IBM

INTERNATIONAL BUSINESS MACHINES, INC.

# The PowerPE Architecture:

A SPECIFICATION FOR A NEW FAMILY OF RISC PROCESSORS

## The **PewerPC** Architecture:

A SPECIFICATION FOR A NEW FAMILY OF RISC PROCESSORS

Second Edition (May 1994)

This edition notice applies to *The PowerPC Architecture: A Specification for A New Family of RISC Processors*. The following paragraph does not apply to the United Kingdom or any country or state where such provisions are inconsistent with local law.

The specifications in this manual are subject to change without notice. This manual is provided "AS IS." Neither Morgan Kaufmann nor International Business Machines Corp. make any warranty of any kind, either expressed or implied, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose.

Neither Morgan Kaufmann nor International Business Machines Corp. warrant that the contents of this publication or the accompanying source code examples, whether individually or as one or more groups, will meet your requirements or that the publication or the accompanying source code examples are error-free.

This publication could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication.

Requests for copies of this publication should be made to Morgan Kaufmann Publishers at (800) 745-7323 or to your IBM Marketing Representative.

Address comments to IBM Corporation, Internal Zip 9630, 11400 Burnett Road, Austin, Texas 78758-3493 or to Morgan Kaufmann Publishers at 340 Pine Street, San Francisco, California 94104. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

The following terms are trademarks of the International Business Machines Corporation in the United States and/or other countries:

IBM PowerPC RISC/System 6000 POWER POWER2 IBM System/370

The following are trademarks of other companies:

Apple is a trademark of Apple Computer Inc.

Motorola is a trademark of Motorola Inc.

DEC and VAX are trademarks of Digital Equipment Corporation.

Intel is a trademark of Intel Corporation.

© International Business Machines Corporation 1993, 1994. All rights reserved.

Notice to U.S. Government Users—Documentation Related to Restricted Rights—Use, duplication or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corporation.

## The **PowerPC** Architecture:

A SPECIFICATION FOR A NEW FAMILY OF RISC PROCESSORS

Edited by Cathy May, Ed Silha, Rick Simpson, Hank Warren To order copies of this book, please contact the publisher at (800)745-7323 or your IBM Marketing Representative.

Morgan Kaufmann Publishers, Inc. Editorial Office: 340 Pine Street, Sixth Floor San Francisco, CA 94104

Executive Editor: Bruce M. Spatz Production Manager: Yonie Overton

Assistant Editor: Douglas Sery

Assistant Production Editor: Vicki Van Ausdall

Production Coordinator: Julie Pabst Composition: Ed Sznyter, Babel Press Cover and Text Design: Carron Design

Copyediting: Fran Taylor Proofreading: Gary Morris Printer: Courier Corporation

Printed in the United States of America

98 97 96 95 94 5 4 3 2 1

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means—electronic, mechanical, photocopying, recording, or otherwise—without the prior written permission of the publisher.

Library of Congress Cataloging-in-Publication Data is available for this book.

ISBN 1-55860-316-6

#### **Foreword**

By

Phil Hester

Vice President

IBM RISC System/6000 Division—Systems and Technology

IBM first introduced the POWER architecture with the RISC System/ 6000 in early 1990. POWER, an acronym for "Performance Optimization With Enhanced RISC," was one of the first superscalar RISC microprocessors. The original microprocessor for these products consisted of a multi-chip implementation which set new performance and price/performance standards at the time of announcement. However, it soon became apparent that a single-chip version would be needed in order to include future lower cost members in the RISC System/6000 family. Systems would be needed that could span the range from personal computers through high end computers. As a result, work was started on a singlechip version of the POWER architecture. In early 1991 it became evident that this single-chip design could potentially become a high volume standard in the industry. Accomplishing this objective would clearly require the development of a superior family of single-chip microprocessors, and the ability to supply these at competitive prices. IBM then began discussions with Motorola concerning potential collaboration to develop this family of microprocessors. As these discussions progressed, it became clear that both our general microprocessor requirements and our belief that the high performance and low cost of these microprocessors could be exploited in systems was shared by another of Motorola's large customers, Apple. This lead to discussions among Apple, IBM, and Motorola, in which it became clear that we did share common objectives for the microprocessors. Based on this, we could define complementary roles for each of the companies in the development of these microprocessors as well as the object-oriented and multi-media software technology needed to exploit them.

Through both a commitment by all three companies to make this alli-

ance a success and the dedication of extremely talented people from each company, negotiations were completed and PowerPC ("PC" stands for "Performance Computing") was born in October of 1991. With Apple's personal computer systems experience, Motorola's high volume microprocessor and silicon knowledge, and IBM's RISC expertise and silicon technology capability, the components were in place to begin development of an entire family of RISC microprocessors which support a common architecture and can span a wide range of computing requirements. Within six months a new development site, now known as the Somerset Design Center, was dedicated, and staffing was well underway for the design teams.

Time to market for the first PowerPC microprocessor was viewed as a critical factor in the future success of PowerPC. As a result, an aggressive plan was put together to allow development of the first PowerPC microprocessor (PowerPC 601) as quickly as possible. It was also important that this microprocessor not sacrifice competitiveness as a result of its aggressive schedule. To achieve these goals, we combined the work already going on in IBM developing a single-chip version of the POWER architecture with the 88110 work going on in Motorola. This allowed us to develop a microprocessor very quickly that was compliant with the PowerPC architecture and utilized the expertise of both IBM and Motorola.

Additional microprocessors were planned as part of the initial effort to be tailored to the various segments of the computing marketplace. The 603 microprocessor is intended for very low end and battery powered products. Satisfying mid-range system needs, primarily optimizing price/performance and permitting symmetric multiprocessor (SMP) scalability, is the major goal for the 604. The 620 is optimized for high end scientific and commercial environments, in which raw performance is critical. This microprocessor, with a goal of achieving the best possible performance from a single-chip technology, supports SMP and implements the 64-bit PowerPC architecture. In 32-bit mode, the 620 is fully compatible with all the 32-bit members of the PowerPC family (601, 603, and 604).

As of November 1993 we are well on our way to delivering this family of PowerPC microprocessors. In September 1993 IBM announced the first product using the PowerPC 601—the RISC System/6000 Model 25. In October 1993 IBM and Motorola announced functional first silicon for the 603. It is important to note that the 601 and 603 were both completed on schedule while also achieving their performance, functionality, and die size objectives. This success gives us high confidence that we will achieve similar results for the 604 and 620. In addition, by having fabricated the 603 separately in both IBM and Motorola manufacturing facil-

Foreword vii

ities, we have validated the compatibility of our manufacturing processes. Since these same processes will be used for the 604 and 620, we feel confident of our ability to produce these microprocessors.

Over time, the Somerset Design Center will continue to broaden and improve the product line to exploit both the PowerPC architecture and advances in silicon technology as they become available. Our vision of providing one architecture, implemented in a family of microprocessors each of which is optimized for a particular environment ranging from "palmtops to teraFLOPS," is well on the way to becoming a reality.

## **Contents in Brief**

Foreword

| List of Figures                                        | xxiii |

|--------------------------------------------------------|-------|

| List of Tables                                         | xxvii |

| Preface                                                | ххіх  |

| Book I PowerPC User Instruction Set Archite            | cture |

| Chapter 1 Introduction                                 | 3     |

| Chapter 2 Branch Processor                             | 31    |

| Chapter 3 Fixed-Point Processor                        | 47    |

| Chapter 4 Floating-Point Processor                     | 133   |

| Appendix A Optional Instructions                       | 197   |

| Appendix B Suggested Floating-Point Models             | 203   |

| Appendix C Assembler Extended Mnemonics                | 215   |

| Appendix D Little-Endian Byte Ordering                 | 233   |

| Appendix E Programming Examples                        | 249   |

| Appendix F Cross-Reference for Changed POWER Mnemonics | 267   |

| Appendix G Incompatibilities with the POWER  Architecture | 271  |

|-----------------------------------------------------------|------|

| Appendix H New Instructions                               | 287  |

| Appendix I Illegal Instructions                           | 291  |

| Appendix J Reserved Instructions                          | 293  |

| Appendix K PowerPC Instruction Set Sorted by Opcod        | e295 |

| Appendix L PowerPC Instruction Set Sorted by<br>Mnemonic  | 305  |

| Book II PowerPC Virtual Environment Architecture          |      |

| Chapter 1 Storage Model                                   | 319  |

| Chapter 2 Effect of Operand Placement on<br>Performance   | 339  |

| Chapter 3 Storage Control Instructions                    | 343  |

| Chapter 4 Time Base                                       | 351  |

| Appendix A Cross-Reference for Changed POWER  Mnemonics   | 359  |

| Appendix B New Instructions                               | 361  |

| Appendix C PowerPC Virtual Environment Instruction Set    | 363  |

| Book III PowerPC Operating Environment Architecture       |      |

| Chapter 1 Introduction                                    | 367  |

| Chapter 2 Branch Processor                                | 373  |

| Chapter 3 Fixed-Point Processor                           | 381  |

Contents in Brief xi

| Chapter 4  | Storage Control                                                                 | 391 |

|------------|---------------------------------------------------------------------------------|-----|

| Chapter 5  | Interrupts                                                                      | 453 |

| Chapter 6  | Timer Facilities                                                                | 479 |

| -          | Synchronization Requirements for Special<br>Registers and for Lookaside Buffers | 483 |

| Appendix A | Optional Facilities and Instructions                                            | 489 |

| Appendix E | Assembler Extended Mnemonics                                                    | 495 |

| Appendix ( | Cross-Reference for Changed POWER  Mnemonics                                    | 497 |

| Appendix D | New Instructions                                                                | 499 |

| Appendix E | Implementation-Specific SPRs                                                    | 501 |

| Appendix F | Interpretation of the DSISR as Set by an Alignment Interrupt                    | 503 |

| Appendix C | PowerPC Operating Environment Instruct                                          | ion |

|            | Set                                                                             | 511 |

| Index      |                                                                                 | 513 |

### **Contents**

| Foreword        | •    |

|-----------------|------|

| List of Figures | xxii |

| List of Tables  | xxvi |

| Proface         | vvi  |

#### **Book I PowerPC User Instruction Set Architecture**

| Cha  | oter 1 | Introduction                          | 3  |

|------|--------|---------------------------------------|----|

| 1.1  | Overv  | iew                                   | 3  |

| 1.2  | Comp   | utation Modes                         | 3  |

|      | 1.2.1  | 64-bit Implementations                | 4  |

|      | 1.2.2  | 32-bit Implementations                | 4  |

| 1.3  | Instru | ction Mnemonics and Operands          | 4  |

| 1.4  | Comp   | atibility with the POWER Architecture | 4  |

| 1.5  | Docun  | nent Conventions                      | 5  |

|      | 1.5.1  | Definitions and Notation              | 5  |

|      | 1.5.2  | Reserved Fields                       | 8  |

|      | 1.5.3  | Description of Instruction Operation  | 8  |

| 1.6  | Proces | ssor Overview                         | 11 |

| 1.7  | Instru | ction Formats                         | 12 |

|      | 1.7.1  | Instruction Fields                    | 19 |

| 1.8  | Classe | es of Instructions                    | 23 |

|      | 1.8.1  | Defined Instruction Class             | 23 |

|      | 1.8.2  | Illegal Instruction Class             | 24 |

|      | 1.8.3  | Reserved Instruction Class            | 24 |

| 1.9  | Forms  | of Defined Instructions               | 25 |

|      | 1.9.1  | Preferred Instruction Forms           | 25 |

|      | 1.9.2  | Invalid Instruction Forms             | 25 |

|      | 1.9.3  | Optional Instructions                 | 26 |

| 1.10 | Excep  | tions                                 | 26 |

| 1.11 | Storag | ge Addressing                         | 27 |

|      |        | Storage Operands                      | 27 |

|      |        | Effective Address Calculation         | 29 |

| Chap | oter 2  | <b>Branch Processor</b>                          | 31  |

|------|---------|--------------------------------------------------|-----|

| 2.1  | Branch  | n Processor Overview                             | 31  |

| 2.2  | Instru  | ction Fetching                                   | 31  |

| 2.3  | Branch  | n Processor Registers                            | 32  |

|      |         | Condition Register                               | 32  |

|      |         | Link Register                                    | 35  |

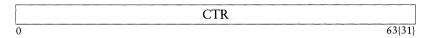

|      |         | Count Register                                   | 35  |

| 2.4  |         | n Processor Instructions                         | 35  |

|      |         | Branch Instructions                              | 35  |

|      |         | System Call Instruction                          | 41  |

|      |         | Condition Register Logical Instructions          | 42  |

|      |         | Condition Register Field Instruction             | 46  |

| Chap | oter 3  | Fixed-Point Processor                            | 47  |

| 3.1  | Fixed-  | Point Processor Overview                         | 47  |

| 3.2  | Fixed-  | Point Processor Registers                        | 47  |

|      | 3.2.1   | General Purpose Registers                        | 47  |

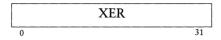

|      | 3.2.2   | Fixed-Point Exception Register                   | 48  |

| 3.3  | Fixed-  | Point Processor Instructions                     | 49  |

|      | 3.3.1   | Storage Access Instructions                      | 49  |

|      | 3.3.2   |                                                  | 49  |

|      | 3.3.3   | Fixed-Point Store Instructions                   | 61  |

|      | 3.3.4   | Fixed-Point Load and Store with Byte Reversal    |     |

|      |         | Instructions                                     | 68  |

|      | 3.3.5   | Fixed-Point Load and Store Multiple Instructions | 70  |

|      |         | Fixed-Point Move Assist Instructions             | 72  |

|      | 3.3.7   | Storage Synchronization Instructions             | 76  |

|      |         | Other Fixed-Point Instructions                   | 80  |

|      | 3.3.9   | Fixed-Point Arithmetic Instructions              | 81  |

|      |         | Fixed-Point Compare Instructions                 | 98  |

|      | 3.3.11  | Fixed-Point Trap Instructions                    | 101 |

|      | 3.3.12  | Fixed-Point Logical Instructions                 | 105 |

|      | 3.3.13  | Fixed-Point Rotate and Shift Instructions        | 115 |

|      | 3.3.14  | Move to/from System Register Instructions        | 128 |

| Chap | oter 4  | Floating-Point Processor                         | 133 |

| 4.1  | Floatir | ng-Point Processor Overview                      | 133 |

| 4.2  | Floatir | ng-Point Processor Registers                     | 135 |

|      | 4.2.1   | Floating-Point Registers                         | 135 |

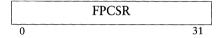

|      | 4.2.2   | Floating-Point Status and Control Register       | 137 |

| 4.3  | Floatir | ng-Point Data                                    | 141 |

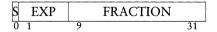

|      |         | Data Format                                      | 141 |

|      | 4.3.2   | Value Representation                             | 143 |

|      | 4.3.3   | Sign of Result                                   | 146 |

|      | 4.3.4   | Normalization and Denormalization                | 147 |

|      |         | Data Handling and Precision                      | 147 |

|      |         | Rounding                                         | 149 |

| 4.4  |         | ng-Point Exceptions                              | 150 |

|      |         | Invalid Operation Exception                      | 155 |

|      |         | Zero Divide Exception                            | 158 |

|      |         | Overflow Exception                               | 159 |

|      |         | Underflow Exception                              | 169 |

|      | 445     | Inexact Exception                                | 162 |

| 4.5         | Floati | ng-Point Execution Models                                                | 162        |

|-------------|--------|--------------------------------------------------------------------------|------------|

|             | 4.5.1  | Execution Model for IEEE Operations                                      | 163        |

|             | 4.5.2  |                                                                          |            |

| 4.6         |        | ng-Point Processor Instructions                                          | 167        |

|             | 4.6.1  |                                                                          | 167        |

|             | 4.6.2  |                                                                          | 168        |

|             |        | Floating-Point Store Instructions Floating-Point Move Instructions       | 173<br>178 |

|             |        | Floating-Point Move Instructions  Floating-Point Arithmetic Instructions | 179        |

|             |        | Floating-Point Rounding and Conversion Instruction                       |            |

|             |        | Floating-Point Compare Instructions                                      | 191        |

|             |        | Floating-Point Status and Control Register                               |            |

|             |        | Instructions                                                             | 193        |

| Арр         | endix  | A Optional Instructions                                                  | 197        |

| A.1         | Floati | ng-Point Processor Instructions                                          | 197        |

|             |        | Floating-Point Store Instruction                                         | 197        |

|             |        | Floating-Point Arithmetic Instructions                                   | 198        |

|             |        | Floating-Point Select Instruction                                        | 202        |

|             |        | _                                                                        |            |

|             |        | B Suggested Floating-Point Models                                        | 203        |

| B.1         |        | ng-Point Round to Single-Precision Model                                 | 203        |

| B.2         |        | ng-Point Convert to Integer Model                                        | 209        |

| B.3         | Floati | ng-Point Convert from Integer Model                                      | 212        |

| App         | endix  | C Assembler Extended Mnemonics                                           | 215        |

| C.1         | Symbo  | ols                                                                      | 215        |

| C.2         | Brancl | h Mnemonics                                                              | 216        |

|             | C.2.1  | BO and BI Fields                                                         | 216        |

|             | C.2.2  | Simple Branch Mnemonics                                                  | 217        |

|             | C.2.3  | Branch Mnemonics Incorporating Conditions                                | 219        |

|             | C.2.4  | Branch Prediction                                                        | 220        |

| C.3         | Condi  | tion Register Logical Mnemonics                                          | 222        |

| C.4         | Subtra | act Mnemonics                                                            | 223        |

|             | C.4.1  | Subtract Immediate                                                       | 223        |

|             | C.4.2  | Subtract                                                                 | 223        |

| C.5         | Comp   | are Mnemonics                                                            | 223        |

|             | C.5.1  | Doubleword Comparisons                                                   | 224        |

|             | C.5.2  | Word Comparisons                                                         | 225        |

| C.6         | Trap N | /Inemonics                                                               | 225        |

| C.7         | Rotate | e and Shift Mnemonics                                                    | 227        |

|             | C.7.1  | Operations on Doublewords                                                | 228        |

|             | C.7.2  | Operations on Words                                                      | 229        |

| C.8         | Move   | To/From Special Purpose Register Mnemonics                               | 230        |

| <b>C</b> .9 | Misce  | llaneous Mnemonics                                                       | 231        |

| App         | endix  | D Little-Endian Byte Ordering                                            | 233        |

| D.1         |        | Ordering                                                                 | 233        |

| D.1<br>D.2  | -      | ure Mapping Examples                                                     | 234        |

|             |        | Big-Endian Mapping                                                       | 235        |

|             |        | Little-Endian Mapping                                                    | 235        |

|             | ···    |                                                                          |            |

| D.3 | Powe   | rPC Byte Ordering                                        | 236  |

|-----|--------|----------------------------------------------------------|------|

|     | D.3.1  | Controlling PowerPC Byte Ordering                        | 236  |

|     | D.3.2  | PowerPC Little-Endian Byte Ordering                      | 237  |

| D.4 | Powe   | rPC Data Storage Addressing in Little-Endian Mode        | 240  |

|     | D.4.1  | Individual Aligned Scalars                               | 240  |

|     | D.4.2  | Other Scalars                                            | 240  |

|     | D.4.3  | Segment Tables and Page Tables                           | 242  |

| D.5 | Powe   | rPC Instruction Storage Addressing in Little-            |      |

|     | Endia  | n Mode                                                   | 242  |

| D.6 | Powe   | rPC Cache Management and Lookaside Buffer                |      |

|     | Mana   | gement Instructions in Little-Endian Mode                | 245  |

| D.7 | Powe   | rPC I/O in Little-Endian Mode                            | 245  |

| D.8 | Origir | n of Endian                                              | 246  |

| Арр | endix  | E Programming Examples                                   | 249  |

| E.1 | Synch  | ronization                                               | 249  |

|     | E.1.1  | Synchronization Primitives                               | 250  |

|     | E.1.2  | Lock Acquisition and Release                             | 253  |

|     | E.1.3  | List Insertion                                           | 254  |

|     | E.1.4  | Notes                                                    | 255  |

| E.2 | Multi  | ple-Precision Shifts                                     | 256  |

| E.3 | Floati | ng-Point Conversions                                     | 259  |

|     | E.3.1  | Conversion from Floating-Point Number to Floating        | g-   |

|     |        | Point Integer                                            | 259  |

|     | E.3.2  | <b>Conversion from Floating-Point Number to Signed</b>   |      |

|     |        | Fixed-Point Integer Doubleword                           | 260  |

|     | E.3.3  | Conversion from Floating-Point Number to Unsigne         | ed   |

|     |        | Fixed-Point Integer Doubleword                           | 260  |

|     | E.3.4  | <b>Conversion from Floating-Point Number to Signed</b>   |      |

|     |        | Fixed-Point Integer Word                                 | 261  |

|     | E.3.5  | <b>Conversion from Floating-Point Number to Unsigne</b>  | ed   |

|     |        | Fixed-Point Integer Word                                 | 261  |

|     | E.3.6  | <b>Conversion from Signed Fixed-Point Integer Double</b> | word |

|     |        | to Floating-Point Number                                 | 262  |

|     | E.3.7  | Conversion from Unsigned Fixed-Point Integer             |      |

|     |        | Doubleword to Floating-Point Number                      | 262  |

|     | E.3.8  | Conversion from Signed Fixed-Point Integer Word          | to   |

|     |        | Floating-Point Number                                    | 263  |

|     | E.3.9  | Conversion from Unsigned Fixed-Point Integer Wor         | d to |

|     |        | Floating-Point Number                                    | 264  |

| E.4 | Floati | ng-Point Selection                                       | 264  |

|     | E.4.1  | Comparison to Zero                                       | 265  |

|     | E.4.2  | Minimum and Maximum                                      | 265  |

|     | E.4.3  | Simple if-then-else Constructions                        | 265  |

|     | E.4.4  | Notes                                                    | 266  |

| Арр | endix  | F Cross-Reference for Changed POWER                      |      |

|     |        | Mnemonics                                                | 267  |

| App              | endix G Incompatibilities with the POWER                   |     |  |  |  |

|------------------|------------------------------------------------------------|-----|--|--|--|

| Architecture 271 |                                                            |     |  |  |  |

| G.1              | New Instructions, Formerly Privileged Instructions         | 271 |  |  |  |

| G.2              | Newly Privileged Instructions                              | 272 |  |  |  |

| G.3              | Reserved Bits in Instructions                              | 272 |  |  |  |

| G.4              | Reserved Bits in Registers                                 | 272 |  |  |  |

| G.5              | Alignment Check                                            | 272 |  |  |  |

| G.6              | Condition Register                                         | 273 |  |  |  |

| <b>G.7</b>       | Inappropriate use of LK and Rc Bits                        | 273 |  |  |  |

| G.8              | BO Field                                                   | 274 |  |  |  |

| G.9              | Branch Conditional to Count Register                       | 274 |  |  |  |

| G.10             | System Call                                                | 274 |  |  |  |

| G.11             | Fixed-Point Exception Register (XER)                       | 275 |  |  |  |

| G.12             | Update Forms of Storage Access                             | 275 |  |  |  |

| G.13             | Multiple Register Loads                                    | 275 |  |  |  |

| G.14             | Alignment for Load/Store Multiple                          | 276 |  |  |  |

| G.15             | Move Assist Instructions                                   | 276 |  |  |  |

| G.16             | Synchronization                                            | 276 |  |  |  |

| G.17             | Move To/From SPR                                           | 276 |  |  |  |

| G.18             | Effects of Exceptions on FPSCR Bits FR and FI              | 277 |  |  |  |

| G.19             | Floating-Point Store Instructions                          | 278 |  |  |  |

| G.20             | Move From FPSCR                                            | 278 |  |  |  |

| G.21             | Zeroing Bytes in the Data Cache                            | 278 |  |  |  |

| G.22             | Floating-Point Load/Store to Direct-Store Segment          | 278 |  |  |  |

| G.23             | Segment Register Instructions                              | 278 |  |  |  |

| G.24             | TLB Entry Invalidation                                     | 279 |  |  |  |

| G.25             | Floating-Point Interrupts                                  | 279 |  |  |  |

| G.26             | Timing Facilities                                          | 279 |  |  |  |

|                  | G.26.1 Real-Time Clock                                     | 279 |  |  |  |

|                  | G.26.2 Decrementer                                         | 280 |  |  |  |

| G.27             | Deleted Instructions                                       | 280 |  |  |  |

| G.28             | Discontinued Opcodes                                       | 282 |  |  |  |

| G.29             | POWER2 Compatibility                                       | 283 |  |  |  |

|                  | <b>G.29.1 Cross-Reference for Changed POWER2 Mnemonics</b> | 283 |  |  |  |

|                  | G.29.2 Floating-Point Conversion to Integer                | 284 |  |  |  |

|                  | G.29.3 Storage Ordering                                    | 284 |  |  |  |

|                  | G.29.4 Floating-Point Interrupts                           | 285 |  |  |  |

|                  | G.29.5 Trace Interrupts                                    | 285 |  |  |  |

|                  | G.29.6 Deleted Instructions                                | 285 |  |  |  |

|                  | G.29.7 Discontinued Opcodes                                | 285 |  |  |  |

| Арр              | endix H New Instructions                                   | 287 |  |  |  |

| H.1              | New Instructions for All Implementations                   | 287 |  |  |  |

| H.2              | New Instructions for 64-Bit Implementations Only           | 289 |  |  |  |

H.3 New Instructions for 32-Bit Implementations Only

290

| Ap      | pendix I Illegal Instructions                          | 291        |

|---------|--------------------------------------------------------|------------|

| Ар      | pendix J Reserved Instructions                         | 293        |

| Ap      | pendix K PowerPC Instruction Set Sorted by             | Opcode295  |

| Ар      | pendix L PowerPC Instruction Set Sorted by<br>Mnemonic | 305        |

| Book II | PowerPC Virtual Environment                            |            |

|         | Architecture                                           |            |

| Ch      | apter 1 Storage Model                                  | 319        |

| 1.1     | Definitions and Notation                               | 319        |

| 1.2     | Introduction                                           | 321        |

| 1.3     | Virtual Storage                                        | 321        |

| 1.4     | Single-Copy Atomicity                                  | 322        |

| 1.5     | Memory Coherence                                       | 323        |

|         | 1.5.1 Coherence Required                               | 324        |

|         | 1.5.2 Coherence Not Required                           | 324        |

| 1.6     | 9                                                      | 325        |

| 1.7     |                                                        | 327        |

|         | 1.7.1 Split or Dual Caches                             | 328        |

|         | 1.7.2 Combined Cache 1.7.3 Write Through Data Cache    | 332<br>332 |

| 1.8     |                                                        | 333        |

| 1.0     | 1.8.1 Storage Access Ordering                          | 333        |

|         | 1.8.2 Atomic Update Primitives                         | 336        |

| Ch      | apter 2 Effect of Operand Placement on                 |            |

|         | Performance                                            | 339        |

| 2.1     | Instruction Restart                                    | 341        |

| 2.2     | Atomicity and Order                                    | 342        |

| Ch      | apter 3 Storage Control Instructions                   | 343        |

| 3.1     | Parameters Useful to Application Programs              | 343        |

| 3.2     |                                                        | 344        |

|         | 3.2.1 Instruction Cache Instructions                   | 344        |

|         | 3.2.2 Data Cache Instructions                          | 346        |

| 3.3     | Enforce In-order Execution of I/O Instruction          | 350        |

| Ch      | apter 4 Time Base                                      | 351        |

| 4.1     |                                                        | 352        |

| 4.2     | Reading the Time Base on 64-bit Implementations        | 353        |

| 4.3     |                                                        | 354        |

| 4.4     | Computing Time of Day from the Time Base               | 354        |

Contents xix

| Ар       | pendix A Cross-Reference for Changed POWER  Mnemonics         | 359        |

|----------|---------------------------------------------------------------|------------|

| Ар       | pendix B New Instructions                                     | 361        |

| Ар       | pendix C PowerPC Virtual Environment Instructio<br>Set        | n<br>363   |

| Book III | PowerPC Operating Environment Architecture                    |            |

| Cha      | apter 1 Introduction                                          | 367        |

| 1.1      | Overview                                                      | 367        |

| 1.2      | Compatibility with the POWER Architecture                     | 367        |

| 1.3      | Document Conventions                                          | 367        |

|          | 1.3.1 Definitions and Notation                                | 368        |

|          | 1.3.2 Reserved Fields                                         | 369        |

|          | 1.3.3 Description of Instruction Operation                    | 369        |

| 1.4      |                                                               | 369        |

| 1.5      |                                                               | 370        |

|          | 1.5.1 Instruction Fields                                      | 370        |

| 1.6      |                                                               | 371        |

| 1.7      |                                                               | 371        |

|          | 1.7.1 Context Synchronization 1.7.2 Execution Synchronization | 371<br>372 |

|          | 1.7.2 Execution Synchronization                               | 3/2        |

| Cha      | apter 2 Branch Processor                                      | 373        |

| 2.1      | Branch Processor Overview                                     | 373        |

| 2.2      | Branch Processor Registers                                    | 373        |

|          | 2.2.1 Machine Status Save/Restore Register 0                  | 373        |

|          | 2.2.2 Machine Status Save/Restore Register 1                  | 374        |

|          | 2.2.3 Machine State Register                                  | 374        |

| 2.3      |                                                               | 378        |

|          | 2.3.1 System Linkage Instructions                             | 378        |

| Cha      | apter 3 Fixed-Point Processor                                 | 381        |

| 3.1      | Fixed-Point Processor Overview                                | 381        |

| 3.2      | PowerPC Special Purpose Registers                             | 381        |

| 3.3      |                                                               | 381        |

|          | 3.3.1 Data Address Register                                   | 381        |

|          | 3.3.2 Data Storage Interrupt Status Register                  | 382        |

|          | 3.3.3 Software-Use SPRs                                       | 382        |

|          | 3.3.4 Processor Version Register                              | 383        |

| 3.4      | · · · · · · · · · · · · · · · · · · ·                         | 384        |

|          | 3.4.1 Move to/from System Register Instructions               | 384        |

| Chap | oter 4         | Storage Control                                                        | 391        |

|------|----------------|------------------------------------------------------------------------|------------|

| 4.1  | Storag         | e Addressing                                                           | 391        |

| 4.2  | Storag         | e Model                                                                | 392        |

|      | 4.2.1          | Storage Segments                                                       | 393        |

|      |                | Storage Exceptions                                                     | 393        |

|      |                | Instruction Fetch                                                      | 394        |

|      |                | Data Storage Access                                                    | 395        |

|      |                | Speculative Execution                                                  | 396        |

|      |                | 32-Bit Mode on a 64-Bit Implementation                                 | 398        |

| _    |                | Real Addressing Mode                                                   | 399        |

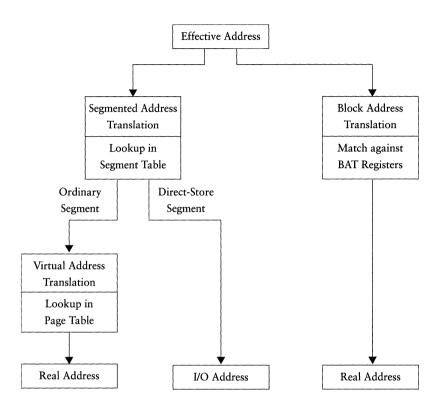

| 4.3  |                | ss Translation Overview                                                | 399        |

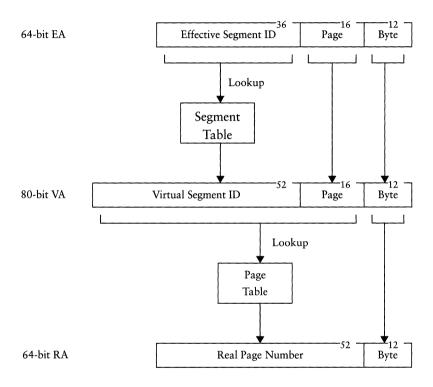

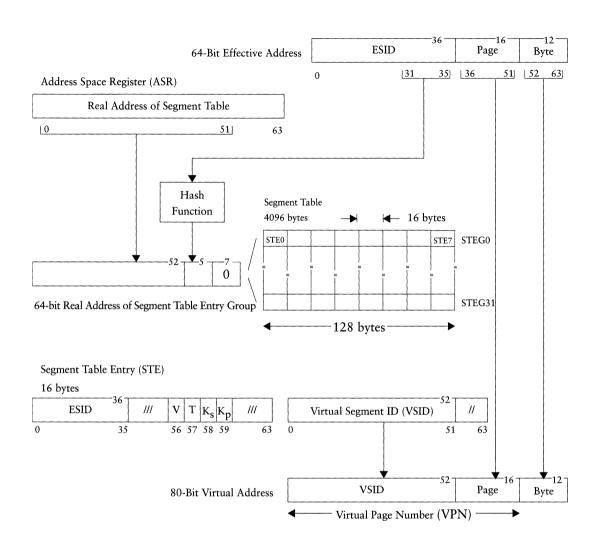

| 4.4  |                | ented Address Translation, 64-bit Implementations                      | 401        |

|      |                | Virtual Address Generation, 64-bit Implementations                     |            |

|      |                | Virtual to Real Translation, 64-bit Implementations                    | 406        |

| 4.5  | _              | ented Address Translation, 32-bit Implementations                      | 412        |

|      |                | Virtual Address Generation, 32-bit Implementations                     |            |

|      |                | Virtual to Real Translation, 32-bit Implementations                    | 415        |

| 4.6  |                | Store Segments                                                         | 421        |

|      |                | Completion of Direct-Store Access                                      | 421        |

|      | 4.6.2          |                                                                        | 422        |

|      | 4.6.3          | Instructions Not Supported for T=1 Instructions with No Effect for T=1 | 422<br>423 |

|      |                |                                                                        |            |

| 4.7  |                | Address Translation                                                    | 423<br>423 |

|      | 4.7.1<br>4.7.2 |                                                                        | 425        |

|      |                |                                                                        | 429        |

| 4.8  |                | e Access Modes                                                         | 429        |

|      | 4.8.1          | W, I, M, and G bits<br>Supported Storage Modes                         | 430        |

|      |                | Mismatched WIMG Bits                                                   | 433        |

| 4.9  |                |                                                                        | 433        |

| 4.9  | 4.9.1          | nce and Change Recording Synchronization of Reference and Change Bit   | 433        |

|      |                | Updates                                                                | 436        |

| 4.10 |                | e Protection                                                           | 436        |

| 4.10 |                | Page Protection                                                        | 430        |

|      |                | BAT Protection                                                         | 438        |

| 4.11 |                | e Control Instructions                                                 | 438        |

| 4.11 |                | Cache Management Instructions                                          | 438        |

|      |                | Segment Register Manipulation Instructions                             | 440        |

|      |                | Lookaside Buffer Management Instructions                               |            |

|      |                | (Optional)                                                             | 442        |

| 4.12 |                | Update Synchronization Requirements                                    | 446        |

|      |                | Page Table Updates                                                     | 447        |

|      |                | Segment Table Updates                                                  | 450        |

|      |                | Segment Register Updates                                               | 452        |

| Chap | oter 5         | Interrupts                                                             | 453        |

| 5.1  | Overvi         | iew                                                                    | 453        |

| 5.2  | Interru        | upt Synchronization                                                    | 453        |

| 5.3  | Interru        | upt Classes                                                            | 454        |

|      | 5.3.1          | Precise Interrupt                                                      | 454        |

|      | 5.3.2          | -                                                                      | 455        |

| 5.4  | Interru        | upt Processing                                                         | 456        |

| 5.5  |                | upt Definitions                                                        | 457        |

|          | 5.5.1   | System Reset Interrupt                          | 457  |

|----------|---------|-------------------------------------------------|------|

|          | 5.5.2   | Machine Check Interrupt                         | 459  |

|          |         | Data Storage Interrupt                          | 460  |

|          | 5.5.4   | Instruction Storage Interrupt                   | 463  |

|          |         | External Interrupt                              | 464  |

|          |         | Alignment Interrupt                             | 464  |

|          |         | Program Interrupt                               | 467  |

|          |         | Floating-Point Unavailable Interrupt            | 469  |

|          |         | Decrementer Interrupt                           | 470  |

|          |         | System Call Interrupt                           | 470  |

|          |         | Trace Interrupt                                 | 470  |

|          |         | Floating-Point Assist Interrupt                 | 471  |

| 5.6      | Partial | ly Executed Instructions                        | 472  |

| 5.7      |         | ion Ordering                                    | 473  |

|          |         | Unordered Interrupt Conditions                  | 474  |

|          | 5.7.2   | Ordered Exceptions                              | 474  |

| 5.8      | Interru | upt Priorities                                  | 475  |

| Cha      | pter 6  | Timer Facilities                                | 479  |

| 6.1      | Overvi  | ew                                              | 479  |

| 6.2      | Time E  | lase                                            | 479  |

|          | 6.2.1   | Writing the Time Base                           | 481  |

| 6.3      |         | menter                                          | 481  |

|          |         | Writing and Reading the Decrementer             | 482  |

| Cha      | pter 7  | Synchronization Requirements for Specia         | ı    |

|          | •       | Registers and for Lookaside Buffers             | 483  |

| Δnn      | endiv   | A Optional Facilities and Instructions          | 489  |

|          |         |                                                 |      |

| A.1      |         | al Control                                      | 489  |

|          |         | External Access Register                        | 490  |

|          | A.1.2   | External Access Instructions                    | 491  |

| Арр      | endix   | B Assembler Extended Mnemonics                  | 495  |

| B.1      | Move    | To/From Special Purpose Register Mnemonics      | 495  |

| <b>J</b> | More    | ion form special rai pose negister innernolines | 455  |

| App      | endix   | C Cross-Reference for Changed POWER             |      |

|          |         | Mnemonics                                       | 497  |

| A n.n    | ondiv   | D New Instructions                              | 499  |

| App      | enaix   | New Instructions                                | 433  |

| Арр      | endix   | E Implementation-Specific SPRs                  | 501  |

| Ann      | endix   | F Interpretation of the DSISR as Set by an      |      |

| PP       | CHUIN   | Alignment Interrupt                             | 503  |

|          |         | Angimient interrupt                             | JU3  |

| Арр      | endix   | G PowerPC Operating Environment Instruc         | tion |

|          |         | Set                                             | 511  |

|          |         |                                                 |      |

| Inde     | ex      |                                                 | 513  |

## **Figures**

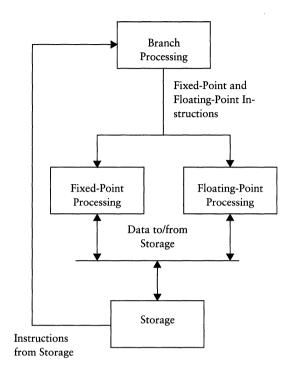

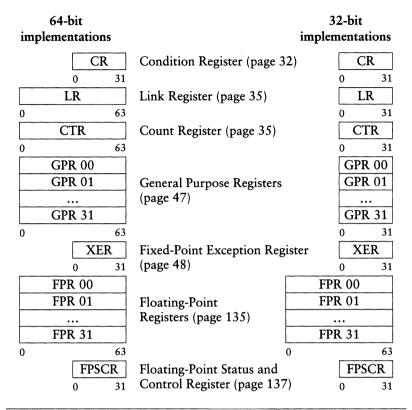

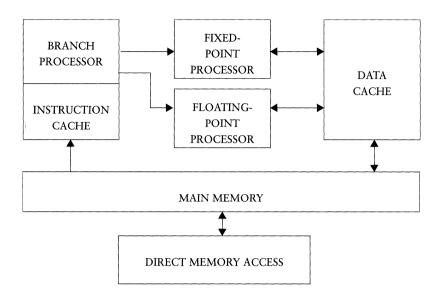

| 1.  | Logical processing model                             | 12  |

|-----|------------------------------------------------------|-----|

| 2.  | PowerPC user register set                            | 13  |

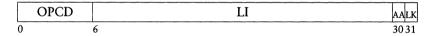

| 3.  | I instruction format                                 | 14  |

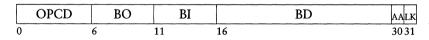

| 4.  | B instruction format                                 | 14  |

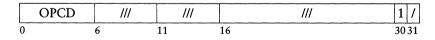

| 5.  | SC instruction format                                | 14  |

| 6.  | D instruction format                                 | 15  |

| 7.  | DS instruction format (64-bit implementations only)  | 15  |

| 8.  | X instruction format                                 | 16  |

| 9.  | XL instruction format                                | 17  |

| 10. | XFX instruction format                               | 17  |

| 11. | XFL instruction format                               | 17  |

| 12. | XS instruction format (64-bit implementations only)  | 17  |

| 13. | XO instruction format                                | 18  |

| 14. | A instruction format                                 | 18  |

| 15. | M instruction format                                 | 18  |

| 16. | MD instruction format (64-bit implementations only)  | 18  |

| 17. | MDS instruction format (64-bit implementations only) | 19  |

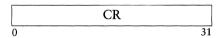

| 18. | Condition Register                                   | 32  |

| 19. | Link Register                                        | 35  |

| 20. | Count Register                                       | 35  |

| 21. | General purpose registers                            | 47  |

| 22. | Fixed-Point Exception Register                       | 48  |

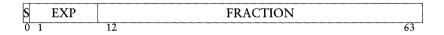

| 23. | Floating-point registers                             | 136 |

| 24. | Floating-Point Status and Control Register           | 137 |

| 25. | Floating-Point Result Flags                          | 140 |

| 26. | Floating-point single format                         | 141 |

| 27. | Floating-point double format                         | 141 |

| 28. | IEEE floating-point fields                           | 142 |

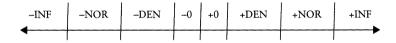

| 29. | Approximation to real numbers                        | 143 |

| 30. | Selection of Z1 and Z2                               | 150 |

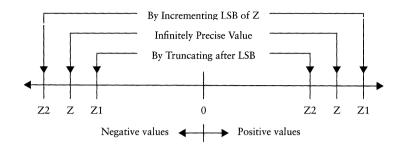

| 31. | IEEE 64-bit execution model                          | 163 |

| 32. | Interpretation of G, R, and X bits                   | 164 |

| 33. | Location of the Guard, Round, and Sticky bits        | 165 |

| 34. | Multiply-Add execution model                         | 166 |

| 35. | C structure 's', showing values of elements          | 235 |

| 36. | Big-Endian mapping of structure 's'                             | 235 |

|-----|-----------------------------------------------------------------|-----|

| 37. | Little-Endian mapping of structure 's'                          | 236 |

| 38. | PowerPC Little-Endian, structure 's' in storage subsystem       | 238 |

| 39. | PowerPC Little-Endian, structure 's' as seen by processor       | 239 |

| 40. | Little-Endian mapping of word 'w' stored at address 5           | 241 |

| 41. | PowerPC Little-Endian, word 'w' stored at address 5 in storage  |     |

|     | subsystem                                                       | 241 |

| 42. | Assembly language program 'p'                                   | 242 |

| 43. | Big-Endian mapping of program 'p'                               | 243 |

| 44. | Little-Endian mapping of program 'p'                            | 243 |

| 45. | PowerPC Little-Endian, program 'p' in storage subsystem         | 243 |

| 46. | Performance effects of storage operand placement, Big-Endian    |     |

|     | mode                                                            | 340 |

| 47. | Performance effects of storage operand placement, Little-Endian |     |

|     | mode                                                            | 341 |

| 48. | Time Base                                                       | 351 |

| 49. | TBR encodings for mftb                                          | 353 |

| 50. | Logical view of the PowerPC processor architecture              | 370 |

| 51. | Save/Restore Register 0                                         | 374 |

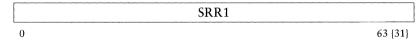

| 52. | Save/Restore Register 1                                         | 374 |

| 53. | Machine State Register                                          | 375 |

| 54. | Data Address Register                                           | 382 |

| 55. | Data Storage Interrupt Status Register                          | 382 |

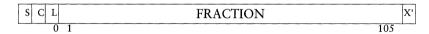

| 56. | Software-use SPRs                                               | 382 |

| 57. | Processor Version Register                                      | 383 |

| 58. | SPR encodings for mtspr                                         | 385 |

| 59. | SPR encodings for mfspr                                         | 387 |

| 60. | PowerPC address translation                                     | 400 |

| 61. | Address translation overview (64-bit implementations)           | 401 |

| 62. | Translation of 64-bit effective address to virtual address      | 403 |

| 63. | Address Space Register                                          | 404 |

| 64. | Segment Table Entry format                                      | 405 |

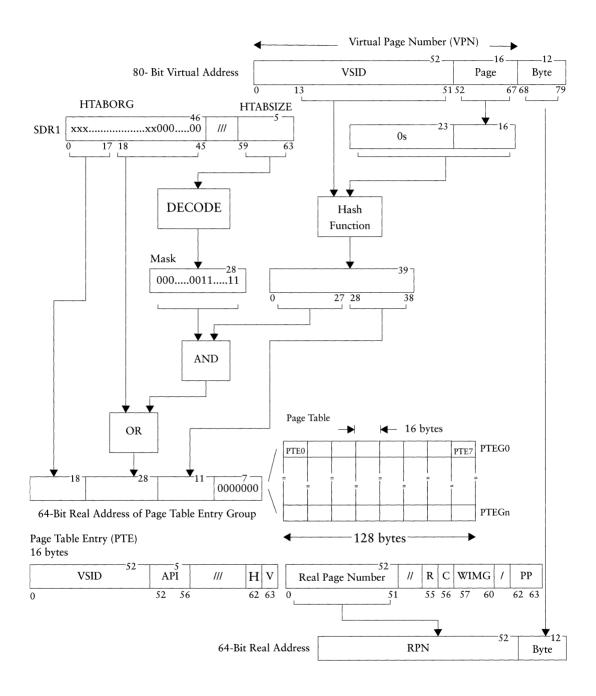

| 65. | Translation of 80-bit virtual address to 64-bit real address    | 407 |

| 66. | Page Table Entry, 64-bit implementations                        | 408 |

| 67. | SDR1, 64-bit implementations                                    | 409 |

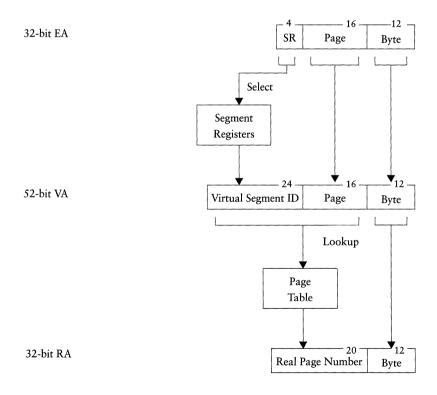

| 68. | Address translation overview (32-bit implementations)           | 412 |

| 69. | Translation of 32-bit effective address to virtual address      | 414 |

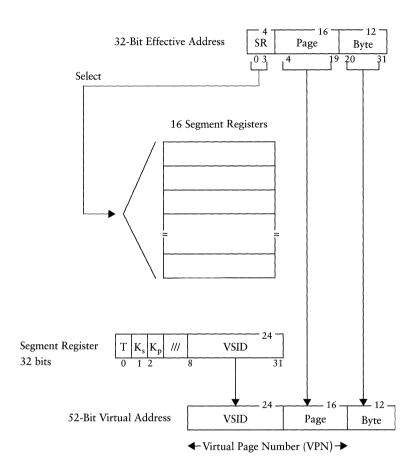

| 70. | Segment Register format                                         | 415 |

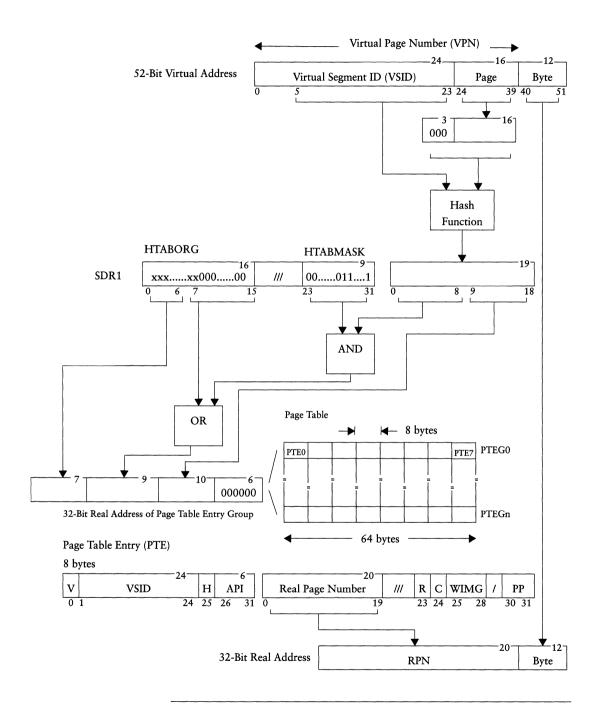

| 71. | Translation of 52-bit virtual address to 32-bit real address    | 416 |

| 72. | Page Table Entry, 32-bit implementations                        | 417 |

| 73. | SDR1, 32-bit implementations                                    | 418 |

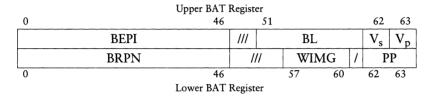

| 74. | BAT registers, 64-bit implementations                           | 425 |

| 75.         | BAT registers, 32-bit implementations                     | 426 |

|-------------|-----------------------------------------------------------|-----|

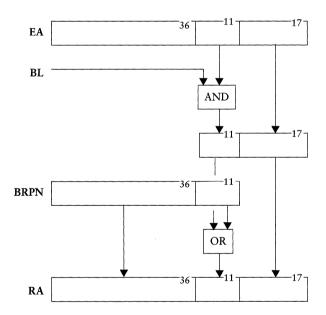

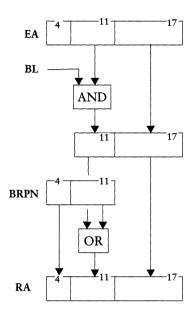

| 76.         | Formation of real address via BAT, 64-bit implementations | 428 |

| 77.         | Formation of real address via BAT, 32-bit implementations | 429 |

| 78.         | Setting the Reference and Change bits                     | 435 |

| 79.         | Protection Key processing                                 | 438 |

| BO.         | MSR setting due to interrupt                              | 458 |

| B1.         | Offset of interrupt vector by interrupt type              | 459 |

| <b>32</b> . | Time Base                                                 | 480 |

| 83.         | Decrementer                                               | 481 |

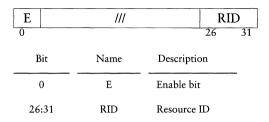

| <b>R</b> 4  | External Access Register                                  | 491 |

## **Tables**

| 1.  | Operator precedence                                       | 11  |

|-----|-----------------------------------------------------------|-----|

| 2.  | Simple branch mnemonics                                   | 218 |

| 3.  | Branch mnemonics incorporating conditions                 | 220 |

| 4.  | Condition Register logical mnemonics                      | 222 |

| 5.  | Doubleword compare mnemonics                              | 224 |

| 6.  | Word compare mnemonics                                    | 225 |

| 7.  | Trap mnemonics                                            | 227 |

| 8.  | Doubleword rotate and shift mnemonics                     | 229 |

| 9.  | Word rotate and shift mnemonics                           | 230 |

| 10. | Extended mnemonics for moving to/from an SPR              | 231 |

| 11. | PowerPC Little-Endian, effective address modification for |     |

|     | individual aligned scalars                                | 238 |

| 12. | Synchronization requirements for data access              | 485 |

| 13. | Synchronization requirements for instruction fetch and/or |     |

|     | execution                                                 | 486 |

| 14. | Extended mnemonics for moving to/from an SPR              | 496 |

#### **Preface**

#### **Preamble**

Some of us wanted to send this book to every household in America, or even in the world, so that everyone who might potentially be interested in PowerPC would easily be able to learn about it. But saner heads prevailed, realizing that some few households might not welcome such a gift, so the book is offered in the normal manner.

#### **About This Book**

The PowerPC Architecture supports a family of processors that spans a wide range of system and application environments. It also provides a stable base for software, allowing applications that run on one PowerPC processor to run consistently on any other PowerPC processor and well-designed operating systems to be moved from one processor implementation to another by making a few minor changes. These desirable yet seemingly conflicting attributes are achieved by structuring the architecture specification into three *Books*, and relegating all implementation-specific aspects of the architecture to a fourth Book that is unique for each implementation. The first three Books correspond to three levels of the architecture, as follows.

#### ■ Book I, User Instruction Set Architecture

This Book describes the registers, instructions, storage model, and execution model that are available to all application programs.

#### ■ Book II, Virtual Environment Architecture

This Book describes features of the architecture that permit application programs to create or modify code, to share data among programs in a multiprocessing system, and to optimize the performance of storage accesses.

#### ■ Book III, Operating Environment Architecture

This Book describes features of the architecture that permit operating systems to allocate and manage storage, to handle errors encountered by application programs, to support I/O devices, and to provide the other services expected of secure, modern, multiprocessor operating systems.

This volume consists of Books I, II, and III. The fourth Book, called Book IV, *PowerPC Implementation Features*, differs for each implementation and is not included herein.

An important attribute of Books I, II, and III is that they do not constrain implementations on matters that would not affect software compatibility. For example, the effects of executing an invalidly coded instruction are not defined and can differ between implementations. Compilers and assemblers are responsible for generating only correctly coded instructions.

An even more important attribute of these three Books is that they specify the architecture in a manner that is independent of implementation. For example, Book III specifies the rules by which storage addresses are translated from the "effective addresses" generated by a program to the "real addresses" that are used to access storage, including the format of related tables and registers that are needed by the operating system. However, it does not specify *how* a processor should accomplish the translation. Thus, it permits translation lookaside buffers (TLBs) to be used, but does not require that they be used and does not specify their organization or contents. Book IV for each processor specifies all such implementation details, and use of the related facilities can be isolated to small portions of the operating system.

All PowerPC processors conform to Book I. The PowerPC processors being developed jointly by Motorola and IBM for the general computer market conform to Books II and III as well. Other implementations may support only a subset of the features described in these two Books. (In effect, such an implementation would have its own private Book II or III.) For example, a processor used as an embedded controller might conform to Books I and II but implement a simpler storage model than the one described in Book III.

Because the features described in Book III are available only to "privileged" programs such as operating systems, application binary compatibility is assured even for processors that implement a different Book III. The ability to change portions of Book III in the future may prove very

Preface xxxi

useful, to support new developments in operating system and hardware technology and unforeseen processor requirements.

As used in this volume, the term "PowerPC Architecture" refers generically to the instructions and facilities described in Books I, II, and III. However, it is important to remember that these Books define three distinct levels of the architecture, and thus three different levels of compatibility.

#### **Acknowledgements**

We would like to acknowledge Keith Diefendorff, Ron Hochsprung, Rich Oehler, and John Sell for providing the technical leadership that made it possible for the group of architects, programmers, and designers from Apple, Motorola, and IBM to produce an architecture that met the goals established by the alliance these companies formed.

Many people contributed to the definition of the architecture, and it is not practical to name each of them here. However, a core group worked long hours over an extended period contributing ideas, evaluating options, debating costs and benefits of each proposal, and working together toward the goal of establishing a competitive architecture for the member companies of the alliance. This group of dedicated professionals included Richard Arndt, Roger Bailey, Al Chang, Barry Dorfman, Greg Grohoski, Randy Groves, Bill Hay, Marty Hopkins, Jim Kahle, Chin-Cheng Kau, Cathy May, Chuck Moore, Bill Moyer, John Muhich, Brett Olsson, John O'Quin, Mark Rogers, Tom Sartorius, Mike Shebanow, Ed Silha, Rick Simpson, Hank Warren, Lynn West, Andy Wottreng, and Mike Yamamura.

## Book

This book describes the base instruction set and related facilities available to the application programmer. It covers data and instruction formats, instruction classes and descriptions, registers accessible to the application programmer, and compatibility with the POWER architecture.

# PowerPC User Instruction Set Architecture

| Cha  | oter 1 Introduction                       | 3   |

|------|-------------------------------------------|-----|

| 1.1  | Overview                                  | 3   |

| 1.2  | Computation Modes                         | 3   |

| 1.3  | Instruction Mnemonics and Operands        |     |

| 1.4  | Compatibility with the POWER Architecture | 4   |

| 1.5  | Document Conventions                      |     |

| 1.6  | Processor Overview                        | 1   |

| 1.7  | Instruction Formats                       | 1:  |

| 1.8  | Classes of Instructions                   | 23  |

| 1.9  | Forms of Defined Instructions             | 2!  |

| 1.10 | Exceptions                                | 20  |

| 1.11 | Storage Addressing                        | 27  |

| Cha  | oter 2 Branch Processor                   | 31  |

| 2.1  | Branch Processor Overview                 | 3.  |

| 2.2  | Instruction Fetching                      | 3.  |

| 2.3  | Branch Processor Registers                | 32  |

| 2.4  | <b>Branch Processor Instructions</b>      | 3!  |

| Chap | oter 3 Fixed-Point Processor              | 47  |

| 3.1  | Fixed-Point Processor Overview            | 47  |

| 3.2  | Fixed-Point Processor Registers           | 47  |

| 3.3  | Fixed-Point Processor Instructions        | 49  |

| Chap | oter 4 Floating-Point Processor           | 133 |

| 4.1  | Floating-Point Processor Overview         | 133 |

| 4.2  | Floating-Point Processor Registers        | 13  |

| 4.3  | Floating-Point Data                       | 14  |

| 4.4  | Floating-Point Exceptions                 | 150 |

| 4.5                            | Floating-Point Execution Models                 | 162 |  |

|--------------------------------|-------------------------------------------------|-----|--|

| 4.6                            | Floating-Point Processor Instructions           | 167 |  |

| App                            | endix A Optional Instructions                   | 197 |  |

| <b>A.1</b>                     | Floating-Point Processor Instructions           | 197 |  |

| App                            | endix B Suggested Floating-Point                |     |  |

|                                | Models                                          | 203 |  |

| B.1                            | Floating-Point Round to Single-Precision Model  | 203 |  |

| B.2                            | Floating-Point Convert to Integer Model         | 209 |  |

| B.3                            | Floating-Point Convert from Integer Model       | 212 |  |

| App                            | endix C Assembler Extended                      |     |  |

|                                | Mnemonics                                       | 215 |  |

| C.1                            | Symbols                                         | 215 |  |

| C.2                            | Branch Mnemonics                                | 216 |  |

| C.3                            | Condition Register Logical Mnemonics            | 222 |  |

| C.4                            | Subtract Mnemonics                              | 223 |  |

| C.5                            | Compare Mnemonics                               | 223 |  |

| C.6                            | Trap Mnemonics                                  | 225 |  |

| C.7                            | Rotate and Shift Mnemonics                      | 227 |  |

| C.8                            | Move To/From Special Purpose Register Mnemonics | 230 |  |

| C.9                            | Miscellaneous Mnemonics                         | 230 |  |

|                                | endix D Little-Endian Byte Ordering             | 233 |  |

| ДРР<br>D.1                     | Byte Ordering                                   | 233 |  |

| D.1<br>D.2                     | Structure Mapping Examples                      | 234 |  |

| D.2<br>D.3                     | PowerPC Byte Ordering                           | 236 |  |

| D.4                            | PowerPC Data Storage Addressing in Little-      | 230 |  |

| DT                             | Endian Mode                                     | 240 |  |

| D.5                            | PowerPC Instruction Storage Addressing in       |     |  |

|                                | Little-Endian Mode                              | 242 |  |

| <b>D.6</b>                     | PowerPC Cache Management and Lookaside But      | fer |  |

|                                | Management Instructions in Little-Endian Mode   |     |  |

| D.7                            | PowerPC I/O in Little-Endian Mode               | 245 |  |

| D.8                            | Origin of Endian                                | 246 |  |

| App                            | endix E Programming Examples                    | 249 |  |

| E.1                            | Synchronization                                 | 249 |  |

| E.2                            | Multiple-Precision Shifts                       | 256 |  |

| E.3                            | Floating-Point Conversions                      | 259 |  |

| E.4                            | Floating-Point Selection                        | 264 |  |

| Appendix F Cross-Reference for |                                                 |     |  |

|                                | <b>Changed POWER Mnemonics</b>                  | 267 |  |

| Appendix G Incompatibilities with the POWER  |                                             |            |  |

|----------------------------------------------|---------------------------------------------|------------|--|

|                                              | Architecture                                | 271        |  |

| F.1                                          | New Instructions, Formerly Privileged       |            |  |

|                                              | Instructions                                | 273        |  |

| G.2                                          | Newly Privileged Instructions               | 272        |  |

| G.3                                          | Reserved Bits in Instructions               | 272        |  |

| <b>G.4</b>                                   | Reserved Bits in Registers                  | 272        |  |

| G.5                                          | Alignment Check                             | 272        |  |

| <b>G</b> .6                                  | Condition Register                          | 273        |  |

| G.7                                          | Inappropriate use of LK and Rc Bits         | 273        |  |

| G.8                                          | BO Field                                    | 274        |  |

| G.9                                          | Branch Conditional to Count Register        | 274        |  |

| G.10                                         |                                             | 274        |  |

| G.11                                         |                                             | 275        |  |

| G.12                                         |                                             | 275        |  |

| G.13                                         |                                             | 275        |  |

| G.14                                         | <b>9</b>                                    | 276        |  |

| G.15                                         |                                             | 276        |  |

| G.16<br>G.17                                 |                                             | 276<br>276 |  |

| G.17                                         |                                             | 276        |  |

| G.18                                         |                                             | 277        |  |

| G.20                                         |                                             | 278        |  |

| G.21                                         |                                             | 278        |  |

| F.22                                         | Floating-Point Load/Store to Direct-Store   | 270        |  |

| 1.22                                         | Segment                                     | 280        |  |

| G.23                                         | Segment Register Instructions               | 278        |  |

| G.24                                         | TLB Entry Invalidation                      | 279        |  |

| G.25                                         | Floating-Point Interrupts                   | 279        |  |

| G.26                                         | Timing Facilities                           | 279        |  |

| G.27                                         | Deleted Instructions                        | 280        |  |

| G.28                                         | Discontinued Opcodes                        | 282        |  |

| G.29                                         | POWER2 Compatibility                        | 283        |  |

| App                                          | endix H New Instructions                    | 287        |  |

| H.1                                          | New Instructions for All Implementations    | 287        |  |

| G.2                                          | New Instructions for 64-Bit Implementations |            |  |

|                                              | Only                                        | 291        |  |

| G.3                                          | New Instructions for 32-Bit Implementations | 202        |  |

|                                              | Only                                        | 292        |  |

| App                                          | endix I Illegal Instructions                | 291        |  |

| App                                          | endix J Reserved Instructions               | 293        |  |

| Appendix K PowerPC Instruction Set Sorted by |                                             |            |  |

| l- la                                        | Opcode                                      | 295        |  |

|                                              | opcode                                      | 293        |  |

| App                                          | endix L PowerPC Instruction Set Sorted      | by         |  |

| • •                                          | Mnemonic                                    | 305        |  |

# Introduction

# 1.1 Overview

This chapter describes computation modes, compatibility with the POWER Architecture, document conventions, a processor overview, instruction formats, storage addressing, and instruction fetching.

# 1.2 Computation Modes

The PowerPC Architecture allows for the following types of implementation:

- 64-bit implementations, in which all registers except some Special Purpose Registers are 64 bits long and effective addresses are 64 bits long. All 64-bit implementations have two modes of operation: 64-bit mode and 32-bit mode. The mode controls how the effective address is interpreted, how status bits are set, and how the Count Register is tested by *Branch Conditional* instructions. All instructions provided for 64-bit implementations are available in both modes.

- 32-bit implementations, in which all registers except Floating-Point Registers are 32 bits long and effective addresses are 32 bits long.

Instructions defined in this document are provided in both 64-bit implementations and 32-bit implementations unless otherwise stated. Instructions that are provided only for 64-bit implementations are illegal in 32-bit implementations, and vice versa.

# 1.2.1 64-bit Implementations

In both 64-bit mode and 32-bit mode of a 64-bit implementation, instructions that set a 64-bit register affect all 64 bits, and the value placed into the register is independent of mode. In both modes, effective address computations use all 64 bits of the relevant registers (General Purpose Registers, Link Register, Count Register, etc.) and produce a 64-bit result. However, in 32-bit mode, the high-order 32 bits of the computed effective address are ignored when accessing data and are set to 0 when fetching instructions.

# 1.2.2 32-bit Implementations

For a 32-bit implementation, all references to 64-bit mode in this document should be disregarded. The semantics of instructions are as shown in this document for 32-bit mode in a 64-bit implementation, except that in a 32-bit implementation all registers except Floating-Point Registers are 32 bits long. Bit numbers for registers are shown in braces ({ }) when they differ from the corresponding numbers for a 64-bit implementation, as described in Section 1.5.1, "Definitions and Notation," on page 5.

# 1.3 Instruction Mnemonics and Operands

The description of each instruction includes the mnemonic and a formatted list of operands. Some examples are the following.

stw RS,D(RA) addis RT,RA,SI