Personal System/2 Hardware Interface Technical Reference

42G2193

S42G-2193-00

– Video Subsystems

Before using this information and the product it supports, be sure to read the general information under "Notices" on page xiii.

#### First Edition (September 1992)

The following paragraph does not apply to the United Kingdom or any country where such provisions are inconsistent with local law: INTERNATIONAL BUSINESS MACHINES CORPORATION PROVIDES THIS PUBLICATION "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some states do not allow disclaimer of express or implied warranties in certain transactions, therefore, this statement may not apply to you.

This publication could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication. IBM may make improvements and/or changes in the product(s) and/or the program(s) described in this publication at any time.

It is possible that this publication may contain reference to, or information about, IBM products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that IBM intends to announce such IBM products, programming, or services in your country.

Requests for technical information about IBM products should be made to your IBM Authorized Dealer or your IBM Marketing Representative.

#### © Copyright International Business Machines Corporation 1989, 1992. All rights reserved.

Note to U.S. Government Users — Documentation related to restricted rights — Use, duplication or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corp.

# Contents

| Figures                           | <b>v</b>    |

|-----------------------------------|-------------|

| Notices                           | . xiii      |

| Trademarks and Service Marks      |             |

| Preface                           | . <b>xv</b> |

| Section 1. Introduction           | . 1-1       |

| Video Subsystem                   | . 1-3       |

| Video BIOS                        |             |

| Type 2 Video Subsystems           |             |

| Type 3 Video Subsystems           | . 1-8       |

| Section 2. VGA Function           | . 2-1       |

| VGA Function Introduction         |             |

| Major Components                  |             |

| Hardware Considerations           |             |

| Type 1 Subsystem Parameters       |             |

| Video Memory Organization         |             |

| Registers                         |             |

| VGA Programming Considerations    |             |

| Video Digital-to-Analog Converter |             |

| VGA Video Extensions              | 2-104       |

| Section 3. XGA Function           | . 3-1       |

| XGA Function Introduction         | . 3-7       |

| VGA Compatibility                 | 3-14        |

| 132-Column Text Mode              | 3-14        |

| Extended Graphics Mode            | 3-18        |

| XGA Display Controller Registers  |             |

| Coprocessor Description           |             |

|                                   | 3-128       |

|                                   | 3-163       |

|                                   | 3-170       |

|                                   | 3-185       |

|                                   | 3-220       |

| Programming the XGA Subsystem     | 3-227       |

| Section 4. Display Connector      | . 4-1       |

| Display Connector Introduction    | . 4-3       |

| Section 5. XGA Sample Code        | . 5-1       |

| XGA Sample Code | 5-3 |

|-----------------|-----|

| Index           | X-1 |

# Figures

| 1-1.  | BIOS Video Modes                                     | . 1-4 |

|-------|------------------------------------------------------|-------|

| 1-2.  | Double Scanning and Border Support                   | . 1-5 |

| 2-1.  | Diagram of the VGA Function                          | . 2-6 |

| 2-2.  | Graphics Controller                                  | . 2-9 |

| 2-3.  | Graphics Controller                                  | 2-10  |

| 2-4.  | Data Flow for Write Operations                       |       |

| 2-5.  | Color Compare Operations                             | 2-13  |

| 2-6.  | Character/Attribute Format                           | 2-15  |

| 2-7.  | Attribute Byte Definitions                           | 2-15  |

| 2-8.  | BIOS Color Set                                       |       |

| 2-9.  | Video Memory Format                                  | 2-17  |

| 2-10. | Pel Format, Modes Hex 4 and 5                        | 2-18  |

| 2-11. | Color Selections, Modes Hex 4 and 5                  | 2-18  |

| 2-12. | Pel Format, Mode Hex 6                               | 2-19  |

| 2-13. | Bit Definitions C2,C0                                | 2-20  |

| 2-14. | Compatible Color Coding                              | 2-22  |

| 2-15. | 256KB Video Memory Map                               |       |

| 2-16. | Video Subsystem Register Overview                    | 2-39  |

| 2-17. | General Registers                                    |       |

| 2-18. | Miscellaneous Output Register, Hex 03CC/03C2         | 2-40  |

| 2-19. | Display Vertical Size                                | 2-41  |

| 2-20. | Clock Select Definitions                             |       |

| 2-21. | Input Status Register 0, Hex 03C2                    | 2-42  |

| 2-22. | Input Status Register 1, Hex 03DA/03BA               |       |

| 2-23. | Feature Control Register, Hex 03DA/03BA and 03CA     |       |

| 2-24. | Video Subsystem Enable Register, Hex 03C3            | 2-44  |

| 2-25. | , Sequencer Registers                                | 2-45  |

| 2-26. | Sequencer Address Register                           | 2-45  |

| 2-27. | Reset Register, Index Hex 00                         |       |

| 2-28. | Clocking Mode Register, Index Hex 01                 |       |

| 2-29. | Map Mask Register, Index Hex 02                      |       |

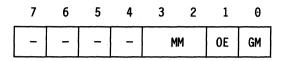

| 2-30. | Character Map Select Register, Index Hex 03          | 2-50  |

| 2-31. | Character Map Select A                               |       |

| 2-32. | Character Map Select B                               |       |

| 2-33. | Memory Mode Register, Index Hex 04                   |       |

| 2-34. | Map Selection, Chain 4                               |       |

| 2-35. | CRT Controller Registers                             |       |

| 2-36. | CRT Controller Address Register, Hex 03B4/03D4       | 2-54  |

| 2-37. | Horizontal Total Register, Index Hex 00              |       |

| 2-38. | Horizontal Display Enable-End Register, Index Hex 01 |       |

| 2-39. | Start Horizontal Blanking Register, Index Hex 02     |       |

| 2-40. | End Horizontal Blanking Register, Index Hex 03       | 2-56  |

| 2-41. | Display Enable Skew                                   | 2-56 |

|-------|-------------------------------------------------------|------|

| 2-42. | Start Horizontal Retrace Pulse Register, Index Hex 04 | 2-57 |

| 2-43. | End Horizontal Retrace Register, Index Hex 05         | 2-58 |

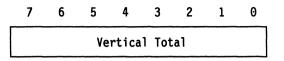

| 2-44. | Vertical Total Register, Index Hex 06                 | 2-59 |

| 2-45. | CRT Overflow Register, Index Hex 07                   | 2-60 |

| 2-46. | Preset Row Scan Register, Index Hex 08                | 2-61 |

| 2-47. | Maximum Scan Line Register, Index Hex 09              |      |

| 2-48. | Cursor Start Register, Index Hex 0A                   | 2-63 |

| 2-49. | Cursor End Register, Index Hex 0B                     | 2-64 |

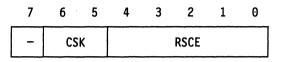

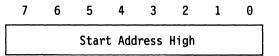

| 2-50. | Start Address High Register, Index Hex 0C             | 2-65 |

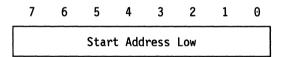

| 2-51. | Start Address Low Register, Index Hex 0D              | 2-65 |

| 2-52. | Cursor Location High Register, Index Hex 0E           | 2-66 |

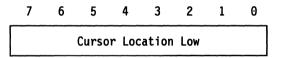

| 2-53. | Cursor Location Low Register, Index Hex 0F            | 2-66 |

| 2-54. | Vertical Retrace Start Register, Index Hex 10         |      |

| 2-55. | Vertical Retrace End Register, Index Hex 11           | 2-67 |

| 2-56. | Vertical Display-Enable End Register, Index Hex 12    |      |

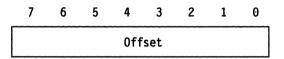

| 2-57. | Offset Register, Index Hex 13                         | 2-69 |

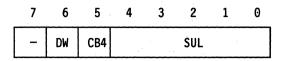

| 2-58. | Underline Location Register, Index Hex 14             | 2-70 |

| 2-59. | Start Vertical Blanking Register, Index Hex 15        | 2-71 |

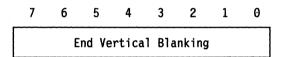

| 2-60. | End Vertical Blanking Register, Index Hex 16          | 2-71 |

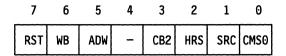

| 2-61. | CRT Mode Control Register, Index Hex 17               | 2-72 |

| 2-62. | CRT Memory Address Mapping                            |      |

| 2-63. | Line Compare Register, Index Hex 18                   |      |

| 2-64. | Graphics Controller Register Overview                 |      |

| 2-65. | Graphics Controller Address Register, Hex 03CE        |      |

| 2-66. | Set/Reset Register, Index Hex 00                      | 2-77 |

| 2-67. | Enable Set/Reset Register, Index Hex 01               | 2-78 |

| 2-68. | Color Compare Register, Index Hex 02                  | 2-79 |

| 2-69. | Data Rotate Register, Index Hex 03                    | 2-80 |

| 2-70. | Operation Select Bit Definitions                      |      |

| 2-71. | Read Map Select Register, Index Hex 04                |      |

| 2-72. | Graphics Mode Register, Index Hex 05                  | 2-82 |

| 2-73. | Write Mode Definitions                                | 2-83 |

| 2-74. | Miscellaneous Register, Index Hex 06                  | 2-84 |

| 2-75. | Video Memory Assignments                              | 2-84 |

| 2-76. | Color Don't Care Register, Index Hex 07               |      |

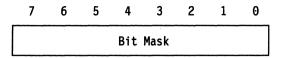

| 2-77. | Bit Mask Register, Index Hex 08                       |      |

| 2-78. | Attribute Controller Register Addresses               |      |

| 2-79. | Address Register, Hex 03C0                            | 2-87 |

| 2-80. | Internal Palette Registers, Index Hex 00 - 0F         | 2-88 |

| 2-81. | Attribute Mode Control Register, Index Hex 10         | 2-89 |

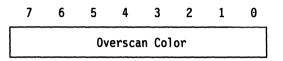

| 2-82. | Overscan Color Register, Index Hex 11                 |      |

| 2-83. | Color Plane Enable Register, Index Hex 12             |      |

| 2-84. | Horizontal Pel Panning Register, Index Hex 13         |      |

| 2-85. | Image Shifting                                        |      |

| 2-86. | Color Select Register, Index Hex 14                   | 2-93 |

| 2-87. | Character Table Structure                             | 2-98  |

|-------|-------------------------------------------------------|-------|

| 2-88. | Character Pattern Example                             | 2-99  |

| 2-89. | Split Screen Definition                               |       |

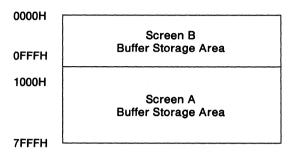

| 2-90. | Screen Mapping within the Display Buffer Address      |       |

|       | Space                                                 | 2-100 |

| 2-91. | Video DAC Register                                    | 2-101 |

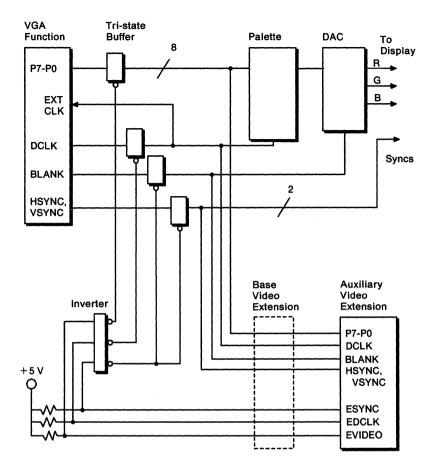

| 2-92. | Auxiliary Video Connector Interface                   | 2-105 |

| 2-93. | Video Extension                                       | 2-106 |

| 2-94. |                                                       | 2-108 |

| 3-1.  | XGA Video Subsystem                                   | . 3-8 |

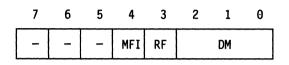

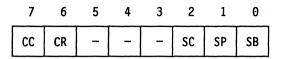

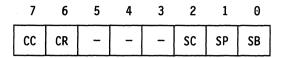

| 3-2.  | MFI Attribute Byte                                    | 3-16  |

| 3-3.  | MFI Blink Rates                                       | 3-16  |

| 3-4.  | Intel Order of the XGA Memory Map                     | 3-19  |

| 3-5.  | Motorola Order of the XGA Memory Map                  | 3-20  |

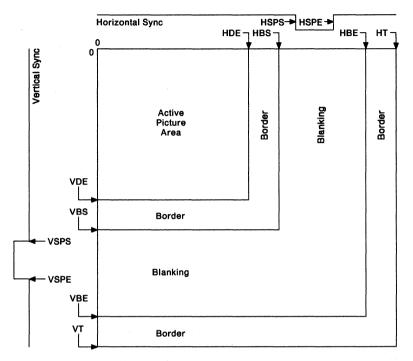

| 3-6.  | CRT Controller Register Definitions                   | 3-23  |

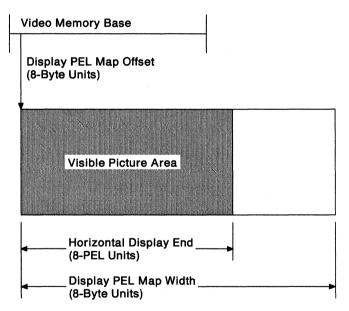

| 3-7.  | Display Pel Map Offset and Width Definitions          | 3-24  |

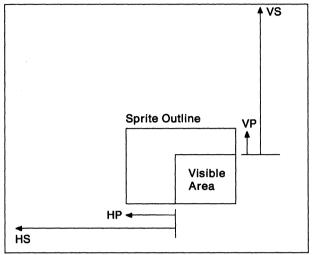

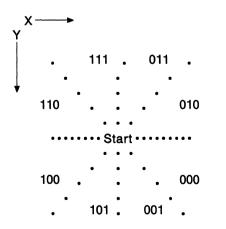

| 3-8.  | Sprite Appearance Defined by 2-Bit Pel                | 3-25  |

| 3-9.  | Sprite Positioning                                    | 3-27  |

| 3-10. | Direct Color Mode Data Word                           | 3-30  |

| 3-11. | XGA Direct Color Palette Load                         | 3-31  |

| 3-12. | Display Controller Register Addresses                 | 3-33  |

| 3-13. | Operating Mode Register, Address Hex 21x0             | 3-35  |

| 3-14. | Display Mode Bit Assignments                          | 3-36  |

| 3-15. | Aperture Control Register, Address Hex 21x1           | 3-37  |

| 3-16. | Aperture Size and Location Bit Assignments            | 3-37  |

| 3-17. | Interrupt Enable Register, Address Hex 21x4           | 3-38  |

| 3-18. | Interrupt Status Register, Address Hex 21x5           | 3-40  |

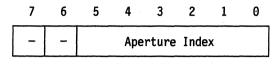

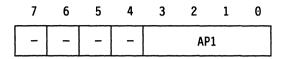

| 3-19. | Aperture Index Register, Address Hex 21x8             | 3-42  |

| 3-20. | Aperture Index Bit Assignments                        | 3-42  |

| 3-21. | Memory Access Mode Register, Address Hex 21x9         | 3-43  |

| 3-22. | Pel Size Bit Assignments                              | 3-43  |

| 3-23. | Index Register, Address Hex 21xA                      | 3-44  |

| 3-24. | XGA Index Register Assignments                        | 3-45  |

| 3-25. | Auto-Configuration Register, Index Hex 04             | 3-48  |

| 3-26. | System Interface Bus Size                             | 3-48  |

| 3-27. | System Bus Type                                       | 3-49  |

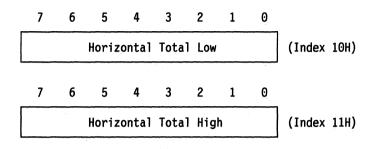

| 3-28. | Horizontal Total Registers, Indexes Hex 10 and 11     | 3-50  |

| 3-29. | Horizontal Total Registers Value Assignments          | 3-50  |

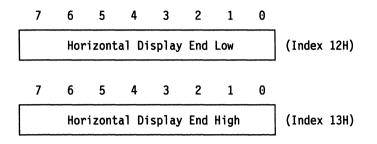

| 3-30. | Horizontal Display End Registers, Indexes Hex 12 and  |       |

|       | 13                                                    | 3-51  |

| 3-31. | Horizontal Display End Registers Value Assignments    | 3-51  |

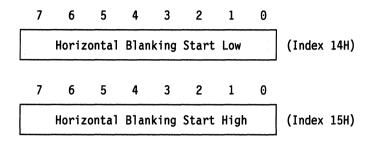

| 3-32. | Horizontal Blanking Start Registers, Indexes Hex 14   |       |

|       | and 15                                                | 3-52  |

| 3-33. | Horizontal Blanking Start Registers Value Assignments | 3-52  |

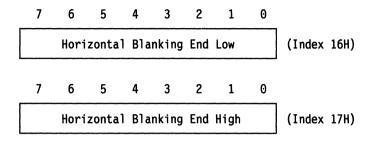

| 3-34. | Horizontal Blanking End Registers, Indexes Hex 16 and |       |

|       | 17                                                    | 3-53  |

٠

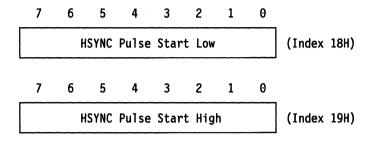

| 3-35.<br>3-36. | Horizontal Blanking End Registers Value Assignments<br>Horizontal Sync Pulse Start Registers, Indexes Hex 18 | 3-53 |

|----------------|--------------------------------------------------------------------------------------------------------------|------|

| 3-37.          | and 19                                                                                                       | 3-54 |

| 5-57.          | Assignments                                                                                                  | 3-54 |

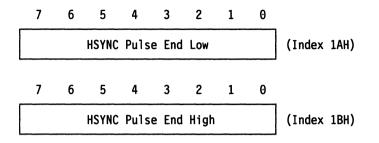

| 3-38.          | Horizontal Sync Pulse End Registers, Indexes Hex 1A                                                          | 0-04 |

| 0 00.          | and 1B                                                                                                       | 3-55 |

| 3-39.          | Horizontal Sync Pulse End Registers Value                                                                    |      |

|                | Assignments                                                                                                  | 3-55 |

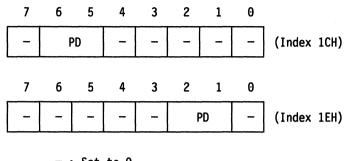

| 3-40.          | Horizontal Sync Pulse Position Registers (Index 1C and                                                       |      |

|                | 1E)                                                                                                          | 3-56 |

| 3-41.          | Horizontal Sync Pulse Delay Bit Assignments                                                                  | 3-56 |

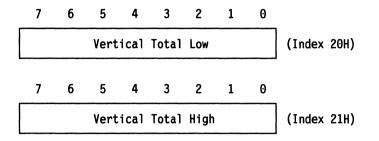

| 3-42.          | Vertical Total Registers, Indexes Hex 20 and 21                                                              | 3-57 |

| 3-43.          | Vertical Total Registers Value Assignments                                                                   | 3-57 |

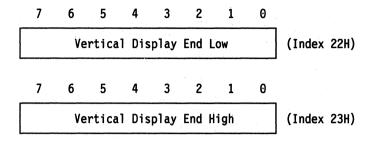

| 3-44.          | Vertical Display End Registers, Indexes Hex 22 and 23                                                        | 3-58 |

| 3-45.          | Vertical Display End Registers Value Assignments                                                             | 3-58 |

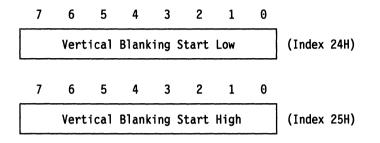

| 3-46.          | Vertical Blanking Start Registers, Indexes Hex 24 and                                                        |      |

|                | 25                                                                                                           | 3-59 |

| 3-47.          | Vertical Blanking Start Registers Value Assignments                                                          | 3-59 |

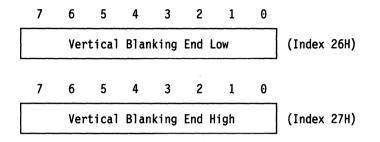

| 3-48.          | Vertical Blanking End Registers, Indexes Hex 26 and 27                                                       | 3-60 |

| 3-49.          | Vertical Blanking End Registers Value Assignments                                                            | 3-60 |

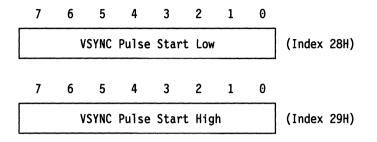

| 3-50.          | Vertical Sync Pulse Start Registers, Indexes Hex 28<br>and 29                                                | 3-61 |

| 3-51.          | Vertical Sync Pulse Start Registers Value Assignments                                                        | 3-61 |

| 3-52.          | Vertical Sync Pulse End Register, Index Hex 2A                                                               | 3-62 |

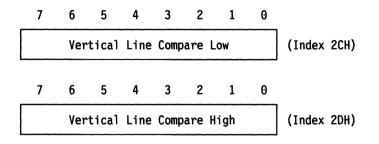

| 3-53.          | Vertical Line Compare Registers, Indexes Hex 2C and                                                          | 0.05 |

| 0.00.          | 2D                                                                                                           | 3-63 |

| 3-54.          | Vertical Line Compare Registers Value Assignments                                                            | 3-63 |

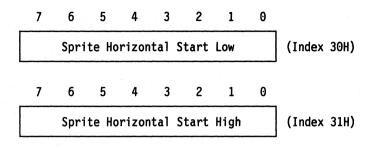

| 3-55.          | Sprite Horizontal Start Registers, Indexes Hex 30 and                                                        |      |

|                | 31                                                                                                           | 3-64 |

| 3-56.          | Sprite Horizontal Start Registers Value Assignments                                                          | 3-64 |

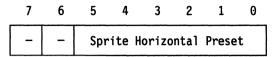

| 3-57.          | Sprite Horizontal Preset, Index Hex 32                                                                       | 3-65 |

| 3-58.          | Sprite Horizontal Preset Value Assignments                                                                   | 3-65 |

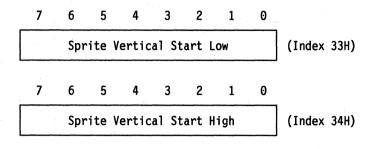

| 3-59.          | Sprite Vertical Start Registers, Indexes Hex 33 and 34                                                       | 3-66 |

| 3-60.          | Sprite Vertical Start Registers Value Assignments                                                            | 3-66 |

| 3-61.          | Sprite Vertical Preset, Index Hex 35                                                                         | 3-67 |

| 3-62.          | Sprite Vertical Preset Value Assignments                                                                     | 3-67 |

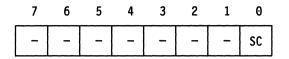

| 3-63.          | Sprite Control Register, Index Hex 36                                                                        | 3-68 |

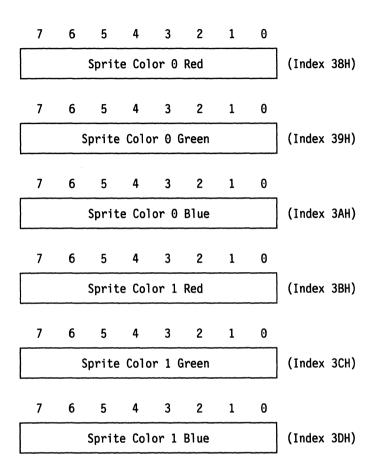

| 3-64.          | Sprite Color Registers, Indexes Hex 38-3D                                                                    | 3-69 |

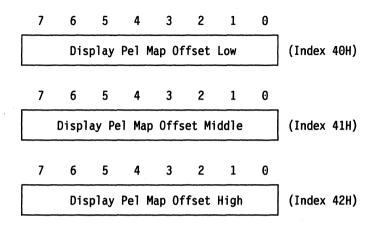

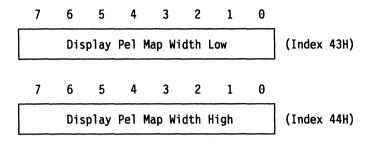

| 3-65.          | Display Pel Map Offset Registers, Indexes Hex 40-42                                                          | 3-70 |

| 3-66.          | Display Pel Map Offset Registers Value Assignments .                                                         | 3-70 |

| 3-67.          | Display Pel Map Width Registers, Indexes Hex 43 and                                                          |      |

|                | 44                                                                                                           | 3-71 |

| 3-68.          | Display Pel Map Width Registers Value Assignments                                                            | 3-71 |

| 3-69.          | Display Control 1 Register, Index Hex 50                                                                     | 3-72 |

| 3-70.          | Sync Polarity Bit Assignments                                                                                | 3-72 |

| 3-71.  | Display Blanking Bit Assignments                        | 3-73  |

|--------|---------------------------------------------------------|-------|

| 3-72.  | Display Control 2 Register, Index Hex 51                | 3-74  |

| 3-73.  | Vertical Scale Factor Bit Assignments                   |       |

| 3-74.  | Horizontal Scale Factor Bit Assignments                 |       |

| 3-75.  | Display Control 2 Register Pel Size Bit Assignments     |       |

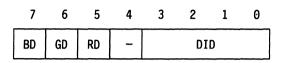

| 3-76.  | Display ID and Comparator, Index Hex 52                 | 3-76  |

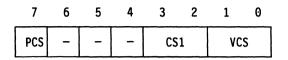

| 3-77.  | Clock Frequency Selector Register, Index Hex 54         |       |

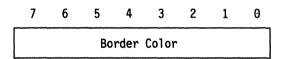

| 3-78.  | Border Color Register, Index Hex 55                     |       |

| 3-79.  | Programmable Pel Clock register, Index Hex 58           |       |

| 3-80.  | Programmable Frequency Ranges                           | 3-78  |

| 3-81.  | Direct Color Control register, Index Hex 59             | 3-79  |

| 3-82.  | Direct Color Modes                                      | 3-79  |

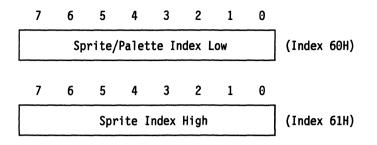

| 3-83.  | Sprite/Palette Index Registers, Indexes Hex 60 and 61   | 3-80  |

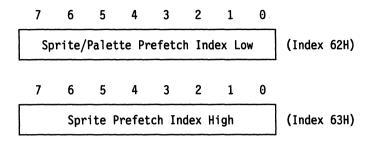

| 3-84.  | Sprite/Palette Prefetch Index Registers, Indexes 62 and |       |

|        | 63                                                      | 3-81  |

| 3-85.  | Palette Mask Register, Index Hex 64                     | 3-82  |

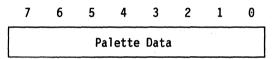

| 3-86.  | Palette Data Register, Index Hex 65                     | 3-82  |

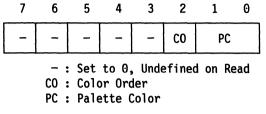

| 3-87.  | Palette Sequence Register, Index Hex 66                 | 3-83  |

| 3-88.  | Palette Sequence Register Color Order Bit Assignment    | 3-83  |

| 3-89.  | Palette Sequence Register Color Bit Assignments         | 3-83  |

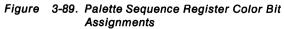

| 3-90.  | Palette Red Prefetch Register, Index Hex 67             | 3-84  |

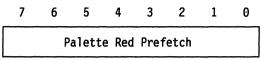

| 3-91.  | Palette Green Prefetch Register, Index Hex 68           | 3-84  |

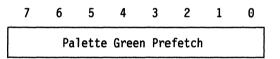

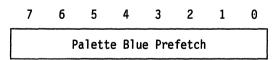

| 3-92.  | Palette Blue Prefetch Register, Index Hex 69            |       |

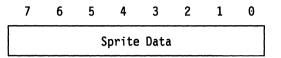

| 3-93.  | Sprite Data Register, Index Hex 6A                      | 3-85  |

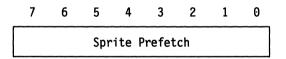

| 3-94.  | Sprite Prefetch Register, Index Hex 6B                  | 3-85  |

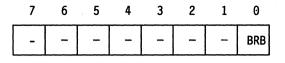

| 3-95.  | Miscellaneous Control Register, Index 6C                | 3-86  |

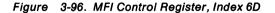

| 3-96.  | MFI Control Register, Index 6D                          | 3-86  |

| 3-97.  | Clock Frequency Select Registers                        | 3-88  |

| 3-98.  | Clock Selected Bit Assignments                          |       |

| 3-99.  | Video Clock Scale Factor Bit Assignments                |       |

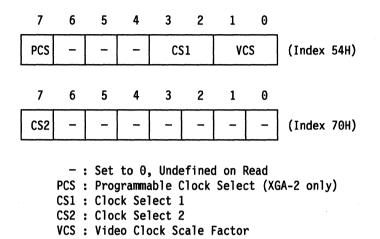

| 3-100. | Coprocessor Data Flow                                   |       |

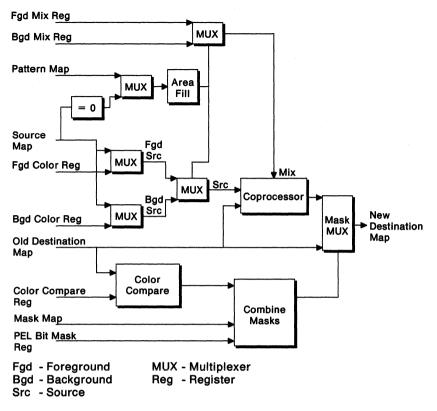

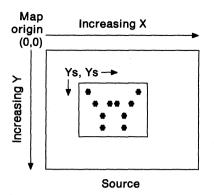

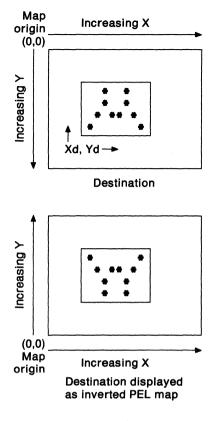

| 3-101. | XGA Pel Map Origin                                      |       |

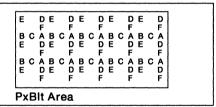

| 3-102. | Repeating Pattern (Tiling)                              | 3-97  |

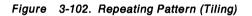

| 3-103. | Destination Map Guardband                               | 3-98  |

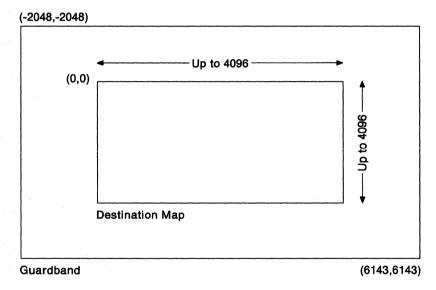

| 3-104. | Mask Map Origin X and Y Offsets                         |       |

| 3-105. | Destination Boundary Scissor                            | 3-101 |

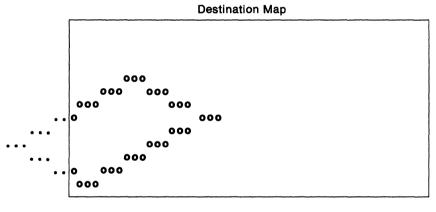

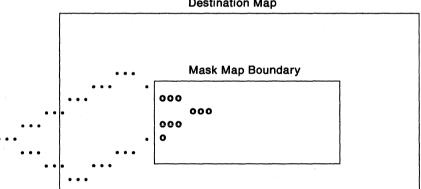

| 3-106. | Mask Map Boundary Scissor                               | 3-102 |

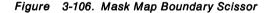

| 3-107. | Mask Map Enabled Scissor                                | 3-103 |

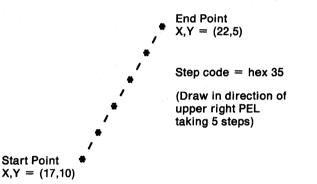

| 3-108. | Draw and Step Code                                      | 3-105 |

| 3-109. | Draw and Step Example                                   | 3-106 |

| 3-110. | Draw and Step Direction Codes                           | 3-107 |

| 3-111. | Programming Fewer Than Four Step Codes                  | 3-108 |

| 3-112. | Bresenham Line Draw Octant Encoding                     | 3-109 |

| 3-113. | Memory-to-Memory Line Draw Address Stepping             | 3-111 |

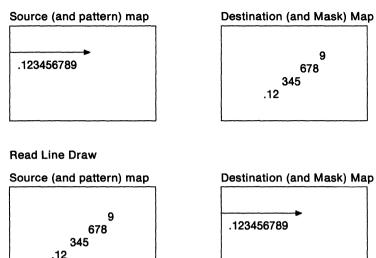

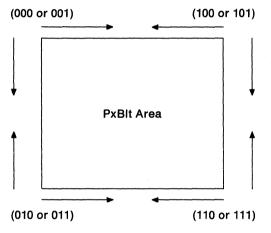

| 3-114. | PxBlt Direction Codes                                   | 3-114 |

| 3-115. | Inverting PxBlt                                         | 3-116 |

| 3-116. | Pattern Filling                                      | 3-117 |

|--------|------------------------------------------------------|-------|

| 3-117. | Foreground and Background Mixes                      | 3-120 |

| 3-118. | Carry Chain Mask for an 8-Bit Pel                    | 3-121 |

| 3-119. | Color Compare Conditions                             | 3-123 |

| 3-120. | XGA Coprocessor Register Space, Intel Format         | 3-130 |

| 3-121. | XGA Coprocessor Register Space, Motorola Format      | 3-131 |

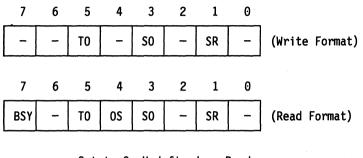

| 3-122. | Auxiliary Coprocessor Status Register, Offset Hex 09 | 3-133 |

| 3-123. | Coprocessor Control Register, Offset Hex 11          | 3-134 |

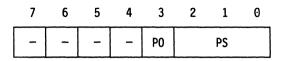

| 3-124. | Pel Map Index Register, Offset Hex 12                | 3-137 |

| 3-125. | Pel Map Index                                        | 3-138 |

| 3-126. | Pel Map n Base Pointer Register, Offset Hex 14       | 3-138 |

| 3-127. | Pel Map n Width Register, Offset Hex 18              | 3-139 |

| 3-128. | Pel Map n Height Register, Offset Hex 1A             | 3-140 |

| 3-129. | Pel Map n Format Register, Offset Hex 1C             | 3-141 |

| 3-130. | Pel Size Value Assignments                           | 3-141 |

| 3-131. | Bresenham Error Term E Register, Offset Hex 20       | 3-142 |

| 3-132. | Bresenham Constant K1 Register, Offset Hex 24        | 3-143 |

| 3-133. | Bresenham Constant K2 Register, Offset Hex 28        | 3-143 |

| 3-134. | Direction Steps Register, Offset Hex 2C              | 3-144 |

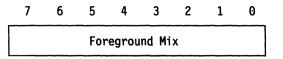

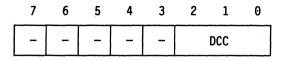

| 3-135. | Foreground Mix Register, Offset Hex 48               | 3-145 |

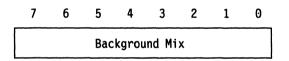

| 3-136. | Background Mix Register, Offset Hex 49               | 3-145 |

| 3-137. | Destination Color Compare Condition Reg, Offset Hex  |       |

|        | 4A                                                   | 3-146 |

| 3-138. | Destination Color Compare Condition Bit Definition   | 3-146 |

| 3-139. | Destination Color Compare Value Register, Offset Hex |       |

|        | 4C                                                   | 3-147 |

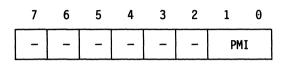

| 3-140. | Pel Bit Mask (Plane Mask) Register, Offset Hex 50    | 3-148 |

| 3-141. | Carry Chain Mask Field Register, Offset Hex 54       | 3-149 |

| 3-142. | Foreground Color Register, Offset Hex 58             | 3-150 |

| 3-143. | Background Color Register, Offset Hex 5C             | 3-150 |

| 3-144. | Operation Dimension 1 Register, Offset Hex 60        | 3-151 |

| 3-145. | Operation Dimension 2 Register, Offset Hex 62        | 3-151 |

| 3-146. | Mask Map Origin X Offset Register, Offset Hex 6C     | 3-152 |

| 3-147. | Mask Map Origin Y Offset Register, Offset Hex 6E     | 3-152 |

| 3-148. | Source X Address Register, Offset Hex 70             | 3-153 |

| 3-149. | Source Y Address Register, Offset Hex 72             | 3-153 |

| 3-150. | Pattern C Address Register, Offset Hex 74            | 3-154 |

| 3-151. | Pattern Y Address Register, Offset Hex 76            | 3-154 |

| 3-152. | Destination X Address Register, Offset Hex 78        | 3-155 |

| 3-153. | Destination Y Address Register, Offset Hex 7A        | 3-155 |

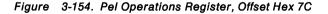

| 3-154. | Pel Operations Register, Offset Hex 7C               | 3-156 |

| 3-155. | Pel Operations Register, Byte 3                      | 3-157 |

| 3-156. | Pel Operations Register Background Source Value      |       |

|        | Assignments                                          | 3-157 |

| 3-157. | Pel Operations Register Foreground Source Value      |       |

|        | Assignments                                          | 3-158 |

| 3-158.      | Pel Operations Register Step Function Value         |         |

|-------------|-----------------------------------------------------|---------|

|             | Assignments                                         | 3-158   |

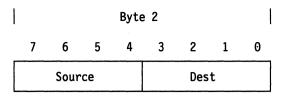

| 3-159.      | Pel Operations Register, Byte 2                     | 3-159   |

| 3-160.      | Pel Operations Register Source Pel Map Value        |         |

|             | Assignments                                         | 3-159   |

| 3-161.      | Pel Operations Register Destination Pel Map Value   |         |

|             | Assignments                                         | 3-160   |

| 3-162.      | Pel Operations Register, Byte 1                     | 3-160   |

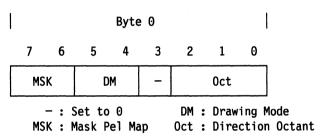

| 3-163.      | Pel Operations Register Pattern Pel Map Value       |         |

|             | Assignments                                         | 3-161   |

| 3-164.      | Pel Operations Register, Byte 0                     |         |

| 3-165.      | Pel Operations Register Mask Pel Map Value          | • • • • |

| • • • • • • | Assignments                                         | 3-161   |

| 3-166.      | Pel Operations Register Drawing Mode Value          | 0.01    |

| • • • • • • | Assignments                                         | 3-162   |

| 3-167.      | Pel Operations Register Direction Octant Values     | 3-162   |

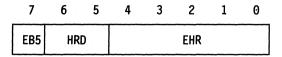

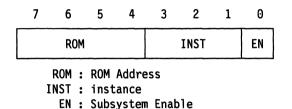

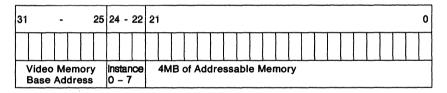

| 3-168.      | POS Register 2, Base Address + 2                    | 3-165   |

| 3-169.      | XGA ROM, Memory-Mapped Register Assignments         | 3-166   |

| 3-170.      | I/O Device Address Bit Assignment                   | 3-167   |

| 3-171.      | POS Register 4, Base Address + 4                    | 3-168   |

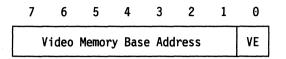

| 3-172.      | XGA Video Memory Base Address                       | 3-168   |

| 3-173.      | POS Register 5, Base Address + 5                    | 3-169   |

| 3-173.      | 1MB Aperture Base Address Value Assignments         | 3-169   |

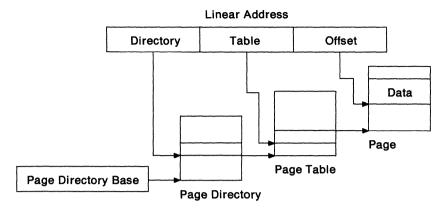

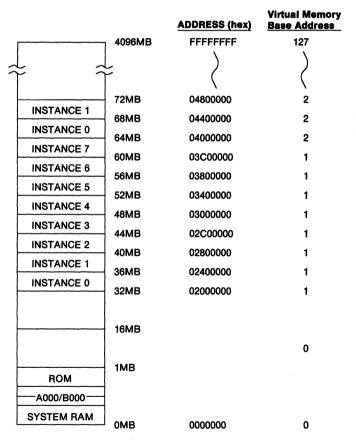

| 3-174.      | Linear Address Fields                               | 3-170   |

| 3-175.      | Linear to Physical Address Translation              | 3-170   |

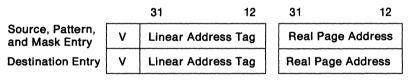

| 3-170.      | Page Directory and Page Table Entry                 | 3-172   |

| 3-177.      |                                                     | 3-172   |

| 3-1/0.      | Page Directory and Page Table Access Rights in User | 0 170   |

| 0 170       |                                                     | 3-173   |

| 3-179.      | Translate Look-Aside Buffer                         | 3-174   |

| 3-180.      | Page Directory Base Address Register, Offset Hex 0  | 3-179   |

| 3-181.      | Current Virtual Address Register, Offset Hex 4      | 3-180   |

| 3-182.      | Virtual Memory Control Register                     | 3-181   |

| 3-183.      | Virtual Memory Interrupt Status Register            | 3-183   |

| 3-184.      | DMQS Display Information File Structure             | 3-193   |

| 3-185.      | DMQS Display Information File Layout                | 3-194   |

| 3-186.      | DMQS Display Information File Mode Data             | 3-195   |

| 3-187.      | DMQS Extended Graphics Mode Register Settings       | 3-197   |

| 3-188.      | DMQS Display Color Characteristics                  | 3-199   |

| 3-189.      | DMQS Display Pre-selected Colors                    | 3-200   |

| 3-190.      | DMQS Customized Tag Syntax                          | 3-203   |

| 3-191.      | XGA Video Memory Base Address                       | 3-208   |

| 3-192.      | The XGA Video Memory Base Address Diagram           | 3-208   |

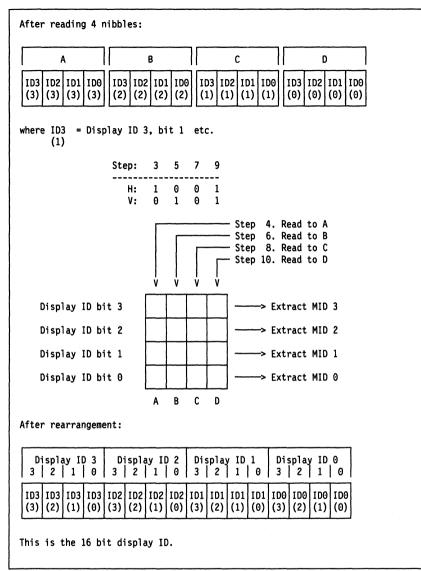

| 3-193.      | Reading the Display ID                              | 3-211   |

| 3-194.      | Video Memory Size Determination                     | 3-212   |

| 3-195.      | Availability of Extended Graphics Modes             | 3-213   |

| 3-196.      | Capability of Graphic Displays                      | 3-214   |

| 3-197. | Extended Graphics Mode Register Settings             | 3-215      |

|--------|------------------------------------------------------|------------|

| 3-198. | VGA Mode Write Sequence                              | 3-221      |

| 3-199. | 132-Column Text Mode First Write Sequence            | 3-224      |

| 3-200. | 132-Column Text Mode Second Write Sequence           | 3-225      |

| 3-201. | Coprocessor Register Write Values (Example A)        | 3-237      |

| 3-202. | Background and Foreground Mixes and Colors           | 3-238      |

| 3-203. | Bit Layout Pel Operations Register                   | 3-241      |

| 3-204. | Operation Direction Diagram                          | 3-244      |

| 3-205. | Definition for Pel Operations Register (Example)     | 3-245      |

| 3-206. | Palette Color Line Draw Steps                        | 3-245      |

| 3-207. | Background and Foreground Mixes and Colors           | 3-246      |

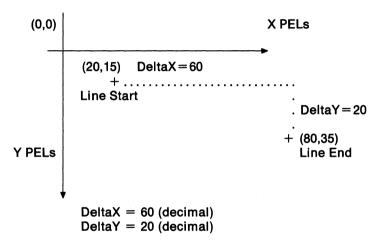

| 3-208. | Line Draw Example in Octant 0                        | 3-247      |

| 3-209. | Bit Layout Pel Operations Register                   | 3-250      |

| 3-210. | Direction Octant (Example)                           | 3-253      |

| 3-211. | Definition for Pel Operations Register (Example)     | 3-254      |

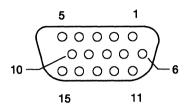

| 4-1.   | Display Connector                                    | 4-3        |

| 4-2.   | Display Connector Signals                            | 4-3        |

| 4-3.   | Vertical Size of Display                             | 4-4        |

| 4-4.   | VGA Mode Display Timing—Set 1                        | <b>4-6</b> |

| 4-5.   | VGA Mode Display Timing—Set 2                        | <b>4-6</b> |

| 4-6.   | VGA Mode Display Timing—Set 3                        | <b>4-6</b> |

| 4-7.   | Pel Frequencies (MHz) for Various Display Modes      | 4-7        |

| 4-8.   | Display Modes 1, 2 and 3.                            | 4-7        |

| 4-9.   | Extended Graphics Mode 1024 x 768 Interlaced Display | ý          |

|        | Timing                                               | 4-8        |

| 4-10.  | Pel Frequencies (MHz) for Various Display Modes      | 4-9        |

# Notices

References in this publication to IBM products, programs, or services do not imply that IBM intends to make these available in all countries in which IBM operates. Any reference to an IBM product, program or service is not intended to state or imply that only IBM's product, program, or service may be used. Any functionally equivalent product, program, or service that does not infringe any of IBM's intellectual property rights or other legally protectable rights may be used instead of the IBM product, program, or service. Evaluation and verification of operation in conjunction with other products, programs, or services, except those expressly designated by IBM, are the user's responsibility.

IBM may have patents or pending patent applications covering subject matter in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to the IBM Director of Commercial Relations, IBM Corporation, Purchase, NY 10577.

### **Trademarks and Service Marks**

The following terms, denoted by an asterisk (\*) in this publication, are trademarks of the IBM Corporation in the United States and/or other countries:

IBM Micro Channel OS/2 Personal System/2 PS/2 XGA AT

The following terms, denoted by a double asterisk (\*\*) in this publication, are trademarks of other companies as follows:

| Intel     | Intel Corporation             |

|-----------|-------------------------------|

| Lotus     | Lotus Development Corporation |

| Microsoft | Microsoft Corporation         |

| Motorola  | Motorola, Incorporated        |

| Windows   | Microsoft Corporation         |

## Notes:

# Preface

This technical reference is for those who develop hardware and software products for IBM Personal Computers and IBM Personal System/2 products. Readers should understand computer architecture and programming concepts.

This technical reference should be used with the following publications, which contain additional information about many of the subjects discussed in this document.

IBM Personal System/2 Hardware Interface Technical Reference – AT-Bus Systems

IBM Personal System/2 Hardware Interface Technical Reference – Architectures

IBM Personal System/2 Hardware Interface Technical Reference – Common Interfaces

IBM Personal System/2 Hardware Interface Technical Reference – System-Specific Information

IBM Personal System/2 and Personal Computer BIOS Interface Technical Reference

Information about diskette drives, hard disk drives, adapters, and external options are in separate option technical references.

**Warning:** The term *reserved* describes certain signals, bits, and registers that should not be changed. Use of reserved areas can cause compatibility problems, loss of data, or permanent damage to the hardware. When the contents of a register are changed, the state of the reserved bits must be preserved. When possible, read the register first and change only the bits that must be changed.

Notes:

# Section 1. Introduction

| Video Subsystem         |                   |        |            |     | <br>1-3 |

|-------------------------|-------------------|--------|------------|-----|---------|

| Type 1 Video            |                   |        |            |     | <br>1-3 |

| Type 2 Video            |                   |        |            |     | <br>1-3 |

| Type 3 Video            |                   |        |            |     | <br>1-3 |

| Video BIOS              |                   |        |            |     | <br>1-4 |

| Type 2 Video Subsystems |                   |        |            |     | <br>1-6 |

| VGA Mode                |                   |        |            |     | <br>1-6 |

| 132-Column Text Mode    |                   |        |            |     | <br>1-6 |

| Extended Graphics Mode  |                   |        |            |     | <br>1-6 |

| IBM PS/2 8514/A Adapter | <sup>-</sup> Inte | erface | Compatibil | ity | <br>1-6 |

| High Resolution Support |                   |        |            |     | <br>1-6 |

| Direct Color Mode       |                   |        |            |     | <br>1-6 |

| Packed Pel Format       |                   |        |            |     | <br>1-7 |

| Hardware Sprite         |                   |        |            |     | <br>1-7 |

| Display Identification  |                   |        |            |     | <br>1-7 |

| Coprocessor             |                   |        |            |     | <br>1-7 |

| Type 3 Video Subsystems |                   |        |            |     | <br>1-8 |

## **Notes:**

# Video Subsystem

This technical reference specifies the hardware interface to the Video Graphics Array (VGA), Extended Graphics Array (XGA'), and Extended Graphics Array-2 (XGA-2), video subsystems. These video subsystems are found in IBM' Micro Channel' - and Industry Standard Architecture (ISA)-based personal computer systems. The system video can be generated by a Type 1, Type 2, or Type 3 video subsystem:

- Type 1 video—Video Graphics Array (VGA)

- Type 2 video—Extended Graphics Array (XGA)

- Type 3 video—Extended Graphics Array-2 (XGA-2)

### **Type 1 Video**

The Type 1 video provides VGA function. The capabilities and operation of the VGA function are described in Section 2, "VGA Function" on page 2-1.

Only one video subsystem can be enabled into VGA or 132-column text mode at any one time. Some Type 1 video subsystems contain the VGA function and 132-column text mode. The hardware interface for the VGA function is fully specified in this technical reference. BIOS should be used to determine the full capability of a Type 1 video subsystem.

### Type 2 Video

The Type 2 video contains the XGA function, which supports the VGA mode, 132-column text mode, and extended graphics mode. The capabilities and operation of the XGA function are described in Section 3, "XGA Function" on page 3-1. One to eight Type 2 video subsystems are allowed in a system.

### Type 3 Video

The Type 3 video contains all the functions of the Type 2 video, along with other enhancements. The capabilities and operation of the XGA-2 function are also described in Section 3, "XGA Function" on page 3-1.

Trademark of the IBM Corporation

## Video BIOS

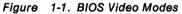

The video function is classified by BIOS mode numbers, which in turn define the screen size, colors, and associated parameters of the specific mode.

The following figure describes the alphanumeric (A/N) and all points addressable (APA) graphics modes supported by BIOS. Each color is selected from 256K possibilities, and gray shades are selected from 64 possibilities. The variations within the basic BIOS modes are selected through BIOS calls that set the number of scan lines. The scan line count is set before the mode call is made.

BIOS should be used to determine the modes that are supported on a given subsystem.

| Mode<br>(hex) | Туре | Colors | Alpha<br>Format | Buffer<br>Start | Box<br>Size | Max.<br>Pgs. | Vert. Pels |

|---------------|------|--------|-----------------|-----------------|-------------|--------------|------------|

| 0,1           | A/N  | 16     | 40 x 25         | B8000           | 8x8         | 8            | 320 x 200  |

| 0†,1†         | A/N  | 16     | 40 x 25         | B8000           | 8x14        | 8            | 320 x 350  |

| 0‡,1‡         | A/N  | 16     | 40 x 25         | B8000           | 9 x 16      | 8            | 360 x 400  |

| 2,3           | A/N  | 16     | 80 x 25         | B8000           | 8x8         | 8            | 640 x 200  |

| 2†,3†         | A/N  | 16     | 80 x 25         | B8000           | 8x14        | 8            | 640 x 350  |

| 2‡,3‡         | A/N  | 16     | 80 x 25         | B8000           | 9x16        | 8            | 720 x 400  |

| 4,5           | APA  | 4      | 40 x 25         | B8000           | 8x8         | 1            | 320 x 200  |

| 6             | APA  | 2      | 80 x 25         | B8000           | 8x8         | 1            | 640 x 200  |

| 7             | A/N  | -      | 80 x 25         | B0000           | 9x14        | 8            | 720 x 350  |

| 7‡            | A/N  | -      | 80 x 25         | B0000           | 9x16        | 8            | 720 x 400  |

| D             | APA  | 16     | 40 x 25         | A0000           | 8x8         | 8            | 320 x 200  |

| E             | APA  | 16     | 80 x 25         | A0000           | 8x8         | 4            | 640 x 200  |

| F             | APA  | -      | 80 x 25         | A0000           | 8x14        | 2            | 640 x 350  |

| 10            | APA  | 16     | 80 x 25         | A0000           | 8x14        | 2            | 640 x 350  |

| 11            | APA  | 2      | 80 x 30         | A0000           | 8x16        | 1            | 640 x 480  |

| 12            | APA  | 16     | 80 x 30         | A0000           | 8 x 16      | 1            | 640 x 480  |

| 13            | APA  | 256    | 40 x 25         | A0000           | 8x8         | 1            | 320 x 200  |

| 14            | A/N  | 16     | 132 x 25        | B8000           | 8 x 16      | 4            | 1056 x 400 |

|               |      |        |                 |                 | or          |              | or         |

|               |      |        |                 |                 | 9 x 16      |              | 1188 x 400 |

In the 200-scan-line modes, the data for each scan line is scanned twice. This double scanning allows the 200-scan-line image to be displayed in 400 scan lines.

Certain modes on previous IBM display adapters distinguished between monochrome and color displays. For example, mode 0 was the same as mode 1 with the color burst turned off. Because color burst is not supported by the PS/2<sup>\*</sup> video, the mode pairs are exactly the same. The support logic for the VGA function recognizes the type of display, and adjusts the output accordingly. When a monochrome display is attached, the colors for the color modes appear as shades of gray.

Mode 3+ is the default mode with a color display attached and mode 7+ is the default mode with a monochrome display attached.

Border support and double scanning depend on the mode selected. The following table shows which modes use double scanning and which support a border.

| Mode<br>(Hex)   | Double<br>Scan | Border<br>Support |

|-----------------|----------------|-------------------|

| 0, 1            | Yes            | No                |

| 0*, 1*          | No             | No                |

| 0+,1+           | No             | No                |

| 2, 3            | Yes            | Yes               |

| 2*, 3*          | No             | Yes               |

| 2+,3+           | No             | Yes               |

| 4, 5            | Yes            | No                |

| 6               | Yes            | Yes               |

| 7               | No             | Yes               |

| 7+              | No             | Yes               |

| D               | Yes            | No                |

| E               | Yes            | Yes               |

| F               | No             | Yes               |

| 10              | No             | Yes               |

| 11              | No             | Yes               |

| 12              | No             | Yes               |

| 13              | Yes            | Yes               |

| 14              | No             | Yes               |

| Note: * or + En | hanced modes   |                   |

Figure 1-2. Double Scanning and Border Support

<sup>\*</sup> Trademark of the IBM Corporation

# **Type 2 Video Subsystems**

The Base XGA function (including the VGA function) is generated by the Type 2 video subsystem.

The XGA function has three modes.

- VGA

- 132-column text

- Extended Graphics.

### VGA Mode

In VGA mode, the XGA video subsystem is VGA register compatible, as defined in the VGA function description.

### **132-Column Text Mode**

In this mode, text is displayed in 132 vertical columns, and is accessible through BIOS mode 14.

### **Extended Graphics Mode**

Extended Graphics mode provides the following software and hardware support.

#### IBM PS/2 8514/A Adapter Interface Compatibility

Compatibility is provided through the XGA Adapter Interface, a device driver supplied with the subsystem as programming support for applications operating in the disk operating system (DOS) environment.

#### **High Resolution Support**

Depending on the display attached and the size of video memory installed, the image on a screen can be defined using 1024 pels and 768 scan lines with 256 colors.

#### **Direct Color Mode**

In this mode, each 16-bit pel in video memory specifies the color of the pel directly. This allows 65,536 colors to be displayed using 640 pels and 480 scan lines.

#### **Packed Pel Format**

In the packed pel format, reads and writes to the video memory access all the data that defines a pel (or pels) in a single operation.

#### **Hardware Sprite**

The sprite is a  $64 \times 64$  pel image. When enabled, it overlays the picture that is being displayed. It can be positioned anywhere on the display without affecting the contents of video memory.

#### **Display Identification**

Signals from the attached display identify its characteristics. Applications use this information to determine the maximum resolution and whether the display is color or monochrome.

#### Coprocessor

The coprocessor provides hardware drawing-assist functions throughout real or virtual memory. The following functions can be used with the XGA Adapter Interface.

- Pel-block and bit-block transfers (PxBIt)

- Line drawing

- Area filling

- Logical and arithmetic mixing

- Map masking

- Scissoring

- X and Y axis addressing

### Type 3 Video Subsystems

All functions of the Type 2 video subsystem are included in the Type 3 video subsystem. The Type 3 video subsystem is an enhanced version of the Type 2 Video subsystem. These enhancements include the following functions.

- Higher refresh rates, such as 75 Hz and 72 Hz, noninterlaced, for improved screen stability, even at higher resolution (1024 x 768)

- Coprocessor support for Direct Color mode operation

- The digital-to-analog converter (DAC) has been expanded from 18 bits to 24 bits, which allows up to 256 colors available from a palette of more than 16 million colors.

- Supports both VGA and mainframe interactive (MFI) character attributes in text mode.

# Section 2. VGA Function

| VGA Function Introduction                            | . 2-5 |

|------------------------------------------------------|-------|

| Major Components                                     | . 2-7 |

| BIOS                                                 | . 2-7 |

| Support Logic                                        |       |

| VGA Components                                       |       |

| CRT Controller                                       | . 2-7 |

| Sequencer                                            | . 2-8 |

| Graphics Controller                                  | . 2-8 |

| Attribute Controller                                 | 2-10  |

| Hardware Considerations                              | 2-11  |

| Differences in Type 1 and Other Video Subsystems     | 2-11  |

| Memory Write Operations                              | 2-12  |

| Memory Read Operations                               | 2-13  |

| Type 1 Subsystem Parameters                          | 2-14  |

| Alphanumeric Modes                                   | 2-14  |

| Graphics Modes                                       | 2-17  |

| 320 x 200 Four-Color Graphics (Modes Hex 4 and 5)    | 2-17  |

| 640 x 200 Two-Color Graphics (Mode Hex 6)            | 2-19  |

| 640 x 350 Graphics (Mode Hex F)                      | 2-20  |

| 640 x 480 Two-Color Graphics (Mode Hex 11)           | 2-21  |

| 16-Color Graphics Modes (Modes Hex D, E, 10, and 12) | 2-21  |

| 256-Color Graphics Mode (Mode Hex 13)                | 2-21  |

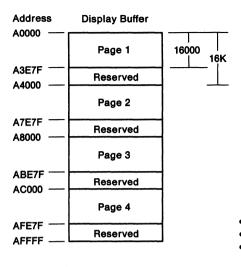

| Video Memory Organization                            | 2-23  |

| Memory Modes                                         | 2-23  |

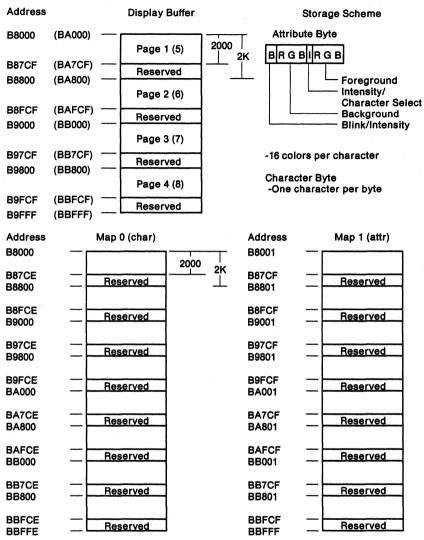

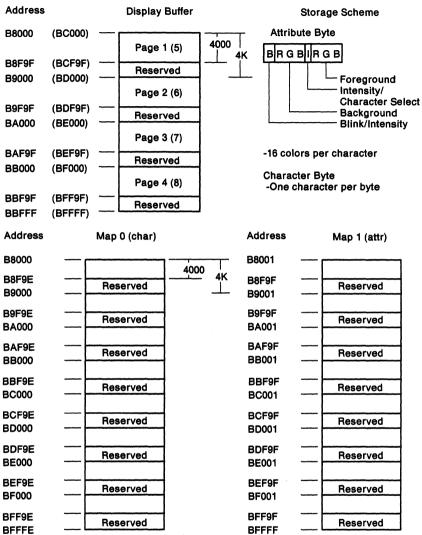

| Modes Hex 0, 1                                       | 2-24  |

| Modes Hex 2, 3                                       | 2-25  |

| Modes Hex 4, 5                                       | 2-26  |

| Mode Hex 6                                           | 2-27  |

| Mode Hex 7                                           | 2-28  |

| Mode Hex D                                           | 2-29  |

| Mode Hex E                                           | 2-31  |

| Mode Hex F                                           | 2-33  |

| Mode Hex 10                                          | 2-34  |

| Mode Hex 11                                          | 2-35  |

| Mode Hex 12                                          | 2-36  |

| Mode Hex 13                                          | 2-37  |

| Mode Hex 14                                          | 2-38  |

| Registers                                            | 2-39  |

| General Registers                                    | 2-40  |

| Miscellaneous Output Register                        | 2-40  |

| Input Status Register 0                              | 2-42  |

| Input Status Register 1                              | 2-43  |

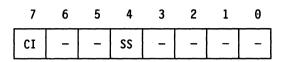

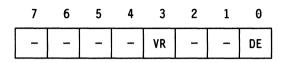

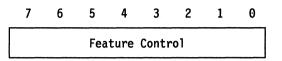

| Facture Control Desister                | 0 44 |

|-----------------------------------------|------|

| Feature Control Register                | 2-44 |

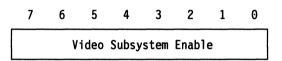

| Video Subsystem Enable Register         | 2-44 |

| Sequencer Registers                     | 2-45 |

| Sequencer Address Register              | 2-45 |

| Reset Register                          | 2-46 |

| Clocking Mode Register                  | 2-47 |

| Map Mask Register                       | 2-49 |

| Character Map Select Register           | 2-50 |

| Memory Mode Register                    | 2-52 |

| CRT Controller Registers                | 2-53 |

| Address Register                        | 2-54 |

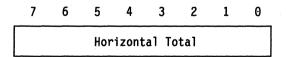

| Horizontal Total Register               | 2-54 |

| Horizontal Display-Enable End Register  | 2-55 |

| Start Horizontal Blanking Register      | 2-55 |

| End Horizontal Blanking Register        | 2-56 |

| Start Horizontal Retrace Pulse Register | 2-57 |

| End Horizontal Retrace Register         | 2-58 |

| Vertical Total Register                 | 2-59 |

| Overflow Register                       | 2-60 |

| Preset Row Scan Register                | 2-61 |

| Maximum Scan Line Register              | 2-62 |

| Cursor Start Register                   | 2-63 |

| Cursor End Register                     | 2-63 |

|                                         | 2-64 |

| Start Address High Register             |      |

| Start Address Low Register              | 2-65 |

| Cursor Location High Register           | 2-66 |

| Cursor Location Low Register            | 2-66 |

| Vertical Retrace Start Register         | 2-67 |

| Vertical Retrace End Register           | 2-67 |

| Vertical Display-Enable End Register    | 2-69 |

| Offset Register                         | 2-69 |

| Underline Location Register             | 2-70 |

| Start Vertical Blanking Register        | 2-71 |

| End Vertical Blanking Register          | 2-71 |

| CRT Mode Control Register               | 2-72 |

| Line Compare Register                   | 2-75 |

| Graphics Controller Registers           | 2-76 |

| Address Register                        | 2-76 |

| Set/Reset Register                      | 2-77 |

| Enable Set/Reset Register               | 2-78 |

| Color Compare Register                  | 2-79 |

| Data Rotate Register                    | 2-80 |

| Read Map Select Register                | 2-81 |

| Graphics Mode Register                  | 2-82 |

| Miscellaneous Register                  |      |

| Color Don't Care Register               | 2-85 |

|                                         | ~-UU |

| Bit Mask Register                   | 2-86 |

|-------------------------------------|------|

| Attribute Controller Registers      | 2-87 |

|                                     | 2-87 |

|                                     | 2-88 |

|                                     | 2-89 |

|                                     | 2-91 |

|                                     | 2-91 |

|                                     | 2-92 |

|                                     | 2-93 |

|                                     | 2-94 |

|                                     | 2-97 |

|                                     | 2-98 |

| Creating a Split Screen             | 2-99 |

|                                     | -101 |

|                                     | -101 |

|                                     | -101 |

|                                     | -103 |

|                                     | -104 |

|                                     | -106 |

| Base Video Extension                | -106 |

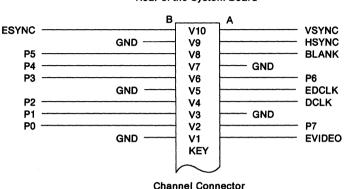

| Video Extension Signal Descriptions | -107 |

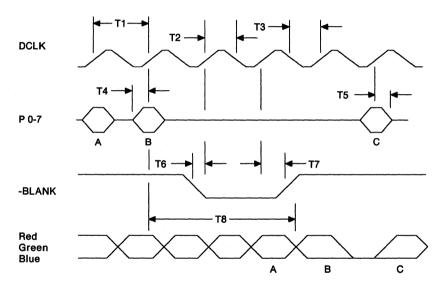

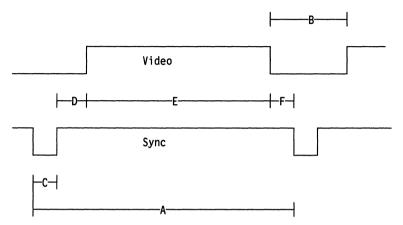

| Video Extension Signal Timing       | -108 |

## Notes:

# **VGA Function Introduction**

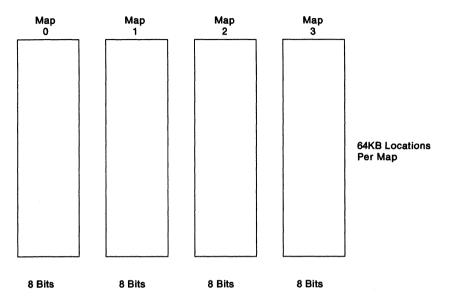

The circuitry that provides the VGA function includes a video buffer, a video digital-to-analog converter (DAC), and test circuitry. Video memory is mapped as four planes of 64KB by 8 bits (maps 0 through 3). The video DAC drives the analog output to the display connector. The test circuitry determines the type of display attached, color or monochrome.

The video subsystem controls the access to video memory from the system and the cathode-ray tube (CRT) controller. It also controls the system addresses assigned to video memory. Up to three starting addresses can be programmed for compatibility with previous video adapters.

In the graphics modes, the mode determines the way video information is formatted into memory, and the way memory is organized.

In alphanumeric modes, the system writes the ASCII character code and attribute data to video memory maps 0 and 1, respectively. Memory map 2 contains the character font loaded by BIOS during an alphanumeric mode set. The font is used by the character generator to create the character image on the display.

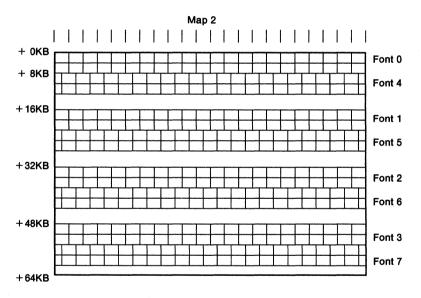

Three fonts are supplied with the system. These fonts are either 8 or 9 pels wide, and either 8, 14, or 16 pels high. Up to eight 256-character fonts can be loaded into the video memory map 2; two of these fonts can be active at one time, allowing a 512-character font.

The video subsystem formats the information in video memory and sends the output to the video DAC. For color displays, the video DAC sends three analog color signals (red, green, and blue) to the display connector. For monochrome displays, BIOS translates the color information in the DAC, and the DAC drives the summed signal onto the green output.

The auxiliary video connector allows video data to be passed between the video subsystem and an adapter plugged into the channel connector. See "VGA Video Extensions" on page 2-104. When it is disabled, the video subsystem will not respond to video memory or I/O reads or writes; however, the video image continues to be displayed.

Note: Compatibility with other hardware is best achieved by using the BIOS interface or operating system interface whenever possible.

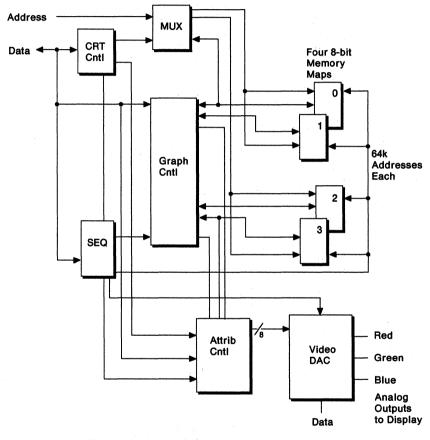

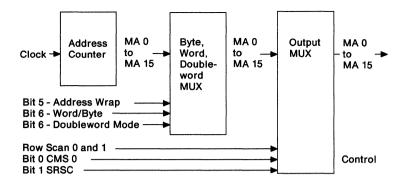

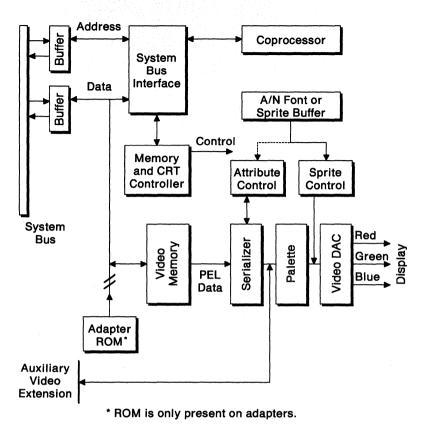

The following is a diagram of the VGA function.

Figure 2-1. Diagram of the VGA Function

## **Major Components**

The video subsystem contains all circuits necessary to generate the timing for the video memory and generates the video information going to the video DAC. The major components are: BIOS, support logic, and Video Graphics Array interface.

### BIOS

BIOS provides software support and contains the character fonts and the system interface to run the video subsystem.

### **Support Logic**

The support logic consists of the video memory, the clocks, and the video DAC. The video memory consists of at least 256KB; its use and mapping depend on the mode selected.

Two clock sources provide the dot rate. The clock source is selected in the Miscellaneous Output register.

The video DAC contains the color palette that is used to convert the video data into the video signal sent to the display. Three analog signals (red, green, and blue) are output from the DAC.

The maximum number of colors displayed is 256 out of 256K, and the maximum number of gray shades is 64 out of 64.

### **VGA** Components

The VGA function has four major functional areas: the CRT controller, the sequencer, the graphics controller, and the attribute controller.

#### **CRT Controller**

The CRT controller generates horizontal and vertical synchronization signal timings, addressing for the regenerative buffer, cursor and underline timings, and refresh addressing for the video memory.

#### Sequencer

The sequencer generates basic memory timings for the video memory and the character clock for controlling regenerative buffer fetches. It allows the system to access memory during active display intervals by periodically inserting dedicated system microprocessor memory cycles between the display memory cycles. Map mask registers in the sequencer are available to protect entire memory maps from being changed.

#### **Graphics Controller**

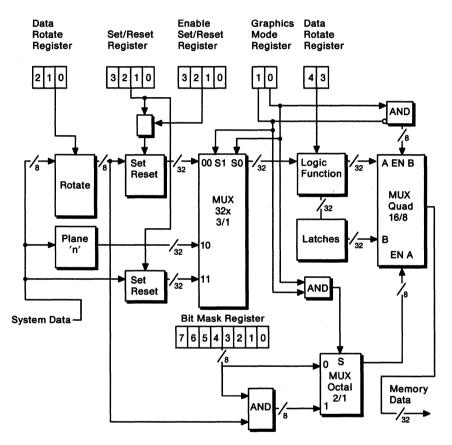

The graphics controller is the interface between the video memory and the attribute controller during active display times, and between video memory and the system microprocessor during memory accesses.

During active display times, memory data is latched and sent to the attribute controller. In graphics modes, the memory data is converted from parallel to serial bit-plane data before being sent; in alphanumeric modes, the parallel attribute data is sent.

During system accesses of video memory, the graphics controller can perform logical operations on the memory data before it reaches video memory or the system data bus. These logical operations are composed of four logical write modes and two logical read modes. The logical operators allow enhanced operations, such as a color compare in the read mode, individual bit masking during write modes, internal 32-bit writes in a single memory cycle, and writing to the display buffer on nonbyte boundaries.

Figure 2-2. Graphics Controller

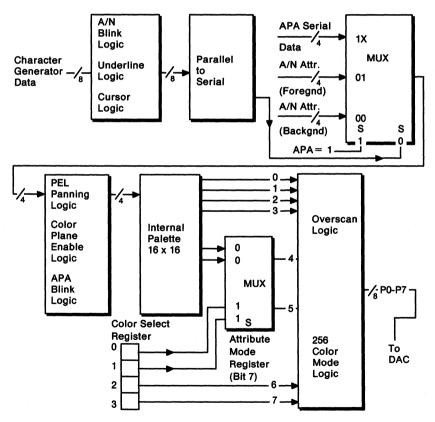

#### **Attribute Controller**

The attribute controller takes in data from video memory through the graphics controller and formats it for display. Attribute data in alphanumeric mode and serialized bit-plane data in graphics mode are converted to an 8-bit color value.

Each color value is selected from an internal color palette of 64 possible colors (except in 256-color mode). The color value is used as a pointer into the video DAC where it is converted to the analog signals that drive the display.

Blinking, underlining, cursor insertion, and pel panning are also controlled in the attribute controller.

Figure 2-3. Attribute Controller

# **Hardware Considerations**

The following are hardware characteristics of the Type 2 or Type 3 video subsystem that must be considered to ensure program compatibility with the Type 1 video subsystem.

# **Differences in Type 1 and Other Video Subsystems**

To ensure program compatibility between Type 1 and Type 2 or between Type 1 and Type 3 video subsystems, the following hardware characteristics of the Type 2 and Type 3 video subsystem must be considered.

**Performance:** Type 2 and Type 3 video subsystems generally run faster than the Type 1 video subsystem. Programs that depend on execution time of the video subsystem will operate differently.

**Video Buffer Compatibility:** For each of the video modes, the Type 2 and Type 3 video subsystems maintain a memory mapping that is the same as the Type 1 video subsystem. To maintain this compatibility, the internal addresses to video memory are manipulated so that video memory looks the same. When switching video modes, video data may not be at the same address in video memory.

BIOS calls to set and change modes make allowances for changes in addresses, and should be used for all mode switches.

**Character Generator:** Differences in the character generator for the Type 2 and Type 3 video subsystems increase the time it takes to load a new font. Because of the additional load time, there is a chance of briefly observing spurious data on the display. BIOS compensates for this during video mode sets.

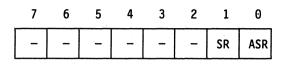

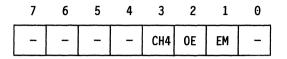

**Register Differences:** The following bits for the Type 2 and Type 3 video subsystems differ from the Type 1 video sybsystem.

- Bits 2 and 4 in the Clocking Mode register

- Bits 5 and 6 in the End Horizontal Blanking register

- Bits 2 and 4 in the Preset Row Scan register

- Bit 5 in the Address register of the attribute controller.

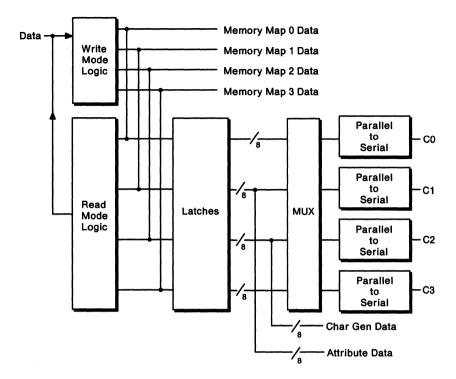

## **Memory Write Operations**

When the system is writing to the display buffer, the maps are enabled by the logical decode of the memory address and the Map Mask register. The addresses used for video memory depend on the mode selected. The data flow for a system write operation is illustrated in the following figure.

Figure 2-4. Data Flow for Write Operations

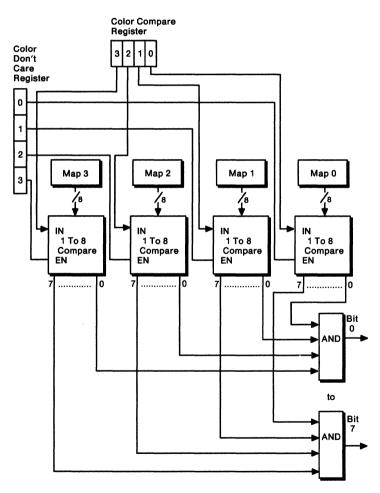

# **Memory Read Operations**

The two ways to read the video buffer are selected through the Graphics Mode register in the graphics controller. The mode 0 read operation returns the 8-bit value determined by the logical decode of the memory address and, if applicable, the Read Map Select register. The mode 1 read operation returns the 8-bit value resulting from the color compare operation controlled by the Color Compare and Color Don't Care registers. The data flow for the color compare operation is shown in the following figure.

Figure 2-5. Color Compare Operations

# **Type 1 Subsystem Parameters**

# **Alphanumeric Modes**

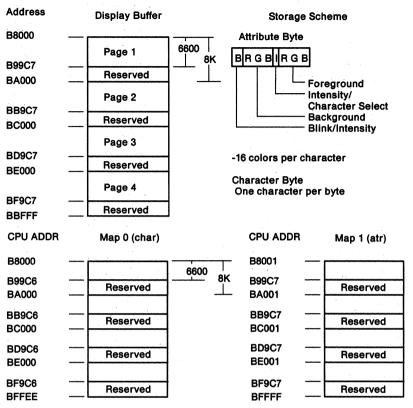

The alphanumeric modes are modes hex 0 through 3 and 7. The mode chart lists the variations of these modes (see Figure 1-1 on page 1-4). The data format for alphanumeric modes is the same as the data format on the IBM Color/Graphics Monitor Adapter, the IBM Monochrome Display Adapter, and the IBM Enhanced Graphics Adapter.

BIOS initializes the video subsystem according to the selected mode and loads the color values into the video DAC. These color values can be changed to give a different color set from which to select. Bit 3 of the attribute byte can be redefined by the Character Map Select register to act as a switch between character sets, giving the programmer access to 512 characters at one time.

When an alphanumeric mode is selected, the BIOS transfers character font patterns from the ROM to map 2. The system stores the character data in map 0, and the attribute data in map 1. In the alphanumeric modes, the programmer views maps 0 and 1 as a single buffer. The CRT controller generates sequential addresses and fetches one character code byte and one attribute byte at a time. The character code and row scan count are combined to make up the address into map 2, which contains the character font. The appropriate dot patterns are then sent to the attribute controller, where color is assigned according to the attribute data. Every display-character position in the alphanumeric mode is defined by two bytes in the display buffer. Both the color/graphics and the monochrome emulation modes use the following 2-byte character/attribute format.

| D | Display Character Code Byte |   |   |   |   |   |   |   |    | Att  | ribu | te B | yte |   |   |

|---|-----------------------------|---|---|---|---|---|---|---|----|------|------|------|-----|---|---|

| 7 | 6                           | 5 | 4 | 3 | 2 | 1 | 0 | 7 | 6  | 5    | 4    | 3    | 2   | 1 | 0 |

|   | Even Address                |   |   |   |   |   |   |   | 00 | id A | ddre | ess  |     |   |   |

Figure 2-6. Character/Attribute Format

.

See "Characters and Keystrokes" for characters loaded during a BIOS mode set.

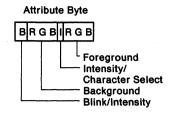

The functions of the attribute bytes are defined in the following table. Bit 7 can be redefined in the Attribute Mode Control register to give 16 possible background colors; its default is to control character blinking. Bit 3 can be redefined in the Character Map Select register as a switch between two character fonts; its default is to control foreground color selection.

| Bit | Color | Function                                      |

|-----|-------|-----------------------------------------------|

| 7   | B/I   | Blinking or Background Intensity              |

| 6   | R     | Background Color                              |

| 5   | G     | Background Color                              |

| 4   | в     | Background Color                              |

| 3   | I/CS  | Foreground Intensity or Character Font Select |

| 2   | R     | Foreground Color                              |

| 1   | G     | Foreground Color                              |

| 0   | в     | Foreground Color                              |

|     |       | -                                             |

Figure 2-7. Attribute Byte Definitions

For more information about the attribute bytes, see "Character Map Select Register" on page 2-50 and "Attribute Mode Control Register" on page 2-89.

The following are the color values loaded by BIOS for the 16-color modes.

|    | Intensity | Red | Green | Blue | Color                  |

|----|-----------|-----|-------|------|------------------------|

|    | 0         | 0   | 0     | 0    | Black                  |

|    | 0         | 0   | 0     | 1    | Blue                   |

|    | 0         | 0   | 1     | 0    | Green                  |

|    | 0         | 0   | 1     | 1    | Cyan                   |

|    | 0         | 1   | 0     | 0    | Red                    |

| l. | 0         | 1   | 0     | 1    | Magenta                |

|    | 0         | 1   | 1     | 0    | Brown                  |

|    | 0         | 1   | 1     | 1    | White                  |

|    | 1         | 0   | 0     | 0    | Gray                   |

|    | 1         | 0   | 0     | 1    | Light Blue             |

|    | 1         | 0   | 1     | 0    | Light Green            |

|    | 1         | 0   | 1     | 1    | Light Cyan             |

|    | 1         | 1   | 0     | 0    | Light Red              |

|    | 1         | 1   | 0     | 1    | Light Magenta          |

|    | 1         | 1   | 1     | 0    | Yellow                 |

|    | 1         | 1   | 1     | 1    | White (High Intensity) |

Figure 2-8. BIOS Color Set

Both 40-column and 80-column alphanumeric modes are supported. The features of the 40-column alphanumeric modes (all variations of modes hex 0 and 1) are:

- 25 rows of 40 characters

- 2KB of video memory per page

- One character byte and one attribute byte per character.

The features of the 80-column alphanumeric modes (all variations of modes hex 2, 3, and 7) are:

- 25 rows of 80 characters

- 4KB of video memory per page

- One character byte and one attribute byte per character.

# **Graphics Modes**

The colors described in this section are generated when the BIOS is used to set the mode. BIOS initializes the video subsystem and the DAC palette to generate these colors. If the DAC palette is changed, different colors are generated.

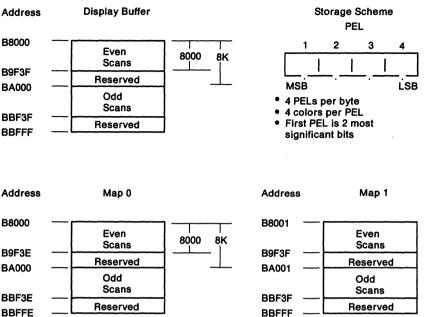

#### 320 x 200 Four-Color Graphics (Modes Hex 4 and 5)

Addressing, mapping, and data format are the same as the 320 x 200 pel mode of the IBM Color/Graphics Monitor Adapter. The display buffer is configured at hex B8000. Bit image data is stored in memory maps 0 and 1. The two bit planes (C0 and C1) are each formed from bits from both memory maps.

Features of this mode are:

- A maximum of 200 rows of 320 pels

- Double scanned to display as 400 rows

- Memory-mapped graphics

- Four colors for each pel

- Four pels per byte

- 16KB of read/write memory.

The video memory is organized into two banks of 8KB each, using the following format. Address hex B8000 contains the pel information for the upper-left corner of the display area.

| Memory Address | Function                  |  |  |

|----------------|---------------------------|--|--|

| B8000          | Even Scans                |  |  |

| B9F3F          | (0,2,4,,198)              |  |  |

|                | Reserved                  |  |  |

| BA000          | Odd Scans<br>(1,3,5,,199) |  |  |

| BBF3F          | <b>D</b>                  |  |  |

| BBFFF          | Reserved                  |  |  |

Figure 2-9. Video Memory Format

## The following figure shows the format for each byte.

| Bit | Function                |  |

|-----|-------------------------|--|

| 7   | C1 - First Display Pel  |  |

| 6   | C0 - First Display Pel  |  |

| 5   | C1 - Second Display Pel |  |

| 4   | C0 - Second Display Pel |  |

| 3   | C1 - Third Display Pel  |  |

| 2   | C0 - Third Display Pel  |  |

| 1   | C1 - Fourth Display Pel |  |

| 0   | C0 - Fourth Display Pel |  |

| Figure 2 | 2-10. | Pel Format. | Modes | Hex 4 and 5 |  |

|----------|-------|-------------|-------|-------------|--|

|----------|-------|-------------|-------|-------------|--|

The color selected depends on the color set that is used. Color set 1 is the default. For information on changing the color set, see the *IBM Personal System/2 and Personal Computer BIOS Interface Technical Reference*.

| Bits  |                   | Color Selected |

|-------|-------------------|----------------|

| C1 C0 | Color Set 1       | Color Set 0    |

| 0 0   | Black             | Black          |

| 0 1   | Light Cyan        | Green          |

| 10    | Light Magenta     | Red            |

| 1 1   | Intensified White | Brown          |

Figure 2-11. Color Selections, Modes Hex 4 and 5

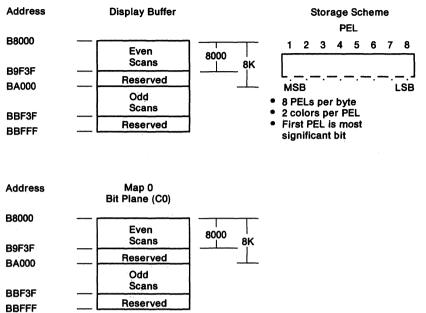

## 640 x 200 Two-Color Graphics (Mode Hex 6)

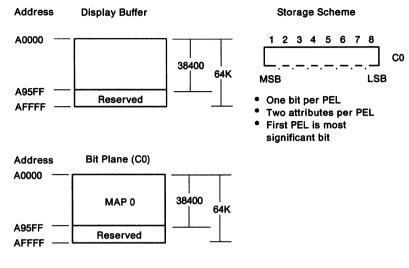

Addressing, scan-line mapping, and data format are the same as the 640 x 200 pel black and white mode of the IBM Color/Graphics Monitor Adapter. The display buffer is configured at hex B8000. Bit image data is stored in memory map 0 and comprises a single bit plane (C0). Features of this mode are:

- A maximum of 200 rows of 640 pels

- Double scanned to display as 400 rows

- Same addressing and scan-line mapping as 320 x 200 graphics

- Two colors for each pel

- Eight pels per byte

- 16KB of read/write memory.

The following shows the format for each byte.

| Bit | Function            |

|-----|---------------------|

| 7   | First Display Pel   |

| 6   | Second Display Pel  |

| 5   | Third Display Pel   |

| 4   | Fourth Display Pel  |

| 3   | Fifth Display Pel   |

| 2   | Sixth Display Pel   |

| 1   | Seventh Display Pel |

| 0   | Eighth Display Pel  |

Figure 2-12. Pel Format, Mode Hex 6

The bit definition for each pel is 0 equals black and 1 equals intensified white.

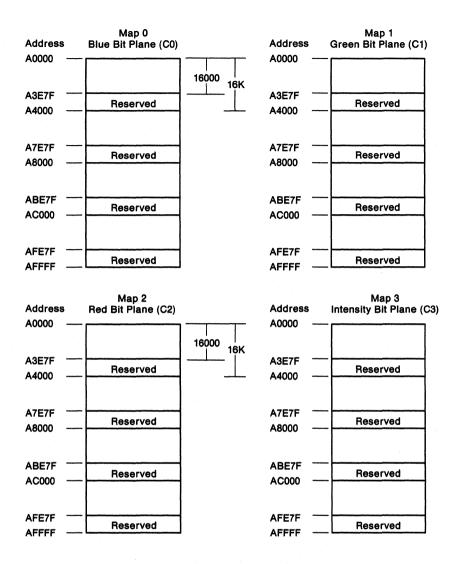

#### 640 x 350 Graphics (Mode Hex F)

This mode emulates the EGA graphics with the monochrome display and the following attributes: black, video, blinking video, and intensified video. A resolution of 640 x 350 uses 56KB of video memory to support the four attributes. This mode uses maps 0 and 2; map 0 is the video bit plane (C0), and map 2 is the intensity bit plane (C2). Both planes reside at address hex A0000.

The two bits, one from each bit plane, define one pel. The bit definitions are given in the following table.

| C2 C0 | Pel Color         |

|-------|-------------------|

| 0 0   | Black             |

| 0 1   | White             |

| 1 0   | Blinking White    |

| 1 1   | Intensified White |

Figure 2-13. Bit Definitions C2,C0

Memory is organized with successive bytes defining successive pels. The first eight pels displayed are defined by the byte at hex A0000, the second eight pels by the byte at hex A0001, and so on. The most-significant bit in each byte defines the first pel for that byte.

Because both bit planes reside at address hex A0000, the user must select the plane to update through the Map Mask register of the sequence controller (see "Video Memory Organization" on page 2-23).

## 640 x 480 Two-Color Graphics (Mode Hex 11)

This mode provides two-color graphics with the same data format as mode 6. Addressing and mapping are shown under "Video Memory Organization" on page 2-23.

The bit image data is stored in map 0 and comprises a single bit plane (C0). The video buffer starts at hex A0000. The first byte contains the first eight pels; the second byte, at hex A0001, contains the second eight pels, and so on. The bit definition for each pel is 0 equals black and 1 equals intensified white.

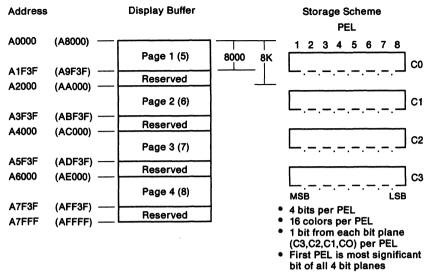

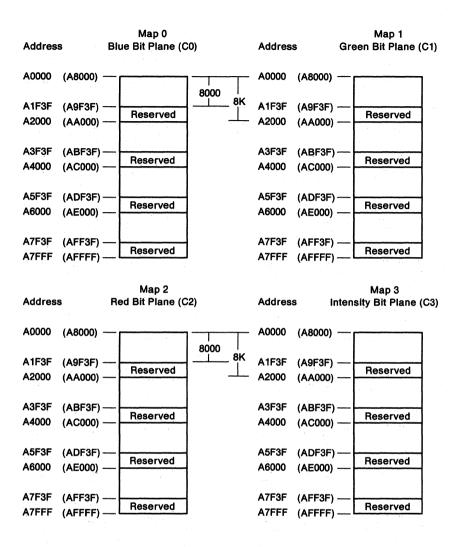

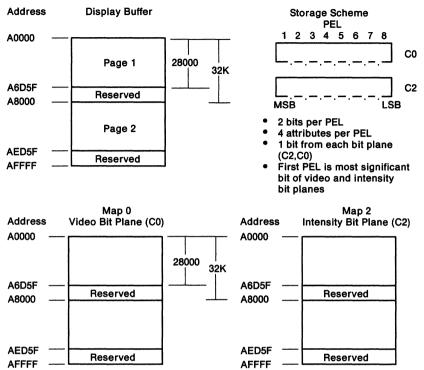

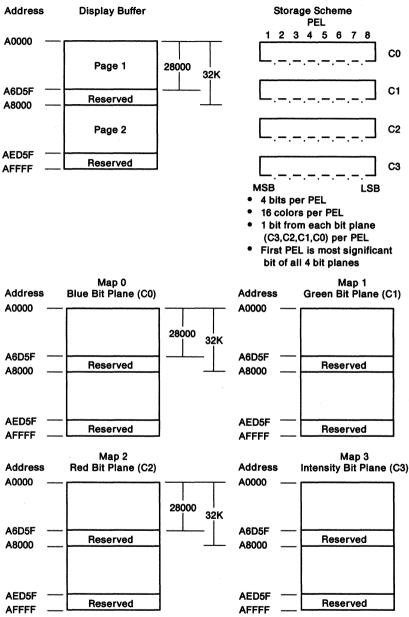

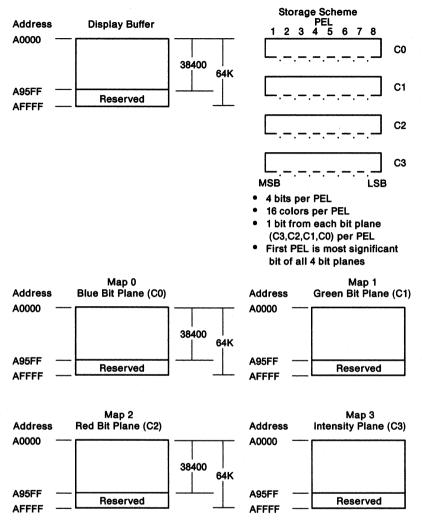

# 16-Color Graphics Modes (Modes Hex D, E, 10, and 12)

These modes support 16 colors. For all modes, the bit image data is stored in all four memory maps. Each memory map contains the data for one bit plane. The bit planes are C0 through C3 and represent the following colors.

C0 = Blue C1 = Green C2 = RedC3 = Intensified

The four bits define each pel on the screen by acting as an address (pointer) into the internal palette in the Extended Graphics mode.

The display buffer resides at address hex A0000. The Map Mask register selects any or all of the maps to be updated when the system writes to the display buffer.

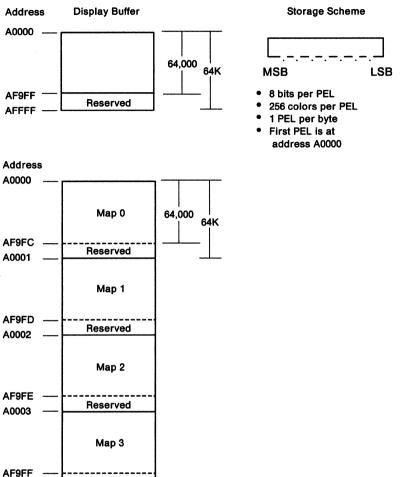

# 256-Color Graphics Mode (Mode Hex 13)

This mode provides graphics with the capability of displaying 256 colors at one time.

The display buffer is sequential, starts at address hex A0000, and is 64,000 bytes long. The first byte contains the color information for the upper-left pel. The second byte contains the second pel, and so on, for 64,000 pels (320 x 200). The bit image data is stored in all four memory maps and comprises four bit planes. The four bit planes are sampled twice to produce eight bit-plane values that address the video DAC.

In this mode, the internal palette of the video subsystem is loaded by BIOS and should not be changed. The first 16 locations in the external palette, which is in the video DAC, contain the colors compatible with the alphanumeric modes. The second 16 locations contain 16 evenly spaced gray shades. The next 216 locations contain values based on a hue-saturation-intensity model tuned to provide a usable, generic color set that covers a wide range of color values.

| Pel Bits |                   |  |

|----------|-------------------|--|

| 76543210 | Color Output      |  |

| 0000000  | Black             |  |

| 0000001  | Blue              |  |

| 0000010  | Green             |  |

| 00000011 | Cyan              |  |

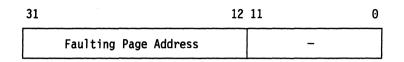

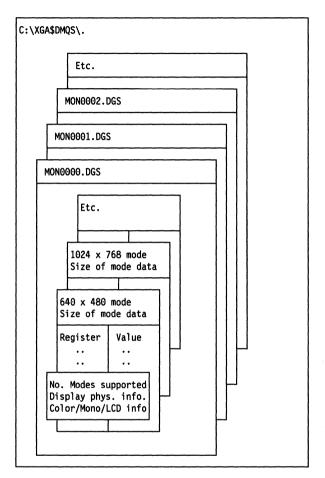

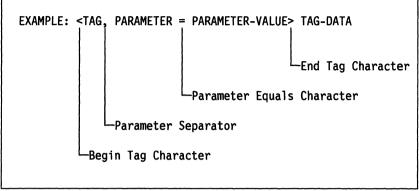

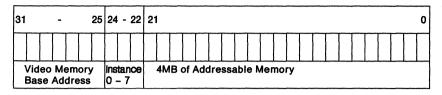

| 00000100 | Red               |  |