## The Design of

Virtual Memory Dynamic Linking Multitasking I/O Management 80286/80386/80486 SAA **Micro Channel** Architecture Multiprocessing OSI LAN Support Processes **Multimedia** Threads **Open Systems** Shared Memory Multiuser OS/2 Windows Compatibility Semaphores Queues Pipes Sessions

### 32-BIT OS/2

Named Pipes Portability **Presentation Manager** Installable File Systems Paging Segmentation **Device Drivers IBM PS/2** TCP/IP **DOS Compatibility** 16-bit OS/2 Scheduling Interprocess Communication **SNA Cache Management**

### 2-BIT

Vesley

leitel

ogan

The Design

<u>o</u>

## H.M. Deitel M.S. Kogan

### Foreword by James A. Cannavino

IBM Vice President and General Manager, Personal Systems

# The Design of OS/2

100

#### H. M. Deitel

Nova University

M. S. Kogan

**IBM** Corporation

#### ADDISON-WESLEY PUBLISHING COMPANY

Reading, Massachusetts • Menlo Park, California • New York Don Mills, Ontario • Wokingham, England • Amsterdam • Bonn Sydney • Singapore • Tokyo • Madrid • San Juan • Milan • Paris Sponsoring Editor: Keith Wollman Electronic Production Administrator: Beth Perry Text Designer: Herb Caswell Technical Art Consultant: Joe Vetere Illustrators: Tech-Graphics Cover Designer: Peter Blaiwas Manufacturing Coordinator: Judy Sullivan

#### Library of Congress Cataloging-in-Publication Data

Deitel, Harvey M., 1945– The design of OS/2 / H.M. Deitel, M.S. Kogan.

p. cm.

Includes bibliographical references and index.

ISBN 0-201-54889-5

1. OS/2 (Computer operating system) I. Kogan, M.S. (Michael S.) II. Title.

QA76.76.063D455 1992

005.4'469—dc20

91-17015 CIP

Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and Addison-Wesley was aware of a trademark claim, the designations have been printed in initial caps or all caps.

The programs and applications presented in this book have been included for their instructional value. They are not guaranteed for any particular purpose. The publisher and the authors do not offer any warranties or representations, nor do they accept any liabilities with respect to the programs or applications.

Copyright © 1992 by Addison-Wesley Publishing Company, Inc.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. Printed in the United States of America.

This manuscript represents the opinions of the authors only, and in no way expresses any view or opinion of the IBM Corporation.

2 3 4 5 6 7 8 9 10-DO-9594939291

To the designers, implementors, and testers of OS/2: For bringing edge-of-the-art distributed computing capabilities to the desktop of the 1990s

To Dean Edward Simco:

For his indefatigable efforts in creating and nurturing the Center for Computer and Information Sciences at Nova University

~

## Foreword

It is a pleasure to write these opening comments for Deitel and Kogan's, *The Design of* OS/2. We at IBM believe strongly that the new 32-bit OS/2 2.0 will have an important place in the market for personal computers, workstations, and network servers. The book clearly and thoroughly explains the architecture of the operating system in a manner appropriate both for technical professionals who want to understand OS/2's internal structure, and for software developers considering investing in OS/2 applications development. It provides insights into *why* various key design decisions were made.

Dr. Michael Kogan is the chief architect of OS/2 2.0; Dr. Harvey Deitel is the author of one of the world's most widely used operating systems textbooks. Their combined experience covers every major current IBM operating system, as well as the UNIX system, networking, multimedia, and open systems. Dr. Kogan, through his position at IBM, is well apprised of IBM architectural trends. Dr. Deitel consults in the open systems arena with activities related to open operating systems, object orientation, OSI protocols, and international computing and communications standards.

#### Why OS/2?

Computer systems are evolving rapidly, and OS/2 is designed to support these changes. There are radical changes in hardware, from older systems supported by modest 8- or 16-bit microprocessors, to newer high-powered 32-bit microprocessors such as the Intel 80386 and 80486. RISC systems and multiprocessing systems offer the potential for massive increases in net processing power.

Radical changes in user support also are demanded. The personal computers of the early to mid-1980s tended to be standalone systems. In the 1990s, personal computers will be networked in local and wide area networks. OS/2 is designed to support missioncritical applications—that is, applications that must function continuously and reliably to support key activities of businesses and other organizations. OS/2 is designed to enhance personal productivity. End users working in OS/2 environments can get more done because of the ease of use, high performance, high reliability, information accessibility, and system integrity provided by OS/2.

#### vi Foreword

The shift in application development toward object-orientation is gaining momentum. To become more productive software developers need to reuse components, to develop prototypes more rapidly, and to implement polished and tuned applications faster. OS/2 provides an environment conducive to object-oriented systems development.

The following sections briefly describe OS/2 2.0 and its capabilities. As you read this book, you will come to understand what is "under the hood," and how these capabilities are implemented.

#### The Integration Platform

We call OS/2 2.0 the "integration platform" because you can run your existing DOS applications, DOS extender (such as the popular Windows) applications, and OS/2 1.3 applications on OS/2 2.0, and they will run more efficiently on the same hardware than they do under their originally intended operating systems. You can also run the new, high-performance 32-bit applications designed to take advantage of 32-bit architectures. Applications run better from the standpoint of performance, integrity, and usability, translating into productivity gains.

#### Protected Multitasking

OS/2 2.0 represents the evolution of DOS into the world of protected multitasking. It uses the protection mechanisms of the 80386/80486 architecture to ensure robust operation. It runs many applications simultaneously without the danger of misbehaved applications destroying one another or the operating system—precisely what is needed in mission-critical application environments. An application may not access the private data of other applications. This level of protection is facilitated by the fact that OS/2 applications execute in separate address spaces; DOS extender applications, on the other hand, share a single address space. An errant DOS application may destroy a DOS extender's kernel, thus requiring a reboot, and work may be lost; the OS/2 kernel is protected from errant applications. OS/2 can run multiple versions of the same software simultaneously, making it ideal as an application developer's platform. Its multitasking capabilities make it appropriate as a network server. It uses preemptive scheduling, so it offers good responsiveness to applications of differing characteristics. Priorities are calculated dynamically, so OS/2 can multitask timing-critical applications in both the foreground and the background.

#### Mission-Critical Systems

OS/2 has many features that support mission-critical business applications. It provides protected multitasking, processes, threads, interprocess communication, and virtual memory, as well as reliability/availability/service (RAS) features that help to isolate software problems and to ensure robust operation.

#### **Applications**

There are already 2500 OS/2 software applications announced or available, including 300 Presentation Manager applications. Popular software packages are available, such as Lotus 1-2-3, DBase, WordPerfect, and many others. Many 32-bit OS/2 applications have appeared, and hundreds more are under development. OS/2 2.0 is a critical platform for

IBM's Systems Application Architecture (SAA), our plan for integrating the IBM mainframe, minicomputer, workstation, and personal computer product lines. OS/2 2.0 is designed for machines based on Intel's 32-bit 80386/80486 architecture. In particular, 80386-based systems have proliferated, creating the installed base needed to attract the resources of the independent software vendors. With the appearance of 32-bit OS/2, major user organizations and independent software vendors are making substantial commitments to developing OS/2 applications. OS/2 2.0 provides a powerful base for future growth; 32-bit applications provide dramatic performance improvements over their 16-bit counterparts. Our PMREXX application, for example, demonstrated a 60 percent improvement when used in the 32-bit programming environment.

#### Memory Management and Virtual Memory

OS/2 2.0's virtual memory model provides 4-gigabyte addressing. The large, flat, paged 32-bit memory model frees the application developer from the memory constraints of the 16-bit segmented model, and from the complexity of managing memory in the 16-bit environment. The 32-bit paging model achieves better utilization of memory and higher performance. The DOS extenders that use virtual memory are typically constrained to a small virtual space; Windows 3.0 applications, for example, share a virtual memory no larger than four times the size of physical memory. In OS/2 2.0, each application has a 512MB virtual memory limit, so the key memory limit is the available disk space. DOS extenders generally use the segmented memory model, in which each piece of memory can only be as large as 64KB; in OS/2 2.0, memory objects can be as large as they need to be (up to the limits of virtual memory). OS/2 runs multiple DOS applications, each with more real memory and far more virtual memory than is available through DOS extenders such as Windows, and each protected from the others to ensure more robust operation. DOS applications can use the DOS Protected Mode Interface (DPMI) to access up to 512MB of extended memory.

#### Productivity and Ease of Use

OS/2 2.0 provides numerous productivity and ease-of-use improvements. It provides a graphical installation procedure, and it uses an object-oriented, graphical user interface with the drag-and-drop environment implemented consistently across the entire system. Local area network requestor capabilities are integrated into the shell. Intelligent font technology is employed. OS/2 2.0 supports a great variety of printers. It provides an online, interactive tutorial, and includes various utilities, games, and productivity applications to help the user become familiar with the system quickly. Extensive on-line help capabilities are provided. In a typical OS/2 environment, the operating system manages the environment transparently to the user. OS/2 worries about the network, and determines whether it has the latest software updates and data updates. The user does not see all that activity. Rather, the user sees only the graphical user interface, which will continue to be enhanced.

#### Workplace Model

OS/2 2.0 implements the SAA Common User Access Workplace model, which uses the desktop metaphor of how people work. It derives from our OfficeVision system, and

works in the object-oriented paradigm. The Workplace model provides an intuitive user interface for managing any objects, including programs, files, and devices.

#### Presentation Manager

Given that we can run Windows applications out of the box, why do we encourage the development of Presentation Manager (PM) applications? PM applications offer better integration with the Workplace model. Threads can be used to maximize the advantages of multitasking, and to increase system responsiveness. PM applications can take advantage of the capabilities of the OS/2 Database Manager and Communications Manager. In general, PM applications can use the more powerful capabilities provided in OS/2 2.0 for interprocess communication, tasking, semaphores, multithreading, and graphics. The High-Performance File System (HPFS) offers greater data integrity, minimizes disk fragmentation, exploits SCSI performance features, uses sophisticated input/output caching algorithms, and supports huge disks and long filenames. Finally, OS/2 2.0 uses installable file systems, which makes it easy to support new kinds of media, such as CD-ROM.

#### Portability

The popularity of flat, 32-bit virtual address spaces across many platforms facilitates porting OS/2 to those platforms. This portability enables OS/2 to compete effectively with UNIX in the workstation marketplace. Porting to RISC platforms is underway. The 32-bit API is portable to multiprocessor architectures, as well as to uniprocessor architectures.

#### Multimedia

OS/2 2.0's exploitation of the 80386/80486 architecture is important for high-performance applications, such as speech synthesis and recognition, full-motion color video with sound, and the integration of these technologies under the rubric of multimedia. OS/2 is a particularly strong system for multimedia applications. It encapsulates system resources, freeing the developer from having to control them directly, and it offers powerful graphics capabilities. Multitasking supports the multiple data streams common in multimedia applications. OS/2 2.0 supports the notion of fast threads specifically for multimedia applications. Multimedia also demands the manipulation of huge objects such as bitmaps; this capability is facilitated by the large, flat, 32-bit virtual addressing model.

#### **Object** Orientation

Through extended attributes, OS/2 provides file-system support for object-oriented capabilities, and we are enhancing support for object-orientation. The motivation for this support is clear. Object orientation enables developers to write collaborative software without having a detailed understanding of all components. It yields reusability of sub-stantial functions, dramatically improving the productivity of developers working on so-phisticated new applications—surely a source of excitement in our industry. Projects underway emphasize the use of object-oriented programming techniques and of other edge-of-the-art technologies (such as multimedia, expert systems, and visual programming) to create applications useful across a wide range of hardware and operating

system platforms. These efforts focus on developing applications by combining reusable software objects. Their work products will become available on OS/2, AIX, UNIX, and Macintosh systems, among others, ensuring wide distribution.

#### Networking and Distributed Computing

IBM has endorsed the Distributed Computing Environment (DCE) of the Open Software Foundation. DCE supports heterogeneous, multivendor distributed computing. IBM's SAA is being extended to include DCE. OS/2 is a key SAA system and will support DCE. In particular, OS/2 will include remote procedure calls (RPCs), the distributed naming service (in conformance with OSI's X.500 standard), the time service, the security service, the threads service, and the distributed file system. OS/2 provides many features that support networked environments, DCE, and cooperative processing. Perhaps most crucial is OS/2's support of key networking standards, such as SNA, TCP/IP, and OSI. OS/2 LAN support includes key local area networking standards, such as token ring and Ethernet, and wide area networking standards, such as X.25.

#### Overview of the Book

Deitel and Kogan describe the evolution of personal-computer operating systems through the early years of DOS and its various versions, and the development of OS/2 through its 16-bit and 32-bit versions. They discuss the microprocessor architectures, hardware system architectures, and operating system architectures of the IBM-compatible, personal computing marketplace. They explain how protected multitasking is implemented, and provide insights into the relationships between threads and processes. A detailed discussion of memory management is presented, including explanations of the segmented model of OS/2 1.X and the flat model of OS/2 2.0. The various interprocess communication mechanisms are considered, including shared memory, semaphores, signals, queues, and pipes. The I/O management chapter explains the notions of files, devices, installable file systems, device drivers, and DevHelp services. With all the attention on graphical user interfaces today, the reader will appreciate the discussion of the Presentation Manager and windowing concepts. The book's highly detailed treatment of providing compatibility for DOS, Windows 3.0, and OS/2 1.3 is superb. The communications features of OS/2-including OSI, X.25, LANs, SNA, and TCP/IP-are covered in depth. The book concludes with a look to the future, considering such important topics as open systems, competition and cooperation between OS/2 and UNIX, IBM's Systems Application Architecture, multiprocessing, security, and multimedia. Deitel and Kogan have written a clear, thorough, well-illustrated, frank, and insightful analysis of the architecture of OS/2 2.0. Their work is an important contribution to the operating systems literature.

James A. Cannavino IBM Vice President and General Manager, Personal Systems

## Preface

The goal of this work is to provide insights into the design decisions and philosophies of the OS/2 operating system. We discuss the motivation, architecture, and realization of OS/2 in the personal computing marketplace. The designs of the major components of OS/2 are described. Each area bridges operating systems theory to the design and implementation of OS/2. Where appropriate, a comparison of the technical aspects of OS/2 and UNIX is provided. The evolution of personal computer operating systems from DOS through 16-bit OS/2 and 32-bit OS/2 is presented.

Chapter 1 recounts the history and evolution of the DOS and OS/2 operating systems. It sets the stage as we illustrate how the OS/2 development teams reconciled real-world development constraints with providing the functionality and performance demanded by a maturing PC industry.

Chapter 2 describes the microprocessor architectures on which the DOS and OS/2 systems execute. We consider the 8088/8086 processor family, the 80286, the 80386, and 80486 CISC-style processors. Looking towards the future, we consider RISC-style processors such as the Intel 80860 and the IBM POWER architecture used in IBM System/6000 workstations.

Chapter 3 presents the hardware system architectures of the personal computer systems that use the processors discussed in Chapter 2. We consider key personal computer bus architectures—the original Industry Standard Architecture (ISA), the Micro Channel Architecture, and the Extended Industry Standard Architecture (EISA). Uniprocessor and multiprocessor configurations are discussed. The programming tools available for the various hardware architectures are described, and the evolution of these is traced across the operating system platforms.

Chapter 4 overviews the architectures of 16-bit and 32-bit OS/2 systems and programs. A discussion of the DOS system gives the technical foundations of the precursor to the OS/2 system.

Chapters 5 through 10 describe the architecture and design of the major components of the 16-bit and 32-bit OS/2 systems. When a component provides the same functional-

#### xii Preface

ity in both the 16-bit and 32-bit systems, a single discussion is rendered and differences in the two versions of the component are noted where significant (as in Chapter 5 on multitasking). When the 16-bit and 32-bit versions of a single component are substantially different, separate treatments of the component are presented for each version (as in Chapter 6 on memory management). Each major component is discussed in terms of its API calls, internal algorithms, and data structures. These specify the behavior and content of 16-bit OS/2 and 32-bit OS/2.

Chapter 5 discusses OS/2 multitasking. The overall architecture, internal data structures, and major algorithms that compose the OS/2 task manager, dispatcher, and scheduler are detailed.

Chapter 6 describes OS/2 memory management. Both the segmented 16-bit memory model and the paged 32-bit memory model are discussed.

Chapter 7 deals with interprocess communication issues in the multitasking environment. Shared memory, semaphores, signals, pipes, queues, and exceptions are examined in both the 16-bit and 32-bit OS/2 systems.

Chapter 8 describes the I/O components of OS/2. The architectures for devices, file systems, and device drivers are elaborated along with their respective APIs or interfaces.

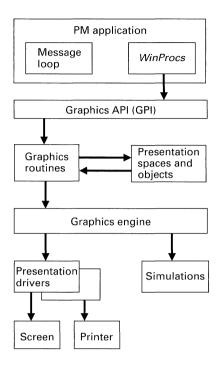

Chapter 9 describes the presentation management aspects of OS/2. The roles of the keyboard, mouse, and screen devices are examined and analyzed with respect to OS/2's session management architecture. The function and design of the graphical user interface of OS/2, as provided by the Presentation Manager, are also described.

Chapter 10 explores issues in providing compatibility. Both the 16-bit and 32-bit versions of OS/2 provide DOS compatibility. The 32-bit version also provides Windows 3.0 compatibility and 16-bit OS/2 compatibility.

Chapter 11 examines the role of OS/2 in the communications arena. IBM's System Application Architecture and the ISO Open Systems Interconnection reference model are described, as well as OS/2 Extended Edition and LAN Manager. The role of OS/2 in networked workstation and multiuser environments is also considered.

Chapter 12 discusses future issues for OS/2. We examine the technical requirements placed on OS/2 to support open systems, RISC architectures, multiprocessor platforms, and multimedia.

It is a pleasure to acknowledge the people who helped us throughout the writing, review, and production phases of this project. Thanks to the individuals in IBM management, communications, and legal areas for their support in this endeavor. We are also grateful for the comments of many IBM OS/2 designers, testers, planners, and developers.

The book was reviewed by many people, includingJack Boyce (IBM Corporation)Byron PazeyGlenn Brew (IBM Corporation)Raymond PeRoss Cook (IBM Corporation)Dr. FreemanGreg Gruse (CITRIX)Dr. Edward SEdward Iacobucci (CITRIX)Dr. Raisa SzDr. Edward Lieblein (Nova University)Raymond WJim Macon (IBM Corporation)Jim Macon (JBM Corporation)

Byron Pazey (Consultant)

Raymond Pedrizetti (Microsoft Corporation) Dr. Freeman Rawson (IBM Corporation)

Dr. Edward Simco (Nova University)

Dr. Raisa Szabo (Nova University)

Raymond Westwater (FutureWare)

Iris Boshell took dictation of major portions of the first draft of the manuscript.

Our efforts were encouraged by IBM managers including Lee Reiswig, Tommy Steele, Roy Clauson, Oscar Fleckner, Janis Walkow, and Shon Saliga. We are especially grateful to James Cannavino for taking the time out of an incredibly busy schedule to prepare the foreword to the book.

Special thanks are due to Ross Cook of IBM for many insights into the intriguing subtleties of the operating system design process, and to Glenn Brew of IBM for serving as a constant technical sounding board, for his friendship, and for his encouragement.

Thanks to Barbara Deitel for handling the development of the manuscript from the author's side, and for coordinating the production of the book with Addison Wesley. Her tireless efforts enabled us to concentrate on preparing the technical material.

Framingham, MassachusettsH. M. D.Delray Beach, FloridaM. S. K.

## Contents

|      | ILLUSTRATIONS                      | xxi |

|------|------------------------------------|-----|

|      | ABOUT THE AUTHORS                  | ххv |

|      | CHAPTER 1<br>HISTORICAL BACKGROUND | 1   |

| 1.1  | Introduction                       | 3   |

| 1.2  | DOS History                        | 3   |

| 1.3  | DOS Limitations                    | 6   |

| 1.4  | OS/2 History                       | 10  |

| 1.5  | The Evolving Market                | 14  |

| 1.6  | OS/2 1.2                           | 16  |

| 1.7  | OS/2 1.3                           | 17  |

| 1.8  | Windows 3.0                        | 17  |

| 1.9  | OS/2 2.0                           | 19  |

| 1.10 | The 1990s                          | 21  |

|      | Summary                            | 21  |

|      |                                    | 05  |

|      | MICROPROCESSOR ARCHITECTURES       | 25  |

| 2.1  | Introduction                       | 28  |

| 2.2  | Intel 8088/8086                    | 28  |

| 2.3  | Intel 80286                        | 32  |

| 2.4  | Intel 80386                        | 42  |

| 2.5  | Intel 80486                        | 52  |

| 2.6  | RISC Processors                    | 53  |

|      | Summary                            | 53  |

|            | CHAPTER 3<br>HARDWARE ARCHITECTURES   | 59       |

|------------|---------------------------------------|----------|

| 3.1        | Introduction                          | 61       |

| 3.2        | IBM PC                                | 61       |

| 3.3        | IBM PC/AT                             | 62       |

| 3.4        | AT 80386                              | 63       |

| 3.5        | Micro Channel Architecture            | 63       |

| 3.6        | IBM PS/2                              | 64       |

| 3.7        | Extended Industry System Architecture | 66       |

| 3.8        | Cache Systems                         | 66       |

| 3.9        | Multiprocessor Systems                | 68       |

| 3.10       | Multiprocessor System Interconnection | 69       |

|            | Summary                               | 71       |

|            | CHAPTER 4                             |          |

|            | OPERATING SYSTEM ARCHITECTURES        | 75       |

| 4.1        | Introduction                          | 77       |

| 4.2        | DOS System                            | 77       |

| 4.3        | DOS API                               | 78       |

| 4.4        | DOS Programs                          | 80       |

| 4.5        | OS/2 1.X System                       | 86       |

| 4.6        | OS/2 1.X API                          | 93       |

| 4.7        | OS/2 1.X Programs                     | 94<br>94 |

| 4.8<br>4.9 | OS/2 2.X System<br>OS/2 2.X API       | 94<br>98 |

| 4.9<br>410 | OS/2 2.X APT<br>OS/2 2.X Programs     | 98<br>98 |

| 410        | Summary                               | 98<br>99 |

|            | Summary                               |          |

|            | CHAPTER 5                             |          |

|            | MULTITASKING                          | 105      |

| 5.1        | Introduction                          | 107      |

| 5.2        | Processes                             | 108      |

| 5.3        | Threads                               | 112      |

| 5.4        | Scheduling                            | 115      |

| 5.5        | Kernel Architecture                   | 118      |

| 5.6        | Multitasking API                      | 135      |

|            | Summary                               | 135      |

|            | CHAPTER 6                             |          |

|            | MEMORY MANAGEMENT                     | 141      |

| 6.1 | Introduction | 143 |

|-----|--------------|-----|

|     |              |     |

| 6.2          | OS/2 1.X Memory Management                              | 144        |

|--------------|---------------------------------------------------------|------------|

| 6.3          | OS/2 2.X Memory Management                              | 163        |

| 6.4          | Segmented vs. Flat Memory Model                         | 189        |

| 6.5          | Memory Management API                                   | 189        |

| 6.6          | Dynamic Linking API                                     | 189        |

|              | Summary                                                 | 189        |

|              | CHAPTER 7<br>INTERPROCESS COMMUNICATION                 | 197        |

| 7.1          | Introduction                                            | 199        |

| 7.2          | Shared Memory                                           | 199        |

| 7.3          | Semaphores                                              | 200        |

| 7.4          | Signals                                                 | 216        |

| 7.5          | Queues                                                  | 218        |

| 7.6          | Pipes                                                   | 219        |

| 7.7          | Exceptions                                              | 222        |

| 7.8          | System Integrity Issues                                 | 227        |

|              | Summary                                                 | 228        |

|              | CHAPTER 8                                               | 004        |

|              | I/O MANAGEMENT                                          | 231        |

| 8.1          | Introduction                                            | 233        |

| 8.2          | Devices                                                 | 233        |

| 8.3          | Installable File System Architecture                    | 233        |

| 8.4          | File System Name Space                                  | 234        |

| 8.5          | File System Objects                                     | 235        |

| 8.6          | File System API                                         | 235        |

| 8.7          | OS/2 1.X File System Drivers                            | 238        |

| 8.8          | OS/2 2.X File System Drivers                            | 240        |

| 8.9          | Device Drivers                                          | 241        |

| 8.10<br>8.11 | Hardware Device Structure<br>Hardware Device Attributes | 241<br>242 |

| 8.11<br>8.12 | Hardware Device Independence                            | 242<br>244 |

| 8.12         | OS/2 1.X Device Drivers                                 | 244<br>245 |

| 8.13         | Device Driver Structure                                 | 245        |

| 8.15         | Device Driver Header                                    | 243        |

| 8.16         | Device Attribute Flags                                  | 248        |

| 8.17         | Request Packets                                         | 248        |

| 8.18         | Strategy Commands                                       | 249        |

| 8.19         | DevHelp Services                                        | 24)        |

| 8.20         | OS/2 2.X Device Drivers                                 | 254        |

|              | Summary                                                 | 256        |

|              |                                                         |            |

|       | CHAPTER 9                          |     |

|-------|------------------------------------|-----|

|       | PRESENTATION MANAGEMENT            | 261 |

| 9.1   | Introduction                       | 263 |

| 9.2   | Session Management                 | 263 |

| 9.3   | Presentation Manager               | 267 |

| 9.4   | Windows Architecture               | 268 |

| 9.5   | Message Architecture               | 271 |

| 9.6   | Graphics Architecture              | 274 |

| 9.7   | Resources                          | 274 |

| 9.8   | Application Data Exchange          | 276 |

| 9.9   | Multitasking Issues                | 276 |

|       | Summary                            | 278 |

|       | CHAPTER 10                         |     |

|       | COMPATIBILITY                      | 281 |

| 10.1  | Introduction                       | 283 |

| 10.2  | DOS Compatibility                  | 283 |

| 10.3  | 80286 DOS Compatibility            | 283 |

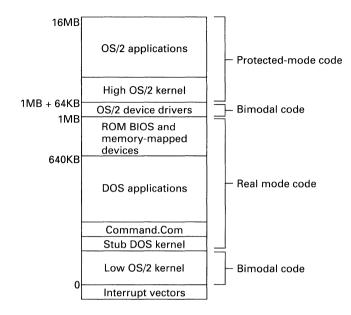

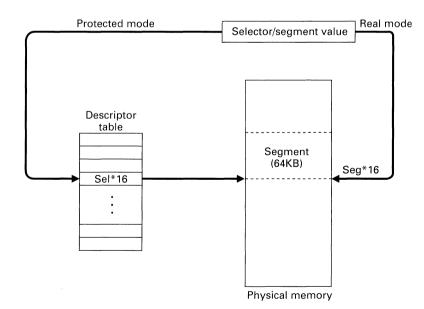

| 10.4  | 80386 DOS Compatibility            | 290 |

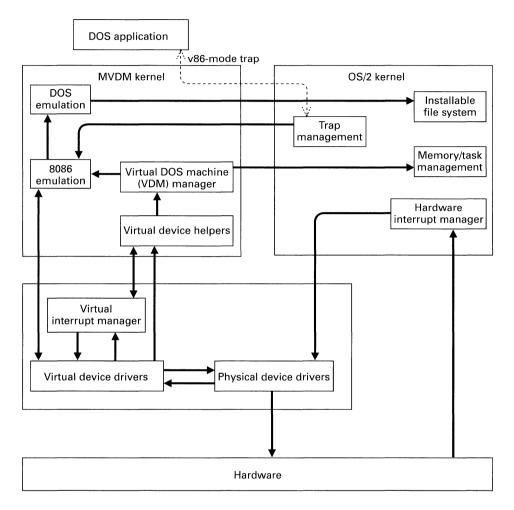

| 10.5  | OS/2 2.X Windows 3.X Compatibility | 300 |

| 10.6  | OS/2 2.X 16-Bit Compatibility      | 301 |

| 10.7  | Hybrid System Strategies           | 301 |

| 10.8  | Memory Model Coexistence           | 301 |

| 10.9  | LDT Tiling                         | 303 |

| 10.10 | Thunks                             | 307 |

|       | Summary                            | 310 |

|       | CHAPTER 11                         |     |

|       | COMMUNICATIONS                     | 315 |

| 11.1  | Introduction                       | 317 |

| 11.2  | Networks                           | 317 |

| 11.3  | Open Systems Interconnection       | 318 |

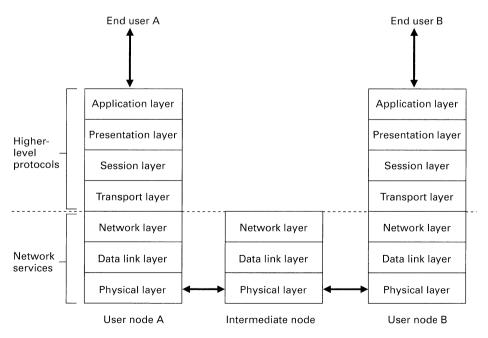

| 11.4  | OSI Reference Model                | 319 |

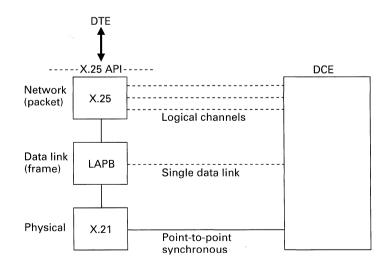

| 11.5  | X.25                               | 321 |

| 11.6  | LANs322                            |     |

| 11.7  | System Network Architecture        | 324 |

| 11.8  | TCP/IP                             | 326 |

| 11.9  | Network Coexistence                | 327 |

|       | OS/2 Extended Edition              | 329 |

| 11.11 | Multiuser OS/2                     | 331 |

|       | Summary                            | 332 |

\*

#### X

|      | CHAPTER 12<br>THE FUTURE         | 337 |

|------|----------------------------------|-----|

|      | THE FOTORE                       | 337 |

| 12.1 | Introduction                     | 339 |

| 12.2 | Open Systems                     | 339 |

| 12.3 | Open UNIX                        | 340 |

| 12.4 | Systems Application Architecture | 342 |

| 12.5 | System Portability               | 345 |

| 12.6 | Multiprocessor Systems           | 345 |

| 12.7 | Security                         | 346 |

| 12.8 | Multimedia                       | 349 |

|      | Summary                          | 349 |

|      | BIBLIOGRAPHY                     | 353 |

|      | INDEX                            | 361 |

## Illustrations

| Fig. 1.1  | DOS system structure.                                 | 4  |

|-----------|-------------------------------------------------------|----|

| Fig. 1.2  | DOS memory map.                                       | 7  |

| Fig. 1.3  | DOS system call.                                      | 9  |

| Fig. 1.4  | DOS system extensions.                                | 10 |

| Fig. 1.5  | Software development process.                         | 12 |

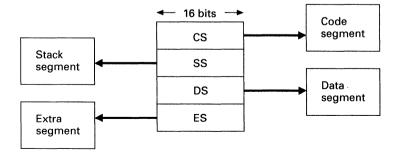

| Fig. 2.1  | 8088 segment registers.                               | 28 |

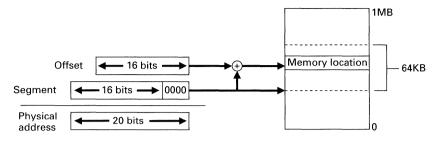

| Fig. 2.2  | 8088 address calculation.                             | 29 |

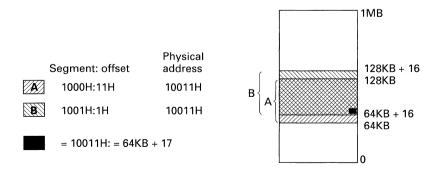

| Fig. 2.3  | 8088 address aliasing.                                | 29 |

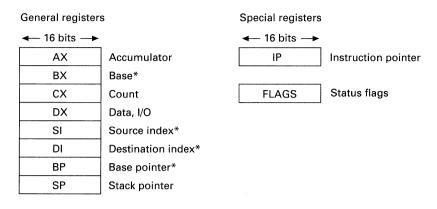

| Fig. 2.4  | 8088 register set.                                    | 30 |

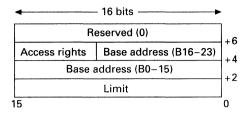

| Fig. 2.5  | 80286 segment descriptor.                             | 33 |

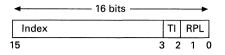

| Fig. 2.6  | 80286 selector format.                                | 34 |

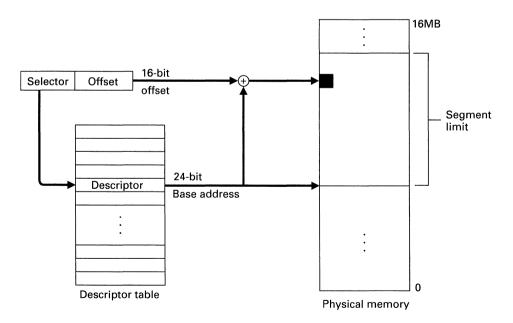

| Fig. 2.7  | 80286 protected-mode address translation.             | 34 |

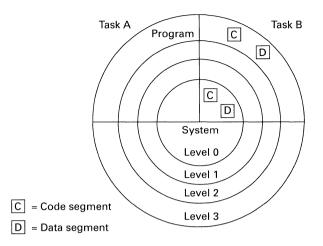

| Fig. 2.8  | 80286 access rights information.                      | 36 |

| Fig. 2.9  | 80286 privilege levels and the ring protection model. | 37 |

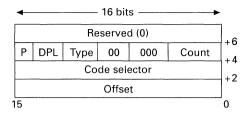

| Fig. 2.10 | 80286 call gate descriptor.                           | 39 |

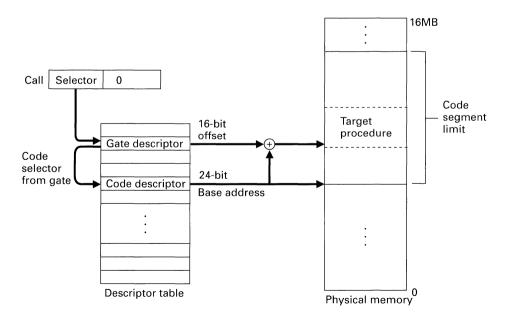

| Fig. 2.11 | 80286 call gate control transfer.                     | 39 |

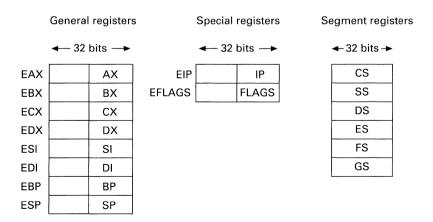

| Fig. 2.12 | 80386 register set.                                   | 43 |

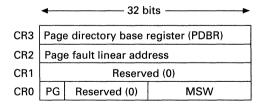

| Fig. 2.13 | 80386 control registers.                              | 44 |

| Fig. 2.14 | 80386 segment descriptor.                             | 45 |

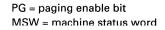

| Fig. 2.15 | 80386 linear address.                                 | 47 |

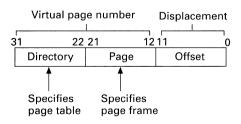

| Fig. 2.16 | 80386 paged linear address translation.               | 48 |

| Fig. 2.17 | 80386 page table entry (PTE).                         | 48 |

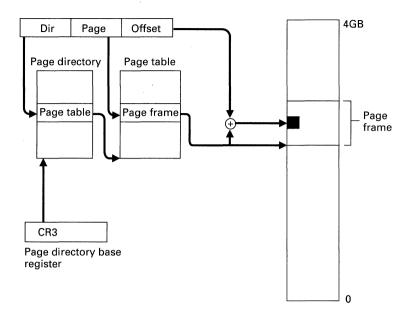

| Fig. 2.18 | 80386 address translation.                            | 50 |

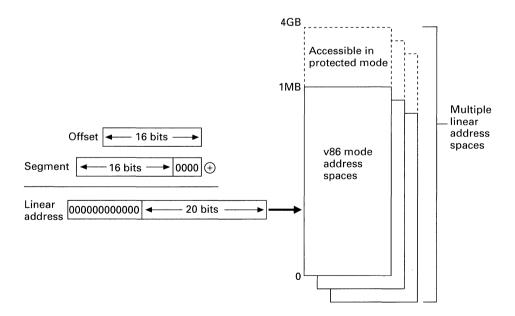

| Fig. 2.19 | Multiple v86 mode address spaces.                     | 51 |

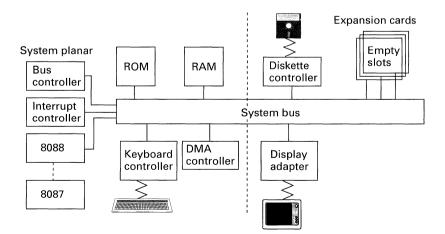

| Fig. 3.1  | IBM PC system architecture.                           | 61 |

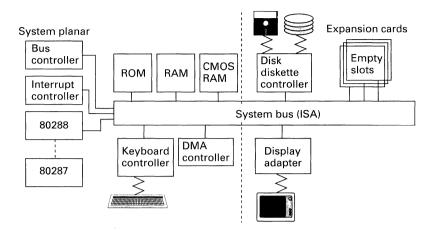

| Fig. 3.2  | IBM PC/AT system architecture.                        | 63 |

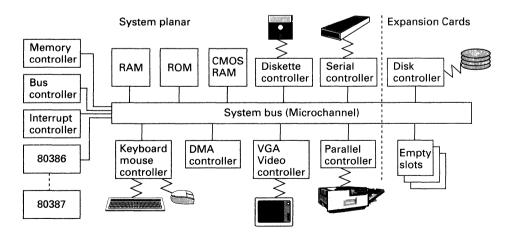

| Fig. 3.3  | IBM PS/2 system architecture.                         | 65 |

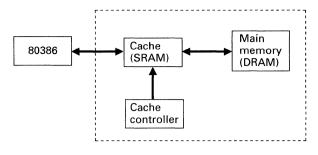

| Fig. 3.4  | Cache memory subsystem.                               | 67 |

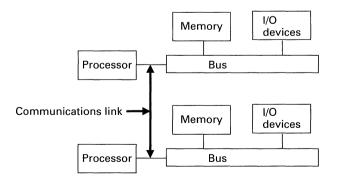

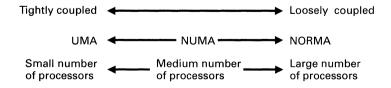

| Fig. 3.5  | Loosely-coupled multiprocessor.                            | 69  |

|-----------|------------------------------------------------------------|-----|

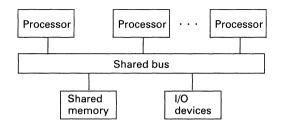

| Fig. 3.6  | Tightly-coupled multiprocessor.                            | 70  |

| Fig. 3.7  | Relationship between processor coupling and memory access. | 70  |

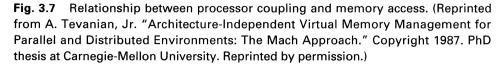

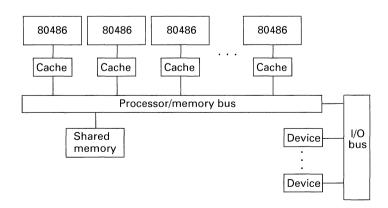

| Fig. 3.8  | Uniform-memory-access multiprocessor (UMA).                | 71  |

| Fig. 3.9  | Nonuniform-memory-access multiprocessor (NUMA).            | 72  |

| Fig. 4.1  | DOS system structure.                                      | 77  |

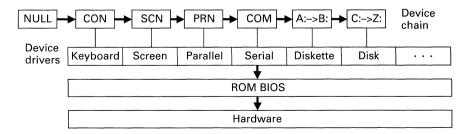

| Fig. 4.2  | DOS device chain.                                          | 78  |

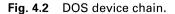

| Fig. 4.3  | DOS system call.                                           | 79  |

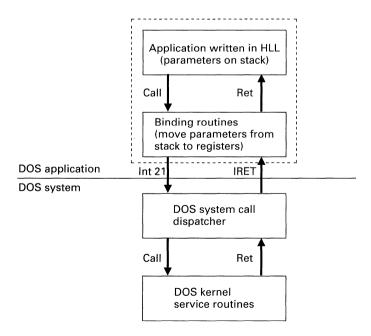

| Fig. 4.4  | Program development process.                               | 81  |

| Fig. 4.5  | DOS (EXE) executable file.                                 | 82  |

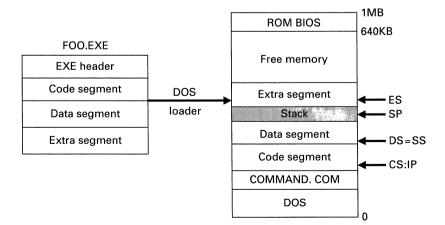

| Fig. 4.6  | Example of segment-relative fixup.                         | 83  |

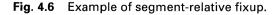

| Fig. 4.7  | Small-model program.                                       | 84  |

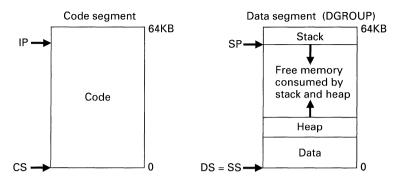

| Fig. 4.8  | DOS example program (static linking).                      | 85  |

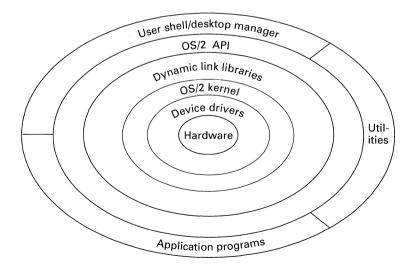

| Fig. 4.9  | OS/2 system structure.                                     | 86  |

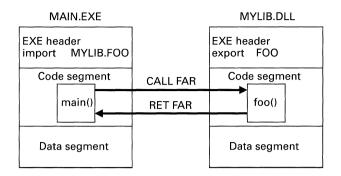

| Fig. 4.10 | Dynamic linking.                                           | 90  |

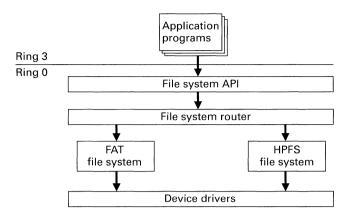

| Fig. 4.11 | OS/2 file system architecture.                             | 91  |

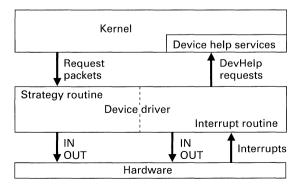

| Fig. 4.12 | Device driver interfaces.                                  | 91  |

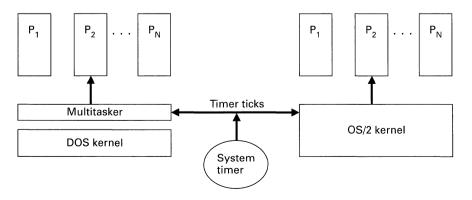

| Fig. 5.1  | DOS versus OS/2 multitasking.                              | 107 |

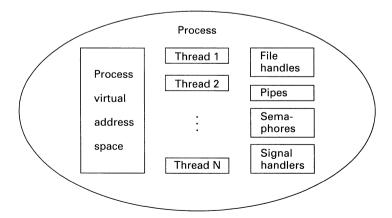

| Fig. 5.2  | Process layout.                                            | 108 |

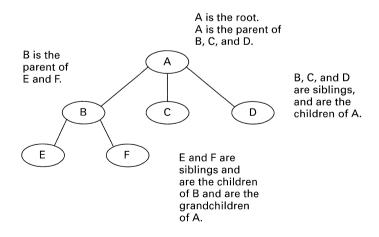

| Fig. 5.3  | Process hierarchy.                                         | 110 |

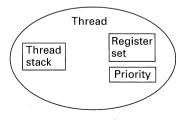

| Fig. 5.4  | Thread layout.                                             | 112 |

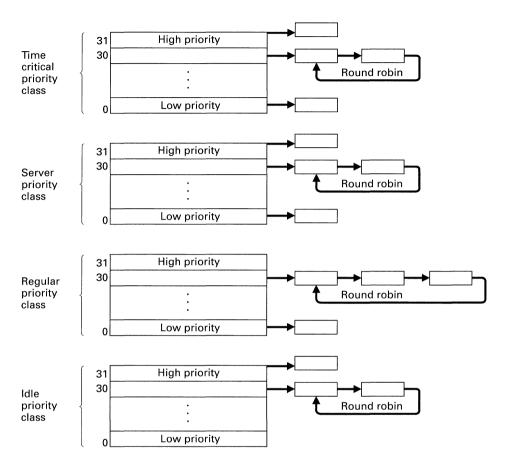

| Fig. 5.5  | Multilevel priority structure.                             | 116 |

| Fig. 5.6  | Multitasking kernel components.                            | 119 |

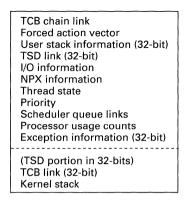

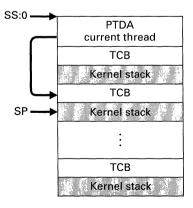

| Fig. 5.7  | Per-task data area (PTDA).                                 | 121 |

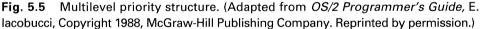

| Fig. 5.8  | Thread control block (TCB).                                | 122 |

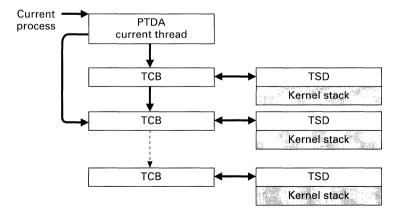

| Fig. 5.9  | Layout of 16-bit PTDA and TCB.                             | 122 |

| Fig. 5.10 | Layout of 32-bit PTDA, TCB, and TSD.                       | 123 |

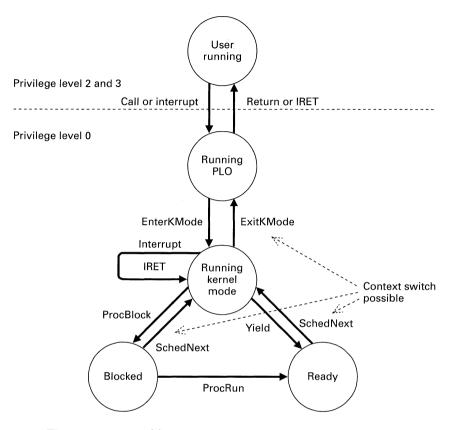

| Fig. 5.11 | Thread state transitions.                                  | 128 |

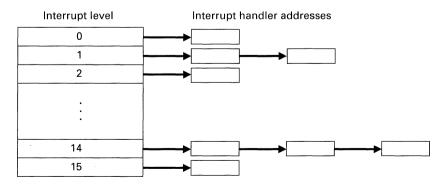

| Fig. 5.12 | Interrupt table.                                           | 129 |

| Fig. 5.13 | ProcBlock calling sequence.                                | 134 |

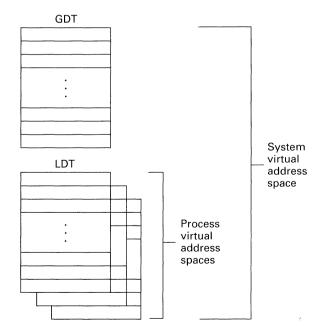

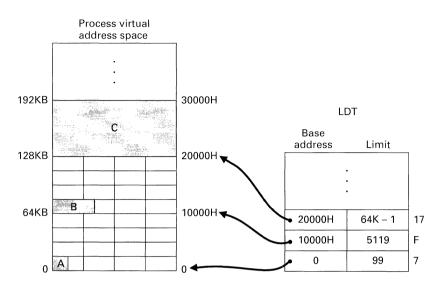

| Fig. 6.1  | 16-bit virtual address spaces.                             | 145 |

| Fig. 6.2  | 16-bit memory sharing.                                     | 148 |

| Fig. 6.3  | 16-bit handle table entry (HTE).                           | 152 |

| Fig. 6.4  | 16-bit virtual memory management data structures.          | 155 |

| Fig. 6.5  | 16-bit executable file format.                             | 156 |

| Fig. 6.6  | 16-bit physical memory map.                                | 158 |

| Fig. 6.7  | 16-bit arena header.                                       | 159 |

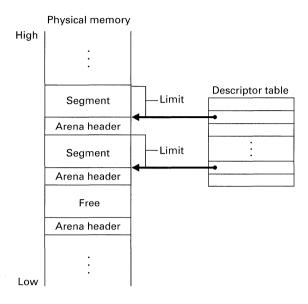

| Fig. 6.8  | 16-bit arena physical layout.                              | 160 |

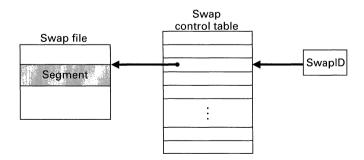

| Fig. 6.9  | 16-bit swapper data structures.                            | 162 |

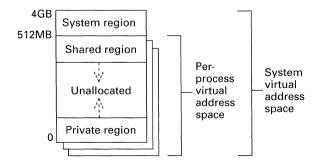

| Fig. 6.10 | 32-bit virtual address spaces.                             | 164 |

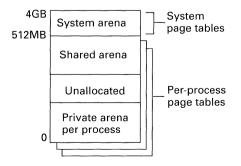

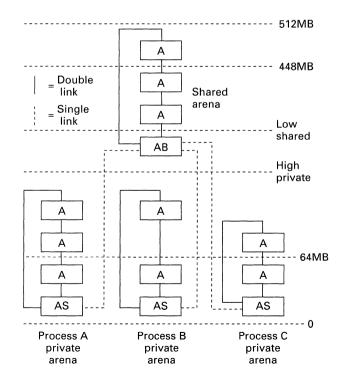

| Fig. 6.11 | 32-bit arena structures.                                   | 171 |

| Fig. 6.12 | 32-bit arena record.                                       | 172 |

| Fig. 6.13 | 32-bit arena layout for three processes.                   | 173 |

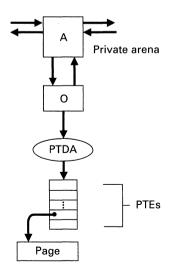

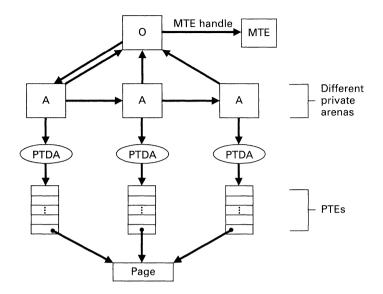

| Fig. 6.14 | 32-bit object record.                                      | 174 |

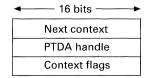

| Fig. 6.15 | 32-bit context record.                                  | 175 |

|-----------|---------------------------------------------------------|-----|

| Fig. 6.16 | Private-address, private-storage object.                | 176 |

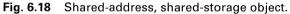

| Fig. 6.17 | Private-address, shared-storage object.                 | 177 |

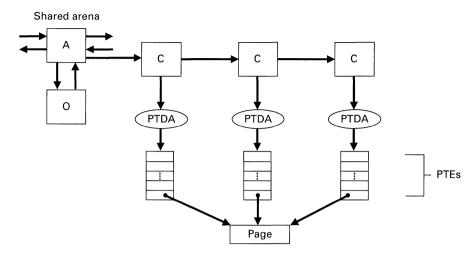

| Fig. 6.18 | Shared-address, shared-storage object.                  | 178 |

| Fig. 6.19 | Shared-address, private-storage object.                 | 178 |

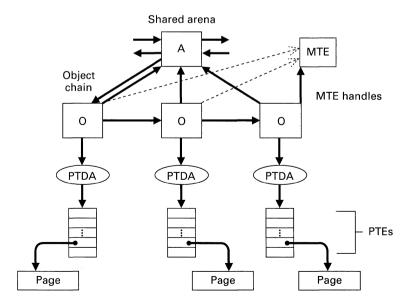

| Fig. 6.20 | Page table entry (PTE).                                 | 182 |

| Fig. 6.21 | Page frame (PF) array entry.                            | 182 |

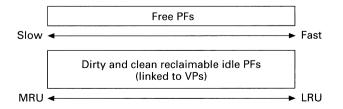

| Fig. 6.22 | Free and idle page frame lists.                         | 183 |

| Fig. 6.23 | Virtual page (VP) structure.                            | 184 |

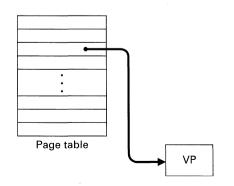

| Fig. 6.24 | Page structures for initially allocated committed page. | 184 |

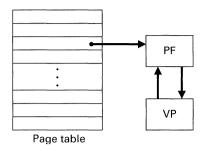

| Fig. 6.25 | Page structures after page fault.                       | 187 |

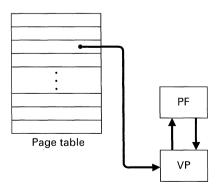

| Fig. 6.26 | Page structures for idle page.                          | 188 |

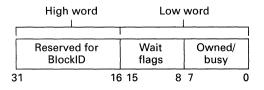

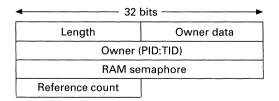

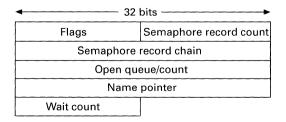

| Fig. 7.1  | RAM semaphore structure.                                | 204 |

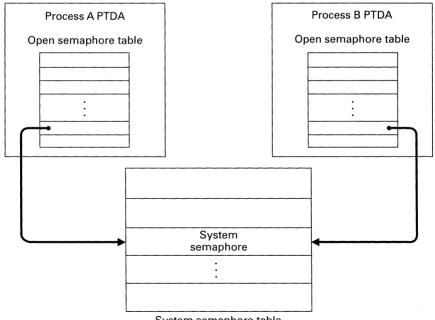

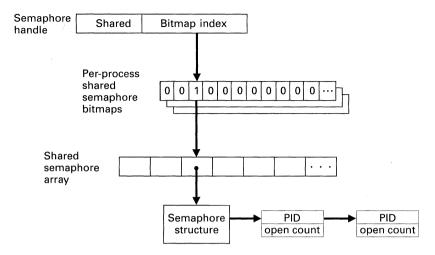

| Fig. 7.2  | System semaphore tables.                                | 206 |

| Fig. 7.3  | System semaphore structure.                             | 207 |

| Fig. 7.4  | Fast-safe RAM semaphore structure.                      | 208 |

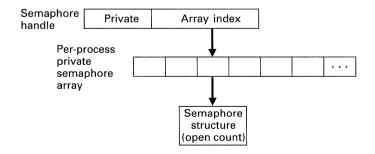

| Fig. 7.5  | Private semaphore structures.                           | 212 |

| Fig. 7.6  | Shared semaphore structures.                            | 213 |

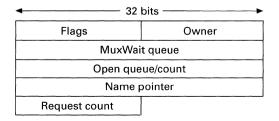

| Fig. 7.7  | Mutual-exclusion (mutex) semaphore structure.           | 213 |

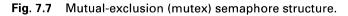

| Fig. 7.8  | Event semaphore structure.                              | 215 |

| Fig. 7.9  | Muxwait semaphore structure.                            | 215 |

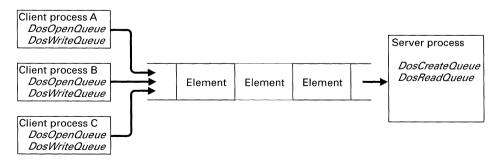

| Fig. 7.10 | IPC queue.                                              | 218 |

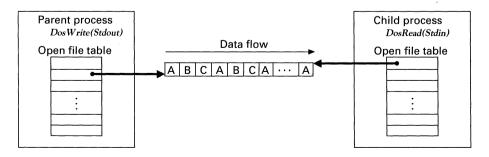

| Fig. 7.11 | Anonymous pipe.                                         | 220 |

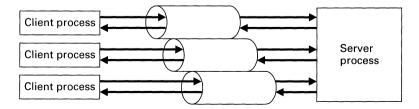

| Fig. 7.12 | Named pipe (three-channel full duplex).                 | 221 |

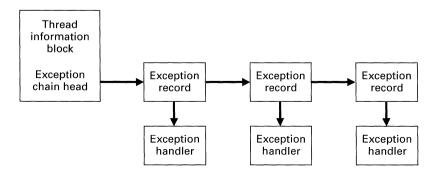

| Fig. 7.13 | Per-thread exception chain.                             | 226 |

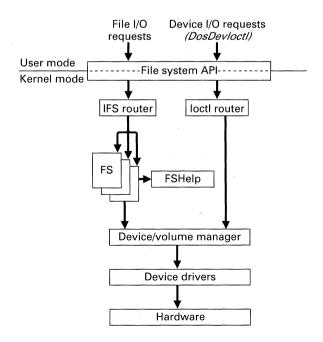

| Fig. 8.1  | File and device I/O subsystem.                          | 234 |

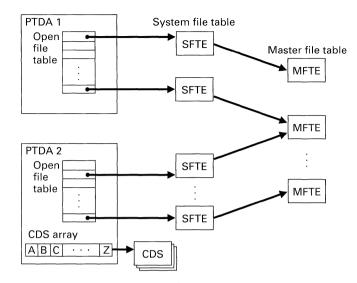

| Fig. 8.2  | File and path management file system data structures.   | 237 |

| Fig. 8.3  | Device driver file structure.                           | 246 |

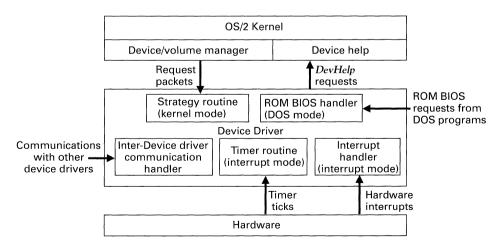

| Fig. 8.4  | OS/2 1.X device driver interfaces.                      | 247 |

| Fig. 8.5  | Device driver header.                                   | 248 |

| Fig. 8.6  | Device driver attribute flags.                          | 249 |

| Fig. 8.7  | Device driver request packet format.                    | 249 |

| Fig. 8.8  | OS/2 2.0 extended device driver interfaces.             | 255 |

| Fig. 8.9  | Request list.                                           | 256 |

| Fig. 9.1  | Session structure.                                      | 263 |

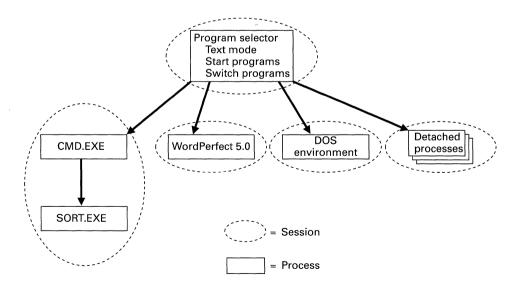

| Fig. 9.2  | OS/2 1.0 session and process hierarchy.                 | 264 |

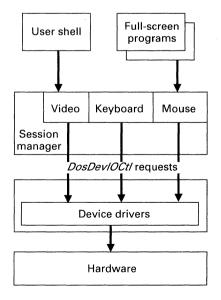

| Fig. 9.3  | Full-screen user-I/O subsystem architecture.            | 265 |

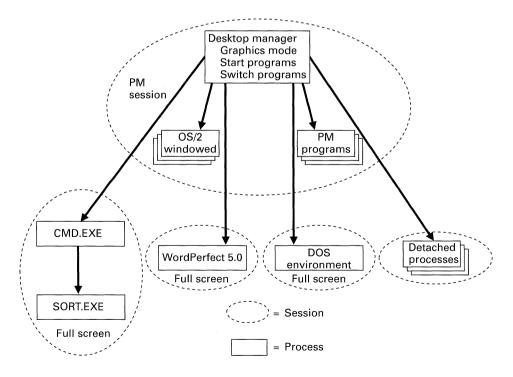

| Fig. 9.4  | 16-bit OS/2 session and process hierarchy with the PM.  | 266 |

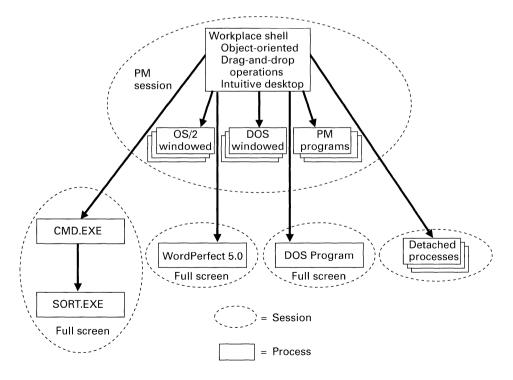

| Fig. 9.5  | OS/2 2.0 session and process hierarchy.                 | 267 |

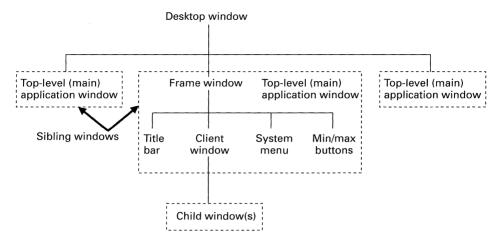

| Fig. 9.6  | Window hierarchy.                                       | 270 |

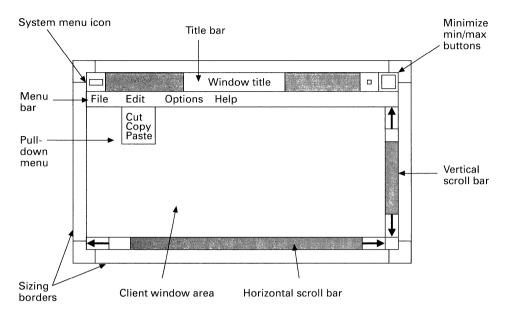

| Fig. 9.7  | Standard window with menu bar and scroll bars.          | 271 |

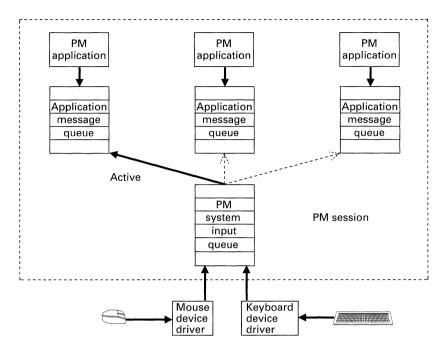

| Fig. 9.8  | PM message architecture.                                | 272 |

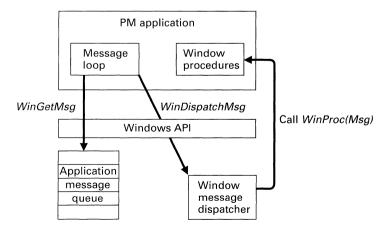

| Fig. 9.9  | PM application message loop processing.                 | 273 |

| Fig. 9.10 | PM device-independent graphics architecture.            | 274 |

|           |                                                         |     |

| Fig. 10.1  | 16-bit physical memory layout with DOS compatibility.   | 287 |

|------------|---------------------------------------------------------|-----|

| Fig. 10.2  | 16-bit memory tiling.                                   | 289 |

| Fig. 10.3  | MVDM architecture.                                      | 293 |

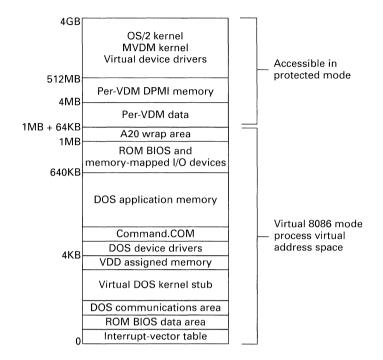

| Fig. 10.4  | Virtual DOS machine memory layout.                      | 295 |

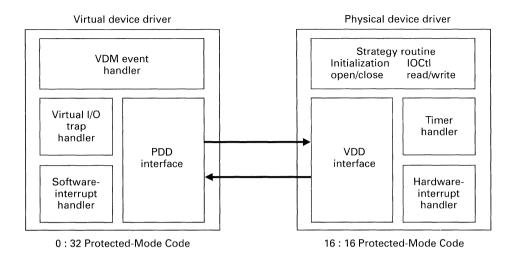

| Fig. 10.5  | 32-bit model for physical and virtual device drivers.   | 299 |

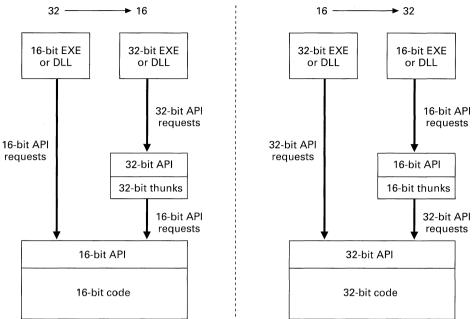

| Fig. 10.6  | Coexistence strategies for 16-bit and 32-bit API.       | 302 |

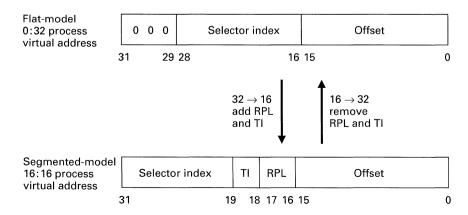

| Fig. 10.7  | 0:32 and 16:16 address conversion.                      | 304 |

| Fig. 10.8  | LDT tiling.                                             | 305 |

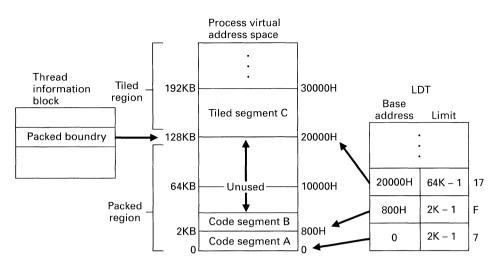

| Fig. 10.9  | LDT tiling with 16-bit private code packing.            | 307 |

| Fig. 11.1  | OSI reference model.                                    | 319 |

| Fig. 11.2  | X.25 architecture.                                      | 322 |

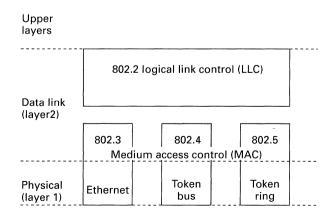

| Fig. 11.3  | IEEE 802 LAN standards.                                 | 323 |

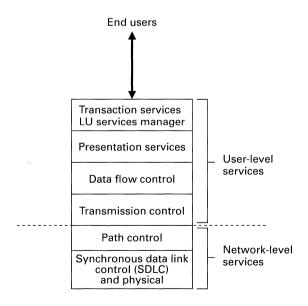

| Fig. 11.4  | IBM SNA architecture.                                   | 325 |

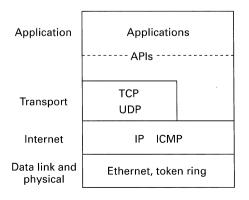

| Fig. 11.5  | TCP/IP architecture.                                    | 326 |

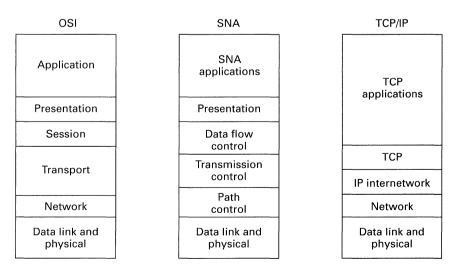

| Fig. 11.6  | Comparison of OSI, SNA, and TCP/IP.                     | 329 |

| Fig. 11.7  | OS/2 protocol stacks.                                   | 331 |

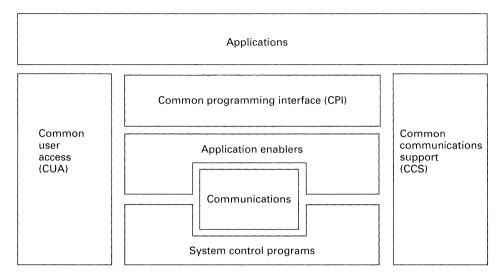

| Fig. 12.1  | Components of the IBM Systems Application Architecture. | 343 |

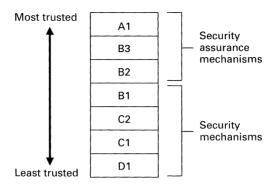

| Fig. 12.2  | Orange Book security levels.                            | 347 |

| Table 1.1  | DOS evolution.                                          | 6   |

| Table 1.2  | OS/2 evolution.                                         | 20  |

| Table 3.1  | PS/2 product line.                                      | 65  |

| Table 4.1  | OS/2 API content.                                       | 94  |

| Table 5.1  | Multitasking API calls.                                 | 136 |

| Table 6.1  | Memory object types.                                    | 147 |

| Table 6.2  | Memory management API.                                  | 190 |

| Table 6.3  | Dynamic linking API.                                    | 190 |

| Table 7.1  | OS/2 1.X semaphores API.                                | 203 |

| Table 7.2  | OS/2 1.X semaphore model usage.                         | 209 |

| Table 7.3  | OS/2 2.X semaphores API.                                | 211 |

| Table 7.4  | OS/2 1.X signals API.                                   | 217 |

| Table 7.5  | OS/2 Queueing API.                                      | 219 |

| Table 7.6  | OS/2 pipes API.                                         | 222 |

| Table 7.7  | 16-bit exceptions.                                      | 223 |

| Table 7.8  | 32-bit exceptions.                                      | 225 |

| Table 7.9  | OS/2 exceptions API.                                    | 227 |

| Table 8.1  | File System API.                                        | 239 |

| Table 8.2  | Device driver strategy commands.                        | 251 |

| Table 8.3  | DevHelp functions.                                      | 253 |

| Table 8.4  | 32-bit DevHelp functions.                               | 257 |

| Table 10.1 | Segmented- and flat-model programming environments.     | 302 |

#### **ABOUT THE AUTHORS**

**Dr. Harvey M. Deitel** has 30 years experience in the computer field. He participated in the research and development of several large-scale operating systems and in the design and implementation of numerous commercial systems. His current research is in the areas of open systems and open systems interconnection (OSI)—the emerging international standards in computer networking. He received the Bachelor of Science and Master of Science Degrees from the Massachusetts Institute of Technology where he did extensive development work on the Multics operating system. He received the Doctor of Philosophy Degree from Boston University where his dissertation research examined the problems of developing very large-scale structured software systems.

Dr. Deitel has been interested in operating systems since 1963. He worked on the pioneering teams that developed IBM's OS, IBM's TSS, and M.I.T.'s Multics; these systems led to today's MVS, VM, and UNIX operating systems. He has consulted for Epson, Advanced Computer Techniques Corporation, Computer Usage Corporation, Harbridge House, American Express, IBM Systems Development Division, IBM Advanced Systems Development Division, IBM Thomas J. Watson Research Center, M.I.T.'s Project MAC, Microsoft, Apple, Digital Equipment Corporation, Sun Microsystems, and the Corporation for Open Systems International (COS).

Dr. Deitel is the former chairman of the Computer Science Department at Boston College where he developed and implemented the graduate program in computer science. He currently serves as Full Professor of Computer Science and Full Professor of Computer Information Systems at Nova University in Fort Lauderdale, Florida, where he has been involved in the implementation of Nova's Master of Science Program in Computer Science at IBM's Entry Systems Division in Boca Raton. He has received numerous teaching commendations, and has been rated nationally among the top computing educators in the country.

Dr. Deitel is a member of several professional honoraries including Tau Beta Pi (engineering), Eta Kappa Nu (electrical engineering), Sigma Xi (scientific research), and Beta Gamma Sigma (management). He holds the CDP certification of the Institute for the Certification of Computer Professionals, and is a member of various professional societies including the Association for Computing Machinery, and the Computer Society of the Institute of Electrical and Electronics Engineers.

Dr. Deitel's publications include Absentee Computations in a Multiple-Access Computer System, MAC-TR-52, Advanced Research Projects Agency, Department of Defense, 1968; Introduction to Computer Programming, Prentice-Hall, 1977; Structured Software Development, Ph.D. dissertation published by University Microfilms, 1980; Operating Systems (with H. Lorin of the IBM Systems Research Institute), Addison-Wesley, 1980, "Functions of Operating Systems," (with H. Lorin) Software World, Vol. 12, No. 2, 1981, "Computers and Communications: Improving the Employability of Persons with Handicaps," Journal for Vocational Needs Education, 1984; An Introduction to Operating Systems, Addison-Wesley, 1990 (Second Edition); VAX-11 BASIC, Prentice-Hall, 1985; Computers and Data Processing (with B. Deitel), Academic Press, 1985; An Introduction to Information Processing (with B. Deitel), Academic Press, 1986, *Microsoft Macintosh BASIC* (with P. Deitel), Prentice-Hall, 1988; *Microsoft IBM QuickBASIC* (with P. Deitel), Prentice-Hall, 1989.

Dr. Deitel is currently writing four other books including: C Programming (with P. Deitel) (Prentice Hall), SPARC System Software and the Sun Operating System: UNIX System V Release 4 (Addison Wesley), SunNET: Sun's Approach to Distributed Computing (Addison Wesley), and the third edition of his book, Operating Systems (Addison Wesley)—now considered a classic in the field of computer science—whose previous editions have been used in 1000 universities in more than 100 countries throughout the world.

Dr. Deitel's current research is in the area of open systems interconnection (OSI) the emerging worldwide standards for computer networking. He is the series editor of the *Open Systems Series* sponsored by the Corporation for Open Systems International (COS) and published by Addison-Wesley. This series includes advanced texts on key aspects of OSI and the Integrated Services Digital Network (ISDN). He is currently writing the lead text, *Open Systems Interconnection*, for this series. He has given operating system seminars at the International Congress Center in West Berlin. His books have been translated into Japanese, Chinese, Spanish, and Russian.

**Dr. Michael S. Kogan** has 10 years of experience in the computer field. In 1984, he received the Bachelor of Science degree in Computer Science and Mathematics from Emory University in Atlanta, Georgia. At Emory he work in Berkeley UNIX and CP/M environments on VAX and 8080-based systems. In 1986, he earned the Master of Science degree in Computer Science from Nova University in Ft. Lauderdale, Florida. In 1991, he received the Doctor of Science degree in Computer Science at Nova University. His dissertation examined the motivation and design of 32-bit OS/2.

In 1984, Dr. Kogan joined IBM in Boca Raton, where he developed and tested several products in the IBM Engineering/Scientific software series. This experience included the testing of a DOS-based FORTRAN compiler, and the development and testing of DOS device drivers for hardware cards used to interface with engineering devices. He led the effort to redesign the device driver architecture of XENIX 2.0 for the 80286 processor, and developed and tested several XENIX device drivers.

In 1985, he was drafted into the OS/2 project. He was a lead developer for two and one half years during the design, development, and testing of the 16-bit versions of OS/2. He had responsibilities in many areas of the 16-bit system including device drivers, memory management, debugging, queues, DOS compatibility, and system initialization. This was followed by another two and one half years as the principal architect of the 32-bit version of OS/2.

Dr. Kogan has published articles on OS/2 in the *IBM Systems Journal* (Ko88) and in *IBM Personal Systems Developer* (Ko90)(Ko90a)(Ko90b). Several of these articles have been reprinted in other publications worldwide. Dr. Kogan is also credited with numerous software inventions, and has several patents pending for technologies he developed for the 32-bit OS/2 system. He frequently represents IBM internationally in a consulting capacity to IBM customers who are moving to the OS/2 platform.

## 1 Historical Background

Nothing endures but change. Heraclitus

It is always good when a man has two irons in the fire. Francis Beaumont and John Fletcher

That's a better hardware base [the PS/2] than what UNIX started with, and there's a good possibility that OS/2 will be better than UNIX.

Dan Bricklin

#### Outline

- **1.1** Introduction

- **1.2** DOS History

- 1.3 DOS Limitations

- **1.3.1** Memory Management

- 1.3.2 I/O Management

- 1.3.3 Multitasking

- **1.3.4** System Extendibility

- **1.3.5** Graphical User Interface

- 1.4 OS/2 History

- 1.4.1 IBM-Microsoft Joint Development

- 1.4.2 Multisite Development

- 1.4.3 OS/2 1.0

- **1.4.4** OS/2 1.1

- **1.5** The Evolving Market

- 1.5.1 Microsoft Windows

- **1.5.2** DOS Expanded Memory

- 1.5.3 DOS Extended Memory

- **1.5.4** DOS Extenders

- 1.5.5 Intel 80386

- **1.5.6** DOS Multitaskers

- **1.6** OS/2 1.2

- **1.7** OS/2 1.3

- **1.8** Windows 3.0

- **1.9** OS/2 2.0

- 1.10 The 1990s Summary

#### **1.1 INTRODUCTION**

This chapter reviews the history of personal computers and operating systems. It traces the evolution of personal computer hardware from the original IBM Personal Computer to the latest IBM PS/2, and examines how this process has affected the content and design of DOS and OS/2.

Before 1980 most computers were mainframes and minicomputers, large computing resources that were mainly job- and transaction-processing systems. Operating system technology had evolved from its early simplistic control program stages to sophisticated multiprogrammed virtual memory systems such as VM, MVS, and later versions of UNIX. In the era of large, centralized computing resources, computer time was expensive, learning was time consuming, assistance was difficult to obtain, and computing resources were scarce. Users rarely had opportunities to interact privately with a local computing resource.

The advent of the microprocessor and of inexpensive, off-the-shelf computer components enabled the creation of the first microcomputer systems. The Altair, a primitive computer kit based on the Intel 8080, was one of the most popular early systems. The Altair was surpassed by the Apple I and II computers created by Steve Jobs and Steve Wozniak. The Apples used the MOS Technology 6502 chip and included a keyboard and display. Also gaining acceptance were microcomputer systems configured with the Intel 8080 and Zilog Z80 processors. Besides the Apple, which had its own proprietary operating system, the Intel and Zilog systems principally ran the CP/M operating system. CP/M was primarily designed for 8-bit single-user microcomputers that had floppy-disk drives.

At this point, during the late 1970s, IBM decided to spin off an independent business unit (IBU) to investigate the potential of an IBM microcomputer system. In the late 1970s, IBM used IBUs to respond rapidly to new opportunities, and granted them considerable freedom within IBM's business processes. An IBU is similar to a venture capital operation that attempts to exploit evolving technologies. The IBU ultimately became the current Entry Systems Division (ESD) of the IBM Corporation, which is responsible for personal computer hardware and operating system development.

#### 1.2 DOS HISTORY

The DOS era of microcomputer operating system technology began when the first IBM Personal Computer (PC) was designed. The first IBM PC went beyond the current 8-bit technology available and used the then-new 16-bit Intel 8088 processor. This choice was made because the current 8-bit systems were being eclipsed by the newer 16-bit systems, and the 16-bit system architecture provided a base for more robust software. The 8088 and 8086 processors are functionally identical, but the 8088 was used in the IBM PC since it was cheaper to configure in hardware. The 8088 processor could address up to 1MB of memory; few designers could envision using all that memory in a desktop personal computer in 1979. IBM also chose the 8088 microprocessor because porting software from existing 8080-based systems to the 8088 would be relatively straightforward.

#### 4 Historical Background

With the hardware for the first PC under development, IBM sought to adapt existing software for the system. Developing a new operating system and software tools would have taken too long. IBM contracted Microsoft, at the time a new company, to provide a BASIC interpreter, assembler, and link editor for the machine. IBM chose Microsoft because of Bill Gates's experience in writing the most popular BASIC interpreter to date for the Altair systems.

Since many CP/M-based programs were available, IBM initially attempted to interest Digital Research, Inc. (DRI) in providing a 16-bit version of the CP/M operating system for the IBM PC. However, DRI did not foresee the success of the 8088 microprocessor and declined to participate in the venture. IBM then approached Microsoft and, after explaining the requirements, asked Microsoft whether it was interested in providing the operating system software as well as the tools. The main concern of both IBM and Microsoft at the time was whether Microsoft had the resources to develop both the software tools and the operating system in the time required. Realizing that writing a new system was not feasible due to the schedules, Microsoft acquired from Seattle Computing Products a CP/M clone called SCP-DOS. With the SCP-DOS technology as a base, Microsoft predicted that it could complete the operating system, and the original operating system agreement between IBM and Microsoft was established.

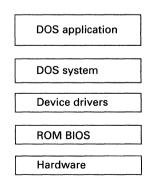

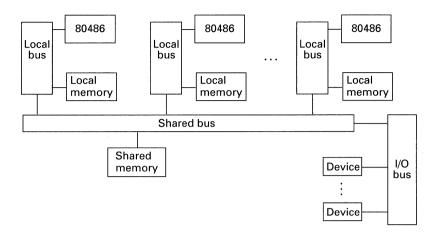

In 1981, the first version of the DOS operating system, 1.0, was shipped for IBM PCs. The system supported PCs with up to 256KB RAM, two 180KB floppy-disk drives, and included a Basic Input Output System (BIOS) built into the system ROM. DOS 1.0 was similar to CP/M in the way it managed the diskette devices and files, and it provided the base platform for the first 8088 DOS applications. Since the primary data structure used by the DOS file system to map file blocks to diskette addresses was the *file allocation table (FAT)*, the DOS file system became known as the FAT file system. Figure 1.1 illustrates the DOS system structure.

In 1982, IBM began shipping PCs with 360KB floppy disk drives. Since the new diskette medium had a format different from that of the 180KB diskettes, DOS had to

Fig. 1.1 DOS system structure.

be updated. IBM shipped DOS 1.1 when the new diskette drives became available in 1982.

IBM next enhanced its PC line in 1983 with the addition of the IBM PC/XT. The PC/XT had a hard disk that could store far more data than could traditional floppy diskettes. This development illustrates how mainframe technology was becoming less expensive and more widely available in the PC market. The IBM PC/XT also included a new system board that allowed 640KB of memory to be installed.

At this point, a trend emerged that continues to this day in the computer industry: The hardware drives the software. The addition of a hard disk to the PC was a problem for DOS 1.1, since the FAT file system was written for floppy-disk systems in which a single 360KB diskette could contain a maximum of 64 files. This limitation had to be removed; even the smallest hard disks could hold 10MB of data.

Responding to this requirement, the DOS team at Microsoft explored different harddisk and file-allocation strategies to select one that would enable DOS software to exploit future improvements in storage technology. Merely extending the limit of 64 files per disk would yield too many files to manage in a single file space, so the Microsoft team chose a hierarchical file-management approach similar to the one found in UNIX. They implemented this approach to support both diskettes and hard drives.

Another requirement for the next version of DOS was an architecture for extending the system to support different peripheral devices. This support took the form of *device drivers*, user-installable program modules that interface the DOS system and applications to devices. The version of DOS that included the hierarchical FAT file system, support for hard disks, and a device-driver model for extending the system was shipped as DOS 2.0 in 1983.

IBM's next PC enhancements involved providing faster systems with larger hard disks. The Intel 80286 chip was selected for the next-generation IBM PC, the PC/AT. The 80286 has two modes of operation called *real mode* and *protected mode*. In real mode, the 80286 functions as a fast 8088. In protected mode, the 80286 allows up to 16MB of memory to be addressed and provides features that support a protected multi-tasking environment. These protection features allow an operating system to separate the memory spaces associated with different programs. However, since the 80286 was not designed to allow existing DOS applications to run in protected mode, they could neither be executed concurrently, nor use more than 1MB of memory. Therefore, DOS applications used the 80286 as a fast 8088. Other operating systems—such as Intel's RMX or Microsoft's XENIX—used the protected mode of the 80286, but neither of these systems was considered to be a mainstream desktop system due to a lack of applications compared to the number of DOS applications.

The PC/AT was also the first PC to use 1.2MB 5.25-inch diskette drives. Since several modifications to DOS 2.0 were necessary for the PC/AT hardware, DOS 3.0 was not released until August 1984. DOS 3.1 was released in 1985 to provide support for PC local-area networks (LANs). Another update to the system (DOS 3.2) was made for supporting 3.5-inch diskettes in 1986. Table 1.1 shows the evolution of the DOS operating system.

#### 6 Historical Background

| Year | Version | System contents                                              |

|------|---------|--------------------------------------------------------------|

| 1981 | 1.0     | IBM PC<br>5.25" 180KB diskette<br>Single task<br>Single user |

| 1982 | 1.1     | 5.25" 360KB diskette                                         |

| 1983 | 2.0     | IBM PC/XT<br>Hard disk<br>FAT file system<br>Device drivers  |

| 1984 | 2.1     | IBM PC Jr.                                                   |

| 1984 | 3.0     | IBM PC AT<br>80286/80287 real mode<br>5.25" 1.2MB diskette   |

| 1985 | 3.1     | IBM PC network                                               |

| 1986 | 3.2     | IBM PC Convertible 3.5" 720KB diskette                       |

| 1987 | 3.3     | IBM PS/2<br>80386/80387 real mode<br>3.5" 1.4MB diskette     |

| 1989 | 4.0     | User shell<br>LIM expanded memory<br>More user memory        |

Table 1.1 DOS evolution.

#### **1.3 DOS LIMITATIONS**

Between 1983 and 1985, IBM, Microsoft, and most application developers began to be aware of certain limitations of DOS and the 8088 environment. These limitations were in the areas of memory management, I/O management, multitasking, system extendibility, and graphical user interfaces.

#### 1.3.1 Memory Management

The 1MB address space, which seemed large in 1980, became a major limitation for larger DOS programs. Applications such as spreadsheets and database systems allowed users to create large volumes of data that needed to be in memory to be processed. The lack of memory became known as the *640KB barrier*, since only 640KB of the 8088 address space mapped RAM. The memory at addresses from 640KB to 1MB in the PC mapped the system ROMs and memory-mapped I/O devices such as the display buffer. The DOS system used from 50KB to 60KB, and device drivers also consumed a portion of

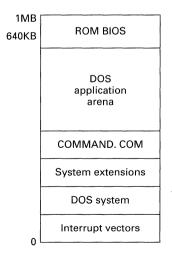

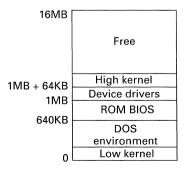

the 640KB address space. Thus, application software had less than 640KB available of the 1MB memory addressable by an 8088. Figure 1.2 illustrates the DOS memory layout.

One of the mechanisms DOS applications developers devised to relieve this memory constraint was the *overlay* scheme. Overlays allowed portions of a program not currently needed to reside on a secondary-storage device, usually a hard disk. Since DOS contains only a primitive memory manager, DOS applications had to provide their own overlay management, further increasing their size and complexity.

These memory integrity problems were exacerbated by the behavior of *terminate-and-stay-resident (TSR) modules*. TSRs are loaded like any other DOS program but stay resident in memory after terminating. A TSR is accessed after terminating by either a hardware or a software interrupt. TSRs that monitor keystrokes by intercepting keyboard interrupts are called *hot-key pop-up applications*. The DOS print spooler is a TSR that intercepts timer and printer interrupts to allow the simultaneous queueing and printing of files.

Since TSRs can never be guaranteed that the memory needed will be available when they are invoked, they must allocate when they are loaded all the memory they will ever need. Also, since TSRs are not aware of one another's existence and resource requirements, they can easily cause the system to behave unpredictably. For example, their behavior may depend on the order in which they are loaded.

The 8088 processor provides no memory-protection features, since it was designed to run one application at a time. All 8088 programs execute using actual physicalmemory addresses with no distinction between accessing the DOS system's memory or application memory. This lack of protection allows programs to modify one another and the system inadvertently, often causing the system to hang. In a protected system, illegal memory accesses are trapped by the hardware. The operating system is given control; it usually terminates the offending application.

Fig. 1.2 DOS memory map.

#### 8 Historical Background

#### 1.3.2 I/O Management

Another area in which the DOS environment is limited is I/O control. Any application may read from or write to any I/O device without having access granted by DOS. Although this limitation is really a shortcoming of the 8088/8086 processor, rather than one of DOS, it is still an integrity problem. Application program errors can cause the system to hang, or, even more serious, can cause data on a secondary storage unit to be destroyed inadvertently.

Another I/O problem is that applications have the capability of disabling interrupts to the 8088/8086 processor with a single instruction. If an application disables interrupts and executes a spin loop, the system will remain in the loop forever. Even intermittent disabling of the interrupts to the system can cause applications to behave incorrectly. For example, if an application disables interrupts while a TSR print spooler is using timer tick interrupts to pace its spooling, the spooler will not receive interrupts to continue moving data to the printer. Disabling interrupts can also disrupt communications applications that depend on receiving periodic interrupts for maintaining communications sessions.

#### 1.3.3 Multitasking

DOS was designed to run one application at a time; it is a *single-task* or *single-thread* environment. Even in a single-user, one-program-at-a-time environment, there are requirements for being able to multiprogram the system. A common scenario is using a TSR print spooler to print a file in the background while the user is editing another file from the keyboard. Since DOS provides no multitasking services, programs that require multitasking must do it themselves. However, there is a catch—since DOS is not reentrant, only one program can correctly use the DOS system services at a time. Therefore, competing applications and TSRs can inadvertently both enter DOS, confuse it, and disrupt the system.

A major benefit of building multitasking into the system, instead of into the applications, is that the system can allocate the processor more efficiently than can the applications. When one application attempts to do I/O, it will block, and the system scheduler can resume another application until the I/O is completed. In the DOS environment, an application that requests I/O typically spins in a loop waiting for the device status to indicate that the I/O is complete. This is called *polling*, and wastes many processor cycles that could be spent on other tasks. Since each DOS application that needs to multitask has to do it itself, putting together two DOS applications that need to multitask frequently results in unpredictable behavior.

#### 1.3.4 System Extendibility

DOS applications request DOS system services by issuing *software interrupts*, an 8088specific form of transferring control between routines. An interrupt causes a transfer of control to an address that is retrieved from an interrupt vector table (IVT) based on the interrupt number invoked. The main difference between a software interrupt and a hardware interrupt is that the software interrupt is caused by the synchronous execution of an INT instruction rather than by an external hardware-device interrupt request. Figure 1.3 illustrates how the DOS system services are invoked using software interrupts.

Since DOS and BIOS system services are routed through software interrupts, the application requesting the service must pass as a parameter information that specifies which service is desired. Since the information that binds the application with a specific service is hard coded into the application, this is called a *statically linked interface*. DOS and BIOS software interrupt requests specify the software interrupt number and the function code of the service. Thus, there are two levels of decode for each static link. The software interrupt number is decoded by the processor, and the function code is decoded by the software providing the service.

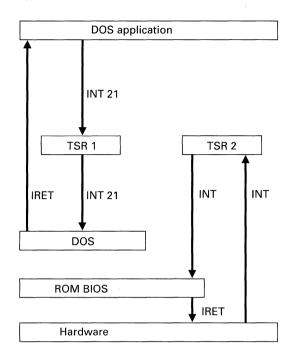

Because all DOS and BIOS (device) services are accessed through the 8088 interrupt mechanism, the memory in which the interrupt-vector table resides is not protected from applications and TSRs. Thus, any application or TSR can *hook an interrupt* and intercept program control when an interrupt is invoked. The result is that the system can be extended by hooking interrupts, but, as more extensions are loaded (usually in the form of TSRs or device drivers), the system's behavior becomes increasingly unpredictable. Also, the order in which the extensions are loaded can change the semantics of the system's behavior. Figure 1.4 illustrates a DOS system with two TSRs loaded.

#### 1.3.5 Graphical User Interface

DOS is packaged with a line-oriented command processor; thus, users must learn DOS commands before they can use the system. New users often find DOS overwhelmingly complex; they complain about the lack of an intuitive paradigm that would make using the system easier. The Apple Macintosh computers were the first microcomputers to exploit successfully the graphical user interface (GUI) technology developed by Xerox at

ivi (interrupt vector ta

**Fig. 1.4** DOS system extensions. (*OS/2 Programmer's Guide,* E. lacobucci, Copyright 1988. McGraw-Hill Publishing Company. Reprinted by permission.)

its Palo Alto Research Center (PARC) in the 1970s. This GUI technology allows users to interact with the system via a user-friendly pointing device such as a mouse, and visual display keys or icons that parallel the user's tasks. More advanced GUIs provide a *device-independent programming model* that applications use for user I/O functions. This model enables these applications to take advantage of whatever user I/O devices are attached to the system, regardless of the devices' particular physical characteristics. GUIs often provide a *what-you-see-is-what-you-get (WYSIWYG)* capability for displaying graphical information on a variety of output devices.

# 1.4 OS/2 HISTORY

The need for a more robust version of DOS to provide solutions to these shortcomings was recognized by both IBM and Microsoft, and each company initiated projects devoted to this end. IBM undertook several projects to extend the functionality of DOS while providing compatibility for current DOS applications by using the protected mode of the 80286. Microsoft began DOS 4.0 (not the one that was shipped in 1989) or MT-DOS (for multitasking DOS), a project to define a real-mode multitasking environment that could run on 80286 and 8088/8086 systems. Although none of these projects led to released products in the PC market, both companies learned about the limitations of DOS and of the 80286 architecture and the scope of independent development efforts.

#### 1.4.1 IBM-Microsoft Joint Development

In 1985, IBM and Microsoft signed an agreement to define and ship the operating system that would extend the capabilities of DOS. Under the agreement, both companies would jointly design, develop, and own the resulting product. By 1990 the practice of software companies joining forces to define and develop products had become common in the computer industry. Alliances among computer companies such as Open Software Foundation and UNIX International, and many smaller joint projects among applications developers, are now leading the computer software industry into an era of *open systems*. Emerging software standards will lead to greater software portability and, thus, to better software productivity. Chapter 12 discusses the open-systems platform and the role it will play in the future.

To understand why IBM and Microsoft worked together, we must explore the goals of the product they desired to create and the attributes of both companies' development methodologies. Both companies realized that, if two different advanced DOS systems were developed, the software market would be confused about which was the "right" one. So it made sense for IBM and Microsoft to combine their efforts, and to create a single industry-standard operating system that was endorsed by the two leading companies in the PC market.

IBM has traditionally been known as a hardware company, although it writes most of the software marketed for its larger systems. IBM is by far the largest computer company and wields the most influence in the computer industry. IBM projects are typically large, comprising many layers of management, staff, and technical personnel in the product organization. On the other hand, Microsoft became the leading independent software vendor (ISV) during the 1980s. Microsoft has led the PC software industry in the development of DOS, Windows, and a variety of programming tools. Microsoft also is a leader in applications software for both the Apple Macintosh and the IBM PC systems. Unlike those at IBM, most Microsoft projects are implemented by a small core team of programmers who manage themselves, with extra staff added as needed. Therefore, the combination of the companies created a good team in the design, development, and testing areas.

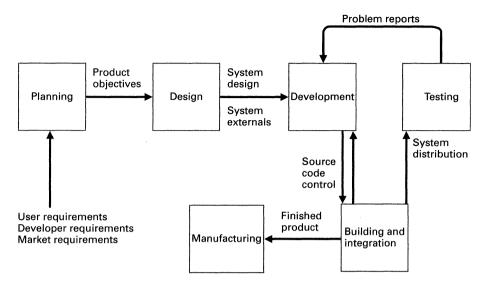

To facilitate both companies participating in the design and development of the system, they constructed a *software-development process* to describe the methodology for building the product. Figure 1.5 illustrates the general process framework.

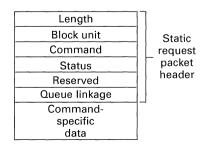

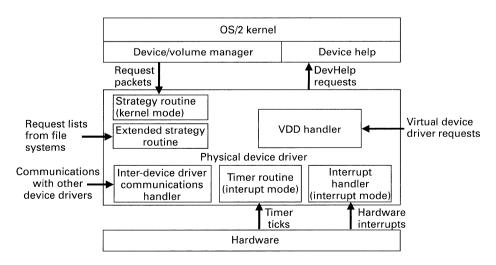

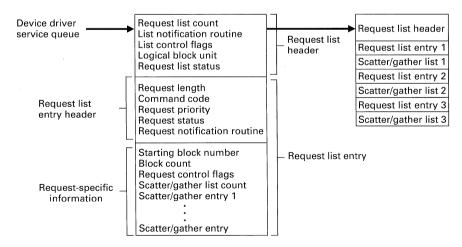

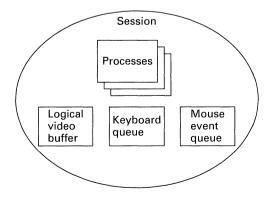

#### 1.4.2 Multisite Development