**Systems**

IBM 2922 Programmable Terminal RPQ 810563, 810564, and 810565 Component Description

# PREFACE

This publication for systems planners, programmers, and operators, presents the functional description and operating procedures of the IBM 2922 Programmable Terminal. The 2922 consists of a 2922-1 Terminal Control Unit, RPQ 810563, cable-connected to a 2922-2 Terminal Printer, RPQ 810564, and a 2922-3 Terminal Card Reader, RPQ 810565. In addition, the IBM 2152 Printer-Keyboard, RPQ 810581, and the IBM 1442 Card Punch Model 5, RPQ AD1629, can be attached (optional). In this publication:

- Chapter 1 describes the 2922-1:data formats, instructions, time-sharing, arithmetic and logical functions, and gives programming suggestions and terminal console operations.

- Chapter 2 presents operating procedures and associated instructions for the reader, printer, and optional printer-keyboard, and an optional card punch.

- Chapter 3 discusses the binary synchronous communications adapter: operating principles, transmission codes, instruction sets, control characters, and sense information.

- Appendixes contain reference information: conversion tables, operation and condition codes, instruction examples, stop codes, and a glossary.

# Second Edition (December 1972)

This is a reprint of GL24-3597-0 incorporating changes released in Technical Newsletter GN24-0500, dated September 22, 1972.

Changes or additions to the specifications contained in this publication are continually being made. When using this publication in connection with the service or operation of IBM equipment, check with your local IBM branch office to ensure that you have the latest edition.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

This manual has been prepared by the IBM System Products Division, Product Publications, Dept. K10, P.O. Box 6, Endicott, New York 13760. A form has been provided at the back of this publication for reader's comments. If the form has been removed, comments may be directed to the above address. Comments become the property of IBM.

© Copyright International Business Machines Corporation 1972

# CONTENTS

| 2922 PROGRAMMABLE TERMINAL   |         |         |          |   |   |   |      |

|------------------------------|---------|---------|----------|---|---|---|------|

| INTRODUCTION                 | •       | •       | •        | • | • | • | 1 –1 |

| TERMINAL CONTROL UNIT .      |         | •       | •        |   | • |   | 1-2  |

| Main Storage                 |         | •       | •        | • | • | • | 1-2  |

| General Registers            |         | •       | •        | • | • | • | 1-3  |

| Parity Checking              | •       | •       | •        | • | • | • | 1 -3 |

| Data Formats                 |         | •       | •        | • |   | • | 1-3  |

| Instruction Format           | •       | •       | •        | • | • | • | 1-5  |

| Instruction Execution .      | •       | •       | •        | • | • | • | 1-6  |

| Information Positioning .    | •       | •       |          | • | • | • | 1-7  |

| Addressing                   |         | •       | •        | • | • | • | 1-8  |

| Operands                     | •       | •       | •        | • | • | • | 1-10 |

| Time Sharing                 |         | •       | •        | • | • | • | 1-11 |

| Arithmetic and Logical Opera | tions . |         | •        | • | • | • | 1-13 |

| Binary Arithmetic .          | •       |         | •        | • | • | • | 1-13 |

| Decimal Arithmetic .         | •       | •       | •        | • | • | • | 1-21 |

| Logical Operations .         |         |         | •        | • | - | • | 1-34 |

| Branching                    |         | •       | •        | • | • | • | 1-49 |

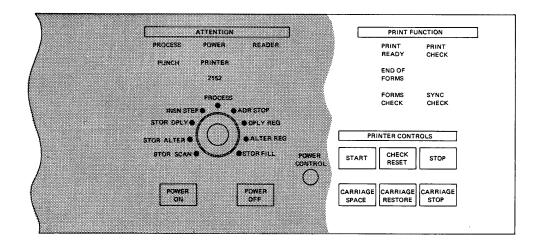

| Terminal Control Unit Consol | е .     |         |          | • | • | • | 1-54 |

| Operating Keys and Indic     |         | -       | •        | • | • | • | 1-54 |

| Input/Output Operations      |         | •       | •        |   | • | • | 1-67 |

|                              | •       | •       | •        | · | • | • |      |

| INPUT/OUTPUT DEVICES .       |         | _       |          |   |   | • | 2-1  |

| 2922-3 Terminal Card Reader  |         | •       | •        | • |   | • | 2-1  |

| Machine Features .           | •       |         | •        | • | • | • | 2-2  |

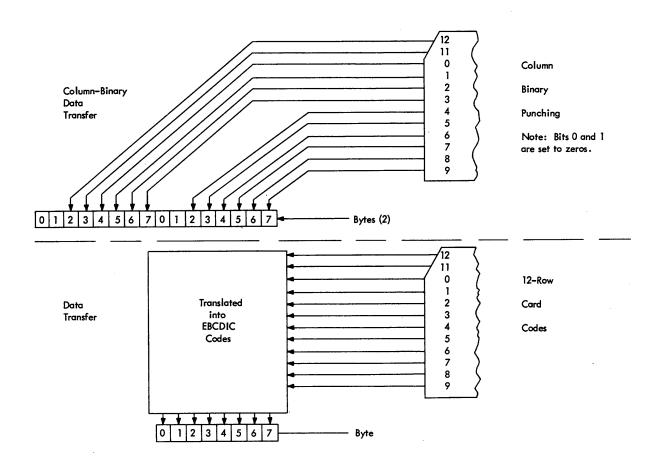

| Data Flow                    |         | -       | •        | • | • | - | 2-8  |

| Programming                  | •       | •       | •        |   | • |   | 2-10 |

| Operating Procedures         | •       | •       | •        | • | • |   | 2-12 |

| Input/Output Considerati     | ons .   | •       | •        | • | • | • | 2-13 |

| Instructions                 |         | •       |          | • | • |   | 2-14 |

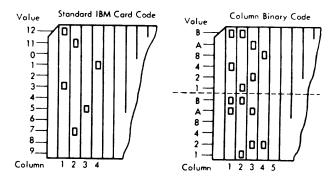

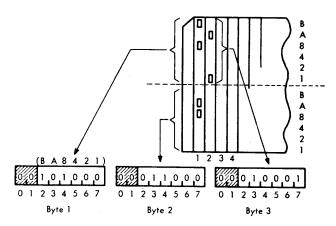

| Column Binary Code .         | •       | •       |          | • | - | _ | 2-16 |

| 2922 Terminal Printer .      |         | •       | •        | • | • | • | 2-18 |

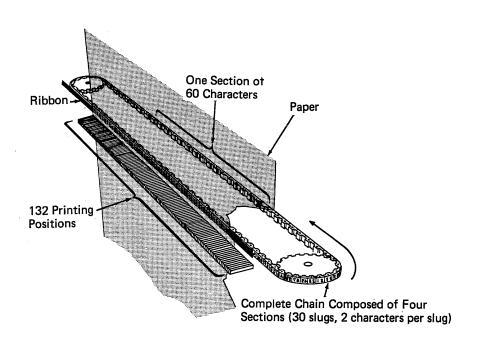

| Printing Method .            |         | •       | 1        | • | • | • | 2-19 |

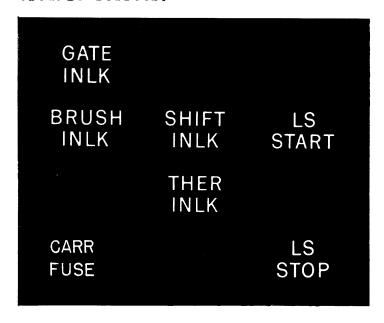

| Machine Covers and Safet     | v .     | •       |          | • | • | • | 2-20 |

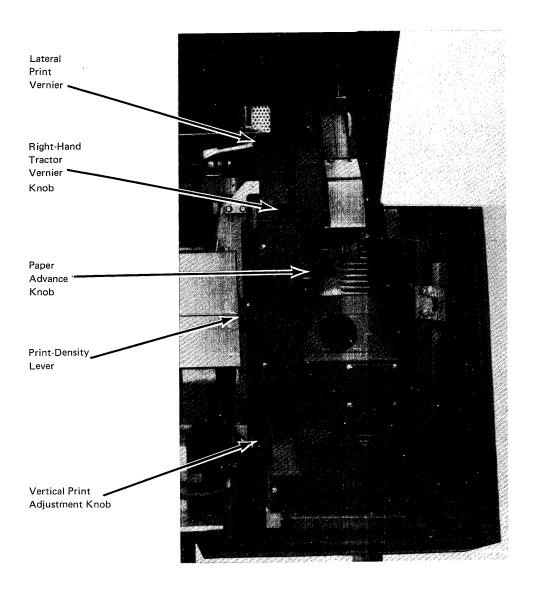

| Operating Information        | · •     | •       | •        | • |   | • | 2-20 |

| Operator Procedures .        |         | •       |          |   |   | _ | 2-36 |

| Print Quality Requiremen     | ts .    | •       | •        | • | • |   | 2-42 |

| Instructions                 |         | •       | •        | • | • | • | 2-49 |

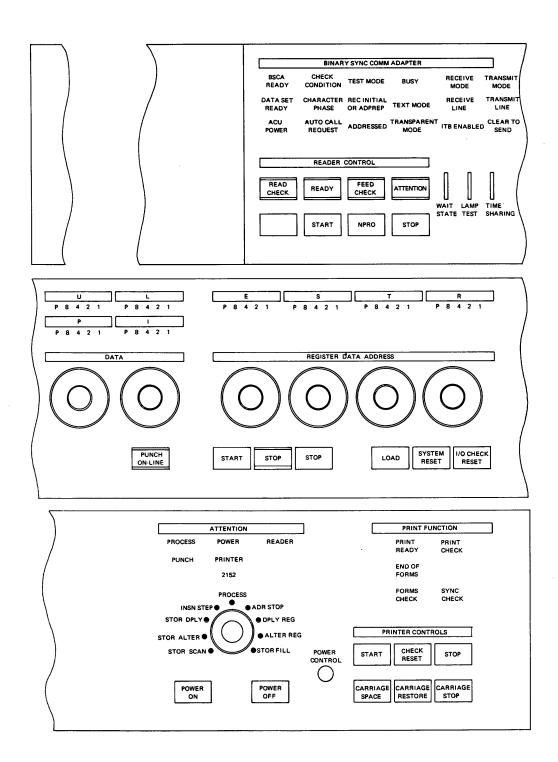

| IBM 2152 Printer-Keyhoard (O | ptional | Feature | )        | _ | • | _ | 2-53 |

| General Operation .          |         | _       | <b>,</b> | _ | _ | _ | 2-53 |

| Instructions                 |         | •       |          | _ | • | _ | 2-55 |

| Ready Condition .            |         | •       | -        |   | • |   | 2-57 |

| Condition Code               | •       | •       | •        | • |   | • | 2-57 |

| 2152 Interrupts .            |         | •       | •        | • | • | • | 2-58 |

| Principles of Operation      |         | •       | •        | • | • | • | 2-59 |

| Printer Character Set        | •       | •       | •        | • | - | - | 2-64 |

| Keys and Lights .            | •       | •       | -        | • | - | • | 2-66 |

| Paper Handling               | •       | •       | •        | - | • | - | 2-68 |

| Ribbon                       | •       | •       | •        | • | • | • | 2-69 |

| Features                     | •       | •       | •        | • | • | • | 2-69 |

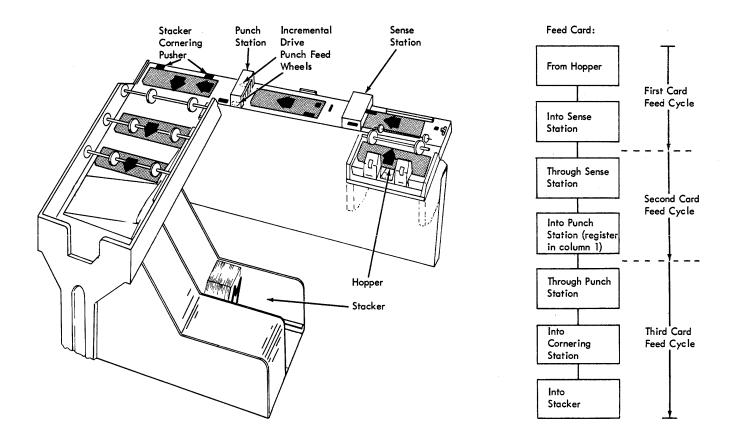

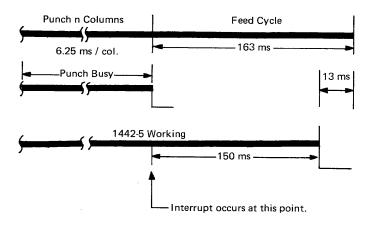

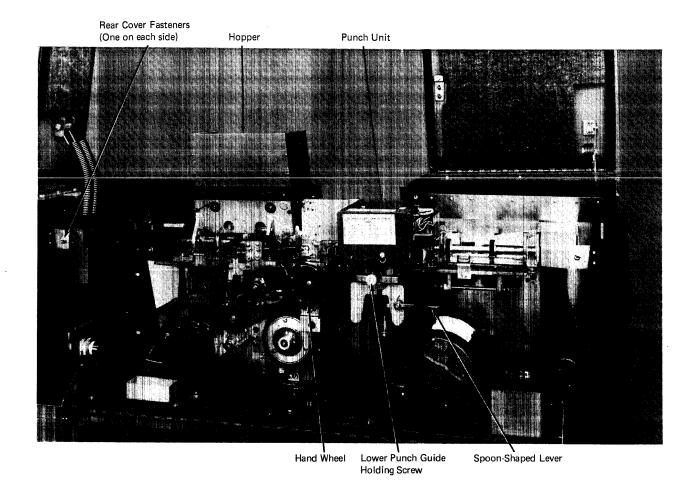

| IBM 1442 Ca | rd Punch Mode | el 5    | (0pt | tional  | Feat  | ure)   | •     | •      | •   | 2-70         |

|-------------|---------------|---------|------|---------|-------|--------|-------|--------|-----|--------------|

|             | med Operation |         |      | •       | •     | •      | •     | •      | •   | 2-72         |

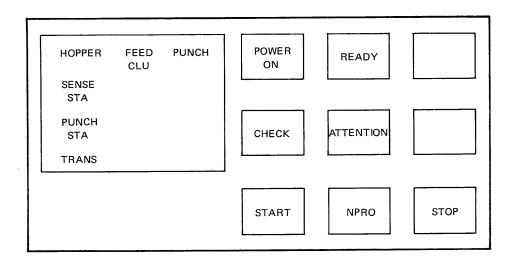

|             | r Controls    |         | •    | •       | •     |        | •     |        |     | 2-76         |

| -           | ng Procedure  | s       | •    | •       | •     | •      | •     | •      | •   | 2-79         |

| BINARY SYNC | HRONOUS COMM  | UNICA   | TIOI | IS ADAI | PTER  | •      | •     | •      | •   | 3-1          |

| Transmi     | ssion Codes   | •       |      | •       | •     | •      |       | •      | •   | 3-2          |

| Interfa     |               | •       | •    | •       | •     | •      | •     | •      | •   | 3 <b>-</b> 3 |

| Modems      | • •           | •       | •    | •       | •     | •      | •     | •      | •   | 3-4          |

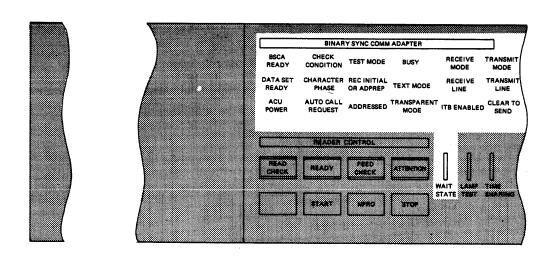

|             | tion (BSCA)   | •       |      | •       | •     | •      | •     | •      | •   | 3-4          |

|             | tion Set and  | Cont    | rol  | Charac  | cters | (Sum   | nary) | •      | •   | 3-4          |

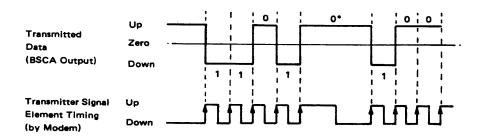

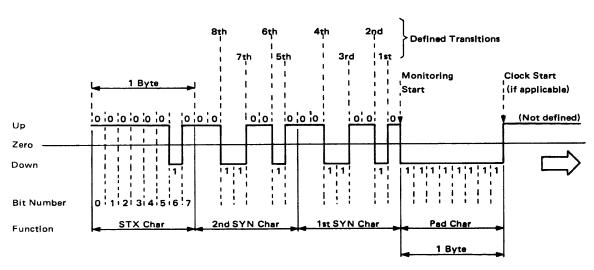

|             | ng Principle  |         |      | •       | •     |        | •     | •      | •   | 3 <b>-</b> 6 |

|             | diate Block   |         | ing  | Mode    | •     | •      | •     | •      | •   | 3-12         |

|             | tions (BSCA)  |         |      | •       | •     | •      | •     | •      | •   | 3-14         |

|             | nformation    | •       | •    | •       | •     | •      | •     | •      | •   | 3-35         |

|             | ject Conditi  | ons     | •    | •       | •     | •      |       | •      | •   | 3-38         |

|             | hecking Metho |         | •    | •       | •     | •      | •     | •      | •   | 3-39         |

| BSCA Co     |               | •       | •    | •       | •     | •      | •     | •      | •   | 3-40         |

|             | op Test .     | •       | •    | •       | •     | _      | •     | •      | •   | 3-43         |

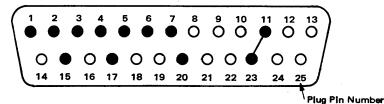

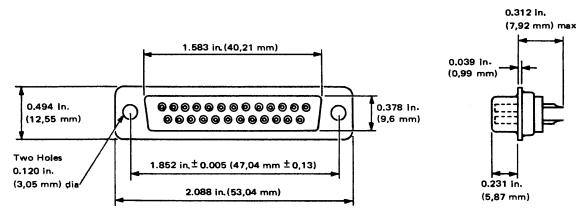

| Interfa     |               | •       | •    | •       | •     | •      | •     | •      | •   | 3-45         |

|             | nd Receptacl  | •<br>ec | •    | •       | •     | •      | •     | •      | •   | 3-58         |

| r Lugs a    | na keceptaci  | CO      | •    | •       | •     | •      | •     | -      | •   | 3 3.         |

| APPENDIX .  |               | •       | •    | •       | •     | •      | •     | •      | •   | A-1          |

| Appendix A  | Formats       | •       | •    | •       | •     | •      | •     | •      | •   | A-1          |

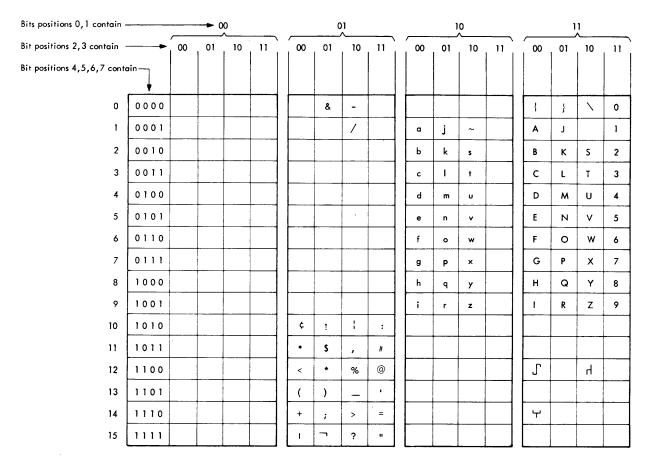

| Appendix B  | EBCDICC and   | ASCI    | I C  | harts   | •     | •      | •     | •      | •   | A-2          |

| Appendix C  | Powers-of-T   |         |      | •       | •     | •      | •     | •      | •   | A-4          |

| Appendix D  | Binary and    |         |      |         |       |        |       | •      | • 1 | A <b>-</b> 5 |

| Appendix E  | Hexadecimal   | -Deci   | mal  | Conve   | rsion | Table  | es    | •      | •   | A-8          |

| Appendix F  | Operation C   | odes    | •    | • ,     | •     | •      | •     | •      | •   | A-13         |

| Appendix G  | Condition C   | ode     | •    | •       | •     | •      | •     | •      | •   | A-14         |

| Appendix H  | Terminal Ti   | mings   | •    | •       | •     | •      | •     | •      | •   | A-15         |

| Appendix I  | Instruction   | Use     | Exar | nples   | •     | •      | •     | •      | •   | A-18         |

| Appendix J  | 4-of-8/EBCD   | IC Co   | nve  | rsion ! | rable | •      | •     | •      | •   | A-28         |

| Appendix K  | Extended Bi   | nary-   | Code | ed Dec  | imal  | Inter  | chang | e Code | е   |              |

|             | ,             | _       |      | (EBCD   | IC) C | ard Co | ode T | able   | •   | A-30         |

| Appendix L  | BSCA Code T   | ables   | •    | •       | •     | •      | •     | •      | •   | A-31         |

| Appendix M  |               |         |      | •       | •     | •      | •     | •      | •   | A-34         |

| Appendix N  | Glossary      | •       | •    | •       | •     | •      | •     | •      | •   | A-35         |

| • •         | •             | •       |      |         |       |        |       |        |     |              |

|             |               |         |      |         |       |        |       |        |     | ** 4         |

The IBM 2922 Programmable Terminal is a communications system designed for teleprocessing applications that require extensive printouts. It can be used for batch data entry and to make inquiries into a computer's data base. The kinary synchronous method of transmission is employed to exchange information over telephone lines with either an IBM System/360 or an IBM System/370 (via a 2701 Data Adapter Unit or 2703 Transmission Control); or with another 2922 terminal.

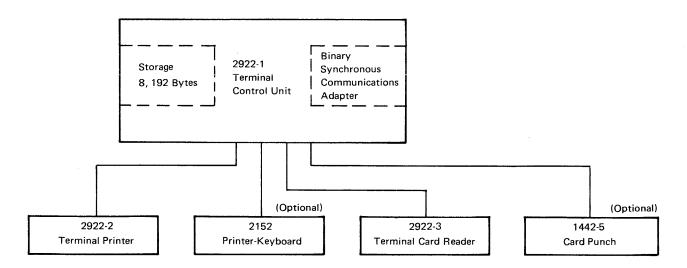

The IBM 2922 Programmable Terminal consists of interconnected functional units operating under the control of a series of instructions, called a program, stored in the IBM 2922-1 Terminal Control unit. Main storage access to one byte is 3.6 microseconds. Figure 1-1 shows a typical (schematic) configuration of units. The 2922-1 Terminal Control Unit is the central figure in the group, and attached to it is the IBM 2922-2 Terminal Printer and the IBM 2922-3 Terminal Card Reader. The IBM 2152 Printer-Keyboard and the IBM 1442 Card Punch Model 5 are available as options.

Data is entered through the terminal card reader, then transmitted to the central computer. After processing the jobs, the central computer can transmit reports and listings hack to the remote terminal for rapid printing.

An optional 2152 Printer-Keyboard can provide interaction between the terminal and the central computer for inquiry and update, job status analysis, and program development. An optional 1442 Card Punch can provide punched-card output, serially, at a maximum rate of 160 columns per second.

The programmable terminal uses 36 System/360 compatible machine instructions that work with the microprogram and hardware circuitry to accomplish the assigned taks.

This reference manual provides detailed information on the operation and characteristics of the programmable terminal. The 2922-1 Terminal Control Unit is hereafter referred to as "Control Unit" and the Programmable Terminal is hereafter referred to as "Terminal."

Figure 1-1. System Configuration

# TERMINAL CONTECL UNIT

#### MAJN STORAGE

Main storage consists of 8,192 positions of magnetic core storage. Each position has an address and contains an eight-bit unit of information referred to as a byte. Coded combinations of bits within a byte can represent alphabetic, numeric, binary, or logical data.

Main storage is used to hold all the data that is to be operated upon, or processed, at a given time. It also holds the instructions, or program, which control the operation of the terminal. For each individual job performed by the terminal, certain portions of main storage are assigned to store instructions, and certain portions to store data to be processed.

#### GENERAL REGISTERS

Eight general purpose registers, small auxiliary storage units, are provided for temporary storage of small amounts of data. Each register is the equivalent of two bytes (one halfword) and is loaded or unloaded under the control of the stored program. Information may flow from register to register, main storage to register, or from register to main storage.

The registers are numbered 8-15 and are selected by the four-bit R or B field of an instruction.

#### PARITY CHECKING

To ensure the accurate transfer of data, an extra (parity) bit is generated for each four bits transferred to or from main storage or register storage. The parity bit is added during transfer, if it is needed, to maintain an odd number of bits. The bit count is monitored continuously, and any missing or extra bits which result in an even number of bits cause a control unit parity error.

#### DATA FORMATS

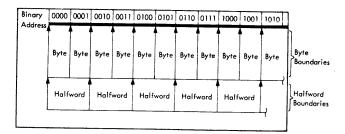

The basic unit of addressable data is an eight-bit byte. Each address contains eight bits of data and can be considered a byte boundary.

The byte is divided into two sections of four bits each. A check (parity) bit is provided for each four bits.

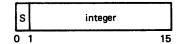

# Halfword Binary Number

A halfword binary number has a fixed length of two bytes (16 bits). The leftmost bit is reserved for sign (+ or -) control.

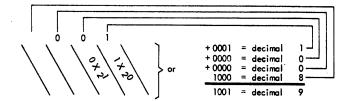

# Decimal Number

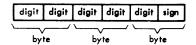

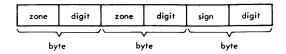

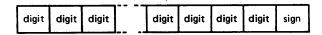

A decimal number may be in either of two forms: packed decimal or zoned decimal.

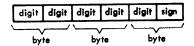

<u>Packed Decimal</u>: This format allows two numeric digits to be stored within one eight-bit byte.

An eight-bit byte may contain two numeric digits, except in the case of the rightmost byte, which has a sign to the right. Variable field length in this format allows for fields up to 16 bytes in length.

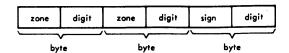

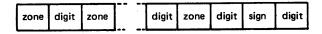

Zoned Decimal: This format contains one digit in the rightmost four positions of each byte.

The left four bits of each byte in this format are called zone bits, and are not used except for the low-order (rightmost) byte which uses them for the sign. Zone bits do not affect the value of the numeric digit contained in the right four bits of the byte.

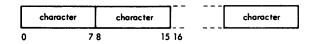

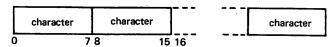

# Logical Data

Logical data may be contained in the instruction or it may reside in core storage as an operand (an operand is data contained in, or addressed by the instruction and used to execute the instruction). Logical data may have a fixed length of one byte or may be variable in length up to a maximum of 256 bytes.

# Fixed-Length Logical Data

| logical data |   |

|--------------|---|

| 0            | 7 |

# Variable-Length Logical Data

#### INSTRUCTION FORMAT

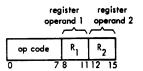

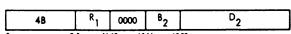

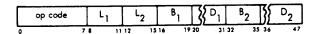

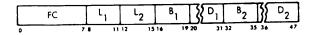

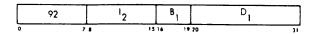

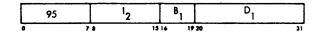

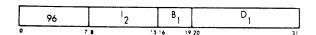

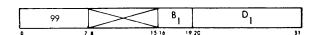

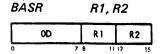

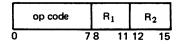

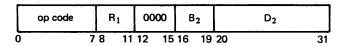

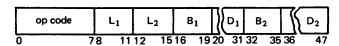

The instruction format specifies the length of the instruction and the type of operation to be performed. The length of the instruction can be one, two, or three halfwords. The types of instruction formats are RR, RX, SI, and SS (Figure 1-2). RR Format: Denotes a register-to-register operation.

RX Format: Denotes a register-tc-storage or a storage-to-register operation. In this format, bits 12 through 15 must be zero.

<u>SI Format</u>: Denotes a stoage-immediate operation. In this format the I2 field of the instruction is the second operand.

SS Format: Denotes a storage-to-storage operation.

In each format, the first instruction halfword consists of two parts. The first byte contains the operation code (op code). The length and format of an instruction are specified by the first two bits of the operation code. The second byte may be used to contain data, specify operand lengths, or specify registers to be used by the operation.

|                   | First I<br>Byte 1 | Halfword<br>Byte 2                        | Second            | d Halfword      | Thi            | rd Halfword         | d          |

|-------------------|-------------------|-------------------------------------------|-------------------|-----------------|----------------|---------------------|------------|

|                   | Regis Open        | ter Regis<br>and 1 Opera                  |                   |                 | 1              |                     |            |

| RR Format         | Op Code           | R <sub>1</sub> R <sub>2</sub><br>8 111215 |                   |                 | 1              |                     |            |

|                   |                   | egister<br>perand 1                       | Address<br>Operar |                 |                |                     | 1          |

| RX Format         | Op Code           | R1 0000                                   | R <sub>2</sub>    | D <sub>2</sub>  | 31             |                     | 1          |

|                   | 1                 | Immediate<br>Operand                      |                   | ress<br>rand 1  |                |                     |            |

| SI Format         | Op Code           | 1 <sub>2</sub><br>8 15                    | B <sub>1</sub>    | D <sub>1</sub>  | 311            |                     | i<br>!     |

|                   | l Opero           | Length<br>and 1 Opera                     | Addi<br>nd 2 Ope  |                 |                | ddress<br>Operand 2 | <br> -<br> |

| SS Decimal Format | Op Code           | l <sub>1</sub> L <sub>2</sub>             | B <sub>1</sub>    | D <sub>1</sub>  | B <sub>2</sub> | D <sub>2</sub>      | 47         |

|                   | <br>              | Length                                    | Add<br>Ope        | ress<br>erand 1 |                | ddress              |            |

| SS Logical Format | Op Code           | L                                         | 8 <sub>1</sub>    | Dl              | B <sub>2</sub> | D <sub>2</sub>      | 47         |

Figure 1-2. Instruction Formats

# INSTRUCTION EXECUTION

For purposes of describing the execution of instructions, operands are designated as first and second operands.

These names refer to the manner in which the operands participate. The operand to which a field in an instruction format applies is generally denoted by the number following the code name of the field, for example, R1, B1, L2, D2. Normally, the operation of the terminal is controlled by instructions taken in sequence. An instruction is fetched from a location specified by the current instruction address. The current instruction address itself is located in the Program Status Word (PSW). After the fetch operation, the current instruction address is increased by the number of bytes in the fetched instruction to enable addressing of the next instruction in sequence.

The instruction is then executed by adding, subtracting, multiplying etc. The result that is thus obtained usually replaces operand 1. Upon the execution of certain instructions, a condition code, which reflects the nature of the result, is set into the PSW.

Subsequently, the updated address in the FSW is used to read out the next instruction from main storage and the processing continues.

#### INFORMATION POSITIONING

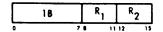

Byte locations in storage are consecutively numbered from 0, each number being considered the address of the corresponding byte. Bytes may be handled singly or strung together in fields. A group of two consecutive bytes is called a 'halfword'. The location of any field or group of bytes is specified by the address of the leftmost byte.

Information positioned in storage may be in fixed-length format or variable-length format. The length of fields is either implied by the operation to be performed or stated explicitly as part of the instruction. When the length is implied, the information is said to have a fixed length, which can be one, two, or four bytes.

Fixed-length fields must be located in main storage on an integral (halfword) boundary (Figure 1-3) for that unit of information. A boundary is called integral for a unit of information when its storage address is a multiple of the length of the unit in bytes. For example, a halfword (two bytes) must have an address that is a multiple of the number 2.

In the control unit unit, all instructions and all data with fixed word length (operands addressed by RX-format instructions) must begin on a halfword boundary. An instruction (or data with fixed word length) is properly located at a halfword boundary when its address is even or, in other words, when the low-order bit of the address is zero. An improperly placed instruction causes an error stop.

When the length of a field is not implied by the operation code, but is stated explicitly, the information is said to have a variable-length field.

within any instruction format or any fixed-length operand format, the bits are consecutively numbered from left to right starting with bit number 0.

Variable-length fields are not restricted to halfword boundaries, and may contain up to 256 bytes. Length is variable in increments of one byte.

Figure 1-3. Integral Boundaries

# ADDRESSING

Byte locations in storage are expressed in binary form and consecutively numbered from 0000 to the upper limit of available storage. Appendix D explains the binary number system, and Appendix E contains the hexadecimal representation for addresses 0000 to 4095. The first 144 bytes (bytes 0000-0143) are reserved for internal control and are not available to the program. The location of any field or group of bytes is specified by the address of the leftmost byte.

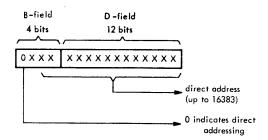

An address used to refer to main storage may be specified by either of two methods; direct addressing or effective address generation.

Note: Neither a direct address nor an effective address can be zero, pertain to the protected area, or exceed the storage capacity.

Direct Addressing: Direct addressing is used when the high-order hit in the B-field of an instruction is zero.

When the direct addressing method is employed, the low-order 14 bits of the combined B- and D-fields are used to refer directly to byte locations in main storage. The 12 binary bits in the D-field allow an address specification of up to 4095. To address additional

storage, the adjacent two bits in the lcw-order position of the B-field are used, allowing address specification of up to 8192.

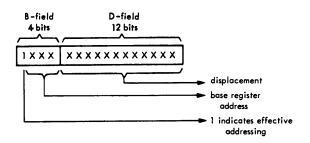

Effective Addressing: Effective addressing is used when the high-order bit in the B-field of an instruction is one.

In the effective-address generation method, the contents of the general register specified by the B-field of an instruction, are added to the contents of the D-field of the instruction to form the effective address. The content of the general register specified by the B-field is referred to as the 'base address'. The content of the D-field is referred to as the 'displacement". (This type of address modification is commonly referred to as indexing.) Effective addressing may be either in a positive or a negative direction, and is determined by the sign of the tase address. Caution should be exercised because a resultant effective address that is negative or that refers to the first 144 bytes of main storage results in an error condition.

Any of the eight general registers, 8 through 15, may be specified in the B-field as the location of the base address for effective-address generation.

If there are zeros either in the general register specified, or in the displacement field of the instruction when effective-address generation is specified, the effective address generated is the same as direct addressing with the nonzero component.

Effective addressing is useful for program routines which require address modification.

<u>Upper Limit of Main Storage</u>: Data can be stored up to (and including) the last available byte of main storage. However, the user must exercise caution when loading a program into the upper available space of main storage. The last instruction must be located so that at least one byte of main storage remains. (Actually, two bytes of main storage have to remain unused, otherwise the last instruction would not be located on a halfword boundary.) The remaining byte is required to avoid a storage overflow which can occur because, when the instruction is read out, the internal controls automatically update the current

instruction address by an increment equal to the length of this instruction.

# OPERANDS

For addressing purposes, operands can be grouped in three classes: explicitly addressed operands in main storage, immediate operands placed in main storage as part of the instruction stream, and operands located in the general registers.

### EXPLICITLY ADDRESSED OPERANDS

An explicitly addressed operand is selected from a main-storage location not related to the location of the instruction referring to it. It is always specified by means of a storage address. When the operand contains more than one byte, the address gives the location of the first byte of the field, subsequent bytes being located in higher addresses. Both the first and second operands of an instruction can be explicitly addressed.

Explicitly addressed operands can be of fixed length or variable length. The length of variable-field-length operands is specified in the L-field of the instruction. The L-field, either four or eight bits long, specifies the length in terms of the number of bytes to the right of the addressed byte, and thus can specify a maximum field length of 256 bytes.

#### IMMEDIATE OPERANDS

An immediate operand consists of one 8-bit byte of data which is located in the instruction itself. Only the instructions in the SI format contain immediate data. The immediate data is always the second operand; the first operand is located in the main-storage location specified by the B1-D1 field.

#### OPERANDS IN REGISTERS

Information referred to by an instruction may be located in one of eight general registers. The registers are identified by numbers 8-15 and are selected by the four-bit R or B field of an instruction. The registers are not designated by main-storage addresses.

An operand located in a register has a fixed length of one halfword, or 16 bits.

### TIME SHARING

The 2922 has the ability to operate in a mode referred to as 'time sharing'. Time sharing is a means of overlapping input/output operations with each other and with processing. Time sharing is based on a system of monitoring the operation of input/output devices and sequencing the transfer of data to or from the I/O devices so as to make the most efficient use of processing time.

Processing operations in the control unit are time shared with the transfer of data between main storage and the I/O devices. When an I/O device requests service, processing is suspended only for the time required to send or to accept the input/output data.

Time sharing allows the control unit to perform useful processing functions while card or forms rovement is taking place. A system of signaling that the I/O device is finished with the data transfer to or from the control unit is referred to as an 'interruption' system.

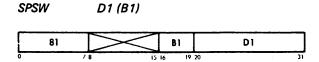

# PROGRAM STATUS WORD (PSW)

The PSW contains the inforamtion necessary for proper program execution. It is located in an internal register in the control unit and is not directly addressable. The programmer can change the PSW by means of a Set PSW instruction. The PSW has a fixed-length format of two halfwords (Figure 1-4).

The PSW is used to control instruction sequencing and to hold and indicate the status of the system in relation to the program being executed. The active or controlling PSW is called the 'current PSW'.

By storing the current PSW during an interrupt, the status of the control unit can be preserved for subsequent inspection. By loading a new PSW or part of a PSW, the state of the control unit can be

initialized or changed. The functions of the PSW are further described under "Branching".

When the current PSW is stored during an input/output interruption, the status of the control unit and the next sequential address are preserved for use after the interruption is serviced. An instruction to load a new PSW is equivalent to an unconditional branch to the instruction address contained in the new PSW.

| СС                                     | O C DA FS                                                                                         | Instruction Address |

|----------------------------------------|---------------------------------------------------------------------------------------------------|---------------------|

| 0 1 2 3                                | 4 5 6 7 8 11 12 15                                                                                | 16 31               |

| 0 - 1<br>2 - 3<br>4<br>5               | Not Used<br>Condition Code<br>Zero                                                                |                     |

| 6<br>7<br>8 - 11<br>12 - 15<br>16 - 31 | ASCII Mode Bit<br>Channel Mask<br>Device Address<br>Function Specification<br>Instruction Address |                     |

Figure 1-4. PSW Format

Operation of the Program Load key or System Reset key causes the condition code (bits 2-3), the overlap mode bit (bit 5), the ASCII mode bit (bit 6), and the channel mask bit (bit 7) of the current PSW to be reset to zero.

# INTERRUPTION

In the 2922, an automatic interrupt system is provided to make optimum use of the I/O devices and available processing time. The I/O devices signal the control unit to store an end condition when a data transfer has been terminated. Upon completion of the execution of each instruction, during the time that the control unit is in an interruptible mode, the control unit checks the various end conditions according to a built-in priority sequence. The first end condition thus found causes the actual interrupt. The interrupt is an automatic branch from the main program to a subroutine. This subroutine may be designed to test the received data for validity or to perform some other action. Since the interrupt occurs at the earliest moment possible after a data transfer has been completed, it is the primary means of controlling I/O operations.

The branch to the subroutine is accomplished by replacing the current PSW with a new PSW which contains the start address of the subroutine in its instruction address portion. The former current PSW is stored into a particular core-storage location and thus becomes the old PSW. During the transfer, the old PSW is furnished with the device address and the function specification of the I/O unit that caused the interrupt.

To initiate a branch back to the main program, the old PSW must be fetched from storage to function as the current PSW again. This is done by addressing the old PSW in the B1-D1 fields of a Set PSW instruction placed at the end of the subroutine. The entire exchange of the program status words is fully automatic; however, the channel mask bit in the PSW, which determines whether the control unit is interruptible or not, may be set or reset under program control. The control unit is interruptible when the channel mask bit is set to 1; it is not interruptible if the channel mask bit is 0. The channel mask bit is zero when the control unit is in a reset state.

# ARITHMETIC AND LOGICAL OPERATIONS

The arithmetic and logical operations are employed to process binary numbers of fixed length, decimal numbers of variable length, and logical information of either fixed or variable length.

Arithmetic and logical operations performed by the control unit fall into three classes: binary arithmetic, decimal arithmetic, and logical operations. These three classes differ in the data formats used, the registers involved, the operations provided, and in the way the field length is stated.

# BINARY ARITHMETIC

The binary arithmetic operand is the 16-bit binary halfword. The binary instruction perform binary arithmetic on operands serving as addresses, index quantities, and counts, as well as binary data. One operand is always in a general register. The second operand may be either in main storage or in a general register.

# Data Format

Binary numbers occupy a fixed length format consisting of a one-bit sign followed by the 15-bit binary field. When held in one of the general registers, a binary quantity has a 15-bit binary field and occupies all 16 bits of the register.

Binary data in main storage also occupies a 16-bit halfword, with a binary field of 15 bits. This data must be located on integral storage boundaries for this unit of information, that is, the low-order binary address bit is zero.

# Halfword Binary Number

| sign | ı | number |

|------|---|--------|

| 0    | 1 | 15     |

#### NUMBER REPRESENTATION

All binary operands are treated as signed numbers. Positive numbers are represented in true binary notation with the sign bit set to 0. Negative numbers are represented in two's-complement notation with a 1 in the sign bit. The two's complement of a number is obtained by inverting each bit of the number and adding a one in the low-order bit position.

The number obtained by inverting each binary bit represents the one's complement of the original number. To represent the two's complement, a one must be added to the low-order position of the one's complement.

```

0 1 1 1 C 1 C 1 0 0 1 C 1 1 1 0 = original number 1 0 0 0 1 0 1 0 1 0 1 0 0 0 1 = one's complement 1 0 0 0 1 0 1 0 1 0 1 0 0 0 1 0 = two's complement | |

```

Two s-complement notation does not include a negative zero. It has a number range in which the set of negative numbers is one larger than the set of positive numbers. The maximum positive number consists of an all-one integer field with a sign bit of zero, whereas the maximum negative number consists of an all-zero integer field with a 1 bit for sign.

The control unit cannot represent the complement of the maximum negative number. When an operation, such as a subtraction from zero, produces the complement of the maximum negative number, the number remains unchanged, and a binary overflow condition is recognized. An overflow does not result, however, when the number is complemented and the final result is within the representable range. An example of this case is a subtraction from minus one.

The sign bit is leftmost in a number. An overflow carries into the sign-bit position and changes the sign.

Figure 1-5 illustrates some sample values of 16-bit binary integers and their equivalents in decimal form.

| Number              |   | Signed<br>Decimal |   | S      |      | INTEGER |      |   |

|---------------------|---|-------------------|---|--------|------|---------|------|---|

| 2 <sup>15</sup> -1  | = | 32767             | = | 0111   | 1111 | 1111    | 1111 |   |

| 28                  | = | 256               | = | 0000   | 0001 | 0000    | 0000 |   |

| 20                  | = | 1                 | = | 0000 0 | 000  | 0000    | 0001 |   |

| 0                   | = | 0                 | = | 0000 0 | 000  | 0000    | 0000 |   |

| -2 <sup>0</sup>     | = | -1                | = | 1111 1 | 111  | 1111    | 1111 |   |

| -2 <sup>1</sup>     | = | -2                | = | 1111 1 | 111  | 1111    | 1110 |   |

| -28                 | = | -256              | = | 1111 1 | 111  | 0000    | 0000 |   |

| -2 <sup>15</sup> +1 | = | -32767            | = | 1000 0 | 000  | 0000    | 0001 |   |

| -2 <sup>15</sup>    | = | -32768            | × | 1000 0 | 000  | 0000    | 0000 | · |

Figure 1-5. Binary Representation

#### CONDITION CODE

The results of binary add, subtract, and compare operations are used to set the condition code in the Program Status Word (PSW). All other binary operations leave this code undisturbed. The condition code can be used for decision-making by subsequent branch-on-condition instructions.

The condition code is set to reflect three types of results for binary arithmetic. For most operations, the status 0(00), 1(01), or 2(10) indicate a zero, less than zero, or greater than zero content of the result register. An overflow results in a Binary Overflow Check condition.

For a compare operation, the states 0, 1, or 2 indicate that the first operand is equal, 1cw, or high compared to the second operand. Condition code settings are shown in Figure 1-6.

|                                                                          | 0                                     | 1                                                                                               | 2                                |

|--------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------|

| Compare Halfword<br>Add Halfword<br>Subtract Halfword<br>Add<br>Subtract | equal<br>zero<br>zero<br>zero<br>zero | low <zero <zero="" <zero<="" td=""><td>high &gt; zero &gt; zero &gt; zero &gt; zero</td></zero> | high > zero > zero > zero > zero |

Figure 1-6. Condition Code Settings for Binary Arithmetic

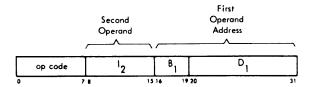

#### INSTRUCTION FORMAT

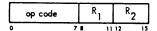

Binary instructions use the following two formats:

# RR Format

# RX Format

|   | op code | R <sub>1</sub> | 0000 | <sup>8</sup> 2 | D <sub>2</sub> |  |

|---|---------|----------------|------|----------------|----------------|--|

| • |         |                |      |                | **             |  |

In these formats, R1 specifies the address of the general register containing the first operand. The second operand location, if any, is defined differently for each format.

In the RR format, the R2 field specifies the address of the general register containing the second operand.

In the RX format, the address which designates the storage location of the second operand is derived from the contents of the B2 and D2 fields of the instruction. This address may be taken directly from the B2 and D2 fields, or an effective address may be formed by adding the contents of the general register specified by the B2 field to the contents of the D2 field. See "Addressing."

Bits 12 thorugh 15 of the RX format must be zero. The second operand, addressed by B2-D2, must begin on a halfword boundary, that is, its address, must be even, otherwise a program error stop occurs.

Results of operations replace the first operand exceet for a store operation. The result replaces the second operand for the store operation.

An instruction can specify the same general register both for address modification and for operand location. Address modification is always completed before execution of the operation.

The contents of all general registers and storage locations participating in the addressing or execution part of an operation remain unchanged, except for the storing of the final result.

# Instructions

The binary arithmetic instructions and their mnemonics, formats, and operation codes are listed in Figure 1-7.

| Name              | Mnemonic | Format | Operation<br>Code |

|-------------------|----------|--------|-------------------|

| Load Halfword     | LH       | RX     | 48                |

| Add Halfword      | AH       | RX     | 4A                |

| Subtract Halfword | SH       | RX     | 48                |

| Compare Halfword  | СН       | RX     | 49                |

| Store Halfword    | STH      | RX     | 40                |

| Add               | AR       | RR     | 1A                |

| Subtract          | SR       | RR     | 18                |

Figure 1-7. Binary Instructions

# Load Halfword (RX)

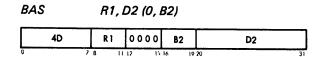

LH R1, D2 (0, B2)

| 48  | R <sub>1</sub> | 0000  | <sup>B</sup> 2 | D <sub>2</sub> |

|-----|----------------|-------|----------------|----------------|

| 0 7 | 8 11           | 12 15 | 16 19          | 20 31          |

The second operand is placed in the first operand location. The instruction uses FX format and provides for loading a halfword from

the main-storage location specified by the B2-D2 fields into the register specified by the R1 field. The condition code is not changed.

# Add Halfword (RX)

AH R1, D2 (0, B2)

|   | 4A | R <sub>1</sub> | 0000  | B <sub>2</sub> | D <sub>2</sub> |

|---|----|----------------|-------|----------------|----------------|

| 0 | 7  | 8 11           | 12 15 | 16 19          | 20 31          |

The second operand is added to the first operand and the sum is placed in the first operand location. Both operands are halfword length. The first operand is contained in the register specified by the R1 field. The second operand is located at a main-storage location specified by the B2-D2 fields of the instruction.

Addition is performed by adding all 16 bits of both operands. If the 'carries' out of the sign-bit position and the high-order numberic bit position agree, the sum is satisfactory; if they disagree, an overflow occurs. The sign bit is not changed after the overflow. A positive overflow yields a negative final sum, and a negative overflow results in a positive sum. The overflow causes a binary-overflow-check condition. The condition code is set to 00, 01, or 10 to indicate that the result is zero, less than zero, or greater than zero.

#### Subtract Halfword (RX)

SH R1, D2 (0, B2)

The second operand is subtracted from the first operand and the difference is placed in the first operand location. Both operands are halfword length. The first operand is contained in the register specified by the R1 field. The second operand is located at a main-storage location specified by the B2-D2 fields of the instruction.

Subtraction is performed by adding the two's complement of the second operand to the first operand. All 16 bits of both operands participate, as in ADD. If the 'carries' out of the sign-bit position and the high-order numeric bit position agree, the difference is satisfactory; if they disagree an overflow occurs, resulting in a bianry-overflow-check condition. The condition code is set to 00, 01, or 10 to indicate that the result is zero, less than zero, or greater than zero.

Compare Halfword (RX)

CH R1, D2 (0, B2)

|   | 49 | R <sub>1</sub> | 0000  | B <sub>2</sub> | D <sub>2</sub> |

|---|----|----------------|-------|----------------|----------------|

| 0 | 7  | 8 II           | 12 15 | 16 19          | 20 31          |

The first operand is compared with the second operand, and the result of the compare is indicated by the setting of the condition code in the PSW. The first operand is contained in the register specified by the R1 field. The second operand is located at a main-storage location specified by the B2-D2 fields of the instruction.

Comparison is algebraic, treating both comparands as 16-bit signed integers. Operands in registers or storage are not changed as a result of the operation.

The condition code is 00 if the operands are equal, 01 if the first operand is lower than the second operand, and 10 if the first operand is higher than the second.

Store Halfword (FX)

STH R1, D2 (0, B2)

|   |     |                |         |                |                | _        |

|---|-----|----------------|---------|----------------|----------------|----------|

| İ | 40  | R <sub>1</sub> | 0000    | <sup>B</sup> 2 | D <sub>2</sub> | 1        |

|   | 0 7 | <b>8</b> 11    | 12 15 1 | 6 19           | 20 1           | <u> </u> |

The first operand is stored at the second operand location. The instruction uses RX format and provides for storing a halfword from the register specified by the R1 field into the main-storage location specified by the B2-D2 fields of the instruction. The condition code remains unchanged.

Add (RR)

AR R1, R2

The second operand is added to the first operand, and the sum is placed in the first operand location. The halfword contained in the register

specified by the R1 field is added to the halfword contained in the register specified by the R2 field and the sum replaces the contents of the register specified by R1.

Addition is performed by adding all 16 bits of both operands. If the 'carries' out of the sign-bit position and the high-order numeric bit position agree, the sum is satisfactory; if they disagree, an overflow occurs. The sign bit is not changed after the overflow. A positive overflow yields a negative final sum, and a negative overflow results in a positive sum. The overflow causes a binary-overflow-check condition. The condition code is set to 00, 01, or 10 to indicate that the result is zero, less than zero, or greater than zero.

Subtract (RR)

SR R1, R2

The second operand is subtracted from the first operand, and the difference is placed in the first operand location.

The halfword contained in the register specified by the R2 field is subtracted from the halfword contained in the register specified by the R1 field and the difference replaces the contents of the register specified by R1.

Subtraction is performed by adding the two's complement of the second operand to the first operand. All 16 bits of both operands participate, as in ADD. If the 'carries' out of the sign-bit position and the high-order numeric bit position agree, the difference is satisfactory; if they disagree, an overflow occurs. The overflow causes a binary-overflow-check condition. The condition code is set to 00, 01, or 10 to indicate that the results is zero, less than zero, or greater than zero.

### BINARY ARITHMETIC ERROF CONDITIONS

Error conditions which may occur during the instruction or exeuction phase of binary operations are:

1. Operation code invalid.

# 2. Addressing error.

- a. An insturciton address or an operand address refers to the protected first 144 bytes of main storage (addresses 0 through 143).

- b. An instruction address or an operand address is outside available storage.

- c. In the 2922-1, the last (highest) main-storage position contains any part of an instruction to be executed.

- d. The R1 or R2 fields of a binary instruction contain values 0 through 7.

# 3. Specification error.

- a. The low-crder bit of an instruciton address is one.

- b. The halfword second operand is not located on a 16-bit boundary.

- c. Bits 12 through 15 of an RX format instuction are not all zero.

- 4. Binary overflow check.

- 5. Control Unit parity error.

### DFCIMAL ARITHMETIC

Decimal arithmetic operations include addition, subtraction, multiplication, division, and comparison. Both operands and results are located in storage.

All decimal arithmetic operations are performed with data in the packed mode for optimum use of storage. Since data is often communicated to or from peripheral devices in the zoned form, operations are provided for changing from zoned to packed format and vice versa.

Operand fields can be located on any byte boundary, except for the first 144 bytes of main storage, which are protected. They can have a length of up to 31 digits and sign, except for multiplier and divisor operands which are limited to 15 digits.

Each address specifies the leftmost byte of an operand. Associated with each address is a length field which indicates the number of additional bytes that the operand extends beyond the first byte.

#### DATA FORMAT

Decimal operands reside in main storage only. They occupy fields that may start at any byte address and are composed of one to 16 eight-bit bytes. All operaions use a two-address format.

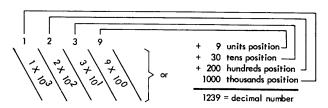

Lengths of the two operands specified in the instruction need not be the same. Regardless of length, the two operands are treated as if the rightmost integers were aligned before the operation begins. For example, in an add operation, the rightmost integers must be aligned to ensure that units are added to units, tens are added to tens, hundreds to hundreds, etc. The programmer may add high-order zeros as needed, to ensure that the result field is always large enough to contain all the digits of the result.

Processing takes place from right to left, as in simple manual arithmetic operations, treating the rightmost position of each operand as the units position, the next position to the left as the tens position, and so on.

Lost 'carries' or lost digits from arithmetic operations are signaled by a decimal-overflow condition. Operands are either in the packed or zoned format. Negative numbers are carried in true form.

# Packed Decimal Number

In the packed format, each eight-bit byte can contain the binary equivalents to two decimal digits, except for the rightmost four bits of the rightmost byte of the field, which represent the sign. Decimal digits 0 through 9 are equivalent to binary values 0000 through 1001.

The decimal digits range from 0 to 9 while any value from 10 to 15 (in hexadecimal representation 'A' to 'F') is regarded as a valid sign. In decimal arithmetic, all numbers must be arranged in the packed format. By means of the Pack instruction, it is possible to change zoned decimal numbers into packed numbers. Decimal number fields may overlap only when their rightmost bytes are identical. During the execution of all decimal arithmetic instructions, all data is checked for validity. A sign code found in any other but the sign position leads to an error stop as does a decimal value that is found in the sign position.

### Zoned Decimal Numbers

In the zoned format, each eight-tit byte can contain one decimal digit in the right four bits and a zone code in the left four bits. However, the rightmost byte of a zoned decimal number field contains the digit in the right half and the sign in the left half.

The zone bits act only as fill characters and do not affect the value of the decimal digits. The zoned format is needed for decimal data that is sent to character-set sensitive I/O devices. all decimal data that is received from card I/O devices comes in the The zone is either 15 (F) in the Extended Binary-Codedzoned format. Decimal Interchange Code (EBCDIC) or 5 in the American National Standard Code for Information Interchange (ASCII). Since the zone F is identical with one of the general plus signs, all data received from punched cards is recognized as positive unless it is explicitly specified as negative data. Data can be changed from the packed to the zoned format by means of the Unpack instruction. During unpacking, the correct zone is automatically supplied by the control unit. The zone used depends on the mode indicated in bit 6 cf the PSW. If the mode bit is zero, the EBCDIC-zone F is used; if the mode bit is one, the ASCIIzone 5 is used.

#### AUTOMATIC SIGN STANDARDIZATION

During the processing of all arithmetic instructions that handle decimal data, the control unit supplies the final result with the correct sign, according to the rules of algebra. The resultant sign is either a ASCII plus or minus sign, or an FBCDIC plus or minus sign (Figure 1-8). Whether the result sign is standardized in the ASCII mode or in the EBCDIC mode depends on mode bit 6 in the PSW. For example, if the result sign is positive and the mode bit is zero, the sign code 1100 is selected. If the result sign is negative and the mode bit is 1, the sign code 1011 is selected. Thus, the result can have only a ASCII or an EBCCIC sign.

| Valid Sign Codes | ASCII | EBCDIC |  |

|------------------|-------|--------|--|

| (A) 1010 +       | +     |        |  |

| (B) 1011 -       | •     |        |  |

| (C) 1100 +       |       | +      |  |

| (D) 1101 -       |       | -      |  |

| (E) 1110 +       |       |        |  |

| (F) 1111 +       |       |        |  |

Figure 1-8. Sign standardization

#### CONDITION CODE

The results of all add-type and comparison operations are used to set the condition code in the PSW. All other decimal arithmetic operations leave the code unchanged. The condition code can be used for decisionmaking by subsequent Branch-cn-Condition instructions.

The condition code is set to reflect the types of results for decimal arithmetic. Four different result types can occur:

- 1. The result is zero, indicated by condition code 00.

- 2. The result is less than zero (negative), indicated by condition code 01.

- 3. The result is more than zero (rositive), indicated by condition code 10.

- 4. The result does not fit into the result field (overflow) indicated by condition code 11.

For the comparison operation, the condition code settings 0, 1, and 2 indicate that the first operand compared equal, low, or high as shown in Figure 1-9.

|                  | 0     | 1      | 2      | 3        |

|------------------|-------|--------|--------|----------|

| Add Decimal      | zero  | < zero | > zero | overflow |

| Compare Decimal  | equal | low    | high   |          |

| Subtract Decimal | zero  | < zero | > zero | overflow |

| Zero and Add     | zero  | < zero | > zero |          |

Figure 1-9. Condition Code Settings for Decimal Operations

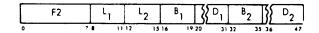

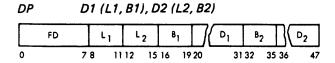

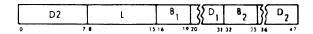

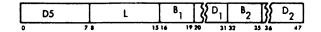

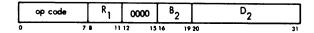

#### INSTRUCTION FORMAT

Decimal instruction use the following format:

# SS Format

In this format, the address which specifies the core-storage location of the leftmost byte of the first operand field is derived from the contents of the E1 and D1 fields of the instruction. The number of operand bytes to the right of this byte is specified by the L1 field of the instruction. Therefore, the length in bytes of the first operand field is 1 to 16 corresponding to a length code in L1 of 0000 to 1111. The second operand field is specified similarly by the L2, B2, and D2 instruction fields.

As previously described in the section "Addressing", the address of each operand may be taken directly from the respective B and D fields of the instruction, or effective addresses may be formed by adding the contents of the general register specified by the B field to the contents of the D field.

Results of operations replace the first operand field. The result is never stored outside the field specified by the address and length. The second operand field remains unchanged, except in those cases where overlapping fields, which are permitted, actually occur. The contents of the general registers remain unchanged.

#### INSTRUCTIONS

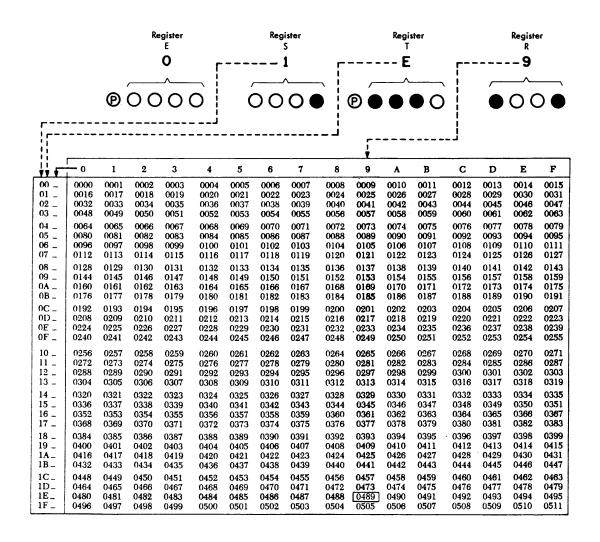

The decimal arithmetic instructions and their mnemonics and operation codes are shown in Figure 1-10.

| Name             | Mnemonic | Format | Operation<br>Code |

|------------------|----------|--------|-------------------|

| Pack             | PACK     | SS     | F2                |

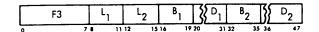

| Unpack           | UNPK     | SS     | F3                |

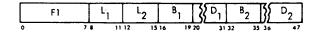

| Move with Offset | MVO      | SS     | Fl                |

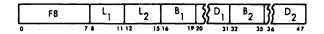

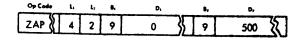

| Zero and Add     | ZAP      | SS     | F8                |

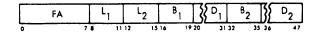

| Add Decimal      | AP       | SS     | FA                |

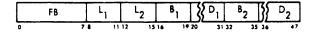

| Subtract Decimal | SP       | SS     | FB                |

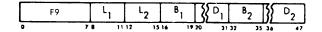

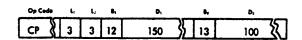

| Compare Decimal  | CP       | SS     | F9                |

| Multiply Decimal | MP       | SS     | FC                |

| Divide Decimal   | DP       | SS     | FD                |

Figure 1-10. Decimal Instructions

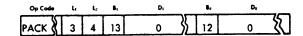

# Pack (SS)

PACK D1 (L1, B1), D2 (L2, B2)

The format of the second operand is changed from zoned to packed, and the result is placed in the first operand location.

The second operand is assumed to have the zoned format. All zones are ignored, except the zone over the low-order digit, which is assumed to represent a sign. The sign is placed in the right four bits of the low-order byte, and the digits are placed adjacent to the sign and to each other in the remainder of the result field. The sign and digits are moved unchanged to the first operand field and are not checked for valid codes.

The fields are processed right to left. If the second operand does not fill the first operand completely, the remaining high-order positions of the first operand are filled with zeros. If the first operand field is too short to contain all the significant digits of the second operand field, the remaining digits are ignored. Overlapping fields may occur and are processed by storing each result byte immediately after the necessary operand bytes are fetched.

The condition code remains unchanged.

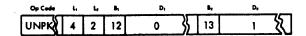

### Unpack (SS)

UNPK D1 (L1, B1), D2 (L2, B2)

The format of the second operand is changed from packed to zoned, and the result is palced in the first operand location.

The digits and sign of the packed operand are placed unchanged in the first operand location, using the zoned format. Zones with coding 1111 in EBCDIC mode and coding 0101 in the ASCII mode are supplied for all bytes except the rightmost byte, which receives (in its high-order four bits) the sign of the packed operand. The operand sign and digits are not checked for valid codes.

The fields are processed right to left. If the second operand does not fill the first operand completely, the remaining high-order bytes of the first operand are each filled with a zero and a zone. If the first operand field is too short to contain all significant digits of the second operand, the remaining digits are ignored. The first and second operand fields may overlap and are processed by storing a result byte immediately after the necessary operand bytes are fetched. Caution must be exercised when overlapping the operands, otherwise bytes which have already been unpacked may be unpacked a second time during a single operation, thus giving an incorrect result.

The condition code remains unchanged.

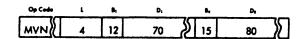

Move with Offset (SS)

MVO D1 (L1, B1), D2 (L2, B2)

The second operand is placed to the left of and adjacent to the loworder four bits of the first operand.

The low-order four bits of the first operand are attached as low-order bits to the second operand, the second operand bits are offset by four bit positions, and the result is placed in the first operand location. Thus, the second operand is effectively offset by half a

byte and, after the operand, the two halves of each original byte are located in two adjacent bytes. The first and second operand bytes are not checked for valid codes.

The fields are processed right to left. If necessary, the second operand is extended with high-order zeros. If the first operand field is too short to contain all bytes of the second operand, the remaining information is ignored. Overlapping fields may occur and are processed by storing a result byte as soon as the necessary operand bytes are fetched.

The condition codes remains unchagned.

Zero and Add (SS)

ZAP D1 (L1, B1), D2 (L2, B2)

The second operand is placed in the first operand location.

The operation is equivalent to an addition to zero. The sign code is made 1100 for positive and 1101 for negative results in EBCDIC and 1010 for positive and 1011 for negative results in the ASCII mode. A zero result is always positive.

When the length of the second operand (L2) is greater than the length of the first operand (L1) a specification error stop occurs. The instruction is not executed.

The second operand is checked for valid sign and digit codes. Extra high-order zeros are supplied if needed. The first and second operand fields may overlap when the rightmost byte of the first operand field is coincident with or to the right of the rightmost byte of the second operand.

The condition code is set to 00, 01, or 10 to indicate that the result is zero, less than zero, or greater than zero.

### Add Decimal (SS)

AP D1 (L1, B1), D2 (L2, B2)

The second operand is added to the first operand, and the sum is placed in the first operand location.

When the length of the second operand (L2) is greater than the length of the first operand (L1), a specification-error stop occurs. The instruction is not executed.

Addition is algebraic, taking into account the sign and all digits of both operands. All signs and digits are checked for validity. If necessary, high-order zeros are supplied for the second operand.

The first and second operand fields may overlap when their loworder bytes coincide: therefore, it is possible to add a number to itself.

The sign of the result is determined by the rules of algebra. A zero sum is always positive. When high-order digits are lost because of an overflow, a zero result has the sign of the correct sum.

The condition code is set to CC, C1, 10 or 11 to indicate that the result is zero, less than zero, greater than zero, or overflow. A decimal overflow is not considered to be an error; that is, no machine stop occurs.

# Subtract Decimal (SS)

SP D1 (L1, B1), D2 (L2, B2)

The second operand is subtracted from the first operand, and the difference is placed in the first operand location.

When the length of the second operand (L2) is greater than the length of the first operand (L1) a specification error stop occurs. The instruction is not executed.

Subtraction is algebraic, taking into account the sign and all digits of both operands. The Subtract Decimal instruction is similar to the Add Decimal instruction, except that the sign of the second operand is changed from positive to negative or from negative to positive after the operand is obtained from storage and before the arithmetic operation.

The sign of the result is determined by the rules of algebra. A zero difference is always positive. When high-order digits are lost because of overflow, a zero result has the sign of the correct difference.

The operands of a Subtract instruction may overlap when their low-order bytes coincide even when their lengths are unequal. This property may be used to make an entire field or the low-order part of a field zero. The condition code is set to 00, 01, 10, or 11 to indicate that the result is zero, less than zero, greater than zero, or an overflow condition. A decimal overflow is not considered to be an error; that is, no machine stop occurs.

# Compare Decimal (SS)

CP D1 (L1, B1), D2 (L2, B2)

The first operand is compared with the second, and the condition code indicates the comparison result.

When the length of the second operand (I2) is greater than the length of the first operand (L1), a specification-error stop occurs. The instruction is not executed.

Comparison is right to left, taking into account the sign and all digits of both operands. All signs and digits are checked for validity. If the second operand field is shorter in length than the first operand field, the second operand field is extended with high-order zeros. A positive zero compares equal to a negative zero. Neither operand is changed as a result of the operation. Overflow cannot occur in this operation.

The first and second fields may overlap when their low-order bytes coincide. It is possible, therefore, to compare a number to itself.

A Decimal Compare instruction differs in several respects from a Logical Compare instruction. Signs, zeros, and invalid characters are considered and fields are extended when unequal in length. The

condition code is made 00 if the operands are equal, 01 if the first operand is low, and 10 if the first operand is high.

Multiply Decimal (SS)

MP D1 (L1, B1), D2 (L2, B2)

The product of factor one (the first operand) times factor two (the second operand) replaces the first operand. A multiplication can be performed only on data in the packed format. The length codes contained in the L1 and L2 fields specify the number of bytes that extend to the left of the units byte. The units byte is the rightmost byte of a packed decimal operand and it contains one digit and the sign. Factor two is limited to a size of 15 digits plus the sign, or in other words, the length code of factor two must not be greater than 7. Furthermore, the length code of factor two must always be smaller than the length code of factor 1. If L2 is greater or equal to L1, or if L2 exceeds 7, a program error stor occurs.

Factor one is limited to a size of 16 bytes (length code 15). The main storage location of factor one is specified by the B1-D1 field according to the rules for direct or effective-address generation. Similarly, the location of factor two is specified by the B2-D2 field.

Since the number of digits in the product (the result) is the sum of the number of digits in both operands, factor one must have as many leading (high-order) zero bytes as factor two has data bytes (L2+1). This requirement for the factor one field ensures that no product overflow can occur. If factor one has insufficient high-order zeros, a program error stop occurs. The sign of the product is developed from the signs of both operands according to the rules of algebra. This is true also when one or both operands are zero. If the larger of the two factors is 15 digits or less, the most efficient use of this instruction is realized when the larger factor is used in the second operand.

The factor two field may everlap the product field when the loworder bytes of both fields coincide. The condition code is not changed by a Multiply Decimal instruction.

# <u>Divide Decimal (SS)</u>

The dividend (the first operand) is divided by the divisor (the second operand) and is replaced by the quotient and remainder. A divide operation must be performed on data in the packed format only. Length codes, contained in the L1 and L2 fields, specify the number of bytes to the left of the units byte. Each byte contains two arithmetic digits, except the units byte which contains one digit and a sign. The location of the dividend is specified by the B1-D2 field, and the location of the divisor is specified by the B2-D2 field. The result consists of the quotient and the remainder.

The quotient field is placed leftmost in the first operand field. The remainder field is placed rightmost in the first operand field and has a size equal to the divisor size. Together, the quotient and remainder occupy the entire former dividend field; therefore, the address of the quotient field is the address of the first operand. The size of the quotient field in eight-bit bytes is L1-L2, and the length code for this field is one less (L1-L2-1). When the divisor length code is larger than seven (15 digits and sign) or larger than or equal to the dividend length code, the operation is not executed and an error stop occurs.

The dividend, divisor, quotient, and remainder are all signed integers, right-aligned in their fields. The sign of the quotient is determined by the rules of algebra from dividend and divisor signs. The sign of the remainder is the same as the dividend sign. These rules are true even when quotient or remainder is zero.

A divide check occurs when the quotient is larger than the number of digits allowed for it, or if the dividend does not have at least one leading zero. If a divide check cccurs, the operation is not executed and a decimal-divide-error stop occurs. Divisor and dividend remain unchanged in their storage locations.

The divisor and dividend fields may overlap only if their low-order bytes coincide.

The condition code remains unchanged for division, and overflow cannot occur.

# Programming Nctes

The maximum dividend size is 30 digits and sign (16 packed bytes). Since the smallest remainder size is one digit and sign, the maximum quotient size is 29 digits and sign.

The condition for a divide check can be determined by a trial subtraction. The leftmost digit of the divisor field is aligned with the leftmost-plus-one digit of the dividend field. When the divisor, so aligned, is less than or equal to the dividend, a quotient overflow is indicated.

By programming a Divide Decimal instruction so that the dividend field (the first operand) has a number of high-order zero digits equal to the field size of the diviscr field (the second operand), a divide check occurs only when a division by zero is attempted.

#### DECIMAL ARITHMETIC EFROR CONDITIONS

The following error conditions may occur during the instruction or execution phases of decimal arithmetic operations:

- 1. Operation code invalid.

- 2. Addressing error.

- a. An instruction address or an operand address refers to the protected first 144 bytes of main storage.

- b. An instruction address or an operand address is outside available storage.

- c. An instruction occupies the last two (highest) main storage positions.

- 3. Specification error.

- a. The low-order bit of an instruction address is 1.

- b. For Zero and Add, Compare Decimal, Add Decimal, and Subtract Decimal instructions, the length code L2 is greater than the length code L1.

- c. For Multiply Decimal and Divide Decimal instructions, the length code L2 is greater than 7 or greater than or equal to the length code L1.

#### 4. Data error.

- Decimal, Add Decimal, Subtract Decimal, Multiply Decimal, or Divide Decimal instruction is incorrect, or the operand fields in these instructions overlap incorrectly.

- b. The factor one field (first operand) in a Multiply Decimal instruction has insufficient high-order zeros.

- 5. Pecimal divide check. The resultant quotient in a Divide Decimal instruction exceeds the specified data field instruction (including division by zero) or the dividend has no leading zero.

- 6. Control Unit parity error.

# LCGICAL CPERATIONS

A set of operations is provided for the logical manipulation of data. Generally the operands are treated as characters, eight bits at a time. In a few cases the left or right four bits of a byte are treated separately. The operands are either in storage or are introduced from the instruction stream.

Processing of data in storage proceeds left to right through fields which may start at any byte resition.

Except for the Edit instruction, data is not treated as numbers in this section. Editing provides a transformation from packed decimal digits to alphameric characters.

The set of logical operations includes move, comparison, editing, testing, and hit-connective operations.

The condition code is set as a result of all logical connective, comparison, editing, and testing operations.

#### DATA FORMAT

Data resides in storage, or is introduced from the instruction itself. The data size may be a single character, or variable in length. When two operands participate they have equal length, except in the Edit instruction.

In storage-to-storage operations, data has a variable field-length format, starting at any byte address (except for the first 144 storage-protected bytes) and continuing to a maximum of 256 bytes. Processing is left to right.

Operations which introduce data from the instruction into storage are restricted to an eight-hit byte. Only one byte is introduced from the instruction, and only one byte in storage participates.

Editing requires a packed decimal field; in other operations no internal data structure is required and all bit configurations are considered valid.

In storage-to-storage operations, the operand fields may be defined in such a way that they overlap. The effect of this overlap depends upon the operation. When the operands remain unchanged, as in compare, overlapping does not affect the execution of the operation. In the case of move and edit operations, one operand is replaced by new data, and the execution of the operation may be affected by the amount of overlap and the manner in which data is fetched or stored. For purposes of evaluating the effect of overlapped operands, it can be considered that data is always handled one eight-bit byte at a time. All overlapping fields are considered valid, but in the edit operations overlapping fields give unpredictable results.

#### CONDITION CODE

The results of most logical operations are used to set the condition code. The move operations leave this code undisturbed. The condition code can be used for deicison-making by subsequent branch-on-condition instructions.

There are four types of condition code settings for logical instructions. For the Edit instruction the codes 00, 01, and 10 indicate a zero, less than zero, and greater than zero content of the last result field.

For the logical connective operations, the codes 00 and 01 indicate a zero or nonzero result field.

For the Compare Logical instruciton, the codes 00, 01, and 10 indicate that the first operand compared equal, low or high.

Figure 1-11 shows the condition code for logical operations.

|                                                         | 00                                    | 01                                             | 10                         | 11              |

|---------------------------------------------------------|---------------------------------------|------------------------------------------------|----------------------------|-----------------|

| Test under Mask<br>AND<br>Compare Logical<br>OR<br>Edit | zero<br>zero<br>equal<br>zero<br>zero | mixed<br>not zero<br>low<br>not zero<br>< zero | <br><br>high<br><br>> zero | one<br><br><br> |

Figure 1-11. Condition Code Settings for Logical Operations

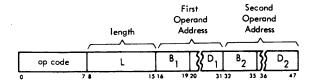

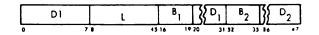

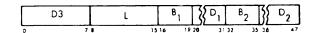

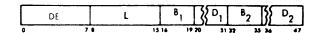

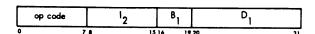

### INSTRUCTION FORMAT

Logical instructions use the SI or SS formats.

# SI FORMAT

In the SI format, the address which specifies the core-storage location of the first operand field is derived from the contents of the B1-D1 fields of the instruction. The address may be taken directly from the B1-D1 fields (direct addressing) or an effective address may be formed by adding the contents of the general register specified by the B1 field to the contents of the D1 field (effective addressing).

Results replace the first operand. The contents of the general registers are not changed.

### SS Format

The address which specifies the core-storage location of the first operand field is derived from the B1-D1 fields of the instruction. The B2-D2 fields specify the leftmost byte of the second operand field. The first and second operand fields are the same length, except in the Edit instruction. The number of bytes extending to the right of the first byte is specified by the I field of the instruction.

The address of each operand may be derived by either direct or effective addressing. The result of the operation replaces the first operand, and is never stored cutside the field specified by the address and length fields of the instruction. The contents of the general registers remain unchanged.

#### INSTRUCTIONS

The logical instructions, their mnemonics, formats, and operation codes are shown in Figure 1-12.

| Name             | Mnemonic | Format | Operation<br>Code |

|------------------|----------|--------|-------------------|

| Move             | MVI      | SI     | 92                |

| Move             | MVC      | ss     | D2                |

| Move Numerics    | MVN      | ss     | DI                |

| Move Zones       | MVZ      | ss     | D3                |

| Compare Logical  | CLI      | SI     | 95                |

| Compare Logical  | CLC      | SS     | D5                |

| Edit             | ED       | SS     | DE                |

| AND              | NI       | SI     | 94                |

| OR               | 01       | SI     | 96                |

| Test under Mask  | TM       | SI     | 91                |

| Halt and Proceed | HPR      | SI     | 99                |

| Translate        | TR       | ss     | DC                |

Figure 1-12. Logical Instructions

## Move (SI)

MVI D1 (B1), 12

## Move (SS)

MVC D1 (L, B1), D2 (B2)

The second operand is placed in the first operand location.

The SS format is used for a storage-to-storage move. The SI format introduces one eight-bit byte from the instruction stream.

In storage-to-storage movement, the fields may overlap in any desired way. Movement is left to right through each field, a byte at a time.

The bytes to be moved are not changed or inspected. The condition code remains unchanged. It is possible to propagate one character through an entire field by having the first operand field start one character to the right of the second operand field.

## Move Numerics (SS)

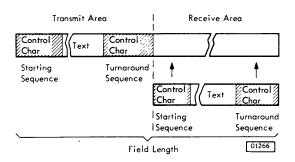

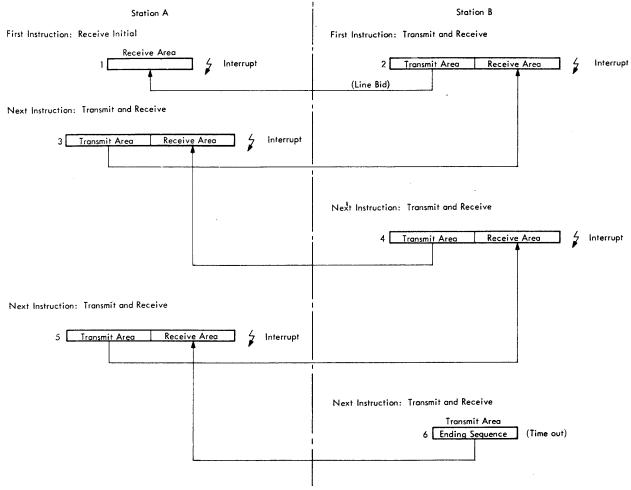

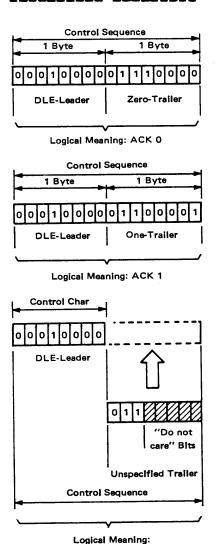

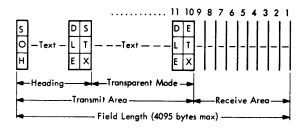

MVN D1 (L, B1), D2 (B2)