# IBM 9020 A System processing AND Control

## **JUNE 1971**

DEPARTMENT OF TRANSPORTATION FEDERAL AVIATION ADMINISTRATION AERONAUTICAL CENTER FAA ACADEMY

CBB-9A0

## Archival notes

Chapter 5 I/O Operations was missing from the source document.

This training manual was produced in July 1968 several years before the first operational installation was deployed. The text does not reflect the final 9020 version in several respects. It was still being used as training course material in the late 1970s, long after all the 9020 systems (with a slightly different configuration) were operational.

The handwritten notes are from 1975, and several of them reflect the differences between the 1968 configuration described in the text and what was finally delivered.

Amongst the differences are the following:

At the time the text was written there was only a single 9020 version, hence the reference to just "9020" in the title. A second, more powerful, version was added later, namely the "9020D". The version described in this text became the "9020A".

The text does not mention disks (DASD). These were added later to 9020As and 9020Ds and referred to as Storage Control Units (SCUs). See the handwritten amendment on page 6-64.

The 9020 was originally conceived as a maximum three-CE configuration. The final 9020A version included up to four CEs. The text and diagrams reflect either the three or four CEs maximum configuration in different sections, presumably depending on when that section was written.

The text refers to Large Capacity Storage (LCS) elements. These were deleted from the final delivered configurations.

The Storage Elements (SEs) referred to in the text are the 128 KB Model-03 and 256 KB Model-04. The final 9020A version used 256 KB Model-08 and 512 KB Model-08A SEs.

April 2025

## SYSTEM PROCESSING AND CONTROL

## CHAPTER 1

## GENERAL INTRODUCTION TO IBM-9020 HARDWARE

| 1-1. | GEN | ERAL   | CONCEPTS OF SYSTEM OPERATION                         | 1-1  |

|------|-----|--------|------------------------------------------------------|------|

| 1-2. | FUN | ICTI O | NAL USE OF COMPONENT ELEMENTS                        | 1-5  |

|      | A.  | Com    | pute Element                                         | 1-5  |

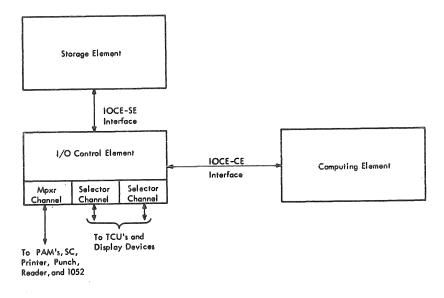

|      | B.  | I/0    | Control Element                                      | 1-5  |

|      | C.  | Sto    | rage Element                                         | 1-5  |

|      | D.  | Per    | ipheral Adapter Module                               | 1-6  |

|      | Ε.  | The    | System Console (SC)                                  | 1-6  |

|      | F.  | 0th    | er Input/Output Control Units                        | 1-7  |

|      |     | 1.     | Integrated Control Unit (2821)                       | 1-7  |

|      |     | 2.     | Tape Control Unit                                    | 1-8  |

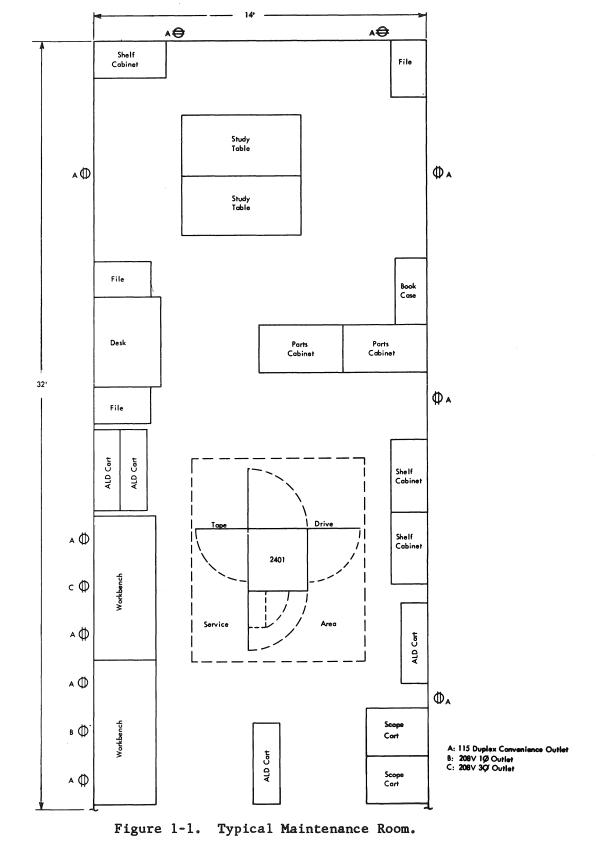

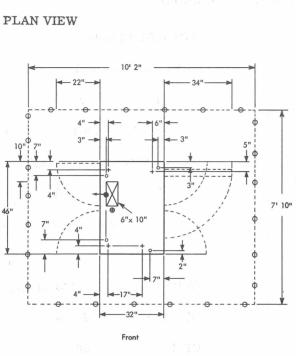

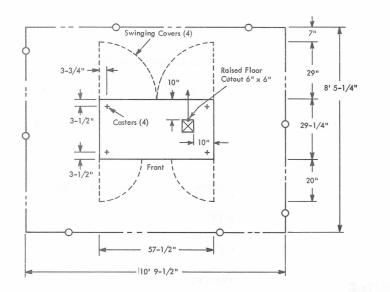

| 1-3. | PRE |        | ALLATION PLANNING                                    |      |

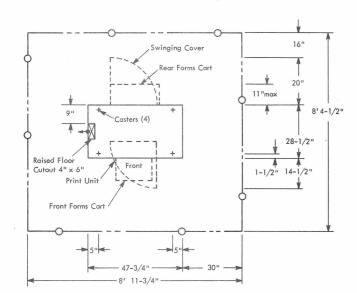

|      | A.  | Bui    | lding Requirements                                   | 1-8  |

|      |     | 1.     | Equipment Layout                                     |      |

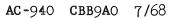

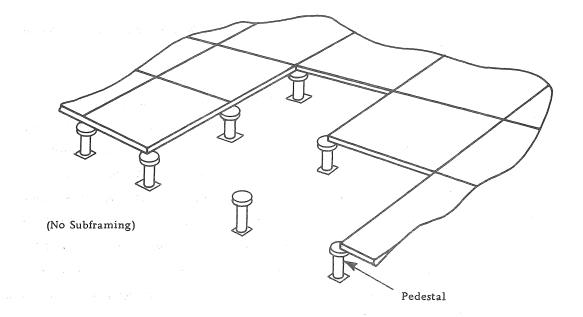

|      |     | 2.     | Floor Construction                                   |      |

|      |     | 3.     | Acoustical Treatment                                 |      |

|      |     | 4.     | Lighting                                             |      |

|      |     | 5.     | Vibration                                            |      |

|      |     | 6.     | Tape Storage                                         | 1-17 |

|      | В.  | Air    | Conditioning                                         | 1-18 |

|      |     | 1.     | Temperature and Humidity Requirements                | 1-18 |

|      |     | 2.     | Air Filtration                                       |      |

|      |     | 3.     | Air Distribution and Types of Systems                | 1-21 |

|      |     |        | a. Single Duct - Overhead System                     |      |

|      |     |        | b. Two Duct - Two Air-Conditioning-Unit System       |      |

|      |     |        | c. Two Duct - Single Air-Conditioning-Unit System    |      |

|      |     |        | d. Underfloor System                                 |      |

|      |     |        | e. Temperature and Humidity Recording Instruments    |      |

|      | C.  | Saf    | ety and Fire Precautions                             | 1-25 |

|      |     | 1.     | Locating a Computer Area                             | 1-25 |

|      |     | 2.     | Structural Safety                                    |      |

|      |     | 3.     | Type of Fire Prevention Equipment in a Computer Area | 1-26 |

| -    |     | 4.     | Data Storage                                         | 1-27 |

|      |     | 5.     | Supporting Facilities                                | 1-28 |

|      |     |        | a. Air Conditioning Systems                          | 1-28 |

|      |     |        | b. Electric Systems                                  |      |

|      |     | 6.     | Preplanning to Continue Operation in an Emergency    | 1-29 |

|      |     | 7.     | General Precautions and Personnel Training           |      |

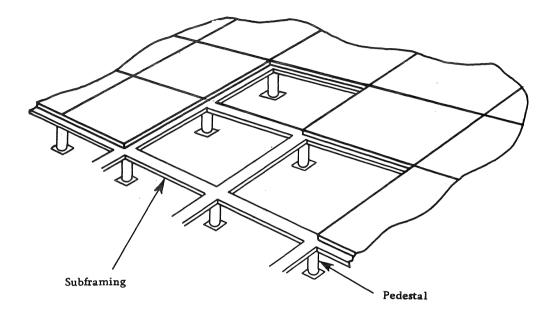

|      | D.  |        | er Requirements                                      |      |

|      |     | 1.     | Phase Rotation                                       |      |

|      |     | 2.     | Convenience Outlets                                  |      |

|      |     | 3.     | Lightning Protection                                 | 1-32 |

|      |     | 4.     | System Grounding                                     | 1-33 |

|      |     | 5.     | Surge Currents                                       | 1-33 |

iii

罐

|      | Ε.  | Physical Planning        |                                        | 1-34  |

|------|-----|--------------------------|----------------------------------------|-------|

|      | F.  | Cabling                  |                                        | 1-47  |

| 1-4. |     |                          |                                        |       |

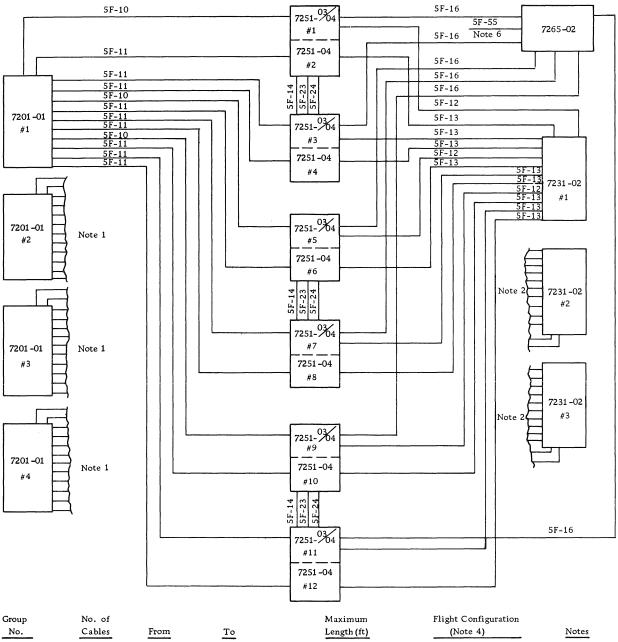

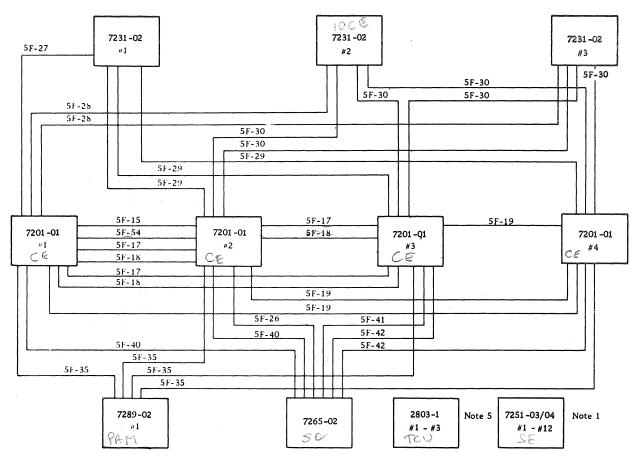

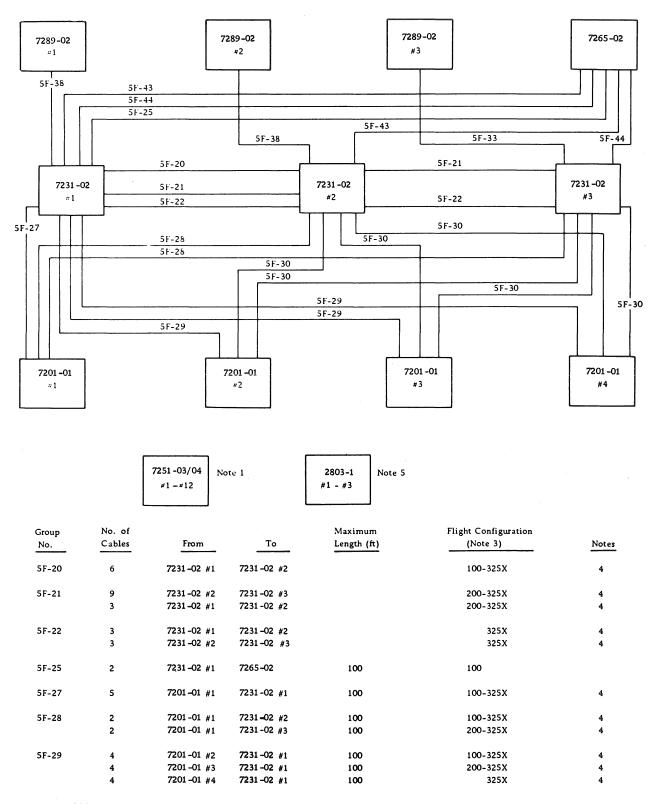

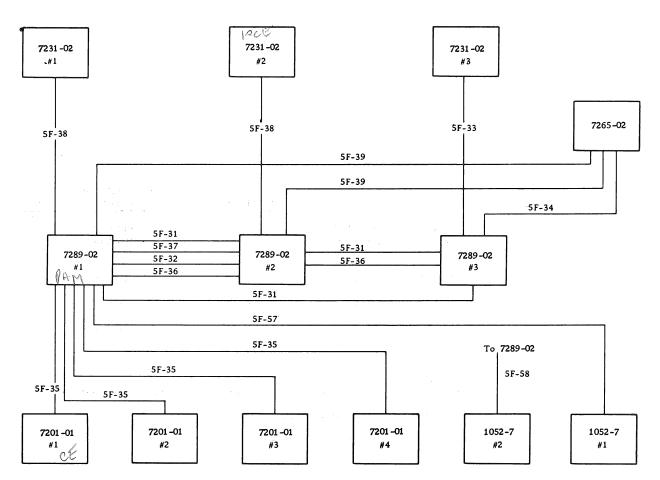

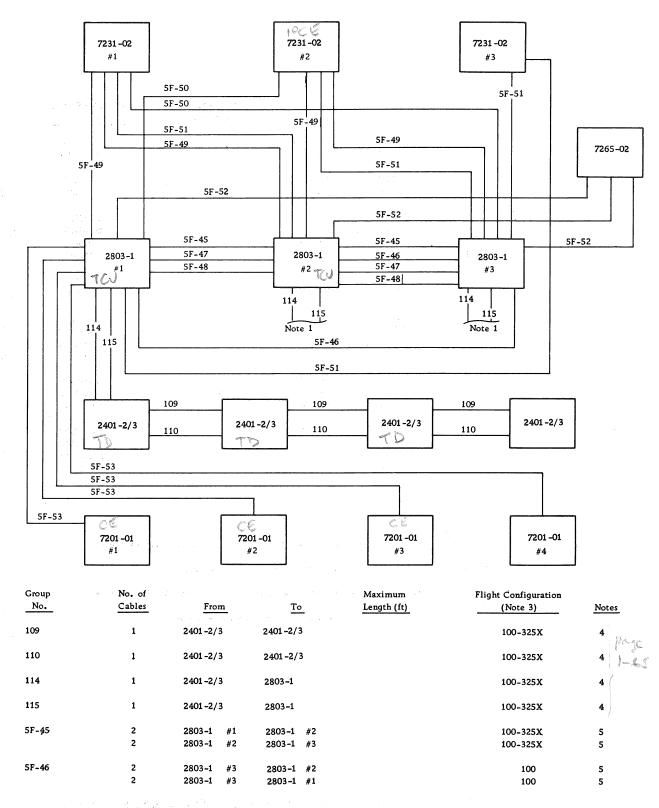

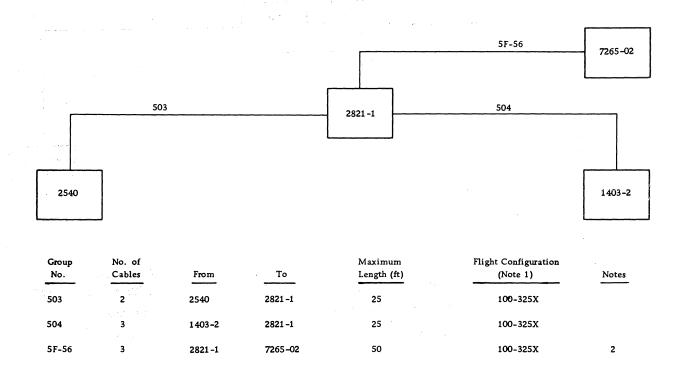

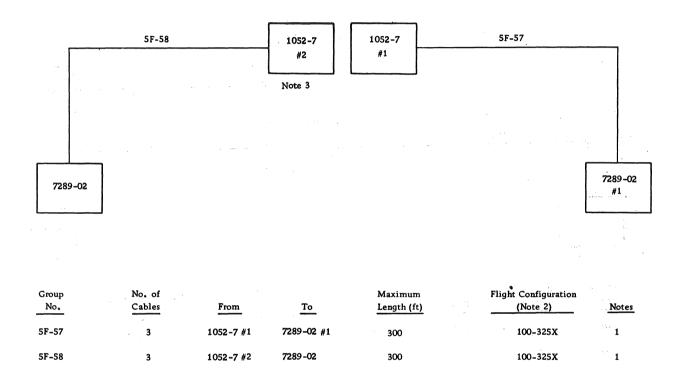

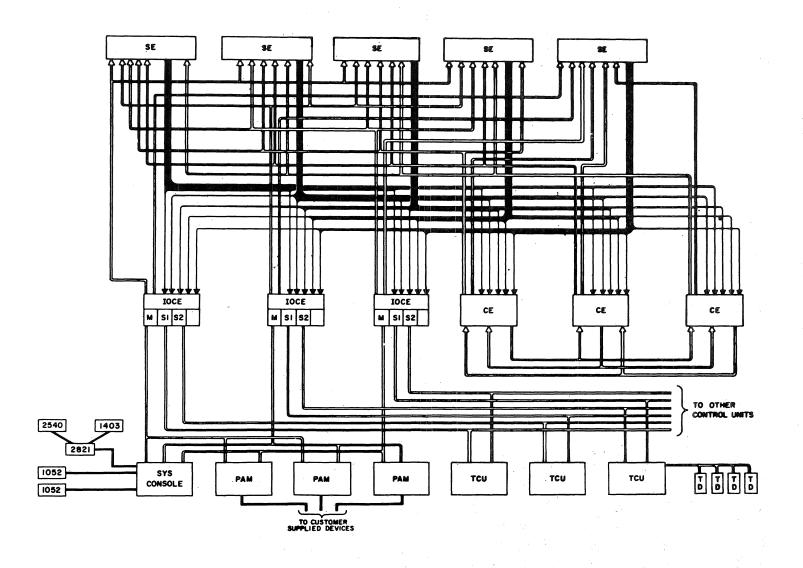

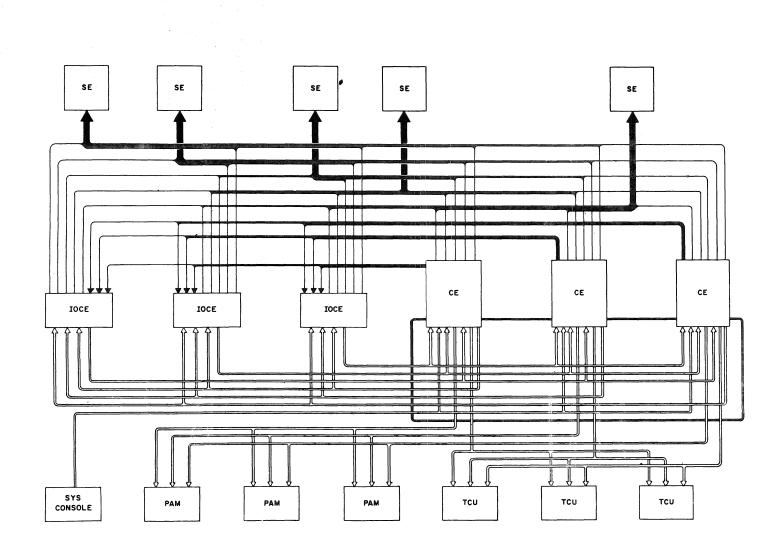

| 1-5. | INI | ER ELEMENT CABLING       |                                        | 1-70  |

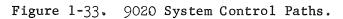

|      | Α.  | CE - CE Interfacing      |                                        | 1-70  |

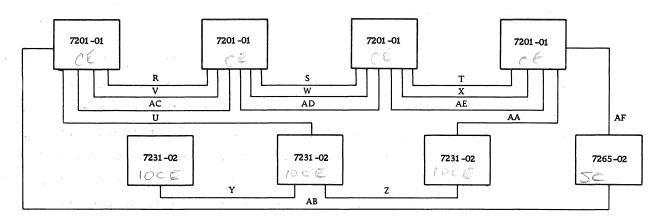

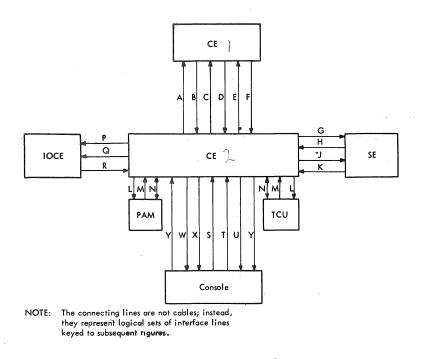

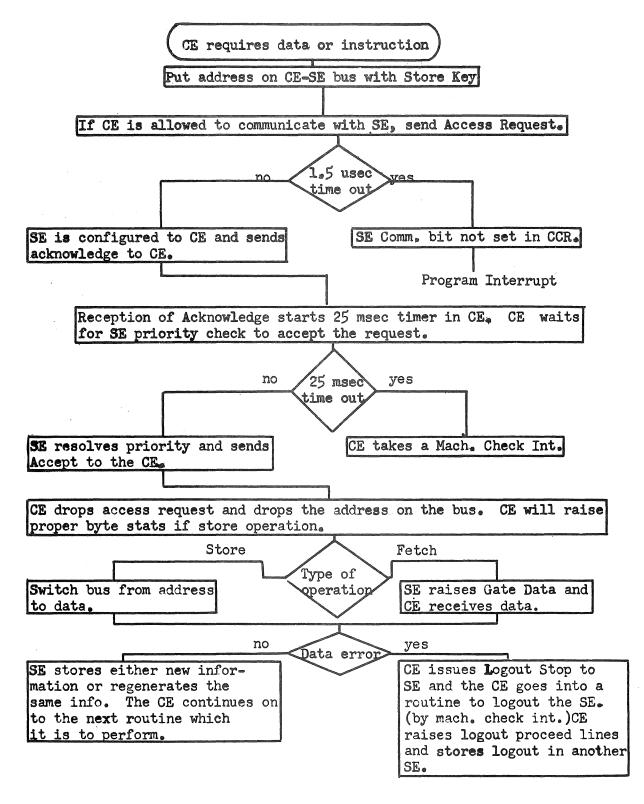

|      | В.  | CE - SE Interfacing      |                                        | 1-73  |

|      | C.  | CE - IOCE Interfacing    |                                        | 1-79  |

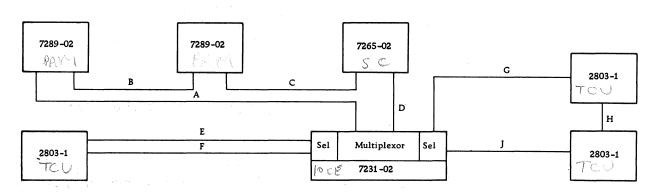

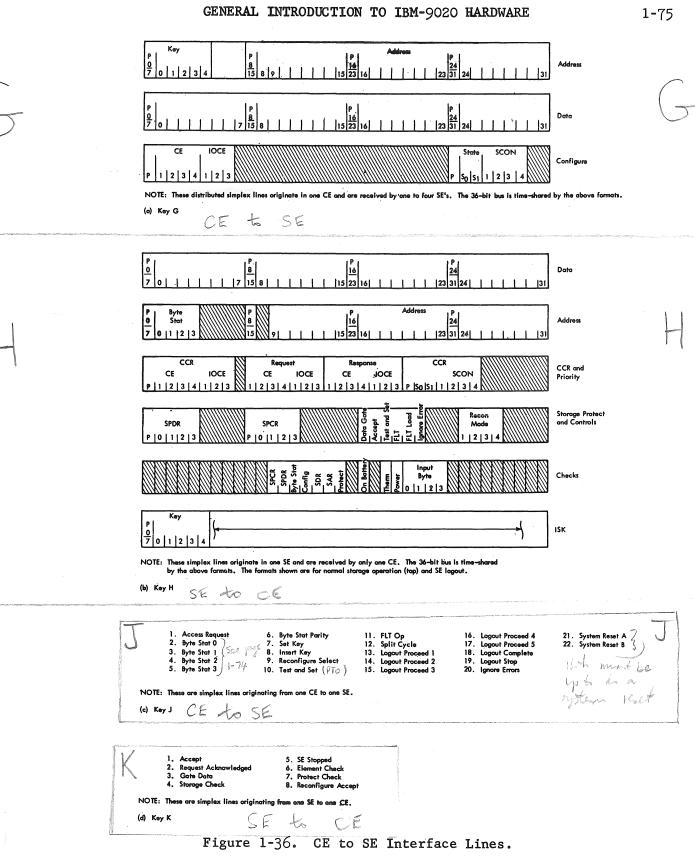

|      | D.  | CE - PAM and TCU Interf  | acing                                  | 1-86  |

|      | Е.  | CE - System Console Inte | erfacing                               | 1-88  |

|      | F.  | IOCE Interfacing         |                                        | 1-93  |

|      | G.  | IOCE - SE Interfacing    |                                        | 1-94  |

|      | Η.  | IOCE - SC Interfacing    | ······································ | 1-95  |

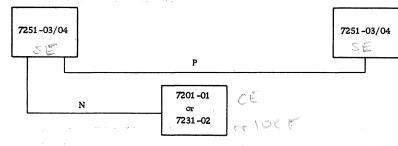

|      | I.  | SE Interfacing           |                                        | 1-95  |

|      | J.  | PAM Interfacing          |                                        | 1-96  |

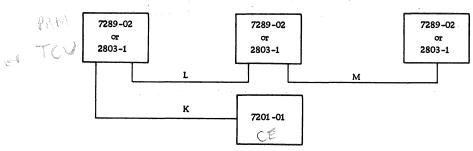

|      | K.  | TCU Interfacing          |                                        | 1-97  |

|      | L.  | System Console Interfac: | ing                                    | 1-98  |

| 1-6. | SYS | TEM COMMUNICATIONS       |                                        | 1-99  |

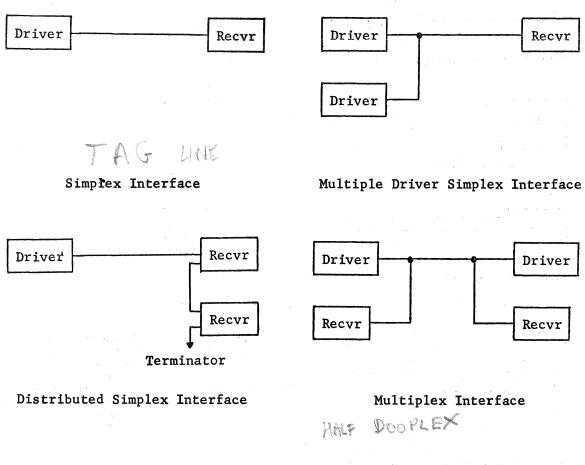

|      | Α.  | CE to CE and IOCE Commu  | nications                              | 1-99  |

|      | В.  |                          |                                        |       |

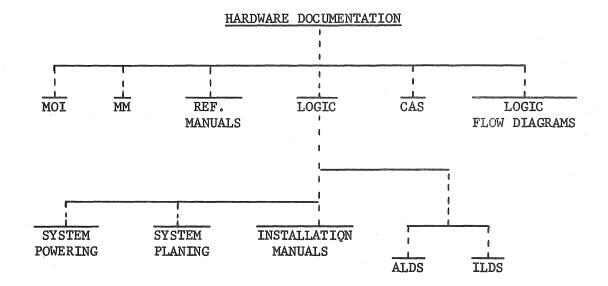

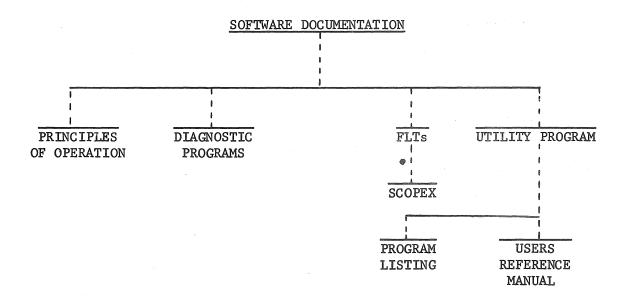

| 1-7. | IBM |                          | 0N                                     |       |

|      | Α.  |                          |                                        |       |

|      | B.  | Operation and Software   | Documentation                          | 1-107 |

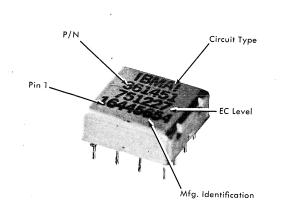

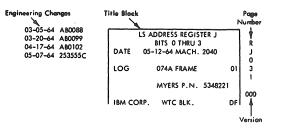

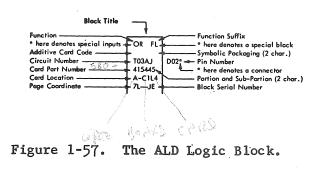

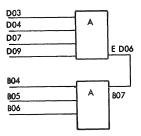

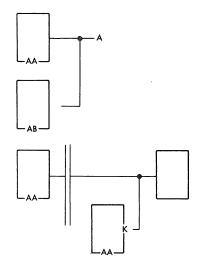

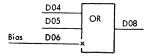

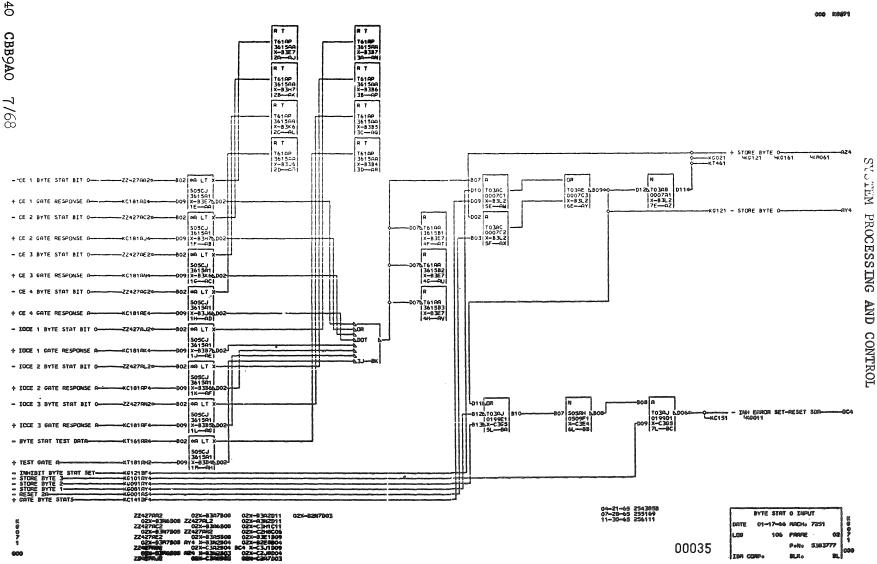

|      | C.  | Description of the Logi  | c Contained in Documentation           | 1-108 |

|      |     |                          | 0n                                     |       |

|      |     | a. Information Inst      | ide the Logic Block                    | 1-123 |

|      |     | b. Information Out       | side the Block                         | 1-127 |

|      |     | c. Information on        | the Side of the Block                  | 1-127 |

|      |     | d. Line Names            |                                        | 1-132 |

|      |     | 2. SMS Description       |                                        | 1-133 |

## CHAPTER 2

## COMPUTING ELEMENT

| 2-1.            | COMPUTI | NG ELEMENT2-1                           |   |

|-----------------|---------|-----------------------------------------|---|

| 2-2.            |         | NG ELEMENT FUNCTIONAL UNITS2-2          |   |

|                 | A. Reg: | isters2-3                               |   |

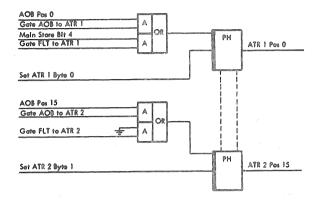

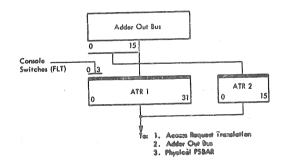

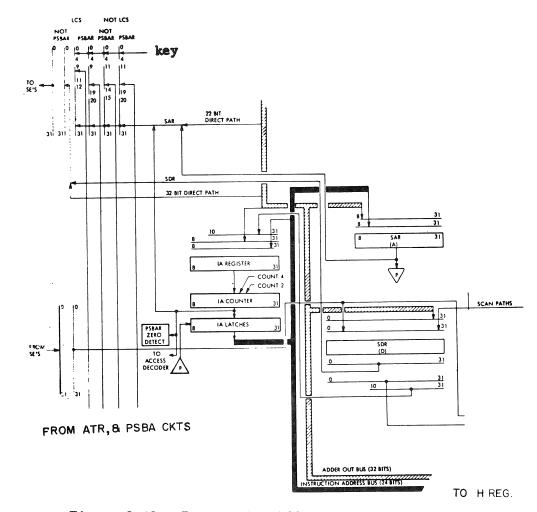

|                 | 1.      | Address Translation Register2-3         |   |

|                 | 2.      | Check Registers2-4                      |   |

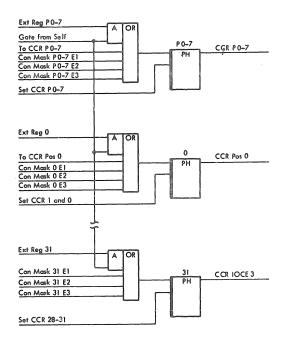

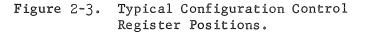

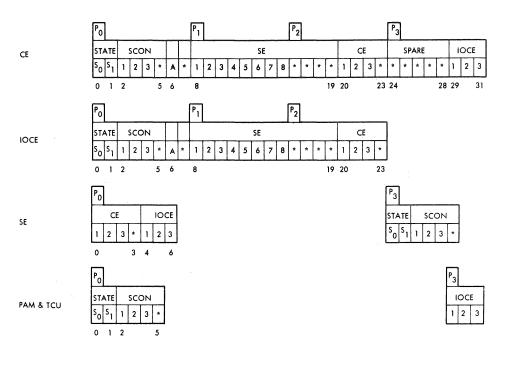

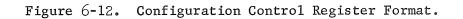

|                 | 3.      | Configuration Control Register (CCR)2-5 |   |

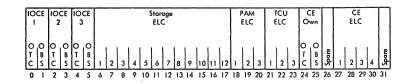

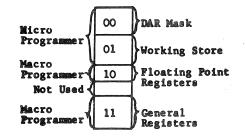

|                 | 4.      | Diagnose Accessible Register2-6         |   |

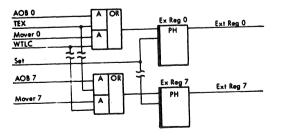

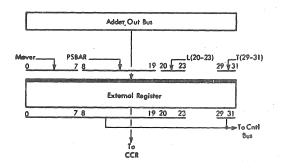

|                 | 5.      | External Register2-7                    |   |

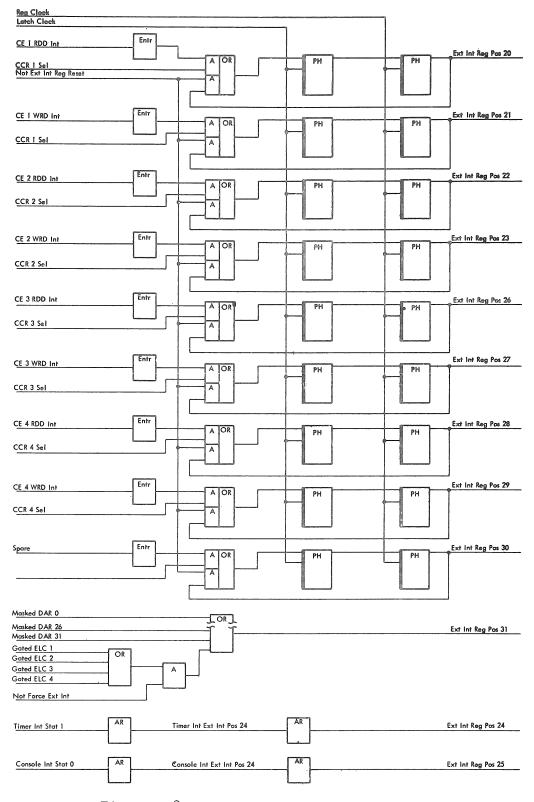

|                 | 6.      | External Interrupt Register2-8          |   |

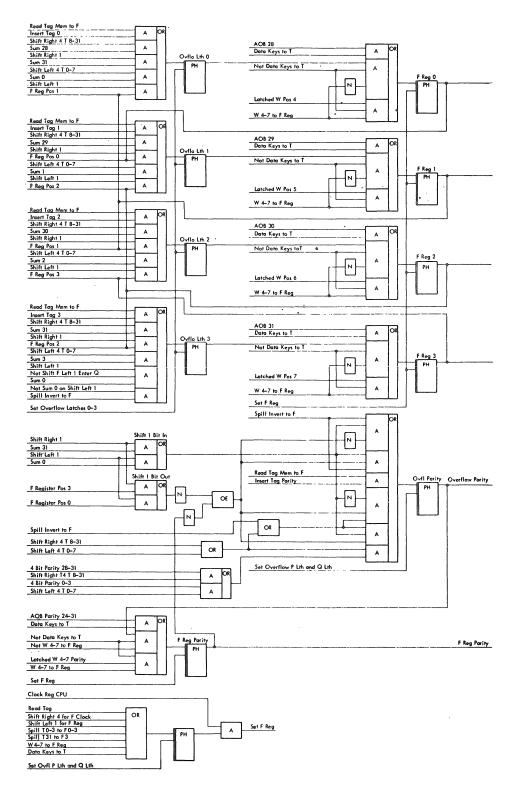

|                 | 7.      | F Register2-8                           |   |

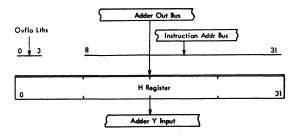

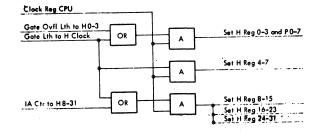

|                 | 8.      | H Register2-11                          | L |

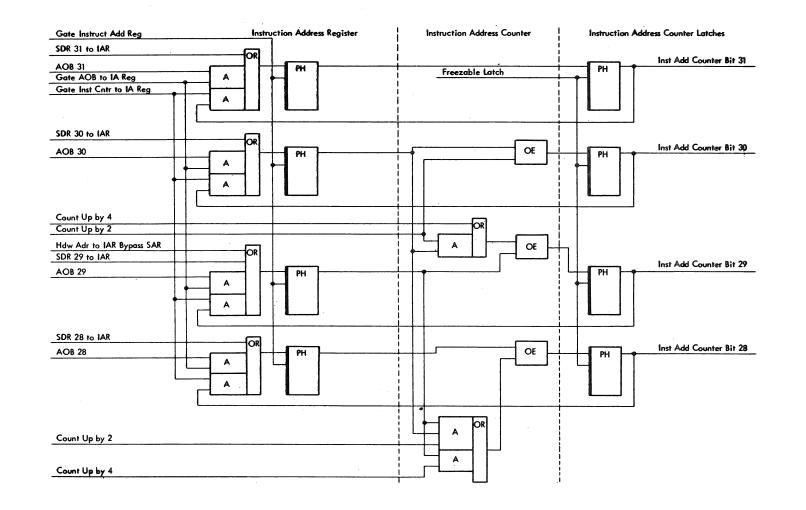

|                 | 9.      | Instruction Address Register2-12        | 2 |

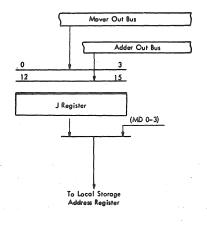

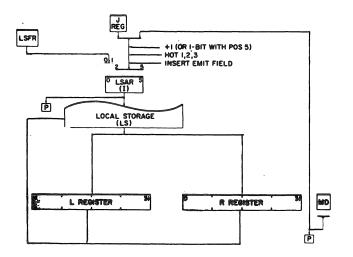

|                 | 10.     | J Register2-12                          |   |

|                 | 11.     | L Register2-12                          | 2 |

| A <b>C-</b> 940 | CBB9A0  | 7/68 iv                                 |   |

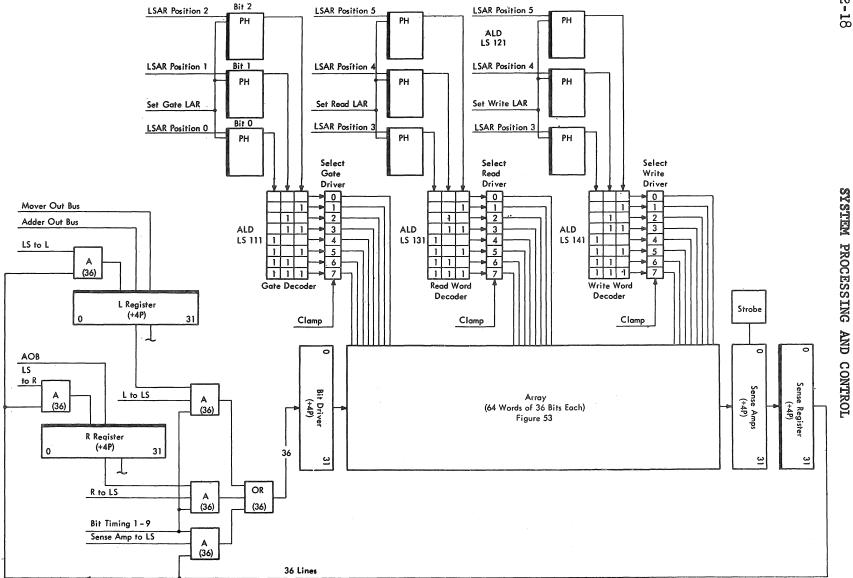

|      |                  | 12.             | Local Store Address Register                           | 2-15  |

|------|------------------|-----------------|--------------------------------------------------------|-------|

|      |                  | 13.             | Local Store Function Register                          | 2-17  |

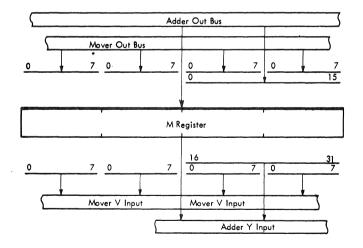

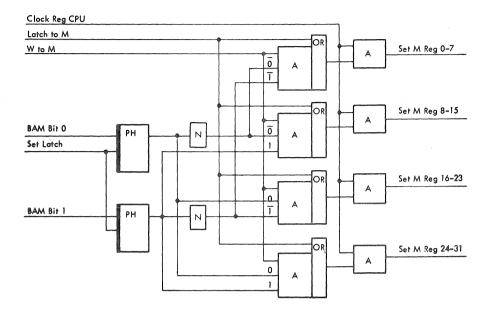

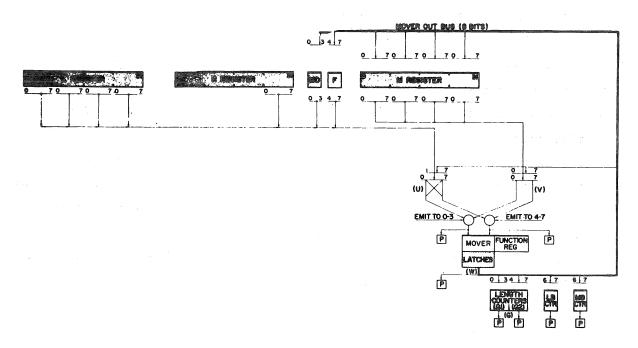

|      |                  | 14.             | M Register                                             | 2-19  |

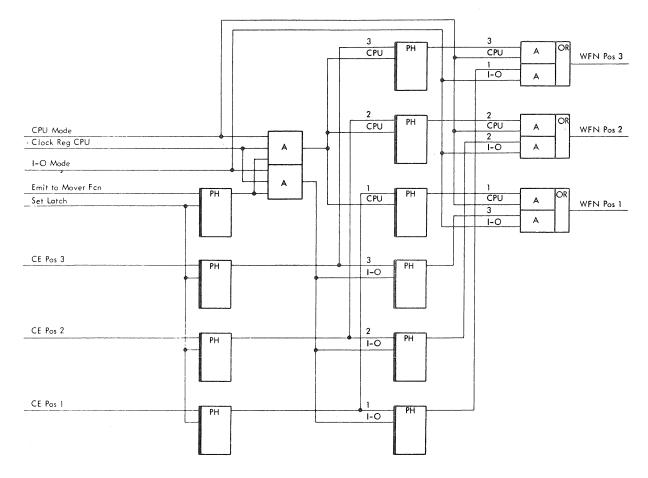

|      |                  | 15.             | Mover Function Register                                | 2-20  |

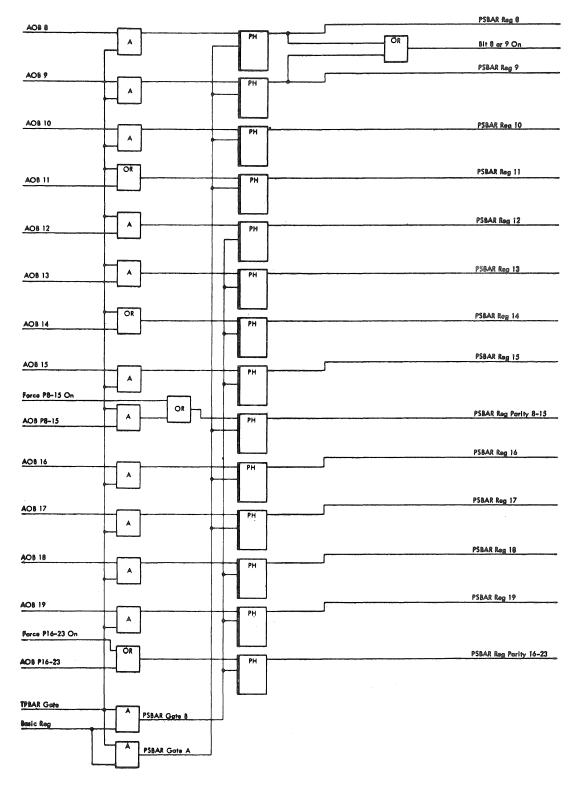

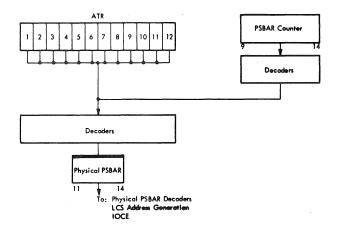

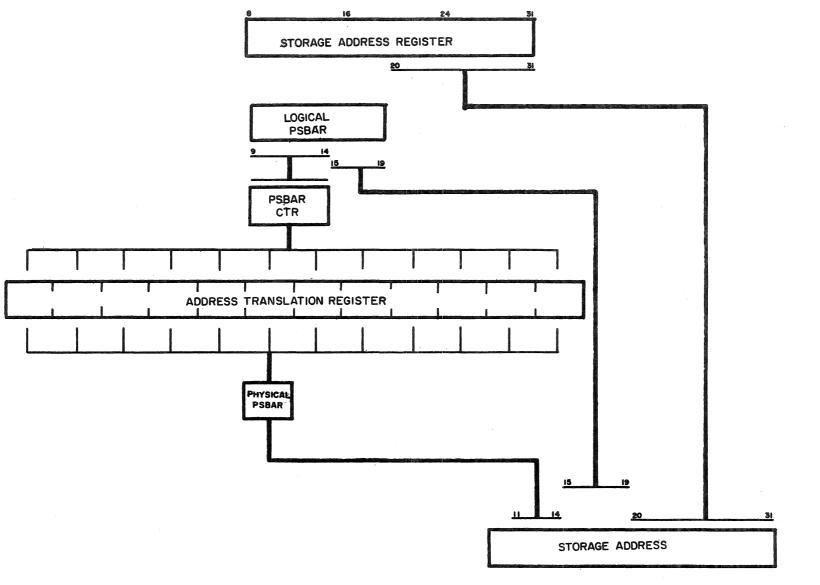

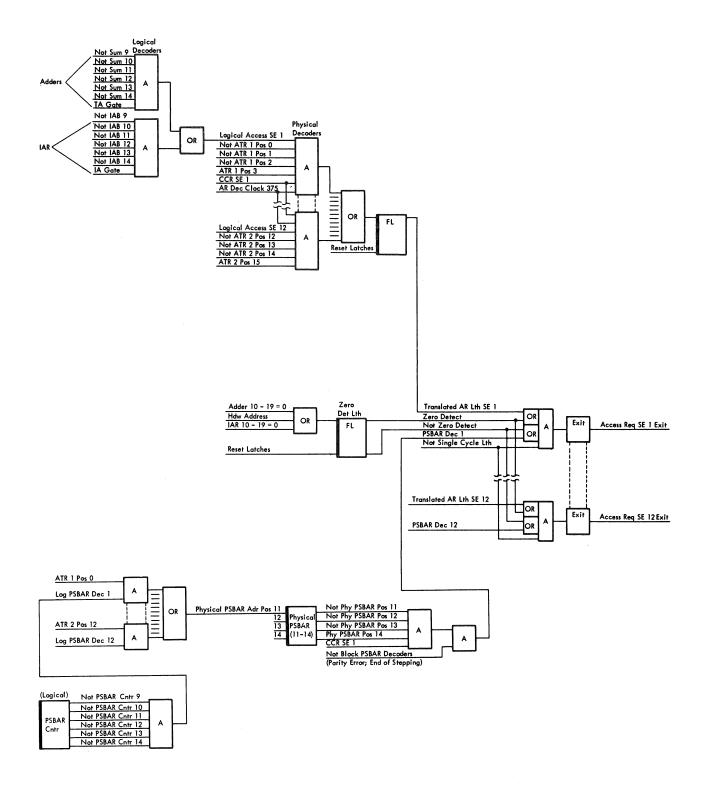

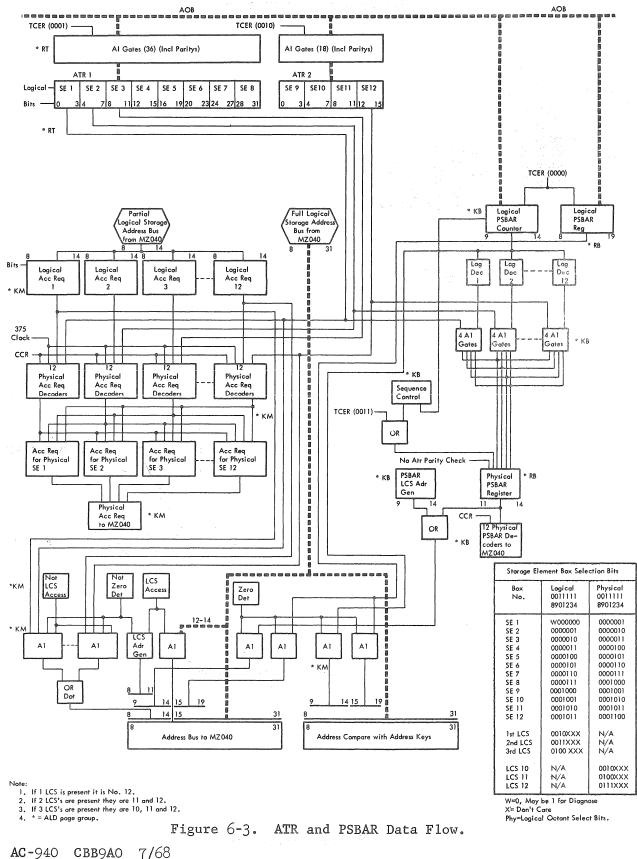

|      |                  | 16.             | Preferential Storage Base Address Register             | 2-20  |

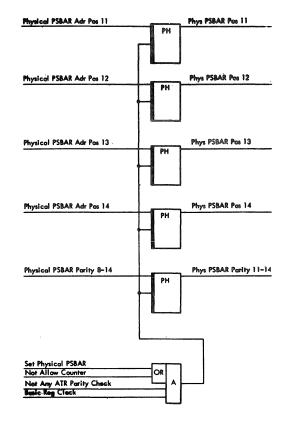

|      |                  | 17.             | Logical PSBAR                                          | 2-22  |

|      |                  | 18.             | Physical PSBAR                                         |       |

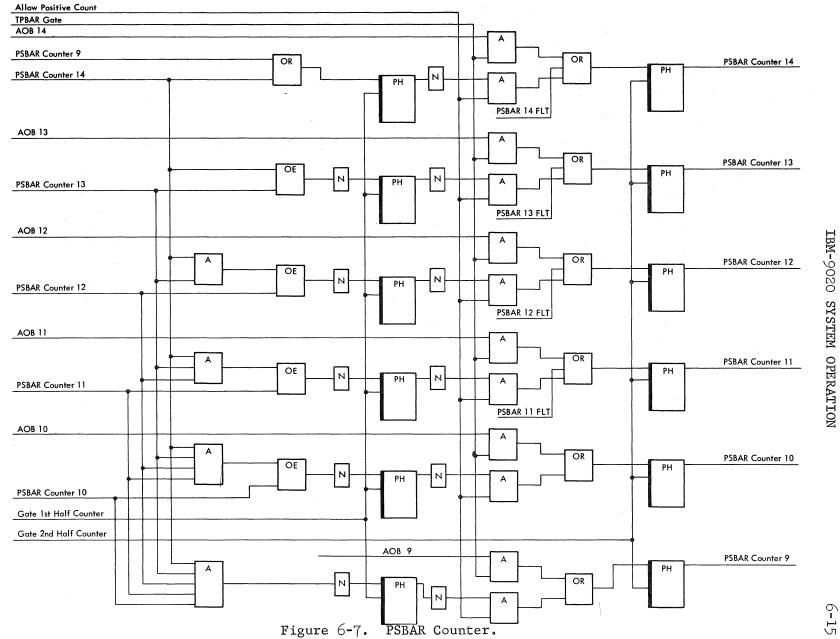

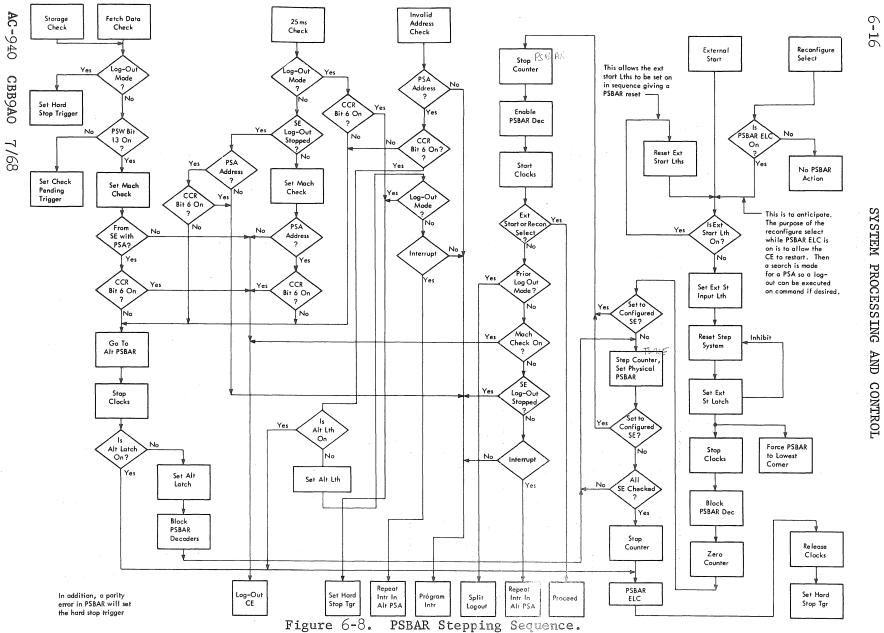

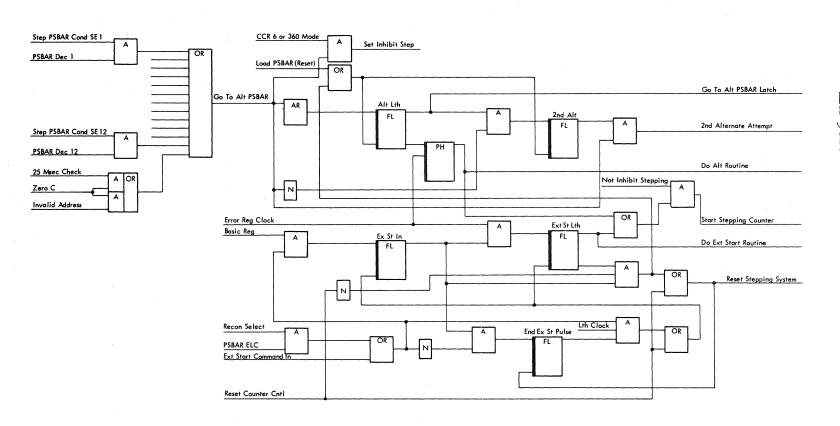

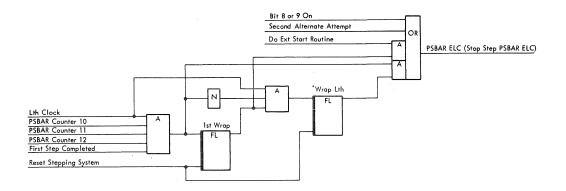

|      |                  | 19.             | PSBAR Counter                                          |       |

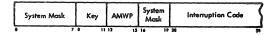

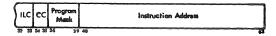

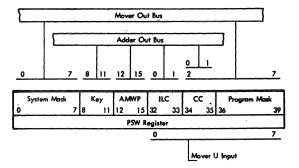

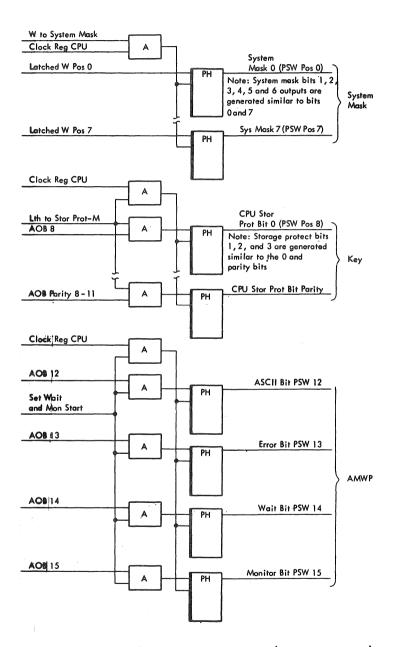

|      |                  | 20.             | Program Status Word Register                           | 2-25  |

|      |                  | 21.             | Q Register                                             |       |

|      |                  | 22.             | R Register                                             |       |

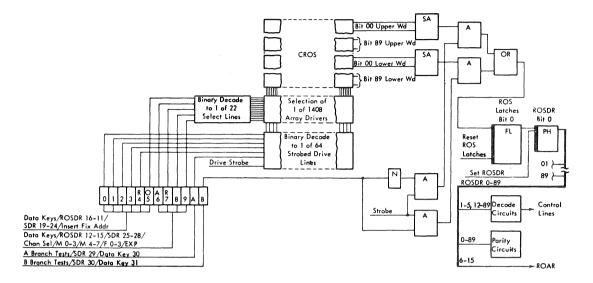

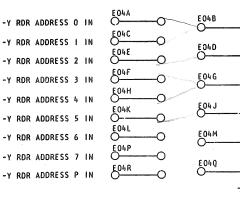

|      |                  | 23.             | Read Only Address Register                             | 2-31  |

|      |                  | 24.             | Read Only Storage Data Register                        | 2-33  |

|      |                  | 25.             | Read Direct Register                                   | 2-33  |

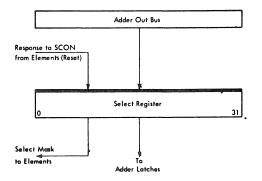

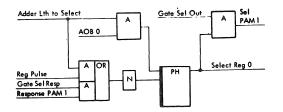

|      |                  | 26.             | Select Register                                        | 2-34  |

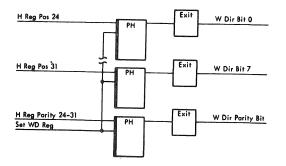

|      |                  | 27.             | Write Direct Register                                  |       |

|      |                  | 28.             | Storage Address Register                               | 2-36  |

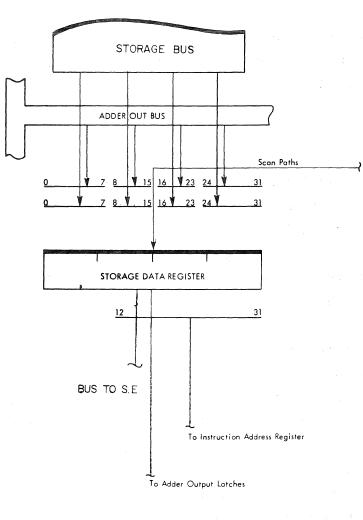

| 2-3. | <b>a</b> 01      | 29.             | Storage Data Register                                  | 2-36  |

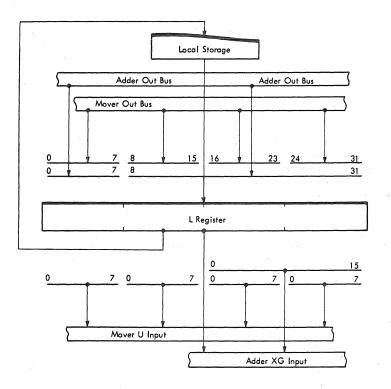

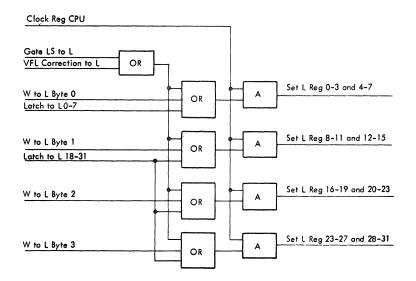

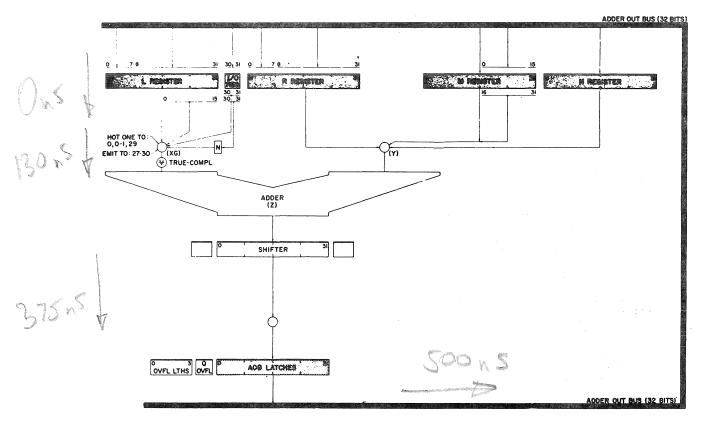

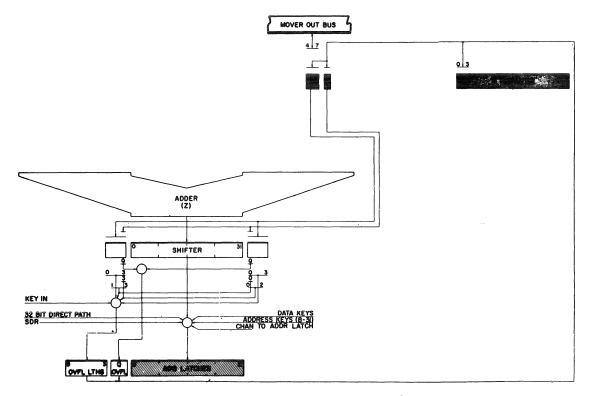

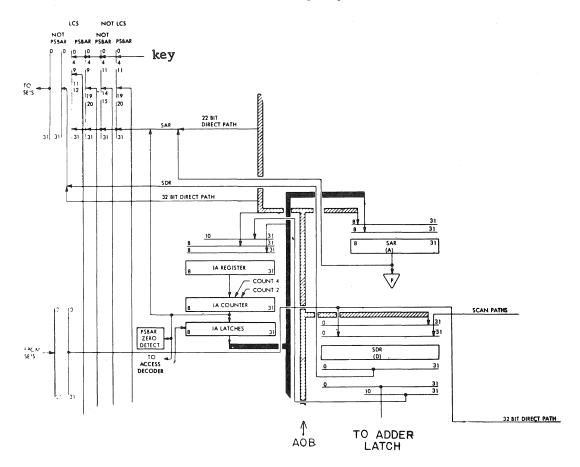

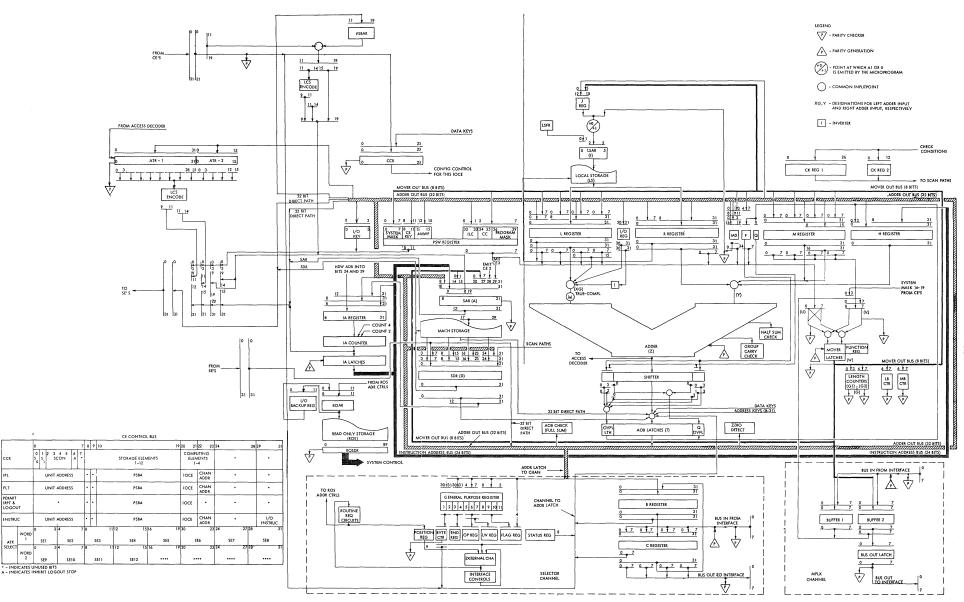

| 2-3. |                  | 1PUTT           | NG ELEMENT INTERNAL DATA PATHS                         | 2-38  |

|      | A.               |                 | fter                                                   |       |

|      | B.<br>C.         |                 | er                                                     |       |

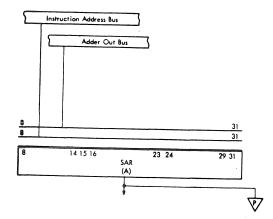

|      | С.<br>D.         |                 | truction Address Data Path                             |       |

|      | <i>р</i> .<br>Е. |                 | al Store Data Path                                     |       |

|      | F.               | Mai             | n Storage In-Out Data Path                             | 2-43  |

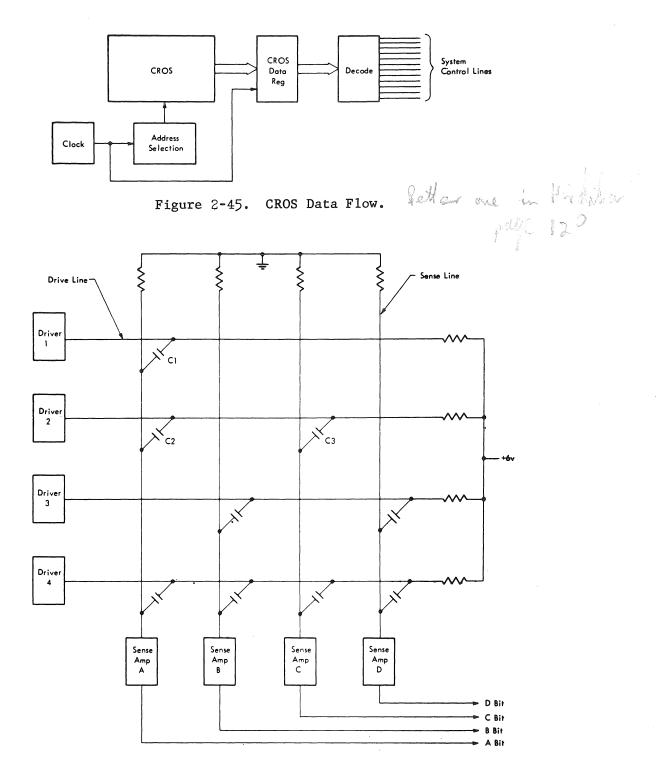

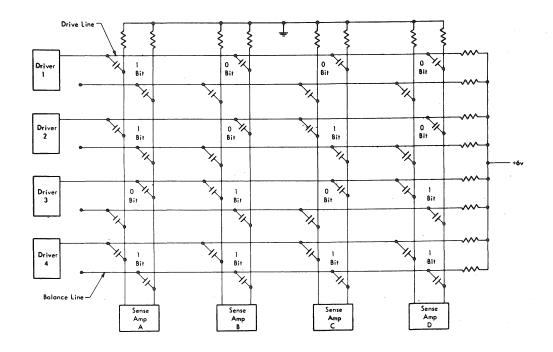

| 2=4. |                  | ידשוו<br>דדווקו | NG ELEMENT INTERNAL CONTROL                            | 2-47  |

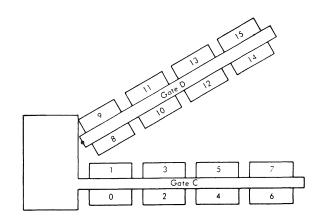

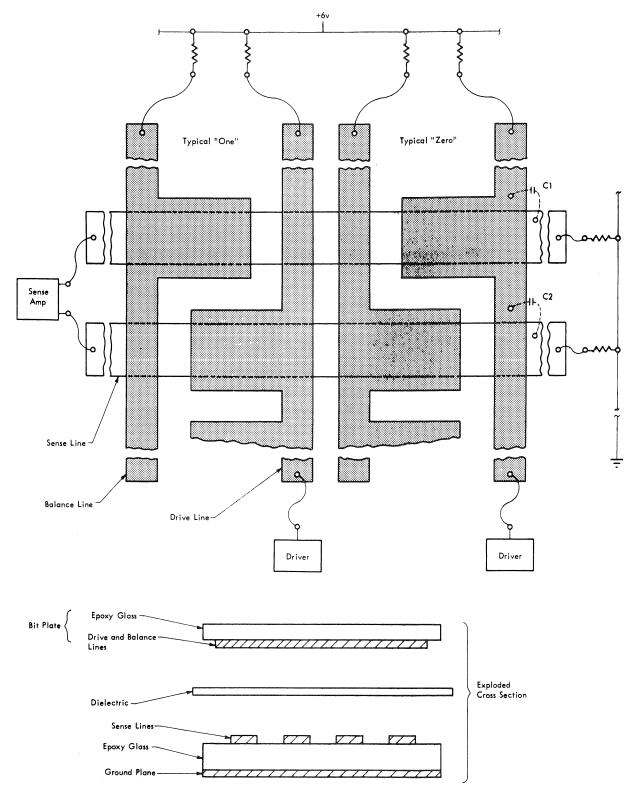

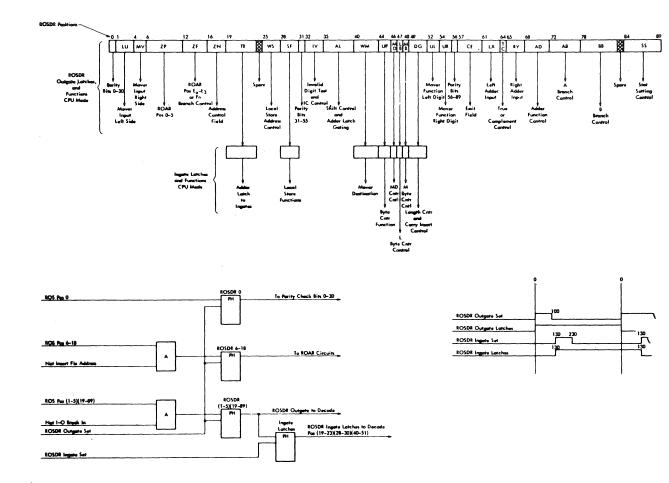

|      | Α.               | Phv             | sical Construction                                     | 2-49  |

|      | Β.               |                 | ory of Operation                                       |       |

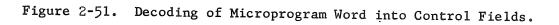

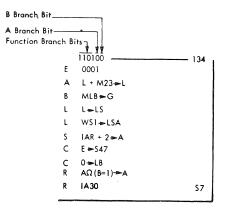

|      |                  | 1.              | Control Fields                                         |       |

|      |                  | 2.              | Micro-Orders                                           |       |

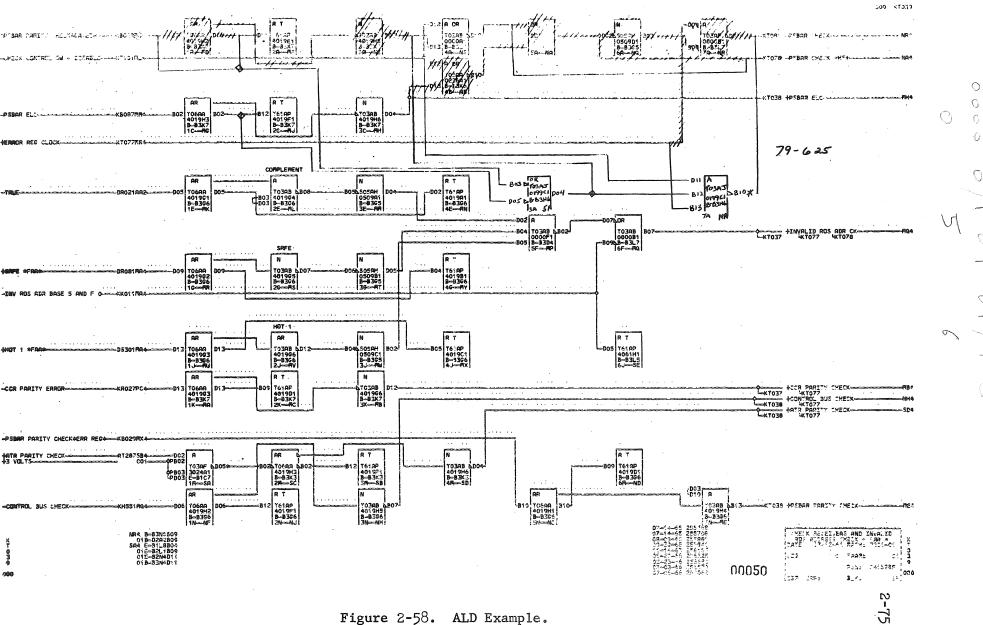

|      |                  | 3.              | CAS Logic Diagrams (CLDs)                              |       |

|      |                  | 4.              | Example Routines Showing Part of the CROS Microprogram |       |

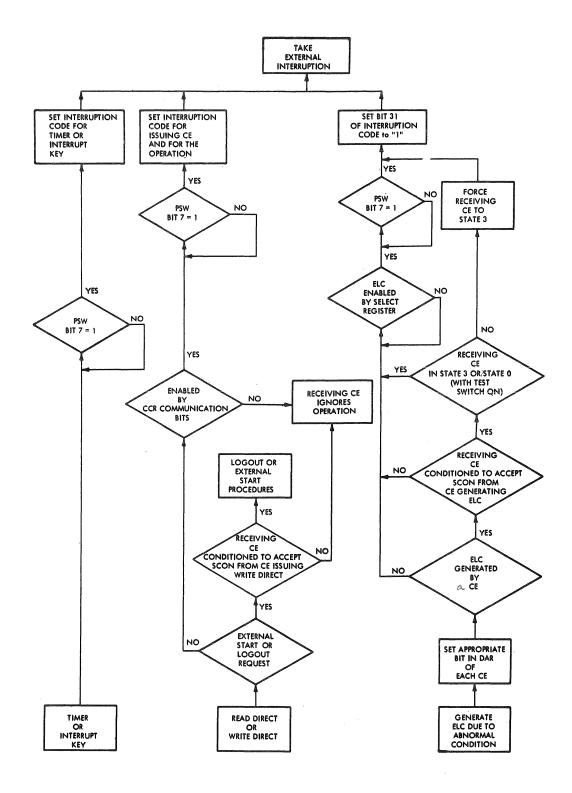

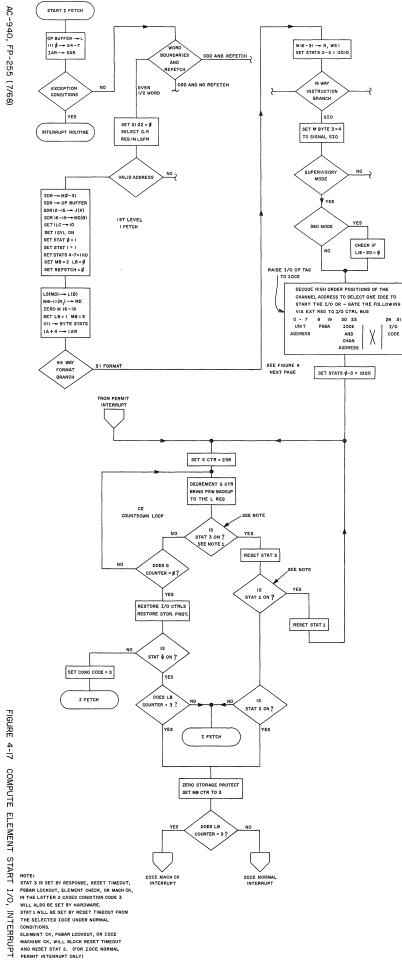

| 2-5. | COM              | IPUTI           | NG ELEMENT INTERRUPT SCHEME                            |       |

|      | Α.               | The             | <pre>Input/Output Interrupt</pre>                      | -2-60 |

|      | B.               | The             | Program Interrupt                                      | -2-61 |

|      | C.               | The             | Supervisor-Call Interruption                           | -2-63 |

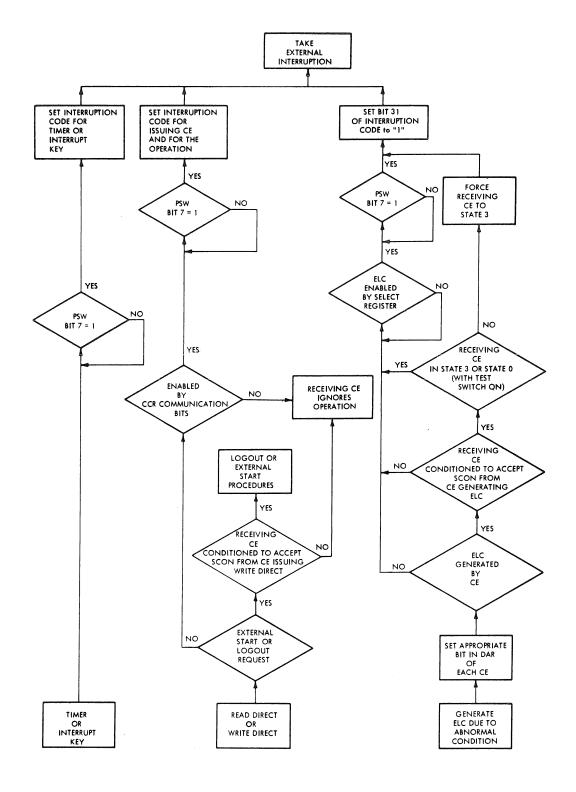

|      | D.               | The             | External Interruption                                  | -2-63 |

|      |                  | 1.              | External Interrupt Caused by a Time Out or the         |       |

|      |                  |                 | 1 2                                                    | -2-64 |

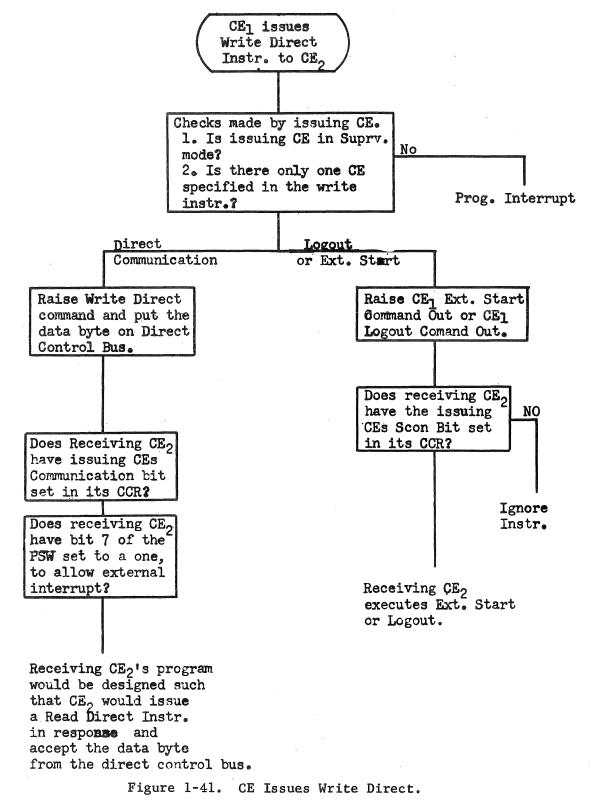

|      |                  | 2.              | External Interrupt Caused by a Read Direct or Write    |       |

|      |                  |                 | Direct Instruction Execution                           | -2-64 |

|      |                  | 3.              | The External Interrupt Caused by an Element Check      |       |

|      | _                |                 | Due to Abnormal Conditions                             |       |

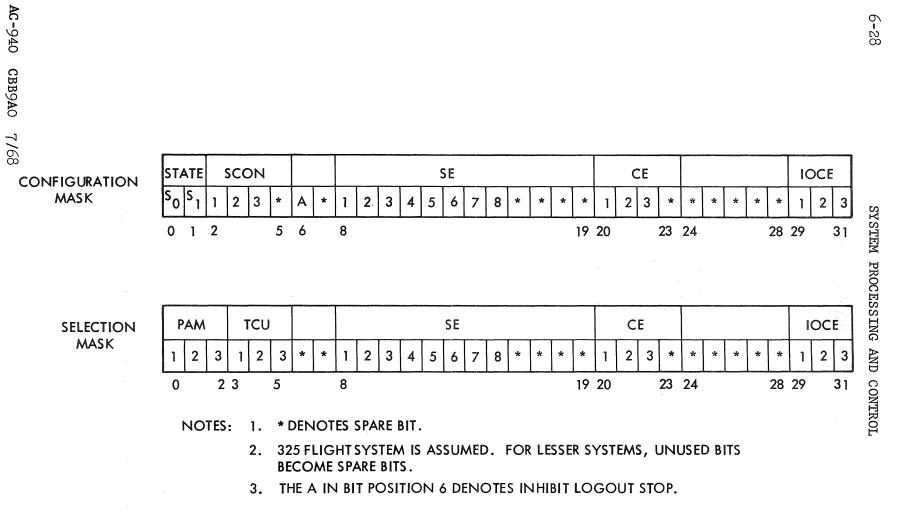

|      | Ε.               | The             | Machine Check Interrupt                                | -2-68 |

| 0 (  | F.               | Sum             | mary of the Interrupt Scheme                           | -2-68 |

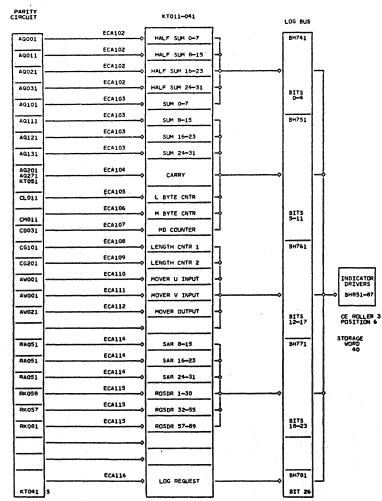

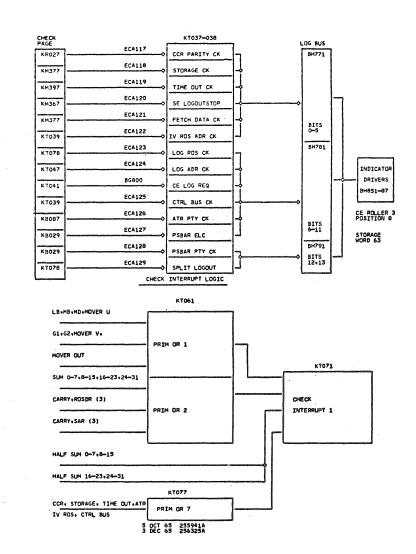

| 2-6. |                  |                 | NG ELEMENT INTERNAL ERROR CHECKING                     |       |

|      | Α.               |                 | ity Tests                                              |       |

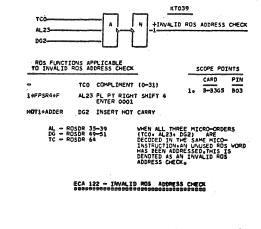

|      | В.               |                 | or Check Analysis Diagrams                             |       |

|      | С.               | гоgo            | out Analysis                                           | -2-/4 |

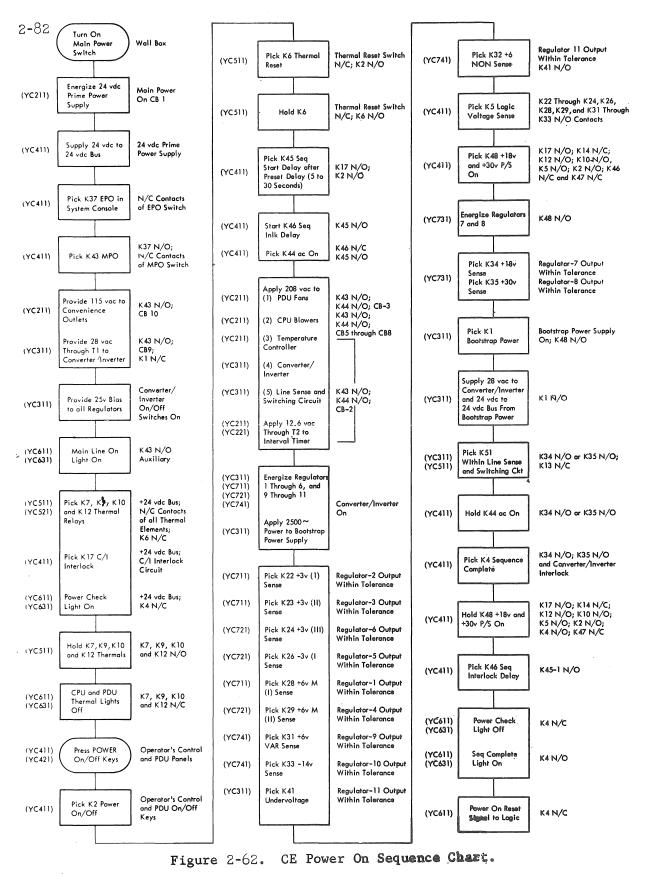

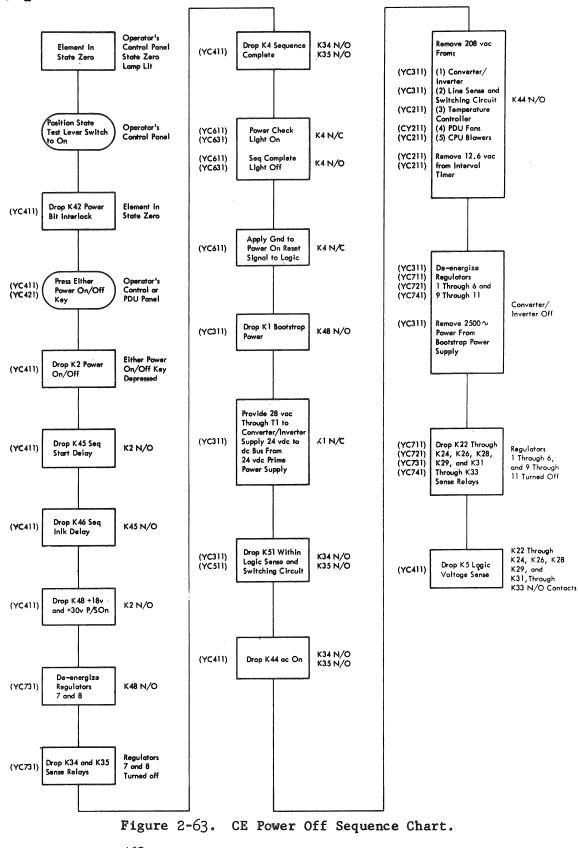

| 2-7. | COM | PUTING ELEMENT POWERING              | 2-76 |

|------|-----|--------------------------------------|------|

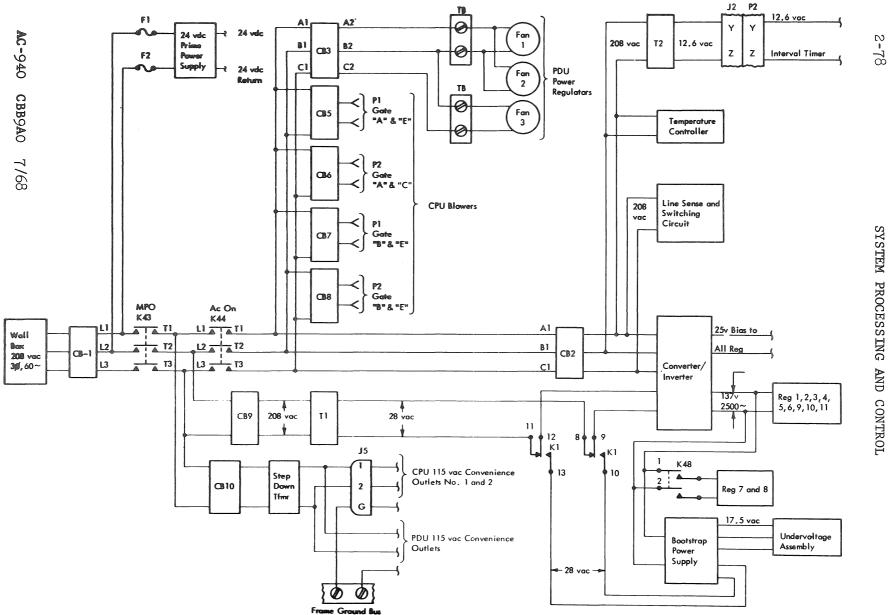

|      | Α.  | AC Distribution                      | 2-77 |

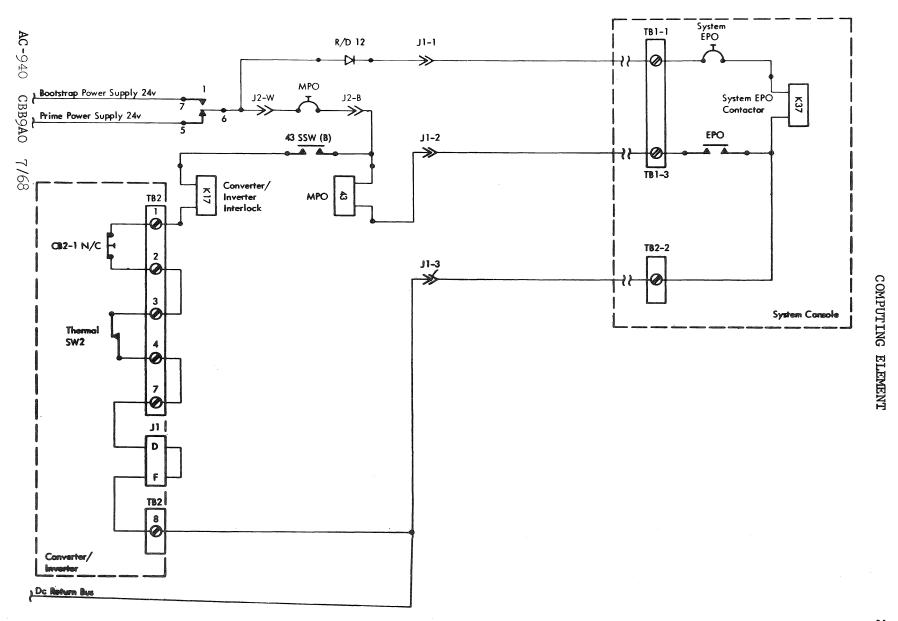

|      | В.  | Converter/Inverter Interlock Circuit | 2-80 |

|      | C.  | DC Distribution                      | 2-80 |

|      | D.  | Power On Sequencing                  | 2-80 |

|      | Ε.  | Normal Power Off                     |      |

|      | F.  | Battery Back-Up Power Control        | 2-85 |

|      | G.  | Emergency Power Off                  |      |

|      | H.  | Special Power-Off Sequences          |      |

|      | I.  | PDU Circuit Breaker Trip             |      |

|      | J.  | Controls and Indicators              |      |

|      |     | 1. Introduction                      | 2-88 |

|      |     | 2. Operator's Control Panel          | 2-89 |

|      |     | 3. PDU                               |      |

| 2-8. | COM | PUTING ELEMENT TESTING               | 2-90 |

## CHAPTER 3

# STORAGE ELEMENT

| 3-1.  | 7351-04 STORAGE ELEMENT                   |      |

|-------|-------------------------------------------|------|

| 3-2.  | THEORY OF MAGNETIC CORE STORAGE           | 3-2  |

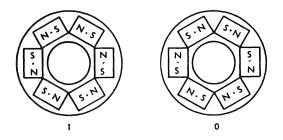

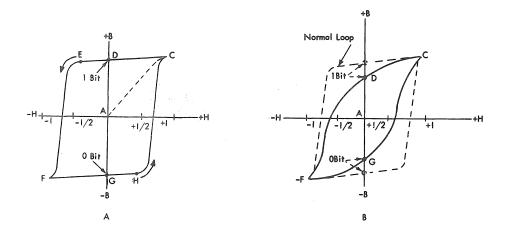

|       | A. Ferrite Core                           | 3-2  |

|       | B. Magnetic Properties                    | 3-2  |

|       | C. Hysteresis Loop                        | 3-6  |

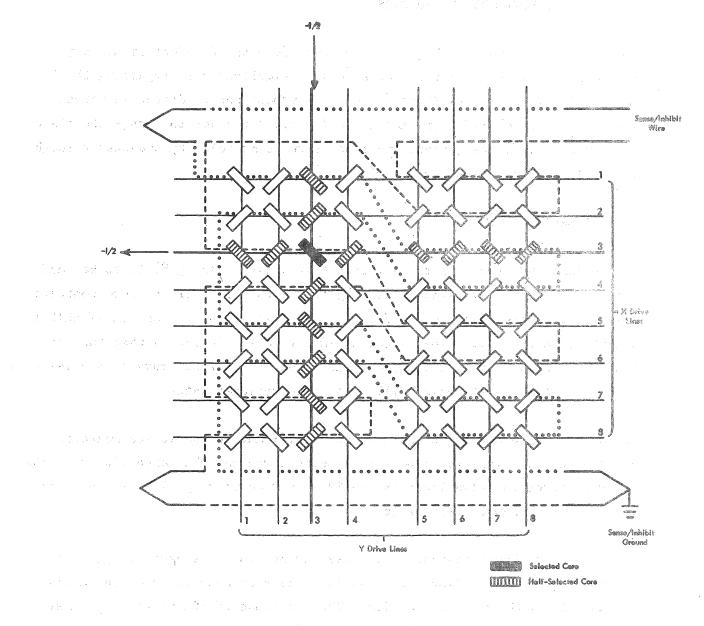

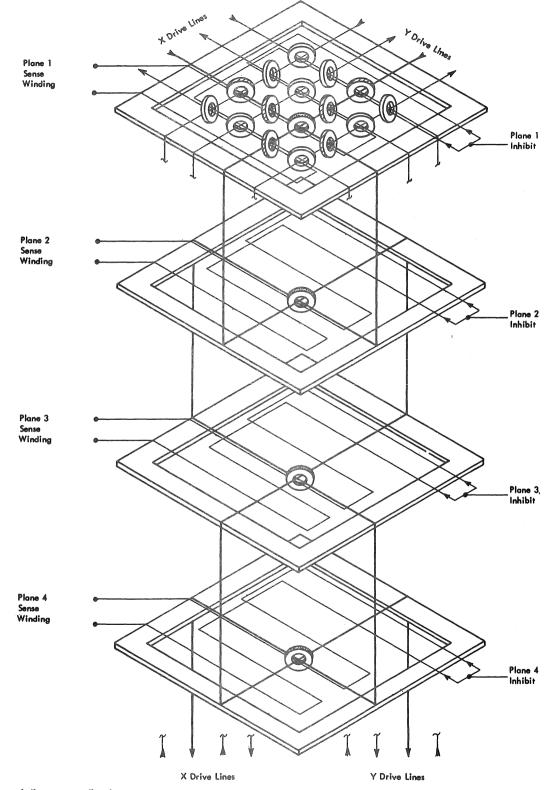

| 3-3.  | CORE PLANES                               |      |

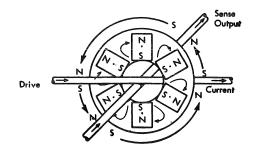

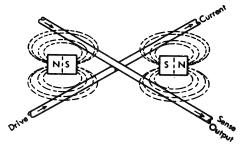

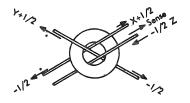

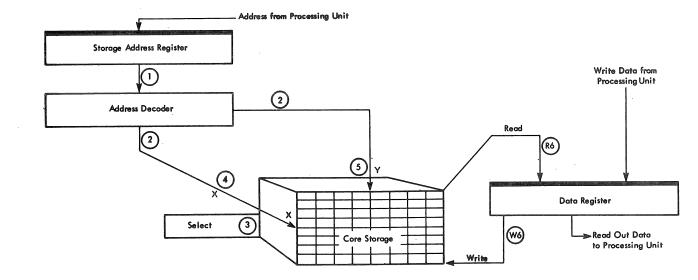

| 3-4.  | COINCIDENT CURRENT ADDRESSING             | 3-10 |

| 3-5.  | READ-OUT, SENSE                           | 3-10 |

| 3-6.  | WRITE, STORE                              | 3-11 |

| 3-7.  | CORE ARRAY                                | 3-11 |

| 3-8.  | CA PACI TY                                | 3-13 |

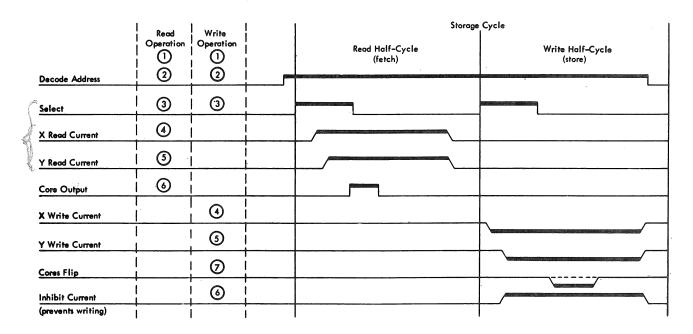

| 3-9.  | STORAGE CYCLE                             | 3-14 |

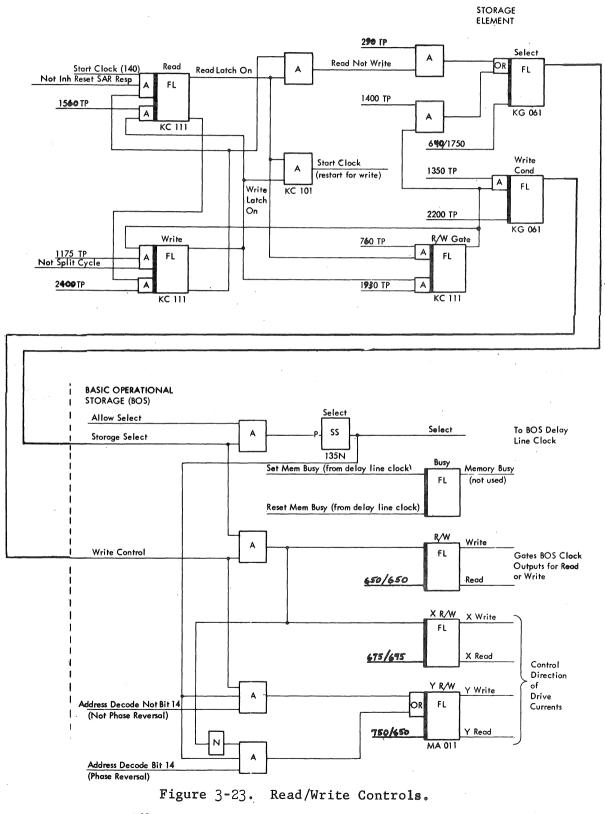

| 3-10. | READ OPERATION                            | 3-16 |

| 3-11. | WRITE OPERATION                           | 3-16 |

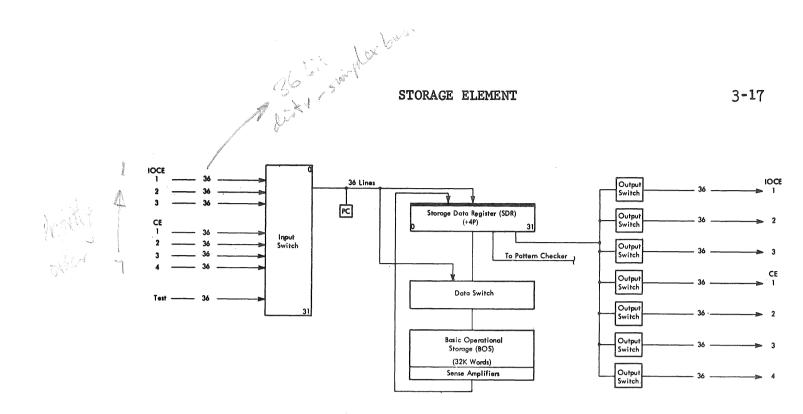

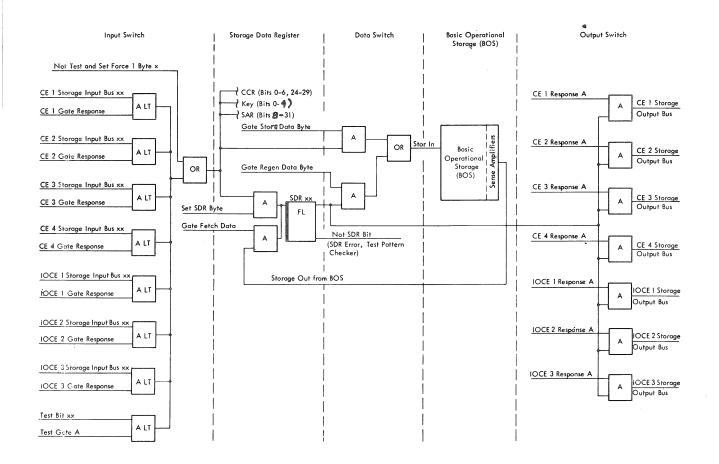

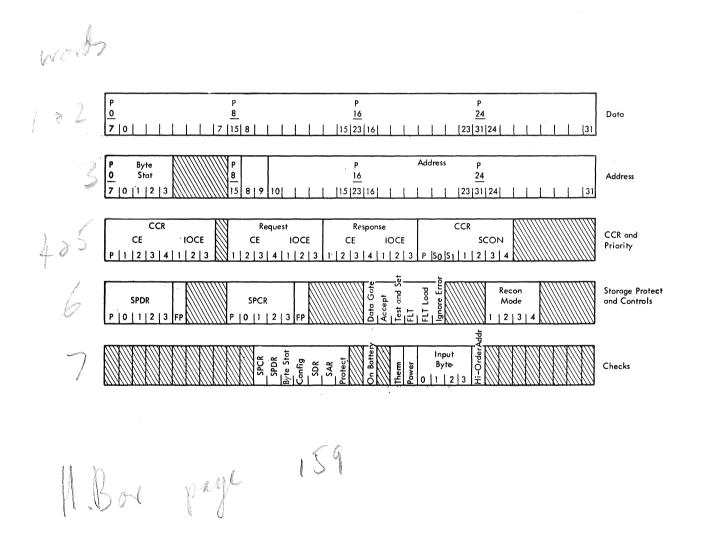

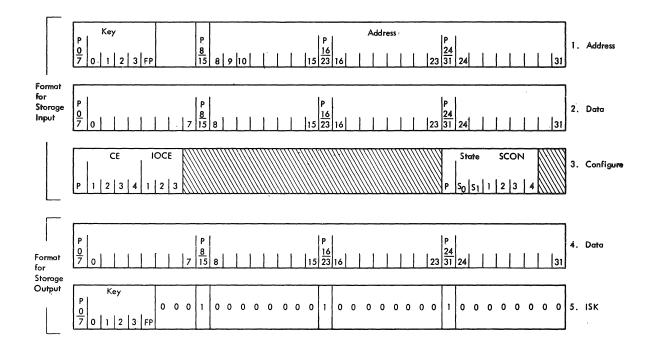

| 3-12. | 7251 DATA FLOW                            |      |

| 3-13. | CONTROLS                                  |      |

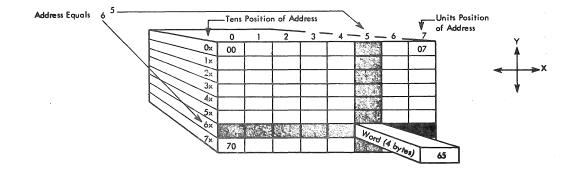

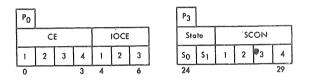

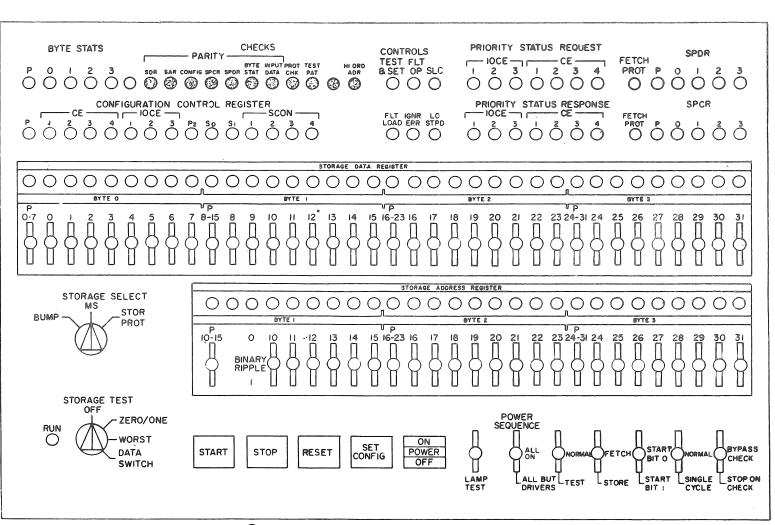

|       | A. Configuration                          | 3-19 |

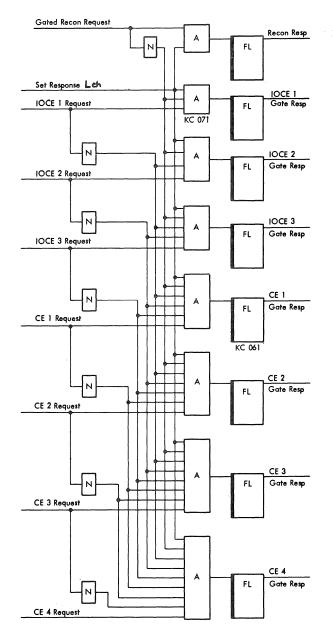

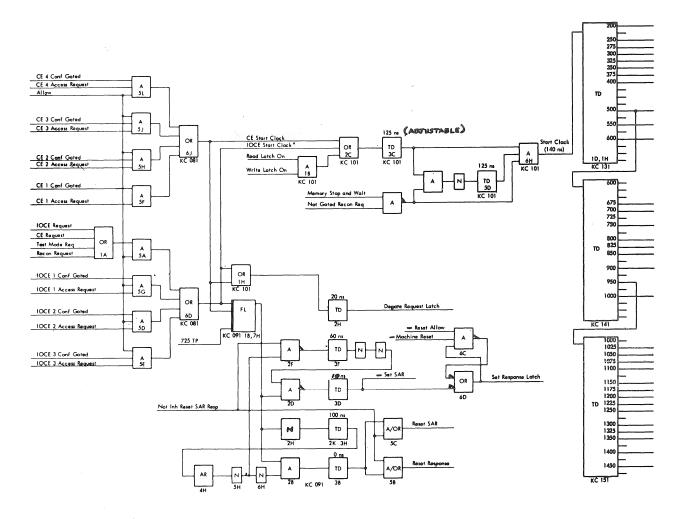

|       | B. Priority Controls                      |      |

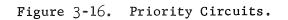

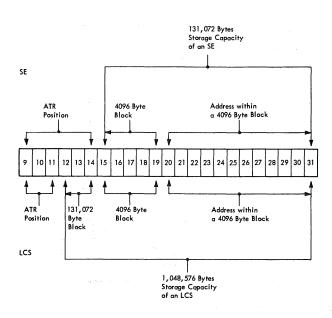

|       | C. Addressing                             | 3-21 |

|       | D. Integral Boundaries                    | 3-24 |

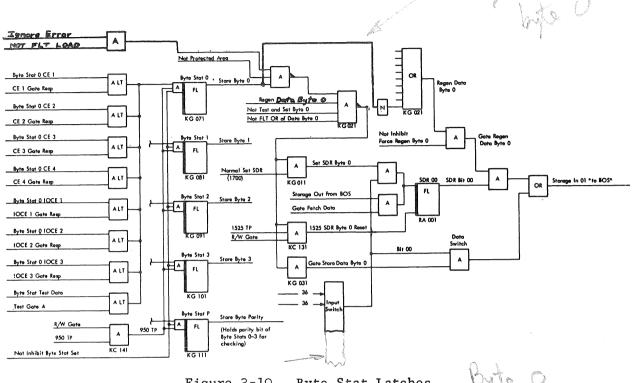

|       | E. Byte Stats                             | 3-25 |

| 3-14. | STORAGE ELEMENT TIMING                    | 3-25 |

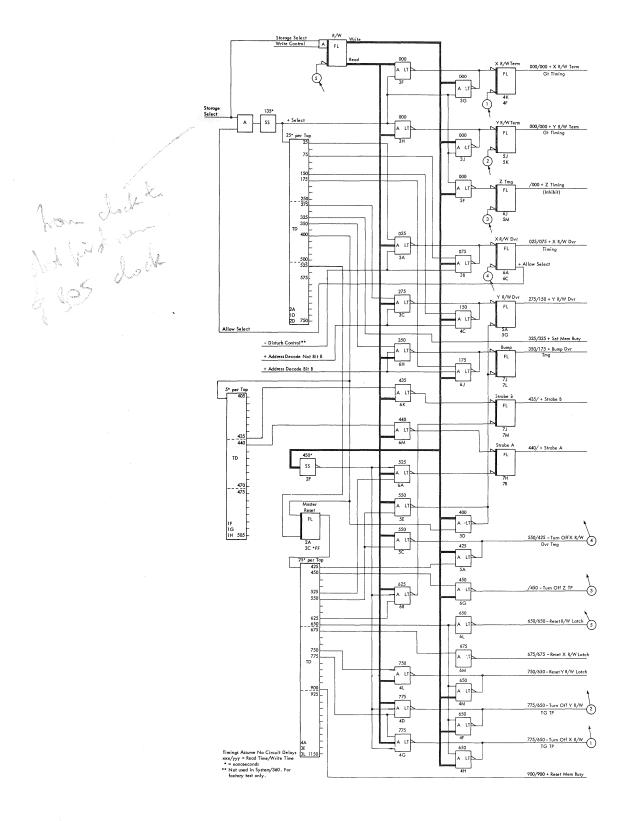

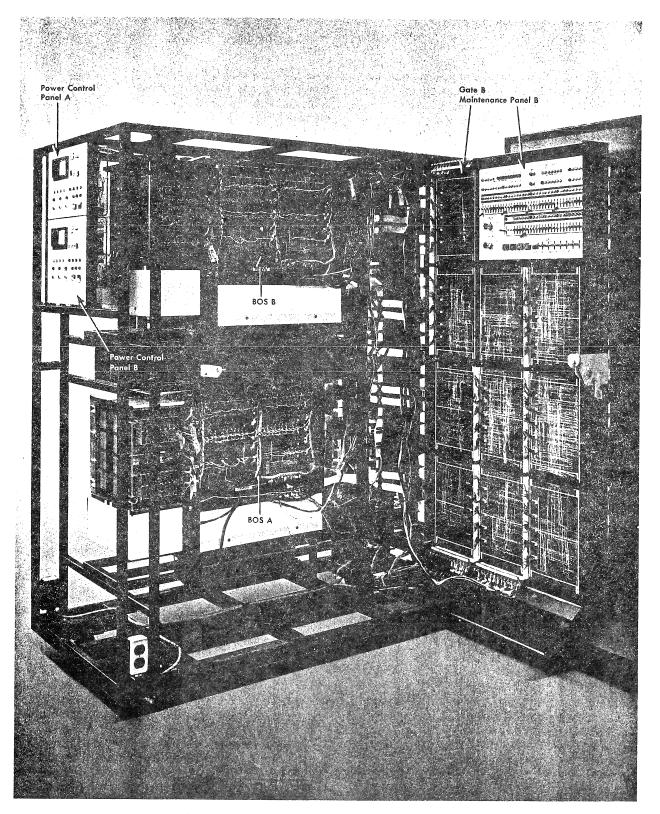

|       | A. Basic Operational Storage (BOS) Timing | 3-29 |

|       | B. Read/Write Controls                    | 3-30 |

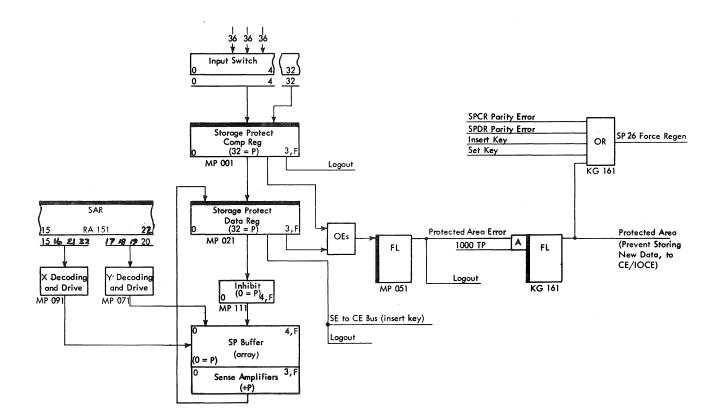

| 3-15. | STORAGE PROTECTION                        | 3-32 |

| 3-16. | LOGOUT                                    |      |

| 3-17. | TEST AND SET                              |      |

|       |                                           |      |

| 3-18.          | ERROR CHECKS                               | 3-34 |

|----------------|--------------------------------------------|------|

|                | A. Element Check                           |      |

|                | B. Storage Check                           | 3-35 |

|                | C. Protected Area                          | 3-36 |

|                | D. Logic Check                             | 3-37 |

|                | E. Power Check                             | 3-37 |

|                | F. On Battery                              | 3-37 |

|                | G. Master Power Off                        | 3-37 |

| 3-19.          | STORAGE ELEMENT TESTING                    | 3-37 |

|                | A. OFF-LINE Testing                        | 3-38 |

|                | a. Indicators                              |      |

|                | b. Switches                                |      |

|                | c. Pushbuttons                             |      |

|                | d. Rotary Switches                         |      |

|                | e. Level Switches                          | 3-43 |

|                | f. Miscellaneous Maintenance Panel Items   | 3-45 |

|                | B. ON-LINE Testing                         | 3-45 |

| 3-20.          | CE/IOCE TO STORAGE ELEMENT INTERFACE LINES | 3-46 |

|                | A. CE/IOCE to SE Bus                       |      |

|                | B. Access Request                          |      |

|                | C. Byte Stats                              | 3-47 |

|                | D. Set Storage Key                         |      |

|                | E. Insert Storage Key                      |      |

|                | F. FLT Op                                  |      |

|                | G. FLT Load                                |      |

|                | H. Test and Set                            |      |

|                | I. Split Cycle                             |      |

|                | J. Logout Stop                             |      |

|                | K. Logout Proceed 1-5                      |      |

|                | L. Logout Complete                         |      |

|                | M. Reconfigure Select                      |      |

|                | N. System Reset A-B and CE Gate            | 3-49 |

|                | O. Ignore Error                            |      |

|                | P. Suppress Log Check                      |      |

| 3-21.          | STORAGE ELEMENT TO CE/IOCE INTERFACE LINES |      |

|                | A. SE to CE/IOCE Bus                       |      |

|                | B. Accept                                  | 3-50 |

|                | C. Request Acknowledged                    | 3-51 |

|                | D. Gate Data                               |      |

|                | E. Protected Area Violated                 |      |

|                | F. Storage Check                           |      |

|                | G. Element Check                           | 3-52 |

|                | H. Reconfigure Response                    | 3-52 |

|                | I. Logout Stopped                          | 3-52 |

| 3-22.          | SYSTEM CONSOLE TO SE INTERFACE             | 3-52 |

| 3-23.          | POWER INTERFACE LINES                      | 3-53 |

| 3-24.          | LATCHES AND REGISTERS ALD PAGE             | 3-54 |

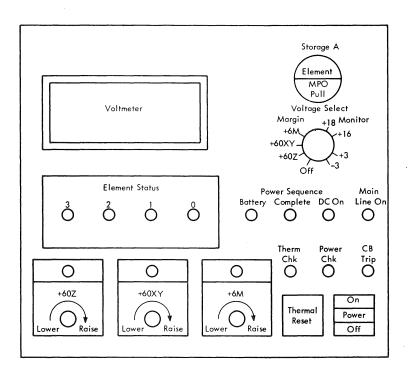

| 3 <b>-</b> 25. | POWE R                                     | 3-57 |

|                |                                            |      |

| 3-26. |     | VER SWITCHES AND INDICATORS |      |

|-------|-----|-----------------------------|------|

|       | Α.  | Marginal Conditions         | 3-58 |

|       |     | 1. Thermal Check            | 3-58 |

|       |     | 2. Power Check              | 3-58 |

|       | Β.  | Catastrophic Conditions     | 3-58 |

|       |     | 1. Battery Power            |      |

|       |     | 2. Emergency Power Off      |      |

|       |     | 3. Element Power Isolation  | 3-59 |

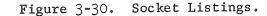

| 3-27. | DOC | CUMENTATION ON THE SE       | 3-60 |

|       | Α.  | Socket Listings             | 3-62 |

|       | Β.  | Logic Diagrams              | 3-62 |

## CHAPTER FOUR

# INPUT/OUTPUT CONTROL ELEMENT

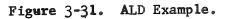

| 4-1. | INTRODUCTION                                            |      |

|------|---------------------------------------------------------|------|

| 4-2. | PHYSICAL MAKE-UP                                        | 4-3  |

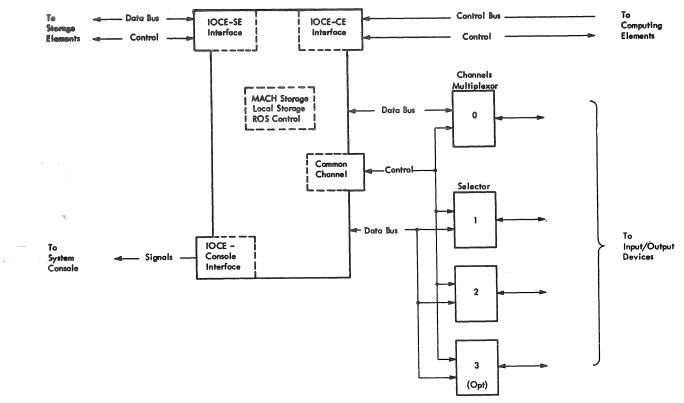

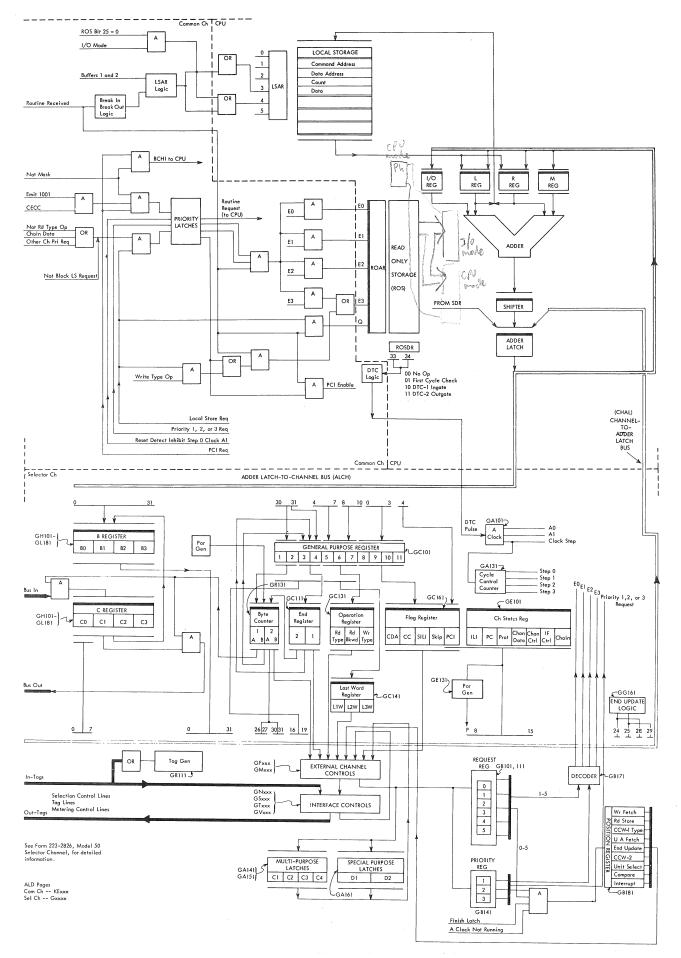

| 4-3. | UNIQUE IOCE FUNCTIONAL UNITS FOR SELECTOR CHANNEL       | 4-3  |

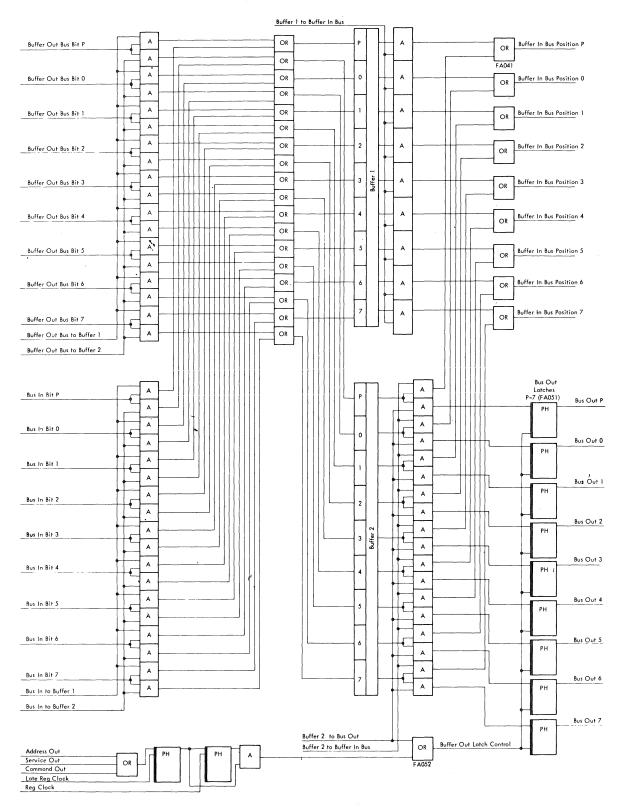

|      | A. B Register                                           | 4-4  |

|      | B. C Register                                           | 4-4  |

|      | C. General Purpose Register                             | 4-5  |

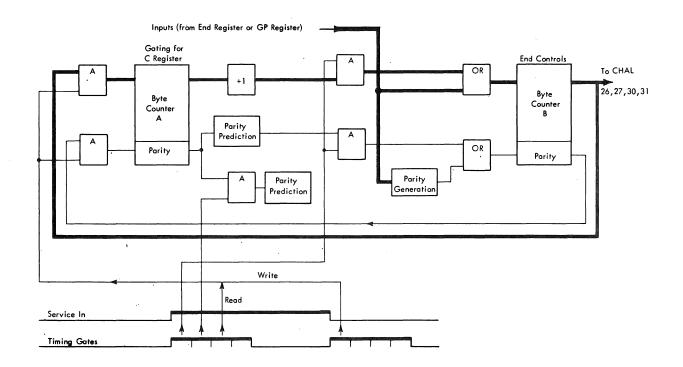

|      | D. Byte Counter                                         | 4-7  |

|      | E. End Register                                         | 4-8  |

|      | F. Last Word Register and Operation Register            |      |

|      | G. Flag Register                                        | 4-8  |

|      | H. Channel Status Register                              | 4-9  |

|      | I. Routine Request Circuitry, I/O External Channel, and |      |

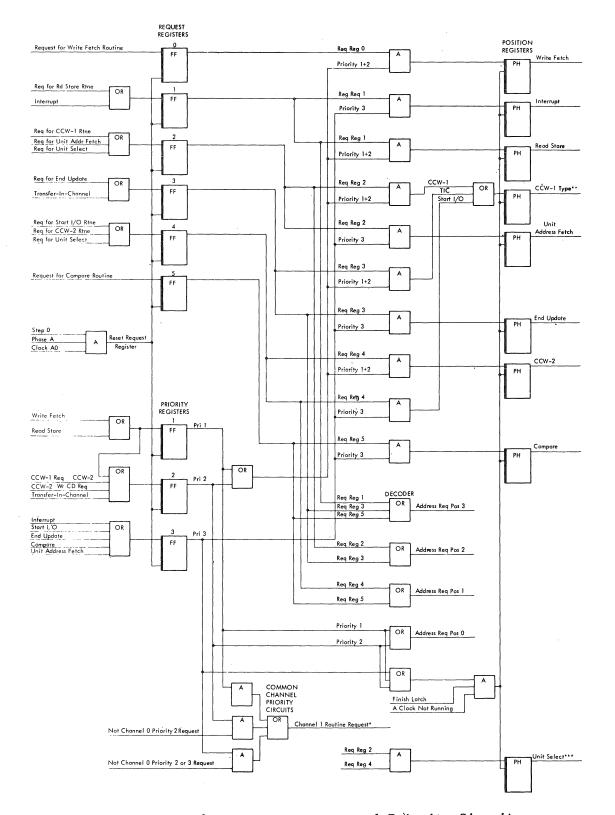

|      | Interface Controls                                      | 4-9  |

| 4-4. | CHANNEL ROS RELATIONS                                   | 4-10 |

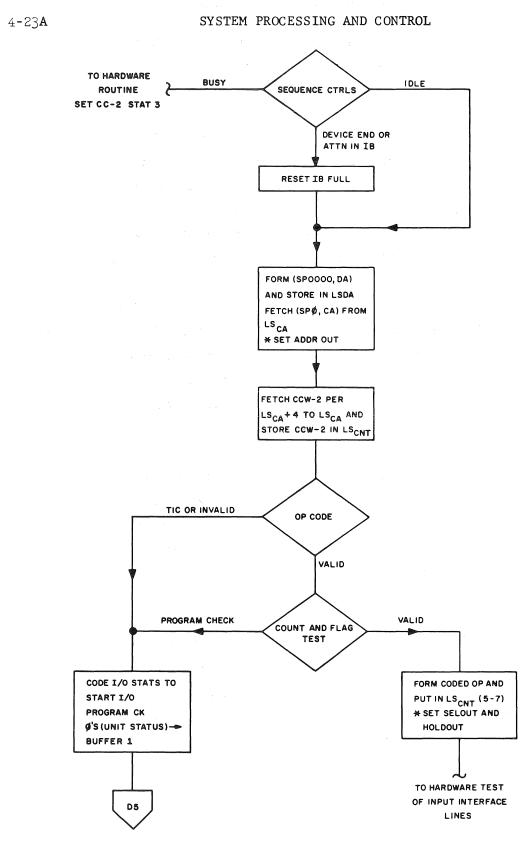

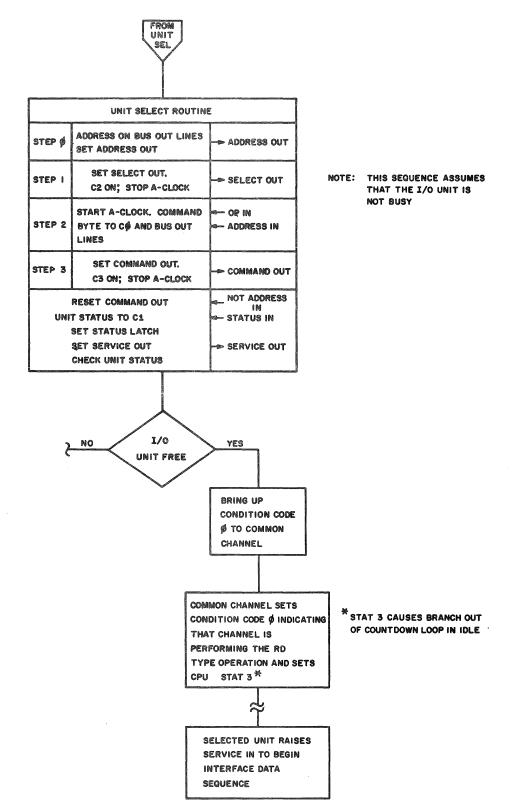

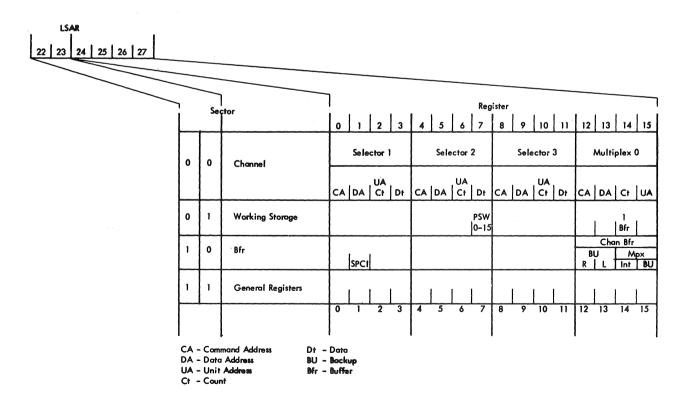

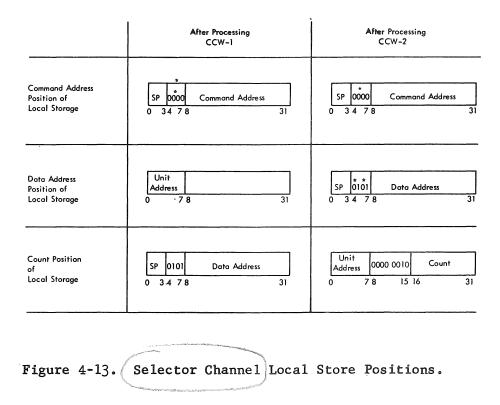

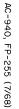

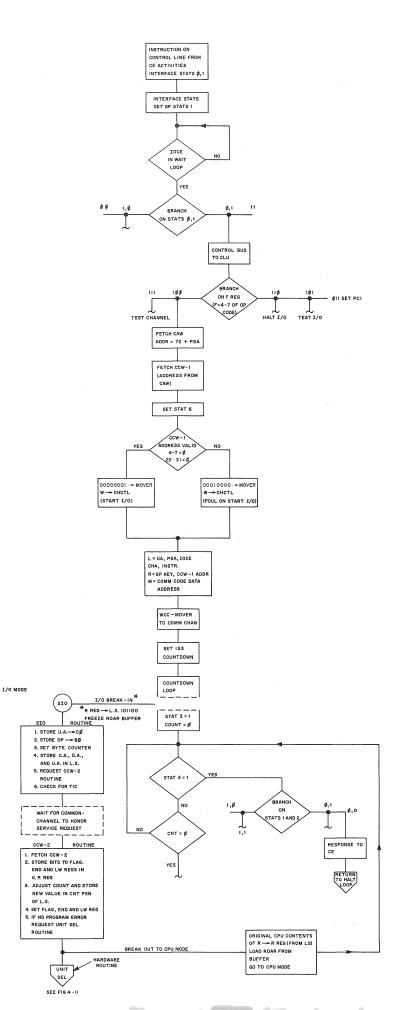

| 4-5. | CE - IOCE SELECTOR CHANNEL OPERATION                    | 4-13 |

| 4-6. | IOCE MULTI PLEXOR CHANNEL                               |      |

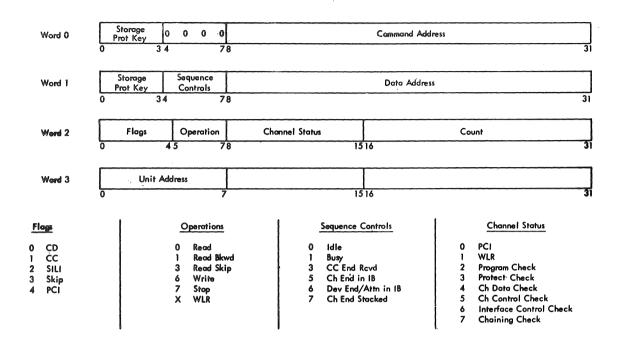

| 4-7. | UNIT CONTROL WORDS                                      | 4-24 |

| 4-8. | IOCE STANDARD INTERFACE                                 | 4-27 |

|      | A. Bus Information                                      | 4-28 |

|      | B. Interface Tag Lines                                  | 4-30 |

|      | C. Selection Control Lines                              |      |

|      | D. Metering Control Lines                               |      |

| 4-9. | IOCE STAND ALONE OPERATION                              |      |

## CHAPTER 5

# I/O OPERATIONS

| 5-2.       IBM-7265-2 SYSTEM CONSOLE - 9020 SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-1. |     | RODUCTION                                     |        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----------------------------------------------|--------|

| <pre>1. Operator Intervention</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-2. | IBM | 1-7265-2 SYSTEM CONSOLE - 9020 SYSTEM         | 5-1    |

| <pre>1. Operator Intervention</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      | A.  | System Console Communication with 9020 System | 5-2    |

| b. Manual Entry of Information or Display5-6<br>2. Printer Keyboard Entry5-6<br>3. Sense Switch Entry5-6<br>4. Storage Modification or Display5-7<br>5. Display of Information from Local Storage (LS)5-8<br>6. Modification of CE Configuration Control Register (CCR)5-9<br>7. Modification of CE Instruction Counter (IAR)5-10<br>8. I/O Switching5-10<br>9. Programming the System Console5-11<br>B. START I/O Instruction5-12<br>C. TEST I/O and HALT I/O Instructions5-12<br>C. TEST I/O and HALT I/O Instructions |      |     | 1. Operator Intervention                      | 5-4    |

| 2. Printer Keyboard Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |     | a. Initial Program Load (IPL)                 | 5-4    |

| 3. Sense Switch Entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |     | b. Manual Entry of Information or Display     | 5-6    |

| 4. Storage Modification or Display5-7 5. Display of Information from Local Storage (LS)5-8 6. Modification of CE Configuration Control Register (CCR)5-9 7. Modification of CE Instruction Counter (IAR)5-10 8. I/O Switching                                                                                                                                                                                                                                                                                            |      |     | 2. Printer Keyboard Entry                     | 5-6    |

| 5. Display of Information from Local Storage (LS)5-8<br>6. Modification of CE Configuration Control Register (CCR)5-9<br>7. Modification of CE Instruction Counter (IAR)5-10<br>8. I/O Switching                                                                                                                                                                                                                                                                                                                         |      |     | 3. Sense Switch Entry                         | 5-6    |

| 6. Modification of CE Configuration Control Register (CCR)5-9<br>7. Modification of CE Instruction Counter (IAR)5-10<br>8. I/O Switching5-10<br>9. Programming the System Console                                                                                                                                                                                                                                                                                                                                        | ,    |     | 4. Storage Modification or Display            | 5-7    |

| 7. Modification of CE Instruction Counter (IAR)5-10<br>8. I/O Switching5-10<br>9. Programming the System Console                                                                                                                                                                                                                                                                                                                                                                                                         |      |     |                                               |        |

| 8. I/O Switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |     |                                               |        |

| 9. Programming the System Console                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |     |                                               |        |

| B. START I/O Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |     |                                               |        |

| <pre>C. TEST I/O and HALT I/O Instructions</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |     | 9. Programming the System Console             | 5-11   |

| D. Console Control Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |     |                                               |        |

| E. Status Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |     |                                               |        |

| F. Sense Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |     |                                               |        |

| G. Printer Keyboard Control Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | -•  |                                               |        |

| H. Commands5-22<br>I. Status Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |     |                                               |        |

| <pre>I. Status Information</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |     |                                               |        |

| <pre>J. Sense Information5-29 K. Data Format5-31 L. Operator Monitoring5-32 1. Mode of Operation Indicators5-32 2. Unit Status Indicators5-32 3. Unit Alarm Indicators</pre>                                                                                                                                                                                                                                                                                                                                             |      | •   |                                               |        |

| <ul> <li>K. Data Format5-31</li> <li>L. Operator Monitoring5-32</li> <li>1. Mode of Operation Indicators5-32</li> <li>2. Unit Status Indicators5-32</li> <li>3. Unit Alarm Indicators</li></ul>                                                                                                                                                                                                                                                                                                                          |      |     |                                               |        |

| <ul> <li>L. Operator Monitoring5-32</li> <li>1. Mode of Operation Indicators5-32</li> <li>2. Unit Status Indicators5-32</li> <li>3. Unit Alarm Indicators</li></ul>                                                                                                                                                                                                                                                                                                                                                      |      |     |                                               |        |

| <ol> <li>Mode of Operation Indicators</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |     |                                               |        |

| <ol> <li>Unit Status Indicators5-32</li> <li>Unit Alarm Indicators</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | L.  | Uperator Monitoring                           | ·-)-32 |

| 3. Unit Alarm Indicators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |     | 1. Mode of Operation Indicators               |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |     |                                               |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |     | 4. Configuration Indicator Registers          |        |

| 5. Audible Alarms5-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |     | 4. Configuration indicator Registers          | -5-33  |

| 6. Printer Keyboard5-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |     |                                               |        |

| 5-3. TAPE OPERATIONS5-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-3  | тΔР |                                               |        |

| A. Magnetic Tape5-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5.5. |     |                                               |        |

| B. Writing and Reading Magnetic Tape                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |     |                                               |        |

| C. Tape Markers5-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      | -   | Tape Markers                                  | -5-40  |

| D. File Protection Device5-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |     |                                               |        |

| E. Tape Blocks5-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | -   |                                               |        |

| F. Checking Tape Validity5-43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |     | Checking Tape Validity                        | -5-43  |

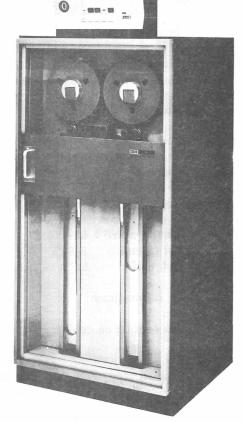

| G. Tape Drive Units (2401-02 and 03)5-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |     | Tape Drive Units (2401-02 and 03)             | -5-44  |

| 1. Moving Tape Forward5-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | -   | 1. Moving Tape Forward                        | -5-44  |

| 2. Moving Tape Backward5-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |     | 2. Moving Tape Backward                       | -5-46  |

| 3. Drive Capstans5-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |     | 3. Drive Capstans                             | -5-46  |

| 4. Stop Capstans5-47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |     | 4. Stop Capstans                              | -5-47  |

| 5. Prolays5-47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |     | 5. Prolays                                    | -5-47  |

| 6. Vacuum Columns5-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |     | 6. Vacuum Columns                             | -5-48  |

|      |      | 7. Column Control Switches                                                                           | 5-51 |

|------|------|------------------------------------------------------------------------------------------------------|------|

|      |      | 8. Tape Handling Operations                                                                          | 5-51 |

|      |      | a. Rewind and Rewind-Unload Operations                                                               | 5-51 |

|      |      | b. Manual Load Operation                                                                             | 5-52 |

|      |      | c. Manual Unload Operation                                                                           | 5-52 |

|      |      | 9. Data Flow During Read Operations                                                                  | 5-52 |

|      | 1    | 0. Tape Unit Selection                                                                               | 5-54 |

|      | 1    | 1. Data Flow During Write Operations - NRZI                                                          | 5-55 |

|      | 1    | 2. Erase Head                                                                                        | 5-56 |

|      | 1    | 3. File Protection                                                                                   |      |

|      | 1    | 4. IBM Tape Unit Keys and Lights                                                                     | 5-57 |

|      |      | a. Operator Keys - All Models                                                                        | 5-57 |

|      |      | b. Operator Lights - All Models                                                                      | 5-60 |

|      |      | 5. Tape Load Procedure                                                                               |      |

|      |      | 6. Tape Unload Procedure                                                                             | 5-62 |

|      |      | 7. Tape Transport Cleaning Procedure                                                                 | 5-64 |

|      |      | 8. Tape Timings                                                                                      |      |

|      |      | IBM-2803 Tape Control Unit                                                                           |      |

|      |      | 1. TCU Designation                                                                                   |      |

|      |      | 2. Configuration Control                                                                             |      |

|      |      | <ol> <li>IBM-9020 System Monitoring of TCU</li> <li>Magnetic Tape Input/Output Operations</li> </ol> |      |

|      |      | <ol> <li>Magnetic Tape Input/Output Operations</li></ol>                                             |      |

|      |      | b. Commands====================================                                                      |      |

|      |      | c. Status Information and Sense Data                                                                 |      |

|      |      | d. Special Status Information                                                                        |      |

|      |      | e. Special Sense Information                                                                         | 5-76 |

| 5-4. | IBM- | 2821 CONTROL UNIT                                                                                    | 5-77 |

|      |      | Data Movement                                                                                        |      |

|      | В.   | Concurrent Operation                                                                                 | 5-78 |

|      |      | Attachment Method                                                                                    |      |

|      | D.   | 2821 Switches                                                                                        | 5-79 |

|      |      | 1. Control Panel Meter Switch                                                                        |      |

|      |      | a. Use Meter (2821)                                                                                  | 5-79 |

|      |      | 2. CE Panel Mode Switch                                                                              |      |

|      |      | Buffering                                                                                            |      |

|      |      | System Reset                                                                                         |      |

|      | G. I | Malfunction Reset (Selective Reset)                                                                  | 5-81 |

|      |      | Interface Disconnect                                                                                 |      |

| 5-5. |      | 2540 CARD READ-PUNCH                                                                                 |      |

|      | A. 4 | Addressing                                                                                           | 5-84 |

|      | В.   | IBM-2540 Reader - Method of Operation                                                                | 5-84 |

|      | C    | IBM-2540 Punch - Method of Operation                                                                 |      |

|      | D. 1 | IBM-2540 Punch-Feed-Read - Method of Operation                                                       | 2-8/ |

|      | E    | Fermination Operations<br>Operation Commands                                                         | 60°C |

|      |      |                                                                                                      |      |

|      |      | l. Read, Feed, and Select Stacker (Type AA)                                                          |      |

|      |      | 3. Read, Feed, and No Stacker Selection (Type AB)                                                    |      |

|      |      | 4. Feed and Select Stacker (Type BA)                                                                 | 5-93 |

|      | -    | ··· reed and bereet bedener (rype bay)                                                               | 5 ,5 |

|    | 5. PFR Write, Feed, and Select Stacker (Type BA)                                                                        | 5-93  |

|----|-------------------------------------------------------------------------------------------------------------------------|-------|

|    | 6. Write, Feed, and Select Stacker (Type BB)                                                                            | 5-94  |

|    | 7. Sense, and No Op                                                                                                     | 5-94  |

|    | 8. Test I/0                                                                                                             |       |

| G. | Data Codes                                                                                                              |       |

|    | 1. Data Mode 1                                                                                                          |       |

|    | 2. Data Mode 2 (Special Feature)                                                                                        | 5-95  |

| H. | Status Byte                                                                                                             | 5-96  |

| I. | Sense Byte                                                                                                              | 5-98  |

| J. | Status Byte Bit Combinations                                                                                            | 5-100 |

|    | 1. 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                |       |

|    | 2. 0 0 0 0 1 0 0                                                                                                        |       |

|    | 3. 0 0 0 0 0 1 0                                                                                                        |       |

|    | 4. 0000001                                                                                                              |       |

|    | 5. 00000110                                                                                                             |       |

|    | 6. 0 0 0 0 1 0 1                                                                                                        |       |

|    | 7. 00000111                                                                                                             |       |

|    | 8. 0000011                                                                                                              |       |

|    | 9. 00011000                                                                                                             |       |

|    | 10. 0 0 0 1 1 1 0 0                                                                                                     |       |

|    | 11. 0 0 0 1 1 0 1 0                                                                                                     |       |

|    | 12. 0 0 0 1 1 0 0 1                                                                                                     |       |

|    | 13. 0 0 0 1 1 1 1 0                                                                                                     |       |

|    | 14. 0 0 0 1 1 1 0 1                                                                                                     |       |

|    | 15. 0 0 0 1 1 1 1 1 1                                                                                                   |       |

|    | 16. 0 0 0 1 1 0 1 1                                                                                                     |       |

|    | 17. 0 0 0 0 1 0 0 0                                                                                                     |       |

|    | 18. 0 0 0 0 1 1 0 0                                                                                                     |       |

|    | 19. 0 0 0 0 1 0 1 0                                                                                                     |       |

|    | 20. 0 0 0 0 1 0 0 1                                                                                                     |       |

|    | 21. 0 0 0 0 1 1 1 0                                                                                                     |       |

|    | 22.       0       0       0       1       1       1         23.       0       0       0       1       1       1       1 |       |

|    |                                                                                                                         |       |

|    |                                                                                                                         |       |

|    |                                                                                                                         |       |

|    |                                                                                                                         |       |

|    |                                                                                                                         |       |

|    |                                                                                                                         |       |

|    |                                                                                                                         |       |

|    |                                                                                                                         |       |

|    |                                                                                                                         |       |

| 17 |                                                                                                                         |       |

| К. | Possible Combinations of Sense Bits in a Sense Byte                                                                     |       |

| L. | Diagnostic Commands for the 2540 Controls<br>1. Diagnostic Write - 100101                                               | D=10/ |

|    | <ol> <li>Diagnostic Write - 100101</li> <li>Diagnostic Read 11000010</li> </ol>                                         |       |

|    |                                                                                                                         | 5.100 |

| м  | 3. Diagnostic Check Read 11000110<br>Keys, Switches, and Indicators                                                     | 5 100 |

| Μ. | 1. Common Reader-Punch Switch and Indicators                                                                            | 5-100 |

|    | 2. Card-Reader Keys and Indicators                                                                                      | 5-100 |

|    | 2. UALU-NEAUEL NEYS ANU INUICALOIS                                                                                      |       |

|      |     | ~   | ~   |     | -   | ,   | -   | -   | 1 1.0 .                                 |               | F 110 |

|------|-----|-----|-----|-----|-----|-----|-----|-----|-----------------------------------------|---------------|-------|

|      |     | 3.  | Ça  | rd- | -Pu | ncl | n ŀ | Key | s and Indicators                        |               | 5-110 |

|      | Ν.  |     | gra | mmi | ing | T:  | imi | Ĺng | Considerations                          |               | 5-111 |

|      |     | 1.  |     |     |     |     |     |     |                                         |               | 5-111 |

|      |     | 2.  |     |     |     |     |     |     |                                         |               | 5-113 |

|      |     | 3.  |     |     |     |     |     |     |                                         |               | 5-113 |

|      |     | 4.  | De  | vic | ce  | End | d t | 0   | Clutch Decision Po                      | int Timing    | 5-113 |

|      | 0.  |     |     |     |     |     |     |     |                                         |               | 5-114 |

| 5-6. | 140 |     |     |     |     |     |     |     |                                         |               | 5-114 |

|      | Α.  | Pri | nti | ng  | Ро  | si  | tic | ons | and Type Format                         |               | 5-115 |

|      | B.  | Тар | e-C | ont | tro | 110 | ed  | Са  | riage                                   |               | 5-116 |

|      | C.  | Pri |     |     |     |     |     |     |                                         |               | 5-116 |

|      |     | 1.  |     |     |     |     |     |     |                                         |               | 5-116 |

|      |     | 2.  |     |     |     |     |     |     |                                         |               | 5-116 |

|      |     | 3.  |     |     |     |     |     |     |                                         |               | 5-117 |

|      |     | 4.  | Me  | thc | od  | of  | OF  | bei | ation of the IBM 1                      | 403 Printer-  | 5=117 |

|      | D.  | 0pe |     |     |     |     |     |     |                                         |               | 5-118 |

|      |     | 1.  | Te  | st  | I/  | 0   |     |     |                                         | ***********   | 5-120 |

|      |     | 2.  |     |     |     |     |     |     |                                         |               | 5-120 |

|      |     | 3.  | Se  | nse | εB  | yte | e   |     | ******                                  |               | 5-123 |

|      | E.  | Pos | sib | le  | Со  | mb: | ina | ati | ons of Status Bits                      | s in a Status | Byte  |

|      |     |     |     |     |     |     |     |     |                                         |               | 5-125 |

|      |     | 1.  | 0   | 0 ( | 0 0 | 0   | 0   | 0   | )                                       |               | 5-125 |

|      |     | 2.  | 0   | 0 0 | 0 0 | 0   | 1   | 0   | )                                       |               | 5-126 |

|      |     | 3.  | 0   | 0 ( | 0 0 | 0   | 0   | 1   | ) = = = = = = = = = = = = = = = = = = = |               | 5-126 |

|      |     | 4.  | 0   | 0 ( | 0 0 | 0   | 0   | 0   |                                         |               | 5-126 |

|      |     | 5.  | 0   | 0 ( | 0 0 | 0   | 1   | 1   | )                                       |               | 5-126 |

|      |     | 6.  | 0   | 0 0 | 0 0 | 0   | 1   | 0   |                                         |               | 5-127 |

|      |     | 7.  | 0   | 0 ( | 0 0 | 0   | 1   | 1   |                                         |               | 5-127 |

|      |     | 8.  | 0   | 0 0 | 0 0 | 0   | 0   | 1   | -                                       |               | 5-128 |

|      |     | 9.  |     |     |     |     |     |     |                                         |               | 5-128 |

|      |     | 10. |     |     |     |     |     |     |                                         |               | 5-128 |

|      |     | 11. |     |     |     |     |     |     |                                         |               | 5-128 |

|      |     | 12. | Õ   |     |     |     |     |     |                                         |               | 5-129 |

|      |     | 13. | -   |     |     |     |     |     |                                         |               | 5-129 |

|      |     | 14. | •   |     |     |     |     |     |                                         |               | 5-130 |

|      |     | 15. |     |     |     |     |     |     |                                         |               | 5-130 |

|      |     | 16. |     |     |     |     |     |     |                                         |               | 5-131 |

|      |     | 17. |     |     |     |     |     |     |                                         |               | 5-131 |

|      |     | 18. |     |     |     |     |     |     |                                         |               | 5-131 |

|      |     | 19. |     |     |     |     |     |     |                                         |               | 5-132 |

|      |     | 20. |     |     |     |     |     |     |                                         |               | 5-132 |

|      |     | 20. |     |     |     |     |     |     |                                         |               | 5-132 |

|      |     |     |     |     |     |     |     |     |                                         |               |       |

|      |     | 22. |     |     |     |     |     |     |                                         |               | 5-133 |

|      |     | 23. |     |     |     |     |     |     |                                         |               | 5-133 |

|      |     | 24. |     |     |     |     |     |     |                                         |               |       |

|      |     | 25. |     |     |     |     |     |     |                                         |               | 5-134 |

|      |     | 26. |     |     |     |     |     |     |                                         |               | 5-134 |

|      |     | 27. |     |     |     |     |     |     |                                         |               | 5-134 |

|      |     | 28. |     |     |     |     |     |     |                                         |               | 5-135 |

|      |     | 29. | 0   | 0 0 | ) 1 | 0   | 1   | 1   | )                                       |               | 5-135 |

|      |     | 30. 0 0 0 1 0 1 0 1                                                    |                      |

|------|-----|------------------------------------------------------------------------|----------------------|

|      |     | 31. 0 0 0 1 0 1 1 1                                                    | 5-135                |

|      |     | 32. 0 0 0 1 0 0 1 1                                                    | 5-135                |

|      | F.  | Possible Combinations of Sense Bits in a Sense Byte                    | 5-135                |

|      | G.  | Diagnostic Commands for the 1403 Controls                              | 5-138                |

|      |     | 1. Diagnostic Write (101)                                              | 5-138                |

|      |     | 2. Diagnostic Data Read (00000010)                                     | 5-138                |

|      |     | 3. Diagnostic Check Read (00000110)                                    | 5-139                |

|      | H.  | Use Meter                                                              | 5-139                |

|      | I.  | Printer Keys and Indicators                                            |                      |

|      |     | 1. Print Start Key                                                     | 5-139                |

|      |     | 2. Check-Reset Key                                                     | 5-140                |

|      |     | 3. Print Stop Key                                                      | 5-140                |

|      |     | 4. End-of-Forms Light                                                  | 5-140                |

|      |     | 5. Forms Check Light                                                   | 5-141                |

|      |     | 6. Ready Light                                                         | 5-141                |

|      |     | 7. Print Check Light                                                   | 5-141                |

|      |     | 8. Sync Check Light                                                    | 5-141                |

|      |     | 9. Single-Cycle Key                                                    |                      |

|      | J.  | Carriage Keys                                                          | 5-142                |

|      | 0.  | 1. Restore Key                                                         |                      |

|      |     | <ol> <li>Carriage Stop Key</li> </ol>                                  |                      |

|      |     | 3. Space Key                                                           | 5-1/13               |

|      | ĸ.  | Universal Character Set Special Feature (1403-2, -3,                   |                      |

|      | K.  | -N1 Only)                                                              |                      |

|      |     | 1. Description                                                         |                      |

|      |     | 2. Method of Operation                                                 |                      |

|      |     | 3. Dualing of Graphics/Codes with the Universal Characte               |                      |

|      |     | Set Feature                                                            |                      |

|      |     | 4. Changing Codes in the 240-Character Storage                         |                      |

|      |     | 5. Data Check Control                                                  |                      |

|      |     | 6. Printing Speeds                                                     |                      |

|      |     | <ol> <li>7. Universal Character Set Utility Program</li> </ol>         |                      |

|      |     | 8. Configurations                                                      | 5-156                |

|      |     | <ol> <li>9. Print Chaings and Trains (Selection and Design)</li> </ol> | 5-157                |

|      |     | 10. Chain or Train Design                                              | J-1J/<br>            |

|      | L.  | Programming Timing Considerations (For Printers without                | <b></b>              |

|      | ь.  | the Universal Character Set Feature)                                   |                      |

| 5-7. | тра | 4 7289-02 PERIPHERAL ADAPTER MODULE                                    |                      |

| J=/. |     | General Characteristics                                                |                      |

|      | Α.  | 1. PAM Common                                                          |                      |

|      |     | <ol> <li>PAM Adapters</li> </ol>                                       |                      |

|      | D   | PAM Input/Output Operations                                            | J=100<br>5171        |

|      | Β.  | 1. START I/O Instruction                                               |                      |

|      |     |                                                                        | ====J=1/1<br>5 172   |

|      | C   | 2. TEST I/O and HALT I/O InstructionsPAM Common                        | (/⊥=ر====<br>. ر=⊥-ر |

|      | С.  | PAM CommonPAM Addressing                                               |                      |

|      | D.  | ram Address Assistant                                                  | 5-1/4                |

|      | Е.  | IOCE-PAM Address Assignment                                            | J-1/0<br>5 100       |

|      | F.  | Configuration Control                                                  | J-LOU                |

|      |     | 1. IOCE Assignment                                                     | J-TQA                |

.

| 3.       State Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 2. SCON Assignment                       | 5-181          |