# Direct Access Storage Devices Description

# GA23-0053

# Direct Access Storage Devices Description

#### Third Edition (April 1984)

This revision obsoletes GA23-0053-1.

This publication is for planning purposes and may be subject to minor changes. The functions and capabilities it describes reflect the information previously available in the *IBM 8130 Processor Description*, GA27-3196, and in the *IBM 8140 Processor Description*, GA27-2880.

References in this publication to IBM products, programs, or services do not imply that IBM intends to make these available in all countries in which IBM operates. Any reference to an IBM program product in this publication is not intended to state or imply that only IBM's program product may be used. Any functionally equivalent program may be used instead.

Publications are not stocked at the address given below. Requests for IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for readers' comments is provided at the back of this publication. Address any additional comments to IBM Corporation, Department 52Q, Neighborhood Road, Kingston, N.Y., U.S.A. 12401. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

© Copyright International Business Machines Corporation 1978, 1984

# Preface

This manual describes the physical characteristics and specific implementation of the 8100 disk and diskette storage facilities. It is intended primarily to help a programming audience understand (1) how, for some operations, programming can control the way the hardware operates and (2) the significance of hardware status information that is accessible to programming. The manual is divided into three chapters, as follows:

Chapter 1 introduces the 8100 system units.

Chapter 2 describes the hardware components of the 8100 disk storage facility. The chapter describes the components, functional elements, and registers of the disk direct access storage device (DASD), and the commands implemented by the disk adapter. Examples of typical data transfer operations show the relationship between the programmed input/output (PIO) commands implemented by the disk adapter and the way data is transferred by use of channel I/O (CHIO) operations.

Chapter 3 describes the hardware components of the 8100 diskette storage facility. The chapter describes the physical characteristics and functional elements of the diskette storage facility. Like the previous chapter, it provides examples of typical data transfer operations for the diskette adapter.

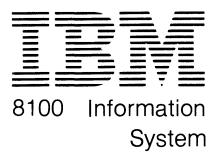

# **Using 8100 System Description Publications**

The following publications are companions to this one:

- IBM 8100 Information System Principles of Operation, GA23-0031

- IBM 8130 Processor Description, GA27-3196

- IBM 8140 Processor Description, GA27-2880

- IBM 8150 Processor Description, GA27-0122

- IBM 8101/8102 Storage and Input/Output Unit Description, GA27-2882

- IBM 8130/8140 Processor Operator's Guide, GA27-3197

- IBM 8150 Processor Operator's Guide, GA23-0123

- IBM 8140 Processor Expanded Function Operator Panel Feature Description, GA27-2879

The following figure shows the topics each publication includes.

.

.

.

.

# Contents

Chapter 1. Introduction 1-1 Chapter 2. 8100 Disk Storage Facility 2-1 Disk DASD Components and Functional Elements 2-1 Disk Surfaces 2-1 Sector Fields 2-1 Sector Positions 2-4 Magnetic Heads 2-4 8130, 8140, and 8101 Spiral Format 2-4 Adapter 2-7 **Operations 2-7** Disk Adapter Error Detection and Reporting 2-9 Disk Adapter Control Registers 2-9 Burst Register 2-10 Control CHCV Register 2-10 Data Transfer CHCV Register 2-11 **Residual Count Register 2-11** Next Function Register (NFR) 2-11 Seek Register 2-12 Skip Factor Register 2-13 Physical Sector Counter (PSC) 2-14 Disk Adapter Status Registers 2-14 Disk BSTAT 2-15 Data Handler Extended Status Register 2-17 FCB Processor Status Register 2-18 Seek Status Register 2-19 **Data Transfer Operations 2-20** Disk Adapter PIO Address Assignments 2-21 I/O Interrupts 2-21 Programmed I/O (PIO) Operations 2-22 **Disk PIO Commands 2-23 Diagnostic Error-Recovery Commands 2-26** Disk Channel I/O (CHIO) Operations 2-28 CHIO Request Priority 2-32 **CHIO Control Operations 2-32** CHIO Data Transfer Operations 2-35 Examples of Disk Data Transfer Operations 2-45

Chapter 3. 8100 Diskette Storage Facility 3-1 **Diskette Storage Physical Characteristics 3-1** Read/Write Heads (Loading/Unloading) 3-1 Diskette Format 3-1 **Track Format 3-2** Sector Format 3-2 Diskette Storage Functional Elements 3-4 Diskette Adapter 3-4 Diskette Adapter Data Buffers 3-4 Diskette Adapter Control Registers 3-5 Channel Pointer (CHP) Number Register 3-5 **Diskette Control Register 3-5** Drive Control Register 3-7 Record Count Register 3-7 **Record Number Register 3-8** Diskette Adapter Status Registers 3-9 Diskette BSTAT Summary 3-9 **Diskette BSTAT Description 3-9** Diskette Status Extension Register Description 3-15 **Diskette Functional Characteristics 3-15** Diskette Adapter PIO Address Assignments 3-15 Diskette Adapter I/O Interrupts 3-16 Programmable Priority Level Assignment 3-16

Diskette PIO Operations 3-17 Register-Oriented Commands 3-18 Data Transfer Commands 3-21 PIO Execution 3-21 Locating the Selected Record 3-21 Transferring the Data 3-22 Data Transfer Command Description 3-25 Seek Commands 3-33 Diskette Channel I/O (CHIO) Operations 3-35 CHIO Request Priority 3-35 Diskette CHIO Operation Introduction 3-35 Initiating a CHIO Burst Transfer 3-37 Examples of Diskette Data Transfer Operations 3-39 Diskette Adapter Error Detection and Reporting 3-44

Appendix A. Data Storage Capacities A-1 Disk DASD Data Storage Capacities by Model A-1 Diskette DASD Data Storage Capacities A-2

Appendix B. DASD Physical Specifications B-1

Disk DASD Functional Specifications and Access Times B-1

Disk Format B-1

Access Times B-1

Diskette DASD Physical Specifications B-2

Diskette DASD Functional Specifications and Access Times B-2

#### Appendix C. Error Status Summary C-1

Disk Error Status Summary C-1 Conditions for Setting Equipment Check (BSTAT 13) Bit C-1 Conditions for Setting Device Error (BSTAT 9) Bit C-1 Diskette Error Status Summary C-2

#### Appendix D. Sample 8100 Assembler Language Code to Generate Cyclic Redundancy Check (CRC) D-1

**Glossary GL-1**

Index X-1

# **Figures**

- 1-1. 8100 Information System Units 1-2

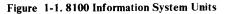

- 2-1. Disk Format 2-3

- 2-2. Sector Displacement 2-4

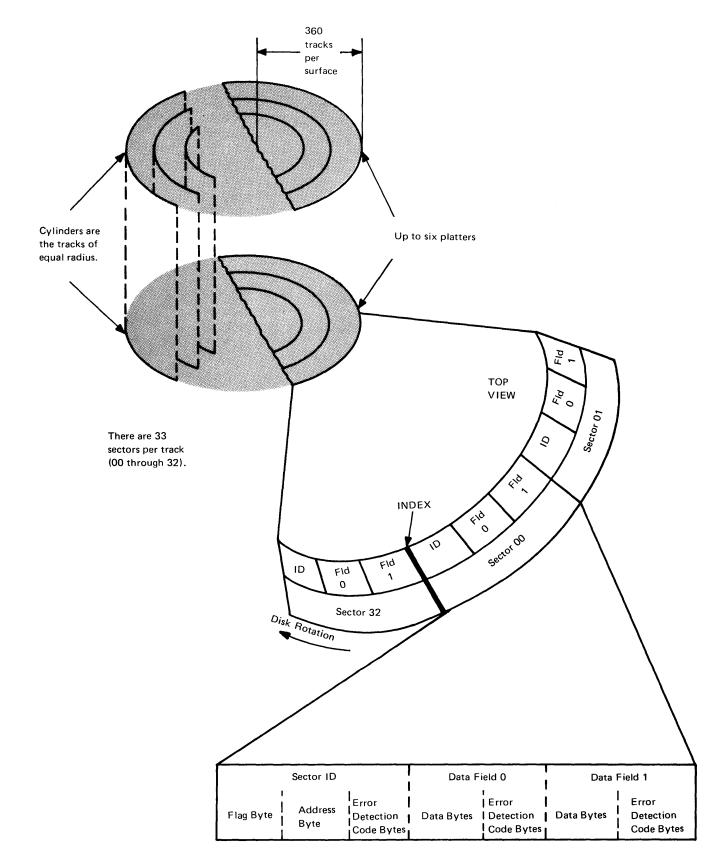

- 2-3. Spiral Format 2-5

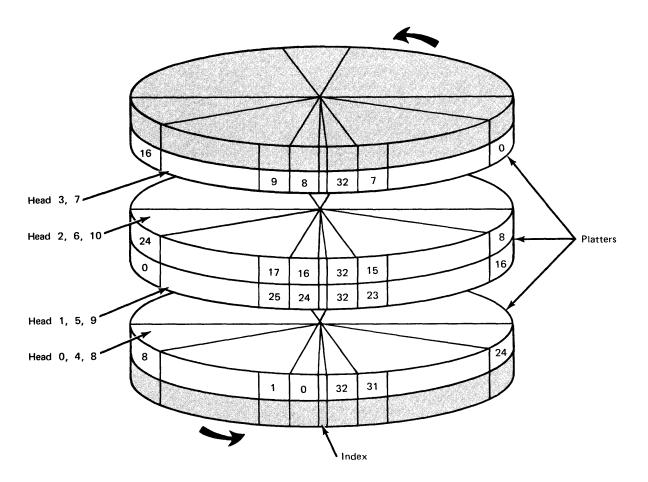

- 2-4. Sector Numbering 2-6

- 2-5. Disk Adapter Data Buffers 2-8

- 2-6. Multifield Transfers with Skip Factor Values 2-14

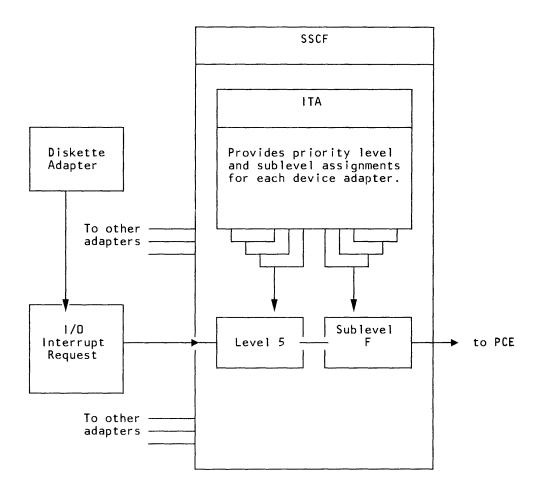

- 2-7. Priority and Sublevel Assignment in the ITA 2-22

- 2-8. Function Control Block (FCB) 2-29

- 2-9. Example of a Channel I/O Operation 2-31

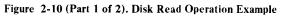

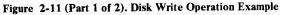

- 2-10. Disk Read Operation Example 2-46

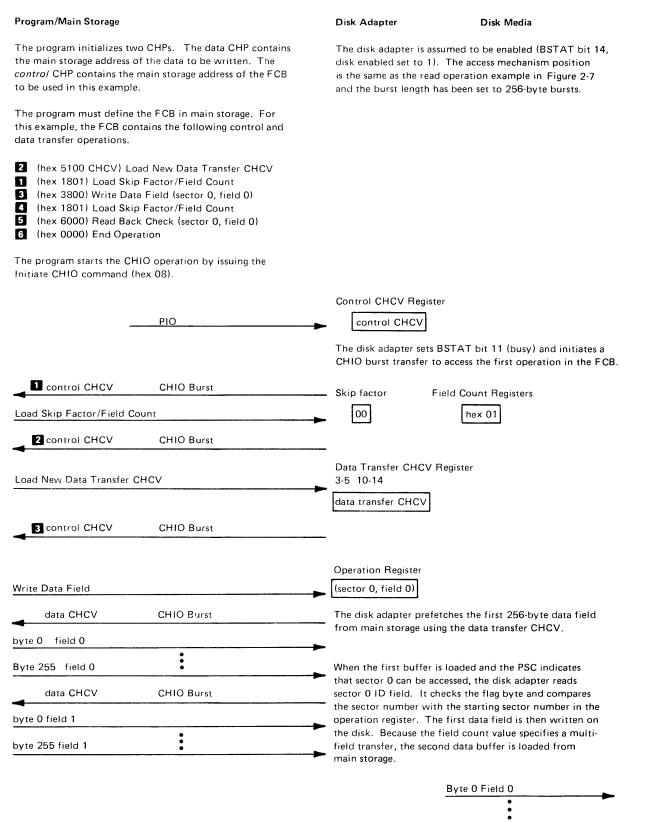

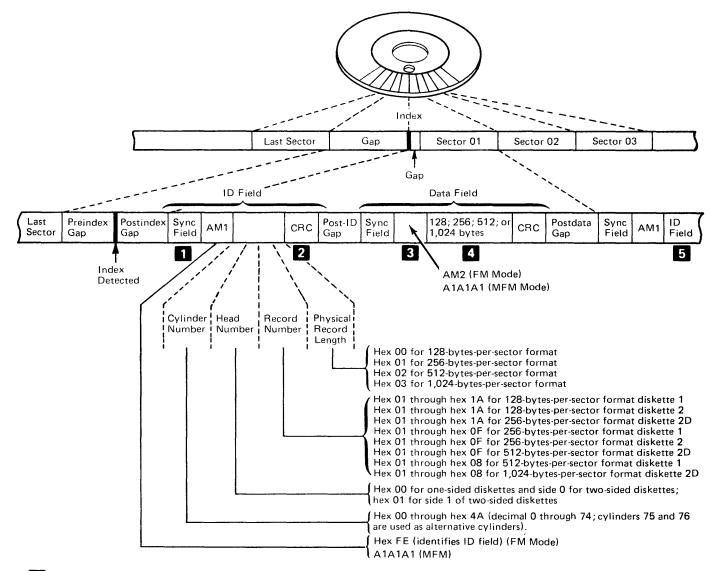

- 2-11. Disk Write Operation Example 2-48

- 3-1. Diskette Sector Format 3-3

- 3-2. Priority and Sublevel Assignment in the ITA 3-17

- 3-3. Single-Density Write Track Control Information Format 3-31

- 3-4. Double-Density Write Track Control Information Format 3-32

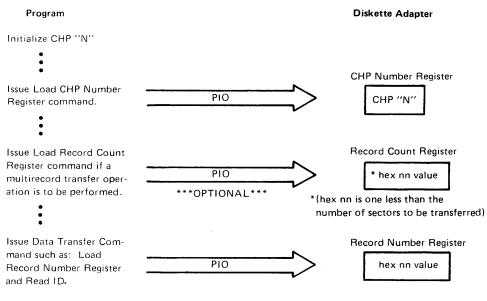

- 3-5. Example of CHIO Preparation 3-36

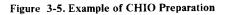

- 3-6. Initiating CHIO Burst Transfers 3-37

- 3-7. Sample Multirecord Read Operation 3-40

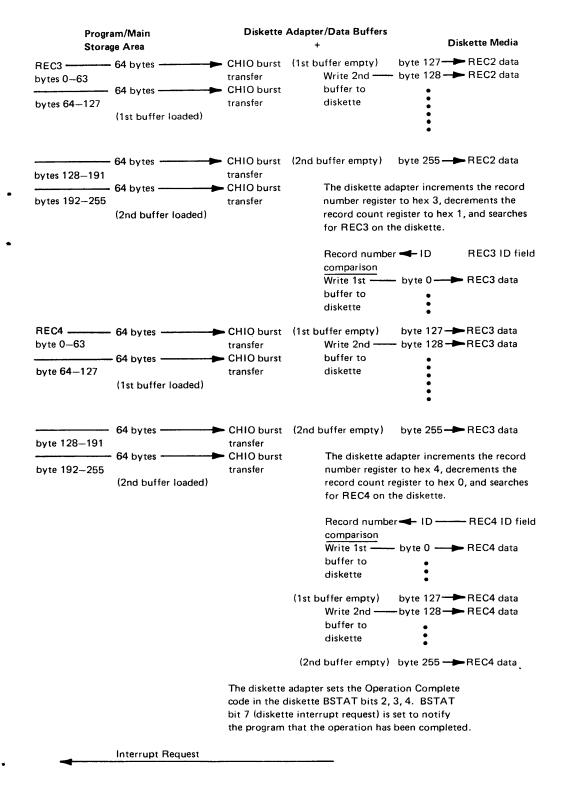

- 3-8. Sample Multirecord Write Operation 3-42

# **Summary of Changes**

# Third Edition (April 1984)

The following changes were made to this edition:

- The term *DASD* is used to refer specifically to a single direct-access storage device, which includes a disk or diskette, an access mechanism, and a disk or diskette adapter.

- Chapter 2 has been updated to include references to the 8102 Models A15 and A17 with an enhanced disk DASD.

- Miscellaneous corrections and clarifications have been made throughout this manual.

# Second Edition (March 1982)

The following changes were made to this edition:

- The term "processor storage" has been changed to "main storage" to match the other 8100 description manuals.

- The word "processor" has been changed to "processing and control element (PCE)" when referring to the processing unit within the 8100 system. The word "processor" was not changed when referring to the 8130 and 8140 processor.

- All chapters have been updated to include references to the 8140 Model C.

- Appendix C, "Sample 8100 Assembler Language Code to Generate CRC", has been added.

- Miscellaneous corrections and clarifications have been made throughout this manual.

# **Chapter 1. Introduction**

.

The IBM 8100 Information System is a communication-oriented stand-alone system capable of being attached to a host System/370 or 4300, or to other 8100 systems. The 8100 processors and operating systems provide a flexible base for a wide variety of products.

Direct access storage devices are contained in the following 8100 Information System units:

8130 Processor8140 Processor8101 Storage and I/O Unit8102 Storage and I/O Unit

Storage capacity varies with each 8100 unit model. See Figure 1-1.

Disks are permanently sealed in an enclosure, which protects them from external contaminants; the user cannot remove them. Diskettes are inserted into the diskette drive when needed, but are stored outside the 8100 unit when not in use. An optional diskette lock, provided on 8140B and C Processors and also available on some other models, restricts access to the diskette drive.

#### 8130/8140 Processor A Models

Disk Storage 23MB to 64MB 2D Diskette Drive

Communication Port Attachment Loop Attachment Display and Printer Attachment (8130B only)

## 8140 Processor B Models

Disk Storage 58MB to 123MB 2D Diskette Drive

#### 8140 Processor C Models

Disk Storage 123MB 2D Diskette Drive

Communication Port Attachment Display and Printer Attachment Loop Attachment

#### 8101 Storage and Input/Output Unit

Disk Storage 29MB to 128MB

With optional 2D Diskette, the disk storage is from 29MB to 64MB.

Note: Disk storage is available only on 8101 Models A11, A13, A23, A25

Communication Port Attachment Display and Printer Attachment Loop Attachment Storage and I/O Unit Switch Feature

8102 Storage and Input/Output Unit

Disk Storage 129MB to 259MB

Display and Printer Attachment Magnetic Tape Attachment Storage and I/O Unit Switch Feature

# Chapter 2. 8100 Disk Storage Facility

.

-

.

.

|                        | 8101 an                                                                               | 0 disk storage facility, incorporated in 8130 and 8140 Processors and in d 8102 Storage and I/O Units, provides high-speed, large-capacity disk for data-base, data-communication, or general use.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | (DASDs<br>movable                                                                     | s storage facility consists of one or more direct access storage devices<br>b). Each disk DASD is composed of a disk, which stores data; fixed or<br>magnetic heads, which transfer data to or from the disk; and a disk<br>which links the disk to the 8100 unit and provides the logic that controls<br>ce.                                                                                                                                                                                                                                                                                                                           |

|                        | type of I<br>greater c                                                                | age capacities of 8100 unit models differ according to the number and DASDs the models contain. (The 8102 contains a disk DASD with capacity and enhanced error-correction capability.) The storage as of all 8100 unit models are listed in Appendix A.                                                                                                                                                                                                                                                                                                                                                                                |

| Disk DASD Components a | and Func                                                                              | tional Elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | elements                                                                              | tion describes the physical characteristics of the disk DASD and the s that enable it to store and transfer data. Refer to Appendix C for format specifications and for access times.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Disk Surfaces          |                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | two disk<br>surfaces,<br>reserved<br>tracks. T<br>cylinders<br>closest to<br>0 to 32; | a consists of a stack of up to six magnetic-coated platters, each providing<br>surfaces, permanently mounted on a motor-driven spindle. Up to 11 disk<br>, numbered from 0 to 10, are available for storing data; one surface is<br>for servo coding. Each surface is divided into several hundred circular<br>Tracks from different surfaces but with the same radius are grouped into<br>s. Cylinders and tracks are numbered starting from zero, with zero<br>to the center. Each track is divided into 33 equal sectors, numbered from<br>any data record stored on a disk can be identified by its cylinder, track,<br>or numbers. |

| Sector Fields          |                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | fields. T                                                                             | ctor is divided into three fields: one identification (ID) field and two data<br>the ID field consists of one flag byte, three address bytes, and two cyclic<br>ncy check (CRC) bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                        |                                                                                       | <i>byte</i> defines the status of the sector and whether an alternate sector has igned. This byte contains the following bits:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                        | Bit                                                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                        | 0                                                                                     | Defective field 1 (factory defect in 8102)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                        | 1                                                                                     | Defective field 0 (field defect in 8102)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                        | 2                                                                                     | Write protect field 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                        | 3                                                                                     | Write protect field 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                        | 4                                                                                     | Sector displaced                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                        | 5                                                                                     | Sector reassigned                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                        | 6                                                                                     | Sector defective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                        | 7                                                                                     | Alternate sector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

7 Alternate sector

The *address bytes* contain the sector, head, and cylinder numbers that identify a particular sector. The following table shows the bit meanings for the address bytes:

#### Sector Number

| 0 | 0  |

|---|----|

| 1 | 32 |

| 2 | 16 |

| 3 | 8  |

| 4 | 4  |

| 5 | 2  |

| 6 | 1  |

| 7 | 0  |

# **Head Number**

| Bit | Decimal Value                             |

|-----|-------------------------------------------|

| 0   | 0                                         |

| 1   | (Designates a fixed head when equal to 1) |

| 2   | 8                                         |

| 3   | 4                                         |

| 4   | 2                                         |

| 5   | 1                                         |

Cylinder Number

| Bit | Decimal Value         |

|-----|-----------------------|

| 6   | 0 (512 for 8102 only) |

| 7   | 256                   |

| 0   | 128                   |

| 1   | 64                    |

| 2   | 32                    |

| 3   | 16                    |

| 4   | 8                     |

| 5   | 4                     |

| 6   | 2                     |

| 7   | 1                     |

The cyclic redundancy check (CRC) bytes are error detection code bytes used to check the accuracy of data as it is read from the disk. They are described in more detail under "Disk Adapter Error Detection and Reporting."

Each data field contains 256 data bytes, used to store data, and two CRC bytes (four Error Correction Code—ECC—bytes in the 8102), which function similarly to the ID field CRC bytes described above.

Each data field can be transferred separately, or multiple fields can be transferred when record-length requirements exceed 256 bytes. The maximum number of data fields that can be read or written during a multiple field operation is 64, or the equivalent of one track. Figure 2-1 depicts the disk and its surface format.

Figure 2-1. Disk Format

#### Sector Positions

On each disk surface, sectors are usually positioned in sequential order. The only sectors that may appear out of sequence are Sector 32 (which precedes the index) and any sector that has been reassigned or displaced because of defects. Defective sectors are reassigned as follows:

At the factory, the first defective sector on a track is reassigned as Sector 32; data and the original ID of the defective sector are displaced one sector, as are all subsequent sectors to the end of the track (Figure 2-2). The next defective sector on the same track is reassigned to Track 64 (in the 8102, either to the closest spare sector within 10 cylinders or to Track 64).

During normal operation, any defective sector is reassigned to Track 64 (in the 8102, either to the closest spare sector within 10 cylinders or to Track 64).

Track "X": all sectors good.

| 1 |   |   | · · · · · · · · · · · · · · · · · · · |   |   |   |   | 1 |    |    |    |    |    | • |

|---|---|---|---------------------------------------|---|---|---|---|---|----|----|----|----|----|---|

|   | 0 | 1 | 2                                     | 3 | 4 | 5 | 6 |   | 28 | 29 | 30 | 31 | 32 |   |

Track ''X'': sector 4 becomes defective and is displaced.

| 0 1 2 3 32 4 5 27 28 29 30 | 31 |

|----------------------------|----|

|----------------------------|----|

**Figure 1. Sector Displacement**

# **Magnetic Heads**

Over each disk surface are suspended one or more magnetic heads for transferring data. The heads may be either fixed or movable.

A movable-head configuration uses one head per disk surface. A pivoting arm suspends the head over the surface, enabling it to move to any track. The head can access any data record on a surface, but there is a brief delay in data transfer whenever the head moves to a different track.

In a *fixed-head configuration*, eight heads are suspended over one disk surface. The heads are permanently positioned over their respective data tracks and can access only those eight tracks. When transferring data, fixed heads read each track on a surface in succession; they can transfer 131,072 successive bytes of data to or from their tracks without the delay of access motion.

# 8130, 8140, and 8101 Spiral Format

On each successive disk surface, Sectors 0-31 are skewed one quarter turn. This places Sector 0 of each surface over Sector 8 of the previous surface and arranges the tracks into a spiral twisting around the disk. (See Figure 2-3 for a depiction of the spiral format.)

The spiral format synchronizes the movement of the disk with the access delay of the heads. Switching to the next higher head in a cylinder takes up a 5-millisecond (ms) "head select" delay, during which the disk rotates one quarter turn. The spiral format prevents the first eight sectors on the next surface from rotating past the next active head. The first sector rotates into position only after the head becomes active, so the head can resume data transfer immediately. Figure 2-4 lists each sector number with its physical position on the disk surface.

Figure 2-3. Spiral Format

|                                            | Heads<br>0, 4, 8 |     | Heads<br>1, 5, 9 |      | Heads<br>2, 6, 1 |     | Heads<br>3, 7    |     |                         |

|--------------------------------------------|------------------|-----|------------------|------|------------------|-----|------------------|-----|-------------------------|

| Physical<br>Sector<br>Number<br>(Position) | ID<br>on<br>Disk | LSN | ID<br>on<br>Disk | LSN  | ID<br>on<br>Disk | LSN | ID<br>on<br>Disk | LSN |                         |

|                                            | DISK             |     | DISA             | LOIN | 17158            |     | DISK             |     | <index< th=""></index<> |

| 0                                          | 00               | 0   | 30               | 24   | 20               | 16  | 10               | 8   |                         |

| 1                                          | 02               | 1   | 30               | 25   | 20               | 10  | 12               | 9   |                         |

| 2                                          | 04               | 2   | 34               | 26   | 24               | 18  | 14               | 10  |                         |

| 23                                         | 06               | 3   | 36               | 20   | 26               | 19  | 16               | 11  |                         |

| 4                                          | 08               | 4   | 38               | 28   | 28               | 20  | 18               | 12  |                         |

| 5                                          | 0A               | 5   | 3A               | 29   | 2A               | 21  | 1A               | 13  |                         |

| 6                                          | 0C               | 6   | 3C               | 30   | 2C               | 22  | 10               | 14  |                         |

| 7                                          | 0E               | 7   | 3E               | 31   | 2E               | 23  | 1E               | 15  |                         |

| 8                                          | 10               | 8   | 00               | 0    | 30               | 24  | 20               | 16  |                         |

| 9                                          | 12               | 9   | 02               | 1    | 32               | 25  | 22               | 17  |                         |

| 10                                         | 14               | 10  | 04               | 2    | 34               | 26  | 24               | 18  |                         |

| 11                                         | 16               | 11  | 06               | 3    | 36               | 27  | 26               | 19  |                         |

| 12                                         | 18               | 12  | 08               | 4    | 38               | 28  | 28               | 20  |                         |

| 13                                         | 1A               | 13  | <b>0</b> A       | 5    | 3A               | 29  | 2A               | 21  |                         |

| 14                                         | 1C               | 14  | 0C               | 6    | 3C               | 30  | 2C               | 22  |                         |

| 15                                         | 1E               | 15  | 0E               | 7    | 3E               | 31  | 2E               | 23  |                         |

| 16                                         | 20               | 16  | 10               | 8    | 00               | 0   | 30               | 24  |                         |

| 17                                         | 22               | 17  | 12               | 9    | 02               | 1   | 32               | 25  |                         |

| 18                                         | 24               | 18  | 14               | 10   | 04               | 2   | 34               | 26  |                         |

| 19                                         | 26               | 19  | 16               | 11   | 06               | 3   | 36               | 27  |                         |

| 20                                         | 28               | 20  | 18               | 12   | 08               | 4   | 38               | 28  |                         |

| 21                                         | 2A               | 21  | 1A               | 13   | 0A               | 5   | 3A               | 29  |                         |

| 22                                         | 2C               | 22  | 1C               | 14   | 0C               | 6   | 3C               | 30  |                         |

| 23                                         | 2E               | 23  | 1E               | 15   | 0E               | 7   | 3E               | 31  |                         |

| 24                                         | 30               | 24  | 20               | 16   | 10               | 8   | 00               | 0   |                         |

| 25                                         | 32               | 25  | 22               | 17   | 12               | 9   | 02               | 1   |                         |

| 26                                         | 34               | 26  | 24               | 18   | 14               | 10  | 04               | 2   |                         |

| 27                                         | 36               | 27  | 26               | 19   | 16               | 11  | 06               | 3   |                         |

| 28                                         | 38               | 28  | 28               | 20   | 18               | 12  | 08               | 4   |                         |

| 29                                         | 3A               | 29  | 2A               | 21   | 1A               | 13  | 0A               | 5   | 1                       |

| 30                                         | 3C               | 30  | 2C               | 22   | 1C               | 14  | 0C               | 6   |                         |

| 31                                         | 3E               | 31  | 2E               | 23   | 1E               | 15  | 0E               | 7   |                         |

| 32                                         | 40               | 32  | 40               | 32   | 40               | 32  | 40               | 32  |                         |

|                                            |                  |     | ļ                |      |                  |     | ļ                |     |                         |

|                                            |                  |     |                  |      |                  |     |                  |     | <index< th=""></index<> |

.

LSN = Logical Sector NumberingSector 32 ("X40") is the alternate sector and precedes the index code, unless logically displaced or reassigned. When fixed heads are used, movable head 0 is not present.

Figure 2-4. Sector Numbering

# Adapter

The disk adapter includes the following elements:

- The Function Control Block (FCB) processor, which decodes commands, fetches control information from main storage, and initiates seek, file status, and sense operations to the disk.

- The data handler, which controls the movement of stored data between the disk and main storage.

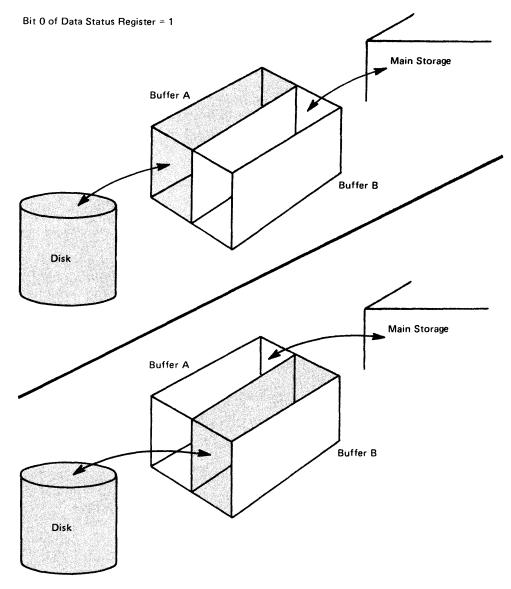

- Data buffers, which hold data being transferred between the disk and main storage. There are two 256-byte buffers, labeled A and B.

- Adapter registers, which control and keep track of the disk adapter's data transfer operations. The disk adapter control registers control data transfer operations; the disk adapter status registers record the operational status of the disk adapter and identify error conditions detected by the disk adapter.

The disk adapter uses these elements to transfer data in two types of operations:

- Channel I/O (CHIO) operations, or the transfer of data between main storage and the disk, initiated by control logic and controlled by channel logic. (CHIO operations are described in greater detail under the heading "Disk Channel I/O [CHIO] Operations.")

- Disk Programmed I/O (PIO) operations, or the transfer of data between main storage and the disk, controlled by I/O instructions. (PIO operations are described in greater detail under the heading "Programmed I/O [PIO] Operations.")

During these data transfer operations, the adapter logic receives control signals from the channel and returns the appropriate responses.

If the transfer is a CHIO operation, the adapter uses buffers A and B to hold the data between the disk and main storage. It controls the buffers with bit 0 of its data handler extended status register. When this bit is set to 1, data buffer A transfers data between itself and main storage, and data buffer B transfers data between itself and the disk; when the bit is reset to 0, the buffers are conditioned oppositely. After a buffer is loaded, the disk adapter inverts the state of the bit, enabling the buffer to transfer its data out in the opposite direction. For multifield transfers, the disk adapter repeatedly inverts the state of the bit, enabling one buffer to start loading data in while the other transfers data out. (See Figure 2-5.)

When an I/O operation has been completed, or when an error condition has been detected by the disk adapter and recorded in its status registers, the disk adapter notifies the program by presenting I/O interrupt requests to the processing and control element (PCE).

#### **Operations**

8

Bit 0 of Data Status Register = 0

Figure 2-5. Disk Adapter Data Buffers

#### **Disk Adapter Error Detection and Reporting**

When data is written to the disk, the disk adapter automatically generates an error detection code for each ID or data field. When each field is subsequently read, the disk adapter compares the field's error detection code with a newly generated code. If the code bytes do not match, the disk adapter reports the error by presenting an I/O interrupt request to the PCE and setting the appropriate bits in one of its registers (BSTAT); the software and hardware can then attempt to recover from the failing operation.

The disk adapter checks the parity of all internal data transfers, and if incorrect parity is detected on data within the adapter, the disk adapter sets the appropriate bits in four of its registers (BSTAT, data status register, FCB processor register, and seek register).

The disk adapter also checks the parity of all commands and data that are received from the program. If incorrect parity is detected, the disk adapter sets the appropriate status bits and suppresses the response for the data or the command, forcing an I/O time-out check. The I/O time-out condition results in a system check interruption in the PCE, with the I/O operation being terminated when the Halt signal is activated by the PCE's channel logic. Again, the data status register, the FCB processor register, and the seek register contain additional information concerning the cause of the error.

Appendix C lists all adapter-detected errors with the register settings used to report them.

## **Disk Adapter Control Registers**

The disk adapter uses the following seven control registers and the physical sector counter to control data transfer operations:

- Burst register

- Control CHCV register

- Data transfer CHCV register

- Residual count register

- Next function register

- Seek register

- Skip factor register

and

• Physical sector counter

The following sections describe each disk adapter control register and the physical sector counter.

# **Burst Register**

The burst register is a three-bit register whose value represents the maximum number of halfword transfers that can occur during one CHIO burst. One CHIO operation consists of one or more CHIO bursts during which data is transferred between the adapter and main storage. Some CHIO bursts may include *fewer* halfwords than the maximum defined by the burst register value.

Listed below are the burst register values which represent specific lengths of CHIO burst transfers:

| Burst Value<br>(in binary) | Burst Length<br>(in halfwords) |

|----------------------------|--------------------------------|

| 000                        | 1 (2 bytes)                    |

| 001                        | 2 (4 bytes)                    |

| 010                        | 4 (8 bytes)                    |

| 011                        | 8 (16 bytes)                   |

| 100                        | 16 (32 bytes)                  |

| 101                        | 32 (64 bytes)                  |

| 110                        | 64 (128 bytes)                 |

| 111                        | 128 (256 bytes)                |

The burst register is set to binary 111 by the Reset Disk Adapter command (hex 02) and by system reset.

**Programming Note:** The contents of the burst register are loaded using bits 13-15 of the CHIO Load Burst Register operation, are read using the Read Burst Skip Factor and Spiral command (hex 21), and are returned in bits 13-15 of the data returned to the program.

# **Control CHCV Register**

**Channel Control Vector Format**

| 0 | 0 | 0 | 0 | 0 | CHP<br>No.<br><0> |   | Command<br>Code <0 3> | CHP Numb | er <15> | Command<br>Code <4><br>or Flag |   |

|---|---|---|---|---|-------------------|---|-----------------------|----------|---------|--------------------------------|---|

| 0 |   |   |   | 4 | 5                 | 6 | 9                     | 10       | 14      | 15                             | _ |

The control CHCV register contains bits 3-5 and bits 10-14 of the CHCV used by the disk adapter to access control and data transfer operations from main storage. Bits 0-2 and 15 are used only for diagnostic purposes. The disk adapter generates bits 6-9, which are presented to the channel when the CHIO operation is initiated.

ς.

**Programming Note:** Bits 3 and 4 are reserved in the CHCV and must be set to 0 to prevent system check interruptions when the CHCV is sent to the PCE's channel logic.

This register is loaded during execution of the Initiate CHIO command (hex 08) by the Write Control CHCV Register (hex 24) and with the Load New Control

CHCV operation. The contents of this register cannot be read directly; the Diagnostic Read Control CHCV Register commands (hex 3B, 3D, and 3F) access its contents besides forcing other CHCV bits active during their execution.

# Data Transfer CHCV Register

The data transfer CHCV register contains bits 3-5 and 10-14 of the CHCV used during disk data transfer operations to or from main storage. Bits 0-2 and 15 are not implemented. The disk adapter generates bits 6-9, which are presented to the channel when the CHIO operation is indicated.

**Programming Note:** Bits 3 and 4 are reserved in the CHCV and must be set to zero. If a CHCV is sent to the PCE's channel logic with 1's in bit 3 or 4, a system check interruption results and the CHIO operation is terminated.

This register is loaded during execution of the Write Data CHCV Register command (hex 26) and during execution of the Load New Data Transfer CHCV control operation. The contents of this register cannot be read directly; the Diagnostic Read Data CHCV Register commands (hex 31, 33, 35, and 37) access its contents besides forcing other CHCV bits active during their execution.

# **Residual Count Register**

The residual count register is a 6-bit register designating the number of data fields remaining to be transferred by a CHIO data transfer operation. The register contains a value one less than the number of fields to be transferred. The register may contain hex values within the range 00 to 3F (0 to 63 decimal).

During a CHIO operation, the contents of the residual count register are decremented by the disk adapter as each field is transferred. At the normal completion of a CHIO data transfer operation, the residual count register has been decremented to zero. However, if an error condition has terminated a CHIO data transfer operation, the register contains the number of data fields remaining to be transferred.

**Programming Note:** The contents of the residual count register are loaded from bits 10-15 of the CHIO Load Skip Factor/Field Count operation, are read using the Read Residual Count Register command (hex 05), and are returned in bits 10-15 of the data returned to the program.

# Next Function Register (NFR)

The NFR is a halfword register containing the current or next CHIO operation to be performed by the disk adapter. As CHIO control and data transfer operations are accessed from main storage, they are placed in the NFR. The NFR contains only the next operation to be performed when a moving head seek operation is being executed and the adapter has prefetched the next operation. Prefetching CHIO operations is described under "CHIO Control Operations."

**Programming Note:** The contents of the NFR can be loaded under program control by issuing the Write NFR command (hex 22), and can be accessed by issuing the Read NFR command (hex 39).

# Seek Register

The seek register is a halfword register whose bits are grouped into fields identifying the location of the access mechanism and the current head selection value.

| Bit                                | Description                                                                                                                                                                                                              |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                                  | <b>Recalibrate.</b> This bit is set when the Recalibrate operation is executed by the disk adapter. The Recalibrate operation returns the access mechanism to home position and sets the head selection value to head 1. |

| 1–5<br>(8130, 8140, and 8101 only) | Head Selection Value. The head selection field identifies the current head selection value. In fixed-head configurations, bit 1 set indicates a fixed head; bit 1 reset indicates a moving head.                         |

| 1<br>(8102 only)                   | Reserved. This bit is always zero.                                                                                                                                                                                       |

| 2-5<br>(8102 only)                 | Head Selection Value. The head selection field identifies the current head selection value.                                                                                                                              |

| 6<br>(8130, 8140, 8101 only)       | <b>Reserved.</b> This bit is always zero.                                                                                                                                                                                |

| 7–15<br>(8130, 8140, 8101 only)    | <b>Cylinder Selection Value.</b> The cylinder selection field identifies the current location of the access mechanism.                                                                                                   |

| 6-15<br>(8102 only)                | Cylinder Selection Value. (Described above.)                                                                                                                                                                             |

| -                                  |                                                                                                                                                                                                                          |

**Programming Note:** The contents of the seek register can be loaded using the Seek or Recalibrate operations, or by issuing the Load Seek Register from NFR command (hex 2A). The head selection field is loaded from bits 2 to 6 of the operation register. The contents of the seek register can be read by issuing the Read Seek Register command (hex 29).

\$

8

# Skip Factor Register

The skip factor register is a 2-bit register that defines the sequence in which data fields are transferred from the disk surface during multifield transfers. The contents of the skip factor register are encoded as follows:

# Bit

| Value | Skip Factor Description                                                       |

|-------|-------------------------------------------------------------------------------|

| 00    | No Skip. Access each data field sequentially from the disk.                   |

| 01    | Skip One Field. Access every other physical field location from the disk.     |

| 10    | Skip Three Fields. Access every fourth physical field location from the disk. |

| 11    | Skip Seven Fields. Access every eighth physical field location from the disk. |

Figure 2-6 shows the data field transfer sequence of physical data field locations for each skip factor value, beginning with sector 0 field 0. The figure shows the field transfer sequence for a full track, or 64 fields. When fewer than 64 fields are to be transferred, the sequence shown in Figure 2-6 is valid, but the starting sector value determines where in this sequence the data transfer operation begins and ends.

**Programming Note:** The contents of the skip factor register are loaded from bits 8 and 9 of the Load Skip Factor/Field Count operation. They are accessed by issuing the Read Burst, Skip Factor, and Spiral command (hex 21), and are returned in bits 8, 9 of the data returned to the program.

| Skip Factor<br>00 |      | Skip Factor<br>01 |       | Skip Factor<br>10 |      | Skip Factor<br>11 |      |

|-------------------|------|-------------------|-------|-------------------|------|-------------------|------|

| 0-0               | 16-0 | 0-0               | 0-1   | 0-0               | 1-0  | 0-0               | 2-0  |

| 0-1               | 16-1 | 1-0               | 1 - 1 | 2-0               | 3-0  | 4-0               | 6-0  |

| 1-0               | 17-0 | 2-0               | 2-1   | 4-0               | 5-0  | 8-0               | 10-0 |

| 1-1               | 17-1 | 3-0               | 3-1   | 6-0               | 7-0  | 12-0              | 14-0 |

| 2-0               | 18-0 | 4-0               | 4-1   | 8-0               | 9-0  | 16-0              | 18-0 |

| 2-1               | 18-1 | 5-0               | 5-1   | 10-0              | 11-0 | 20-0              | 22-0 |

| 3-0               | 19-0 | 6-0               | 6-1   | 12-0              | 13-0 | 24-0              | 26-0 |

| 3-1               | 19-1 | 7-0               | 7-1   | 14-0              | 15-0 | 28-0              | 30-0 |

| 4-0               | 20-0 | 8-0               | 8-1   | 16-0              | 17-0 | 0-1               | 2-1  |

| 4-1               | 20-1 | 9-0               | 9-1   | 18-0              | 19-0 | 4-1               | 6-1  |

| 5-0               | 21-0 | 10-0              | 10-1  | 20-0              | 21-0 | 8-1               | 10-1 |

| 5-1               | 21-1 | 11-0              | 11-1  | 22-0              | 23-0 | 12-1              | 14-1 |

| 6-0               | 22-0 | 12-0              | 12-1  | 24-0              | 25-0 | 16-1              | 18-1 |

| 6-1               | 22-1 | 13-0              | 13-1  | 26-0              | 27-0 | 20-1              | 22-1 |

| 7-0               | 23-0 | 14-0              | 14-1  | 28-0              | 29-0 | 24-1              | 26-1 |

| 7-1               | 23-1 | 15-0              | 15-1  | 30-0              | 31-0 | 28-1              | 30-1 |

| 8-0               | 24-0 | 16-0              | 16-1  | 0-1               | 1-1  | 1-0               | 3-0  |

| 8-1               | 24-1 | 17-0              | 17-1  | 2-1               | 3-1  | 5-0               | 7-0  |

| 9-0               | 25-0 | 18-0              | 18-1  | 4-1               | 5-1  | 9-0               | 11-1 |

| 9-1               | 25-1 | 19-0              | 19-1  | 6-1               | 7-1  | 13-0              | 15-0 |

| 10-0              | 26-0 | 20-0              | 20-1  | 8-1               | 9-1  | 17-0              | 19-0 |

| 10-1              | 26-1 | 21-0              | 21-1  | 10-1              | 11-1 | 21-0              | 23-0 |

| 11-0              | 27-0 | 22-0              | 22-1  | 12-1              | 13-1 | 25-0              | 27-0 |

| 11-1              | 27-1 | 23-0              | 23-1  | 14-1              | 15-1 | 29-0              | 31-0 |

| 12-0              | 28-0 | 24-0              | 24-1  | 16-1              | 17-1 | 1-1               | 3-1  |

| 12-1              | 28-1 | 25-0              | 25-1  | 18-1              | 19-1 | 5-1               | 7-1  |

| 13-0              | 29-0 | 26-0              | 26-1  | 20-1              | 21-1 | 9-1               | 11-1 |

| 13-1              | 29-1 | 27-0              | 27-1  | 22-1              | 23-1 | 13-1              | 15-1 |

| 14-0              | 30-0 | 28-0              | 28-1  | 24-1              | 25-1 | 17-1              | 19-1 |

| 14-1              | 30-1 | 29-0              | 29-1  | 26-1              | 27-1 | 21-1              | 23-1 |

| 15-0              | 31-0 | 30-0              | 30-1  | 28-1              | 29-1 | 25-1              | 27-1 |

| 15-1              | 31-1 | 31-0              | 31-1  | 30-1              | 31-1 | 29-1              | 31-1 |

Figure 2-6. Multifield Transfers with Skip Factor Values

# **Physical Sector Counter (PSC)**

The physical sector counter (PSC) contains the number of the next physical sector available. The PSC is set to zero by the index signal and is incremented for each sector area on the disk surface. The PSC is used by the disk adapter to control data transfer operations, and cannot be accessed or modified through programming.

4

.

# **Disk Adapter Status Registers**

The disk adapter uses the following four status registers to record the operational status of the disk adapter and to identify error conditions detected by the disk adapter.

- Disk basic status register (Disk BSTAT)

- Data handler extended status register

- FCB processor status register

- Seek status register

The bits in these registers can be reset by activating the Reset interface line or by decoding a Reset Adapter PIO command.

**Disk BSTAT** The following sections list and describe the bits in each disk adapter status register.

The disk BSTAT is a 2-byte register.

#### Bit Description

- 0 **FCB Processor Error.** This bit is set when a parity error is detected in the disk adapter control logic.

- 1 **Data Handler Error.** This bit is set when a data buffer parity check or a hardware failure is detected in the disk adapter control logic.

- 2 **Check Error.** This bit is set during disk read operations when the error detection code read from the disk does not match the error detection code generated by the disk adapter. When this bit is set, either bit 3 (ID error) or bit 4 (data field error) is set to identify the field containing the error.

- 3 **ID Error.** This bit is set under one of the following conditions:

- A CRC error is detected while the ID field is being read.

- The PSC indicates that the correct sector has been reached for a read or write operation, but one of the cylinder, head, or sector bytes does not compare with the value in the seek or NFR.

- The "defective" bit in the ID flag byte is set, and a Read-Normal operation or any data-field read or write operation is in progress.

- 4 **Data Field Error.** This bit is set during a read operation if a CRC/ECC error is detected on a data field; it is set during a write operation when the "write protect" bit is set for the selected data field in the sector ID field flag byte.

- 5 Sector Not Found. This bit is set when a second index signal is detected by the disk adapter and the selected sector ID has not yet been located. This bit is also set if a displaced ID is met or if no byte sync field is detected in the ID.

- 6 MCK-Halted CHIO Data Transfer. This bit is set to indicate that the disk adapter received the Halt signal from the channel during a CHIO burst transfer of data. This bit is not set during CHIO control operation transfers. The Halt signal also sets BSTAT bit 13 (disk equipment check).

## Bit Description

- 7 **File Write Gate Error.** This bit is set when the Write Gate Return signal does not match the internal signal that activates the Write signal from the adapter to the file. When activating or deactivating the Write signal, the adapter waits 890 ns for the Write Gate Return signal before declaring an error.

- 8\* **Program-Controlled Interrupt (PCI).** This bit is set when the PCI operation is performed by the disk adapter. This bit can also be set through programming; however, BSTAT bit 15 is not automatically set in this case.

- 9\* **Device Error.** This bit is set whenever the disk adapter detects an error condition. When this bit is set, BSTAT bit 11 (busy) is reset by the disk adapter and BSTAT bit 15 is set to present an I/O interrupt request to the PCE.

When this bit is reset through programming, bits 10 and 11 of the seek status register are reset, as are BSTAT bits 0-7 and FCB processor status register bits 8-15 if they contain a value in the range hex 38-3F.

- 10 **File Interrupt Disabled.** This bit is set only by a Set Basic Status command. When set, the bit causes the adapter to ignore any file interrupts. It is reset by a Reset Adapter or Reset Basic Status command.

- 11 Busy. This bit is set during execution of the Initiate CHIO command (hex 08) to indicate that a CHIO operation is in progress. This bit is reset by one of the following conditions:

- The CHIO operation is completed normally with an End operation or a Terminate operation being performed by the disk adapter.

- BSTAT bit 9 (disk adapter error) is set by an error condition other than a control operation time-out.

- The disk adapter is reset.

This bit cannot be set or reset using the Set or Reset BSTAT under Mask commands (hex 04 or 06).

- 12 **Channel Request Frozen.** When this bit is set, the disk adapter is unable to activate the Channel Request signal to initiate a CHIO burst transfer. This bit is only set and reset through programming.

- 13\* Equipment Check. This bit is set under one of the following conditions:

- A Halt signal is received from the channel during PIO or CHIO operations.

- A tag signal sequence error or a command error occurs, setting seek status register bit 8 or 9.

- An out-of-parity command or out-of-parity write data is received.

When this bit is reset through programming, seek status register bits 8 and 9 are also reset.

- Bit Description

- 14 **Requests Enabled.** This bit, when set, permits the disk adapter to initiate CHIO burst transfers and to present interrupt requests to the PCE. When this bit is reset, these functions are inhibited. This bit is only set through programming.

- 15 Interrupt. This bit is set when the disk adapter is attempting to present an I/O interrupt request to the PCE. If bit 14 (requests enabled) is reset, the interrupt request is held in the disk adapter until bit 15 is reset or bit 14 is again set.

\*When this bit is set, BSTAT bit 15 (interrupt) is also set.

#### Programming Notes:

- 1. BSTAT bits 0-7 cannot be changed using the Set or Reset Disk BSTAT under Mask commands (hex 04 or 06). These bits can only be reset by resetting BSTAT bit 9 with the Reset BSTAT under Mask command (hex 04).

- 2. BSTAT bit 11 cannot be reset using the Reset BSTAT under Mask command (hex 04).

- 3. The Reset Disk Adapter command (hex 02) resets the disk BSTAT to zeros.

- 4. The contents of the disk BSTAT can be read by issuing the Read Disk BSTAT command (hex 07) and are returned to the program as a halfword operand.

# Data Handler Extended Status Register

The data handler extended status register is a 2-byte register.

#### Bit Description

0 **Buffer A to Disk.** This bit is controlled by the disk adapter. It indicates which of the 256-byte buffers is being used to transfer data to or from main storage. When this bit is set, buffer A is used to transfer data to or from the disk and buffer B is used to transfer data to or from main storage.

When this bit is reset, buffer A is used to transfer data to or from main storage and buffer B is used to transfer data to or from the disk.

1 **Disk Speed Good.** This bit is set to indicate that the disk speed is correct. This bit is reset by the disk adapter when a speed error condition is detected.

#### Bit Description

- 2-7 **ID Flags.** Each time an ID field is read from the disk, the contents of the flag byte, bits 2-7, are set into the data status register by the disk adapter. The flag bits correspond directly with the status register bits into which they are loaded. The flag bits are as follows:

- 2 Write protected field 1.

- 3 Write protected field 0.

- 4 Sector displaced.

- 5 Sector reassigned.

- 6 Sector defective.

- 7 Alternate sector.

- 8 **Reserved.** Always zero.

- 9 **Reserved.** Always zero.

- 10-15 Residual Field Count. Bits 10-15 reflect the contents of residual count register bits 10-15. When data transfer operations are ended without errors, these bits contain a hex zero value. If a data transfer operation is terminated with an error, the residual count register contains the number of data fields that remain to be transferred minus 1. This value is returned as the residual (bits 10-15) of the data handler extended status register.

**Programming Note:** The contents of the data handler extended status register can be read by issuing the Read Residual Count command (hex 05). Read-only access is provided for the contents of this register; the data handler extended status register cannot be written through programming. This register is reset to zeros by the Reset Disk Adapter command (hex 02). Bits 2–7 are not reset; they reflect the contents of the last flag byte read.

#### FCB Processor Status Register

The FCB processor status register is a 1-byte register. Its first two bits are reserved and are always set to "0, 0" ("1, 1" in the 8102). The other six bits identify error conditions detected by the disk adapter. This publication does not describe these bits in greater detail, because they are provided for maintenance use only.

**Programming Note:** Read-only access is provided for the contents of the FCB processor status register by issuing the Read FCB Processor Status Register command (hex 0B). When this command is executed by the disk adapter, byte 0 of the data returned to the program contains bits 0-7 of the disk BSTAT register and byte 1 contains the contents of the FCB processor status register.

# Seek Status Register

The seek status register is a 1-byte register whose contents may be used for failure analysis or for error-recovery operations. Its bits are numbered from 8 to 15.

#### Bit Description

- 8 **Tag Sequence Error.** This bit is set when an incorrect signal sequence is received by the disk adapter. When this bit is set, disk BSTAT bit 13 (equipment check) is also set. It is reset when BSTAT bit 13 (equipment check) is reset.

- 9 **Command Error.** This bit is set under the following conditions:

- During a PIO operation directed to the disk adapter, an invalid command was received.

- During a PIO operation directed to the disk adapter, a command with incorrect parity was received.

- The disk adapter received a command that is not permitted while BSTAT bit 11 (busy) is set. These PIO commands are hex 08, 0B, 22, 24, 26, 2A, 2D, and 2E.

When this bit is set, BSTAT bits 13 (disk equipment check) and 15 (disk interrupt request) are also set. It is reset when BSTAT bit 13 (disk equipment check) is reset.

10 **Card 1 Error.** This bit is set when the disk adapter detects incorrect parity on a PIO command or detects a byte of PIO write data that was received with incorrect parity.

When this bit is set, BSTAT bit 9 (device error) and bit 15 (interrupt) are also set. It is reset when BSTAT bit 9 (device error) is reset.

11 FCB Time-Out. This bit is set when a minimum of 6.5 seconds (8 seconds for the 8102) have elapsed between channel requests to access control or data transfer operations. This condition can be caused through programming if BSTAT bit 12 (channel request frozen) or BSTAT bit 14 (requests enabled) is reset for this time period.

When this bit is set, BSTAT bits 9 (device error) and 15 (interrupt) are also set. It is reset when BSTAT bit 9 (device error) is reset.

- 12 **Cable Continuity.** This bit is set as long as the cable path through the adapter is intact. This bit is only reset when the cable path through the adapter is interrupted; it cannot be set or reset through programming, or reset with system reset.

- 13-15 Seek Activity Bits. These bits indicate whether any of the following seek activities are in progress.

- Moving Head Seek (MHS)

- Fixed Head Select (FHS-8130, 8140, and 8101 only)

- Head Shift (HDS—8102 only)

- Recalibrate (RECAL)

These seek activities are designated by the following settings:

| Bits 13, 14, and 15<br>Set To:     | Description                                                                                                                                                                |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000                                | No seek activities in progress.                                                                                                                                            |

| 001                                | A RECAL was begun and has not been completed.                                                                                                                              |

| 010<br>(8130, 8140, and 8101 only) | An FHS operation was begun and<br>has not been completed. No MHS or<br>RECAL is in progress.                                                                               |

| 010<br>(8102 only)                 | An HDS operation was begun and<br>has not been completed. No other<br>seek activity is in progress.                                                                        |

| 100                                | An MHS operation was begun and<br>has not been completed. No other<br>seek activity is in progress.                                                                        |

| 101<br>(8130, 8140, and 8101 only) | An MHS operation was begun,<br>followed by an FHS. The FHS has<br>been completed, but the MHS has<br>not.                                                                  |

| 110<br>(8130, 8140, and 8101 only) | An MHS operation was begun,<br>followed by an FHS. Neither has<br>been completed.                                                                                          |

| 111<br>(8130, 8140, and 8101 only) | An MHS operation was begun,<br>followed by an FHS. The MHS has<br>been completed, but the FHS has not.<br>No data transfer will begin until the<br>FHS has been completed. |

**Programming Note:** Read-only access is provided for the contents of the seek status register by using the Read Seek Status Register command (hex 0D). Byte 0 of the data returned to the program contains byte 0 of the disk BSTAT. Byte 1 contains bits 8-15 of the seek status register.

# **Data Transfer Operations**

The following sections describe the PIO address assignments for the disk adapter, its priority level assignments, the PIO commands implemented by the disk adapter, and the CHIO operations implemented by the disk adapter. The last section in this chapter is a set of examples of data transfer operations performed by the disk adapter. These examples include the PIO operations needed to prepare the disk adapter for the CHIO operations that follow. The commands and CHIO operations are shown in the sequence in which they are executed by the disk adapter.

# Disk Adapter PIO Address Assignments

The disk adapter PIO addresses depend upon the system component that contains the disk adapter. Address assignments for the disk adapters in each system component are listed in the following publications:

- 8101/8102 Storage and Input/Output Units Description, GA27-2882

- 8130 Processor Description, GA27-3196

- 8140 Processor Description, GA27-2880

Ask your IBM representative for additional information on configuring an 8100 system and placing a system order.

# **I/O Interrupts**

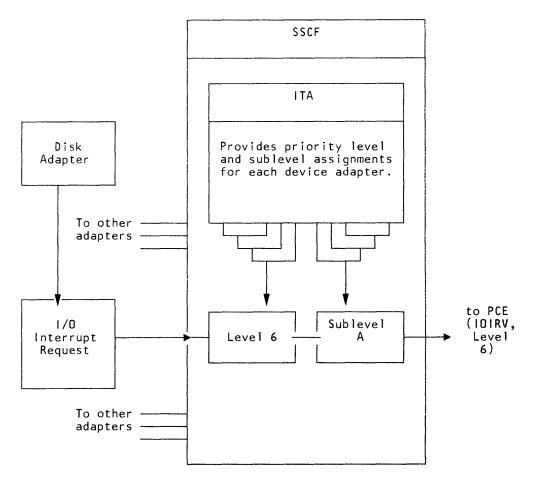

The disk adapter presents an I/O interrupt request to the PCE when BSTAT bits 14 and 15 are set. This interrupt request receives the appropriate priority level from the SSCF to which the adapter is attached.

Several adapters may be attached to one SSCF. The SSCF defines the priority level of each adapter by assigning it to a location in an interrupt translation array (ITA). An adapter's location in the ITA corresponds to the second hex digit of the adapter's PIO address. For example, the disk adapter with a PIO address of 91 is assigned to ITA location 1.

ITA also provides a means of assigning a unique identification to the interrupt request presented by the disk adapter, called the *sublevel assignment*. Both the priority level assignment and the sublevel assignment are defined in the ITA location to which the disk adapter is assigned, as illustrated in Figure 2-7.

Figure 2-7. Priority and Sublevel Assignment in the ITA

For a detailed description of assigning priority levels and sublevels and of the ITA, refer to IBM 8130 Processor Description, GA27-3196, IBM 8140 Processor Description, GA27-2880, and 8101/8102 Storage and Input/Output Units Description, GA27-2882.

# **Programmed I/O (PIO) Operations**

Programs initiate PIO operations by executing I/O instructions to direct a command and one byte or one halfword of data to the disk storage facility. The channel and the disk adapter exchange control signals that ensure that the data and the control information are presented in the correct sequence. The PIO command determines whether data is transferred to or from the disk storage facility. The specific PIO commands implemented by the disk storage facility are described under "Disk PIO Commands." Specific I/O instructions and general programmed I/O operations are described in detail in the 8100 Information System Principles of Operation, GA23-0031.

The disk adapter decodes and executes programmed I/O (PIO) commands as they are received from a program. These PIO commands are generally used to inspect or modify the contents of a status register, since they only transfer a halfword or a byte of data during their execution. PIO operations are also used to prepare the disk adapter for subsequent CHIO operations. The PIO command "Initiate CHIO" defines the beginning of a CHIO operation. The following sections list and describe the disk PIO commands and the diagnostic error-recovery commands.

#### **Disk PIO Commands**

| Code     |                     |

|----------|---------------------|

| (in Hex) | Command Description |

02

**Reset Disk Adapter.** This command resets all disk adapter status registers to hex 0 with the following exceptions:

- Residual count register bits 2-7 reflect the contents of the last flag byte read by the disk adapter. These bits cannot be reset through programming.

- Seek status register bit 12 (cable continuity) cannot be reset through programming.

- The burst register is set to binary 111 (256-byte bursts).

CHIO operations in progress when this command is executed are terminated by the disk adapter.

After execution of this command, the disk adapter is disabled from presenting I/O interrupt requests to the PCE and from initiating CHIO operations.

Warning: Do not issue this command while the adapter is writing data to the file, because partial writes will result.

**Reset Basic Status under Mask.** This command resets basic status register (BSTAT) bits that are selected by the mask operand. The mask bits correspond directly to the BSTAT bits. A mask bit with the value 1 resets the associated BSTAT bit; a mask bit with the value 0 does not affect the associated BSTAT bit.

Only BSTAT bits 8-10 and 12-15 can be reset using this command. BSTAT bits 0-7 and bit 11 (busy) cannot be changed using this command.

- 05 **Read Residual Count.** This command causes the disk adapter to return the contents of the data status register to the program. Bits 0 -15 of the data status register correspond directly to bits 0 -15 of the data returned to the program. Bits 8, 9 are always returned as zeros.

- 06

04

Set Basic Status under Mask. This command transfers a mask operand to the disk adapter. The mask operand corresponds directly to bits 8 – 15 of the disk BSTAT. Active mask bits cause the corresponding BSTAT bits to be set, except for bits 0–7 and bit 11 (busy); these bits cannot be set using this command. When mask bits are set to zero, the corresponding BSTAT bit is not changed.

| Code<br>(in Hex) | Command Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

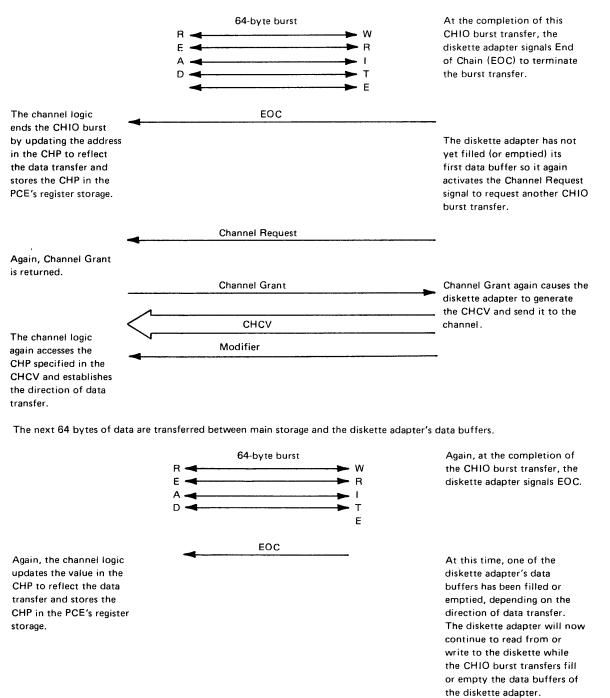

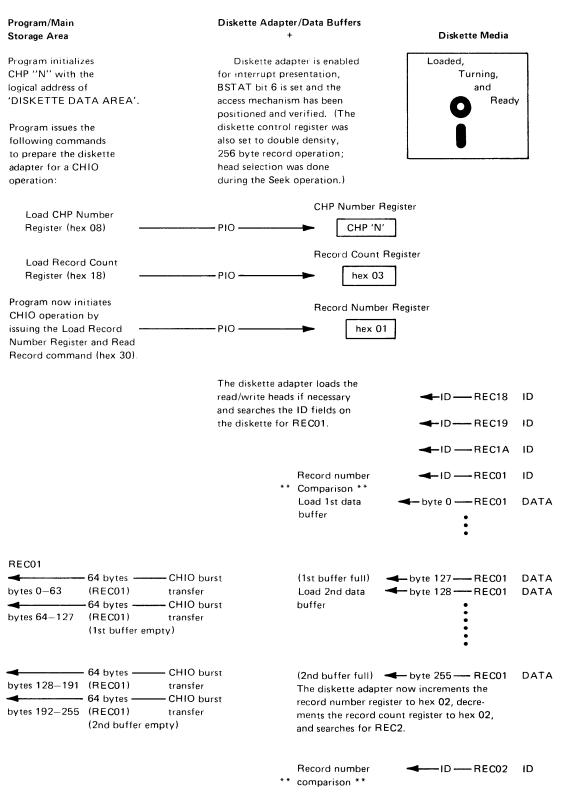

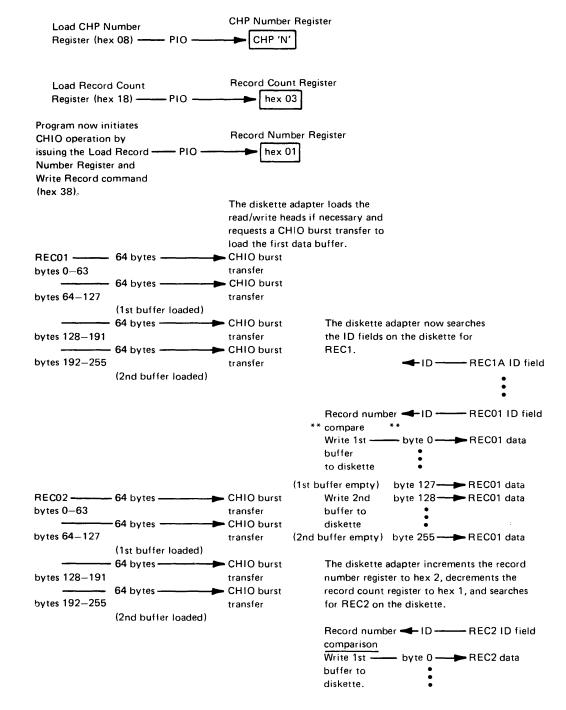

| 07               | <b>Read Disk Basic Status.</b> This command causes the disk adapter to return the contents of the disk BSTAT to the program. This command is executed by the disk adapter regardless of whether a CHIO operation is in progress.                                                                                                                                                                                                                                                                                                                                 |  |  |  |