# Principles of Operation

## Principles of Operation

#### Fifth Edition (March 1984)

This is a revision of, and obsoletes, GA23-0031-3. The changes include both technical and editorial clarification to improve accuracy and usability of the publication, and are indicated by a vertical line in the left margin. Changes are continually made to the information herein; before using this publication in connection with the operation of IBM systems, consult the latest *IBM System/370 Bibliography*, GC20-001, for the editions that are applicable and current.

It is possible that this material may contain reference to, or information about, IBM products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that IBM intends to announce such IBM products, programming, or services in your country.

Publications are not stocked at the address given below; requests for IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for reader's comments is provided at the back of this publication. If the form has been removed, comments may be addressed to IBM Corporation, Department 52Q. Neighborhood Road, Kingston, New York 12401. IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation whatever. You may, of course, continue to use the information you supply.

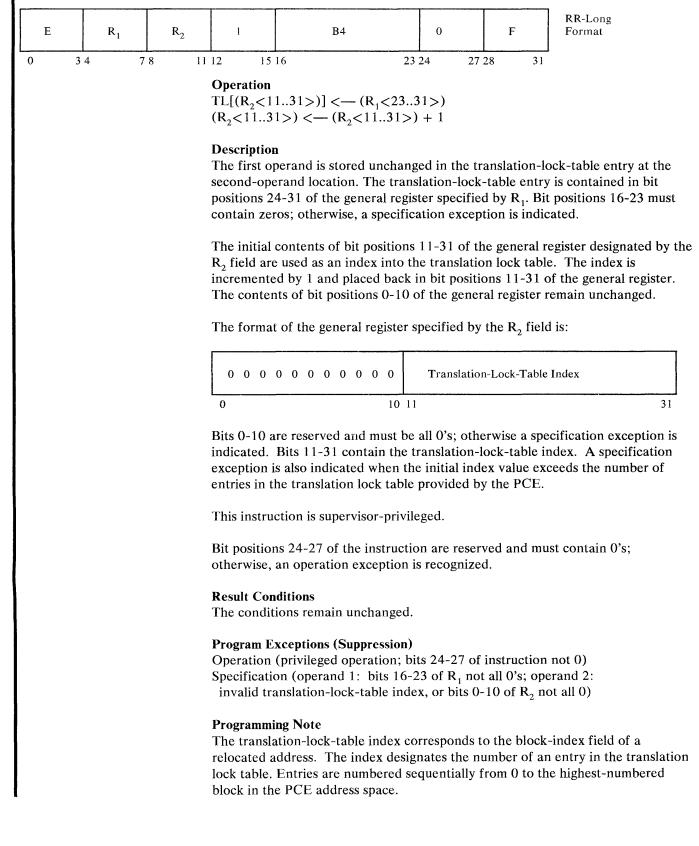

© Copyright International Business Machines Corporation 1979, 1984

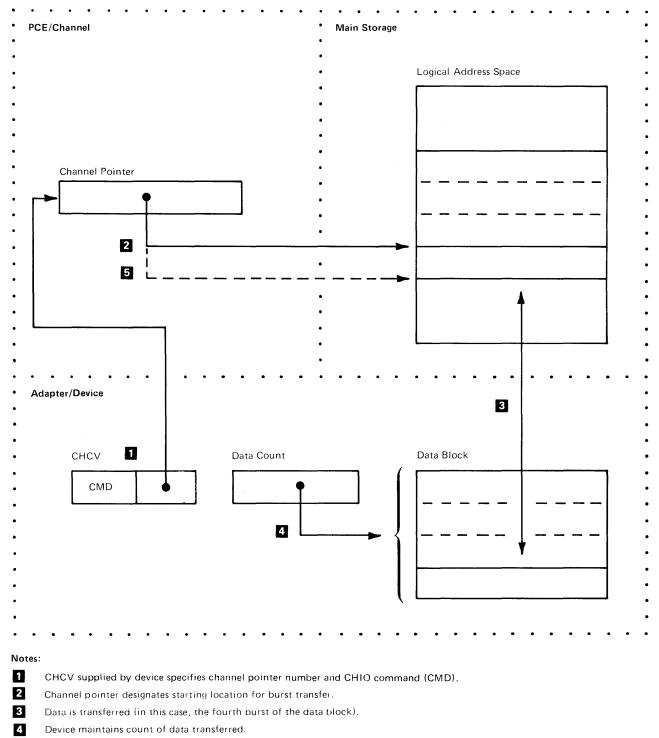

## Preface

The IBM 8100 Information System provides a coordinated set of information processing equipment. The logical structure of the 8100 system, including the processing and control element (PCE), is unique and permits several levels of performance with the preservation of program compatibility.

This publication provides, for reference purposes, a detailed definition of the machine functions performed by the PCE within an IBM 8100 Information System processor. For purposes of this publication, the PCE is defined as the logical entity that is the controlling center of the system. Additional definitions are included in Chapter 1 and in the Glossary.

The manual describes each function to the level of detail that must be understood to prepare a program that relies on that function. It does not, however, describe all the notation and conventions employed in preparing such a program; for this information, the user must instead refer to the appropriate assembler language manual, such as *IBM 8100 DPPX Assembler Programming: Language Reference and Guide*, SC27-0412.

The information in this publication is provided principally for use by assembler language programmers, although anyone concerned with the functional details of the IBM 8100 Information System processors will find it useful.

This manual is written as a reference document and should not be considered an introduction or a textbook for the IBM 8100 Information System. It assumes the user has a basic knowledge of data processing systems and, specifically, the IBM 8100. Such basic knowledge can be derived by selecting the appropriate hardware and/or software publications from the IBM 8100's system library.

All facilities discussed in this publication are not necessarily available on every processor model in the IBM 8100 system. Furthermore, in some instances the definitions are structured to allow certain extension capabilities to be described even though they are not offered on any currently available processor model. An example is the provision for the number of bits in an adjunct register. The allowance for this type of extension should not be construed as implying any intention by IBM to provide such capabilities. Appendix G provides a summary of processor-specific parameters and functions identified as such within this manual. For information about the characteristics and availability of features on a specific processor model, refer to the appropriate publications for that model. The availability of features on processor models is summarized in *An Introduction to the IBM 8100 Information System*, GA27-2875.

Although processor models of the IBM 8100 system may differ in implementation and physical capabilities, logically they are compatible. That is, within the limitations described below, any program gives identical results on any model. The compatibility rule has four limitations:

- 1. The system's facilities used by the program should be the same in each case. For example, the optional processor features and the storage capacity, as well as the quantity and type of input/output equipment, should be equivalent.

- 2. The program should be independent of the relation between instruction execution times, input/output data rates, storage access times, and elapsed time values.

- 3. The program should not depend on functions identified in this manual as processor-model dependent, on operations explicitly not defined, on results defined to be unpredictable, or on special-purpose functions that are not described in this manual.

- 4. The program should not use or depend on reserved fields unless they are explicitly made available for program use. Additionally, the program should not be designed to cause interruptions by means of format errors, such as the use of undefined operation codes.

The information presented in this manual is grouped into 10 chapters and several appendixes. The 10 chapters are organized in three parts: Part I, the first chapter, is an overview description of the processing facilities provided by the IBM 8100 system. Part II consists of the next four chapters and pertains to functions that are useful to all assembler language programmers. Part III, the last five chapters, contains information normally used by programmers who develop or maintain supervisory-type programs.

Chapter 1, Introduction to the Logical Structure, describes the processing facilities available with the IBM 8100 Information System. It summarizes the information provided in the remaining nine chapters.

## Part II. Information Processing Facilities

Chapter 2, Storage and Registers, describes how the program refers to instruction-operand information in main storage or a general register.

Chapter 3, Program Execution, explains the role of instructions and their formats in program execution. It provides a detailed description of sequence of the instructions and storage references. Program exceptions and the action taken by the PCE as a result of these exceptions are also described.

Chapter 4, General Instructions, describes in detail the instructions available to all programs for general use.

Chapter 5, Floating-Point Instructions, describes in detail the instructions provided with the floating-point feature. Program exceptions relating to floating-point operations are also described in this chapter.

## Part III. Supervisory Facilities

Chapter 6, Register Organization, explains the organization and use of the groups of register sets available to the program, and contains the descriptions of the instructions for retrieving or storing information in any register set.

Chapter 7, Dynamic Address Relocation and Translation, explains the operation of the machine facilities, including dynamic address relocation and dynamic address translation, that ease the task of controlling the allocation and use of main storage. The instructions used to manipulate the translation table are also described.

Chapter 8, Input/Output Operations, explains the programmed control of I/O devices by the channel and by the PCE. It includes detailed descriptions of the I/O instructions and other I/O control formats.

Chapter 9, PCE Control, describes in depth the facilities for the switching of system status, for protecting the system against the unauthorized modification of system status, for defining a relative processing priority among programs, and for temporarily disallowing the processing of one or more programs. It deals specifically with PCE states, program modes, the program status vector, the floating-point status vector, priority levels, control vectors, interruptions, and the dispatching mechanism. It includes the detailed descriptions of the instructions available for reading or altering PCE status information, and for directly controlling certain attached system facilities.

Chapter 10, Dual-Mode Processing, describes the differences between processors containing one PCE and processors containing two PCEs. It also describes dual-mode processing and how it is implemented in those models that contain two PCEs.

The Appendixes include:

|                                 | • Lists of the instructions arranged in several sequences (App A)                                                                                                                                                                                                                                                                                                        |  |  |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                 | • Explanation of assembler language notation used in this manual (App B)                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                 | • Summaries of instruction operations and result conditions (App C)                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                 | • List of instruction formats arranged by operation code (App D)                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                 | • Summaries of important formats (App E)                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                 | • Summary of permanently assigned register sets (App F)                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                                 | • Summary of processor-specific functions (App G)                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                 | • Table of the powers of 2 (App H)                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                 | • Tabular information helpful in dealing with hexadecimal numbers (App I)                                                                                                                                                                                                                                                                                                |  |  |  |

|                                 | • An EBCDIC chart (App J)                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                 | • Information about number representation (App K)                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                 | A glossary of important terms used in this publication is provided at the ba<br>the manual, preceding the Index.                                                                                                                                                                                                                                                         |  |  |  |

|                                 | Primarily because the manual is arranged for reference purposes, certain words<br>and phrases appear, of necessity, earlier in the manual than the principal<br>discussions explaining them. The reader who encounters a problem of this sort<br>should refer to the Index, which will indicate the location of the key description<br>for the word or phrase concerned. |  |  |  |

| Prerequisite Publications       |                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                                 | An Introduction to the IBM 8100 Information System, GA27-2875                                                                                                                                                                                                                                                                                                            |  |  |  |

| <b>Corequisite Publications</b> |                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                                 | IBM 8130 Processor Description, GA27-3196                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                 | IBM 8140 Processor Description, GA27-2880                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                 | IBM 8150 Processor Description, GA23-0122                                                                                                                                                                                                                                                                                                                                |  |  |  |

| <b>Related Publications</b>     |                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                                 | <i>IBM 8100 DPPX Assembler Programming: Language Reference and Guide</i> , SC27-0412                                                                                                                                                                                                                                                                                     |  |  |  |

|                                 | IBM 8130 and 8140 Processors Operator's Guide, GA27-3197                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                 | IBM 8150 Processor Operator's Guide, GA23-0123                                                                                                                                                                                                                                                                                                                           |  |  |  |

## Contents

Chapter 1. Introduction to the Logical Structure 1-1 Logical Structure 1-1 Information Formats 1-3 Main Storage Addressing 1-5 **Registers** 1-5 Instructions 1-6 **Operands** 1-7 **Operation Classes and Instruction Formats 1-8** Register-to-Register 1-8 Register-and-Immediate 1-11 Register-and-Storage - Address Generation 1-12 Sequencing 1-14 Storage-to-Storage 1-14 General Instructions 1-15 Data Movement 1-15 Fixed-Point Arithmetic 1-19 Logical Operations 1-20 Sequencing 1-22 Floating-Point Instructions 1-23 Program - Environment Definition 1-24 Dynamic Address Transformations 1-26 Logical Addressing of Main Storage 1-27 **Dynamic Address Relocation 1-27 Dynamic Address Translation 1-32 Register Organization 1-41** Principal Registers 1-41 Adjunct Registers 1-41 Floating-Point Registers 1-41 Access to Register Groups 1-41 PCE Control 1-41 Priority Levels 1-43 Interrupt Requests 1-45 Priority Level Dispatching 1-45 Interruption Action 1-46 Instructions for PCE Control 1-47 Input/Output Operations 1-47 Programmed I/O Operations 1-47 Channel I/O Operations 1-49 Chapter 2. Storage and Registers 2-1 Information Units 2-1 Main Storage 2-2 Addressing 2-2 **Integral Boundaries 2-2 General Registers 2-3** Floating-Point Registers 2-9 Chapter 3. Program Execution 3-1 Instructions 3-1 **Operands 3-1** Instruction Formats 3-2 **Register Operand Specification 3-2 Immediate Operand Specification 3-4** Storage Operand Specification 3-4 Address Generation 3-4 Base Address 3-4 Displacement 3-5 Execution of a Program 3-7 Program Status Vector 3-8 Floating-Point Status Vector 3-8 Instruction Execution 3-8 Branching 3-8 Introduction of a New PSV 3-10 Interruptible Instructions 3-10 Sequence of Storage References 3-10 Instruction Fetch 3-11

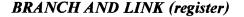

Storage-Operand References 3-11 Storage-Operand Fetch References 3-11 Storage-Operand Store References 3-12 Storage-Operand Update References 3-12 Program Exceptions 3-12 Types of Ending 3-13 **Exception Information 3-14** Program Exception Conditions 3-14 Specification Exception (code 0) 3-15 Access Exception (code 1) 3-17 Operation Exception (code 2) 3-18 Separation Exception (code 3) 3-19 Address Exception (code 4) 3-19 Register-Indirect Exception (code 5) 3-20 Fixed-Point-Overflow Exception (code 6) 3-21 Floating-Point Exception (code 7) 3-21 Handling of Multiple Program Exceptions 3-21 Chapter 4. General Instructions 4-1 Data Formats 4-1 Fixed-Point Numbers 4-1 Extended Fixed-Point Numbers 4-3 Instruction Descriptions 4-5 Instruction Name 4-6 Assembler Language Statement 4-6 Machine Instruction Format 4-6 **Operation 4-7** Description 4-7 **Result Conditions 4-9** Program Exceptions 4-9 Instructions 4-10 ADD (byte, register) 4-10 ADD (byte, register-immediate) 4-11 ADD WITH CARRY (byte, register) 4-11 ADD (halfword, register) 4-12 ADD (halfword, register-immediate) 4-13 ADD WITH CARRY (halfword, register) 4-14 ADD WITH CARRY (halfword, register, extended) 4-14 AND (byte, register) 4-16 AND (byte, register-immediate) 4-17 AND (halfword, register) 4-17 **BRANCH AND LINK 4-18** BRANCH AND LINK (register) 4-19 **BRANCH ON CONDITION 4-20** BRANCH ON CONDITION (register) 4-21 BRANCH ON COUNT (byte, register) 4-23 BRANCH ON INDEX (byte) 4-24 CALL PSV 4-25 COMPARE (byte, register) 4-26 COMPARE (halfword, register) 4-27 COMPARE WITH CARRY (halfword, register, extended) 4-28 COMPARE LOGICAL (bytes, storage) 4-29 COMPARE LOGICAL (halfwords, storage) 4-31 COUNT LEADING ZEROS (halfword) 4-33 DIVIDE (halfword, register) 4-34 EXCLUSIVE OR (byte, register) 4-35 EXCLUSIVE OR (byte, register-immediate) 4-36 EXCLUSIVE OR (halfword, register) 4-36 JUMP ON BIT ZERO (halfword) 4-37 **JUMP ON CONDITION 4-38** LOAD ADDRESS 4-39 LOAD (byte) 4-40 LOAD (byte, with index) 4-41 LOAD (byte, with index decremented) 4-41 LOAD (byte, with index incremented) 4-42 LOAD (byte, register) 4-43 LOAD (byte, register-immediate) 4-44 LOAD (halfword) 4-44 LOAD (halfword, short form) 4-45 LOAD (halfword, with index) 4-46

LOAD (halfword, with index decremented) 4-46 LOAD (halfword, with index incremented) 4-47 LOAD (halfword, register) 4-48 LOAD (halfword, register, lower half from upper) 4-48 LOAD (halfword, register, upper half) 4-49 LOAD (halfword, register, upper half from lower) 4-49 LOAD (halfwords, quadrant) 4-50 LOAD (word) 4-51 MOVE (bytes, storage) 4-52 MOVE (halfwords, storage) 4-54 MULTIPLY (halfword, register) 4-55 OR (byte, register) 4-56 OR (byte, register-immediate) 4-57 OR (halfword, register) 4-58 **PROGRAM EXCEPTION 4-58** ROTATE LEFT (byte) 4-59 ROTATE LEFT (halfword) 4-60 SHIFT LEFT (byte, logical) 4-61 SHIFT LEFT (halfword, logical) 4-62 STORE (byte) 4-63 STORE (byte, with index) 4-63 STORE (byte, with index decremented) 4-64 STORE (byte, with index incremented) 4-65 STORE (halfword) 4-65 STORE (halfword, short form) 4-66 STORE (halfword, with index) 4-67 STORE (halfword, with index decremented) 4-68 STORE (halfword, with index incremented) 4-69 STORE (halfwords, quadrant) 4-69 STORE (word) 4-71 SUBTRACT (byte, register) 4-71 SUBTRACT WITH CARRY (byte, register) 4-72 SUBTRACT (halfword, register) 4-73 SUBTRACT (halfword, register-immediate) 4-74 SUBTRACT WITH CARRY (halfword, register) 4-75 SUBTRACT WITH CARRY (halfword, register, extended) 4-76 TEST AND SET (byte) 4-77 TEST (byte, register-immediate) 4-78

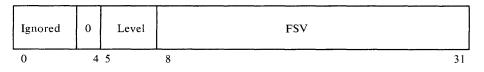

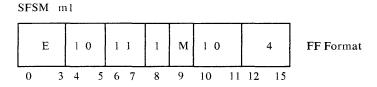

**Chapter 5. Floating-Point Instructions 5-1** Data Format 5-1 Guard Digit 5-2 Number Representation 5-2 Normalization 5-3 Floating-Point Status Vector 5-4 Referring to the FSV 5-4 Precision Modes 5-5 Exception Masks 5-5 Program Exceptions 5-5 Instructions 5-7 ADD NORMALIZED 5-8 ADD NORMALIZED (register) 5-8 ADD UNNORMALIZED 5-10 ADD UNNORMALIZED (register) 5-10 COMPARE 5-11 COMPARE (register) 5-11 DIVIDE 5-12 DIVIDE (register) 5-13 LOAD 5-14 LOAD (register) 5-14 LOAD AND TEST (register) 5-15 LOAD COMPLEMENT (register) 5-15 LOAD NEGATIVE (register) 5-16 LOAD POSITIVE (register) 5-16 LOAD ROUNDED (register) 5-17 MULTIPLY 5-18 MULTIPLY (register) 5-18 **READ FLOATING-POINT CONTROL 5-20 READ FLOATING-POINT STATUS VECTOR 5-20** SET OVERFLOW MASK 5-21

SET PRECISION MODE 5-22 SET SIGNIFICANCE MASK 5-22 SET UNDERFLOW MASK 5-23 STORE 5-23 SUBTRACT NORMALIZED 5-24 SUBTRACT NORMALIZED (register) 5-24 SUBTRACT UNNORMALIZED 5-25 SUBTRACT UNNORMALIZED (register) 5-25 WRITE FLOATING-POINT CONTROL 5-26 WRITE FLOATING-POINT STATUS VECTOR 5-27

#### Chapter 6. Register Organization 6-1

Organization 6-1 Principal Registers 6-1 Adjunct Registers 6-4 Floating-Point Registers 6-11 Access to Register Contents 6-12 Instructions 6-13 LOAD (byte, register-indirect) 6-13 LOAD (halfword, register-indirect) 6-14 STORE (byte, register-indirect) 6-14 STORE (halfword, register-indirect) 6-15

#### Chapter 7. Dynamic Address Relocation and Translation 7-1

Logical Addressing of Main Storage 7-1 **Dynamic Address Relocation** 7-1 Address Control Vector 7-3 Address-Space Size 7-3 Address-Space Origin 7-5 **Relocation Process 7-6** Dynamic Address Translation 7-7 **Translation-Table Entries 7-8 Translation Process 7-9** Storage Access Protection 7-10 Separation Protection 7-11 Protection Keys 7-12 Translation Locks 7-12 Translation Lock and Protection Key Operation 7-12 Addresses Relocated and Translated 7-13 Translation-Table and Translation-Lock-Table Instructions 7-13 LOAD FROM ADDRESS TRANSLATION TABLE 7-13 LOAD FROM ADDRESS TRANSLATION LOCK TABLE 7-15 STORE TO ADDRESS TRANSLATION TABLE 7-16 STORE TO ADDRESS TRANSLATION LOCK TABLE 7-17 Chapter 8. Input/Output Operations 8-1 Attachment of Input/Output Devices 8-2 Input/Output Devices 8-2 Adapters 8-2 Channel 8-2 Types of Input/Output Operations 8-3 Methods of Data Transfer 8-3 Data-Unit Size 8-3 Programmed Input/Output 8-4 Compatibility of Operation 8-4 Programmed Input/Output Addressing 8-5 Programmed Input/Output Commands 8-5 **Result Conditions 8-6** Program-Exception Interruptions 8-7 Abnormal Ending of Programmed Input/Output Operations 8-7 Instructions 8-8 INPUT/OUTPUT (byte) 8-8 INPUT/OUTPUT (byte, immediate) 8-10 INPUT/OUTPUT (halfword) 8-11 Basic Status Register 8-12 Equipment Check 8-13 Enabled 8-13 Interrupt Request 8-14 PIO Commands Related to the BSTAT 8-14

Reset BSTAT Under Mask 8-14 Set BSTAT Under Mask 8-15 Read BSTAT 8-15 Input/Output Interruptions 8-15 Priority Level Assignment 8-15 Input/Output Interrupt Requests 8-16 Multiple Interruptions for the Same Priority Level 8-17 Resetting I/O Devices 8-17 I/O System Reset 8-17 I/O Selective Reset 8-17 Channel Input/Output 8-18 Channel Input/Output Operation 8-18 Execution of Channel Input/Output Operations 8-22 Blocking of Data 8-22 Channel Pointer 8-22 Designation of Storage Area 8-23 Channel Input/Output Commands 8-25 Channel Pointer Usage 8-26 Conclusion of Channel Input/Output Operations 8-27 Types of Conclusion 8-28 Enabling and Disabling of Channel Input/Output Operations 8-30 Channel Mask 8-31 Error Interrupt Request Vector 8-31 Channel Control Vector 8-31 Channel Control Vector Format 8-32 Command Code 8-33 Command Code Modifier Bits 8-33 Chapter 9. PCE Control 9-1 PCE States 9-1

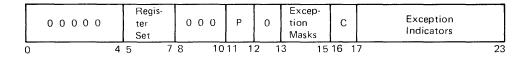

Program Modes 9-2 Program Status Vector 9-2 Program Status Vector Format 9-3 Exceptions Associated with PSV Introduction 9-5 **PSV Format Exceptions 9-5** Other Exceptions 9-5 Address Control Vector 9-6 Exceptions Associated with ACV Introduction 9-6 **ACV Format Exceptions 9-6** Other Exceptions 9-6 Floating-Point Status Vector 9-7 Floating-Point Status Vector Format 9-7 Referring to the FSV 9-8 Exceptions Related to the FSV 9-9 Priority Levels 9-9 Dual PSV/ACV Facility 9-10 Primary and Secondary PSV/ACV Pairs 9-10 Program Activation Vector 9-10 Interruptions 9-11 Interrupt Requests 9-12 I/O Interrupt Request Vector 9-13 Programmed Interrupt Request Vector 9-13 Error Interrupt Request Vector 9-14 Enabling and Disabling 9-15 Master Mask 9-15 Common Mask 9-16 Priority Level Dispatching 9-17 Current and Last Priority Levels 9-18 Summary of the Priority Level Dispatching Process 9-18 Interruption Action 9-20 Control Given to a Program at a New Priority Level 9-20 Control Given to a New Program at the Current Level 9-21 Point of Interruption 9-21 Types of Ending 9-22 Execution of Interruptible Instructions 9-24 Interruption Information 9-24 Source Identification 9-25 System-Check Interruption 9-25 Error Interrupt Request Vector Format 9-25 System Checks 9-26

Instructions for PCE Control 9-31 AND WITH PROGRAMMED INTERRUPT REQUEST VECTOR 9-32 **DISPATCH NEW LEVEL 9-32 OR WITH PROGRAMMED INTERRUPT REQUEST VECTOR 9-34 READ CHANNEL MASK 9-34 READ COMMON MASK 9-35 READ CONDITION INDICATORS 9-35 READ CURRENT AND LAST LEVELS 9-36 READ ERROR INTERRUPT REQUEST VECTOR 9-36 READ I/O INTERRUPT REQUEST VECTOR 9-37 READ MASTER MASK 9-37 READ PRIMARY REGISTER SET NUMBER 9-38 READ PROGRAM ACTIVATION VECTOR 9-38 READ PROGRAMMED INTERRUPT REQUEST VECTOR 9-39 READ SECONDARY REGISTER SET NUMBER 9-39 RESET CHANNEL MASK 9-40 RESET MASTER MASK 9-40 RESET PROGRAMMED INTERRUPT REQUEST 9-40** SET CHANNEL MASK 9-41 SET MASTER MASK 9-41 SET PROGRAMMED INTERRUPT REQUEST 9-42 WRITE COMMON MASK 9-42 WRITE CONDITION INDICATORS 9-43 WRITE ERROR INTERRUPT REQUEST VECTOR 9-43 WRITE PRIMARY REGISTER SET NUMBER 9-44 WRITE PROGRAM ACTIVATION VECTOR 9-44 WRITE SECONDARY REGISTER SET NUMBER 9-45 Instruction for Direct Control 9-46 **CONTROL DIRECT OUT 9-46** Instructions for Diagnostic Control Vector 9-46 **READ DIAGNOSTIC CONTROL VECTOR 9-46** WRITE DIAGNOSTIC CONTROL VECTOR 9-47 Chapter 10. Dual-Mode Processing 10-1 Logical Structure 10-1 Storage and Registers 10-2

Program Execution 10-3 Execution 10-3 Sequence of Execution 10-4 Program Exceptions 10-4 General Instructions 10-4 Floating-Point Instructions 10-5 Register Organization 10-5 Dynamic Address Relocation and Translation 10-5 Input/Output Operations 10-6 PCE Control 10-6

#### Appendix A. Lists of Instructions A-1

Instructions Arranged by Name A-2 Instructions Arranged by Mnemonic A-6 Instructions Arranged by Type A-10

#### Appendix B. Assembler Language Operand Specification B-1

Generic Specification B-1 IBM 8100 DPPX Assembler Language Register Specifications B-4 General Registers B-4 Floating-Point Registers B-6

Appendix C. Instruction Operations and Condition Settings C-1 Instruction Operations C-2 Result Conditions C-11

Appendix D. Instruction Formats D-1 Operation Code D-1 Displacement Representation D-3 Comprehensive List of Instruction Formats D-4

Appendix E. Control Information Formats E-1

#### Appendix F. Assigned Register Locations F-1

Appendix G. Processor-Specific Functions G-1 Logical Storage Addressing G-1 Other Processor-Specific Functions G-1 Address Range Control G-2 Processor-Specific Error Reporting G-2 Disabling System-Check Interrupt Requests G-2 Reserved Program Information Code (PIC) Field G-3 Write Program Activation Vector Instruction G-3 Reserved Operand Bits in PCE-Control Instructions G-3 Reserved Channel Control Vector (CHCV) Command Codes G-3 Specification of Count for Interruptible Instructions G-3 Suspended PCE Operation in Dual-PCE Processors G-4 Instruction Address G-4 Address Exception G-4 Unit of Operation G-5 Prefetch Errors G-5 EIRV Variations G-5 Detection of Concurrent Program Exceptions G-6 Address Range Error G-6

Appendix H. Tables of Powers of 2 H-1

#### Appendix I. Hexadecimal Tables I-1

Direct Conversion Tables I-1 Conversion Table: Hexadecimal and Decimal Integers I-6 Conversion Table: Hexadecimal and Decimal Fractions I-8 Hexadecimal Addition and Subtraction Table I-9 Hexadecimal Multiplication Table I-10

Appendix J. EBCDIC Chart J-1

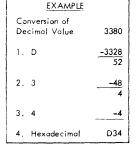

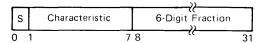

Appendix K. Number Representation K-1 Fixed-Point with Two's Complement K-1 Floating Point K-3 Conversion Example K-4

**Glossary GL-1**

Index X-1

## Figures

- 1-1. IBM 8100 Information System Logical Structure 1-2

- 1-2. Examples of Information Formats and Alignment 1-4

- 1-3. Storage Addresses 1-5

- 1-4. Organization of Registers Assigned to a Program 1-6

- 1-5. Data Unit Allocation for a General Register 1-7

- 1-6. Example of Register-to-Register Operation (lower halfwords) 1-9

- 1-7. Example of Register-to-Register Operation (bytes) 1-10

- 1-8. Example of Register-and-Immediate Operation 1-11

- 1-9. Address Generation Using Base and Displacement Values 1-13

- 1-10. LOAD (halfword, register) Operations 1-15

- 1-11. LOAD (byte, register) Operations 1-16

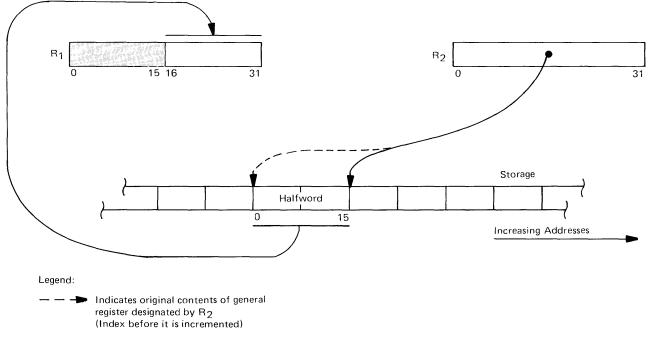

- 1-12. LOAD (halfword, with index incremented) Operation 1-17

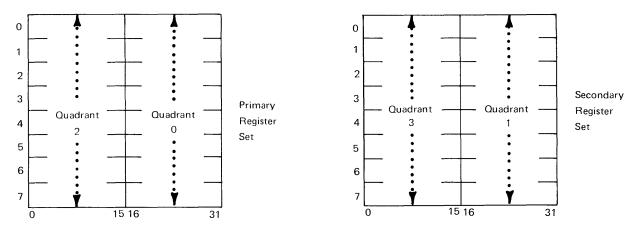

- 1-13. General Register Quadrants 1-18

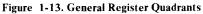

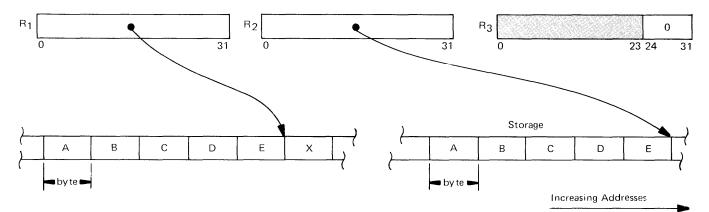

- 1-14. Example of MOVE (bytes, storage) 1-18

- 1-15. Example of Extended-Precision Addition 1-19

- 1-16. SHIFT and ROTATE (halfwords) Operations 1-21

- 1-17. Example of COMPARE (bytes, storage) 1-21

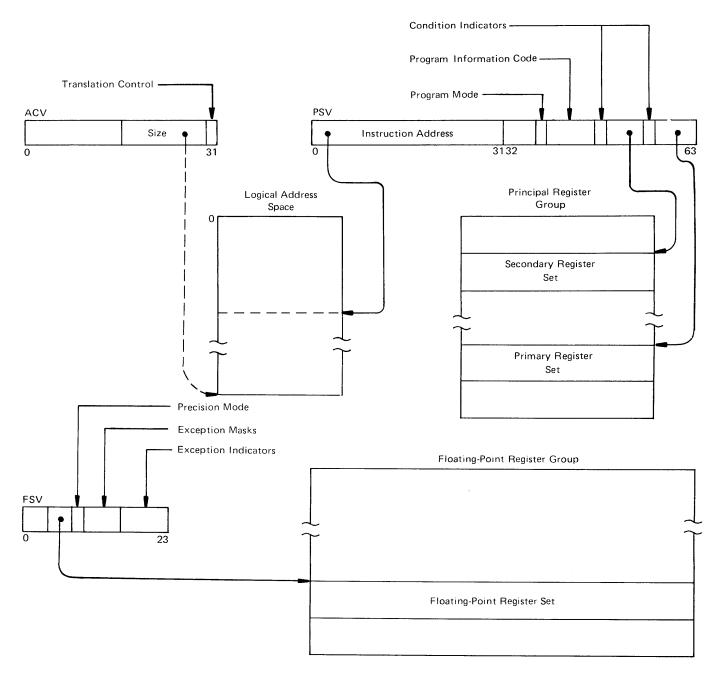

- 1-18. Program-Execution Environment 1-26

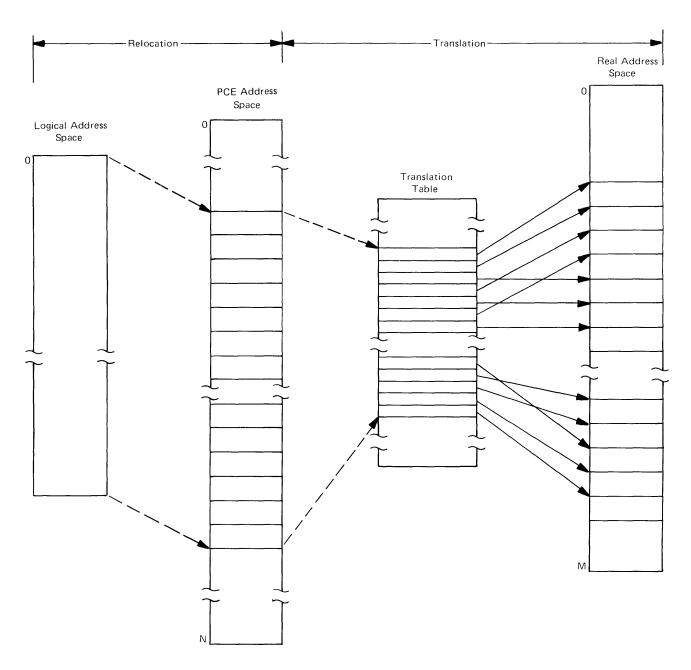

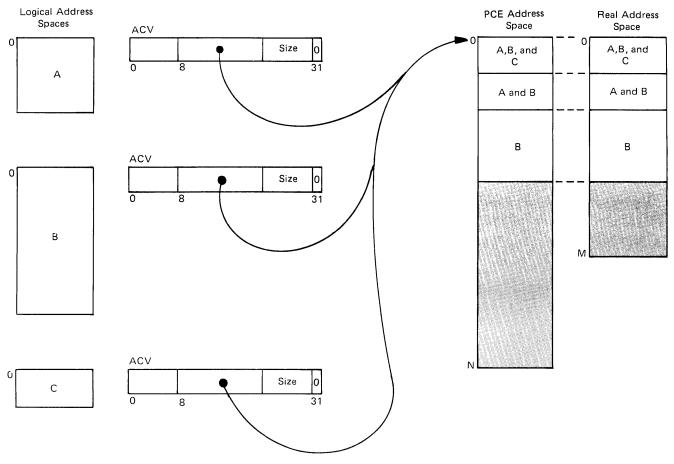

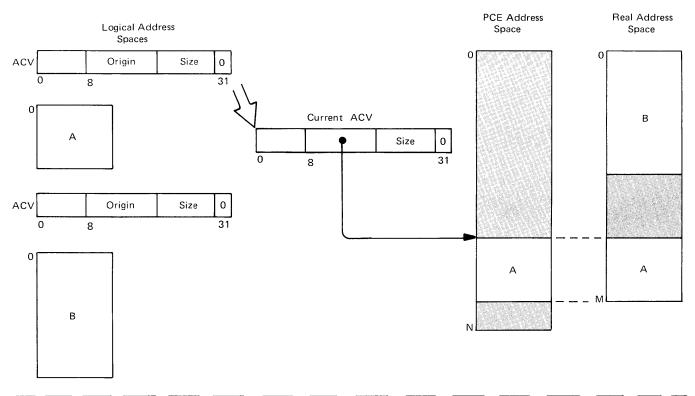

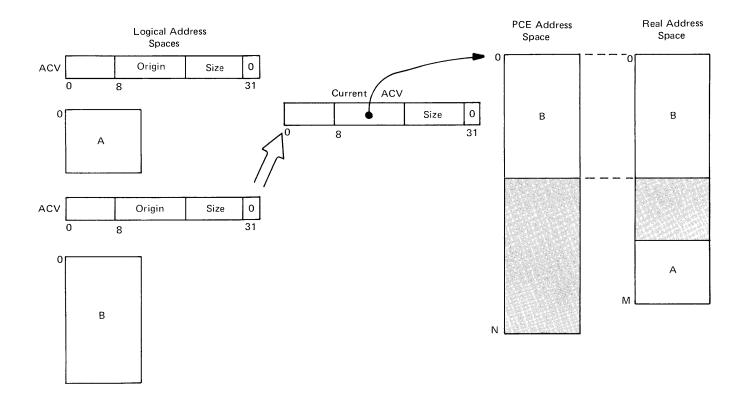

- 1-19. Dynamic Address Relocation and Translation 1-28

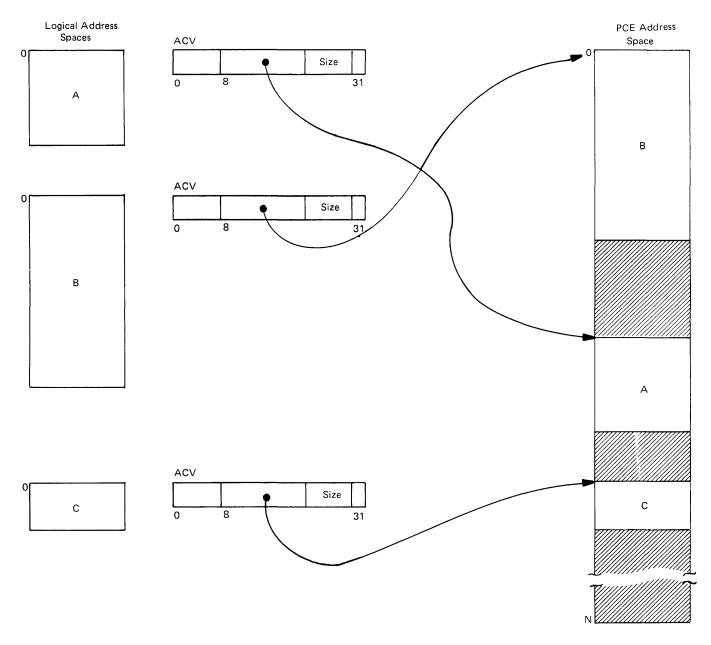

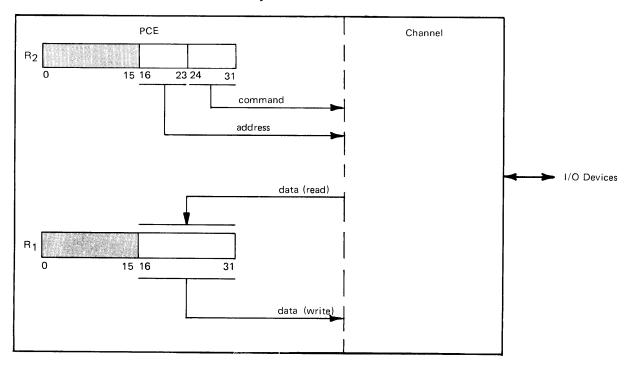

- 1-20. ACV Control of Dynamic Address Relocation 1-29

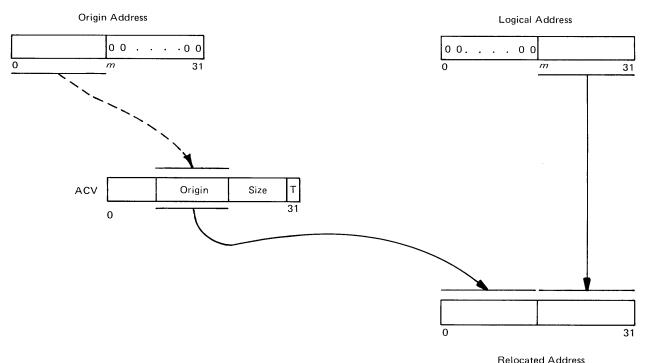

- 1-21. Relocation Process 1-30

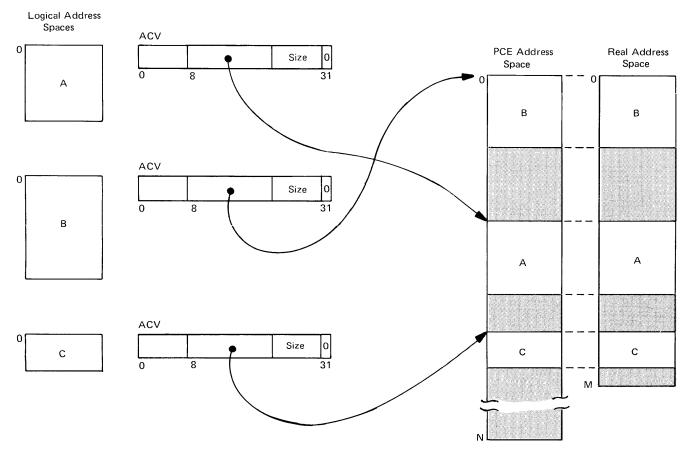

- 1-22. Dynamic Address Relocation (Translation Not Specified) 1-31

- 1-23. Nested Logical Address Spaces 1-32

- 1-24. Information Protection in Main Storage 1-33

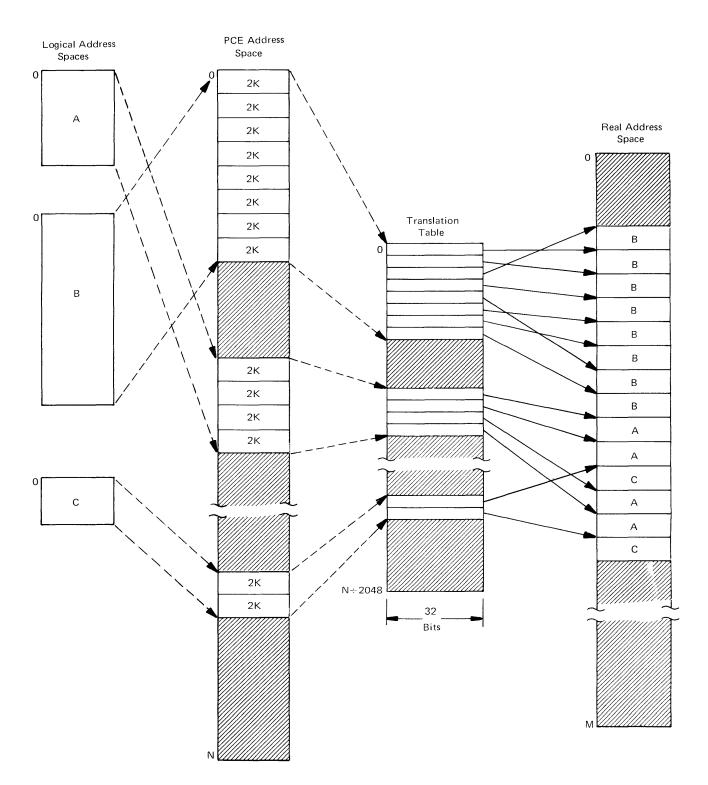

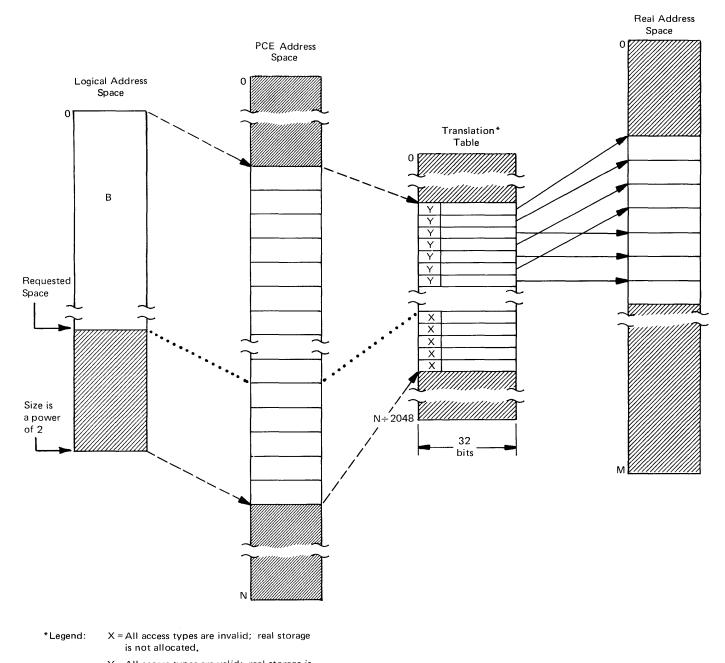

- 1-25. Dynamic Address Translation 1-34

- 1-26. Translation Process 1-35

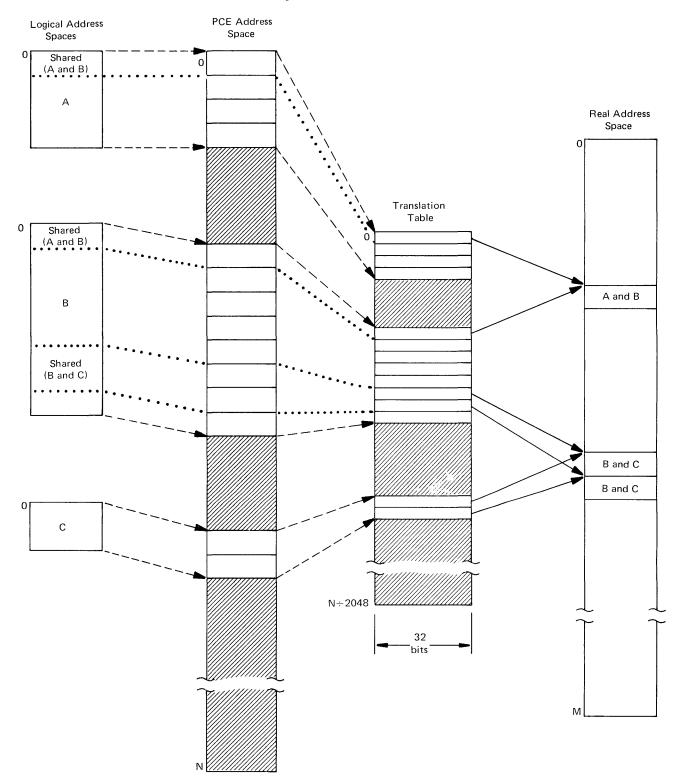

- 1-27. Information Sharing 1-36

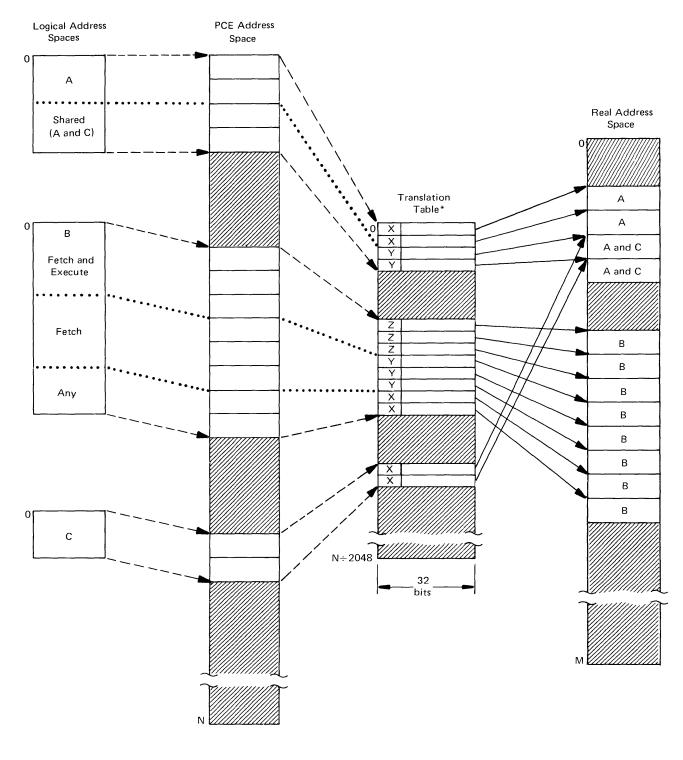

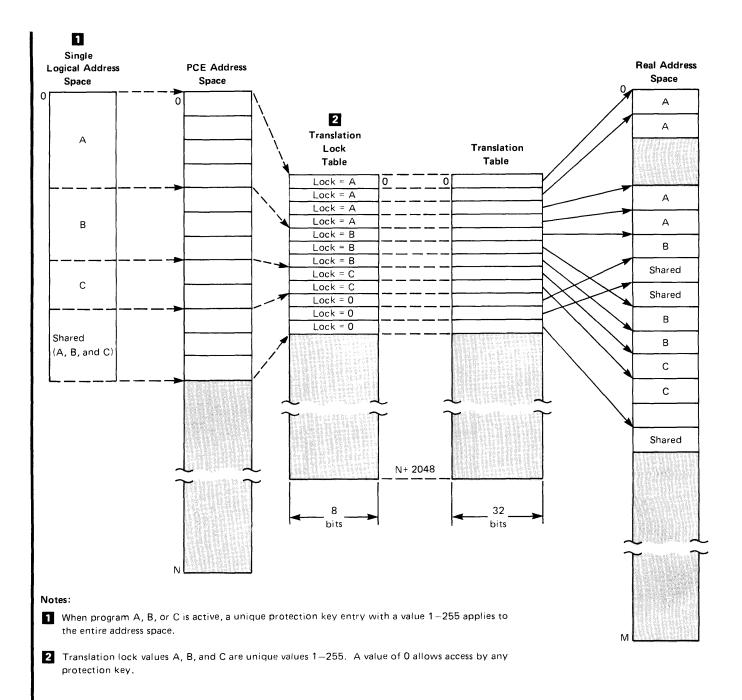

- 1-28. Information Sharing with Different Types of Access 1-38

- 1-29. Example of Conservation of Main Storage 1-39

- 1-30. Example of Separation Protection 1-40

- 1-31. Principal and Adjunct Register Assignments 1-42

- 1-32. PSV and ACV/EBI Register Locations 1-44

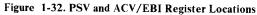

- 1-33. PIO Operation (halfword) 1-48

- 1-34. Channel I/O Storage-Addressing Information 1-50

- 2-1. Integral Boundaries for Halfwords and Words 2-3

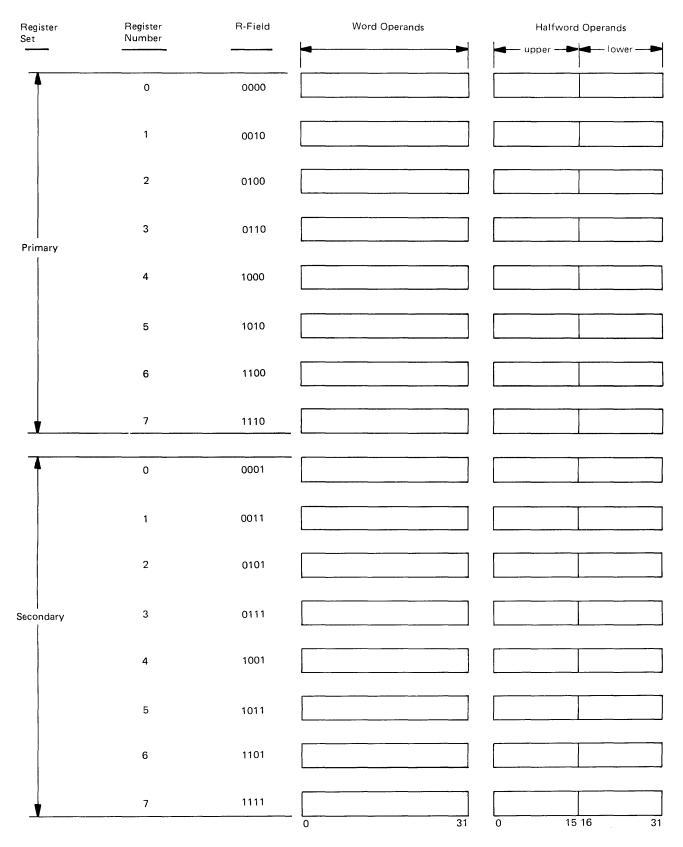

- 2-2. General Registers Within a Register Set 2-5

- 2-3. General-Register Word and Halfword Operands 2-7

- 2-4. General-Register Byte Operands 2-8

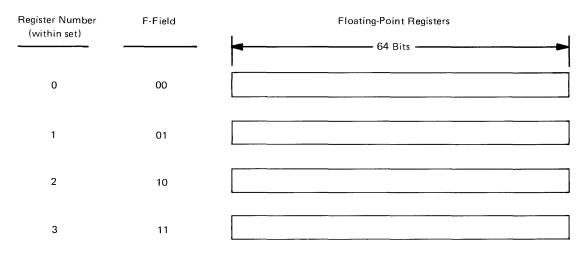

- 2-5. Registers in a Floating-Point Register Set 2-9

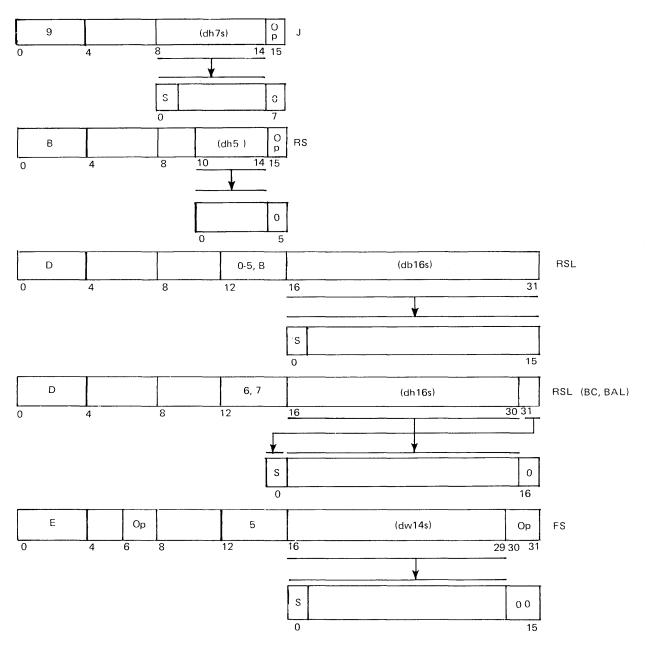

- 3-1. General Formats of Instructions 3-3

- 3-2. Displacement of RS-Long Format BRANCH Instructions 3-7

- 4-1. Symbols Used in Instruction Descriptions 4-8

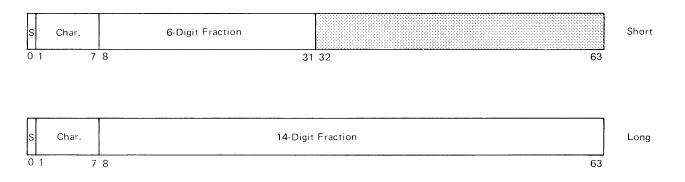

- 5-1. Formats of Short and Long Floating-Point Numbers 5-2

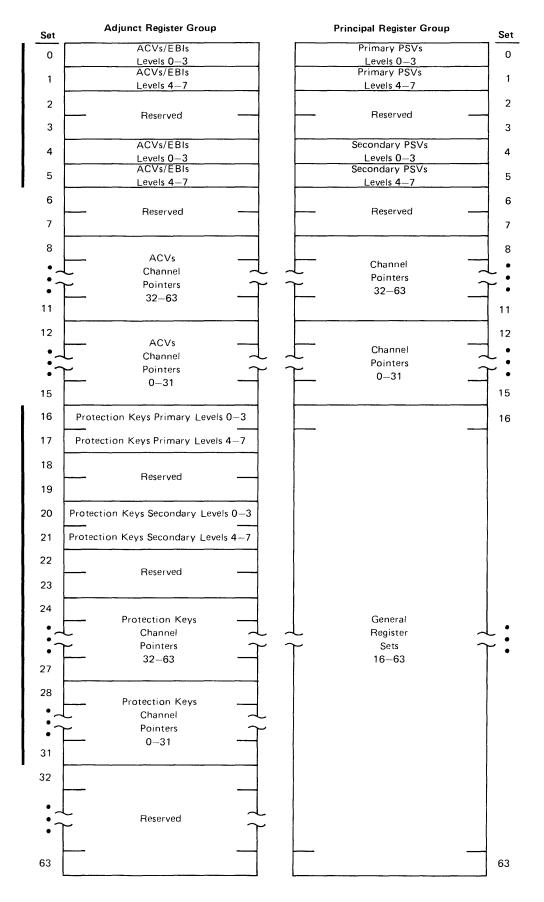

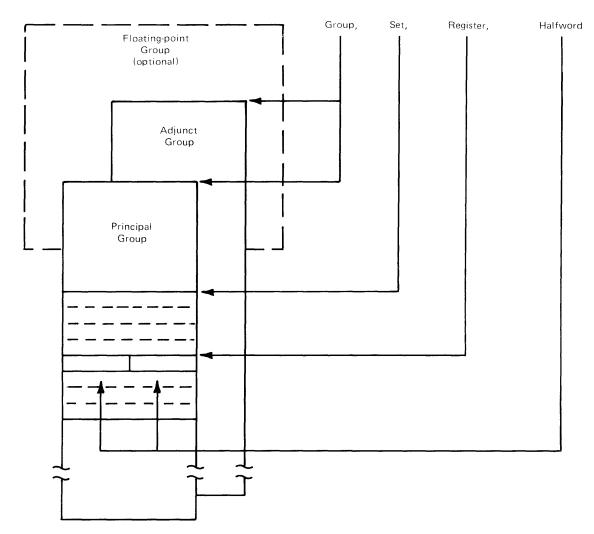

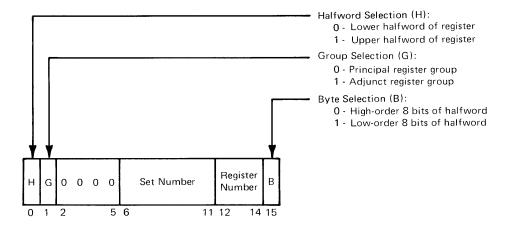

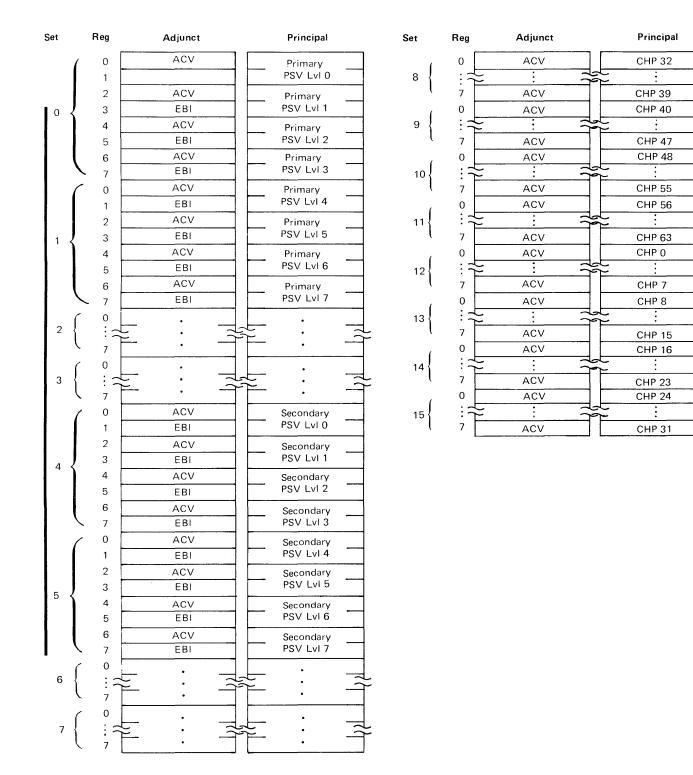

- 6-1. Register Organization and Information Selection 6-2

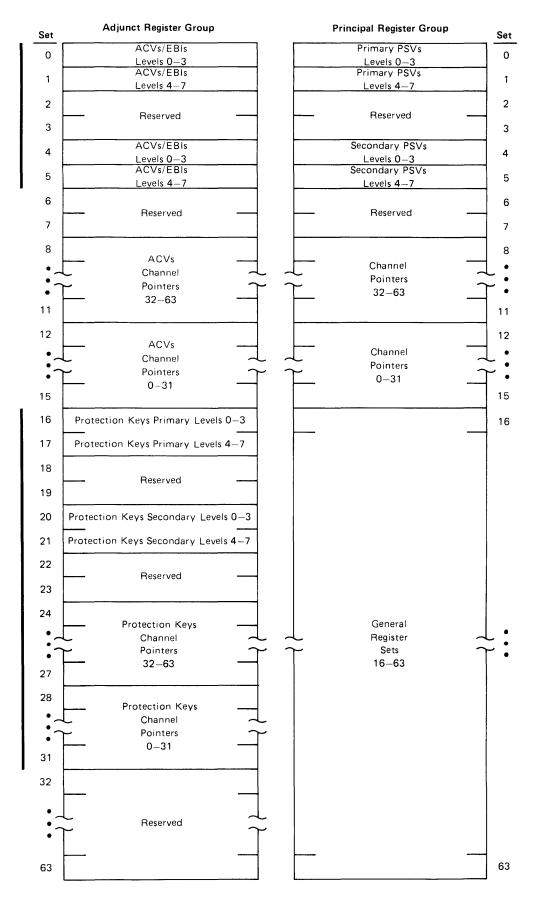

- 6-2. Assignment of Principal and Adjunct Register Sets 6-3

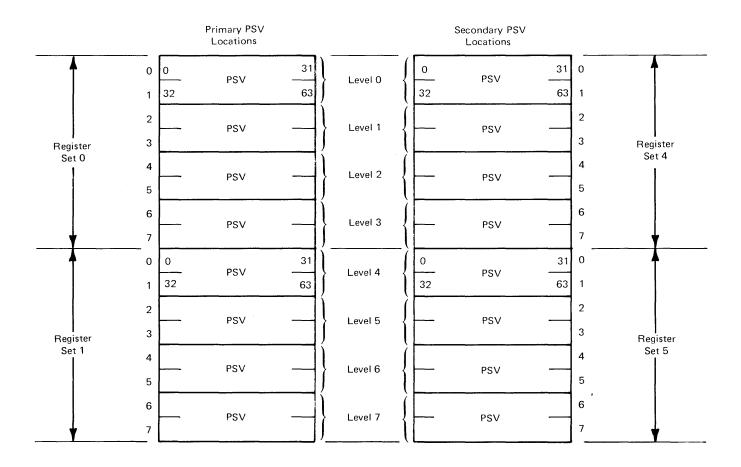

- 6-3. PSV Locations in Principal Register Sets 6-4

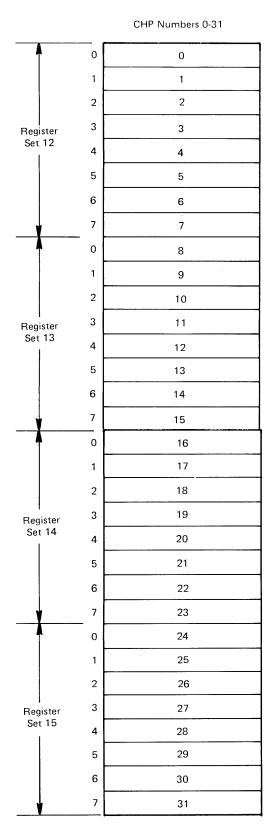

- 6-4. Channel Pointers 6-5

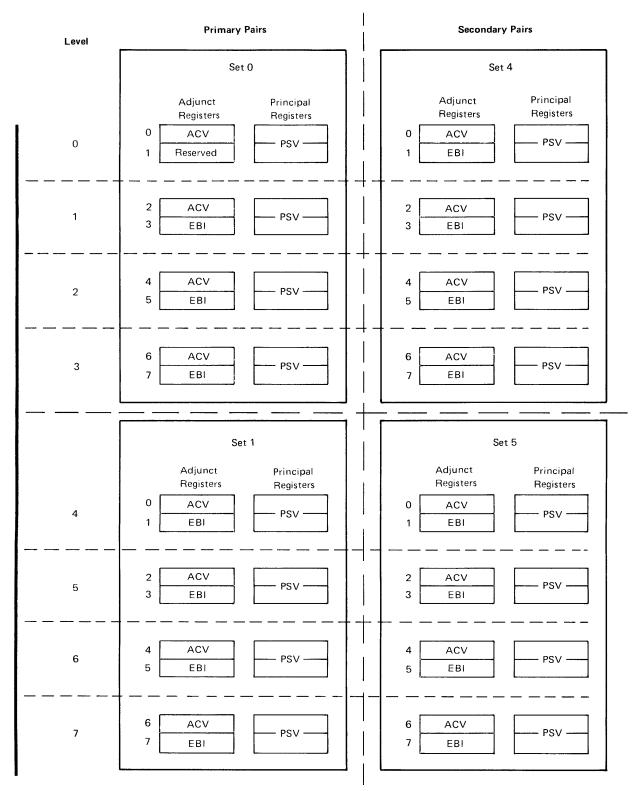

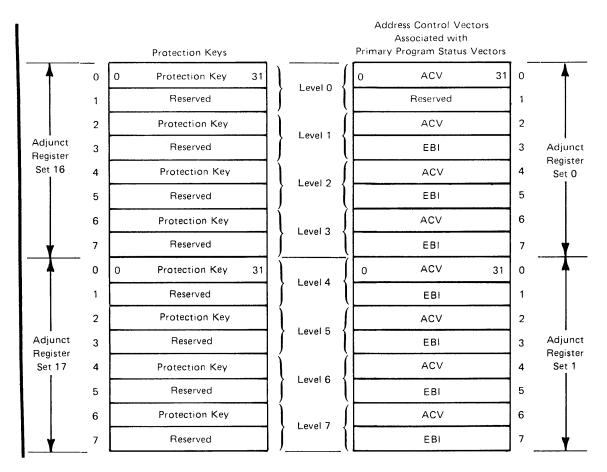

- 6-5. ACV/EBI Pairs Associated with Primary PSVs 6-6

- 6-6. ACV/EBI Pairs Associated with Secondary PSVs 6-7

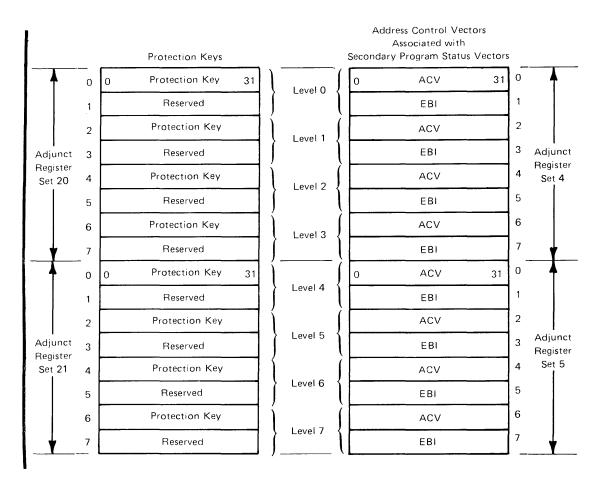

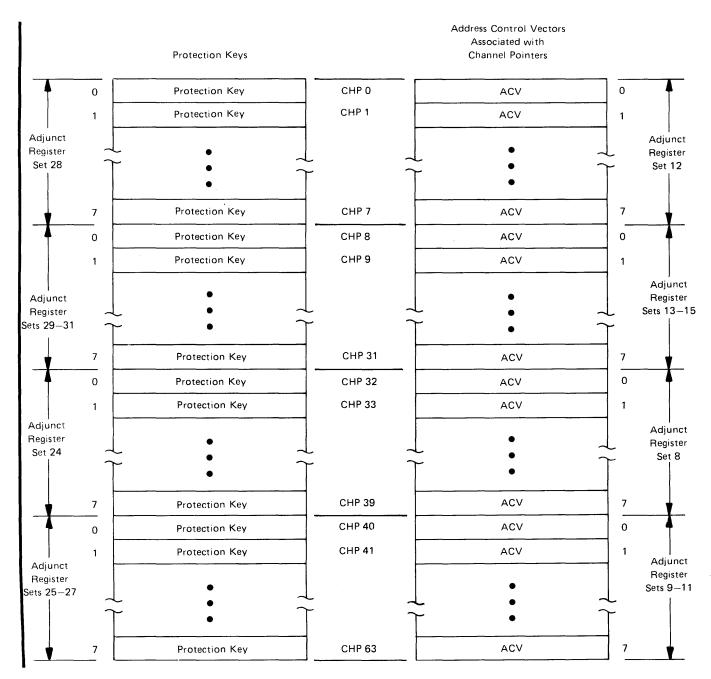

- 6-7. ACVs Associated with Channel Pointers 6-8

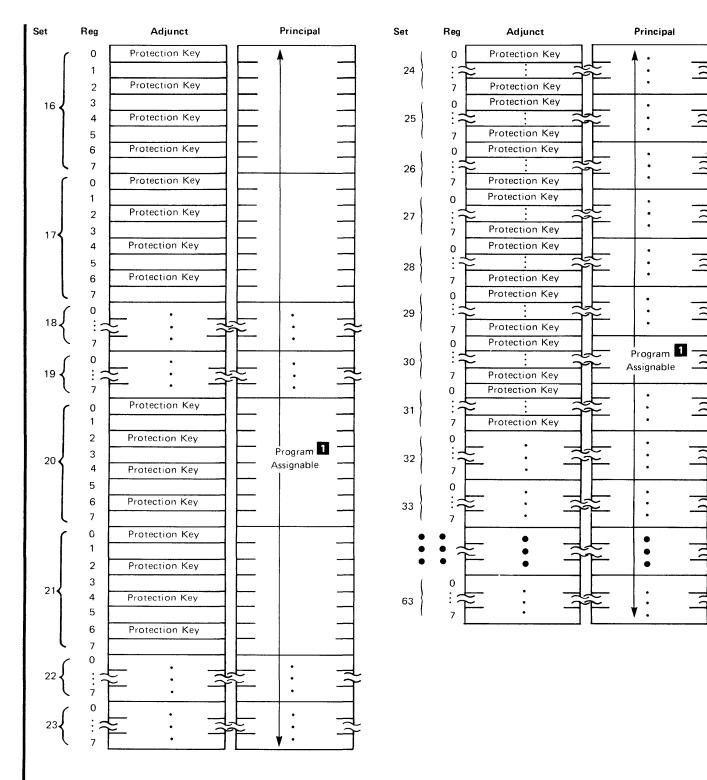

- 6-8. How Protection Keys Correspond to ACVs Associated with Primary PSVs 6-9

- 6-9. How Protection Keys Correspond to ACVs Associated with Secondary PSVs 6-10

- 6-10. How Protection Keys Correspond to ACVs Associated with Channel Pointers 6-11

- 7-1. Dynamic Address Relocation 7-2

- 7-2. Address Control Vector 7-3

- 7-3. Address Control Vector Formats 7-4

- 7-4. Logical Address Used by the Program or Channel 7-5

- 7-5. Correspondence of m and k to Address Space Sizes 7-5

- 7-6. Origin Address 7-6

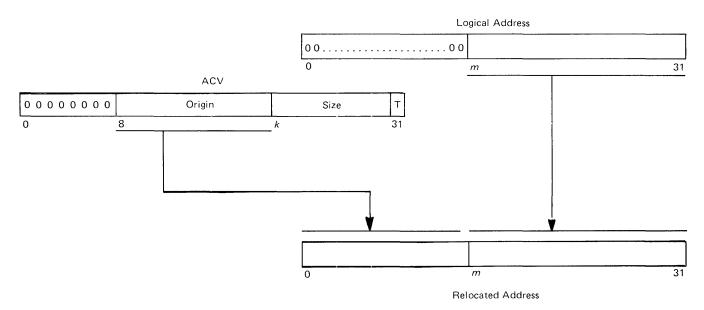

- 7-7. Dynamic Address Relocation Process 7-7

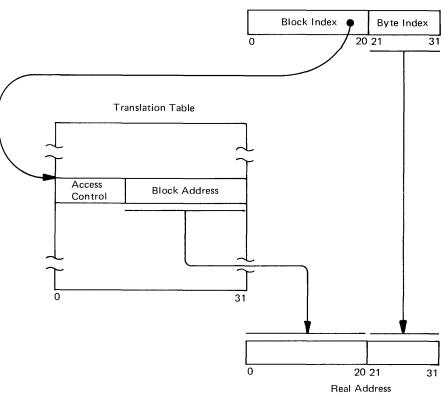

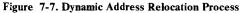

- 7-8. Block-Index and Byte-Index Fields of an Address to Be Translated 7-8

7-9. Translation-Table Entry 7-8

- 7-10. Dynamic Address Translation 7-9

- 7-11. Format of Access-Control Field 7-10

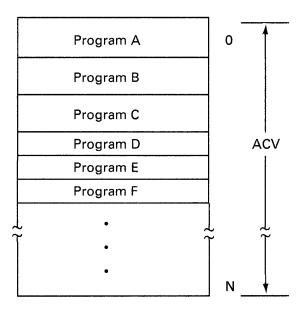

- 7-12. Multiple Programs within a Logical Address Space 7-11

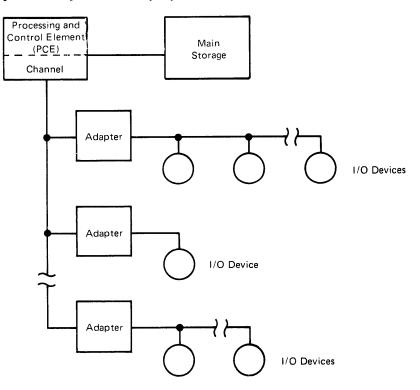

- 8-1. Logical Interconnection of I/O Devices to PCE and Main Storage 8-1

- 8-2. Channel I/O Data Transfer Operation 8-21

- 8-3. Designation of Logical Storage Area 8-25

- 9-1. Program Status Vector Format 9-3

- 9-2. Floating-Point Status Vector Format 9-7

- 9-3. Determining the Dispatchable Priority Levels 9-19

- 9-4. Summary of Interruption Information 9-23

- 9-5. Format of Error Interrupt Request Vector 9-25

- 10-1. Logical Structure of Dual-PCE Processors 10-1

- B-1. General Register Specifications B-5

- B-2. Byte Operand Specifications B-5

- B-3. Floating-Point Register Specifications B-6

## **Summary of Changes**

## Fifth Edition (March 1984)

This edition includes information that relates to:

- Separation protection, which uses translation locks and protection keys.

- Exception block index (EBI) registers.

- The LOAD FROM TRANSLATION LOCK TABLE (LATL) and STORE TO TRANSLATION LOCK TABLE (STATL) instructions.

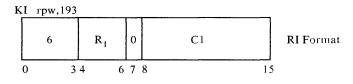

- The control immediate WRITE DIAGNOSTIC CONTROL VECTOR (KI 192) and READ DIAGNOSTIC CONTROL VECTOR (KI 193) instructions.

- The 8130 Model B and the 8150, where applicable.

- Corrections and clarifications of the previous revision level.

## PART I. OVERVIEW

Chapter 1. Introduction to the Logical Structure

## **Chapter 1. Introduction to the Logical Structure**

**Note:** Before using this manual, review the Preface that precedes the table of contents. The Preface (1) describes the purpose and content of this manual, (2) defines some assumptions made, (3) identifies the intended user, and (4) indicates the prerequisite knowledge needed by the user.

Also, be aware that not all 8100 processor models implement every architectural function. For example, the floating-point feature, exception block index (EBI) registers, separation protection, two channels in dual-PCE processors, and certain instructions are not available on all models. Refer to "Appendix G" for processor-specific functions.

This chapter serves as an introduction to the major information formats and processing facilities provided by the IBM 8100 Information System. The description is mainly tutorial; it is not intended as a rigorous specification. The remaining chapters and appendixes provide such a specification. Chapter 1 should be read before using this publication as a reference.

Available on all processors are control facilities that provide system functions, such as I/O interrupt request identification, programmable assignment of I/O devices to priority levels, execution of direct-control (KDO) instructions, initial program load (IPL), and system and I/O reset. These facilities for system control as they apply to 8100 operation are described in the respective processor description manuals listed in the Preface under "Corequisite Publications".

## **Logical Structure**

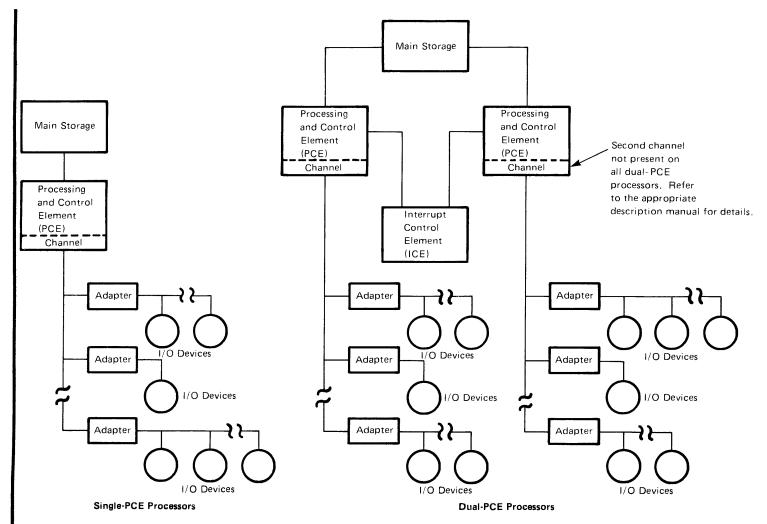

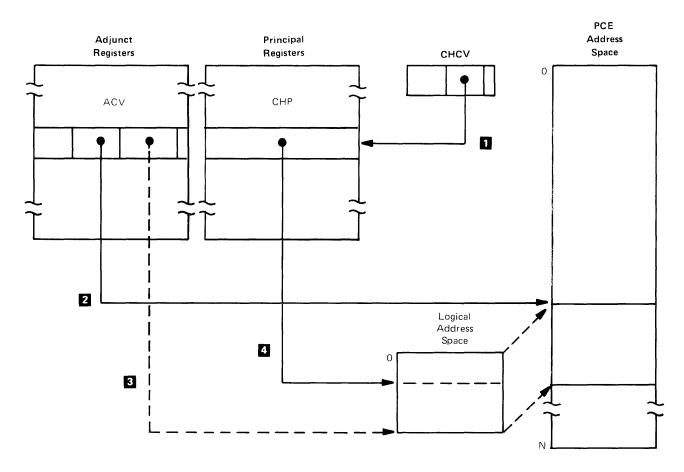

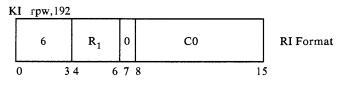

The logical structure of an IBM 8100 Information System consists of main storage, a processing and control element (PCE), a channel, and input/output devices attached to the channel through adapters. In IBM 8100 Information Systems having the dual-mode capability, the logical structure includes an interrupt control element (ICE) and a second PCE. Figure 1-1 shows this logical structure.

The PCE is the logical entity that is the controlling center of the system. It contains the sequencing and processing controls for instruction execution, interruption action, dynamic address transformations, and other control or processing functions. The physical makeup of the PCE in the processor models of the 8100 system may be different, but the logical function remains the same.

Some processor models contain two PCEs (primary and secondary) and also an interrupt control element (ICE) that enables communication between the PCEs. These models are referred to as dual-PCE processors, which can operate either in dual or single mode. Dual mode is the normal operational mode and uses both PCEs; single mode uses only the primary PCE.

Each PCE includes 32-bit registers used as general-purpose registers. Also included are registers that are permanently assigned to hold control information. Floating-point registers having 64 bits each are optionally available.

Three distinct types of processing are provided by the PCE: (1) logical manipulation of bits, fixed-length information units, and character strings; (2) fixed-point binary arithmetic; and (3) (optionally) floating-point arithmetic.

The 8100 system is designed for use with a supervisory program that coordinates the use of the system's resources. The PCE includes facilities for protection, dynamic address transformations, interruption handling, and PCE control.

Figure 1-1. IBM 8100 Information System Logical Structure

## **Information Formats**

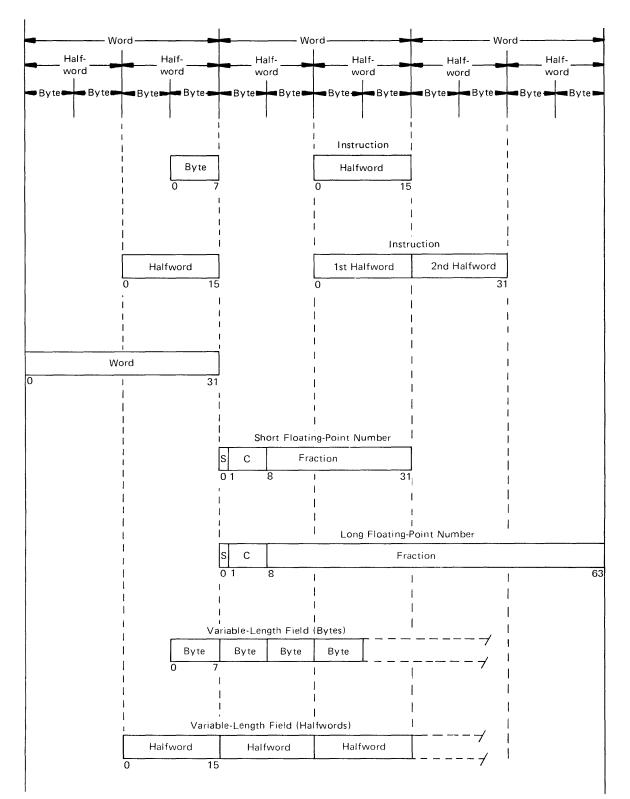

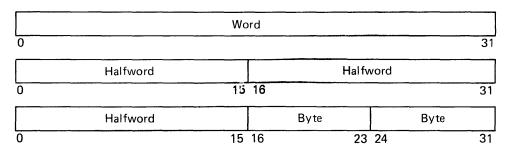

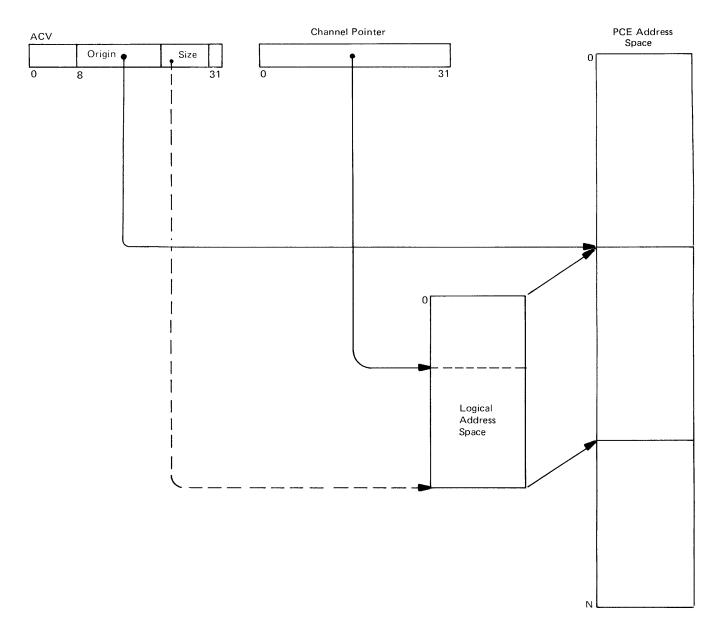

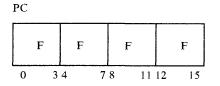

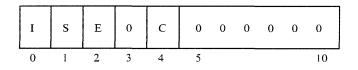

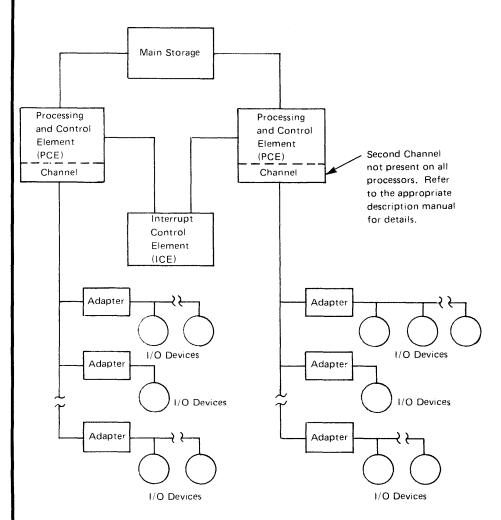

Within any information format in the 8100 system, the bits making up the format are numbered consecutively left to right, starting with 0. The basic building block of all formats is an 8-bit unit of information. Fixed-length fields of one, two, four, and eight consecutive 8-bit units are called *bytes, halfwords, words, and doublewords,* respectively. For instructions operating on fixed-length fields, the operation implies one of these four lengths as the operand length. When the length of a field is not implied by the operation but is stated explicitly, the information format is said to have *variable field length*. Variable field lengths are variable by increments of a byte or a halfword.

The location of a field in main storage is identified by the address of the leftmost byte of the field. Except for doubleword information formats, fixed-length fields must be aligned in main storage on an *integral boundary*. That is, the field's location must have an address that is a multiple of its length in bytes. For example, a halfword integral boundary has an address which is a multiple of 2; a word integral boundary has an address which is a multiple of 4. Doubleword information formats must be aligned on a word boundary. Halfwords are the basic building blocks of instructions. Instructions, thus, must be located at addresses that are a multiple of 2.

Variable-length fields that are variable in increments of 1 byte may start at any byte address. On the other hand, variable-length fields that are variable in increments of 1 halfword must start at an address that is a multiple of 2. Figure 1-2 shows some examples of the information formats and alignment possibilities.

Figure 1-2. Examples of Information Formats and Alignment

## **Main Storage Addressing**

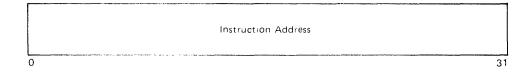

Main storage is addressed in units of bytes. Byte locations in storage are numbered consecutively, left to right, starting with 0. Each number is considered the address of the corresponding byte location. Storage addresses are represented by unsigned 32-bit positive binary integers (see Figure 1-3).

|   | 0    | 1    | 2    | 3    | 4    |          | 2 <sup>32</sup> –1 |   |

|---|------|------|------|------|------|----------|--------------------|---|

|   | Byte | Byte | Byte | Byte | Byte | <br>Byte | Byte               |   |

| 1 | 0    | 7    |      |      |      | (        | 7 (                | 1 |

#### Figure 1-3. Storage Addresses

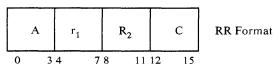

For purposes of addressing main storage, two types of addresses are recognized: real and logical. *Real addresses* are the addresses assigned to physical main storage locations. The addresses used by a program, or in a channel I/O operation, to refer to storage locations are called *logical addresses*. Logical addresses are transformed into real addresses by two means: dynamic address relocation and dynamic address translation. Dynamic address relocation is always applied to all logical addresses; dynamic address translation is controlled by a supervisory program. These facilities are described under "Dynamic Address Transformations" in this chapter.

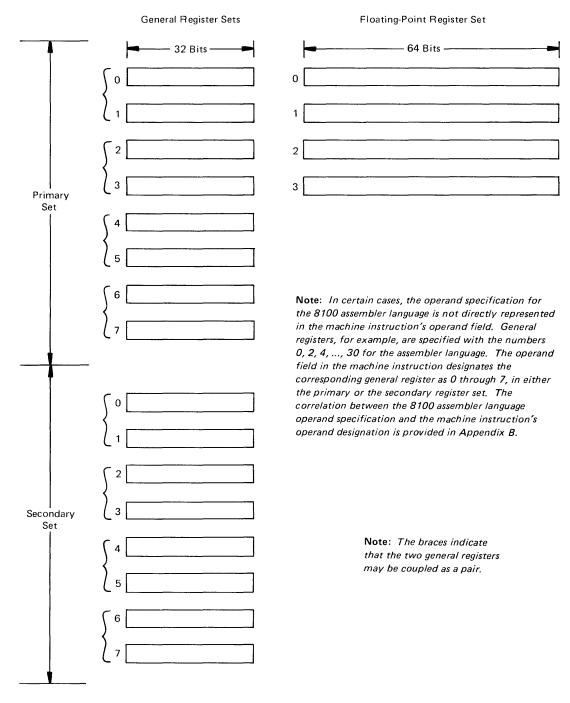

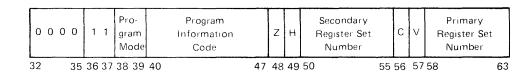

## Registers

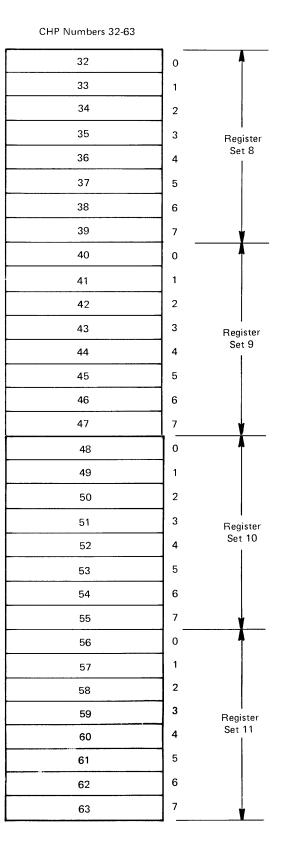

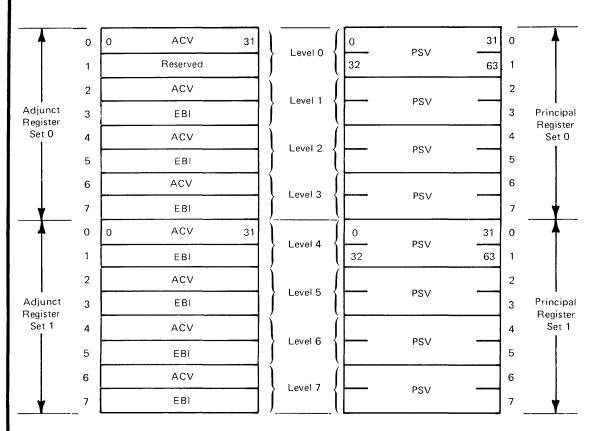

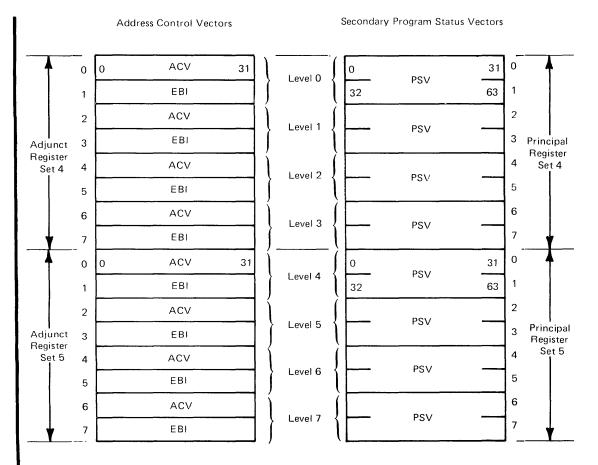

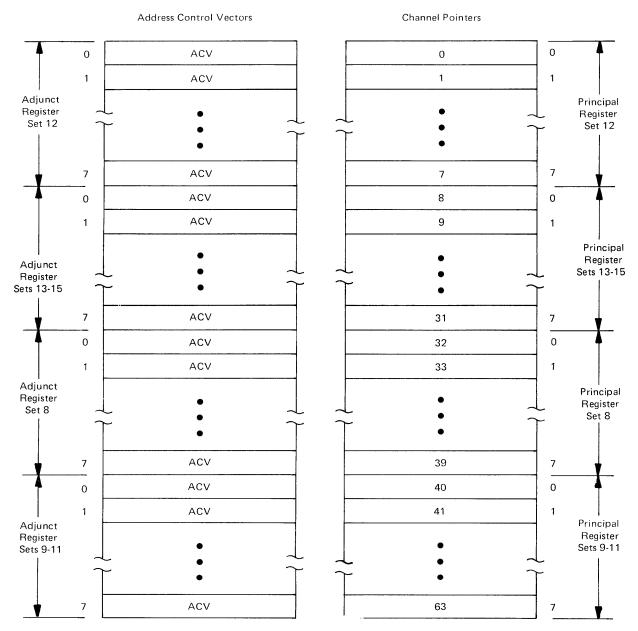

Registers are organized in *register groups* and *register sets*. Sixty-four sets of registers are provided in each of two register groups; each set consists of eight 32-bit registers numbered 0-7. One group of 64 register sets is known collectively as the *principal register group*. Of these, 12 sets are permanently assigned to hold control information, 4 are reserved, and the remaining 48 sets are available for use by programs as general-purpose registers. The second group of 64 register sets is known as the *adjunct register group*. Of these, 24 sets are permanently assigned to hold control information, and the remaining sets are reserved.

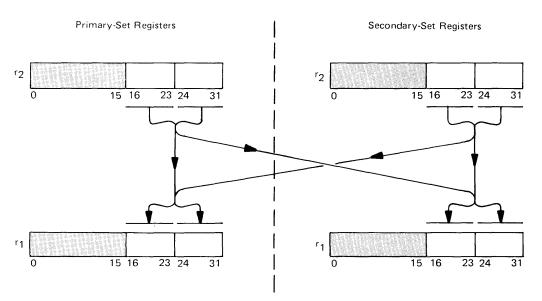

A program has two sets from the principal register group assigned to it and, thus, can address information in 16 general-purpose registers. General-purpose registers can be used for addressing and to hold operands and results in arithmetic and logical operations. Of the two register sets assigned to a program, one is designated the *primary set* and the other the *secondary set*.

For processor models having the optional floating-point feature installed, programs can address data in floating-point registers. Eight sets of floating-point registers are provided in the *floating-point register group*. All eight sets are available for assignment to programs. A program may address one set; each set consists of four 64-bit registers numbered 0-3.

The assignment of register sets to programs is discussed further under "Program-Environment Definition" in this chapter. Figure 1-4 shows the organization of registers assigned to a program. A description of all register groups is found under "Register Organization" in this chapter.

Figure 1-4. Organization of Registers Assigned to a Program

## Instructions

Operations performed by the PCE are controlled by sequences of instructions, which are the building blocks of programs. Each instruction consists of two major parts: (1) operation-code fields which specify the operation to be performed by the PCE, and (2) fields which specify the operands that participate in the operation.

|          | In the following sections, operands, operand specifications, and instruction<br>formats for the general instructions are discussed. Floating-point numbers,<br>operand specifications, and instruction formats are described under<br>"Floating-Point Instructions" in this chapter. PCE-control instructions are<br>summarized in other sections of this chapter where the associated control<br>functions are also described.                                                                                                         |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|          | During instruction execution, the PCE monitors the existence of certain program exceptions, including those resulting from improper specification or use of instructions and data. These program exceptions normally result in an interruption of the program. (See "PCE Control" in this chapter for a discussion of interruptions.)                                                                                                                                                                                                   |  |  |  |

|          | <b>Note:</b> Instructions are described in Chapters 4 through 10, and Appendix A contains three lists that summarize these descriptions. These lists arrange the instructions by name, by mnemonic, and by instruction type.                                                                                                                                                                                                                                                                                                            |  |  |  |

| Operands |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|          | Operands can be grouped into three classes according to their location: operands in general registers, immediate operands, and operands in main storage.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

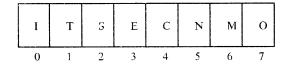

|          | Operands located in general registers may be 1-byte, 2-byte (halfword), or 4-byte (word) information units. The length of an operand in a general register is implied by the operation-code fields of the instruction. The distinction between the primary and secondary register sets applies in general to processing of byte operands and is explained in detail later in this chapter.                                                                                                                                              |  |  |  |

|          | A general register can be used to hold multiple information units, each of which<br>can be processed independently. Figure 1-5 shows the allocation of operands in a<br>general register. Bit positions 0-15 are referred to as the <i>upper halfword</i> of a<br>general register and bit positions 16-31 as the <i>lower halfword</i> . Byte operands may<br>be located in bit positions 16-23 (upper byte) and 24-31 (lower byte) of a general<br>register. Thus in the 16 registers assigned to a program there are a maximum of 32 |  |  |  |

register. Thus in the 16 registers assigned to a program there are a maximum of 32 halfword-operand locations and a maximum of 32 byte-operand locations. For operations which place the result in a general register, if the result is a byte or halfword, only the indicated bit positions of the register are used for the result; the remaining register bit positions are not changed.

Figure 1-5. Data Unit Allocation for a General Register

Immediate operands are contained in a field within the instruction. The immediate data may be 4 bits or 1 byte, depending on the instruction.

Operands in main storage may have either a fixed length implied by the operation-code fields of the instruction, or a variable length specified by the contents of a general register.

#### **Operation Classes and Instruction Formats**

Instruction formats differ primarily in the method of operand specification and, in most cases, also in the allocation of fields for operation-code bits. Some instructions contain fields that vary somewhat from the general format descriptions.

An instruction is 1 or 2 halfwords long. Each instruction is in one of eight general formats. Six of the eight formats are used for all instructions other than floating-point instructions. The two remaining formats are used only for instructions provided with the optional floating-point feature.

The first four bit positions of all instructions are an operation-code field which identifies a general form for the instruction. Specification of the complete operation code generally requires more than 4 bits. Bits 12-15 of most instruction formats are used for this purpose; other fields may also be used in certain formats to completely specify the operation code.

Differences among the operand-specification parts of the various instruction formats depend on two factors: the number of operands required for the operation, and their locations. For purposes of description, operands are designated as first and second operands, and in some cases, third operands. In general, two operands participate in an operation and the result replaces the first operand. An exception is instructions with STORE in the name, where the result replaces the second operand.

Operation classes are identified by the locations of the operands that participate in the operation. The classes are: register-to-register, register-and-immediate, register-and-storage, storage-to-storage, and sequencing. Operation classes and the various instruction formats that are used for each operation class are discussed in the following sections. Note that instruction-format names express, in general terms, the form of operand specification provided, not the operation class that may employ a particular format. An instruction format is used for more than one operation class when these classes require similar forms of operand specification.

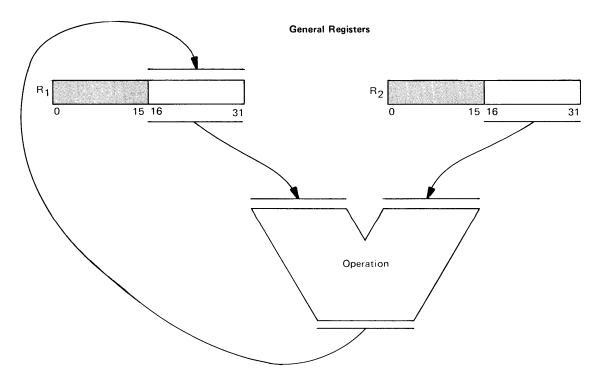

#### **Register-to-Register**

Operations in which the operands and result are held in general registers are called *register-to-register operations*. All fixed-point arithmetic and logical operations fall in this class. These operations generally use two operands and produce a result which always replaces the first operand. Except for multiplication and division, the first and second operands and the result all have the same length. In certain operations, such as data movement, only the second operand is used as input to the operation; the first operand is treated as an explicit result field having the same length as the second operand.

For most arithmetic and logical operations on halfword data, both operands are located in the lower halves of general registers. Several operations are also provided in which operands are located in the upper halves (arithmetic) or in either half (data movement). The operation code implies the register halves (upper or lower) that contain the operands. Figure 1-6 shows arithmetic and logical halfword operations, which can be described by the following general expressions:

#### Arithmetic and Logical:

$$(R_1 < 16..31 >) < (R_1 < 16..31 >)$$

(Y  $(R_2 < 16..31 >)$  lower half

$(R_1 < 0..15 >) < (R_1 < 0..15 >)$  (Y  $(R_2 < 0..15 >)$  upper half

#### Data Movement:

| $(R_1 < 1631 >)$ | < (R <sub>2</sub> <1631>) | lower half to lower |

|------------------|---------------------------|---------------------|

| $(R_1 < 015 >)$  | $<-(R_2 < 1631>)$         | lower half to upper |

| $(R_1 < 1631 >)$ | $<-(R_2 < 015>)$          | upper half to lower |

| $(R_1 < 015 >)$  | $<-(R_2 < 015>)$          | upper half to upper |

where:

- <--- means "is replaced by"

- Y represents an arithmetic or logical operation

- () denotes "the contents of the register designated by"

- $R_1, R_2$  designate general registers containing the first and second operand, respectively

- <a..b> designates bit positions a through b of the general register.

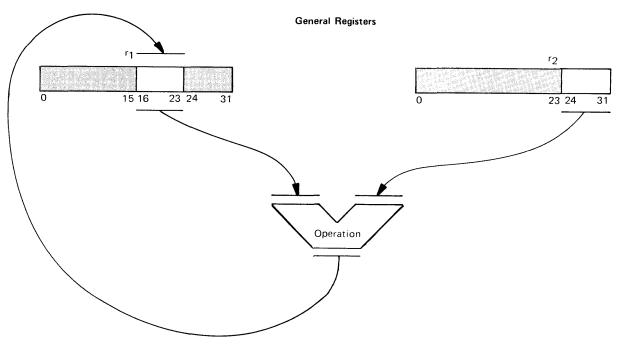

Figure 1-6. Example of Register-to-Register Operation (lower halfwords)

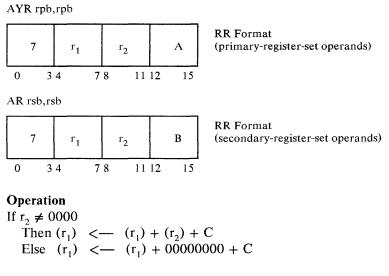

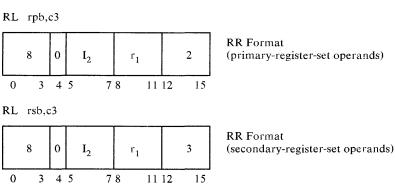

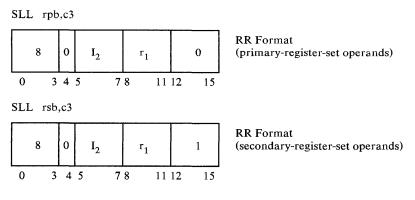

Register-to-register operations on byte operands are also provided. For arithmetic and logical operations on byte operands (see Figure 1-7), both the first and second operand must be in the same register set. Two instructions are provided for each such operation on byte operands: one obtains both operands from the primary register set; the other obtains both from the secondary set.

Data-movement operations are provided in which the operand locations may be in either set. Operation codes indicate the register set(s) that contains the operands. General expressions for register-to-register operations on byte data, where r is used to indicate specification of a byte operand, are:

$(r_1) < -(r_1) \bigcirc (r_2)$  arithmetic, logical  $(r_1) < -(r_2)$  data movement

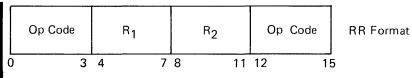

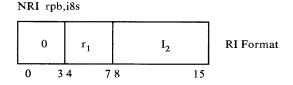

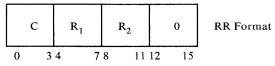

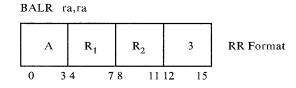

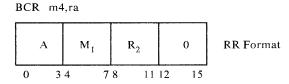

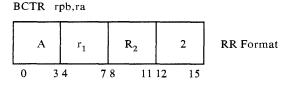

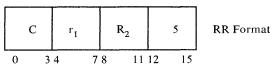

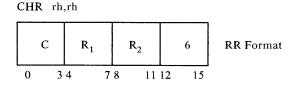

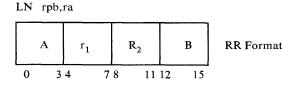

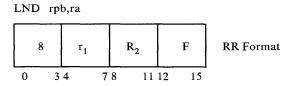

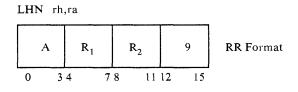

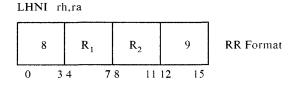

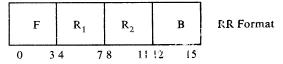

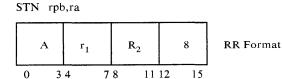

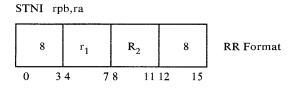

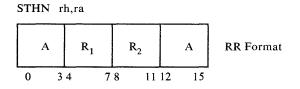

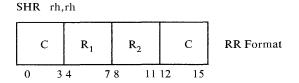

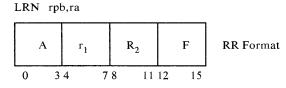

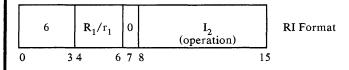

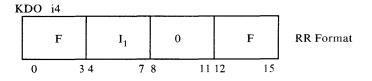

Register-to-register operations require specification of two register operands. The RR format is used for these operations. For this, as well as all other formats, the format name expresses, in general, the types of operand specification, not the operation class. In the format shown below, two registers are specified and thus the name is RR. The RR format is also used for other classes of operations, such as register-and-storage, where specification of two registers is required for a particular instruction.

For register-to-register operations on halfword operands, each R field designates one of the general registers that contains an operand:  $R_1$  designates the first-operand register and  $R_2$  designates the second-operand register.

Operations on byte operands in general registers are also specified by instructions in the RR format. In this case, the register-specification fields of the instruction designate one of the 16 byte-operand positions in either the primary or the secondary register set. The particular set is designated by an operation-code field of the instruction.

Figure 1-7. Example of Register-to-Register Operation (bytes)

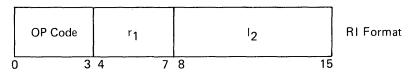

Operations in which the first operand is located in a register and the second operand is an immediate field in the instruction are called *register-and-immediate operations*. The result always replaces the first operand. Figure 1-8 shows an example of this type of operation.

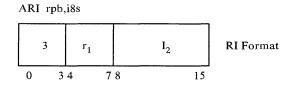

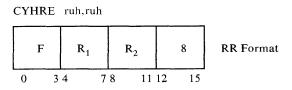

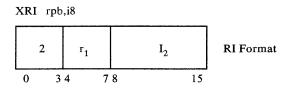

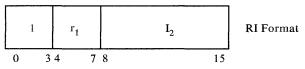

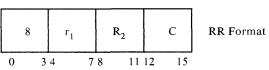

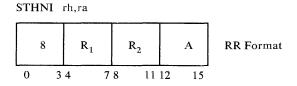

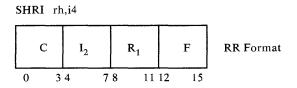

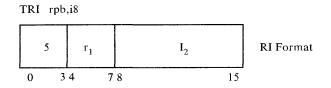

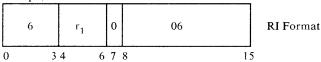

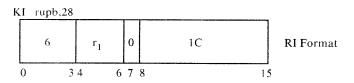

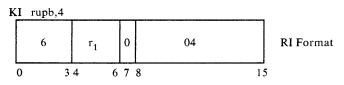

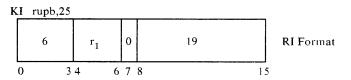

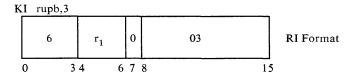

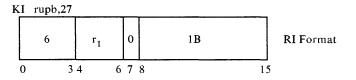

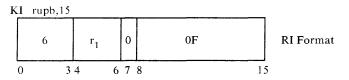

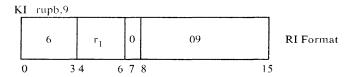

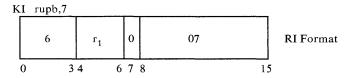

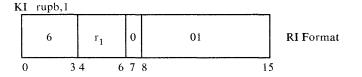

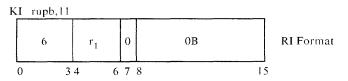

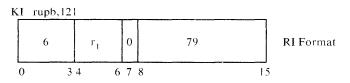

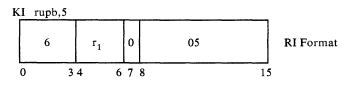

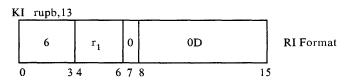

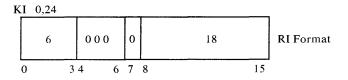

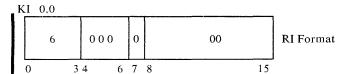

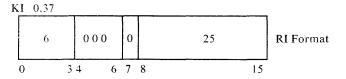

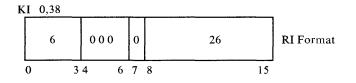

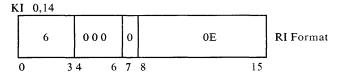

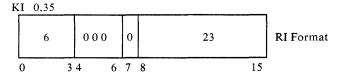

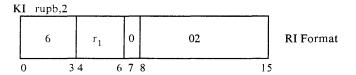

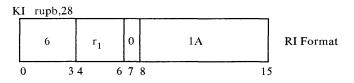

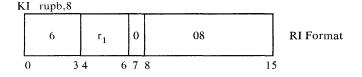

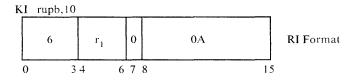

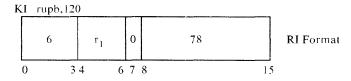

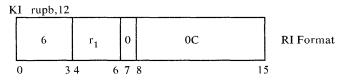

For register-and-immediate operations on byte operands, the instruction format shown below is used. Because a register and an immediate field are specified, this format is called the RI format. In the RI format, the  $r_1$  field designates one of the 16 byte-operand positions in the primary register set.

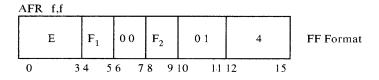

Certain register-and-immediate arithmetic operations are specified with RR format instructions in which a 4-bit immediate-data field is defined in place of one of the register-specification fields.

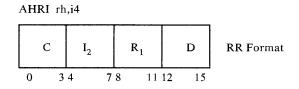

The RI format is also used for other classes of operations, such as programmed input/output (PIO) and PCE-control. For PIO operations, the immediate field contains a command code for an I/O device; for PCE-control instructions, it is used as an extension to the operation code. For PCE-control instructions, instruction bit positions 4-6 designate the first operand byte (located in register bit positions 16-23) or word of a general register in the primary register set. When a PCE-control operation does not use a register operand, the  $r_1$  field should contain 0's.

Figure 1-8. Example of Register-and-Immediate Operation

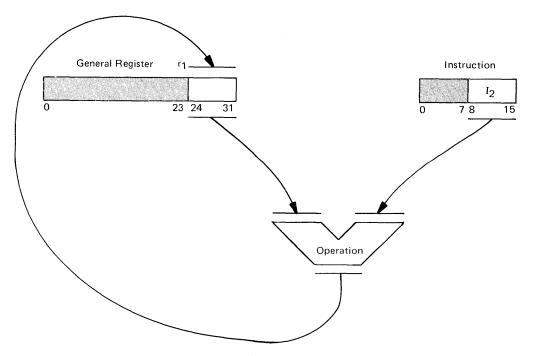

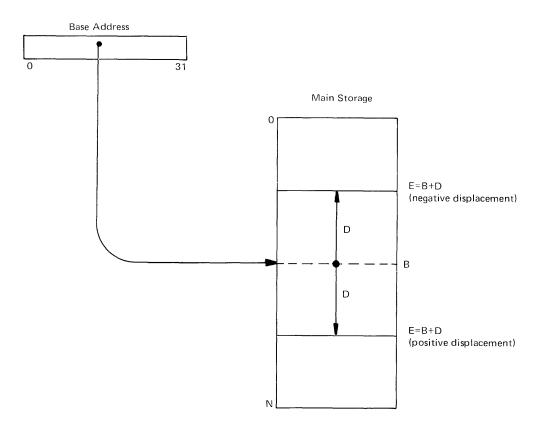

### **Register-and-Storage** — Address Generation

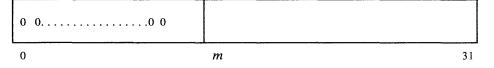

All operations that refer to information in main storage (register-and-storage, storage-to-storage), or that alter the sequence of instructions executed, require specification of logical main-storage addresses. Addresses are specified by means of instruction formats that designate the contents of a general register as all or part of the address. All logical addresses used by the program to refer to main storage are treated as unsigned 32-bit positive binary integers.

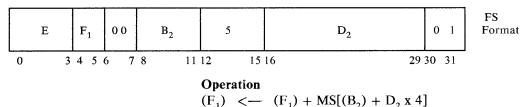

Operations in which the first operand is located in a register and the second operand is located in main storage are called *register-and-storage operations*. Except for floating-point arithmetic, all register-and-storage operations are used only for data movement between a register and main storage.

For register-and-storage operations, the simplest address specification is obtained when the address is contained in one of the general registers. When this address specification is used, the instruction has the RR format. The register containing the first operand is specified by the  $R_1$  field; the  $R_2$  field designates a register that contains the address of the second operand. The address so specified is usually considered an index; that is, the address is used to select an element from a one-dimensional array of like elements. Several instructions are provided that include modification of the address as part of the operation.

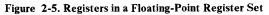

More generally, address specification involves generation of an effective storage address. An *effective storage address*, E, is an unsigned 32-bit positive binary number given by E = B + D. Here, B represents an unsigned 32-bit positive number called the *base address*. Base addresses can be used for independently addressing different areas of storage. In many types of processing, the base address is useful for locating a data structure (such as an array or record). The base address may also be used for indexing purposes; for example, to select a record from an array of records having a common format.

D represents a binary number, usually signed, called the *displacement*, which is taken from a field in the instruction. The displacement provides for addressing relative to the location specified by the base address; for example, for addressing an elementary unit or field within a record.

The base and displacement are added as binary integers with the displacement logically expanded to 32 bits. The result of this addition is used as the effective address (see Figure 1-9).

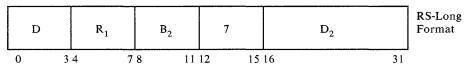

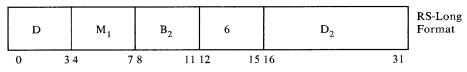

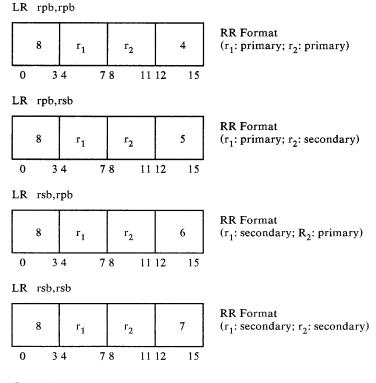

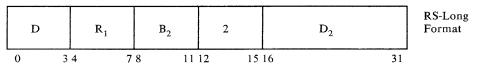

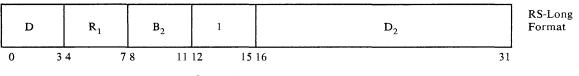

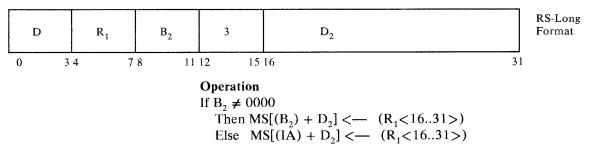

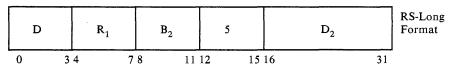

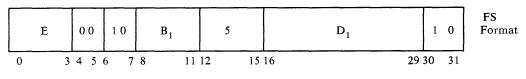

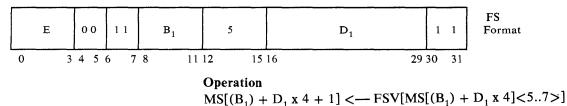

The principal instruction format for register-and-storage operations using a base and displacement is RS-Long, which is shown below. In this format, the  $R_1$  field designates the register containing the first operand; the  $B_2$  and  $D_2$  fields designate the components of the second-operand address. The  $B_2$  field designates the general register containing the base address; any of 15 general registers may be used to hold the base address. The  $D_2$  field is used to represent the displacement as a signed binary integer.

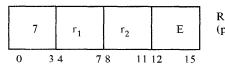

| Op Code |   | R <sub>1</sub> | B <sub>2</sub> | (    | Op Code | D <sub>2</sub> |    | RS-Long<br>Format |

|---------|---|----------------|----------------|------|---------|----------------|----|-------------------|

| 0 3     | 4 | 7              | 8 1            | 1 12 | . 15    | 16             | 31 |                   |

Figure 1-9. Address Generation Using Base and Displacement Values

A special case of base-and-displacement address generation is provided when the  $B_2$  field of an RS-Long format instruction contains all 0's. In this case, the updated instruction address (address of the next sequential instruction) is used as the base, instead of the contents of a general register. This provides for addressing instructions and data relative to the current instruction's address. It is particularly useful for branch addresses and references to local data because a register is not needed to hold the base.

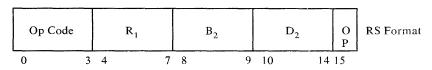

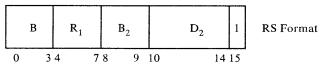

Base-and-displacement address generation for certain register-and-storage operations is provided in an abbreviated format, called the RS format, which is shown below. The  $B_2$  field designates one of four general registers that can contain the base address. The  $D_2$  field is used to represent an unsigned binary integer.

Initialization, modification, and testing of addresses in general registers can be performed using the operations for data movement and fixed-point arithmetic. Further, an instruction can designate the same general register as containing an address and as the location of an operand. Address generation is completed before the register is used for an operand. One instruction that provides several functions is the LOAD ADDRESS instruction, which has the RS-Long format. The operation of LOAD ADDRESS is given by the following expressions:

| $(R_1) < (B_2) + D_2$ | where $B_2$ designates a general register                                |

|-----------------------|--------------------------------------------------------------------------|

|                       | or                                                                       |

| $(R_1) < IA + D_2$    | where IA is the updated instruction address (the $B_2$ field is all 0's) |

This instruction performs the calculation E = (B) + D and places the 32-bit value, E, in the general register specified by  $R_1$  LOAD ADDRESS is also useful as an add-immediate operation in which the  $D_2$  field is used as signed immediate data. When the same general register is specified for  $R_1$  and  $B_2$ , a convenient update of that register's contents is obtained.

Sequencing operations are used to alter the sequential order of instruction execution. These operations require specification of a main storage address that designates the new sequence of instructions to be executed. Most sequencing operations are specified in both RR and RS-Long format instructions. In the RR format, the  $R_2$  field designates a general register containing the address. When specified in the RS-Long format, the address is formed by a base and displacement calculation.

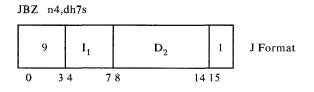

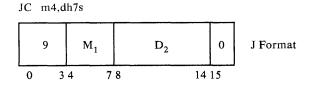

A special case of address specification in sequencing operations applies to instructions with JUMP in the name. These operations are specified with J format instructions (shown below). The  $D_2$  field is used as a signed displacement which is added to the updated instruction address to form the new instruction address.

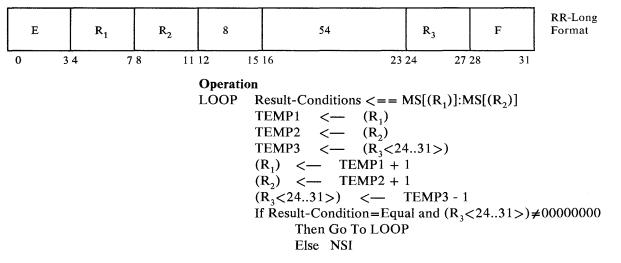

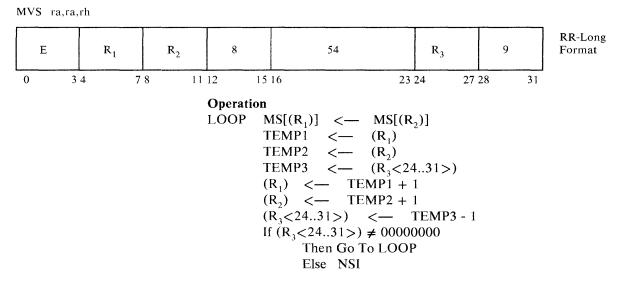

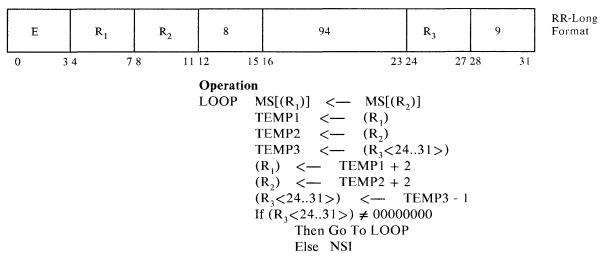

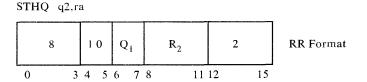

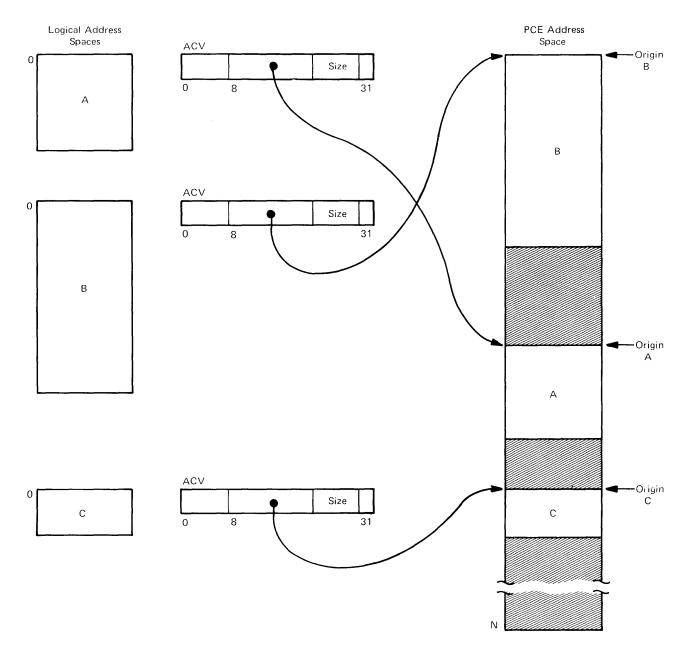

Operations on variable-length fields are called *storage-to-storage operations*. Operand specification for these operations requires two addresses and a field length (both fields are the same length). The length may vary from 1 to 256 units; the unit is a byte or halfword, depending on the operation.

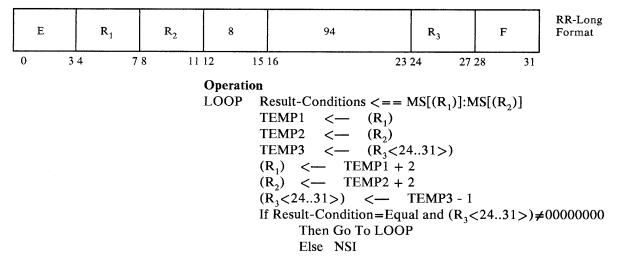

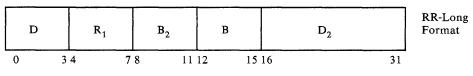

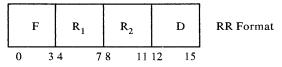

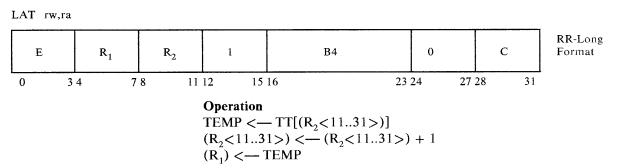

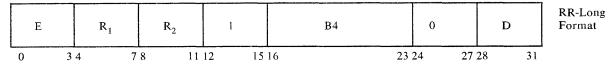

Storage-to-storage operations are specified in the RR-Long instruction format which is shown below. The starting addresses of the first and second operands are contained in the registers designated by the  $R_1$  and  $R_2$  fields, respectively. The length is contained in bit positions 24-31 of the register designated by the  $R_3$  field.

| Op | Code | R <sub>1</sub> | R <sub>2</sub> | Op Code | Op Code | R <sub>3</sub> | Op Code | RR-Long<br>Format |

|----|------|----------------|----------------|---------|---------|----------------|---------|-------------------|

| 1  | 3 4  | 4 7            | 8 11           | 12 15   | 16 23   | 24 27          | 28 31   |                   |

In storage-to-storage operations, the data units are processed proceeding from left to right. As the operands are processed, the storage addresses in the  $R_1$  and  $R_2$ registers are increased accordingly. The length in the  $R_3$  register is used as a count of the units remaining to be processed and is reduced accordingly until a count of 0 is reached. Because address and count information is maintained in general

#### Sequencing

#### Storage-to-Storage

registers, these operations are interruptible and can be resumed automatically following an interruption. This capability prevents delaying the execution of other, high-priority programs while a long storage-to-storage operation is being performed.

### **General Instructions**

The following sections briefly summarize most general instructions, grouped according to the operations they cause the PCE to perform. The types of general instructions are: data movement, fixed-point arithmetic, logical operations, and sequencing. In this discussion, the general instructions are described in terms of these types as well as in terms of the classes of operations and the instruction formats discussed in the previous section. Certain specialized operations are not discussed.

## **Data Movement**

Operations are provided that allow data to be moved unchanged (1) from one general register to another, (2) between main storage and a general register, and (3) from one main storage location to another.

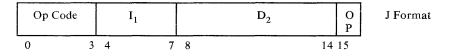

**Register-to-Register:** In register-to-register load operations, the unchanged second operand replaces the first operand. Four LOAD (halfword, register) operations are provided, one for each combination of operand positions in upper and lower halves of two general registers (see Figure 1-10).

General Registers

Figure 1-10. LOAD (halfword, register) Operations

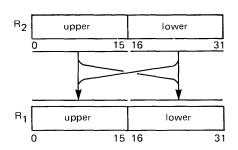

Movement of byte operands is accomplished by the LOAD (byte, register) operation. Four instructions of this type are provided, one for each combination of movement among primary and secondary register sets (see Figure 1-11).

**Register-and-Storage**: Operations for data movement from main storage to a register (LOAD) and from a register to main storage (STORE) are provided. For all LOAD or STORE operations that move 1 byte of information, the register operand is located in the primary register set.

Figure 1-11. LOAD (byte, register) Operations

The following are general expressions for data-movement operations specified in the RS-Long format:

| $(R_1) $                             | LOAD (word)      |

|--------------------------------------|------------------|

| $(R_1 < 1631 >) $                    | LOAD (halfword)  |

| $(r_1) < MS[(B_2) + D_2]$            | LOAD (byte)      |

| $MS[(B_2) + D_2] < (R_1)$            | STORE (word)     |

| $MS[(B_2) + D_2] < - (R_1 < 1631 >)$ | STORE (halfword) |

| $MS[(B_2) + D_2] < (r_1)$            | STORE (byte)     |

where  $MS[(B_2) + D_2]$  represents the contents of a main-storage location with an address specified by the base and displacement.

These instructions provide for relative addressing of up to 32,768 bytes preceding the base address and 32,767 bytes beyond it. LOAD (halfword) and STORE (halfword) instructions are also provided in an abbreviated specification that uses the RS format. These instructions provide for addressing data structures consisting of up to 32 contiguous halfwords.

Register-and-storage data movement operations are also provided with RR format instructions. These LOAD and STORE operations comprise a set of 12 instructions useful for processing one-dimensional arrays (or stacks) of halfword or byte elements. The storage address contained in the register designated by  $R_2$  is considered to be an index (or stack pointer). Operations are provided that include increasing or decreasing the address by the length of the data unit (1 for bytes, 2 for halfwords). See Figure 1-12 for an example from this group of instructions.

The 12 instructions are obtained from all combinations of the following specifications:

| Operation     | Data Unit        | Addressing                                |

|---------------|------------------|-------------------------------------------|

| LOAD<br>STORE | byte<br>halfword | index unchanged<br>index post-incremented |

|               |                  | index pre-decremented                     |

Figure 1-12. LOAD (halfword, with index incremented) Operation

It is often convenient to transfer information between main storage and multiple registers in a single operation (for example, as part of subroutine linkage). Groups of eight halfword operands may be addressed as a single unit — the *quadrant*. In the 16 general registers assigned to a program, there are four quadrants as illustrated in Figure 1-13.

The instructions LOAD (halfwords, quadrant) and STORE (halfwords, quadrant) transfer 8 halfwords between the consecutive operand positions in a quadrant and consecutive locations in main storage.

The instruction LOAD (byte, register-immediate) is provided to place a byte of immediate data into a general register in the primary set.

**Storage-to-Storage:** Movement of variable-length fields from one main storage location to another is accomplished with MOVE operations. Two RR-Long format instructions are provided: one that moves a field of consecutive byte data units, and one that moves a field of consecutive halfword data units (see Figure 1-14).

General Registers

#### At Completion

The basic arithmetic operand is the 16-bit fixed-point signed binary number. Byte operands (8-bit fixed-point signed binary numbers) may also be specified for most operations.

Fixed-point numbers may be signed or unsigned integers. In an unsigned number, all bits are used to represent the magnitude of the number. In signed numbers, the leftmost bit indicates the sign. Positive numbers are represented in true binary notation with the sign bit set to 0. Negative numbers are represented in twos-complement binary notation with a 1 in the sign-bit position. The value zero is represented by all bits being 0.

Most fixed-point arithmetic is performed with register-to-register operations specified in the RR instruction format. Unless otherwise stated, the halfword operands occupy the lower half (bit positions 16-31) of a general register. Byte operands may be located in either the primary or the secondary register set; however, both operands are located in the same set.

ADD and SUBTRACT operations are provided for both 8-bit and 16-bit binary numbers. MULTIPLY and DIVIDE operations are provided for unsigned 16-bit multipliers, multiplicands, and divisors. Products and dividends are unsigned and occupy 32 bit positions. Quotients and remainders are unsigned 16-bit binary numbers.

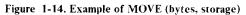

Extended-and-mixed-precision fixed-point arithmetic is made convenient by use of twos-complement representation and by provision for recognition and retention of the carry from one field to another. One example of extended-precision arithmetic, useful particularly for address modification, applies to 32-bit binary numbers contained in general registers. ADD WITH CARRY and SUBTRACT WITH CARRY operations are provided that combine operands in the upper halves (bit positions 0-15) of two general registers with the carry resulting from a previous operation on the lower halves (see Figure 1-15).

#### Figure 1-15. Example of Extended-Precision Addition

ADD WITH CARRY and SUBTRACT WITH CARRY operations are also provided that combine operands in the lower halves of general registers with the value of the carry from a previous operation. Operations on both 8-bit and 16-bit fields are provided. Addition and subtraction of halfword and byte operands may also be performed with register-and-immediate operations.

All arithmetic operations indicate certain result conditions that reflect the outcome of the operations (equal to 0, greater than 0, less than 0, overflow, or carry). These result conditions can be tested by operations that control the sequence of instructions executed.

Arithmetic-compare operations are provided for comparing 8-bit, 16-bit, and extended-precision fixed-point binary numbers. COMPARE operations are similar to the corresponding SUBTRACT operations except that the first operand is not replaced (no result is stored).

### **Logical Operations**

A set of instructions is provided for the logical manipulation of data. The set of logical instructions includes comparing, boolean, bit testing, shifting, and rotating operations.

As in fixed-point arithmetic, the boolean operations (AND, OR, EXCLUSIVE OR) are provided as register-to-register operations. Fixed-length logical data may be processed in 8-bit or 16-bit lengths. The boolean operations are applied bit-by-bit. All boolean operations indicate certain result conditions reflecting their outcome (all 0's, all 1's, or mixed 0's and 1's).

Halfword operands are taken from the lower half of a general register. Byte operands may be located in either the primary or the secondary register set; both operands are located in the same set. Boolean operations on byte operands in the primary register set are also provided as register-and-immediate operations.

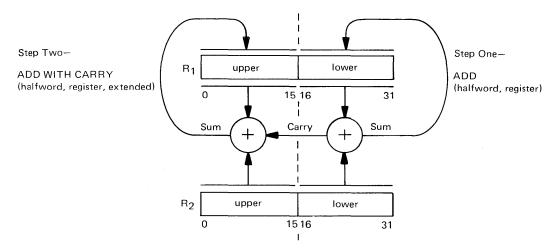

Shifting and rotating operations are provided for use in isolating, concatenating, and aligning groups of contiguous bits. SHIFT LEFT and ROTATE LEFT operations are provided in the RR instruction format for both 8-bit and 16-bit fixed-length fields. In this format, the number of bits moved is specified with immediate data in place of one R field.

SHIFT operations cause bits shifted out of the high-order bit positions of the operand to be lost; 0's are supplied in vacated low-order bit positions (see Figure 1-16). ROTATE operations wrap the operand; that is, bits shifted out of the high-order bit positions are entered consecutively in vacated low-order bit positions.

Operations are provided for testing and comparing logical data. TEST (byte, register-immediate) is provided for testing byte operands in the primary register set. The operation selects for testing those bits in the byte that are designated by 1's in the corresponding bit positions of a mask. The collection of bits so selected are tested for three conditions: all 0's, all 1's, and mixed 0's and 1's. If the mask and operand are identical, this is also indicated.

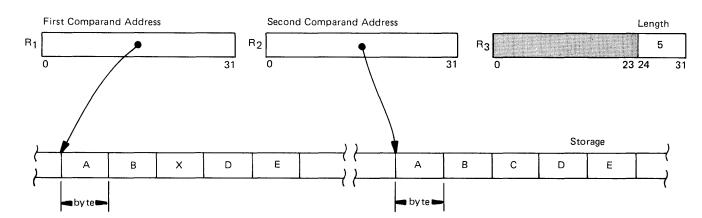

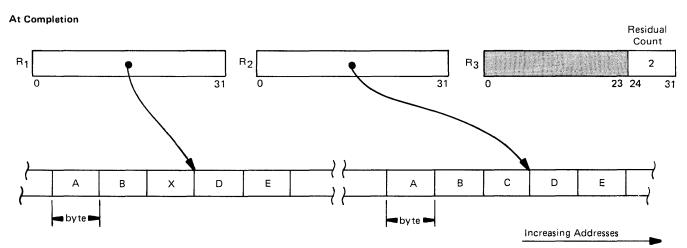

Logical comparison of two variable-length fields in storage is provided by the COMPARE LOGICAL operations. Two RR-Long format instructions are provided: one that compares fields of consecutive byte data units, and one that compares fields of consecutive halfwords (see Figure 1-17). Fields are logically compared by treating each byte or halfword as an unsigned positive binary number. The operation ends when an inequality between two corresponding units is found or when the end of the fields is reached. Three result conditions may be indicated: equal, low, or high.

Figure 1-16. SHIFT and ROTATE (halfwords) Operations

**General Registers**

Figure 1-17. Example of COMPARE (bytes, storage)

### Sequencing

Normally the PCE takes instructions in sequence. After an instruction is fetched from the location specified by the instruction address, the instruction address is increased by the number of bytes in the instruction. This addition is effectively performed before the fetched instruction is executed.

The normal sequence of instruction execution may be changed by use of branching operations to perform decision making, loop control, and subroutine linkage.

Conditional branching is accomplished by BRANCH ON CONDITION and JUMP ON CONDITION operations. These operations test five logical entities, called *result conditions*, which describe the outcome of arithmetic, logical, and I/O operations. Each of the five result conditions can be set in one of two possible states: *indicated* or *not-indicated*. A conditional branch or jump operation can select combinations of result conditions as a criterion for branching.

The specific meaning associated with any of the five result conditions depends on the particular instruction for which result conditions are specified. For example, results such as 0 sum, first operand high, equal, overflow, and non-0 may be indicated. Once set, the states of the result conditions remain unchanged until modified by a subsequent operation. Each operation that indicates result conditions sets the state of all five conditions. The states are derived from condition-indicator bits held in the PCE.