# Image: Customer Engineering Manual of Instruction

Tape Adapter Units

| ssued to:                      |                            |              |

|--------------------------------|----------------------------|--------------|

| Department or<br>Branch Office | Telepho                    | ne           |

| Branch Office                  | Number                     | <u></u>      |

| Address                        | City                       | State        |

|                                |                            |              |

| lome Address                   | City                       | State        |

|                                |                            |              |

| If this manual is mis          | laid, please notify the ab | ove address. |

© 1959 by International Business Machines Corporation Printed in U.S.A. Form 223-6847

# CONTENTS

| 1.0.00 GENERAL INFORMATI     | ON           | •     |       |     | • |   |   |   | • |   |   | •  | •   |   |   | B3            |

|------------------------------|--------------|-------|-------|-----|---|---|---|---|---|---|---|----|-----|---|---|---------------|

| 1.1.00 Introduction          |              | •     |       |     |   |   |   |   |   |   |   |    |     |   |   | B3            |

| 1.2.00 General Machine Logic |              |       |       |     |   |   |   |   |   |   |   |    |     |   |   | B3            |

| 1.2.01 Write                 |              |       |       |     |   |   |   |   |   |   |   |    |     |   |   | B3            |

| 1.2.02 Read                  |              |       |       |     |   |   |   |   |   |   |   |    |     |   |   | B5            |

| 1.2.03 Backspace             | •            | •     | •     | •   | • |   | • |   |   |   |   | •  |     |   |   | B5            |

| 1.2.04 Write Tape Mark       | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | B6            |

| 1.2.05 Rewind                | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | B6            |

|                              | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | B6            |

|                              | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | В7            |

| 1.2.07 Error Checking        | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • |               |

| 1.3.00 Physical Layout       | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | B8            |

| 1.4.00 Machine Language .    | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | <b>B</b> 8    |

|                              |              |       |       |     |   |   |   |   |   |   |   |    |     |   |   |               |

| 2.0.00 TIMING AND CONTROL    | • •          | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | В9            |

| 2.1.00 Timing                | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | <b>B</b> 9    |

| 2.1.01 Read Clock            | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | В9            |

| 2.1.02 Write Clock           | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | ٠ | • | $\mathbf{B9}$ |

| 2.1.03 Delay Counter .       |              | •     | •     |     | • |   |   |   | • |   | • | •  | •   | • |   | B9            |

| 2.2.00 Input-Output Controls |              |       | •     |     |   |   |   |   | • |   |   |    |     |   |   | B11           |

| 2.2.01 Interrupts            |              |       |       |     |   |   | • |   |   |   |   |    | •   |   |   | B11           |

| -                            |              |       |       |     |   |   |   |   |   |   |   |    |     |   |   |               |

| 3.0.00 FUNCTIONAL UNITS      |              |       |       |     |   |   |   |   |   |   |   |    |     |   |   | B13           |

| 3.1.00 Amplifiers            |              |       |       |     |   |   |   |   |   |   |   |    |     |   |   | B13           |

| 3.1.01 Final Amplifier       | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | B13           |

| 3.2.00 Registers             | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | B13           |

|                              | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | · | B13           |

|                              | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • |               |

| 3.2.02 Read-Write Register   | • •          |       | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | B13           |

|                              | •            |       | •     |     | • | • | • | • | • | • | • | •  | •   | • | • | B14           |

| 3.3.01 Vertical Redundancy ( |              |       |       | •   | • | • | • | • | • | • | • | •  | •   | • | • | B14           |

| 3.3.02 Longitudinal Redundar | ncy Ch       | eck I | Regis | ter | • | • | • | • | • | • | • | •  | •   | • | • | B14           |

| 3.3.03 Echo Error            | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | B14           |

| 3.3.04 Write Compare .       | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | B14           |

| 3.4.00 Clocks and Counters   | •            | •     |       |     |   | • |   |   | • | • | • |    | • 1 |   |   | B14           |

| 3.4.01 Read Check            | •            | •     |       |     |   |   | • |   | • | • |   | •  |     |   |   | B14           |

| 3.4.02 Write Clock           |              |       |       |     |   |   |   |   |   |   |   |    |     |   |   | B15           |

| 3.4.03 Delay Counter .       | •            |       |       |     |   |   |   |   |   |   |   | •  |     | • | • | B15           |

| -                            |              |       |       |     |   |   |   |   |   |   |   |    |     |   |   |               |

| 4.0.00 INTERNAL OPERATION    | $\mathbf{s}$ | •     |       |     |   |   |   |   | • |   |   |    |     |   |   | B16           |

| 4.0.01 Figure References .   |              |       |       |     |   |   |   |   |   |   |   |    |     |   |   | B16           |

| 4.1.00 Basic TAU Operations  |              |       |       |     |   |   |   |   |   |   |   |    |     |   |   | B16           |

| 4.1.01 Write Operation .     |              |       |       |     |   |   |   | • |   | • |   |    | •   | • | • | B16           |

| 4.1.02 Read Operation        | •            | •     | •     | •   | • | • | • |   | • | • | • | •  | •   | • | • | B28           |

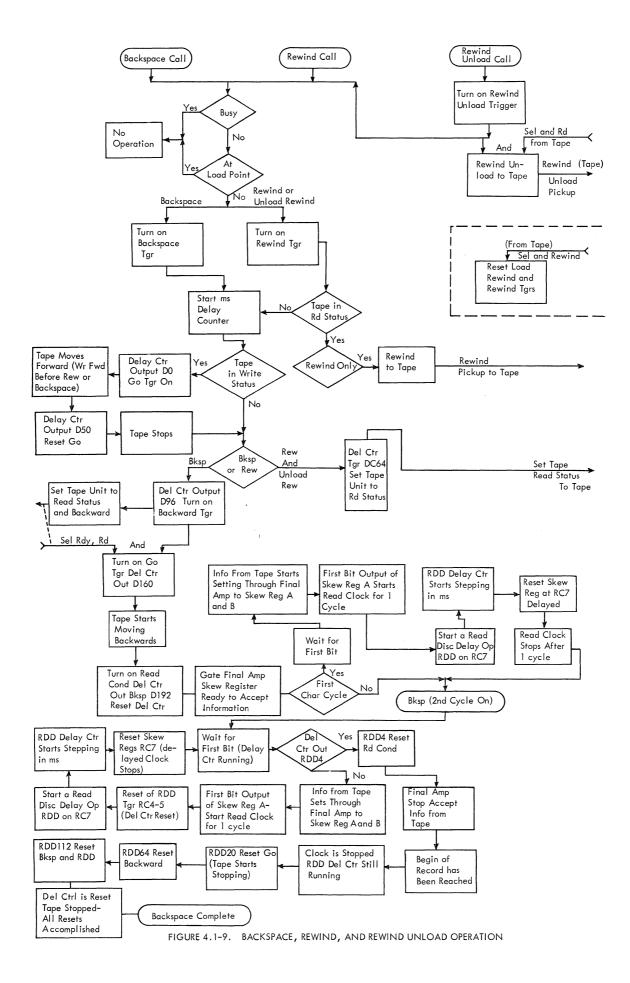

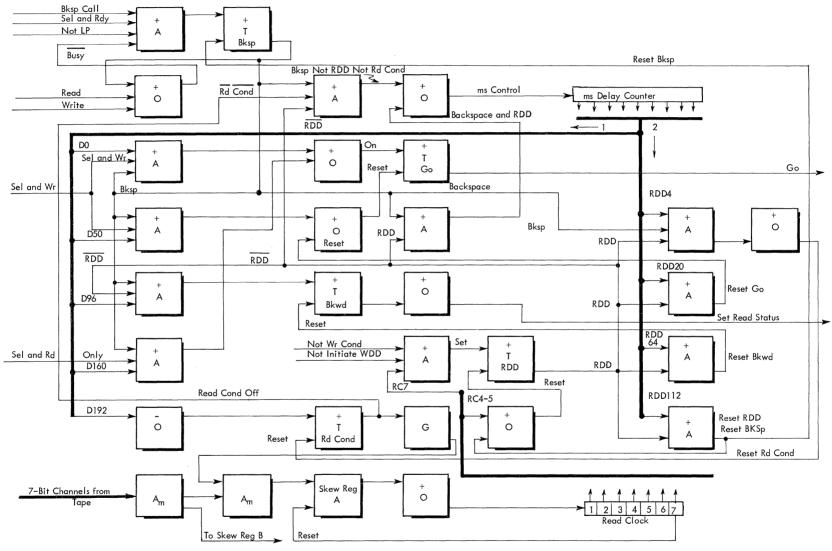

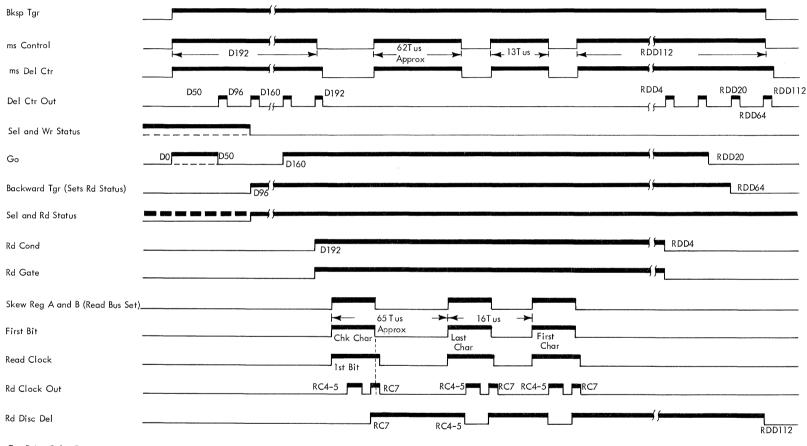

| 4.1.03 Backspace             | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | B20<br>B37    |

| 4.1.04 Tape Mark.            | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • |               |

|                              | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | B43           |

| 4.1.05 Erase                 | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | B44           |

| 4.1.06 Odd Redundancy .      | •            | •     | •     | ·   | • | • | • | • | • | • | • | •. | •   | • | • | B44           |

| 4.1.07 Manual Operation .    | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | B44           |

| 4.2.00 TAU 1 (Sliding Gate)  | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | B45           |

| 4.2.01 Dual Density          | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   | • | • | B45           |

| 4.3.00 TAU 2 (Swinging Gate) | •            | •     | •     | •   | • | • | • | • | • | • | • | •  | •   |   | • | B48           |

| 4.3.01 Dual Density          | •            | •     | •     |     | • | • |   |   |   |   |   |    |     |   |   | B48           |

| 4.3.02 Rewind-Rewind Unload  | d.           | •     |       | •   | • |   |   | • |   |   |   |    |     |   |   | B48           |

# FOREWORD

This manual discusses the basic functions of the IBM Tape Adapter Unit (TAU). Because TAU can be used by several systems, no attempt is made to tie TAU to any particular system. Instead, "external system" or "external system control unit" are used to refer to an outside control.

This manual has been prepared for teaching and as an aid for learning. Engineering changes may alter timings, logic, and other information presented here; therefore, the reader should not use this information alone as a reference manual or servicing aid.

The first section of the manual covers general information and logic of the basic TAU. Timing, input-output control, and functional units are discussed. These TAU functions are shown in flow diagrams, block diagrams, and sequence charts. A section explaining in detail the internal operations of the basic TAU is included. Operations peculiar to only TAU 1 and TAU 2 are covered in the final section.

# 1.0.00 GENERAL INFORMATION

## 1.1.00 INTRODUCTION

The IBM Tape Adapter Unit (TAU) is a standard assembly used to control the operation of 729 II and IV tape units. Previous magnetic tape control units contained several common operations and controls. These basic features are now included in TAU, and it is no longer necessary to design a complete magnetic tape control unit. By adding circuits, peculiar to any system, the complete control unit can be achieved.

Contained in TAU are the controls for tape movement, the controls for all timing pulses, and controls for information handling. With the exception of tape unit selection, TAU controls all timings and data flow for a complete tape operation, both system to tape and tape to system. Timings and data lines are made available by TAU for use with an external system.

# 1.2.00 GENERAL MACHINE LOGIC

Except for selection circuits, tape units are under complete control of TAU. Any tape operation called for by an external system must make the request to TAU. Upon receiving the request for operation signal, TAU will start and control the timing and data transfer from beginning to end. TAU circuits provide all necessary timings for initiating and stopping tape movement, developing all necessary delays for any read or write operation and for all data transfer and checking procedures. Following is a logical description of TAU operations.

# 1.2.01 Write

To perform a write operation on a tape unit (Figure 1.2-1), TAU must first receive a write request signal from the system. This signal is called "write call" and initiates the proper circuits in TAU. TAU sends a "go" signal to the tape unit and tape starts moving. Because it takes time for the tape to reach its proper speed, TAU initiates a write delay before the write circuits become active. When the write delay is completed, TAU starts a write clock to control writing. Input data lines from the system are active to TAU. The write clock pulses set the data into a read-write (R-W) register in TAU. As soon as the data is in the R-W register, it becomes available to the tape unit. Another write clock pulse is developed into a write pulse and sent to the tape unit, where it initiates the writing action. The write clock, when started, is in repetitive cycles, and the writing action continues until stopped by another request signal from the system. This request signal, called "disconnect call," initiates circuits in TAU to complete the operation. The operation is completed by stopping the tape and writing a check character, under TAU timing control.

As data flow through TAU, error checking circuits are active to insure proper operation. These error circuits are explained in Section 3.3.00.

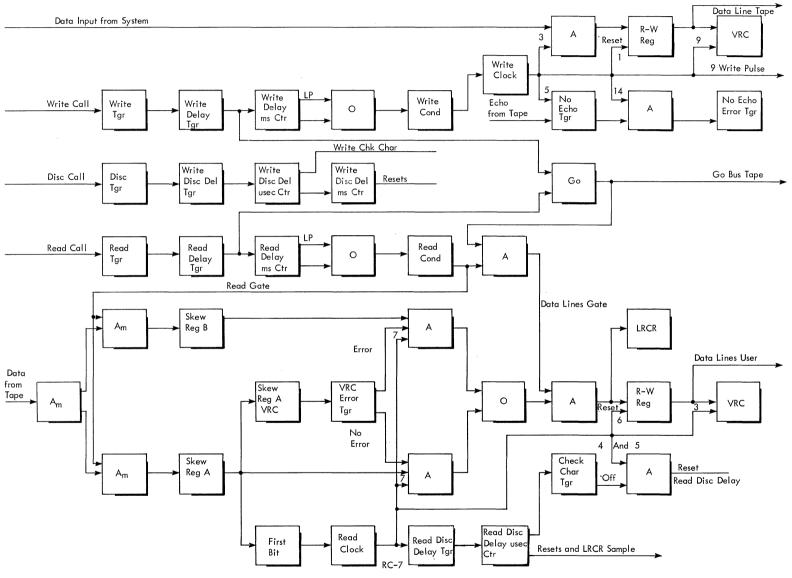

FIGURE 1.2-1. TAU READ-WRITE

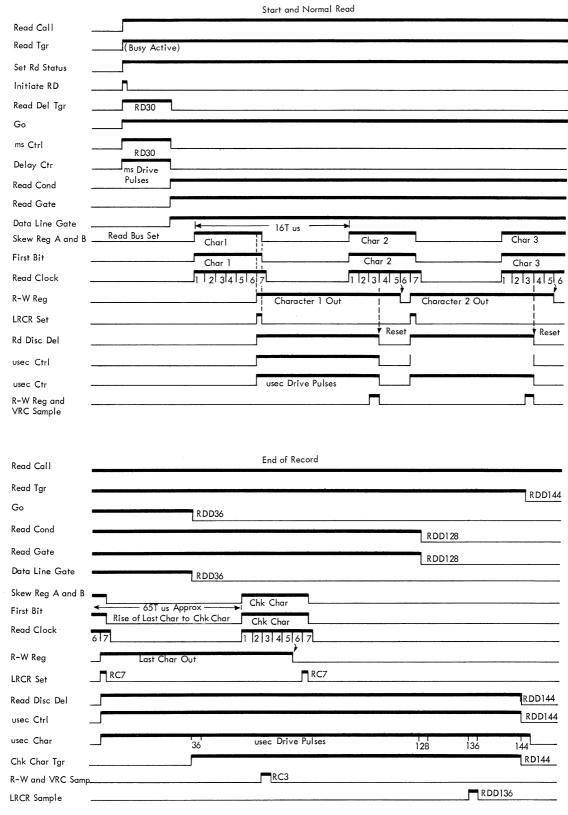

# 1.2.02 Read

A read operation (Figure 1.2-1) is started when TAU receives a "read call" signal from the system. As in the write operation, TAU develops a "go" signal to start tape moving. A read delay is initiated before the read circuits become active, to allow the tape to attain proper speed. When the read delay is completed, final amplifiers are conditioned to accept information from TAU. When a character is read from the tape, it is sent to TAU through the final amplifier, and set into two registers call skew register A and skew register B. The two skew registers have different acceptance levels to discriminate against noise pulses (skew register A) and low output levels (skew register B). The first character set into the skew registers starts a read clock for one cycle. The read clock controls the data flow through TAU. During the read clock cycle, skew register A is checked for error. If skew register A is in error, a read clock pulse sets the read-write (R-W) register to skew register B. If skew register A has no error, the read clock pulse sets the R-W register to skew register A. Once the character is set into the R-W register, it becomes available to the system. The read clock stops after the R-W register is set. The next character setting into the skew registers starts the clock again for one more cycle and so on, until the complete record is read. In each read clock cycle, a timing circuit is activated to try to stop the read operation. As long as characters arrive in specified time intervals, the timing circuit is reset before it can complete its function. Because the check character time is greater than the normal character time interval, the timing circuit activated during the last normal character cycle is allowed to run long enough to initiate the stopping action. The end operation circuits process the check character, perform read circuit resets, complete error checking procedures, and stop the tape.

During the read operation, error detection circuits are active to insure proper read operation. The checking procedures during a read operation are covered in Section 4.1.02.

# Read During Writing

The 2-gap head on the tape unit makes it possible to read the record being written. The read portion of the write operation is used to check the record on tape for error. The write control circuits initiate a read operation. This read operation operates the same as a normal read operation, except that the data being read are never set into the R-W register. All checking of the record read is done with the data in the skew registers. The write operation is not completed until the complete read operation is finished. The error conditions in the read check during writing are covered in Section 4.1.02.

#### 1.2.03 Backspace

A backspace operation is essentially a read operation in a backward direction. The only difference is that, in a backspace operation, no data are transferred from the tape to the system. The operation consists only of getting from the end of a record back to its beginning.

When the "backspace call" request signal is received in TAU, the operation is started. All tape motion in a backward direction must be done with the tape unit in read status. TAU first checks the status of the tape unit. If the tape unit is in write status, TAU initiates forward tape movement for a short time before setting read status to insure that noise, created in changing to read status, will be far enough out on the tape to be erased in the next write operation. Once the tape unit is in read status, TAU will set backward and then start the tape moving. Characters are set into the skew registers and start the read clock as in any read operation. A timing circuit is started from each read clock cycle and, providing characters arrive in timed intervals, the timing circuit is reset on the next character cycle. When the beginning of the record is reached, the timing circuit stops the operation and resets the tape unit to forward status. The R-W register is not set during the backspace operation and no error checking circuits are active.

# 1.2.04 Write Tape Mark

A write tape mark operation is a 1-character write operation. On receiving the write tape mark call signal, TAU activates the normal write operation circuits. Because this is a write tape mark operation, the R-W register is conditioned internally within TAU to set to 8, 4, 2, and 1, the bit structure of a tape mark. A write clock pulse then sets the character into the R-W register, making it available to the tape unit write circuits. Another clock output is developed into a write pulse and sent to the tape unit initiating the writing action. At the same time the write operation is started, a disconnect operation is also started to end the operation. This insures a 1-character record (tape mark), and a check character is written on tape. All normal checking circuits are active.

In a read operation, TAU recognizes a tape mark and makes the recognition available to the system. In every read operation a first character trigger is turned on for the first read cycle. If the character that sets into skew register A is a tape mark, a "first character tape mark" line is made available to the system.

# 1.2.05 Rewind

There are two rewind operations included in TAU. One is a normal rewind operation, and the other is a rewind-unload operation. Both operations are identical for the actual rewind operation, but the rewind-unload operation causes the tape to unload.

A rewind call signal turns on a rewind trigger in TAU. The output of the rewind trigger is sent to the tape unit, where it initiates the rewind. As soon as the tape unit goes into rewind status, TAU resets the rewind trigger and the TAU operation is complete.

A rewind-unload call signal turns on a rewind unload trigger in TAU. The output of the trigger initiates the rewind action in the tape unit in addition to setting control circuits for unloading the tape when the rewind is completed. As soon as the tape unit is in rewind status, the rewind-unload trigger is turned off and TAU operation is complete.

## 1.2.06 Erase

An erase call signal to TAU turns on an erase trigger. With the erase trigger on, the next write operation is forced to take a longer write delay before allowing writing to begin. In effect, it causes a tape unit to skip over a section of tape.

# 1.2.07 Error Checking

In all operations where data are being transferred from TAU to either the system or tape unit, the information, while in TAU, is checked for various errors. The error checks performed in TAU consist of vertical redundancy checks, write echo checks, write compare checks, and a longitudinal redundancy check. Any type error turns on a TAU error trigger. The output of the trigger is available to the system, and is the only indication of an error to the external system. Besides the TAU error trigger, a skew register A vertical redundancy error, a R-W register vertical redundancy error, and an echo error will turn on triggers in the TAU that are used only to light indicator lamps. Following is a description of each type of error condition.

# Vertical Redundancy Check

The vertical redundancy checker (VRC) determines the vertical bit structure of a character for either an odd or even bit count. Normally the VRC is set to check for an even bit count, but an "odd redundancy call" signal from the system turns on an odd redundancy trigger that conditions the VRC for an odd bit count. Whenever a character bit structure count does not agree with the type of vertical redundancy check called for, a VRC error line becomes active. There are two VRC's in TAU. The outputs of skew register A condition one VRC and the outputs of the R-W register condition the other. Any time data appear in the R-W register they are checked. If the bit count is different from the type of check called for (odd or even), a clock pulse samples the error line and turns on the TAU error trigger and the R-W register VRC error trigger. The R-W register VRC error trigger is used only as a neon indication on the TAU wiring panel.

In any read operation, the output of skew register A is checked. If a vertical redundancy error exists in a read check during writing operation, the TAU error trigger and skew register A VRC error trigger are turned on. If the error exists in a normal read, the skew register A VRC error trigger is turned on but the TAU error trigger is not. The VRC error line in a normal read is used to gate the outputs of either skew register A (no error) or skew register B (error) to the R-W register.

# Echo Check

To insure that something is being written on tape during a write operation, TAU checks for return echoes from the tape unit. During the write operation, a no echo trigger is turned on. When writing takes place on the tape unit, the tape write circuits develop an echo and return it to TAU. Any echo return will reset the no echo trigger. If the tape writing circuits are not active, no echoes are developed and the no echo trigger remains on. At the end of the write cycle, the no echo trigger output is sampled. If the trigger is on, the echo error and the TAU error triggers are turned on.

#### Write Compare

While read checking during a write operation, the character in skew register A is compared against the character in skew register B. If they do not compare, the TAU error trigger is turned on.

# Longitudinal Redundancy Check Register (LRCR)

The LRCR is a 7-trigger binary register which keeps an odd-even count of each bit track. The count of bits in a horizontal track in a write operation should always be even. Assuming no error, the record that is read should also have an even count for each bit track. Before completing any read operation, the LRCR output is sampled. If any trigger is on at this time, the TAU error trigger will be turned on.

# 1.3.00 PHYSICAL LAYOUT

TAU is an assembly of internally cabled gates. The unit is made up in two forms to fit either the standard large module (sliding gate) or the standard small module (swing-ing gate). The card chassis assembly for the sliding gate module is designed for mount-ing in gate positions B or D. The card chassis assembly for the swinging gate module is designed for mounting in gate positions 1, 2, 3, and 4 of the lower module.

The system designer mounts TAU in an available frame. He must provide the power supply, CE test panel, and external cables necessary for the efficient operation and maintenance of the unit.

The circuits used in TAU are the standard alloy junction transistor current switching circuits.

# 1.4.00 MACHINE LANGUAGE

TAU operates on one character at a time. A character in TAU is made up of a 6-bit combination plus a check bit. The 6-bit combination can be in either a straight binary form or a binary coded decimal form. The check bit can be written or read to make the bit structure either odd or even, depending upon the operation being performed. The character received from a system or the tape is not altered in TAU, but is simply routed through in the form in which it was received. The registers in TAU are in the BCD form with a C-bit trigger for the check bit, but the data passing through TAU can be either straight binary or BCD.

#### 2.0.00 TIMING AND CONTROL

# 2.1.00 TIMING

All the necessary timings and delays required by TAU are generated by oscillator driven binary counters. The timing circuits included in TAU consist of a read clock, a write clock and a delay counter. Because TAU can operate with 729 II and IV tape units, the timings of the various control circuits must vary. By selecting different oscillators, the output of the timing circuits can be varied. Figures 2.1-1 and 2.1-2 list the timings and clock pulses for the two different speeds.

## 2.1.01 Read Clock

The read clock is a 3-stage modified binary counter. The clock triggers are labeled RC1, RC2 and RC4. By gating combinations of the three triggers, pulses from RC1 through RC7 can be obtained. All timings from the read clock will be referred to as RC1, RC2, RC3 and so on to RC7.

Each first bit of a character read during a read operation allows oscillator drive pulses to start stepping the clock. Since the read clock is a binary counter, it takes eight stepping pulses to fully step through the clock for one cycle. To start the clock for another cycle, another first bit is necessary. All necessary timings required for data flow and checking on any read operation are obtained from the read clock. The clock is gated with the RC4 trigger to insure that all triggers will be off when the clock stops.

# 2.1.02 Write Clock

The write clock is a 4-stage modified binary counter. Write clock triggers are labeled WC1, WC2, WC4 and WC8. As in the read clock, by gating combinations of the triggers, pulses from WC1 through WC15 can be obtained. All write clock pulses will be referred to as WC1, WC2, WC3 and so on.

Early in a write operation, TAU turns on a control trigger (write condition) which gates oscillator drive pulses to the clock. Since the clock is a binary counter , 16 drive pulses are necessary for one complete cycle. As long as write condition remains on, the clock is in repetitive cycles. When the write operation is ending, write condition is turned off and the clock stops. The clock input is gated also with the WC8 trigger, which insures that all clock triggers are off when the clock stops. All timing pulses for data flow through TAU during a write operation are obtained from the write clock.

#### 2.1.03 Delay Counter

The delay counter is a 9-stage modified binary counter. The delay counter triggers are labeled in binary order from DC1 to DC256. Since the delays required by TAU range from microseconds to milliseconds, the delay counter has the ability to count in both the microsecond mode and the millisecond mode. It also has facilities for starting and stopping at any specified point in a cycle. The outputs of the delay counter are

| WRITE CLOCK                                                                                |                                                                                    | READ CLOCK                                                                                                    |                                                                                                           |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Oscillator<br>Drive Pulse Frequency<br>WC1<br>WC3<br>WC9<br>WC14<br>1 Complete Write Cycle | 240 kc<br>4.2 usec<br>4.2 usec<br>12.6 usec<br>37.8 usec<br>58.8 usec<br>67.2 usec | Oscillator<br>Drive Pulse Frequency<br>RC1<br>RC3<br>RC4 and 5<br>RC6<br>RC7<br>RC7 (DL4)<br>1 Complete Cycle | 240 kc<br>4.2 usec<br>12.6 usec<br>16.8 and 21.0 usec<br>25.2 usec<br>29.4 usec<br>29.8 usec<br>33.6 usec |

# DELAY COUNTER

| MILLISECOND MODE      |         | MICROSECOND MO        | DE       |

|-----------------------|---------|-----------------------|----------|

| Oscillator            | 6.7 kc  | Oscillator            | 240 kc   |

| Drive Pulse Frequency | 0.15 ms | Drive Pulse Frequency | 4.2 usec |

| D50                   | 7.5 ms  | RDD36                 | 151 usec |

| D96                   | 14.4 ms | RDD128                | 538 usec |

| D160                  | 24 ms   | RDD136                | 571 usec |

| R D30                 | 4.5 ms  | RDD144                | 605 usec |

| RD160                 | 24 ms   | WDD60                 | 252 usec |

| RDD4                  | 0.6 ms  |                       |          |

| RDD20                 | 3 ms    |                       |          |

| RDD20                 | 3 ms    |                       |          |

| RDD64                 | 9.6 ms  |                       |          |

| RDD96                 | 14.4 ms |                       |          |

| RDD112                | 16.8 ms |                       |          |

| WD50                  | 7.5 ms  |                       |          |

| WD58                  | 8.7 ms  |                       |          |

| WD80                  | 12 ms   |                       |          |

| WD320                 | 48 ms   |                       |          |

| WDD17                 | 2.55 ms |                       |          |

| BKSP190               | 28.5 ms |                       |          |

FIGURE 2.1-1. TIMING RELATIONSHIPS USING 729 II

| WRITE CLOCK            |         | READ CLOCK            |              |  |

|------------------------|---------|-----------------------|--------------|--|

| Oscillator             | l meg   |                       |              |  |

| Drive Pulse Frequency  | lusec   | Oscillator            | l meg        |  |

| WC1                    | lusec   | Drive Pulse Frequency | l usec       |  |

| WC3                    | 3 usec  | RC1                   | l usec       |  |

| WC9                    | 9 usec  | RC3                   | 3 usec       |  |

| WC14                   | 14 usec | RC4 and 5             | 4 and 5 usec |  |

| 1 Complete Write Cycle | 16 usec | RC6                   | 6 usec       |  |

| . ,                    |         | RC7                   | 7 usec       |  |

|                        |         | RC7 (DLY)             | 8 usec       |  |

|                        |         | 1 Complete Cycle      |              |  |

# DELAY COUNTER

| MILLISECOND MODE      |         | MICROSECOND MODE |                       |          |

|-----------------------|---------|------------------|-----------------------|----------|

| Oscillator            | 10 kc   |                  | Oscillator            | lmeg     |

| Drive Pulse Frequency | .1 ms   |                  | Drive Pulse Frequency | lusec    |

| D50                   | 5 ms    |                  | RDD36                 | 36 usec  |

| D96                   | 9.6 ms  |                  | RDD128                | 128 usec |

| D160                  | 16 ms   | 1                | RDD136                | 136 usec |

| R D30                 | 3 ms    | 1                | RDD144                | 144 usec |

| RD160                 | 16 ms   |                  | WDD60                 | 60 usec  |

| RDD4                  | .4 ms   | 1                |                       |          |

| RDD20                 | 2 ms    | 1                |                       |          |

| RDD64                 | 6.4 ms  |                  |                       |          |

| RDD96                 | 9.6 ms  |                  |                       |          |

| RDD112                | 11.2 ms |                  |                       |          |

| WD50                  | 5 ms    |                  |                       |          |

| WD58                  | 5.8 ms  |                  |                       |          |

| WD80                  | 8 ms    | 1                |                       |          |

| WD320                 | 32 ms   | 1                |                       |          |

| WDD17                 | 1.7 ms  |                  |                       |          |

| BK SP190              | 19 ms   |                  |                       |          |

FIGURE 2.1-2. TIMING RELATIONSHIPS USING 729 IV

obtained by gating combinations of the triggers. Because the delay counter is widely used in all TAU applications, the outputs are labeled according to the gating lines and the count at the output circuit. Listed in Figures 2.1-1 and 2.1-2 are the timing outputs for 729 II and IV operation.

The counter operation is controlled from control triggers turned on during specific TAU operations. Depending upon the timing necessary, either millisecond or microsecond control is conditioned by the controlling trigger. The millisecond or microsecond control gates the proper oscillator drive pulses to the counter. The drive pulses are obtained from outputs of four oscillators. Two oscillators are used for 729 IV operation for the millisecond and microsecond mode, and two oscillators are used for 729 II operation in the millisecond and microsecond mode. The correct oscillators are conditioned by a "sel and rdy Mod II" from the tape unit. All outputs of the delay counter are used to obtain all the delays for tape motion and for completing TAU operations.

# 2.2.00 INPUT-OUTPUT CONTROLS

Input data and control lines to TAU from the external system are listed in Figure 2.2-1. Also listed are all output lines from TAU to the tape unit. The timing and control data lines required by the external system from TAU are made available at edge connectors. Figure 2.2-2 lists all the lines that are available at the edge connectors.

# 2.2.01 Interrupts

An interrupt is a control or timing pulse line that passes through jumpered edge connector points before completing its function. By opening the edge connector points, the logic operation at that point can be interrupted. By use of the interrupts available in TAU, the normal function of the interrupted line can be altered by conditioning the line in the external control unit. The interrupts are listed in Figure 2.2-3.

| FROM CONTROL UNIT                                                                                                                                                                        | FROM TAPE UNIT                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Lines<br>All Request Signals<br>Turn on TI<br>Turn off TI<br>Manual Op<br>Manual Data Lines<br>Manual Write Disc<br>Manual Stop of Error<br>Manual Error Reset<br>Machine or Pwr-On | Data Lines<br>Write Echoes<br>Sel and Rdy M4<br>Sel and Rdy M2<br>Sel and LP<br>Sel, Rdy and Rd<br>Sel, Rdy, and Wr<br>Sel Not LP<br>Sel and TI Off<br>Sel and TI On |

| Reset                                                                                                                                                                                    |                                                                                                                                                                      |

FIGURE 2.2-1. TAU EXTERNAL INPUTS

| TC               | CONTROL UNIT  |                  |

|------------------|---------------|------------------|

| RC3              | WD            | GoReset          |

| WC5              | WD52          | Set Read Status  |

| WC9              | WD80          | Read Condition   |

| Write Pulse      | WD320         | Set Write Status |

| WC14             | WDD           | Erase            |

| DC8              | WDD17         | Backspace        |

| DC16             | WDD60         | Backward         |

| DC32             | Data Lines    | Rewind           |

| DC128            | Check Char    | Rewind-Unload    |

| RDD              | First Char TM | Sel and Rew      |

| RDD112           | TAU Error     | Sel and Not LP   |

| RDD128           | Busy          | Sel and TI On    |

| RDD136           | Load Point    | Sel and TI Off   |

| RDD144           | Sel and Load  | TR Reset         |

|                  | Point         |                  |

|                  | Go            | Reset WR Tgrs    |

| Т                | O TAPE UNIT   |                  |

| <u></u>          |               |                  |

| Write Bus        | Reset Wr Tgrs | Rewind-Unload    |

| Go               | Write Pulse   | Turn off TI      |

| Set Read Status  | Backward      | Turn on TI       |

| Set Write Status | Rewind        |                  |

# FIGURE 2.2-2. TAU EXTERNAL OUTPUTS

| LINE                | TO (Function)                |

|---------------------|------------------------------|

|                     |                              |

| RC7                 | Turn on Read Delay Disc      |

| WC3                 | Set R-W Reg to Input Data    |

| Initiate Write Cond | Write Clock Drive            |

| RDD TR Reset        | Normal Read Reset of RDD Tgr |

| RDD144              | Reset of RDD Tgr             |

| RDD4                | Backspace Reset of Read Cond |

| Odd Redundancy      | C-Bit for Write TM           |

| Ungated VRC         | R-W Reg VRC Error            |

| Read LRCR           | TAU Error Tgr                |

| Sel and Rdy         | Read only Tgr                |

|                     | Write Tgr                    |

|                     | Write TM Tgr                 |

|                     | Backspace Tgr                |

|                     | Rewind Tgr                   |

| Bksp or Rew         | Go Tgr - Bksp or Rew Oper    |

FIGURE 2.2-3. TAU INTERRUPTS

# 3.0.00 FUNCTIONAL UNITS

## 3.1.00 AMPLIFIERS

# 3.1.01 Final Amplifier

There are seven final amplifiers, each fed from the 7-bit read bus channel from the tape unit. The inputs to the amplifiers are peak amplitude sensed. The final amplifiers have two outputs, a high level and a low level. Seven high and seven low output signals are developed for input to the skew registers. The nominal signal input is eight volts peak-to-peak (VPP). The minimum signal levels are as follows:

|         | Minim    | Minimum Signal |  |  |  |  |  |

|---------|----------|----------------|--|--|--|--|--|

| Channel | Read     | Read Check     |  |  |  |  |  |

| А       | 3.2  VPP | 4.0 VPP        |  |  |  |  |  |

| В       | 1.6 VPP  | 2.0 VPP        |  |  |  |  |  |

# 3.2.00 REGISTERS

# 3.2.01 Skew Registers

TAU has two skew registers; one, skew register A, is set from the high level output signals from the final amplifier, and the other, skew register B, is set from the low level output signals from the final amplifier. Each skew register contains seven triggers, one for each bit of the 7-bit code. Because of skew on the tape, the character bits remain in the skew registers for a length of time determined by the read clock cycle. This is done to insure that all the bits of a particular character have been received by TAU, before the character is placed in the R-W register. The length of time the character bits are allowed to remain in the skew registers is a little less than half of the normal character time interval. If the full character is not in the skew registers by this time an error is indicated in the read cycle.

In a normal read, the character in either skew register A or skew register B is gated to the R-W register. If the character in skew register A is correct (no vertical redundancy error) it is sent to the R-W register; however, if the character in skew register A is not correct (skew register A vertical redundancy error), the character in skew register B is unconditionally sent to the R-W register. Besides setting the R-W register, the LRCR is also set. The operation is the same for a read check during writing operation, except the character is sent only to the LRCR and not to the R-W register.

# 3.2.02 Read-Write Register (R-W)

The R-W register is a group of seven triggers, one for each bit of the 7-bit code. All data passing between the external system and a tape unit passes through the R-W register. The R-W register is the swinging door through which the data are allowed to flow either way. During writing, the input data lines are set into the R-W register, and the register output is the data output of TAU to the tape unit. During reading, the R-W register is set from the skew register and the R-W register output is again the output of TAU, only this time to the external system.

# 3.3.00 ERROR CHECKING

# 3.3.01 Vertical Redundancy Checker (VRC)

The outputs of skew register A and the R-W register feed VRC's. Both VRC's are conditioned by an odd redundancy trigger that can be turned on and off by the external system. The VRC's are a combination of plus and minus OR circuits that determine the vertical bit structure of a character. The output of the VRC is an error line. By use of the odd redundancy trigger, the VRC error line can be conditioned to be active for either odd or even redundancies.

# 3.3.02 Longitudinal Redundancy Check Register (LRCR)

The LRCR is a group of seven triggers, one for each bit of the 7-bit code. All the triggers are binary triggers. At the start of any read operation all triggers are off. As character bits set into the LRCR, each trigger being set will be turned on with the first bit, off with the second, on again with the third and so on throughout the record. Since a record, when written, is always made even when the check character is written, the LRCR, after setting to the check character, should finish with all triggers off (even count). If this is the case, no error is indicated. However, if any trigger is on after the check character sets, the active trigger output will indicate an LRCR error.

# 3.3.03 Echo Error

In each write cycle, a no echo trigger is turned on before sending a write pulse to the tape unit. When any writing takes place on the tape unit (from a TAU generated write pulse), the active write circuits develop an echo pulse and send them to TAU. Any echo pulse received by TAU resets the no echo trigger. Late in the write cycle the status of the no echo trigger is sampled. If the no echo trigger is on, the TAU error trigger and a no echo error trigger will be turned on. If the trigger is off, (echo return), no error will be indicated.

# 3.3.04 Write Compare

In every read during a write operation, skew register A and skew register B are compared against each other. Any uneven comparison will indicate an error by turning on the TAU error trigger. The compare circuit is a group of -AND circuits conditioned by the outputs of both registers.

# 3.4.00 CLOCKS AND COUNTER

## 3.4.01 Read Clock

The read clock consists of three binary triggers separated by a 400 milli-microsecond delay line. These three triggers are driven in parallel by a 400 milli-microsecond timing pulse derived from a clamped oscillator and a single shot. The first bit of each character read unclamps the oscillator, allowing drive pulses to feed the clock. The first drive pulse turns on the RC1 trigger, the second drive pulse turns RC1 off and RC2 on, the third turns RC1 on again (RC3 time), the fourth turns off both RC1 and RC2 and turns on RC4, and so on through the cycle. At RC7 time the RC1, RC2 and RC4 triggers are all on. To complete the cycle, another drive pulse is needed to turn off all the clock triggers. Since the first bit line is not active after RC7 (reset skew register A), the RC4 trigger on output conditions the oscillator to produce the eighth drive pulse. The eighth drive pulse resets the RC1, RC2, and RC4 triggers. The oscillator is then clamped off again and the clock is stopped. Another first bit is needed to start the clock again.

Note: During a read check during a write operation, the RC7 pulse from the read clock actually comes at RC5 time. An active "Write" line conditions the clock during this operation. The reason for this is an added marginal check on the record being read. Each character not completely in the skew registers by RC5 time indicates an error, whereas, on a normal read, the skew registers are not checked until RC7 time.

# 3.4.02 Write Clock

The write clock consists of four binary triggers separated by a 400 milli-microsecond delay line. The triggers are driven in parallel by a 400 milli-microsecond timing pulse derived from a crystal oscillator. A control trigger (write condition) comes on early in a write operation and gates oscillator pulses to the clock. The clock operates in a binary fashion similar to the read clock (1 on, 2 on, 1 and 2 on, and so on). After the fifteenth drive pulse the WC1, 2, 4, and 8 triggers will be on. The sixteenth drive pulse resets all the triggers to normal, and one cycle is complete. Since write condition is still on, the oscillator continues driving the clock and another write cycle is started. As long as write condition is on, the clock remains in repetitive cycles. The WC8 trigger also conditions the oscillator drive pulses to insure the write clock will complete its cycle when write condition goes off.

## 3.4.03 Delay Counter

The delay counter consists of nine binary triggers separated by delay lines, the first five of which are driven in parallel by a 400 milli-microsecond timing pulse, while the next four are driven in series by the output of the preceding trigger. The counter operates in a binary mode just as the read and write clocks.

The drive pulses to the clock are conditioned from a speed control circuit. This circuit has either a millisecond control output or a microsecond control output. Since the operation of the counter is so varied, each operation needing the delay counter outputs has a control trigger to start the delay counter at the proper time and in the proper mode. Whenever an operation using the delay counter is complete, the control trigger resets the counter in preparation for the next operation.

The frequency of the drive pulses to the counter is determined by either 729 II or IV operation.

## 4.0.00 INTERNAL OPERATIONS

# 4.0.01 Figure References

#### Flow Diagrams

To clarify TAU operation, flow diagrams have been included for write, read, read check, backspace, and rewind. The flow diagrams show the word sequence of the way TAU performs an operation, and in no way show how the operations have been performed. With TAU operating correctly, the flow charts tell the sequence of events TAU uses in completing an operation from beginning to end. The diagrams use a 3-block notation. The oval block is used at the beginning to indicate the operation to be performed. It is also used at the end when the operation is complete. The rectangles indicate the event TAU is performing. The diamond blocks are decision blocks with the outputs labeled. The write-up that follows in this section has a brief explanation of each block of the flow diagram.

# Block Diagrams

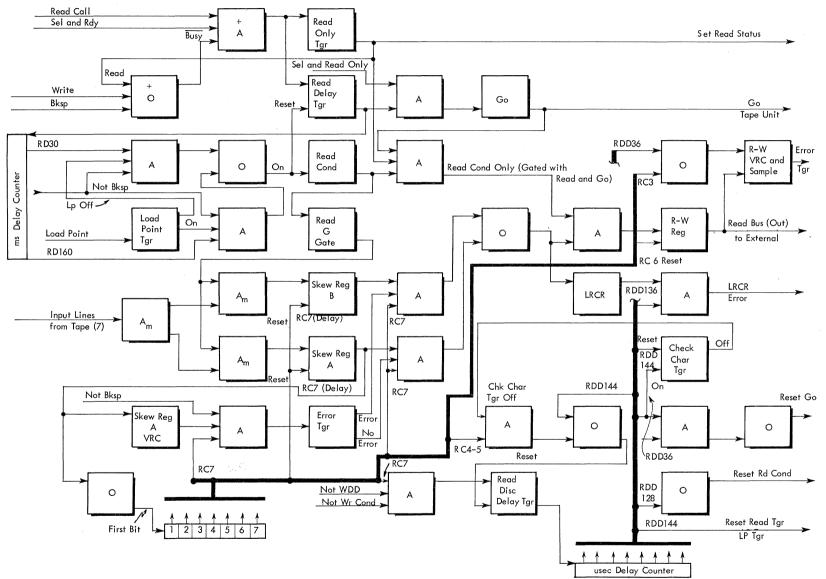

Included for read, write, error while writing, and backspace are block diagrams for each of the operations. The block diagrams represent all the necessary timings, conditions, and writing lines TAU uses to perform the operation.

#### Sequence Charts

A timing sequence chart is also included for read, write, backspace and error conditions while writing. The sequence chart shows the timing relationships for existing conditions of an operation during the operating cycle.

# 4.1.00 BASIC TAU OPERATIONS

# 4.1.01 Write Operation

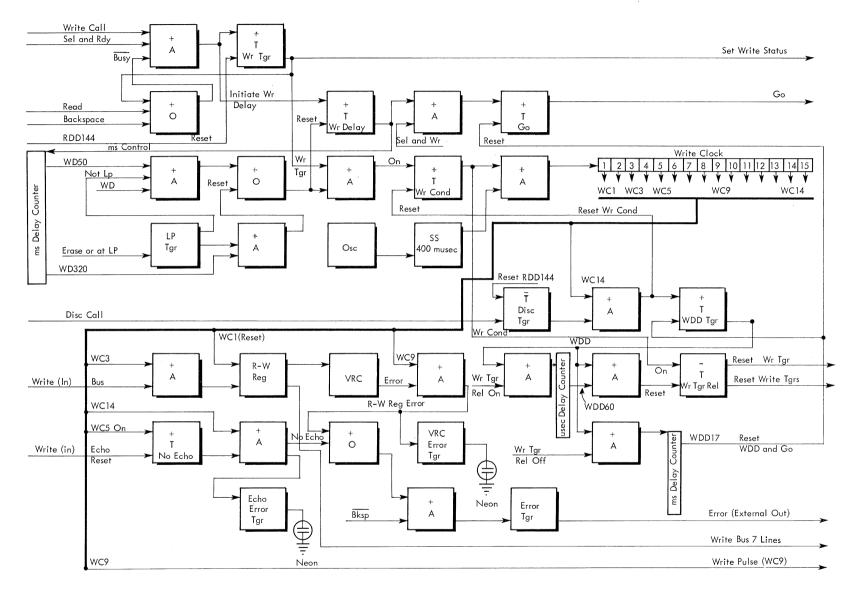

To initiate a write operation, the external system must generate a write call and send it to the TAU. The TAU directly controls all tape movement, develops the write pulses, and controls the data flow from the system through TAU to the tape. The complete write operation of TAU is shown in Figures 4.1-1 through 4.1-5. Following is a brief explanation of each block of the flow diagram.

# Write Call

This call is a request signal generated within the external system and sent to the TAU to start the operation.

#### Busy

If the TAU were performing another operation at the time of the request signal, the busy line would be active and prevent the write call from performing its function. If the TAU were idle, however, the write call signal would initiate action in TAU.

FIGURE 4.1-1. WRITE OPERATION

FIGURE 4.1-2. TAU WRITE OPERATION DETAIL

| Starting Tape and Normal Writing (No Errors)               | End of Record Routine (Busy                          |

|------------------------------------------------------------|------------------------------------------------------|

| Write Call                                                 | Write Tgr RDD144 Inactiv                             |

| Wr Tgr Busy is Active                                      | Go WDD17                                             |

| Set Wr Status                                              | Wr Cond WC14                                         |

| Initiate Wr 🔲                                              | Wr Cond WC14                                         |

| Wr Delay Tgr                                               | Wr Clock                                             |

| Go                                                         | R-W Reg                                              |

| ms Control                                                 |                                                      |

| Delay Ctr WD50 (WD320 if at LP)                            | Wr Bus                                               |

| Wr Cond16Tus                                               |                                                      |

| Wr Clock 1 3 5 7 9 14 1 3 57 9 14 1 3 57 9 14 1 3 5 7 9 14 | Wr Pulse9 ↓ Write Point                              |

| R-W Reg 3 1 3 1 3 1 3 1                                    | Disc Tgr                                             |

| Write Bus Tape                                             |                                                      |

| Wr Pulse79797979                                           | WDD Tgr WC14 WDD17                                   |

| T = Drive Pulse Freq Echo Checking                         | usec CtrlGates Usec Pulses to Ctr                    |

| No Echo Tgr555                                             | usec Del Ctr                                         |

| Echo from Tap <u>e</u> No real Echo                        |                                                      |

| No Echo Samp <u>le141414</u>                               | usec Del Ctr Out WDD60                               |

| Echo Error Tap <u>e</u>                                    | Wr Tr Rel Write Chk Char                             |

| TAU Error Tgr                                              | Wr Tr Re! (On with Wr Cond) <sub>Reset</sub> Wr Tgrs |

| VRC Checking                                               | ms CtrlGate ms Pulses to Ctr                         |

| Input to VRC                                               |                                                      |

| VRC Error                                                  | ms Del Ctr                                           |

| VRC Sample999                                              | ms Del Ctr Out WDD17                                 |

| VRC Error Tgr                                              | RDD]44                                               |

| TAU Error Tgr                                              |                                                      |

FIGURE 4.1-3. TAU WRITE OPERATION

FIGURE 4.1-4. ERROR CONDITIONS WHEN WRITING

|                                                           | Writing Only Error Conditions                                                                                   | Read Check While Writing Erro          | or Conditions     |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------|

| Write Tgr                                                 |                                                                                                                 |                                        |                   |

| Write Clock                                               | 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 6 1                                                                         | 2 3 Skew Reg A                         | <b>-</b> L1       |

| R-W Reg                                                   |                                                                                                                 | Skew Reg B                             | η                 |

| Write Pulse                                               |                                                                                                                 | First Bit                              | <b>_</b>          |

| Echo                                                      |                                                                                                                 | Read Clock 1 2 3 4 5 6                 | 7                 |

| No Echo Tgr                                               |                                                                                                                 |                                        | <b>_</b>          |

| No Echo Sample                                            |                                                                                                                 | Skew Reg A VRC Er <u>ror</u>           | ]_ <sub>1</sub>   |

| Echo Error Tgr                                            | Neon                                                                                                            | —————————————————————————————————————— |                   |

| TAU Error Tgr                                             | Neon                                                                                                            | <br>Skew Reg A Error T <u>gr</u>       |                   |

| Input to VRC                                              |                                                                                                                 | TAU Error Tgr                          |                   |

| VRC Error                                                 | R-W Reg                                                                                                         | Skew Reg A and B Comp                  | ]_ <sub>{</sub> , |

| VRC Sample                                                | 9                                                                                                               | Comp Sample                            | L <sub>1</sub>    |

| VRC Error Tgr                                             | Neon                                                                                                            | - — – –<br>TAU Error Tgr               |                   |

| TAU Error Tgr                                             | Neon                                                                                                            |                                        | L_ <sub>1</sub>   |

| Error                                                     | Conditions Neons                                                                                                | LRCR Output                            | <u>\}</u>         |

| 1. No Echo<br>2. R-W VRC                                  | Fail to Receive Echo from Tape Echo Error Tg<br>Even or Odd Redundancy VRC Error Tgr                            | LRCR Sample                            | RDD136            |

| <ol> <li>3. Skew Reg A VRC</li> <li>4. Compare</li> </ol> | Even or Odd Redundancy<br>Skew Reg A-Skew Reg B Odd Comparison TAU Error Tgr                                    | rror Tgr LRCR Error                    | <u>\</u>          |

| 5. LRCR<br>In All Cases the TAU                           | Horizontal Redundancy at End of TAU Error Tgr<br>Operation                                                      | TAU Error Tgr                          | {}                |

| Error Tgr Neon will k<br>on with Other Neons              | be a second s |                                        |                   |

Dotted Lines Represent Error Conditions. Solid Lines Represent Normal Conditions.

FIGURE 4.1-5. ERRORS DURING WRITING

## Write Trigger

The write call signal turns on the write trigger in TAU. With the write trigger on, the busy line becomes active and prevents another operation until writing is complete. The write trigger output is sent to the tape unit where it sets the unit in write status. When the tape unit is in write status it returns "sel and write" to the TAU.

#### Write Delay Trigger (WD)

At the same time the write trigger is turned on, the write delay trigger is also turned on. The write delay trigger controls the starting of the tape and the necessary time delay before the actual writing circuits become active.

# Go Trigger

With the write delay trigger on and "sel and write status" active from the tape unit, the go trigger in TAU is turned on. The go trigger output is sent to the tape unit and initiates tape movement.

#### Millisecond Delay Counter

At the same time the go trigger is turned on, the write delay trigger starts the delay counter. The write delay trigger conditions the counter for millisecond control and the counter starts stepping. The counter drive pulses are determined by the oscillator, selected by either 729 II or IV operation. The reason for the delay is to allow the tape to reach its proper speed before initiating the active write circuits.

#### Load Point

If the tape unit is at load point when it is selected, the load point trigger in TAU will be on. The load point trigger conditions the write delay counter output.

#### Delay Counter Output

If the load point trigger is off, the delay counter WD50 pulse will turn on write condition. If the load point trigger is on, the delay counter must count to WD320 before an output is available to turn on write condition. The added delay, if at load point, is necessary to insure that the load point reflective spot is well beyond the R-W head before writing is allowed to take place. In either case the tape is up to speed before write condition is turned on. The same delay pulse used to turn on write condition also resets the write delay trigger and the delay counter.

# Write Condition

This trigger is turned on upon completion of the write delay. Write condition has the direct control of the actual writing by controlling the write clock. The flow of data through TAU and the timing relationships for control are originated with the write clock. Write condition allows oscillator drive pulses to start stepping the clock. As long as write condition remains on, the write clock will be in repetitive cycles. When write condition comes on, the write trigger release trigger is turned on. This trigger is used at the end of the write operation to write the check character.

# Read Condition

Also upon completion of the write delay, read condition is turned on to read the information being written as a check of the write operation. The read checking operation is covered under the read flow diagram (Figure 4.1-6).

#### Write Clock

This clock produces basic timing pulses for actual writing. The actual timing of the pulses is listed in Figures 2.1-1 and 2.1-2. All clock outputs are listed with a WC designation; for example, WC1 time, WC5 time, and so on.

#### Reset R-W Register

At WC1 time of any write clock cycle, the R-W register is reset. This clears out the last character in the R-W register in preparation for setting it to the input data lines for a new character.

#### Set R-W Register

At WC3 time of the write clock cycle, the input data lines are sampled. All lines that are active are set into corresponding triggers in the R-W register with the WC3 pulse. With data in the R-W register, the output lines to the tape are active.

#### No Echo Trigger

Unconditionally, at every WC5 time, a no echo trigger is turned on. This trigger is sampled later in the write cycle as an echo check for writing.

## Write Pulse

Powered from the clock at WC9 time, the write pulse is sent to the tape unit to initiate the writing action. Since the data lines are already active to the tape (output of R-W register), the arrival of the write pulse causes the character to be written.

# R-W Register VRC Sample

Also at WC9 time the R-W register output is sampled for a vertical redundancy check. Whenever data appear in the R-W register, its output, besides being available on the output tape bus, is also sent through a VRC. Depending upon the type of vertical redundancy check called for (odd or even), the VRC error line will be active from the wrong type bit structure. At WC9 time the VRC error line is sampled.

#### R-W Register VRC

If the VRC error line is active at WC9 time, the R-W register VRC error trigger will be turned on. This trigger only gives a neon indication of the error. In addition to the R-W register VRC trigger being turned on, the TAU error trigger is turned on. The output of the TAU error trigger is available to the external system and is TAU's only method of indicating any write or read error.

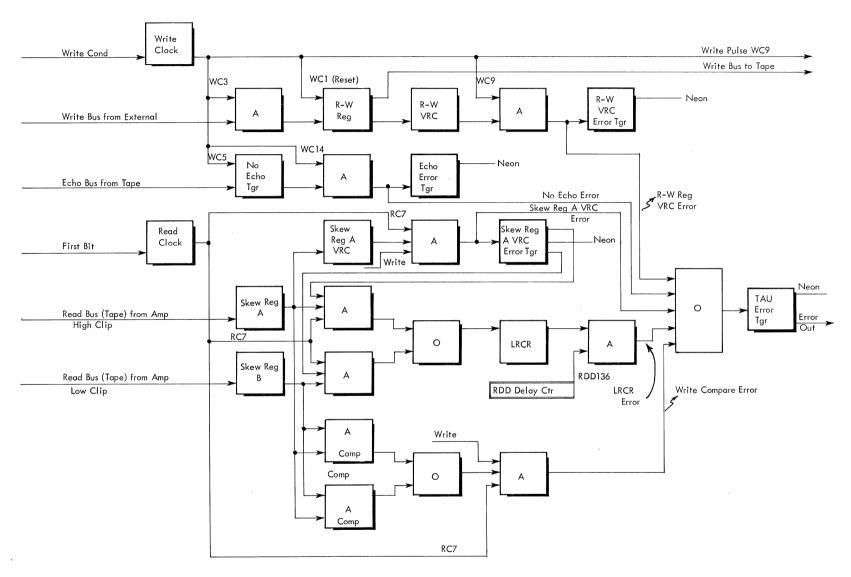

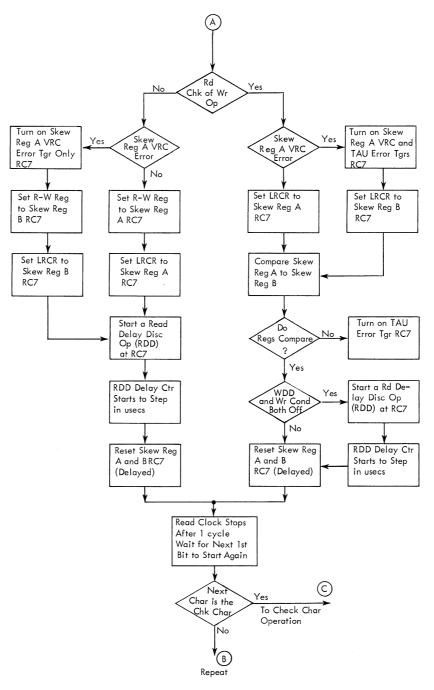

FIGURE 4.1-6A. READ AND READ CHECK OPERATION

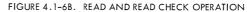

FIGURE 4.1-6C. READ AND READ CHECK OPERATION

# Echo

When writing action takes place in the tape unit, the write circuits develop an echo pulse. The echo pulse is immediately sent to TAU. When any echo is received from the tape unit, the no echo trigger is reset. Note: It takes only one echo from the tape to reset the no echo trigger. If the write circuits in the tape unit are not activated for any bits, no echos are develped and the no echo trigger remains on. This check insures that something was written, but does not indicate what.

## No Echo Error Sample

At WC14 time, the no echo trigger output is sampled. If the no echo trigger is off, no action takes place. However, if the no echo trigger is on (no echoes from tape), an echo error trigger and the TAU error trigger will be turned on with the WC14 pulse. The echo error trigger is a neon indicating trigger only. The TAU error trigger output is the only error indication to the external system.

## Disconnect (Disc) Trigger On

This trigger is turned on by a request from external system control to end the operation. If an end-of-write operation is not requested with disc call, the write operation continues to repeat. The next clock pulse WC1 resets the R-W register and so on through the complete write cycle again.

The write operation continues until the information from the external system is written. To end the write operation, the system must generate a disc call signal and send it to TAU. This signal arrives sometime during the last write character cycle. Upon receiving the disc call, TAU writes a check character, stops the tape, and provides the necessary resets for the write circuits. The disc operation is shown in Figure 4.1-1.

## Disc Call

This call is a signal generated within the external system control to end the write operation.

#### Disc Trigger

This trigger is turned on when the disc call line to TAU is activated.

Disc Trigger On

If the disc trigger is on when the write clock output is at WC14, the write delay disc trigger is turned on (Figure 4.1-1).

# Write Delay Disc (WDD)

This trigger is the controlling trigger in TAU that initiates the end-of-write operation. It is turned on at WC14 time of the last character cycle when the TAU disc trigger is on.

# Reset Write Condition

Write condition is reset at WC14 also if the WDD trigger is on. When write condition goes off, it blocks further oscillator drive pulses to the write clock. The clock stops with all triggers off.

# Microsecond Delay Counter

The WDD trigger starts the delay counter by initiating microsecond control. The oscillator drive pulses are determined by 729 II or IV operation. Figures 2.1-1 and 2.1-2 show the drive pulse for each type operation. The delay counter, while in the microsecond mode, gives the necessary time delay and then causes the check character to be written.

## Reset Write Trigger Release

When the delay counter output is WDD60 (refer to Figures 2.1-1 and 2.1-2 for timing), the write trigger release is reset, causing "reset wr trigger" to reset the write triggers in the tape unit. When the write triggers in the tape unit are reset, a check character will be written. All write triggers that were on write a bit when they are reset. The WDD60 pulse also resets the delay counter.

#### Millisecond Delay Counter

With the WDD trigger on, the write trigger release trigger going off causes millisecond control to condition the delay counter. The delay counter now begins stepping in a millisecond mode. (Refer to Figures 2.1-1 and 2.1-2 for timings.) This delay conditions the tape unit to stop at the proper time and perform the necessary write circuit resets.

# Reset WDD and Go Triggers

When the delay counter output reaches WDD17, the go trigger, the WDD trigger, and the delay counter are reset. Because the tape is still reading after the writing has finished (physical location of 2-gap head), the tape is allowed to run to complete the read check. This is the reason for the WDD17 delay. When the go trigger is reset after the delay, the tape starts to stop, but there is still the normal mechanical stop delay which further insures the time necessary to complete the read check operation.

# Reset Write Trigger

The complete write operation is not completed until all operations, including the read check, are finished (Figure 4.1-6C). Since the read portion of the write operation is the last to finish, the write trigger remains on to keep the TAU in a busy status. At the completion of the read checking operation, the write trigger is reset and "busy" becomes inactive. The write operation is complete.

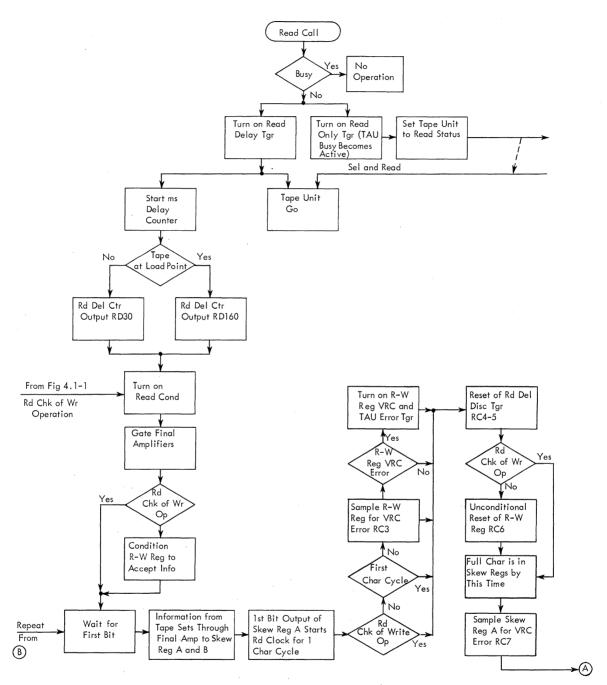

# 4.1.02 Read Operation

To initiate a read operation, the external system must generate a read call signal and send it to the TAU. The TAU controls all tape movements and controls the flow of data from tape through the TAU to the external system. In all operations performed during a read operation, TAU performs necessary checks for error conditions. The diagrams for reading are Figures 4.1-6, 4.1-7, and 4.1-8. Included in these flow diagrams is the read check during a write operation. Since a normal read and a read check during a write operation are similar in many instances, both have been included. Any deviation from a normal read is represented by a decision block labeled "read check of write operation." The outputs of the decision blocks are correspondingly labeled to cover the individual cases. A brief explanation follows.

## Read call

This call is a request signal generated within the external system and used to start the read operation.

#### Busy

If TAU were performing another operation at the time of receiving the read call, the busy line would be active and prevent any operation on the read call signal until the other operation is completed. If "busy" were inactive, the read call signal would initiate action in TAU.

## Read Only Trigger

The read only trigger is turned on with the read call signal. The output of the read only trigger activates the busy line, which prevents any other operation until reading is complete. The read only trigger output is also sent to the tape unit where read status is set. When the tape unit is in read status, it returns "sel and rd" to TAU.

## Read Delay Trigger (RD)

At the same time that the read only trigger is turned on, the read delay (RD) trigger is also turned on. The RD trigger controls the starting of tape and necessary delay before the actual reading circuits become active.

#### Go Trigger

With the RD trigger on and "sel and rd" active from the tape unit, the go trigger in TAU is turned on. The output of the go trigger is sent to the tape unit and starts the tape moving.

## Millisecond Delay Counter

At the same time the go trigger is turned on, the read delay trigger starts the delay counter. The RD trigger conditions the counter for millisecond control and the counter starts stepping. The counter drive pulses are determined by the oscillator, selected by either 729 II or IV operation (Figures 2.1-1 and 2.1-2). The reason for the delay is to allow the tape to reach its proper speed before the actual reading circuits become conditioned.

# Load Point

If the tape unit is at load point when it is selected, the load point trigger in the TAU is turned on. The load point trigger conditions the delay counter output.

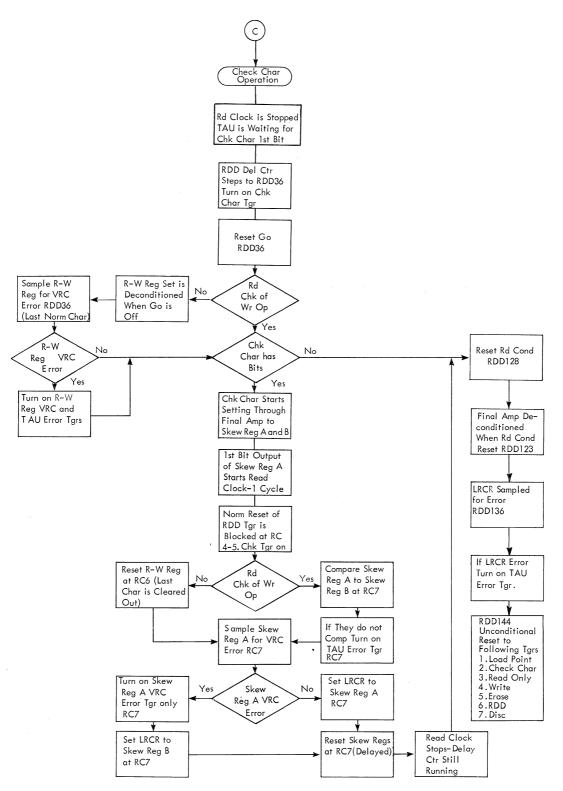

FIGURE 4.1-7. READ OPERATION DETAIL

T = Osc Drive Pulse Freq

FIGURE 4.1-8. READ OPERATION

# Delay Counter Output

If the load point trigger is off when the read operation is started, the RD30 output turns on the read condition trigger. If the load point trigger is on at the start of the read operation, the read condition trigger cannot be turned on at RD30, but must wait for the RD160 output of the delay counter. The reason for the longer delay, if at load point, is to insure that the load point reflective spot is away from the R-W head before reading begins. Notice that the delays taken for a read operation are shorter than those of a write operation. The shorter delays when reading are to insure that the read circuits become active soon enough to read the first bit of the written record. If the read and write delays were the same, there will be the chance that the first character when reading might be missed.

# Read Condition

Normal Read. This trigger is turned on when the read delay operation is complete. With read condition on, the actual read circuits are conditioned for operation.

Read Check During Writing. This trigger is turned on by the same pulse that turns on write condition. Read condition in this case is limited to its function of conditioning the read circuits.

#### Gate Final Amplifiers

Read condition activates a read gate line which conditions the final amplifier in TAU. With the read gate conditioning the final amplifier, any data appearing on the input data bus from the tape unit will be amplified and routed to the skew registers.

#### Condition R-W Register

Normal Read. In a normal read operation, read condition, the read only trigger, and go condition the inputs to the R-W register. Since TAU must make the tape data available to the system, the R-W register must be set to these data.

Read Check During Writing. In a read check operation, the data being read from tape need only to be checked within TAU. In this operation the only data appearing in the R-W register are the data that are being written on tape. These written data are read by the read head and sent to TAU for various checks, and are not gated to the R-W register.

#### Wait for First Bit

Because of variable starting times between tape units and the shorter read delay, TAU does not know at exactly what time the first character will be read. Once the first bit of a character is read, a timing relationship for that character is established. TAU performs no operations until the first bit of a character is read.

#### Set Skew Registers A and B

Whenever the read head reads data from the tape, the information is sent from the tape to the final amplifier in the TAU. The final amplifier has two outputs, a high level and a low level. The high level output sets to skew register A and the low level output sets to skew register B.

#### First Bit

As soon as any trigger in skew register A is set, a first bit line becomes active. The first bit line unclamps the read clock oscillator and allows the read clock to start stepping. A read clock cycle is started.

#### Sample R-W Register for Vertical Redundancy

Normal Read. In a normal read operation, the R-W register is the data output to the system. The character that is being sent to the system is checked for a vertical redundancy error while in the R-W register at RC3 time of the read clock cycle. The character being checked is the character that was processed through the TAU in the previous read clock cycle. The first character of a record is not in the R-W register at RC3 time of the first clock cycle; therefore, no check is made of the R-W register at this time. During the second read clock cycle, the first character read is in the R-W register and is checked. The second character read is checked in the third read clock cycle and so on through the record. The last normal character of the record is checked during the check character processing cycles. Since the check character never appears in the R-W register, no vertical redundancy check is necessary.

Read Check During Writing. The read clock does not sample the R-W register when reading during a write operation. The data read in this operation never appear in the R-W register. The R-W register in the read during writing operation contains the data to be written on tape. The R-W register is sampled from a write clock pulse.

## R-W Register Vertical Redundancy Error

If, in a normal read operation, the R-W register VRC line is active at RC3 time, the R-W register VRC error trigger and the TAU error trigger will be turned on. The R-W VRC error trigger is for neon indication only, while the TAU error trigger is available to the system.

#### Reset of Read Delay Disc Trigger (RDD)

Each time the read clock runs (except check character) an unconditional reset is applied to the read delay disc trigger at RC4-5 time. This trigger is used to control the read end operation and is always turned on at the end of every normal read character cycle. Normally, the trigger is not on long enough to start the end operation because it is reset at each character time interval with the RC4-5 pulse. The only time the trigger is not reset in the timed interval is when the check character is the next character. In this case the check character time is much longer than normal character time intervals, and the RDD trigger remains on long enough to start the end operation.

#### Reset R-W Register

Normal Read. In every normal read cycle the R-W register is reset with the RC6 pulse from the read clock. The reset clears out the data from the previous cycle, so the character now in the skew registers can be set into the R-W register.

Read Check During Write. Since the R-W register is used only for the writing operation, the reset from the read clock is blocked during this operation.

# Skew Registers

By this time skew reigsters A and B have the full character setting in them. Before the character can be available to the system, it must first be set into the R-W register.

#### Skew Register A VRC

Normal Read. At RC7 time of the read clock cycle, skew register A is sampled for a vertical redundancy error. The outputs of the register are immediately available to a VRC. By RC7 time the full character is setting in the register and the VRC will have determined if the bit structure of the character is correct (odd or even depending upon the type check called for). If the character is redundant, the skew register A error line is active. At RC7 time, the line is sampled, and if an error is indicated, the skew register A VRC error trigger will be turned on. In this case the TAU error trigger is not turned on. The only indication of a skew register A VRC is the neon indicating skew register A error trigger. The skew register A error line is used to gate either skew register A (no error) or skew register B (error) to the R-W register and an LRCR.

Read Check During Writing. Because this is a read check of information that was just written, the TAU error trigger is also turned on by a skew register A vertical redundancy error. The skew register A VRC error trigger is also on, giving a neon indication in TAU of the error. The skew register A VRC error line is also used in this operation to gate either skew register A (no error) or skew register B (error) to an LRCR register. The data in the skew registers are not set into the R-W register when doing a read during a write operation.

#### Set R-W Register

Normal Read. At RC7 time of a normal read clock cycle, the R-W register is set from either skew register A or skew register B. If skew register A shows a vertical redundancy error, the data in skew register B is unconditionally gated to the R-W register. If, however, skew register A shows no vertical redundancy check, the data in skew register A is set into the R-W register at RC7 time. Besides setting the R-W register, the same data is also set into the LRCR register.

Read During Write. If the operation is a read check of the writing operation, the data sets only into the LRCR register and does not appear in the R-W register. The data appearing in the LRCR register is from either skew register A or skew register B, depending upon the skew register A vertical redundancy error condition.

#### Compare Skew Register A to Skew Register B

Read Check During a Write Operation Only. At RC7 time of the read clock cycle, the output of skew register A is compared to the output of skew register B. If the two registers compare, no error is indicated. If however, the two registers do not compare, the TAU error trigger is turned on at RC7 time. The TAU error trigger activates the error line to the external systems.

#### Read Delay Disconnect (RDD)