223-2712-1

# IIIC Customer Engineering Maintenance Manual

IBM 7040-7044 Data Processing Systems

Channels  $\mathbf{B}_{i}$   $\mathbf{C}_{i}$   $\mathbf{D}_{i}$  and  $\mathbf{E}$

Customer Engineering Maintenance Manual IBM 7040-7044 Data Processing Systems Channels B, C, D, and E

#### PREFACE

This manual contains logic diagrams of tape operations, Simplex interface operations, and direct data operations. A brief description of each of these operations precedes the diagrams in each major section. A detailed description of the operations diagrammed can be found in <u>Channels B, C, D, E</u> <u>CE Manual of Instruction</u>, Form 223-2755.

Your ideas and comments concerning Customer Engineering manuals are of value to Product Publications. Please use the comments sheet at the back of this manual.

#### SAFETY

Accidents do not always happen to "the other fellow." Be smart! When servicing any equipment, remove rings and watches, roll up your sleeves, and tuck in your tie. Put on your safety glasses! If power must be on when working on power supplies, probe with one hand only; keep the other hand off the frame. You know the safety rules--follow them!

MAJOR REVISION (December 1963) This edition, Form 223-2712-1, obsoletes Form 223-2712-0 and all earlier editions. The "Tape Interface" section has been updated and the "Simplex" and "Direct Data" sections are new.

Copies of this and other IBM publications can be obtained through IBM Branch Offices. Address comments concerning the contents of this publication to: IBM Corporation, CE Manuals, Dept. B95, PO Box 390, Poughkeepsie, N.Y. 12602

#### CONTENTS (TEXT)

| PHYSICAL DESCRIPTION               |     |     |    |       |     |   |   |   |   |    |   | 5        |

|------------------------------------|-----|-----|----|-------|-----|---|---|---|---|----|---|----------|

| Frame Configuration                |     |     |    |       |     |   |   |   |   |    |   | 5        |

| I-O Connector Panel                |     |     |    |       |     |   |   |   |   |    |   | 5        |

| Power                              |     |     |    |       |     |   |   |   |   |    |   | 5        |

| Power Supplies                     |     |     |    |       |     |   |   |   |   |    |   | 5        |

| Power Switches                     |     |     |    |       |     |   |   |   |   |    |   | 5        |

| Tape Drive Power Gate              |     |     |    |       |     |   | ÷ |   |   |    | ÷ | 5        |

| Power Input and Output Connector   |     |     |    |       |     |   |   |   |   |    |   | 6        |

| Channel Indicator Lights           |     |     |    |       |     |   |   | Ē | Ē | Ţ. | Ī | 6        |

| Basic Cable Arrangement Between C  |     |     |    |       |     |   |   |   | : |    | · | 6        |

| Bable Cable In rangement Detween C | 10  | ana | 01 | 10011 | nor | 5 | • | · | • | •  | • | Ū        |

| TAPE INTERFACE LOGIC               |     |     |    |       |     |   |   |   |   |    |   | 12       |

|                                    | ·   | ·   | ·  | ·     | ·   | · | • | · | · | ·  | • | 12       |

| Write Tape Operation               |     |     |    |       |     |   |   |   | ٠ | ٠  | • |          |

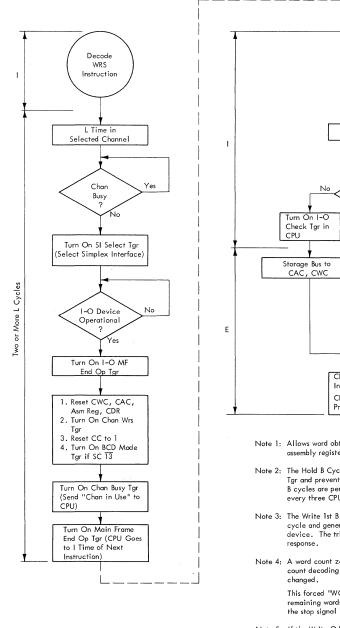

| Write Selecting the Channel (WRS)  |     |     |    | ٠     | ·   | ٠ | ٠ | ٠ | ٠ | ٠  | ٠ | 12       |

| Command Word Loading (RCH) .       |     | ٠   | ·  | ٠     | ٠   | ٠ | ٠ | ٠ | ٠ | ٠  | ٠ | 12       |

| B Cycle                            | •   | •   | ٠  | ٠     | ٠   | ٠ | ٠ | ٠ | ٠ | ٠  | ٠ | 12       |

| Character Transmission             | •   | •   | •  | •     | •   | • |   | • | • | ٠  |   | 12       |

| End Operation and Disconnect .     |     |     |    |       |     |   |   |   |   |    |   | 12       |

| Read Tape Operation                |     |     |    |       |     |   |   |   |   |    |   | 28       |

| Read Selecting the Channel (RDS)   |     |     |    |       |     |   |   |   |   |    |   | 28       |

| Command Word Loading (RCH) .       |     |     |    |       |     |   |   |   |   |    |   | 28       |

| Character Transmission             |     |     |    |       |     |   |   |   |   |    |   | 28       |

| B Cvcle                            |     |     |    |       |     |   | ÷ | ÷ | ÷ | ÷  | ÷ | 28       |

| 5                                  |     |     |    |       |     |   |   |   |   |    |   | 28       |

|                                    | •   | •   | •  | •     | ·   | · | · | • | · | •  | • |          |

| SIMPLEX INTERFACE LOGIC            |     |     |    |       |     |   |   |   |   |    |   | 45       |

| Simplex Interface Write Operation  | •   | •   | ÷  | •     | ·   | • | · | · | • | •  | • | 45       |

| Write Selecting the Channel (WRS)  | 、•  | ·   |    | ·     | •   | • | · | • | • | ·  | • | 45<br>45 |

| write belecting the Channel (WRS   | ) • | ٠   | ٠  | ·     | ·   | • | ٠ | • | ٠ | •  | ٠ | 40       |

| Command Word Loading (RCH) .        |     |               |   |  |   |  | • | • | 45 |

|-------------------------------------|-----|---------------|---|--|---|--|---|---|----|

| B Cycle                             |     |               |   |  | • |  |   |   | 45 |

| Character Transmission              |     |               |   |  |   |  |   |   | 45 |

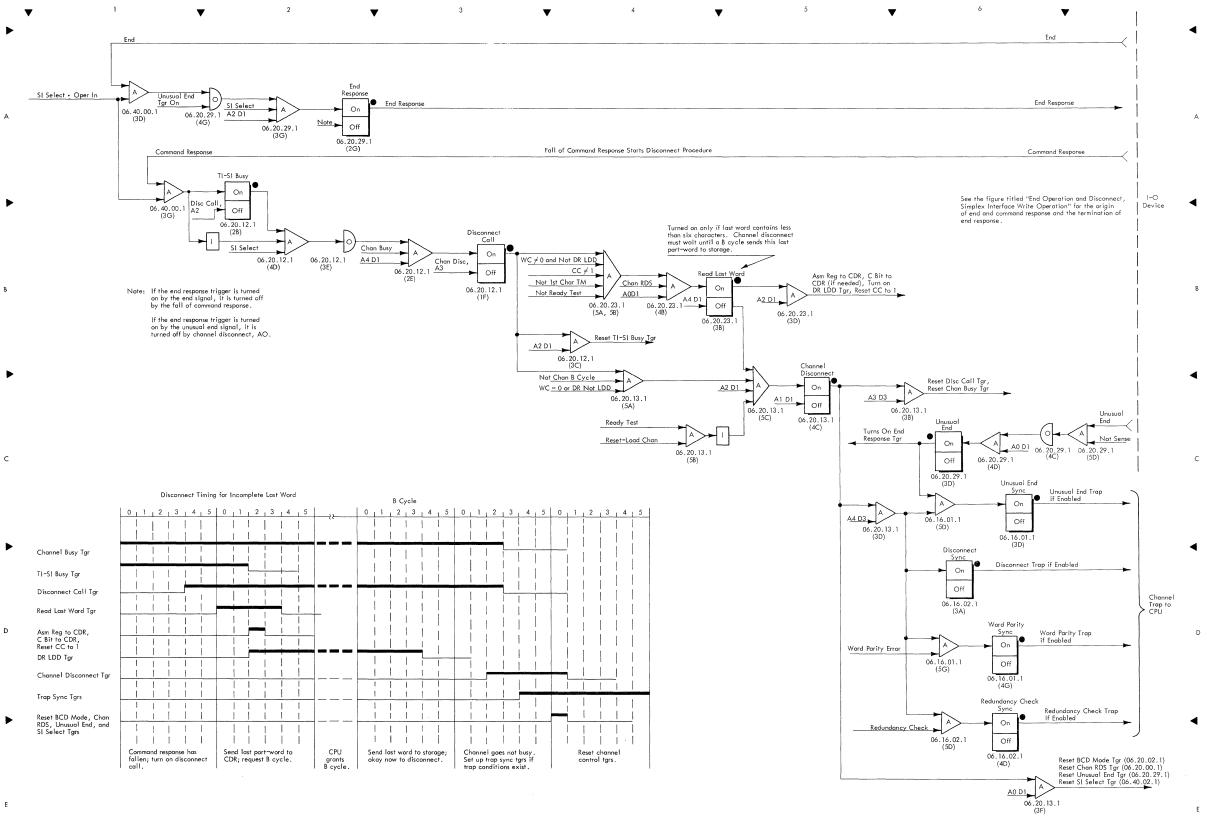

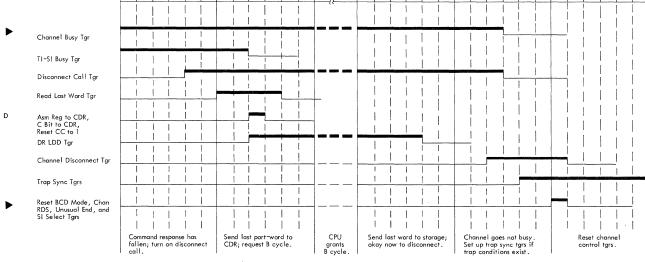

| End Operation and Disconnect .      |     |               |   |  |   |  |   |   | 45 |

| Simplex Interface Control Operation |     |               | • |  |   |  |   |   | 53 |

| Simplex Interface Read Operation .  |     |               |   |  |   |  |   |   | 57 |

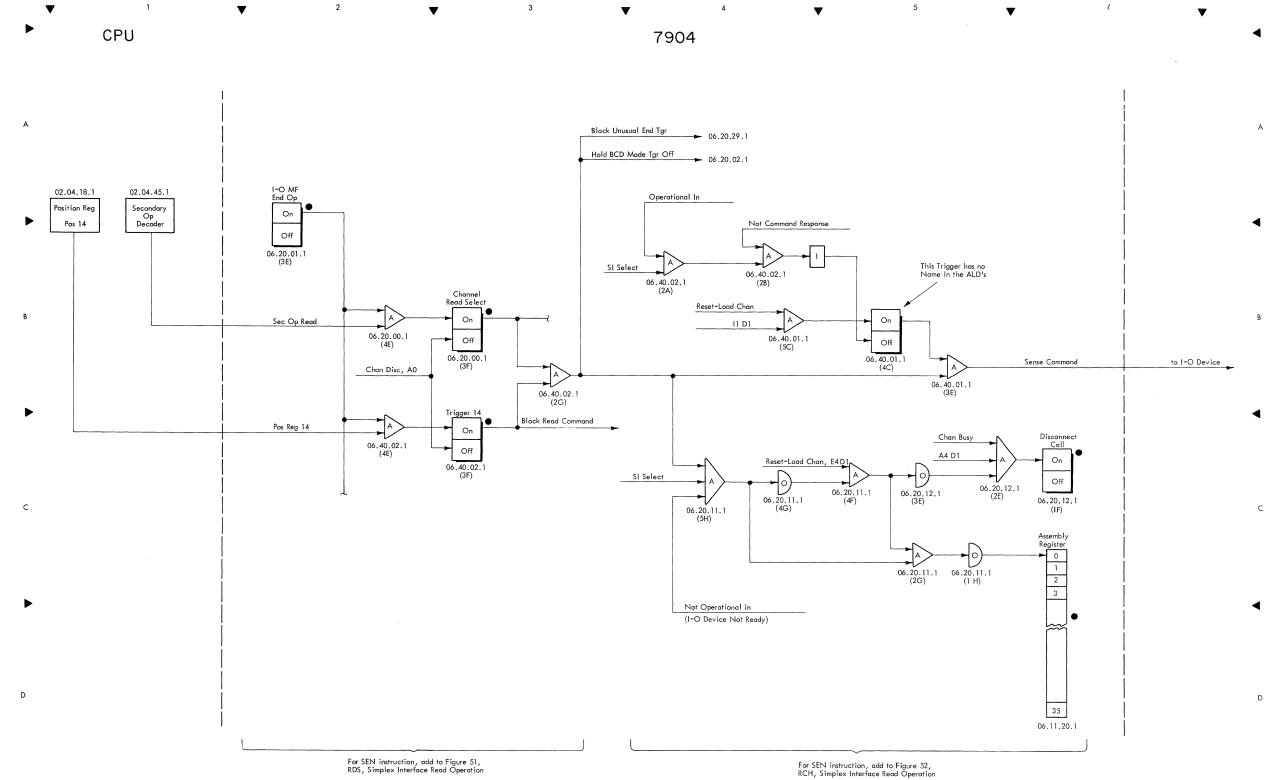

| Read Selecting the Channel (RDS)    |     |               |   |  |   |  |   |   | 57 |

| Command Word Loading (RCH) .        | •   |               |   |  |   |  |   |   | 57 |

| Character Transmission              |     |               |   |  |   |  |   |   | 57 |

| B Cycle                             |     |               |   |  |   |  |   |   | 57 |

| End Operation and Disconnect .      |     |               |   |  |   |  |   |   | 57 |

| Simplex Interface Sense Operation . | •   |               |   |  |   |  |   |   | 65 |

|                                     |     |               |   |  |   |  |   |   |    |

| DIRECT DATA LOGIC                   |     |               |   |  |   |  |   |   | 69 |

| Direct Data Write Operation         |     |               |   |  |   |  |   |   | 69 |

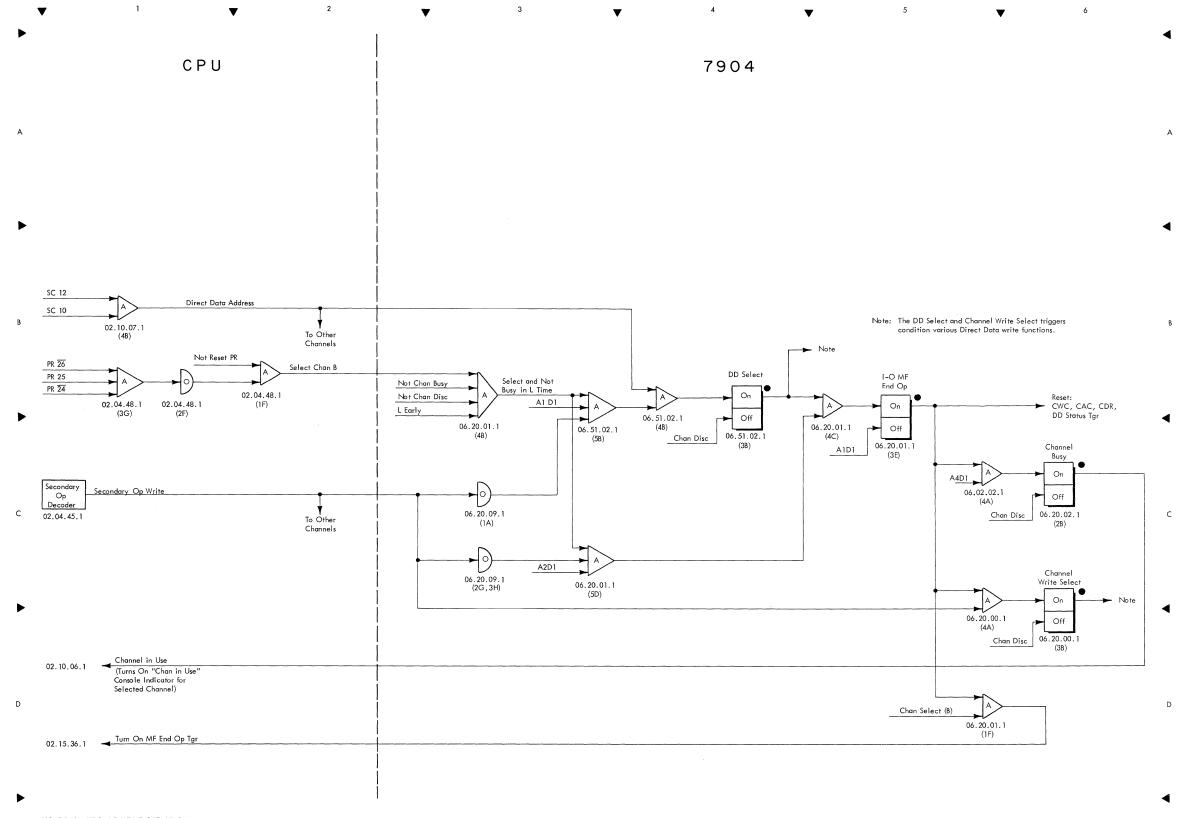

| Write Selecting the Channel (WRS)   | ).  |               |   |  |   |  |   |   | 69 |

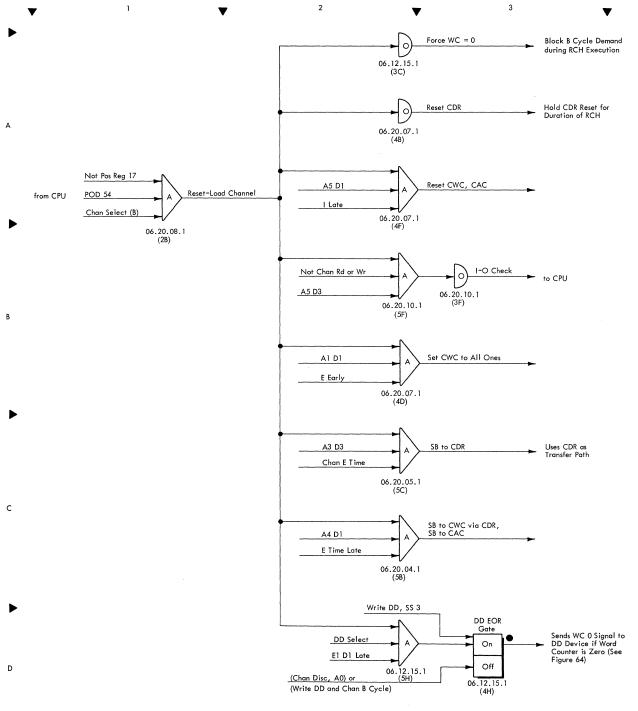

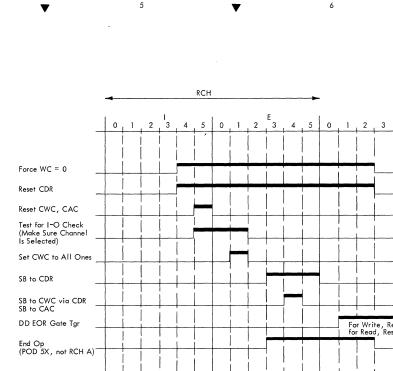

| Command Word Loading (RCH) .        | •   |               |   |  |   |  |   |   | 69 |

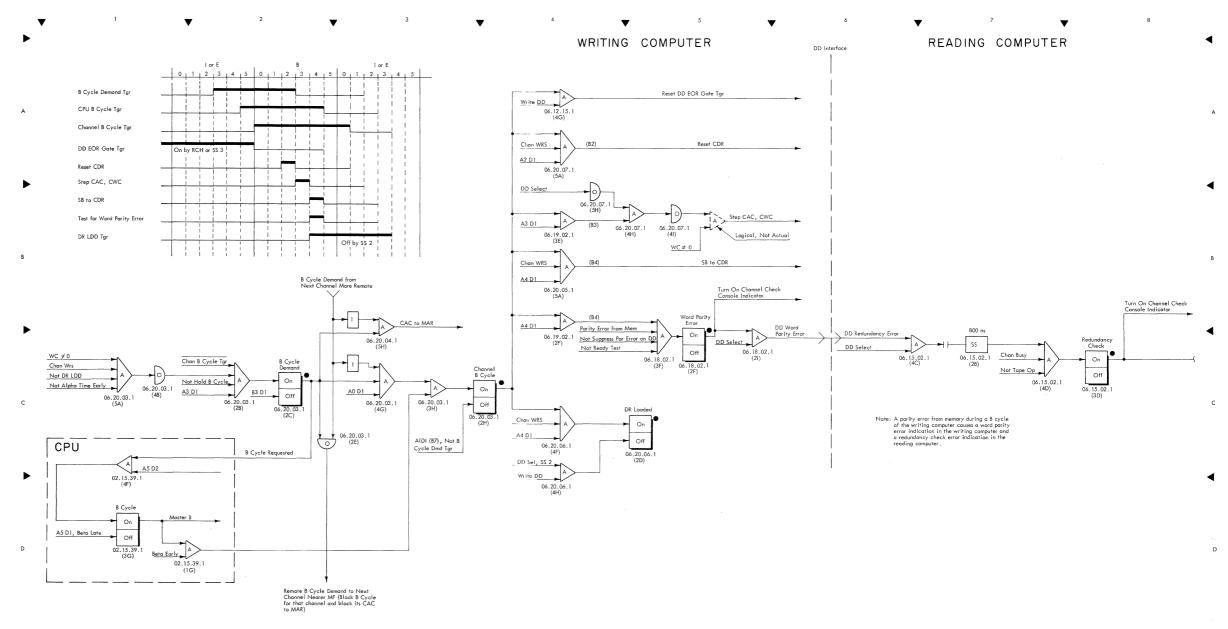

| B Cycle                             |     |               |   |  |   |  |   |   | 69 |

| Data Transfer                       |     |               |   |  |   |  |   |   | 69 |

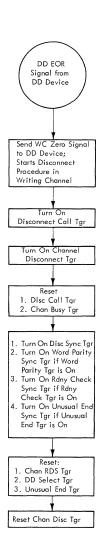

| End Operation and Disconnect .      |     |               |   |  |   |  |   |   | 69 |

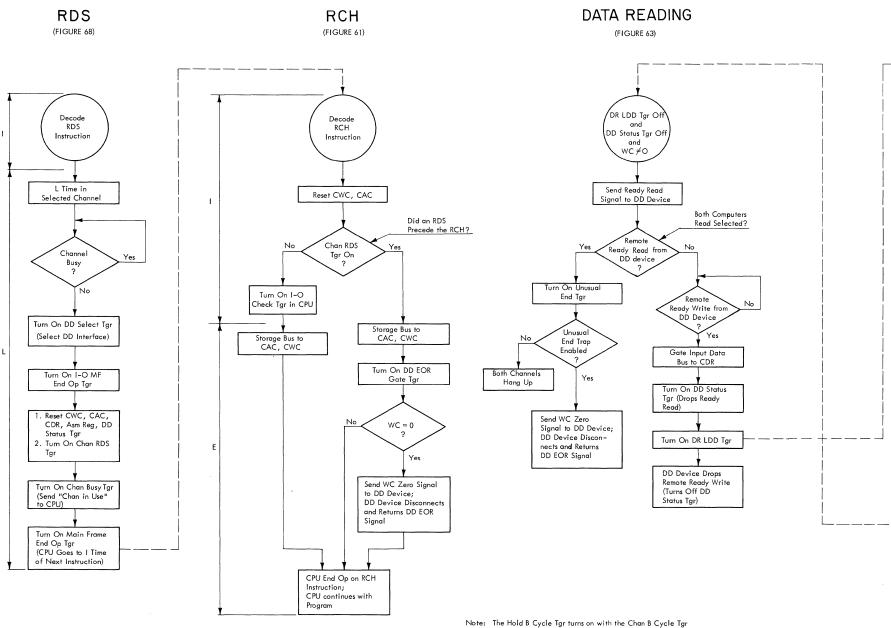

| Direct Data Read Operation          |     |               |   |  |   |  |   |   | 79 |

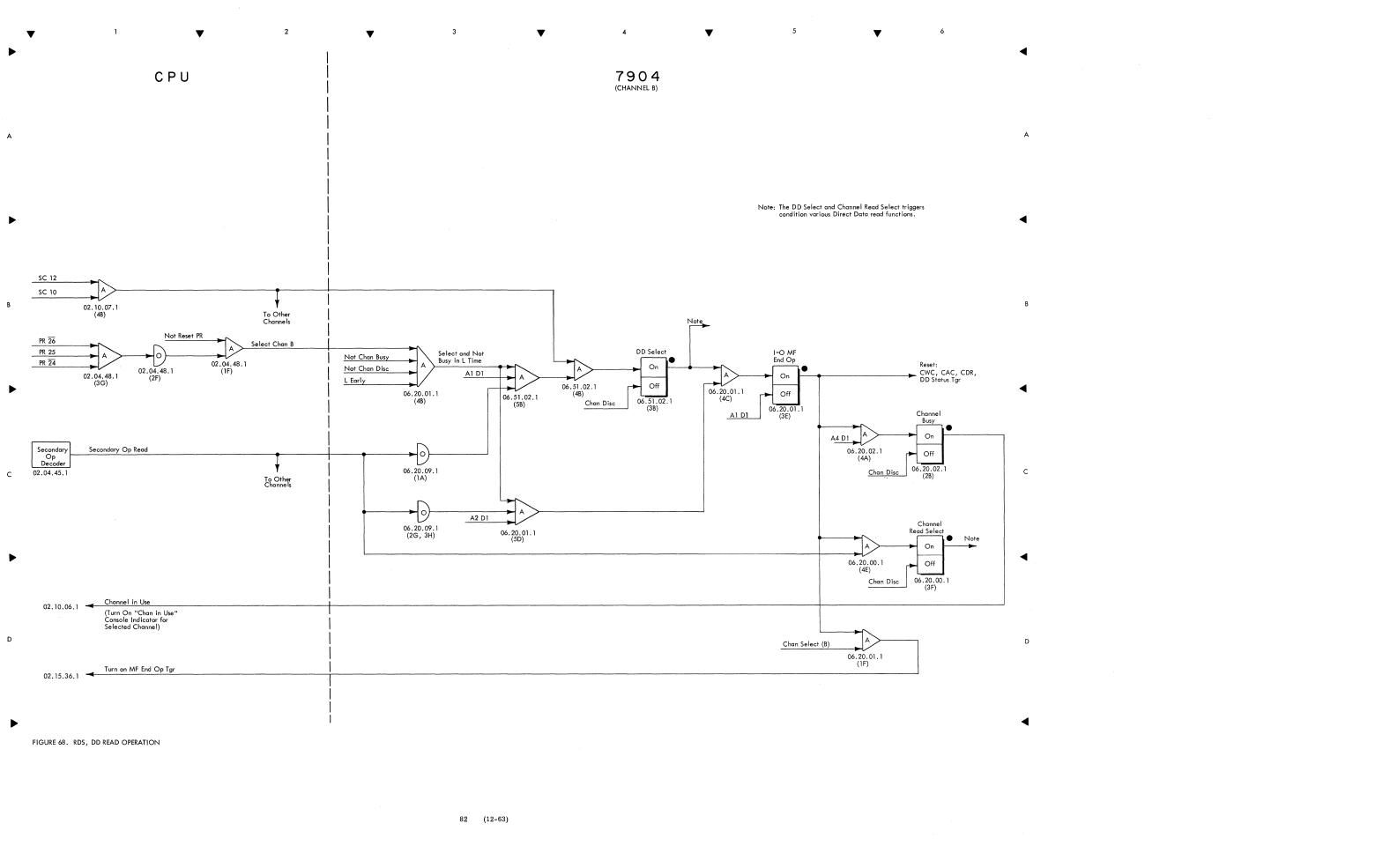

| Read Selecting the Channel (RDS)    |     |               |   |  |   |  |   |   | 79 |

| Command Word Loading (RCH) .        |     |               |   |  |   |  |   |   | 79 |

| Data Transfer                       |     |               |   |  |   |  |   |   | 79 |

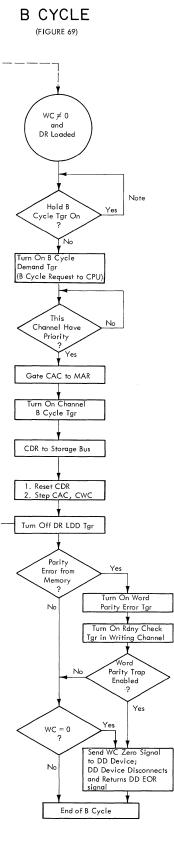

| B Cycle                             |     |               |   |  |   |  |   |   | 79 |

| End Operation and Disconnect .      |     |               |   |  |   |  |   |   | 79 |

| -                                   |     |               |   |  |   |  |   |   |    |

| DIAGNOSTIC INSTRUCTIONS AND R       | ESE | $\mathbf{TS}$ |   |  |   |  |   |   | 85 |

|                                     |     |               |   |  |   |  |   |   |    |

## CONTENTS (ILLUSTRATIONS)

Page

| Figure | Title                                 | Page |

|--------|---------------------------------------|------|

| PHYSIC | AL DESCRIPTION                        |      |

| 1      | Frame 02 - Front Layout (Wiring Side) | 7    |

| 2      | I-O Connector Panel                   | 7    |

| 3      | 7904 Rear View                        | 8    |

| 4      | 7904 Front View                       | 9    |

| 5      | Channel Indicators                    | 10   |

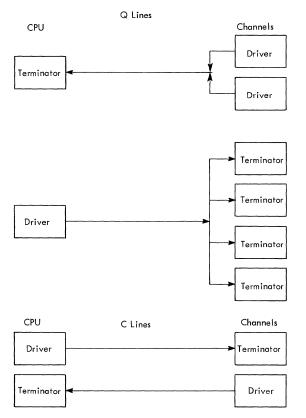

| 6      | Q Line and C Line Examples            | 11   |

|        |                                       |      |

| 6 | Q Line and C Line Examples                     |

|---|------------------------------------------------|

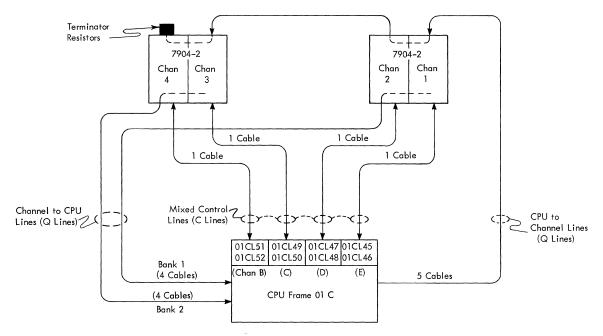

| 7 | Basic Cable Arrangement, 7904 Channels and CPU |

#### WRITE TAPE LOGIC

| 8         | Tape Interface Signal Lines                          | 13        |

|-----------|------------------------------------------------------|-----------|

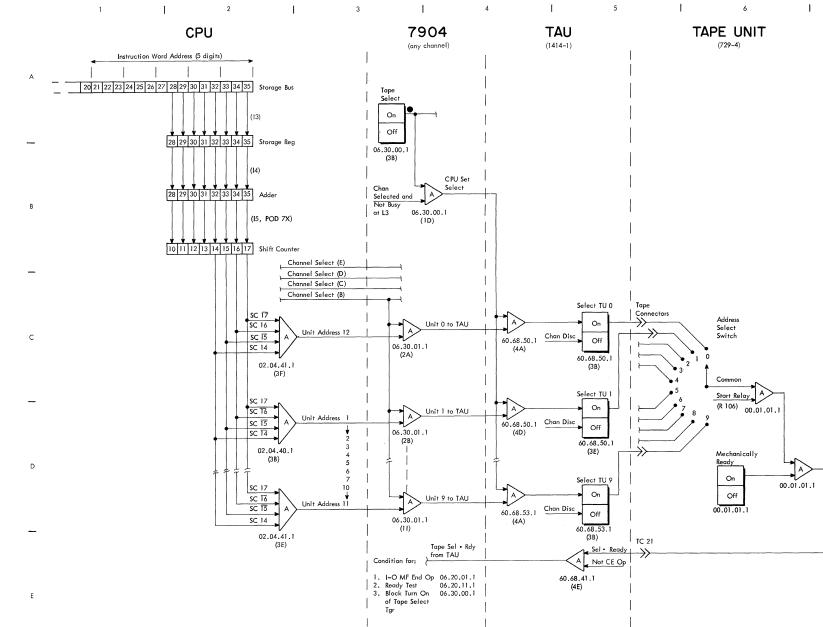

| 9         | Tape Unit Selection                                  | 14        |

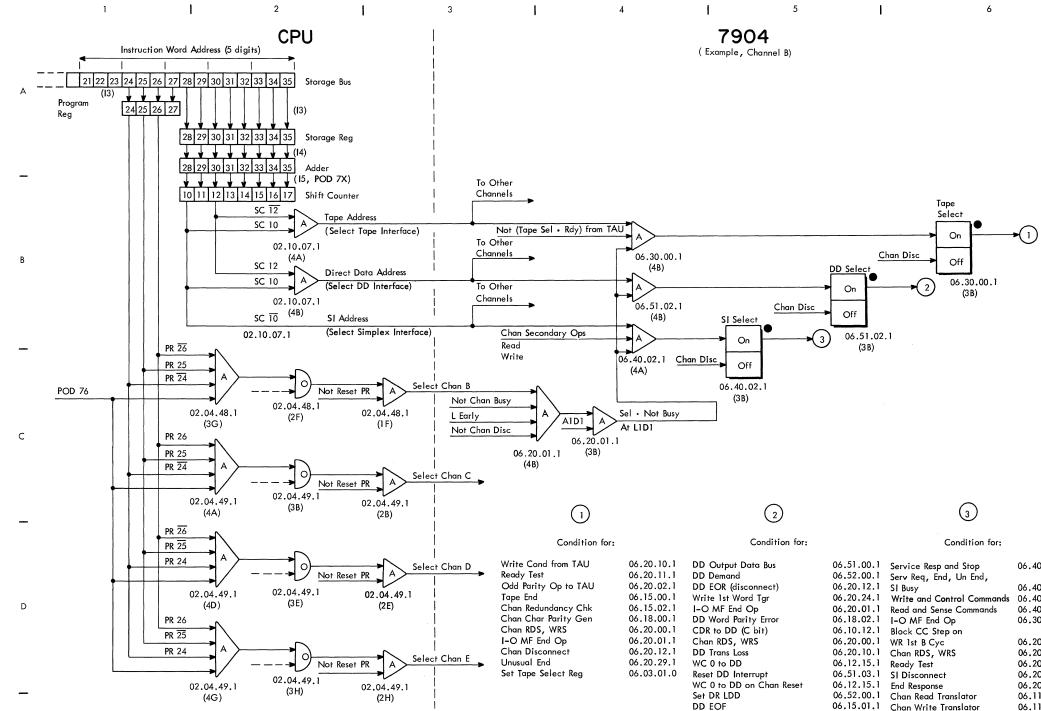

| 10        | Channel and Interface Selection                      | 15        |

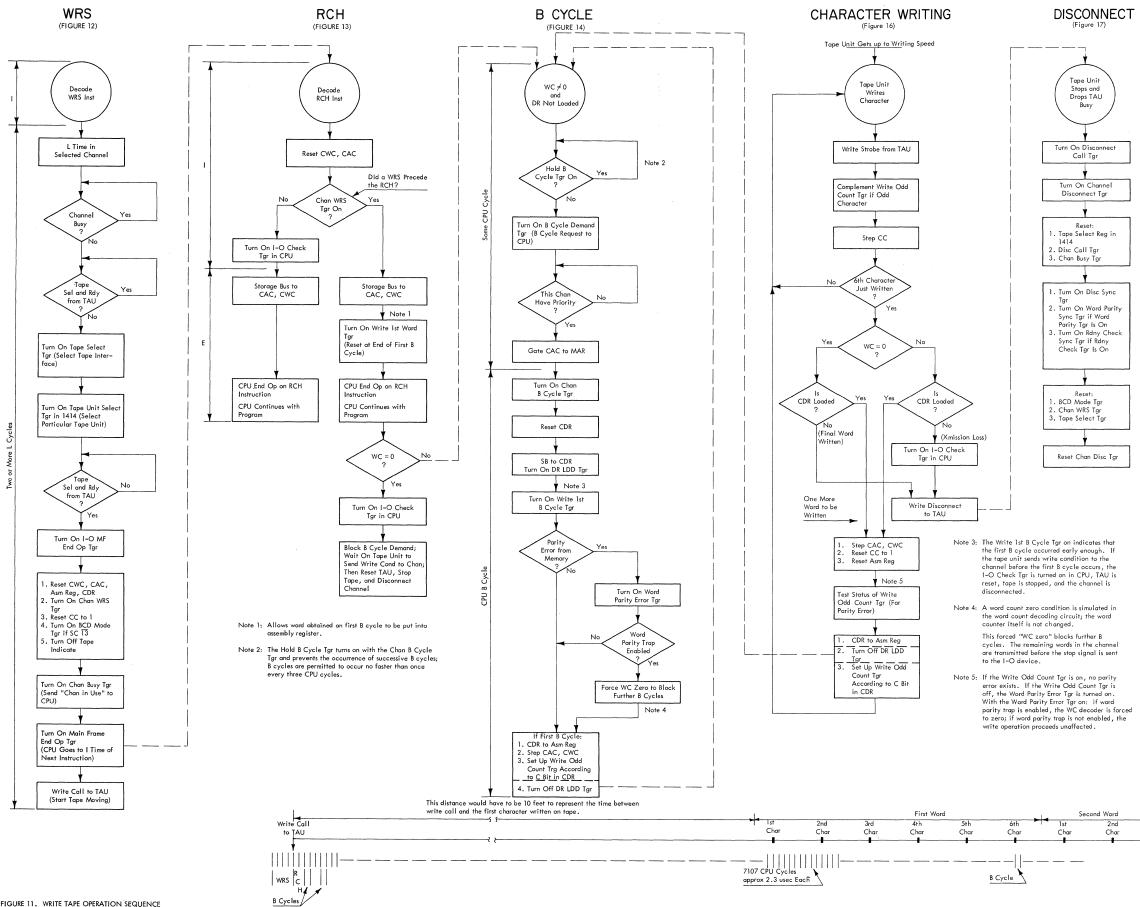

| 11        | Write Tape Operation Sequence                        | 16        |

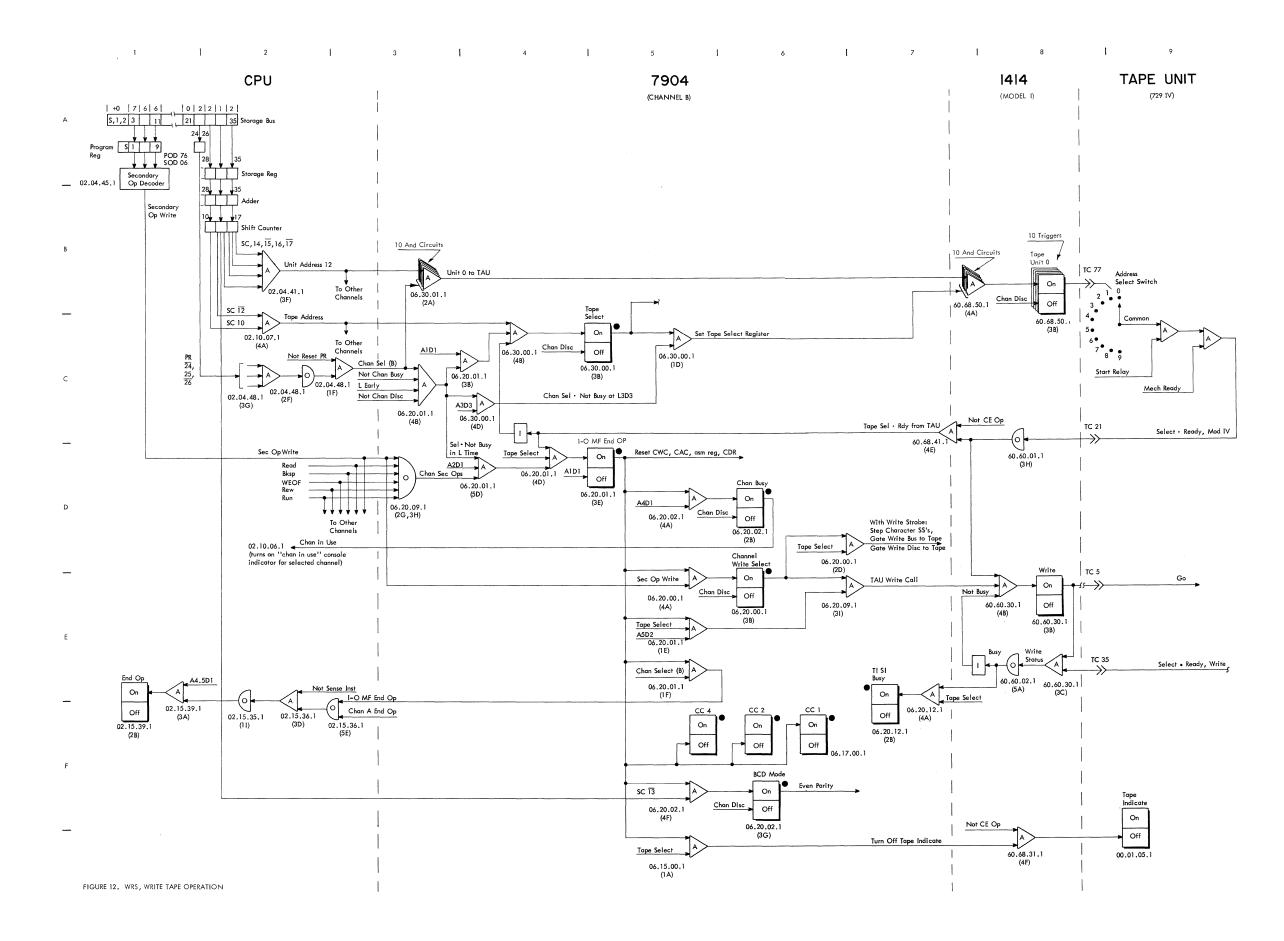

| <b>12</b> | WRS, Write Tape Operation                            | 17        |

| 13        | RCH, Write Tape Operation                            | 18        |

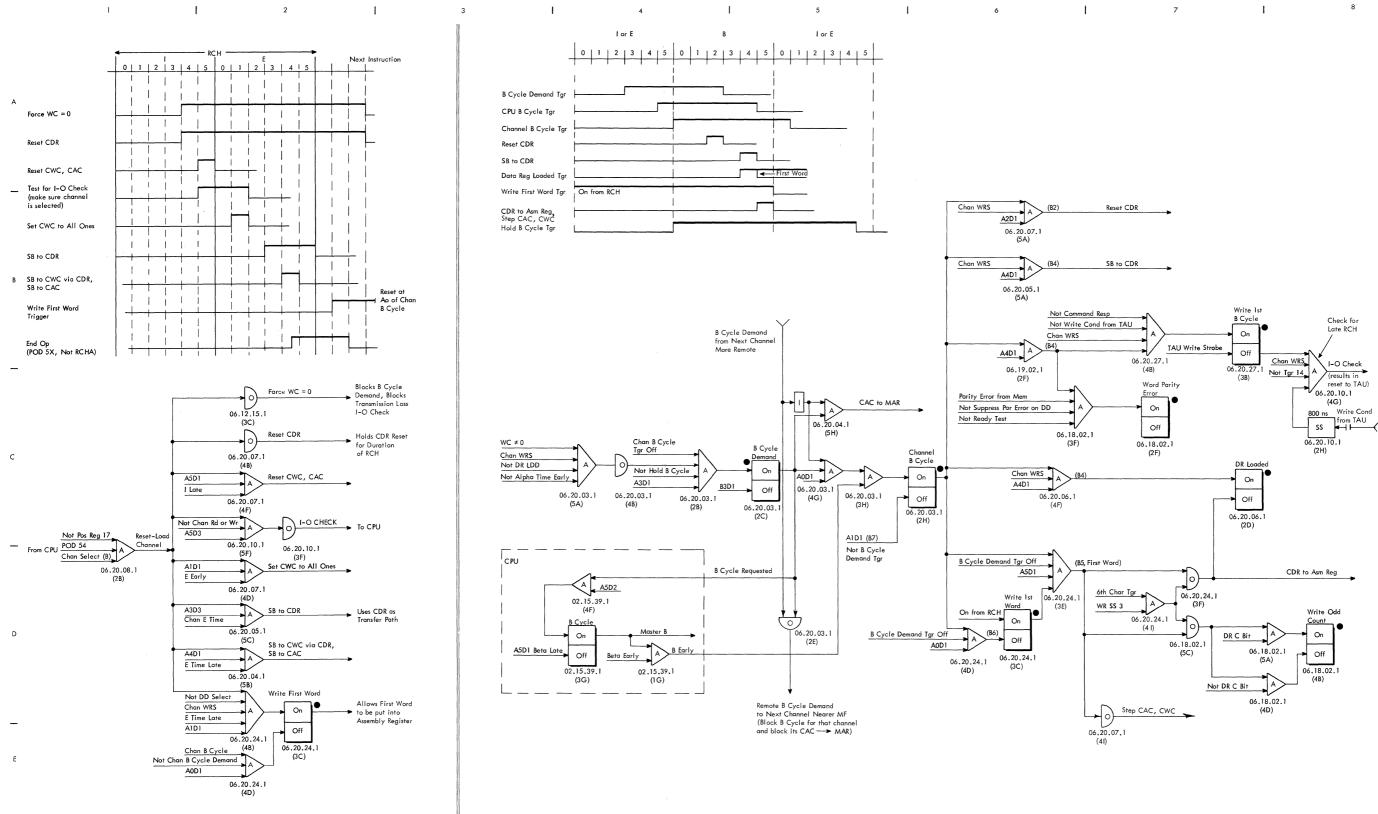

| <b>14</b> | B Cycle, Write Tape Operation                        | 18        |

| 15        | B Cycle Priority                                     | 19        |

| 16        | Character Writing, Write Tape Operation              | 20        |

| 17        | End Operation and Disconnect, Write Tape Operation   | 21        |

| 18        | Data Flow, Write Tape Operation                      | 22        |

| 19        | I-O Check and Redundancy Check, Write Tape Operation | 23        |

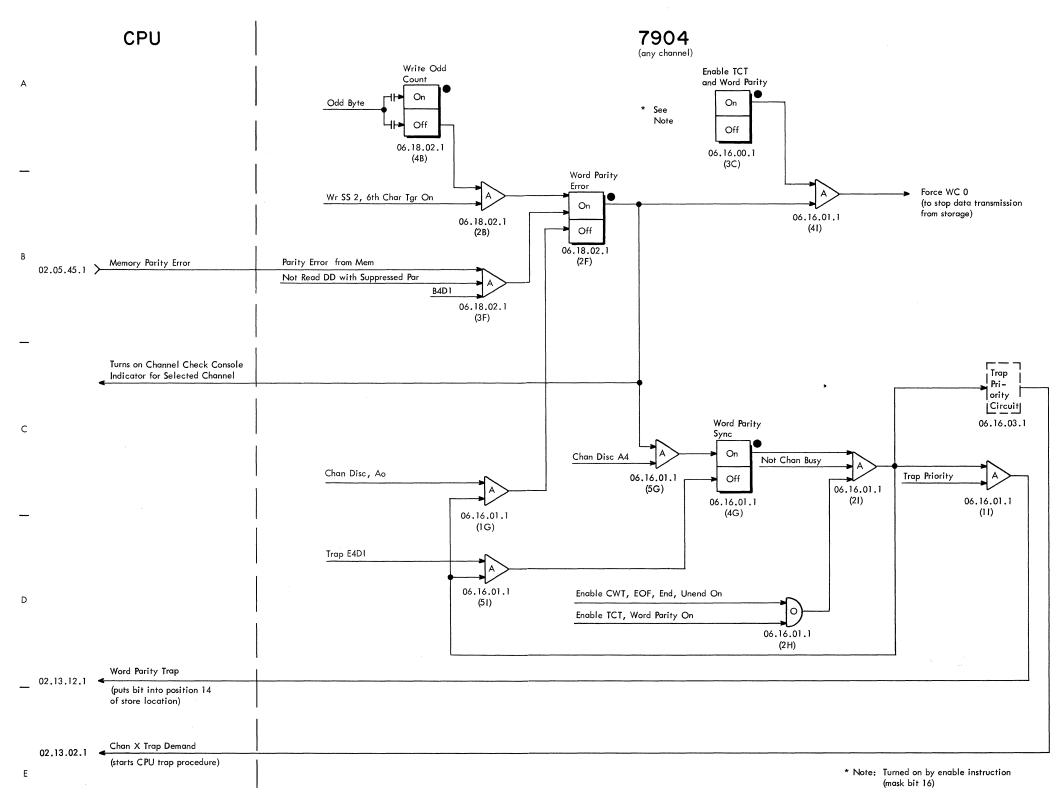

| 20        | Word Parity Error, Write Tape Operation              | <b>24</b> |

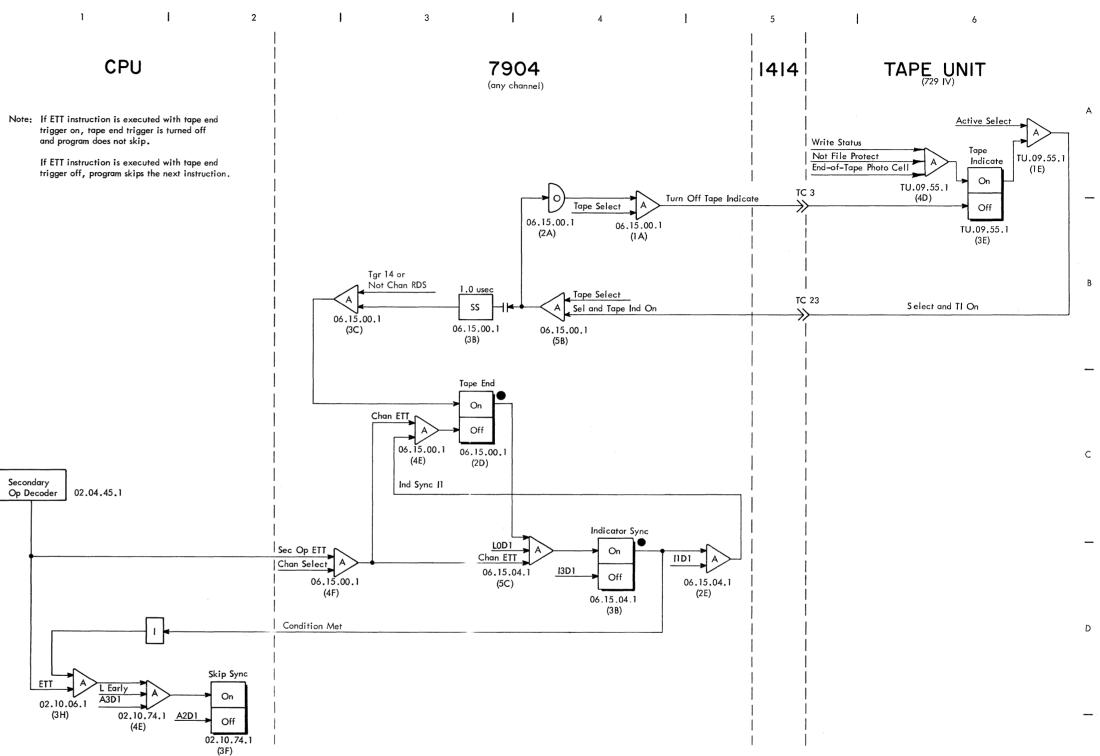

| <b>21</b> | ETT, End-of-Tape Operation                           | 25        |

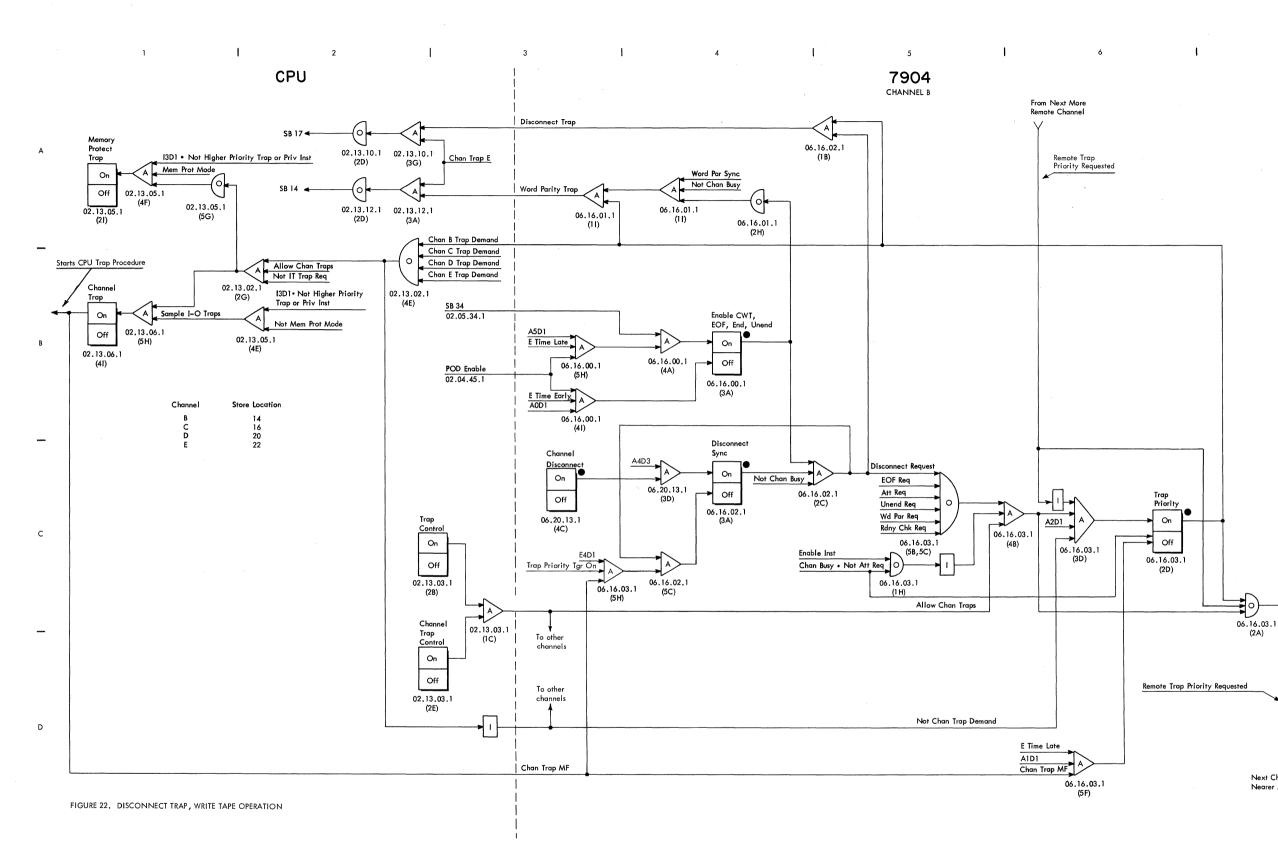

| 22        | Disconnect Trap, Write Tape Operation                | <b>26</b> |

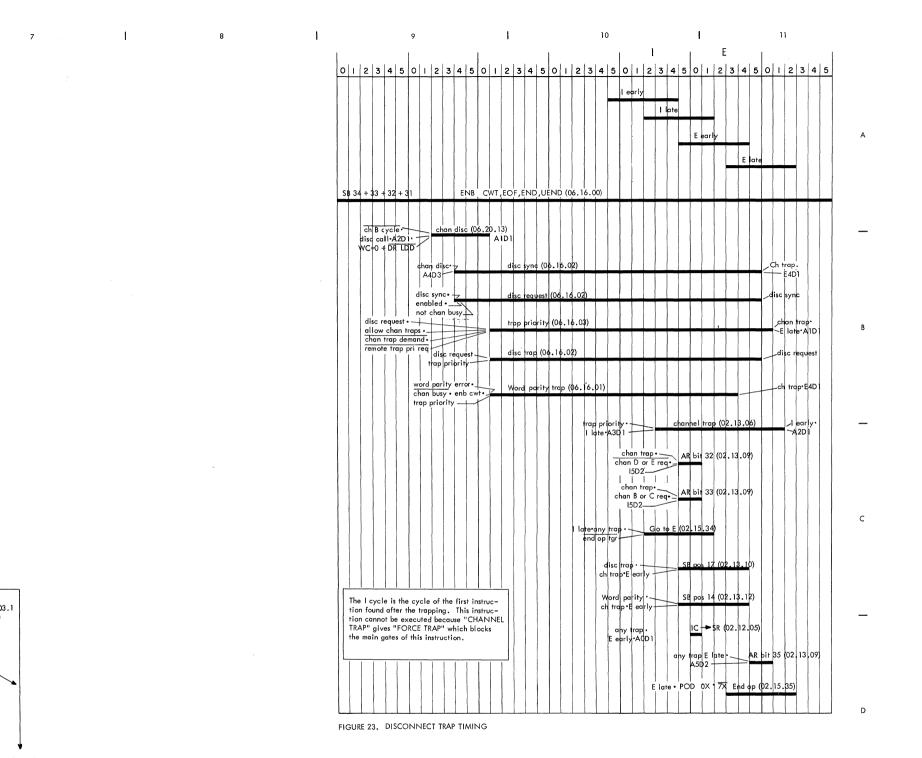

| 23        | Disconnect Trap Timing                               | 26        |

| <b>24</b> | Error and Trap Conditions, Tape Operation            | 27        |

|           |                                                      |           |

#### READ TAPE LOGIC

.

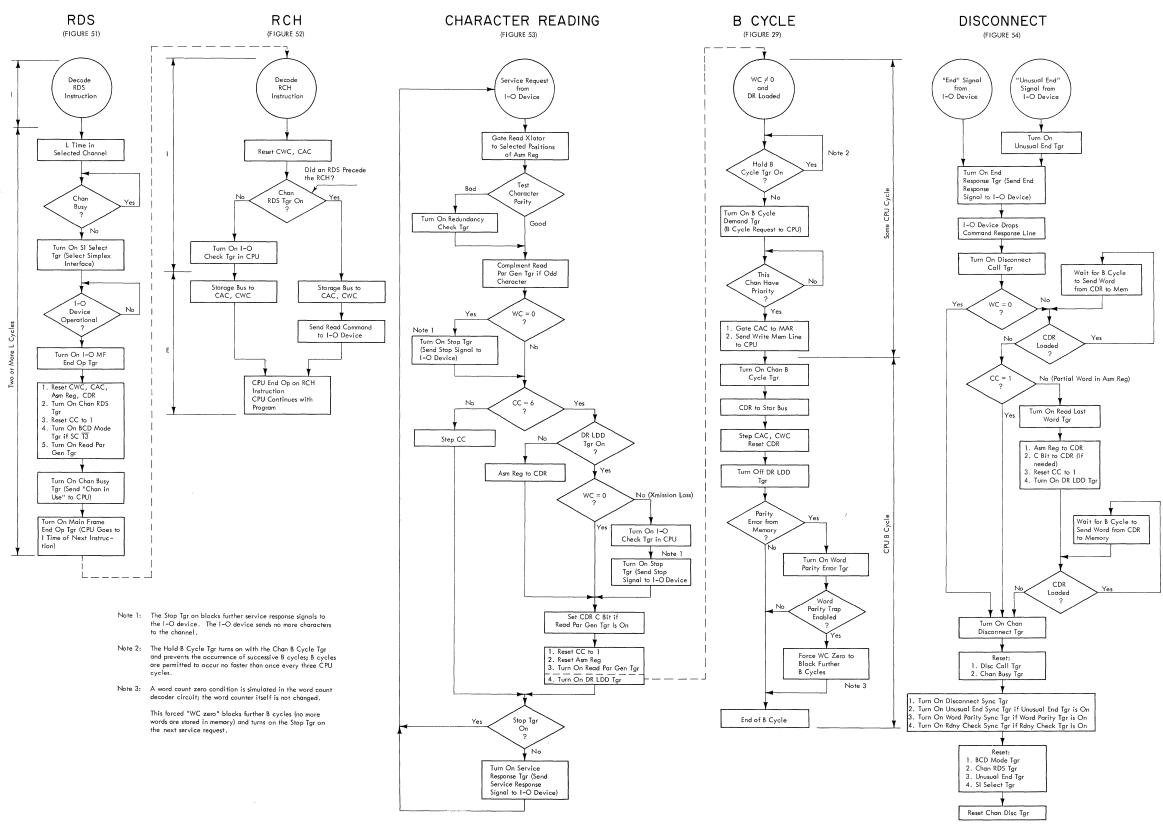

| 25 | Read Tape Operation Sequence                        | 29 |

|----|-----------------------------------------------------|----|

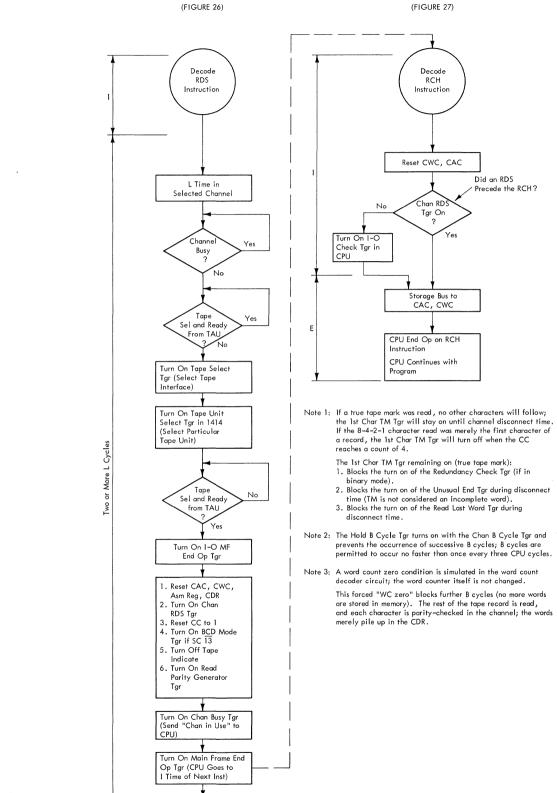

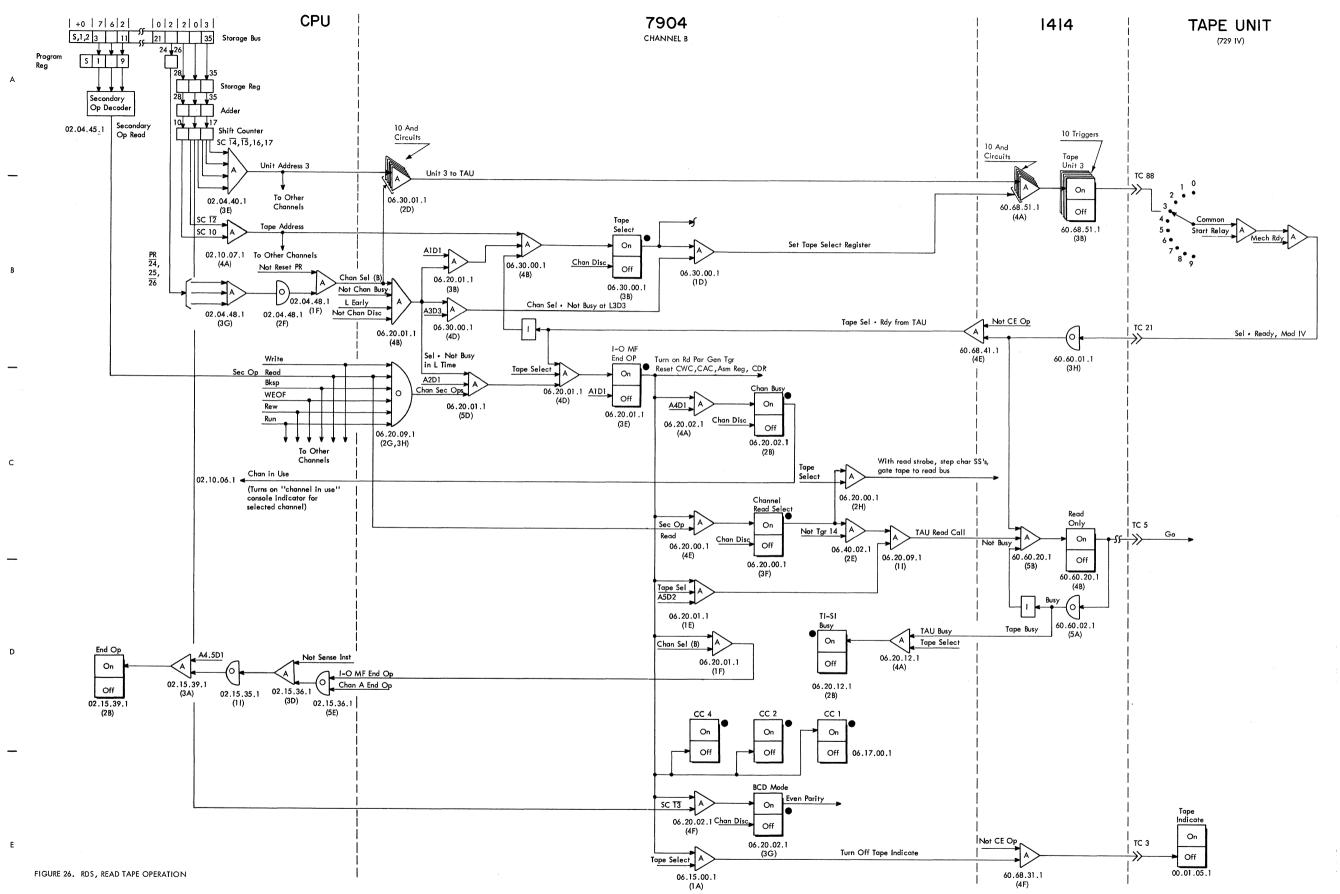

| 26 | RDS, Read Tape Operation                            | 30 |

| 27 | RCH, Read Tape Operation                            | 30 |

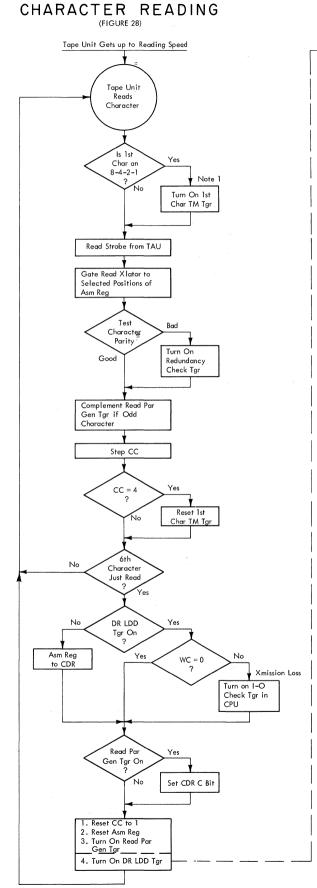

| 28 | Character Reading, Read Tape Operation              | 31 |

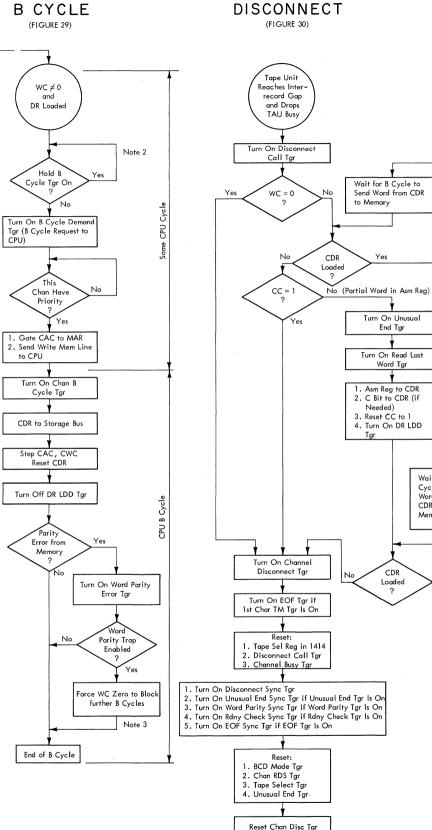

| 29 | B Cycle, Read Tape Operation                        | 32 |

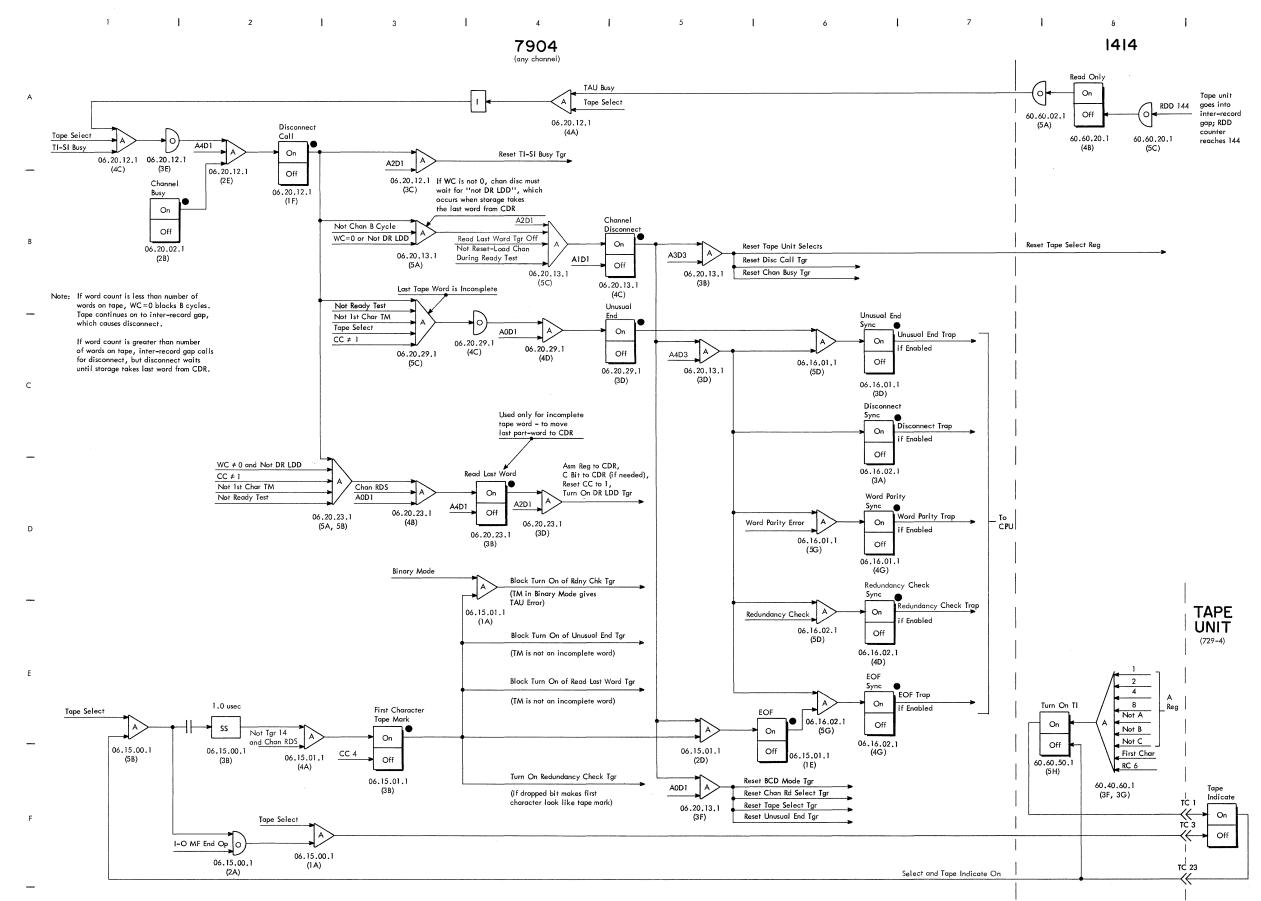

| 30 | End Operation and Disconnect, Read Tape Operation   | 33 |

| 31 | Data Flow, Read Tape Operation                      | 34 |

| 32 | I-O Check and Redundancy Check, Read Tape Operation | 35 |

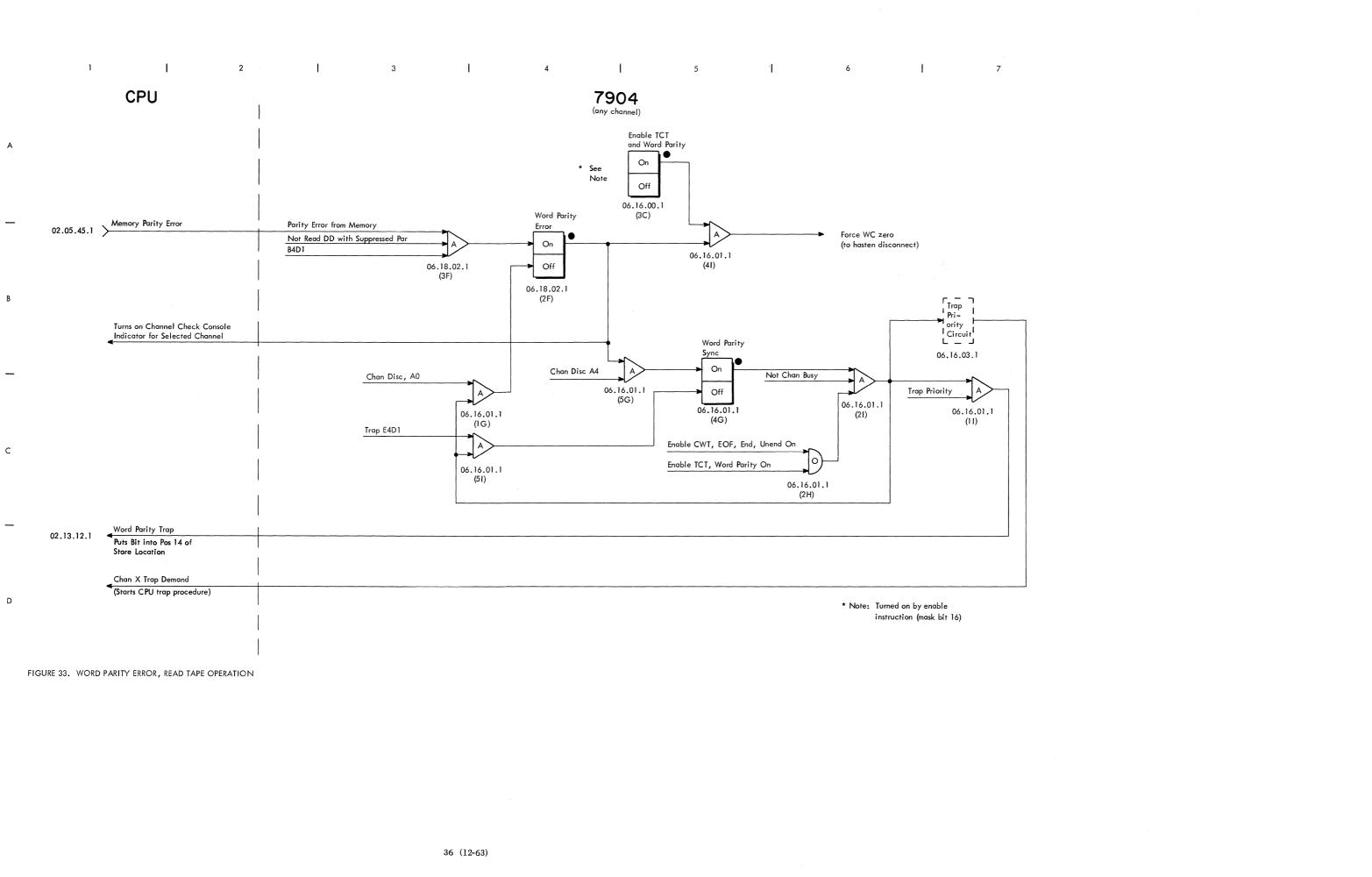

| 33 | Word Parity Error, Read Tape Operation              | 36 |

|    |                                                     |    |

| 34    | BSR, Backspace Operation                               | 3 |

|-------|--------------------------------------------------------|---|

| 35    | WEF, Write-End-of-File Operation                       | 3 |

| 36    | REW, Rewind Operation                                  | 3 |

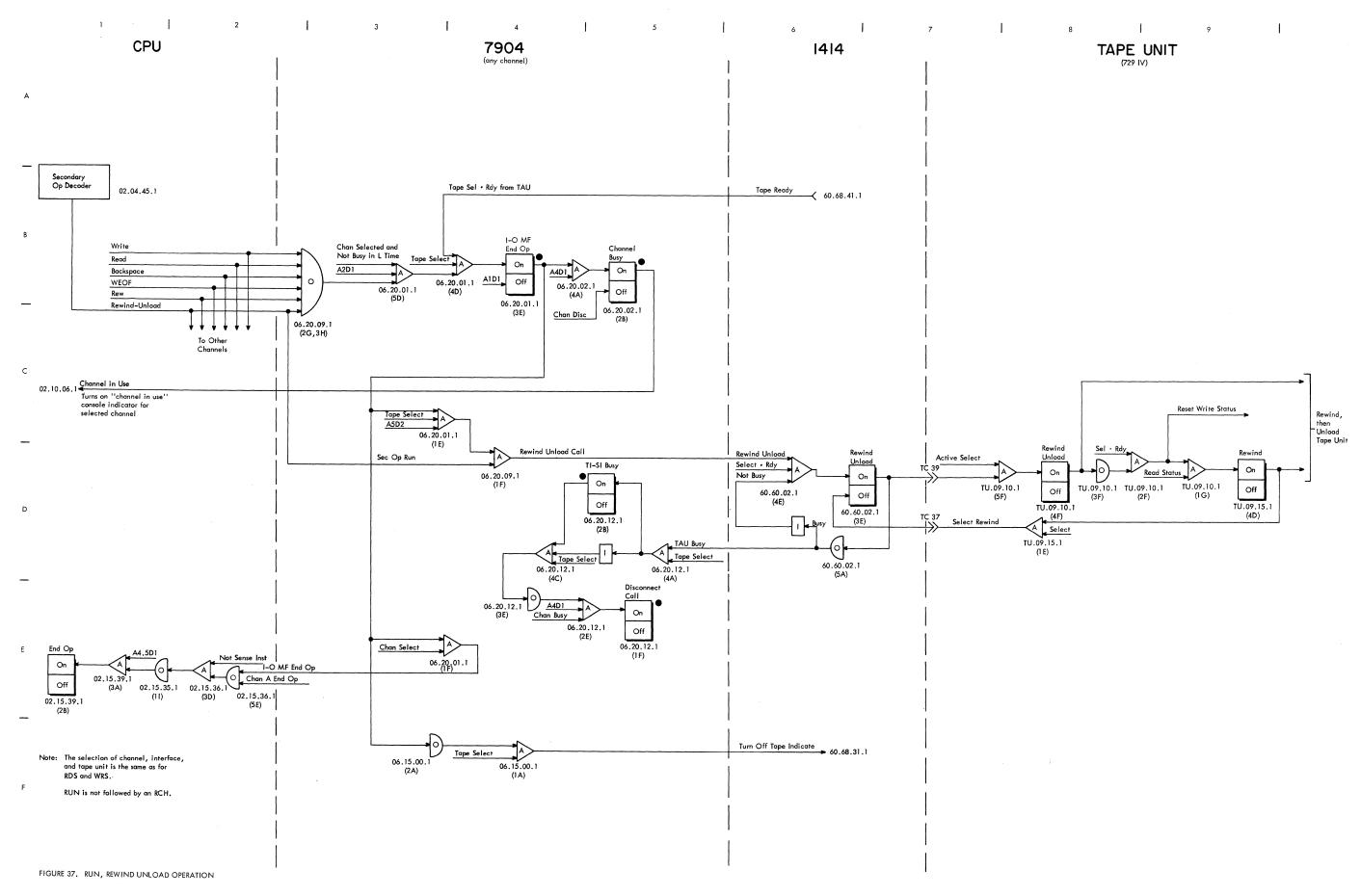

| 37    | RUN, Rewind Unload Operation                           | 4 |

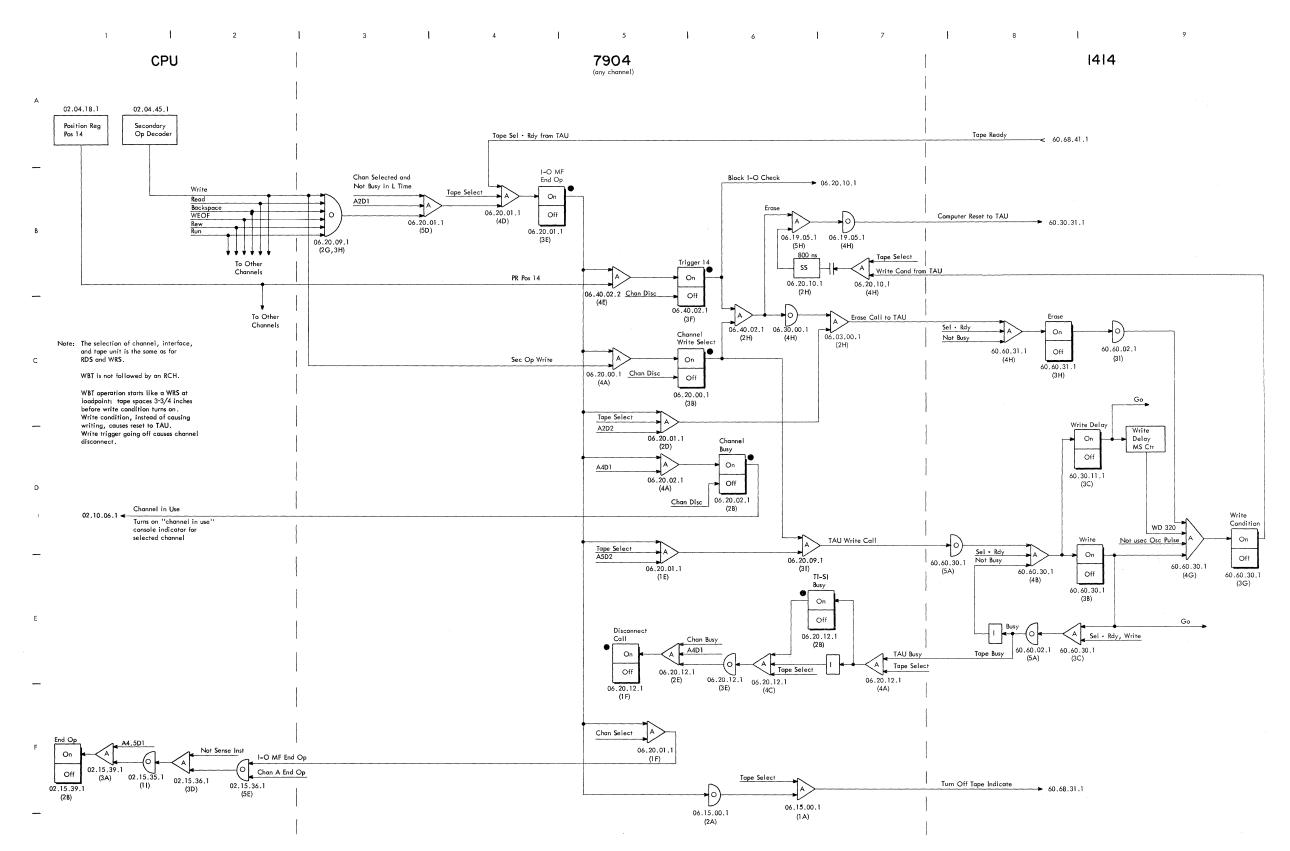

| 38    | WBT, Write Blank Tape Operation                        | 4 |

| TAPE  | READY TEST                                             |   |

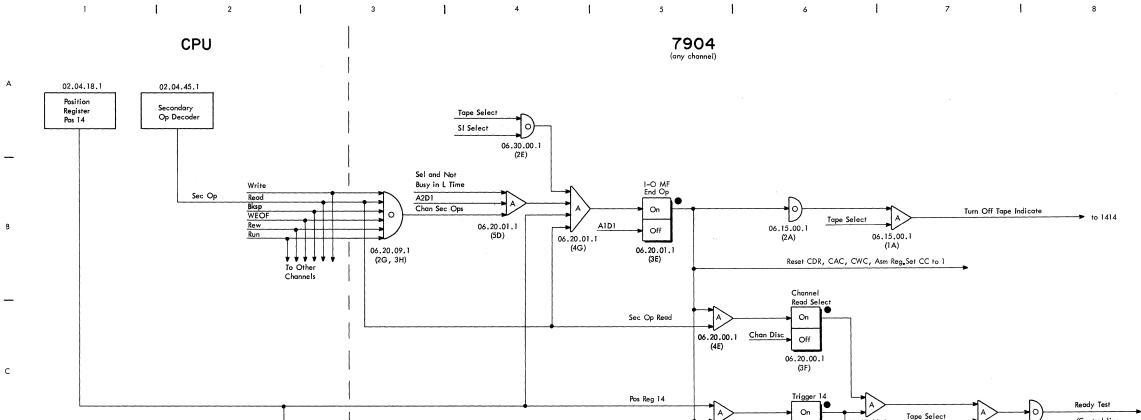

| 39    | SEN, Tape Ready Test Operation                         | 4 |

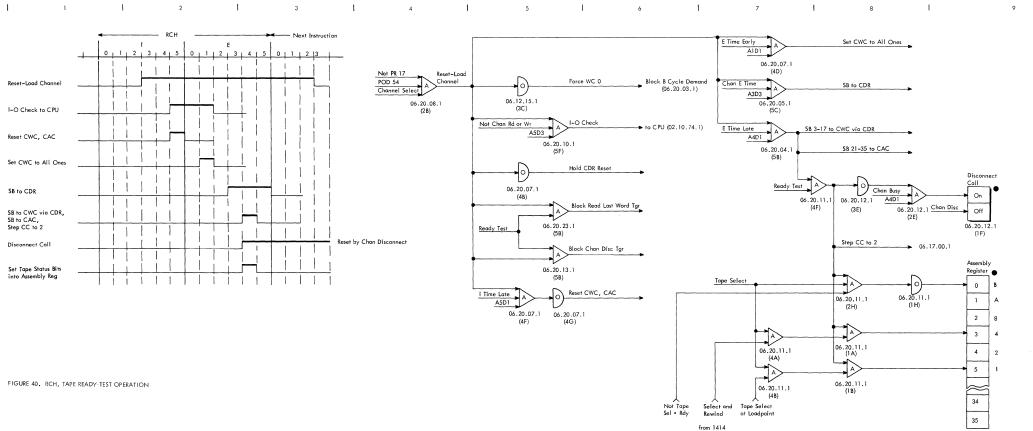

| 40    | RCH, Tape Ready Test Operation                         | 4 |

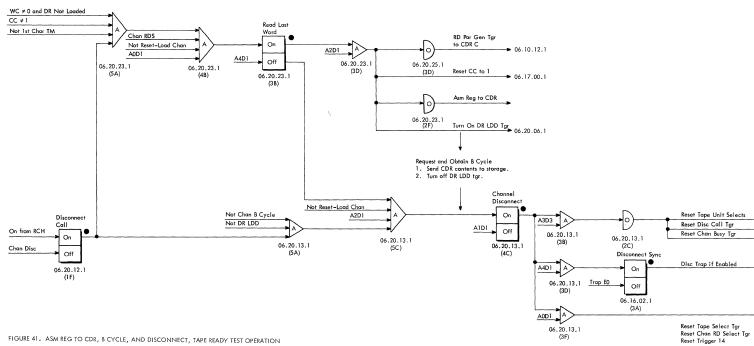

| 41    | Asm Reg to CDR, B Cycle, and Disconnect,               |   |

|       | Tape Ready Test Operation                              | 4 |

| WRITI | E SIMPLEX LOGIC                                        |   |

| 42    | Simplex Interface Signal Lines                         | 4 |

| 43    | Write Simplex Operation Sequence                       | 4 |

| 44    | WRS, Simplex Interface Write Operation                 | 4 |

| 45    | B Cycle, Simplex Interface Write Operation             | 4 |

| 46    | Character Writing, Simplex Interface Write Operation   | 5 |

| 47    | End Operation and Disconnect, Simplex Interface        |   |

|       | Write Operation                                        | 5 |

| SIMPI | EX INTERFACE CONTROL                                   |   |

| 48    | Control Command, Simplex Interface Control Operation   | 5 |

| 49    | Attention, Simplex Interface                           | 5 |

| READ  | SIMPLEX LOGIC                                          |   |

| 50    | Read Simplex Operation Sequence                        | 5 |

| 51    | RDS, Simplex Interface Read Operation                  | 6 |

| 52    | RCH, Simplex Interface Read Operation                  | 6 |

| 53    | Character Reading, Simplex Interface Read Operation    | 6 |

| 54    | End Operation and Disconnect, Simplex Interface        |   |

|       | Read Operation                                         | 6 |

| 55    | Error and Trap Conditions, Simplex Interface Operation | 6 |

Figure Title

11

56 Sense Command, Simplex Interface Sense Operation 67

## CONTENTS (ILLUSTRATIONS)

WRITE DIRECT DATA LOGIC

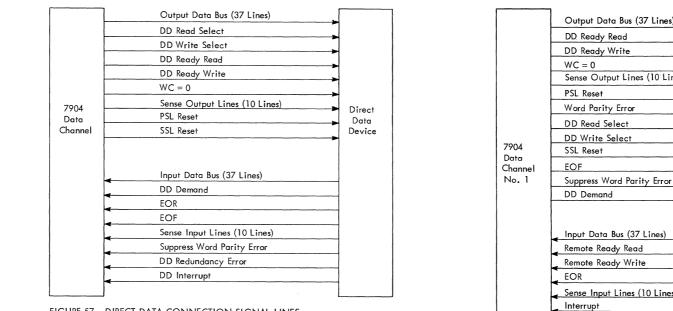

| 57   | Direct Data Connection Signal Lines                 | 71 |

|------|-----------------------------------------------------|----|

| 58   | Direct Data Signal Lines for 7040 and 7090          | 71 |

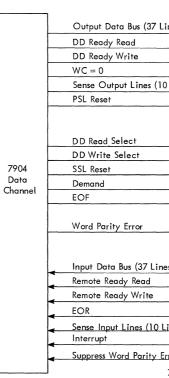

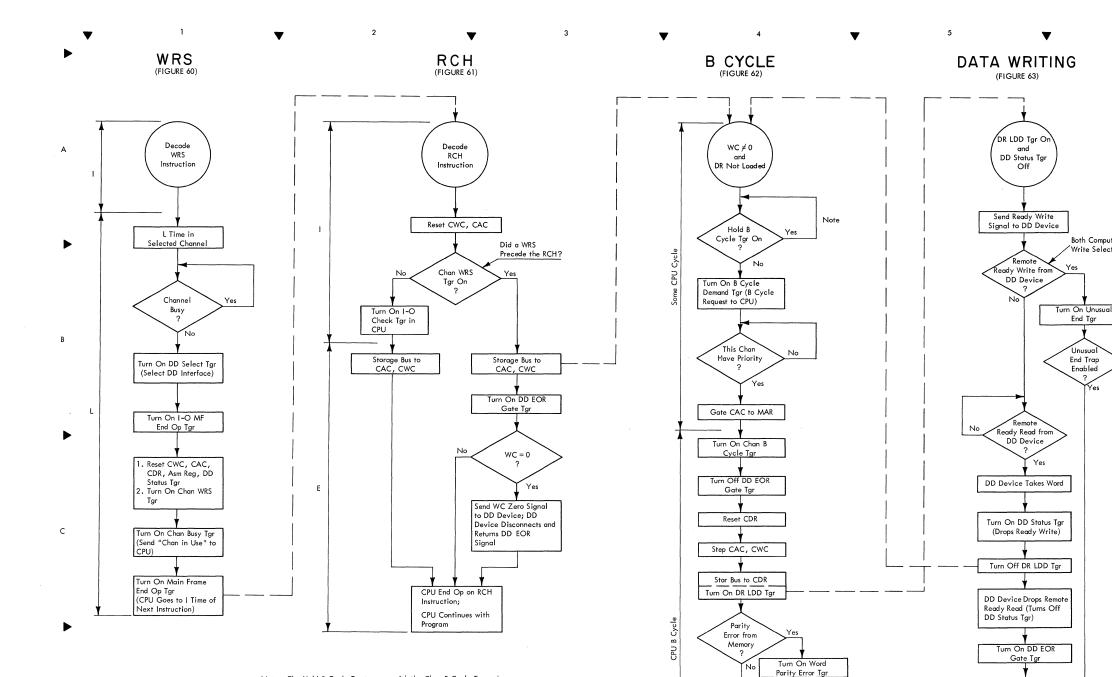

| 59   | Direct Data Write Operation Sequence                | 72 |

| 60   | WRS, DD Write Operation                             | 73 |

| 61   | RCH, Direct Data Operation                          | 74 |

| 62   | B Cycle, DD Write Operation                         | 75 |

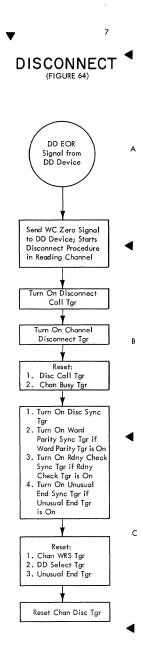

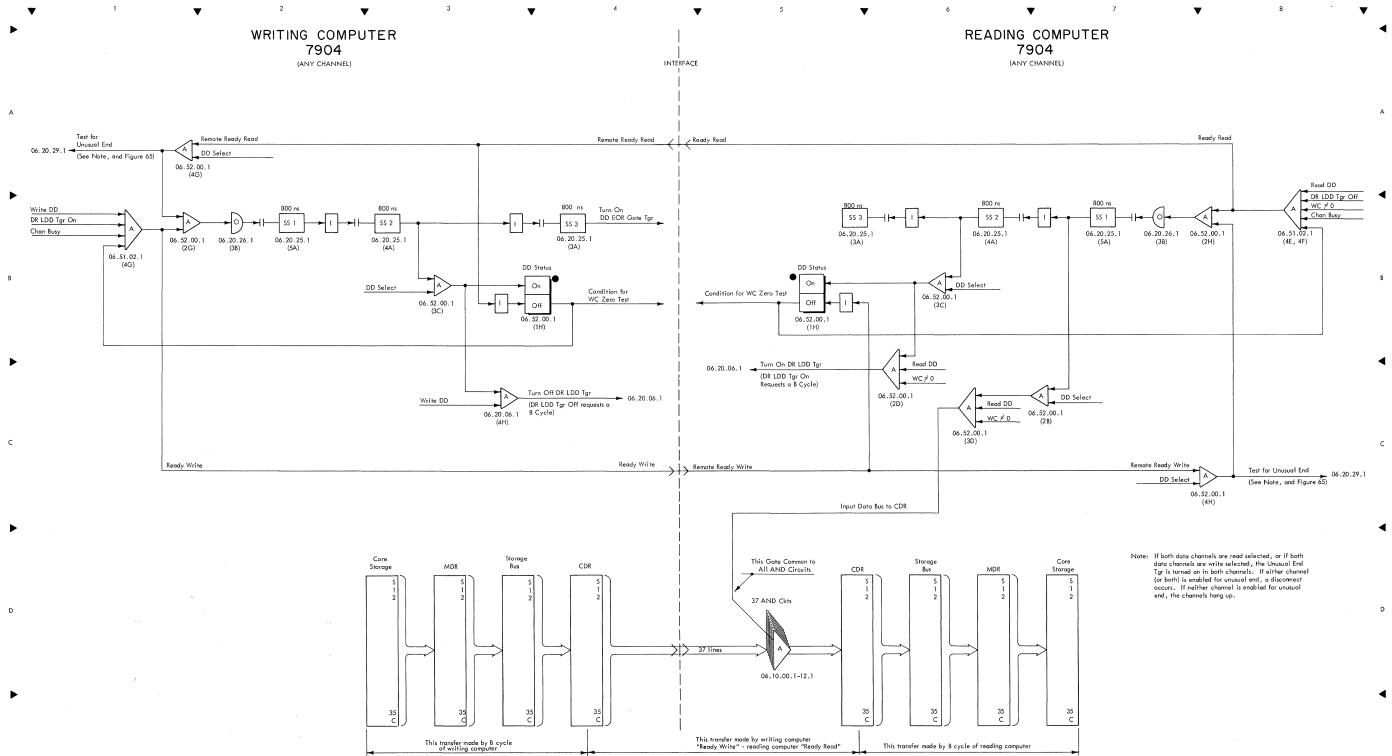

| 63   | Data Transfer Control, Direct Data Operation        | 76 |

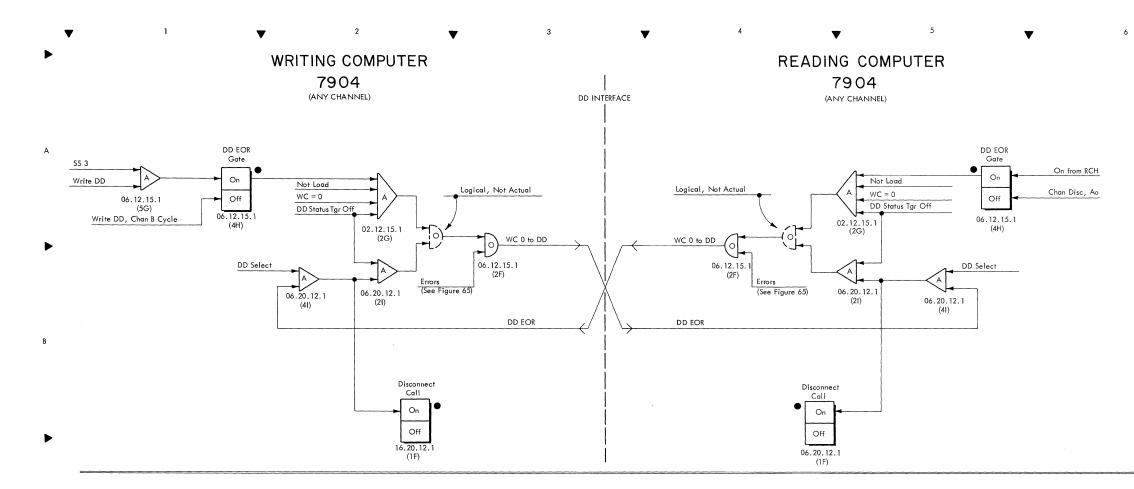

| 64   | End Operation and Disconnect, Direct Data Operation | 77 |

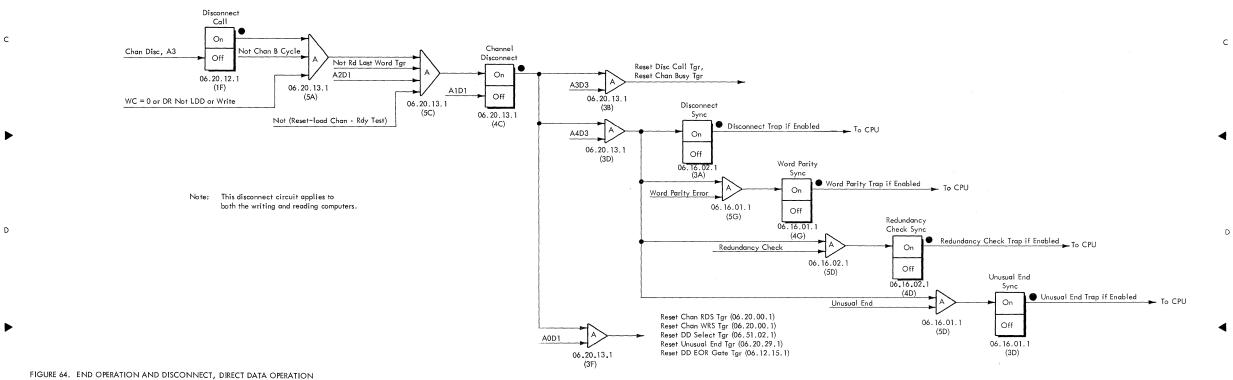

| 65   | Error Conditions, Direct Data Operation             | 78 |

| 66   | Error and Trap Conditions, DD Operation             | 78 |

|      |                                                     |    |

| READ | DIRECT DATA LOGIC                                   |    |

| 67 | Direct Data Read | Operation | Sequence |

|----|------------------|-----------|----------|

|----|------------------|-----------|----------|

## ILLUSTRATIONS (ALPHABETICAL)

| Figure    | Title                                                  | Page      |

|-----------|--------------------------------------------------------|-----------|

| 41        | Asm Reg to CDR, B Cycle, and Disconnect, Tape          |           |

|           | Ready Test Operation                                   | 43        |

| 49        | Attention, Simplex Interface                           | 56        |

| 7         | Basic Cable Arrangement, 7904 Channels and CPU         | 11        |

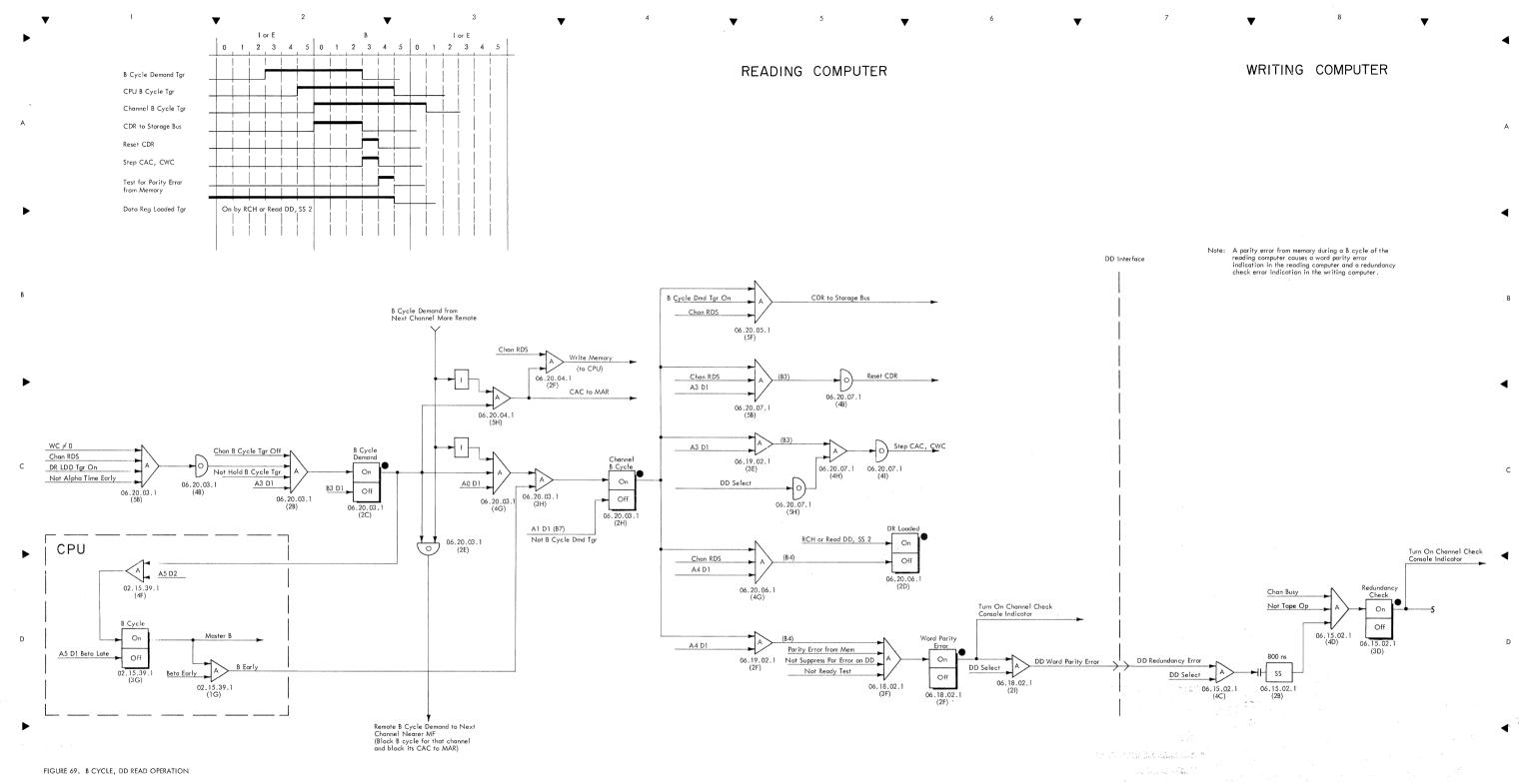

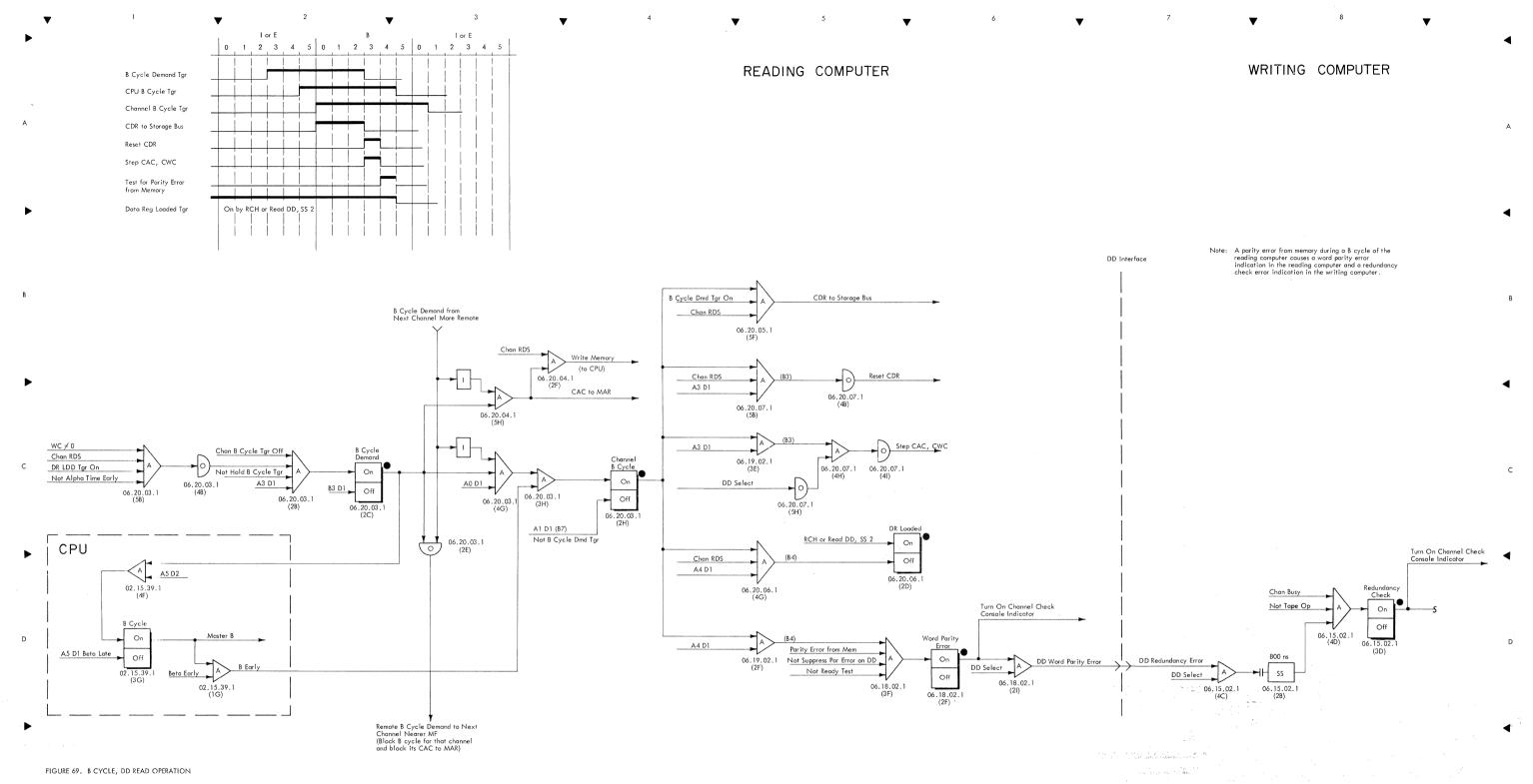

| 69        | B Cycle, DD Read Operation                             | 83        |

| 62        | B Cycle, DD Write Operation                            | 75        |

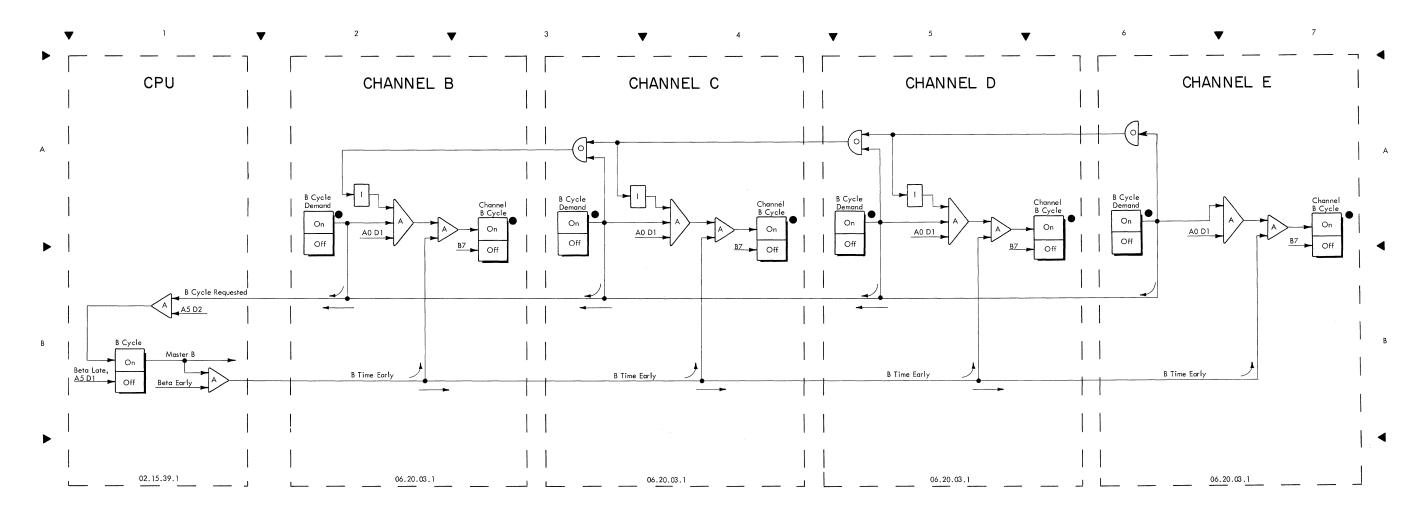

| 15        | B Cycle Priority                                       | 19        |

| 29        | B Cycle, Read Tape Operation                           | 32        |

| 45        | B Cycle, Simplex Interface Write Operation             | 49        |

| 14        | B Cycle, Write Tape Operation                          | 18        |

| 34        | BSR, Backspace Operation                               | 37        |

| 10        | Channel and Interface Selection                        | 15        |

| 5         | Channel Indicators                                     | 10        |

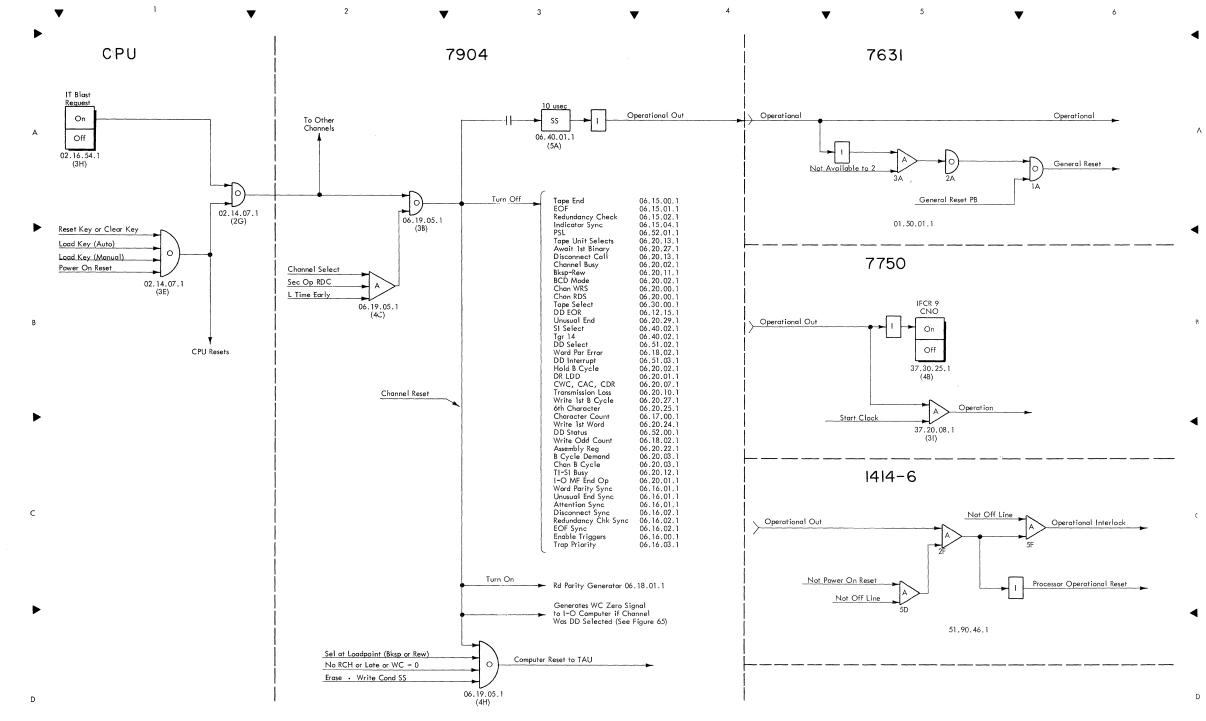

| 74        | Channel Resets                                         | 89        |

| <b>28</b> | Character Reading, Read Tape Operation                 | 31        |

| 53        | Character Reading, Simplex Interface Read Operation    | 62        |

| 46        | Character Writing, Simplex Interface Write Operation   | 50        |

| 16        | Character Writing, Write Tape Operation                | 20        |

| 48        | Control Command, Simplex Interface Control Operation   | 55        |

| 31        | Data Flow, Read Tape Operation                         | <b>34</b> |

| 18        | Data Flow, Write Tape Operation                        | 22        |

| 63        | Data Transfer Control, Direct Data Operation           | 76        |

| 57        | Direct Data Connection Signal Lines                    | 71        |

| 67        | Direct Data Read Operation Sequence                    | 81        |

| 58        | Direct Data Signal Lines for 7040-44 and 7090-94       | 71        |

| 59        | Direct Data Write Operation Sequence                   | 72        |

| 23        | Disconnect Trap Timing                                 | 26        |

| 22        | Disconnect Trap, Write Tape Operation                  | 26        |

| 64        | End Operation and Disconnect, Direct Data Operation    | 77        |

| 30        | End Operation and Disconnect, Read Tape Operation      | 33        |

| 54        | End Operation and Disconnect, Simplex Interface        |           |

|           | Read Operation                                         | 63        |

| 47        | End Operation and Disconnect, Simplex Interface        |           |

|           | Write Operation                                        | 51        |

| 17        | End Operation and Disconnect, Write Tape Operation     | 21        |

| 66        | Error and Trap Conditions, DD Operation                | 78        |

| 55        | Error and Trap Conditions, Simplex Interface Operation | 64        |

| 24        | Error and Trap Conditions, Tape Operation              | 27        |

| 68    | RDS, DD Read Operation               | 82 |

|-------|--------------------------------------|----|

| 69    | B Cycle, DD Read Operation           | 83 |

|       |                                      |    |

| PRESE | NT SENSE LINES AND STORE SENSE LINES |    |

|       |                                      |    |

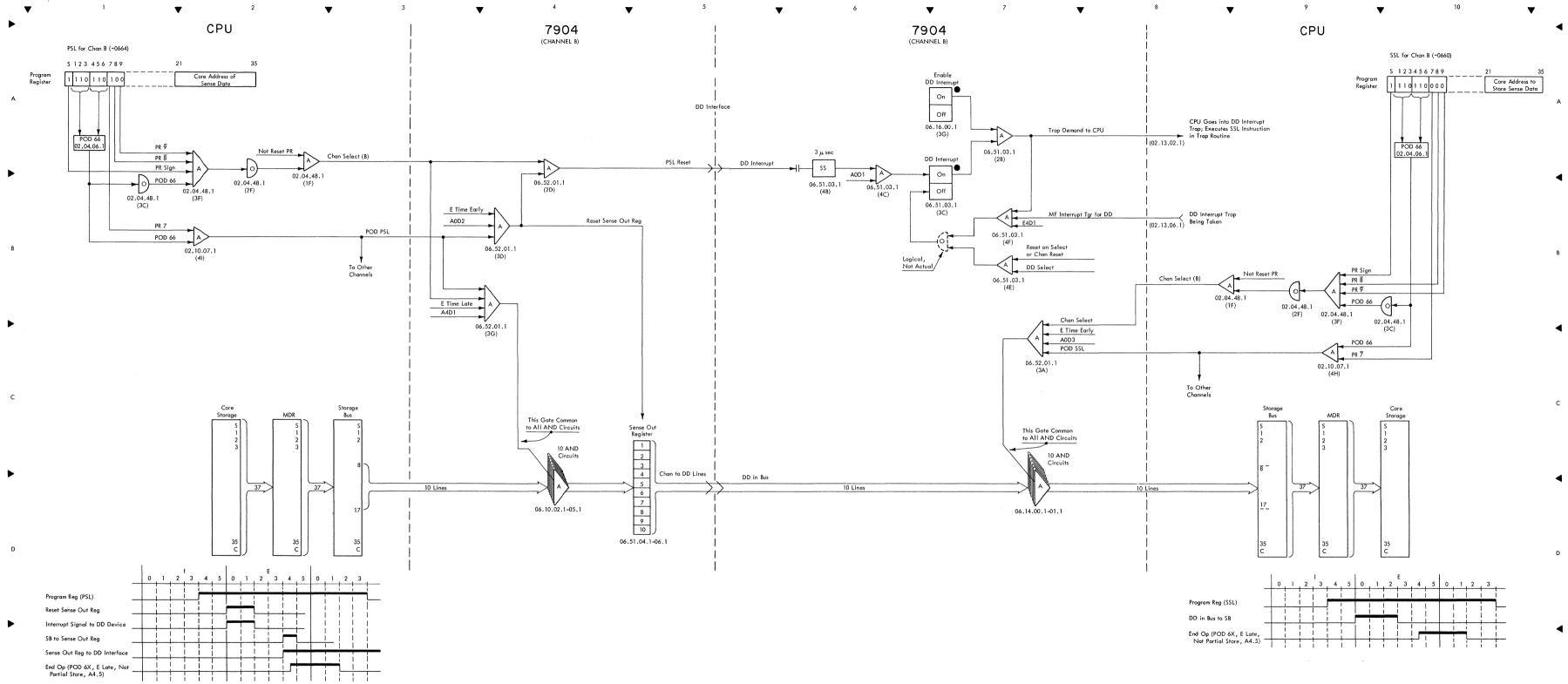

| 70    | PSL and SSL, Direct Data Operation   | 84 |

|       |                                      |    |

| DIAGN | OSTIC INSTRUCTIONS                   |    |

|       |                                      |    |

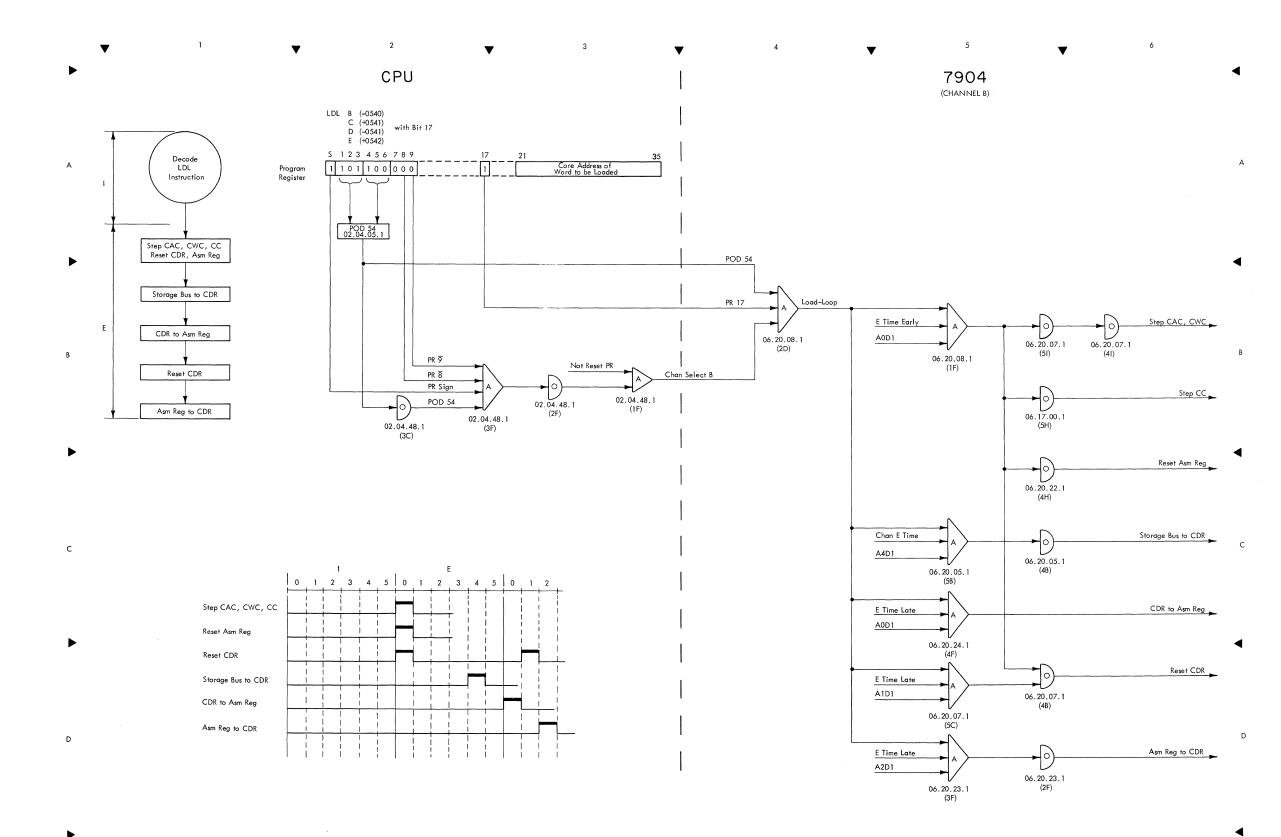

| 71    | Load Data Register and Loop (LDL)    | 87 |

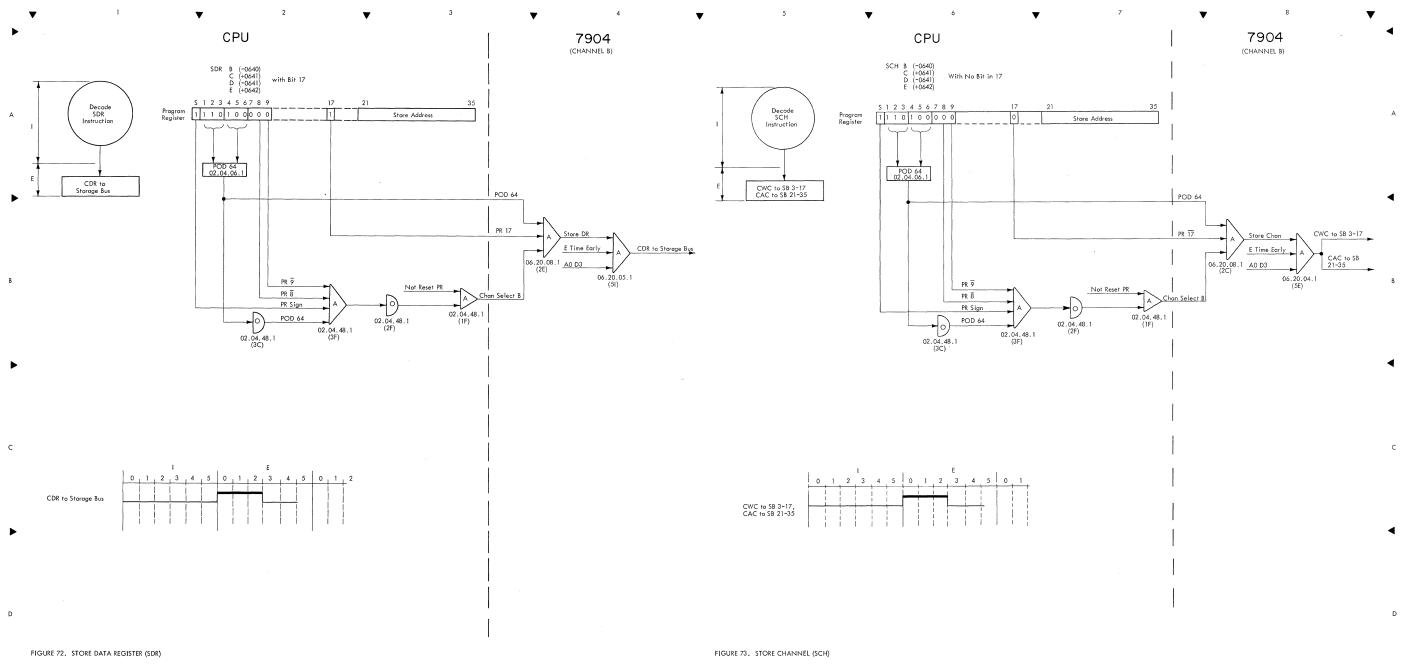

| 72    | Store Data Register (SDR)            | 88 |

| 73    | Store Channel (SCH)                  | 88 |

|       |                                      |    |

| RESET | 'S                                   |    |

|       |                                      |    |

| 74 | Channel Resets | 89 |

|----|----------------|----|

#### Figure <u>Title</u>

81

## Page

| 65     | Error Conditions, Direct Data Operation              | 78 |

|--------|------------------------------------------------------|----|

| 21     | ETT, End-of-Tape Operation                           | 25 |

| 1      | Frame 02 - Front Layout (Wiring Side)                | 7  |

| 32     | I-O Check and Redundancy Check, Read Tape Operation  | 35 |

| 19     | I-O Check and Redundancy Check, Write Tape Operation | 23 |

| $^{2}$ | I-O Connector Panel                                  | 7  |

| 71     | Load Data Register and Loop (LDL)                    | 87 |

| 70     | PSL and SSL, Direct Data Operation                   | 84 |

| 6      | Q Line and C Line Examples                           | 11 |

| 61     | RCH, Direct Data Operation                           | 74 |

| 27     | RCH, Read Tape Operation                             | 30 |

| 52     | RCH, Simplex Interface Read Operation                | 61 |

| 40     | RCH, Tape Ready Test Operation                       | 43 |

| 13     | RCH, Write Tape Operation                            | 18 |

| 68     | RDS, DD Read Operation                               | 82 |

| 26     | RDS, Read Tape Operation                             | 30 |

| 51     | RDS, Simplex Interface Read Operation                | 60 |

| 50     | Read Simplex Operation Sequence                      | 59 |

| 25     | Read Tape Operation Sequence                         | 29 |

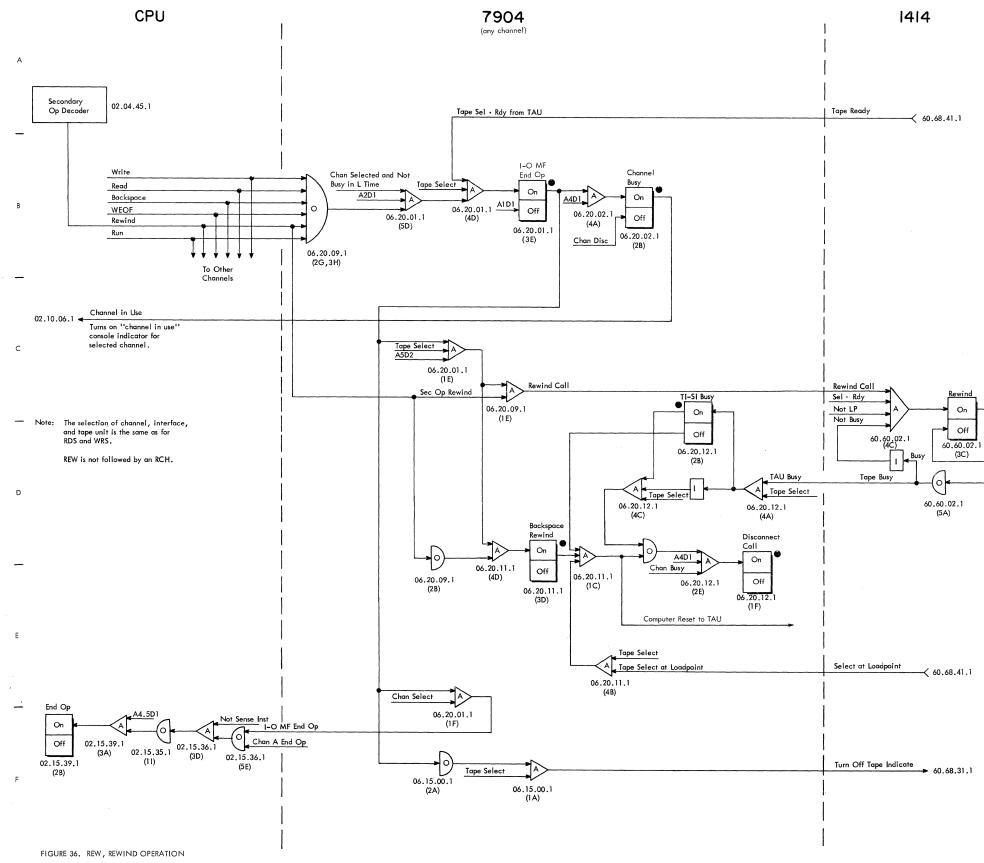

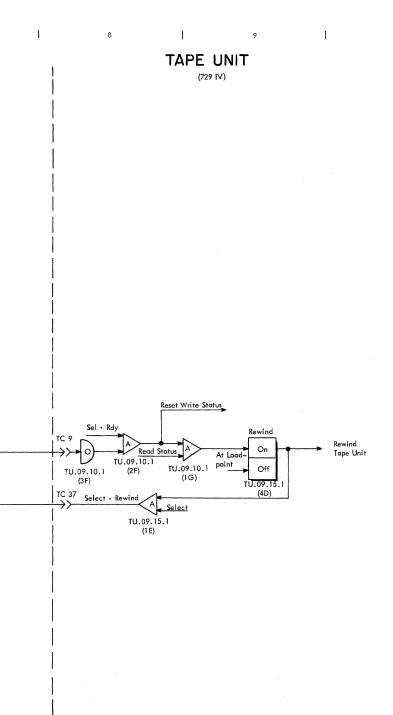

| 36     | REW, Rewind Operation                                | 39 |

| 37     | RUN, Rewind Unload Operation                         | 40 |

| 56     | Sense Command, Simplex Interface Sense Operation     | 67 |

| 39     | SEN, Tape Ready Test Operation                       | 42 |

| 42     | Simplex Interface Signal Lines                       | 46 |

| 73     | Store Channel (SCH)                                  | 88 |

| 72     | Store Data Register (SDR)                            | 88 |

| 8      | Tape Interface Signal Lines                          | 13 |

| 9      | Tape Unit Selection                                  | 14 |

| 38     | WBT, Write Blank Tape Operation                      | 41 |

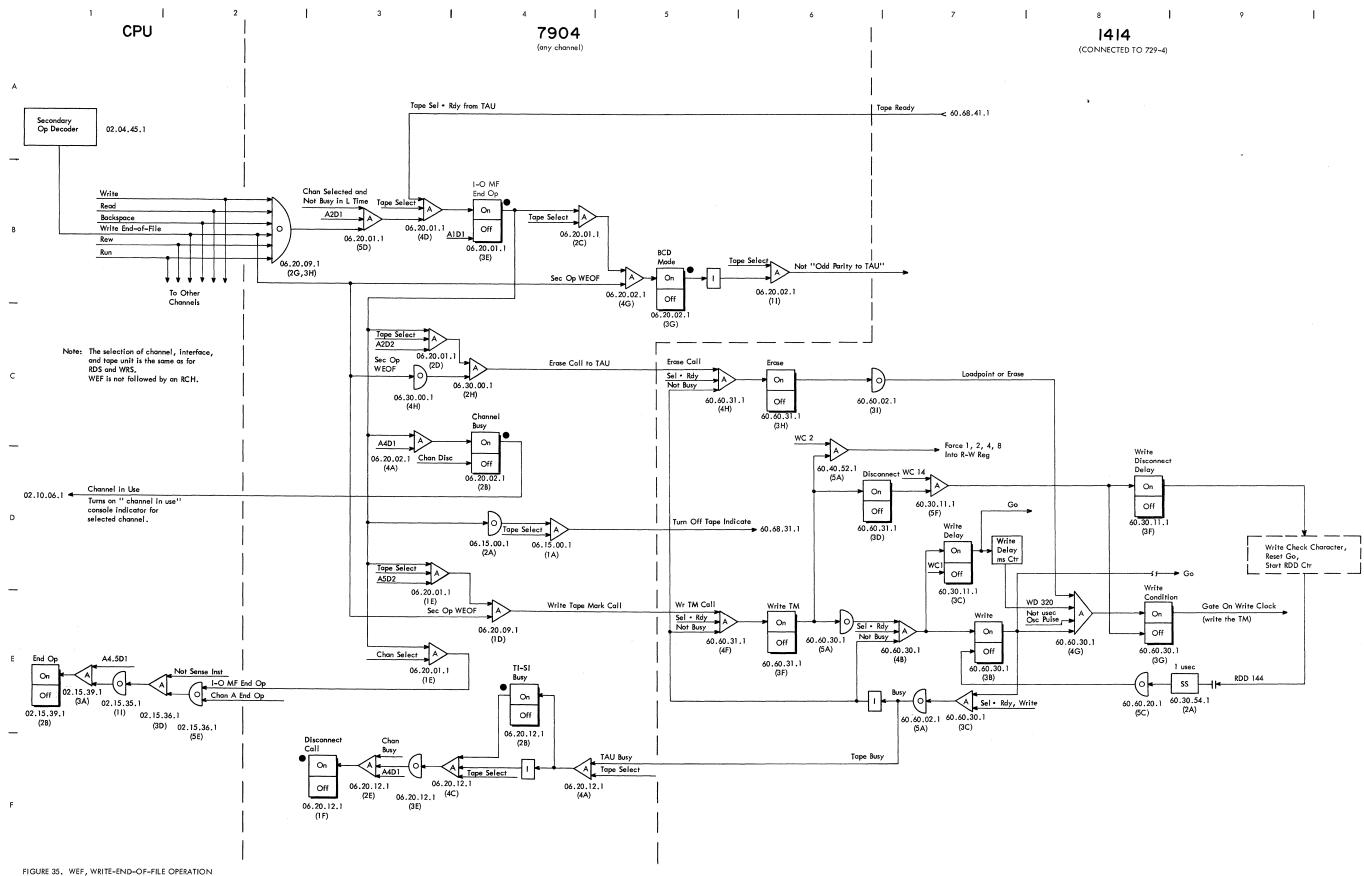

| 35     | WEF, Write-End-of-File Operation                     | 38 |

| 33     | Word Parity Error, Read Tape Operation               | 36 |

| 20     | Word Parity Error, Write Tape Operation              | 24 |

| 43     | Write Simplex Operation Sequence                     | 47 |

| 11     | Write Tape Operation Sequence                        | 16 |

| 60     | WRS, DD Write Operation                              | 73 |

| 44     | WRS, Simplex Interface Write Operation               | 48 |

| 12     | WRS, Write Tape Operation                            | 17 |

| 4      | 7904 Front View                                      | 9  |

| 3      | 7904 Rear View                                       | 8  |

| -      |                                                      | -  |

#### PHYSICAL DESCRIPTION

#### FRAME CONFIGURATION

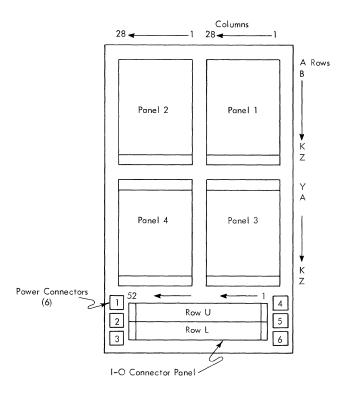

The 7904-1 and 7904-2 are packaged in a standard rack and panel frame (Figure 1). The frame is divided into four panels that provide space for the logic circuitry required for two channels. Panels 1 and 3 accommodate the logic circuits for one channel, and panels 2 and 4 accommodate the circuits for the second channel.

The frame is identified as frame 02. In a system where two frames are used (more than two channels), the frames are designated as frames 02 A and 02 B. This designation would be used, for example, in a system containing two 7904-2 data channels.

To locate cards, pins, or components, each panel is divided into rows (A through K) and columns (1 through 28) as shown in Figure 1. The two adjacent rows identified as Y and Z are used to jumper card connections from panel 3 to panel 1, and from panel 4 to panel 2, respectively. Row Z of panels 3 and 4 provide connections for dot OR'ing signal lines from the two channels to the I-O connector panel.

Logic cards are on the rear side of the panels and are accessible through the rear of the machine.

#### I-O CONNECTOR PANEL

Cables containing the data and signal lines from the CPU and associated I-O units are connected to the I-O connector panel (Figures 1 and 2). The I-O connector panel consists of two rows of connectors designated as the upper row (U) and the lower row (L). Each row has 52 positions. Figure 2 shows the connector positions grouped according to functions.

#### POWER

#### Power Supplies

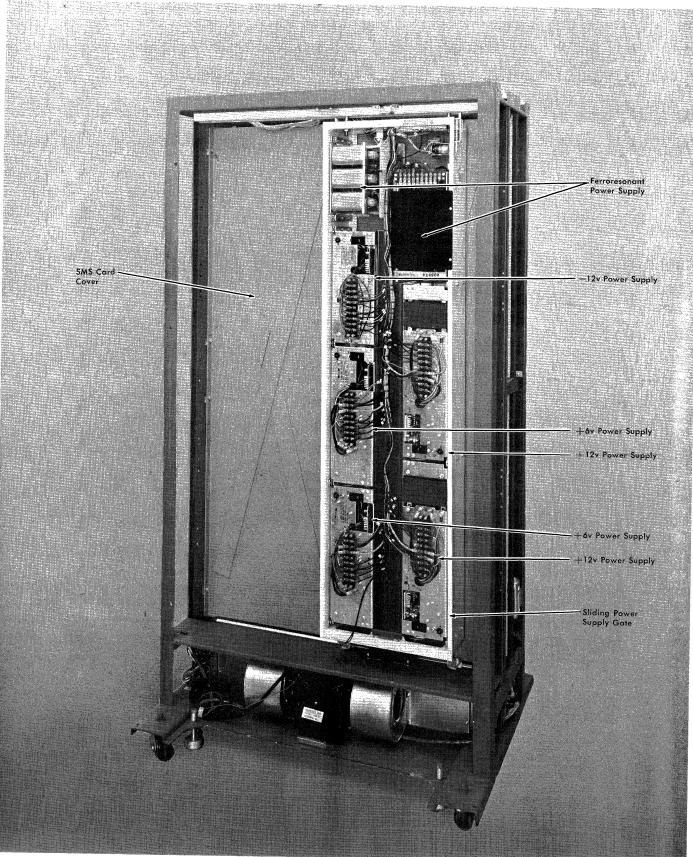

The dc power required for the operation of electronic circuitry in a 7904-1 or 7904-2 is furnished by five self-contained power supplies on a sliding gate at the rear of the frame (Figure 3). The dc power supplies are numbered 1 through 5, and in that order provide the following voltages: -12v, +12v, +6v, +12v, and +6v.

A -12v (mc) output from power supply 1 is used for marginal check purposes. A connector is provided so that a portable  $\pm 3$ -volt marginal check power supply may be connected in series with the -12 vm output. Refer to Figure 4 for the location of the marginal check connector.

Located on each dc power supply are two circuit breakers designated as CB 1 and CB 2. CB 2 is a

thermal-type circuit breaker connected to the input of the power supply to protect it from damage in the event of a component failure within the supply. The contacts may be operated manually by means of a reset plunger, which resets the circuit breaker. The plunger has a white ring around its base that is exposed when the circuit breaker is tripped. CB 1 is connected on the output of each power supply and provides overload protection. This circuit breaker may be operated manually with an on-off switch used to reset the contacts.

Input power to the five dc power supplies is supplied by a 1,250 watt ferroresonant power supply that regulates the input voltage. The ferroresonant supply is also on the sliding gate at the rear of the frame, and provides a regulated output of approximately 133 vac.

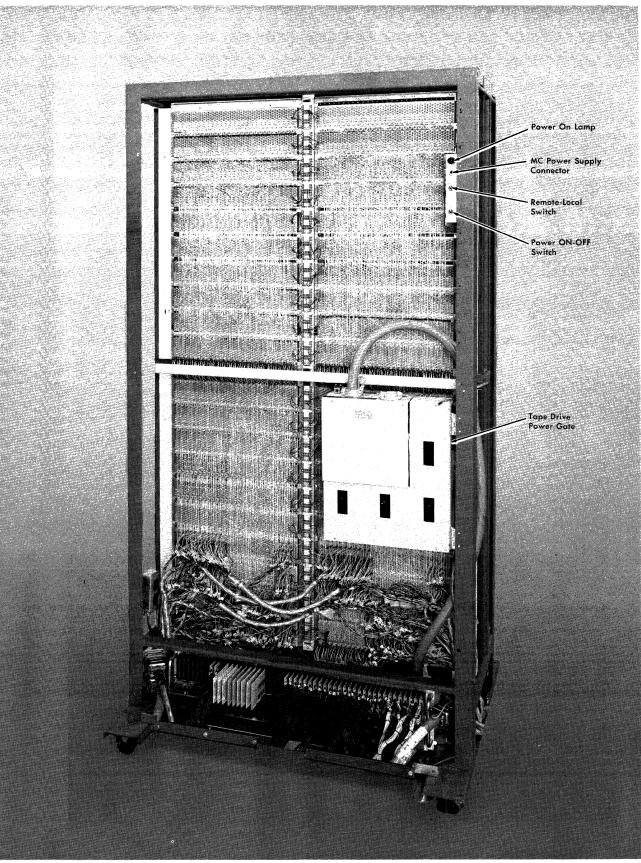

#### Power Switches

Two power switches and a power on lamp are on the upper right portion of the front of the frame (Figure 4). The switches are the remote-local switch and the power on-off switch.

Input power to the 7904 is distributed from the CPU. With the remote-local switch in the remote position, input power to the 7904 is controlled solely by the CPU power switches. With the remote-local switch in the local position, input power may be locally controlled with the power on-off switch. Local power control is used primarily for off-line operation of the 7904. The power on-off switch is ineffective when the remote-local switch is in the remote position.

The power on lamp, when on, indicates that dc power is up.

#### Tape Drive Power Gate

The tape drive power gate is essentially a junction box from which 115 vac and 208v, 3 phase power is distributed to tape drives associated with a particular 7904. The tape drive power gate is mounted on the front of the frame (Figure 4), and is hinged so that it will swing out to permit access to the wiring directly behind it (panel 3). Four separate power outputs are available from the tape drive power gate. Each output provides power for a bank of five tape units. A circuit breaker for each separate tape power output is in the tape drive power gate. Input power to the tape drive power gate is supplied from the CPU.

#### Power Input And Output Connectors

There are six connectors for attaching power cables to a 7904 (Figures 1 and 2). The connectors are numbered 1 through 6 and are on each side of the I-O connector panel. Input power from the CPU is fed through connectors 1 and 2 to the 1,250 watt ferroresonant power supply and the tape drive power gate. The four power outputs from the tape drive power gate are fed to connectors 3, 4, 5, and 6.

#### CHANNEL INDICATOR LIGHTS

Neon indicators that show the status of various control triggers, error triggers, and register positions are on the wiring side of the panels associated with each channel. The location of the indicators and their Systems page reference are shown in Figure 5.

## BASIC CABLE ARRANGEMENT BETWEEN CPU AND CHANNELS

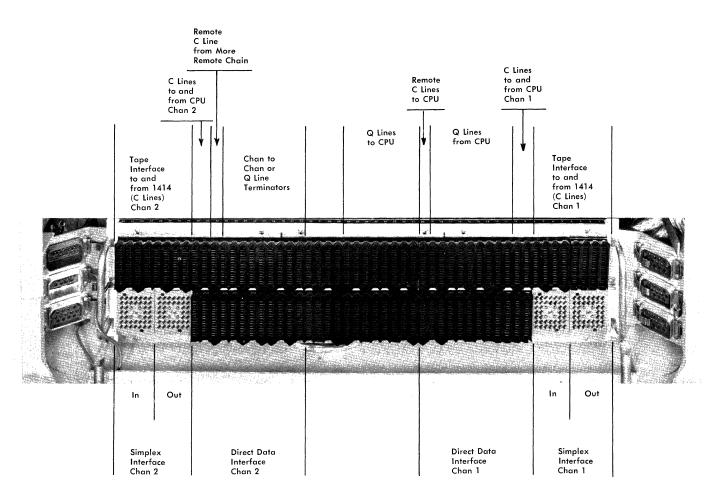

This section describes the basic groups of interconnecting cables between the CPU and 7904 data channels. This information is not intended for use as a guide or as instructions for connecting the cables; a cable chart should be referred to for this purpose.

The interconnecting cables consisting of signal and data lines may be divided into three groups: the channel to CPU lines (Q lines), the CPU to channel lines (Q lines), and a group of mixed control lines (C lines). Q lines are distributed lines, or lines that are shared on either end. Two examples are shown in Figure 6. C lines are point-to-point lines as illustrated in Figure 6.

The three basic groups of cables are shown in Figure 7. Two 7904-2 data channels are used as an example in the figure. The channel to CPU lines are in eight cables that are divided into two banks, with each bank consisting of four cables from each 7904-2. Each bank of four cables contains the channel to storage bus lines, trap identification bit lines, and certain control lines (such as B cycle demand) for the two channels in the respective 7904-2. These lines are jumpered (dot OR'ed) in each 7904-2 and are shared by the two channels. The cables are attached to module C of the CPU.

The second group consists of five cables that contain the CPU to channel lines (Q lines). These lines are shared by all four channels and generally consist of:

- 1. Storage bus to channel lines.

- 2. Tape unit address lines.

- 3. Primary and secondary operation decoder lines.

- 4. Interface select (address) lines.

- 5. Clock pulse lines.

- 6. Miscellaneous control lines.

The method of distributing the lines contained in the five cables is shown in Figure 7. The lines from the CPU are attached to channel 1, where they are jumpered internally to channel 2, and then routed to the second 7904-2 by cables. The lines are internally distributed to channels 3 and 4 in a like manner. In the last channel, the lines are terminated with terminating resistor loads. The sequence in which the channels are connected to the lines establishes the relative remoteness of the channels with respect to the CPU. Therefore, the sequence determines the channel priority status for B cycle and trap requests. The channel with the terminating resistor loads (Figure 7), in this case, channel 4, is always the most remote channel and thus has priority over other channels for B cycle and trap service. Channel 3 has second priority, and the remaining two channels are connected in the order of decreasing priority.

The third group of cables contains mixed control lines (C lines): control lines from the CPU to channel, and lines from the channel to CPU. There is one cable for each channel in the system, and each cable contains control lines that are not shared by other channels. These lines are:

| CPU to channel | 1. | Channel select.            |

|----------------|----|----------------------------|

|                | 2. | Trap enable lines.         |

|                | 3. | Tape density switch lines. |

| Channel to CPU | 1. | Channel in use.            |

|                | 2. | Direct data interrupt.     |

|                | 3. | Channel trap demand.       |

4. Channel check indicator.

The specific connector locations for attaching these cables to module C of the CPU are shown in Figure 7. These locations determine the identification (B, C, D, or E) of the respective channels, and thus the trap store location. Each location consists of two edge connector positions for attaching a cable.

<u>Note:</u> A channel's designation, B, C, D, or E, is not indicative of its priority status for B cycles and trap servicing. The priority status (remoteness from the CPU) is determined by the sequence in which the channels are connected to the CPU to channel lines.

FIGURE 3. 7904 REAR VIEW

FIGURE 4. 7904 FRONT VIEW

|   | 28     | 27          | 26         | <b>2</b> 5  | 24            | 23                | 22          | 21    | 20             | 19    | 18 | 17                  | 16    | 15                | 14    | 13                | 12        | 11                | 10    | 9                    | 8           | 7     | 6            | 5           | 4                 | 3           | 2           | 1          |   |

|---|--------|-------------|------------|-------------|---------------|-------------------|-------------|-------|----------------|-------|----|---------------------|-------|-------------------|-------|-------------------|-----------|-------------------|-------|----------------------|-------------|-------|--------------|-------------|-------------------|-------------|-------------|------------|---|

|   |        | Tape<br>Sel | SI<br>Sel  | DD<br>Sel   |               |                   | Chan<br>WRS |       | Ctrl<br>Sense  |       |    |                     |       | IO/M<br>End<br>Op | F     | DD<br>EOR<br>Gate | Wd<br>Ctr | Dr<br>Load-<br>ed | Char  | Write<br>1st<br>Word | Last        |       |              |             | B<br>Cycle<br>Dmd | B<br>Cycle  |             | lst<br>BIN |   |

| В |        | TI          | SI         | DD          |               |                   |             |       |                |       | TI | TI SI               |       | Op                |       | DD                | - 0       | eu                |       | TI SI                |             |       |              |             | Dinu              |             | Cycle       | TI         | В |

|   |        | 30.00       | 40.02      |             |               |                   |             |       | 40.02          |       |    |                     |       | 20.01             |       | 12.15             | 12.15     | 20.06             |       |                      | 20.23       | 20.13 | 20.12        |             |                   |             | 20.27       | 20.27      |   |

|   |        |             |            | Tape<br>End |               | lst<br>Char<br>TM | of          |       | Redun<br>Check |       |    | Prog<br>Ind<br>Sync |       |                   |       |                   |           |                   |       | Serv<br>Resp         |             |       | Attn<br>Resp |             | Stop              | Unus<br>End | End<br>Resp |            | с |

| С |        |             |            | ΤI          |               |                   | TI DD       |       |                |       |    |                     |       |                   |       |                   |           |                   |       | SI                   |             | SI    | SI           |             | SI                |             | SI          |            | C |

|   |        |             |            | 15.00       |               | 15.01             | 15.01       | 18.02 | 15.02          | 20.10 |    | 15.04               |       |                   |       |                   |           |                   |       | 20.26                |             | 20.28 | 20.28        |             | 20.27             | 20.29       | 20.29       |            |   |

|   |        |             | Enb<br>CWT | 1           | Enb<br>ICT Wo | ł                 | Enb<br>Attn |       | Enb<br>DD      |       |    |                     |       | Par               | Sync  | Redun<br>Check    |           |                   |       |                      | Trap<br>PRI |       |              | DD<br>Inter |                   |             |             |            |   |

| D |        |             |            |             | Par           |                   | sı          |       | Int<br>DD      |       |    | SI                  | Sync  | Sync              |       | Sync              | TIDD      |                   |       |                      |             |       |              | DD          |                   |             |             |            | D |

|   |        |             | 16.00      |             | 16.00         |                   | 16.00       |       | 16.00          |       |    | 16.01               | 16.01 | 16.01             | 16.02 | 16.02             | 16.02     |                   |       |                      | 16.03       |       |              | 51.03       |                   |             |             |            |   |

| ž | L<br>r |             |            |             |               |                   |             |       |                |       |    |                     |       |                   |       |                   |           |                   |       |                      |             |       |              |             |                   |             |             | L<br>T     | 2 |

|   |        |             |            |             |               |                   |             |       |                |       |    |                     |       |                   |       |                   |           | aracte<br>Countei |       |                      |             |       |              |             |                   |             |             |            |   |

| Н |        |             |            |             |               |                   |             |       |                |       |    |                     |       |                   |       |                   | 4         | 2<br>TI SI .      | 1     |                      |             |       |              |             |                   |             |             |            | н |

|   |        |             |            |             |               |                   |             |       |                |       |    |                     |       |                   |       |                   | 17.00     | 17.00             | 17.00 |                      |             |       |              |             |                   |             |             |            |   |

02A1 or 02A2 (06.XX.YY.1)

|   |                                 |        |        | nbly R<br>Charc |               | r      |       |        |                  |        | embly<br>Char | Regist<br>acter    | er     |        |       |             |       | embly<br>d Char | ,<br>Registe<br>acter | er    |       |   |             |              |              |            |   |   | ] |

|---|---------------------------------|--------|--------|-----------------|---------------|--------|-------|--------|------------------|--------|---------------|--------------------|--------|--------|-------|-------------|-------|-----------------|-----------------------|-------|-------|---|-------------|--------------|--------------|------------|---|---|---|

| В | •                               | 0 (B)  | 1 (A)  | 2 (8)<br>— TI   | 3 (4)<br>SI — | 4(2)   | 5 (1) |        | 6 (B)            | 7 (A)  |               | 9 (4)<br>SI —      |        | 11 (1) |       | 12 (B)<br>ৰ | 13 (A |                 | 15(4)<br>SI —         |       | 17(1) |   |             |              |              |            |   |   | В |

|   |                                 | 11.20  | 11.20  | 11.20           | 11.21         | 11.21  | 11.21 |        | 11.22            | 11.22  | 11.22         | 11.23              | 11.23  | 11.23  |       | 11.24       | 11.24 | 11.24           | 11.25                 | 11.25 | 11.25 |   |             |              |              |            |   |   |   |

| с |                                 |        |        | mbly<br>th Cho  |               |        |       |        |                  | 5      | th Ćho        | Registe<br>aracter | •      |        |       |             | 6     | th Cho          | Regist<br>aracter     |       |       |   | DR C<br>Bit | Odd          | Rd<br>Par    | DD<br>Stat |   |   | с |

| C |                                 | 18 (B) | 19 (A) |                 | 21(4)<br>SI   | 22 (2) | 23(1) |        | 24(B)            | 25 (A) |               | 27(4)<br>SI —      | 28 (2) | 29(1)  |       | 30 (B)      | 31 (A |                 | 33(4)<br>SI           | 34(2) | 35(1) |   |             | Cnt<br>TI SI | Gen<br>TI SI | DD         |   |   |   |

|   |                                 | 11.26  | 11.26  |                 |               | 11.27  | 11.27 |        | 11.28            | 11.28  |               |                    | 11.29  | 11.29  |       | 11.30       | 11.30 |                 | 11.31                 | 11.31 | 11.31 |   | 10.12       | 18.02        |              |            |   |   |   |

|   |                                 | -      |        | - (-)           |               | - (-)  |       |        | Word             |        |               | 2.0 (0)            |        | 25(4)  | 1     |             | -     |                 |                       |       |       |   |             |              |              |            |   |   |   |

|   |                                 | 3 (4)  | 4 (2)  | 5(1)            | 6 (4)         | 7 (2)  | 8 (1) | 9 (4)  | 10(2)            | 11(1)  | 12(4)         | 13(2)              | 14(1)  | 15(4)  | 16(2) | 17(1)       |       |                 |                       |       |       |   |             |              |              |            |   |   |   |

| D |                                 |        |        |                 |               |        |       |        |                  |        |               |                    |        |        |       |             |       |                 |                       |       |       |   |             |              |              |            |   |   |   |

|   |                                 | 12.00  | 12.00  | 12.00           | 12.01         | 12.01  |       | 1      | 12.02            |        |               | 12.03              | 12.03  | 12.04  | 12.04 | 12.04       | L     |                 |                       |       |       |   |             |              |              |            |   |   | 4 |

|   |                                 | 21 (4) | 00 (0) | 22/1)           | 24(4)         | 25 (2) |       |        | ddress<br>28 (2) |        |               | 31 (2)             | 32(1)  | 33(4)  | 34(2) | 35(1)       | 1     |                 |                       |       |       |   |             |              |              |            |   |   |   |

|   |                                 | 21 (4  | 22(2)  | 23(1)           | 24(4)         | 25(2)  | 20(1) | 27 (4) | 20(2)            | 27(1)  | 30(4)         | 51(2)              | 52(1)  | 55(4)  | 54(2) | 00(1)       |       |                 |                       |       |       |   |             |              |              |            |   |   |   |

| E |                                 |        |        |                 |               |        |       |        |                  |        |               |                    |        |        |       |             |       |                 |                       |       |       |   |             |              |              |            |   |   | E |

| l |                                 |        |        |                 |               |        |       |        | 13.02            |        |               |                    |        |        |       |             |       | L.,,            |                       | L     |       |   | ,           | L            | L            |            |   | L | ] |

|   | 28                              | 27     | 26     | 25              | 24            | 23     | 22    | 21     | 20               | 19     | 18            | 17                 | 16     | 15     | 14    | 13          | 12    | 11              | 10                    | 9     | 8     | 7 | 6           | 5            | 4            | 3          | 2 | I |   |

|   | 02A3<br>or (06.XX.YY.1)<br>02A4 |        |        |                 |               |        |       |        |                  |        |               |                    |        |        |       |             |       |                 |                       |       |       |   |             |              |              |            |   |   |   |

FIGURE 5. CHANNEL INDICATORS

10 (12-63)

FIGURE 6. Q LINE AND C LINE EXAMPLES

FIGURE 7. BASIC CABLE ARRANGEMENT, 7904 CHANNELS AND CPU

#### WRITE TAPE OPERATION (Figures 8-24)

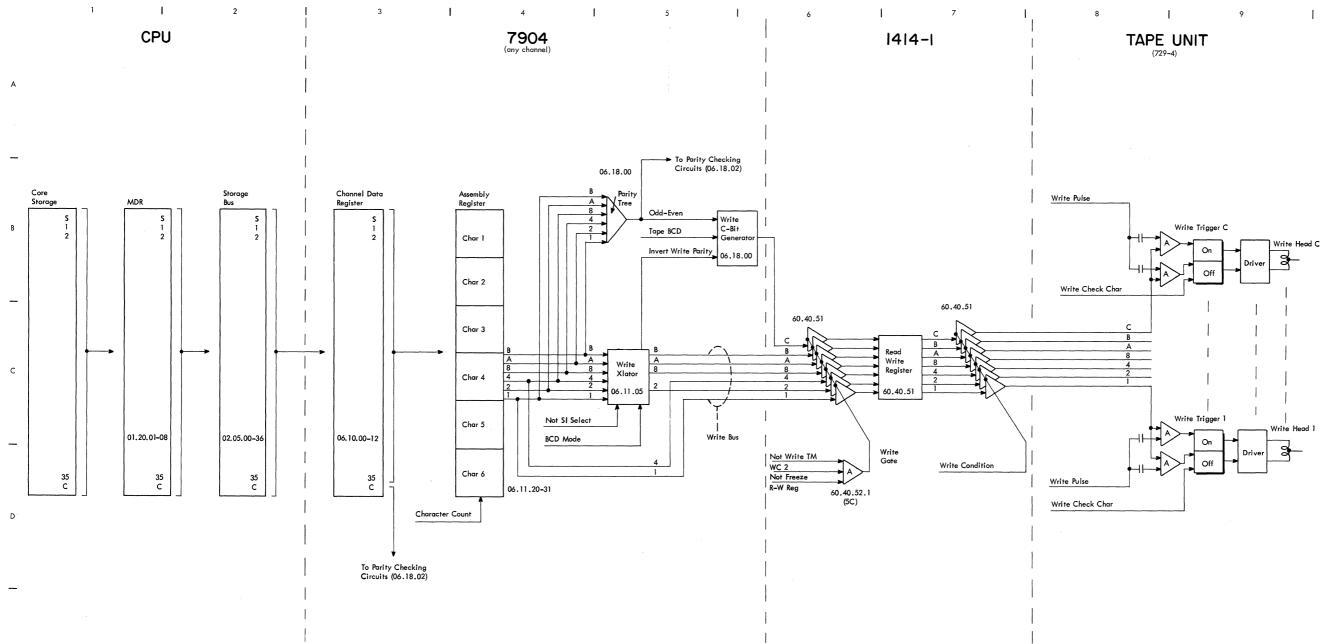

Words are transferred (in parallel) from storage to a 7904 channel, and then sent a character at a time to the 1414 attached to the tape interface of that channel.

The word counter in the 7904 channel determines the number of words transmitted. It is initially set for the desired number of words, and reduced by one as each word is transmitted. When the counter reaches zero, transmission stops.

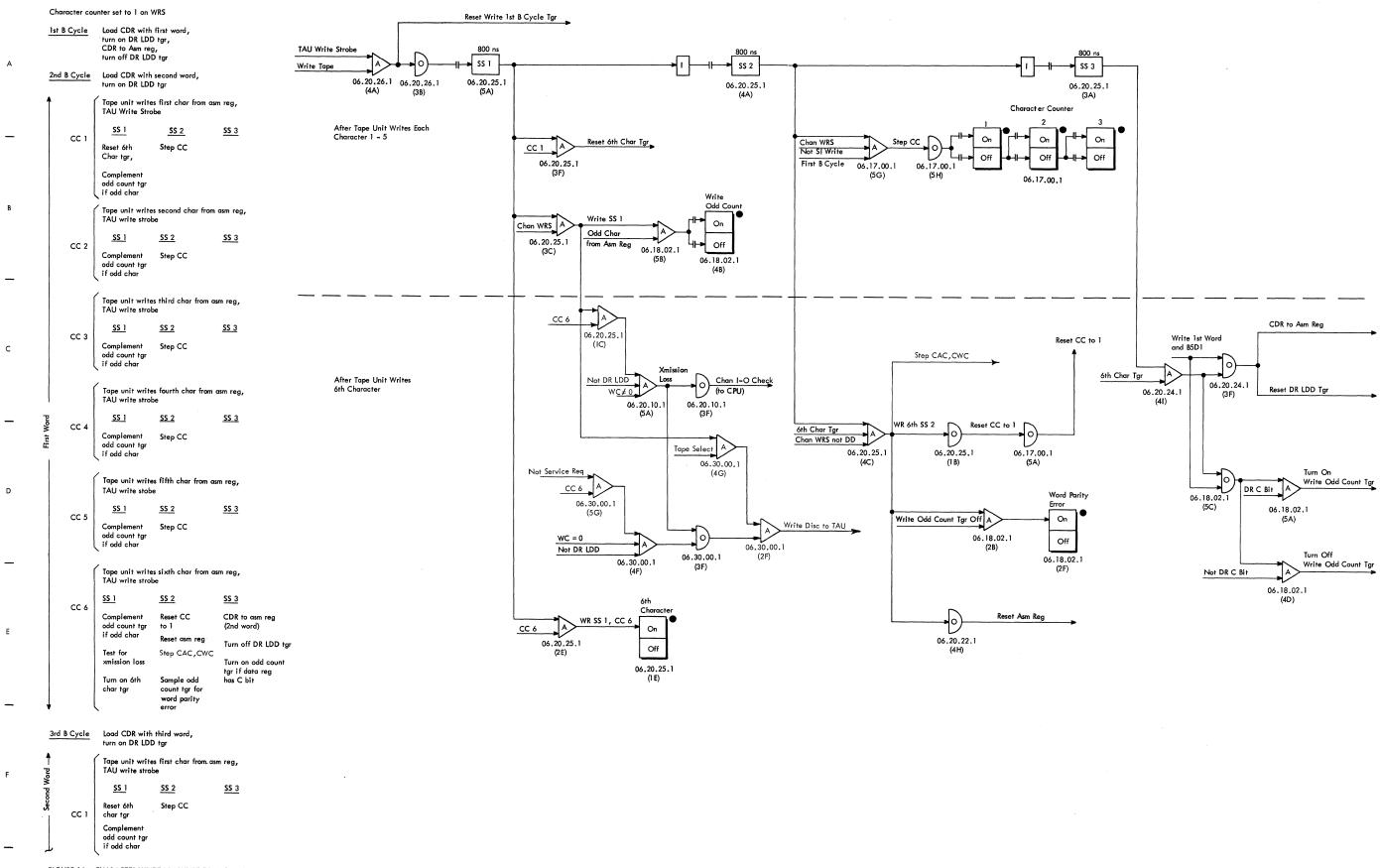

Figure 11 shows the sequence of the write tape operation.

#### Write Selecting the Channel (WRS)

The address portion of the WRS instruction selects channel B, C, D, or E, selects the tape interface of that channel, and selects a particular tape unit on that interface (Figure 12). The operation portion of the WRS instruction sets up the channel for writing; that is, it conditions certain circuits in the channel that will allow writing to the 1414 (and on to the tape unit) through the tape interface. During the WRS operation, tape motion is started. The WRS operation ends and the program goes on with the next instruction while the tape unit is getting up to speed.

#### Command Word Loading (RCH)

An RCH instruction for the channel just selected is executed, causing a command word to be sent from storage to the channel. The command word, when entered into the channel, sets the word counter and address counter. The RCH instruction requires an I cycle and an E cycle, after which the CPU proceeds with the next instruction.

The word counter not zero and the data register not loaded cause a B cycle demand. See Figure 13 for actions in the channel caused by the RCH.

#### B Cycle

The word counter not zero and the data register not loaded cause a B cycle demand to be sent to CPU (Figure 14). The next CPU cycle following the request becomes a B cycle, during which the first word to be transmitted is sent from storage to the channel's data register. During this first B cycle, the first word immediately moves on to the assembly register.

Because the data register is now empty, another B cycle is requested; during this B cycle, the data reg-

ister is loaded with the second word. At this point, the tape unit is nearly up to writing speed, the first word is waiting in the assembly register, and the second word is in the data register.

#### Character Transmission

While the first word is in the assembly register, the first character of this word is being gated to the write bus (by the character counter). When the tape unit gets to writing speed, it writes the first character and sends a write strobe signal to the channel. The write strobe signal tells the channel that the tape unit has written a character and will soon need another one.

Each write strobe trips off a series of three singleshots in the channel (Figure 16). The single-shots check each character sent for the proper parity, and control the character counter (make sure each of the six characters is gated out of the assembly register in the proper order). After each group of six characters is transmitted, the next word (always waiting in the data register) moves to the assembly register. This action causes a B cycle, which again fills the data register.

As words move from storage to the data register on B cycles, the word counter is stepped down. When the word counter reaches zero, no more B cycles are allowed. The last word moves into the assembly register and is sent to the tape unit. After the tape unit writes the last character of the last word and sends the write strobe to the channel (firing the single-shots for the last time), all conditions are present in the channel to end the write operation. The channel initiates the ending of the write operation by sending a write disconnect signal to TAU.

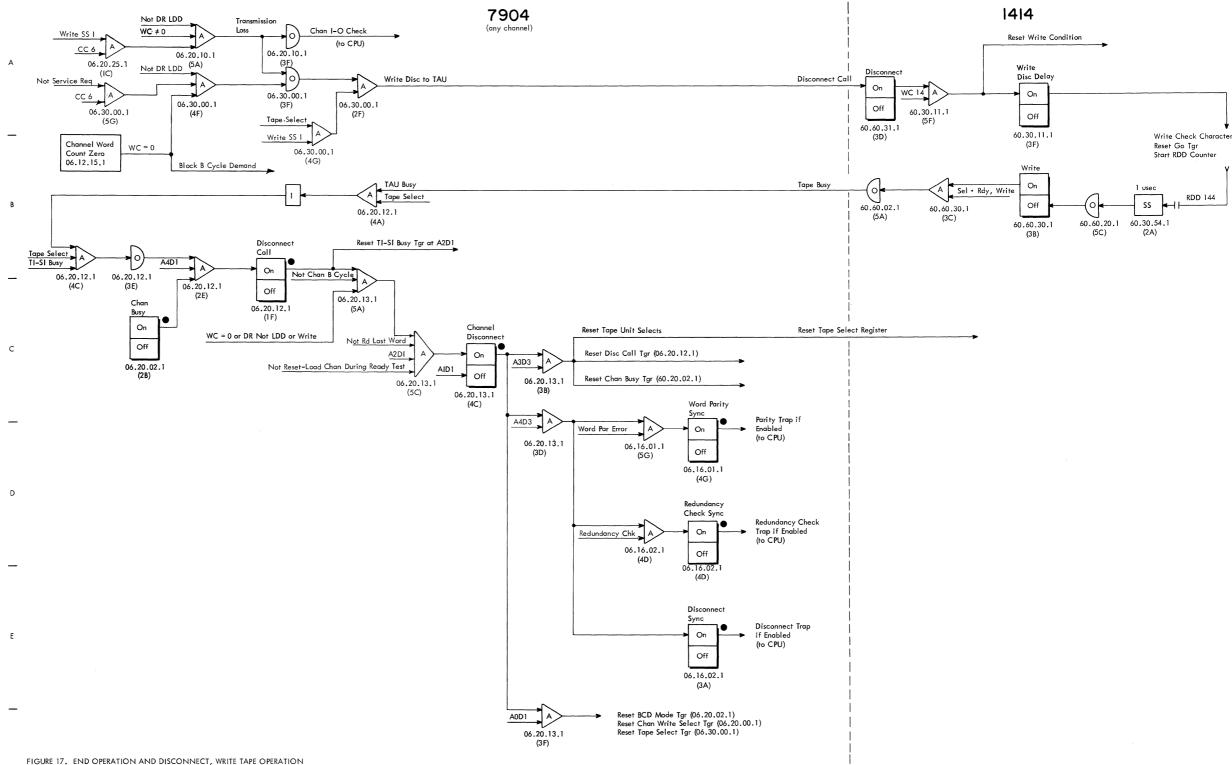

#### End Operation and Disconnect

The disconnect signal at the 1414 causes the tape unit to write the check character, read-check the check character, and then turn off the write trigger in the 1414 (Figure 17). When this trigger goes off, the TAU busy line drops to the channel. In the channel, the fall of TAU busy turns on the disconnect call trigger, which subsequently turns on the channel disconnect trigger. The channel disconnect trigger resets the triggers that were maintaining the channel in a write tape status, and sets up trap sync triggers for any trap conditions that might have occurred during the write operation. The channel is now not busy and may be used by CPU for another read or write.

| [                       | Unit Number Lines (10) to TAU                                                                                                                                                                                                                      |                                                                                     |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|                         | Write Bus Lines CBA8421                                                                                                                                                                                                                            | ▶                                                                                   |

|                         | Set Tape Select Register                                                                                                                                                                                                                           | >                                                                                   |

|                         | Call Lines (7)                                                                                                                                                                                                                                     | ▶                                                                                   |

|                         |                                                                                                                                                                                                                                                    | >                                                                                   |

| 1                       | Odd Parity OP to TAU                                                                                                                                                                                                                               | ->                                                                                  |

|                         | Computer Reset to TAU                                                                                                                                                                                                                              | >                                                                                   |

|                         | Write Disconnect to TAU                                                                                                                                                                                                                            | >                                                                                   |

|                         | Reset Tape Unit Selects                                                                                                                                                                                                                            | -                                                                                   |

|                         | Turn Off Tape Indicator                                                                                                                                                                                                                            | >                                                                                   |

| 7904<br>Data<br>Channel | Density 556 and 200 to TAU Density 556 and 200 to TAU Lines from Density 800 and 556 to TAU Data Lines CBA8421 TAU Busy Line Tape Sel and Ready from TAU Write Condition from TAU Tape Select at Load Point Select and Tape Indicator On TAU Error | <ul> <li>1414 I, II,<br/>or VII</li> <li>I-O</li> <li>Synchro-<br/>nizer</li> </ul> |

|                         | TAU Write Strobe                                                                                                                                                                                                                                   |                                                                                     |

|                         | TAU Read Strobe                                                                                                                                                                                                                                    |                                                                                     |

|                         | Tape Select and Rewind                                                                                                                                                                                                                             | 1                                                                                   |

|                         |                                                                                                                                                                                                                                                    |                                                                                     |

Note: 7904 line nomenclature shown. Refer to Systems 06.03.01.1 for 1414 line nomenclature.

FIGURE 8. TAPE INTERFACE SIGNAL LINES

FIGURE 9. TAPE UNIT SELECTION

14 (12-63)

FIGURE 10. CHANNEL AND INTERFACE SELECTION

| DD Output Data Bus       | 06.51.00.1 | Service Resp and Stop      | 06.40.01.1 |

|--------------------------|------------|----------------------------|------------|

| DD Demand                | 06.52.00.1 | Serv Req, End, Un End,     |            |

| DD EOR (disconnect)      | 06.20.12.1 | SI Busy                    | 06.40.00.1 |

| Write 1st Word Tgr       | 06.20.24.1 | Write and Control Commands | 06.40.01.1 |

| I-O MF End Op            | 06.20.01.1 | Read and Sense Commands    | 06.40.01.1 |

| DD Word Parity Error     | 06.18.02.1 | I-O MF End Op              | 06.30.00.1 |

| CDR to DD (C bit)        | 06.10.12.1 | Block CC Step on           |            |

| Chan RDS, WRS            | 06.20.00.1 | WR 1st B Cyc               | 06.20.27.1 |

| DD Trans Loss            | 06.20.10.1 | Chan RDS, WRS              | 06.20.00.1 |

| WC 0 to DD               | 06.12.15.1 | Ready Test                 | 06.20.11.1 |

| Reset DD Interrupt       | 06.51.03.1 | SI Disconnect              | 06.20.12.1 |

| WC 0 to DD on Chan Reset | 06.12.15.1 | End Response               | 06.20.29.1 |

| Set DR LDD               | 06.52.00.1 | Chan Read Translator       | 06.11.02.1 |

| DD EOF                   | 06.15.01.1 | Chan Write Translator      | 06.11.05.1 |

| Chan Redundancy Chk      | 06.15.02.1 |                            |            |

FIGURE 13. RCH, WRITE TAPE OPERATION

í

FIGURE 14. B CYCLE, WRITE TAPE OPERATION

Note: Any channel's B Cycle Demand trigger on requests a B cycle of CPU. The next CPU cycle becomes the B cycle, the B cycle being granted to the requesting channel.

If more than one channel requests a B cycle at the same time, the B cycle is granted to the most remote requesting channel.

FIGURE 15. B CYCLE PRIORITY

с

С

FIGURE 16. CHARACTER WRITING, WRITE TAPE OPERATION

Α

\_

\_\_\_\_

\_\_\_\_

F

1

9

I

FIGURE 18. DATA FLOW, WRITE TAPE OPERATION

1 | 2 | 3 | 4 | 5 | 6 |

FIGURE 20. WORD PARITY ERROR, WRITE TAPE OPERATION

.

ş.

02.10.06.1 (3H)

FIGURE 21. ETT, END-OF-TAPE OPERATION

.

26 (12-63)

•

Next Channel Nearer MF

.

•

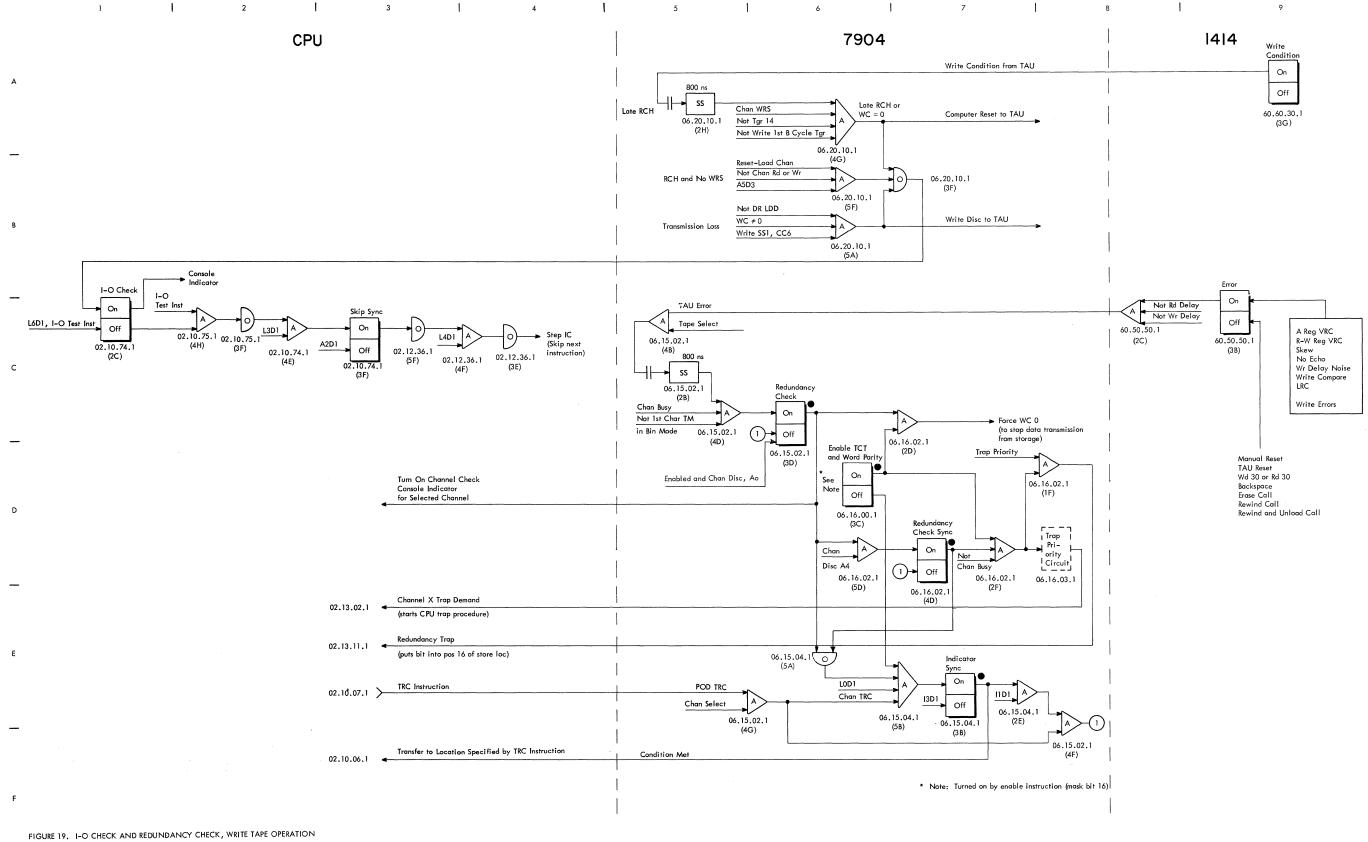

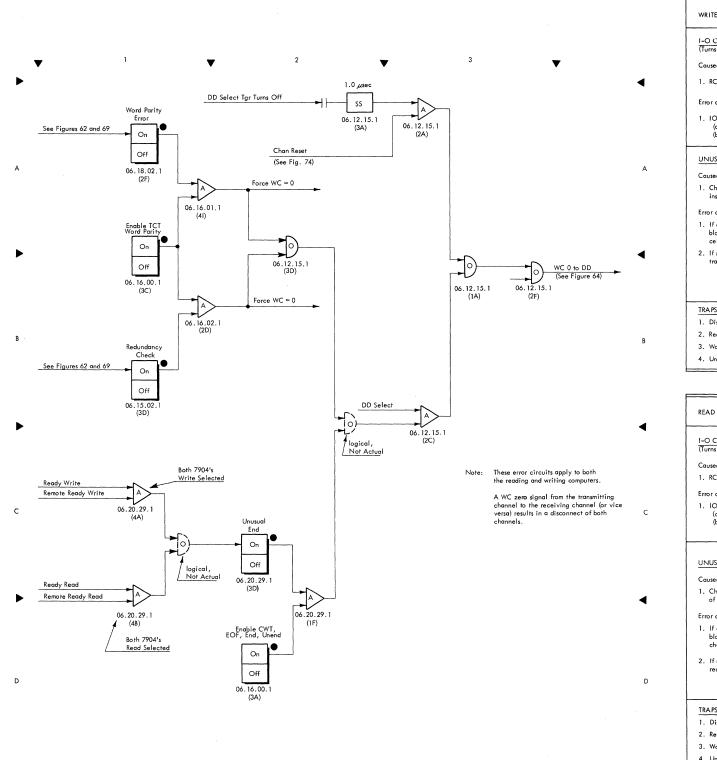

| I-O CHECK<br>(Turns on console I-O check light)                                                                                                                                                                                                                                                                                                                                                                                                                 | REDUNDANCY CHECK<br>(Turns on console channel check light)                                                                                                                                                                                                                                                                                                                                                                                                                       | WORD PARITY ERROR<br>(Turns on console channel check light)                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Caused by:</li> <li>1. Late RCH or initial WC zero. <ul> <li>(a) Causes computer reset to TAU at write condition time.</li> </ul> </li> <li>2. RCH and no WRS.</li> <li>3. Transmission loss. <ul> <li>(a) Causes write disconnect to TAU.</li> </ul> </li> <li>Error detection: <ol> <li>IOT instruction. <ul> <li>(a) If 1-O check, execute next instruction.</li> <li>(b) If not 1-O check, skip next instruction.</li> </ul> </li> </ol></li></ul> | Caused by:<br>1. Tape write error.<br>(a) A reg VRC<br>(b) R-W reg VRC<br>(c) Skew<br>(d) No echo<br>(e) Write delay noise<br>(f) Write compare<br>(g) LRC<br>Error detection:<br>1. If not enabled for trap, redundancy check is tested<br>by TRC instruction.<br>(a) If redundancy check, turn off redundancy<br>check tgr and transfer.<br>(b) If not redundancy check, proceed with program.<br>2. If enabled for trap, force WC zero on error and trap<br>after disconnect. | <ol> <li>Caused by:</li> <li>B cycle storage bus parity.</li> <li>Odd-even count of six characters does not agree with word C bit from CDR.</li> <li>Error detection:</li> <li>If enabled for word parity trap, force WC zero on error and trap after disconnect.</li> <li>If not enabled for word parity trap, but disconnect trap is enabled, store parity flag bit along with disconnect flag bit when disconnect trap is taken.</li> </ol> |

| TRAPS (Taken after channel disconnects) 1. Disconnect: enabled by "Enb CWT, EOF, End, Uner 2. Redundancy check: enabled by "Enb TCT and Word Parity" 3. Word parity: enabled by "Enb TCT and Word Parity"                                                                                                                                                                                                                                                       | Carity" trigger.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                |

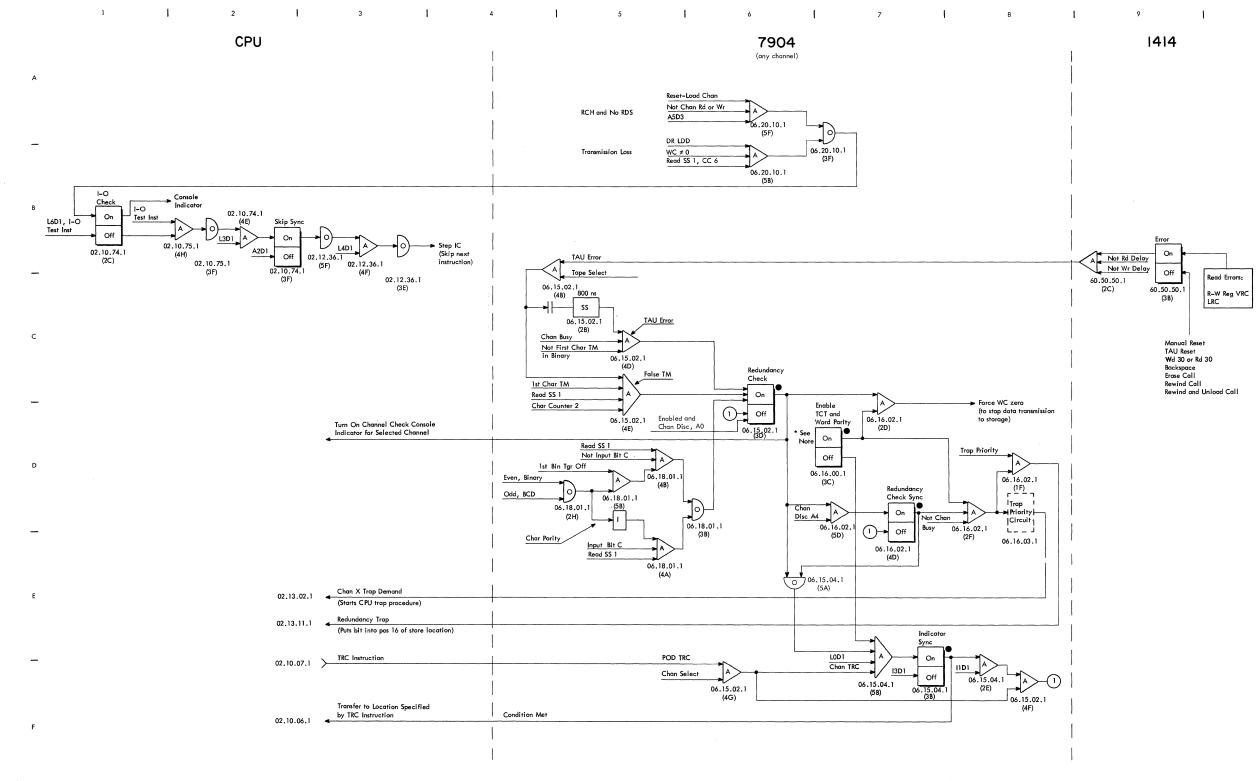

| READ TAPE                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I-O CHECK<br>(Turns on console I-O check light)<br>Caused by:<br>1. RCH and no RDS.<br>2. Transmission loss.<br>Error detection:<br>1. IOT instruction.<br>(a) If I-O check, execute next instruction.<br>(b) If not I-O check, skip next instruction. | REDUNDANCY CHECK<br>(Turns on console channel check light)         Caused by:         1. Tape read error.<br>(a) R-W reg VRC<br>(b) LRC         2. Bit count of character does not agree with C bit<br>received with character.         Error detection:         1. If not enabled for trap, redundancy check is tested<br>by TRC instruction.<br>(a) If redundancy check, turn off redundancy check<br>tgr and transfer.<br>(b) If not redundancy check, proceed with program.         2. If enabled for trap, force WC zero on error and trap<br>after disconnect. | <ul> <li>WORD PARITY ERROR<br/>(Turns on console channel check light)</li> <li>Caused by: <ol> <li>B cycle storage bus parity.</li> </ol> </li> <li>Error detection: <ol> <li>If enabled for word parity trap, force WC zero<br/>on error and trap after disconnect.</li> </ol> </li> <li>If not enabled for word parity trap, but disconnect<br/>trap is enabled, store parity flag bit along with<br/>disconnect flag bit when disconnect trap is taken.</li> </ul> |

| TRAPS (Taken after channel disconnects)                                                                                                                                                                                                                | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

- 1. Disconnect: enabled by "Enb CWT, EOF, End, Unend" trigger.

- 2. Redundancy check: enabled by "Enb TCT and Word Parity" trigger.

- 3. Word parity: enabled by "Enb TCT and Word Parity" trigger.

- 4. Unusual end (last tape word incomplete): enabled by "Enb CWT, EOF, End, Unend" trigger.

- 5. End of file (tape mark read from tape): enabled by "Enb CWT, EOF, End, Unend" trigger.

FIGURE 24. ERROR AND TRAP CONDITIONS, TAPE OPERATION

#### **READ TAPE OPERATION (Figures 25-41)**

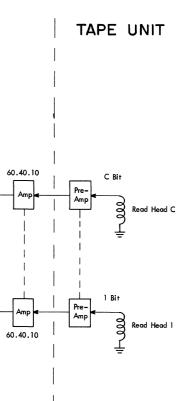

Characters are read from the tape unit through the 1414 into the assembly register of the channel. When each group of six characters is assembled, the 6-character word is transferred to the data register and then to storage.

The word counter in the channel is normally set higher than the number of words in the record; transmission stops when the tape reaches the inter-record gap. Figure 25 shows the sequence of the read tape operation.

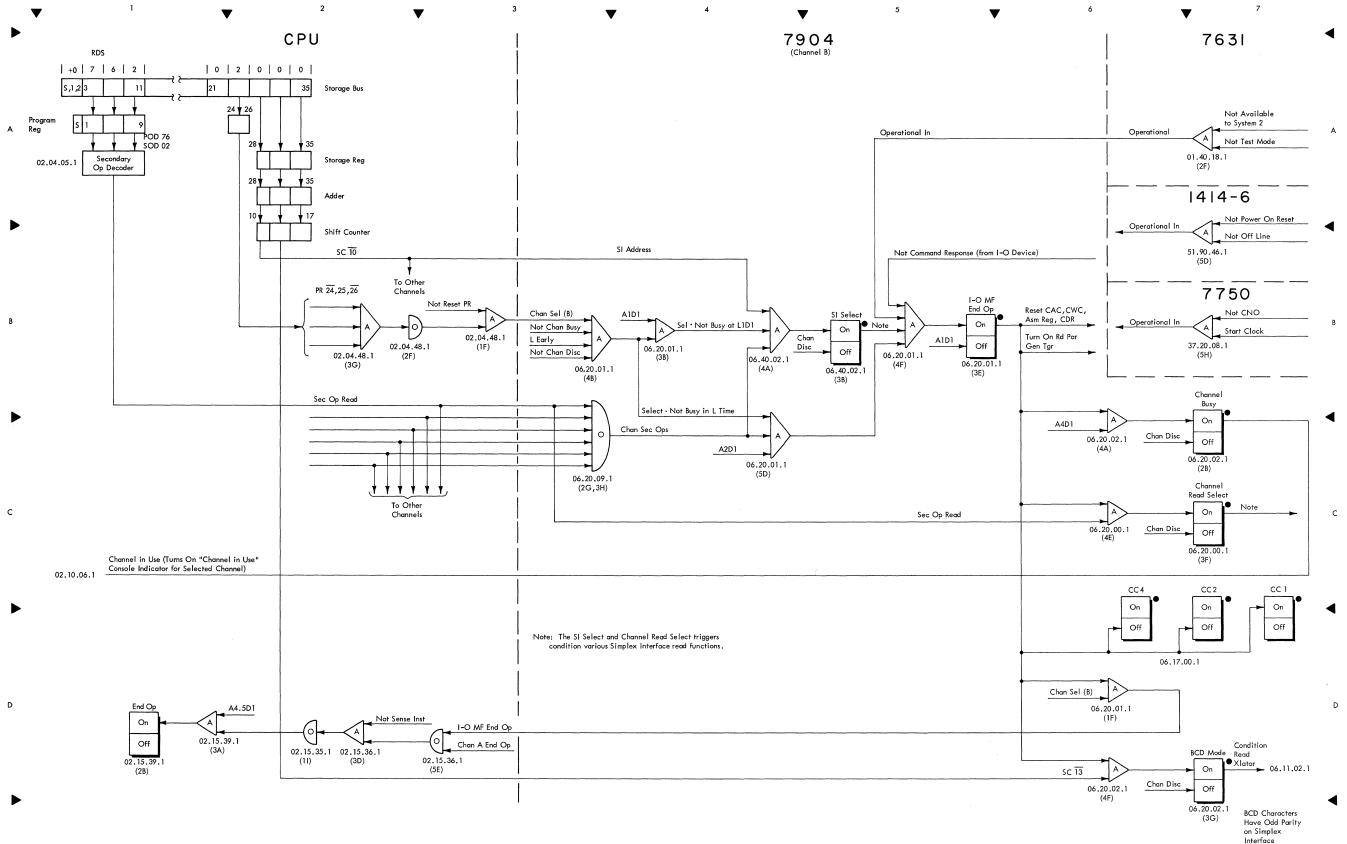

#### Read Selecting the Channel (RDS)

The RDS instruction initiates the read operation (Figure 26). The address portion of the RDS instruction selects channel B, C, D, or E, selects the tape interface of that channel, and selects a particular tape unit on that interface. The operation portion of the RDS instruction sets up the channel for reading; that is, it conditions certain circuits that will allow data read from the tape unit (through the 1414) to enter the channel through the tape interface. The RDS operation ends, and the program goes on with the next instruction while the tape unit is getting up to speed.

#### Command Word Loading (RCH)

An RCH instruction for the channel just selected is executed, causing a command word to be sent from storage to the channel. The command word, when entered into the channel, sets the word counter and address counter. The word count in a tape read operation is usually insignificant, because if the tape inter-record gap is to stop the data transmission, the tape will reach the gap before the word counter reaches zero. The RCH instruction requires an I cycle and an E cycle, after which the program proceeds with the next instruction. See Figure 27 for actions in the channel caused by the RCH.

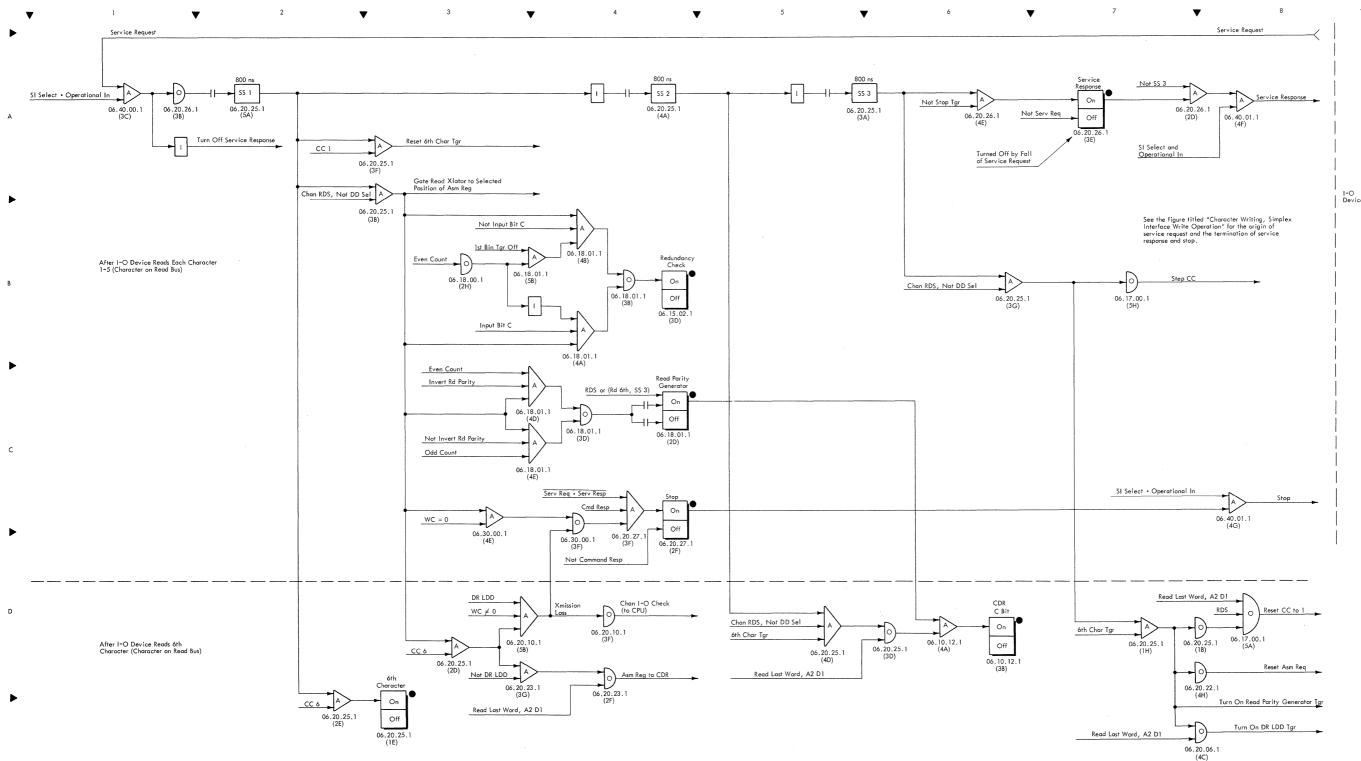

#### Character Transmission

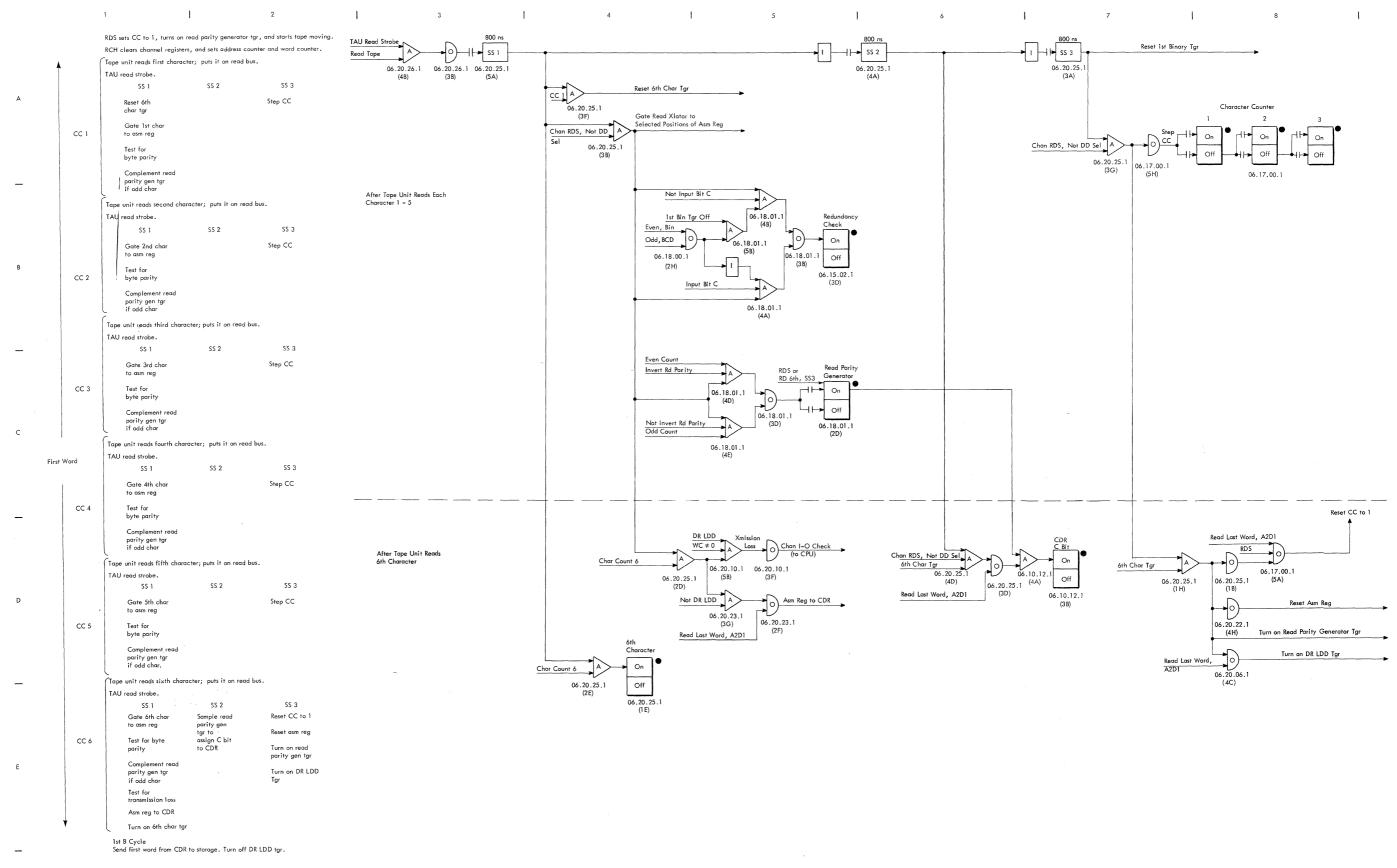

The tape unit reads the first character, puts it on the read bus, and sends a read strobe signal to the channel (Figure 28). The read strobe signal trips off a series of three single-shots in the channel. The single-shots check each character received for proper parity, control the character counter (make sure each character goes into its proper place in the assembly register), and control a circuit that keeps track of the odd-even count of each group of six characters. This latter job is necessary because a parity bit must be assigned to the assembled word before the word is put into storage.

After each group of six characters is received, the 6-character word moves from the assembly register to the data register. The assembly register is now empty and ready to receive the next group of characters. Because the data register is loaded, a B cycle is requested to move the word from the data register to storage.

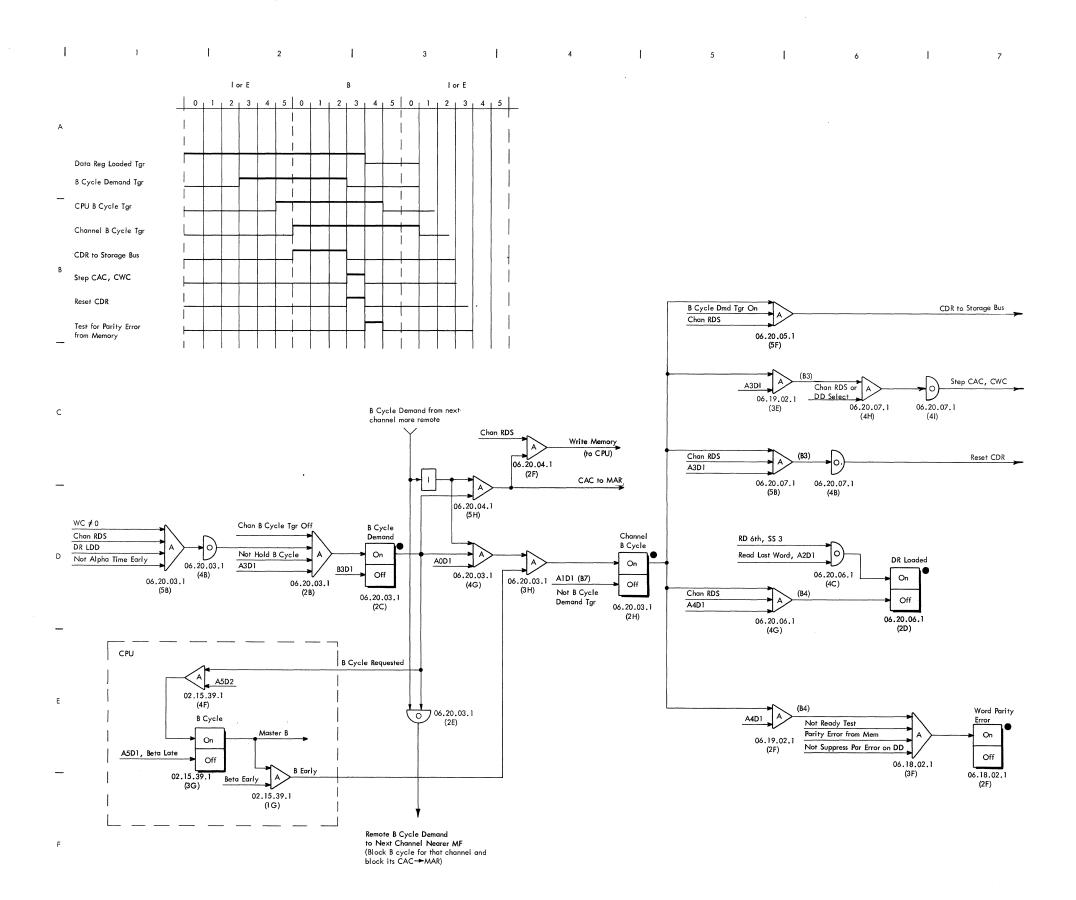

## B Cycle

On a read operation, the word counter not zero and the data register loaded cause a B cycle demand to be sent to CPU (Figure 29). The next CPU cycle following the request becomes a B cycle, during which the word in the data register moves to storage. The data register is now empty and ready to receive the next word from the assembly register.

As words move from the data register to storage on B cycles, the word counter steps down. If the word counter was initially set lower than the number of words in the record, it will reach zero before the tape reaches the inter-record gap. No more B cycles are allowed, but the tape continues to the interrecord gap.

#### End Operation and Disconnect

The tape moves into the inter-record gap, causing the read only trigger in the 1414 to turn off (Figure 30). This action drops the TAU busy line to the channel. The fall of TAU busy at the channel turns on the disconnect call trigger. When the last word moves from the CDR to storage, the channel disconnect trigger turns on. This trigger resets all the triggers that were maintaining the channel in a read tape status, and sets up the trap sync triggers for any trap conditions that might have occurred on the read operation. The channel is now not busy and may be used by CPU for another read or write.

RDS

Read Call to TAU (Start Tape Moving)

RCH

- and each character is parity-checked in the channel; the words merely pile up in the CDR.

Reset Chan Disc Tgr

Wait for B Cycle to Send Word from CDR

Turn On Unusual

End Tgr

Turn On Read Last

Word Tgr

Asm Reg to CDR

C Bit to CDR (if

Needed) 3. Reset CC to 1 4. Turn On DR LDD

CDR Loaded

Wait for B

CDR to

Memory

Cycle to Send Word from

Tgr

to Memory

#### 7 1 8 9 1 10 1 11

Force WC = 0

Reset CDR

SB to CDR

SB to CAC

I

0 1 2 3 4 5 0 1 2 3 4 5 Next Instruction 1 1 1 1 1 1 1 Reset CWC, CAC Test for I-O Check (make sure channel is selected) Set CWC to All Ones SB to CWC via CDR End Op (Pod 5X, Not RCH A)

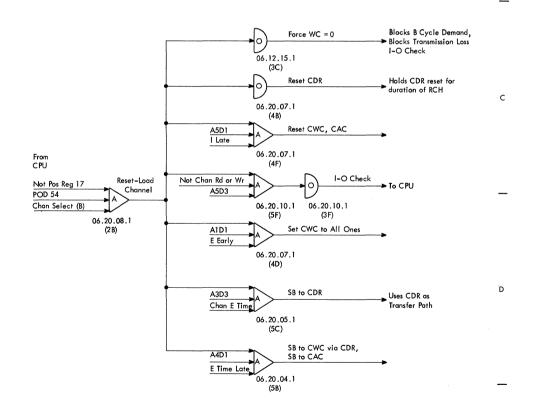

FIGURE 27. RCH, READ TAPE OPERATION

Ε

В

-

FIGURE 28. CHARACTER READING, READ TAPE OPERATION

FIGURE 29. B CYCLE, READ TAPE OPERATION

FIGURE 30. END OPERATION AND DISCONNECT, READ TAPE OPERATION

A CPU 7904 **1414** (729-4) 1 (any channel) Storage Bus Channel Data Register Assembly Register S 06.11.20-31 RC 7, A Reg Error Char 1 2 \_\_\_\_ Low Clip Not Freeze R-W Reg Read Cond Char 2 Read Only Not Check Char Read Tape Read Reg Go В Read Bu 60.60.20 В BCD Mode Char 3 60.40.20-22 60.40.20-22 Read– Write Registe Read Xlator Char 4 \_\_\_\_ 06.11.02

06.11.00-01

3 | 4 | 5 | 6 | 7 | 8 | 9 |

60.40.50-51

60.40.50

60.40.20-22

RC 7, No A Reg Error

Read Reg

А

High Clip

60.40.20-22

FIGURE 31. DATA FLOW, READ TAPE OPERATION

35

С

06.10.00-12

I

2

ł

Char 5

Char 6

Redundancy Check

Character Count

Invert Read Parity

Word Parity Generato

06.18.01 Odd-<u>Even</u>

Read Parity Check

06.18.01

Parit Tree

06.18.00

C Bit Read SS 1 Time

Odd

Even

1

С

35 C

02.05.00-36

FIGURE 32. I-O CHECK AND REDUNDANCY CHECK, READ TAPE OPERATION

\* Note: Turned on by unable instruction (mask bit 16)

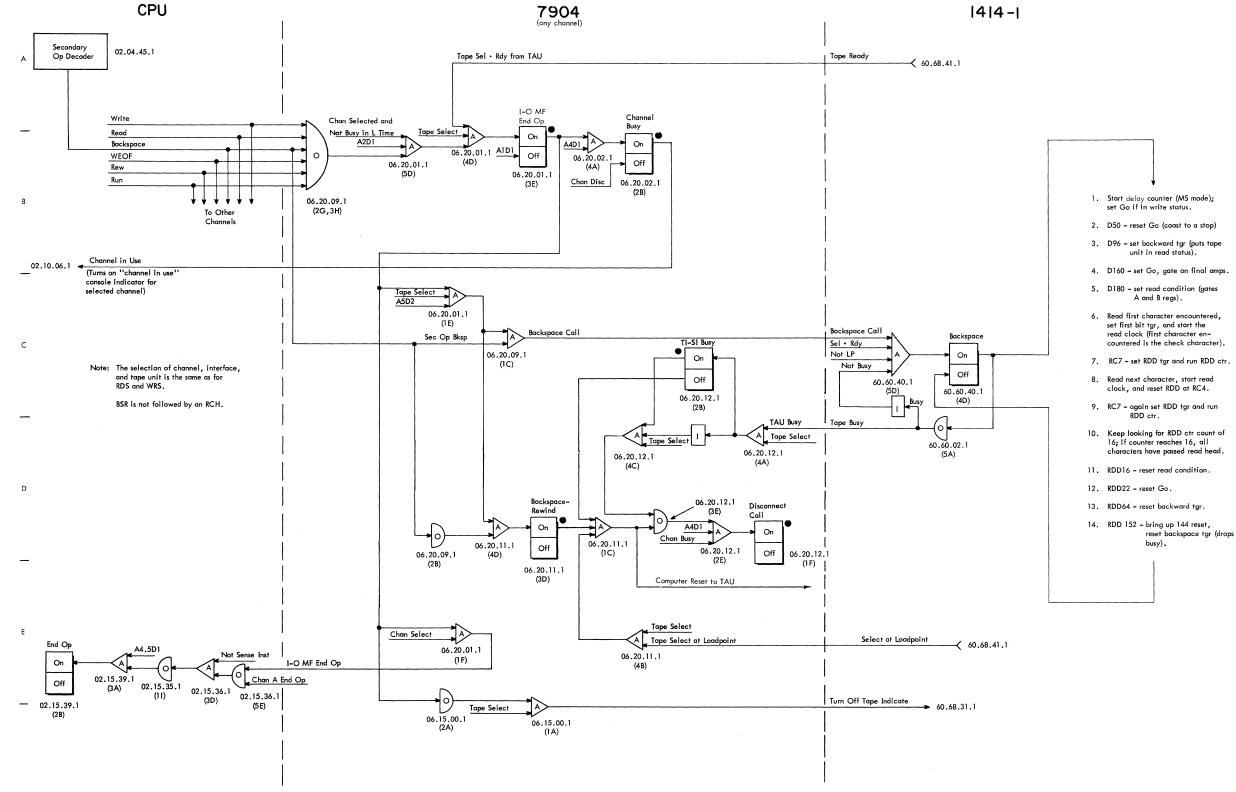

FIGURE 34. BSR, BACKSPACE OPERATION

ł

40 (12-63)

40 (12-6)

FIGURE 38. WBT, WRITE BLANK TAPE OPERATION

٠

So. WDI, WKIE BEAKK IAFE OFERATION

FIGURE 39. SEN, TAPE READY TEST OPERATION

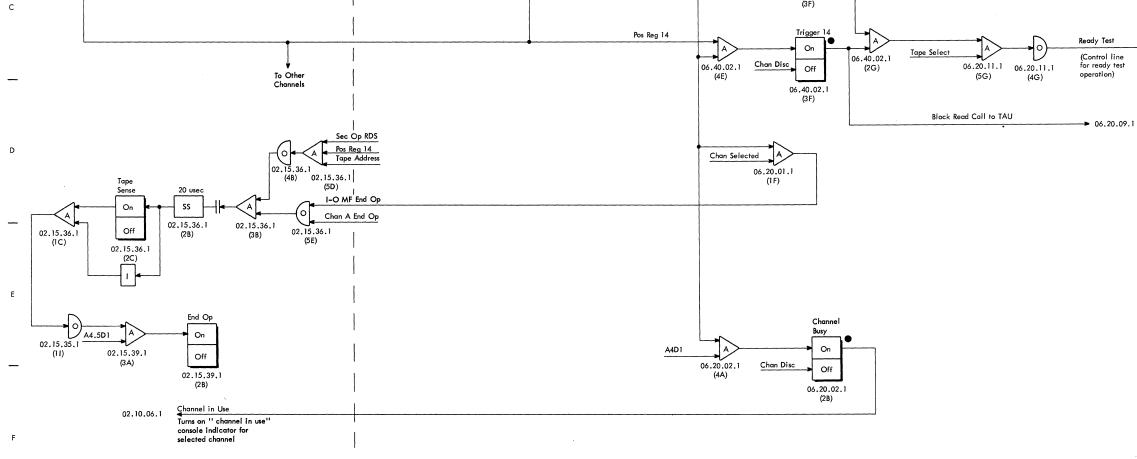

FIGURE 41. ASM REG TO CDR, B CYCLE, AND DISCONNECT, TAPE READY TEST OPERATION

| Selects | to 1414                      |

|---------|------------------------------|

| Tgr     |                              |

| Tgr     | → 06.20.12.1<br>→ 06.20.02.1 |

|         |                              |

|         |                              |

06.30.00.1 06.20.00.1 06.40.02.1

С

D

Ε

G

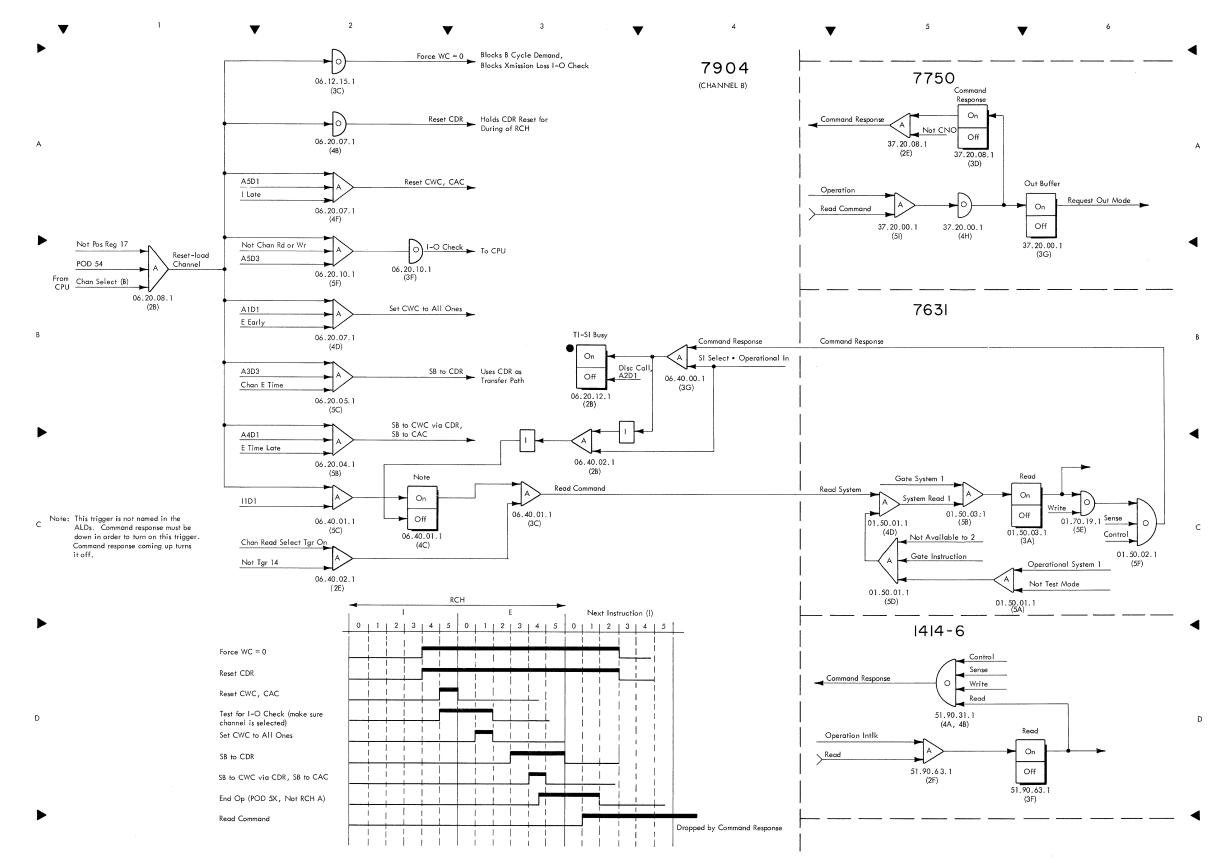

#### SIMPLEX INTERFACE LOGIC

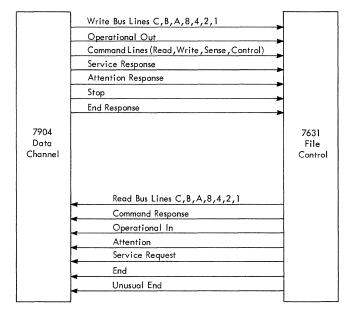

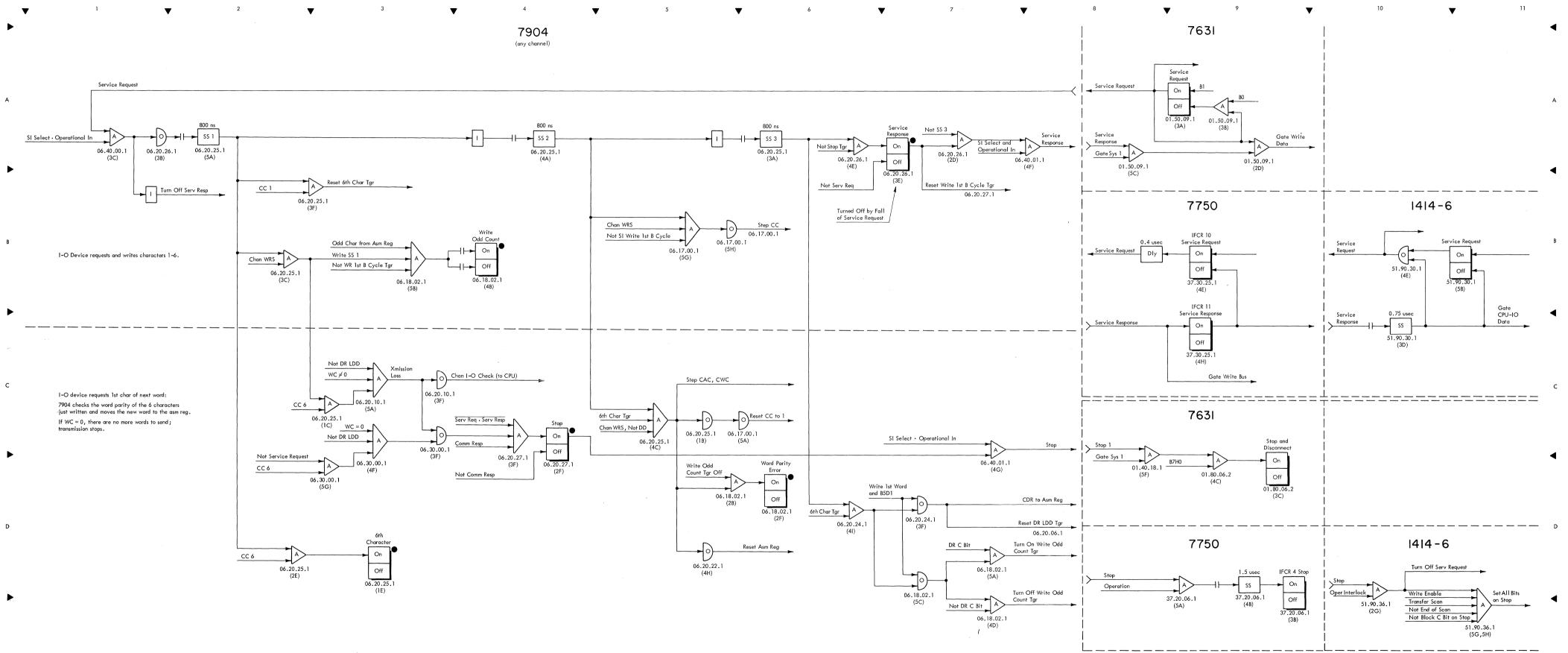

## SIMPLEX INTERFACE WRITE OPERATION (Figures 42-47)

Words are transferred (in parallel) from storage to a 7904 channel, and then sent a character at a time to the I-O device attached to the Simplex interface of that channel.

The word counter in the 7904 channel determines the number of words transmitted. It is initially set for the desired number of words, and reduced by one as each word is transmitted. When the counter reaches zero, transmission stops.

Figure 43 shows the sequence of the write Simplex operation.

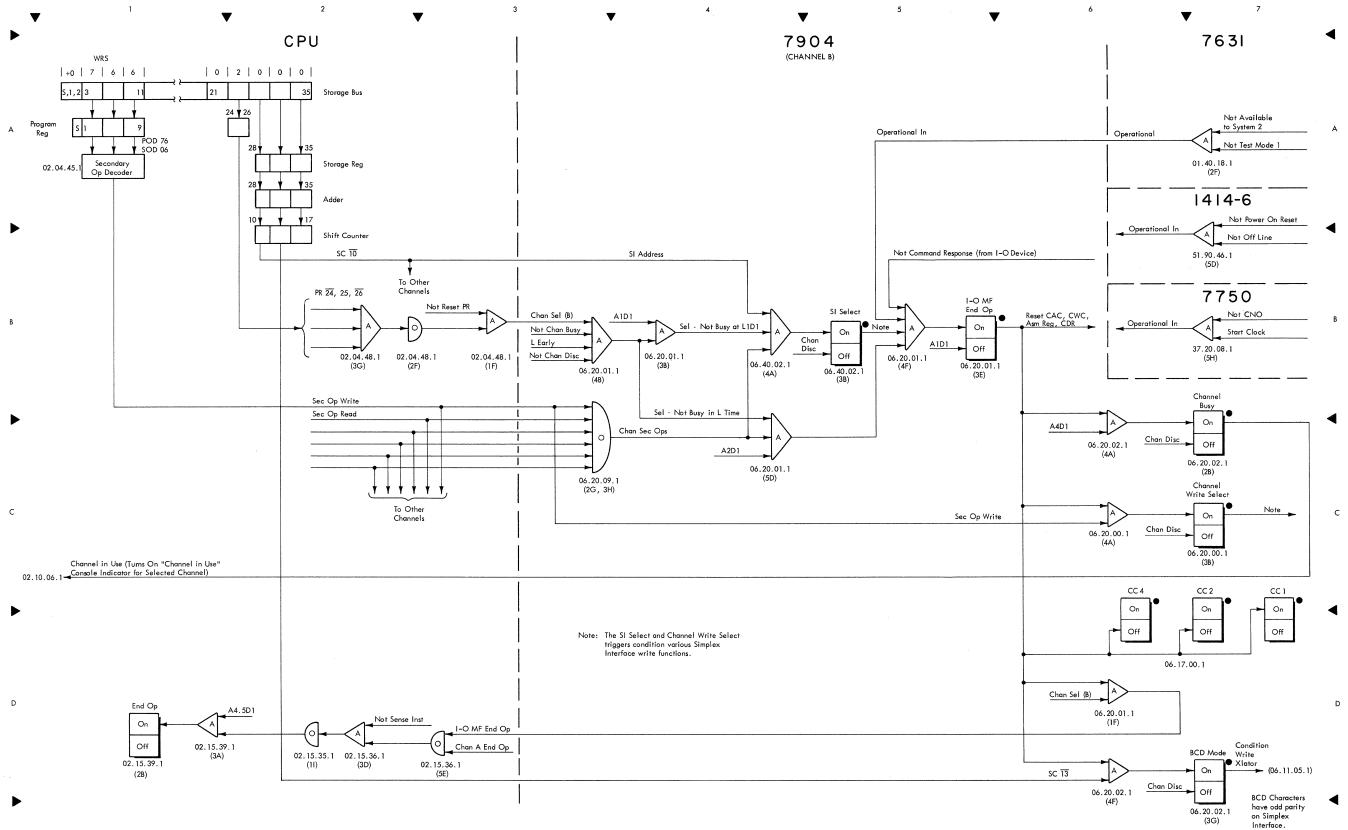

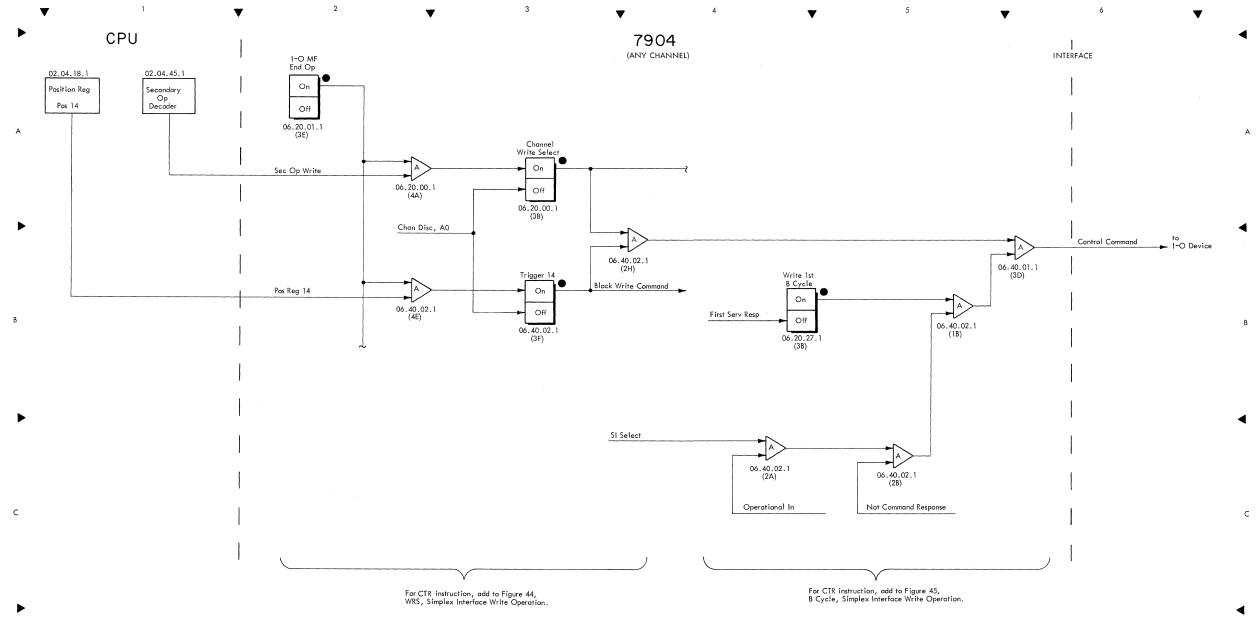

#### Write Selecting the Channel (WRS)

The WRS instruction initiates the write operation (Figure 44). The address portion of the instruction selects channels B, C, D, or E, and selects the Simplex interface of that channel. The operation portion of the instruction sets up the channel for writing; that is, it conditions certain circuits in the channel that will allow writing to the I-O device through the Simplex interface. If the device is ready to receive data, the WRS operation ends, and the program goes on with the next instruction.

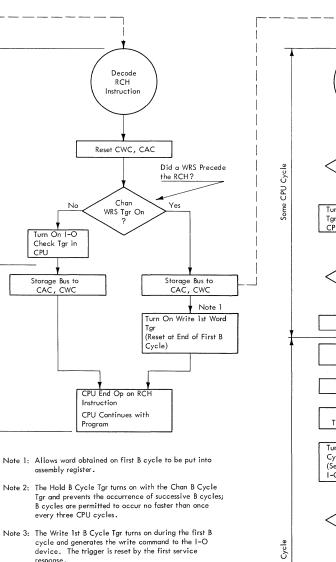

#### Command Word Loading (RCH)

An RCH instruction for the channel just selected is executed, causing a command word to be sent from storage to the channel. The command word, when entered into the channel, sets the word counter and address counter. The RCH instruction requires an I cycle and an E cycle, after which the program proceeds with the next instruction.

The word counter not zero and the data register not loaded cause a B cycle demand. See Figure 13 for actions in the channel caused by the RCH. Although this figure is in the write tape section of the manual, it is valid for RCH, Simplex interface write.

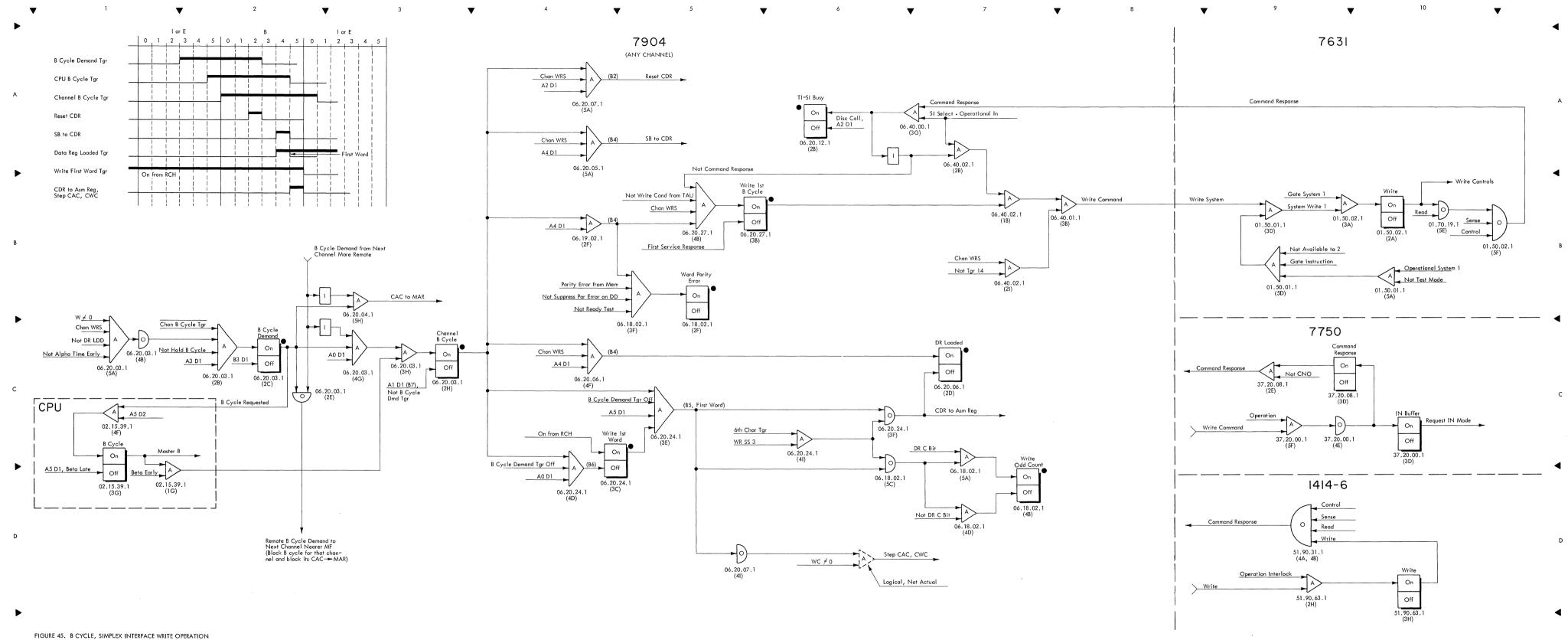

## B Cycle

The word counter not zero and the data register not loaded cause a B cycle demand to be sent to CPU (Figure 45). The next CPU cycle following the request becomes a B cycle, during which the first word to be transmitted is sent from storage to the channel's data register. During this first B cycle, the first word immediately moves on to the assembly register, and a write command is sent to the I-O device. Because the data register is now empty, another B cycle is requested; during this B cycle, the data register is loaded with the second word. At this point, the I-O device has been told that the channel wants to write, the first word is waiting in the assembly register, and the second word is in the data register. The channel now waits for the first service request from the I-O device.

## Character Transmission

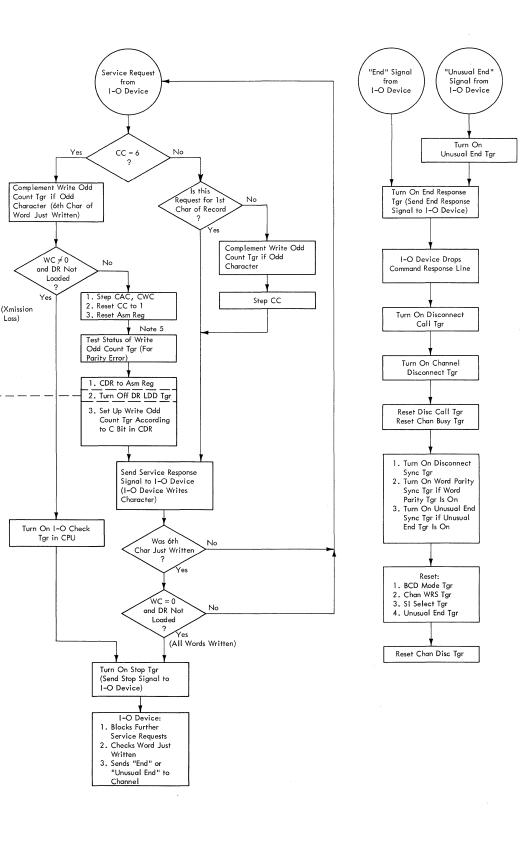

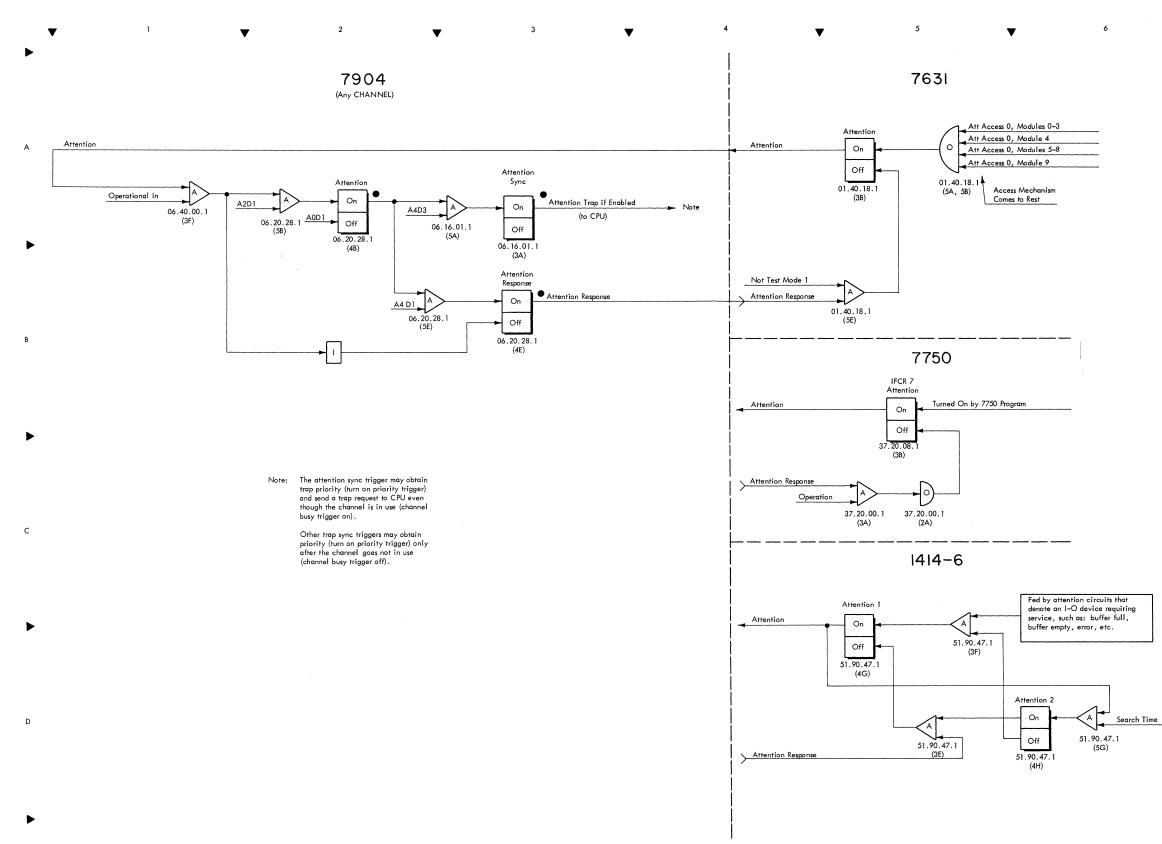

Characters are transmitted on demand of the I-O device. The device asks for a character by sending a service request signal to the channel. The channel places the proper character on the write bus and tells the I-O device to take it by sending a service response signal to the device.

Each service request trips off a series of three single-shots in the channel (Figure 46). The singleshots check each character sent for the proper parity, control the character counter (make sure each of the six characters is gated out of the assembly register in the proper order), and generate the service response signal. After each group of six characters is transmitted, the next word (always waiting in the data register) moves to the assembly register. This action causes a B cycle, which again fills the data register.

As words move from storage to the data register on B cycles, the word counter is stepped down. When the word counter reaches zero, no more B cycles are allowed. The last six characters are sent to the I-O device. The I-O device does not know this is the last word and asks for another character (service request). Because the word counter is zero and the data register is not loaded, the channel sends a stop signal to the I-O device in place of a service response. The stop signal causes the I-O device to start the procedure that will end the write operation and disconnect the channel.

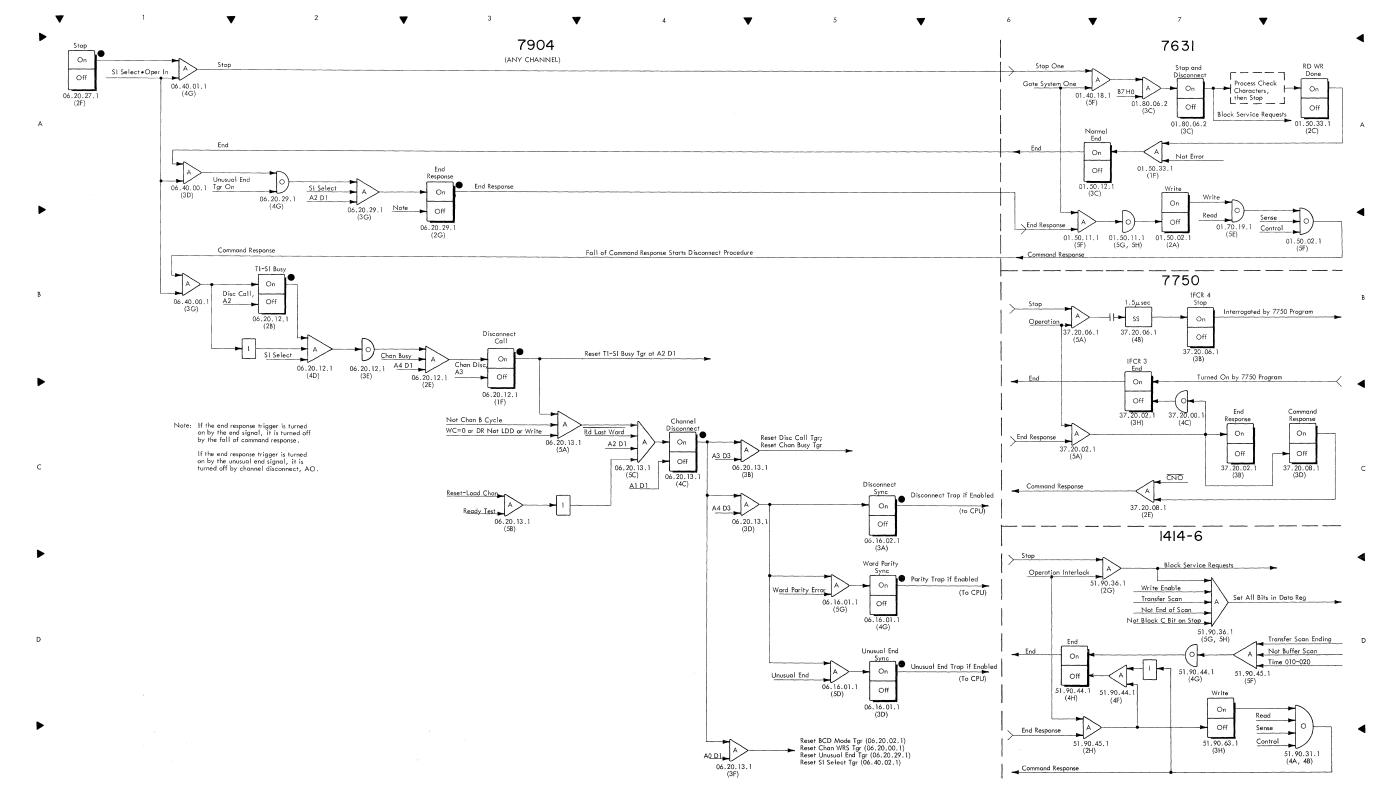

#### End Operation and Disconnect

The stop signal is received by the I-O device. The device checks to see that the transmission was correct, and if it was, sends the end signal to the channel (Figure 47). The end signal in the channel generates end response, which is sent to the I-O device. If the transmission had not been correct, the I-O device would have sent unusual end instead of end. Unusual end would have also generated end response, but, in addition, would have caused an unusual end trap.