GC20-1755-3 File No. S370-01

**Systems**

A Guide to the IBM System/370 Model 168 for System/370 Model 165 Users

# **Systems**

# A Guide to the IBM System/370 Model 168 for System/370 Model 165 Users

This guide presents hardware, programming systems, and other pertinent information about the IBM System/370 Model 168 that describes its significant new features and advantages. Knowledge of the IBM System/370 Model 165 is assumed. Features common to Models 165 and 168 are indicated but not discussed in detail. The contents of the guide are intended to acquaint the reader with the Model 168 and to be of benefit in planning for its installation.

Associated with this guide are three optional supplements that describe operating systems for the Model 168 that support a virtual storage environment. Each supplement has its own form number and must be ordered individually, if required. Optional supplements are the following:

- OS/Virtual Storage 1 Features Supplement (GC20-1752)

- OS/Virtual Storage 2 Single Virtual Storage (SVS) Features Supplement (GC20-1753)

- Virtual Machine Facility/370 Features Supplement (GC20-1757)

# Fourth Edition (September 1976)

This is a major revision obsoleting GC20-1755-2. Text has been added to include information about the multiprocessing feature and Attached Processor Systems. Miscellaneous other changes have been made throughout the publication as well. Changes to the text and illustrations are indicated by a vertical line in the left margin.

This guide is intended for planning purposes only. It will be updated from time to time; however, the reader should remember that the authoritative sources of system information are the system library publications for the Model 168, its associated components and its programming support. These publications will first reflect any changes.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form has been provided at the back of this publication for readers' comments. If this form has been removed, address comments to: IBM Corporation, Technical Publications/Systems, Dept. 824, 1133 Westchester Avenue, White Plains, New York 10604. Comments become the property of IBM.

© Copyright International Business Machines Corporation 1972, 1974, 1975, 1976

It is assumed that the reader of this publication is familiar with System/370 Model 165 hardware features, channels, I/O devices, and programming support as described in A <u>Guide to the IBM System/370 Model 165</u>, GC20-1730, and/or system library publications concerning Model 165 hardware and programming systems support. This guide discusses in detail only the hardware features of the Model 168 that are different from those of the Model 165 and the programming support provided for new features of the Model 168.

Those familiar with a System/360 model only or a System/370 model other than the Model 165 should obtain A Guide to the IBM System/370 Model 168 for System/360 Users, GC20-1787, which discusses the differences between the Model 168 and the System/360 Model 65.

There are three versions of the Model 168: the Model 1, Model 3, and Model A3. The hardware differences between Model 1 of the Model 168 and the Model 165 are discussed in Sections 01 to 60. The differences between Models 3 and 1 of the Model 168 (both uniprocessor and multiprocessor systems) are discussed in Section 65. The Model A3, which together with the 3062 Attached Processing Unit forms the Model 168 Attached Processor System, is discussed in Section 67.

The Model 168 is not compared with a Model 165 II, which is a purchased Model 165 (storage model J, K, or KJ) with the optional Dynamic Address Translation Facility installed. However, functional descriptions of Model 168 features that are also part of the Dynamic Address Translation Facility of the Model 165 II apply to the Model 165 II as well, unless otherwise noted. This publication applies to systems with 60-cycle power.

The total Model 168 guide consists of this base publication (Sections 01 to 70), which covers virtual storage and virtual machine concepts and Model 168 hardware and I/O devices, and from one to three optional supplements (Sections 90 to 110). The optional supplements describe the facilities of the IBM programming systems that support a virtual storage environment using the dynamic address translation hardware of the Model 168. Each optional supplement has its own unique form number and each supplement desired must be ordered separately and inserted in this base publication, which is distributed without the automatic inclusion of any optional supplements.

The following optional supplements can be inserted in this base publication:

- OS/Virtual Storage 1 Features Supplement (GC20-1752) assumes knowledge of OS MFT

- OS/Virtual Storage 2 Single Virtual Storage (SVS) Features Supplement (GC20-1753) - assumes knowledge of OS MVT

- Virtual Machine Facility/370 Features Supplement (GC20-1757) does not assume knowledge of CP-67/CMS

All optional supplements also assume knowledge of virtual storage, dynamic address translation, and other new Model 168 features as described in this base publication or appropriate system library documents. However, no optional supplement requires knowledge of the contents of any other optional supplement.

This base publication, as well as each optional supplement, begins with page 1 and includes its own table of contents and index. The base publication or supplement title is printed at the bottom of each page as a means of identification.

The optional programming systems supplements contain System/370 model-independent information, unless otherwise noted, and are designed to be included in the guides for System/370 Models 135, 145, 158, and 168 as shown below.

|                                                                                                | Supplements                                     |                                                 |                                                        |                                                 |  |  |

|------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------------|--------------------------------------------------------|-------------------------------------------------|--|--|

| Base<br>Publications                                                                           | DOS/VS<br>Features<br>Supplement<br>(GC20-1756) | OS/VS1<br>Features<br>Supplement<br>(GC20-1752) | OS/VS2<br>SVS<br>Features<br>Supplement<br>(GC20-1753) | VM/370<br>Features<br>Supplement<br>(GC20-1757) |  |  |

| A Guide to the IBM<br>System/370 Model 135<br>(GC20-1738-4 or<br>later editions)               | x                                               | х                                               |                                                        | х                                               |  |  |

| A Guide to the IBM<br>System/370 Model 145<br>(GC20-1734-2 or<br>later editions)               | x                                               | x                                               | х                                                      | x                                               |  |  |

| A Guide to the IBM<br>System/370 Model 158<br>for System/370<br>Model 155 Users<br>(GC20-1754) | х                                               | х                                               | х                                                      | х                                               |  |  |

| A Guide to the IBM<br>System/370 Model 158<br>for System/360 Users<br>(GC20-1781)              | х                                               | X                                               | x                                                      | <b>x</b>                                        |  |  |

| A Guide to the IBM<br>System/370 Model 168<br>for System/370<br>Model 165 Users<br>(GC20-1755) |                                                 | х                                               | <b>x</b>                                               | х                                               |  |  |

| A Guide to the IBM<br>System/370 Model 168<br>for System/360 Users<br>(GC20-1787)              |                                                 | x                                               | x                                                      | x                                               |  |  |

Additional, more detailed information regarding System/370 Model 168 hardware and programming systems support can be found in system library publications.

# CONTENTS

| Base Pul | olication Sections (Sections 01 to 70)                        |          |

|----------|---------------------------------------------------------------|----------|

| Section  | 01: System Highlights of Models 1 and 3                       | 1        |

| Section  | 10: Major Components and System Technology for Models 1 and 3 | 6        |

| Section  |                                                               | _        |

| 20.05    | Model 1                                                       | 9        |

|          |                                                               | 9        |

| 20:10    |                                                               | 13<br>13 |

|          |                                                               | 13<br>19 |

|          |                                                               | 19<br>19 |

|          |                                                               | 20       |

|          |                                                               | 20<br>21 |

| 20:15    |                                                               | 25<br>25 |

| 20:15    |                                                               | 25<br>25 |

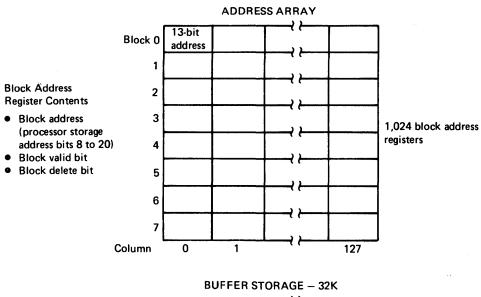

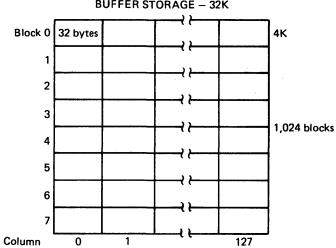

|          | High-Speed Buffer Storage                                     | 23<br>28 |

| 20:20    |                                                               | 32       |

| 20:25    |                                                               | 34       |

| 20:30    | Standard and Optional System Features                         | 34       |

| 20.00    | Standard Features                                             | 34       |

|          |                                                               | 35       |

|          |                                                               | 36       |

| 30:05    |                                                               | 36       |

|          |                                                               | 36       |

|          |                                                               | 40       |

|          | General Advantages Offered by IBM Operating Systems that      |          |

|          |                                                               | 46       |

|          | Virtual Storage and Dynamic Address Translation               | 53       |

| 30:10    |                                                               | ) )      |

| 20110    |                                                               | 58       |

|          |                                                               | 58       |

|          | Operation of Dynamic Address Translation Hardware             | 59       |

|          | Features to Support Demand Paging                             | 66       |

|          |                                                               | 69       |

| 30:15    |                                                               | 71       |

| ******   | System Resources Required to Support a Virtual Storage        | _        |

|          | Environment                                                   | 72       |

|          | New Factors that Affect System Performance                    | 75       |

|          | Relationship Between Virtual Storage Size and System          |          |

|          |                                                               | 78       |

|          | Increasing System Performance in a Virtual Storage            |          |

|          | Environment                                                   | 82       |

| Section  | 40: Virtual Machines                                          | 86       |

| 40:05    |                                                               | 86       |

|          | General Advantages of a Virtual Machine Environment           | 93       |

| Section  |                                                               | 96       |

| 50:05    | I/O Device Support                                            | 96       |

| 50:10    | 3333 Disk Storage and Control Model 11 and 3330 Disk Storage  |          |

|          |                                                               | 96       |

|          | Attachment via Integrated Storage Controls.                   | 97       |

| 50:1         |                                                                                                                                                       |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | 3340 Disk Storage Drives and the 3348 Data Module 101                                                                                                 |

|              | Attachment via 3830 Storage Control Model 2 116                                                                                                       |

|              | Attachment via Integrated Storage Controls 119                                                                                                        |

|              | Intermixing 3340 and 3330-Series Strings on an                                                                                                        |

|              | Attachment                                                                                                                                            |

|              | Summary                                                                                                                                               |

|              |                                                                                                                                                       |

| Sectio       | n 60: Multiprocessing                                                                                                                                 |

| 60:0         |                                                                                                                                                       |

|              | Introduction                                                                                                                                          |

|              | Definition of Multiprocessing                                                                                                                         |

|              | The Model 168 Multiprocessing System                                                                                                                  |

|              | Advantages of Model 168 Tightly Coupled Multiprocessing                                                                                               |

|              | Configurations                                                                                                                                        |

|              |                                                                                                                                                       |

|              | Advantages of Loosely Coupled Multiprocessing                                                                                                         |

|              | Configurations                                                                                                                                        |

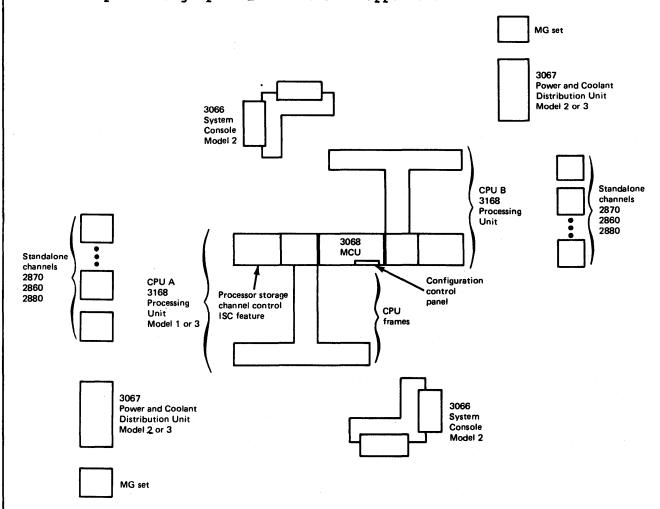

| 60:1         |                                                                                                                                                       |

|              | Uniprocessor and Multiprocessor Hardware Differences 142                                                                                              |

|              | 3068 Multisystem Communication Unit                                                                                                                   |

|              | Prefixing                                                                                                                                             |

|              | CPU Addressing                                                                                                                                        |

|              | Time-of-Day Clock                                                                                                                                     |

|              | Interprocessor Programmed Communication                                                                                                               |

|              | Interprocessor Hardware Communication                                                                                                                 |

|              | Channel Reconfiguration Hardware                                                                                                                      |

| 60:1         |                                                                                                                                                       |

| 60:2         | 0 Planning Considerations 162                                                                                                                         |

| 00,2         | O Planning Considerations                                                                                                                             |

|              | ridingling for Maximum Dyscem Availability.                                                                                                           |

| Sectio       | n 65: Differences Between the Model 3 and the Model 1 165                                                                                             |

| 65:0         |                                                                                                                                                       |

| 65:1         | 0 The Service Processor                                                                                                                               |

| 02:1         | Functions and General Operation                                                                                                                       |

|              | runctions and General Operation                                                                                                                       |

|              | Processor Unit                                                                                                                                        |

|              | Trace Unit                                                                                                                                            |

|              | Counters                                                                                                                                              |

|              | Internal Disk File                                                                                                                                    |

|              | CE Panel                                                                                                                                              |

|              | Printer Control                                                                                                                                       |

|              | Corporate Standard Interface                                                                                                                          |

|              | Modem                                                                                                                                                 |

|              | Advantages                                                                                                                                            |

|              |                                                                                                                                                       |

| Section      | n 67: Attached Processor System                                                                                                                       |

| 67:0         |                                                                                                                                                       |

| 67:1         | 0 The 3062 Attached Processing Unit                                                                                                                   |

| 67:1         |                                                                                                                                                       |

|              | Differences 183                                                                                                                                       |

| 67:2         | Differences                                                                                                                                           |

| 67.2         | 5 Recording and Diagnostic Routines                                                                                                                   |

| 0/12         | A MECOLATINA SING DISABLESCIP MONOCINES                                                                                                               |

|              |                                                                                                                                                       |

| - فروست      | n 70. Companion Mahloo                                                                                                                                |

|              | n 70: Comparison Tables                                                                                                                               |

| Section 70:0 | 5 Comparison Table of Hardware Features of the System/360                                                                                             |

|              | 5 Comparison Table of Hardware Features of the System/360 Model 65 and System/370 Models 158 (Models 1 and 3), 165,                                   |

| 70:0         | 5 Comparison Table of Hardware Features of the System/360 Model 65 and System/370 Models 158 (Models 1 and 3), 165, 165 II, and 168 (Models 1 and 3). |

| 70:0         | 5 Comparison Table of Hardware Features of the System/360 Model 65 and System/370 Models 158 (Models 1 and 3), 165,                                   |

| 70:0<br>70:1 | 5 Comparison Table of Hardware Features of the System/360 Model 65 and System/370 Models 158 (Models 1 and 3), 165, 165 II, and 168 (Models 1 and 3). |

| Optional           | <u>Sections</u> (See each supplement for detailed contents and index)                                                                                     |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 9          | 0: OS/Virtual Storage 1 Features                                                                                                                          |

| Section 1          | 00: OS/Virtual Storage 2 Single Virtual Storage (SVS) Features                                                                                            |

| Section 1          | 10: Virtual Machine Facility/370 Features                                                                                                                 |

| fe                 | is guide does not have a Section 80. DOS/Virtual Storage atures are discussed in the Section 80 supplement and the Model 8 is not supported by DOS/VS.    |

| FIGURES (          | Sections 01 to 70)                                                                                                                                        |

| 10.1               | System/370 Model 168 6                                                                                                                                    |

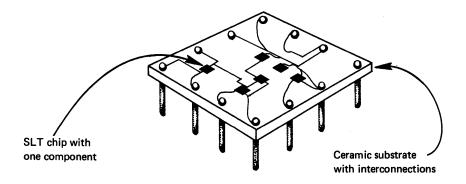

| 10.2               | SIT substrate                                                                                                                                             |

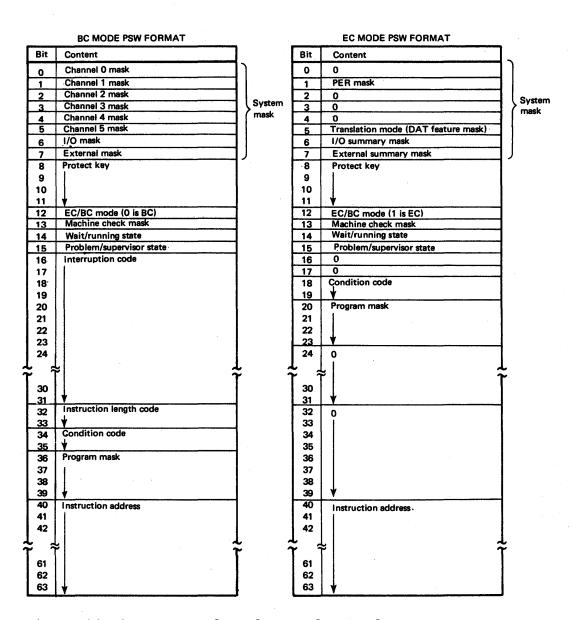

| 20.10.1<br>20.10.2 | BC mode and EC mode PSW formats                                                                                                                           |

| 20.10.2            | BC and EC modes                                                                                                                                           |

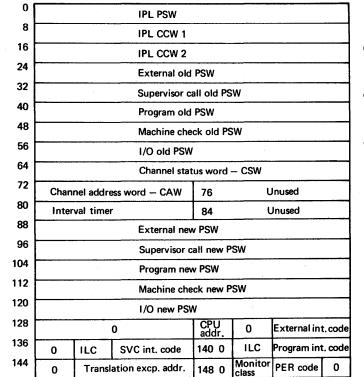

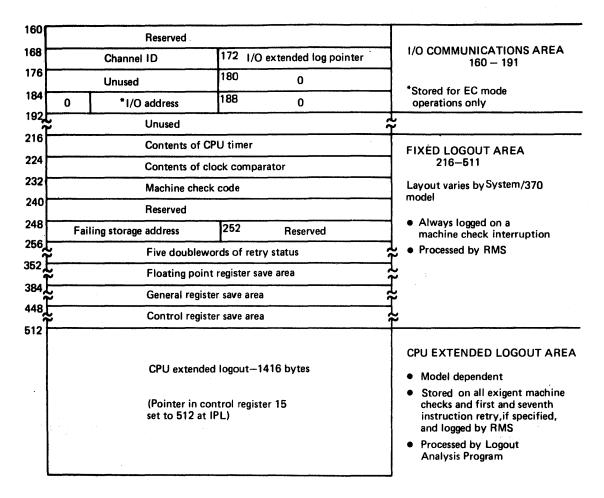

| 20.10.3            | Model 168 (Model 1) model-dependent fixed storage                                                                                                         |

|                    | locations                                                                                                                                                 |

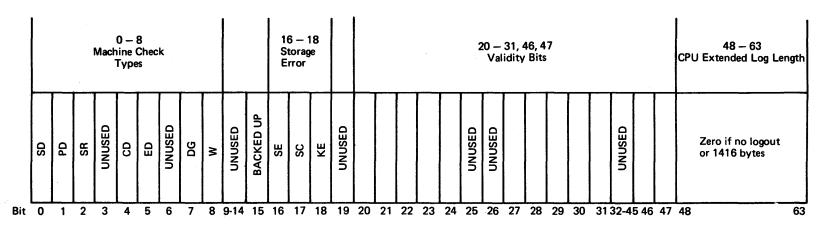

| 20.10.4            | Model 168 machine check code                                                                                                                              |

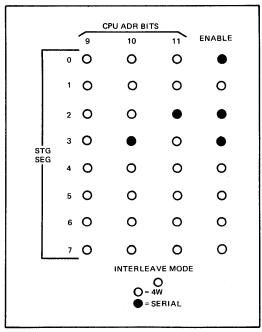

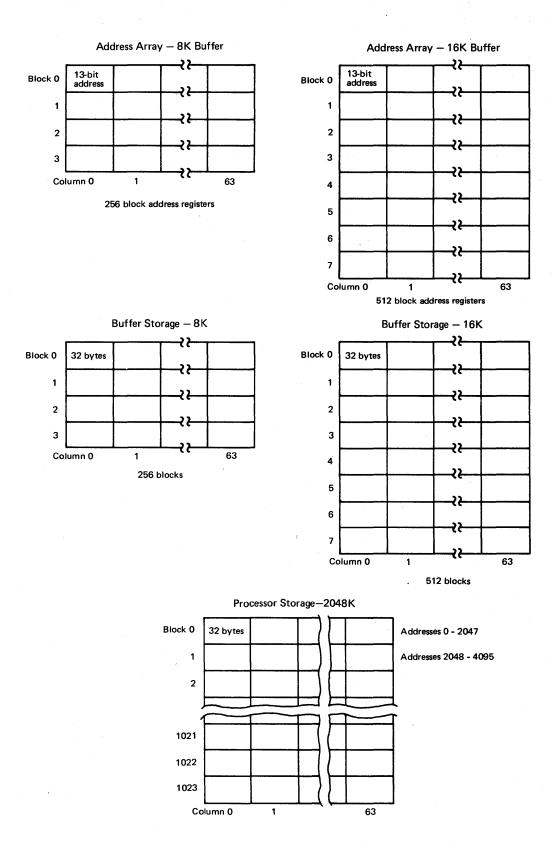

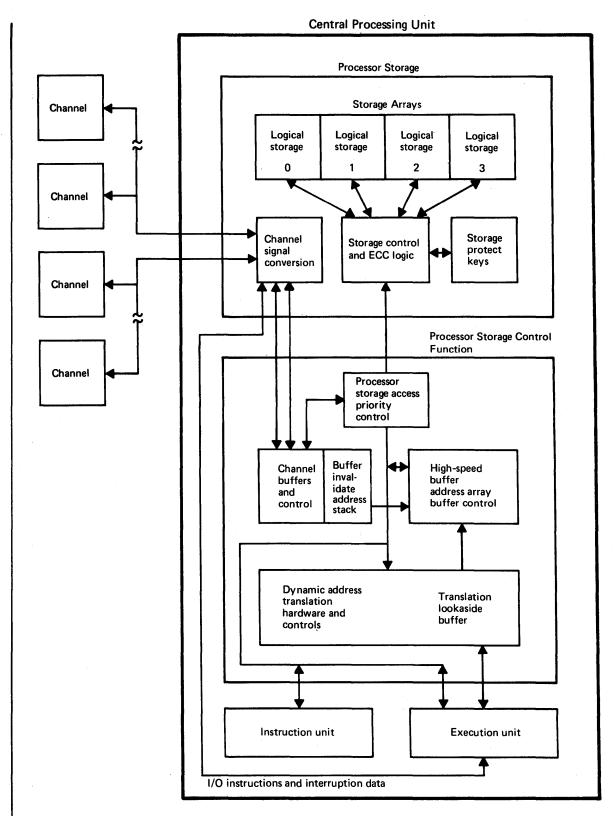

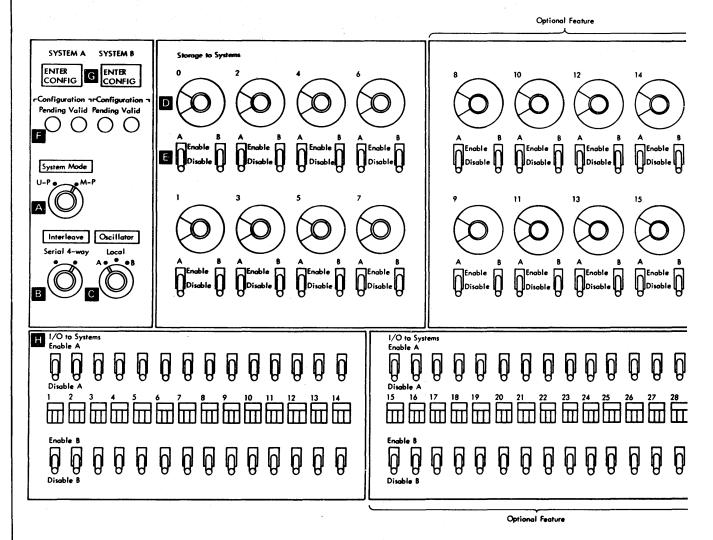

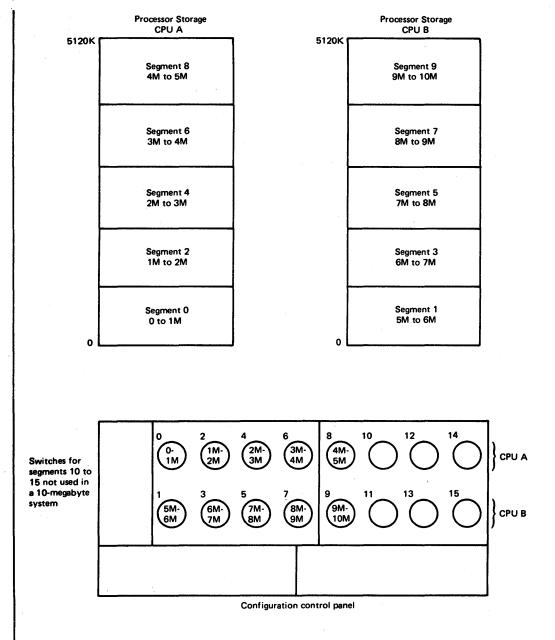

| 20.15.1            | Model 168 processor storage organization and configuration panel                                                                                          |

| 20.15.2            | configuration panel                                                                                                                                       |

| 20.15.3            | Model 168 components and controls                                                                                                                         |

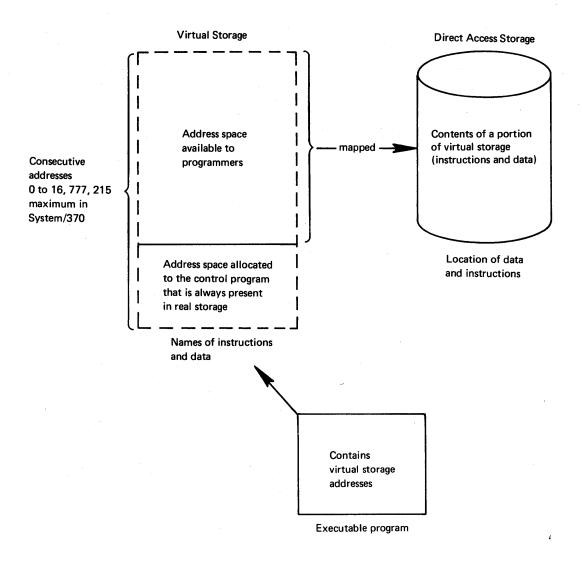

| 30.05.1            | Names and location of instructions and data in a virtual                                                                                                  |

| 30.05.2            | storage environment                                                                                                                                       |

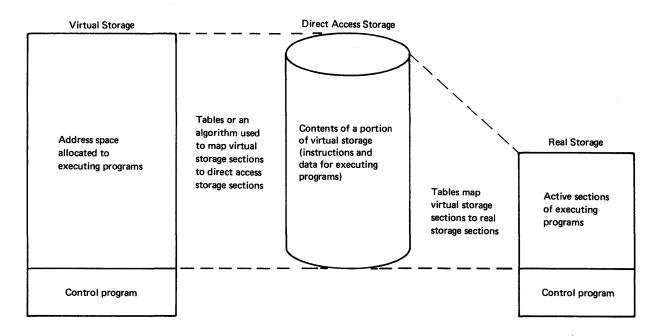

| 30.05.3            | and real storage                                                                                                                                          |

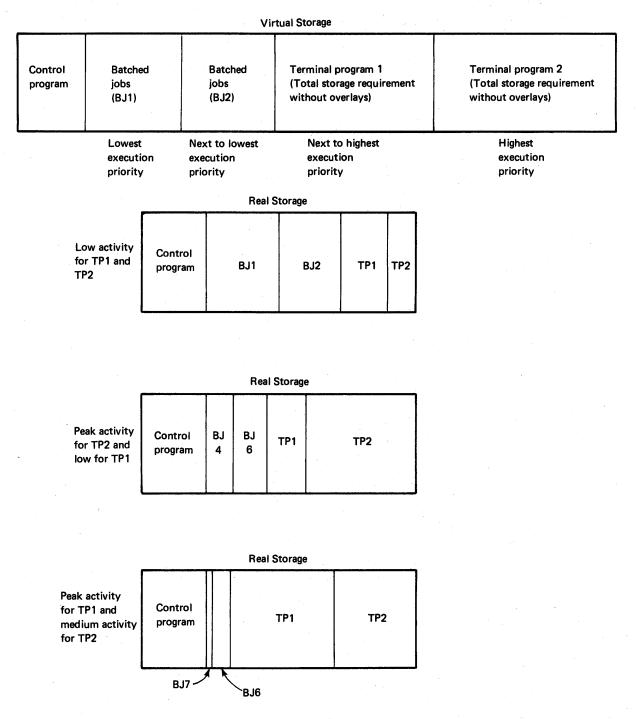

|                    | a mixed batch and online virtual storage environment 52                                                                                                   |

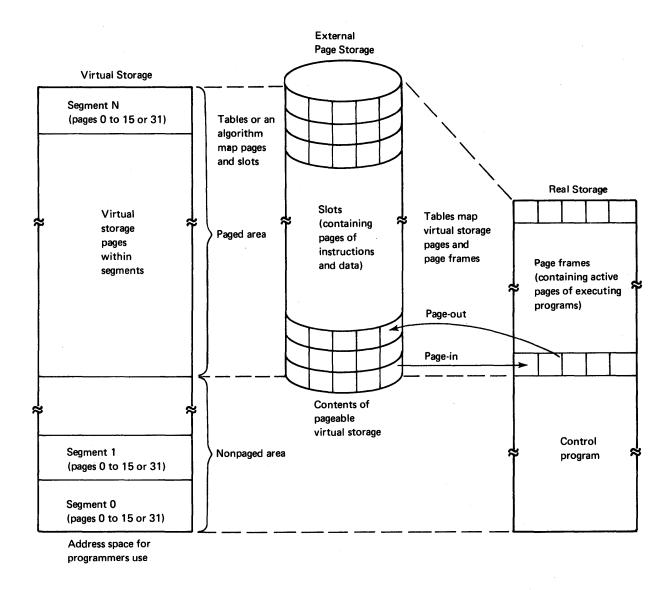

| 30.05.4            | Layout of virtual storage, external page storage, and real storage                                                                                        |

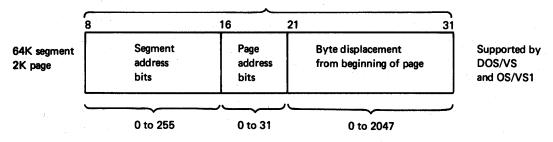

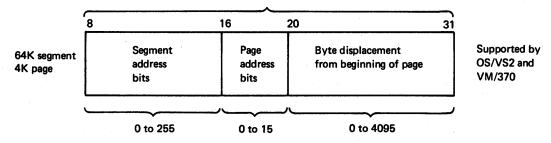

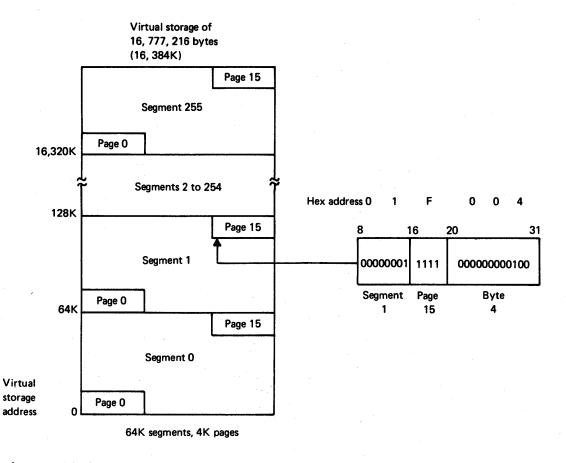

| 30.10.1            | Virtual storage address fields for a 64K segment. 60                                                                                                      |

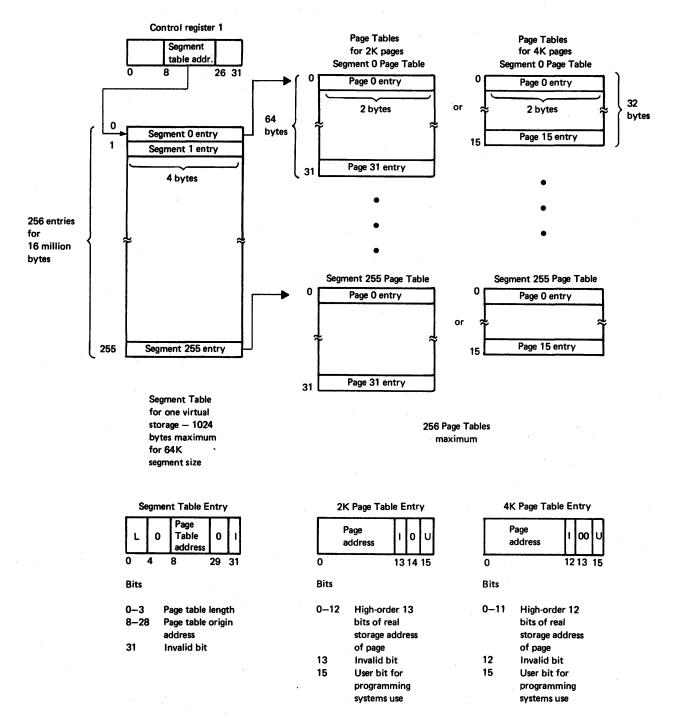

| 30.10.2            | Segment table and page tables used for dynamic address                                                                                                    |

|                    | translation                                                                                                                                               |

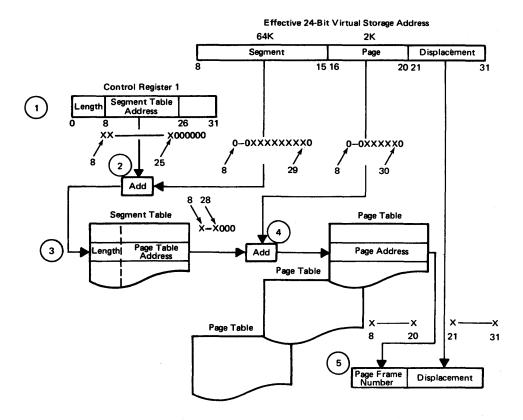

| 30.10.3            | Dynamic address translation procedure 63                                                                                                                  |

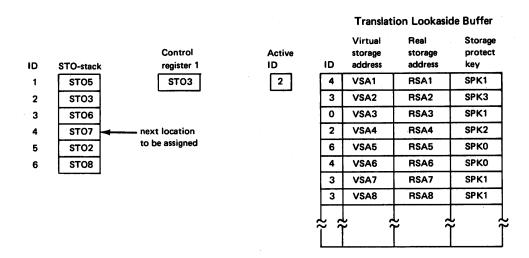

| 30.10.4            | TLB purging when control register 1 is changed 65                                                                                                         |

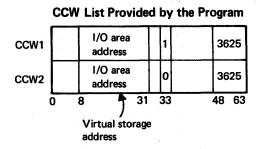

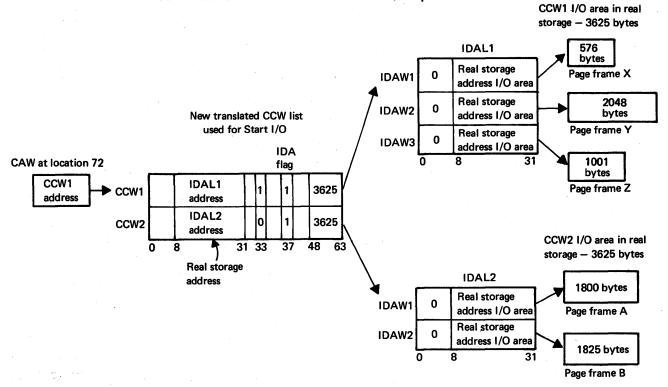

| 30.10.5            | Example of IDALs required for a CCW list when page size is 2K                                                                                             |

| 30.15.1            | Possible system performance when a virtual storage operating system is used with a Model 168 with the same I/O configuration and real storage size as the |

| 30.15.2            | replaced Model 165                                                                                                                                        |

|                    | virtual storage used to real storage present in the                                                                                                       |

|                    | system                                                                                                                                                    |

| 30.15.3            | General effect on system performance of the paging factor                                                                                                 |

| 30.15.4            | only                                                                                                                                                      |

| 30.15.5            | General system performance curve for a virtual storage                                                                                                    |

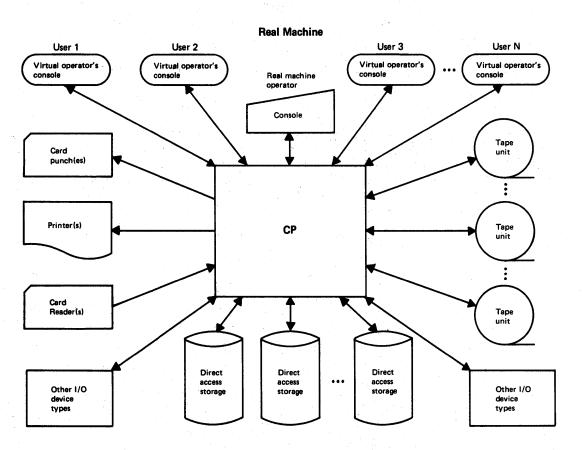

| 40.05.1            | Conceptual illustration of the real and virtual machine                                                                                                   |

| #A AF A            | environment that is supported by VM/370                                                                                                                   |

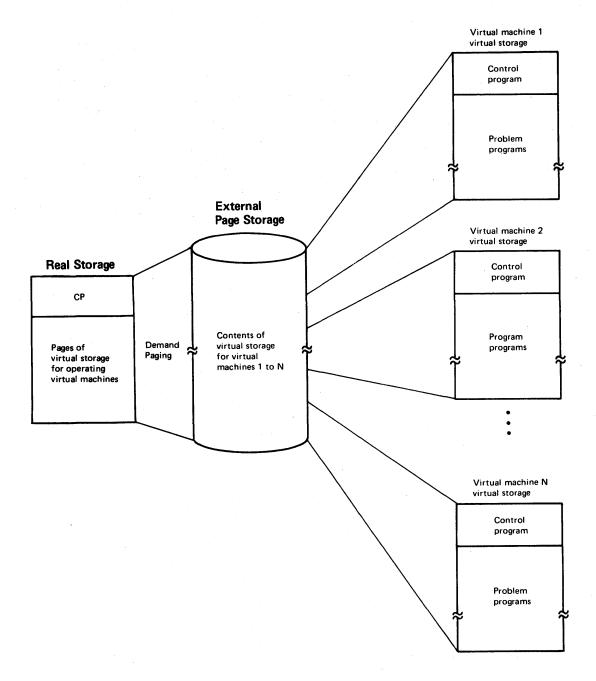

| 40.05.2            | Conceptual illustration of the implementation of virtual storage in a virtual machine environment                                                         |

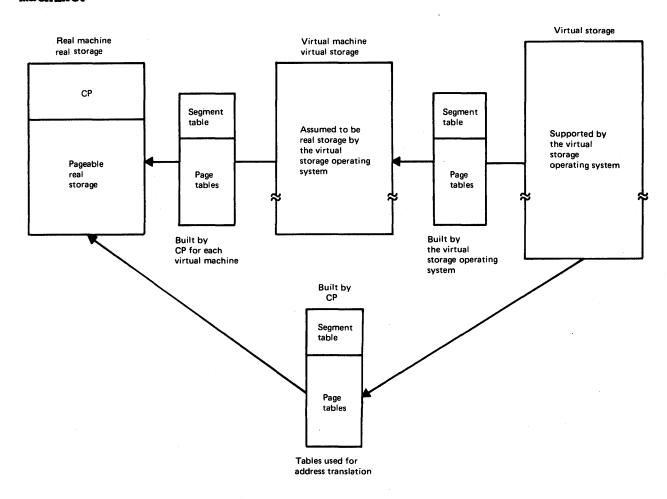

| 40.05.3            | Segment table and page tables built when a virtual                                                                                                        |

|                    | storage operating system executes in a virtual machine 91                                                                                                 |

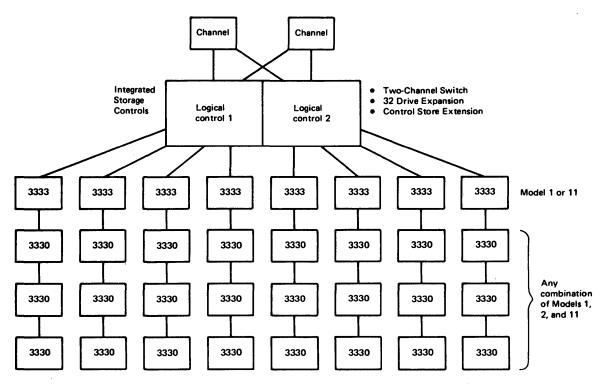

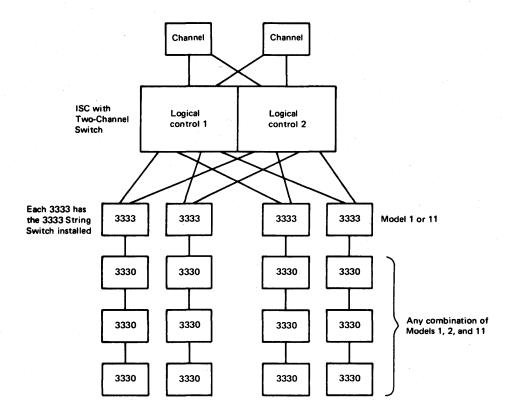

| 50.10.1            | Permissible 3330-series string configurations for the Model 168 Integrated Storage Controls feature 99                                                    |

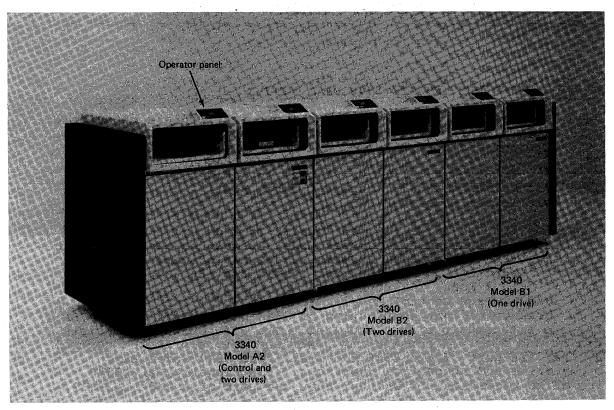

| 50.15.1 A five-drive 3340 string with 3340 Model AZ, BZ, and Bl units                                                                                                                                            | 50.10.2                                                                                                               | Sample 3330-series string configuration with string                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bl units.                                                                                                                                                                                                        |                                                                                                                       | switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

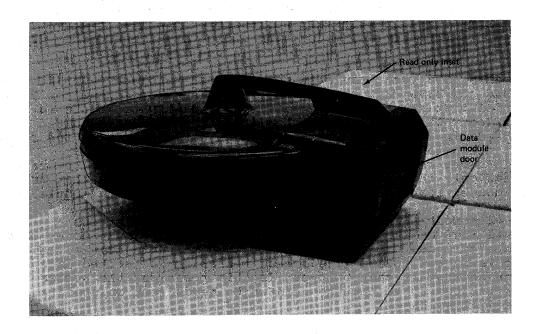

| 50.15.2 The 3348 bata Module                                                                                                                                                                                     | 50.15.1                                                                                                               | A five-drive 3340 string with 3340 Model A2, B2, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

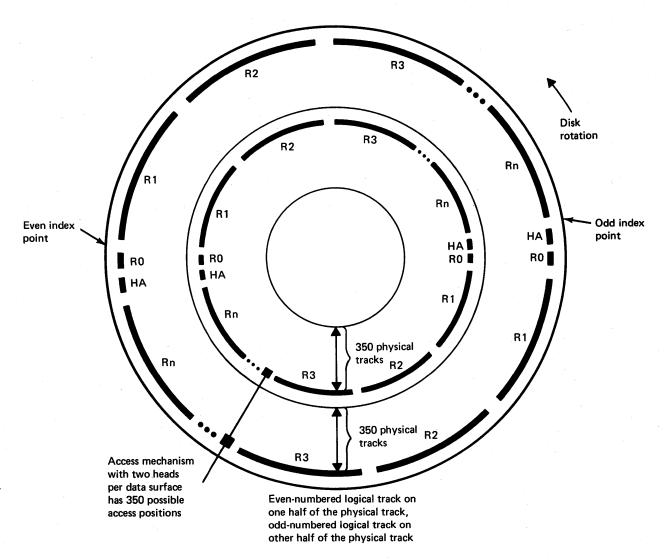

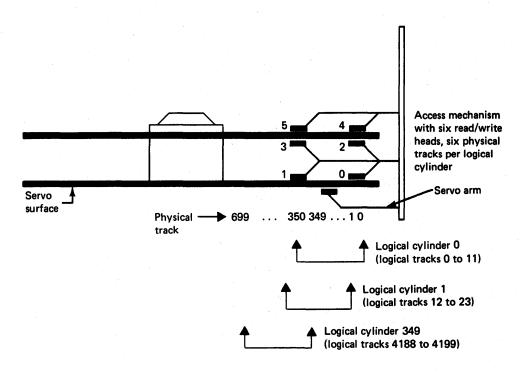

| 50.15.3 Location of physical and logical tracks and read/write heads on a data surface in a 3348 Data Module                                                                                                     |                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| heads on a data surface in a 3348 Data Module                                                                                                                                                                    |                                                                                                                       | The 3348 Data Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

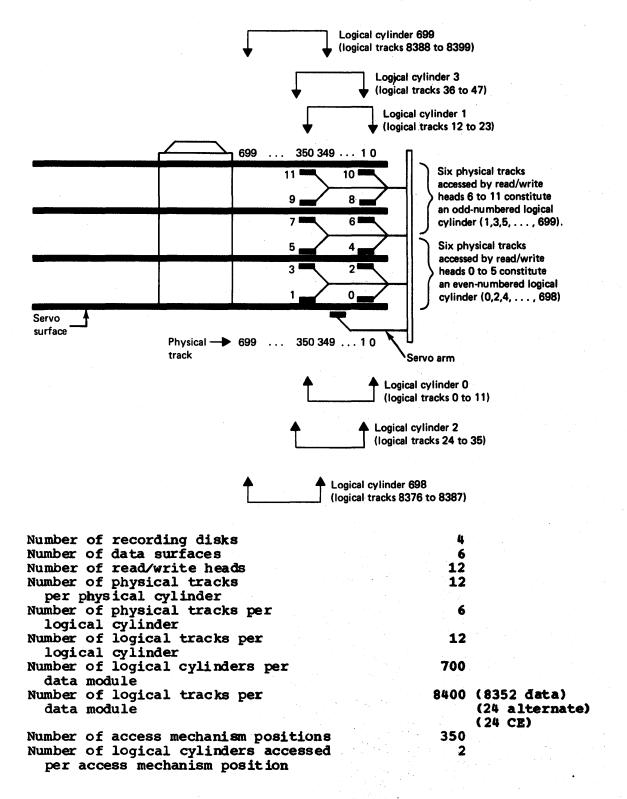

| 50.15.4   Cylinder and read/write head layout for a 3348 Model 35 Data Module                                                                                                                                    | 50.15.3                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 35 Data Module                                                                                                                                                                                                   |                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

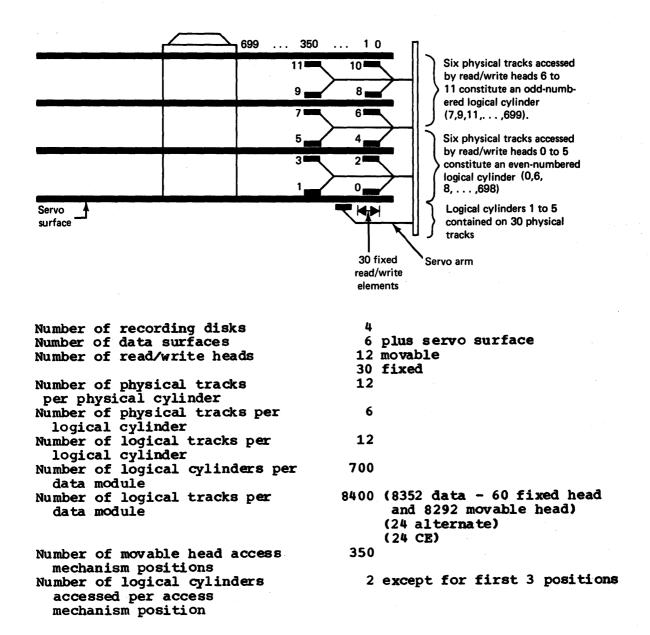

| 50.15.5   Cylinder and read/write head layout for a 3348 Model   70 Data Module                                                                                                                                  | 50.15.4                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 70 Data Module                                                                                                                                                                                                   |                                                                                                                       | 35 Data Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 50.15.6 Cylinder and read/write head layout for a 3348 Model 70F Data Module                                                                                                                                     | 50.15.5                                                                                                               | Cylinder and read/write head layout for a 3348 Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 70F Data Module                                                                                                                                                                                                  |                                                                                                                       | 70 Data Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 70F Data Module                                                                                                                                                                                                  | 50.15.6                                                                                                               | Cylinder and read/write head layout for a 3348 Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

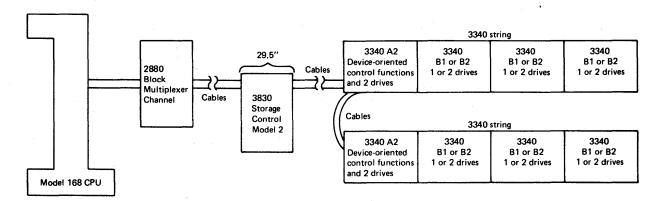

| attached via 3830 Storage Control Model 2                                                                                                                                                                        |                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

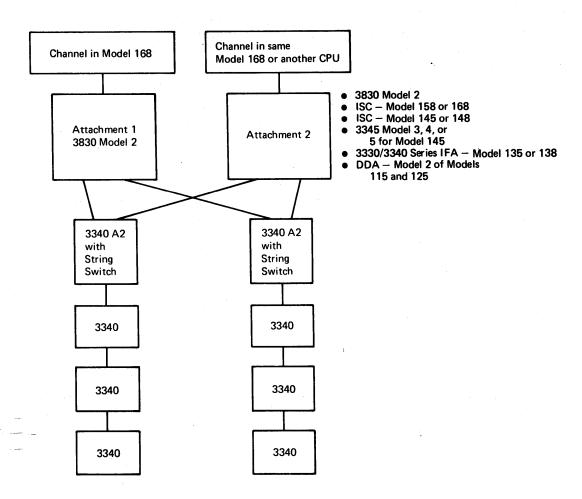

| attached via 3830 Storage Control Model 2                                                                                                                                                                        | 50.15.7                                                                                                               | A Model 168 configuration with 3340 disk storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 50.15.8 String switching for the 3340 facilities attached to a 3830 Model 2                                                                                                                                      |                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| a 3830 Model 2                                                                                                                                                                                                   | 50 15 8                                                                                                               | String switching for the 3340 facilities attached to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

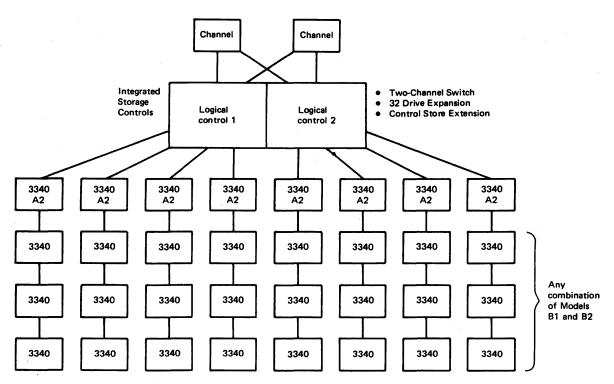

| 16.15.9 Permissible 3340 string configurations for the Model 168 Integrated Storage Controls feature                                                                                                             | 30.13.0                                                                                                               | a 3830 Model 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 168 Integrated Storage Controls feature                                                                                                                                                                          | 50 15 0                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

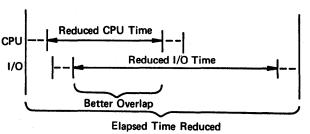

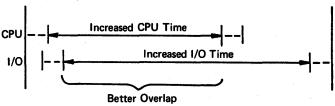

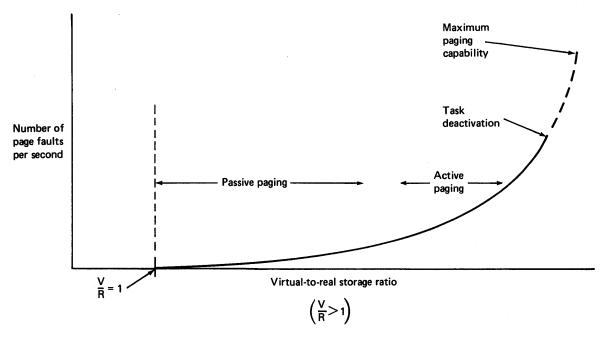

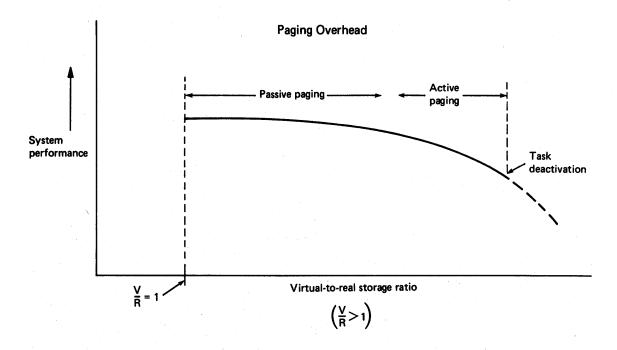

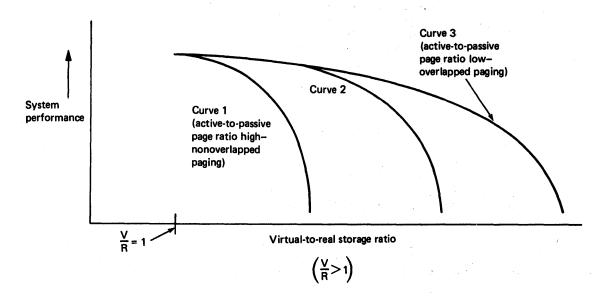

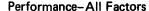

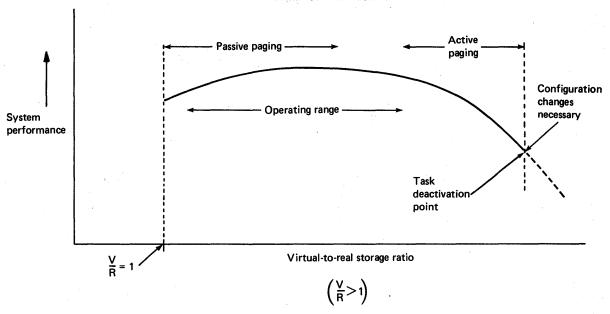

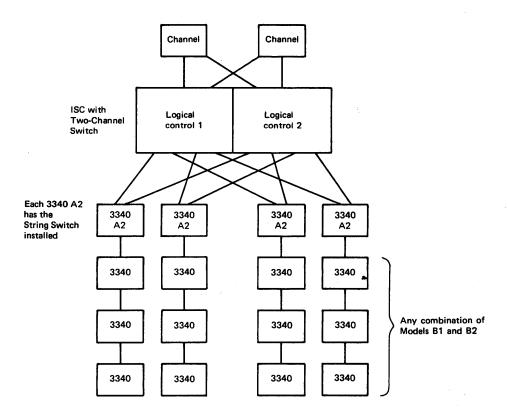

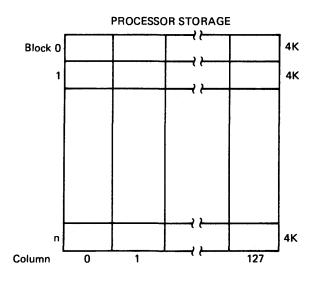

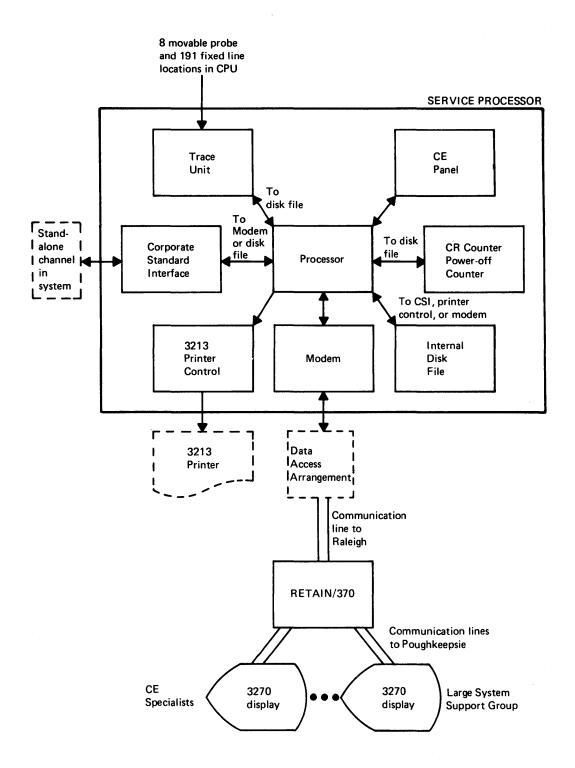

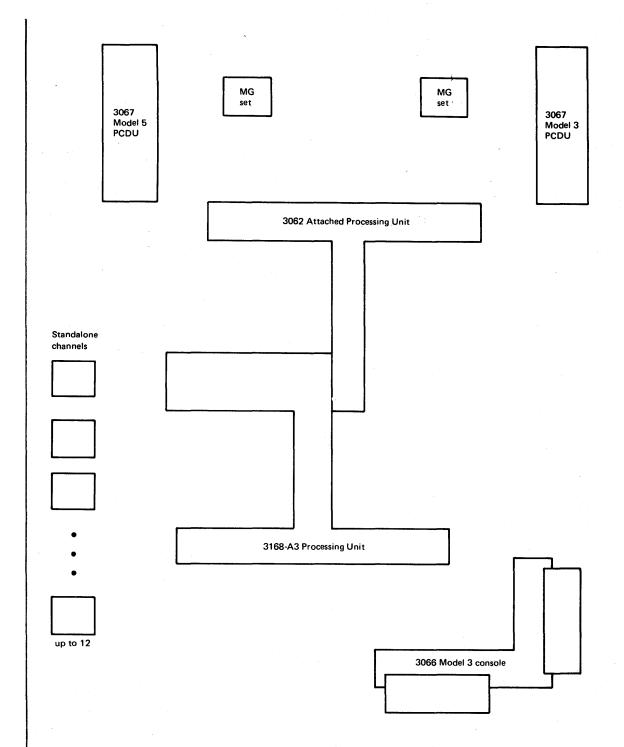

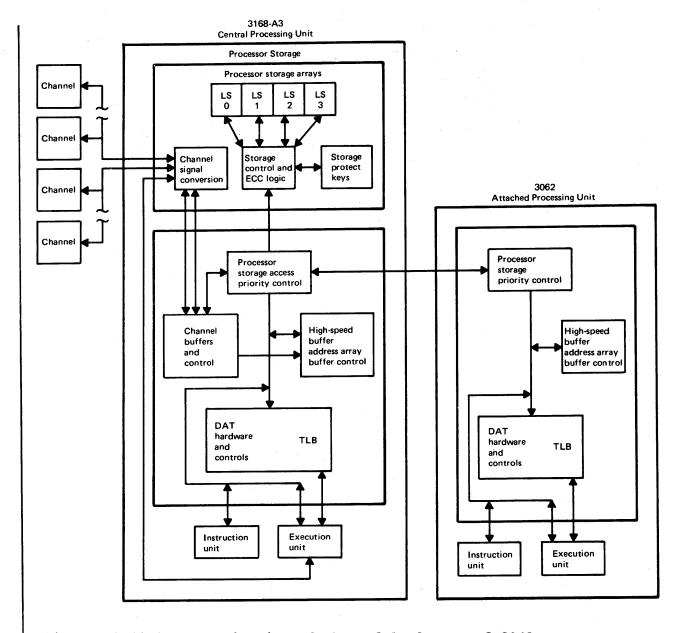

| String switching for 3340 facilities attached to one ISC                                                                                                                                                         | 20.12.3                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |