# Program Logic

# IBM System/360 Time Sharing System

System Logic Summary

Program Logic Manual

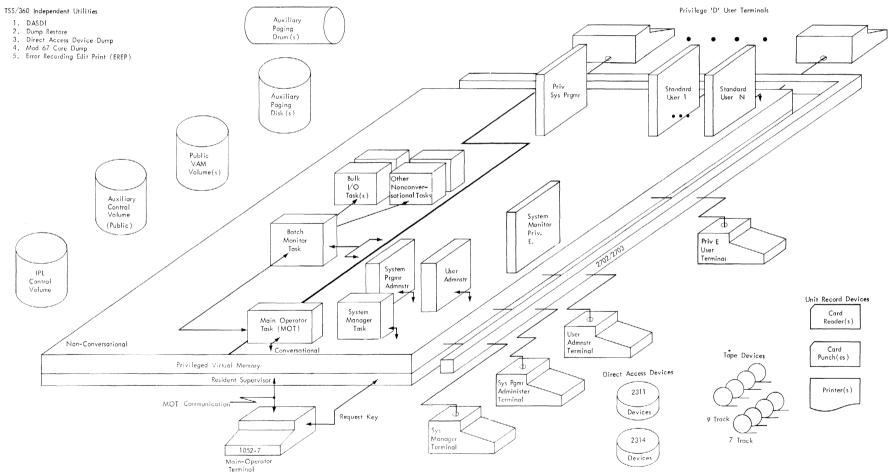

This publication describes the logic of the IBM System/360 Time Sharing System (TSS/360). The emphasis is on describing the interrelationship of system components in performing system functions. Where an individual component is described, only the highest level of logic is discussed.

This program logic manual is directed to the IBM customer engineer who is responsible for program maintenance. It can be used to determine the interrelationship among the various areas of the system, and it enables the reader to relate these areas to the corresponding program logic manuals.

## PREFACE

This publication is divided into three parts. The first part contains a systematic description of TSS/360. The second part explains various detailed features of TSS/360 such as allocation algorithms, sharing, and paging and gives examples of system operation. The third part discusses the relationship of language processors and auxiliary programs to the system.

There are three appendixes. One relates major system components to the appropriate Program Logic Manual, the second contains a summary of important system control blocks, and the third is a directory listing all modules for which flowcharts exist and the PLM which contains each flowchart.

## PREREQUISITE PUBLICATIONS:

IBM System/360 Time Sharing System: <u>Concepts and Facilities</u>, Form C28-2003

In addition, the following TSS/360 publications can be used to supplement an understanding of the interrelationships described in this manual:

- IBM System/360 Time Sharing System: <u>Command System User's Guide</u>, Form C28-2001

- IBM\_System/360 Time Sharing System: Assembler Programmer's Guide, Form C28-2032

- IBM System/360 Time Sharing System: <u>Manager's and Administrator's Guide</u>, Form C28-2024

- IEM System/360 Time Sharing System: Assembler Language, Form C28-2000

- IEM System/360 Time Sharing System: Assembler User Macro Instructions, Form C28-2004

- IBM System/360 Time Sharing System: IBM FORTRAN IV, Form C28-2007

- <u>IBM\_System/360 Time\_Sharing\_System:</u> <u>Linkage\_Editor</u>, Form C28-2005

- IBM System/360 Time Sharing System: Operator's Guide, Form C28-2033

#### Third Edition (June 1970)

This is a major revision of, and makes cbsolete, <u>IBM System/360 Time</u> <u>Sharing System: System Logic Summary</u>, Form Y28-2009-1, and Technical Newsletters Y28-3094, Y28-3102, Y28-3111, and Y28-3112. Changes to the text and illustrations have been made throughout and this edition should be reviewed in its entirety.

This edition is current with Version 7, Modification 0, and remains in effect for all subsequent versions or modifications of IBM System/360 Time Sharing System unless otherwise indicated. Significant changes or additions to this publication will be provided in new editions or Technical Newsletters. Before using this publication in connection with the operation of IBM systems, refer to the latest edition of <u>IBM</u> <u>System/360 Time Sharing System: Addendum</u>, Form C28-2043, for the editions of publications that are applicable and current.

This publication was prepared for production using an IBM computer to update the text and to control the page and line format. Page impressions for photo-offset printing were obtained from an IBM 1403 Printer using a special print chain.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form is provided at the back of this publication for reader's comments. If the form has been removed, comments may be addressed to IBM Corporation, Time Sharing System/360 Programming Publications, Department 643, Neighborhood Road, Kingston, New York 12401.

© Copyright International Business Machines Corporation 1967, 1968, 1970

IBM System/360: Model 67 Functional Characteristics, Form A27-2719

## CONTENTS

| PART I: GENERAL SYSTEM DESCRIPTION       |

|------------------------------------------|

| INTRODUCTION                             |

| Command Repertoire 4                     |

| SYSTEM ENVIRONMENT                       |

| Operational Environment                  |

|                                          |

| System Users5Privilege Classes5          |

| Authcrization Code                       |

| Tasks                                    |

| Ccnversaticnal Tasks                     |

| Nonconversational Tasks                  |

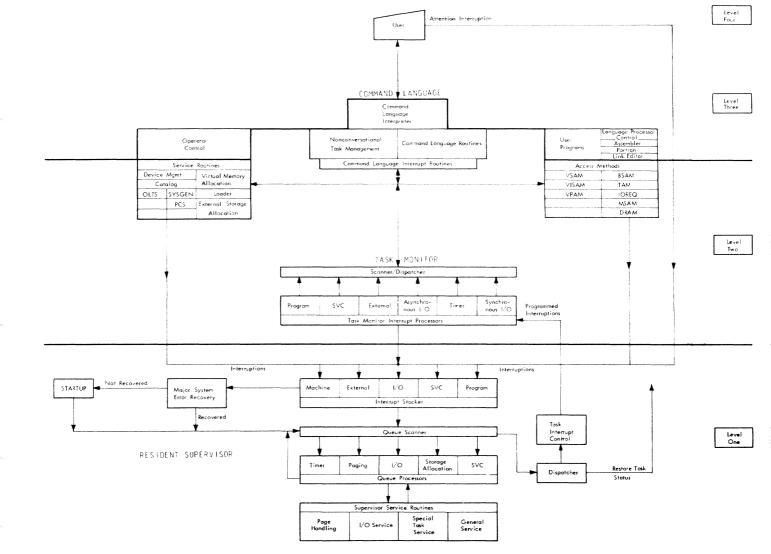

| System Program Structure                 |

| Resident Supervisor                      |

| Task Monitor and System Service Routines |

| IBM-Supplied Problem Programs            |

| Auxiliary Programs                       |

| Time Sharing Support System              |

|                                          |

| Utility Programs                         |

| System Build Program                     |

| STARTUP Program                          |

| System Storage                           |

| Public Storage                           |

| Private Storage                          |

| System Storage                           |

| Multiprogramming Environment             |

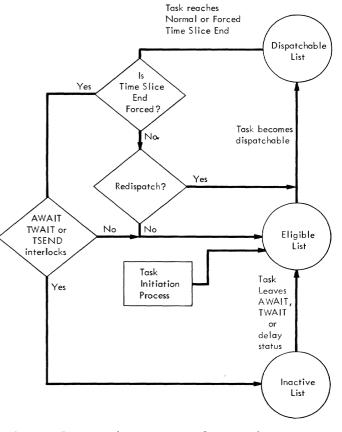

| Time-Slicing                             |

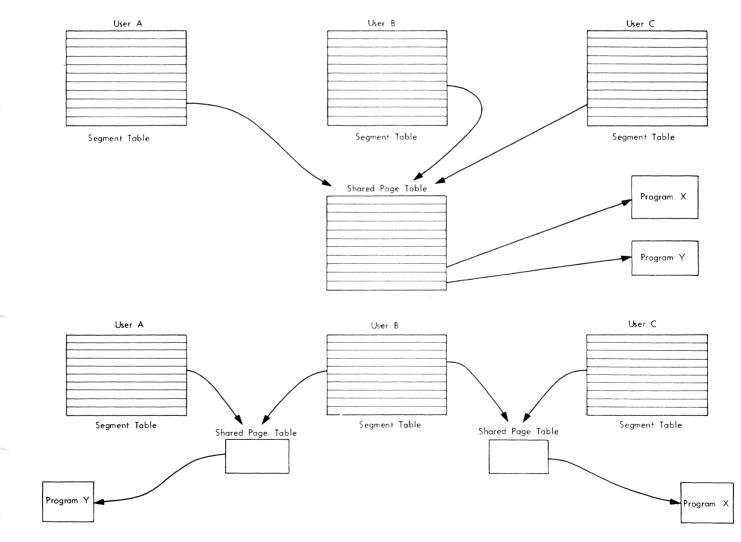

| Dynamic Program Relocation               |

| Configuration                            |

| Interconnection of System Components     |

| System Partitioning                      |

| Multiprocessing Features                 |

| Signaling                                |

| Malfunction Indication                   |

| Programmed Initialization                |

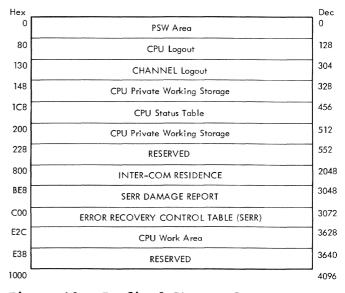

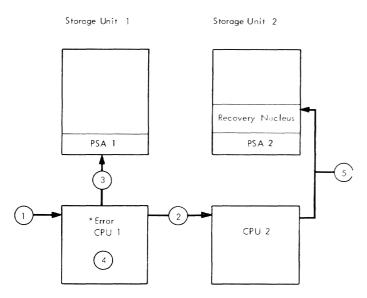

| Prefixed Storage Areas                   |

| Prefixed Storage Areas                   |

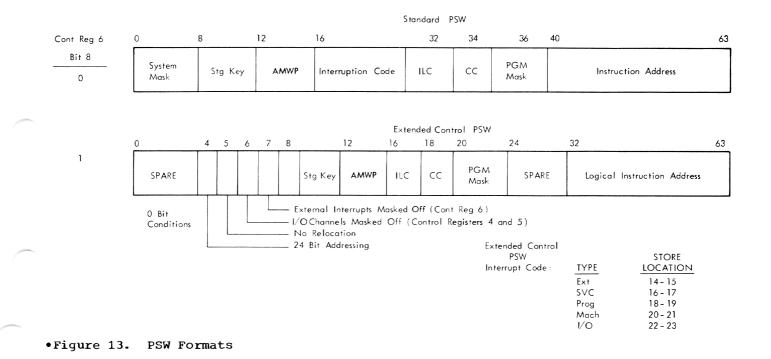

| Extended Mode                            |

| Extended Mode                            |

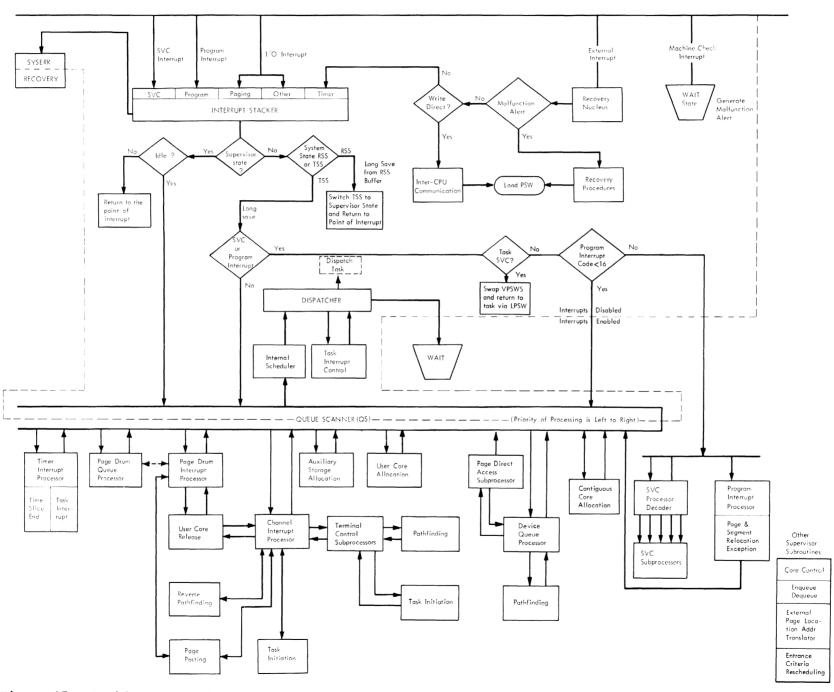

| CONTROL ARCHITECTURE                     |

| Resident Supervisor                      |

| Interrupt Stacker                        |

| Queue Scanner                            |

| Dispatcher                               |

| Queue Processors                         |

| Supervisor Service Subroutines           |

| Majer Error Recovery Routines            |

|                                          |

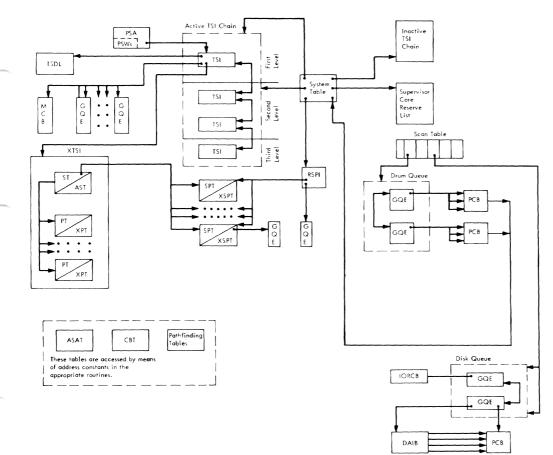

| Control Blocks                           |

| General Queue Entry (GQE)                |

| Scan Table                               |

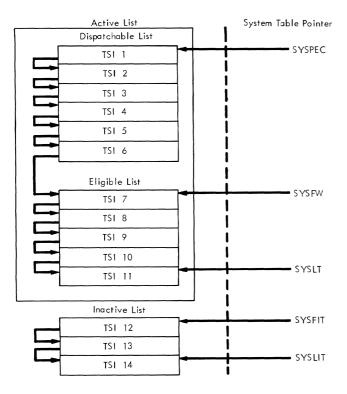

| Task Status Index (TSI)                  |

| Extended Task Status Index (XTSI)        |

| Page Control Block                       |

| Task Monitor                             |

| Interface With Resident Supervisor       |

| Interruption Processing                  |

| Task Integrity                           |

|                                          |

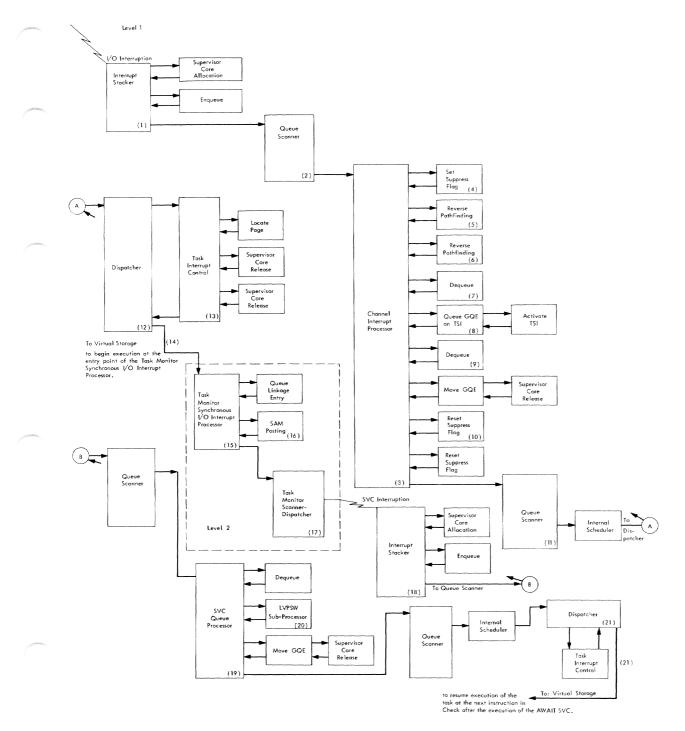

| INTERRUPTION HANDLING                    |

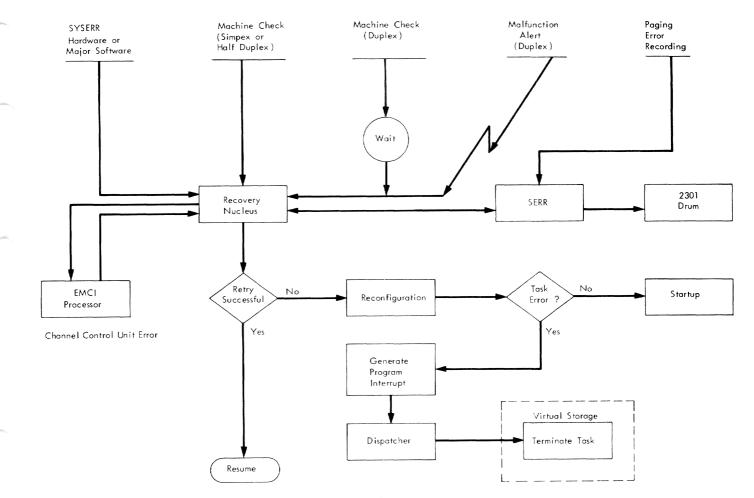

| Machine Check Interruption               |

| External Interruption                                                                                                                                                                                                                               | •••                                                                                             |                                       | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7<br>7                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Write Direct Interruptions                                                                                                                                                                                                                          | •••                                                                                             |                                       | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7                                                                                      |

| Program Interruption                                                                                                                                                                                                                                |                                                                                                 |                                       | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7                                                                                      |

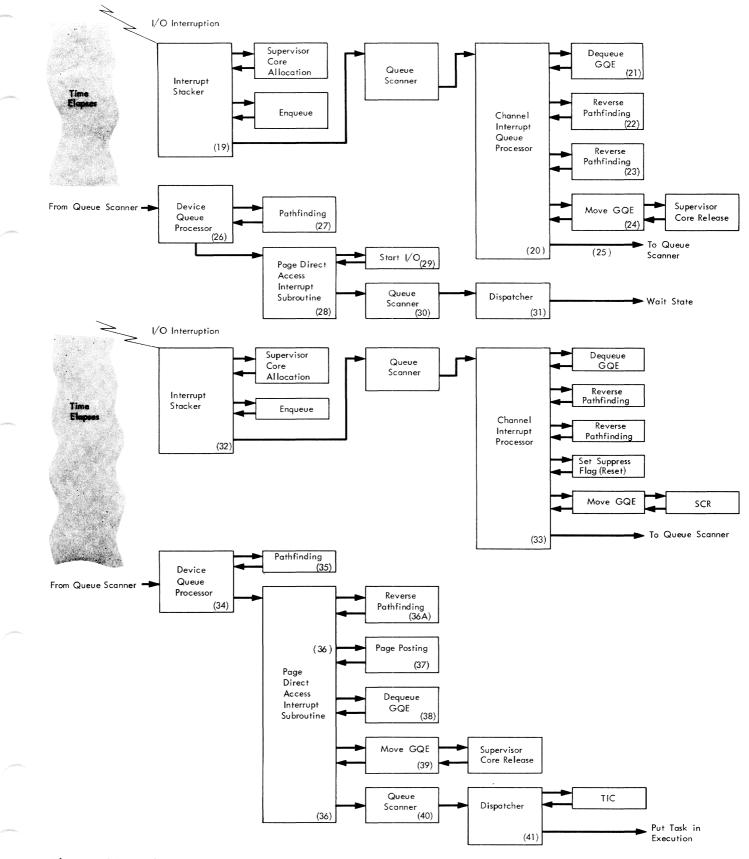

| I/O Interruption                                                                                                                                                                                                                                    | • •                                                                                             |                                       | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8                                                                                      |

| Supervisor Call Interruption                                                                                                                                                                                                                        | •••                                                                                             | •••                                   | •••5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                      |

| RESIDENT TERMINAL ACCESS METHOD/MULTITERMINAL TASK                                                                                                                                                                                                  |                                                                                                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

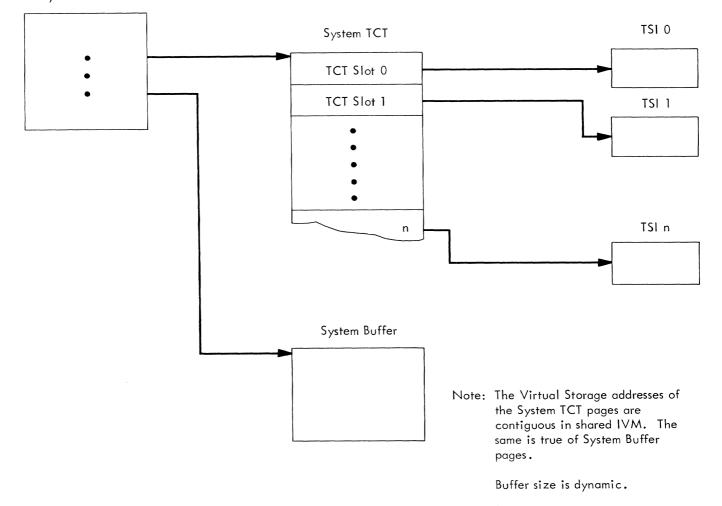

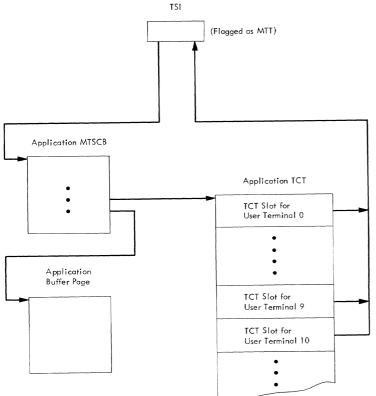

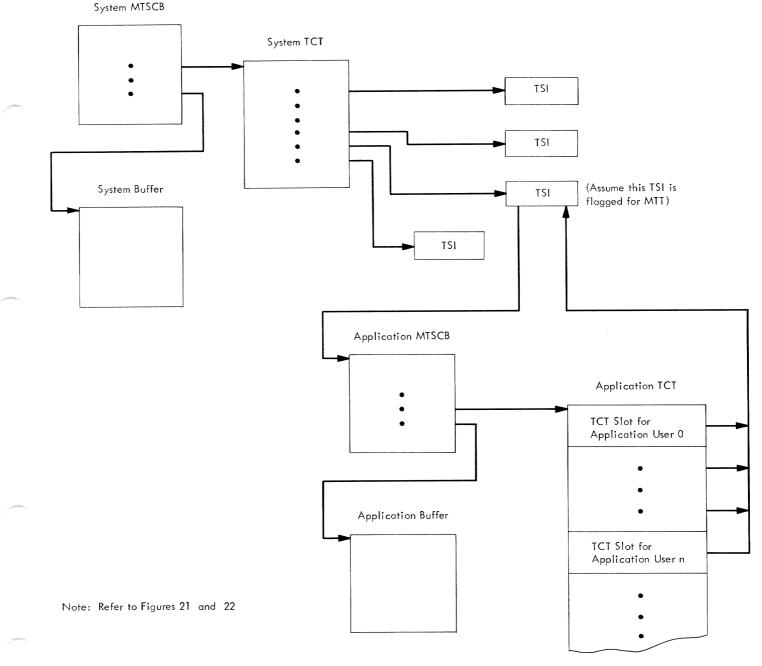

| RTAM Control Blocks                                                                                                                                                                                                                                 | • •                                                                                             |                                       | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                                                                                      |

| RTAM TSS Initialization                                                                                                                                                                                                                             |                                                                                                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

| RTAM TSS Mode Operation                                                                                                                                                                                                                             | • •                                                                                             | • • •                                 | ••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4                                                                                      |

| RTAM MTT Initialization By Administrator                                                                                                                                                                                                            | • •                                                                                             | •••                                   | ••••5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                                                                      |

| RTAM MTT Initialization By User                                                                                                                                                                                                                     | • •                                                                                             | • • •                                 | ••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4                                                                                      |

|                                                                                                                                                                                                                                                     | •••                                                                                             | • • •                                 | ••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4                                                                                      |

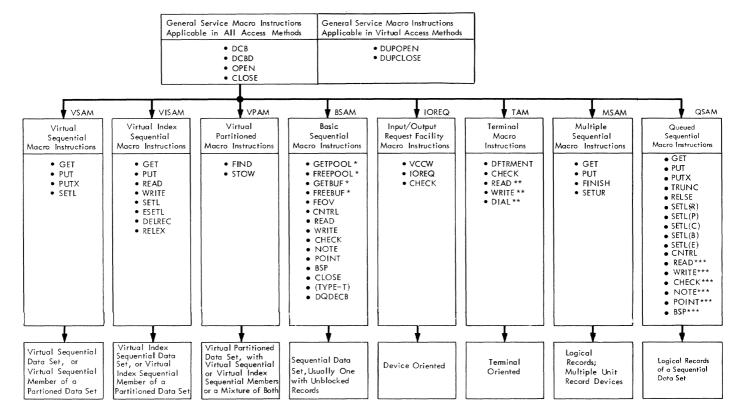

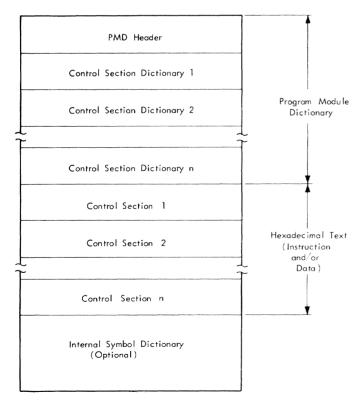

| DATA MANAGEMENT ACCESS METHODS                                                                                                                                                                                                                      |                                                                                                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

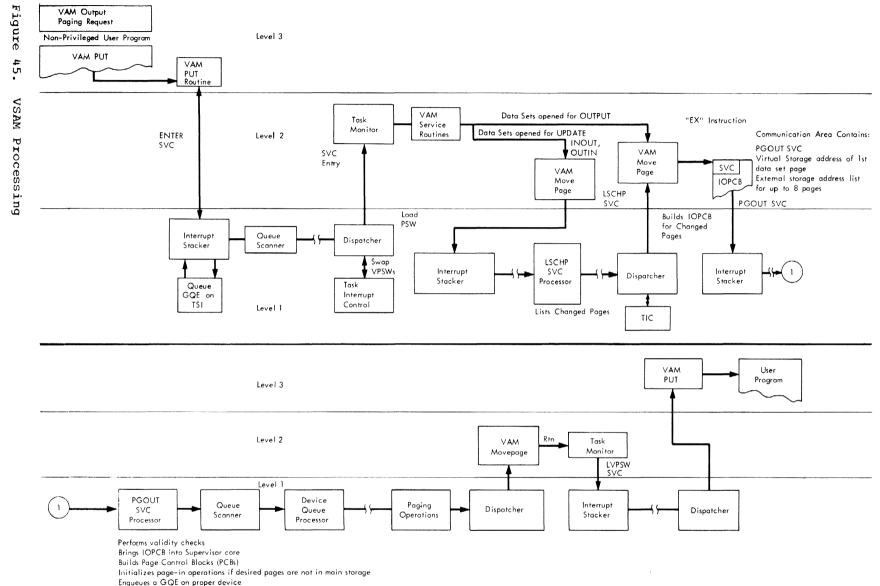

| Virtual Access Methods                                                                                                                                                                                                                              |                                                                                                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

| Implementation                                                                                                                                                                                                                                      | • •                                                                                             | • • •                                 | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9                                                                                      |

| Virtual Sequential Data Sets                                                                                                                                                                                                                        |                                                                                                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

| Virtual Index Sequential Data Sets                                                                                                                                                                                                                  | •••                                                                                             | • • •                                 | ••••5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9                                                                                      |

| Virtual Partitioned Data Sets                                                                                                                                                                                                                       | • •                                                                                             | • • •                                 | ••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                      |

| Sequential I/O Access Methods                                                                                                                                                                                                                       | • •                                                                                             | • • •                                 | ••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0                                                                                      |

| Queued Sequential Access Method                                                                                                                                                                                                                     | • •                                                                                             | • • •                                 | ••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                      |

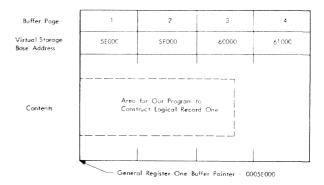

| Blocking Logical Records                                                                                                                                                                                                                            |                                                                                                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

| Deblocking Logical Records                                                                                                                                                                                                                          | •••                                                                                             | ••••                                  | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\frac{2}{2}$                                                                          |

| Buffering Blocks of Data                                                                                                                                                                                                                            |                                                                                                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

| Issuing I/O Requests, Checking, and Positioning                                                                                                                                                                                                     | for                                                                                             | Block                                 | sof                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                      |

| Data                                                                                                                                                                                                                                                |                                                                                                 |                                       | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                                                                                      |

| Multiple Sequential Access Method                                                                                                                                                                                                                   |                                                                                                 |                                       | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                                                                                      |

| TAM                                                                                                                                                                                                                                                 | • •                                                                                             |                                       | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                                                                                      |

| IOREQ                                                                                                                                                                                                                                               |                                                                                                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

| OLTAM                                                                                                                                                                                                                                               | • •                                                                                             | • • •                                 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                                                                                      |

| DRAM                                                                                                                                                                                                                                                | • •                                                                                             | • • •                                 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                                                      |

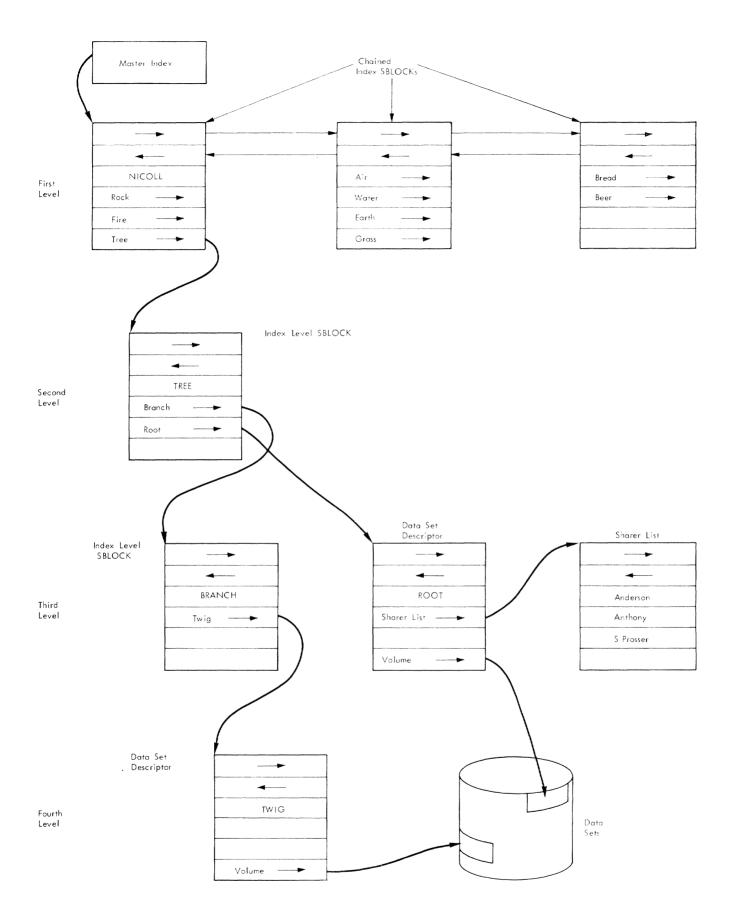

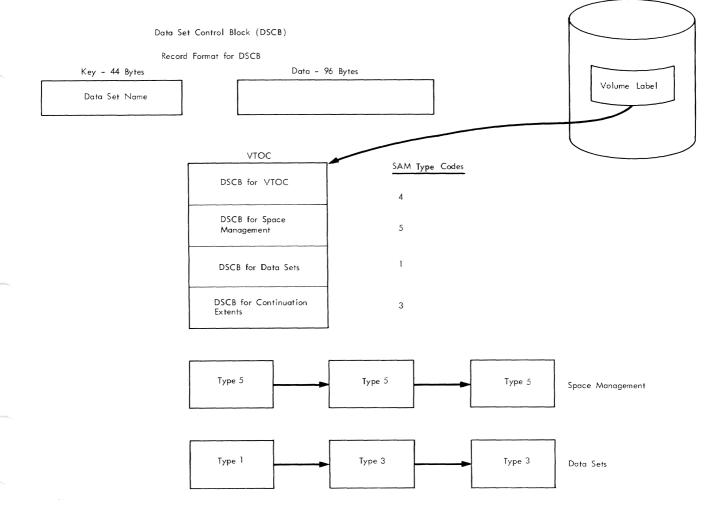

| THE CATALOG                                                                                                                                                                                                                                         | • •                                                                                             |                                       | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                                                      |

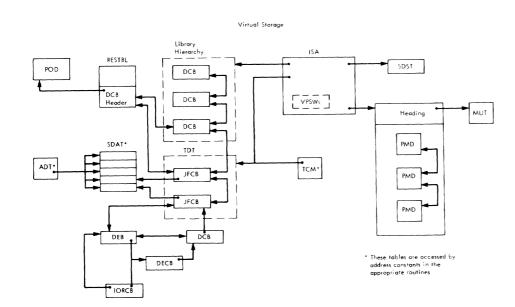

| LIBRARIES                                                                                                                                                                                                                                           |                                                                                                 |                                       | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | a                                                                                      |

| Object Libraries                                                                                                                                                                                                                                    |                                                                                                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

| Symbolic Libraries                                                                                                                                                                                                                                  |                                                                                                 |                                       | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                      |

|                                                                                                                                                                                                                                                     |                                                                                                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •                                                                                      |

| PROTECTION                                                                                                                                                                                                                                          |                                                                                                 |                                       | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                      |

| CPU References                                                                                                                                                                                                                                      |                                                                                                 |                                       | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                      |

| External and Auxiliary Storage References                                                                                                                                                                                                           | • •                                                                                             |                                       | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                      |

| Channel References to Main Storage                                                                                                                                                                                                                  | • •                                                                                             | • • •                                 | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                                                                                      |

| Classes of I/O Operation                                                                                                                                                                                                                            |                                                                                                 |                                       | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                        |

| Classes of Storage                                                                                                                                                                                                                                  |                                                                                                 |                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                        |

| Assignment of Keys                                                                                                                                                                                                                                  |                                                                                                 |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

|                                                                                                                                                                                                                                                     |                                                                                                 | · · ·                                 | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                                                                                      |

|                                                                                                                                                                                                                                                     |                                                                                                 | · · ·                                 | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                                                                                      |

| -                                                                                                                                                                                                                                                   | •••                                                                                             | · · ·<br>· · ·                        | · · · · 7<br>· · · 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2<br>2                                                                                 |

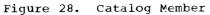

| PROGRAM MODULE STRUCTURE                                                                                                                                                                                                                            | •••<br>•••                                                                                      | · · · ·                               | · · · · 7<br>· · · 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2<br>2<br>4                                                                            |

| PROGRAM MODULE STRUCTURE                                                                                                                                                                                                                            | · · ·                                                                                           | · · · · · · · · · · · · · · · · · · · | · · · · 7<br>· · · · 7<br>· · · 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2<br>2<br>4<br>4                                                                       |

| PROGRAM MODULE STRUCTURE                                                                                                                                                                                                                            | <br><br><br>                                                                                    | · · · · · · · · · · · · · · · · · · · | · · · · 7<br>· · · · 7<br>· · · · 7<br>· · · 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2<br>2<br>4<br>5                                                                       |

| PROGRAM MODULE STRUCTURE                                                                                                                                                                                                                            | · · · · · · · · · · · · · · · · · · ·                                                           | · · · ·                               | · · · · 7<br>· · · · 7<br>· · · · 7<br>· · · · 7<br>· · · 7<br>· · · 7<br>· · · 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2<br>2<br>4<br>5<br>6                                                                  |