File Number S/360-00 Form C20-1647-0

# IBM Systems Reference Library

# System/360 Model 67 Time Sharing System Preliminary Technical Summary

This document is being furnished for System/360 planning use only. It contains preliminary technical information, and the contents are subject to change. The content represents "best available information" as of the publication date. This material is to be considered automatically replaced by the normal SRL publication upon its release.

The System/360 Model 67 Technical Summary is a selfcontained description of the system, its components, and the Time-Sharing System programming support. The objective of the document is to provide consistent material to support branch office preparation of customer proposals. Performance information unique to the Model 67 is provided. A brief section on reliability and maintainability is included.

Copies of this and other IBM publications can be obtained through IBM branch offices. Address comments concerning the contents of this publication to IBM, Technical Publications Department, 112 East Post Road, White Plains, N.Y. 10601

© International Business Machines Corporation, 1966

### CONTENTS

| SYSTEM SUMMARY                | 5         |

|-------------------------------|-----------|

| System Features               | 5         |

| System Components             | 5         |

| Programming System            | 6         |

| SYSTEM PHILOSOPHY             | 8         |

| General Concepts              | 9         |

| Processing Unit Features      | 12        |

| Multiprocessing               | <b>13</b> |

| Systems Data Flow             | 19        |

| SYSTEM COMPONENTS             | 21        |

| IBM 2067 Processing Unit      | <b>21</b> |

| IBM 2365 Processor Storage    | <b>28</b> |

| Channels                      | <b>28</b> |

| I/O Control Units             | 30        |

| I/O Devices                   | <b>31</b> |

| Graphic and Display Terminals | 33        |

| Remote Transmission           | 35        |

| Remote Computer Systems or    |           |

| High-Volume Terminals         | 36        |

| PROGRAMMING SYSTEMS           | <b>38</b> |

| General Description           | 38        |

| Supervisor                    | <b>38</b> |

| Command System                | 38        |

| Data Management               | 38        |

| Growth                        | 38        |

| Interfaces                    | 39        |

| The Command Language          | <b>39</b> |

| Language Processors           | 41        |

| Data Management               | 43        |

|                               |           |

| Identifying and Locating Data        | 44        |

|--------------------------------------|-----------|

| Organizing Data                      | 45        |

| Storing and Retrieving Data          | 46        |

| System Facilities for Program        |           |

| Construction                         | <b>46</b> |

| Use of the Language Processors       | 48        |

| Linkage Editor                       | 49        |

| Dynamic Loader                       | 50        |

| Program Checkout System              | 50        |

| System Design Considerations         | 51        |

| PERFORMANCE ANALYSIS                 | 55        |

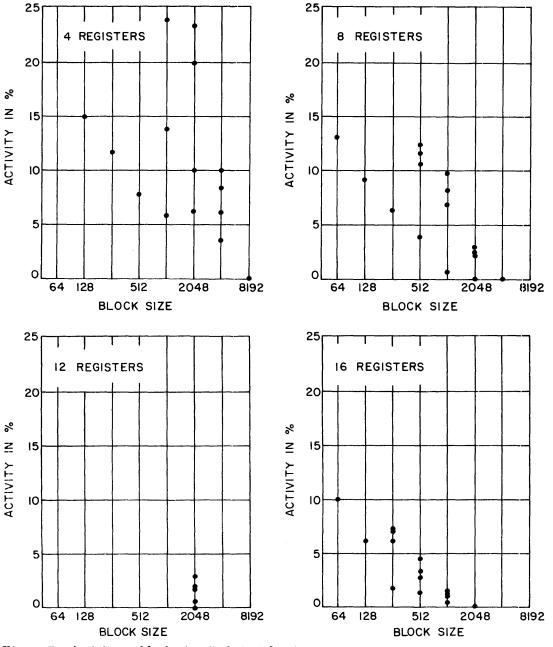

| Relocation Timing                    | 55        |

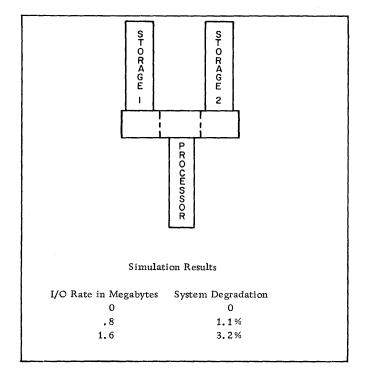

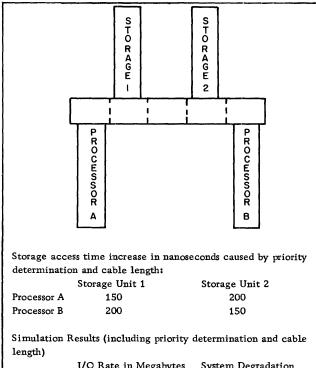

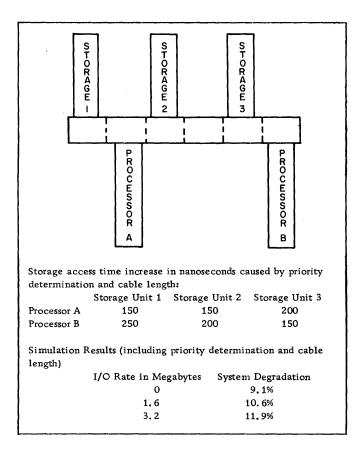

| Shared Storage Interference and      |           |

| Delays                               | 57        |

| RELIABILITY AND MAINTAINABILITY      | 59        |

| Introduction                         | 59        |

| Facilities                           | 59        |

| Maintenance Programming              | 60        |

| Built-in Diagnostics and Checking    |           |

| Features                             | 61        |

| Power and Thermal Malfunctions       | 61        |

| Packaging                            | 61        |

| EXTENDED DYNAMIC ADDRESS             |           |

| TRANSLATION                          | 62        |

| Address Translation (32-Bit Version) | 62        |

| Relocation Mode                      | 63        |

| Extended Control (32-Bit Version)    | <b>64</b> |

| New Instructions (32-Bit Version)    | 66        |

#### SYSTEM SUMMARY

#### SYSTEM FEATURES

The basic architecture of the IBM System/360 makes it ideally suited to processing in a multiprogramming and multiprocessing environment. The Model 67 extends this basic architecture to provide the additional capabilities of an advanced time-sharing system, offers multiple users real-time processing, efficient conversational-mode operation, and almost instantaneous turnaround. The Model 67 is designed to:

- Enable all processors in a system to access directly or to control all components of the system, including core storage units, I/O channels, and I/O control units. The facilities of the system can be dynamically allocated to meet changing job requirements.

- Allow direct connection of channels to the processor storage units. Thus, I/O transfers to storage are independent of the processor.

- Enable each processor of a multiprocessor system to operate:

- 1. As a single processor with its own I/O subsystem.

- 2. Jointly with other processors in a symmetric multiprocessing configuration.

- Allow extensive growth without impacting programming support or programming compatibility, and without disrupting the total system operation. For example:

- 1. For additional computing power growth, a total of four processors can be attached.

- 2. For additional core storage requirements, up to eight processor storage units can be attached to provide more than 2 million bytes of physical core storage.

- 3. To gain additional system throughput, many channels, channel controllers, and hundreds of I/O devices can readily be added.

- Enable system components to be physically partitioned from the rest of the system by centrally-located switches. Multiple computing systems can therefore operate independently.

#### SYSTEM COMPONENTS

#### Processor

The System/360 Model 67 time-sharing processor has the full capabilities of the System/360 processor plus additional features to strengthen its capabilities for time sharing. Some of these features are:

- Extended control capability. Masking facilities are extended so that a processor can control all channels in a system. The system can address up to 28 channels.

- Dynamic address translation (dynamic relocation). Special hardware and associated support programming permit each user to program as though he had sole use of a large, contiguously addressable virtual memory, which may be very much larger than the size of the physical core memory present. The programmer need not be concerned with the size of physical memory or with other users who have simultaneous claims on memory. Only active blocks (pages) of each program reside in physical memory. They may be placed temporarily on a secondary storage device and returned to different areas of core storage regardless of their execution status. Without this feature, it is very costly in time and space to activate many programs simultaneously as is necessary in a true timesharing environment. The address translate feature eliminates the need for the programmer to organize large programs into overlays and allows simultaneous responses to a large number of users even though their total memory demands far exceed actual memory.

- Extended storage protection. The System/360 provides protection of storage from erroneous updating. This is especially important in a time-sharing mode. The Model 67 has extended protection so that even unauthorized reading of storage is prevented. Two bits are added to the store and fetch protect feature which monitor the use of blocks of memory (reference and change).

- High-resolution timer. A timer is provided with a 13-microsecond interval. Automatic interruption occurs on clock runout to permit control to be transferred rapidly between programs. Only with this feature can the monitor effectively assign resources in a time-sharing environment.

#### Processor Storage

The Model 67 utilizes core storage units with a cycle time of 750 nanoseconds per doubleword (64 bits + 8 parity). These units are available with a capacity of 262,000 bytes. The total core storage capacity supported ranges from 262,000 bytes to

over 2 million bytes. References within each unit can be interleaved to obtain effective storage cycles approaching one-half the cycle time of the unit. Although there are delays caused by storage access conflicts and cable length considerations, these storage units are capable of supplying the demands of multiprocessor configurations with large amounts of I/O activity without serious system performance degradation.

#### I/O Components

Increase in system throughput is highly dependent upon the ability of the system to increase the number of channels and I/O devices. The Model 67, with its powerful I/O control element (channel controller), provides the ability to greatly increase system throughput and offers maximum flexibility in system configuration.

Some of the I/O highlights are:

- Channel controller provides for maximum data rates up to 6,400,000 bytes per second

- Four channel controllers can be attached to a system

- controller)

- I/O data transfer proceeds concurrently with processor operation

- Each processor in a system can address all channels in the system (addressing capability provided for 28 channels)

- I/O devices can be shared by the interconnecting channels or device

#### Remote Devices

A wide range of terminals for both low-volume and high-volume jobs can be remotely attached to the System/360 Time-Sharing System. The terminals include manual keyboards, printers, and visual displays.

In addition, smaller computers, such as the IBM 1800 Data Acquisition and Control System and the Models 20 and 30 of the System/360, can be remotely attached through the IBM 2701 Data Adapter Unit.

#### PROGRAMMING SYSTEM

A fundamental of IBM programming systems support has always been to furnish a computer system with in-depth programming systems so that the computer is used not only efficiently but also conveniently.

This becomes increasingly important with a time-sharing system that offers its full facilities to a large number of users.

The Time-Sharing System (TSS) employs new concepts, such as dynamic relocation, multiple access to system components, and extended storage protection, and furnishes a wide range of remote terminals.

To give users fast, efficient service the operating system must be designed to take full advantage of these features. Also, to permit easy, remote use of the computing system, the supervisor incorporates a wide range of user-oriented programs and languages. Close man-machine relationship is essential.

IBM is furnishing such a supervisor with the Time-Sharing System--a time-sharing, multiprogramming supervisor with assemblers, compilers, and debugging facilities designed specifically for it.

The new Time-Sharing System contains many of the features found in Operating System/360. Much of the task scheduling and interrupt handling is similar to Operating System/360. In addition, TSS contains special features specifically designed for efficient use of terminals, multiple processors, and virtual storage.

The system features a flexible and powerful • As many as 28 channels in a system (7 per channel command set for remote terminal users and a conversational mode of operation with terminals to perform line-by-line editing during input. With minor exceptions, the system is source-languagecompatible with Operating System/360 language processors.

The Time-Sharing System includes:

- Time-sharing control program for efficient facilities scheduling

- A mnemonic assembly language compiler with macro capability -- batch and conversational syntax analysis modes

- A FORTRAN IV compiler -- batch and conversational syntax analysis modes

- A Programming Language One (PL/I) compiler -- batch and conversational syntax analysis modes

- COBOL compiler -- batch mode

- A sort/merge program

- A terminal command language to remotely process and manipulate data and programs

- A library of mathematical and utility programs. open-ended so that user-developed programs and routines can be added easily

- Data management and cataloging facilities

#### The Monitor

The Time-Sharing System is the interface between the equipment and the users. Many of the functions traditionally considered part of the supervisory system are implemented in TSS as service routines subject to relocation in user's memory. For this

purpose, the system is structured into two principal subsystems: a supervisor that supervises and allocates the equipment configuration, and command programs that enable remote users to process and manipulate data and programs. The programming design is organized to separate machine-oriented functions from user-oriented functions. This results in a compact monitor that:

1. Maintains status indices of system facilities (attachments, assignments, and usages), processing times, storages (primary core units and secondary drums), I/O devices (tapes, peripheral equipment, and terminals), and files (disks).

2. Supervises all interrupts.

3. Records basic data for job scheduling and for determining individual user system charges.

4. Allocates the resources of the system to achieve short response times to the users of the system. To meet this requirement, the timesharing monitor responds rapidly to all interrupts and has an efficient processing scheduling algorithm that controls the processing time-slice allotted to active programs. The monitor is designed so that this scheduling algorithm can be modified to meet any changing requirements of the operating environment.

5. Achieves high utilization of core storage through the use of reentrant coding that allows multiple independent programs to use the same copy of a subroutine, compiler, etc.

6. Provides the nucleus of a recovery program so that when some portion of the system malfunctions, the rest of the system can keep operating. This function may be expanded by the user at his option so that, for example, the system can maintain a fast response time for high-priority users, or retain the same number of terminal users with a slower response time.

Other functions, such as error routines, checkpoints, and restarts, are separated from the monitor and are performed by a modular set of routines that are:

- Independent of the monitor.

- Not necessarily permanently resident in core.

- Capable of shared usage -- that is, they are reentrant.

- Identical with the problem programs written by system users except for priority (for processor time and space) and for a privileged authorization to use and change the status indices.

This approach is used because:

1. Core space for system residence is kept to a minimum.

2. The startup-shutdown, checkpoint-recovery, and reconfiguration procedures are simplified,

since a minimum of information must be periodically recorded.

3. Complete flexibility is provided for the installation to revise or write its own routines.

#### Program Support

Development of the supervisor is only one step in the development of a practical real-time, time-sharing system. To be convenient to use, the system must also have conventional program support such as compilers and utility routines. This support must be capable of conversational use with remote terminals.

A number of programs are designed specifically for support of remote terminals or consoles:

- An assembly program is designed to operate under the time-sharing monitor. The mnemonics, data definitions, macros, etc., are for the most part similar to those of Operating System/360. However, this assembly program is reentrant and allows for entry through a terminal of source language programs with editing and diagnostic checking in a conversational mode. Symbolic updating of the program is possible at any time after initial entry of the program into the program library; symbolic listings are available at any time. Storage is allocated at execute time instead of during assembly time.

- The FORTRAN IV provided with TSS is designed to be reentrant and to produce reentrant code. The FORTRAN IV system may be used in either batch or conversational syntax analysis mode, and is source-languagecompatible with the OS/360 FORTRAN IV. Some debugging commands of the QUIKTRAN type are provided.

- TSS includes a PL/I compiler, designed for use in batch and conversational syntax analysis modes. The compiler is reentrant and produces reentrant code.

- The COBOL may be used in batch/background mode only and is similar to OS/360 COBOL.

- The sort/merge program provides a capability for this function under the time-sharing mode of operation.

- The provided terminal command language is open-ended and may be extended indefinitely. It provides online functions for program or data manipulations and program debugging facilities, and offers the user tremendous flexibility in working with the time-sharing system.

The time-sharing supervisor and the programming systems provided with it constitute an effective means of utilizing the data processing power of the System/360 Model 67 multiprocessor system.

7

#### SYSTEM PHILOSOPHY

IBM's Model 67 Time-Sharing System provides a solution to the problem of optimizing the relationship of the man and his problem to the computer and its facilities. Through a combination of machine and program features, the system described appears to everyone using it during the same time period as a complete computing system. These users present a wide variety of applications to the system, ranging from conversational compiling to conventional batch-processing jobs. Since each application receives a share of the available time, many jobs are performed simultaneously within a given time period.

Using TSS, the individual job may take more time than if it occupied the entire computer facilities exclusively until completion, but far more use of the computing system is made. The major saving of time sharing, however, is in the reduction of the overall time between problem definition and solution (turnaround time). The use of terminals at remote locations permits the person defining a problem to call in the facilities of a complete computing system to his desk (the terminal). Thus time sharing eliminates much of the normal delay in human effort associated with the turnaround time problem of a batch system.

The Model 67 system is characterized by a close interaction of machine and program features. The objective is a time-sharing, multiple-access, multiprocessor, general purpose, online computing system. A description of these various characteristics follows.

• Time sharing. This technique interleaves many different tasks in a computer system by using a timing mechanism, in conjunction with a supervisor program's scheduling and dispatching routines, to signal the end of the time interval given to one task and permit the transfer of a processor to another task. Although it is analogous to the communications technique of time-division multiplexing, computer time sharing makes use of hundreds of thousands of instruction executions per time division, whereas communication multiplexing is at the bit level, per time division. It differs, also, in that communications multiplexing is for fixed intervals over a fixed number of channels, whereas time sharing is for varying intervals over a varying number of tasks. In conventional multiprogramming, control is taken from one task and given to another only when the first task is incapable of using, or indicates that it does not wish to use, a processor. Time sharing also uses this means of task switching. By additionally using the interval timer to transfer control from one executing task to another, however, time sharing provides a service that

generally makes the most efficient use of the total computer facility and also facilitates the online multiple-access nature of the system by providing response times compatible with human reaction times.

• Multiple access. In contrast to conventional computing systems, where only one task is performed in a specific period of time and only one system input and system output device need be defined, many such devices are defined in a multiple-access system at any one time, one for each task currently being performed in the system. A multiple-access system allows many users to share the total system facility concurrently, as if each had sole use of the system. It also permits terminal intercommunication, making possible several new ways of using computer systems, such as gaming situations, multiconsole teaching situations, and design team computer systems. One reason for providing multiple access in online systems is that one user does not usually require the total system facility on a continuous basis. If, in such a case, multiple access is not provided, a brief pause by a user idles the entire system and its capability to serve. This unused capability can be profitably deployed to serve some other user at the same time, the cost of doing this being small compared with the facility time recovered.

• Multiprocessor. The number of jobs that can be handled in a time-sharing system is increased by adding processors in parallel. The operation of processors in parallel is the mode normal to the system described in this manual. Other modes, such as partitioned systems and direct-coupled master-slave systems, are possible. In the parallel processor operation, the same monitor can be executed simultaneously by each of several processors independently executing programs, accessing memory, and controlling input/output. Programmed and wired-in interlocks are provided to prevent interference between processors. The monitor itself is reentrant (not changed by execution), and simultaneous usage presents no problems. Some sections of the monitor must modify tables of system data. To prevent confusion, these modifications must be made sequentially, rather than in parallel. In these circumstances, the first processor to begin modifying such tables will lock out all others until its modification has been safely completed. These lockout procedures are inserted only when necessary, and the lockout time is held to a minimum.

• <u>General purpose</u>. This system is not limited to operating in just one mode, such as online interpretive FORTRAN systems, QUIKTRAN, or "desk calculator" systems. The system is capable of performing in every way as conventional batchprocessing operating systems, and yet can do much more. Teleprocessing, real-time monitoring and multiprocessing types of jobs can be handled by the time-sharing system as by-products of its extremely versatile basic design.

• On line. This system was designed primarily to couple users of computation facilities more closely to computer systems. This close usersystem contact is provided at several levels within the system described in this manual. For example, it is possible not only to economically employ console-type debugging techniques at a terminal. but also to employ interpretive and conversational modes of operation that may considerably shorten the overall time to complete the user's job. Furthermore, the immediate access time enables a great many relatively short jobs to be performed in a reasonably short period of time without incurring significant delays. In addition, by employing large, direct-access storage devices (typical of the system described here), users may gain access to the data and programs of interest without losing time because of operator intervention. Also, the online situation does not require physical proximity of the attached terminals. All the apparatus of communications technology (communication lines, dial connections, etc.) may be used to convey computational power over any distance.

#### GENERAL CONCEPTS

The IBM Model 67 Time-Sharing System is a general purpose, remote computing system. A remote computing system enables a terminal operator to use computing equipment at his own convenience, that is, at the <u>times</u> and <u>places</u> of his own choosing. A general purpose, remote computing system is one that will accommodate a wide variety of problems, expressed in a variety of computing languages (including the language of the computer itself) introduced from several different types of sources.

The user of a remote computing system operates an input/output device called a terminal. The terminal may be adjacent to the computer itself, or it may be hundreds of miles from the computer. In either case, communication between computer and terminal occurs via standard communication devices or direct cabling.

The simplest kind of terminal is a typewriterlike device, with the keyboard serving as the input unit to the system, and the printing mechanism as the output unit. More complex terminals, such as the IBM 2250 Display Unit, contain both a keyboard and a cathode ray tube display. These displays are powerful tools for the generation and control of graphic material. Any remote computing system is capable of handling many terminals. The time-sharing type of remote computing system is designed to provide each user at each terminal with essentially immediate response. It does so by taking advantage of the fact that a modern computer can generate responses much faster than the terminal user can ask questions.

Time slicing is a technique used in remote computing systems to provide equal response to a number of simultaneous computer users. In a time-sharing system utilizing time slicing, the many programs that may be executed are (1) swapped successively into high-speed core storage from some auxiliary device, usually a drum, (2) executed for fixed periods of time, and (3) swapped out again. Each program thus gets a slice of computer time periodically. Within a short cycle of time, all programs are in some sense responded to.

#### Paging

The 24-bit addressing capability of the standard System/360 allows a maximum of 16 million addressable bytes. In practice, however, the programmer is restricted to using addresses that represent the actual physical storage on his machine. Thus, the programmer does not have the ability to write a program addressing 16 million contiguous bytes. If his total program size exceeds the physical core available, he must overlay his program. The System/360 Model 67 processors remove this restriction by allowing the problem program to address a virtual memory limited only by the page table handling capacity of the memory system.

The installation may establish the maximum number of addressable bytes that each programmer/ user may address, representing his virtual memory. (Virtual memory is defined as the maximum addressing capability of a computer system.) A program's demand on virtual memory is a subset defined as logical memory, that is, the total claim actually made on virtual memory by a program.

In a multitasking environment, the supervisor has the job of placing active programs into whatever actual core storage is available. The program runs in core storage, but because of space limitations or relocation of programs, the logical program may be scattered throughout core storage. The execution of programs requires that this physical fragmenting of programs be transparent to the user, so he can think of his program as being in contiguous logical memory locations. Indeed, his listings depict these logical addresses to him.

The more users that are in core storage, the faster the control can be transferred to another waiting user and the lower the resulting overhead cost. In Model 67 systems, the basic element for relocation (and fragmentation) is a 4096-byte unit called a page. By breaking programs up into pages, core memory may be allocated in page increments. Only the actively used pages of a program are brought into core storage. At execution time, core memory holds only a small part of a user's program, but, more important, it holds only the active parts.

The heart of the paging technique is a hardware development called dynamic address translation. It involves the transformation of one address into another by means of a table-lookup procedure implemented in hardware. The tables provide mapping of the task's virtual memory into core memory. Each task in the system requires, for its operation, one segment table and a page table for each segment used. These tables are developed by the supervisor, as the task is created and as new page requirements are made by the task. As a required page is fetched into core storage, the supervisor enters in the page table the actual location of the logical page.

During program execution, the equipment automatically does a table lookup on each address as it is referenced by the user, and the actual address is chosen for each logical address reference. If the user references a location in a page that is not in core storage, the supervisor receives an automatic interrupt; the supervisor then sets up a "page-turning" routine to fetch the missing page, and assigns the processor to another task in the queue. The waiting program is held in the wait status until its required page has been assigned and fetched somewhere in core storage. It is then returned to the queue of active users sharing processor time. This activity is not apparent to the user, being performed without his knowledge.

"Page turning" has the following effects:

- The entire program need not be in core storage to operate. Bits and pieces of many programs may be present, and several may be in operating condition. The system, therefore, has many opportunities to do useful work while swapping a page.

- Program "swap time" is greatly reduced as an overhead factor, since only active pages of a program ever require movement between core storage and auxiliary storage.

- The size of core storage ceases to have any significance to a programmer. Although written and executed as a classical set of contiguous instructions and working space, a program may exist in the machine as scattered pages. The programmer's concept of the program in execution becomes "virtual memory" rather than actual core storage.

• With so much virtual memory space available, it becomes possible to extend the pageturning concept to input/output operations upon prestored data files. If a program in virtual memory is operating upon a data set in the system's bulk files, the file space which the data set occupies can be treated as an extension of the virtual memory, and can be operated upon directly without explicit Read or Write commands. Again, as each "page" of the data set is referred to, it will be page-turned into core storage by the system. The effect, to the programmer, is the same as if the entire file were always present in high-speed memory.

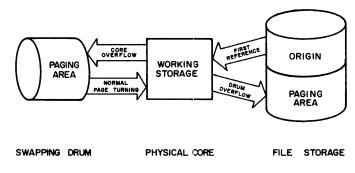

The page-turning concept (Figure 1) provides for efficient use of the equipment, while allowing the system to handle many programs in rapid succession. In addition, it frees the computer user from arbitrary bounds of core memory size.

#### Segmentation

Just as space need not be allocated in core memory for currently inactive portions of a user's program, auxiliary storage space need exist only for portions of the user's virtual memory actually used by his program, that is, his logical memory. The user can take advantage of this in setting aside areas of virtual memory large enough to hold data sets or tables of very large size, without tying up storage for such tables except to the extent that they are actually used.

Such use of virtual memory is facilitated in the Model 67 by dividing virtual memory into 1,048,576-byte units (256 pages) called segments. Virtual memory consists of 16 (or optionally 4096) segments depending on whether 24- or 32-bit addressing is utilized, and logical memory thus can consist of up to 16 (or optionally 4096) segments, each of which can contain from 1 to 256 pages. A segment can contain programs and data, or can constitute a million-byte area for working space.

Segmentation is implemented by making the table lookup of address translation a two-stage

Figure 1. Page-turning concept

process. Instead of a single page table for the task, there exists a page table for each segment. The high-order bits of the page number are interpreted as a segment number, and a segment table entry is accessed to obtain the address of the page table to be used in the second stage of translation.

The advantage of implementing segmentation in the hardware is that it is possible to load virtual memory sparsely (thereby leaving room for data sets to grow), without requiring page table entries for unused pages.

#### Reentrant Code

The time-sharing system is based on reentrant coding. A reentrant program is one that is not in any way modified by execution. Such a program can be shared by several other time-shared programs that can be executed by one or more processors. All parameters, data locations, and working storage spaces are passed to the reentrant program. The integrity of each user's data is maintained regardless of the number of users who have entered the program.

Reentrant coding of programs enhances system efficiency. In situations where there is multiple usage of a single program or subroutine, only one copy need be present in memory or on the paging drum. It also reduces overhead for paging because of the read-only nature of the coding.

#### Data Set Management

To the user, a remote computing system can be a file space as well as a computing device. The user need not keep programs (that is, problem statements) or data files on his own premises. They can be introduced to the system, left within it, and recalled and manipulated at will.

Therefore the system must maintain large sets of files with complete safety and security. To this end, the system contains a catalog of all data files within its storage devices, and provides many modes of protection for these files. A user can specify that his files be accessible to himself only or to specific individuals or groups other than himself. Various modes of access can be specified. Some accesses may be for read-only purposes, others for both reading and writing.

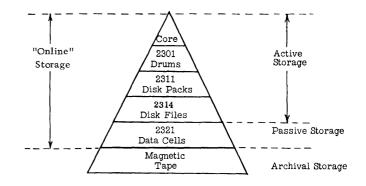

The system can also regulate the location of files in accordance with the activity against them. In general, storage devices range from smallvolume, fast-access units to large-volume, slowaccess units. The large units store information at a lower unit cost, but usually at the price of increased access time. Files also vary in terms of the activity rate against them. It is generally desirable to keep frequently used files in a storage device that can deliver them quickly. Files that are used less frequently can be kept more economically in larger storage devices. The system is designed to keep the content of a storage device at some level slightly below its capacity. If this content builds up to the point where the device might "overflow", the system automatically scans the device "table of contents" for low-activity files. Such files are then moved out of the loaded device, and are rewritten into a larger, slower-access unit. Subsequent references to the same file will again cause it to be brought back to a faster-access device. Thus, the data files are dynamically adjusted to the proper class of storage.

#### User Commands

The user at a terminal can request that the system take certain actions in his behalf. Each action that he can specify is a command, which in the case of a typewriter-like terminal is a one-line message. Commands are always acted upon by the commandlanguage interpreter. This system program receives the incoming message, scans it to determine the nature of the action requested, and fetches from the system files the command program that will carry out the action.

The command system (the set of actions that the command-language interpreter can recognize) provides the capability for a program to be:

- Entered from the terminal, line by line, with immediate diagnostic feedback from the system after each line

- Cataloged, stored permanently in the system for later manipulation, then made part of the user's prestored library

- Compiled or assembled

- Executed

To the system, the user is an active terminal and is presenting a series of tasks to be performed. As long as these tasks are system commands, the system is fetching its own programs and executing them on behalf of the user. In most cases, these command programs are in one part of the user's "virtual memory", operating upon the user's program (or data file), which is in another part of the "virtual memory". System commands are not very different from user programs; they are timeshared, multiprogrammed, and page-turned as they execute. When the user initiates execution of his own program he retains complete control over it. Thus the command system also allows a program to be:

- Stopped

- Modified or displayed -- for debugging purposes

- Checkpointed (this will create a new file for later use)

- Restarted

- Terminated

The program as entered may be in a variety of source languages. Initially the system will accept FORTRAN IV and an assembly language, and will accept PL/I when it becomes available.

Beyond these basic capabilities of entering, executing, and controlling programs from terminals, the command system provides for:

1. System accounting. A user must LOGON at a terminal before any other action can be taken, and LOGOFF when his terminal operations are complete. These commands initiate time charges to the user for use of the terminal itself and of other hardware facilities as required. They also serve to identify the user to the system. If, in succeeding commands, he requests access to files, his identity will be matched against the file-protection and security data.

2. File maintenance. A user can request that his files be moved from one storage unit to another, or be removed from the system. He can also modify them, combine them, or change their protection status.

Commands can be initiated from terminals, as previously described, or they can in most cases be embedded in programs as the equivalent of subroutine calls. They can also be included as "control card" functions to specify the type of processing to be applied to batch jobs entering the system. The command functions are, in essence, the verbs of a terminal control language. All instructions to the system are intercepted by the command language interpreter.

The command system has been discussed thus far in terms of its appearance to the remote computer user. This, of course, is its primary orientation. It allows the user to direct the system in its manipulation of files and the solution to problems. More than this, however, it is the universal interface between the system and the outside world. From the machine-room console, for example, installation personnel control the partitioning and recovery functions of the system, using special commands reserved only for their use. Batch jobs entering the system from peripheral equipment or tape drives are controlled by the command system. And finally, since commands are programs in the system files, the command system itself can be augmented or modified by terminal action.

This general concepts discussion has been presented from a remote-computing point of view. It is, however, a system capable of performing batchprocessing operations introduced both locally and remotely -- as well as of providing immediate response to terminals. It is expected that any given installation workload will be a blend of batchprocessing work (where response is not necessarily critical) and conversational computing (where response is often basic to the operation).

#### PROCESSING UNIT FEATURES

#### Program Switching

Switching between programs may be (1) initiated by the program (as when a problem program calls the supervisor or a supervisor returns control to a problem program), or (2) caused by a condition external to the currently operating program (as when the completion of an I/O operation is signaled by an interruption, or a timer interrupt).

Rapid program switching is facilitated by the program status word (PSW). This word contains all information required for proper execution of a given program. It contains the instruction address, condition code, mask and status bits, and other fields indicating the status of the program at the time of interruption. The current PSW is automatically stored during an interruption; thus the status of the processor is preserved for subsequent inspection and resumption.

#### Interruption and Priority

An interruption consists of the automatic storing of the current PSW and the fetching of a new PSW. Processing resumes in the state and at the location indicated by the new PSW. To permit proper program action following an interruption, the cause of the interruption is identified and provision is made to locate the last instruction executed under control of the old PSW.

The five classes of interruption conditions are: Input/output

- Program Supervisor call External

- Machine check

The mask bits make it possible to assign relative priorities to the various interruption sources. The processor accepts interruptions only when they come from a specific interruption source, as determined by the mask. When masked off, an interruption either remains pending or is ignored, depending on the type of interrupt. Input/output and external interruptions may be kept pending by the system mask. Four of the standard 15 program interruptions may be masked off by the program mask. The machine-check interruption may be masked by the machine-check mask. If, for example, the external interruption has a higher priority than an I/O interruption, the mask bits can be set up so that an external interruption will come in while an I/O interruption is being processed; an I/O interruption would not be allowed to come in while an external interruption is being processed. The mask bits may also be set to cause a reverse of priority between external and I/O interruptions.

#### Storage Protection

The basic design of the System/360 includes a flexible memory protection system. Complete memory protection is essential for time sharing.

For the time-sharing system, the storage protection feature is augmented by fetch protection and two indicators that indicate whether a block of storage has been referenced and whether the block has been changed. Three bits have been added to the storage key for this purpose. The protection keys, however, in the PSW and channel address word (CAW) remain unchanged.

#### Dynamic Relocation

To explain the operation of dynamic relocation, consider a specific instruction.

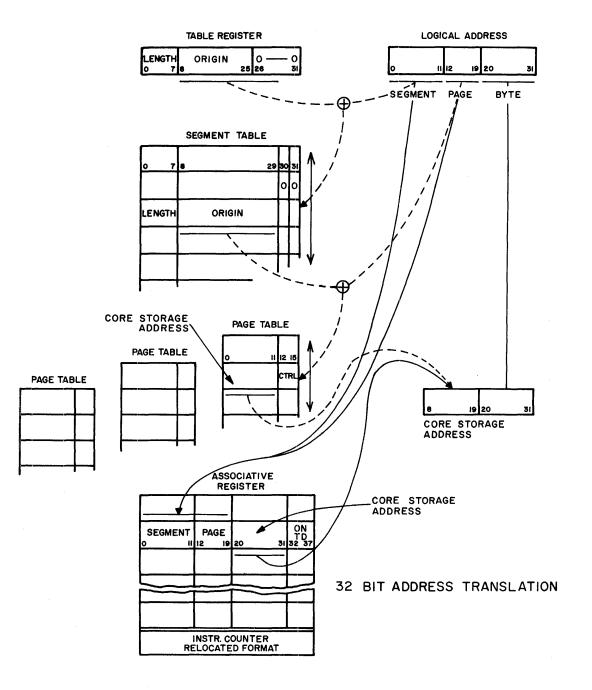

Within this instruction, the logical storage address is represented by the sum of the displacement, the index register, and the base register. Before the supervisor begins processing a task, the location of a table, called a segment table, is loaded into a special register called the table register.

The segment table contains an entry for each segment called for by the task. Each segment entry contains the location of a page table. The page table contains the physical address of the 4096-byte block (page) in which the data or instruction is located. There may be more than one page entry in the page table for any one entry in the segment table.

The page tables referred to by one segment table need not be contiguous; however, the page entries of each page table must be contiguous.

The supervisor loads the location of the particular task's segment table into the table register. The logical address is broken into segment, page, and byte portions. To call the proper element from the segment table, the segment portion of the logical address is added to the segment table origin. This entry, located in the segment table, contains a page table origin which, when combined with the page portion of the logical address, selects the proper entry in the page table. The page entry contains the core storage address of a 4096-byte block which, when combined with the byte portion of the logical address, produces the core storage address of the operand. While the logical addresses would be sequential, the operands could spill over from one page to the next. Since a new page would be referred to, a different entry in the page table would produce a different core storage block address. Consequently, the use of randomly located blocks does not affect program operation.

To speed up the operation when constant reference to a specific page or group of pages is occurring, a group of eight associative registers is added. These registers are transparent to the program, and affect only the rate at which the program runs. A register is loaded with the logical and core storage page addresses each time a new page not already in the associative register is referred to. The registers may contain up to eight entries. A high-speed parallel search is made for the segment and page in the associative register. If the desired segment and page values are found in one of the associative registers, the core storage address portion is routed to replace that which would otherwise have been supplied by the page table.

If the logical page address were not found in an associative register, the original translation operation would be performed and an entry made in an associative register that had probably not been referenced recently.

There is another register that contains the instruction counter in relocated form. Sequential instructions are referenced using this register instruction by instruction. Should a page boundary be crossed, or a branch out of this page occur, the conversion of a logical address to a core storage address is performed and the new relocated address is entered into this register.

#### MULTIPROCESSING

The multiprocessing capability of the system provides reliability and continuity of operation and provides as well for growth in throughput capability. It is truly a polymorphic system that can ensure a single multiprocessing configuration or a symmetric multiprocessing relationship between two or more subsystems. The power, reliability, and flexibility of the system can be increased by expanding up to four computing units and up to 2 million bytes of actual core storage. It must be possible to interconnect the system components so that they may interact with one another. It must also be possible to partition a system, that is, to operate a selected processor plus storage and certain I/O devices as an autonomous unit.

#### Interconnection of System Components

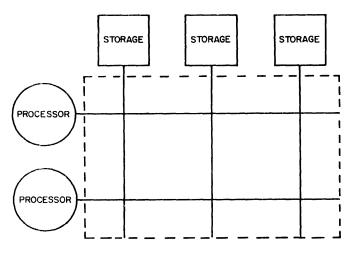

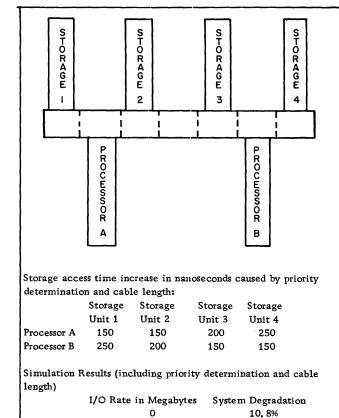

The simplest interconnecting structure for a series of processing units and associated storage units is the crossbar switch arrangement shown in Figure 2.

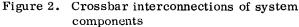

Figure 3. Distributed-switching interconnection of system components

For the time-sharing system, however, the switching arrangement is not a centralized switching point, but has been distributed among the various components that form the system (see Figure 3).

The reasons for adopting the distributed approach are improved availability and flexibility. A centralized piece of equipment represents a crucial link within the system, since its failure would cause the entire system to fail; it would be more costly to remedy this by duplicating equipment. The distributed approach is more flexible and facilitates extension of the system by addition of more processors or storage units.

The interconnecting structure shown in Figure 3 shows that the necessary switching equipment is distributed among the system components, central

processor, channel controller, and core storage units. Drivers are added to the processors as required, and the equipment needed for selection of any of the processor bus systems is added to the core storage units. Instead of the single bus connection or tail of the simplex system, multiple tails are provided for a multiprocessing system. The design of the circuits that select from among the tails is such that if a storage unit should fail (including power failure), the other storage units connected to the storage bus would remain operative. When the bus control unit within a processor fails, the entire bus driven by this unit is, of course, inoperative. This bus will not, however, prevent proper functioning of the storage units with the remaining processors.

I/O channels within a multiprocessor system are flexible in the System/360 design. The channels perform the transmission function. All controlling functions for I/O devices have been placed within the control units for these devices. Thus, the channel design is general and applies to all I/O devices.

As with the processors and core storage units, a control unit can be attached to more than one channel by means of multiple tails. The switching equipment is modular, a design that avoids the problems of cost and poor reliability of centralized switches.

A channel operates concurrently with the processing unit and may be treated as an independent entity within the system. As shown in Figure 3, the channels are grouped into two sets, each provided with its own channel controller; thus there are two systems for I/O operations. Storage units are equipped with the necessary tails to accommodate the additional buses. Channels are addressable by either processor and can return their interruptions to either unit.

Sharing of external storage media can be achieved by interconnecting their channels, their control units, or the devices themselves. Special attention has been given to availability considerations, with minimal duplication of equipment.

#### System Partitioning

A system with sufficient elements may, in effect, be divided or partitioned into at least two systems that can operate independently as single systems. This type of partitioning can be achieved by relying on the programs in each system to refer only to those components that have been assigned for their use. This approach can be enforced by a program that supervises storage assignment and protection and assigns I/O devices. System/360 was designed for operation with such a supervisory program. Where it is desirable to experiment with new and as yet undebugged supervisors, however, a more absolute means of partitioning may be required. Such a means is provided in the Model 67 by manual partitioning switches.

Partitioning is detected dynamically by sampling a single wire -- the availability signal. When the signal is up, the unit is available to the processor; when the signal is down, the unit is unavailable.

An availability signal is provided for each processor bus system from each storage unit within the multiprocessing system. Absolute partitioning is achieved by making these lines manually switchable. One storage array, therefore, may be available to one part of the system and unavailable to another part of the system. An invalid address indication results if the system attempts to address an array designated as not available.

Partitioning of the control units and channels is similar. The control units can be selected from the multiple interface tails; this selection can be overridden by manual switches.

Partitioning, therefore, makes it possible to operate the processors within the multisystem as single processors, as independent processors sharing common storage facilities, and as part of a multiprocessing system.

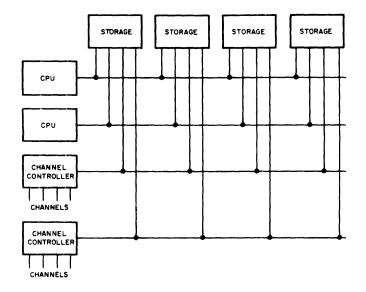

Figure 4 shows a representative multiprocessor configuration. Each circled X denotes a partition

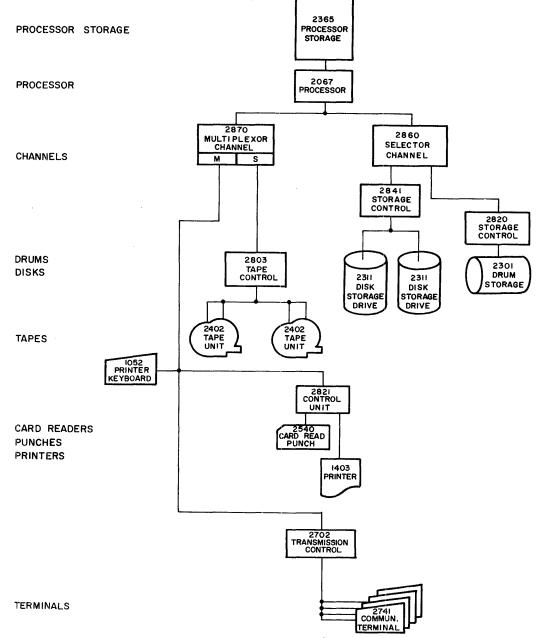

Figure 4A. Small, single-processor IBM System/360 time-sharing system

15

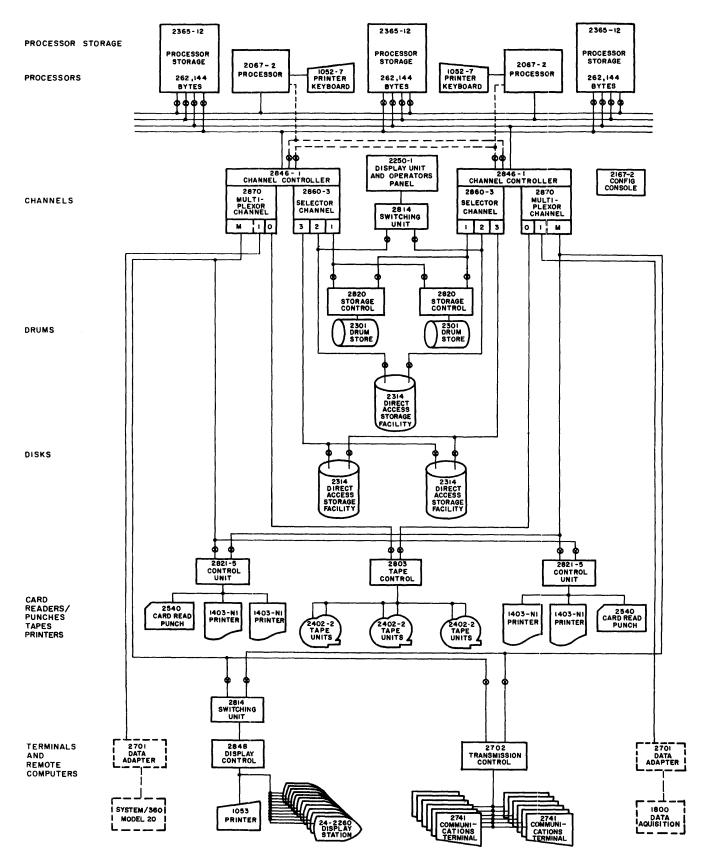

Figure 4B. Typical IBM system/360 model 67 dual-processor, time-sharing system with manual partitioning switches

point. Each storage unit can be assigned to all processors and channel controllers in any desired configuration.

Each channel controller may be controlled by any processor in the system via buses connecting the two. A partitioning switch either permits this control or causes the channel controller to ignore any attempt by this CPU to initiate an I/O function. When the processor-to-channel controller path is inactive, commands to the channels and devices attached to that channel controller are not executed and cause condition code 3 to be set in the PSW. This indicates to the processor that the channel is not operational.

The control units for the high-speed drum and disk files can have two interface connections (tails) each, thus permitting each control unit to be physically attached to two channels. The logical connection between the control units and the channels is under program control, thus providing the program with the facility to connect the control unit to any of its channels. Once a connection is established, it is preserved until the control unit is released by a command from the connected channel. Release causes the control unit to assume the neutral state in which it is available to any channel.

In the IBM 2702 Transmission Control Unit, which provides for attachment of communication lines to the multiplexor channel, the switch connecting the control unit with either of the channels is placed in the neutral position upon resetting the control unit. The first programmed selection of a communication line subsequently causes the control unit and all associated communication lines to be switched to the selecting channel. This connection is maintained until the control unit is reset or a release function is performed.

When a control unit has been disconnected from a channel by the partitioning switch, that channel does not have access to the control unit and all devices on the control unit appear to the channel to be not operational. The not-operational state of a control unit or device is indicated by setting condition code 3 in the PSW. To restore switching under program control, the control unit must be reconnected to the system by the partitioning switch.

The condition of all partitioning switches can be sensed by the Store Multiple Control instruction.

#### Aids to Intrasystem Communication

Communication between the processors of a multiprocessing system is supplemented with means for:

- Signaling that a message has been or is to be transmitted

- Interlocking the use of storage to prevent conflict

- Requesting intervention in case of malfunction

- Permitting initialization to attempt recovery from malfunction

#### Signaling

For communications through a common storage facility, a processor must be alerted when a message has been prepared for it by another processor. The extended direct-control feature and external interrupt lines of the Model 67 perform this function.

Associated with the direct-control instructions is an interface at which eight signals are made available. A signal from one processor is connected to one of the external interruption lines of another processor. By means of the Read Direct or Write Direct instruction, the program in one processor causes an external interruption in another processor.

#### Interlocking

When shared storage is used as a common medium for data, restart information, programs, or results that are updated by different processors, interlocks must be provided to prevent mutual interference. The interlocks are provided within the device when I/O devices are the common storage media. The operating nature of devices that can maintain only one data transfer operation to or from the storage medium at a time, provides the desired interlock.

A longer interlocking period is required during the time between the physical arm movement in disk files and the read or write command. Additional controls can therefore be supplied so that a program can reserve an access mechanism.

The requirement for interlocking is apparent in cases where each processor simultaneously attempts to update a single record. One processor could read the record to perform the updating and the other processor could immediately attempt to read the same record. Processor 1 performs the updating and writes back the record, and processor 2 updates and writes back the record. Without interlocking, a complete transaction could have been lost. With interlocking, processor 1 would have reserved the file during an update and then released it, at which time processor 2 could have performed its updating without any chance of interference.

When main storage is the means of communication, electrical interlocks are provided for the period of one storage cycle. When two processors simultaneously request access to storage, a tiebreaking priority circuit grants access to one processor, then gives the next cycle to the other processor. This simple rule prevents one processor from locking out and therefore effectively halting

17

another processor. I/O is always granted higher priority than a processor.

Access to storage is granted for the duration of one storage cycle, not for the duration of an entire instruction. Since, as a rule, information is processed in internal registers, a typical procedure is to fetch data from storage, process the data in registers, and place the results in storage. The storage-interlocking mechanism, unaware of the relationship between successive storage accesses, makes it possible for one processor to store results in a location after the second processor has fetched its operands from that location, but before the second processor stores the results. This possibility necessitates a programmed interlock in the use of core storage as a shared medium. This requirement becomes even stronger when one processor is to use an entire storage area before permitting a second processor to use it.

The Test and Set instruction is designed specifically for this requirement. When this instruction is performed, a bit is tested and subsequently changed to 1 without access to the particular bit by any other processor in the intervening period; the instruction is available to the problem program and supervisor program alike. By means of the protection feature, testing and setting of particular control bits can be reserved for the supervisor program. A concise description of the Test and Set instruction is included under "System Components".

#### Malfunction Alert

In a multiprocessing system designed for high availability, the system should be alerted when a malfunction occurs in one of the components. A malfunction signal, similar to the direct control signal, is issued as soon as a machine malfunction is detected. This signal may be transmitted to other processors in the system, using the external interruption inputs of those processors.

The extensive checking included in all System/360 equipment is useful not only in error detection but in the improvement of fault location. A high degree of checking makes it possible to recognize malfunctions on short notice and thus preserve the state of the CPU for later diagnosis. Furthermore, the detailed error information made available to the customer engineer reduces the repair time and contributes to the overall system availability.

#### **Programmed Initialization**

Each IBM System/360 processor uses permanently assigned storage locations (0-127) for program status words, channel address and status words, the

timer, and initial program loading. If these locations were common, they would be shared by several processors and interference among processors would result. To provide each processor with separate assigned storage, a quantity called a prefix is used for dynamic relocation of all addresses referring to the first 4096 storage locations. In a multiprocessor system each processor is normally assigned a different prefix, and the sharing of these preferred locations is therefore avoided.

The prefix relocates all locations that can be directly addressed (using zero-index specifications) by the displacement. During program switching, such direct addressing is necessary when the supervisor must store the general purpose registers. The prefix makes this programming technique possible even if locations 0-4095 are not available to the system.

When a malfunction occurs only in storage, a system can resume operation immediately by eliminating the faulty storage unit. If the faulty storage contains the permanently assigned storage locations for the processor, new locations can be provided by introducing an alternate prefix. For this reason, a second prefix quantity is provided for a CPU as part of the System/360 multisystem feature.

Normally, the two prefix quantities relocate the preferred storage locations to different storage units; the processor therefore becomes independent of the specific storage unit for its operation.

The identity of the processor executing a program may be determined by setting apart one of the addresses in the range 0-4095 as the address of an identifying location, and loading identifying quantities in each of the corresponding physical locations. Since the physical location actually selected is determined by the prefix number, inspection of the addressed location identifies the processor and prefix currently used.

When a processor is reintroduced into a multiprocessor system, it is desirable to minimize operator action. Introduction of a new program status word and the corresponding instructions may best be performed by the still-operating part of the multiprocessor system. For this reason, means are provided for one processor to start another processor. This signaling again has been defined consistent with the signals of the direct-control circuits. Two signal inputs are provided, each of which causes an action similar to initial program loading. The choice between the two signals determines which prefix is used, and hence, the location of the permanently assigned storage addresses. In this case, the external start consists of loading an initial PSW from location 0 and performing the necessary system reset. Before the external start, the necessary PSW's should have been established by the active part of the system.

#### SYSTEMS DATA FLOW

#### General Information

Data is transmitted throughout the system along paths whose number, width, and data-rate capabilities are designed for efficient information flow and minimum interference.

In general, paths are widest where data rates are highest. The number of paths between major elements of the system is a function of the requirement for simultaneous operation and availability.

Data is transmitted eight bytes at a time between main storage and the processors and channels. It is transmitted one byte at a time between channels and I/O control units. Parity checking throughout the system is at the byte level.

#### Storage Bus

Each processor and each channel controller has a separate bus connecting it to each storage unit in the system. A system having two processors and two channel controllers has four buses. Expansion facilities provide for a total of eight buses, divided among processors and channel controllers. Each bus is connectable to as many as eight storage units.

Conflicts that occur among the several buses connected to each storage unit are resolved at the storage unit. This conflict resolution adds 150 nanoseconds to storage access time. Channel controller requests for storage cycles are given priority over processor requests.

Each processor has a bus control unit (BCU) that controls the storage bus associated with it. The processor can place data in core storage selectively by bytes. To initiate a store-type reference, the processor requests a storage cycle by providing to the BCU the address of a doubleword, accompanied by one or more mark signals. There is one mark line for each of the eight bytes that can be stored in a single cycle, and presence of signals on these lines indicates which bytes are to be replaced in the storage unit. Bytes that are not replaced remain unchanged. When the BCU indicates that the addressed storage unit has been selected and is available, data is provided to the storage unit.

When the processor requests a storage cycle without any signals on the mark lines, a fetch operation is initiated. The IBM 2067 processor expects data in a fetch operation to be available a fixed time after the initiation of the request. If the storage unit does not provide the data at the anticipated instant, operation of the processor is inhibited until data is available. During fetching, storage always provides full doublewords of data.

When a storage unit is shared by multiple processors or among processors and channel controllers, multiple concurrent references to the storage unit are possible. As far as the BCU and the channel controller are concerned, execution of storage cycles is the same as in a nonshared storage unit, except that the time interval between the initiation of a storage request and the acceptance of the request by the storage unit is variable. Whenever the storage unit is busy with the execution of a request from another bus, the new request remains pending on its bus until accepted by the storage unit. The storage units execute references in a fixed priority, established among those references that are pending at the instant of sampling. When multiple requests are pending, establishment of the priority is overlapped with the execution of the preceding cycle.

In the data transfer function, the channel controller performs two types of tasks: it communicates with the storage units and it serves the requests from its channels.

Channel servicing consists of establishing priority among the channel requests and initiating storage references in response to these requests. Channel priority is established by a priority network on the basis of requests from the channels. When more than one request signal is present at time of sampling, the channel controller establishes priority among the requests in the order of ascending channel addresses. Establishment of priority is overlapped with the execution of the preceding storage cycle to make maximum use of the storage bus.

When priority has been established for a particular channel, the channel controller requests the storage address and mark signals from the channel and initiates a storage cycle. Communication between the channel controller and the storage units is identical to that between the BCU and the storage units.

#### Channel Data Path

The channel data path provides for the transfer of data between the channel controller and the attached channels. This path is eight bytes wide, including the associated parity bits. All data transfer between the channel controller and the attached channels takes place over a single path; the time sharing of the path is under the control of the channel controller. The definition of signals on this path, other than those required for establishing priority among channels, is the same as for signals on the storage bus.

#### Input/Output Interface Data Path

All communication between channels and I/O control units is via I/O interface data buses (one in each direction), which are one byte wide (eight data bits and one parity bit). The connection between channels and control units is standardized. Further information is given in IBM System/360 I/O Interface --Channel to Control Unit OEMI (A22-6843).

#### Data Path Bandwidth

A channel controller can achieve a maximum data rate of 800,000 doublewords or 6,400,000 bytes per second.

Two types of channels can be attached to a channel controller: the IBM 2860 Selector Channel and the IBM 2870 Multiplexor Channel. The 2860 Selector Channel can sustain data rates of 1, 300, 000 bytes per second. The basic interface of the IBM 2870 Multiplexor Channel can handle an aggregate rate of 110,000 bytes per second, when no mediumspeed interfaces are provided. Table 1 illustrates the data rates that can be sustained by the basic interface and the selector subchannels of the IBM 2870 Multiplexor Channel:

| Table 1: Selector Subchannels |            |     |     |     |

|-------------------------------|------------|-----|-----|-----|

| Basic                         | <u>1st</u> | 2nd | 3rd | 4th |

| 110                           | x          | x   | x   | x   |

| 88                            | 180        | x   | х   | х   |

| 66                            | 180        | 180 | x   | x   |

| 44                            | 180        | 180 | 180 | x   |

| 30                            | 180        | 180 | 180 | 100 |

#### Nonstandard Component Interfaces

IBM System/360 is designed to permit attachment of special as well as non-IBM components. This versatility is achieved by providing well defined interfaces for certain components of the system. Many non-IBM components, such as processors, core storage units, control units, or I/O devices, may be incorporated in the system by designing to the interface specifications.

Detailed descriptions of these interfaces will be published as Original Equipment Manufacturers Information (OEMI) manuals. These descriptions will be made available upon request.

#### SYSTEM COMPONENTS

The IBM System/360 is a versatile, all-purpose system that can accommodate all applications which may be encountered in a diversified computing activity. The system is unique in its capability to grow easily with increasing needs for computational capability. If the particular I/O equipment is outgrown, more or faster I/O can be added. Core storage can also easily grow in capacity. The important point, however, is that any or all of this growth can be accomplished with no changes in system programming or in problem programming.

This section briefly outlines most of the components in the System/360. Specific emphasis has been placed on those devices and features which are unique to the time-sharing, multiaccess, and multiprocessing aspects of the system.

#### IBM 2067 PROCESSING UNIT

#### General Information

The 2067 Processing Unit provides the necessary arithmetic, logical, and control functions for the System/360.

The processor contains the facilities for addressing core storage, for fetching and storing information across the storage bus to which it is connected, for arithmetic and logical processing of data, for instruction sequencing, and for initiating the communication between core storage and external devices.

Information is transmitted between the processor and core storage across a storage bus 72 bits wide. These 72 bits constitute a doubleword of eight 8-bit bytes plus eight parity bits. Byte manipulations are possible, and any number of bytes up to a maximum of eight can be transferred in a single cycle.

The processor operates with a basic internal cycle time of 200 nanoseconds. A 60-bit parallel adder handles the full-length fraction in floatingpoint operations. An eight-bit adder handles simultaneous exponent arithmetic in floating-point operations, and is also used in serial variable-fieldlength decimal arithmetic.

The processor contains 16 general registers for fixed-point binary arithmetic, address manipulations, and indexing purposes. Each has a capacity of 32 bits (one word) and may be addressed by four bits in the instruction. For certain operations, pairs of registers may be coupled to form single 64-bit registers. Four additional registers each contain a 64 data-bit doubleword. They can be used for both short (one word) or long (doubleword) floating-point arithmetic. A capacitor read-only storage (ROS) etched on a glass substrate provides logical control for the processor. The flexibility of ROS control permits incorporation of specialized instructions or functions into the processors. The readout time of this storage is 140 nanoseconds. Sixteen planes, of 176 words each, provide an ROS capacity of 2816 hundred-bit words.

In addition to the above, the processor incorporates several features that provide dynamic address translation, protection, extended I/O control capability, communication between multiple processors, a high-resolution interval timer, and facilities for the programmed inspection of partitioning switches.

#### Dynamic Relocation

By its very nature, time sharing requires extremely large storage capacity. Not all information needs to be immediately available in core storage, however, since all programs and data sets are not simultaneously active. When programs or data sets or portions thereof become active, they must be quickly moved into core storage so that delays seen by the users are minimized. The dynamic relocation feature on the Model 2067 provides a means of doing this quickly and efficiently.

The dynamic relocation feature permits the use of a "virtual store" concept, whereby the total memory addressed is far larger than the actual core storage. The virtual addresses are translated to actual addresses by relocation tables that are set up and changed on a continuing basis by the supervisory program as information is moved back and forth between core storage and drums or other slower, larger-capacity storage devices.

This moving of information is done by the control program to satisfy user demands. The unit of information moved is 4096 bytes, commonly referred to as a page of information -- hence the term "page turning" to refer to this process of dynamically relocating information.

A set of eight associative registers is provided to minimize the effect that repeated references to relocation tables in core storage would have on processor performance. These registers are called associative registers since, in a translation process, a register is referenced by its contents rather than its physical location.

One other feature provided to minimize delays due to address translation is storage of the instruction address (that is, the instruction counter) in the translated or relocated form. This feature obviates the need for instruction address translation until a branch occurs or a page boundary is crossed.

The 2067 processor uses 24-bit addressing for the time-sharing system; in this mode of operation, a program may have up to 16 segments of 256 pages each. TSS also permits an extension of this addressing scheme to 32 bits, allowing the use of up to 4096 segments of 256 pages each. The dynamic relocation extension feature permits both 24- and 32-bit addressing.

The processor recognizes the relocation mode only when it has previously been switched into the extended control mode (see "Extended Control" later in this section). In the extended control mode, bit 4 of the PSW specifies the extent of logical addressing. That is, when bit 4 is a zero, 24-bit logical addressing takes place, and when bit 4 is a one, 32-bit logical addressing takes place. Bit 5 of the PSW (in extended control mode) specifies relocation vs nonrelocation mode. When bit 5 is a one, relocation takes place, and when bit 5 is a zero, no relocation takes place. When bit 4 is a one, bit 5 must be a one; otherwise, a specification exception is recognized.

The following table summarizes the modes of operation specified by bits 4-5 of the PSW (in extended control mode):

| Bit 4 | Bit 5 | Mode of Operation                                                                                                    |

|-------|-------|----------------------------------------------------------------------------------------------------------------------|

| 0     | 0     | No relocation, 24-bit address arithmetic                                                                             |

| 0     | 1     | Relocation, 24-bit address arithmetic                                                                                |

| 1     | 0     | Specification exception                                                                                              |

| 1     | 1     | Relocation, 32-bit address<br>arithmetic (specification exception<br>if 32-bit addressing option is not<br>provided) |

#### Address Translation (24-Bit Version)

The relocation tables used to translate a logical address into an actual address consist of "segment" tables and "page" tables. These tables are placed in main storage at the "segment table origin" and "page table origin" respectively. Each table occupies the number of storage locations specified by the respective "table length" amount.

Segment table origin is specified by the contents of bit positions 8-31 of the "table register" (control register 0). The length is always 64 bytes or one group of entries (16 entries per group, four bytes per entry). The address of the table origin must be a multiple of 64; hence, bits 26-31 of the table register must be zeros or a data exception is recognized. Each four-byte entry in the segment table defines a page table. The first byte (bits 0-7) defines the length of the page table, and the remaining three bytes (bits 8-31) define the page table origin. The unit of length for a page table is a two-byte entry. Thus, the table is variable in multiples of two bytes. Each page table's origin is located at a byte address that is a multiple of two. Thus, bit 31 of each segment table entry that defines a page table is zero. If bit 31 is one, no translation takes place and a segment relocation exception is recognized (program interruption with interruption code 16).

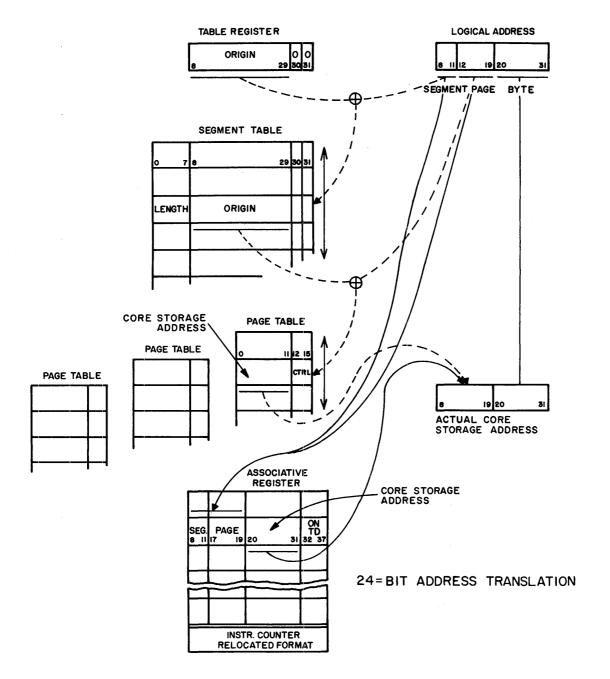

Figure 5 illustrates the translation action when the 24-bit addressing mode is used. Bits 8-19 of the "logical" (or virtual) address are first compared with the corresponding bits of each associative register having bit 36 set to one. If a match is found, bits 20-31 of that register are used as bits 8-19 of the actual address and bit 37 at the associative register is set to one. Bits 20-31 of the logical address are used directly as bits 20-31 of the actual address.