File Wo. S360 (Mod.20)-21 Of the Mo. GC26 3602-5

## Systems Reference Library

# IBM System/360 Model 20 Card Programming Support Basic Assembler Language

This reference publication provides programmers with the information required to write programs in the Basic Assembler language of the IBM System/360 Model 20.

The Basic Assembler language provides the user with a convenient means of making full use of the operational capabilities of the Model 20. Programs written in the Basic Assembler language (source programs) are translated into machine-language by means of the Basic Assembler program.

The description of the language includes rules for writing source programs and explanations of the instructions for controlling the Basic Assembler program. In addition, this publication includes a number of tables for convenient reference and conversion. Time and storage requirements are listed in a separate section. An extensive sample program is given to illustrate Basic Assembler language programming.

The description of the card and tape versions of the Basic Assembler program is confined to the aspects that affect the planning and writing of source programs.

Readers of this publication should be thoroughly familiar with the contents of the SRL publication <u>IBM</u> <u>System/360 Model 20</u>, Functional Characteristics, Order No. GA26-5847. Titles and abstracts of other Model 20 SRL publications are contained in the publication <u>IBM</u> <u>System/360 Model 20</u>, <u>Bibliography</u>, Order No. GA26-3565.

CPS

Seventh Edition (May, 1969; reprinted January, 1971)

This is a reprint of GC26-3602-5 incorporating changes issued in Technical Newsletter GN33-8612, dated April 6, 1970.

This edition applies to the following program version and modification levels of IBM System/360 Model 20, Card Programming Support, Basic Assembler, and to all subsequent versions and modifications until otherwise indicated in new editions and Technical Newsletters.

| Program Number | Version/Modification |

|----------------|----------------------|

| 360T-AS-001    | 3/7                  |

| 360T-AS-110    | 2/0                  |

| 360U-AS-130    | 2/2                  |

| 360U-AS-153    | 2/0                  |

Changes are continually made to the information herein; before using this publication in connection with the operation of IBM systems, consult the latest SRL Newsletter, Order No. GN20-0361, for the editions that are applicable and current.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for reader's comments is provided at the back of this publication. If the form has been removed, comments may be addressed to IBM Laboratory, Publications Department, P.O. Box 24, Uithoorn, Netherlands.

© Copyright International Business Machines Corporation 1965,1966,1967,1969

Prerequisite to using this publication is a thorough knowledge of IBM System/360 Model 20 machine operations, particularly storage addressing, data formats, and machine instruction formats and functions. It is assumed that the reader has experience with programming concepts and techniques or has completed basic courses of instruction in these areas.

Publications closely related to this one are:

IBM\_System/360\_Model\_20:

<u>Functional Characteristics</u>, Form A26-5847.

<u>Card Programming Support, Basic Assembler (Card), Operating Procedures</u>, Form C26-3802. <u>Card Programming Support, Basic Assen-</u> <u>bler (Tape), Operating Procedures</u>, Form C24-9011.

Card Programming Support, Input/Output Control System, Form C26-3603.

Input/Output Control System for the Communications Adapter, Form C26-3606.

<u>Input/Output Control System for the</u> <u>Binary Synchronous Communications Adapt-</u> <u>er</u>, Form C33-4001.

<u>Card Programming Support, Basic Utility</u> <u>Programs, Functions and Operating Proce-</u> <u>dures</u>, Form C26-3604.

Titles and abstracts of other Model 20 SRL publications are contained in the <u>IBM</u> <u>System/360 Model 20 Bibliography</u>, Form A26-3565.

## CONTENTS

| IN       | De<br>Ba<br>BA<br>Mi<br>La             | fi<br>si<br>SI<br>ni<br>xi            | n<br>C<br>C<br>m                                                                                 | it<br>A<br>A<br>un                             | i<br>IS<br>IS                                                                   | s<br>s<br>s<br>s<br>s | n<br>E<br>Y<br>y           | s<br>m)<br>Ml<br>s'<br>s' | b]<br>31<br>t@      | le<br>LE<br>en             | er<br>CR                                                                                    |                        |                      | ar<br>AN<br>nf             | ig<br>IG           | u<br>U<br>g       | a<br>A<br>u | g<br>G<br>r<br>r | e<br>E<br>ai                    | :<br>F<br>ti        | st<br>FE      | a<br>A<br>n | t<br>T | en<br>UF      | ie<br>E         | S | •           | •           | •.               | 6<br>6<br>7                                      |  |

|----------|----------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------|-----------------------|----------------------------|---------------------------|---------------------|----------------------------|---------------------------------------------------------------------------------------------|------------------------|----------------------|----------------------------|--------------------|-------------------|-------------|------------------|---------------------------------|---------------------|---------------|-------------|--------|---------------|-----------------|---|-------------|-------------|------------------|--------------------------------------------------|--|

| LA<br>Co | Sy:<br>Ex                              | UA<br>ng<br>La<br>lf<br>mb            | G<br>ei<br>Cl                                                                                    | E<br>C<br>g<br>u<br>h<br>a<br>D<br>e<br>S<br>S | n<br>ia<br>ia<br>ia<br>ia<br>ia<br>ia<br>ia<br>ia<br>ia<br>ia<br>ia<br>ia<br>ia | vt<br>gai             | •<br>e<br>c<br>n<br>•<br>n | n<br>Fo<br>te             | ·<br>si<br>si<br>ng |                            | n<br>ia<br>S<br>T                                                                           | ·<br>st<br>c<br>e<br>e | s<br>t<br>r          | •<br>•<br>•<br>•           |                    | đ                 | • • • • •   | С                | •                               | nf                  |               | • • • • • • | e      | •<br>•<br>•   | · · · · · · · · |   | •           | •           | •<br>•<br>•<br>• | 9<br>9<br>11<br>14<br>14<br>15<br>16<br>17<br>19 |  |

| St       | Sy<br>Ex<br>Ab<br>ne<br>se<br>Us       | ag<br>fe<br>pl<br>so<br>ra<br>R<br>in | e<br>o<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i | A<br>Li<br>ci<br>ut<br>at                      | d<br>.c.t.e.n<br>.s                                                             | d<br>d<br>t           | r<br>(A<br>(<br>eU         | e:<br>A(<br>D:<br>P:<br>s |                     | se<br>lr<br>pl<br>re<br>eu | i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i<br>i | s<br>e<br>s<br>t<br>o  | s<br>ay<br>i         | ir<br>ng<br>Re             |                    |                   | d<br>rs     | r<br>et<br>s     | ·<br>·<br>·<br>·<br>·<br>·<br>· |                     |               | n<br>g      | g      | •             | • • • • • • •   |   | •           | • • • • •   | •                | 20<br>20<br>20<br>21<br>22                       |  |

| A E      | 850                                    | LU                                    | T:                                                                                               | Е                                              | A                                                                               | N                     | D                          |                           | R I                 | EI                         | 20                                                                                          | C                      | A                    | Γ <i>Ι</i>                 | A E                | BL                | , E         |                  | P                               | RC                  | 00            | R           | A      | MM            | II              | N | G           | •           | •                | 26                                               |  |

| PF       | ROG<br>Sa                              |                                       |                                                                                                  |                                                |                                                                                 |                       |                            |                           |                     |                            |                                                                                             | •                      |                      | •                          |                    |                   |             |                  | •                               |                     |               |             |        | •             |                 |   | •           |             | •                | 27<br>28                                         |  |

| DE       | EFI<br>EQ<br>DC<br>DS                  | U<br>U<br>-                           | T .                                                                                              |                                                | )N<br>E<br>)e                                                                   | q<br>f<br>f           | I<br>u<br>i                | N<br>a<br>n<br>e          | S!<br>Ee            |                            | St                                                                                          | C<br>yı<br>n           | T<br>m<br>s          | IC<br>bc<br>ta<br>ag       |                    | t                 | •           |                  | •                               |                     | •             | •           |        | •<br>•<br>•   | • • •           |   | •           | •<br>•<br>• | •<br>•<br>•      | 29<br>29<br>29<br>32                             |  |

| BA       | SI<br>ST<br>EN<br>OR                   | C<br>A R<br>D<br>G                    | A :<br>T<br>                                                                                     | 5 S<br>-<br>-                                  | E                                                                               | n<br>e                | B<br>S<br>d<br>S           | L)<br>ta<br>e             |                     | R<br>ct<br>E<br>L          | C<br>P                                                                                      | P<br>P<br>C            |                      | r H<br>og<br>gr<br>t i     | RC<br>II<br>a      | a<br>m            | m           | I<br>C           | N :<br>0 1                      | 51<br>ur            | r F           | U           | C<br>r | т I<br>•<br>• | :0              | N | s<br>•<br>• | •           | •<br>•<br>•      | 34<br>34<br>34<br>35                             |  |

| In       | PU<br>XI<br>CI<br>TI<br>Se<br>Pu<br>'0 | 0<br>0E<br>gu<br>t/                   | e:                                                                                               | -<br>-<br>nc                                   | E<br>C<br>e                                                                     | x<br>o<br>T<br>u      | e<br>n<br>e<br>o<br>t      | ci<br>ti<br>si            |                     | te<br>5]<br>I/<br>ac       |                                                                                             | I:<br>P:<br>O          | n)<br>nj<br>u†<br>I: | pu<br>pu<br>t/<br>ns<br>In | it<br>1<br>7<br>St | /<br>/<br>u<br>:t | 00<br>tur   | u<br>p<br>c<br>u |                                 | pu<br>pu<br>t<br>ic | it<br>a<br>on | n<br>S      | d<br>s | E             | Br              | a | •           |             |                  | 37<br>37<br>39<br>40<br>40<br>41                 |  |

| Ma       | CH<br>ich<br>ist<br>RR<br>RX           | in<br>ru<br>F                         | ie<br>ic<br>'o                                                                                   | -]<br>ti<br>cn                                 | In<br>.o<br>na                                                                  | n<br>t                | t                          | r)<br>Fo                  |                     | ct<br>כת<br>•              | i<br>a                                                                                      | o<br>t:                | n                    | ľ                          | 1 n                | ie                | m           | 0                | n                               | ic                  |               | C           | 0      |               |                 |   | •           | • • •       | • • •            | 43<br>45<br>45<br>45<br>45                       |  |

|           |             |                |            |          | -            |                  | ıt       |              | •        |        | •        | •          |            | •      | •   | •       | •        | •       |     | •        | •        | •          | •           | •       | •       | • | 47       |   |

|-----------|-------------|----------------|------------|----------|--------------|------------------|----------|--------------|----------|--------|----------|------------|------------|--------|-----|---------|----------|---------|-----|----------|----------|------------|-------------|---------|---------|---|----------|---|

|           | S           | S              | F          | 0        | r i          | n a              | ιt       |              | •        |        | •        | •          | ·          | •      | •   |         | •        | •       |     | •        | •        | •          | •           | •       | ٠       | • | 48       |   |

| Ту        | P           | e              | 5          | 0        | f            | ľ                | la       | Ċh           | ii       | n      | е        | C          | )p         | e      | ra  | ı t     | i        | or      | s   |          | •        | •          | •           | •       | •       | • | 49<br>49 |   |

|           | B:          | ir             | ıa         | r        | У            | P                | ΙĽ       | it           | h        | M      | e        | t i        | C          |        |     | ,       | •        | •       |     | •        | •        | • •        | •           | •       | •       | • | 49       |   |

|           | 1           | n s            | 5t         | r        | u            | ct               | :i       | or           | ۱S       |        | f        | 21         |            | В      | iı  | ۱a      | r        | У       | A   | ri       | .th      | Μe         | et.         | ic      | •       |   | 51       |   |

|           | D           | ec             | :i         | m        | a]           | L                | A        | ri           | t        | hı     | m e      | et         | i          | с      |     |         | •        | •       |     | •        | •        | •          | •           |         | •       | • | 53<br>55 |   |

|           | I           | n٩             | st         | r        | u            | c t              | :i       | on           | ۱s       | : :    | f        | 21         |            | D      | ec  | :i      | m        | a l     |     | Ar       | it       | hn         | ie          | ti      | с       |   | 55       |   |

|           | No          | or             | <u>-</u>   | A        | ri           | i t              | h        | мe           | et       | i      | С        | C          | )p         | e      | Γâ  | ١t      | i        | o r     | s   |          | •        |            |             |         |         |   | 61       |   |

|           |             |                |            |          |              |                  |          |              |          |        |          |            |            |        |     |         |          |         |     |          | iet      |            |             |         |         |   |          |   |

|           |             |                |            |          |              |                  |          |              |          |        |          |            |            |        |     |         |          |         |     | •        |          |            |             |         |         |   | 62       |   |

|           |             |                |            |          |              |                  |          | 5            |          |        |          |            |            |        |     |         | :        |         |     |          |          | •          | •           | •       | •       |   | 69       |   |

|           | T           | . c            | - <b>-</b> | -        | ,1 -<br>11 - | ~ 4              | 9        | ~ <b>r</b>   |          |        | •<br>•   |            |            |        |     |         |          |         |     | •        |          | ::         | :           |         | •       | : |          |   |

|           | Ŧ           | 11 2           | sι         | r        | u            | - 1              | - 1      | 01           | 15       | •      | T (      | 51         | •          | D      | τc  | . 11    | С.       | n       | 0   | pe       | :La      | -u         | .0          | ns      | •       | • | 10       |   |

|           |             |                |            | ~        |              | ~                |          | ~ ~          |          |        |          |            |            |        |     |         | ~        |         |     |          |          |            |             |         |         |   | -        |   |

| TH        |             |                |            |          |              |                  |          |              |          |        |          |            |            |        |     |         |          |         |     |          | •.       | •          | •           | ٠       | •       |   | 72       |   |

| Ba        | S.          | 10             | 2          | A        | SS           | 5 E              | em       | pT           | e        | r      |          | (0         | a          | r      | d   | V       | e:       | C S     | :1  | on       | s)       |            |             |         | •       | • | 72       |   |

| Ba        | S           | 10             | 2          | A        | s            | 56               | em       | bl           | .e       | Γ      |          | ( ]        | 'a         | P      | е   | V       | e        | rs      | 51  | on       | ıs)      |            | •           | •       | ٠       | ٠ | 73       |   |

|           |             |                |            |          |              |                  |          |              |          |        |          |            |            |        |     |         |          |         |     |          |          |            |             |         |         |   |          |   |

| DI        | A           | G١             | 10         | S        | T:           | ΣC               | :        | ΜE           | S        | Si     | A (      | GE         | S          |        |     |         | •        |         |     | •        | •        | •          | •           | •       | •       | • | 74       |   |

| Lo        | a           | đj             | . n        | q        | (            | ٦t               | ŗ        | ec           | t        | ]      | Pı       | c          | q          | r      | an  | າຣ      |          |         |     |          | :        |            |             |         | •       | • | 74       |   |

|           |             |                |            |          |              |                  |          |              |          |        |          |            |            |        |     |         |          |         |     |          |          |            |             |         |         |   |          |   |

| ΡE        | R           | F (            | )R         | M        | A I          | N C              | E        | E            | A (      | Т      | A        |            |            |        |     |         |          |         |     |          | •        |            |             |         |         |   | 75       |   |

|           | M           | a ·            | i n        |          | S            | h r              | n r      | ao           |          | . 1    | R        | a r        | r 13       | i      | re  | Э ПП «  | 6        | n t     | . 5 | •        | •        |            | Ţ           | Ţ       | Ţ       |   | 75       |   |

|           | τι·<br>π·   | i n            | 20         |          | D/           | 20               |          | ir           | 6        |        | <u> </u> |            | ۳.<br>ح    | -      |     | - 11    | ř        |         | Ā   | U        |          | . i        |             | n •     | •       | • | 75       |   |

|           | 1.<br>m     |                | e          |          | ne<br>D      | =9               | u        | 11           | e        | tu e   | =1       |            | 3          |        |     |         | ر ب<br>س | ar      | u   |          | er       | 51         | .0.         | n       | •       | • | 75       |   |

|           | T.          | 11             | ne         |          | R (          | 9 G              | Įu       | 11           | e        | m      | eı       | יח         | s          |        |     | •       | T        | a Į     | e   | v        | er       | <b>S</b> 1 | .0          | n       | ٠       | • | 15       |   |

|           |             | _              |            | _        |              |                  | _        | • •          | _        | _      |          |            | _          |        |     |         | _        |         |     |          |          |            |             |         |         |   |          |   |

|           |             |                |            |          |              |                  |          |              |          |        |          |            |            |        |     |         |          |         |     |          | SE       |            |             |         |         |   |          |   |

| LA        | N (         | G١             | JA         | G        | Е            |                  |          | •            | •        |        | •        | •          |            | ٠      |     | ,       | •        | •       |     | •        | •        | •          | •           | •       | •       | • | 76       |   |

| St        | a           | tj             | . n        | a        | i f          | t h              | ıe       | Ē            | 'r       | o      | b]       | Le         | m          |        |     |         |          |         |     |          |          |            |             |         |         | • | 76       |   |

| Wr        | i           | t.:            | i n        | a        | ł            | E P              | ne       | S            | 0        | u      | г        | ce         |            | p      | ra  | λa      | ra       | аπ      | ı   |          |          |            |             |         |         | • | 76       |   |

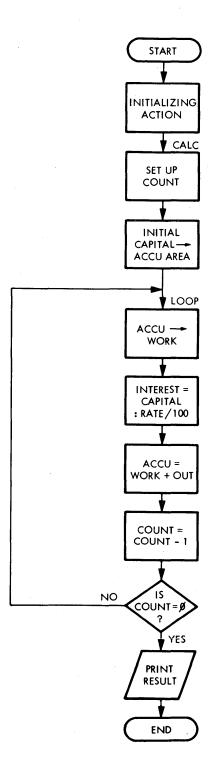

|           | TT 1        | h d            | <u> </u>   | ट .<br>म | 1,           | <br>             |          | ha           | r        | + '    |          |            |            |        | _   | - 9     | -        |         | •   | - ·      | -        | -          | •           | •       | •       | • | 76       |   |

|           | 1 I<br>T    | n e            |            | 1        | τĊ           | ) W<br>1         | -        | 11 a         |          | Ľ      | • 1      | •          |            | •      | _   |         | •        | •       |     | •        | •        | •          | •           | •       | •       | • | 70       | ( |

|           | 1           | n.             | Lt         | 1        | d.           | 11               | . Z      | 11           | ig       |        | τ        | ne         | •          | P      | L.C | )g      | L        | a II    | ł   |          |          |            |             |         |         |   | 74       |   |

|           | (:          | 51             | . W        | T        | 1-           | - 5              | T        | МТ           | 3        | )      |          | •          |            | •      | •   |         | •        | •       |     | •        | eas      | ٠          | ٠           | ٠       | ٠       | ٠ | 76       |   |

|           | D           | at             | za         |          | C            | ЪI               | ۱S       | ta           | n        | t      | s        | а          | l n        | d      | ľ   | ł٥      | r        | k       | A   | re       | eas      |            |             |         |         |   |          |   |

|           | (           | 51             | M          | т        | 4-           | - S              | Т        | ΜT           | 1        | 5)     | )        |            |            | •      |     |         | •        | •       |     |          | •        | •          | •           | •       | •       | • | 77       |   |

|           | P           | r              | bd         | r        | a١           | m                | R        | ou           | ۱t       | i      | ne       | э          | (          | S      | TI  | 1T      | 1        | 6-      | ٠S  | ΤĽ       | 1T2      | 4)         |             |         |         |   | 78       |   |

|           | 01          | n t            | ر.<br>م    | 11       | t            | 1                | S        | тM           | T        | 2      | 5-       | - 9        | :m         | M      | T : | 35      | ١.       |         |     |          | •        | .'         | _           |         | -       |   | 79       |   |

|           | D           |                | .t.        | -        | ə ı          | י<br>ת           | E        | nđ           | -        | 1      | 5,       | г N        | i T        | ົຈ     | 61  |         | '        | •       |     | •        | •        | •          | •           | •       |         | • |          |   |

| 10        |             | ~ "            | /9<br>.h   | ī        |              | <br>             | , "      | 11.u<br>+ h  | ٠<br>_   | V.     | с.<br>С/ |            |            | 2      | 2,  | n       |          | •       |     | •        | .*       | •          | •           | •       | •       | • | 80<br>80 |   |

| AS        | 5           | en             | 10         | T.       | T 1          | 19               |          | ιn           | e        |        | 50       | <b>)</b> U | L          | Ç      | e   | P       | T        | 99      | μ   | aii      | l        | •          | •           | •       | •       | • | 00       |   |

|           | C           | 01             | lt         | r        | 0.           | L                | C        | aı           | d        |        | ٠        | •          |            | ٠      | •   |         | ٠        | •       |     | •        | •        | •          | ٠           | •       | •       | ٠ | 80       |   |

|           | D:          | ĺð             | ١g         | n        | 0.5          | st               | <b>i</b> | С            | R        | u      | 1]       | •          |            | ٠      |     | •       | •        | •       |     | •        | •        | ٠          | •           | •       | . •     | • | 80       |   |

|           |             |                |            |          |              |                  |          |              |          |        |          |            |            |        |     |         |          |         |     |          |          |            |             |         |         |   |          |   |

|           |             |                |            |          |              |                  |          |              | U        | Μ      | M        | A F        | Y          |        | OI  | 2       | Β.       | AS      | SI  | С        | AS       | SI         | ΕM          | ΒL      | ER      |   |          |   |

| IN        | S'          | ΓI             | RU         | С        | T I          | I C              | ) N      | S            |          |        |          |            |            |        |     |         |          |         |     |          |          | •          |             |         |         | • | 82       |   |

|           |             |                |            |          |              |                  |          |              |          |        |          |            |            |        |     |         |          |         |     |          |          |            |             |         |         |   |          |   |

| AP        | P           | E              | ID         | т        | Y            | F                | ٤.       | · c          | : n      | M      | MI       | A F        | v          |        | OF  | 2       |          |         |     |          |          |            |             |         |         |   |          |   |

| MA        |             |                |            |          |              |                  |          |              |          |        |          |            |            |        |     |         |          |         |     |          |          |            |             |         |         |   | 83       |   |

| ΓA        | C           | п.             |            | Ŀ,       |              | LD               | 10       | ΤU           | U        | С.     | 1.       | LC         | NI V       | ວ      | •   |         | •        | •       |     | •        | •        | •          | •           | •       | •       | • | 03       |   |

|           |             |                |            | _        |              |                  | _        | -            |          |        |          |            |            |        |     | _       | _        |         |     | _        |          |            | _           |         |         |   |          |   |

|           |             |                |            |          |              |                  |          |              |          |        |          |            |            |        | 01  | 2       | I        | NF      | 0   | T/       | ′0 U     | ΤF         | יטי         | т       |         |   |          |   |

| IN        | S           | Τł             | ۲U         | C        | T:           | ΓC               | ) N      | S            | ٠        |        | •        |            |            | •      | •   | •       | •        | •       |     | •        | •        | •          | ٠           | •       | ٠       | • | 84       |   |

|           |             |                |            |          |              |                  |          |              |          |        |          |            |            |        |     |         |          |         |     |          |          |            |             |         |         |   |          |   |

| AP        | P           | El             | ١D         | I        | X            | Ε                | ).       | 5            | ; U      | M      | M        | A F        | Y          |        | OI  |         | D        | IA      | G   | NC       | )ST      | IC         | 2           |         |         |   |          |   |

| ΜE        | S           | s I            | G          | E        | S            |                  |          | •            |          |        | _        |            |            | _      |     |         |          |         |     | _        |          |            |             |         |         |   | 86       |   |

|           | ~           |                |            | -        | ~            | •                |          | •            | •        |        | •        | . •        |            | •      | •   |         | •        | •       |     | •        | •        | •          | •           | •       | •       | • | 00       |   |

| ۸ T       |             |                | a D        | +        | v            | τ                | ,        | ~            | • ^      |        |          | T IT       | · <b>-</b> | ~      | NT  | ~       | 0        |         |     |          |          |            |             |         |         |   | 00       |   |

| AP        | · • •       |                | N D        | T        | X            | r                | •        | C            | .0       | N.     | υ.       | 11         | 1          | 0      | N   | C       | 0.       | DE      | 2   |          | •        | •          | •           | •       | ٠       | • | 88       |   |

|           | <b>P</b>    |                |            |          |              |                  | _        | -            |          | _      | _        |            |            | _      |     |         |          |         |     |          |          |            |             |         |         |   |          |   |

|           |             |                |            |          |              |                  |          |              | ٩Η.      | A      | R        | A (        | T          | Е      | R   | С       | 0        | DE      | S   |          | •        | •          | -           |         |         |   | 89       |   |

| A P       |             |                | ١D         | I        | Х            | ł                | •        | U.           |          |        |          |            |            |        |     |         |          |         |     |          |          |            | •           | •       | •       | • |          |   |

| A P       |             |                | ١D         | I        | X            | 1 .              | •        |              |          |        |          |            |            |        |     |         |          |         |     |          |          |            | •           | •       | •       | • |          |   |

|           | P           | El             |            |          |              |                  |          |              |          |        | A :      | DI         | EC         | I      | MZ  | ۱L      | - ;      | DE      | EC  | IM       | IAL      | N          |             | •<br>MB | •<br>ER | • |          |   |

| A P       | P<br>P      | E I<br>E I     | ٧D         | I        | X            |                  | ;.       | Н            | ΙE       | X      |          |            |            |        |     |         | - 1      | DE      | EC  | IM.      | IAL      | N          | U           | MB      | ER      |   |          |   |

|           | P<br>P      | E I<br>E I     | ٧D         | I        | X            |                  | ;.       | Н            | ΙE       | X      |          |            |            |        |     | \L<br>• | - ;      | DH<br>• | C   | IM.      | IAL<br>• |            | 101         | мв<br>• | ER      | • | 93       |   |

| A P<br>CO | P<br>P<br>N | EI<br>EI<br>VI | N D<br>E R | IS       | X            |                  | ;.<br>I  | H            | I E<br>B | X<br>L | E        | •          | ۰.         | •      |     | •       | •        | DH<br>• | EC  | IM.      | IAL<br>• |            | יטו<br>י    | MB      | ER      | • | 93       |   |

| A P       | P<br>P<br>N | EI<br>EI<br>VI | N D<br>E R | IS       | X<br>I(      |                  | ;.<br>I  | H            | I E<br>B | X<br>L | E        | •          | ۰.         | •      |     | •       | •        | DH      | C   | IM.<br>• | IAL<br>• | N<br>•     | יטו<br>יייי | мв<br>• | ER<br>• | • |          |   |

| A P<br>CO | P<br>N<br>P |                |            | IS       | X<br>X       | C<br>N<br>C<br>F |          | H<br>TA<br>G |          | L<br>D | E<br>S   | SF         | R          | •<br>Y | •   | •       | •        | •       |     | •        | •        | •          | •           | •       | •       | • | 93       |   |

Computer programs may be expressed either in machine language, in other words, language directly interpreted by the computer, or in a symbolic language, which is more meaningful to the programmer. The symbolic language, however, must be translated into machine language before the computer can execute the program. This function is accomplished by an associated processing program.

Of the various symbolic programming languages, Assembler languages are closest to machine language in form and content.

The Basic Assembler language discussed in this manual is a symbolic programming language for the IPM System/360 Model 20. It enables the programmer to use all Model 20 machine functions, as if he were coding in Model 20 machine language.

The Basic Assembler program translates or processes programs written in Basic Assembler language into machine language for execution by the computer. The program written in the Basic Assembler language used as input to the Basic Assembler program is called the <u>source program</u>; the machine-language program produced as output from the Basic Assembler program is called the <u>object program</u>. The translation or processing procedure performed by the Basic Assembler program to produce the object program is called <u>assembling</u> or <u>assembly</u>.

Four versions of the Basic Assembler program are available:

- a. Two card versions. These are two-pass programs for a Model 20 system that includes only card input/output devices. One of the versions permits the assembly of the macro instructions associated with the Input/Output Control System for the Binary Synchronous Communications Adapter (BSCA IOCS).

- b. Two tape versions. These versions differ from the card versions by being one-pass programs and by using magnetic tape as an intermediate storage medium, thus reducing card-handling and assembly time.

<u>Note</u>: The CPS Input/Output Control System (IOCS) routines can be assembled by means of either version.

#### DEFINITIONS

Terms used in this publication are defined in the glossary provided in <u>Appendix H</u>.

#### BASIC ASSEMBLER LANGUAGE STATEMENTS

Program statements (source statements) written in Basic Assembler language may consist of: a name to identify the statement; a symbolic operation code (mnemonic) to identify the function the statement represents; one or more items called operands, to designate the data or storage locations used in the operation; and comments.

Programs written in Basic Assembler language may consist of up to five types of instructions: definition instructions, program linking instructions, Basic Assembler control instructions, input/output instructions (including IBM-supplied I/O macro instructions), and machine instructions. There are predefined mnemonic codes for all instructions in the Basic Assembler language.

Definition instructions are used to reserve storage, to define constants, and to equate symbols to the attributes of an expression.

Program linking instructions are used to link program sections for joint execution.

Basic Assembler control instructions are used to begin assembly, end assembly, and set the location counter.

Input/output instructions designate the units used as I/O devices, and control their operation. The use of IOCS macro instructions saves programming time because it relieves the user of having to code, test, and provide linkages to his own I/O routines.

Machine instructions direct the computer to execute certain operations. The Basic Assembler produces an equivalent internal machine instruction in the object program from each machine instruction in the source program.

#### BASIC ASSEMBLER LANGUAGE FEATURES

## Variety in Data Representation

Decimal, hexadecimal, or character representation of machine-language binary values may be employed by the programmer in writing source statements. The programmer selects the representation best suited to his purpose.

## Base Register Address Calculation

The Model 20 Basic Assembler language provides for two methods of addressing:

- The address may be specified as a displacement plus a base register the contents of which are added to the displacement. The base register may be one of the general registers 8 through 15 or one of the pseudo base registers 0 through 3. (If a Submodel 5 is used, pseudo registers 0-7 are available. However, 0-3 are the only pseudo registers.)

- When using a general register, the register contents can be controlled by the programmer.

- b. When using a pseudo base register, the register contents are assumed to be fixed (i.e., 0, 4096, 8192, and 12288). This corresponds to what is termed direct addressing in the Model 20 SRL publication <u>Func-</u> <u>tional Characteristics</u>, Form A26-5847.

- The address may be specified symbolically without the use of a base register. In this case, the Basic Assembler assumes the clerical burden of computing storage locations in terms of a base address and a displacement.

## Relocatability

The object programs produced by the Basic Assembler may be in a format enabling relocation from the originally assigned storage area to any other suitable area.

## <u>Program Linking</u>

The linking facilities of the Basic Assembler language and program allow symbols to be defined in one assembly and referred to in another, thus effecting a link between separately assembled programs. This permits reference to data and/or transfer of control between programs. A discussion of linking is contained under <u>Program Linking</u>.

6 System/360 Model 20 Basic Assembler Language

## <u>Program Listings</u>

A listing of the source-program statements and the resulting object-program statements is produced by the Basic Assembler for each source program it assembles. The programmer can partly control the form and contents of the listing.

## Error Indications

As a source program is assembled, it is analyzed for actual or potential errors in the use of the Basic Assembler language. Detected errors are indicated in the program listing.

#### MINIMUM SYSTEM CONFIGURATION

The minimum system configuration for assembling and executing Basic Assembler programs is as follows. The configuration applies to all versions of the program except where indicated.

#### <u>Submodel 2</u>

- An IBM 2020 Central Processing Unit, Model B2 for the normal version, or C2 for the BSCA version (4096 or 8192 bytes of main storage);

- one of the following card units: IBM 2560 Multi-Function Card Machine, Model A1, IBM 2520 Card Read-Punch, Model A1, IBM 2501 Card Reader, Model A1 or A2 with either an IBM 2520 Card Punch, Model A2 or A3, or an IBM 1442 Card Punch, Model 5;

- an IBM 2415 Magnetic Tape Unit, Model 1 or 4 (for the tape versions only);

- one of the following printers: IBM 1403 Printer, Model N1, 2, or 7, IBM 2203 Printer, Model A1;

#### <u>Submodel 3</u>

- an IBM 2020 Central Processing Unit, Model B3 (4096 bytes of main storage);

- an IBM 2560 Multi-Function Card Machine, Model A2;

- an IBM 2203 Printer, Model A2.

#### Submodel 4

- an IBM 2020 Central Processing Unit, Model B4 (4096 bytes of main storage);

- an IBM 2560 Multi-Function Card Machine, Model A2;

• an IBM 2203 Printer, Model A2.

## <u>Submodel 5</u>

- an IBM 2020 Central Processing Unit, Model C5 (8192 bytes of main storage);

- one of the following card units: IBM 2560 Multi-Function Card Machine, Model A1, IBM 2520 Card Read Punch, Model A1, IBM 2501 Card Reader, Model A1 or A2 with either an TBM 2520 Card Punch, Model A2 or A3, or an IBM 1442 Card Punch, Model 5;

- an IBM 2415 Magnetic Tape Unit, Model 1 or 4 (for the tape versions only);

- one of the following printers: IBM 1403 Printer, Model N1, 2, or 7, IBM 2203 Printer, Model A1.

Note 1: CPS does not support main storage sizes of 24K and 32K, but CPS programs will run on Models DC5 and E5 although only 16K bytes are used. (The maximum value of the location counter is X'3FFF'. Therefore, the Basic Assembler will not permit references to addresses greater than this.)

<u>Note 2</u>: If 7-track tapes are used, the data-conversion feature is required.

MAXIMUM SYSTEM CONFIGURATION

Basic Assembler object programs may be produced for the following maximum system configurations.

#### Submodel 2

- An IBM 2020 Central Processing Unit, Model D2 (16,384 bytes of main storage); with or without IBM Binary Synchronous Communications Adapter, Feature No. 2074;

- two IBM 2311 Disk Storage Drives, Model 11 or 12 (both must be the same model);

- an IBM 2415 Magnetic Tape Unit, Model 1 through 6;

- an IBM 2501 Card Reader, Model A1 or A2;

- an IBM 1442 Card Punch, Model 5;

- one of the following card units: IBM 2520 Card Read-Punch, Model A1, IBM 2520 Card Punch, Model A2 or A3, IBM 2560 Multi-Function Card Machine, Model A1;

- one of the following printers: IBM 1403 Printer, Model N1, 2, or 7, IBM 2203 Printer, Model A1;

- one of the following magnetic character readers: IBM 1419 Magnetic Character Reader, Model 1 or 31, IBM 1259 Magnetic Character Reader, Model 1, 31, or 32;

- an IBM 2152 Printer-Keyboard.

#### <u>Submodel 3</u>

- an IBM 2020 Central Processing Unit, Model D3 (16,384 bytes of main storage);

- an IBM 2560 Multi-Function Card Machine, Model A2;

- an IBM 2203 Printer, Model A2.

## Submodel 4

- an IBM 2020 Central Processing Unit, Model D4 (16,384 bytes of main storage); with or without IBM Binary Synchronous Communications Adapter, Feature No. 2074;

- two IBM 2311 Disk Storage Drives, Model 12;

- an IBM 2560 Multi-Function Card Machine, Model A2;

- an IBM 2203 Printer, Model A2;

- an IBM 2152 Printer-Keyboard.

## <u>Submodel 5</u>

- an IBM 2020 Central Processing Unit, Model D5 (16,384 bytes of main storage); with or without IBM Binary Synchronous Communications Adapter, Feature No. 2074;

- four IBM 2311 Disk Storage Drives, Model 11 or 12;

- an IBM 2415 Magnetic Tape Unit, Model 1 through 6;

- an IBM 2501 Card Reader, Model A1 or A2;

- an IBM 1442 Card Punch, Model 5;

- one of the following card units: IBM 2520 Card Read-Punch, Model A1, IBM 2520 Card Punch, Model A2 or A3, IBM 2560 Multi-Function Card Machine, Model A1;

- one of the following printers: IBM 1403 Printer, Model N1, 2, or 7, IBM 2203 Printer, Model A1;

- one of the following magnetic character readers:

Introduction 7

IBM 1419 Magnetic Character Reader, Model 1 or 31, IBM 1259 Magnetic Character Reader, Model 1, 31, or 32;

an IBM 2152 Printer-Keyboard.

<u>Note</u>: CPS does not support main storage sizes of 24K and 32K, but CPS programs will run on Models DC5 and E5 although only 16K bytes are used.

#### LANGUAGE COMPATIBILITY

The IBM System/360 Model 20 Basic Assembler language is compatible with the Basic Assembler language for the other models of the IBM System/360, except where differences in machine design make it necessary to include some instructions in the Model 20 Basic Assembler language that are not contained in the System/360 Basic Assembler language. The mnemonics of these Model 20 instructions are: BAS BASR CIO HPR SPSW TIOB XIO

The use of the CIO, SPSW, TIOB, and XIO instructions in Model 20 programs can be avoided by using IOCS macro instructions to satisfy input/output requirements.

Programs that are written in the Model 20 Basic Assembler language and contain statements with blank operands cannot be assembled by other System/360 Assembler programs.

In addition, the use and the functions of registers 0 through 3 in Model 20 programming differ from the corresponding registers on other models of the IBM System/360.

## CHARACTERISTICS OF THE BASIC ASSEMBLER LANGUAGE

## CODING CONVENTIONS

Statements in Basic Assembler language can be written in free format; in other words, the statement components need not begin in a specified column of the coding sheet. (The <u>name</u> of a statement, which must begin in column 25, is an exception to this rule.) However, the statement components must be separated from each other by at least one blank column.

For the purpose of clarity, most programmers do not use the free format but prefer to begin each type of statement component in a specific column of the coding sheet.

#### The Coding Form

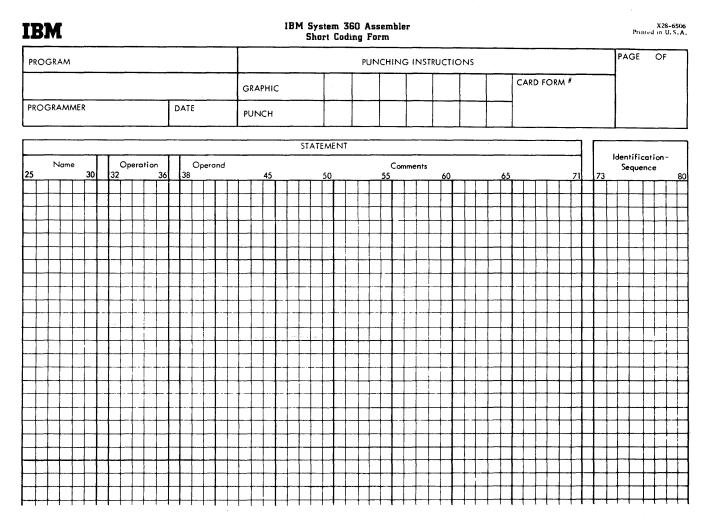

The coding form shown in Figure 1 is designed to satisfy this preference. This form -- the IBM System/360 Assembler Short Coding Form (No. X28-6506-2) -- contains a statement field which extends from column 25 to column 71 and is broken down into three sub-fields: the name field (cols. 25-30), the operation field (cols. 32-36), and the operand field (cols. 38-71).

The column numbers on the coding form refer to the column numbers on the cards into which the source program is to be punched.

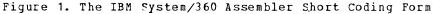

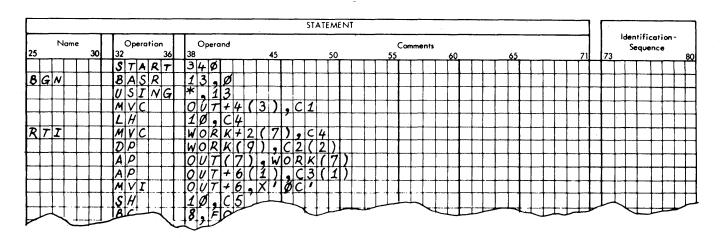

For the purpose of alignment, each entry in one of the sub-fields should begin in the leftmost column of the sub-field. Thus, the operation entry should begin in column 32 and the operand entry should begin in column 38. (Note that the name entry <u>must</u> begin in column 25.) Figure 2 shows a coding form with a number of typical statements in the Basic Assembler language.

Figure 2. Typical Statements on a Short Coding Form

## STATEMENT FORMATS AND COMPONENTS

A source program that is written in the Basic Assembler language is composed of a sequence of statements. These statements have the following format:

| - | · •        | Operand (s) |  |

|---|------------|-------------|--|

| < | Instructio | >n>I        |  |

Each source statement is punched into a separate card. The deck of cards that contains all the statements of one source program is referred to as the source program deck.

A statement may consist of (1) an instruction only, or (2) an instruction and a comments portion. Instruction entries and comments entries are described in two separate sections below.

## Instruction Entries

The instruction entry must contain an operation entry, and may contain a name and an operand entry. These three types of entry are described in the subsequent sections.

The Name Entry: The name entry consists of a symbol that is placed in the name field of the coding form to identify the associated statement. The use of such names is optional.

In the Basic Assembler language, names must conform to the following rules.

- 1. The first character of the name must be alphabetic.

- 2. The name must not be longer than four characters.

- The name must not contain special characters or embedded blanks.

- The name must begin in column 25 of the coding form and in column 25 of the source card.

- 5. The name must be separated from the operation entry by at least one blank.

Examples of valid names:

RNT1 C345

Α

BGN

| 0 |  |

|---|--|

|   |  |

|   |  |

Examples of invalid names:

| 3NBR  | (the first character is not      |

|-------|----------------------------------|

|       | alphabetic)                      |

| START | (the symbol contains more than 4 |

|       | characters)                      |

RL+8 (the symbol contains a special character)

A programming example that demonstrates the use of the name entry is shown in Figure 3.

Note 1: For all joint assemblies (i.e., whenever the programmer uses the IOCS and wishes to assemble the generated IOCS routines with his source program) user programs must not contain a name that begins with the letter I followed by three numerical characters (0-9). In addition to this, the name assigned to a file must not appear in the name field of any statement in the source program.

Note 2: User programs for joint assemblies with the BSCA Basic Assembler <u>must not con-</u> tain a name that begins with the letters ID followed by two numerical characters. User programs for both joint and <u>separate</u> assemblies of the BSCA Basic Assembler must not include the type codes of the BSCA macro instructions in a name field.

<u>The Operation Entry</u>: The operation entry consists of a <u>mnemonic</u> operation code that represents a <u>machine instruction</u>, a Basic Assembler instruction, or an IOCS macro instruction.

A mnemonic operation code consists of up to five alphabetic characters. It must be separated from the name entry and the operand entry by at least one blank column each.

To understand the terms used in this publication, a clear distinction must be made between (1) a machine instruction written in Basic Assembler language and (2) a Basic Assembler instruction.

A machine instruction written in the Basic Assembler language is an instruction to the computer. General descriptions of these instructions are contained in the section <u>Machine Instruction Statements</u>. Detailed descriptions of machine instructions are contained in the SRL publication IBM System/360 Model 20, Functional Characteristics, Form A26-5847.

A Basic Assembler instruction is an instruction to the Basic Assembler program. The functions of Basic Assembler instructions are summarized in Appendix A. Detailed descriptions are contained in the pertinent sections of this publication.

Characteristics of the Basic Assembler Language 11

The IOCS macro instructions are summarized in the section <u>Input/Output Macro</u> <u>Instructions</u>. Detailed descriptions of these macro instructions are contained in the SRL publication <u>IBM\_System/360\_Model\_20</u> <u>Card Programming Support, Input/Output Con-</u> <u>trof\_System</u>, Form C26-3603.

The following are examples of valid operation codes:

| LH   | load halfword          |

|------|------------------------|

| A H  | add halfword           |

| MVC  | move characters        |

| ORG  | reset location counter |

| TIOB | test I/O and branch    |

|      |                        |

<u>The Operand Entry</u>: The operand entry provides the Basic Assembler program or the computer with the information required to carry out the instruction specified in the operation field.

An operand entry may consist of one or two operands. Operands are used to designate storage addresses, to specify register numbers, or to define 1/0 devices, immediate data, masks, and lengths of storage areas.

An operand may consist of a symbol (name), a constant, or a compound expression. Two examples of compound expressions are shown below.

- X'BF' -- defines the hexadecimal constant PF, which is equal to decimal 191.

- GAMA-150 -- designates the storage address of GAMA minus 150 bytes.

Each operand entry must be separated from the associated operation entry by at least one blank column. In addition, each operand entry must be delimited by at least one blank column; i.e., any associated comments entry must be separated from the operand entry by at least one blank column.

For example, the AH instruction requests the computer to ad<sup>a</sup> a halfword to the contents of a register. The operand, therefore, must specify (1) the number of the register and (2) the storage address of this halfword, as shown in the sample statement

AH 8,VALX

The above statement specifies that the value (halfword) stored at the location whose address is VALX be added to the contents of register <sup>9</sup>.

The operand entry of the AH instruction in the above example consists of two operands: the register number 8 and the symbolic address VALX. These two operands must be separated from each other by a comma.

<u>Note</u>: Operand entries that consist of two operands must conform to the format

operand1,operand2

and must not contain a blank column. When the computer encounters a blank column in an operand entry, it considers the operand entry to be terminated.

The attributes and functions of symbols and expressions that may appear in the operand field of a statement are described in a later section.

## <u>Comments Entries</u>

The comments entry in a statement provides for the insertion of explanatory information into a program listing. Comments do not affect the assembly or the execution of a program, but they facilitate the reading and understanding of a program listing by explaining the purpose or function of a particular statement.

Any valid character, including blanks, can be used in a comment. Comments entries are punched into a statement card to the right of the operand entry and separated from it by at least one blank column. Comments entries must not extend beyond column 71.

If the desired comments entry cannot be accommodated in the space available on the right of the operand entry, or if comments consist of general information that pertains to a sequence of statements, the "comments card" can be used.

Comments cards must contain an asterisk in column 25; columns 1-24 and 26-71 are available for comments. Any number of comments cards may be inserted anywhere in a source-program deck.

#### <u>Identification-Sequence Entries</u>

The identification-sequence field (columns 73-80 of the coding form) can be used to specify identifying information and/or to provide the statements of a program with sequence numbers. Some typical identification-sequence entries are shown in the example below.

| Example | 1: | SALE0001<br>S AL E0002 |

|---------|----|------------------------|

|         |    | •                      |

|         |    | •                      |

|         |    | •                      |

|         |    | SALE0813               |

|   | Example 2: | MAINOO1<br>MAINOO2 |

|---|------------|--------------------|

|   |            | •                  |

|   |            | •                  |

| • |            | •                  |

|   |            | MAIN097            |

|   |            | ROUT 1/01          |

|   |            | •                  |

|   |            | •                  |

|   |            | •                  |

|   |            | ROUT 1/65          |

|   |            | MAIN098            |

|   |            | •                  |

|   |            | •                  |

|   |            | MAIN466            |

|   | Example 3: | MILLEP             |

|   | ryambie 2. |                    |

|   |            | MILLEP             |

|   |            | •                  |

|   |            | •                  |

|   |            |                    |

MILLEP

Any identification-sequence entry is printed in the program listing as it is read. Identification-sequence entries do not affect the assembly or the execution of the program.

#### Sample Sequence of Statements

Figure 3 shows a sample sequence of statements in the Basic Assembler language. This example illustrates the writing and the general function of the statements and their components as discussed in the preceding sections.

The comments entries in Figure 3 refer to the subsequent notes.

## Note 1:

The instruction CALC SR 9,10 causes the contents of register 10 to be subtracted from the contents of register 9. When this subtraction has been completed, control is transferred to the physically next statement. (Refer to Note 2.)

Note 2:

The instruction BC 12,RES1 causes a test to determine if the contents of register 9 -the register whose contents were changed by means of the preceding instruction -- are equal to or less than zero.

If they are, this BC instruction causes a branch to the symbolic address RES1. (Refer to Note 3.) If the contents of register 9 are greater than zero (positive), the BC instruction causes the physically next statement (SH instruction) to be executed. (Refer to Note 4.)

#### Note 3:

The instruction RES1 STH 9,0UTA is executed only if the contents of register 9 were found to be less than or equal to zero (refer to Note 2).

This STH instruction causes the contents of register 9 to be transferred to an (output) area named OUTA. When this transfer has been completed, the physically next statement of the program (not shown in this example) is executed.

## Note 4:

The instruction SH 9,CON2 is executed only if the contents of register 9 were found to be greater than zero (refer to Note 2).

This SH instruction causes the value stored at the symbolic address CON2 to be subtracted from the current contents of register 9. When this subtraction has been completed, the physically next statement is executed. (Refer to Note 5.)

Note 5:

The instruction BC 2,CALC causes a conditional branch to the symbolic address CALC, which is the address of the SR instruction referred to in Note 1.

Note that this BC instruction is executed only if the contents of register 9 were found to be greater than zero in the test caused by the instruction BC 12,RES1.

#### Note 6:

The program "loops" through the statement sequence beginning with the instruction CALC SR 9,10 and ending with the instruction BC 2,CALC until the contents of register 9 are found to be less than or equal to zero. When this is the case, the instruction BC 12,RES1 causes an exit from the loop to the instruction RES1 STH 9,OUTA (refer to Note 3).

| PROGRAM    | •        |         | PUN | снім | g inst | RUCTIC | NS |             | PAG | E OF |

|------------|----------|---------|-----|------|--------|--------|----|-------------|-----|------|

|            | <u> </u> | GRAPHIC |     |      |        |        |    | CARD FORM # |     |      |

| PROGRAMMER | DATE     | PUNCH   |     |      |        |        |    |             |     |      |

|          |    |     |              |          |              |          |               |     |      |         |              |                |          |     |    |     |     |     |   |    |   |   | ST. | AT | ÊM | EN | Т |   |   |     |   |              |              |     |     |    |   |   |   |               |    |   |              |   |              |   |    |   |    |    |    |   |          |               |        | ٦  |

|----------|----|-----|--------------|----------|--------------|----------|---------------|-----|------|---------|--------------|----------------|----------|-----|----|-----|-----|-----|---|----|---|---|-----|----|----|----|---|---|---|-----|---|--------------|--------------|-----|-----|----|---|---|---|---------------|----|---|--------------|---|--------------|---|----|---|----|----|----|---|----------|---------------|--------|----|

| 25       |    | Nam | ne           | 30       |              | 32       | Ор            | era | itio | n<br>36 |              | 38             |          | per | an | 4   |     |     | 4 | 15 |   |   |     |    | 50 |    |   |   |   | 5   |   | mm           | nen          | its | 6   | ٥  |   |   |   |               | 55 |   |              |   |              |   | 71 |   | 73 |    |    |   | ationce  |               |        | 30 |

| Ī        |    | Τ   | Γ            | Ĺ        |              | S        | T             | A   | R    |         |              |                |          | Γ   | Γ  |     | T   |     | Ţ | Ĩ  |   |   |     |    | Ĺ  |    |   | L |   | Ţ   | Í | Ι            | T            |     | Ť   | Ť  |   | Τ | Ţ | Ĩ             | Ĩ  |   |              |   |              |   | Ì  |   | Ĩ  |    |    | _ | П        | $\Box$        | Ţ      | Ĩ  |

|          | +  | -   | ┾            | +        |              |          |               | ł   | -    |         | -            |                | -        | F   | ╞  | +   | +   | +   | ╇ | +  |   |   |     | -  | ╞  |    | - | ╞ | + | -   |   | ╀            | ╀            | +   | +   | +  | + | + | + | +             | -  | + | +            | - | $\downarrow$ | 4 | -  | _ | _  |    | +  | - | $\vdash$ | $\vdash$      | -+     | _  |

|          | ╈  | +   | ┢            | +        | $\square$    | $\vdash$ |               | ł   | ╞╌   | ┢       |              | $\vdash$       |          | ┢   | ╀  | ╈   | ╈   | +   | ╈ | -  |   | - |     | -  | ┢╴ | ┢  | 1 | ┢ | ╈ | ╀   | ╀ | ╈            | ╉            | ╉   | +   | ╉  | + | ╈ | ╉ | +             | ╉  | ╉ | -+           | ┥ | +            | - | +  | - |    | +  | -+ |   | H        | $\rightarrow$ | +      | -  |

| C,       | 41 |     |              |          |              | S        |               |     |      |         |              | 9              |          |     | ļ  | ø   |     |     |   |    |   |   |     |    |    |    | 0 |   |   |     | 1 |              |              |     |     | T  |   |   |   |               |    |   |              |   |              |   |    |   |    |    |    |   | $\Box$   |               |        |    |

|          | +  | +   | ╞            | $\vdash$ |              | 8<br>S   | <u>C</u>      |     |      |         | -            | 1              | 2        | 1.  | 1  | 2 4 | v 2 | 5/2 | 4 |    |   |   |     |    |    |    |   |   |   |     | ľ |              | +            | +   | _   | +  | - |   | + | +             | +  | - | +            |   |              | _ | -  |   | _  |    | _  |   | H        | $\vdash$      |        | 4  |

| $\vdash$ | +  | ╉   | +            | +        |              | S<br>B   | $\frac{H}{C}$ |     | -    | +-      | ┢            |                | 9        | C   | 1  |     |     |     | + | +  | - | - |     | -  |    |    |   |   |   |     | 4 |              | ╉            | +   | ╉   | ╉  | ┥ | ┽ | + | +             | ╉  | + | +            | + | +            | - |    |   |    |    | +  |   | H        | $ \dashv$     | +      | -  |

| R        | ΞŚ | 51  |              |          |              | S        |               |     |      |         |              | $\overline{q}$ |          | 0   | ì  | 17  | -/  | 1   | 1 |    |   |   |     |    | Ĺ  | _  | 0 |   |   | : 3 |   | 3            | 3            |     | A / | ٧Ť | D | 1 | 6 |               |    |   |              |   |              |   |    |   |    |    |    |   |          |               |        |    |

|          | _  |     |              | +        |              |          |               | ł   |      | -       | -            |                | Ĺ        | -   |    | -   | +   |     | ╉ | 4  |   |   |     |    | -  |    | ╞ | ╞ | + | +   | + | +            | +            | +   | +   | +  | + | - | - |               | +  | + | +            | - | +            |   |    | _ |    | _  |    |   | $\vdash$ | $\vdash$      | -      | _  |

| ┝┼       | +  | +   | +            | +        | $\mathbb{H}$ |          |               | ł{  | -    | ┢       | ┢            | ┢              | $\vdash$ | ┢   | ┢  | ╋   | +   | ╉   | ┥ | +  |   |   |     | -  | ┝  | ┢  | ┢ | ╀ | ╀ | ╈   | ╉ | ╉            | +            | +   | +   | ╉  | + | + | ╉ | -             | +  | ╉ | +            | + | +            | - |    | - | -  |    | -  | _ | H        | H             | $\neg$ | -  |

|          |    |     | T            |          |              |          |               | ¥   |      |         | T            |                | T        |     | t  |     |     |     | 1 |    |   |   |     |    |    |    |   | t | t | T   | t | T            | 1            |     |     | 1  |   |   | 1 |               |    |   |              |   |              |   |    |   |    |    |    |   |          |               |        |    |

| $\vdash$ | 4- | +   | $\downarrow$ |          |              | E        | N             | D   |      | -       | $\downarrow$ |                |          | -   | Ļ  | -   | +   | -   | - |    | _ |   |     |    | -  | _  | - | + | 1 |     | 1 | $\downarrow$ | $\downarrow$ | 4   | 4   | 4  | + | _ | 4 | -             | 4  |   | $\downarrow$ | - | $\downarrow$ | 4 | 4  |   | _  | 4  | -  |   | $\vdash$ | H             | ⊢┤     | _  |

| $\vdash$ |    | +   | +            | +        |              |          |               |     | ╞    | +-      | +            | -              | ┝        | ┢   | ╀  | +   | ╋   | ╉   | + | -  | - |   | -   |    | ╀  | -  |   | ╀ | + | +   | + | +            | ╉            | +   | +   | ╉  | + |   | + | $\rightarrow$ | -+ | + | +            | + | +            |   | -  | + |    | -+ | +  |   | H        | ┍┥            |        | -  |

Figure 3. Sample Sequence of Statements

#### THE LANGUAGE STRUCTURE

#### THE CHARACTER SET

The following 44 characters can be used in statements written in the Basic Assembler language.

26 alphabetic characters: A through Z 10 numerical characters: 0 through 9 8 special characters: \*+-,)('blank

The punch combinations that represent these characters are shown in <u>Appendix F</u>. However, constants and character selfdefining terms may contain any of the 256 punch combinations listed in <u>Appendix F</u>.

#### SELF-DEFINING TERMS

A self-defining term is a term whose value is not assigned by the Basic Assembler program, but is inherent in the term itself. Thus, the decimal digit 3, representing the value 3, is a self-defining term.

The three types of self-defining terms are decimal, hexadecimal, and character terms. They can be used to specify immediate data, masks, registers or addresses, and constants. Self-defining terms must not be confused with data constants, which are described in the section <u>Definition Instructions</u>. There is a clear distinction in the use of each: the Basic Assembler program assembles the <u>value</u> of a self-defining term, but it assembles the <u>address</u> of a data constant.

A self-defining term is considered absolute because its value is not changed on program relocation.

## Decimal Self-Defining Terms

A decimal self-defining term is an unsigned decimal number with a maximum of five digits, e.g., 007, 11900, or 3. Its value must not exceed 16383. A decimal selfdefining term is assembled as its binary equivalent.

#### <u>Hexadecimal Self-Defining Terms</u>

A hexadecimal self-defining term is a sequence of up to four hexadecimal digits enclosed in apostrophes and preceded by the prefix X (e.g., X'9',X'A4',X'20B3'). The highest hexadecimal self-defining term is 3FFF. This value corresponds to the maximum decimal self-defining term 16383. Each hexadecimal digit is assembled as its 4-bit binary equivalent, as shown in Figure 4.

| Hexadecimal<br>  Digit | Binary<br>Equivalent |

|------------------------|----------------------|

| 0                      | 0000                 |

| 1                      | 0001                 |

| 2                      | 0010                 |

| 3                      | 0011                 |

| 1 4                    | 0100                 |

| 1 5                    | 0101                 |

| 6                      | 0110                 |

| 1 7                    | 0111                 |

| 8                      | 1000                 |

| 9                      | 1001                 |

| A A                    | 1010                 |

| В                      | 1011                 |

| I C                    | 1100                 |

| D.                     | 1 1101               |

| E                      | 1 1110 1             |

| I F                    | 1111                 |

Figure 4. Table of Hexadecimal Self-Defining Terms

A hexadecimal-to-decimal conversion table is shown in <u>Appendix\_G</u>.

#### Character Self-Defining Terms

A character self-defining term consists of a single character, enclosed in apostrophes and preceded by the prefix C (e.g., C'A', C'/', C'5', C''). Any of the 256 EBCDIC punch combinations shown in Appendix F can be used for character specification. However, ampersands and apostrophes that are to be specified as self-defining characters must be doubled within the enclosing apostrophes. Thus, a single apostrophe must be written as C'''' and a single ampersand as C'&&'.

Each character self-defining term is assembled as its 8-bit EBCDIC code equivalent (see Appendix F).

#### SYMBOLS

Symbols are used to refer to locations in main storage by name rather than by the actual address.

A symbol may be placed in the name field of one statement and in the operand entry of another statement. However, if a symbol is to be placed in the operand entry of a statement, it must be "defined" elsewhere in the program.

A symbol is considered "defined" when it appears

(a) in the name field of some statement within the same program, or

## (b) in the operand of an EXTRN statement within the same program.

A prerequisite for defining a symbol by method (b) is that the same symbol appear in the operand entry of an ENTRY statement and in the name field of some statement in another program section. (Refer to the section <u>Program Linking</u> for further information about the use of EXTRN and ENTRY statements.)

## Defining Symbols

The Basic Assembler program maintains an internal table -- the symbol table -- where it stores all symbols that are used as names within a program. Each symbol in the table is associated with a storage address, which is the setting of the location counter at the time the symbol is read. program-generated length attribute and a name identification are added. The length attribute depends on the basic instruction format. The name identification indicates whether the symbol is relocatable or absolute, and whether it is external (defined in a separately assembled program section). Thus, a symbol entered in the name field of a statement is considered to be defined.

All symbols that are used as expressions, i.e., as operands of a statement, must be defined. Normally, this can be done at the most convenient position in the program. The ORG and the EQU instructions, however, require the symbols in their operands to be previously defined. Otherwise, the Basic Assembler identifies these statements in the program listing by the diagnostic message U (undefined).

## Relocatable and Absolute Symbols

In general, a symbol is considered to be relocatable because relocatability is its inherent purpose. (Refer to the section <u>Absolute and Relocatable Programming</u>.) However, for the convenience of relating the meaning of the stored information to its symbolic address, a symbol can be equated to an absolute address by means of the Basic Assembler instruction EQU, which is described in the section <u>EQU-Equate</u> <u>Symbol</u>.

The Basic Assembler program generates the relocatable or absolute attribute of a symbol as part of the name identification. This attribute is then stored with the symbol in the symbol table.

#### External Symbols

Limited main storage availability may require a program to be divided into a number of sections, each of which can be assembled separately.

Characteristics of the Basic Assembler Language 15

In one program section, the operand entry of a statement may contain a symbol that is defined in a different program section. This symbol must be introduced by an EXTRN statement into the section in which it is not defined. In the program section where the symbol is defined, it must be specified in an ENTRY statement. The Basic Assembler instructions, ENTRY and EXTRN, are described in the section <u>Program</u> <u>Linking</u>.

## <u>Restrictions on Symbols</u>

Each symbol can represent one specific storage address only. Therefore, it must not be defined twice. The number of symbols that can be specified in a program depends on the available storage capacity, as shown in Figure 5.

| r-<br> <br> | Storage<br>Capacity | •    | of Symbols Allowed<br>Source Program | ר<br> <br> |

|-------------|---------------------|------|--------------------------------------|------------|

|             | 4096                | 165  |                                      |            |

|             | 8192                | 847  | 805*                                 | 1          |

| 1           | 12288               | 1530 | 1487*                                | 1          |

| 1           | 16384               | 2213 | 2170*                                |            |

| L           |                     | L    |                                      |            |

\* for the BSCA version

## Figure 5. Number of Symbols versus Storage Capacity

If the number of symbols exceeds the applicable maximum, a symbol-table overflow occurs. The card versions of the Basic Assembler program require an additional assembly run to compensate for the overflow; the tape versions (after an informative halt) deal with the situation automatically. Detailed explanations are supplied in the section <u>The Basic Assembler Program</u>.

#### Relative Addressing

To avoid a symbol-table overflow, the number of symbols can be reduced by means of relative addressing.

The term relative addressing refers to the method of specifying storage locations by means of a defined symbol plus or minus a displacement, or by means of the setting of the location counter plus or minus a displacement. The following examples show some relative addresses.

| FLDA-200  | (symbol minus displacement) |

|-----------|-----------------------------|

| *+12      | (location counter plus      |

|           | displacement)               |

| FLDB+X'F' | (symbol plus hexadecimal    |

|           | displacement)               |

<u>Note</u>: The asterisk (\*) represents the value of the location counter after the preceding instruction has been read in,

16 System/360 Model 20 Basic Assembler Language

and, if required, boundary alignment has taken place.