## Restricted Distribution

This manual is intended for internal use only and may not be used by other than IBM personnel without IBM's written permission.

Processing Unit -- Volume 4

I, FXP, FLP Operations

#### Restricted Distribution

This manual is intended for internal use only and may not be used by other than IBM personnel without IBM's written permission.

Processing Unit -- Volume 4

I, FXP, FLP Operations

#### PREFACE

This is one of five volumes of the IBM 2091 Processing Unit, Field Engineering Maintenance Diagrams Manual (FEMDM). The organization of the FEMDM, the general content of each volume, and the form numbers of the five volumes are:

| Title<br>Volume 1 - Diagnostic Techniques, | Contents<br>DIAGNOSTIC TECHNIQUES<br>Diagrams 1-1 to 1-XX |                                         |  |

|--------------------------------------------|-----------------------------------------------------------|-----------------------------------------|--|

| ECAD's (Form Y22-6671)                     |                                                           |                                         |  |

|                                            | ERROR CONDIT                                              | TIONS                                   |  |

|                                            | Diagrams 2-1 to 2-XX                                      |                                         |  |

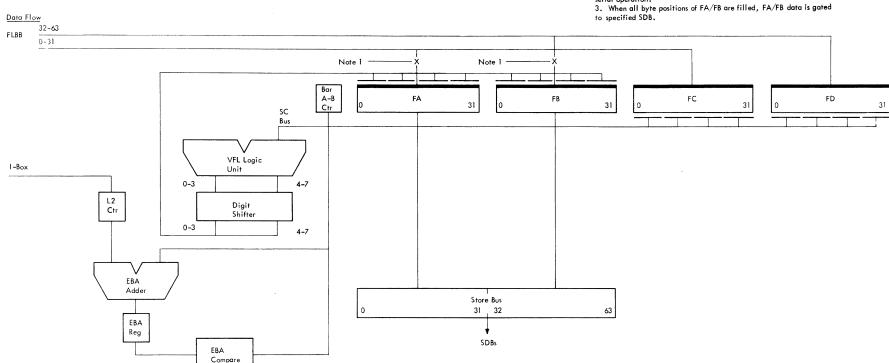

| Volume 2 - Data Flow; I, FXP, FLP,         | DATA FLOW                                                 |                                         |  |

| Functional Units (Form Y22-6672)           | Diagram                                                   |                                         |  |

|                                            | 3-1                                                       | System Data Flow                        |  |

|                                            | 3-2                                                       | I Unit Data Flow                        |  |

|                                            | 3-3                                                       | Fixed Point Data Flow                   |  |

|                                            | 3-4                                                       | Floating Point Data Flow                |  |

|                                            | 3-5                                                       | MSCE Data Flow                          |  |

|                                            | 3-6                                                       | PSCE Data Flow                          |  |

|                                            | 3-7                                                       | MC Data Flow                            |  |

|                                            | 3-8                                                       | PSCE Storage Channel (SC) Data          |  |

|                                            | 3-9                                                       | System Control Panel                    |  |

|                                            | 3-10                                                      | PSCE Control Panel                      |  |

|                                            | FUNCTIONAL UNITS                                          |                                         |  |

|                                            | Diagrams                                                  |                                         |  |

|                                            | 4-1 to 4-XX                                               | I Unit                                  |  |

|                                            | 4-100 to 4-1XX                                            |                                         |  |

|                                            | 4-200 to 4-2XX                                            |                                         |  |

| Volume 3 - MSCE, PSCE, MC,                 | FUNCTIONAL UNITS (Cont'd)                                 |                                         |  |

| Functional Units (Form Y22-6673)           | 4-300 to 4-3XX                                            | MSCE                                    |  |

|                                            | 4-400 to 4-4XX                                            | PSCE                                    |  |

|                                            | 4-500 to 4-5XX                                            | MC                                      |  |

| Volume 4 - I, FXP, FLP Operations          | OPERATIONS                                                |                                         |  |

| (Form Y22-6674)                            | 5-1 to 5-XX                                               | I Unit Operations                       |  |

|                                            | 5-100 to 5-1XX                                            | Fixed Point Operations                  |  |

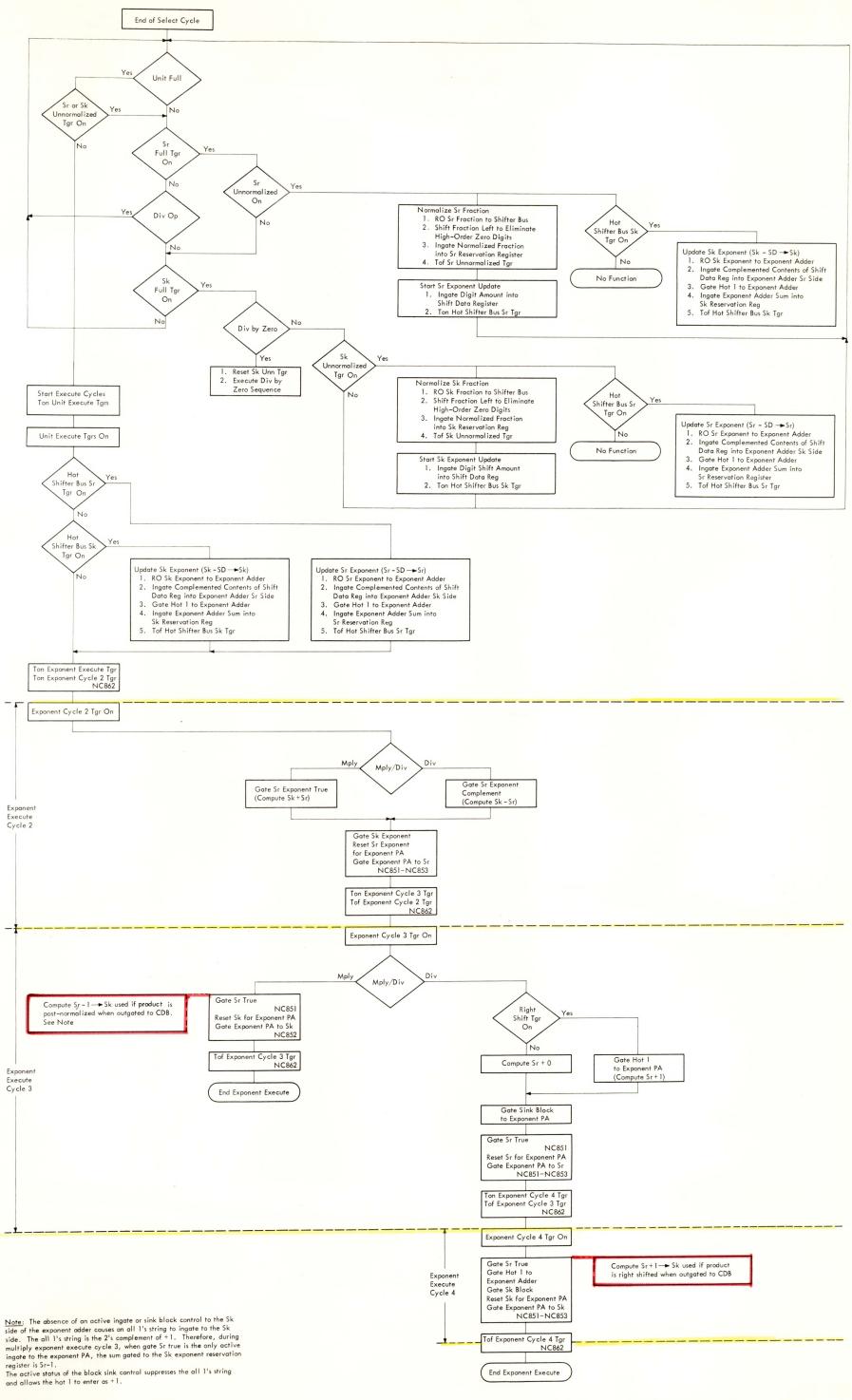

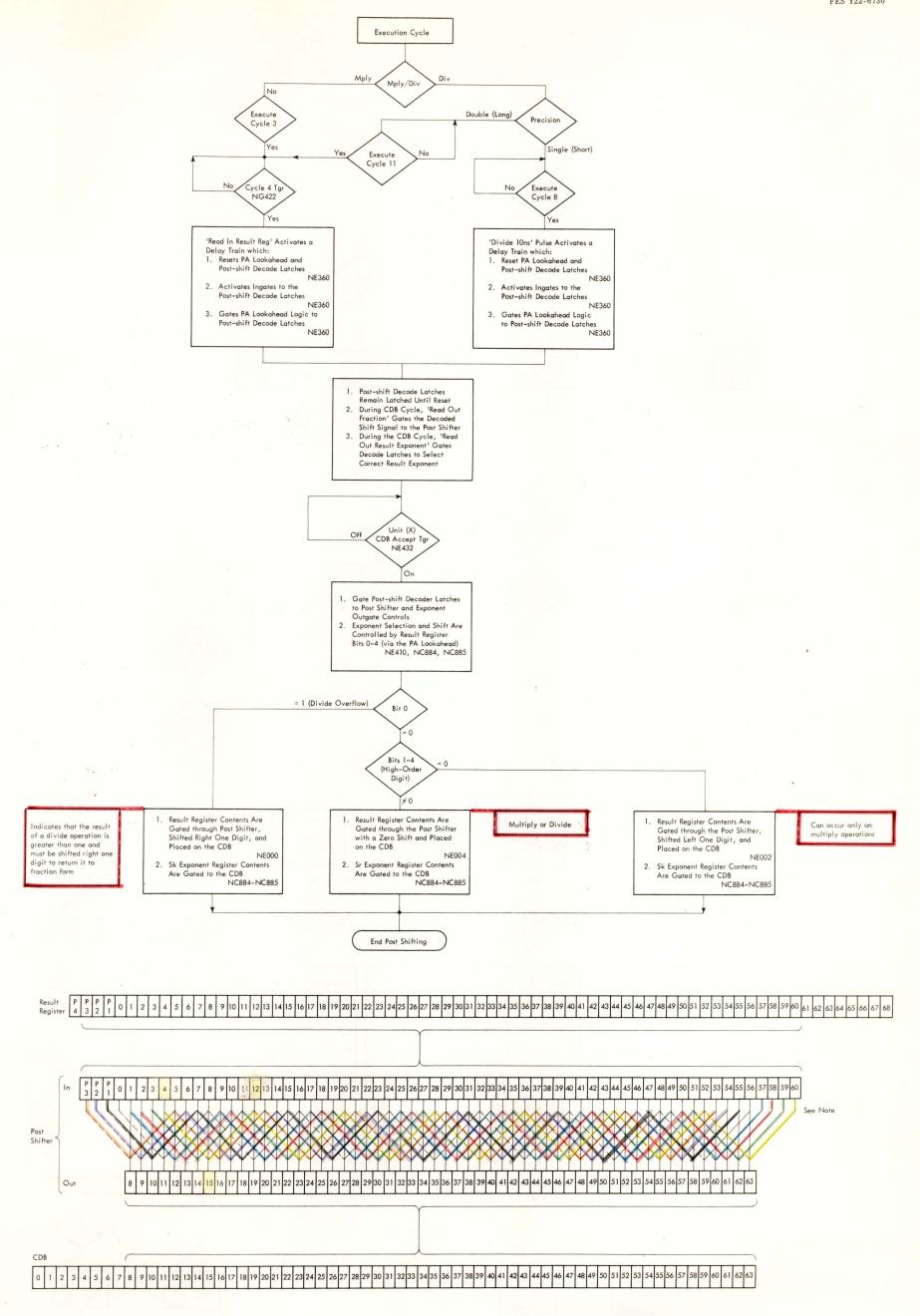

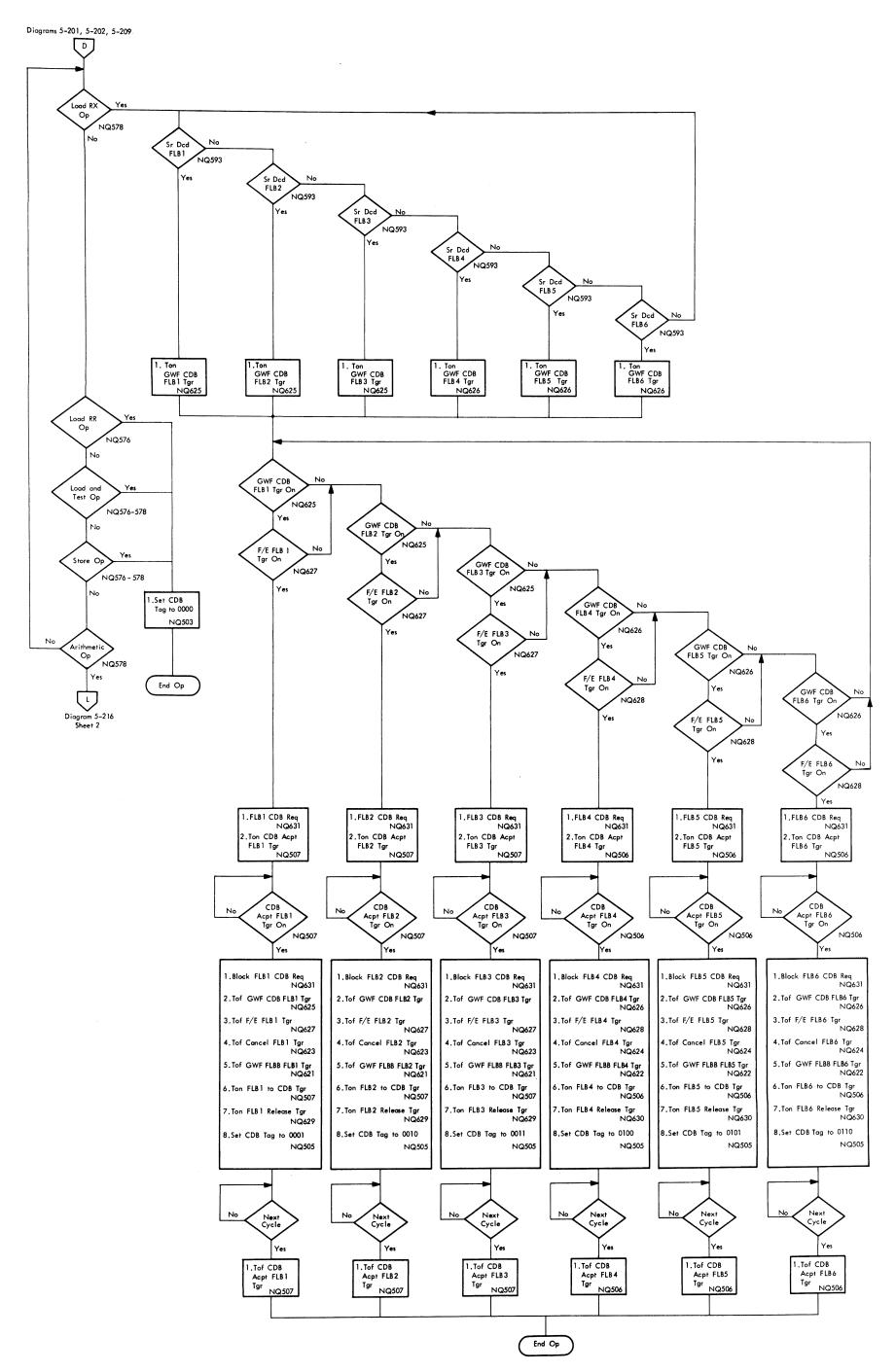

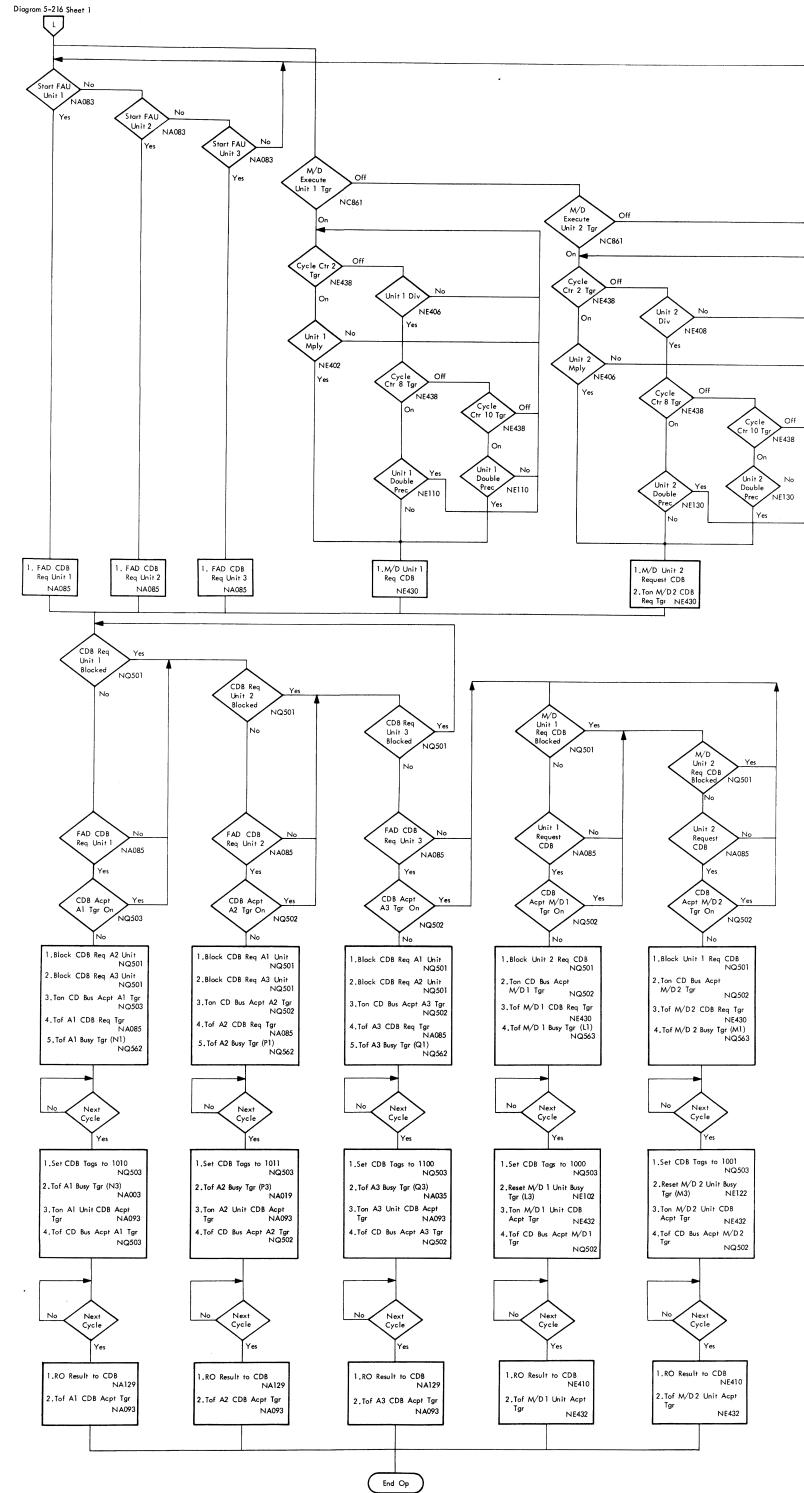

|                                            | 5-200 to 5-2XX                                            | Floating Point Operations               |  |

| Volume 5 - MSCE, PSCE, MC                  | OPERATIONS (Cont'd)                                       |                                         |  |

| Operations; Power (Form Y22-6675)          | 5-300 to 5-3XX                                            | MSCE Operations                         |  |

|                                            | 5-400 to 5-4XX                                            | • • • • • • • • • • • • • • • • • • • • |  |

|                                            | 5-500 to 5-5XX                                            | MC Operations                           |  |

|                                            | POWER SUPPLIES                                            |                                         |  |

|                                            | 6-1 to 6-XX                                               |                                         |  |

Diagrams contained in this manual are referenced from the seven 2091 Field Engineering Theory of Operation Manuals (FETOM's). References to FEMDM diagrams take the form "Diagram 5-103"; references to figures in a FETOM take the form "Figure 3-22." The seven 2091 FETOM's are:

IBM 2091 Processing Unit, FE Theory of Operation Manuals:

System Introduction, Instruction Processor, Form Y22-6622

Power Supplies and Control, Form Y22-6623

Console and Maintenance Features, Form Y22-6624

Fixed Point Execution Element, Form Y22-6625

Main Storage Control Element, Form Y22-6626

Peripheral Storage Control Element, Form Y22-6627

Floating Point Execution Element, Form Y22-6628

Other FE Manuals containing information pertinent to the 2091 are: 2091 Processing Unit, FE Maintenance Manual, Form Y22-6659

2091 Processing Unit, 2395 Processor Storage, FE Installation Manual, Form Y22-6634

Advanced Solid Logic Technology Packaging, Tools, Wiring Change and Repair Procedures, FE Theory-Maintenance Manual, Form Y22-6620

Solid Logic Technology, Packaging, Tools, Wiring Change Procedure FE Theory of Operation Manual, Form Y22-2800

Component Circuits — SLT (Solid Logic Technology), SLD (Solid Logic Dense), ASLT (Advanced Solid Logic Technology), FE Theory of Operation Manual, Form Z22-2798 — IBM Confidential

Power Supplies -- SLT (Solid Logic Technology), SLD (Solid Logic Dense), ASLT (Advanced Solid Logic Technology), FE Theory of Operation Manual, Form Y22-2799

## Second Edition (March 1968)

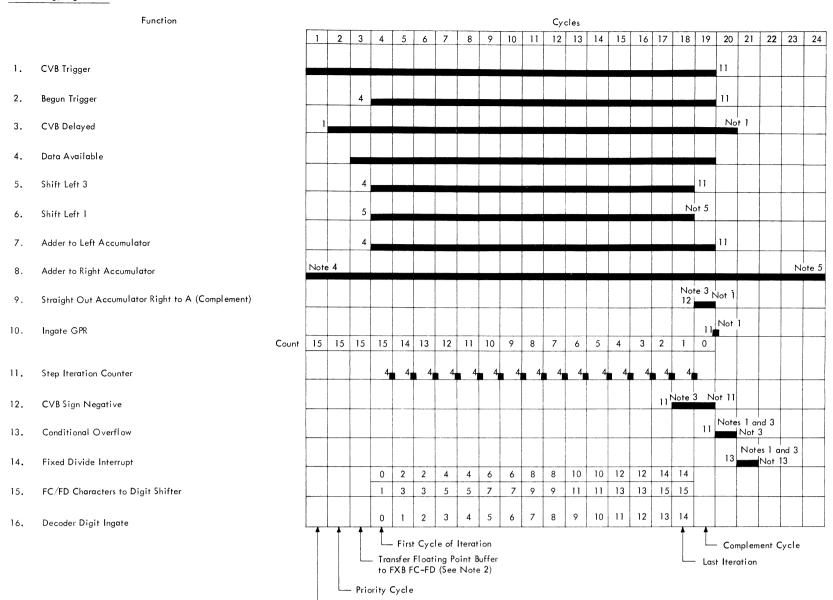

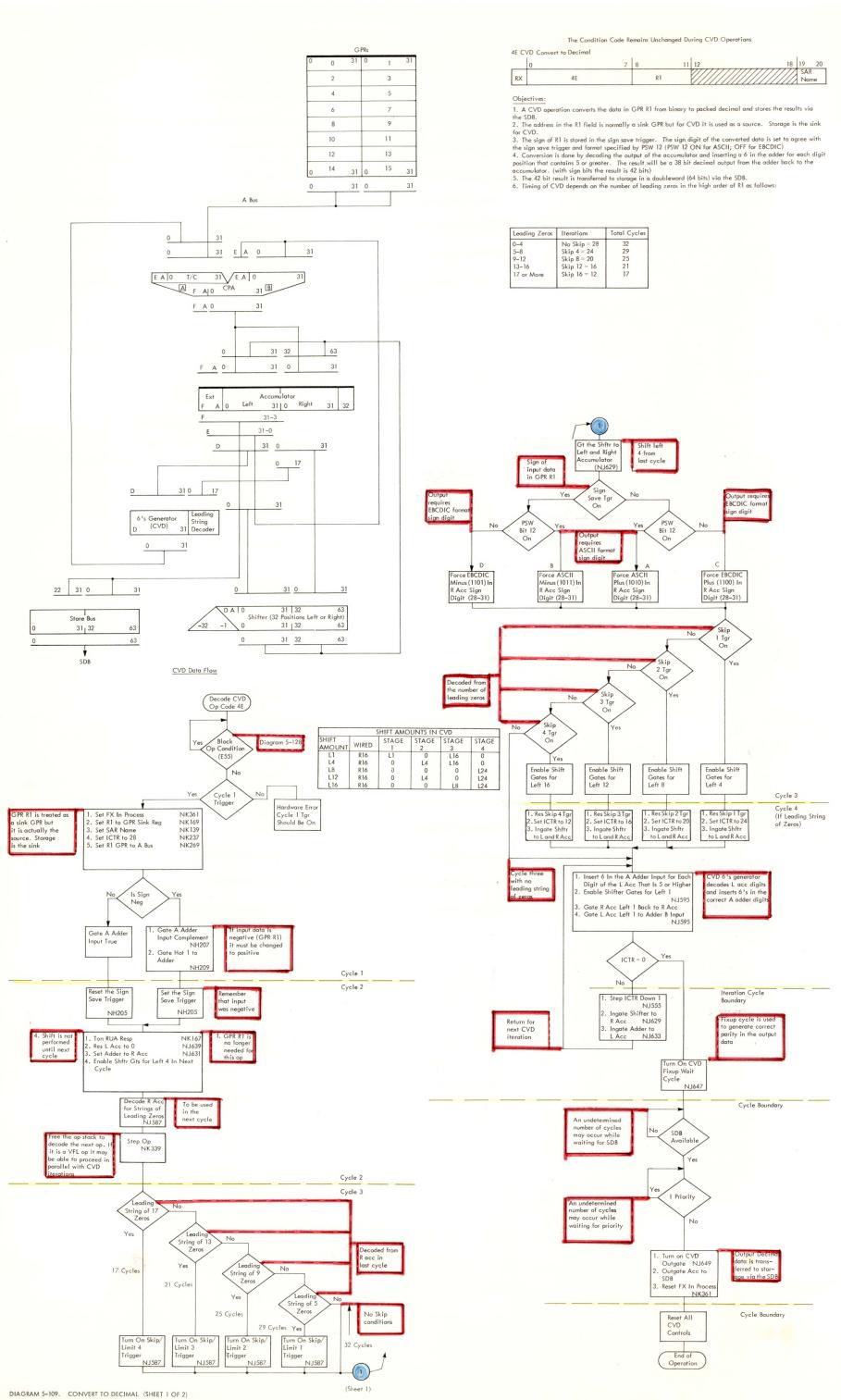

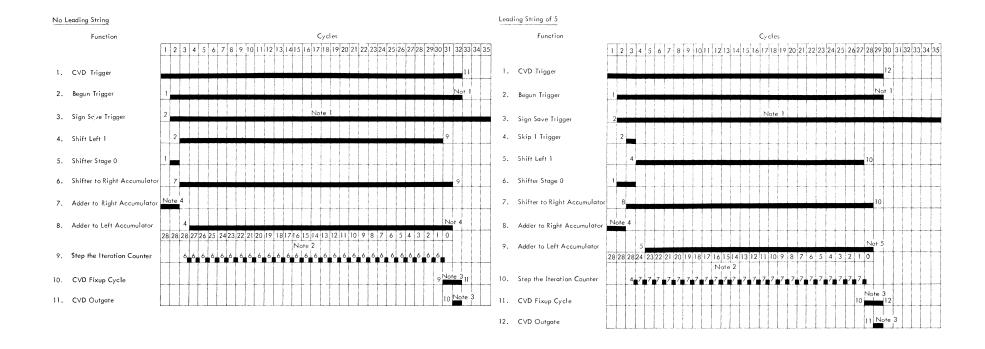

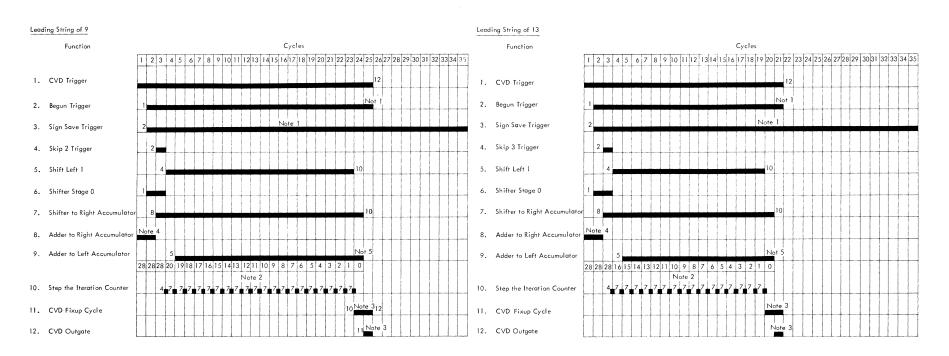

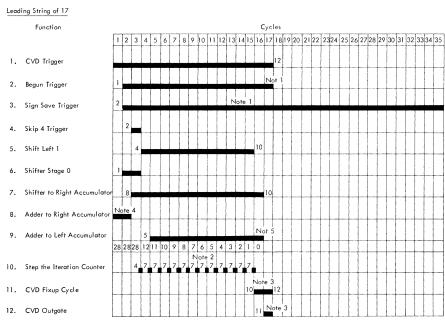

This edition, Form Y22-6674-1, is a major revision of and obsoletes, Form Y22-6674-0 and FES Y22-6681. Diagrams 5-36, 5-131, and 5-132 have been added. Major changes have been made to Diagrams 5-1, 5-2, 5-6, and 5-122 through 5-126. Timing charts have been added to Diagrams 5-101, 5-102, 5-108, 5-109, and 5-112. Minor changes have been made to most of the remaining diagrams. New or changed diagrams are indicated by a page date of 3/68 and by a vertical bar to the left of the diagram number on the Contents page.

Changes are periodically made to the specifications herein; any such changes will be reported in subsequent revisions or FE Supplements.

This manual has been prepared by the IBM Systems Development Division, Product Publications, Dept. B95, PO Box 390, Poughkeepsie, N.Y. 12602. A form for readers' comments is provided at the back of this publication. If the form has been removed, comments may be sent to the above address.

# **CONTENTS**

| Diagram | Title                                                        | Diagran | m Title                                         |

|---------|--------------------------------------------------------------|---------|-------------------------------------------------|

| I UNIT  | OPERATIONS                                                   | 5-107   | Insert                                          |

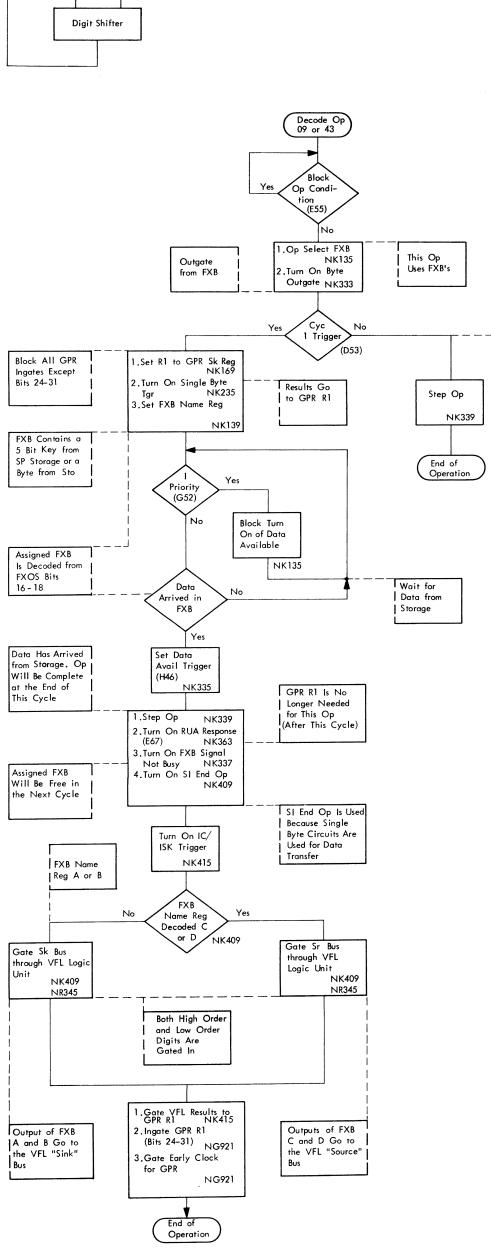

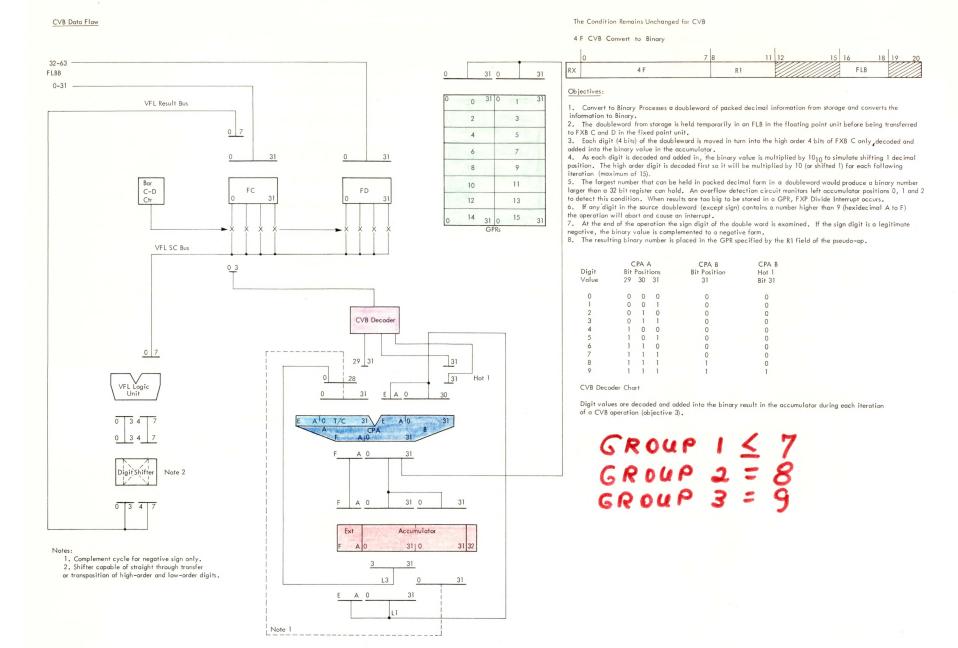

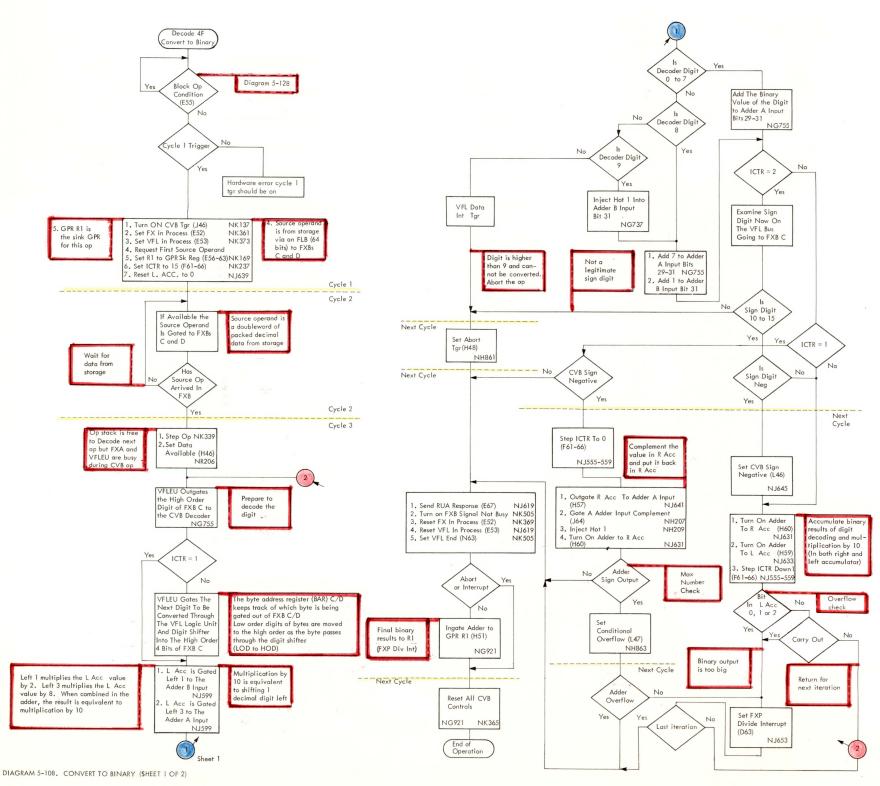

|         |                                                              | 5-108   | Convert to Binary (2 sheets)                    |

| 5-1     | Instruction Fetch                                            | 5-109   | Convert to Decimal (2 sheets)                   |

| 5-2     | Instruction Fetch Return and Op Register Ingate Controls     | 5-110   | Load Multiple (2 sheets)                        |

| 5-3     | Array Word Outgate, Fetch Protect Interrupt and Step AOC,    | 5-111   | Store Multiple                                  |

|         | Temp Fetch Bypass                                            | 5-112   | Shift Instructions (3 sheets)                   |

| 5-4     | AOC Invalid Address, Valid Trigger Turn Off, and Turn        | 5-113   | NI, OI, and XI Instructions                     |

|         | Off Loop Mode                                                | 5-114   | TM and CLI Instructions (2 sheets)              |

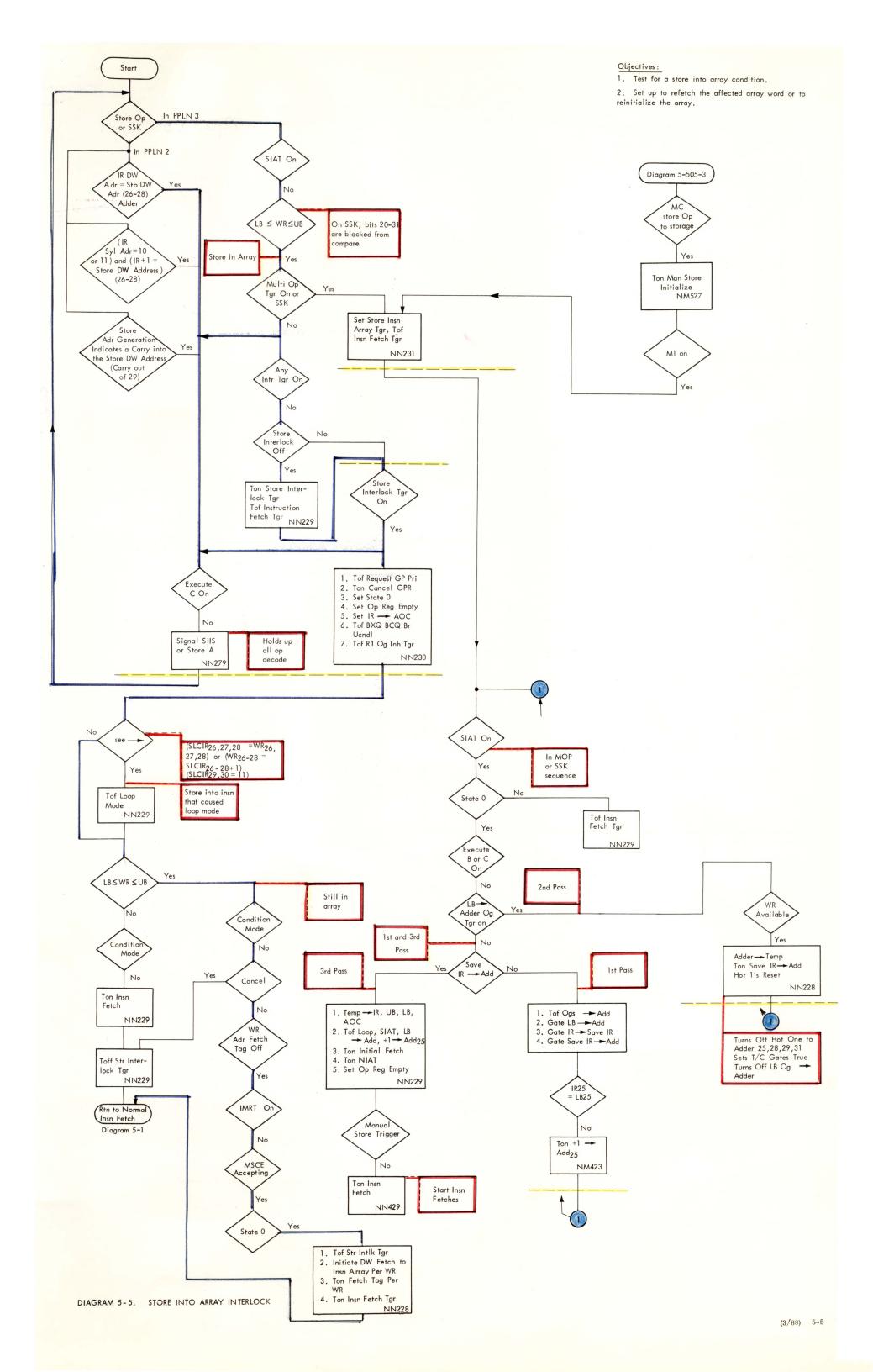

| 5-5     | Store into Array Interlock                                   | 5-115   | MVI Instructions                                |

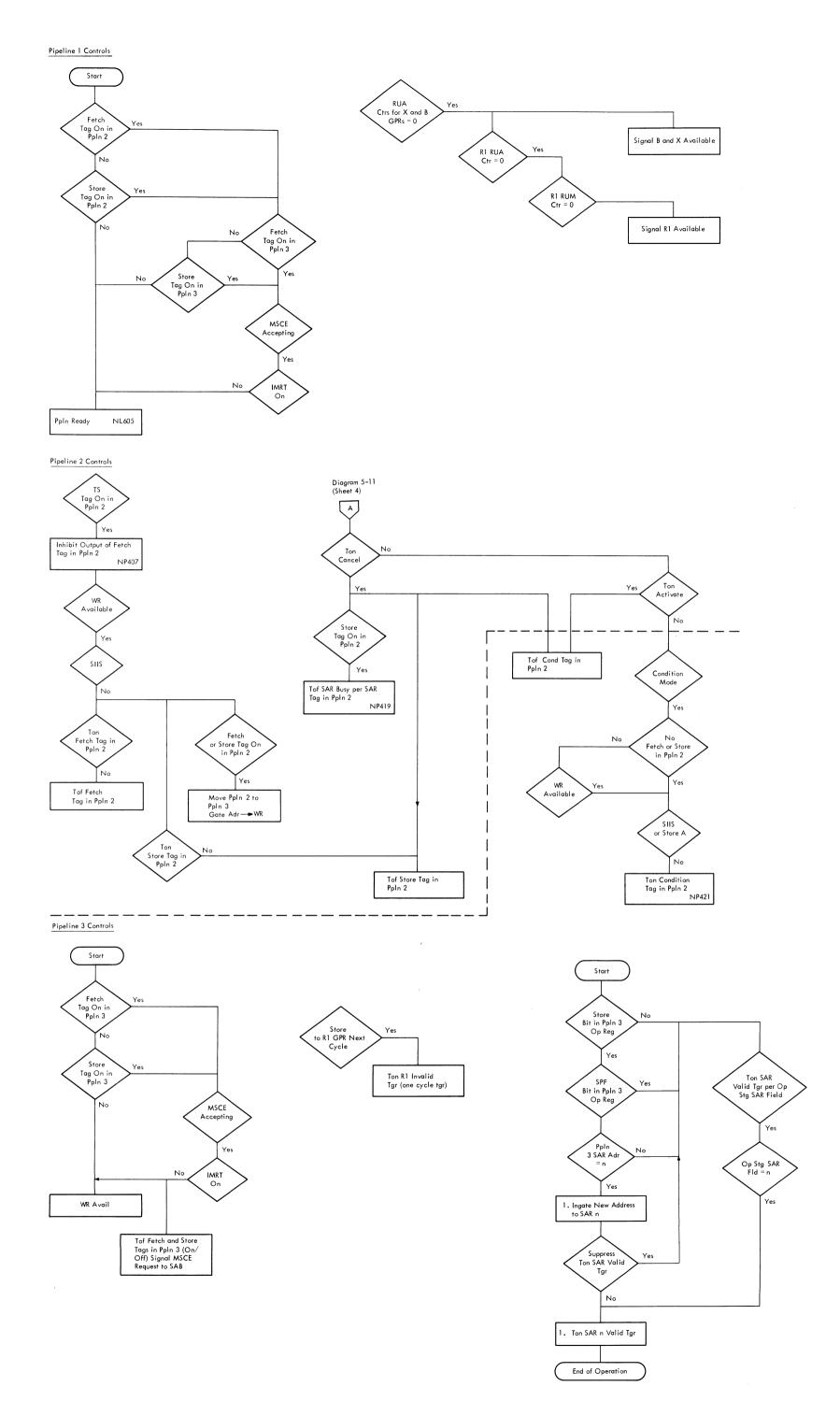

| 5-6     | Pipeline 2 and 3 Control                                     | 5-116   | TS Instruction                                  |

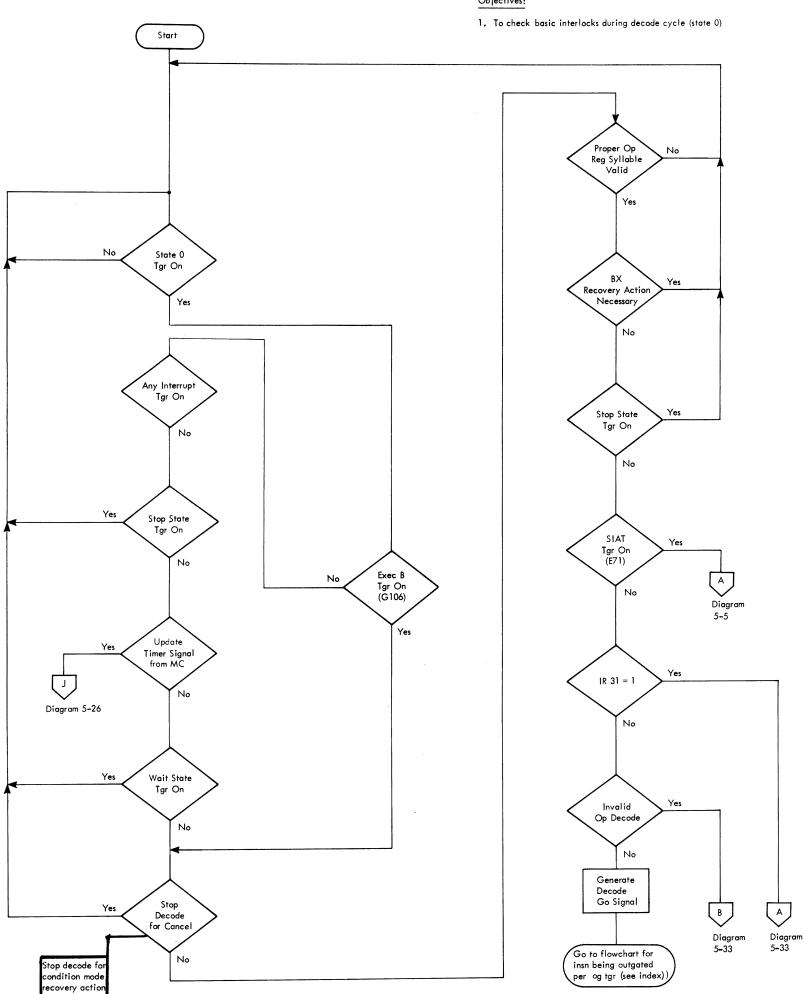

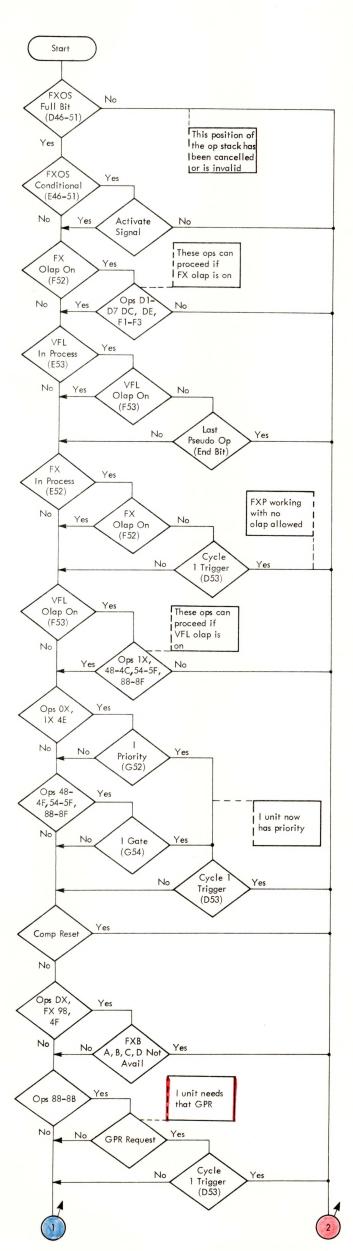

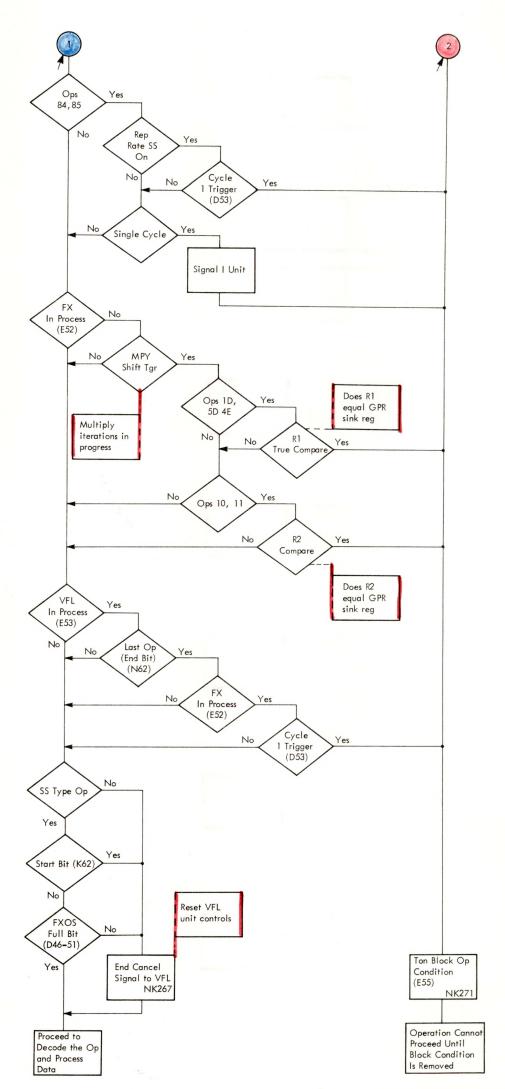

| 5-7     | Decode Cycle (State 0) Basic Interlock Check                 | 5-117   | SSM Instruction                                 |

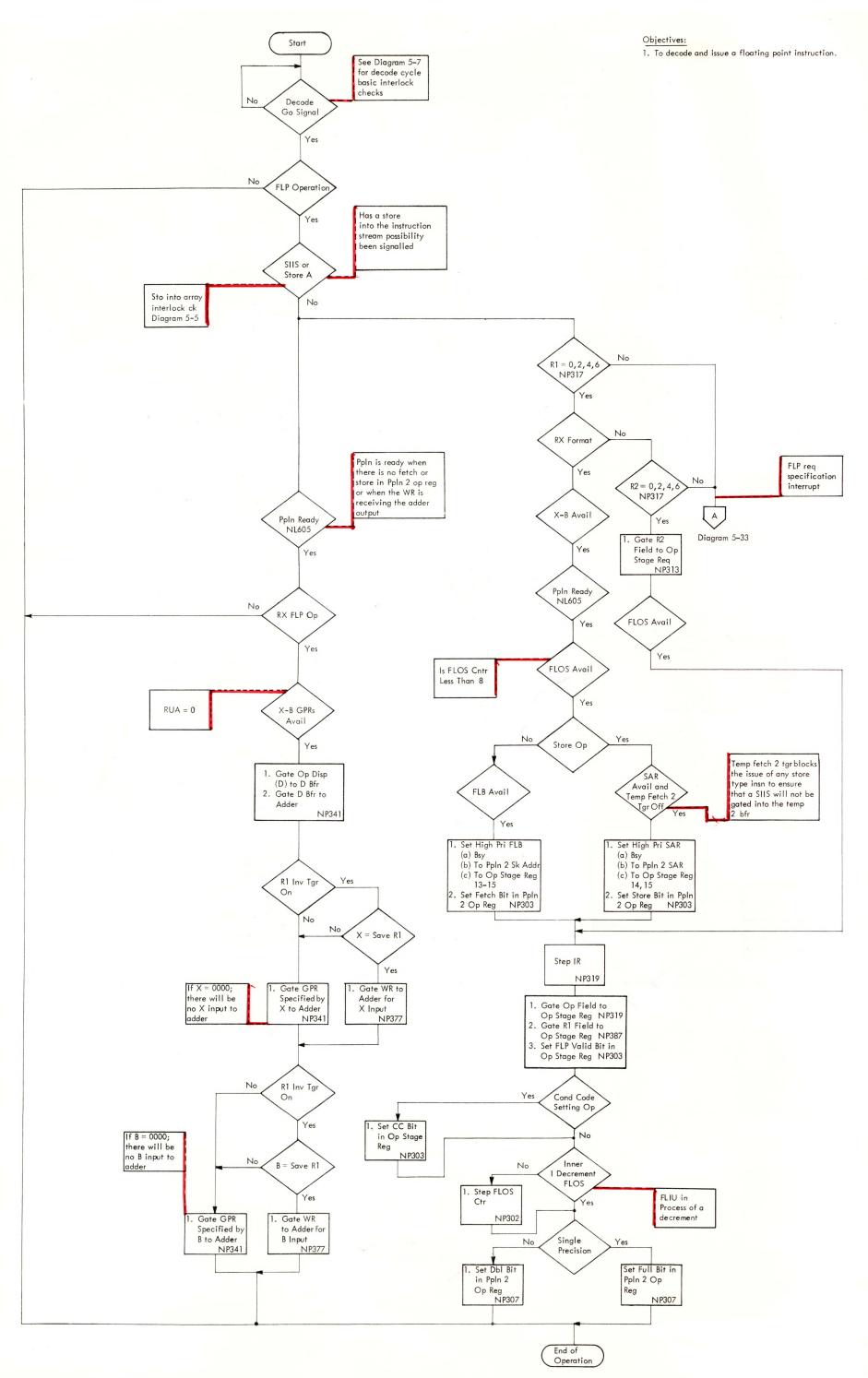

| 5-8     | Floating-Point Issue Sequence                                | 5-118   | RDD Instruction                                 |

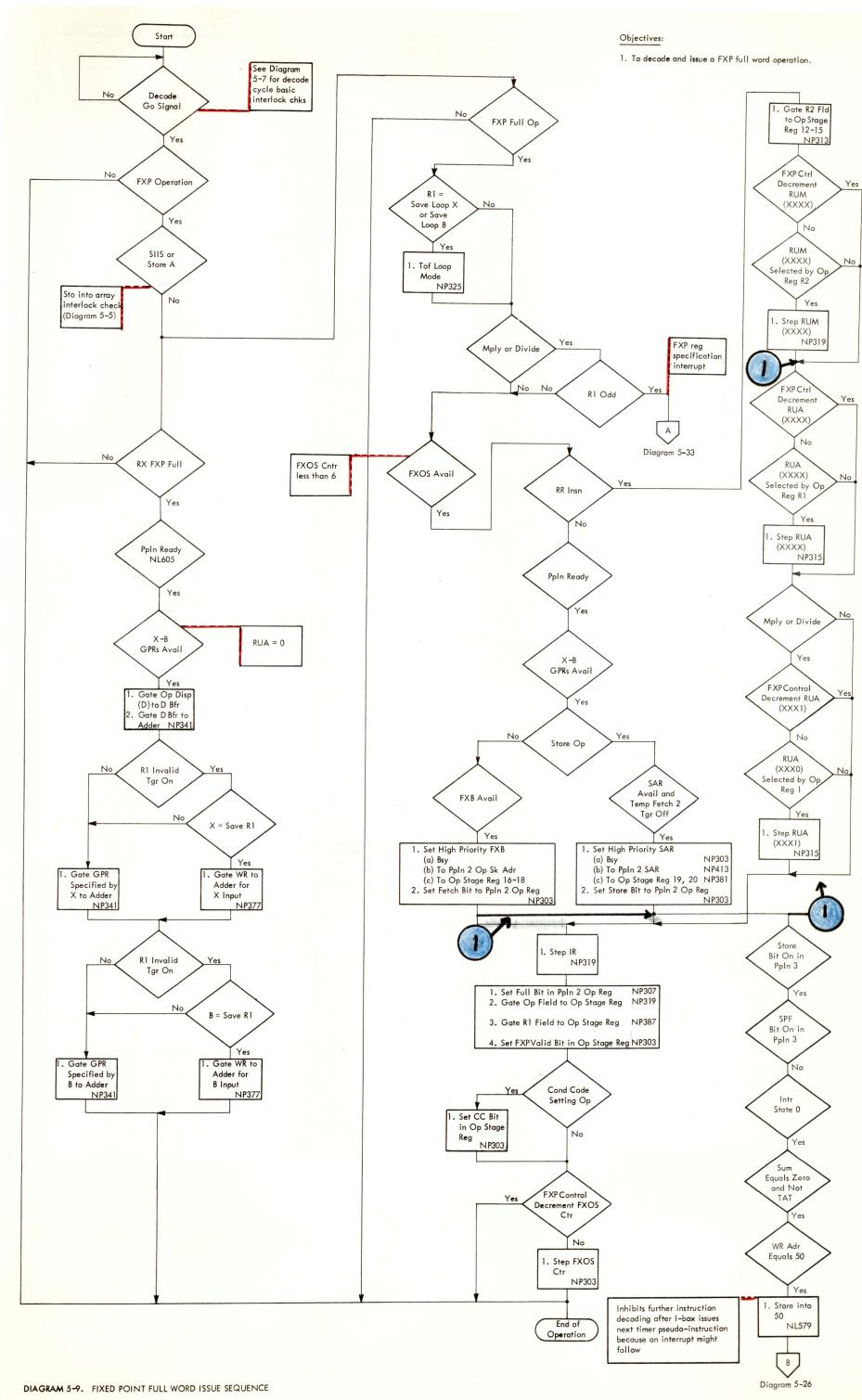

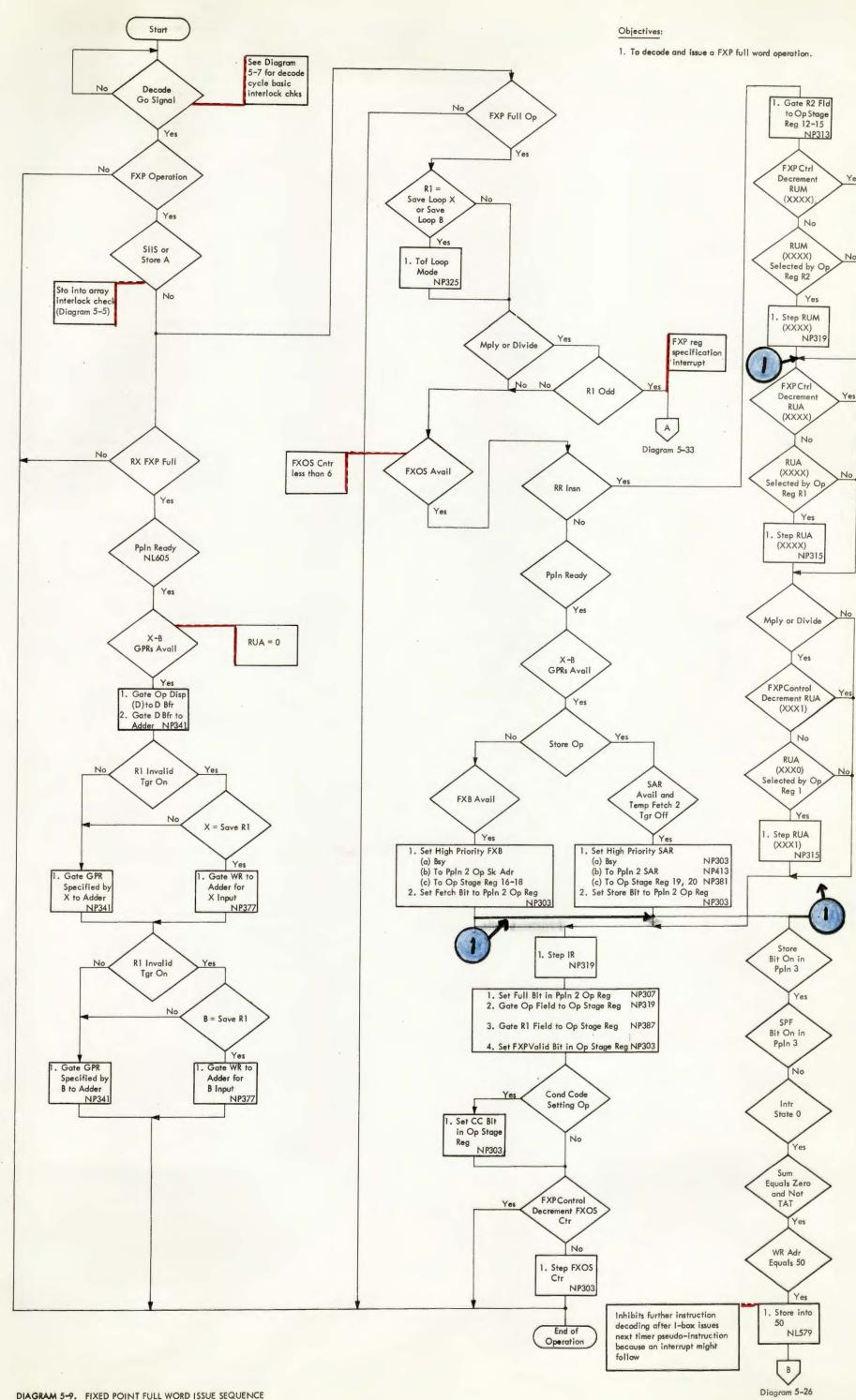

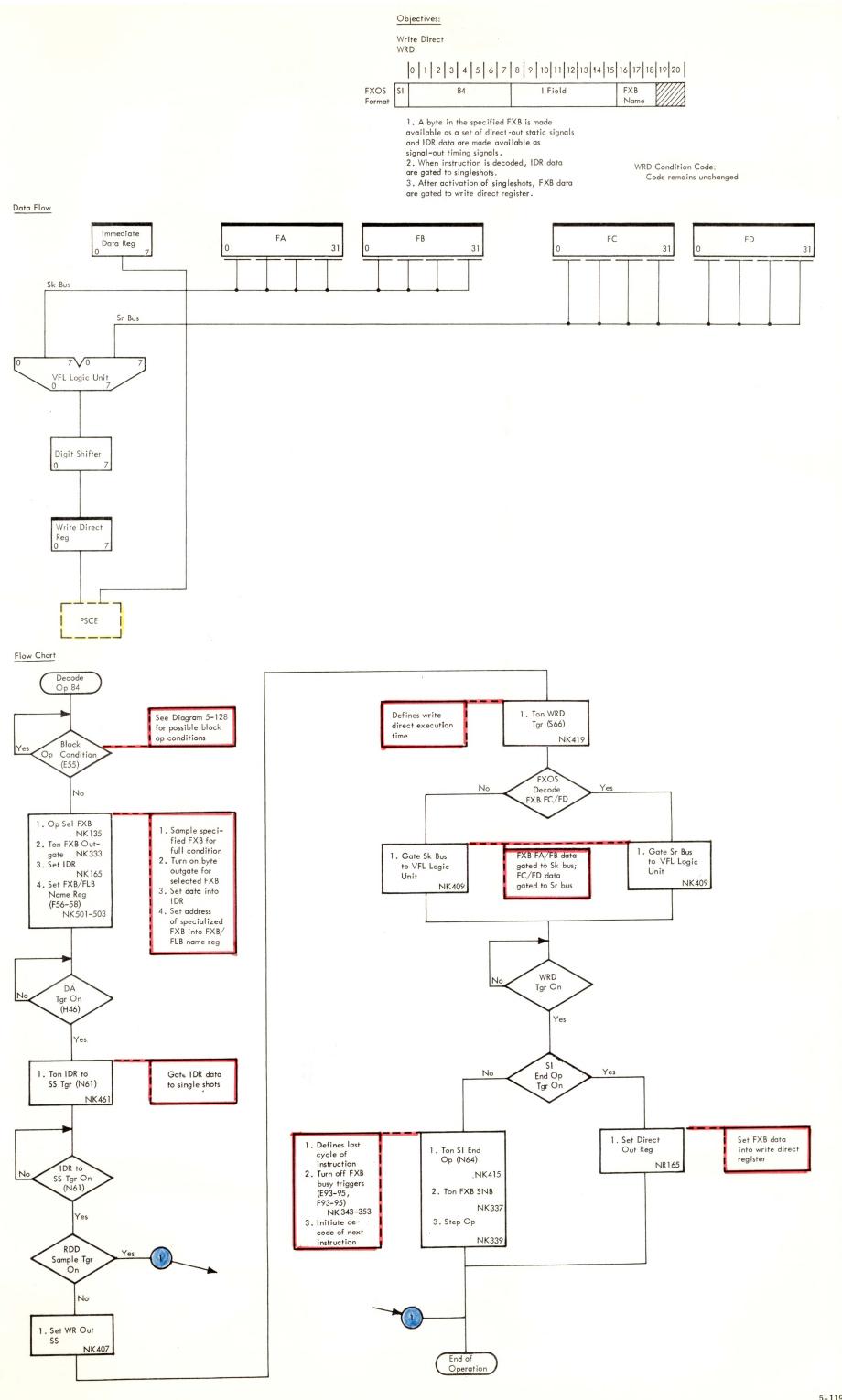

| 5-9     | Fixed-Point Full Word Issue Sequence                         | 5-119   | WRD Instruction                                 |

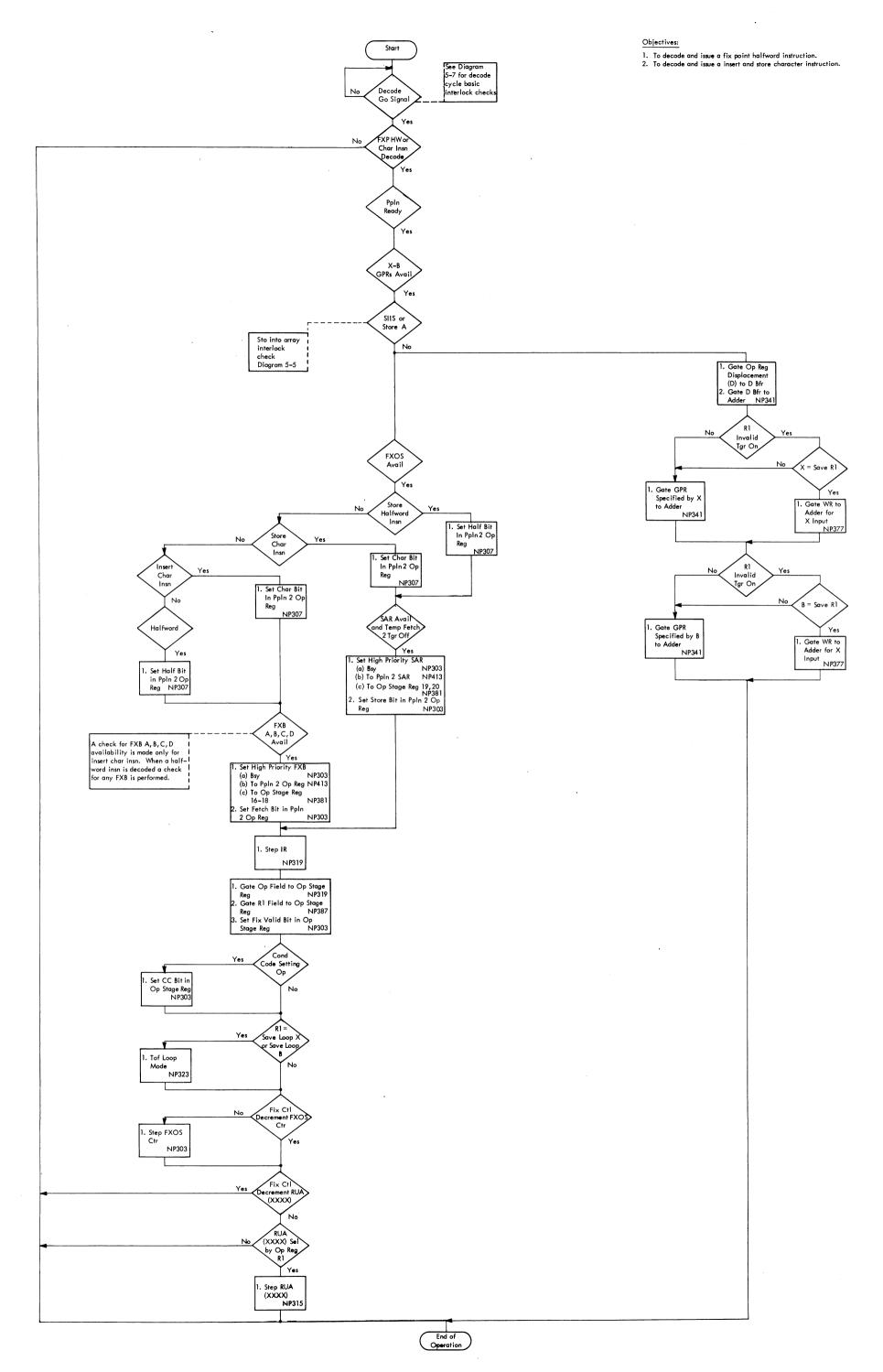

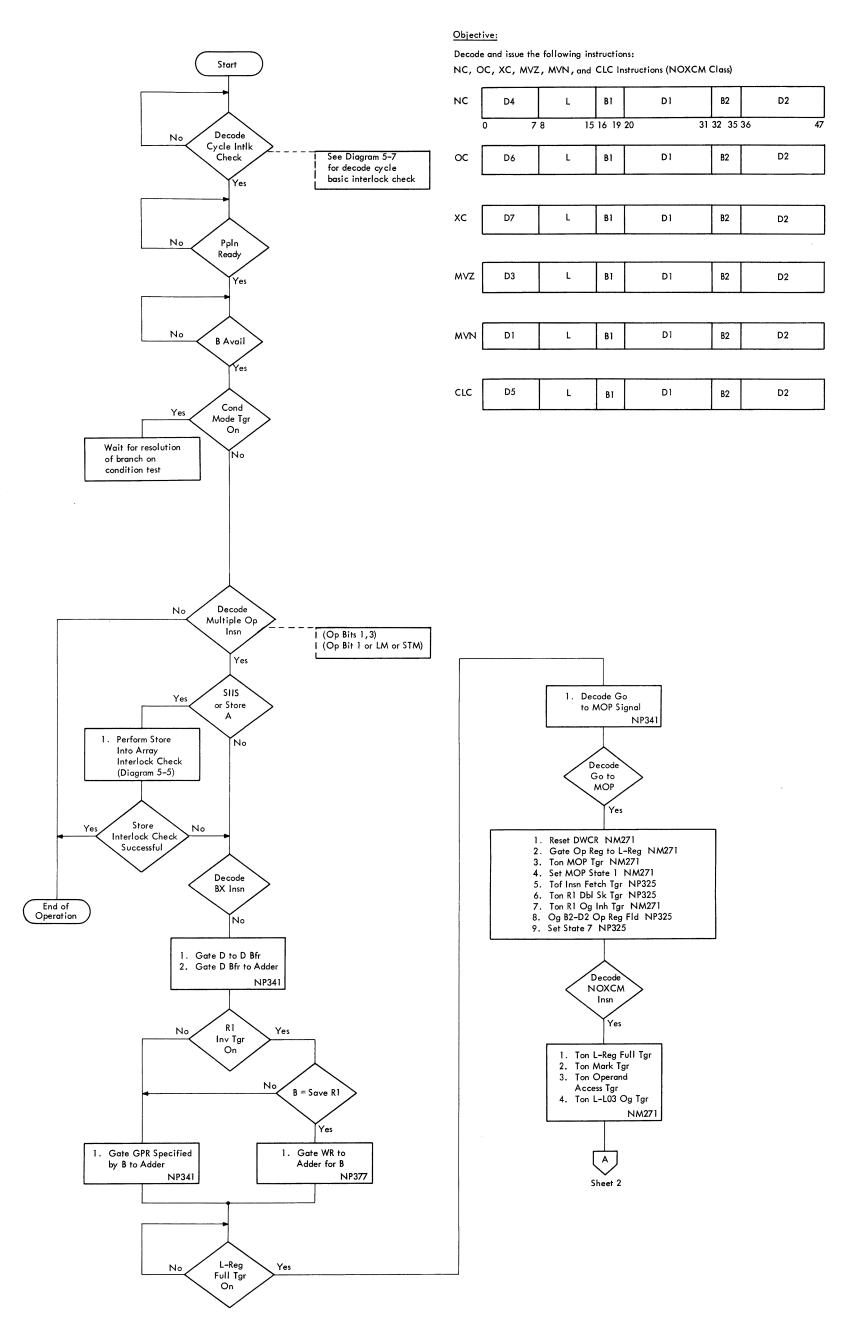

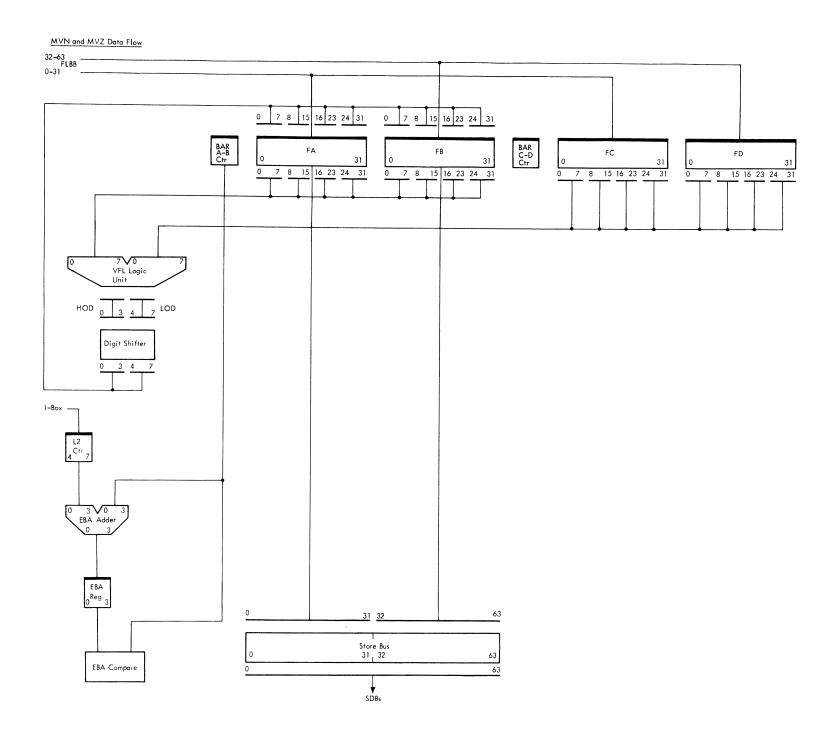

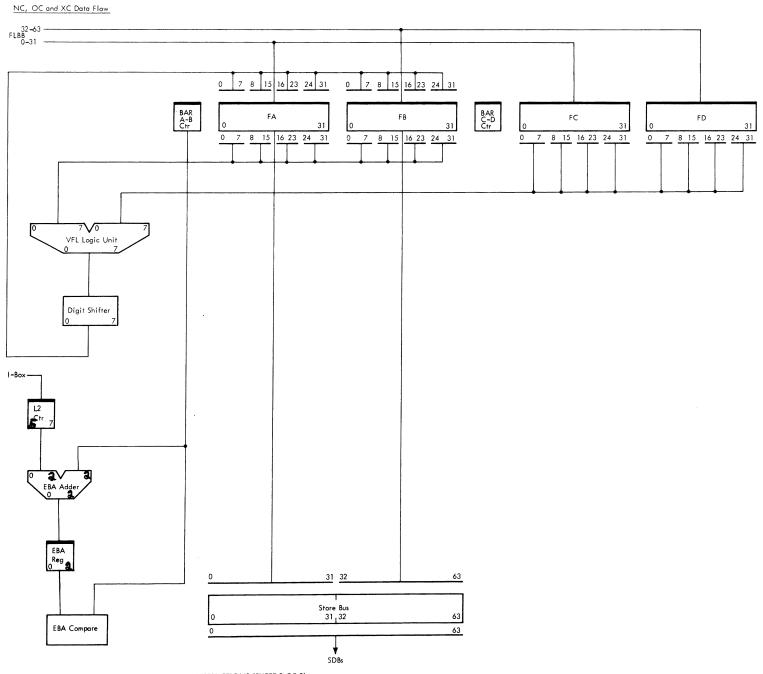

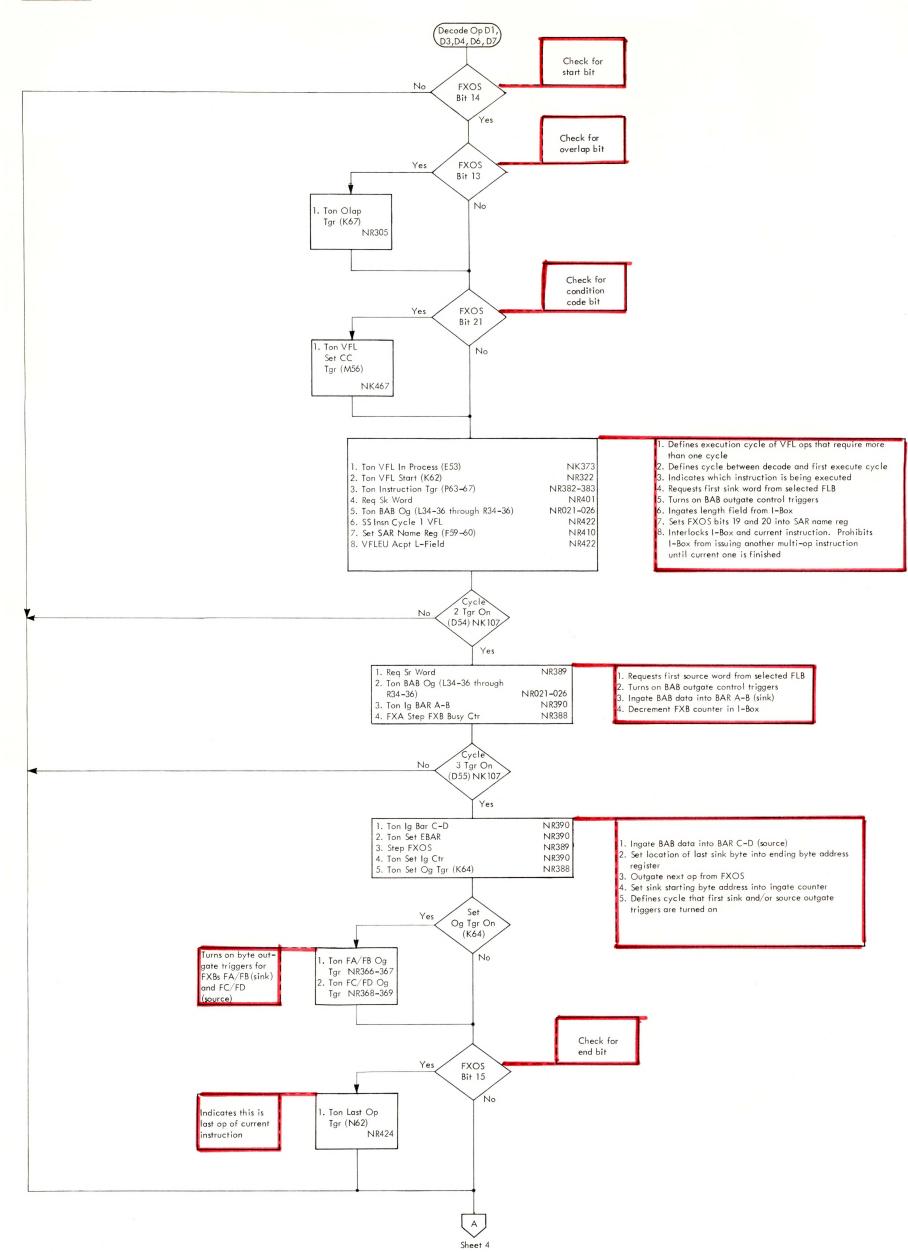

| 5-10    | Fixed-Point Halfword and Insert and Store Character          | 5-120   | NC, OC, XC, MVN and MVZ Instructions (8 sheets) |

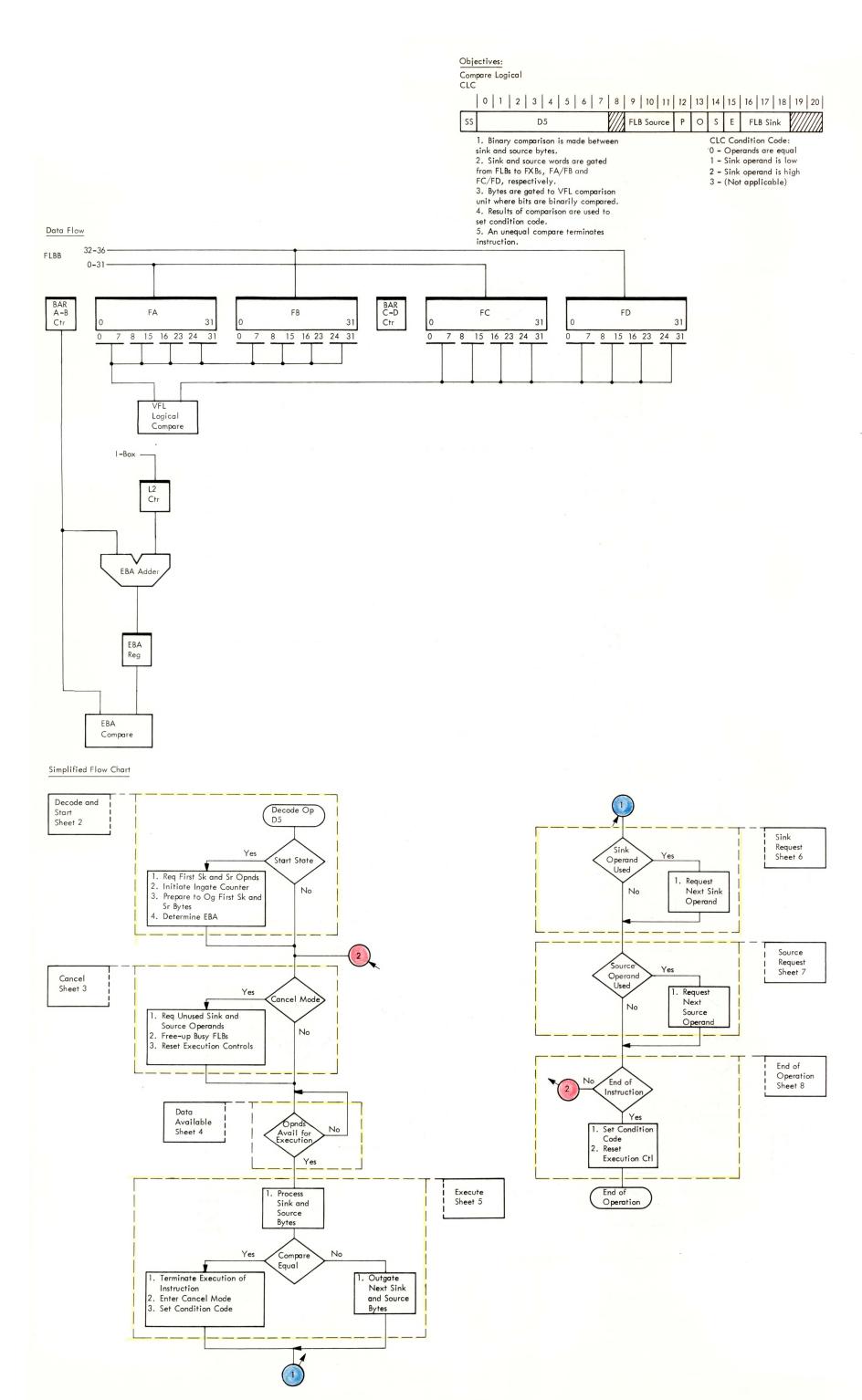

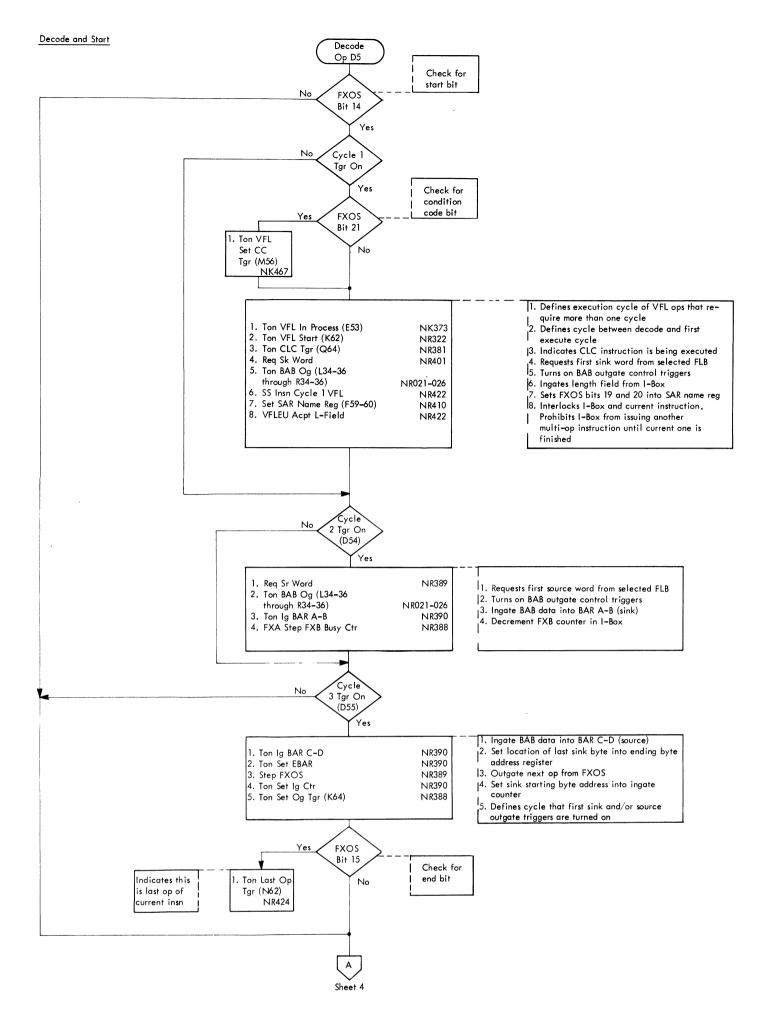

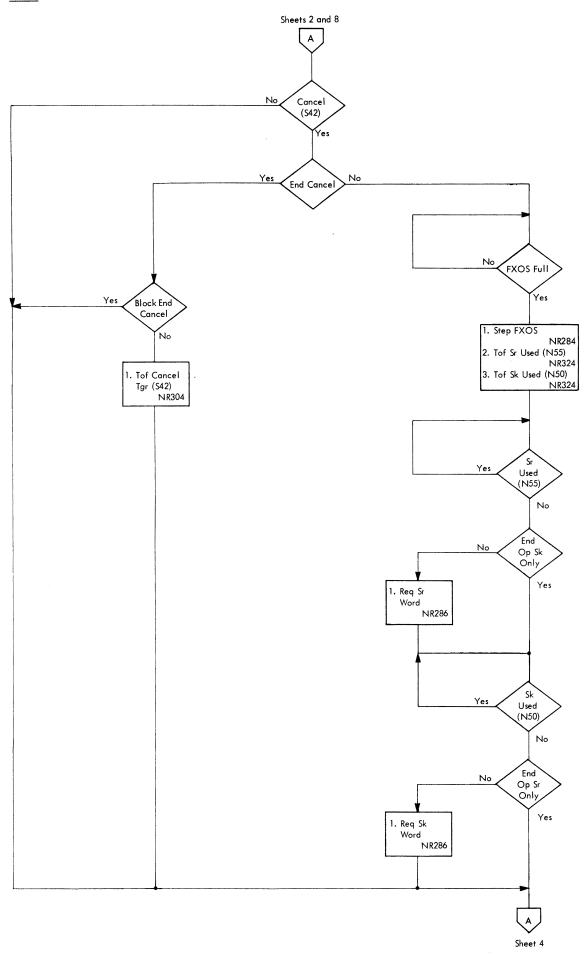

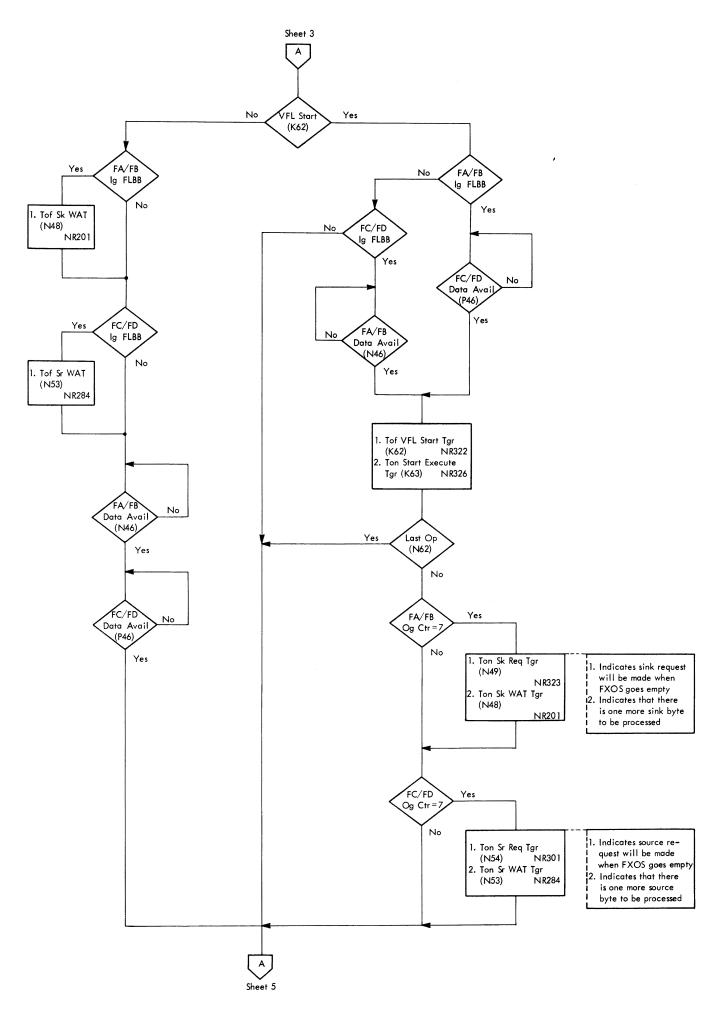

|         | Issue Sequence                                               | 5-121   | CLC Instruction (8 sheets)                      |

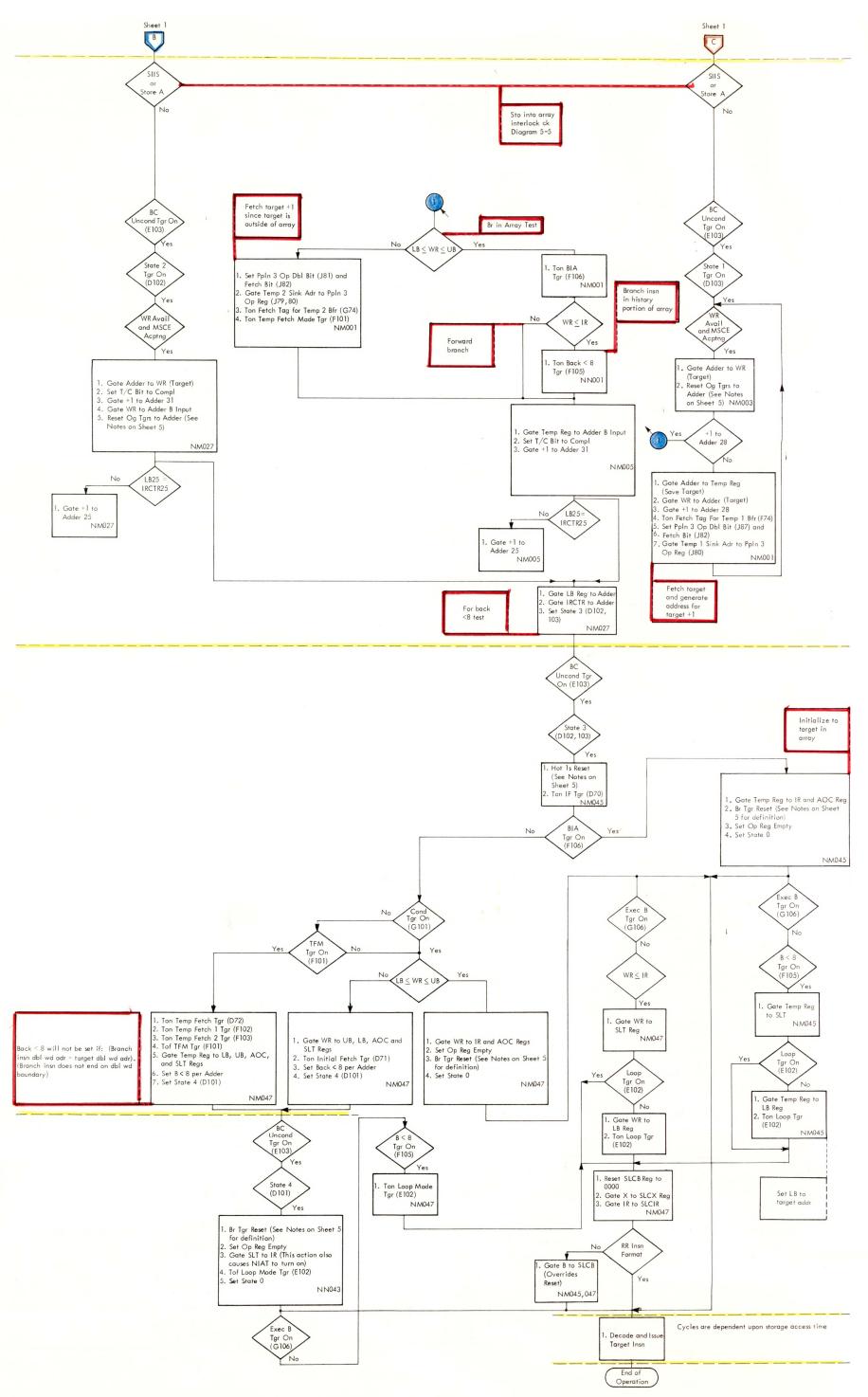

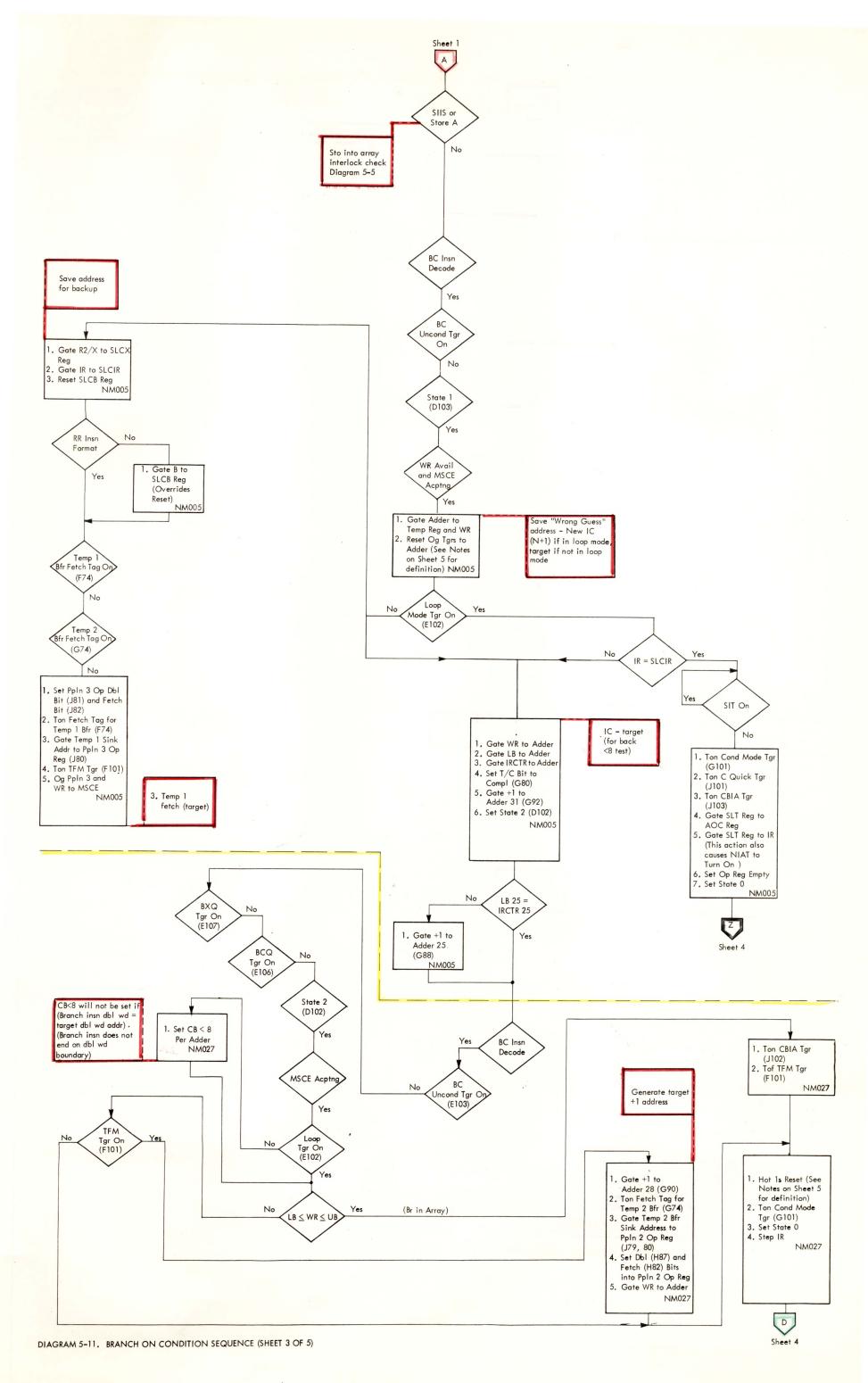

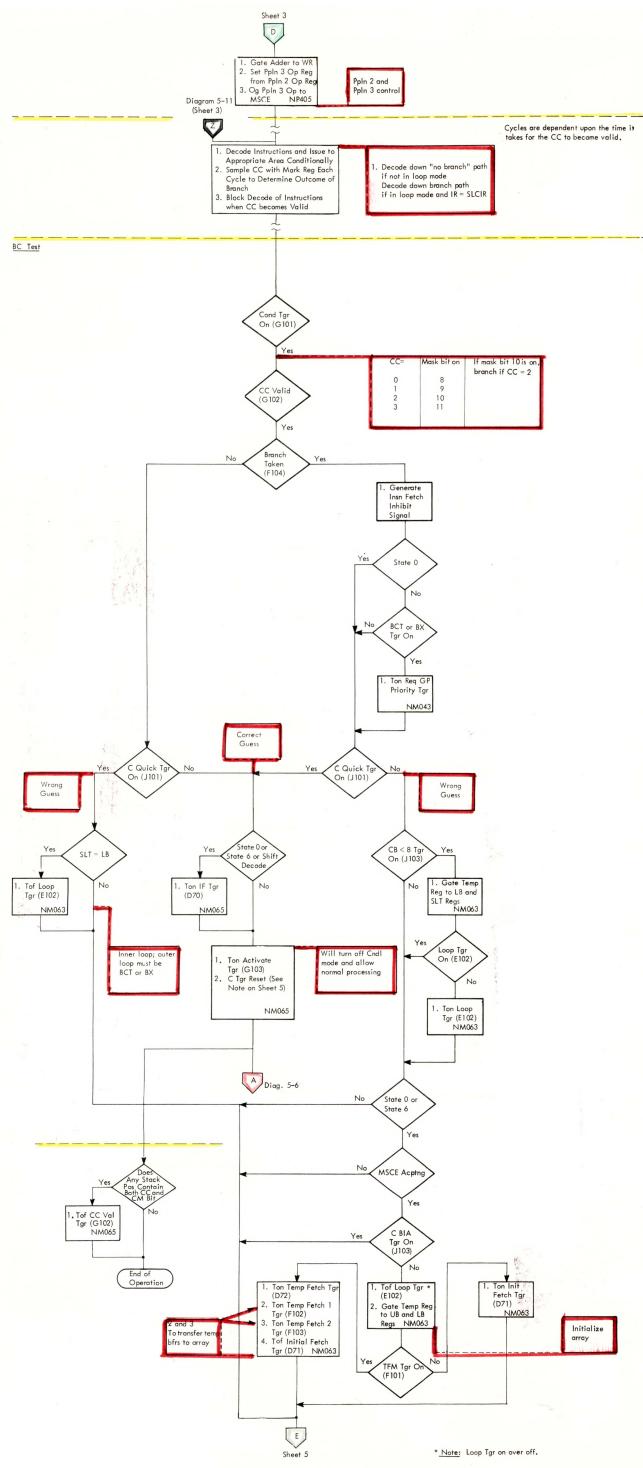

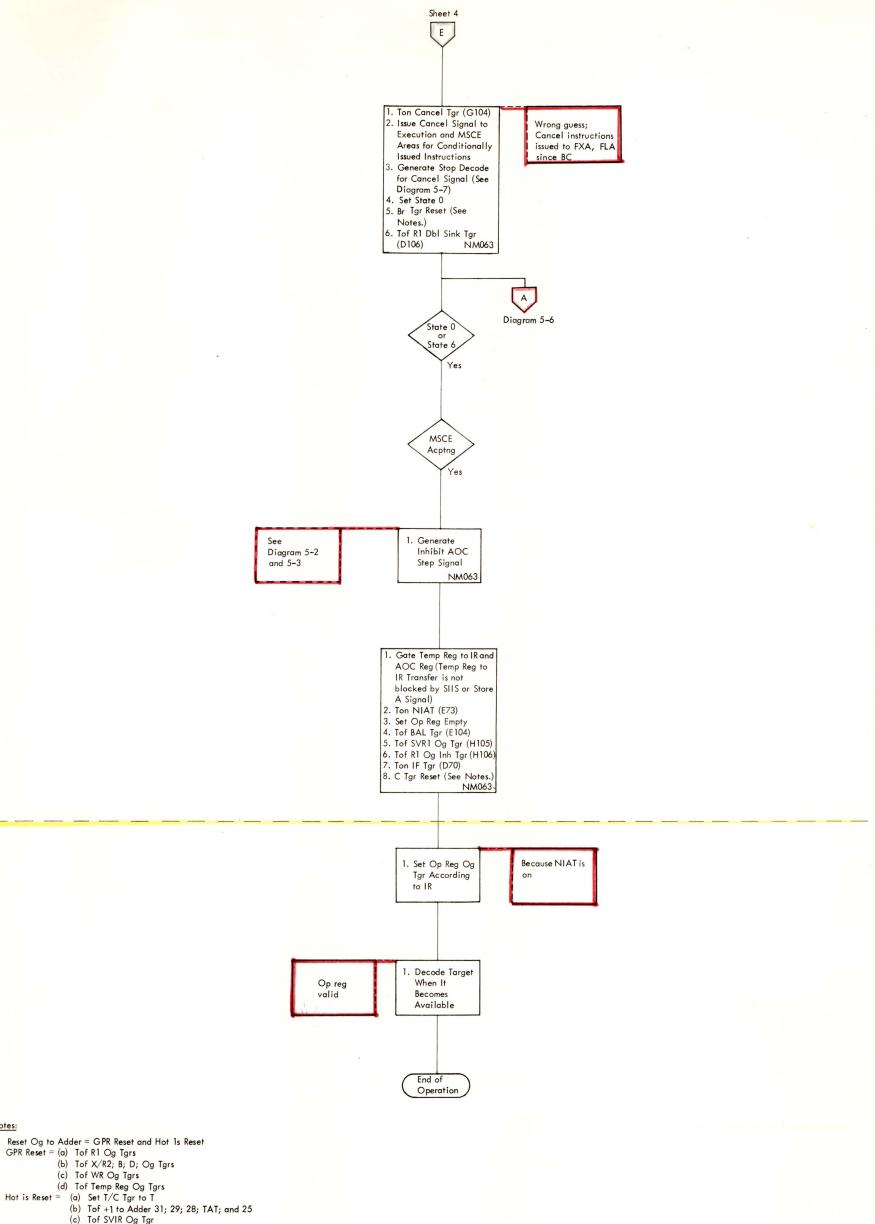

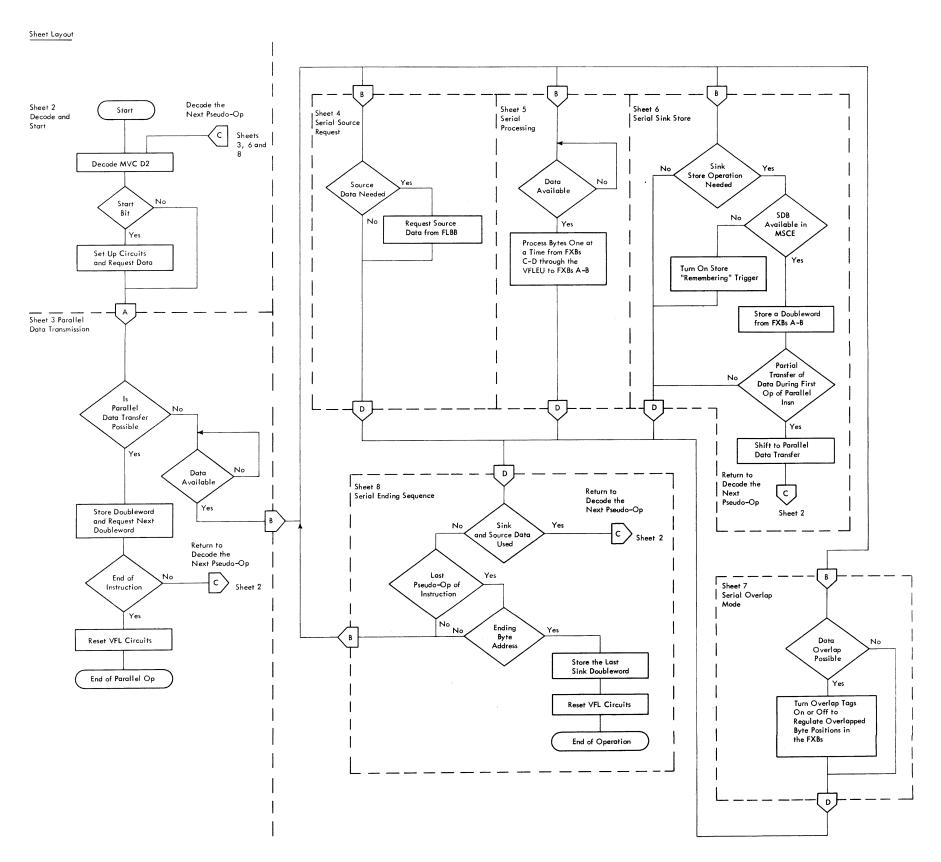

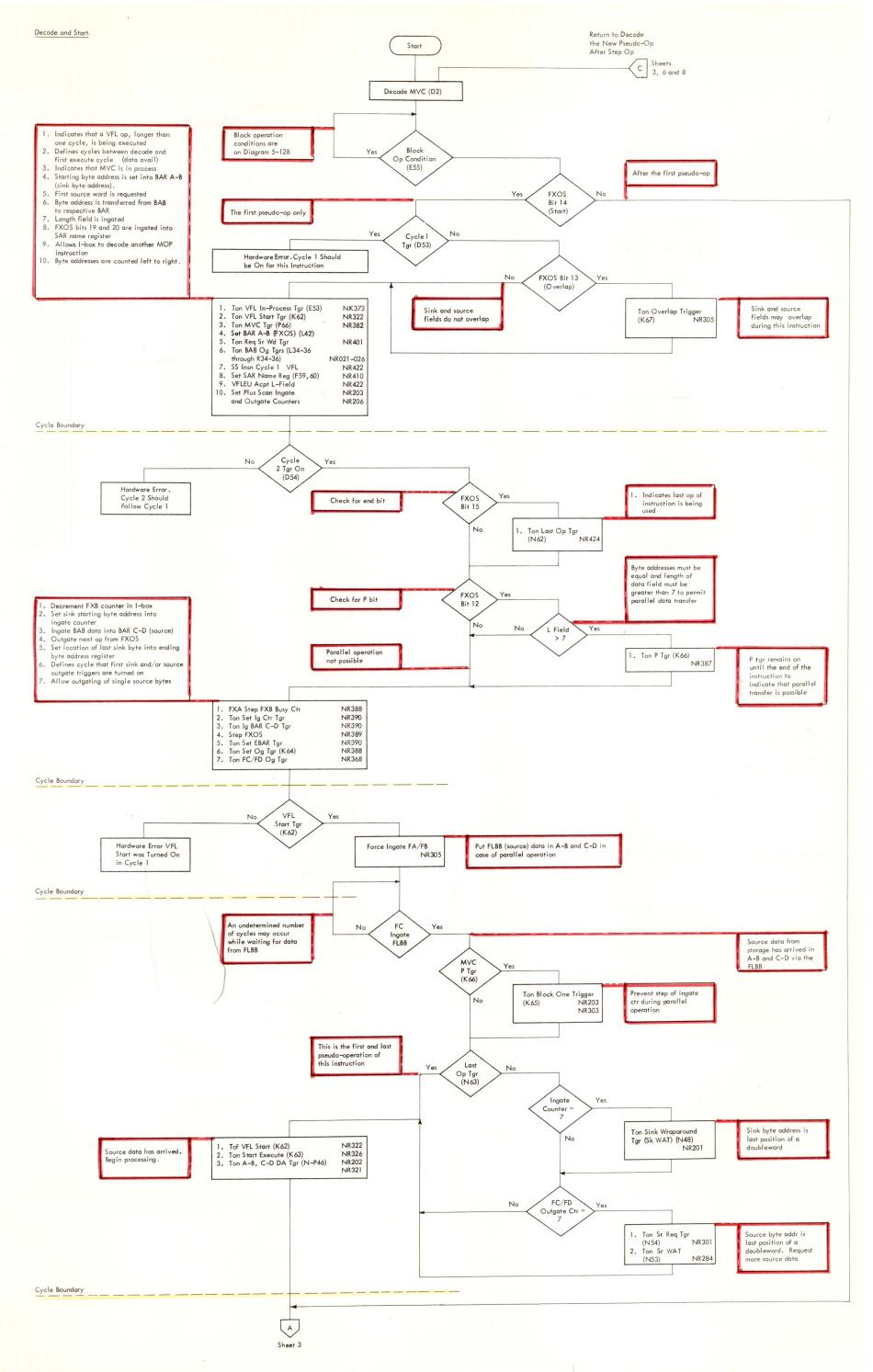

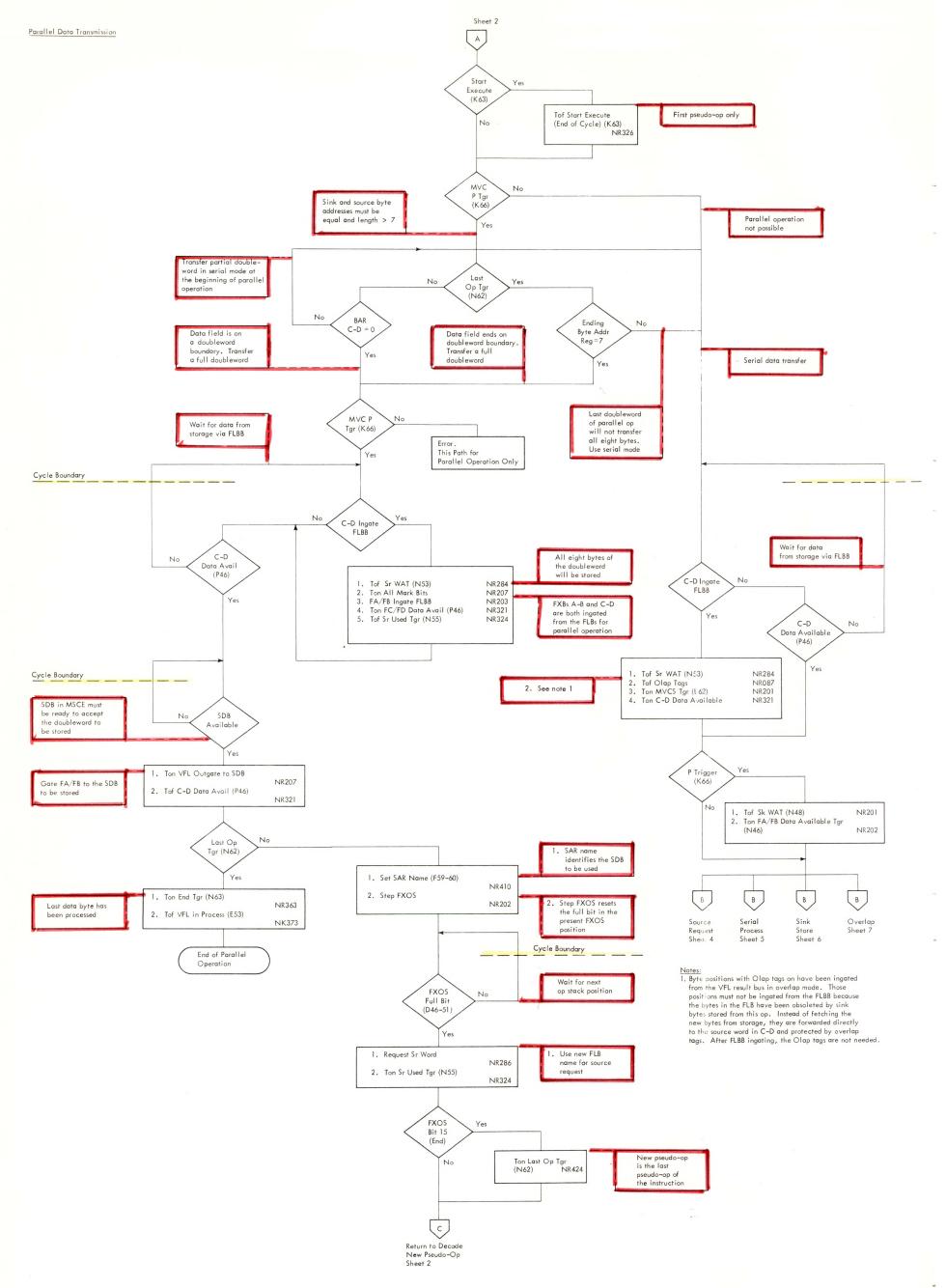

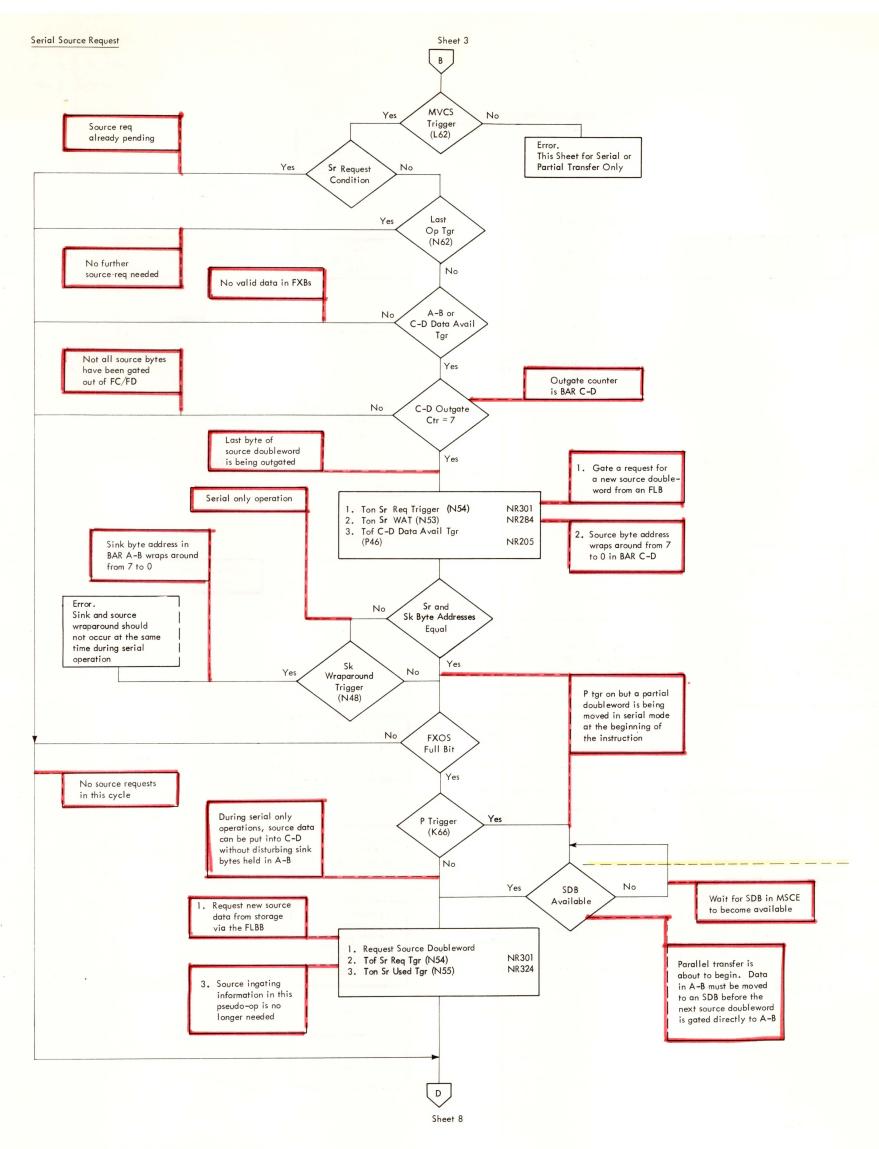

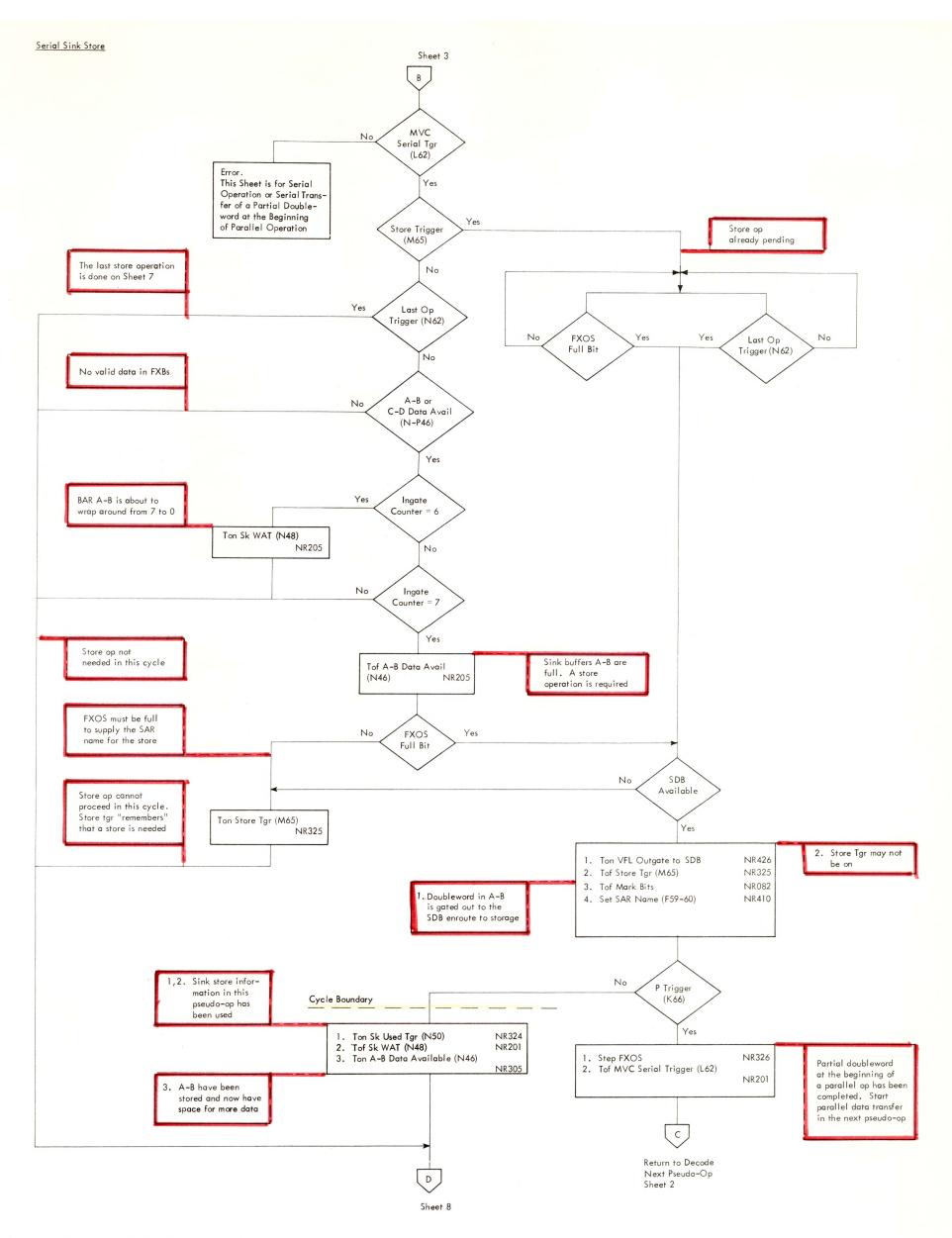

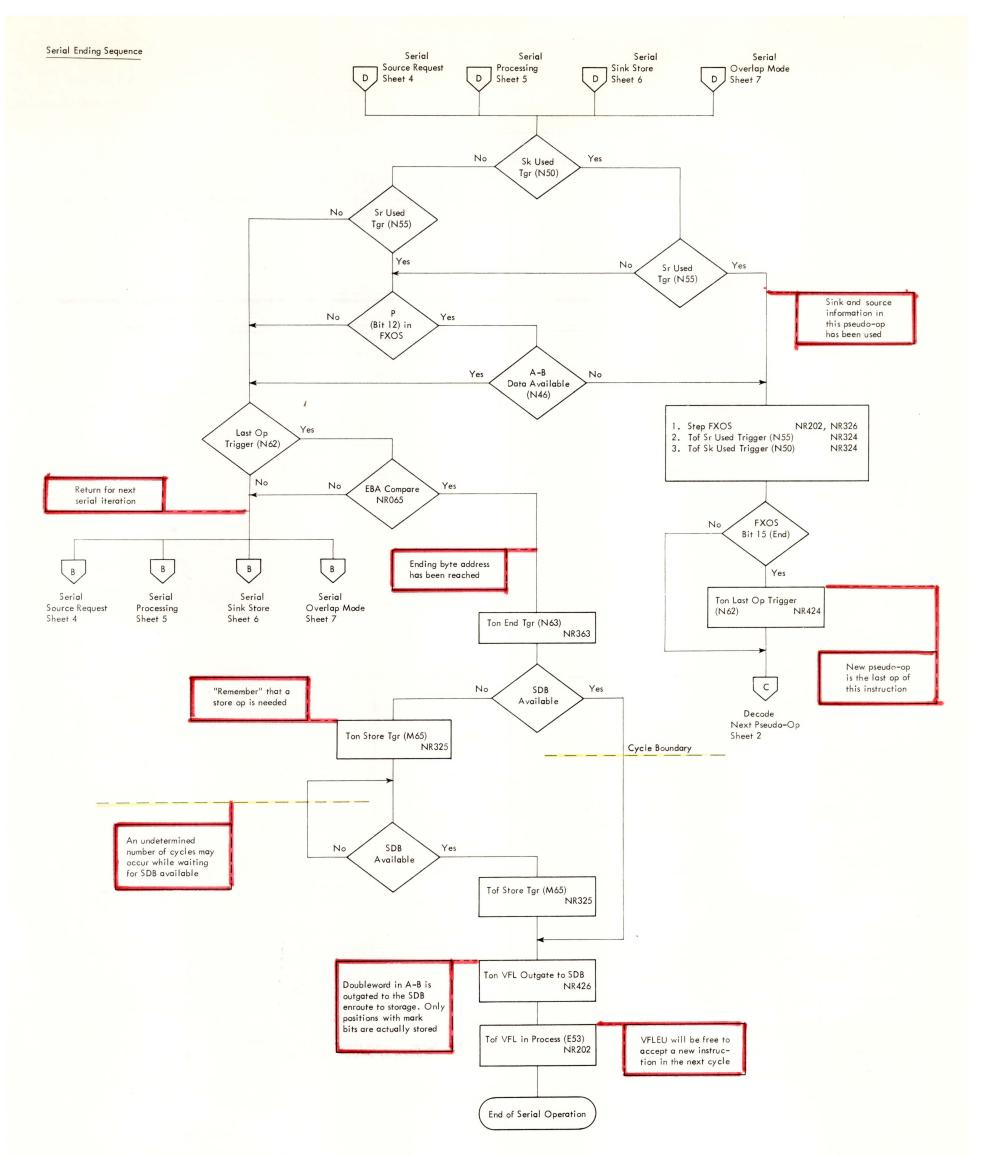

| 5-11    | Branch on Condition Sequence (5 sheets)                      | 5-122   | MVC Instruction (8 sheets)                      |

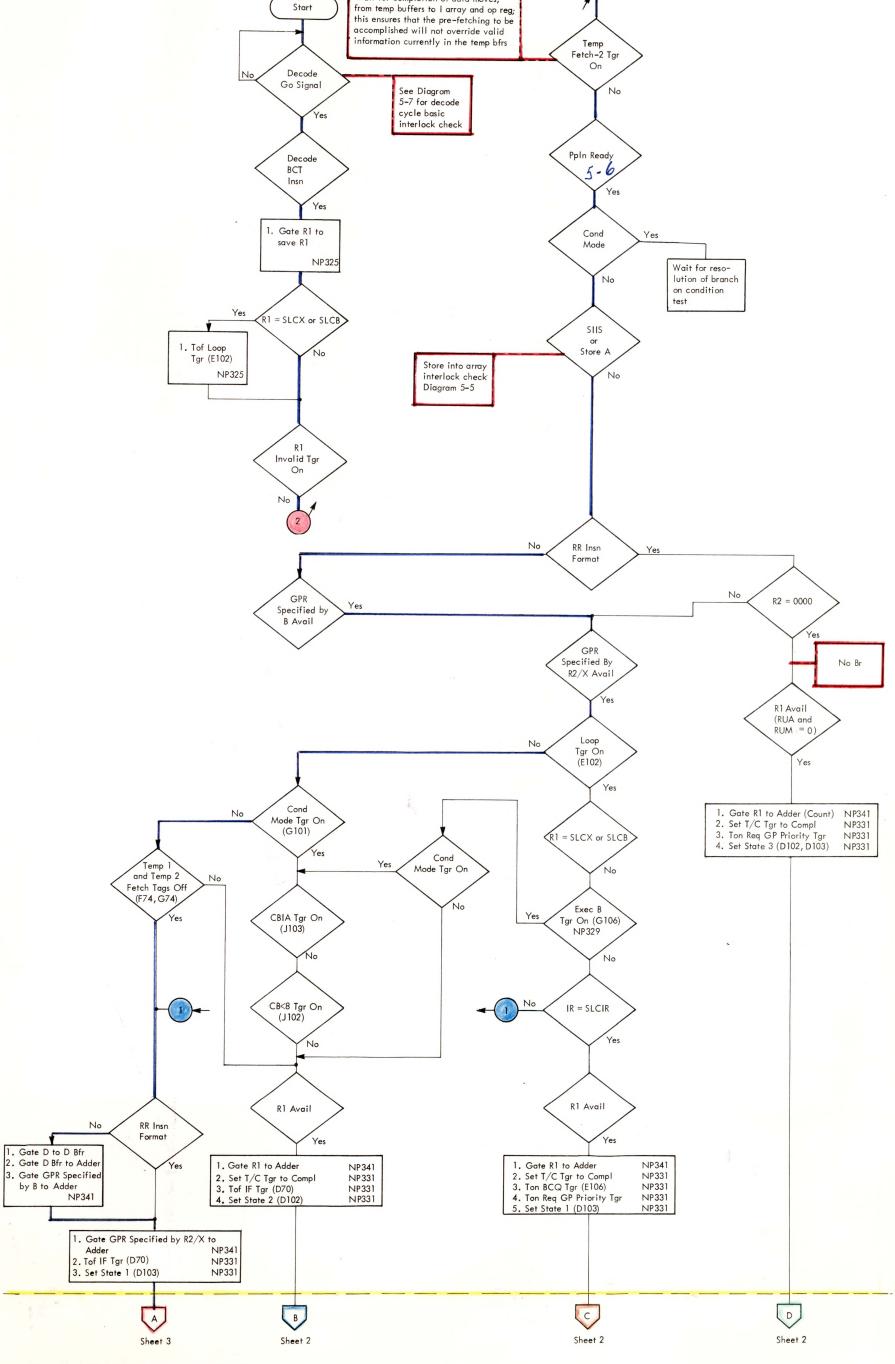

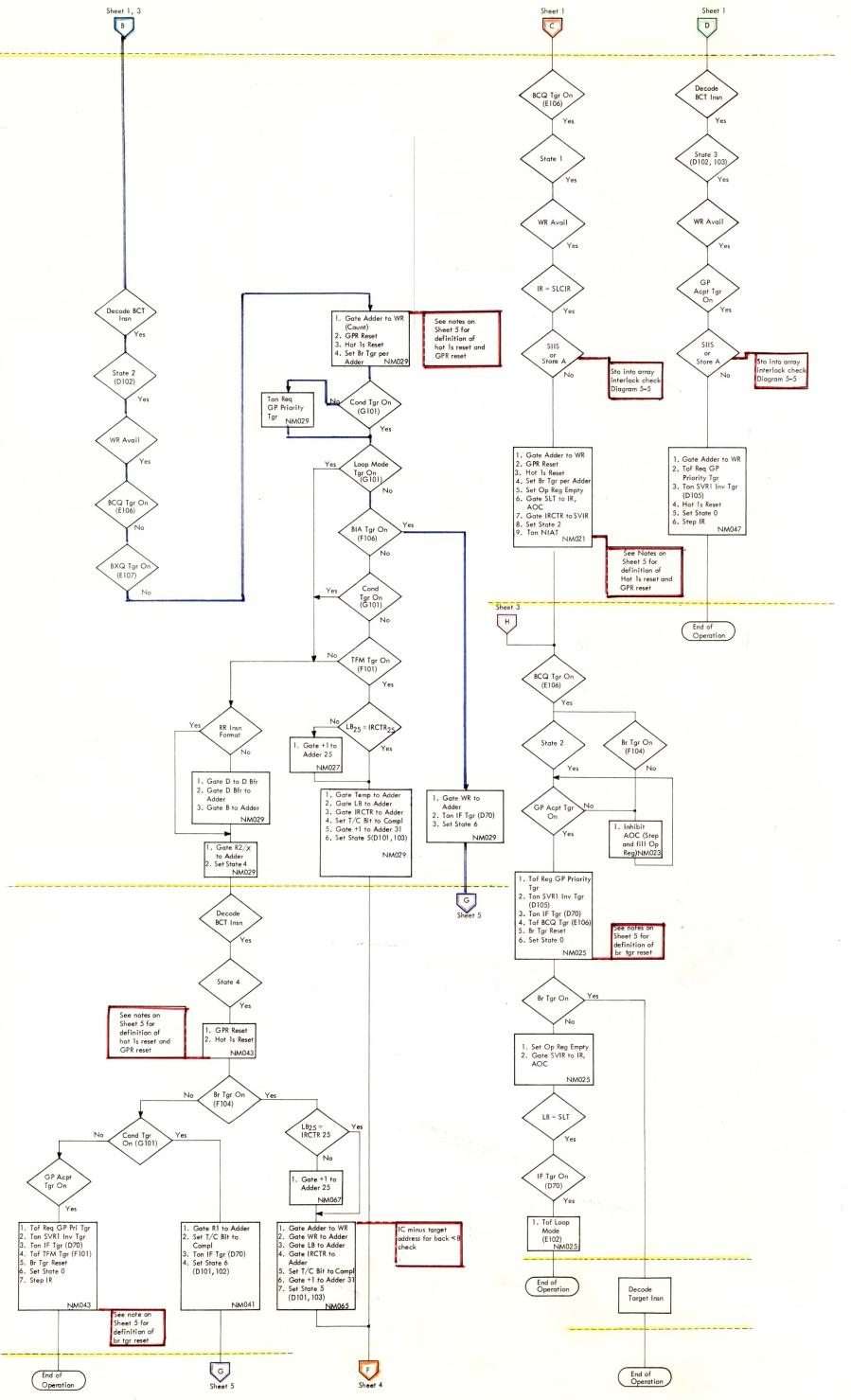

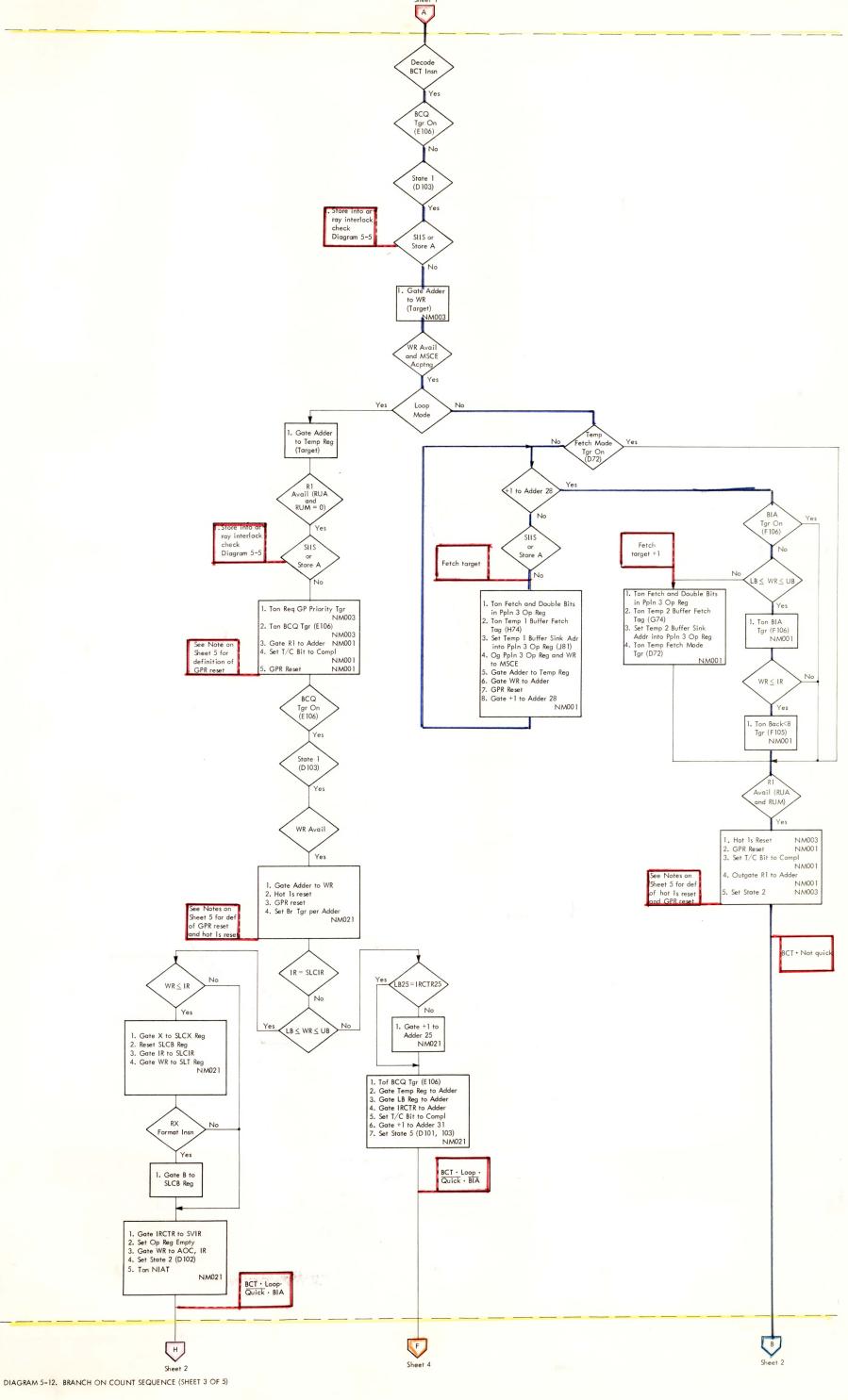

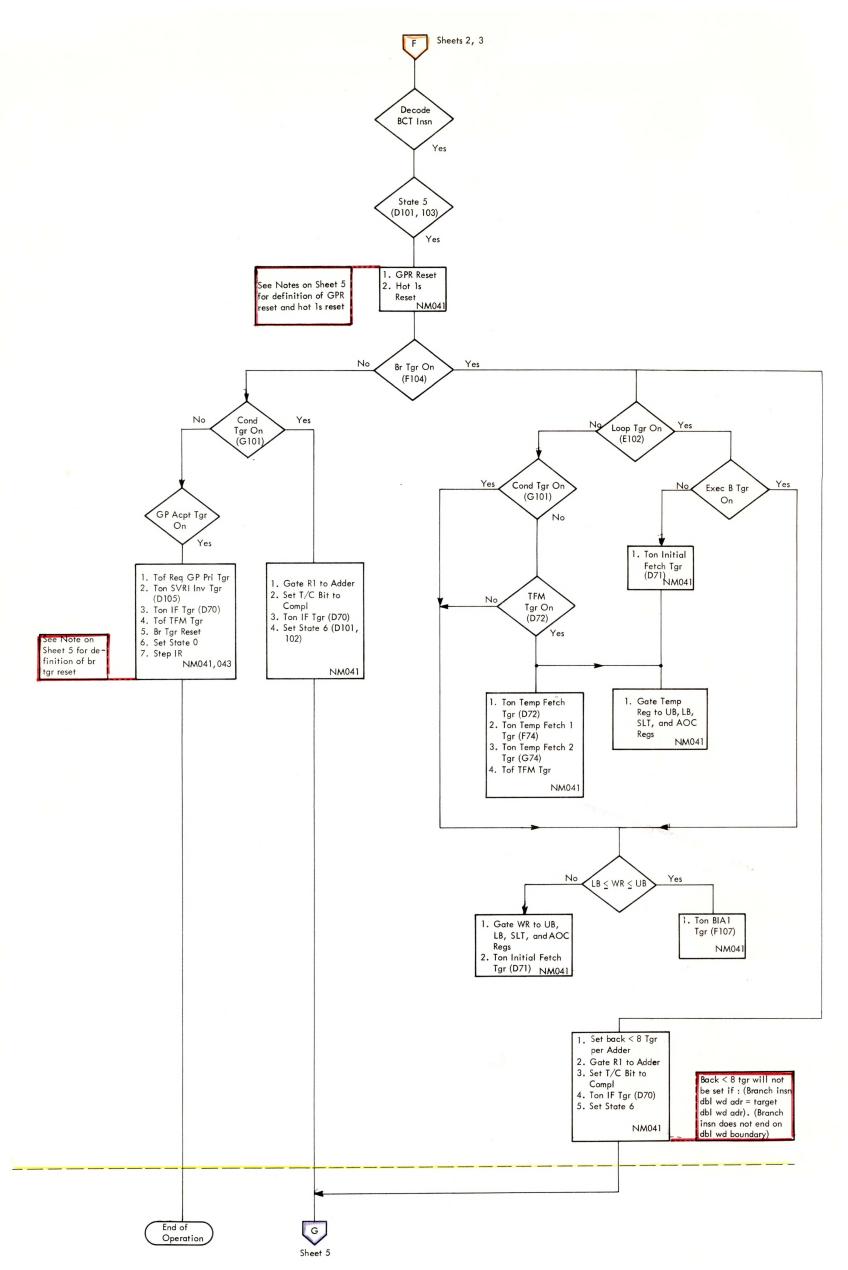

| 5-12    | Branch on Count Sequence (5 sheets)                          | 5-123   | MVO Instruction (7 sheets)                      |

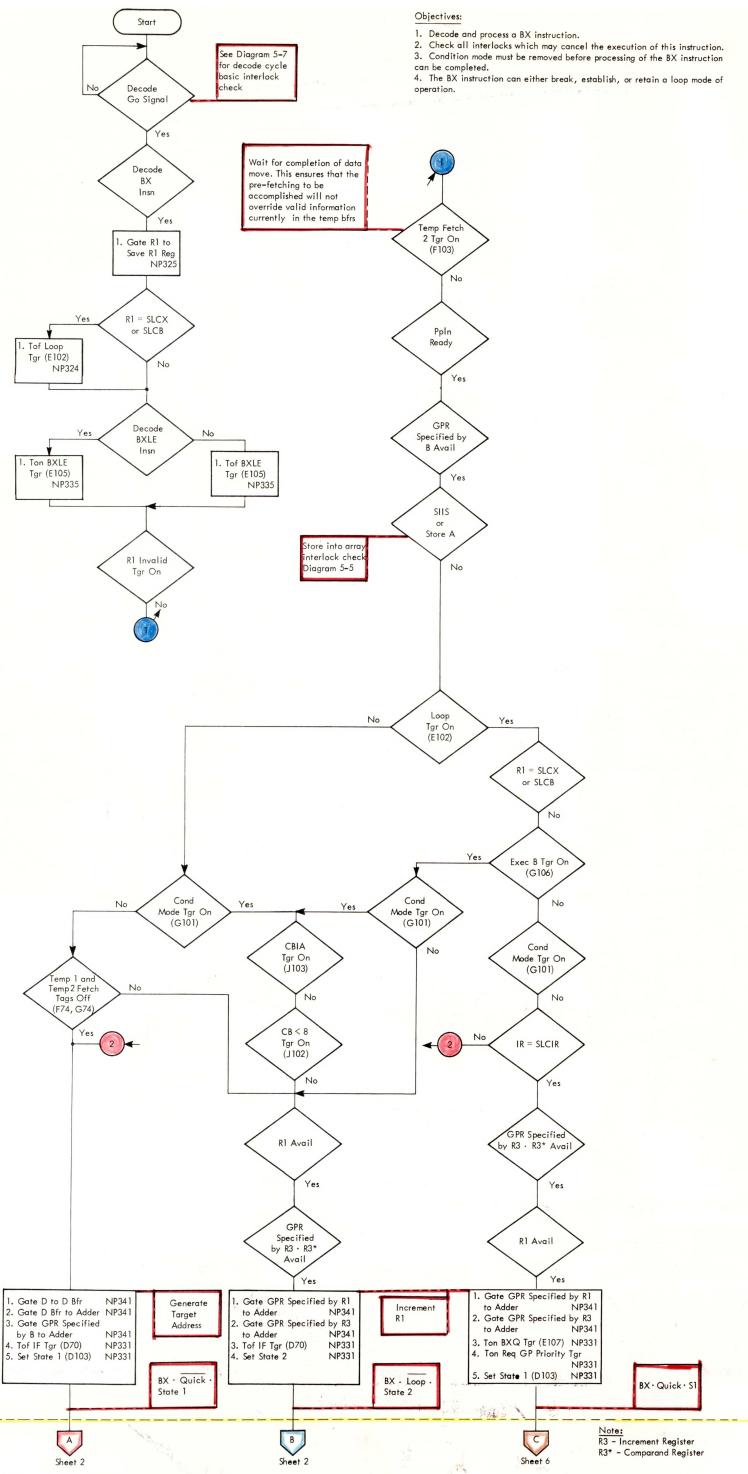

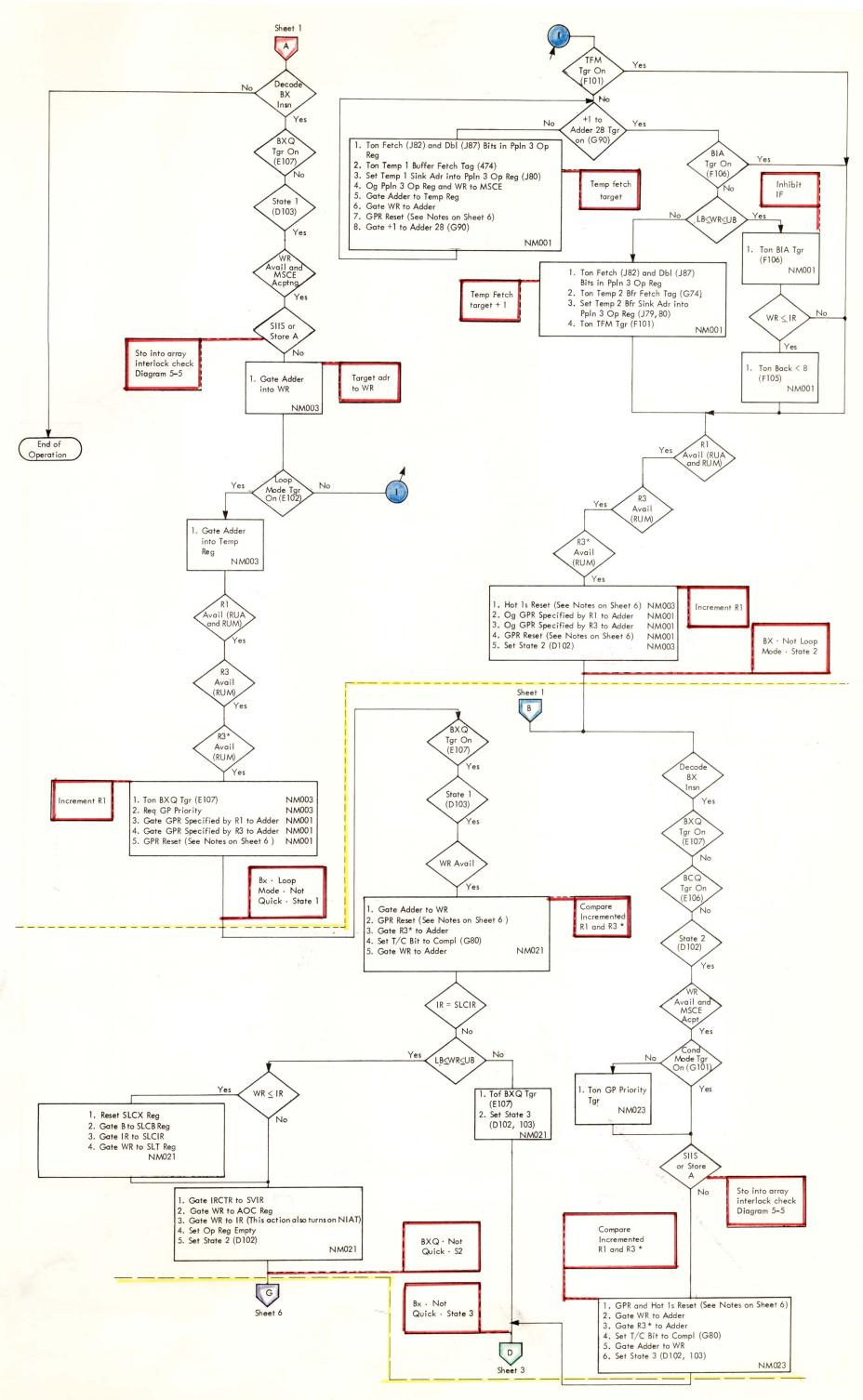

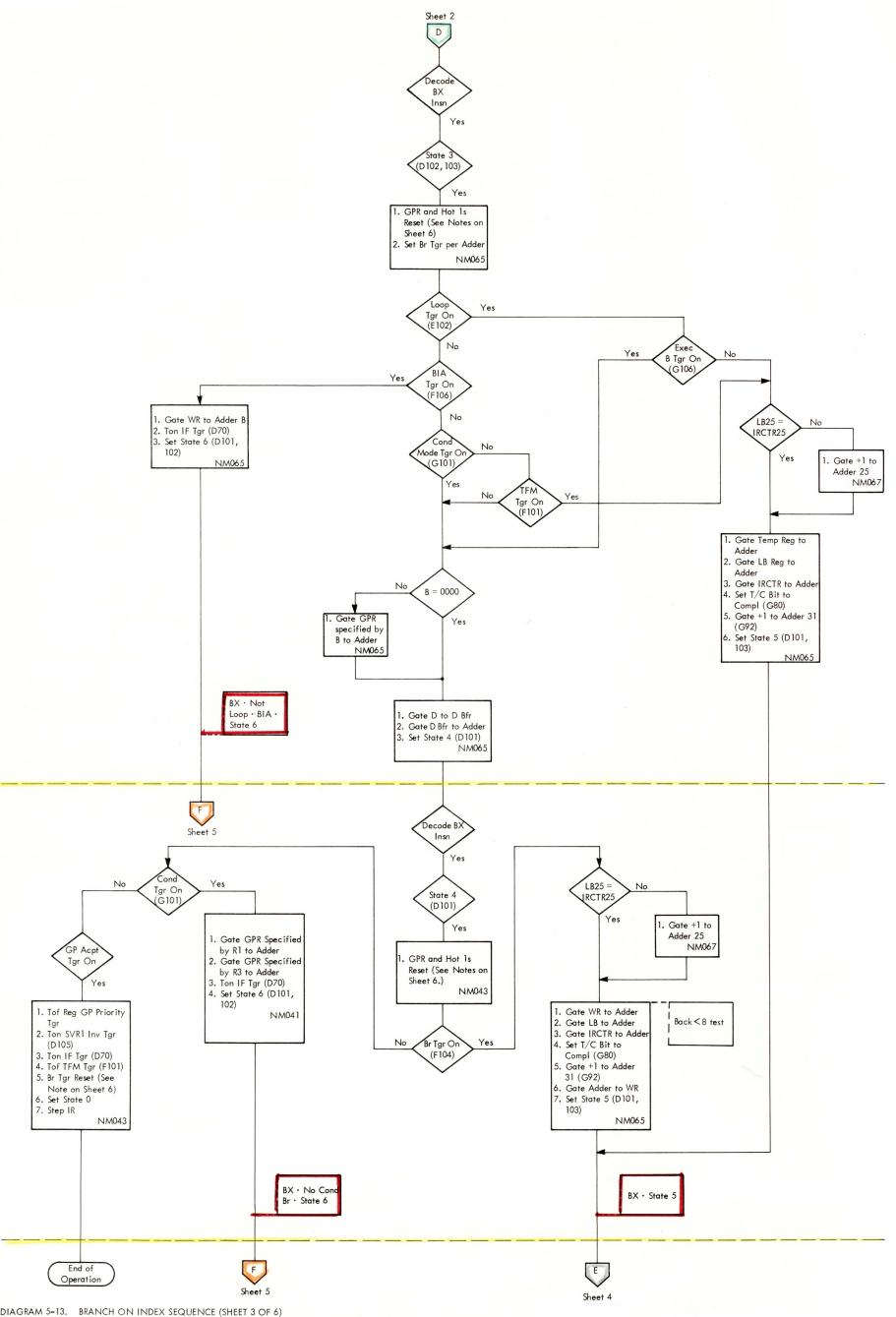

| 5-13    | Branch on Index Sequence (6 sheets)                          | 5-124   | Pack and Unpack Instructions (7 sheets)         |

| 5-14    | Branch and Link Sequence (2 sheets)                          | 5-125   | ED and EDMK Instructions (8 sheets)             |

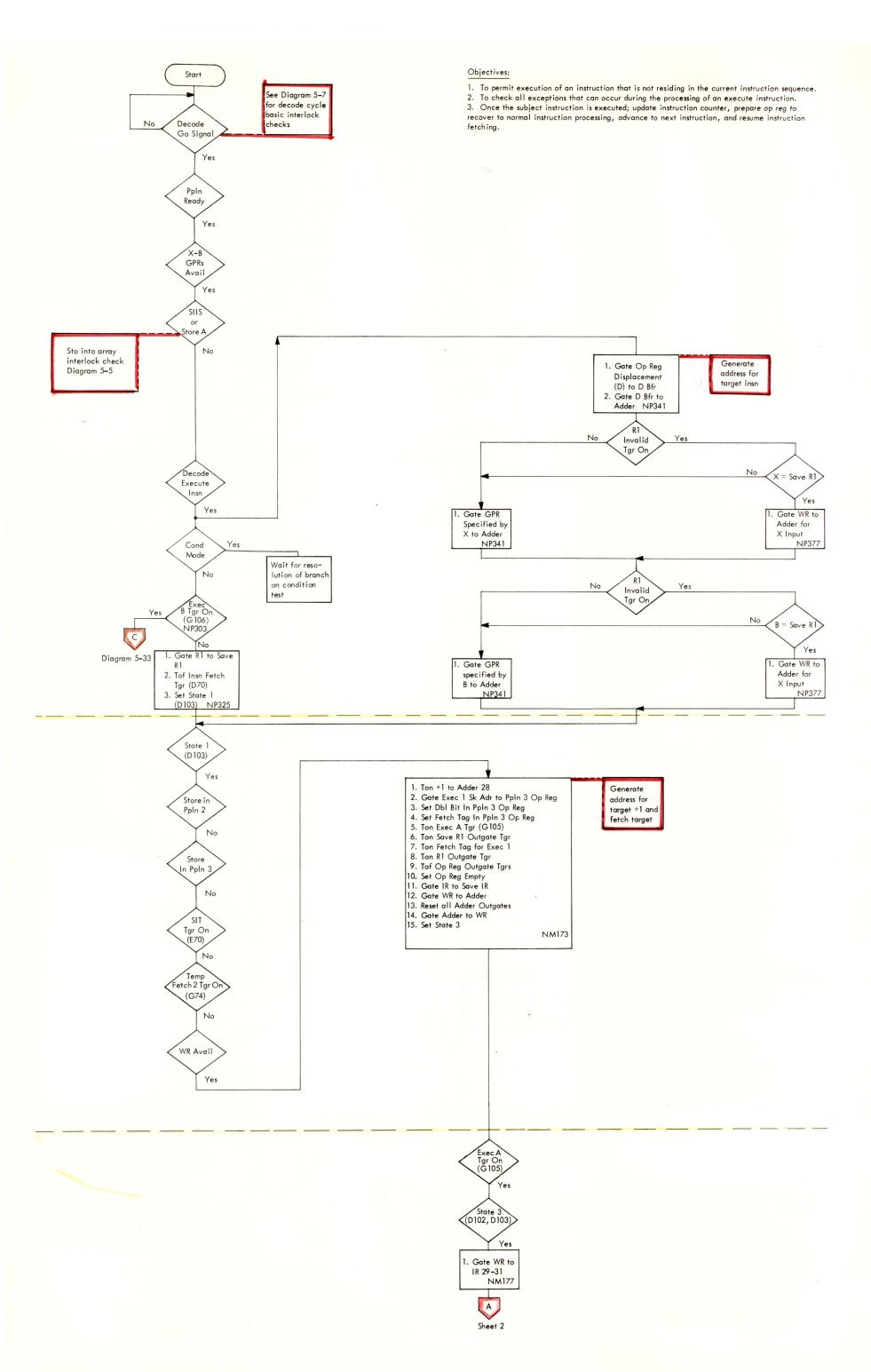

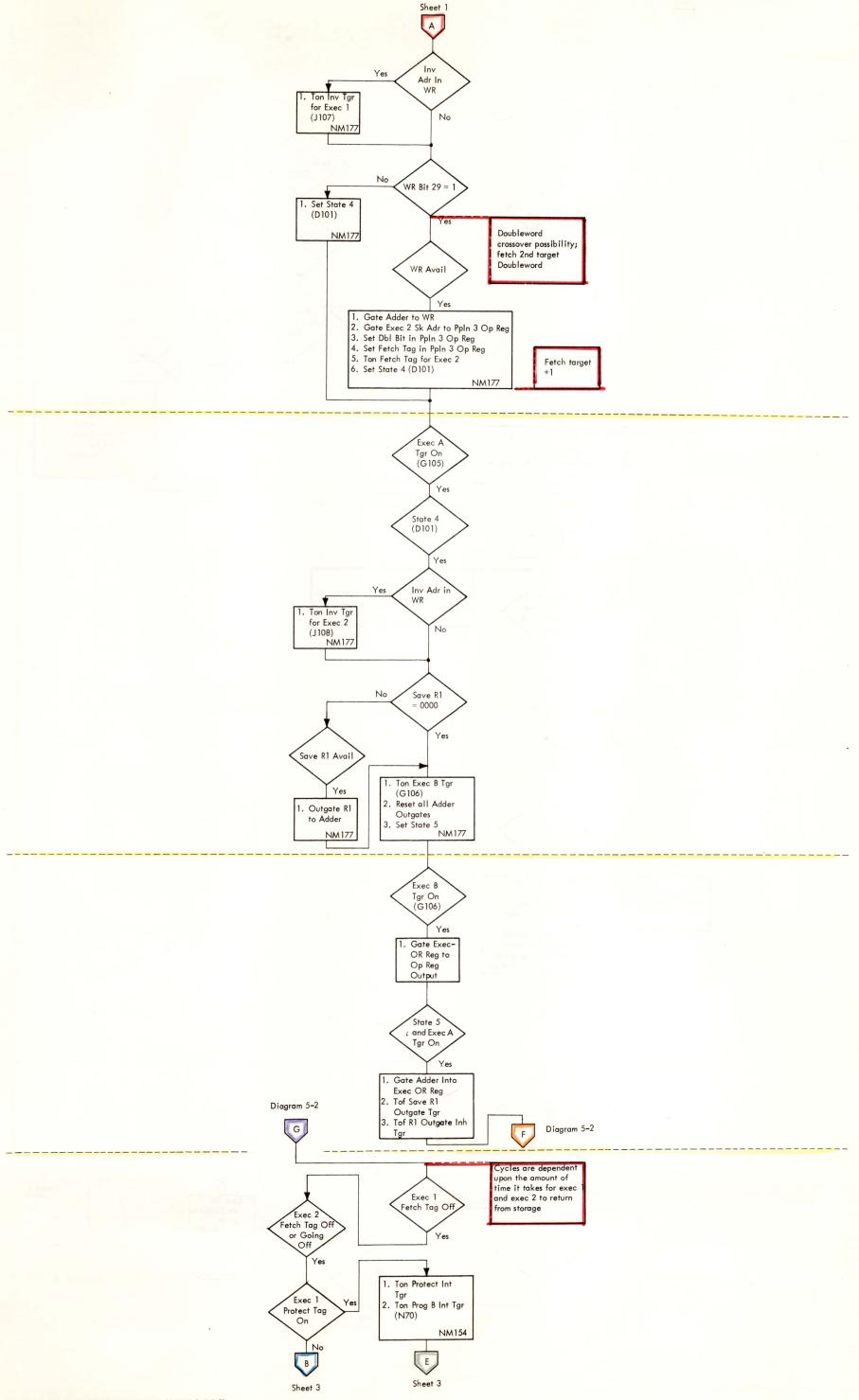

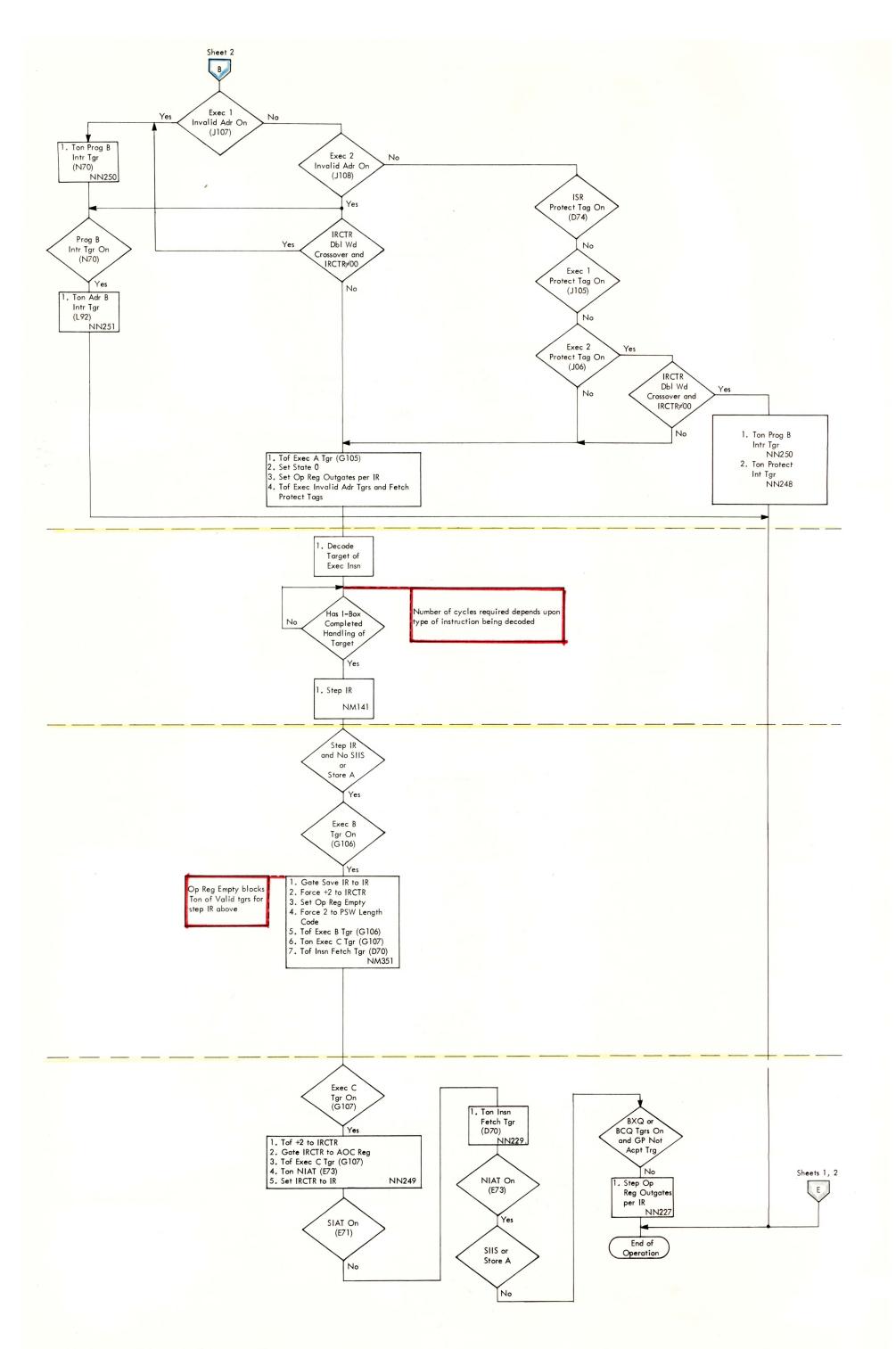

| 5-15    | Execute Sequence (3 sheets)                                  | 5-126   | · ·                                             |

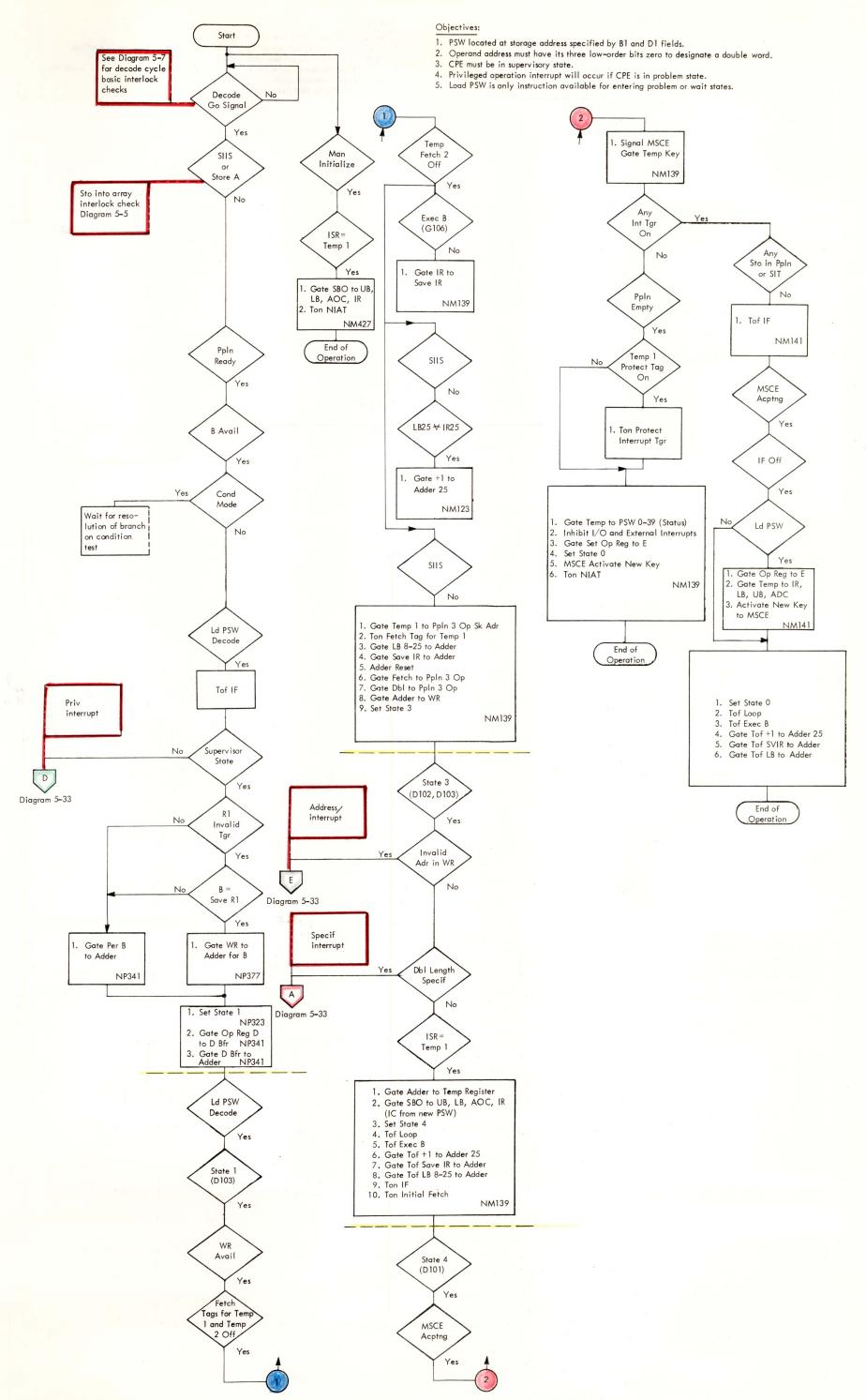

| 5-16    | Load PSW Sequence                                            | 5-127   | VFL Controls                                    |

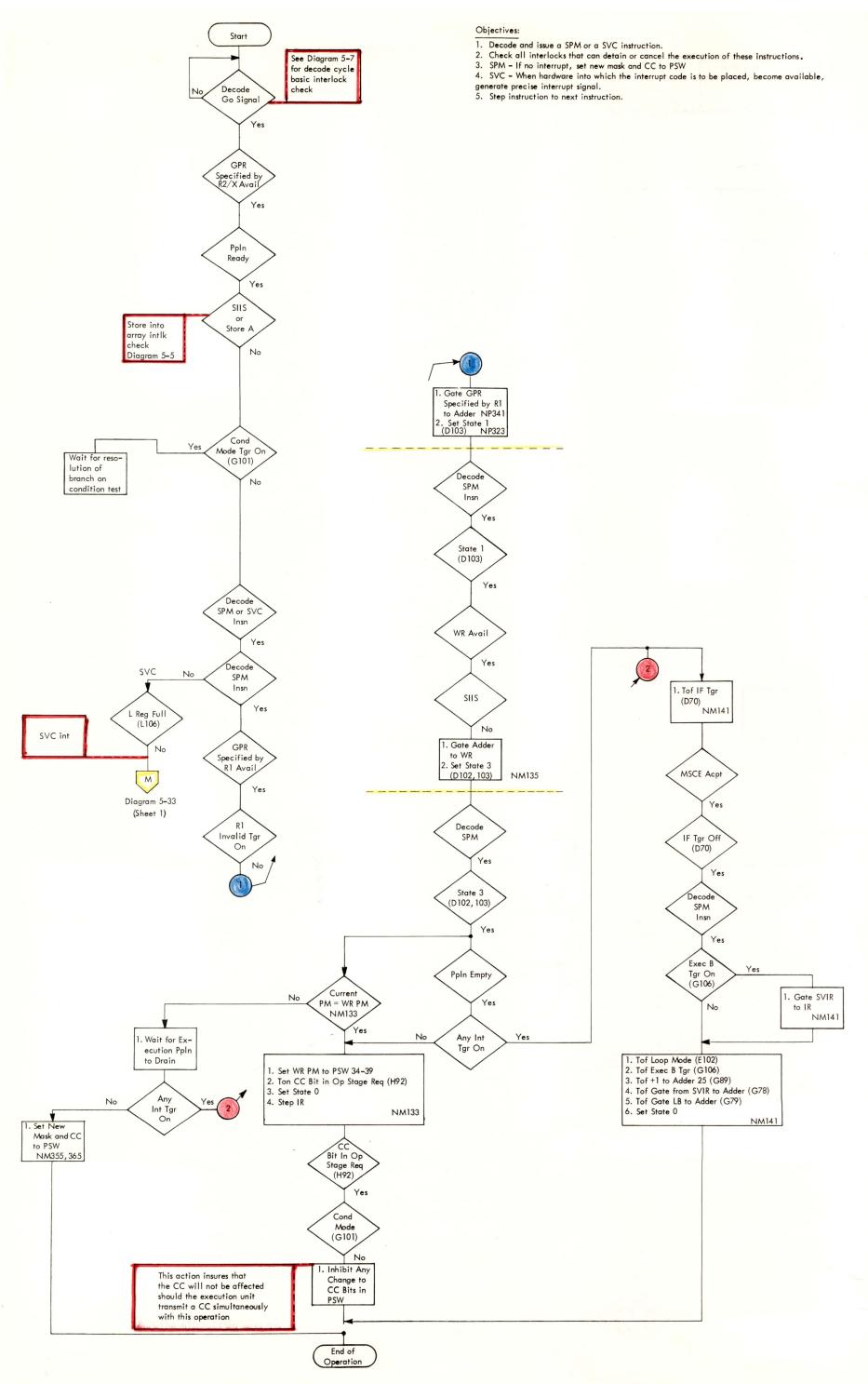

| 5-17    | Set Program Mask and Supervisor Call Sequence                | 5-128   | Block Operation                                 |

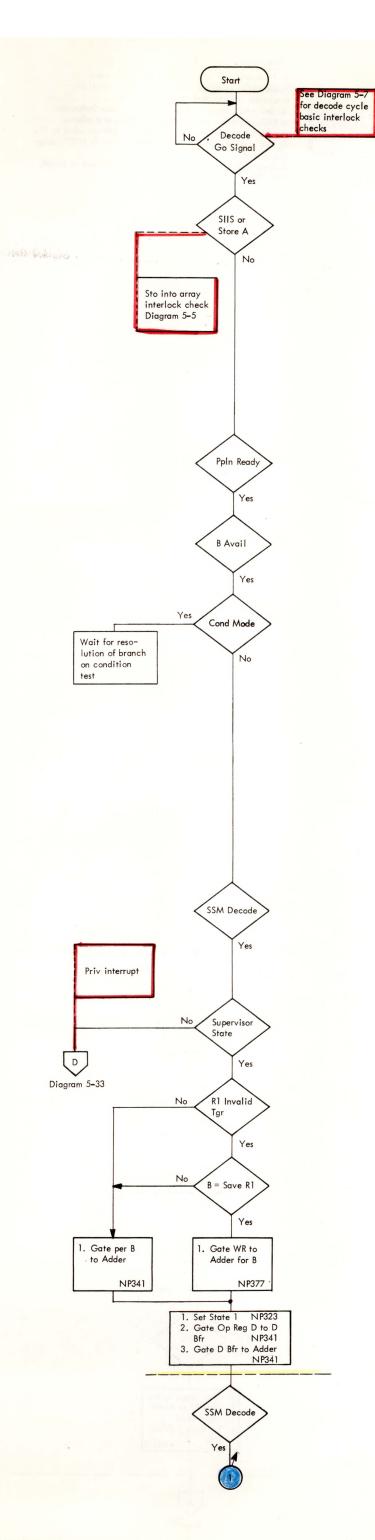

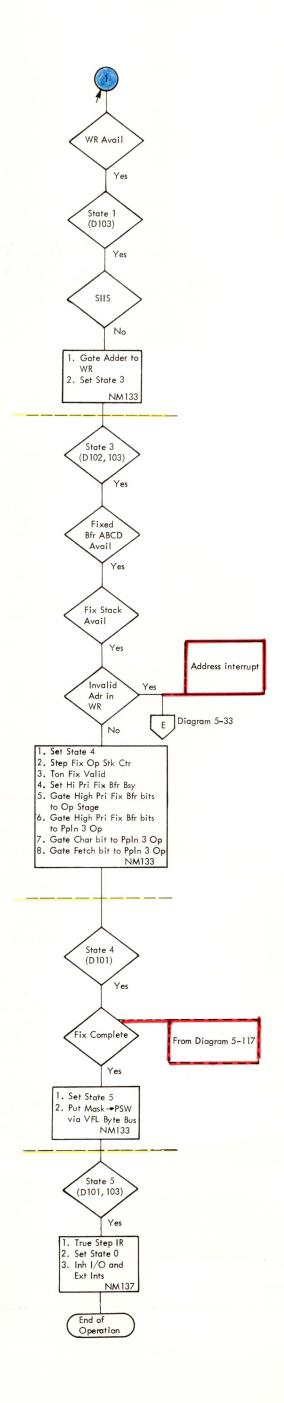

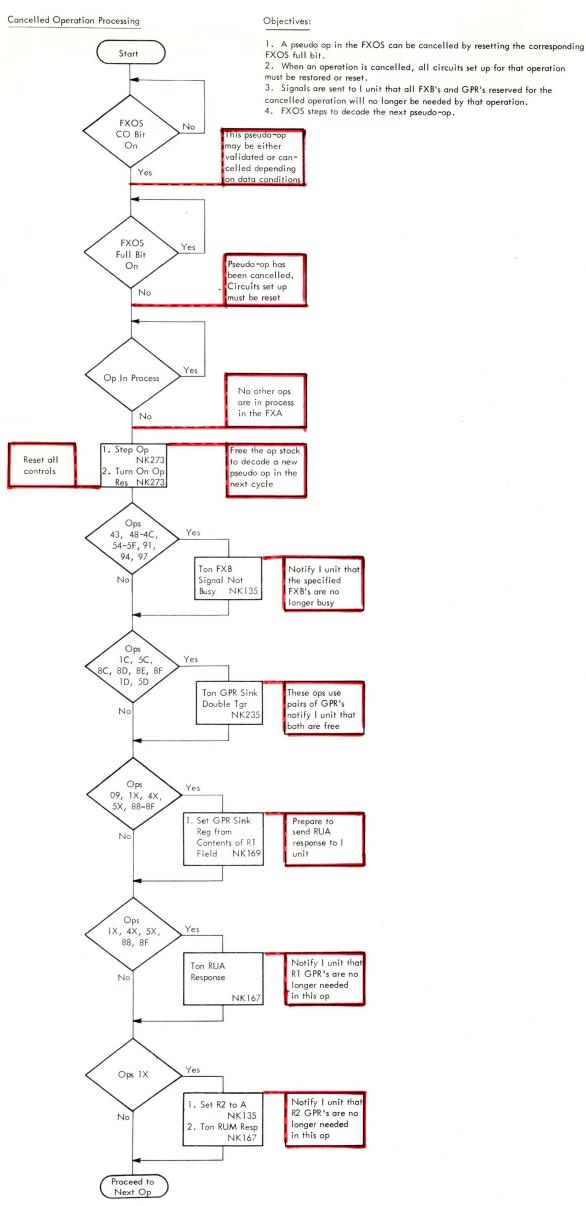

| 5-18    | Set System Mask Sequence                                     | 5-129   | Cancelled Operation Processing                  |

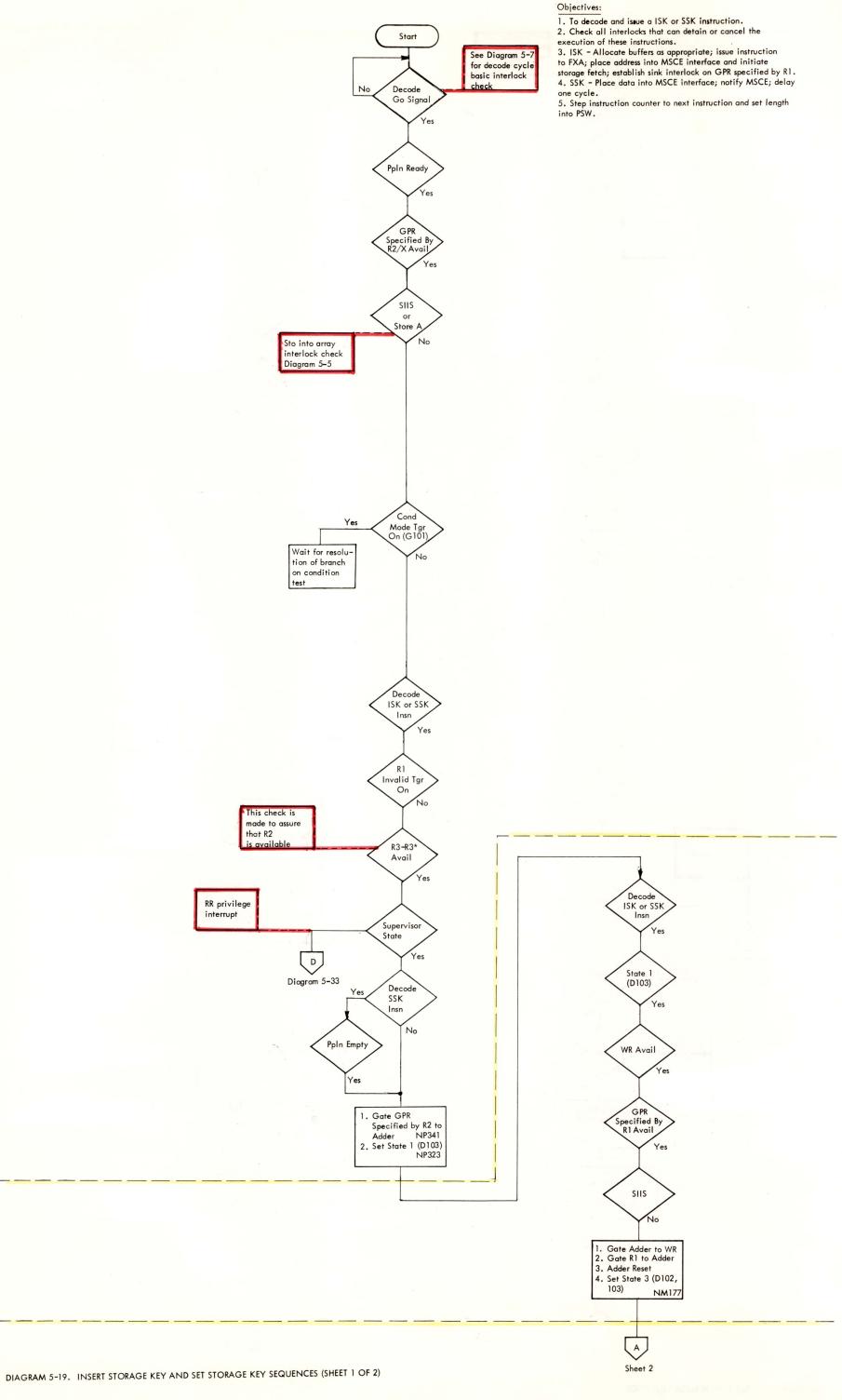

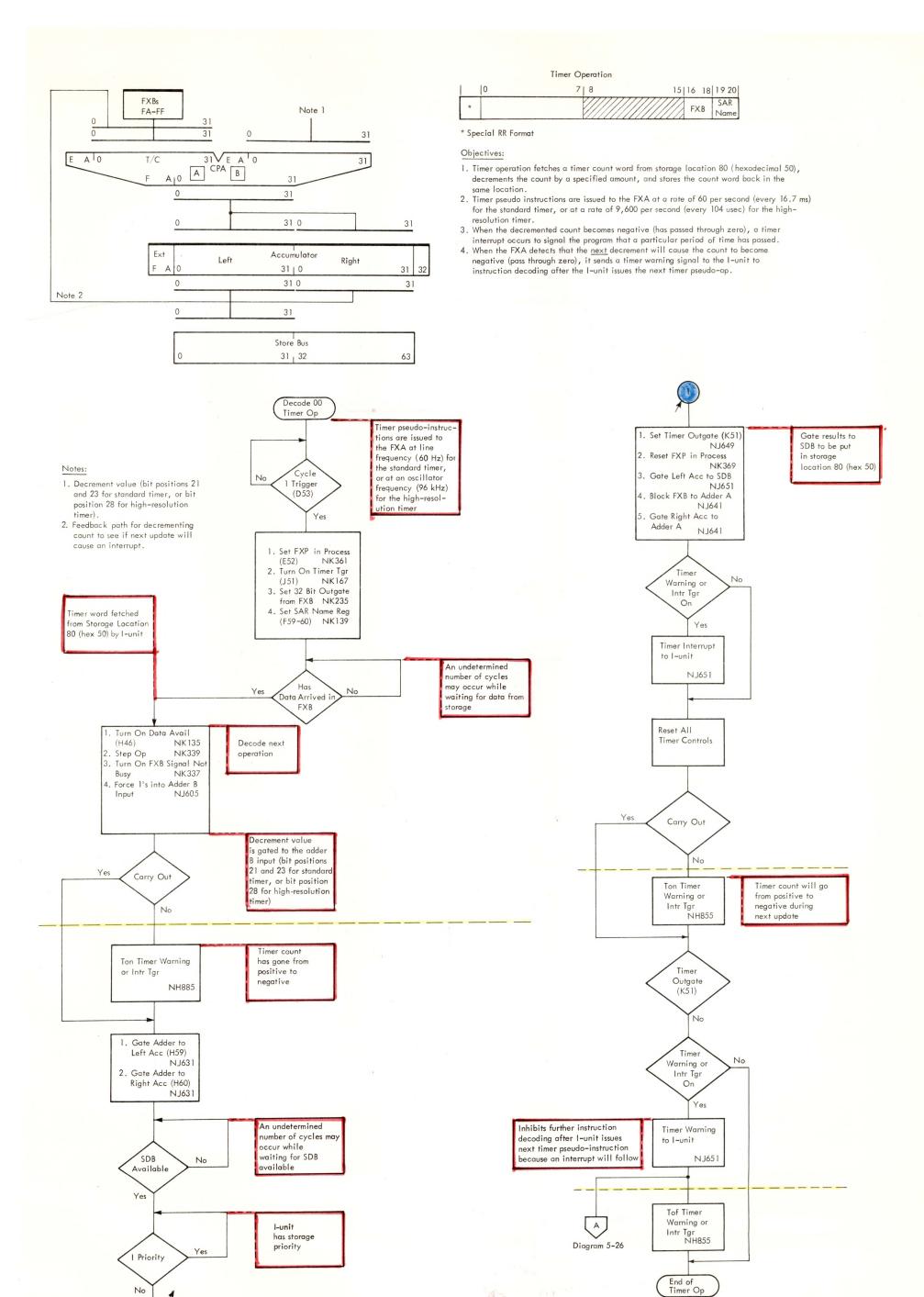

| 5-19    | Insert Storage Key and Set Storage Key Sequences (2 sheets)  | 5-130   | Timer Operation                                 |

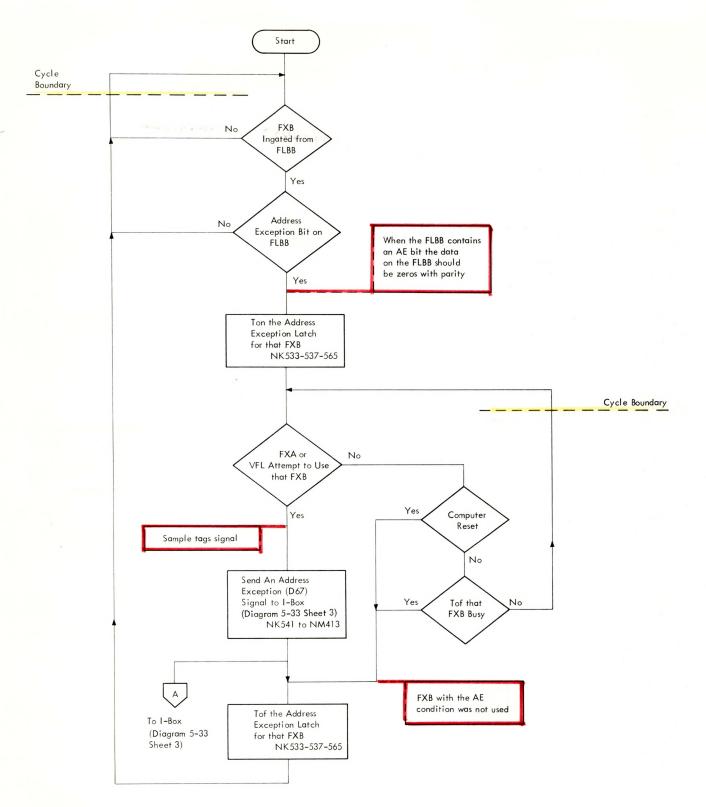

| 5-20    | Read, Write Direct Sequence                                  | 5-131   | Address Exception Interrupt                     |

| 5-21    | Diagnose Sequence                                            | 5-132   | Fixed-Point Trigger List (3 sheets)             |

| 5-22    | Insert Character, Store Character, and Test and Set Sequence |         | 35 ( ,                                          |

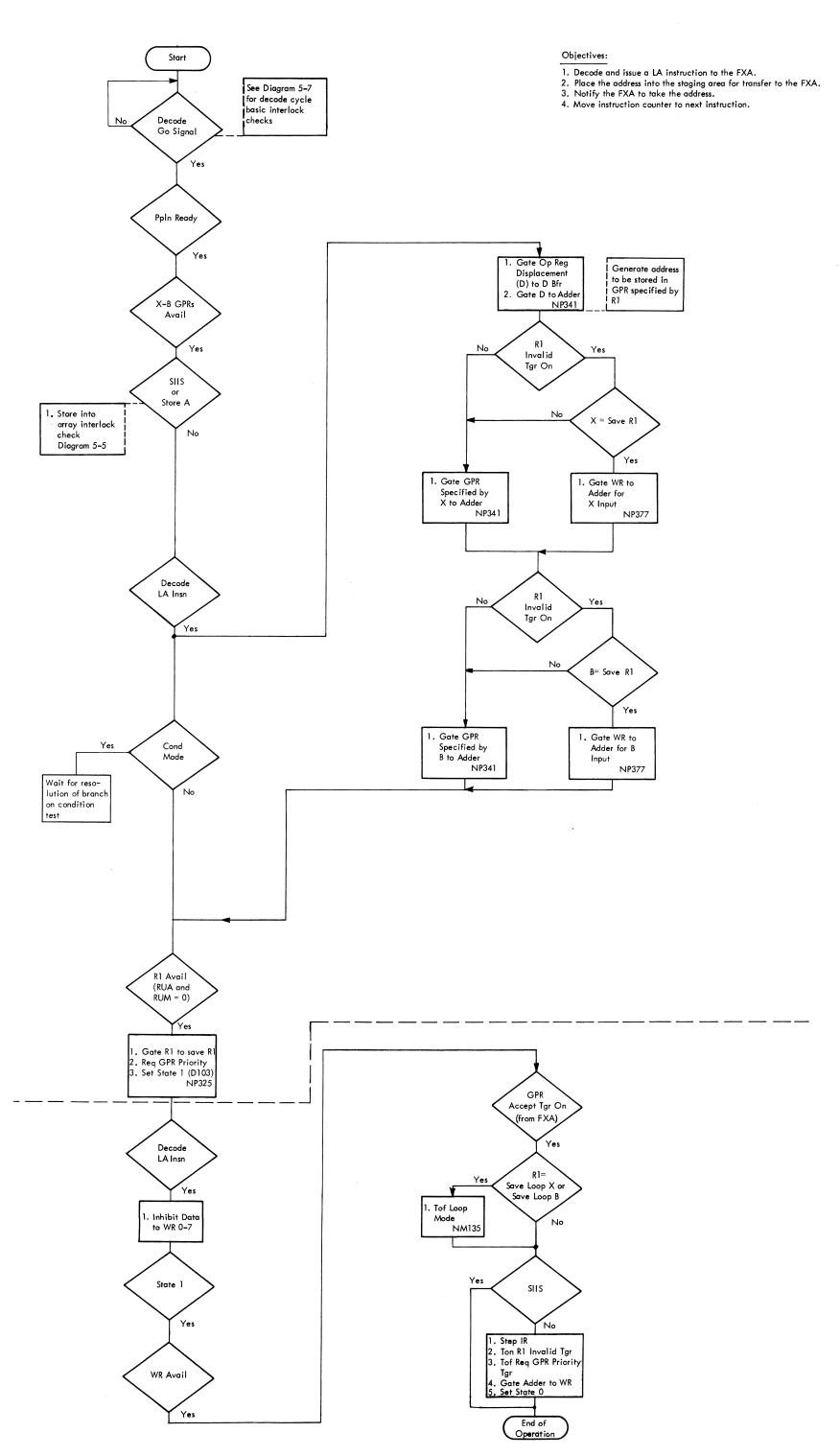

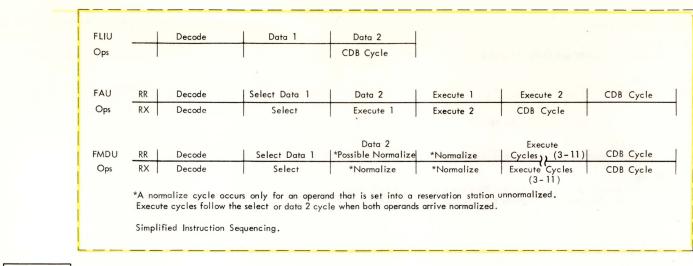

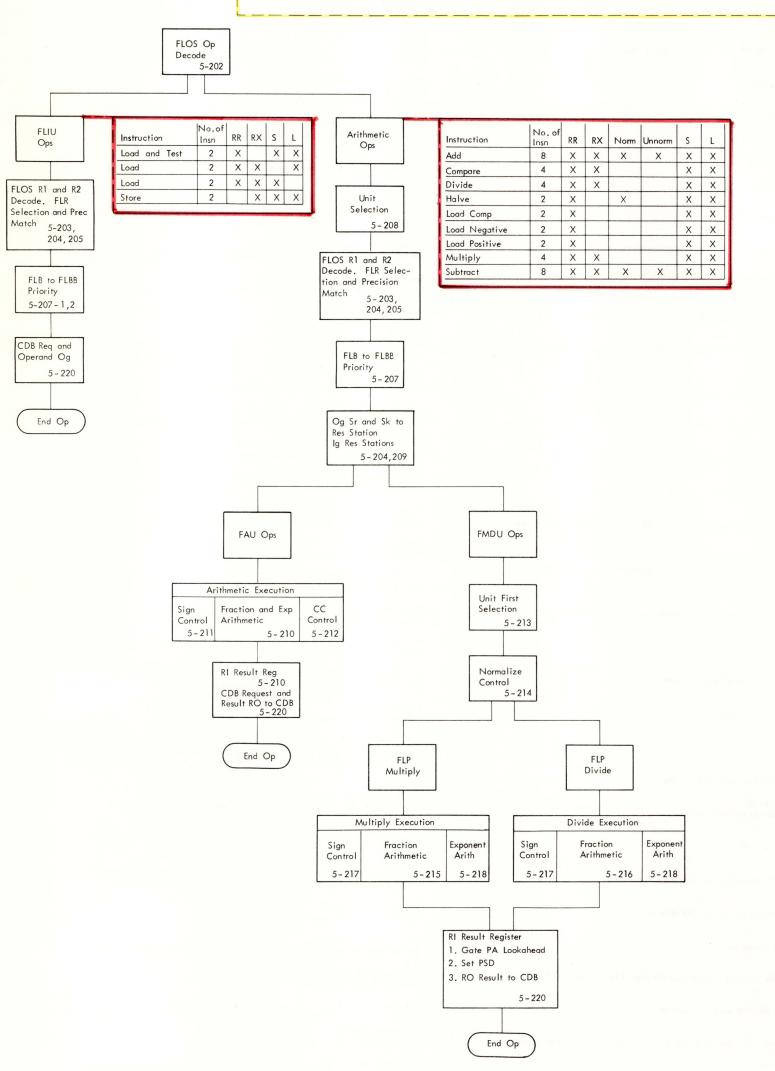

| 5-23    | Load Address Sequence                                        | FIOATI  | ING-POINT OPERATIONS                            |

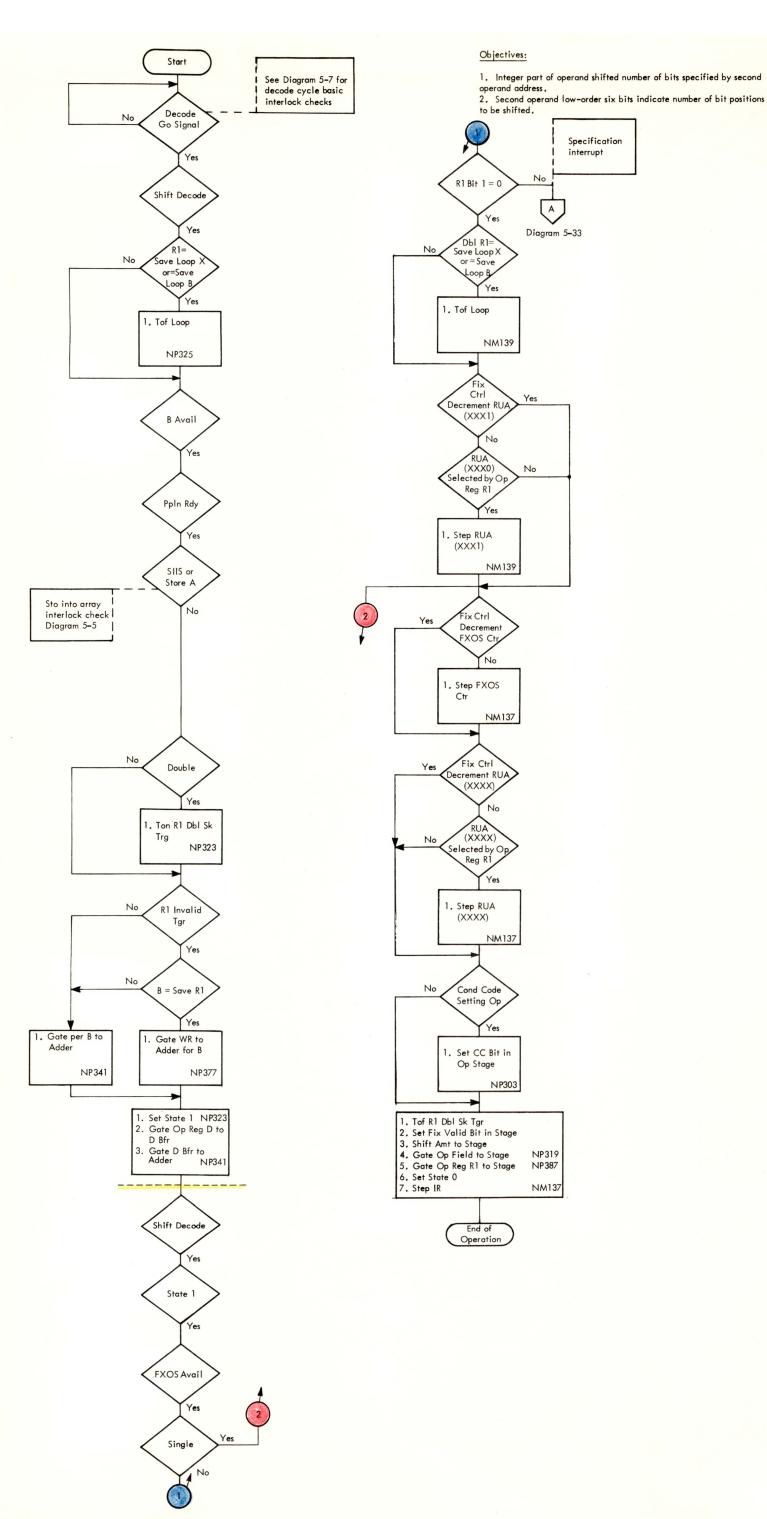

| 5-24    | Shift Sequence                                               | ILOAII  | ING-FORT CIERATIONS                             |

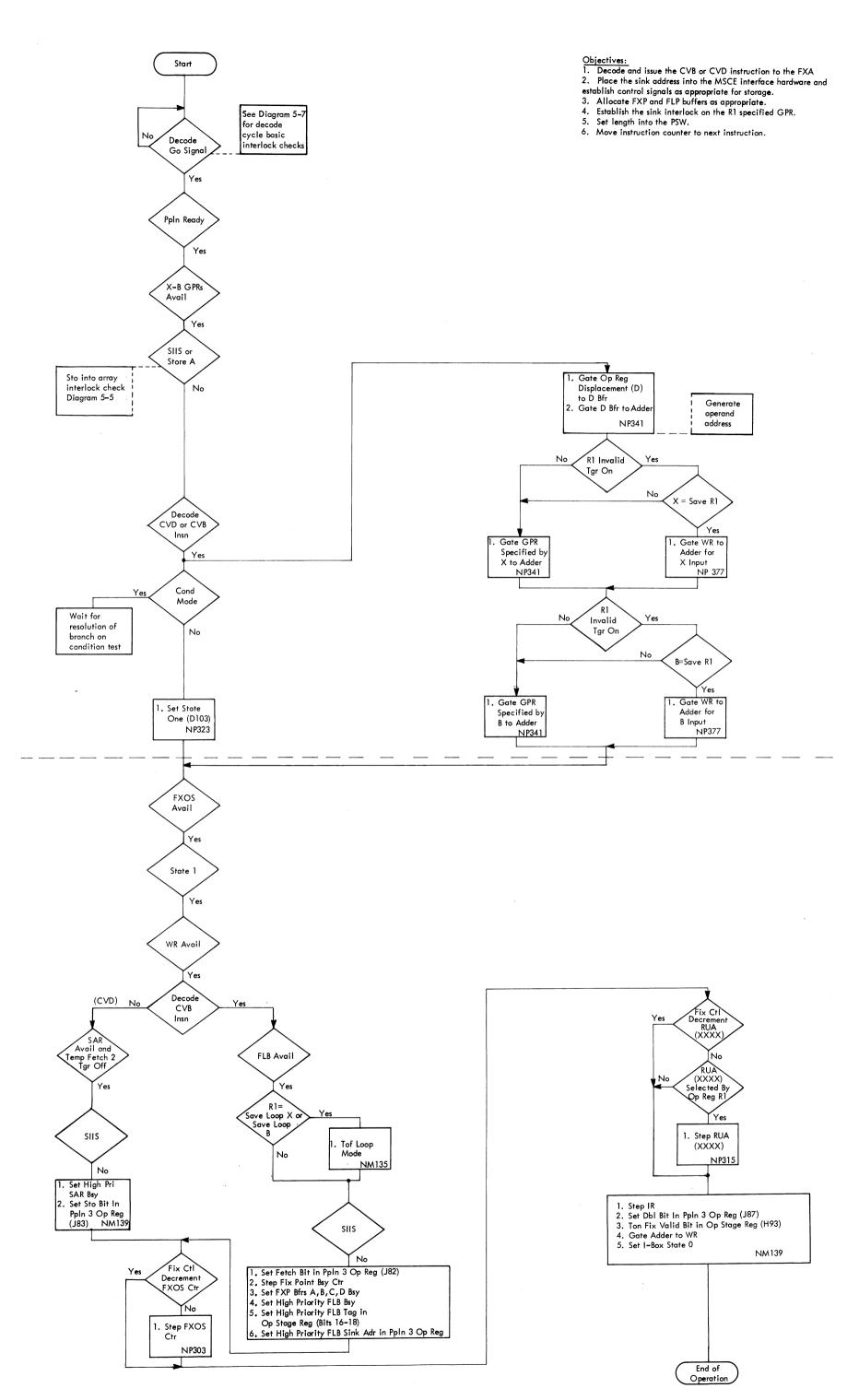

| 5-25    | Convert Sequence                                             | 5-200   | Floating-Point Operation                        |

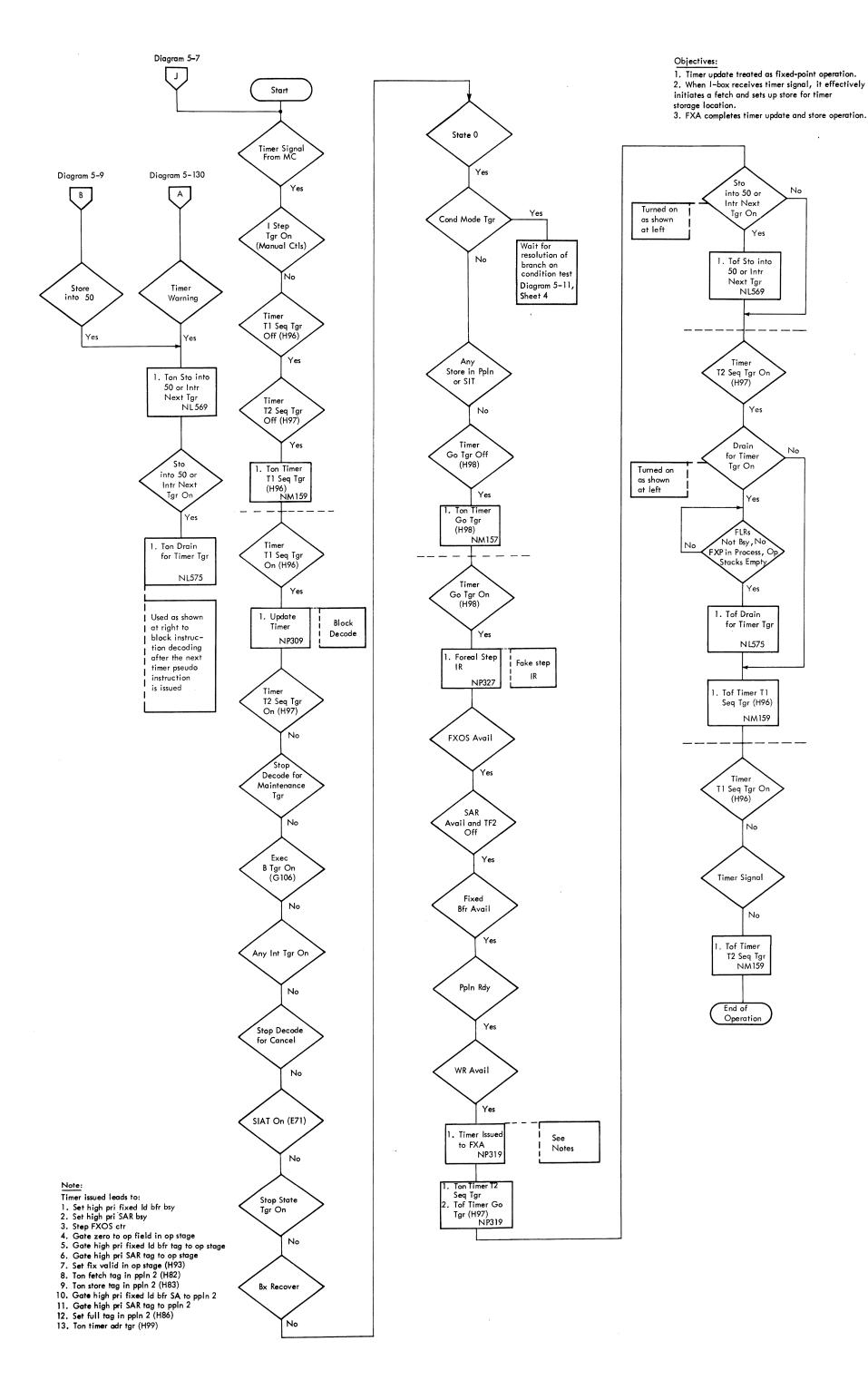

| 5-26    | Timer Update Sequence                                        | 5-201   | FLOS Controls                                   |

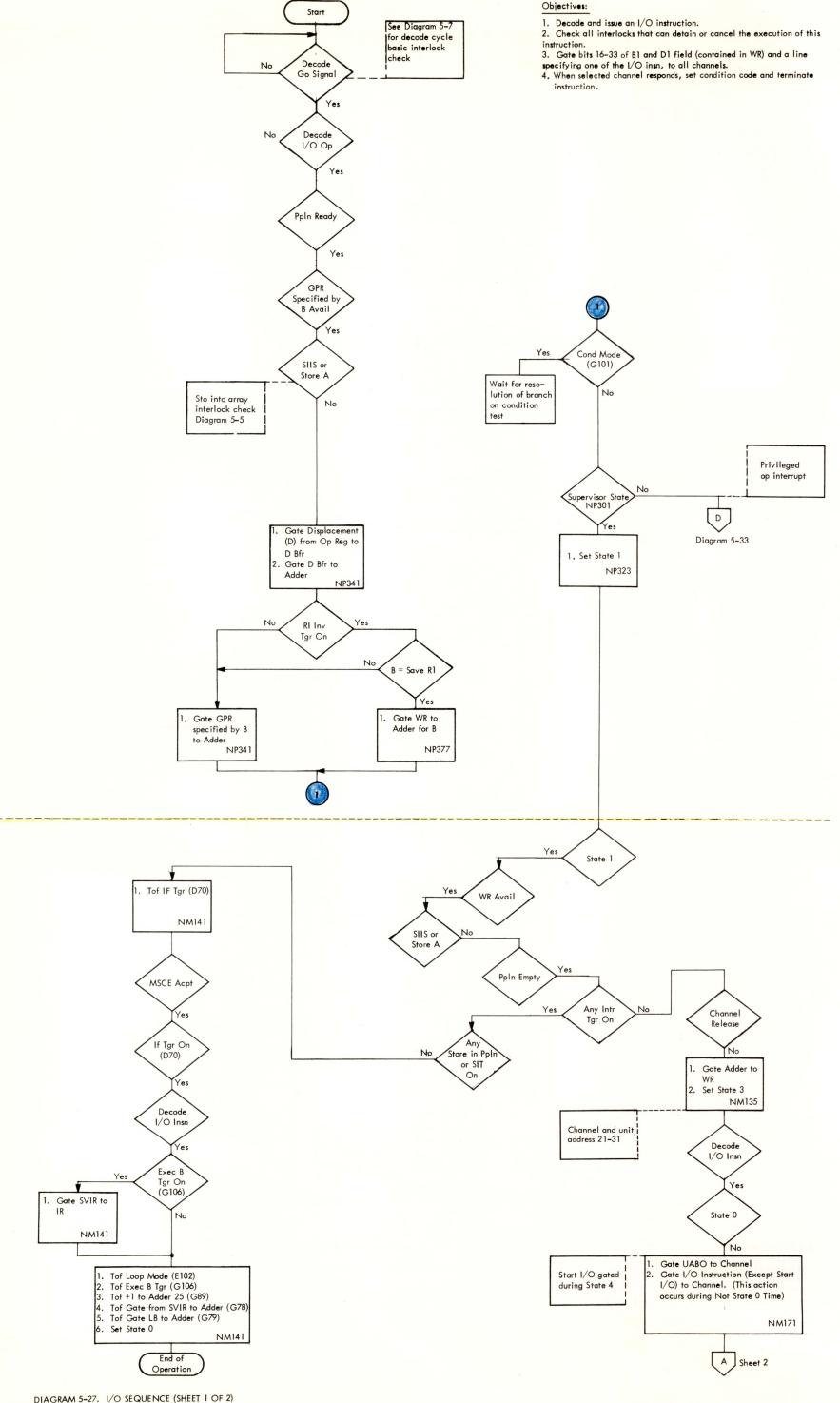

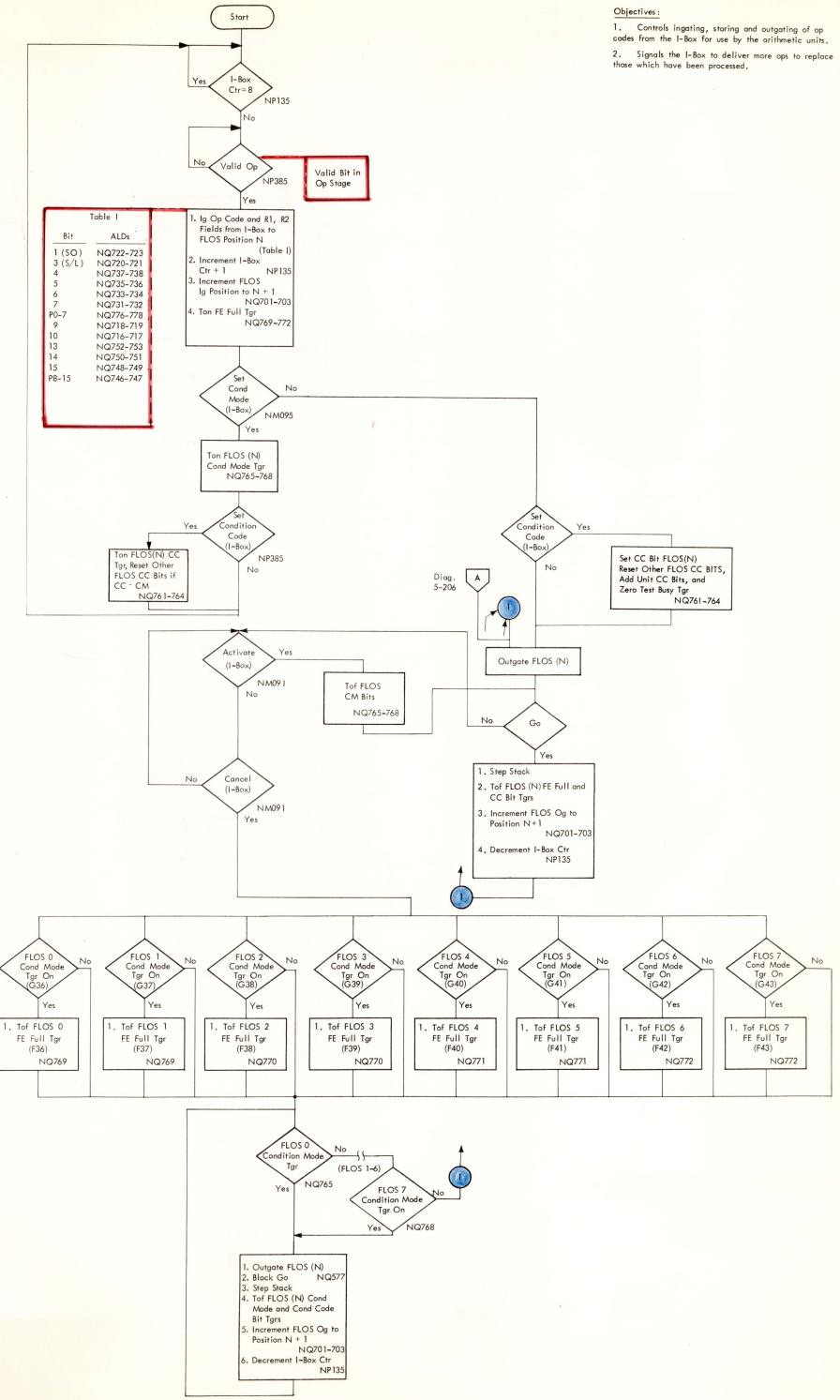

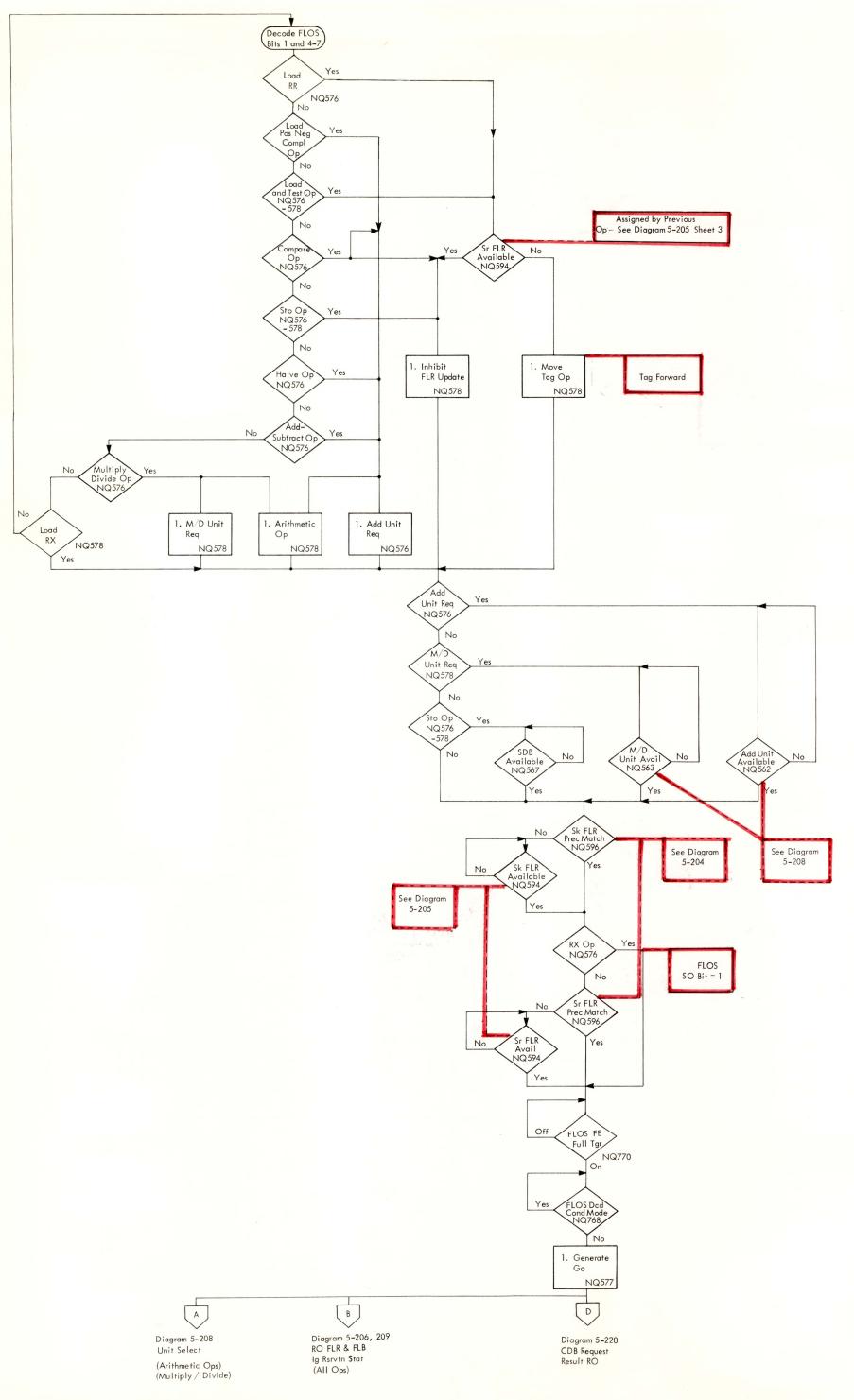

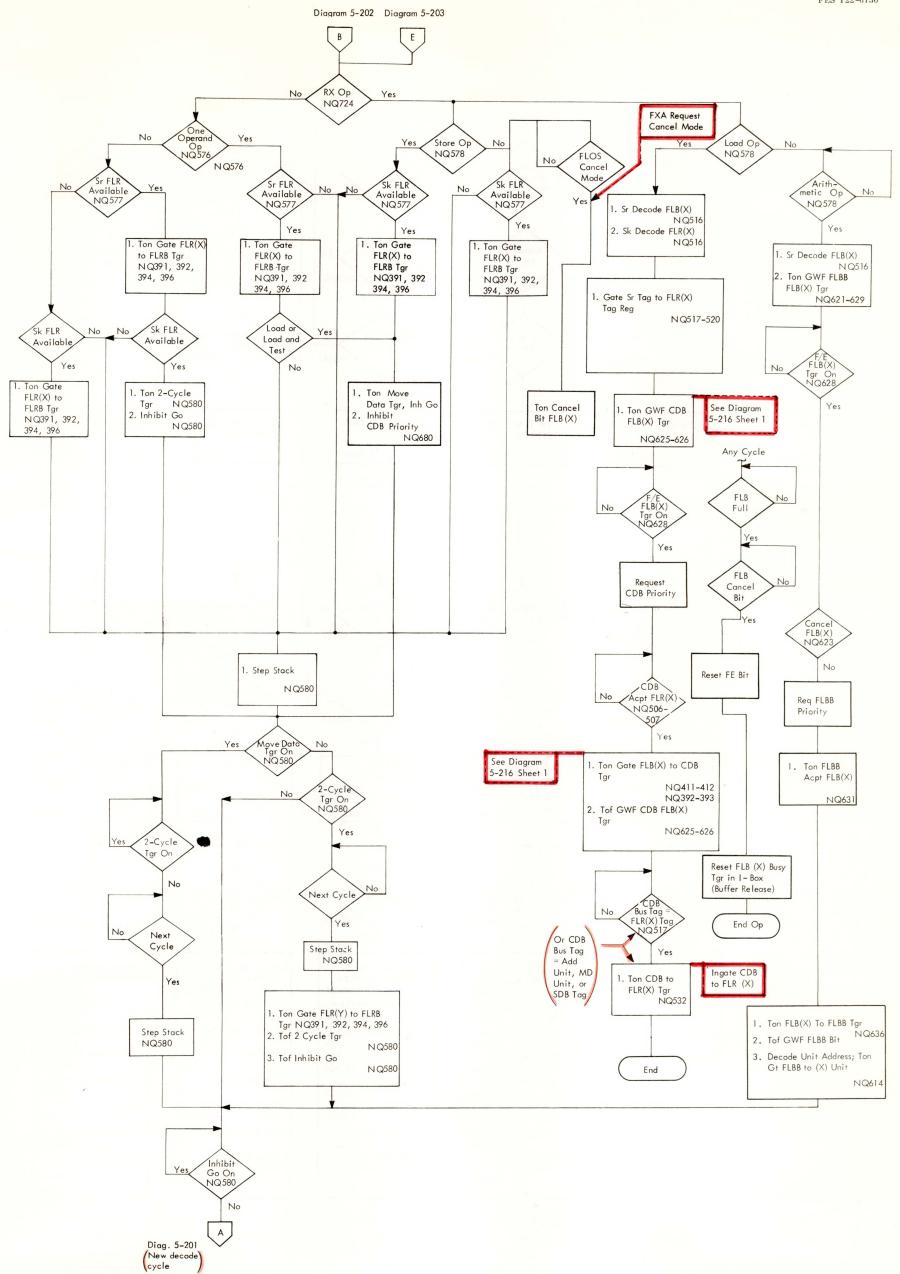

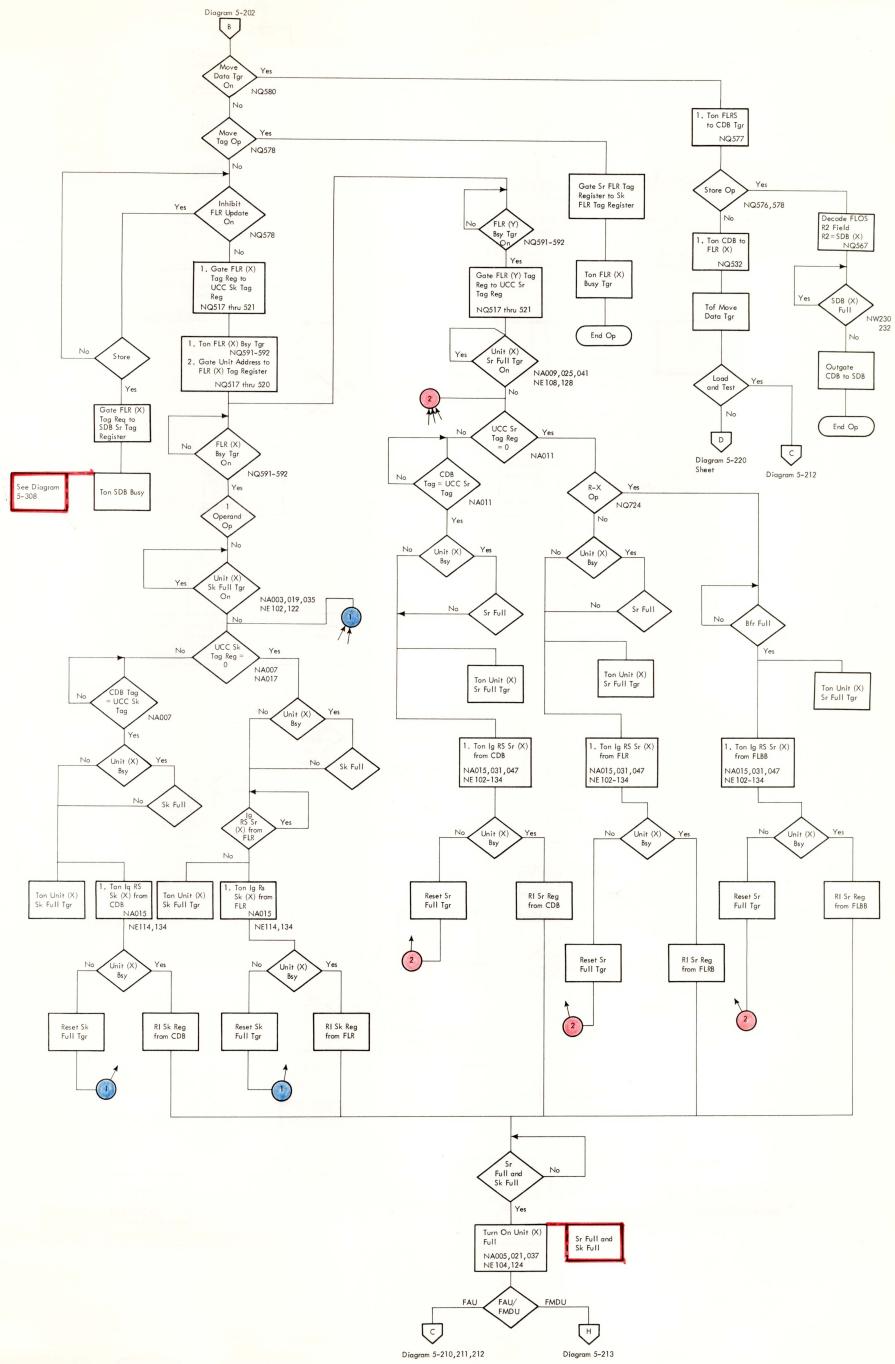

| 5-27    | I/O Sequence (2 sheets)                                      | 5-202   | FLOS OP Decode-Go Generation                    |

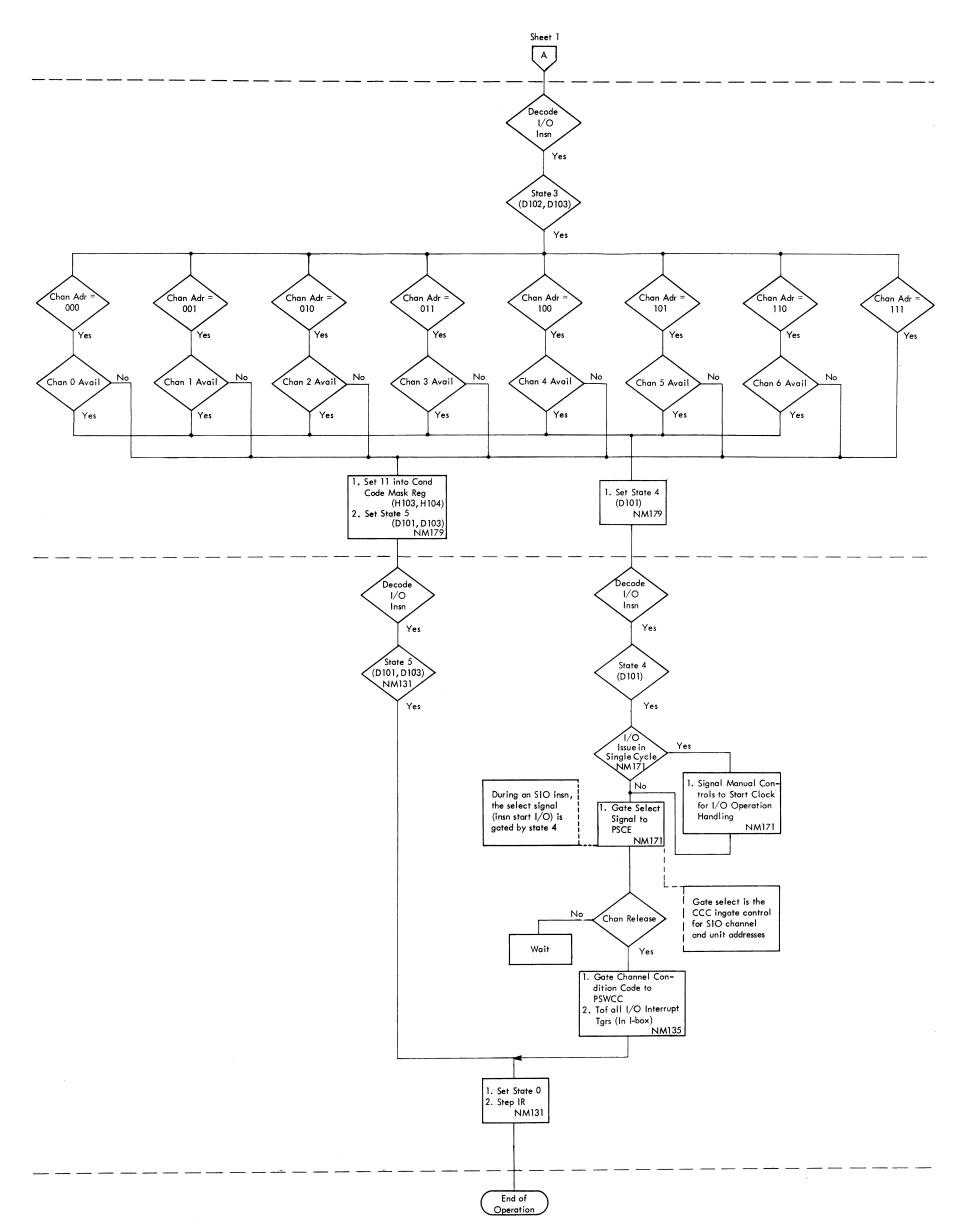

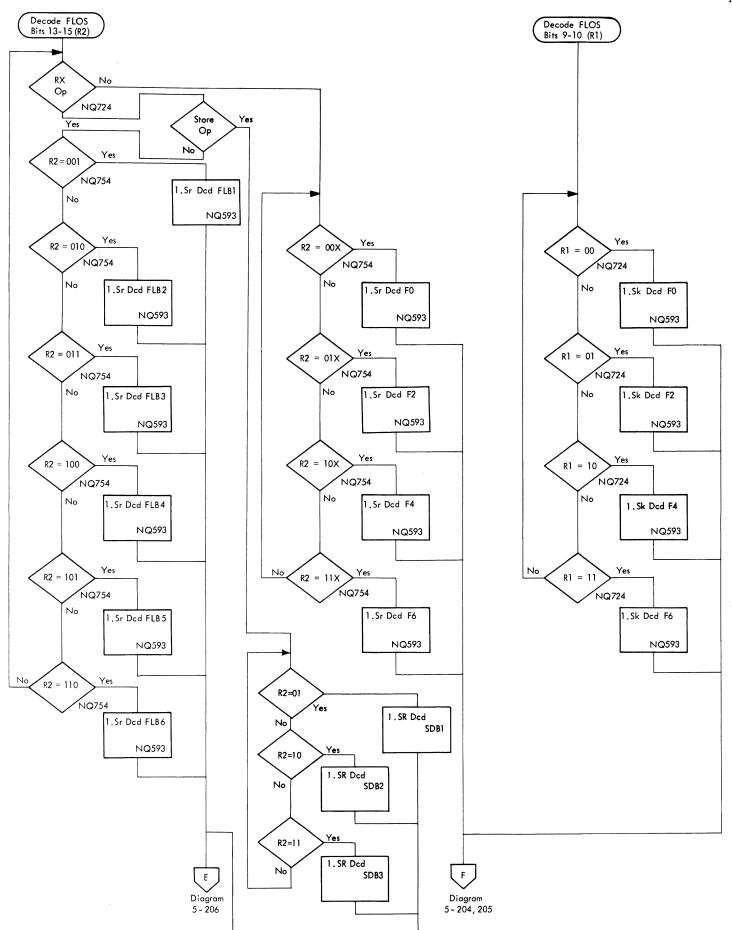

| 5-28    | LM, STM Sequence (3 sheets)                                  | 5-203   | FLOS R1 and R2 Decode                           |

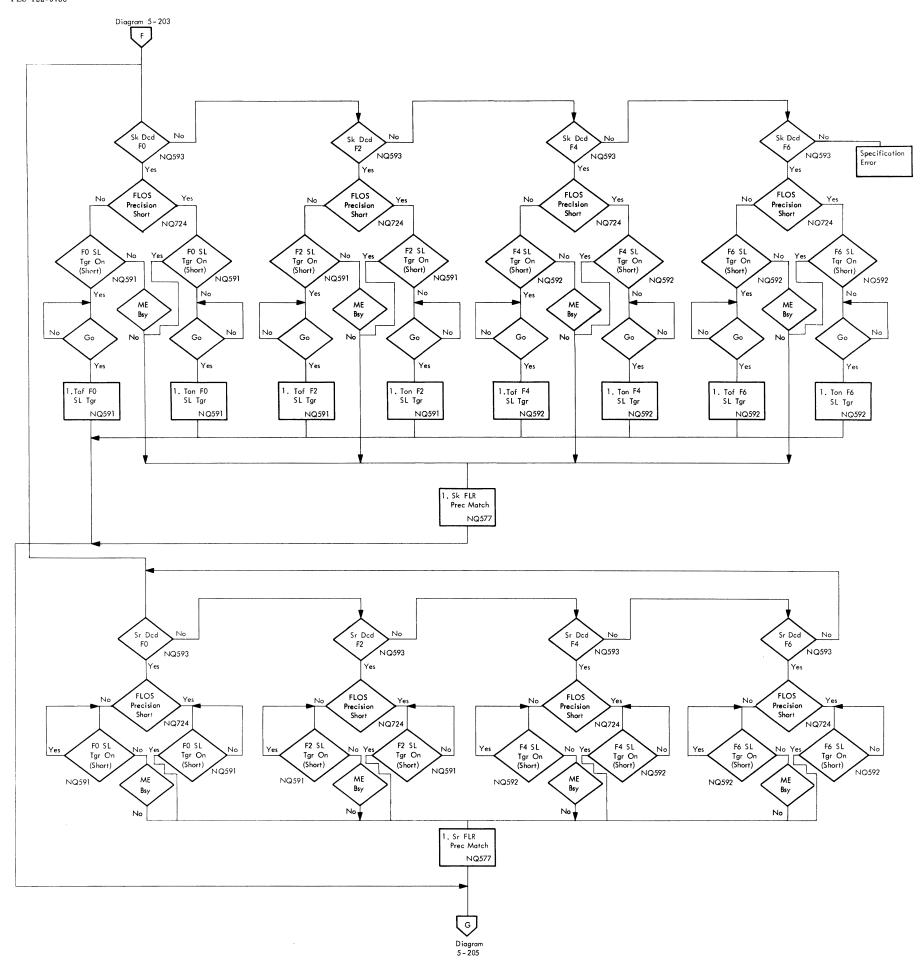

| 5-29    | TR, TRT Sequence (5 sheets)                                  | 5-204   | FLR Precision Match                             |

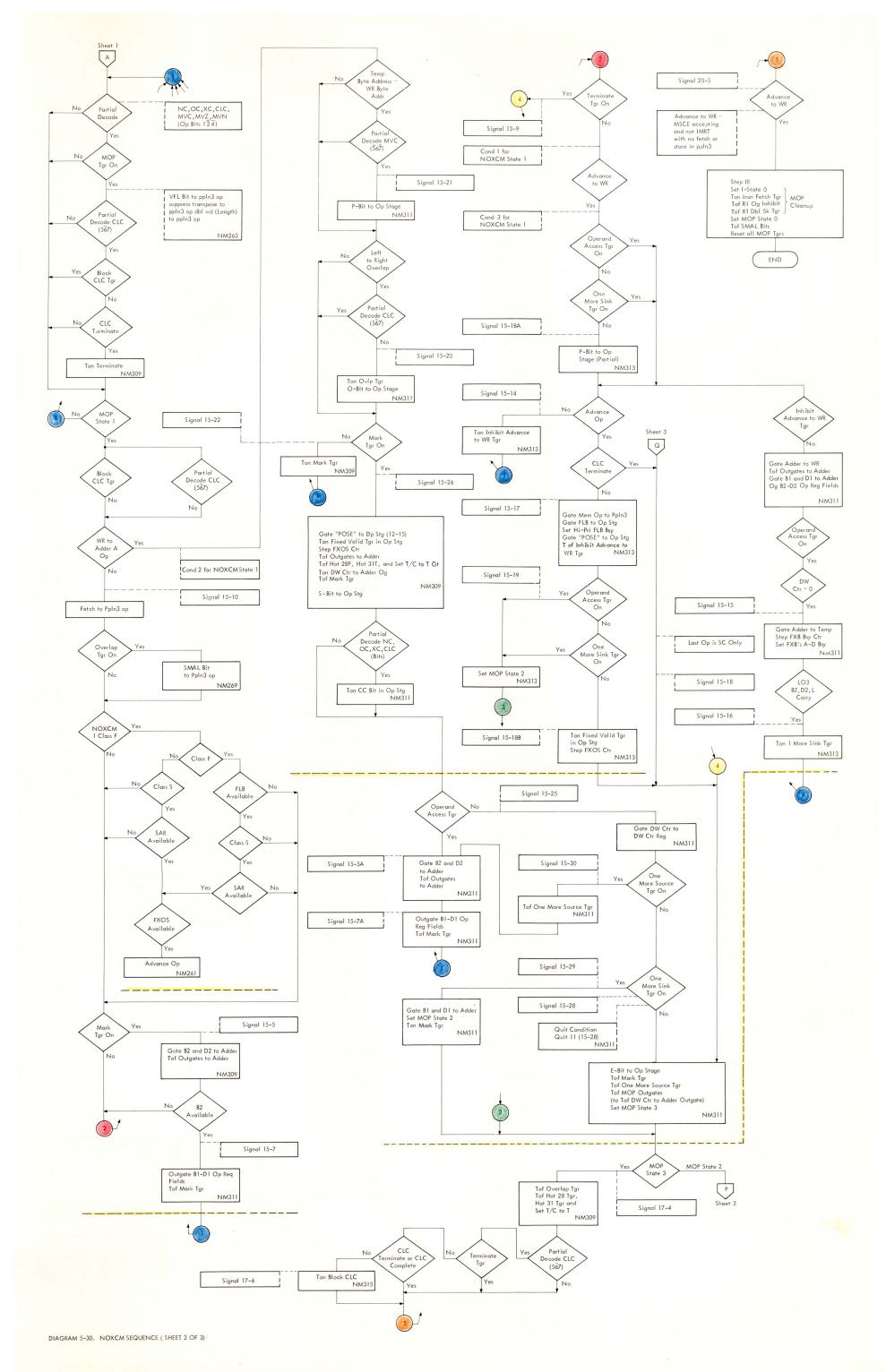

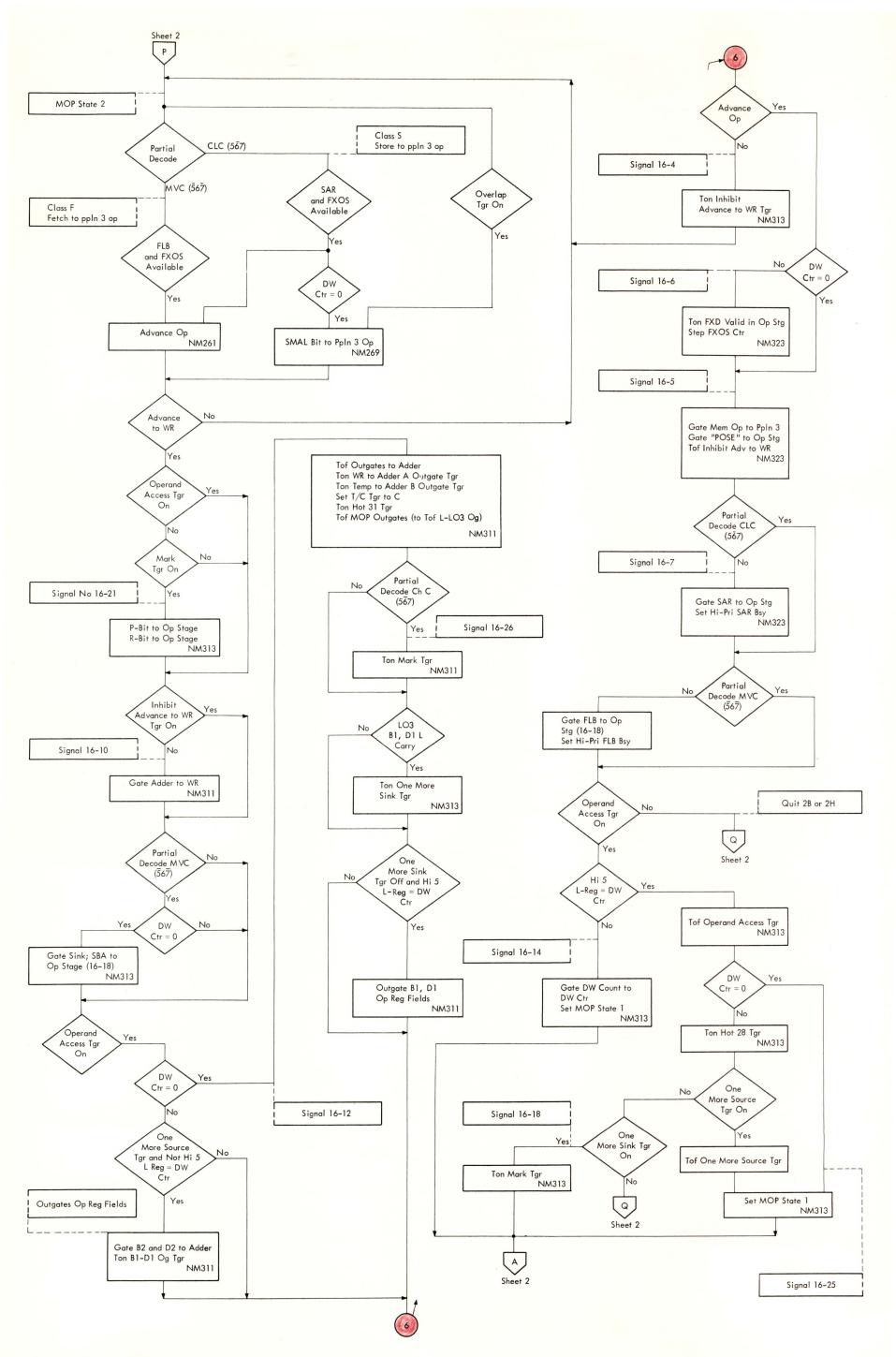

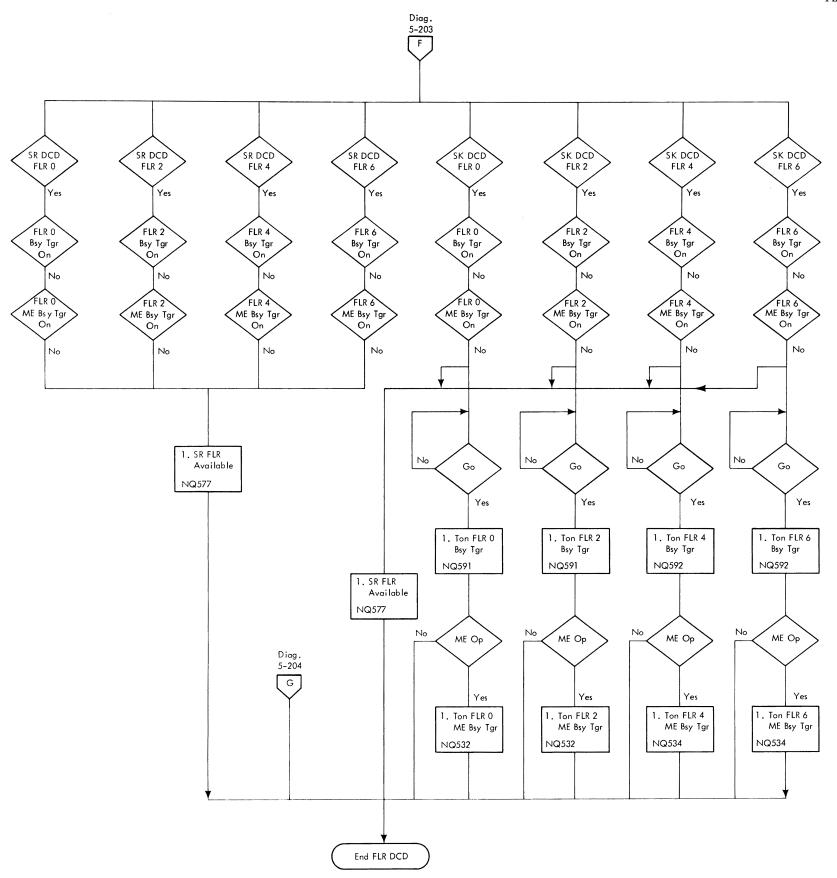

| 5-30    | NOXCM Sequence (3 sheets)                                    | 5-205   | FLR Availability                                |

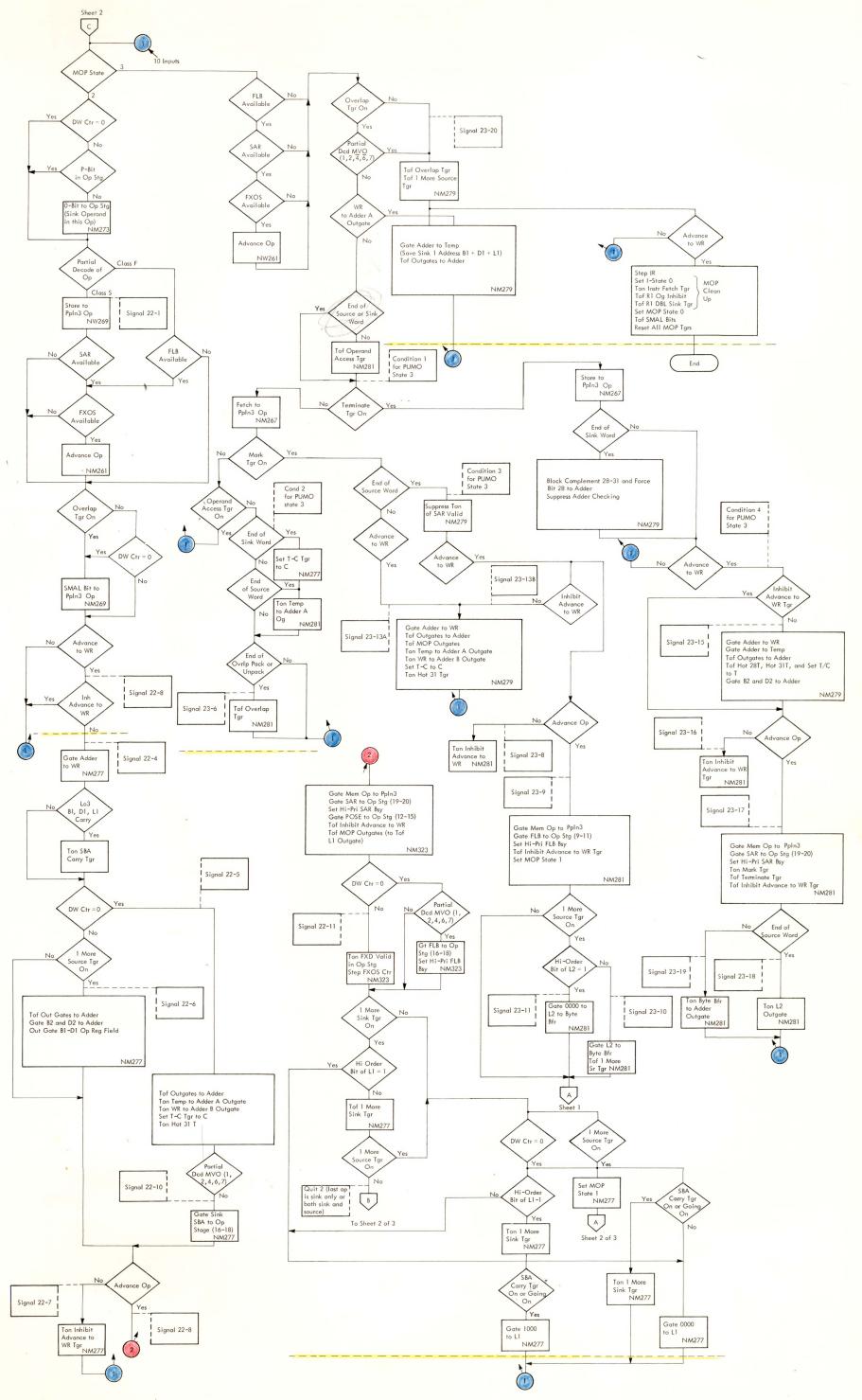

| 5-31    | PUMO Sequence (3 sheets)                                     | 5-206   | FLR Outgating                                   |

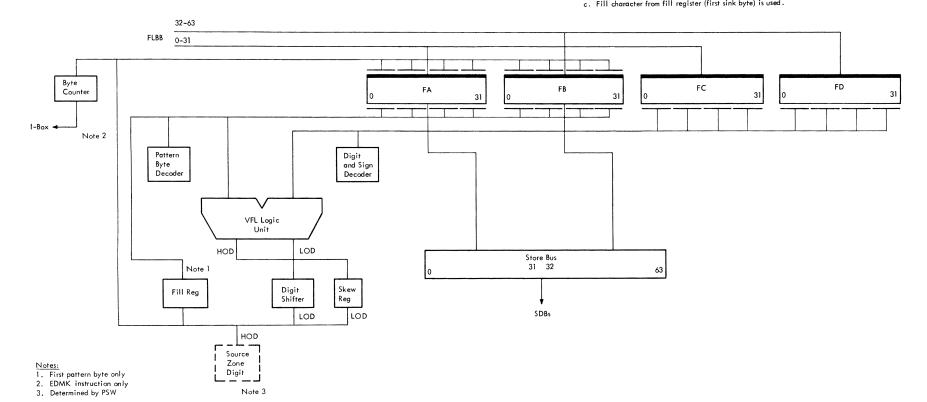

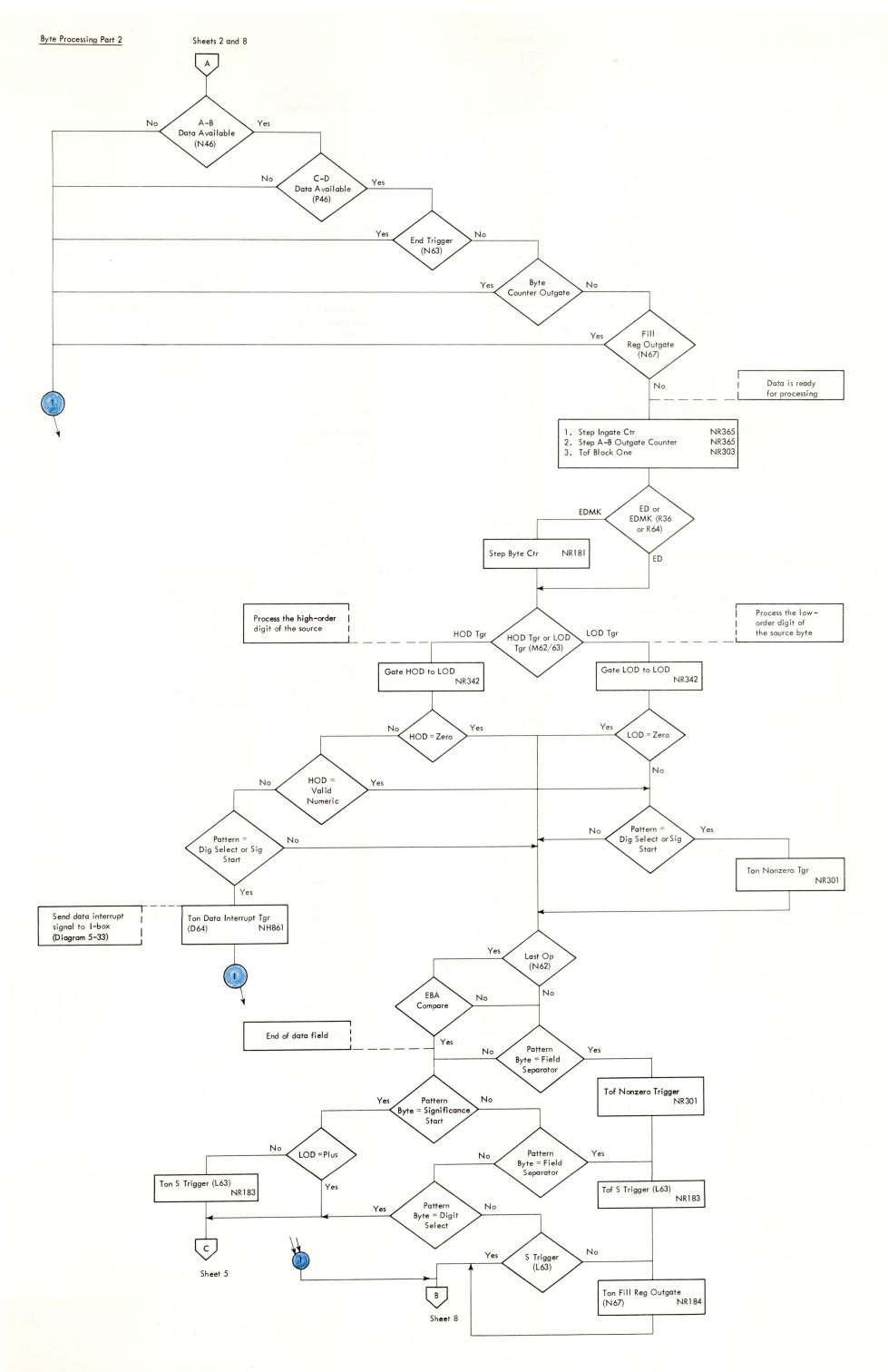

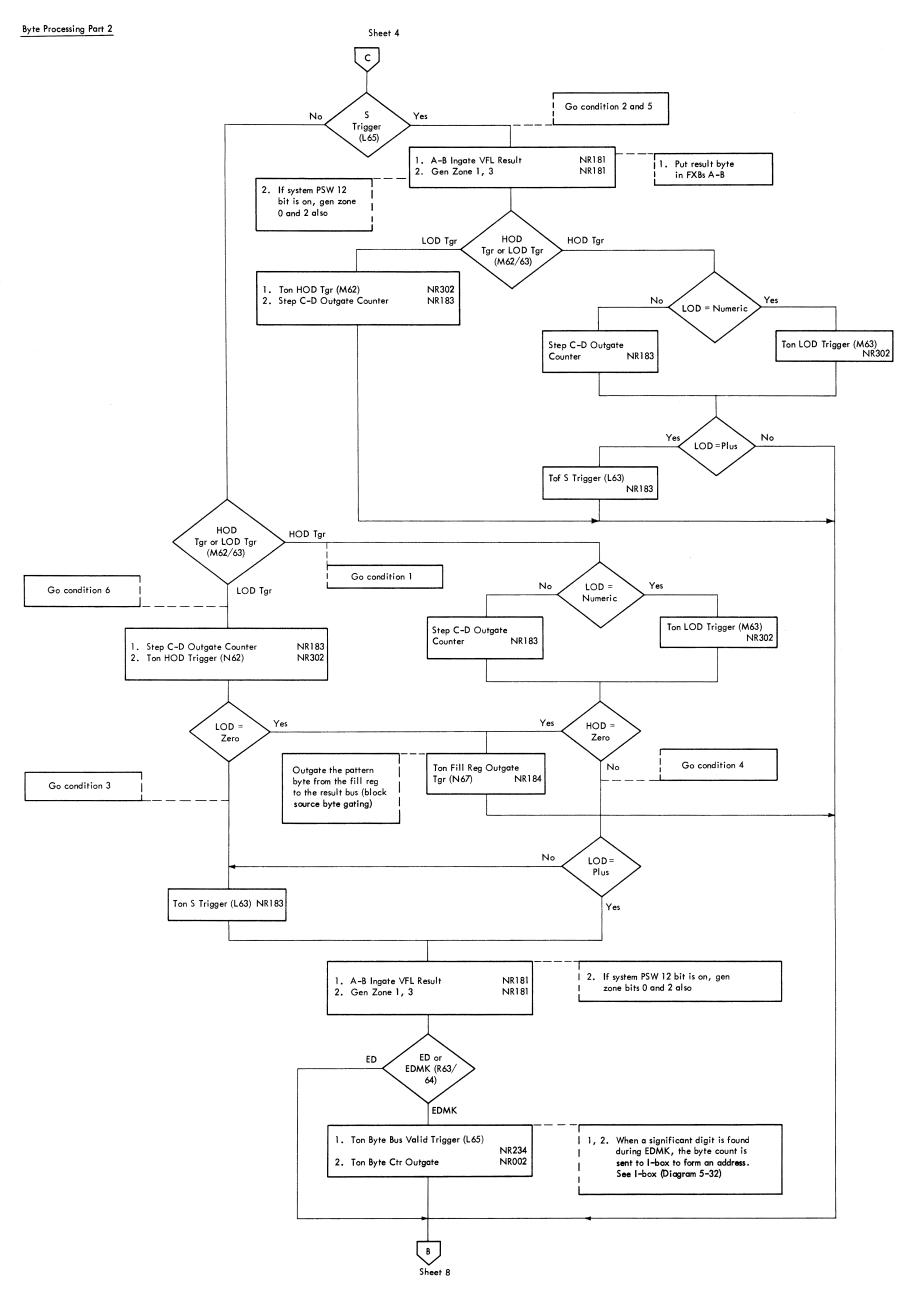

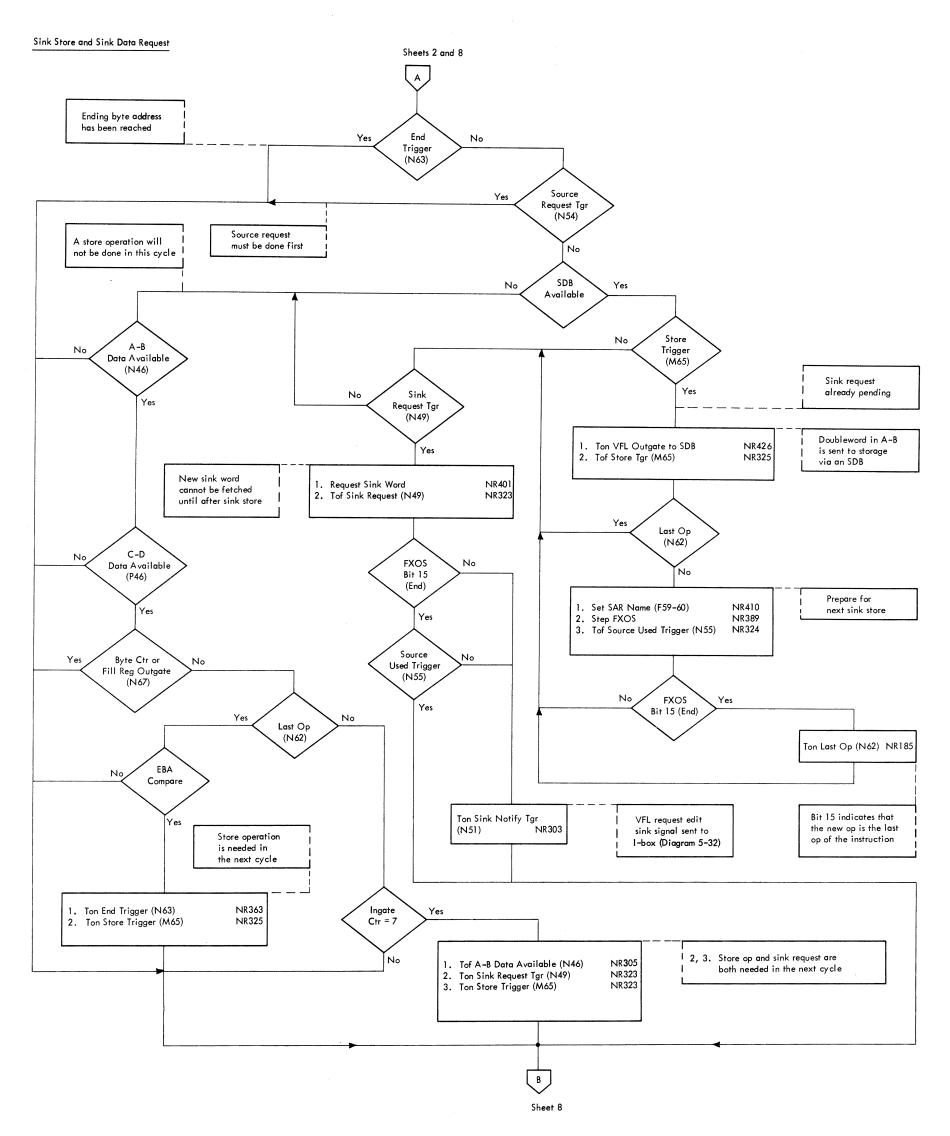

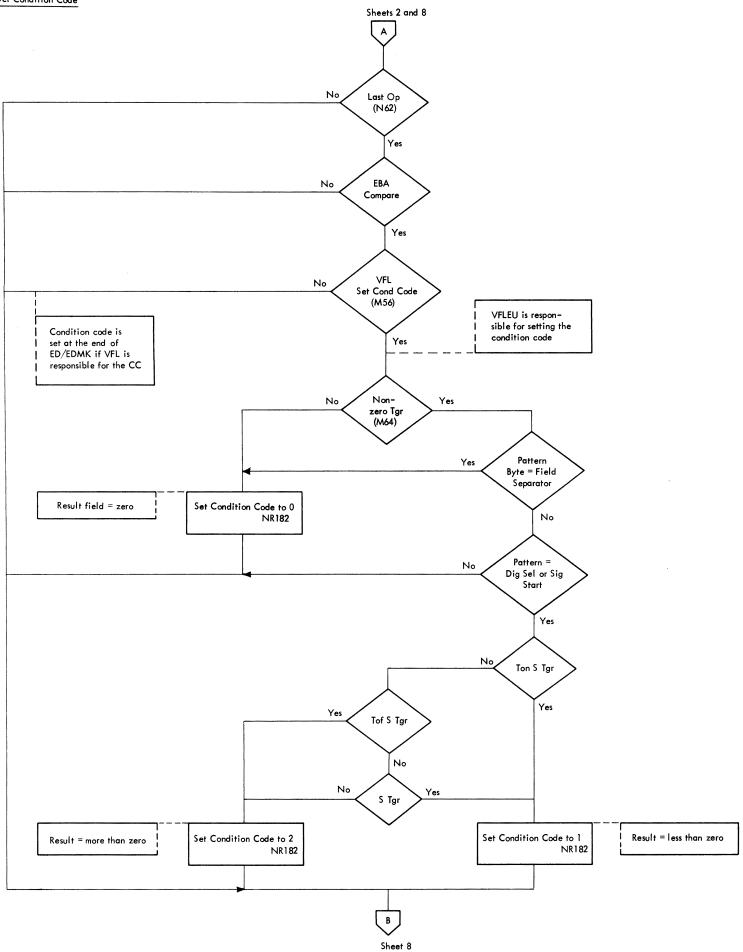

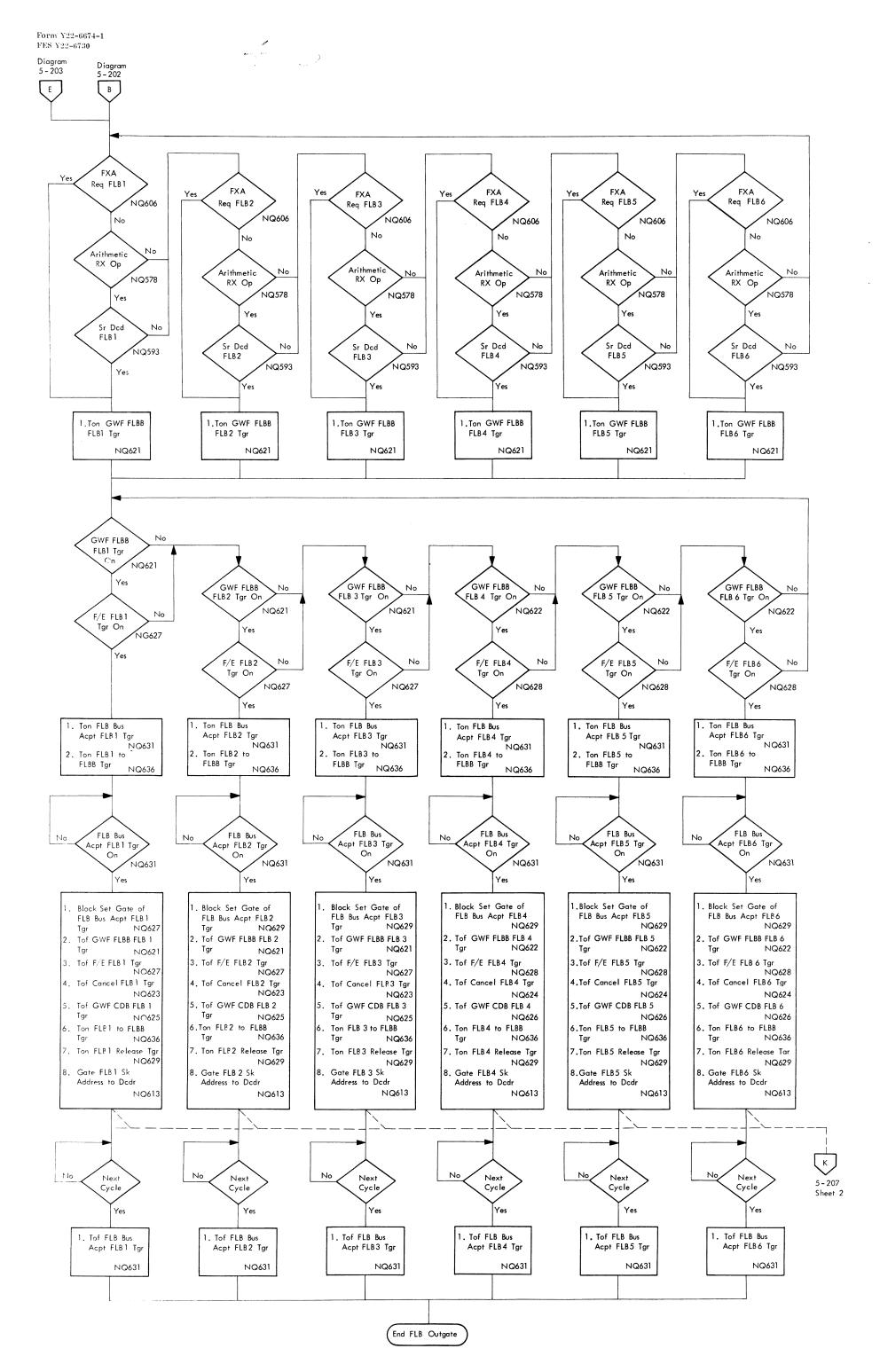

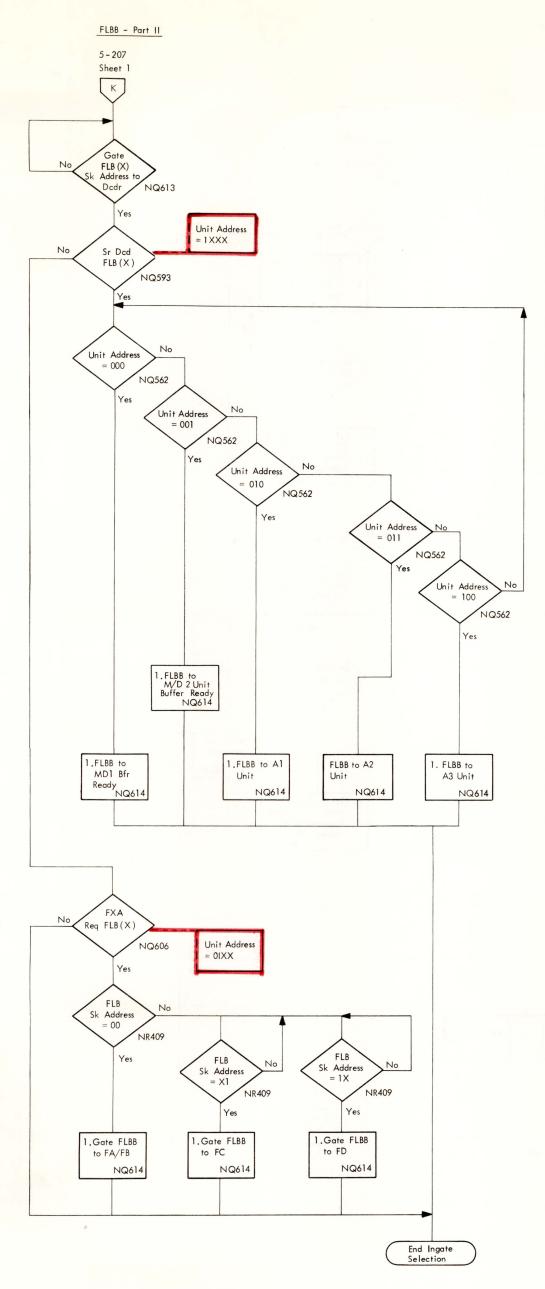

| 5-32    | ED, EDMK Sequence (4 sheets)                                 | 5-207   | FLBB Priority and FLB Outgating (2 sheets)      |

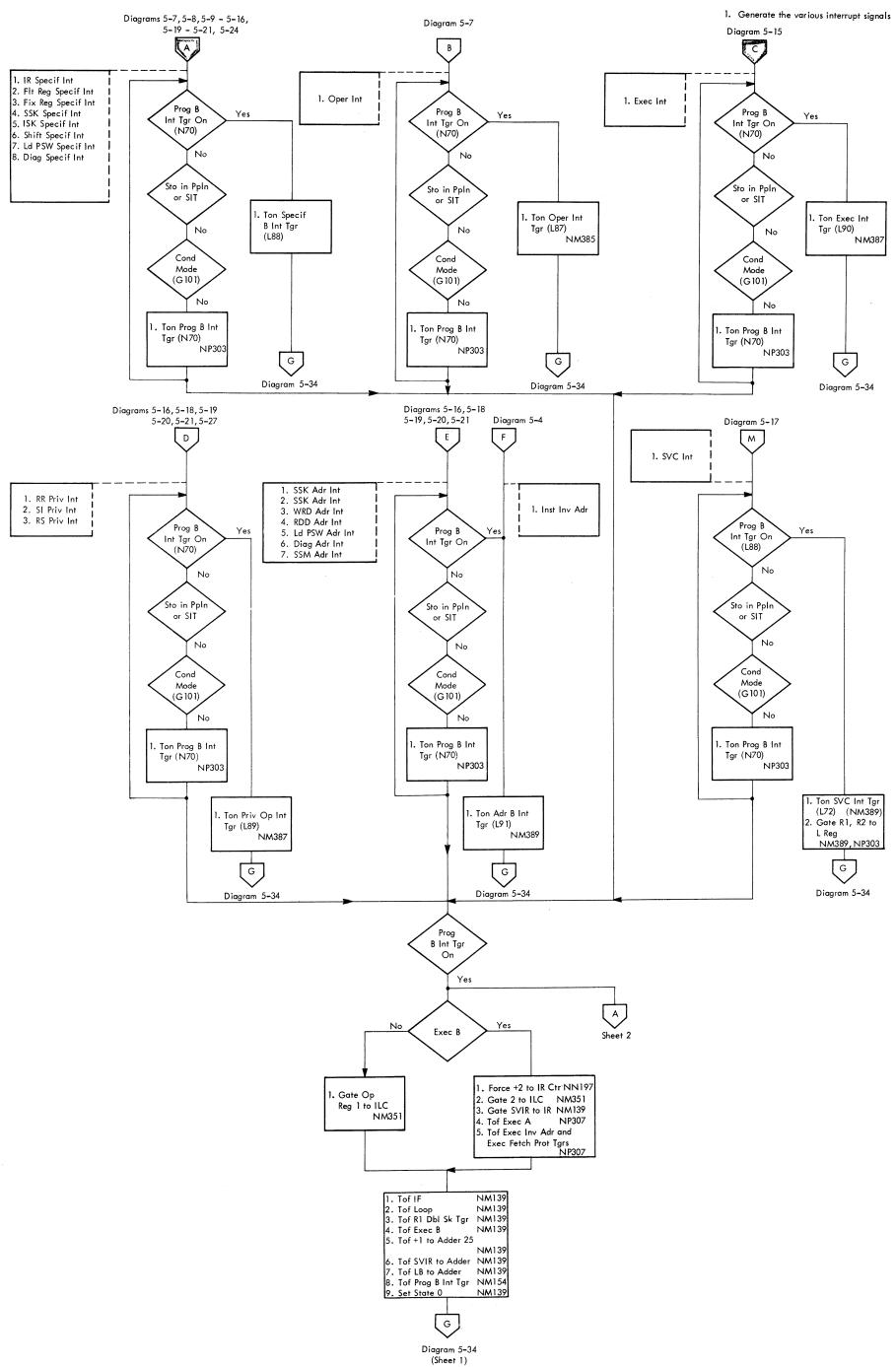

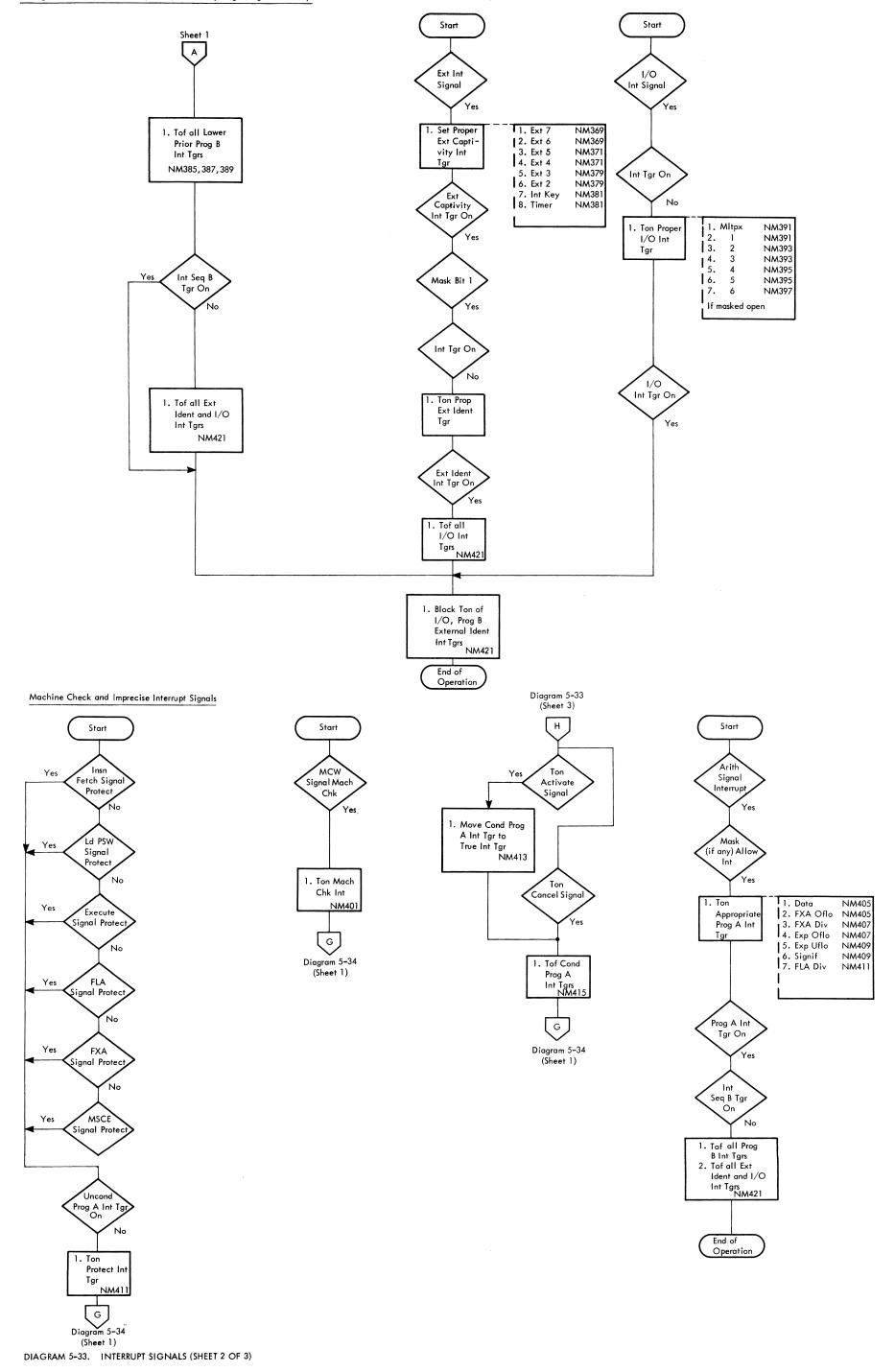

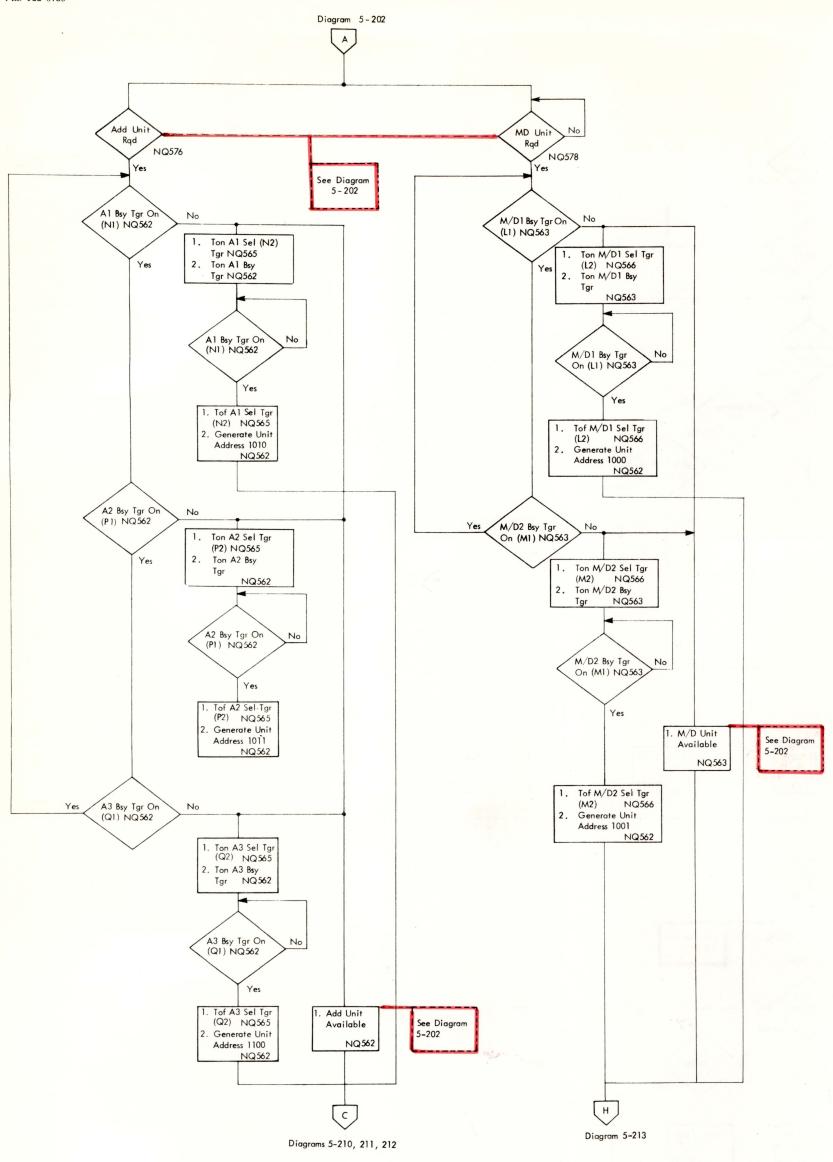

| 5-33    | Interrupt Signals (3 sheets)                                 | 5-208   | Unit Selection                                  |

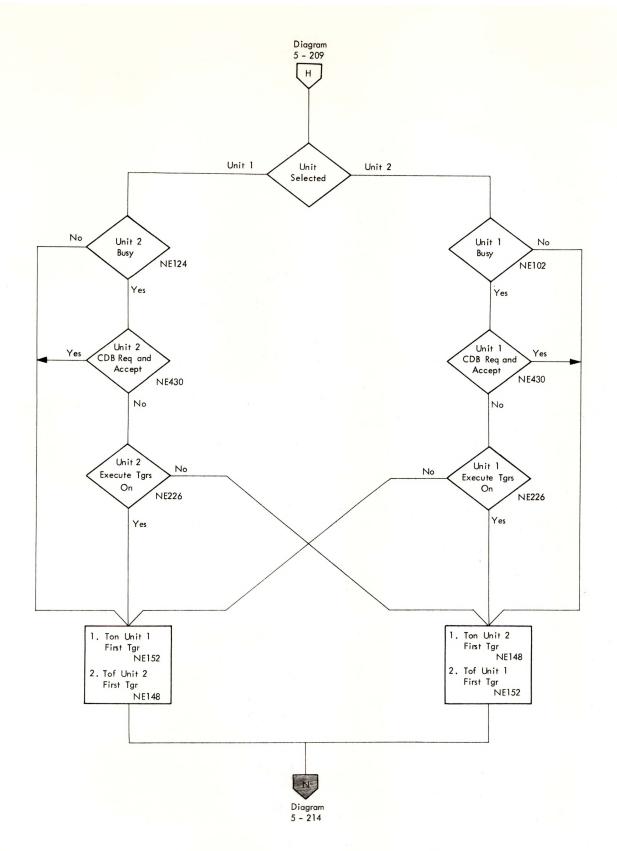

| 5-34    | Interrupt Sequencing (2 sheets)                              | 5-209   | Reservation Station Ingating                    |

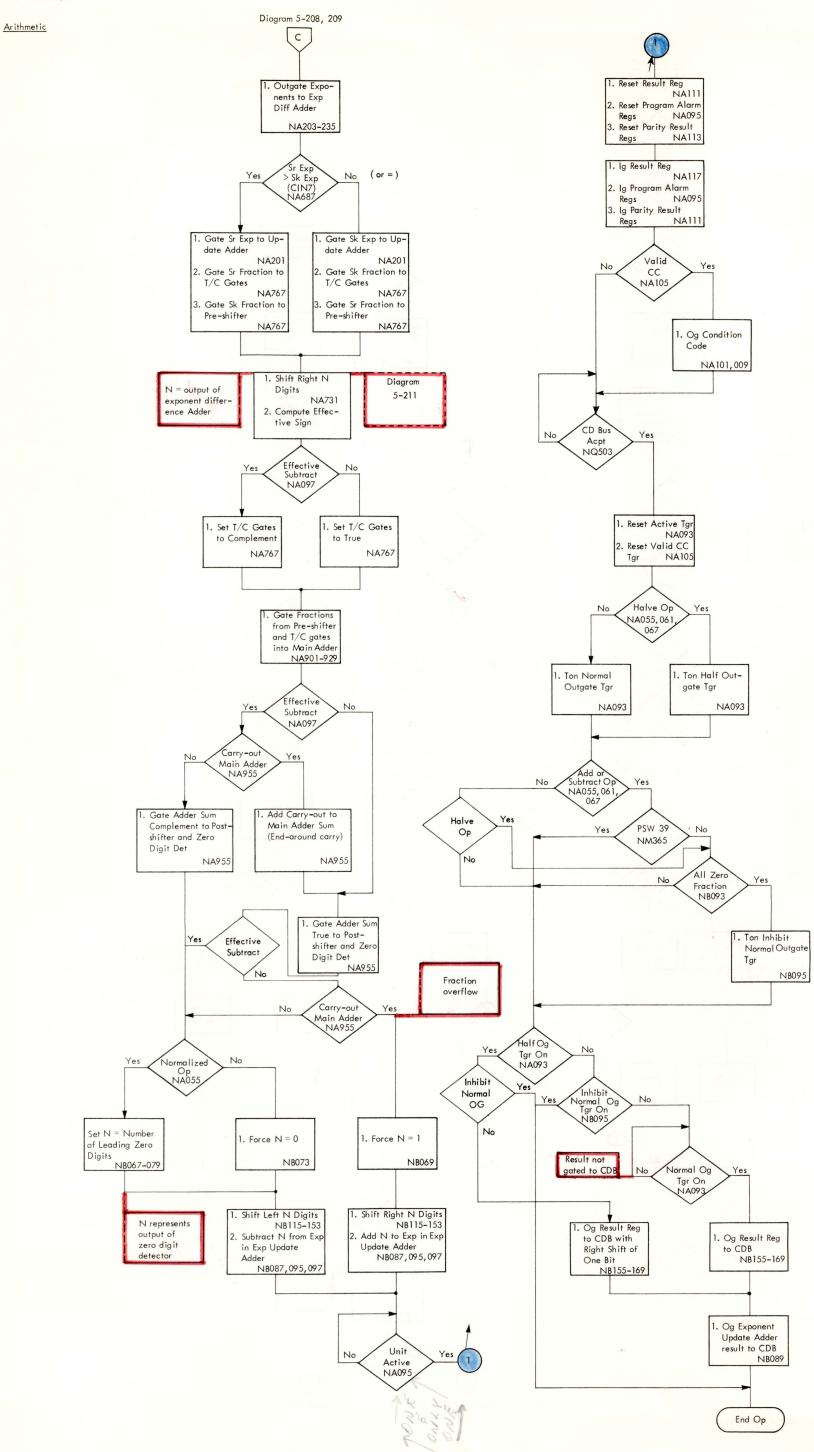

| 5-35    | MOP Definitions                                              | 5-210   | FAU Execution Fraction and Exponent             |

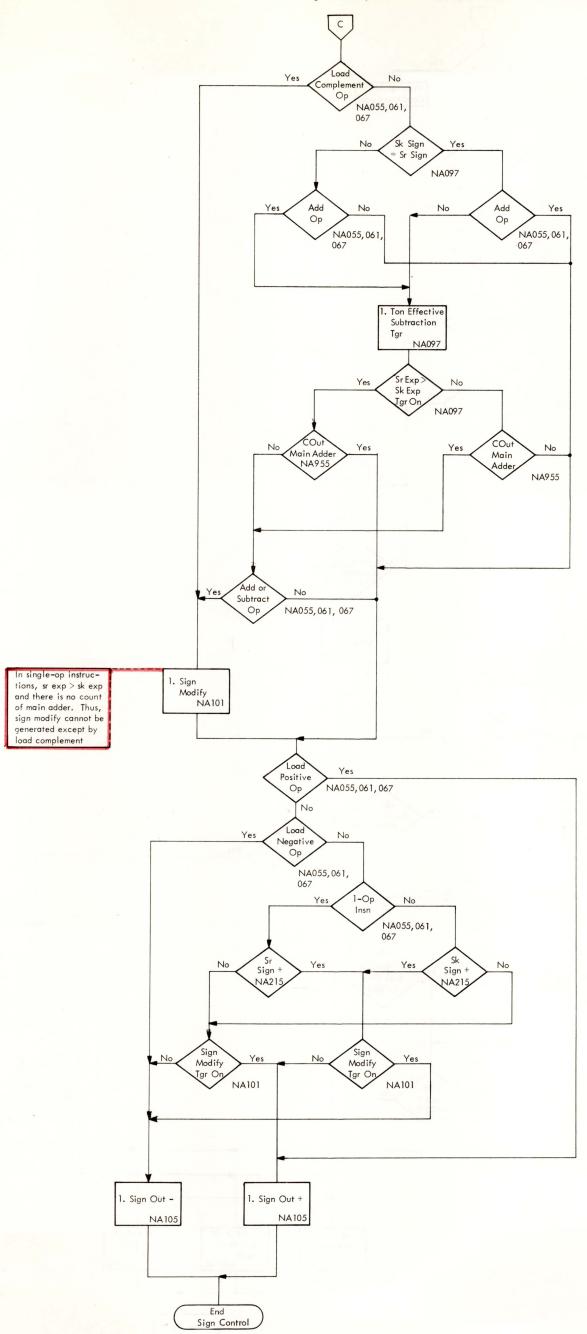

| 5-36    | I-Unit Trigger List (3 sheets)                               | 5-211   | FAU Sign Control                                |

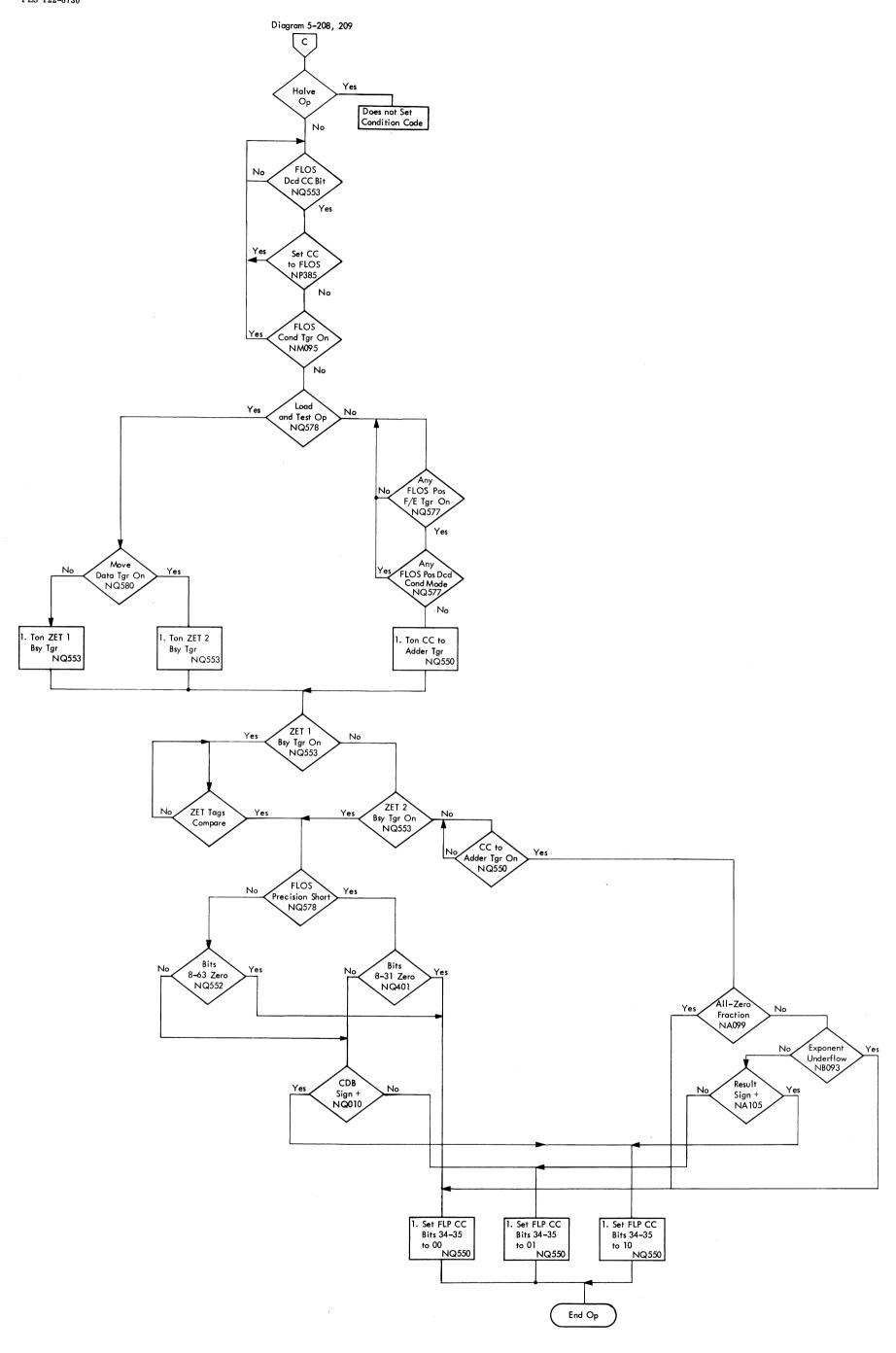

|         | ,                                                            | 5-212   | FAU and ZET Condition Code Control              |

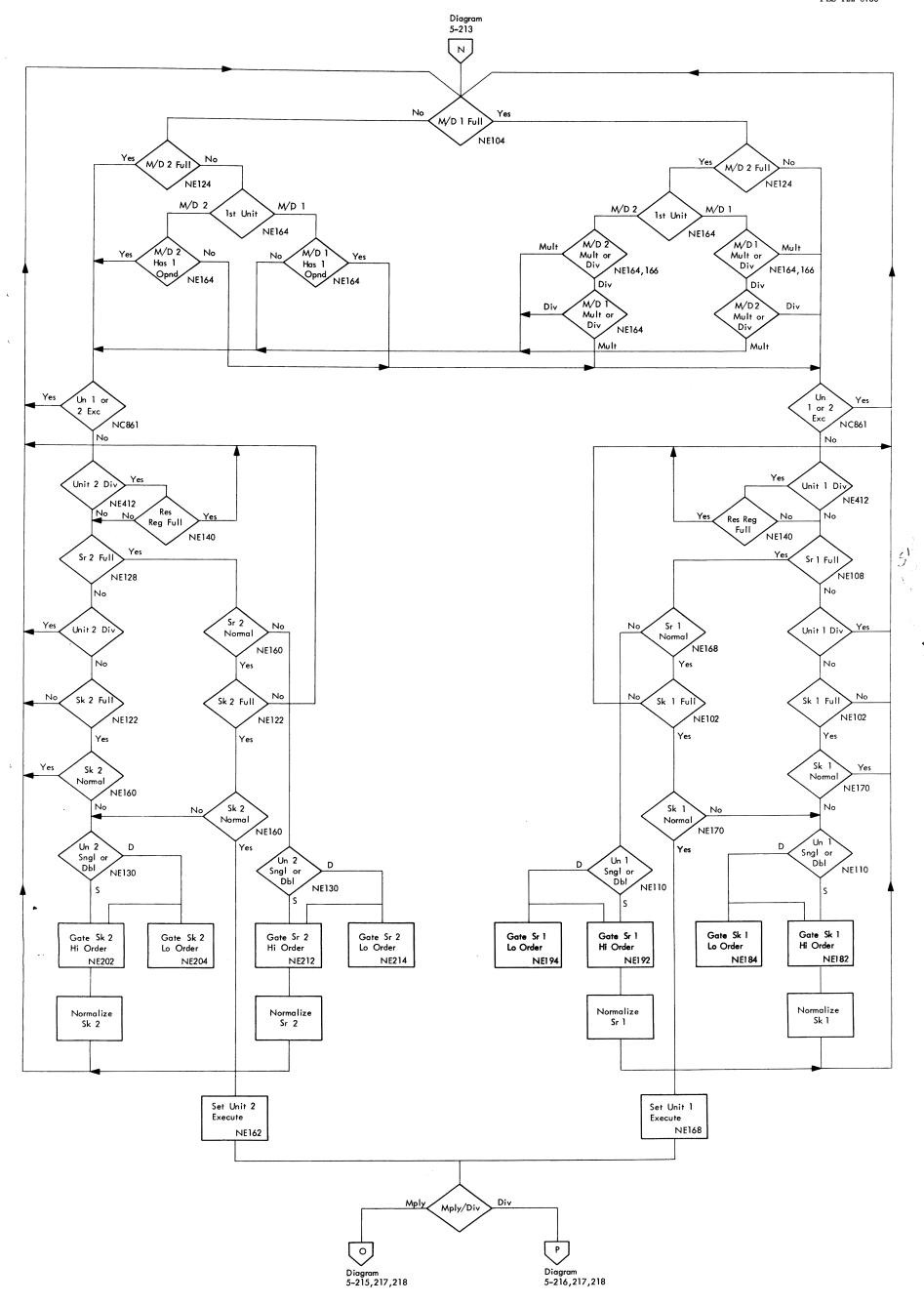

|         | •                                                            | 5-213   | FMDU Unit First Selection                       |

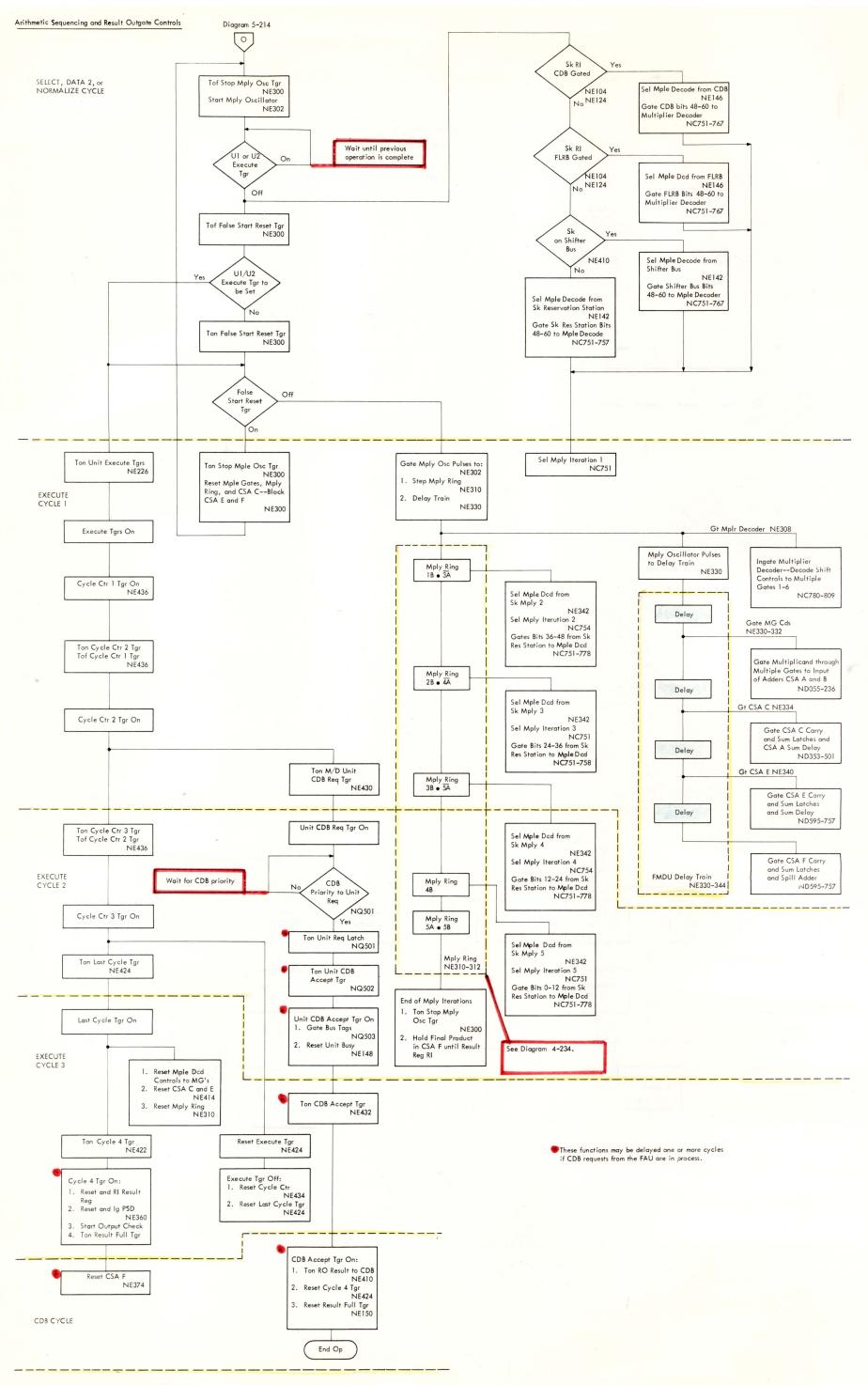

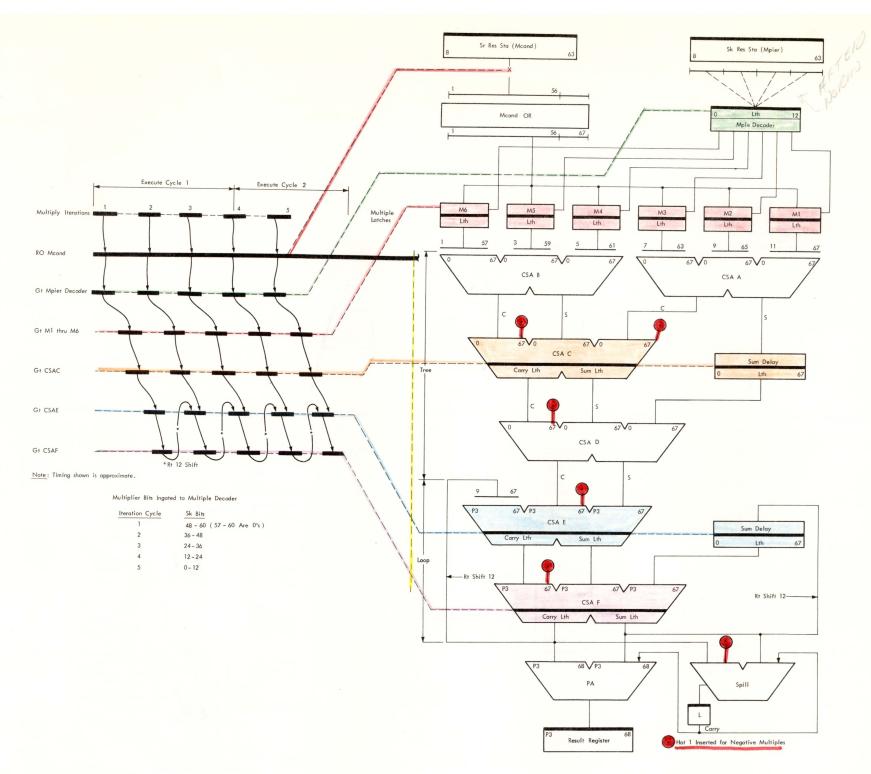

| FIXED-F | POINT OPERATIONS                                             | 5-214   | FMDU Normalize Control                          |

|         |                                                              | 5-215   | Multiply Execution (2 sheets)                   |

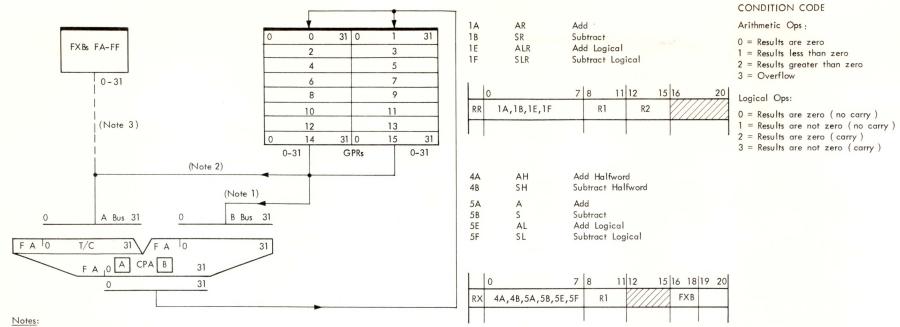

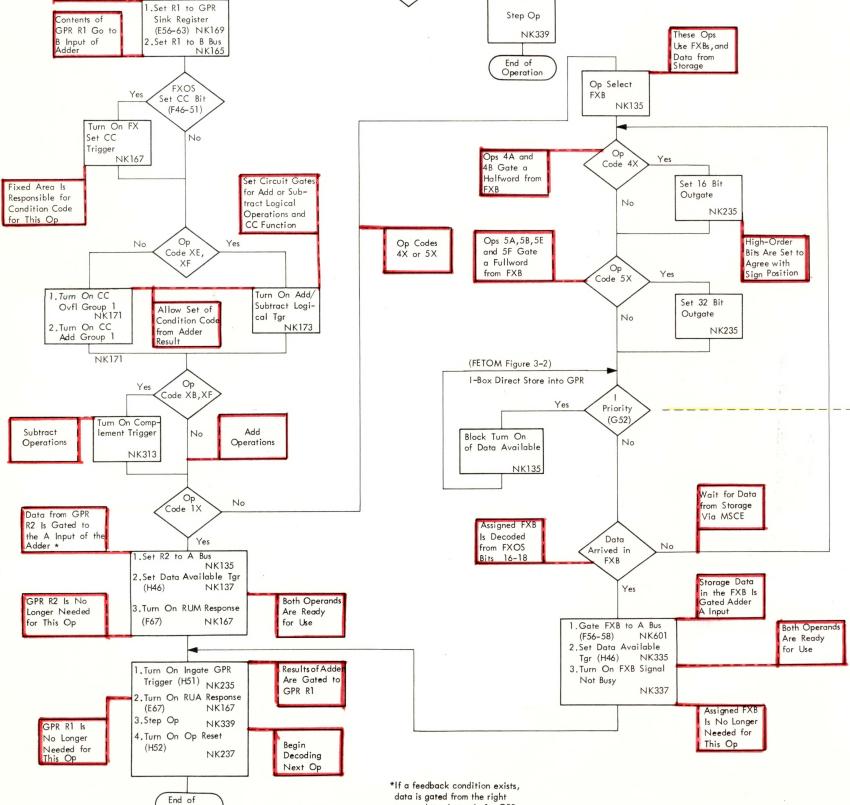

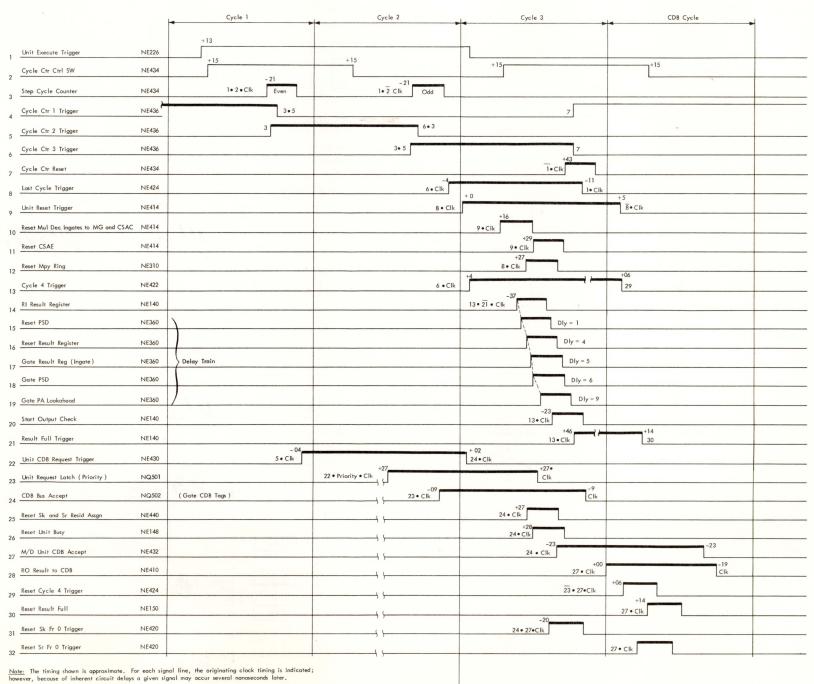

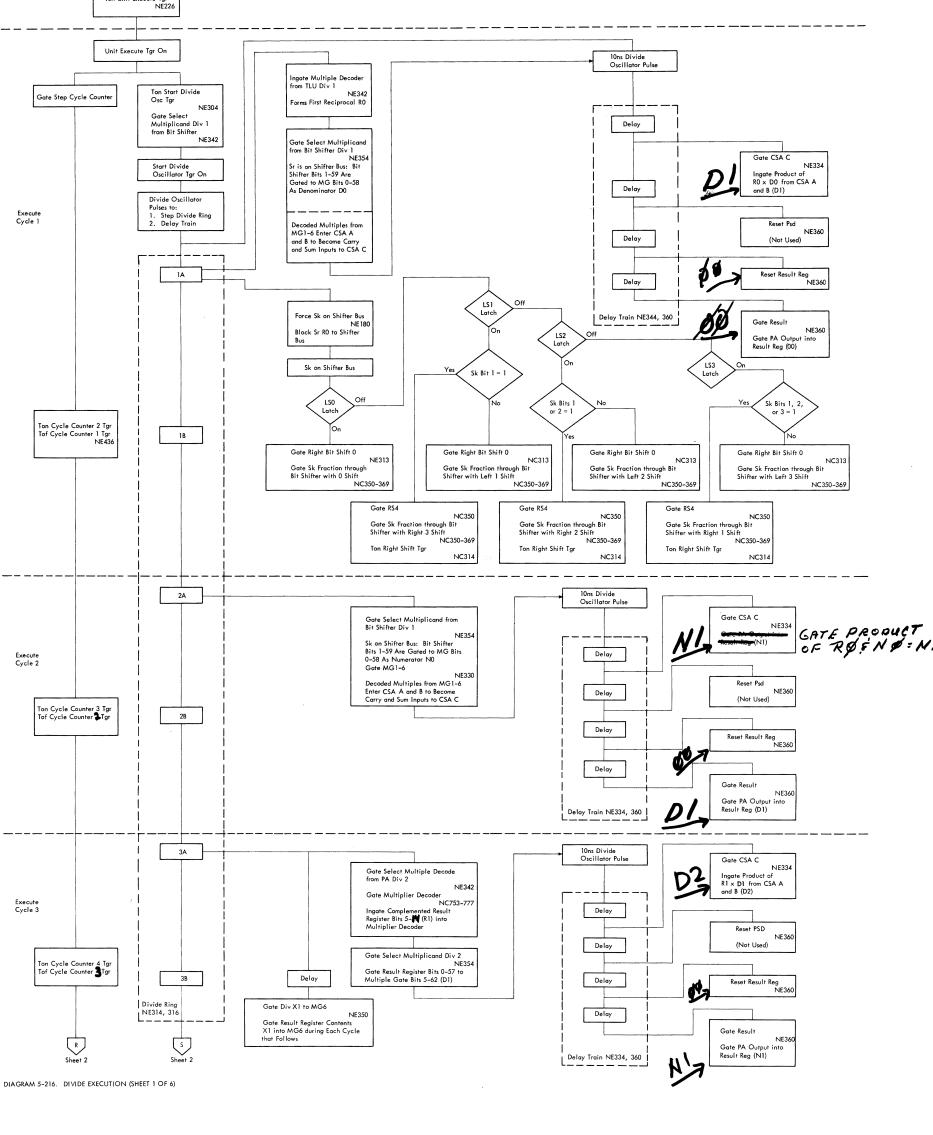

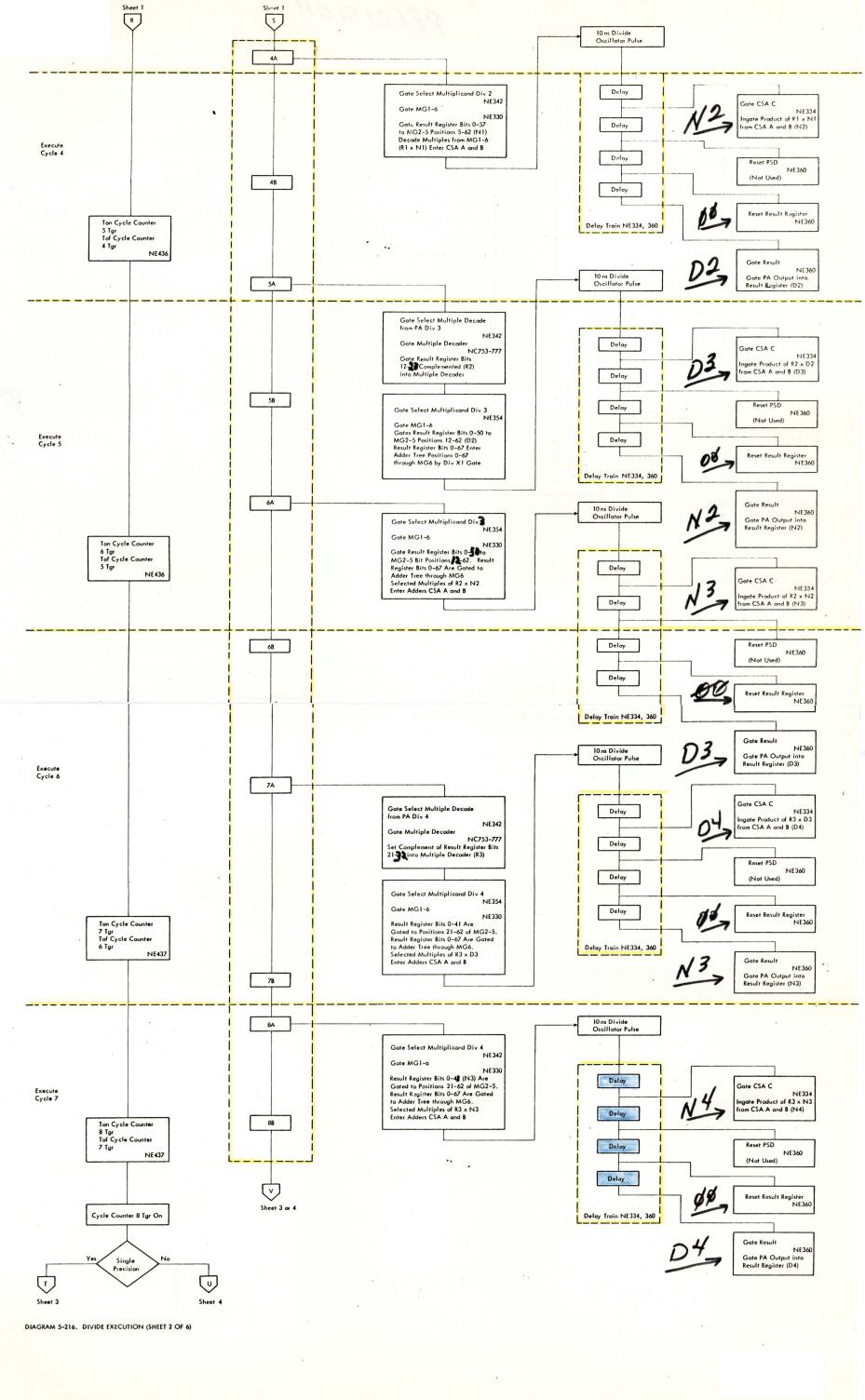

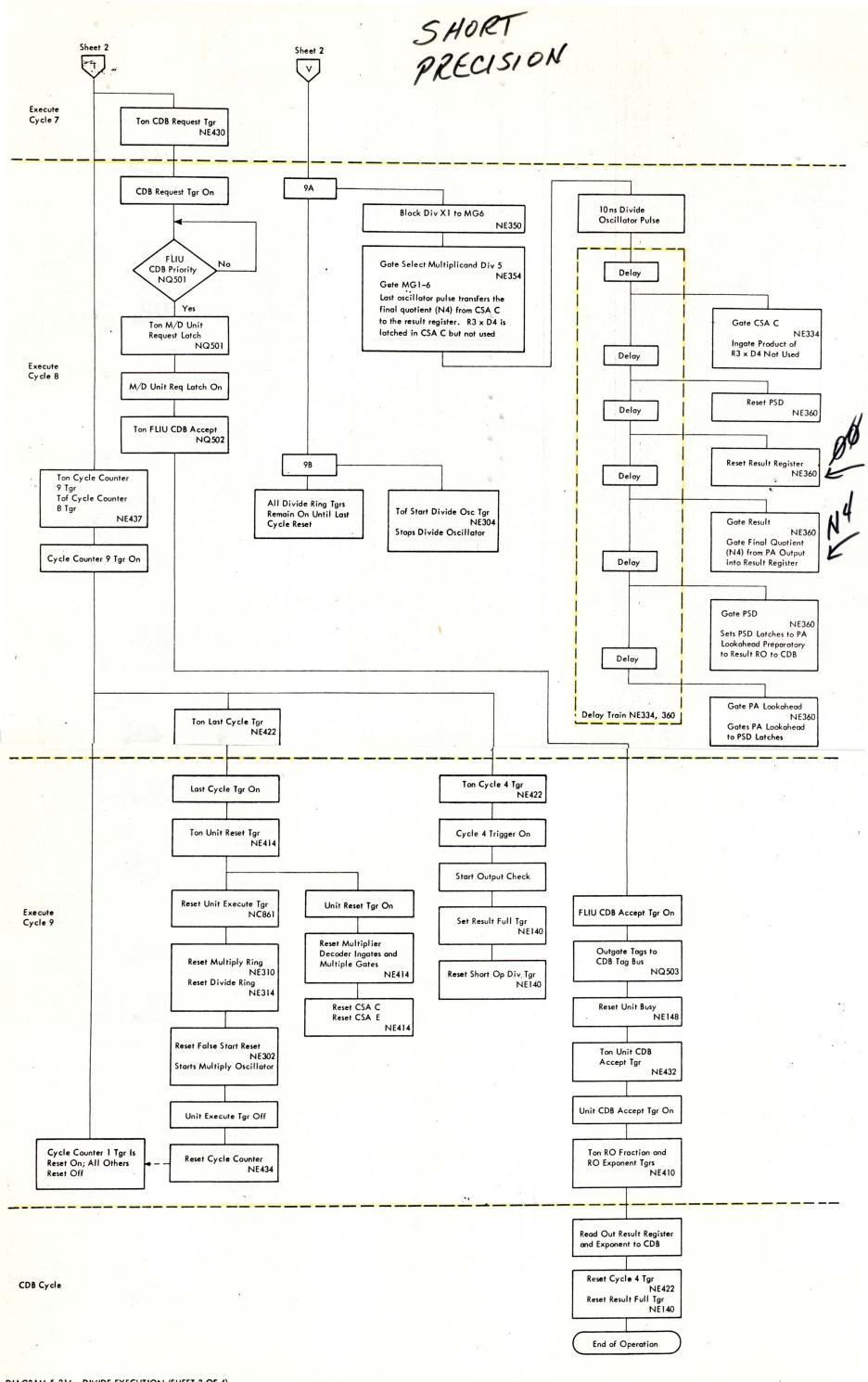

| 5-100   | Add and Subtract                                             | 5-216   | Divide Execution (6 sheets)                     |

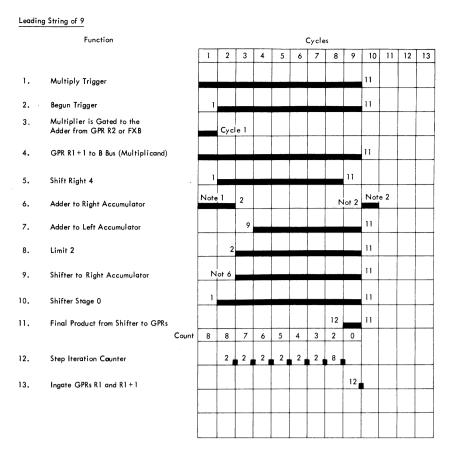

| 5-101   | Multiply (3 sheets)                                          | 5-217 • | FMDU Sign Control                               |

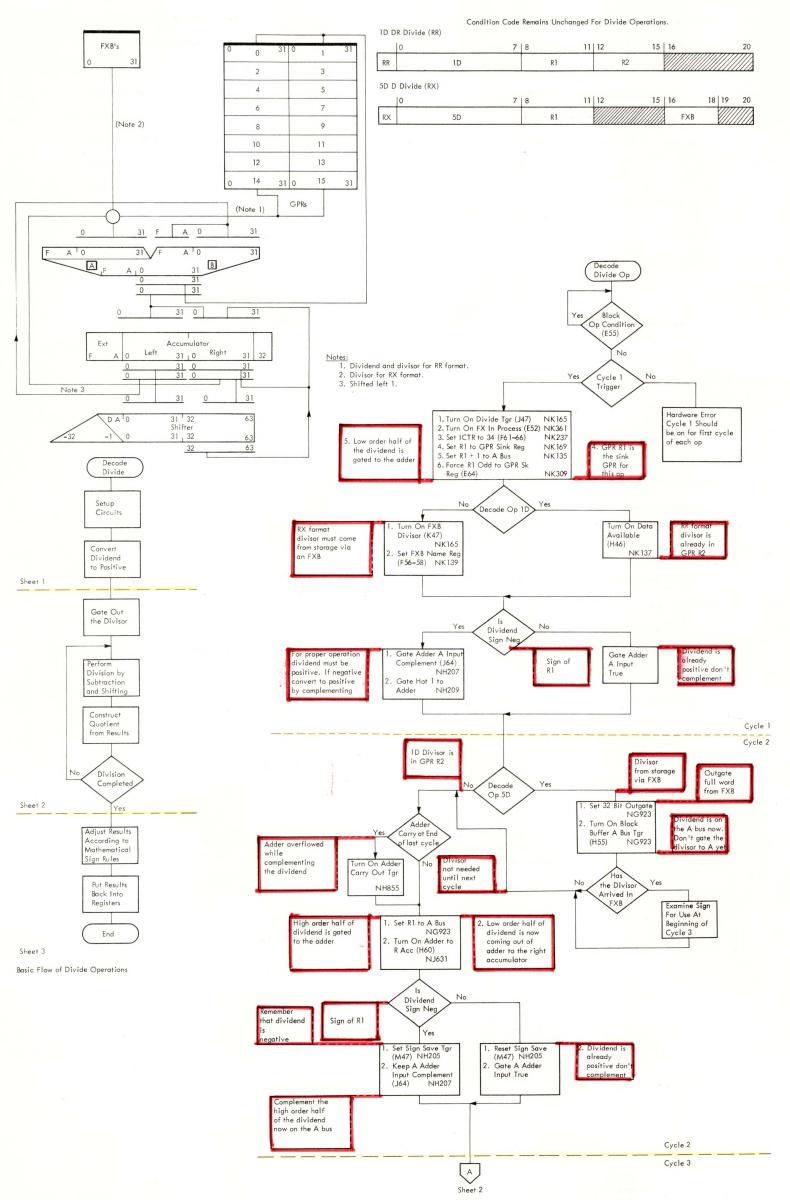

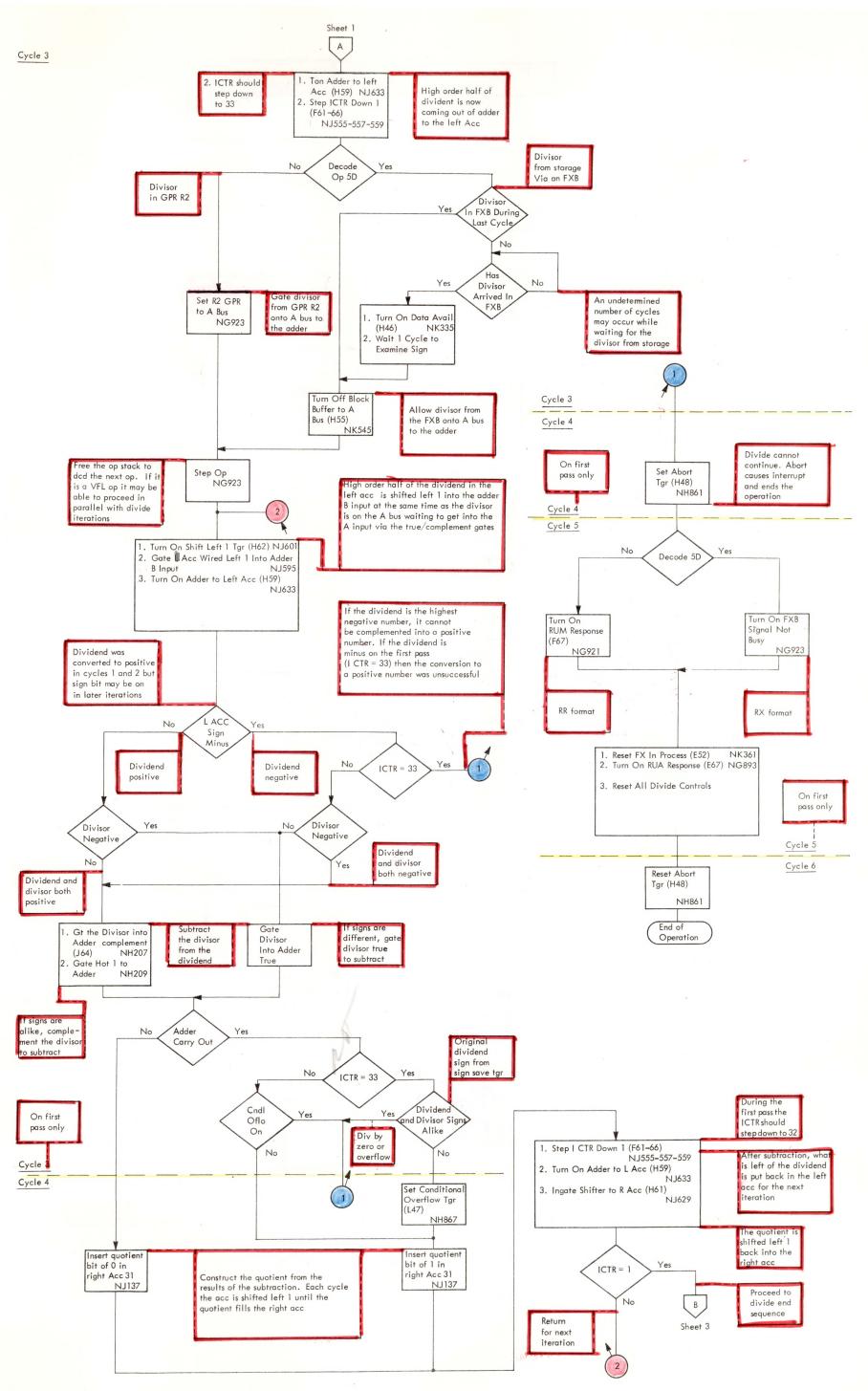

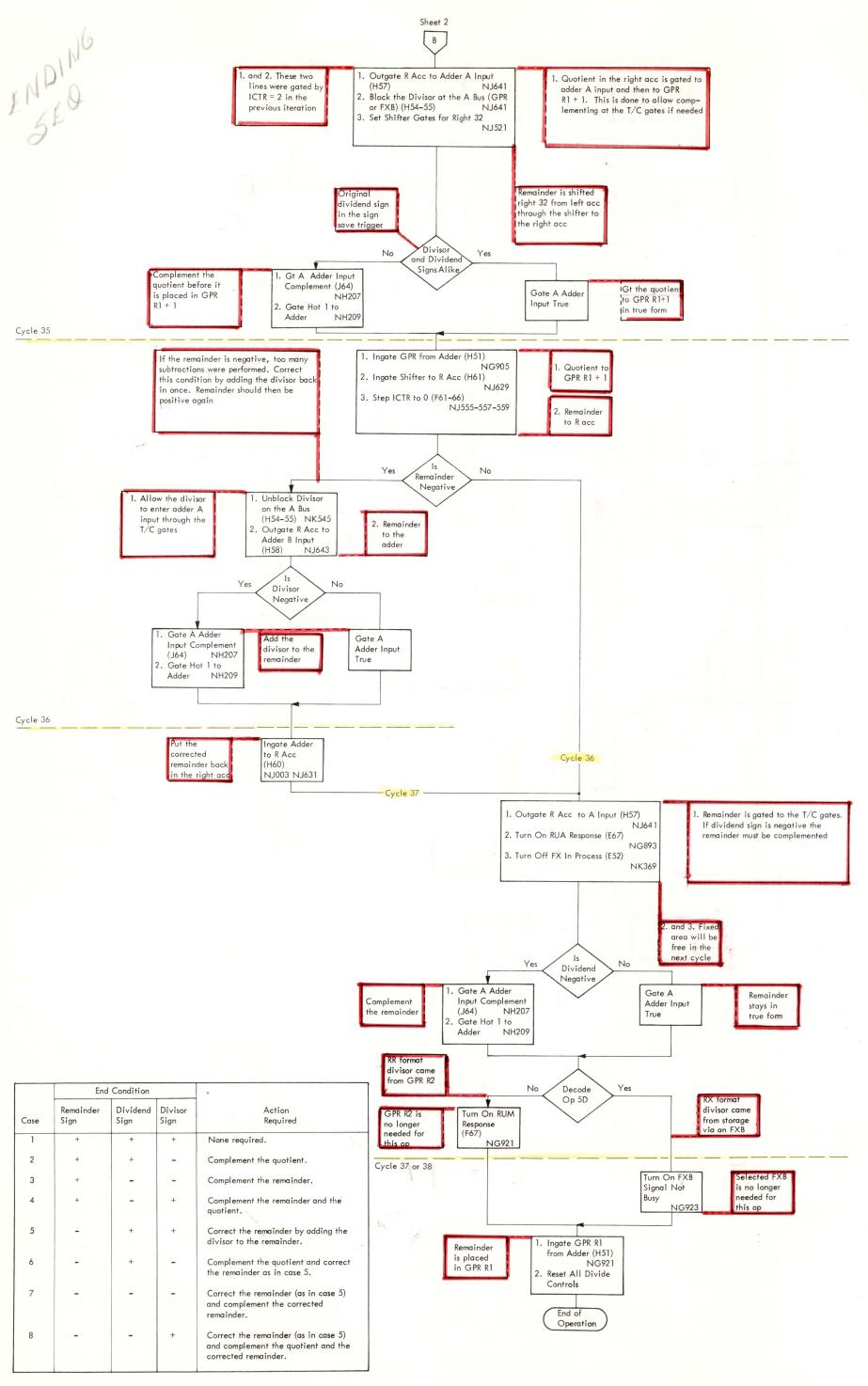

| 5-102:  | Divide (4 sheets)                                            | 5-218   | FMDU Exponent Execution                         |

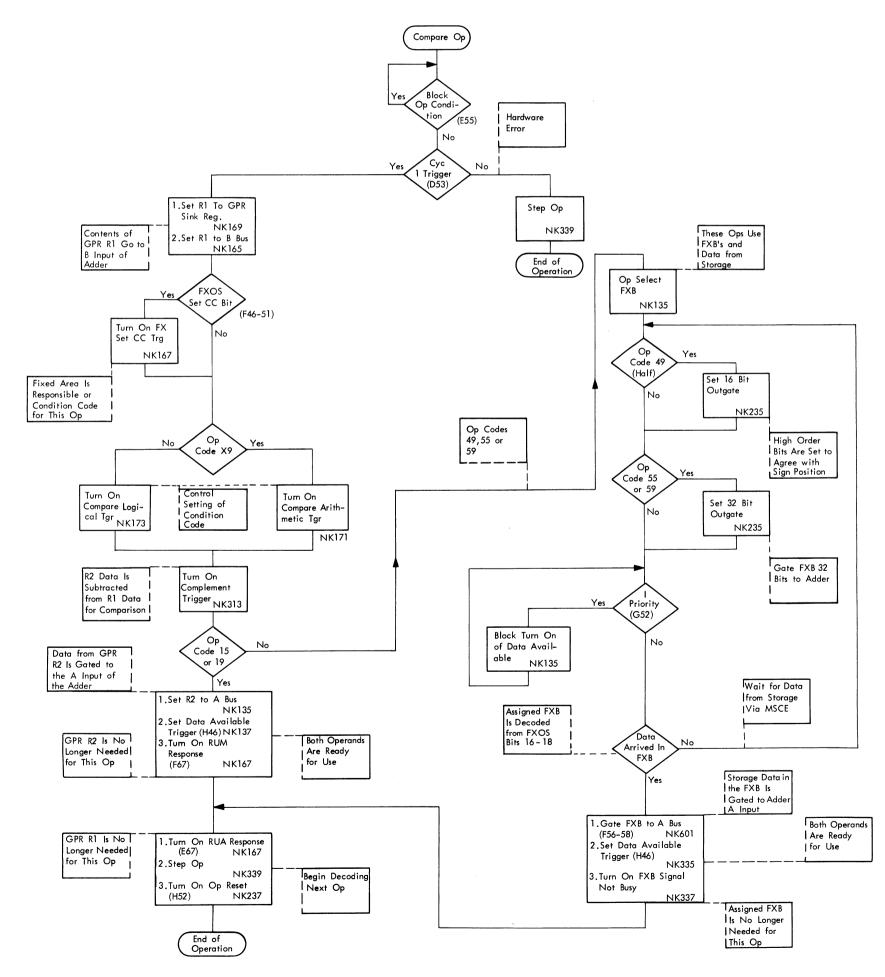

| 5-103   | Compare                                                      | 5-219   | FMDU Post Decoding and Post Shifting            |

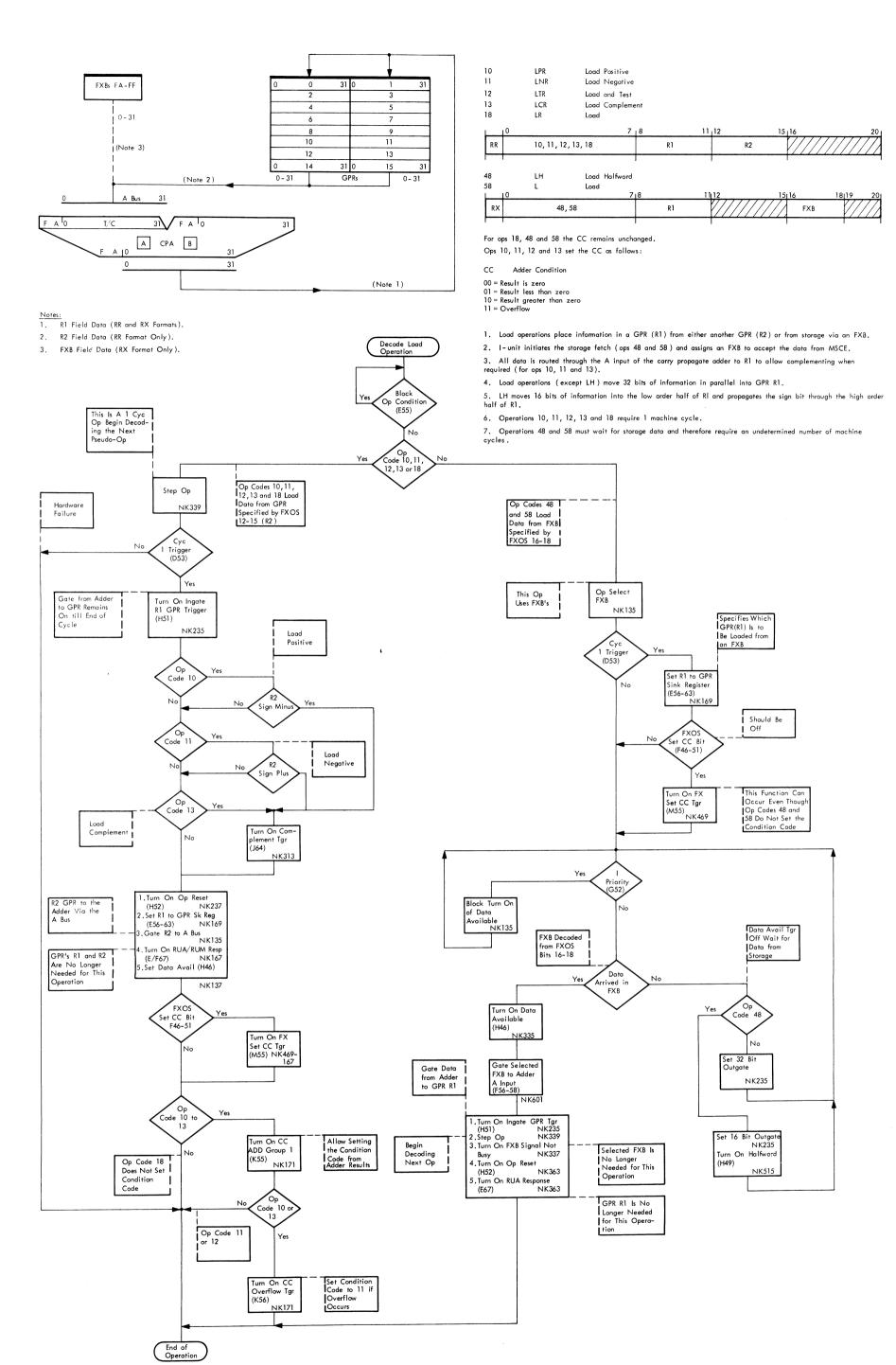

| 5-104   | Loads                                                        | 5-220   | Outgates to CDB (2 sheets)                      |

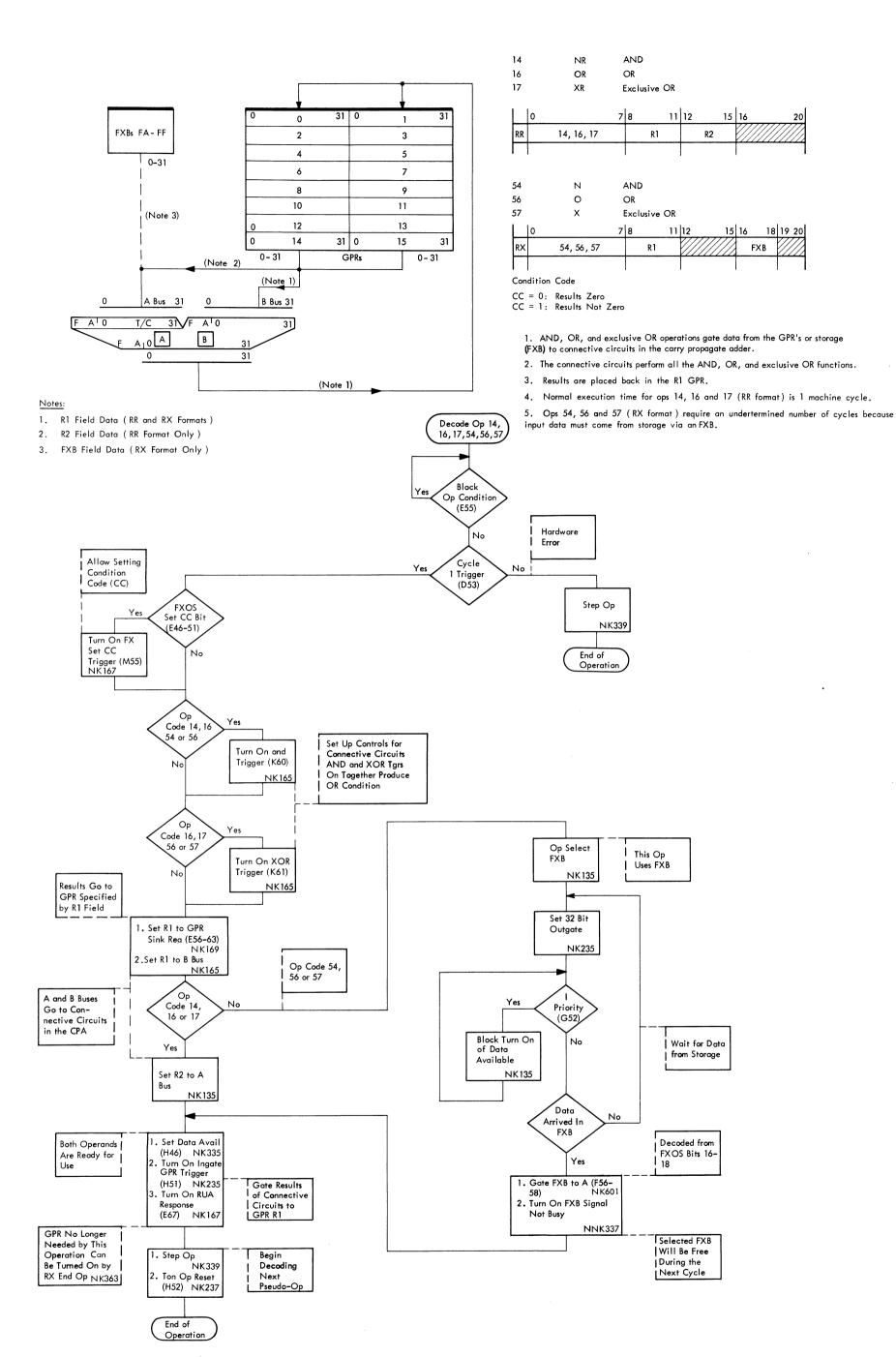

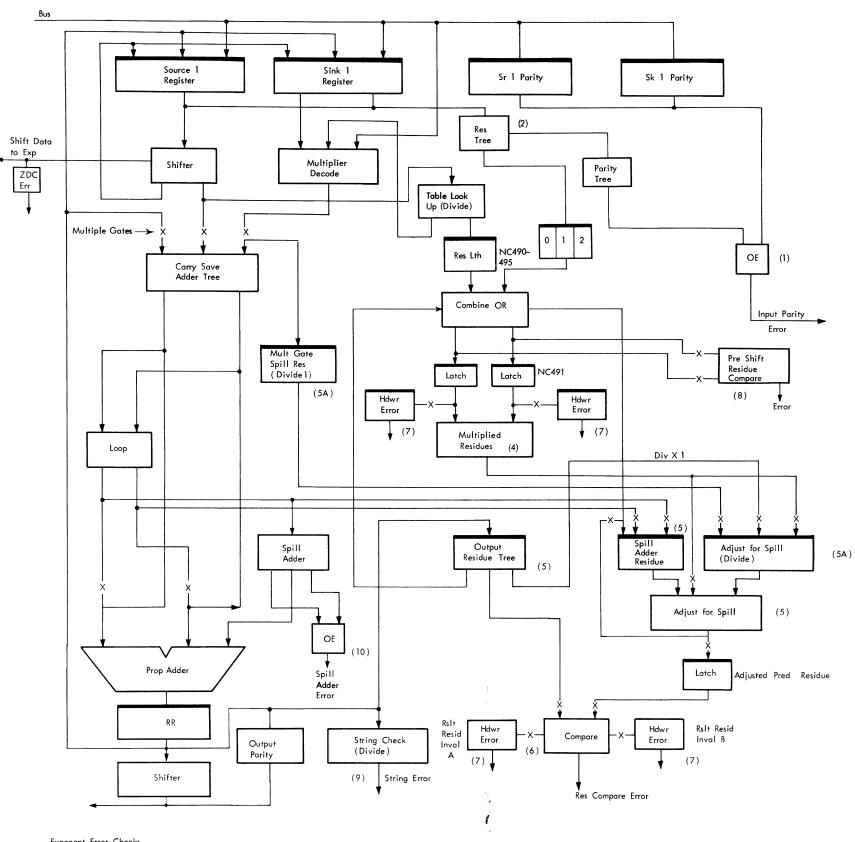

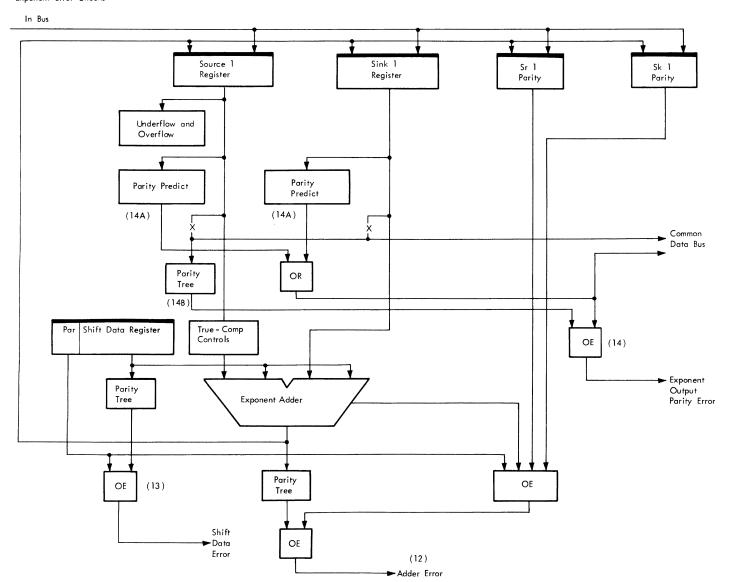

| 5-105   | AND, OR, and EXCLUSIVE OR                                    | 5-221   | Multiply/Divide Error Checking                  |

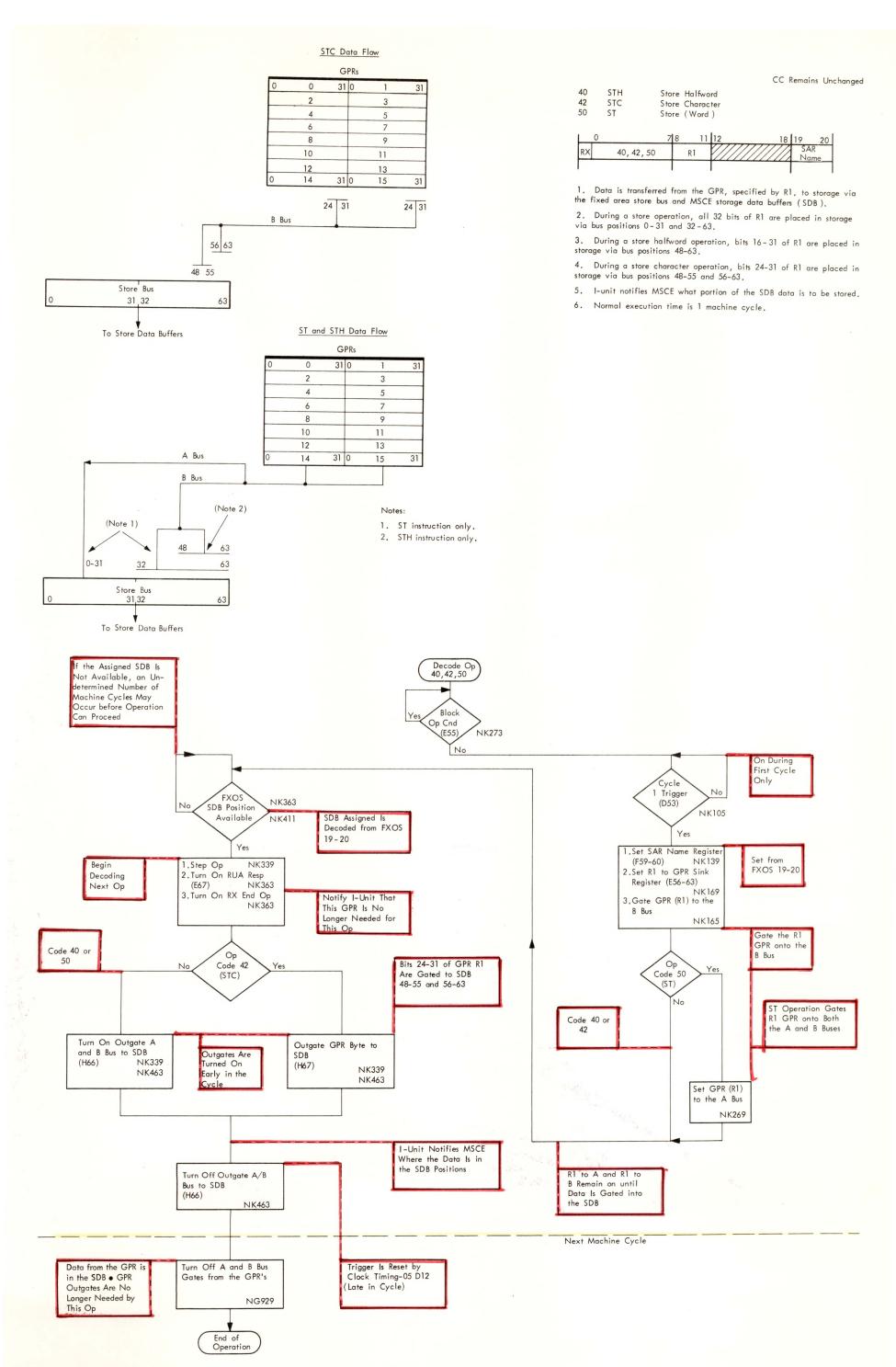

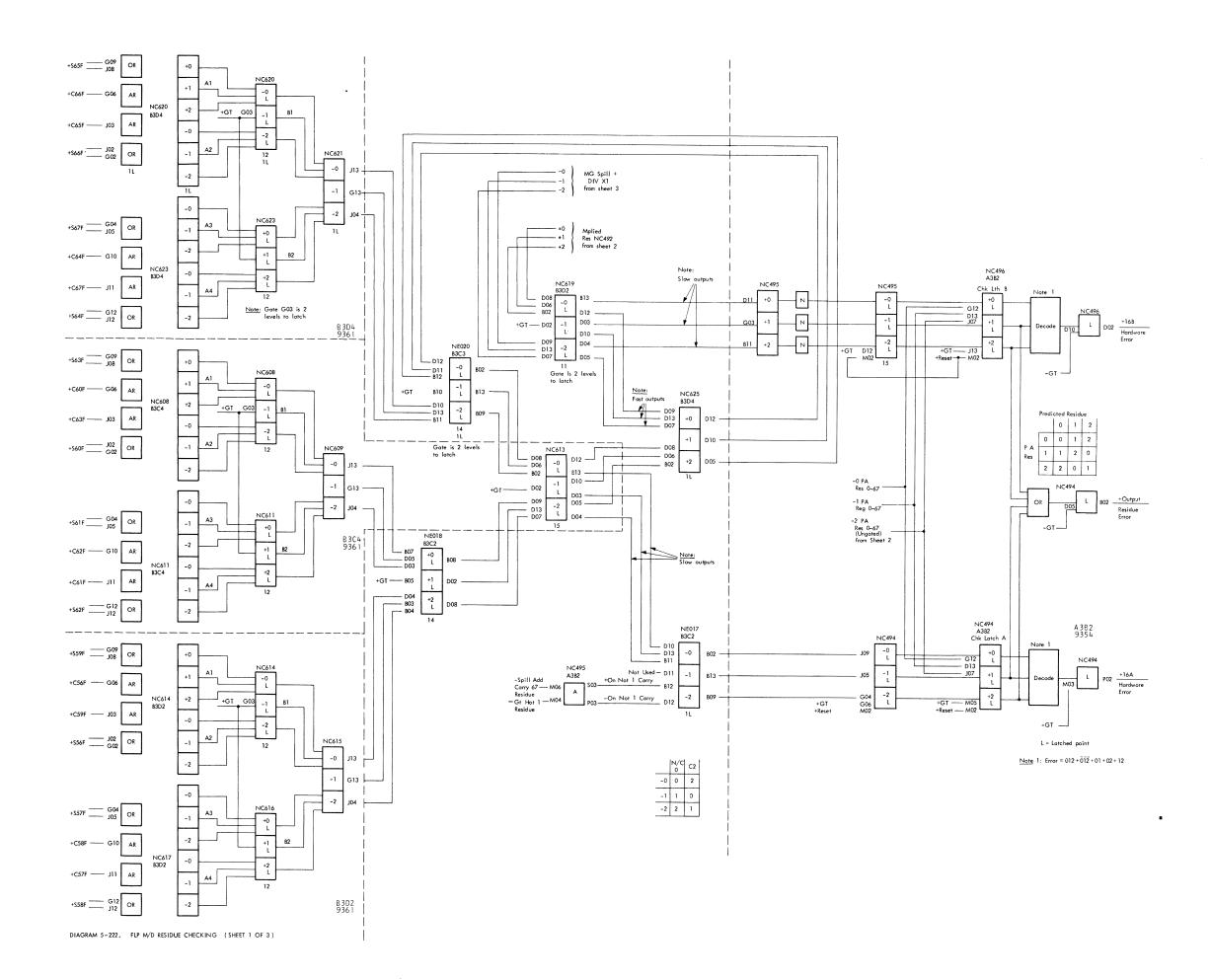

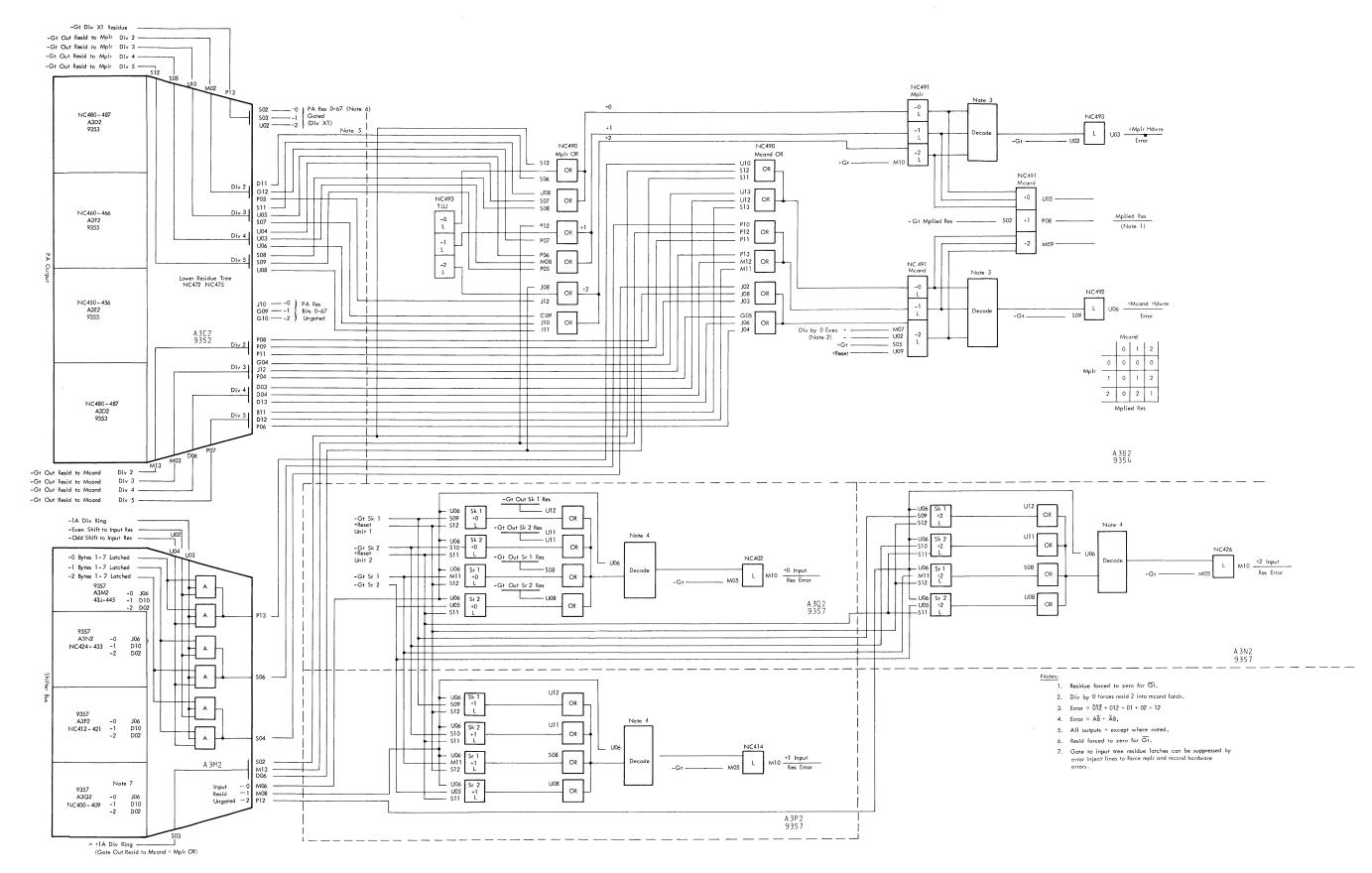

| 5-106   | Store, Store Halfword, and Store Character                   | 5-222   | FLP M/D Residue Checking (3 sheets)             |

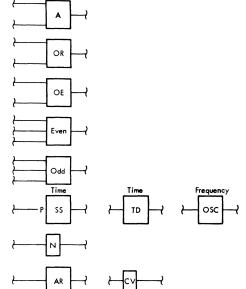

## **ABBREVIATIONS**

| A              | AND                                                                   | CPU          | Central Processing Unit                             |

|----------------|-----------------------------------------------------------------------|--------------|-----------------------------------------------------|

| AC             | Address Check                                                         | C QUICK T    | Conditional Quick Trigger                           |

| Acc            | Access; Accumulator                                                   | CR           | Control Register                                    |

| Acpt           | Accept                                                                | Crip         | Cripple                                             |

| Acptng<br>Addr | Accepting                                                             | CSA          | Carry Save Adder                                    |

| Adr            | Address<br>Address                                                    | CSW          | Channel Status Word                                 |

| Adv            | Advance                                                               | Ctl          | Control                                             |

| AE             | Address Exception                                                     | Ctr          | Counter                                             |

| ALD            | Automated Logic Diagram                                               | Ctrl         | Control                                             |

| Altr           | Alteration                                                            | CV           | Converter                                           |

| Amt            | Amount                                                                | CVB          | (Mnemonic) Convert to Binary (RX)                   |

| AOC            | Array Out Counter                                                     | CVD<br>CXR   | (Mnemonic) Convert to Decimal (RF)                  |

| AR             | Amplifier                                                             | CAR          | Console Auxiliary Register                          |

| Arg            | Argument                                                              | D            | Displacement                                        |

| Arg Wd         | Argument Doubleword                                                   | Dbl          | Double                                              |

| AS             | Accept Stack                                                          | DC           | Data Check; Display Check                           |

| ASLT           | Advanced Solid Logic Technology                                       | Dcd          | Decode  Decode                                      |

| ATI            | Auxiliary Tape Input                                                  | Dcdr         | Decoder                                             |

| Avail          | Available                                                             | Des          | Designation                                         |

|                |                                                                       | Det          | Detection; Detector                                 |

| В              | Bit                                                                   | DG           | Display Gate                                        |

| BAB            | Byte Address Buffer                                                   | Diag         | Diagnose                                            |

| BAC            | Buffer Address Counter                                                | D <b>I</b> G | Data Ingate                                         |

| BAL            | (Mnemonic)Branch and Link (RX)                                        | Disp         | Displacement                                        |

| BALR           | (Mnemonic) Branch and Link (RR)                                       | Dist         | Distributor                                         |

| BAR            | Byte Address Register                                                 | Div          | Divide                                              |

| BB<br>BC       | Bank Bit                                                              | Dly          | Delay, Delayed                                      |

| BC R           | (Mnemonic) Branch on Condition; Bus Control                           | Dlyd         | Delayed                                             |

| BCQT           | (Mnemonic) Branch on Condition (RR) Branch on Condition Quick Trigger | DM           | Diagnostic Monitor                                  |

| BCT            | (Mnemonic) Branch on Count (RX)                                       | DOG          | Data Outgate                                        |

| BCTR           | (Mnemonic) Branch on Count (RR)                                       | DPC          | Display Parity Check                                |

| BCU            | Bus Control Unit                                                      | Dsbl<br>Dt   | Disable                                             |

| BCUNCONT       | Unconditional Branch Trigger                                          | DW           | Data<br>Doubleword                                  |

| Bd             | Board                                                                 | DWC          | Doubleword Counter                                  |

| Bdy            | Boundary                                                              | DWCR         | Doubleword Count Register                           |

| Bfr            | Buffer                                                                |              | Double Hotal Count Register                         |

| BIA            | Branch In Array                                                       | EBA          | Ending Byte Address                                 |

| BIAT           | Back in Array Trigger                                                 | EBAR         | Ending Byte Address Register                        |

| BOM            | Basic Operating Memory                                                | EBCDIC       | Extended Binary Coded Decimal Interchange Code      |

| Br             | Branch                                                                | EC           | Engineering Change                                  |

| BRT            | Branch Trigger                                                        | ECAD         | Error Check Analysis Diagram                        |

| BSM            | Basic Storage Module                                                  | ED           | (Mnemonic) Edit (SS)                                |

| Bsy            | Busy                                                                  | EDMK         | (Mnemonic) Edit and Mark (SS)                       |

| BXH            | (Mnemonic) Branch on Index High (RS)                                  | EMS          | Extended Main Storage (Same as LCS)                 |

| BXLE           | (Mnemonic) Branch on Index Low or Equal (RS)                          | Eq           | Equals                                              |

| BXQT<br>BZ     | Branch on Index Quick Trigger                                         | Err          | Error                                               |

| BZTP           | Busy<br>Busy-to-Priority                                              | EX           | (Mnemonic) Execute (RX)                             |

| BZTPSCE        | Busy-to-PSCE                                                          | Excpn        | Exception                                           |

| BZTTSCE        | Busy-to-Request                                                       | Exce<br>Exp  | Execute Exponent                                    |

| 22111          | Day to request                                                        | шхр          | Exponent                                            |

| CAB            | Channel Address Bus                                                   | FAU          | Floating Point Add Unit                             |

| CAR            | Console Address Register;                                             | FE           | Field Engineering                                   |

| CAR            | Channel Address Register                                              | FEMDM        | Field Engineering Maintenance Diagram Manual        |

| CAW            | Channel Address Word                                                  | FETOM        | Field Engineering Theory of Operation Manual        |

| C BACKL8 T     | Condition Back Less than Eight Trigger                                | FIFO         | First-In, First-Out                                 |

| C BIA T        | Conditional Back in Array Trigger                                     | Fir          | First                                               |

| CBR            | Console Buffer Register                                               | FIWADFO      | First-In-With-Available-Data, First-Out             |

| CC             | Command Counter; Condition Code                                       | FIWAMFO      | First-In-With-Available-Memory, First-Out           |

| CCC            | Common Channel Control                                                | FLA          | Floating Point Area                                 |

| CCW            | Channel Command Word                                                  | FLB          | Floating Point Buffer                               |

| CD             | Chain Data                                                            | FLBB         | Floating Point Buffer Bus                           |

| CDB            | Common Data Bus                                                       | Fld          | Field                                               |

| CDBI           | Console Data Bus In                                                   | FLEU         | Floating Point Execution Unit                       |

| CDBO           | Console Data Bus Out                                                  | FLIU         | Floating Point Instruction Unit                     |

| Ch             | Channel                                                               | FLOS         | Floating Point Op Stack                             |

| Chan<br>Ch Fr  | Channel Channel Frame                                                 | FLP          | Floating Point                                      |

| Chk            | Check                                                                 | FLR<br>FLRB  | Floating Point Register Floating Point Register Bus |

| Ck             | Check                                                                 | FLU          | Floating Point Unit                                 |

| Chn            | Chain                                                                 | FMDU         | Floating Point Multiply/Divide Unit                 |

| CIn            | Carry In                                                              | FP           | Fetch Protect                                       |

| CLC            | (Mnemonic) Compare Logical (SS)                                       | FPA          | Floating Point Area                                 |

| Clk            | Clock                                                                 | Frm          | Frame                                               |

| CM             | Conditional Mode; Console Mode; Cripple Mode                          | Frac         | Fraction                                            |

| Cncl           | Cancel                                                                | FS           | False Start                                         |

| Cndl           | Conditional                                                           | FSB          | Fixed Store Bus                                     |

| Cnt            | Count                                                                 | Fth          | Fetch                                               |

| со             | Conditional Op                                                        | Fwd          | Forward; Forwarding                                 |

| Comp           | Compare; Comparator                                                   | FXA          | Fixed Point/VFL Area                                |

| Cond           | Condition                                                             | FXB          | Fixed Point Buffer                                  |

| COut           | Carry Out                                                             | FXEU         | Fixed Point Execution Unit                          |

| CPA            | Carry Propagate Adder                                                 | FXIU         | Fixed Point Instruction Unit                        |

| CPC            | Cyclic Program Counter                                                | FXOS         | Fixed Point Op Stack                                |

| CPE<br>Cpr     | Central Processing Element                                            | FXP          | Fixed Point                                         |

| Cp.            | Computer                                                              |              |                                                     |

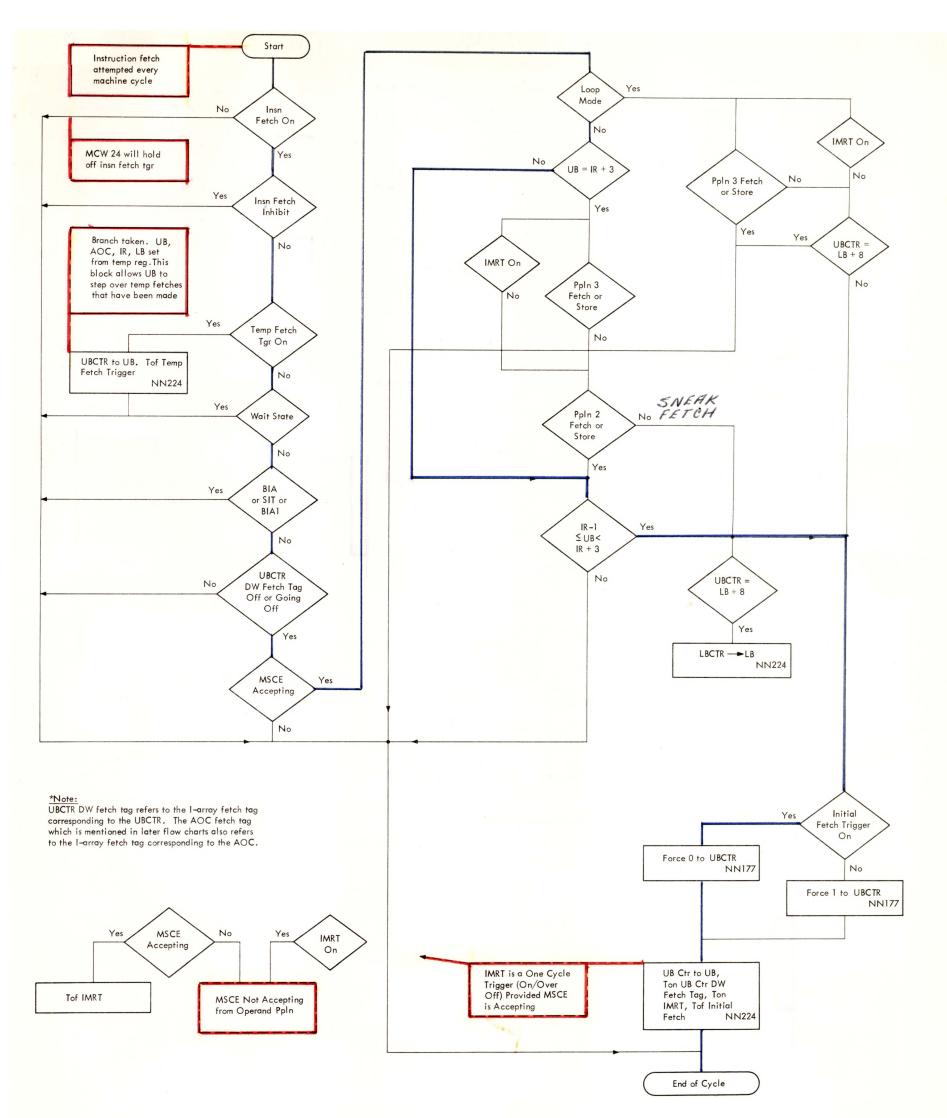

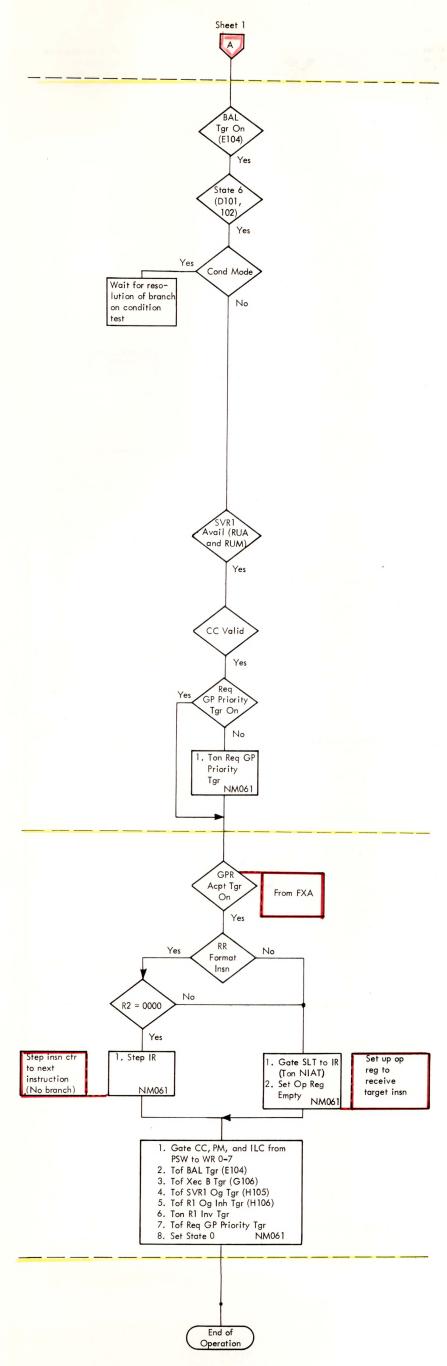

DIAGRAM 5-1. INSTRUCTION FETCH

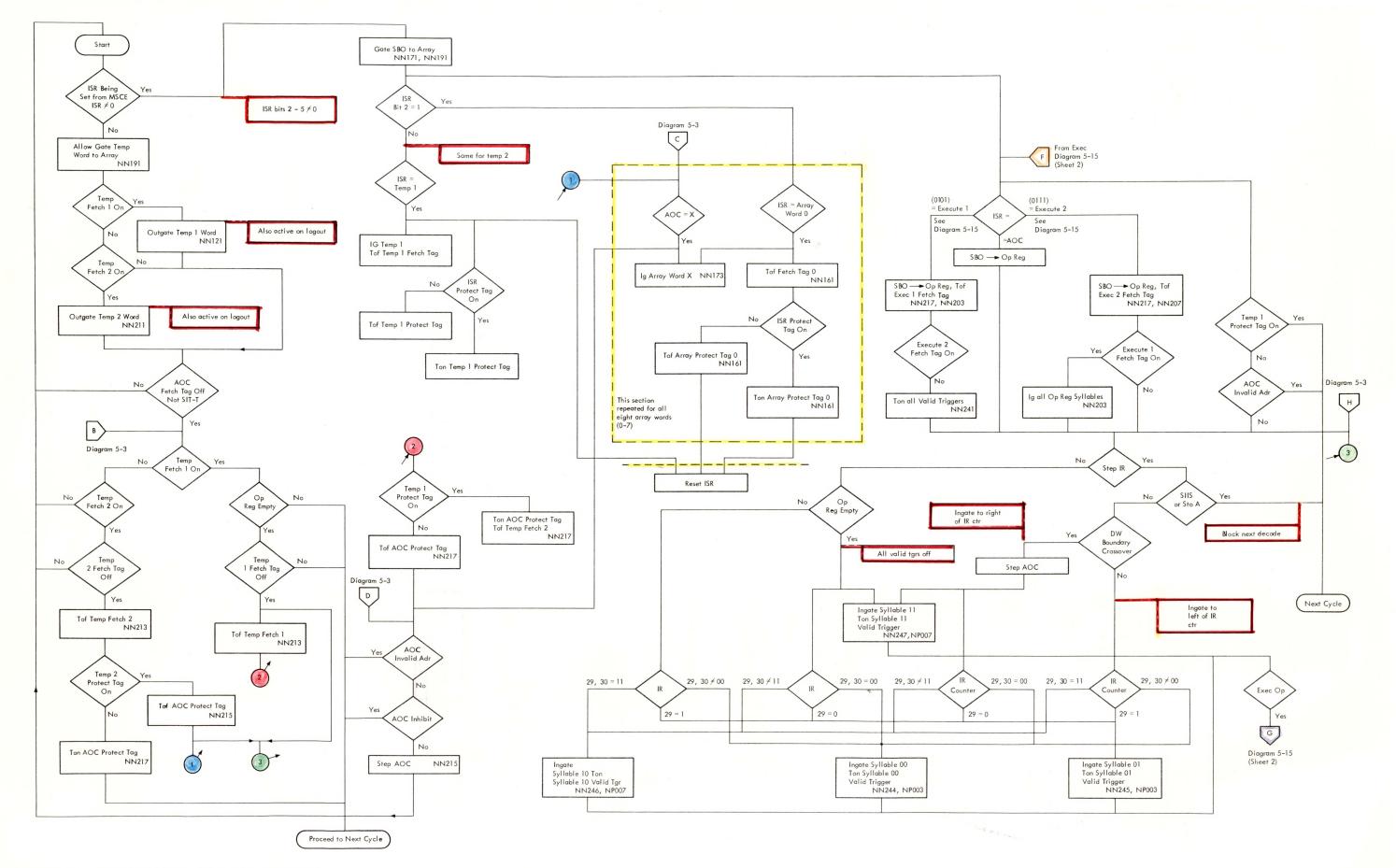

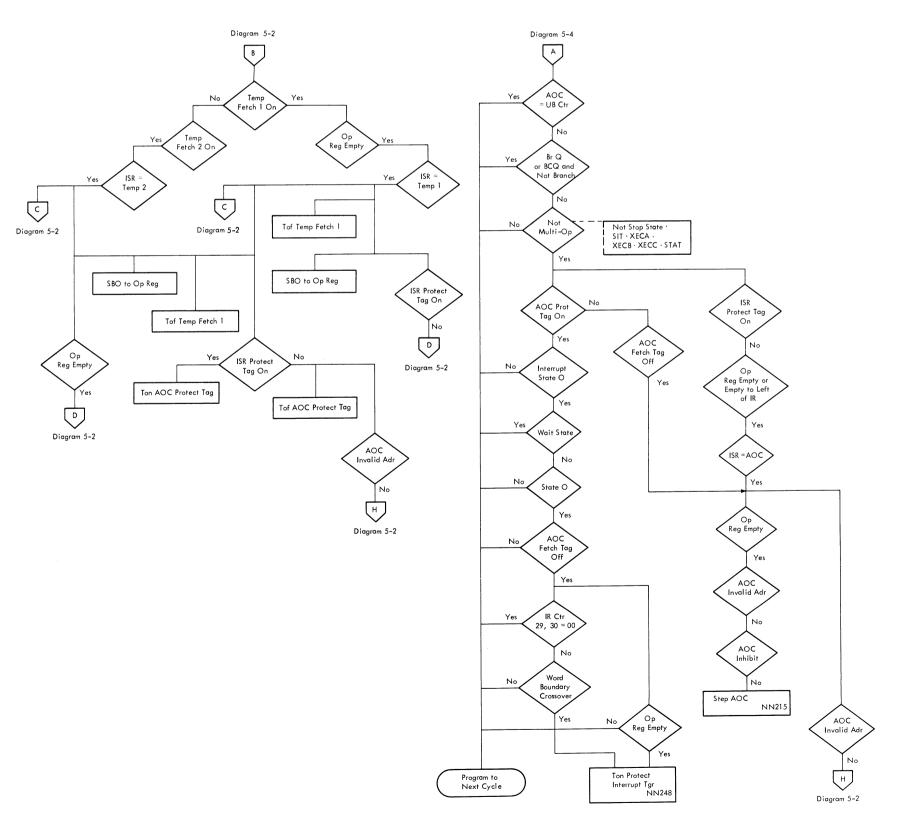

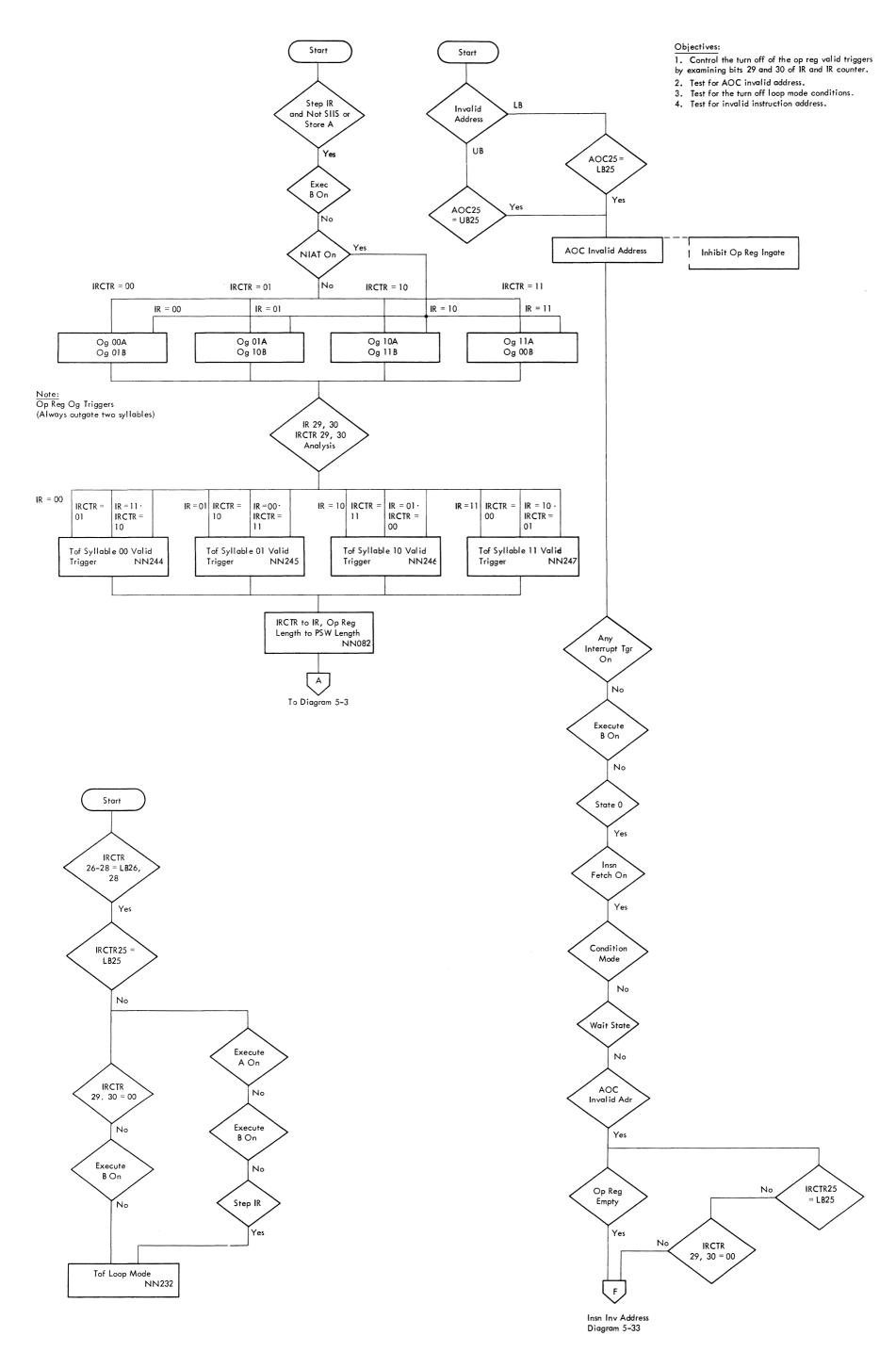

DIAGRAM 5-4. AOC INVALID ADDRESS, VALID TRIGGER TURN OFF AND TURN OFF LOOP MODE

DIAGRAM 5-6. PIPELINE 2 AND 3 CONTROL

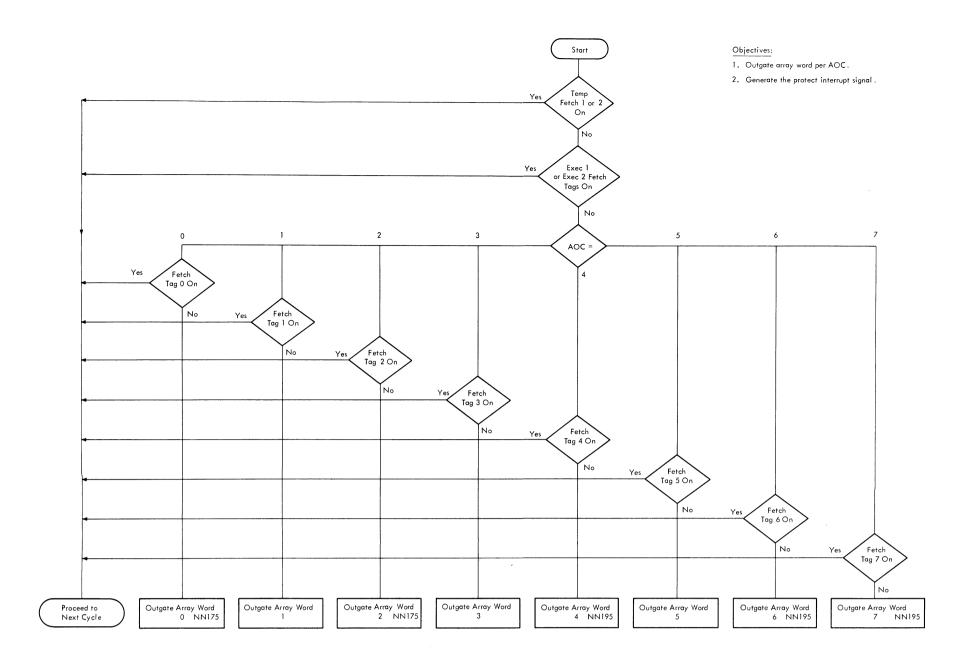

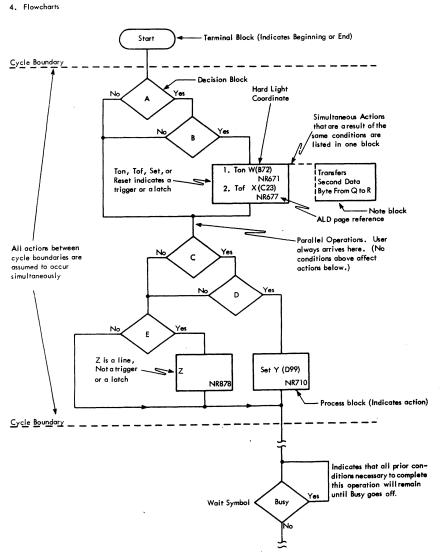

#### Objectives:

DIAGRAM 5-7. DECODE CYCLE (STATE 0) BASIC INTERLOCK CHECK

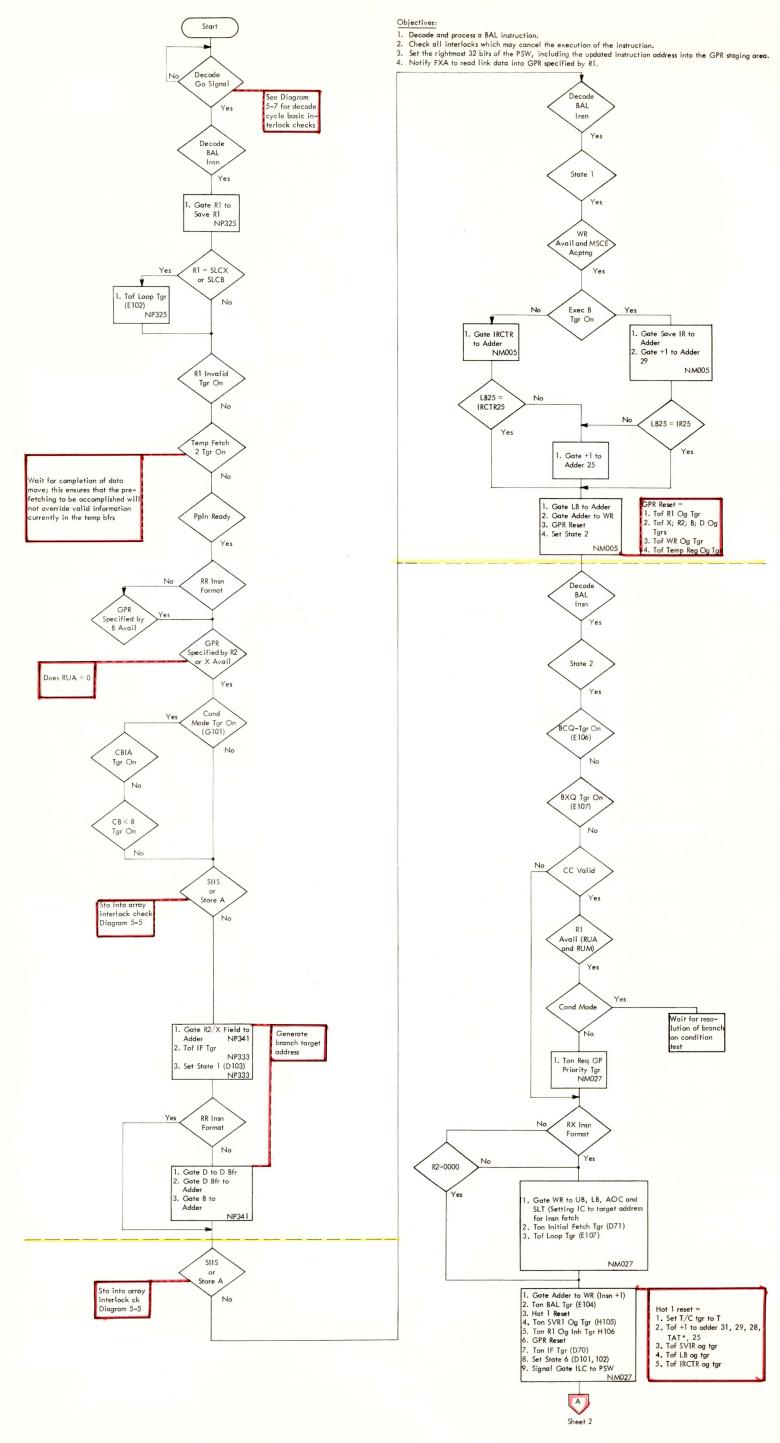

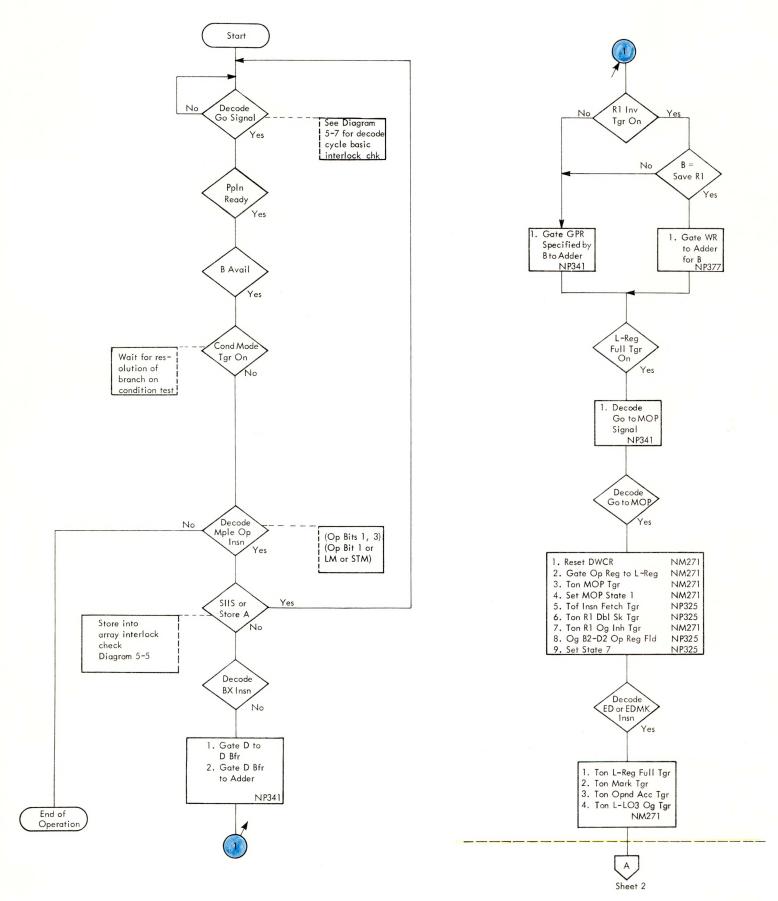

#### Objectives: 1. Decode and process a BC instruction. 2. Check all interlocks which may cancel the execution of this instruction. 3. Establish condition mode if the condition code is not immediately valid. 4. Establish an unconditional branch when the M1 (four bit mask) field in the BC instruction format contains all ones. Start see Diagram 5–7 for decode cycle basic interlock che all ones. 5. If conditions permit, establish loop mode. Decode Go Signal Yes When all 4 mask bits are zero or when the R2 field in the RR Decode BC Insn format contains zero, the branch instruction is equivalent to a Yes o-operation No Op M1 = 0000No RR Insn Format No No Op and Pipeline Drain R2 = 0000No PpIn Empty NP319 Yes R1 Inv Tgr On Wait for completion of data move; this ensures that the prefetching to be accomplished will not override valid information currently SIIS or Store A No No Temp Fetch 2 Tgr O (G74) in the temp bfrs 1. Step IR NP319 No End of Operation PpIn Ready Yes RR Insn Format GPR Specified by Does RUA for this GPR = 0 Yes B Avail Yes Does RUA for this GPR = 0 GPR Specified by R2/X Avail Sto into array interlock ck Diagram 5–5 Yes SIIS or Store A No No M1 = 1111 oranch Yes Exec B Tgr On (G106) Cond Mode Igr On (G101 RR Insn Format BC is target RR Insn of Exec Wait for Gate D to D Bfr No Format resolution of 2. Gate D Bfr to Adder 3. Gate GPR Specified by B to Adder Yes branch on condition test .Gate D to D Bfr Yes Gate D Bfr to Adder Gate GPR Specified by B to Adder NP341 . Gate GPR NP341 Specified by R2/X to Ad-der NP341 Loop Tgr Or (E102) 1.Gate GPR Specified by R2/X to Adde Yes Exec B Tgr On (G106) NP341 IR = SLCIR Did this BC Loop Mode On (E102) CC Valid (G102) Yes RR Insn Format Gate LB Reg to Adder Gate IRCTR to Adder No IR = SLCIR Yes is same insn that caused . Gate D to D Bfr . Gate D Bfr to Adder . Gate GPR Specified Cond Mode Tgr On (G101) NP33 Br Taken Addr Gen New IC (used if no branch) by B to Adder NP341 IRCTR 25 : LB25 (F104) 1. Gate SLT Reg to AOC 2. Set Op Reg Empty 3. Gate SLT Reg to IR (This action also causes NIAT to turn on) NP333 CBIA Tgr On (J103) Temp 1 and Temp 2 Fth Tags Off Yes No Νo (F74, G74) Gate GPR Specified by R2/X to Adder NP341 Gate +1 to Adder 25 Yes CB<8 Tgr On (J103) 1. Step IR Loop Tgr On (E102) NP333 NP333 Gate R1 to CC Mask Reg Tof IF Tgr (D70) 1. Ton BC Uncond Tgr (E103) 2. Tof IF Tgr (D70) 3. Set State 2 (D102) 1. Ton BC Uncond Tgr (E103) 2. Tof IF Tgr (D70) 3. Set State 1 (D103) 2. Tof IF Tgr (D/U) 3. Set State 1 (D103) NP333 State 2• no temp fetching State 1• State 1 · BC cond NP333 NP333 A End of Operation B Sheet 2 C End of Operation Sheet 2

DIAGRAM 5-11. BRANCH ON CONDITION SEQUENCE (SHEET 4 OF 5)

# Notes:

```

1. Reset Og to Adder = GPR Reset and Hot 1s Reset

2. GPR Reset = (a) Tof R1 Og Tgrs

(b) Tof X/R2; B; D; Og Tgrs

(b) Tot X/R2; B; D; Og Igrs

(c) Tof WR Og Tgrs

(d) Tof Temp Reg Og Tgrs

3. Hot is Reset = (a) Set T/C Tgr to T

(b) Tof +1 to Adder 31; 29; 28; TAT; and 25

(c) Tof SVIR Og Tgr

(d) Tof LB Og Tgr

(e) Tof IRCTR Og Tgr

4. Br Tar Reset = (a) Tof Br Tar

(e) Tof IRCTR Og Tgr

(a) Tof Br Tgr

(b) Tof BIA Tgr

(c) Tof BIA 1 Tgr

(d) Tof BSR Tgr

(e) Tof Exec Tgr

(f) Tof BCUNCON Tgr

(a) Tof Cond Tgr

(b) Tof CBIA Tgr

(c) Tof CBSR Tgr

(d) Tof CQUick Tgr

(e) Tof CTFM Tgr

4. Br Tgr Reset =

5. C Tgr Reset =

(e) Tof TFM Tgr

```

DIAGRAM 5-11. BRANCH ON CONDITION SEQUENCE (SHEET 5 OF 5)

#### Objectives:

Wait for completion of data moves;

- 1. Decode and process a BCT instruction.

- Check all interlocks which may cancel the execution of this instruction.

Condition mode must be removed before processing of the BCT instruction can be completed.

- 4. The BCT instruction can either break, establish, or retain a loop mode of operation.

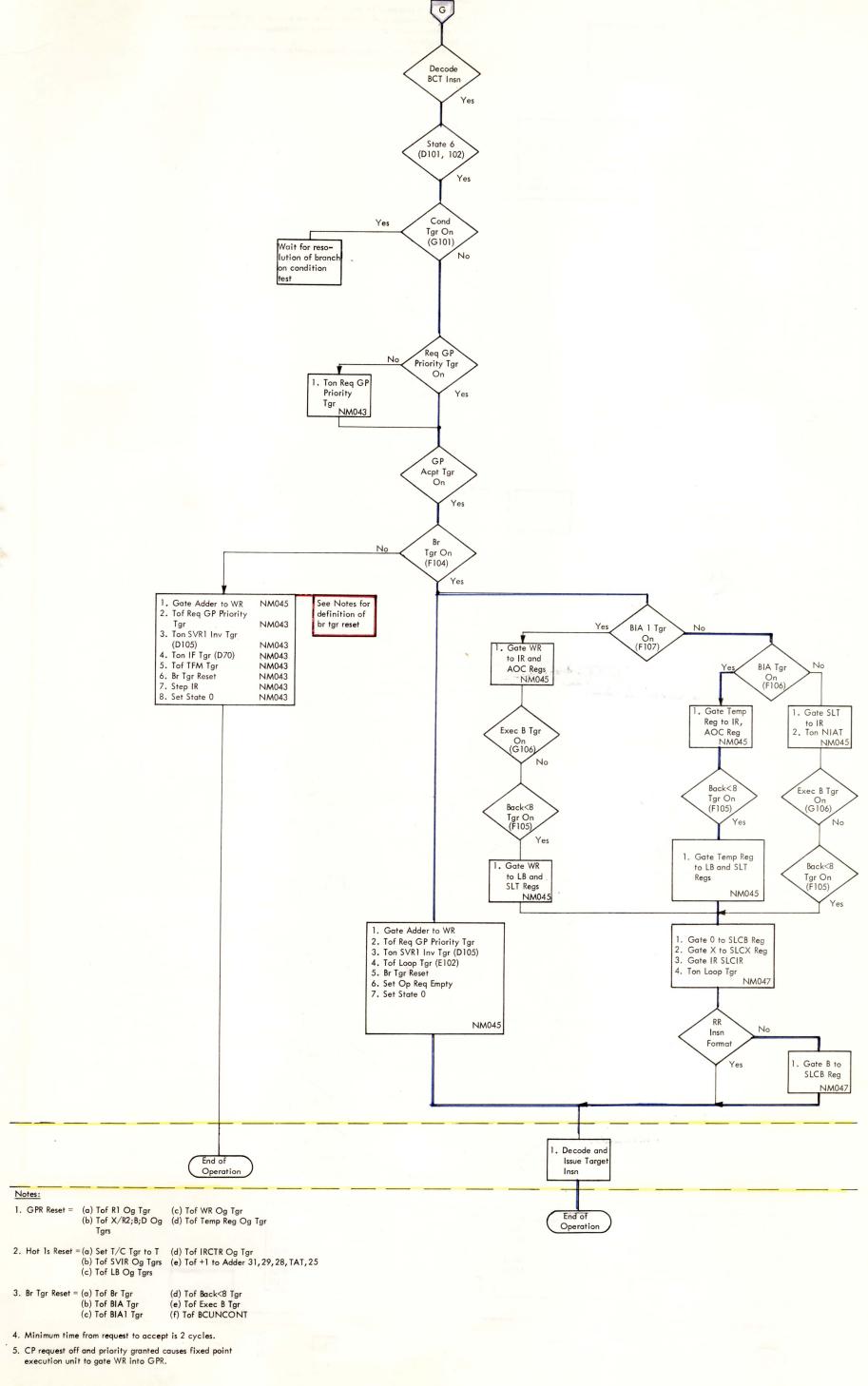

DIAGRAM 5-12. BRANCH ON COUNT SEQUENCE (SHEET 4 OF 5)

Sheets 2, 4

DIAGRAM 5-12. BRANCH AND COUNT SEQUENCE (SHEET 5 OF 5)

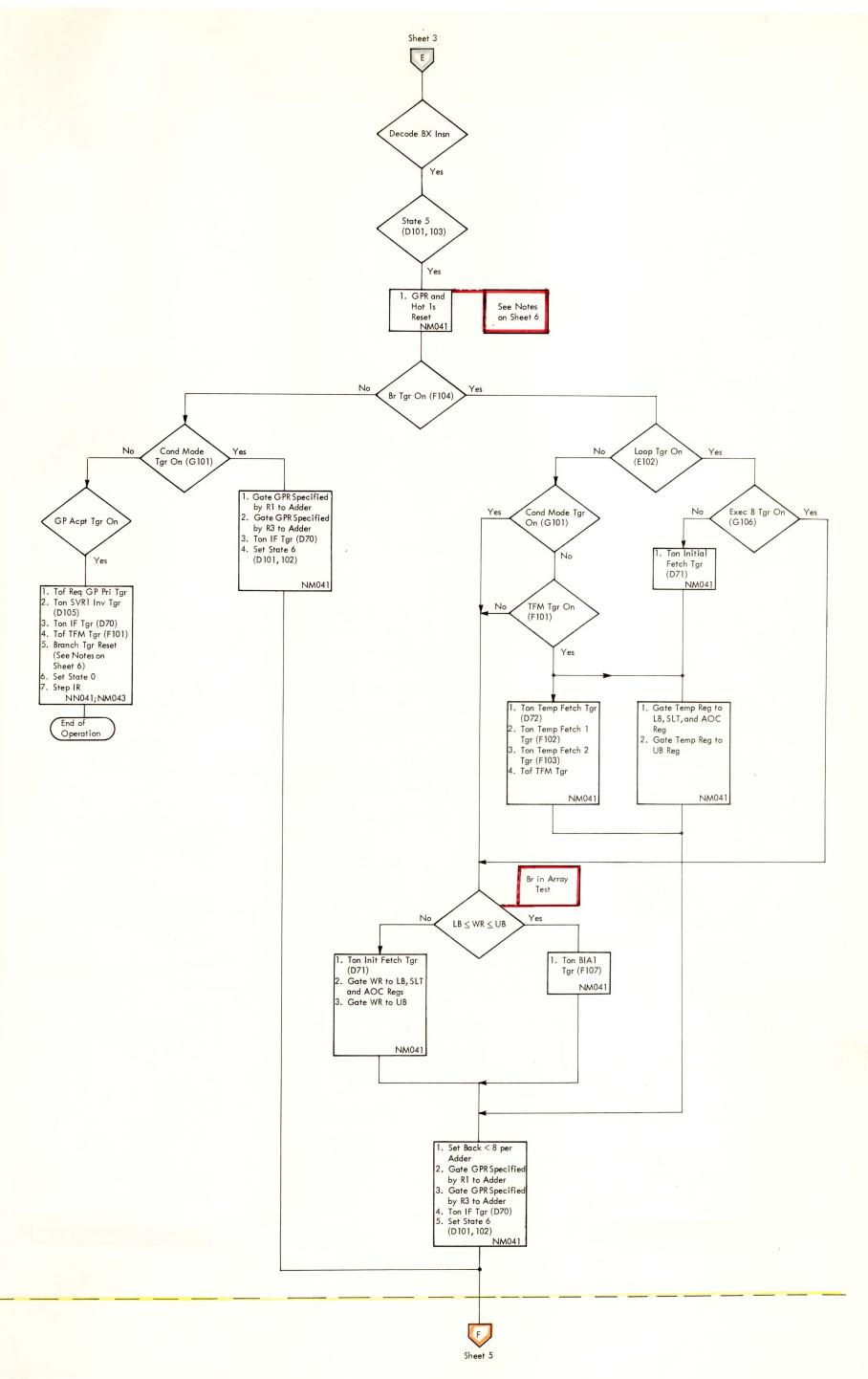

DIAGRAM 5-13. BRANCH ON INDEX SEQUENCE (SHEET 3 OF 6)

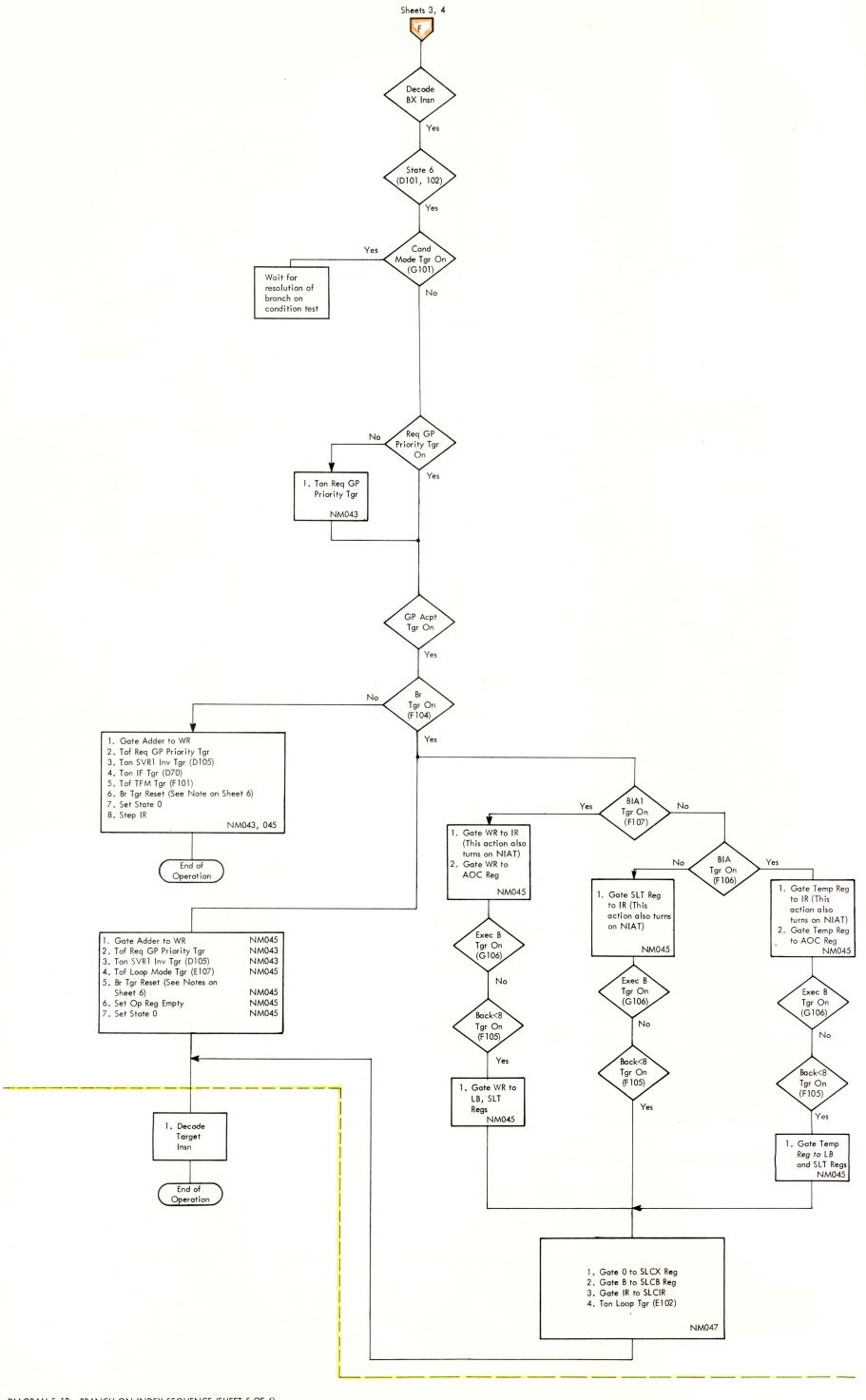

DIAGRAM 5-13. BRANCH ON INDEX SEQUENCE (SHEET 6 OF 6)

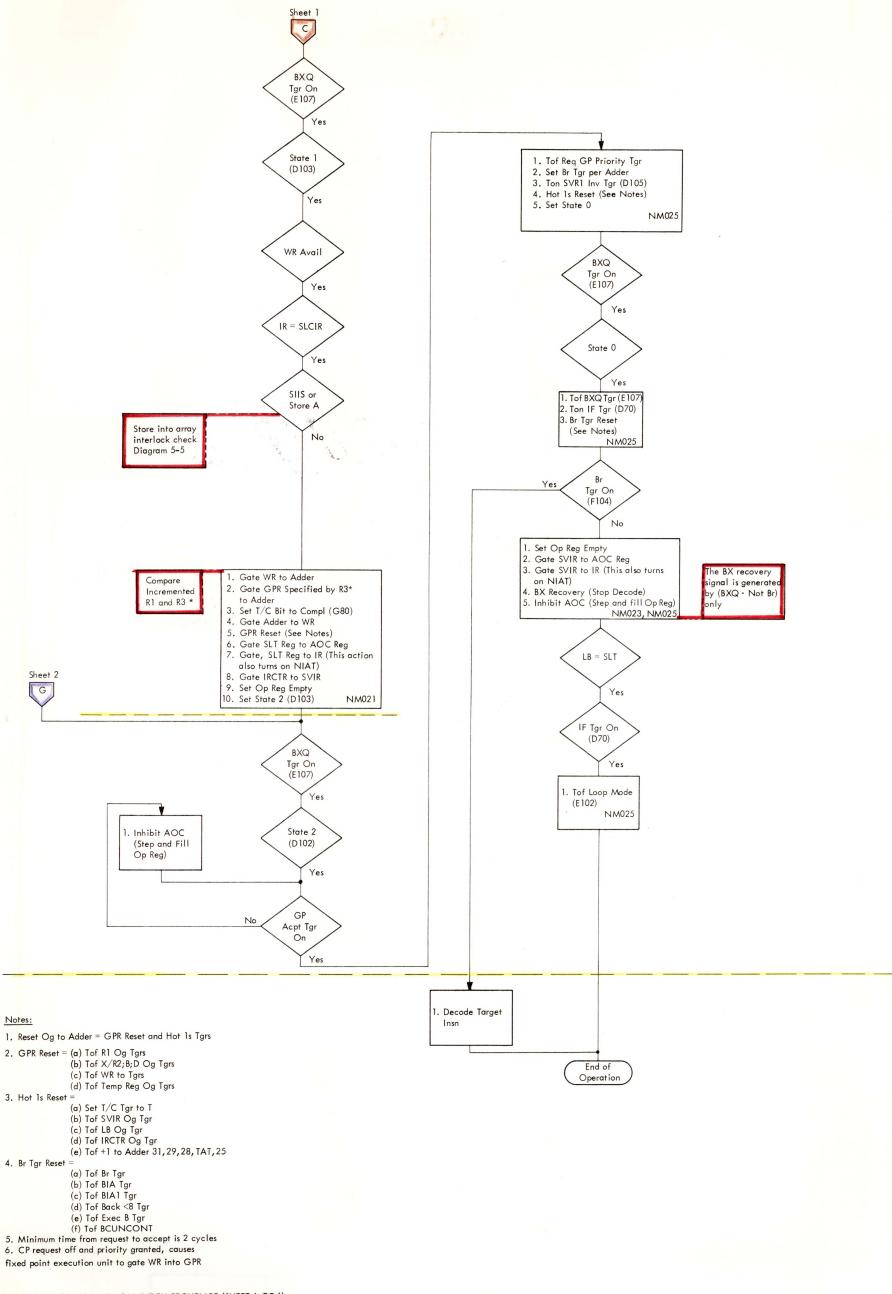

DIAGRAM 5-14. BRANCH AND LINK SEQUENCE (SHEET 2 OF 2)

DIAGRAM 5-17. SET PROGRAM MASK AND SUPERVISOR CALL SEQUENCE

execution.

- The byte located at the B1 and D1 instruction fields replaces system mask of current PSW.

- VFLEU does byte selection for storage operand.

Correct system mask is stored because I/O and external interrupts are inhibited during instruction

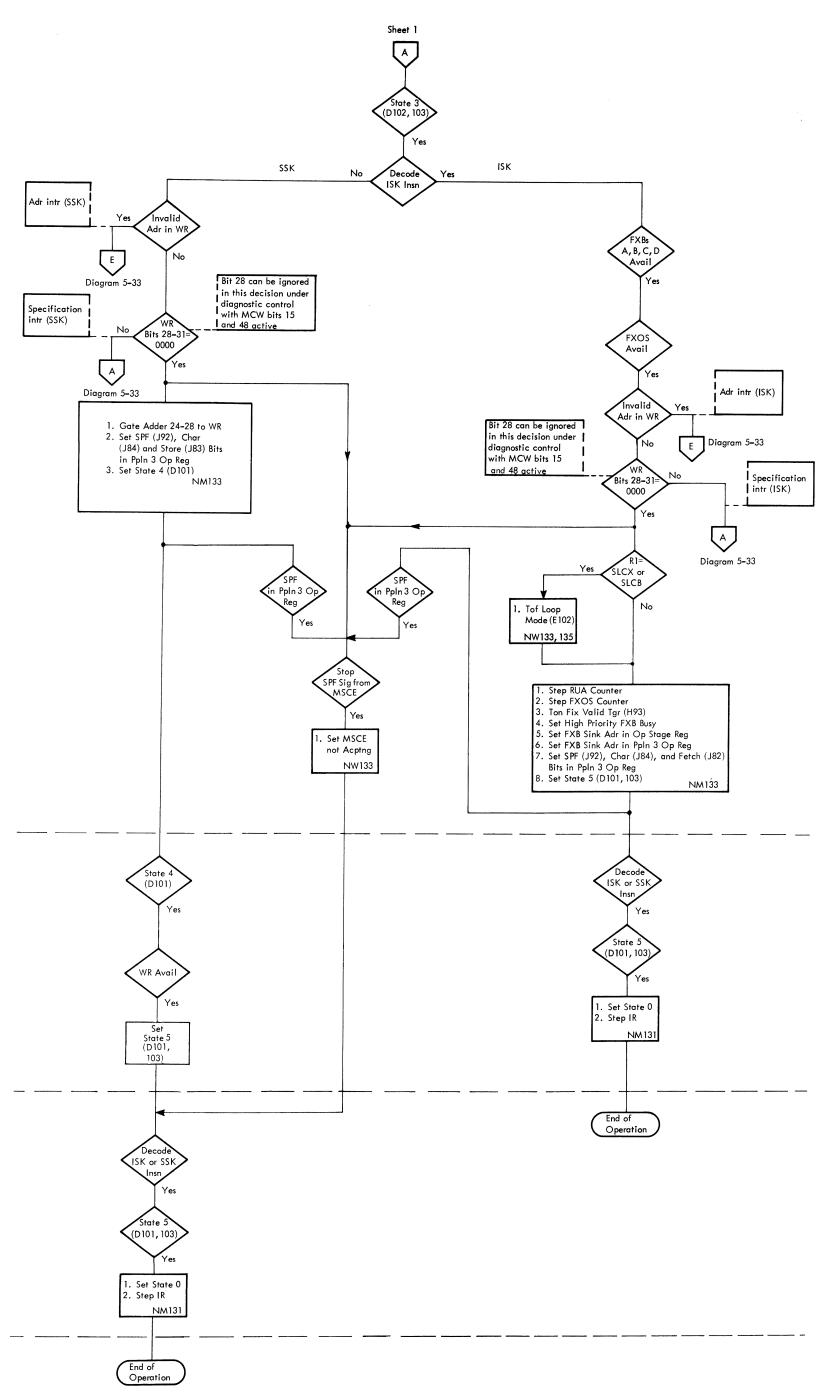

DIAGRAM 5-19. INSERT STORAGE KEY AND SET STORAGE KEY SEQUENCES (SHEET 2 OF 2)

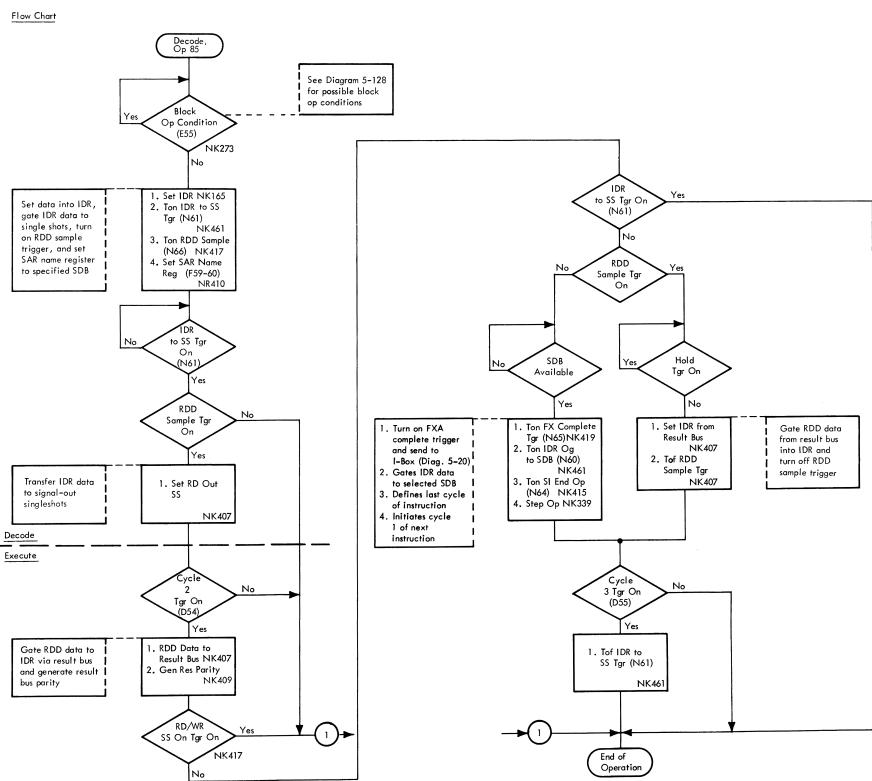

- 1. Decode and issue a RDD or WRD instruction.

- Check all interlocks that can detain or cancel these instructions.

RDD Generate address and test for valid storage; check for FXOS and SAR availability; issue instruction to FXA; wait for FXA completion of this instruction before proceeding to decode cycle.

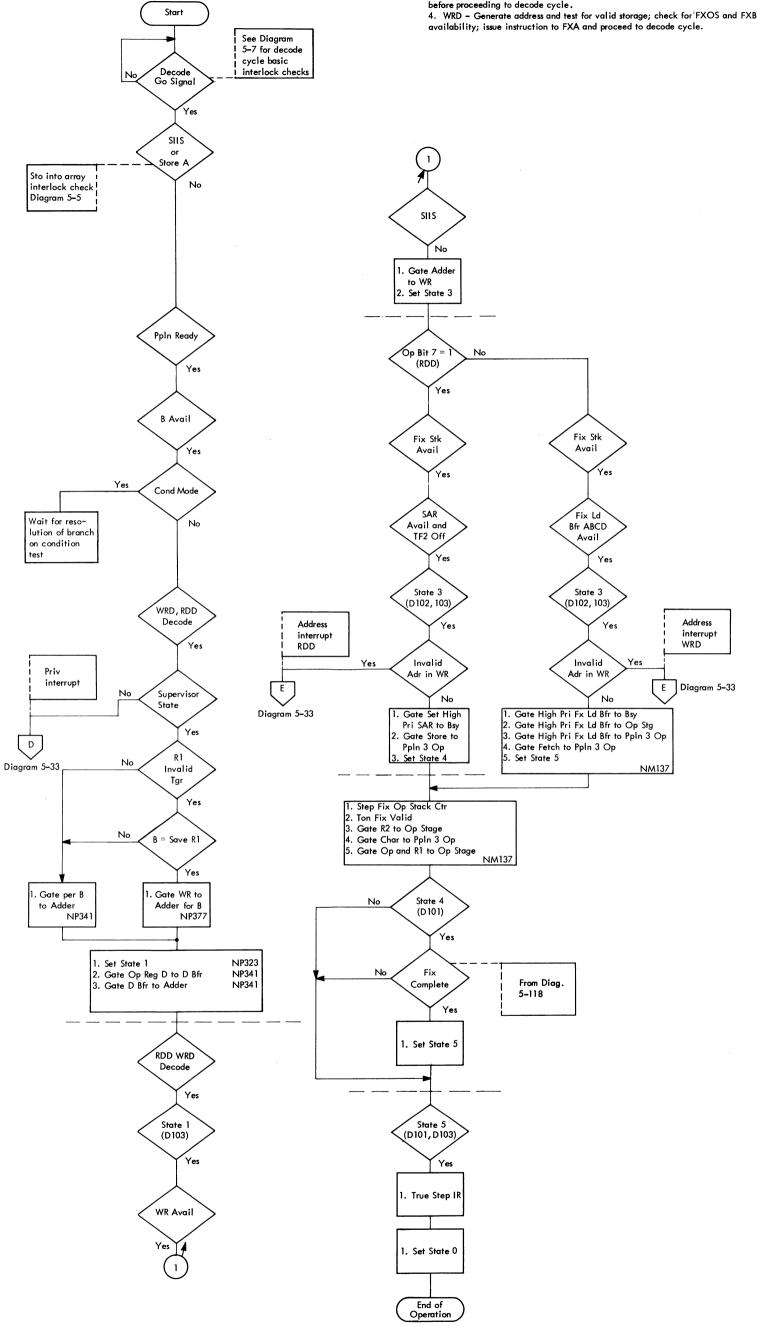

DIAGRAM 5-20. READ, WRITE DIRECT SEQUENCE

#### Start Objectives: Decode and issue diagnose instruction. Set MCW register which controls CPE and channel functions. Verification of proper CPU equipment functions. See Diagram 5-7 for decode cycle basic interlock No Decode Go Signal Yes Store A Sto into array interlock check No Diagram 5-5 PpIn Ready Yes B Avail Yes Yes Cond Mode Yes Any Int Tgr On Wait for No resolution of Any Sto in PpIn or No branch on condition test SIIS No 1. Tof IF Diag Decode No NM141 1. Add → WR 2. Set State 3 Yes Priv interrupt NM135 MSCE Acptng No Supervisor State D State 3 Yes (D102, D103) Yes Diagram 5-33 IF Off Yes No R1 Invalid Tgr Address in WR Invalid Yes Yes Address E 1/0 or interrupt Diag Op No No Diagram 5-33 SPM B = Save R1 Dbl Length Yes Specification in WR Specification interrupt (Type A 1. Gate per B 1. Gate WR to Adder for B NP377 B precise) $\mathsf{Exec}\ \mathsf{B}$ to Adder NP341 1. Ton Stop Tgr 2. Set State 4 Yes Start MC 1. Gate SVIR stop sequence to IR Set State 1 Gate Op Reg D → D Bfr Gate D Bfr → Adder NP323 NM141 NP341 NP341 State 4 1. Set State 0 (D101) 2. Tof Loop 3. Tof Exec B 4. Gate Tof + 1 to Adder 25 Gate SVIR to Adder Gate Tof LB to Adder 12 field to MC Signal MCW Diagnose to MC Gate Bit 1 to Ppln 3 Op Sk Adr Gate Dbl to Ppln 3 Op Fetch MCW; set NM141 sink address equal to MC Diag Decode End of 4. Gate Fetch to PpIn 3 Op Operation NM135 5. Set State 5 Yes (D103) (D101, D103) Yes Yes PpIn Empty 1. Set State 0 2. True Step IR End of

Operation

DIAGRAM 5-21. DIAGNOSE SEQUENCE

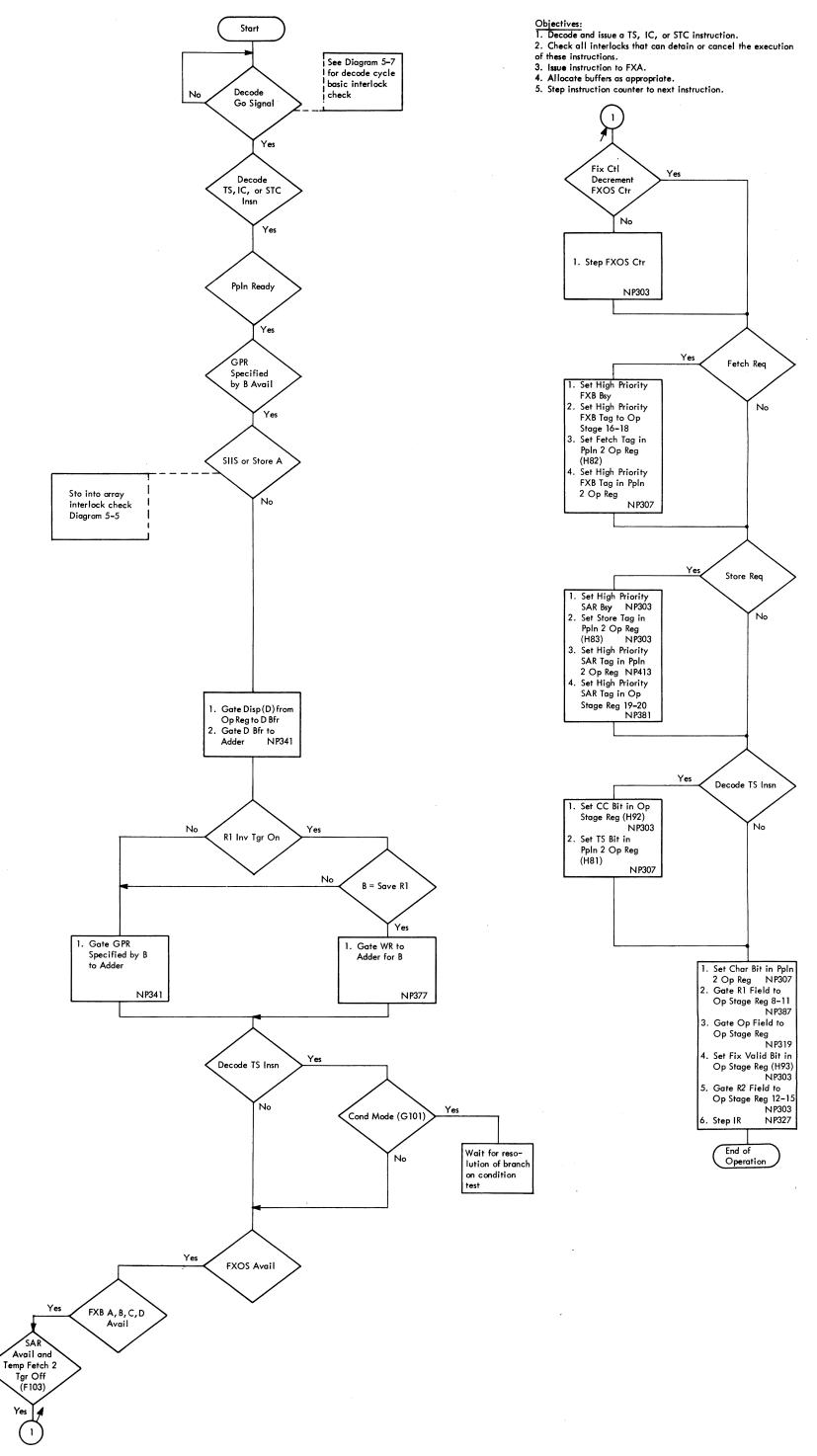

DIAGRAM 5-22. INSERT CHARACTER, STORE CHARACTER, AND TEST AND SET SEQUENCE

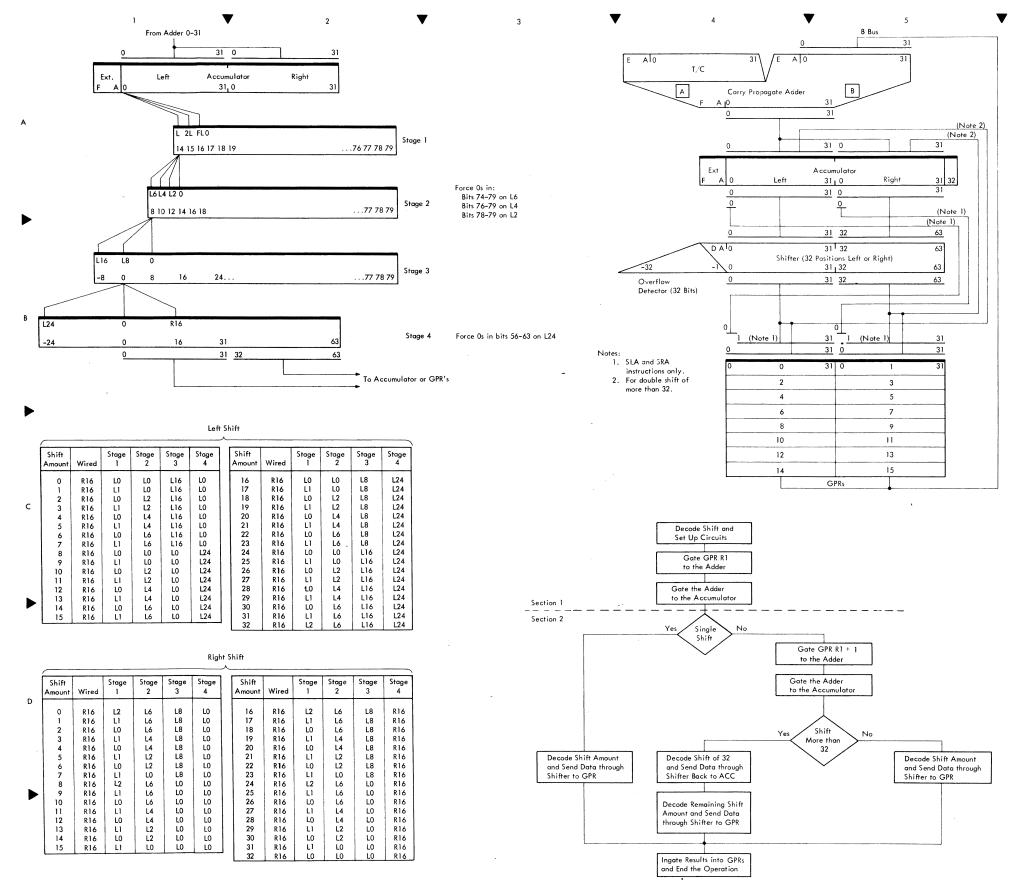

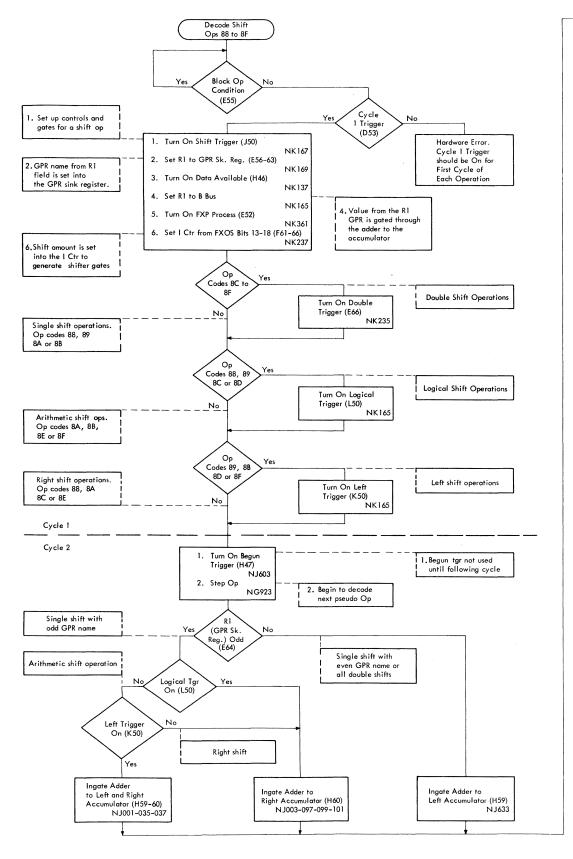

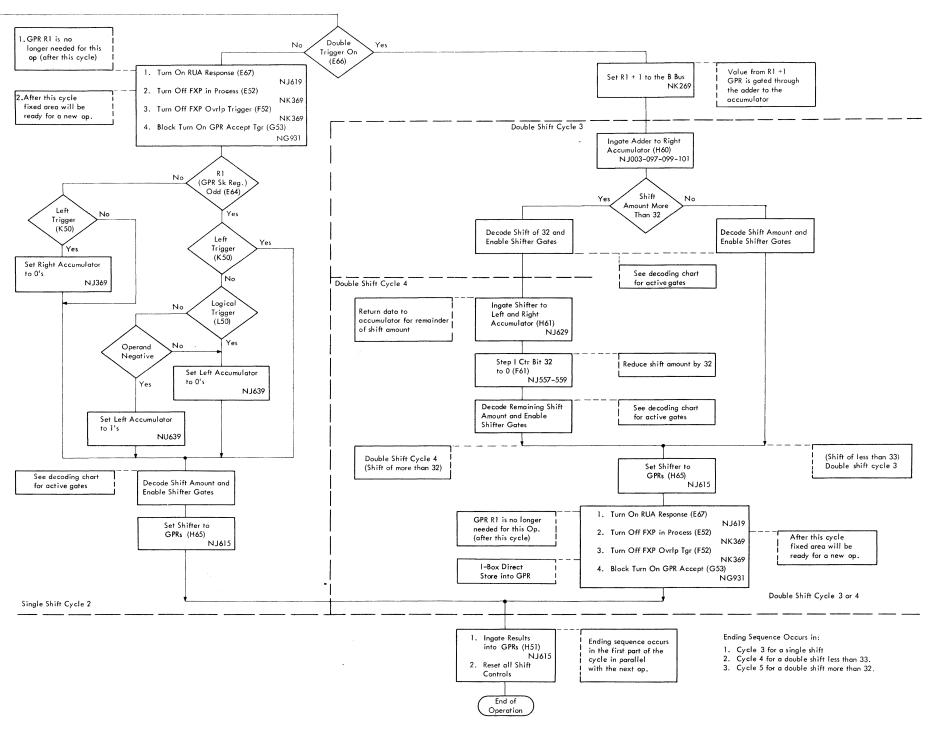

DIAGRAM 5-24. SHIFT SEQUENCE

DIAGRAM 5-27. I/O SEQUENCE (SHEET 2 OF 2)

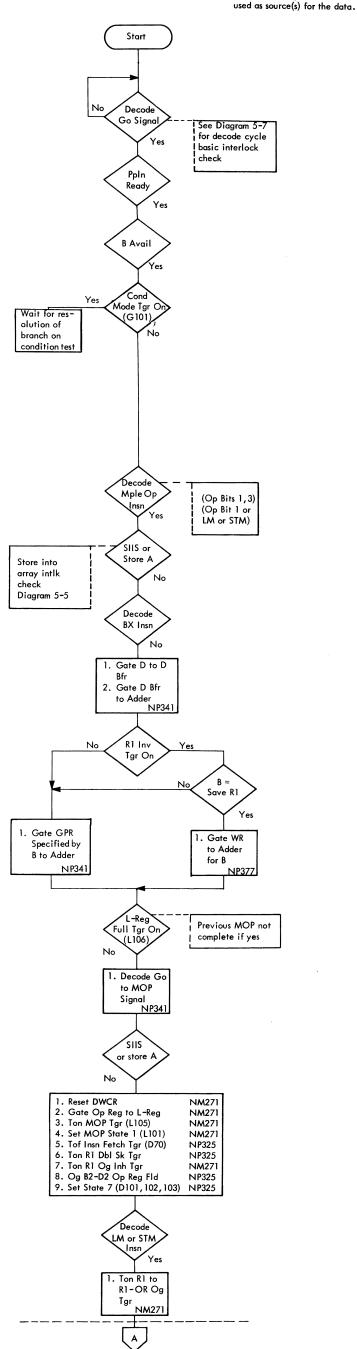

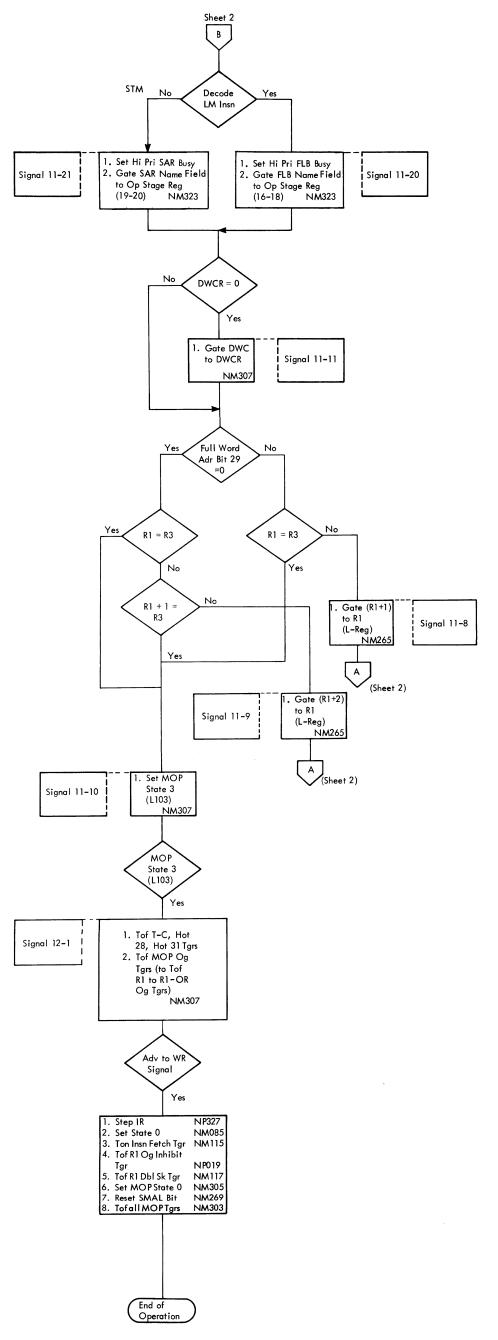

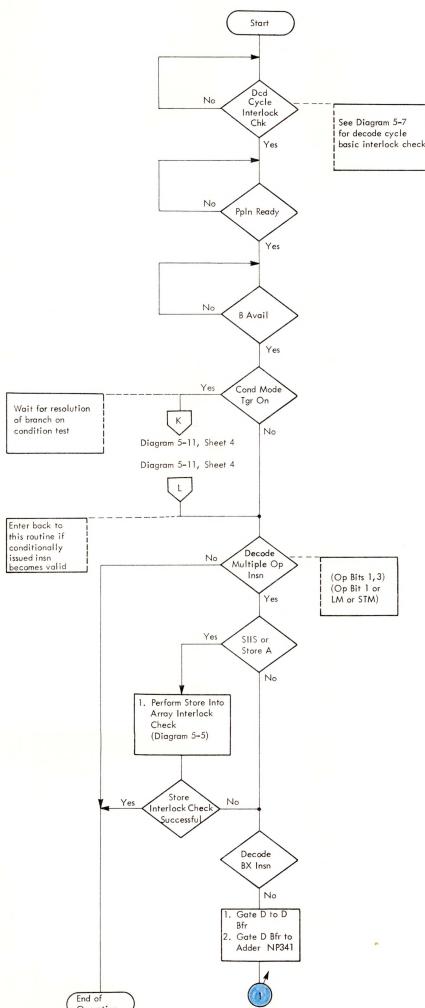

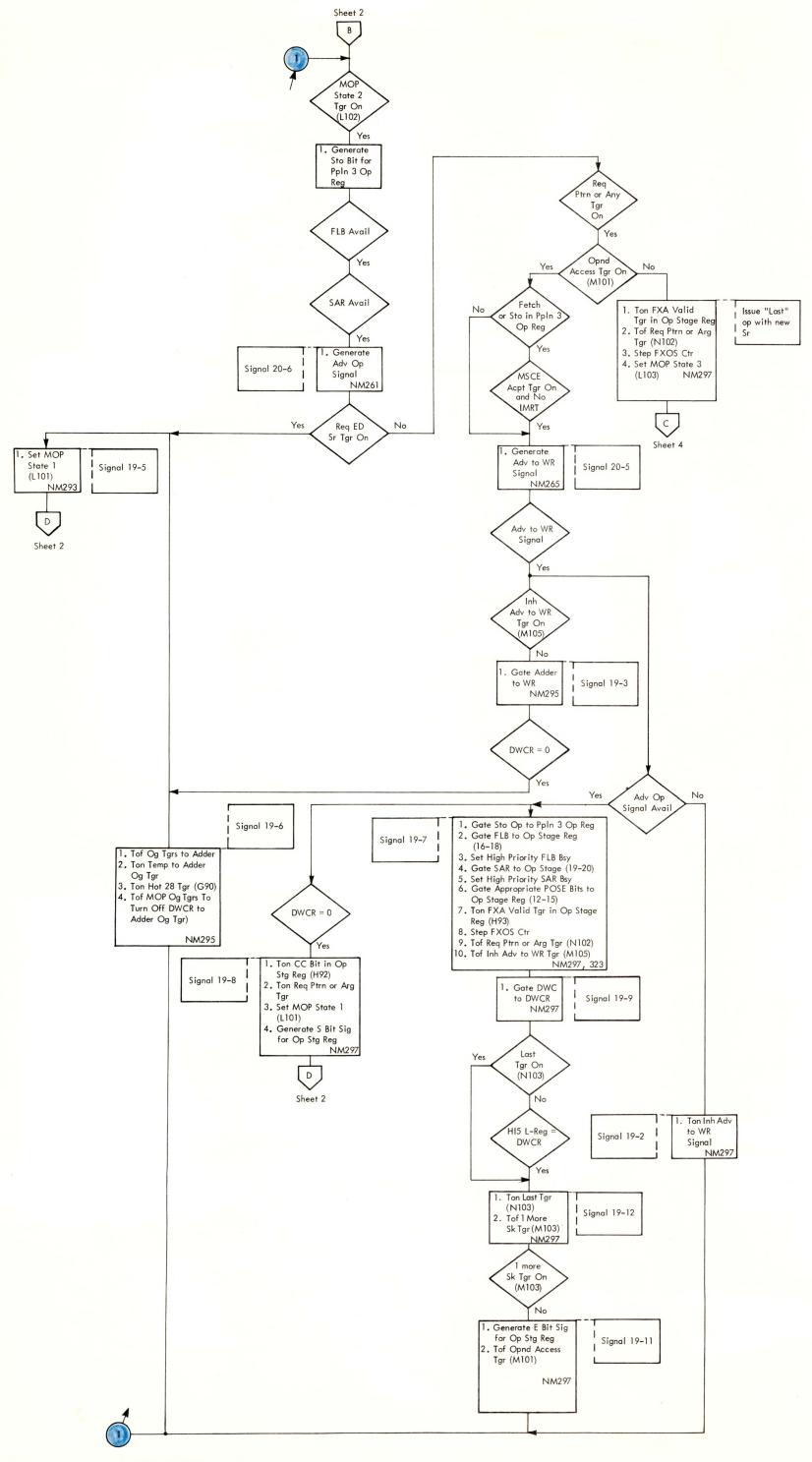

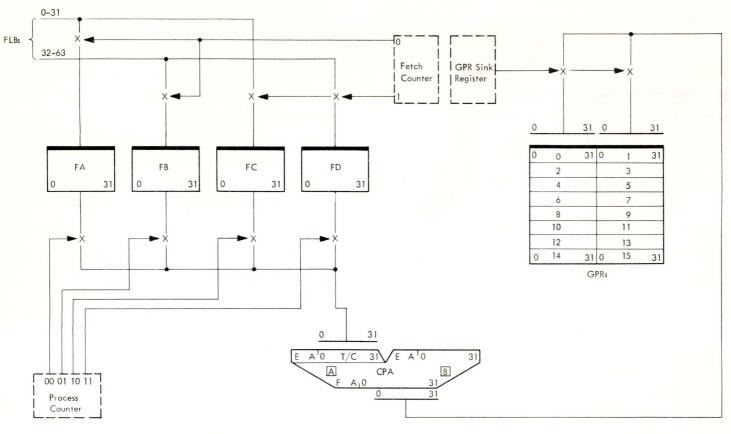

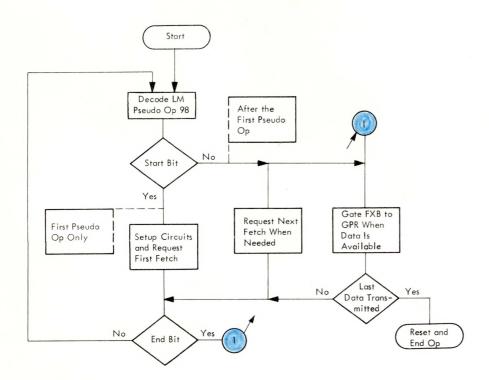

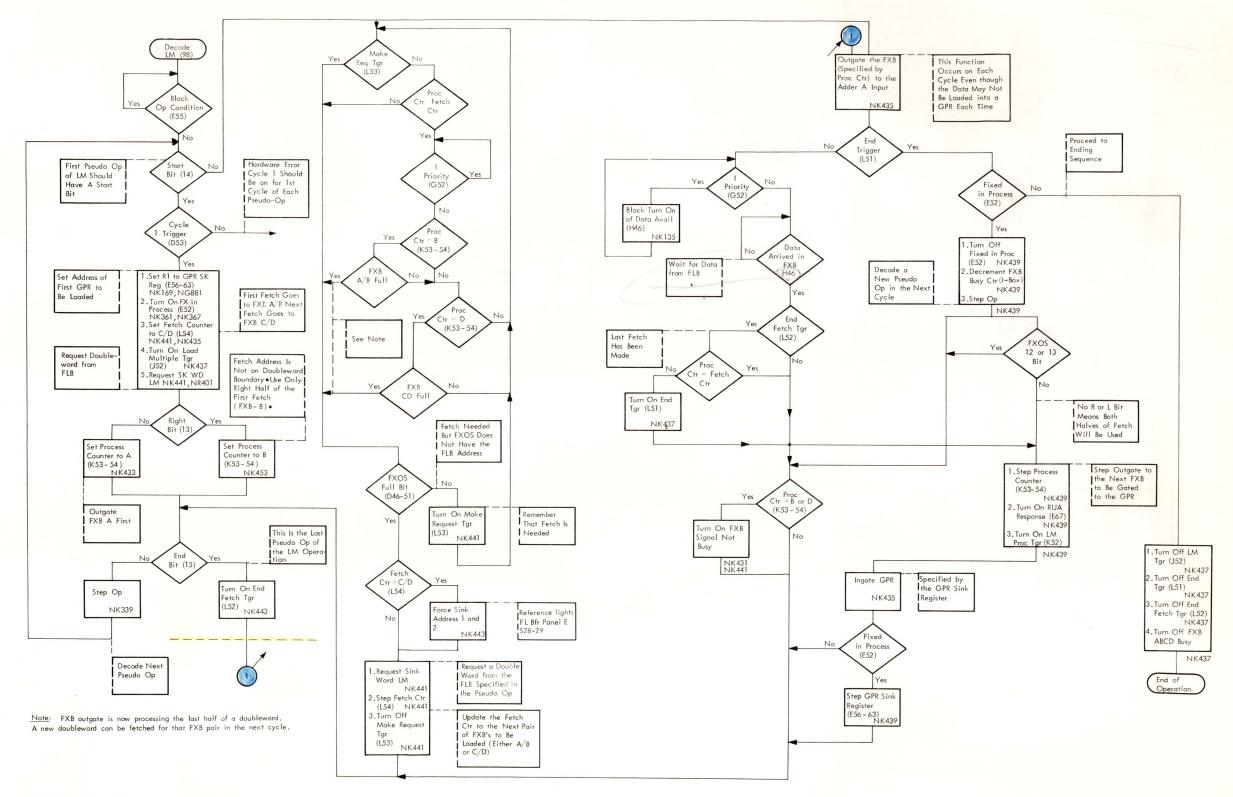

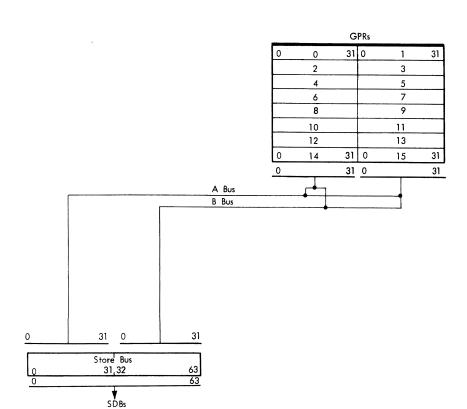

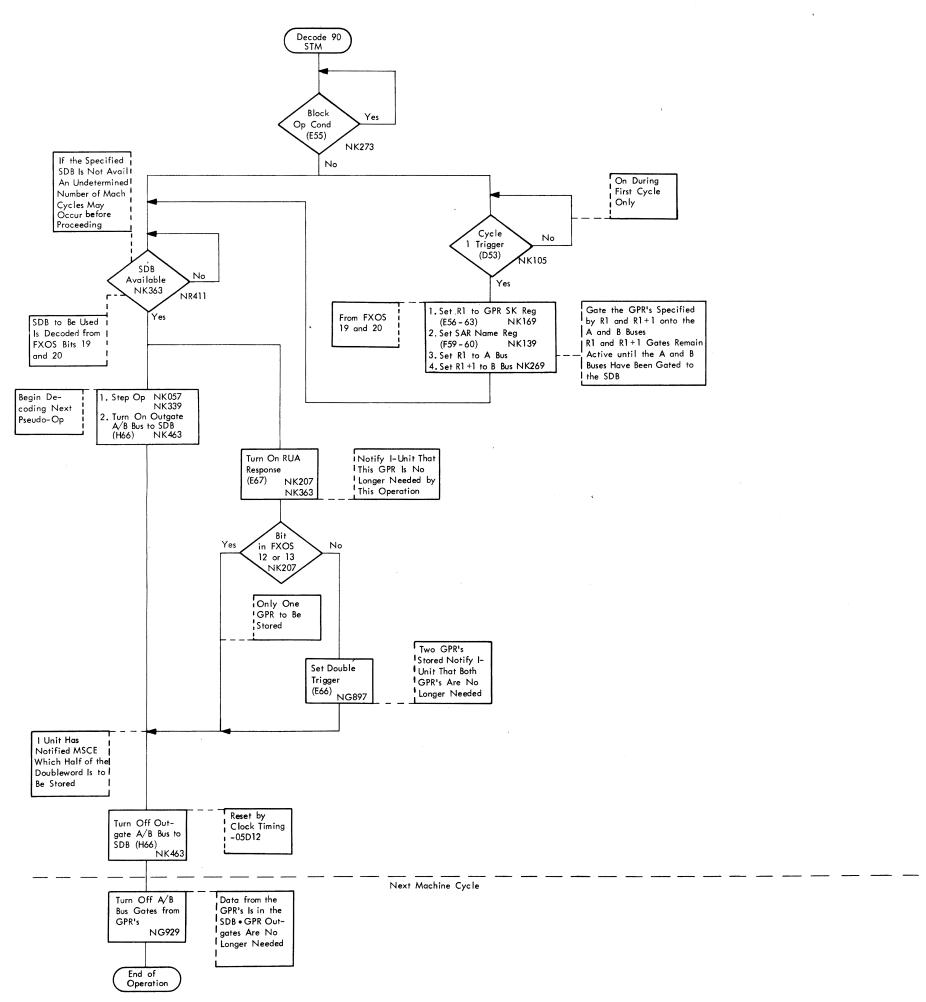

- 1. Decode and issue LM or STM instruction.

- Decode and issue LM or STM instruction.

Check all interlocks that might detain or cancel the instruction.

LM Fetch a doubleword; inform FXA of the FLB assigned for this fetch, the position of the data within the doubleword; and the GPR(s) that the data should fill.

STM Set up a store for a doubleword; inform FXA of the SAR assigned for this store, the position of the data within the doubleword, and the GPR(s) to be used as source(s) for the data.

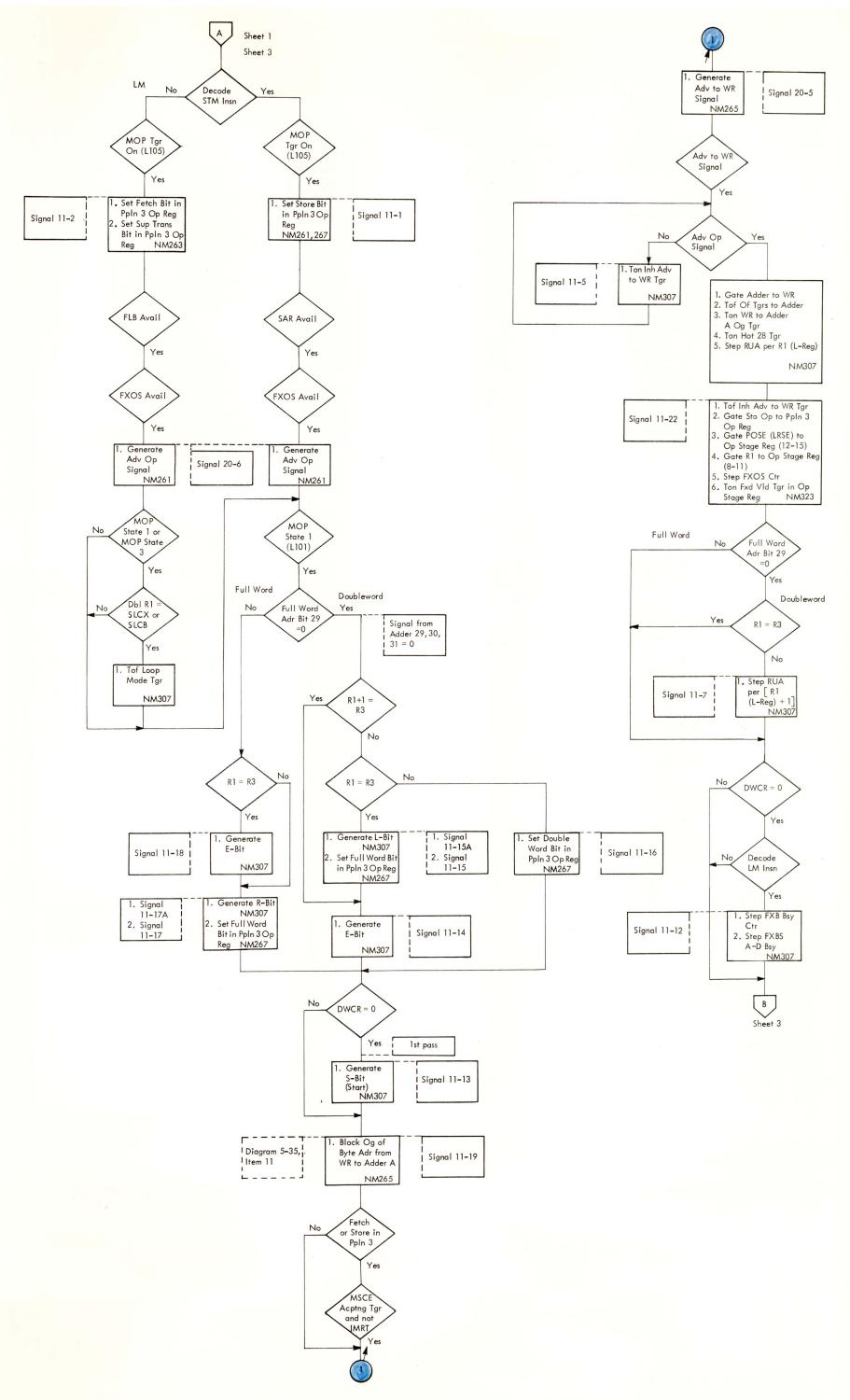

DIAGRAM 5-28. LM, STM SEQUENCE (SHEET 1 OF 3)

DIAGRAM 5-28. LM, STM SEQUENCE (SHEET 3 OF 3)

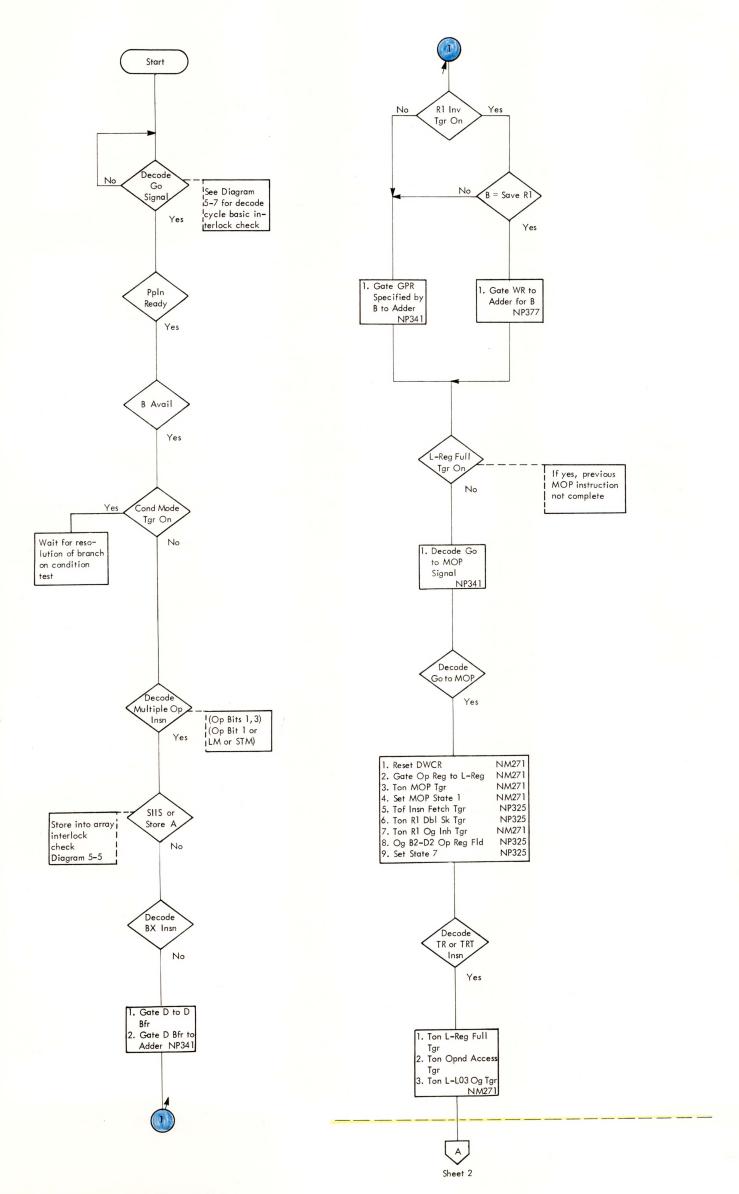

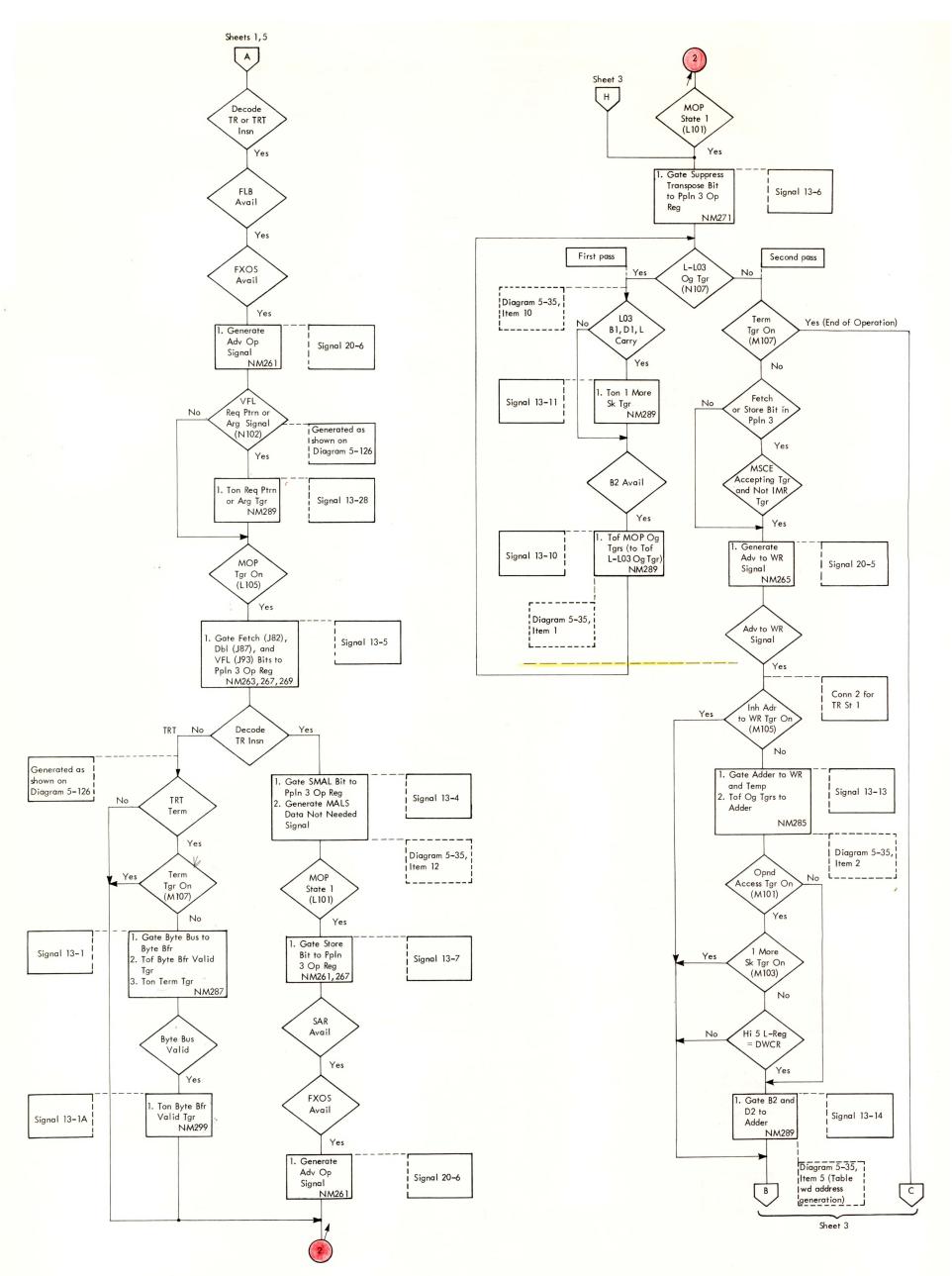

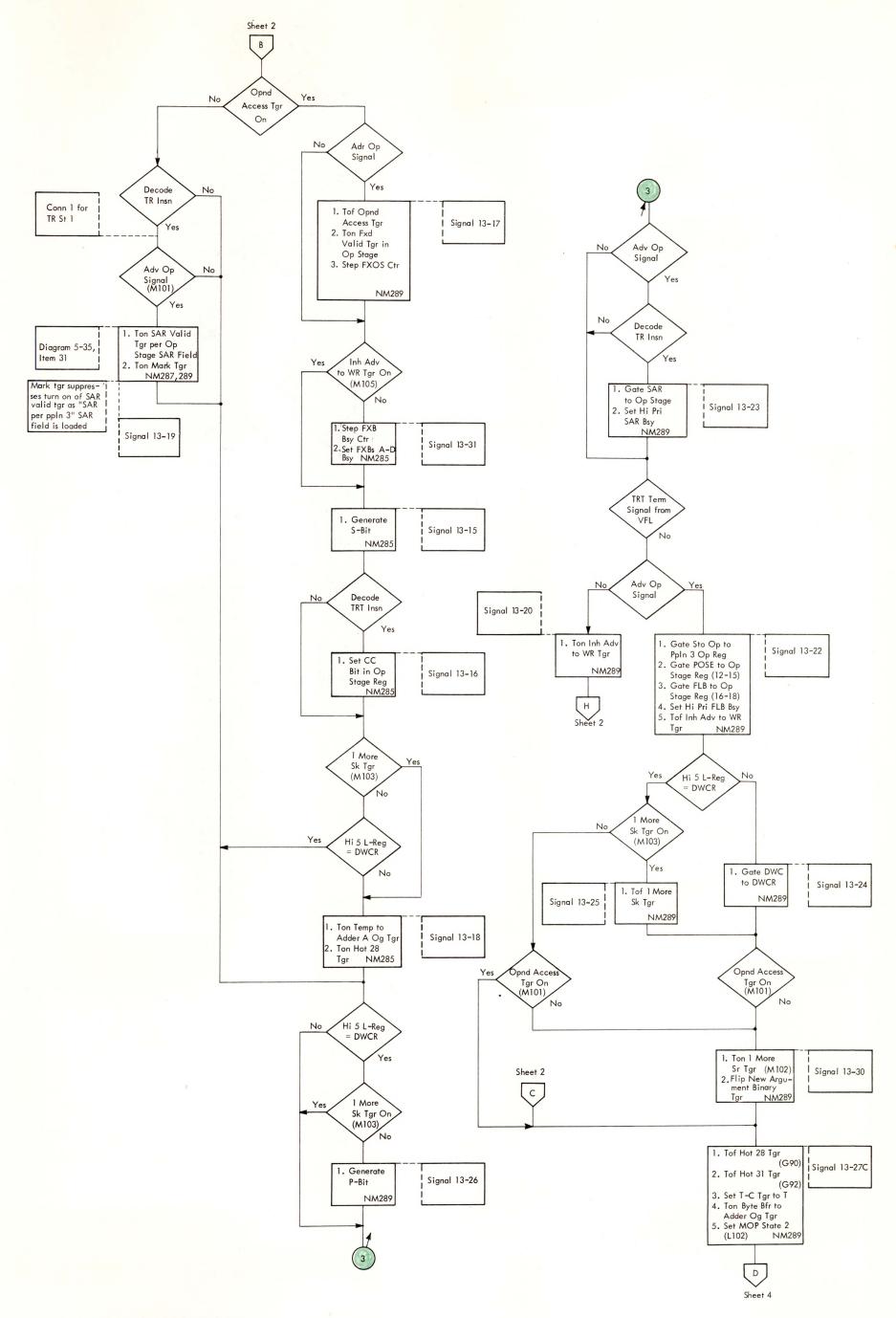

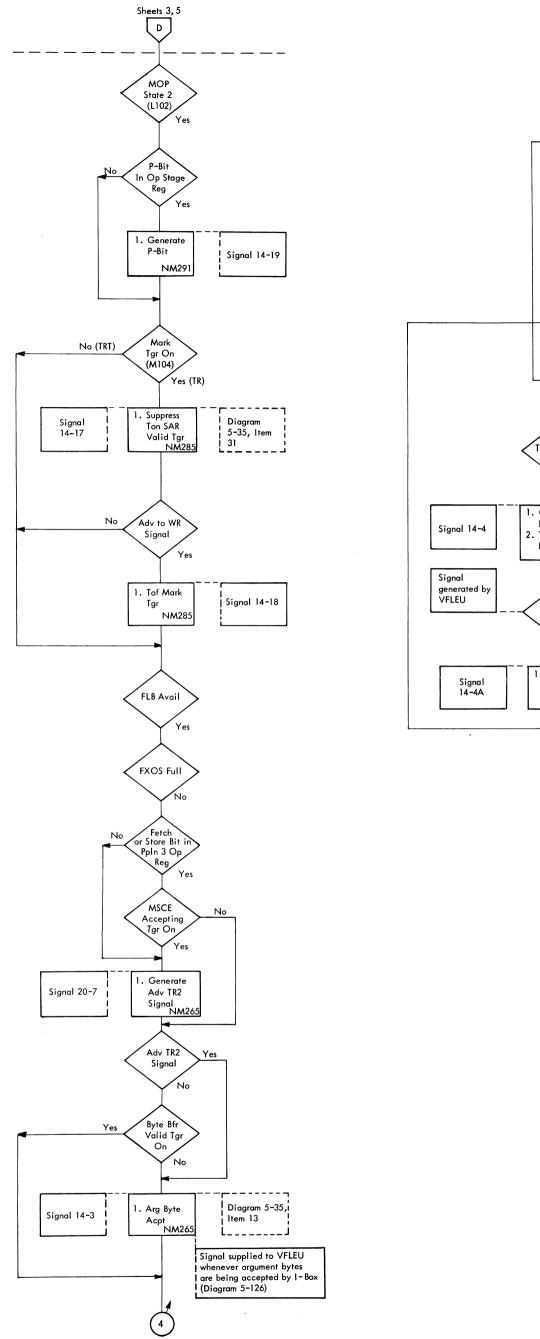

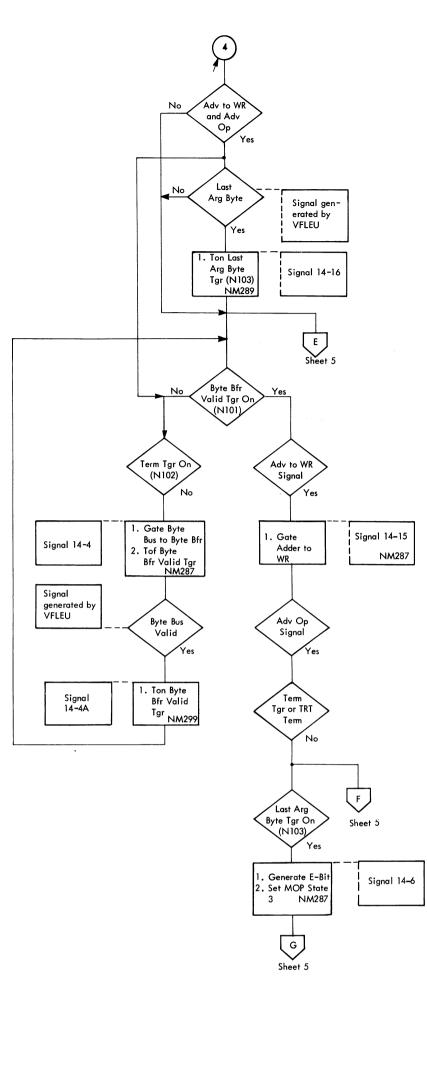

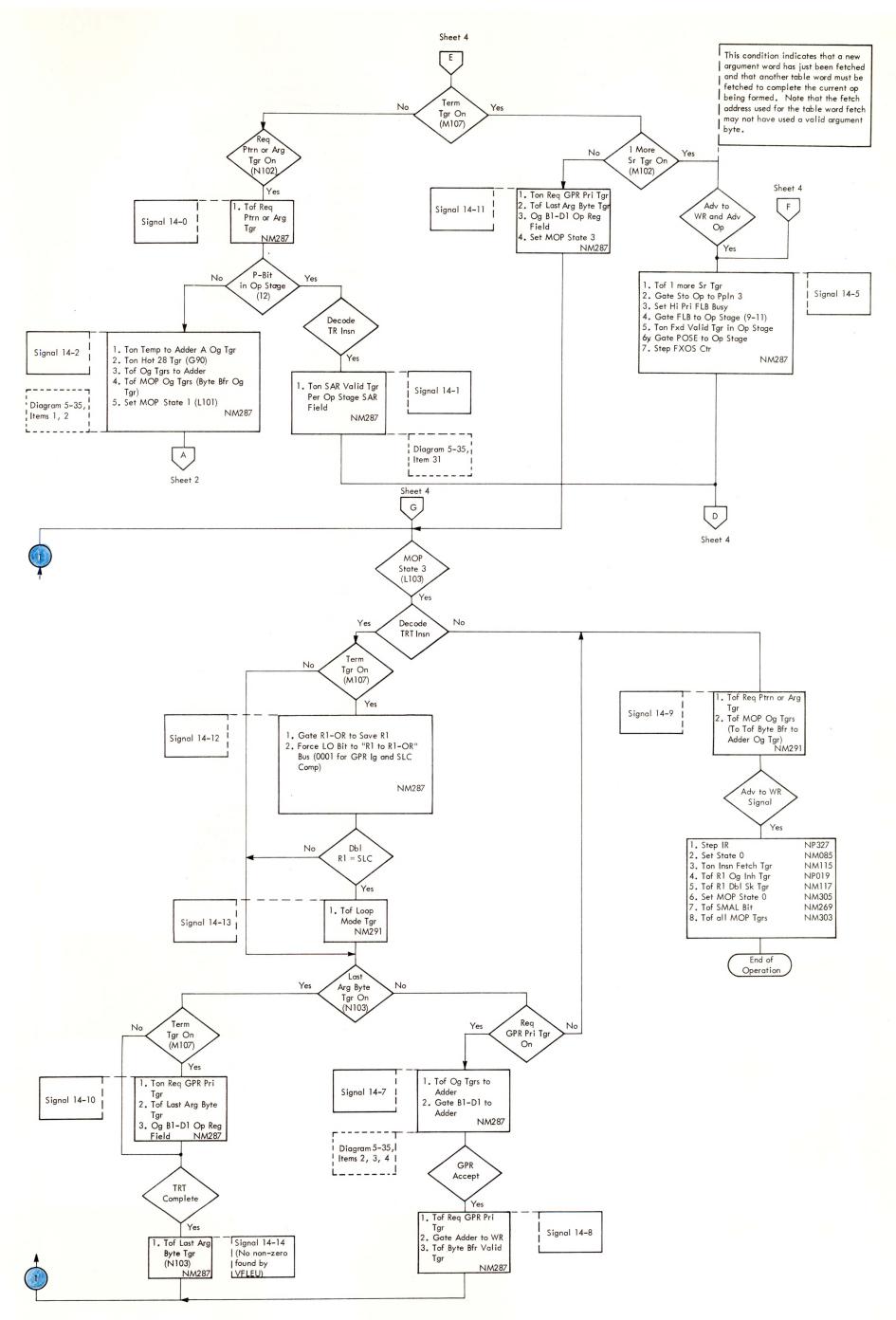

- 1. Decode and issue TR or TRT instruction.

2. Check all interlocks that might detain or cancel the instruction.

3. TR-Fetch and set up store for argument double word(s), and inform FXA of the assigned FLB(s) and SAR(s); suppress MSCE multi-accessing; fetch table word(s), and inform FXA of the assigned FLB(s).

- 4. TRT-Fetch argument double word(s), and inform FXA of the assigned FLB(s); fetch table word(s) and inform FXA of the assigned FLB(s); generate required argument byte address and save it in GPR 1.

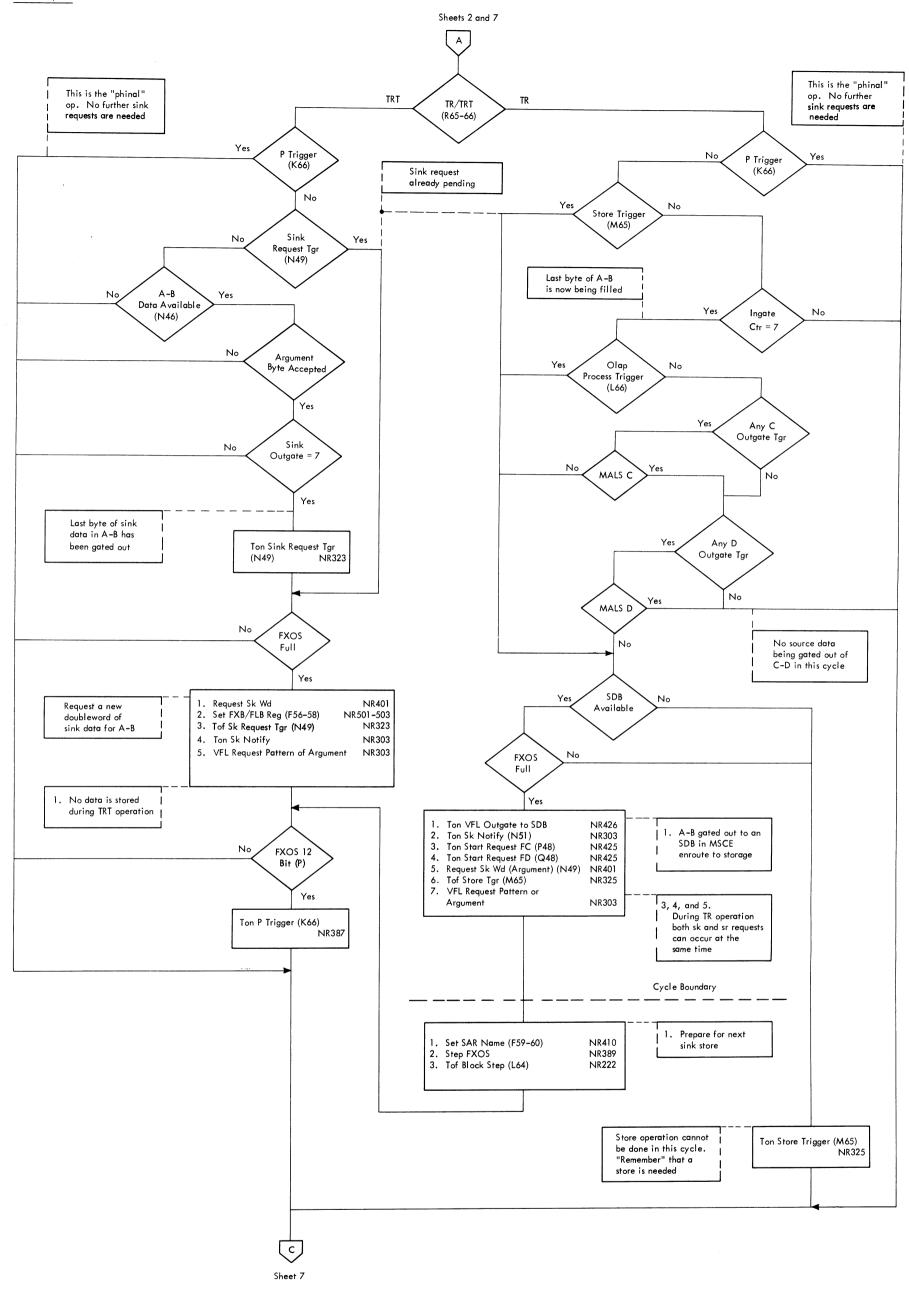

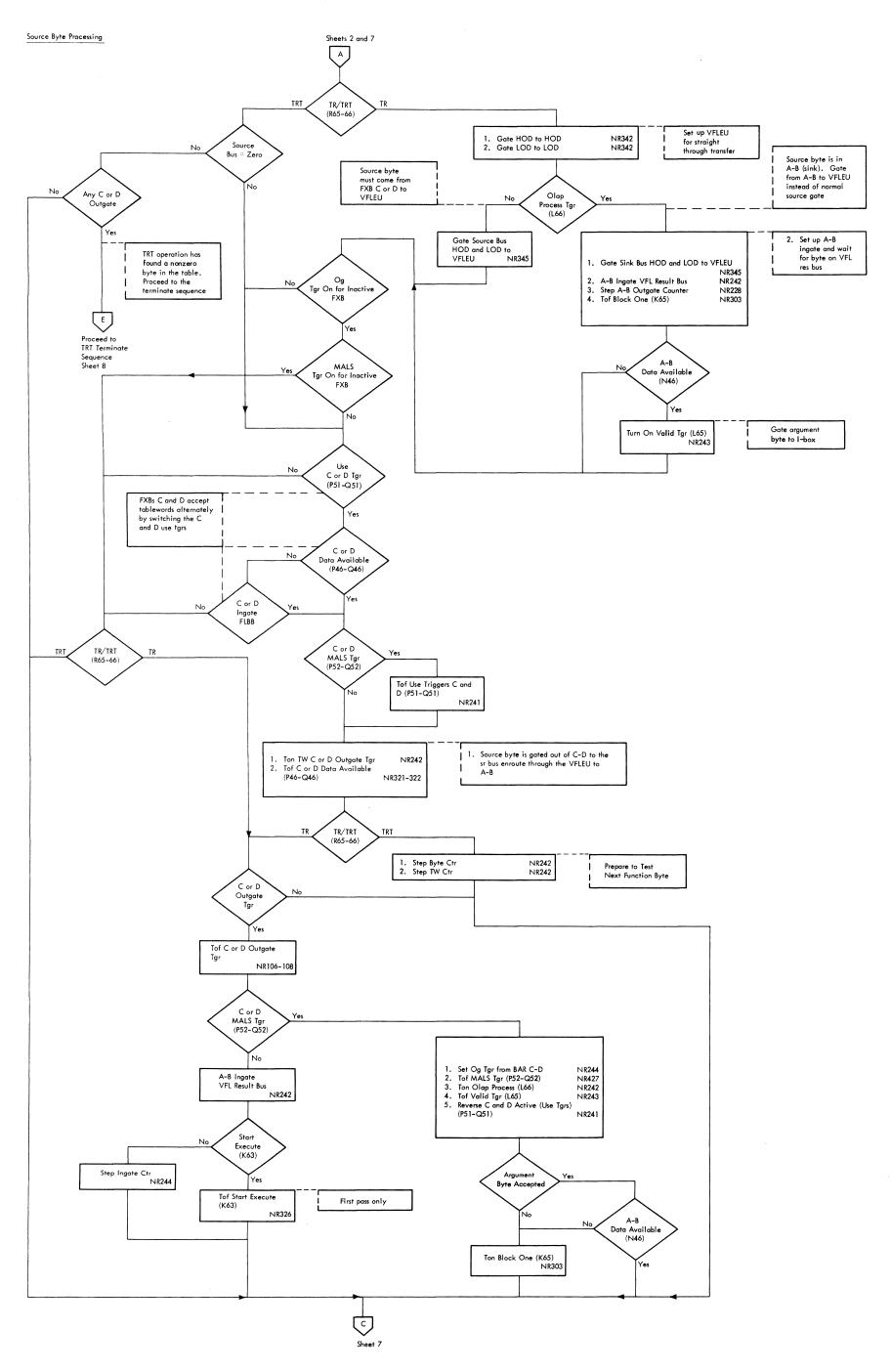

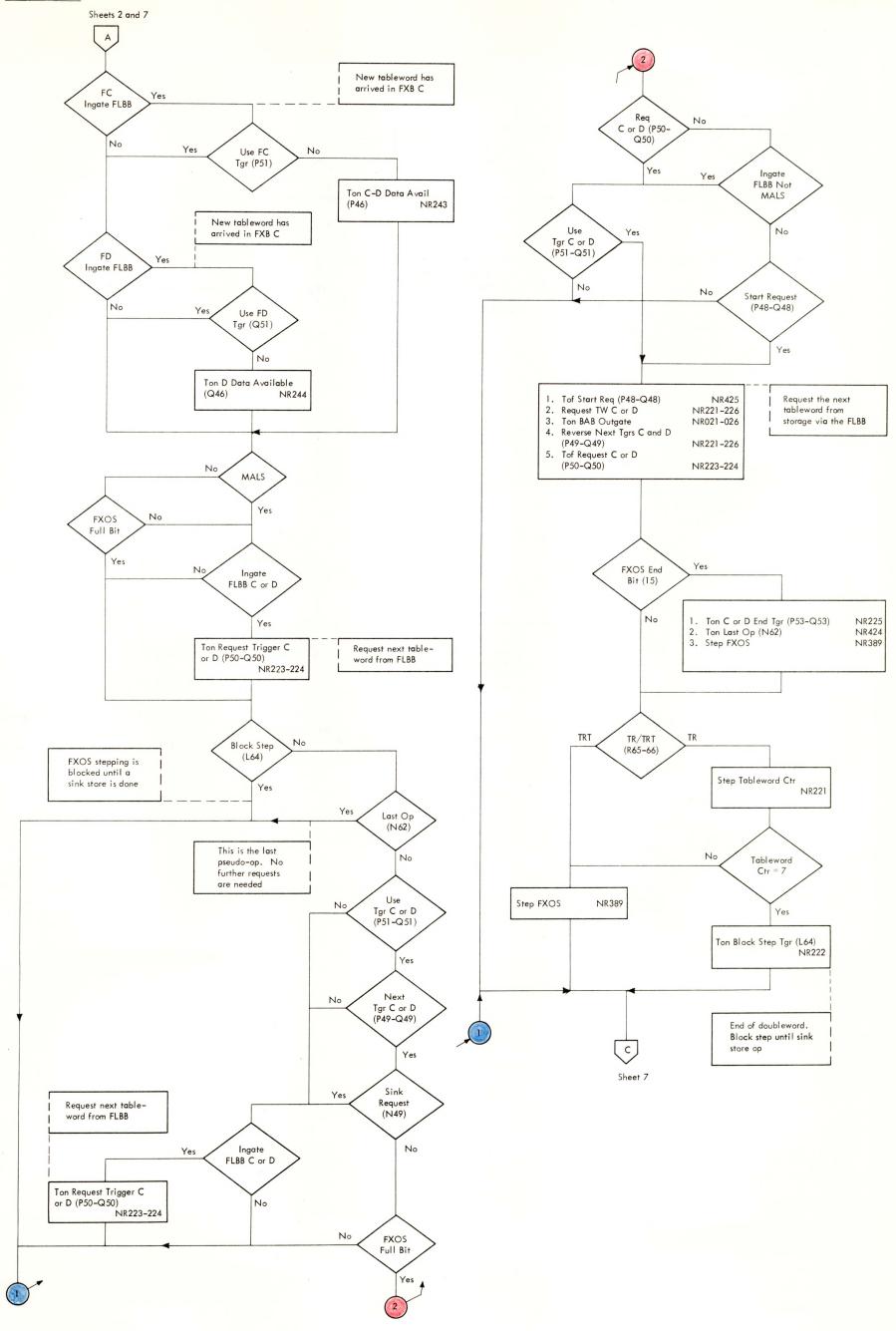

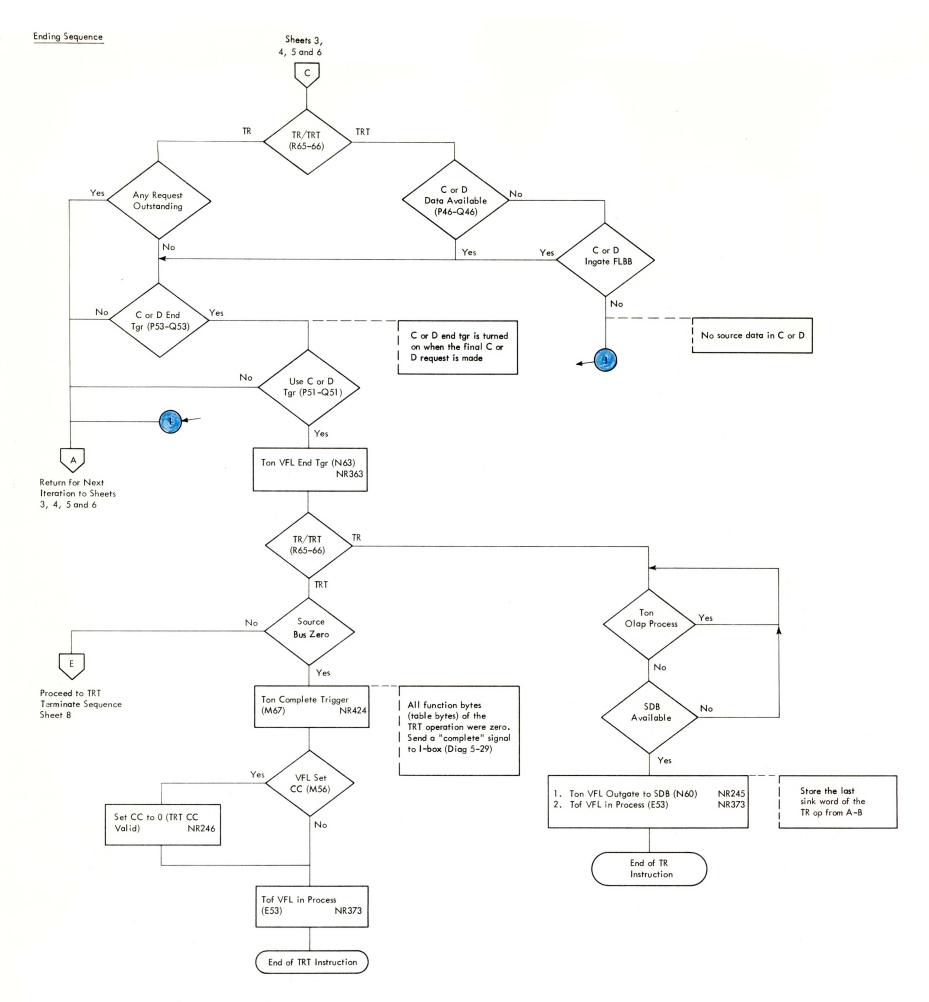

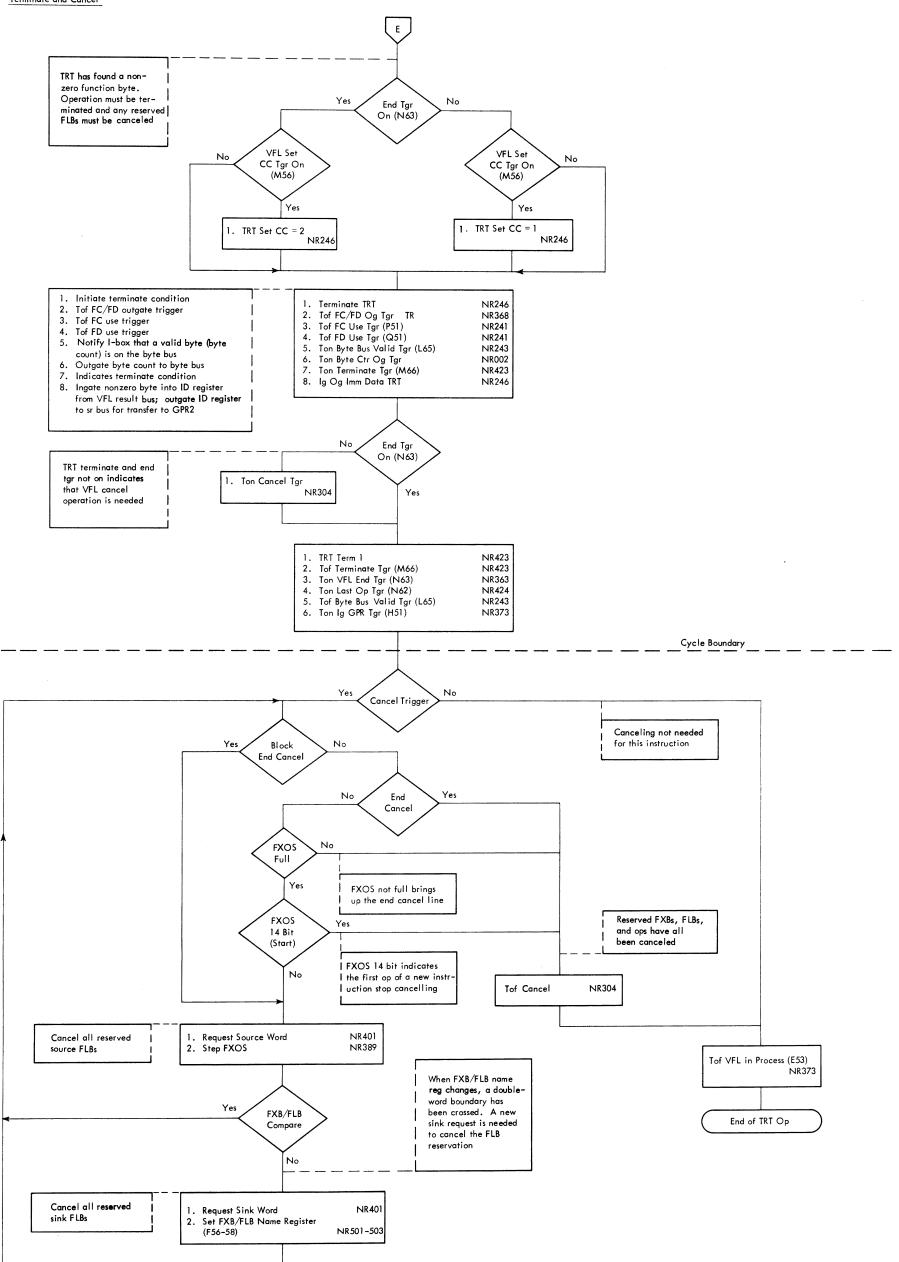

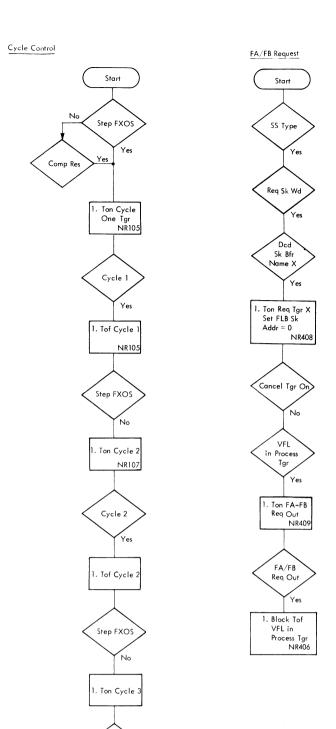

DIAGRAM 5-29. TR, TRT SEQUENCE (SHEET 1 OF 5)

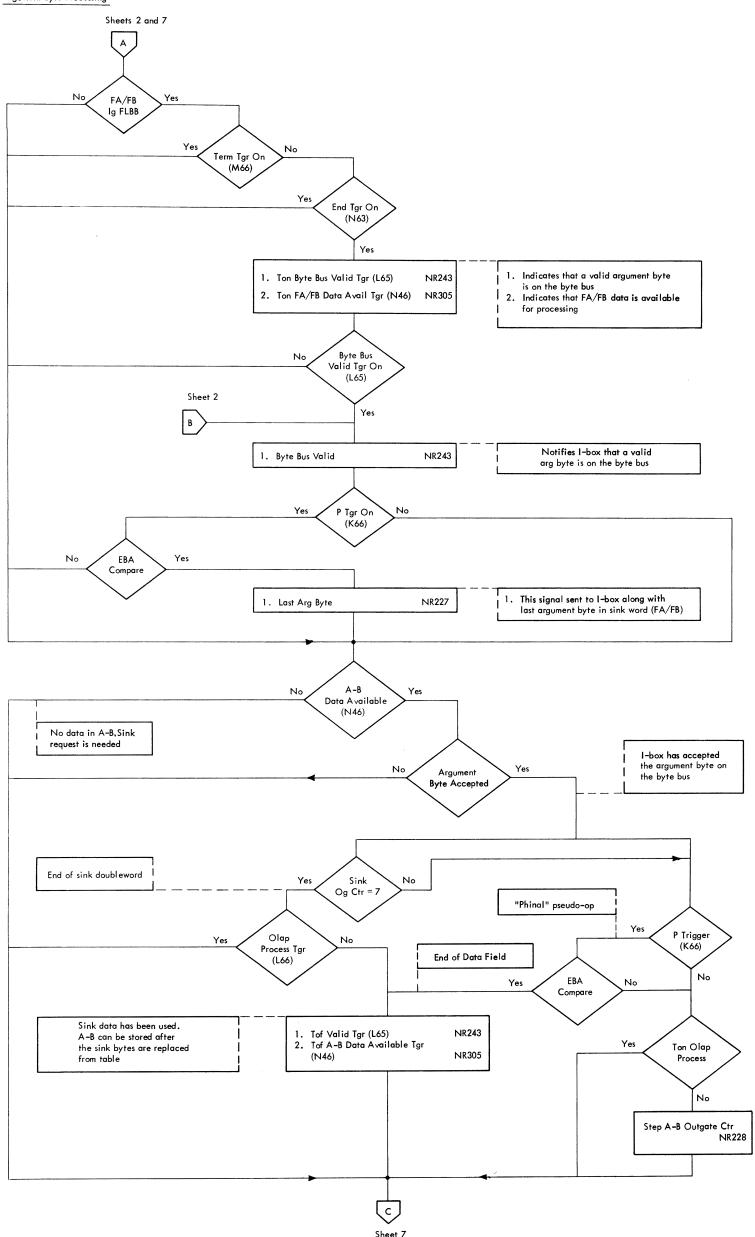

DIAGRAM 5-29. TR, TRT SEQUENCE (SHEET 2 OF 5)

DIAGRAM 5-29. TR, TRT SEQUENCE (SHEET 3 OF 5)

DIAGRAM 5-29. TR, TRT SEQUENCE ( SHEET 4 OF 5 )

DIAGRAM 5-29. TR, TRT SEQUENCE (SHEET 5 OF 5)

DIAGRAM 5-30. NOXCM SEQUENCE (SHEET 1 OF 3)

DIAGRAM 5-30. NOXCM SEQUENCE (SHEET 3 OF 3)

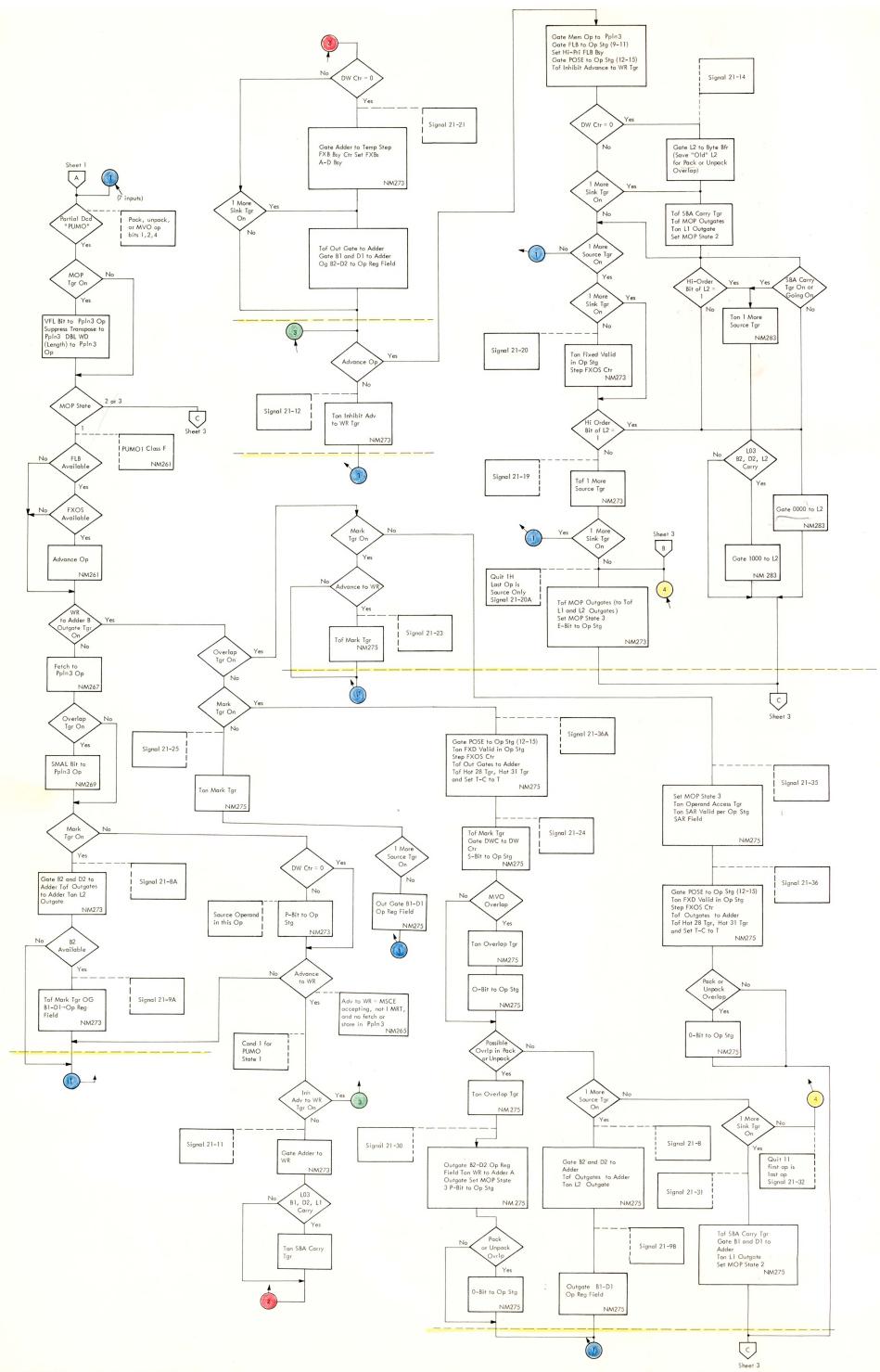

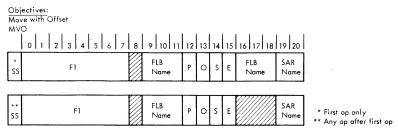

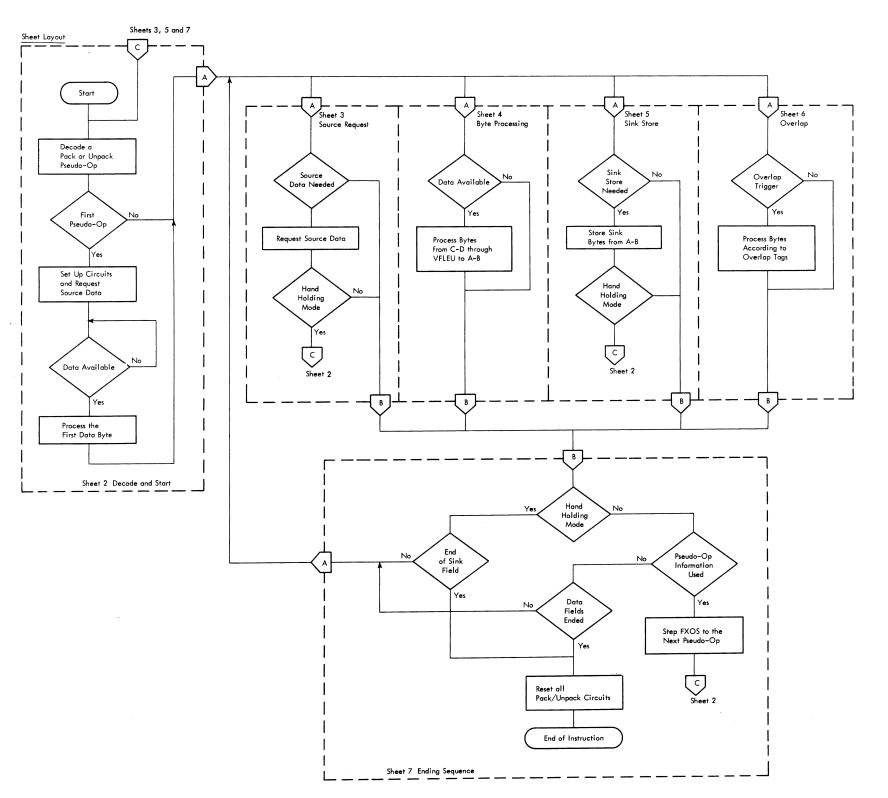

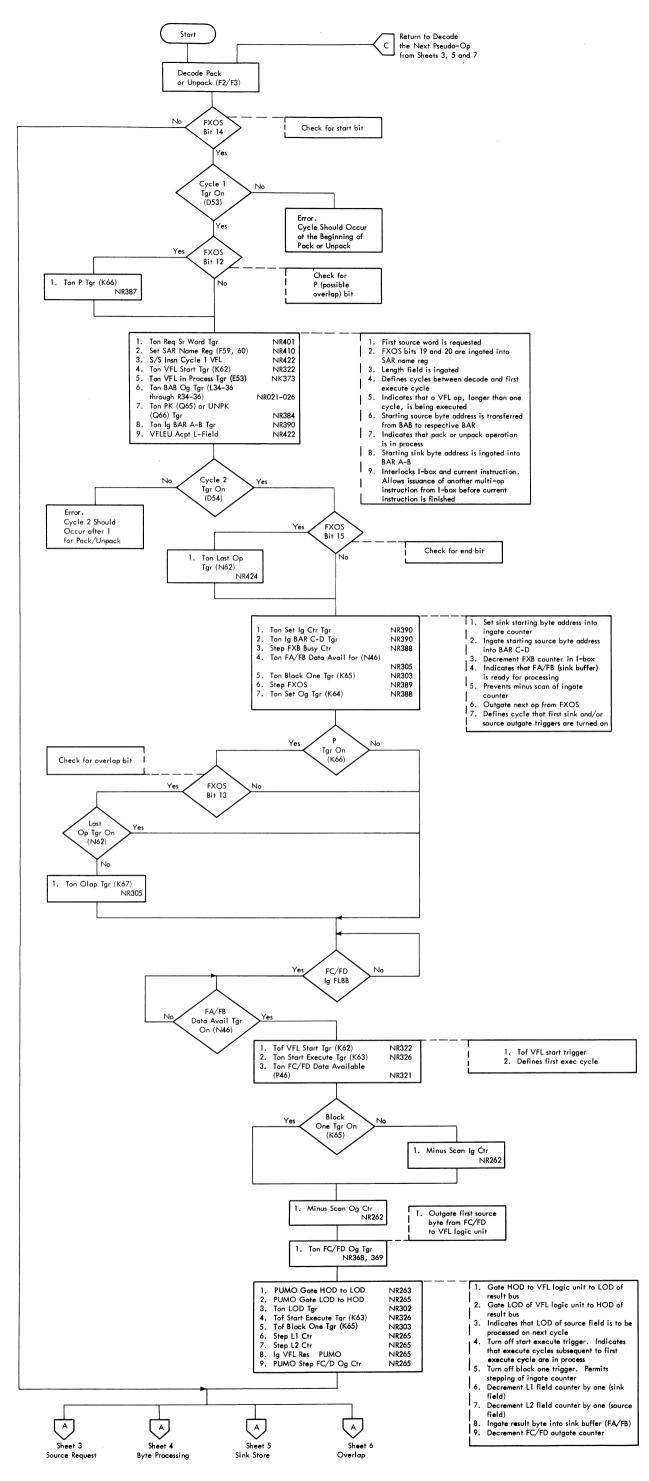

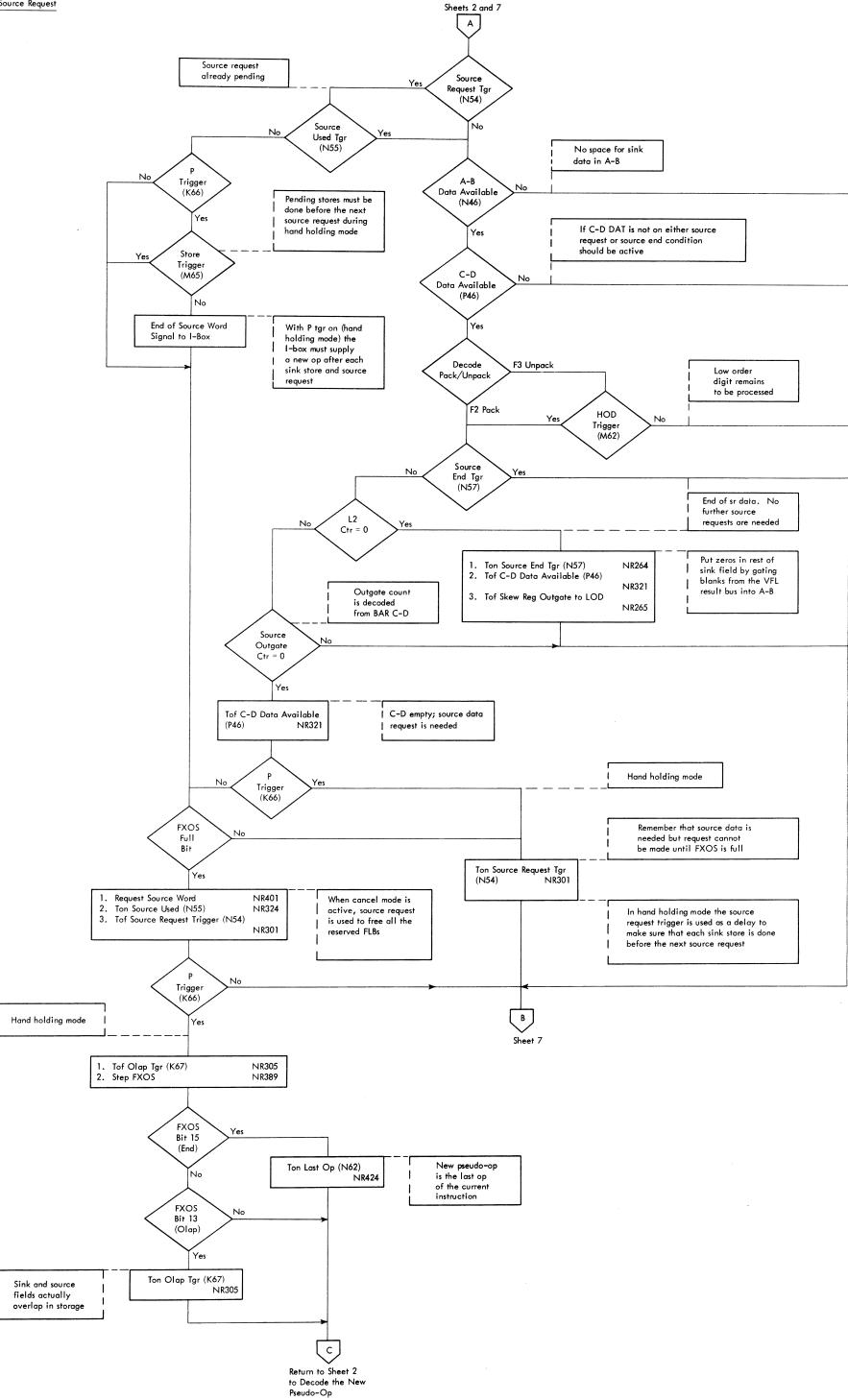

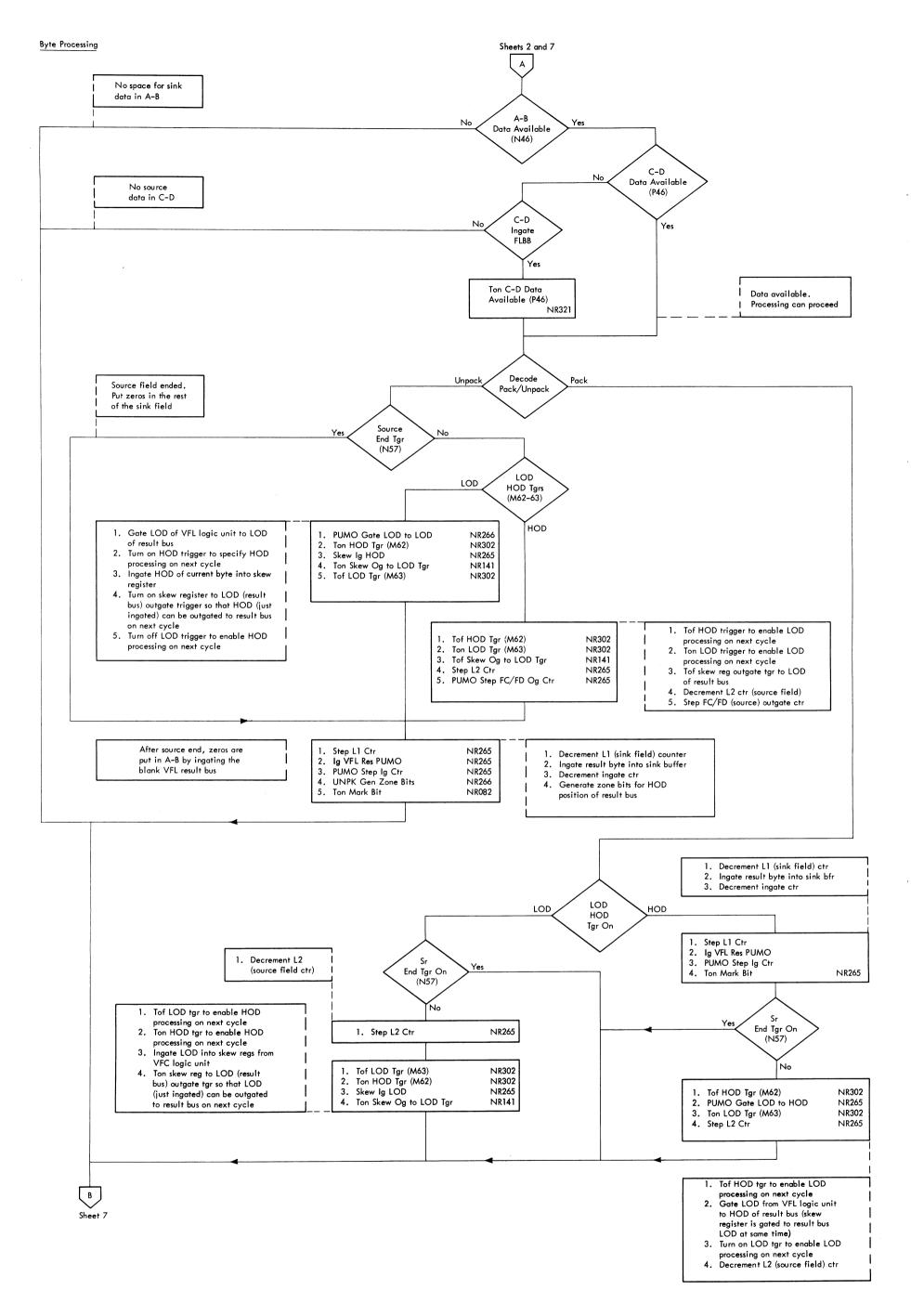

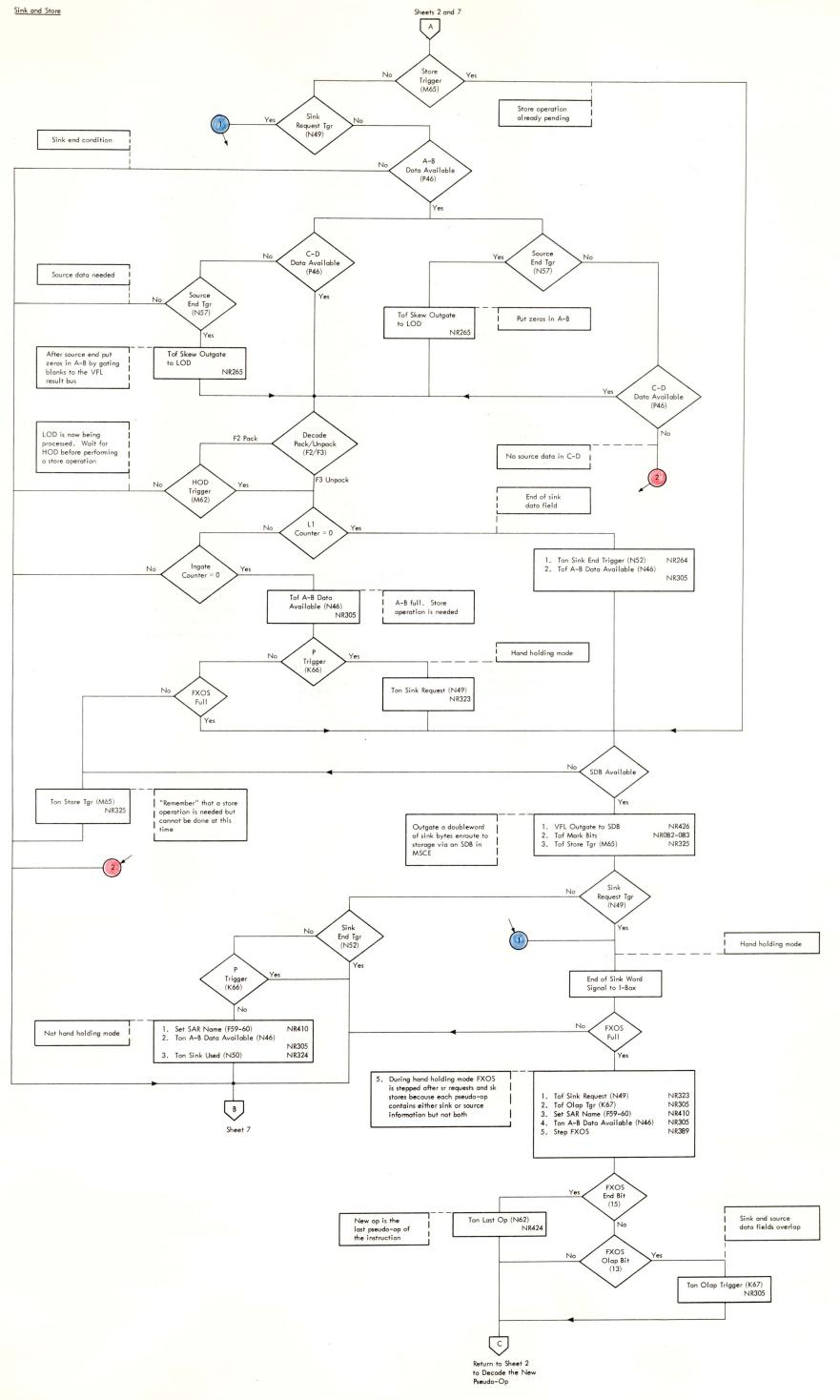

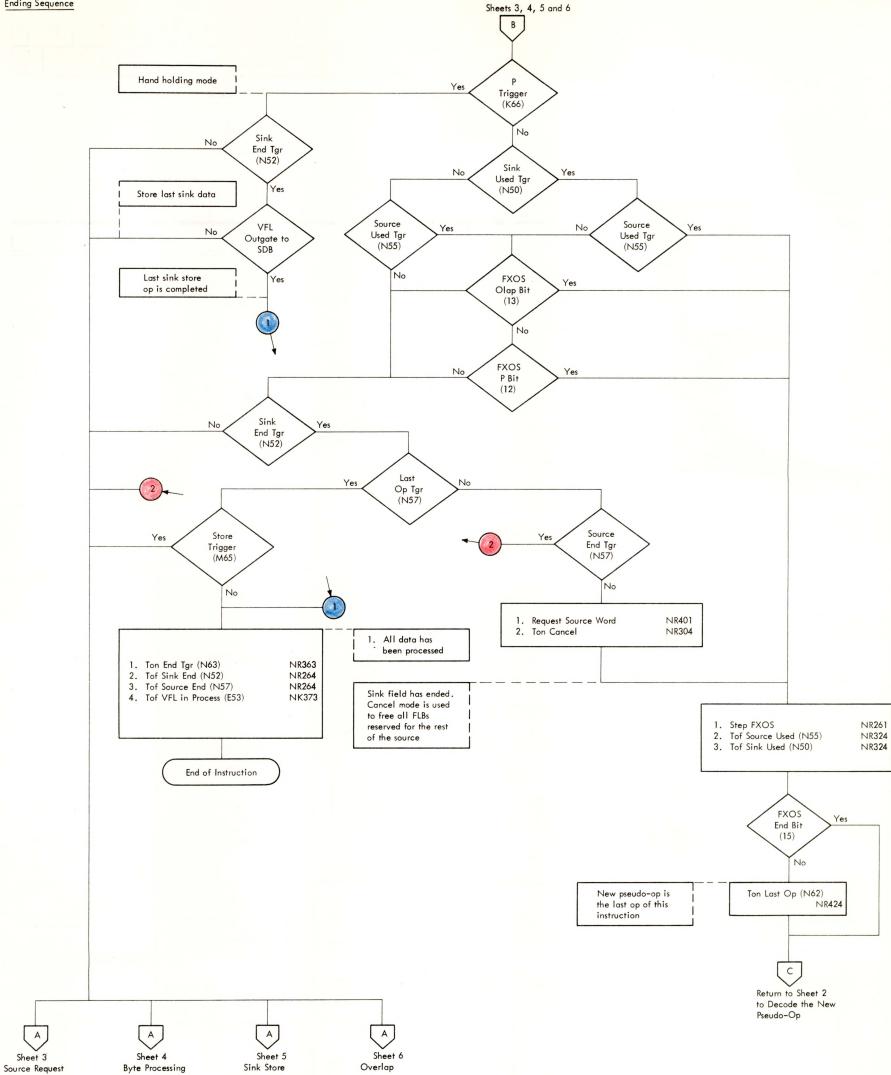

Decode and issue the following instructions: Pack, Unpack, and Move With Ofset

|        | F2 | L1     | L2    | B1    | D1 |    | B2    | D2 |    |

|--------|----|--------|-------|-------|----|----|-------|----|----|

| Pack   | 0  | 78 11  | 12 15 | 16 19 | 20 | 31 | 32 35 | 36 | 47 |

|        | F3 | L1     | L2    | В1    | DI |    | B2    | D2 |    |

| Unpack | 0  | 78 11  | 12 15 | 16 19 | 20 | 31 | 32 35 | 36 | 47 |

|        | F1 | L1     | L2    | B1    | D1 |    | B2    | D2 |    |

| MVO    | 0  | 7 8 11 | 12 15 | 16 19 | 20 | 31 | 32 35 | 36 | 47 |

See Diagram 5–7 for decode cycle basic interlock check R1 Inv Yes No Tgr On B = Save R1 Yes Gate GPR Gate WR to Specified by  ${\sf B}$ Adder for B to Adder NP341 NP377 L-Reg Full Tgr On Yes Decode Go to MOP Signal NP341 Decode Go to MOP Yes 1. Reset DWCR 2. Gate Op Reg to L-Reg 3. Ton MOP Tgr NM271 NM271 NM271 NM271 4. Set MOP State 1 5. Tof Insn Fetch Tgr NP325 6. Ton R1 Dbl Sk Tgr

7. Ton R1 Og Inh Tgr

8. Og B2-D2 Op Reg Fld

9. Set State 7 NP325 NM271 NP325 NP325 Decode PUMO Insn Yes 1. Ton L-Reg Full Tgr 2. Ton Mark Tgr NM271 End of Operation

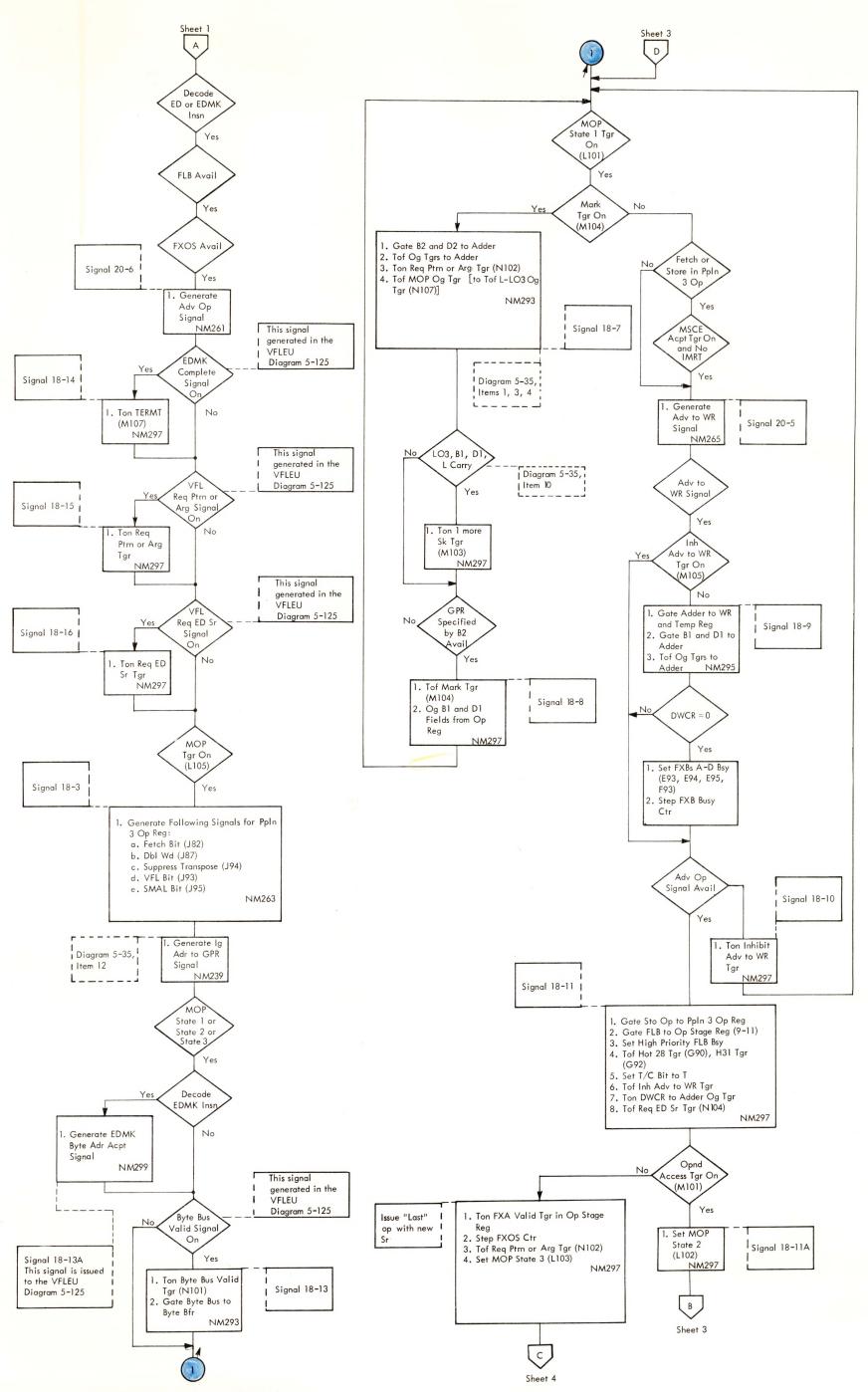

DIAGRAM 5-31. PUMO SEQUENCE (SHEET 1 OF 3)

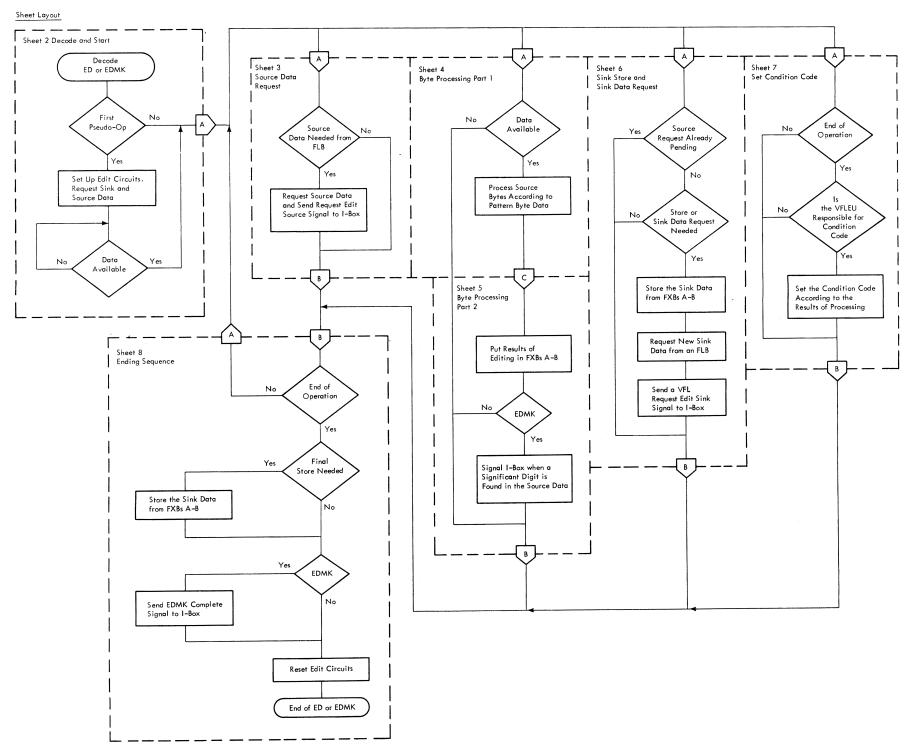

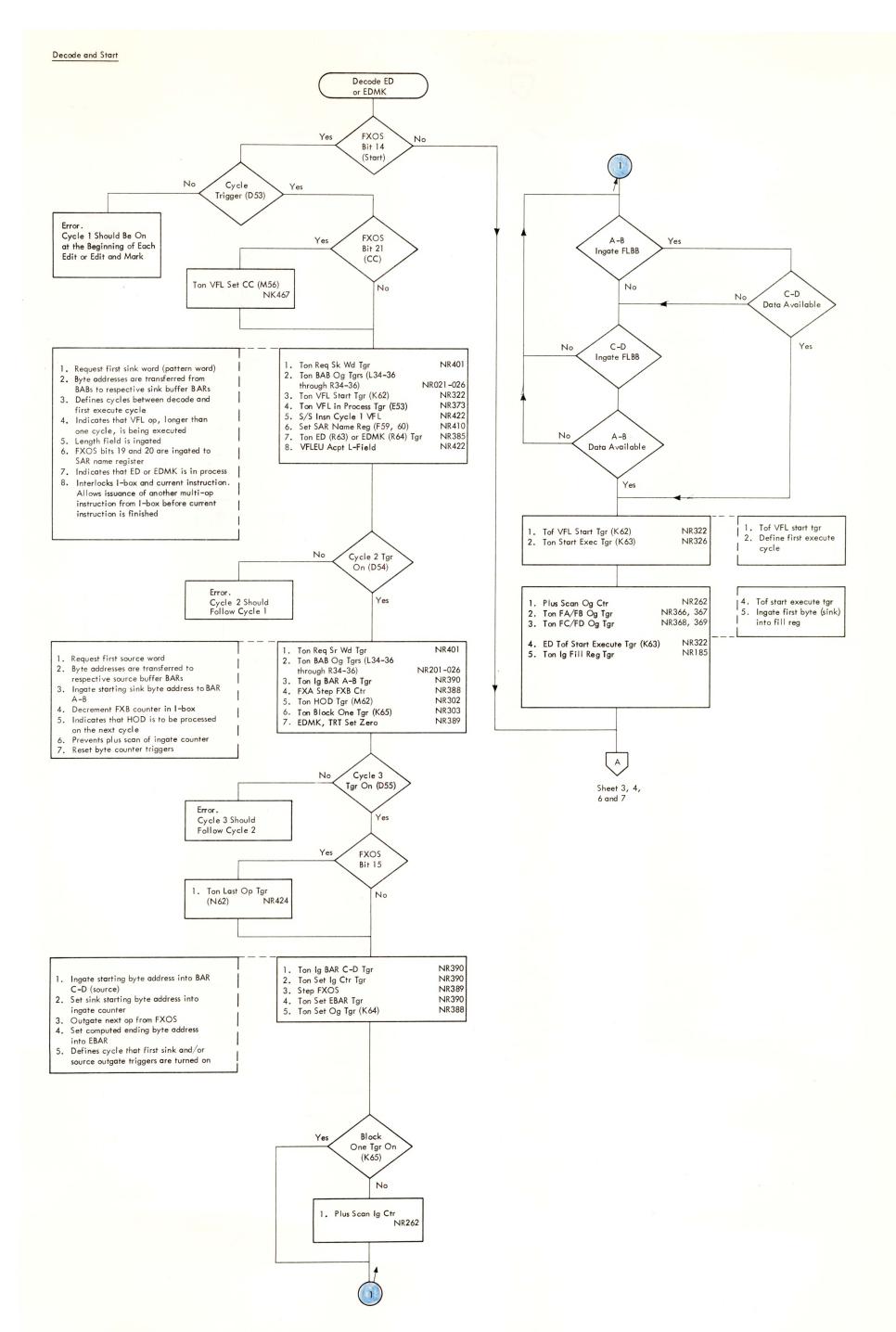

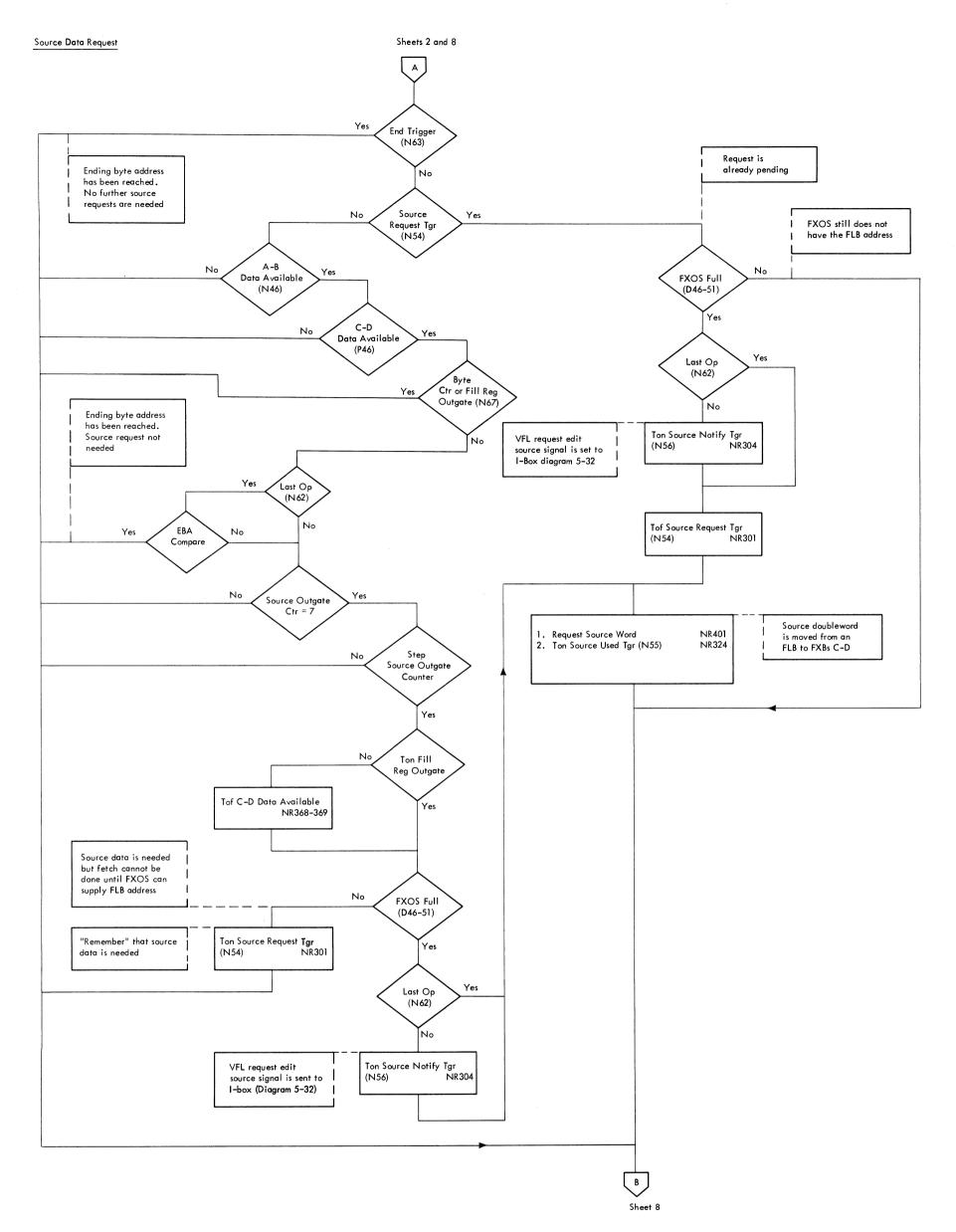

- 1. Decode and issue an ED or EDMK instruction.

- 2. Check all interlocks that may detain or cancel the instruction.

- Initially fetch two pattern and source words for VFLEU.

After first pattern (or source) word is requested by VFLEU, a subsequent reference for a pattern (or source) word is made each time the VFLEU finishes processing a pattern (or source) word.

- 5. VFLEU steps off an Op whenever it requests a pattern word, and the I-Box issues an op whenever

- it references a pattern word.

6. EDMK Record byte address for first significant result digit by forming byte address and causing this byte address to be stored in GPR1.

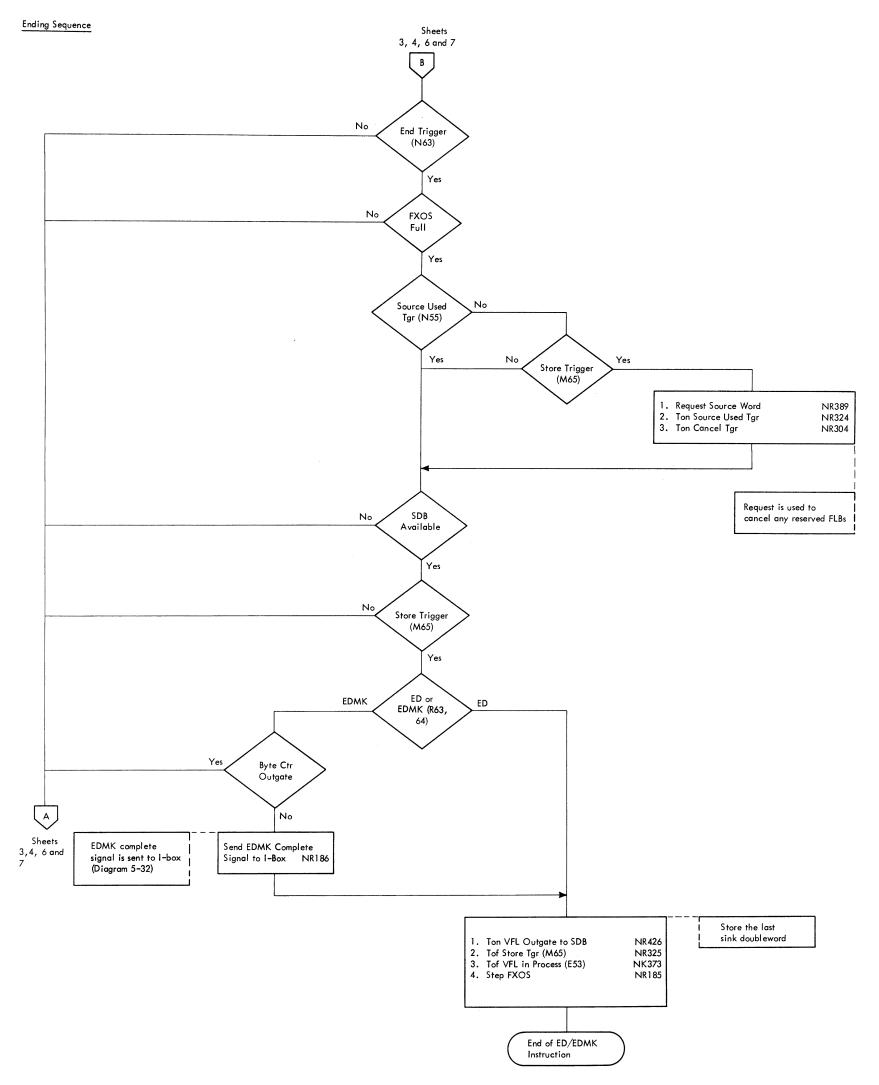

DIAGRAM 5-32. ED, EDMK SEQUENCE (SHEET 1 OF 4)

DIAGRAM 5-32. ED, EDMK SEQUENCE (SHEET 2 OF 4)

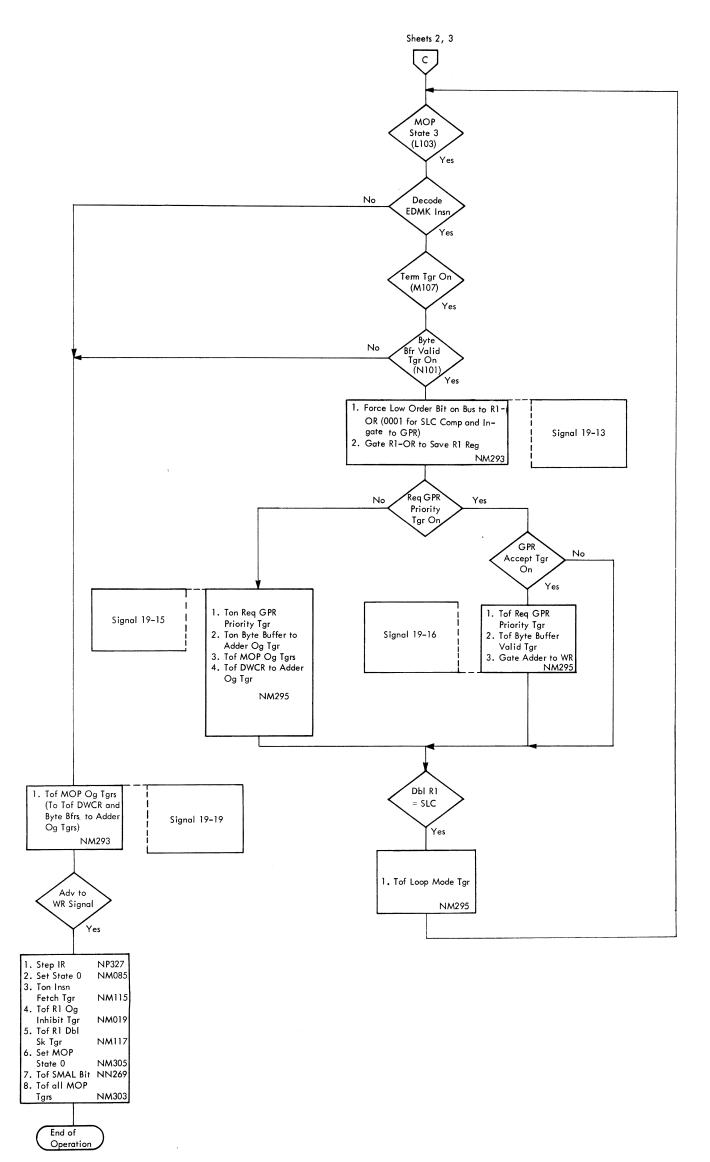

DIAGRAM 5-32. ED, EDMK SEQUENCE (SHEET 4 OF 4)

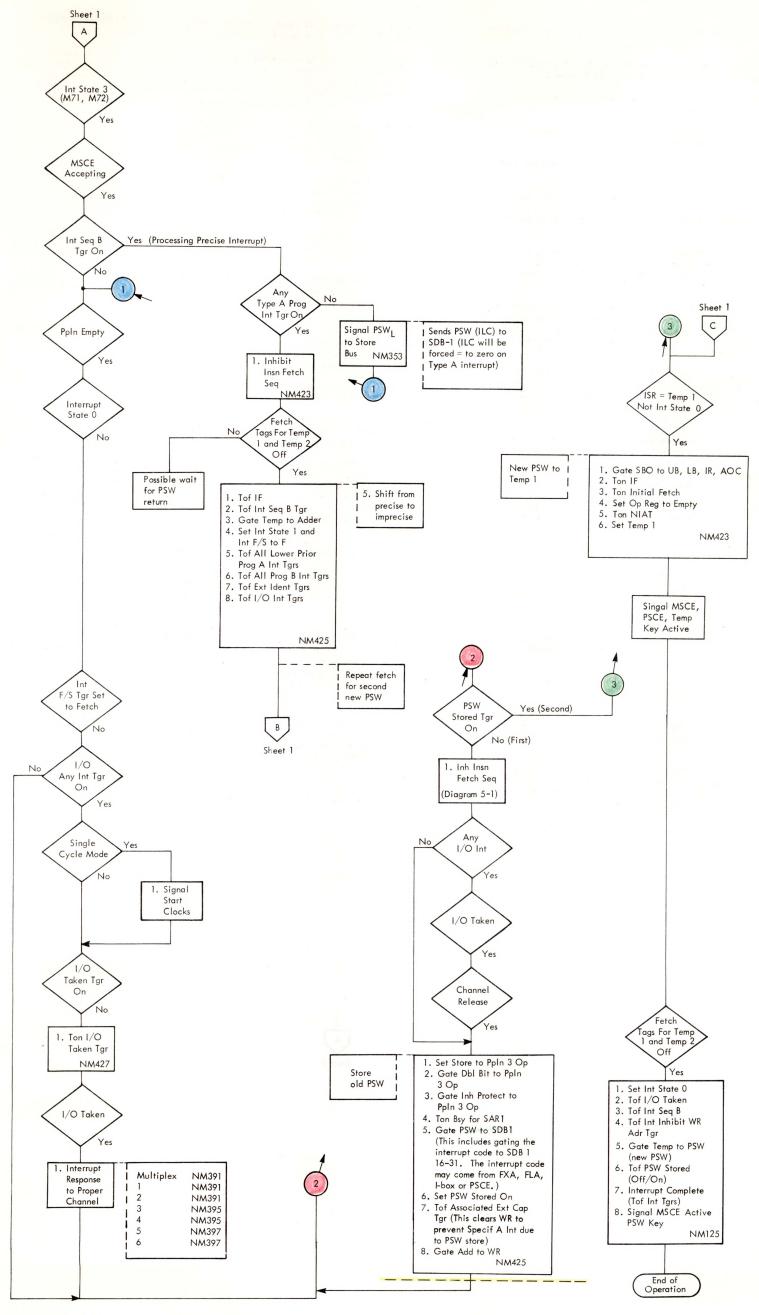

Diagram 5-34 (Sheet 1)

Diagram 5–33 (Sheet 2)

DIAGRAM 5-33. INTERRUPT SIGNALS (SHEET 3 OF 3)

H

Diagram 5–33 (Sheet 2)

Diagram 5-34 (Sheet 1)

DIAGRAM 5-34. INTERRUPT SEQUENCING (SHEET 2 OF 2)

- 1. Tof MOP Og Tgrs This line turns off the following outgate triggers: DWCR; Byte Buffer; R1 to R1 OR; L1; L2; and L-L03.

- 2. Tof Og Tgrs to Adder This line turns off the following outgate triggers: all "B" and "X" outgate triggers; D-Bfr; Temp to Adder A; Temp to Adder B; WR to Adder A; WR to Adder B.

- 3. Gate B1 (B2) to Adder This line turns on the B outgate trigger which is specified by a decode of the B-field outgated from the Instruction Register.

- 4. Gate D1 (D2) to Adder This line turns on the D-Bfr outgate trigger and ingates to the D-Bfr the D-Field which is outgated from the Instruction Register.

- 5. Gate B1 (B2) and D1 (D2) to Adder This line combines the functions of the lines described in items 3 and 4.

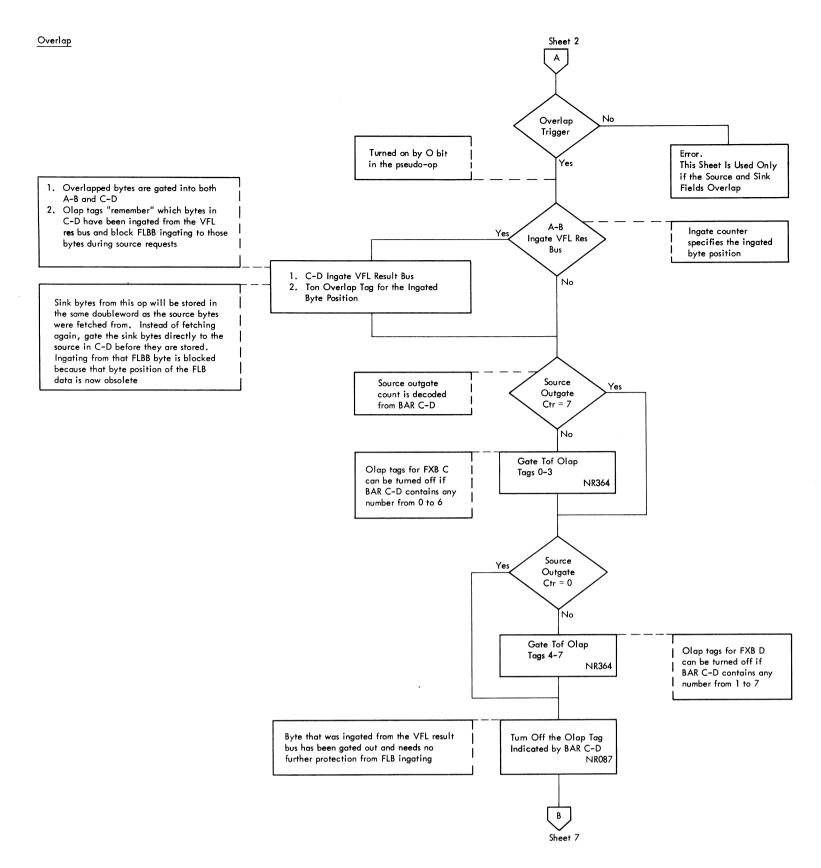

- 6. Lf to Rt Olap This signal is used in the NOXCM sequence to indicate an overlapping condition between the sink and source operand fields which requires special handling by the VFLEU. This line is conditioned by: 0 < [Sink Starting Address (to byte level) Source Starting Address (to byte level)] < 8; i.e., 0 < [(B1 + D1) (B2 + D2)] < 8.

- 7. MVO Olap This signal is used in the PUMO sequence to indicate an overlapping condition between the sink and source operand fields which requires special handling by the VFLEU. This line is conditioned by: 0 < D < 8, where D = [(B2 + D2 + L2) (B1 + D1 + L1)] = (Source Starting Address Sink Starting Address).</p>

- 8. Possible Olap in PACK or UNPK This signal is used in the PUMO sequence to indicate an overlapping condition between the sink and source operand fields which may require special handling by the VFLEU. (See also item 9.) This line is conditioned by the following logical relationship: (Decode UNPK) ( $-8 \le D \le 0$ ) or (0 < D < 16). (D is defined in item 7.) This condition will prompt the PUMO sequence to go into a special "hand-in-hand" relationship with the VFLEU.

- 9. PACK or UNPK Olap This signal is used in the PUMO sequence to indicate that a particular source doubleword has the same address as a particular sink doubleword and that special handling of this pair of operands is required in the VFLEU. This line is conditioned when: (-8 ≤ D < 8) (Sink Dbl Wd Adr Bit, Bit 28) = (Source Dbl Wd Adr Bit, Bit 28); i.e., Sink Double Word Address = Source Double Wd Address. (D is defined in item 7.)</p>

- 10. LO3, B, D, L Carry This signal is used as operand fetching is begun, to aid in determining how many doublewords are involved in a particular operand stream. A three-bit sum is determined by the addition of the low-order three bits of the register specified by B to the low-order three bits of the D field. This sum is then added to the low-order three bits of the L-field; a carry out of the high-order position of this three-bit add is known as an "LO3, B, D, L Carry".

- 11. Block Og of Byte Adr from WR to Adder A When this line is conditioned, it suppresses the outgating of bits 29-31 from the WR which would otherwise take place when the WR to Adder A Og Tar is on.

- 12. MALS Data Not Needed This line signals the MSCE that the data for a fetch are not needed.

- 13. Arg Byte Accp This signal is generated by the MOP sequence for TR and TRT. Its presence indicates to the VFLEU that any argument byte which is presently on the Byte Bus may be taken off. Note that this signal consists of two lines to the VFLEU the signal is present only when both lines are negative.

- 14. Blk End Cancel This line is conditioned by the MOP logic whenever the Term Tgr is on. It is used in connection with the op cancelling process. When the line is conditioned, it prevents the VFLEU from completing its cancelling process until the MOP sequence can guarantee that no more ops will be issued to the FXOS.

- 15. Byte Bus Valid This signal from the VFLEU indicates to the TR or TRT sequence that a valid argument byte is on the Byte Bus, or to the ED or EDMK sequence that a byte count is on the Byte Bus

- 16. CLC Complete This signal is generated by the VFLEU when it finds that the operands in a CLC instruction are equal. The signal is used in the NOXCM sequence as part of the control for the Blk CLC Tgr.

- 17. CLC Term This signal is generated by the VFLEU based on the fact that a pair of CLC operand bytes are unequal. If the unequal byte pair is compared during cycle n, this signal is transmitted to the I-Box during cycle (n+1). CLC Term is used in the NOXCM sequence to prevent further operand accessing and as part of the control for the Blk CLC Tgr.

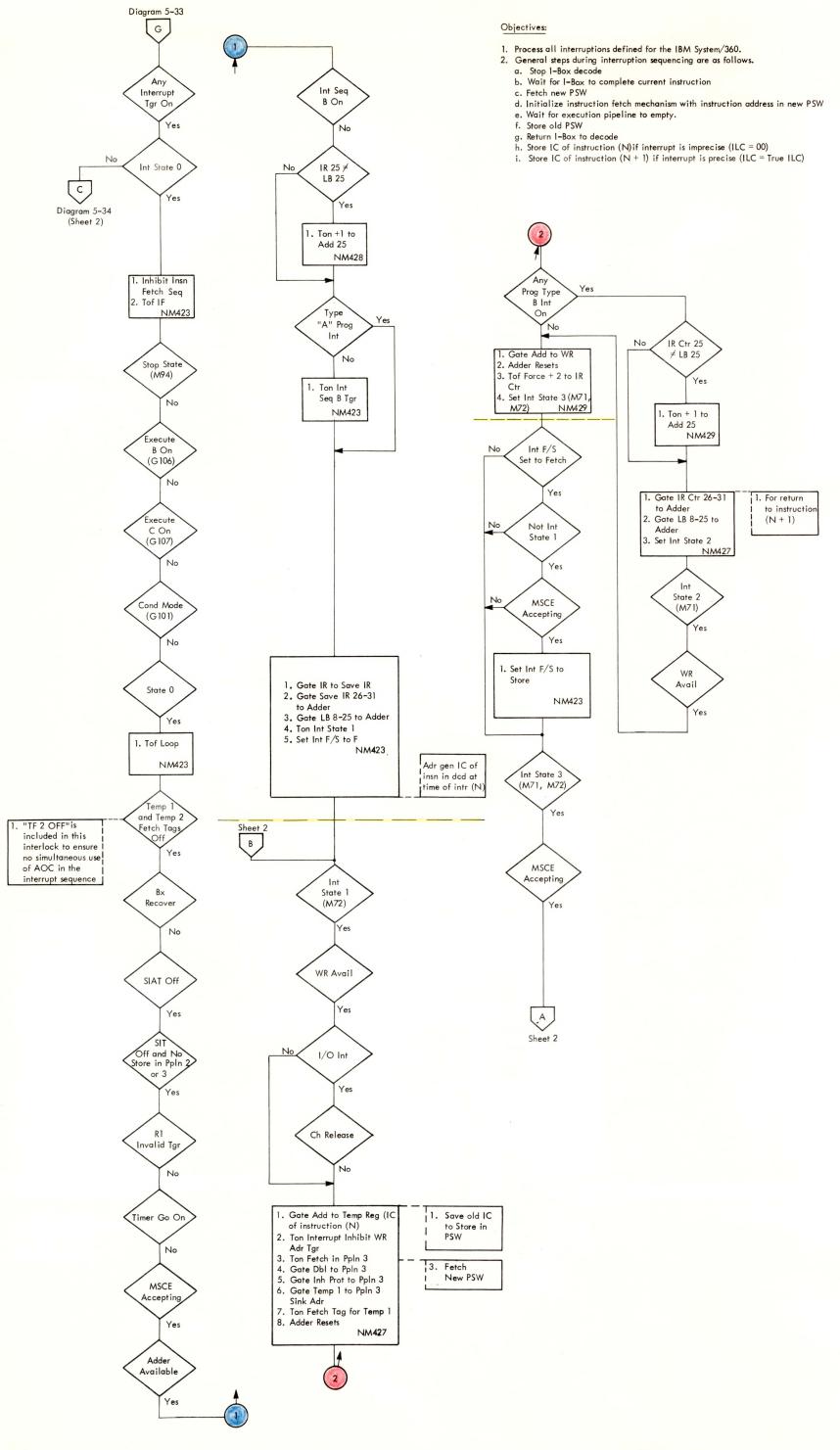

DIAGRAM 5-35. MOP DEFINITIONS

- 18. EDMK Byte Adr Accp This signal is generated by the MOP sequence for ED and EDMK. Its presence indicates that the byte count has been gated into the Byte Buffer.

- 19. EDMK Complete This signal is generated by the VFLEU and is transmitted to the I-Box in parallel with the transmission of the last pattern word to an SDB. It causes the ED or EDMK sequence to turn on the Term Tgr which will then lead to an exit from the sequence. This communication relative to the completion of EDMK execution is necessary since the I-Box must stand-by until there is no further chance that a byte address may have to be generated and stored in GPR1.

- 20. End of Olap PACK or UNPK This signal is generated by the VFLEU in connection with the special approach used for particular overlap situations in PACK and UNPK. It is transmitted to the I-Box in parallel with the transmission of the last sink word to an SDB and is used in the PUMO sequence to motivate an exit.

- 21. End of Sr Wd This signal, generated by the VFLEU, is used only in certain overlapped PACK or UNPK situations. It is transmitted to the I-Box during the cycle following the outgate of the last byte from the source word and is used in the PUMO sequence to initiate the fetch for the next source word and the setting up of another store for the present sink word.

- 22. End of Sk Wd This signal, generated by the VFLEU, is used only in certain overlapped PACK or UNPK situations. It is transmitted to the I-Box during the cycle following the ingate of the last byte into the sink word, and is used in the PUMO sequence to initiate a store for the next sink word.

- 23. GPR Accept This signal is the output of the GPR Accept Trigger which is a part of the GPR ingate priority scheme in the FXA. If the GPR Accept Tgr is turned on at the start of cycle n, data from the I-Box are gated into an addressed GPR at the start of cycle (n+2).

- 24. Ig Adr to GPR This line is conditioned by the MOP logic whenever the MOP Tgr is on to block the ingate to the addressed GPR of the high-order eight bits from the I-Box. This covers the byte-address-saving situations which arise in TRT and EDMK, and requires the high-order eight bits of GPRI to remain unchanged.

- 25. Last Arg Byte This signal accompanies the last argument byte to be sent from the VFLEU to the I-Box in the course of a TR or TRT instruction.

- 26. TRT Complete This signal is generated by the VFLEU when there is no non-zero function byte in the course of a TRT instruction. It is transmitted to the I-Box during the cycle following the examination of the last function byte and causes an exit from the TR or TRT sequence.

- 27. TRT Term This signal is generated by the VFLEU based on the fact that a non-zero function byte has been found. It is transmitted to the I-Box during the cycle following the examination of the non-zero function byte, and in parallel with the transmission to the I-Box of the byte count necessary for the generation of the culprit argument byte address. TRT Term is recorded by the Term Tgr, and motivates argument byte address generation and storing into GPR1. It then leads to an exit from the TR or TRT sequence.

- 28. <u>VFLEU</u> This signal is sent to the I-Box from the FXA during the FXOS decode cycle for an SS instruction. Its presence will cause the L-Reg Full Tgr to be turned off.

- 29. VFL Req ED Sr This signal is sent to the I-Box by the VFLEU whenever, in the course of an ED or EDMK, it makes a request for a source word from an FLB. VFL Req ED Sr is recorded by MOP in the Req ED Sr Tgr and motivates the fetch of the next source word.

- 30. VFL Req Ptrn or Arg Tgr This signal is generated by the VFLEU in connection with pattern word requests in ED or EDMK and argument word requests in TR or TRT. The signal is recorded by Req Ptrn or Arg Tgr. The TR or TRT sequence is notified for all argument word requests except the first; and the Req Ptrn or Arg Tgr initiates the fetch of the next argument word. The ED or EDMK sequence receives this signal for all pattern word requests except the first (and in one case the end of the pattern word from the "END" Op); and the Req Ptrn or Arg Tgr initiates the fetch of the next pattern word.

- 31. Ton SAR Valid Tgr Associated with each of the three SARs is a valid trigger. A SAR is set "Valid" when a new address is set into the SAR. Once the SAR is valid, its address is compared with all incoming addresses. Situations arise in the multiple op sequences for handling TR and PACK or UNPK in which an address may be set into a SAR before it is desirable to subject it to comparisons. In such cases it becomes necessary to modify the general procedure for setting a SAR valid. The logic used to accomplish this modification makes use of the signals: Suppress Ton SAR Valid Tgr, and Ton SAR Valid Tgr per Op Stage SAR Field. The flow chart below shows how these special signals interact with the general procedure for setting a SAR valid.

#### Instruction Fetch Control Triggers

Array Fetch Protect Tags (Array Words 0-7, Temp 1 and 2) - NN161-167, 181-187, 207 Indicate when an instruction fetch has violated a protected block of storage. There are ten array protect tags corresponding to the 8 array doublewords and the two temp locations. Should an attempt be made to decode any portion of an array or a temp doubleword with a protect tag on, a fetch protect interrupt results. The tags are turned on or off respectively, as a storage return which violates or satisfies fetch protect is gated to the associated array word.

Array Fetch Tags (Array Words 0-7, Temp 1 and 2) - NN161-167, 181-187, 201 Indicate when a fetch for the corresponding doubleword of instruction array has been made and the data has not yet returned from storage. There are ten fetch tags, corresponding to the 8 array doublewords and the two temp locations. The tags are turned on by the instruction fetch mechanism and turned off on the same cycle that the data from the memory bus is ingated.

#### Initial Fetch - NN177

Used to gate a zero into the UBCTR, allowing an unmodified transfer of the UB register contents to the UBCTR output. This requirement is necessary because instruction fetching is initiated via the UB register even though the next instruction fetch address is always taken after UB is updated by the UBCTR output. The initial fetch trigger is used to gate a zero into the UBCTR. This allows an unmodified transfer of the UB register contents through the UBCTR and back to UB.

#### Instruction Fetch Trigger (IFT) - NM115

Master control trigger for instruction fetch logic. This trigger must be on for any fetches that take place using the UB register.

#### Instruction From Memory Request Trigger (IMRT) - NN225

Signals MSCE of an instruction fetch. This signal also inhibits operand fetching to give instruction fetching CPU priority to the address bus to storage. Initiating an instruction fetch turns IMRT on; MSCE accepting to the CPU turns IMRT off.

#### ISR Protect Tag - NN249

This trigger is turned on or off by the MSCE to indicate that the immediately following storage return to the 1-Box has violated protected storage. It is used to turn on or off the appropriate array or execute protect tags.

#### Store Interlock Trigger (SIT) - NN230

Set on when it is detected that a store instruction in the ppln 3 op register has stored within the UB and LB boundaries. SIT effectively cancels the affected instruction array word by initiating a fetch to storage for the doubleword stored into. The trigger is turned off when the re-fetch has been initiated.

#### Store Into Array Trigger (SIAT) - NN231

On SS format store operation or a store multiple doubleword, if the store falls within UB and LB, multiple instruction array words may become invalid. SIAT simplifies the recovery control by initializing the whole array starting with the current instruction address. SIAT is turned on by the detection of a store between the UB and LB bounds when processing an SS store or a store multiple instruction. It goes off following the completion of the instruction and completion of the reinitialization.

#### Temp Fetch Trigger - NN226

This trigger is turned on when the instruction fetch area is initialized following a branch that did temp fetching. The trigger causes the updating of the UB without initiating storage fetches, thereby preventing re–fetching of branch targets already fetched to the temp 1 and temp 2 locations. The UBCTR output is then correctly positioned to fetch the instruction word after the doubleword fetched for temp 2. The temp fetch trigger goes off on completion of the UB update.

#### Temp Fetch 1 and 2 - NN205

Signify that the respective instruction array doubleword (temp 1 and temp 2) has been activated by a branch decision and is to be gated to the op register and also to the instruction array word designated by the AOC register. The triggers are turned on as a result of a successful branch that did temp

#### Pipeline Stage 1 (Instruction Decode) Control Triggers

#### Fixed Buffer Busy Counter - NP139

A three-bit control register that properly sequences the releasing of fixed operand buffers when an instruction requiring more than one of these buffers is encountered. These instructions require the fetching of 64 bit operands and therefore utilize the floating buffers as well as the fixed buffers. The fixed buffer busy counter is required when these instructions are stacked.

## Fixed Buffer Busy Tags A-F (FXB-BSY) - NP343-353

A set of six triggers, one for each 32 bit fixed storage operand buffer, utilized to control allocation of buffers to storage fetches initiated for fixed operations. A buffer is made busy by turning its tag on as a fetch to the buffer is initiated. The tag is turned off when the fixed area utilizes the buffer contents, whereupon the buffer becomes available for re-assignment.

## Fixed Operation Stack Count (FXOS) - NP131

A three-bit control register interlock on issuing to the fixed area. As an instruction is issued to the fixed area, the FXOS counter is incremented; when an instruction is completed by fixed execution, the counter is decremented. A maximum of six operations can be outstanding prior to the interlock preventing more issuing.

# Floating Buffer Busy Tags 1-6 (FLB-BSY) - NP357-361

A set of six triggers, one for each 64 bit floating storage operand buffer, identical in function to the fixed buffer busy tags, except applying to the floating buffers.

# Floating Operation Stack Count (FLOS) - NP135

A four-bit control register identical in function to the FXOS, except applying to the floating area. A maximum of eight operations can be outstanding prior to the interlock preventing more issuing.

# New Instruction Address Trigger (NIAT) - NN227

Sets the op register outgate triggers according to the value in IR after a new instruction address has initialized the array counters and IR.

## Op Register Outgate Triggers (2 per halfword) – NP009–015

# Used to control the outgating of the op register.

# Op Register Valid Triggers (one per halfword) - NN244-247

Used to indicate which of the four halfwords of the op register are valid and available for decoding. A particular valid trigger is turned on by ingating new data to its associated op register halfword and turned off when the instruction processing has utilized that halfword.

#### Register Unavailable For Addressing (RUA Tags) - NP145-285 Order is: UAO, 1; RUM 0, 1; RUA 2, 3; RUM 2, 3; etc.

A set of sixteen (one for each GPR) 3-bit control tags used to guarantee logically correct address generation by the I-Box. As an operation is issued to the fixed area, any GPR altered by that operation (R1) has its RUA tag incremented. The fixed area will decrement the tag upon execution of the operation. A nonzero tag indicates to any subsequent decode that the associated GPR is unavailable as an address generating parameter. Three bits are required to cover the number of operations that can be outstanding in the fixed area.

#### Register Unavailable For Modification (RUM Tags) - NP145-285 Order is: RUA 0, 1; RUM 0, 1; RUA 2. 3-RUM 2. 3: etc.

A set of sixteen (one for each GPR) 3-bit control tags used in conjunction with the RUA tags to guarantee the proper sequencing of I-Box results into the GPRs. As an operation is issued to the fixed area, any GPR required as a source parameter by that operation (R2) has its RUM tag incremented. The fixed area decrements the tag upon execution of the operation. A nonzero RUM or RUA indicates to any subsequent decode that the I-Box cannot change this register, as an outstanding operation requires the current contents. Three bits are required to cover the number of possible outstanding fixed area operations.

# DIAGRAM 5-36. I-UNIT TRIGGER LIST (SHEET 1 OF 3)

#### R1 Double Sink Trigger - NM117

Set by the decoder during all MOP instructions. It is meaningful only for LM and STM, double length shifts, and multiply/divide. It is used to make the R1 equal SLCX and R1 equal SLCB comparator compare not only R1 but R1 plus one, if R1 is even.

#### State Triggers (3) - NM083

General sequence control triggers. S0 is the decode state of all instructions. S7 is entered at the start of a multi-op instruction. MOP logic uses its own state triggers. The interrupt sequences are executed in S0 and have their own sequence triggers.

#### Store Address Register Busy Tags (SAR-BSY) - NP369

A set of three triggers, one for each store address buffer register. As a store is issued, one of the buffers is assigned to hold its address until executed. The buffer is freed following execution and becomes available for reassignment.

#### SVR1 Invalid Trigger (R1 Invalid) - NM113

Indicates, for one cycle, to the decoder that the GPR addressed by SVR1 has just been changed by the I-Box. If the address generate following this decode cycle used this GPR, the SVR1 invalid trigger substitutes the WR contents (WR contains the address parameter) for the GPR (which has not

#### Pipeline Stage 2 - Adder and Execution Staging Control Triggers

#### B Outgate Triggers - NP435-441

Sixteen triggers, one for each value of B. Allows gating the associated 32-bit GPR quantity to the A adder input 0-31.

#### D Outgate Trigger - NP473

Enables gating the 12-bit D buffer quantity to the D adder input 0-11.

#### Fixed Valid Trigger - NP385

Notifies the fixed area that the staging register contains an instruction for the fixed area. The trigger is turned on when an instruction is set into the stage and remains on for one cycle.

#### Floating Valid Trigger - NP385

Notifies the floating area that the staging register contains a floating point instruction. The trigger is turned on when an instruction is set into the stage and remains on for one cycle.

#### Hot Ones Triggers - NP467-481

Four triggers that allow gating particular single bit entries to the adder. The entry positions are into the D adder input.

- 1. Bit 31

- 3. Bit 28 4. Bit 25

#### IR Counter Outgate - NP471

Gates the five IR counter bits (26-30) to D adder input positions 26-30.

#### LB Outgate - NP471

Gates LB 8–25 to A adder input positions 8–25.

#### Set Condition Code Trigger - NP385

Notifies the execution areas that a condition code affecting instruction has just been issued or handled by the I-Box. The signal inhibits any outstanding instructions from changing the code. It is a one-cycle signal.

#### SVIR Outgate Trigger - NP479

Gates the five SVIR bits to the A adder input positions 26-30.

#### Temp Outgate Triggers - NP477

Two triggers allowing the 24-bit temp quantity to be gated to either the A or B adder inputs 8-31.

# Timer Address Trigger (TAT) - NP483

Forces the address of the timer storage location into the adder when a timer update is required. Feeds hot inputs to D input positions 25 and 27.

## True/Complement Trigger - NP467

Enables complementing the data gated to the B adder input 0-31.

#### WR Outgate Triggers - NP469 Two triggers allowing the 32-bit WR quantity to be gated to either the A or B adder inputs 0-31.

X Outgate Triggers - NP447-457

Sixteen triggers, one for each value of X. Allows gating the associated 32-bit GPR quantity to the B adder input 0-31.

# Pipeline Stage 3 - Interface with Storage Control Triggers

## MSCE Not Accepting - NL551

Indicates that no CPU address will be taken on the following cycle. Controlled by the MSCE.

## **Branch Control Triggers**

## Activate Trigger - NM091

Set for one cycle when test of CC shows branch condition guess is correct. It notifies both stacks to start processing conditional ops, i.e., render them normal.

# Back Less Than Eight Trigger (BACK8T) - NM103

Indicates that the target of the current branch is back less than 8 doublewords. It can be set in two ways: (1) When LB  $\leq$  WR  $\leq$  UB and WR  $\leq$  IR or (2) When the adder output indicates back less than 8 (LB plus IRCTR minus the target).

# BAL Trigger - NM111

Indicates a BAL op has entered state 6.

# BCQ Trigger - NM119

Set during the decode of a quick loop BCT instruction (loop trigger on and IR equals SLCIR). Branch In Array Trigger (BIAT) - NM107

Indicates the target of a branch (not BC) is in the array. It is set by the LB  $\leq$  WR  $\leq$  UB comparator after the first temp fetch is made.

#### Branch In Array 1 Trigger (BIA1T) - NM107 Similar to BIAT but set when a temp fetch sequence has not been used.

Branch Trigger (BRT) - NM107 Indicates whether the branch in process will be taken. It is set according to the adder output and the op (BXLE, BXH, BCT).

# BXLE Trigger - NM103

Turned on during the decode of a BXLE instruction, off by the decode of BXH. It tells the branch sequences how to interpret the adder output, i.e., whether a plus or D sum indicates branch or whether a minus sum indicates branch.

BXQ Trigger - NM118

Set during the decode of a quick loop BX instruction (loop trigger on and IR equals SLCIR). It is also used for BX ops in loop (but not quick) mode.

Cancel GPR Request Trigger - NM109

A store in the instruction stream may occur after the request GPR priority trigger has been turned on. The cancel GPR request trigger allows the request GPR priority trigger to be turned off without ingating the GPRs.

Cancel Trigger - NM091

Set for one cycle when test of CC shows BC guess is wrong. It notifies both stacks, FXOS and FLOS, and MSCE to destroy all outstanding conditional ops.

CC Valid - NM095

Tells test sequence when CC is available for testing. It is a data trigger and is kept off by (1) any CC op outstanding in the FXA or FLA, (2) a CC bit on in the op stage and not conditional mode, and (3) by the turn on of the activate trigger for one cycle (set to on again if a CC bit was issued in conditional mode).

Conditional BACK8T - NM093

On during conditional mode caused by a BC operation whose target is back less than 8 doublewords.

Conditional BIAT - NM093

On during conditional mode caused by a BC whose target is in the instruction array.

Conditional Quick Trigger – NM089 On during conditional mode caused by a BC closing a loop in the instruction array .

Conditional Trigger - NM095

Indicates machine is in conditional mode, i.e., the I-Box has processed a BC op but the test of the CC has not yet been made.

Loop Trigger - NM087

Indicates machine in loop mode. May be reset by decode of any fixed op that changes the GPR pointed to by SLCB or SLCX.

R1 Outgate Inhibit Trigger - NP019

Inhibits the op register R1 fields from being outgated to the R1 decoder when a substitute field is utilizing the decode hardware.

Request GPR Priority Trigger - NM117

Requests the FXA to give the I-Box priority on ingating into the GPRs. The turn off of this trigger causes the WR to be set into the GPR addressed by the SVR1 register.

SVR1 Outgate Trigger - NM109

Outgates SVR1 to the R1 OR. It is set and reset by the XEC and BAL sequences.

Temp Fetch Made Trigger (TFMT) - NM089

Indicates that two temp fetches have been made for the branch in process. (Target is out of

Unconditional Branch Trigger (BCUNCONT) - NM118

Set during the decode of a BC with an all ones mask field to distinguish it from a conditional branch.

#### Execute Control Triggers

Execute A Trigger - NM152

Indicates that an execute instruction is being processed. Required because the op register will be changed by the target fetch during the processing. This trigger is reset after target returns from

Execute B Trigger - NM103

Indicates that the op in process is the target of an XEC instruction.

Execute C Trigger - NN249

Controls housekeeping following the completion of an execute target that has not resulted in a branch being taken. It controls the adjusting of the AOC and IR register contents to point to the instruction subsequent to the execute instruction, and activates instruction fetching. It is turned on for one cycle as a result of the completion of the target.

Execute Fetch Protect Tags - NN209

Two execute fetch protect tags are turned on as a result of fetching the execute target from a protected array. An interrupt will result from an attempt to use any portion of a protected word. Turn on and off is identical to that of the array protect tags.

Execute 1 and 2 Fetch Tags - NN203

Indicate outstanding fetches for the execute target. When the data arrives, it will be routed only to the op register and not to any array location. Two fetches may be required because the XEC target may cross a doubleword boundary.

Execute 1 Invalid Trigger - NM152

Turned on when the fetch for an execute target is to an invalid address.

Execute 2 Invalid - NM155

Indicates the second fetch for execute target is invalid. This fetch is made because the target instruction may cross a doubleword boundary. No action results from this indicator unless the fetch is utilized.

Plus 2 To IRCTR Trigger - NN197

Used to set the IRCTR to the correct value after an execute has been processed. The IR must be updated by two halfwords following the target completion irrespective of the target length. It is turned on for one cycle following the completion of the execute target.

## Interrupt Control Triggers

Channel Release Trigger - NM383

Captures the release signal from the channels to provide a timing base on which to terminate I/O instructions and I/O interrupts. Trigger is off whenever there is no turn-on signal.

External Identity Triggers

Set of eight triggers used to indicate which of the external, interrupt key, and timer interrupts are currently being processed

Inhibit WR Address Trigger - NM551

Blocks the output of the WR from the address bus to MSCE during interrupt sequencing. This action allows the PSW addresses to be forced via the same bus.

Interrupt Fetch/Store Trigger - NM153

Indicates and causes the PSW fetch or store address to be formed based on the interrupt class being sequenced.

Interrupt Sequence B Trigger - NM160

Indicates a precise interrupt is currently being processed. Enables imprecise interrupts that occur during the process to usurp the control and cancel the precise interrupt.

Interrupt Sequence 1 and 2 Triggers - NM151

Provide clocking for handling interrupt sequencing.

I/O Interrupt Taken Trigger - NM158

Signals the channels that an I/O interrupt has been honored and that status may be stored.

I/O Interrupt Triggers - NM391-397

Set of seven triggers, one for each channel, turned on when the associated channel signals interrupt.

DIAGRAM 5-36. I-UNIT TRIGGER LIST (SHEET 2 OF 3)

Pipeline Not Empty Trigger - NM158

Used whenever logical correctness demands a pipeline drain. The requirements for pipeline

- 1. FXOS and FLOS empty

- 2. I-Box state zero

- 3. All FXBs, FLBs, and SARs available

- 4. Not step IR

- 5. FLRs not busy

- 6. No FXA execution in process

- 7. Instruction fetch trigger on

- 8. All SDBs empty

- Ppln empty from PSCE

No CPE request in CPE buffer

- b. No active CPU request in any queue register.

- 10. CC valid

Program A Interrupt Triggers

Set of triggers identifying the various imprecise interrupts. In order of priority the imprecise interrupts are:

- 1. Data NM417

- 2. Fixed Overflow NM417

- 3. Divide NM407

- 4. Exponent Overflow NM407

- 5. Exponent Underflow NM409 6. Significance - NM409

7. Floating Divide - NM411

- 8. Protect NM411

- Specification A NM413

Address A NM413

Two additional triggers indicate imprecise interrupts on conditionally issued instructions. These triggers turn on the normal program A interrupt triggers if the conditional instructions are activated.

- Conditional Specification A NM415

- 2. Conditional Address A NM415

Program B Interrupt Triggers

Set of triggers identifying the various program exceptions and the supervisor call exception, all of which are precise. In order of priority:

- 1. Operation NM385

- 2. Specification B NM385

- 3. Privileged Op NM387

- 4. Execute NM387

- Address B NM389

- Supervisor Call NM389

Program B Interrupt Trigger - NM154

Indicates a precise interrupt condition has been signaled. Establishes correct timing platform on which to begin sequencing the interrupt.

PSW Stored Trigger - NM157

Indicates that the PSW has been stored to prevent a second store for a single interrupt.

#### Multiple Operation (MOP) and Timer Control Triggers

Block CLC Trigger (BLK CLCT) - NM259

Used to block the MOP sequence for CLC (the NOXCM sequence) in case a prior CLC has not yet been terminated or completed. It is turned on when a MOP sequence completes a CLC prior to its completion or termination by the VFLEU. It is turned off when the VFLEU signals completion or termination.

Byte Buffer Outgate Trigger - NM319 Outgates the 8 bits of the byte buffer to input B, bits 24-31 of the address adder. This outgate function is used in the TR or TRT, ED, EDMK and PUMO sequences.

Byte Buffer Valid Trigger - NM301 Turned on whenever the byte bus is gated into the byte buffer and the byte bus valid line from the VFLEU is conditioned. This trigger goes off whenever the data in the byte buffer has been used and no new data has been gated in. TR, TRT (in TR or TRT sequence) and EDMK (in ED, EDMK sequence) instructions make use of this trigger.

DWCR To Adder Outgate Trigger - NM319 Outgates the 5 bits of the doubleword count register to input B, bits 24-28 of the address adder. This outgate function is used in the NOXCM and ED, EDMK sequences.

Inhibit Advance to Working Register Trigger - NM248

Prevents ingating the address adder sum to the working register (or temp). This trigger is turned on whenever an address is ingated to the WR but the associated ppln op bits are not set into the ppln 3 register. This condition occurs during operand accessing whenever advance to WR is present but advance is not. The trigger is turned off as the ppln op bits are set into the ppln 3 op register.

Last or SBA Carry Trigger (LAST) - NM247

Used in three contexts. It is used in the TR or TRT sequence to record the last argument byte signal which accompanies the last byte of the argument stream from the VFLEU to the I-Box. It is used in the ED, EDMK sequence to aid in sequencing and addressing the last pattern word fetch. It is used in the PUMO sequence to record the occurrence of a LO3 B, D, L, carry to set the one more source trigger or the one more sink trigger correctly.

Outgates the L1 field from the L register (bits 0-3) to input B, bits 28-31 of the address adder, and also gates the low-order 3 bits of the L1 field to the LO3 carry propagate logic (see LO3, B, D, L, carry in the MOP definitions - Diagram 5-35, item 10). This outgate function is used in the PUMO sequence (covering all MOP instructions which have two 4-bit L fields, L1 and L2).

Outgates the L2 field from the L register (bits 4-7) to input B, bits 28-31 of the address adder and also gates the low-order 3 bits of the L2 field to the LO3 carry propagate logic (see LO3, B, D, L, carry in the MOP definitions – Diagram 5–35, item 10). This outgate function is used in the PUMO sequence (covering all MOP instructions which have two 4-bit L fields, L1 and L2).

L-LO3 Outgate - NM201

Outgates the low-order 3 bits of the L register to the carry propagate logic (see LO3, B, D, L, carry in the MOP definitions - Diagram 5-35, item 10). This outgate function is used in the TR or TRT, NOXCM and ED, EDMK sequences (covering all MOP instructions which have a single 8-bit

L Register Full Trigger – NM245 Turned on when the L (or L1-L2) field is set into the L register at the beginning of each MOP sequence except LM or STM. While on, it serves as an interlock to prevent the I-Box from beginning a subsequent MOP instruction. It is turned off on the cycle following the FXOS decode of the first op of the associated MOP instruction.

Mark Trigger - NM243

Provides an assortment of special functions in all MOP sequences except LM or STM.

Multiple Op State Triggers - NM305

Define the 3 major states used in the MOP (multiple op) sequences. There are five MOP sequences: LM or STM; TR or TRT; NOXCM which covers NC, OC, XC, CLC, MVC, MVZ and MVN; ED, EDMK; and PUMO which covers PACK, UNPK, and MVO. Each of the sequences is entered in MOP state 1 and is completed in MOP state 3.

- 1. MOP State 1 This trigger defines state 1 for each MOP sequence.

- 2. MOP State 2 This trigger defines state 2 for all MOP sequences. (Note that the LM or STM sequence does not use state 2.)

- 3. MOP State 3 This trigger defines state 3 for all MOP sequences.

#### Multiple Op Trigger - NM239

Turned on as each MOP sequence is entered and is turned off as each MOP sequence is completed. While on, it: aids in control of ingating to the op stage and ppln 3 op; modifies the handling of the store into instruction array situation; and calls for partial (24-bit address field only) GPR ingating whenever required.

#### New Argument Binary Trigger (NABT) - NM260

Used in TRT to aid in the cancellation of an unused argument buffer in case the TRT instruction terminates rather than completes. The NABT is off as the I-Box TRT sequence initiates the first argument fetch and is then alternately turned on and off as succeeding argument doubleword fetches are initiated. When NABT is on, it forces a bit to op stage position 13 (in the POSE field).

#### One More Sink Trigger - NM253

Used in all MOP sequences except LM or STM as an aid in counting the doublewords involved in the sink operand field.

#### One More Source Trigger - NM251

Used in NOXCM and PUMO sequences as an aid in counting the doublewords involved in the source operand field. This trigger is also used in the TR or TRT sequence as described on the TR and TRT flowchart (Diagram 5-126).

#### Operand Access Trigger - NM241

Used in all MOP sequences except LM or STM. It derives its name from its use in the NOXCM and ED or EDMK sequences wherein it is used (in conjunction with one more source trigger and one more sink trigger) as a part of the operand doubleword fetching mechanism. In this context, the operand access trigger will be on as fetching is begun and will be turned off when operand accessing is almost complete. In the TR or TRT and PUMO sequences, this trigger provides general sequencing functions.

DIAGRAM 5-36. I-UNIT TRIGGER LIST (SHEET 3 OF 3)

#### Overlap Trigger (OLAPT) - NM257

Used as an aid to handle certain overlapping operand situations that may be discovered during the NOXCM and PUMO sequences. It is turned on whenever the operand fields overlap in such a way that special handling will be (or may be, in case of PACK and UNPK) necessary in the VFLEU.

#### Request Edit Source Trigger - NM301

Used in the ED, EDMK sequence to record that the VFLEU has requested a source word from an FLB. When on, it causes the ED, EDMK sequence to fetch the next source doubleword.

#### Request Pattern or Argument Trigger - NM301

Used in the TR or TRT sequence to record that the VFLEU has requested an argument word from an FLB. When on, it causes a fetch for the next argument word. This trigger is used in the ED, EDMK sequence to record that the VFLEU has requested a pattern word from an FLB; and then it causes the fetching of the next pattern doubleword, and the issuance of an associated op to the  $\mathsf{FXOS}$ .

#### R1 to R1 OR Outgate Trigger - NM201

Used only in the LM or STM sequence. Gates the R1 field from the L register (bits 0–3) to the R1 OR. The decoded output of this 4-bit OR is used to step the appropriate RUA counter(s) when stepping is signaled by the LM or STM sequence.

#### Terminate Trigger (TERMT) - NM255