IBM

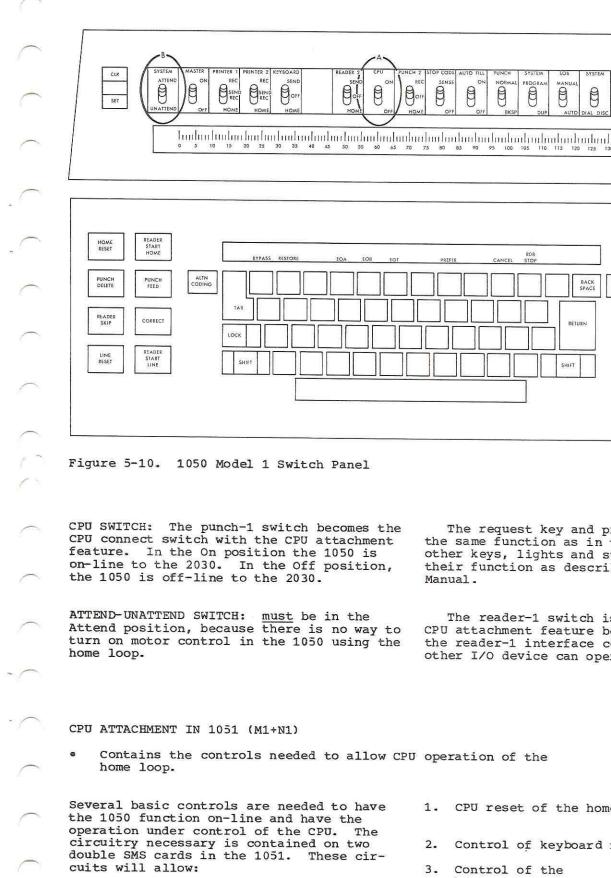

# Field Engineering Theory of Operation

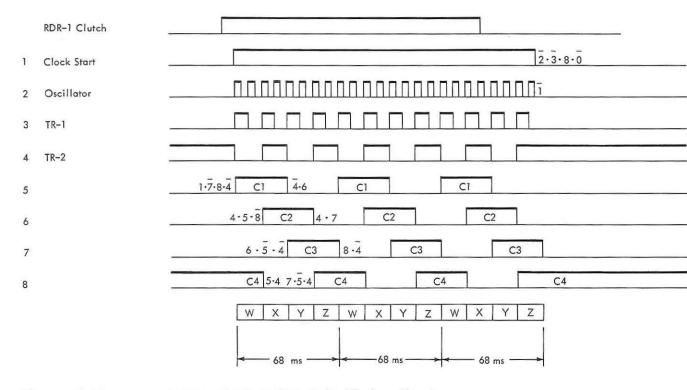

# **Restricted** Distribution

This manual is intended for internal use only and may not be used by other than IBM personnel without IBM's written permission.

Specifications contained herein are subject to change without notice. Revisions and/or supplements to this publication will be issued periodically.

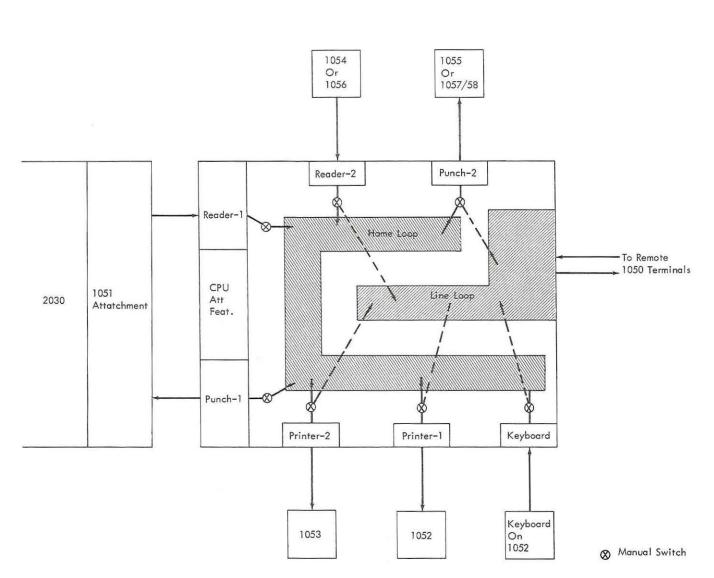

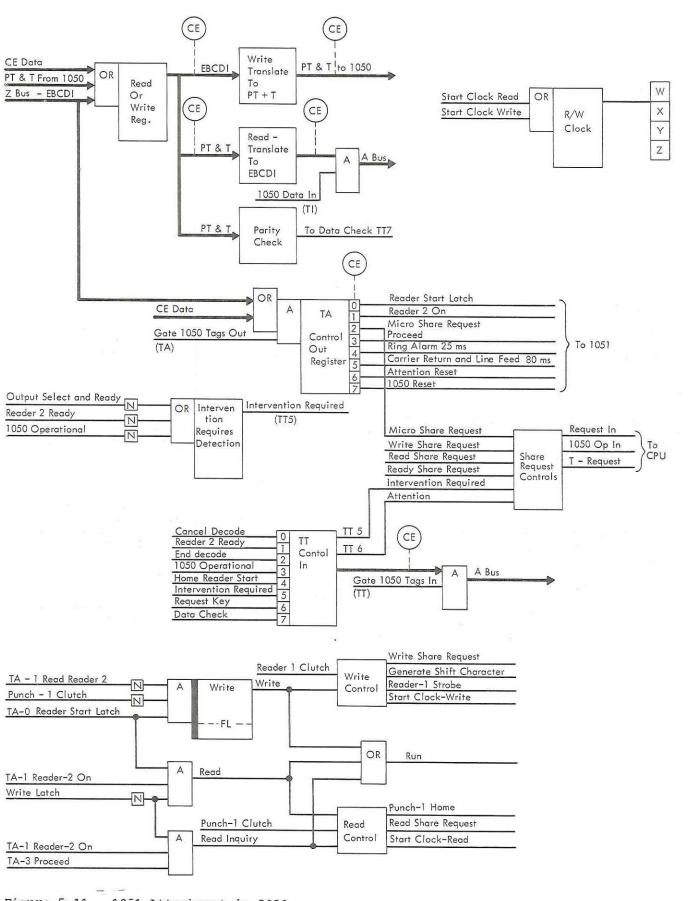

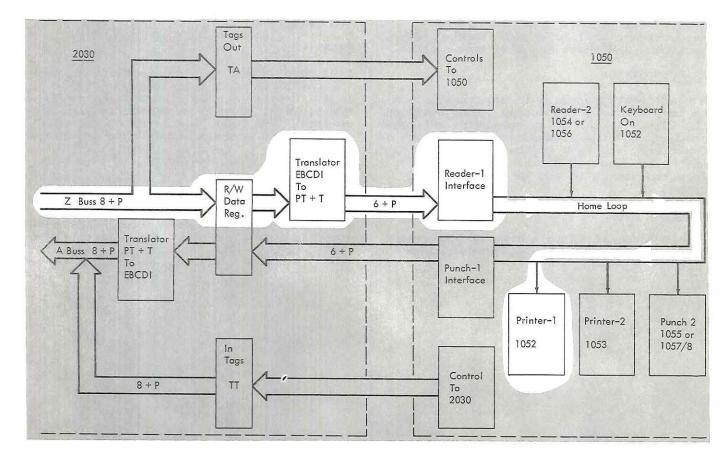

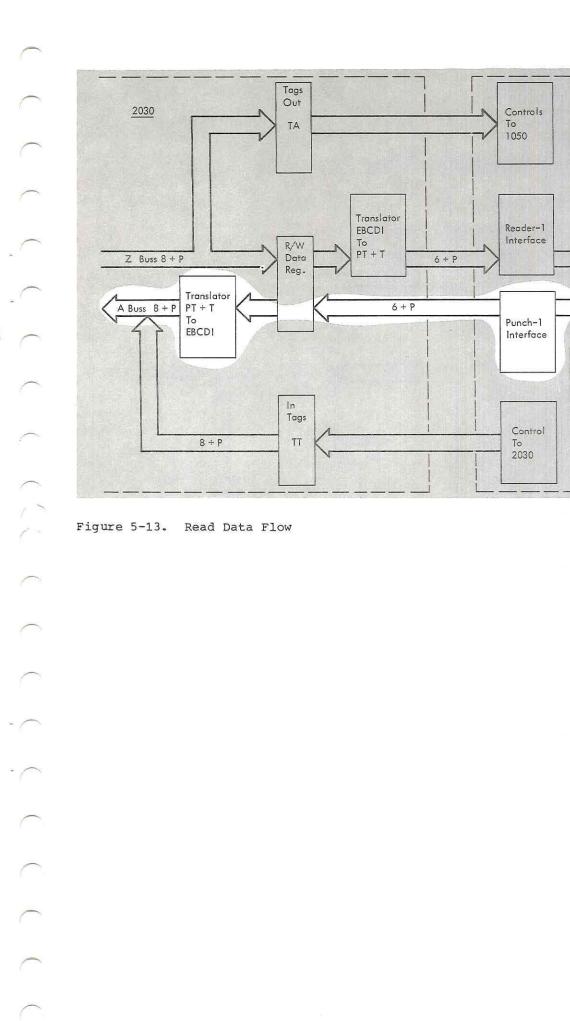

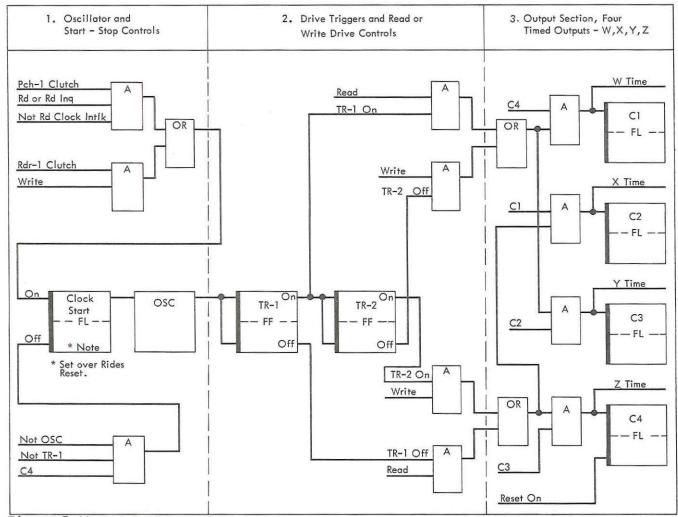

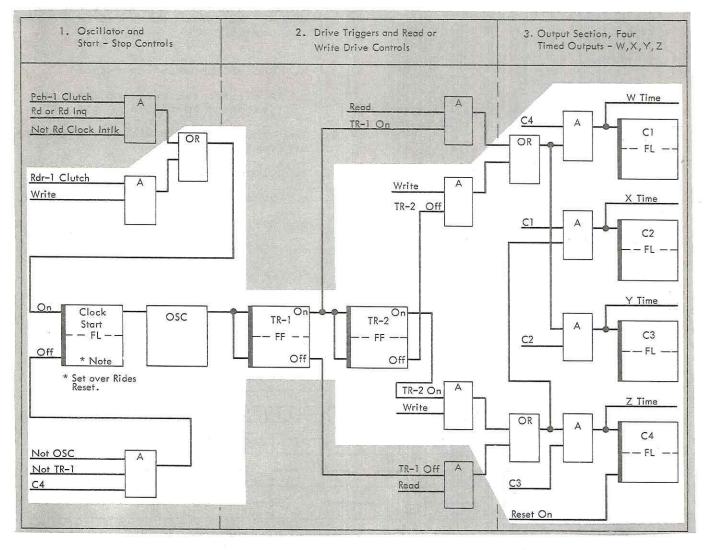

2030

I/O Control System/360 Model 30 2030 I/O Control System/360 Model 30

Field Engineering Theory of Operation

(

$\left( \begin{array}{c} \\ \\ \\ \end{array} \right)$

$\frown$

$\overline{}$

I/O Control

System/360 Model 30

#### PREFACE

This manual contains information about the Input/Output controls of the System/360 Model 30. A knowledge of the IBM 2030 Processing Unit is assumed. Information pertaining to the 2030 Processing Unit is contained in a companion Field Engineering manual, <u>2030 Processing Unit</u>, Form Y24-3360. Maintenance information is contained in the Field Engineering Maintenance Manual, <u>2030 Processing Unit</u>, Form Y24-3390.

# Fifth Edition (November 1966)

This edition, Y24-3362-1 contains minor changes to, but does not obsolete the previous edition, Y24-3362-0. Changed text is marked with a vertical line in the margin; changed figures are marked with a large bullet to the left of the figure title.

Copies of this and other IBM publications can be obtained through IBM Branch Offices. This manual has been prepared by the IBM Systems Development Division, Product Publications, Department 171, P.O. Box 6, Endicott, New York 13760. Address comments concerning the manual to this address.

(c) International Business Machines Corporation 1965

| $\frown$   | SECTION 1. COMPREHENSIVE INTRODUCTION.                                             | 1-1                                                  |

|------------|------------------------------------------------------------------------------------|------------------------------------------------------|

| (          | Channels                                                                           | 1-1<br>1-2<br>1-7<br>1-8<br>1-14<br>1-15             |

| •          | SECTION 2. I/O INTERFACE                                                           | 2-1                                                  |

| $\sim$     | Scan Controls                                                                      | 2-2<br>2-3<br>2-10                                   |

| (          | Inbound Tag Lines                                                                  | 2-16<br>2-18                                         |

|            | SECTION 3. MULTIPLEXOR CHANNEL                                                     | 3-1                                                  |

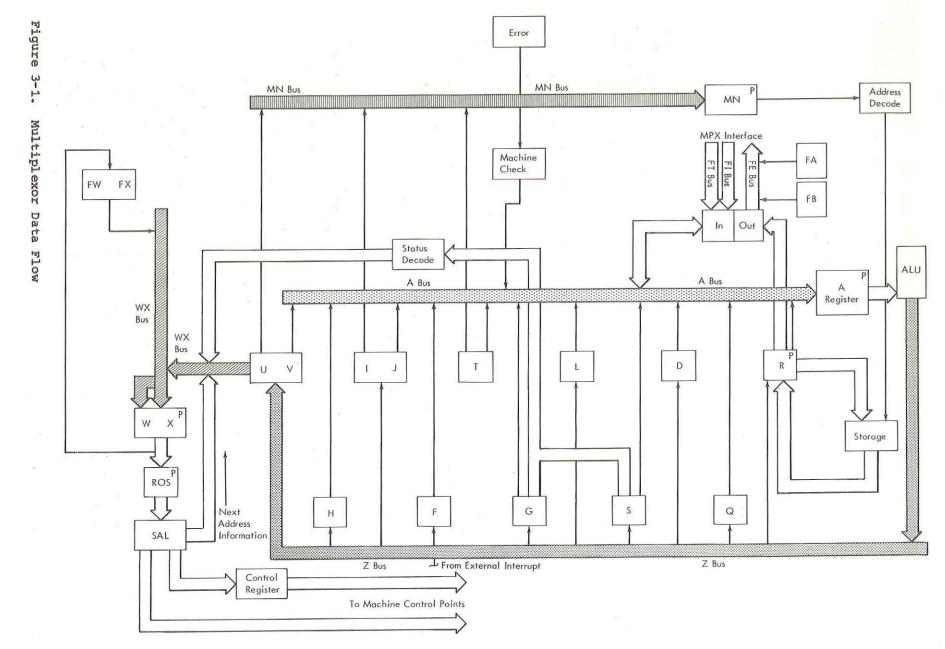

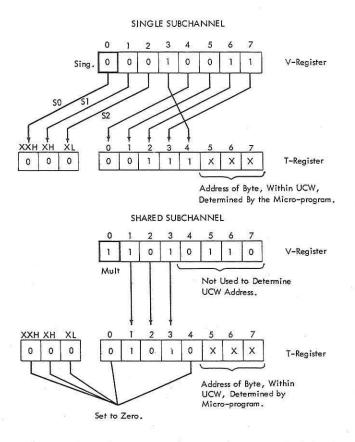

|            | Data Flow                                                                          | 3-5                                                  |

|            | THEORY OF OPERATION                                                                | 3-15                                                 |

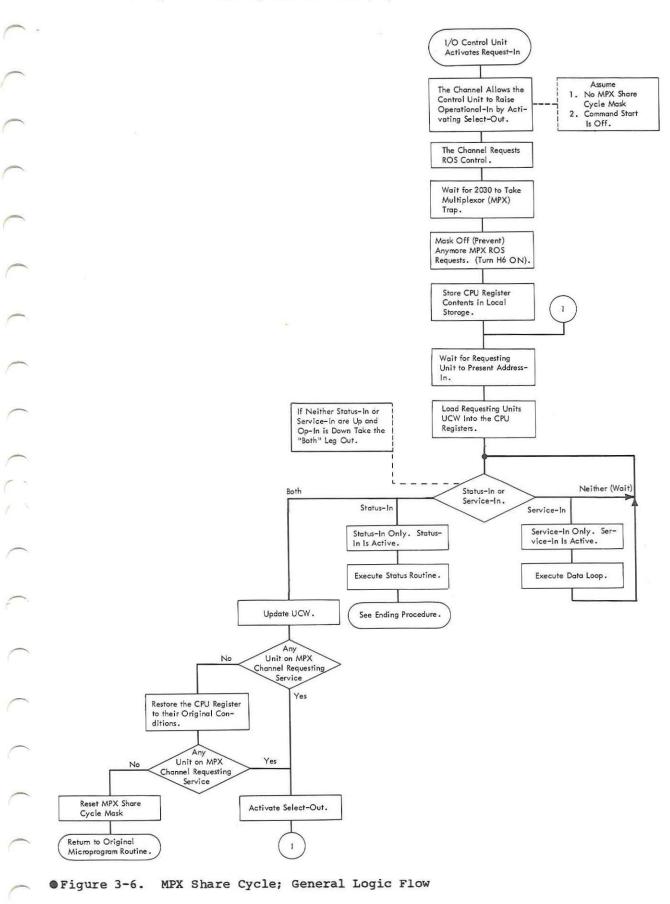

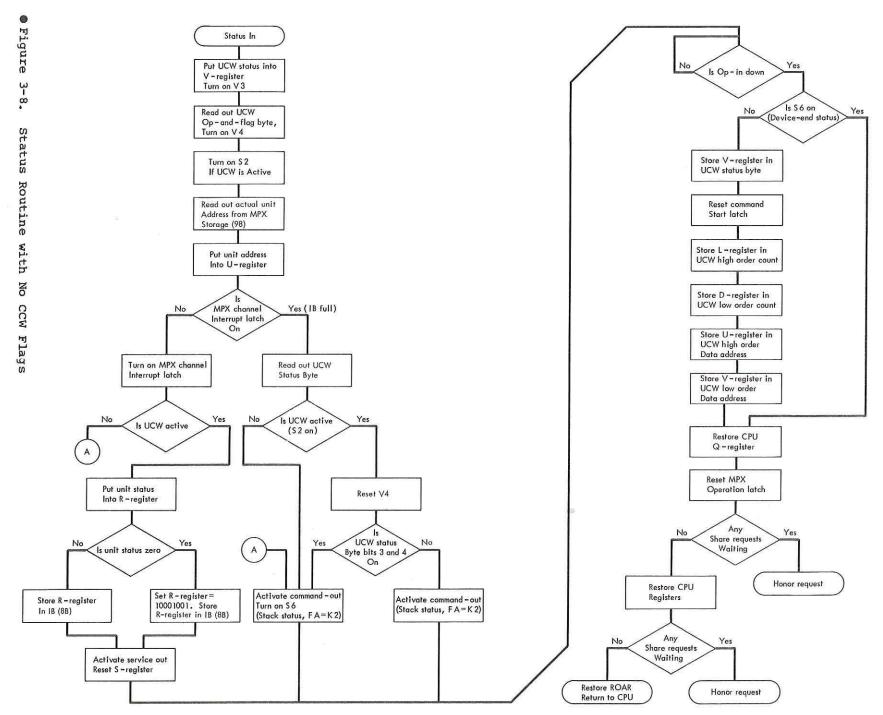

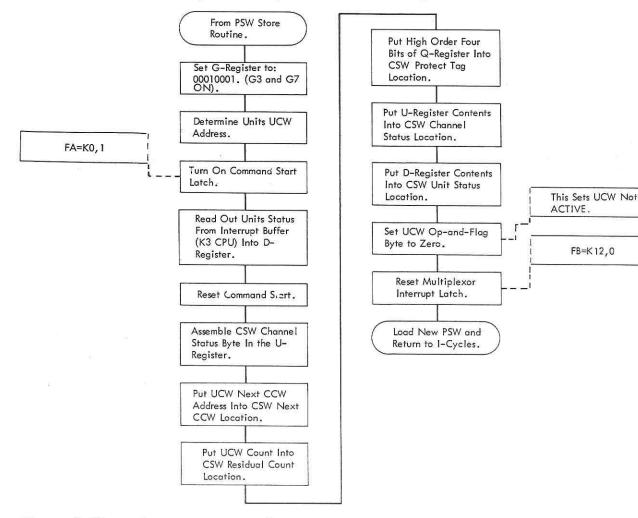

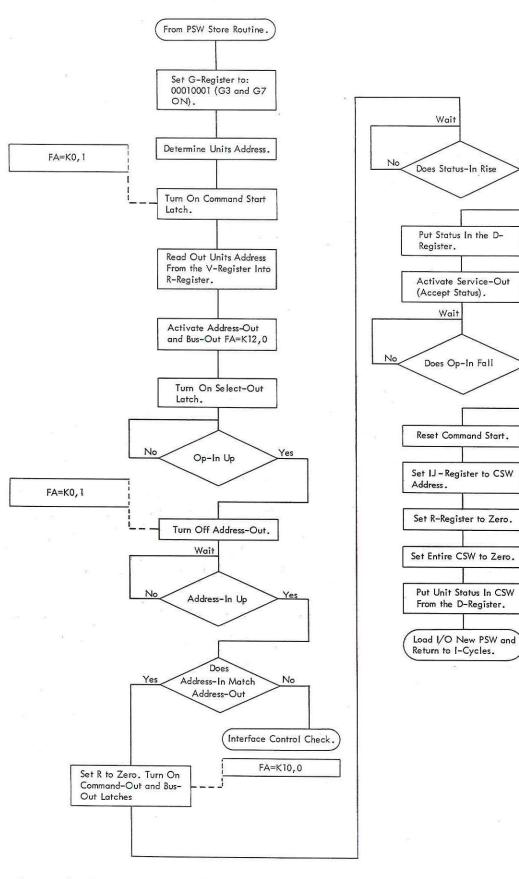

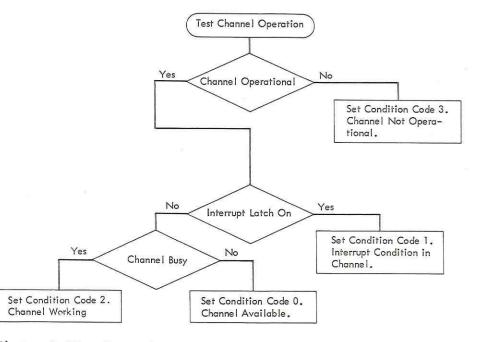

| (          | I/O Interrupt                                                                      | 3-15<br>3-16<br>3-27<br>3-28<br>3-29<br>3-33<br>3-33 |

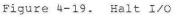

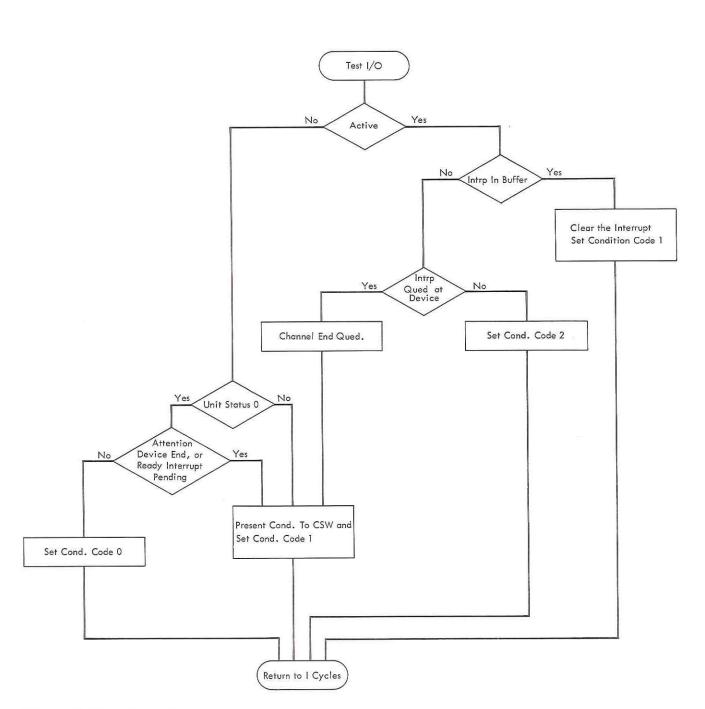

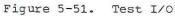

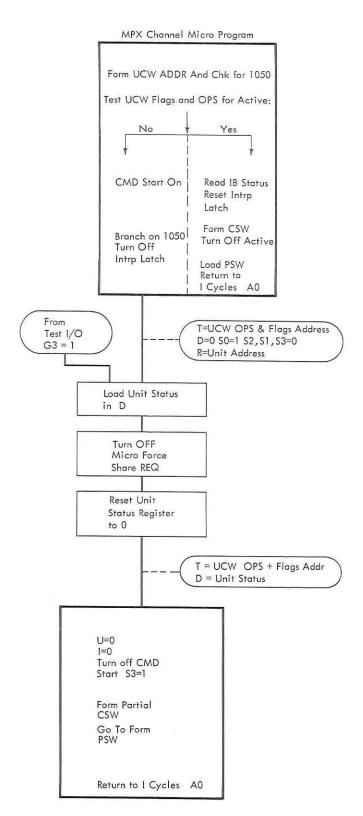

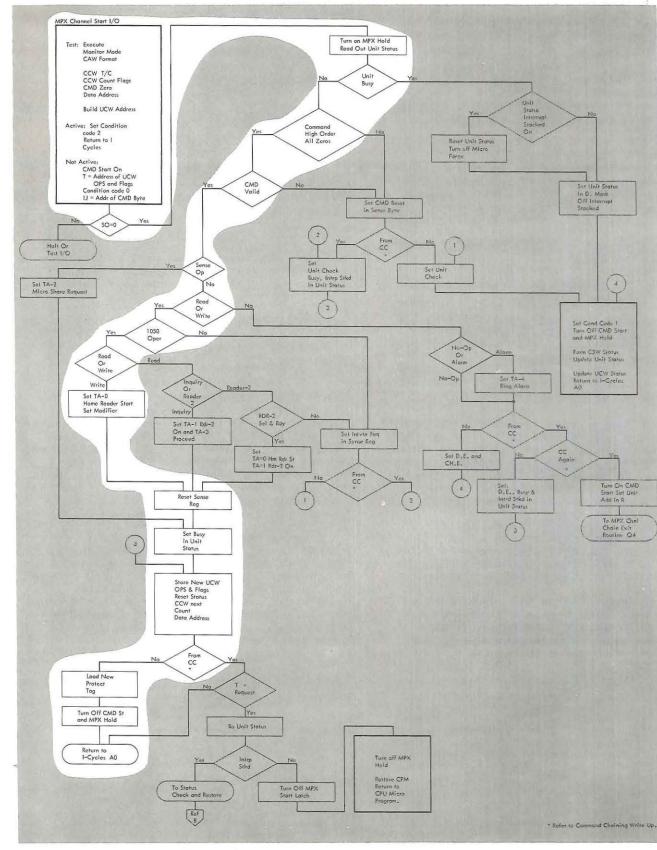

| (          | Initial Program Load (IPL)         Test I/O         Halt I/O         Test Channel. | 3-42<br>3-42<br>3-44<br>3-45<br>3-46                 |

|            | Error Handling                                                                     | 3-47                                                 |

|            | Comprehensive Introduction                                                         | 4-1                                                  |

|            | FUNCTIONAL-UNITS                                                                   | 4-4                                                  |

| $\frown$   | GA Register                                                                        | 4-4<br>4-5<br>4-6<br>4-6<br>4-6                      |

|            | GG Register                                                                        | 4-7<br>4-7<br>4-8<br>4-8                             |

| $\bigcirc$ | GJ Assembler                                                                       | 4-9<br>4-9                                           |

$\bigcirc$

| GO       | Re  | gj         | S   | te     | r.      | 8        | •    | s.       | e.    | ÷    | •          | 3         | í -        |       | •    |      | ×.      | ۰.              | •    | ۲    | 4-1               | 0_  |

|----------|-----|------------|-----|--------|---------|----------|------|----------|-------|------|------------|-----------|------------|-------|------|------|---------|-----------------|------|------|-------------------|-----|

| GR       | Re  | gj         | S   | te     | r.      | e        | •    | •        | •     | •    | ٠          | - 13      | •          | •     | •    | •    | •       | •               | •    | •    | 4-1               | 10  |

| GR,      | , 0 | ss,        |     | an     | d       | G        | т    | Βυ       | ISS   | es   | з.         | 55        |            | •     | •    | •    | •       | •               | •    | •    | 4-]               | 11  |

| GU       | an  | nd         | G   | V      | Re      | eg       | is   | ste      | rs    | ٠    | •          | į,        | ŝ.         | •     | •    |      |         | •               | 8    | ÷.   | 4-]               | L2  |

| GW,      | , 0 | SX         | R   | eg     | is      | st       | er   | S        | •     | •    | •          | - 32      | •          | •     | •    | •    | •       |                 | •    |      | 4-]               | L2  |

| Mod      | lif | ie         | er  |        |         |          |      |          |       | ÷    |            |           |            |       |      | •    |         | ÷               |      |      | 4-1               | L3  |

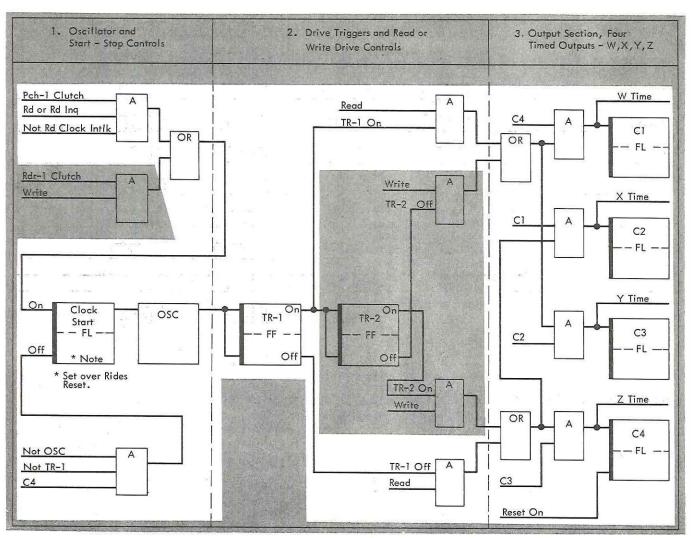

| Clc      | ock |            | (S  | el     | .ec     | ct       | or   | : 0      | ha    | n    | ne         | 1         | )          |       |      |      |         |                 | •    |      | 4-]<br>4-]        | L5  |

|          |     |            |     |        |         |          |      |          |       |      |            |           |            |       |      |      |         |                 |      |      |                   |     |

| THE      | EOF | ۲Y         | 0   | F      | OI      | PE       | RA   | TI       | ON    |      |            |           | •          | •     | •    | ¥    | •       |                 | ×    | ÷    | 4-3               | L8  |

| <u></u>  |     |            | - / | 0      |         | <b>-</b> |      |          | 7.    |      |            |           | <b>~</b> - |       |      | -    | **      | e e             |      |      |                   | 10  |

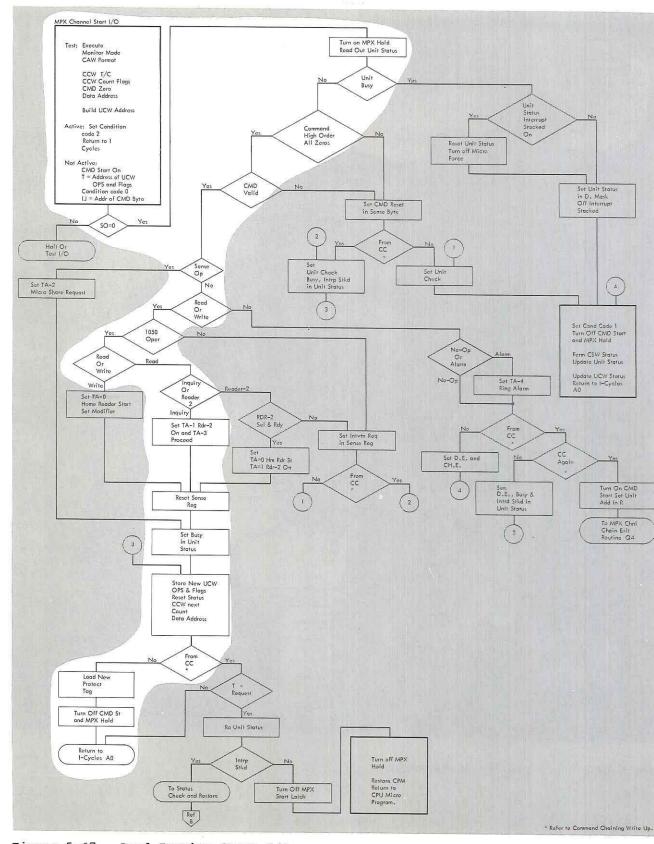

| Sta      | art | ŝ, s       | L/  | 0;     | C       | 20       | mn   | lar      | nds   | 1    | tC         | ) (       | 0          | nt    | rc   | T    | Ur      | llt             | S    | ٠    | 4-1               | 18  |

| 1/0      | 2   | n          | ce  | rı     | cul     | pt       | E    | Xe       | ecu   | It.  | 10         | n         | •          | ÷     |      | •    | •       | •               |      | ٠    | 4-4<br>4-4<br>4-5 | 40  |

| CCI      | NI  | 718        | ag  | C      | )pe     | er       | at   | ic       | ons   |      | •          |           | •          |       | ٠    |      | ٠       | •               | 8    | ٠    | 4-4               | 41  |

| Tra      | ans | sfe        | er  | j      | n       | C        | ha   | anr      | nel   |      | (T         | 'I(       | C)         |       |      |      |         |                 |      |      | 4-5               | 50  |

| Tes      | st  | I,         | 10  | i .    |         | •        |      | *        |       |      |            |           |            |       |      |      |         |                 |      |      | 4-!<br>4-!        | 51  |

| Ha       | lt  | I,         | 10  | ι,     |         |          |      |          |       |      |            |           |            |       |      |      |         |                 |      |      | 4-!               | 53  |

| Tes      | st  | Cl         | na  | nr     | ne.     | 1        |      |          |       |      |            |           |            | 2     |      |      |         |                 |      |      | 4-!<br>4-!        | 55  |

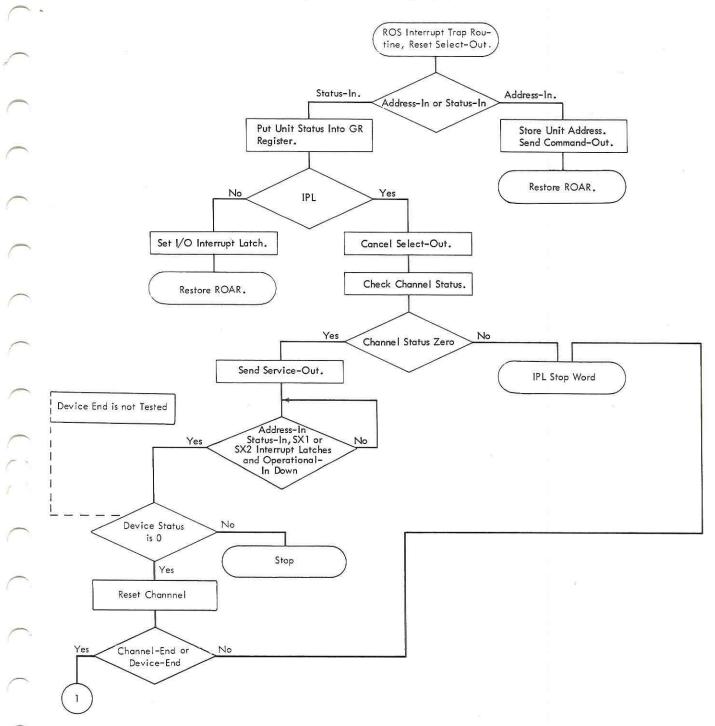

| In       | it  | La         | L   | Pr     | :00     | ar       | an   | n I      | 50    | d    | (          | T         | PI         | )     |      |      |         |                 |      |      | 4-1               | 56  |

| Er       | roi | c 1        | De  | te     | ec.     | ti       | or   | 1.       |       |      |            |           |            |       |      |      |         |                 |      |      | 4-                | 59  |

|          |     |            |     |        |         |          |      |          |       |      |            |           |            |       |      |      |         |                 |      |      |                   |     |

| SPI      | EC  | IA         | L   | FI     | EA      | ΓU       | IRE  | ES       |       | •    |            | e:        | •          | ٠     | •    |      | •       | •               | :0): | •    | 4-                | 60  |

| Mei      | mo  | ry         | P   | rc     | ot      | ec       | :t   | ٠        | •     | ٠    | 0.00       |           | •          | ٠     | •    | ٠    | ٠       | ٠               | ٠    | ٠    | 4-                | 60  |

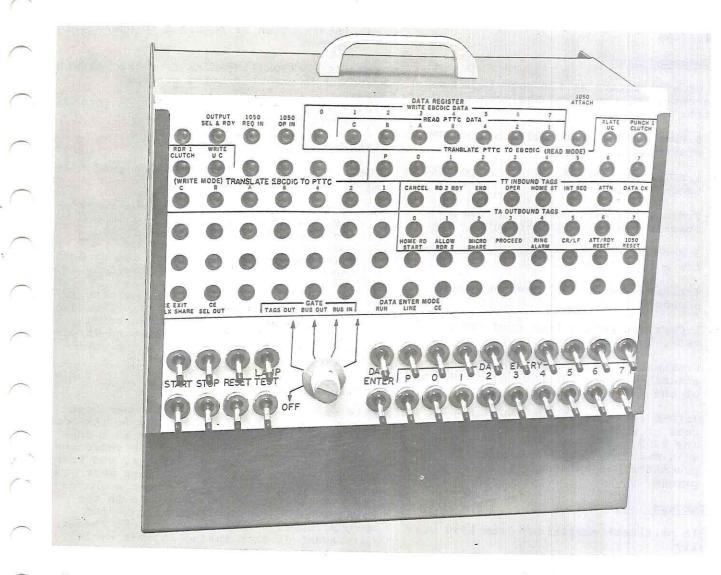

| SE       | CT: | IOI        | N   | 5.     |         | C        | :01  | NS(      | DLE   | C    | CF         | IA        | NN         | EI    |      | •    | 305     | 300             |      |      | 5-                | l   |

| Coi      | mp  | rei        | he  | ens    | si      | ve       | 1    | Int      | tro   | bd   | uc         | ct        | ic         | n     |      |      |         | 3 <b>.</b>      |      |      | 5-                | 1   |

| FU       | NC  | rI)        | ON  | IAI    | 5       | UN       | II.  | гs       |       | •    | 2          |           | ٠          | •     | ٠    | ٠    | ۲       | •               |      |      | 5-                | 18  |

| IB.      | M   | 10         | 51  |        | At      | ta       | ıcl  | hme      | ent   | 2    | CI         | Lo        | ck         |       | •    |      | •       | <b>.</b>        | •    | •    | 5-                | 18  |

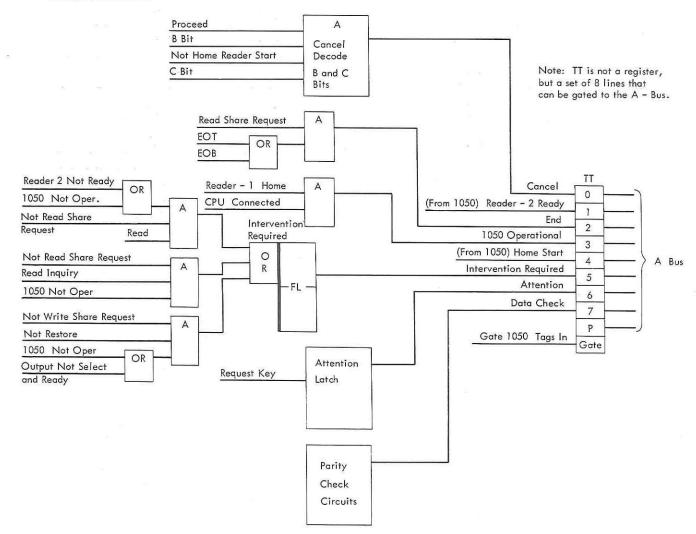

| Co       | nt  | ro         | 19  | 5      | In      | -1       | T    |          |       |      |            |           | -          | 2.002 | 1.00 | 000  | 1142    | 1040            | 1941 | 1.00 | 5-                | 24  |

| Co       | nt  | ro         | 19  | 5 (    | Ju      | t-       | -T   | Α.       |       | 1945 | 8          | 15        |            |       | 141  |      | 125     | 100             | 1207 | 22   | 5-                | 25  |

| Re       | ad  | -W         | ri  | t      | 2       | Re       | a    | is       | ter   | ٢.   | 25         | 7.5<br>•  |            | 1075  |      | 9.85 |         | 1.55            | 1070 | 1.42 | 5-<br>5-<br>5-    | 26  |

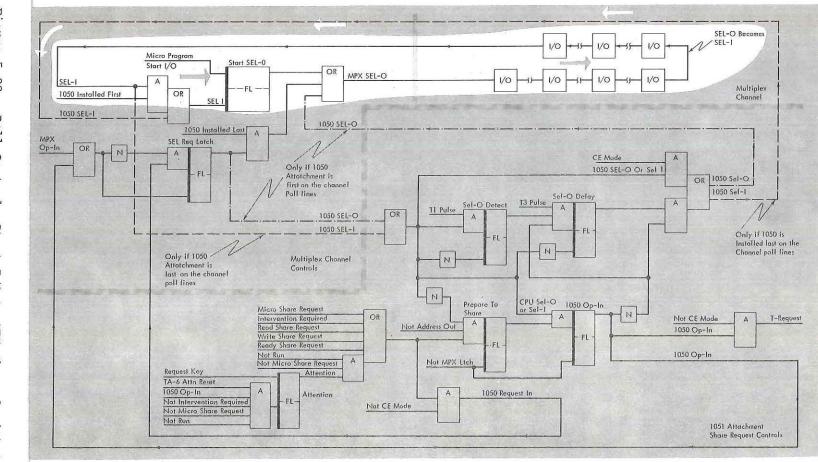

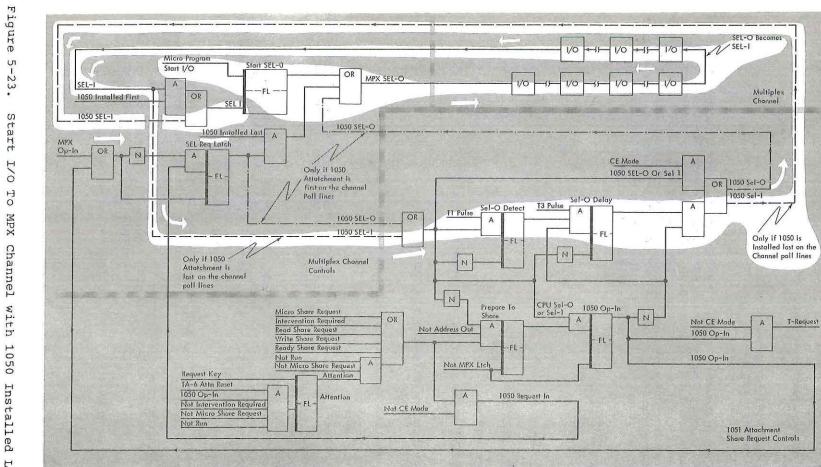

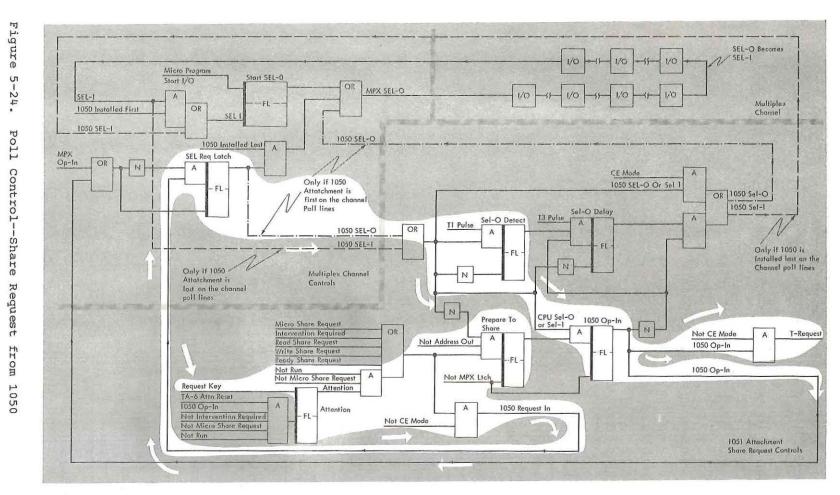

| Sh       | ar  | e -        | Re  | a      | ie      | st       | - (  | Cot      | nti   | ro   | 1          | -<br>-    | Pr         | 11    | 6    | 701  | $h^{-}$ | ro <sup>-</sup> | 1    |      | 5-                | 27  |

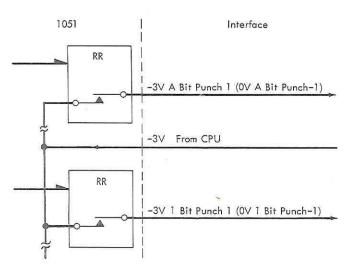

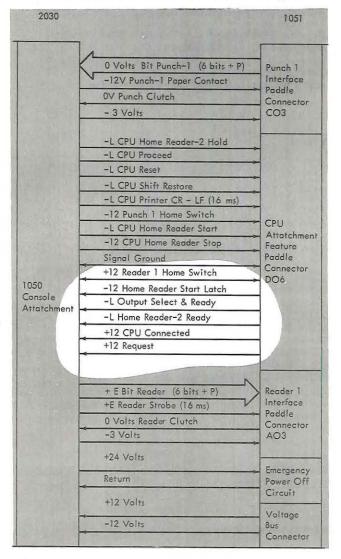

| TB       | M   | 10         | 51  | - 1    | to      | 5        | 20   | 30       | T     |      | 01         | rf        | ac         | 10    |      |      |         | -0.             |      |      | 5-                | 32  |

| Do       | ri. | +17        | 2   | -<br>h | 20      | le i     |      | 20       | 11    | 10   |            |           | au         | ,e    | ٠    |      |         | 13              |      |      | 5                 | 12  |

| ra<br>Do |     | Ly<br>Ly   | T   |        | =C<br>⊾ | 27       |      | y.       | · ÷ . | •    | ~          | •         |            | 125   | 2.   | 2.91 | ۰       |                 |      |      | 5-<br>5-<br>5-    | 4.5 |

| ra       | τт  | LY         | ц.  | ът     | L       | Ge       | 2110 | er       | all   | דכ   | 5          | •         | ٠          | •     | ٠    | ٠    | ٠       | •               | •    | •    | 5-                | 44  |

| TH       | ΕO  | RY         | C   | F      | 0       | PI       | ER   | AT       | IOI   | .Ν.  |            | •         | •          |       |      | ÷    | ٠       | 2               | •    | •    | 5-                | 45  |

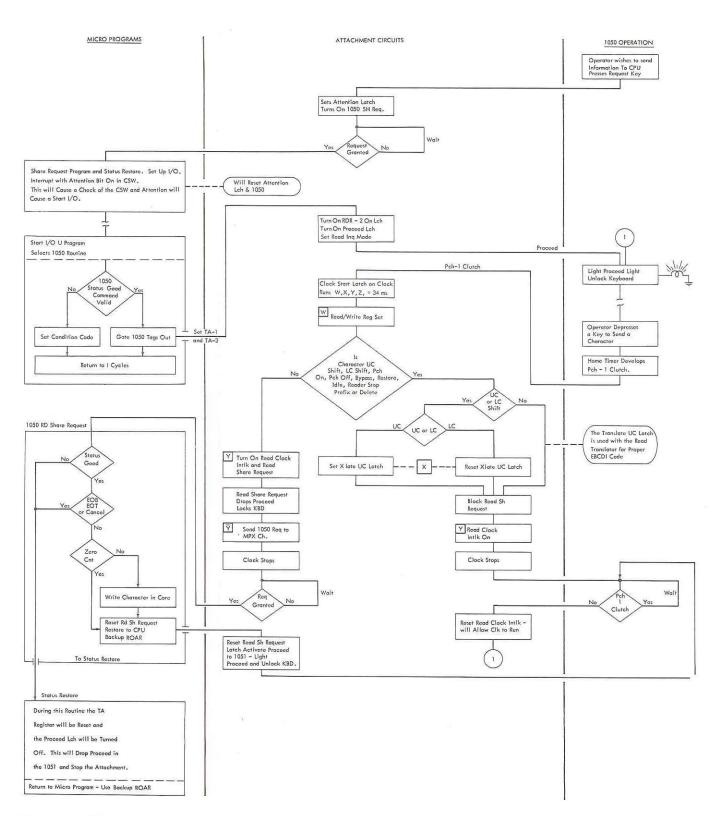

| Mi       | cr  | qo         | r   | pa     | ra      | ms       | 5.   |          |       |      |            |           |            |       | -    |      |         |                 |      |      | 5-                | 45  |

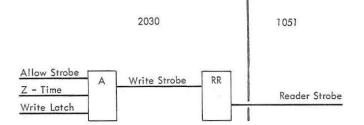

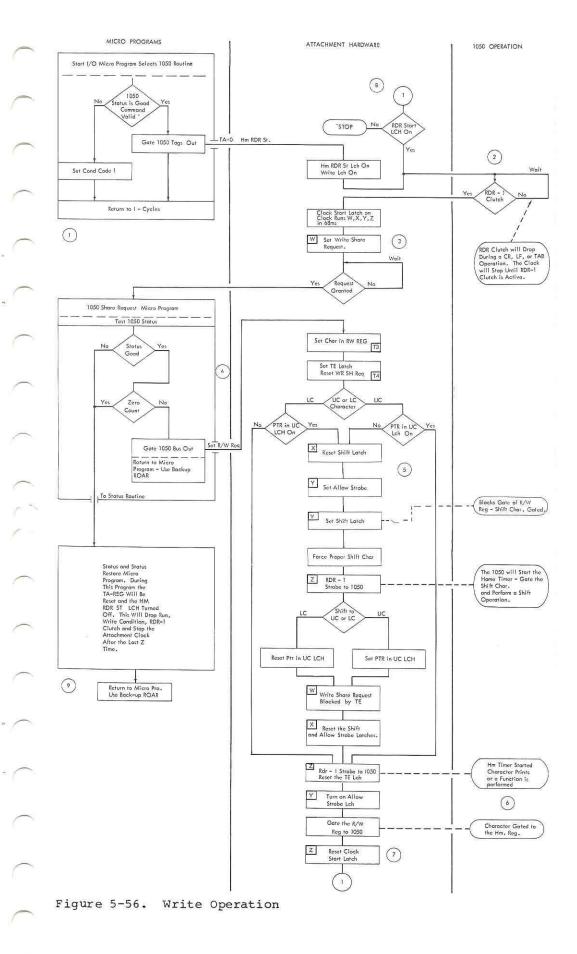

| Wr       | it. | e          | Or  | De     | ra      | t.       | io   | n.       |       |      |            |           | 0          | 2     |      | - 0  | - 2     | - 2             | - 2  | - 2  | 5-                | 53  |

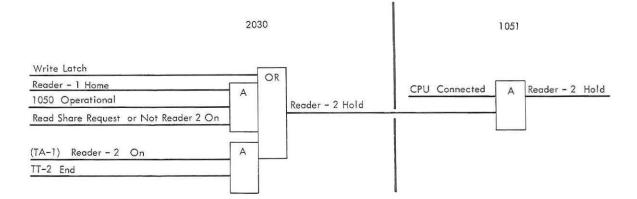

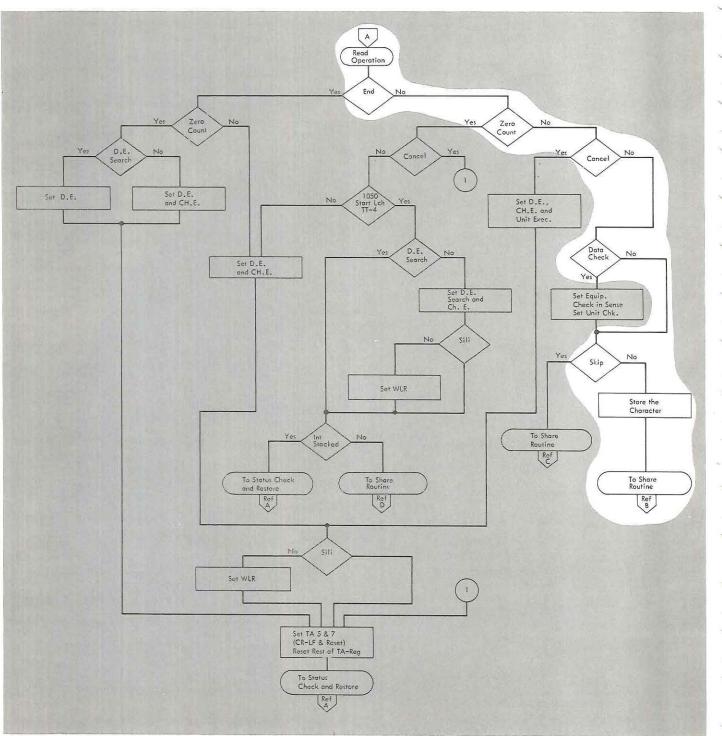

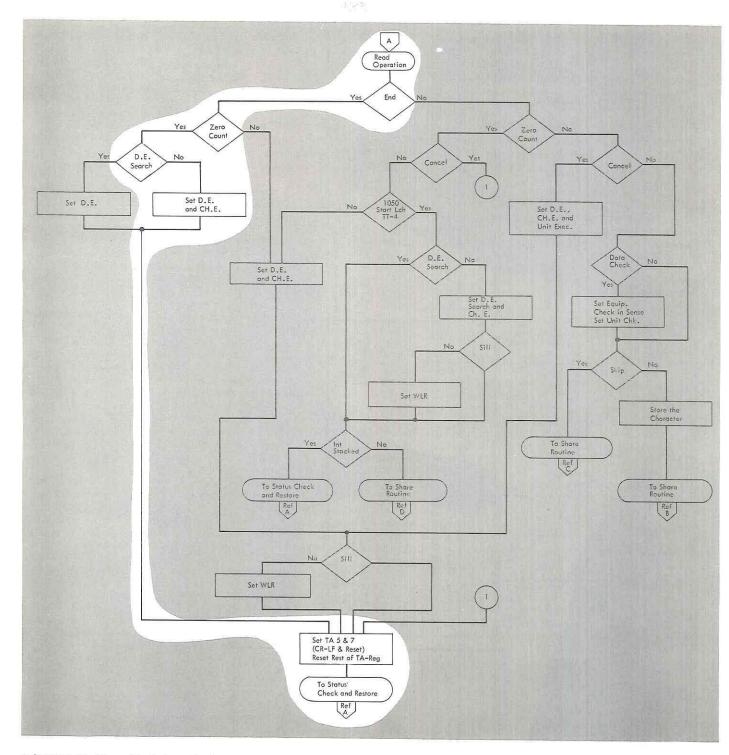

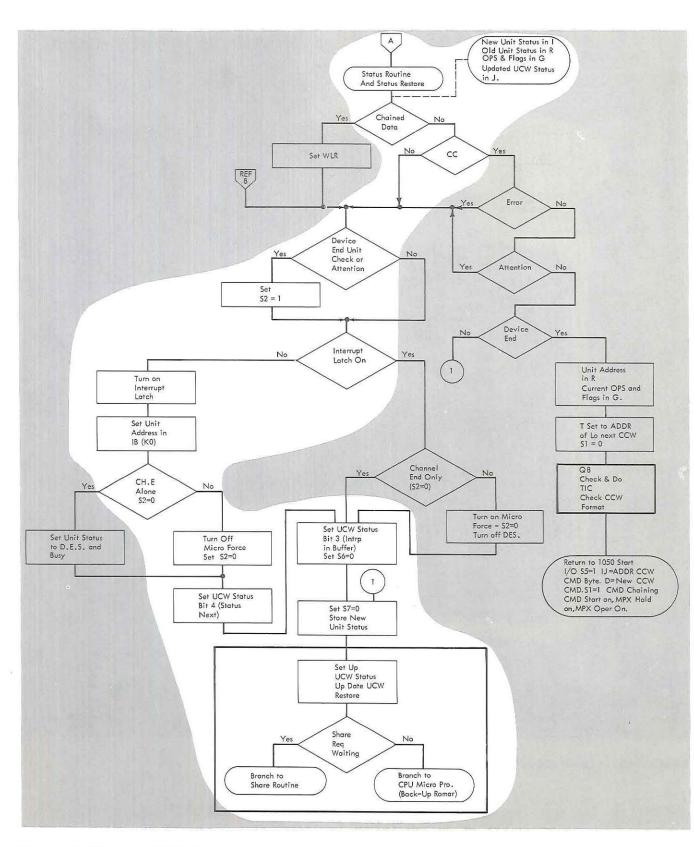

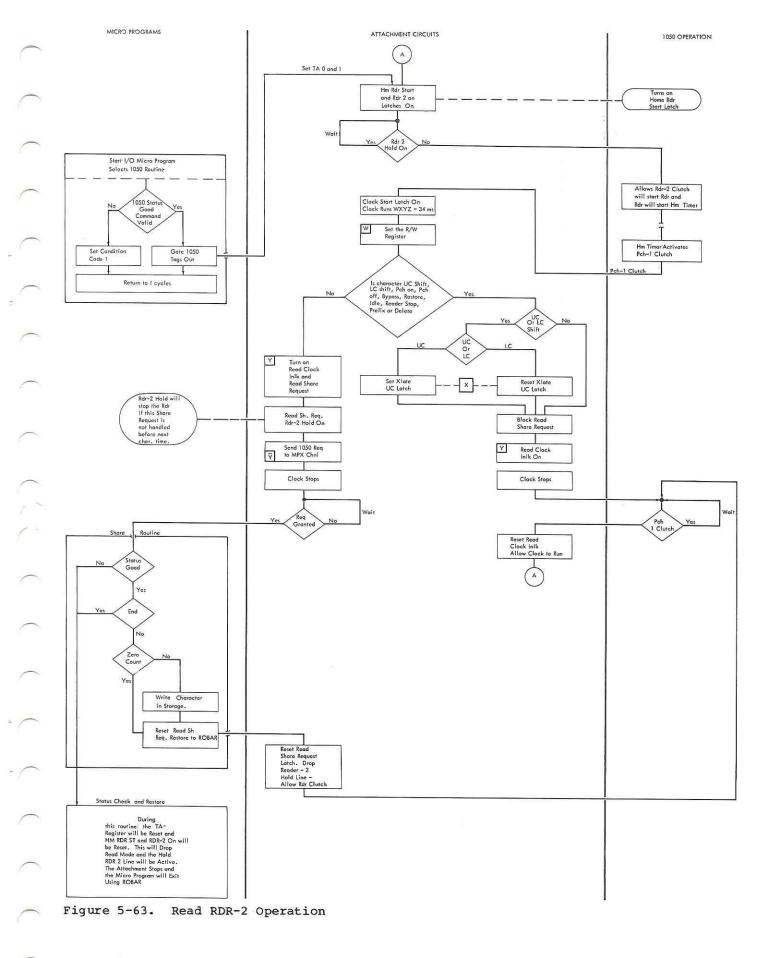

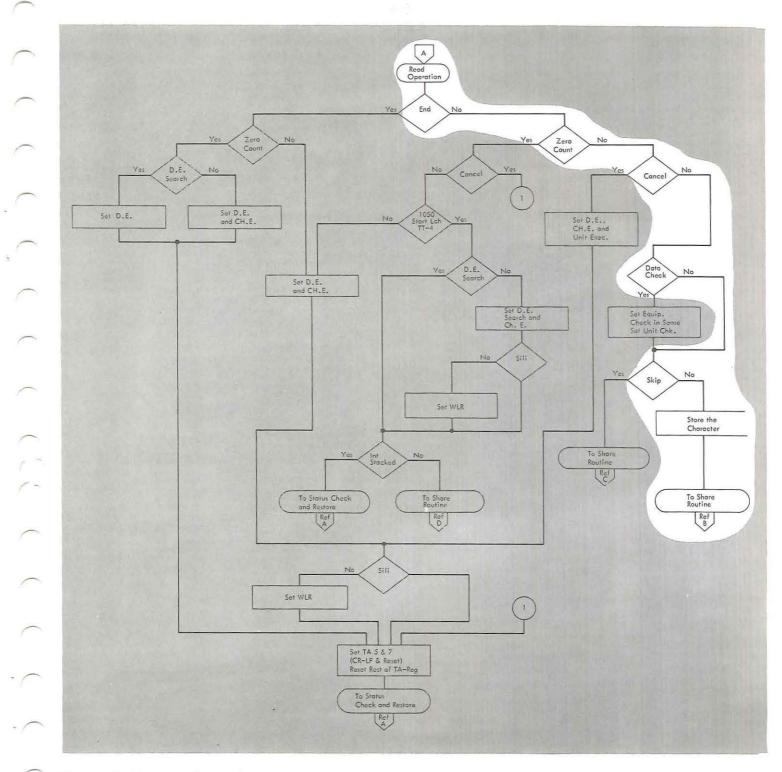

| Re       | ad  | R          | e   | be     | er      | -        | 2    | Op       | er    | a†   | i          | on        |            |       |      |      | 10      |                 | 51   | -    | 5-                | 69  |

| Ro       | ad  | Т          | n   | 117    | ir      |          | 0    | no       | ra    | + i  | 0          | n.        |            |       | ÷.   |      |         |                 |      | ÷.   | 5-                | 73  |

| Po       | ad  | • <u> </u> | CI  | 14     | 20      | <u>x</u> | Po   | pc<br>an | 20    | +    | 0          | 2         | · · ·      | ·+·   |      | . ·  | •       |                 |      |      | 5_                | 01  |

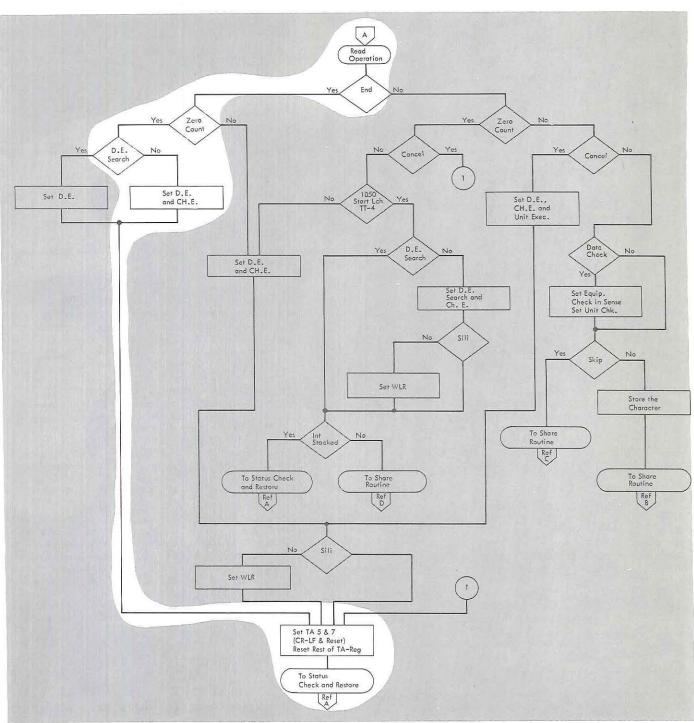

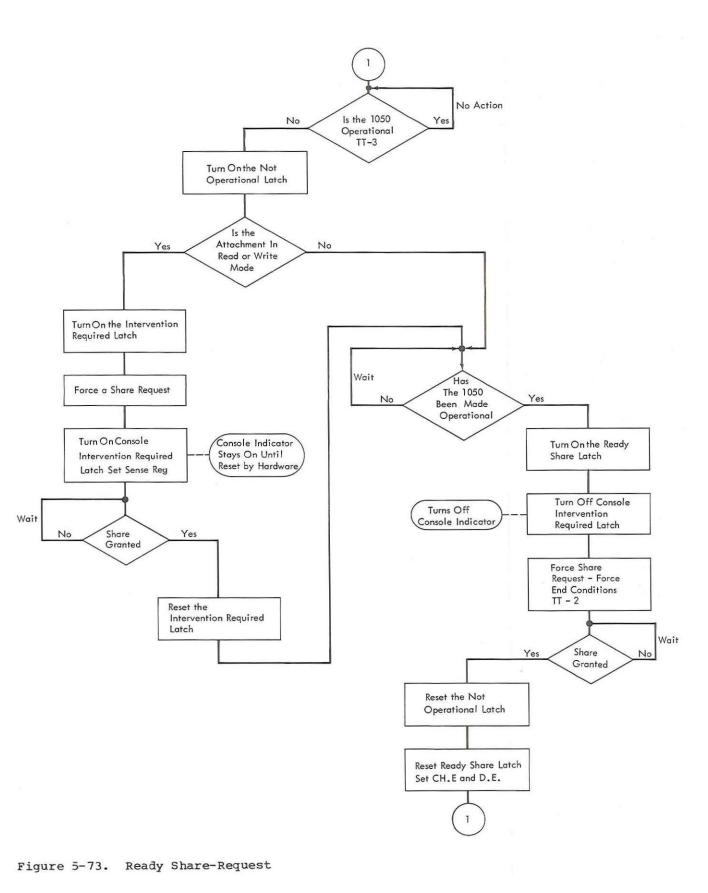

| ne       | au  | Y          | 01  | a      | те      | 7        | i.e  | yu<br>S  | es    | L    | U          | he        | ι L d      | a L.  | LO.  |      | •       |                 | ٠    | •    | 5-                | 04  |

| De       | ins | e          | J.  | .e     | 1 d     | . L.     | 10   | 11.      | •     | 1    |            | •         | •          |       |      | •    | •       |                 |      |      | 5-<br>5-<br>5-    | 00  |

| Cn       | lar | ne         | a   | D      | at      | d        | 0    | pe       | Id    | LT   | -0.        | <u>11</u> |            |       |      | •    |         |                 | ۲    | •    | 5-                | 00  |

| Co       | mm  | an         | d   | C      | ha      | 11       | nı.  | ng       | 0     | pe   | r          | at        | 10         | on    | . *  | .*   | ٠       | ٠               | •    | ٠    | 5-                | 87  |

| Co       | mm  |            |     |        |         |          |      |          |       |      |            |           |            | nma   | an   | d    |         |                 |      |      | ÷.                | 00  |

|          | TW  | me         | α.  | ıa     | τe      | 3970     | ٠    | ٠        | •     |      | 63         | •         | •          | •     | ٠    | ٠    | ۲       |                 |      | •    | 5-                | 88  |

| PC       | WE  | R          | S   | UP     | PI      | Y        | A    | ND       | I     | NЛ   | ΓE         | RI        | 200        | CK    | s.   | ٠    | ٠       | •               | ٠    | •    | 5-                | 90  |

| SP       | PEC | IA         | L   | F      | EA      | TI       | UR   | ES       |       |      | <b>1</b> 0 | •         | •          |       | •    |      |         |                 | :•)  |      | 5-                | 91  |

| Cc       | ont | rc         | 1   | A      | la      | ir       | m    | Op       | er    | at   | :i         | or        | ı.         |       |      |      |         |                 |      |      | 5-                | 91  |

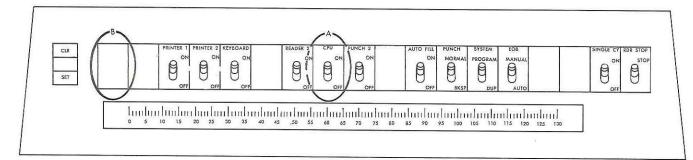

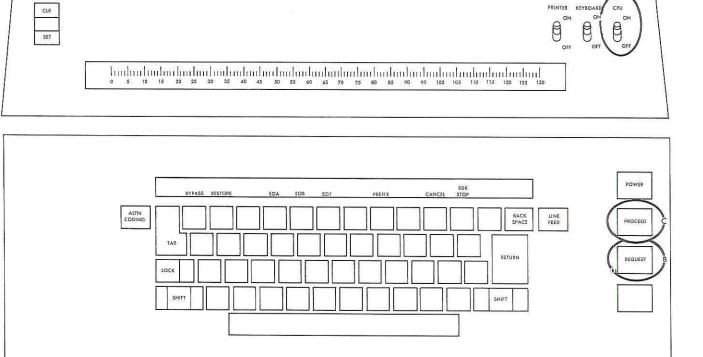

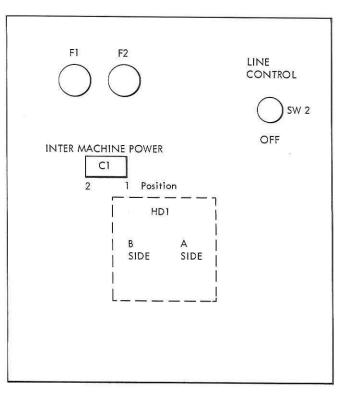

| SH       | IAR | EL         | )   | I/     | 0       | P.       | AN   | EL       |       | 5    |            | •         | •          |       |      |      |         | 141             | 2.   | 18   | 5-                | -92 |

|          |     |            |     |        |         |          |      |          |       |      |            |           |            |       |      |      |         |                 |      |      | 5-                |     |

|          |     |            |     |        |         |          |      |          |       |      |            |           |            |       |      |      |         |                 |      |      |                   |     |

|          |     |            |     |        |         |          |      |          |       |      |            |           |            |       |      |      |         |                 |      |      |                   |     |

| Review Question Answers           |   | • | 5-99 |

|-----------------------------------|---|---|------|

| SECTION 6. DIRECT CONTROL FEATURE | • | • | 6-1  |

| Introduction                      |   | • | 6-1  |

| Write Direct                      |   |   | 6-1  |

| Read Direct                       | • |   | 6-1  |

| Definitions of Interface Lines    |   |   | 6-3  |

| Application                       |   |   | 6-4  |

| Data Flow                         | · | ٠ | 6-5  |

| SECTION 7. APPENDIX               |   | • | 7-1  |

| INDEX                             | • | • | X-1  |

INPUT/OUTPUT CONTROL

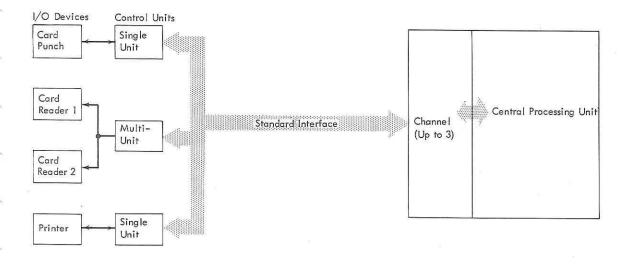

- The IBM 2030 communicates with I/O devices through Channels.

- The Channel is a physical part of the CPU, but functionally separate.

- The Channels are connected to, and communicate with, the I/O control units via a standard interface.

- Each I/O device attached to a channel must have an associated control unit.

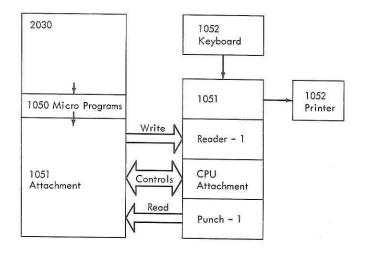

The transfer of information between the 2030 processing unit and an I/O device is by I/O control circuits and micro programs. These control circuits and micro programs, together, are called channels. Existing channel circuitry is located in the CPU, but in actual operation, the channels are completely separate units.

A channel is connected to an I/O control unit by a cable containing 34 signal lines. The 34 signal lines, and the sequence in which they become active and inactive, constitute the standard interface. By using a standard set of lines and signal sequences, the same I/O control units and devices can be used on most models of System/360.

When an I/O device is attached to the IBM 2030, a control unit must be used. The

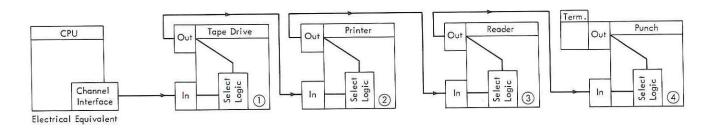

control unit can be separate from, or contained within the I/O device. Each device could have its own control unit, or several devices can be controlled by one control unit. The control unit acts as a buffer and compensates for a difference in the rate of flow of data, or the time of occurrence of events, when transferring information between the 2030 and an I/O device. Figure 1-1 shows the concept of data flow between the CPU and I/O devices.

The channel itself can have many I/O devices physically connected to it but only <u>one</u> I/O device can be operational with the channel at any one time. To ensure that only one control unit and device is selected, each is given a unique address. This address is assigned by the customer and wired on an address card by the CE at the time of installation.

Figure 1-1. CPU to I/O Device Data Path

#### CHANNELS

- The IBM 2030 has two basic types of channels:

- 1. Multiplexor

- 2. Selector (one or two)

- A console subchannel is also available for the 1050 attachment.

The two channel types used by the 2030 perform the same function. They differ however, in the method by which they obtain their objectives:

- The multiplexor channel is basically a microprogram routine. It can sustain operations with several I/O devices at a time on a time shared basis.

- The selector channel is a highspeed channel. It operates with

## CHANNEL INSTRUCTIONS

The CPU uses four instructions to communicate with a channel:

Start I/0 Test I/0 Halt I/0

Test Channel

The start I/O instruction is used by the CPU to initiate all I/O operations. Test I/O is the CPU's means of obtaining information regarding the status of a particular I/O control unit and device. The halt I/O instruction is issued by the CPU to disconnect a particular I/O control unit and device from the channel. The test channel instruction involves only a channel and the CPU. It is used to determine the status of the channel.

These four instructions specify only the address of the channel, I/O control unit, and device. For the test I/O, halt I/O, and test channel instructions, this is sufficient. The channel must, however, obtain operating information to execute a start I/O instruction. It gets this information from a channel address word (CAW) at location 72 (hex 48) and a channel command word (CCW), located in CPU main storage. The CAW consists of:

A storage protection key for the I/O operation.  A command address, designating the location in main storage where the associated first CCW is located.

The CCW consists of:

- The specific command to be executed by the I/O unit.

- A data address that specifies the area of core storage to be used for the data transfers.

- A count that specifies the number of data transfers, in the form of bytes, that are to be made.

- Five flag bits that may extend or modify the basic command.

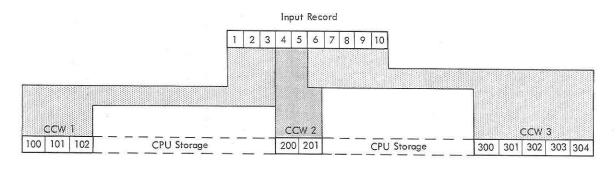

A separate CCW is necessary for each command the channel is to perform. For example, a read, write, rewind instruction to a tape drive is actually three separate commands and therefore would require three separate CCW's to execute the commands.

1-2

one I/O device until a complete data record has been transferred. It does not use microprogram routines to accomplish data transfers.

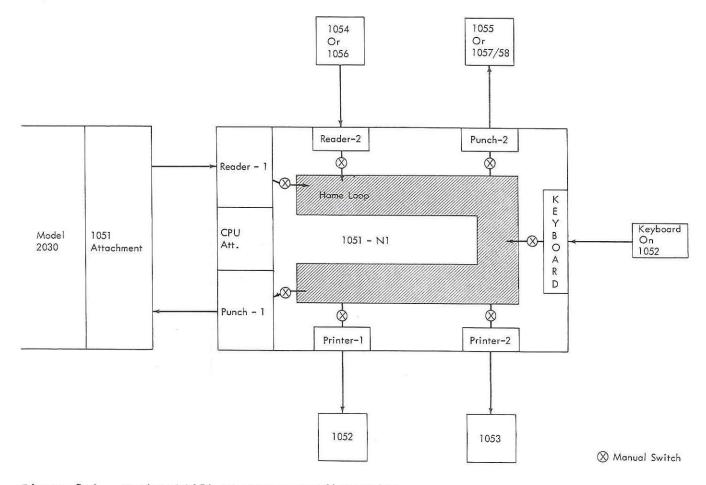

The console subchannel operates only with the 1050 attachment. It uses the microprogram routines of the multiplexor channel to accomplish many of its functions. The circuits for the console are also located in the 2030 frame.

#### I/O INSTRUCTIONS

- The start I/O instruction selects the channel, control unit, and device.

- The channel, control unit, and device are connected electrically by the standard interface.

- After executing the instruction, the control unit presents ending status and causes an interrupt.

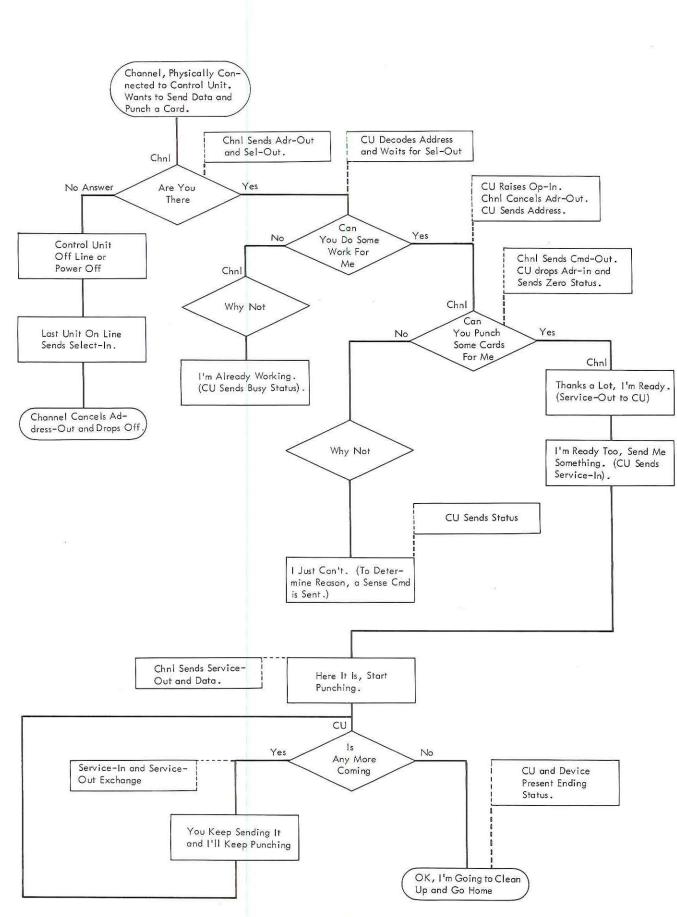

When the CPU issues a start I/O instruction to a channel, the channel selects the I/O device and control unit by executing an initial selection sequence.

The channel issues the I/O command to the control unit during the initial selection sequence, and electrically connects the control unit to the interface. The control unit decodes the command and raises control lines to the I/O device.

A control unit that is electrically connected to the channel can operate in either burst mode, or data interleave (byte) mode. When operating in burst mode, the control unit remains electrically connected to the channel after initial selection, until a complete data record has been transmitted. When operating in byte mode, the control unit disconnects from the channel after initial selection and between each data byte. When a control unit is connected to a selector channel, it always operates in burst mode. This is because a selector channel is a high speed channel that operates with one I/O device at a time.

When a control unit is connected to a multiplexor channel, it operates in either burst or byte mode, depending on the design of the control unit. Normal data transfer from the I/O unit to the multiplexor channel is in byte mode. The control unit may force burst mode operation. Normally, the low speed control units operate in byte mode and high speed units in burst mode. Intermediate speed units have a switch that can be set to either byte or burst mode. The selector channel overrides the switch setting and forces burst mode. When the channel is operating in byte mode, it may service several I/O units on a time-shared It must disconnect from one I/O basis. device before it can operate with another This means that the control unit device. must initiate a selection sequence each time it requires service from the channel.

When a channel and control unit have transferred the number of bytes required by the I/O command, the control unit sends its channel-end and device-end status to the channel. These may be sent together or separately, depending on the control unit.

The control unit always sends channelend status to the channel at the end of the data transfer portion of a command. Channel-end may be alone or accompanied by other status bits. Device-end is sent when the control unit is in a position to accept another command.

When a channel receives ending status, it may either accept the status or it may command the control unit to hold (stack) the status. Once the channel responds to channel-end status with either an acceptance response or a stack response, the control unit disconnects from the channel. Figure 1-2 illustrates a basic selector channel data transfer.

When a channel accepts the control units device end status, it will either obtain new operating information (a new CCW), or initiate on I/O interrupt of the current program.

If the channel must obtain a new CCW because of the presence of the command chaining bit in the CCW, it must wait until it receives device-end status from the I/O device control unit.

An I/O interrupt causes the status of the interrupting channel and I/O unit to be placed in the channel status word (CSW) and the execution of the I/O interrupt program to begin.

Note: The CPU can begin the execution of an I/O interrupt only after it has completed the execution of the instruction it is currently executing when it receives the interrupt.

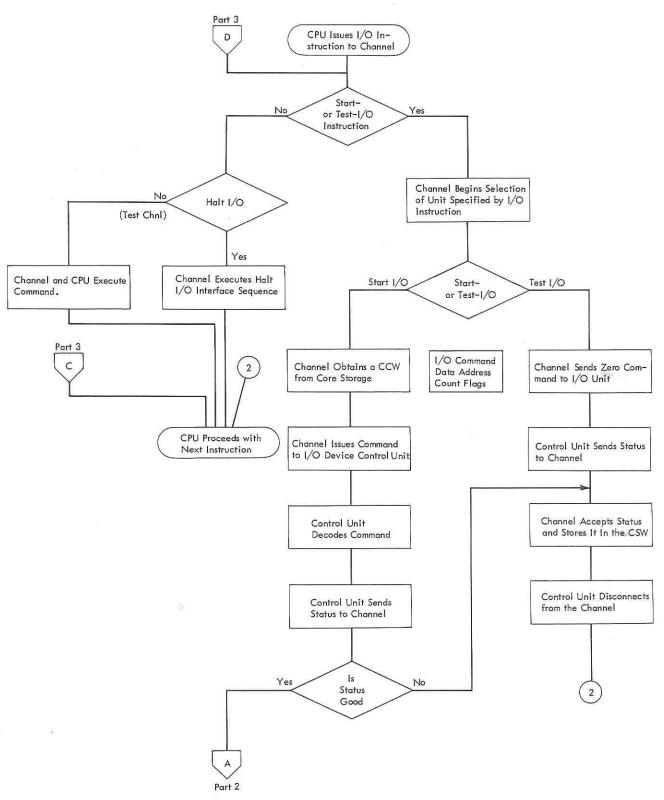

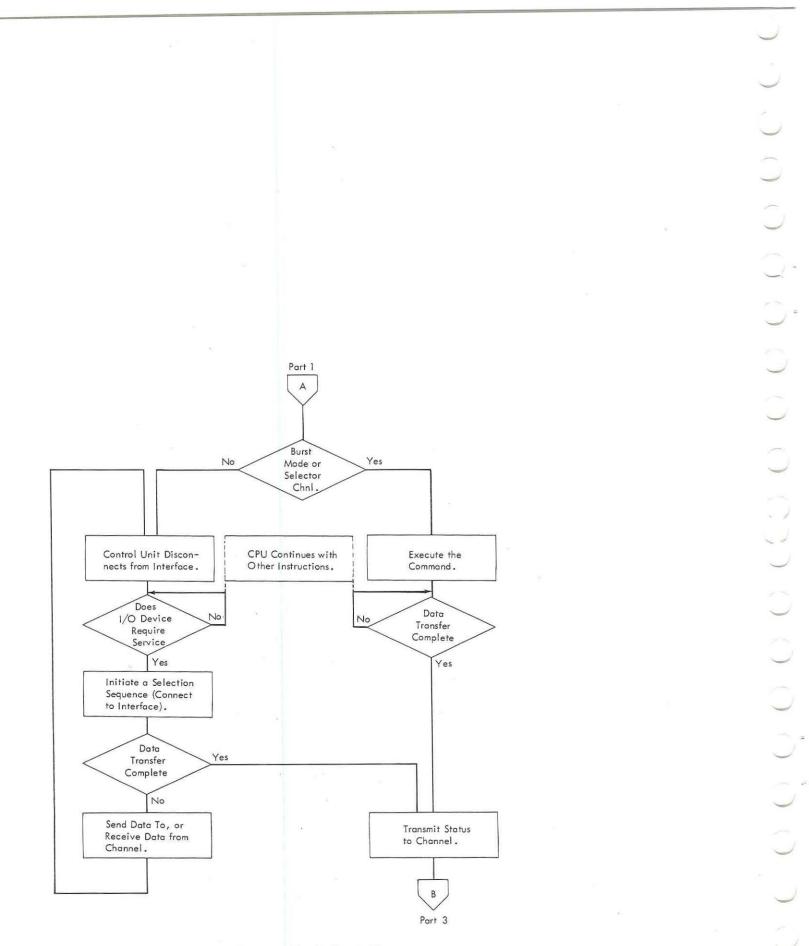

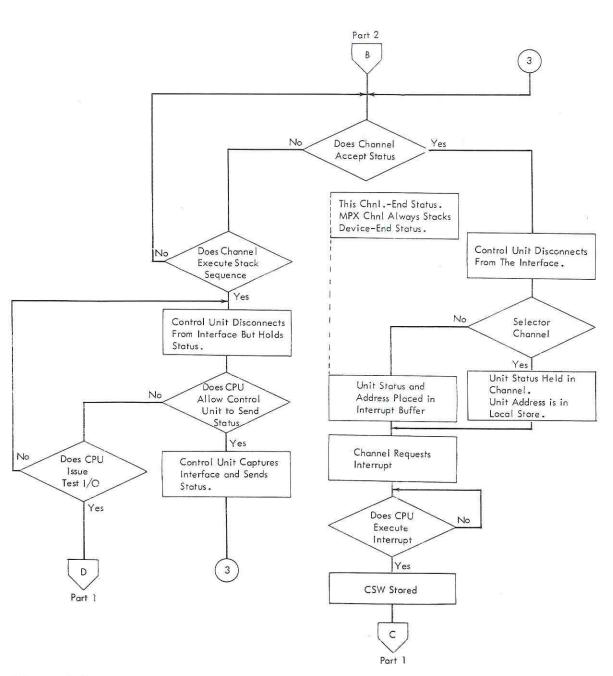

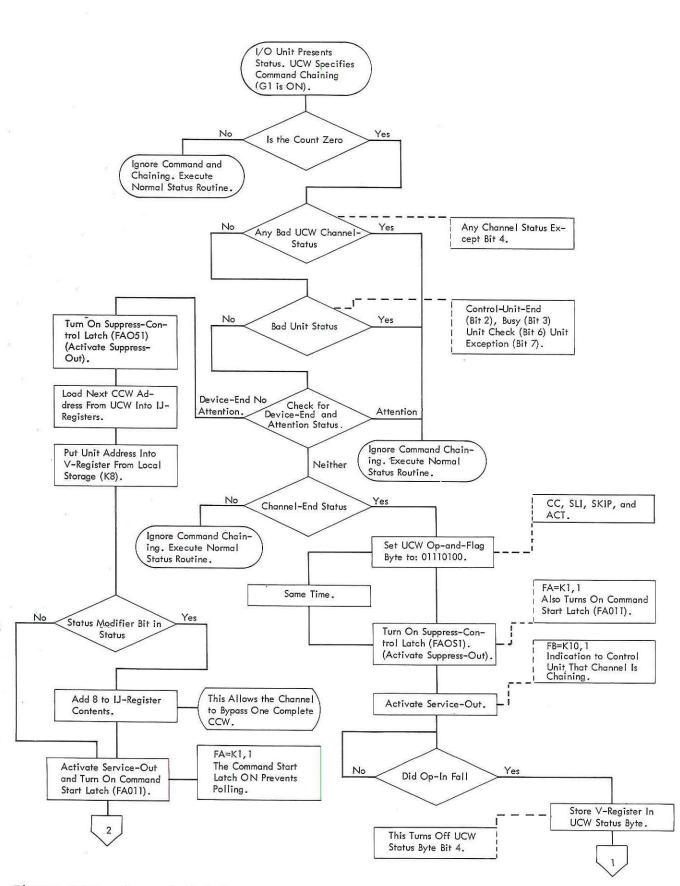

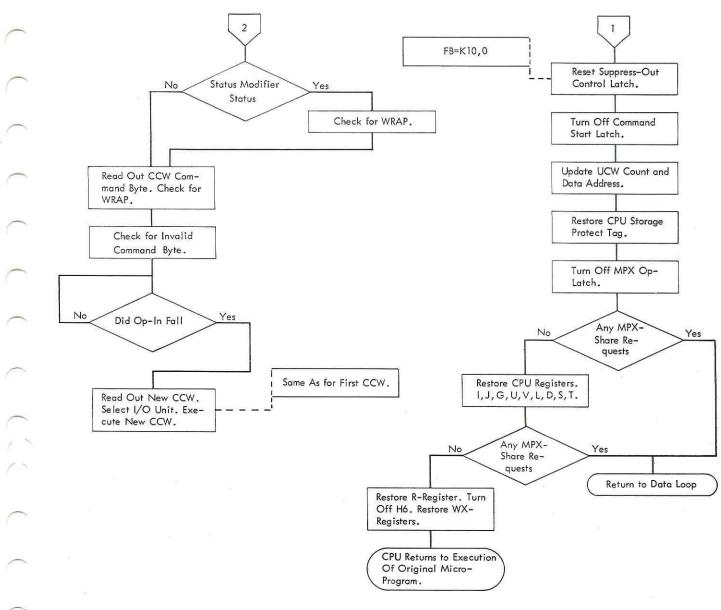

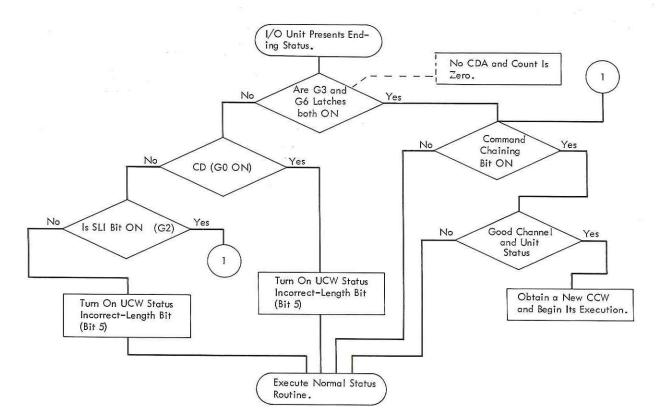

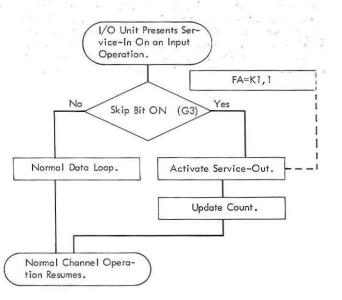

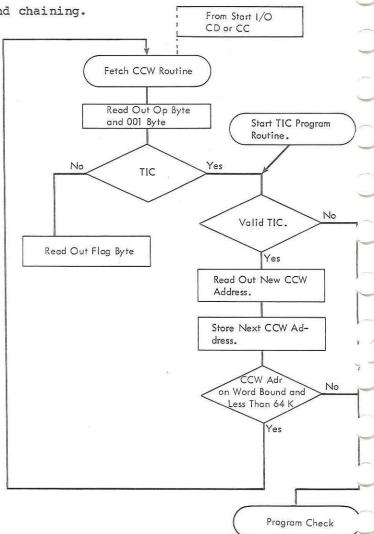

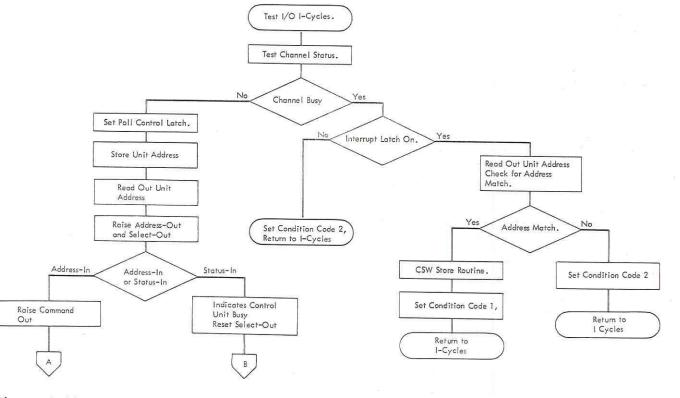

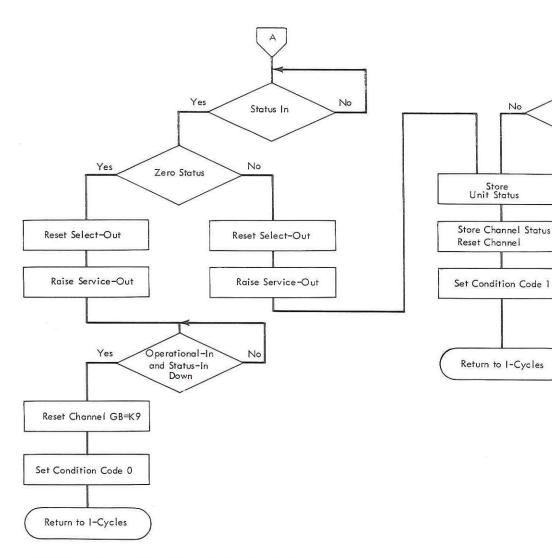

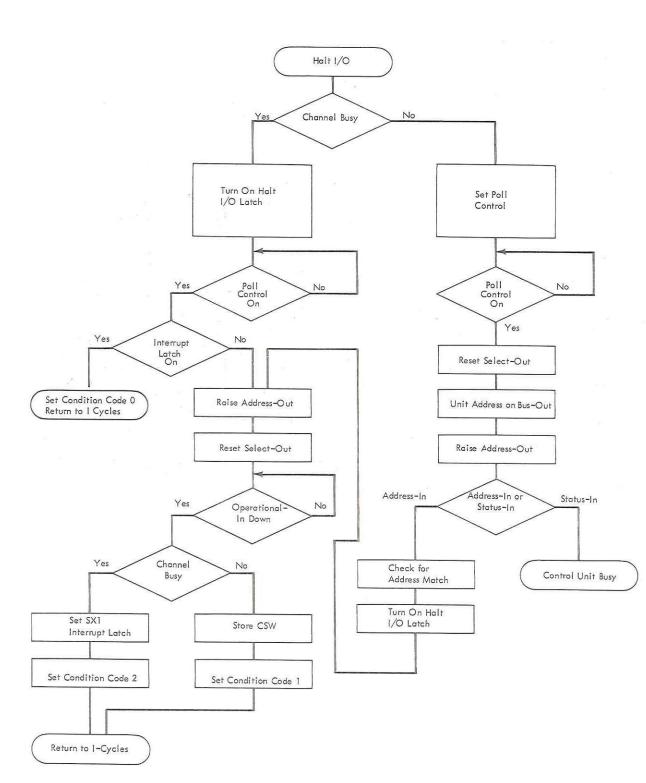

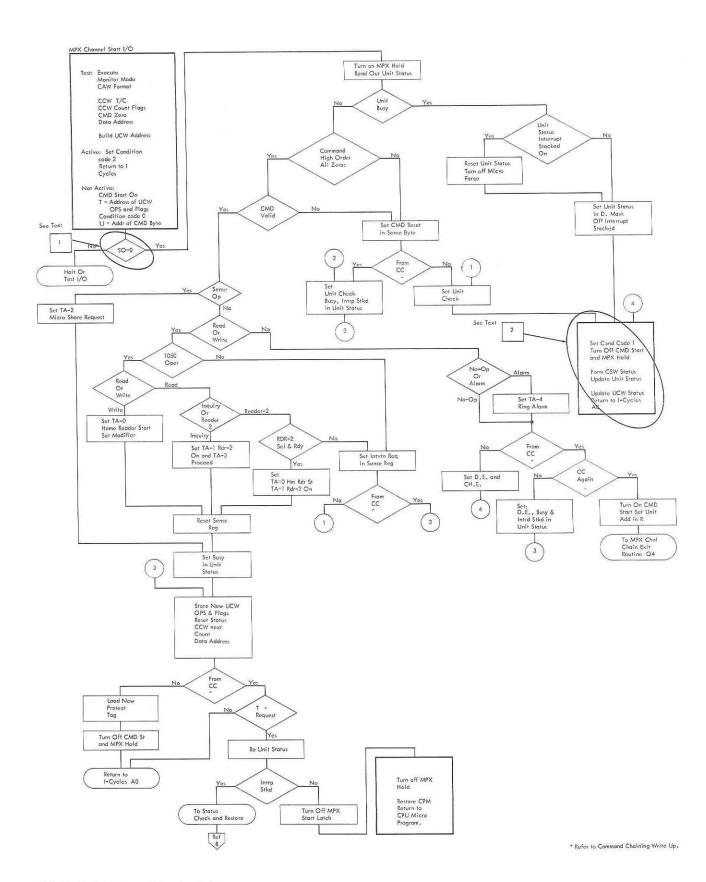

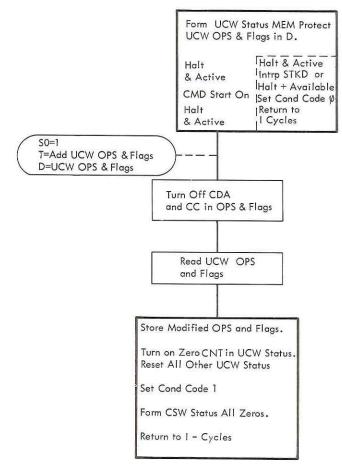

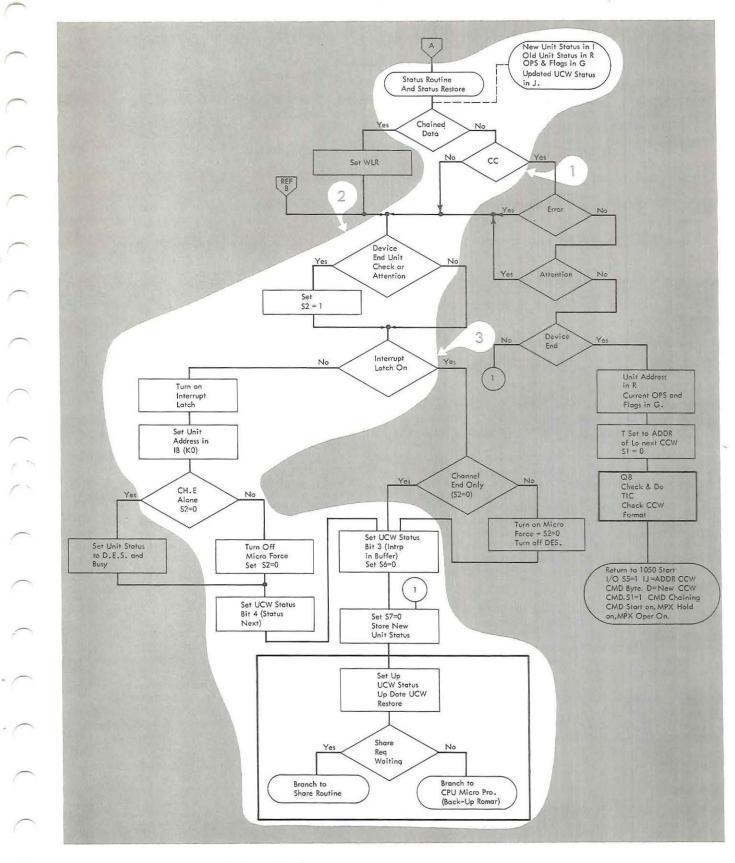

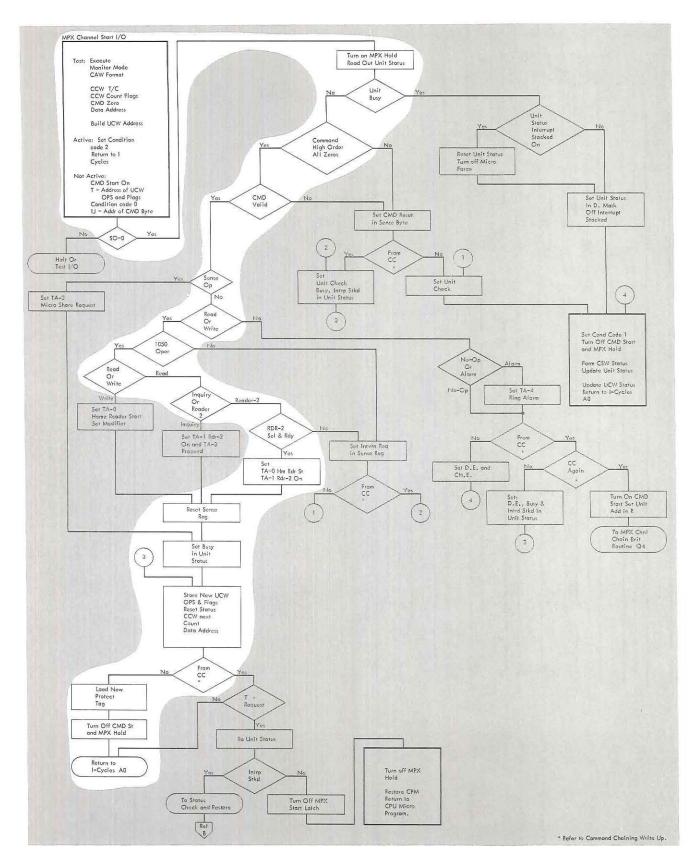

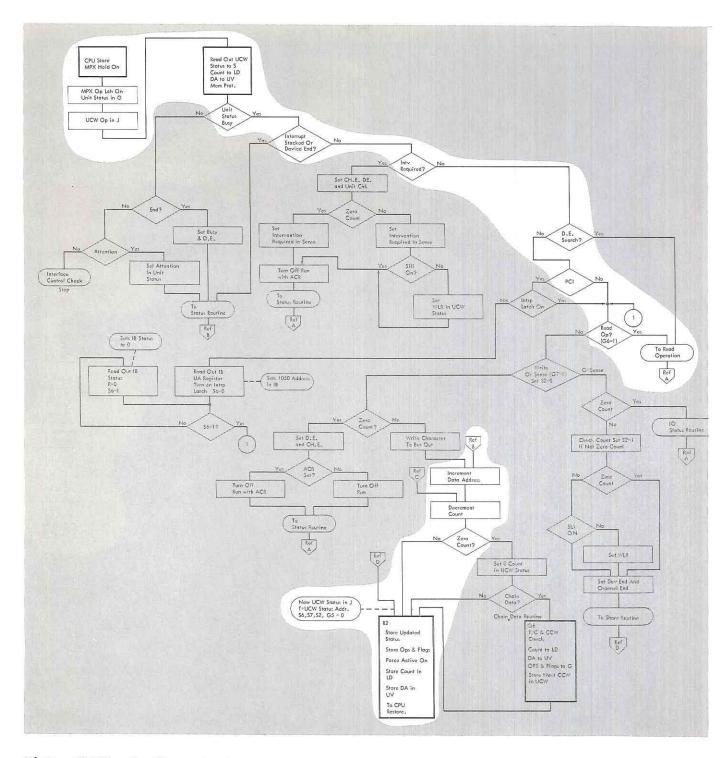

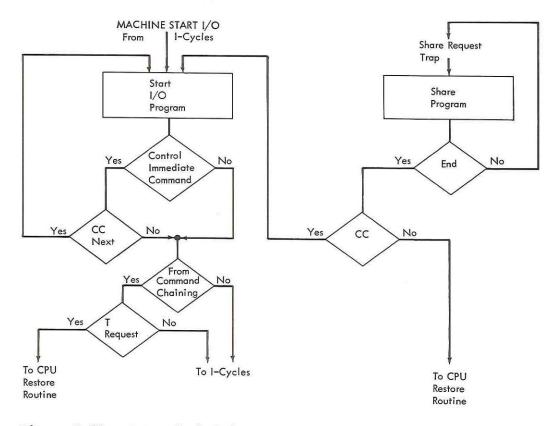

Refer to Figure 1-3 for a flowchart of the four channel and I/O instructions.

Figure 1-2. Basic Selector Channel Operation

1 - 4

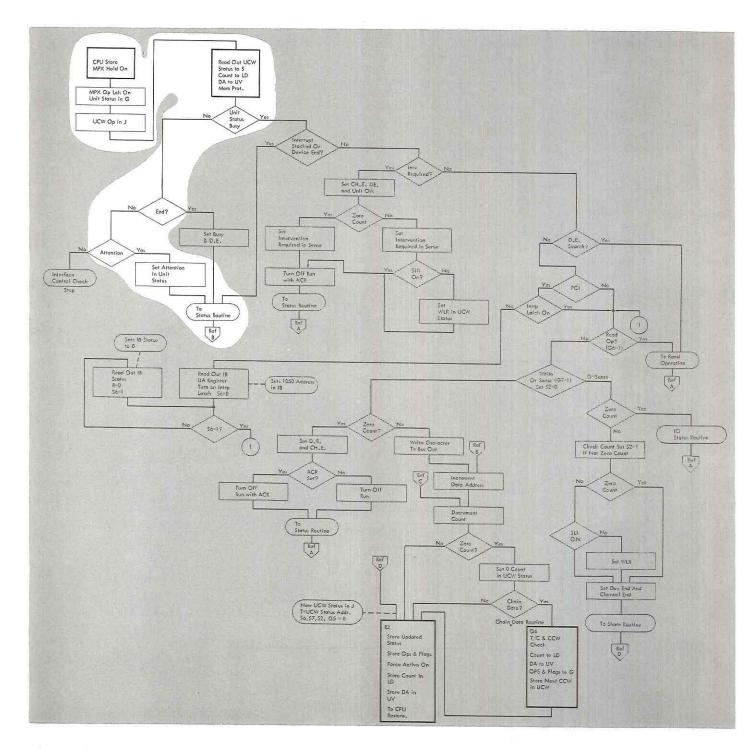

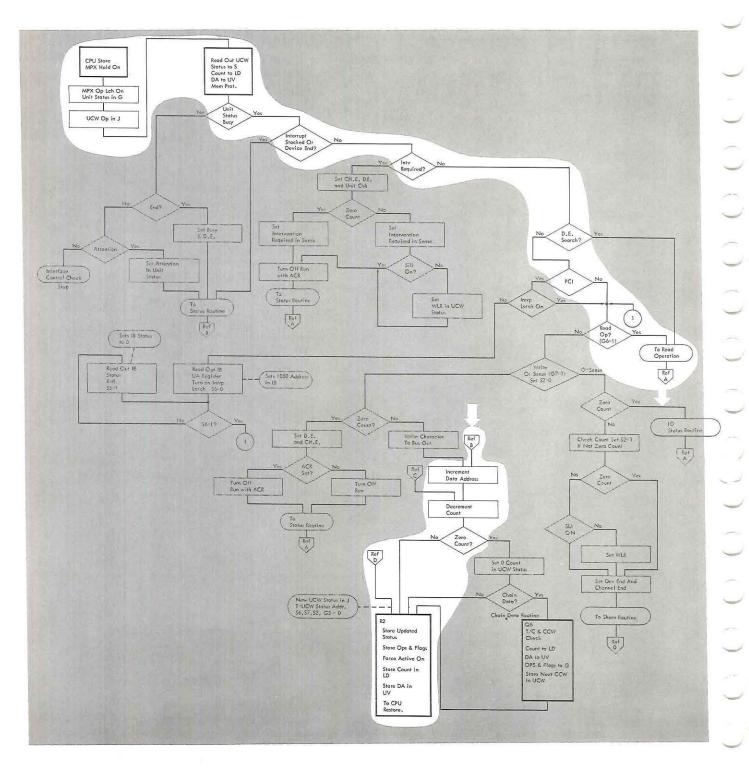

Figure 1-3. I/O Instructions (Part 1 of 3)

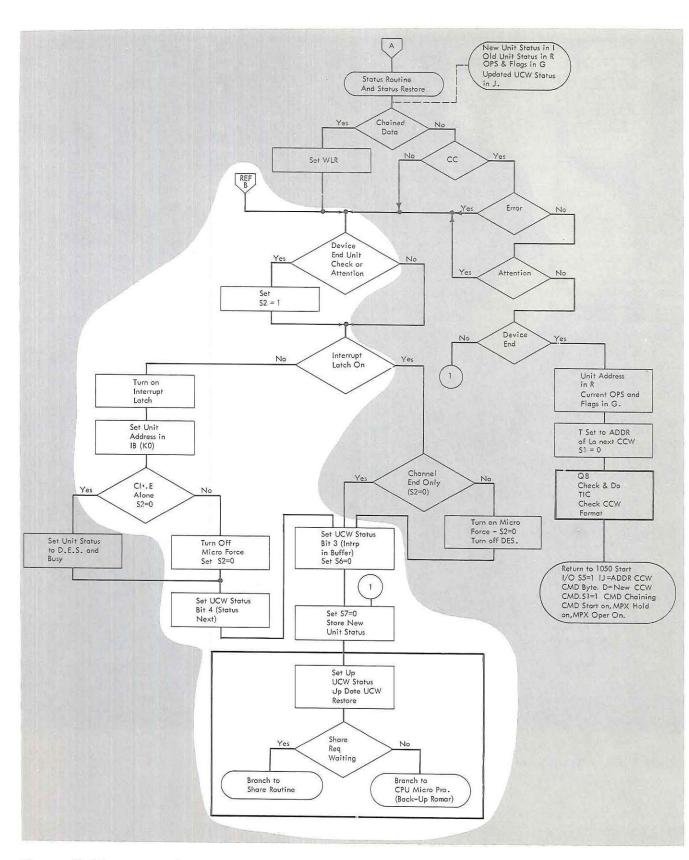

Figure 1-3. I/O Instructions (Part 2 of 3)

1-6

Figure 1-3. I/O Instructions (Part 3 of 3)

# INPUT/OUTPUT INSTRUCTION FORMAT

• The four I/O instructions have the SI format in a 32 bit word.

The I/O instruction format is as follows:

| 0   | 718  | 15      | 16 | 191 | 20 | 31 |

|-----|------|---------|----|-----|----|----|

| Op. | Code | Ignored | B1 | j   | D1 |    |

BITS 0-7: An eight-bit field giving the operation code of the instruction as fol-

| lows:    |      |              |

|----------|------|--------------|

| 10011100 | (9C) | Start I/O    |

| 10011101 | (9D) | Test I/O     |

| 10011110 | (9E) | Halt I/O     |

| 10011111 | (9F) | Test channel |

BITS 8 - 15: These eight bits are not used and are ignored.

<u>BITS 16 - 19:</u> A four-bit field which designates a 32-bit general purpose register in local storage. A zero in the B1 field is used to indicate the absence of a base register component, and a value of zero is used in forming the address regardless of the contents of general register zero.

BITS 20 - 31: A 12-bit field which holds a literal value known as the displacement.

The contents of the general purpose register designated by B1 is added to the value of D1. This forms the channel and unit address. In the resulting 32-bit summary: Bits 0-20: Ignored

BITS 21 - 23: These three bits for channel address are assigned as follows: 000 - Multiplexor Channel 001 - 010 Selector Channels 1 & 2 (011-110, Selector Channels 3-6, are invalid on the 2030) 111 - Unused

BITS 24 - 31: These eight bits define the unit number to a maximum of 256 units, each unit having a unique address.

#### I/O CONTROL WORDS

Four control words are common to I/O operations:

- 1. Channel Address Word (CAW))

- 2. Channel Command Word (CCW) Start I/O Only

- 3. Channel Status Word (CSW)

- 4. I/O New and Old Program Status Words (PSW)

COMMAND ADDRESS WORD (CAW)

- The CAW is a 32-bit word located in main storage 72 75 (48-4B hex).

- It provides the address of the first Channel-Command Word (CCW) to be used in the I/O operation.

- It provides the I/O protection key to be used in the I/O operation.

- It is automatically read out when the instruction start I/O is given.

The CAW is a 32-bit word stored in the fixed location 72-75 in main memory. The CAW is loaded into the channel by the instruction start I/O and specifies the address of the first control word. The CAW has the following format:

| 0   |            | 31  | 4 7   | 18   | 31      |

|-----|------------|-----|-------|------|---------|

| I/0 | Protection | Key | Zeros | ICCW | Address |

BITS 0 - 3: A four-bit I/O protection key which is compared with the four-bit storage key obtained from the storage-protect stack when a main storage location is addressed. If the protection key and the storage key do not compare, the protection key is not zero, and the operation is INPUT, the address is violating a protected area. This causes the channel to generate an I/O interrupt, with the protection-check indicated in the channel-status of the associated CSW.

BITS 4 - 7: This four-bit field must be zeros.

BITS 8 - 31: A 24-bit field which defines the address of the first control word used in the I/O operation. The CCW specified in this address must not be a Transfer-in-Channel command.

1-8

# CHANNEL COMMAND WORD (CCW)

- The CCW is a 64-bit word located in a main-storage area designated by the program.

- It contains control information specifying:

- 1. Type of operation (command code).

- Main storage area to be used (data address and byte count).

- 3. Action to be taken upon completion of operation (Flags).

- Accessed only during the start I/O microprogram when initiating the I/O operation or chaining from one CCW to another.

- Used as a basis to form the unit-control word (for multiplexor channel only).

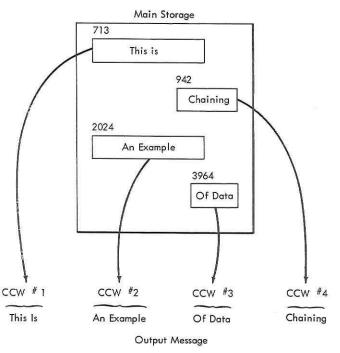

The address contained in the CAW is the address in main storage of the first CCW to be used in an I/O operation. This CCW is a 64-bit word and specifies the operation to be performed. Because the CCW must be located on a double word boundary, the three low-order bits of its address must be zeros.

The information contained in the CCW defines:

- 1. The operation to be performed.

- 2. The main-storage area to be used.

- The action to be taken upon completion of the operation.

The format of a CCW is:

| 10    |                 | 7 8 |                 | 31 32 |       | 36 |

|-------|-----------------|-----|-----------------|-------|-------|----|

| 1     | Command<br>Code | 1   | Data<br>Address |       | Flags |    |

| !<br> | Code            |     | Address         |       |       |    |

| 37    | 39 | 40 | 47     | 48 |       | 63 |

|-------|----|----|--------|----|-------|----|

| Zeros | 1  | I  | gnored | Ì  | Count |    |

<u>BITS 0 - 7:</u> Command Code. These eight bits specify one of the following six channel commands:

- 1. Read Backward

- 2. Write

- 3. Read

- 4. Control

- 5. Sense

- 6. Transfer-in-Channel

Each of the six commands, with the exception of Transfer-in- Channel (TIC), initiates the I/O operation. The TIC command CCW contains the address of another CCW in bits 8 - 31. The remaining bits (32 - 63) are ignored.

Figure 1-4 shows the CCW command code format. Bits marked x and M have the significance: x = ignored

TO T (T)

m = modifier

|                     |    |   |   | B: | ΕT |   |   |   |

|---------------------|----|---|---|----|----|---|---|---|

| Command             | 10 | 1 | 2 | 3  | 4  | 5 | 6 | 7 |

| Invalid             | ×  | x | x | x  | 0  | 0 | 0 | 0 |

| Sense               | m  | m | m | m  | 0  | 1 | 0 | 0 |

| Transfer in channel | x  | x | x | x  | 1  | 0 | 0 | 0 |

| Read Backward       | m  | m | m | m  | 1  | 1 | 0 | 0 |

| Write               | m  | m | m | m  | m  | m | 0 | 1 |

| Read                | m  | m | m | m  | m  | m | 1 | 0 |

| Control             | m  | m | m | m  | m  | m | 1 | 1 |

|                     |    |   |   | _  |    |   |   |   |

Figure 1-4 Command Code.

The modifier bits of the command code specify to the I/O unit the detail conditions under which the operation is to be executed. It covers such conditions as recording-density, parity, and byte size. The meaning of the modifier bits depends on the type of I/O device.

<u>BITS 8 - 31</u>: Data Address. These 24 bits specify the location of an eight-bit byte in main storage. It is the first location referred to in the area defined by the CCW. The location is the starting address from which data is to be fetched or the starting address of the locations where data is to be stored.

<u>BITS 32 - 36:</u> Flags. Five flag bits modify the basic CCW command :

- Bit 32, Chain Data CD. This bit specifies chain data addresses. It allows a channel to obtain the data address and count from the next CCW after the CCW in which it appears has been fully executed.

- Bit 33, Chain Command (CC). This bit specifies chain command. It allows the channel to obtain and execute the next CCW if the CCW in which it appears is successfully executed.

- 3. Bit 34, Suppress Length Indication (SLI). This bit allows the channel to ignore incorrect length indications when an I/O device signals the end of an operation before the number of bytes specified by the CCW count have been transferred, or vice versa.

- Bit 35, Skip. This bit allows the channel to bypass storing input information in main storage.

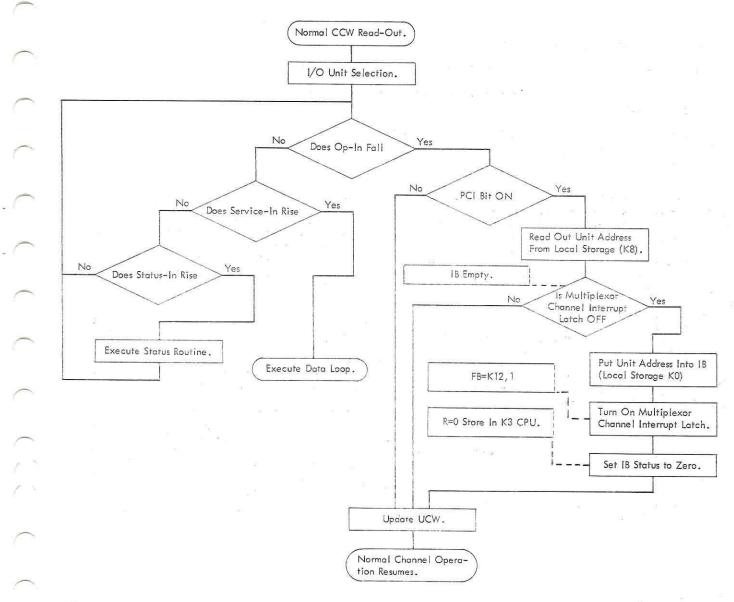

5. Bit 36, Program Controlled Interrupt (PCI). This forces the channel to attempt an interrupt of the major program. It is used by programmers to force an interrupt to the major program during the execution of a chain of CCW's. It allows the CPU to find out how the operation is going, and to initiate other action if the conditions warrant it.

<u>BITS 37 - 39</u>: These three bits must be zero. If they do not contain zeros, the operation is terminated with a program error indication.

BITS 40 - 47: These eight bits are not used and are ignored.

BITS 48 - 63: Count. This 16-bit field defines the number of byte storage locations in the area defined by the CCW. The count in conjunction with the data address specifies the complete storage area used by the current CCW.

# CHANNEL STATUS WORD (CSW)

- The CSW is a 64-bit word located at main-storage word location 64 (40).

- It describes the status of the I/O operation just completed.

- It identifies the I/O protection key, the last CCW address used plus eight, the residual count, and channel and unit status at end time.

- It is stored in main-storage location 64 at the completion of an I/O operation when the I/O interruption (for that operation) is taken.

- During the initiation of an I/O instruction, the status portion of the CSW may be stored in main-storage storage 68 and 69 (44 and 45 hex) due to the I/O instruction being rejected, or if an immediate operation has been performed.

When the I/O operation sequence is completed at the unit an interruption to the CPU program is generated. The interruption informs the program that the operation initiated by the start I/O instruction has been completed. The CPU, in accepting the interruption, also stores, in a fixed memory location, a channel-status word. This 64-bit channel status word refers to the unit and operation that has just terminated and describes the results obtained with the status conditions prevailing. The CSW is formed in the process of an interruption and it is stored upon interruption at the fixed location 64 in main storage. It is available at this location (for interpretation by the program) until a new CSW is

stored.

| 0          | 3 4 | 7    | 8       | 31      |

|------------|-----|------|---------|---------|

| Protection | ic  | 0000 | Command | Address |

| кеу<br>L   |     |      | <br>    |         |

| 32     | 47   48 | 63  |

|--------|---------|-----|

| Status | Cou     | int |

<u>Bits 0 - 3:</u> Protection Key. This fourbit key is the same as the protection key described previously under <u>Command</u> <u>Address Word (CAW).</u> Form Y24-3362-1, Page modified by FES Y24-0055, 9/67

- 2. Bits 4-7: These four bits must be zero.

- Bits 8-31: Command Address. Identifies the last CCW address used plus eight.

- Bits 32-47: Status. This area defines the conditions in the I/O device and channel that caused the storing of the CSW.

- Bits 32-39 indicate the conditions detected by the I/O unit or its control unit and are sent via the interface in a status byte. Bits 40-47 indicate the conditions detected by the channel.

- Bits 48-63: Count. This area contains the residual count for the last CCW used.

#### PROGRAM STATUS WORD (PSW)

- Four PSW's are associated with input/output operations:

- 1. Current PSW

- Initial Program Load PSW

- 3. I/O old PSW

- 4. I/O new PSW.

The bit positions in a PSW which are utilized in an I/O operation are listed with their function:

Bits 0-7: System mask

- Bit 0 Multiplexor Channel Mask

- Bit 1 Selector Channel 1 Mask

- Bit 2 Selector Channel 2 Mask

- Bits 3-7 are not used.

Bits 16-31: Interruption Code (I/O Old PSW)

Bits 34-35: Condition Code (CC)

The system mask bits 0, 1, and 2 provide the facility to prevent all I/O interruptions occurring when the appropriate bit is zero. This gives the possibility of preventing I/O interrupts from one channel while allowing I/O interrupts on another channel.

The 16 bits which form the interruption code (PSW 16-31) are stored in the I/O old PSW in main storage 56 when an I/O interruption is accepted by the CPU. The interruption code in this case contains the channel and unit address which caused the interrupt. The channel and unit address occupy PSW bit positions 21 - 31. PSW bits 16 - 20 are made zero. Because only the channel and unit causing the interrupt are identified in the interruption code, the program must now refer to the status field of the CSW to determine the cause of the interrupt.

The condition code is set after the initiation of an I/O instruction and informs the program if the I/O instruction was successfully started or if it was rejected. The I/O instruction could be rejected because the channel or unit were unavailable or busy. The condition-code settings for each of the four I/O instructions are:

|                 | 0               | <br>  1        | 2                 | 3            |  |

|-----------------|-----------------|----------------|-------------------|--------------|--|

| Halt<br>I/O     | not<br>working  | halted         | stopped           | not<br>oper. |  |

| Start<br>I/O    | avail-<br> able | CSW<br> stored | busy              | not<br>oper. |  |

| Test<br>Channel | not<br>working  | CSW<br> ready  | working           | not<br>oper. |  |

| Test<br>I/O     | avail-<br> able | CSW<br> stored | +<br> working<br> | not<br>oper. |  |

The meanings of the condition codes are:

| 1. Available   | Unit and channel availa-<br>ble                            |

|----------------|------------------------------------------------------------|

| 2. Busy        | Unit or channel busy                                       |

| 3. CSW ready   | Channel status word<br>ready for test or inter-<br>ruption |

| 4. CSW stored  | Channel status word<br>stored                              |

| 5. Halted      | Data transmission<br>stopped. Unit in halt-<br>reset mode  |

| 6. Not oper    | Unit or channel not<br>operational                         |

| 7. Not working | Unit or channel not<br>working                             |

| 8. Stopped     | Data transmission<br>stopped                               |

| 0 Working      | Unit or channel working                                    |

9. Working Unit or channel working

The condition code also may be changed by LOAD PSW, SET SYSTEM MASK, and by an interrupt.

# Current PSW

• The fields of the current PSW are scattered throughout local storage and CPU-registers

The current PSW fields and locations are:

- 1. <u>System Mask:</u> Located in local storage K24. It is also in CPU latches.

- Storage Protect Key: Located in four high-order bits of local storage location K25 and Q-register. This is the storage protect key for CPU operation. It is not the same as the I/O storage protect key in the CAW.

- 3. <u>AMWP</u>: Located in the four low-order bits of local storage location K25.

- <u>Instruction Length Code (ILC)</u>: Located in the four low-order bits of local storage K4.

- <u>Condition Code (CC)</u>: Located in four <u>high-order bits of local storage K27</u>.

- 6. <u>PSW bit:</u> Located at bit-1 of local storage location K4.

- 7. <u>Instruction Counter (IC):</u> Located in local storage locations K17 and K18 when the PSW bit is on. It is in the IJ-registers when the PSW bit is off.

1-12

# Initial Program Load (IPL) PSW

- The IPL PSW is loaded from the first input record on IPL operations.

- After the first three records have entered the CPU, the IPL PSW enters local storage as the current PSW.

# I/O NEW PSW

- Located at main storage location 120 (hex 78).

- The I/O new PSW enters local storage on I/O interrupts as the current PSW.

# I/O Old PSW

$\widehat{}$

- Located at main storage location 56 (hex 38).

- The current PSW is loaded into the I/O Old PSW location during I/O interrupts.

UNIT CONTROL WORD (UCW)

- The UCW is actually a subchannel of the multiplexor channel.

- Refer to subchannels under the multiplexor channel functional units for a description of the UCW.

#### FUNCTIONAL UNITS

LOCAL STORAGE

- The contents of the CPU data flow registers are stored in local storage when a channel microprogram routine is being executed.

- Two local storage positions serve as the multiplexor channel interrupt buffer.

- Local storage also contains the K-addressable byte positions.

A channel breaks into the CPU microprogram at various times. For this reason the channel's microprogram must store the contents of the CPU data-flow registers in local storage. This allows the channel microprogram to use the CPU data-flow registers. When the channel is finished with the the CPU data-flow registers, they are restored to their original state from the information that was stored in local storage.

Local storage also serves as storage for other channel operating information. This information is stored in the K-addressable byte locations. The K-addressable byte locations also contain some of the current PSW.

The K-addressable byte utilization is as follows:

- 1. KO (hex 88) is the Interrupt Buffer (IB) for the address of a MPX channel I/O unit that is requesting an interrupt.

- 2. K1 (hex 89) stores the T-register during MPX channel operations.

- 3. K2 (hex 8A) stores the R-register during MPX channel operations. K3 (hex 8B) is the interrupt buffer

- 4. for the status of a MPX channel I/O unit that is requesting an interrupt.

- K4 (hex 8C) contains the current PSW 5. instruction length counter (ILC) in the four low-order bits. Bit 1 serves as the PSW bit. The instruction counter (IC) is in local storage at K17 and K18 when the PSW bit is on.

- K5 (hex 8D) holds the unit address of 6. the I/O unit operating on selector channel 1.

- 7. K6 (hex 8E) holds the high-order address of selector channel 1 next-CCW address.

- 8. K7 (hex 8F) holds the low-order of selector channel 1 next-CCW address.

- K8 (hex 98) serves as temporary stor-9. age for the unit address of a unit on the MPX channel.

- 10. K9 (hex 99) is used by the console subchannel to store unit status.

- K 10 (hex 9A) through K15 (hex 9E) is 11. CPU working storage.

- 12. K16 (hex A8) is instruction counter unavailable.

- K17 (hex A9) holds the high-order byte 13. of the instruction counter when it must be stored in local storage.

- K18 (hex AA) holds the low-order byte 14. of the Instruction Counter (IC) when it must be stored in local storage.

- 15. K19 (hex AB) is not assigned.

- 16. K20 (hex AC) stores the R-register during selector channel microprogram routines.

- K21 (hex AD) contains the addresses of 17. an I/O unit operating on selector channel 2.

- K22 (hex AE) holds selector channel 2 18. next-CCW address high-order byte.

- 19. K23 (hex AF) holds selector channel 2 next-CCW address low-order byte.

- K24 (hex B8) contains the current PSW 20. system mask.

- K25 (hex B9) contains the current PSW 21. storage protect key and AMWP. K26 (hex BA) is not assigned

- 22.

- 23. K27 (hex BB) contains the current PSW condition register and program mask. 24.

- K28 (hex BC) is not assigned. K29 (hex BD) stores the S-register 25. during selector channel microprogram operations.

- 26. K30 (hex BE) stores the U-register during selector channel microprogram operations.

- 27. K31 (hex BF) stores the V-register during selector channel microprogram operations.

#### THEORY OF OPERATION

- The I/O instruction I-cycles are named SI format I-cycles.

- After reading out the instruction the CPU reads out the channel address word (CAW).

- The channel microprogram reads out the CCW and begins its execution.

- When the execution of the CCW is complete the channel either obtains new operating information or attempts to interrupt the CPU program.

- An I/O interrupt loads the CSW with the required information.

Before issuing an I/O instruction, the CPU program loads the CAW with the address of the CCW to be executed, and loads the CCW with the required information. Also the CPU must be in the supervisory state before issuing any I/O instructions. These are privileged instructions that may be issued in the supervisory state only, or a program error results.

During I/O I-cycles the instruction reads out normally. The instruction code enters the G-register. The B-field and D-field specify the channel and device address. The channel address enters the U-register, the device address enters the V-register. When this is complete, the CPU reads out the CAW. The storage protect key enters the high order of the U-register and the CCW address enters the IJ-registers. During the read out of the CAW, the PSW is interrogated to determine if the CPU is in the supervisory state, and the CCW address is checked to ensure that it is on a double word boundary.

When the CAW has been read out, the channel microprogram program reads out the CCW, the channel selects the desired I/O device and issues a command. The I/O device responds with status. After this is accomplished, the channel microprogram analyzes the status byte received from the I/O device during initial selection, and sets the PSW condition code. The channel microprogram then branches to CPU I-cycles.

In the case of a start I/O instruction that has been successfully started, the channel continues to operate with the I/O device either on a time-share basis with other I/O devices and the CPU or constantly with the I/O device until the entire record specified by the CCW count is transferred. This depends on the channel and I/O device whose address the start I/O instruction specifies. In most case the CPU begins the execution of the next instruction. The channel and CPU operate concurrently on a time-share basis. It is possible for the CPU to be executing a program while all three channels are operating concurrently, all on a time-share basis.

When an I/O device has completed the execution of a CCW, it sends an end signal to the channel. The channel in turn either obtains new operating information or attempts to generate an interrupt to the CPU program. The CCW flag bits determine if the channel is to obtain new operating information. The current PSW system mask determines whether or not a particular channel can generate an interrupt.

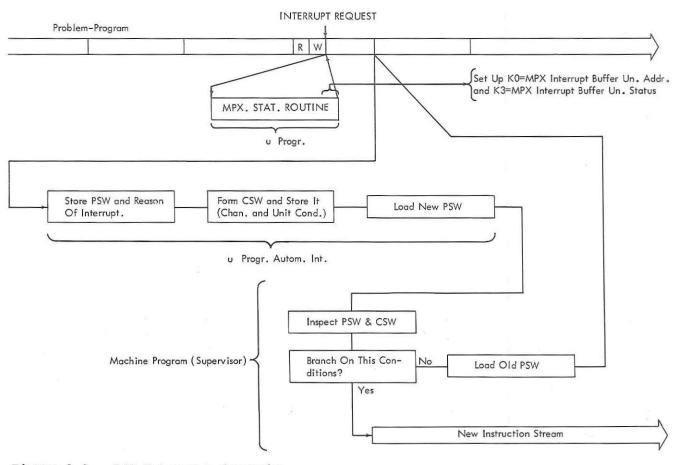

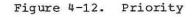

When the CPU executes an interrupt, it does so at the end of the execution of its current instruction. An I-O interrupt consists of:

- Storing the current PSW at the I/O old PSW.

- Loading the CSW with the required information.

- Loading the I/O new PSW into the current PSW locations in local storage and corresponding registers. The CPU now executes the I/O program defined by the I/O new PSW.

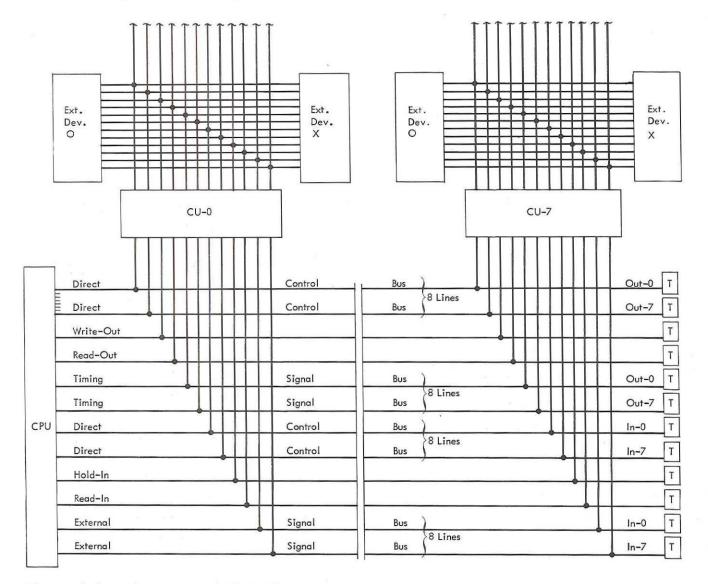

- The IBM System/360 I/O interface provides a uniform method of attaching I/O equipment to the System/360.

- This interface consists of 34 data and control lines.

- Up to eight input/output control units may be attached to one System/360 channel.

- Most control units can accommodate one input/output device although some can accommodate more than one device.

The input/output interface provides a uniform method of attaching input/output (I/O) control units to IBM System/360 channels. The interface can accommodate up to eight control units with addressing capabilities for up to 256 I/O devices. This means that some control units can control a single I/O device and some can control a number of I/O devices.

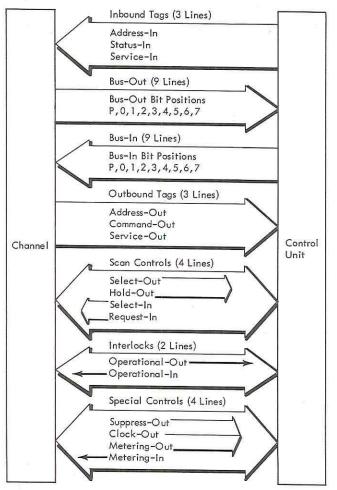

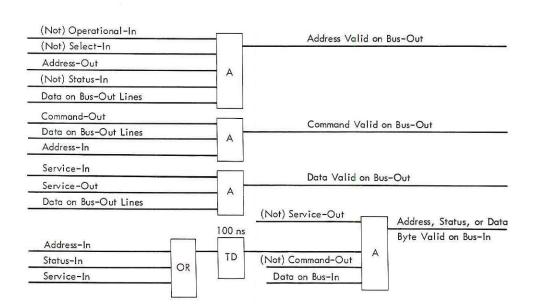

The interface, consisting of 34 lines, establishes requirements for signal transfers between control units and the servicing channel. Therefore, interface lines provide a common information format and signal sequence for all input/output devices. Figure 2-1 categorizes interface lines according to their general functions.

Except for signals that establish priority among control units, all interface signals are sent over a common bus. Any interface signals that the channel generates is available to all control units, although only one control unit may be serviced by the channel at any given time.

After a control unit is selected, it remains logically connected to the channel until it transmits or receives the required information or until the channel signals the control unit to disconnect.

The rise and fall of signals transmitted over the interface are interlocked with the corresponding responses. This interlocking makes the interface applicable to a wide variety of circuits and data rates, and permits the connection of control units of different circuit speeds and data rates.

Each control unit contains an address card that designates its interface address; no two control units on the same interface can have identical addresses. To begin an I/O operation, the channel must transmit the address of the desired unit. During the selection sequence, the selected control unit must identify itself by transmitting its address to the channel.

A similar identification procedure is necessary if the control unit initiates the signal sequence: the control unit must identify itself by transmitting its address before it can indicate the purpose of the sequence.

Figure 2-1. Interface Lines

Interface adapter circuits located in each control unit must:

Convert interface-line sequences and coded commands to control lines necessary to operate the control unit. In turn, the control unit controls the desired I/O device.

Establish communication between the control circuits in the unit and the interface.

# INTERFACE LINES

• Interface lines are divided into five types:

Bus lines Scan controls Tag lines Interlock lines Special controls

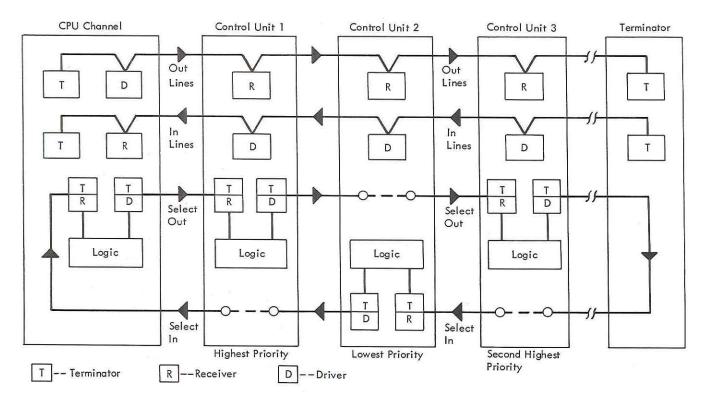

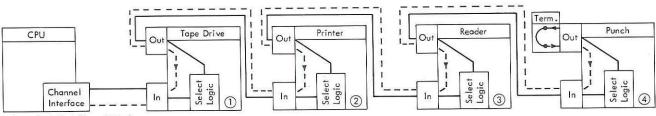

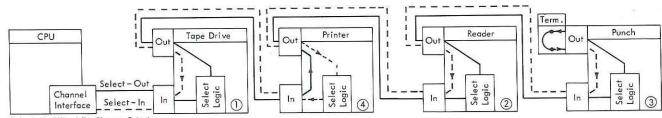

Figure 2-2 shows channel and control unit connections to the interface. Observe that the select lines (select-out and select-in) connect serially through each control unit for the purpose of establishing priority, other lines connect in parallel.

Priority is assigned to the different control units on the channel during installation. The customer establishes priority of control units by evaluating the type of channel involved, the data rates of the control units to be attached, and the type of operations to be performed. The highest priority control unit can receive the most service from the channel, whereas the lowest priority control unit receives the least service from the channel.

Figure 2-2. Interface Connections

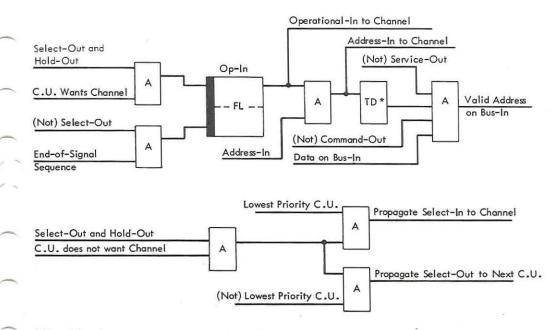

# SCAN CONTROLS (FIGURE 2-3).

- Select-out, hold-out, and select-in are controlled by the channel.

- Request-in is controlled by the control unit.

- The scan controls are independent of processing unit non-I/O operations.

- The purpose of the scan controls is to establish initial communication between the channel and attached control units.

- The scan controls establish contact between the channel and the control units on a priority basis.

\* Time delay duration dependent upon control unit.

# •Figure 2-3. Scan Controls

The primary objective of scanning is to establish a connection with a control unit. During initial selection any control unit that receives select-out and hold-out at the same time compares its address to the one on bus-out. An equal compare is the first part of any selection sequence. Scanning, then, is the process of presenting select-out and hold-out in an established sequence until a control unit indicates that its address compares equal. The sequence in which select-out and hold-out is presented to the control units is called priority. The first control unit to compare-equal blocks the select-out line to the next control unit in line. To further define priority, the first control unit that can receive select-out has the highest priority, the last, the lowest. In reality, there are two ways to establish priority. The method presented here is the simplest and is used primarily for clarity.

Interface Physical Connection

Select - In Added (Dotted Wire)

Select - In Wired To Change Priority

Figure 2-4. Select-In, Select-Out Priority Control

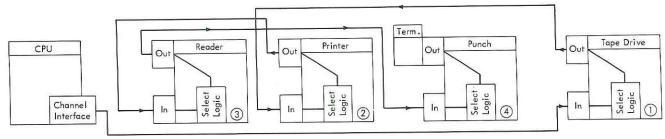

For this example, consider four control units positioned by the customer in this sequence:

- 1. Reader (closest to the processing unit)

- 2. Printer

- 3. Punch

- Tape Drive (farthest from the processing unit)

For the system to operate efficiently,

assume that the desired order of priority is:

- 1. Tape Drive (highest priority)

- 2. Printer

- 3. Reader

- 4. Punch (lowest priority)

To establish this priority, the CE must connect the tape drive to the system interface first, then connect the tape drive to the printer, the printer to the reader, and

2 - 4

the reader to the punch. The output of the punch is connected to a terminator.

Disregarding, then, the physical location of the units, they are electrically coupled in the desired priority sequence. That is, the first control unit to receive select-out is the tape drive. If this unit compares addresses and finds them equal, it connects to the interface. Select-out is prevented from reaching the other control units by the selection logic. This prevents two or more units from connecting to the interface at the same time. If the unit compares addresses and finds them unequal, it propagates the select-out signal to the next control unit in line. This indicates that the highest priority unit does not require service and others are free to use the interface.

To complete the process of establishing priority, each unit must be jumper wired internally for "high-priority." This term means that each control unit, as it receives select-out, attempts to compare addresses. This wiring also causes selectout to be passed along to the next control unit if the addresses compare unequal.

Using the same cabling sequence, this priority can be altered by jumper wiring a control unit internally for a condition

called low priority. Low-priority jumper wiring essentially shorts out the selectout signal directly to the next control unit and picks up the selection pulse on its return path to the processing unit. This return line is called select-in for physical identification only. Electrically, it is the select-out line on its return path to the processing unit. Thus, if any one of the four units in the example is wired for "low priority" its priority would change to the last in the series. Figure 2-4 shows the printer altered from the number 2 position to the number 4 position simply by changing the jumper wiring from high-priority to lowpriority.

Considering only one unit wired for low priority, these are the possibilities:

| Unit | 1 | (Tape Drive) | highest or lowest     |

|------|---|--------------|-----------------------|

| Unit | 2 | (Printer)    | 2nd highest or lowest |

| Unit | 3 | (Reader)     | 3rd highest or lowest |

| Unit | 4 | (Punch)      | no change             |

Except for the first unit, altering two or more control units offers unlimited priority arrangements. The first unit can only be first or last, not 2 or 3.

#### SELECT-OUT

- The select-out line connects each control unit in series.

- Control unit priority is determined by the order that the select-out line goes through the control unit logic.

The select-out line provides the scan loop that allows the channel to interrogate each control unit in priority sequence.

When an I/O control unit receives the select-out signal, it must either raise its operational-in line in response to it (request service) or immediately propagate the select-out signal to the next control unit in the series. Once a control unit has propagated select-out, it cannot raise its operational-in line until the next incoming select-out line to the control unit rises.

The channel must hold select-out active until it receives a signal on either the select-in or the address-in line. When select-out is transferred to the control unit with the lowest priority, the control unit either:

- raises its operational-in line, and later, its address-in line, initiating a signal sequence with the channel, or

- propagates the incoming select-out to the channel (select-in).

If a control unit conditions operational-in when the incoming select-out is active, it does not transfer select-out to the next control unit (or select-in to the channel). By conditioning operationalin, the control unit interrupts the channel's scan loop. Then, the control unit transmits an address byte on bus-in lines and conditions address-in. The control unit must hold operationalin active until communication with the channel is complete. The channel can drop select-out after receiving address-in, or can hold select-out active through the complete I/O operation. In no case can the control unit cancel operational-in before the channel drops select-out.

## SELECT-IN

- Select-in is the select-out line's return path to the channel.

- The select-in signal notifies the channel that no control unit has decoded the address sent out.

The control unit provides an option of connecting its selection logic in series on either the select-out or select-in line (see Figure 2-2). Descending-order priority from the channel can be established on the select-out line, and the remaining control units can maintain the descendingorder priority to the channel on the select-in logic. For clarity, assume that the selection logic is connected to the select-out line. Select-in is a line from the lowest priority control unit to the channel. It is the outgoing select-out line of that control unit and provides a return path to the channel for the select-out signal. The definition of the select-in line is the same as that of a select-out line coming from any control unit.

## REQUEST-IN

- Request-in allows a control unit to indicate to the channel that it needs service.

- At the channel, request-in initiates the polling sequence.

A control unit conditions the request-in line to indicate that it will initiate a signal sequence when select-out polls that unit again. The channel need not condition select-out to scan the attached control units until the request-in line indicates that a control unit requires servicing. This operation allows the control unit with the highest priority to receive attention in a minimum amount of time after the request-in line is conditioned. To illustrate the function of request-in, consider the following example. Assume that the highest interface priority is assigned to the I/O device with highest data rate and that the device with the slowest data rate has the lowest priority. The unit with the lowest priority can wait longest for service; so, each time that the request-in line is conditioned, that unit is the last to be polled. Because the I/O device with the highest priority can wait the least period of time for service, each request-in indication causes that unit to be polled first.

2-6

## HOLD-OUT

- The hold-out signal controls the effect of select-out.

- This signal allows additional channel control over the polling operation.

The channel conditions the hold-out line to all control units in parallel to allow select-out to perform its function in a control unit. The hold-out line allows the channel to cancel the effects of select-out at each control unit at the same time. If the channel is holding select-out active and cancels hold-out, no control unit can make use of select-out. A unit can only propagate the incoming select-out to the next unit. Therefore, the channel can interrupt the polling sequence and cause select-out to fall in all units in the shortest possible time.

## BUS LINES

- The bus lines carry information between the channel and all attached control units.

- There are nine bus-in lines and nine bus-out lines.

- The basic unit of information in the System/360, the 8-bit byte, may be transmitted over the bus lines.

- A parity bit is added to the 8-bit byte when necessary to maintain odd parity.

Figure 2-5. Bus Lines

Information is transmitted over the interface from the channel to a control unit on bus-out, and from a control unit to the channel on bus-in. Figure 2-5 shows the different conditions necessary to have information on bus-in and bus-out at the correct time. Bus-in and bus-out each contain eight information lines and one line for odd parity. Thus the basic unit of information in the System/360, the 8-bit byte, can be transmitted over the interface.

Information on the in and the out bus is arranged so that bit position 7 on a bus always carries the lowest order bit within an 8-bit byte. The highest-order bit is in position 0, and intervening bits are in descending order from position 1 to position 6.

When a byte transmitted over the interface consists of fewer than eight bits, the bits must be placed in the highest-numbered bit positions of the bus (low area). Any unused lines of the bus must include the low-numbered positions of the bus. Thus, if a paper tape reader reads 5-channel tape, bus-in positions 0, 1, and 2 are always zero. The parity bit of any byte must appear in the parity position (P). The byte formed by the nine bits must always contain odd parity. BUS-OUT

- Bus-out transfers information from the channel to a control unit.

- The information can be either data, control, or address information.

- Tag lines identify the bus-out data.

- Bus-out consists of eight data lines and one parity line.

The nine bus-out lines transfer information from the channel to control units. The channel conditions an out- bound tag line to identify the type of data transmitted on bus-out lines. For example, when the address-out tag and bus-out lines are active concurrently, the information on the bus-out lines designates an address.

Tag lines control the period during in which bus-out lines contain valid informa-

tion. When the address of an I/O device is transferred, the information on bus-out lines is valid from the rise of address-out to the rise of one of the following: operational-in, select-in, or status-in. When information other than an address is transferred, signals on bus-out lines are valid from the rise of the identifying outbound tag to the fall of the responding inbound tag.

## BUS-IN

- Bus-in transfers information from a control unit to the channel.

- Bus-in information can be either data, addresses, or controls.

- Inbound tag lines identify the information on bus-in.

- Bus-in consists of eight data lines and one parity line.

The nine bus-in lines transfer information from the selected control unit to the channel. The control unit conditions an inbound tag line to identify the type of information transmitted on bus-in lines. For example, when the status-in tag and bus-in lines are active concurrently, the bus-in lines contain a status byte.

Tag lines control the period during which bus-in lines contain valid information. Signals on bus-in lines are considered valid from 100 nanoseconds after the rise of the identifying inbound tag to the rise of the responding outbound tag.

The primary objective of scanning is to establish a connection with a control unit. Any control unit that receives select-out and hold-out at the same time compares its address to the one on bus-out. An equal

- Select-out, hold-out, and select-in are controlled by the channel.

- Request-in is controlled by the control unit.

- The scan controls are independent of processing unit non-I/O operations.

- The purpose of the scan controls is to establish initial communication between the channel and attached control units.

- The scan controls establish contact between the channel and the control units on a priority basis.

compare is the first part of any selection sequence. Scanning, then, is the process of presenting select-out and hold-out in an established sequence until a control unit indicates that its address compares equal.

Section 2 2-9

#### OUTBOUND TAG LINES

- There are three outbound tag lines:

- 1. Address-Out

- 2. Command-Out

- 3. Service-Out

- These lines control the basic communication between the channel and a control unit.

- No two of these lines can be active at the same time.

lines is a command.

Each of the outbound tag lines has a basic purpose:

| Address-Out | The data on the bus-out |

|-------------|-------------------------|

|             | lines is an address.    |

| Command-Out | The data on the bus-out |

Service-Out Responds to data received from the control unit on a read operation, and indicates data being sent to the control unit on a write operation. These signals have a positive sequence depending on the operation involved. Example: Initial selection share-cycle, ending procedure. It is as much the sequence that governs the operation as the exact name or purpose of the line. These sequences must be thoroughly understood to become completely familiar with the operation of the interface.

#### ADDRESS-OUT

- The basic function of address-out is to indicate to a control unit that the information on bus-out is an address.

- Address-out can also be activated at the same time as select-out to disconnect a selected control unit from the interface.

The channel transmits a signal over the address-out line (Figure 2-6) to indicate either of two conditions:

- Address-out initiates selection of an I/O device causing all attached control units to attempt to decode the address on the bus-out lines. Because each control unit address is different, only one unit can decode the address. If the control unit that recognizes the address is not busy, it must respond by conditioning operational-in when select-out is conditioned to the control unit.

- Address-out precedes the rise of select-out by 400 nanoseconds. The channel must hold address-out active

until it receives operational-in, select-in, or status-in. Select-in indicates that no control unit decoded the address. This occurs when the specified control unit is off-line. Status-in indicates that the designated control unit is busy and cannot be interrupted to execute another operation. The channel responds to the status-in reply by cancelling selectout. It then waits for status-in to fall, and cancels address-out.

Address-out causes a control unit to disconnect from the interface. The channel:

a. Conditions the select-out line,

- Receives operational-in from a control unit,

- c. Conditions the address-out line (or allows address-out to remain active), then after 250 ns,

- d. Cancels select-out and holds address-out active until the con-

trol unit allows operational- in to fall.

The control unit must cancel operational-in within 6 microseconds after receiving the interface disconnect indication. The I/O operation proceeds to the normal end, but no data is transferred across the inter-face.

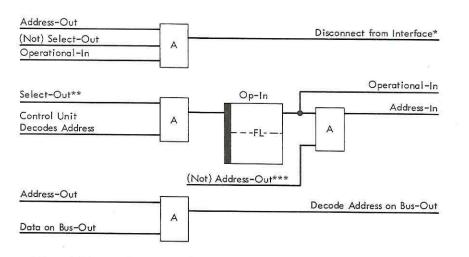

\* Control Unit must drop op-in within 6 usec .

\*\* Select-out rises a minimum of 400 ns after address-out

\*\*\* Rise of Op-in causes address-out to fall.

Figure 2-6. Address-Out

Section 2 2-11

# COMMAND-OUT

- The basic function of command-out is to indicate to a control unit that the information on bus-out is a command.

- Command-out also is used to indicate "proceed" at the end of initial selection.

- In response to status-in command-out signals a control unit to "stack" its status.

- In response to service-in, command-out indicates "stop".

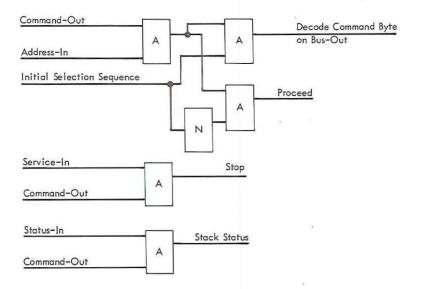

Figure 2-7. Command-Out

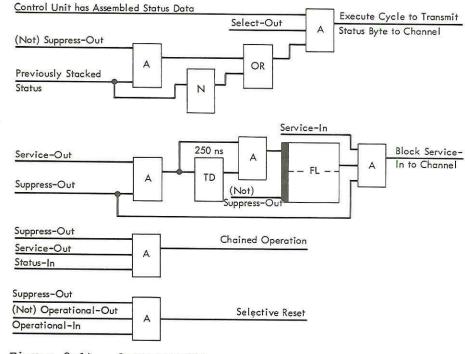

The channel conditions the command-out line (Figure 2-7) to respond to a signal on an inbound tag line. During the initial selection sequence, the channel activates command-out to reply to address-in, indicating that a command byte is on the busout lines. This command byte specifies the I/O operation to be performed. Only at this point in the initial selection sequence does command-out cause the selected control unit to decode the byte on busout lines. After the initial selection sequence, the command-out response to address-in means proceed. A command-out response to service-in means "stop", and causes the control unit to terminate the operation and reset. Whether during the initial selection sequence or at the end of the operation, the command-out reply to status-in causes the selected control unit to "stack" (hold) the status data. The control unit can present the stacked status only if suppress-out and address-out are down when select-out rises at the control unit.

SERVICE-OUT

- The basic function of service-out is to indicate to a control unit that data has been received or is being sent.

- Service-out responds to service-in on read or write operations and to status-in during a status sequence.

#### Figure 2-8. Service-Out

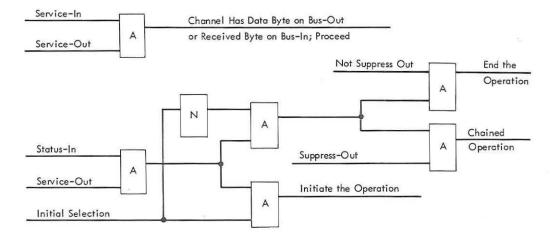

Service-out is a line from the channel to all attached control units and is used to signal the selected device in recognition of a signal on the service-in or status-in line (Figure 2-8). A signal on the service-out line indicates to the selected device that the channel has accepted the information on bus-in or has provided on bus-out the data requested by service-in.

When service-out is sent in response to service-in during read, read-backwards, or sense operations, or to status-in, the service-out signal must rise after the channel accepts the information on bus-in. In these cases, the rise of service-out indicates that the information on bus-in has been received. When service-out is sent in response to service-in during a write or control operation, the rise of service-out indicates that the channel has provided the requested information on bus-out. In this case, the signal must rise after the information is placed on the bus. Service-out must stay up until the fall of the associated service-in or status-in signal. Serviceout cannot be up concurrently with any other out-tag.

A service-out response to status-in while suppress-out is up indicates to the control unit that the operation is being chained. See <u>Suppress-Out</u> for further details. The status is accepted by the channel.

Sect

Section 2 2-13

#### INBOUND TAG LINES

• There are three inbound tag lines:

Address-In Status-In Service-In

- These lines control the basic communication between a control unit and the channel

- No two of these lines can be active at the same time.

The data on the bus-in

The data on the bus-in lines is status informa-

The information the bus-in

operation, this line indi-

lines is data on a read

operation. On a write

cates that the control

lines is an address.

Each of these lines has a single basic purpose:

tion.

unit is ready to receive data.

The control unit uses the inbound tag lines to respond to signal sequence developed by the channel. For example, during an initial selection sequence the channel activates address-out. The control unit that is selected responds with address-in. The channel then sends command-out. When the control unit receives the command, it sends status-in. The channel responds with service-out. When the control unit is ready to send or receive data, it activates service-in.

ADDRESS-IN

Address-In

Status-In

Service-In

- Address-in identifies the information on the bus-in lines as a control unit address.

- When the channel identifies the control unit, it responds with command-out.

| Address-In     |   | Decode Address Byte on Bus-In |

|----------------|---|-------------------------------|

| Operational-In | A | Decode Address byte on bus-in |

Figure 2-9. Address-In

Address-in is a line from all attached control units to the channel (Figure 2-9). It is used to signal the channel that the address of an I/O unit is on bus-in. The channel responds to address-in with command-out.

During the initial selection sequence, the channel checks the address received against the address initially sent out. If they are equal, the operation can proceed. If not, the channel branches to an error routine. During data transfer cycles, the channel identifies the control unit when address-in is received. The channel can then select the correct information to proceed with data transfer.

Address-in remains active until the rise of command-out. It must then fall in order that command-out can fall.

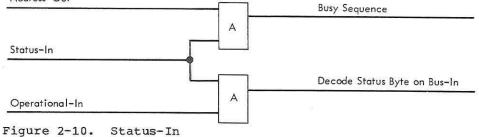

STATUS-IN

- Status-in identifies the information on \*he bus-in lines as a status byte.

- The line must remain active until the channel responds.

- Address-Out

A control unit activates the status-in line to indicate to the channel that a status byte is on the bus-in lines (Figure A-10). The status byte has a fixed format and contains bits describing the current status at the control unit.

2. Command-out, indicating that the chan-

nel has stacked the status.

1.

- Status-in must remain up until the chan- t nel responds with:

- If status-in is the control unit's reply to address-out during initial selection, it must remain up until select-out falls.

Service-out, indicating that the channel accepted the status.

### SERVICE-IN

- On a read operation, service-in indicates that data is ready on the bus-in lines.

- On a write operation, service-in indicates that the control unit is ready to receive data.

- This line remains active until the rise of either commandout or service-out.

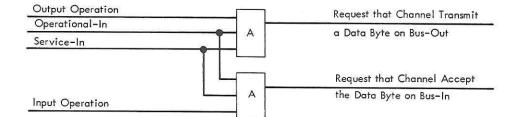

•Figure 2-11. Service-In

A control unit activates the service-in line (Figure 2-11) to:

on the bus-in lines (read, read backward, and sense operations).

1. Signal the channel that a data byte is

2. Request that the channel transmit a

Section 2 2-15

data byte on the bus-out lines (write or control operations).

- Service-out, when data is accepted or transmitted.

- Command-out, to stop data transfers and end the operation.

The channel responds to service-in with:

## INTERLOCK LINES

There are two interlock lines:

Operational-in Operational-out

These lines permit only one control unit at a time to communicate with the channel.

The interlock lines provide additional control of the interface. They are used to gate other signals, reset all control units and signal the channel that a unit is selected.

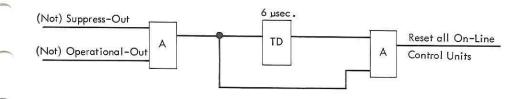

### OPERATIONAL-OUT

- All outbound lines are controlled by operational-out.

- To reset all the control units, the channel drops operational-out and suppress-out.

Operational-out originates at the channel when the processing unit is power-on-reset. It stays up as long as the channel is operable. The operational-out line enables all control units on the interface to communicate with the channel (providing the correct signal sequences are maintained). If operational-out is down, all interface signals become ineffective.

The fall of operational-out resets control units on the interface either selectively or concurrently, depending on the status of suppress-out, a special control line (Figure 2-12). If the channel drops operational-out while a control unit is operating on the interface, the control unit is reset. If the channel wishes to reset <u>all</u> control units on the interface, the suppress-out and operational-out lines are both dropped (for a period of at least 6 microseconds to ensure a complete reset).

### OPERATIONAL-IN

- Operational-in signals the channel that a device is selected.

- When select-out falls and the signal sequence is completed, operational-in is dropped.

To initiate an interface signal sequence, a control unit conditions operational-in when the incoming select-out line is up. At the same time, the control unit blocks selectout from reaching the next control unit. No other control unit can connect to the interface while operational-in is up.

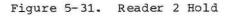

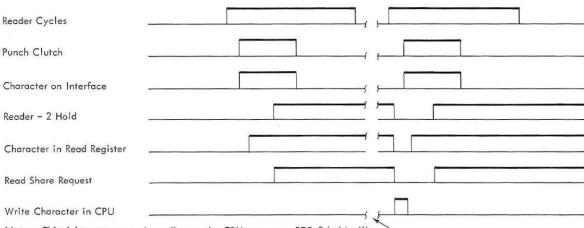

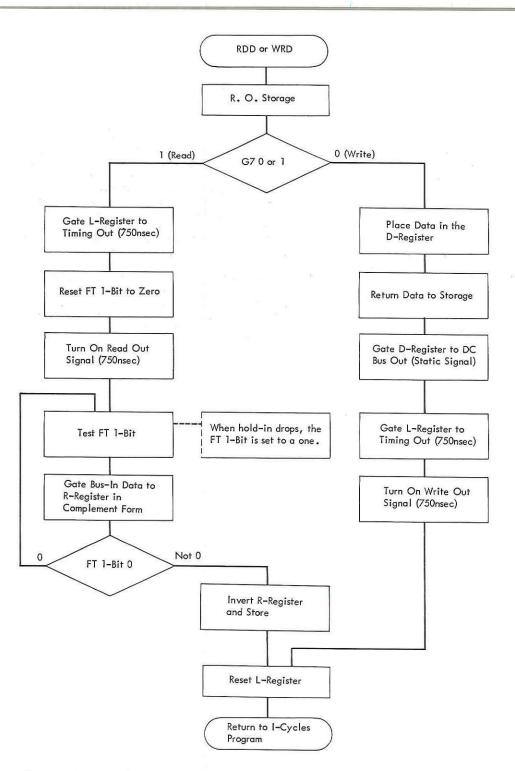

When operational-in is raised for a particular signal sequence, it stays up until all required information is transmitted between the channel and the device. Operational-in drops at the same time as the transfer of the last byte of information, if select-out is down. Signals on bus-in and on the inbound tag lines are significant only when operational-in is up, except in the case of the control-unit-busy selection sequence. When operational-in is down, the channel disregards any signal on these lines. However, most control units are interlocked so that no signals are placed on any inbound lines when operational-in is down. This is necessary to prevent erroneous indications to the channel when another control unit first raises its operational-in line.