IBW

Field Engineering Manual of Instruction

Processing Unit System/360 Model 30

## PREFACE

This manual contains information about the IBM 2030 Processing Unit. A companion manual on input/output control should be obtained for information pertaining to the attachment of I/O devices to the IBM System/360 Model 30. The companion manual is the IBM 2030 I/O Control Field Engineering Manual of Instruction, Form 225-3362.

Minor Revision, August 1965

This edition, 225-3360, is identical in content to the previous edition, Z25-3360. The IBM Confidential classification has been removed and the form number has been changed to allow free access to the manual.

Address comments concerning the content of this publication to IBM Product Publications, Endicott, New York 13764.

| SECTION 1. COMPREHENSIVE INTRODUCTION<br>System Concepts<br>Numbering Systems<br>Arithmetic Principles<br>Data Flow<br>Basic Programming<br>Instruction Sequencing and Branching<br>The System/360 and Interrupts<br>Storage Protection                                                                              | 1-1<br>1-5<br>1-21<br>1-25<br>1-31<br>1-35<br>1-43<br>1-49<br>1-69                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| SECTION 2. FUNCTIONAL UNITS<br>SLT Circuitry<br>Remembering Devices<br>Combined Components<br>Central Processing Unit (CPU) Clock.<br>Arithmetic Logical Unit (ALU)<br>Registers<br>Core Storage<br>Memory Control                                                                                                   | 2-1<br>2-3<br>2-4<br>2-5<br>2-10<br>2-22<br>2-23<br>2-62                                    |

| SECTION 3. THEORY OF OPERATION<br>Concepts of Capacitor                                                                                                                                                                                                                                                              | 3-1                                                                                         |

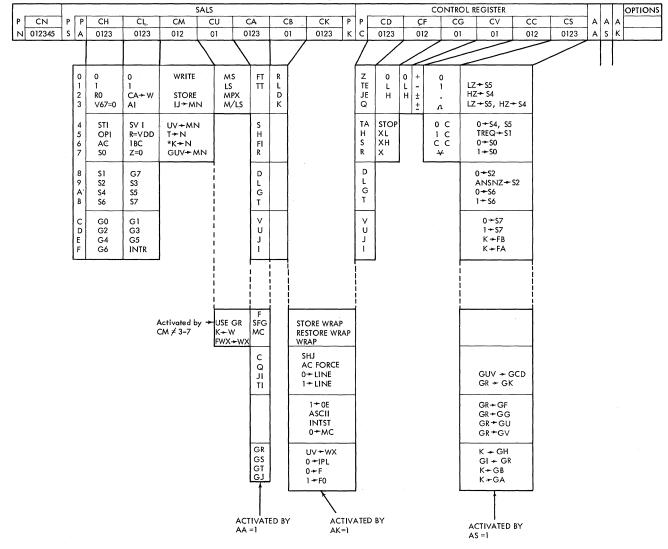

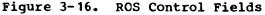

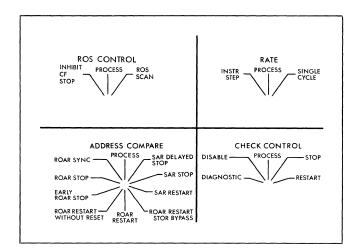

| Concepts of Capacitor<br>Read Only Storage<br>Micro Programming Introduction<br>Micro Program Examples<br>Control Field Mnemonics<br>Parity Bits<br>ROS Addressing<br>ROAR Controls<br>ROS Timings<br>Physical Description<br>Machine Check Handling<br>Forced Micro Program Entries<br>Overall Timing Relationships | 3-1<br>3-15<br>3-23<br>3-44<br>3-51<br>3-53<br>3-60<br>3-63<br>3-66<br>3-71<br>3-76<br>3-80 |

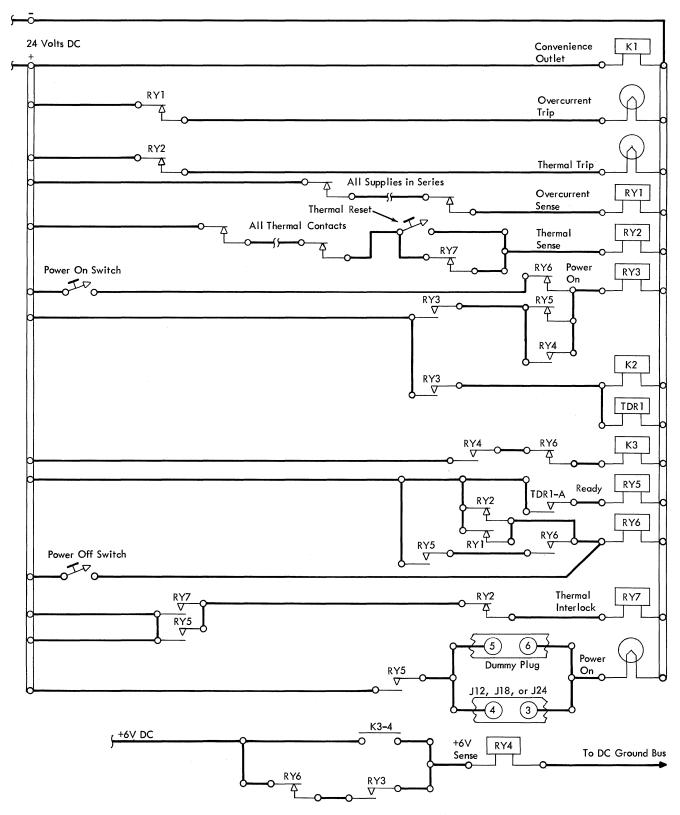

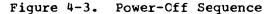

| SECTION 4. POWER SUPPLY                                                                                                                                                                                                                                                                                              | 4-1                                                                                         |

| SECTION 5. SPECIAL FEATURES<br>1401, 1440, and 1460<br>Compatibility Features<br>Interval Timer                                                                                                                                                                                                                      | 5-1                                                                                         |

| APPENDIX 1                                                                                                                                                                                                                                                                                                           | 6-2                                                                                         |

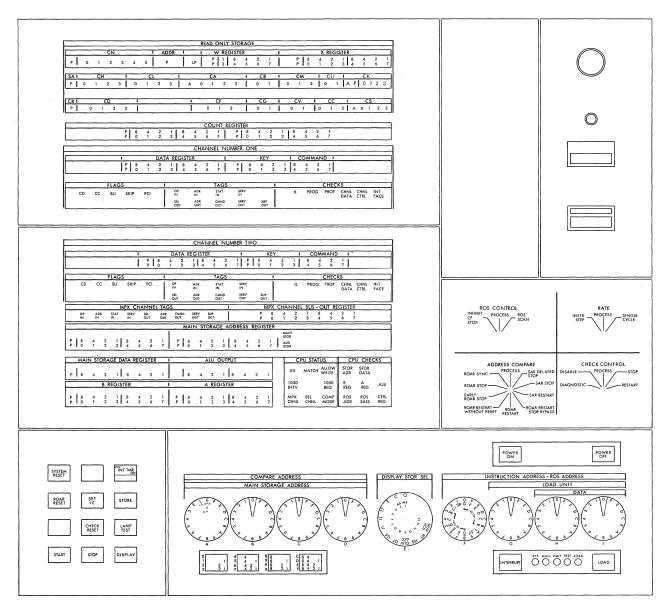

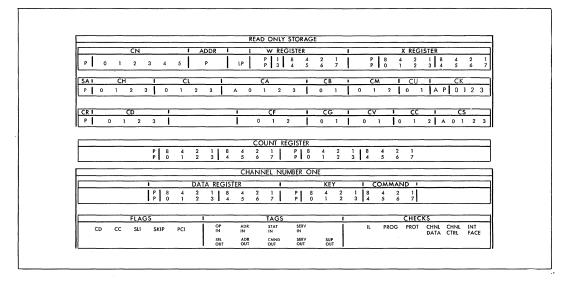

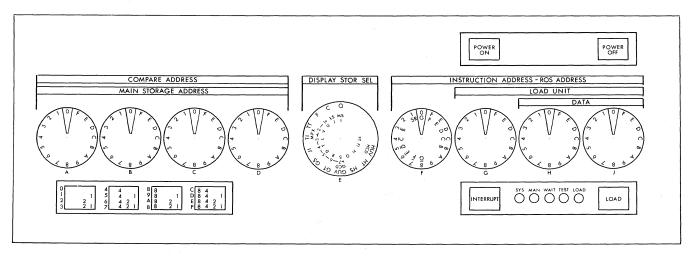

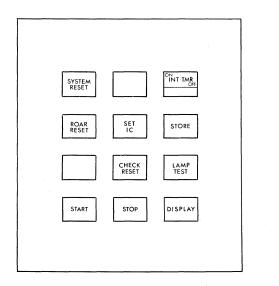

| APPENDIX 2<br>Upper Indicator Panel<br>Lower Indicator Panel<br>Operator Panel<br>Control Keys<br>Mode Control Panel<br>Meter Panel                                                                                                                                                                                  | 6-5<br>6-7<br>6-9<br>6-11<br>6-15<br>6-17                                                   |

| ANSWERS TO REVIEW QUESTIONS                                                                                                                                                                                                                                                                                          | 6-19                                                                                        |

| INDEX                                                                                                                                                                                                                                                                                                                | 7-1                                                                                         |

# SECTION 1. COMPREHENSIVE INTRODUCTION

## SYSTEM CONFIGURATIONS

- Single system concept.

- Different models provide a variety of processing speeds and storage sizes.

- Broad range of input/output devices.

- Uses an 8-bit coding structure to represent data.

- Program compatibility throughout system models.

Behind the decision to design the IBM System/360 - a single system which encompasses all areas of data processing lies the awareness that apparently unrelated applications have more similarities than differences. For example, because of teleprocessing and other factors, scientific applications require high-speed input/output similar to that required by commercial applications. In addition to this versatility, the System/360, because of its modularity, adaptability and compatibility, can handle the many kinds of growth that normally occur in computer installations.

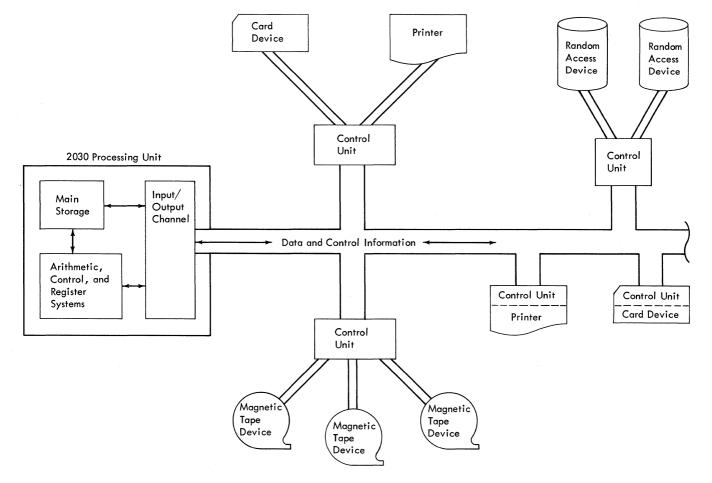

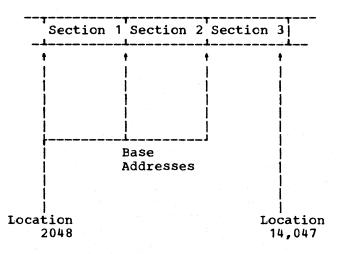

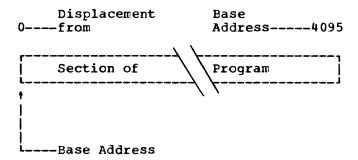

Modularity in the System/360 is achieved through the availability of seven models. A typical Model 30 system is shown in Figure 1-1. In addition to a choice of processing speed through model selection, each model offers a choice of storage capacities.

Figure 1-1. IBM System/360, Model 30

As problems and workloads grow or change, the System/360 can easily be expanded or changed to handle additional or different operations. Storage can be added and input/output and processing speeds increased -- in small increments, as needed. This adaptability makes provision for the inclusion, either initially or subsequently, of a broad range of input/output devices.

Versatile performance characteristics permit handling of data in virtually any desired character representation. Instead of the usual six-bit character, the System/360 employs a new eight-bit coding structure to represent data. An 8-bit unit of data is called a byte. This 8-bit coding structure allows 256 possible combinations for letters, digits and symbols, providing greater versatility in both binary and decimal operations. It also means that System/360 can accept a character code of fewer bits, such as a telegraph code.

More important than the modularity and adaptability of the System/360 is its compatibility. A program written for one configuration will run on any other, if there is enough memory capacity and input/output equipment, and if the program is not geared to the operating speed of any particular unit. Subject to these constraints, a program written for a smaller System/360 will run without modification on a larger one. While this "upward" compatibility is certainly an advantage, "downward" compatibility can be even more valuable; for example, a small user can utilize programs written for larger systems. This places a total library of programs at all users' disposal.

Compatibility further allows a System/360 to be tailored to fit either centralization or decentralization. That is, a company's installation can be either a large central processor or a number of smaller processors. Shifts between the extremes are possible within the same system.

Traditionally there have been constraints on computer versatility, so that one processor has lent itself to scientific and engineering application, another to commercial data processing applications, another to process control, and still another to communications.

The System/360 provides a versatile set of instructions that permit operating quickly and efficiently regardless of the system application.

#### MODELS AND SPEEDS

- Different processor models provide a variety of processing speeds and core storage sizes.

- The 2030 is the processor for the System/360, Model 30 (Figure 1-2).

- The 2030 is available in four core storage sizes, represented as System/360, Models C30, D30, E30, and F30.

Figure 1-2. IBM 2030 Processing Unit

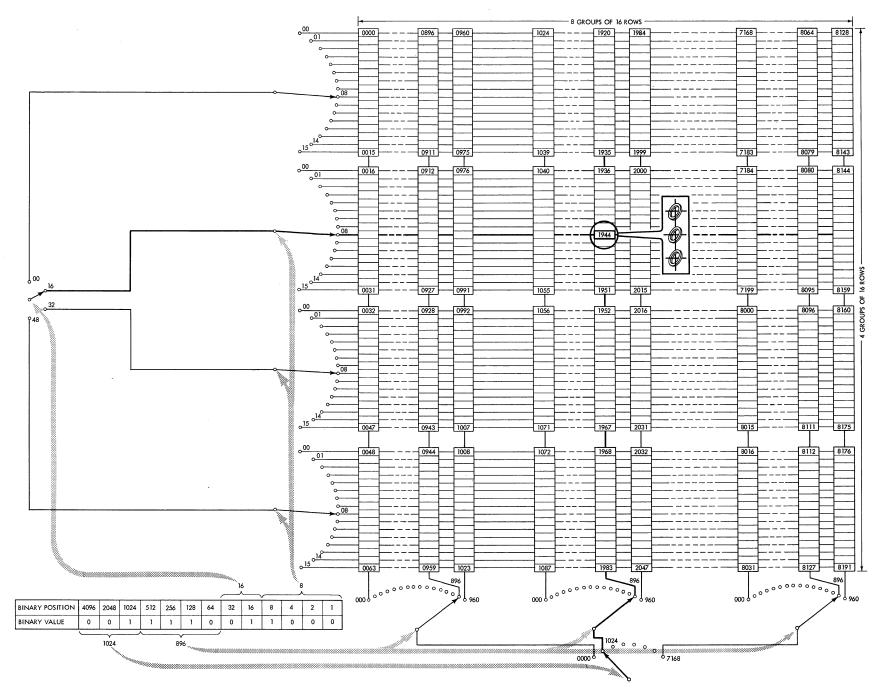

To fit the widely varied cost and volume needs of all computer users, the IBM System/360 is available in many different models. For instance, to fit the needs of the user who needs a minimal number of answers per month, a Model 30 is available at a minimal cost. For the user who needs a greater number of answers per month, a Model 70 is available that will give approximately 50 times as many answers per month as a Model 30. The answers will be the same; only the number of answers in a given period of time will be different. There are two basic differences between models: core storage capacity and internal processing speeds. Figure 1-3 shows the core storage capacities for the different System/360 models. Internal processing speed is largely dependent on the speed of the core storage unit and the amount of data involved on each core

storage access. Core storage speed in the System/360 varies from 2 microseconds per single byte access on the Model 30's to 1 microsecond per eightbyte access on the Model 70's (Figure 1-4).

| Storage Capacity<br>in Bytes | System/360 Models |     |     |     |     |     |

|------------------------------|-------------------|-----|-----|-----|-----|-----|

| 524,288                      |                   |     |     | 160 | 162 | 170 |

| 262,144                      |                   | H40 | H50 | H60 | H62 | H70 |

| 131,072                      |                   | G40 | G50 | G60 |     |     |

| 65,536                       | F30               | F40 | F50 |     |     |     |

| 32,768                       | E30               | E40 |     |     |     |     |

| 16,384                       | D30               | D40 |     |     |     |     |

| 8,192                        | C30               |     |     |     |     |     |

Figure 1-3. System/360 Storage Sizes

| Processor | System/360 Models       | Bytes/<br>Access | Memory Speed     |

|-----------|-------------------------|------------------|------------------|

| 2030      | C30, D30, E30, F30      | ]                | 2.0 microseconds |

| 2040      | D40, E40, F40, G40, H40 | 2                | 2.5 microseconds |

| 2050      | F50, G50, H50           | 4                | 2.0 microseconds |

| 2060      | G60, H60, I60           | 8                | 2.0 microseconds |

| 2062      | H62, 162                | 8                | 1.0 microseconds |

| 2070      | H70, 170                | 8                | 1.0 microseconds |

Figure 1-4. System/360 Storage Access and Speed

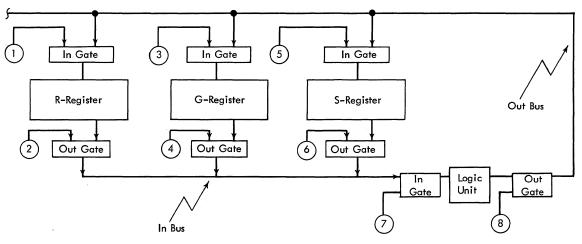

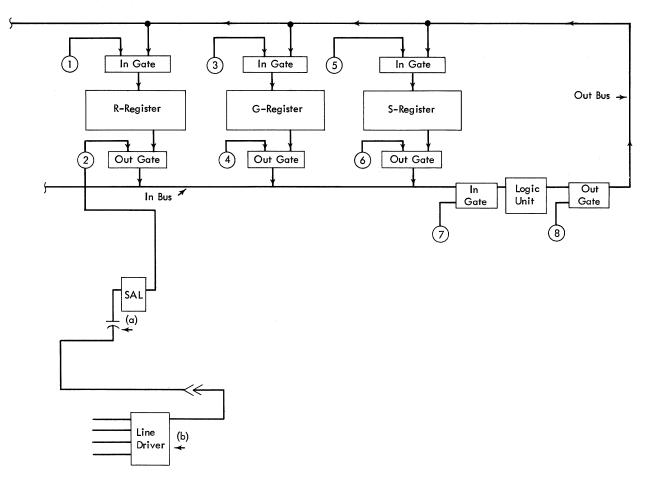

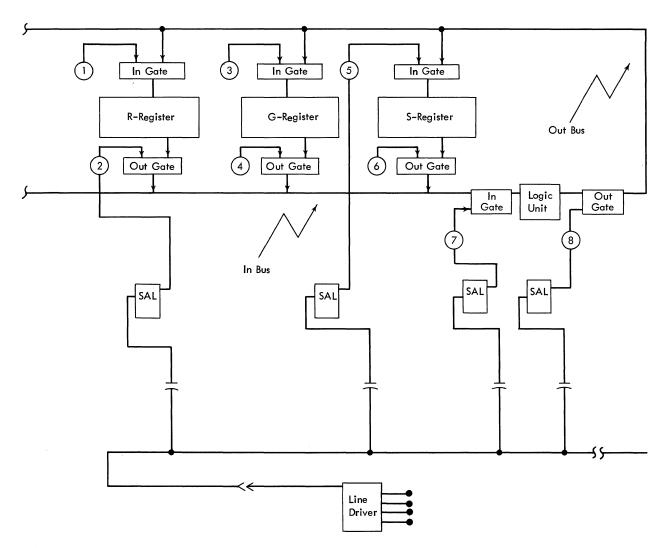

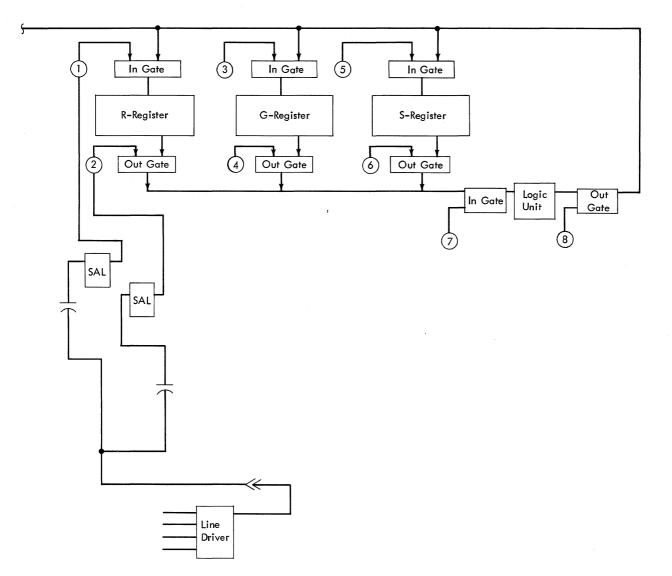

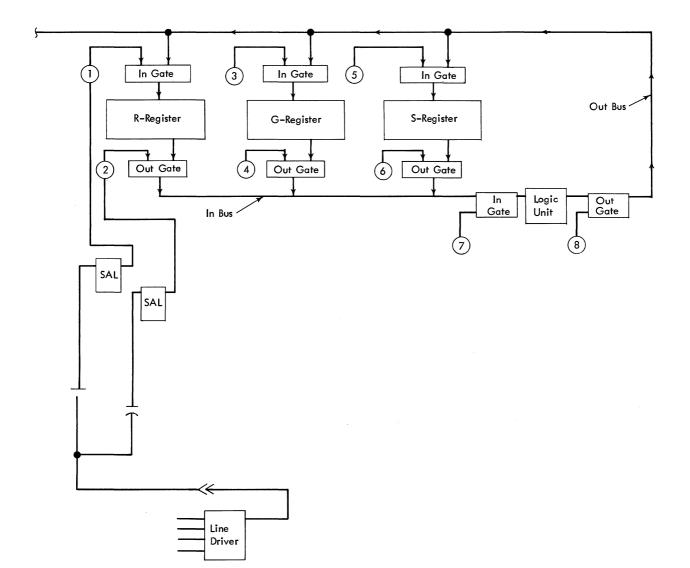

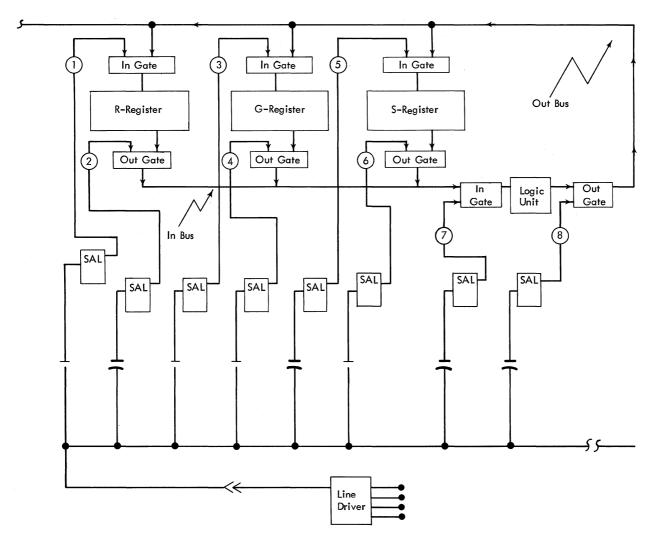

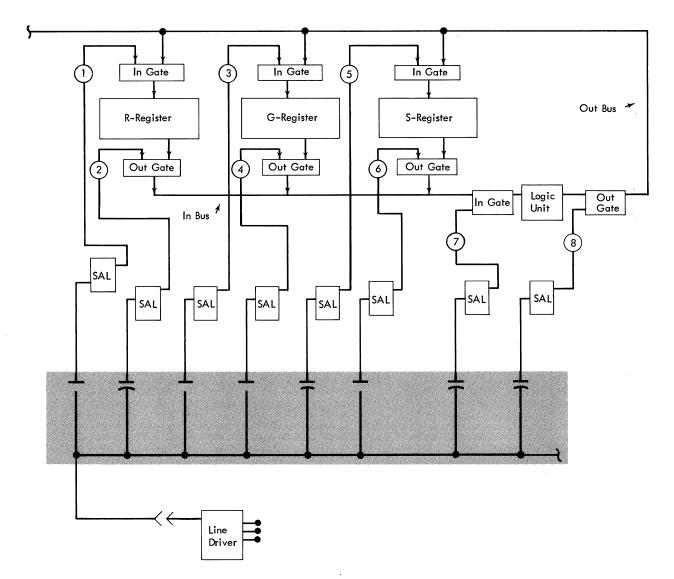

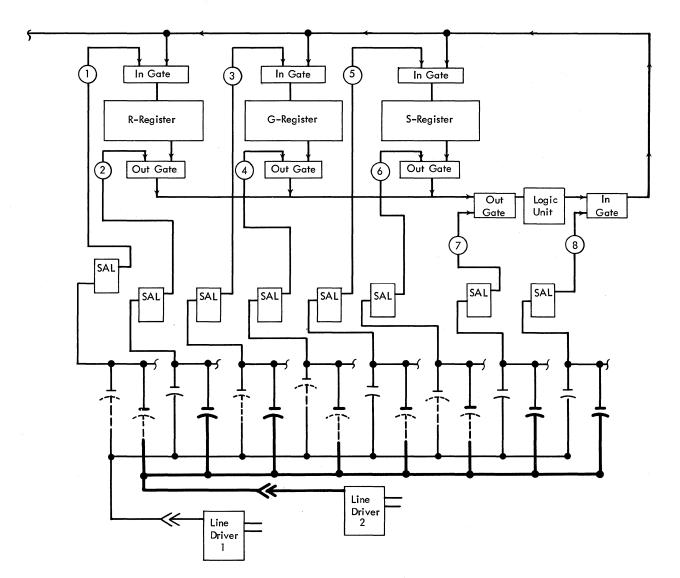

GENERAL DATA FLOW

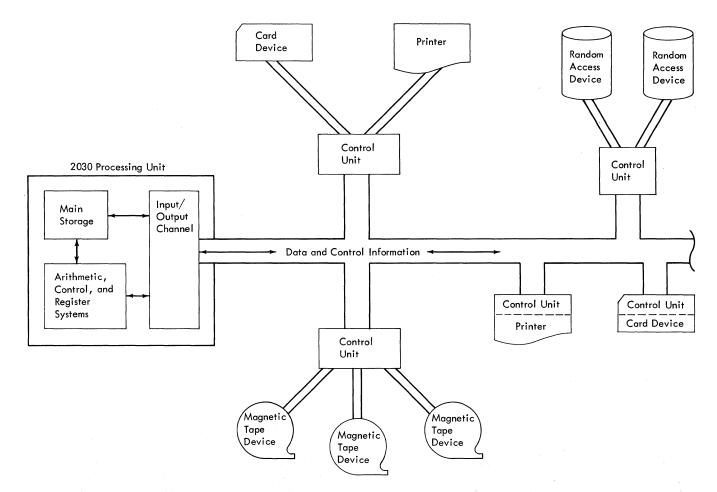

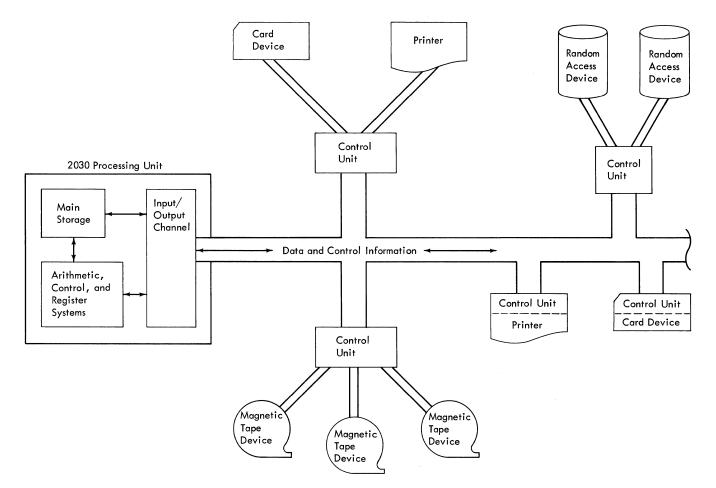

- The processing unit controls the system.

- Information enters the system from an input device.

- The information is manipulated by the processing unit to develop the required answers.

- The answers are sent to an output device to be stored.

In the System/360, Model 30, the 2030 processing unit provides all system control. The processing unit is given instructions by a programmer. These instructions are interpreted and executed by the processing unit. Execution of an instruction might involve adding two numbers together, or it might involve causing a printer to print a check. Regardless of the instruction, the interpretation and control lies in the 2030 processing unit.

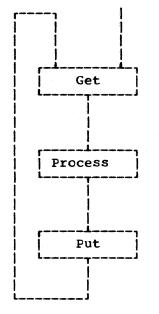

General data flow is divided into three operations (Figure 1-5). First, information comes into the processing unit via some input device. This information is then used along with input information from other devices and constant information contained in main storage to develop the required result or output. This output is then sent to an output device where the resultant information is stored. The information storage may be a printed report, punched cards, or magnetized spots on a reel of magnetic tape.

Figure 1-5. General Data Flow

## SYSTEM CONCEPTS

- Programming Systems support of the IBM System/360 is called Operating System/360.

- The Operating System/360 supports the Computing System/360. Together they make up the IBM System/360.

The introduction of the IBM System/360 marks the achievement of a truly allpurpose computer that can solve any type of data-handling problem with greater speed and efficiency than ever before. This opens up greatly increased computer potential in every area.

In order to realize this potential, it was apparent to the designers that the programming support needed to be as powerful and as extensive as the computer. In fact, programming support should make the IBM System/360 an even more powerful system.

This lead to the concept of the Computing System/360 (hardware) being supported by the Operating System/360 (programming), together making up the System/360.

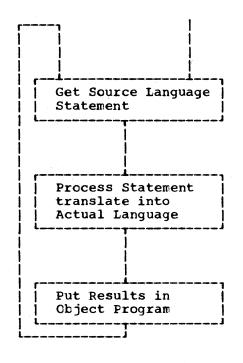

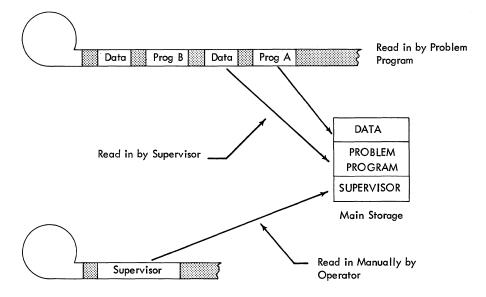

This means that a customer is getting a system that is powerful and flexible, yet, due to extensive programming support, he can easily apply his problem to the System. For one thing, he can write problem solving programs without the necessity of translating them into a language understandable by the machine. Once written, the operation of his program is controlled or supervised by Cperating System/360, relieving the operator of many tasks and increasing the utilization of the Computing System/360.

# **CPERATING SYSTEM/360 CONCEPTS**

- Control programs allowing monitored operation of a system have been proven by experience to produce optimum computer utilization.

- Cperating System/360 includes both control programs, and IBM and userwritten processing programs.

- Basic Programming Support programs will be provided for System/360 systems with 8K bytes of storage.

As stated previously, IBM's single system approach with the System/360 recognizes that computing systems and programming systems should be integrated and not developed independently. Experience in the past decade has proved that the optimum method of producing this result is with monitored operation.

Early monitors were designed to minimize human intervention. The new and sophisticated control techniques included in programming systems with the System/360 extend its capabilities so that the monitor and control functions make up what is called an operating system.

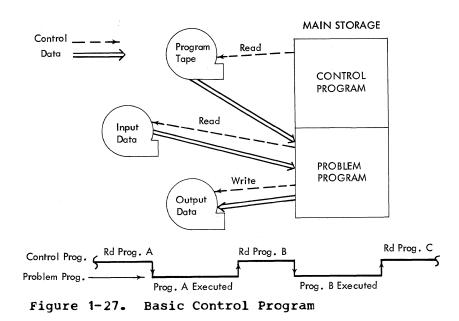

The basic purpose of Operating System/360 is to permit the user to solve problems and process information effectively. Included in Operating System/360 are both processing and control programs. Processing programs include all application-oriented programs, including both IBM and userwritten.

For systems having 16K bytes of main storage, basic control program functions will be supplied with magnetic tapes or direct access devices. Additional capability can be utilized as more main storage is added.

For systems having 8K bytes of main storage, programming systems is supplying basic programming support programs, which perform many of the functions of operating systems, including control functions.

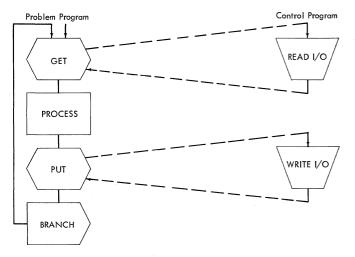

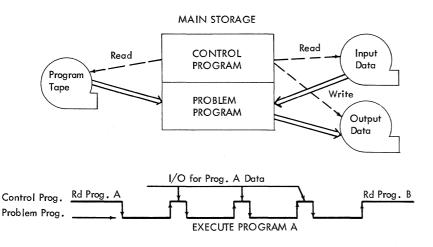

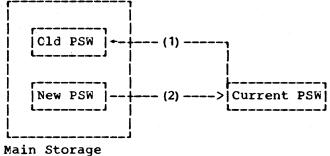

#### Control Programs

Control programs perform functions such as control of administrative operations, job flow control, Input/Cutput control, and program execution control.

A basic key to achievement of high operating efficiency in a computing or data processing installation is a good control procedure. This procedure must include many functions: administrative control of job schedules, workflow, and computer usage records; control over data and program libraries; control over computer operations; and control over the flow of programs and data within the computing system during job runs.

The control programs for the IBM System/360 set up a comprehensive control framework to assist the user in satisfying the above objectives. The control programs operate at various levels of concept. For example:

- Operations control of installation and administration and workflow, including instructions from and to the computer operator, administrative records, logs of system operation, and control over library programs.

- Job flow control, including I/O transition between jobs and job segments, unit assignments, initial loading and initialization when the computer is first turned on, control between jobs, and control over the type of operation mode, ranging from simple stacked jobs through teleprocessing systems performing concurrent operations.

- Input/Output control, including physical and logical control over I/O records, files and units; buffer control; teleprocessing terminal and message handling; random access I/O

control; labeling of files, and error recovery procedures.

4. Program execution control that manages the flow of program instructions from one routine to another, including the instantaneous transitions that take place when any interrupt occurs, the decisions that control the next program series to be executed, the return of control to an interrupted program, storage allocation and protection, diagnostic programs, program loading, and management of the interval timer.

# Processing Programs

- Processing programs function under control of operating system control programs.

- Some IBM supplied processing programs are, the System/360 Assembler, FORTRAN, new programming language, CCBOL, report program generator, utility programs, and sort/merge programs.

Complementing the control programs and functioning under them are those programs necessary to handle users' specific data processing needs. These programs, known collectively as processing programs, include application programs both IBM and user written, compilers, Report Program Generators, sort/merge, and utility programs.

Symbolic programming languages and the programs that translate them (assemblers and compilers) offer valuable aids to the programmer in solving data processing problems.

The System/360 Assembler language is a symbolic language that permits the coding of source programs in convenient, report program generators, sort/merge, specialized language, it can be used in all kinds of applications, including both commercial and scientific.

The FORTRAN language allows the programmer to code a mathematical or scientific problem in terms closely resembling those he uses in stating the problem mathematically.

The new programming language has some features that are characteristic of FORTRAN and incorporates some of the best features of other languages, such as extensive editing capabilities, to take advantage of recent developments in computer technology.

The COBOL language provides a convenient method of coding programs in a form closely resembling the English language, using the method sponsored by the Conference on Data Systems Languages (CCDASYL), a cooperative effort by a number of computer manufacturers and users.

The report program generator (RPG) provides a convenient method for producing a wide variety of reports, using IBM-provided coding forms.

Utility programs provide the user with standard, efficient handling of routine operations involving data transfer between I/O devices. These include such operations such as card to printer, card to punch, card to tape, tape to tape, tape to punch, tape to disk, and many others.

The sort/merge program is designed to satisfy the sorting and merging requirements of all tape-oriented or random storage-oriented IBM System/360 installations. It is a generalized program that can produce many different sorting/merging programs in accordance with control information specified by the user.

### COMPUTING SYSTEM/360 CONCEPTS

- System/360 uses binary and BCD.

- System/360 uses variable and fixed length fields.

- System/360 uses a new technology called solid logic technology.

The System/360 is a general purpose computer system. By this we mean it is designated to be used for commercial, scientific, and communications applications. In the past, these applications were handled by separate computer families (Figure 1-6).

| •      | 7090             | 7080       |  |

|--------|------------------|------------|--|

|        | 709              | 705 111    |  |

| Growth | 704              | 705 11     |  |

|        | 701              | 702        |  |

| SC     | <u>CIENTIFIC</u> | COMMERCIAL |  |

|        |                  | COMMERCIAL |  |

|        |                  |            |  |

One scientific computer family and its comparable commercial equivalent.

Figure 1-6. Commercial vs. Scientific Computers The scientific computers were usually fixed word length machines and used a pure binary form of coding. On the other hand, the commercial computers were usually variable word length (character oriented) machines and used a binary coded representation of decimal information. The System/360 uses binary as well as BCD and has both fixed and variable length fields.

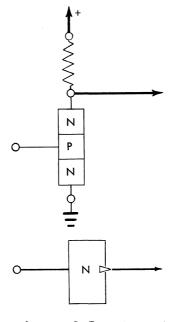

The System/360 also uses a new technology known as solid logic technology (SLT). It consists of printed circuitry instead of physical wiring on the back panel. It also uses packaged logic circuits. This new technology reduces manufacturing costs, increases reliability and reduces maintenance time.

In Figure 1-7, you can see the components that make up a data processing system.

Figure 1-7. Typical Data Processing System

### Primary Storage

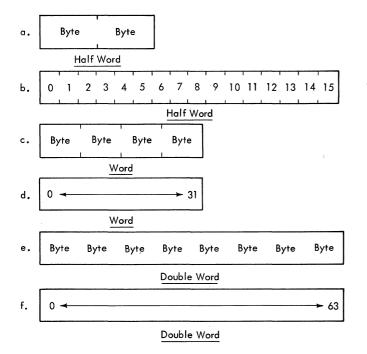

- The smallest main storage addressable unit is called the byte.

- A byte consists of 8 data bits and 1 parity bit. Cdd parity is maintained.

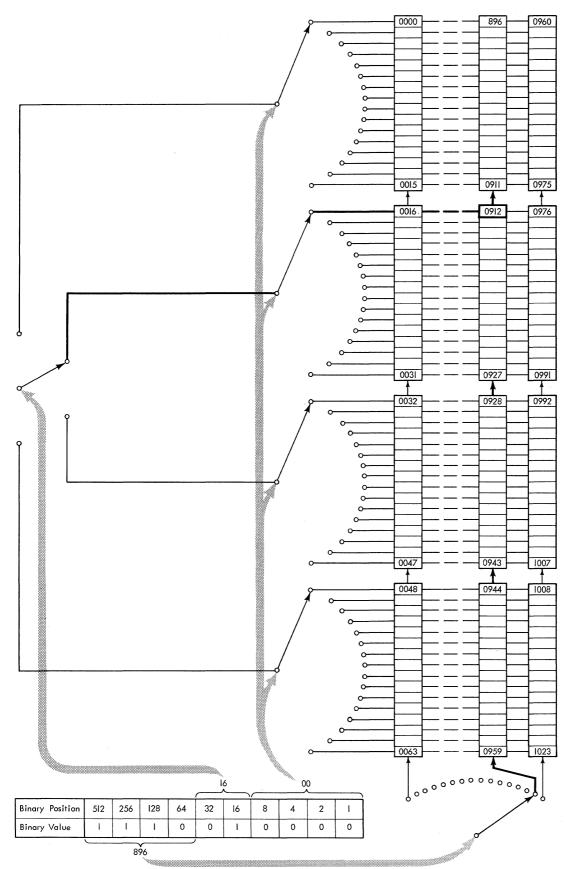

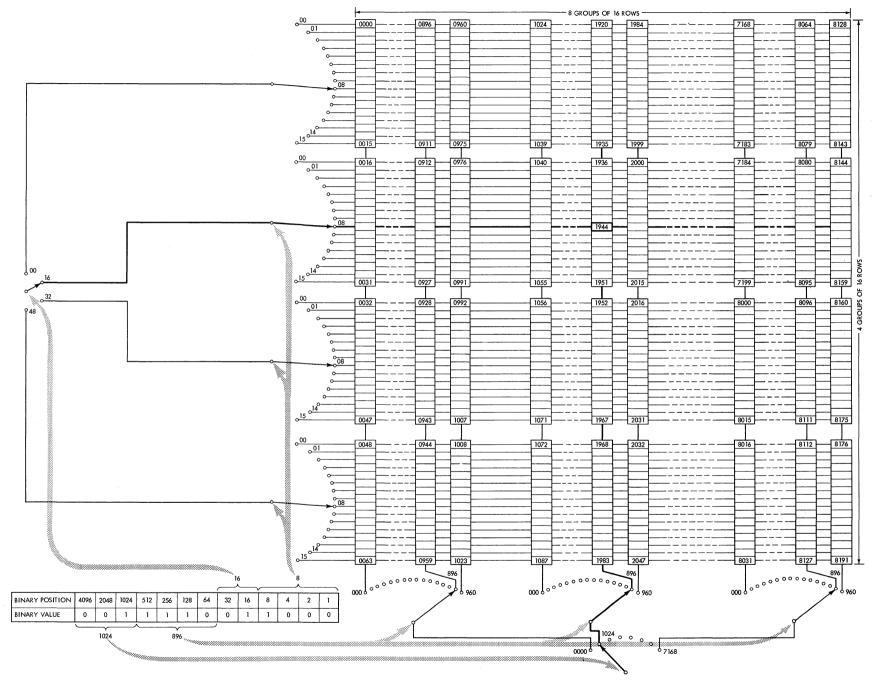

- The System/360 uses a 24 bit binary address.

- A byte can represent characters, binary numbers, or many different codes.

- A half word is 2 bytes.

- A word is 4 bytes.

- A double word is 8 bytes.

- Data can be fixed length (2, 4, or 8 bytes) or variable length (up to 256 bytes).

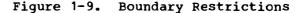

- Fixed length data must reside on the correct boundaries in main storage.

- A program check occurs if the boundary restriction is violated.

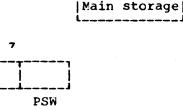

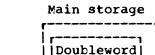

The primary storage is that section of a computing system that contains the program to be executed as well as the data to be processed. All data entering the system goes into the primary storage before it can be processed. After processing, the data must be placed back into primary storage before it can be sent to an output device. Primary storage is sometimes referred to as main storage. The System/360 also uses ferrite cores for its main storage.

The smallest addressable unit of main storage in the System/360 is called the byte. The byte consists of eight data bits and one parity bit.

|   |   | - 1 | T |  |   |   | <b>F</b> -1 |

|---|---|-----|---|--|---|---|-------------|

|   |   | 1   | 1 |  |   |   |             |

|   |   |     |   |  |   |   | İP          |

| 7 | 6 |     |   |  | 2 | 0 | Ρ           |

#### The Byte

As can be seen in the preceding example, the left-most bit of a byte is the parity bit. The IBM System/360 maintains odd parity for all bytes in main storage. The parity bit is added or removed to make the total bit-count odd for any byte. This method of coding provides convenient error checking: an even number of bits indicates an error condition.

One thing you should get clear is that the byte is the smallest addressable unit of main storage. This means that each and every byte of main storage is individually addressable. To read out the first eight bytes of main storage, the Model 30 takes eight storage cycles. For each cycle, the Model 30 changes its storage address by one, using addresses 0-7.

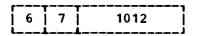

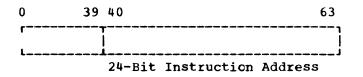

Main storage addresses start with 00000 for the first byte and increase by one for each byte in the particular main storage unit. Valid storage addresses for a Model 30 would start with 00000 and continue up to 65535. To allow for program compatibility as well as for future growth, the System/360 uses a 24 bit binary address to address main storage. age. A 24-bit binary number allows us to go as high as 16777215 for You can see the future an address. growth that is possible here! A binary rather than a binary coded decimal address is used because it is more efficient with large addresses.

The 24-bit binary address that would be used to address byte location 0007 is written 000000000000000000111.

You are probably a little perplexed about this byte by now. You know that a byte consists of eight data bits and a parity bit. You know that each byte is individually addressable by a 24 bit binary address! You know that main storage size can vary from approximately 8K bytes on a Model 30 to over 500K bytes on a Model 70. You know that the Model 30 has access to one byte per storage cycle.

However, you are probably asking

yourself:

Is the byte a character?

Is it a binary number?

Just what is it?

The answer to these questions is simple. The eight data bits of a byte can be coded to represent characters, binary numbers, or anything you want it to be. The instructions of the System/360 are many and varied. Some of the instructions treat bytes as charac-Some instructions treat bytes as ters. part of a binary number. So the answer to the question, "What does a byte represent?" is: It depends on the particular instruction being executed at the time. This question will be answered more to your satisfaction after you study the data formats and some of the instructions.

As was previously stated, the System/360 is a general purpose data processing system. As such it is designed to operate with fixed length as well as variable length data. The byte as you have already learned is a very versatile unit. It is individually addressable. By further specifying the number of desired bytes, we can have a variable length field in main storage starting and ending at any byte address.

To be truly general purpose, the System/360 must also be capable of operating with fixed length data. Whereas variable length data has a variable number of bytes, fixed length data always has a fixed number of bytes. Let's go on and define these fixed length fields.

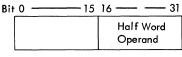

A half word is two bytes in length (Figure 1-8a).

The data bit positions of a half word are numbered 0-15 from left to right (Figure 1-8b).

Notice that the parity bits are not shown. They will not be shown form here on, since they do not represent data. Remember, however, that every byte does contain a parity bit for checking purposes.

A word is 4 bytes long (Figure 1-8c).

The data bit positions of a word are numbered 0-31 from left to right (Figure 1-8d).

A double word is 8 bytes long (Figure 1-8e).

The data bit positions of a double word are numbered 0-63 from left to right (Figure 1-8f).

Figure 1-8. Word Formats

Remember that each byte of a half word, word, or double word carries its own parity bit.

Remember also that it is the instruction being executed that determines whether to consider data as variable or fixed. The instruction also determines in the case of fixed length data whether it is a half word, word, or double word.

Before leaving the definitions of fixed length data, you must learn the restrictions placed on the use of fixed length data.

| Byte<br>0000 | Byte<br>0001 | Byte<br>0002 | Byte<br>0003 | Byte<br>0004 | By <u>t</u> e<br>0005 | Byte<br>0006 | Byte<br>0007 | Byte<br>0008 |

|--------------|--------------|--------------|--------------|--------------|-----------------------|--------------|--------------|--------------|

| Half         | Word         | Half         | Word         | Half         | Word                  | Half         | Word         |              |

| Word Word    |              |              |              |              |                       |              |              |              |

| Double Word  |              |              |              |              |                       |              |              |              |

The rule is that fixed length data must reside on the correct boundaries in main storage (Figure 1-9).

Fixed length data is addressed by the high order (left-most byte) of the field.

- For half words this address must be divisible by two.

- For words this address must be divisible by four.

- For double words this address must be divisible by eight.

Another way of stating this rule is to say the 24 bit binary address:

- 1. Of a half word must have one loworder zero bit.

- Of a word must have two low-order zero bits.

- 3. Of a double word must have three low- order zero bits.

The boundary restriction placed on the use of fixed length fields is a restriction placed on the user. Violation of these rules does not produce a <u>machine</u> check. Instead, violation of these rules is considered a <u>program</u> check.

Because there are other restrictions placed on the programmer, you should be able to identify program checks by type. The type of program check caused by a violation of fixed length boundaries is known as a <u>specification</u> exception. Another exception to valid programming is addressing a byte location that is not available on your particular model of System/360. The largest size main storage that is available on the Model 30 is 65,536 bytes. Any address other than 00000-65535 results in a program check. This type of check is known as an <u>addressing</u> exception.

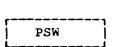

### Central Processing Unit (CPU)

- The two main sections of the CPU are

the control section and (2) the

arithmetic and logical unit (ALU).

- The CPU uses variable field length instructions for storage to storage operations.

- Variable fields can be up to 256 bytes long.

- The CPU uses fixed length instructors for storage to register or register to register operations.

- Fixed length fields can be half-word, word, or double-word fields.

- Register-to-register or storage to register operations use any of 16 general purpose registers.

- Floating point operations use any of 4 double-word floating-point registers

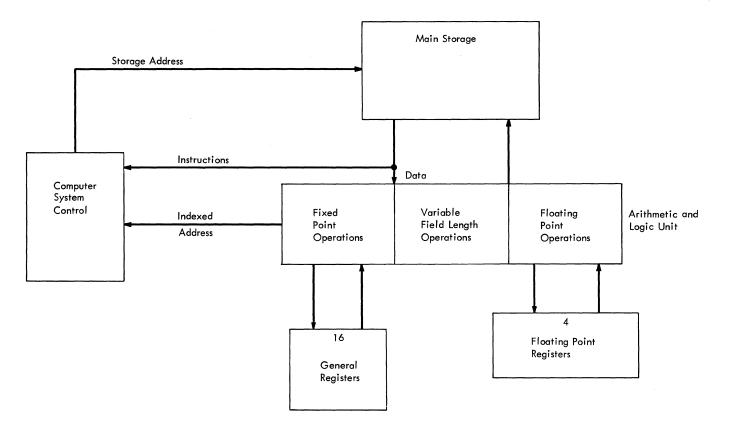

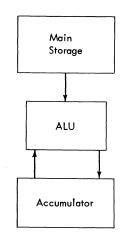

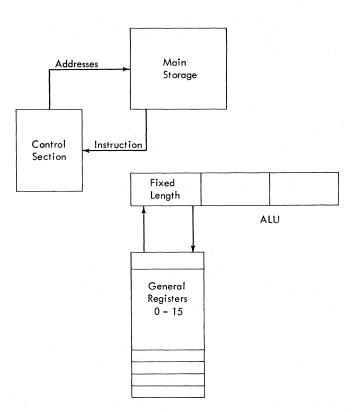

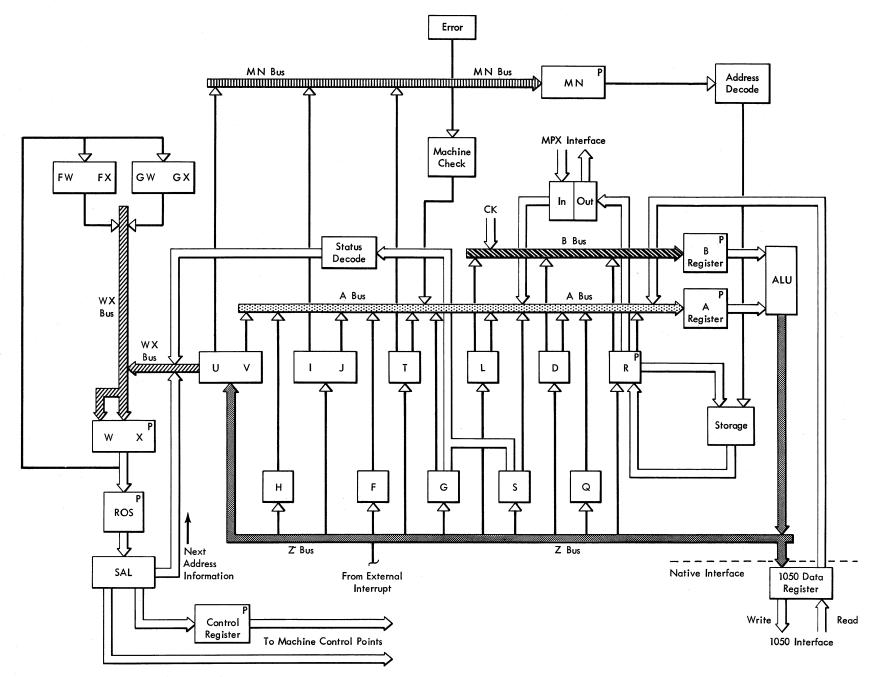

In Figure 1-10, you can see the logical

structure of the CPU for the System/360 and its relationship to the main storage.

There are two main sections in CPU. They are (1) the control section and (2) the arithmetic and logical unit (ALU).

From Figure 1-10, you should be able to see some of the functions of the control section. They are:

- All references to main storage, whether for instructions or for data, are made by the control section.

- 2. During the first part of any instruction, the control section addresses main storage and causes the instruction to be fetched and sent to the control section. The instruction is then decoded by the control section and executed during the latter part.

The ALU contains the circuits necessary for adding and comparing data fields as well as the other circuits necessary for operating on data fields.

As can be seen from Figure 1-10, the ALU can do:

- 1. Variable field length operations.

- 2. Fixed-point operations involving fixed-length fields.

- 3. Floating point operations.

Figure 1-10. Processing Unit Logic Flow

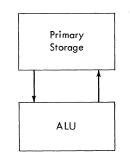

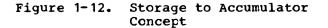

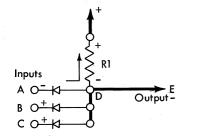

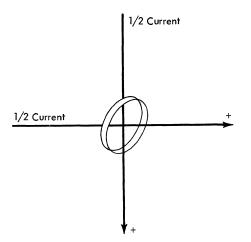

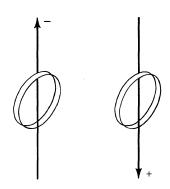

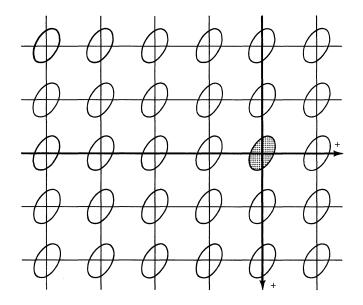

Variable Field Length Operations: In looking at the ALU, let us first consider variable length fields as used in many commercial computers of the past. Two main concepts were used. The storage-to-storage concept was used by computers of the IBM 1401 family. In it the data fields were brought out of main storage, operated upon, and the results went back into main storage (Figure 1-11).

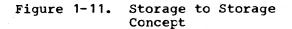

Other computers such as those of the IBM 702-705 family used a storage-to-accumulator concept. The accumulator was a small storage device. The storage medium could be core

Storage to Storage Concept

storage, vacuum tubes or transistorized registers. In the storage to accumulator concept one of the data fields would be in main storage and the other would be in an accumulator. Both fields would be brought out to the ALU, operated upon, and the result would go back into the accumulator (Figure 1-12).

Storage to Accumulator Concept

For its variable length operations the System/360 uses the storage-tostorage storage concept (Figure 1-13).

Figure 1-13. System/360 Storage to Storage Operations

As you have previously learned, variable length fields can start at any byte location in main storage. They are not restricted by storage boundaries as are fixed length operands. However, there fixed length operands. (Data fields are sometimes referred to as operands.) However, there must be some way of indicating to the system the length of the fields. In computers of the past, this was done several ways. The 1401 used a special word mark bit over the high-order position of the The IBM 705-II used zone bits. data. In the System/360 variable length operations use binary and decimal operands. In order to be code independent, System/360 specifies the length of these fields by a length code in the instruction.

The length code can be either 4 or 8 bits long, depending on the instruction. The length code is in binary. As a result the maximum length can be either 16 or 256 bytes. The values of the code is one less than the total number of bytes.

Length code of 0000 = 1 Byte

Length code of 1111 = 16 Bytes

Length code of 11111111 = 256 Bytes

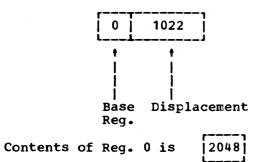

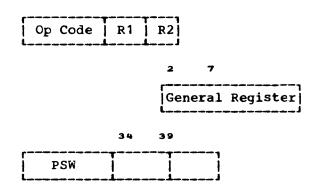

Fixed-Length Operations: When operating on fixed-length fields (such as half words, words, or double words), the System/360 uses the storage-to-accumulator concept. These fixed-length operations use binary operands. For use as accumulators, the System/360 has 16 registers available to the programmer. As these registers can be used for purposes other than accumulating, they are called general registers (Figure 1-14).

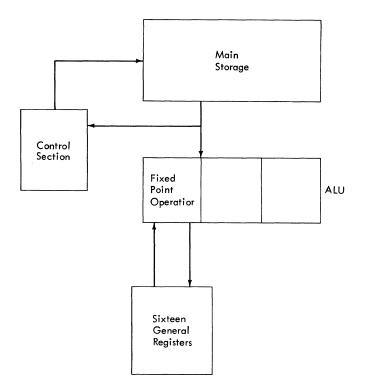

None of the General Registers 0-15 can contain a double word. For those operations that use a double word operand, such as fixed length divide, a pair of adjacent registers are used. In these cases, an even-odd pair of registers (such as 0-1 or 6-7) are used, and the even register is addressed.

In this case bits 0-63 of the double word would be in the registers as shown in Figure 1-16.

Figure 1-14. 16 General Registers

<u>Fixed-length operands</u> in main storage <u>must be on integral boundaries</u> or a program check will occur indicating a specification exception.

These registers are numbered 0-15 and are addressed in an instruction by a 4-bit binary address field.

Being a word in length, a general register can easily contain a half word data field.

As can be seen in Figure 1-15, the bits of a general register are numbered left to right starting with the number 0. Also we can see that a half word operand is placed in the low-order half (bits 16-31) of a General Register.

GENERAL REGISTER

Figure 1-15. General Register

The general registers are also used for purposes other than accumulating. For example, a general purpose register can be used as an index register. Indexing is a form of indirect addressing. An increment contained in an index register is added to the data address in the instruction to form an effective main storage address. Neither the index

register nor the instruction in storage

is changed by indexing.

<u>Register-to-Register:</u> With sixteen general registers, sometimes <u>both</u> fixed length binary operands will be in general registers. In these cases, another data flow concept is used (register-to-register operation, Figure 1-17).

Figure 1-17. System/360 Register to Register Operations

<u>Floating-Point Operation:</u> Floating point is the term given to arithmetic operations involving a fraction and an exponent. For instance:

217,000 can be expressed as:  $.217 \times 10^6$

296,000 can be expressed as: .296 x 10<sup>6</sup>

Fixed point arithmetic would add the numbers thusly:

|   | 217, | 000 |

|---|------|-----|

| ŧ | 296, | 000 |

|   | 513, | 000 |

Floating point arithmetic would do it like this:

$$-217 \times 10^{6}$$

+  $-296 \times 10^{6}$

$-513 \times 10^{6}$

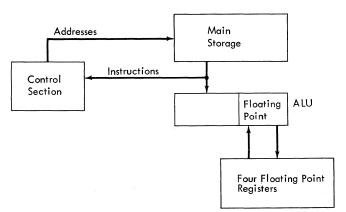

Floating-point arithemetic is most useful for expressing very large numbers and operating on them with much precision. To do floating point arithmetic the System/360 has four floating point registers (Figure 1-18).

### Figure 1-18. Floating Point Registers

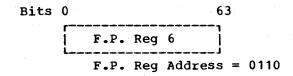

The four floating point registers are numbered 0, 2, 4, 6. These are not the same as general registers 0, 2, 4, 6. The floating point registers are separate registers used only as accumulators during floating point operations.

The floating point registers are double word registers and are addressed by a four bit binary address in floating point instructions.

Logical vs Hardware Structure of System/360: The structure of the System/360 which you have been learning is its logical structure: By this we mean that this is the way the System/360 appears to the programmer. The manner in which this logical structure is implemented will vary between the different models of the System/360. For example:

- In Models 60, 62, and 70 of the System/360, the general and floating point registers are transistor registers.

- In Models 40 and 50 a core array is used. This array is similar to main storage but is a separate physical entity.

- 3. In Model 30 the general and floating point registers are located in the main storage unit. However, they do not use any of the available main

storage addresses. The area of the main storage unit used for registers is called auxiliary storage.

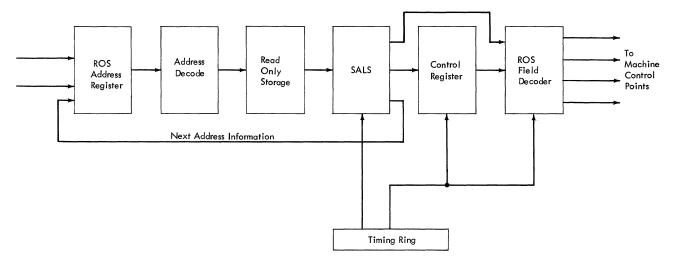

Another example of hardware differences is in the control section of the System/360. In the Model 70, the control section is made up of high speed transistorized circuits. However, other models of System/360 use a capacitor- or a transformer-storage device for most of their control functions. This device is called Read Only Storage (ROS). The ROS is a storage device and cannot be changed by the programmer. It is strictly a control device.

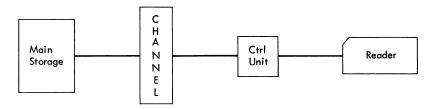

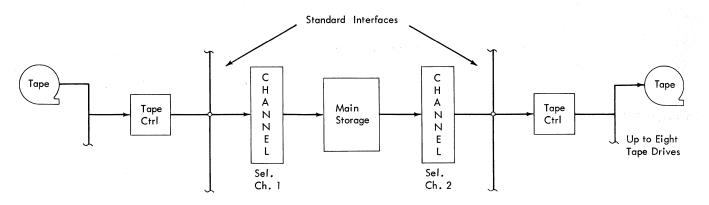

# Channels (Figure 1-19)

- Channels handle data transfers between main storage and I/O devices.

- All I/O devices are connected to channels via a standard interface.

- There are 2 types of channels: selector and multiplexor.

- Selector channels are designed for high data rates.

- Multiplexor channels are designed for low data rates.

One of the main functions of a channel is to handle I/O requests for a main storage cycle. The channel receives data from the I/O devices one byte at a time. When enough data has been received to justify the use of main storage, the channel requests a storage cycle. The amount of data handled varies depending on the particular model of System/360. After the data has been placed in main storage, the channel waits for additional information from the input device. For an output device the procedure reverses. The channel requests a main storage cycle and brings out data. It passes this data to the output device one byte at a time.

Since the channel is taking care of main storage cycles for the I/O device, the central processing unit is now logically free to continue processing instructions. We say that processing is overlapped with the I/O operation.

# Figure 1-19.

Channel Operations

On some models of the System/360, overlapping channel with CPU operations is allowed only at certain times. Once the CPU has started a channel operation, it has to wait for the channel operation to finish before it can continue processing instructions.

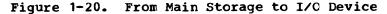

Each I/C device ties into the channel through a control unit (Figure 1-20).

Another name for a control unit is adapter. For some I/O devices the control unit or adapter is built into the device. For other devices, the control unit is external to the device.

Some adapters can control only one I/O device while others can control a number of similar I/O devices. The IBM 1443 Printer Model N1 is an example of an I/O device with a self-contained adapter. The IBM 2803 tape control is an example of a stand-alone adapter which can control up to eight IBM 2401 magnetic tape units (Figure 1-21).

Selector Channels: Selector channels are available on all models of the System/360. The maximum number per model varies from two for a Model 30 to six for a Model 70. The Selector channel is so named because only one I/O device can be selected on the channel at any one time. Once selected, a complete record is transferred over the channel one byte at a time.

Once the record has been transferred, the channel is free to select another I/C device. When a channel is transferring an entire record between main storage and an I/O device, it is said to be operating in burst mode. Because a selector channel always transfers an

Figure 1-21. Control Units and Adapters

Figure 1-22. Dual Channel Operation

entire record, it can only operate in burst mode.

Although only one I/O device can be operating on a selector channel at any one time, multiple selector channels can be in operation simultaneously. Figure 1-22 shows an input record being read in from tape over selector channel 1 at the same time an output record is being transferred over selector channel 2.

Selector channels are designed to operate with high data rates. I/O devices such as magnetic tape, disk units, drums, and buffered card devices are the devices most likely to be connected to a selector channel.

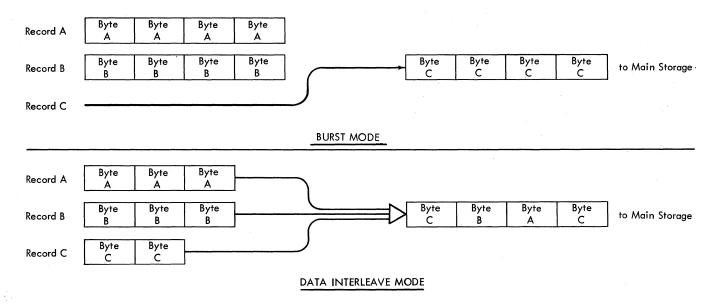

<u>Multiplexor Channels:</u> A multiplexor channel is designed to operate with a number of I/O devices simultaneously on a byte basis. That is, several I/O devices can be transferring a record over the multiplexor channel, timesharing it on a byte basis. When the multiplexor channel is being time shared by several devices, it is said to be operating in data-interleave mode. The multiplexor channel can also operate in burst mode for higher-speed units (Figure 1-23).

Figure 1-23. Burst Mode vs. Multiplex Mode

A comparison of <u>burst</u> versus <u>multiplex</u> mode can be seen in Figure 1-23.

To handle data flow from an I/O device, the channel needs to know certain information such as:

- 1. In which direction must data flow (input or output)?

- 2. Where in main storage should data be placed or taken from?

- How many bytes should be sent to an output device or accepted from an input device?

Information of this type is contained in the I/O command addressed to a particular I/O device. For a selector channel which operates with only one I/O device at time, this information may be placed in the channel registers and left there

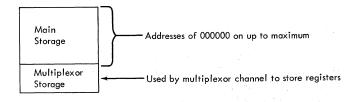

Cn a multiplexor channel it is possible to have I/O devices operating simultaneously. To have all this information in the multiplexor channel's registers would require a set of registers for each I/O device. Therefore, the multiplexor channel keeps this information in a compact storage area known as auxiliary storage. Auxiliary storage is part of the physical core array used for the main storage unit.

Auxiliary storage does <u>not</u> use any of the main storage addresses (Figure 1-24).

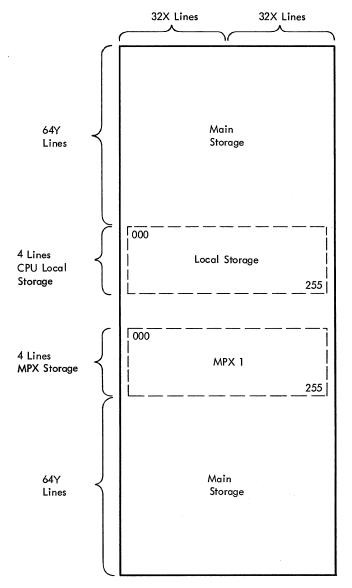

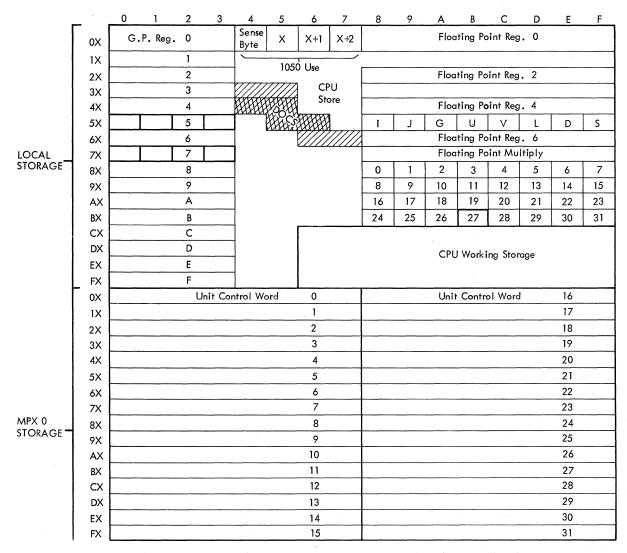

Figure 1-24. Local Storage

It is a physical part of the core array used by the main storage unit. However, logically auxiliary storage is separate from local storage. On the Model 30, part of the auxiliary storage is used to contain the sixteen general registers mentioned previously.

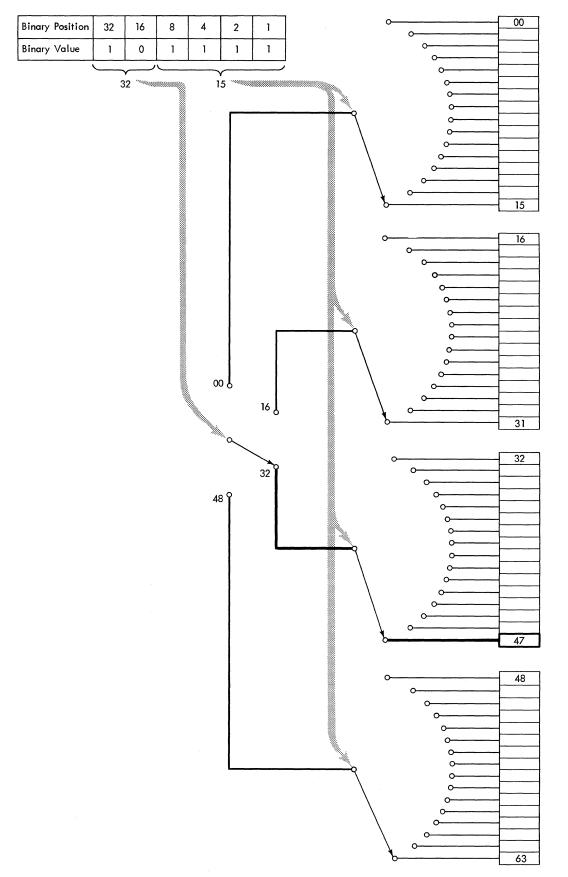

#### NUMBERING SYSTEMS

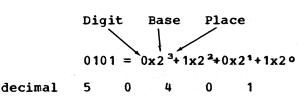

Numbering systems were developed by man so that he could count. A number basically is a group of symbols. Each symbol in a number has a definite place and value.

The place value of the digit symbol is some power of the base. The power of the base starts with zero and increases by one from right to left. The base of the decimal numbering system in common usage is ten (10).

Example:

$444 = 4x10^{2}+4x10^{1}+4x10^{\circ} (10^{\circ} = 1)$ Digit Base Place

444 = 400+40+4

The maximum value of a symbol is always one less than the base. In our above example, the base is ten (10) so the maximum value is nine (9). If when adding two symbols the total exceeds the base, a carry (value of one) is added to the next higher place.

Example:

6 +<u>6</u> Carry 12

### BASIC BINARY

Units of Binary

This is a numbering system using a base of two. All of the rules which we discussed for a numbering system apply here. Let us check.

The base is two so the maximum symbol value is one. The binary numbering system has only two valid symbols, 0 and 1.

Example:

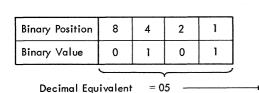

### **Binary-Decimal Conversion**

The decimal place values of a six position binary number are:

| 32   | 16   | 8                | 4    | 2    | 1    |

|------|------|------------------|------|------|------|

| 1x25 | 1x24 | 1x2 <sup>3</sup> | 1x2² | 1x21 | 1x2° |

| 1    | 1    | 1                | 1    | 1    | 1    |

The preceding binary number equals 63 when the place values are added.

The following chart shows conversion from decimal to binary:

| <u>Decimal</u> | <u>Binary</u> |

|----------------|---------------|

| 0              | 0000          |

| 1              | 0001          |

| 2              | 0010          |

| 3              | 0011          |

| 4              | 0100          |

| 5              | 0101          |

| 6              | 0110          |

| 7              | 0111          |

| 8              | 1000          |

| 9              | 1001          |

| 10             | 1010          |

| 11             | 1011          |

| 12             | 1100          |

| 13             | 1101          |

| 14             | 1110          |

| 15             | 1111          |

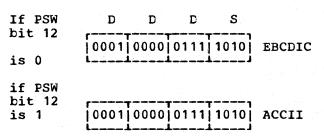

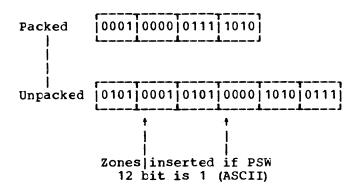

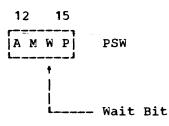

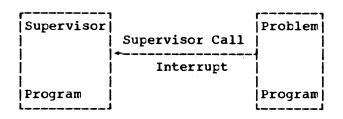

ZONED DECIMAL - EXTENDED BINARY CODED DECIMAL (BCD)

Zoned decimal is a decimal number representing a BCD alphanumeric character. A zoned decimal has eight places divided into two 4-place sections. The highorder places represent the alphanumeric zone bit and the low-order places represent the alphanumeric decimal.

Example: 1101 0111=P

11 7 (zone) (digit) PACKED DECIMAL

The packed decimal coding system allows two decimal digits to be stored in one byte-location:

Example:

| Binary<br>Position    | 8421 | 8421 |

|-----------------------|------|------|

| Binary<br>Value       | 1001 | 0011 |

| Decimal<br>Equivalent | 9    | 3    |

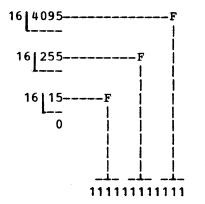

#### HEXADECIMAL

The hexadecimal system uses the decimal value of sixteen as its base.

16<sup>3</sup> 16<sup>2</sup> 16<sup>1</sup> 16<sup>0</sup> 4096 256 16 1

In the hexadecimal system you can count to fifteen before a carry occurs.

To express the values ten to fifteen, the symbols A-F are used. Thus, the sixteen hexadecimal symbols are: 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F.

The following charts lists some sample decimal to binary to hexadecimal conversion.

| <u>Decimal</u> | Bin  | ary  | <u>Hexadecimal</u> |

|----------------|------|------|--------------------|

| 1              |      | 0001 | 1                  |

| 5              |      | 0101 | 5                  |

| 9              |      | 1001 | 9                  |

| 10             |      | 1010 | Α                  |

| 11             |      | 1011 | В                  |

| 12             |      | 1100 | С                  |

| 13             |      | 1101 | D                  |

| 14             |      | 1110 | E                  |

| 15             |      | 1111 | F                  |

| 16             | 0001 | 0000 | 10                 |

| 17             | 0001 | 0001 | 11                 |

| 18             | 0001 | 0010 | 12                 |

| 19             | 0001 | 0011 | 13                 |

| 20             | 0001 | 0100 | 14                 |

| 30             | 0001 | 1110 | 1E                 |

| 40             | 0010 | 1000 | 28                 |

| 50             | 0011 | 0010 | 32                 |

| 60             | 0011 | 1100 | 3C                 |

Examples: Express the hexadecimal (hex) numbers as a sum of terms in decimal. hex: 482=4x162+8x161+2x160 =4x256+8x16+2x1 = 1024+128+2 = 1154 decimal hex: 8C6=8x162+12x161+6x160 =8x256+12x16+6x1 =2048 +192 +6 = 2246 decimal

Rules for Converting from Decimal to Hexadecimal

- Divide decimal number by the new base (16).

- 2. Remainder becomes low order of new number.

- 3. Divide quotient by the new base (16).

- 4. Remainder becomes next digit of new number.

- 5. Repeat steps 3 and 4 until a quotient of zero is obtained.

Example: Decimal 456 to hexadecimal 1C8

1

|       |           |    | 1C8<br>+++<br>                            |

|-------|-----------|----|-------------------------------------------|

| 0     |           |    |                                           |

| 16 1  | Remainder | of | 1                                         |

| 16 28 | Remainder | of | 12 or C                                   |

| 6 456 | Remainder | of | ز<br>ــــــــــــــــــــــــــــــــــــ |

# Binary - Hexadecimal Conversion

The base of the binary system is 2<sup>1</sup> while the hexadecimal system uses a base of 2<sup>4</sup> (16). There is a direct 4 to 1 relationship (2<sup>4</sup> to 2<sup>1</sup>) between the exponents of the two bases. Every hexadecimal digit becomes four binary digits. Every four binary digits in turn can be converted to a single hexadecimal digit.

| Hexadecimal | 8    | 3       | - 4   | 9    | E    |

|-------------|------|---------|-------|------|------|

| Binary      | 1000 | 1011    | 0100  | 1001 | 1110 |

| Einary      | 1000 | 1.0 1 1 | 0.100 | 1001 |      |

### FLCATING POINT

#### Description

Various computer computations frequently involve lengthy and complex calculations in which it is necessary to manipulate numbers that may vary widely in magnitude. To obtain a meaningful answer, problems of this type usually require that as many significant digits as possible be retained during calculation and that the decimal point always be properly located. When applying such problems to a computer, several factors must be taken into consideration, the most important of which is the decimal point location.

Generally speaking, a computer does not recognize the decimal point present in any quantity used during the calculation. Thus, a product of 414154 will result regardless of whether the factors are 9.37 X 44.2, 93.7 X 0.442, or 937 X 4.42, etc. A system must be employed in which information regarding the magnitude of all numbers accompanies the quantities in the calculation. Thus, if all numbers are represented in some standard, predetermined format which instructs the computer in an orderly and simple fashion concerning the location of the decimal point, and if this representation is acceptable to the routine doing the calculation, then quantities which range from minute fractions having many decimal places to large whole numbers having many integer places can be handled. The arithmetic system used, in which all numbers are expressed in a format having the feature just described, is called floating point arithmetic.

The notation used in floating point arithmetic is basically an adaptation of the scientific notation widely used today. In scientific work, very large or very small numbers are expressed as a number, between one and ten, times a power of ten. Thus 427.93456 is written as 4.2793456 X 10<sup>2</sup> and 0.0009762 as 9.762 X 10-4.

The System/360 uses hexadecimal floating point and the hexadecimal point

of all numbers is placed to the left of the high-order (leftmost) nonzero digit. Hence, all quantities may be thought of as a hexadecimal fraction times a power of 16. In addition to the advantages inherent in scientific notation, the use of floating point numbers during processing eliminates the necessity of analyzing the operations to determine the positioning of the decimal point in intermediate and final results since the decimal point is always immediately to the left of the high-order nonzero digit in the fraction.

Floating-point arithmetic simplifies programming by automatically maintaining hexadecimal point placement (scaling) during computations in which the range of values used varies widely or is unpredictable.

The key to floating-point data representation is the separation of the significant digits of a number from the size (scale) of the number. Thus, the number is expressed as a fraction times a power of 16.

A floating-point number has two associated sets of values. One set represents the significant digits of the number and is called the fraction. The second set specifies the power (exponent) to which 16 is raised and indicates the location of the binary point of the number. The term Mantissa is often used instead of fraction. Characteristic is another term for exponent.

## <u>Sign</u>

These two numbers (the fraction and exponent) are recorded in a single word or double-word.

Since each of these two numbers is signed, some method must be employed to express two signs in an area that provides for a single sign. This is accomplished by having the fraction sign use the sign associated with the word (or double word) and expressing the exponent in excess 64 arithmetic. That is, the exponent is added as a signed number to 64. Above 64 is a positive exponent and below 64 is a negative exponent. The resulting number is called the characteristic. The characteristic can vary from 0 to 127, permitting the exponent to vary from -64 through 0 to +63. This

provides a decimal range of  $7.2 \times 10^{75}$  to 2.4 X  $10^{-78}$ .

Floating-point data in the System/360 may be recorded in short or long formats, depending on the precision required. Both formats use a sign bit in bit position 0, followed by a characteristic in bit positions 1-7. Shortprecision floating-point data operands contain the fraction in bit positions 8-31; long-precision operands have the fraction in bit positions 8-63.

Short-Precision Floating-Point Format

| s | Ì | Exponent | Fraction |

|---|---|----------|----------|

| 0 | 1 | 78       | 31       |

Long-Precision Floating Point Format

| s | 1 | Exponent | r | Fraction |

|---|---|----------|---|----------|

| 0 | 1 | 7        | 8 | 63       |

The sign of the fraction is indicated by a zero or one bit in bit position 0 to denote a positive or negative fraction, respectively.

#### ARITHMETIC PRINCIPLES

BINARY FIXED POINT

### Positive and Negative Numbers

A fixed point number has a signed value recorded as a binary integer. The first bit position (high order) holds the sign of the number, with the remaining bit positions used to designate the magnitude of the number.

Positive fixed-point numbers are represented in true binary form with a zero sign bit. Negative fixed-point numbers are represented in two's complement notation with a one bit in the sign position. In all cases, the bits between the sign bit and the leftmost significant bit of the integer are the same as the sign bit (i.e., all zeros for positive numbers, all ones for negative numbers).

Negative fixed-point numbers are formed in two's complement notation by inverting each bit of the positive binary number and adding one. For example, the true binary form of the decimal value (plus 26) is made negative (minus 26) in the following manner:

| S | INTEGER |  |

|---|---------|--|

|   |         |  |

| +26    | 0 0000000 | 00011010 |               |

|--------|-----------|----------|---------------|

| Invert | 1 1111111 | 11100101 |               |

| Add 1  |           | 1        |               |

| -26    | 1 1111111 | 11100110 | (Two's com-   |

|        |           |          | plement form) |

This is equivalent to subtracting the number from 1 00000000 00000000.

## **Binary Addition**

|   |   | 0 | + | 0 | = | 0 |      |   |       |    |    |

|---|---|---|---|---|---|---|------|---|-------|----|----|

|   |   | 1 | + | 0 | = | 1 |      |   |       |    |    |

|   |   | 0 | + | 1 | = | 1 |      |   |       |    |    |

|   |   | 1 | + | 1 | = | 0 | with | а | carry | of | 1  |

| 1 | ŧ | 1 | + | 1 | = | 1 | with | а | carry | of | 1. |

The following addition examples illustrate two's complement arithmetic. Only eight bit positions are used. The left-most position is the sign position, the next position to the right is the high-order position.All negative numbers are in two's complement form.

An overflow condition occurs when carries out of the sign position and high order numeric position disagree. When overflow occurs the sign of the result is incorrect. This condition must be noted and properly used by the processor.

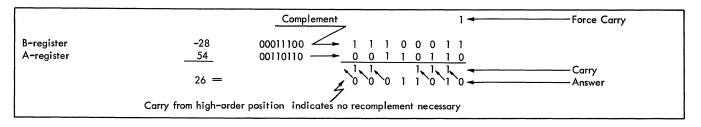

When there is no carry out of the high order position, the answer is in complement form. This is the final answer in fixed point binary subtract. The model 30 does not recomplement. Examples:

# sign indication.

| S                                                                                        | COMMENTS                                                                                                                                                     |                                                                                                                              |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| _                                                                                        |                                                                                                                                                              | Dinama Cubhrachian                                                                                                           |

| +37 = 00111001<br>+35 = 00100011<br>+92 = 01011100                                       | No high-order carry,<br>no sign-position carry,<br>no overflow.                                                                                              | Binary Subtraction                                                                                                           |

|                                                                                          | Result is in true form.                                                                                                                                      | $\begin{array}{r} 678 \\ -456 \\ 222 \end{array} \begin{array}{r} 001010100110 \\ +111000111000 \\ 000011011110 \end{array}$ |

| $\begin{array}{r} +57 = 00111001 \\ -35 = 11011101 \\ +22 = 00010110 \end{array}$        | High-order carry,<br>sign-position carry,<br>no overflow.                                                                                                    |                                                                                                                              |

|                                                                                          | Result is in true form.                                                                                                                                      | Notice that binary<br>adding the two's co<br>ber to be subtracte                                                             |

| -57 = 11000111                                                                           | No high-order carry,<br>no sign-position carry,<br>Bit in sign position<br>indicates result is in                                                            | Examples of Fixed P                                                                                                          |

|                                                                                          | complement form.                                                                                                                                             | The following are 1<br>numbers. The first<br>tive number and the                                                             |

| $\begin{array}{rrrr} -57 &=& 11000111\\ -35 &=& 11011101\\ -92 &=& 10100100 \end{array}$ | High-order carry,<br>sign-position carry,<br>no overflow.                                                                                                    | negative number.                                                                                                             |

|                                                                                          | Bit in sign position<br>indicates result is in<br>complement form.                                                                                           | $\begin{array}{rrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrrr$                                                                         |

| -92 = 10100100                                                                           | High-order carry,<br>sign-position carry,<br>overflow. No bit in<br>sign-position indicates<br>result is in true form,<br>but overflow sign<br>is incorrect. | Table 1 shows 32<br>numbers. The first<br>tive number that ca<br>32 bits, and the la<br>negative number.                     |

| +92 = 01011100                                                                           | High-order carry, no<br>sign-position carry,<br>overflow. Sign-position<br>indicates a complement<br>result, but overflow<br>signals are incorrect           |                                                                                                                              |

|                                                                                          |                                                                                                                                                              |                                                                                                                              |

ce that binary subtraction is simply ing the two's complement of the num-to be subtracted.

# ples of Fixed Point Numbers:

following are 16-bit fixed-point ers. The first is the largest posinumber and the last, the largest tive number.

| 215 -1 | =  | 32,737  | =0  | 11111111 | 11111111 |

|--------|----|---------|-----|----------|----------|

| 20     | =  | 1       | =0  | 00000000 | 0000001  |

| 0      | =  | 0       | = 0 | 00000000 | 00000000 |

| -20    | =  | -1      | =1  | 11111111 | 11111111 |

| -215   | =- | -32,768 | =1  | 00000000 | 00000000 |

able 1 shows 32-bit fixed-point ers. The first is the largest posinumber that can be represented by bits, and the last is the largest ative number.

| NUMBE         | R | DI | ECIM       | AL         | da dala nije daja daja | S | <br>INTEGER                             | <br>                                        |

|---------------|---|----|------------|------------|------------------------|---|-----------------------------------------|---------------------------------------------|

| 231-          | • | 2  | 147        |            | 647                    |   |                                         | 11111111                                    |

| 216           | H |    |            | 65         | 536<br>1               | - |                                         | <br>000000000000000000000000000000000000000 |

| 0             | = |    |            |            | 0                      |   |                                         | 00000000                                    |

| -2º<br> -21   | = |    |            |            | -1<br>-2               |   |                                         | 111111111                                   |

| -216          | = | -  |            | -65        |                        |   |                                         | 00000000                                    |

| -231<br> -231 |   |    | 147<br>147 | 483<br>483 | 647<br>648             |   | 000000000000000000000000000000000000000 | <br>00000001                                |

Table 1. Fixed Point Numbers

The following is an example of hexadecimal complement addition. The general method is the same as binary but the base is sixteen.

> Problem: E7A4 -<u>A48E</u>

First, convert the number to be subtracted to its sixteen- complement.

> FFFF -<u>A48E</u> 5B71 +1 5B72

Now, add the sixteen's complement of A48E to E7A4.

|        | E | 7 | A | 4 |

|--------|---|---|---|---|

| +      |   |   |   |   |

| Carry+ | 4 | 3 | 1 | 6 |

Presence of the high-order carry means the answer is in true form. If there had been no carry, the result would have been in complement form.

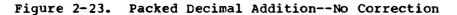

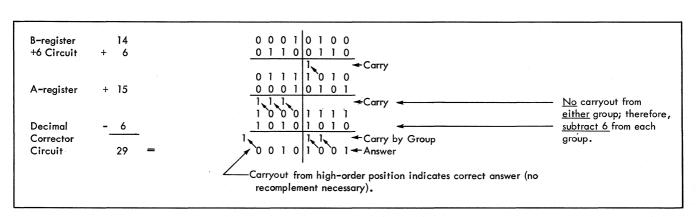

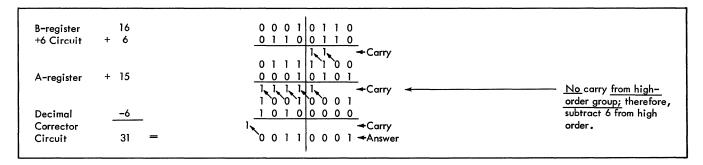

#### PACKED DECIMAL

#### Sign-Operation Analysis

Before any packed decimal arithmetic can take place, a sign- operation analysis must be performed. The result of this analysis determines whether the operation is to be a true add or a complement add. There are three conditions that are analyzed to determine the type of operation. These are:

| 1. | operation<br>r subtract | + or - |

|----|-------------------------|--------|

|    |                         |        |

- 2. sign of first operand: + or -

- 3. sign of second operand: + or -

An even number of minus signs calls for a true-add operation to combine the two operands. An odd number of minus signs calls for a complement-add operation to combine the two operands. Thus, eight conditions can occur. These eight are analyzed as follows:

| First   | Operation | Second  | True or    |

|---------|-----------|---------|------------|

| Operand | Sign      | Operand | Complement |

|         |           |         | _          |

| +X      | +         | +Y      | True       |

| -x      | +         | +Y      | Complement |

| -X      | +         | -Y      | True       |

| +X      | +         | -Y      | Complement |

| +X      | -         | +Y      | Complement |

| -X      | -         | +Y      | True       |

| -X      | -         | -Y      | Complement |

| +X      | -         | -Y      | True       |

The signs of the operands are maintained in the low-order half byte (four bit positions). The actual bit-coding of the sign depends on the data-coding scheme being used.

### Packed-Decimal True Add

In the packed-decimal data format, we want each four bits to represent one decimal digit. The range of this decimal digit is, of course, 0 - 9. However, four bits with the packed-decimal value of 1, 2, 4, and 8 can represent any decimal number from 00 to

15. If we are simply storing packeddecimal data, no problem exists because we make sure that the digit we store at each packed decimal location is in the range 0 to 9. However, if we add two packed-decimal digits together, and their total exceeds nine, we are in trouble. Remember that in a decimal system, we wish to carry from the units position to the tens position when the units total exceeds nine. Using the packed-decimal system just described, if we added two decimal digits together, and if their total exceeded nine, the result would be in hexadecimal form. For example, if we added nine and four, the result would be 13, instead of three with a carry. To compensate for this discrepancy between the actual capacity of the 4-bit packed-decimal digit (00-15) and the desired capacity of the 4-bit packed decimal digit (0-9), we add a correction factor of six to our rules for true odd.

#### Packed-Decimal True Add

The following general rules for packeddecimal true add provide decimal correction as mentioned previously.

- Add six to each packed-decimal digit (4-bit group) of the first operand.

- Add the result to the second operand. This should be a conventional binary add, allowing carries from one 4-bit group to the next.

- 3. Now, considering each 4-bit group (packed-decimal digit) separately, subtract six from each group where no high-order carry occurred. If a high-order carry <u>did</u> occur, add 0000 to that 4-bit group. Remember, that to subtract six really means complement add six. The result will be the correct decimal number in true form.

| Example:  | 16 = First operand<br>$\frac{18}{34}$ = Second operand<br>$\frac{34}{34}$ = Result of true add |

|-----------|------------------------------------------------------------------------------------------------|

| 8421 8421 | Packed-decimal value                                                                           |

| 0001 0110 | First operand                                                                                  |

| $\begin{array}{c} 0110 \\ 0111 \\ 1100 \end{array}$              | Add six per Rule 1                          |   |

|------------------------------------------------------------------|---------------------------------------------|---|

| 0001 1000                                                        | Second operand                              |   |

| NC C<br>1001 0100                                                |                                             |   |

| $\begin{array}{c} 1010 & 0000 \\ \hline 0011 & 0100 \end{array}$ | Subtract six per Rule<br>Result of true add | 3 |

### Packed-Decimal Complement Add

The following general rules are for packed-decimal complement add. Notice that the necessary correction factor of six is employed differently than in the previous example of true add.

- Develop the binary complement of the second operand.

- 2. Add the complement of the second operand to the first operand.

- 3. Considering each 4-bit group (packed-decimal digit) separately, subtract six from each group where no high-order carry occurred. If a high-order carry occurred, add 0000 to that 4-bit group. Remember, that to subtract six, you must add the binary complement of six (1010).

- If there is a carry out of the high-4 order group of four bits at the completion of the original add (Rule 2), the answer will be in true form. If there is no carry out of the high-order group at the completion of the original add, the answer will be in complement form and will have to be recomplemented. To obtain the correct result when recomplementing, we must subtract six from each 4-bit group of the recomplemented number. To condition this correction operation, we must first add the recomplemented number to zero to give us the no-carry indication and apply Rule 3.

Note: When subtracting six from each 4-bit group, any carry from a group is ignored. Example: Packed-Decimal Complement Add 1st Operand +49 2nd Operand -92 +49 = 0100 1001-92 =1001 0010 0110 1110 Complement 2nd Oper. 0100 1001 Add 1st Cper. NC C NC From High order 1011 0111 Position indicates Recomplement Rule 4 1011 0111 1010 0000 Rule 3 0101 0111 1010 1001 Recomplement 0000 0000 Add to Zero Rule 4 NC NC 1010 1001  $-43 = \frac{1010}{0100} \frac{1010}{0011}$  Rule 3 Result

### FLCATING-POINT ARITHMETIC

#### Description.

Floating-point is basically a mathematical shorthand by which numbers are expressed as a fraction and an exponent. This notation is an adaptation of the scientific notation used today. In scientific work, very large or very small numbers are expressed as some number one through ten times a power of ten.

Example  $427.93456 = 4.2793456 \times 10^{2}$ 0.0009762 = 9.762 × 10<sup>-4</sup>

System/360 uses hexadecimal floatingpoint, and the decimal point is always to the left of the high-order digit. The hexadecimal fraction may be thought of as a number (base 16) X a power of 16.

Decimal numbers must first be converted to numbers the system may use in floating-point operations. The sign of the fraction will be noted in the sign position of the floating-point word, a 0 for plus a 1 for minus. The sign of the exponent will be contained in the characteristic which will represent the exponent and its sign.

To develop the characteristic, the exponent is expressed in excess 64 arithmetic. The signed exponent is algebraically added to 64. A result above 64 indicates a positive exponent; a result below 64 indicates a negative exponent.

Conversion Example:

- 1. The decimal number must be separated into a decimal integer and a decimal fraction. 123.725 = 123+.725

- The decimal integer is converted to its hexadecimal representation. decimal 123 = hexadecimal 7B

- The decimal fraction is converted to its hexadecimal representation. decimal .725 = hexadecimal .2D5

- 4. Combine the integer and the fraction and express as a fraction times a power of 16. 7B.2D5 = .7B2D5 X 162

- 5. Develop the characteristics and convert to binary 64+2 = 66 = 1000010

- 6. The fraction is converted to binary and grouped hexadecimally.

.7B2D5 = 0111 1011 0010 1101 0101

- 7. The characteristic and the fraction are stored in floating-point format. The sign position contains the sign of the fraction

- Sign Characteristic 0 1000010

<u>Fraction</u> 0111 1011 0010 1101 0101 00

System/360 provides four floatingpoint registers, each eight bytes in length, for use in floating-point operations. The first operand of any floating-point instruction is always contained in one of these registers. The result of a floating-point operation replaces the first operand except in a store operation.

### <u>Normalization</u>

A quantity can be represented with the greatest precision by a floating-point number of given fraction length when that number is normalized. A normalized floating-point number has a nonzero high-order hexadecimal fraction digit. The process of normalization consists of shifting the fraction left until the high-order hexadecimal digit is nonzero and reducing the characteristic by the number of hexadecimal digits shifted. A zero fraction cannot be normalized, and its associated characteristic therefore remains unchanged when normalization is called for.

Normalization usually takes place when the intermediate arithmetic result is changed to the final result. This function is called postnormalization. In performing multiplication and division, the operands are normalized before the arithmetic process. This function is called prenormalization.

Floating-point addition and subtraction may be performed with or without normalization.

When an operation is performed without normalization, high-order zeros in the result fraction are not eliminated. The result may or may not be normalized, depending on the original operands.

In both normalized and unnormalized operations, the initial operands need not be in normalized form.

#### Floating-Point Addition and Subtraction.

Addition or subtraction of two floatingpoint numbers consists of characteristic comparison and fraction addition. The characteristics of the two operands are compared, and the fraction with the smaller characteristic is right shifted; its characteristic is increased by one for every hexadecimal digit shift (four binary places), until the two characteristics agree. The fractions are then added algebraically to form an intermediate sum. Subtraction differs here only in that the sign of the second operand is inverted before fraction addition.

Normalization may be called for in either addition or subtraction. Normalization consists of shifting the fraction left and decreasing the characteristic one for every hexadecimal digit shift.

### Floating-Point Multiply and Divide

The multiplication of two floating-point numbers consists of a characteristic addition and a fraction multiplication. The sum of the characteristics less 64 is used as the characteristic of an intermediate product.

The product fraction is normalized by prenormalizing the operands before the operation, and postnormalizing the intermediate result if necessary.

Division of two floating-point numbers consists of subtracting the characteristics and dividing the fractions. The difference between the dividend and divisor characteristics plus 64 is used as an intermediate characteristic.

The quotient fraction is normalized by prenormalizing the operands before the operation. Postnormalizing the intermediate quotient is never necessary.

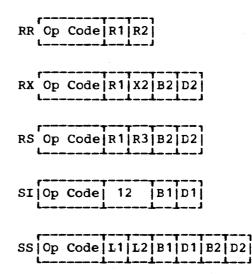

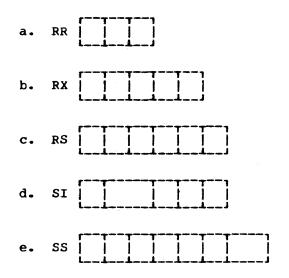

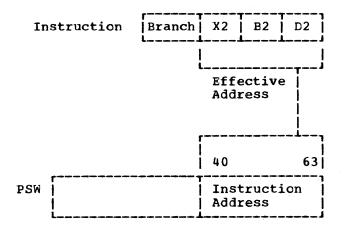

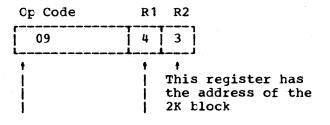

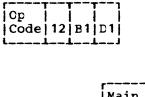

#### Instruction Format

Floating-point instructions use the following two formats:

RR Format

|   |   | R <sub>1</sub> |    |   | R2 |    |  |  |

|---|---|----------------|----|---|----|----|--|--|

| 0 | 7 | 8              | 11 | 1 | 2  | 15 |  |  |

**RX** Format

| Op | Code | R | 1  | X2 | X <sub>2</sub> |    | . B <sub>2</sub> |    | D2 |   |

|----|------|---|----|----|----------------|----|------------------|----|----|---|

| 0  | 7    | 8 | 11 | 12 | 15             | 16 | 19               | 20 | 3  | 1 |

In these formats, R1 designates the address of a floating-point register. The contents of this register will be called the first operand. The second operand location is defined differently for two formats.

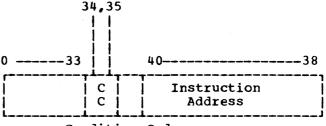

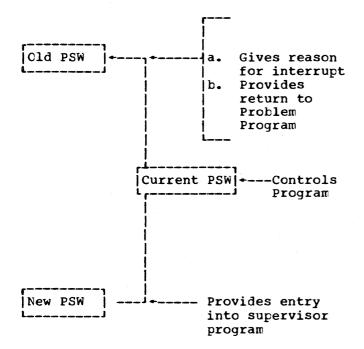

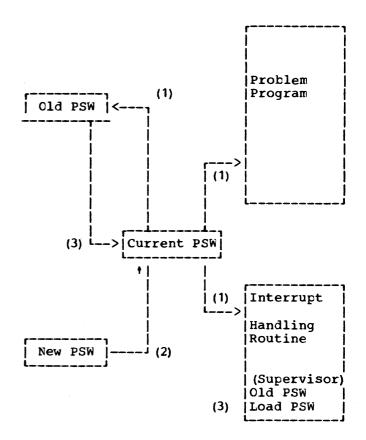

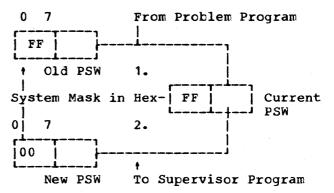

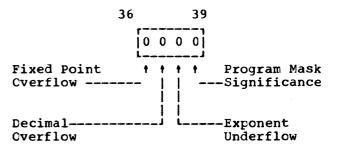

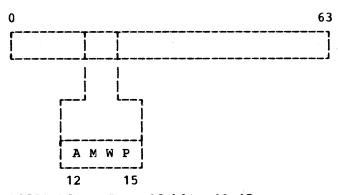

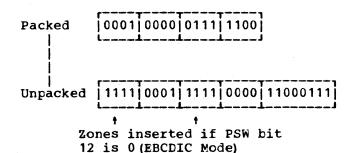

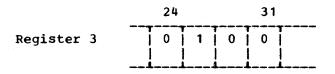

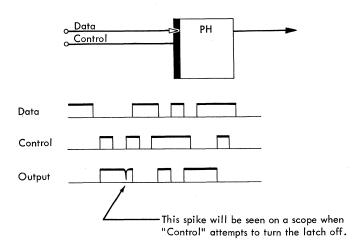

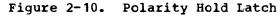

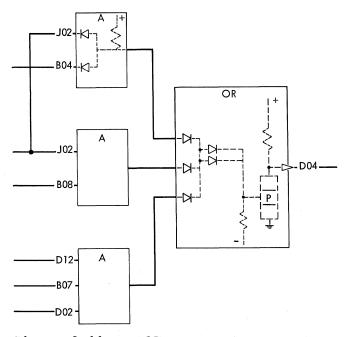

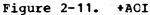

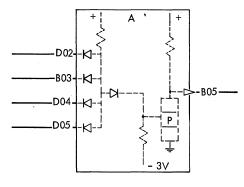

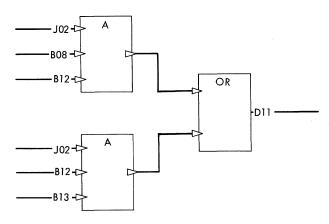

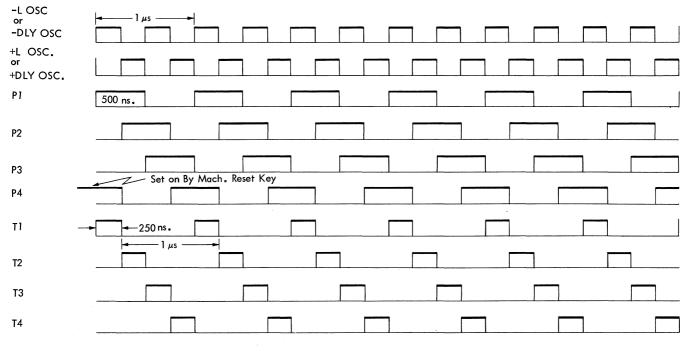

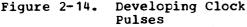

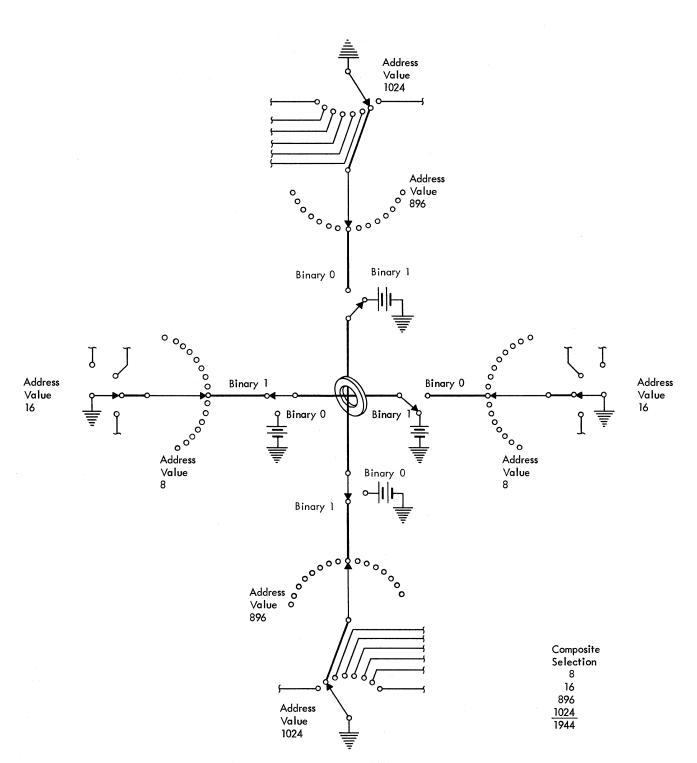

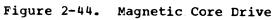

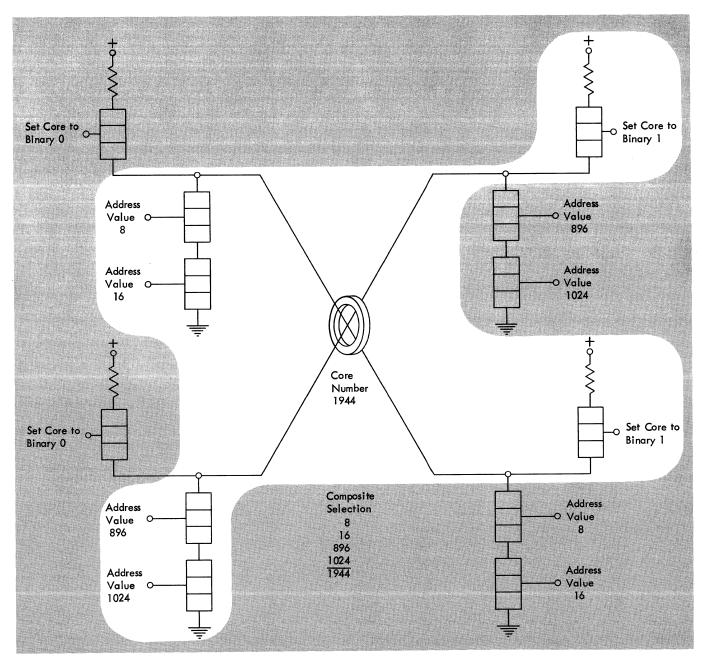

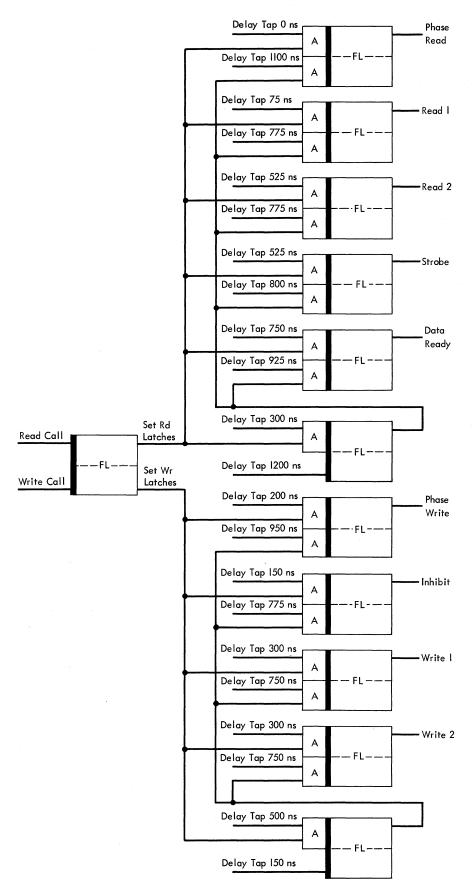

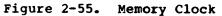

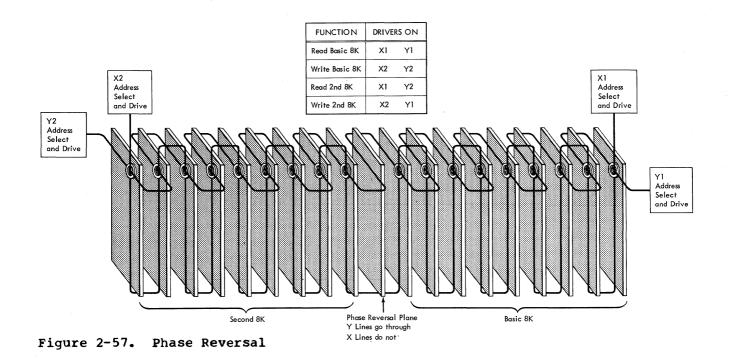

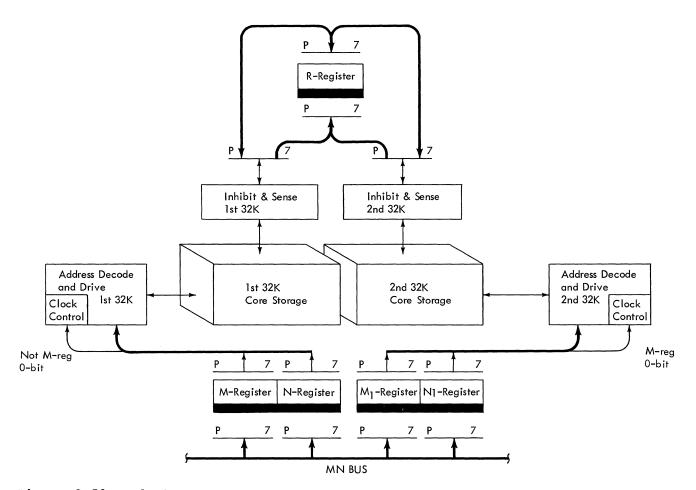

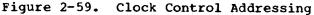

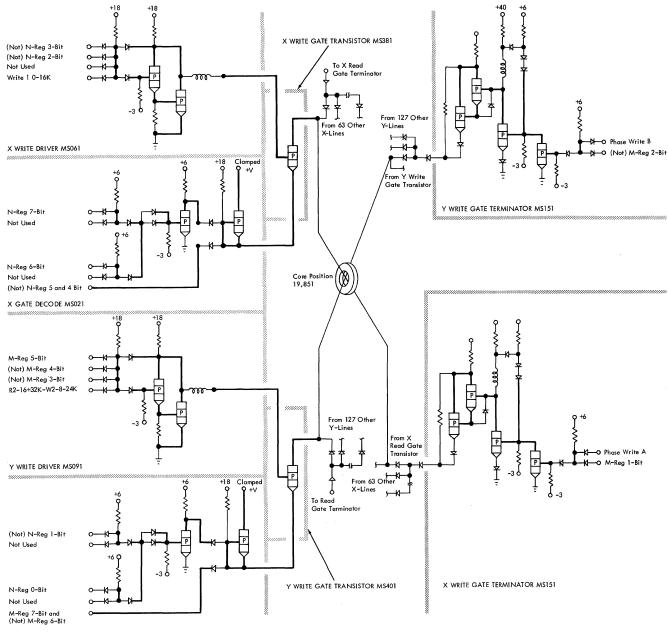

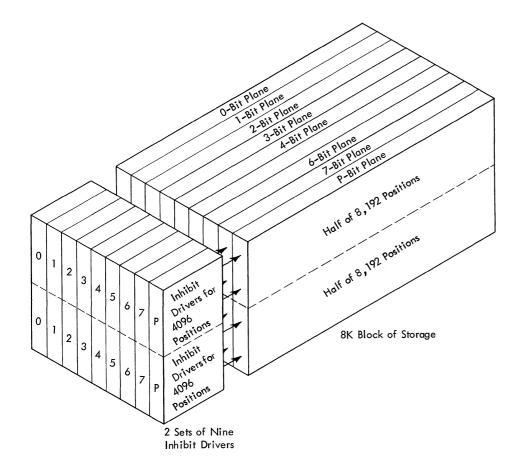

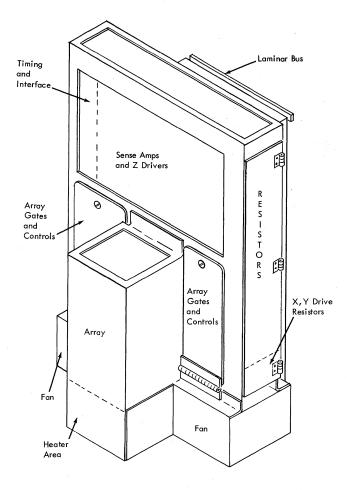

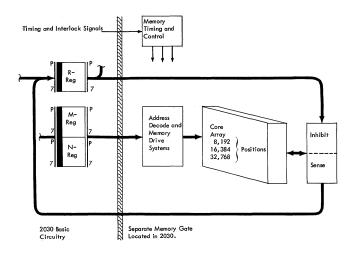

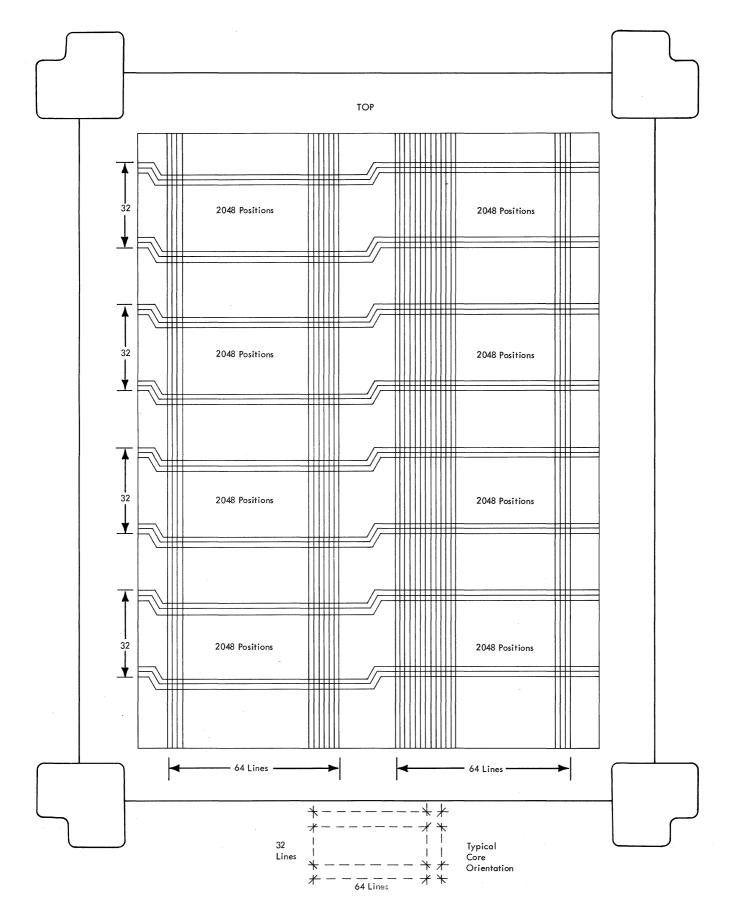

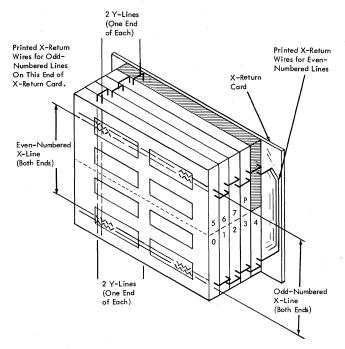

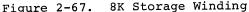

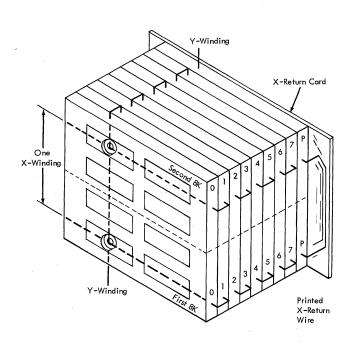

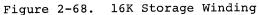

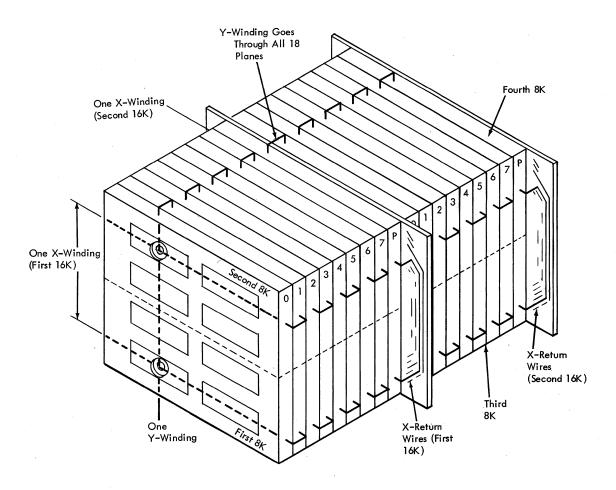

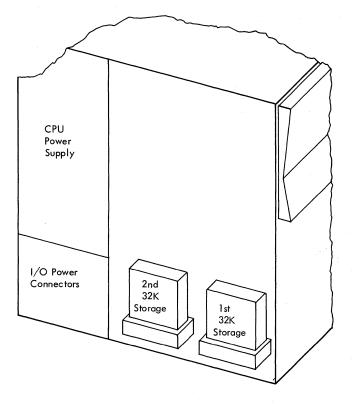

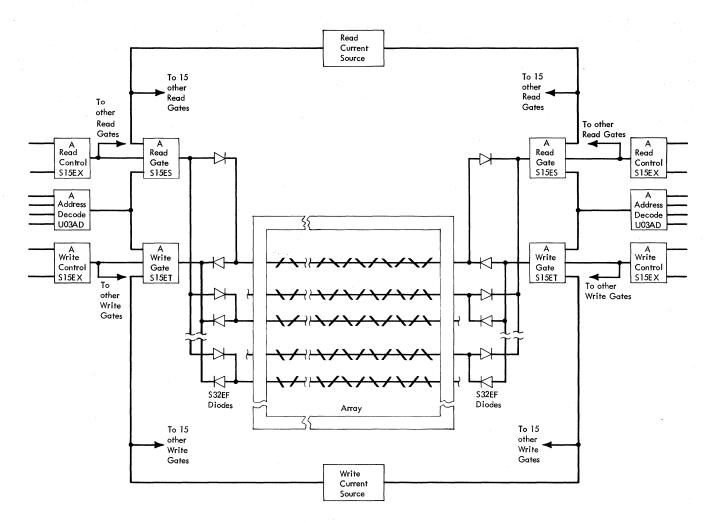

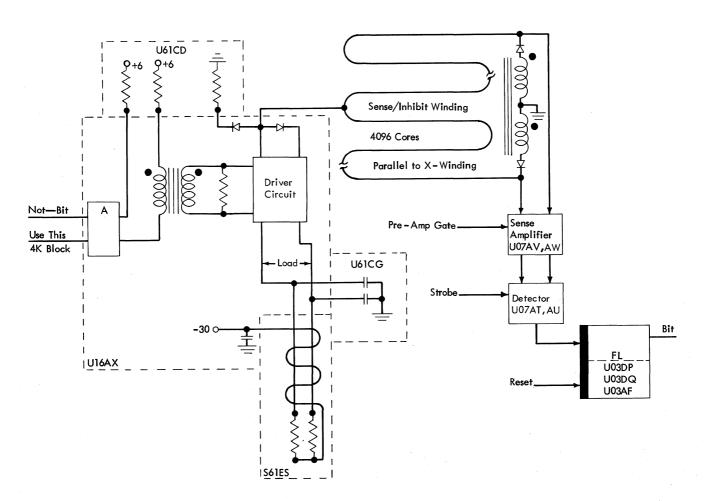

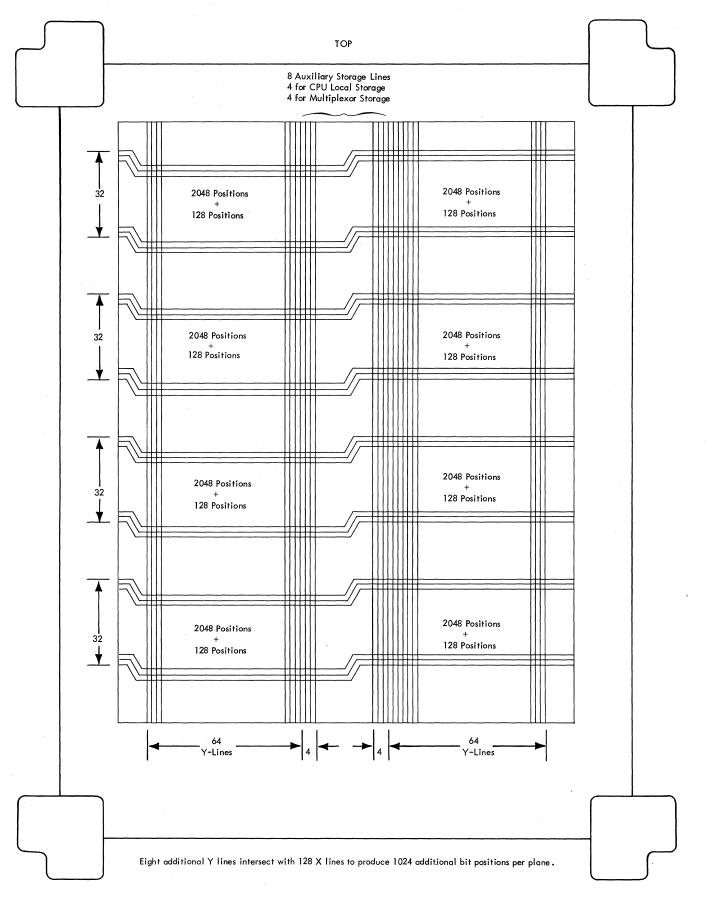

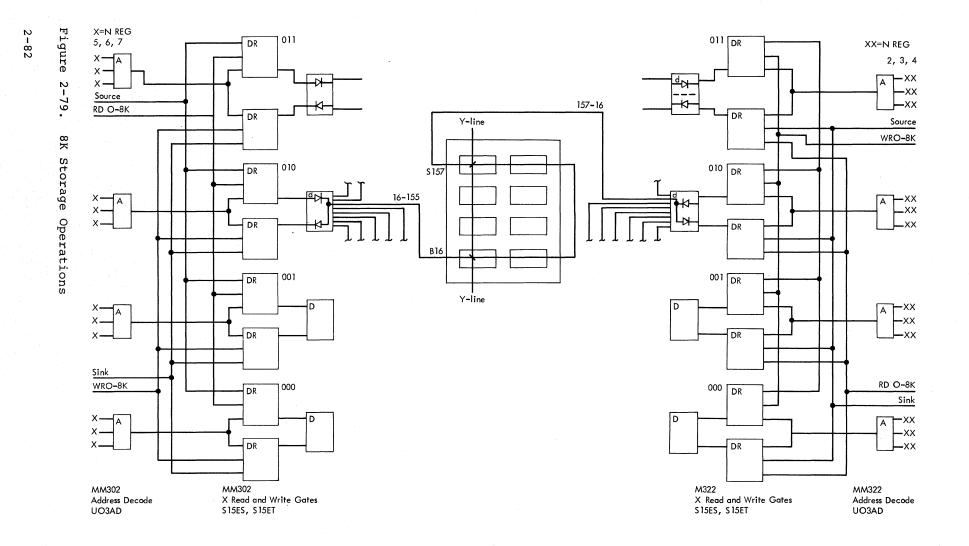

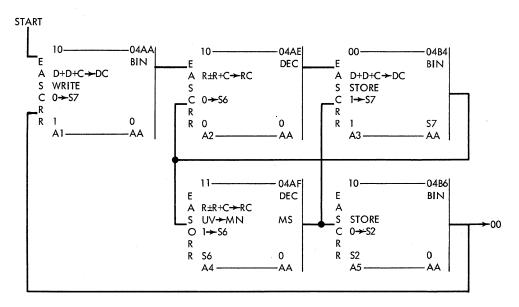

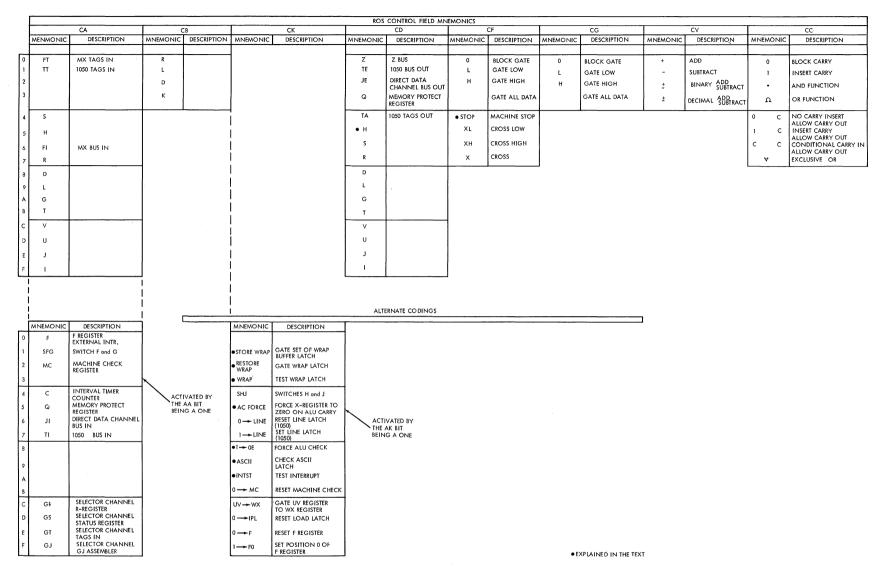

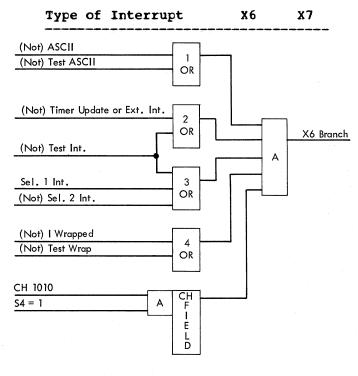

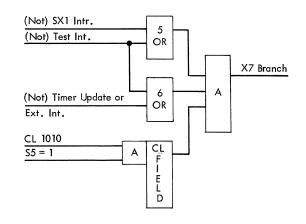

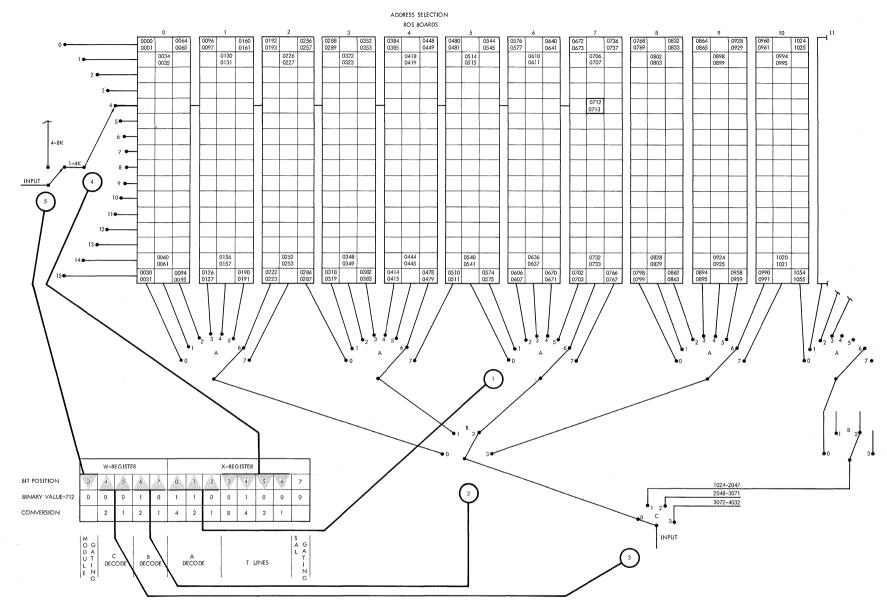

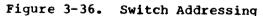

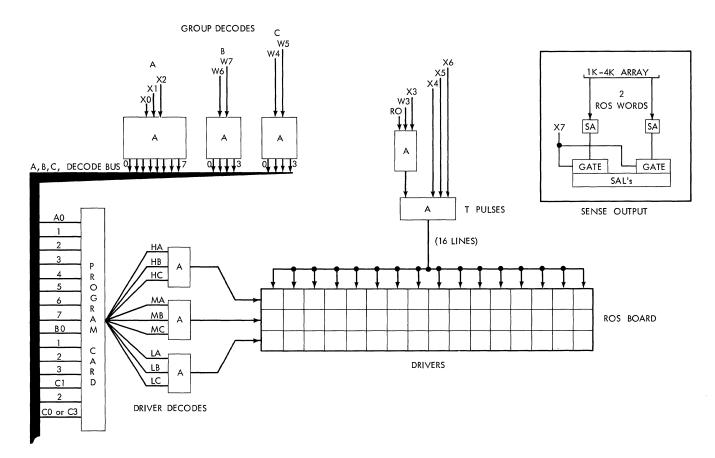

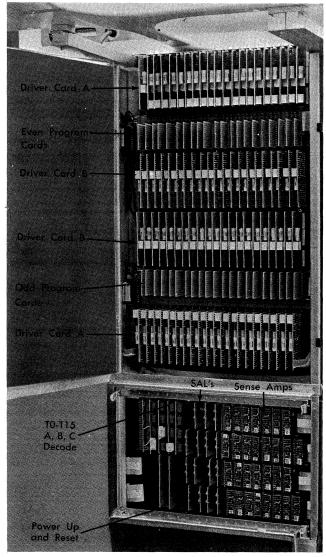

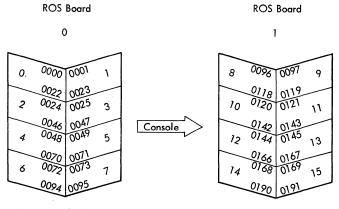

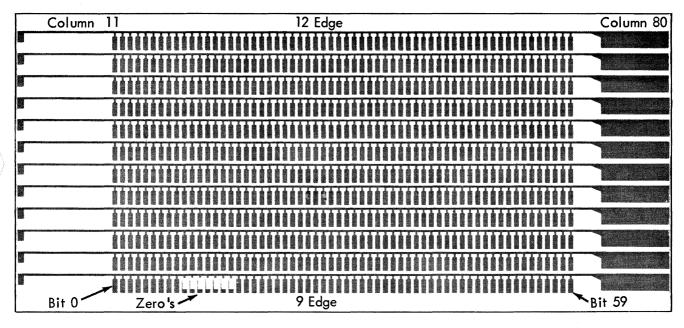

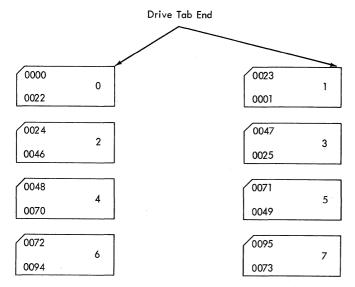

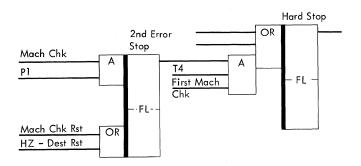

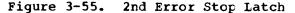

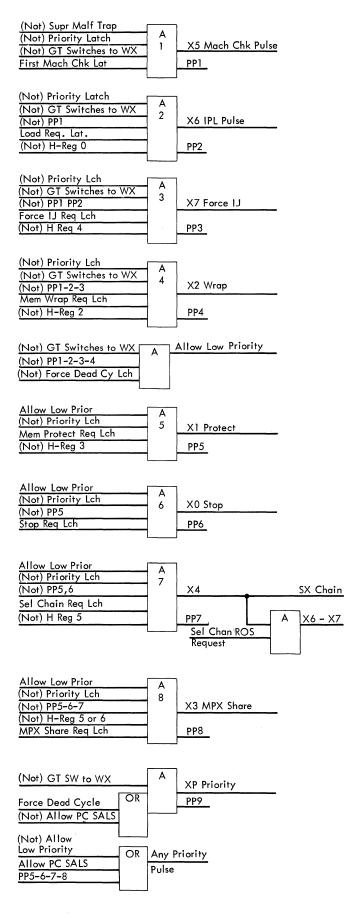

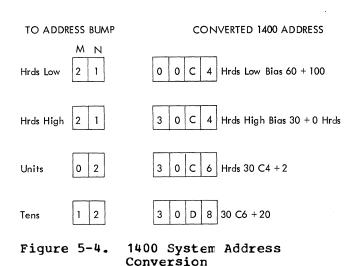

In the RR format, the  $R_2$  field specifies the address of a floating-point register containing the second operand. The same register may be specified for the first and second operand.