# Maintenance Library

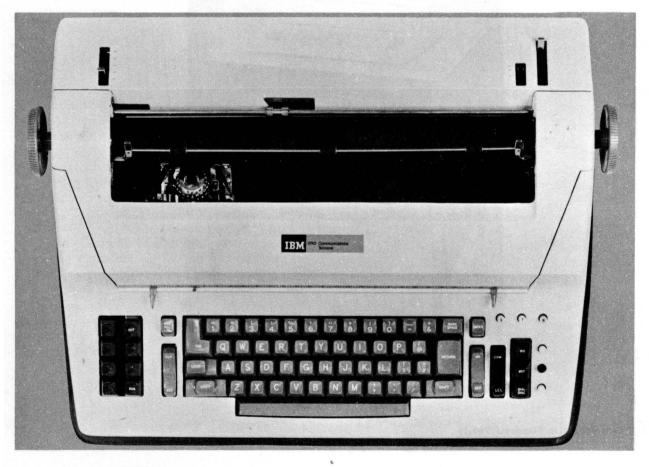

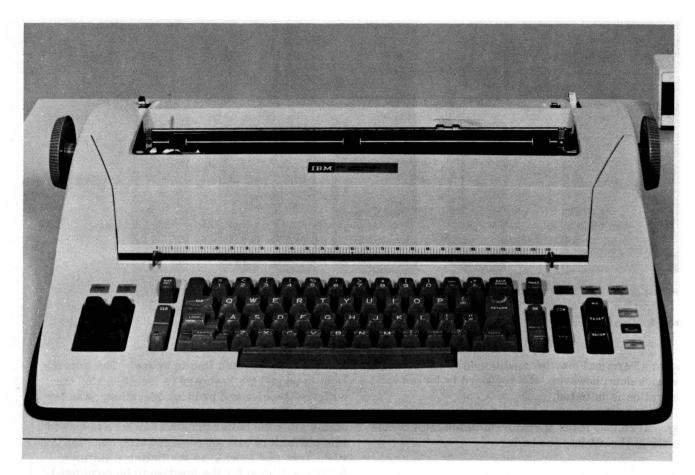

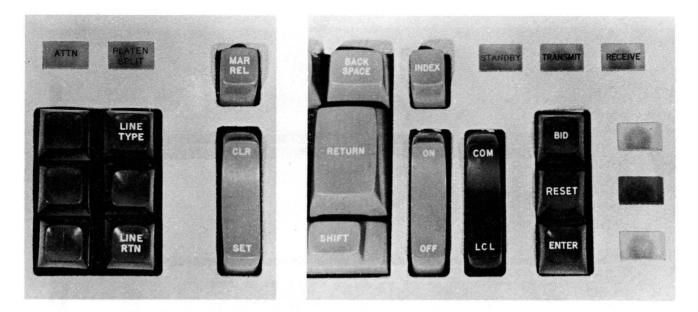

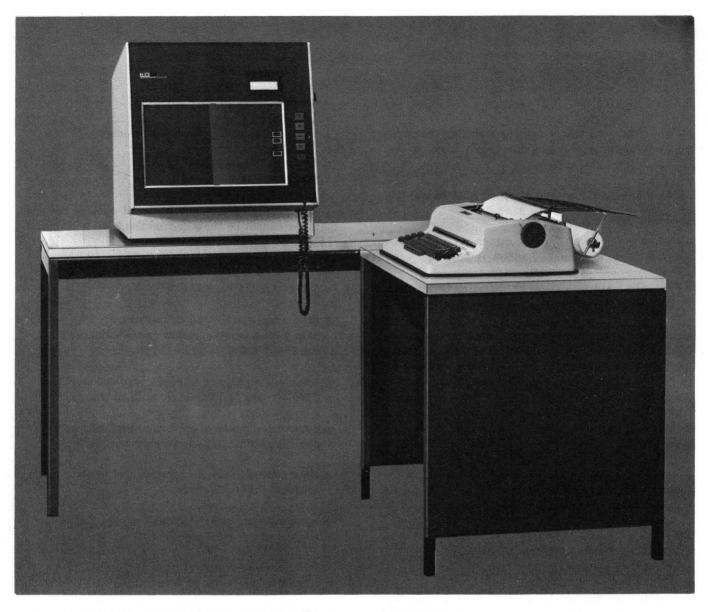

2740 Communication Terminal Model 1

2740 Communication Terminal Model 2

2741 Communication Terminal Theory of Operation

Maintenance Library

2740 Communication Terminal Model 1

2740 Communication Terminal Model 2

2741 Communication Terminal Theory of Operation

# PREFACE

This manual describes the theory of operation of the IBM 2740 Model 1 (2740-1), 2740 Model 2 (2740-2), and 2741 Communication Terminal and special features. To use this manual, the reader must be thoroughly familiar with these publications:

- 1. SLT Packaging and Documentation, SR23-2916

- 2. Introduction to Teleprocessing, Z25-2522

- 3. Common-Carrier Facilities for Teleprocessing, Z25-2529

- 4. 2740/2741 Communication Terminal, Operator's Guide, GA27-3001

- 5. IBM Line Adapters (Modems), S226-3003

In addition, the reader must completely understand the operation of the Selectric  $\bigcirc$  I/O.

The 2740/41 Communication Terminal Model 1, 2740 Communication Terminal Model 2, FE Diagram Manual, SY27-0014, is required to follow the explanations in the "Functional Units," "Principles of Operation," and "Features" sections of this manual.

All figures in this manual are positive logic--that is, a positive level is required to condition ANDs, ORs, etc. Triggers and latches also require a positive level to be turned on or off.

#### Sixth Edition (January 1973)

This is a reprint of SY27-0013-3 incorporating changes issued in Technical Newsletter SY27-1056, dated June 10, 1970.

Changes are periodically made to the information herein; before using this publication in connection with the operation and/or repair of the system or equipment, refer to the latest Technical Newsletter that is applicable and current.

This manual has been prepared by the IBM Systems Development Division, Publications Center, Department E01, P.O. Box 12195, Research Triangle Park, North Carolina 27709. A form for reader's comments is provided at the back of this manual. If the form has been removed, comments may be sent to the above address. Comments become the property of IBM.

© Copyright International Business Machines Corporation 1966, 1968, 1969, 1973

# CONTENTS

| CHAPTER 1. INTRODUC       |                                        |       | ·    |      | •    | • | • | • | 1-1           |

|---------------------------|----------------------------------------|-------|------|------|------|---|---|---|---------------|

| 2740 COMMUNICATION        | FERM                                   | IINA  | L, М | ODE  | L 1  |   | • | • | 1-1           |

| Modes of Operation        | •                                      | •     | •    | •    | •    | • | • | • | 1-3           |

| Local                     | •                                      | •     | •    | •    | •    | • | • | • | 1-3           |

| Communicate .             | •                                      | •     | •    | •    | •    | • | • | • | 1-3           |

| Special Features (2740-1) |                                        | •     | •    | •    | •    | • | • | • | 1-3           |

| Record Checking           | •                                      | •     | •    | •    | •    | • | • | • | 1-3           |

| Automatic EOB .           |                                        | •     | •    | •    | •    | • |   |   | 1-3           |

| Dial-Up                   |                                        |       |      |      |      |   | • | • | 1-4           |

| Transmit Control          |                                        |       |      |      |      |   |   |   | 1-4           |

| Station Control .         |                                        |       |      |      |      | • |   | • | 1-4           |

| 2760 Attachment           |                                        |       | •    | •    |      | • |   | • | 1-4           |

| 2741 Communication Terr   | mina                                   | 1     |      |      |      |   |   |   | 1 <b>-</b> 4A |

| Special Features (2741)   |                                        | -     |      |      |      |   |   |   | 1-5           |

|                           | •                                      | :     | :    | •    |      |   |   |   | 1-5           |

| •                         | •                                      | •     | •    | •    | •    | • | • | • | 1-5           |

| Receive Interrupt •       | •                                      | •     | •    | •    | •    | • | • | • |               |

| Transmit Interrupt •      | •                                      | •     | •    | •    | •    | • | • | • | 1-5           |

| - <i>) F</i> ======       |                                        | •     | •    | •    | •    | • | • | • | 1-5           |

| Print Inhibit CPU Contr   |                                        | •     | •    | •    | •    | • | • | • | 1-5           |

| 2740 COMMUNICATION        | TERN                                   | ИINA  | L, N | 10DE | EL 2 |   | • | • | 1-6           |

| Modes of Operation        | •                                      | •     | •    | •    | •    | • | • | • | 1-7           |

| Local                     | •                                      | •     | •    | •    | •    | • | • | • | 1-7           |

| Communicate .             |                                        | •     | •    |      | •    |   |   |   | 1-7           |

| Special Features (2740-2) |                                        | •     |      |      |      |   |   |   | 1-8           |

| Buffer Expansion          |                                        |       |      |      |      |   |   |   | 1-8           |

| Buffered Receive          |                                        |       |      |      |      |   |   |   | 1-8           |

| Telegraph Line Adapte     | r                                      |       |      |      |      |   | • |   | 1-8           |

| Speed Base 600 bps        |                                        |       |      |      |      |   |   |   | 1-8           |

| Header Control .          |                                        |       |      |      |      |   |   |   | 1-9           |

| Edit                      |                                        |       |      |      |      |   |   |   | 1-9           |

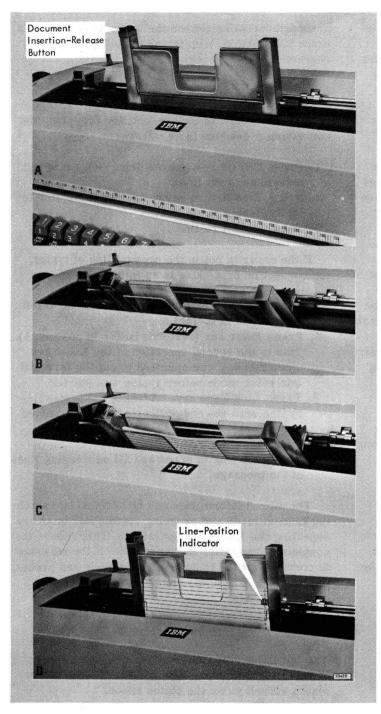

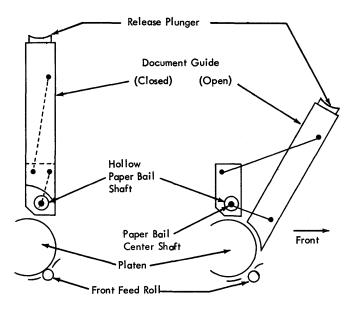

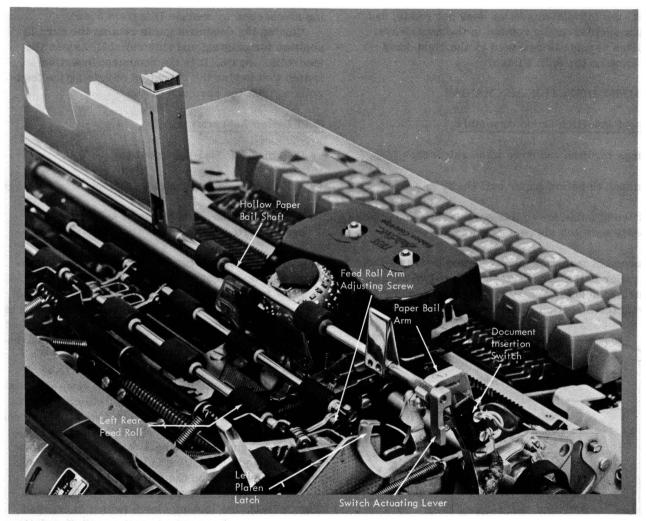

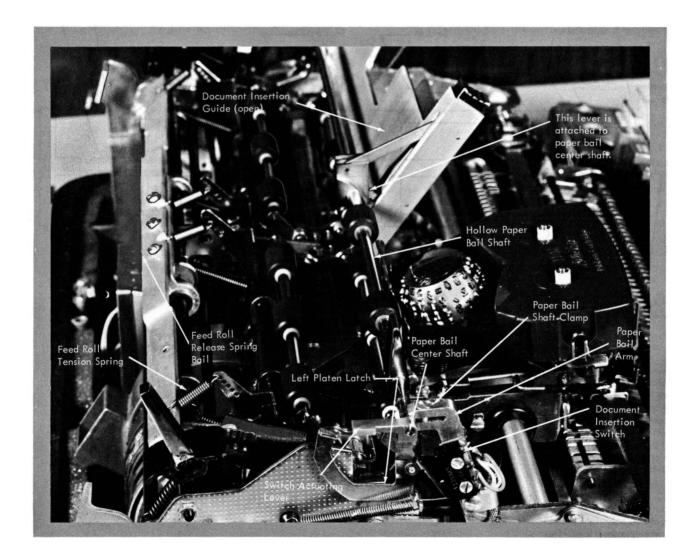

| Document Insertion        |                                        | •     |      |      |      |   |   | • | 1-9           |

| Split Platen              | •                                      | •     | •    | •    | •    | • | • | • | 1-10          |

| Record Checking           | •                                      | •     | •    | •    | •    | • | • | • | 1-10          |

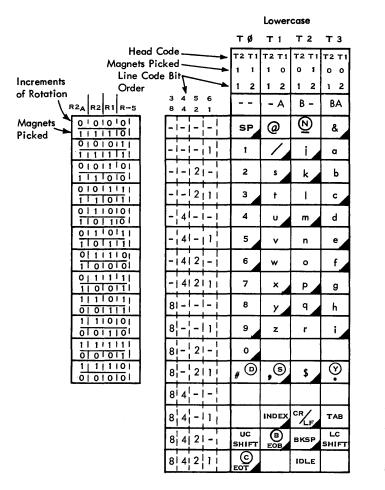

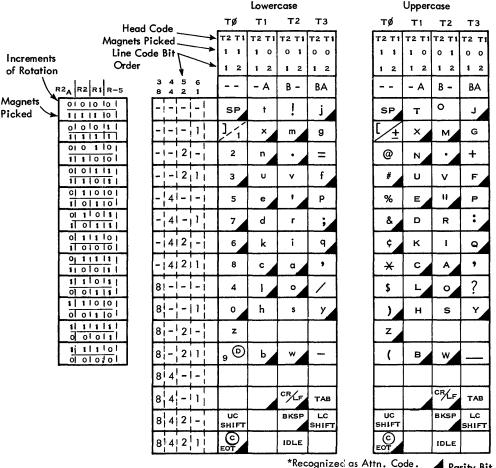

| Data Representation       | •                                      | •     | •    | •    | •    | • | • | • | 1-10          |

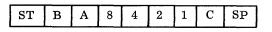

| Character Format          | •                                      | •     | •    | •    | •    | • | • | • | 1-11          |

|                           | ·                                      | •     | •    | •    | •    | • | • | • |               |

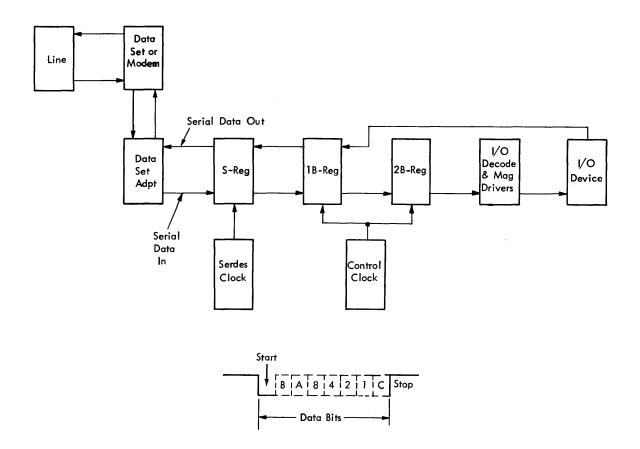

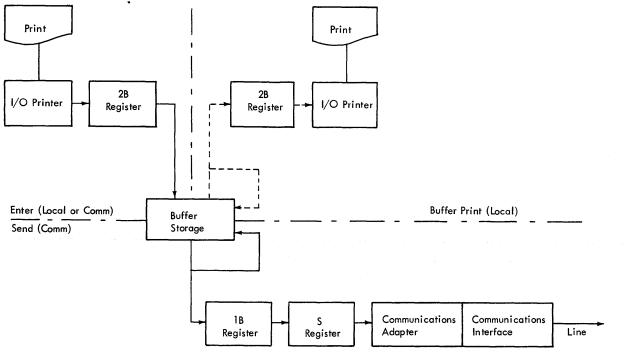

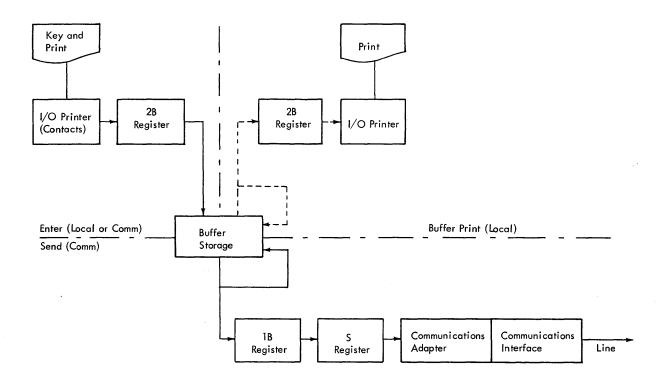

| Data Flow (2740-1/2741)   |                                        | •     | •    | •    | •    | • | • | • | 1-12          |

| Data Flow (2740-2)        | •                                      | •     | •    | •    | •    | • | • | • | 1-13          |

| Enter                     | ·                                      | •     | •    | •    | •    | • | • | • | 1-13          |

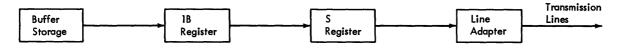

| Transmit                  | •                                      | •     | •    | •    | •    | • | • | • | 1-14          |

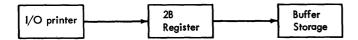

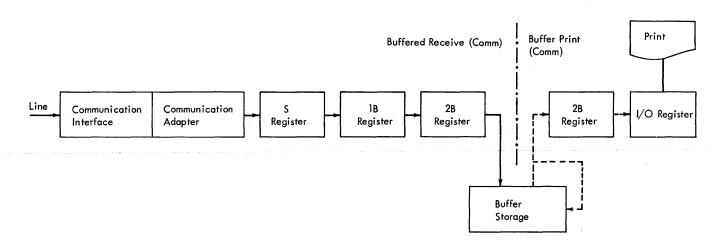

| Receive                   | •                                      | •     | •    | •    | •    | • | • | • | 1-14          |

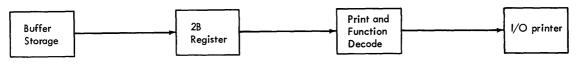

| Buffer Print .            | •                                      | •     | •    | •    | •    | • | • | • | 1-14          |

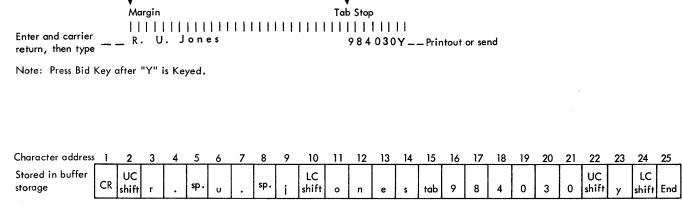

| Buffer Storage            | •                                      | •     | •    | •    | •    | • | • | • | 1-14          |

| Storage Operation         | •                                      | •     | •    | •    | •    | • | • | • | 1-16          |

| Character Storage Con     | cepts                                  |       | •    | •    | •    | • | • | • | 1-16          |

| Buffered Receive Feat     | ure                                    |       | •    | •    | •    | • | • | • | 1-19          |

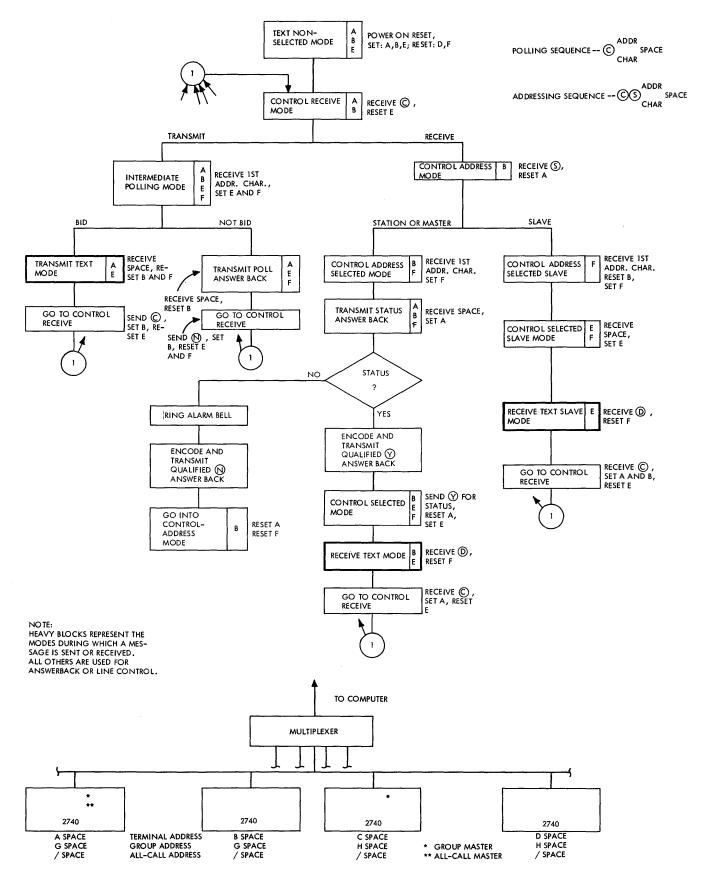

| Transmit Status/Answerba  | .ck (2                                 | 2740- | -2)  |      | •    | • | • | • | 1-19          |

|                           |                                        |       |      |      |      |   |   |   |               |

| CHAPTER 2. FUNCTION       | AL U                                   | NIT   | S    |      |      |   |   |   |               |

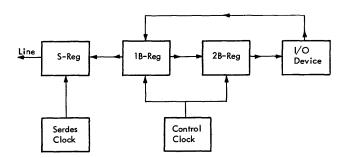

| S-Register                | •                                      | •     | •    |      |      | • |   |   | 2-1           |

| Serialization (Sending)   |                                        |       |      |      |      |   | • |   | 2-1           |

| Deserialization (Receiv   | ving)                                  |       |      |      |      |   |   |   | 2-1           |

| Serdes Clock              | •                                      |       |      |      |      |   |   |   | 2-2           |

| Control Clock             |                                        |       |      | •    |      |   |   |   | 2-3           |

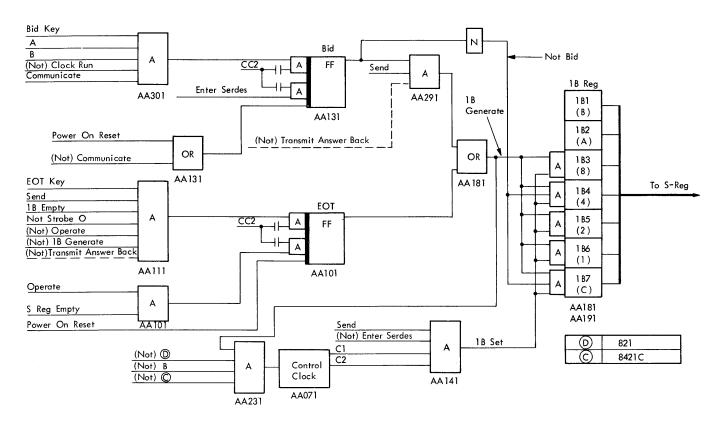

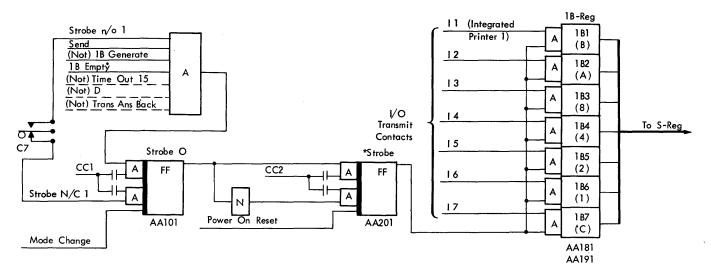

| 1B-Register (2740-1/2741  | )                                      |       |      |      |      |   |   |   | 2-3           |

| 1B-Register (2740-2)      | <i>.</i>                               |       |      |      |      |   |   |   | 2-4           |

| Generated Data            |                                        |       |      |      |      |   |   |   | 2-4           |

| 2B-Register (2740-1/2741  | `````````````````````````````````````` | •     | •    | •    | •    | • | • | • | 2-4           |

| 2B-Register (2740-2)      | .,                                     | •     | •    | •    | •    | • | • | • | 2-5           |

| Generated Data            | •                                      | •     | •    | •    | •    | • | • | • | 2-5           |

|                           |                                        |       |      |      |      |   |   |   |               |

| Print and Function Deco                                                                                                                                                                                              |                 |              | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-5                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|-------|-----------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------------|------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------|

| Print Decode                                                                                                                                                                                                         | •               | •            | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-5                                                                                  |

| Function Decode                                                                                                                                                                                                      | •               | •            | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-6                                                                                  |

| Strobe and I/O Cycle                                                                                                                                                                                                 |                 | •            | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-6                                                                                  |

| Communicate/Local and                                                                                                                                                                                                |                 | us           | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-6                                                                                  |

| Communicate/Local                                                                                                                                                                                                    |                 | •            | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-6                                                                                  |

| Status                                                                                                                                                                                                               |                 |              | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-7                                                                                  |

| Operate Trigger .                                                                                                                                                                                                    | •               | •            | •     | •                                                                                                         | •         | •                                                                       | ٠                                              | •                     | 2-7                                                                                  |

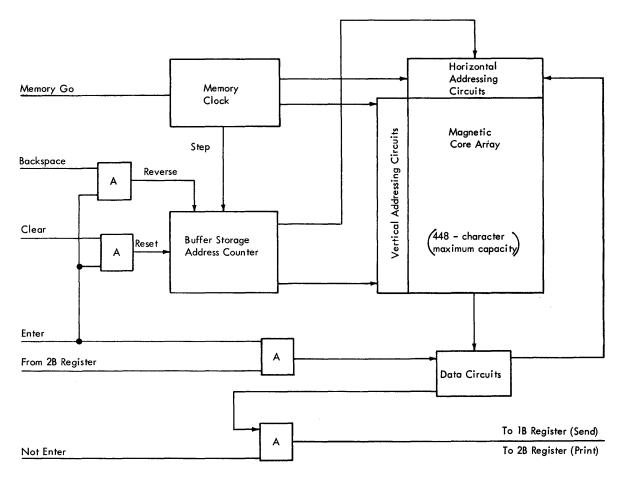

| Buffer Storage                                                                                                                                                                                                       |                 | •            | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-7                                                                                  |

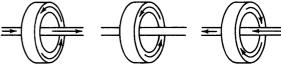

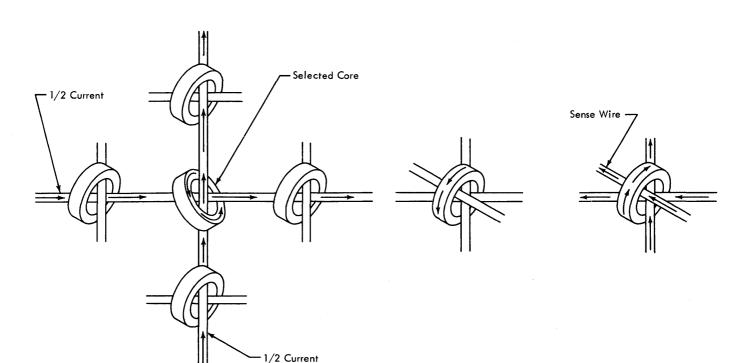

| Magnetic Core Theor                                                                                                                                                                                                  | •               | •            | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-7                                                                                  |

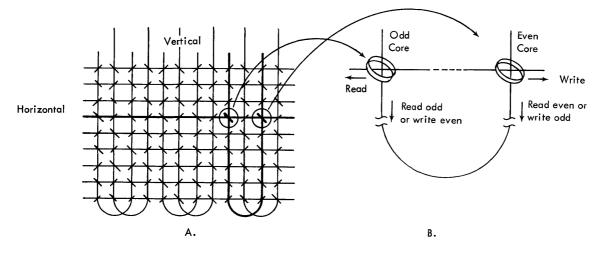

| Odd-Even Core Sche                                                                                                                                                                                                   |                 |              | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-10                                                                                 |

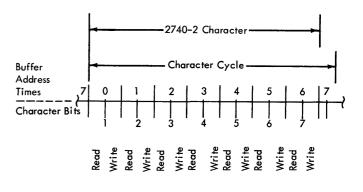

| Character Cycle                                                                                                                                                                                                      |                 |              | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-11                                                                                 |

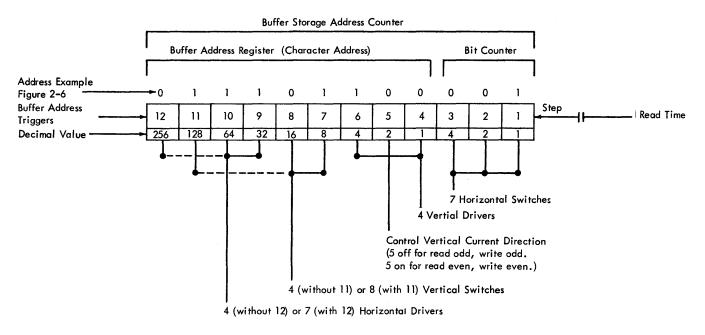

| Buffer Storage Addres                                                                                                                                                                                                |                 |              |       | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-11                                                                                 |

| Bit Counter .                                                                                                                                                                                                        |                 | •            | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-12                                                                                 |

| Buffer Address Regist                                                                                                                                                                                                |                 | •            | •     | •                                                                                                         |           | •                                                                       | •                                              | •                     | 2-12                                                                                 |

| Address Register Con                                                                                                                                                                                                 |                 | •            | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-12                                                                                 |

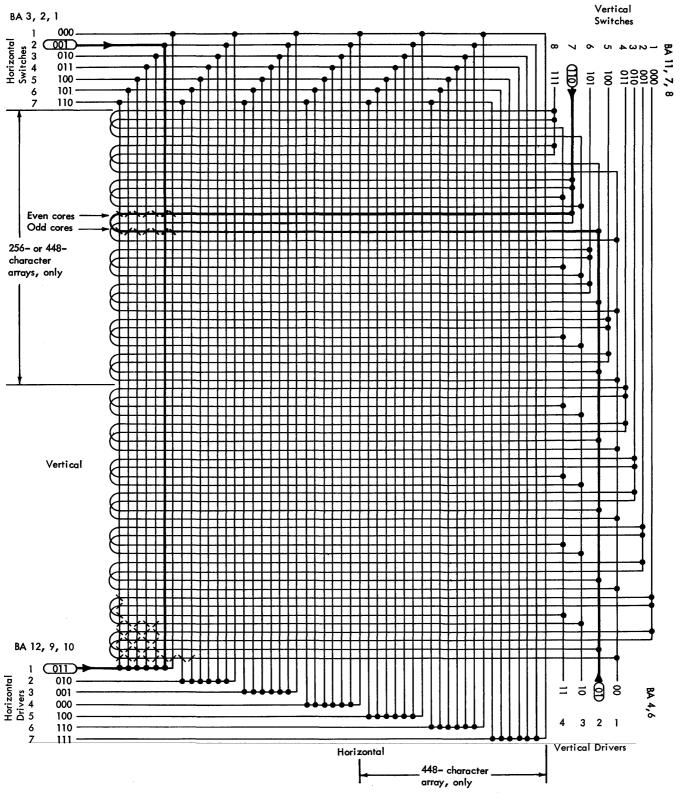

| Buffer Storage Array                                                                                                                                                                                                 |                 |              |       |                                                                                                           | •         | •                                                                       | •                                              | •                     | 2-15                                                                                 |

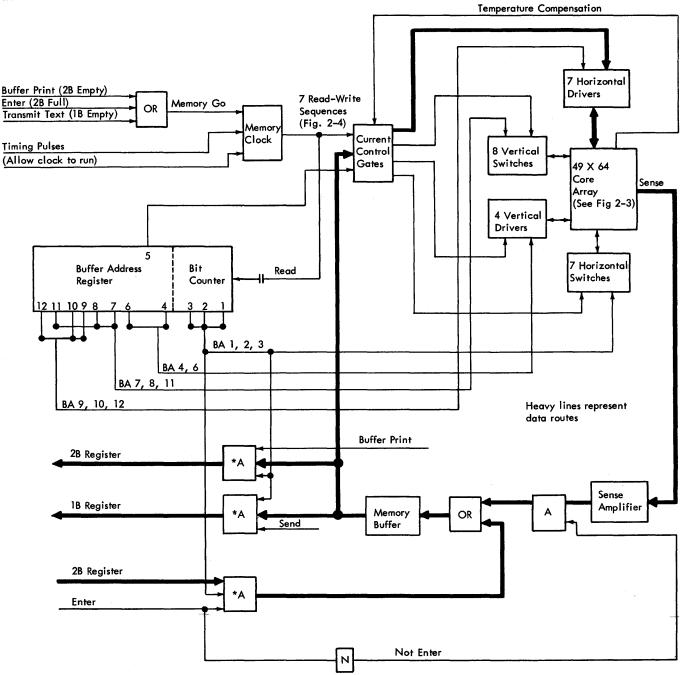

| Memory Clock .                                                                                                                                                                                                       |                 | •            | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-15                                                                                 |

| Buffer Data Control                                                                                                                                                                                                  |                 | •            | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-16                                                                                 |

| Summary of Buffer St                                                                                                                                                                                                 |                 | Ope          | ratio | n                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-17                                                                                 |

| Temperature Compensat                                                                                                                                                                                                | tion            | •            | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 2-17                                                                                 |

|                                                                                                                                                                                                                      |                 |              |       |                                                                                                           |           |                                                                         |                                                |                       |                                                                                      |

|                                                                                                                                                                                                                      |                 |              |       |                                                                                                           |           |                                                                         |                                                |                       |                                                                                      |

| CHAPTER 3. PRINCIPL                                                                                                                                                                                                  | es of           | OPE          | RAT   | ION                                                                                                       |           |                                                                         | •                                              |                       | 3-1                                                                                  |

| 2740 COMMUNICATION                                                                                                                                                                                                   | TER             | MINA         | L, N  | NODI                                                                                                      | EL 1      |                                                                         |                                                | •                     | 3-1                                                                                  |

| Basic Terminal Mode Co                                                                                                                                                                                               | ntrol           |              | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 3-1                                                                                  |

| Transmit (Point-to-Point                                                                                                                                                                                             | :)              | •            | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 3-1                                                                                  |

| Load Control Charact                                                                                                                                                                                                 | ers in          | to 1B        | -Reg  | ister                                                                                                     |           | •                                                                       | •                                              | •                     | 3-2                                                                                  |

| Load Text Characters                                                                                                                                                                                                 | into            | 1B-R         | egist | er                                                                                                        | •         | •                                                                       | •                                              | •                     | 3-2                                                                                  |

| Transfer Characters fr                                                                                                                                                                                               | om 11           | B-Re         | giste | r to S                                                                                                    | S-Re      | giste                                                                   | er                                             | •                     | 3-2                                                                                  |

| S-Register to 'Serial                                                                                                                                                                                                | Data            | Out'         | Line  |                                                                                                           |           | •                                                                       | •                                              | •                     | 3-3                                                                                  |

| End-of-Transmission                                                                                                                                                                                                  |                 |              | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 3-3                                                                                  |

| Receive (Point-to-Point)                                                                                                                                                                                             | )               | •            | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 3-4                                                                                  |

| Receive Bid Characte                                                                                                                                                                                                 | rs D            | •            | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 3-4                                                                                  |

| Receive Text Charac                                                                                                                                                                                                  | ters            | •            | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 3-5                                                                                  |

| Receive End-of-Tran                                                                                                                                                                                                  | smi <b>s</b> si | on C         | harac | ter (                                                                                                     | 2         | •                                                                       | •                                              | •                     | 3-5                                                                                  |

| 2B Overflow Reset                                                                                                                                                                                                    | •               | •            | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 3-5                                                                                  |

| Power On Reset (2740-1,                                                                                                                                                                                              |                 |              | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 3-6                                                                                  |

| I/O Motor Control (2740                                                                                                                                                                                              | -1/27           | 41)          |       | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 3-6                                                                                  |

| Keyboard Lock (2740-1/                                                                                                                                                                                               | 2741 <b>)</b>   |              | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 3-6                                                                                  |

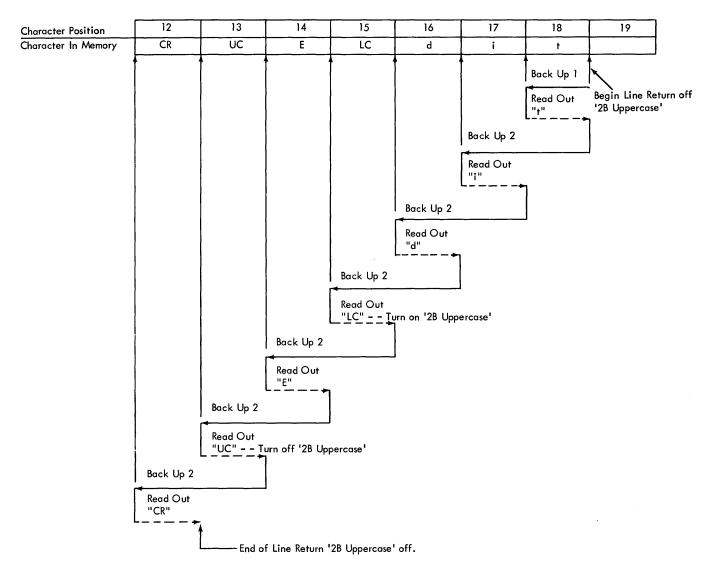

| Initial Lowercase (2740-                                                                                                                                                                                             |                 |              | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 3-7                                                                                  |

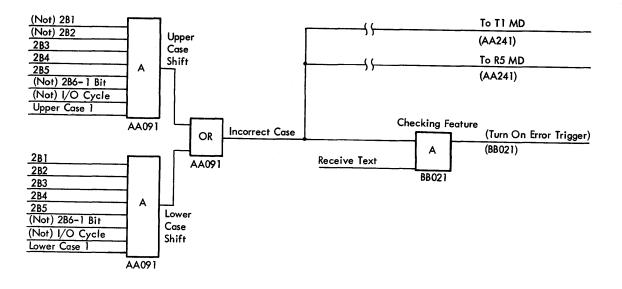

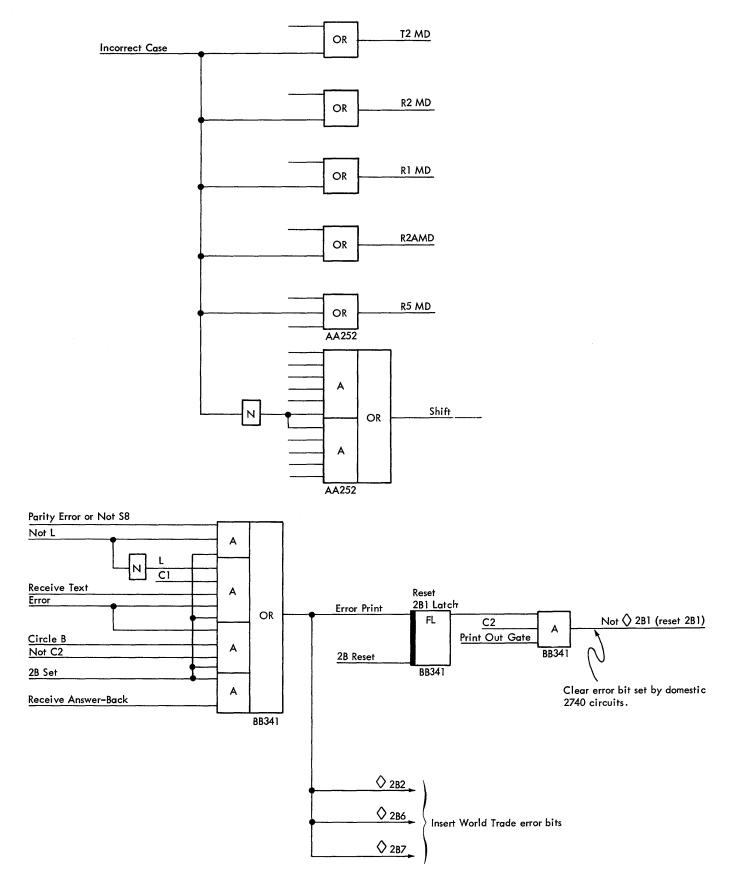

| Incorrect Case (2740-1/2                                                                                                                                                                                             | 2741)           |              | •     | •                                                                                                         | •         | •                                                                       | •                                              | •                     | 3-7                                                                                  |

| 2741 COMMUNICATION                                                                                                                                                                                                   | TFR             | <b>ΛΤΝΙΔ</b> | 7     |                                                                                                           |           |                                                                         |                                                | •                     | 3-8                                                                                  |

| 2740 COMMUNICATION                                                                                                                                                                                                   |                 |              |       | ٠                                                                                                         | ٠         | •                                                                       | •                                              |                       |                                                                                      |

|                                                                                                                                                                                                                      |                 |              |       | NODI                                                                                                      |           | •                                                                       |                                                | •                     | 3-8<br>3-10                                                                          |

| Terminal Mode Operatio                                                                                                                                                                                               | TER             |              |       | 10Di                                                                                                      |           | •                                                                       | •                                              | •                     |                                                                                      |

|                                                                                                                                                                                                                      | TER             |              | L, N  | /ODI                                                                                                      |           | •                                                                       | •                                              | •<br>•<br>•           | 3-10                                                                                 |

| Terminal Mode Operatio                                                                                                                                                                                               | TER             |              | L, N  | /ODI                                                                                                      | EL 2<br>• | •                                                                       | •<br>•<br>•                                    | •<br>•<br>•           | 3-10<br>3-10                                                                         |

| Terminal Mode Operation<br>Control Unit                                                                                                                                                                              | TER             |              | L, N  | ,<br>NODI                                                                                                 | EL 2<br>• | • • • •                                                                 | • • • •                                        |                       | 3-10<br>3-10<br>3-10                                                                 |

| Terminal Mode Operatio<br>Control Unit .<br>Enter                                                                                                                                                                    | TERI<br>n       |              | .L, N | /ODI                                                                                                      | EL 2<br>• | • • • •                                                                 | •<br>•<br>•<br>•                               | •<br>•<br>•<br>•      | 3-10<br>3-10<br>3-10<br>3-10                                                         |

| Terminal Mode Operation<br>Control Unit .<br>Enter<br>Start Enter                                                                                                                                                    | TER             | MINA         | AL, N | •<br>10Di<br>•<br>•                                                                                       | EL 2<br>• | • • • • •                                                               | •<br>•<br>•<br>•<br>•                          | •<br>•<br>•<br>•      | 3-10<br>3-10<br>3-10<br>3-10<br>3-10                                                 |

| Terminal Mode Operatio<br>Control Unit .<br>Enter<br>Start Enter<br>Enter Characters<br>Store Character into H<br>End Enter                                                                                          | TER             | MINA         | AL, N | •<br>10DI<br>•<br>•<br>•                                                                                  | EL 2      | •<br>•<br>•<br>•                                                        | •                                              |                       | 3-10<br>3-10<br>3-10<br>3-10<br>3-10<br>3-11                                         |

| Terminal Mode Operation<br>Control Unit<br>Enter<br>Start Enter<br>Enter Characters<br>Store Character into H                                                                                                        | TER             | MINA         | AL, N | •<br>10Di<br>•<br>•<br>•                                                                                  | EL 2      | •<br>•<br>•<br>•<br>•                                                   | • • • • • • • • •                              | •<br>•<br>•<br>•<br>• | 3-10<br>3-10<br>3-10<br>3-10<br>3-10<br>3-11<br>3-11                                 |

| Terminal Mode Operatio<br>Control Unit .<br>Enter<br>Start Enter<br>Enter Characters<br>Store Character into H<br>End Enter                                                                                          | TER)<br>m       | MINA         | AL, N | •<br>10DH<br>•<br>•<br>•<br>•                                                                             | EL 2      | •<br>•<br>•<br>•<br>•<br>•                                              | • • • • • • • • • •                            |                       | 3-10<br>3-10<br>3-10<br>3-10<br>3-10<br>3-11<br>3-11<br>3-12                         |

| Terminal Mode Operation<br>Control Unit<br>Enter<br>Start Enter<br>Enter Characters<br>Store Character into H<br>End Enter<br>Transmit (2740-2)                                                                      | TER             | MINA         | AL, N | •<br>ИОДН<br>•<br>•<br>•<br>•<br>•                                                                        | EL 2      | •<br>•<br>•<br>•<br>•<br>•                                              | • • • • • • • • • • • • • • • • • • • •        |                       | 3-10<br>3-10<br>3-10<br>3-10<br>3-11<br>3-11<br>3-11<br>3-12<br>3-13                 |

| Terminal Mode Operation<br>Control Unit .<br>Enter<br>Start Enter<br>Enter Characters<br>Store Character into H<br>End Enter<br>Transmit (2740-2)<br>Generate and Transm                                             | TER             | MINA         | AL, N | AODI                                                                                                      | EL 2      | •<br>•<br>•<br>•<br>•<br>•                                              | • • • • • • • • • • • • • • • • • • • •        |                       | 3-10<br>3-10<br>3-10<br>3-10<br>3-11<br>3-11<br>3-11<br>3-12<br>3-13<br>3-13         |

| Terminal Mode Operation<br>Control Unit<br>Enter<br>Start Enter<br>Enter Characters<br>Store Character into H<br>End Enter<br>Transmit (2740-2)<br>Generate and Transm<br>Transmit Text Charac                       | TER             | MINA         | AL, N | 10DH                                                                                                      | EL 2      | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                               | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• |                       | 3-10<br>3-10<br>3-10<br>3-10<br>3-11<br>3-11<br>3-11<br>3-12<br>3-13<br>3-13<br>3-13 |

| Terminal Mode Operation<br>Control Unit<br>Enter<br>Start Enter<br>Enter Characters<br>Store Character into H<br>End Enter<br>Transmit (2740-2)<br>Generate and Transm<br>Transmit Text Charac<br>Transmit () or (B) | TER             | MINA         | AL, N | •<br>//ODI<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | EL 2      | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | • • • • • • • • • • • • • • • • • • • •        |                       | 3-10<br>3-10<br>3-10<br>3-10<br>3-11<br>3-11<br>3-12<br>3-13<br>3-13<br>3-13<br>3-13 |

| Buffer Print Operation                                                                                                                                                                                                                                                                                                                                          |                                      | •                                                                                                               | •                                                                                           | •                                              | •                                         | •                                         | •                          | 3-14                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------|-------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| End Buffer Print                                                                                                                                                                                                                                                                                                                                                | •                                    | •                                                                                                               | •                                                                                           | •                                              | •                                         | •                                         | •                          | 3-15                                                                                                                                                               |

| Initial Lowercase (2740–2)                                                                                                                                                                                                                                                                                                                                      | •                                    | •                                                                                                               | •                                                                                           | •                                              | •                                         | •                                         | •                          | 3-15                                                                                                                                                               |

| Incorrect Case                                                                                                                                                                                                                                                                                                                                                  | •                                    | •                                                                                                               | •                                                                                           | •                                              | •                                         | •                                         | •                          | 3-16                                                                                                                                                               |

| Keyboard Lock (2740-2)                                                                                                                                                                                                                                                                                                                                          | •                                    | •                                                                                                               | •                                                                                           | •                                              | •                                         | •                                         | •                          | 3-16                                                                                                                                                               |

| 1/O Motor Control (2740-2)                                                                                                                                                                                                                                                                                                                                      | •                                    | •                                                                                                               | •                                                                                           | •                                              | •                                         | •                                         | •                          | 3-16                                                                                                                                                               |

| Line Parity Error (2740-2)                                                                                                                                                                                                                                                                                                                                      | •                                    | •                                                                                                               | •                                                                                           | •                                              | •                                         | •                                         | •                          | 3-17                                                                                                                                                               |

| Storage Latches for Error Respo                                                                                                                                                                                                                                                                                                                                 | onses                                |                                                                                                                 | •                                                                                           | •                                              | •                                         | •                                         | •                          | 3-17                                                                                                                                                               |

| Electronic Error Latch                                                                                                                                                                                                                                                                                                                                          | •                                    | •                                                                                                               |                                                                                             | •                                              | •                                         | •                                         | •                          | 3-17                                                                                                                                                               |

| I/O Error Latch                                                                                                                                                                                                                                                                                                                                                 | •                                    |                                                                                                                 | •                                                                                           | •                                              | •                                         | •                                         | •                          | 3-17                                                                                                                                                               |

| Receive Parity Error Latch                                                                                                                                                                                                                                                                                                                                      |                                      | •                                                                                                               | •                                                                                           | •                                              | •                                         | •                                         | •                          | 3-18                                                                                                                                                               |

| Transmit Parity Error Latch                                                                                                                                                                                                                                                                                                                                     |                                      | •                                                                                                               | •                                                                                           | •                                              | •                                         | •                                         | •                          | 3-18                                                                                                                                                               |

| Transmit-Status/Answerback                                                                                                                                                                                                                                                                                                                                      |                                      |                                                                                                                 | •                                                                                           | •                                              | •                                         | •                                         | •                          | 3-18                                                                                                                                                               |

| Status and Operational Error                                                                                                                                                                                                                                                                                                                                    | r Con                                | ditio                                                                                                           | ns                                                                                          |                                                | •                                         | •                                         | •                          | 3-19                                                                                                                                                               |

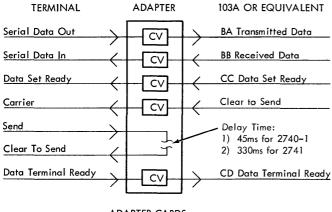

| Terminal to Line Adapter Inter                                                                                                                                                                                                                                                                                                                                  | rface                                | (A11                                                                                                            | Mod                                                                                         | els)                                           |                                           | •                                         | •                          | 3-19                                                                                                                                                               |

| Signal Ground-AB .                                                                                                                                                                                                                                                                                                                                              | •                                    | •                                                                                                               | •                                                                                           | •                                              | •                                         | •                                         | •                          | 3-19                                                                                                                                                               |

| Transmitted Data (Serial D                                                                                                                                                                                                                                                                                                                                      | ata O                                | ut)-E                                                                                                           | <b>BA</b>                                                                                   |                                                | •                                         | •                                         | •                          | 3-19                                                                                                                                                               |

| Received Data (Serial Data                                                                                                                                                                                                                                                                                                                                      | In)-l                                | BB                                                                                                              |                                                                                             | •                                              | •                                         | •                                         | •                          | 3-19                                                                                                                                                               |

| Data Set Ready-CC .                                                                                                                                                                                                                                                                                                                                             | •                                    | •                                                                                                               | •                                                                                           | •                                              | •                                         | •                                         | •                          | 3-19                                                                                                                                                               |

| Request to Send-CA .                                                                                                                                                                                                                                                                                                                                            | •                                    | •                                                                                                               | •                                                                                           |                                                | •                                         | •                                         | •                          | 3-19                                                                                                                                                               |

| Clear to Send-CB .                                                                                                                                                                                                                                                                                                                                              | •                                    | •                                                                                                               | •                                                                                           |                                                | •                                         | •                                         | •                          | 3-19                                                                                                                                                               |

| Carrier-CF                                                                                                                                                                                                                                                                                                                                                      | •                                    | •                                                                                                               |                                                                                             | •                                              | •                                         | •                                         |                            | 3-20                                                                                                                                                               |

| Originate (used only for 103                                                                                                                                                                                                                                                                                                                                    | BF da                                | ata se                                                                                                          | et)                                                                                         |                                                |                                           |                                           | •                          | 3-20                                                                                                                                                               |

| Data Terminal Ready (used                                                                                                                                                                                                                                                                                                                                       |                                      |                                                                                                                 |                                                                                             | data                                           | ı set)                                    | -CD                                       |                            | 3-20                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                 |                                      |                                                                                                                 |                                                                                             |                                                |                                           |                                           |                            |                                                                                                                                                                    |

| CHAPTER 4. FEATURES                                                                                                                                                                                                                                                                                                                                             |                                      |                                                                                                                 |                                                                                             |                                                |                                           |                                           |                            |                                                                                                                                                                    |

| SECTION 1. RECORD CHECK                                                                                                                                                                                                                                                                                                                                         | ING                                  | (274                                                                                                            | 0-1/3                                                                                       | 2740                                           | -2)                                       |                                           |                            | 4-1                                                                                                                                                                |

| Introduction                                                                                                                                                                                                                                                                                                                                                    |                                      |                                                                                                                 |                                                                                             |                                                | •                                         |                                           |                            | 4-1                                                                                                                                                                |

| Vertical Redundancy Check                                                                                                                                                                                                                                                                                                                                       | (VR                                  | C)                                                                                                              |                                                                                             |                                                |                                           | •                                         |                            | 4-1                                                                                                                                                                |

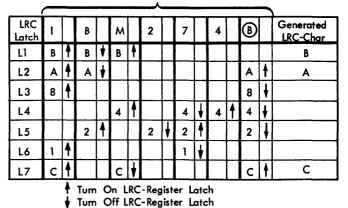

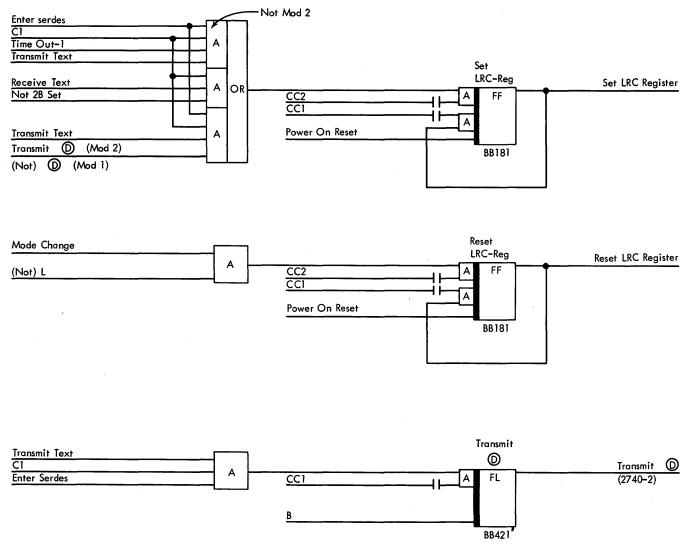

| Longitudinal Redundancy C                                                                                                                                                                                                                                                                                                                                       | •                                    | •                                                                                                               | 2)                                                                                          |                                                |                                           | •                                         |                            | 4-1                                                                                                                                                                |

| End-of-Block (EOB) Check                                                                                                                                                                                                                                                                                                                                        |                                      |                                                                                                                 | '                                                                                           | •                                              | •                                         | •                                         |                            | 4-1                                                                                                                                                                |

| End-of-Block (EOB) Check                                                                                                                                                                                                                                                                                                                                        |                                      | -                                                                                                               |                                                                                             | •                                              | •                                         | •                                         |                            | 4-2                                                                                                                                                                |

| Functional Units                                                                                                                                                                                                                                                                                                                                                | •                                    | . '                                                                                                             |                                                                                             | •                                              | •                                         | •                                         | •                          | 4-2                                                                                                                                                                |

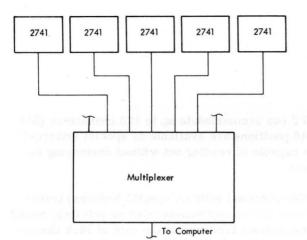

| Parity Error (VRC)                                                                                                                                                                                                                                                                                                                                              |                                      | •                                                                                                               |                                                                                             |                                                | •                                         | •                                         | •                          | 4-2                                                                                                                                                                |