# HEWLETT-PACKARD

HP 7936 AND HP 7937 DISC DRIVES

# HARDWARE SUPPORT MANUAL

# CERTIFICATION

.

Products, materials, parts, and services furnished on this order have been provided in accordance with all applicable Hewlett-Packard specifications. Actual inspection and test data pertaining to this order is on file and available for examination.

Hewlett-Packard's calibration measurements are traceable to the National Bureau of Standards to the extent allowed by the Bureau's calibration facilities.

The Hewlett-Packard Quality Program satisfies the requirements of FAR 52.246-15.

# HP 7936 and HP 7937 Disc Drives Hardware Support Manual

Manual part number: 07937-90903 Microfiche part no. 07937-90803

Printed: JANUARY 1987 Printed in U.S.A. Edition 1 E0187

#### **MODELS COVERED**

This manual covers the following models: HP 7936H, 7937H, 7936XP, 7937XP.

#### **OPTIONS COVERED**

In addition to the standard model, this manual covers the following options: 015, 017.

HEWLETT-PACKARD P.O. Box 39, Boise, Idaho 83707-0039 The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. HEWLETT-PACKARD shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

HEWLETT-PACKARD assumes no responsibility for the use or reliability of its software on equipment that is not furnished by HEWLETT-PACKARD.

This document contains proprietary information, which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of HEWLETT-PACKARD Company.

#### Copyright © 1987 by HEWLETT-PACKARD

# FOR U.S.A. ONLY

The Federal Communications Commission (in 47 CFR 15.818) has specified that the following notice be brought to the attention of the users of this product.

#### FEDERAL COMMUNICATIONS COMMISSION RADIO FREQUENCY INTERFERENCE STATEMENT

Warning: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with the limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference. New editions are complete revisions of the manual. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The dates on the title page change only when a new edition or a new update is published. No information is incorporated into a reprinting unless it appears as a prior update; the edition does not change when an update is incorporated.

A software code may be printed before the date; this indicates the version level of the software product at the time the manual or update was issued. Many product updates and fixes do not require manual changes and, conversely, manual corrections may be done without accompanying product changes. Therefore, do not expect a one-to-one correspondence between product updates and manual updates.

Edition 1.....JANUARY 1987

#### Herstellerbescheinigung

Hiermit wird bescheinigt, daß das Gerät/System HP 7936/7937 in Übereinstimmung mit den Bestimmungen von Postverfügung 1046/84 funkentstört ist.

Der Deutschen Bundespost wurde das Inverkehrbringen dieses Gerätes/Systems angezeigt und die Berechtigung zur Überprüfung der Serie auf Einhaltung der Bestimmungen eingeräumt.

#### **Manufacturer's Declaration**

This is to certify that the product(s) HP 7936/7937 is in accordance with the Radio Interference Requirements of Directive FTZ 1046/1984. The German Bundespost was notified that this equipment was put into circulation; the right to check the series for compliance with the requirements was granted.

Additional Information for Test and Measurement Equipment

If Test and Measurement Equipment is operated with unscreened cables and/or used for measurements on open setups, the user has to assure that under operating conditions the Radio Interference Limits are still met at the border of his premises.

**GENERAL** - This product and related documentation must be reviewed for familiarization with safety markings and instructions before operation.

#### SAFETY SYMBOLS

Instruction manual symbol: the product will be marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect the product against damage.

Indicates hazardous voltages.

Indicates earth (ground) terminal.

# WARNING

The WARNING sign denotes a hazard. It calls attention to a procedure or practice that, if not correctly performed or adhered to, could result in personal injury. Do not proceed beyond a WARNING sign until the indicated conditions are fully understood and met.

# CAUTION

The CAUTION sign denotes a hazard. It calls attention to an operating procedure or practice that, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the product. Do not proceed beyond a CAUTION sign until the indicated conditions are fully understood and met.

SAFETY EARTH GROUND - This is a safety class I product and is provided with a protective earthing terminal. An uninterruptible safety earth ground must be provided from the main power source to the product input wiring terminals, power cord, or supplied power cord set. Whenever it is likely that the protection has been impaired, the product must be made inoperative and be secured against any unintended operation.

**BEFORE APPLYING POWER** - Verify that the product is configured to match the available main power source according to the input power configuration instructions provided in this manual.

If this product is to be operated with an autotransformer make sure that the common terminal is connected to the earth terminal of the main power source.

SERVICING

# WARNING

Any servicing, adjustment, maintenance, or repair of this product must be performed only by service-trained personnel.

Adjustments described in this manual may be performed with power supplied to the product while protective covers are removed. Energy available at many points may, if contacted, result in personal injury.

Capacitors inside this product may still be charged after the product has been disconnected from the main power source.

To avoid a fire hazard, fuses with the proper current rating and of the specified type (normal blow, time delay, etc.) must be used for replacement. To install or remove a fuse, first disconnect the power cord from the device. Then, using a small flat-bladed screw driver, turn the fuseholder cap counterclockwise until the cap releases. Install either end of a properly rated fuse into the cap. Next, insert the fuse and fuseholder cap into the fuseholder by pressing the cap inward and then turning it clockwise until it locks in place. The List of Effective Pages shows the edition or update number of all pages. Within the manual, any page changed since the last edition is indicated by printing the update number on the bottom of the page. Changes are marked with a vertical bar in the margin. If an update is incorporated when an edition is reprinted, these bars are removed. No information is incorporated into a reprinting unless it appears as a prior update. To verify that your manual contains the most current information, check that the version printed at the bottom of the page matches the version listed below for that page.

| Effective Pages | Version   |

|-----------------|-----------|

| all             | Edition 1 |

| Chapter 1                | Page |

|--------------------------|------|

| Product Information      | 1-1  |

| Introduction             | 1-1  |

| Product Description      | 1-1  |

| Documentation Supplied   |      |

| Supporting Documentation | 1-2  |

| Product Structure        | 1-2  |

| Specifications           |      |

| Serial Number            |      |

| Supported Equipment      | 1-2  |

| Test Equipment Required  |      |

| Warranty                 |      |

| Support Strategy         | 1-2  |

# Chapter 2 Site Planning and Requirements

# **Page** 2-1

| Introduction        | 2-1 |

|---------------------|-----|

| Site Planning       | 2-1 |

| Specifications      | 2-1 |

| Cabling Limitations | 2-1 |

| Chapter 3<br>Installation And Configuration | Page<br>3-1 |

|---------------------------------------------|-------------|

| Introduction                                | 3_1         |

| Shipping Latch                              |             |

| Drive Installation                          | 3-2         |

| Primary Power Requirements                  |             |

| Controls, Indicators, and Connectors        | 3-2         |

| Line~ Switch                                | 3-2         |

| Channel Address/Diagnostic Switch           |             |

| Run Time Mode                               | 3-3         |

| Diagnostic Mode                             | 3-3         |

| LED Display                                 | 3-4         |

| HP-IB Connector                             | 3-4         |

| Power Fuse                                  |             |

| Line Connector                              | 3-4         |

| CPU Connection - HP-IB Systems              | 3-4         |

# **Contents (continued)**

| HP-IB Cabling        | 3-4 |

|----------------------|-----|

| HP-IB Device Address | 3-5 |

| Page |  |

|------|--|

| 4-1  |  |

| 4-1  |  |

|      |  |

| Chapter 5                               | Page |

|-----------------------------------------|------|

| Functional Description                  | 5-1  |

| Introduction                            | 5-1  |

| Block Diagrams                          |      |

| Signal Notation                         |      |

| List of Mnemonics                       |      |

| Disc Format                             |      |

| Addressing Structure                    |      |

| Addressing Mode                         |      |

| Disc Sparing                            |      |

| Sector Sparing                          |      |

| Track Sparing                           |      |

| Controller PCA-A6                       |      |

| Servo System                            |      |

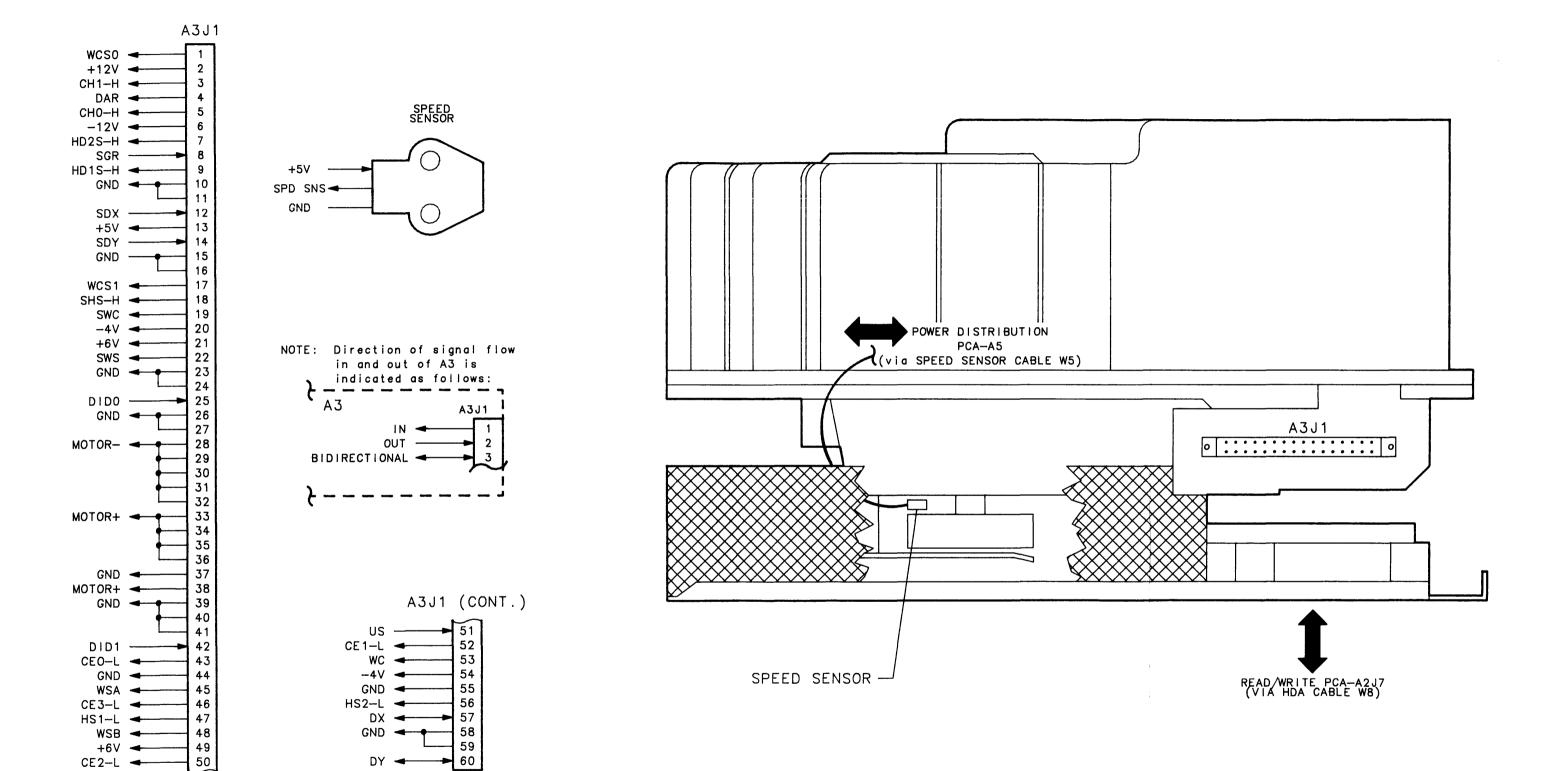

| Head-Disc Assembly A3                   |      |

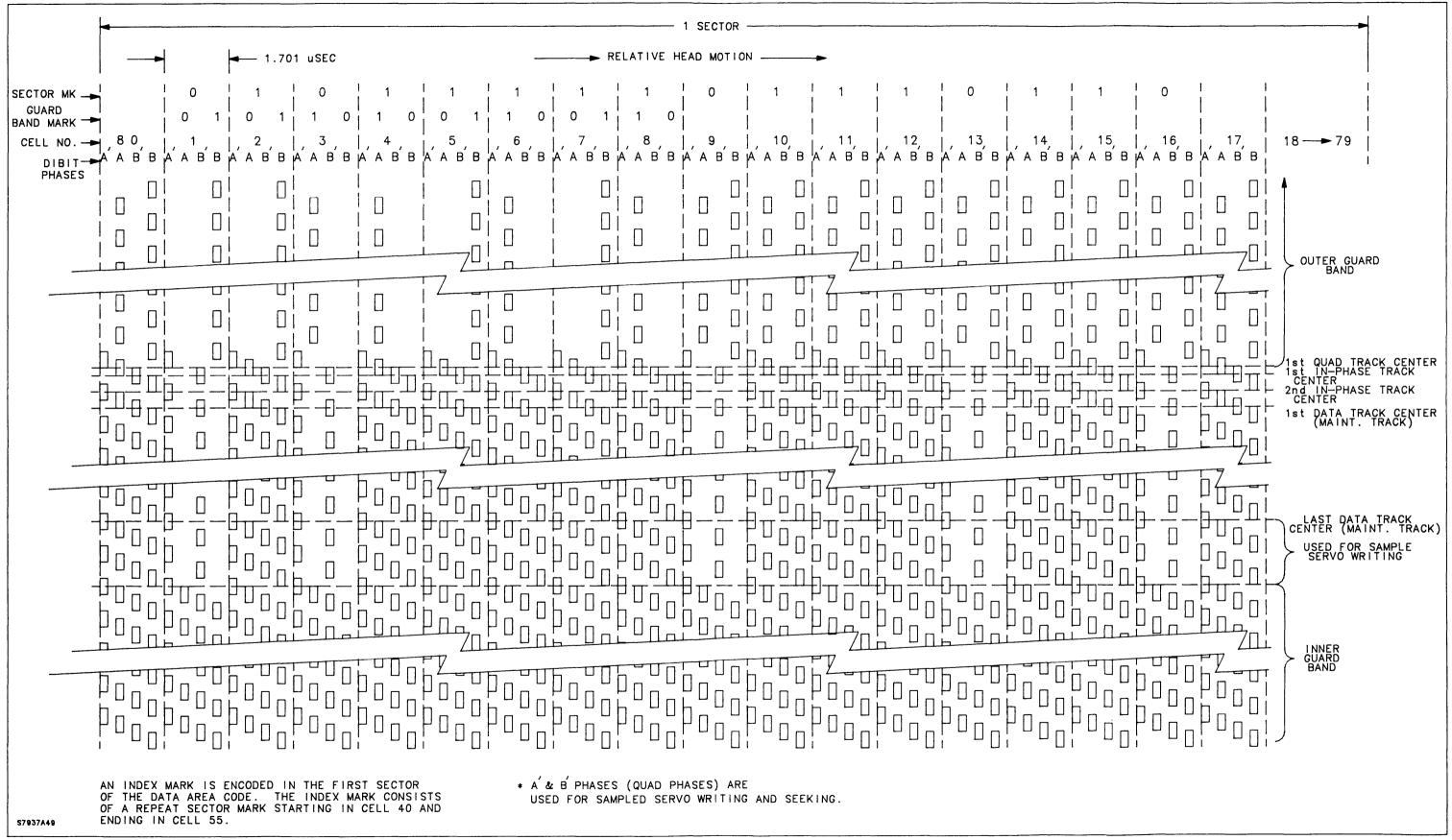

| Dedicated Servo Code                    |      |

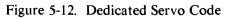

| Sampled Servo Code                      |      |

| Servo Head                              |      |

| Servo Read Preamplifier/Write Driver IC |      |

| Drive ID Circuit                        |      |

| Head Gain Reference PROM and DAC        |      |

| Actuator                                |      |

| Speed Sensor                            |      |

| Read/Write PCA-A2                       |      |

| Dedicated Servo AGC Amplifier           |      |

| Sampled Servo Switch                    |      |

| Sampled Servo AGC Amplifier             |      |

| Servo PCA-A1                            |      |

| Servo Controller                        |      |

| 2-Bit ADC                               |      |

| Dedicated Servo AGC Circuit             |      |

| Sampled Servo AGC Circuit               |      |

| Sector Mark Decoder                     |      |

| Dedicated Servo Circuit                 |      |

| Sampled Servo Circuit                   |      |

| Sampled/Dedicated Select Switch    |       |

|------------------------------------|-------|

| Slew Rate Limiter                  |       |

| Slew Rate Limit Switch             | .5-20 |

| Off-Track Detector                 | .5-20 |

| Track Crossing Detector            | .5-20 |

| Fault Latches                      | .5-21 |

| Servo Power Amplifier              | .5-21 |

| Amplifier Error Detection          | .5-24 |

| Servo System Errors                | .5-25 |

| Track Follower - PLL Errors        | .5-25 |

| Seek Errors                        | .5-26 |

| Power Amplifier Error              | .5-26 |

| Error Reporting                    | .5-27 |

| Flowcharts                         |       |

| Read/Write System                  | .5-27 |

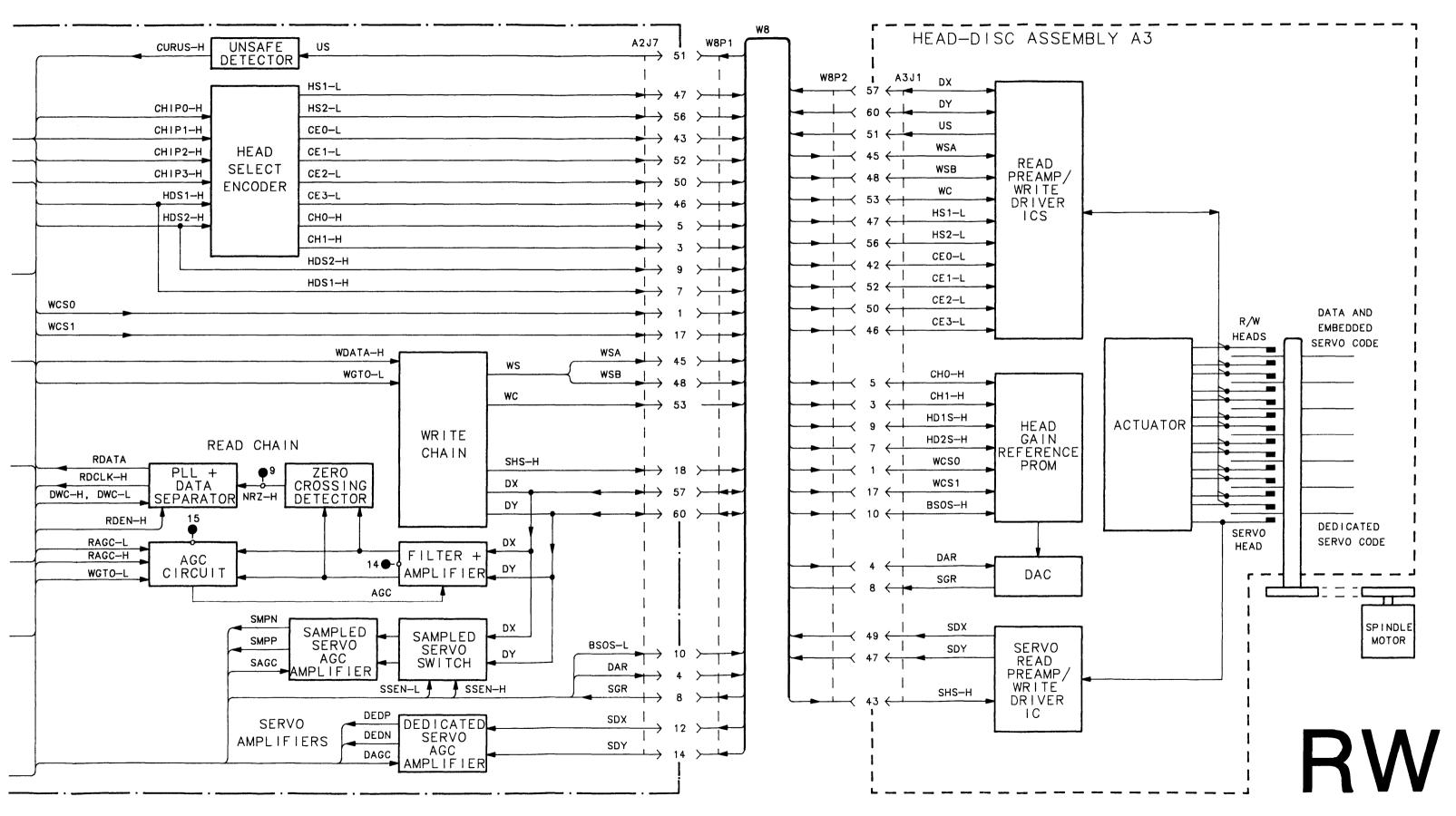

| Head-Disc Assembly A3              | .5-28 |

| Recording Medium                   | .5-28 |

| Read/Write Heads                   | .5-28 |

| Read Preamplifier/Write Driver ICs |       |

| Read/Write PCA-A2                  | .5-29 |

| Read/Write Controller IC           | .5-29 |

| Head Select Encoder                | .5-32 |

| Read Chain                         | .5-32 |

| Write Chain                        | .5-33 |

| Read/Write System Errors           | .5-33 |

| Error Reporting                    | .5-34 |

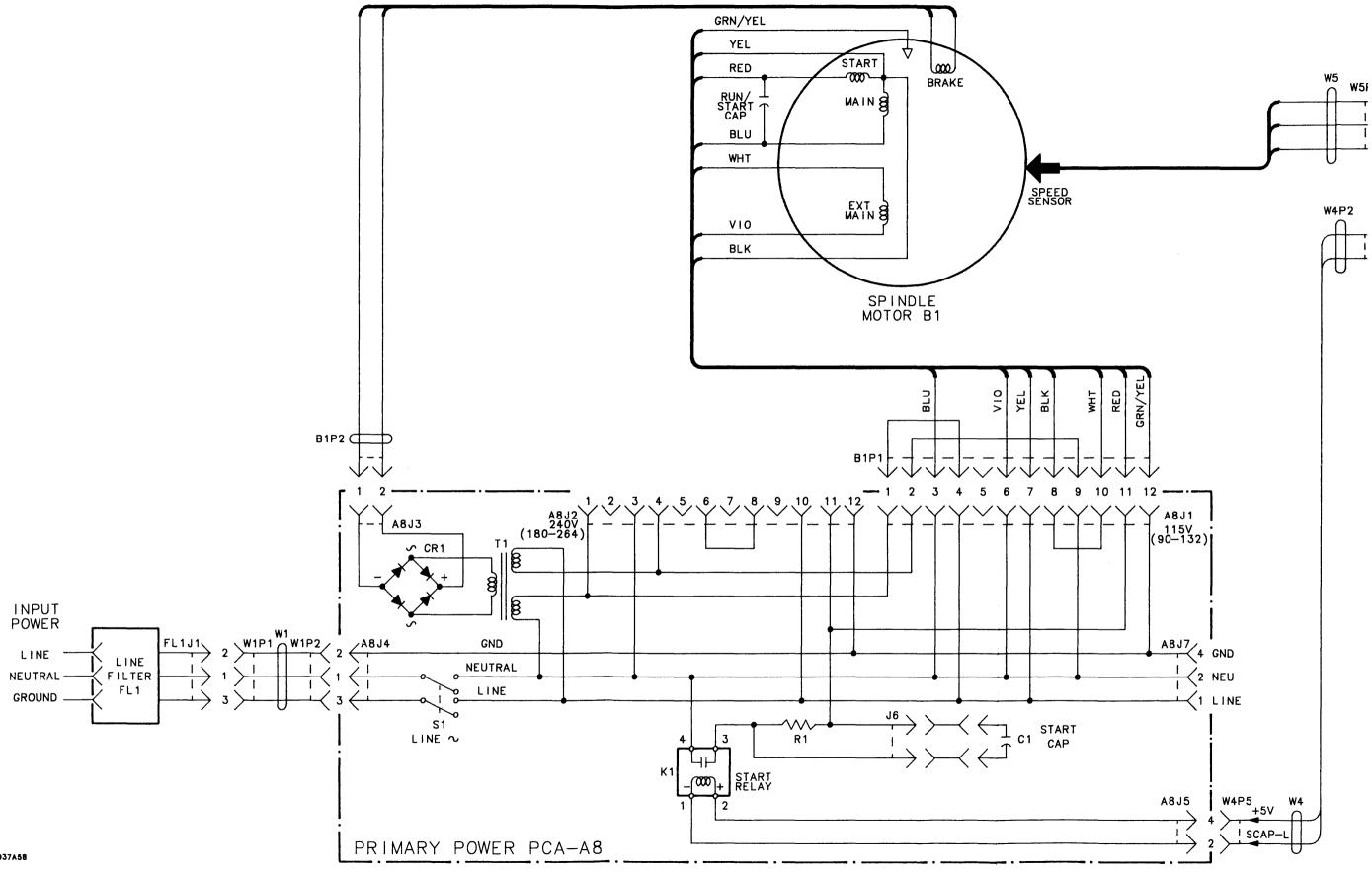

| Spindle Drive System               | .5-34 |

| AC Input Circuit                   | .5-35 |

| Spindle Motor B1                   | .5-35 |

| Primary Power PCA-A8               | .5-35 |

| LINE~ Switch                       | .5-35 |

| Start Capacitor and Relay          | .5-35 |

| Brake Voltage Source               | .5-36 |

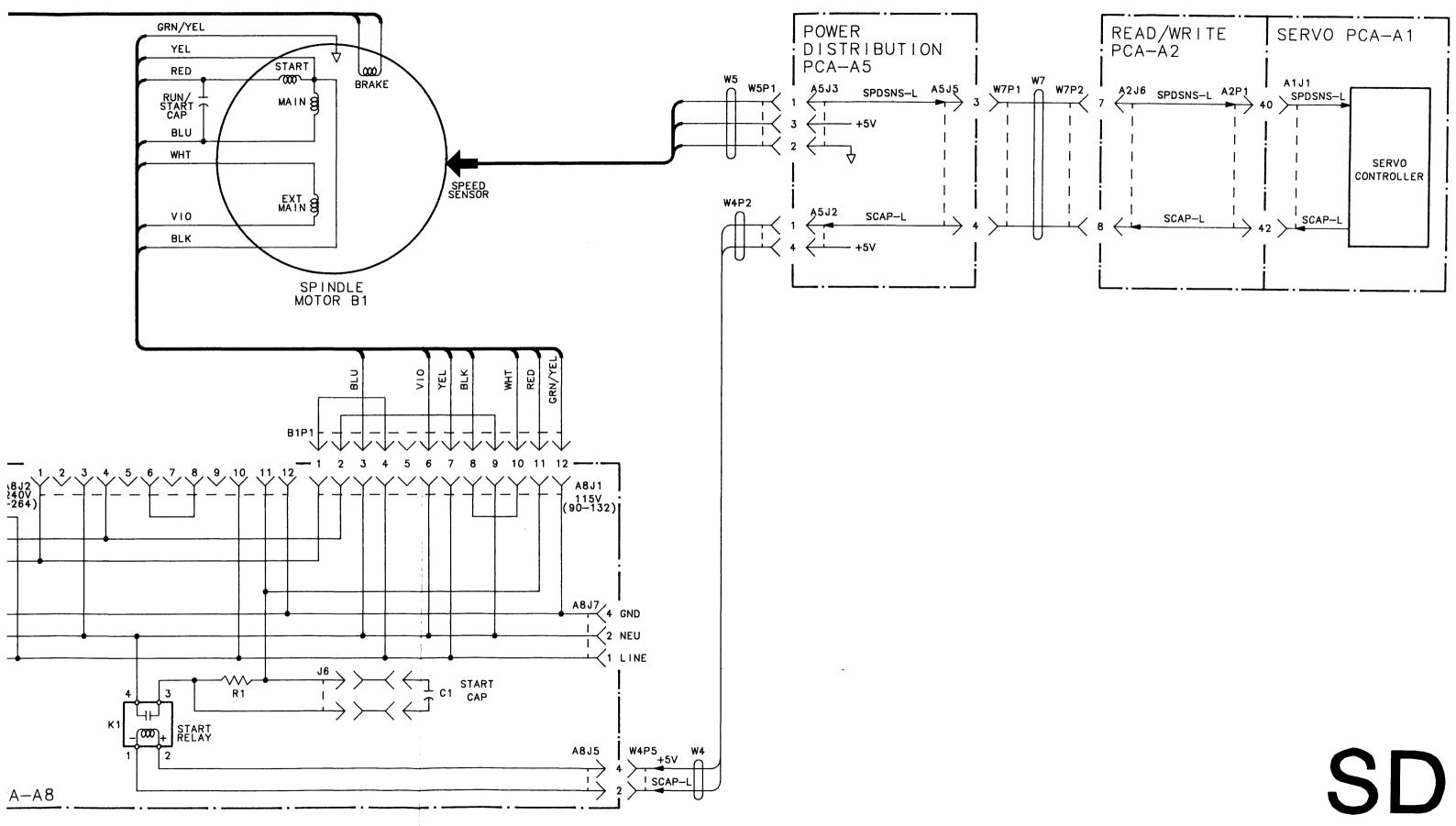

| Speed Sensor                       | .5-36 |

| Servo PCA-A1                       | .5-36 |

| Read/Write PCA-A2                  |       |

| Power Distribution PCA-A5          |       |

| Power Supply System                |       |

| AC Input Circuit                   |       |

| Primary Power PCA-A8               |       |

| Power Supply PCA-A4                |       |

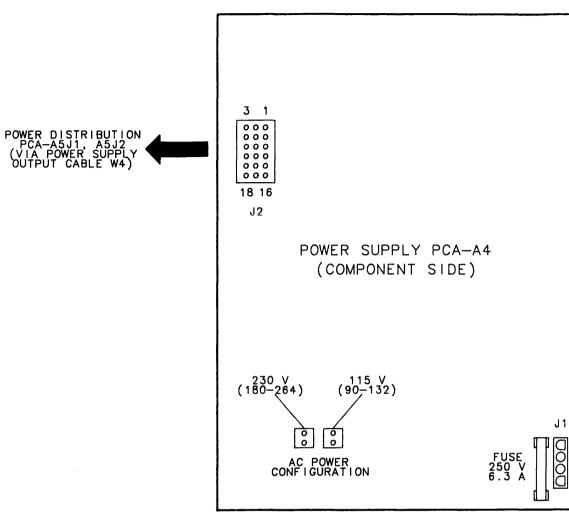

| Primary Power Selection            |       |

| Primary Control Circuit            |       |

| Output Section.                    |       |

| Fault Detection and Protection     |       |

| Power Distribution PCA-A5.         |       |

| Read/Write PCA-A2.                 |       |

| Servo PCA-A1                       |       |

|                                    |       |

# **Contents (continued)**

| LED Display                           | 5-38 |

|---------------------------------------|------|

| HDA Air Filtration                    |      |

| Recirculating Filter                  |      |

| Breather Filter                       |      |

| Chemical Filter and Desiccant Chamber |      |

| Drive Air Flow                        |      |

# Chapter 6 Removal And Replacement

| Introduction                             | 6-1         |

|------------------------------------------|-------------|

| Tools Required                           | 6-1         |

| Illustrations                            | 6-2         |

| Drive Preparation For Service            | 6-2         |

| Drive Removal And Replacement Procedures | 6-2         |

| Rear Cover                               | 6-2         |

| HP-IB Assembly                           |             |

| Front Panel                              |             |

| Front Cover                              | 6-3         |

| Controller PCA-A6                        | 6-3         |

| EPROM Kit, Controller PCA-A6             | 6-3         |

| Read/Write PCA-A2                        | 6-4         |

| Servo PCA-A1                             | 6-4         |

| Power Distribution PCA-A5                | 6-4         |

| Line Filter Assembly FL1                 | 6-4         |

| Drive Belt, Motor Pulley                 | 6-5         |

| Power Supply PCA-A4                      | 6-5         |

| Primary Power PCA-A8                     | 6-6         |

| Start Capacitor C1                       | 6-6         |

| Motor B1                                 | <b>6-</b> 7 |

| Head-Disc Assembly A3                    | 6-7         |

| Chapter 7    | Page |

|--------------|------|

| Adjustments  | 7-1  |

| Introduction |      |

| Chapter 8                       | Page |

|---------------------------------|------|

| Troubleshooting and Diagnostics | 8-1  |

| Introduction                    |      |

| Safety Considerations           |      |

| Troubleshooting Strategy       | 3-1 |

|--------------------------------|-----|

| Self-Test Diagnostics          | 8-1 |

| Diagnostic Switch              | 8-2 |

| Run Time Mode                  | 3-2 |

| Diagnostic Mode                | 3-2 |

| LED Display                    | 3-3 |

| Assembly Identification        | 3-3 |

| CS/80 External Exerciser       | 8-3 |

| Error Logs                     | 3-4 |

| Error Rate Test (ERT) Log      | 3-4 |

| Run Time Log                   |     |

| Fault Log                      | 8-5 |

| Error Codes                    | B-5 |

| TERRORS                        | 8-6 |

| DERRORS                        | 3-6 |

| Servo Controller Error Codes   | 8-6 |

| Data Error Troubleshooting     | 8-7 |

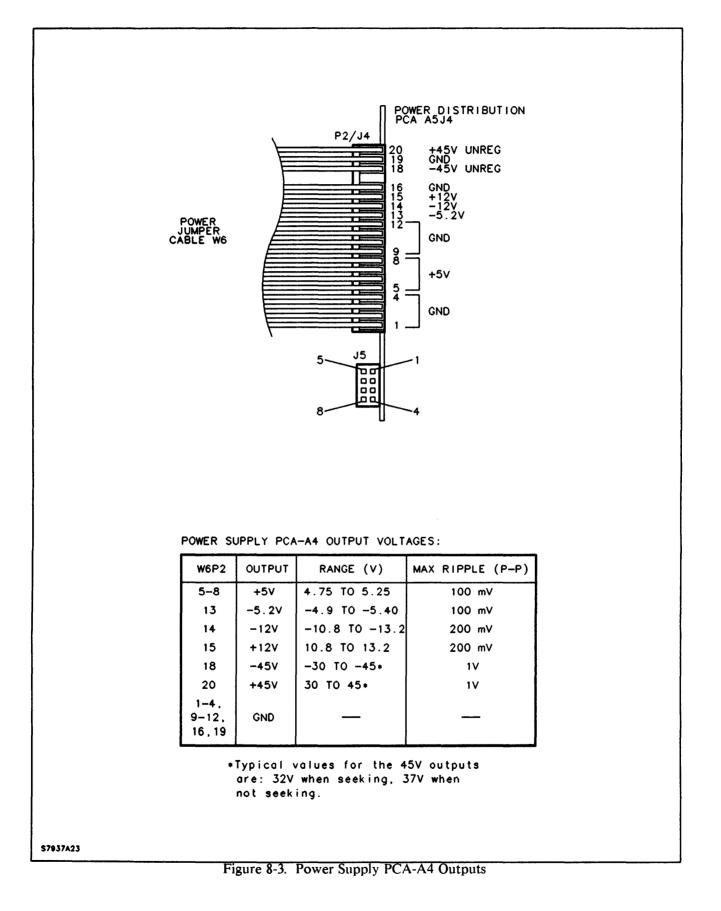

| Checking Power Supply Voltages | 8-7 |

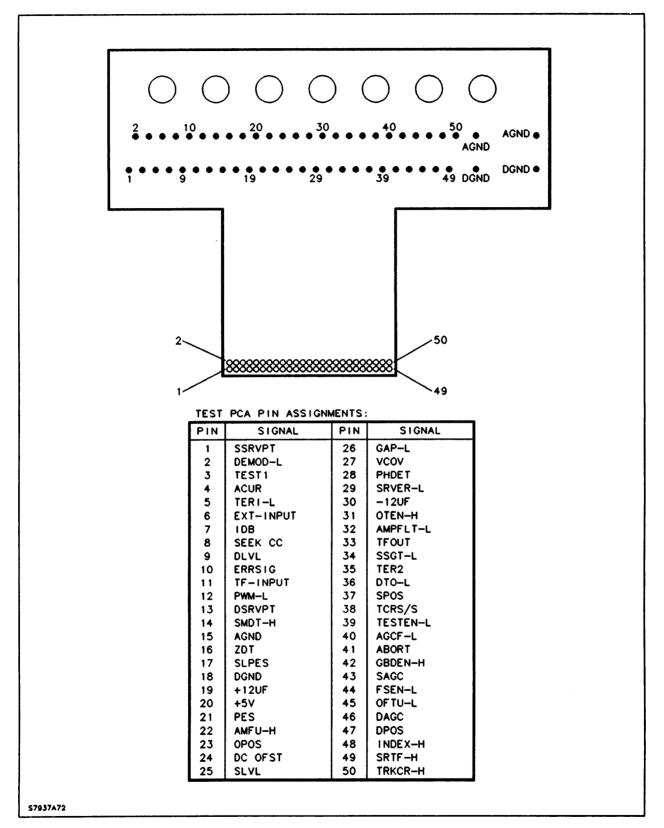

| Servo Test Point PCA           | 8-8 |

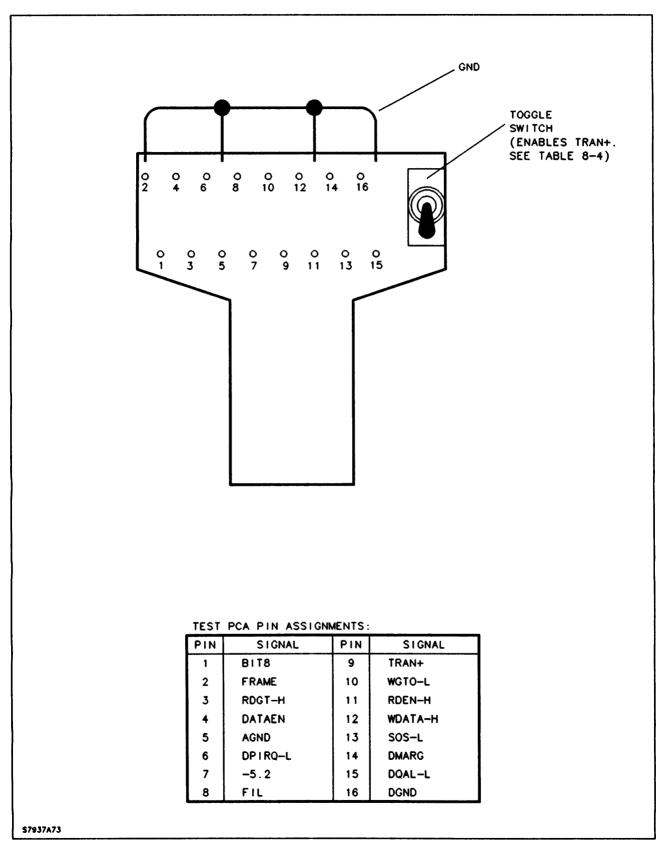

| Read/Write Test Point PCA      | 8-8 |

.

,

,

| Chapter 9            | Page |

|----------------------|------|

| Replaceable Parts    | 9-1  |

| Introduction         |      |

| Ordering Information |      |

| Service Kit Contents |      |

| Chapter 10        | Page |

|-------------------|------|

| Reference         | 10-1 |

| Controller PCA-A6 |      |

| Chapter 11      | Page |

|-----------------|------|

| Product History | 11-1 |

| ·               |      |

| Introduction    |      |

# **Contents (continued)**

| Chapter 12<br>Diagrams      | <b>Page</b><br>12-1                   |

|-----------------------------|---------------------------------------|

| Introduction                |                                       |

| Dimensions                  |                                       |

| Air Circulation             |                                       |

| Assembly Location           |                                       |

| Signal Distribution         |                                       |

| Functional Block Diagrams   | 12-2                                  |

| Appendix A                  | Page                                  |

| HP-IB Controller            | A-1                                   |

| Introduction                |                                       |

| Controller Interfaces       |                                       |

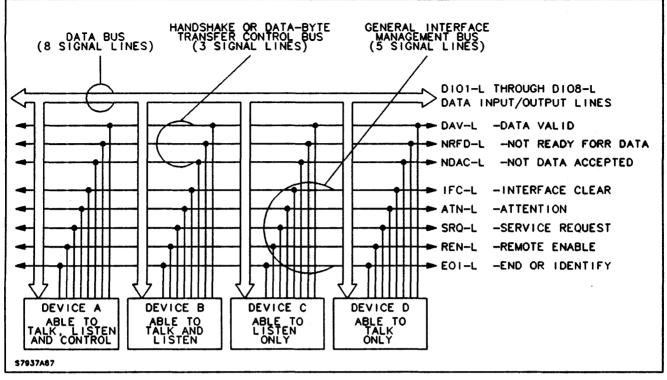

| НР-ІВ                       |                                       |

| HP-IB Communications        |                                       |

| Channel Management          |                                       |

| Message Structure           |                                       |

| CS/80 Instruction Set       |                                       |

| ESI.                        |                                       |

| Disc Data Bus               |                                       |

| Data Path Control Bus       |                                       |

| Servo Control Bus           |                                       |

| Miscellaneous Signals       |                                       |

| Human Interface             |                                       |

| Functional Operation        |                                       |

| Power-Up.                   |                                       |

| Head Positioning.           |                                       |

| Write                       |                                       |

| Read                        |                                       |

| Error Correction.           |                                       |

| Hardware Architecture       |                                       |

| HP-IB Circuitry             |                                       |

| HP-IB Interface.            | · · · · · · · · · · · · · · · · · · · |

| DMA                         |                                       |

| ESI Circuitry.              |                                       |

| Disc Data Interface         |                                       |

| DMA<br>ECC                  |                                       |

| Data Path Control Interface |                                       |

|                             |                                       |

| Interrupt Controller           | A-13 |

|--------------------------------|------|

| Bus Error Timer                |      |

| Human Interface Circuitry      |      |

| HP-IB Address/Selftest Switch  |      |

| LED Drivers.                   |      |

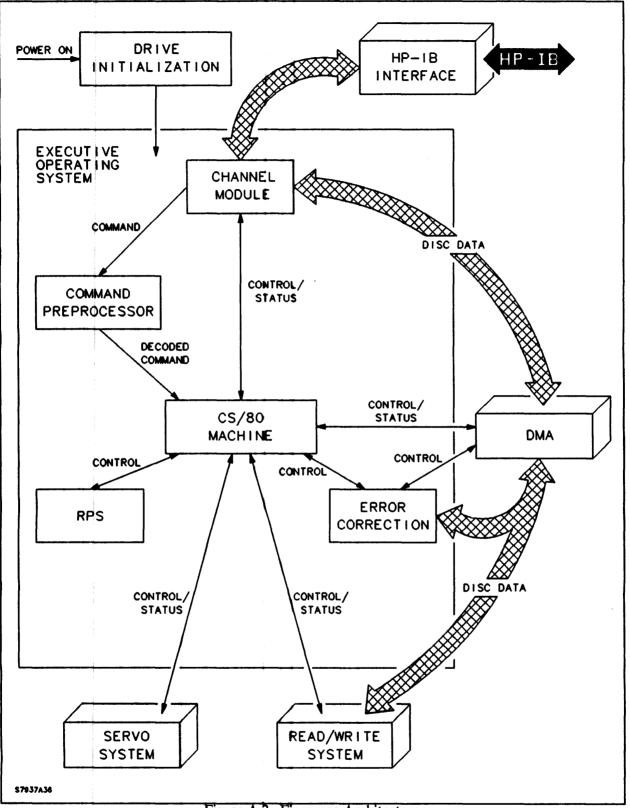

| Firmware Architecture          |      |

|                                |      |

| Drive Initialization Firmware. |      |

| Multi-Tasking Executive        |      |

| Channel Module                 |      |

| Command Preprocessor           | A-17 |

| CS/80 Module                   | A-17 |

| RPS Task                       | A-17 |

| Error Correction Task          | A-18 |

| Diagnostics.                   | A-18 |

| Disc Caching.                  |      |

| Cache Functional Operation     |      |

| Read With Disc Caching         |      |

| Write With Disc Caching.       |      |

| Cache Flushing                 |      |

| Cache Hardware                 |      |

| Cache Diagnostics              |      |

.

# **Figures and Tables**

# Figure or Table

#### Page

| Figure 1-1. HP 7937 Disc Drives in HP 19511A Cabinet1-3                      |

|------------------------------------------------------------------------------|

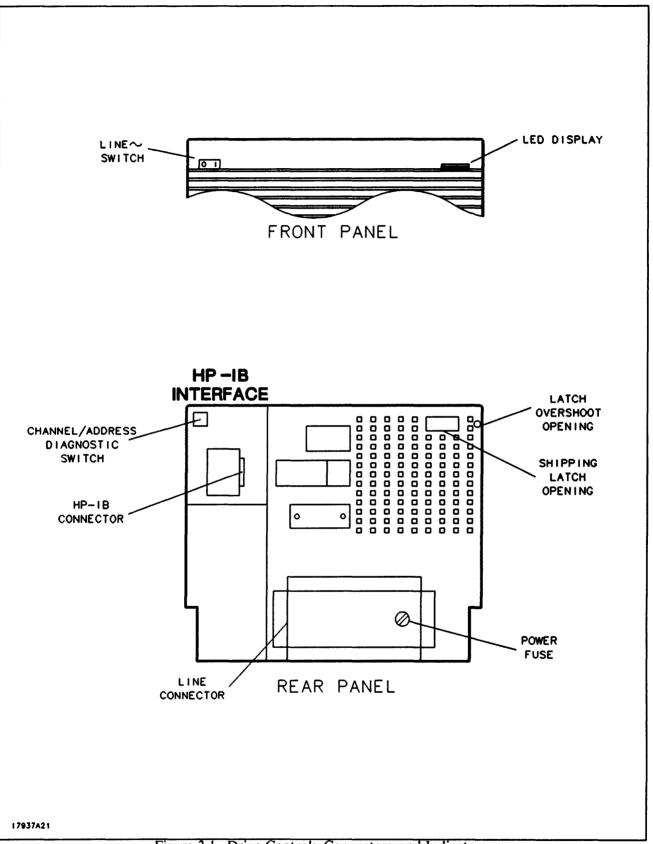

| Figure 3-1. Drive Controls, Connectors, and Indicators                       |

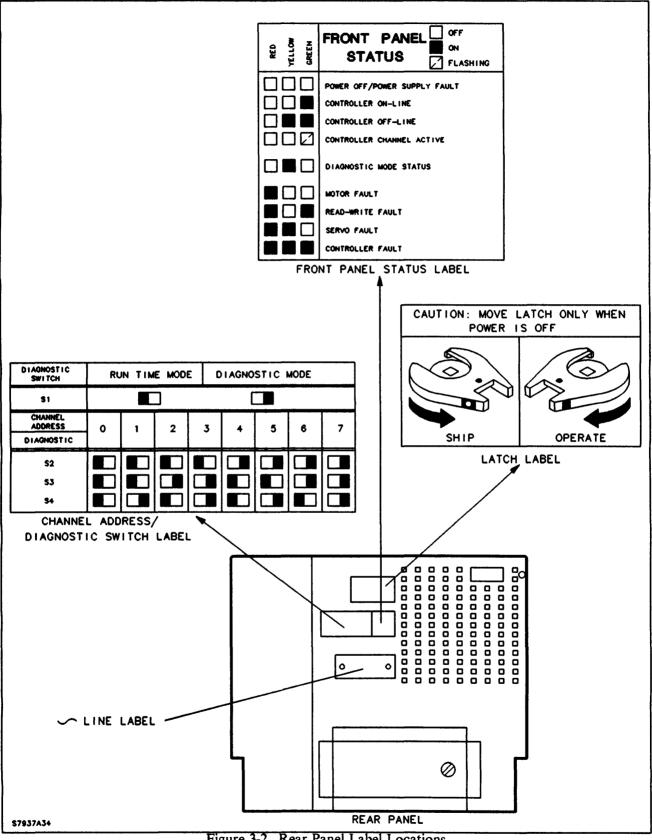

| Figure 3-2. Rear Panel Label Locations                                       |

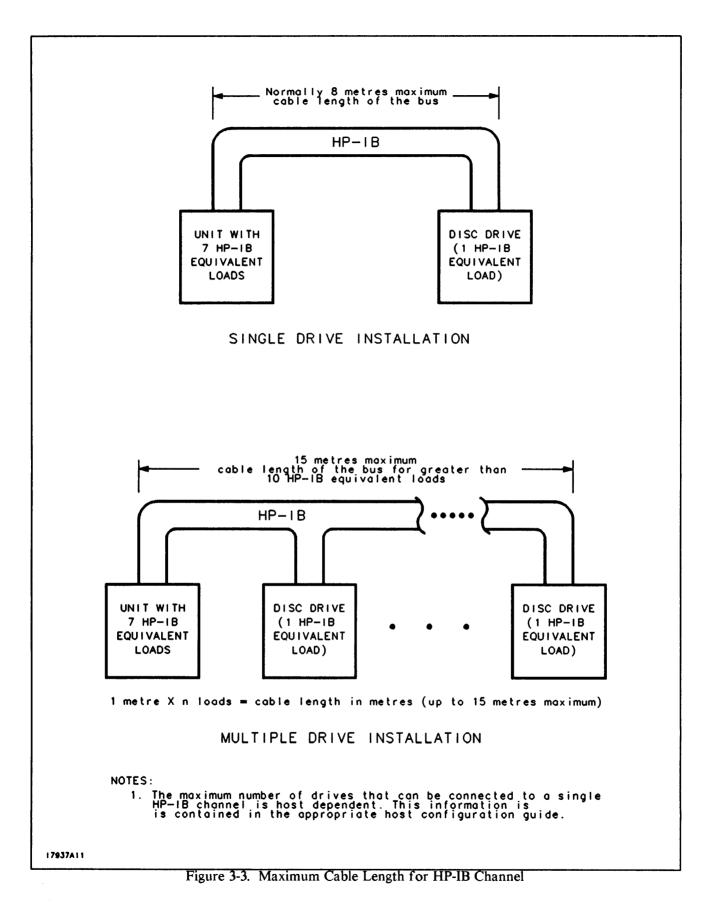

| Figure 3-3. Maximum Cable Length for HP-IB Channel                           |

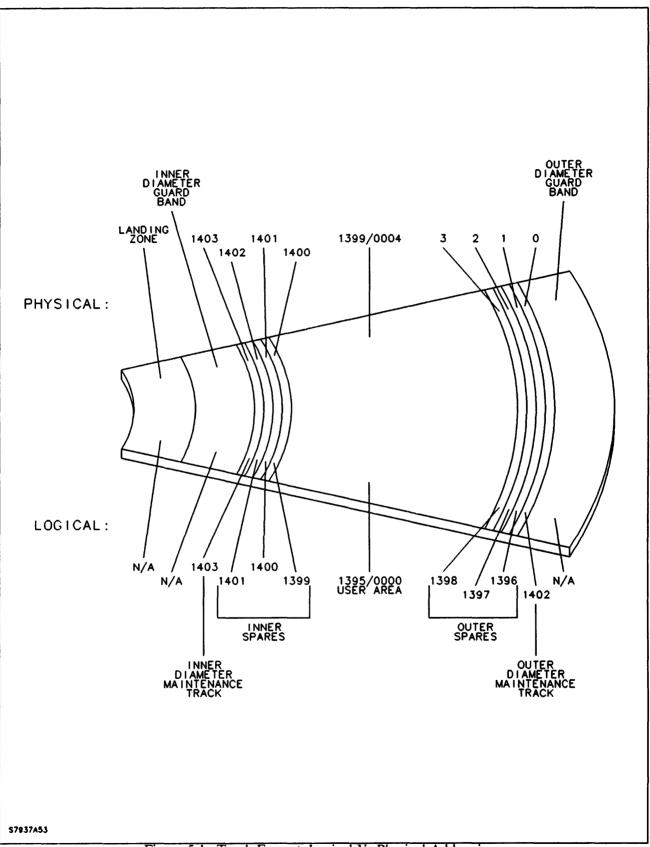

| Figure 5-1. Track Format, Logical Vs Physical Addressisng                    |

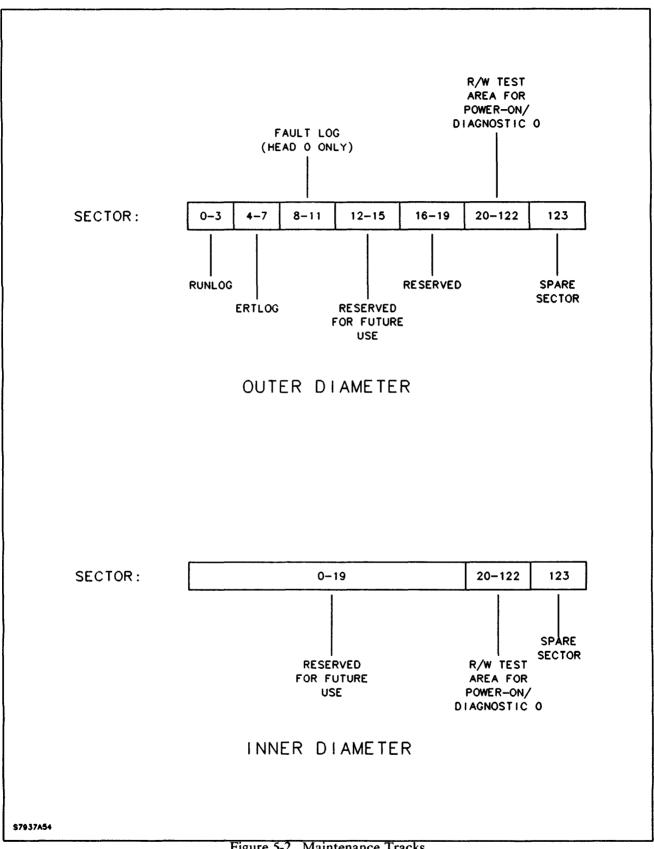

| Figure 5-2. Maintenance Tracks                                               |

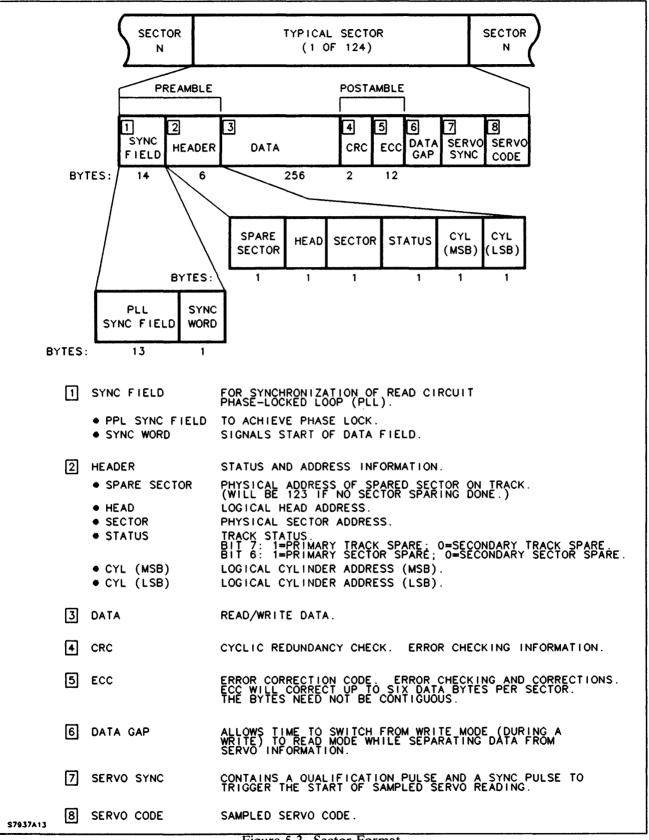

| Figure 5-3. Sector Format                                                    |

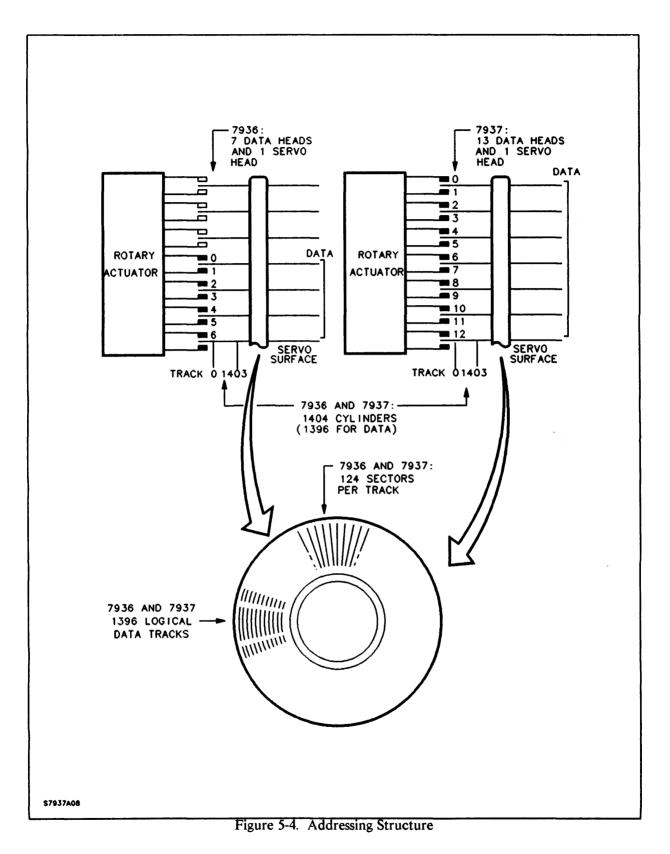

| Figure 5-4. Addressing Structure                                             |

| Figure 5-5. Spare Track Scalar Values                                        |

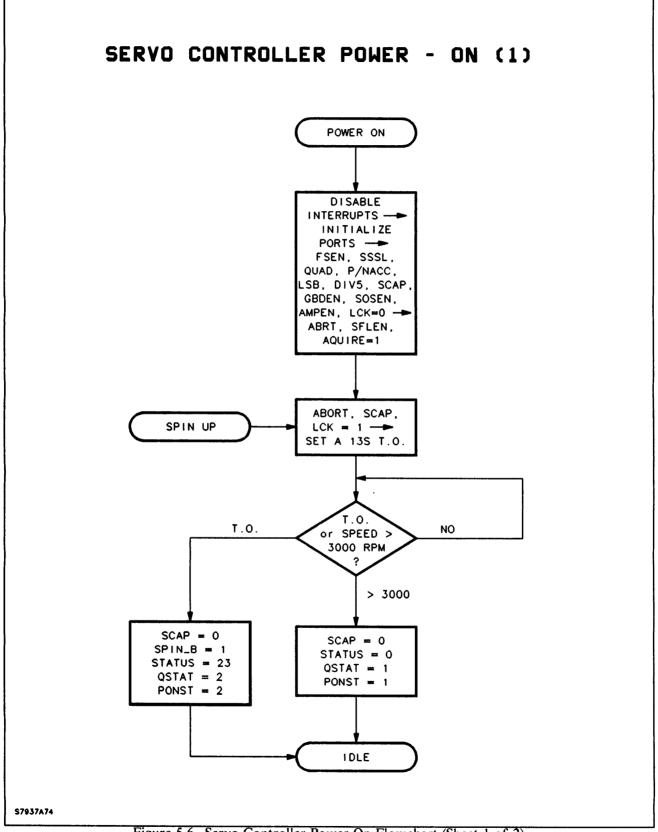

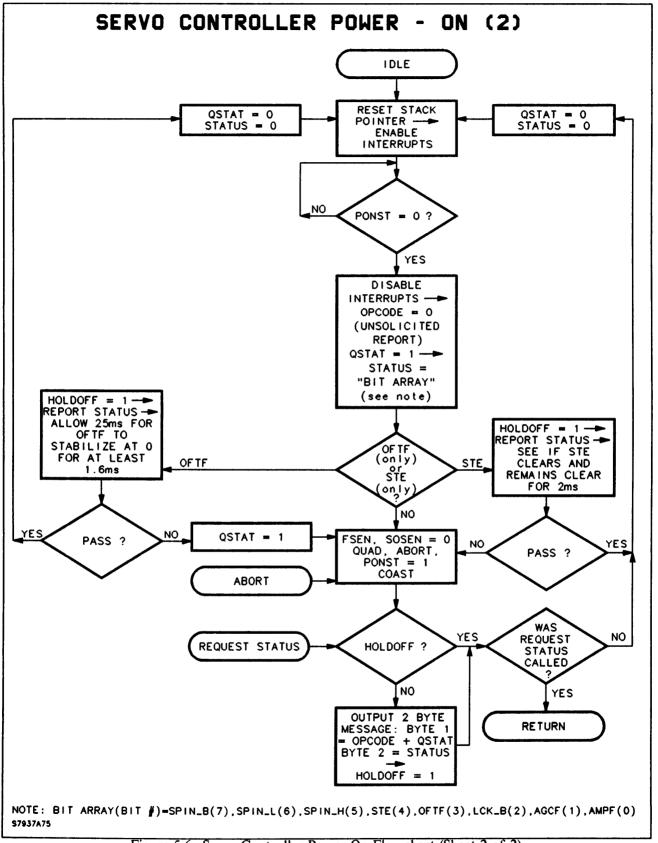

| Figure 5-6. Servo Controller Power On Flowchart                              |

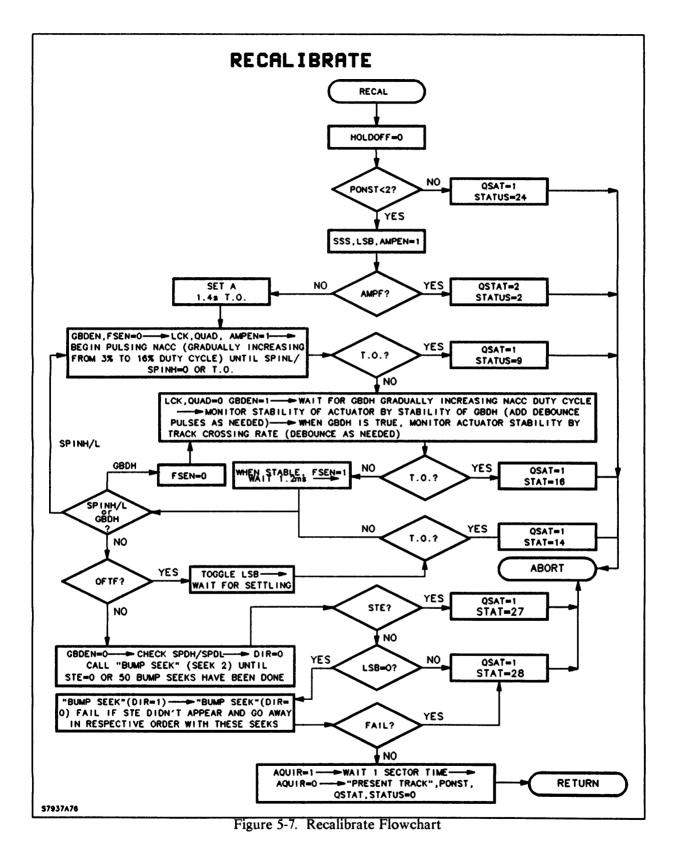

| Figure 5-7. Recalibrate Flowchart                                            |

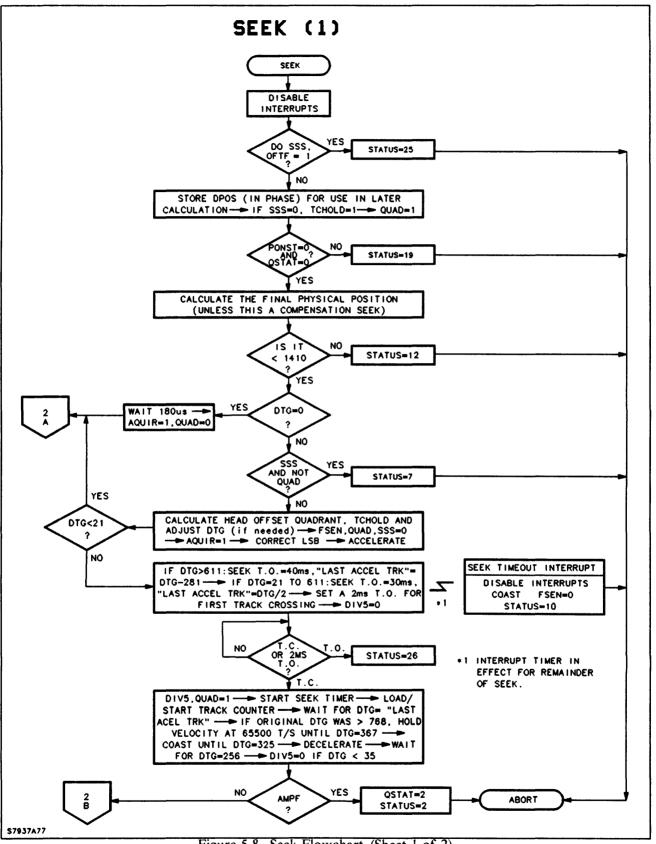

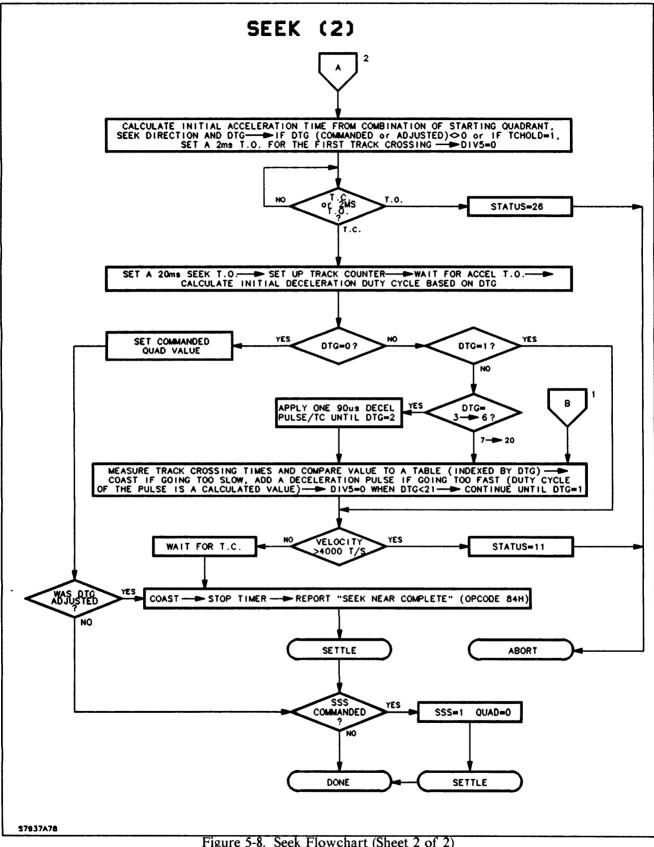

| Figure 5-8. Seek Flowchart                                                   |

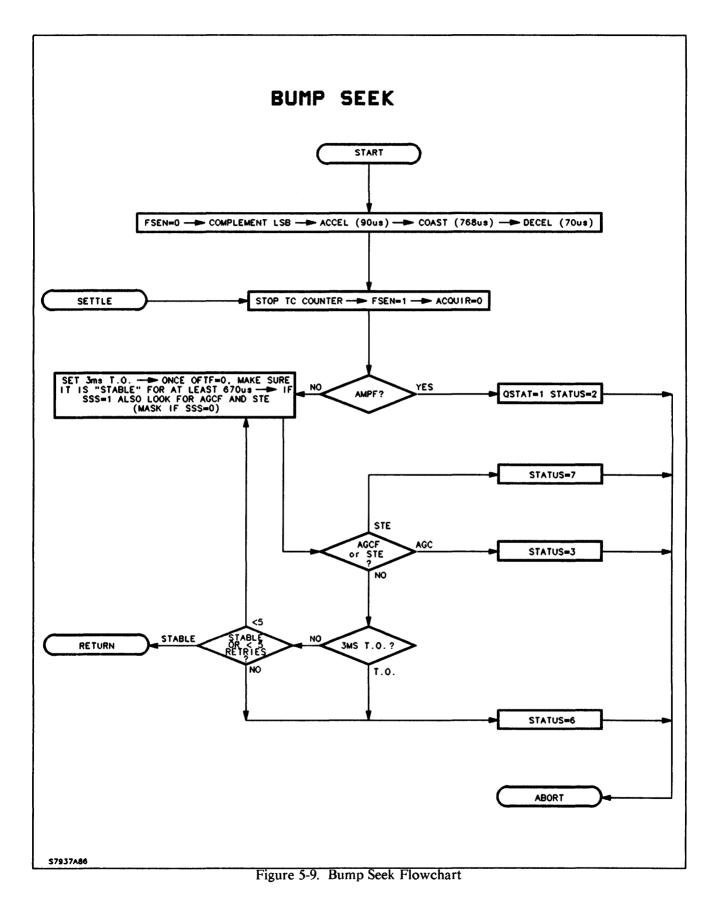

| Figure 5-9. Bump Seek Flowchart                                              |

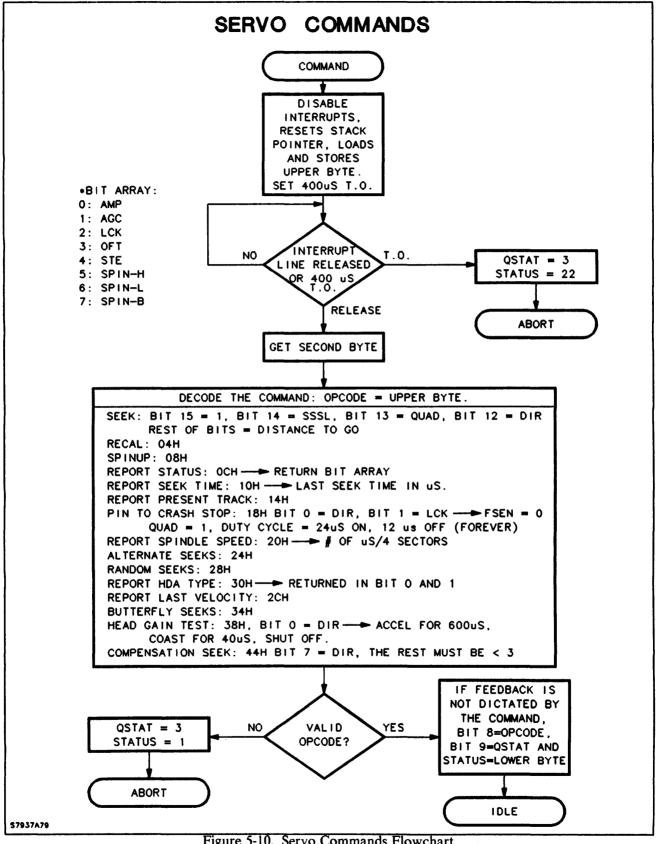

| Figure 5-10. Servo Commands Flowchart                                        |

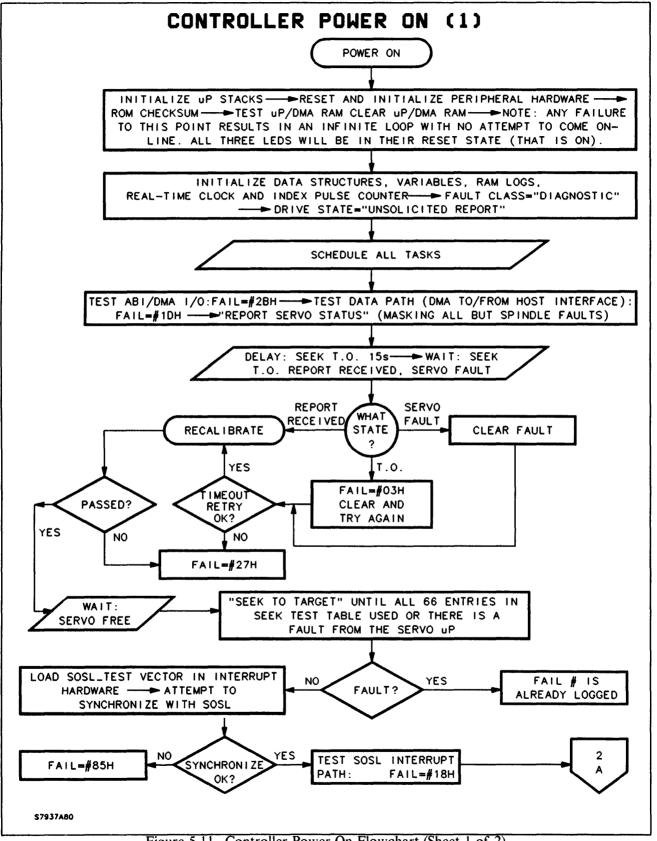

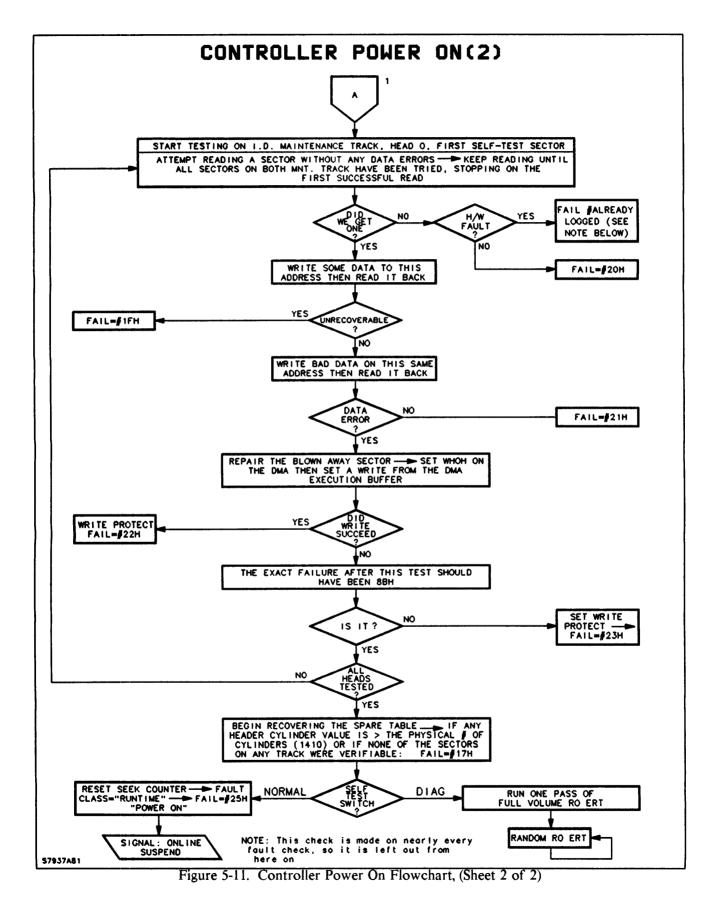

| Figure 5-11. Controller Power On Flowchart                                   |

| Figure 5-12. Dedicated Servo Code                                            |

| Figure 5-13. Sampled Servo Code                                              |

| Figure 5-14. Dedicated Servo Circuit Timing                                  |

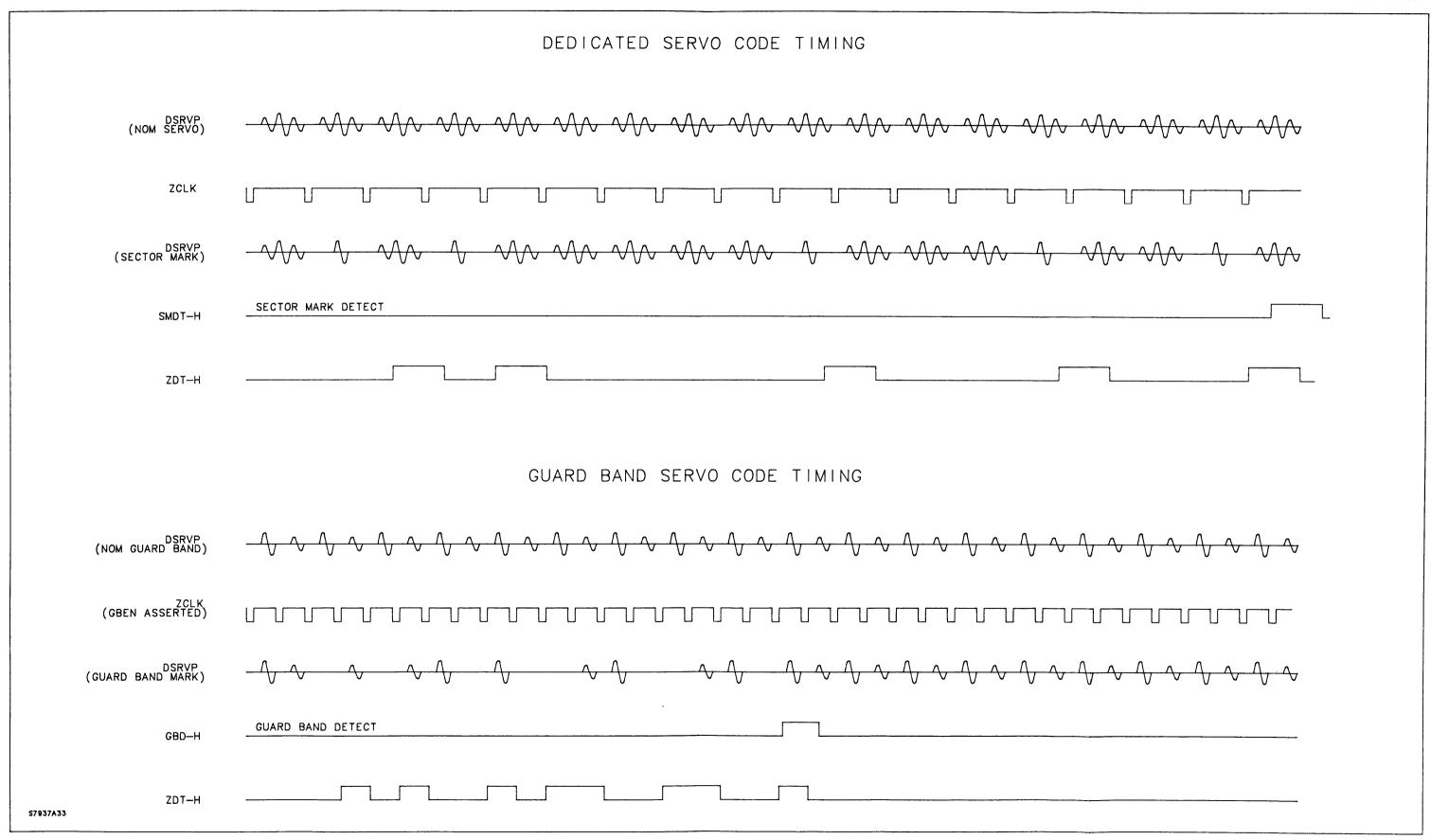

| Figure 5-15. Sampled Servo Circuit Timing                                    |

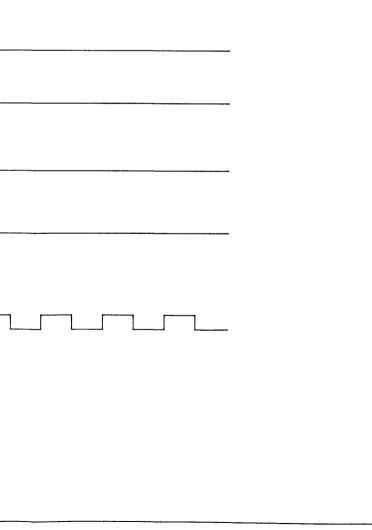

| Figure 5-16. Disc Drive Basic Block Diagram                                  |

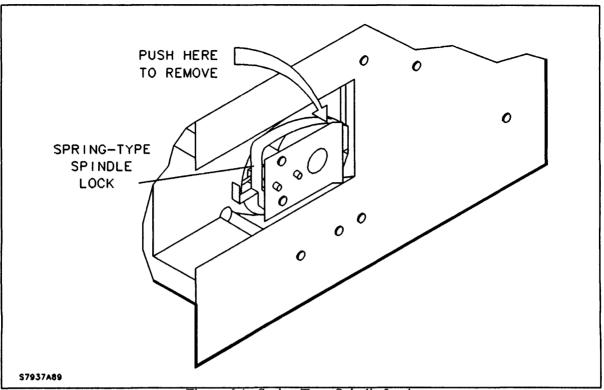

| Figure 6-1. Spring-Type Spindle Lock                                         |

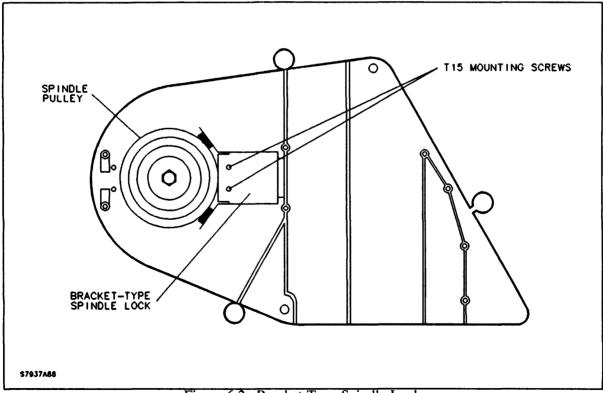

| Figure 6-2. Bracket-Type Spindle Lock                                        |

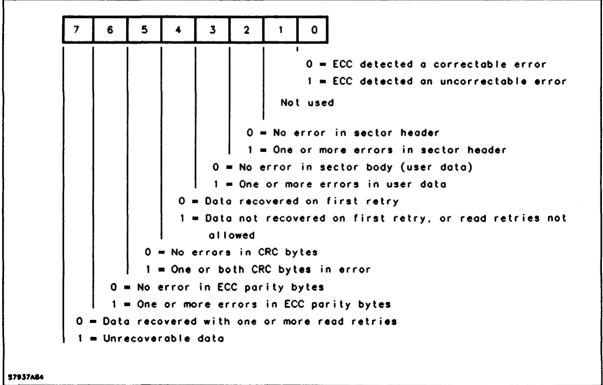

| Figure 8-1. ERT Log Error Code Byte                                          |

| Figure 8-2. Run Time Log Error Code Byte                                     |

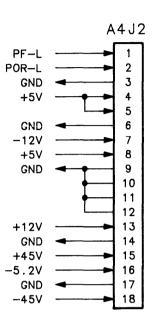

| Figure 8-3. Power Supply PCA-A4 Outputs                                      |

| Figure 8-4. Servo System Test Point PCA                                      |

| Figure 8-5. Read/Write Test Point PCA                                        |

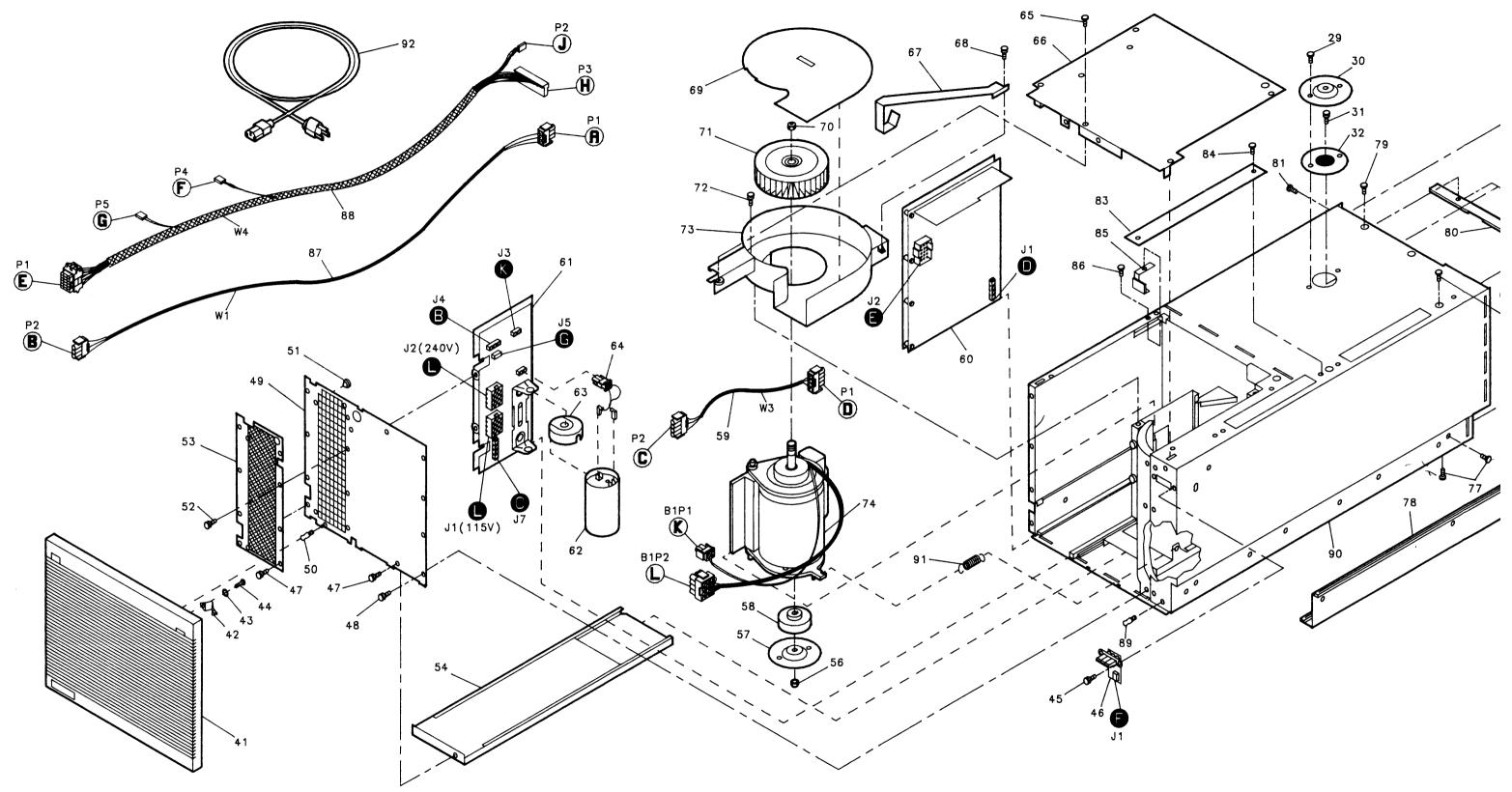

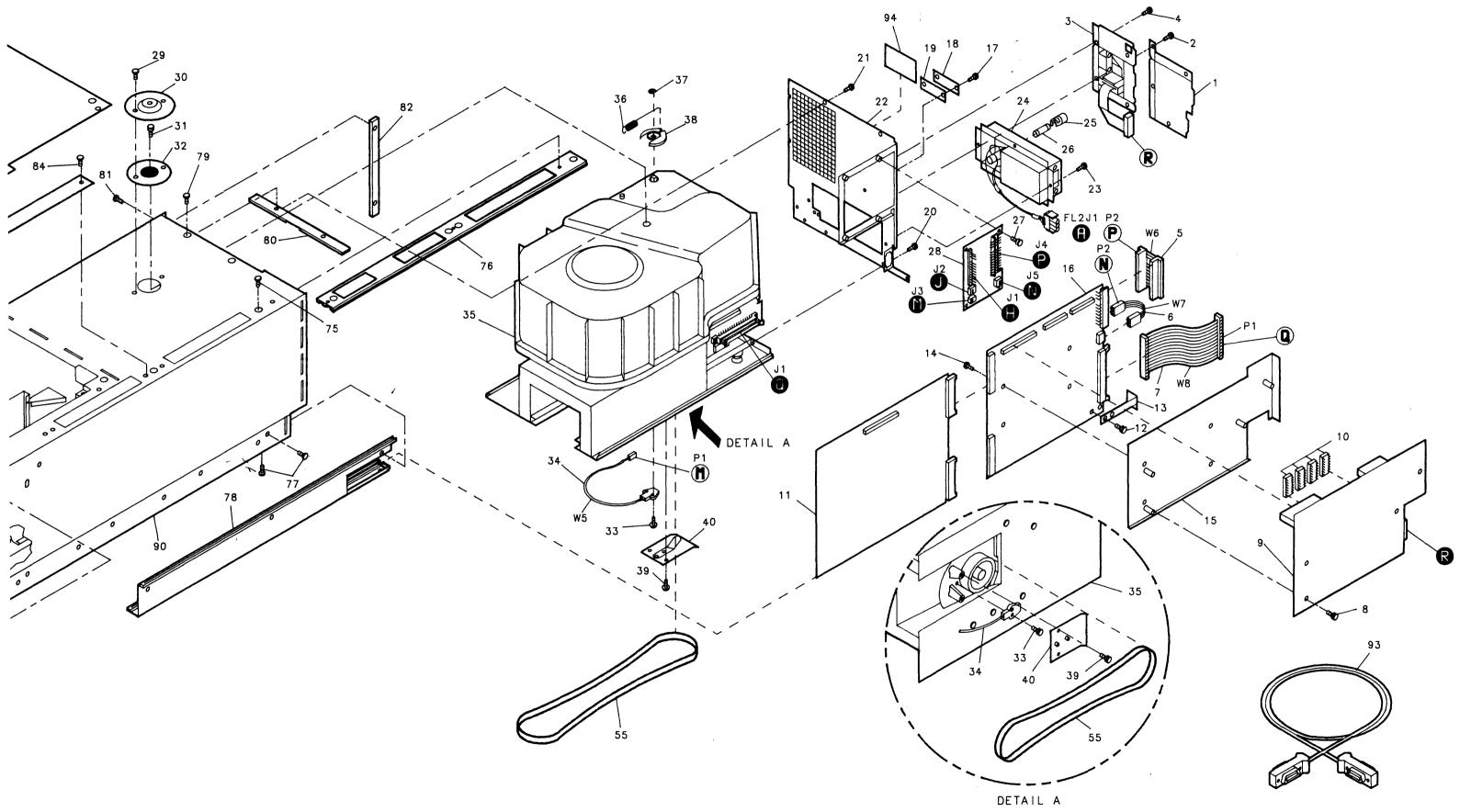

| Figure 9-1. Disc Drive, Exploded View                                        |

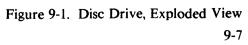

| Figure 9-2. HP 19511A Cabinet, Exploded View                                 |

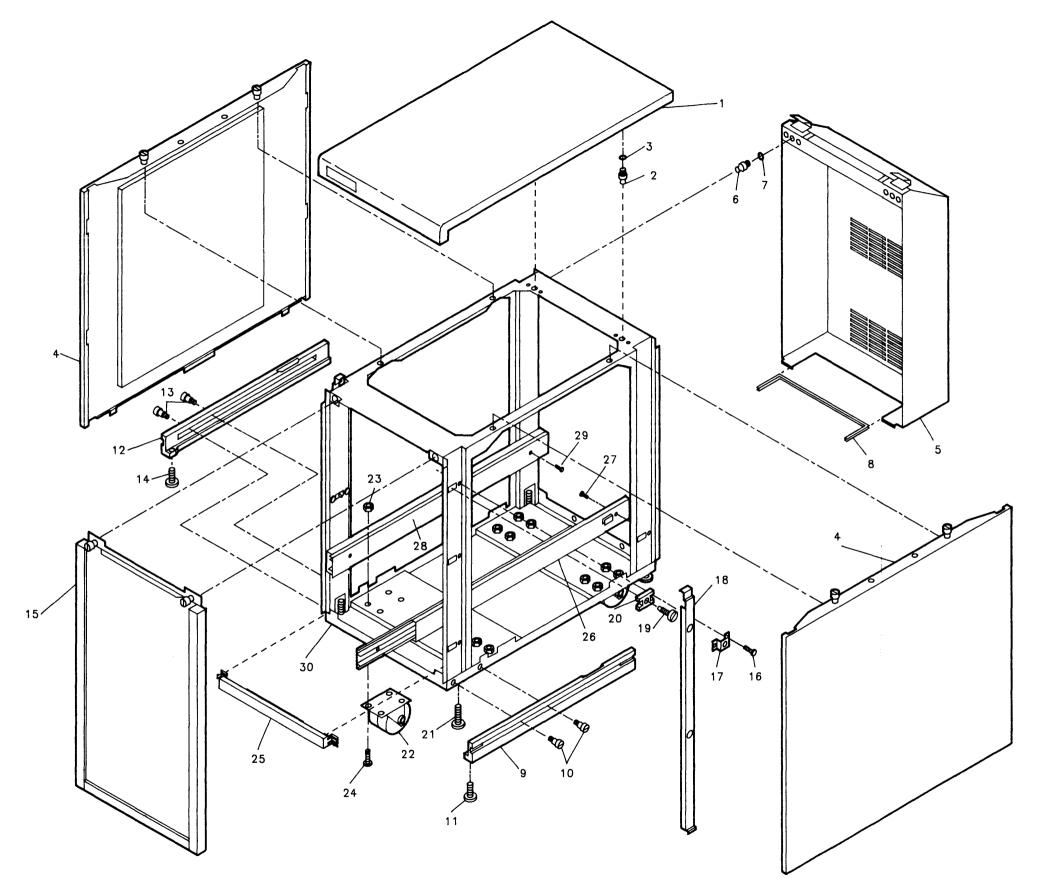

| Figure 9-3. HP 19512A Rack Slide Kit, Exploded View                          |

| Figure 12-1. Drive Dimensions                                                |

| Figure 12-2. HP 19511A Cabinet Dimensions                                    |

| Figure 12-3. Airflow Within Drive.                                           |

| Figure 12-4. Location of Assemblies and Parts                                |

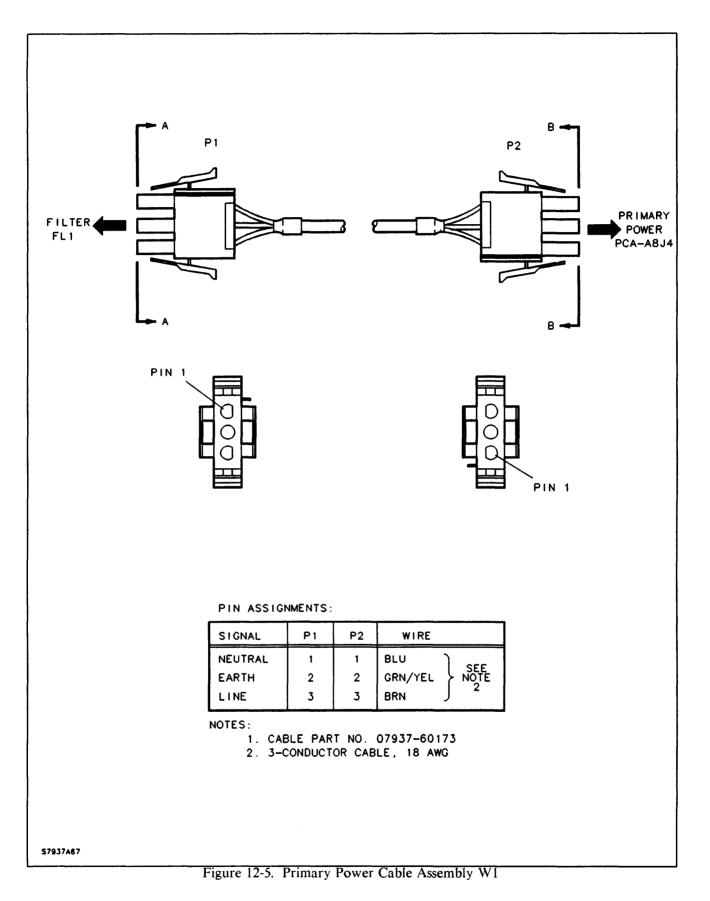

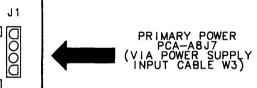

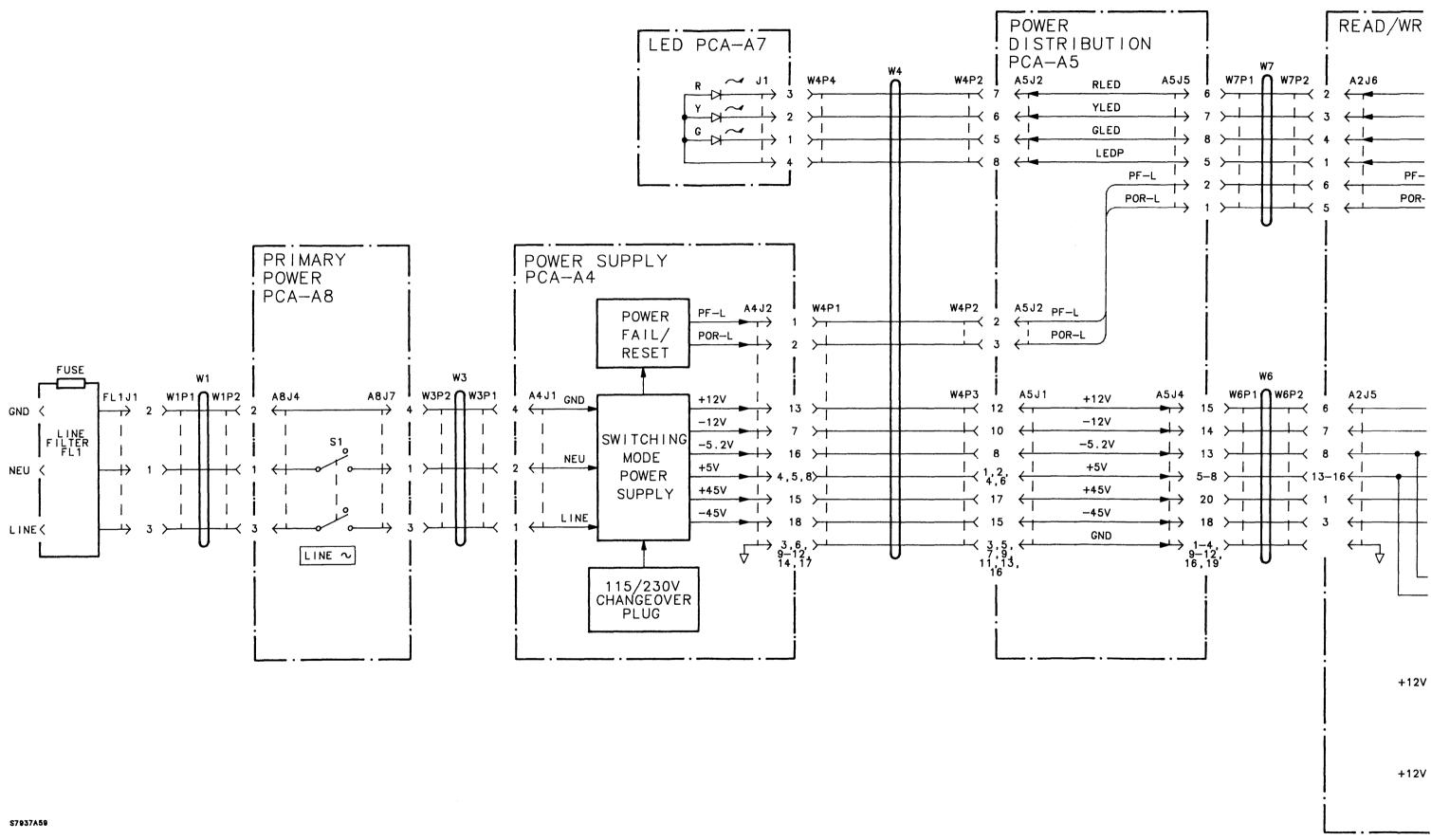

| Figure 12-5. Primary Power Cable Assembly W1                                 |

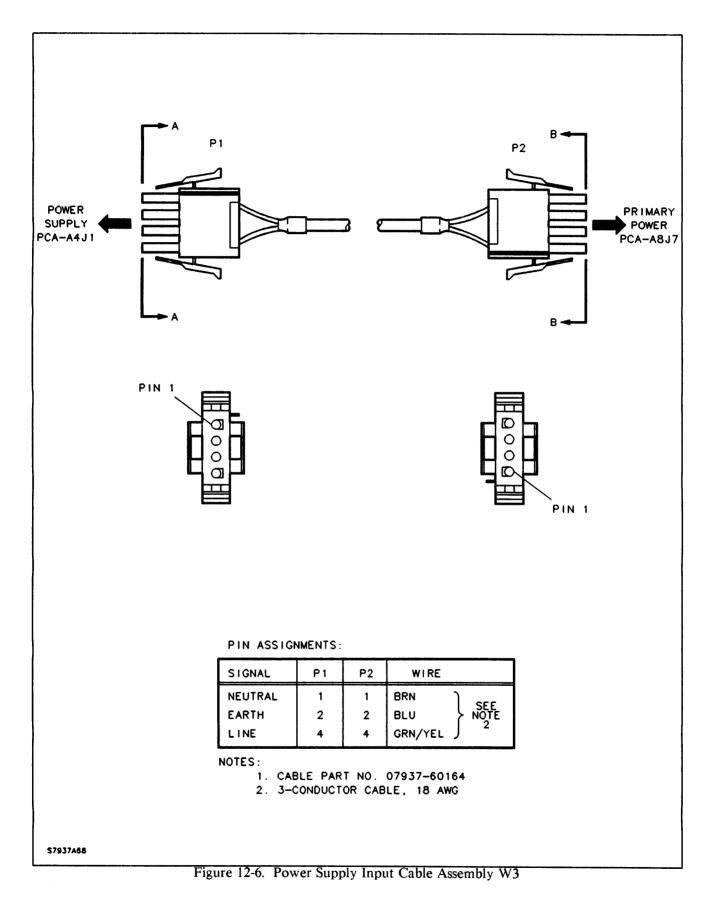

| Figure 12-6. Power Supply Input Cable Assembly W3                            |

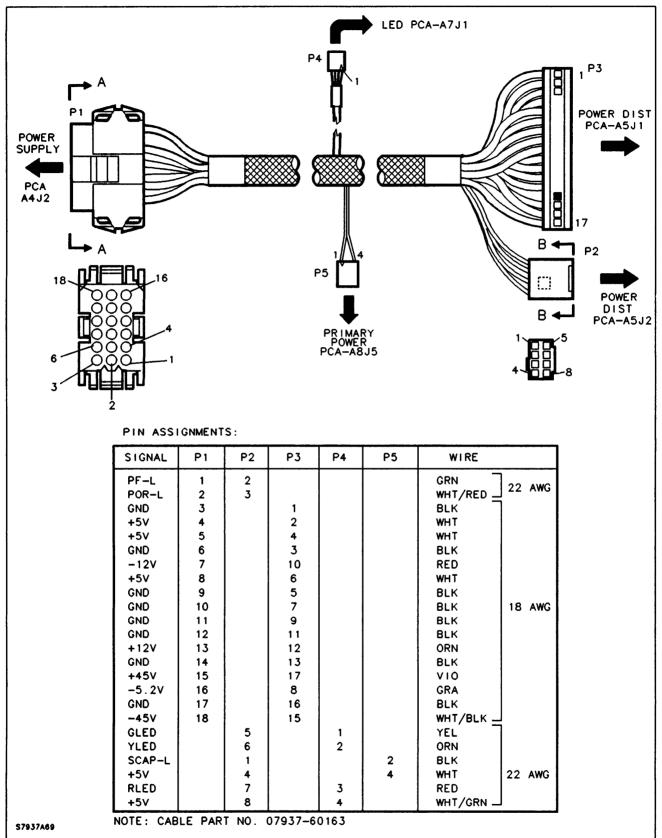

| Figure 12-7. Power Supply Output Cable Assembly W4                           |

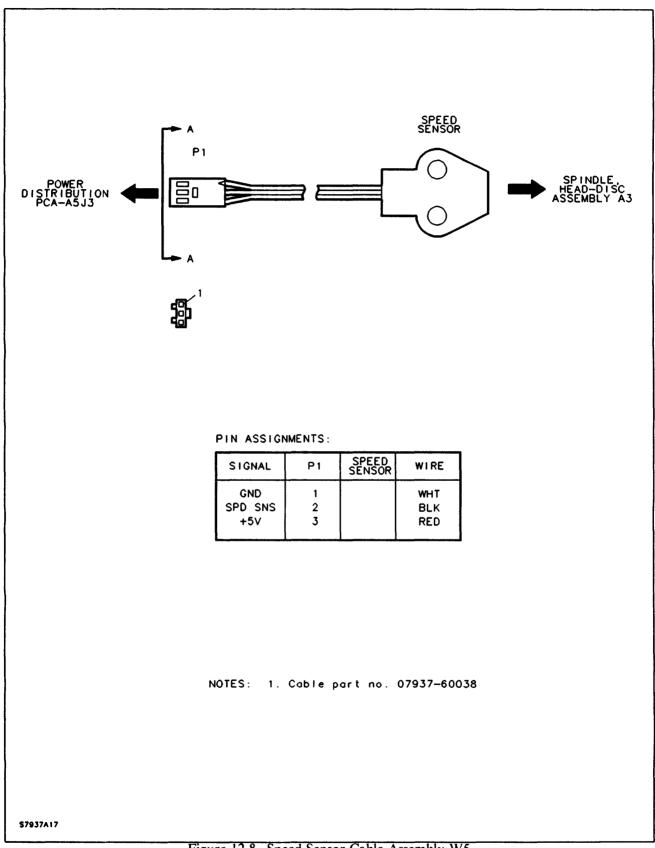

| Figure 12-8. Speed Sensor Cable Assembly W5                                  |

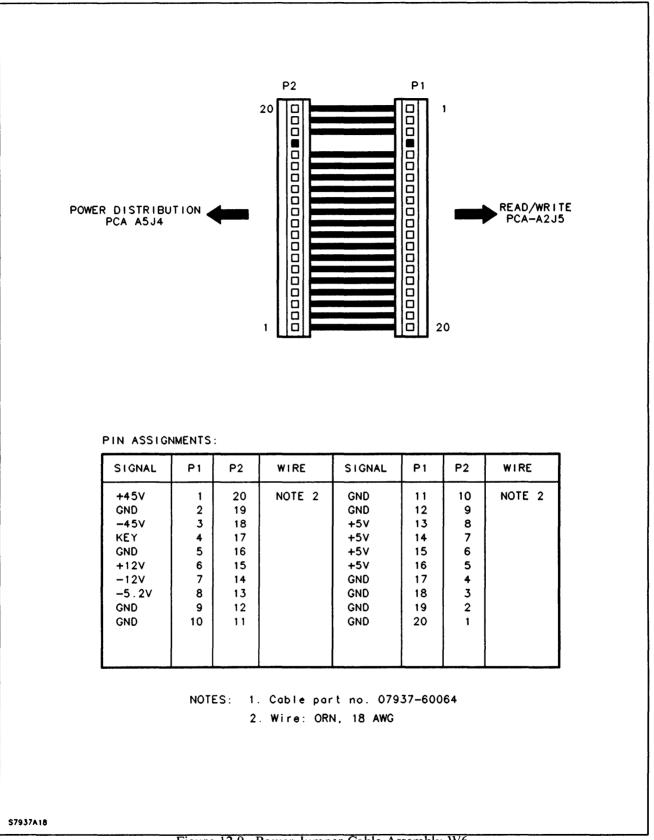

| Figure 12-9. Power Jumper Cable Assembly W6                                  |

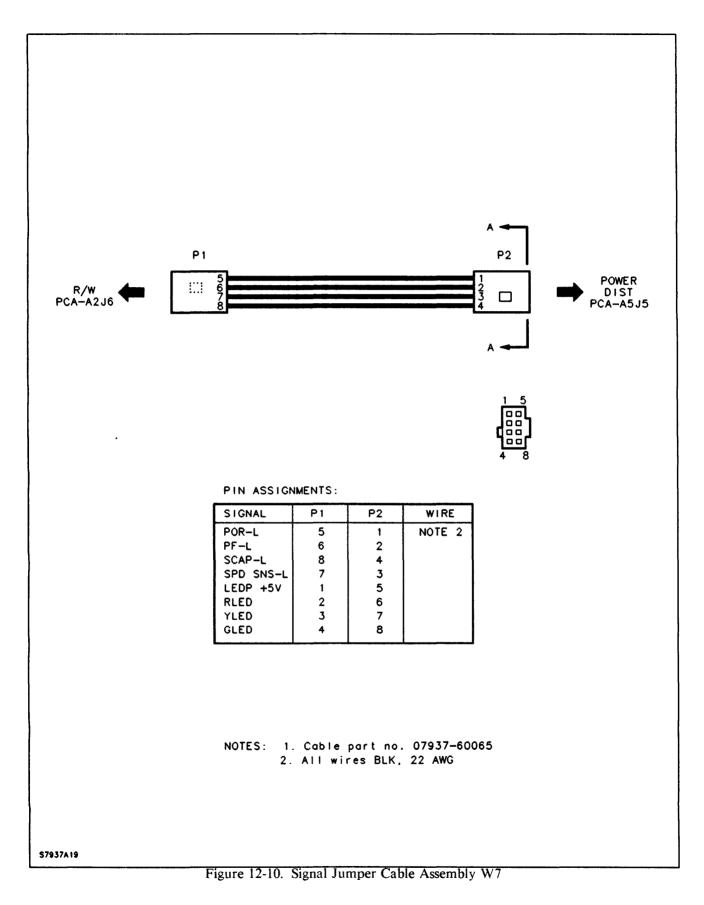

| Figure 12-10. Signal Jumper Cable Assembly W7                                |

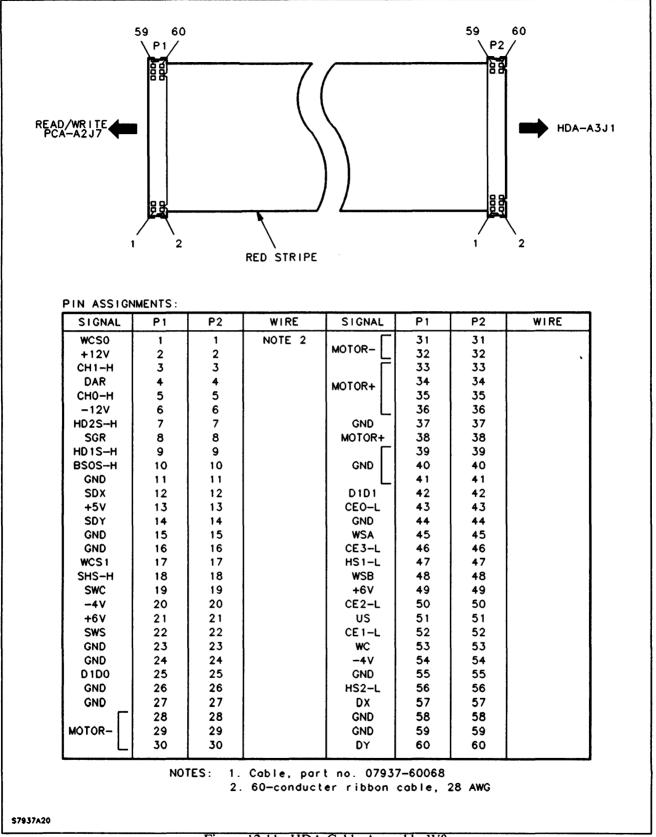

| Figure 12-11. HDA Cable Assembly W8                                          |

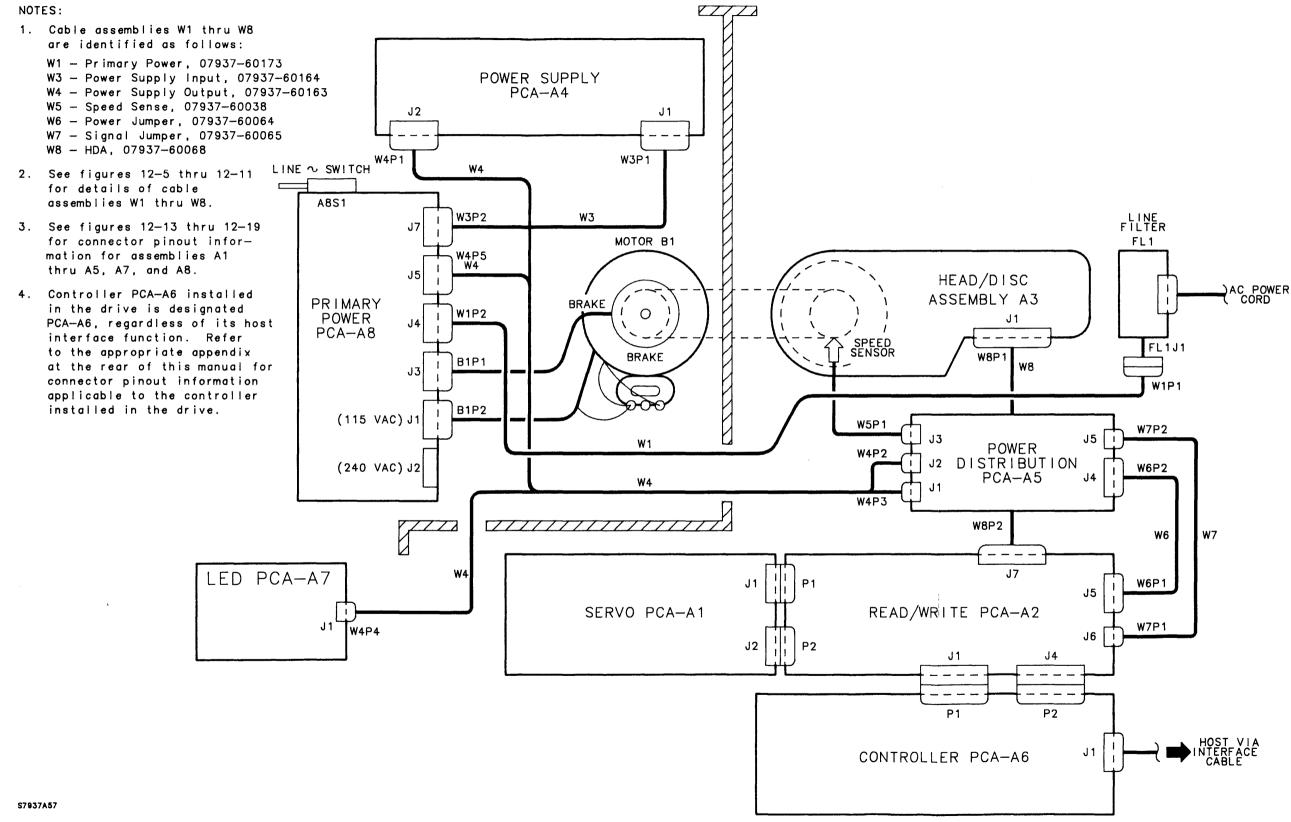

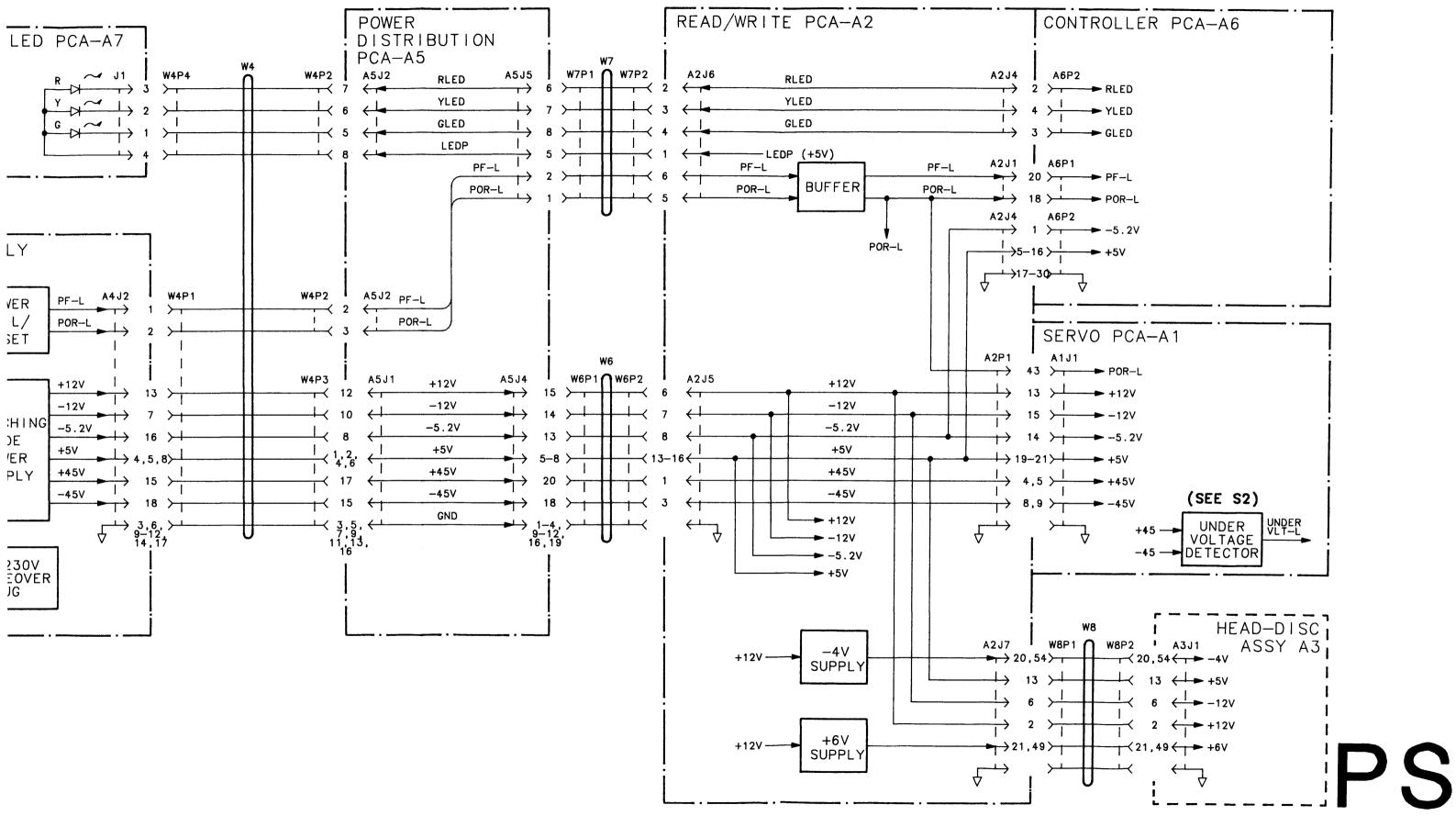

| Figure 12-12. Cabling Diagram                                                |

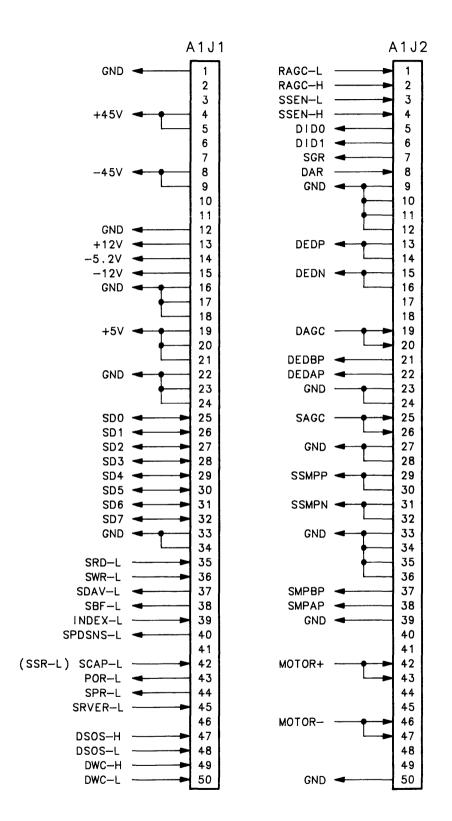

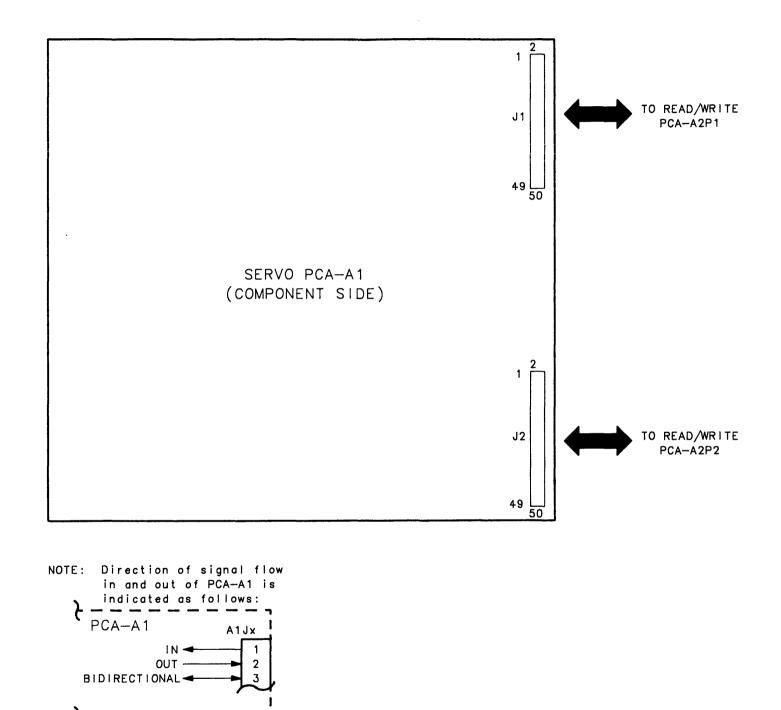

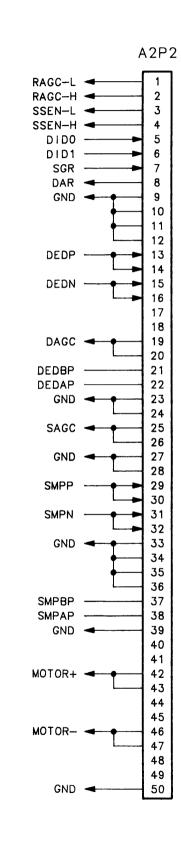

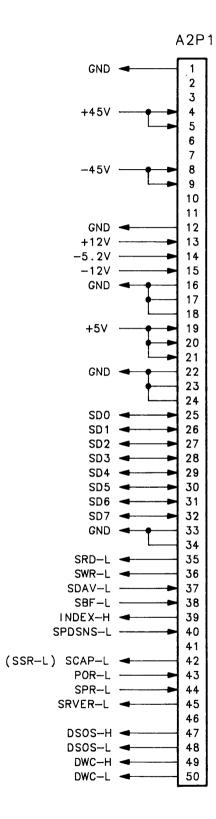

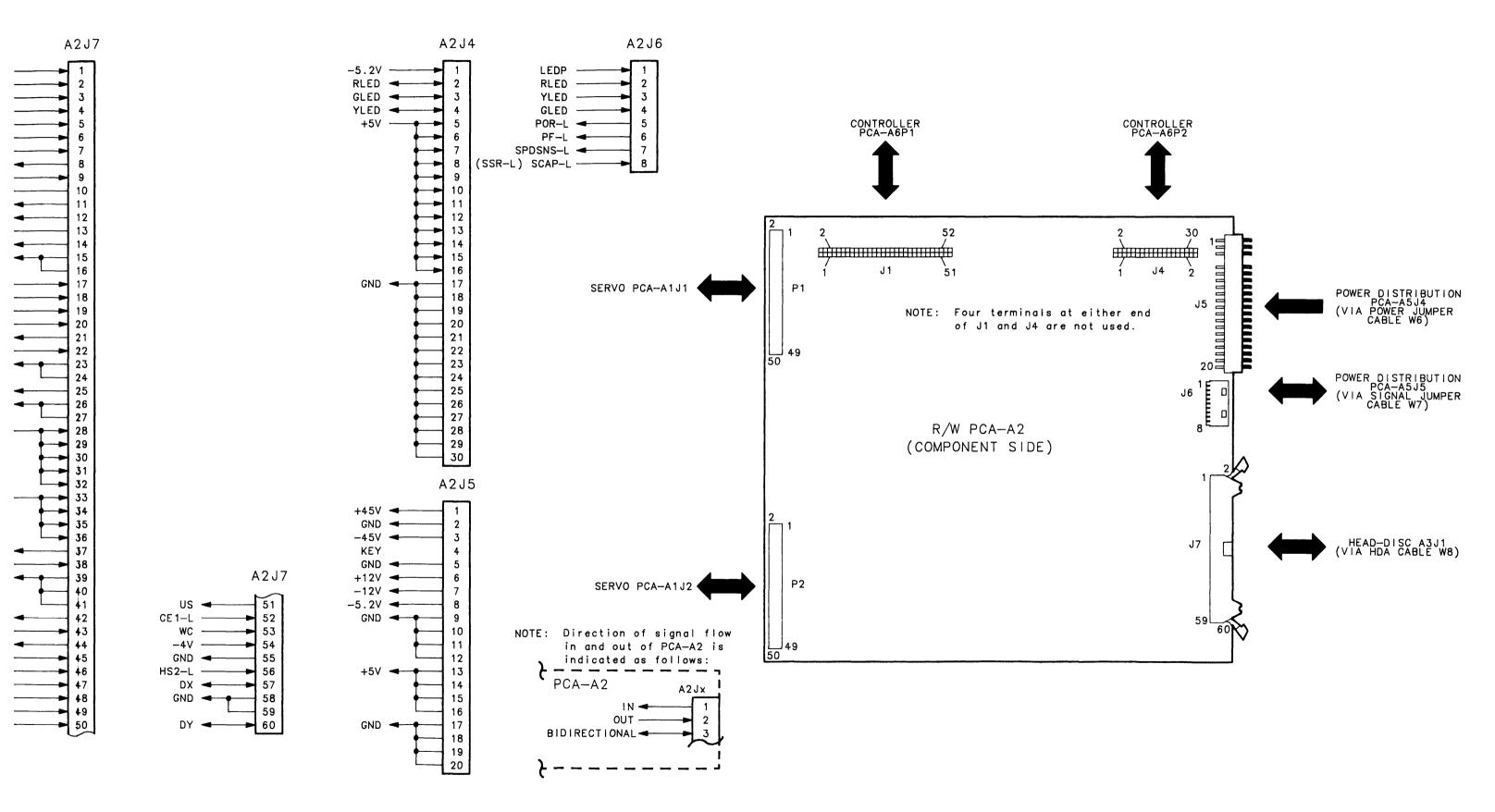

| Figure 12-13. Servo PCA-A1, Parts Location and Connector Pinout              |

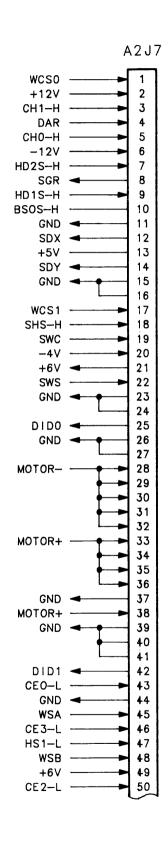

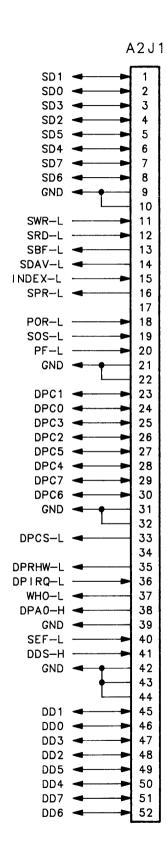

| Figure 12-14. R/W PCA-A2, Parts Location and Connector Pinout                |

| Figure 12-15. HDA Assembly A3, Parts Location and Connector Pinout           |

| Figure 12-16. Power Supply PCA-A4, Parts Location and Connector Pinout 12-29 |

# Figures and Tables (continued)

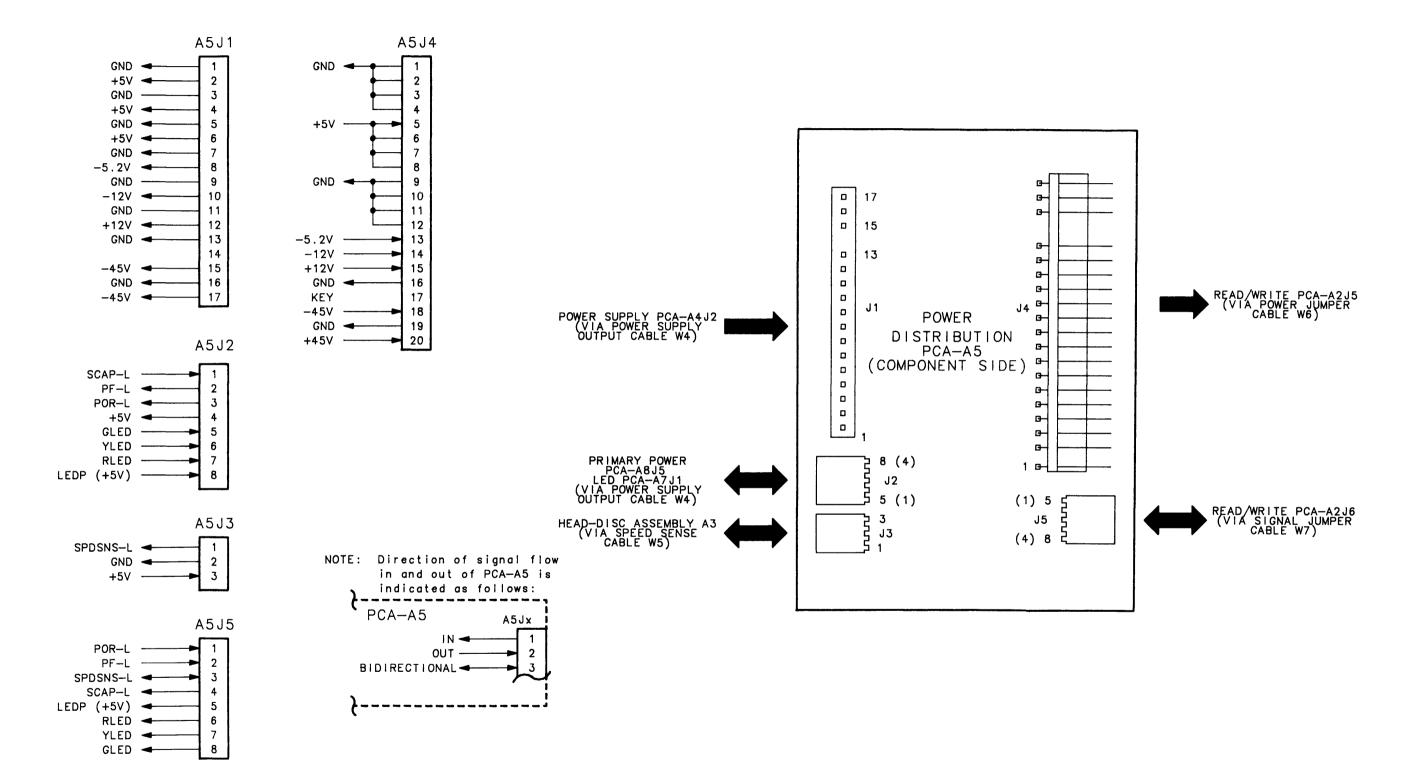

| Figure 12-17. Power Distribution PCA-A5, Parts Location and Connector Pinout | 12-31 |

|------------------------------------------------------------------------------|-------|

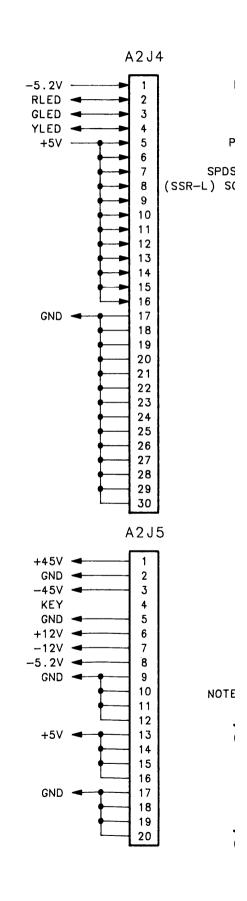

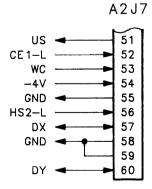

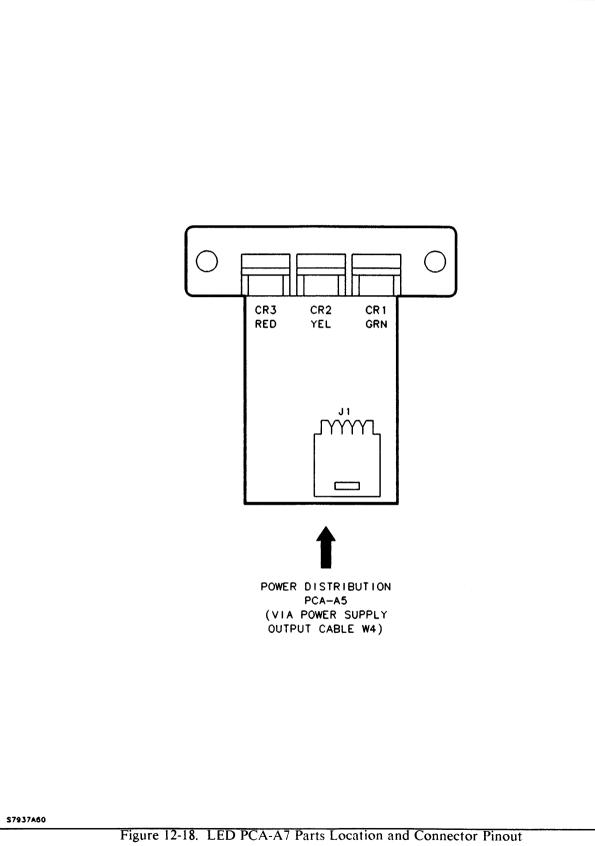

| Figure 12-18. LED PCA-A7, Parts Location and Connector Pinout                | 12-32 |

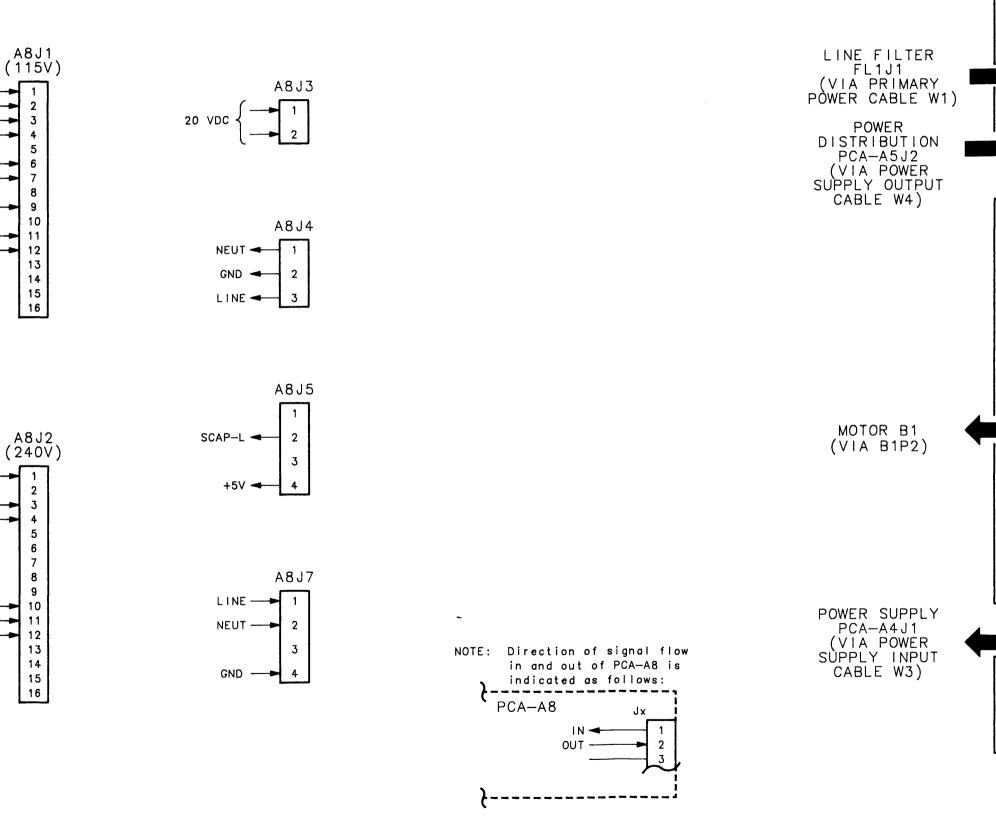

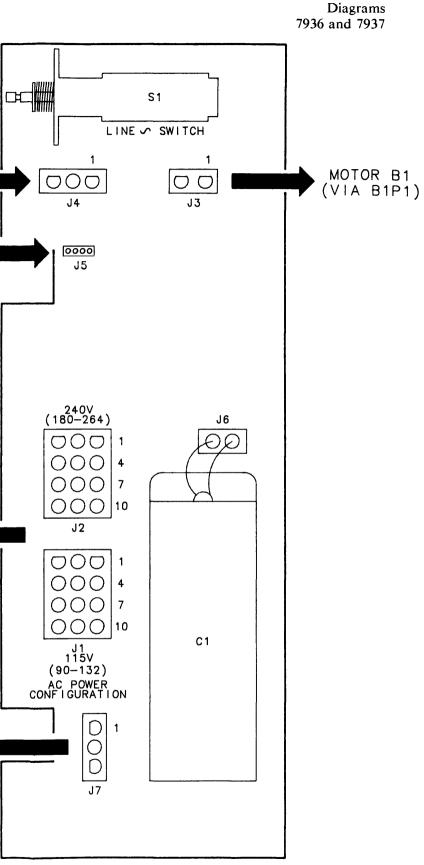

| Figure 12-19. Primary Power PCA-A8, Parts Location and Connector Pinout      | 12-33 |

| Figure 12-20. Servo System, Functional Block Diagram.                        | 12-35 |

| Figure 12-21. Read/Write System, Functional Block Diagram                    |       |

| Figure 12-22. Spindle Drive System, Functional Block Diagram                 | 12-41 |

| Figure 12-23. Power Supply System, Functional Block Diagram                  | 12-43 |

| Figure A-1. HP-IB Signal Lines.                                              |       |

| Figure A-2. Firmware Architecture                                            |       |

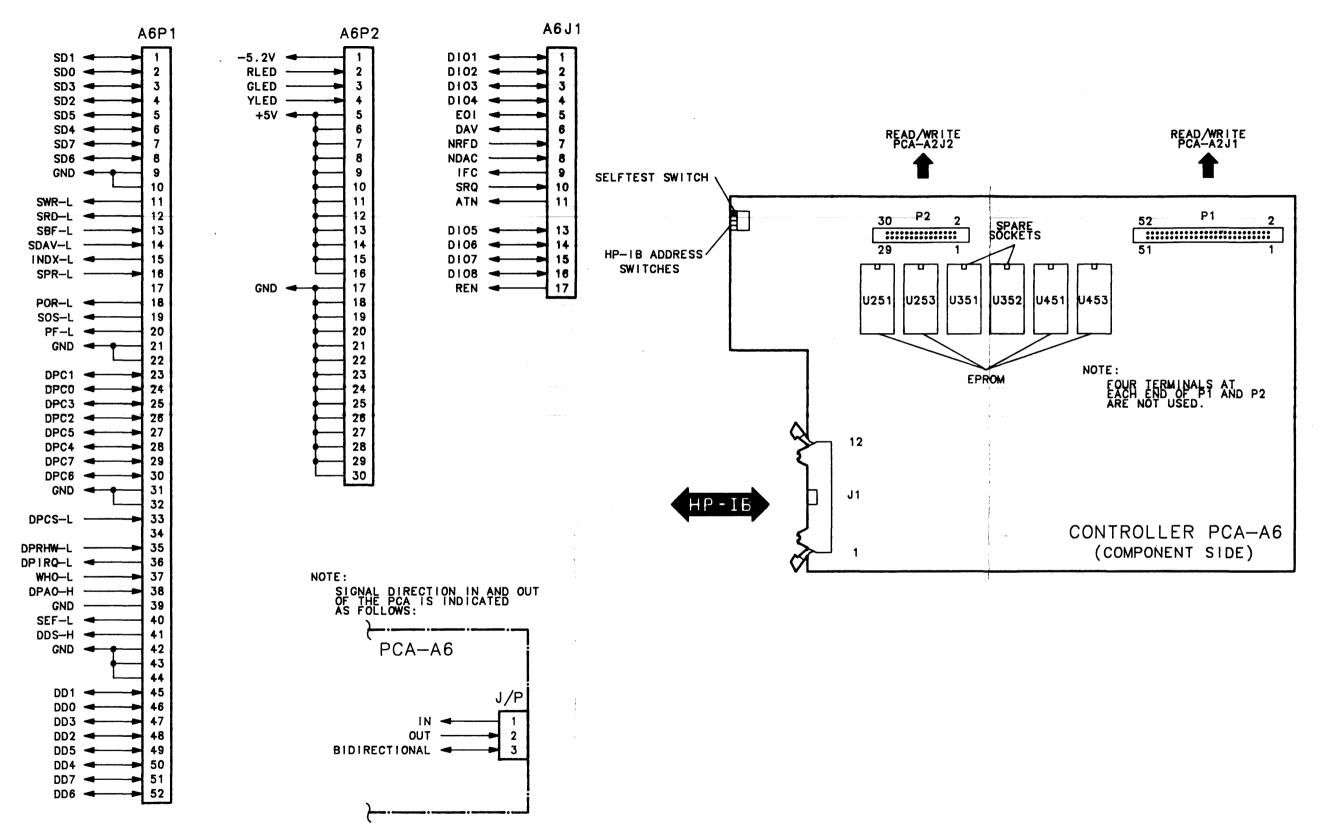

| Figure A-3. HP-IB Controller PCA-A6 Functional Block Diagram                 |       |

| Figure A-4. HP-IB Controller PCA-A6, Parts Location and Connector Pinout     | A-23  |

|                                                                              |       |

| Table 1-1. Disc Drive, Product Structure.                                    |       |

| Table 5-1. List of Mnemonics                                                 |       |

| Table 8-1. External Exerciser Commands                                       |       |

| Table 8-2. List of DERROR/TERRORS                                            |       |

| Table 8-3.         Servo System Test Connector A1J3, Mnemonics.              |       |

| Table 8-4. Read/Write System Test Fixture, Mnemonics                         |       |

| Table 9-1. Disc Drive, Replaceable Parts                                     |       |

| Table 9-2. HP 19511A Cabinet, Replaceable Parts                              |       |

| Table 9-3. HP 19512A Rack Slide Kit, Replaceable Parts                       |       |

| Table 9-4.    Abbreviations                                                  |       |

| Table 9-5. Code List Of Manufacturers                                        |       |

| Table 12-1. Signal Distribution List                                         |       |

| Table 12-2.    Voltage Distribution List                                     |       |

| Table A-1. HP-IB Definitions                                                 |       |

| Table A-2. Universal Command Formats                                         | A-3   |

| Table A-3. HP-IB Message Structure                                           | A-5   |

| Table A-4. Supported CS/80 Commands                                          | A-6   |

|                                                                              |       |

·

#### 1-1. INTRODUCTION

This chapter contains product information for the Hewlett-Packard Model 7936 and 7937 Disc Drives. The information provided includes a general description of the HP 7936 and HP 7937, a list of equipment supplied, details of the product structure, test equipment required, and support strategy.

# **1-2. PRODUCT DESCRIPTION**

The HP 7936 and HP 7937 Disc Drives are highperformance, random access, data storage devices designed for use with medium- and large-sized computer systems. In this manual, unless otherwise specified, "drive" refers to both the HP 7936 and HP 7937.

A microprocessor-based controller is factoryinstalled in the drive to provide an interface to the host computer. Two HP-IB controllers are available for this purpose. In the HP 7936H and HP 7937H Disc Drives, interface to the host is via an Hewlett-Packard Interface Bus (HP-IB) controller. In the HP 7936XP and HP 7937XP, the controller has HP-IB Cache added. Both of the controllers interface with the drive electronics via an HP-developed standard interface (ESI).

A sealed head-disc assembly (HDA) in the drive contains a spindle with a stack of seven nonremovable 210-millimetre (8.3-inch) diameter discs. The spindle is belt-driven by a motor mounted adjacent to the sealed HDA. There are seven (HP 7936) or 13 (HP 7937) thin-film surfaces on the discs for data storage. An additional surface is used for dedicated servo code.

The formatted storage capacity of the drive is 307 megabytes (HP 7936) or 571 megabytes (HP 7937). Each data surface uses a movable read/write head to service its data tracks. The bottom surface of the lowest disc in the stack contains prerecorded servo code which is used to position the read/write heads over the desired data track. Head positioning is performed by a rotary actuator and a dual closed-loop servo positioning system. Control of the servo system is derived from the dedicated servo code on the servo surface and also from servo code embedded between data sectors on all of the data surfaces.

Mechanical and contamination protection for the discs, heads, and rotary actuator is achieved by enclosing these components in the sealed head-disc assembly. The head-disc assembly includes a self-contained air filtration system which supplies clean air and equalizes temperature throughout the HDA.

A self-contained power supply in the drive supplies dc voltages to the controller and the drive electronics. The standard drive is configured for operation from a 90-132V, 60 Hz power source. Options 015 and 017 permit operation from 50 Hz and 180-264V, respectively.

The drive is contained in an enclosed housing and is fitted with removable covers to permit easy access for servicing. A total of two drives can be installed on the rack slides of a desk-height HP 19511A Cabinet. See figure 1-1. An HP 19512A Rack Slide Kit is available for mounting the drive in an EIA 19-inch rack cabinet. A special lifter tool makes it possible for one person to install the 56.7 kg (125 lb) drive in either cabinet.

An upgrade kit is available for the drive: HP 97521A Controller Cache Upgrade.

Self-test diagnostics and a fault-finding system contained within the drive exercise key functions of its operation. Self test is performed automatically at power on and also can be initiated by the host. Drive status is indicated by three lightemitting diodes (LEDs) on the front panel. See figure 3-1. In the event of a self-test failure, the LEDs will identify the failed subassembly in the drive.

# 1-3. DOCUMENTATION SUPPLIED

The drive is supplied with one each of the following publications:

- HP 7936 and HP 7937 Disc Drives Operating and Installation Manual, part no. 07937-90902

- Site Environmental Requirements for Disc/Tape Drives Manual, part no. 5955-3456

# 1-4. SUPPORTING DOCUMENTATION

The following supporting documentation for the drive may be ordered from your nearest Hewlett-Packard Sales and Support Office:

- HP 7936 and HP 7937 Disc Drives Hardware Support Manual, part no. 07937-90903

- CS/80 Instruction Set Programming Manual, part no. 5955-3442

- CS/80 External Exerciser Manual, part no. 5955-3462

# 1-5. PRODUCT STRUCTURE

The drive product structure is outlined in Table 1-1.

#### **1-6. SPECIFICATIONS**

Specifications for the drive are listed in the Site Environmental Requirements for Disc/Tape Drives Manual, part no. 5955-3456. This manual is supplied with the drive.

#### 1-7. SERIAL NUMBER

The serial number of the drive is recorded on a serial number label attached to the front cover of the drive, below the front panel. The drive model

number and full serial number should be quoted in any communication with Hewlett-Packard regarding the drive.

# **1-8. SUPPORTED EQUIPMENT**

This manual is intended to provide the information needed to support service of the drive and all of its accessories and options.

# 1-9. TEST EQUIPMENT REQUIRED

No special test equipment is needed for installation and normal maintenance of the drive. However, when using the special diagnostics available for troubleshooting the drive, the following equipment is needed:

- HP 85B Personal Computer

- CS/80 External Exerciser Tapes, part numbers 5010-0566 and 5010-0567.

- CS/80 External Exerciser Manual, part no. 5955-3462.

# 1-10. WARRANTY

The drive is covered by a 90-day Hewlett-Packard warranty. However, this warranty is voided if the sealed head-disc assembly is opened or otherwise tampered with. The warranty does not include installation or rack mounting.

#### 1-11. SUPPORT STRATEGY

The drive may be repaired on site to the field replaceable assembly level. Troubleshooting is aided by firmware controlled self-test diagnostics with the malfunctioning assembly identified on a front-panel display, error codes returned by the drive to the CPU, and diagnostics available through the use of the HP 85B Personal Computer and an external exerciser or a host-supported external exerciser.

Figure 1-1. HP 7937 Disc Drives in HP 19511A Cabinet

#### **DISC DRIVE**

HP 7936H/7937H - 307/571 Mbyte Disc Drive, HP-IB Controller

HP 7936XP/7937XP - 307/571 Mbyte Disc Drive, HP-IB Controller with Cache

#### CABINET

HP 19511A - Desk-height Cabinet for up to two 7936/7937 Disc Drives.

#### **CABINET OPTIONS**

208 - Adds 07937-60214 Power Tap to HP 19511A Cabinet. Designed for environments using NEMA 6-30R power receptacles (208 Vac, 60 Hz).

#### **RACK SLIDE KIT**

HP 19512A - Rack Slide Kit for mounting a 7936/7937 Disc Drive in an EIA 19-inch rack cabinet

#### **POWER OPTIONS**

015 - 50 Hz operation

017 - 180-264 Vac operation

#### **UPGRADE KITS**

HP 97521A - HP-IB Cache Controller

# 2-1. INTRODUCTION

This chapter defines site preparation and requirements needed to ensure a proper operating environment for the drive.

# 2-2. SITE PLANNING

No site preparations are required for the drive other than those specified for the host system.

# 2-3. SPECIFICATIONS

Detailed electrical, environmental, and physical specifications for the drive are provided in the Site Environmental Requirements for Disc/Tape Drives

Manual, part no. 5944-3456. This publication is supplied with the drive.

In order for the drive to operate properly, it must be operated within the environmental specifications given in the above mentioned publication.

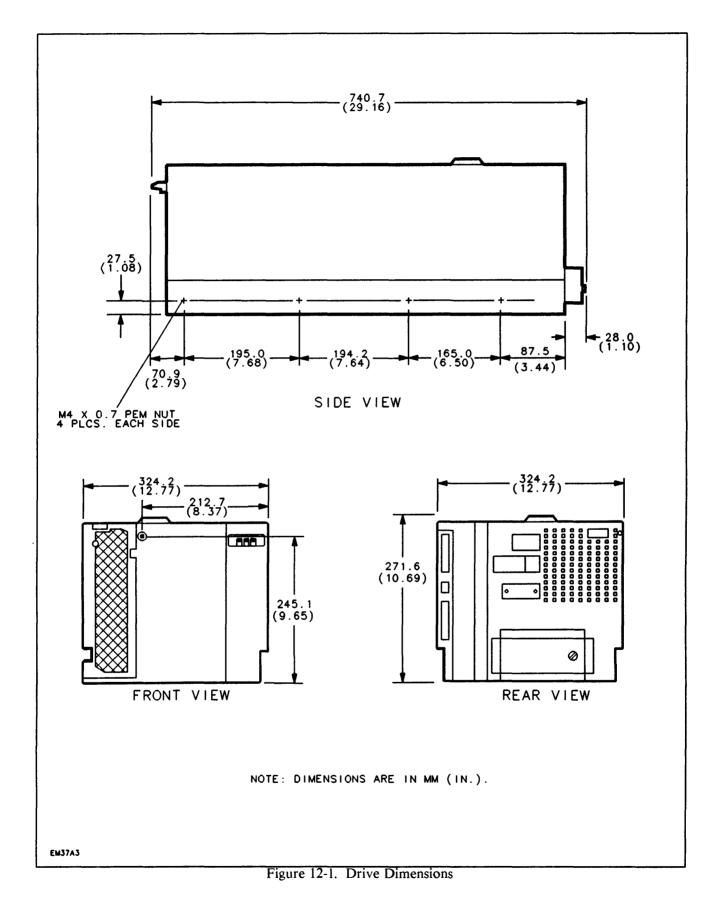

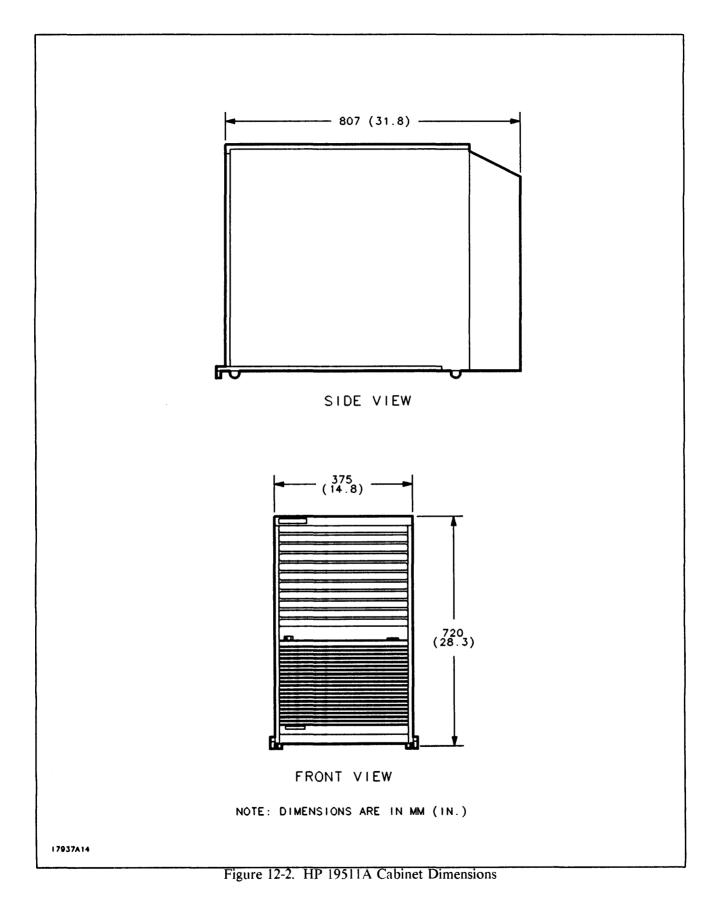

Detailed dimensional specifications for the drive are given in figure 12-1. The dimensions of the HP 19511A Cabinet are shown in figure 12-2.

# 2-4. CABLING LIMITATIONS

The drive adheres to the cabling limitations set forth in the interface documentation applicable to the controller installed in the drive. This documentation is listed in chapter 1. .

# 3-1. INTRODUCTION

This chapter contains a summary of drive installation information, compiled for use by servicetrained personnel. For detailed installation information, including unpacking instructions, cabinet installation procedures, input voltage and frequency configuration, and initial checkout tests, refer to the *HP* 7936 and 7937 Disc Drives Operating and Installation manual, part no. 07937-90902.

# WARNING

The drive does not contain operatorserviceable parts. To prevent electrical shock, refer all maintenance activities to service-trained personnel.

# 3-2. SHIPPING LATCH

# CAUTION

Do not operate the Shipping Latch when the drive LINE~ switch is in the 1 (in) position. The drive must be in a powered-down state before the latch is moved.

Do not attempt to operate the drive with the Shipping Latch in the (Ship) position. If the drive is powered up with the latch in the position, a servo fault will occur (Red and Yellow LEDs illuminated). To recover from this situation, power down the drive, move the latch to the (Operate) position, and then power up the drive.

The drive shipping latch prevents the drive headdisc assembly from being damaged by vibration and shock during shipment and installation of the drive. The latch is located behind the rear panel and can be activated by a medium-sized flat-blade screwdriver through a rectangular opening in the rear panel. See figure 3-1.

The latch settings are indicated by symbols on the latch, visible through the rectangular opening. The symbol is the "Ship" setting and the symbol is the "Operate" setting. The latch must remain in the o (Ship) position until the drive is installed at its operating location and is ready to be powered on. At this time, the latch should be set to the (Operate) position and then the drive powered on.

If the latch is inadvertently moved to the (Ship) setting after the drive is powered on, the latch may overshoot the (Ship) setting. (The latch is in an overshoot state if the (Ship) symbol moves to the right, past the range of visibility of the rectangular opening.)

If an overshoot occurs, the drive will continue to operate normally as long as power is not turned off. However, to ensure that data is not destroyed, the following procedure should be performed immediately to reset the latch:

1. Power down the drive by setting the LINE~ switch to the 0 (out) position.

2. Disconnect the HP-IB connector.

3. Power up the drive.

4. Wait for the drive to finish its internal self-test diagnostic routine (approximately 10 seconds).

5. Insert the tip of a small flat-blade screwdriver through the round over-shoot opening in the rear panel (see

figure 3-1) and return the latch to the Operate) position.

- 6. Power down the drive.

- 7. Reconnect the HP-IB connector.

- 8. Power up the drive.

# 3-3. DRIVE INSTALLATION

# WARNING

Anti-tip feet must be in position on the cabinet when the drive is installed and any time the drive is extended out of the cabinet on its rack slides.

A total of two drives can be installed in the HP 19511A Cabinet or up to four drives can be installed in a EIA 19-inch rack cabinet using HP 19512A Rack Slide Adapter Kits. A special lifter tool, part no. 07937-60141, allows one person to install the drive in either cabinet. For instructions on how to install the drive in the HP 19511A Cabinet and EIA rack cabinet, refer to the HP 7936 and HP 7937 Disc Drive Operating and Installation Manual, part no. 07937-60602.

#### 3-4. PRIMARY POWER REQUIREMENTS

# CAUTION

Do not operate a drive configured for 90-132 Vac on 180-264 Vac, or vice versa. Also, do not operate a drive configured for 60 Hz on 50 Hz, or vice versa. Failure to observe these precautions may result in damage to the drive.

The drive has been factory preset for the proper line voltage and frequency in your area. The standard model is configured for an ac input of 90-132 Vac, 60 Hz and a drive with option 017 is configured for an input of 180-264 Vac, 60 Hz. A drive with option 15 is configured for an input of 50 Hz.

The voltage and frequency for which the drive has been configured at the factory is marked on the ~LINE label attached to the rear panel of the drive. The location of the label is shown in figure 3-2. Make sure that your power source meets the requirements marked on the label.

Voltage configuration (standard/option 017) is accomplished within the drive by moving plug-in connectors in power supply PCA-A4 and primary power PCA-A8.

Frequency configuration (standard/option 015) is accomplished by changing the spindle motor pulley and drive belt.

Details of how to change the drive voltage and/or frequency configuration are provided in the HP 7936 and HP 7937 Disc Drive Operating and Installation Manual, part no. 07937-90902.

# 3-5. CONTROLS, INDICATORS, AND CONNECTORS

The drive front and rear panel controls, indicators, and connectors are identified in figure 3-1. The functions of these components are described in the following paragraphs.

#### 3-6. LINE~ SWITCH

The LINE~ switch controls the application of ac power to the drive. Power is "on" when the switch is in the 1 (in) position and "off" when it is in the 0 (out) position. The 1 and 0 markings correspond to international symbology presently in use.

#### 3-7. CHANNEL ADDRESS/DIAGNOSTIC SWITCH

The Channel Address/Diagnostic switch is a 4-segment switch assembly which selects the system channel address and the drive self-test diagnostics. The switch segments are read by the controller at power-on. The segments can be set with any sharp-pointed tool, such as the tip of a ball point pen. CHANNEL ADDRESS switch segments S2, S3, and S4 permit the selection of one of eight unique channel addresses. The address settings, 0 through 7, are shown on the Channel Address/Diagnostic Switch label on the rear panel. See figure 3-2. Switches S2, S3, and S4 can also be used to initiate diagnostic tests. (This function is not implemented in the drive at this time.)

DIAGNOSTIC SWITCH segment S1 selects which internal diagnostic routine the drive will execute at power-on. The two diagnostic modes are described in the following paragraphs.

**3-8. RUN TIME MODE.** When switch S1 is set to the RUN TIME MODE position, a series of hardware tests are performed at power-on. Following successful completion of the hardware diagnostic routines, the drive comes on line. The diagnostic normally takes approximately 10 seconds to complete.

Successful completion of the diagnostic is indicated by the Green LED remaining lit. If the drive fails the hardware diagnostic, the Red LED will remain lit and the Yellow and Green LEDs will be coded to indicate the malfunctioning assembly. A power supply failure or loss of input power is indicated by all LEDs extinguished. The coding for the LEDs is shown on a label on the rear panel. See figure 3-2.

# NOTE

A drive fault condition (Red LED lit) does not necessarily mean that the drive controller is incapable of communication with the host. In most cases, details of the fault condition (over and above the information encoded by the LEDs), can still be obtained by commands from the host. Refer to Chapter 8 for details.

#### 3-9. DIAGNOSTIC MODE.

NOTE

The DIAGNOSTIC MODE position is for service purposes and should not be used during normal operation of the drive.

If S1 is set to the DIAGNOSTIC MODE position, the same hardware diagnostic executed in RUN TIME MODE is invoked when power is applied. However, the controller does not bring the drive on line following the completion of the hardware diagnostic routines. Instead, the drive performs a full-volume RO ERT (7.5 minutes) followed by a continuous loop of random RO ERTs.

When the drive successfully completes the hardware diagnostics and begins the RO ERTs, both the Yellow and Green LEDs will be illuminated. If any uncorrectable or marginal data errors occur during the RO ERTs, the Green LED is extinguished leaving only the Yellow LED lit.

A hardware diagnostic failure is indicated by the Red LED remaining lit and the Yellow and Green LEDs coded to indicate the source of the most likely malfunctioning assembly. A power supply failure or loss of input power is indicated by all LEDs extinguished. The coding for the LEDs is listed on a label on the rear panel. See figure 3-2.

When the DIAGNOSTIC MODE position is selected, the drive will not come on line (be capable of communication with the host) until the Power switch is turned off, switch S1 returned to the RUN TIME MODE position, and the drive powered on again.

# NOTE

Failure information gathered during this time will be logged in the internal error logs of the drive. Refer to Chapter 8 for details on how to retrieve this data.

#### **3-10.** LED DISPLAY

The front panel LED display provides the operator with a visual indication of the operational status of the drive. The LED display consists of single red, green, and yellow LEDs. As explained in the preceding paragraphs, the significance of the LED patterns is determined by the operating mode of the drive (RUN TIME or DIAGNOSTIC). The Front Panel Status label affixed to the rear of the drive indicates the significance of the LED patterns (see figure 3-2).

In addition to its role as a status display, the Green LED also serves as an activity indicator, flashing any time the drive is exchanging data or commands with the host.

#### **3-11. HP-IB CONNECTOR**

The HP-IB connector provides the mechanical connection for the HP-IB cable which connects the host and the drive.

#### **3-12. POWER FUSE**

#### WARNING

The power fuse is not an operatorserviceable part and should only be replaced by service-trained personnel.

The power fuse protects the drive from an ac power overload. The same fuse is used regardless of the input operating voltage. The fuse value is listed below.

| OPERATING | FUSE        | HP        |

|-----------|-------------|-----------|

| VOLTAGE   | DESCRIPTION | PART NO.  |

| ALL       | 5AS - 250V  | 2110-0030 |

#### **3-13.** LINE CONNECTOR

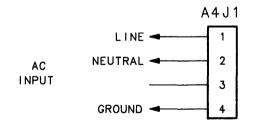

The line connector allows the drive to be connected to an ac power source via a suitable power cord. The input power configuration of the drive is listed on the ~LINE label.

#### 3-14. CPU CONNECTION - HP-IB SYSTEMS

# CAUTION

Do not connect or disconnect the HP-IB cable(s) from the drive while the system is in active state.

The interconnection of the drive is dependent on the system configuration. The location of the HP-IB connector for the drive is shown in figure 3-1. The major considerations concerning the connection of the drive to an HP-IB channel are contained in the following paragraphs.

#### 3-15. HP-IB CABLING

The Hewlett-Packard Interface Bus (HP-IB) has certain rules which must be observed or successful installation of the drive. Cabling is limited to 1 metre per HP-IB load. Typically the Central Processing Unit (CPU) is 7 equivalent loads and the drive is 1 equivalent load. See figure 3-3.

The CPU adheres to an HP standard which allows 7 metres of HP-IB cable between the CPU and the nearest device connected to it and 1 metre of cable between each additional device. The maximum configuration is 8 devices (excluding the CPU) per HP-IB channel of a maximum of 15 metres of 10 equivalent loads.

The maximum number of devices that can be connected to a single HP-IB channel is host dependent. This information is contained in the appropriate host configuration guide.

#### 3-16. HP-IB DEVICE ADDRESS

The Channel Address switches located on the rear panel of the drive are used to set the HP-IB device address. See figure 3-1. The switches permit setting one of eight unique addresses. The switches can be set with any pointed tool. When setting the HP-IB address, disregard any markings on the switch body. Set the switches according to the information on the Channel Address/Diagnostic switch label. See figure 3-2.

# NOTE

Before using the drive, check the address switches to ensure that no two devices in the system have the same address.

Figure 3-1. Drive Controls, Connectors, and Indicators

# 4-1. INTRODUCTION

# WARNING

The drive does not contain operatorserviceable parts. To prevent electrical shock, refer all maintenance activities to service-trained personnel.

No preventive maintenance procedures are required to be scheduled for the drive.

•

# 5-1. INTRODUCTION

The HP 7936 and HP 7937 Disc Drives are high performance, random access, data storage devices designed for use in medium-and large-sized computer systems. In this chapter, unless otherwise specified, "drive" refers to all models of the HP 7936 and HP 7937.

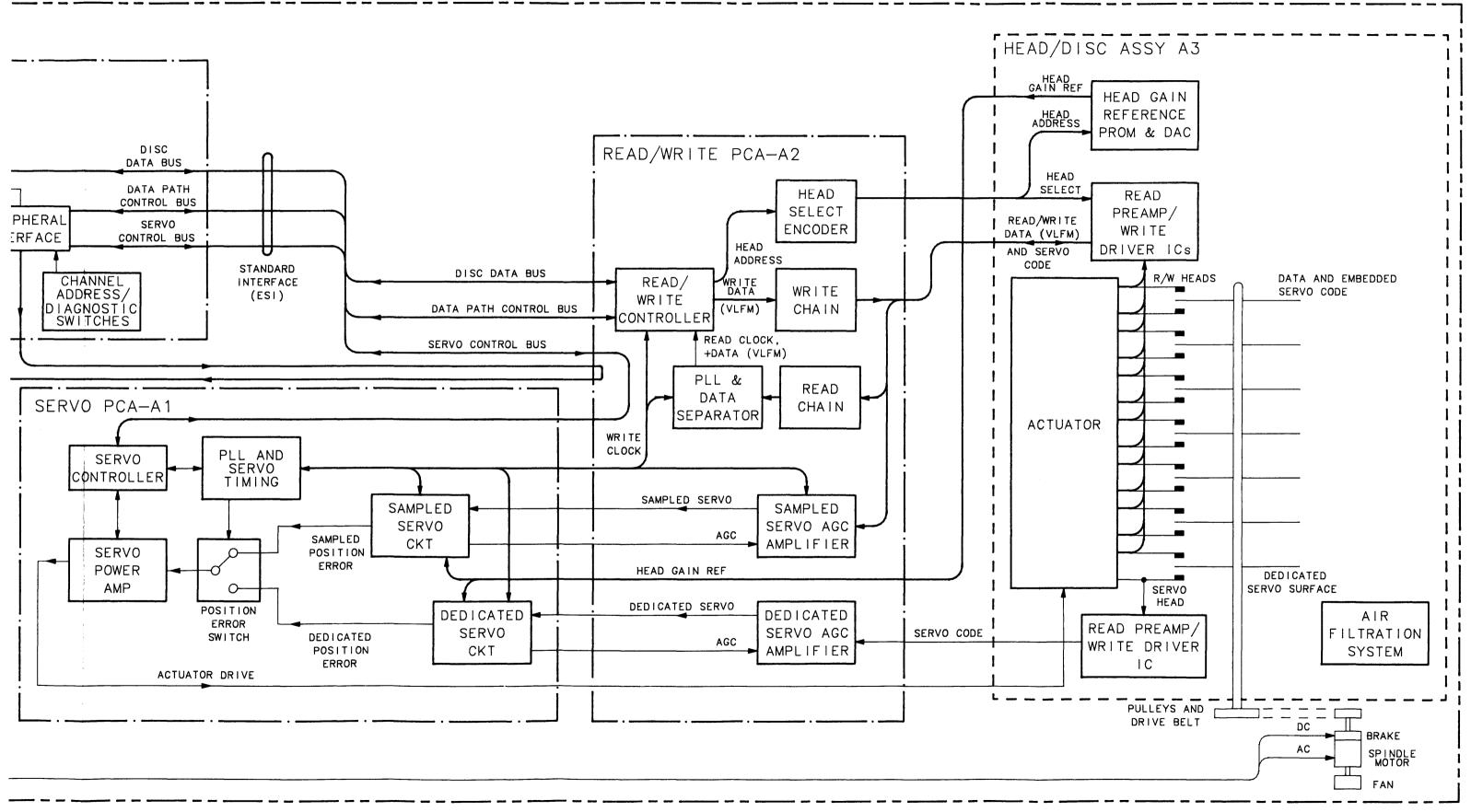

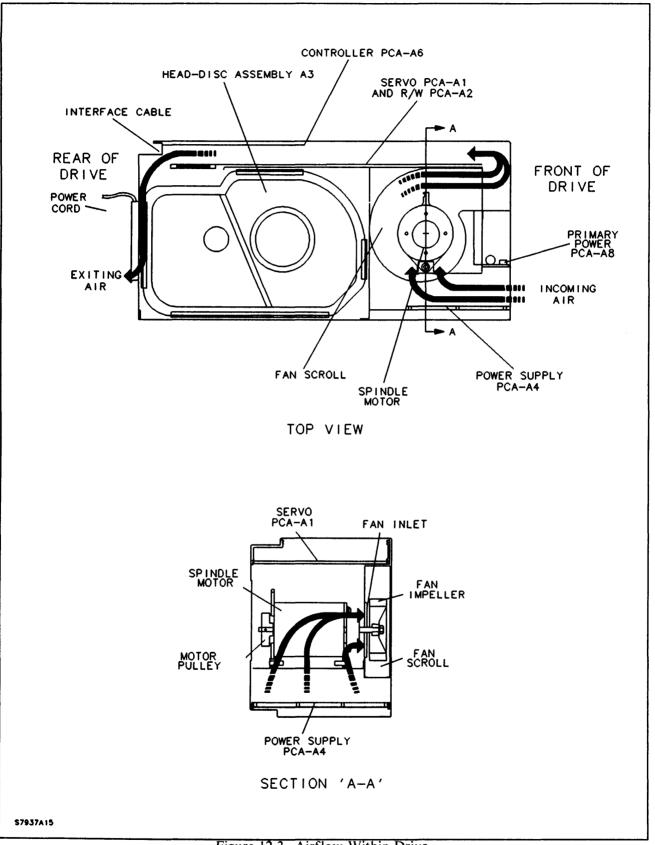

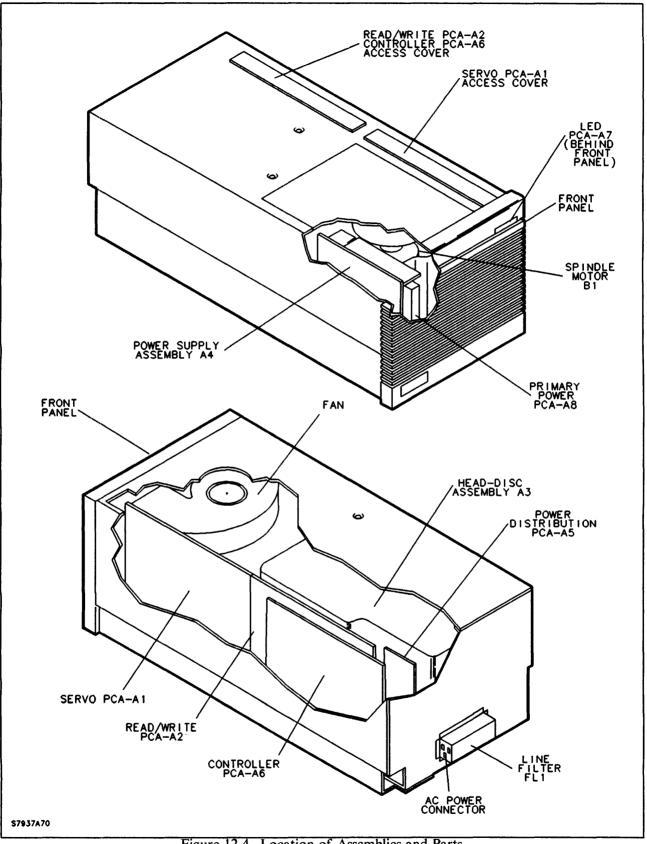

The drive is housed in a rigid enclosure designed to be mounted on rack slides in a cabinet. Contained within the enclosure is a sealed head-disc assembly (HDA), with spindle and disc stack, read/write heads, servo head, electromagnetic head positioning mechanism (actuator), read preamplifiers, write drivers, head gain reference PROM and DAC, and air filtration system. See figure 5-16. The spindle is belt driven by an ac induction motor mounted adjacent to the sealed HDA. The motor speed is regulated by the line frequency. This motor also drives a squirrel-cage type cooling fan.

The disc stack is composed of seven 210-millimetre (8.3-inch) diameter nonremovable discs. These discs have seven (HP 7936) or 13 (HP 7937) thin-film magnetic surfaces for data storage. (The same number of discs are used in both drives in order to maintain the dynamic design parameters of the The formatted head-disc assembly.) storage capacity of the drive is 307 megabytes (HP 7936) or 571 megabytes (HP 7937). One movable head is used to service each surface. The bottom surface the lowest disc in the stack contains of prerecorded dedicated servo code which is used to generate timing and seeking information. When on track, embedded servo code prerecorded between data sectors on all of the data tracks is sampled to keep the heads on track.

In addition to head-disc assembly A3, a number of printed-circuit assemblies (PCAs) are contained within the enclosure. These include servo PCA-A1, read/write PCA-A2, power supply PCA-A4, power distribution PCA-A5, controller PCA-A6, LED PCA-A7, and primary power PCA-A8.

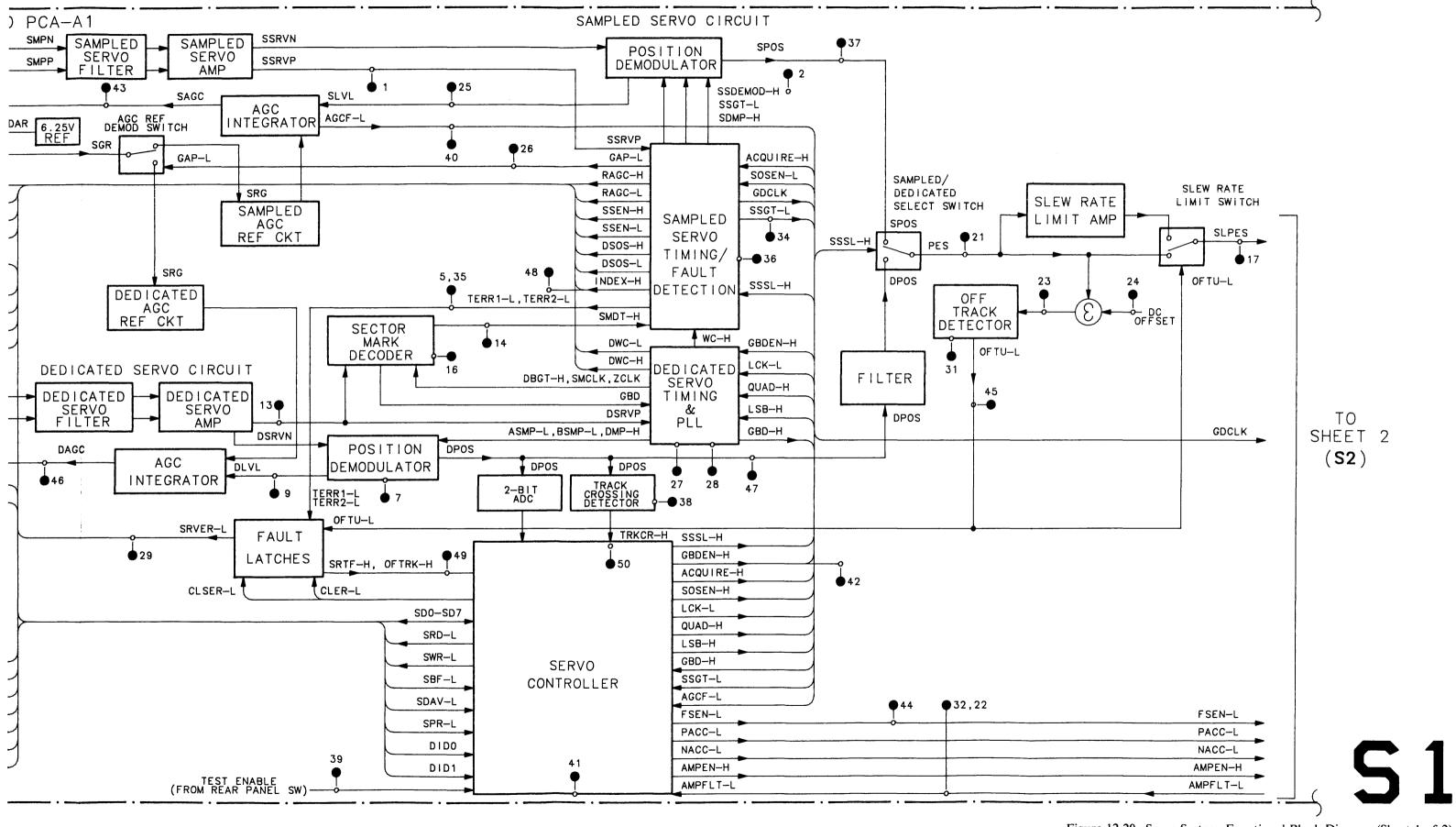

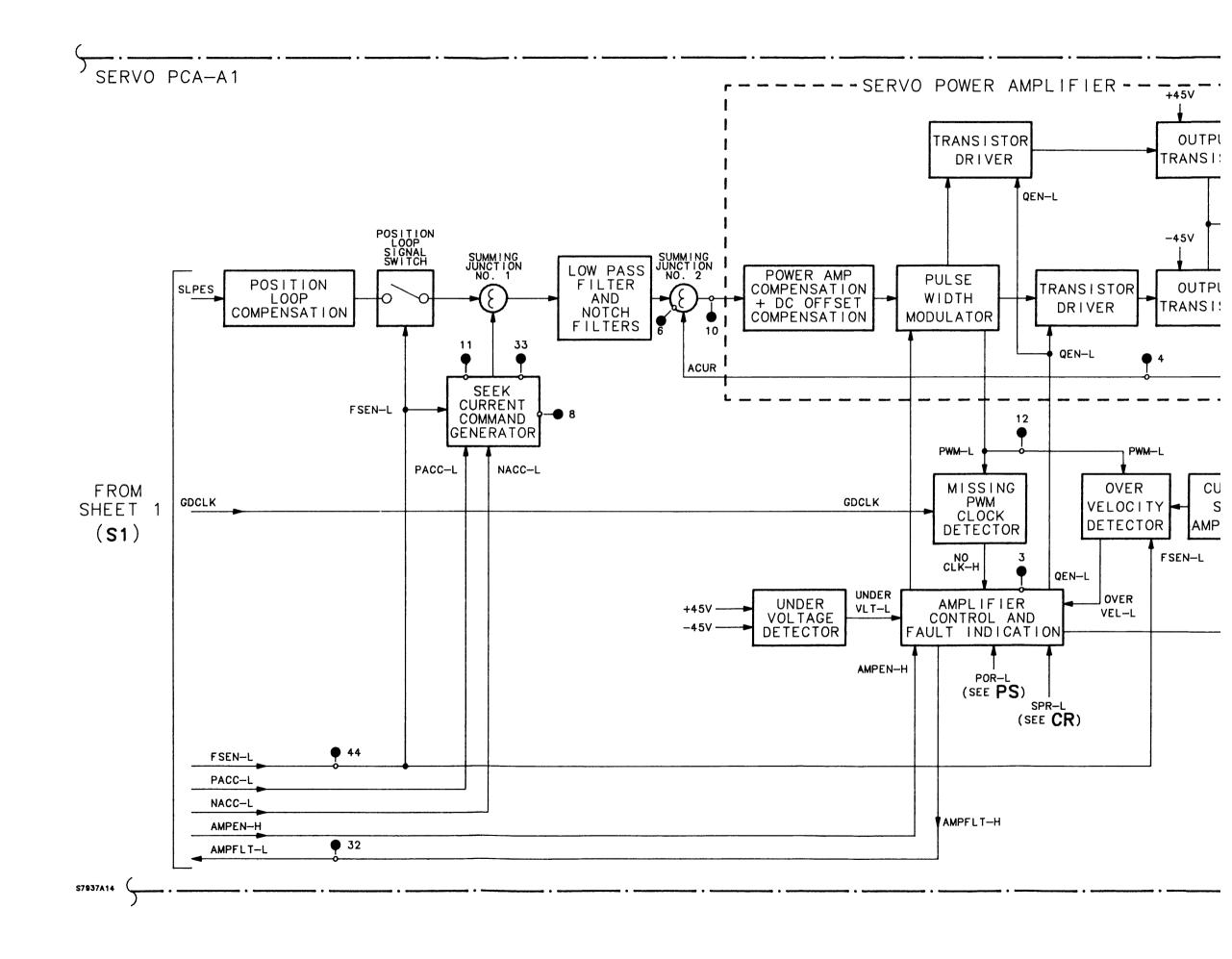

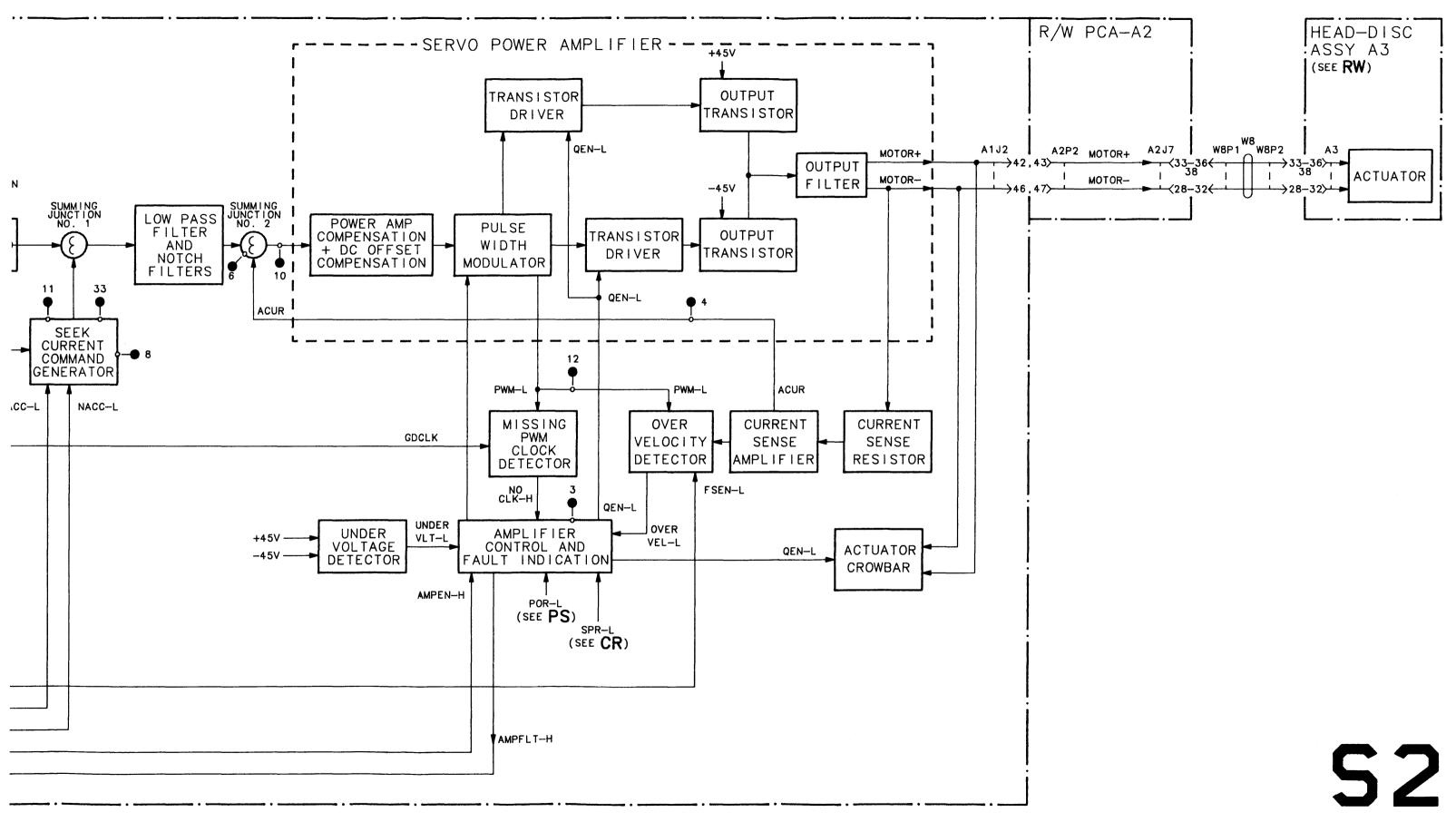

Servo PCA-A1 contains a servo controller, phase-locked loop (PLL) and servo timing counters,

dedicated servo circuit, sampled (embedded) servo circuit, and servo power amplifier. These circuits provide sector timing information, control seeks, and maintain the heads on track.

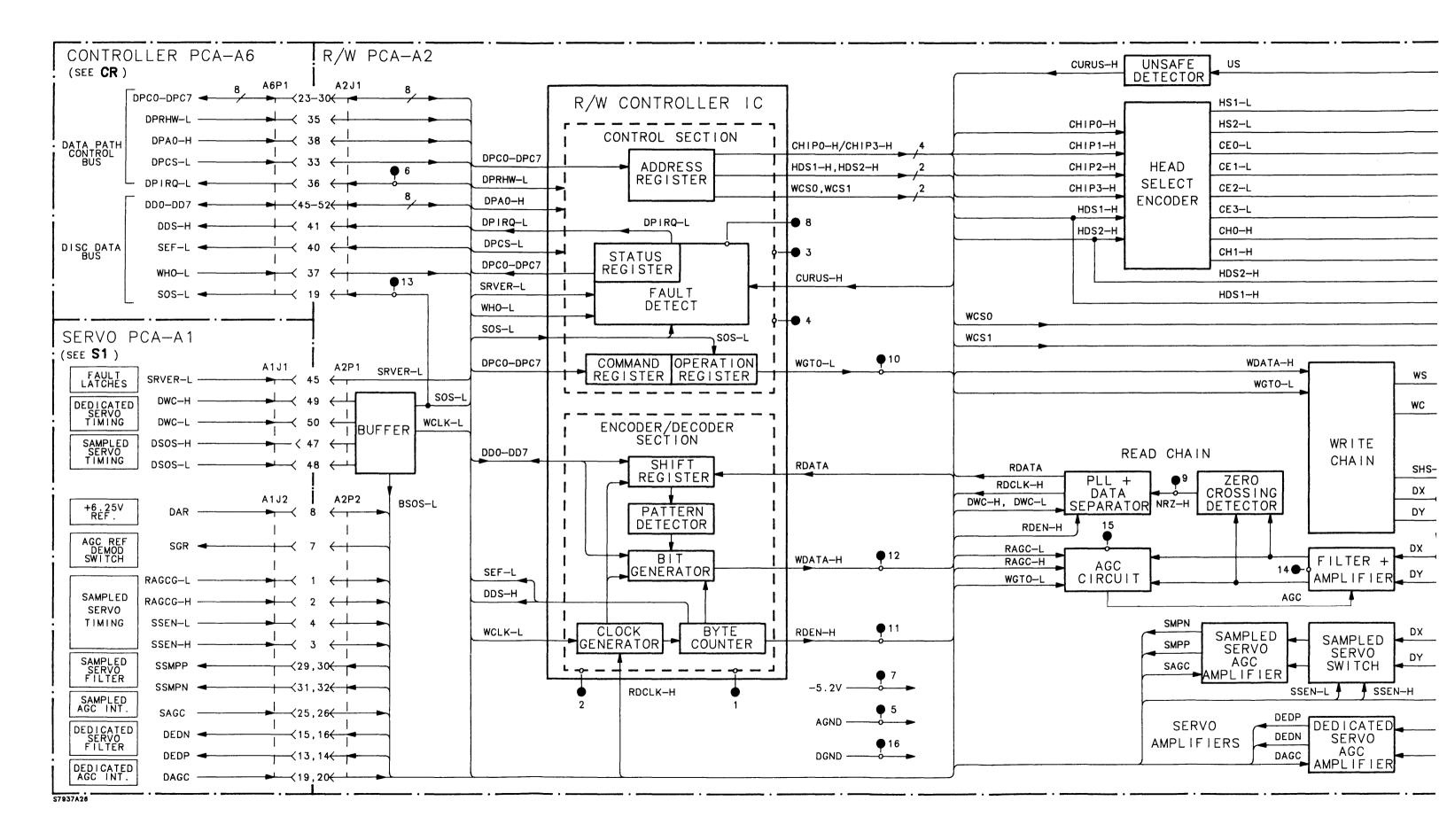

Read/write PCA-A2 includes a custom-designed read/write controller that, together with associated read chain, write chain, and head select electronics, transfers data to and from the disc media. The PCA also maintains data communication with controller PCA-A6, and performs amplification of the sampled and dedicated servo codes.

Power supply PCA-A4, in addition to supplying DC voltages for the controller and drive electronics, provides power-on reset and power fail signals.

Power distribution PCA-A5 filters and distributes the outputs from power supply PCA-A4 to the controller and drive electronics.

Controller PCA-A6 is factory-installed а microprocessor-based controller which provides an interface to the host computer. Two different HP-IB controllers are available for this purpose. In the HP 7936H and HP 7937H Disc Drives, interface to the host is via an Hewlett-Packard Interface Bus (HP-IB) controller. In the HP 7936XP and HP 7937XP, the controller has HP-IB Cache added. (In this manual, the controllers are identified collectively as PCA-A6.) Both controllers interface with the drive electronics via an HP-developed standard interface (ESI).

Self-test diagnostics and fault-finding firmware contained within the controller PCA-A6 exercise key functions of drive operation. Self test is performed automatically at power on and can also be initiated by the host. Drive status is indicated by three LEDs mounted on the front panel. In the event of a self-test failure, this LED display identifies the most likely failed assembly within the drive.

LED PCA-A7 contains three light-emitting diodes (LEDs) that signal to the user the operating status of the drive.

Functional Description 7936 and 7937

Primary power PCA-A8 contains the drive LINEswitch and the spindle motor start capacitor and control relay. Also mounted on PCA-A8 are connectors that facilitate the changeover of the spindle motor wiring when the drive power configuration is changed from 90-132 Vac to 180-264 Vac, or vice versa.

#### 5-2. BLOCK DIAGRAMS

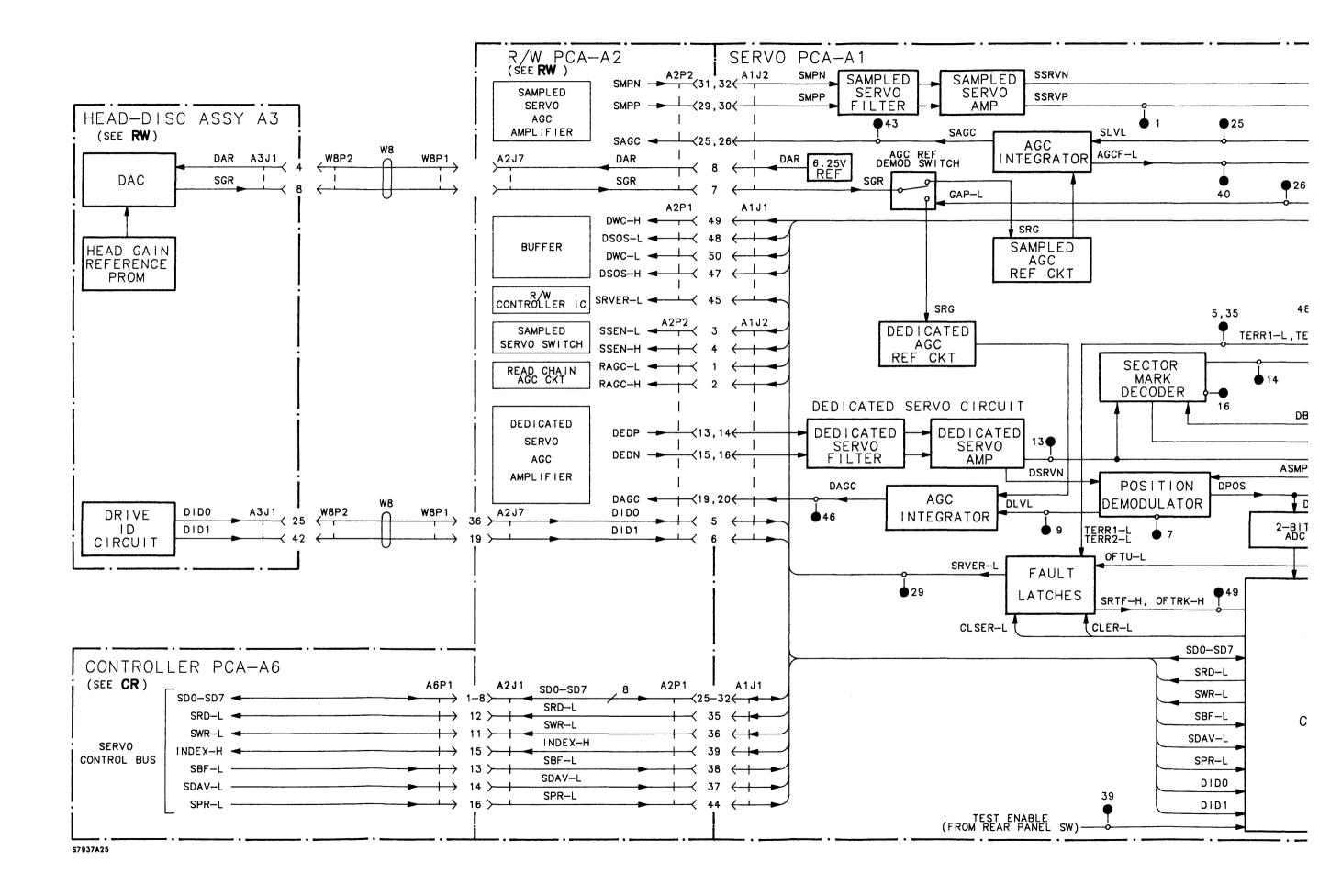

A basic block diagram (figure 5-16) for the controller and drive electronics is provided in this chapter. Functional block diagrams (figures 12-20 through 12-23) for the servo, read/write, spindle, and power supply systems within the drive are located in chapter 12. A functional block diagram for the two HP-IB controllers available for use in the drive is contained in Appendix A at the rear of the manual.

In order to facilitate text and table references to the functional block diagrams in chapter 12 and the appendixes, each diagram is identified by two large characters in the lower right-hand corner of the page. For example, the read/write system diagram is identified with the characters  $\mathbf{RW}$ . These characters are boxed in the text and tables thus:  $\mathbf{RW}$ .

The diagrams are identified as follows:

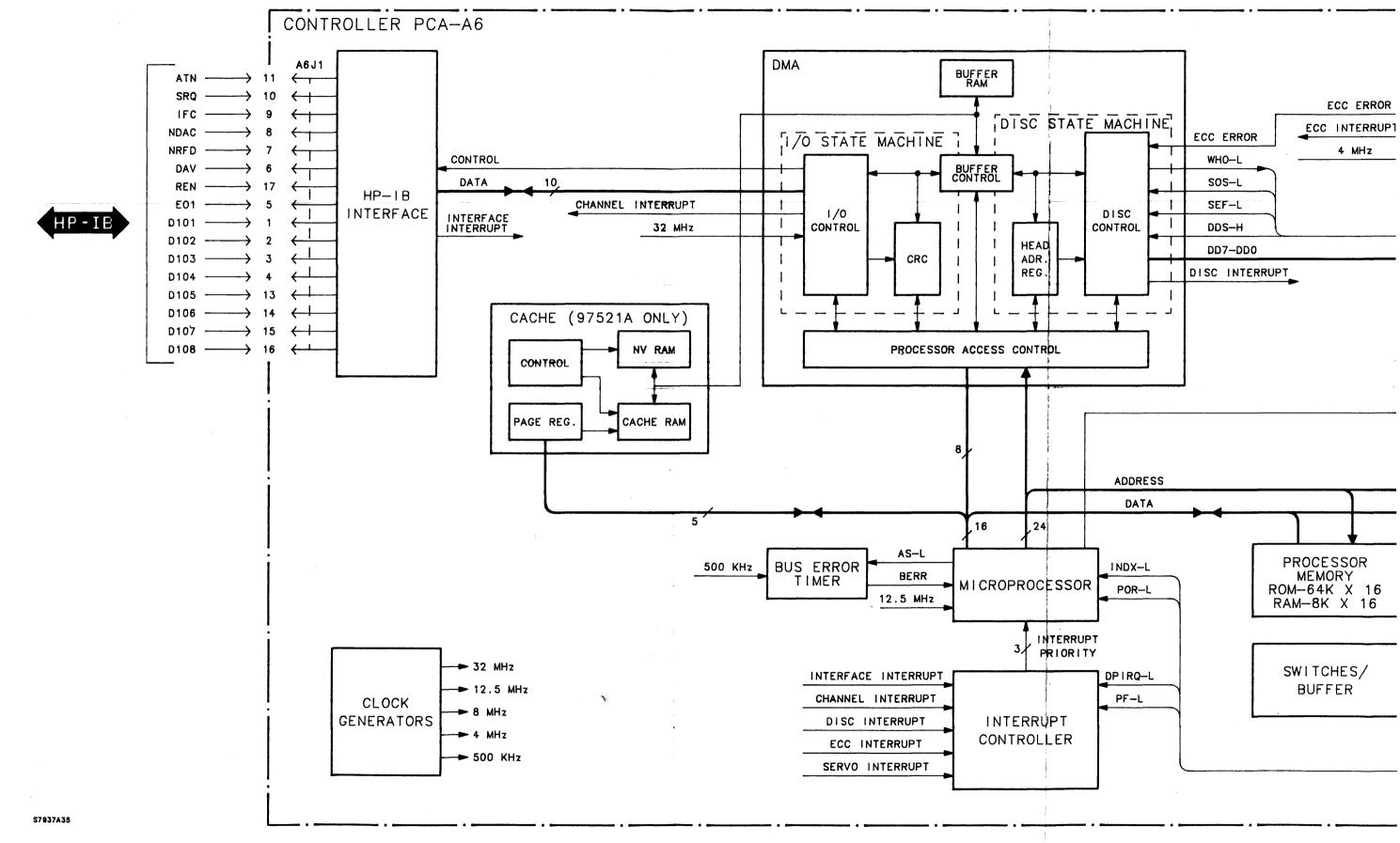

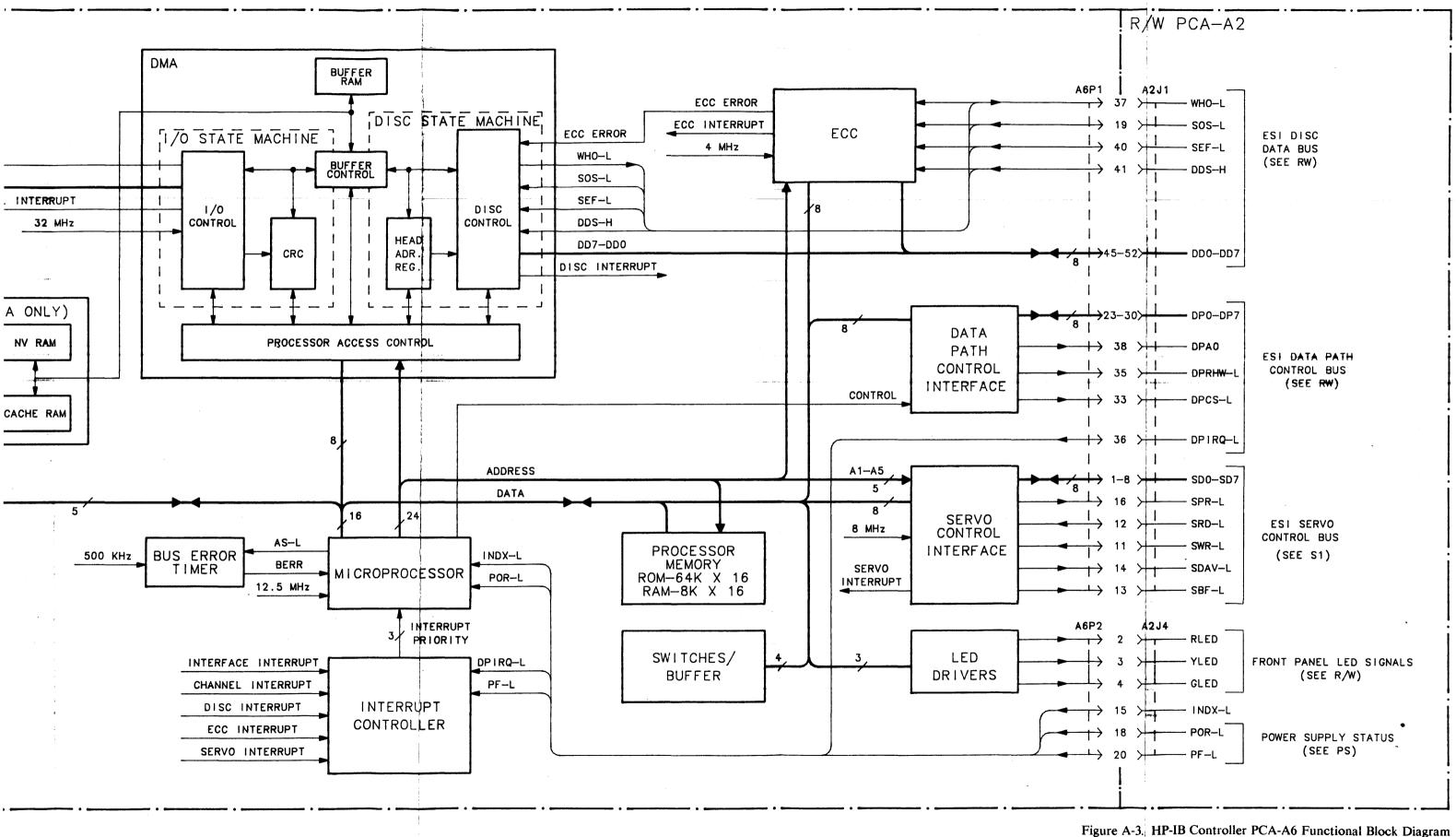

**CR** = Figure A-3, Controller, Functional Block Diagram, in Appendix A.

Appendix A describes the two HP-IB controllers available for use in the drive. Refer to figure A-3 when **CR** is used in this chapter to identify the functional block diagram for controller PCA-A6.

**S1** = Figure 12-20. Servo System, Functional Block Diagram (Sheet 1 of 2)

**S2** = Figure 12-20. Servo System, Functional Block Diagram (Sheet 2 of 2)

**RW** = Figure 12-21. Read/Write System,

Functional Block Diagram

The numbers which identify the test points in the servo and read/write functional block diagrams are the pin numbers on the read/write and servo test PCAs. Refer to chapter 8 for details.

**SD** = Figure 12-22. Spindle Drive System, Functional Block Diagram

**PS** = Figure 12-23. Power Supply System, Functional Block Diagram

#### 5-3. SIGNAL NOTATION

In the controller and drive logic circuits, a digital signal is applied to its destination in one of two states: active or inactive. The signal is active when its voltage level (high or low) makes the action occur for which the signal was designed. This action is usually identified by a signal mnemonic. A mnemonic with an "-L" suffix indicates a logic signal with an active low voltage level. A mnemonic with an "-H" suffix indicates a logic signal with an active high voltage level. Signal mnemonics without an "-L" or "-H" suffix usually indicate analog, data bus, or control bus signals.

#### 5-4. LIST OF MNEMONICS

The mnemonics used in the functional block diagrams and accompanying text are defined in table 5-1. The **SOURCE** column of table 5-1 gives the identification characters for the functional block diagram where the signal appears, followed by the number of the assembly where the signal originates.

The following assembly numbers appear in the **SOURCE** column of table 5-1:

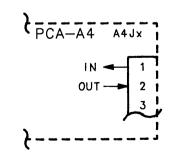

A1 = Servo PCA-A1 A2 = Read/Write PCA-A2 A3 = Head-Disc Assembly A3 A4 = Power Supply PCA-A4 A5 = Power Distribution PCA-A5 A6 = Controller PCA-A6 A7 = LED PCA-A7 A8 = Primary Power PCA-A8

Certain of the signals listed in table 5-1 may be monitored with test PCAs that can be connected to servo PCA-A1 and read/write PCA-A2. Refer to chapter 8 for details. In the SIGNAL column of table 5-1, the servo test signals are identified with an asterisk (\*), and the read/write test signals with a double asterisk (\*\*).

In the **DESCRIPTION** column of table 5-1, the circuits listed in upper case (capital) letters are blocks in the functional diagrams.

# 5-5. DISC FORMAT

Each data surface is divided into a number of concentric circles called tracks. See figure 5-1. From the outer diameter (OD) of the disc to the inner diameter (ID), there are a number of OD guard band tracks, one OD maintenance track, three spare tracks, 1396 user data tracks, three spare tracks, one ID maintenance track, a number of ID guard band tracks, and a landing zone.

The OD guard band is used for calibration. Both the OD and ID guard band tracks allow for overshooting when seeking to the outermost and the innermost data tracks. The maintenance tracks contain service information including run time error logs, fault log (data surface 0 only), and error rate test logs. See figure 5-2. The maintenance tracks are also used when reading and writing during self test. The data tracks are used for reading and writing host data. The spare tracks are used for sparing out any data tracks containing media defects. The head comes to rest on the landing zone when power is removed from the drive.

Each data track is organized into smaller sequentially-numbered blocks of data called sec-

tors. On each track, there are 124 of these physical sectors, with each sector having 256 bytes of data. See figure 5-3.

In addition to the 256 bytes of data, each sector contains a 14-byte sync field, a 6-byte header, a 2-byte CRC field, a 12-byte ECC field, a data gap, a servo field, and a servo code field.

The 14-byte formatter/separator field and the 6-byte header field comprise a 20-byte preamble. This information is used for synchronization and addressing purposes. The header field specifies status, head, cylinder, and sector addresses, and provides the spare sector information. The head and cylinder are logical addresses and the spare sector and sector bytes are physical addresses. The status byte is used to determine whether a spare is classified as primary (factory) or secondary (field). If bit 6 of the status byte is zero, the sector is spared secondary; if 1, the sector is spared primary. If bit 7 of the status byte is zero, the entire track has been field spared; if 1, the track has been spared primary.

The data field is used to store 256 bytes of data. Only the data field is transferred from the system during most data operations. The preamble and the postamble are checked by controller PCA-A6.

The 2-byte CRC field and 12-byte ECC field form a 14-byte postamble. Controller PCA-A6 generates the CRC and ECC information during a write operation and appends it to the other information written in the sector. The check information itself depends on the value of every bit from the first bit in the header field to the last bit in the data field. During a read operation, this check information is regenerated and compared in such a way that the presence of errors is detected. The controller ECC firmware corrects any data errors detected by the hardware in the background while the hardware is busy transferring subsequent sectors in a multiple-sector transfer. In most cases, this scheme will result in no loss of performance for correctable data errors.

Figure 5-1. Track Format, Logical Vs Physical Addressisng

Figure 5-3. Sector Format

The data gap, servo sync, and servo code fields which follow the postamble comprise the sampled (embedded) servo data. This code is described in more detail in the description of the servo system electronics.

# 5-6. ADDRESSING STRUCTURE

The head-disc assembly in the HP 7936 contains seven data surfaces, with the data being accessed with seven read/write heads. See figure 5-4. The HDA in the HP 7937 contains 13 data surfaces, with data being accessed with 13 read/write heads.

Head positioning information and sector clocking are derived from the dedicated servo surface through the read-only servo head. There are 1396 ensured cylinder positions available for data storage (HP 7936 and HP 7937). Cylinder addresses range from 0 to 1395. Each cylinder consists of seven (HP 7936) or 13 (HP 7937) data tracks, one for each data surface. Tracks are addressed when both cylinder and head addresses are specified. Each data track is divided into 123 logically addressable physical sectors (HP 7936 and HP 7937). Sectors are addressed when both head and sector addresses are specified for a given cylinder. Head addresses range from zero to 6 (HP 7936) or zero to 12 (HP 7937).

All addressing in the drive is logical. Controller PCA-A6 assigns logical addresses to the physical addresses. Figure 5-1 shows logical versus physical track addressing. When a defective physical track is encountered, a new physical track (spare track) will be assigned to the same logical address. This eliminates dual seeks to obtain the the correct data and reduces system overhead in managing the discs and spare tracks. A total of 1396 tracks are guaranteed as logical tracks through the the use of spares, which the controller assigns as required.

There are 124 physical sectors. Of these, 123 sectors (addressed from 0 to 122) are available for data storage and one sector is reserved for use as a spare in the event that one of the original 123 becomes defective. Sectors are spared by the controller. In the event that the spare sector is already used, the entire logical track will then be assigned a new physical address (one of the spare tracks). This sparing action is transparent to the host CPU, except that the host may note the decision to spare, and issue the spare command.

# 5-7. ADDRESSING MODE

The drive operates in a cylinder mode to access the data storage areas of the drive. In the cylinder mode, the heads are positioned over a particular cylinder and then data is written or read, starting at the lowest numbered head and continuing to the highest numbered head. A cylinder of information consists of all sectors on all tracks at a given cylinder address. Head switching occurs after the data in sector 123 of the current track has been transferred. Head switching is sequential, that is, head 1 will be selected after head 0, and so on. Data transfers will continue with sector 0 of the next track after the address fields and track status indicators of a sector of that track have been verified by the drive.

# 5-8. DISC SPARING

One sector per track and six tracks per data surface (head) are allocated for sparing bad sectors discovered during data transfers. When performing a sparing operation, controller PCA-A6 attempts a sector spare on the target address (sector). If the allocated spare sector has been used, the entire data track is spared. When sparing, the host has the option of retaining or not retaining data. If the host chooses not to retain data, all data on the target track is destroyed. If the host chooses to retain data, all data on the target track, excluding the sector being spared, is kept.

## 5-9. SECTOR SPARING

When performing a sector sparing operation that retains data, controller PCA-A6 copies the entire contents of the target track (excluding the defective sector) to the nearest available spare track for temporary storage. The controller then reformats the original track, placing the spare sector into user accessible area and mapping out the bad sector. The data is then copied from the spare track back to the reformatted track with the bad sector being skipped. This shifts all those sectors with logical addresses greater than the bad sector to the next higher sector address. By reformatting the entire Functional Description 7936 and 7937

track in this manner, an additional latency is not incurred when accessing a track containing a spared sector.

When reformatting the target track, the controller writes the physical address of the bad sector in the header of each sector on the track. Using this information, the controller knows which sector to skip in subsequent accesses to the track. On tracks that have not undergone a sparing operation, the field in the sector headers contains the physical address of the spare sector (logical sector 123).

## 5-10. TRACK SPARING

If the spare sector has been used, controller PCA-A6 must copy the entire track on which the defective sector resides to an available spare track. Each data head has 6 spare tracks allocated for this purpose. Like data tracks, these spare tracks are organized into cylinders and, to improve sparing efficiency, are located in two bands on each data surface. See figure 5-1. A spare track table, which is stored in controller RAM, is generated at power on by reading the ID and OD spare pools sequentially until a track is found that has not been spared out. This table is then searched before a seek begins to determine if a particular logical address has been reallocated and if so the address is pulled from the table. To reduce the amount of controller RAM consumed by the spare track table, scalar values, rather than explicit addresses, are used to record the physical location of each spare track. Figure 5-5 shows the relationship of scalar values to physical spare track locations.

When performing a track sparing operation, the controller first determines the nearest (in terms of seek time) from the spare pool. Then the next sequential scalar in the pool is the track that is used in the spare. If the track to be spared resides at logical cylinder 0-697, then the OD spare pool is

used (scalar number 39-77). If the track is at cylinder 698-1395, the the ID spare pool is used (scalar number 0-38).

If all of the spare tracks are used up in one of the spare pools, then the next sequential scalar from the opposite spare pool will be chosen.

Defective maintenance tracks are spared automatically by controller PCA-A6. No host intervention is required when sparing a maintenance track.

# 5-11. CONTROLLER PCA-A6

Controller PCA-A6 provides an interface between the host computer and the drive electronics. One of two available HP-IB controllers is factory installed in the drive mainframe.

Appendix A at the rear of this manual provides details of the controllers, including a functional block diagram and accompanying circuit description. Refer to Appendix A for details of the controller installed in the drive.

## NOTE

In this manual, the controllers are referred to collectively as "PCA-A6".

Each controller includes: host interface, a data buffer for data examination and speed matching, disc memory access (DMA) for control of data transfer, error correction (ECC), firmware in read only memory (ROM) for an on-board microprocessor to execute drive commands and monitor status, a peripheral interface for command and status interface with the drive electronics, and channel address/diagnostic control switches. See figure 5-16.

|                                              |           | 1402      | 1401     | 1400     |             | 3       | 2         | 1        | (P                  | HYSICAL)      |

|----------------------------------------------|-----------|-----------|----------|----------|-------------|---------|-----------|----------|---------------------|---------------|

|                                              | CYLINDERS |           |          | 1399     |             |         | -<br>1397 |          |                     | LOGICAL)      |

|                                              |           |           | 1        | 1        |             | 1       | 1         | I        |                     |               |

|                                              |           | I<br>ID I | 1        |          |             | 1       | 1         |          | 00                  |               |

|                                              |           | ID  <br>O | <br>13   | ا<br>26  |             | 1<br>39 | ا<br>52   | l<br>65  | <u>مە</u>           | 1             |

|                                              |           | 1         | 14       | 27       |             | 40      | 53        | 66       | - î                 |               |

|                                              |           |           |          |          |             |         |           |          |                     |               |

| <u> </u>                                     |           | 2         | 15<br>16 | 28<br>29 |             | 41      | 54<br>55  | 67<br>68 | - <sup>2</sup><br>3 |               |

|                                              |           |           |          |          |             |         |           |          | J                   |               |

| ــــــر                                      | _         | 4         | 17       | 30       |             | 43      | 56        | 69       | _ 1                 |               |

| ·                                            |           | 5         | 18       | 31       |             | 44      | 57        | 70       | 5                   | 7937          |

| <u>)                                    </u> |           | 6         | 19       | 32       |             | 45      | 58        | 71       | 6                   | HEADS         |

|                                              |           | 7         | 20       | 33       |             | 46      | 59        | 72       | 7                   |               |

| ١                                            |           | 8         | 21       | 34       |             | 47      | 60        | 73       | 8                   |               |

|                                              |           | 9         | 22       | 35       |             | 48      | 61        | 74       | 9                   |               |

|                                              |           | 10        | 23       | 36       |             | 49      | 62        | 75       | 10                  |               |

|                                              | -         | 11        | 24       | 37       |             | 50      | 63        | 76       | 11                  |               |

|                                              |           | 12        | 25       | 38       |             | 51      | 64        | 77       | 12                  |               |

|                                              | -         | <u></u>   |          |          |             |         | <br>      |          | 12                  | ]             |

|                                              | $\sim$    | ·<br>I    | i        | Ì        |             | i       | I         | i i      |                     |               |

|                                              |           | I         | I        | I        |             | I       | I         | Ì        |                     |               |

|                                              |           | I         | I        | 1        |             | 1       | 1         | I        |                     |               |

|                                              |           | I         | Ι        | Ι        |             | Ι       | I         | I        |                     |               |

| )                                            |           |           |          |          |             |         |           |          |                     |               |

| (                                            |           | 1         | 1        | ł        |             | 1       | i         |          |                     |               |

| ,                                            |           | 1         | I<br>I   | 1        |             | 1       | 1         | 1        |                     |               |

| (                                            |           |           | 1        |          |             | 1       |           |          |                     |               |

|                                              |           | I         | Ì        | I        |             | 1       | I         | I        |                     |               |

| }                                            |           | 1         | 1        | 1        |             |         | 1         |          |                     |               |

|                                              |           | <br>0     | <br>7    | <br>14   |             | <br>21  | <br>28    | <br>35   | ~_                  | 1             |

| ~                                            | ŀ         | 1         |          | 14       |             | 22      | 28        | 35       | - °                 |               |

|                                              |           |           |          |          |             |         |           |          |                     |               |

| ≻                                            | _         | 2         | 9        | 16       |             | 23      | 30        | 37       | 2                   |               |

| ·                                            |           | 3         | 10       | 17       |             | 24      | 31        | 38       | 3                   | 7936<br>HEADS |

| )                                            |           | 4         | 11       | 18       |             | 25      | 32        | 39       | 4                   | -             |

| ( <u> </u>                                   |           | 5         | 12       | 19       | •           | 26      | 33        | 40       | 5                   |               |

| Ŋ                                            |           | 6         | 13       | 20       |             | 27      | 34        | 41       | 6                   |               |

| (                                            | ┓         |           |          |          |             |         |           |          |                     | -             |

| \$7937482                                    |           |           |          |          | Track Scala |         |           |          |                     |               |

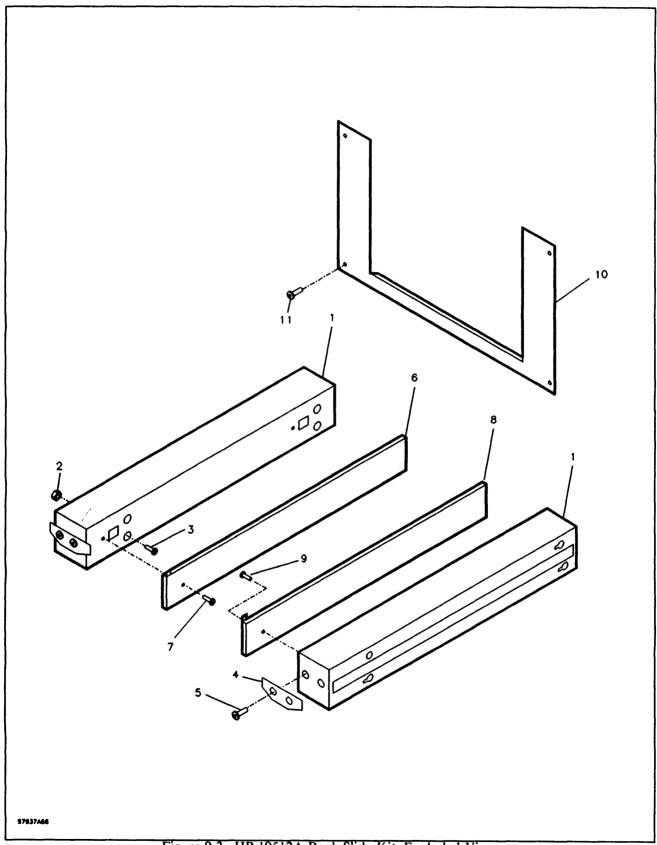

Figure 5-5. Spare Track Scalar Values

Both of the controllers interface to the drive electronics via a standard interface (ESI). This interface consists of a Disc Data Bus, a Data Path Control Bus, and a Servo Control Bus. Each bus is a bidirectional parallel 8-bit bus with associated control and handshake lines. The mnemonics which identify the bus signals are listed below. Refer to table 5-1 for a description of the signal functions.

#### **DISC DATA BUS**

| DD0-DD7 | Disc Data Bus    |

|---------|------------------|

| DDS-H   | Disc Data Strobe |

| SEF-L   | Start ECC Field  |

| SOS-L   | Start of Sector  |

| WHO-L   | Write Hold Off   |

#### DATA PATH CONTROL BUS

| DPC0-DPC7 | Data Path Control Bus          |

|-----------|--------------------------------|

| DPA0-H    | Data Path Address Zero         |

| DPCS-L    | Data Path Control Select       |

| DPIRQ-L   | Data Path Interrupt Request    |

| DPRHW-L   | Data Path Read High, Write Low |

#### SERVO CONTROL BUS

| SD0-SD7 | Servo Data Bus        |

|---------|-----------------------|

| SBF-L   | Servo Buffer Full     |

| SDAV-L  | Servo Data Available  |

| SPR-L   | Servo Processor Reset |

| SRD-L   | Servo Read            |

| SWR-L   | Servo Write           |

The controller also supplies drive signals for the three LEDs in LED PCA-A7 that indicate the operating status of the drive. These signals are labeled Red LED (RLED), Green LED (GLED), and Yellow LED (YLED). The signals reach PCA-A7 via read/write PCA-A2, signal jumper cable W7, power distribution PCA-A5, and power supply output cable W4. See figure **S**.

The +5V supply for the LEDs, labeled LED Power (LEDP), originates in read/write PCA-A2, and is connected to PCA-A7 via the same path as the LED drive signals.

# 5-12. SERVO SYSTEM

Control of the servo system is based on dedicated servo code (prerecorded on the single servo surface) and embedded servo code (prerecorded on all of the data surfaces between data sectors). The servo system follows the specified track while reading or writing and when needed, initiates and controls seeks between cylinders. In addition, the servo system is responsible for determining the type of HDA being addressed (7936 or 7937), monitoring the spindle speed, reporting current servo system status, and interpreting incoming commands from controller PCA-A6.