# REFERENCE MANUAL for the CPD N-MOS II PROCESSOR

Calculator Products Division August 1976

| ananananananana CHAPTERS anananana                | nunu | アロロ | ローローロ |

|---------------------------------------------------|------|-----|-------|

| PREFACE · · · · · · · ·                           |      |     | viii  |

| PROCESSOR                                         |      |     |       |

| DESCRIPTION OF THE PROCESSOR · · · ·              |      |     | . 1   |

| GENERAL INFORMATION                               |      |     | . 2   |

| MEMORY CONVENTIONS                                |      |     | . 3   |

| MEMORY CYCLES · · · · ·                           |      |     | . 5   |

| THE BYTE LINE                                     |      |     | . 6   |

| RAL LINE · · · · · ·                              |      |     | • 7   |

| FUNCTIONAL DESCRIPTION OF THE BPC · · · ·         | 1.   |     | . 8   |

| INDIRECT ADDRESSING                               |      |     | . 8   |

| MULTI-LEVEL INDIRECT ADDRESSING                   |      |     | . 8   |

| SINGLE-LEVEL INDIRECT ADDRESSING.                 |      |     | . 9   |

| MEMORY REFERENCE INSTRUCTIONS AND PAGE ADDRESSING | 2    |     | . 9   |

| ABSOLUTE ADDRESSING                               |      |     | .11   |

| RELATIVE ADDRESSING · · · ·                       |      |     | .11   |

| BASE PAGE ADDRESSING                              |      |     | .11   |

| CURRENT PAGE ADDRESSING                           | •    | ·   | .12   |

|                                                   | •    | •   | .12   |

| SUBROUTINES.                                      | •    | •   | .15   |

| FLAGS · · · · · · · ·                             | •    | •   | .15   |

| BUS REQUESTS AND INTERRUPTS · · ·                 | •    | •   |       |

| FUNCTIONAL DESCRIPTION OF THE IOC · · · ·         | •    |     | .18   |

| GENERAL INFORMATION ABOUT I/O · · · ·             | •    | •   | .18   |

| I/O BUS CYCLES · · · · · · ·                      |      | •   | .18   |

| STANDARD I/O · · · · · · ·                        | ٠    | ٠   | .21   |

| ADDRESSING THE PERIPHERAL · · ·                   | •    | ٠   | .21   |

| CHECKING STATUS · · · · ·                         | •    | •   | .21   |

| INITIATING I/O BUS CYCLES · · · ·                 | •    | •   | .21   |

| THE ODDBALL POSSIBILITIES                         | ٠    | ·   | .22   |

| THE INTERRUPT SYSTEM · · · · ·                    | •    | •   | .23   |

| PRIORITY                                          |      | •   | .23   |

| INTERRUPT POLLS                                   | •    | •   | .23   |

| INTERRUPT TABLE                                   | •    |     | .24   |

| INTERRUPT PROCESS SUMMARY                         | •    |     | .26   |

| INTERRUPT SERVICE ROUTINES                        |      |     | .26   |

----- PROCESSOR -----

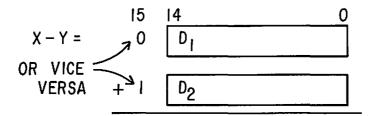

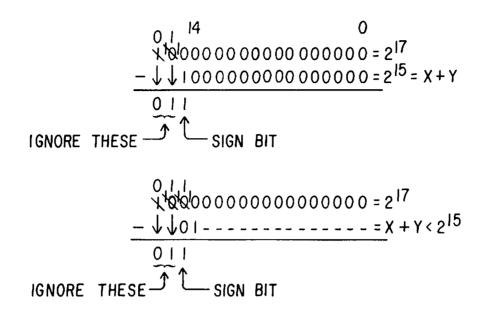

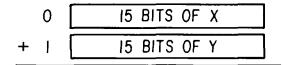

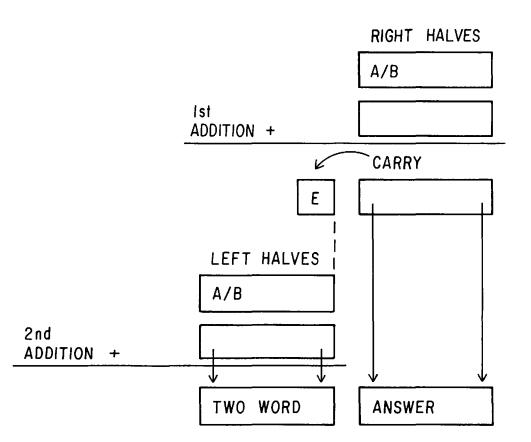

#### FUNCTIONAL DESCRIPTION OF THE IOC THE INTERRUPT SYSTEM (CONT.) HOW A PERIPHERAL KNOWS WHETHER TO USE INTERRUPT OR SIMPLE I/O . .28 BOMBPROOFING THE MAINLINE FIRMWARE . . .28 140 "SIMULTANEOUS" ACTIVITIES . . 5.00 . .28 . WHEN TO CEASE INTERRUPT MODE OPERATION . .29 • • RETURNING FROM INTERRUPT SERVICE ROUTINES . .30 12 12 DISABLING THE INTERRUPT SYSTEM . . . .30 1 1 DIRECT MEMORY ACCESS · · · · . . 31 ENABLING AND DISABLING THE DMA MODE . . .31 . . REGISTER SET-UP . . . .32 221 . DMA INITIATION . . . .32 . 141 . . DATA REQUEST AND TRANSFER . . .33 . . . . DMA TERMINATION . . . .33 . . . . . THE PULSE COUNT MODE . . .33 .34 PLACE AND WITHDRAW . . . 1.0 1.0 THE NOTATION OF A STACK . .34 . . . . . STACK OPERATIONS . . . .34 2 PLACE AND WITHDRAW FOR BYTES . .35 . . .38 INITIALIZATION OF TURN-ON · · . . GENERAL INFORMATION ABOUT THE EMC . . . .39 . . . .39 NOTATION . . . . . . . .40 . DATA FORMAT. . . . . A BEGINNER'S LOOK AT CALCULATOR ARITHMETIC .41 . . . NUMERICAL REPRESENTATIONS · · .41 . . . . . BINARY . . .41 121 .42 BINARY-CODED DECIMAL . . . .... . . .43 BINARY ARITHMETIC · · . . . . . . BINARY COMPLEMENTS .43 . . TWO'S COMPLEMENT SUMMATION . .45 . 22 .45 TWO'S COMPLEMENT SUBTRACTION . . . . TWO'S COMPLEMENT OVERFLOW . .50 .

11

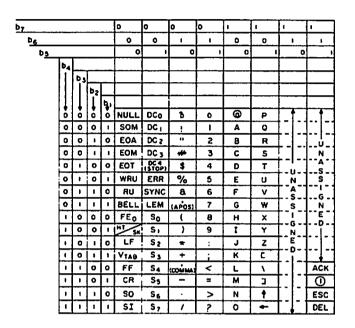

and an and an and a CHAPTERS and a descent and a second and as ----- PROCESSOR ------A BEGINNER'S LOOK AT CALCULATOR ARITHMETIC (CONT.) .52 MULTI-PRECISION BINARY ARITHMETIC • .53 ARITHMETIC SHIFTS · . . . . . • • .55 BINARY MULTIPLY · · · · · · • • • .55 • • . BCD ARITHMETIC · · • . . . . .56 DECIMAL CARRY • • . .56 TEN'S COMPLEMENT FOR BCD . . • • • TEN'S COMPLEMENT ARITHMETIC DEMONSTRATION . .59 • .61 FLOATING-POINT SUMMATIONS · · • • • . . .61 OFFSETS. . . . . . • • • • MANTISSA ADDITION. . . . . .62 • • • .63 NORMALIZATION · · • • • • • . • • ROUNDING · · • • . • .63 • .64 FLOATING-POINT MULTIPLICATION · • • • • • .66 FLOATING-POINT BCD DIVISION • • • • • • THE DIVISION ALGORITHM. . • • .66 • . . • .68 THE FDV INSTRUCTION • • • • • SAMPLE DIVISION ROUTINE . . . . . . .71

## ----- INSTRUCTIONS ------

| INT | RODUCTION | TO THE   | MACH     | INE  | INSTR | JCTIO | NS. | • | • | • | • | . 1 |

|-----|-----------|----------|----------|------|-------|-------|-----|---|---|---|---|-----|

|     | NOTATION  | •        | •        | •    | •     | •     | •   | • | • | • | • | . 1 |

| BPC | MACHINE   | INSTRUC  | TIONS    | •    | •     | •     | •   | • | • | • | • | . 2 |

|     | MEMORY RI | EFERENCI | e gro    | UP   | •     | •     | •   | • | • | • | • | . 2 |

|     | SHIFT-RO  | TATE GRO | OUP      | •    | •     | •     | •   | • | • | • | • | . 4 |

|     | ALTER-SK  | IP GROU  | <b>.</b> | •    | •     | •     | •   | • | • | • | • | . 5 |

|     | COMPLEME  | NT-EXECU | ЛЕ G     | Roup | ••    | •     | •   | • | • | • | • | .10 |

| IOC | MACHINE   | INSTRUC  | TIONS    | ٠    | •     | •     | •   | • | • | • | • | .12 |

|     | STACK GRO | OUP.     | •        | •    | •     | •     | •   | • | • | • | • | .12 |

|     | I/O GROUI | >.       | •        | ٠    | •     | •     | •   | • | • | • | • | .14 |

|     | INTERRUP  | T GROUP  | •        | •    | •     | •     | •   | • | • | • | • | .14 |

|     | DMA GROUI | <b>.</b> | •        | •    | •     | •     | •   | • | • | • | • | .15 |

| $\phi$                        | HAP    | <b>FER</b> | S 🗠   | orond | היימיימי | orone | nonor | mm   |

|-------------------------------|--------|------------|-------|-------|----------|-------|-------|------|

| —— I N S T                    | RU(    | стι        | O N   | s –   |          |       |       |      |

| EMC MACHINE INSTRUCTIONS .    |        |            |       |       | _        | -     | _     | .16  |

| THE FOUR WORD GROUP           | •      | •          | •     | •     |          |       |       | .16  |

| THE MANTISSA SHIFT GROUP      | •      | •          | •     | •     | •        | •     | •     | .16  |

| THE ARITHMETIC GROUP ·        | •      |            | •     | •     | •        | •     | •     | .17  |

|                               |        |            |       |       |          |       |       |      |

| ——— A S :                     | SEN    | 1 B L      | . E R |       |          |       |       |      |

| INTRODUCTION TO THE ASSEMBLE  | ξ.     | •          | •     | •     | •        | •     | •     | . 1  |

| GENERAL INFORMATION .         | •      | •          | •     | •     | •        | •     | •     | . 1  |

| INSTRUCTION FORMAT •          | •      | •          | •     | •     | •        | •     | •     | . 2  |

| STATEMENT CHARACTERIS         | STICS  | •          | •     | •     | •        | •     | •     | . 2  |

| LABEL FIELD                   | •      | •          | •     | •     | •        | •     | •     | . 3  |

| OPCODE FIELD.                 | •      | •          | •     | •     | •        | •     | •     | . 4  |

| OPERAND FIELD .               | •      | •          | •     | •     | •        | •     | •     | . 5  |

| SYMBOLIC TERMS .              | •      | •          | •     | •     | •        | •     | •     | . 6  |

| NUMERIC TERMS .               | •      | •          | •     | •     | •        | •     | •     | . 8  |

| THE ASTERISK                  | •      | •          | •     | •     | •        | •     | •     | . 8  |

| EXPRESSIONS                   | •      | •          | •     | •     | •        | •     | •     | . 8  |

| INDIRECT ADDRESSING           | •      | •          | •     | •     | •        | •     | •     | . 9  |

| BASE PAGE AND CURRENT         | r page | ADD        | RESSI | NG.   | •        | •     | •     | . 9  |

| COMMENT FIELD .               | •      | •          | •     | •     | •        | •     | •     | . 9  |

| STATEMENT LENGTH .            | •      | ٠          | •     | •     | •        | •     | •     | .10  |

| ASSEMBLER PSEUDO INSTRUCTIONS | 3.     | •          | •     | •     | •        | •     | •     | .11  |

| ASSEMBLER CONTROL ·           | •      | •          | •     | •     | •        | •     | •     | .11  |

| ORG AND ORR · ·               | •      | •          | •     | •     | •        | •     | •     | .11  |

| NEW INSTRUCTION DEFIN         | NITION | ۱.         | •     | •     | •        | •     | •     | .12  |

| PARTITIONING A BINAR          | Y TAPE |            | •     | •     | •        | •     | •     | .14  |

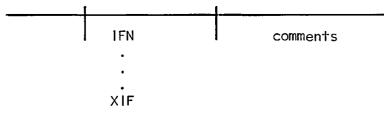

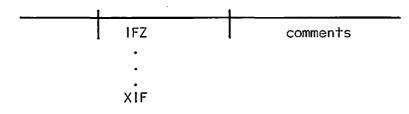

| CONDITIONAL ASSEMBLY          | •      | •          | •     | •     | •        | •     | •     | .15  |

| AUTOMATIC STATEMENT           | REPETI | TION       |       | •     | •        | •     | •     | . 17 |

| SOURCE TERMINATION            | •      | •          | •     | •     | •        | •     | •     | .17  |

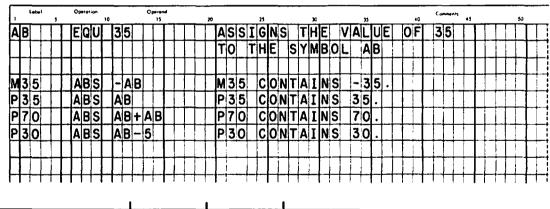

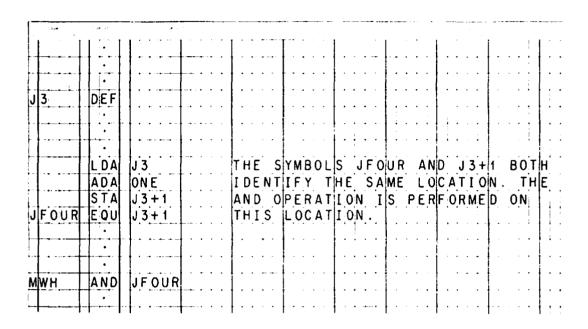

| ADDRESS AND SYMBOL DEFIN      | ITION  | •          | •     | •     | •        | •     | •     | .18  |

| CONSTANT DEFINITION •         | •      | •          | •     | •     | •        | •     | •     | .20  |

| STORAGE ALLOCATION ·          | •      | •          | •     | •     | •        | •     | •     | .23  |

| ASSEMBLY LISTING CONTROL      | •      | •          | •     | •     | •        | •     | •     | .23  |

ī٧

| ananananananana CHAPTERS              | anana | monor | or or or | mmo |     |

|---------------------------------------|-------|-------|----------|-----|-----|

| ASSEMBLE                              | R —   |       |          |     |     |

| ASSEMBLER INPUT AND OUTPUT · · ·      | •     | •     | •        | •   | .26 |

| THE CONTROL STATEMENT · · · ·         | •     |       | •        | •   | .26 |

| THE SOURCE PROGRAM · · · ·            | •     | •     | •        | •   | .27 |

|                                       | •     |       | •        | •   | .27 |

| BINARY OUTPUT                         | •     | •     | •        | •   | .28 |

| APPENDIX                              | <     |       |          |     |     |

| APPENDIX · · · · · ·                  |       |       |          |     | . 1 |

| ASSEMBLER ERROR MESSAGES · · ·        | •     | •     | •        | •   | . 1 |

| BINARY LOADERS                        |       | •     | •        | •   | . 3 |

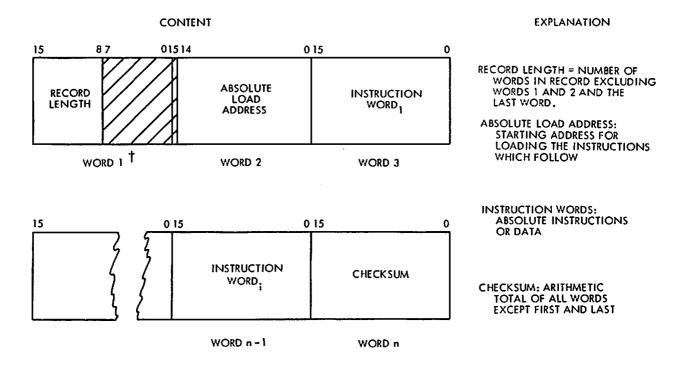

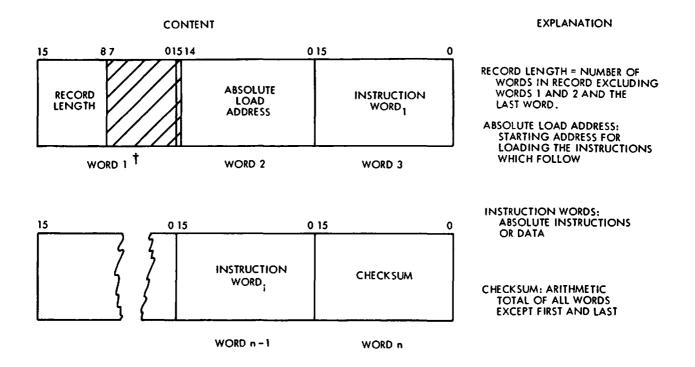

| OUTPUT PAPER TAPE FORMAT              | •     | •     | •        | •   | . 5 |

| ABSOLUTE BINARY OBJECT PROGRAM .      | •     | •     | •        |     | . 5 |

| ADDING PRE-DEFINED SYMBOLS TO ASMA ·  |       | •     | •        | •   | . 6 |

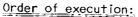

| THE STRUCTURE OF THE ASSEMBLER · ·    |       | •     | •        | •   | . 9 |

| PSEUDO INSTRUCTIONS · · · ·           |       | •     | •        | •   | .11 |

| MACHINE INSTRUCTIONS · · · ·          |       | •     | •        | •   | .12 |

| INSTRUCTION BIT PATTERNS · · ·        |       | •     | •        | •   | .18 |

| MEMORY REFERENCE GROUP                |       | •     | •        | •   | .18 |

| SHIFT-ROTATE GROUP                    |       | •     | •        | •   | .18 |

| SKIP GROUP                            |       | •     | •        | •   | .19 |

| RETURN GROUP                          |       | •     | •        | •   | .19 |

| COMPLEMENT GROUP                      |       | •     | •        | •   | .20 |

| ALTER GROUP                           |       | •     | •        | •   | .20 |

| EXECUTE GROUP                         |       | •     | •        | •   | .21 |

| 16-BIT IOC ONLY GROUP                 | • •   | •     | •        | •   | .21 |

| STACK GROUP                           | • •   | •     | •        | •   | .22 |

| INTERRUPT GROUP                       | • •   | •     | •        | •   | .22 |

| DMA GROUP                             | • •   | •     | •        | •   | .22 |

| FOUR WORD OPERATION GROUP             | • •   | •     | •        | •   | .23 |

| MANTISSA SHIFT GROUP                  | • •   | •     | •        | •   | .23 |

| ARITHMETIC GROUP                      | •     | •     | •        | •   | .23 |

| 15/16 BIT BPC CONSOLIDATED CODING SHE | EET · | •     | •        | ٠   | .24 |

| 15/16 BIT IOC CONSOLIDATED CODING SHE | EET · | •     | •        | •   | .24 |

| 15/16 BIT EMC CONSOLIDATED CODING SHE | EET . | •     | •        |     | .24 |

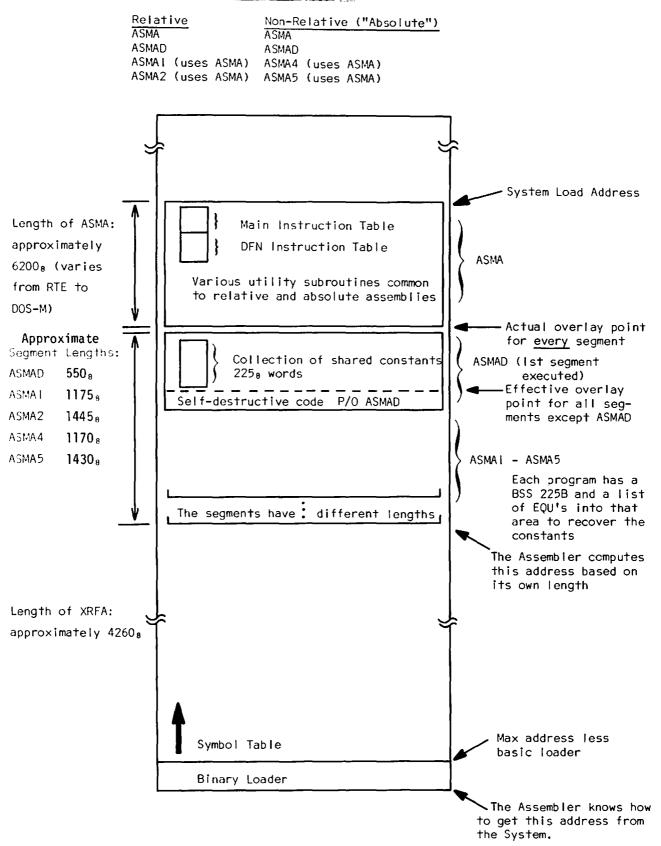

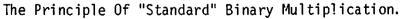

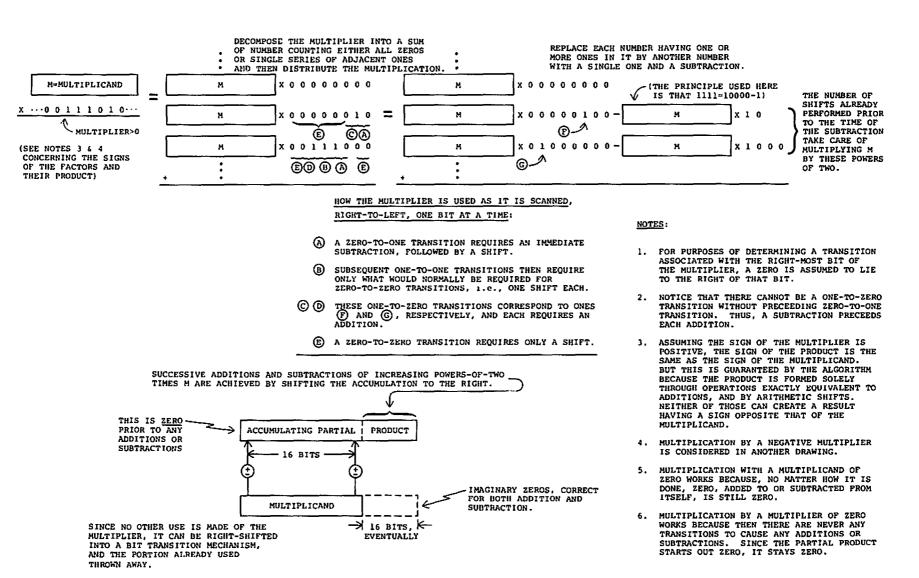

——— APPENDIX —— APPENDIX (CONT.) HP CHARACTER SET. . . .25 • CHARACTER CODES · · · · .26 • • • • . BPC INSTRUCTION EXECUTION TIMES. .27 • • • • EMC INSTRUCTION EXECUTION TIMES. .28 • • • . . IOC INSTRUCTION EXECUTION TIMES. .29 • • ٠ • • EXPLANATION OF BOOTH'S ALGORITHM · · · .30 • •

1

and a second a second and a sec

----- PROCESSOR ----

| Figure P-1.  | Simplified Block Diagram of the Processor .                                             | •     | •     | . 1  |

|--------------|-----------------------------------------------------------------------------------------|-------|-------|------|

| Figure P-2.  | Nature of the BIB's                                                                     | •     | •     | . 3  |

| Figure P-3.  | Simplified Read Memory Cycle                                                            |       | •     | . 5  |

| Figure P-4.  | Simplified Write Memory Cycle                                                           | •     | •     | . 6  |

| Figure P-5.  | Base Page Description                                                                   | •     | •     | .10  |

| Figure P-6.  | Relative Addressing                                                                     | •     | •     | .14  |

| Figure P-7.  | Bus Request Protocol                                                                    | •     | •     | .16  |

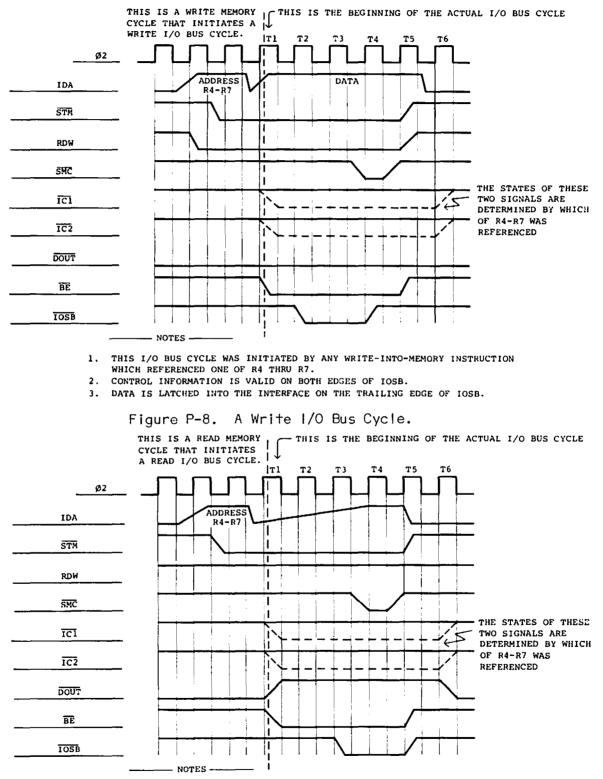

| Figure P-8.  | A Write I/O Bus Cycle                                                                   | •     | •     | . 20 |

| Figure P-9.  | A Read I/O Bus Cycle                                                                    | •     | •     | .20  |

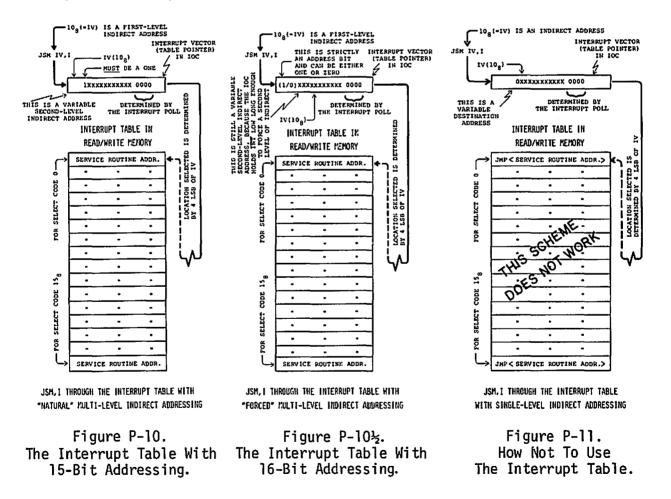

| Figure P-10. | The Interrupt Table With 15-Bit or 16-Bit A                                             | \ddre | ssing | .25  |

| Figure P-II. | How Not To Use The interrupt Table                                                      | •     | •     | .25  |

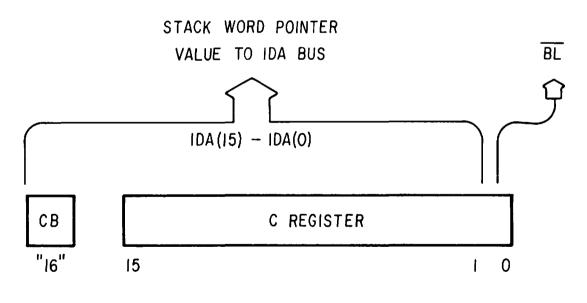

| Figure P-12. | Sixteen-Bit Stack Pointer Addressing                                                    |       | •     | .36  |

| Figure P-13. | Floating-Point Data Format                                                              | •     | •     | .40  |

| Figure P-14. | The Internal Floating-Point Representation .003587219 ( = $3.587219 \times 10^{-3}$ ) . | of    | •     | .43  |

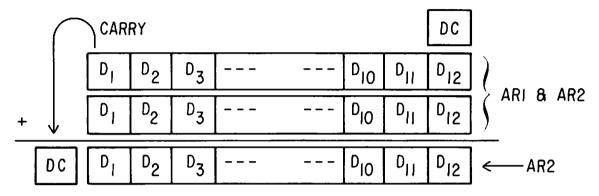

| Figure P-15. | Multi-Word Binary Addition Using the Extend                                             | d Reg | ister | . 52 |

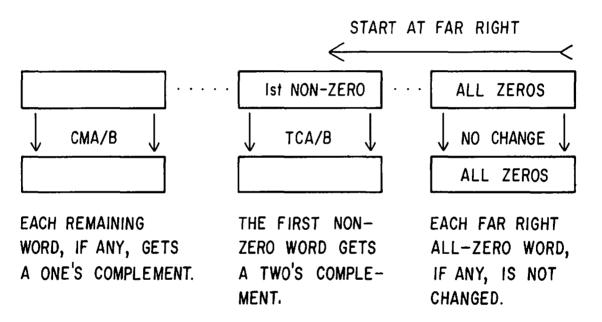

| Figure P-16. | Two's Complements of Multi-Word Binary Numb                                             | pers  | •     | .53  |

| Figure P-17. | Floating-Point Data Format                                                              |       | •     | .54  |

2

and a contraction of TABLES and a contraction of the contraction of th

-

-----

### ----- PROCESSOR ------

| Table P-I. | Addressable Registers                       | . 4 |

|------------|---------------------------------------------|-----|

| Table P-2. | Current Page Absolute Addressing for Memory |     |

|            | Reference Instructions                      | .13 |

| Table P-3. | Comparison of Decimal, Binary, and Octal    | .41 |

### ----- ASSEMBLER ------

This book is the result of an extensive revision of the "CPD PROCESSOR" manual first issued in early 1975. Things have changed a bit since then, and the old manual was getting pretty shakey. The development of the 16-bit version of the processor provided the opportunity to revise the entire book.

PREFACE

First, this book covers both versions of the processor; one with 15-bit (32K) addressing, and the other with 16-bit (64K) addressing. The assembler (ASMA) described herein has also been updated to work with the 16-bit version.

Next, numerous mistaken and misleading explanations have been corrected. Also, the information relating to the general attributes and operation of the hardware has been collected together and organized as an introduction and overview of the entire processor. However, the book does not educate the reader in the general notion of what a processor is, or in the ins and outs of assembly language programming; it is still very helpful if one is familiar with the 2100-series computers.

As before, the book is aimed primarily at engineers and technicians within HP who will recognize the attributes of the processor and apply them to their own situation. Even so, there are still places where the explanation becomes detailed. The explanations of the interrupt process and of arithmetic are examples. There are other areas which the reader is simply expected to absorb on his own. The assembler is a good example; all the explanation in the world (and we give quite a bit) won't remove the need for a little bit of experience.

If you are a beginner, you probably shouldn't try to read the book from cover to cover, in the order given. It would be better if you mix your exposure to the system overview (at least skip the arithmetic), machine-instructions, and the assembler.

A comment on the section on arithmetic is in order. First, it would be impossible to understand the EMC arithmetic instructions without reference to some detailed examples. Second, its been my experience that typically there's one guy who sits in a corner, mutters out loud a lot, and who writes all the math routines. He's the only guy who knows how they work, and even he makes frequent references to the texts he used in school. And in general, if you ask three differenct people about some aspect of arithmetic, you'll get three different answers.

I don't suppose that too many people are really concerned about the nature of the EMC instruction set. But it needs explanation none the less. To do that, detailed examples are needed. To understand the examples, some familiarity with arithmetic techniques is needed. So I went the last mile and started at the beginning.

At present, there is exactly zero interfacing information that would allow a designer to create hardware that will function with the processor. We hope to remedy this shortly.

### PREFACE

If you find a snarf in the book, please bring it to my attention. If it's serious enough, you may win a six-pack of Coors.

May 1977 Revision

Affecting pages:

PROCESSOR -1 -3 -4 -13\* -25 -28 -37 -38 \_44\* -55 INSTRUCTIONS-17 ASSEMBLER -6 -7 APPENDIX -6 -8 -10

\*Non-significant typing error only

June 1978 Revision

Affecting pages:

PROCESSOR -1 -4 -5 -6 -24\* -38\* -59

# PREFACE

June 1978 Revision (Cont.)

INSTRUCTIONS-3\* -12 -14 -15 -17 -19 -7 ASSEMBLER -9 -8 APPENDIX -14 -16 -29 -32 -34 -35

\*Non-significant typing error only

.....

Ed Miller Ft. Collins CPD June 1978

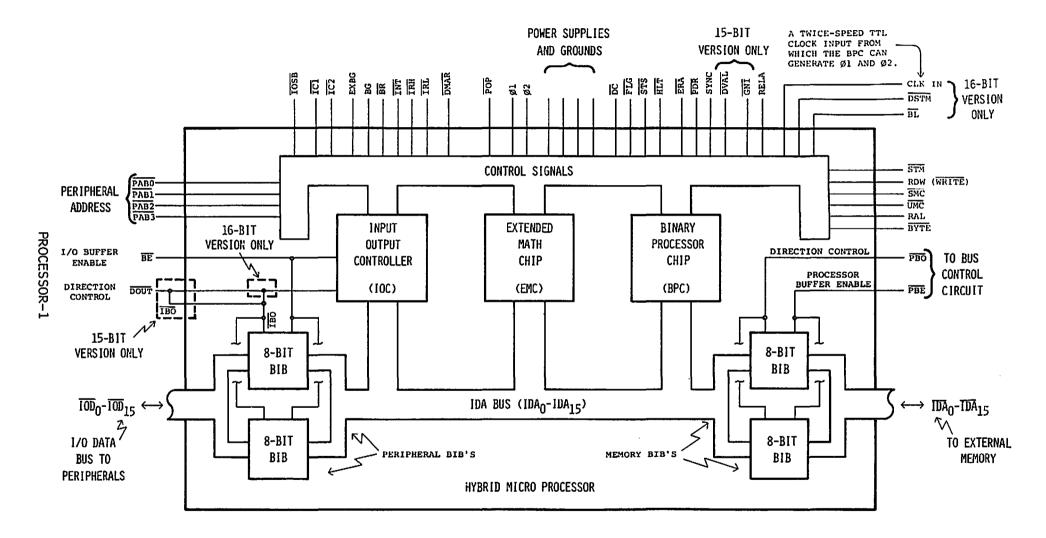

Figure P-1. Simplified Block Diagram of the Processor.

### GENERAL INFORMATION

The CPD Processor consists of seven integrated circuits mounted on a ceramic substrate. Of these, three are N-channel MOS LSI chips. The remaining four chips are entirely bi-polar and serve as buffers to connect the LSI circuitry of the other chips to circuitry external to the substrate. Because the processor is an assemblage of components mounted on a substrate, it is often referred to as the "hybrid", "hybrid micro-processor", or simply as the "processor".

Figure P-I is a simplified block diagram of the processor. The LSI chips are the Binary Processor Chip (BPC), Input-Output Controller (IOC), and the Extended Math Chip (EMC). All of the processing capability of the processor resides in those three chips; except for inversion the four Bi-Directional Interface Buffers (BIB's) are logically powerless. The three LSI chips communicate among themselves, and also with the outside world, via a collection of control signals and a I6-bit bus called the IDA Bus (IDA stands for Instruction/Data/Address).

The processor is available in two versions. One version uses 15-bit addressing for a maximum memory size of 32K words, and implements multilevel indirect addressing. The other version uses 16-bit addressing for a maximum memory size of 64K words, and implements a single level of indirect addressing. The 15-bit processor uses 15-bit versions of the BPC and IOC; the 16-bit processor uses 16-bit versions. The EMC is currently a 16-bit version that works in either processor; an obsolete 15-bit version of the EMC also exists but is not currently being produced.

The two versions of the processor are far more alike than they are different. Some new machine-instructions were added for the 16-bit IOC. However, they represent an alternate method of doing something (in light of the different way the 16th address bit is used) rather than a major extension of capability. Other than for size, both processors are alike in the general way they interface to memory. Their sets of machineinstructions are nearly identical; in fact, an assembler exists that can be used for both. The information in this book is generally applicable to both processors; information that applies to a particular version is labeled as such.

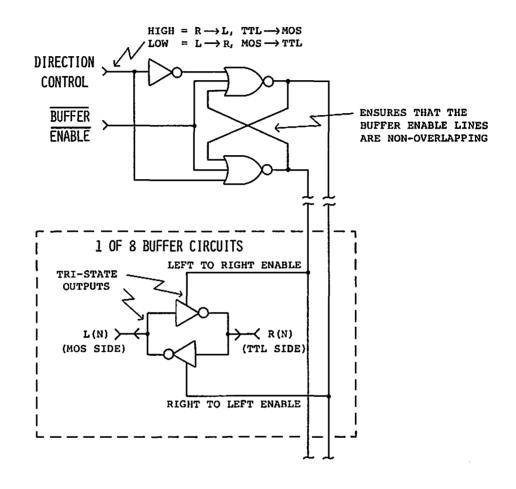

The IDA Bus is buffered as it leaves the hybrid, but the control signals are not. The BIB's are grouped together to buffer the IDA Bus in a way that allows it to perform two different functions. Each BIB can buffer eight bits of the IDA Bus. Two BIB's are grouped together to connect the IDA Bus to the (main and external) memory; those BIB's are called the Memory BIB's. The remaining two BIB's are grouped together to connect the IDA Bus to the IOD Bus. The IOD Bus (I/O Data Bus) is the data bus that serves peripheral devices. Accordingly, the BIB's connecting the IDA Bus with the IOD Bus are called the Peripheral BIB's. The Memory BIB's are enabled by a circuit (external to the hybrid) which detects memory traffic on the IDA Bus. The Peripheral BIB's are controlled by the IOC as the various types of input-output operations are performed.

### GENERAL INFORMATION (CONT.)

Figure P-2 illustrates the nature of the BIB's. Each bit of the IDA Bus is buffered in both directions by tri-state buffers controlled by nonoverlapping buffer enable signals.

Figure P-2. Nature of the BIB's.

#### MEMORY CONVENTIONS

The term "memory" will be used to refer to any addressable memory location, regardless of whether that location is physically within the hybrid micro-processor, or external to it. The term "external memory" refers to memory that is not physically within the hybrid. The term "register" refers to various storage locations within the hybrid micro-processor itself. These registers range in size from 1 to 16 bits. Most of the registers are 16 bit registers. The term "addressable register" refers to a register within one of the LSI chips that responds as memory when addressed. Most registers are not addressable. In most of the discussions that follow the context clarifies whether or not a register is addressable so that it is deemed unnecessary to explicitly differentiate between addressable and nonaddressable registers. Those registers that are addressable are included in the meaning of the term "memory". The term "memory cycle" refers to a read or write operation involving a memory location.

### MEMORY CONVENTIONS (CONT.)

The first 32 memory addresses do not refer to external memory. Instead, these addresses  $(0-37_8)$  are reserved to designate addressable registers within the micro-processor. Table P-I lists the addressable registers within the micro-processor.

| 16 or 16)<br>or 16) |

|---------------------|

|                     |

|                     |

|                     |

| or 16)              |

|                     |

|                     |

|                     |

|                     |

|                     |

|                     |

| of 16)              |

|                     |

| Add. Reg.           |

| er (16)             |

|                     |

|                     |

|                     |

|                     |

|                     |

|                     |

|                     |

|                     |

| •                   |

Table P-1. Addressable Registers.

Not available for general use. Part of processes internal to a chip. It is best to pretend that these registers co not exist.

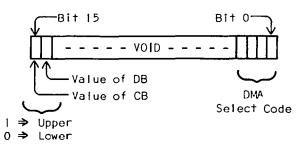

<sup>+</sup> Read register 13<sub>8</sub> produces:

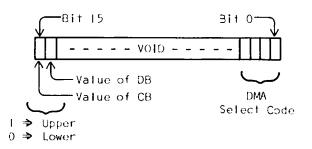

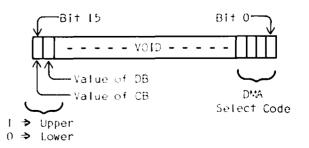

CB and DB are actually discrete registers, and while they can only be read by reading R13, storinging into R13 will not alter their values. Use the CBL, CBU, DBL and DBU machine instructions for that purpose. CB and DB exist in the 16-bit version only.

#### MEMORY CONVENTIONS (CONT.)

Most of the traffic on the IDA Bus has to do with memory. Both address of memory locations, and the contents of those locations (data and machineinstructions) are transmitted over the same 16-bit bi-directional bus (the IDA Bus). Further, memory can be physically distributed along the Bus. Each of the three chips in the processor contains registers which are addressable, and addressable memory also exists external to the processor.

#### MEMORY CYCLES

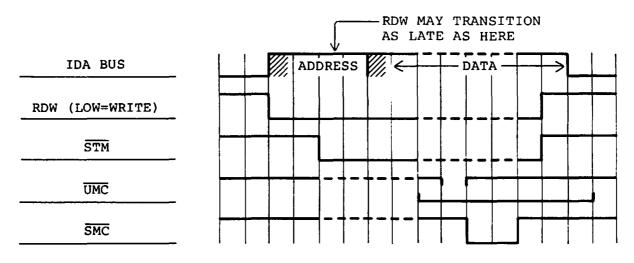

A memory cycle involves some control lines as well as the IDA Bus. Start Memory (STM) is used to initiate a memory cycle by identifying the contents of the IDA Bus as an address. Memory Complete\* is used to identify the conclusion of a memory cycle. A line called Read/Write (RDW) specifies the direction of data movement; out of or into memory, respectively.

Each element in the system decodes the addresses for which it contains addressable memory. To initiate a memory cycle, an element of the processor puts the address of the desired location on the IDA Bus, sets the Read/Write line, and gives Start Memory. Then, elsewhere in the system the address is decoded and recognized, and that agency begins to function as memory. It is part of the system definition that whatever is on the IDA Bus when a Start Memory is given is an address of a memory (or register) location.

Here is a complete description of the entire process: An originator originates a memory cycle by putting the address on the IDA Bus, setting the Read/Write line, and giving a Start Memory. The respondent identifies itself as containing the object location of the memory cycle, and handles the data. If the originator is a sender (write) it puts and holds the data on the IDA Bus until the respondent acknowledges receipt by sending Memory Complete. If the originator is a receiver (read) the respondent obtains and puts the data onto the IDA Bus and then sends Memory Complete. The originator then has one clock time to capture the data; no additional acknowledgement is involved.

DATA IS CAPTURED

Figures P-3 and P-4 illustrate typical memory cycles.

IDA BUS

ADDRESS

RDW (HIGH=READ)

STM

UMC

SMC

Figure P-3. Simplified Read Memory Cycle.

There is no single signal called "Memory Complete". Instead there is Unsynchronized Memory Complete (UMC) and Synchronized Memory Complete (SMC). They mean the same thing for our present purposes, and their exact differences need not concern us here.

#### MEMORY CONVENTIONS

MEMORY CYCLES (CONT.)

Figure P-4. Simplified Write Memory Cycle.

#### THE BYTE LINE

The IOC generates a signal called BYTE that affects memory operation. BYTE signifies that a memory cycle is to involve a left-half or right-half of a word rather than the entire word. The IOC is the only entity that is allowed to generate BYTE, which is used during the execution of certain IOC machine-instructions (the place and withdraw byte instructions).

During a read memory cycle the memory can supply the entire word regardless of the status of the BYTE line; the IOC will automatically extract the desired byte from the supplied word. However, during a write memory cycle the memory must merge the transmitted byte with the existing other half of the word (which is already in memory). The transmitted byte will be sent as the left-half or right-half of a word (that is, on the upper eight bits or on the lower eight bits of the IDA Bus), as is appropriate for whichever byte it is supposed to be.

The 15-bit and 16-bit versions of the IOC differ in the way they indicate which half of the word is being sent to memory. (These indicators are actually in force for both read and write memory cycles, but may be entirely ignored during read memory cycles.) For 15-bit IOC's the left-right information appears in the left-most bit of the address word; only 15 bits are needed for addressing the word anyway. In this scheme a one in bit 15 indicates a left-half. For 16-bit IOC's the entire 16 bits is required for addressing, and a separate signal ( $\overline{BL}$  - Byte Left Not) is supplied to the memory. When bit 15 is used to designate the byte, bit 15 must be latched by the memory at the time the address is sent, as it is effectively sent as part of the address. On the other hand,  $\overline{BL}$  is a steady state signal valid for the duration of the memory cycle.

When acting as memory themselves, none of the BPC, IOC, or EMC utilize the BYTE line during a write memory cycle. This means that a byte can be

### MEMORY CONVENTIONS

THE BYTE LINE (CONT.)

read from a register in any of those chips, but that only entire words can be written to those registers.

RAL LINE

Among several service functions performed by the BPC for the IOC and EMC is the generation of a signal called RAL (Register Access Line) whenever an address on the IDA Bus is within the range reserved for register designation. RAL functions to prevent the external memory from responding to any memory cycle having such an address.

The BPC has two main functions. The first is to fetch machine-instructions from memory for itself, the IOC, and for the EMC. A fetched instruction may pertain to one or more of those chips. A chip that is not associated with a fetched instruction simply ignores that instruction. The second main function of the BPC is to execute the 56 instructions in its own repertoire. These instructions include general purpose register and memory reference instructions, branching instructions, bit manipulation instructions, and some binary arithmetic instructions. Most of the BPC's instructions involve one of the two accumulator registers: A and B.

There are four addressable registers within the BPC and they have the following functions: The A and B registers are used as accumulator registers for arithmetic operations, and also as source or destination locations for most BPC machine-instructions referencing memory. The R register is an indirect pointer into an area of read/write memory designated to store return addresses associated with nests of subroutines encountered during program execution. The P register contains the program counter; its value is the address of the memory location from which the next machine-instruction will be fetched.

Upon the completion of each instruction the program counter (P register) has been incremented by one, except for the instructions JMP, JSM, RET, and SKIP instructions whose SKIP condition has been met. For those instructions the value of P will depend on the activity of the particular instruction.

#### INDIRECT ADDRESSING

Indirect addressing is a technique in which an instruction that references memory treats the first one or more references as intermediate steps to referencing the final destination. Each intermediate reference yields the address of the next location to be referenced. When an intermediate location can point to yet another intermediate location, such addressing is termed *multi-level* indirect addressing. Indirect addressing is not a property of the memory; it is property of the chips that use the memory. Any chip that is to implement instructions employing indirect addressing must contain a special gear works for that purpose.

#### MULTI-LEVEL INDIRECT ADDRESSING

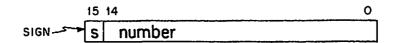

BPC's that can address 32K of memory can perform multi-level indirect addressing. Memory addresses appear on the IDA Bus as 15-bit patterns during the address portion of a memory cycle. The BPC machine-instructions that reference memory are capable of multi-level indirect addressing. The initial indirect indicator is a particular bit in the machine-instruction itself (the most-significant, or left-most, bit: Bit 15). The internal operation of the BPC is so arranged that if the memory content of that address also has a one in bit 15, the other bits of the contents are themselves taken as an indirect address. The process of accessing via an indirect address continues

#### INDIRECT ADDRESSING

MULTI-LEVEL INDIRECT ADDRESSING (CONT.)

until a location is accessed which does not have a one in bit 15. At that time the content of that location is taken as the final address; that is, it is taken to be the address of the desired location and the memory cycle is completed when that final desired location is accessed.

#### SINGLE LEVEL INDIRECT ADDRESSING

BPC's that can address 64K of memory are not capable of multi-level indirect addressing; they can perform only one level of indirect addressing. As before, bit 15 of the particular memory reference instruction will be set. The contents of the referenced location will be read, and its entire 16-bit contents treated as the address of the final destination to be read from or written into. This is because addressing 64K of memory requires the use of bit 15 as an actual address bit; thus bit 15 is not available to indicate that the remaining bits are an indirect address. The format of the memory reference instructions themselves has not changed; bit 15 of those instructions still indicates an initial indirect reference, but no further indirect references can be indicated as memory is read. Hence only one level of indirect addressing is possible.

#### MEMORY REFERENCE INSTRUCTIONS & PAGE ADDRESSING

Machine-instructions fetched from memory are 16-bit instructions. Some of those bits represent the particular type to which the particular instruction belongs. Other bits differentiate the instruction from others of the same type. If a BPC machine-instruction is one that involves reading from, storing into, or otherwise manipulating the contents of a memory location, it is said to be a memory reference instruction. Load into A (LDA), Store from B (STB), and Jump (JMP) are examples. There are 14 memory reference instructions and they each contain bits to represent the address of the location that is to be referenced by the instruction. Only ten bits are devoted to indicating the address to be referenced. Those ten bits represent one of 102410 locations on either the base page or the current page of memory. An additional bit in the machine-instruction indicates which. The base page is always a particular, non-changing, range of addresses, exactly 102416 in number. A memory reference machine-instruction fetched from any location in memory (i.e., from any value of the program counter) may directly reference (that is, need not use indirect addressing) any location on the base page.

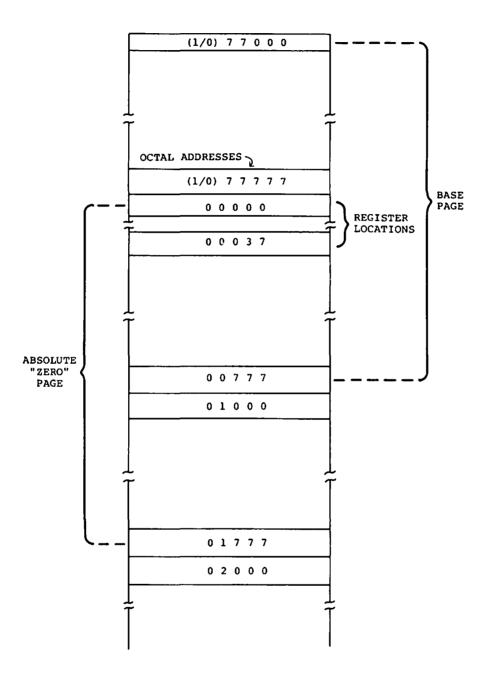

For 15-bit addressing the base page is addresses  $00000_8-00777_8$  and  $77000_8-77777_8$ . For 16-bit addressing the base page addresses are  $000000_8-000777_8$  and  $177000_8-17777_8$ . Figure P-5 depicts the base page.

There are two types of current pages. Each type is also  $1024_{10}$  consecutive words in length. Except for base page references, a memory reference machine-instruction can directly reference only locations that are on the same current page as it; that is, locations that are within the page containing the current value of the

MEMORY REFERENCE INSTRUCTIONS & PAGE ADDRESSING (CONT.)

Figure P-5. Base Page Description.

program counter (P).\* Thus the value of P determines the particular collection of addresses that are the current page at any given time. This is done in one of two distinct ways, and the particular way is determined by whether the signal called RELA is grounded or not. If RELA is ungrounded, the BPC is said to address memory in the "relative" mode. If RELA is grounded it is said to operate in the "absolute" mode.

\* Off-page references that are not base page references must be made using indirect addressing.

### MEMORY REFERENCE INSTRUCTIONS & PAGE ADDRESSING (CONT.)

During the execution of each memory reference machine-instruction the BPC forms a full 15-bit or 16-bit address based on the ten bits of address contained within the instruction. How the supplied ten bits are manipulated before becoming part of the actual address, and how the remaining five or six bits are supplied, depends upon whether the instruction calls for a base page reference or not, and upon whether the addressing mode is relative or absolute. The differences are determined primarily by the two different definitions of the current page; one for each mode of addressing. Base page addressing is the same in either mode.

#### ABSOLUTE ADDRESSING

In the absolute mode of addressing the memory address space is divided into a base page and 32 or 64 possible current pages. The possible current pages are the consecutive  $1024_{10}$  word groups beginning with  $00000_8$ . The possible current pages can be numbered, 0 through  $3l_{10}$ ; or 0 through  $63_{10}$ . Thus the "zero page" is addresses  $00000_8-0177_8$ . Note that the base page is not the same as the zero page; the base page overlaps pages zero and 31 for 32K machines, and overlaps pages zero and 63 for 64K machines.

#### RELATIVE ADDRESSING

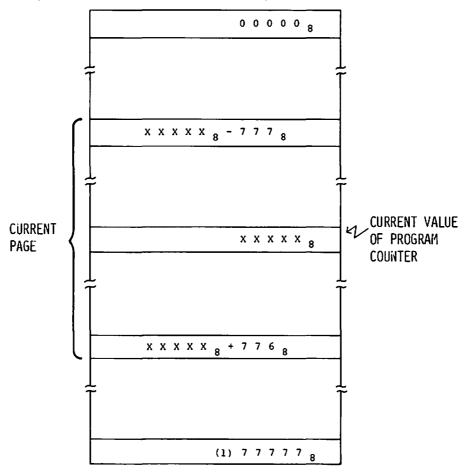

In relative addressing there are as many possible current pages as there are values of the program counter. In the relative addressing mode a current page is the  $5|2_{10}$  consecutive locations prior (that is, having lower valued addresses) to the current location (value of P), and the  $5|1_{10}$  consecutive locations following the current location.

#### BASE PAGE ADDRESSING

All memory reference machine-instructions include a 10-bit field that specifies the location referenced by the instruction. What goes in this field is a displacement from some reference location, as an actual complete address has too many bits in it to fit in the instruction. This 10-bit field is bit 0 through bit 9. Bit 10 tells whether the referenced location is on the base page, or someplace else. Bit 10 is called the B/C bit, as it alone is used to indicate base page references. Bit 10 will be a zero if the reference is to the base page, and a one if otherwise.

If bit 10 is zero for a memory reference instruction (base page reference), the 10-bit field is sufficient to indicate completely which of the 1024 locations on the base page is to be referenced. There are two way to describe the rule that is the correspondence between bit patterns in the 10-bit field, and the locations that are the base page: (1) the least significant 10 bits of the "real address" (i.e., (1)77,000<sub>8</sub> through 777<sub>8</sub>) are put into the 10-bit field, bit for bit; (2) as a displacement between  $+777_8$  and  $-1000_8$  about 0, with bit 9 being the sign.

The 32 register addresses are considered to be a part of the base page. Base page addressing is always done in the manner indicated above, regardless of whether relative or non-relative addressing is employed by the BPC.

# MEMORY REFERENCE INSTRUCTIONS & PAGE ADDRESSING (CONT.)

CURRENT PAGE ADDRESSING

Current page addressing refers to memory reference instructions which reference a location which is not on the base page. The same IO-bit field of the machine-instruction is involved, but the B/C bit is a one (C). Now, since there are more than IO24 locations that are not the base page, the IO-bit field by itself, is not enough to completely specify the exact location involved. An assumption has to be made about which page of the memory is involved.

For absolute addressing the assumption is that the most significant 5 (or 6) bits of the P register correspond to the page, and the last 10 bits of the machine-instruction determine the location within that page. This assumption requires that there will be no page changes except by certain ways. This means that once the program counter is set to a particular location the top 5 (or 6) bits need not be changed for any addressing on that (which ever it is) page. When the assembler assembles a memory reference instruction, it computes the least 10 bits and puts them in the instruction. When the BPC executes the instruction it concatenates its own top 5 (or 6) bits of P with the address represented by the least 10 bits of the instruction; that produces the complete address for the location referenced by the instruction.

However, the least 10 bits produces by the assembler and placed in the machine-instruction do not correspond exactly to the "real" memory address that is referenced. Bit 9 (the 10th bit) is complemented before it is placed in the address field of the instruction. The other 9 bits are left unchanged. This induces a one-half page offset whose effect is to make current page addressing relative to the middle of the page. Table P-2 depicts current page absolute addressing. This similarity between current page and base page addressing is deliberate, and results in simplified hardware in the BPC.

Page changes can be accomplished in two ways: incrementing or decrementing the program counter in the BPC, and through indirect addressing. An example of incrementing to a new page is a continuous block of code that spans two adjacent pages. A page change through an increment or decrement can occur in the same general way due to skip instructions.

Indirect addressing allows page changes because the object of an indirect reference is always taken as a full I5-bit or I6-bit address. Indirect addressing is the method used for an instruction on a given page to either reference a memory location on another page (LDA, STA, etc.), or, to jump (JMP or JSM) to a location on another page.

Instructions on any page can make references to any location on the base page without using indirect addressing. This is because the B/C bit designates whether the IO-bit field in the instruction refers to the base page or to the current page. If B/C is a zero (B), the BPC automatically assumes the upper 5 or 6 bits are all zeros, and thus the IO-bit field refers to the base page. If B/C is a one (C), the top 5 or 6 bits are taken for what they are, and the current page is referenced (whichever it is).

### MEMORY REFERENCE INSTRUCTIONS & PAGE ADDRESSING

CURRENT PAGE ADDRESSING (CONT.)

| LEAST 10 BITS<br>OF ASSEMBLER | "REAL OCTAL ADDRESS" |               |  |  |  |  |  |

|-------------------------------|----------------------|---------------|--|--|--|--|--|

| OUTPUT (octal)                | TOP 5 (6) BITS OF P  | LOWER 10 BITS |  |  |  |  |  |

| 1000                          | X X START OF PAGE    | 0 0 0 0       |  |  |  |  |  |

| 1001                          | хх                   | 0001          |  |  |  |  |  |

| 1002                          | хх                   | 0002          |  |  |  |  |  |

|                               |                      | •             |  |  |  |  |  |

|                               |                      | •             |  |  |  |  |  |

|                               | •                    | •             |  |  |  |  |  |

| 1777                          |                      | 0777          |  |  |  |  |  |

| 0 0 0 0                       |                      | 1000          |  |  |  |  |  |

| 0001                          | •                    | 1001          |  |  |  |  |  |

| 0002                          |                      | 1002          |  |  |  |  |  |

|                               |                      |               |  |  |  |  |  |

|                               |                      | •             |  |  |  |  |  |

|                               |                      |               |  |  |  |  |  |

| 0777                          | X X END OF PAGE      | 1777          |  |  |  |  |  |

Table P-2. Current Page Absolute Addressing for Memory Reference Instructions.

It is the responsibility of the assembler to control the B/C bit at the time the machine-instruction is assembled. It does this easily enough by determining if the address of the operand (or its "value") of an instruction is in the range of  $(1)77,000_8$  through 0, or, 0 through  $777_8$ . If it is, then it is a base page reference and B/C is made a zero for that instruction.

Relative addressing does not require the concept of a fixed page, as in absolute addressing. The word "page" can still be used, but requires a new definition:

#### MEMORY REFERENCE INSTRUCTIONS & PAGE ADDRESSING

CURRENT PAGE ADDRESSING (CONT.)

In relative addressing, a page is  $1024_{10}$  consecutive locations, having  $512_{10}$  locations prior to the current location, and  $511_{10}$  locations following the current location.

As before, direct addressing is possible anywhere within the page. But off-page references (other than to the base page) require indirect addressing, which, once started, works as before - it is not relative, but produces a full 15-bit or 16-bit absolute address.

Figure P-6 illustrates relative addressing. Relative current page addressing is done much the same way as base page addressing. The IO-bit field in the memory reference instructions is encoded with a displacement relative to the current location.

Bit 9 (the 10th, and most significant bit of the 10) is a sign bit. If it is a zero, then the displacement is positive, and bits 0-8 are taken at face value. If bit 9 is a one, the displacement is negative. Bits 0-8 have been complemented and then incremented (two's complement) before being placed in the field. To get the absolute value of the displacement, simply complement them again, and increment, ignoring bit 9.

Figure P-6. Relative Addressing.

#### SUBROUTINES

The processor implements subroutines in the following way. The JSM memory reference instruction is used to cause a jump (change in value of P) to the start of the subroutine. Also as part of the JSM, the BPC saves the value of P that corresponds to the word of programming that is the JSM. That value is saved in a section of read/write memory called the *return stack*.

The return stack is a group of contiguous locations, whose starting address less one was initially stored in the R register (in the BPC). Thus R is an indirect pointer. What a JSM does is to increment the value in R and then use that new value as the address at which to store the value of P that is to be saved. Once this activity is complete, P is actually set to the address of the first word of the subroutine and its execution commences.

A subroutine is terminated with a RET n instruction. The essence of this instruction is to read the location that R points at, set P to that value plus n, and then decrement R. The garden variety return is a RET I. Different values of n permit different returns corresponding to error or other special conditions.

Subroutines can be nested as deep as the size of the return stack will allow. The subroutines themselves can be either in ROM or read/write memory.

#### FLAGS

The BPC is capable of branching based on the condition of each of four signals externally supplied to the chip. These signals are Decimal Carry (DC), Hait (HLT), Fiag (FLG), and Status (STS). The EMC acts as a source for Decimal Carry, which represents an overflow condition during certain arithmetic operations performed by the EMC. The other signals can be defined in any way that is suitable for the system in which the processor is operating; they are not used for inter-chip communication within the processor.

#### BUS REQUESTS AND INTERRUPTS

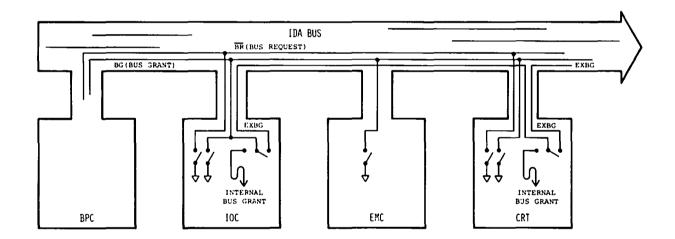

Two protocols that do involve inter-chip communication are those of Bus Request and Interrupt. Bus Request  $(\overline{BR})$  provides a way for a chip in the processor, or even a device external to the processor, to request unfettered use of the IDA Bus. A signal called Bus Grant (BG) is generated if all chips and any other interested entities agree to do so. The requesting agency can use the IDA Bus for whatever purpose it wants, (typically to do memory cycles). During the time that Bus Grant is in effect all chips suspend their activity. Bus Grants can be given even in the middle of the execution of an instruction. Because of this, the chips do not grant bus requests indiscriminately. Furthermore, a Bus Grant not requested by the IOC is used by the IOC to create *Extended Bus Grant* (EXBG), which is routed from chip to chip in a definite order; chips or other entities not at the top of the chain can exercise the right not to pass along the signal. This

### BUS REQUESTS AND INTERRUPTS (CONT.)

allows a Bus Request from the IOC to have a higher priority than any entity further down the chain. Even if both are requesting the bus, the IOC can "steal" EXBG by not passing it along. Further down the chain from the IOC, BG serves to indicate only that the bus is being granted to somebody; a paticular requesting device must wait until it sees EXBG before it can use the bus.

The Bus Request protocol includes these additional considerations: Any entity on the bus may ground BG as long as BG is not already being given. This allows any entity anywhere in the chain to protect its own access to the bus against all agencies. Further, the BPC itself refuses to issue a BG as long as any memory cycle is in progress.

Figure P-7 illustrates the usage of the Bus Request, Bus Grant, and Extended Bus Grant protocol.

Figure P-7. Bus Request Protocol.

Following is a description of how the inter-chip mechanism for interrupt acts. During an instruction fetch a line called Interrupt ( $\overline{INT}$ ) can signal that the IOC has agreed to allow an interrupt requested by a peripheral. The management of this decision is complicated and its description belongs with a description of the IOC. However, once the decision is made, the IOC signals the BPC with  $\overline{INT}$ . This has to occur during a certain period of time ending with the end of the instruction fetch. (A signal called SYNC indentifies the instruction fetch.)

What the chips in the system must do when an interrupt occurs is to abort the execution of the instruction just fetched (it will be fetched again, later). Then the BPC executes the instruction JSM  $IO_8$  Indirect.

### BUS REQUESTS AND INTERRUPTS (CONT.)

Register address  $10_8$  is located in the IOC, and is the Interrupt Vector register (IV). That register is a pointer into a stack of addresses of the starting locations for the various interrupt service routines. These routines handle the traffic needed by the interrupting peripheral. A special mechanism in the IOC sets the bottom four bits of IV to correspond to the particular peripheral that requested the interrupt. Thus IV points to different service routines, according to which peripheral interrupted.

In any event, the JSM  $IO_8$  Indirect causes the value of P for the aborted instruction to be saved on the return stack. A RET 0 at the end of the service routine results in that very instruction being fetched over again, at the conclusion of the service routine.

The IOC has two main functions. One is to manage the transfer of information between the processor and external peripheral devices. This is done by providing capabilities classified as Standard I/O, Interrupt and Direct Memory Access (DMA). The second main function is to provide machine-instructions allowing software management of two stacks in Read/Write Memory.

To implement these tasks the IOC contains a number of addressable registers. The function of each will be discussed as the various topics of IOC operation are covered.

#### GENERAL INFORMATION ABOUT 1/0

The IOC allows up to 16 peripheral devices to be present at one time. Each peripheral device is connected to the IOD Bus, Peripheral Address Bus, and the various control signals necessary for that particular device's operation. Individual I/O operations (exchanges of single words) occur between the processor and one peripheral at a time, although Interrupt and DMA modes of operation can cause automatic interleaving of individual operations. A select code transmitted by the Peripheral Address Bus (PABO-PAB3) indentifies which of the 16 devices is the object of an individual I/O operation.

In addition, the peripheral interface is the source of the Flag and Status bits for the BPC instructions SFS, SFC, SSS, and SSC. Since there can be many interfaces, but only one each of Flag and Status, only the interface addressed by the select code is allowed to ground these lines. Their logic is such that if the addressed peripheral is not present on the I/O Bus, Status and Flag are logically false.

ICI and IC2 are two control lines that are sent to each peripheral interface by the IOC. The state of these two lines during the non-DMA transfer of information can be decoded to mean something by the interface. Just what 'something' will be is subject to agreement between the firmware designer and the interface designer - it can be anything they want, and might not be the same for different interfaces. These two lines act as a four position mode switch on the interface, controlled by the IOC during an I/O operation.

### I/O BUS CYCLES

There are no specific machine-instructions for which the IOC responds by doing I/O operations. That is, there is no "output instruction", and no "input instruction". The real workhorse of I/O is a thing called an *I/O Bus Cycle*. An I/O Bus Cycle is an exchange of a word between the IDA Bus and the IOD Bus, via the Peripheral BIB's. The exchange is not of the handshake variety. I/O Bus Cycles are termed read or write I/O Bus Cycles, depending upon whether information is being read from, or written to, a peripheral.

Each of the three modes of I/O operation (Standard I/O, Interrupt, and

### I/O BUS CYCLES (CONT.)

DMA) utilize I/O Bus Cycles. After we have examined how an I/O Bus Cycle works, the explanation of the various modes of I/O will amount to showing different ways to initiate I/O Bus Cycles.

For example, during Standard I/O operation, an I/O Bus Cycle is initiated by a reference to one of R4 through R7 in the IOC. One way that can be done is with a BPC memory reference instruction; for instance, STA R4 (for a write cycle), or LDA R4 (for a read cycle).

The IOC includes a register called the Peripheral Address Register (PA) which is used in establishing the select code surrently in use. The peripheral address is established by storing the desired select code into PA with an ordinary memory reference instruction. The bottom four bits of this register are brought out of the IOC as PABO through PAB3. Each peripheral interface decodes PABO-PAB3 and thus determines if it is the addressed interface.

Consider a write 1/0 Bus Cycle as illustrated in Figure P-8. This is initiated with a reference to one of R4-R7. The IOC sees this as an address between 4 and 7 on the IDA Bus while STM is low. The Read line is low to denote a write operation. The IOC enables the Peripheral BIB's and specifies the direction. It also sets the control lines ICI and IC2, according to which of R4 through R7 was referenced. Meanwhile, the BPC has put the word that is to be written onto the IDA Bus. Because both the Memory BIB's and Peripheral BIB's are enabled, that word is felt at all peripheral interfaces. The interface that is addressed uses DOUT to understand it's to read something, and uses IOSB as a strobe for doing it. After IOSB is given, the IOC gives [Synchronized] Memory Complete (SMC) and the process terminates. The BPC has written a word to the interface whose select code matched the number in the PA register.

A read I/O Bus Cycle is similar, as shown in Figure P-9. Here the BPC expects to receive a word from the addressed peripheral interface. Read, DOUT and BE are different because the data is now moving in the other direction.

In either case, the critical control signals  $\overline{SMC}$  and  $\overline{IOSB}$  are given by the IOC, and their timing is fixed. There can be no delays due to something's not being ready, nor is there any handshake between the interface and the IOC.

It is the responsibility of the firmware not to initiate an I/O Bus cycle involving a device that is not ready. To do so will result in lost data, and there will be no warning that this has happened.

# I/O BUS CYCLES (CONT.)

THIS I/O BUS CYCLE WAS INITIATED BY ANY READ-FROM-MEMORY INSTRUCTION 1.

WHICH REFERENCED ONE OF R4 THRU R7. 2. CONTROL INFORMATION IS VALID ON BOTH EDGES OF IOSB. 3. DATA FROM THE INTERFACE IS LATCHED INTO THE BPC DURING T4.

Figure P-9. A Read I/O Bus Cycle.

#### STANDARD I/O

۰.

Standard (programmed) 1/0 involves three activities:

- 1) Setting the peripheral address

- 2) Investigating the status of the peripheral

- 3) Initiating an I/O Bus Cycle

#### ADDRESSING THE PERIPHERAL

A peripheral is selected as the addressed peripheral by storing its octal select code into a 4-bit register called PA (Peripheral Address - address II<sub>B</sub>). Only the four least significant bits are used to represent the select code.

#### CHECKING STATUS

The addressed peripheral is allowed to control the Flag and Status lines. (That is, it is up to the interface to not ground Flag or Status unless it is the addressed interface.) These lines have an electrical logic such that when floating they appear false (clear, or not set) for SFS, SFC, SSS, and SSC.

The basic idea (and it can be done in a variety of ways) is to use sufficient checks of Flag and Status before and amongst the I/O Bus Cycles such that there is no possibility of initiating an I/O Bus Cycle to a device that is not ready to handle it. One way to do this with Standard I/O is to precede every I/O Bus Cycle with the appropriate checks.

#### INITIATING I/O BUS CYCLES

An I/O Bus Cycle occurs once each time one of R4 - R7  $(4_8-7_8)$  is accessed as memory. An instruction that "puts" something into R4-R7 results in an output (write) I/O Bus Cycle. Conversely, an instruction that "gets" something from R4-R7 results in an input (read) I/O Bus Cycle. However, there are no R4 through R7. The use of address 4-7 is just a device to get an I/O Bus Cycle started; they do not correspond to actual physical registers in the IOC.

Consider the following hypothetical case, (specially invented for purposes of illustration) - Suppose we are to write a driver for a smarter than average paper tape punch: Upon a single command it can output 50 feedframes for leader. The routine is to have two entry points; one for outputting a single word of data, and one for causing the leader. Also, the punch sets the status line if it gets low on tape. Prior to calling our driver, the main program puts the word to be outputted into DATA, and the select code of the punch in PUNSC.

| ۱.  | PUNCH | JSM | SETUP | SET SELECT CODE, CHECK AVAILABILITY     |

|-----|-------|-----|-------|-----------------------------------------|

| 2.  |       | LDA | DATA  | GET OUTPUT DATA WORD                    |

| 3.  |       | STA |       | OUTPUT THE DATA (ICI = 0, IC2 = 0)      |

| 4.  |       | RET | 1     | RETURN TO MAIN PROGRAM                  |

| 5.  | LEADR | JSM |       | SET SELECT CODE, CHECK AVAILABILITY     |

| б.  |       |     | R5    | OUTPUT LEADER ( $ C  = 1$ , $ C2 = 0$ ) |

| 7.  |       | RET | I     | RETURN TO MAIN PROGRAM                  |

| 8.  | SETUP | LDA |       | GET SELECT CODE                         |

| 9.  |       | STA | PA    | PUT IT INOT PERIPHERAL ADDRESS REG      |

| 10. |       | SFC | *     | WAIT IF PUNCH NOT AVAILABLE             |

### STANDARD I/O

INITIATING I/O BUS CYCLES (CONT.)

| 11.<br>12.<br>13. | BXCRS | SSS<br>RET<br>:<br>: | BXCRS<br>I | SKIP IF PUNCH OUT OF TAPE<br>OK, DO OUTPUT OPERATION<br>HANDLE THE OUT OF TAPE SITUATION |

|-------------------|-------|----------------------|------------|------------------------------------------------------------------------------------------|

| 14.               | PUNSC | NOP                  |            | TAPE PUNCH SELECT CODE                                                                   |

| 15.               | DATA  | NOP                  |            | OUTPUT DATA WORD                                                                         |

Lines I and 5 invoke lines 8 through 12. Lines 8 and 9 set the select code, and line 10 checks for presence and availability (both must be "yes", or, at the interface the Flag will be false). Line II checks for the out-of-tape condition; it is the responsibility of the punch-interface combination to set Status high when the tape supply is low and the punch is addressed by PA. The routine at BXCRS handles the out of tape condition.

Lines 2 and 3 punch a word of data onto the tape. Line 3 causes a "write" (output) I/O Bus Cycle. The contents of (in this case) A are written to the addressed peripheral. Because it is R4 that is referenced, ICI and IC2 are both zeros. The interface understands an output I/O Bus Cycle with IC1 and IC2 both zeros to be a command to punch the supplied word.

Line 6 gives the command to punch leader. Because it is a write operation referencing R5, an output I/O Bus Cycle is done with ICI = I and IC2 = 0. In this instance the contents of B is sent to the punch (we will assume that it is ignored, however). The interface understands an output I/O Bus Cycle with ICI = I and IC2 = 0 as the command to generate leader.

The 16-bit word transmitted from B need not be ignored. An even smarter punch might use it as the number of feed-frames to punch. A more general approach would be for the interface to recognize that ICI = I and IC2 = 0 signifies that the accompanying word is to be decoded to determine the instruction/control information. The possibilities are numerous.

#### THE ODDBALL POSSIBILITIES

By this time in your reading you no doubt instantly recognize LDB R4 as an input operation where a word is read from the addressed peripheral and placed into B. But what about the <u>other</u> memory reference instructions? What, for instance, does ADA R4 do, or a CPA R4, or an ISZ R4, or worse still, a LDB R4,I? Some of these things do not have a known practical use, but they each work in a logically straight-forward manner.

An ADA R4 will read a word of data from the addressed peripheral, and then add it to the contents of A, leaving the result in A.

A CPA R4 will read a word of data from the addressed peripheral, and then compare that with the existing contents of A. The BPC will skip the next instruction if the two are unequal.

#### STANDARD I/O

THE ODDBALL POSSIBILITIES (CONT.)

An ISZ R4 is an input/increment-and-skip/output instruction. It reads a word of data from the addressed peripheral and increments the resulting value. If the sum is zero, the next instruction is skipped. But in any case, the incremented value is written back to the same peripheral it came from. The interface sees a read I/O Bus Cycle followed a very short time later by a write I/O Bus Cycle.

An LDB R4,I does the obvious thing. A word of data is read from the addressed peripheral. Once the data is read it is treated exactly as if it had come from regular memory, and the action proceeds just as for any other Load B-indirect.

### THE INTERRUPT SYSTEM

The idea behind interrupt is that for certain kinds of peripheral activity, the processor can go about other business once the I/O activity is intiated, leaving the bulk of the I/O activity to an interrupt service routine. When the peripheral is ready to handle another ration of data (it might be a single byte or a whole string of words) it requests an interrupt. When the processor grants the interrupt, the program segment currently being executed is automatically suspended, and there is an automatic JSM to an interrupt service routine that corresponds to the device that interrupted. The service routine uses Standard I/O to accomplish its task. A RET 0,P terminates the activity of the service routine and causes resumption of the suspended program.

#### PRIORITY

The interrupt system allows even an interrupt service routine to be interrupted and is therefore a multi-level interrupt system, and it has a priority scheme to determine whether to grant or ignore an interrupt request.

The IOC allows two levels of interrupt, and has an accompanying two levels of priority. Priority is determined by select code; select codes  $0-7_8$  are the lower level (priority level I), and select codes  $10_8-17_8$  are the higher level (priority level 2). Level 2 devices have priority over level I devices; that is, a disc drive operating at level 2 could interrupt a plotter operating at level I, but not vice versa. Within a priority level all devices are of "equal" priority, and operation is of a first come-first served basis; a level I device cannot be interrupted by another level I device, but only by a level 2 device. However, priorities are not equal in the case of simultaneous requests by two or more devices on the same level. In such an instance the device with the higher numbered select code has priority. With no interrupt service routine in progress, any interrupt will be granted.

#### INTERRUPT POLLS

Devices request an interrupt by pulling on one of two interrupt request lines (IRL and IRH - one for each priority level). The IOC determines the requesting select code by means of an interrupt poll, to be described in the next paragraph. If the IOC grants the interrupt it saves the existing select

#### THE INTERRUPT SYSTEM

#### INTERRUPT POLLS (CONT.)

code located in PA, puts the interrupting select code in PA, and does a JSM-Indirect through an interrupt table to get to the interrupt service routine.

An interrupt poll is a special I/O Bus Cycle to determine which interface(s) is (are) requesting an interrupt. An interrupt poll is restricted to one level of priority at a time, and is done only when the IOC is prepared to grant an interrupt for that level.

The interfaces distinguish an Interrupt Poll Bus Cycle from an ordinary <u>1/0</u> Bus Cycle through the INT line being low. Also, during this Bus Cycle PAB3 specifies which priority level the poll is for. An interface that is requesting an interrupt on the level being polled responds by grounding the nth 1/0 Data line of the 1/0 Bus, where n equals the device's select code module eight. If more than one device is requesting an interrupt, the one with the higher select code will have priority.

The IOC has a three-deep first-in last-out hardware stack. The top of the stack is the Peripheral Address register (PA-II<sub>8</sub>). The stack is deep enough to hold the select code in use prior to any interrupts, plus the select codes for two levels of interrupt. When an interrupt is granted, the IOC automatically pushes the select code of the interrupting device (as determined by the interrupt poll) onto the stack. Thus the previous select code-in-use is saved, and the new select code-in-use becomes the one of the interrupting device.

#### INTERRUPT TABLE

It is the responsibility of the firmware to maintain an interrupt table of 16 consecutive words, starting at some Read/Write Memory address whose four least-significant bits are zeros. The words in the interrupt table are set to the starting addresses of the various interrupt service routines in use for the 16 different select codes. When a peripheral is allowed to interrupt its select code is used to determine which interrupt service routine to JSM to. The interrupt service routine then handles the I/O operations needed by the interrupting device.

The firmware must also store the address of the first word of the interrupt table in the IV register (Interrupt Vector register, address 10<sub>8</sub>, located in the IOC). Those contents will merge with the select code to produce the address of the appropriate table entry. In either version of the processor a two-level indirect jump is used to arrive at the interrupt service routine. This happens automatically because the BPC generates a JSM IV, I as part of what it does during an interrupt. See Figures P-10 and P-10½. In 15-bit processors the indirect chain could be longer if desired. It cannot be shorter, however, due to a bug in the 15-bit IOC. Thus, the scheme depicted in Figure P-11 cannot be used. Even with 16-bit processors the scheme in Figure P-11 is not possible; in 16-bit processors the IOC forces the BPC to do two consecutive "first-level" indirect accesses, so that the effect is exactly that shown in Figure P-11, except that it doesn't matter then whether bit 15 of IV is set or not.

In I5-bit processors bit 15 of IV must be set. This does two things. First, it guarantees that the JSM  $10_8$ , I involves at least two levels of indirect. Second, it avoids a bug in the IOC. If bit 15 were a zero, the machine would attempt to implement the situation shown in Figure P-II. But

## THE INTERRUPT SYSTEM INTERRUPT TABLE (CONT.)

a race condition between the BPC and IOC is involved; its effect is to make bit 15 of IV look like a one even when it was a zero. The bug is somewhat dependent upon clock frequency. Reliable operation can be ensured only by using a two-level JSM through IV and the interrupt table.

In 16-bit processors the bug was fixed by permanently deciding the race condition in the IOC's favor. Nothing was done to the BPC; it still only understands one level of indirect addressing. But the IOC keeps the INT line grounded long enough to force the BPC to treat the contents of IV itself as an *indirect address*. This causes the BPC to read the next address (the one in the interrupt table) and treat *its* contents as the destination address, just as in multi-level indirect addressing. Thus, in the I6-bit processor the JSM through the interrupt table is always a two-level process as shown in Figure P-IO<sup>1</sup>/<sub>2</sub>, regardless of whether bit 15 of IV is set or not. Bit 15 of IV becomes simply an address bit, helping indicate where in memory the interrupt table is located.

After the interrupt poll is complete the select code of the interrupting device is made to be the four least-significant bits of the IV register. Thus IV now points at the word in the Interrupt Table which corresponds to the appropriate interrupt service routine. All that is needed now is a JSM IV, I,

#### PROCESSOR-25

# THE INTERRUPT SYSTEM

### INTERRUPT TABLE (CONT.)

and the interrupt service routine will be under way. This is accomplished by the BPC as summarized below.

### INTERRUPT PROCESS SUMMARY

The IOC inspects the interrupt requests IRL and IRH during the time sync is given. Based on the priority of the interrupt requests, and the priority of any interrupt in progress, the IOC decides whether or not to grant an interrupt. If it decides to allow an interrupt it immediately pulls INT to ground, and also begins an interrupt poll.

The grounding of  $\overline{INT}$  serves three purposes: It allows the interfaces to identify the forthcoming I/O Bus Cycle as an interrupt poll; it causes any other chips in the system, except the BPC, to abort their instruction decode process (which by this time is in progress) and return their idle states; and it causes the BPC to abort its instruction decode and execute a JSM  $IO_8$ , I instead.

The IOC uses the results of the interrupt poll to form the interrupt vector, which is then used by the JSM  $10_8$ , l. It also pushes the new select code onto the peripheral address stack, and puts itself into a configuration where all interrupt requests except those of higher priority will be ignored.

#### INTERRUPT SERVICE ROUTINES

The majority of the interrupt activity described so far is accomplished automatically by the hardware. All the firmware has been responsible for has been the IV register, the maintenance of the interrupt table, and (probably) the initiation of the particular peripheral operation involved (plotting a point, backspace, finding a file, etc.). Such operations (initated through a command given by simple programmed I/O) may involve many subsequent I/O Bus Cycles, done at odd time-intervals, and requested by the peripheral through an interrupt. It is the responsibility of the interrupt service routine to handle the I/O activity required by the peripheral without upsetting the routine that was interrupted.

It's difficult to say specific things about interrupt service routines in general; a lot depends upon the particulars of the host software system. In the next few pages we will examine some generalities relating to interrupt service routines, and sketch some examples. The result may leave some readers with an unsatisfied feeling; specific information is not available except as part of a description of a particular software system.

Our first observation is on the number of service routines. In general, there is not one service routine for each select code, or even for each peripheral. The usual case is collections of routines that perform related functions within the needs of a certain class of peripheral activity; each class of activity has it own collection.

## THE INTERRUPT SYSTEM

INTERRUPT SERVICE ROUTINES (CONT.)

For instance, it is unlikely that there would be a single interrupt service routine for a disc. On the customer's level there are many commands in the disc operating system. On the firmware level there are a series of routines that perform 'fundamental units' of activity, where each 'fundamental unit' involves some amount of I/O. Most commands in the user's disc operating system are made up of a series of these 'fundamental units' of activity. 'Fundamental units' of activity for the disc are things like: moving the head to a given track, reading a given sector from a track into such and such a buffer, and writing from such and such a buffer into a given sector. It is these types of activity that are most likely to have corresponding interrupt service routines.

Let's sketch a hypothetical example. Assume a fairly involved disc user's command is to be performed, one requiring reading the directory on the disc to determine the location of certain file on the disc, and then loading that file into memory. The kind of thing that happens here is to move the head to the start of the directory, read through the information in the directory sector by sector until the information about the desired file is found, moving the head to the file's location, reading its header, reading its first sector, etc.

Each service routine is smart enough to know which service routine follows it for the particular high level task at hand, and, if it has a choice based on the way events turn out (error conditions, etc.), it knows how to handle that, too. As each new step in the sequence requiring a different interrupt service routine is reached, the concluding routine changes the appropriate entry of the interrupt table to the starting address of the next service routine. In this way a versitile collection of interrupt service routines can serve many purposes.

As another example of this, consider a smart tape cassette, whose internal architecture was of variable length files composed of fixed length records. Such a cassette would resemble a cisc from the user's point of view, and it is possible that some of the disc interrupt service routines would work for the cassette, also.

And lastly, consider the case of formatted output to line printers, punches, teletypes and CRT's. Some of these devices may differ slightly in their mainline firmware drivers, but there is an excellent chance that they could use the same general purpose interrupt service routine(s).

So much for the chicken, now for the egg. At the beginning of the operation the mainline firmware sets up any initial conditions that are required (e.g., selecting a buffer and setting a word count or a value of a pointer). The mainline firmware also selects the interrupt service routine by modifying an entry in the interrupt table. It also gives the first I/O Bus Cycle, which wakes up the peripheral and gets things going. After this first I/O Bus Cycle the mainline firmware can go on about its other business.

### THE INTERRUPT SYSTEM

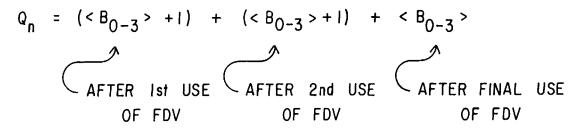

INTERRUPT SERVICE ROUTINE (CONT.)