# **HP 3000 Computer Systems**

# HP 30242 LAN/3000 Link Local Area Network Interface Controller (LANIC)

**Installation and Service Manual**

Update 1 (July 1986)

Manual Part No. 30242-90001

E0285

Printed in U.S.A

February 1985

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of Hewlett-Packard Company.

Copyright © 1985, 1986 by HEWLETT-PACKARD COMPANY

# PRINTING HISTORY

The Printing History below identifies the Edition of this Manual and any Updates that are included. Periodically, update packages are distributed which contain replacement pages to be merged into the manual, including an updated copy of this Printing History page. Also, the update may contain write-in instructions.

Each reprinting of this manual will incorporate all past updates; however, no new information will be added. Thus, the reprinted copy will be identical in content to prior printings of the same edition with the user-inserted update information. New editions of this manual will contain new information, as well as updates.

#### 30242-90001

| First Edition | ٠ |  |  |  |  |  |  |  |  |  |  |  |  | ] | ₹e | b | ru | aı  | ry | 19 | 8 | 5 |

|---------------|---|--|--|--|--|--|--|--|--|--|--|--|--|---|----|---|----|-----|----|----|---|---|

| Update 1      |   |  |  |  |  |  |  |  |  |  |  |  |  |   |    |   | J  | lu! | lv | 19 | 8 | 6 |

# SAFETY CONSIDERATIONS

GENERAL - This product and related documentation must be reviewed for familiarization with safety markings and instructions before operation.

#### SAFETY SYMBOLS

Instruction manual symbol: the product will be marked with this symbol when it is necessary for the user to refer to the instruction manual in order to protect the product against damage.

Indicates hazardous voltages.

Indicates earth (ground) terminal (sometimes used in manual to indicate circuit common connected to grounded chassis).

The WARNING sign denotes a hazard. It calls attention to a procedure, practice, or the like, which, if not correctly performed or adhered to, could result in injury. Do not proceed beyond a WARNING sign

until the indicated conditions are fully understood and met.

CAUTION

The CAUTION sign denotes a hazard. It calls attention to an operating procedure, practice, or the like, which, if not correctly performed or adhered to, could result in damage to or destruction of part or all of the product. Do not proceed beyond a CAUTION sign until the indicated conditions are fully understood and met.

## CAUTION

#### STATIC SENSITIVE DEVICES

When any two materials make contact, their surfaces are crushed on the atomic level and electrons pass back and forth between the objects. On separation, one surface comes away with excess electrons (negatively charged) while the other is electron deficient (positively charged). The level of charge that is developed depends on the type of material. Insulators can easily build up charges in excess of 20,000 volts. A person working at a bench or walking across a floor can build up a charge of many thousands of volts. The amount of static voltage developed depends on the rate of generation of the charge and the capacitance of the body holding the charge. If the discharge happens to go through a semiconductor device and the transient current pulse is not effectively diverted by protection circuitry, the resulting current flow through the device can raise the temperature of internal junctions to their melting points. MOS structures are also susceptible to dielectric damage due to high fields.

The resulting damage can range from complete destruction to latent degradation. Small geometry semiconductor devices are especially susceptible to damage by static discharge.

The LANIC card is shipped in a transparent static shielding bag. The card should be kept in this bag at all times until it is installed in the system. Save this bag for storing or transporting the card. When installing the card in the system, do not touch any components. Hold the card by its edges.

# WARNING

**SAFETY** GROUND - The EARTH computer on which this product is installed is a safety class I product and is provided with a protective earthing terminal. An uninterruptible safety ground must be provided from the main source to the product input wiring terminals, power cord. or supplied power cord set. Whenever it is likely that the protection has been impaired, or before the power cord is removed from the wall receptacle, the AUI cable connector must be removed from the junction panel and insulated from exposed conductive surfaces.

# WARNING

At infrequent intervals, exposed metal surfaces of the AUI cable may be subject to transient hazardous voltages due to strong electrical disturbances (such as lightning or disturbances in the electrical utilities power grid) in the area surrounding the network to which this product is connected. These surfaces should be handled with caution when the AUI cable is not connected to a properly grounded HP 3000 Computer System.

#### SER VICING

# WARNING

Any servicing, adjustment, maintenance, or repair of assemblies within the HP 3000 cabinet must be performed only by qualified personnel.

## WARNING

This product is not designed for attachment to a network serving an area which contains multiple unconnected power system safety grounds. Before installing this product, verify that all of the power system safety grounds are securely interconnected in the area served by the local network.

# WARNING

Do not connect this product to an ungrounded network coaxial cable.

# **CONTENTS**

| Section 1 GENERAL INFORMATION        |                   |

|--------------------------------------|-------------------|

| General Description                  | 1-1               |

| Equipment Supplied                   | . 1-3             |

| System Interface.                    | 1-4               |

| Link Address                         | . 1 – 5           |

| Specifications                       | 1-5               |

| Section 2 INSTALLATION               |                   |

| Current Requirements                 | 2-1               |

| Channel Address Switch               | 2-1               |

| Cables                               | 2-3               |

| Installing the LANIC                 | . 2-4             |

| Start Up                             | 2-6               |

| Reshipment                           | 2-6               |

|                                      |                   |

| Section 3 PRINCIPLES OF OPERATION    |                   |

| LAN Interface Controller (LANIC)     | 3-1               |

| Host to LANIC Communication          | . 3-1             |

| LANIC MPU and Firmware               | . 3-3             |

| Local Communications Controller      | 3-3               |

| Direct Memory Access                 | . 3-3             |

| Firmware Download and Configuration. | . 3-3             |

| Firmware Download                    | . 3-3             |

| Setting Station Address              | 3-3               |

| Queue Initialization                 | 3-4               |

| Transmit Operation                   | 3-4               |

| Types of Packets Transmitted.        | 3-4               |

| Transmit Buffer Management           | 3-4               |

| Queuing of Transmit Buffers          |                   |

| Transmit Operation Example           | . 3-4             |

| Receive Operation                    | 3-4               |

| Types of Packets Received.           |                   |

| Receive Buffer Management            | 3-5               |

| Queuing of Received Packets          | 3-3               |

| Receiver Blind Spots                 | . 3-5             |

| Receive Operation Example            |                   |

| Error Management                     | 3-5               |

| Self-Test Operation                  |                   |

| System Interrupt.                    | . 3 <del>-(</del> |

# **CONTENTS** (continued)

| SINTRO Self-Test Interrupt          | . 3-6                    |

|-------------------------------------|--------------------------|

| SINTR1 LANIC Interrupt              | 3-6                      |

| Interactive Command Completion      | 3-1                      |

| Interactive Command Acknowledgement | 3-1                      |

| Batch Command Completion.           | 3-8                      |

| Fatal Error Response.               | 3-8                      |

| LANIC Resets.                       | 3-8                      |

| Power-On Reset                      | 3_0                      |

| Hard Reset                          | 3-0                      |

| Soft Reset                          | 3_0                      |

| Z-80 Reset.                         | 3-10                     |

| Power-Fail Warn.                    | 3 _ 1 C                  |

| Self-Test.                          | 3 - 1 C                  |

| Manually Initiated Self-Test.       | 3-10                     |

| Remotely Initiated Self-Test.       | ) 10<br>1_10             |

| Idle Self-Test                      | )-10<br>1_10             |

| Visual Indicators.                  | )-10<br>210              |

| Attachment Unit Interface (AUI).    | )-10<br>2-10             |

| MAU Power Control Circuit.          | )-10<br>1-10             |

| LEDs.                               | ) - 12<br>1 - 1 <b>2</b> |

| DO LED Pair.                        | ) - 12<br>1 - 15         |

| CL LED Pair                         | )-13<br>!-16             |

| CR LED Pair.                        | ,-10<br>l-16             |

| H through N and * LEDs.             | 1-16                     |

| TX, RX, MN, DL, RO, Q, and IT LEDs  | 1-16                     |

| Medium Attachment Unit (MAU)        | 1 1 0                    |

| Receiver                            | 1-10                     |

| Transmitter                         | -10                      |

| Collision Detection                 | - 10<br>- 10             |

| Jabber Fault Detection              | -10                      |

| J                                   | -20                      |

|                                     |                          |

| Section 4                           |                          |

| MAINTENANCE                         |                          |

|                                     |                          |

| Repair Philosophy                   | 4-1                      |

| Self-Test                           | 4-1                      |

|                                     |                          |

| A man and the A                     |                          |

| Appendix A                          |                          |

| CONFIGURATION INFORMATION           |                          |

| Configuration Dialog                |                          |

| Coming an auton Dialog              | Δ 1                      |

# **GENERAL INFORMATION**

SECTION

1

This manual presents installation and service instructions for the HP 30242A LAN/3000 Link Local Area Network Interface Controller. This section contains general information covering the HP 30242A LAN/3000 link product, and includes a description and specifications.

#### GENERAL DESCRIPTION

The HP 30242A LAN/3000 link is an implementation of the IEEE 802.2 and IEEE 802.3 Local Area Network (LAN) standards and is used in HP 3000 computer systems. The HP 30242A allows the HP 3000 to communicate with other HP 3000s over an IEEE 802.3, 0.4-inch baseband Local Area Network (LAN).

The IEEE 802. 3 Local Area Networks (LANs) consist of three major elements: a coaxial cable transmission medium, units to access this medium (Medium Attachment Units, or MAUs), and controllers. For the HP 30242A, the controller is the Local Area Network Interface Controller (LANIC).

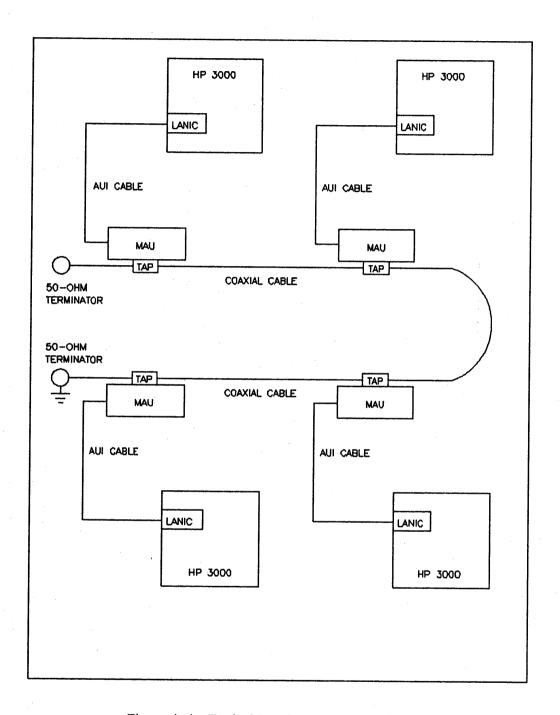

A fitting, called a tap, pierces the coaxial cable and provides a connection from the cable to the Medium Attachment Unit (MAU). An Attachment Unit Interface (AUI) cable connects the MAU to the LAN Interface Controller (LANIC). The LANIC, in addition to controlling the other LAN elements, functions as the interface from the Local Area Network to the computer system. A typical Local Area Network is shown in figure 1-1. Each host computer system, including LANIC, AUI, tap, and MAU is called a node on the Local Area Network. The LANIC, AUI, tap, and MAU are all part of the HP 30242A LAN/3000 link.

The HP 30242A LAN/3000 link is available for use with the HP 3000 Series 39, 40, and 42; and the HP 3000 Series 44, 48 64, and 68. The LANIC, MAU, and AUI cable are the same for all HP 3000 Series; however, two different LANIC cables are offered (see the paragraph "Equipment Supplied").

The LAN/3000 link functions as an intelligent Direct Memory Access (DMA) channel which communicates with the host system via the system I/O backplane. Local intelligent control is provided by a microprocessor and firmware on the LAN Interface Controller (LANIC). An 8-bit Z-80B microprocessor (MPU) on the LANIC handles all the LAN/3000-to-host communication and performs many link-level operations independently of the host. A type 82586 Local Communications Controller (LCC) on the LANIC performs high-speed serial operations, packet address checking, network contention control, packet formatting, and Cyclic Redundancy Check (CRC) generation and checking. The LCC is controlled by the Z-80B through local (card resident) memory.

Figure 1-1. Typical Local Area Network (LAN)

The Medium Attachment Unit (MAU) connects the coaxial cable to the LANIC, through a tap and an Attachment Unit Interface (AUI) cable. The MAU has three major functions:

- Receive data from the coaxial cable and pass it along to the LANIC controller.

- Transmit data from the LANIC controller onto the coaxial cable.

- Detect collisions on the coaxial cable, and report the condition to the LANIC.

In addition, the MAU performs various housekeeping and support functions. These functions are covered in Section 3, Principles of Operation.

# **Equipment Supplied**

Standard equipment supplied with the HP 30242A is listed below:

#### Standard Equipment

| 1   | Medium Attachment Unit Assembly          | 30241-60101  |

|-----|------------------------------------------|--------------|

| 1   | Coaxial Cable Tap Kit                    | 0362-0819    |

| . 1 | 6-meter AUI Cable                        | HP 92254A    |

| •   | (Includes 6 Wallplate/Cable Labels       | 30241-80004) |

|     | (Includes 6 Protector Labels             | 30241-80003) |

| 1   | LAN/3000 Installation and Service Manual | 30242-90001  |

In addition, one of the following options (depending on the HP 3000 type) adds the following equipment:

# Option 300 for the HP 3000 Series 39, 40, and 42

```

Series 4X/6X LAN Interface Controller (LANIC card) 30242-60001

Series 39/40/42 LANIC Internal Cable ................ 30241-60002

```

#### Option 400 for the HP 3000 Series 44 and 48

| 1 | Series | 4X/6X | LAN I | nterface | Controller | (LANIC | card) | 30242-60001 |

|---|--------|-------|-------|----------|------------|--------|-------|-------------|

| • | Series | 44/48 | LANTO | Internal | Cable      |        |       | 30241-60003 |

## Option 500 for the HP 3000 Series 64 and 68

| 1 | Series | 4X/6X | LAN Interface Controller (LANIC card) | 30242-60001 |

|---|--------|-------|---------------------------------------|-------------|

| 1 | Series | 64/68 | LANIC Internal Cable                  | 30241-60003 |

#### General Information

Option 241 is specified if the MAU and AUI cable are not desired. Option 241 deletes the following standard equipment:

#### Option 241

#### Deletes

| 1<br>1<br>1 | - 1000 101 00010 1111111111111111111111 | 0362-0819<br>HP 92254A |

|-------------|-----------------------------------------|------------------------|

|             | (Including 6 Wallplate/Cable Labels     | 30241-80004)           |

|             | (Including 6 Protector Labels           | 30241-80003)           |

# System Interface

As noted previously, the LAN/3000 link interfaces to the host computer system through the LAN Interface Controller (LANIC). The LANIC functions as an I/O channel and fits into the backplane of HP 3000 Series 39, 40, 42, 44, 48, 64, and 68 computers.

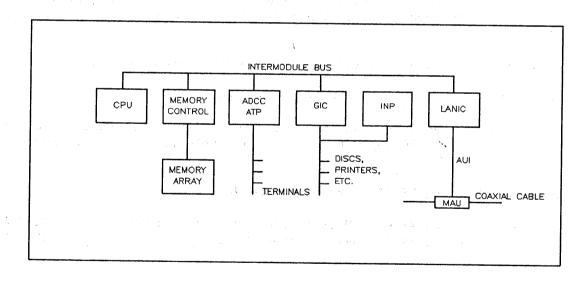

Figure 1-2 shows how the LANIC connects to a Series 39, 40, 42, 44, or 48 computer system. The CPU, Memory, Asynchronous Data Communications Controller (ADCC) or Advanced Terminal Processor (ATP), General Input/Output Controller (GIC), Intelligent Network Processor (INP), and LANIC all physically fit into the backplane (the backplane is called the Intermodule Bus (IMB)).

Figure 1-2. HP 3000 Series 39 through 48 System Architecture

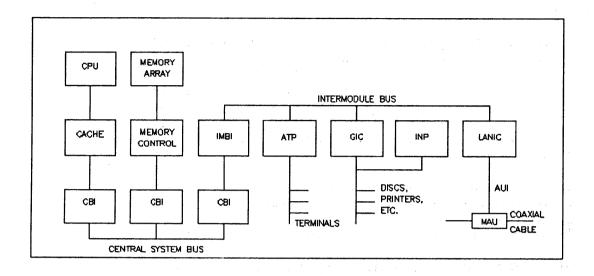

The architecture for the Series 64 and 68 computers is significantly different than the other HP 3000 series, as shown in figure 1-3. The CPU and memory fit into the Central System Bus (CSB), and one or more IMBs connect to the CSB via Common Bus Interfaces (CBIs) and IMB Interfaces (IMBIs). I/O DMA operations do not go directly to memory, but are handled by the IMBI.

Figure 1-3. HP 3000 Series 64 and 68 System Architecture

# Link Address

The last 6 hex digits of the link level address for the LANIC are indicated on the board stiffener to the left of the channel address switch (CHAN ADDR) on a label titled "Station Address". The full address is 08 00 09 XX XX XX, where XX XX XX represents the value on the label.

## **SPECIFICATIONS**

Table 1-1 lists the specifications of the HP 30242A LAN/3000 link.

#### Table 1-1. Specifications

#### **FEATURES**

Compatible with IEEE 802.3 Standard for access to 0.4-inch diameter baseband coaxial cable

Carrier-Sense Multiple Access with Collision Detection (CSMA/CD) protocol controls network access using no master node

On-board node self-test that checks the operation of the node hardware including the AUI and MAU

Every node on the network cable is accessible by any other node on the network with no store and forward

10 megabit-per-second hardware data transfer rate

Each 500-meter cable segment supports up to 100 nodes

Nodes may be attached or removed while network is active

VLSI implementation for reliability and lower cost

Microprocessor off-loads host computer and gathers network statistics

#### ELECTRICAL CHARACTERISTICS

#### Data Rate:

Transmitted in bursts of 10 Mbits/sec

Maximum Coaxial Cable Length:

500 meters for one segment

Maximum Distance from Node to Network Trunk:

48 meters maximum for external AUI cable

Required Distance Between Taps on Coaxial Cable Trunk:

Each MAU with its cable tap must be located on the coaxial cable at a position that is an exact multiple of 2.5 meters from the end of the cable. The coaxial cable available from HP is marked every 2.5 meters to show where MAUs may connect.

#### Table 1-1. Specifications (Continued)

#### LANIC at AUI Connector:

AUI signalling conforms to IEEE 802.3

CO not driven

VP +12V +/-6% @ 0.5A; overcurrent protected @ 1.2A maximum

Interframe spacing = 9.6 usec minimum

#### MAU at AUI Connector:

AUI signalling conforms to IEEE 802.3

CO terminated but unused

Jabber is reset by VP shutdown only

Operating voltage: 9.5V to 15.75V at 460mA maximum

#### MAU at Coaxial Cable:

Coax signalling compatible with IEEE 802.3 recommended signalling levels  $\frac{1}{2}$

Receiver based collision detection

Will tap any 0.4 inch coaxial cable meeting IEEE 802.3 physical specifications

#### MAU Coaxial Cable to AUI Cable Isolation:

+/-707V DC, 500V AC RMS, 50/60Hz Will conduct repetitive surges of up to 4A without damage (between the shields)

DC Impedance, Coaxial Shield to AUI Shield: 928K ohms

Table 1-1. Specifications (Continued)

#### LANIC PHYSICAL CHARACTERISTICS

Size:

331 mm long by 285 mm wide by 22.5 mm thick

(13.04 by 11.2 by 0.89 inches)

Weight:

739 grams (26 ounces)

#### LANIC POWER REQUIREMENTS

Voltage

Current

Power Dissipation

+5V +/-0.5V

4.7A

23.5W

+12V +/-0.6V

0.5A

6.0W (with MAU attached)

#### MAU PHYSICAL CHARACTERISTICS

Size:

320 mm long by 95 mm wide by 30 mm thick

(12.25 by 3.75 by 1.25 inches)

Weight:

0.55 kg (1.2 lbs)

#### MAU POWER REQUIREMENTS

9.5 to 15.75 volts

0.5 amp maximum

#### **ENVIRONMENTAL SPECIFICATIONS**

Complete environmental specifications are contained in the LAN/3000 Cabling and Installation Guide, part number 30242-90002

# INSTALLATION

SECTION

2

This section contains information on installing and verifying proper operation of the LANIC card, part number 30242-60001. This manual assumes that the coaxial cable medium, tap, and MAU have been installed and that the AUI cable has been connected to the MAU and has been routed from the MAU to the host computer system containing the LANIC. Information on installing the MAU and the AUI cable is contained in the Local Area Network Cabling and Installation Guide, part number 30242-90002.

# CAUTION

SOME OF THE COMPONENTS USED IN THIS PRODUCT ARE SUSCEPTIBLE TO DAMAGE BY STATIC DISCHARGE. REFER TO THE SAFETY CONSIDERATIONS INFORMATION AT THE FRONT OF THIS MANUAL BEFORE HANDLING THE CARD.

#### **CURRENT REQUIREMENTS**

The LANIC circuit card obtains its operating voltages from the host computer. The current requirements of the card are listed in the power requirements entry of table 1-1.

All HP 3000 Computer systems can supply adequate current to accommodate the LANIC card without the need for any power supply modification. However, it is possible that the +12V supply in the HP 3000 system may be set to a low voltage such that the VP lead on the AUI cable may not provide the minimum voltage specified by IEEE 802.3 (+11.28V). If MAU replacement does not correct an apparent MAU problem, the VP voltage should be checked. This is done by connecting an accurate voltmeter between the +12 and GND test points near the LEDs on the LANIC card. This must be done when the MAU is connected to the LANIC and MAU power is on (as indicated by the VP LED). MAU power can be turned on by executing the LANIC self-test. Consult the HP 3000 CE Handbook for instructions on adjusting the +12V power on the HP 3000.

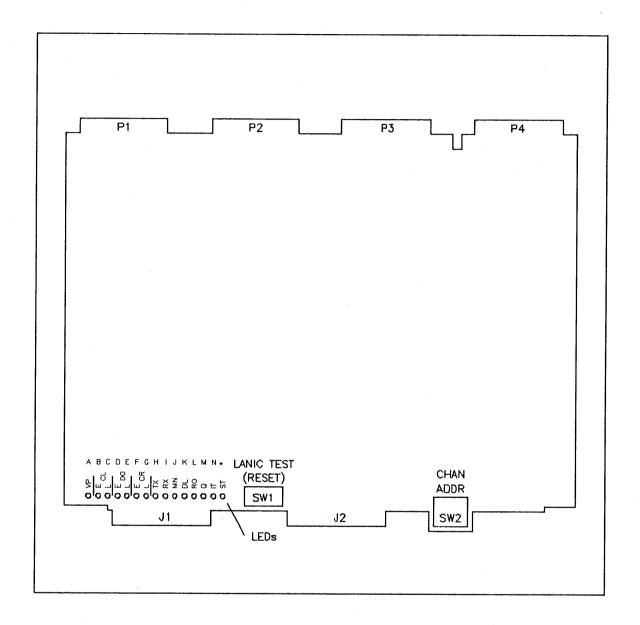

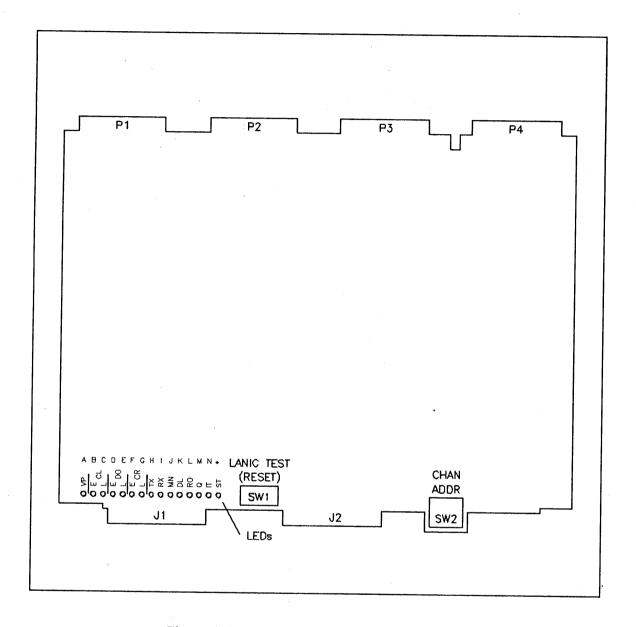

#### CHANNEL ADDRESS SWITCH

For the LANIC card, the channel address is set by a CHAN ADDR rotary switch, SW2, located on the front edge of the card. See figure 2-1 for the location of SW2. SW2 can be set to any value between 1 and 15, however, ensure that no GICs, ADCCs, or SIBs are set to the same channel number. Once you have set SW2 to a value, jot the value down. For 3x and 4x systems, this value times 8 will be the DRT number. For 6x systems, the DRT number is computed as follows: (CHAN ADDR x 8) + (IMB x 128) = DRT.

Figure 2-1. LANIC Switch and LED Locations

#### **CABLES**

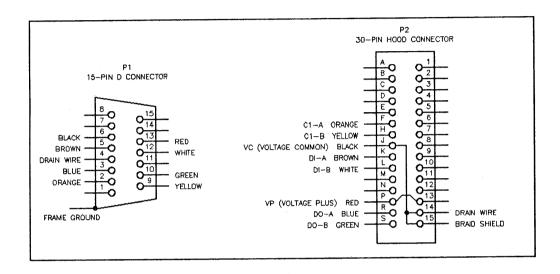

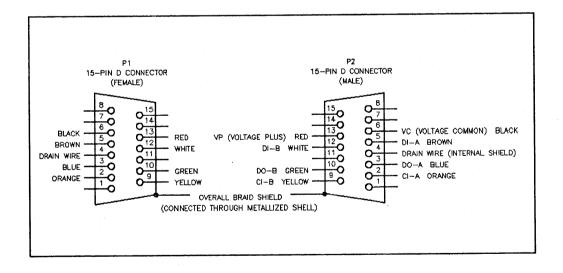

Two cables are used to connect the LANIC to the MAU: an internal LANIC cable and the AUI cable. The LANIC cable has a hood connector on one end and a female 15-pin D connector on the other. A cabling diagram for the LANIC cable is shown in figure 2-2. The AUI cable uses a male 15-pin D connector on one end and a female 15-pin D connector on the other. A cabling diagram for the AUI cable is shown in figure 2-3.

Figure 2-2. LANIC Cable Diagram

Figure 2-3. AUI Cable Diagram

# INSTALLING THE LANIC

## CAUTION

SOME OF THE COMPONENTS USED IN THIS PRODUCT ARE SUSCEPTIBLE TO DAMAGE BY STATIC DISCHARGE. REFER TO THE SAFETY CONSIDERATIONS INFORMATION AT THE FRONT OF THIS MANUAL BEFORE HANDLING THE CARD.

Install the LANIC as follows:

#### CAUTION

ALL SYSTEM POWER MUST BE OFF WHEN INSTALLING OR REMOVING ANY DEVICE OR CARD IN THE SYSTEM.

- 1. Before installing the LANIC, perform a full HP 3000 backup.

- 2. Shut down MPE.

- 3. Ensure that SW2 is set to the intended channel address. (It may be useful to obtain an IOMAP of all devices presently on the system. Refer to the HP 3000 System Operation and Resource Management Reference Manual, part number 32033-90005 for details.)

- 4. Turn off all system power.

- 5. Open the door of the I/O section card cage on the back of the HP 3000 Computer system.

- 6. Insert the LANIC card into a vacant card cage slot as follows:

The LANIC is considered to be a high-speed channel and, as such, must be configured so that its priority is higher than any GIC. Priority is established by the position of I/O cards in the card cage; the closer to the CPU (or the IMBI in the case of the Series 64 and 68), the higher the priority.

Series 39, 40, 42. The LANIC can be installed in any slot in the range of 13 through 25. The adding of the LANIC card may require the movement of cards in the card cage to give the LANIC the required relative priority.

Slots 13 and 14 are unique in the Series 39, 40, and 42 in that they are interdependent upon slot 15 in some situations. Specifically, if either a GIC, SIB, or LANIC occupies slot 13 and/or 14, and if slots 16 through 25 have one or more GICs, SIBs, or LANICs, then a GIC, SIB, or LANIC MUST be in slot 15.

Note that the card in slot 15 need not be identical to the others under consideration. For instance, if a GIC is in slot 13, and a GIC, SIB, or LANIC is in 16 through 25, then any one of the three may be installed in 15.

If ADCCs are installed in 13 and 14, as is commonly the case, there are no special considerations involving slot 15.

Series 44 and 48. The LANIC can be installed in any slot in the range of 14 through 24 (card cage 1) and any slot in the range of 1 through 7 (card cage 2). The adding of the LANIC card may require the movement of cards in the card cage(s) to give the LANIC the required relative priority.

Series 64 and 68. The LANIC must be installed in the I/O portion of the card cage. The adding of the LANIC card may require the movement of cards in the card cage to give the LANIC the required relative priority.

Special considerations apply to the placement of GICs, SIBs, and LANICs in Series 64 and 68 systems:

Between a GIC, SIB, or LANIC, and the next GIC, SIB, or LANIC, there may be a maximum of nine slots.

The "next" card need not be identical to its neighbor as long as it is one of the three types (GIC, SIB, or LANIC)

As an example, an SIB in slot 10 with a LANIC in slot 21, and GICs in slots 22 and 23, is not legal because there are greater than nine slots between the SIB and the LANIC. (The device cards such as INPs, AIBs, etc., do not matter in this case.)

An SIB in slot 10, LANIC in slot 17, and GIC in slot 22 is legal because there are nine or fewer slots between each card.

Finally, this limitation does not span IMBs. Each IMB must conform only individually.

- 7. Record the location of the LANIC in the configuration section of the System Support Log.

- 8. Connect the hood connector of the appropriate LANIC cable (part number 30241-60002 for Series 39, 40, and 42; part number 30241-60003 for Series 44, 48, 64, and 68) to connector J2 of the LANIC card. Connect the other end of the LANIC cable as follows:

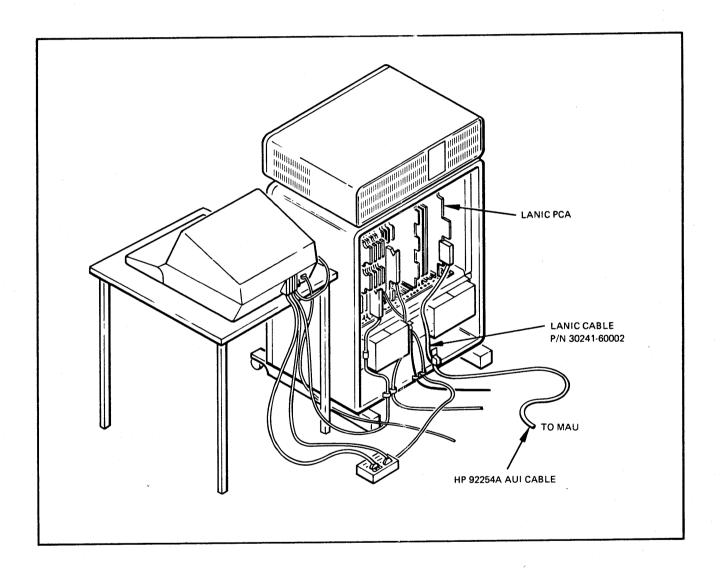

- Series 39, 40, 42. Fasten the LANIC cable connecting box to the grounding strip at the bottom of the SPU (system processor unit) frame with the captive thumbscrew attached. Be sure the raised mounting lug is inserted in a hole in the grounding strip. Tighten the thumbscrew securely. Connect the AUI cable to the LANIC cable connector. See figure 2-4.

- Series 44 and 48. Fasten the LANIC cable connector, with its mounting panel attached, to the junction panel on the side of the card cage. Use only cutout numbers 2, 3, 5, 6, 7, or 8 for the LANIC cable. Connect the AUI cable to the LANIC cable connector. See figure 2-5 for details.

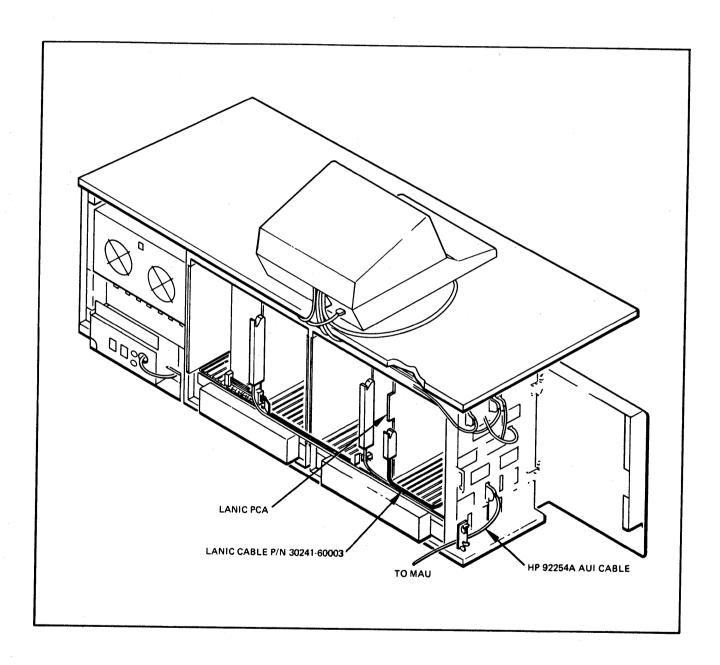

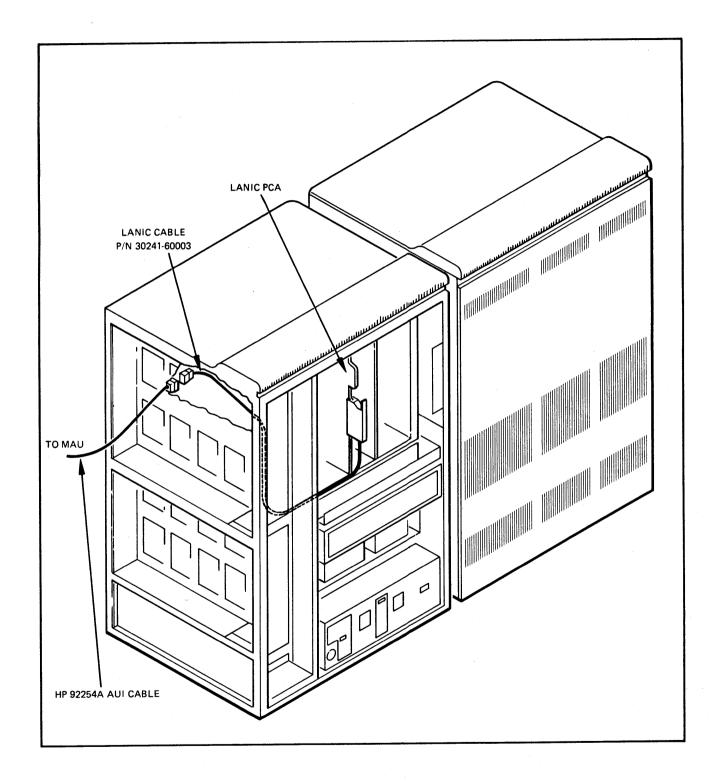

- Series 64 and 68. Fasten the LANIC cable connector, with its mounting panel attached, to the junction panel on the side of the card cage. Connect the AUI cable to the LANIC cable connector. See figure 2-6 for details. Note that the junction panel on Series 64 and 68 systems consists of two sets of 24 slots with a cable trough above and below each set. In each set of 24 slots, there are 12 upper and 12 lower slots. If the LANIC internal cable is installed in one of the lower 12 slots, the AUI cable should be routed into the *upper* cable trough. If the LANIC internal is installed in one of the upper 12 slots, the AUI cable should be routed into the *lower* cable trough.

- 8. Connect the AUI cable to the MAU, or to a MAU with a test hood. (A MAU is required for complete testing.)

# START UP AND VERIFICATION

For start up and preliminary verification of the LANIC, perform the following:

- 1. Turn on computer system power.

- 2. A self-test, which is contained on the card, will execute at power on. There are 15 LEDs located on the front edge of the LANIC card (see figure 2-1). The seven LEDs on the top are used to indicate activity on the AUI cable. The eight LEDs on the bottom are used by self-test.

The power-on self-test begins with all eight self-test LEDs blinking on and off in unison for approximately 10 seconds. Thereafter, the bottom LED (labeled "ST") is lit to indicate that the self-test is in progress, and the remaining seven self-test LEDs will perform a binary count, incrementing from 0000001 to 0101110 and executing a self-test for each binary code displayed. Some tests require several seconds to execute, some tests require much less, but the LEDs will be lit for at least 100 milliseconds for every test, thus each code will be visible as the LEDs increment the count. No binary codes are skipped. The binary codes and the self-tests they represent are listed in Section 4.

Watch the LEDs as the self-test program executes. If the self-test completes with no errors, the ST LED will be on and the other seven LEDs will be off (a code of all zeros) for five seconds. After five seconds, the ST LED will go off, and the remaining LEDs will reflect activity on the LANIC. If the self-test fails, the code of the test that failed will be displayed for a minimum of 20 seconds. This display will continue until the system accesses the link, while the self-test LED blinks slowly.

Note that if the self test indicates failure 36H or 46H, this could indicate that the AUI cable and MAU are not connected. Verify that these items are connected. If the failures are still indicated, the error could be in the AUI, MAU, or the coaxial cable. If the LANIC fails self-test, refer to Section 4 for maintenance procedures, and for further information on the self-test.

- 3. Start up the system in accordance with the procedures contained in Appendix A of this manual and in the HP 3000 System Operation and Resource Management Reference Manual, part number 32033-90005.

- 4. Run the LAN diagnostic on the LANIC/AUI/MAU combination. Refer to the LAN/3000 Diagnostic and Troubleshooting Guide, part number 30242-90003 for information on running the diagnostic.

#### RESHIPMENT

If any item of the LAN/3000 link is to be shipped to Hewlett-Packard for any reason, attach a tag identifying the owner and indicating the reason for shipment. Include the part number of the item being shipped.

Pack the item in the original factory packing material, if available. If the original material is not available, good commercial packing material should be used. Commercial packing and shipping companies have the facilities and materials to repack the item. BE SURE TO OBSERVE ANTI-STATIC PRECAUTIONS.

Figure 2-4. Series 39, 40, and 42 LANIC Cabling Detail

Figure 2-5. Series 44 and 48 LANIC Cabling Detail

Figure 2-6. Series 64 and 68 LANIC Cabling Detail

# PRINCIPLES OF OPERATION

3

# **FUNCTIONAL DESCRIPTION**

The HP 30242A LAN/3000 link is an implementation of the IEEE 802.2 and IEEE 802.3 Local Area Network (LAN) standards and is used to allow HP 3000 computer systems to communicate with other HP 3000s over a Local Area Network (LAN). The IEEE 802.2 Local Area Network standard defines a logical link control protocol, and IEEE 802.3 Local Area Network standard defines a bus utilizing CSMA/CD (Carrier Sense Multiple Access/Collision Detect) as the access method.

The LAN/3000 link functions as an intelligent Direct Memory Access (DMA) channel which communicates with the host system via the system backplane. Local intelligent control is provided by a microprocessor and firmware on the LAN Interface Controller (LANIC).

The LAN/3000 link consists of a LAN Interface Controller (LANIC), an Attachment Unit Interface (AUI) cable, and a Medium Attachment Unit (MAU). The MAU attaches to a coaxial cable which connects the various computer systems together on the Local Area Network; the AUI connects the MAU to the LANIC; and the LANIC provides the interface between the LAN and the computer system.

# LAN INTERFACE CONTROLLER (LANIC)

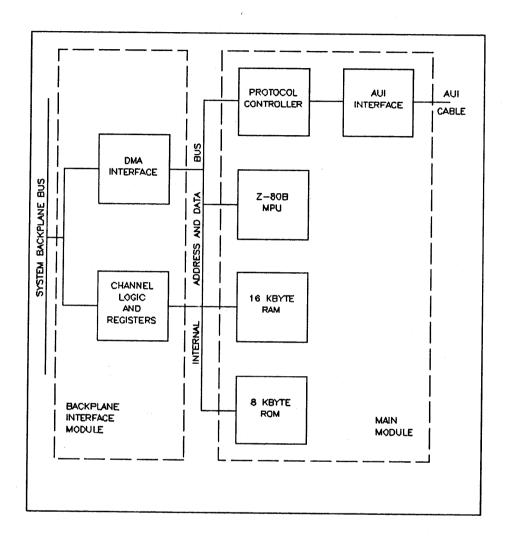

The LANIC is an intelligent DMA channel which communicates with the host system via the system backplane. On the network end of the LANIC, the AUI carries bit-serial data and control information to and from the MAU, which attaches directly to the network coaxial cable. A functional block diagram of the LANIC is shown in figure 3-1.

# Host to LANIC Communication.

The host communicates with LANIC through channel registers and data structures stored in system memory. Basic channel communication registers provide for channel identification, interrupt control, and diagnostics. Of primary importance are the Control Register (CR) and Status Register (SR), which provide for the input and output of control and status information. Link-level commands and status are passed via two queue structures stored in system memory shared by the LANIC and the host.

Figure 3-1. LANIC Functional Block Diagram

#### LANIC MPU and Firmware.

Local intelligent control is provided by a microprocessor (MPU) and firmware on the LANIC card. An 8-bit microprocessor of type Z-80B handles all the LANIC-to-host communication and performs many link-level operations independently of the host. The MPU also is responsible for performing an on-board self-test to detect and locate hardware faults. The firmware for the MPU resides in both ROM and RAM. The ROM firmware contains the self-test, MPU interrupt control, and bootstrap programs. The link-level operational firmware is downloaded into LANIC RAM from system memory.

#### Local Communications Controller.

The Local Communications Controller (LCC) is a high-performance LSI device that performs most of the data link and physical link functions for the local network architecture. The LCC performs high-speed serial operations, packet address checking, network contention control, packet formatting, and CRC (Cyclic Redundancy Check) generation/checking. The LCC is controlled by the MPU through local memory.

# **Direct Memory Access.**

The LANIC can transfer data directly to and from system memory. Once the host has given the LANIC the location of data buffers in system memory, data is transferred without host intervention. This allows maximum system performance by uploading the task of packet transmission and reception from the host, allowing the host to spend more of its time on other processing.

# Firmware Download and Configuration

Although the self-test, diagnostic, and bootstrap firmware are all resident in ROM, the operational firmware must be downloaded from the host into the LANIC local memory. After the firmware is downloaded, control is passed to it and the LANIC is ready to be configured. Configuration comprises the 82586 chip configuration, setting the station address, and initializing the command response queues.

FIRMWARE DOWNLOAD. The host initiates the downloading of firmware from system memory to the LANIC local RAM. The LANIC performs the actual transfer via its DMA facility. After the transfer, the LANIC computes the checksum of the data in local RAM and compares it with the checksum computed by the host. This ensures that the download firmware is transferred correctly. The entire firmware may be downloaded via a sequence of download operations. The host has full control of firmware operation and can suspend firmware execution at any time and dump LANIC memory and hardware status to system memory.

SETTING STATION ADDRESS. The LANIC supports both globally and locally administered addressing. Globally administered addressing is supported by a ROM on the LANIC that contains a unique 48-bit address code. This address can be read by the host. Setting the station address is accomplished by a process involving the Duplicate Address Check (DAC) protocol. The host supplies the LANIC with a candidate station address. The LANIC sends an Exchange Identification (XID) packet with this address in the destination field. If any node is using the same station address, it sends the packet back to the LANIC. The LANIC waits for any response to come back before establishing its station address. If the DAC protocol fails, the host is notified to take further action.

QUEUE INITIALIZATION. Once operational, most of the communication between the host and the LANIC is via a pair of queue structures in system memory. One queue, the Command Queue (CQ), is used by the host to send commands to the LANIC. The other queue, the Response Queue (RQ), is used by the LANIC to return status to the host. Each queue is fixed in size with fixed-length entries, however these parameters are programmable when the queues are configured by the host. The head and tail pointers are stored in system memory along with each queue. The host informs the LANIC of new entries in the CQ by means of the READ\_QUEUE command. The LANIC informs the host of new RQ entries by means of the system interrupt facility.

# **Transmit Operation**

TYPES OF PACKETS TRANSMITTED. The LANIC can transmit any size packet up to the maximum packet size. Short packets are automatically padded to meet minimum packet length requirements.

TRANSMIT BUFFER MANAGEMENT. The host is responsible for setting aside transmit buffers in system memory. The starting address and length of each buffer is sent to the LANIC via the XMIT request. Each buffer is identified by a unique ID number. When the LANIC has successfully transmitted a transmit buffer, or when it encounters an irrecoverable error, it returns the ID number and status to the host via the Response Queue (RQ). The host must ensure that transmit buffers are frozen in system memory from the time the XMIT request is entered into the CQ until the LANIC returns the buffer ID in the RQ.

QUEUING OF TRANSMIT BUFFERS. The transmit operation requires a number of steps and there in no way to predict when a transmit buffer is actually sent. Transmit buffers queue up in the CQ and in an internal transmit queue. The buffer at the head of the transmit queue is processed when no receive packets are being processed. Even then, there may be a delay due to the CSMA/CD protocol.

TRANSMIT OPERATION EXAMPLE. A transmit frame is assembled by the host in system memory. The host then adds to the CQ an XMIT request containing the address and length of the transmit frame and the ID number. The LANIC will process this command after it completes operations in progress and gets the command from the CQ. The LANIC then copies the contents of the frame buffer from system memory to its local memory. The next phase is undertaken by the 82586 LCC chip. The 82586 handles the CSMA/CD protocol, serializes the data from the local memory buffer, sends it out on the network, and generates the frame check sequence. After the 82586 LCC is finished with the frame, LANIC firmware records the frame completion status and ID number in the RQ.

# **Receive Operation**

TYPES OF PACKETS RECEIVED. The LANIC will only receive packets addressed to its station address (except when promiscuous mode is configured). These packets may be individually addressed, broadcast, or multicast, if the LANIC has been configured for such operation. Packets that are shorter than minimum or longer than maximum are not returned to the host, however, the statistical counters are updated.

RECEIVE BUFFER MANAGEMENT. The host is responsible for setting aside receive buffers in system memory. The starting address and length of each buffer are sent to the LANIC via the RECV command. These buffers are identified via a unique ID number. When the LANIC fills a receive buffer, it returns the ID number to the host via the Response Queue (RQ). From the time that the host enters the buffer descriptor into the CQ until the LANIC returns the ID number in the RQ, the host must ensure that the buffer is frozen in physical memory. Since neither the host nor the LANIC have control over what time a packet arrives, there must be a sufficient number of buffers ready for the LANIC to receive bursts of packets, otherwise packets will be lost. For further information on lost packets, see the paragraph "Receiver Blind Spots".

QUEUING OF RECEIVED PACKETS. Received packets may be queued by the LANIC before being reported to the host. In order to report received packets to the host, the LANIC microprocessor must access system memory. However, it may not be able to do this during a burst of receive packets because the LANIC DMA capability will be saturated with packet transfers to system memory. The microprocessor will update the RQ as soon as a lull in received packet traffic occurs.

RECEIVER BLIND SPOTS. Under certain conditions, the LANIC can fail to receive a packet. The following conditions are necessary for the LANIC to receive a packet at any time:

The receiver must be turned on.

There must be a buffer ready to receive the packet.

The LANIC must be able to write to memory fast enough to prevent losing data.

If any of the above conditions are not met, receive packets will be lost.

RECEIVE OPERATION EXAMPLE. The host allocates one or more receive buffers and enters RECV commands containing the buffer descriptors and IDs into the CQ. The LANIC removes these descriptors from the CQ and puts them on an internal queue, and turns the 82586 LCC receiver on. The LCC prepares for packet reception by taking the first buffer descriptor off the internal queue. The LCC looks at the destination address of all packets on the network. When the destination address matches the LANIC's station address, the LCC descrializes the packet and starts writing it to system memory using the current receive buffer descriptor. At the end of the packet, the LCC compares the CRC and re-uses the buffer descriptor if there was an error in packet reception. Otherwise, the LCC records the packet reception, prepares the next buffer descriptor from the internal queue, and interrupts the microprocessor. When the microprocessor acknowledges the interrupt, the LCC adds the status and ID number of the completed packet(s) to the RQ.

# **Error Management**

The LANIC detects command, system, and network errors, takes recovery action when appropriate, and reports status to the host. Command format errors are simply reported to the host, but do not result in any interruption of operations in progress. The LANIC attempts recovery of certain errors, such as MAU jabber, and if recovery is successful, the LANIC reports the recovery to the host for logging, and continues operation. When the LANIC detects a non-recoverable error, such as a system memory error, it aborts all operations in progress, reports the nature of the error to the host via the system interrupt mechanism, and waits for further action by the host.

# Self-Test Operation

The LANIC executes a self-contained self-test program on system reset, or under host software control. Additionally, self-test can be initiated via a switch on the card, or by power-on. The LANIC self-test program tests a portion of the LANIC hardware. The self-test result code is displayed visually on the LANIC card (see Section 4), and can be programmatically read by the host via a channel register dedicated to self-test result codes.

# System Interrupt

The LANIC can request a host software interrupt via two pseudo-device interrupts. When the host issues the OBII command to the LANIC, the data returned contains either a zero or a one in bit 15, corresponding to the interrupting device number. Device number zero corresponds to the interrupt called SINTRO, and device number one corresponds to the interrupt called SINTR1. If both interrupt requests, SINTRO and SINTR1, are active simultaneously the interrupt code for SINTRO is returned.

Operation of the LANIC IRQ (Interrupt Request) is as follows:

If either or both of SINTR0 and SINTR1 are set and the interrupt mask, MASKF, is set, then the channel asserts the IRQ line on the backplane. Eventually, the host detects that IRQ is asserted and invokes the microcode routine to handle interrupts. This microcode performs an IPOLL to determine which channel(s) are requesting, and then an OBII to determine which device on the channel to service. After determining which channel and device to service, the microcode issues a WIOC command to clear SINTR, and dispatches the appropriate software interrupt routine.

SINTRO SELF-TEST INTERRUPT. The SINTRO interrupt request is activated by the ROM-based self-test firmware when the self-test sequence completes or whenever an idle self-test failure is detected. The host software reads the STR channel register to determine the type of error detected. A more detailed description of the self-test is contained in Section 4.

SINTR1 LANIC INTERRUPT. This interrupt is activated by either the ROM-based kernel firmware or by the downloaded operational firmware to signal the host software that some event in the LANIC has occurred. Host software reads the SR channel register to determine what type of event has occurred. The types of events fall into two groups: those related to a command issued to LANIC by the host software, and those resulting from internal LANIC operations.

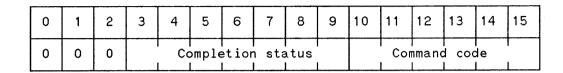

INTERACTIVE COMMAND COMPLETION. This response is given when the LANIC completes the execution of an interactive command. The command-specific bits of the response code contain status and error codes whose meanings depend on the associated command as shown below.

Command code

= Command code originally given

Completion status = See below and paragraph "Self-test"

00 - command executed correctly

01 - sync between driver and LANIC established (e.g., an all-ones word written into CR)

02 - illegal length command

03 - command not found

04 - command doesn't match length

08 - host buffer crosses bank boundary

09 - non-word address on download or dump

OA - checksum didn't check (DOWNLOAD command)

OB - illegal start address (START CODE command)

INTERACTIVE COMMAND ACKNOWLEDGEMENT. This response is given after the firmware reads the first word of a multiple-word command from the CR. This response is useful for avoiding the host software busy-wait on CRFULL after the first word of a multiple-word command has been written to the DR. This problem is due to the fact that the first word may not be accepted by the LANIC for several milliseconds, but the succeeding words are handshaken with negligible delay. A command acknowledgement response is not given for a single-word command as it is followed by a command completion response anyway. See below.

| 0 | 1 | 2 | 3 | 4         | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15     |

|---|---|---|---|-----------|---|---|---|---|---|----|----|----|----|----|--------|

| 0 | 0 | 1 |   | Undefined |   |   |   |   |   |    |    |    |    |    | l<br>I |

#### Principles of Operation

BATCH COMMAND COMPLETION. The response shown below is given when the firmware completes the execution of a batch command:

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7    | 8     | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

|---|---|---|---|---|---|---|------|-------|----|----|----|----|----|----|----|

| 0 | 1 | 0 |   |   |   |   | Unde | efine | ed | 1  |    |    |    |    |    |

FATAL ERROR RESPONSE. The fatal error response is given when and event occurs that requires the LANIC to be re-initialized. All operations in progress are aborted and pending operations are suspended. The LANIC is in the KERNEL state after giving this response.

| 0 | 1 | 2 | 3 | 4                | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12   | 13   | 14    | 15   |

|---|---|---|---|------------------|---|---|---|---|---|----|----|------|------|-------|------|

| 1 | 1 | 0 |   | Catastrophe Code |   |   |   |   |   |    |    | onal | info | ormai | tion |

Catastrophe code = fatal error type (41H = SW, 42H = HW) Additional information = error number

## **LANIC Resets**

There are three types of resets on the LANIC: power-on reset, hard reset, and soft reset. The power-on reset is the highest priority and the soft reset is the lowest priority. The resets are nested such that a higher priority reset includes all lower priority resets. Table 3-1 summarizes the LANIC reset operations.

Table 3-1. LANIC Resets and their Effects

| AFFECTED<br>FUNCTION                                                                  | PON                                                               | HARDRST                          | INIT<br>IOCL                                                | SOFTRST                                         |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------|-------------------------------------------------|

| MAUPOWER SELFTEST VISIND MHSEN SLVHS MASTER H/S CRFULL MASKF SINTRO SINTR1 Z-80 RESET | OFF<br>YES<br>ON<br>OFF<br>RESET<br>RESET<br>O<br>O<br>O<br>PULSE | OFF YES ON OFF RESET 0 0 0 PULSE | OFF<br>NO<br>ON<br>OFF<br><br>RESET<br>O<br>O<br>O<br>LATCH | OFF<br>NO<br><br>OFF<br><br>RESET<br><br><br>NO |

**POWER-ON RESET.** The PON signal on the backplane causes a power-on reset. The entire hardware and firmware state of LANIC is initialized and all LANIC operations on the backplane cease. When the PON goes active, the LANIC enters the SELFTEST state.

HARD RESET. Hard reset aborts all operations in progress on the LANIC, resets all control registers, and forces the LANIC into the SELFTEST state. Self-test is then performed and the internal status of the firmware prior to the reset is unrecoverable. LANIC commands (except further hard resets) must not be issued until the self-test sequence has completed. At the end of the self-test sequence, the LANIC will go to the KERNEL state, waiting for commands from the host.

Hard reset is started by the backplane commands PON, SRST, IOCL, INIT, WREG14, WREG15, and by activating the self-test switch.

The HARDRST clears the channel interrupt mask flip-flop MASKF, clears both SINTR0 and SINTR1 interrupt requests, and illuminates the VISIND visual indicators (LEDs). In addition, the master handshake enable flip-flop, MHSEN, is cleared.

SOFT RESET. Soft reset suspends all hardware operations in progress and puts the LANIC into the KERNEL state, waiting for further commands. In this way, most of the LANIC's internal state information is preserved. The microprocessor is not reset and information pertaining to the RQ entries remains valid. The firmware is forced to the KERNEL state and communication with the host software is restricted to the CR and SR only.

The soft reset is typically issued when a LANIC failure has been detected by the host (e.g., LANIC is unresponsive). The firmware is thus forced to communicate with the host software. Since self- test has not been performed, diagnostics of the firmware can take place by issuing the MEMORY\_DUMP command.

#### Principles of Operation

Soft reset can be initiated by the LANIC or by host software. The LANIC hardware initiates soft reset by detecting certain system bus errors. These errors are: system bus timeout, memory parity error, bus parity error, or memory bounds violation. System software can initiate a soft reset by writing register 14 (ABORT register) on the LANIC with bit 15=1.

**Z-80 RESET.** The IOCL and INIT commands effect a HARDRST, but the microprocessor remains reset. This feature is useful for diagnostics which need to reset the hardware registers without initiating the self-test sequence. The microprocessor remains reset until a normal HARDRST in issued.

**POWER-FAIL** WARN. When the backplane power-fail warn signal (PFW) is active, the LANIC is prevented from requesting or initiating a system bus master handshake. If the PFW signal becomes active while the LANIC is requesting, but has not yet been acknowledged bus master, then the LANIC backs off from requesting the bus while PFW is active.

#### Self-Test

The LANIC contains a self-test feature that performs tests of internal circuitry and provides a status code indicating the result. Before the execution of each self-test step, the step number is written to the STR and the VISIND registers. When the self-test is complete, the LANIC interrupts the host and enters the KERNEL state where it is ready to accept interactive commands.

MANUALLY INITIATED SELF-TEST. Self-test is manually initiated by the self-test switch on the LANIC card. The location of this switch is shown in figure 2-1 in Section 2.

**REMOTELY INITIATED SELF-TEST.** Self-test is remotely initiated by the backplane command WREG15, or by the backplane signals PON or SRST (Power On or System Reset).

IDLE SELF-TEST. During operation of the LANIC, various tests of hardware are performed when no other tasks are being processed. If a hardware failure is detected, an error code is placed into the STR register and the host interrupt request is set.

VISUAL INDICATORS. Fifteen light-emitting diodes (LEDs) are used on the LANIC card to indicate LANIC activity. The locations of the LEDs are shown in figure 2-1 in Section 2. Eight of the LEDs are used for self-test results and are described in Section 4; the remaining seven LEDs are used for indicating activity on the LANIC card and the LAN network. These LEDs are described in the paragraph "LEDs", later in this section.

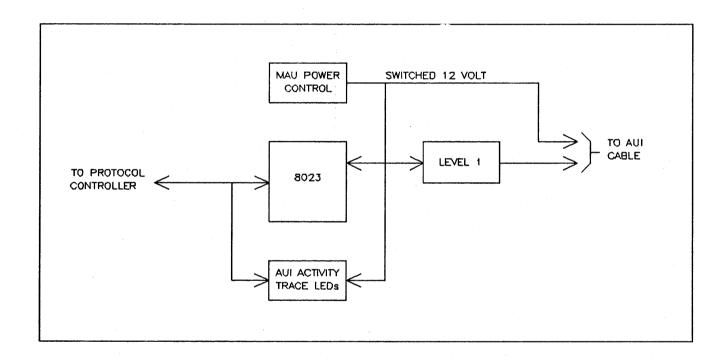

# Attachment Unit Interface (AUI) Circuitry

The Attachment Unit Interface (AUI) is the interface between the LANIC board and the Medium Attachment Unit (MAU). The AUI, MAU, and the coaxial trunk cable comprise an analog network. The analog network provides the physical connection between Local Area Network (LAN) nodes.

The AUI cable has a 15-pin D-type connector on each end for connecting the LANIC to the MAU. The pin connections for the AUI cable are presented in Section 2.

A block diagram of the AUI interface circuitry is shown in figure 3-2. The AUI interface consists of four blocks:

- A type 8023 chip

- · Level 1 circuitry

- MAU power control

- AUI activity trace LEDs

Figure 3-2. AUI Interface Block Diagram

The 8023 chip performs the following functions:

Decodes receive clock

Decodes receive data

Generates transmit clock

Encodes transmit data with clock

Decodes CONTROL IN

Detects carrier present

Loops transmit data to receive data for diagnostics

The AUI side of the 8023 chip consists of two balanced receivers (DATA 5IN + CONTROL 5IN) and one balanced driver (DATA 5OUT). The signals from these circuits are put through a passive balancing network and are then transformer coupled to the AUI pairs.

#### Principles of Operation

MAU POWER CONTROL CIRCUIT. The MAU power control circuit provides three functions:

#### 12-Volt Switch

The Z-80B MPU can turn the 12V to the AUI on or off.

#### 12-Volt Current Protect

If the current to the AUI goes above 1.2A, the power control circuit causes the +12V to turn off, thus protecting the LANIC and the system from shorts in the AUI cable or the MAU. The Z-80B will detect the fault and attempt to restart MAU power. If the attempt fails, the Z-80B notifies the host system of the fault.

#### 12-Volt Sense

The Z-80B can determine if power to the AUI is on or off. However, it is not able to accurately measure the exact voltage being supplied. The IEEE 802.3 standard requires VP (+12V) to be greater than 11.28 volts. It is possible that the +12-volt power supply may be adjusted low enough such that less than 11.28 volts is present at the LANIC edge under load. This will cause difficulty for the HP 30241A MAU only when AUI cables near the maximum length are used. If faulty MAU operation is suspected, and MAU replacement has not corrected the problem, the VP voltage should be checked. The VP voltage can be checked by attaching an accurate voltmeter between the +12V and GND test points on the LANIC. If the voltage under load is found to be less than 11.28V, the system +12V power supply must be checked and adjusted to the upper end of the allowable range. If the power supply is already set at the upper end of its range, the LANIC may need to be replaced. Consult the appropriate CE Handbook for details.

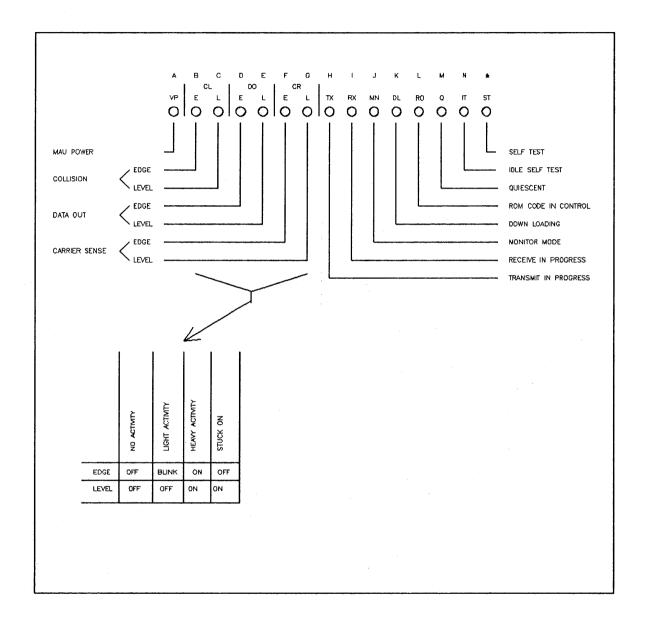

#### LEDs.

The LANIC uses 15 LEDs to monitor activities on the card and the LAN network. The locations of the LEDs are shown in Section 2, figure 2-1; the labels and functions of the LEDs are shown in figure 3-3.

The seven LEDs labeled A through G monitor activity on the AUI interface. The eight LEDs labeled H through N and \* monitor LANIC MPU activity. A great deal of information about the state of the network and the LANIC and system software can be gained by studying the LEDs. They are provided as an aid in problem detection and resolution.

Each of the 15 LEDs is labeled with two different labels. The single alphabetic labels are helpful for quick reference to the LEDs; the two-letter mnemonics are intended to remind users of the function being indicated by the LED.

Figure 3-3. LANIC LEDs

The meanings of the eight MPU (microprocessor unit) activity monitoring LEDs are as follows:

#### Mnemonic MPU Activity in Progress TX On when the LANIC is processing and transmitting a frame. RX On when the LANIC is processing a frame that was received at an address which the LANIC recognized as its own. MN On when the LANIC is monitoring all link activity, or is monitoring activity sent to a particular address not its own. DL On when the LANIC receives a command from the SPU (system processor unit) to start downloading operating firmware. Off when the SPU commands the MPU to begin to execute the downloaded feature. RO On when ROM-resident firmware is being executed by the MPU. when downloaded firmware is being executed by the MPU. Q On when the MPU is quiescent. During such times, it is checking for activity that requires attention. IT On when the MPU is executing an idle test of internal LANIC circuitry. During idle test, the MPU tests hardware on the LANIC that can be exercised without affecting readiness to process frames. The idle test also runs before the operational on the link. ST On when the MPU is executing the ROM-resident self-test, which verifies proper operation of the LAN hardware subsystem. When the ST LED is lit, the other seven MPU activity LEDs are interpreted as self-test progress and failure indicators, rather than according to the mnemonics given above. For details of the use of self-test, see Section 4 of this manual and the LAN/3000 Diagnostic and

The seven AUI activity LEDs are intended to be used as aids in determining activity on the network, and whether the source of this activity is this node or some other node on the network. These seven LEDs monitor the four functions shown below.

Troubleshooting Guide, part number 30242-90003.

| Mnemonic | Function Monitored                                                                                                                                                                                                                                                                                                                  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DO       | $\underline{D}\text{ata}$ $\underline{O}\text{ut}$ . On when data is transferred from this LANIC to the Data $\overline{O}\text{ut}$ $A\overline{U}I$ pair.                                                                                                                                                                         |

| CL       | Collision Detect. On when a collision is detected by the MAU on this node. Since the HP 30241A MAU detects collisions whether it is transmitting or not, the CL indicator comes on for every collision that occurs on this coaxial cable. The CL indicator does not come on when the MAU sends an SQE heartbeat after transmission. |

- CR <u>CaRrier Sense</u>. On when data is detected coming into the node on the Data In AUI pair, or on when the collision function is detecting collisions. The CR indicator does not come on due to SQE heartbeat.

- VP Voltage Plus. This LED indicates the voltage present on this 12-volt supply lead to the MAU.

Each of the indicators for DO, CL, and CR consist of a pair of LEDs, labeled E and L. The pair is driven in such a manner that all conditions of activity from occasional isolated events to continuous events can be distinguished by the unaided eye. This is accomplished in the following manner:

Each time that the event being monitored by an LED pair begins, the *E* LED is turned on and remains on for 6 msec regardless of the length of the event. The *L* LED turns on at the beginning of the event and turns off at the end of the event.

Following this algorithm, a single isolated event of short duration produces a 6 msec blink of the E LED, and the L LED is on for the length of the event, which is short. Therefore, the L LED appears to remain of f.

As the frequency of events of short duration increases, the E LED appears to be constantly lit, and the L LED begins to glow.

When short duration events occur constantly, both the E and L LEDs will appear to be constantly lit.

A single event of very long duration produces a single 6 msec blink of the E LED at the beginning of the event, and the L LED turns on and stays on for a long time, until the event is completed.

Continuously occurring events of very long duration will cause the E LED to blink at the beginning of each event for 6 msec, and the L LED will appear to be constantly lit.

Events on a normally-operating network are all of short duration. For instance, a maximum length frame requires only 1.2 msec to transmit; a minimum length frame requires only 51 µsec to transmit. Collisions have a maximum duration of only 49 µsec. For events of short duration such as these, the E and L LEDs can be visualized as a sort of two-column bar graph. Frequency of activity is increasing as the frequency of flashing of the E LED increases while the L LED is off or very dim. When the E LED is always on, the L LED indicates further increase in activity by becoming brighter and brighter until it reaches full intensity. This state of the E and L LEDs indicates continuous short events.

To understand the indications given by the DO, CL, and CR LEDs, it is necessary to understand how the signals that drive these LEDs are related to the signals on the AUI cable.

**DO LED PAIR.** The event indicated by the DO LED pair is the enabling of the data encoder by the protocol controller on the LANIC. The event begins when the encoder is turned on. While the encoder is on, a continuous stream of encoded data bits is transmitted by the LANIC to the DO AUI pair. The event ends when the data encoder is disabled. When the encoder is disabled, data bits are no longer sent to the DO pair. The transmission of a single frame to the AUI DO pair is one event, and will cause the E LED to blink on for 6 msec. The L LED will be lit for the length of time required to transmit the data bits to the AUI pair, a maximum of 1.2 msec for a maximum length frame.

CL LED PAIR. The event indicated by the CL LED pair is the occurrence of the Signal Quality Error (Collision) signal on the Control In pair of the AUI cable. When the HP 30241A MAU, whether it is transmitting to the coaxial cable or not, detects a collision on the cable, it sends the SQE signal to the LANIC on the CI pair. SQE is signalled by a 10 MHz signal on the CI pair. The event begins when the first transition is received at the LANIC, and ends 200 nsec after the last transition is received.

The SQE heartbeat, which is a short burst of 10 MHz signal on the CI pair after each transmission by the LANIC on DO, does not cause the E LED to blink, although it does cause the L LED to light for approximately 1  $\mu$ sec, which is too short to be seen. Likewise, no collision occurring on the network within 5.3  $\mu$ sec of cessation of transmission by the LANIC will light the E LED. The SQE heartbeat is blocked from triggering the E LED so that the CL LEDs will indicate the frequency of collisions occurring on the network.

CR LED PAIR. The event indicated by the CR LED pair is the reception of data on the Data In pair in the AUI cable, or the occurrence of the collision event described above. The event begins when the first data transition arrives on the AUI DI pair, or when the collision event begins, whichever occurs first. The event ends 200 nsec after the last data transition on the DI pair, or when the collision event ends, whichever occurs last.

H THROUGH N AND \* LEDs. When the LANIC has been reset either by power-up of the system or by the operating software, all eight of the MPU activity indicators (LEDs H through N and \*) will be on continuously. This indicates that the MPU is not executing. Additionally, the VP LED will be off, which indicates that the MAU is not powered. The other AUI activity indicator LEDs will all be off.

After the LANIC has successfully passed self-test, and the pass code pattern has been displayed as required, the \*LED will be off, and the other seven MPU activity indicator LEDs will now indicate the MPU activity. The \*LED being off indicates that the H-N LEDs are to be interpreted as individual activity indicators according to their two-letter mnemonics. (See the following paragraphs.)

TX, RX, MN, DL, RO, Q, AND IT LEDs. When self-test passes, the SPU is interrupted and notified of the event. Between the time that this interrupt is given and the time when the SPU begins to access the LANIC, the RO and Q LEDs will be lit. This indicates that the LANIC is executing ROM code and is quiescent, while waiting for the SPU to take control. In addition, the VP LED will be lit, indicating that the MAU is powered. Any activity on the network coaxial cable will be indicated by the state of the CL and CR LED pairs. The LANIC will never transmit in this state, and therefore, the DO LED pair will remain inactive.

When the SPU prepares the LANIC for operation, it first must download the operating firmware from system memory to the LANIC. When this process begins, the DL LED turns on, and the Q and IT LEDs will go off. After each download command, the Q LED lights for a few milliseconds. At least seven download commands occur, but they may not be separately distinguishable. However, the pattern that occurs on one working system will occur on all other working systems, so if suspicious, compare the download pattern on the suspected system with a system that works.

After the download is complete, the SPU will instruct the MPU to begin to execute the downloaded firmware. When this occurs, the RO and DL LEDs will go off. The Q and IT LEDs will turn on.

A short time later the SPU will instruct the LANIC to set its individual address. When this occurs, the LANIC performs a duplicate address check, which is accomplished by transmitting 10 frames to the network with a 500 msec separation between frames. The TX and the DO E LED will both come on for each of the 10 frames. In addition, the CR E LED will indicate that the frames were sent to the coaxial cable and caused the carrier to come on. If collisions are encountered, the frames will be retried up to 15 times each, with resultant activity indicated by the CL LEDs. The RX LED will not light during the duplicate address check due to our own transmission, even though the duplicate address check frame is addressed to the transmitting LANIC. If the RX LED lights during duplicate address checking, it is due either to a duplicate station being detected or to an ordinary frame being address to the LANIC. If a reply to the duplicate address check is received, this will cause the address check to fail, no further check frames will be sent, and the system software will close the link and clear the LANIC, forcing all the LANIC MPU LEDs to come on and stay on.

If the duplicate address check passes, the link is opened, and frame transmission and reception will commence. The LEDs will indicate activity as it occurs.

During normal network operation, frame transmission causes the LEDs to operate in the following manner, assuming that the network and the LANIC were both idle before the transmit request arrived at the LANIC from the SPU:

While idle, the VP, Q, and IT LEDs are on.

When the MPU begins processing the transmit command, the Q and IT LEDs go off, and the TX LED comes on. The LANIC begins the transmit process by reading the frame from the system to the on-card memory.

Once the frame is in LANIC local memory, and the network is free, the serial transmission process begins. This causes the DO E LED to light. The DO L LED will also be turned on for the duration of the frame transmission, but this may or may not be visible, depending upon the length of the individual frame being sent.

The serial data reaches the MAU and is transmitted to the coaxial cable. The MAU begins to receive its own signal from the coax, and sends it back down the AUI cable. The LANIC detects data arriving on the DI pair of the AUI cable, and the CR E LED is lit. The CR L LED will also be lit for the duration of the frame, but this may or may not be visible. If the DO L LED is visible, the CR L LED will also be visible for approximately the same length of time.

If no collision is encountered, the CR and DO E LEDs will go off after 6 msec, followed quickly by the transmit LED going off, and the Q and IT LEDs coming on. If a collision is encountered, the CL E LED will come on, and the frame will be retransmitted up to 15 times. The retransmissions will cause the DO and CR E LEDs to appear to be on, and the DO and CR L LEDs will probably appear to be partially lit, with the intensity of the L LEDs determined by frame length, number of retransmissions required, and the time separation of the retransmissions. The CL LEDs will also display behavior similar to the CR and DO LEDs if multiple retransmissions are required before the frame is successfully transmitted. In the collision case, it must be remembered that other network activity will also cause the CL and CR LEDs to light, and the activity caused by the LANIC will be superimposed on the network activity being displayed by the CR and CL LEDs. A little experience at observing the LEDs will allow the occurrence of single or multiple collisions to be easily distinguished.

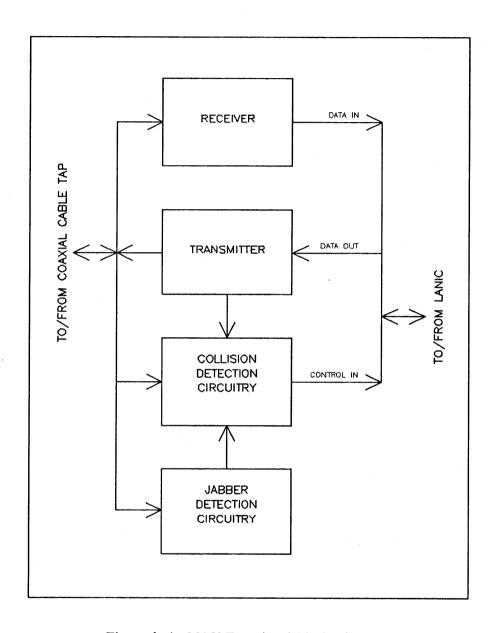

## Medium Attachment Unit

A functional block diagram of the HP 30241A MAU is shown in figure 3-4. As shown, the MAU has four functional areas:

Receive Function. Receives serial data bit streams from the coaxial cable and sends these to the LANIC.

Transmit Function. Accepts serial data bit streams from the LANIC, and transmits this data to the coaxial cable.

Collision Detection. Detects the presence of two or more simultaneous transmissions on the coaxial cable and informs the LANIC of this condition.

Jabber Fault Detection. Detects an abnormally long output data stream ("jabber") from the LANIC, and inhibits transmission to the coaxial cable.

RECEIVER. The coaxial receiver has a high input impedance. (The high impedance is necessary to allow up to 100 users to connect to the coax and not load down the cable.) The data received from the coax is then amplified, shaped, and compensated for attenuation by the coaxial cable. The data is then sent through a cable driver to the LANIC via the twisted pair of the AUI cable. The MAU also has a DC squelch function which turns off the AUI cable driver when no data is present on the coax as indicated by a lack of DC component in signals on the coaxial cable.

Since the receiver passes all data from the coaxial cable to the AUI cable, the receiver also monitors data sent by its own LANIC, thus implementing a local loop-back and monitoring function.

TRANSMITTER. The transmitter accepts data from the LANIC and transmits this data to the coaxial cable. Data is transmitted to the cable using a high-impedance current sink. Current drive of the coaxial cable causes multiple transmitters' signals to add without damage to the transmitters. The coaxial cable driver adheres to the recommended values for drive level specified in the IEEE 802.3 Standard.

COLLISION DETECTION. When a collision occurs on the coaxial cable, the DC voltage on the cable increases in magnitude and the collision detection circuitry senses this condition. The LANIC is informed of this condition by a signal sent from the MAU on the CONTROL IN (CI) cable pair (part of the AUI cable). The collision detection scheme employed implements receiver-based collision detection. This means that the presence of two or more transmitters can be detected even when the MAU is not transmitting.

To insure that the collision detection circuitry is working satisfactorily, it is tested each time a data packet is sent. At the end of each transmitted packet, a 'Heartbeat', or SQE (Signal Quality Error) test signal (which is a short burst of the collision indicator signal) is sent to the LANIC.

Figure 3-4. MAU Functional Block Diagram

#### Principles of Operation

JABBER FAULT DETECTION. If the LANIC should try to send data for a time longer than the longest data packet allowed, the network throughput could be affected. (If the LANIC transmitted continuously, no other node could access the network.) The jabber fault detection circuitry detects any attempt by the MAU to transmit for longer than 25 milliseconds, and prevents this from happening by turning the transmitter off permanently. The LANIC is informed of the shut-off condition by a continuous signal (SQE) on the CI pair of the AUI cable. The MAU is prevented from transmitting until it is powered off and then on again.

# **MAINTENANCE**

SECTION

4

This section contains general maintenance instructions for the LANIC card. Included is the repair philosophy for the LANIC card and information on the self-test. See the LAN/3000 Diagnostic and Troubleshooting Guide, part number 30242-90003, for detailed procedures to be used in troubleshooting networks containing the LAN/3000 link, and for diagnostic procedures to be used in isolating failures in LAN/3000 nodes to the field replaceable assembly.

#### CAUTION

SOME OF THE COMPONENTS USED IN THIS PRODUCT ARE SUSCEPTIBLE TO DAMAGE BY STATIC DISCHARGE. REFER TO THE SAFETY CONSIDERATIONS INFORMATION AT THE FRONT OF THIS MANUAL BEFORE HANDLING THE CARD.

#### REPAIR PHILOSOPHY

Field repair of the LANIC cards is limited to the replacement of the card itself. To exchange a LANIC card, remove it from the system and prepare it for reshipment to Hewlett-Packard in accordance with the instructions presented in Section 2.

#### SELF-TEST

A self-test is included in ROM on the LANIC card. The self-test runs at power-on, when the LANIC TEST (RESET) switch on the LANIC card is pressed, or when invoked by the LAN diagnostic.

#### NOTE

The self-test consists of several tests which check approximately half the circuitry on the LANIC card as well as performing a simple test of the AUI cable and the MAU. The LAN/3000 link diagnostic must be run to perform a complete test of the LANIC card. See the LAN/3000 Diagnostic and Troubleshooting Guide, part number 30242-90003 for a description of the diagnostic.

#### CAUTION

PRESSING THE LANIC TEST SWITCH PERFORMS A HARD RESET ON THE LANIC CARD BEFORE THE SELF-TEST IS INITIATED. NETWORKING OPERATIONS IN PROGRESS WILL BE DISRUPTED BY PRESSING THE RESET SWITCH. ONCE SELF-TEST HAS STARTED, ALLOW IT TO COMPLETE PRIOR TO PRESSING THE SWITCH AGAIN. PRESSING THE SELF-TEST SWITCH WHEN THE LINK IS OPEN OR WHILE SELF-TEST IS ACTIVE HAS A SLIGHT POSSIBILITY OF CRASHING THE SYSTEM.

#### Maintenance

To run the LANIC self-test, perform the following:

1. Determine that the LANIC is not in use. This can be done by typing

:SHOWDEV nn

at any terminal on the system, where nn is the logical device number of the LANIC. If you see