## 27140A

## SIX CHANNEL MODEM MUX

### FEATURES

o Six full duplex modem/terminal channels

o EIA RS-232-C AND CCITT V.28 compatability

o Selectable number of bits/char: 5,6,7, or 8 plus partity

o Selectable number of stop bits: 1,1.5,2

o Two transmission modes: Full duplex hardwire or modem

o Selectable parity: None, odd, or even

o Internal clock

o Programmable baud rate: 50,75,110,134.5,150,300,600,900, 1200,1800,2400,3600,4800,7200, 9600, or 19200. Default is 9600

o Break detection and generation

- o Programmable device controlled X-ON/X-OFF handshaking

- o On board self-test which will automatically test frontplane circuitry if test hood is present

- o Timer for various modem functions

o Optional interrupt for asynchronus event sensed

TERMINAL HANDSHAKING X-ON/X-OFF - A Peripheral paces data transfer - A to stop card: X-OFF + To start xmit: X- ON ENQIACE -A Sender paces data

-> Sender sends ENQ to request start -> Receiver responds with ACK

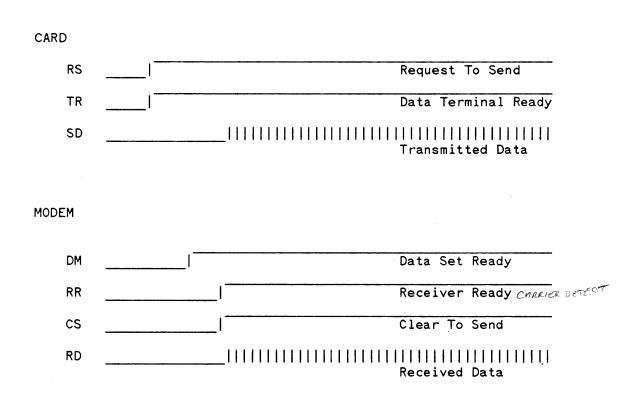

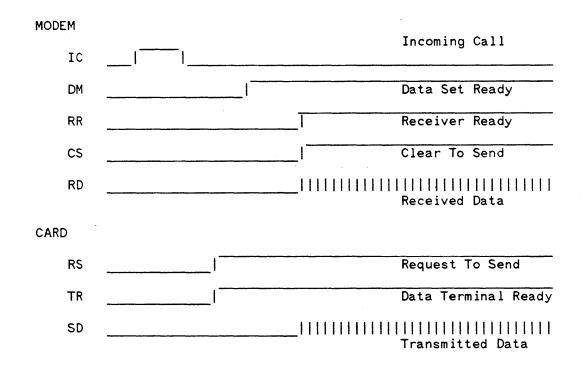

## MODEM CONTROL

|                            | Card<br>Abbr               | Common<br>Abbr.                              | Description                                                                                                                                    |  |

|----------------------------|----------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| I<br>N<br>P<br>U<br>T<br>S | RD<br>CS<br>RR<br>DM<br>IC | RD<br>CTS<br>CD <sup>CAND</sup><br>DSR<br>RI | Received Data<br>Clear To Send<br>Receiver Ready (Received Line Signal Detect)<br>Data Mode (Data Set Ready)<br>Incoming Call (Ring Indicator) |  |

| O U<br>T P<br>U T<br>S     | SD<br>RS<br>TR<br>SR       | SD<br>RTS<br>DTR<br>SR                       | Transmitted Data<br>Request To Send<br>Data Terminal Ready<br>Frequency Select                                                                 |  |

|                            | SG                         |                                              | Signal Ground                                                                                                                                  |  |

Modem Line Definitions

DM: Local modern is ready RR! Remote modern is ready RD: Data, valid only while RR is active Cs: Remote receiver ready to receive

### CARD CALLS OUT

.

## REMOTE MODEM CALLS

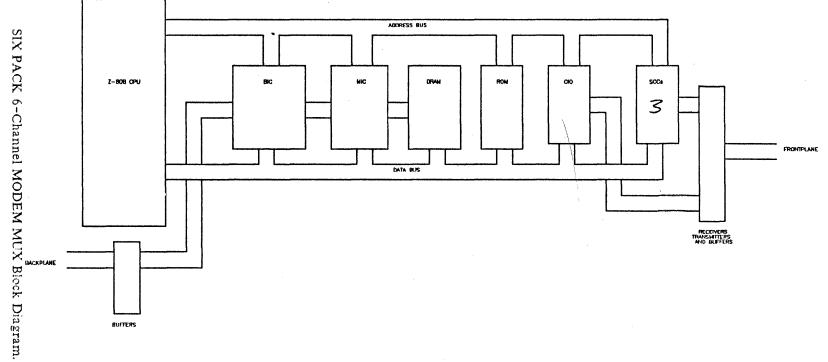

# FUNCTIONAL BLOCK OVERVIEW

CPU & COMTROL

Ilo control PAL Clock divident Ilo enable PAL

Frontplane Interface

75189A Receivers

75188A Drivers

JZ-BZ +SU line not used

Data Com Circuit 3 SCCS 1 CIO (Parallel I/Of counter(timer) XMTR-DIS forces marking state

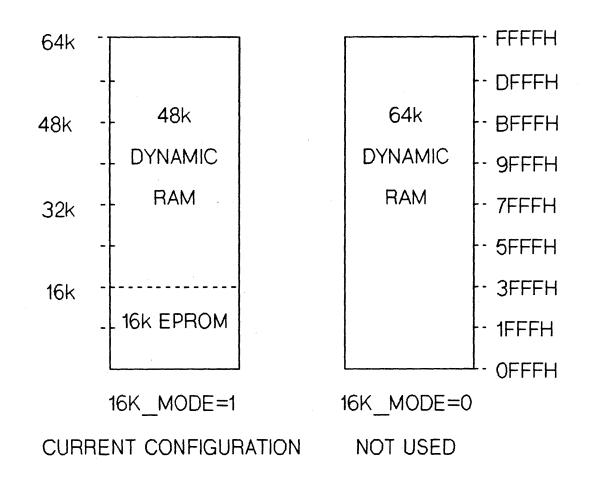

Memory Interface MIC Chip Hidden 161= unused

#### MEMORY ADDRESS SPACE

#### ABEHPD1

MEMORY INTERFACE CONTROLLER

A controls up to Y8K of DRAM

A controls up to 16K of ROM

A Two programmable DMA channels

A 280 computible interrupts

A 12 programmable registers

REGISTER 0 = MIC Configuration Register (read/write) Bit 7 = DM2, which selects which of IRQ1 or IRQ2 is the DMA request sensed by DMA channel B. If DM2 = 1, IRQ2 is sensed If DM1 = 0, IRQ1 is sensed Bit 6 = XNT, external interrupt enable. The IINT line to be sensed as an interrupt by the MIC interrupt control when XNT = 1. Bit 5 = DEND, when this bit = 1, the function of OEND pin is disabled. Bit 4 through 0 are not used. NOTE: All of the above bits are zeroed upon reset. REGISTER 1 = DMA B Upper Byte of Memory Address (write only) NOTE: This register is not effected by reset. REGISTER 2 = DMA B Lower Byte of Memory Address (write only) NOTE: This register is not effected by reset. REGISTER 3 = DMA B Configuration Register (read/write) Bit 7 = DMA channel B enable bit. 1 = enable, 0 = disable.Bit 6 = Transfer from/to memory. 0 =from memory, 1 =to memory. Bit 5 = Direction of memory address counter. 0 = increment, 1 = decrement.Bit 4 = DMA channel B interrupt enable. 0 = disable interrupt,1 = enable interrupt. Bit  $3 = \setminus$ Bit  $2 = \setminus$  Upper four bits of transfer Bit 1 = / byte count for DMA B Bit 0 = /NOTE: Bits 4 through 7 are zeroed upon reset. Bits 0 through 3 are not effected by reset. REGISTER 4 = Lower Byte of Transfer Byte Count (read/write) Channel B. NOTE: This register is not affected by reset. REGISTER 5 = DMA B I/O Port Address Register (read/write) NOTE: This register is not effected by reset. REGISTER 6 = DMA A Upper Byte of Memory Address (write only) (same as Register 1) REGISTER 7 = DMA A Lower Byte of Memory Address (write only) (same as Register 2) REGISTER 8 = DMA A Configuration Register (read/write) (same as Register 3)

- REGISTER 9 = Lower Byte of Transfer Byte Count channel A (read/write) (same as Register 4)

- REGISTER A = DMA A I/O Port Address Register. (same as Register 5)

- REGISTER B = Interrupt Vector (read/write) Bits 3 through 7 contain bits 3 through 7 of the interrupt vector address.

Bits 1 and 2 are modified automatically by the highest priority device requesting interrupt service. The following function shows how bits 2 and 1 are determined based on the interrupts sensed at interrupt acknowledge time.

| +      | DMA A | DMA B | +        | +<br>  VE | CTOR BI | rs | +<br> <br>+ |

|--------|-------|-------|----------|-----------|---------|----|-------------|

|        |       |       |          | 2         | 1       | 0  | +           |

|        | 1     | X     | X<br>  X |           | 0       | 0  | -<br> <br>  |

| <br> + | 0     | 0     | 1<br>    | 1         | 0<br>+  | 0  | <br> <br>+  |

where X = don't care.

Bit 0 is always a logical zero.

NOTE: This register is not effected by reset.

I/O A DORESSES

|   | I/O PORT FUNCTION   |      |   |       |   |   |     |   | I/O  <br>PORT   REF | REF  |     |

|---|---------------------|------|---|-------|---|---|-----|---|---------------------|------|-----|

|   |                     | 1 71 | 6 | 5     | 4 | 3 | 2   | 1 | 0                   | ADDR | DSG |

| - | MIC REGISTER 0      | 1    | 1 | 1     | 0 | 0 | 0   | 0 | 0                   | EOH  | U57 |

|   | MIC REGISTER 1      | 1    | 1 | 1     | 0 | 0 | 0   | 0 | 1                   | E1H  |     |

|   | MIC REGISTER 2      | 1    | 1 | 1     | 0 | 0 | 0   | 1 | 0                   | E2H  |     |

|   | MIC REGISTER 3      | 1    | 1 | 1     | 0 | 0 | 0   | 1 | 1                   | E3H  |     |

|   | MIC REGISTER 4      | 1    | 1 | 1     | 0 | 0 | 1   | 0 | 0                   | E4H  |     |

|   | MIC REGISTER 5      | 1    | 1 | 1     | 0 | 0 | 1   | 0 | 1                   | E5H  |     |

|   | MIC REGISTER 6      | 1    | 1 | 1     | 0 | 0 | 1   | 1 | 0                   | E6H  |     |

|   | MIC REGISTER 7      | 1    | 1 | 1     | 0 | 0 | 1   | 1 | 1                   | E7H  |     |

|   | MIC REGISTER 8      | 1    | 1 | 1     | 0 | 1 | 0   | 0 | 0                   | E8H  |     |

|   | MIC REGISTER 9      | 1    | 1 | 1     | 0 | 1 | 0   |   | 1                   |      |     |

|   | MIC REGISTER 10     | 1    | 1 | 1     | 0 | 1 | 0   | 1 | 0                   | EAH  |     |

|   | MIC REGISTER 11     |      | 1 | 1     | 0 | 1 | 0   | 1 | 1                   | EBH  |     |

|   |                     |      |   |       |   | • |     |   |                     |      |     |

|   | BIC REGISTER O      | 1    | 0 | 1     | 1 | x | 0   | 0 | 0                   | вон  | U42 |

|   | BIC REGISTER 1      | 1    | õ |       | 1 | x | õ   | 0 | 1                   | B1H  | 012 |

|   | BIC REGISTER 2      | 1    | 0 |       | 1 |   |     | 1 | 0                   | B2H  |     |

|   | BIC REGISTER 3      | 1    | 0 |       | 1 |   |     |   | 1                   | ВЗН  |     |

|   | BIC REGISTER 4      | 1    | 0 |       | 1 |   |     | 0 |                     | B4H  |     |

|   |                     | -    | 0 | 1     | 1 | x |     |   |                     | B5H  |     |

|   | BIC REGISTER 5      | 1    | 0 | 1     | 1 | x | 1   | 1 | 0                   | B6H  |     |

|   | BIC REGISTER 6      |      |   | ,<br> |   |   | -   | 1 | 0                   | воп  |     |

|   |                     | •    | • |       |   |   | v   | ^ | ~                   | 2011 |     |

|   | SCC 0: CH B CONTROL | 0    | 0 |       | 1 |   | X   | 0 | 0                   | 30H  | U85 |

|   | SCC 0: CH B DATA    |      |   | 1     |   |   | X   |   | 1                   | 31H  |     |

|   | SCC 0: CH A CONTROL | 0    |   | 1     |   | X |     | 1 | 0                   | 32H  |     |

|   | SCC 0: CH A DATA    | 0    | 0 | 1     | 1 | Х | Х   | 1 | 1                   | 33H  |     |

|   | SCC 1: CH B CONTROL | 1    | 0 | 0     | 1 |   | х   | 0 | 0                   | 9 ÅH | U73 |

|   | SCC 1: CH B DATA    | 1    | 0 | 0     | 1 | Х | Х   | 0 | 1                   | 95H  |     |

|   | SCC 1: CH A CONTROL | 1    | 0 | 0     | 1 | Х | Х   | 1 | 0                   | 96H  |     |

|   | SCC 1: CH A DATA    | 1    | 0 | 0     | 1 | Х | х   | 1 | 1                   | 97H  |     |

|   | SCC 2: CH B CONTROL | 1    | 1 | 1     | 1 | x | х   | 0 | 0                   | F8H  | U83 |

|   | SCC 2: CH B DATA    | 1    | 1 | 1     | 1 | Х | Х   | 0 | 1                   | F9H  |     |

|   | SCC 2: CH A CONTROL | 1    | 1 | 1     | 1 | Х | Х   | 1 | 0                   | FAH  |     |

|   | SCC 2: CH A DATA    | 1    | 1 | 1     | 1 | X | X   | 1 | 1                   | FBH  |     |

|   | CIO PORT C          | 1    | 0 | 1     | 0 | x | x   | 0 | 0                   | АОН  | U75 |

|   | CIO PORT B          | 1    | õ | 1     | õ | x | x   | 0 | 1                   | A1H  |     |

|   | CIO PORT A          | •    | õ | 1     | õ | x | x   | 1 | o<br>o              | A2H  |     |

|   | CIO CONTROL         | 1    | õ | 1     | õ | x | x   | 1 | 1                   | АЗН  |     |

|   |                     |      | ~ | •     | ~ | ~ | • • | • | •                   |      |     |

## INTERRUPTS

MASEABLE

+ Controlled by 280 commands

- IMO: Set interrupt mode 0, 8080A mode. CPU will execute as an instruction whatever vector the interrupting device outputs.

- IM1: Set interrupt mode 1, CPU will execute a restart from location 38H.

- IM2: Set interrupt mode 2, indirect call using register I and 8 bits from interrupting device as pointer.

I Register Contents | 7 bits from peripheral | 0 | Upper address byte Lower address byte

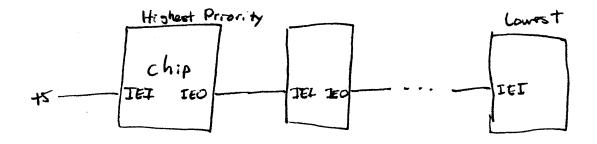

- Prioritized by daisy chain

NON- MASKABLE

-A Restart from address 66H

DAISY CHAIN INTERRUPTS

| PRIORITY | DEVICE                                                                                                                                | SUBFUNCTION                                                                                                                                          |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Highest  | SCC 0           SCC 0 | Channel A Receiver<br>Channel A Transmitter<br>Channel A External/Status<br>Channel B Receiver<br>Channel B Transmitter<br>Channel B External/Status |  |  |  |  |

|          | SCC 1                 | Channel A Receiver<br>Channel A Transmitter<br>Channel A External/Status<br>Channel B Receiver<br>Channel B Transmitter<br>Channel B External/Status |  |  |  |  |

|          | SCC 2<br>SCC 2<br>SCC 2<br>SCC 2<br>SCC 2<br>SCC 2<br>SCC 2                                                                           | Channel A Receiver<br>Channel A Transmitter<br>Channel A External/Status<br>Channel B Receiver<br>Channel B Transmitter<br>Channel B External/Status |  |  |  |  |

|          | CIO<br>CIO<br>CIO<br>CIO<br>CIO                                                                                                       | Counter/Timer 3<br>Port A<br>Counter/Timer 2<br>Port B<br>Counter/Timer 1                                                                            |  |  |  |  |

| Lowest   | MIC<br>MIC<br>BIC                                                                                                                     | DMA Channel A<br>DMA Channel B                                                                                                                       |  |  |  |  |

# OMA PATH

RAM - MIC - BIC

- SILO Buffers used to maintain performance

+ HP-ux use character at a time Ilo

+ Each character stored in a OMA guad in silo buffer Daty

Naty Attribute (errors or spec. cind.) Port number Number of data char=1

### SELF-TEST DETAILS

ROM TEST: The contents of the EPROM are verified using a Cyclic Redundancy Check (CRC) algorithm. The contents of the ROM are read one at a time in 4K blocks. Each byte is included in the algorithm and the resulting 16 bit number is checked against a 16 bit reference number stored in the EPROM. The two numbers must match.

RAM TEST: RAM is checked for stuck-at-0 and stuck-at-1 conditions. The address decoder is also checked. If reset was due to a RST, then the short RAM test is executed. If reset was due to a DCL, then the long RAM test is executed.

SCC TEST: The SCC is checked by performing basic asynchronus internal transmit and receive functions. If a loopback hood is sensed, a loopback is performed through the line drivers and receivers on the external data (RD and SD), and control lines connected to the SCC (RS, RR, CS, TR, and IC).

CIO TEST: Detects stuck-at faults in the data lines, system control, interrupt control, and the ?timers are checked? If the loopback hood is sensed, the modem signal lines (DM and SR) are checked through the line drivers and receivers.

BIC TEST: The BIC is tested for functional faults. Registers which can be tested like RAM by writing to them and then reading them have that done. The chip is also tested using the internal loopback functionality built into it. The testing of the BIC and the backplane receivers and drivers must be done in the system test.

MIC TEST: The MIC is tested for functional faults. The registers which can be written to and read from are tested for stuck-at-1 and stuck-at-0 faults. Some MIC registers cannot be tested (they are read only).

DMA TEST: This test transfers data between memory and the BIC through the MIC. The BIC operates in self-test mode in this operation.

- 1. A 6 byte pattern is written to the BIC FIFO (6 is the FIFO size)

- The BIC is turned around by changing its configuration from host to device, which will cause the BIC to interrupt through the MIC (BIC interrupts are passed to the Z80 through the MIC).

- 3. The interrupt will initiate the BIC interrupt service routine which then sets up the DMA between the BIC and RAM.

- 4. When the transfer is complete, the MIC interrupts the Z80 and the Z80 compares the data in the RAM with the data it wrote into the BIC FIFOs.

When the card has completed self-test successfully, the LEDs are turned off on the card and on the hood and the card jumps to its standard firmware.