# HP 27130A

# EIGHT-CHANNEL MULTIPLEXER (MUX)

**Technical Reference Manual**

Card Assembly: 5061-4929 Date Code: A-2301

HEWLETT-PACKARD COMPANY Roseville Networks Division 8000 Foothills Boulevard Roseville, California 95678 Manual Part No. 27132-90006 Printed in U.S.A. June 1983 The Printing History below identifies the Edition of this Manual and any Updates that are included. Periodically, update packages are distributed which contain replacement pages to be merged into the manual, including an updated copy of this Printing History page. Also, the update may contain write-in instructions.

Each reprinting of this manual will incorporate all past updates; however, no new information will be added. Thus, the reprinted copy will be identical in content to prior printings of the same edition with its user-inserted update information. New editions of this manual will contain new information, as well as updates.

First Edition.....June 1983

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied or reproduced without the prior written consent of Hewlett-Packard Company.

Copyright (c) 1983 by HEWLETT-PACKARD COMPANY

| Section 1              | Page |

|------------------------|------|

| GENERAL INFORMATION    | -    |

| Physical Description   |      |

| Functional Description | 1-1  |

| Equipment Supplied     |      |

| Identification         |      |

| The Product            |      |

| Printed Circuit Card   |      |

| Manuals                |      |

| Specifications         |      |

| Section II Page INSTALLATION                             |

|----------------------------------------------------------|

| Determining Current Requirements                         |

| Firmware (EPROM) Installation2-1                         |

| Jumpers                                                  |

| Memory Configuration Jumper2-3                           |

| Signature Analysis Jumper2-3<br>I/O Channel Interface2-5 |

| I/O Channel Interface                                    |

| Peripheral Device Interface                              |

| Installing the MUX2-12                                   |

| Checkout                                                 |

| Reshipment                                               |

| ection III Pag<br>RINCIPLES OF OPERATION        | 3e |

|-------------------------------------------------|----|

| Functional description                          | -1 |

| System Clocks                                   | -3 |

| Manany Address Cases                            | _2 |

| Memory Address Space                            | -3 |

| I/O Address Space                               | -6 |

| Z-80B Microprocessor CPU                        |    |

| Z-80 SID/2 (Serial I/D Controller)              |    |

| CTC (Counter Timer Circuit                      |    |

| Interfacing to the BIC                          | 19 |

| Memory Interface Circuit (MIC)                  | 24 |

| Register 0 - MIC Configuration                  |    |

| Register 1 - DMA B Upper Byte of Memory Address |    |

| Register 2 - DMA Lower Byte of Memory Address   |    |

| Register 3 - DMA B Configuration                |    |

| Register 4 - Lower Byte of Transfer Byte Count  |    |

| Register 5 - DMA B I/D Port Address             |    |

|                                                 |    |

| Register 6 - DMA A Upper Byte of Memory Address |    |

| Register 7 - DMA A Lower Byte of Memory Address |    |

| Register 8 - DMA A Configuration                | 26 |

| Register 9 - Lower Byte of Transfer Byte Count | . 3-26 |

|------------------------------------------------|--------|

| Register A - DMA A I/O Port Address            |        |

| Register B - Interrupt Vector                  | 3-26   |

| Priority Interrupt Structure                   |        |

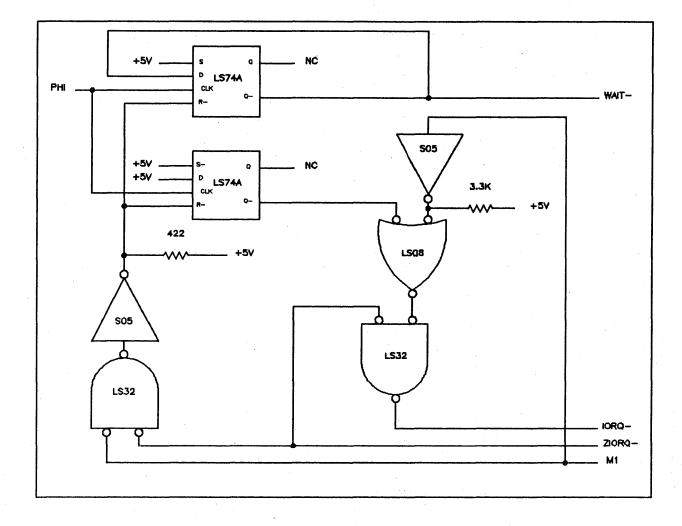

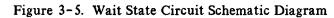

| Wait State Circuits for Interrupt Acknowledge  |        |

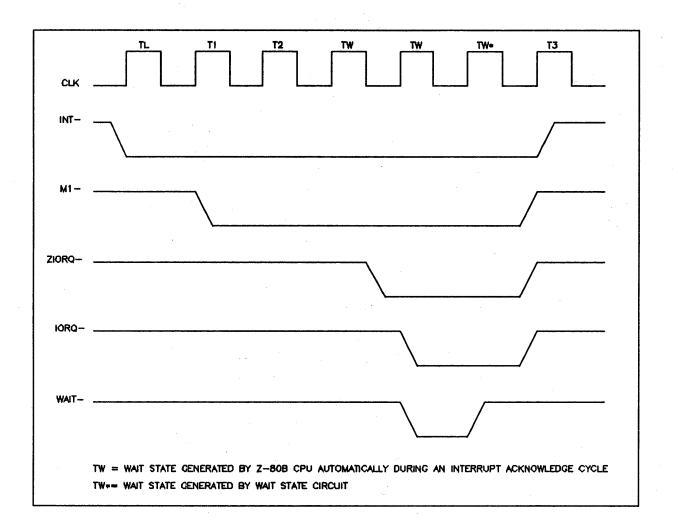

| Diagnostic Hood for External Loop Back         | 3-28   |

| Section IV Pag                           | ge |

|------------------------------------------|----|

| PROGRAMMING                              |    |

| MUX Programmable Features                | -1 |

| Transactions                             | -2 |

| Connect Logical Channel Request Format   |    |

| Capabilities                             | -4 |

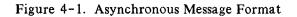

| Receive Character Processing4            | -4 |

| Receive Error Conditions                 | -5 |

| Signal Character                         | -5 |

| Edit Mode                                | -6 |

| Backspace                                | -6 |

| Line Deletion                            | -6 |

| Software Handshake with the Device4      | -7 |

| Host ENQ/ACK Handshake4                  | -7 |

| Device X-ON/X-DFF Handshake4             | -8 |

| Host X-DN/X-DFF Handshake4               |    |

| Single Text Termination4                 | -9 |

| End-On-Count Text Termination4.          | -9 |

| Alert 1 Mode                             | -9 |

| Type Ahead and Echoing                   | 10 |

| Receiving Transparent or Binary Data     | 11 |

| Read Request Length                      | 11 |

| Host Initiated Text Termination          | 12 |

| Transmit Character Processing4-          | 12 |

| Automatic Dutput Separators Appendage    |    |

| Transmitting Transparent or Binary Data  | 12 |

| Buffer Flushing                          | 12 |

| Programming the Receiver and Transmitter | 13 |

| Parity in Transmitted or Received data   | 15 |

| Break Detection                          | 15 |

| Handshake Timer                          | 15 |

| Additional Options                       | 16 |

| Error Handling                           | 16 |

| Quoting Character Mode Option            |    |

| Conditional Output Separators Appendage  | 18 |

| Speed Sense Mode                         | 18 |

| Asynchronous Events                      |    |

| Solicited Events                         | 19 |

| Diagnostics                              |    |

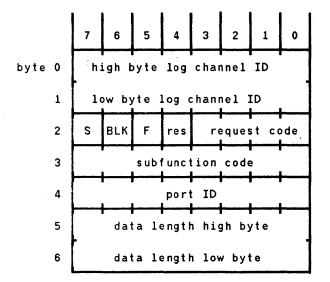

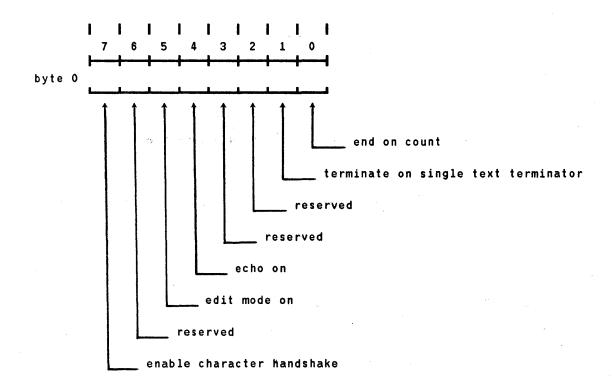

| Connect Logical Channel Request Definitions                   |

|---------------------------------------------------------------|

| Read Device Data, Request Code = 1                            |

| Write Device Data, Request Code = 2                           |

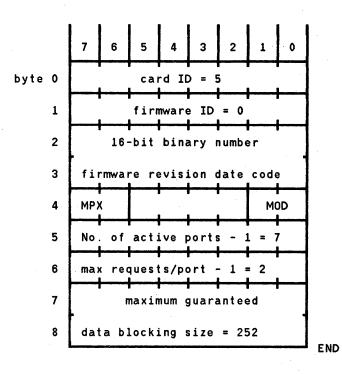

| Read Card Information, Request Code = 4                       |

| Subfunctions 0 through 334-23                                 |

| Subfunction 249 - Read Data Status                            |

| Subfunction 250. Get Card RAM                                 |

| Subfunction 254. Get Card Status                              |

| Write Card Configuration, Request Code = 5                    |

| Subfunction 0                                                 |

| Subfunction 1. Configure Read Option                          |

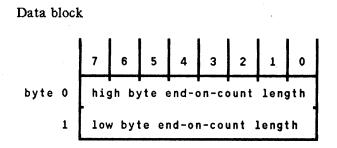

| Subfunction 2. End-On-Count Length                            |

| Subfunction 3. Alert 1 Read Mode                              |

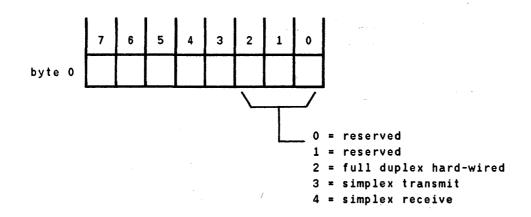

| Subfunction 5. Transmission Mode                              |

| Subfunction 6. Backspace Character                            |

| Subfunction 7. Line Delete Character                          |

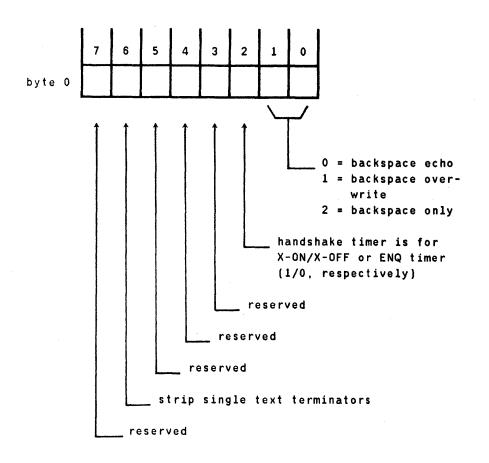

| Subfunction 8. Backspace and Other Options                    |

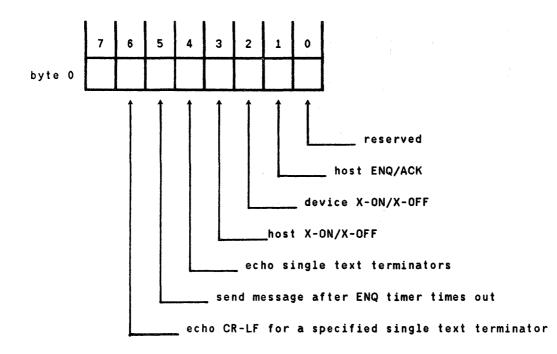

| Subfunction 9. Device Handshake Option                        |

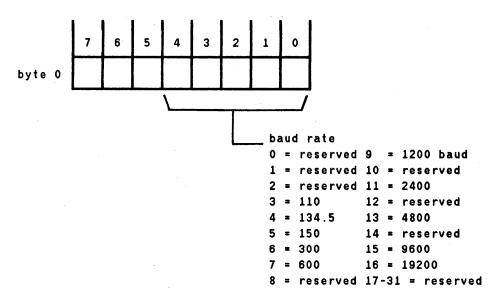

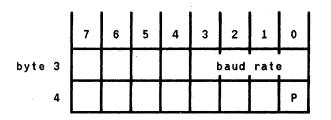

| Subfunction 10. Baud Rate                                     |

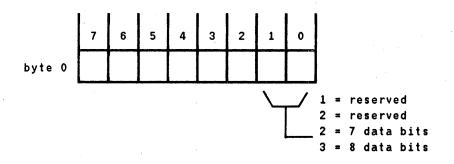

| Subfunction 11. Character Length                              |

| Subfunction 12. Number Of Stop Bits                           |

|                                                               |

| Subfunction 13. Parity                                        |

|                                                               |

| Subfunction 21. Host Interrupt Mask                           |

| Subfunction 22. Host X-ON/X-OFF Characters                    |

| Subfunction 23. Device X-DN/X-DFF Characters                  |

| Subfunction 24. Host ENQ/ACK Characters                       |

| Subfunction 25. Host ENQ/ACK Pacing Counter                   |

| Subfunction 27. Single Text Terminator for Echoing CR-LF 4-37 |

| Subfunction 28. Output Separator                              |

| Subfunction 31. Additional Options                            |

| Subfunction 32. Single Text Terminator                        |

| Subfunction 33. Card Write Register                           |

| Subfunction 34. Set Port ID                                   |

| Control Card, Request Code = 6                                |

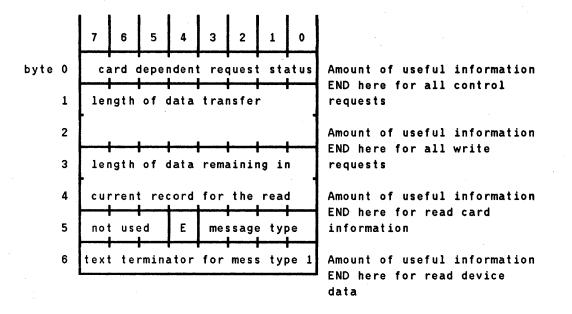

| RTS and WTC Block Definitions                                 |

| Event Block Description                                       |

| Read Status Request Block Definitions                         |

| Identity Information Block Definitions                        |

| Default MUX Configuration                                     |

| Subfunction Assignment Summary                                |

| Read Device Data                                              |

| Write Device Data                                             |

| Read Card Information                                         |

| Write Card Configuration                                      |

| Control Card. 4-51                                            |

| Section V                       | Page |

|---------------------------------|------|

| MAINTENANCE                     | 5-1  |

|                                 |      |

| Section VI<br>REPLACEABLE PARTS | Page |

| Replaceable Parts               | 6-1  |

| Ordering Information            | 6-1  |

| Section VII                     | Page |

| SCHEMATIC DIAGRAMS              | 7-1  |

|                                 |      |

| Appendix A       |            |       | Page |

|------------------|------------|-------|------|

| ASCII CHARACTERS | AND BINARY | CODES | A-1  |

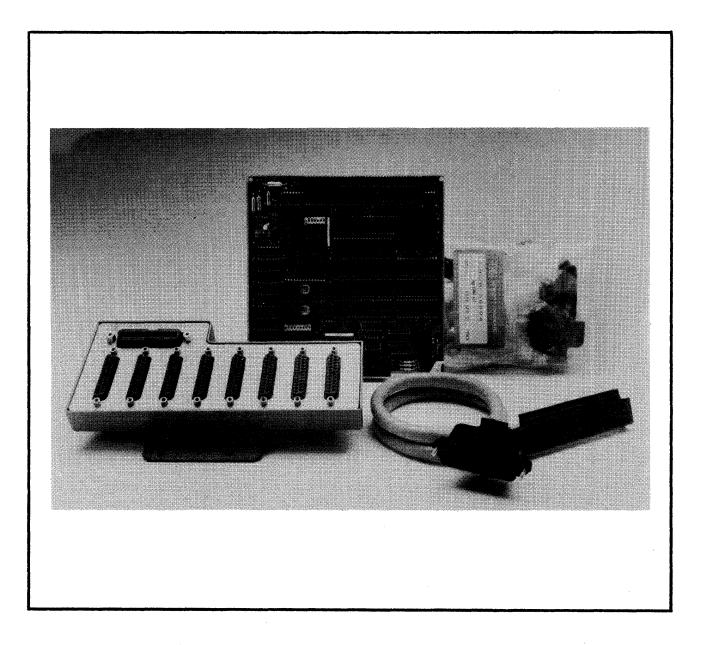

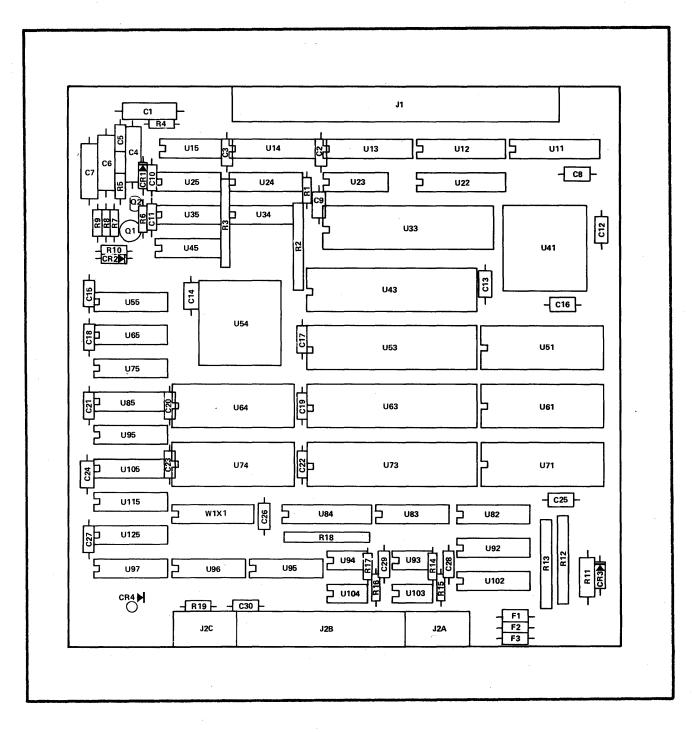

Figure 1-1. HP 27130A MUX

# GENERAL INFORMATION

SECTION

This manual provides general information, installation, theory of operation, maintenance instructions, replaceable parts information, and servicing diagrams for the Hewlett-Packard HP 27130A Eight-Channel Multiplexer (MUX). This chapter contains general information concerning the MUX, and includes a description and specifications.

#### PHYSICAL DESCRIPTION

The HP 27130A Eight-Channel Multiplexer (MUX) is shown in figure 1-1 and consists of a printed circuit card, a cable, an RS-232-C connection box, and an installation manual.

### FUNCTIONAL DESCRIPTION

The HP 27130A Eight-Channel Multiplexer provides multiplexed connections between a Hewlett-Packard computer system and up to eight EIA RS-232-C/RS-423-A/RS-422-A type devices (not including modems).

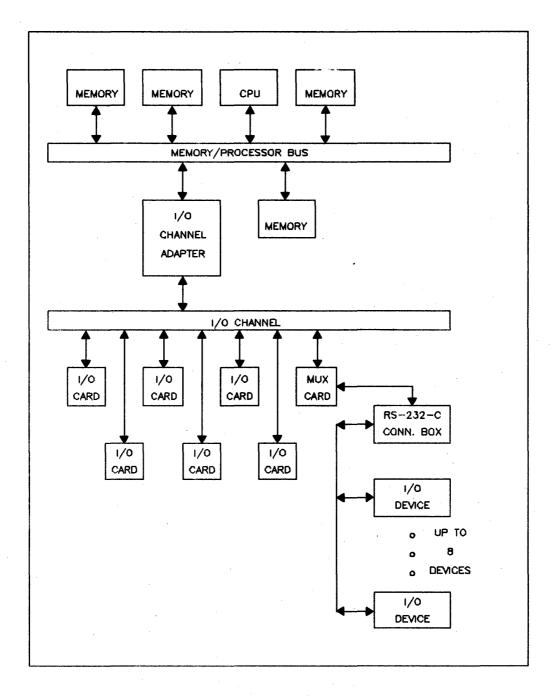

Figure 1-2 shows a Hewlett-Packard computer system using CHANNEL I/O and the MUX. (CHANNEL I/O is a Hewlett-Packard standard defining the physical and electrical characteristics for an I/O system consisting of an I/O channel, an I/O channel adapter, and I/O cards. The MUX is one of the I/O cards.)

Note that the computer system CPU and memory communicate directly along a Memory/Processor Bus (MPB). I/O data to/from peripheral devices reaches the CPU/memory through the I/O channel, the I/O channel adapter, and an I/O card such as the MUX card. The I/O data is received from and transmitted to peripheral devices by the I/O card, which converts device-specific data to a format compatible with the I/O channel, and thus the computer. The I/O channel adapter (see figure 1-2) controls the flow of traffic between the I/O channel and the memory/processor bus.

Figure 1-2. MUX in a Typical Hewlett-Packard Computer System

The HP 27130A uses several of the Z-80A family of microprocessor components to relieve the host computer of much of the overhead. This permits a wide range of configurable transmission modes and formats, thus allowing connections to various CRT terminals, printing terminals, printers, and plotters.

#### EQUIPMENT SUPPLIED

The standard HP 27130A Eight-Channel Multiplexer consists of the following items (see figure 1-1):

Printed circuit card, part number 5061-4929

Seventy centimeter (27.5 inch) RS-232-C connection box cable, part number 8120-4076

RS-232-C connection box, part number 12828-60001

Extension cable kit, part number 12828-60004

EPROMs, part numbers 27130-80003 and 27130-80004

Installation manual, part number 27130-90001

#### **IDENTIFICATION**

#### The Product

Up to five digits and a letter (27130A in this case) are used to identify Hewlett-Packard products. The five digits identify the product; the letter indicates the revision level of the product.

#### Printed Circuit Card

The printed circuit card supplied with the HP 27130A product is identified by a part number marked on the card. In addition to the part number, the card is further identified by a letter and a four-digit date code (e.g., A-2301). This designation is placed below the part number. The letter identifies the version of the etched circuit on the card. The date code (the four digits following the letter) identifies the electrical characteristics of the card with components mounted. Thus, the complete part number on the MUX card is:

5061-4929 A-2301

If the date code stamped on the card does not agree with the date code on the title page of this manual, there are differences between your card and the card described herein. These differences are described in manual supplements available at the nearest Hewlett-Packard Sales and Service Office (a list of Hewlett-Packard Sales and Service Offices is contained at the back of this manual).

#### Manuals

The Installation Manual (part number 27130-90001, supplied with the HP 27130A product) and this manual (HP 27130 Technical Reference Manual, part number 27132-90006) are identified by name and part number. (Note that this manual is part of the HP 27132A Technical Reference Package.) The name, part number, and publication date are printed on the title page of each manual. If the manual is revised, the publication date is changed. In this manual, the "Printing History" page (page ii) records the reprint dates and manual update record. Reprint dates for the Installation Manual are printed on the title page.

## SPECIFICATIONS

Table 1-1 lists the specifications of the MUX.

#### Table 1-1. Specifications

## **FEATURES**

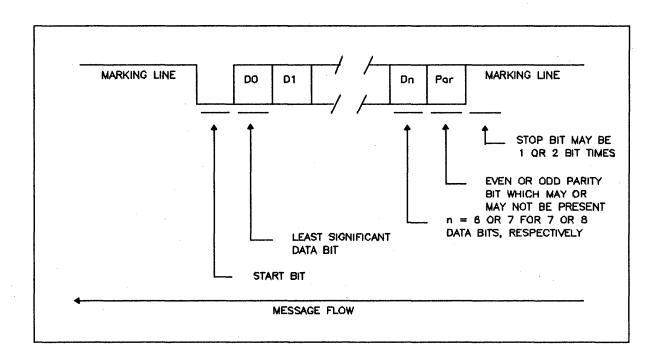

- \* Eight full-duplex asynchronous serial I/O ports

- \* EIA RS-232-C/RS-423-A compatible

- \* Simplex, echoplex, half-duplex, or full-duplex mode operation

- \* Asynchronous baud rates from 110 baud to 19.2K baud

- \* Programmable character size of 7 or 8 bits

- \* 1 or 2 stop bits

- \* Parity: programmable even, odd, forced 1, forced 0, or none

- \* Break detection

- \* Parity, overrun, and framing error detection

- \* Firmware based self-test

- \* Optional device handshakes: host or device controlled X-ON/X-OFF, or host controlled ENQ/ACK

- \* 16-bit parallel interface to I/O channel (backplane)

| PHYSICAL CHARACTER         | ISTICS                                                                                  |

|----------------------------|-----------------------------------------------------------------------------------------|

| Size:                      | 193.04 mm long by 171.45 mm wide<br>by 16.383 mm thick<br>(7.6 by 6.75 by 0.645 inches) |

| Weight:                    | 283.5 grams (0.625 pound)                                                               |

| I/O Channel Interconnects: | 80-pin connector, J1                                                                    |

| Device Interconnects:      | 72-pin connector, J2                                                                    |

| POWER REQUIREMENTS         | 3                                                                                       |

| Current (amps              | a) Power Dissipation (watts)                                                            |

| Voltage (typical) (2-si    | gma) (typical) (2-sigma)                                                                |

| -    |        | -      | ••    | -     |

|------|--------|--------|-------|-------|

| +5V  | 1.672A | 1.890A | 8.36W | 9.45W |

| +12V | 0.052A | 0.062A | 0.62W | 0.74W |

| -12V | 0.075A | 0.085A | 0.90W | 1.02W |

|      |        |        |       |       |

MTBF= 32KHRS (6-19-86)

# the state of the second state of the second

. . .

INSTALLATION

SECTION

11

This section provides information on installing and checking the operation of the MUX.

## DETERMINING CURRENT REQUIREMENTS

The MUX circuit card obtains its operating voltages from the host computer power supply through the I/O channel. Before installing the card, it is necessary to determine whether the added current will overload the power supply. The current requirements of the card are listed in the power requirements entry of table 1-1. Current requirements for all other I/O cards can be found in the appropriate Technical Reference Manuals.

# FIRMWARE (EPROM) INSTALLATION

#### CAUTION

SOME OF THE COMPONENTS USED IN THIS PRODUCT ARE SUSCEPTIBLE TO DAMAGE BY STATIC DISCHARGE. REFER TO THE SAFETY CONSIDERATIONS INFORMATION AT THE FRONT OF THIS MANUAL BEFORE HANDLING THE CARD OR REMOVING OR REPLACING COMPONENTS.

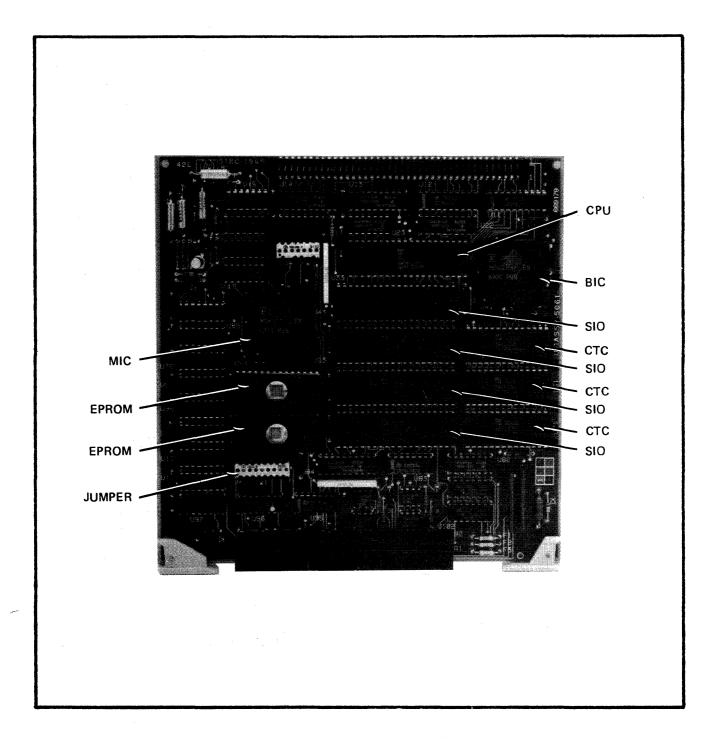

The EPROMs are installed in sockets provided on the MUX card as shown in figure 2-1. Ensure that they are installed properly, and that they have not been damaged or loosened from their sockets during shipping.

Figure 2-1. Component and Jumper Locations

Additionally, when installing or removing EPROMs, guard against bending or breaking the pins on the component. These pins also can become folded between the component and its socket, which would result in intermittent operation of the MUX. In most cases, a bent or damaged pin can be straightened with careful use of needle-nose pliers.

#### JUMPERS

There are two jumpers on the MUX card: a Memory Configuration jumper, and a Signature Analysis jumper. The locations of these two jumpers are shown on figure 2-1.

#### Memory Configuration Jumper

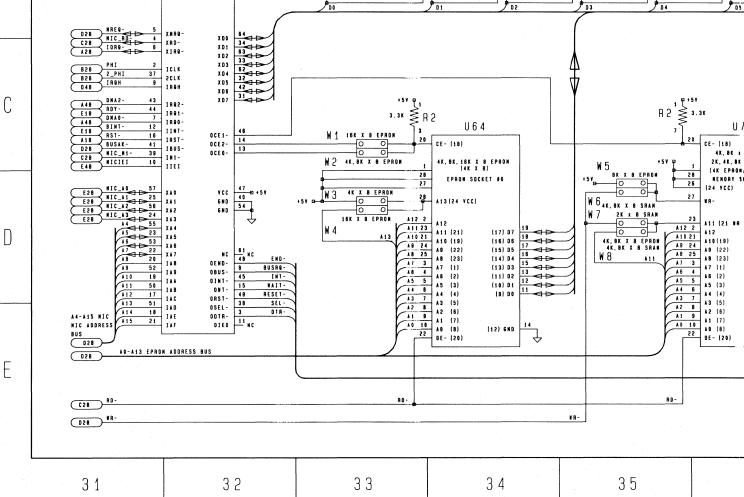

The Memory Configuration jumper, W1, is an internally-connected, 18-pin dual in-line package (DIP) shunt network. The jumper is used to configure the two memory sockets (U64 and U74) to accomodate different kinds of EPROMs and static RAMs. The pin diagram of W1 is shown in figure 2-2, pin functions are listed in table 2-1.

| 18       | 17 | 16 | 15 | 14 | . 13 | 12 | 11 | 10 |  |

|----------|----|----|----|----|------|----|----|----|--|

| <u>_</u> |    |    |    |    |      |    | 1  |    |  |

| 0        | 0  | ٥  | 0  | 0  | 0    | 0  | 0  | 0  |  |

| ) ^      | 8  | C  | D  | E  | F    | G  | н  | J. |  |

| 0        | 0  | ο  | 0  | 0  | 0    | 0  | 0  | 0  |  |

|          | Τ  |    | T  | T  |      | Ţ  |    |    |  |

| 1        | 2  | 3  | 4  | 5  | 6    | 7  | 8  | 9  |  |

Figure 2-2. Memory Configuration Jumper

#### Signature Analysis Jumper

The Signature Analysis jumper, U34, is a 14-pin pre-programmed shunt network. The internal connections of this jumper are set at the factory and are shown in figure 2-3 for information only.

| Table 2-1. | Functions of | the Memory | Configuration Jumper |

|------------|--------------|------------|----------------------|

|            |              |            |                      |

| JUMPER | FUNCTION                                                                                                                                                                                                                                                                                                                                       |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A      | Installed only when a 16K byte EPRDM is used in socket U64.<br>Position A connects DCE2- of the Memory Interface Circuit (MIC)<br>to pin 20 (CE-) of the EPRDM in socket U64. This enables the<br>EPRDM in socket U64 whenever the lower 16K bytes of memory are<br>addressed.                                                                 |

| В      | Installed only when a 4K or 8K byte EPROM is used in socket U64.<br>Position B connects OCEO- of the MIC to pin 18 (CE-) of the 4K<br>byte EPROM or pin 20 (CE-) of the 8K byte EPROM, depending on<br>which EPROM is installed in socket U64. This enables the EPROM<br>in socket U64 whenever the lower 8K bytes of memory are<br>addressed. |

| С      | Installed only when a 4K byte EPROM is used in socket U64.<br>Position C connects +5V power to pin 24 (VDD) of the 4K byte<br>EPROM.                                                                                                                                                                                                           |

| D      | Installed only when a 16K byte EPRDM is used in socket U64.<br>Position D connects A13 of the address bus to pin 24 (A13) of<br>the 16K byte EPRDM.                                                                                                                                                                                            |

| Е      | Installed only when an 8K byte EPROM is used in socket U74.<br>Position E connects +5V power to pin 27 (VPP-) of the 8K byte<br>EPROM.                                                                                                                                                                                                         |

| F      | Installed only when an 8K byte static RAM is used in socket U74.<br>Position F connects WR- of the Z-80B CPU to pin 27 (WE-) of the<br>static RAM, thus enabling the CPU to write to the RAM.                                                                                                                                                  |

| G      | Installed only when a 2K byte static RAM is used in socket U74.<br>Position G connects WR- of the Z-80B CPU to pin 21 (WE-) of the<br>static RAM, thus enabling the CPU to write to the RAM.                                                                                                                                                   |

| н      | Installed only when a 4K or 8K byte EPROM or an 8K byte static<br>RAM is used in socket U74. Position H connects A11 of the Z-80B<br>CPU address bus to pin 23 (A11) of the 4K or 8K byte EPROM or 8K<br>byte RAM, depending on which device is installed in socket U74.                                                                       |

| J      | Installed to enable the MIC wait state signal when slow EPROMs<br>(access time greater than 250 nsec) are used in U64 or U74.                                                                                                                                                                                                                  |

Figure 2-3. Signature Analysis Jumper Internal Connections

# **I/O CHANNEL INTERFACE**

All interface between the MUX and the host computer occurs on the I/O channel. An 80-pin connector (J1) located on the MUX mates with a receptacle on the I/O channel. Connections to J1 are listed in table 2-2.

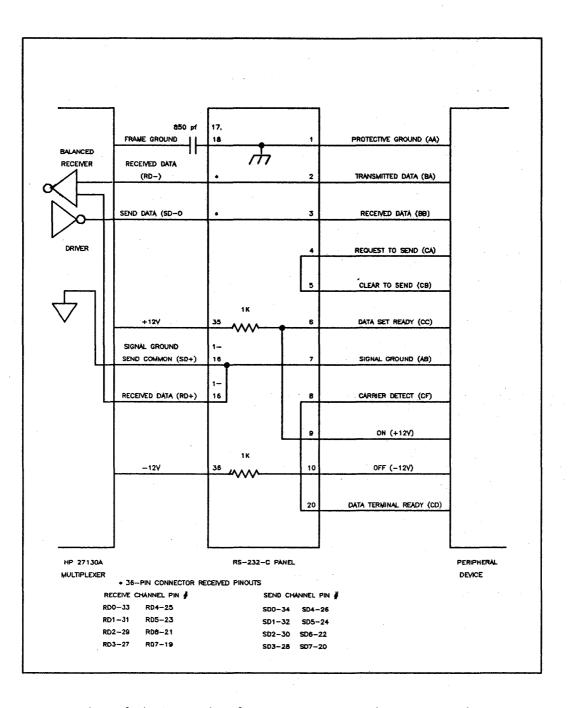

## PERIPHERAL DEVICE INTERFACE

Interface between the MUX card and up to eight peripheral devices is via a 72-pin connector (J2) to a connection panel (RS-232-C Connection Box, part number 12828-60001) and from there, via eight separate connectors and eight cables, to the peripheral devices. A connection diagram for the connection box is shown in figure 2-4.

Connector J2 pin assignments are shown in table 2-3. Pin assignments for J2 and the connection panel are shown in table 2-4. Note that, in table 2-4, there are eight pairs of Send Data (SD) and Signal Ground (SG) lines, and eight pairs of Receive Data (RD) and Signal Ground (SG) lines; that is, one pair of Send Data lines and one pair of Receive Data lines for each of the eight connectors (J0 through J7) to the eight peripheral devices.

Figure 2-4. Connections from MUX to Connection Box to Device

| Table | 2-2. | I/0 | Channel | Connector | <b>J1</b> |

|-------|------|-----|---------|-----------|-----------|

|       |      |     |         |           |           |

|   | PIN NO.    | SIGNAL MNEMONIC | SIGNAL DEFINITION              |

|---|------------|-----------------|--------------------------------|

|   |            |                 |                                |

|   |            |                 |                                |

|   | A1         | RES             | Not used                       |

|   | A2         | DB14-           | Data Bus, Bit 14               |

|   | A3         | DB12-           | Data Bus, Bit 12               |

|   | A4         | GND             | Ground                         |

|   | A5         | DB10-           | Data Bus, Bit 10               |

|   | AG         | DB8-            | Data Bus, Bit 8                |

|   | A7         | GND             | Ground                         |

|   | AB         | DB6-            | Data Bus, Bit 6                |

|   | A9         | DB4-            | Data Bus, Bit 4                |

|   | A10        | GND             | Ground                         |

|   | A11        | DB2-            | Data Bus, Bit 2                |

|   | A12        | DB0-            | Data Bus, Bit O                |

|   | A13        | GND             | Ground                         |

|   | A14        | AD2-            | Address Bus, Bit 2             |

|   | A15        | AD0-            | Address Bus, Bit O             |

|   | A16        | GND             | Ground                         |

|   | A17        | DOUT-           | Data Out                       |

|   | A18        | BP0-            | Bus Primiti∨e Bit O            |

|   | A19        | CEND-           | Channel End                    |

|   | A20        | SYNC-           | Synchronize                    |

|   | A21        | GND             | Ground                         |

|   | A22        | CCLK            | Common Clock                   |

| ł | A23        | GND             | Ground                         |

|   | A24        | BR-             | Burst Request                  |

|   | A25        | DBYT-           | Device Byte                    |

|   | A26        | MYAD-           | My Address                     |

|   | A27        | GND             | Ground                         |

|   | A28        | <b>-</b>        | Not used                       |

|   | A29        |                 | Not used                       |

|   | A30<br>A31 | RES             | Not used                       |

|   | A32        | PFW-            | Not used<br>Power-Fail Warning |

|   |            | PPON            | Primary Power Op               |

|   | A33<br>A34 | GND             | Primary Power On<br>Ground     |

|   | A35        | AC-             | Not used                       |

|   | A36        | AC+             | Not used                       |

|   | A37        | -12             | -12V                           |

|   | A38        | +12             | +12V                           |

|   | A39        | +12             | Not used                       |

|   | A40        | +55<br>+5P      | +5P                            |

| L | UTU        |                 |                                |

| PIN NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SIGNAL MNEMONIC                                                                                                                                                                                                                                                                                                               | SIGNAL DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B1<br>B2<br>B3<br>B4<br>B5<br>B6<br>B7<br>B8<br>B9<br>B10<br>B11<br>B12<br>B13<br>B14<br>B15<br>B16<br>B17<br>B18<br>B19<br>B20<br>B21<br>B22<br>B23<br>B24<br>B25<br>B26<br>B27<br>B28<br>B29<br>B30<br>B31<br>B32<br>B34<br>B35<br>B36<br>B37<br>B38<br>B39<br>B31<br>B32<br>B34<br>B35<br>B36<br>B37<br>B38<br>B39<br>B31<br>B32<br>B34<br>B35<br>B36<br>B37<br>B38<br>B39<br>B31<br>B32<br>B34<br>B35<br>B36<br>B37<br>B38<br>B39<br>B31<br>B32<br>B34<br>B35<br>B36<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B38<br>B37<br>B37<br>B38<br>B37<br>B37<br>B37<br>B37<br>B37<br>B37<br>B37<br>B37<br>B37<br>B37 | DB15-<br>DB13-<br>GND<br>DB11-<br>DB9-<br>GND<br>DB7-<br>DB5-<br>GND<br>DB3-<br>DB1-<br>GND<br>AD3-<br>AD1-<br>GND<br>UAD-<br>BP1-<br>CBYT-<br>POLL-<br>GND<br>IOSB-<br>GND<br>IOSB-<br>GND<br>IOSB-<br>GND<br>IOSB-<br>GND<br>ARQ-<br>DEND-<br>IFC-<br>GND<br>ISPU<br>NMI-<br>SPON<br>GND<br>AC-<br>AC+<br>-12<br>+5S<br>+5P | Not used<br>Data Bus, Bit 15<br>Data Bus, Bit 13<br>Ground<br>Data Bus, Bit 9<br>Ground<br>Data Bus, Bit 9<br>Ground<br>Data Bus, Bit 7<br>Data Bus, Bit 3<br>Data Bus, Bit 3<br>Data Bus, Bit 1<br>Ground<br>Address Bus, Bit 1<br>Ground<br>Unary Address<br>Bus Primitive Bit 1<br>Channel Byte<br>Poll<br>Ground<br>I/O Strobe<br>Ground<br>Attention Request<br>Device End<br>Interface Clear<br>Ground<br>Not used<br>Not used |

Table 2-2. I/O Channel Connector J1 (Continued)

| J2<br>PIN NO.     | J2<br>MNEMONIC            | SID<br>MNEMONIC | J2<br>PIN. NO. | J2<br>MNEMONIC     | SIO<br>MNEMONIC |

|-------------------|---------------------------|-----------------|----------------|--------------------|-----------------|

| B25<br>B26<br>B27 | SD0 (A)<br>SG0<br>SD0 (B) | TxD0            | B4<br>B6       | RDO (A)<br>RDO (B) | RxD0            |

| A25<br>A26<br>A27 | SD1 (A)<br>SG1<br>SD1 (B) | TxD1            | A4<br>B7       | RD1 (A)<br>RD1 (B) | RxD1            |

| B28<br>B29<br>B30 | SD2 (A)<br>SG2<br>SD2 (B) | TxD2            | AG<br>B8       | RD2 (A)<br>RD2 (B) | RxD2            |

| A28<br>A29<br>A30 | SD3 (A)<br>SG3<br>SD3 (B) | TxD3            | A8<br>B9       | RD3 (A)<br>RD3 (B) | RxD3            |

| B31<br>B32<br>B33 | SD4 (A)<br>SG4<br>SD4 (B) | TxD4            | A1 0<br>B1 0   | RD4 (A)<br>RD4 (B) | RxD4            |

| A31<br>A32<br>A33 | SD5 (A)<br>SG5<br>SD5 (B) | TxD5            | A12<br>B11     | RDS (A)<br>RDS (B) | RxD5            |

| B34<br>B35<br>B36 | SDG (A)<br>SGG<br>SDG (B) | TxDG            | A14<br>B12     | RDG (A)<br>RDG (B) | RxDG            |

| A34<br>A35<br>A36 | SD7 (A)<br>SG7<br>SD7 (B) | TxD7            | B15<br>B13     | RD7 (A)<br>RD7 (B) | RxD7            |

| Table 2-3. Connector | J2 Pin | Assignments |

|----------------------|--------|-------------|

|----------------------|--------|-------------|

2-9

#### HP 27130A

| J2<br>PIN NO. | J2<br>MNEMONIC   | SID<br>MNEMONIC | J2<br>PIN NO. | J2<br>MNEMONIC  | SIO<br>MNEMONIC |

|---------------|------------------|-----------------|---------------|-----------------|-----------------|

| A17<br>B17    | SD0<br>SC0       | TxD0            | A21<br>B21    | SD4<br>SC4      | TxD4            |

| A18<br>B18    | SD1<br>SC1       | TxD1            | A22<br>B22    | SD5<br>SC5      | TxD5            |

| A19<br>B19    | SD2<br>SC2       | TxD2            | A23<br>B23    | SD6<br>SC6      | TxD6            |

| A20<br>B20    | SD3<br>SC3       | TxD3            | A24<br>B24    | SD7<br>SC7      | TxD7            |

| A3<br>B3      | HOOD_ON-<br>HLED | CTSA0-<br>      | B14<br>A16    | SG<br>GND       |                 |

| A2<br>B2      | -12V<br>+12V     |                 | B1<br>A1      | +5V<br>GND(PWR) |                 |

Table 2-3. Connector J2 Pin Assignments (Continued)

Table 2-4. RS-232-C/RS-423-A Cables

| <b></b>                                                                                                                      |                                                                                                                                                                                                                                                                                       | ·····                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                    |                                                                                                                                                               |                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| J2<br>PIN NO.                                                                                                                | J2<br>MNEMONIC                                                                                                                                                                                                                                                                        | PANEL<br>PIN NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PANEL<br>MNEMONIC                                                                                                                                                                                  | COLOR                                                                                                                                                         | PAIR<br>ND.                                                                                      |

| *<br>A17<br>B17<br>A18<br>B18<br>A19<br>B19<br>A20<br>B20<br>A21<br>B21<br>A22<br>B22<br>A23<br>B23<br>A24<br>B24            | SD0<br>SC0<br>SD1<br>SC1<br>SD2<br>SC2<br>SD3<br>SC3<br>SD4<br>SC4<br>SD5<br>SC4<br>SD5<br>SC5<br>SD6<br>SC6<br>SD7<br>SC7                                                                                                                                                            | SC0         16         SG (J02)           SD1         32         SD (J12)           SC1         14         SG (J12)           SD2         30         SD (J22)           SC2         12         SG (J22)           SD3         28         SD (J32)           SC3         10         SG (J32)           SD4         26         SD (J42)           SC4         8         SG (J42)           SC5         6         SG (J52)           SD6         22         SD (J52)           SD6         22         SD (J62) |                                                                                                                                                                                                    | LT RED<br>BLACK<br>DK GREEN<br>BLACK<br>DK VIOLET<br>BLACK<br>LT BLUE<br>BLACK<br>DK BLUE<br>BLACK<br>LT VIOLET<br>BLACK<br>BROWN<br>BLACK<br>DK RED<br>BLACK | 11<br>12<br>12<br>13<br>13                                                                       |

| B4<br>B6 **<br>A4<br>B7 **<br>A6<br>B8 **<br>A8<br>B9 **<br>A10<br>B10 **<br>A12<br>B11 **<br>A14<br>B12 **<br>B15<br>B13 ** | RD0       (A)         RD0       (B)         RD1       (A)         RD2       (A)         RD2       (A)         RD2       (B)         RD3       (A)         RD3       (B)         RD4       (A)         RD5       (A)         RD5       (B)         RD6       (A)         RD7       (A) | 33<br>15<br>31<br>13<br>29<br>11<br>27<br>9<br>25<br>7<br>23<br>5<br>21<br>3<br>19<br>1                                                                                                                                                                                                                                                                                                                                                                                                                     | RD (J0)<br>SG (J0)<br>RD (J1)<br>SG (J1)<br>RD (J2)<br>SG (J2)<br>RD (J3)<br>SG (J3)<br>RD (J3)<br>SG (J4)<br>SG (J4)<br>RD (J5)<br>SG (J5)<br>RD (J5)<br>SG (J5)<br>RD (J6)<br>SG (J7)<br>SG (J7) | NATURAL<br>BLACK<br>WHITE<br>BLACK<br>YELLDW<br>BLACK<br>DRANGE<br>BLACK<br>TAN<br>BLACK<br>GRAY<br>BLACK<br>LT GREEN<br>BLACK                                | 1<br>1<br>2<br>2<br>3<br>3<br>4<br>4<br>4<br>5<br>5<br>5<br>6<br>6<br>6<br>7<br>7<br>7<br>8<br>8 |

#### HP 27130A

| J2<br>PIN NO.                                                                                                                                                                   | J2<br>MNEMONIC | PANEL<br>PIN ND. | PANEL<br>MINEMONIC | COLOR               | PAIR<br>ND. |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|--------------------|---------------------|-------------|--|--|--|--|

| B14 **                                                                                                                                                                          | SG             |                  |                    |                     |             |  |  |  |  |

| B2                                                                                                                                                                              | +12V           | 35               | ON                 | DK RED<br>(SINGLE)  | 1           |  |  |  |  |

| A2                                                                                                                                                                              | -12V           | 36               | OFF                | DK BLUE<br>(SINGLE) | 2           |  |  |  |  |

| <ul> <li>* - Shield connected to chassis ground through a decoupling<br/>capacitor in J2 connector hood.</li> <li>** - These signals bused together at connector J2.</li> </ul> |                |                  |                    |                     |             |  |  |  |  |

Table 2-4. RS-232-C/RS-423-A Cables (Continued)

## INSTALLATION

#### CAUTION

ALWAYS ENSURE THAT THE POWER TO THE COMPUTER IS OFF BEFORE INSERTING OR REMOVING THE MUX CIRCUIT CARD AND CABLE. FAILURE TO DO SO MAY RESULT IN DAMAGE TO THE MUX.

#### CAUTION

SOME OF THE COMPONENTS USED ON THE PRINTED CIRCUIT CARD ARE SUSCEPTIBLE TO DAMAGE BY STATIC DISCHARGE. REFER TO THE SAFETY CONSIDERATIONS INFORMATION AT THE FRONT OF THIS MANUAL BEFORE HANDLING THE CARD.

Install the MUX as follows:

1. Determine if your computer system can supply the power needed for the MUX card. Refer to table 1-1 in Section I for power requirements.

- 2. Verify that the Memory Configuration jumper is configured correctly for the EPROMs/RAMs installed on the card. To verify that the jumper is configured correctly, determine what types of EPROMs/RAMs are installed in sockets U64 and U74, then refer to table 2-1 to verify that the correct jumpers are closed.

- 3. Install the card in the appropriate slot in the computer. Refer to the computer system installation manual to determine the correct slot. When installing the card, use care not to damage components or traces on the card or on adjacent cards. Press the MUX card firmly into place.

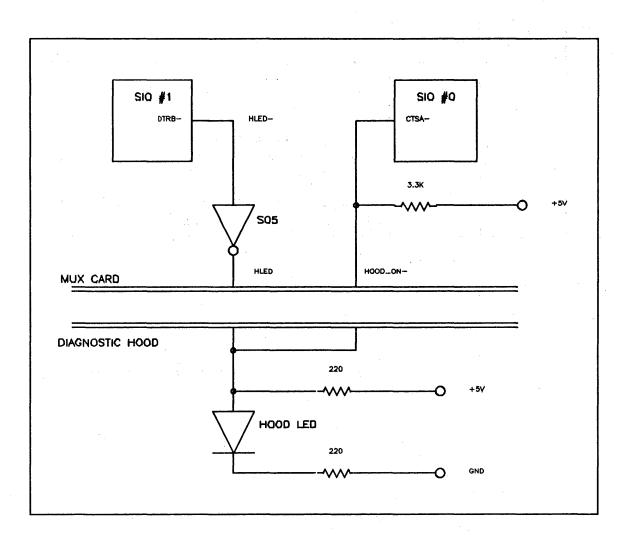

- 4. Connect the cable supplied with the card from J2 to the RS-232-C connection box. If you have the test hood, which exercises more of the card's circuitry, and can be ordered (Hewlett-Packard part number 0950-1659), connect it to J2 instead of connecting the cable.

#### CAUTION

BE SURE AND INSTALL THE DIAGNOSTIC TEST HOOD SO THAT ITS COMPONENT SIDE (THE SIDE WITH THE LED) MATCHES THE COMPONENT SIDE ON THE MUX CARD. DAMAGE TO THE MUX CARD CAN RESULT IF THE COMPONENT SIDES OF THE TWO DEVICES DO NOT MATCH.

#### START-UP

To start up and verify correct operation of the MUX, perform the following:

1. Turn on computer system power.

- 2. A self-test is contained on the card. The host computer system determines if the self-test is run automatically at power-on or must be invoked by the user. Refer to the appropriate manual for your system for a description of self-test initiation.

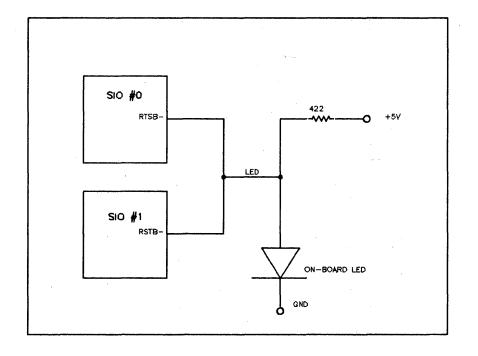

- a. If the diagnostic test hood is not installed when the self-test executes, the LED located on the card should light briefly and go out. This indicates that the card passed self-test. If the LED does not light at all, the card is defective. If the LED stays on, the card did not pass self-test. For either of these latter two cases, it is recommended that you return the card to Hewlett-Packard; refer to the next paragraph for reshipment information. If you wish to perform maintenance on the card, however, refer to Sections V, VI, and VII for maintenance information, replaceable parts lists, and schematic logic diagrams, respectively.

- b. If the diagnostic test hood is installed when the self-test executes, the conditions in step 2.a. should occur, plus the LED located on the test hood should light briefly and go out. If the LEDs (the one mounted on the card and the one on the diagnostic test hood) do not light at all, or if they light and stay on, the causes are the same as in step 2.a.

- 3. Refer to your system documentation for information on using the MUX in your system.

HP 27130A

## RESHIPMENT

If the MUX is to be shipped to Hewlett-Packard for any reason, attach a tag identifying the owner and indicating the reason for shipment. Include the part number of the MUX.

Pack the card in the original factory packing material, if available. If the original material is not available, good commercial packing material should be used. Reliable commercial packing and shipping companies have the facilities and materials to repack the item. BE SURE TO OBSERVE ANTI-STATIC PRECAUTIONS.

# PRINCIPLES OF OPERATION

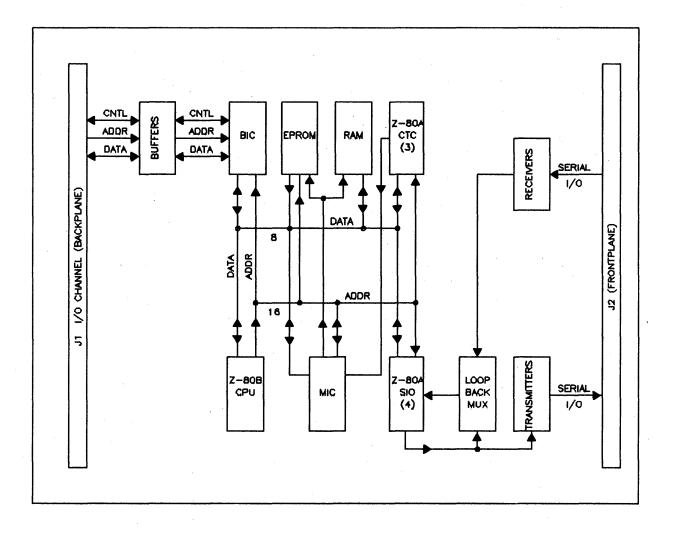

## FUNCTIONAL DESCRIPTION

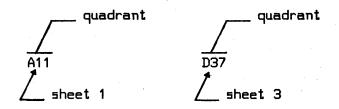

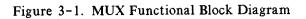

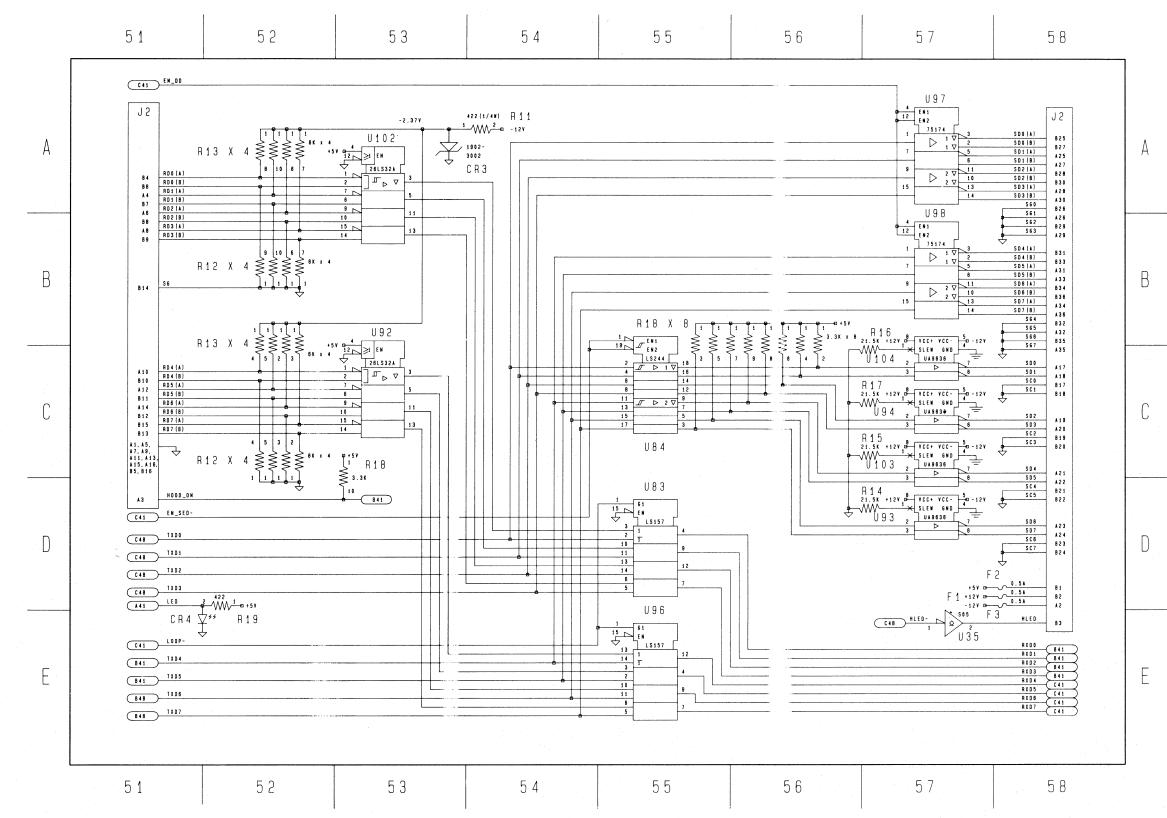

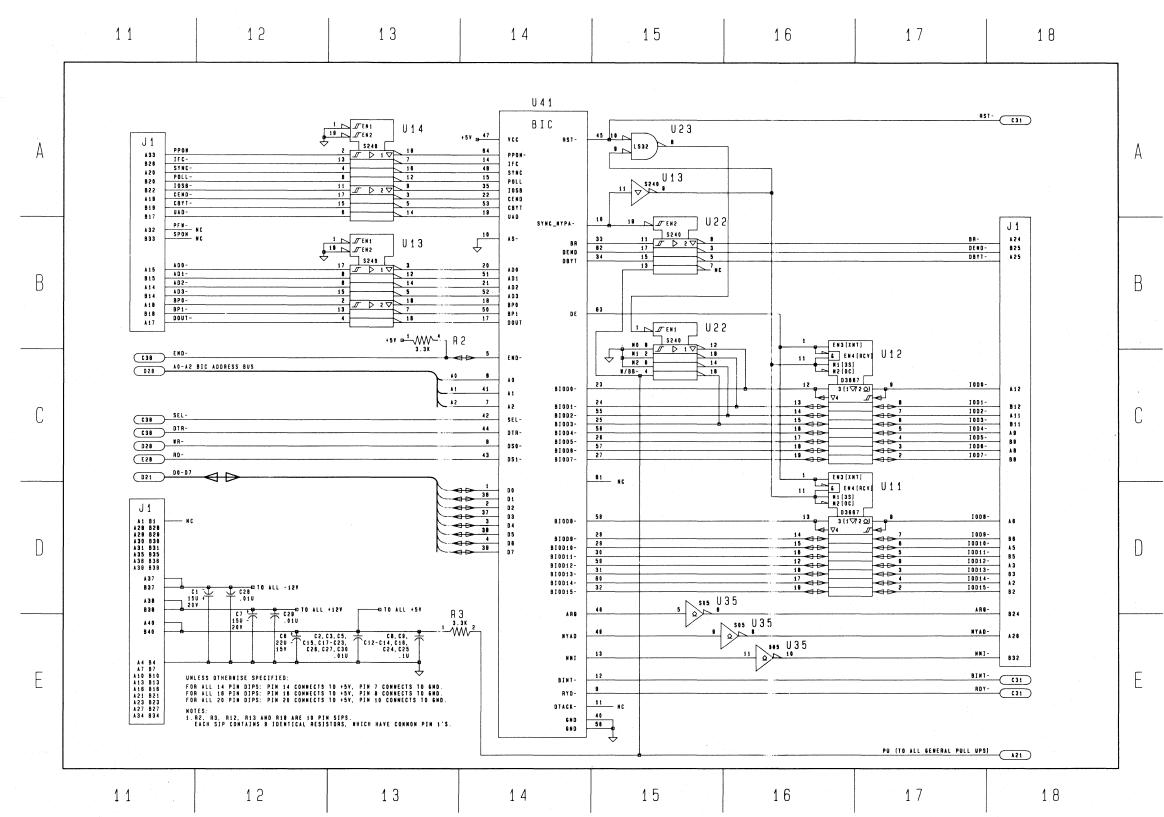

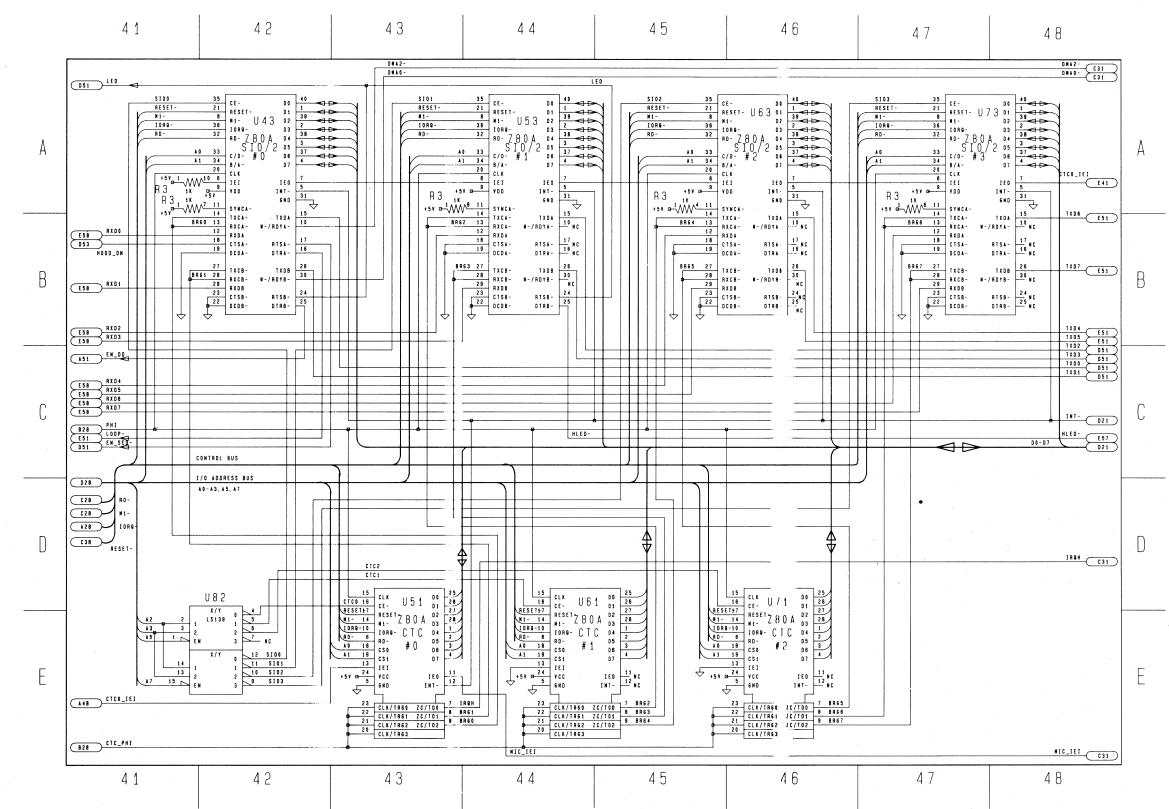

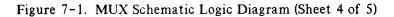

A functional block diagram of the HP 27130 Eight-Channel Multiplexer is shown in figure 3-1. Reference will also be made to the schematic logic diagram contained in Section VII, figure 7-1. Note that figure 7-1 consists of five sheets. References to this figure will be as follows: A11, 7-1; C23, 7-1; D37, 7-1, etc., where the first digit (1, 2, 3, 4, or 5) refers to the sheet number; the combination of letters A through E and numbers 11 through 58 (A11, D37, etc.) refer to the quadrants on the individual sheets; and 7-1 refers to the figure number. For example,

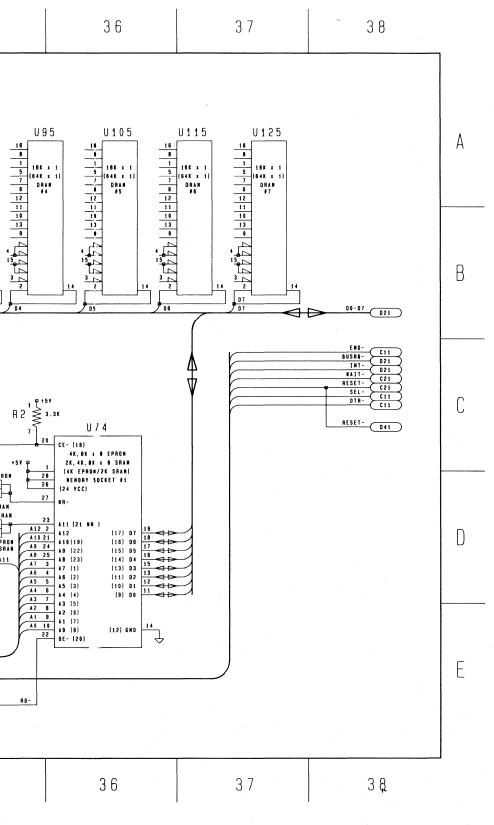

Circuitry contained on the MUX card includes a Backplane Interface Circuit (BIC) gate array and its support circuits, a Z-80B microprocessor (CPU), three Z-80 Counter Timer Circuits (CTCs), four Z-80 Serial I/O circuits (SIO/2s), up to 16K bytes of EPROM in two 28-pin sockets, a Memory Interface Circuit (MIC) gate array, 64K bytes of dynamic RAM (48K available) RS-422-A/RS-423-A transmitters and receivers (compatible with RS-232-C and CCITT V.28), and I/O channel (backplane) and peripheral device panel (frontplane) connectors.

The heart of the MUX card is the Z-80B CPU (U33, see D24, 7-1), which through a program stored in EPROM controls the functions of the card.

The Backplane Interface Circuit (BIC, U41, see A14, 7-1) is a custom gate array integrated circuit which controls the communication and handshaking with the I/O channel (backplane). The BIC is accessed by the Z-80B CPU as an I/O device for control information, and through Direct Memory Access (DMA) for data transfer to memory.

The Counter Timer Circuits (CTC, U51, U61, and U71, see E43, 7-1) divide the system clock to provide baud rate clocks and other necessary clocks for the MUX. They are accessed by the Z-80B CPU as I/O devices.

The Memory Interface Circuit (MIC, U54, see A32, 7-1) is a custom gate array integrated circuit which handles dynamic refresh and address multiplexing for the 64K bytes of dynamic RAM. The MIC also contains the DMA controller, provides interrupt vectors for backplane interrupts, decodes addresses and provides wait states for the slow EPROMs, and provides reset for the for the rest of the MUX card.

The Serial I/O circuits (SIOs, U43, U53, U63 and U73, see A42, 7-1) and their associated multiplexers, receivers, and drivers (see figure 7-1, sheet 5), provide serial data communication to the frontplane connector J2.

### System Clocks

Three synchronized system clocks (1.8432 MHz, 3.6864 MHz, and 7.3728 MHz), all derived from the 14.7456 MHz clock signal CCLK+ (see A21, 7-1), perform the following functions:

1.8432 MHZ (PHI\_CTC): Provides input to the CLK/TRG pins on the CTCs to generate baud rates and system timing intervals.

3.6864 MHz (PHI): Used to provide a system clock to the Z-80B CPU, the SIOs and MIC, and the CTCs.

7.3728 MHz (2 PHI): Drives the MIC.

#### Memory Address Space

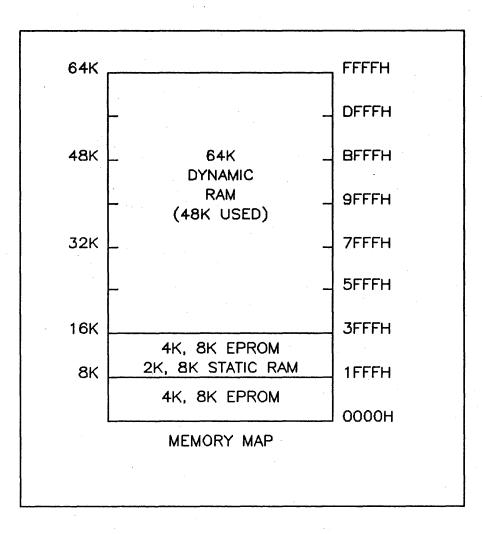

The Z-80B CPU address space of 64K bytes is divided into several sections as shown in figure 3-2.

The two memory sockets, U64 and U74, are reserved for EPROMs and/or static RAMs. Socket U64 can be configured for 4K, 8K, or 16K byte EPROMs. Socket U74 can be configured for 4K byte EPROM, 8K byte EPROM, 2K byte static RAM, or 8K byte static RAM. Note, however, that when a 16K byte EPROM is installed in U64, socket U74 must be left empty to avoid bus contention.

The address space of U64 is from 0H to 3FFFH when this socket is configured for the 16K byte EPROM. The address space is from 0H to 1FFFH when the socket is configured for 4K or 8K byte EPROMs.

The address space of U74 is fixed between 2000H to 3FFFH.

The following types of EPROMs can be installed in socket U64:

4K by 8 (Intel 2732) 8K by 8 (Intel 2764) 16K by 8 (Intel 27128)

The following types of EPROMs and static RAMs can be installed in socket U74:

4K by 8 EPROM (Intel 2732) 8K by 8 EPROM (Intel 2764) 2K by 8 static RAM (Hitachi HM-6116) 8K by 8 static RAM (Hitachi HM-6164)

Memory Configuration jumper W1 is used to configure the two memory sockets. W1 contains nine jumper positions: A, B, C, D, E, F, G, H, and J. Positions A through D configure socket U64; positions E through H configure U74; and position J enables the WAIT- signal of the MIC to the Z-80B CPU. The MIC always asserts the WAIT- signal when the lowest 16K byte address is accessed. Position J should be closed (a jumper installed) when EPROMs/RAMs with access times greater than 250 nsec are used. The jumper is shown in Section II, figure 2-2.

#### NOTE

The jumpers are set at the factory and need no further adjustment unless the EPROMs or RAMS are changed.

HP 27130A

The 4K by 8 EPROMs and 2K by 8 static RAMs are 24-pin packages and are installed to the back of the sockets (pins 1, 2, 27, and 28 are not used).

Tables 3-1 and 3-2 show the settings of W1 for different types of EPROMs/RAMs.

Figure 3-2. Memory Map

| ADDRESS                 |        | SETTI  | NGS            | SOCKET |                           |                                |

|-------------------------|--------|--------|----------------|--------|---------------------------|--------------------------------|

| SPACE                   | A      | B      | , C            | D      | U64                       | COMMENTS                       |

| 0000H-<br>0FFFH<br>(4K) | OPEN   | CLOSED | CLOSED         | OPEN   | 4K x 8<br>Intel<br>2732   |                                |

| 0000H-<br>1FFFH<br>(8K) | OPEN   | CLOSED | DON "T<br>CARE | OPEN   | 8K x 8<br>Intel<br>2764   |                                |

| 0000H<br>3FFFH<br>(16K) | CLOSED | OPEN   | OPEN           | CLOSED | 16K x 8<br>Intel<br>27128 | Socket<br>U74 must<br>be empty |

Table 3-1. Memory Configuration Jumper (W1) Settings for Socket U64

Table 3-2. Memory Configuration Jumper (W1) Settings for Socket U74

| ADDRESS                |               | SETTI  | NGS    | SOCKET |                              |                                        |

|------------------------|---------------|--------|--------|--------|------------------------------|----------------------------------------|

| SPACE                  | E             | F      | Ģ      | G H    |                              | COMMENTS                               |

| 2000H<br>2FFFH<br>(4K) | DON'T<br>CARE | OPEN   | OPEN   | CLOSED | 4K x 8<br>Intel              | 4K byte<br>EPROM<br>configuration      |

| 2000H<br>3FFFH<br>(8K) | CLOSED        | OPEN   | OPEN   | CLOSED | 8K x 8<br>Intel<br>2764      | 8K byte<br>EPROM<br>configuration      |

| 2000H<br>27FFH<br>(2K) | OPEN          | CLOSED | CLOSED | OPEN   | 2K x 8<br>Hitachi            | 2K byte<br>static RAM<br>configuration |

| 2000H<br>3FFFH<br>(8K) | OPEN          | CLOSED | OPEN   | CLOSED | 8K x 8<br>Hitachi<br>HM-6264 | 8K byte<br>static RAM<br>configuration |

### I/O Address Space

The Z-80B CPU provides addressing capability for 256 distinct I/O port registers. The MUX card uses only 47 I/O port register addresses: 16 are reserved for the four Z-80 SIOs, 12 are reserved for the three Z-80 CTCs, 12 are reserved for the MIC, and seven are reserved for the BIC.

Table 3-3 shows the I/O addresses used by the card.

#### CAUTION

# THE USE OF ANY OTHER ADDRESSES MAY CAUSE IMPROPER OPERATION.

#### Z-80B Microprocessor CPU

The Z-80B CPU (U33) is an MOS LSI microprocessor which operates from a single +5-volt supply, uses a single-phase clock, and has a typical instruction execution time of 1 microsecond. The data bus is eight bits wide, and the address bus is 16 bits wide. All CPU pins are TTL compatible.

The Z-80B CPU employs a register-based architecture which includes two sets of six generalpurpose registers which can be used as individual 8-bit registers or 16-bit register pairs. Additional 8-bit registers include two sets of accumulator and flag registers, and the interrupt vector and memory refresh registers. Additional 16-bit registers include the stack pointer, program counter, and two index registers. The Z-80B CPU provides the intelligence for the MUX card to function as a preprocessor for the I/O devices, thus relieving the host computer of a considerable amount of processing.

The functions of the Z-80B CPU signals are shown in table 3-4.

#### Z-80 SIO/2 (Serial I/O Controller)

The MUX card uses four Z-80 SIO/2 controller circuits (U43, U53, U63, and U73, see A42, 7-1). The Z-80 SIO/2 is a programmable serial I/O controller with two independent full-duplex channels, each of which contains separate control and status lines. Each channel can be independently programmed. On the MUX card, each of the eight channels is used as a fully programmable asynchronous terminal controller.

Each SIO channel has two I/O addressable ports: one port for data transfer, and one for control information. Each control port has three read registers and eight write registers available for control information. The functions performed by the registers are shown in table 3-5.

Several of the SIO number 0 (U43) and SIO number 1 (U53) modem control output and modem status input signals are used for special functions, such as turning on the card's LED, sensing the diagnostic test hood, etc. These special functions are described in table 3-6.

Table 3-3. I/O Address Space

| I/O ADDRESS LINES                                                                                                                                                                                                                            |                                                |                            |                                                          |                                                     |                                                |                                                | I/O<br>PORT                                         |                                                |                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------|----------------------------------------------------------|-----------------------------------------------------|------------------------------------------------|------------------------------------------------|-----------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------|

| I/O PORT FUNCTION                                                                                                                                                                                                                            | 7                                              | 6                          | 5                                                        | 4                                                   | 3                                              | 2                                              | 1                                                   | 0                                              | ADDR                                                                                                 |

| MIC Register 0<br>MIC Register 1<br>MIC Register 2<br>MIC Register 3<br>MIC Register 4<br>MIC Register 5<br>MIC Register 6<br>MIC Register 7<br>MIC Register 7<br>MIC Register 9<br>MIC Register 10<br>MIC Register 11                       | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1           |                            | 1 1 1 1 1 1 1 1 1 1 1                                    | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1      | 0<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>0      | 0<br>0<br>1<br>1<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0      | E0 H<br>E1 H<br>E2 H<br>E3 H<br>E4 H<br>E5 H<br>E6 H<br>E7 H<br>E8 H<br>E9 H<br>EA H<br>EB H         |

| CTC 0: Channel 0<br>CTC 0: Channel 1<br>CTC 0: Channel 2<br>CTC 0: Channel 3<br>CTC 1: Channel 0<br>CTC 1: Channel 1<br>CTC 1: Channel 1<br>CTC 1: Channel 2<br>CTC 1: Channel 3<br>CTC 2: Channel 0<br>CTC 2: Channel 1<br>CTC 2: Channel 3 | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 1 1 1 1 1 1 1 1 1 1        | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 111111111111111111111111111111111111111             | 0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0 | 0<br>0<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | D0 H<br>D1 H<br>D2 H<br>D3 H<br>D4 H<br>D5 H<br>D6 H<br>D7 H<br>D8 H<br>D9 H<br>D9 H<br>DA H<br>DB H |

| BIC Register 0<br>BIC Register 1<br>BIC Register 2<br>BIC Register 3<br>BIC Register 4<br>BIC Register 5<br>BIC Register 5<br>BIC Register 7<br>X = Don't care                                                                               | 1<br>1<br>1<br>1<br>1<br>1                     | 0<br>0<br>0<br>0<br>0<br>0 | 1<br>1<br>1<br>1<br>1<br>1                               | 1 1 1 1 1 1 1                                       | X X X X X X X X X X X X X X X X X X X          | 0<br>0<br>0<br>1<br>1<br>1                     | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1                | 0<br>1<br>0<br>1<br>0<br>1<br>0                | B0 H<br>B1 H<br>B2 H<br>B3 H<br>B4 H<br>B5 H<br>B6 H<br>B7 H                                         |

HP 27130A

|                                                                                                                                                                                                                                                                                                                                                                                                                             | I/O ADDRESS LINES |                                           |                                         |                                         |                                           |                                           |                                                     |                                                     | I/D<br>PORT                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------|-----------------------------------------|-----------------------------------------|-------------------------------------------|-------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| I/D PORT FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                           |                   | 6                                         | 5                                       | 4                                       | 3                                         | 2                                         | 1                                                   | 0                                                   | ADDR                                                                                                                         |

| SIO 0: Channel A Data<br>SIO 0: Channel A Control<br>SIO 0: Channel B Data<br>SIO 0: Channel B Data<br>SIO 0: Channel B Control<br>SIO 1: Channel A Data<br>SIO 1: Channel A Control<br>SIO 1: Channel B Data<br>SIO 1: Channel B Control<br>SIO 2: Channel A Data<br>SIO 2: Channel A Data<br>SIO 2: Channel B Data<br>SIO 2: Channel B Data<br>SIO 2: Channel B Data<br>SIO 3: Channel A Data<br>SIO 3: Channel A Control |                   | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 0<br>0<br>0<br>0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>0 | 0<br>0<br>1<br>1<br>0<br>1<br>1<br>0<br>1<br>1<br>0 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0 | 70 H<br>71 H<br>72 H<br>73 H<br>74 H<br>75 H<br>76 H<br>77 H<br>78 H<br>78 H<br>79 H<br>78 H<br>78 H<br>78 H<br>70 H<br>70 H |

| SIO 3: Channel B Data<br>SIO 3: Channel B Control                                                                                                                                                                                                                                                                                                                                                                           | 0                 | 1                                         |                                         |                                         |                                           | 1                                         | 1                                                   | 0<br>1                                              | 7E H<br>7F H                                                                                                                 |

Table 3-3. I/O Address Space (Continued)

## Table 3-4. Z-80B CPU Signals

| SIGNAL NAME                        | FUNCTION                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AO - A15<br>(Address Bus)          | Tri-state output, active high.<br>A0 - A15 are a 16-bit address bus (A0 is the<br>least significant bit). This bus provides<br>address capability for up to 64K of memory data<br>exchanges, and for I/O device data exchanges.<br>I/O addressing uses the 8 lower address bits                                                           |

|                                    | to allow direct addressing of up to 256 input<br>or 256 output ports.                                                                                                                                                                                                                                                                     |

| D0 - D7<br>(Data Bus)              | Tri-state input/output, active high.<br>D0 - D7 are an 8-bit bidirectional data bus<br>used for data exchanges with memory and I/O<br>devices.                                                                                                                                                                                            |

| M1-<br>(Machine Cycle 1)           | Output, active low.<br>Indicates that the current machine cycle is<br>the OP code fetch cycle of an instruction<br>execution.                                                                                                                                                                                                             |

| MREQ-<br>(Memory Request)          | Tri-state output, active low.<br>Indicates that the address bus holds a valid<br>address for a memory read or write.                                                                                                                                                                                                                      |

| IDRQ-<br>(Input/Dutput<br>Request) | Tri-state output, active low.<br>Indicates that the lower half of the address<br>bus holds a valid I/O address for an I/O read<br>or write. IORQ- is also generated with M1-<br>when an interrupt is being acknowledged.<br>Interrupt acknowledge operations occur during<br>M1 time, while I/O operations never occur<br>during M1 time. |

HP 27130A

| Table 3 | 3-4. | Z-80B | CPU | Signals | (Continued) |

|---------|------|-------|-----|---------|-------------|

|---------|------|-------|-----|---------|-------------|

| SIGNAL NAME                         | FUNCTION                                                                                                                                                                                                                            |  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RD-<br>(Read)                       | Tri-state output, active low.<br>Indicates that the CPU wants to read data<br>from memory or an I/O device. Memory or<br>I/O device uses this signal to gate data onto<br>the CPU data bus.                                         |  |

| WR-<br>(Write)                      | Tri-state output, active low.<br>Indicates that the CPU data bus holds valid<br>data for the addressed memory or I/O device.                                                                                                        |  |

| RFSH-<br>(Refresh)                  | Not used by the MUX card.                                                                                                                                                                                                           |  |

| HALT-                               | Not used by the MUX card.                                                                                                                                                                                                           |  |

| WAIT-                               | Input, active low.<br>Indicates to the Z-80B CPU that the addressed<br>memory or I/O devices are not ready for a<br>data transfer. This signal allows memory<br>or I/O devices of any speed to be<br>synchronized to the Z-80B CPU. |  |

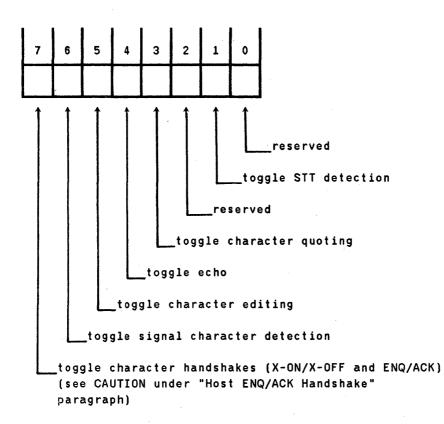

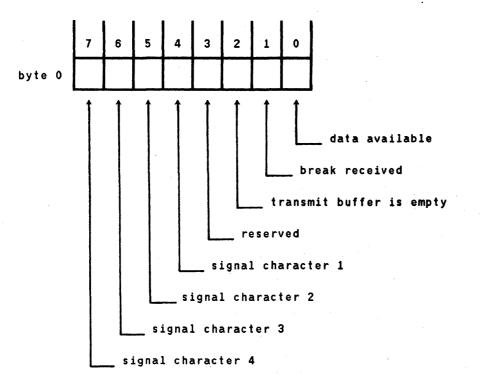

| INT-<br>(Interrupt<br>Request)      | Input, active low.<br>Generated by I/O devices. A request will be<br>honored at the end of the current instruction<br>if an internal Interrupt Enable flip-flop<br>is enabled and if the BUSRQ- signal is not<br>active.            |  |