HEWLETT PACKARD

HP-CIO I/O EIGHT CHANNEL TERMINAL MULTIPLEXER

FIRMWARE INTERNAL MAINTENANCE SPECIFICATION (IMS)

PROJECT YUBA

HEWLETT-PACKARD COMPANY Roseville Networks Division 8000 Foothills Boulevard Roseville, California 95678

HEWLETT-PACKARD PRIVATE

HP-CIO I/O EIGHT CHANNEL TERMINAL MULTIPLEXER

# FIRMWARE INTERNAL MAINTENANCE SPECIFICATION (IMS)

PROJECT YUBA

HEWLETT

PACKARD

27130A

July 14, 1983

Terry Gong Greg Dolkas

HEWLETT-PACKARD PRIVATE

HEULETT-PACKARD COMPANY

Roseville Networks Division 8000 Foothills Boulevard

Roseville, California 95678

July 14, 1983

Terry Gong Greg Dolkas

History

date description

821111 Original document

830510 Complete document

830714 Added debug monitor to the product firmware for trouble shooting.

1.1 Scope

INTRODUCTION

This document describes the internal structure of the firmware that as implemented for the HP-CIO RS-232-C/RS-422/3 8 channel terminal multiplexer card. Specially, this document describes:

CHAPTER 1

o all symbols used by the firmware except for symbols used as labels in the instruction sequence,

\_\_\_\_\_

- o the firmware data structure,

- o the function of each firmware modules, and

- o any other information pertinent to the understanding of the firmware.

The reader is referred to the following related documents.

- o Zilog Z80 CPU Technical Manual.

- o Zilog Z80-SIO Technical Manual.

- o Zilog Z80-CTC Technical Manual.

- o CSG I/O EIGHT CHANNEL TERMINAL MULTIPLEXER, FIRMWARE EXTERNAL REFERENCE SPECIFICATION (ERS) by Greg Dolkas (RVD).

- BACKPLANE INTERFACE CIRCUIT (BIC) ERS by Bill Martin, Roseville Division (RVD).

o CSG STANDARD I/O BACKPLANE by R. B. Haagens, Computer Systems Division (CSY).

STANDARD DATACOM DRIVER by Greg Dolkas, Roseville Division (RVD).

o CSG I/O STANDARD BACKPLANE PROTOCOL FOR SMART DATACOM

1

HEWLETT-PACKARD PRIVATE

HEWLETT-PACKARD PRIVATE

CARDS by Greg Dolkas, Roseville Division (RVD).

- O GUIDEBOOK TO DATA COMMUNICATIONS, Part No. 5955-1715, Hewlett-Packard, 1977.

- o HP-1000 SERIES, Z80 REAL TIME SCHEDULER, TECHNICAL SPECIFICATION by Tom Szolyga, June, 1979.

This document assumes the reader has the full understanding of all the information given in the MUX ERS.

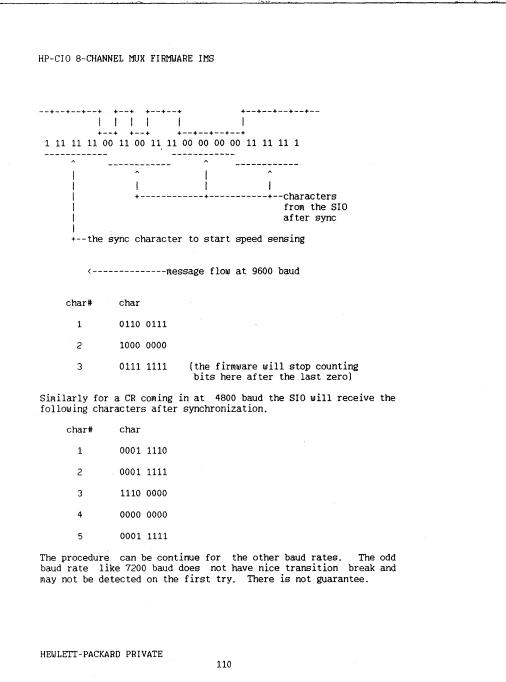

Note that this document does not contain complete documentation of the self-test. Much of the code was leverage from the HP-CIO ASI and PSI self-test and from the MEF/L/A PSI self-test. The listing of the self-test subprogram contains most of the required documentation. HP-CIO 8-CHANNEL MUX FIRMWARE IMS

| +                                     |           |

|---------------------------------------|-----------|

| 1                                     | 1         |

| EQUATE & VARIABLE SYMBOLS DICTIONARY  | CHAPTER 2 |

|                                       |           |

| · · · · · · · · · · · · · · · · · · · |           |

This chapter defines all the symbols which are not used as a label or subprogram name. However, all the symbols used in the self-test is not defined here because it is a self-contained module (that is, leverage from the ASI and PSI self-test). See the listing for documentation information.

Each global and local equate and variable symbols are defined in this chapter. Each symbol will have 3 or 4 attribute descriptions follow by the usage description.

The attribute descriptions are as follow:

- o The first attribute is whether the symbol is globally defined. The symbol is globally defined if it is used in an COPY file or if it is given the PUBLIC attribute. Otherwise, the symbol is locally defined within the module.

- o The second attribute is the type of the symbol which includes:

- code if the symbol is defined in the CSEG area by using either DEFW or DEFB,

- define label if the symbol is defined by using the DEFL pseudo op,

- equate if the symbol is defined by using the EQU pseudo op,

- FBIT if the symbol is defined by using the FBIT macro,

- variable if the symbol is defined by using the DEFS pseudo op,

- macro if the symbol is used to define offset to access the content .

- o The third attribute or information parameter is the name of the source file where the symbol is defined.

- o The fourth attribute is included only if the second attribute is defined as being a variable. This defined the

3

HEWLETT-PACKARD PRIVATE

HEWLETT-PACKARD PRIVATE

# size of the variable.

- ABD global, equate, [MUX; BIC register 2 status code, abort done

- ABORT global, equate, [MUX; WTC order request code to abort a given transaction

- ABRT\_TBL local, code, &BCWTC, 12 bytes; jump table to abort processing routines

- ACTPRIO global, variable, &MUXVR, 1 byte; contains the priority of the active transaction

- ACTREQ global, variable, &MUXVR, 2 bytes; contains the address to the active request block

- ACTSTAT global, variable, &MUXVR, 1 byte; contains the RTS code for the active transaction

- ACTTID global, variable, &MUXVR, 2 bytes; contains the transaction ID (TID) of the active transaction

- AES global, equate, [MUX; BIC registr 2 status code, asynchronous event

- ALERT1 global, equate, [MUX; bit assignment for alert 1 option in ALRT OPT

- ALOC global, macro, [MUX; macro to assign offset value to a given symbol

- ALOC\_CNT global, define label, [MUX; offset assignment to be used with the macro ALOC

- ALRT OPT global, ALOC, [MUX, 1 byte; alert 1 option

- ARQ\_BUF local, variable, &BPISR, 16 bytes, the FIFO buffer to queue ARQ status code for the host

- ARQ\_PTRA local, variable, &BPISR, 2 bytes, the buffer pointer to ARQ BUF for the writing the next ARQ status code

- ARQ\_PTRB local, variable, &BPISR, 2 bytes, the buffer pointer to ARQ BUF for the reading the next ARQ status code

- BACK\_SP global, ALOC, [MUX, 1 byte; contains the character fo backspacing when edit mode is enabled

- BAUD\_RAT global, ALOC, [MUX, 1 byte; contains the baud rate value

4

HEWLETT-PACKARD PRIVATE

HP-CIO 8-CHANNEL MUX FIRMWARE IMS

- BAUD\_TAB local, code, &SPDSN, 17 bytes; the baud rate table to match the first zero's count which is the start bit, used in speed sensing

- BEGSTACK global, equate, [MUX; beginning address of the stack

- BICEND local, equate, &BPISR; bit assignment for BIC registers 5 and 6, the BIC END bit

- BIC\_0 local, equate, &BPISR; I/O port address for BIC register 0

- BIC\_1 local, equate, &BPISR; I/O port address for BIC register 1

- BIC 2 local, equate, &BPISR; I/O port address for BIC register 2

- BIC 3 local, equate, &BPISR; I/O port address for BIC register 3

- BIC\_4 local, equate, &BPISR and &MUXMN; I/O port address for BIC register 4

- BIC\_5 local, equate, &BPISR and &MUXMN; I/O port address for BIC register 5

- BIC\_6 local, equate, &BPISR and &MUXMN; I/O port address for BIC register 6

- BIC\_ENI local, equate, &BPISR; bit assignment for MIC register 0, set to enable the BIC interrupt

- BLK\_BIT global, equate, [MUX; bit assignment for block mode in the WIC order request code

- BLK\_MASK global, equate, [MUX; mask to get the block mode bit from the WIC order request code

- BP\_CMD local, variable, &BPISR, 1 byte; contains the current command from the BIC register 1

- BP\_INT local, variable, &BPISR, 1 byte; contains the current interrupt status from BIC register 5

- BP\_ORDER global, variable, &BPISR, 1 byte; contains the current BIC order being processed

- BPTX\_PTR global, ALOC, [MUX, 2 bytes; backplane transmit buffer pointer

- BRK\_ON global, equate, [MUX; bit assignment for PORTSTAT+1 set when break detection is actively in progress

BRK\_RX - global, equate, [MUX; bit assignment for INT\_STAT set when

HEWLETT-PACKARD PRIVATE

#### break event occurred

- BS global, equate, [MUX; ASCII backspace character

- BSLASH global, equate, [MUX; ASCII back slash character

- BP\_PTR global, ALOC, [MUX, 1 byte; RX buffer location of the last backspace action

- BUF\_ADDR local, variable, &BPISR, 2 bytes; the buffer address for continuing the data transfer when the buffer wrap around in the circular buffer

- BUF\_ADRW local, variable, &BPISR, 2 bytes; contains the beginning address of the host write request for the bad BIC fix

- BUF\_LEN local, variable, &BPISR, 2 bytes; the length of the data transfer for the wrap around buffer of the circular buffer data transfer

- BUF\_LENU local, variable, &BPISR, 2 bytes; contains the data transfer length for the host write request for the bad BIC fix

- BYTE local, equate, &BPISR; bit assignment for BIC register 2, set when want byte wide data transfer

- CAR\_WREG global, variable, &MUXVR, 1 byte; contains pseudo card write register content which defines the control for the card LED, self-test mode, hood LED, single-ended driver, and differential driver

- CDC local, equate, &BPISR; bit assignment for BIC register 3, the clear device clear bit

- CHAR\_LEN global, ALOC, [MUX, 1 byte; contains the character length for the SIO

- CH\_AL1 global, equate, [MUX; bit assignment for RX FLAGS+1 set when alert 1 mode is enabled and no alert 1 has been sent yet

- CH\_ECHO global, equate, [MUX; bit assignment for RX\_FLAGS set when echoing is enabled

- CH\_EDIT global, equate, [MUX; bit assignment for RX\_FLAGS set when edit mode is enabled

- CH\_HAND global, equate, [MUX; bit assignment for RX\_FLAGS set when handshaking is enabled

HEWLETT-PACKARD PRIVATE

6

#### HP-CIO 8-CHANNEL MUX FIRMWARE IMS

- CH\_QUOT global, equate, [MUX; bit assignment for RX\_FLAGS set when quoting mode is enabled

- CH\_SIGN global, equate, [MUX; bit assignment for RX\_FLAGS set when signal character detection is enabled

- CH\_SIT global, equate, [MUX; bit assignment for RX\_FLAGS set when single text termination is enabled

- CMD local, equate, &BPISR; bit assignment for BIC registers 5 and 6, the command bit

- CMD\_TBL local, code, &BPISR, 32 bytes; jump table containing processing routine address which correspond to the command to be processed

- CONF\_BUF global, ALOC, [MUX, CONF\_SIZ bytes; the write card configuration staging buffer

- CONF\_SIZ global, equate, [MUX; size of the write card configuration table which is currently 60 bytes

- COUNT global, equate, [MUX; bit assignment for RD\_OPT set when the end-on-count option is enabled

- COUNT local, variable, &DMAA, 2 bytes; counter in the MIC channel A ISR to measure how many time the MIC failed by generating an interrupt for channel A DMA, the MUX card never uses the MIC channel A DMA

CR - global, equate, [MUX; ASCII carriage-return character

- CTC0\_TAB local, code, &MXWCC, 34 bytes; CTC baud rate generator programming values, each entry consists of 2 bytes, the first byte is the control byte for the CTC, the second byte is the time constant

- CTCIVECO global, code, &MUXIV, 16 bytes; contains the interrupt service routine addresses for CTC #0

- CTCVEC global, equate, [MUX; low byte of the starting address for the CTC interrupt table

- CTC\_0\_CO global, equate, [MUX; CTC #0 channel 0 I/O port address, the DMA pacer for the MIC DMA card or the firmware real

7

HEWLETT-PACKARD PRIVATE

time clock for the Z80 DMA card

- CTC\_0\_C1 global, equate, [MUX; CTC #0 channel 1 I/O port address, port #1 baud rate generator

- CTC\_0\_C2 global, equate, [MUX; CTC #0 channel 2 I/O port address, port #0 baud rate generator

- CTC\_0\_C3 global, equate, [MUX; CTC #0 channel 3 I/O port address, the firmware real time clock for the MIC DMA card or the BIC interrupt generator for the Z80 DMA card

- CTC\_1\_CO global, equate, [MUX; CTC #1 channel 0 I/O port address, port #2 baud rate generator

- CTC\_1\_C1 global, equate, [MUX; CTC #1 channel 1 I/O port address, port #3 baud rate generator

- CTC\_1\_C2 global, equate, [MUX; CTC #1 channel 2 I/O port address, port #4 baud rate generator

- CTC\_1\_C3 global, equate, [MUX; CTC #1 channel 3 I/O port address, unused

- CTC\_2\_CO global, equate, [MUX; CTC #2 channel 0 I/O port address, port #5 baud rate generator

- CTC\_2\_C1 global, equate, [MUX; CTC #2 channel 1 I/O port address, port #6 baud rate generator

- CTC\_2\_C2 global, equate, [MUX; CTC #2 channel 2 I/O port address, port #7 baud rate generator

- CTC\_2\_C3 global, equate, [MUX; CTC #2 channel 3 I/O port address, unused

- CTC\_BAUD global, ALOC, [MUX, 1 byte; contains the CTC I/O port address for the baud rate generator

- CTC\_TBL local, code, &MUXMN, 8 bytes; table of CTC I/O port address for the baud rate generator corresponding to the port, index by the port number

- C\_OUTSP global, equate, [MUX; bit assignment for UNIX\_OPT set when the conditional output separator appendage option is enabled

- DATALEN global, ALOC, [MUX, 2 bytes; the data transfer length from the transaction request block of the WIC order

DATA AVA - global, equate, [MUX; bit assignment for INT STAT, set

8

HEWLETT-PACKARD PRIVATE

HP-CIO 8-CHANNEL MUX FIRMWARE IMS

when data is available in the receive buffer, i.e., a receive record is available for the host

- DATA MSK global, ALOC, [MUX, 2 bytes; the data and parity mask

- DCL local, equute, &BPISR; bit assignment for BIC register 3, the device clear bit

- DEL global, equate, [MUX; ASCII DEL character

- DEVEND local, equate, &BPISR; bit assignment for BIC register 4, the device end bit

- DEV HAND global, ALOC, [MUX, 1 byte; the handshake options

- DIFFDVR global, equate, [MUX; bit assignment for CAR\_WREG, set to disabled the front end differential driver

- DIFFX local, variable, &SPDSN, 1 byte; the tolerance band width to determine if the speed sensed value is within the potential baud rate

- DLF global, equate, [MUX; BIC register 2 status code, download failed

- DMAB\_SW local, equate, &BPISR; bit assignment for MIC register 0, the DMA B switch bit, clear for backplane DMA, set for frontplane DMA

- DMACT local, equate, &MUXMN; the size of DMAI

- DMAHRD global, FBIT, [MUX; set when doing host read DMA with the Z80 DMA card

- DMAHRDA local, variable, &BPISR, 14 bytes; contains the Z80 DMA programming instructions for doing a host read

- DMAHRDAR local, variable, &BPISR, 2 bytes; this is part of array DMAHRDA, contains the buffer address for the data transfer from the card to the host

- DMAHRDBL local, variable, &BPISR, 2 bytes; this is part of array DMAHRDA, contains the buffer length for the dta transfer from the card to the host

- DMAHRDCT local, equate, &BPISR; the length of array DMAHRDA

- DMAHWD local, variable, &BPISR, 12 bytes; contains the Z80 DMA programming instructions for data transfer from the host to the card

g

HEWLETT-PACKARD PRIVATE

- DMAHWDAR local, variable, &BPISR, 2 bytes; this is part of array DMAHWD, contains the buffer address for the data transfer from the host to the card

- DMAHWDBL local, variable, &BPISR, 2 bytes; this is part of array DMAHWD, contains the buffer length for the data transfer from the host to the card

- DMAHUDCT local, equate, &BPISR; the length of array DMAHUD

- DMAI local, code, &MUXMN, 7 bytes; programming instructions to initialize the Z80 DMA

- DMAINIT local, code, &BPISR, 26 bytes; programming instructions to initialize the Z80 DMA

- DMAWRAP global, FBIT, [MUX; set when have wrap around on the circular buffer when using the Z80 DMA card

- DMA\_DIR local, equate, &BPISR; bit assignment for MIC registers 3 and 8, data transfer direction bit, clear for from memory, set for to memory

- DMA\_END local, equate, &BPISR; bit assignment for MIC register 0, clear to assert END on the last byte in the host read data transfer

- DMA\_ENI local, equate, &BPISR; bit assignment for MIC registers 3 and 8, set when the MIC is to generate an interrupt after the data transfer completes

- DMA\_ENO local, equate, &BPISR; bit assignment for MIC registers 3 and 8, set to enable the DMA operation

- DMA\_MEM local, equate, &BPISR; bit assignment for MIC registers 3 and 8, clear to increment for the memory address, set to decrement for the memory address

- DOD global, equate, [MUX; BIC register 2 status code to host, dead or dying

- EAK global, equate, [MUX; WTC order request code, event acknowledge

- EBLEN global, equate, [MUX; length of the echo buffer

- ECHO global, equate, [MUX; bit assignment for RD\_OPT, set when for echoing the receive character

- ECHOBUF global, variable, &MUXVR, 1024 bytes; the starting address for the echo buffers for all 8 ports

HEWLETT-PACKARD PRIVATE

10

# HP-CIO 8-CHANNEL MUX FIRMWARE IMS

- ECHOPTRI global, ALOC, [MUX, 2 bytes; contains the address for the next echo character to be inserted into the echo buffer

- ECHOPTRO global, ALOC, [MUX, 2 bytes; contains the address for the next echo character to be transmitted from the echo buffer

- ECHO\_SIN global, equate, [MUX; bit assignment for DEV\_HAND, set when the single text terminator is to be echoed

- ECHO\_TBL local, code, &MUXMN, 16 bytes; table of echo buffer address for each port, index by the port number

- ECH\_CRLF global, equate, [MUX; bit assignment for DEV\_HAND, set when the single text terminator defined in SIN\_TEXT is to cause the echoing of the CR-LF characters in place of it

- EDIT global, equate, [MUX; bit assignment for RD\_OPT, set when the edit mode option is enabled

- EDITCHAR global, equate, [MUX; bit assignment for the special character tables POSCHTBL, PISCHTBL, ..., PTSCHTBL, set when the corresponding character is an edit character for editing

- EHCTR local, equate, &MUXMN; the host ENQ/ACK pacing counter default value

- END global, equate, [MUX; UTC order request code for the end-of-data

- END\_CT global, ALOC, [MUX, 2 bytes; contains the end-on-count value from the host for the end-on-count option

- ENQ\_TIMR global, ALOC, [MUX, 1 byte; the host ENQ/ACK or handshake timer value

- EONCT local, equate, &MUXMN; the default end-on-count value

- EQ\_DCNTR global, ALOC, [MUX, 1 byte; the host ENQ/ACK character down counter

- EVBITMSK local, code, &MXWCC, 9 bytes; the bit mask corresponding the bit position in INT STAT for the corresponding event

- EVB LEN global, equate, [MUX; length of the event block

- EVENTQ global, variable, &MUXVR, 2 bytes; contains the link list adress of the pending event queue

HEWLETT-PACKARD PRIVATE

- EVNTABLE local, code, &BCRTS, 32 bytes; a table of masks to remove the appropriate event which was sent to the host, each entry consists of 2 bytes

- EVNT\_BRK global, equate, [MUX; event code for break received

- EVNT\_MSG global, equate, [MUX; event code for data message available

- EVNT\_SC1 global, equate, [MUX; event code for signal character 1 detected

- EVNT\_SC2 global, equate, [MUX; event code for signal character 2 detected

- EVNT\_SC3 global, equate, [MUX; event code for signal character 3 detected

- EVNT\_SC4 global, equate, [MUX; event code for signal character 4 detected

- EVNT TIM global, equate, [MUX; event code for handshake timed out

- EVNT\_TX global, equate, [MUX; event code for transmit buffer is empty

- EVNUM global, equate, [MUX; the maximum number of pending events per card

- EVPRITBL local, code, &MXWCC, 9 bytes; the event priority value corresponding to each event

- EVQFREE global, variable, &MUXVR, 2 bytes; contains the link list address to the free event blocks

- EV\_BLKS global, variable, &MUXVR, EVNUM\*EVB\_LEN bytes (640 bytes); the event blocks storage area

- EV\_CODE global, ALOC, [MUX, 1 byte; index into the event block for the event code if an event was sensed

- EV\_DISB global, equate, [MUX; bit assignment for PORTSTAT+1, set when an event is sent to the host, it is cleared when an event acknowledge is received from the host with no more event on the queue

- EV\_LEN global, ALOC, [MUX, 2 bytes; index into the event block containing the length of the message received buffer

HEWLETT-PACKARD PRIVATE

12

#### HP-CIO 8-CHANNEL MUX FIRMWARE IMS

- EV\_NEXT global, ALOC, [MUX, 2 bytes; link address to the next event block

- EV\_PID global, ALOC, [MUX, 1 byte; index into the event block containing the port ID number

- EV\_PRIO global, ALOC, [MUX, 1 byte; index into the event block containing the event block priority

- EV\_QUED global, equate, [MUX; bit assignment for PORTSTAT+1, set when an event is queued on the RTS queue for this port

- EV\_RTS\_S global, ALOC, [MUX, 1 byte; index into the event block containing the RTS status code

- EV\_TID global, ALOC, [MUX, 2 bytes; index into the event block containing the transaction ID number, if any

- FBIT global, macro, [MUX; macro used to define the flag to be used with macros FCLR, FSET, and FTST

- FCL local, equate, &BPISR; bit assignment for BIC register 3, the fifo clear bit

- FCLR global, macro, [MUX; macro to clear the flag defined by using macro FBIT

- FF global, equate, [MUX; the character OFFH

- FFR local, equate, &BPISR; bit assignment for BIC registers 5 and 6, the FIFO ready bit

- FIFORBPI local, equate, &BPISR; control word for BIC register 4 for read byte, pre-end, srq-immediate

- FIFOWBI local, equate, &BPISR; control word for BIC register 4

for write byte, srq-immediate

- FIFOWWI local, equate, &BPISR; control word for BIC register 4 for write word, srq-immediate

HEWLETT-PACKARD PRIVATE

- FIFO\_SRQ local, equate, &BPISR; control word for BIC register 4 for SRQ for the next order

- FILLER1 global, ALOC, [MUX, 1 byte; filler in the port configuration information

- FILLER10 global, ALOC, [MUX, 1 byte; filler in the port configuration information

- FILLER11 global, ALOC, [MUX, 1 byte; filler in the port configuraion information

- FILLER12 global, ALOC, [MUX, 1 byte; filler in the port configuration information

- FILLER13 global, ALOC, [MUX, 1 byte; filler in the port configuration information

- FILLER14 global, ALOC, [MUX, 1 byte; filler in the port configuration information

- FILLER15 global, ALOC, [MUX, 1 byte; filler in the port configuration information

- FILLER16 global, ALOC, [MUX, 1 byte; filler in the port configuration information

- FILLER2 global, ALOC, [MUX, 1 byte; filler in the port configuration information

- FILLER3 global, ALOC, [MUX, 2 bytes; filler in the port configuration information

- FILLER4 global, ALOC, [MUX, 1 byte; filler in the port configuration information

- FILLER5 global, ALOC, [MUX, 1 byte; filler in the port configuration information

- FILLER6 global, ALOC, [MUX, 1 byte; filler in the port configuration information

- FILLER7 global, ALOC, [MUX, 1 byte; filler in the port configuration information

- FLAGS local, variable, &MUXVR, (FLBIT+7)/8 bytes (2 bytes); the first byte is the interrupt counter for the macros INTS OFF and INTS RES; the second byte contains the flags defined by using the macro FBIT

- FLBIT global, define label, [MUX; flag bit position assignment

HEWLETT-PACKARD PRIVATE

14

## HP-CIO 8-CHANNEL MUX FIRMUARE IMS

counter for used with macro FBIT to define flags

- FSET global, macro, [MUX; macro to set the flag defined by using macro FBIT

- FTST global, macro, [MUX; macro to test the flag defined by using macro FBIT

- FULL WIR global, equate, [MUX; transmission mode code for full duplex hardwired link

- F\_BIT global, equate, [MUX; bit assignment for the WIC order request code specifying that the received buffer is to be flushed

- GEN\_NULL global, equate, [MUX; bit assignment for UNIX\_OPT, set to generate a null character instead of an event for the received break event

- HANDSHAK global, equate, [MUX; bit assignment for the special character tables POSCHTBL, PISCHTBL, ..., P7SCHTBL, set when the corresponding character is an handshake character

- HAND\_EN global, equate, [MUX; bit assignment for RD\_OPT, set when the handshake option is enabled

- HEN\_TCT global, ALOC, [MUX, 2 bytes; the host ENQ/ACK or handshake timer counter, the first byte is millisecond down counter, and the second byte is the second down counter

- HLED\_ON global, equate, [MUX; bit assignment for CAR\_UREG, set when the hood LED is on

- HOST\_X\_X global, equate, [MUX; mask for the host X-ON/X-OFF bit in DEV HAND

- HOWTOSRQ global, FBIT, [MUX; flag set when a data transfer occurred which tells subprogram SRQ HOST to send a 10H to BIC register 5 to generate an SRQ; otherwise, send a 10H to BIC register 4 to generate an SRQ

- HST\_MASK global, ALOC, [MUX, 1 byte; the first byte of the host interrupt mask, if the corresponding bit is set, the card will generate an event to the host if the card encountered the event

- HST\_MASL global, ALOC, [MUX, 1 byte; the second byte of the host interrupt mask, same comment as for HST MASK

HEWLETT-PACKARD PRIVATE

- HTIMEOUT global, equate, [MUX; bit assignment for INT\_STAT+1, set when the handshake timer timed out

- HUDONE global, FBIT, [MUX; flag set for the Z80 DMA MUX when the host write is doing a 1 byte transfer

- HWD\_XFER global, FBIT, [MUX; flag set when the card is doing a host write data transfer

- H ACK global, ALOC, [MUX, 1 byte; the host ENQ/ACK ACK character

- H\_D1\_D3 global, equate, [MUX; bit assignment for DEV\_HAND, set when the host X-ON/X-OFF handshake is enabled

- H ENQ global, ALOC, [MUX, 1 byte; the host ENQ/ACK ENQ character

- H\_EN\_CTR global, ALOC, [MUX, 1 byte; the host ENQ/ACK pacing counter value

- H\_EQ\_AK global, equate, [MUX; bit assignment for DEV\_HAND, set when the host ENQ/ACK handshake is enabled

- H\_XOFF global, ALOC, [MUX, 1 byte; contains the host X-ON/X-OFF X-OFF character

- H\_XON global, ALOC, [MUX, 1 byte; contains the host X-ON/X-OFF X-ON character

- IDY\_BUF local, code, &BCIDY, 9 bytes; contains the IDY information for the MUX card

- IDY LEN local, equate, &BCIDY; the length of the MUX IDY block

- IDY\_RAM local, variable, &BCIDY, 9 bytes; the RAM area for the IDY block, the MIC is unable to transfer data to the host from the ROM area, therefore the ROM data must first be moved to the RAM area

- IFC local, equate, &BPISR; bit assignment for BIC register 5, the interface clear bit

- IM\_XON global, equate, [MUX; bit assignment for UNIX\_OPT, set when the receiver is to restart the transmitter when any character is received while the transmitter is stopped due to an device X-OFF

- INTS\_CNT global, equate, [MUX; equivalent to the first byte of FLAGS which is used as the interrupt counter, see also FLAGS

INT STAT - global, ALOC, [MUX, 2 bytes; contains the interrupt

HEWLETT-PACKARD PRIVATE

16

#### HP-CIO 8-CHANNEL MUX FIRMWARE IMS

status

- IOBUFLN global, equate, [MUX; length of each I/O buffer

- IOBUFRS global, variable, &MUXVR, NPORTS\*2\*IOBUFLN bytes (8192 bytes); the I/O buffer for each port

- IVECTOR global, code, &MUXIV, 144 bytes; contains the interrupt service routine addresses, the receive interrupt cell addresses, the receive interrupt service routine addresses, and the speed sense interrupt service routine addresses

- IV SIZE global, equate, [MUX; the size of the interrupt table

- LED\_OFF global, equate, [MUX; bit assignment for CAR\_WREG, set when the card LED is off

- LEN local, code, &MXWCC, 4 bytes; the data mask for the number of significant data bits, index by the character length code

LF - global, equate, [MUX; the ASCII linefeed character

- LINE\_DEL global, ALOC, [MUX, 1 byte; contains the character to be used as the line delete character for edit mode

- MAXEV global, equate, [MUX; maximum number of events per port

- MAX\_RX global, equate, [MUX; maximum block size for the receive buffer

- MAX\_TX global, equate, [MUX; maximum block size for the transmit buffer

- MICVEC global, equate, [MUX; the low byte of the interrupt vector address for the MIC

- MIC 0 local, equate, &BPISR; I/O port address for MIC register 0

MIC 1 - local, equate, &BPISR; I/O port address for MIC register 1

MIC 2 - local, equate, &BPISR; I/O port address for MIC register 2

MIC 3 - local, equate, &BPISR; I/O port address for MIC register 3

HEWLETT-PACKARD PRIVATE

MIC\_4 - local, equate, &BPISR; I/O port address for MIC register 4

MIC 5 - local, equate, &BPISR; I/O port address for MIC register 5

MIC 6 - local, equate, &BPISR; I/O port address for MIC register 6

MIC 7 - local, equate, &BPISR; I/O port address for MIC register 7

MIC 8 - local, equate, &BPISR; I/O port address for MIC register 8

MIC 9 - local, equate, &BPISR; I/O port address for MIC register 9

- MIC\_A local, equate, &BPISR; I/O port address for MIC register OAH

- MIC\_B local, equate, &BPISR; I/O port address for MIC register OBH

- MIC\_FLAG global, define label, [MUXA; flag set to 0 when using Z80 DMA or to 1 when using MIC DMA. This flag is used in the conditional assembly statements in the following sources: &MUXMN, &BPISR, &MUXST, and &BCIDY.

- MIC\_IVEC global, code, &MUXIV, 16 bytes; contains the MIC interrupt service routine addresses

- MTERM global, equate, [MUX; the offset within the RSR status block for the message termination character

- MTYPE global, equate, [MUX; the offset within the RSR status block for the message termination type code

- MUX\_BERR global, equate, [MUX; the RSR error code for block mode is not allowed for the given request

- MUX\_DAOV global, equate, [MUX; the RSR error code for data overrun in the write data transfer

- MUX\_IREQ global, equate, [MUX; the RSR error code for illegal request or request not implemented

- MUX\_IVSU global, equate, [MUX; the RSR error code for illegal subfunction

- MUX\_NORX global, equate, [MUX; the RSR error code for receive not allowed in simplex transmit mode

HEWLETT-PACKARD PRIVATE

18

#### HP-CIO 8-CHANNEL MUX FIRMWARE IMS

- MUX\_NOSP global, equate, [MUX; the RSR error code for data transfer length too long

- MUX\_NOTX global, equate, [MUX; the RSR error code for transmit not allowed in simplex receive mode

- MUX\_PARA global, equate, [MUX; the RSR error code for illegal configuration parameter values

- MUX\_PLEN global, equate, [MUX; the RSR error code for illegal configuration parameter length

- MUX\_PORT global, equate, [MUX; the RSR error code for illegal port ID

- NEEDTXSP global, equate, [MUX; bit assignment for PORTSTAT+1, set when no more space exist in the transmit buffer to continue the host write request

- NMK local, equate, &BPISR; bit assignment for BIC registers 5 and 6, the NMI acknowledge bit

- NO\_PAR global, equate, [MUX; bit assignment for UNIX\_OPT, set when the "do not terminate receive record on errors" option is desired, the character in error will be replace by the replacement character found in RP BAD

- NPORTS global, equate, [MUX; the number of ports on the card

- OLDMASK1 local, variable, &MXWCC, 1 byte; temporary storage to save the old content of HST\_MASK while reconfiguring

- OLDMASK2 local, variable, &MXWCC, 1 byte; temproary storage to save the old content of HST MASL while reconfiguring

- ONE\_ADDR local, variable, &BPISR, 2 bytes; the buffer address for the last data byte in the host write request, used in the Z80 DMA MUX to process 1 data byte transfer and for fixing a BIC bug when both FFR and END condition are set at the same time

- ORD local, equate, &BPISR; bit assignment for BIC registers 5 and 6, the order bit

- ORD\_TBL local, code, &BPISR, 32 bytes; jump table containing processing routine addresses corresponding each of the order being processed

- OSEP\_1 global, ALOC, [MUX, 1 byte; contains the first output separator character

HEWLETT-PACKARD PRIVATE

- OSEP\_2 global, ALOC, [MUX, 1 byte; contains the second output separator character

- OSEP\_CT global, ALOC, [MUX, 1 byte; specify the number character for the output separator

- OTHER\_RQ global, ALOC, [MUX, 2 bytes; contains the address pointer to the other request block

- POECHO global, variable, &MUXVR, EBLEN bytes (128 bytes); port 0 echo buffer

- POSCHTBL global, variable, &MUXVR, 256 bytes; port 0 special character table

- POSTUFF global, variable, &MUXVR, P\_MAPLEN bytes (185 bytes); port 0 port stuff information including port configuration, buffer pointers, counters, and so on

- P1ECHO global, variable, &MUXVR, EBLEN bytes (128 bytes); port 1 echo buffer

- PISCHTBL global, variable, &MUXVR, 256 bytes; port 1 special character table

- PISTUFF global, variable, &MUXVR, P\_MAPLEN bytes (185 bytes); port 1 port stuff information including port configuration, buffer pointers, counters, and so on

- P2ECH0 global, variable, &MUXVR, EBLEN bytes (128 bytes); port 2 echo buffer

- P2SCHTBL global, variable, &MUXVR, 256 bytes; port 2 special character table

- P2STUFF global, variable, &MUXVR, P\_MAPLEN bytes (185 bytes); port 2 port stuff information including port configuration, buffer pointers, counters, and so on

- P3ECH0 global, variable, &MUXVR, EBLEN bytes (128 bytes); port 3 echo buffer

- P3SCHTBL global, variable, &MUXVR, 256 bytes; port 3 special character table

- P3STUFF global, variable, &MUXVR, P\_MAPLEN bytes (185 bytes); port 3 port stuff information including port configuration, buffer pointers, counters, and so on

- P4ECH0 global, variable, &MUXVR, EBLEN bytes (128 bytes); port 4 echo buffer

HEWLETT-PACKARD PRIVATE

20

HP-CIO 8-CHANNEL MUX FIRMWARE IMS

- P4SCHTBL global, variable, &MUXVR, 256 bytes; port 4 special character table

- P4STUFF global, variable, &MUXVR, P\_MAPLEN bytes (185 bytes); port 4 port stuff information including port configuration, buffer pointers, counters, and so on

- P5ECHO global, variable, &MUXVR, EBLEN bytes (128 bytes); port 5 echo buffer

- P5SCHTBL global, variable, &MUXVR, 256 bytes; port 5 special character table

- P5STUFF global, variable, &MUXVR, P\_MAPLEN bytes (185 bytes); port 5 port stuff information including port configuration, buffer pointers, counters, and so on

- P6ECHO global, variable, &MUXVR, EBLEN bytes (128 bytes); port 6 echo buffer

- P6SCHTBL global, variable, &MUXVR, 256 bytes; port 6 special character table

- P6STUFF global, variable, &MUXVR, P\_MAPLEN bytes (185 bytes); port 6 port stuff information including port configuration, buffer pointers, counters, and so on

- P7ECHO global, variable, &MUXVR, EBLEN bytes (128 bytes); port 7 echo buffer

- P7SCHTBL global, variable, &MUXVR, 256 bytes; port 7 special character table

- P7STUFF global, variable, &MUXVR, P\_MAPLEN bytes (185 bytes); port 7 port stuff information including port configuration, buffer pointers, counters, and so on

- PAR local, equate, &BPISR; bit assignment for BIC register 3, the perpherial address ready bit

- PARITY global, ALOC, [MUX, 1 byte; contains the parity option, 0 for no parity, 1 for odd, 2 for even, 3 for force '0', and 4 for force '1'

- PER global, equate, [MUX; BIC register 2 status code for protocol error

- PID global, ALOC, [MUX, 1 byte; use to get the port ID number from the WIC request block

PIDTABLE - global, variable, &MUXVR, NPORTS bytes (8 bytes); the

HEWLETT-PACKARD PRIVATE

port ID table to map the logical port ID given in the WIC request to the physical port ID, the table is indexed by the physical port number

- PORTABLE local, code, &MUXMN, 16 bytes; table of addresses to the port stuff array, index by port number

- PORTSTAT global, ALOC, [MUX, 2 bytes; contains various flag for the port

- PORT\_DEF local, code, &MUXMN, 60 bytes; the default port configuration

- PORT DFE local, equate, &MUXMN; the ending address of PORT DEF

- PRIO\_ABT global, equate, [MUX; RTS op code priority for abort status

- PRIO\_CON global, equate, [MUX; RTS op code priority for continue status

- PRIO\_END global, equate, [MUX; RTS op code priority for end-of-data transfer

- PRIO\_ERR global, equate, [MUX; RTS op code priority for error trap status

- PRIO\_IDL global, equate, [MUX; RTS op code priority for nothing to do

- PRIO\_REC global, equate, [MUX; RTS op code priority for data message received event

- PRIO\_SIG global, equate, [MUX; RTS op code priority for signal character detected event

- PRIO\_SSM global, equate, [MUX; RTS op code priority for speed sense status

- PRI0\_TIM global, equate, [MUX; RTS op code priority for handshake timeout

- PRIO\_TX global, equate, [MUX; RTS op code priority for transmit buffer is empty

- P\_MAPLEN global, equate, [MUX; the length of port information block for each port

HEWLETT-PACKARD PRIVATE

22

## HP-CIO 8-CHANNEL MUX FIRMWARE IMS

- QS local, equate, &MUXMN; the default quotable single text terminator

- QUOTABLE global, equate, [MUX; bit assignment for the special character table POSCHTBL, PISCHTBL, ..., P7SCHTBL, set for the corresponding character when it is quotable

- QUOTE global, ALOC, [MUX, 1 byte; the quotable character specified by the user

- RAM END global, equate, [MUX; the RAM ending address

- RAM STRT global, equate, [MUX; the RAM starting address

- RD\_BUFR global, ALOC, [MUX, 2 bytes; contains the buffer pointer to the next receive record for the backplane for the next read request; if no receive buffer is available, the pointer value will be zero

- RD\_BUF\_N global, ALOC, [MUX, 1 byte; the offset into the current backplane receive buffer for the next character

- RD\_CARD global, equate, [MUX; the WIC request code for read card information

- RD\_DEV global, equate, [MUX; the WIC request code for read device data

- RD\_OPT global, ALOC, [MUX, 1 byte; contains the frontplane control options for processing the received data

- RD\_SUSP global, equate, [MUX; bit assignment for PORTSTAT+1, set when the host read request is suspended

- READ\_RQ global, ALOC, [MUX, 2 bytes; contains the address pointing the the read request block

HEWLETT-PACKARD PRIVATE

- REC\_SEP global, ALOC, [MUX, 1 byte; contains the record separator character to be used for searching for the conditional output separator option

- REQ global, ALOC, [MUX, 1 byte; index into the request block for the request code

- RESUME global, equate, [MUX; WTC op code to resume a transaction

- RET\_ADDR local, variable, &BPISR, 2 bytes; contains the return address to the calling subprogram which requested a data transfer by calling H CIR, H READ, or H WRITE

- RFC global, equate, [MUX; BIC register status code for ready for command

- RLOG global, equate, [MUX; offset into the status block for the residual count

- RP\_BAD global, ALOC, [MUX, 1 byte; contains the replacement character to replace the receive character which contains an error. This option must be enabled by setting the NO PAR bit in UNIX\_OPT

- RQA local, equate, &BPISR; bit assignment for BIC registers 5 and 6, the request attention bit

- RQB LEN global, equate, [MUX; request block length

- RQ\_FLIST global, variable, &MUXVR, 2 bytes; link list of free request blocks

- RQ\_PSTUF global, ALOC, [MUX, 2 bytes; index into the request block which contains the pointer to the port stuff for the request

- RQ\_TBLES global, variable, [MUX, NPORTS\*3\*RQB\_LEN bytes (480 bytes); allocate space for the request blocks

- RSR\_CODE global, ALOC, [MUX, 1 byte; to contain the RSR status code

- RSR LEN local, equate, &BCRSR; the length of the RSR block

HEWLETT-PACKARD PRIVATE

24

HP-CIO 8-CHANNEL MUX FIRMWARE IMS

- RSR\_RESD global, ALOC, [MUX, 2 bytes; to contain the transmission residual count for the host read request

- RSR\_STT global, ALOC, [MUX, 1 byte; to contain the single text terminator character for the host read request if the receive buffer is terminated by a single text terminator

- RSR\_TERM global, ALOC, [MUX, 1 byte; to contain the text termination code for the host read request

- RSR\_TLOG global, ALOC, [MUX, 2 bytes; to contain the transmission log for any data transfer between the host and the card

- RSUB\_STA local, code, &MXRCI, 14 bytes; the jump table to the appropriate processing routine for the get status request (read card information)

- RTSQ global, variable, &MUXVR, 2 bytes; link list of the RTS response queue

- RTS\_CONT global, equate, [MUX; the RTS status op code to continue the given transaction

- RTS\_END global, equate, [MUX; the RTS status op code to terminate the data transfer phase of the given transaction

- RTS\_EROR global, equate, [MUX; the RTS status op code to notify the host that the given transaction caused an error condition

- RTS\_EVNT global, equate, [MJX; the RTS status op code to notify the host of an event (asynchronous interrupt)

- RTS\_IDLE global, variable, &MUXVR, 1 byte; the RTS status op code to notify the host that the card has nothing to do, this value is not in ROM because the MIC will not DMA data from ROM to the host

- RTS\_NONE global, equate, [MUX; the RTS status op code for nothing to do (not used)

- RTS\_TEMP global, variable, &MUXVR, 2 bytes; temporary storage area for subprogram BC RTS

RWD TABL - local, code, &BCRWD, 10 bytes; jump table to the

HEWLETT-PACKARD PRIVATE

continuation processing routines after the data transfer

- RXD\_CTR global, ALOC, [MUX, 1 byte; frontplane receive record down counter

- RXD\_CTRI global, ALOC, [MUX, 1 byte; frontplane receive record down counter initial value

- RXTX local, equate, &BPISR; bit assignment for the I/O buffer address, clear for the receive buffer, set for the transmit buffer

- RX\_BFULL global, equate, [MUX; bit assignment for RX\_FLAGS, set when the receive buffer is full

- RX\_BUF\_H global, ALOC, [MUX, 2 bytes; frontplane active receive buffer header pointer

- RX DCTR global, ALOC, [MUX, 2 bytes; end-on-count down counter

- RX FLAGS global, ALOC, [MUX, 1 byte; receive configuration flags

- RX\_LOC global, code, &MUXIV, 16 bytes; table of receive interrupt cell for each receive port

- RX\_NXT\_C global, ALOC, [MUX, 2 bytes; frontplane active receive buffer next character pointer

- RX\_TABLE local, code, &MUXMN, 8 bytes; table of high byte receive buffer address for each port, index by the port number

- RX\_TEMP global, variable, &MUXVR, 2 bytes; temporary storage area for the receive interrupt service routine

- RX\_TXOFF global, equate, [MUX; bit assignment for PORTSTAT, set when a device X-OFF is received and waiting for an X-ON

- RX\_VEC global, code, &MUXIV, 16 bytes; a table of receive interrupt service routine address for each port

- R\_E\_SENT global, equate, [MUX; bit assignment for PORTSTAT+1, set when a message receive event was sent

SBIT MSK - global, equate, [MUX; mask to get the S-bit from the WIC

HEWLETT-PACKARD PRIVATE

26

#### HP-CIO 8-CHANNEL MUX FIRMWARE IMS

request code

- SCHARPTR global, ALOC, [MUX, 1 byte; the high byte address of the special character table for the given port

- SCR global, equate, [MUX; BIC register 2 status code for subchannel connect request

- SELF\_TST global, equate, [MUX; bit assignment for CAR WREG, set when the card internal loopback mode is enabled for self-test

- SEND\_MES global, equate, [MUX; bit assignment for DEV\_HAND, set when the option to continue transmitting the message after the ENQ/ACK timer times out

- SGENDDVR global, equate, [MUX; bit assignment for CAR\_WREG, set when the single-ended driver is enabled

- SIGNAL global, equate, [MUX; bit assignment in the special character table, set when the corresponding character is a signal character

- SIGNALA global, equate, [MUX; bit assignment for UNIX\_OPT, set when the signal character detection option is enabled

- SIGNAL 1 global, ALOC, [MUX, 1 byte; contains the signal character 1

- SIGNAL\_2 global, ALOC, [MUX, 1 byte; contains the signal character 2

- SIGNAL\_3 global, ALOC, [MUX, 1 byte; contains the signal character 3

- SIGNAL\_4 global, ALOC, [MUX, 1 byte; contains the signal character 4

- SIG\_1 global, equate, [MUX; bit assignment for INT\_STAT, set when the signal character 1 is detected

- SIG\_1\_X global, equate, [MUX; mask to get the signal character 1 value

- SIG\_2 global, equate, [MUX; bit assignment for INT\_STAT, set when the signal character 2 is detected

HEWLETT-PACKARD PRIVATE

- SIG\_3 global, equate, [MUX; bit assignment for INT\_STAT, set when the signal character 3 is detected

- SIG\_4 global, equate, [MUX; bit assignment for INT\_STAT, set when the signal character 4 is detected

- SIM\_RX global, equate, [MUX; the transmission code for simplex receive

- SIM\_TX global, equate, [MUX; the transmission code for simplex transmit

- SINGLE global, equate, [MUX; bit assignment for RD\_OPT, set when the frontplane control is to terminate the receive record when a single text terminator is encountered

- SINGTEXT global, equate, [MUX; bit assignment for the special character table, set when the corresponding character is to be used as a single text terminator

- SIN\_TEXT global, ALOC, [MUX, 1 byte; the single text terminator character to cause the echoing of the CR-LF characters

- SIOCMD local, code, &MXCCD, 8 bytes; programming instructions to put the SIO in synchronous mode for speed sensing

- SIOIVECO global, code, &MUXIV, 16 bytes; the table of interrupt service routine addresses to service SIO #0

- SIOIVEC1 global, code, &MUXIV, 16 bytes; the table of interrupt service routine addresses to service SIO #1

- SIOIVEC2 global, code, &MUXIV, 16 bytes; the table of interrupt service routine addresses to service SIO #2

- SIOIVEC3 global, code, &MUXIV, 16 bytes; the table of interrupt service routine addresses to service SIO #3

- SIOLEN local, equate, &MXCCD; the size of SIOCMD

- SIOVEC global, equate, [MUX; the starting low byte address for the SIO interrupt vector table

- SI0\_0\_AC global, equate, [MUX; the I/O port address for the control channel of the SIO #O channel A

- SI0\_0\_AD global, equate, [MUX; the I/O port address for the data channel of the SIO #O channel A

- SI0\_0\_BC global, equate, [MUX; the I/O port address for the control channel of the SIO #0 channel B

HEWLETT-PACKARD PRIVATE

28

#### HP-CIO 8-CHANNEL MUX FIRMWARE IMS

- SIO\_0\_BD global, equate, [MUX; the I/O port address for the data channel of the SIO #O channel B

- SI0\_1\_AC global, equate, [MUX; the I/O port address for the control channel of the SIO #1 channel A

- SI0\_1\_AD global, equate, [MUX; the I/O port address for the data channel of the SIO #1 channel A

- SI0\_1\_BC global, equate, [MUX; the I/O port address for the control channel of the SIO #1 channel B

- SIO\_1\_BD global, equate, [MUX; the I/O port address for the data channel of the SIO #1 channel B

- SI0\_2\_AC global, equate, [MUX; the I/O port address for the control channel of the SIO #2 channel A

- SIO\_2\_AD global, equate, [MUX; the I/O port address for the data channel of the SIO #2 channel A

- SIO\_2\_BC global, equate, [MUX; the I/O port address for the control channel of the SIO #2 channel B

- SIO\_2\_BD global, equate, [MUX; the I/O port address for the data channel of the SIO #2 channel B

- SI0\_3\_AC global, equate, [MUX; the I/O port address for the control channel of the SIO #3 channel A

- SI0\_3\_AD global, equate, [MUX; the I/O port address for the data channel of the SIO #3 channel A

- SI0\_3\_BC global, equate, [MUX; the I/O port address for the control channel of the SIO #3 channel B

- SI0\_3\_BD global, equate, [MUX; the I/O port address for the data channel of the SIO #3 channel B

- SIO\_BRK global, equate, [MUX; bit assignment for SIO channel B read register 0 indicating the break receive condition

- SIO\_CS global, equate, [MUX; bit assignment for SIO read register 0 indicating the state of the clear-to-send modem signal

- SIO\_CTRL global, ALOC, [MUX, 1 byte; contains the SIO I/O port address of the control channel for the port

- SIO\_DEF local, code, &MUXMN, 8 bytes; contains the programming instructions for initializing the SIO

HEWLETT-PACKARD PRIVATE

- SIO\_EXEN global, equate, [MUX; bit assignment for SIO write register 1 to enable the SIO external status interrupt

- SIO\_FRER global, equate, [MUX; bit assignment for SIO read register 1 for the framing error bit

- SIO\_LEN global, equate, &MUXVR; the length of the SIO programming instructions

- SIO\_PAR global, equate, [MUX; bit assignment for SIO read register 1 for the parity error bit

- SIO\_RR global, equate, [MUX; bit assignment for SIO read register 0 indicating the state of the receiver ready modem signal

- SIO\_RS global, equate, [MUX; bit assignment for SIO write register 5 to set the request-to-send modem signal state

- SIO\_RXAV global, equate, [MUX; bit assignment for SIO read register 0 indicating whether a receive character is available

- SIO\_RXEN global, equate, [MUX; bit assignment for SIO write register 3 to enable or disalbe the receive interrupt

- SIO\_RXIN global, equate, [MUX; bit assignment for SIO write register 3 to set the receive interrupt mode to interrupt on all receive characters

- SIO\_RXOV global, equate, [MUX; bit assignment for SIO read register 1 for the data overrun error bit

- SIO\_SNBK global, equate, [MUX; bit assignment for SIO write register 5 to enable and disable the break generator

- SIO\_TBL local, code, &MUXMN, 8 bytes; table of SIO I/O port address for the control channel for each port, index by the port number

- SIO\_TR global, equate, [MUX; bit assignment for SiO write register 5 to set or clear the terminal ready modem signal

- SIO\_TXEM global, equate, [MUX; bit assignment for SIO read register 0 indicating whether the transmit buffer is empty

- SIO\_TXEN global, equate, [MUX; bit assignment for SIO write register 1 to enable the transmitter

- SIO\_TXIN global, equate, [MUX; bit assignment for SIO write register 1 to enable the transmit interrupt

HEWLETT-PACKARD PRIVATE

30

## HP-CIO 8-CHANNEL MUX FIRMWARE IMS

- SIO\_W global, variable, &MUXVR, 8 bytes; array of SIO programming instructions

- SIO\_W3 global, variable, &MUXVR, 1 byte; contains the SIO write register 3 content

- SIO\_U4 global, variable, &MUXVR, 1 byte; contains the SIO write register 4 content

- SIO\_W5 global, variable, &MUXVR, 1 byte; contains the SIO write register 5 content

- SPACE global, equate, [MUX; the ASCII space character

- SQUOTE global, ALOC, [MUX, 1 byte; the single text terminator to be used as a quoting character when quoting mode is enabled in UNIX

- SRE local, equate, &BPISR; bit assignment for BIC registers 5 and 6, the status register is empty bit

- SS\_CHAR global, ALOC, [MUX, 1 byte; contains the previous character processing in speed sense mode

- SS\_CTR global, ALOC, [MUX, 10 bytes; 5 16-bit counter for speed sensing

- SS\_DCTR global, ALOC, [MUX, 1 byte; the down counter for the number of remaining speed sense counter for counting

- SS\_PTR global, ALOC, [MUX, 2 bytes; the address pointer to the current counter in SS CTR

- SS\_VEC global, code, &MUXIV, 16 bytes; the table of speed sense interrupt service routine addresses for each port

- ST1 local, equate, &MUXMN; the default single text terminator

- STATUS global, equate, &MUXVR; equivalent to FLAGS since no status bits were defined

- STERM global, ALOC, [MUX, 8 bytes; an array of single text terminators

- STERM\_CT global, ALOC, [MUX, 1 byte; the number of valid single text terminators in array STERM

- STOP\_BIT global, ALOC, [MUX, 1 byte; specify the stop bit option, 0 for 1, 1 for 1.5, and 2 for 2

STP - local, equate, &BPISR; bit assignment for BIC register 3, the

HEWLETT-PACKARD PRIVATE

### self-test pass bit

- STRP\_MSK global, ALOC, [MUX, 1 byte; contains the stripping option information

- STRP\_TRM global, equate, [MUX; bit assignment for STRP\_MSK, set the text terminators are to be stripped from the receive buffer

- ST\_CT local, equate, &MUXMN; the default number of single text terminator

- ST\_TEMP global, ALOC, [MUX, 9 bytes; contains the new single text terminator information which will be enabled after the current frontplane record is terminated. If the first byte is zero, no new single text terminator configuration is available.

- SUBFCN global, ALOC, [MUX, 1 byte; the subfucntion code of the WIC request

- SUB\_PSE global, FBIT, [MUX; flag set when the subchannel is paused

- S\_BIT global, equate, [MUX; bit assignment for the WIC request code for the S-bit which specify whether to keep the partial buffer (if any) for the next read

- TEMP global, variable, &MUXVR, 2 bytes; temporary storage

- TEMP\_BUF local, variable, &MXWDD, 2 bytes; buffer address for the next data transfer

- TEMP\_LEN local, variable, &MXWDD, 2 bytes; buffer length for the next data transfer

- TERM\_AL1 global, equate, [MUX; termination code in the receive buffer header for alert 1

- TERM\_BOF global, equate, [MUX; termination code in the receive buffer header for receive buffer overflow

- TERM\_BUF global, equate, [MUX; termination code in the receive buffer header for terminated by card, user buffer full

- TERM\_CNT global, equate, [MUX; termination code in the receive buffer header for termination on count

HEWLETT-PACKARD PRIVATE

32,

HP-CIO 8-CHANNEL MUX FIRMWARE IMS

- TERM\_FER global, equate, [MUX; termination code in the receive buffer header for framing error

- TERM\_HOS global, equate, [MUX; termination code in the receive buffer header for termination initiated by the host

- TERM\_OVF global, equate, [MUX; termination code in the receive buffer header for SIO data overrun error

- TERM\_PER global, equate, [MUX; termination code in the receive buffer header for parity error

- TERM\_PRT global, equate, [MUX; termination code in the receive buffer header for termination by card, partial record

- TERM\_STT global, equate, [MUX; termination code in the receive buffer header for single text termination

- TID global, ALOC, [MUX, 2 bytes; the transaction ID number from the WIC request block

- TIMR\_TYP global, equate, [MUX; bit assignment for STRP\_MSK, set to specify an event to be generated when the handshake timer timed out

- TLOG global, equate, [MUX; offset into the RSR status block for the transmission log

- TOGL\_MSK global, ALOC, [MUX, 1 byte; contains the frontplane features toggle mask

- TR\_ADDR global, ALOC, [MUX, 2 bytes; contains the data transfer address for the transaction

- TR\_LEN global, ALOC, [MUX, 2 bytes; contains the data transfer length for the transaction

- TX\_BUSY global, equate, [MUX; bit assignment for PORTSTAT, set when the transmitter is busy transmitting data

- TX\_CTR global, ALOC, [MUX, 1 byte; the frontplane transmitter down counter

- TX\_ECHO global, equate, [MUX; bit assignment for PORTSTAT+1, set when the echo buffer is not empty

TX EMPTY - global, equate, [MUX; bit assignment for INT STAT, set

HEULETT-PACKARD PRIVATE

#### when the transmit buffer is empty

- TX\_ENQ global, equate, [MUX; bit assignment for PORTSTAT, set when an ENQ character is to be transmitted on the next transmit interrupt for the port

- TX\_HXOFF global, equate, [MUX; bit assignment for PORTSTAT, set when the transmitter needs to transmit the host X-OFF character on the next transmit interrupt

- TX\_HXON global, equate, [MUX; bit assignment for PORTSTAT, set when the transmitter needs to transmit the host X-ON character on the next transmit interrupt

- TX\_MODE global, ALOC, [MUX, 1 byte; contains the transmission mode option, 2 for full duplex hardwired, 3 for simplex transmit, and 4 for simplex receive

- TX\_OUT2 global, equate, [MUX; bit assignment for PORTSTAT, set when the second character of the output separator needs to be transmitted for the conditional output separator option

- TX\_PTR global, ALOC, [MUX, 2 bytes; contains the address pointing to the next character for data transmission

- TX\_TABLE local, code, &MUXMN, 8 bytes; table of the high byte transmit buffer address for each port, index by the port number

- T\_D1\_D3 global, equate, [MUX; bit assignment for DEV\_HAND, set when the device X-ON/X-OFF handshake is enabled

- $T_{EQ}AK$  global, equate, [MUX; bit assignment for DEV\_HAND, set when the device ENQ/ACK handshake is enabled

- T XOFF global, ALOC, [MUX, 1 byte; device X-OFF character

- T XON global, ALOC, [MUX, 1 byte; device X-ON character

- UNIX\_OPT global, ALOC, [MUX, 1 byte; contains the miscellaneous flags to implement some of the UNIX features

- WAIT\_ACK global, equate, [MUX; bit assignment for PORTSTAT, set when the firmware is waiting for the ACK character for the ENQ character sent

- WAPPEND global, equate, [MUX; bit assignment for the subfunction code in the WIC write device data request, set to append the output separators to the message being written

HEWLETT-PACKARD PRIVATE

34

### HP-CIO 8-CHANNEL MUX FIRMWARE IMS

- WHAND global, equate, [MUX; bit assignment for the subfunction code in the WIC write device data request, set to toggle the handshake option

- WCC\_LEN global, code, &MXWCC, 35 bytes; a table containing the length for each corresponding subfunction parameters. If the entry contains a zero, then the length is variable and is checked in the code. If the entry contains a OFFH value, the corresponding subfunction is not used by this firmware. Otherwise, the nonzero value is the length of the parameters that must be given by the user.

- WCC\_TAB global, code, &MXWCC, 105 bytes; a table containing the offset from the start of the port stuff array for the subfunction parameter and the processing routine address to validate the parameters

- WIC\_TEMP global, variable, &MUXVR, 2 bytes; temporary storage area for subprogram BC WIC

- WRITE\_RQ global, ALOC, [MUX, 2 bytes; contains the address pointing to the write request block

- WR\_CARD global, equate, [MUX; WIC request code for write card configuration

- WTC\_BUFR global, variable, &MUXVR, 3 bytes; buffer area for the WTC order request block

- WTC\_LEN global, equate, [MUX; WTC request block length

WTC OPCD - global, ALOC, [MUX, 1 byte; contains the WTC op code

- WTC\_PID global, ALOC, [MUX, 1 byte; contains the port ID in the WTC request block

- WTC\_TID global, ALOC, [MUX, 2 bytes; contains the transaction ID in the WTC request block

Z80DMA - global, equate, [MUX; the Z80 DMA I/O port address

HEWLETT-PACKARD PRIVATE

| +                               | +       | + |

|---------------------------------|---------|---|

|                                 | 1       | 1 |

| SUBPROGRAM & JUMP ENTRY SYMBOLS | CHAPTER | 3 |

|                                 | 1       |   |

|                                 | +       | + |

The following is description for each subprogram and jump entry symbols used in the MUX firmware. There are many multiple entries in each module to reduce the memory space required. This may cause a little difficulty in understanding and modifying the firmware, but the primary objective of fitting the firmware into an 16K EPROM was met.

The symbol is listed first followed by the source file where it is defined. The linkage and the subprogram called are given next, respectively, if the symbol represent a subprogram which can be CALL. Following this is the list of all subprograms calling or jumping to this symbol. Finally a short functional description is given.

ABRT REQ - source: &BCRSR

linkage: CALL ABRT REQ

Register IY contains the address of the request block.

calls: FREE RQB, NOTHIN

jump to: none

called by: BIC RSR, BIC WTC

used by: none

Subprogram to kill off a request and deallocate its resource.

ADD Q - source: &MUXEV

linkage: CALL ADD Q, register DE contains the address of the queue header, register HL contains the address of the block

calls: SRQ HOST

jump to: none

HEWLETT-PACKARD PRIVATE

36

HP-CIO 8-CHANNEL MUX FIRMWARE IMS

called by: BIC RTS, EAK IT

used by: none

Routine to add an event block to the RTS or event queues. Blocks are queued in priority order (0 = highest).

AL1 EVNT - source: &RXISR

linkage: CALL AL1 EVNT

On entry register IY = address of port's stuff.

calls: EVNT MGR, GET\_EVB

jump to: none

called by: RDD\_CONT, RX\_ISR0, RX\_ISR1, RX\_ISR2, RX\_ISR3, RX\_ISR4, RX\_ISR5, RX\_ISR6, RX\_ISR7, WCC\_CONT

used by: none

Subprogram to generate an alert-1 event to the host.

ARQ HOST - source: &BPISR

linkage: CALL ARQ HOST

On entry register C contains the ARQ status code.

calls: none

jump to: none

called by: BIC ABT, BIC ERR, BIC SC, DIE

used by: none

The subprogram to send the ARQ status code to the host through the BIC register 2. If the BIC register is busy, queue the status until the host is ready for it.

BIC ABT - source: &BPISR

linkage: JP BIC ABT

calls: ARQ HOST

HEWLETT-PACKARD PRIVATE

jump to: none

called by: none

used by: BIC\_ISR

The BIC abort command processor.

BIC DIS - source: &BPISR

linkage: JP BIC DIS

calls: none

jump to: BIC\_EXIT

called by: none

used by: BIC ISR

BIC disconnect order processor.

BIC ERR - source: &BIC ERR

linkage: JP BIC\_ERR

calls: ARQ\_HOST

jump to: BIC\_EXIT

called by: none

used by: BIC\_ISR, BIC\_RD, BIC\_UD, BIC\_WIC, BIC\_WTC

Send the protocol error status to the host.

BIC EXIT - source: &BPISR

linkage: JP BIC EXIT

calls: none

jump to: none

called by: none

used by: BIC DIS, BIC END, BIC ERR, BIC PSE, BIC SC, DMAB\_ISR, HCIR\_IO, HRD\_IO, HWD\_IO, ORD\_EXIT

HEWLETT-PACKARD PRIVATE

38

# HP-CIO 8-CHANNEL MUX FIRMWARE IMS

# SRE RTN

Restore the registers and return from BIC or MIC interrupt.

BIC\_IDY - source: &BCIDY

linkage: CALL BIC\_IDY

calls: HRD IO, SRQ HOST

jump to: BIC\_EXIT

called by: BIC\_ISR

used by: none

The MUX IDY order handler. Move the IDY information to RAM, and then send it to the host. The information is moved to RAM first, because the MIC cannot DMA out of the ROM area.

BIC\_INIT - source: &BPISR

linkage: CALL BIC\_INIT

calls: none

jump to: none

called by: MUX\_MAIN

used by: none

The subprogram to initialize the BIC ISR, the BIC, and the MIC.

BIC\_ISR - source: &BPISR

linkage: CALL BIC\_ISR

calls: ARQ\_HOST, BIC\_IDY, BIC\_RD, BIC\_RSR, BIC\_RTS, BIC\_WD, BIC\_WIC, BIC\_WTC

jump to: BIC EXIT

called by: BIC interrupt

HEWLETT-PACKARD PRIVATE

used by: MIC IVEC

BIC and MIC interrupt service routine.

BIC PSE - source: &BPISR

linkage: JP BIC\_PSE

calls: SRQ\_HOST

jump to: BIC\_EXIT

called by: none

used by: BIC ISR

BIC PAUSE order handler.

BIC\_RES - source: &BPISR

linkage: JP BIC\_RES calls: SRQ\_HOST jump to: none called by: none used by: BIC\_ISR BIC RESUME command processor.

BIC\_RD - source: &BCRWD

linkage: CALL BIC RD

calls: BIC\_ERR, HCIR\_IO HRD\_IO, HWD\_IO

jump to: ORD\_EXIT, RCI\_CONT, RDD\_CONT, WCC\_CONT, WDD\_CONT

called by: BIC\_ISR

used by: none

RD and WD order handler.

BIC\_RSR - source: &BCRSR

HEWLETT-PACKARD PRIVATE

40

# HP-CIO 8-CHANNEL MUX FIRMWARE IMS

linkage: CALL BIC\_RSR

calls: ABRT REQ, HRD IO

jump to: ORD\_EXIT

called by: BIC ISR

used by: none

This subprogram returns the read request status block for the current transaction to the host.

BIC\_RTS - source: &BCRTS

linkage: CALL BIC RTS

calls: ADD\_Q, FREE\_EVB, GET\_EVB, HRD\_IO, NOTHIN, SRQ HOST, UPDTID

jump to: BIC EXIT

called by: BIC ISR

used by: none

This subprogram handles all RTS order processing.

BIC SC - source: &BPISR

linkage: JP BIC SC

calls: ARQ\_HOST, SRQ\_HOST

jump to: BIC EXIT

called by: none

used by: BIC ISR

BIC subchannel connect command handler.

BIC WD - same as BIC RD

BIC\_WIC - source: &BCWIC

linkage: CALL BIC\_WIC

HEWLETT-PACKARD PRIVATE

calls: CCD\_BEG, CDV\_BEG, EVNT\_MGR, GET\_EVB, GET\_RQB, HWD\_IO, RCI\_BEG, RDD\_BEG, SRQ\_HOST, WCC\_BEG, WDD\_BEG

jump to: BIC\_EXIT, DIE

called by: BIC\_ISR

used by: none

WIC order handler.

BIC WTC - source: &BCWTC

linkage: CALL BIC\_WTC

calls: ABRT\_REQ, ADD\_Q, CCD\_ABT, CDV\_ABT, FREE\_EVB, HWD\_TO, RCI\_ABT\_RDD\_ABT, SET\_EVNT, WCC\_ABT, WDD\_ABT, WDD\_END

jump to: BIC\_ERR, ORD\_EXIT

called by: BIC\_ISR

used by: none

WTC order handler.

CCD ABT - source: &MXCCD

linkage: CALL CCD ABT

calls: none

jump to: none

called by: BIC\_WTC

used by: none

Abort the control card transaction.

CCD BEG - source: &MXCCD

linkage: CALL CCD\_BEG

On entry register BC contains the port stuff address, register IY contains the request block

HEWLETT-PACKARD PRIVATE

42

### HP-CIO 8-CHANNEL MUX FIRMUARE IMS

#### address.

On exit the C flag is set to continue the transaction, the S flag is set if the transaction contains an error, the Z flag is set to suspend the transaction (not used).

calls: CHUCK RX, DATA TX, ECHO CK, MSG EVNT, PACKITUP, PRG\_CTC, RESYNC, RX\_COMPL, SEND\_XON, SET\_CNTR, SET\_EVNT, SET\_SIO

jump to: none

called by: BIC WIC

used by: none

Control card request processor.

CDV ABT - source: &MXCDV

linkage: CALL CDV\_ABT

calls: none

jump to: none

called by: BIC\_WTC

used by: none

Abort the control device request processor.

CDV\_BEG - source: &MXCDV

linkage: CALL CDV BEG

calls: none

jump to: none

called by: BIC\_WIC

used by: none

Control device request processor.

CHEK\_XOF - source: &RXISR

HEWLETT-PACKARD PRIVATE

On entry register IY = address of port's stuff.

calls: PUT\_CHAR, SET\_CNTR, SP\_LEFT

jump to: none

called by: RX\_ISR0, RX\_ISR1, RX\_ISR2, RX\_ISR3, RX\_ISR4, RX\_ISR5, RX\_ISR6, RX\_ISR7, SPC\_ISR0, SPC\_ISR1, SPC\_ISR2, SPC\_ISR3, SPC\_ISR4, SPC\_ISR5, SPC\_ISR6, SPC\_ISR7

used by: none

The frontplane down counter has hit zero; check to see if it is time to send an X-OFF to the device. If so (and it is enabled) send the character. Unless called from RX COUNT subprogram, the frontplane down counter is updated.

CHUCK RX - source: &MXCCD

linkage: CALL CHUCK RX

Register IY contains the port stuff address.

calls: EDIT IT

jump to: none

called by: CCD BEG

used by: none

Clean up the receive event.

CTCIVECO - source: &MUXIV

linkage: none

calls: none

jump to: none

called by: none

used by: none

HEWLETT-PACKARD PRIVATE

44

HP-CIO 8-CHANNEL MUX FIRMWARE IMS

The CTC #0 interrupt vector table.

DATA\_CK - source: &TXISR

linkage: CALL DATA CK

On entry register C = SIO data channel I/O port address, register D = parity mask, register E = data mask, register IY = port stuff address.

calls: none

jump to: DATA TXC

called by: none

used by: ECHO CK

Subprogram to set up pointers & counters to start data transmission.

DATA CKA - source: &TXISR

linkage: JP DATA CKA

On entry registers C, D, E, and IY must be set up the same as for DATA\_CK. In addition the buffer address must be set in register HL.

calls: none

jump to: none

called by: none

used by: PUT DATA

Same function as for DATA\_CK except register HL is already set and it bypass some of the checking which is unnecessary.

DATA TX - source: &TXISR

linkage: CALL DATA TX

On entry register C = SIO data channel I/O port address, register D = parity mask, register E = data mask, register IY = port stuff address.

HEULETT-PACKARD PRIVATE

# calls: SET EVNT, TX SP CK

jump to: none

called by: DATA TX, TX\_ISR0, TX\_ISR1, TX\_ISR2, TX\_ISR3, TX\_ISR4, TX\_ISR5, TX\_ISR6, TX\_ISR7

used by: none

Subprogram to send the next character, update the buffer pointer and counter.

DATA TXC - source: &TXISR

linkage: JP DATA TXC

On entry the content of registers C, D, E, and IY are the same as for entry into DATA TX except register HL must contain the buffer pointer for the next output character.

calls: see DATA\_TX

jump to: none

called by: none

used by: DATA CK

Same function as DATA\_TX except register HL has the buffer pointer already and need not be set up again.

DIE - source: &BPISR

linkage: JP DIE

calls: ARQ HOST

jump to: none

called by: none

used by: GET\_EVB, RX\_ISR0, RX\_ISR1, RX\_ISR2, RX\_ISR3, RX\_ISR4, RX\_ISR5, RX\_ISR6, RX\_ISR7

Subprogram to send the dead-or-dying status error to the host and then jump to 0 to reinitialize the card.

HEWLETT-PACKARD PRIVATE

46

HP-CIO 8-CHANNEL MUX FIRMWARE IMS

DMAA ISR - source: &DMAA

linkage: CALL DMAA ISR

calls: none

jump to: none

called by: MIC channel A DMA interrupt

used by: MIC IVEC

This subprogram keep track of DMA channel A interrupts which should never occur, except under bad condition.

DMAB ISR - source: &BPISR

linkage: CALL DMAB ISR

calls: none

jump to: BIC EXIT, return to the subprogram which calls HCIR\_IO, HRD\_IO, or HWD\_IO

called by: MIC interrupt

used by: MIC\_IVEC

MIC channel B DMA interrupt service routine.

EAK IT - source: &BCWTC

linkage: CALL EAK IT

calls: ADD Q, GET\_STUF

jump to: none

called by: BIC\_WTC, EDIT\_IT

used by: none

Subprogram to process the EAK request of the WTC order.

ECHO CK - source: &TXISR

linkage: CALL ECHO CK

HEWLETT-PACKARD PRIVATE

On entry register C = SIO data channel I/O port address, register D = parity mask, register E = data mask, register IY = port stuff address.

calls: HENQ CK, PUT CHAR

jump to: DATA CK

called by: ECHO\_CK, TX\_ISR0, TX\_ISR1, TX\_ISR2, TX\_ISR3, TX\_ISR4, TX\_ISR5, TX\_ISR6, TX\_ISR7

used by: none

Subprogram to check echo buffer and transmit next echo character. If echo buffer is empty, go check the user buffer.

EDIT IT - source: &MUXEV

linkage: CALL EDIT\_IT, (Q\_TEMP) = the event to be edited

calls: EAK IT, EDIT Q

jump to: none

called by: CHUCK\_RX, RCI\_BEG, RDD\_BEG, WCC\_CONT, WDD\_BEG

used by: none

Routine to do all the editing, busy work, etc. to remove an event from the system.

EDIT Q - source: &MUXEV

linkage: CALL EDIT\_Q, (Q\_TEMP) = event code, (Q\_TEMP+1) =

port ID, register DE = address of the queue

header, interrupt system must be off

calls: FREE EVB

jump to: none

called by: EDIT IT

used by: none

Routine to remove events from either the RTS queue or the event queue.

HEWLETT-PACKARD PRIVATE

48

HP-CIO 8-CHANNEL MUX FIRMWARE IMS

EVNT MGR - source: &MUXEV

linkage: CALL EVNT MGR, register HL contains the address of the RTS or event queue

All registers will be destroyed except for register IY.

calls: ADD Q

jump to: none

called by: AL1\_EVNT, BIC\_WIC, GENSEVEN, MSG\_EVNT, SET\_EVNT

used by: none

Routine to manage the queue of events and RTS responses.

EXT\_ISR0 - source: &EXISR

linkage: CALL EXT\_ISR0

calls: SET\_EVNT

jump to: none

called by: external status interrupt on SIO #0 channel A (port 0)

used by: SIOIVECO

Process the external status interrupt generated by the SIO #0 channel A. The ISR only process the break condition. All other conditions are ignored.

EXT ISR1 - source: &EXISR

linkage: CALL EXT\_ISR1

calls: SET\_EVNT

jump to: none

called by: external status interrupt on SIO #0 channel B (port 1)

used by: SIOIVECO

HEULETT-PACKARD PRIVATE

Process the external status interrupt generated by the SIO #0 channel B. The ISR only process the break condition. All other conditions are ignored.

EXT ISR2 - source: &EXISR

linkage: CALL EXT\_ISR2

calls: SET EVNT

jump to: none

called by: external status interrupt on SIO #1 channel A (port 2)

used by: SIOIVEC1

Process the external status interrupt generated by the SIO #1 channel A. The ISR only process the break condition. All other conditions are ignored.

EXT ISR3 - source: &EXISR

linkage: CALL EXT ISR3

calls: SET EVNT

jump to: none

called by: external status interrupt on SIO #1 channel B (port 3)

used by: SIOIVEC1

Process the external status interrupt generated by the SIO #1 channel B. The ISR only process the break condition. All other conditions are ignored.

EXT ISR4 - source: &EXISR

linkage: CALL EXT\_ISR4

calls: SET EVNT

jump to: none

called by: external status interrupt on SIO #2 channel A (port 4)

HEULETT-PACKARD PRIVATE

50

## HP-CIO 8-CHANNEL MUX FIRMWARE IMS

# used by: SIOIVEC2

Process the external status interrupt generated by the SIO #2 channel A. The ISR only process the break condition. All other conditions are ignored.

EXT ISR5 - source: &EXISR

linkage: CALL EXT ISR5

calls: SET EVNT

jump to: none

called by: external status interrupt on SIO #2 channel B (port 5)

used by: SIOIVEC2

Process the external status interrupt generated by the SIO #2 channel B. The ISR only process the break condition. All other conditions are ignored.

EXT ISR6 - source: &EXISR

linkage: CALL EXT ISR6

calls: SET EVNT

jump to: none

called by: external status interrupt on SIO #3 channel A

used by: SIOIVEC3

Process the external status interrupt generated by the SIO #3 channel A. The ISR only process the break condition. All other conditions are ignored.

EXT ISR7 - source: &EXISR

linkage: CALL EXT ISR7

calls: SET EVNT

jump to: none

called by: external status interrupt on SIO #3 channel B

HEULETT-PACKARD PRIVATE

# used by: SIOIVEC3

Process the external status interrupt generated by the SIO #3 channel B. The ISR only process the break condition. All other conditions are ignored.

FIND TID - source: &BCWTC

linkage: CALL FIND TID

On exit the Z flag is set if the subprogram cannot find the request block containing the TID. Otherwise, register DE contains the request block address.

calls: none

jump to: none

called by: BIC\_WIC

used by: none

Subprogram to find the location of the request block containing the TID specified in the WTC request block.

# FP W1000 - source: &MXWCC

linkage: JP FP W1000

calls: none

jump to: none

called by: none

used by: RCI BEG

Entry in  $\ensuremath{\texttt{WCC}}\xspace_{\ensuremath{\texttt{BEG}}}$  to return the request cannot be block error.

FP W1060 - source: &MXWCC

linkage: JP FP W1060

calls: none

jump to: none

HEWLETT-PACKARD PRIVATE

52

# HP-CIO 8-CHANNEL MUX FIRMWARE IMS

called by: none

used by: RCI BEG

Entry in WCC\_BEG to return the invalid subfunction code error.

FP W1200 - source: &MXWCC

linkage: JP FP W1200

calls: none

jump to: none

called by: none

used by: RCI\_BEG

Entry in WCC\_BEG to return the illegal request length error.

FREE EVB - source: &MUXEV

linkage: CALL FREE\_EVB, register HL contains the block address

calls: none

jump to: none

called by: BIC\_RTS, BIC\_WTC, EDIT\_Q, MUX\_MAIN

used by: none

Routine to return an event block to the free space storage area.

FREE RQB - source: &BCWIC

linkage: CALL FREE RQB

On entry register H1 contains the address of the block to be returned to free storage.

calls: none

jump to: none

HEWLETT-PACKARD PRIVATE

called by: BIC RSR, MUX MAIN

used by: none

Routine to return a request block to free storage.

GENSEVEN - source: &SSISR

linkage: CALL GENSEVEN

Register B contains the baud rate index sensed, register C contains the 8th bit value of character sensed, register IY contains the port stuff address.

calls: EVNT MGR, GET EVB

jump to: none

called by: SS\_ISR0, SS\_ISR1, SS\_ISR2, SS\_ISR3, SS\_ISR4, SS\_ISR5, SS\_ISR6, SS\_ISR7

used by: none

Generate the solicited speed sensed event.

GET EVB - source: &MUXEV

linkage: CALL GET EVB

Returns the address to the block in register HL. Register A is trashed.

calls: none

jump to: DIE

called by: AL1\_EVNT, BIC\_RTS, BIC\_WIC, GENSEVEN, MSG\_EVNT, SET\_EVNT

used by: none

Allocate an event block from free storage.

GET RQB - source: &BCWIC

linkage: CALL GET RQB

HEWLETT-PACKARD PRIVATE

54

#### HP-CIO 8-CHANNEL MUX FIRMUARE IMS

On exit the Z flag bit is set if there is no space. Otherwise register HL will contain the address of the block

calls: none