HP 9000 Series 500 and Series 800 Computer Systems

# HP 27110B

# **CIO HP-IB Interface Card**

**Installation and Reference Manual**

Hewlett-Packard Company Roseville Networks Division 8000 Foothills Boulevard Roseville, California 95678 Manual Part Number 27110-90005 E0288 Printed in U.S.A. February 1988

# **Printing History**

New editions are complete revisions of the manual. Update packages, which are issued between editions, contain additional and replacement pages to be merged into the manual by the customer. The dates on the title page change only when a new edition or a new update is published. No information is incorporated into a reprinting unless it appears as a prior update; the edition does not change when an update is incorporated.

| Edition 1. |   |  | • |   |   |   |   | • |   | • |   | • |   |   |   |   | November 1986 |

|------------|---|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---------------|

| Edition 2. | • |  |   | • | • | • | • | • | • | • | • |   | • | • | • | • | February 1988 |

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD COMAPANY MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANT-ABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

Hewlett-Packard assumes no responsibility for the use or reliability of its software on equipment that is not furnished by Hewlett-Packard.

This document contains proprietary information, which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced, or translated into another language without the prior written consent of Hewlett-Packard Company.

#### Copyright © 1986, 1988 by HEWLETT-PACKARD COMPANY

# Notice

#### For U.S.A. Only

The Federal Communications Commission (in 47 CFR 15.838) has specified that the following notice be brought to the attention of the users of this product.

#### FEDERAL COMMUNICATIONS COMMISSION RADIO FREQUENCY INTERFERENCE STATEMENT

Warning: This equipment generates and uses radio frequency energy and, if not installed and used properly, that is, in strict accordance with the manufacturer's instructions, may cause interference to radio and television reception. It has been type tested and found to comply with the limits for a Class A computing device in accordance with the specifications in Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

If this equipment does cause interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures: re-orient the receiving antenna; relocate the equipment with respect to the receiver; move the equipment away from the receiver; plug the equipment into a different branch circuit. If necessary, the user should consult the dealer or authorized field service representative for additional suggestions. The user may find the following booklet prepared by the Federal Communications Commission helpful: "How to Identify and Resolve Radio-TV Interference Problems". This booklet is available from the U.S. Government Printing Office, Washington, DC 20402. Stock No. 004-000-00345-4.

# Notice

#### For JAPAN Only

#### VCCI RADIO FREQUENCY INTERFERENCE STATEMENT

This device is a Class 1 ITE (data processing equipment for use in industrial and commercial areas), and meets the VCCI standards for prevention of radio interference in industrial and commercial areas. The operation of this device in residential or adjacent areas may interfere with radio and television reception.

Use this device in accordance with its operating manuals.

この装置は,第一種情報装置(商工業地域において使用されるべき情報装置) で商工業地域での電波障害防止を目的とした情報処理装置等電波障害自主規制 協議会(VCCI)基準に適合しております。 従って,住宅地域またはその隣接した地域で使用すると,ラジオ,テレビジ ョン受信機等に受信障害を与えることがあります。 取扱説明書に従って正しい取り扱いをして下さい。

| General        | This product and related documentation must be reviewed for familiariza-<br>tion with safety markings before operation.                                                                                                                                                                                                                          |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Safety Symbols |                                                                                                                                                                                                                                                                                                                                                  |

| $\triangle$    | Instruction manual symbol: the product will be marked with this symbol<br>when it is necessary for the user to refer to the instruction manual in order<br>to protect the product against damage.                                                                                                                                                |

| 4              | Indicates hazardous voltages.                                                                                                                                                                                                                                                                                                                    |

| ÷              | Indicates earth (ground) terminal. This symbol is sometimes used in the manual to indicate circuit common connected to a grounded chassis.                                                                                                                                                                                                       |

|                |                                                                                                                                                                                                                                                                                                                                                  |

| Warning        | The warning sign denotes a hazard. It calls attention to a procedure,<br>practice,or the like, which, if not correctly performed or adhered to, could<br>result in injury. Do not proceed beyond a warning sign until the indi-<br>cated conditions are fully understood and met.                                                                |

|                | ······································                                                                                                                                                                                                                                                                                                           |

| Caution        | The caution sign denotes a hazard. It calls attention to an operating proce-<br>dure, practice, or the like, which, if not correctly performed or adhered to,<br>could result in damage to or destruction of part or all of the product. Do<br>not proceed beyond a caution sign until the indicated conditions are fully<br>understood and met. |

| Servicing      |                                                                                                                                                                                                                                                                                                                                                  |

Any servicing, adjustment, maintenance, or repair of this product must be performed only by service-trained personnel.

## Grounding

#### Warning

SAFETY EARTH GROUND – The computer on which this product is installed is a safety class I product and is provided with a protective earthing terminal. An uninterruptible safety earth ground must be provided from the main power source to the product input wiring terminals, power cord, or supplied power cord set. Whenever it is likely that the protection has been impaired, the product must be made inoperative and be secured against any unintended operation.

**BEFORE APPLYING POWER – Verify that the computer system is configured to match the available main power. Consult your system installation manuals.**

## Handling

#### Caution

STATIC SENSITIVE DEVICES - When any two materials make contact, their surfaces are crushed on the atomic level and electrons pass back and forth between the objects. On separation, one surface comes away with excess electrons (negatively charged) while the other surface is electron deficient (positively charged). The level of charge that is developed depends on the type of material. Insulators can easily build up charges in excess of 20,000 volts. A person working at a bench or walking across a floor can build up a charge of many thousands of volts. The amount of static voltage developed depends on the rate of generation of the charge and the capacitance of the body holding the charge. If the discharge happens to go through a semiconductor device and the transient current pulse is not effectively diverted by protection circuitry, the resulting current flow through the device can raise the temperature of internal junctions to their melting points. MOS structures are also susceptible to dielectric damage due to high fields.

The resulting damage can range from complete destruction to latent degradation. Small geometry semiconductor devices are especially susceptible to damage by static discharge.

This product contains static devices. Transport or store the printed circuit board assembly in an antistatic container. When installing or removing the printed circuit board assembly, do not touch any components. Hold the board by its edges. Component replacement operations must be performed at a static-free workstation using proper anti-static procedures.

# Preface

This is the second edition of the HP 27110B CIO/HP-IB Interface Card Reference Manual. The manual contains information needed to install and check out the operation of the interface card. There are twelve chapters in the manual:

Chapter 1 General Information - introductory and should be read first.

Chapter 2 Site Preparation – not applicable to the product covered by this manual.

Chapter 3 Installation and Configuration – should be read before installing the product.

Chapter 4 **Preventive Maintenance** – read this before attempting any repairs or maintenance of the product.

Chapter 5 Functional Description – read when it is necessary to understand the technical operation of the product.

Chapter 6 **Removal and Replacement** – refer to this chapter when it is necessary to remove or replace this product in the host computer.

Chapter 7 Adjustments – refer to this chapter if it is considered necesary to tune the product.

Chapter 8 **Troubleshooting** – refer to this chapter when it is necessary to diagnose a problem in the product.

Chapter 9 **Component Parts** – refer to this chapter when it is necessary to identify a component in the product that must be removed and a new component installed.

Chapter 10 Reference – lists information source for the product.

Chapter 11 **Product History** – compares previous versions of this product.

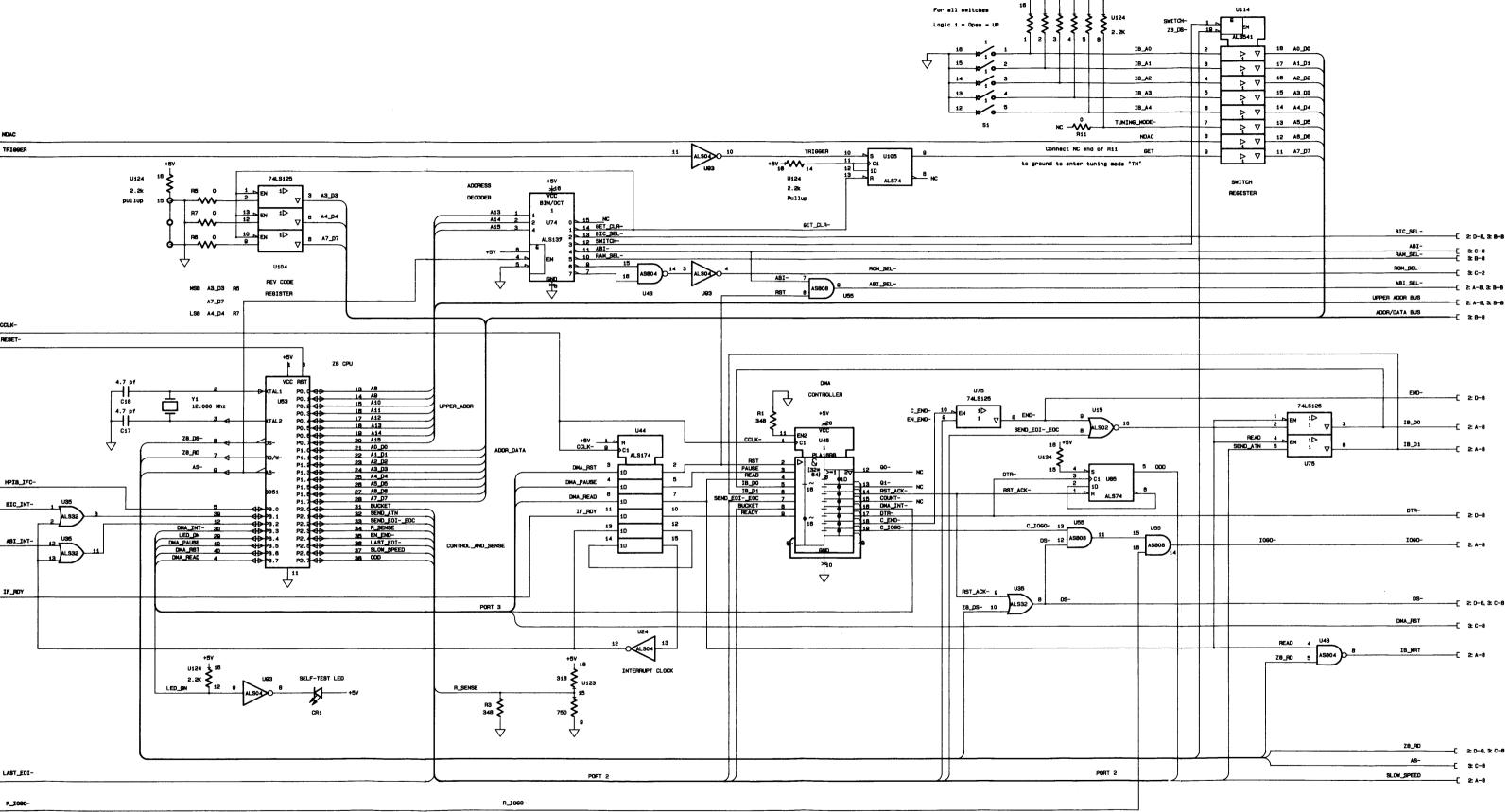

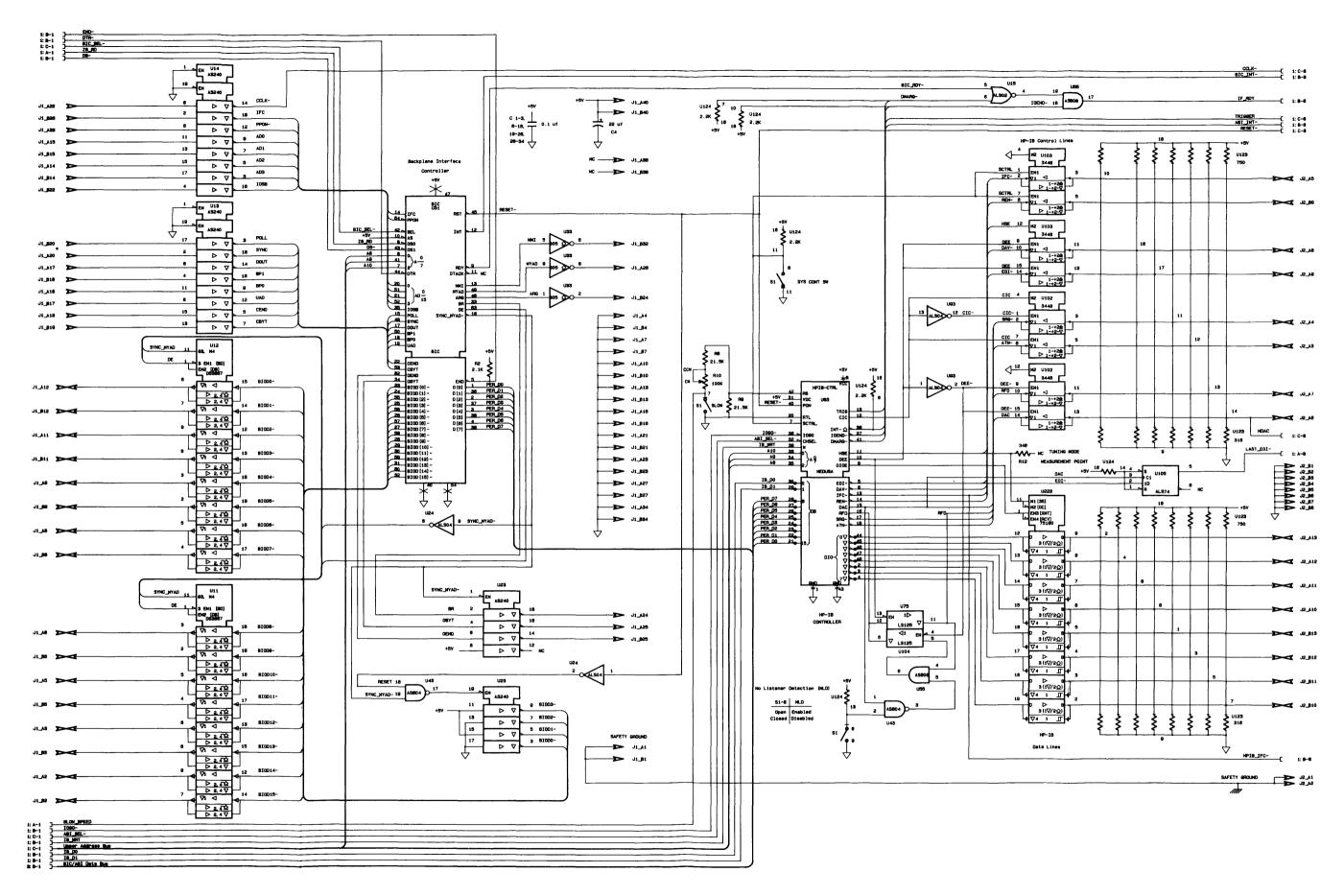

Chapter 12 Diagrams – contains functional block and schematic drawings for the product.

# Contents

### **1** General Information

| Standard Product               | 1-1 |

|--------------------------------|-----|

| Specifications                 | 1-2 |

| Maximum Transfer Rates         | 1-2 |

| Data Settling Time             | 1-2 |

| HP-IB Address                  |     |

| HP-IB Signal Line Terminations | 1-2 |

| HP-IB Signal Line Drivers      | 1-2 |

| HP-IB Line Receivers           | 1-2 |

| Maximum Cable Length           |     |

| Environmental Limits           | 1-3 |

| Physical Characteristics       | 1-3 |

| Power Requirements             | 1-3 |

| HP-IB Supported Functions      | 1-4 |

### 2 Site Preparation

### 3 Installation

| Unpacking and Examining the HP-IB Card     | 3-1 |

|--------------------------------------------|-----|

| Storage                                    | 3-1 |

| General Guidelines for HP-IB Configuration | 3-2 |

| Slow-Speed and Medium-Speed Configurations | 3-3 |

| High-Speed Configuration                   | 3-3 |

| Installation and Checkout                  | 3-5 |

| Reshipment                                 | 3-8 |

### 4 **Preventive Maintenance**

| Preventive Maintenance and Cleaning Instructions |  |  | ••• |  | 4-1 |

|--------------------------------------------------|--|--|-----|--|-----|

|--------------------------------------------------|--|--|-----|--|-----|

### 5 Functional Description

| Overview                    |

|-----------------------------|

| Backplane Interface         |

| HP-IB Interface             |

| DMA Requirements            |

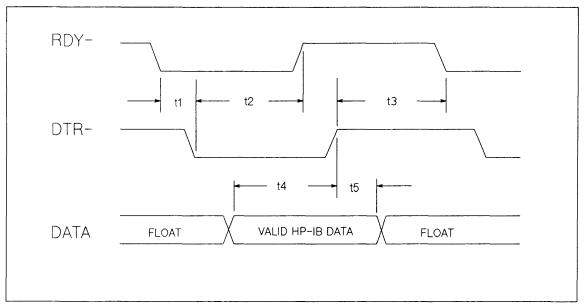

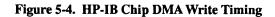

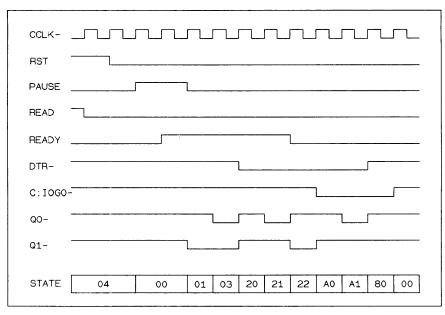

| HP-IB Chip DMA Read Timing  |

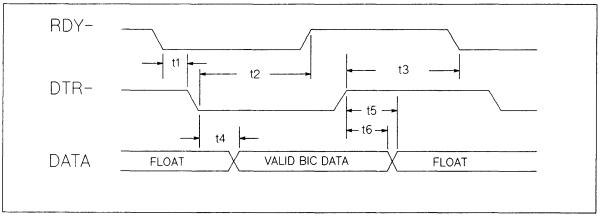

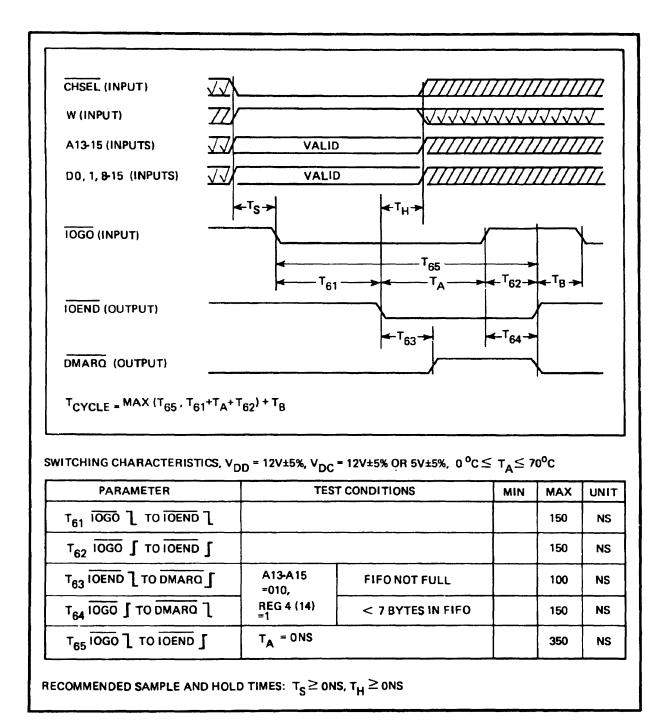

| HP-IB Chip DMA Write Timing |

| <b>Z8</b> Interface         |

| Addressing                  |

| Switch Register Interface   |

| Revision Code Register                   | 5-19   |

|------------------------------------------|--------|

| Z8 Control Signals                       | . 5-19 |

| SEND:ATN, SEND:EOI, LAST:EOI, and LED:ON | 5-20   |

| Interrupts                               | . 5-21 |

| Direct Memory Access Interface (DMA)     | . 5-22 |

| DMA Write                                | . 5-24 |

| DMA Read                                 | . 5-25 |

### 6 Removal and Replacement

| Required Tools                     | <br> | <br>••  | ••• | · · · · · ·                            |

|------------------------------------|------|---------|-----|----------------------------------------|

| Repair Environment                 | <br> | <br>• • | ••  | •••••••••••••••••••••••••••••••••••••• |

| Removal and Replacement Procedures | <br> | <br>    |     | 6-2                                    |

### 7 Adjustments

| 8 | Troubleshooting    |

|---|--------------------|

|   | Card Self-Test     |

|   | LED Interpretation |

## 9 Replaceable Parts

| Replaceable Parts |     |   |   | • |   |   |   |   | • | • |   |   | • |   | • | • | • | • |   | • |   | • | • | • |   |   |   | • | • | .9-1 |

|-------------------|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|

| Ordering Parts .  | ••• | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | .9-1 |

#### 10 Reference

٠

| HP Computer Users Docum    | entation Index | <br>• |  | • | • | • | • | • | • • | · •        | . 10-1 |

|----------------------------|----------------|-------|--|---|---|---|---|---|-----|------------|--------|

| HP-IB Tutorial Description |                | <br>• |  | • |   |   | • | • |     | , <b>.</b> | . 10-1 |

### 11 **Product History**

### 12 Diagrams

The HP 27110B Hewlett-Packard Interface Bus (HP-IB) Interface Card is Hewlett-Packard's implementation of the IEEE Standard 488-1978 and Supplement 488-1978A-1980. The HP 27110B is an input/output (I/O) card and is used with the Hewlett-Packard HP 9000, Series 500 and Series 800, computers.

The HP 27110B can connect up to 14 slow-speed to medium-speed peripheral devices (such as instruments), or up to eight high-speed peripheral devices (such as disc drives). (Standard-speed and high-speed devices can NOT be mixed on the high-speed bus.)

The HP 27110B supports Command Set 80 protocol for HP CS/80-based discs and tape drives.

For error detection, the HP 27110B has parity check and cyclic redundancy check (CRC) as included features, and a firmware-based self-test is in read-only-memory (ROM). Parallel-poll mode can be programmatically enabled or disabled. A no-listener-detection circuit can be enabled or disabled with a switch on the HP 27110B.

## **Standard Product**

The standard HP 27110B HP-IB Interface Card consists of the following parts:

| Item                                | Part Number |

|-------------------------------------|-------------|

| HP-IB printed circuit card assembly | 27110-60301 |

| HP 27110B to HP-IB cable            | 27110-63001 |

| HP 27110B manual (this manual)      | 27110-90005 |

| HP-IB connector backing plate       | 30070-00043 |

The descriptors that identify the card are product number, card assembly number, and date code. The card assembly number and date code are printed on a sticker attached to the card.

# Specifications

| Maximum Transfer<br>Rates         | Medium/Slow-Speed:<br>High-Speed:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 500 kilobytes/second<br>980 kilobytes/second                  |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|

|                                   | (Note: transfer rates are host-computed on the second seco | er and software dependent)                                    |  |

| Data Settling Time                | Medium/Slow-Speed Operation:<br>High-Speed Operation:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | May exceed 500 ns (i.e., 2 µs)<br>350 ns maximum              |  |

| <b>HP-IB Address</b>              | Switch-selectable (set to 30 decimal when acting as the HP-IB System Controller).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                               |  |

| HP-IB Signal Line<br>Terminations | Without the optional load resistor pack installed (the card configured for medium/slow-speed operation), each of the 16 HP-IB signal lines is termi-<br>nated with a 2.3K-ohm resistor to Vcc and a 4.7K-ohm resistor to com-<br>mon. With the installation of the load resistor pack for high-speed<br>operation, signal line termination values are changed except for the REN<br>line, which is not affected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                               |  |

| HP-IB Signal Line<br>Drivers      | Each of the 16 HP-IB signal lines is driven with a circuit having the follow-<br>ing typical characteristics:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                               |  |

|                                   | Type:<br>Output Voltage, Low State:<br>Output Voltage, High State:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Tri-state, open collector<br>0.5 V, 48 mA<br>2.5 V, -5.2 mA   |  |

| HP-IB Line Receivers              | Each of the 16 HP-IB signal lines is re lowing characteristics:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ceived with a circuit having the fol-                         |  |

|                                   | Type:<br>Threshold, Positive Transition:<br>Threshold, Negative Transition:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Schmitt Trigger<br>1.6 V<br>0.9 V for data lines, 1.0 V for   |  |

|                                   | Input Current, Low State:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | control lines<br>-1.3 mA minimum to -3.2 mA<br>maximum @ 0.5V |  |

|                                   | Input Current, High State:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.7 mA minimum to 2.5 mA<br>maximum, between 5V and 5.5V      |  |

| Maximum Cable<br>Length     | Medium/Slow-Speed Operation: |         | 2 metres per device connected,<br>or 20 metres total, whichever is<br>less |  |

|-----------------------------|------------------------------|---------|----------------------------------------------------------------------------|--|

|                             | <b>High-Speed</b> Operation  |         |                                                                            |  |

|                             | Number of Devices            |         | Maximum Total Cable Length<br>(metres)                                     |  |

|                             | 1                            |         | 8                                                                          |  |

|                             | 2                            |         | 9                                                                          |  |

|                             | 3                            |         | 10                                                                         |  |

|                             | 4                            |         | 11                                                                         |  |

|                             | 4<br>5                       |         | 12                                                                         |  |

|                             | 6                            |         | 13                                                                         |  |

|                             | 7                            |         | 14                                                                         |  |

|                             | 8 (ma                        | ximum)  | 15                                                                         |  |

|                             |                              |         |                                                                            |  |

| <b>Environmental Limits</b> | <b>Operating Temperatur</b>  | es:     | 0° to 55° Celsius                                                          |  |

|                             | Operating Humidity:          |         | 5% to 95% relative humidity at 40° Celsius                                 |  |

|                             | <b>Operating Altitude:</b>   |         | 4600 metres (15,000 feet)<br>maximum                                       |  |

|                             |                              |         | me environment, consult your HP<br>Sales and Support Office.)              |  |

| Physical<br>Characteristics | Size:                        |         | 172.7 mm (6.80 inches) long,<br>172.0 mm (7.75 inches) wide                |  |

|                             | Weight:                      |         | 265 grams                                                                  |  |

| I/O Channel Connector       |                              | r:      | 80-pin connector, J1                                                       |  |

|                             | Device Connector:            |         | 26-pin connector, J2                                                       |  |

| <b>Power Requirements</b>   | Voltage                      | Current | Power Usage                                                                |  |

| i ower requirements         | -                            |         | -                                                                          |  |

|                             | + 5 V                        | 1.68 A  | 8.4 Watts                                                                  |  |

## HP-IB Supported Functions

The HP 27110B card is designed to support the following HP-IB Interface Functions as defined by the IEEE Standard 488-1978. These functions are fully supported by the HP 27110B unless noted otherwise.

| Mnemonic               | Controller Functions                                                                                                          |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| C1                     | System Controller                                                                                                             |

| C2                     | Send Interface Clear and Take Charge                                                                                          |

| C3                     | Send Remote Enable                                                                                                            |

| C4                     | Respond to Service Request                                                                                                    |

| C5                     | Send Interface Messages, Receive Control, Pass<br>Control, Pass Control to Self, Parallel Poll, Take<br>Control Synchronously |

|                        |                                                                                                                               |

| Mnemonic               | Controlled Device Functions                                                                                                   |

| <b>Mnemonic</b><br>SR1 | <b>Controlled Device Functions</b><br>Service Request                                                                         |

|                        |                                                                                                                               |

| SR1                    | Service Request                                                                                                               |

| SR1<br>RL2             | Service Request<br>Remote Local                                                                                               |

The following utility functions are provided to support the above listed functions:

| Mnemonic   | Utility Functions                                                                                                                                           |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SH1        | Source Handshake                                                                                                                                            |

| AH1        | Acceptor Handshake                                                                                                                                          |

| <b>T</b> 1 | Basic Talker, Serial Poll, Talk Only                                                                                                                        |

| TE1        | Basic Extended Talker, Serial Poll, Talk Only,<br>Unaddress if My Listener Address and My Secondary<br>Address (requires host software support)             |

| L1         | Basic Listener, Listen Only Mode                                                                                                                            |

| LE1        | Basic Extended Listener, Listener Only Mode,<br>Unaddress if My Secondary Address and Talker<br>Primary Addressed State (requires host software<br>support) |

Note

There are no site preparation requirements specific to the HP 27110B HP-IB interface card. Refer to your computer system manuals for general site preparation procedures. This chapter provides information for you to install, configure, and verify correct operation of the HP 27110B HP-IB Interface card. You will also need your computer system installation manual for reference.

# Unpacking and Examining the HP-IB Card

Caution

Many of the components of the HP 27110B are susceptible to destruction or degradation by electrostatic discharge. See the safety considerations in the front of this manual. To handle this card, use only the edges and extractor levers to avoid damage to components.

Remove the HP-IB card from its protective envelope and place it on *anti-static material* in a clean workspace. Inspect the card itself for damage or missing parts, and verify the part number. Also, check the other sub-assemblies (cables, etc.) for damage.

## Storage

If you store the card for any reason, place it in an electrically and mechanically safe container. The safest place for the card is in the computer card cage. If you must store the card outside of the computer, use the original packaging material or have the card packed by a commercial packaging firm. You must protect the card from static electricity and impact. Place the package containing the card upright (like a book on a shelf) to avoid crushing.

# General Guidelines for HP-IB Configuration

The following general guidelines should be observed when configuring an HP-IB system:

1. Devices or cable segments should not be added to an HP-IB system that is active.

If a device is to be added to an active HP-IB system, the possibility of errors will be minimized if the following procedure is used:

- a. Attach all new cables to the new device to be added. Do not attach any unterminated cables to the existing bus.

- b. Power on the new device.

- c. Attach the new device (with power on) and its cable to the existing bus as a unit.

- 2. On an active HP-IB system, all devices attached should be poweredon to avoid excessive loads caused by powered-down devices.

- 3. The HP 27110B HP-IB Interface Card is shipped from Hewlett-Packard properly configured as system controller and set for highspeed operation. [Switch S1(6) is in the up, or open, position.] The 18-pin Dual In-Line Package (DIP) resistor pack (1810-0081) is also pre-installed in the socket (U123) to support this configuration.

Depending on both the number and performance characteristics of the attached devices, the HP-IB card may be reconfigured for slow and medium operating speeds. Devices that talk at a slower rate may be configured as high-speed devices in the same system, provided all of the requirements for high-speed operation are med. (See "High-Speed Configuration" below.)

### Caution

Adding termination resistors to more than one interface card on an HP-IB bus may result in permanent damage to any or all cards on the bus.

Note

A System Controller that is powered off will not allow the HP-IB bus to be used (as long as the System Controller is connected) because HP-IB bus drivers cannot drive the powered-down termination resistors.

4. Bus configuration guidelines in the following paragraphs should be observed.

| Slow-Speed and<br>Medium-Speed | For proper operation of the HP-IB bus at slow and medium operating speeds, observe the following guidelines:                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configurations                 | 1. Counting the HP-IB interface card as a device, up to 15 HP-IB devices may be connected to the bus.                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                | 2. The maximum length of cable permitted is two metres per connected device, or 20 metres total, whichever is less. For example, when connecting an HP-IB card to one peripheral device, a cable of up to 4 metres is allowed (2 devices X 2 metres/device). The length between adjacent devices is not normally critical as long as the overall limit is not exceeded.                                                                                                                                           |

|                                | 3. At least four out of every five devices should be powered on.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

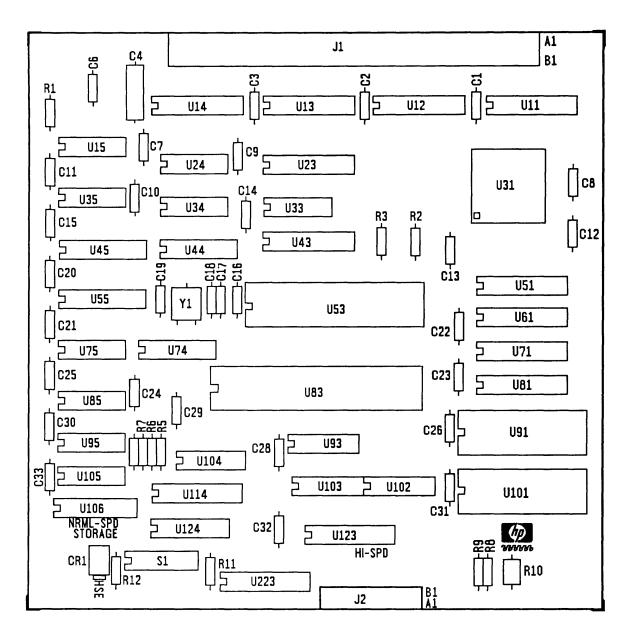

|                                | 4. The 18-pin Dual In-Line Package (DIP) resistor pack (1810-0081)<br>must be removed from socket U123 behind connector J2 and placed<br>in socket U106, labeled "NRML-SPD STORAGE". (See parts<br>location diagram, figure 9-1, in Chapter 9.)                                                                                                                                                                                                                                                                   |

| High-Speed<br>Configuration    | To achieve the maximum possible data transfer rate within a system, the following guidelines must be followed:                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                | 1. Switch S1(7) (see figure 9-1), marked "SLOW", should be set to the high speed position (down, or closed). Switch S1(7) determines the delay between data assertion and DAV (data valid) during an HP-IB write from the computer to the device. With the switch in SLOW position (up, or open), a delay of approximately 500 ns is realized. In the high-speed (down) position, the delay is reduced to approximately 350 ns.                                                                                   |

|                                | 2. All devices expected to talk at high speed must use a settling time of 350 nanoseconds or less.                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                | 3. All devices expected to talk at the higher rates should use 48 mA, three-state drivers.                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                | 4. The device capacitance on each HP-IB line, except REN (Remote<br>Enable) and IFC (Interface Clear), should be less than 50 pF per<br>device. In a system configuration, the total device capacitance should<br>be no more than 50 pF for each equivalent resistive load in the system                                                                                                                                                                                                                          |

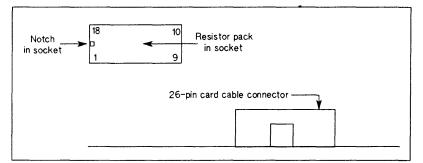

|                                | 5. When the HP-IB interface card is the HP-IB System Controller<br>[switch S1(6), marked "SCTL", is in the up, or open, position], the<br>18-pin Dual In-Line Package (DIP) load resistor pack (1810-0081)<br>must also be installed. Verify that the resistor pack is installed in the<br>socket U123, labeled "HI-SPD", located directly behind connector J2<br>(peripheral device cable connector), with pins 1 and 18 on the pack-<br>age oriented toward the half-circle notch on the socket. See figure 3-1 |

6. Interconnecting cable links should be as short as possible, with a maximum of 15 metres total length per system (see table 3-1). There should be AT LEAST one equivalent resistive load per metre of cable. With the HP-IB interface card as the System Controller, each peripheral device provides a resistive load, and the high-speed resistor pack adds seven equivalent resistive loads.

Thus a maximum system would be composed of the HP-IB card as the System Controller (with its high-speed resistor pack installed) and eight HP-IB peripherals.

7. All devices on the cable should be powered-on to avoid excessive loads caused by powered-down devices.

Figure 3-1. Top View of U123 Socket

| Table 3-1. | Maximum | HP-IB | Cable  | Lengths |

|------------|---------|-------|--------|---------|

|            |         |       | 04.010 |         |

| Number of Peripheral Devices | Maximum Total Cable Length<br>(metres) |

|------------------------------|----------------------------------------|

| 1                            | 8                                      |

| 2                            | 9                                      |

| 3                            | 10                                     |

| 4                            | 11                                     |

| 5                            | 12                                     |

| 6                            | 13                                     |

| 7                            | 14                                     |

| 8 (maximum)                  | 15                                     |

## Installation and Checkout

Warning

Install and check the operation of the HP-IB card as follows:

Before attempting to install this (or any) card, follow the computer "shut down" procedure and TURN OFF the computer power supply. Failure to disconnect the power could result in an electrical shock; and it may damage both the computer and the card. Any resultant damage will not be covered by the warranty.

- 1. All I/O cards draw their power from the host computer system. Determine if your computer system can supply the power needed for the HP-IB card. Refer to Chapter 1 for power requirements of the HP-IB card.

- 2. Set the card switches. Table 3-2 provides a summary of switch positions. Note that UP (open) is logic one, and DOWN (closed) is logic zero.

- a. Set switch S1(7), marked "SLOW", either up (for medium/slowspeed operation) or down (for high-speed operation). Check that the optional load resistor pack (see the "HIGH-SPEED OPERATION" paragraph) is installed if high-speed devices are going to be connected to the card AND the card is the HP-IB System Controller.

- b. Set switch S1(6), marked "SCTL", either up (System Controller ON) or down (System Controller OFF) depending on whether the card is going to operate as the System Controller.

- c. Set switches S1(1) through S1(5) to the card HP-IB address. If the card is to be the System Controller [switch S1(6) up], set the address to 30 decimal [S1(1) down, S1(2) through S1(5) up].

- d. Ensure that switch S1(8) is in the down/disabled position.

- 3. Turn off your computer power following system shutdown procedures compatible with your computer operating system. All HP-IB devices should also be powered-down. Insert the HP-IB card into the desired slot in the I/O channel. Make sure that the components on the card are on the same side as other installed cards. When installing the card, use care not to damage the components or traces on the card or on adjacent cards. Press the card firmly into place.

4. Connect the interface cable supplied to the 26-pin connector (J2) on the card. Table 3-3 shows the pin signal definitions for connector J2. Connect the other end to the HP-IB device(s).

### Note

A "grounding grommet" on the interface cable allows the cable shield to be electrically grounded, which helps to reduce electromagnetic interference generated by some systems. Refer to your computer installation manual for additional information.

- 5. The HP-IB interface has a self-test in ROM. Depending on the power on sequence and logic of the host computer system, card self-test may be initiated at power on or system reset, or it may have to be invoked by you through software. Refer to the appropriate manual for your system for a description of self-test initiation.

- 6. Power-up the computer following procedures compatible with your operating system. To provide an indication that the HP-IB card is working properly:

- a. Some systems have a Computer Service Panel that has LEDs (light emitting diodes) for each I/O slot. These LEDs indicate that the interface card in the specified slot failed to pass self-test. Consult your computer system installation manual for additional information.

- b. For systems that do not have a Computer Service Panel, system software will provide console messages relating I/O slot status. Consult your system manuals.

| Switch      | Function                                                        | Settings                                                                                                                 |

|-------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| S1(8)       | No Listener<br>Detection                                        | Should be down/disabled                                                                                                  |

| S1(7)       | Data Settling<br>Time Selection                                 | Up = Medium/Slow speed,<br>Down = High speed                                                                             |

| S1(6)       | System Controller<br>Selection                                  | Up = System Controller,<br>Down = Not System Controller                                                                  |

| S1(1)–S1(5) | HP-IB Address<br>Selection when<br>not Controller-<br>In-Charge | S5 = MSB (Most Significant Bit);<br>S1 = LSB (Least Significant Bit);<br>Up = Logic 1 = Open;<br>Down = Logic 0 = Closed |

**Table 3-2. Configuration Switch Functions**

The original factory switch settings are as follows:

| 0     |   |      |

|-------|---|------|

| S1(1) | = | DOWN |

| S1(2) | = | UP   |

| S1(3) | = | UP   |

| S1(4) | - | UP   |

| S1(5) | = | UP   |

| S1(6) | = | UP   |

| S1(7) | = | DOWN |

| S1(8) | = | DOWN |

|       |   |      |

Which set these conditions:

| Speed              | – HIGH       |

|--------------------|--------------|

| System Controller  | – ON         |

| Address            | - 30 Decimal |

| No-Listener Detect | – Disabled   |

Table 3-3.

Device Connector J2

| Pin<br>Number | Signal<br>Mnemonic | Signal Definition                   |

|---------------|--------------------|-------------------------------------|

| A1            | SAFETY             | Cable outer shield (chassis ground) |

| A2            | SAFETY             | Cable outer shield (chassis ground) |

| A3            | ATN                | Attention                           |

| A4            | SRQ                | Service Request                     |

| A5            | IFC                | Interface Clear                     |

| A6            | NDAC               | Not Data Accepted                   |

| A7            | NRFD               | Not Ready For Data                  |

| A8            | DAV                | Data Valid                          |

| A9            | EOI                | End Or Identify                     |

| A10           | DIO4               | Data Input/Output, Bit 4            |

| A11           | DIO3               | Data Input/Output, Bit 3            |

| A12           | DIO2               | Data Input/Output, Bit 2            |

| A13           | DIO1               | Data Input/Output, Bit 1            |

| B1            | GND                | Ground                              |

| B2            | GND                | Ground                              |

| B3            | GND                | Ground                              |

| B4            | GND                | Ground                              |

| B5            | GND                | Ground                              |

| <b>B</b> 6    | GND                | Ground                              |

| B7            | GND                | Ground                              |

| <b>B</b> 8    | GND                | Ground                              |

| <b>B</b> 9    | REN                | Remote Enable                       |

| B10           | DIO8               | Data Input/Output, Bit 8            |

| B11           | DIO7               | Data Input/Output, Bit 7            |

| B12           | DIO6               | Data Input/Output, Bit 6            |

| B13           | DIO5               | Data Input/Output, Bit 5            |

### **Reshipment** If the HP-IB card is to be shipped to Hewlett-Packard for any reason, attach a tag identifying the owner and indicating the reason for shipment. Pack the HP-IB card in the original factory packing material, if available. If the original material is not available, good commercial packing material

If the original material is not available, good commercial packing material should be used. Reliable commercial packing and shipping companies have the facilities and materials to repack the item. BE SURE TO OB-SERVE ANTI-STATIC PRECAUTIONS.

| There are no operator adjustments on the HP 27110B card. Do not adjust potentiometer R10. This control was set permanently at the factory. Service, troubleshooting, or other maintenance of the HP 27110B should only be done by qualified electronic maintenance personnel.                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Removal and replacement of the HP 27110B card should only be done<br>with all power removed from the host computer. Power connected to the<br>host computer in normal operation is dangerous and can cause serious<br>injury or death if not switched off during service operations.                                                                                                                                                                                                       |

| Static electricity can cause permanent damage to, or catastrophic failure<br>of, the HP 27110B card. All work performed on electronic assemblies<br>such as the HP 27110B must be at static-safe work stations that have cor-<br>rect static grounding for the card and the service person. Keep the card in<br>a static protection bag whenever it is possible. Use the two plastic ejector<br>levers to handle the card when it is not in a static protection bag or in the<br>computer. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| No regularly scheduled preventive maintenance is recommended for the<br>HP 27110B card except the preventive maintenance recommended in the<br>manual for the host computer.<br>Refer to the cleaning instructions in the host computer manual, and use<br>the same procedures to clean the HP 27110B card.                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

•

The HP 27110B HP-IB card provides an interface between a Hewlett-Packard computer system and an HP-IB bus of up to 14 additional devices. Several such HP-IB devices, each connected to an HP-IB interface card, can be connected to one host computer.

### **Overview**

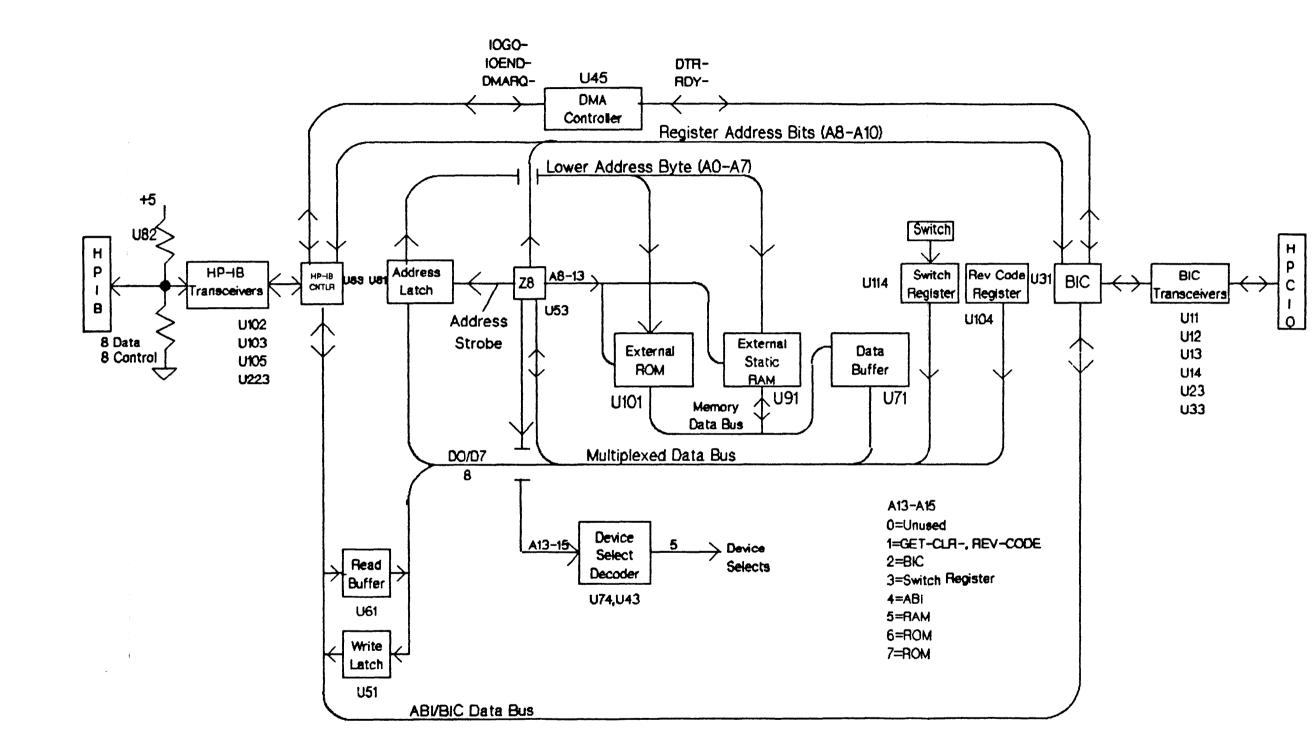

Block and schematic diagrams for the HP-IB card are in Chapter 12.

Eight devices are connected to the Z8 address/data bus as shown below:

#### Device

HP-IB Controller Address Latch Z8 Microcomputer External ROM External RAM Switch Register Backplane Interface Circuit (BIC) Hardware Revision Code Register Access Direction Buffered Read/Write Write Read/Write Buffered Read Buffered Read/Write Read Buffered Read/Write Read

The devices are controlled by the Z8 and/or the DMA controller.

Interface between the HP-IB card and the I/O channel is accomplished via the Backplane Interface Circuit (BIC), U31, gate array and transceivers. Interface between the card and the HP-IB bus is through the HP-IB circuit: U103, U102, and U223.

Direct memory access (DMA) is used on HP-IB data transfers, and is done with a DMA state machine controller in a programmable logic array, and controlled by the Z8 microcomputer. The Z8 does not allow other devices (including itself) to use the data bus while DMA is in progress.

The Address Latch latches the lower eight address bits (A0-A7) from the multiplexed Address/Data bus. Only the memory components (ROM, RAM) require these address bits – all other devices are addressed via A8–A15.

The Switch Register buffers the HP-IB address of the card to the Z8.

The Hardware Revision Code Register has the hardware revision level.

The BIC, HP-IB circuit, RAM and ROM are buffered from the Z8 data bus to prevent timing problems caused by the Z8 interfacing requirements.

#### **Backplane** Interface The Backplane Interface Circuit (BIC), which is a CMOS gate array integrated circuit or "chip", provides a standard method of interfacing to the I/O channel (backplane).

From a hardware standpoint, the BIC performs as a simple microprocessor peripheral. As used in the HP-IB card, the BIC has the following standard signal lines:

- Eight-bit bi-directional tri-state data bus

- Three-bit address bus

- Chip Select line to enable the chip for addressed data transfers

- Data Strobe line to strobe incoming data

- Read/Write line to specify data transfer direction

- Interrupt line to alert the Z8 of important events occurring on the I/O channel

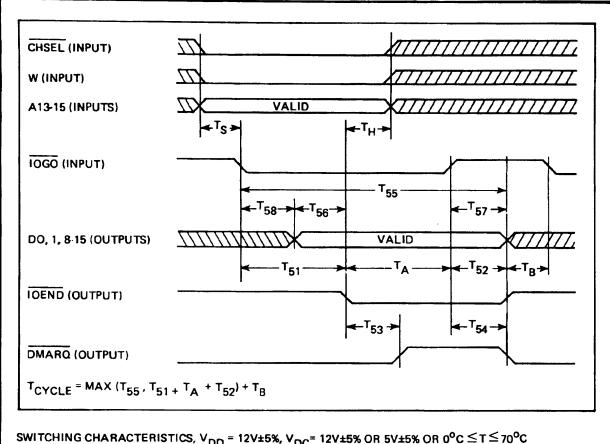

Table 5-1 lists pin connections and describes signals to the BIC.

| Table 5-1. | BIC | <b>Chip Pin</b> | Connections |

|------------|-----|-----------------|-------------|

|------------|-----|-----------------|-------------|

| Pin<br>No. | Signal<br>Mnemonic | BIC<br>Mnemonic | Description                                                           |  |

|------------|--------------------|-----------------|-----------------------------------------------------------------------|--|

| 1          | D0                 | D0              | Data Bus, Bit 0                                                       |  |

| 2          | D2                 | D2              | Data Bus, Bit 2                                                       |  |

| 3          | D4                 | D4              | Data Bus, Bit 4                                                       |  |

| 4          | D6                 | D6              | Data Bus, Bit 6                                                       |  |

| 5          | END-               | END-            | Indicates end of data read or write                                   |  |

| 6          | A8                 | A0              | Register Address, Bit 0                                               |  |

| 7          | A10                | A2              | Register Address, Bit 2                                               |  |

| 8          | Z8RD               | DS0-            | Z8 Read (Read Data Strobe)                                            |  |

| 9          | RDY-               |                 | Asserted by BIC when ready for data transfer                          |  |

| 10         |                    |                 | Not used                                                              |  |

| 11         |                    |                 | Not used                                                              |  |

| 12         | BIC:INT-           | INT-            | BIC Interrupt                                                         |  |

| 13         | NMI                | NMI             | Non-Maskable Interrupt                                                |  |

| 14         | IFC (RST)          | IFC             | Interface Clear (Reset)                                               |  |

| 15         | POLL               | POLL            | Poll                                                                  |  |

| 16         |                    | SYNC_MYAD-      | In conjunction with DE, determines data bus drivers mode of operation |  |

| 17         | DOUT               | DOUT            | Data Out, specifies data bus direction                                |  |

| 18         | BP0                | BP0             | Bus Primitive, Bit 0-with BP1, specifies bus primitive operation      |  |

| 19         | UAD                |                 | Unary Address, latches BIC channel address after a PPON or IFC        |  |

| 20         | AD0                | AD0             | Address Bus, Bit 0                                                    |  |

| 21         | AD2                | AD2             | Address Bus, Bit 2                                                    |  |

| 22         | CEND               | CEND            | Channel End                                                           |  |

| 23         | DB0                | BIOD0-          | Backplane I/O Data, Bit 0                                             |  |

| 24         | DB1                | BIOD1-          | Backplane I/O Data, Bit 1                                             |  |

| 25         | DB3                | BIOD3-          | Backplane I/O Data, Bit 3                                             |  |

| 26         | DB5                | BIOD5-          | Backplane I/O Data, Bit 5                                             |  |

| 27         | DB7                | BIOD7-          | Backplane I/O Data, Bit 7                                             |  |

| 28         | DB9                | BIOD9-          | Backplane I/O Data, Bit 9                                             |  |

| 29         | <b>DB</b> 10       | BIOD10          | Backplane I/O Data, Bit 10                                            |  |