# HP 97060A Graphics Processor Service Manual

# HP 97060A Graphics Processor Service Manual

Part No. 97060-90030

© Copyright 1984, Hewlett-Packard Company. All rights reserved.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied, reproduced or translated to another language without the prior written consent of Hewlett-Packard Company. The information contained in this document is subject to change without notice.

**Restricted Rights Legend**

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in paragraph (b)(3)(B) of the Rights in Technical Data and Software clause in DAR 7-104.9(a).

Hewlett-Packard Company 3404 East Harmony Road, Fort Collins, Colorado 80525

# **Printing History**

New editions of this manual will incorporate all material updated since the previous edition. Update packages may be issued between editions and contain replacement and additional pages to be merged into the manual by the user. Each updated page will be indicated by a revision date at the bottom of the page. A vertical bar in the margin indicates the changes on each page. Note that pages which are rearranged due to changes on a previous page are not considered revised.

The manual printing date and part number indicate its current edition. The printing date changes when a new edition is printed. (Minor corrections and updates which are incorporated at reprint do not cause the date to change.) The manual part number changes when extensive technical changes are incorporated.

November 1983...First Edition August 1984...First Edition with update

#### Warranty Statement

Hewlett-Packard products are warranted against defects in materials and workmanship. For Hewlett-Packard computer system products sold in the U.S.A. and Canada, this warranty applies for ninety (90) days from the date of shipment.\* Hewlett-Packard will, at its option, repair or replace equipment which proves to be defective during the warranty period. This warranty includes labor, parts, and surface travel costs, if any. Equipment returned to Hewlett-Packard for repair must be shipped freight prepaid. Repairs necessitated by misuse of the equipment, or by hardware, software, or interfacing not provided by Hewlett-Packard are not covered by this warranty.

HP warrants that its software and firmware designated by HP for use with a CPU will execute its programming instructions when properly installed on that CPU. HP does not warrant that the operation of the CPU, software, or firmware will be uninterrupted or error free.

NO OTHER WARRANTY IS EXPRESSED OR IMPLIED, INCLUDING BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. HEWLETT-PACKARD SHALL NOT BE LIABLE FOR CONSEQUENTIAL DAMAGES.

\* For other countries, contact your local Sales and Support Office to determine warranty terms.

# Table of Contents

| Chapter 1. General Information          |

|-----------------------------------------|

| Introduction                            |

| Description                             |

| Environmental Specifications 1-2        |

| Electrical Characteristics              |

| Functional Specifications               |

| 33/60 Hz Display Mode Selection 1-4     |

| Parallel Interface Pc Assembly Jumpers  |

| GPIO Interface Card Switch Settings 1-6 |

| Warnings, Cautions, and Notes           |

| Repair Philosophy                       |

| Ac Components/Power Cord 1-7            |

| Voltage Options                         |

| Grounding Requirements 1-9              |

| Safety                                  |

|                                         |

#### Chapter 2. Theory of Operation

| Introduction                 |   |

|------------------------------|---|

| System                       | 2 |

| 97060A Graphics Processor    | 3 |

| I/O                          | 3 |

| Processor                    | 3 |

| Microcode PROM               | 3 |

| Processor Address Counters   | 3 |

| Screen Address Counters 2    | 4 |

| Pixel Memory                 | 4 |

| Pan/Zoom                     |   |

| Color Map                    | 4 |

| Digital to Analog Converters | 4 |

| Microcode Word Definition    |   |

| Op Codes                     | 6 |

#### Chapter 3. Testing and Troubleshooting

| Introduction                       | 1  |

|------------------------------------|----|

| Required Equipment                 | 1  |

| Self Test                          | 1  |

| Diagnostic LED Failure Indications | 2  |

| Not Sequencing                     | 2  |

| 2901 Processor                     | .3 |

| Data Bus                           | 3  |

| Loop Counter                       | .3 |

| I/O                                | 3  |

| Scratch Pad                        | .3 |

| Write/Read Back                    |    |

| Signature                          | .3 |

| RAM                                | .4 |

| Troubleshooting Hints              | -5 |

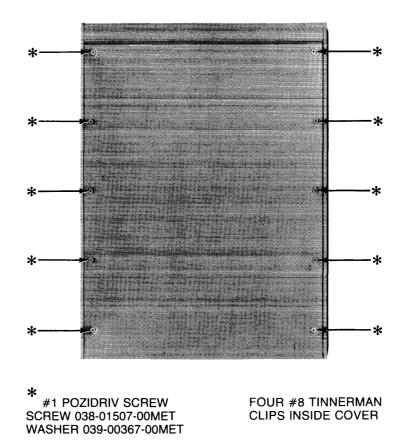

#### Chapter 4. Assembly Access

| Introduction                          |

|---------------------------------------|

| Electrostatic Discharge               |

| Covers                                |

| Top Cover                             |

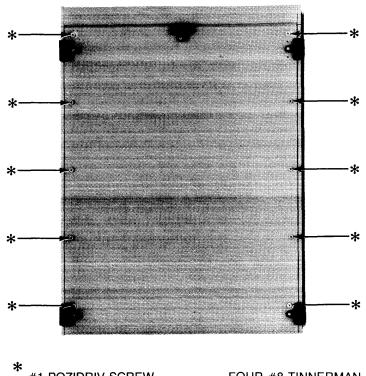

| Bottom Cover                          |

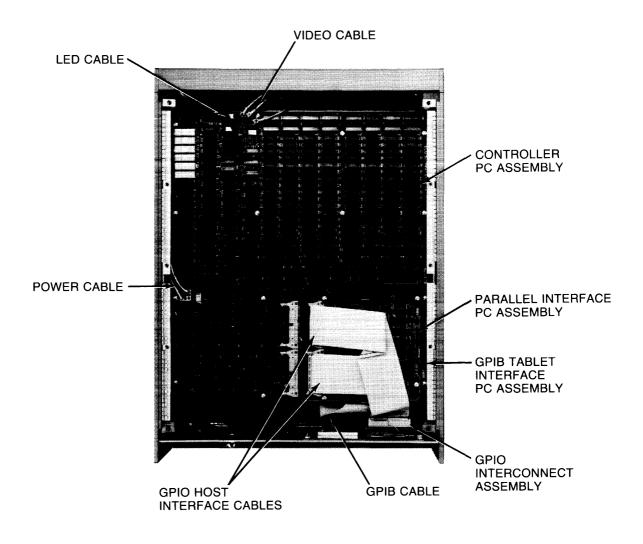

| Replaceable Assemblies                |

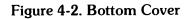

| Parallel Interface Pc Assembly 4-8    |

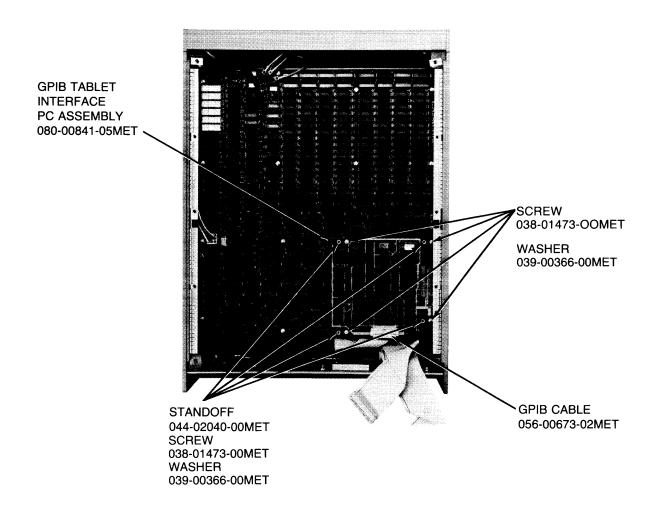

| GPIB Tablet Interface Pc Assembly 4-9 |

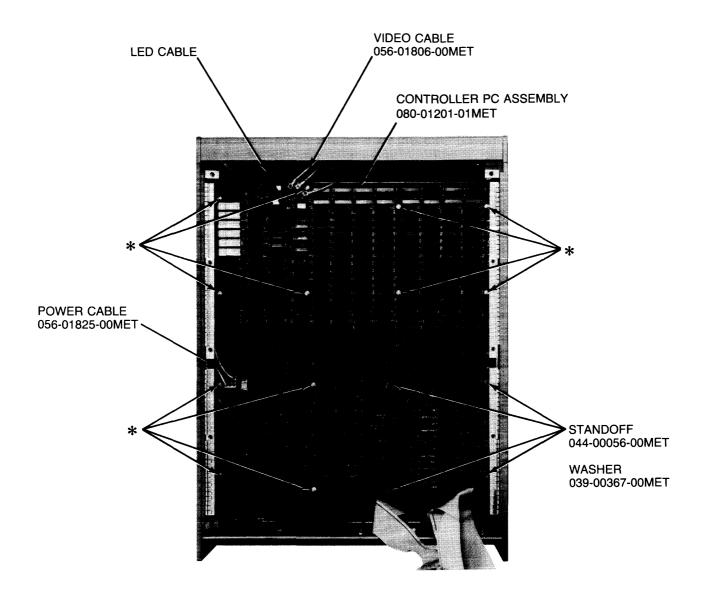

| Controller Pc Assembly                |

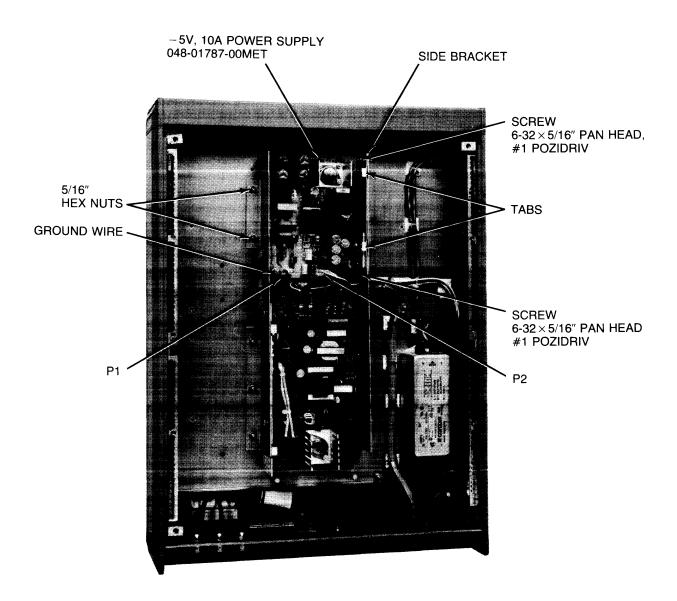

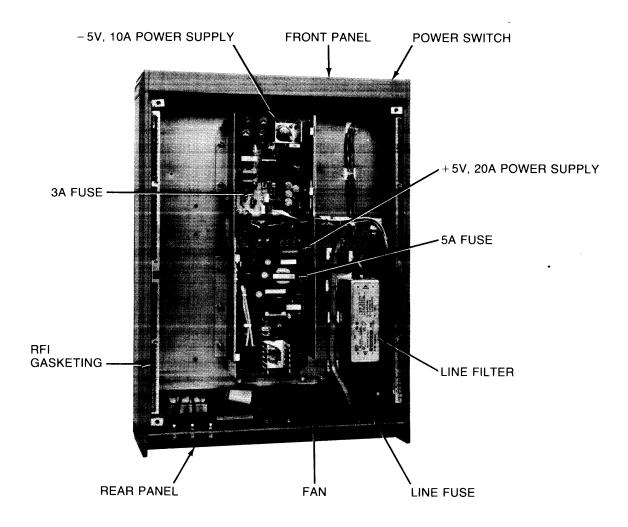

| Power Supply, $-5V$ , $10A$ 4-12      |

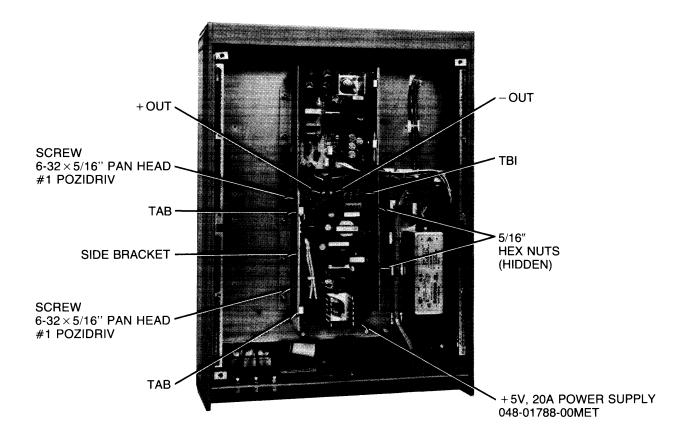

| Power Supply, +5V, 20A                |

| Fan                                   |

#### Chapter 5. Replaceable Parts

| Introduction       | 5-1 |

|--------------------|-----|

| Exchange Part.     | 5-1 |

| Non-Exchange Parts | 5-2 |

#### Figures

| 1-1    | Controller Pc Assembly Jumpers 1-4        |

|--------|-------------------------------------------|

| 1-2    | Parallel Interface Pc Asembly Jumpers 1-5 |

| 1-3    | Power Cords                               |

| 1-4    | Power Supply Voltage Jumpers              |

| 2-1    | System Block Diagram                      |

| 2-2    | 97060A Block Diagram                      |

| 4-1    | Top Cover                                 |

| 4-2    | Bottom Cover                              |

| 4-3    | Parallel Interface Pc Assembly            |

| 4-4    | GPIB Tablet Interface Pc Assembly 4-9     |

| 4-5    | Controller Pc Assembly                    |

| 4-6    | -5V, 10A Power Supply 4-12                |

| 4-7    | + 5V, 20A Power Supply 4-13               |

| 5-1    | Replaceable Parts, Top View               |

| 5-2    | Replaceable Parts, Bottom View 5-4        |

| Tables |                                           |

| 1-1    | Voltage Configuration Part Numbers 1-8    |

| 3-1    | Diagnostic LED Failure Indications        |

| 3-2    | Failed RAM Locater                        |

| 5-1    | Exchange Part                             |

| 5-2    | Non-Exchange Parts                        |

# Chapter 1 General Information

## Introduction

Note Hewlett-Packard assumes no responsibility for customer repairs or modifications.

This manual contains servicing information for the Hewlett-Packard (HP) 97060A Graphics Processor (hereinafter referred to as the 97060A). HP supports repairing the 97060A to the assembly level, that is, isolating the problem to the replaceable assembly. Then the defective assembly is exchanged for a new or rebuilt assembly.

This chapter contains general information about the 97060A and its servicing.

Additional information in this manual includes:

- Theory of Operation

- Testing and Troubleshooting Procedures

- Assembly Access Procedures

- Replaceable Parts

Complete installation instructions are provided in the HP 97060A Graphics Processor Installation Note, part number 97060-90001.

# Description

The HP 97060A is a high-performance graphics processor. The 97060A has eight planes of 1024 X 1024 pixels.

Installation consists of unpacking, connecting power, connecting the RGB coax cables to the monitor, and connecting the interface cable to the GPIO card in the HP 9000 Series 500 computer.

The 97060A has refresh rate and voltage options which are preset at the factory. Refer to 33/60 Hz Display Mode Selection and Voltage Options which follow in this chapter for additional information.

Extensive self-test capability is built into the 97060A, and the **READY** light on the front panel gives a highly reliable indication that the self-tests have passed. Normally, the **READY** light turns on about 8 seconds after the **ON** light turns on at powerup. However, if a fault occurs, the **READY** light does not turn on.

#### **Environmental Specifications**

| Temperature:                            | <ul> <li>- 40°C to + 75°C non-operating</li> <li>0°C to + 55°C operating</li> </ul>        |                                                                                                                                                                            |

|-----------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Humidity:                               | $+40^{\circ}C @ 95\%$ non-condensing operating                                             |                                                                                                                                                                            |

| Vibration:<br>(operating)               | Cycle range:<br>Amplitude (p-p):<br>Sweeptime:<br>Dwell:<br>Amplitude:                     | 5-55-5 Hz<br>0.015 inch<br>1 minute per octave,<br>15 minutes total<br>10 minutes each resonance<br>0.125 inch @ 5-10 Hz<br>0.060 inch @ 10-25 Hz<br>0.015 inch @ 25-55 Hz |

| Shock:<br>(non-operating)               | Magnitude:<br>Duration:<br>No. of shocks:<br>Waveform:<br>Bench drop:                      | 30 G<br>11 msec<br>18 (3 each on 6 surfaces)<br>Half sine<br>4-inch tilt                                                                                                   |

| Altitude:                               | 50,000 feet, 0-55°C, non-operating<br>15,000 feet, 0-55°C, operating                       |                                                                                                                                                                            |

| Drop Test:<br>(non-operating, packaged) | 30 inches each face                                                                        | and corner                                                                                                                                                                 |

| EMI:                                    | VDE Class A<br>FCC Class A                                                                 |                                                                                                                                                                            |

| Safety:                                 | UL114 (Office Mac<br>UL478 (EDP)<br>CSA154 (EDP)<br>IEC380 (Office Mac<br>IEC435 (EDP 1982 | chines with Amendment 1)                                                                                                                                                   |

I

#### **Electrical Characteristics**

| Rated Line Voltage: | Low Range:<br>High Range:                                                              | 90 to 132V ac<br>180 to 264V ac |

|---------------------|----------------------------------------------------------------------------------------|---------------------------------|

| Frequency Range:    | 47 to 66 Hz                                                                            |                                 |

| Power Dissipated:   | <100W; 85W typic                                                                       | al                              |

| Supply Ratings:     | + 5V @ 20A<br>- 5V @ 12A                                                               |                                 |

| Fuse:               | 4A Low Voltage Range, fast blow<br>6.3A High Voltage Range, fast blow                  |                                 |

| Video:              | RS-343 compatible. $1V$ p-p with sync on Green. $0.7V$ video, $0.3V$ sync within $5\%$ |                                 |

# **Functional Specifications**

| Resolution:       | 1024 X 768 @ 33 Hz interlaced<br>736 X 552 @ 60 Hz non-interlaced<br>Other options are soft programmable, such as 640 X 480, 30 Hz, RS-170                                                                                                                                                                                                |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host Interface:   | Compatible with HP 27112A General Purpose I/O (GPIO) Interface Card with Option 001 interface cable                                                                                                                                                                                                                                       |

| Tablet Interface: | Compatible with HP 9111A Data Tablet                                                                                                                                                                                                                                                                                                      |

| Self Test:        | >90% of IC failures detected<br>Data bus counter check<br>Bit slice register increment check<br>Loop counter check<br>I/O loopback check<br>Scratchpad RAM check, load with address<br>Memory test: write all 1s, 0s, 1s, 0s; read back<br>Write Mask, Write Data, check with read back<br>Vector drawing test followed by signature read |

| Reset:            | Power up causes full self-test<br>Host reset causes full self-test                                                                                                                                                                                                                                                                        |

# 33/60 Hz Display Mode Selection

The 97060A may be set for either 33 or 60 Hz frame refresh rate (display mode), as follows:

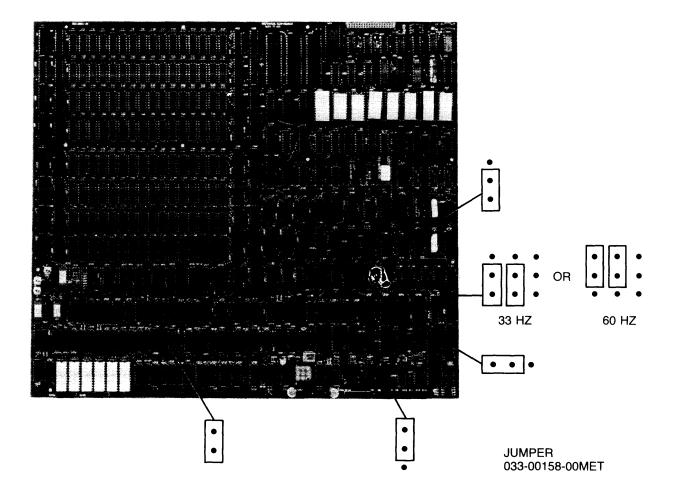

Access the controller pc assembly according to procedures in Chapter 4. Two jumpers near U291 on the controller pc assembly determine display mode selection. Ensure that both jumpers are in either the 33 Hz or the 60 Hz positions, depending on the monitor used. See Figure 1-1 for 33/60 Hz jumper positions. The other four jumpers are set at the factory and should not be changed. Ensure that they are in the positions shown in Figure 1-1.

Figure 1-1. Controller Pc Assembly Jumpers

# Parallel Interface Pc Assembly Jumpers

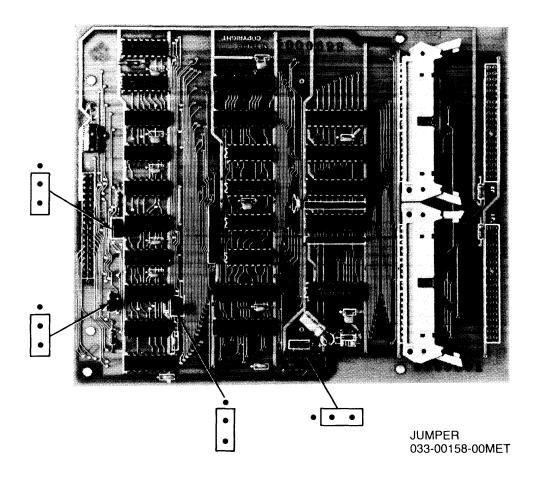

Four jumpers are contained on the parallel interface pc assembly (Figure 1-2). Three concern handshaking, the fourth concerns the INIT signal. The jumpers are set at the factory and should not be changed. Ensure that they are in the positions shown in Figure 1-2.

Figure 1-2. Parallel Interface Pc Assembly Jumpers

# **GPIO Interface Card Switch Settings**

The HP 27112A General Purpose I/O (GPIO) Interface Card interfaces the HP 9000 Series 500 computer to the 97060A. The GPIO card switches should be set as follows. Note that a switch that is up is in the open position and represents a logic one; a switch that is down is in the closed position and represents a logic zero.

SW1: S1 through S8 - Down

SW2: S1, S2, and S5 - Up S3 and S4 - Down

# Warnings, Cautions, and Notes

Warnings, cautions, and notes are used in this manual. Warnings call attention to potential hazards for personnel. Cautions call attention to potential hazards for equipment. Notes emphasize important information or instructions.

# **Repair Philosophy**

The 97060A is repaired at an assembly replacement level. Parts that are most commonly replaced are exchange parts and are on the Computer Support Division (CSD) exchange program. When an exchange part fails, it should be returned to CSD for repair, and a rebuilt part should be obtained. If a new part is purchased instead, it is unnecessary to return the failed part. Chapter 5 contains a list of all replaceable parts. Tables in Chapter 5 also list exchange parts with new and rebuilt part numbers and module-level non-exchange parts.

# Ac Components/Power Cord

A detachable ac power cord plugs into an ac outlet to provide primary power to the 97060A. Other ac components are an on/off **POWER** switch, line fuse, line filter, fan, and wiring.

#### WARNING

IF IT IS NECESSARY TO REPLACE THE POWER CORD, THE RE-PLACEMENT CORD MUST HAVE THE SAME POLARITY AS THE ORIGINAL CORD. OTHERWISE, A SHOCK HAZARD MIGHT EXIST WHICH COULD RESULT IN INJURY OR DEATH. ALSO, THE EQUIPMENT COULD BE SEVERELY DAMAGED IF EVEN A RE-LATIVELY MINOR INTERNAL FAILURE OCCURRED.

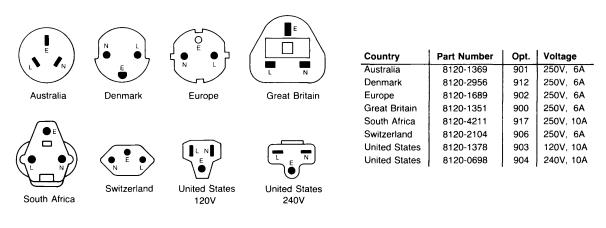

Power cords with different plugs are available for the 97060A; plug configurations are shown in Figure 1-3. Each plug has a ground connector. The cord packaged with the 97060A depends upon where the equipment is to be delivered. If your equipment has the wrong power cord for your area, please contact your local HP Sales and Support Office.

NOTE: Plugs are viewed from connector end. Shape of molded plug may vary within country.

Power cords supplied by HP have polarities matched to the power-input socket on the computer:

- L = Line or Active Conductor (also called "live" or "hot")

- N = Neutral or Identified Conductor

- E = Earth or Safety Ground

Figure 1-3. Power Cords

# **Voltage Options**

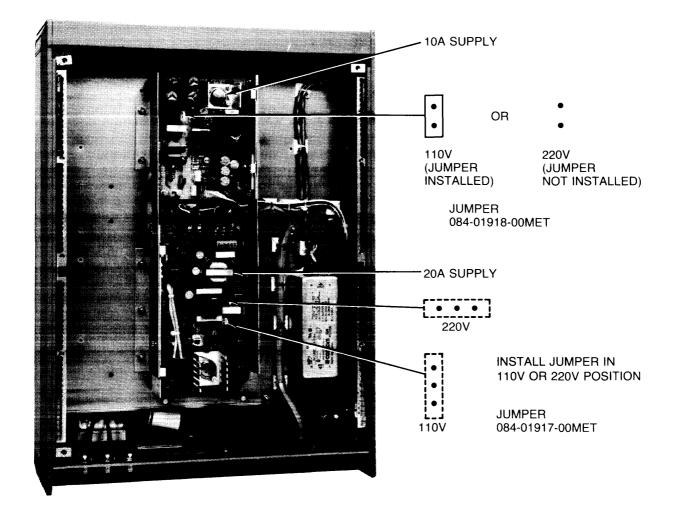

The 97060A is configured at the factory for either 110V or 220V input line voltage. Table 1-1 lists the parts which are unique to the 110V and 220V options. Figure 1-4 shows power supply jumper configurations for the voltage options.

Table 1-1. Voltage Configuration Part Numbers

| Description | 110V            | 220V              |

|-------------|-----------------|-------------------|

| Power cord  | 8120-1378       | Country dependent |

| Fan         | 050-00342-00MET | 050-00694-00MET   |

| Line fuse   | 2110-0055       | 2110-0715         |

Figure 1-4. Power Supply Voltage Jumpers

# **Grounding Requirements**

To protect operating personnel, the National Electrical Manufacturers' Association (NEMA) recommends that the 97060A chassis be grounded. The 97060A is equipped with a three-conductor power cable which, when connected to an appropriate power receptacle, grounds the computer chassis.

# Safety

#### WARNING LETHAL VOLTAGES ARE PRESENT INSIDE THE 97060A. OBSERVE ALL WARNINGS IN THIS MANUAL, AND OBSERVE THE FOLLOWING SAFETY PROCEDURES.

- Do all possible operations with the 97060A unplugged from the power source.

- If installation, maintenance, or repair must be done with the 97060A energized, take the following precautions:

- a. Never work alone in high-voltage areas. In case of accidental shock, a life may depend on rapid removal from the energized source and appropriate first-aid action.

- b. Personnel working in high-voltage areas should know where to obtain respiratory resuscitation and/or cardiopulmonary resuscitation (CPR), in case a fellow worker needs assistance.

- c. In case of burns, treat only after the person is breathing and has a normal heartbeat.

- If primary wiring change is made, perform continuity test between power cord ground and metal chassis. Record results on Repair Order.

#### 1-10 General Information

# Chapter **2** Theory of Operation

## Introduction

The HP 97060A is a high-performance raster graphics processor constructed from a mixture of MOS and bipolar ECL technology. The architectural components include:

- Bit-slice processor with 64-bit microword

- Megabyte of dynamic RAM (DRAM), organized as eight megabit planes of 1024 X 1024

- Integrated signature analyzer

- Hardware pan and zoom

- Line and area pattern generators

- EPROM-based character generator

- 36 MHz pixel clock

# System

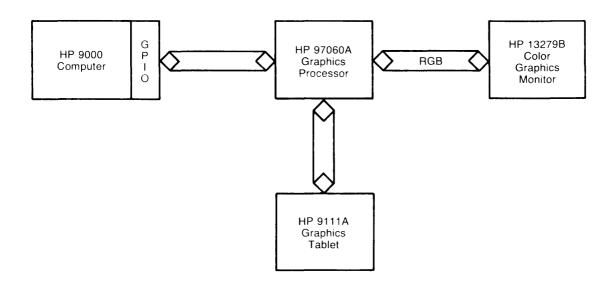

Communications with the HP 9000 computer is via the 16-bit parallel interface with the HP 27112A GPIO interface card and its Option 001 2.5-metre cable.

An HPIB graphics tablet interface option is supported, allowing a local cursor to track the tablet stylus. The HP 9111A Data Tablet is the supported device.

Figure 2-1 shows a fully configured system.

Figure 2-1. System Block Diagram

The link between the computer and 97060A is bidirectional. The computer sends op codes and arguments in the 97060A syntax, and thus builds a picture in display memory. The computer may also read display memory or 97060A status.

The link to the graphics tablet is also bidirectional, although the tablet functions primarily as a sender. The tablet is software configurable and can be set under host control.

The link between the 97060A and monitor is three coaxial cables carrying composite video conforming to the RS-343 standard for RGB transmission.

# 97060A Graphics Processor

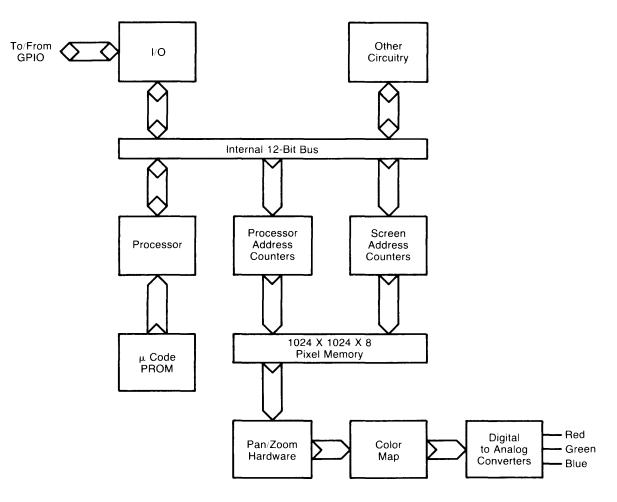

Figure 2-2 is a block diagram of the 97060A hardware. Access to the dynamic RAM bit-map is shared by the processor and screen refresh circuitry.

Figure 2-2. 97060A Block Diagram

The functions of the 97060A blocks are as follows:

#### I/O

This is the interface port to the HP 9000. The 97060A communicates with a "2-wire" handshake, PCTL and PFLG.

#### Processor

Composed of three 2901B bit slices, the 12-bit processor runs at a 220 ns cycle time.

#### Microcode PROM

This is a 64-bit-wide PROM array controlling processor ALU, source and destination for data transfers, load of the processor counters, and other important 97060A functions. Only the high speed functions such as memory cycle timing are performed independently, in state machines or random logic.

#### **Processor Address Counters**

These two 12-bit counters, one for X and one for Y, respond to the commands Load, Up/Down, and Count.

#### **Screen Address Counters**

These two counters, a 6-bit counter for X and a 10-bit counter for Y, only count up. However, they can be loaded with a start count other than zero to achieve the Pan function. They are automatically loaded on each vertical retrace. Counting can be prescaled by a modulo Zoom value.

#### **Pixel Memory**

Pixel memory consists of 128 DRAMs, 16 chips of 64K bits per plane. Memory is organized such that blocks of 16 adjacent pixels on a raster line are each contributed by a different DRAM output. Memory operates at a 220 ns write cycle and a 440 ns read cycle. The eight planes are individually addressable through the Write Mask, Write Data, and Read Mask. These are each 8-bit registers with a flip-flop for each of the eight planes. Only when the Write Mask is set for a particular plane is its write enable line allowed to pulse. When written, the value of the particular Write Data flip-flop determines whether a 1 or a 0 is written. The Read Mask affects the planes read out and has no effect on data read by the processor.

In the following example, plane 0 is neither read nor written. Plane 1 is written with a 1, and is viewed. Plane 2 is not written, but is viewed. Plane 3 is written with a 0, and viewed. Plane 4 is written with a 1, and not viewed, and so forth.

Example:

| Plane | Write Mask | Write Data | Read Mask |

|-------|------------|------------|-----------|

| 0     | 0          | 1          | 0         |

| 1     | 1          | 1          | 1         |

| 2     | 0          | 1          | 1         |

| 3     | 1          | 0          | 1         |

| 4     | 1          | 1          | 0         |

| 5     | 0          | 0          | 1         |

| 6     | 1          | 0          | 1         |

| 7     | 1          | 1          | 0         |

#### Pan/Zoom

This circuitry contains modulo counters which essentially mirror the function of the screen address counters. Zoom is achieved by slowing down the entire pipeline from DRAM to the output digital-to-analog converters, causing pixel replication. Pan is achieved primarily by the screen address counters, but these only address 16 contiguous pixel blocks. To obtain a finer offset, a circular buffer is used as a programmable delay line.

#### **Color Map**

The 8-bit path through Pan/Zoom continues to the Color Map, a 256 X 24 RAM that allows the user to work with 256 colors simultaneously from a palette of 16.7 million colors.

#### Digital to Analog Converters

The 24 bits from the Look Up Table are broken into three groups and routed to three 8-bit Digital to Analog Converters: Red, Green, and Blue. Composite sync is added to the Green output to create a 1V p-p signal.

# **Microcode Word Definition**

The 64-bit microcode word resides in eight 16K PROMs, allowing 2048 steps of control memory. These PROMs are addressed by a 12-bit sequencer comprising two 2911As and a 2909A. The sequencer in turn is driven by microcode control bits and branching conditions from various sections of the hardware. The next section will explain these conditions in more detail.

The microcode word is subdivided into five major groups called fields:

- Control Field. These 13 bits of control lines regulate the processor address counters, the write enable generator for pixel memory, and other functions described below.

- Data Bus Source and Destination Control. Every instruction must specify a driver and a receiver for the internal data bus. This occurs even if no actual data transfer is required, in which case the destination is a dummy location. The sub-fields are:

| Data Source      | 3 bits |

|------------------|--------|

| Data Destination | 5 bits |

• Conditional Branch Control. These 11 bits directly control the activity of the microcode sequencer, which in turn selects the next microcode word decoded. There are three sub-fields:

| Branch Type    | 3 bits |

|----------------|--------|

| Condition Code | 8 bits |

• Bit Slice ALU Controls. These 20 bits specify internal action of the three 2901B bit slice parts. There are five sub-fields:

| External Carry/Borrow | 3 bits |

|-----------------------|--------|

| ALU Destination       | 3 bits |

| ALU Function          | 3 bits |

| ALU Source            | 3 bits |

| Register Address      | 8 bits |

• Data Field. The microcode often must drive the data bus, either to load the ALU with a constant operand, preset data bus destinations to some value, specify a branch location to the sequencer, or other operation. This is a single 12-bit field.

# **Op Codes**

Unless otherwise specified, all writes to pixel memory observe the Write Data, Write Mask, and present Area Pattern. That is, a write in plane k occurs only if bit k of the Write Data Register and Write Mask Register are = 1 and the present Area Pattern function A(x,y) = 1.

Byte arguments are indicated by lower case, word arguments by upper case. Word arguments are read in the order: low byte, high byte.

The following are state variables:

P1 (pointer 1) P2 (pointer 2) WRITE DATA (also called "current color") WRITE MASK (determines planes written) PATTERN REGISTER (including line and area patterns) READ MASK (planes viewed) BLANK BLINK CMAP (contents of 256 locations) CONFIGURATION (33 Hz, 8 planes, tablet) SETCORN, SETCSZ, FSIZE, CSPACE (character information) SZCUR (cursor size) CURRENT POLYGON STRUCTURE (vertex list)

| Mnemonic                     | Hex | Description                                                                                                                                                                                                                 |

|------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AFILL1                       | 68  | Read pixel at P1<br>Do while neighbor color = P1 pixel color<br>Write neighbor with Write Data<br>End<br>P1 and P2 unmodified.                                                                                              |

| AFILL2 <f></f>               | 69  | Read pixel at P1<br>Do until neighbor color = f<br>Write neighbor with Write Data<br>End<br>P1 and P2 unmodified                                                                                                            |

| ARC <1>                      | 62  | Draw arc of length 1 using Write Data and center of curvature P1.<br>Begin at P2. P2 left at end of arc upon completion. 0<1<2047.                                                                                          |

| BLANK <b></b>                | 4B  | b is LSB of argument byte. If $b = 1$ then blank screen and give processor access. If $b = 0$ then return to screen-priority mode.                                                                                          |

| BLINK <b></b>                | 4D  | b is LSB of argument byte. If $b = 1$ then toggle plane 7 at 2 Hz, using Read Mask. If $b = 0$ then restore steady plane 7.                                                                                                 |

| CHAR <c1,c2cn></c1,c2cn>     | 6B  | Draw text starting with P1 pointing to the lower left corner of the 16 X 8 character cell. c1, c2, etc., are ASCII codes 0-127. cn is the ESC character (#27) and terminates text mode. See also SETCSZ, FSIZE, and CSPACE. |

|                              |     | Control characters decoded:                                                                                                                                                                                                 |

|                              |     | CR Return to left margin<br>LF Move pointer down one line<br>BS Move pointer back one space<br>ESC Exit text mode                                                                                                           |

| CLEAR                        | 60  | Fill screen with Write Data.                                                                                                                                                                                                |

| CMAP <a,r,g,b></a,r,g,b>     | 51  | Load color map location a with values r, g, and b.                                                                                                                                                                          |

| COMPDR                       | 72  | Draw a vector between P1 and P2 complementing present pixel values. Leave P1 at P2. WRMASK and SETCOL not used.                                                                                                             |

| CRTWR <r,d></r,d>            | 46  | Write the 6845-1 CRT Controller Register r with d.                                                                                                                                                                          |

| CSPACE <Δx,Δy>               | 48  | Auto increment between successive characters. Apply increment $\Delta x, \Delta y$ from lower left corner of cell, then apply transformation specified by SETORN.                                                           |

| CURS                         | 71  | Draw cursor at P1. Drawn in complement mode, with crosshair width<br>and height as set by SZCUR. Automatically removed upon receipt of<br>next op code. Write Mask and Area Pattern ignored.                                |

| DRAW                         | 61  | Draw vector from P1 to P2. Leave P1 at P2.                                                                                                                                                                                  |

| FFILL                        | 65  | Fill rectangle defined by diagonal P1,P2. Approximately 16 times fast-<br>er than RECT2; no patterns allowed.                                                                                                               |

| FSIZE $<\Delta x, \Delta y>$ | 49  | Font size. $0 < \Delta x \le 8$ , $0 < \Delta y \le 16$ . These define a window on the 16 X 8 character cell.                                                                                                               |

| Mnemonic       | Hex | Description                                                                                                                                                                                                                                                                                             |                                                                                                                                                               |                           |                                     |                       |                      |                   |                     |                                                                 |                                                                    |       |  |

|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------|-----------------------|----------------------|-------------------|---------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|-------|--|

| GRAFIN <f></f> | 4A  | FIN :                                                                                                                                                                                                                                                                                                   | Set Graphic Input (from tablet). The argument (f), which is the GRA-<br>FIN mode select byte, selects the current GRAFIN mode. It is one of<br>the following: |                           |                                     |                       |                      |                   |                     |                                                                 |                                                                    |       |  |

|                |     | 0 Software INIT Mode. This mode resets all GRAFIN attributes to<br>their default values and clears the coordinate queue. The offset and<br>scale factors are also reset to their default values.                                                                                                        |                                                                                                                                                               |                           |                                     |                       |                      |                   |                     |                                                                 |                                                                    |       |  |

|                |     |                                                                                                                                                                                                                                                                                                         | GPIB t<br>hics tab                                                                                                                                            |                           | interf                              | ace pc                | assem                | bly ser           | nds the             | follow                                                          | ring to                                                            | the   |  |

|                |     | The                                                                                                                                                                                                                                                                                                     | DEVIC                                                                                                                                                         | E CLE                     | EAR si                              | gnal.                 |                      |                   |                     |                                                                 |                                                                    |       |  |

|                |     |                                                                                                                                                                                                                                                                                                         | IN mes<br>et to run                                                                                                                                           | -                         |                                     |                       |                      | -                 | -                   |                                                                 |                                                                    | hics  |  |

|                |     |                                                                                                                                                                                                                                                                                                         | DF mes<br>edeterm                                                                                                                                             |                           |                                     |                       |                      | essage            | sets the            | e graphi                                                        | ics table                                                          | et to |  |

|                |     | ] -                                                                                                                                                                                                                                                                                                     |                                                                                                                                                               |                           |                                     |                       | Note                 |                   |                     |                                                                 |                                                                    |       |  |

|                |     |                                                                                                                                                                                                                                                                                                         | Refer to the Hewlett-Packard 9111A Graphics Tablet Us-<br>er's Manual for information about messages sent to the<br>graphics tablet.                          |                           |                                     |                       |                      |                   |                     |                                                                 |                                                                    |       |  |

|                |     | 1 Local Cursor Control Mode. When in this mode, the<br>continuous stream of x,y coordinates in the tablet's us<br>format. The coordinates are buffered on the GPIB ta<br>assembly, and the stylus position is indicated by the<br>attached monitor. The cursor appears in the color<br>existing pixels. |                                                                                                                                                               |                           |                                     |                       |                      |                   |                     | usual 8-bit, 6-byte<br>tablet interface pc<br>the cursor on the |                                                                    |       |  |

|                |     | is de<br>1 ar<br>depr                                                                                                                                                                                                                                                                                   | pressed<br>nd 2 of<br>ressed, t                                                                                                                               | l. The<br>byte<br>the bit | messa<br>1 inc                      | age forn<br>licate tl | mat is s<br>he styli | hown i<br>us posi | n the fo<br>tion. W | ollowing<br>Vhen th                                             | on the tablet<br>ng table. Bits<br>the stylus is<br>n is transmit- |       |  |

|                |     |                                                                                                                                                                                                                                                                                                         | o the ho                                                                                                                                                      |                           |                                     |                       |                      |                   |                     |                                                                 |                                                                    | 1     |  |

|                |     |                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                             |                           |                                     | <u> </u>              |                      | Bit               |                     |                                                                 |                                                                    | 4     |  |

|                |     |                                                                                                                                                                                                                                                                                                         | Byte                                                                                                                                                          | 7                         | 6                                   | 5                     | 4                    | 3                 | 2                   | 1                                                               | 0                                                                  | 4     |  |

|                |     |                                                                                                                                                                                                                                                                                                         | 1<br>2                                                                                                                                                        | 0<br>0                    | $\begin{array}{c} 1\\ 0\end{array}$ | 0<br>x5               | 0<br>x4              | 0<br>x3           | sp<br>x2            | sp<br>x1                                                        | 0<br>x0                                                            |       |  |

|                |     |                                                                                                                                                                                                                                                                                                         | 3                                                                                                                                                             | 0                         | 0                                   | 0*                    | 0*                   | x9                | x8                  | x7                                                              | x6                                                                 |       |  |

|                |     |                                                                                                                                                                                                                                                                                                         | 4<br>5                                                                                                                                                        | 0                         | 0<br>0                              | у5<br>0*              | у4<br>0*             | y3                | y2                  | y1                                                              | y0                                                                 |       |  |

|                |     |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                               |                           | , ,                                 |                       |                      | y9                | y8                  | y7                                                              | <u>y6</u>                                                          | ]     |  |

|                |     | * Coordinates are those of the screen cursor, after applying offset and scaling. Transparent should be used if full tablet precision is required.                                                                                                                                                       |                                                                                                                                                               |                           |                                     |                       |                      |                   | ansparent           | mod                                                             |                                                                    |       |  |

|                |     | sp (stylus position): $1 =$ stylus depressed                                                                                                                                                                                                                                                            |                                                                                                                                                               |                           |                                     |                       |                      |                   |                     |                                                                 |                                                                    |       |  |

| Mnemonic                       | Hex | Description                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GRAFIN <f><br/>(continued)</f> | 4A  | 2 Transparent Mode. Transparent mode allows the host to interact directly with the graphics tablet, without converting the graphics tablet data to the 97060A's 5-byte format. Full-duplex communications continues until a delimiter (default: hex 80) is received to terminate Transparent mode. This mode is useful primarily in two cases: |

|                                |     | Transparent mode may be used to run programs that were not specifi-<br>cally written for use with the 97060A/9111A Graphics Tablet con-<br>figuration. These programs may require graphics tablet data that has<br>not been converted to the 97060A's 5-byte format.                                                                           |

|                                |     | Transparent mode may also be used to issue any of the commands described in the 9111A Graphics Tablet User's Manual, e.g., "RC;" or "RC" <lf>.</lf>                                                                                                                                                                                            |

|                                |     | Note                                                                                                                                                                                                                                                                                                                                           |

|                                |     | When in Transparent mode, do not issue the Input Masks<br>instruction using the Status Mask (S-mask) parameter. The<br>S-mask parameter causes the graphics tablet to respond by<br>activating SRQ (request service message) on the data line.<br>The SRQ function on the data line is not supported on the<br>GPIB tablet interface.          |

|                                |     | In Transparent mode, the graphics tablet sends one 6-byte message in response to each semicolon (;) it receives from the host.                                                                                                                                                                                                                 |

|                                |     | In Transparent mode, all responses from the 9111A are padded to an even number of bytes. Responses that would normally have an odd byte count have a null character (00H) appended to the end.                                                                                                                                                 |

|                                |     | Commands sent to the tablet may be padded with as many ASCII space characters (20H) as desired. These are filtered from the character stream and not sent to the 9111A.                                                                                                                                                                        |

|                                |     | 3 Set Offset and Scale Factors Mode. The device coordinates are<br>subjected to an offset and scale operation in the 97060A for cursor<br>position control. The next eight bytes specify the following in two's<br>complement format:                                                                                                          |

|                                |     | <ol> <li>x offset low byte</li> <li>x offset high byte</li> <li>x multiplier fraction</li> <li>x multiplier integer</li> <li>y offset low byte</li> <li>y offset high byte</li> <li>y offset high byte</li> <li>y multiplier fraction</li> <li>y multiplier integer</li> </ol>                                                                 |

|                                |     | 4 Set Delimiter Mode. The next byte specifies the delimiter, replacing<br>the default delimiter. Transmitting the delimiter during Transparent<br>mode causes exit from Transparent mode. The delimiter can range<br>from 0 to FE (hex); the default delimiter is 80 (hex).                                                                    |

| Mnemonic                                     | Hex | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                |  |  |  |  |  |  |

|----------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| GRAFIN <f><br/>(continued)</f>               | 4A  | <ul> <li>5 Sample Position - Screen Coordinates. This instruction cause full device status message to be sent to the host regardless or device's status message value. (No stylus switch closure is necess See the preceding table under mode 1 for the full device status sage format. The x,y values are returned in 97060A (5-byte) contacts.</li> <li>6 Sample Position - Tablet Coordinates. The full tablet coordinates.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                |  |  |  |  |  |  |

|                                              |     | -                                                                                                                                                                                                                                                                                                                                                                                                                                         | le Position - Tablet Coordina<br>s relayed upon receipt of this                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                |  |  |  |  |  |  |

|                                              |     | 7 Set Mo<br>tions:                                                                                                                                                                                                                                                                                                                                                                                                                        | ode Register. The mode regis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ter has the following bit defini-                                                                              |  |  |  |  |  |  |

|                                              |     | Bit                                                                                                                                                                                                                                                                                                                                                                                                                                       | IF = 0(default)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IF = 1                                                                                                         |  |  |  |  |  |  |

|                                              |     | 1 I<br>2 H<br>3 H                                                                                                                                                                                                                                                                                                                                                                                                                         | Wrap around<br>Level Buttons<br>Button Xmit<br>Report Button Depression<br>During GRAFIN 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Clip to screen Boundary<br>Edge Buttons<br>Button not Xmit<br>No Output During<br>GRAFIN 1                     |  |  |  |  |  |  |

|                                              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                           | ts may be written as a group, $e$ with bits 0, 1, and 2 appropriate the second | by sending GRAFIN 7 followed iately set and bit $7 = 1$ .                                                      |  |  |  |  |  |  |

|                                              |     | the other<br>respective                                                                                                                                                                                                                                                                                                                                                                                                                   | s by setting bit 7 to a zero, bit .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | individual bit without modifying<br>3 to zero or one (for clear or set,<br>pointer value (i.e., 000 for bit 0, |  |  |  |  |  |  |