# INSTALLATION AND MAINTENANCE MANUAL

HP 2116C

# 2116C COMPUTER

# **VOLUME THREE**

HP 2116C

#### MANUAL ADDENDUM

**GENERAL.** The purpose of this addendum is to adapt the attached HP 2116B Input/Output System Operation Manual for use with the HP 2116C Computer with serial numbers prefixed 980- and above. Information in the manual applies, with the exceptions listed below as addendum, to the HP 2116C Computer. When available, the final version of the HP 2116C manual will be provided as a replacement for this manual.

ADDENDUM. To adapt this manual for use with the HP 2116C Computer, make the following changes:

- 1. Change all 2116B references to 2116C.

- Page 2-13, paragraph 2-53. Delete subparagraphs "b. Option 02," and "c. Option 03." These options to the HP 2150B Input/Output and Memory Extender are not available for use with the HP 2116C Computer.

- 3. Page 2-13. Replace table 2-3 with the table included in this addendum.

- 4. Page 2-14, paragraph 2-56. Change all references to a "computer with an 8k or 16k memory" to "computer with an 8k, 16k, 24k, or 32k memory." The replacement table 2-3, above, provides the additional information for a computer with 24k or 32k of memory.

- 5. Page 1-0, figure 1-1. Some 2116C Computers have a toggle-type power switch instead of the illustrated pushbutton switch.

|                                                                           |      | SUPPLY CURRENTS (AMP) |      |        |  |  |  |  |  |

|---------------------------------------------------------------------------|------|-----------------------|------|--------|--|--|--|--|--|

| REQUIREMENTS                                                              | +12V | -12V                  | -2V  | +4.5V  |  |  |  |  |  |

| CURRENT AVAILABLE FROM POWER SUPPLIES                                     | Ĩ    |                       |      |        |  |  |  |  |  |

| Computer Power Supply                                                     | 6    | 6                     | 22.5 | *22.5  |  |  |  |  |  |

| Computer and HP 2160A Power Supplies                                      | 6    | 6                     | 32.5 | **32.5 |  |  |  |  |  |

| CURRENT REQUIRED BY COMPUTER WITH NO<br>PROCESSOR OR INPUT/OUTPUT OPTIONS |      |                       |      |        |  |  |  |  |  |

| Computer with 8k Memory                                                   | 0.15 | 0.25                  | 14.3 | 23.0   |  |  |  |  |  |

| Computer with 16k Memory                                                  | 0.15 | 0.25                  | 15.6 | 24.2   |  |  |  |  |  |

| Computer with 24k Memory                                                  | 0.15 | 0.25                  | 16.9 | 25.4   |  |  |  |  |  |

| Computer with 32k Memory                                                  | 0.15 | 0.25                  | 18.2 | 26.6   |  |  |  |  |  |

| CURRENT AVAILABLE FOR OPTIONS                                             |      |                       |      |        |  |  |  |  |  |

| Computer with 8k Memory                                                   | 5.85 | 5.75                  | 8.2  | †13.8  |  |  |  |  |  |

| Computer with 16k Memory                                                  | 5.85 | 5.75                  | 6.9  | †13.9  |  |  |  |  |  |

| Computer with 24k Memory                                                  | 5.85 | 5.75                  | 5.6  | †14.0  |  |  |  |  |  |

| Computer with 32k Memory                                                  | 5.85 | 5.75                  | 4.3  | †14.1  |  |  |  |  |  |

| Computer with 8k Memory and HP 2160A<br>Power Supply Extender             | 5.85 | 5.75                  | 18.2 | †23.8  |  |  |  |  |  |

| Computer with 16k Memory and HP 2160A                                     | 5.85 | 5.75                  | 16.9 | †23.9  |  |  |  |  |  |

| Power Supply Extender                                                     |      |                       |      |        |  |  |  |  |  |

| Computer with 24k Memory and HP 2160A                                     | 5.85 | 5.75                  | 15.6 | †24.0  |  |  |  |  |  |

| Power Supply Extender                                                     |      |                       |      |        |  |  |  |  |  |

| Computer with 32k Memory and HP 2160A                                     | 5.85 | 5.75                  | 14.3 | †24.1  |  |  |  |  |  |

| Power Supply Extender                                                     |      |                       |      | 1      |  |  |  |  |  |

### Table 2-3. Internal/External Power Supply Requirements

NOTES: \* Plus the current drawn from the -2V supply by the Computer with memory and options. Maximum available from +1.5V supply is 45 amperes.

\*\* Plus the current drawn from the -2V supply by the Computer with memory and options. Maximum available from +4.5V supply is 65 amperes.

† Plus Plus the current drawn from the -2V supply by the selected options.

-

,

-

.

### TABLE OF CONTENTS

| Sec | tion    | Page                                                                                                                               |  |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------|--|

| T   | INTRO   | DUCTION $\cdot \cdot 1-1$                                        |  |

| -   | 1-1.    |                                                                                                                                    |  |

|     | 1-4.    |                                                                                                                                    |  |

|     |         |                                                                                                                                    |  |

| II  | INPUT   | T/OUTPUT STRUCTURE • • • • 2-1                                                                                                     |  |

|     | 2 - 1.  | Introduction $\cdot \cdot \cdot \cdot \cdot \cdot \cdot \cdot 2-1$                                                                 |  |

|     | 2-5.    | Computer System Input/Output                                                                                                       |  |

|     |         | Operations $\cdot \cdot 2-1$                                           |  |

|     | 2-6.    | $General \cdot \cdot \cdot \cdot \cdot \cdot \cdot \cdot 2-1$                                                                      |  |

|     | 2-8.    | Input/Output Instructions • • 2-2                                                                                                  |  |

|     | 2-12.   | Interrupt Requests · · · 2-2                                                                                                       |  |

|     | 2-14.   |                                                                                                                                    |  |

|     | 2-15.   | I/O Control and I/O Address                                                                                                        |  |

|     |         | Cards $\cdot \cdot \cdot \cdot \cdot \cdot \cdot \cdot 2-3$                                                                        |  |

|     | 2 - 17. | Resistance Load Card • • • 2-3                                                                                                     |  |

|     | 2-19.   | Interface Cards • • • • 2-3                                                                                                        |  |

|     | 2-25.   | Input/Output Device Selection • • 2-5                                                                                              |  |

|     | 2-28.   |                                                                                                                                    |  |

|     | 2-31.   | Interrupt System Enable-                                                                                                           |  |

|     |         | $Disable \cdot \cdot \cdot \cdot \cdot \cdot \cdot 2-5$                                                                            |  |

|     | 2 - 34. | Interrupt System Operation • • 2-6                                                                                                 |  |

|     | 2-39.   | Interrupt Processing $\cdot \cdot \cdot \cdot 2-8$                                                                                 |  |

|     | 2-42.   | Interrupt Priority $\cdot$ $\cdot$ $\cdot$ $\cdot$ 2-8                                                                             |  |

|     | 2-48.   | Interrupt Priority                                                                                                                 |  |

|     |         | Continuity $\cdot \cdot \cdot \cdot \cdot \cdot \cdot \cdot 2-11$                                                                  |  |

|     | 2-52.   | Extender Modules $\cdot \cdot \cdot \cdot \cdot \cdot 2-13$                                                                        |  |

|     | 2-54.   |                                                                                                                                    |  |

|     | 2-57.   | Interface Kits $\cdot \cdot \cdot$ |  |

|     |         |                                                                                                                                    |  |

| Sec | tion   |                                                    |   | Page  |

|-----|--------|----------------------------------------------------|---|-------|

| III | I/O CC | ONTROL CARD · · · · · ·                            |   | 3-1   |

|     | 3-1.   |                                                    |   | 3 - 1 |

|     | 3-3.   | Theory of Operation · · · ·                        |   | 3 - 1 |

|     | 3-4.   | Computer Power-On • • •                            |   | 3 - 1 |

|     | 3-10.  |                                                    |   |       |

|     | 3-12.  | Priority-Affecting Instructions                    |   | 3 - 2 |

|     | 3-19.  | • •                                                | • | -     |

|     | 3-21.  | Phase Operation                                    | • | 3-2   |

|     | 3-27.  |                                                    |   |       |

|     |        | Selection $\cdot$ $\cdot$ $\cdot$ $\cdot$ $\cdot$  | • | 3-3   |

|     | 3-29.  | Interrupt System Control •                         |   |       |

|     | 3-36.  | Skip Flag Instructions • •                         | • | 3-5   |

|     | 3-39.  | Replaceable Parts • • • •                          | • | 3-6   |

|     | T/0 47 |                                                    |   |       |

| IV  |        | DDRESS CARD · · · · · ·                            | • | 4-1   |

|     | 4-1.   | Introduction · · · · · · · · · · · · · · · · · · · | • | 4-1   |

|     | 4-3.   | Theory of Operation • • • •                        | • | 4-1   |

|     | 4-4.   |                                                    |   |       |

|     | 4-10.  |                                                    |   |       |

|     | 4-17.  |                                                    |   |       |

|     | 4-19.  | Replaceable Parts • • • •                          | • | 4-6   |

| v   | RESIS  | TANCE LOAD CARD $\cdot \cdot \cdot \cdot \cdot$    |   | 5-1   |

| •   | 5-1.   | Introduction • • • • • •                           |   |       |

|     | 5-3.   | Description · · · · · ·                            |   |       |

|     | 5-5.   | Installation · · · · · · ·                         | • | 5-1   |

|     | 5-7.   |                                                    |   |       |

|     | 5-9.   | Replaceable Parts · · · ·                          |   | 5-1   |

|     | 0-0.   | ropiaceanie i arto                                 | • | 0-1   |

### LIST OF ILLUSTRATIONS

| Numbe         | er Title                                                               |   | Page         |

|---------------|------------------------------------------------------------------------|---|--------------|

| 1 - 1. 2 - 1. | Typical HP 2116B Computer System •<br>Input/Output Structure • • • • • | • | $1-0 \\ 2-2$ |

| 2-2.          | Block Diagram of System Input/Output                                   |   |              |

| 2-3.          | Operations · · · · · · · · · · · · · · · · · · ·                       | • | 2-3          |

|               | Front View • • • • • • • •                                             | • | 2-4          |

| 2-4.          | Interface Card Connectors • • • •                                      | • | 2-5          |

| 2-5.          | Typical Interrupt Logic • • • • •                                      | • | 2-7          |

| 2-6.          | Typical Interrupt System Timing • •                                    |   | 2-9          |

| 2-7.          | Interrupt Priority • • • • • • •                                       | • | 2 - 11       |

| 2-8.          | Priority Continuity • • • • •                                          | • | 2 - 12       |

| 3-1.          | I/O Control Card IEN, PRN, and                                         |   |              |

|               | PRL Signals • • • • • •                                                | • | 3-4          |

| Numbe | er Title                                                                   |   | - | Page  |

|-------|----------------------------------------------------------------------------|---|---|-------|

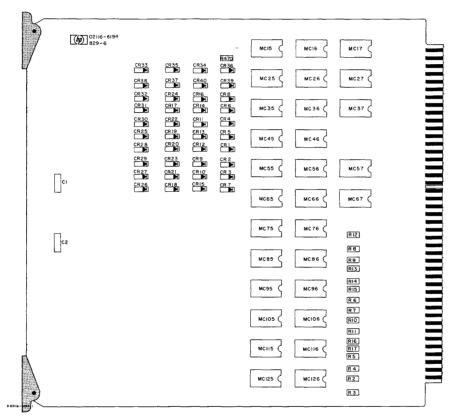

| 3-2.  | I/O Control Card, Component                                                |   |   |       |

|       | $Location \cdot \cdot \cdot \cdot \cdot \cdot \cdot \cdot \cdot$           | • | • | 3-6   |

| 3-3.  | $I/O$ Control Card $\cdot$ $\cdot$ $\cdot$ $\cdot$ $\cdot$ $\cdot$ $\cdot$ | • | • | 3 - 7 |

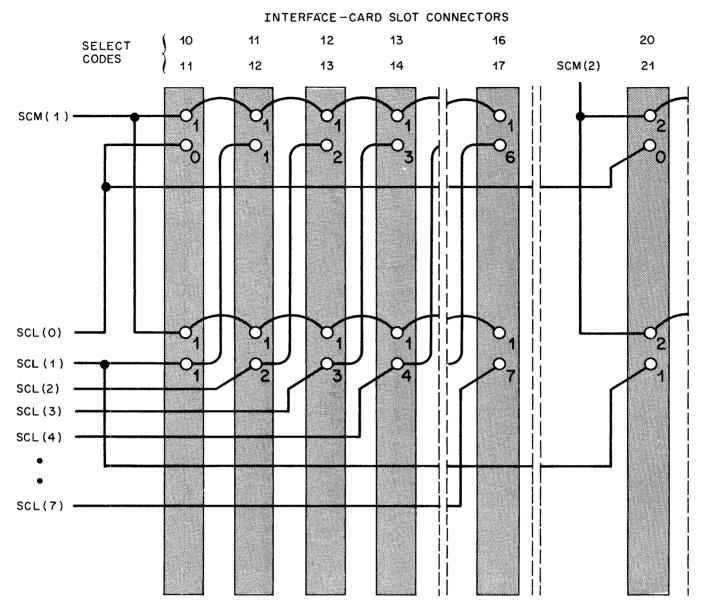

| 4-1.  | SCM and SCL Signal Paths • • •                                             |   |   | 4-2   |

| 4-2.  | I/O Address Card · · · · · ·                                               | • | • | 4-3   |

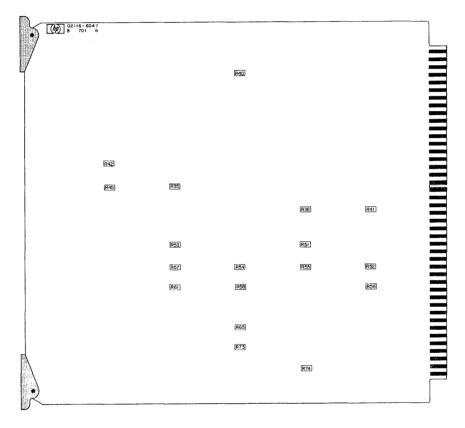

| 4-3.  | I/O Address Card, Component                                                |   |   |       |

|       | Location · · · · · · · ·                                                   | • | • | 4-4   |

| 5-1.  | Resistance Load Card Schematic                                             |   |   |       |

|       | Diagram · · · · · · · ·                                                    | • | • | 5-1   |

| 5-2.  | Resistance Load Card, Component                                            |   |   |       |

|       | Location · · · · · · · ·                                                   | • | • | 5-2   |

|       |                                                                            |   |   |       |

### LIST OF TABLES

| Numbe | er Title                          |   | Page   |

|-------|-----------------------------------|---|--------|

| 2-1.  | Interface Card-to-Computer Pin    |   |        |

|       | Connections · · · · · · ·         |   | · 2-6  |

| 2-2.  | Select Code Assignments • • •     | • | · 2-7  |

| 2-3.  | Internal/External Power Supply    |   |        |

|       | Requirements • • • • • •          |   | . 2-13 |

| 2-4.  | Current Required by Options       | • | · 2-14 |

| 3-1.  | Replaceable Parts for I/O Control |   |        |

|       | Card • • • • • • • • •            | • | ₀ 3-6  |

| Numb         | er Title                                      |   | ] | Page |

|--------------|-----------------------------------------------|---|---|------|

| 4-1.<br>4-2. | I/O Address Card Encoding<br>Examples         | • | • | 4-5  |

| •            | Card $\ldots$ $\ldots$ $\ldots$ $\ldots$      | • | • | 4-6  |

| 5-1.         | Replaceable Parts for Resistance<br>Load Card | • | • | 5-2  |

02809 - 1

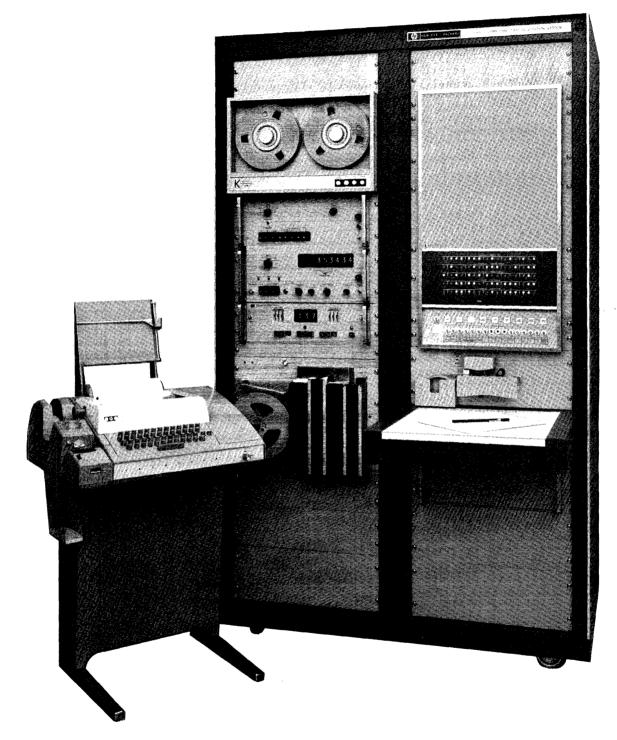

Figure 1-1. Typical HP 2116B Computer System

# SECTION I

#### 1-1. COMPUTER SYSTEM.

1-2. The Computer System (Figure 1-1) consists of the HP 2116B Computer, associated input/output devices, and the necessary interface accessory kits and software.

1-3. The basic Computer is able to control and service up to 16 peripheral devices. Plug-in I/O options are available for expansion of Computer capabilities to 48 devices, and a wide range of input/output options are available. Refer to Volume One for detailed information on the Computer and available processor

options, Volume Two for processor maintenance, and to Volume Four for programming information.

#### 1-4. MANUAL CONTENTS.

1-5. Section II of this manual contains a description of the input/output structure of the HP 2116B Computer. Theory of Operation information and Logic Diagrams for the I/O Control card, the I/O Address card, and the Resistance Load card are contained in Sections III, IV, and V, respectively. Complete Operating and Service manuals are provided with each input/output device and Interface Kit in a system.

# SECTION II INPUT/OUTPUT STRUCTURE

#### 2-1. INTRODUCTION.

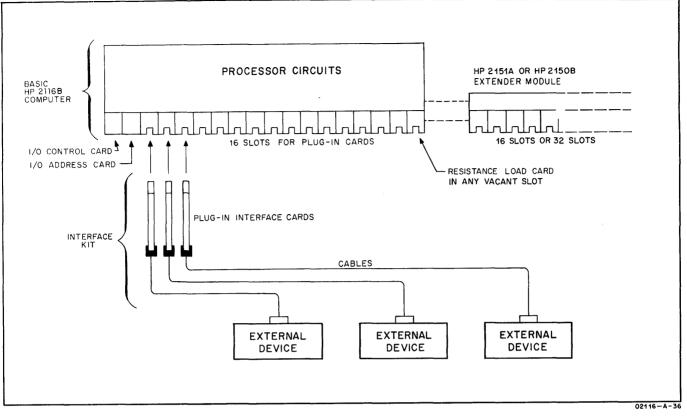

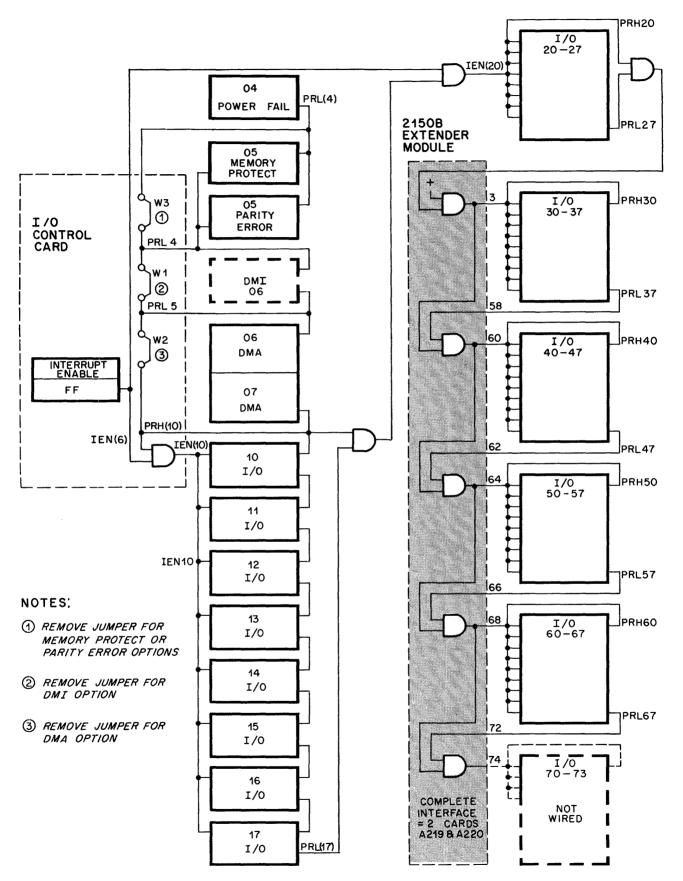

The input/output (I/O) structure of the HP 2 - 2. 2116B Computer system consists of input/output devices, their interface cards and interconnecting cables, an I/O Control card, and an I/O Address card (see Figure 2-1). The Input/Output section of the basic Computer, located directly behind the front panel and toward the bottom of the Computer, provides slots for 16 plug-in interface cards and two slots for the I/OControl and I/O Address cards. (A Resistance Load card is also used when less than 16 interface cards are used in the system; it then plugs into the highestnumbered interface-card slot.) The Computer selects and communicates with the interface cards through the I/O Control card, the I/OAddress card, and through direct wiring to the interface card slot connectors. In most cases, each interface card is capable of interfacing a separate input/output device. Detailed information on computer logic required for control of the input/output devices is contained in the Installation and Maintenance Manual, Volume Two. Paragraphs 2-5 through 2-13 in this section contain a general description of computer logic operation in conjunction with the elements within the input/output structure.

2-3. The input/output structure also provides a means for the input/output devices to interrupt the computer program when they require servicing. When devices request an interrupt, the Computer processes the requests on a priority basis. Each input/output device has its own level of priority and when interrupting, causes program execution of the contents of a memory location uniquely associated with the interrupting device.

2-4. The number of input/output devices in the system is expandable to 32 or 48 devices simply by adding a HP 2151A or HP 2150B Extender Module, respectively, and the appropriate interface cards, cables, and devices. The interface cards and cables required for each input/output device are contained in an Interface Kit. Each addition, then, requires that the Interface Kit and device be ordered separately. Refer to the HP 2116B Computer Data Sheet for a description and ordering information.

#### 2-5. COMPUTER SYSTEM INPUT/OUTPUT OPERATIONS.

#### 2-6. GENERAL.

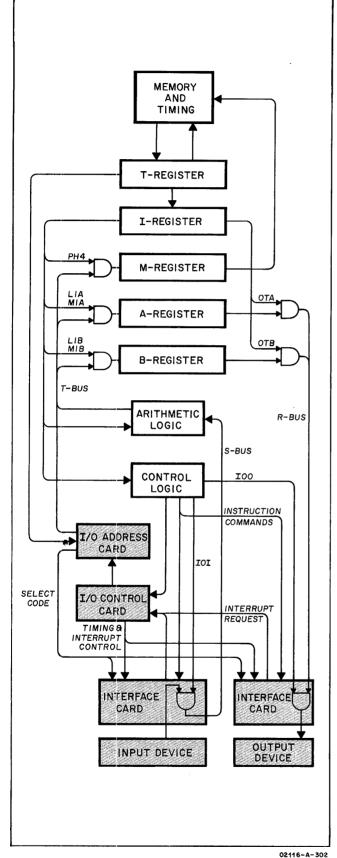

2-7. Figure 2-2 illustrates the main elements of the computer system concerned with the control of input/ output operations. All elements shown are contained in the computer mainframe, except for the external devices. Although the R-, S-, and T-Buses are represented as single lines in Figure 2-2, each bus is actually 16 individual lines. Also, interface arrangements are shown for only two external devices, one input and one output, where as many as 48 devices may exist. The elements illustrated process all input/output operations in two ways, as follows:

a. Processes Input/Output instructions.

b. Processes interrupt requests from the external devices.

Figure 2-1. Input/Output Structure

#### 2-8. INPUT/OUTPUT INSTRUCTIONS.

2-9. Refer to Figure 2-2. Input/Output instructions from memory via the T-Register are decoded by the I-Register and routed to the various register gate inputs and to the Control Logic which translates the instructions into appropriate driving signals. Instruction Commands are routed to a particular interface card and external device as determined by the Select Code from the T-Register via the I/O Address card. These signals can set or reset the Control and Flag flip-flops (FFs) on the interface cards and can test the set or reset condition of the Flag flip-flops. The Control and Flag flip-flops are used to control data transfer between the interface card and the external device.

2-10. The IOI (I/O Input) signal strobes all interface cards for input data as a result of a Load Into A (LIA), Load Into B (LIB), Merge Into A (MIA), or a Merge Into B (MIB) instruction. Only the data from the interface card selected by the Select Code can be enabled. The data is strobed by the IOI signal onto the S-Bus. From there it is transferred via the Arithmetic Logic (to alter or combine the data) and the T-Bus to the A- or B-Register. The particular register which will receive the data is determined by the LIA/B or MIA/B signal present at the register input gate.

2-11. Another driving signal from the Control Logic, the IOO (I/O Output) signal, strobes all interface

cards to output data as a result of an OTA (Output from A) or an OTB (Output from B) instruction. The Select Code from the T-Register via the I/O Address card permits the IOO signal to strobe the data on the R-Bus into the appropriate interface card and external device. (The data was placed on the R-Bus from the A- or B-Register as a result of the OTA/Binstruction.

#### 2-12. INTERRUPT REQUESTS.

2-13. If a specific instruction to the I/O Control card has at some previous time enabled the interrupt system, an external device may request an interrupt to the computer program to obtain new data from the Computer or to feed new data to the Computer. This interrupt request is received by the I/O Control card. The I/O Control card signal to the I/O Address card causes it to interrupt the computer program by forcing the M-Register to be set (via the T-Bus) to a memory location corresponding to the Select Code of the interrupting device. This occurs during the Interrupt phase (Phase 4) machine cycle. The Fetch phase is then entered to make the Computer execute the instruction contained in the specified memory location. Generally, this instruction will be a jump to a service subroutine which will prepare or accept the new data. On completion of service, the subroutine must cause a return to the proper location in the main program. Refer to Paragraphs 2-28 through 2-53 for more detailed information on the interrupt system.

Figure 2-2. Block Diagram of System Input/Output Operations

### 2-14. INPUT/OUTPUT SYSTEM CARDS.

#### 2-15. I/O CONTROL AND I/O ADDRESS CARDS.

2-16. The Computer contains one plug-in I/O Control card and one plug-in I/O Address card. The cards plug into the Computer, adjacent to the interface cards as shown in Figure 2-3. Each card contains extractor handles to aid in their removal from the Computer. The I/O Control card contains the master Interrupt System Enable flip-flop, receives command and timing signals from the Computer for transfer to the interface card slots, and provides the necessary gates and flip-flops for proper control of interface-card operation. For detailed information on the I/O Control card, refer to Section III of this manual. The I/O Address card provides a decoding function for program selection of the desired interface card and an encoding function for interface card interrupt identification. For detailed information on the I/O Address card, refer to Section IV of this manual.

#### NOTE

Possible damage to the I/O Control card or the I/O Address card may result if either one of these cards is inserted in an incorrect slot.

#### 2-17. RESISTANCE LOAD CARD.

2-18. The Computer contains one plug-in Resistance Load card. The card provides 18 150-ohm resistors, connected to the -2 volt supply, to terminate the IOBO (I/O Bus Output) lines from the Computer to the interface cards. The card plugs into any of the input/output slots (Figure 2-3) of the Computer. The card remains in an I/O slot unless the total interface and Priority Jumper cards used in the system equal 16. At that time, the card is no longer required and must be removed. Extractor handles on the card aid in its removal. Refer to Section V for further information on the Resistance Load card.

#### 2-19. INTERFACE CARDS.

2-20. PURPOSE. The interface cards provide channels through which data is transferred between the Computer and the input/output devices, and provide control (via computer commands) of the input/output device operation. An interface card may contain up to 16 or more buffer flip-flops for temporary storage of data to be transferred to the Computer or the input/ output device. The number of buffer flip-flops on a particular interface card depends on the type of device connected to it. Other logic circuitry on the interface card also depends on the device to which it is connected. Certain devices are capable of interrupting the computer program while for others, this capability is not necessary; certain devices require control signals for movement of tape, etc., while others do not, and timing requirements for some devices must be provided on the interface card. For detailed information on a particular interface card, refer to the applicable Interface Kit Operating manual. In some cases, more than one interface card is required for an external device.

| POSITION                                                                                           | 201              | 202              | 203                     | 204                   | 205                          | 206                  | 207 | 208 | 209 | 210      | 211      | 212 | 213 | 214      | 215      | 216      | 217      | 218                    | 219                 | 220                 | 221 | 222 |

|----------------------------------------------------------------------------------------------------|------------------|------------------|-------------------------|-----------------------|------------------------------|----------------------|-----|-----|-----|----------|----------|-----|-----|----------|----------|----------|----------|------------------------|---------------------|---------------------|-----|-----|

|                                                                                                    | I/O CONTROL CARD | I/O ADDRESS CARD | HIGH-SPEED PHOTO READER | HIGH-SPEED TAPE PUNCH | TELEPRINTER INPUT AND OUTPUT | PRIORITY JUMPER CARD |     |     |     |          | ERF      |     |     |          |          |          |          | (RESISTANCE LOAD CARD) | I/O EXTENDER DRIVER | I/O EXTENDER DRIVER |     |     |

| SELECT CODES<br>LOWER<br>SELECT CODE<br>(HIGH PRIORITY)<br>HIGHER<br>SELECT CODE<br>(LOW PRIORITY) |                  |                  | 10                      | 11                    | 12<br>13                     | 13<br>14             | 14  | 15  | 16  | 17<br>20 | 20<br>21 | 21  | 22  | 23<br>24 | 24<br>25 | 25<br>26 | 26<br>27 | 27<br>30               | _                   | -                   | -   |     |

Figure 2-3. Computer Plug-In Card Positions, Front View

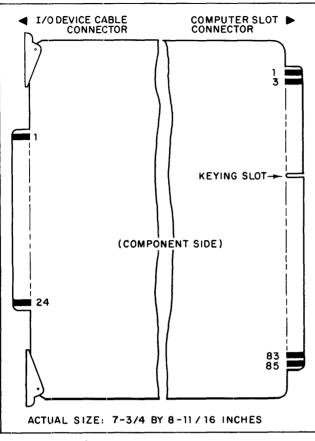

2-21. LOGIC ELEMENTS. Logic elements on the interface cards are provided by microcircuit packages which may contain more than one logic element and which are in numbered locations on the interface cards. The microcircuit package reference designations on the logic diagrams are preceded by MC. The number following MC corresponds to the numbered location of the package on the particular interface card. The individual elements of a package are further identified by a suffix letter. The Appendix in Volume Two provides logic diagrams for each of the microcircuit packages according to HP Part Number which is stamped on the microcircuit package.

2-22. PIN ASSIGNMENTS. Refer to Figure 2-4. One end of each interface card has 86 printed-circuit paths, 43 on each side of the card. This end of the card plugs into a computer slot connector to transfer signals to and from the Computer. It is also keyed to prevent incorrect insertion. The circuit path positions correspond to the pin positions of the slot connector. Odd-numbered pins 1 through 85 are on one side of the card as shown in Figure 2-4, and even-numbered pins 2 through 86 are on the other side of the card. Pins 1 and 2 are directly opposite each other on the card. Pin assignments for this end of the card are identical

2 - 4

for all interface cards to permit the placement of any card in any of the input/output slots of the Computer.

2-23. The other end of most interface cards have 48 printed-circuit paths, 24 on each side of the card. The plug connector of the interconnecting cable to the input/output device plugs into this end of the card to transfer signals to and from the device. The circuitpath positions correspond to the pin positions of the plug connector. Pins 1 through 24 are on one side of the card as shown in Figure 2-4, and consecutivelylettered pins A through BB (with letters G, I, O and Q deleted) are on the other side of the card. Pins 1 and A are directly opposite each other on the card. Also on this end of the card are two extractor handles to aid in the removal of the card from the Computer.

2-24. Refer to Table 2-1 for a list of the pin connections and signals between the interface cards and the slot connectors. Although this table lists all of the pin assignments and signals between the cards and the slot connectors, an individual interface card may not necessarily use all signals. Pin assignments and signals between an interface card and its input/output device is provided in each Interface Kit section of this manual.

Figure 2-4. Interface Card Connectors

#### 2-25. INPUT/OUTPUT DEVICE SELECTION.

2-26. Bits 0 through 5 of the Input/Output instruction form a Select Code to specify one of 64 possible input/ output devices or functions. The Select Code is applied to the I/O Address card. This card decodes the 6-bit code and provides a two-digit octal code output. This output is transferred to the interface-card slot of the selected input/output device to permit program control of the device. Table 2-2 lists the Select Codes and their assignments, and indicates the corresponding interrupt location (i.e., the memory location containing the instruction to be executed when an interrupt occurs). Select Code 00 is the access to the master Interrupt System Enable Flip-Flop on the I/O Control card. Codes 01 through 07 are reserved for processor input/output functions or options, as listed. Codes 10 through 67 (octal) are used for selection of the 48 possible input/output devices and functions, each capable of causing an interrupt when used with the appropriate Extender Module.

2-27. Figure 2-3 illustrates the slots in the Computer card cage which are for the plug-in interface cards associated with input/output operation. These slots are capable of accepting interface cards of two basic types. The first is the parallel data-transfer type interface card. This interface card transfers data information to and from the Computer in parallel groups of bits (8 or 16 bits at a time) and requires the use of only one of the two Select Codes assigned to each I/O slot. This is the type of interface card used with most HP Accessory Kits. The second of the two interface card-types is the serial data-transfer interface card. This card transfers data information to and from the Computer in serial (one bit at a time) and normally requires that both of the Select Codes assigned to each I/O slot be used in order to control input and output functions. When a serial-type interface card is used, the I/O slot directly adjacent to it must contain a Priority Jumper card in order to maintain the priority continuity of the interrupt system. Since the I/O slot connector-wiring (on the Computer backplane) determines the Select Codes of each I/O slot, and interface cards can be inserted into any slot, each interface card assumes the two Select Codes of the slot into which it has been placed.

#### 2-28. INTERRUPT SYSTEM.

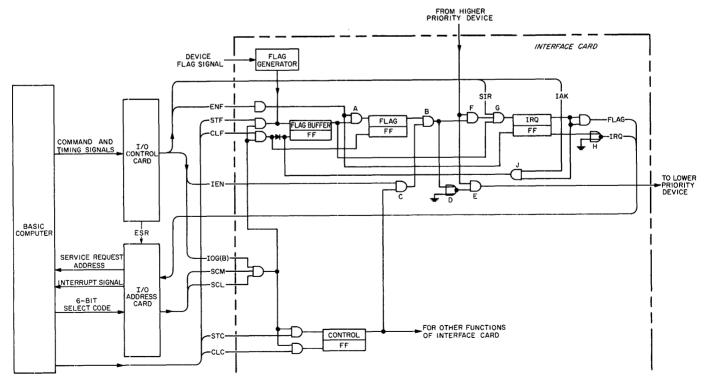

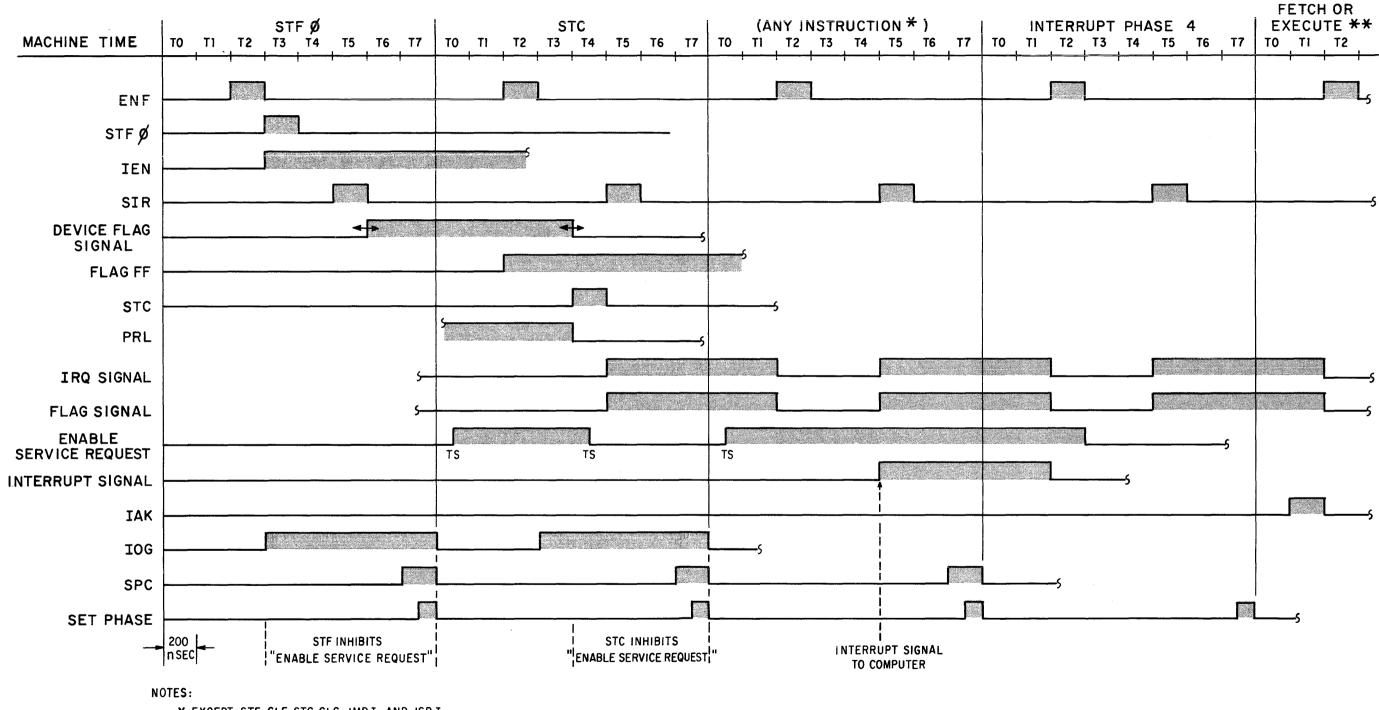

2-29. The Interrupt System provides the means for an external device to interrupt the program in proggress when data is available or when additional output data can be accepted. Figure 2-5 illustrates the relationship between the Computer, the I/O Control and I/O Address plug-in cards, and typical interrupt logic on a particular interface card; Figure 2-5 is for interrupt-logic explanatory purposes only. Refer to Figure 2-6 for a chart of typical interrupt system timing.

2-30. An interrupt request from an external device occurs when the following conditions are met:

a. The Interrupt System is enabled.

b. The Flag flip-flop of the specific device interface card is set.

c. The Control flip-flop of the specific device interface card is set.

d. No priority-affecting instruction (STF, CLF, STC and CLC), JSB,I instruction or JMP,I instruction is in progress.

e. No higher-priority devices satisfy the conditions of steps "b" and "c".

#### 2-31. INTERRUPT SYSTEM ENABLE-DISABLE.

2-32. The computer program determines if interrupt requests from the external devices will be recognized. This is accomplished by enabling or disabling the Interrupt System Enable flip-flop on the I/O Control card. A set Flag (STF) instruction with a Select Code of 00 (octal) sets the FF and enables the interrupt system. A Clear Flag (CLF) instruction with a Select Code of 00 (octal) resets the flip-flop and disables the interrupt system.

2-33. When Computer power is initially turned on, pressing the POWER pushbutton automatically resets the Interrupt System Enable flip-flop, disabling the interrupt system. Initial turn-on also resets all Control flip-flops on the interface cards to prevent input/output devices from running when power is applied, and sets all Flag Buffer and Flag flip-flops on the interface cards. Therefore, to operate any device, it is first necessary to set the Interrupt System Enable flip-flop, reset the individual Flag Buffer and Flag flip-flop.

Table 2-1. Interface Card-to-Computer Pin Connections

| PIN      | SIGNAL                                                                 |        | PIN     | SIGNAL                                                            |

|----------|------------------------------------------------------------------------|--------|---------|-------------------------------------------------------------------|

| 1        | Ground                                                                 |        | 2       | Ground                                                            |

| 3        | PRL: Priority Low                                                      | ł      | 4       | FLGL: Flag signal, Lower Select Code                              |

| 5        | SFC: Skip Flag Clear (Skip next instruction                            |        | 6       | IRQL: Interrupt Request, Lower Select                             |

|          | if Flag FF is reset)                                                   | ł      |         | Code                                                              |

| 7        | CLF: Clear (reset) Flag FF                                             |        | 8       | IEN: Interrupt Enable                                             |

| 9        | STF: Set Flag FF                                                       | ]      | 10      | IAK: Interrupt Acknowledge                                        |

| 11       | T3(B): Machine phase time T3 (Buffered)                                |        | 12      | SKF: Skip Flag (Skip next instruction if SFS or SFC test is true) |

| 13       | CRS: Control Reset                                                     |        | 14      | LSCM: Lower Select Code Most Significant<br>Digit                 |

| 15       | IOG(B): I/O Group instruction (Buffered)                               |        | 16      | LSCL: Lower Select Code Least Significant<br>Digit                |

| 17       | POPIO(B): Power On Preset I/O (Buffered)                               | ]      | 18      | IOBI 16: I/O Bus Input, Bit 16                                    |

| 19       | SRQ: Service Request                                                   | 1      | 20      | IOO: I/O Output                                                   |

| 21       | CLC: Clear (reset) Control FF                                          | 1      | 22      | STC: Set Control FF                                               |

| 23       | PRH: Priority High                                                     | [      | 24      | IOI: I/O Input                                                    |

| 25       | SFS: Skip Flag Set (Skip next instruction if Flag FF is set)           |        | 26      | IOBI 0: I/O Bus Input, Bit 0                                      |

| 27       | IOBI 8: I/O Bus Input, Bit 8                                           |        | 28      | IOBI 9: I/O Bus Input, Bit 9                                      |

| 29       | IOBI 1: I/O Bus Input, Bit 1                                           | }      | 30      | IOBI 2: I/O Bus Input, Bit 2                                      |

| 31       | IOBI 10: I/O Bus Input, Bit 10                                         | 1      | 32      | SIR: Set Interrupt Request                                        |

| 33       | IRQH: Interrupt Request, Higher Select                                 |        | 34      | HSCL: Higher Select Code Least Signifi-                           |

|          | Code                                                                   | í      |         | cant Digit                                                        |

| 35       | IOBO 0: I/O Bus Output, Bit 0                                          |        | 36      | +30 volts, unregulated                                            |

| 37       | HSCM: Higher Select Code Most Significant                              |        | 38      | IOBO 1: I/O Bus Output, Bit 1                                     |

|          | Digit                                                                  |        |         |                                                                   |

| 39       | +4.5 volts                                                             |        | 40      | +4.5 volts                                                        |

| 41       | IOBO 2: I/O Bus Output, Bit 2                                          |        | 42      | IOBO 4: I/O Bus Output, Bit 4                                     |

| 43       | +12 volts                                                              | ļ      |         | +12 volts                                                         |

| 45       | IOBO 3: I/O Bus Output, Bit 3<br>-2 volts                              |        | 46      | ENF: Enable Flag<br>-2 volts                                      |

| 47<br>49 |                                                                        | }      | 50      | RUN                                                               |

| 49<br>51 | FLGH: Flag signal, Higher Select Code<br>IOBO 5: I/O Bus Output, Bit 5 |        | 50      | IOBO 7: I/O Bus Output, Bit 7                                     |

| 53       | IOBO 6: I/O Bus Output, Bit 5                                          |        | 54      | IOBO 8: I/O Bus Output, Bit 7<br>IOBO 8: I/O Bus Output, Bit 8    |

| 55       | IOBO 11: I/O Bus Output, Bit 11                                        |        | 56      | IOBO 9: I/O Bus Output, Bit 9                                     |

| 57       | IOBO 12: I/O Bus Output, Bit 12                                        |        | 58      | IOBO 10: I/O Bus Output, Bit 10                                   |

| 59       | LDS: Load Switch                                                       | ł      | 60      | IOBI 11: I/O Bus Input, Bit 11                                    |

| 61       | IOBO 13: I/O Bus Output, Bit 13                                        |        | 62      | (Not Used)                                                        |

| 63       | (Not Used)                                                             |        | 64      | IOBI 3: I/O Bus Input, Bit 3                                      |

| 65       | IOBO 14: I/O Bus Output, Bit 14                                        |        | 66      | (Not Used)                                                        |

| 67       | (Not Used)                                                             |        | 68      | (Not Used)                                                        |

| 69       | -12 volts                                                              |        | 70      | -12 volts                                                         |

| 71       | (Not Used)                                                             |        | 72      | (Not Used)                                                        |

| 73       | IOBO 16: I/O Bus Output, Bit 16                                        |        | 74      | IOBO 15: I/O Bus Output, Bit 15                                   |

| 75       | (Not Used)                                                             |        | 76      | (Not Used)                                                        |

| 77       | IOBI 4: I/O Bus Input, Bit 4                                           |        | 78      | IOBI 12: I/O Bus Input, Bit 12                                    |

| 79       | IOBI 13: I/O Bus Input, Bit 13                                         |        | 80      | IOBI 5: I/O Bus Input, Bit 5                                      |

| 81       | IOBI 6: I/O Bus Input, Bit 6                                           | 1      | 82      | IOBI 14: I/O Bus Input, Bit 14                                    |

| 83       | IOBI 15: I/O Bus Input, Bit 15                                         |        | 84      | IOBI 7: I/O Bus Input, Bit 7                                      |

| 85       | Ground                                                                 | 1      | 86      | Ground                                                            |

| NOT      | E: Pins 1 & 2, 39 & 40, 43 & 44, 47 & 48, 69 & 70                      | ), and | 85 & 86 | connected together on Slot Connector                              |

and on Interface Card.

#### 2-34. INTERRUPT SYSTEM OPERATION.

2-35. When the external device has completed its operation, it generates a Device Flag signal to the Interface-card Flag Generator which sets the Flag Buffer flip-flop (see Figure 2-5). The output of the Flag Buffer flip-flop, in conjunction with the ENF (Enable Flag) signal from the I/O Control card during

time T2 (Figure 2-6) causes "and" gate A to set the Flag flip-flop. The Flag flip-flop output is "anded" at gate B with the output of "nand" gate C. The gate C output is true when the Control flip-flop is set and when the IEN (Interrupt Enable) signal is received from the I/O Control card during time T3. Unless the Control flip-flop is set by a Set Control (STC) instruction, an interrupt request cannot occur.

| SELECT<br>CODE<br>(OCTAL) | INTERRUPT<br>LOCATION | ASSIGNMENT                                  |

|---------------------------|-----------------------|---------------------------------------------|

| 00                        | None                  | Interrupt System Disable/Enable             |

| 01                        | None                  | Switch Register or Overflow                 |

| 02                        | None                  | DMA Channel 1 Initialize                    |

| 03                        | None                  | DMA Channel 2 Initialize                    |

| 04                        | 00004                 | Power Fail Interrupt/Central Interrupt Load |

| 05                        | 00005                 | Memory Protect/Parity Error Interrupt       |

| 06                        | 00006                 | DMA Channel 1 Completion Interrupt          |

| 07                        | 00007                 | DMA Channel 2 Completion Interrupt          |

| 10                        | 00010                 | I/O Device, Highest Priority                |

| thru                      | thru                  | thru                                        |

| 67<br>70                  | 00067<br>00070        | I/O Device, Lowest Priority                 |

| thru<br>77                | thru<br>00077         | Not wired in the HP 2150B Extender          |

Table 2-2.

Select Code Assignments

2-36. The Control flip-flop is set under program control and therefore, is set at T4 time of a machine cycle. The STC instruction is enabled to the Control flip-flop by the SCM (Select Code Most Significant digit) and SCL (Select Code Least Significant digit) signals from the I/O Address card, and the IOG(B) (I/O Group instruction, Buffered) signal from the I/O Control card. The SCM and SCL signals are enabled on the individual interface card by the IOG(B) signal which occurs when the instruction to be performed is an I/O Group instruction. When the Control flip-flop sets, a true input is applied to "and" gate C. The inputs to "and" gates B and C are then true and gate B applies a true output to inverting "or" gate D. The false output of gate D disables "and" gate E, making

the priority network bus to the lower-priority devices false. This prevents any device of lower priority from requesting an interrupt.

2-37. At the same time that gate B applied a true signal to gate D, it also applied the same true signal to "and" gate F. The priority network signal to gate F will be true if an interface card (device) of higher priority than the one represented in Figure 2-5 is not requesting an interrupt. In this case, the true output of gate F is combined with the SIR (Set Interrupt Request) signal from the I/O Control card at time T5 and the output of the set Flag Buffer flip-flop to provide a true output from "and" gate G. The gate G output sets the IRQ (Interrupt Request) flip-flop.

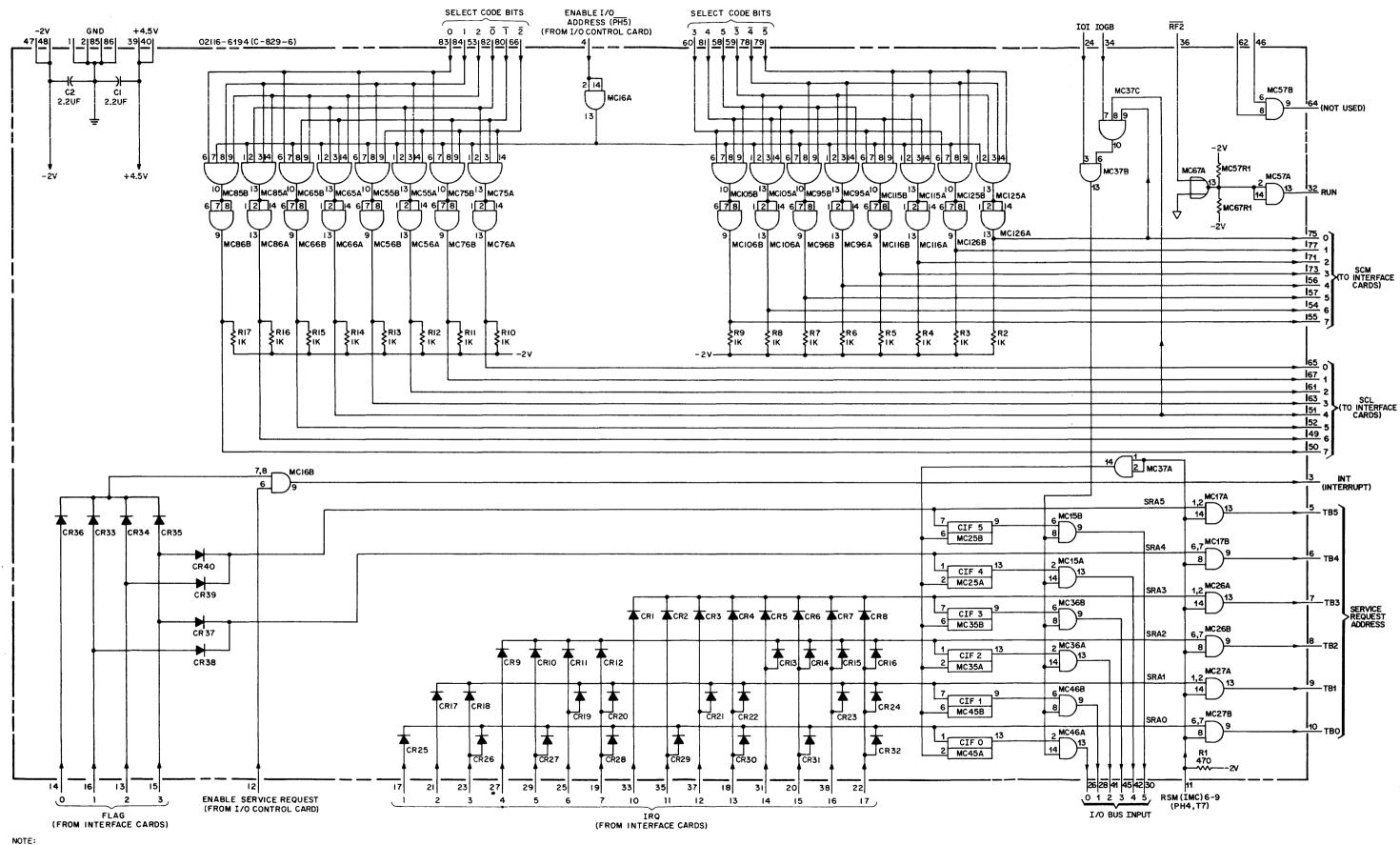

Figure 2-5. Typical Interrupt Logic

2-38. The IRQ flip-flop outputs provide the Flag signal and the IRQ signal to the I/O Address card. (The IRQ signal is obtained by the inversion of the false reset-side output of the IRQ flip-flop by inverting "or" gate H.) The Flag signal is "anded" in the I/O Address card with the Enable Service Request (ESR) signal from the I/O Control card to form an interrupt signal. However, the ESR signal is false for the remainder of the machine cycle during which an instruction occurs that affects device priorities (STC in Figure 2-6) as determined by the I/O Control card. At time T2, the IRQ flip-flop is reset by the ENF signal to allow a higher-priority device to request an interrupt. If the Control flip-flop is still set and no higher-priority devices have requested an interrupt, the IRQ flip-flop will again be set at time T5 (SIR). The Flag and IRQ signals are again sent to the I/O Address card. The signals are used to form a 6-bit Service Request Address which is enabled to the Computer at time T7 of the Interrupt Phase. The Flag signal and the now-true ESR signal cause the Interrupt signal (INT) to be sent to the Computer. This signal causes an interrupt at the end of the current machine phase, switching the Computer into the Interrupt Phase, except when any of the following conditions occur:

a. The Computer is in the HALT mode.

b. A Jump Indirect (JMP,I) or a Jump to Subroutine Indirect (JSB,I) instruction is not fully executed. (These instructions inhibit all interrupts until fully executed for any number of indirect levels of addressing. At the earliest, an interrupt request will be granted at the end of the machine phase immediately following one or more JMP,I or JSB,I instructions.)

c. Direct Memory Access (DMA) option is in process of transferring data. Exception: The Power Fail Interrupt can interrupt a DMA transfer.

d. A STC, CLC, STF or CLF machine cycle is being executed.

#### 2-39. INTERRUPT PROCESSING.

2-40. During the Interrupt Phase, the Computer decrements the P-Register by one to ensure that the proper location in the main program will be returned to after the interrupt is processed. Also, the Computer places the Service Request Address (which is always equal to the Select Code of the interrupting device) from the I/O Address card into the M-Register at time T7. This causes the next instruction to be read from the memory location having the same number as the Service Request Address (Select Code) during the Fetch phase (Phase 1). This location in memory is referred to as the "interrupt location" and is reserved for that particular device. Example: A device specified by a Select Code of 10 will interrupt to (i.e., cause execution of the contents of) memory location 00010. At time T3 of Phase 4, the interrupt system is inhibited by the false Enable Service Request signal until the Fetch phase following the execution of the instruction at the interrupt location. This prevents interrupts from occurring until at least one instruction has been executed (except in the case of JMP, I and JSB,I instructions), which may be more than one instruction.

2-41. At time T1 of Phase 1 the IAK (Interrupt Acknowledge) signal from the I/O Control card and the set-side output of the IRQ flip-flop resets the Flag Buffer flip-flop through "and" gate J (Figure 2-5). Since the set-side output of the Flag Buffer flip-flop is applied to "and" gate G, resetting the flip-flop prevents the setting of the IRQ flip-flop and causing another interrupt from the same Flag signal at time T5 of Phase 1 when the SIR signal is again applied to gate G. (The Flag Buffer flip-flop can also be reset by a programmed CLF (Clear Flag) instruction.) During time T2, the ENF signal resets the IRQ flipflop. The Computer fetches the instruction in the interrupt location which will usually be a jump to a subroutine (JSB) instruction. The contents of the P-Register plus one is stored in the first location (X) of the subroutine. (Since the previous contents of the first memory location are destroyed when P+1 is stored, the first instruction of the subroutine should always be a no-operation (NOP) instruction or equivalent.) The location of the subroutine (X + 1) is placed in the P- and M-Registers, and the Computer resumes normal subroutine operation. Thus, the instruction at location X + 1 is the first instruction of the subroutine to be executed. The contents of the working registers that were in use in the main program should be stored when entering the subroutine and restored before exit from the subroutine. The exit from the subroutine is made with a JMP, I to location X. This places the address of the interrupted program instruction in the P- and M-Registers and normal program operation resumes.

#### 2-42. INTERRUPT PRIORITY.

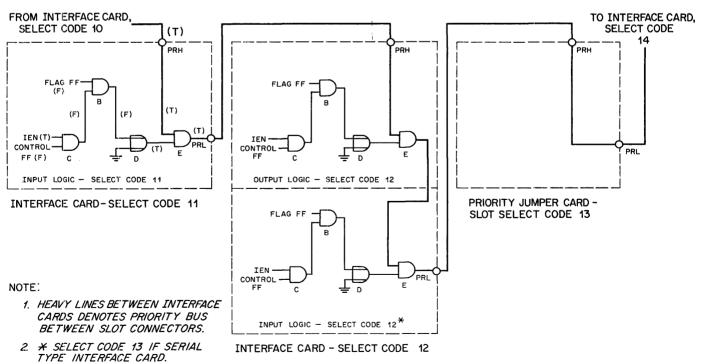

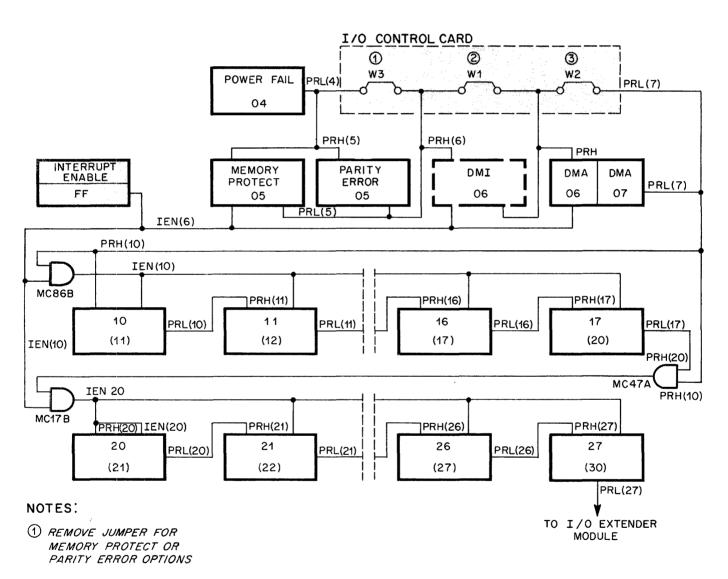

2-43. PRIORITY ASSIGNMENTS. A priority network on the I/O slots allows only one external device at a time to interrupt the computer program regardless of the number of devices requesting an interrupt. The priority network gives highest priority to Select Code 04. reserved for Power Fail Interrupt, and decreasing priority to the remaining Select Codes in order from 05 to 67 (see Table 2-2). (See Figure 2-8, INTERRUPT PRIORITY CONTINUITY.) Select Code 05 is reserved for both the Memory Protect and Parity Error options. Either one, or both, of these options may be used but they always share the same Select Code of 05. When neither one of these two options (Memory Protect or Parity Error) is installed, jumper W3 on the I/O Control card (slot 201 of the computer card cage) must be installed in order to maintain priority continuity (see Figure 2-8). Select Codes 06 and 07 are reserved for the DMA (Direct Memory Access) option Channel 1 and Channel 2, respectively. When the DMA option is installed, jumper W2 on the I/O Control card must be removed. The DMI (Direct Memory Increment) option may be used in place of the DMA option Channel 1 and utilizes Select Code 06 only (see Figure 2-8). When the DMI option is installed, jumper W1 on the I/O Control card must be removed. All I/O slots from Select Code 10 ascending thru 67 may be used for I/O devices as desired by the computer user. The interrupt priority assignments of the I/O slots remain fixed but since any interface card can be inserted into any I/O slot, the interrupt priority of a given device can be easily changed by inserting the device interface card into another I/O slot.

★ EXCEPT STF, CLF, STC, CLC, JMPI, AND JSBI. ★ ★ EXECUTE IF A SINGLE CYCLE INSTRUCTION. 2-44. PRIORITY NETWORK OPERATION. As shown in Figure 2-7, priority is established by a hardwareimplemented priority chain. The "and-or" gates illustrated in Figure 2-7 are identified by letters and correspond to those used in Figure 2-5. The truefalse logic levels for an interface card which is not requesting an interrupt are illustrated on the first interface card (Select Code 11) with the Interrupt System enabled (IEN input is true). Also, the PRH (Priority High) signal is true, indicating that a device of higher priority is not requesting an interrupt. In this case, the "chain" is not broken and a true PRL (Priority Low) signal is available to the next interface card (Select Code 12) as a true PRH signal to that card.

2-45. If the output logic portion of the interface card with Select Code 12 in Figure 2-7 requests an interrupt, all inputs to "and" gate B will be true. Inverting "or" gate D will then apply a false input to "and" gate E. The output of gate E is then false, breaking the "chain", and preventing any interface card of lower priority from interrupting the computer program. A service subroutine can then be entered to process the interrupt of the output logic.

2-46. A service subroutine of any device can be interrupted by a higher-priority device; then after the higher-priority interrupt subroutine is completed, the lower-priority subroutine may continue. In this way, several service subroutines may be in a state of interruption at one time. Each will be permitted to continue when the next higher priority subroutine is completed. 2-47. Interrupt priority can also be program controlled. Since an interrupt cannot occur unless the Control flip-flop of the interface card is set, all Control flip-flops on interface cards of higher priority than the one desired can be reset by a Clear Control (CLC) instruction. This prevents those interface cards from requesting an interrupt and establishes the desired device as the highest-priority device.

2-48. INTERRUPT PRIORITY CONTINUITY.

2-49. Figure 2-8 illustrates the continuity of the interrupt priority network for all possible input/output interface cards and processor option cards capable of interrupting the Computer.

**2-50.** Since the Power Fail Interrupt (Select Code 04) is assigned the highest priority, it can interrupt the Computer (as also can the Memory Protect/Parity Error and the Direct Memory Increment options) regardless of the state of the Interrupt System Enable flip-flop. For all other interface cards and options, the flip-flop must be set before an interrupt can occur. When an interface card requests an interrupt, its false PRL signal is applied to the next interface card as a false PRH signal to prevent it from requesting an interrupt. This sequence continues from card to card until the last interface card receives a false PRH signal. When an interrupt request occurs, the PRL-PRH switching sequence proceeds to the next card and also to the "and" gate following the group of eight cards in which the interrupt request occurs. The false input to the "and" gate causes a false IEN output and all following interface cards are quickly disabled.

#### CARD POSITION 204

#### CARD POSITION 205

#### CARD POSITION 206

Figure 2-7. Interrupt Priority

Figure 2-8. Priority Continuity

2-51. The Memory Protect and Parity Error options share Select Code 05 as they are connected in parallel in the interrupt priority chain (see Figure 2-8). If either one of these options is installed in the Computer, Select Code 05 is operative. If either of the options is installed, it is necessary to remove jumper W3 on the I/O Control card (Figure 2-8) in order to maintain interrupt priority continuity.

#### 2-52. EXTENDER MODULES.

2-53. To increase the number of I/O Channels from 16 or to extend the computer memory from 16K (16,384 words), it is necessary to use one of two available extender modules. The HP 2151A Extender Module provides an additional 16 slots of I/O only and requires the HP 12596A Interface Kit, in order to be used with the HP 2116B Computer. It is easily installed by the use of interconnecting cabling and contains its own internal power supply. The HP 2150B Extender Module provides the Computer with the capability for an additional 32 slots of I/O and an additional 8K or 16K of memory and also contains its own internal power supply. The additional capabilities provided by the HP 2150B Extender Module are dependent upon which of several extender options are incorporated within the basic extender module unit. The options are as follows:

a. Option 01: This option comprises four plug-in cards and two interconnecting cables which are required for the operation of the interface cards (up to 32) added to the extender module.

b. Option 02: This option comprises an 8K memory module, a set of plug-in memory addressing cards, and two interconnecting cables. When combined with the 16K memory in the basic computer, this option gives a combined memory size of 24K(24,576 words).

c. Option 03: This option comprises a second 8K memory module, and set of memory addressing cards in addition to the 8K of Option 02. With Options 02 and 03 installed, the HP 2116B Computer and HP 2150B Extender Module combined provide the computer user with 32K (32,768 words) of memory.

#### 2-54. POWER SUPPLY REQUIREMENTS.

2-55. When using certain combinations of I/O devices which have high current requirements, the Computer internal power supply may be inadequate. In order to furnish the necessary additional power, a HP 2160A Power Supply Extender must be used. The HP 2160A Power Supply Extender is a physically self-contained unit that is connected to the HP 2116B Computer by the use of two interconnecting cables. When connected, the power supply extender is a slaved extension of the computer power supply and provides an additional 20 amperes at +4.5V and 10 amperes at -2V. If desired, the power supply extender may be mounted in a standard 19-inch vertical mounting rack.

2-56. Table 2-3 lists the current available from the Computer power supply and from the combination of Computer power supply and HP 2160A Power Supply. The current available for options in Table 2-3 is

| REQUIREMENTS                                                              | SUPPLY CURRENTS (AMP) |        |                |         |  |  |  |  |  |

|---------------------------------------------------------------------------|-----------------------|--------|----------------|---------|--|--|--|--|--|

|                                                                           | +12V                  | -12V   | -2V            | +4.5V   |  |  |  |  |  |

| CURRENT AVAILABLE FROM POWER SUPPLIES                                     |                       |        |                |         |  |  |  |  |  |

| Computer Power Supply<br>Computer and HP 2160A Power Supplies             | 3<br>3                | 3<br>3 | $22.5 \\ 32.5$ | *22.5   |  |  |  |  |  |

| CURRENT REQUIRED BY COMPUTER WITH NO<br>PROCESSOR OR INPUT/OUTPUT OPTIONS |                       |        |                |         |  |  |  |  |  |

| Computer with 8K Memory                                                   | 540 ma                | 600 ma | 15.2           | 26.4    |  |  |  |  |  |

| Computer with 16K Memory                                                  | 1.0                   | 1.1    | 15.7           | 28.4    |  |  |  |  |  |

| CURRENT AVAILABLE FOR OPTIONS                                             |                       |        |                |         |  |  |  |  |  |

| Computer with 8K Memory                                                   | 2.5                   | 2.4    | 7.3            | ***11.3 |  |  |  |  |  |

| Computer with 16K Memory                                                  | 2.0                   | 1.9    | 6.8            | *** 9.8 |  |  |  |  |  |

| Computer with 8K Memory and HP 2160A                                      |                       |        |                |         |  |  |  |  |  |

| Power Supply Extender                                                     | 2.5                   | 2.4    | 17.3           | ***21.3 |  |  |  |  |  |

| Computer with 16K Memory and HP 2160A                                     | • •                   | 1.9    | 16.8           | ***19.8 |  |  |  |  |  |

| Power Supply Extender                                                     | 2.0                   | 1.9    | 1 10.0         | 1       |  |  |  |  |  |

Table 2-3. Internal/External Power Supply Requirements

NOTES: \* Plus the current drawn from the -2V supply by the Computer with memory and options. Maximum available from +4.5V supply is 45 amperes.

\*\* Plus the current drawn from the -2V supply by the Computer with memory and options. Maximum available from +4.5V supply is 65 amperes.

\*\*\* Plus the current drawn from the -2V supply by the selected options.

obtained by subtracting the current required by the Computer from the current available from the power supplies. Table 2-4 lists the current required by the processor and input/output options. To determine if the Computer power supply is adequate for the options to be used with the Computer or if a HP 2160A Power Supply must be added, proceed as follows:

a. Refer to Table 2-4 and add the currents required in each of the +12V, -12V, -2V, and +4.5Vcolumns for the selected options.

b. Add the sum of the -2V supply currents obtained in step "a" to the value in the +4.5V column of Table 2-3 for a Computer with an 8K or 16K memory (as applicable) under the CURRENT AVAILABLE FOR OPTIONS title. Record this new sum.

c. Again refer to the currents listed for a Computer with 8K or 16K of memory (as applicable) under the CURRENT AVAILABLE FOR OPTIONS title in Table 2-3. If any of the individual +12V, -12V, or -2V supply current sums of step "a" are higher than those listed, or if the +4.5V supply current sum is higher than that recorded in step "b", an HP 2160A Power Supply is required. The current sums cannot then exceed those listed for a Computer with an 8K or 16K memory (as applicable) and an HP 2160A Power Supply. The HP 2160A Power Supply provides only -2V and +4.5V and does not supply +12V or -12V.

#### 2-57. INTERFACE KITS.

2-58. Interface Kits for the HP 2116B Computer system provide the necessary interface cards, priority jumper cards, and cable for connection of external equipment to the Computer. The necessary software for driving the specific peripheral device, and the device diagnostic-program tape are also provided. The kits are identified by a 5-digit accessory number, a suffix revision letter, and a functional name (e.g., 12531B Teleprinter Input/Output). Available interface kits, identified in this manner, are listed on the Accessory Kit Ordering Information sheet that accompanies each HP 2116B Computer Technical Data Sheet.

Table 2-4. Current Required by Options

|                  | OPTIONS                                        |      |      | CURREN<br>RED (AMP |       |

|------------------|------------------------------------------------|------|------|--------------------|-------|

|                  | PROCESSOR OPTIONS                              | +12V | -12V | -2V                | +4.5V |

| 12578A           | Direct Memory Access                           | 0.00 | 0.00 | 0.72               | 6.20  |

| 12579A           | Extended Arithmetic Unit                       | 0.00 | 0.00 | 3.30               | 4.68  |

| 12581A           | Memory Protect                                 | 0.00 | 0.00 | 0.90               | 1.92  |

| 12582A           | Direct Memory Increment                        | 0.00 | 0.00 | 0.12               | 2.04  |

| 12588A           | Power Fail with Auto Restart                   | 0.06 | 0.04 | 0.00               | 0.00  |

| 12591A           | Memory Parity Check                            | 0.00 | 0.00 | 0.5                | 0.91  |

|                  | INPUT/OUTPUT OPTIONS                           |      |      | <u>.</u>           |       |

| 12531B           | Teleprinter Input/Output, Buffered             | 0.05 | 0.10 | 0.05               | 0.76  |

| 12532A           | High-Speed Punched Tape Input                  | 0.03 | 0.01 | 0.48               | 1.10  |

| 12533A           | Digital Voltmeter Program Output (2401C)       | 0.00 | 0.30 | 0.24               | 0.42  |

| 12535A           | Crossbar Scanner Program Output                | 0.01 | 0.04 | 0.84               | 1.10  |

| 12536A           | High-Speed Punched Tape Output                 | 0.01 | 0.01 | 0.30               | 0.72  |

| 12537A           | Incremental Magnetic Tape Output               | 0.00 | 0.06 | 0.48               | 0.90  |

| 12538A           | Magnetic Tape Input/Output (7 Channel)         | 0.09 | 0.18 | 4.20               | 6.00  |

| 12539A           | Time Base Generator                            | 0.01 | 0.00 | 0.42               | 1.10  |

| 12540A           | Data-Phone Interface (103A)                    | 0.11 | 0.05 | 0.90               | 1.40  |

| 12541A<br>12543A | Digital Voltmeter Data Input (2401C and 3440A) | 0.05 | 0.01 | 0.30               | 0.96  |

| 12544A           | Counter/Thermometer Data Input (8 Digits)      | 0.05 | 0.01 | 0.30               | 0.96  |

| 12548A           | Counter Data Input (4, 5, 6, & 7 Digits)       | 0.05 | 0.01 | 0.30               | 0.96  |

| 12550A           | Digital Voltmeter Program Output (2411A)       | 0.00 | 0.06 | 0.30               | 0.42  |

| 12551A           | Relay Output Register (no Interrupt)           | 0.24 | 0.00 | 0.39               | 0.60  |

| 12551B           | Relay Output Register (with Interrupt)         | 0.18 | 0.02 | 0.90               | 0.08  |

| 12554A           | Duplex General Purpose Register                | 0.24 | 0.01 | 0.48               | 2.40  |

| 12555A           | Digital-to-Analog Converter                    | 0.25 | 0.30 | 0.90               | 2.00  |

| 12556A           | 40-Bit Output Register                         | 0.07 | 0.00 | 0.06               | 0.80  |

| 12559A           | 9 Channel Magnetic Tape Input/Output           | 0.18 | 0.18 | 0.24               | 2.58  |

| 12561A           | Disc Memory Interface                          | 0.00 | 0.00 | 0.24               | 2.40  |

| 12564A           | 10-Bit A-to-D Converter                        | 0.15 | 0.22 | 0.09               | 0.90  |

| 12566A           | Microcircuit Interface                         | 0.00 | 0.00 | 0.05               | 1.10  |

| 12596A           | HP 2151A I/O Extender Interface                | 0.00 | 0.00 | 3.00               | 0.80  |

| 12597A           | 8-Bit Duplex Register (Positive-True)          | 0.18 | 0.02 | 0.80               | 0.05  |

|                  | 8-Bit Duplex Register Option 2 (Negative-True) | 0.04 | 0.18 | 0.80               | 0.06  |

## SECTION III I/O CONTROL CARD

#### 3-1. INTRODUCTION.

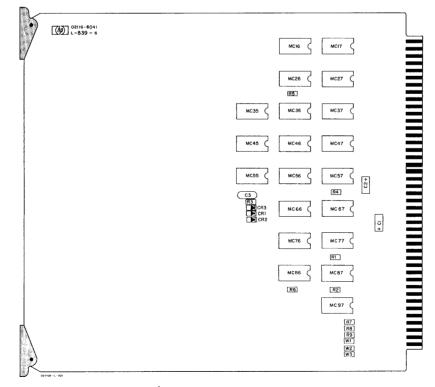

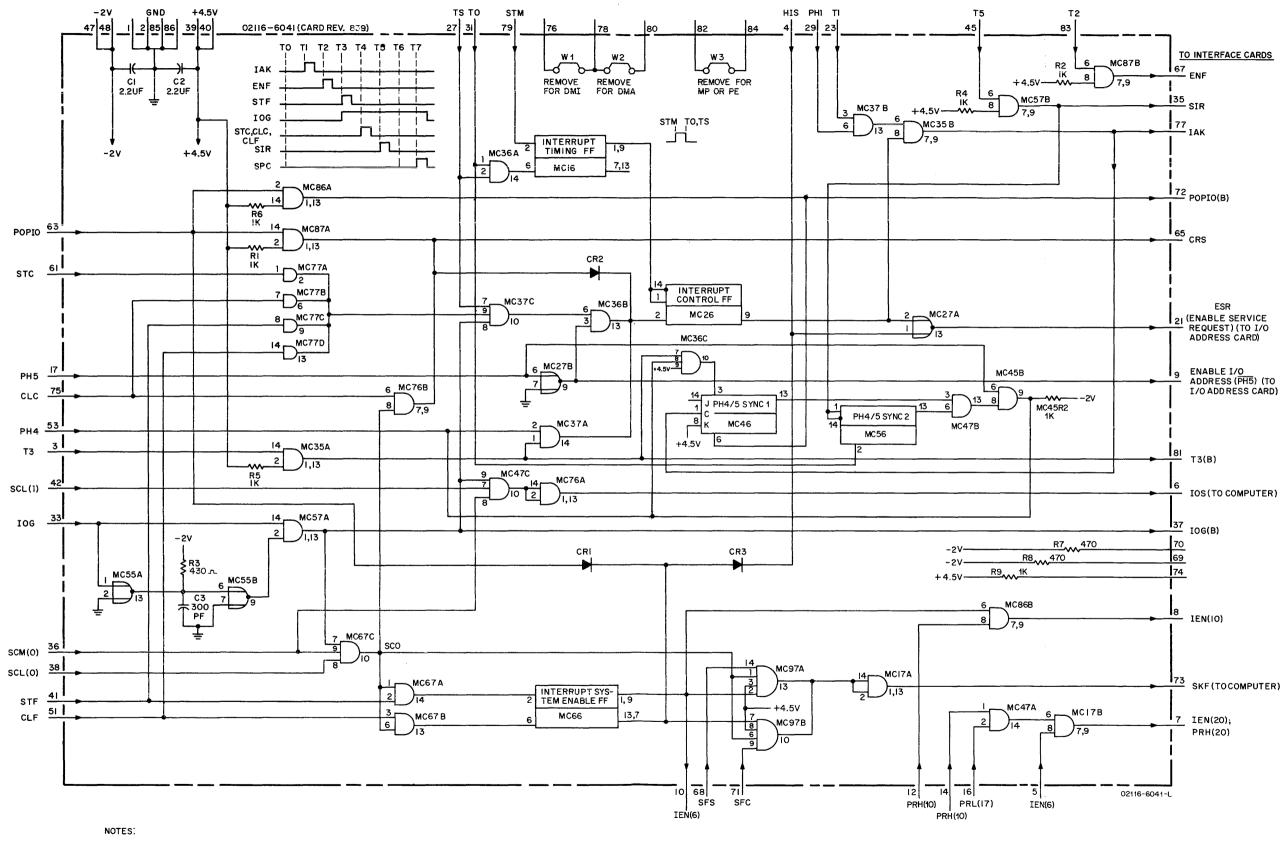

3-2. This section provides theory of operation information for the I/O Control card (HP Part No. 02116-6041). The card is of standard interface-card size and plugs into Position 201 on the left side of the input/output slots of the Computer. The slot connector transfers signals to and from the card; no additional cabling is required. The card output signals are transferred to all interface cards in the Computer, in parallel, through the interface-card slot connectors. The main function of the I/O Control card is to control the interrupt system. Certain clock signals, reset signals, and selection of the Switch Register and the Overflow bit of the Computer are also provided by the I/O Control card.

#### 3-3. THEORY OF OPERATION.

#### 3-4. COMPUTER POWER-ON.

3-5. When power is initially applied, the Computer is set to the HALT mode of Phase 1. At this time, the POPIO signal (Figure 3-3) is received at pin 63 of the I/O Control card. This signal is present for 100 milliseconds. (With power on, pressing the Computer PRESET switch applies the POPIO signal to the I/O Control card for as long as the switch is pressed.) The POPIO signal occurs at time T5 of Phase 1. When the POPIO signal drops, the Computer is still in Phase 1 and the initial conditions have been established for proper interface card operation. The POPIO signal performs the following functions which are described in Paragraphs 3-6 through 3-9.

a. Disables the Interrupt System.

b. Provides a false Enable Service Request signal to the I/O Address card.

c. Sets the Flag Buffer and Flag flip-flops and resets the IRQ flip-flops on all interface cards.

d. Resets the Control flip-flop on all interface cards.

3-6. Disables the Interrupt System: The POPIO signal resets the Interrupt System Enable flip-flop (MC66) through diode CR1, disabling the interrupt system. (The flip-flop consists of two inverting "or" gates which are connected such that the flip-flop can be reset by a true signal to either the reset-side input of the reset-side output of the flip-flop.

#### NOTE

Table 3-1 lists the part numbers of the microcircuit packages identified in Figure 3-3 by reference designations preceded by MC. The Appendix in Volume Two contains logic diagrams of the microcircuit packages according to part number.

3-7. Provides a False Enable Service Request Signal: When the Interrupt System Enable flip-flop was reset, the true reset-side output of the flip-flop is applied to the input of inverting "or" gate MC27A through diode CR3. The output of gate MC27A is a false Enable Service Request signal to the I/O Address card. This prevents the I/O Address card from sending an Interrupt Signal to the Computer which would switch the Computer into the Interrupt Phase, Phase 4.

3-8. Sets the Flag Buffer and Flag Flip-Flops and Resets the IRQ (Interrupt Request) Flip-Flop: The POPIO signal forms the buffered POPIO signal (POPIO(B)), through "and" gate MC86A, to set the Flag Buffer flip-flop on all interface cards. At time T2, the T2 clock signal to the I/O Control card (through "and" gate MC87B) forms the ENF signal. This signal resets the IRQ flip-flop on the interface cards and, with the set Flag Buffer flip-flop output, sets the Flag flip-flop on all interface cards.

3-9. Resets the Control Flip-Flop: The POPIO signal forms the CRS signal through "and" gate MC87A, to reset the Control flip-flop on all interface cards and to reset the Interrupt Control flip-flop (MC26) through diode CR2 on the  $\bar{I}/O$  Control card. (The CRS signal can also be programmed by a CLC instruction with a Select Code of 00 (octal); see Paragraph 3-20.) Resetting the Control flip-flops prevents an interrupt from occurring when the interrupt system is initially enabled (Interrupt System Enable flip-flop on the I/O Control card gets set). Resetting Interrupt Control flip-flop MC26 ensures a false Enable Service Request signal to the I/O Address card when the POPIO signal drops. This prevents an interrupt from occurring until after time T7 of the first machine phase after the POPIO signal drops to permit the execution of at least one program instruction. (The reset-side output of the Interrupt Control flip-flop enables "and" gate MC35B to form the IAK signal at time T1 of Phase 1; the IAK signal has no affect on the interface cards during the presence of the POPIO signal.)

#### 3-10. SIR SIGNAL.

3-11. At each T5 clock time, the T5 signal is sent to the I/O Control card by the Computer (Figure 3-3). After being applied to gate MC57B, this signal is applied to all interface-card slot connectors as the SIR (Set Interrupt Request) signal. The SIR signal enables setting of the IRQ (Interrupt Request) flipflop on all interface cards in order to provide Flag and IRQ signals to the I/O Address card during an interrupt request. This signal is also applied to the set input of the PH4/5 SYNC 2 flip-flop (MC56) on the I/O Control card causing the flip-flop to apply a true output signal to pin 6 of "and" gate MC47B. (For a detailed description of the PH4/5 SYNC 2 flip-flop circuit, refer to Paragraph 3-25, DMA Phase 5.)

#### 3-12. PRIORITY-AFFECTING INSTRUCTIONS.

3-13. Four instructions, STC CLC, STF, and CLF, affect the priority structure of the input/output devices; whether a device can request an interrupt or not depends upon whether its interface-card Control flip-flop is set or reset (STC, CLC) or its Flag flip-flop is set or reset (STF, CLF). If an I/O device cannot request an interrupt, it is not recognized as being part of the interrupt priority structure. In this case, all succeeding I/O devices are effectively moved up the interrupt priority structure by one.

3-14. The four instructions also inhibit all interrupt during the machine phase in which they occur, plus one machine cycle, by removing the ESR (Enable Service Request) signal to the I/O Address card. This prevents interrupts during JMP, I and JSB, I instructions (during entry and exit from subroutines. Also, a combination of two of the four instructions are normally the next-to-last instruction in a service subroutine processing an interrupt (the last being a JMP, I instruction to cause return to the main program or to an address in another service subroutine). If another input/output device could interrupt immediately after execution of these instructions (and before the JMP, I instruction), the possibility would exist that the first device may interrupt a second time before the JMP.I instruction is performed. In this event, the first main-program address (or the other service-subroutine address) stored in the beginning of the service subroutine would be destroyed, preventing a return to the main program or to the other service subroutine.

3-15. (Refer to Figure 3-3). Whenever any of the four instructions are programmed, the STC, CLC, STF, and CLF signals are received by the I/O Control card and applied to one of the MC77A through MC77D isolator gates. The applicable gate output is then a true input to "and" gate MC37C. The MC37C gate output becomes true on receipt of clock signal TS (pin 27) and the IOG signal at time T3 plus 80 nanoseconds from "and" gate MC57A.

3-16. The IOG signal from the Computer is sent to the I/O Control card at time T3 of each machine phase that an I/O Group instruction is performed and is applied to one input of "and" gate MC57A. The other input to gate MC57A is the IOG signal which has been delayed by about 80 nanoseconds to eliminate any noise which may have been generated during its formation. (The delay is caused by inverting "or" gates MC55A and MC55B, resistor R3, and capacitor C3.) At the end of the delay, gate MC57A provides a true output to "and" gate MC37C and a buffered IOG signal to all interface card slots. The IOG(B) signal is an enabling signal for the I/O Group instruction and the Select Code transferred to the selected interface card.

3-17. The true output of gate MC37C is applied to "and" gate MC36B. The other input to gate MC36B is true due to the inversion of the false PH5 signal by inverting "or" gate MC27B. The true output of "and" gate MC36B resets the Interrupt Control flip-flop. The true reset-side output of the Interrupt Control flipflop is applied to inverting "or" gate MC27A, removing the Enable Service Request signal to the I/O Address card. Interrupt signals will not now be enabled to the Computer for the remainder of the current machine phase.

3-18. At time T7 of the current machine phase, the STM signal sets Interrupt Timing flip-flop MC16. At time T0, TS of the next machine phase, true T0 and TS signals are applied to "and" gate MC36A. The true output of gate MC36A resets the Interrupt Timing flip-flop. The set-side output of this flip-flop is applied to the Interrupt Control flip-flop which is set at time T0, TS by the trailing (negative-going) edge of the pulse output of the Interrupt Timing flip-flop. The false reset-side output of the Interrupt Control flip-flop is inverted by inverting "or" gate MC27A, providing a true Enable Service Request input to the I/O Address card, and enabling Interrupt signals to the Computer.

#### 3-19. RESETTING CONTROL FLIP-FLOPS.