# IV HARDWARE OPERATION

The material contained in this section describes the hardware for the Central Processor Unit (CPU).

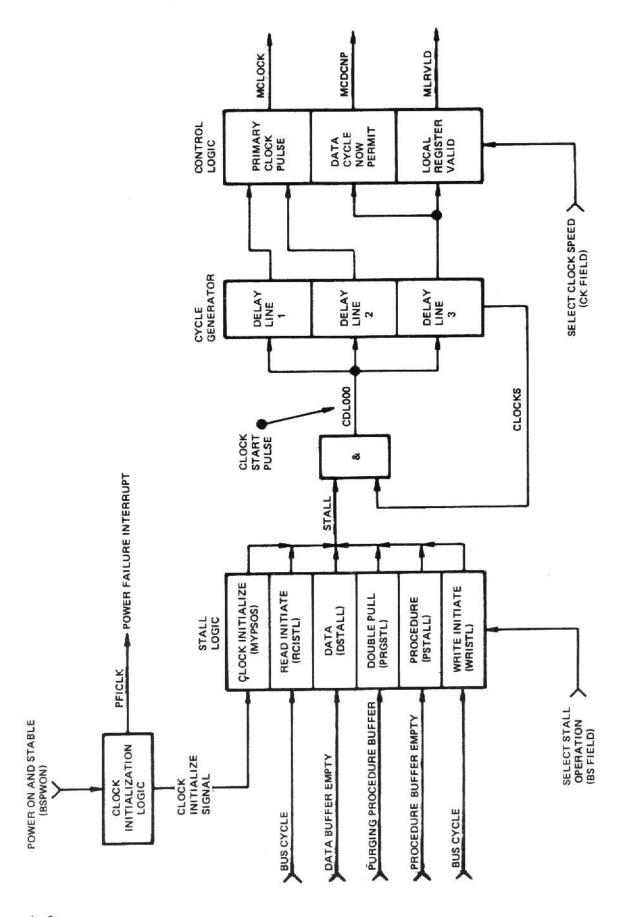

#### 4.1 MASTER CLOCK

The CPU clock (see Figure 4-1) is a two-phase delay line clock that provides one variable and two fixed clock pulses. The variable clock pulse is called Master Clock (MCLOCK); the fixed clock pulses are called Data Cycle Now Permit (MCDCNP) and Local Register Valid (MLRVLD). All three clock pulses are generated by delay lines which are hereafter referred to as the clock cycle generator.

A Master Clock pulse is composed of an 80-nanosecond positive period and a variable length negative period. The negative intervals range from 80- to 240-nanoseconds in duration and are usually selected by bits 20 and 21 of the control store word (CK Field). Combining the selected negative period with the 80-nanosecond positive period produces one complete Master Clock cycle with an overall clock speed as indicated below.

| CLOCK SPEED   | SECOND HALF<br>CYCLE | CK FIELD<br>BITS |    |  |

|---------------|----------------------|------------------|----|--|

| (nanoseconds) | (nanoseconds)        | 20               | 21 |  |

| 160           | 80                   | 1                | 1  |  |

| 180           | 100                  | 1                | 0  |  |

| 200           | 120                  | 0                | 1  |  |

| 320           | 240                  | 0                | 0  |  |

Figure 4-1 Master Clock Logic

A Data Cycle Now Permit pulse indicates that the Megabus address lines are valid; a Local Register Valid pulse indicates that the contents of the control store data register are valid.

The master clock logic can be divided into the following three areas:

- Clock initialization network

- Clock stall network

- Clock cycle generator.

# 4.1.1 Clock Initialization Network

The clock initialization network monitors the Megabus for a power-up sequence to initialize the CPU and the master clock, and to initiate the necessary CPU housekeeping operations when a power supply malfunction occurs. It performs these functions in conjunction with the clock stall network.

# 4.1.2 Clock Stall Network

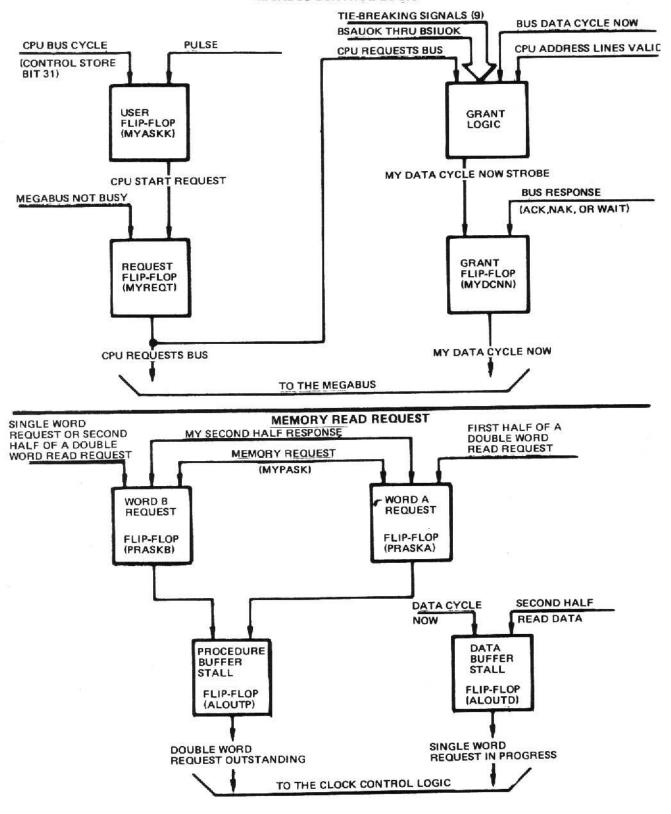

The clock stall network momentarily stalls the clock when additional time is needed to complete one of the following CPU or firmware generated functions:

- A clock initialization that occurs during the CPU powerup sequence.

- A firmware initiated Megabus cycle to which no responding bus activity is expected (e.g., a memory write operation).

The clock remains stalled until the selected unit acknowledges or rejects the request.

- A firmware cycle immediately following one in which a Megabus cycle was initiated and to which a response is expected. The clock remains stalled until the selected unit acknowledges or rejects the request.

- A firmware step that calls for data from a bus buffer that has not yet been filled. The clock remains stalled until the applicable buffer is full.

The clock is stalled by inhibiting the clock cycle generator (specifically MCLOCK pulses) when the CPU is initially powered-up, during a read or write cycle initiate, or for single-word or double-word data transfers from an external device (i.e., memory or I/O). The specific type of stall operation is determined by bits 31 through 35 of the control store word (BS Field).

# 4.1.2.1 Read Cycle Initiate Stalls

A Read Cycle Initiate is defined as a firmware step that requests data from a source external to the CPU (e.g., memory), and is intended to allow firmware to use the data in subsequent

firmware steps. The clock cycle generator is inhibited at the next MCLOCK pulse, preventing any further clock activity until the request is accepted or rejected over the Megabus.

#### 4.1.2.2 Write Initiate Stalls

During a write operation to an external device, the clock is stalled until the device responds with a positive or negative acknowledgment.

#### 4.1.2.3 Data Stalls

A Data Stall operation inhibits MCLOCK pulses to provide any additional time needed to fill the Data (BD) buffer or the Procedure buffer with pertinent data from memory. Two basic signals are used for this purpose. The first, ALOUTD, denotes that the data buffer is empty; the second, ALOUTP, denotes that the procedure buffers are empty. A third signal, PURGEF, inhibits additional double-fetch operations until all previous double-fetch requests have been answered and discarded.

# 4.1.3 Clock Cycle Generator

The clock cycle generator provides the selectable clock pulses used throughout the CPU, and consists of three delay lines plus associated control logic. Delay lines 1 and 2 generate the primary Master Clock (MCLOCK) pulse; delay line 3 generates the two previously described secondary clock pulses (MLRVLD and MCDCNP). All delay lines are tapped at selected intervals to generate their respective clock cycles.

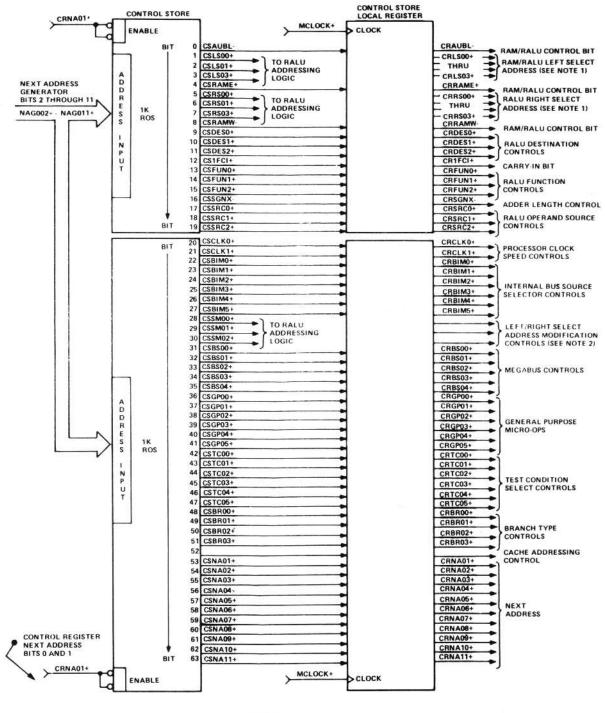

#### 4.2 CONTROL STORE

Control within the CPU is provided by the generation of specifically formatted 64-bit control words. Each word is selectively obtained from a 2,048 location Read Only Storage (ROS) memory, which is called the control store. The 64-bit output from the control store forms the input to the Control Store Local Register (CR). Figure 4-2 illustrates the control store logic and includes the control store local register.

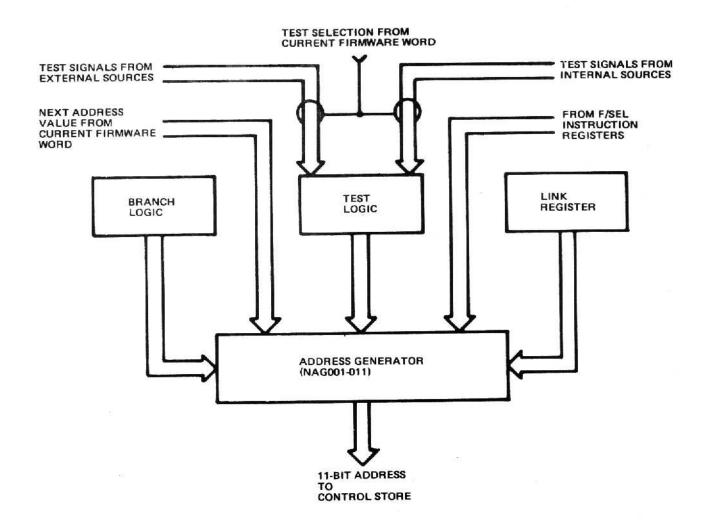

# 4.2.1 Control Store Local Register (CR)

The CR register retains firmware control words that emanate from control store for one complete firmware cycle (i.e., the control store output, or firmware word, is strobed into the local register at the positive transition of the clock input to the register, and it retains this data until new data is available at the positive transition of the next primary clock pulse). Outputs from the CR register are available for distribution throughout the CPU.

NOTES

Figure 4-2 Control Store Local Register

<sup>1.</sup> INPUTS TO THESE SIGNALS ARE OBTAINED FROM THE OUTPUT OF THE RALU ADDRESSING LOGIC (REFER TO SUBSECTION 4.5)

THESE SIGNALS ARE NOT LOADED FROM THE OUTPUT OF THE CONTROL STORE. INSTEAD, THE OUTPUTS FROM CONTROL STORE (8) TS 28 THROUGH 30) ARE FED TO THE RALU ADDRESSING LOGIC TO PARTICIPATE IN GENERATING RAM/RALU ADDRESSES.

The Left and Right Select address bits (i.e., control store bits 1 through 3 and 5 through 7) are not stored directly into the local register. Instead, they are fed to the microprocessor (RALU) addressing logic where they are used in conjunction with the Select Modify bits (i.e., control store bits 28 through 30) to generate the 4-bit left and right select address inputs for the local register. These input signals to the local register and their corresponding output signals are:

# 4.2.2 Control Store Addressing

Control store addressing is primarily controlled by the next address generation logic (refer to subsection 4.3).

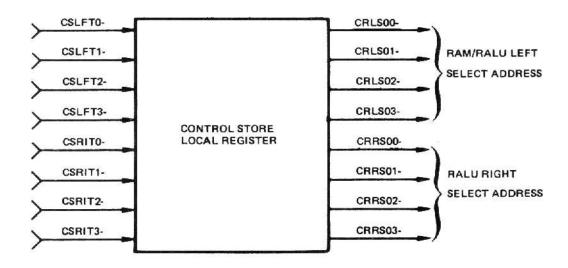

#### 4.3 NEXT ADDRESS GENERATION (NAG) LOGIC

The NAG logic (see Figure 4-3) generates the next firmware address for the control store using one of three methods. All methods use bits 53 through 63 of the firmware word to form a tentative next address. These bits comprise the 11-bit NA field that can directly address any one of the 2,048 control store locations.

Method 1: This method uses as the alternate next address, bits 53 through 61 of the firmware word, in conjunction with logical Ones replacing bits 62 and 63, to form the 11-bit address.

Method 2: This method obtains the alternate next address from the CPU branch logic which generates numerous predefined addresses. The address generated is determined from a decode of the instruction register contents and other control logic.

Figure 4-3 Next Address Generation Logic

Method 3: This method uses the 8-bit contents of the LINK register with three constant bits (as shown below) to form the alternate 11-bit address.

| - |   |   |          |   |

|---|---|---|----------|---|

|   |   |   | LINK     |   |

|   | 0 | 1 | REGISTER | 0 |

The next address generation logic can be divided into four areas: (1) test logic, (2) branch logic, (3) LINK register, and (4) address generator. These logic areas and selected fields of the firmware word make possible the above methods of generating the next firmware address.

#### 4.3.1 Test Logic

The test logic receives inputs from sources both internal and external to the CPU, providing 69 hardware signals that can be used as test conditions. One of the 69 test signals is selected by the TC Field of the current firmware word to participate in generating the next firmware address. These test conditions are too numerous to catalog here, but are defined in Table 3-16.

The output from the test logic (hereafter referred to as the test signal) indicates whether or not the test condition is satisfied, and is fed directly to the address generator. The test signal is used by the address generator to determine whether to substitute the alternate next firmware address for the tentative value (CRNA01-11).

# 4.3.2 Branch Logic

The branch logic contains several branch PROMs that provide the next firmware address for major branch operations.

# 4.3.3 LINK Register (XL)

The XL register is an 8-bit firmware address register (not visible to software) that supplies eight bits of the next firmware address when a Link Branch (or subroutine return) type operation is selected; the most significant two bits of the address are forced to 01 and the least significant bit is forced to Zero.

## 4.3.4 Address Generator

The address generator provides the next firmware address for the control store. The precise manner used to generate the next address is determined by the BR Field of the current firmware word. This field specifies the type of branch operation being performed as a result of a specific test condition. The eight branch types that can be specified include two binary branches (XO and XL) and six major branches (XA, XB, XR, XE, XW, and XF).

#### 4.3.4.1 X0 Branch

The XO branch type consists of both unconditional and conditional branches. The alternate next address is derived by performing a logical OR operation between the NA field and a value of 3 (hexadecimal).

#### 4.3.4.2 XL Branch

The XL branch type returns control to the normal firmware sequence after execution of a firmware subroutine. The alternate next address is determined from the contents of the LINK register.

#### 4.3.4.3 XA Branch

The XA branch type is used as the first step in analyzing each instruction. Formation of the alternate next address for XA branches depends on the instruction form.

#### 4.3.4.4 XB Branch

The XB branch type is used to analyze the address syllable portion of the data descriptor for commercial type instructions.

#### 4.3.4.5 XR Branch

The XR branch type is used to fetch an indirect address, perform indexing, read operand(s) from memory, or execute jump type or I/O type instructions.

#### 4.3.4.6 XE Branch

The XE branch type completes the op-code decoding necessary to begin execution of the single- and double-operand instructions included in the CPU instruction repertoire.

#### 4.3.4.7 XW Branch

The XW branch is used to store a result.

#### 4.3.4.8 XF Branch

The XF branch type is used to exit the instruction currently being executed and return to the Instruction Fetch firmware.

#### 4.4 MICROPROCESSOR

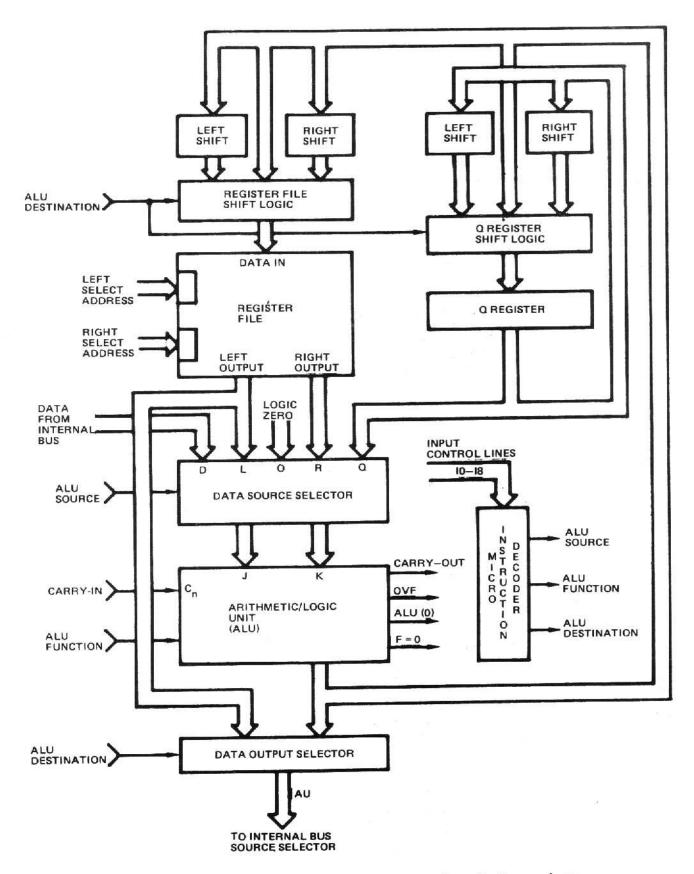

The microprocessor (see Figure 4-4), hereafter referred to as the Register File and Arithmetic Logic Unit (RALU), performs arithmetic, logical, and shift operations as directed by the current firmware word.

The major logic areas of the RALU are:

- Microinstruction decoder

- Register file

- Q register

- Data source selector

- Arithmetic/Logic Unit (ALU)

- Data output selector

- Shift logic.

# 4.4.1 Microinstruction Decoder

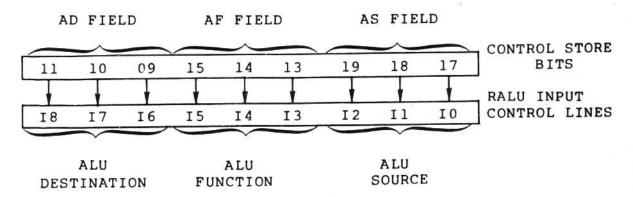

Control store generates a microprocessor instruction by encoding the RALU input control lines (IO through I8) with the microinstruction code necessary to process data through the RALU. This is accomplished using the AD, AF, and AS fields of the current firmware word as shown below:

# 4.4.2 Register File

The Register File (RF) is the operand storage facility of the RALU, consisting of 16 registers; two working registers, seven data registers, and seven base registers. Each register is 20 bits wide.

The two working registers (D0 and B0) are not software-visible, and provide a temporary storage facility when manipulating data during firmware operations. These registers are located in RF locations 0 and 8, respectively.

The seven data registers (Dl through D7) are softwarevisible, representing software registers Rl through R7. These registers are located in RF locations 1 through 7.

The seven base registers (Bl through B7) are software-visible, and are located in RF locations 9 through F.

Of the 16 register file locations, any two can be simultaneously accessed by the firmware, providing dual operands in a single firmware step. The contents of the selected locations (or location, if the addresses are the same) appear as the left and right outputs from the register file. The left output may be routed directly (via the data output selector) to the internal bus source selector, while both the left and right outputs are available as sources for the J and K ports.

Figure 4-4 Microprocessor Functional Overview

# 4.4.3 Q Register

The Q register can function as a scratch pad or an extension of any register file register during shift operations and normal transfers of data. This allows, for example, the retention of the least significant half of a double-length product during a multiply operation. Although the Q register is 20 bits wide, only the least significant 16 bits are used during double-precision shift operations.

# 4.4.4 Data Source Selector

The data source selector is a steering device for data within the RALU, and consists of separate multiplexers for the J and K inputs to the ALU. The sources that serve as inputs to these multiplexers include:

- Register file left and/or right output

- Q register

- Internal bus

- Logical Zero.

The J multiplexer can select any of the above, except the right register file output and the Q register, while the K multiplexer can select any but the internal bus; logical Zero can be selected by either the J or K multiplexer, but not both simultaneously.

# 4.4.5 Arithmetic/Logic Unit (ALU)

The ALU is the heart of the CPU, performing arithmetic, logical, and compare operations as directed by the firmware. The ALU has two inputs (J and K) that are sourced from the data source selector, and one 20-bit output that may be selected as an input to either the register file or the Q register, and is made available to the internal bus source selector via the data output selector (AU).

The ALU can perform 64 arithmetic and logical operations as directed by RALU input control lines IO through I5 (see Table 4-1). These operations include the following features:

- Full Carry Look-Ahead

- Overflow Detection

- Result Sign Detection

- All Zeros Detection.

Other ALU outputs that can be tested and/or copied by the firmware include: (1) overflow, (2) carry out, and (3) ALU output equals Zero. These three test signals can relate to an entire 20-bit operation or only the least significant 16 bits.

Table 4-1 RALU Logical and Arithmetic Operations (Sheet 1 of 2)

|                         | TIONS  | AL OPERA                  | OGIC | ı  |    |    |    |

|-------------------------|--------|---------------------------|------|----|----|----|----|

|                         |        | INSTRUCTION MODIFIER BITS |      |    |    |    |    |

| FUNCTIO                 | GROUP  | 10                        | 11   | 12 | 13 | 14 | 15 |

| L V Q                   | OR     | 0                         | 0    | 0  | 1  | 1  | 0  |

| L V R                   | OR     | 1                         | 0    | 0  | 1  | 1  | 0  |

| Q                       | Pass   | 0                         | 1    | 0  | 1  | 1  | 0  |

| R                       | Pass   | 1                         | 1    | 0  | 1  | 1  | 0  |

| L                       | Pass   | 0                         | 0    | 1  | 1  | 1  | 0  |

| DVL                     | OR     | 1                         | 0    | 1  | 1  | 1  | 0  |

| D V Q                   | OR     | 0                         | 1    | 1  | 1  | 1  | 0  |

| D                       | Pass   | 1                         | 1    | 1  | 1  | 1  | 0  |

| L & Q                   | AND    | 0                         | 0    | 0  | 0  | 0  | 1  |

| L & R                   | AND    | 1                         | 0    | 0  | 0  | 0  | 1  |

| 0                       | Zero   | 0                         | 1    | 0  | 0  | 0  | 1  |

| 0                       | Zero   | 1                         | 1    | 0  | 0  | 0  | 1  |

| 0                       | Zero   | 0                         | 0    | 1  | 0  | 0  | 1  |

| D & L                   | AND    | 1                         | 0    | 1  | 0  | 0  | 1  |

| D & Q                   | AND    | 0                         | 1    | 1  | 0  | 0  | 1  |

| 0                       | Zero   | 1                         | 1    | 1  | 0  | 0  | 1  |

| L & Q                   | Mask   | 0                         | 0    | 0  | 1  | 0  | 1  |

| Ī& R                    | Mask   | 1                         | 0    | 0  | 1  | 0  | 1  |

| Q                       | Pass   | 0                         | 1    | 0  | 1  | 0  | 1  |

| R                       | Pass   | 1                         | 1    | 0  | 1  | 0  | 1  |

| L                       | Pass   | 0                         | 0    | 1  | 1  | 0  | 1  |

| D & L                   | Mask   | 1                         | 0    | 1  | 1  | 0  | 1  |

| D & Q                   | Mask   | 0                         | 1    | 1  | 1  | 0  | 1  |

| 0                       | Pass   | 1                         | 1    | 1  | 1  | 0  | 1  |

| L♥ Q                    | EX-OR  | 0                         | 0    | 0  | 0  | 1  | 1  |

| L₩ R                    | EX-OR  | 1                         | 0    | 0  | 0  | 1  | 1  |

| Q                       | Pass   | 0                         | 1    | 0  | 0  | 1  | 1  |

| R                       | Pass   | 1                         | 1    | 0  | 0  | 1  | 1  |

| L                       | Pass   | 0                         | 0    | 1  | 0  | 1  | 1  |

| D ₩ L                   | EX-OR  | 1                         | 0    | 1  | 0  | 1  | 1  |

| D ₩ Q                   | EX-OR  | 0                         | 1    | 1  | 0  | 1  | 1  |

| D                       | Pass   | 1                         | 1    | 1  | 0  | 1  | 1  |

| LVQ                     | EX-NOR | 0                         | 0    | 0  | 1  | 1  | 1  |

| L ₩ R                   | EX-NOR | 1                         | 0    | 0  | 1  | 1  | 1  |

| $\overline{Q}$          | Invert | 0                         | 1    | 0  | 1  | 1  | 1  |

| র                       | Invert | 1                         | 1    | 0  | 1  | 1  | 1  |

| $\overline{\mathbf{L}}$ | Invert | 0                         | 0    | 1  | 1  | 1  | 1  |

| D # L                   | EX-NOR | 1                         | 0    | 1  | 1  | 1  | 1  |

| D ₩ Q                   | EX-NOR | 0                         | 1    | 1  | 1  | 1  | 1  |

| D                       | Invert | 1                         | ī    | ī  | ī  | 1  | ī  |

# DEFINITIONS

| X = | don't care  | ¥ | = | exc1 | Lusive | OR   |    |             |

|-----|-------------|---|---|------|--------|------|----|-------------|

| + = | addition    | D | = | ALU  | input  | from | ir | nternal bus |

| - = | subtraction |   |   |      |        |      |    | latches     |

| & = | logical AND | R | = | ALU  | input  | from | R  | latches     |

|     | logical OR  | Q | = | ALU  | input  | from | Q  | register    |

Table 4-1 RALU Logical and Arithmetic Operations (Sheet 2 of 2)

| FU   | NCTI | ON                    |                  | SOURC                      | E    | ARITH            | METIC OPERA | TIONS            |           |

|------|------|-----------------------|------------------|----------------------------|------|------------------|-------------|------------------|-----------|

| INST | RUCT | ION                   | MODI             | FIER                       | BITS | $C_{n} = 0$ (Lo  | w)          | $C_n = 1$ (Hi    | gh)       |

| 15   | 14   | 13                    | 12               | Il                         | 10   | GROUP            | FUNCTION    | GROUP            | FUNCTION  |

| 0    | 0    | 0                     | 0                | 0                          | 0    | Add              | L + Q       | Add + 1          | L + Q + 1 |

| 0    | 0    | 0                     | 0                | 0                          | 1    | Add              | L + R       | Add + 1          | L + R + 1 |

| 0    |      |                       | 0                | 1                          | 0    | Pass             | 0           | Increment        | Q + 1     |

| 0    | 0    | 0                     | 0<br>1<br>1<br>1 | 1<br>0<br>0<br>1           | 1    | Pass             | R           | Increment        | R + 1     |

| 0    | 0    | 0                     | 1                | 0                          | 0    | Pass             | L           | Increment        | L + 1     |

| 0    | 0    |                       | 1                | 0                          | 1    | Add              | D + L       | Add + 1          | D + L + 1 |

| 0    | 0    | 0                     | 1                | 1                          | 0    | Add              | D + Q       | Add + 1          | D + Q + 1 |

| 0    | 0    | 0                     | 1                | 1                          | 1    | Pass             | D           | Increment        | D + 1     |

| 0    | 0    | 1                     | 0                | 0                          | 0    | Subtract         | Q - L - 1   | Subtract         | Q - L     |

| 0    | 0    | 1<br>1<br>1<br>1<br>1 | 0<br>0<br>0      | 0<br>1<br>1<br>0<br>0<br>1 | 1    | Subtract         | R - L - 1   | Subtract         | R - L     |

| 0    | 0    | 1                     | 0                | 1                          | 0    | Decrement        | Q - 1       | Pass             | Q         |

| 0    | 0    | 1                     |                  | 1                          | 1    | Decrement        | R - 1       | Pass             | R         |

| 0    | 0    | 1                     | 1                | 0                          | 0    | Decrement        | L - 1       | Pass             | L         |

| 0    |      | 1                     | 1<br>1<br>1      | 0                          | 1    | Subtract         | L - D - 1   | Subtract         | L - D     |

| 0    | 0    | 1                     | 1                | 1                          | 0    | Subtract         | Q - D - 1   | Subtract         | Q - D     |

| 0    | 0    | 1                     | 1                | 1                          | 1    | One's complement | - D - 1     | Two's complement | - D       |

| 0    | 1    | 0                     | 0                | 0                          | 0    | Subtract         | L - Q - 1   | Subtract         | L - Q     |

| 0    | 1    | 0                     | 0                | 0                          | 1    | Subtract         | L - R - 1   | Subtract         | L - R     |

| 0    | 1    | 0                     | 0                | 1                          | 0    | One's complement | - Q - 1     | Two's complement | - Q       |

| 0    | 1    |                       | 0                | 1                          | 1    | One's complement | - R - 1     | Two's complement | - R       |

| 0    | 1    | 0                     | 0<br>0<br>1<br>1 | 0<br>1<br>1<br>0<br>0      | 0    | One's complement | - L - 1     | Two's complement | - L       |

| 0    | 1    | 0                     | 1                | 0                          | 1    | Subtract         | D - L - 1   | Subtract         | D - L     |

| 0    | 1    | 0                     | 1                | 1                          | 0    | Subtract         | D - Q - 1   | Subtract         | D - Q     |

| 0    | 1    | 0                     | 1                | 1                          | 1    | Decrement        | D - Î       | Pass             | D         |

#### DEFINITIONS

| + | = | addition     | D | = | ALU input | from | internal bus             |

|---|---|--------------|---|---|-----------|------|--------------------------|

| - | = | subtraction  | L |   | ALU input | from | left output of register  |

| & | = | logical AND  |   |   | file      |      |                          |

| V | = | logical OR   | R | = | ALU input | from | right output of register |

| V | = | exclusive OR |   |   | file      |      |                          |

|   |   |              | Q | = | ALU input | from | Q register               |

#### 4.4.5.1 Look-Ahead Logic

The RALU consists of five stages, with each stage providing a Carry Generate and a Carry Propagate signal. These signals are used in conjunction with an external carry generator (i.e., external to the RALU) to form the look-ahead logic. This logic determines whether or not the Carry Input (CN) to the RALU is propagated through each stage. The determination is based on an interpretation of the input operand rather than awaiting the ripple carry through each stage.

# 4.4.5.2 Overflow Logic

The overflow logic is internal to the RALU and is used in conjunction with the sign bit during signed arithmetic operations. Overflow reflects the results of an exclusive OR operation between the carry-in and carry-out of the sign bit, and occurs when the result of any addition or subtraction requires more bit positions than the ALU can accommodate. For example, assume that a 4-bit system (three bits plus the sign bit) is used, consisting of one arithmetic unit where the most significant bit is a Zero for positive numbers and a One for negative numbers as shown below:

Under the preceding conditions, only a maximum value of +7 and a minimum value of -8 is possible. Overflow is detected by comparing the carry-in and carry-out of the sign bit via an exclusive OR operation that is internal to the RALU; if the carries disagree, the overflow signal is not used during logical operations.

# 4.4.5.3 Zero Detection Logic

The Zero Detect outputs from the least significant four stages of the RALU are effectively tied together, enabling detection of a logical Zero condition for the 20-bit system.

# 4.4.6 Data Output Selector

The data output selector selects whether the left output from the register file or the ALU output is made available at the output (AU) of the RALU. This output can be used directly in the current firmware step, and is available to the internal bus source selector for distribution to other CPU elements via the internal bus. The output selector also specifies whether the ALU output is to be copied into the register file. If this is done, the register file location modified is the one that supplied the right output to the data input selector.

NOTE

Write operations can be performed only into the right side of the register file.

# 4.4.7 Shift Logic

The RALU shift logic optionally shifts the output of the ALU (or the ALU and the Q register) before delivering the results to the register file (or the register file and the Q register). The shift logic is capable of shifting single- or double-word operands left or right by one bit position as directed by RALU input control lines I6 through I8 (see Table 4-2).

| DESTINATION |    | SHIFT OPERATIONS |                 |                |       |        |  |

|-------------|----|------------------|-----------------|----------------|-------|--------|--|

|             |    | TION<br>BITS     | REGISTE<br>FUNC | ER FILE Q REGI |       | STER   |  |

| 18          | 17 | 16               | SHIFT           | LOAD           | SHIFT | LOAD   |  |

| 0           | 0  | 0                | Х               | х              | None  | ALU    |  |

| 0           | 0  | 1                | Х               | х              | х     | Х      |  |

| 0           | 1  | 0                | None            | ALU            | Х     | x      |  |

| 0           | 1  | 1                | None            | ALU            | х     | х      |  |

| 1           | 0  | 0                | Left            | ALU            | Left  | Q Req. |  |

| 1           | 0  | 1                | Left            | ALU            | х     | X      |  |

| 1           | 1  | 0                | Right           | ALU            | Right | Q Reg. |  |

| 1           | 1  | 1                | Right           | ALU            | Х     | х      |  |

Table 4-2 RALU Shift Operations

X = don't care

In shift operations, the bit shifted into the vacated bit position is designated as SHIN (shift input), and is controlled by three flip-flops: SHIN1, SHIN2, and MISC (refer to subsection 4.8). The SHIN function is selected as follows:

| MISC | SHIN1 | SHIN2 | SHIN                |

|------|-------|-------|---------------------|

| 0    | 0     | 0     | Internal Bus bit 10 |

| 0    | 0     | 1     | Internal Bus bit 10 |

| 0 ,  | 1     | 0     | Zero                |

| 0    | 1     | 1     | Q register bit 1F*  |

| 1    | 0     | 0     | XB register bit 1   |

| 1    | 0     | 1     | Y register bit 7    |

| 1    | 1     | 0     | Zero                |

| 1    | 1     | 1     | Q register bit 1F*  |

<sup>\*</sup>During shift right operations; otherwise undefined.

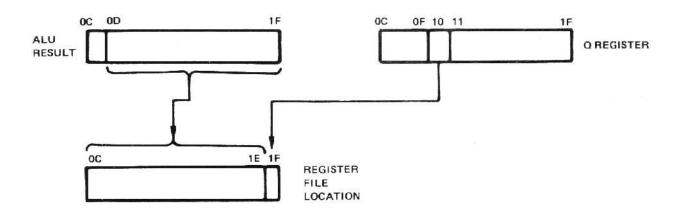

#### 4.4.7.1 Single Left Shift

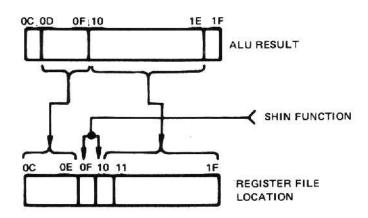

Bits OD through 1F of the ALU result are placed in bits OC through 1E of the selected register file location; bit 1F of the selected register file location receives a copy of Q register bit 10.

#### 4.4.7.2 Double Left Shift

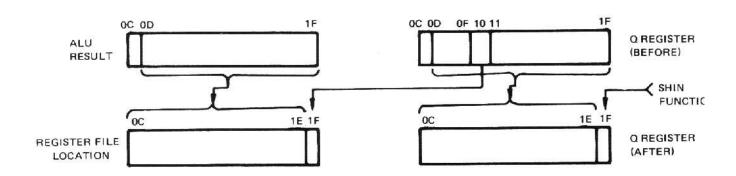

Bits OD through 1F of the ALU result are placed in bits OC through 1E of the selected register file location; bit 1F of the selected register file location receives a copy of Q register bit 10. Q register bits OD through 1F are placed in Q register bits OC through 1E; Q register bit 1F receives a copy of the SHIN function.

Conceptually, the rightmost 16 bits of the ALU result are concatenated with the rightmost 16 bits of the Q register and shifted left one bit position with the SHIN function shifted in

on the right. The result is placed in the rightmost bit positions of the register file location and the Q register, respectively.

# 4.4.7.3 Single Right Shift

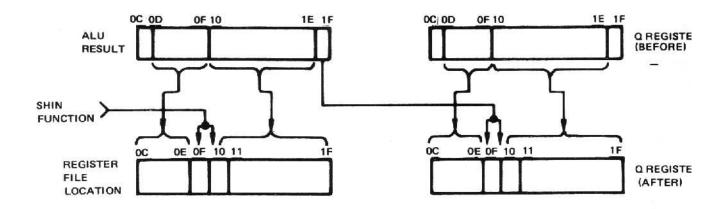

Bits 10 through 1E of the ALU result are placed in bits 11 through 1F of the selected register file location; bit 10 of the selected register file location receives a copy of the SHIN function. Bits 0D through 0F of the ALU result are placed in bits 0C through 0E of the selected register file location; bit 0F of the selected register file location receives a copy of the SHIN function.

Conceptually, the rightmost 16 bits of the ALU result are shifted right one bit position with the SHIN function shifted in on the left. The result is placed in the 16 rightmost bit positions of the register file location.

#### 4.4.7.4 Double Right Shift

Bits 10 through 1E of the ALU result are placed in bits 11 through 1F of the selected register file location; bit 10 of the selected register file location receives a copy of the SHIN function. Q register bits 10 through 1E are placed in Q register bits 11 through 1F; bit 1F of the ALU result is placed in Q register bit 10. Bits 0D through 0F of the ALU result are placed in bits 0C through 0E of the selected register file location; bit 0F of the selected register file location receives a copy of the SHIN function. Q register bits 0D through 0F are placed in Q register bits 0C through 0E; bit 1F of the ALU result is placed in 0 register bit 0F.

Conceptually, the least significant 16 bits of the ALU result and the least significant 16 bits of the Q register are concatenated, shifted right one bit position with the SHIN function filling the most significant bit, and the result placed in the least significant 16 bits of the register file location and the Q register, respectively.

#### 4.5 RALU ADDRESSING

The RALU addressing logic can select any one of the 16 registers located within the register file as directed by the LS, RS, and SM fields of the current firmware word. Eight of these registers are directly addressable by the LS and RS fields when the SM field equals zero (see Tables 3-1 and 3-2). Each of the 16 registers can be addressed by using the SM field to modify the LS or RS register address.

The LS, RS, and SM fields are each configured as 3-bit codes that are allocated within the control store as follows:

- LS: bits 1 through 3

- RS: bits 5 through 7

- SM: bits 28 through 30

These 3-bit fields generate hexadecimal addresses that deliver the contents of a selected register (or registers) to the left and/or right output of the register file. The register selection performed by the above address fields is defined in Table 3-13.

The LS field also provides addressing for the Random Access Memory (RAM) which is external to the RALU (refer to subsection 4.9.1).

Write operations into the register file can be performed only to a register that is accessed by the right select address lines. The SM field selects data from one of two sources to modify the LS or RS address:

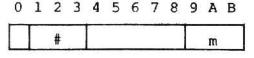

1. The following F register fields (refer to subsection 1.6.2):

F Register Format

SEL Counter

- 2. One of the following three constants:

- D: (1,1,0,1)

- E: (1,1,1,0)

- F: (1,1,1,1)

These signals are ANDed with the applicable LS or RS field, providing the input signals to the local register for the left and right select addresses.

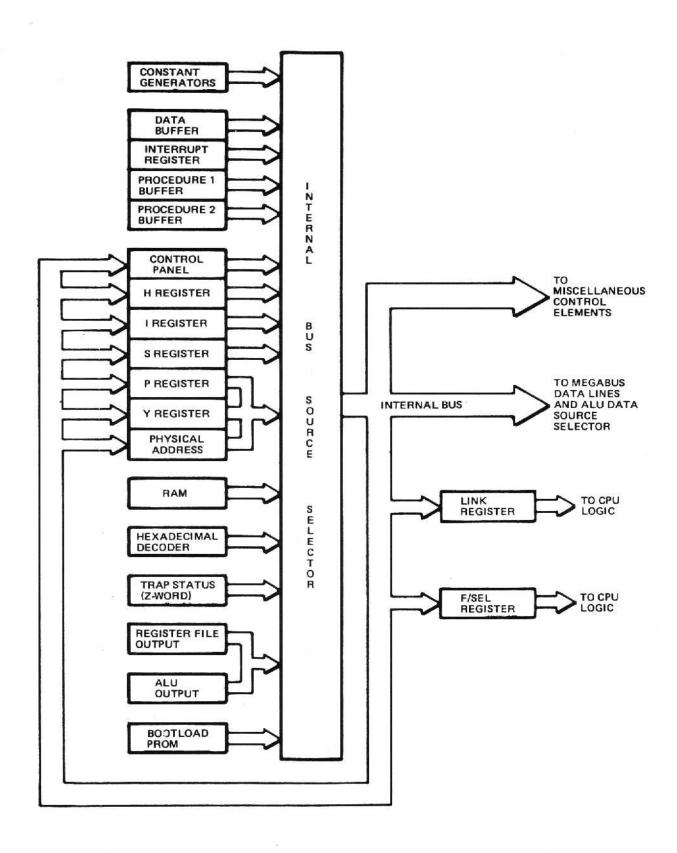

#### 1.6 INTERNAL BUS

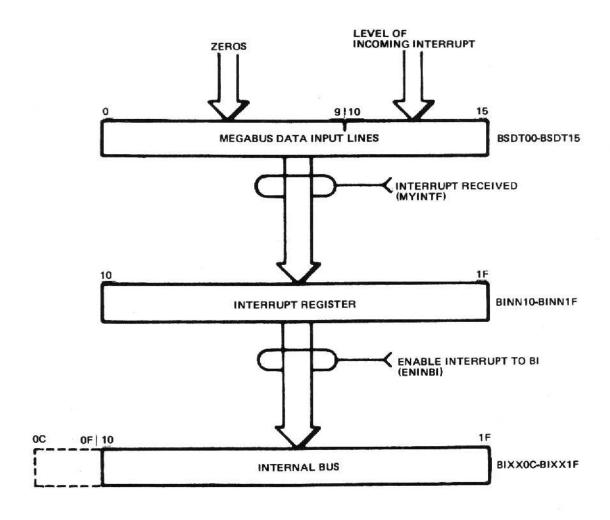

The internal bus (BIXXOC through BIXXIF) provides a 20-bit vide data path that transfers data among elements of the CPU as lirected by the BI Field of the current firmware word (see Tables 3-9 through 3-11). The internal bus receives inputs (via the internal bus source selector) from 14 sources, and makes its data available to 12 destinations (see Figure 4-5). These sources and destinations are:

## Internal Bus Sources

- 1. Constant Generators

- Megabus Data Buffer (BD)

- Megabus Interrupt Register (RUP)

- Megabus Procedure 1 Buffer (BP1) or Procedure 2 Buffer (BP2)

- 5. Control Panel

- 6. H Register

- 7. Indicator Register (I)

- Status/Security Register (S)

- 9. Program Counter (P), or

Memory Address Register (Y), or

MMU Output (Physical Address)

Via Address Bus (BA)

- 10. RAM

- 11. Hexadecimal Decoder

- 12. Trap Status (Z-word)

- Register File (left) Output, or ALU Output (AU)

- 14. Bootload PROM.

# Internal Bus Destinations

- 1. Program Counter (P)

2. Memory Address Register (Y)

- 3. Indicator Register (I) \_\_\_\_\_ Group 2

- 4. RAM \_\_\_\_\_ Group 3

- 5. LINK Register (XL)

- Instruction Register (F/SEL)

- 7. Control Panel Display

- 8. H Register

- 9. Status/Security Register (S)

- 10. Megabus Data Lines

- 11. ALU Data Source Selector

- 12. Miscellaneous Control Elements (Control Flip-Flops, MMU, Test Logic, etc.)

Firmware can select one element (or combinations of several elements) as an internal bus source, and deliver these data to one destination in each of the four groups listed above. The combinations of internal bus elements that are available as internal bus sources are:

Two copies of ALU output (bits OC through OF) and three interleaving Zeros

Group 4

- 2. Eight copies of H register (bit 18) and ALU output (bits 18 through 1F)

- H register (bits 1C through 1F) and contents of Megabus data buffer.

- H register (bits 1C through 1F) and contents of Megabus procedure buffer

- 5. H register (bits 1C through 1F) and control word from control panel

- 6. H register (bits 10 through 17) right justified and sign extended to 16 bits.

# 4.7 CPU REGISTERS

The CPU registers, except those contained within the RALU, are described in the following subsections.

# 4.7.1 Indicator Register (I)

The CPU indicators can be loaded using the firmware controls described in Table 3-11.

#### 4.7.1.1 Arithmetic Indicators

Two indicators can be loaded with the results of arithmetic operations in the CPU; the Overflow (OV) indicator and the Carry (C) indicator. The available inputs to these indicators are:

#### 1. OV Indicator

- OVFL (ALU overflow signal)

- Result of exclusive OR operation between internal bus bits 10 and 11

#### 2. C Indicator

- CRY (ALU carry signal)

- Internal bus bit 10

- Internal bus bit 1F

- Q register bit 1F just prior to right shift in the current firmware step.

#### 4.7.1.2 Bit Test Indicator

Inputs available to the bit test indicator are:

- AUZERO (ALU zero detect signal)

- Internal bus bit 10.

Figure 4-5 Internal Bus Sources and Destinations

# 4.7.1.3 Input/Output Indicator

This indicator stores the results of the last I/O instruction performed by the CPU. This is accomplished by making the Megabus acknowledge signal available at the input to this indicator. If the I/O instruction is accepted, the indicator is set; otherwise, it is cleared.

# 4.7.1.4 Comparison Indicators

Three indicators store the results of the last compare operation performed in the CPU; the Greater Than (G), Less Than (L), and Unlike Signs (U) indicators. The inputs available to these indicators are:

#### 1. G Indicator

- Internal bus bit 10 is zero and the ALU output (16 bits) is not zero

- Complement of the SIGN flip-flop

#### L Indicator

- Internal bus bit 10

- ALU result bit 0C

- SIGN flip-flop

#### U Indicator

Internal bus bit 10.

#### 4.7.2 LINK Register (XL)

Refer to subsection 4.3.3 for a description of the XL register.

# 4.7.3 Counter Type Registers

Counter type registers are versatile in that they are alternately used as a 4-bit counter or as a 4-bit storage register within their respective circuit configurations.

# 4.7.3.1 Counter Register (CTR)

The CTR register (RCTROF through RCTR3F) counts the number of procedure words fetched during instruction execution, and in conjunction with the program counter allows the Trap Handler software to reconstruct the instruction word address in the event an exception condition is detected in the CPU. To accomplish this, firmware initializes the register to a count of 1.

# 4.7.3.2 Select Register (SEL)

The SEL register (RSELOF through RSEL3F) generally holds the least significant hexadecimal digit of the current instruction. At times, it is used to count repetitive actions in Shift, Multiply, or Divide operations. Data are received over internal bus bits 1C through 1F. When the SEL register is used as a counter, it is decremented and its contents tested for zero.

## 4.7.3.3 Byte Indexing Register (XB)

The XB register (RXBOFF through RXB3FF) stores bits shifted out of RALU data registers during half-word, digit, or bit indexing operations. At the start of each instruction, it is cleared to zero. Its output is sent directly to a hexadecimal decoder, and is also available to the internal bus for trap reporting.

# 4.7.4 Instruction Register (F)

The F register (RF00FF through RF08FF) accepts and stores the most significant three hexadecimal digits of instructions from memory for execution in the CPU.

# 4.7.5 H Register

The H register (RH10FF through RH1FFF) is configured into two 8-bit segments that accept data directly from the internal bus. Its output is available to the internal bus source selector for delivery to the internal bus, but as its contents are deposited onto the bus, the least and most significant eight bits of the register are swapped.

# 4.7.6 Status/Security Register (S)

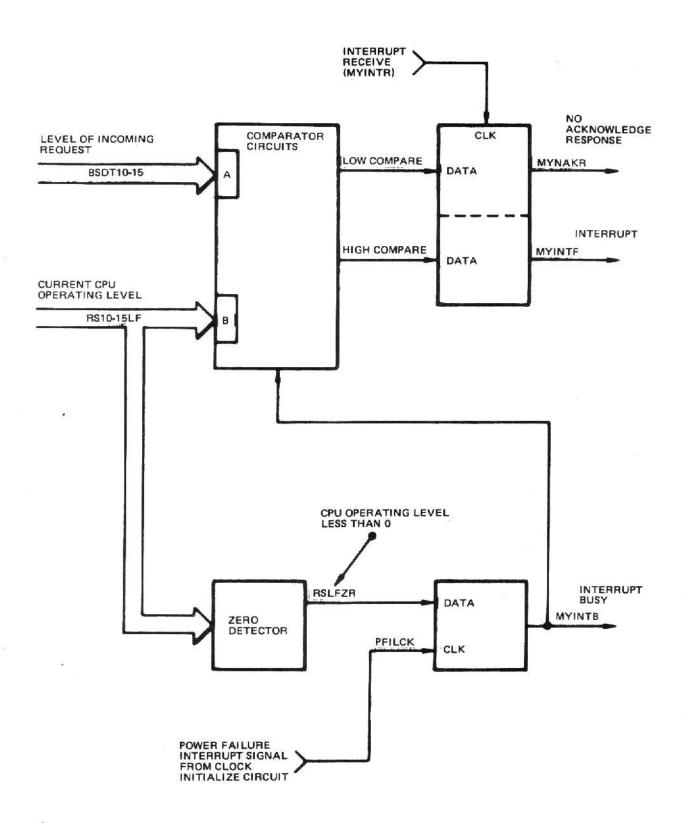

The S register (RS01FF, RS02FF, and RS10FF through RS15FF) retains the system status and security codes for use within the CPU. It is also used for comparing the priority level of an incoming interrupt request with the current CPU operating priority level (refer to subsection 4.11.2). This compare activity is performed to deny acceptance of an incoming request when the request level is equal to or lower than the current CPU priority level. The contents of this register are controlled entirely by firmware, except for the CPU channel number (bits 8 and 9) which are switch controlled.

# 4.7.7 P Register (Program Counter)

The P register (RP03CF through RP22CF) consists of five 4-bit counters capable of being preset that retain and increment the current instruction address originally obtained from the internal bus.

# 4.7.8 Memory Address Register (Y)

The Y register (RY03CF through RY22CF) provides operand addresses (via the address bus) for memory or a peripheral device. Its architecture and functionality are basically the same as the P register (refer to subsection 4.7.7). Also included is a logical switching network which, under firmware control, generates a 16-bit address field by isolating the most significant byte (bits 3 through 6) from the 20-bit address. The 16- and 20-bit address fields are defined in Section I as the Short Address Form (SAF) and the Long Address Form (LAF), respectively.

# 4.7.9 Megabus Registers

The Megabus registers consist of three temporary storage buffers that receive procedure and data words (over the Megabus) from memory. Refer to subsection 4.10.6 for a description of these buffers.

# 4.7.10 Interrupt Register

Refer to subsection 4.11.3 for a description of the interrupt register.

# 4.7.11 M Register

The M register accepts pertinent RAM data (see Table 4-3) as the RAM is being updated, and since this data is not immediately available from the RAM, the M register delivers it to the test logic and next address generation logic for instantaneous action. This data is obtained from several sources and loaded into the M register as directed by the GP Field of the current firmware word. These sources include:

- Y register bit 15

- F register bit OA

- SEL register bits 0 and 2

- H register bits 1A and 1B

- ZERO flip-flop

- AUZERO (ALU Zero Detect signal).

Table 4-3 M Register Format

| BIT         | SIGNAL | DESCRIPTION                             |

|-------------|--------|-----------------------------------------|

| 0           | RMTRAC | Trace Trap Enable                       |

| 1           | RMSCIl | Sl memory operand length is double-word |

| 1<br>2<br>3 | RMSCI2 |                                         |

| 3           | RMSCI3 | S3 memory operand length is double-word |

| 4           | RMSQB6 | B6 is in Stack or Queue mode            |

| 5           | RMSOB7 | B7 is in Stack or Queue mode            |

| 5<br>6      |        | SIP is part of the processor complex    |

| 7           | GOTBPU | CIP is part of the processor complex    |

#### 4.8 CPU CONTROL FLIP-FLOPS

The control flip-flops receive inputs from sources both internal and external to the CPU, permitting modification of firmware actions based on the results of operations performed through the system.

# 4.8.1 SIGN Flip-Flop

The SIGN flip-flop provides temporary storage of control information during instruction execution, and may be set from:

- Internal bus bit 0

- Internal bus bit 4

- Internal bus bit 19

- One

- · Zero.

# 4.8.2 MISC Flip-Flop

The MISC flip-flop provides temporary storage of control information during instruction execution, and is one of the flipflops used to select the SHIN function for RALU shift operations (refer to subsection 4.4.6). The MISC flip-flop may be set from:

- Complement of internal bus bit 19

- Internal bus bits 4 through 9 equal to Zero

- CRY ALU Carry signal

- ACK Megabus Acknowledge signal

- PROV MMU Protection Violation signal

- Zero

- One.

# 4.8.3 SHIN1 Flip-Flop

The SHIN1 flip-flop is primarily used to select the SHIN function for RALU shift operations (refer to subsection 4.4.6), and may be set from:

- I(B) I register Bit Test indicator

- Zero

- One.

# 4.8.4 SHIN2 Flip-Flop

The SHIN2 flip-flop is primarily used to select the SHIN function for RALU shift operations (refer to subsection 4.4.6), and may be set from:

- Complement of SIGN flip-flop

- Zero

- One.

# 4.8.5 ZERO Flip-Flop

The Zero flip-flop is primarily used for temporary storage of an ALU Zero Result condition, and may be set from:

- ALU Zero Detect signal

- QLT active flip-flop from control panel equals One only if the last CPU Quality Logic Test (QLT) failed

- Zero

- One.

# 4.8.6 WRAP Flip-Flop

The WRAP flip-flop facilitates the checking of address-arithmetic firmware to detect attempts to exceed the 20-bit capacity of the address registers. If WRAP is On, any access to the Megabus (read request or write operation) will result in the transmission of an illegal address or I/O channel number. This action results in no response via the Megabus, which is interpreted as an "unavailable resource." The WRAP flip-flop may be set from the inequality of the ALU Carry signal (CRY) and the SIGN flip-flop.

#### 4.8.7 NEWXR Flip-Flop

The NEWXR flip-flop distinguishes between reentrant invocations of the XR "splatter" branch. This flop is set when the SEL register is loaded from the internal bus (e.g., during instruction fetch operations); it is cleared when a branch is performed to XR, XE, XW, or XF, and when the WRAP flip-flop is set or cleared.

# 4.8.8 ACK Flip-Flop

The ACK flip-flop remembers whether the most recent Megabus action was accepted or rejected: if ACK is On, the action was accepted; if ACK is Off, the action was rejected.

#### 4.8.9 YELLOW and PARER Flip-Flops

The YELLOW and PARER flip-flops signal detection of an error in memory or on the Megabus. YELLOW remembers whether at least one data error was corrected by the memory Error Detection And Correction (EDAC) hardware since the last interrogation of this flip-flop; YELLOW is cleared each time it is interrogated by the firmware. PARER remembers whether the most recent Megabus buffer reference (BD or BP) reported either a Megabus parity error or a data error not correctable by memory EDAC hardware. Inless the control panel is in Load, Read, or Write mode, the setting of PARER forces the firmware to control store location 00° for suitable trap generation.

# 4.8.10 EXTRAP, INTBSY, and TICK Flip-Flops

The EXTRAP, INTBSY, and TICK service request flip-flops are set by hardware to signal a requirement for a break in firmware flow.

EXTRAP is true when one or more external processors (CIP or SIP) has detected a trap condition. EXTRAP becomes false when all external processors with trap conditions have delivered their trap words.

INTBSY is set when an external interrupt of high enough priority is received and accepted by the hardware. No further interrupt, regardless of priority, can be accepted until firmware services buffer RUP, reloads the level field in the S register, and clears INTBSY.

TICK is set every 8-1/3 milliseconds by a crystal-controlled oscillator, signaling the need for service of the YELLOW logic, the RTC and/or WDT, and the control panel.

# 4.8.11 LOAD, TRAFFIC, and PANOK Flip-Flops

These flip-flops communicate control information between frimware and the operator.

The LOAD flip-flop can be set and cleared both by the operator and by firmware. During system startup operations, LOAD is normally set by the operator and, when bootload action is completed, cleared by firmware. Thereafter, this flip-flop usually remains OFF, but is sometimes set briefly by firmware as a means of preventing a trap to location 000 when a Megabus cycle is addressed to a possibly unavailable resource.

The TRAFFIC flip-flop is loaded by firmware to control the corresponding indicator on the control panel, but is held OFF by hardware unless the control panel is in Run mode. The TRAFFIC flip-flop may be set from the complement of the ZERO flip-flop, which indicates whether or not the instruction op-code just fetched from memory is an HLT (Halt).

The PANOK flip-flop synchronizes the servicing of operator requests. It is set to Zero whenever the CLEAR or EXECUTE push-button is depressed and when, in register-change mode, a hexadecimal key is depressed. This flip-flop is set to One by the firmware that services the request, and is used to prevent multiple servicing of a single key-stroke.

# 4.8.12 EFFRING, NONPROC, NOCHECK, SEGERR, and PROV Controls

These signals and flip-flops support normal MMU operations, permit temporary alteration of access rules, and report errors detected by the MMU.

EFFRING is a two-bit register containing the effective ring number, which the MMU uses to determine the degree of privilege appropriate to the current instruction, and against which memory access requests are tested. Firmware loads EFFRING from the S register RING field at the start of each instruction. EFFRING is modified to decrease its privilege level whenever, in the course of formulating an address, it uses data that might have been generated by a less privileged program.

NONPROC establishes a temporary change in the rules of access. Memory references which use the P register as the address source normally require "Execute" permission; when NONPROC has been set, they require only "Read" permission.

NOCHEK establishes a temporary suspension of the rules of access (it does not affect the mapping of segmented virtual addresses to physical, nor the detection of illegal, non-existent addresses). The intent of this functionality is to remove restrictions on memory access by system firmware (interrupt and trap handlers, RTC/WDT service, panel routines, etc.).

SEGERR signals that the MMU has detected an error in a virtual address; the referenced segment is not valid, or its size has been exceeded, or a protection violation has been detected. If SEGERR occurs during a memory reference, it causes the transmission of an illegal physical address. This action results in no response via the Megabus, which is interpreted as an unavailable resource. If no memory reference or access-rights test is requested, signal SEGERR is ignored.

PROV signals that the MMU has detected a protection violation (failure of access-rights check) on an otherwise legal address (i.e., an address in a valid segment and within the segment size). If a protection violation occurs during a memory reference, the PROV flip-flop is locked in the set state until cleared by the firmware function NOCHEK (this function is normally issued by the trap-generation firmware). If a protection violation occurs during a firmware step that explicitly requests an access-rights test, the next firmware step may copy PROV to the MISC control flip-flop.

#### 4.9 MISCELLANEOUS CPU HARDWARE

The following subsections describe those CPU elements not previously defined under one of the major CPU logic areas.

#### 4.9.1 Random Access Memory (RAM)

The RAM consists of sixteen 20-bit auxiliary storage registers that the CPU uses as work areas, and to maintain selected system status conditions. Addressing the RAM for a read or write operation is performed by the Left Select portion of the RALU addressing logic (refer to subsection 4.5). However, the actual RAM read or write operation is performed as directed by the DI Field of the current firmware word.

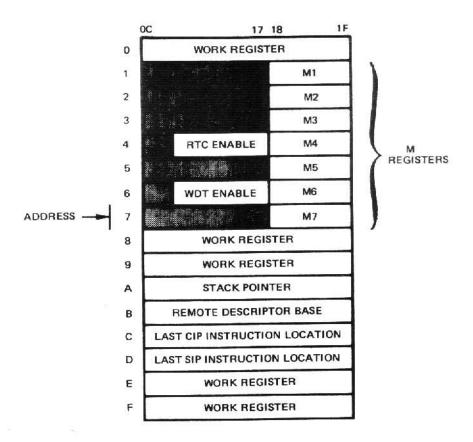

The organization of the RAM is illustrated in Figure 4-6.

Figure 4-6 RAM Format

# 4.9.1.1 RAM Location 0

This RAM location contains the instruction word to be reported when a trap occurs.

# 4.9.1.2 RAM Locations 1 through 3

Bits OC through 17 of these RAM locations are unused; bits 18 through 1F contain software mode registers M1 through M3.

#### 4.9.1.3 RAM Location 4

Bits 10 through 17 of this RAM location contain the mode information for enabling the Real Time Clock (RTC); bits 18 through 1F contain software mode register M4.

#### 4.9.1.4 RAM Location 5

Bits OC through 17 of this RAM location are unused; bits 18 through 1F contain software mode register M5.

#### 4.9.1.5 RAM Location 6

Bits 10 through 17 of this RAM location contain the mode information for enabling the Watch Dog Timer (WDT); bits 18 through 1F contain software mode register M6.

#### 4.9.1.6 RAM Location 7

Bits OC through 17 of this RAM location are unused; bits 18 through 1F contain software mode register M7.

#### 4.9.1.7 RAM Location 8

This RAM location contains a pointer to the next word of procedure.

#### 4.9.1.8 RAM Location 9

This RAM location is unused.

#### 4.9.1.9 RAM Location A

This RAM location contains a stack pointer.

#### 4.9.1.10 RAM Location B

This RAM location contains the Remote Descriptor Base (RDB) register.

#### 4.9.1.11 RAM Location C

This RAM location contains a pointer to the most recently accepted Commercial Instruction Processor (CIP) instruction.

#### 4.9.1.12 RAM Location D

This RAM location contains a pointer to the most recently accepted Scientific Instruction Processor (SIP) instruction.

#### 4.9.1.13 RAM Location E

This RAM location is unused.

# 4.9.1.14 RAM Location F

This RAM location contains a pointer to the next word of procedure.

# 4.9.2 Bootload PROM

The bootload PROM, which consists of four 2K PROMs, is a standard feature of the CPU. Addressing for the boot PROM is provided by bits 14 through 22 of the address bus. The 20-bit output from the boot PROM is delivered to the internal bus either as directed by the BS Field of the current firmware word or when the Load pushbutton on the control panel is depressed.

The bootload operation has the following modes of operation, depending on the contents of the program counter (P):

| P CONTENTS | OPERATION                                                                                                                                                                                                                         |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0000       | Executes Basic Logic Test (BLT). Reads one physical record from channel 010 (hexadecimal) into memory, starting at location 0100 (hexadecimal); branches to 0100 (hexadecimal). The preceding is the default Bootload procedure.* |  |  |  |

| 0002       | Does not execute BLT. Reads one physical record into memory, starting at location 0100 (hexadecimal), using the channel number previously entered into register Dl; branches to 0100 (hexadecimal).                               |  |  |  |

| 0004       | Does not execute BLT. Reads one physical record into memory, starting at the address entered into register Bl, using the channel number entered into register Dl; branches to the address entered into register Bl.               |  |  |  |

<sup>\*</sup>This procedure is used when the control panel is locked. If the control panel is unlocked, procedure will halt after the BLT unless Run (R) pushbutton is depressed.

The devices supported and the Boot record file formats are as follows:

| DEVICES             | RECORD FORMAT                                                                                                                                                                   |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Diskette            | Data portion (128 bytes) of track 0, sector 0 (first sector)                                                                                                                    |

| Card                | The contents of the first card; 80 bytes punches in Bootload format                                                                                                             |

| Paper Tape<br>(ASR) | One record of 256 bytes or less, starting with the character that follows the first non-NUL character and continuing to the first X-OFF or T-OFF character with no escaped data |

| Cartridge           | Data portion (256 bytes) of track 0, sector 0                                                                                                                                   |

| Magnetic<br>Tape    | One record of 256 bytes or less; the record must be the first after BOT                                                                                                         |

#### 4.9.3 Address Bus

The address bus (MYAD03 through MYAD22) accepts addresses from the P and Y registers (refer to subsections 4.7.7 and 4.7.8, respectively) as directed by the BS Field of the current firmware word. The 20-bit output from the address bus is delivered to the Megabus for I/O and memory read or write operations, or to the internal bus for distribution in the CPU.

# 4.9.4 Memory Management Unit (MMU)

The MMU checks all memory addresses before permitting them to take part in a memory reference (either over the Megabus to main memory or to the cache memory). These checks ensure that addresses are legitimate and do not violate any software imposed restrictions. If a memory address is rejected by the MMU, a protection violation results. Addresses before being processed by the MMU are called Virtaul addresses, while addresses after being processed by the MMU are called Physical addresses.

# 4.9.5 Cache Memory

The cache memory contains copies of selected (recently referenced) main memory locations. It has a Megabus interface which allows it to make main memory read references on behalf of the CPU and to monitor the Megabus, copying main memory write data if it currently contains a copy of the main memory location addressed. The cache also has a private interface allowing it to communicate to the CPU to which it is dedicated. It receives main memory read requests across this interface, thereby becoming committed to locate the data for the CPU in its local cache array or in the actual main memory. In either case, the requested data is returned to the CPU with an appropriate handshake.

#### 4.9.6 Hexadecimal Decoder

The hexadecimal decoder (RXBD10 through RXBD1F) generates 16-bit masks for bit test operations (i.e., a single bit within a 16-bit word can be selected). The bit being tested is selected by the 4-bit value from the XB register (refer to subsection 4.7.3.3). This value is used to define which of the 16 bits is zero; the other 15 bits are made all ones.

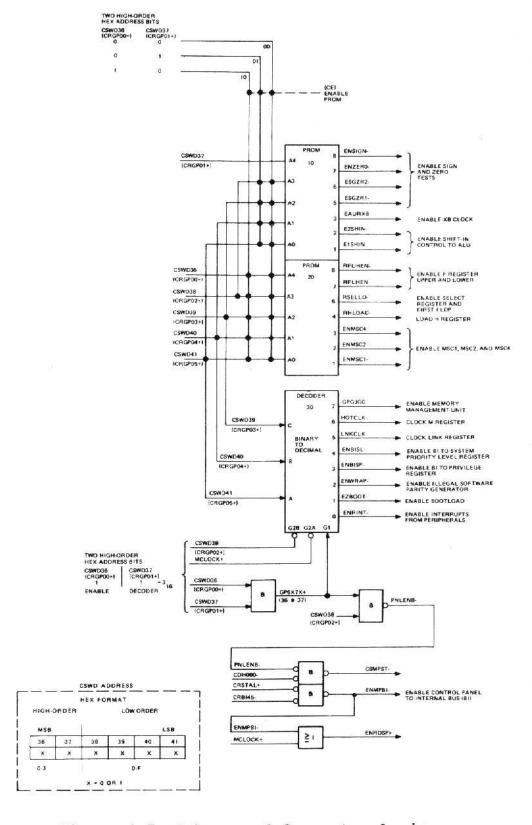

#### 4.9.7 Subcommand Generator

The 6-bit GP field of the Control Store Word (CSWD) is essentially viewed by firmware as three independent hexadecimal subfields: 10, 20, and 30, which control various hardware operations. Actually, these subfields provide a 6-bit hexadecimal address (0 through 3F) to two PROM devices and a binary-to-decimal decoder. These devices comprise the subcommand generator (see Figure 4-7) which provides control signals (subcommands) for the CPU hardware.

Decoder selection occurs when CSWD 36 through 38 equal 6 (110) and MCLOCK+ is inactive. This disables the two PROMs and enables the least significant three bits of the low-order address field (CSWD 39 through CSWD 41) into decoder 30 for selection of the applicable control signal. Also, when CSWD 36 and 37 equal 3 (11), they enable the control panel for service by the CPU.

Selection between the two PROMs is performed by CSWD 36 and 37 as indicated below:

| CS | SWD | PROM  |

|----|-----|-------|

| 36 | 37  | 21    |

| 0  | 0   | 10/20 |

| 0  | 1   | 10    |

| 1  | 0   | 20    |

This enables the respective hexadecimal address field into the selected PROM for selection of the applicable control signal(s).

#### NOTE

Some overlap between the two PROMs can occur to provide adequate control signal selection.

Figure 4-7 Subcommand Generator Logic

### 4.9.8 Constant Generators

The CPU constant generators provide two types of constants, which are available as internal bus sources as directed by the BI Field of the current firmware word. These constants are:

- 1. Numeric constants, and

- 2. Constants used to generate control words for communication with external processors.

# 4.9.9 Control Panel

Refer to subsection 4.12 for a description of the full control panel.

### 4.10 MEGABUS NETWORK

The Megabus provides a common communication path among available system units. The design of the Megabus is asynchronous to make communications possible between units of varying speeds.

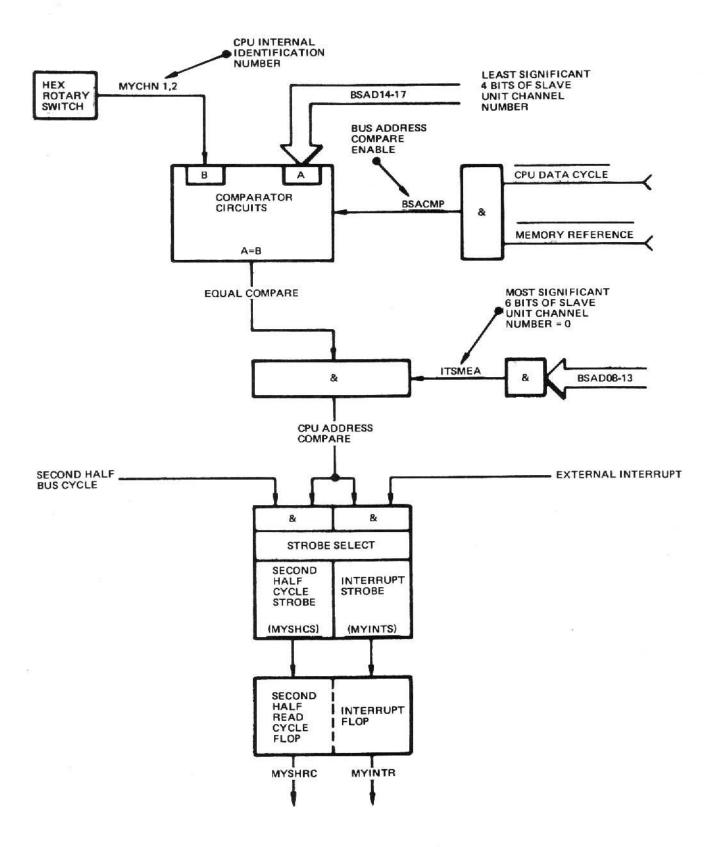

# 4.10.1 Interface Logic

The Megabus interfaces with the CPU via a group of transceivers that provide the equivalent electrical characteristics required of all bus connections to allow data, address, and control signals to be routed to and from the CPU. Table 4-4 provides a complete list of the interface signals, while subsections 4.10.1.1 through 4.10.1.6 provide a brief description of each Megabus/CPU interface signal.

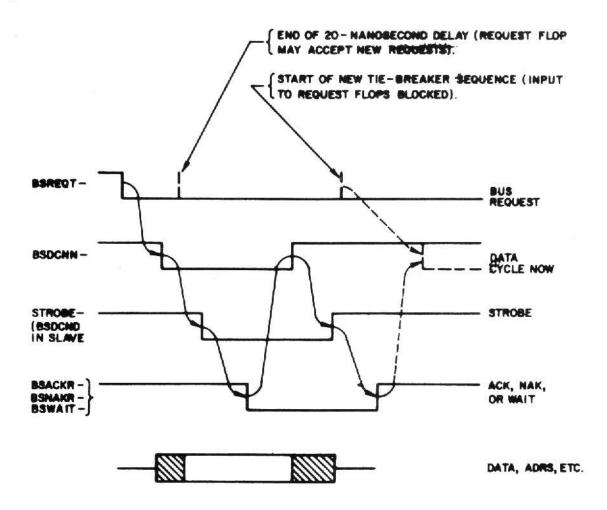

# 4.10.1.1 Timing Signal Lines

The following signals provide the handshake function required by a unit to either initiate, accept, or deny a request for a Megabus cycle from another unit.

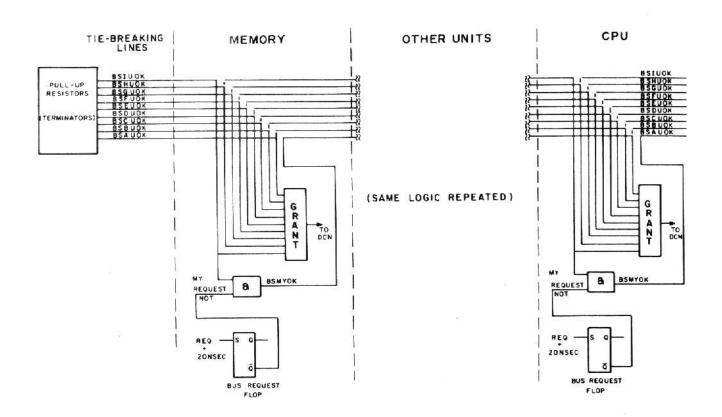

## Bus Request (BSREQT-)

When true, this signal indicates that one or more of the units connected to the Megabus have requested a bus cycle. When the signal is false, no requests are pending.

### Bus Data Cycle Now (BSDCNN-)

When true, this signal indicates that a specific master unit has been granted a requested Megabus cycle and has placed information on the bus for use by a specific slave unit. When this signal is false, the bus is not busy (i.e., between bus cycles).

Table 4-4 Megabus Interface Signals (Sheet 1 of 2)

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                           | CPU SIGNAL                                                                                                                                                                                                                                              |                                                                                                   |                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TYPE                      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                  | DRIVER<br>ENABLE                                                                                                                                                                                                                                        | DRIVER<br>INPUT                                                                                   | RECEIVER<br>OUTPUT                                                                                                                                                                                                                                                                                    | BUS<br>SIGNAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Bus<br>Handshake          | Bus Request<br>Data Cycle Now<br>Acknowledge<br>Negative Acknowledge<br>Wait                                                                                                                                                                                                                                                                                                                                              | GROUND<br>GROUND<br>GROUND<br>GROUND<br>GROUND                                                                                                                                                                                                          | MYREQT+<br>MYDCNN+<br>MYACKR+<br>MYNAKR+<br>GROUND                                                | BSREQT+<br>BSDCNN+<br>BSACKR+<br>BSNAKR+<br>BSWAIT+                                                                                                                                                                                                                                                   | BSREQT-<br>BSDCNN-<br>BSACKR-<br>BSNAKR-<br>BSWAIT-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |