# Honeywell Level 6 Minicomputer Handbook

## SERIES 60 (LEVEL 6) MINICOMPUTER HANDBOOK

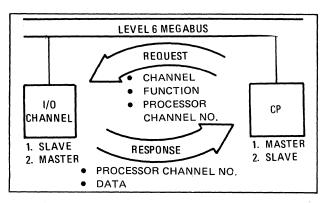

#### SUBJECT

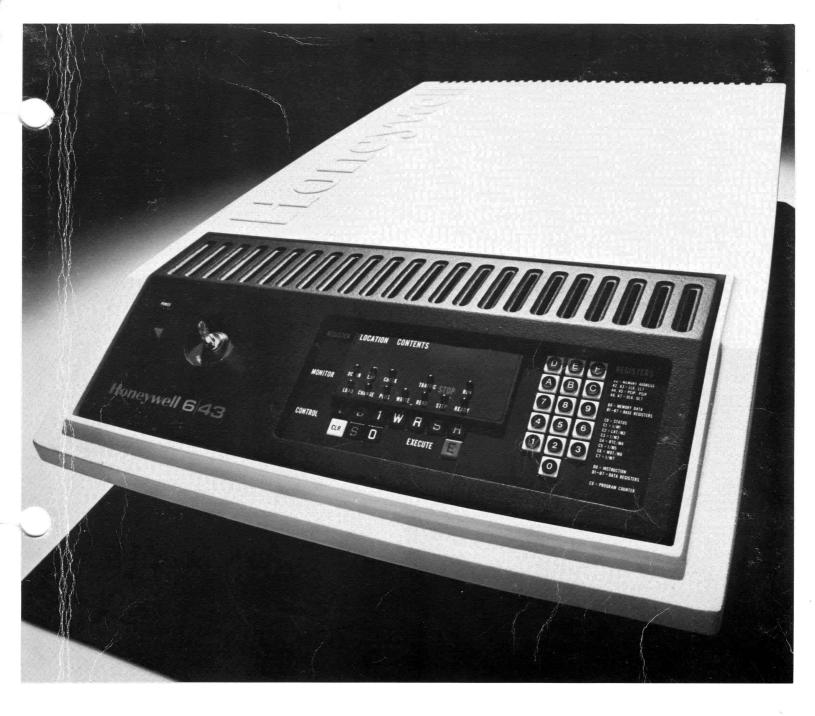

Introduction and Overview of the Models 6/34, 6/36 and 6/43 System Components, Architecture, and Software; Programmer-oriented Discussion of Instruction Set and Peripherals

#### SPECIAL INSTRUCTIONS

This manual supersedes the previous edition, AS22, Rev. 1, dated August 1976. This edition has been so extensively revised that change bars were not used. The Site Preparation Planning and Site Facility Listing sections have been removed from the manual; this information is now contained in the Site Preparation Manual, Order Number AY52.

ORDER NUMBER

AS22, Rev. 2

September 1977

## PREFACE

This Handbook introduces Level 6, Honeywell's family of minicomputer systems, and describes their major system elements in straightforward technical detail. Thus, present minicomputer users and others with an engineering orientation can understand the fundamental design philosophy of Level 6 and make a firm personal evaluation of its merits. They will also become reacquainted with Honeywell as a minicomputer manufacturer.

Honeywell has been a minicomputer manufacturer for over 10 years. In that time it has marketed the products of Computer Control Company, which it acquired in 1966, and has developed and introduced extensions of the original line. Computer Control Company in 1965 built one of the first 16-bit minicomputers, the DDP-116. Honeywell has continued with the DDP-516 (1966), the DDP-416 (1967), the H316 (1969), and System 700 (1972), establishing itself as one of the foremost manufacturers of 16-bit systems.

Level 6 is a 16-bit minicomputer system founded on new concepts of simplicity, flexibility, and reliability. With its open-ended system architecture, its modular, highly functional software, and its low-cost peripherals (including diskettes), Level 6 presages a family of machines with wideranging suitability for both end-use and OEM applications. And as a partner with Honeywell's Series 60 and a member of the Honeywell Information System, Level 6 enjoys the full field engineering service of one of the country's major computer manufacturers.

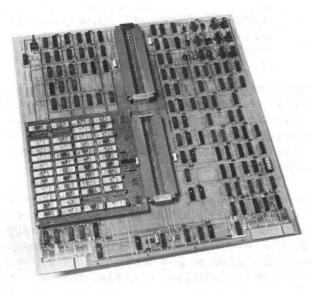

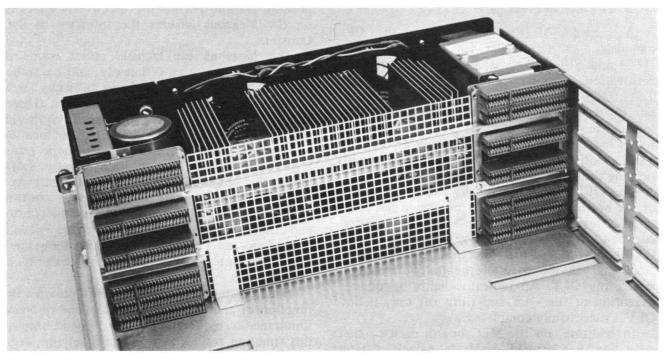

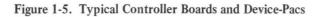

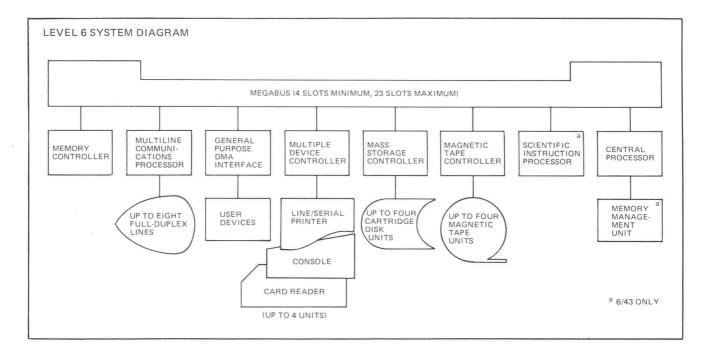

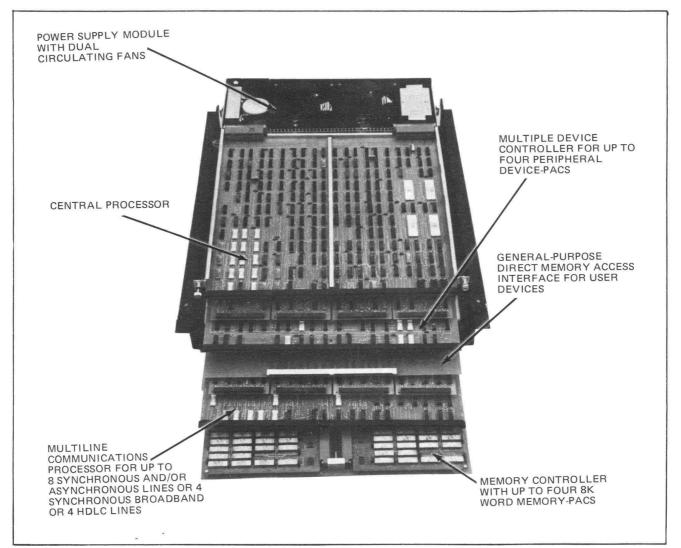

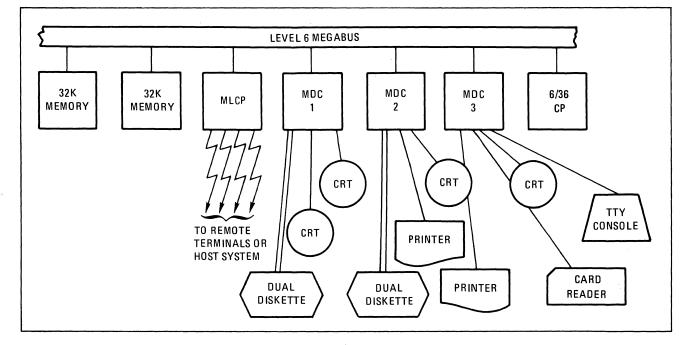

The heart of Level 6 is the Megabus, expandable to 23 slots – each with multiple device capability (diskettes, printers, card readers, communication controllers, etc.). Modularity has reached new levels, with implementation of an entire central processor (up to 32,768 words of memory) on a single circuit board. Indeed, a complete minisystem of five boards (central processor, memory, and device and communication controllers), plus power supply, air circulating unit, and control panel, fits into a standard drawer 5¼ inches high.

Lying behind the advanced technology of Level 6 are not only Honeywell's long experience as a producer of 16-bit machines, but a design philosophy emphasizing the use of commercially established elements and a new factory system promoting error-reducing automated procedures. These have combined to lower manufacturing costs to the point at which Level 6 can offer one of the most attractive cost/performance ratios on the market.

There is much more that is newsworthy about Level 6, and this Handbook can only summarize key aspects. For a full account of Honeywell's new minicomputer and its place in your operations, call a Honeywell Marketing Representative.

# CONTENTS

|                                  | Page  |

|----------------------------------|-------|

| Section 1. System Summary        | 1-1   |

| Models                           |       |

| 6/34                             |       |

| 6/36                             |       |

| 6/43                             |       |

| Configurability                  |       |

| Board Technology                 |       |

| Quality Logic Tests              |       |

| System Elements                  |       |

| Megabus                          |       |

| Central Processor                |       |

| Memory                           |       |

| Semiconductor Storage            | 1-11  |

| Packaging                        |       |

| Functionality                    |       |

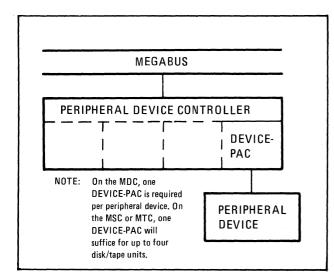

| Multiple Device Controller       |       |

| (MDC9101)                        | 1-12  |

| Mass Storage Controller          |       |

| (MSC9101)                        | 1-12  |

| Multiline Communications         |       |

| Processor (MLCP9103)             | 1-13  |

| Magnetic Tape Controller         |       |

| (MTC9101)                        | 1-14  |

| General-Purpose Direct Memory    |       |

| Access (DMA)                     |       |

| Interface (GIS9001)              | 1-14  |

| Scientific Instruction Processor |       |

| (CPF9503)                        | 1-15  |

| Memory Management Unit           |       |

| (CPF9501)                        |       |

| Power Supply and Fans            | 1-15  |

| Peripheral Devices               |       |

| Programmable Interrupt Levels    | 1-15  |

| Teleprinters and Compatible CRT  |       |

| Devices                          |       |

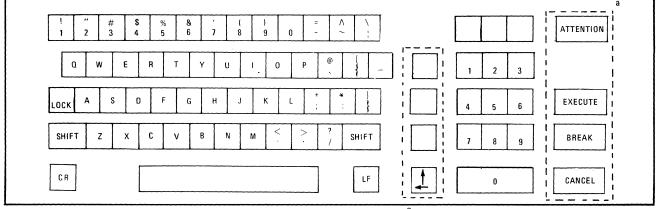

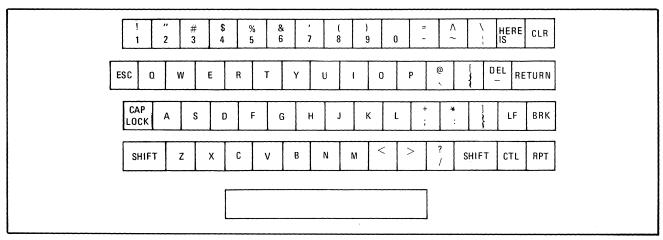

| Keyboard Typewriter Consoles     |       |

| Card Readers                     |       |

| Serial Printers                  |       |

| Line Printers                    |       |

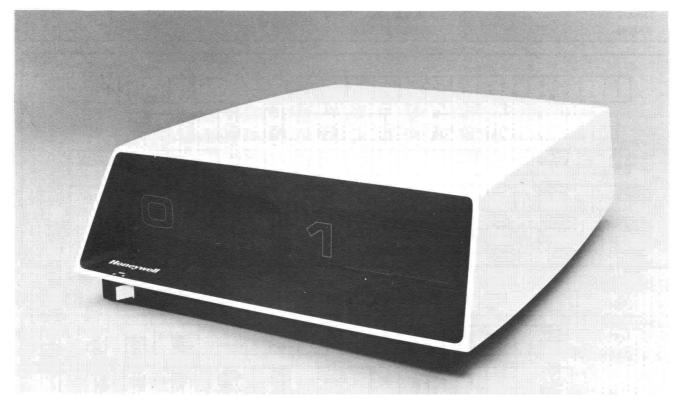

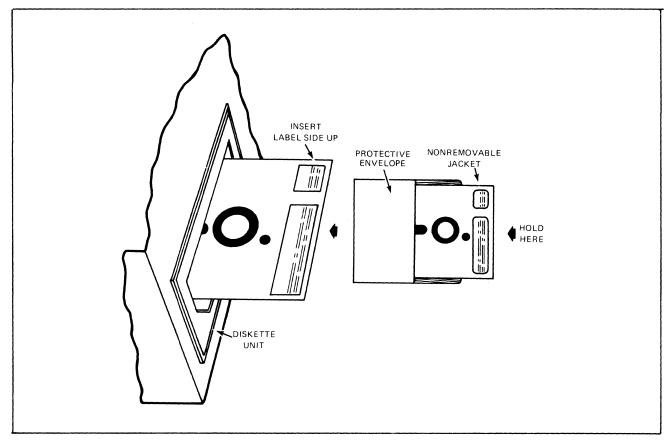

| Diskettes                        |       |

| Cartridge Disk Units             |       |

| Magnetic Tape Units              |       |

| Software                         |       |

| GCOS/BES                         |       |

| GCOS 6/MDT                       | 1-17  |

| Human Factors Engineering and    | 1 1 0 |

| Industrial Design                |       |

| Site Preparation Planning        |       |

| Maintenance                      |       |

| Documentation                    |       |

| Future Developments              | 1-19  |

| Section 2. System Architecture<br>Connectable Units<br>Interunit Communication<br>Megabus Priority<br>Types of CP and Memory Transfers<br>Input/Output Transfers<br>Input/Output Commands<br>Interrupt Levels<br>Interrupt Levels<br>Interrupt Action<br>Context Switching<br>Summary of Bus Operations<br>Memory Addresses | 2-1<br>2-2<br>2-2<br>2-3<br>2-4<br>2-4<br>2-5<br>2-5<br>2-5<br>2-5<br>2-6<br>2-6 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

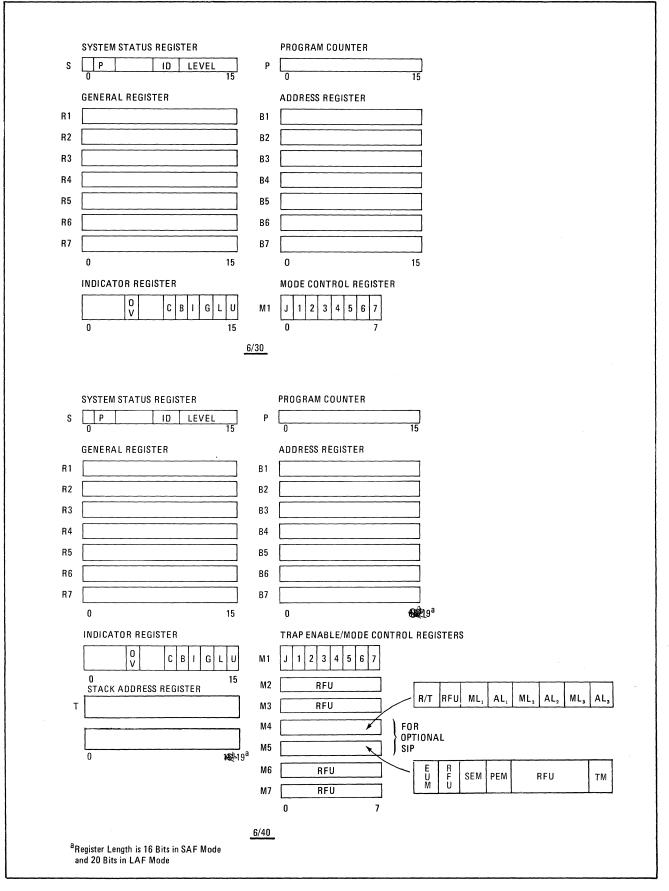

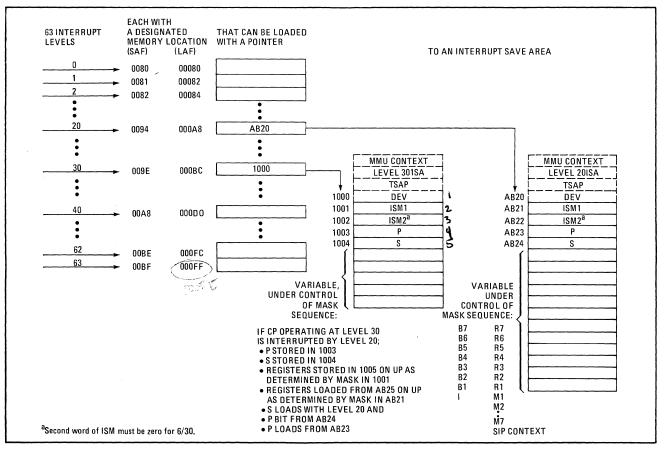

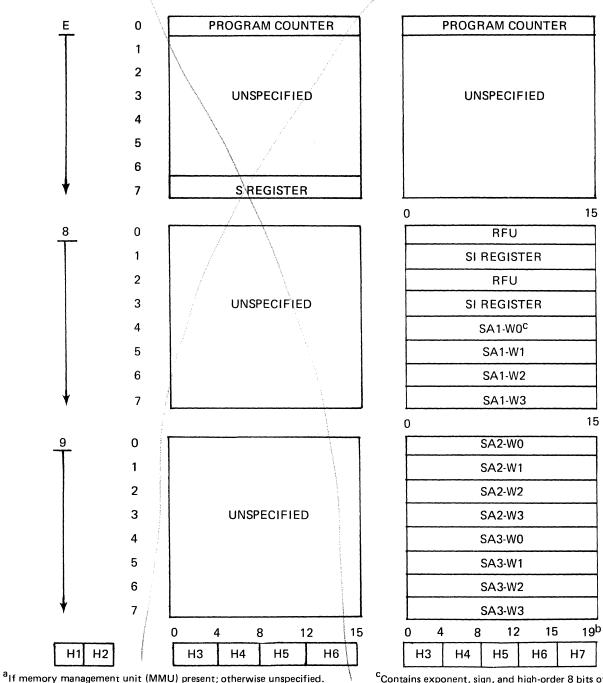

| Section 3. Central Processor Architecture                                                                                                                                                                                                                                                                                   | 3-1                                                                              |

| Registers                                                                                                                                                                                                                                                                                                                   |                                                                                  |

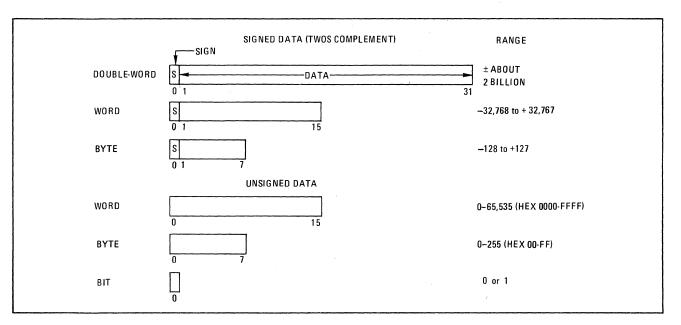

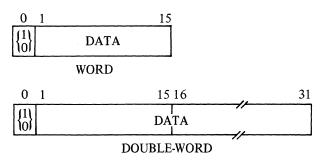

| Data Formats                                                                                                                                                                                                                                                                                                                |                                                                                  |

| General Registers                                                                                                                                                                                                                                                                                                           |                                                                                  |

| Address Registers                                                                                                                                                                                                                                                                                                           |                                                                                  |

| Program Counter                                                                                                                                                                                                                                                                                                             |                                                                                  |

| Indicator Register                                                                                                                                                                                                                                                                                                          |                                                                                  |

| Arithmetic Indicators                                                                                                                                                                                                                                                                                                       |                                                                                  |

| Comparison Indicators                                                                                                                                                                                                                                                                                                       |                                                                                  |

| Bit Test Indicator                                                                                                                                                                                                                                                                                                          |                                                                                  |

| Input/Output Indicator                                                                                                                                                                                                                                                                                                      |                                                                                  |

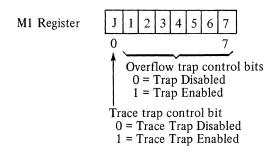

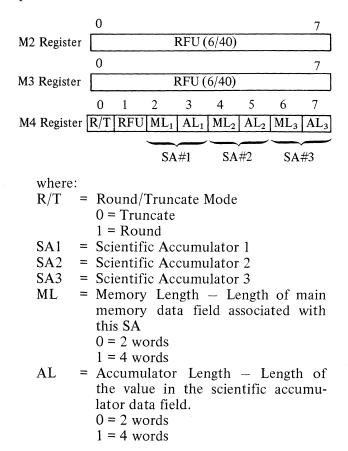

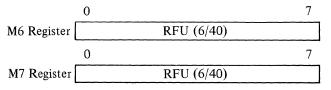

| Mode Control Register                                                                                                                                                                                                                                                                                                       |                                                                                  |

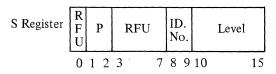

| Status Register                                                                                                                                                                                                                                                                                                             |                                                                                  |

| Privileged State Indicator                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Processor ID                                                                                                                                                                                                                                                                                                                |                                                                                  |

| Priority Level                                                                                                                                                                                                                                                                                                              |                                                                                  |

| Summary of Program Visible                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Registers                                                                                                                                                                                                                                                                                                                   | 3-5                                                                              |

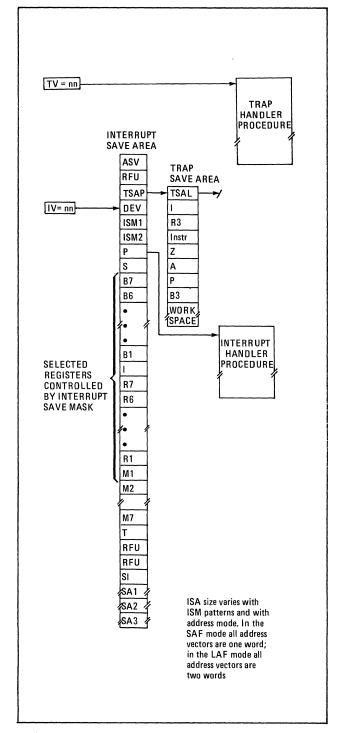

| Interrupts                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Traps                                                                                                                                                                                                                                                                                                                       |                                                                                  |

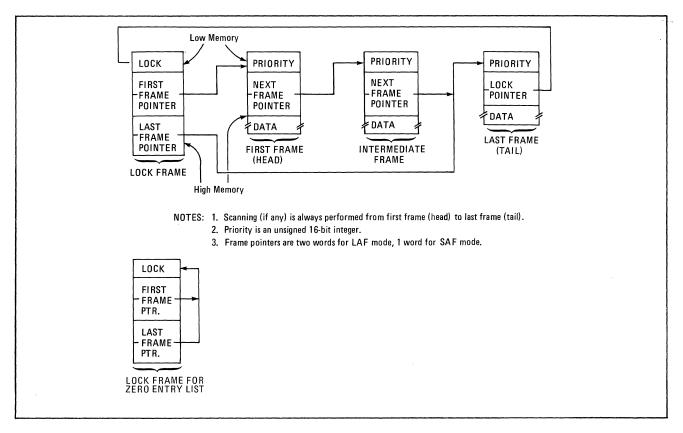

| Queue Management                                                                                                                                                                                                                                                                                                            |                                                                                  |

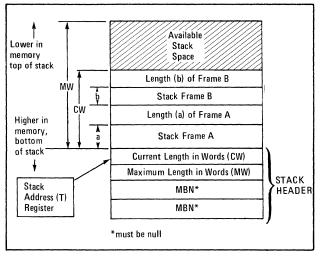

| Stack Management                                                                                                                                                                                                                                                                                                            |                                                                                  |

| Scientific Instruction Processor                                                                                                                                                                                                                                                                                            |                                                                                  |

| Control Registers                                                                                                                                                                                                                                                                                                           | 3-11                                                                             |

| Accumulators                                                                                                                                                                                                                                                                                                                | 3-11                                                                             |

| Automatic Round/Truncate                                                                                                                                                                                                                                                                                                    |                                                                                  |

| Scientific Traps                                                                                                                                                                                                                                                                                                            |                                                                                  |

| Data Formats                                                                                                                                                                                                                                                                                                                |                                                                                  |

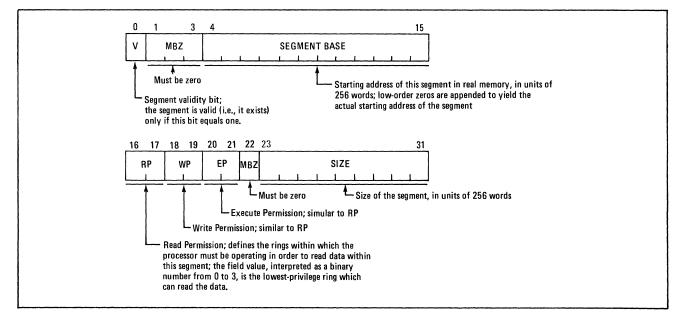

| Memory Management Unit                                                                                                                                                                                                                                                                                                      |                                                                                  |

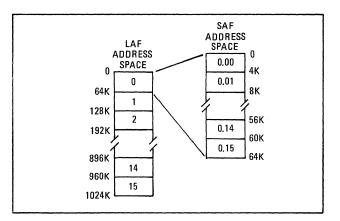

| Segmentation                                                                                                                                                                                                                                                                                                                |                                                                                  |

| Relocation                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Protection                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Segment Descriptor Format                                                                                                                                                                                                                                                                                                   | 3-13                                                                             |

| Section 4. Instructions and Addressing                                                                                                                                                                                                                                                                                      | 4-1                                                                              |

| Instruction Set Summary                                                                                                                                                                                                                                                                                                     |                                                                                  |

| SAF and LAF Mode Impact on                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Instructions                                                                                                                                                                                                                                                                                                                | 4-4                                                                              |

|                                                                                                                                                                                                                                                                                                                             |                                                                                  |

| -                                                                 |          |

|-------------------------------------------------------------------|----------|

| SAF/LAF Independent Code (SLIC)<br>Pre-fetch Capability and Self- | 4-4      |

| Modifying Code                                                    | 4-5      |

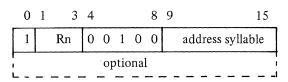

| Instruction Formats and Addressing                                | 4 -      |

| Modes                                                             | 4-5      |

| Single and Double Operand                                         | <u> </u> |

| Instructions                                                      |          |

| Branch Instructions                                               |          |

| Displacement Addressing                                           |          |

| Relative Addressing                                               | 4-7      |

| Absolute Addressing (Immediate                                    |          |

| Address)                                                          |          |

| Short Value Immediate Instructions                                |          |

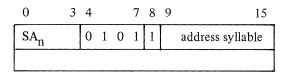

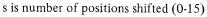

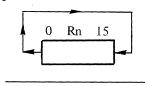

| Shift Instructions                                                |          |

| Generic Instructions                                              |          |

| Input/Output Instructions                                         |          |

| Scientific Instructions                                           |          |

| Instruction Set                                                   | 4-8      |

|                                                                   |          |

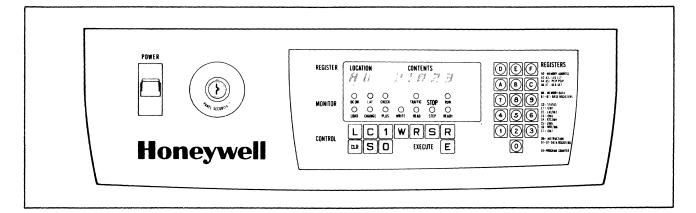

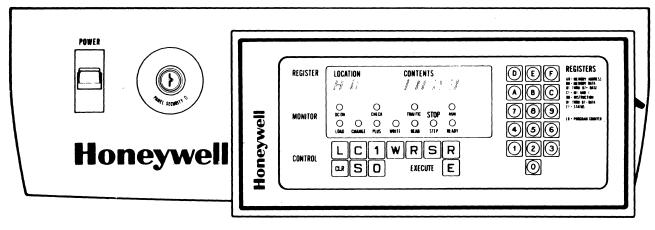

| Section 5. Control Panels                                         | 5-1      |

| Packaging                                                         |          |

| Full Control Panel                                                | 5-1      |

| Register Display                                                  | 5-1      |

| Hexadecimal-Pad Keys                                              |          |

| Panel Display Interpretation                                      | 5-6      |

| Basic Control Panel                                               | 5-7      |

| Options                                                           |          |

| Portable Plug-in Panel                                            |          |

| Vertical Panel Mounting                                           |          |

| Ordering Information                                              |          |

| Control Panel Operating Procedures                                | 5-10     |

| Display Memory                                                    |          |

| Change Memory                                                     |          |

| Display Registers                                                 |          |

| Change Registers                                                  |          |

| Stop Program Execution                                            |          |

| Execute Single Instruction(s)                                     | 5 1 2    |

| Restart Program                                                   |          |

|                                                                   |          |

| Master Clear                                                      |          |

| Board Checking<br>Accessing and Checking Boards                   |          |

|                                                                   | 5-15     |

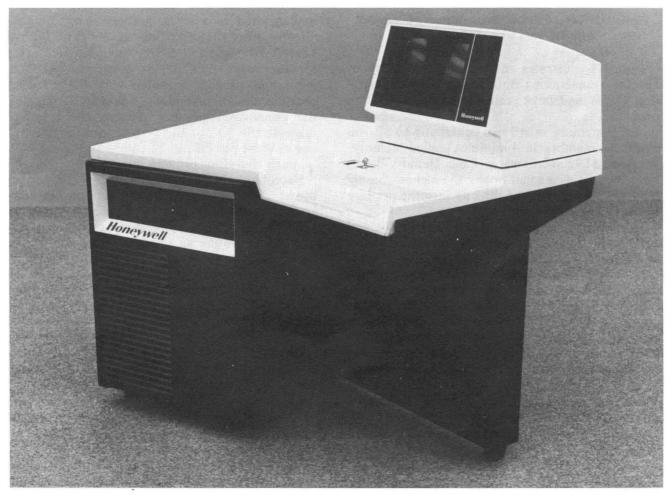

| Freestanding (Tabletop) Central                                   | 5 1 5    |

| Subsystem                                                         | 5-15     |

| Rack-Mounted Central System                                       |          |

| Physical Characteristics                                          |          |

| Section 6. Peripheral Devices                                     |          |

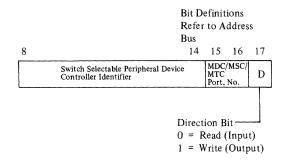

| Peripheral Device Connection                                      | 6-1      |

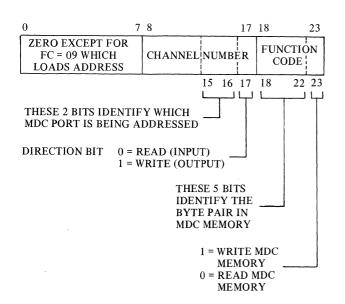

| MDC/MSC/MTC Memory and                                            |          |

| Command Interpretation                                            | 6-2      |

| Bus Responses and Busy                                            |          |

| Conditions                                                        |          |

| Channel Number                                                    |          |

| Device Identification Number                                      | 6-3      |

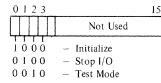

| Test Mode                                                         | 6-3      |

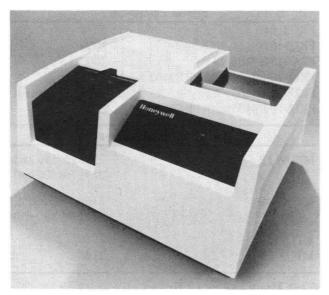

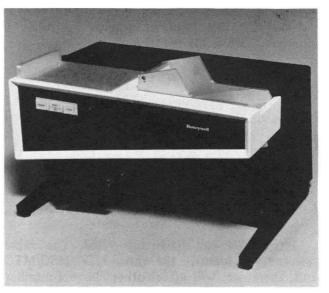

| Card Readers                                                      | 6-3      |

| Features                                                          |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ( )                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                              |

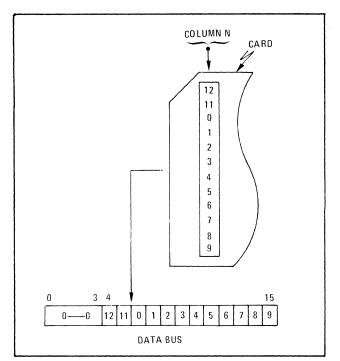

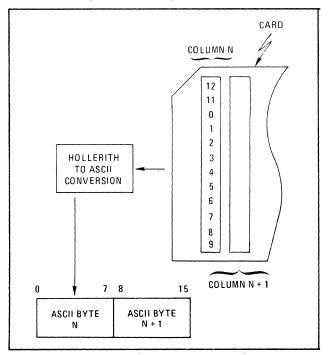

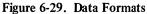

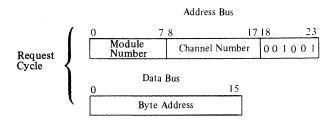

| Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                              |

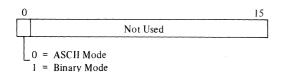

| Binary Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6-5                                                                                                                          |

| ASCII Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-5                                                                                                                          |

| Honeywell Mark Reading Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                              |

| IBM Mark Reading Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                              |

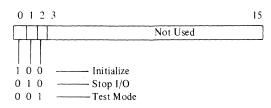

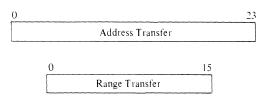

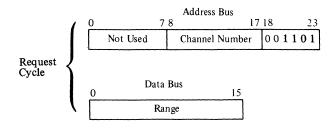

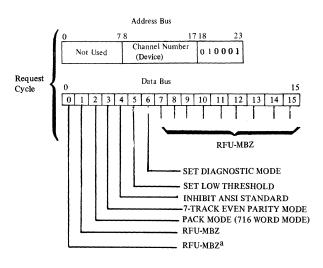

| Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                              |

| Output Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                              |

| Input Commands.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                              |

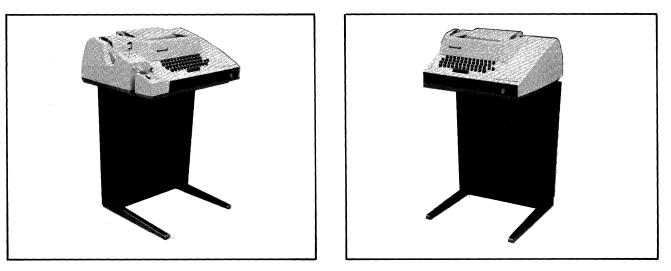

| Teleprinter Consoles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                              |

| Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                              |

| Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-11                                                                                                                         |

| Printer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6-11                                                                                                                         |

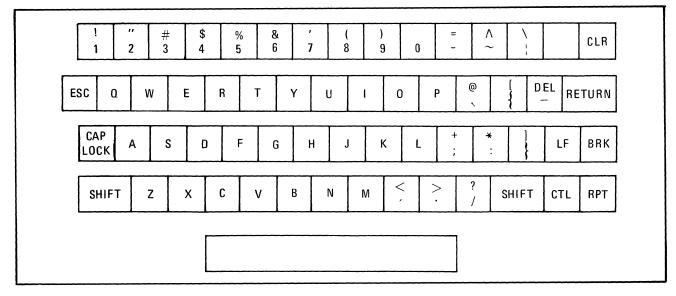

| Keyboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6-12                                                                                                                         |

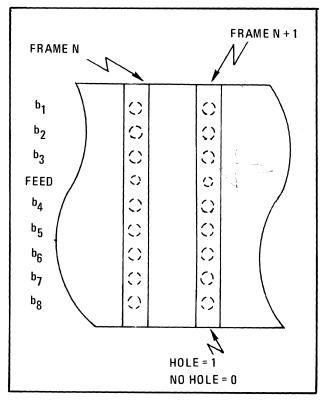

| Paper Tape Reader                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                              |

| Paper Tape Punch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-12                                                                                                                         |

| Data Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                              |

| Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                              |

| Output Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                              |

| Input Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6-16                                                                                                                         |

| Programming Considerations –                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                              |

| Console                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6-18                                                                                                                         |

| Load Console Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                              |

| Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-18                                                                                                                         |

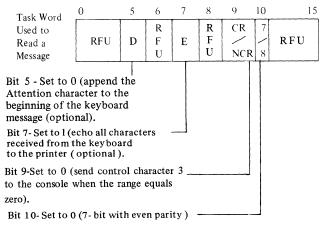

| Read Keyboard Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                              |

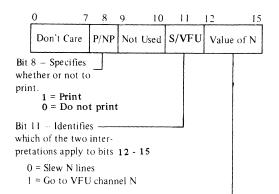

| Print/Display Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6-20                                                                                                                         |

| Console Read Status Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                              |

| Console Stop I/O Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                              |

| Attention                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-21                                                                                                                         |

| Programming Considerations –                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                              |

| Paper Tape                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-21                                                                                                                         |

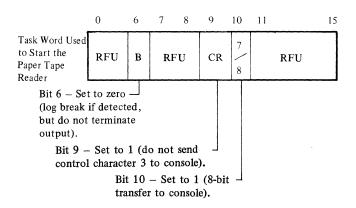

| Load Paper Tape Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                              |

| Uneration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-21                                                                                                                         |

| Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                              |

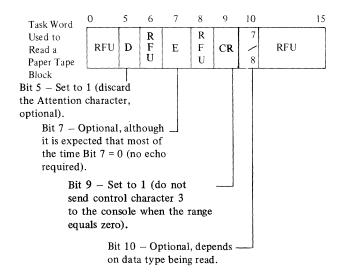

| Read Paper Tape Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-22                                                                                                                         |

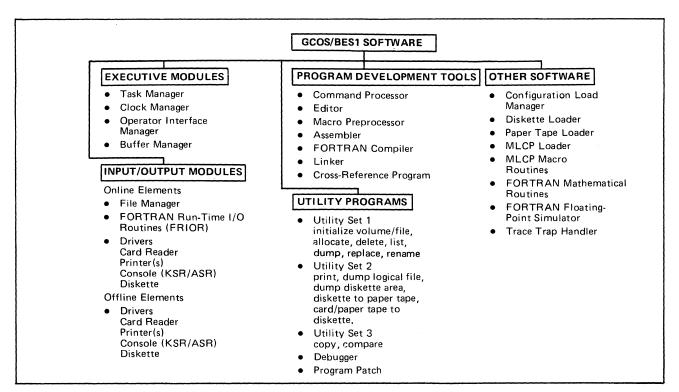

| Read Paper Tape Operation<br>Punch Paper Tape Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6-22                                                                                                                         |