# Honeywell

# SYSTEM CONTROL UNIT WSCU66LA UNIT MANUAL

58009922

#### (FREESTANDING UNIT) DPS 8

This document and the information contained herein are confidential to and the property of Honeywell Information Systems, Inc. and are made available only to Honeywell employees for the sole purpose of conducting Honeywell business. This document, any copy thereof and the information contained herein shall be maintained in strictest confidence; shall not be copied in whole or in part except as authorized by the employee's manager; and shall not be disclosed or distributed (a) to persons who are not Honeywell employees, or (b) to Honeywell employees for whom such information is not necessary in connection with their assigned responsibilities. Upon request, or when the employee in possession of this document no longer has need for the document for the authorized Honeywell purpose, this document and any copies thereof shall be returned to the employee's manager. There shall be no exceptions to the terms and conditions set forth herein except as authorized in writing by the responsible Honeywell Vice President

58009922-040 DIST. CODE NCO, XAN The following notice is provided in accordance with the United States interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference

Federal Communications Commission's (FCC) regulations Warning: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. As temporarily permitted by regulation it has not been tested for compliance with limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause

> A ISSUED JULY 1981

| RECORD OF REVISION |        |               | RECORD OF                                                                                                                                                                                       |     |      |               |

|--------------------|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|---------------|

| REV                | DATE   | AUTHORIZATION | PAGES AFFECTED                                                                                                                                                                                  | REV | DATE | AUTHORIZATION |

| A                  | 7/81   | PHAFPS933     | 58009922-040,1F<br>58009922-014,1F<br>58009922-017,1F<br>58009922-015,1-1 & 1-2F<br>58009922-001,1F<br>58009922-051,2-1F<br>58009922-030,1F<br>58009922-100,3-1 thru 3-30F<br>58009922-200,4-1F |     |      |               |

|                    |        |               |                                                                                                                                                                                                 |     |      |               |

|                    |        |               |                                                                                                                                                                                                 |     |      |               |

|                    |        |               |                                                                                                                                                                                                 |     |      |               |

|                    |        |               |                                                                                                                                                                                                 |     |      |               |

|                    |        |               |                                                                                                                                                                                                 |     |      |               |

|                    |        |               |                                                                                                                                                                                                 |     |      |               |

|                    | •      | -             | -                                                                                                                                                                                               |     |      |               |

|                    | ÷,     |               |                                                                                                                                                                                                 |     |      |               |

|                    |        |               |                                                                                                                                                                                                 |     |      |               |

|                    |        |               |                                                                                                                                                                                                 |     |      |               |

|                    |        |               |                                                                                                                                                                                                 |     |      |               |

|                    |        |               |                                                                                                                                                                                                 |     |      |               |

|                    |        |               |                                                                                                                                                                                                 |     |      |               |

|                    |        |               |                                                                                                                                                                                                 |     |      |               |

|                    |        |               |                                                                                                                                                                                                 |     |      |               |

|                    |        |               |                                                                                                                                                                                                 |     |      |               |

| 10099              | 22-014 | 1 1           | HONEYWELL CONFIDENTIA                                                                                                                                                                           |     |      |               |

# A ISSUED

REVISION

## PAGES AFFECTED

# TABLE OF CONTENTS

# VOLUME 1F

| Binder, B-Size, 4-Ring, 2-Inch               | 58009884-008 |

|----------------------------------------------|--------------|

| Standard Separator Tabs, B-Size, Unit Manual | 58009885-016 |

| Spine, Vol. 1F                               | 58009922-030 |

| Title Page, Vol. 1F                          | 58009922-040 |

| Record of Revisions                          | 58009922-014 |

| Table of Contents                            | 58009922-001 |

| Manual Contents, Vol. 1F                     | 58009922-017 |

| GENERAL TAB              | 58009922-015                           |

|--------------------------|----------------------------------------|

| PHYSICAL OUTLINE TAB     | 58009922-051                           |

|                          |                                        |

| THEORY OF OPERATION TAB  | 58009922-100                           |

| MAINTENANCE AIDS TAB     | 58009922-200                           |

| WIRE LISTS TAB           |                                        |

| Microfiche Index         | See WMMU66LA<br>Option Manual 58009914 |

| CKT/LOGIC TAB            | Microfiche Indexes                     |

| RSS, CIL, Logic Diagrams | See WMMU66LA<br>Option Manual 58009914 |

HONEYWELL CONFIDENTIAL & PROPRIETARY

# MANUAL CONTENTS

# VOLUME 1F

PAGE NO.

3.6.4 3.6.5 3.6.6 3.6.7 3.6.8 3.6.9 3.6.10 3.6.11

|               |                                           | FAGE N  |

|---------------|-------------------------------------------|---------|

| 1.0           | GENERAL                                   | _ 1 – 1 |

| 1.1           | INTRODUCTION                              | . 1-1   |

| 1.1.1         | SCOPE                                     |         |

| 1.1.2         | PURPOSE                                   | 1 - 1   |

|               |                                           | 1 0 5   |

| 1.2           | FEEDBACK                                  |         |

| 1.3           | REFERENCE DOCUMENTATION                   | _ 1-2F  |

| 2.0           | PHYSICAL OUTLINE                          | 2-1F    |

| 3.0           | THEORY OF OPERATION                       | 3-1     |

| 3.1           | SYSTEM OVERVIEW                           | - 3-1   |

| 3.1.1         | SYSTEM CONTROLLER FUNCTIONS               | - 3-1   |

| 3.1.2         | CONFIGURATION PANEL                       | . 3-1   |

| 3.1.3         | INTERFACE DESCRIPTION                     | 3-1     |

| 3.2           | GENERAL                                   |         |

| 3.2.1         | PORT INTERFACES                           | . 3-4   |

| 3.2.2         | STORE INTERFACES                          | 3-5     |

| 3.2.3         | SCU CYCLES                                | - 3-5   |

| 3.3           | FUNCTIONAL DESCRIPTION                    | 3-7     |

| 3.3.1         | PORT INTERFACE SIGNALS                    | 3-7     |

| 3.3.2         | DATA FLOW                                 | 3-10    |

| 3.3.3         | ZAC LOGIC OPERATION                       | 3-10    |

| 3.3.4         | TIMING AND CONTROL                        | . 3-13  |

| 3.4           | SCU COMMANDS                              |         |

| 3.4.1         | MEMORY READ COMMANDS                      | - 3-15  |

| 3.4.2         | MEMORY WRITE COMMANDS                     |         |

| 3.4.3         | SYSTEM CONTROL COMMANDS                   |         |

| 3.3.4         | GENERAL REGISTER COMMANDS                 | 3-18    |

| 3.5           | WRITE NOTIFICATION (HARDWARE CACHE CLEAR) | 3-24    |

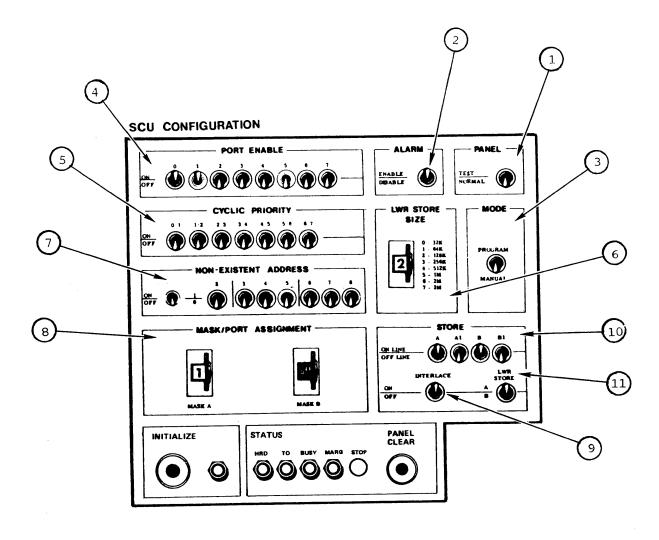

| 3.6           | SCU CONFIGURATION PANEL                   | 3-28    |

| 3.6.1         | PANEL TEST/NORMAL                         | 3-28    |

| 3.6.2         | ALARM ENABLE/DISABLE                      | 3-28    |

| <b>3</b> .6.3 | CONFIGURATION PANEL                       | - 3-28  |

|               |                                           |         |

| PORT ENABLE SWITCHES            | 3-29  |

|---------------------------------|-------|

| CYCLIC PRIORITY SWITCHES        | 3-29  |

| LWR STORE SIZE SWITCH           | 3-29  |

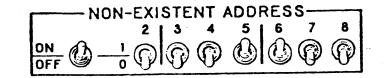

| NON-EXISTENT ADDRESS            | 3-29  |

| MASK/PORT ASSIGNMENT            | 3-30F |

| STORE INTERFACE ON/OFF          | 3-30F |

| STORE ON LINE/OFF LINE          | 3-30F |

| LWR STORE A/B                   | 3-30F |

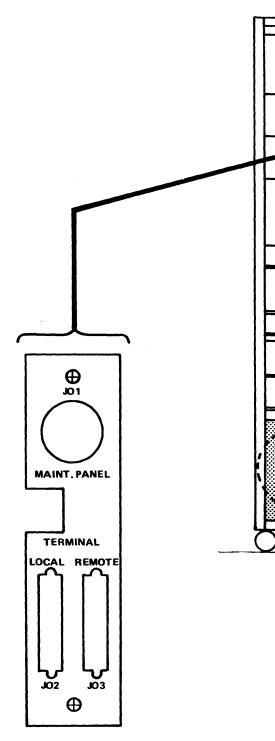

| MAINTENANCE AIDS                | 4-1   |

| DYNAMIC MAINTENANCE PANEL (DMP) | 4 - 1 |

| MAINT PANEL - JO1               | 4 - 1 |

| TERMINAL, LOCAL - JO2           | 4 – 1 |

| TERMINAL, REMOTE - JO3          | 4 – 1 |

| 4.0   | MAINTENANCE AIDS       |

|-------|------------------------|

| 4.1   | DYNAMIC MAINTENANCE PA |

| 4.1.1 | MAINT PANEL - JO1      |

| 4.1.2 | TERMINAL, LOCAL - JO2  |

| 4.1.3 | TERMINAL, REMOTE - JO3 |

...

HONEYWELL CONFIDENTIAL & PROPRIETARY

# A ISSUED

# PAGE NO.

# MANUAL CONTENTS(CONTINUED)

# VOLUME 1F

PAGE NO.

| FIGURE<br>2-1                                                       | SYSTEM CONTROLLER WSCU66LA PHYSICAL<br>OUTLINE                                                                                                                                                                                                                                                                    | 2-1F                                                 |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-10 | 4MW SCU MAJOR BLOCK DIAGRAM<br>SYSTEM PORT INTERFACE<br>STORE PORT INTERFACE<br>EARLY CYCLE TIMING<br>INFORMATION FLOW 4-MEGAWORD SCU<br>FUNCTIONAL DIAGRAM ZAC FLOW<br>SYSTEM CONTROLLER TWO WORD INTERLACE<br>INTERRUPT REGISTER FORMATS<br>INTERRUPT CELL ADDRESS (VECTOR)<br>GENERAL REGISTER COMMAND FORMATS | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

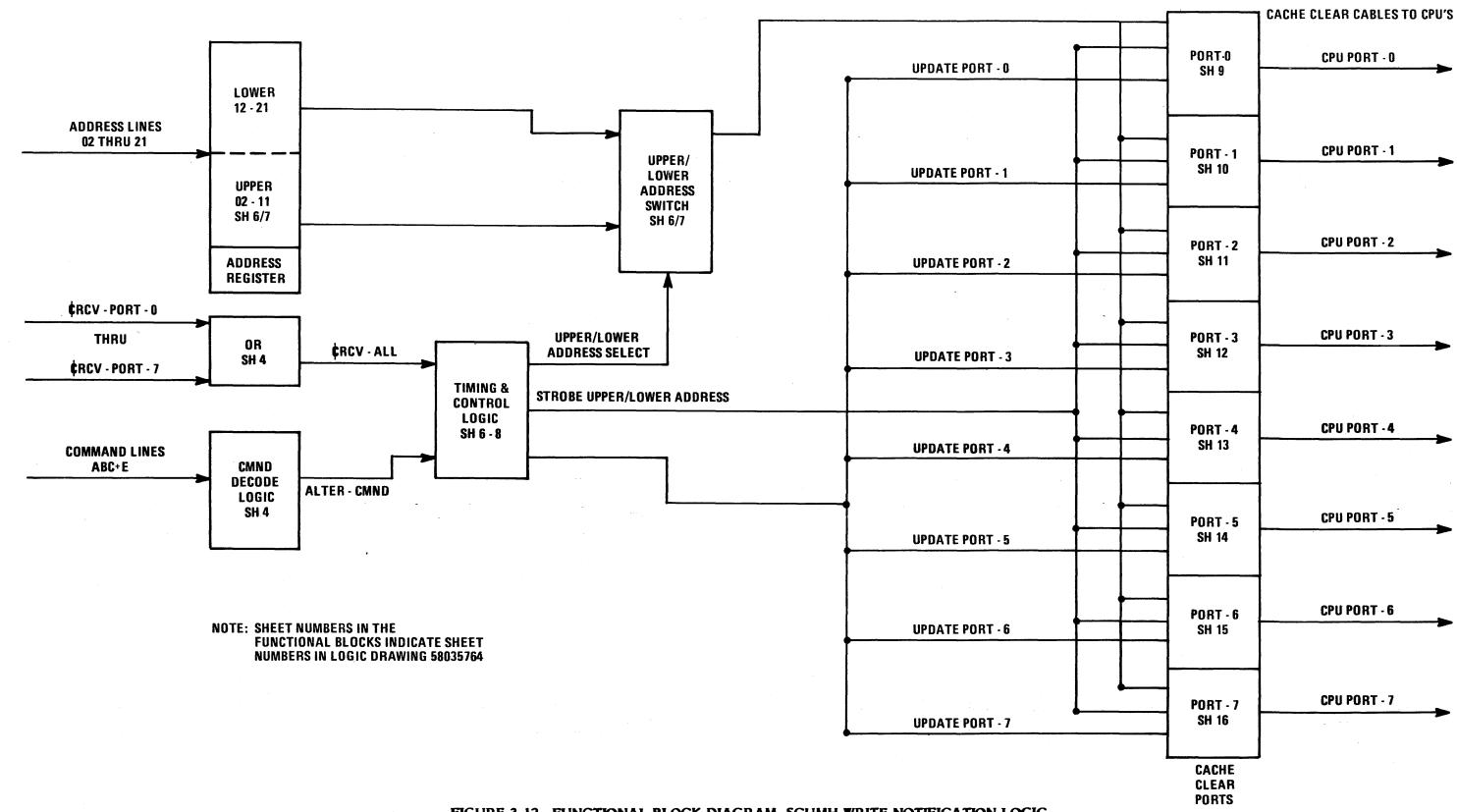

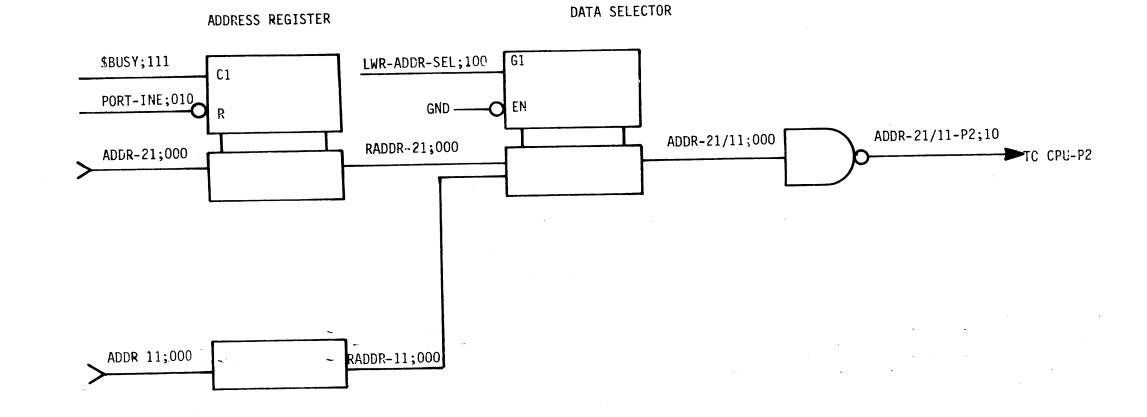

| 3-11<br>3-12<br>3-13<br>3-14                                        | FUNCTIONAL BLOCK DIAGRAM, SCUMH<br>WRITE NOTIFICATION LOGIC<br>ADDRESS TRANSFER LOGIC FOR A21/A11<br>SCU CONFIGURATION PANEL                                                                                                                                                                                      | 3-22<br>3-27                                         |

| TABLE                                                               |                                                                                                                                                                                                                                                                                                                   | 3-16                                                 |

| 0.1   | COMMAND  | SUMMARY | <br>3-16 |

|-------|----------|---------|----------|

| 3 - 1 | COMMITTE |         |          |

# PAGE NO.

1

## 1.0 GENERAL

1.1 INTRODUCTION

1.1.1 SCOPE

This manual is written primarily for the Field Engineering Division (FED) specialists and LISD Manufacturing specialists, and is, Honeywell Confidential and Proprietary. The CSU product maintenance documentation structure is contained in System Manual 58009888.

Unit manuals are sectionalized under six tabs and may consist of one to several volumes (binders) depending on the complexity of the functional unit. The information contained under each tab is as follows:

1.1.1.1 General Tab

This section contains the introductory material.

1.1.1.2 Physical Outline Tab

This section contains a physical outline of the functional unit and its major features, options and ORU's.

1.1.1.3 Theory of Operation Tab

This section contains a multi-level description of unit operation keyed to major block, intermediate block and flow diagrams Coverage will give the specialist the information necessary to trace signals in the logic block diagram (LBD). 1.1.1.4 Maintenance Aids Tab

This section contains references to existing test and diagnostics (T&D) procedures for the functional unit and appropriate troubleshooting techniques. This material supplements the system maintenance software documentation.

1.1.1.5 Wire Lists Tab(Not Required)

The Microfiche Index for the logic wire lists that are on microfiche in the microfiche card box plus pertinent hard-copy wire lists are located in 58009914, WMMU66LA Option Manual.

1.1.1.6 CKT/Logic Tab(Not Required)

The LBD's for the circuit boards and/or the electrical schematics of power supplies and configuration, control and maintenance panels are located in 58009914, WMMU66LA Option Manual. It also contains the revision status sheets (RSS) for each circuit board and the circuit board component installation list (CIL), or installation instructions.

1.1.2 PURPOSE

This unit manual is applicable to multiple users and user environments as follows:

1.1.2.1 Specialist Training

This manual can be used for preparing lesson plans, for classroom use by Field Engineering Training and for field study reference. It is expected that training will always be supported with additional prepared material (handouts, etc.) but the student should become familiar with and be able to effectively use this manual as a primary reference.

# 1.1.2.2 FED Field Maintenance

This manual can be used for direct maintenance of equipment on customer sites to isolate and replace the optimum replaceable unit (ORU) and to resolve failures not corrected by ORU callout and replacement.

# 1.1.2.3 Technical Assistance Center

This manual can be used for remote support of field sites. It should be part of a primary reference library for use in the Technical Assistance Center (TAC) environment by TAC personnel in remote contact with a maintenance computer on site.

# 1.2 FEEDBACK

Send any comments on this manual to Honeywell Large Systems Product Support, P. O. Box 6000, MS K92, Phoenix, Arizona, 85005.

# 1.3 REFERENCE DOCUMENTATION

.

~

HONEY LL CONFIDENTIAL & PROPRIETARY

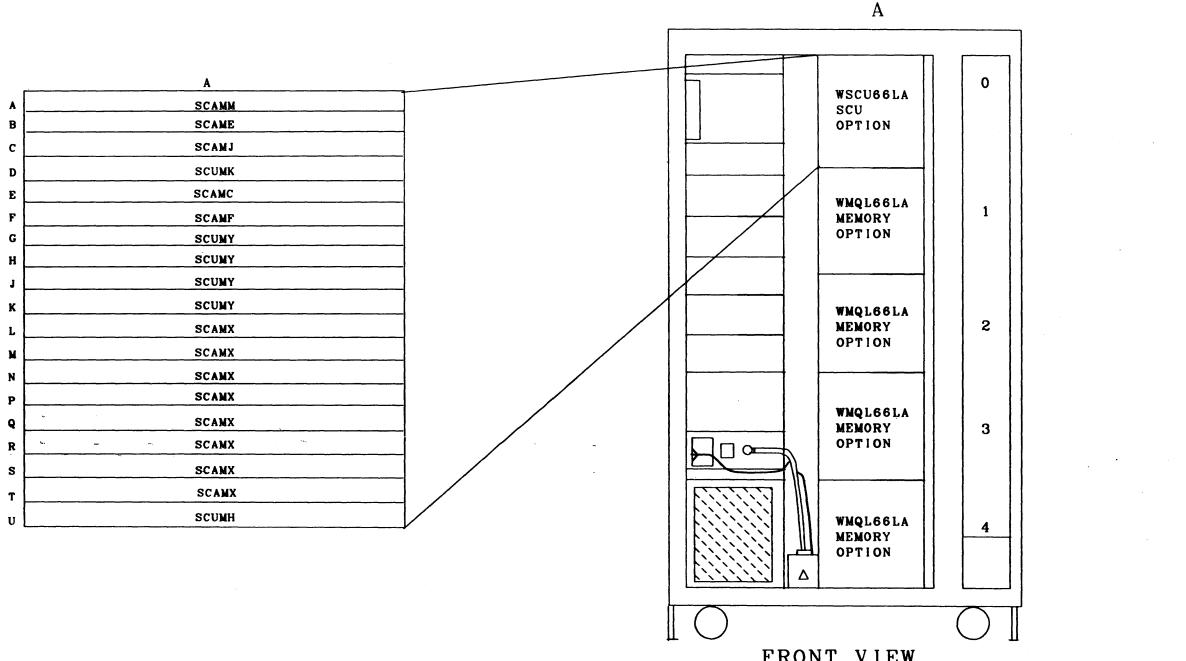

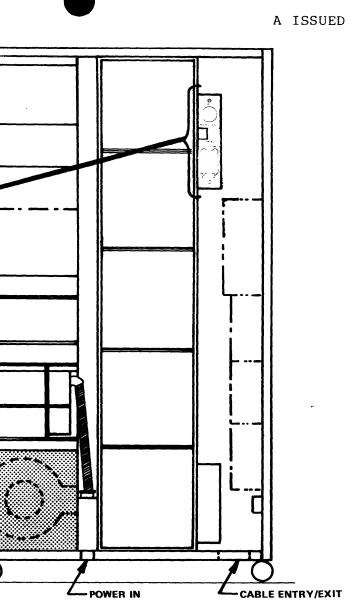

# 2.0 PHYSICAL OUTLINE

FRONT VIEW

FIGURE 2-1. SYSTEM CONTROLLER WSCU66LA PHYSICAL OUTLINE

HONEYWELL CONFIDENTIAL & PROPRIETARY

58009922-051

÷

| 2 0        | THEORY OF OPERATION                                                                                                                                                                                           | 3.1.3     | Interface Description                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 3.0<br>3.1 | SYSTEM OVERVIEW                                                                                                                                                                                               |           | The 4MW SCU has two major i<br>STORE UNIT INTERFACE is the<br>(maximum of four store unit<br>INTERFACE is the link betwee               |

| 3.1.1      | System Controller Functions                                                                                                                                                                                   |           | (processors, input/output module                                                                                                        |

|            | Functions of the SCU are as follows:                                                                                                                                                                          | 3.1.3.1   | System Port Interface                                                                                                                   |

|            | <ul> <li>Synchronize communications between active system modules.</li> </ul>                                                                                                                                 |           | The SCU has 8 board locations                                                                                                           |

|            | <ul> <li>Provide the operating system with a centralized hardware time base.</li> </ul>                                                                                                                       |           | modules. The board locations<br>Depending on the customer's                                                                             |

|            | <ul> <li>Service all valid requests from active system modules in a predeter-<br/>mined port priority scheme.</li> </ul>                                                                                      |           | eight MX boards may be added<br>processor and an input/output<br>options (two MX boards and as                                          |

|            | <ul> <li>Provide the necessary logic control to interface with as many as four<br/>attached storage units.</li> </ul>                                                                                         |           | system with multiple central could utilize all port options (8                                                                          |

|            | <ul> <li>Provide interlace capability between each pair of the attached store<br/>units.</li> </ul>                                                                                                           |           | It should be noted that the<br>determines the hard wired port<br>port priority while port 7 has 1                                       |

|            | <ul> <li>Provide the necessary maintenance logic to test the SCU and the<br/>attached store units.</li> </ul>                                                                                                 |           | means if two or more ports re-<br>the higher priority port will be<br>priority port requesting a cyc<br>slowest active modules (input/c |

| 3.1.       |                                                                                                                                                                                                               |           | priority port locations while th<br>are placed in the lower priorit<br>priority, the port options are                                   |

|            | The configuration panel of the SCU is located in the Main Memory Cabinet.<br>The panel is utilized by the operator to configure the system. The panel provides switchable control of the following functions: |           | (For a complete description of 3.2.1.)                                                                                                  |

|            | • Storage capacity for both storage units (A and B).                                                                                                                                                          |           | The System Port Board (SCAM)                                                                                                            |

|            | • On line/off line mode for store units.                                                                                                                                                                      | <b>w.</b> | Series 60 Level 66, Level 68, a<br>with the System Controller usi<br>active module must contain an                                      |

|            | <ul> <li>Interrupt cell mask assignment switches for mask A and B only.</li> </ul>                                                                                                                            |           | FRE                                                                                                                                     |

|            | • Lower store.                                                                                                                                                                                                |           | Location                                                                                                                                |

|            | • Port enable.                                                                                                                                                                                                |           |                                                                                                                                         |

|            | • Interlace.                                                                                                                                                                                                  |           | AOL<br>AOM                                                                                                                              |

|            | • Cyclic priority.                                                                                                                                                                                            |           | AON<br>AOP                                                                                                                              |

|            | • Upper address boundary.                                                                                                                                                                                     |           | A0Q<br>A0R                                                                                                                              |

|            | Nonexistent address detection enable.                                                                                                                                                                         |           | AOS<br>AOT                                                                                                                              |

|            | <ul> <li>Program/manual configuration mode.</li> </ul>                                                                                                                                                        |           |                                                                                                                                         |

Initialize function

58009922-100

interfaces to external system modules. The he link between the SCU and the storage units its options allowed). The SYSTEM PORT een the SCU and the active system modules ales, etc.).

as dedicated to interfacing with active system as are dedicated to port option boards (MX). needs, varying quantities from two through ed to the SCU. A basic system with a central at multiplexer would require two active port associated cable harnesses). A more complex 1 processors, input/output multiplexers, etc., 8 MX boards and associated cable harnesses).

he physical positioning of the port options rt priority. In the SCU, port 0 has the highest is the lowest port priority. Port priority simply request a cycle from the SCU simultaneously, be serviced first, followed by the next highest ycle, etc. As a general rule of thumb, the /output multiplexers) are placed in the highest the fastest active modules (central processors) ity port locations. With the exception of port identical and may be installed in any other. of the active port interface, see paragraph

#### (XN

and 6000 active system modules can interface sing the system port options listed below. The n active system port for each SCU connection.

#### EE STANDING SCU

| Port | Board |

|------|-------|

| 0    | SCAMX |

| 1    | SCAMX |

| 2    | SCAMX |

| 3    | SCAMX |

| 4    | SCAMX |

| 5    | SCAMX |

| 6    | SCAMX |

| 7    | SCAMX |

#### Store Port Interface

The system controller provides connection to as many as four WMQL66LA Memory Modules. When two modules (store units) (or two pairs of store units) of equal size are connected, the SCU provides for interlacing of addresses and overlapping of cycles in the two (pairs of) units.

For a complete description of the Store Port Interface see paragraph 3.2.2.

## The Store Port Board (SCUMY)

| Location | Store Number |

|----------|--------------|

| A0G      | А            |

| A0H      | AI           |

| A0J      | В            |

| A0K      | B1           |

#### SCU Logic Boards 3.1.3.3

The following paragraphs present a brief description of the functions of the various logic boards used in the SCU, including the Hardware Cache Clear (Write Notification) Option, WHCC66LB.

#### SCAMM (AØA)

This is the early cycle timing board which performs the following logic functions:

- Port priority control.

- Poll for system interrupts.

- Develop early cycle strobes.

- Detect illegal commands from system ports.

- Stop on illegal action.

- Cyclic priority.

- Micro Processor logic for the following functions:

- A. Interupt control for ports 0-8.

- B. Read address logic for bite 02-23.

- C. Read ØRCV ports 0-8.

- D. ZAC logic and control.

#### SCAMC (AØE)

This is the configuration register board which contains the following logic/performs the following functions:

- Configuration register.

- Configuration register mask A.

- Configuration register mask B.

- Configuration register port mask.

- Configuration register store control.

- Mask port decode.

- Mask display logic.

- Mask select.

- Reset mask select.

- Write data drivers.

- - C. Program interrupt timer chip.

- 0-17.

#### SCUMK (AØD)

This board contains the interrupt cells and mask registers. The SCUMK is a high density board that was designed for the low profile equipment. The board contains the following logic/performs the following functions:

- Execute interrupt cells.

- Interrupt cell mask registers.

- Interrupt cell enable logic.

- Execute interrupt (XIP) logic. Interrupt cell priority.

- Execute address generation.

- RMSK and RGR display drivers.

#### SCAME (AØB)

This is the look ahead logic board. It performs store select tasks for all models of the SCU. The SCAME board contains the following logic/performs the following functions:

- Address look ahead.

- Store selection.

- Configuration distribution.

- Illegal action register.

- Illegal action encode.

- Illegal action decode and stop logic.

- - A, Port 8 look ahead logic.

- B. Read illegal action information.

HONEYWELL CONFIDENTIAL AND PROPRIETARY

Microprocessor logic for the following functions:

A. Microprocessor chip 8085A, address/data base control logic. B. USART chips for Remote and Local communication interface logic. D. 8K RAM memory and 12K EPROM memory. E. Read logic for Read Data bite 0-17 and write data drivers for bits

Microprocessor logic for the following functions:

#### SCAMF (AØF)

This is the clock and history register board for all models of the SCU. It contains the calendar clock, history registers, and the control logic.

- Microprocessor logic for the following functions:

- A. Read the read-data bits 18-71.

- B. Write the write-data bits 00-71.

- C. Address counter and logic bits 02-23.

- D. Read the write-data bits 18-71.

- Select logic for writing address as data or data-bits 00-71. Ε.

- F. Parity logic for write-data bits 00-71.

#### SCAMJ (AØC)

This is the late cycle control board which contains the following logic/performs the following functions:

- Logic initialize for SCU. •

- Connect (\$CON) to system ports. •

- SANS and SEOC processing. •

- Generates Data Available (\$DA) strobe. •

- Store A and store B control. •

- Early cycle and late cycle counters. •

- History register (partial) and controls. •

- Mode register. .

- Display drivers. .

- Microprocessor logic for the following functions:

- A. 16K EPROM memory.

- **\$DA logic.** в.

- C. History register and display logic.

- D. Stop on IA control logic.

#### SCUMH (AØU)

This board is part of the write notification (hardware cache clear) option. The function of the cache clear option is to inform the CPU(s) when the contents of a location in main memory is changed. The CPU initiating the change is exempt from notification.

#### SCAMX (AØL-AØT)

This is the system port board which serves as the interface between the active system modules (CPU, IOM, etc.) and the SCU. The quantity of SCAMX boards in any SCU is a function of the number of active modules in the particular system. The board contains the following logic/performs the following functions:

- Port control.

- Parity check. .

.

- Generates receive control (CRCV). .

- Generates transmit (\$XMT) strobe. .

- Generates zone addresses.

- Microprocessor logic to disable MX board.

#### SCUMY (AØG-AØK)

This is the memory port board which serves as the interface between the main memory and the SCU. The quantity of SCUMY boards in any SCU is a function of the quantity of main memory modules in the particular system. The board contains the following logic/performs the following functions:

- Decodes memory commands.

A ISSUED

Transfers commands and addresses to memory. Transfers illegal action codes to active modules. Transfers data between active modules and SCUMY board.

Transfers control signals between the memory modules and the SCU.

Stores and transfers ZAC information to the memory modules. Transfers data between the active modules and the memory modules.

#### GENERAL

3.2

The System Control Unit (SCU) has two basic functions:

.

- 1. Providing priority-controlled memory access for information storage and retrieval functions for the active system modules.

- 2. Providing intermodule communications paths for control of hardware operations within the computer.

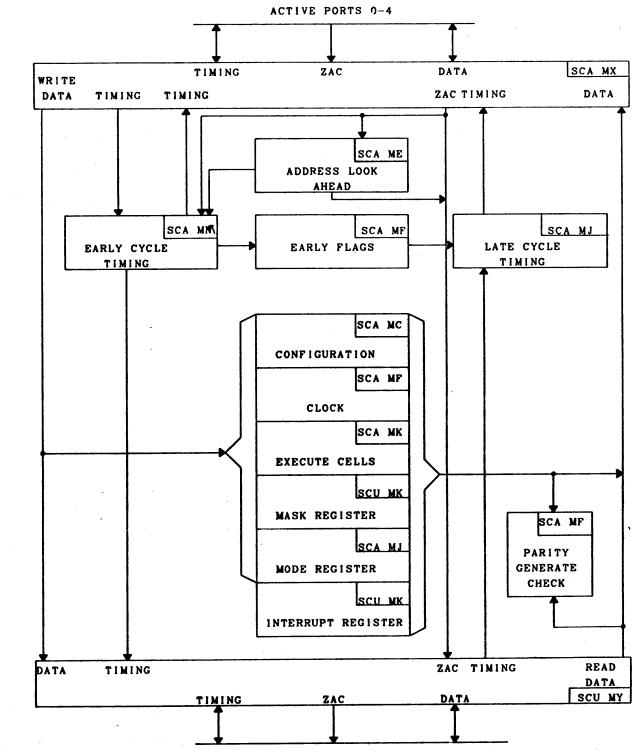

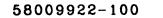

Figure 3-1 presents the major block diagram for the Four Megaword (4MW) SCU.

The SCU contains the port interfaces which enable communication between the system modules and the storage unit, and intercommunication between system modules. Each cycle begins when a system module issues an interrupt strobe to the SCU via one of the active port interfaces.

The SCU also contains store interfaces which act as communications links between the SCU and the storage units.

58009922-100

A ISSUED

Figure 3-1 4MW SCU MAJOR BLOCK DIAGRAM

#### 3.2.1 Port Interfaces

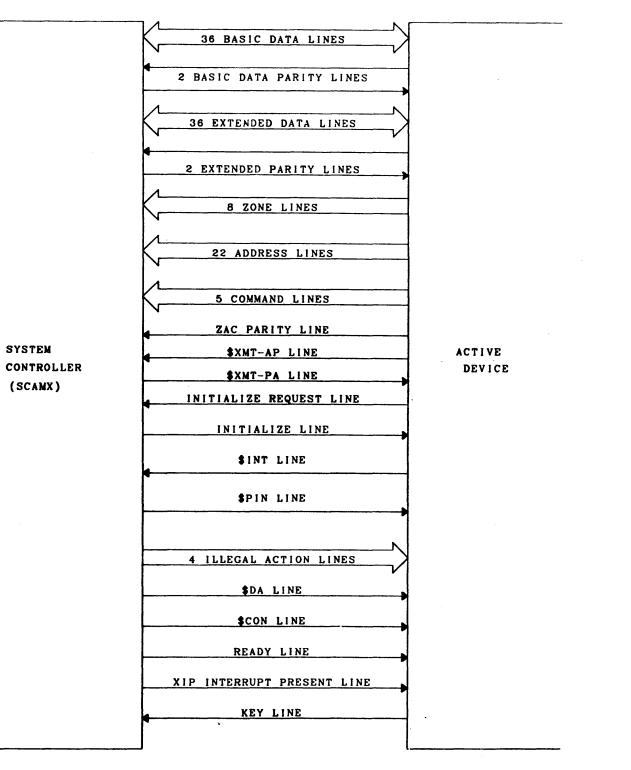

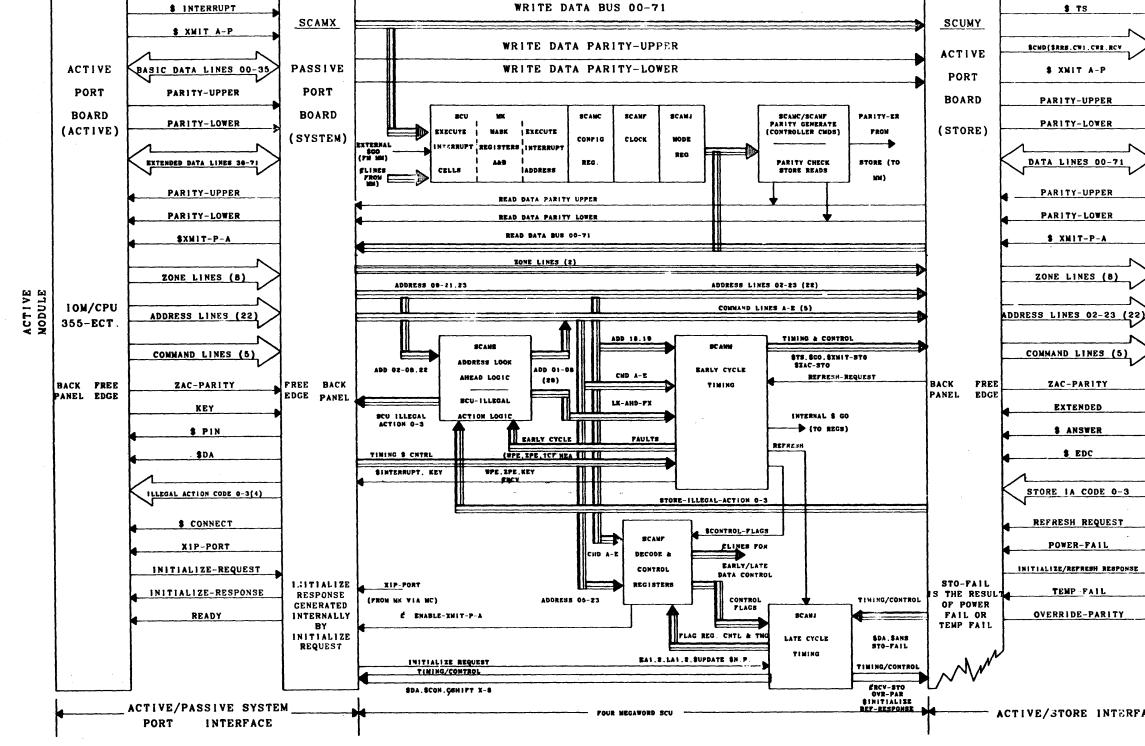

The port interfaces, Figure 3-2, provide the necessary hardware and logic to connect the Communications Processor Unit (CPU), the Input/Output Multiplexer (IOM), and the other active modules to the SCU.

Data at the port interfaces is 72 bits wide plus two parity bits. As with all system modules, the parity is odd. Bit 00 of the data is most significant and bit 71 is least significant. Although the data bus is bidirectional, the parity lines are unidirectional.

ZAC lines (8 Zone, 22 Address, 5 Command) are unidirectional and carry information from the requesting active module to the SCU with each cycle request.

Timing and control signals include the port interface control necessary for a complete SCU cycle, plus various non-cycle oriented controls. The cycle controls include the \$INT (request for cycle), \$PIN (request honored, cycle in progress), \$DA (data available), and the illegal action lines from the SCU indicating status of the just-completed cycle.

In addition to normal cycle controls, others include the Connect Strobe  $(\CON)$  and the Execute Interrupt Present (XIP) to enable intercommunication between active units. To register data from an active unit to the SCU, the active unit issues a Strobe Transmit ( $\XMT-AP$ ) pulse. To register data from the SCU to an active unit, the SCU issues a Strobe Transmit ( $\XMT-PA$ ) pulse.

The SCU is also the distribution center for the System Initialize (INZ) signal. This signal may be issued by any active unit and is distributed by the SCU to all enabled active units attached to the interface.

FIGURE 3-2 SYSTEM PORT INTERFACE

The Ready Line originates with the SCU. It is sent to the attached active units to notify them that the SCU and the storage unit are available for system access.

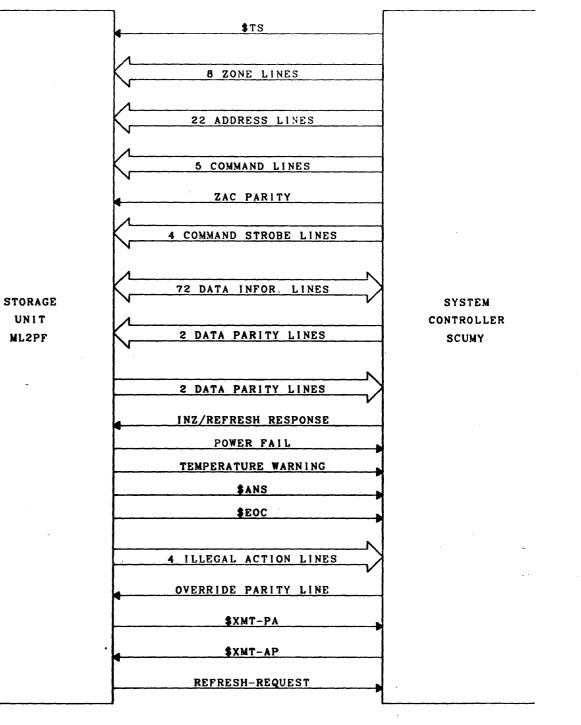

#### 3.2.2 Store Interfaces

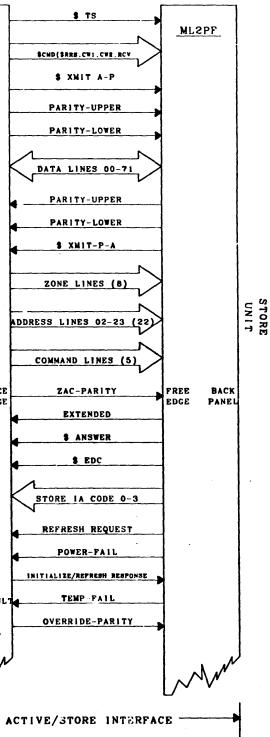

The store interfaces (Figure 3-3) contain the necessary hardware and logic to accomplish interface between the SCU and the storage unit(s).

Data and ZAC exchanges between the SCU and the storage units are the same as between the active units and the SCU. Refer to paragraph 3.2.1 for details.

Timing and control lines at the store interface differ slightly from the port interface. The cycle controls include the following:

- 1. Storage unit start pulse (\$TS) similar to \$INT.

- 2. Storage unit answer pulse (\$ANS) similar to \$PIN.

- 3. Storage unit end of cycle pulse (\$EOC) similar to \$DA.

- 4. Illegal action lines from the storage unit, indicating status of the justcompleted cycle.

In addition to these control signals, four command strobes are issued by the SCU to the storage unit. These command pulses inform the storage unit what type of cycle to perform.

- 1. \$RRS Read Restore

- 2. \$RCL Read and Clear

- 3. \$CW1 Clear Write Zone (Single Precision)

- 4. \$CW2 Clear Write Double Precision

The storage units will also inform the SCU, via the control lines, of power and temperature failures.

#### 3.2.3 SCU Cycles

To start a cycle, an active module (CPU, IOM, etc.) gates the ZAC lines and then transmits an Asynchronous Interrupt Strobe (\$INT) to the SCU. This \$INT strobe, requesting a cycle, initiates the following sequence of events. For a complete early cycle, refer to Figure 3-4.

- 1. SCU uses the look ahead bits of the address to ensure that the memory storage unit may be accessed by the active module.

- 2. SCU receives an \$INT strobe from an active module requesting access to a memory unit.

- 3. SCU stores the strobe on an FREQUEST bistable (FREQ).

- 4. SCU checks priority of the requesting active module. If the requesting port has the highest priority, the SCU gates the data and ZAC onto the data bus.

#### FIGURE 3-3 STORE PORT INTERFACE

| SINT PORT-X1000                 | 0 60                             |

|---------------------------------|----------------------------------|

|                                 | 15 203                           |

| FREQUEST-PX:100                 | 209                              |

| DREQ-PX:110                     | 27                               |

| SET-FPRI-PX;100                 |                                  |

| PRIORITY-REG;000                | 43 87                            |

| \$PRIORITY; 100                 | 51 94                            |

| FPR1-PX:100                     | 61                               |

| SAMPLE-PRI-REG: 100             | 87 274                           |

| LOCK-ZAC;100                    | 79 180                           |

| \$START: 100                    |                                  |

| READ-PRIORITY                   | 102 203                          |

| ØRCV-PORT-X:000                 | 107 209                          |

| SET-BSY-A;110                   | 122 225                          |

| STO-A-SEL:100                   | 128                              |

| \$CONTROL-FLAGS                 | 137 187                          |

| \$START + 40;010                | 150 195                          |

| ILLEGAL CND                     | 150                              |

| FBSY-STO-A:100                  |                                  |

| \$RMSK-SEL;000                  |                                  |

| \$ZAC-STO-A;000                 |                                  |

| \$TS-STO-A:000                  |                                  |

| \$TS-ALL+60;150                 | 180 237                          |

| \$XMT-STO-A;000                 | 183 248                          |

| \$RSET-RPRI;000                 | 197 242                          |

| \$GO-ALL;000                    |                                  |

| FINT-\$G0:000                   | 223 257                          |

|                                 | 228                              |

| FEXT-\$G0:100<br>\$G0-ST0-A:000 |                                  |

|                                 | 271 324                          |

| \$RSET-SAMP-PRI:00              |                                  |

| \$XEG-ADDR;00                   | 0 X = PORT NUMBER 0 TO 7 272 312 |

# FIGURE 3-4

# EARLY CYCLE TIMING

. -

- 5. SCU performs a parity check on the zone, address, and command (ZAC) lines. (SCUMX board)

- SCU sets an error flag (ZPE) if an error is detected. This sets the abort 6. bistable which inhibits the command strobe to the store port.

- 7. SCU sends a Control strobe (\$PIN) to the active module as notification that the requested cycle is being processed.

- 8. SCU accesses the memory storage unit by generating a \$TS pulse.

- 9. SCU decodes the zone, address, and command (ZAC) lines to determine the type of cycle the active module has requested.

- 10. SCU issues a command strobe to the memory storage unit. The strobe is determined by the type of cycle requested by the active module. The strobe may be aborted by an error.

- 11. The accessed memory storage unit sends an Answer Strobe (\$ANS) to the SCU, verifying readiness to receive the data.

Triggering of the \$ANS strobe by the memory storage unit signals the end of the early cycle and the beginning of the late cycle.

The sequence of events in the late cycle are as follows:

- 1. SCU enables the data paths as determined by controls set in the early cycle.

- SCU enables the controls and issues a response according to the type of 2. cycle requested by the active module.

- 3. SCU issues a Data Available (\$DA) strobe to the memory storage unit, signalling transfer of data from the SCU.

- Accessed memory storage unit issues an End of Cycle strobe (\$EOC) to the SCU, indicating that the cycle is nearing completion.

- 5. Illegal action codes from the accessed memory storage unit and within the SCU are examined, encoded, and sent to the requesting active module.

#### FUNCTIONAL DESCRIPTION 3.3

#### Port Interface Signals 3.3.1

The system port interface consists of signal lines to/from the active module as shown in Figure 3-5. All communication between the active module and the SCU takes place over these lines. Subsequent paragraphs describe these lines and their basic timing relationships.

3.3.1.1

The signal lines are listed below. The designation "true" indicates the interface receives/sends a high-level (nominal =5 volts) when the signal is enabled. The designation "false" indicates the interface receives/sends a low level (0 volts) when the signal is enabled.

lines (true = 1).

parity lines (true = 1).

Zone Lines (8 unidirectional lines from active module) (true = 1)

Command Lines (5 unidirectional lines from active module) (true = 1)

ZAC Parity (1 unidirectional line from active module) (true = 1)

(true)

module) (false)

Key Line (1 unidirectional line from active module) (true)

Illegal Action Lines (4 unidirectional lines from SCU) (true = 1)

Connect Strobe (\$CON) Line (1 unidirectional line from SCU) (false)

Transmit Strobe (\$XMT-PA) Line (1 unidirectional line from SCU) (true)

Initialize (INZ) (1 unidirectional line from SCU) (false)

Ready (RDY) (1 unidirectional line from SCU) (false)

Interrupt Present (XIP) Line (1 unidirectional line from SCU) (false)

Basic Data and Extended Data

The 38 basic data lines (36 bidirectional data lines and 2 unidirectional parity lines) plus the 38 extended data lines (36 bidirectional data lines and 2 unidirectional parity lines) make up a 74 line data path for transfer of data with parity to/from the SCU. The sense of parity is odd with bit 72 as the basic data parity bit and bit 73 as the extended data parity bit.

Basic Data Lines (36 bidirectional data lines, and two unidirectional parity

Extended Data Lines (36 bidirectional data lines, and two unidirectional

Address Lines (22 unidirectional lines from active module) (true) = 1)

Transmit Strobe (\$XMT-AP) Line (1 unidirectional line from active module)

Initialize Request Line (1 unidirectional line from active module) (false)

Access Request Strobe (\$INT) Line (1 unidirectional line from active

Acknowledge Strobe (\$PIN) Line (1 unidirectional line from SCU) (false)

Data Available Strobe (\$DA) Line (1 unidirectional line from SCU) (false)

# HONEYWELL CONFIDENTIAL & PROPRIETARY

INFORMATION FLOW 4 MEGAWORD SCU

FIGURE 3-5.

All single precision operations will utilize the basic data lines. During single precision operations, the extended data lines and extended parity line are ignored.

#### 3.3.1.2 Zone Lines

The (8) unidirectional zone lines are used to specify which 6- or 9-bit characters are to be operated on during a single precision write operation (clear write). The store unit will ignore the zone lines for all commands except single precision write.

The following table shows the zone assignments:

| Data Bits | Field Si  | ize  |             |                 |

|-----------|-----------|------|-------------|-----------------|

| Affected  | Character | Byte | Zone        | Line            |

| 00-05     | 6         | 9    | zo          | Zone Zero       |

| 06-08     | 6         |      | ZIU         | Zone One Upper  |

| 09-11     |           |      | ZIL         | Zone One Lower  |

| 12-17     | 6         | 9    | Z2          | Zone Two        |

| 18-23     | 6         | 9    | Z3          | Zone Three      |

| 24-26     | 6         |      | <b>Z4</b> U | Zone Four Upper |

| 27-29     |           |      | Z4L         | Zone Four Lower |

| 30-35     | 6         | 9    | 75          | Zone Five       |

3.3.1.3

#### Address Lines

The 22 unidirectional address lines (A2-A23) are used to specify the location in which a store module access is to occur or, in the case of internal SCU cycles, the address of an internal register. Address line (A2) is the most significant address bit and line (A23) is the least significant address bit.

#### 3.3.1.4 Command Lines

The (5) unidirectional command lines are used to specify the command to be executed when the access request (\$INT) pulse from the active module is acknowledged. Illegal combinations of command lines are trapped and the active module notified via the illegal action lines.

#### 3.3.1.5 ZAC Parity

The active module generates odd parity for the combined zone, address and command (ZAC) lines and furnishes this parity to the system port.

#### 3.3.1.6 Transmit Strobe (\$XMT-AP)

The transmit strobe (\$XMT-AP) is utilized by the active module to control the strobing of data into the SCU port board receive register.

3.3.1.7 Initialize Request The system port accepts the initialize request signal from the active module (usually originated at the IOM or system console). This signal is accepted by the SCU and distributed through other system ports via the initialize line. 3.3.1.8 Access Request Strobe (\$INT) The access request strobe (\$INT) is used by the active module to initiate an SCU command. 3.3.1.9 Acknowledge Strobe (\$PIN) The acknowledge strobe (\$PIN) notifies the active module that the requested cycle is in progress. The time period (at the system port) from SINT to SPIN is a function of whether the SCU is currently busy servicing another port, and the priority of the port that is requesting access. 3.3.1.10 **Illegal** Action Lines The system port provides four unidirectional lines to the active module coded to provide illegal action information. These four lines are valid following the transfer of the data. Parity is not generated on the illegal action lines. 3.3.1.11 Data Available Strobe (\$DA) The data available strobe (\$DA) is the pulse issued by the SCU indicating that the requested data will be valid in the active module port board a short time later. The active module receives \$DA pulse for all SCU cycles (write or read) with SDA preceding the illegal action lines. For write cycles, SDA is effectively and End of Cycle pulse since there is no data sent to the requesting active module. 3.3.1.12 Connect Strobe (SCON) The connect strobe (SCON) is a pulse from the SCU to alert the active module of intermodule communication. \$CON is the result of a connect command to the SCU and will be generated as a function of the \$DA pulse of the connect command. The SCU sends \$CON to the designated system port provided the port is enabled. SCON to a not enabled port will result in an illegal action to the system port originating the connect command. 3.3.1.13 Execute Interrupt Present (XIP) The execute interrupt present (XIP) is a level from the SCU to an active

The execute interrupt present (XIP) is a level from the SCU to an active module designated as a system control module indicating a program interrupt cell requires service. The SCU can designate up to two system ports as control ports via the program interrupt mask register assignment switches on the SCU configuration panel. Under program control, up to eight system ports can be designated as control ports.

HONEYWELL CONFIDENTIAL AND PROPRIETARY

#### Transmit Strobe (\$XMT-PA) 3.3.1.14

The transmit strobe (\$XMT-PA) is the signal used by the SCU to strobe data into the active module port board data receive register.

Initialize (INZ) Line 3.3.1.15

> The Initialize (INZ) signal is a level from the SCU which causes all on-line active modules to go to the initialized state. The initialize signal occurs asynchronous of all system timing.

#### Data Flow 3.3.2

Data flow through the SCU is in two directions and is accomplished on two unique sets of lines.

- 1. Data coming from a requesting active module, and destined for either memory or one of the SCU's internal registers, is transferred via the write-data bus.

- 2. Data read from memory or one of the SCU's internal registers, and destined for a requesting active module, is transferred via the readdata bus.

#### Write Data Bus 3.3.2.1

Incoming data is transferred from the system ports to the store ports via a common bus referred to as the "write-data bus". Data is gated onto the write-data bus by the "receive control" signal CRCV. This control signal is generated by the port priority and timing logic which is located on the SCAMM board. Since this logic determines which requesting system port will be granted store access, only the data from one port will be present on the bus at any given time.

Data on the write-data bus is gated to the memory logic by a transmit strobe \$XMT; XXX. This logic, located on the memory port boards, places the data on the interface line to the memory unit designated by the look ahead address. The contents of these lines is gated into the memory write register by the control logic. The write data is gated internally by the internal command decode logic and is placed on the memory data lines, but it is ignored because the SCU is executing a read data command.

#### Read Data Bus 3.3.2.2

Data read from memory is transferred to the requesting active module via the read data bus. The read data bus is organized in the same manner as the write data bus since a common bus is used to transfer data from the store ports and internal registers to the active system ports. The main difference is that the parity check logic for outgoing data is on the SCAMF board. This logic checks and generates parity on all outgoing data. Control logic for outgoing data is provided on the SCAMX board which formats data, as required by the command being executed, and places it out on the output data lines. It should be noted that the data on the read data bus is presented to the input of all system ports, but is only transmitted by the port that requested the data. Requesting port identification is obtained from the history register logic on the SCAMF board.

#### 3.3.2.3

ZAC Bus

Zone, address, and Command information is carried on 35 unidirectional lines referred to as the ZAC bus.

- o Zone information is carried on 8 lines.

- 0

- Parity information is carried on one line. 0

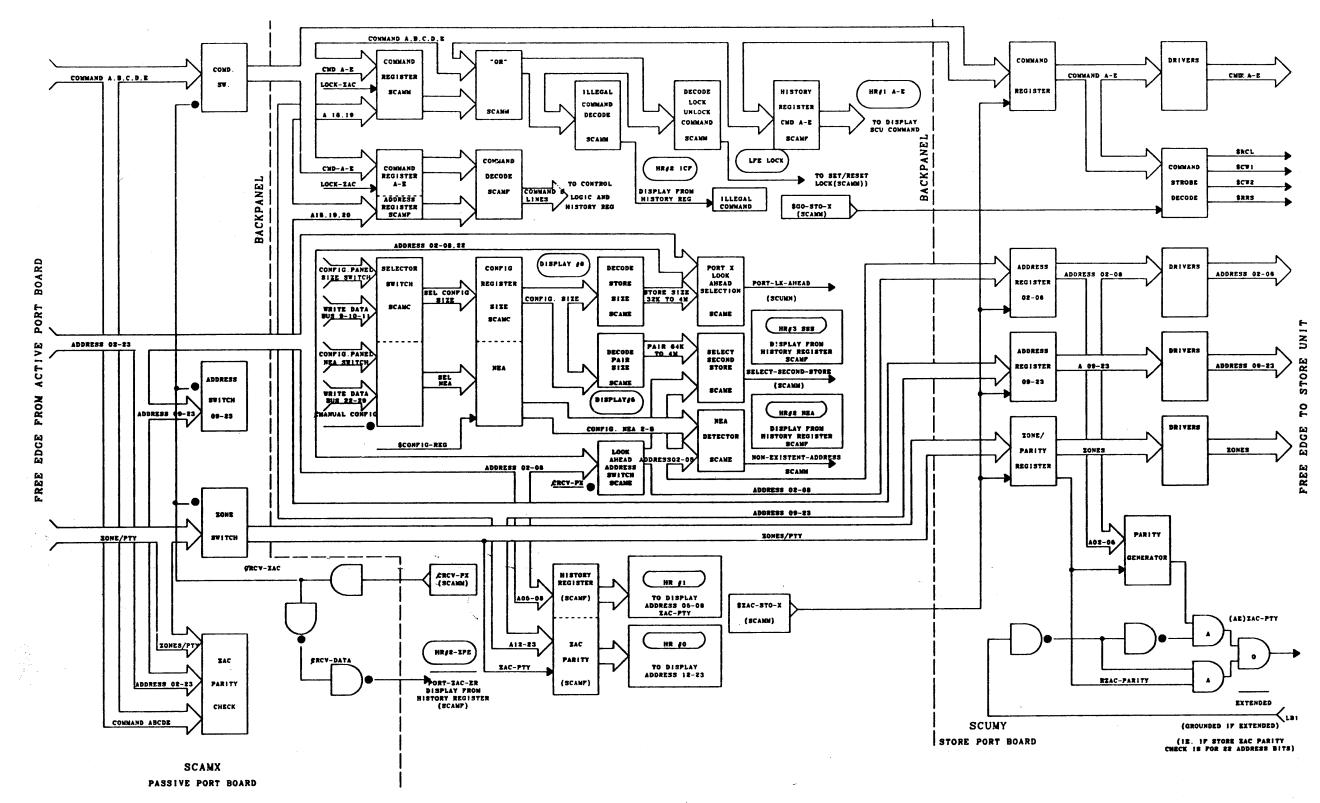

As shown in Figure 3-6, information on these lines flows from the requesting active module to the system port on the SCAMX board. From there it is routed to the SCAMM board where it is decoded and registered. The one exception is that information on the look ahead lines is routed to the SCAME board.

The zone, address, and command switches permit the information contained on 27 ZAC lines to be gated to the internal SCU logic, and to the SCUMY boards when QRCV for the port is detected.

The look ahead portion of the address is gated from the SCAMX board to Look Ahead Address Board (SCAME) by the look ahead address switch. These bits are used as an advance check to determine whether the request is directed at Store A or Store B.

The parity check logic looks for odd parity on the ZAC information. If an error is detected, it is reported to the SCU as a Port-ZAC-Error and a ZPE flag is set. Discovering the error, the SCAMM board aborts the command strobe to the store unit and the SCU's internal registers. The cycle is aborted by an illegal action code of 14-octal.

3.3.2.4

#### Parity

The system extensively checks transmission parity on intermodule data transfers. The SCU checks all data and ZAC parity received from the active modules as well as data parity received from the storage units, and generates an illegal action code if a parity error is detected. For data involved in reading the internal registers, the SCU generates the parity bit and passes it on to the requesting active module.

3.3.3

#### ZAC Logic Operation

The ZAC bus should be present at the input of the SCAMX board at least 10 nanoseconds prior to arrival of the \$INT. \$INT causes the SCU to initiate a new early cycle if it is not busy with another port. This is conditional on the previously sent look ahead address.

Address information is carried on 14 lines plus 8 lines for look ahead. Command information is carried on 5 lines.

#### FIGURE 3-6 FUNCTIONAL DIAGRAM ZAC FLOW

HONEYWELL CONFIDENTIAL AND PROPRIETARY

----

44

In Figure 3-6, note that all ZAC lines are only enabled to the SCU's common ZAC bus when the CRCV for the port is received by the SCAMX port board. The look ahead bits are wired directly to the input of the SCAME look ahead address board. The SCAME board has one look ahead circuit for each of the system ports. The logic for each port is constantly comparing the look ahead bits with the decode of the store size. The store size is made up by decoding the store size field of the programmable configuration register. The output of the decoder is 7 lines, each representing one of the 8 possible sizes of the lower store unit. The configuration register is loaded three ways:

| Conf. Panel<br>Mode Switch | Conf. Reg.<br>Load Source | When Loaded      |

|----------------------------|---------------------------|------------------|

| Manual                     | Conf. Pnl. Sws            | Unconditionally  |

| Program                    | Conf. Pnl. Sws            | Sys. or Pnl INZ  |

| Program                    | SGR-Data Word             | SGR-Conf.Reg Cmd |

As can be seen from the above chart, when the unit is in manual mode or the unit is in program mode with the system or unit initialized, the configuration register SIZE field is loaded from the LWR-Store-Size switch on the configuration panel. System initialize will occur every time the system is bootloaded. So, for program or manual mode, the initial state of the configuration register is set to correspond with the switch settings. In the program mode, the register retains the information read from the switches until such time as a Set General Register Configuration Register is performed. At the present time, only the T&D programs use this command.

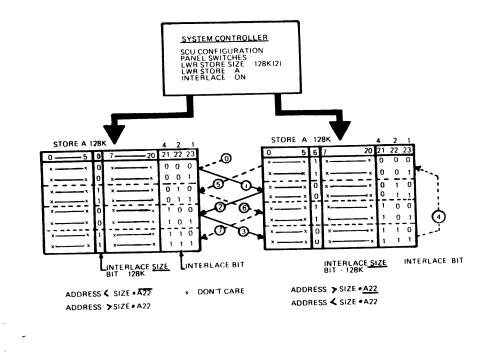

Address line 22 has to do with interlacing, which may or may not be enabled. Interlace is a method of forcing the SCU to address different store units (pairs) for every other sequential access to store. This permits full use of the overlap between the early and late cycles, thus increasing system thruput. For example, if the SCU has two 128K Store units attached as Store A and Store B, (see Figure 3-7), and an active module requests a cycle with all of the address look ahead lines in their zero state (false), the lower store unit (normally address 0-128K-1) is selected for the cycle. If the lower store unit is busy with a current cycle, the request is postponed until it becomes available for a request.

Taking another example, where the interlace function is enabled and the active module requests a cycle with all address look ahead lines in their zero (false) state except line 22 which is a one (true), the upper store unit (normally 128K-256K-1) is selected for the cycle. This is accomplished by decoding the store size from the size field of the configuration register. (See Figure 3-7) The interlace function is controlled by the configuration panel INTERLACE ON/OFF switch or the programmable function in the configuration register.

The address look ahead lines, in effect, interrogate the status (busy or not busy) of the store unit prior to letting the requested cycle proceed.

Rules for interlace:

1. Store A and B must be of equal size. 2. Store A and B must be of equal speed.

Numbers in circles indicate the interlace pattern, assuming the configuration given. The numbers 0 thru 3 show how the sequential addresses are threaded into both Store A and B dependent upon the Interlace bit 22. Note that at 4 the Size bit Address 6 goes to the ONE state. This assumes that all addresses from 0 to 128K-1 follow the same pattern of operation. When the SIZE bit determined by the LWR - STORE - SIZE configuration, goes to the ONE state the pattern reverses itself. Numbers 4 thru 7 show this effect. The SIZE bit corresponds to the following settings of the LWR - STORE - SIZE switch.

| Switch Seting                   | Size                                           | Size Bit (Address Bit)                 |

|---------------------------------|------------------------------------------------|----------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6 | 32K<br>64K<br>128K<br>256K<br>512K<br>1M<br>2M | 08<br>07<br>06<br>05<br>04<br>03<br>02 |

|                                 |                                                |                                        |

A ISSUED

# FIGURE 3-7 SYSTEM CONTROLLER TWO WORD INTERLACE

The address look ahead lines are redriven from the SCAME address look ahead board to become part of the common ZAC bus to the store units. These lines are gated off the SCAME board with QRCV for the port.

The look ahead address, in addition to being gated to the input of the store port boards with the remaining portion of the ZAC bus, are also sent to the select second store and non-existent address logic. The select second store logic on the SCAME board compares the look ahead address with a decode of the pair size to determine which store unit of a pair is to be selected. This is done by developing seven unique pair size lines (Pair - 64K to Pair - 4M), one of which will be true. The pair size bit is then ANDed with an address line one binary power less than the pair size. If the AND condition is met, a check is made to determine if the store unit is on and, if so, the control term Select-2nd-Store is true. This term is used in conjunction with STO-A-SEL to control which store port board will receive \$TS and External \$GO (\$ COMMAND) during the early cycle.

The Non-Existent-Address (NEA) logic on the SCAME board compares address bits 02 to 08 with the contents of the NEA portion of the configuration register. If the address is equal to or greater than the register an NEA results. If the cycle is not a controller only operation, the level ABORT is generated causing the store function to be aborted. Abort inhibits the command strobe from being sent to the selected store unit.

The command lines, in addition to being transmitted to the store port boards, are latched up in two registers. One register is located on the early cycle control board (SCAMM). The other register is located on the SCAMF board.

The command register on the SCAMM board includes address bits 18 and 19 and is used for the decode of all illegal commands.

Of the 32 possible commands with the 5 command lines, only 14 commands are legal. This leaves 18 illegal combinations. Any SCU command which addresses upper store is also defined as an illegal command. Bits 18 and 19 are included in the register and decode because the RGR/SGR commands use this address to define the type of operation to be performed. All the variations of the RGR/SGR commands, except for store mode register operations, are considered controller operations. For store mode register operations, address bits 18 and 19 are true (high). This inhibits the illegal command fault if the upper store is addressed.

The early cycle timing board decodes the read lock and write lock instructions to permit set or reset of the lock bistable.

The WRT-CMD is decoded for loading into the control flag register for data control during the late cycle. Controller-Command is also a term which is decoded for loading into the control flag register.

The command register (SCAMF) is loaded at the same time as the command register on the SCAMM board with LOCK-ZAC. This register includes address bits 18-20 along with command lines A to D. The function of this register is to hold the current early cycle command for decoding. The address bits are included for the RGR/SGR commands. These commands use the address to define the specific variation of the operation. The early cycle operations (writes and set register commands) obtain their control lines directly from the decode of this register. Decodes of commands for late cycle operations (reads) are loaded into the control flag register (SCAMF) during the early cycle. The commands loaded into the control flag register are gated out during the late cycle and become the sense lines to control data flow.

The command lines are loaded into the history register along with address lines 5-8, 12-23, and the ZAC parity bit for display for troubleshooting.

All ZAC lines internal to the SCU feed the inputs of all SCUMY boards. Selection of which store unit pair receives the ZAC input is a function of which store busy bistable is set during the early cycle. Both store units of the pair receive the \$ZAC that causes the ZAC lines to be loaded into the ZAC registers. As soon as these registers are loaded, the output is redriven thru drivers to the store units.

| Store<br>Operation | COMMAND          | Command Strobe |

|--------------------|------------------|----------------|

| Read Data          | RRS-SP, RRS-DP   | <b>\$</b> RRS  |

| Read Data          | RDLCK            | <b>Š</b> RRS   |

| Read Data          | CON              | ŚRRS           |

| n/a                | RMSK-DP, SMSK-DP | <b>Š</b> RRS   |

| n/a*               | RGR/SGR          | <b>Š</b> RRS   |

| n/a                | XEC              | \$RRS          |

| n/a                | SXC              | \$RRS          |

| Write              | CWR-SP           | <b>\$CW1</b>   |

| Write              | WRLCK            | \$CW1          |

| Write              | CWR-DP           | \$CW2          |

\*\$RGR/SGR Store Unit Mode Register commands use \$RRS in the store unit.

There is also parity generation logic on the SCUMY board which is used to generate parity on 22 address bits. LB21, a pin on the free edge connector of the SCUMY board determines that parity will be generated for 22 address lines. This free edge connector is connected by cable to the port board of the store unit. The port board has internal jumpers to denote the address bus size. The term EXTENDED is true (high) and parity is generated on 22 address lines (ZAC bus = 35 bits).

3.3.4

Timing and Control

units:

Early cycle timing and control logic.

HONEYWELL CONFIDENTIAL AND PROPRIETARY

#### A ISSUED

Logic for all SCU timing and control is divided into two major functional

• Late cycle timing and control logic.

An early cycle is initiated when an interrupt strobe (\$INT) from an active module is accepted by the SCU. The cycle is concluded when the command strobe is sent to memory. A late cycle is initiated when the answer strobe (\$ANS) is received from memory. The cycle is concluded when the illegal action code is placed on the output lines.

The early cycle timing and control logic is physically located on the SCAMM board. The late cycle timing and control logic is on the SCAMJ board.

#### Write Data and Parity Control Logic 3.3.4.1

Write Data and parity control logic permits the contents of the write register 00-71 to be gated to the SCU's internal write bus when SENSE RECEIVE (*QRCV*) is detected by the board. The write parity upper and lower are also gated to the SCU's internal lines by QRCV. Two control terms from the SCU (COMMAND-D and QRCV) govern transmission of data from the write register to the SCU's write data bus.

- COMMAND-D (CMD-D) is the command-D received from the active • module via the ZAC bus and is locked up in a register chip on the SCAMX board.

- SENSE RECEIVE is transmitted to the SCAMX board by the SCAMM board during the early cycle.

SENSE RECEIVE and CMD-D, both true (high), cause the SCAMX board to generate two internal control lines: CRCV-DATA and CRCV-SHIFT.

QRCV-DATA causes write register 00-35 to be gated to the SCU's write data bus 00-35 along with the upper parity bit. SENSE RECEIVE DATA also controls the output of the upper word parity. If a parity error is detected, the term Upper-Data-Error is true which, enabled by SENSE RECEIVE DATA, is ORed to the SCU internal logic as WRITE-DATA-ERROR. The SCU responds by causing the Write Parity Error (WPE) fault to be generated, aborting the operation in the early cycle.

QRCV-SHIFT causes write register 36-71 to be gated to the SCU's write data bus 36-71 along with the lower parity bit. It also permits the lower word parity check logic output to be ORed to the SCU internal logic as WRITE-DATA-ERROR if a parity error exists. The SCU responds by aborting the operation with a WPE.

Write Data and Parity Control - Single Precision 3.3.4.2

> CMD-D false (low) indicates a single precision operation. When QRCV is detected by the port and CMD-D is false, the SCAMX generates two internal control lines which are QRCV-DATA and QRCV-SHIFT. QRCV-DATA functions the same as the double precision operation. It gates write register 00-35 onto the SCU write bus 00-35 along with the upper parity bit and the output of the write data parity checker for bits 00-35. CRCV-SHIFT causes write register 00-35 to be gated onto the SCU write data bus 36-71.

The parity bit received from the active module is gated to the SCU as WRITE DATA PARITY LOWER. The output of the write data parity checker for the upper word is enabled to the SCU.

3.3.4.3

Control for transmission and shifting of data is handled by three input signals to the SCAMX port board. The signals are:

- **SDA-PORT**

- ENABLE-XMIT-PA

- SENSE SHIFT-XB-PA

\$DA is sent during the late cycle for any command requested by the active module. ENABLE-XMIT-PA is a function of the control register write bit being decoded during the late cycle. If the write term is low, ENABLE-XMIT-PA is sent to all SCAMX boards. SENSE-SHIFT-XB-PA is decoded by the SCAMJ board by looking at CMD-D and address bit 23 (even/odd). If CMD-D is false (single precision) and address bit 23 is true (odd address), the term SENSE-SHIFT-XB-PA is generated and sent all SCAMX boards. For double precision operation \$DA-PORT is generated, since the port has been flagged for response during the late cycle. SENSE-SHIFT-XB-PA is false because the CMD-D line is true. ENABLE-XMIT-PA is true because a read operation is being performed. The SCAMX board enables two internal control lines (\$XMIT and \$XMIT-SHIFT) and one external strobe (\$XMIT-PA). \$XMIT-SHIFT causes the SCU's read data bus 00-35 to be gated onto the basic bidirectional data lines (00-35) to the active module. This control also gates the read data parity upper bit from the parity register on the SCAMX board to the active module.

- port board parity register.

- bidirectional data lines to the active module.

- bit to the active module.

Read Data and Parity Control - Single Precision (Even Address)

Data and parity control for read operations that are directed to even addresses are identical to the double precision operation except that the active module only accepts the data on the basic data lines. The extended data lines are latched into the active module's MY port board receivers, but are ignored by the module.

HONEYWELL CONFIDENTIAL AND PROPRIETARY

3.3.4.4

58009922-100

Read Data and Parity Control - Double Precision

\$XMIT always strobes the parity bits received from the SCU into the

\$XMIT always enables the SCU read data bus 36-71 to the extended

The lower parity bit from the SCU is always gated to the parity lower

\$XMIT-PA is used by the active module to indicate that data has been trasmitted, and latches it into the receivers on the MY board.

#### SCU COMMANDS

Commands applicable to the SCU are described in this section and summarized in Table 3-1. Symbols and terms used in the command descriptions are as follows:

- Y = absolute address received by the SCU from the active module 0 initiating the command.

- C(Y) = contents of storage location specified by Y. 0

- $\implies$  = replaces. 0

- Basic Data Lines = bits 00-35. 0

- Extended Data Lines = bits 36-71. 0

| COMMAND SUMMARY   |         |    |   |          |   |   |             |  |

|-------------------|---------|----|---|----------|---|---|-------------|--|

| Command           |         |    |   |          |   |   |             |  |

|                   |         | A  | B | <u>C</u> | D | E | Octal Code* |  |

| READ RESTORE SP   | RRS-SP  | 0  | 0 | 0        | 0 | 0 | 00          |  |

| READ RESTORE DP   | RRS-DP  | 0  | 0 | 0        | 1 | 0 | 04          |  |

| READ CLEAR        | RCL     | 0  | 0 | 1        | 0 | 0 | 10          |  |

| READ MASK DP      | RMSK-DP | 0  | 0 | 1        | 1 | 1 | 16          |  |

| CLEAR WRITE SP    | CWR-SP  | 0  | 1 | 0        | 0 | 0 | 20          |  |

| CLEAR WRITE DP    | CWR-DP  | 0  | I | 0        | 1 | 0 | 24          |  |

| SET MASK DP       | SMSK-DP | 0  | 1 | 1        | 1 | 1 | 36          |  |

| LOCK              | RDLK    | 1  | 0 | 0        | 0 | 0 | 40          |  |

| READ GEN REGISTER | RGR     | 1  | 0 | 1        | 1 | 0 | 54          |  |

| SET GEN REGISTER  | SGR     | 1  | 0 | 1        | 1 | 1 | 56          |  |

| UNLOCK            | WRLK    | 1  | 1 | 0        | 0 | 0 | 60          |  |

| CONNECT           | CON     | 1  | 1 | 0        | 0 | 1 | 62          |  |

| EXECUTE           | XEC     | 11 | 1 | 0        | 1 | 1 | 66          |  |

| SET EXECUTE       | SXC -   | 1  | 1 | 1        | 0 | 1 | 72          |  |

Table 3-1.

\*Octal Code adds a pseudo zero-bit in the low order bit position of each command.

#### 3.4.1 Memory Read Commands

Memory read commands are used by the active modules to extract data which is stored in memory.

#### Read Restore Single Precision (RRS-SP) (00<sub>o</sub>) 3.4.1.1

The C(Y) are sent to the requesting system port on the basic data lines. The C(Y) in memory are not altered. The data word is selected using address bits 2-23 of address Y. The C(Y) equals 36 data bits and one parity bit.

3.4.1.2 Read Restore Double Precision (RRS-DP) (04<sub>o</sub>)

The C(Y) are sent to the requesting active module on the basic and extended

(72 data bits) plus two parity bits.

3.4.1.3

to memory as all zeroes.

Memory Write Commands

Read and Clear (RCL) (10<sub>o</sub>)

3.4.2

3.4.2.1

3.4.2.2

3.4.3

Memory write commands are used by the active modules to transfer data into memory. Two types of write commands are used:

- transferred in 3 or 6 bit bytes.

- 0 extended data lines (72 bits) into memory.

Odd parity is checked and generated on each 36 bit increment of write data by the SCU. If an illegal action is detected, the cycle is aborted and the appropriate illegal action code is sent to the active module.

C(Y)C(Y)

Are written into memory in the location specified by the contents of the address lines. The bit positions to be altered must be specified by the contents of the zone lines. Unaltered bits are restored to memory without change.

Clear/Write Double Precision (CWR-DP) 01010 (24) C(Y)The contents of both basic and extended data lines.

C(Y)Are written into the memory location specified by the contents of address lines.

System Control Commands

These commands are used by the active modules to control system operation and to communicate with each other. Intersystem communication and control are implemented by means of registers which are physically located in the SCU.

58009922-100

HONEYWELL CONFIDENTIAL AND PROPRIETARY

#### A ISSUED

data lines. The C(Y) in memory are not altered. The data consist of C(Y)

The RCL command functions the same as RRS-SP except C(Y) are restored

SINGLE PRECISION COMMAND - used with the contents of the zone lines to transfer up to 36 bits of data into memory. Data may be

DOUBLE PRECISION COMMAND -transfers contents of basic and

Clear/Write Single Precision (CWR-SP) 01000 (20.)

= The contents of the basic data lines from the requesting port.

#### Set Execute Cells (SXC) 11101 (72<sub>g</sub>)

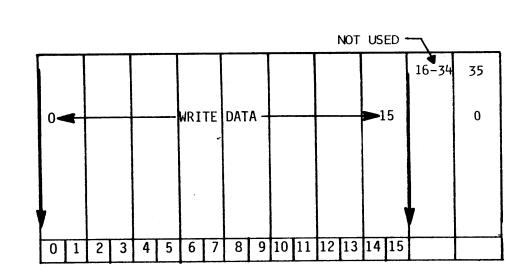

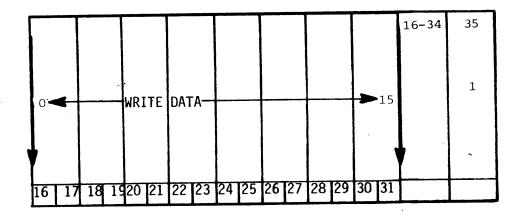

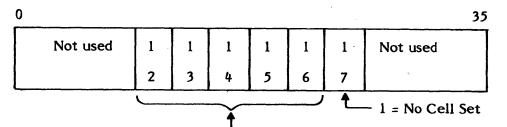

The SXC command is used by the active modules to set (write) the SCU execute interrupt register. The execute interrupt cells (register bits) are used by the active modules for intermodule communication. The most common usage is communication between the IOM and the CPU. In this application, the IOM sets a particular cell with an SXC command. The CPU responds by executing (reading) that cell with an XEC command. SXC is always single precision. SXC is similar in operation to CWR-SP. Figure 3-8 shows the structure of the execute interrupt register and the alignment of the data field presented to the SCU by the active module. As shown in Figure 3-8, data bit 35 of the SXC is the stacking bit during execution of the command. If bit 35 is "0" (false), the upper portion of the execute interrupt register (0-15) is selected. If bit 35 is "1" (true), the lower portion of the execute interrupt register (16-31) is selected. The total 36 bits of the data word are checked for parity and the SXC cycle is aborted if an error is detected.

INTERRUPT REGISTER FORMAT - WRITE DATA 35 = 0 Α. SET UPPER CELLS

INTERRUPT REGISTER FORMAT - WRITE DATA 35 = 1 Β. SET LOWER CELLS

# HONEYWELL CONFIDENTIAL AND PROPRIETARY

58009922-100

# FIGURE 3-8 INTERRUPT REGISTER FORMATS

As with all internal SCU commands, the address field associated with the cycle must access the lower assigned store unit attached to the SCU. Failure to comply results in an illegal command IA code (12 octal) and abort of the cycle. Data sent to the active module during an aborted cycle is whatever happens to be in the store unit location designated by the address. The SCU performs a read restore for aborted cycles and sends the appropriate illegal action code. An SXC command is also aborted if a ZAC parity error is detected by the SCU.

#### 3.4.3.2 Execute Interrupt Cells (XEC) 11011 (66,)

The XEC command is used by the active modules to read/execute an SCU execute interrupt cell (bit). The most common usage is communication between the IOM and the CPU. In this application, the IOM sets one of the 32 execute interrupt cells, using an SXC command. The CPU responds by executing that cell with an XEC. The XEC command is always single precision. It is similar in operation to RRS-SP.

Each execute interrupt cell has a hardwired address associated with it. The system operating software will allocate these addresses in the memory as the vectors associated with each individual interrupt cell. Figure 3-9 shows the hardwired address associated with each execute interrupt cell and the data lines on which this address is transferred to the active module executing the interrupt.