# HONEYWELL

## GENERAL

## Honeywell

## THE MULTICS VIRTUAL MEMORY

MULTICS

#### SUBJECT:

Technical Papers on the Multics Virtual Memory as Designed for Model 645 Implementation.

#### SPECIAL INSTRUCTIONS:

These technical papers are reprinted here for theoretical and historical purposes only.

DATE:

June 1972

ORDER NUMBER:

AG95, Rev. 0

#### PREFACE

This document consists of three technical papers which describe the theory and practice of Multics virtual memory implementation. Multics (<u>Multiplexed Information and</u> Computing Service) is a general purpose computer system which has been designed to be a "computer utility." As such, it is essential that Multics provide its users with sufficient resources to do a wide variety of tasks and that the system be protected from destructive interactions between users. The papers address the theory, the practice, the hardware, and the software used to provide an effectively infinite memory to each user and to protect both the users and the system.

The first paper discusses the concept of a virtual memory and explores several ways in which such a memory could be implemented. The method used to implement the Multics virtual memory on the Series 600 Model 645 processor is developed in detail. This paper is of historical importance and presents valid Multics design theory although the Model 645 is no longer used as the Multics processor.

The second paper extends the discussion further into the subject of protection. The theory of the Multics ring structure is introduced and its implementation on the Model 645 is described. This theory is still valid although the Model 645 is no longer used as the Multics processor.

The third paper shows how the features described in the two earlier papers are handled by hardware under the optional Multics modifications to Series 6000 processors. Several new processor features are introduced and described. Use of these features allows Multics to run on the Series 6000 processors, specifically the Model 6180, with greatly increased efficiency as compared with the earlier implementation of Multics on the Series 600 processors.

The information and specifications in this document are subject to change without notice. This document contains information about Honeywell products or services that may not be available outside the United States. Consult your Honeywell Marketing Representative.

© General Electric Company, U.S.A., 1970 © Honeywell Information Systems Inc., 1972

File No.: 1LW3

An alphabetized list of abbreviations and acronyms used in all three papers has been included as an aid to the reader.

Papers in this document were written to further the understanding of the Multics design philosophy and practices. They are not intended to be specifications of the Multics system or its components. Authors have made simplifying assumptions at times to make the main point clearer and easier to understand. Persons requiring design specification details are requested to contact the Multics development staff for guidance and assistance.

"The Multics Virtual Memory" was first published as Technical Information Series Report R69LSD3, Copyright 1970 by General Electric Company, U.S.A.

"Access Control to the Multics Virtual Memory" was first published as Technical Information Series Report R69LSD4, Copyright 1970 by General Electric Company, U.S.A.

## CONTENTS

|    |                                                     | Page |

|----|-----------------------------------------------------|------|

| Α. | The Multics Virtual Memory                          | v    |

| в. | Access Control to the Multics Virtual Memory        | 119  |

| с. | Series 6000 Features for the Multics Virtual Memory | 165  |

| D. | Abbreviations and Acronyms                          | 191  |

A. The Multics Virtual Memory

#### CONTENTS

| Chapter | Title                                               |

|---------|-----------------------------------------------------|

| 1       | General Properties of the<br>Multics Virtual Memory |

| 2       | Overview of the Implementation                      |

| 3       | Directory Structure                                 |

| 4       | Making a Segment Known to a<br>Process              |

| 5       | Segment Fault Handling                              |

| 6       | Page Fault Handling                                 |

| 7       | Secondary Storage Management                        |

| 8       | Device Interface Modules                            |

#### PREFACE

In the past few years several well-known systems have implemented large virtual memories which permit the execution of programs exceeding the size of available core memory. These implementations have been achieved by demand paging in the Atlas computer, allowing a program to be divided physically into pages only some of which need reside in core storage at any one time, by segmentation in the B5000 computer allowing a program to be divided logically into segments, only some of which need be in core, and by a combination of both segmentation and paging in the 645 and the IBM 360/67 for which only a few pages of a few segments need be available in core while a program is running.

As experience has been gained with remote-access, multiprogrammed systems, however, it has become apparent that, in addition to being able to take advantage of the direct addressibility of large amounts of information made possible by large virtual memories, many applications also require the rapid but controlled sharing of information stored on-line at the central facility. In Multics (<u>Multiplexed Information and Computing Service</u>), segmentation provides a generalized basis for the direct accessing and sharing of on-line information by satisfying two design goals: 1) it must be possible for all on-line information stored in the system to be addressed directly by a processor and hence referenced directly by any computation. 2) it must be possible to control access, at each reference, to all on-line information in the system.

The fundamental advantage of direct addressability is that information copying is no longer mandatory. Since all instructions and data items in the system are processor-addressible, duplication of procedures and data is unnecessary. This means, for example, that core images of programs need not be prepared by loading and binding together copies of procedures before execution; instead, the original procedures may be used directly in a computation. Also, partial copies of data files need not be read, via requests to an I/O system, into core buffers for subsequent use and then returned, by means of another I/O request, to their original locations; instead the central processor executing a computation can directly address just those required data items in the original version of the file. This kind of access to information promises a very attractive reduction in program complexity for the programmer. If all on-line information in the system may be addressed directly by any computation, it becomes imperative to be able to limit or control access to this information both for the self-protection of a computation from its own mishaps, and for the mutual protection of computations using the same system hardware facilities. Thus it becomes desirable to compartmentalize or package all information in a directlyaddressible memory and to attach to these information packages access attributes describing the fashion in which each user may reference the contained data and procedures. Since all such information is processor-addressible, the access attributes of the referencing user must be enforced upon each processor reference to any information package.

Given the ability to directly address all on-line information in the system, thereby eliminating the need for copying data and procedures, and given the ability to control access to this information, then controlled information sharing among several computations follows as a natural consequence.

In Multics, segments are packages of information which are directly addressed and which are accessed in a controlled fashion. Associated with each segment is a set of access attributes for each user who may access the segment. These attributes are checked by hardware upon each segment reference by any user. Furthermore <u>all</u> on-line information in a Multics installation can be directly referenced as segments while in other systems most on-line information is referenced as files.

#### Chapter 1

#### GENERAL PROPERTIES OF THE MULTICS VIRTUAL MEMORY

#### 1. INTRODUCTION

In recent literature the term "virtual memory" has become quite familiar. The adjective "virtual" suggests that this memory is the image of an ideal memory that one would like to have, since it complies with the actual needs of a multiprogramming, multiple-access computer utility. This "ideal memory" is not available as a hardware device and has been simulated by the Multics system using a conventional memory with the assistance of additional hardware and software features.

This chapter describes the properties of the ideal memory, justifies the desire for these properties, and explains the principles of the simulation of this memory.

#### 2. THE IDEAL MEMORY

In order to describe this ideal memory the terms "segment" and "segmented memory" need to be defined first.

#### 2.1. <u>Segments</u>

A segment is an entity defined by:

- 1) A <u>name</u> which uniquely identifies the segment.

- 2) A <u>descriptor</u> which describes the properties or "attributes" associated with the segment.

- 3) A body which is an array of consecutive elements.

The name is a character string of arbitrary length.

The descriptor contains all attributes the system designer needs to attach to the segment: the size and the physical location of the body, access rights for different users with respect to this segment, the date it was created, etc.

The body of the segment is an ordered set of elements, called words, each of which is identified within the segment body by an integer i, its index. The number of elements in the body is called the length of the segment.

## 2.2. Segmented Memory

A segmented memory will be defined as a memory with the following properties:

- 1) It is capable of containing segments and only segments.

- 2) If it contains a segment named n, then n is the address of the descriptor of this segment and the pair [n,i] is the address of the i<sup>th</sup> element in the body of this segment.

- 3) It is capable of performing operations on the descriptor and the body of any segment, in accordance with the attributes recorded in the descriptor.

#### 2.3. Ideal Memory

The ideal memory can now be defined as a large, segmented memory directly accessible by the processor, where by "large" it is meant that the maximum number of segments that one can store in it is adequate for the needs of the system.

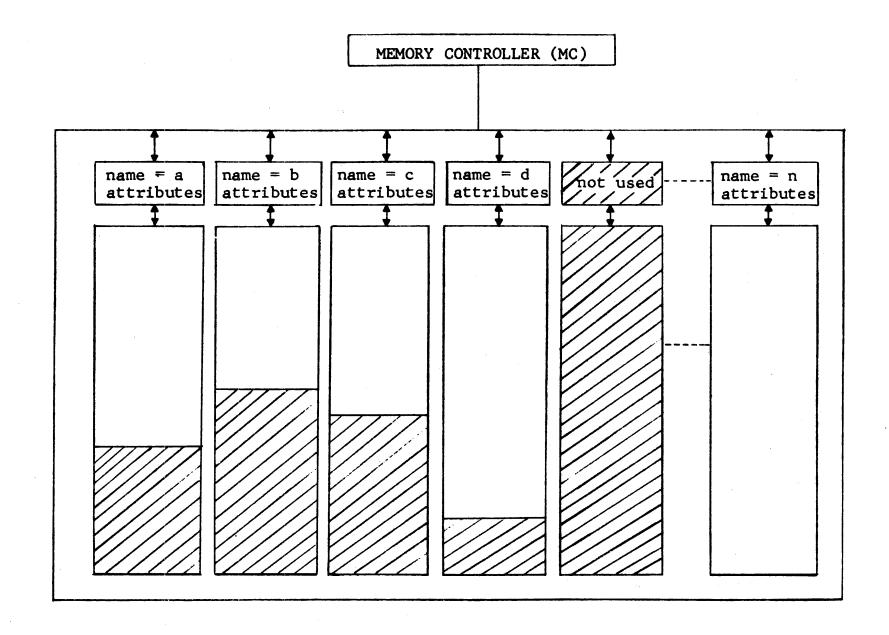

A simple representation of such a memory is shown in Figure 1; it comprises a memory controller (MC), a large number of descriptors each of which contains the name and the attributes of a segment, and a large number of linear memories each of which is connected to a descriptor and can contain the body of a segment.

The processor can send two types of requests to the MC: requests for operations on descriptors and requests for operations on bodies. In both cases the processor must communicate to the MC the identification of the user on behalf of whom the operation is requested.

## 2.4. Operations on Descriptors

The general form of a request sent by the processor to the MC for operations on descriptors is

OPCODE n arguments userid

where:

- OPCODE designates operations, such as "create a segment", "change the length of a segment", "change access rights";

- n is the name of the segment. The MC uses it to locate the appropriate segment descriptor;

- arguments are parameters associated with the function defined by OPCODE;

- userid is the identification of the user on behalf of whom the operation is requested. The MC uses this userid in order to determine from the attributes of the segments whether this particular user has the right to perform this particular operation.

#### 2.5. Operations on Segment Bodies

The general form of a request sent by the processor to the MC for operations on segment bodies is

OPCODE [n,i] userid

where:

- OPCODE designates operations, such as "read", "write", "instruction fetch";

- n is the name of the segment; the MC uses it to locate the appropriate segment descriptor. It then uses the segment descriptor to locate the segment body;

- i is the index of the word within the segment to which the operation is to be applied;

- userid is used by the MC as above.

Figure 1. Organization of the Ideal Memory

4

#### 3. JUSTIFICATION OF THE IDEAL MEMORY PROPERTIES

The ideal memory has been defined as a "large segmented memory directly accessible by the processor". The advantages of such an ideal memory will be explained by successively introducing the advantages of a memory, that is: 1) large (but not segmented); 2) segmented (but not large); and finally, 3) large and segmented.

#### 3.1. Large, Unsegmented Memory

Because the memory is large and directly accessible by the processor, the user is provided with a core memory large enough for any of his computations. Therefore, he can run a program without being concerned with its size. However, no matter how large the core memory is, if it is a linear memory accessible by a single number, no sharing of information in core can be tolerated between programs of different users since no protection mechanism is in effect at the time a word is accessed.

#### 3.2. Small, Segmented Memory

Because the memory is segmented and directly accessible by the processor, the user is provided with several independent linear core memories in each of which he can store one of his segments, deciding who can access it and how. Therefore, the same segment can be shared in core by several user programs without the danger of unauthorized accessed to this segment. However, even though the memory is segmented, if the number of segments that one can store in it is small, the user is faced with the problem of overlays.

#### 3.3. Large, Segmented Memory

By having the two properties "large" and "segmented" a directly accessible memory provides the user with:

- a large machine-independent memory. There is a oneto-one correspondence between the <u>name</u> by which the user references a one-word datum and the physical <u>location</u> in memory where the datum resides. As a consequence, users are provided with a simple means of writing programs such that, when executed, they <u>access</u> common information in core. They merely have to reference this information by its name. - a protection mechanism. This mechanism is in effect during execution at any memory access and protects segments from unauthorized access.

#### 3.4. Note on Information Sharing

It is worth making some remarks about information sharing. Information to be shared consists of data and procedures.

- Sharing data or procedures in core requires:

- a) A mechanism by which a reference to a segment by its name X will cause segment X, and not a copy segment X, to be referenced during program execution.

- b) A mechanism by which the shared information can be protected from unauthorized access while it is in core.

- Sharing procedures in core also requires:

- c) A mechanism by which one can produce pure procedures that can be executed simultaneously by several programs.

The memory described here provides a) and b), but not c). In fact the memory itself cannot provide c); writing a pure procedure implies the ability of communicating as parameters to this procedure the names of any information private to the program on behalf of which the procedure is executing. These names cannot be stored in the memory itself; they have to be stored in processor registers whose names are invariant. During execution of a pure procedure by a processor on behalf of a program, the names of data segments private to the program are stored in processor registers whose names are stored in the pure procedure. The processor requests the data from the memory controller using the name found in the appropriate processor register.

#### 4. PRINCIPLE OF THE SIMULATION

The memory presented here is simulated in the Multics system, this simulation being achieved by a combination of hardware and software features. Hardware segmentation has been implemented in the 645 and constitutes the most important of the hardware features mentioned above. Paging has also been implemented in the 645; although of immense help to the implementation, we do not regard paging as a concept fundamental to a description of the principles of the ideal memory simulation and shall postpone the discussion of paging until the end of this section.

Let us first examine how much of the ideal memory capability has been integrated into the hardware. Then a discussion of the software functions needed to compensate for those capabilities which are not provided by the hardware will follow.

#### 4.1. Hardware Segmentation in the 645

Concepts of segment name, segment descriptor, and segment body have been integrated into the hardware as follows.

4.1.1. <u>Segment Names</u>. A segment name for the hardware is an integer s, called segment number, such that  $0 < s < 2^{18}$ .

4.1.2. <u>Segment Descriptors</u>. The segment descriptor of segment "s" is the sth entry of a table called a Descriptor Segment. The descriptor segment is in core memory and its absolute address is kept in a processor register. A descriptor segment entry is called a Segment Descriptor Word (SDW). SDW number s will be designated by the notation SDW(s).

Attributes that can be recorded in an SDW area are:

- The absolute core address of the head of the segment body.

- The length of the segment body.

- Access rights for only <u>one</u> user with respect to the segment <u>body</u>.

- An invalid attribute flag. F, which, when ON, signals the absence of the above attributes in the SDW and causes the processor to fault.

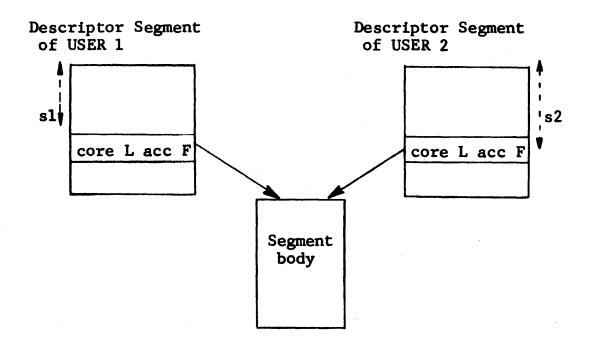

Since an SDW can contain access rights for one user only, each user program must be provided with a private descriptor segment. (See Figure 2.)

## Figure 2. Hardware Segment Descriptors

4.1.3. <u>Segment Bodies</u>. The segment body is an array of contiguous words in core memory and its maximum length is  $2^{18}$  words.

4.1.4. <u>Address Transformations</u>. Word number i of the body of segment s is addressed by the pair [s,i] and is accessed through SDW(s) by the processor.

Provided that the absolute core address  $m_0$  of word 0 of the segment is stored in SDW(s), the processor transforms -

- the processor segment name s into the core memory address  $m_0$  using the descriptor segment which provides the mapping  $m_0 = Z(s)$ .

- the processor address [s,i] into the core memory address  $m_i$  by the translation  $m_i = m_0+i$ , that is  $m_i = Z(s)+i$ .

4.1.5. Access Rights Checking. Before accessing word  $m_i$  the processor performs a check on -

- the length of the segment by comparing i to the length recorded in SDW(s).

- The access rights for the user with respect to segment s by using the access rights recorded in SDW(s).

This hardware organization presents the following advantages over more conventional hardware.

- The set of processor addresses [s,i] is sufficiently large that all words referenced by a program can be assigned unique processor addresses. The user does not have to organize a large program into overlays provided that he uses no more than 2<sup>18</sup> segments.

- Processor addresses are independent of physical memory addresses. Addresses which appear in the instructions of a program are invariant when segments are moved from one location to another in core memory.

- Each access to core memory is subject to access rights checking.

However, the hardware has only a restricted understanding of the concept of segments and needs to be complemented by appropriate software features.

#### 4.2. Software Segmentation

Given the foregoing hardware segmentation capabilities, the corresponding software segmentation capabilities required to implement the Multics virtual memory can be described.

4.2.1. <u>Segment Names</u>. A segment name is a character string called a symbolic segment name. The set of symbolic segment names is larger than  $2^{18}$ . Therefore, the supervisor must map a large set of symbolic segment names into a smaller set of segment numbers.

4.2.2. <u>Segment Descriptors</u>. The hardware does not permit one to -

- retrieve attributes of a segment given the symbolic name of the segment. The software provides this capability.

- store all attributes of a segment in a hardware segment descriptor or SDW. The software provides complete segment descriptors for each segment and stores them in a catalog. See Figure 3.

| Segment<br>name | Segment Attributes        |        |                            |     |      |   |                     |  |

|-----------------|---------------------------|--------|----------------------------|-----|------|---|---------------------|--|

| a               |                           |        |                            | J   |      |   |                     |  |

| Ъ               |                           |        |                            |     |      | • |                     |  |

| с               | core/secondary<br>address | length | Access<br>Access<br>Access | for | user | 2 | other<br>attributes |  |

| d               |                           |        |                            |     |      |   |                     |  |

|                 |                           |        |                            |     |      |   | <u> </u>            |  |

#### Figure 3. Representation of a Catalog

4.2.3. <u>Segment Bodies</u>. The body of a segment is an array of contiguous words in <u>core</u> or in <u>secondary</u> memory. Since the processor can fetch data and instructions only from core-resident segments, the software must intercede when a segment is found to be missing from core.

4.2.4. Address Transformations. Assuming for the moment that all segments are in core memory, the supervisor performs the following three transformations to make segments accessible by the processor.

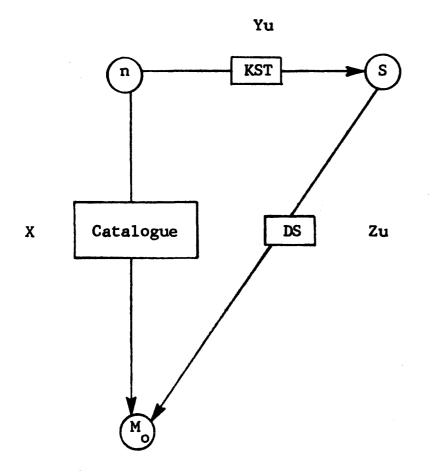

First, for any segment in the system, the supervisor must provide a one to-one mapping from its symbolic name n into its memory address  $m_0$ , where m is the address of the beginning of the segment. This mapping  $m_0 = X(n)^0$  is recorded in the catalog. See Figure 4.

Next, for each segment referenced by a user program, the supervisor must provide a one-to-one mapping from its symbolic name n into the segment number s assigned to it in this user program. This mapping s = Y(n) is recorded in a table associated with the user program and called the Known Segment Table (KST).

Finally, for each segment that has been assigned a segment number s in a user program, the supervisor must provide a one-to-one mapping between the segment number s and its memory address  $m_0$ . This mapping  $m_0=Z(s)$  is recorded in the descriptor segment associated with the user program.

The transformation X is independent of the user program; transformations Y and Z for user program u are userdependent and will be denoted as  $Y_{11}$  and  $Z_{11}$ .

11

In order to permit several user programs to share the same segment by merely referencing it by the same name, these transformations must be such that, for any user program,  $X(n) = Z_u(Y_u(n))$ .

To this point we have assumed that all segments are in core. In fact, core memory being limited, the supervisor has to move segments between core and secondary memory.

The transportation of segment n from core memory address m<sub>o</sub> to secondary memory address M must be associated with the following address mapping modifications:

m must be replaced by M<sub>o</sub> in the catalog entry for n.

m must be replaced by an undefined value in any SDW in which it appears. This is done by setting the invalid attribute flag ON in the SDW.

Note that the mapping between n and s remains unchanged in any user program.

A subsequent reference to segment n by segment number s in a user program will cause the processor to fault since the invalid attribute flag is ON in SDW(s). This fault will be referred to as a <u>missing segment fault</u>. Using the KST associated with this user program, it is possible to determine the name n of the segment s. Knowing n, the catalog entry for n can be found. The segment must be moved from secondary memory address M<sub>0</sub> to some (generally different) core memory address m'. This move must be associated with the following address mapping modifications:

M<sub>0</sub> must be replaced by m' in the catalog entry for n.

The undefined value (Flag) in SDW(s) must be replaced by m'.

Note again that the mapping between n and s remains unchanged by the move.

4.2.5. Access Rights Checking. We have seen how the supervisor responds to a missing segment fault occurring in a user program but the description was not complete. A missing segment fault is a signal to evaluate the segment attributes in a specific SDW. Only the evaluation of the core address attribute has been described. Moreover, when the supervisor extracts core address information from the catalog, it also extracts the length and access rights attributes and stores them in the SDW. Each subsequent hardware reference to the segment by this user program is made through the SDW with the hardware performing access checking. However, when performing operations on segment attributes the supervisor itself must do the necessary validation for any operation requested by a particular user since the hardware does not provide for access checking on attributes.

#### 4.3. Paging

In a system in which the maximum size of any segment were very small compared to the size of the entire core memory, the "swapping" of complete segments into and out of core would be feasible. Even in such a system, if all segments did not have the same maximum size, or had the same maximum size but were allowed to grow from initially smaller sizes, there remains the difficult core management problem of providing space for segments of different sizes.

Multics, however, provides for segments of sufficient maximum size that only a few can be entirely core-resident at any one time. Also, these segments can grow from any initial size smaller than the maximum permissible size.

By breaking segments into equal-sized parts called <u>pages</u> and providing for the transportation of individual pages to and from core as demand dictates, several practical problems encountered in the implementation of a segmented virtual memory are solved.

First, since only the referenced page of a segment need be in core at one instant, segments need not be small compared to core memory.

Second, "demand paging" permits advantage to be taken of any locality of references peculiar to a program by transporting to core only those pages of segments which are currently needed. Any additional overhead associated with demand paging should of course be weighed against the alternative inefficiencies associated with dedicating core to entire segments which have been swapped into core but which may be only partly referenced.

Finally, since pages are all of equal size, space allocation is immensely simplified. The "compaction" of information in core and on secondary storage characteristic of systems dealing with variable-sized segments or pages is thereby eliminated. The basic principles of paging in the Multics virtual memory may be briefly summarized as follows.

When a segment is not paged, the memory location of its element i is defined by relation (1), where  $m_0$  is the memory location of element 0.

(1)

$$m_i = m_0 + i$$

When a segment is paged into pages of K elements, the memory location of its element i is defined by relation (2), where  $m_{pK}$  is the memory location of element pK; that is, the memory location of the page number p of the segment.

(2)

$$\begin{cases} m_i = m_{pK} + j \\ j = i \mod K \\ p = (i-j)/K \end{cases}$$

If N is the number of pages in a segment, paging this segment requires -

- a segment map with N entries, one for each page.

- a relocation capability in the hardware.

In the 645 the N entries of the segment map are provided by a "page table" and the relocation is performed by the processor itself. Furthermore, a page table entry contains a <u>missing-page flag</u> such that, if found ON by the processor while attempting to perform relocation, causes the processor to trap to the supervisor.

The missing-page flag is ON when the corresponding page is not in core. When, upon attempting to access a missing page, the processor traps to the supervisor, the supervisor must move the requested page into core. In order to do so the supervisor must maintain a segment map of N entries in the software descriptor, i.e., in the directory entry. Each time page p is moved from one location to another, this move must be associated with the following address mapping modifications.

- Update the mapping in entry p of the segment map located in the directory entry.

- Update the mapping in entry p of the page table.

Although paging need not be considered essential to a description of the simulation principles of an ideal memory, it is a basic feature for the implementation of such a memory.

The next chapter describes in some detail how the ideal memory has been simulated in the Multics system, using hardware segmentation and hardware paging as implemented on the GE-645.

#### Chapter 2

#### IMPLEMENTATION OF THE MULTICS VIRTUAL MEMORY: OVERVIEW

#### 1. INTRODUCTION

As we have seen in Chapter 1, the Multics virtual memory is a large, segmented memory. Each segment can be referenced by its name in a user program; a reference by name will cause the segment to be accessed by the processor according to the access rights of the user with respect to that segment. The memory is called "virtual" because it is not available as a hardware device. Instead, it is simulated using a conventional non-segmented memory, a set of processor registers which provide the second dimension of a segmented memory and a supervisor which compensates for the difference in capabilities between the 645 hardware and the ideal memory described in Chapter 1.

Although the hardware checks each user's access rights to a segment whenever it accesses that segment, a certain number of additional functions must be provided by the supervisor in order to give the illusion that all segments are directly accessible by name by the processor.

- The hardware cannot <u>retrieve</u> the attributes of a segment using its symbolic name; the supervisor organizes segment attributes into "directories" where it can retrieve them.

- The hardware cannot <u>interpret</u> access rights for segment attributes; all operations on segment attributes are done by the supervisor.

- The hardware cannot <u>reference</u> a segment by a symbolic name; it does it by a segment number. The supervisor translates all symbolic segment names into segment numbers.

- The hardware cannot <u>access</u> a segment if it is not in core memory; each reference to a segment which is not in core will cause the supervisor to move the segment from secondary memory to core memory. In order to help the supervisor in core memory allocation, the hardware provides a paging capability.

17

This chapter builds upon the ideas developed in Chapter 1 to show in some detail how the ideal memory is simulated. The major topics covered are:

- Segmentation and paging on the 645 processor.

- The organization of segment attributes into hierarchically ordered directories and the manipulation of these attributes by the supervisor.

- Segment accessing and all the supervisory functions needed to make a segment directly accessible by the processor.

- The structure of the supervisor itself, showing how parts of the supervisor are able to utilize the virtual memory provided for user programs.

#### 2. THE 645 PROCESSOR

This paper discusses only those features of the 645 processor which are of interest for the implementation of a virtual memory. They can be grouped into two different classes -segmentation and paging -- and are treated separately below.

#### 2.1. Segmentation

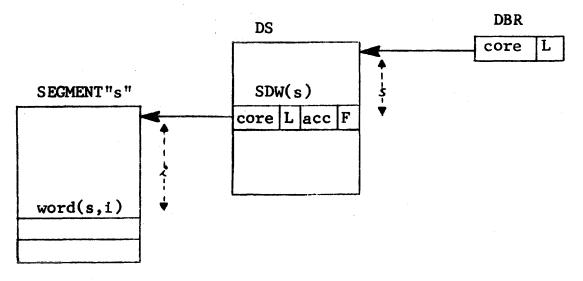

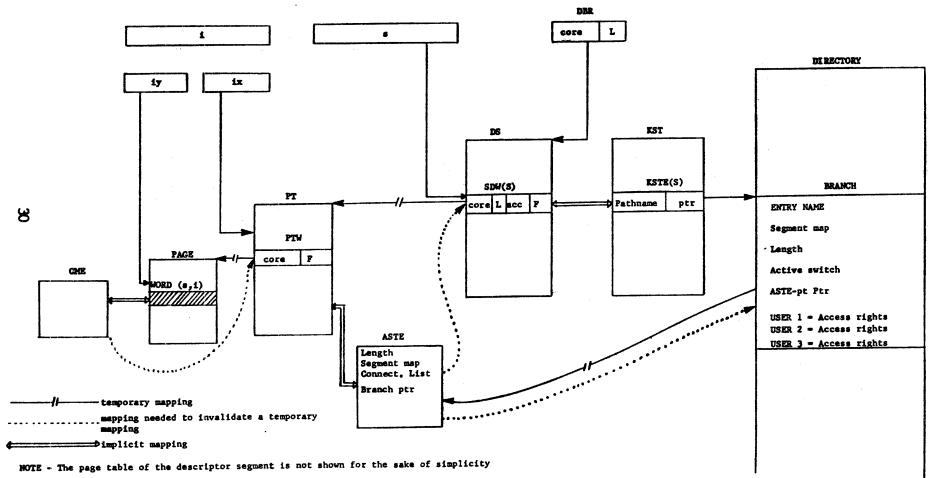

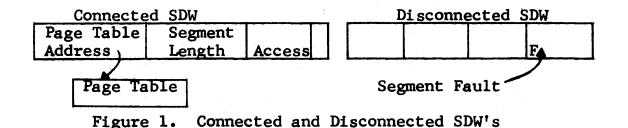

Any address in the 645 consists of a pair of integers [s,i]. The range of s and i is 0 to  $2^{18}$ -1. s is called the segment number, i the index within the segment. Word [s,i] is accessed through a hardware register which is the s<sup>th</sup> word in a table called a <u>descriptor segment</u> (DS). This descriptor segment is in core memory and its absolute address is recorded in a hardware register called a descriptor base register (DBR). Each word of the DS is called a segment descriptor word (SDW); the s<sup>th</sup> SDW will be referred to as SDW(s). See Figure 1.

The DBR contains the following values:

- DBR.core which is the absolute core address of the DS.

- DBR.L which is the length of the DS.

Segment descriptor word number s contains the following values:

- SDW(s).core which is the absolute address of the segment s.

- SDW(s).L which is the length of the segment s.

- SDW(s).acc which describes the access rights for the segment.

- **-** · SDW(s).F which is a flag that can be ON or OFF. This is the invalid attribute flag mentioned in Chapter 1.

The algorithm used by the hardware for executing an instruction of the type OPCODE [s,i] is as follows:

- If DBR.L <s, generate a fault.

Access SDW(s) at absolute location DBR.core + s.</pre>

- If SDW(s).F = ON, generate a missing segment fault.

- If SDW(s).L < i, generate a fault.

- If SDW(s).acc is incompatible with OPCODE, generate a fault.

- Apply OPCODE to the word whose absolute address is SDW(s).core+i.

Figure 1. Hardware Segmentation in the 645

The above description assumes that segments are not paged; in fact, paging is implemented in the 645 hardware.

#### 2.2 Paging

A bit in an SDW indicates whether the corresponding segment is paged or not. Another bit in the SDW indicates whether the page size is 64 or 1024 words. Analogous bits in the DBR serve the same purpose for the descriptor segment.

However, in the Multics implementation, all segments are paged and the page size is always 1024 words. Therefore, this description makes the following two assumptions:

- All segments are paged.

- The page size is a constant, K, equal to 1024 words.

No further reference will be made to these two bits in the SDW and DBR.

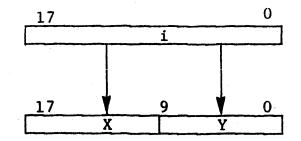

Element i of a segment is the  $y^{th}$  word of the  $x^{th}$  page of the segment, x and y being defined by:

$$\begin{cases} y = i \mod K \\ x = (i-y)/K \end{cases}$$

where K is the page size.

Since  $K = 1024 = 2^{10}$ , the processor can compute x and y from the 18 bit-binary representation of i by merely dividing i into two parts. The right part, which consists of the 10 least significant bits of i, represents the binary value of y; the left part, which consists of the 8 most significant bits of 1, represents the binary value of x. See Figure 2.

Figure 2. Hardware Interpretation of the Word Number

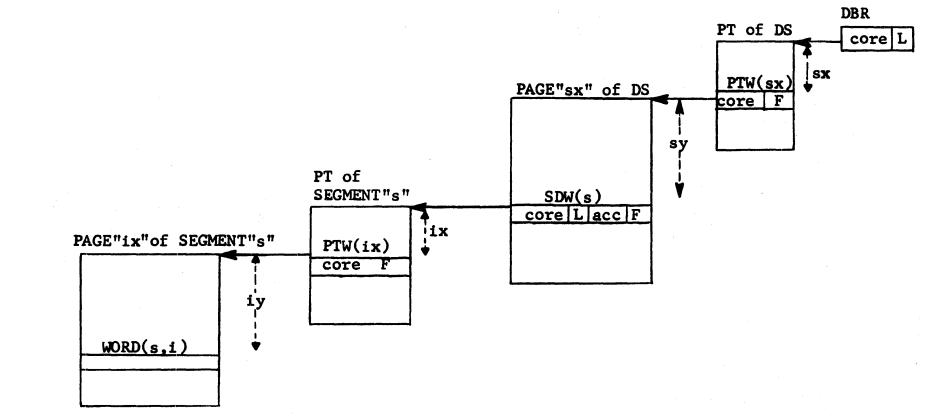

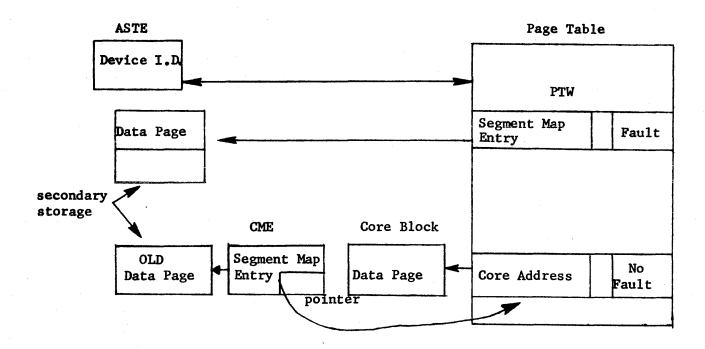

The <u>page table</u> (PT) of a segment is an array of <u>physically</u> <u>contiguous</u> words in core memory. Each element of this array is called a <u>page table word</u> (PTW).

Page table word number x contains the following items.

- PTW(x).core which is the absolute core address of page #x.

- PTW(x).F which is a flag that can be ON or OFF. This is the missing page flag mentioned in Chapter 1.

The meaning of DBR.core and SDW(s).core is now as follows:

- DBR.core = Absolute address of the PT of the DS.

- SDW(s).core = Absolute address of the PT of segment #s.

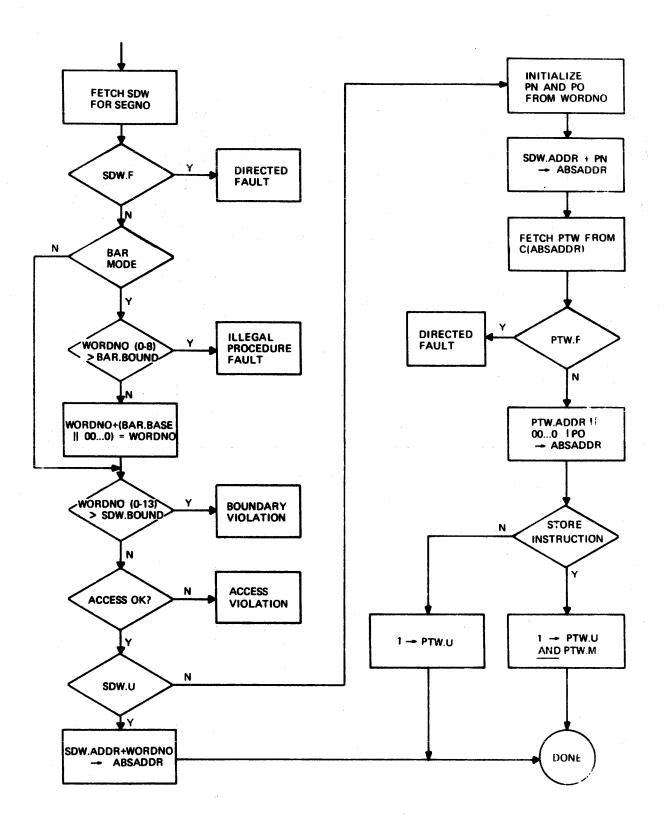

The full algorithm used by the hardware to access word [s,i] is (see Figure 3):

- If DBR.L < s, generate a fault.

- Split s into sx and sy such that sy = s mod K and sx = (s-sy)/K.

- Access PTW(sx) at absolute location DBR.core + sx.

- If PTW(sx).F = ON, generate a missing page fault.

- Access SDW(s) at absolute location PTW(sx).core

+ sy.

- If SDW(s).F = ON, generate a missing segment fault.

- If SDW(s).L < i, generate a fault.

- If SDW(s).acc is incompatible with OPCODE, generate a fault.

- Split i into ix and iy such that iy = i mod K and ix = (i-iy)/K.

- Access PTW(ix) at absolute location SDW(s).core + ix.

- If PTW(ix).F = ON, generate a missing page fault.

- Apply the OPCODE to the word whose absolute location is PTW(ix).core + iy.

## Figure 3. Hardware Segmentation and Paging in the 645

22

#### 3. SEGMENT ATTRIBUTES

#### 3.1. Directory Hierarchy

The association between the name of a segment and its attributes is recorded in a catalogue. This catalogue consists of a table with one entry for each segment in the system. An <u>entry</u> contains the name of the segment and all its attributes (length, memory address, list of users allowed to use that segment with their respective access rights, date the segment was created, etc.).

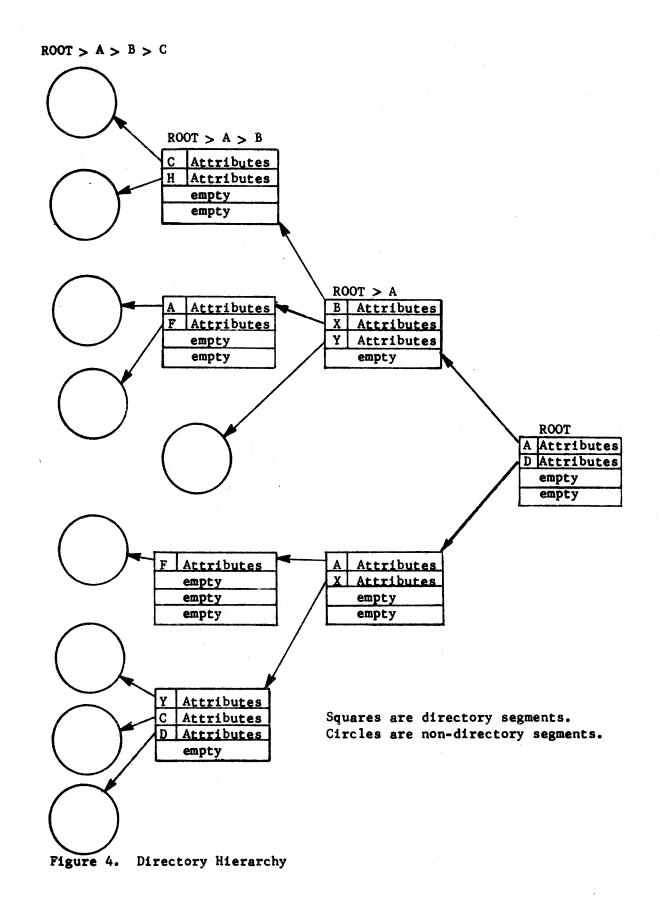

In Multics this catalogue is divided into several segments called <u>directories</u>, which are organized into a tree structure. A naming convention permits one to search the tree structure for a given name without having to search all directories.

A segment name is a list of subnames reflecting the position of the entry in the tree structure, with respect to the beginning of the tree or root directory. By convention, subnames are separated by the character ">". Each subname is called an <u>entryname</u> and the list of entrynames is called a pathname.

There are two types of directory entries called branches and links. A <u>branch</u> is a directory entry which contains all attributes of a segment while a <u>link</u> is a directory entry which contains the pathname of another directory entry. This chapter will deal only with entries of the branch type.

The pathname is the only name by which a segment can be searched for in the directory hierarchy.

The attributes associated with a segment whose pathname is ROOT > A > B > C are found as follows (see Figure 4):

Search the root directory for an entry whose entry name is A. This entry contains attributes for the directory segment whose pathname is ROOT > A. These attributes permit one to locate the directory ROOT> A in memory.

- Search directory ROOT > A for an entry whose entry name is B. This entry contains attributes for the directory segment whose pathname is ROOT > A > B. These attributes permit one to locate the directory ROOT > A > B in memory.

- Search directory ROOT > A > B for an entry whose entry name is C. This entry contains attributes for the segment ROOT > A > B > C.

#### 3.2. Operations on Segment Attributes

All operations on segment attributes are done by supervisor primitives. There is a set of primitives available to the user which allow him, for example, to:

- Create a segment.

- Delete a segment.

- Change the entryname of a directory entry.

- Change the access rights of a segment.

- List a directory.

Any of these operations is performed on behalf of a user by the supervisor only if the user has the right to perform them.

Some further details about one of these operations, segment creation, are important to an understanding of the topic of segment accessing developed in the next section.

Creating a segment whose pathname is ROOT > A > B > C consists basically of taking the following actions:

- Check, by searching the directory hierarchy, that this segment does not exist already in the system.

- Allocate space for a branch in directory ROOT > A > B.

- Store in the branch the following items:

- . The entry name C.

- . The access list, given by the creator.

- . The segment map which consists of a secondary storage address for each page of the segment. This segment map is manufactured by the supervisor.

- The segment status "inactive", meaning that there is no page table for this segment.

Once the segment has been created, the user can reference it. Note that no segment number has been assigned to the segment at creation time, and the only way to refer to it is by the pathname.

#### 4. SEGMENT ACCESSING

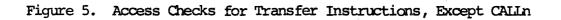

We are now in a position to understand a description of the functions that are provided by the supervisor in order to make accessible by the processor segments which are referenced by name in a user program. Figure 5 is key to an appreciation of the Multics virtual memory implementation. Although frequent references to Figure 5 follow, the full implications of its contents will not be apparent until the entire section has been read.

#### 4.1. Concept of Process and Address Space

A process is generally understood as being a program in execution. A process is characterized by its state-word defining, at any given instant, the history resulting from the execution of the program.

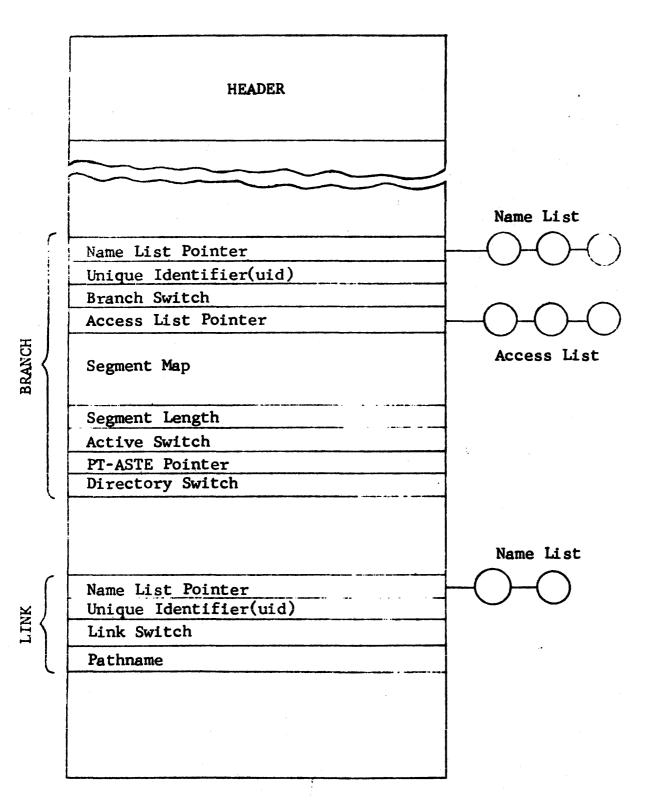

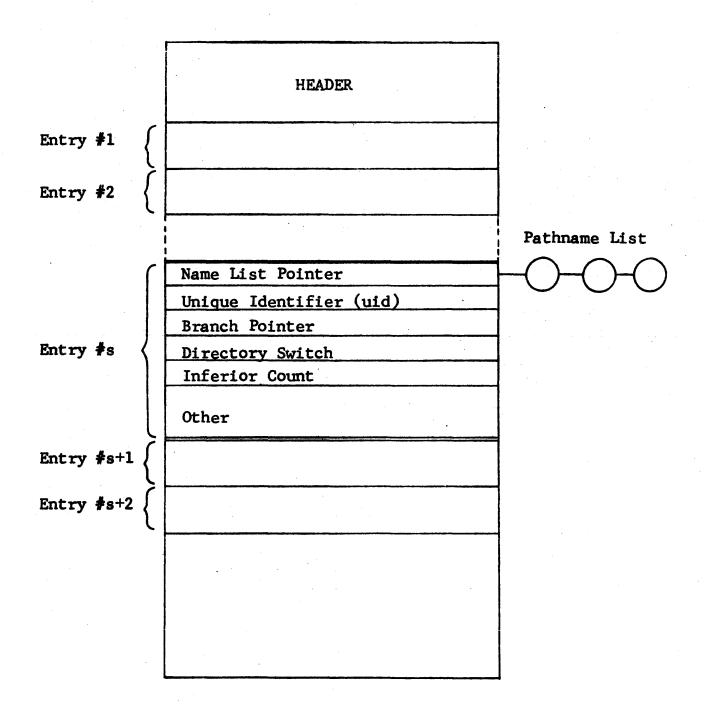

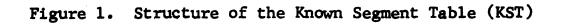

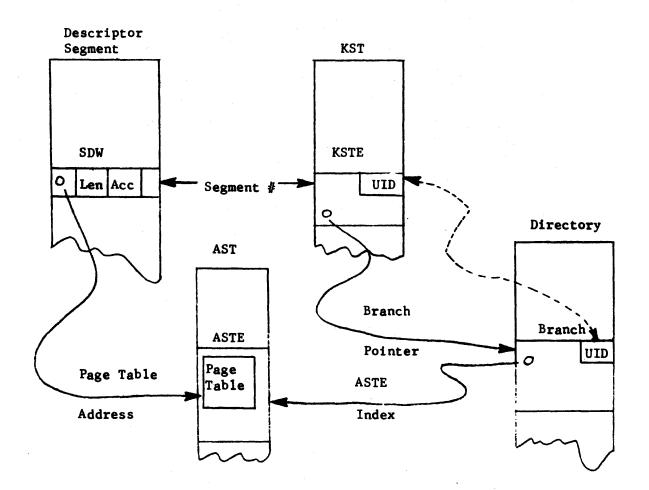

A process is also characterized by its address space. The address space is the set of processor addresses that this process can use to reference the memory. In Multics the address space of a process is defined as the set of segment numbers that the process can use to reference segments in the virtual memory. As explained in Chapter 1, a segment number can be used to reference the virtual memory only if it has been associated with a segment name, i.e., a pathname. This association [pathname, segment number] is recorded in a table called the Known Segment Table (KST) which defines the address space of the process. There is a one-to-one correspondence between Multics processes and address spaces. The action of adding a new pair [pathname, segment number] in a KST is referred to as making the segment with that pathname known to the process.

#### 4.2. Making a Segment Known to a Process

Each time a segment is referenced in a process by its pathname, the pathname must be translated into a segment number in order to permit the processor to address the segment. This translation is done by the supervisor using the KST associated with the process. The KST is an array organized such that the entry number "s", KSTE(s), contains the pathname associated with segment number s. See Figure 5. If the association [pathname, segment number] is found in the KST for this process, then the segment is known to the process and the segment number can be used to reference the segment.

If the association [pathname, segment number] is not found it means that this is the first time the segment is referenced in the process and the segment has to be made known. This is done by assigning an unused segment number "s" in the process and by establishing the pair [pathname, segment number] in the KST by recording the pathname in KSTE(s). Furthermore, the directory hierarchy is searched for this pathname and a pointer to the corresponding branch is entered in KSTE(s) for later use (see Section 4.3.).

This stage is fundamental because, in the Multics system, it is impossible to assign a unique segment number to each segment. The reason is that the number of segments in the system may be larger than the number of segment numbers available in the processor.

When a segment is made known to a process by segment number "s" its attributes are not placed in SDW(s) of the descriptor segment of that process. SDW(s) has been initialized with an invalid attribute flag. Therefore, the first reference in this process to that segment by segment number "s" will cause the processor to generate a fault. In Multics this fault is called a "missing segment fault" and transfers control to a supervisor module called the segment fault handler.

## 4.3. The Segment Fault Handler

Upon the occurrence of a missing segment fault, control is passed to the segment fault handler whose function is to store the proper segment attributes in the appropriate SDW and to set the invalid attribute flag OFF in the SDW.

This information, we recall, consists of:

- The page table address.

- The length of the segment.

- The access rights of the user with respect to the segment.

The information initially available to the supervisor upon occurrence of a missing segment fault is:

- The segment number s.

- The process identification.

The only place where the needed information can be found is in the branch of the segment. Using the process identification, the supervisor can find the KST for this process. It can then search this KST for the segment number s. Having found the KST entry for s, it can find the required branch since a pointer to the branch has been stored in the KST entry when the segment was made known to that process. See Section 4.2.

Using the active switch (see Figure 5) in the branch, the supervisor can determine whether or not there is a page table for this segment. Recall that this switch was initialized in the branch at segment creation time. If there is no page table, one must be constructed. A portion of core memory is permanently reserved for page tables. All page tables are of the same length and the number of them is determined at system initialization.

Figure 5. Basic Tables Used to Implement the Multics Virtual Memory

The supervisor divides these page tables into two lists: the "used list" and the "free list". Manufacturing a page table (PT) for a segment could consist only of selecting a PT from the free list, putting its absolute address in the branch and moving it from the free to the used list. If this were actually done, however, then the servicing of each missing page fault would require access to a branch since the segment map is kept there.

Since all directories cannot be core-resident, page fault handling could thereby require a secondary storage access in addition to the read required to transport the page itself into core. Although this mechanism works, efficiency considerations have led to the "activation" convention between the segment fault handler and the page fault handler.

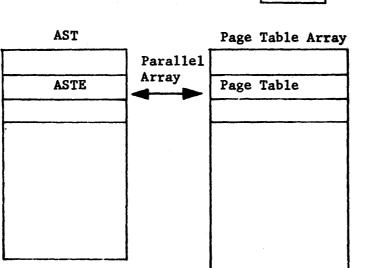

4.3.1. <u>Activation</u>. A portion of core memory is permanently reserved for recording attributes needed by the page fault handler, i.e., the segment map and the segment length. This portion of core is referred to as the <u>active segment</u> <u>table</u> (AST). The AST contains one entry (ASTE) for any segment that has a PT. A PT is always associated with an ASTE, the address of one implying the address of the other. They may be regarded as a single entity and will be referred to as the [PT,ASTE] of a segment.

A segment which has a [PT,ASTE] is said to be <u>active</u>. The property of being active or not active is an attribute of the segment and, therefore, has to be recorded in the branch. When this active switch is set ON it means that both the segment map and the segment length are no longer in the branch but are to be found in the segment's  $\lceil PT,ASTE \rceil$  whose address has been recorded in the branch during "activation" of the segment.

To activate a segment the supervisor must:

- Find a free [PT,ASTE]. Assume temporarily that at least one is available.

- Move the segment map and the segment length from the branch into the ASTE.

- Set the active switch in the branch.

- Record the pointer to [PT,ASTE] in the branch.

Having defined activation, the actions taken up to now by the segment fault handler can be summarized as:

- Use the segment number s to access the KST entry.

- Use the KST entry to find the branch.

- If the active switch is OFF, activate the segment. If it is ON, then activation is unnecessary at this time as the segment was already activated for another process.

By pairing an ASTE with a PT in core, the segment fault handler has guaranteed that the segment attributes needed by the page fault handler are core-resident, thus permitting efficient page fault servicing.

4.3.2. <u>Connection</u>. Now that the segment is active, the corresponding SDW must be "connected" to the segment.

To connect the SDW to the segment the supervisor must:

- Get the absolute address of the PT, using the [PT,ASTE] pointer kept in the branch, and store it in the SDW.

- Get the segment length from the ASTE and store it in the SDW.

- Get the access rights for the user from the branch and store them in the SDW.

- Turn off the flag which caused the fault from the SDW.

Having defined activation and connection, segment fault handling can finally be summarized as:

- Use the segment number s to access the KST entry.

- Use the KST entry to find the branch.

- If the active switch in the branch is OFF, activate the segment.

- Connect the SDW.

Note that segment sharing in core is "automatically" guaranteed by the use of the active switch and [PT,ASTE] pointer kept in the segment branch since all SDW's describing this segment will point to the same PT.

Now that the segment has an SDW pointing to the PT, the hardware can access the appropriate page table word. If the page is not in core, a missing page fault occurs, transferring control to the supervisor module called the page fault handler.

### 4.4. The Page Fault Handler

When a page fault occurs the page fault handler is given control with the following information:

- The PT address.

- The page number.

The information needed to bring the page into memory is:

- The address of a free block of core memory into which the page can be moved.

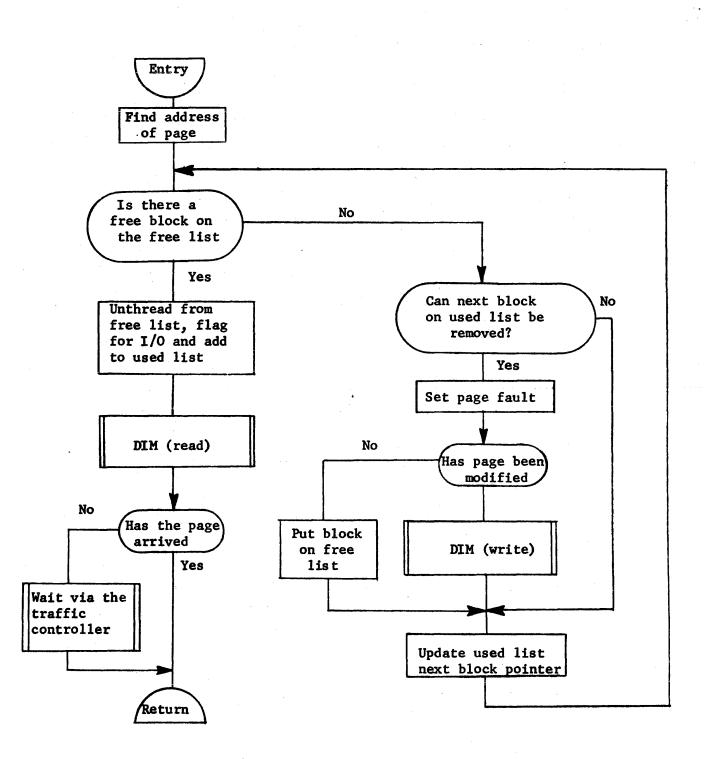

- The address of the page in secondary memory.

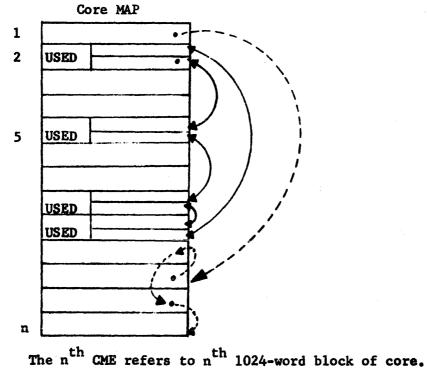

A free block of core must be found. This is done by using a data base called the core map. The core map is an array of elements called core map entries (CME). The n<sup>th</sup> entry contains information about the n<sup>th</sup> block of core (the size of all blocks is 1024 words). The supervisor divides this core map in two lists; the used list and the free list. The job of the page fault handler is to:

- Find a free block of core. (Assume temporarily that there is at least one free block in the free list.)

- Access the ASTE associated with the PT and find the address in secondary memory of the missing page.

- Issue an I/O request to move the page from secondary memory into the free block of core.

- Upon completion of the I/O request, store the core address in the PTW and remove the fault from the PTW.

### 4.5. Page Multiplexing

It was assumed that a free block of core was available in the core map free list; however, this is not always the case since there are many more pages in the virtual memory than there are blocks of core. Therefore, in order to get a free block of core, the page fault handler may have to move a page from core to secondary memory. This requires:

- An algorithm to select a page to be removed.

- Knowing the address of the PTW which holds the address of the selected page in order to set a fault in it.

- Knowing where to put the page in secondary memory.

The selection algorithm is based upon page usage. The hardware provides valuable assistance by the fact that, each time a page is accessed, a bit is set ON in the corresponding PTW. This bit is called the <u>used bit</u>. The selection algorithm will not be described here; however, it should be noted that candidates for removal are those pages described in the core map used list. Therefore, each core map entry which appears in the used list must contain a pointer to the associated PTW in order to permit one to examine the used bit. The action of storing the PTW pointer in the core map entry must be added to the list of actions taken by the page fault handler when a page is moved into core (see Section 4.4.).

- A fault is stored in the PTW.

- The secondary storage address for the page is found in the ASTE whose address can be computed from the PTW address.

- An I/O request is issued to remove the page to secondary storage.

- Upon completion of the I/O request, the core map entry is removed from the used list and put in the free list.

By this mechanism, blocks of core are multiplexed among all pages of all active segments in the system.

It is important to realize that a page is either in core or in secondary storage. There is no such thing as a "copy" of a page. When a page is moved from secondary storage to core, its secondary storage address, located in the ASTE, could be freed; it is no longer needed since the address of the page is now in the PTW. When the page is to be removed, a free block of secondary storage could be assigned to it. It is only for practical reasons that the block of secondary storage is not freed each time a page is moved into core.

Page multiplexing maintains a "perpetual motion" between core and secondary storage of pages of <u>active</u> segments. If the set of active segments in the system were invariant, then pages of other segments would never have a chance to be in core.

## 4.6. [PT, ASTE] Multiplexing

In the description of segment fault handling, when a segment had to be activated, a pair [PT,ASTE] was assumed available for assignment to that segment. In fact, the number of [PT,ASTE] pairs is limited in the system and is, by far, smaller than the number of segments in the virtual memory. Therefore, these [PT,ASTE] pairs must be multiplexed among all segments in the virtual memory.

This means that making a segment active may imply making another segment inactive thereby disassociating this other segment from its [PT,ASTE]. Since each process sharing the same segment will have the address of the PT in an SDW it is essential to invalidate this address in all SDW's before removing the page table. It is also essential to move to secondary memory all pages of that segment which are in core before removing the [PT,ASTE], since the ASTE is needed to remove a page. Then, and only then, can [PT,ASTE] be disassociated from the segment.

This operation requires:

- An algorithm to select a segment to be deactivated.

- Knowing all SDW's that contain the address of the page table of the selected segment in order to invalidate this address.

- The removal of all pages of the selected segment that are still in core.

- Moving the attributes contained in the ASTE back to the branch and changing the status of the segment from active to inactive in the branch.

The selection algorithm is here again based on segment usage. The only thing of interest at this point is that selection is done by scanning the ASTE used list. Therefore, the ASTE must provide all the information needed for removing the [PT,ASTE]. This means that during activation and connection this information must be made available as explained below. During activation, a pointer to the branch must be placed in the ASTE; during connection, a pointer to the SDW must be placed in the ASTE. Since more than one SDW is connected to the same PT when the segment is shared by several processes the supervisor must maintain a list of pointers to connected SDW's. This list is called a <u>connection list</u>. See Figure 5.

Now we are in a position to understand how a [PT,ASTE] can be disassociated from a segment. After the selection algorithm decides on an ASTE to be freed, actions to be taken consist of two steps called "disconnection" and "deactivation".

<u>Disconnection</u> consists of storing a segment fault in each SDW whose address appears in the connection list in the ASTE.

<u>Deactivation</u> consists of removing all pages of this segment that may be in core, moving the segment map from the ASTE back to the branch, resetting the active switch in the branch and putting the [PT,ASTE] in the free list.

## 4.7. Segment Number Multiplexing in a Process

The number of segments that a process can describe in its descriptor segment is limited to  $2^{18}$ . It is unlikely that a process needs to access more than  $2^{18}$  segments from the time it is created to the time it is destroyed. However, if this should happen, a facility is provided to a process to remove an association [pathname, segment-number] by an explicit call to the supervisor. This action is referred to as making a segment unknown. When segment A which is known to a process by the segment number "s" is made unknown to that process, no attempt is made by the supervisor to remove residual [s,i] pairs that may have been generated and stored during the time that s was assigned to A. Making segment A unknown to the process implies freeing KSTE(s). If subsequently another segment, say B, is made known to the process, the supervisor may assign this unused segment number s to segment B, entering the pathname B in KSTE(s). From this point on, any reference by segment number s in this process will cause segment B to be accessed. Therefore, it is entirely the responsibility of the programmer, after segment A is made unknown, not to reuse any residual pair [s,i] that was generated for accessing segment A.

### 4.8. Directory Entry Multiplexing

When a segment is deleted, the branch of that segment is deleted. No attempt is made by the supervisor to remove residual KST entries that contain a pointer to this branch. However, the supervisor can detect references by residual segment numbers, to segments which have been destroyed as follows:

- When segment A is created, the supervisor assigns a unique number  $N_A$  to segment A and stores it in the branch.

- When segment A is made known to a process P by the segment number s, N<sub>A</sub> is copied from the branch to KSTE(s) for process P along with the pointer to branch A.

- If segment A is deleted by any process, the supervisor disconnects the corresponding SDW in process P, if it was connected, and deletes the branch together with  $N_A$ .

- If the same directory entry is reused to record the branch information of another segment B, a new unique identifier  $N_B$  will be stored in the branch.

- Now, if process P uses the segment number s in order to access segment A, a segment fault will occur; the KST entry contains a pointer to the directory entry which is supposed to be the branch A. But by comparing the  $N_A$  of the KST entry and  $N_B$  of the directory entry, the supervisor can discover that segment A has been deleted.

Therefore, it is possible to detect the deletion of a branch even though its former directory entry has been reused for another segment.

### 5. STRUCTURE OF THE SUPERVISOR

Up to now supervisor functions have been described, but supervisor structure has not been discussed. In this section, the different components of the supervisor are covered and the ability of portions of the supervisor to partially utilize the virtual memory is demonstrated.

## 5.1. Functional Modules

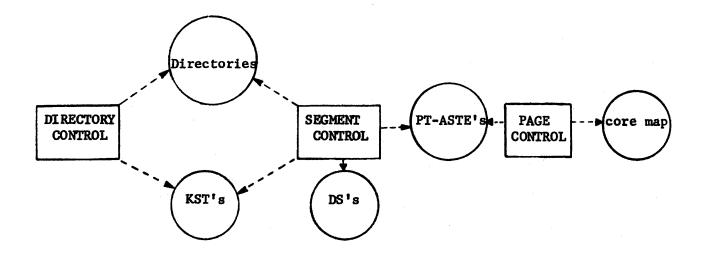

Three functional modules can be identified in the supervisor described; they are called directory control (DC), segment control (SC), and page control (PC).

5.1.1. <u>Directory Control</u>. Directory control is that part of the supervisor which can manipulate all segments in the system. DC identifies a segment by its pathname which uniquely defines a segment in the system. Data bases that are manipulated by DC are the directories and KST's of all processes (see Figure 6). DC provides all primitives to simulate operations on segment attributes; it also provides the assignment of a segment number to a segment within a processe.

5.1.2. <u>Segment Control</u>. Segment control is that part of the supervisor which can manipulate only those segments which are known to at least one process. SC identifies a segment by either its segment number within a particular process, which uniquely defines a segment in the system, or by its [PT,ASTE] address which uniquely defines an active segment in the system. Data bases that are manipulated by SC are directories, KST's of all processes, descriptor segments of all processes and [PT,ASTE] pairs of all active segments. SC provides the functions of activation, connection, disconnection and deactivation.

5.1.3. <u>Page Control</u>. Page control is that part of the supervisor which can manipulate only those segments which are active. PC identifies a segment by its [PT,ASTE] address which uniquely defines an active segment in the system. Data bases that are manipulated by PC are [PT,ASTE] pairs of all active segments and the core map. PC provides the mechanism to move pages of active segments between secondary storage and core.

Figure 6. Supervisor Functional Modules and Data Bases

### 5.2. Use of Segmentation in the Supervisor

Previous to this no assumptions were made about the type of addressing used by the supervisor. It could be written so as not to use segment addressing of course; but organizing the supervisor into procedures and data segments permits one to use in the supervisor the same standard conventions that are used in a user program. For instance, the CALL-SAVE-RETURN conventions made for user programs can be used by the supervisor, the standard way to manufacture pure procedures in a user program can be used in the supervisor, etc. Thus, it seems desirable to use segmentation in the supervisor, and the following (temporary) assumption will be made:

### Assumption 1:

- a. The address space of the supervisor is entirely defined by a descriptor segment.

- b. All segments used by the supervisor are always in core.

Assumption 1.b is not realistic, however, since it generally is not possible to dedicate enough core to contain the entire supervisor. It is, therefore, interesting to determine whether there is a way to use the page fault handler to transport supervisor as well as user pages.

## 5.3. Use of PC in the Supervisor

For the purpose of this paper, let us assume the validity of the following statement. "Page fault handling for a page x must be performed without referencing page x".

It is certainly possible to design a PC module which allows recursive page faults provided that the above condition is always satisfied. Each recursive invocation of the page fault handler should use a set of pages which does not include any of the pages that caused the previous invocations; furthermore, the number of recursive invocations must be guaranteed to be finite. The technique that has been chosen in Multics for page fault handling is to fix this finite number to 1 and thus no recursive page faults will ever occur. This decision has been made for reasons of efficiency and design simplicity. Therefore, it is assumed that all segments used in PC are always in core.

We can observe that the page fault handler need not know if a missing page belongs to a user or to the supervisor; it only expects to find the information it requires in the [PT,ASTE] of the segment to which the missing page belongs. Therefore, if all segments used in SC and DC are always active, then their pages need not be in core since PC can load them when they are referenced.

Thus, assumption 1 can be replaced by the following one (again temporary):

Assumption 2:

- a. The address space of the supervisor is entirely defined by a descriptor segment.

- b. All segments used in PC are always in core.

- c. All segments used in SC and DC must be active and connected.

This convention turned out to be satisfactory in the Multics implementation except for directories. Recall that segments used by SC and DC are: (a) SC and DC procedures, (b) KST's and DS's, and (c) Directories. The number of segments in class (a) and (b) is relatively small. On the contrary, the number of directory segments may be very large and keeping them always active is not a realistic approach, since a large number of [PT,ASTE] pairs would have to be permanently assigned to them. Therefore, it is desirable to use SC to activate and connect directory segments.

### 5.4. Use of Segment Control in the Supervisor

A necessary condition for handling a segment fault for segment x in a process is that segment x be known to that process. If SC is to handle segment faults taken by the supervisor for directories, all directories must be known to the supervisor. This means that the address space of the supervisor must be defined not only by its descriptor segment but also by KST, which contains one entry for each directory. After its KST has been so initialized, the supervisor looks like any other process.

Assuming that all directories are known to the supervisor process, but not necessarily active, a supervisor reference to a directory x may cause a segment fault. Recall that when handling this fault, the segment fault handler must reference the parent directory of segment x, where the branch for x is located. This reference to the parent of x could, in turn, cause a recursive invocation of the segment fault handler. Recursive invocations can propagate from directory to parent directory up to the root. If there is a way of stopping the recursion, then any segment fault on directories can be handled.

One way of stopping the recursion is to keep the root active and connected, so that a segment fault never occurs for it.

Assumption 2 can now be replaced by assumption 3, again temporary.

Assumption 3:

- a. The address space of the supervisor process is defined by a descriptor segment and a KST.

- b. All segments used in PC are always in core.

- c. All segments used in SC and DC are always active and connected, except directories.

d. The root directory is always active and connected.

e. All directories are known to the supervisor process.

However, it is unsatisfactory to keep all directories known. We would like to keep known only those which may possibly be used in a segment fault handling, provided that other directories can be made known by directory control when needed.

### 5.5. Use of the Make Known Facility in the Supervisor

Making a segment x known implies searching for its pathname in the KST. If not found, the parent of x must first be made known and so on up to the root. If the root directory is always known to the supervisor, then any directory can be made known to the supervisor by the supervisor itself.

Assumption 3 will now be replaced by the final assumption:

Final Assumption:

- a. The address space of the supervisor process is defined by a descriptor segment and a KST.

- b. All segments used in PC are always in core.

- c. All segments used in SC and DC, except directories, are always active and connected.

- d. The root directory is always active and connected.

- e. If a segment is known to any process, its parent directory must be known to the supervisor process.

- f. The root directory is always known to the supervisor process.

Given the above assumptions, supervisor segments as well as user segments can be stored in the virtual memory that the supervisor provides.

### 5.6. The Supervisor Address Space

Unlike most supervisors, the Multics supervisor does not operate in a dedicated process or address space. Instead. the supervisor procedure and data segments are shared among all Multics processes. Whenever a new process is created, its descriptor segment is initialized with descriptors for all supervisor segments allowing the process to perform all of the basic supervisory functions for itself. The execution of the supervisor in the address space of each process facilitates communication between user procedures and supervisor procedures. For example, the user can call a supervisor procedure as if he were calling a normal user procedure. Also, the sharing of the Multics supervisor facilitates simultaneous execution, by several processes, of supervisory functions, just as the sharing of user procedures facilitates the simultaneous execution of functions written by users.

Since supervisor segments are in the address space of each process, they must be protected against unauthorized references by user programs. Multics provides the user with a ring protection mechanism which segregates the segments in his address space into several sets with different access privileges. The Multics supervisor takes advantage of the existence of this mechanism and uses it, rather than some other special mechanism, to protect itself.

### 6. SUMMARY

If only a few points discussed here were to be remembered, they should be those mentioned below. They have been separated into two classes: the point of view of the user of the virtual memory, and the point of view of the supervisor itself.

### User Point of View

- The Multics virtual memory is capable of containing a very large number of segments that can be identified by their symbolic names.

- Segment attributes are stored in special segments called directories, which are organized into a tree structure; there is a naming convention, of which the user must be aware, by which a segment name must be the pathname of its branch in the directory tree structure.

- Any operation on directory segments must be done via a call to the supervisor.

- Any operation on a non-directory segment can be done directly in accordance with the access rights that the user has for this segment; any word of any segment which resides in the virtual memory can be referenced with a pair [pathname,i] by the user.

- A process can have only a limited number of segments in its address space. If the programmer wants to overlay a segment A by a segment B in the process address space, he can call the supervisor to do it but he must be aware of the dangers that this operation may present.

#### Supervisor Point of View

- The supervisor must simulate a large segmented memory directly addressable by segment name such that any access to the memory is submitted to access rights checking.

- It maintains a directory tree where it stores all segment attributes. It can retrieve the attributes of a segment given the pathname of that segment.

- The supervisor itself is organized into segments and runs in the user process address space.

- Any segment, be it a directory or a non-directory segment, is identified by its pathname but can be accessed only using a segment number. For each segment name the supervisor must assign a segment number by which the processor will address the segment in the process.

- The processor accesses a word of a segment through the appropriate SDW and PTW and subject to the access rights recorded in the SDW.

- A segment fault is generated by the processor whenever the page table address or access rights are missing in the SDW. The supervisor then, using the KST entry as a stepping stone, accesses the branch where it finds the needed information. If a PT is to be assigned, the supervisor may have to deactivate another segment.

- A page fault is generated by the processor whenever a PTW does not contain a core address. The supervisor then, using the ASTE associated with the PT, moves the missing page from secondary storage to core. This may require the removal of another page.

### Chapter 3

# DIRECTORY STRUCTURE

### 1. INTRODUCTION

A virtual memory system must include some means of storing and retrieving information. A segment is the unit of information in the Multics virtual memory which is so stored and retrieved.

All information about a segment such as its length and its location are called "attributes" of the segment. If the attributes of a segment can be located, then the segment itself can be found.

The attributes of segments are stored in special segments called "directories" and the directories are organized into a tree structure called "the directory hierarchy". All of the attributes of one segment are recorded in one entry in a directory. The entries in a directory can be referenced by literal string names called "entrynames".

The discussion which follows gives some of the details of the directory hierarchy structure, the naming of entries and segments and the contents of directory entries. Segment creation and deletion are also described since those operations are closely related to the creation and deletion of the attributes of a segment.

Other chapters describe the details of the search for a segment and how segments themselves are handled.

### 2. THE DIRECTORY HIERARCHY AND TERMINOLOGY

#### 2.1. The Structure

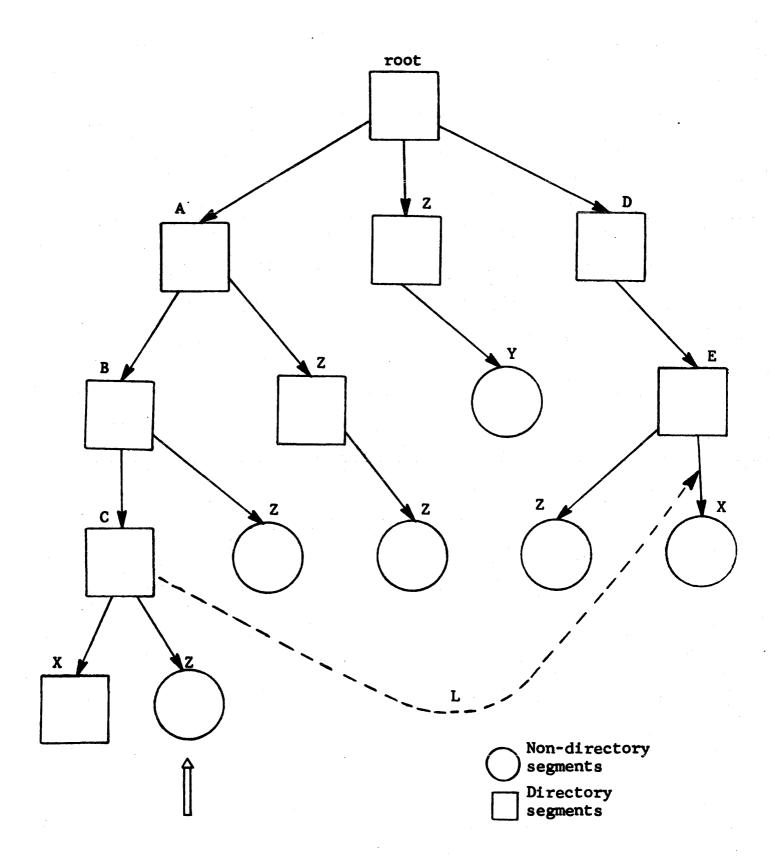

A tree structured directory hierarchy is shown in Figure 1. Directory segments are shown as squares and non-directory segments are shown as circles. The lines between segments are branches of the tree structure and in Multics, denote the fact that the attributes of a segment at the lower end of a line are recorded in an entry in the directory at the upper end of the line. Thus the attributes of the segment labeled C in Figure 1, are recorded in the directory labeled B. The directory entries in which the attributes of segments are recorded are called "branch entries" or "branches". A directory is said to be the parent of a segment if it contains the branch with the attributes of that segment. The parent directory of a segment is said to be "immediately superior to" the segment and the segment is "immediately inferior to" its parent. In Figure 1, the directory at the top of the structure labeled "root" and called "the root directory" or simply "the root" is the parent of or immediately superior to the segment labeled D. The root is superior to the segment labeled E, but not immediately superior to E. The segment labeled E is inferior to the root and the segment labeled D is immediately inferior to the root.

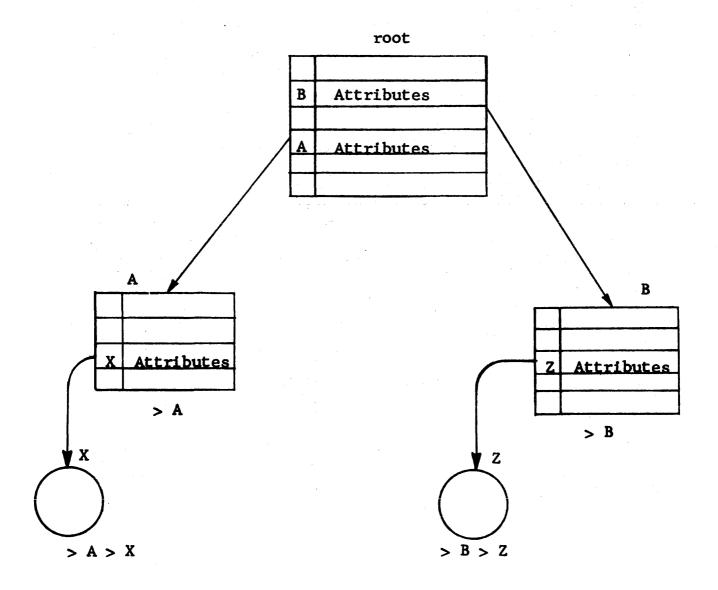

The root is the starting point in the search for segments. Note that the root has no branch. Its attributes, among them its location, are assumed to be known to the modules which perform the search.

There is one and only one branch per segment in the Multics system. This rule arose from the difficulty of finding and updating all the branches of a segment if one of its attributes should be changed. For cases in which it is useful to have a branch in more than one directory a link (see below) can be used.

## 2.2. Entrynames and Pathnames

An entryname is used to locate an entry in a given directory, but a "pathname" is needed to search the directory hierarchy for a particular entry. In order to uniquely locate a particular entry in a directory, an entryname must be unique in that directory. However, an entry can have several names (synonyms).

A pathname is the concatenation of an ordered sequence of entrynames. The entries must be located in the order they were named in order to follow the path from the root to the desired entry. The entrynames are separated by the character ">".

The name of a segment is the pathname which addresses its branch.

Figure 1. Tree structure directory hierarchy

The names root > A and root > D > E > Z are examples of pathnames for segments in the hierarchy shown in Figure 1. The name root > A > B > C > Z is the name of the segment pointed to by the vertical arrow. Since all pathnames begin with root >, the leading symbol > is used to mean root >. The names above become > A, > D > E > Z and > A > B > C > Z.

An example of the search for the attributes of the segment > B > Z in Figure 2 is instructive. The root is searched for a branch with the name B. The segment > B is accessed using the information in this branch. Next, the directory segment > B is searched for a branch with the name Z. When the branch Z is found in the directory > B then the search is finished.

It must be emphasized that the only way in which the search modules can find a segment is through use of a pathname.

A pathname can have synonyms since the entrynames from which it is constructed can have synonyms. However, a given pathname cannot lead to more than one segment.

#### 2.3. Links

There can exist in a directory a second type of entry in addition to the branch entry. This is called a "link entry" or a "link". A link entry has a name just as branch entry does and like a branch is used to access a segment or its attributes. A link contains no attributes but only the "pathname" of another entry. In Figure 1, the dotted line labeled L is an example of a link. The entryname of the link is L. Loops such as might be generated by two links which reference each other should not be allowed in the directory hierarchy.

Links are addressed by pathname just as branches are. Referencing the link, > A > B > C > L, in Figure 1, will cause accessing of the segment > D > E > X, as that pathname is recorded in the link.

## 3. DESIGN CONSIDERATIONS

A directory is needed as a place to look up the addresses of other segments. Once a directory exists, there are other advantages to be gained from it. The directory is a convenient place to store the access rights of a user to a segment so they may be checked at the same time that the address of the segment is located. It may also be useful to reference the attributes of a segment without necessarily accessing the segment body, e.g., to find the length of a segment. For these reasons, all of the attributes of a segment are collected into a list and the lists are stored together in a directory. Why then have more than one directory?

Figure 2. Directories and Attributes