## **LARGE SYSTEMS**

ASSEMBLY INSTRUCTIONS **DPS 8000**

# ASSEMBLY INSTRUCTIONS DPS 8000

## **SUBJECT**

Description of the Assembly Instructions for the DPS 8000 Information System.

#### SOFTWARE SUPPORTED

GCOS 8 Software Release 2500

DATE

March 1987

**ORDER NUMBER**

DZ51-00

Worldwide

Information

**Systems**

## **PREFACE**

This manual contains information that enables the user to code programs in symbolic machine language which is then translated into binary machine instructions.

This manual is directed to users who are experienced in coding within the environment of a large-scale computer installation. Considerable knowledge and practical experience is required in the use of address modification with indirection, hardware indicators, fault interrupts and recovery routines, macro operations, pseudo-operations, and other features normally encountered in a large computer with a flexible instruction repertoire under control of a master executive program. It is assumed that the user is familiar with the two's complement number system.

This manual includes the processor capabilities, modes of operation, detailed descriptions of machine instructions, virtual memory addressing, paging, and the representation of data. It should prove useful to programmers who are responsible for analyzing conditions that cause system failures.

In this document, multiple vertical braces and brackets should be assumed to be a single brace or bracket; for example:

| {      | } |            |     | [     | ] |              |

|--------|---|------------|-----|-------|---|--------------|

| {<br>{ | } | represents | { } | and [ | ] | represents [ |

BULL DISCLAIMS THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE AND MAKES NO EXPRESS WARRANTIES EXCEPT AS MAY BE STATED IN ITS WRITTEN AGREEMENT WITH AND FOR ITS CUSTOMER. IN NO EVENT IS BULL LIABLE TO ANYONE FOR ANY INDIRECT, SPECIAL, OR CONSEQUENTIAL DAMAGES.

THE INFORMATION AND SPECIFICATIONS IN THIS DOCUMENT ARE SUBJECT TO CHANGE WITHOUT NOTICE. CONSULT YOUR BULL MARKETING REPRESENTATIVE FOR PRODUCT OR SERVICE AVAILABILITY.

Copyright © Bull HN Information Systems Inc., 1987, 1990 All Rights Reserved

File No.: 1V13, 1313

DZ51-00

## LISTING AND CORRECTING DOCUMENTS

The Problem Analysis Solution System (PASS) data base is an online tool that provides direct communications between Bull software development organizations and Bull customers. Documentation-related transactions available to customers via PASS include those which:

- Generate a list of all software documents published for the current Software Release.

- Prepare Software Technical Action Requests (STARs) regarding documentation discrepancies.

Logon procedures for these functions and procedures for using PASS can be obtained by contacting the Bull Technical Assistance Center (TAC).

## DOCUMENT LISTING

A list of all GCOS 8 System software documents published for this Software Release and available through the Bull CSO Marketing and Sales Order Entry (telephone 1-800-343-6665) can be displayed via the NEWS facility of PASS. The document lists are available via the PASS meeting SWDOC\_AVAILABILITY.

## DOCUMENTATION CORRECTIONS

Customers can submit documentation error reports via the PASS online STAR Maker facility. Responses to STARs, as well as other documentation changes, also are contained on PASS. (Documentation corrections contained on PASS may apply to prior Software Releases as well as to the current Software Release.)

In addition, corrections to documents will be entered on the PASS data base. Query PASS periodically to determine if any corrections exist. Corrections documented on PASS, if applicable to the next release of the software, will be incorporated into the next update of the manual.

iii/iv DZ51-00

#### CONTENTS

|                                                                                                                                                                                                                                                                                                                                     | Page                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| SECTION 1 INTRODUCTION                                                                                                                                                                                                                                                                                                              | 1-1                                                                                                                  |

| Processor Features.  Pipeline Architecture Of The DPS 8000.  Faults And Interrupts.  Connect/Interrupt Mechanism.  Online Processor Tests.  Operator Modes.  Processor Modes Of Operation.  Non-Extended/Extended Modes.  Memory Addressing Modes.  Virtual Memory Paging.  Absolute Mode.  Reserved Memory Space.  Interval Timer. | 1-1<br>1-2<br>1-2<br>1-3<br>1-4<br>1-4<br>1-6<br>1-7<br>1-7<br>1-8<br>1-8                                            |

| SECTION 2 REPRESENTATION OF DATA                                                                                                                                                                                                                                                                                                    | 2-1                                                                                                                  |

| Character Positions                                                                                                                                                                                                                                                                                                                 | 2-1<br>2-1<br>2-1<br>2-2<br>2-2<br>2-3<br>2-3<br>2-3<br>2-3<br>2-5<br>2-5<br>2-6<br>2-7<br>2-8<br>2-8<br>2-9<br>2-10 |

| SECTION 3 MEMORY ORGANIZATION                                                                                                                                                                                                                                                                                                       | 3-1                                                                                                                  |

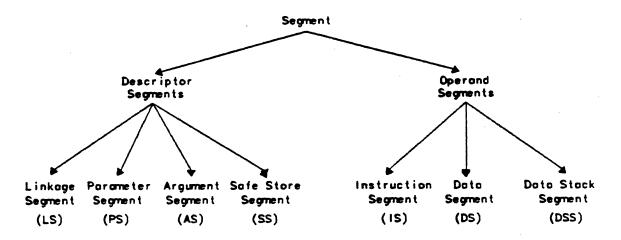

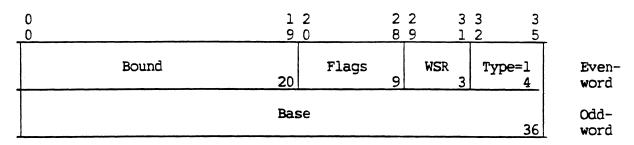

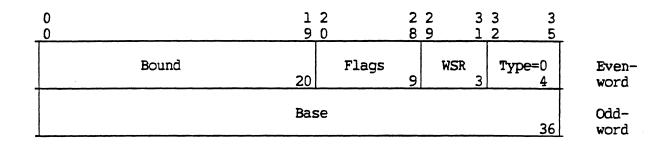

| Virtual Memory.  Working Spaces.  Page Tables.  Domains.  Segments.  Descriptors.                                                                                                                                                                                                                                                   | 3-1<br>3-2<br>3-2<br>3-3<br>3-4<br>3-6                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

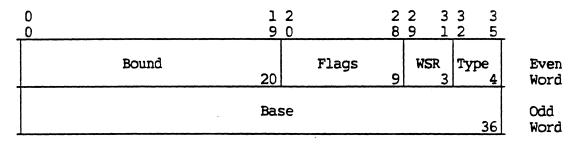

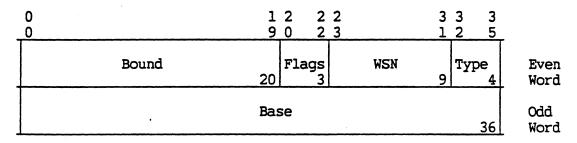

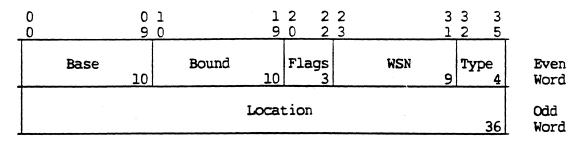

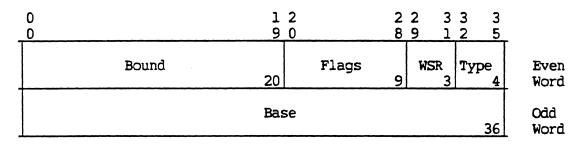

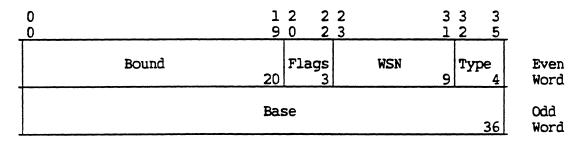

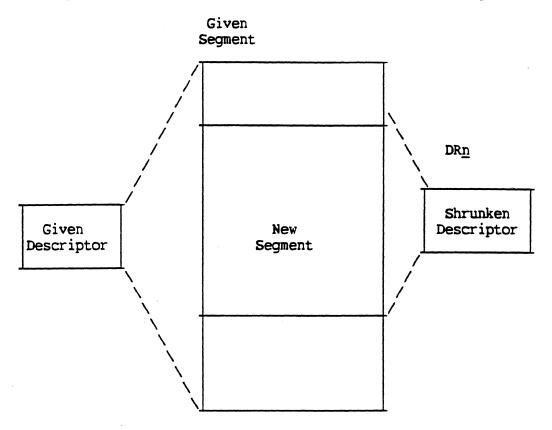

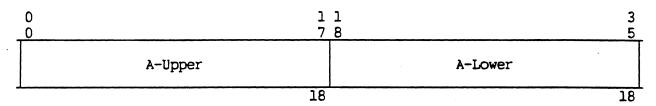

| Standard Descriptor Standard Descriptor With Working Space Number Super Descriptor Super Descriptor With Working Space Number Extended Descriptor Extended Descriptor With Working Space Number Entry Descriptor Dynamic Linking Descriptor Shrinking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-8<br>3-10<br>3-11<br>3-12<br>3-13<br>3-14<br>3-15<br>3-16                                                                            |

| SECTION 4 PROCESSOR ACCESSIBLE REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-1                                                                                                                                    |

| Accumulator Register (A). Quotient Register (Q) Accumulator-Quotient Register (AQ). Exponent Register (E).  Exponent-Accumulator-Quotient Register (EAQ) Low Operand Register (LOR). Index Registers (Xn). General Index Registers (GXn). Indicator Register (IR). Timer Register (TR). Instruction Counter (IC). Address Registers (ARn). Linkage Segment Register (LSR) Instruction Segment Register (ISR). Segment Descriptor Registers (DRn). Segment Identity Registers (SEGIDn). Instruction Segment Identity Register - SEGID(IS). Pointer Register (OR). Option Register (OR). Calendar Clock Register (CCR). Working Space Register (SSR). Safe Store Register (SSR). Stack Control Register (SCR). Argument Stack Register (ASR). Parameter Segment Register (HWMR). Data Stack Descriptor Register (DSDR). | 4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-13<br>3-15<br>4-17<br>4-19<br>4-19<br>4-22<br>4-22<br>4-22<br>4-22<br>4-22<br>4-22<br>4-22<br>4-2 |

| Data Stack Address Register (DSAR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-25<br>4-26                                                                                                                           |

| CPU Mode Register (MR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-26<br>4-28<br>4-30                                                                                                                   |

| Address Trap Register (ATR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-32<br>4-33                                                                                                                           |

|                                                | Page                                         |

|------------------------------------------------|----------------------------------------------|

| CPU Number Register (NR)                       | 4-34                                         |

| Interrupt Mask Register (IMR)                  | 4-35                                         |

| CPU Fault Register (FR)                        | 4-36                                         |

| Extended Fault Register (EFR)                  | 4-40                                         |

| History Register (HR)                          | 4-41                                         |

| Reserve Memory Base Register (RMBR)            | 4-43                                         |

| SCU Fault Register (SCUFR)                     | 4-44                                         |

| Syndrome Register (SYR)                        | 4-46                                         |

| SCU Configuration Register (SCUCR)             | 4-47                                         |

| SCU History Register (SCUHR)                   | 4-49                                         |

| Memory Error Status Register (MSR)             | 4-51                                         |

| Memory Identification Register (MID)           | 4-52                                         |

| SECTION 5 ADDRESS MODIFICATION AND DEVELOPMENT | 5-1                                          |

| Address Modification Features                  | 5-1                                          |

| Address Generation In The NS Mode              | 5-1                                          |

| Basic Modification                             | 5-1                                          |

| Indirect Addressing                            | 5-1                                          |

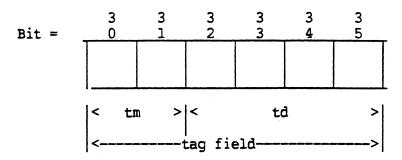

| Tag Field                                      | 5-2                                          |

| Types Of Address Modification                  | 5-3                                          |

| Register (R)                                   | 5-3                                          |

| Register (R)                                   | 5-7                                          |

| Indirect Then Register (IR)                    | 5-9                                          |

| Indirect Then Tally (IT)                       | 5-13                                         |

| Indirect Word Format                           | 5-16                                         |

| Variations Under IT Modification               | 5-17                                         |

| Address Modification Octal Codes               | 5-25                                         |

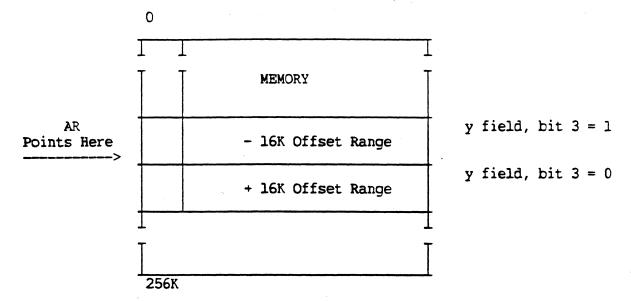

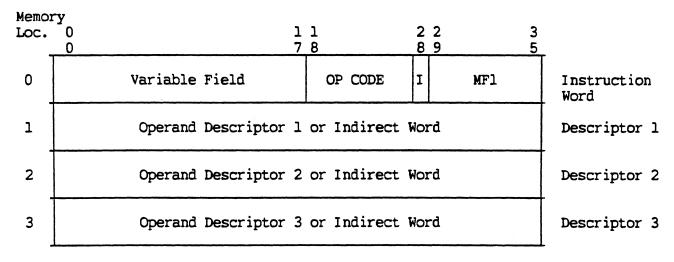

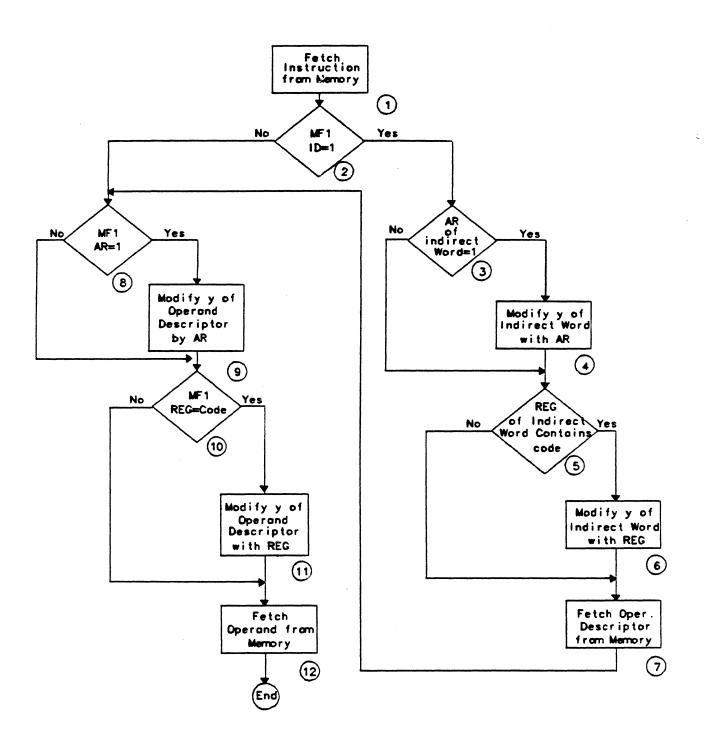

| Address Modification Flowchart                 | 5-26                                         |

| Floatable Code                                 | 5-27                                         |

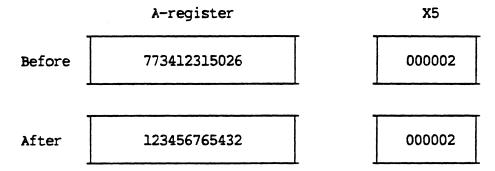

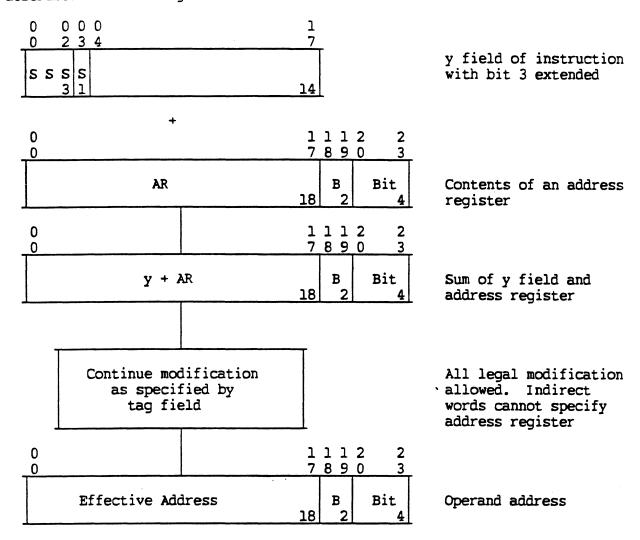

| Address Modification With Address Registers    | 5-27                                         |

| Single-Word Address Modification               | 5-27                                         |

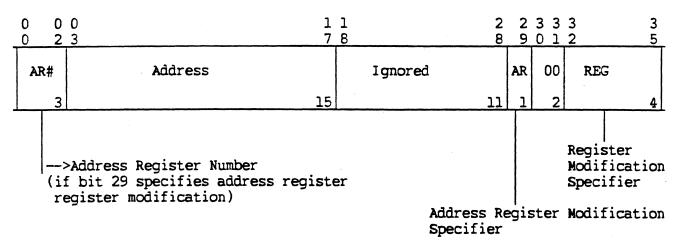

| Multiword Address Modification.                | 5-30                                         |

| Multiword Modification Field.                  | 5-30                                         |

|                                                | 5-35                                         |

| Operand Descriptors                            | 5-35<br>5-35                                 |

| Bit String Operand Descriptor                  |                                              |

| Alphanumeric Operand Descriptors               | 5-36                                         |

| Numeric Operand Descriptors                    | 5-37<br>5-40                                 |

| Indirect Word                                  |                                              |

| Operand Descriptor Address Preparation         | 5-41                                         |

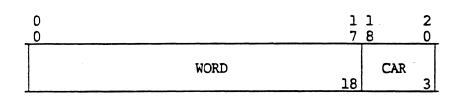

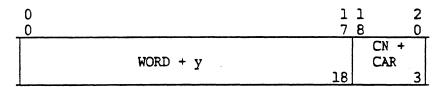

| Bit String Address Preparation                 | 5-43                                         |

| Alphanumeric/Numeric Address Preparation       | 5-44                                         |

| Address Generation In The ES Mode              | 5-49                                         |

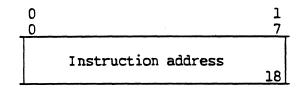

| Instruction Address Field And Register Formats | 5-49                                         |

| Instruction Address Field                      | 5-49                                         |

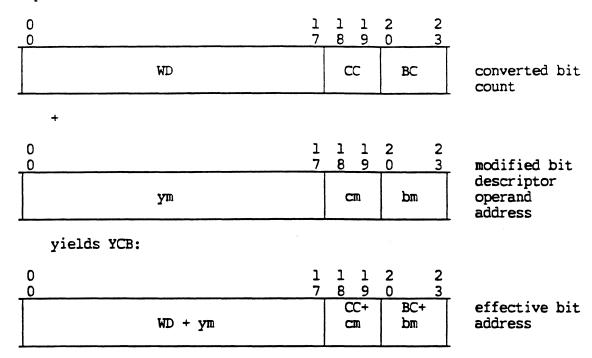

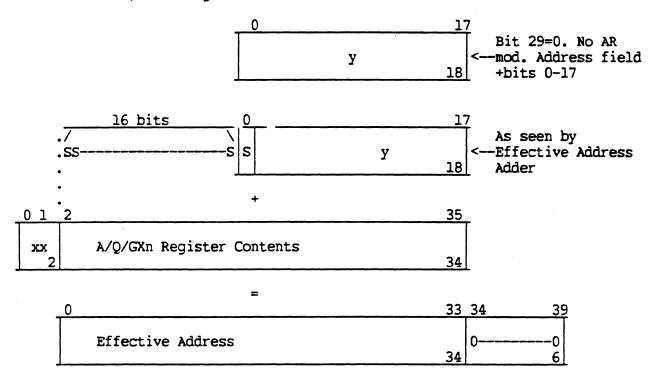

| Address Modification With No AR Indicated      | 5-49                                         |

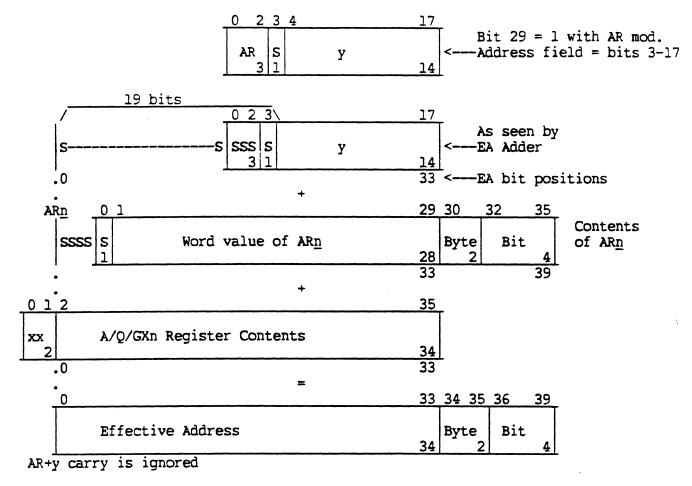

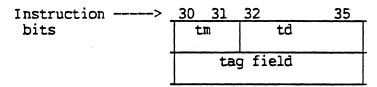

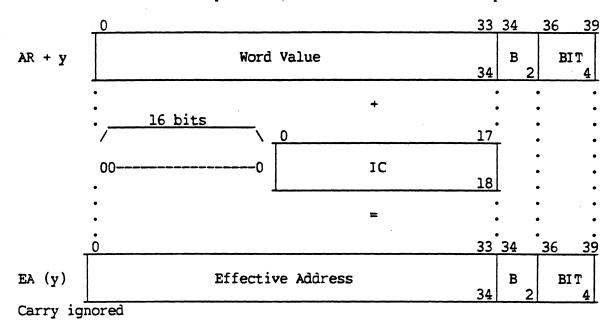

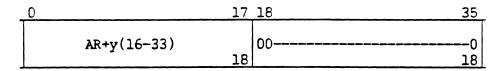

| Address Modification With AR Indicated         | 5-50<br>5-52                                 |

| UDG ELOIG MOGITIGOTION                         | <b>—</b> ——————————————————————————————————— |

vii DZ51-00

|                                                | Page       |

|------------------------------------------------|------------|

| Operand Descriptor Modification                | 5-55       |

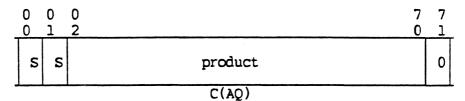

| Address Development                            | 5-57       |

| Virtual Memory Addressing                      | 5-57       |

| Operand Address Procedure                      | 5-58       |

| Instruction Address Procedure                  | 5-59       |

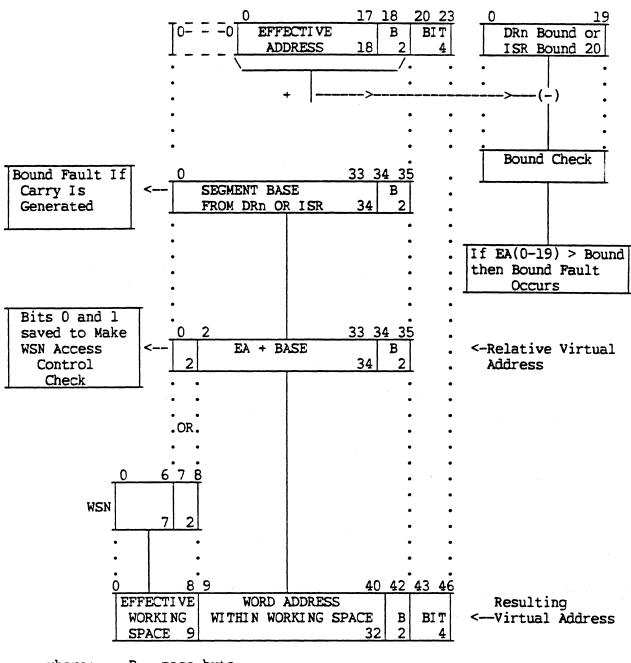

| Virtual Address Generation For NS Mode         | 5-59       |

| Standard Descriptor NS Mode                    | 5-60       |

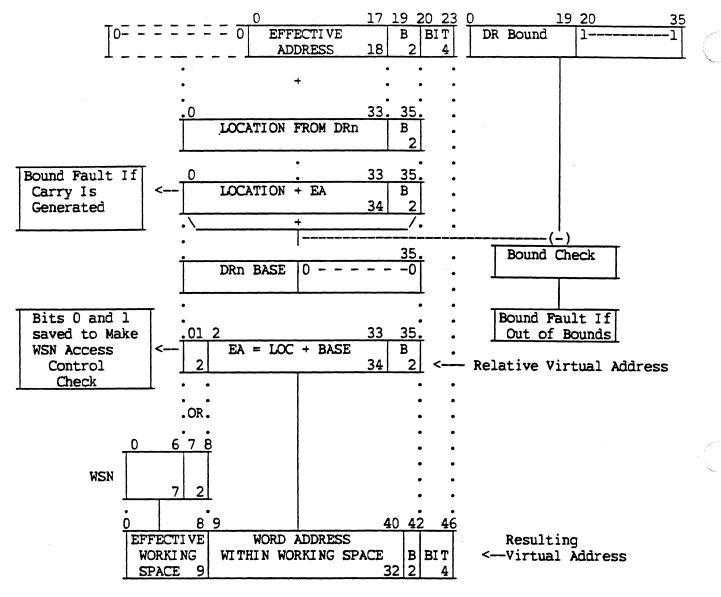

| Super Descriptor NS Mode                       | 5-61       |

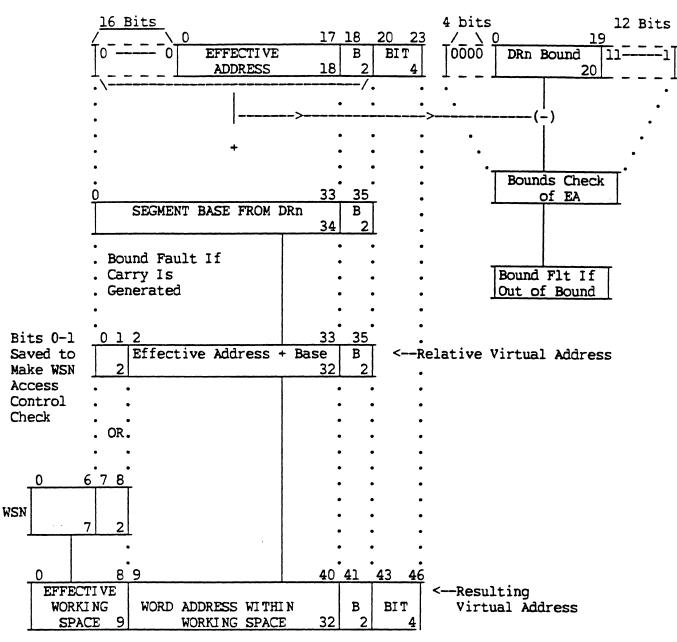

| Extended Segment Descriptor NS Mode            | 5-63       |

| Virtual Address Generation For ES Mode         | 5-64       |

| Standard Descriptor ES Mode                    | 5-64       |

| Extended Segment Descriptor ES Mode            | 5-65       |

| Absolute Addressing Mode                       | 5-67       |

| Paging                                         | 5-68       |

| Address Translation Process                    | 5-68       |

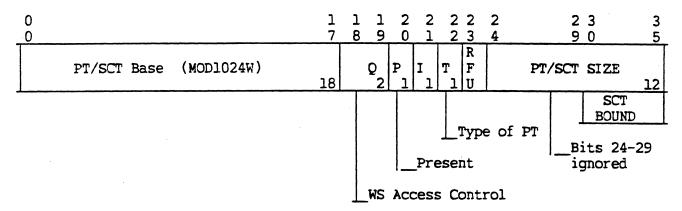

| Page Table Directory Word Format               | 5-68       |

| Page Table Base Word Format                    | 5-69       |

| Page Table Word Format                         | 5-70       |

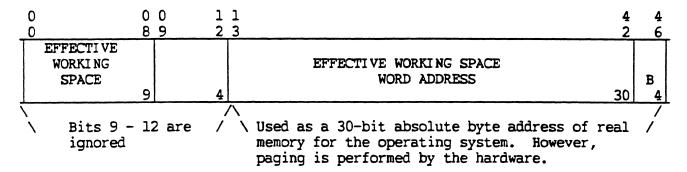

| Mapping The Virtual Address To A Real Address  | 5-71       |

| Dense Page Table                               | 5-72       |

| Locating The Page Table Directory Word         | 5-72       |

| Section Table                                  | 5-75       |

| Associative Memory                             | 5-79       |

| Cache Memory                                   | 5-82       |

| Address Truncation                             | 5-83       |

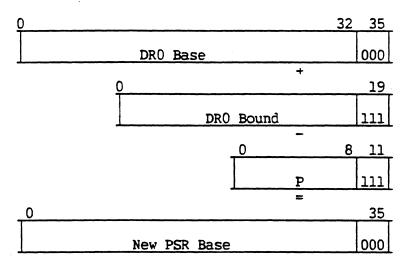

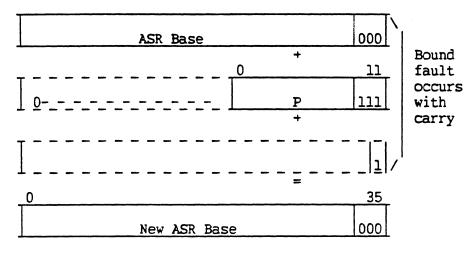

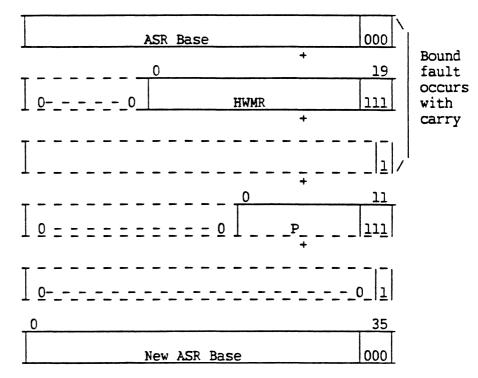

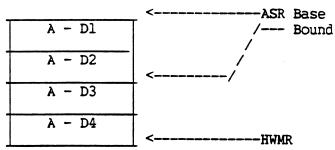

| Bounds Checking                                | 5-83       |

| Word And Double-Word Operations                | 5-84       |

| Byte Operations                                | 5-85       |

| Bit Strings And Table Of Translate Instruction | 5-85       |

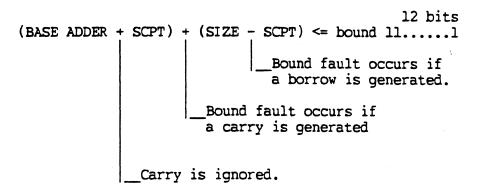

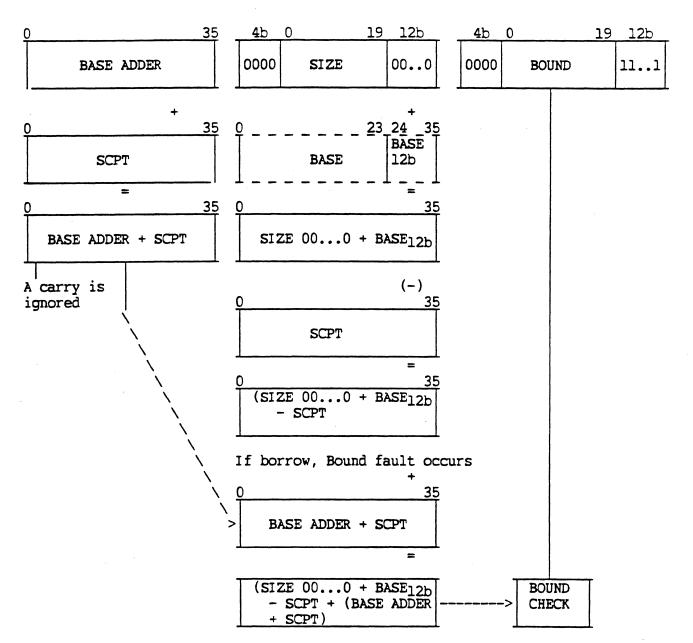

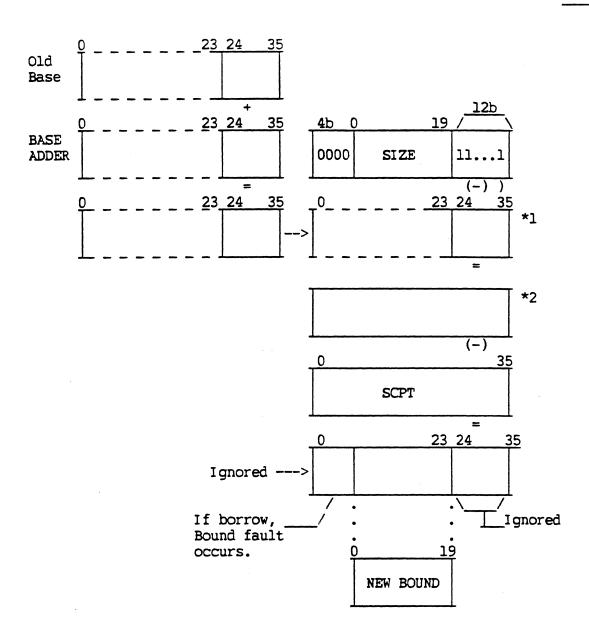

| Bound Check Equations                          | 5-85       |

| Duna Circui Equations                          | 5 05       |

| SECTION 6 FAULTS AND INTERRUPTS.               | 6-1        |

|                                                | <b>~</b> - |

| Description Of Faults And Interrupts           | 6-1        |

| Fault Procedures                               | 6-1        |

| Fault Priority                                 | 6-2        |

| Fault Recognition                              | 6-2        |

| Fault Categories                               | 6-4        |

| Instruction-Generated Faults                   | 6-4        |

| Program-Generated Faults                       | 6-7        |

| Virtual Memory-Generated Faults                | 6-10       |

| Hardware-Generated Faults                      | 6-16       |

| Mode Faults                                    | 6-17       |

| Privileged Master Mode Faults                  | 6-17       |

| Master Mode Faults                             | 6-17       |

| Slave Mode Faults                              | 6-17       |

| Any Mode Faults                                | 6-18       |

| Miscellaneous Faults.                          | 6-18       |

| Segment Descriptor Flag Faults                 |            |

|                                                |            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Page Table Word Control Field Faults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-20<br>6-23<br>6-23<br>6-24<br>6-25                                                    |

| SECTION 7 MACHINE INSTRUCTION FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-1                                                                                     |

| Single-Word Instructions.  Address Register Instructions.  Boolean Operations.  Comparison Operations.  Data Movement Instructions.  Data Shifting Instructions.  Effective Address To Register Instructions.  Fixed-Point Arithmetic Instructions.  Floating-Point Arithmetic Instructions.  Quadruple-Precision Floating-Point Instructions.  Privileged Master Mode Instructions.  Miscellaneous Instructions.  Special Processor Instructions.  Multiword Instructions.  Alphanumeric Instructions.  Numeric Instructions.  Bit String Instructions.  Conversion Instructions.  Edited Move Instructions.  Multiword Instructions.  Edited Move Instructions.  Multiword Instructions. | 7-1<br>7-2<br>7-2<br>7-2<br>7-3<br>7-3<br>7-4<br>7-5<br>7-5<br>7-6<br>7-6<br>7-6<br>7-7 |

| Address Register Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7-9<br>7-10<br>7-10<br>7-10<br>7-12                                                     |

| Boolean Operation Instructions  Boolean Expressions  Evaluation Of Boolean Expressions  Boolean AND  Boolean OR  Boolean EXCLUSIVE OR  Boolean COMPARATIVE AND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-13<br>7-13<br>7-14<br>7-15<br>7-15<br>7-15                                            |

| Boolean COMPARATIVE NOT AND.  Fixed-Point Instructions.  Data Movement Load.  Data Movement Store.  Data Movement Shift.  Fixed-Point Addition.  Fixed-Point Subtraction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-15<br>7-16<br>7-16<br>7-16<br>7-17<br>7-17                                            |

ix DZ51-00

|                                                             | Page |

|-------------------------------------------------------------|------|

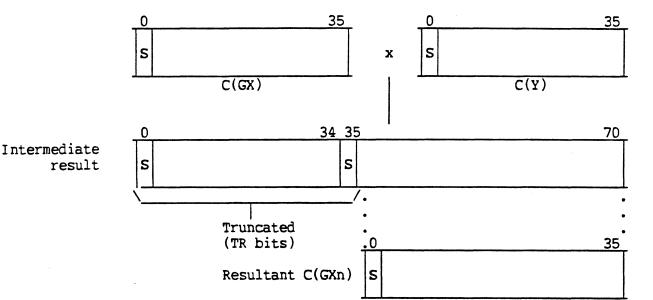

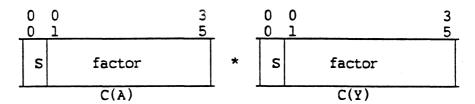

| Fixed-Point Multiplication                                  | 7-18 |

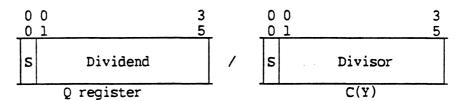

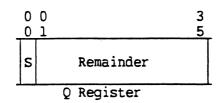

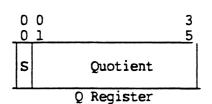

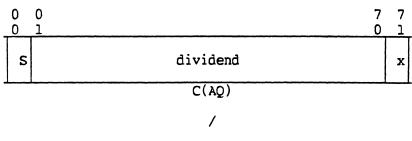

| Fixed-Point Division                                        | 7-18 |

| Fixed-Point Comparison                                      | 7-19 |

| Fixed-Point Negate                                          | 7-19 |

| Floating-Point Instructions                                 | 7-20 |

| Data Movement Load                                          |      |

| Data Movement Store                                         |      |

| Floating-Point Addition                                     |      |

| Floating-Point Subtraction                                  |      |

| Floating-Point Multiplication                               |      |

| Floating-Point Division                                     |      |

| Floating-Point Comparison                                   |      |

| Floating-Point Negate                                       |      |

| Floating-Point Normalize                                    |      |

| Floating-Point Round                                        |      |

| Floating-Point Truncate Fraction                            |      |

| Quadruple-Precision Instructions                            |      |

| Multiword Instructions                                      |      |

| Multiword Instruction Format                                |      |

| Multiword Modification Field                                |      |

| Operand Descriptors And Indirect Words                      |      |

|                                                             |      |

| Operand Descriptor Indirect Word Format                     |      |

| Alphanumeric Instructions                                   |      |

| Alphanumeric Operand Descriptor Format                      |      |

| Alphanumeric Compare                                        |      |

| Alphanumeric Move                                           |      |

| Character Move To/From Register Instructions                |      |

| Operand Descriptor For Character Move Instructions          |      |

| Character Move Instruction Repertoire                       |      |

| Numeric Instructions                                        | 7-30 |

| Numeric Operand Descriptor Format                           |      |

| Numeric Compare                                             |      |

| Numeric Move                                                |      |

| Bit String Instructions                                     | 7-34 |

| Bit String Operand Descriptor Format                        | 7-35 |

| Bit String Combine                                          |      |

| Bit String Compare                                          |      |

| Bit String Set Indicators                                   | 7-36 |

| Data Conversion Instructions                                |      |

| Arithmetic Instructions                                     |      |

| Decimal Addition                                            |      |

| Decimal Subtraction                                         |      |

| Decimal Multiplication                                      |      |

| Decimal Division                                            |      |

| Micro Operations For Edit Instructions MVE, MVNE, And MVNEX | 7-38 |

| Micro Operation Sequence                                    |      |

| Edit Insertion Tables                                       | 7-39 |

| min and and another pifferences                             | 7 40 |

|                                              | Page |

|----------------------------------------------|------|

| Numeric Edit (MVNE AND MVNEX)                | 7-40 |

| Alphanumeric Edit (MVE)                      | 7-41 |

| Micro Operation Repertoire                   | 7-41 |

| Micro Operations Descriptions                | 7-42 |

| Edit Flags                                   | 7-42 |

| Micro Operation Code Assignment Map          | 7-57 |

| Terminating Micro Operations                 | 7-57 |

| Virtual Memory Instructions                  | 7-58 |

| Descriptor Register Instructions             | 7-58 |

|                                              | 7-58 |

| Pointer Register Instructions                |      |

| Domain Transfer (CLIMB)                      | 7-58 |

| Privileged Instructions                      | 7-59 |

| Clear Associative Memory Pages               | 7-59 |

| Clear Cache                                  | 7-59 |

| Register Load                                | 7-59 |

| Register Store                               | 7-60 |

| Memory Control                               | 7-60 |

| System Control                               | 7-60 |

| All Mode Instructions                        | 7-61 |

| ES Mode Instructions                         | 7-62 |

| Register-to-Register Instructions            | 7-62 |

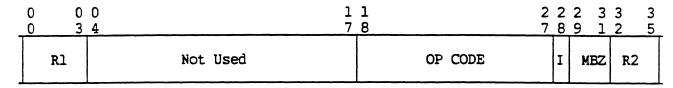

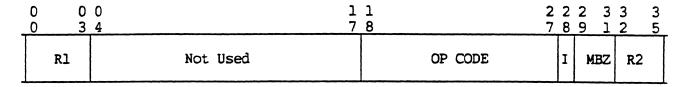

| RR Type Instruction Format                   | 7-62 |

| Movement And Arithmetic Instructions         | 7-64 |

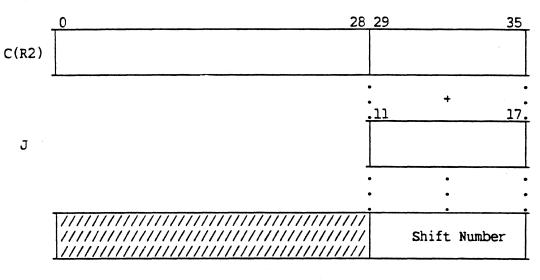

| Shift Instructions                           | 7-65 |

| Fixed-Point Instructions                     | 7-65 |

| Transfer Instructions                        | 7-66 |

| Conditional Transfer                         | 7-66 |

| Unconditional Transfer                       | 7-66 |

| Miscellaneous Instructions                   | 7-67 |

| Option Register Instructions                 | 7-67 |

| Binary-To-BCD Conversion                     | 7-67 |

| Execute Instructions                         | 7-67 |

| Gray-To-Binary-Conversion.                   | 7-67 |

| Programmed Fault                             | 7-67 |

|                                              | 7-68 |

| No Operation                                 | 7-68 |

| Repeat Instructions                          |      |

| Pointer And Length Instructions              | 7-68 |

| Coding Limitations                           | 7-69 |

| CDCMION O MACHINE INCONFICMION ADCCOLUMNIONS | 8-1  |

| SECTION 8 MACHINE INSTRUCTION DESCRIPTIONS   | 0-1  |

| Paymet Of Instruction Description            | 8-1  |

| Format Of Instruction Description            | 8-3  |

| Abbreviations And Symbols                    |      |

| Common Attributes Of Instructions            | 8-7  |

| Illegal Modification                         | 8-7  |

| Parity Indicator                             | 8-7  |

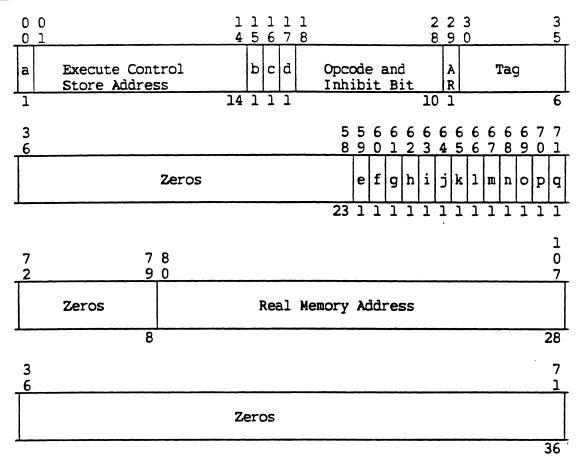

| Instruction Word Formats                     | 8-7  |

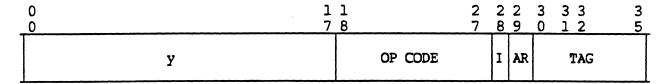

| Single-Word Instructions                     | 8-7  |

хi

| 8-9<br>8-10                                                                            |

|----------------------------------------------------------------------------------------|

| 8-10<br>8-11<br>8-12<br>8-14                                                           |

| <b>A-</b> 1                                                                            |

| B-1                                                                                    |

| C-1<br>C-1<br>C-4<br>C-10<br>C-12                                                      |

| i-1                                                                                    |

|                                                                                        |

| Page                                                                                   |

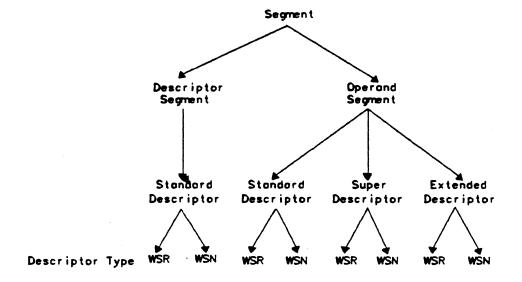

| 3-3<br>3-5<br>3-16<br>1-4<br>1-5<br>1-5<br>1-6<br>1-13<br>1-13<br>1-15<br>1-17<br>1-18 |

|                                                                                        |

## ILLUSTRATIONS (cont)

| Figur | e e                                                             | Page |

|-------|-----------------------------------------------------------------|------|

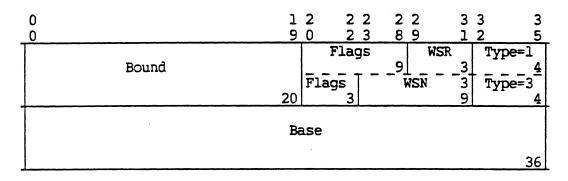

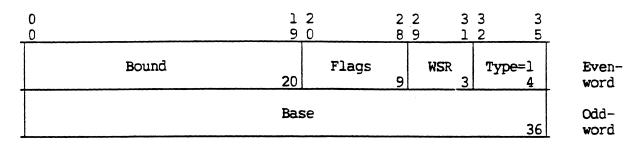

| 4-20  | Working Space Register (WSRn) Format                            | 4-21 |

| 4-21  | Safe Store Register (SSR) Format                                | 4-21 |

| 4-22  | Argument Stack Register (ASR) Format                            | 4-23 |

| 4-23  | Parameter Segment Register (PSR) Format                         | 4-23 |

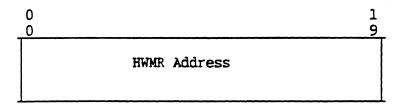

| 4-24  | High Water Mark Register (HWMR) Format                          | 4-24 |

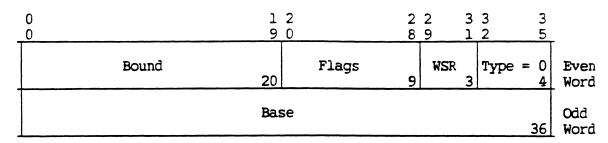

| 4-25  | Data Stack Descriptor Register (DSDR) Format                    | 4-25 |

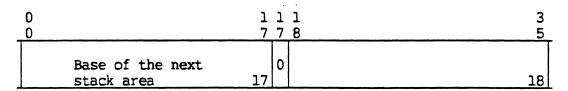

| 4-26  | Data Stack Address Register (DSAR) Format                       | 4-25 |

| 4-27  | Page Directory Base Register (PDBR) Format                      | 4-26 |

| 4-28  | CPU Mode Register (MR) Format                                   | 4-26 |

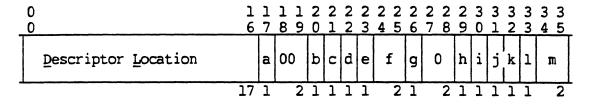

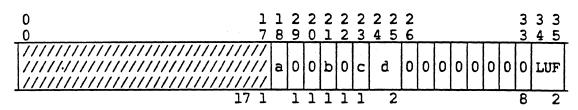

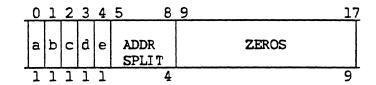

| 4-29  | Cache Mode Register (CMR), Lockup Fault Register Format (LUF)   | 4-28 |

| 4-30  | Configuration Register (Port Assignment ) (CR)                  | 4-30 |

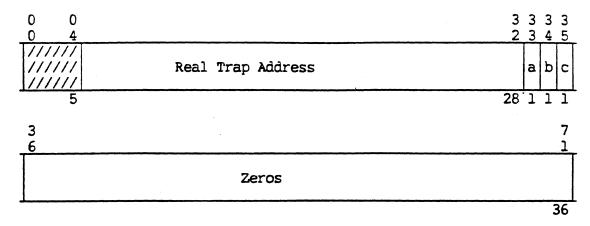

| 4-31  | Address Trap Register (ATR) Format                              | 4-32 |

| 4-32  | Virtual Address Trap Register (VATR) Format                     | 4-33 |

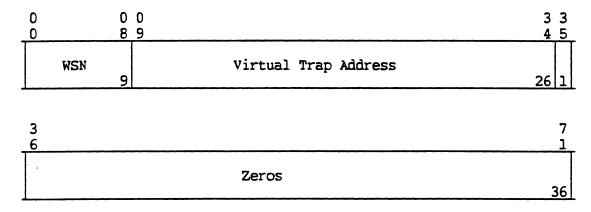

| 4-33  | CPU Number Register (NR) Format                                 | 4-34 |

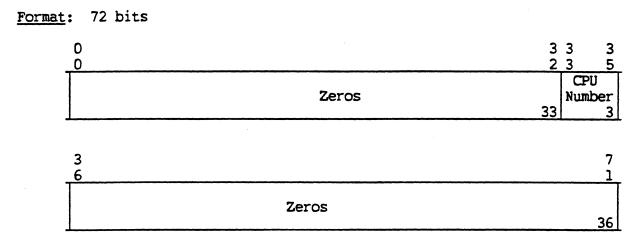

| 4-34  | Interrupt Mask Register (IMR) Format                            | 4-35 |

| 4-35  | Fault Register (FR) Format                                      | 4-36 |

| 4-36  | Extended Fault Register (EFR) Format                            | 4-40 |

| 4-37  | History Register (HR) Format                                    | 4-41 |

| 4-38  | Reserve Memory Base Register (RMBR) Format                      | 4-43 |

| 4-39  | System Control Unit Fault Register (SCUFR) Format               | 4-44 |

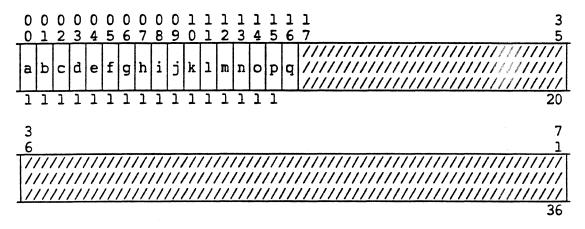

| 4-40  | Syndrome Register (SYR) Format                                  | 4-46 |

| 4-41  | SCU Configuration Register (SCUCR) Format                       | 4-47 |

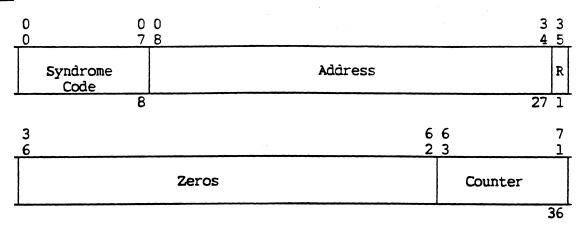

| 4-42  | SCU History Register (SCUHR) Format                             | 4-49 |

| 4-43  | Memory Error Status Register Format                             | 4-51 |

| 4-44  | Memory Identification Register (MID)                            | 4-52 |

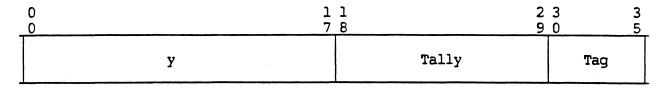

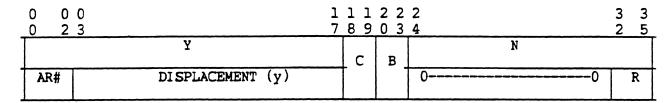

| 5-1   | Indirect Word Format                                            | 5-16 |

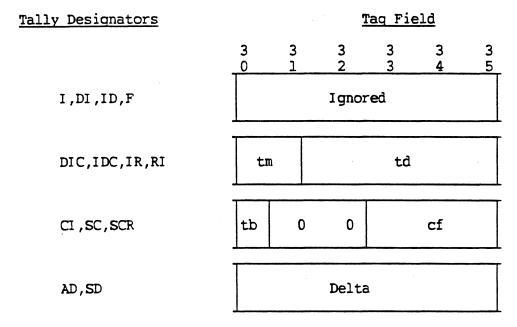

| 5-2   | Address Modification Flowchart                                  | 5-26 |

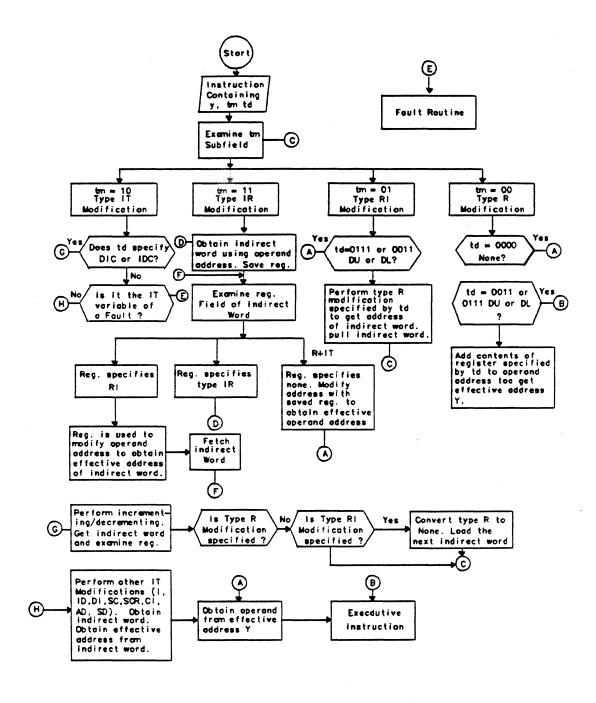

| 5-3   | Single-Word Instruction Format                                  | 5-28 |

| 5-4   | Address Preparation For Single-Word Instruction                 | 5-29 |

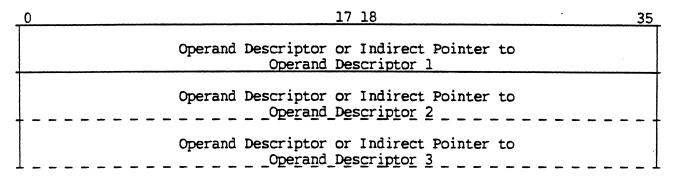

| 5-5   | Multiword Instruction Format                                    | 5-30 |

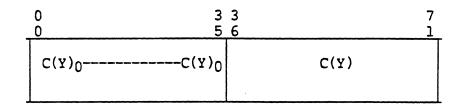

| 5-6   | Bit String Operand Descriptor Format                            | 5-35 |

| 5-7   | Alphanumeric Operand Descriptor Format                          | 5-36 |

| 5-8   | Numeric Operand Descriptor Format                               | 5-37 |

| 5-9   | Indirect Word Format                                            | 5-40 |

| 5-10  | Flowchart For Operand Descriptor Address Preparation            | 5-42 |

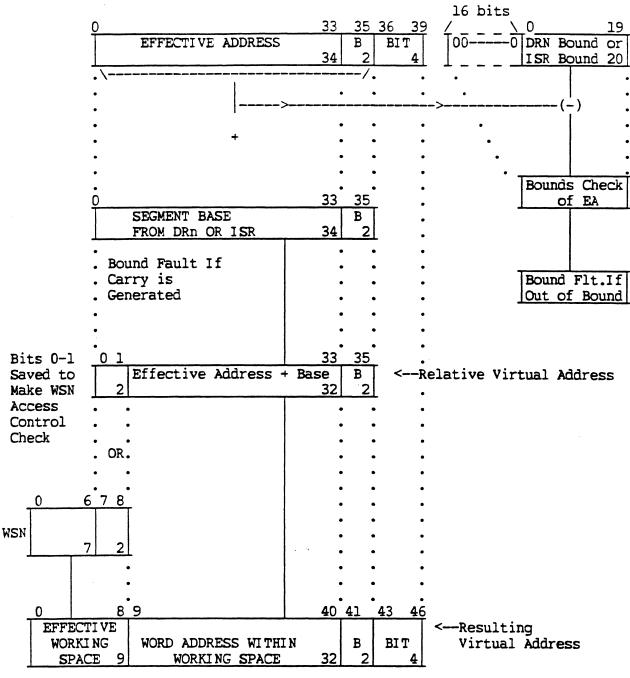

| 5-11  | Virtual Address Generation Using Standard Descriptor (NS Mode). |      |

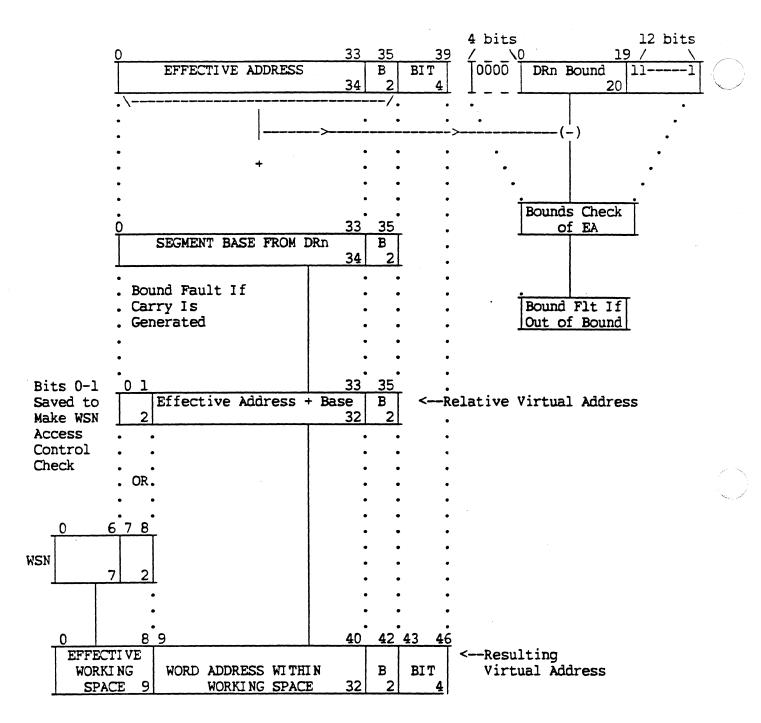

| 5-12  | Virtual Address Generation Using Super Descriptor (NS Mode)     | 5-62 |

| 5-13  | Virtual Address Generation Using Extended Segment Descriptor    |      |

| _     | (NS Mode)                                                       | 5-63 |

| 5-14  | Virtual Address Generation Using Standard Descriptor (ES Mode). | 5-65 |

| 5-15  | Virtual Address Generation Using Extended Segment Descriptor    |      |

|       | (ES Mode)                                                       | 5-66 |

| 5-16  | Effective Absolute Address                                      | 5–67 |

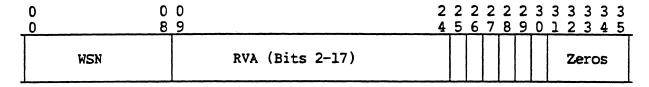

| 5-17  | Page Table Directory Word (PTDW) Format                         | 5-68 |

| 5-18  | Page Table Base Word (PBW) Format                               | 5-69 |

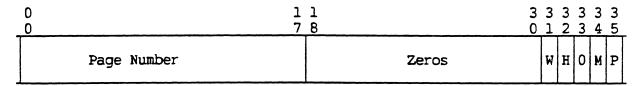

| 5-19  | Page Table Word (PTW) Format                                    | 5-70 |

| 5-20  | Virtual Address                                                 | 5-72 |

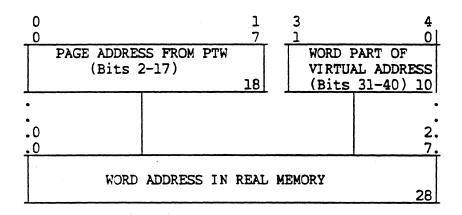

| 5-21  | Address Mapping Using A Dense Page Table                        | 5-73 |

| 5-22  | PTDW Address                                                    | 5-73 |

xiii DZ51-00

## ILLUSTRATIONS (cont)

| Figur                                                                                                                       | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

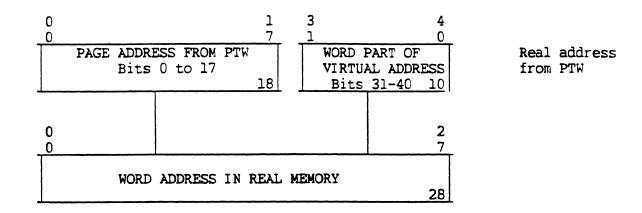

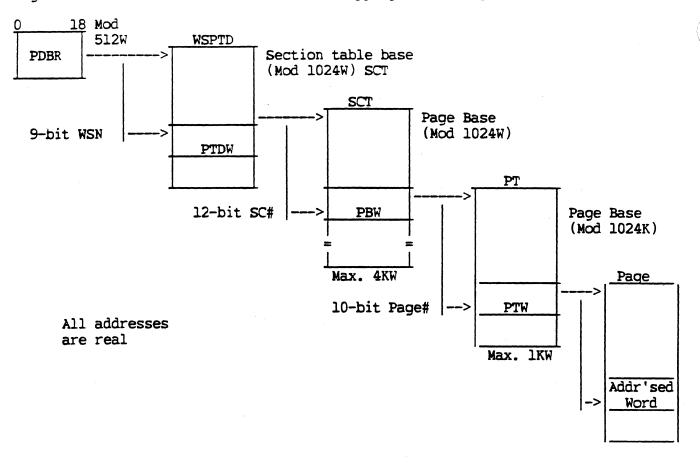

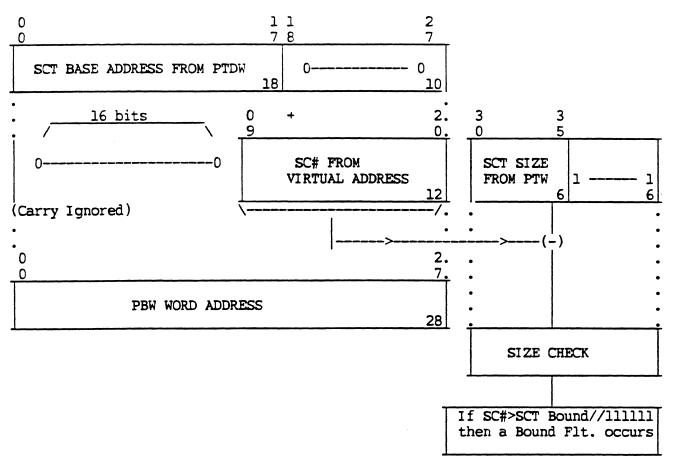

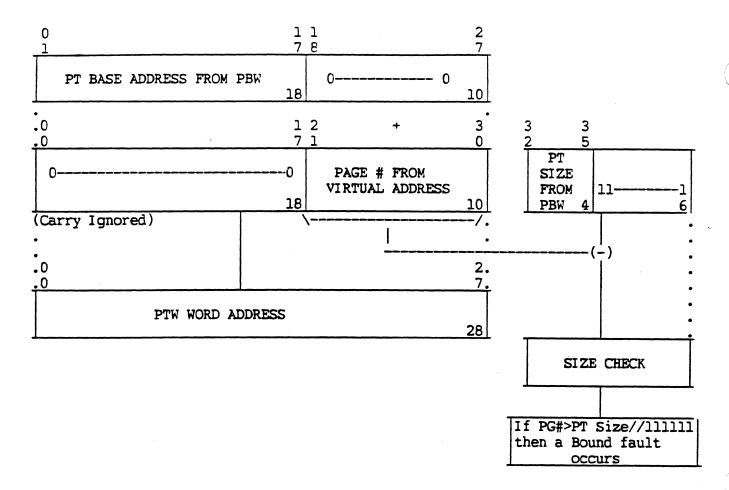

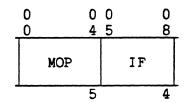

| 5-23<br>5-24<br>5-25<br>5-26<br>5-27<br>5-29<br>5-30<br>5-31<br>7-2<br>7-3<br>7-6<br>7-7<br>8-1<br>8-2<br>8-3<br>8-7<br>8-8 | Word Address. Virtual Address. Virtual Address. Address Mapping Using A Section Table PBW Address. PTW Address. Word Address. Page Table Word Associative Memory (PTWAM) Format. Associative Memory Directory Word. Cache Directory Word. Single-word Instruction With Address Modification. Alter Address Register Contents. Special Address Register Instructions. Multiword Instruction Format. Operand Descriptor Indirect Word Format. Alphanumeric Operand Descriptor Format. Numeric Operand Descriptor Format. Bit String Operand Descriptor Format. Micro Operation (MOP) Character Format. Single-Word Instruction Format. Multiword Instruction Format. Address Register Special Arithmetic Instruction Format Character Move To/From Register Instruction Format. Register To Register Instruction Format Standard I/O Mailbox. Safe Store Stack Format - NS Mode. Safe Store Stack Format - ES Mode. | 5-74<br>5-75<br>5-75<br>5-76<br>5-77<br>5-78<br>5-79<br>5-80<br>5-82<br>7-10<br>7-12<br>7-23<br>7-25<br>7-26<br>7-29<br>7-31<br>7-35<br>7-38<br>8-10<br>8-11<br>8-10<br>8-10<br>8-10<br>8-10 |

|                                                                                                                             | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                              |

| Table                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page                                                                                                                                                                                         |

| 1-1<br>2-1<br>2-2<br>4-1<br>4-2<br>4-3<br>5-1<br>5-2<br>5-3<br>6-1                                                          | Status Of Processor Mode Determinants.  Ranges Of Fixed-Point Numbers.  Ranges Of Binary Floating-Point Numbers.  Processor Accessible Registers.  System Controller Illegal Action Codes.  Source Of Fault Register Errors.  Address Modification Octal Codes.  Register Codes.  Bound Check Equations.  Processor Faults By Fault Code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-5<br>2-4<br>2-7<br>4-2<br>4-38<br>4-39<br>5-25<br>5-33<br>5-86<br>6-3                                                                                                                      |

## TABLES (cont)

| Table |                                                          | Page |

|-------|----------------------------------------------------------|------|

| 6-2   | Processor Modes                                          |      |

| 6-3   | Classes Of Faults And Interrupts (DPS 8000)              | 6-26 |

| 7-1   | Alphanumeric Character Number (CN) Codes                 | 7-27 |

|       | Alphanumeric Data Type (TA) Codes                        |      |

|       | Sign And Decimal Type (S) Codes                          |      |

|       | Default Edit Insertion Table Characters For MVE And MVNX |      |

| 7-5   | Edit Insertion Table Entries For MVNEX                   | 7-40 |

| 8-1   | Binary-To-BCD Conversion Constants                       | 8-78 |

| 8-2   | Character Codes For ASCII And EBCDIC Overpunched Signs   |      |

|       | Operation Code Map (Bit 27 = 0)                          |      |

|       | Operation Code Map (Bit 27 = 1)                          |      |

DZ51-00

#### SECTION 1

#### INTRODUCTION

This manual contains a set of machine instructions used on Honeywell Bull hardware and operating systems. The systems are highly modular, allowing system configuration to be matched to the work load mix. This section describes the essential characteristics of the central processors for these systems.

Each processor module in the system has full program execution capability. The processors conduct all actual computational processing (data movement, arithmetic, logic, comparison, and control operations) within the information system. The processor communicates only with the system controller (DPS 8000: SCU, System Control Unit) and associated memory. The processors contain several special features that make significant contributions to multiprogramming, high throughput, and rapid turnaround. These features are under the control of the operating system which maintains automatic supervision and complete control of the multiprogramming/multiprocessing environment.

#### PROCESSOR FEATURES

- A processor contains the following general features:

- 1. Memory protection to place access restrictions on specified segments

- 2. Capability to interrupt program execution in response to an external signal (e.g., I/O termination), to save processor status and to restore the status at a later time without loss of program continuity

- Capability to fetch instructions and to buffer instructions

- 4. A four-stage pipelined instruction development for greater performance

- 5. Fully interlaced store units addressable by a given SCU

- 6. Ability to hold recently referenced operands and instructions in a 64K high-speed cache memory

- 7. An Extended (ES) mode that uses 36-bit addressing includes a set of general register-to-register instructions

- 8. Real memory configurations of up to 256 megawords are supported.

1-1 DZ51-00

9. Quad-precision arithmetic operations for which the exponents are handled as powers of 16

#### Pipeline Architecture Of The DPS 8000

The four-stage pipeline processor consists of the following cycles:

A cycle: Effective address calculation and virtual address calculation are

performed

V cycle: Virtual address to real address translation and bound checking,

access checking (read, write permission, etc.) are performed

C cycle: Memory is accessed (cache) using the real memory addresss

E cycle: Instruction is executed by firmware control

One instruction execution completes via four cycles. The maximum instruction rate is attained when the processor is executing basic instructions (one memory access and one execution cycle). Because the processor operates as a four-stage pipeline, a new instruction can be issued before the prior one is completed, thereby reducing the effective execution time.

#### Faults And Interrupts

The processor detects illegal instruction usages, faulty communication with main memory, programmed faults, certain external events, and arithmetic faults. Many of the processor fault conditions are deliberately caused by the software and do not necessarily involve error conditions. The processor communicates with the other system modules (I/O processors and other processors) by setting and answering external interrupts. When the processor responds to a fault or interrupt, control is transferred to an operating system module via an interdomain transfer using an entry descriptor obtained from a fixed memory location.

The locations in real memory containing the entry descriptors for interrupt, fault, and system entry (PMME) are as follows:

| <u>Type</u>  | Location      |  |  |  |  |

|--------------|---------------|--|--|--|--|

| Interrupt    | 30-31 (octal) |  |  |  |  |

| Fault        | 32-33 (octal) |  |  |  |  |

| System Entry | 34-35 (octal) |  |  |  |  |

| Backup       | 40-41 (octal) |  |  |  |  |

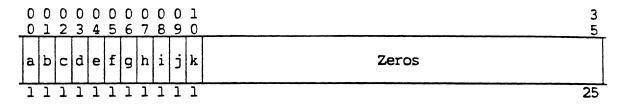

Interrupts and certain low-priority faults are recognized only at specific times during program execution. If, at these times, bit 28 in the instruction word is set ON, the trap is inhibited and program execution continues. The interrupt or fault signal is saved for future recognition and is reset only when the trap is recognized.

#### Connect/Interrupt Mechanism

On a connect to the IMX, the software points to a logical channel mailbox that resides anywhere in main memory. The mailbox is required to be 24 words, beginning at a 0-modul0-8 address. The operating system is responsible for placing specific information into the first eight words.

This mailbox serves as the primary intercommunication vehicle between the IMX and the CPU. Software specifies the (relative) starting location of the mailbox as the effective address of the connect instruction (CIOC). Normal CPU address preparation converts this to a real memory address, which is then used by the IMX.

Successive I/O operations to the same logical channel can be issued via a linked mailbox feature available through IMX's. However, once a connect has been issued by the software, it is the responsibility of the operating system to not issue another connect directed to the same logical channel until the current one is completed or a "lost interrupt" timeout has occurred.

All 128 channels (numbered 0-127) are data channels except channel numbers zero and three. Channel three is used for two-way communication between the CPU and IMX maintenance system (MCA). Channel zero is normally declared invalid, to avoid confusion that would otherwise exist in the operating system as to whether a given channel number field is zero, or the field is currently unused.

The CPU automatically directs the connect command to the "control" SCU. If the system configuration includes two SCU's (i.e., tandem), then the SCU which is designated as "control" is the one which processes all connects and interrupts for the operational system. The control SCU then adds a connect word pair to the destination port's connect queue and notifies the port that a connect is present in its queue. The IMX reads the contents of the queue with the Read Connect Words command instruction (RCW).

An interrupt queue mechanism is used in the DPS 8000 system that allows for up to 256 simultaneous entries for each of eight interrupt levels. Thus, the SCU maintains a queue for each interrupt level. Levels one and seven are for fault and special interrupts, respectively. The interrupt level for marker/terminate interrupts are specified at connect time in the mailbox (GCOS uses levels 5 and 3, respectively).

The control SCU sends an interrupt present signal to all CPU's that are unmasked for this interrupt level (each CPU initializes and modifies its own masks independently). The SCU sends an accept signal to the candidate CPU selected, and automatically shuts off all further interrupt present signals by masking a unique system-wide "all mask".

1-3 DZ51-00

The CPU, selected by the SCU to process the interrupt, transfers to the operating system interrupt handler by executing an interdomain CALL version of the CLIMB instruction, using the entry descriptor at location 30-31 (octal). The software interrupt handler uses the RIW instruction for each pair of interrupt words (one doubleword interrupt queue entry). The next interrupt pair is selected from the highest priority (i.e., lowest numbered), unmasked level, and inserted into the AQ register. When no more entries are available at any level that is unmasked for this CPU, then the AQ register will contain all zeros.

The operating system examines the channel mailbox for status information. On terminate or marker type interrupts, status returns are automatically stored in the channel mailbox. Up to eight words of peripheral extended status are likewise stored.

#### Online Processor Tests

The PATROL feature (Processor Activity Test Runs On Line) is implemented as firmware in its own unique CPU memory. PATROL runs test programs and reports status to the maintainance interface.

#### OPERATING MODES

Three types of modes determine the operation of the CPU.

- o Privileged Master, Master, and Slave modes which determine the processor mode of operation

- o NS and ES (Non-extended/Extended) modes which determine whether 18-bit or 36-bit registers are used and determine the method to be used to generate effective and virtual addresses

- o Memory addressing modes

#### Processor Modes Of Operation

The three processor modes of operation are Privileged Master mode, Master mode, and Slave mode. The master mode bit in the indicator register, the privileged bit in the instruction segment register (ISR), and the housekeeping bit in the page table word (PTW) for the instruction define these processor modes.

1-4 DZ51-00

The status of the determinants for each mode is shown in Table 1-1.

Table 1-1. Status Of Processor Mode Determinants

|                                                                  | Processor Modes <sup>a</sup> |        |       |  |  |  |  |

|------------------------------------------------------------------|------------------------------|--------|-------|--|--|--|--|

| Determinants                                                     | Privileged<br>Master         | Master | Slave |  |  |  |  |

| Master Mode Bit in Indicator Register (bit 28)                   | ON                           | ON     | OFF   |  |  |  |  |

| Privileged Bit in<br>Instruction Segment<br>Register<br>(bit 26) | ON                           | OFF    | OFF   |  |  |  |  |

| Housekeeping Bit in Page Table Word for the Instruction (bit 32) | ОИр                          | ON/OFF | OFF   |  |  |  |  |

a All other combinations are illegal and result in a Class 1 Security Fault.

A fault or an interrupt causes the processor to enter Privileged Master mode. If the processor is in Privileged Master mode, an instruction can change to Master mode by transferring to a segment marked non-privileged. The reverse is also true when transferring to a segment marked privileged. The use of a CLIMB instruction between Master and Privileged Master modes, like the transfer, not only allows a change of processor execution modes but also a change of domains.

b When working space zero is referenced, the housekeeping bit is assumed to be ON and the processor addresses memory through absolute mode page tables.

The Master mode bit in the indicator register can be turned ON as follows:

- 1. Occurrence of an interrupt or a fault

- 2. Execution of the PMME version of the CLIMB instruction, which causes a system entry

- 3. Execution of the OCLIMB version of the CLIMB instruction where the master mode bit of the restored indicator register is ON

The following mode-dependent processor functions are listed by mode. None of these functions are permitted in Slave mode.

Functions allowed in Master and Privileged Master modes:

- 1. Accessing through working space register zero

- 2. Reading operands from a housekeeping page of segment descriptor type T = 0, 2, 4, 6, 12, or 14

- 3. Executing instructions from housekeeping pages of type T = 0 segments

- 4. Executing a CLIMB (ICLIMB or GCLIMB) not invoking a system entry option (PMME)

- 5. Executing a transfer to a privileged executable segment

Functions allowed only in Privileged Master mode:

- 1. Executing Privileged Master mode instructions (e.g., load working space registers)

- 2. Executing Privileged Master mode options of the LDDn, LDPn, or CLIMB instructions, such as copying the safe store register (SSR) to a descriptor register (DRn)

- 3. Writing on housekeeping pages of type T = 0, 2, 4, 6, 12, or 14 segments, using instructions other than CLIMB, SDRn, STDn

#### Non-Extended/Extended Modes

The NS (Non-extended) and ES (Extended) modes are specified with bit 24 of the Instruction Segment Register (ISR).

- o When ISR bit 24 = 0 NS mode.

- o When ISR bit 24 = 1 ES mode.

ISR bit 24 may be altered only with the CLIMB instruction.

Processor operations differ between NS and ES modes for the following:

- o The number of bits in the index and the address registers

- o The method used to generate effective address

- o The execution of some instructions

- o Additional register instructions available in ES mode

#### Memory Addressing Modes

Three types of memory addressing exist in the DPS 8000.

- 1. Virtual memory which is mapped to a real (physical) memory address

- 2. Absolute mode which is used only when Working space zero is referenced

- 3. Reserved memory which is reserved for special use

#### VIRTUAL MEMORY PAGING

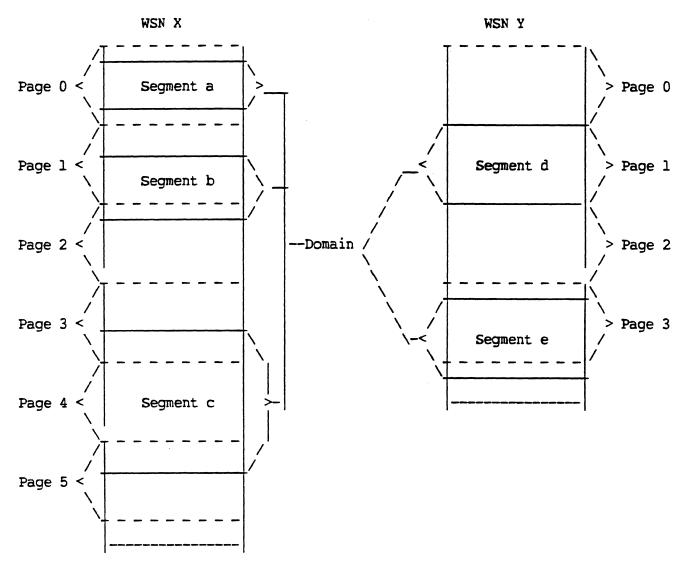

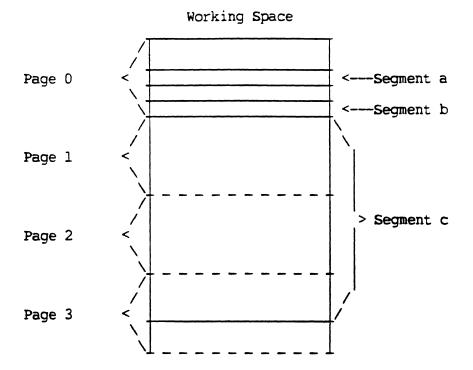

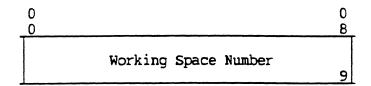

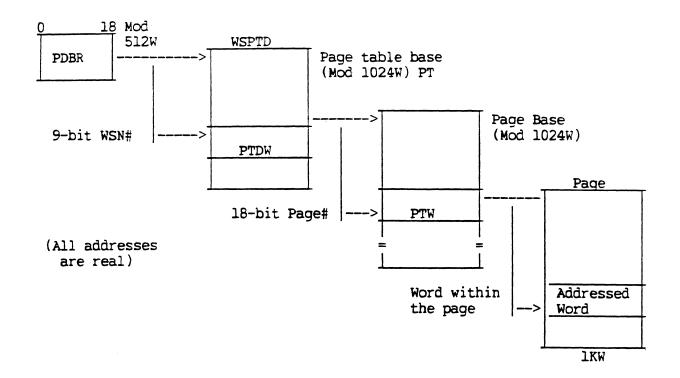

Virtual memory paging mode is an integral part of the address translation process for mapping a virtual memory address to a real memory address. Each of the 512 working spaces (WS) is supported by one page table (PT) or by a section table (SCT) that references multiple page tables.

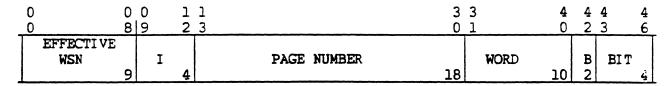

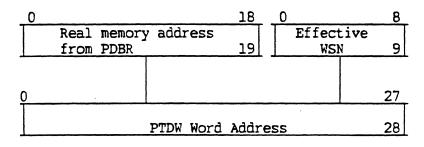

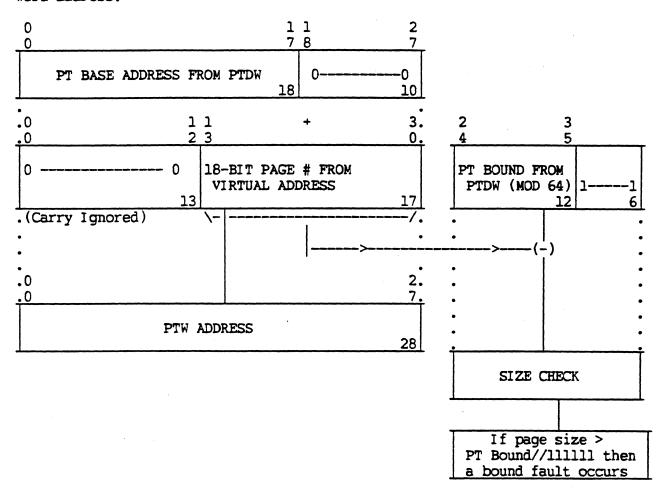

The location of a PT supporting a working space (WS) is indicated by a 9-bit working space number (WSN) that indexes the 512-word page table directory called the working space page table directory (WSPTD). This directory contains the real memory address of the supporting page table. Words in the WSPTD are called page table directory words (PTDW), and words on the page table are called page table words (PTW). The location of a WSPTD is indicated by the page directory base register (PDBR).

The location of the SCT supporting a given WS is indicated by a 9-bit WSN that also indexes the page table directory (WSPTD). The SCT consists of up to 4K words and includes the real memory address of the page table. The individual words in the SCT are called page table base words (PBW). The effect of SCTs is seen when paging is performed; these page tables are distributed throughout memory.

1-7 DZ51-00

#### ABSOLUTE MODE

The processor utilizes the absolute addressing mode each time working space number zero is referenced. However, the virtual address is not mapped to a real address; it is used as the real address with a maximum size limitation of 2\*\*28 words (256 megawords). Any time a working space other than zero (WSN=0) is referenced, the processor uses the paging mode.

To use the absolute addressing mode, the processor must be in Privileged Master mode. The master mode bit in the indicator register and the privileged bit in the instruction segment register must be ON. If these two conditions are not met, any attempted reference to WSN 0 results in a Command fault. The housekeeping bit is assumed ON when WSN 0 is referenced.

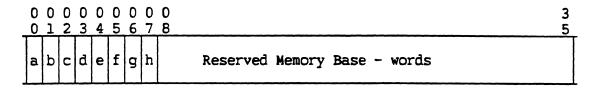

#### RESERVED MEMORY SPACE

Reserved memory space is defined by space above the Reserved Memory Base Register. This page is not represented in the Memory Utilization Table (MUT) and is addressable only in absolute mode.

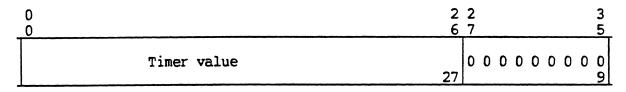

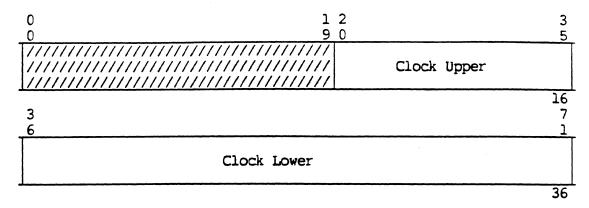

#### INTERVAL TIMER

The processor contains a timer that provides a program interrupt (timer runout fault) at the end of a variable interval. The timer is loaded by the operating system and can be set to a maximum of approximately four minutes total elapsed time.

1-8 DZ51-00

#### SECTION 2

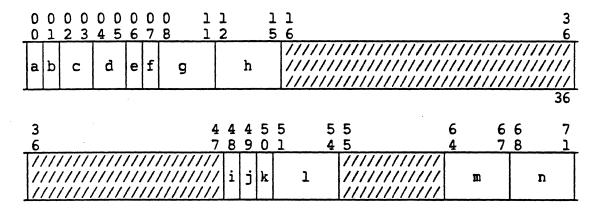

#### REPRESENTATION OF DATA

#### **FORMATS**

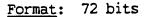

The processor is functionally organized to process 36-bit groupings of information called words. Special features are also included for ease in manipulating 4-bit groups, 6-bit groups, 9-bit groups, 18-bit groups, 72-bit double-precision, and 144-bit quad-precision groups. These bit groupings are used by the hardware and software to represent a variety of forms of information.

#### POSITION NUMBERING

The numbering of bit positions, character positions, words, etc., starts with zero and increases from left to right as in conventional alphanumeric text. Bit zero is the most-significant bit and the right-most bit is the least-significant bit.

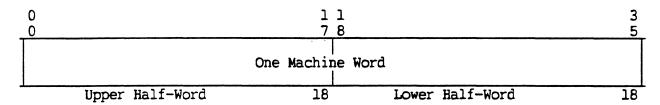

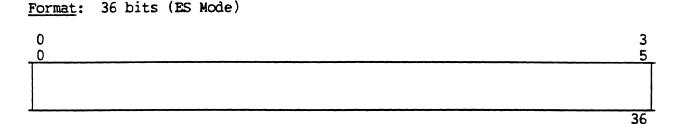

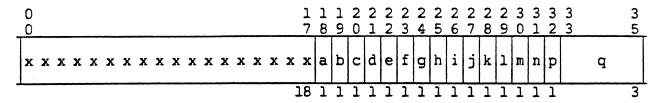

#### THE MACHINE WORD

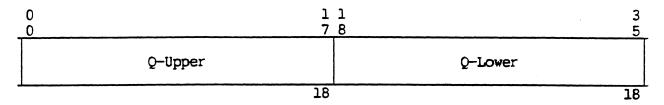

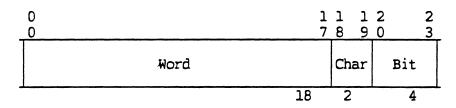

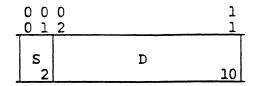

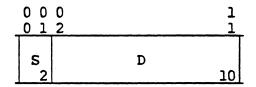

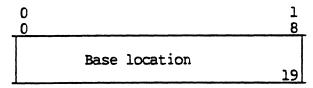

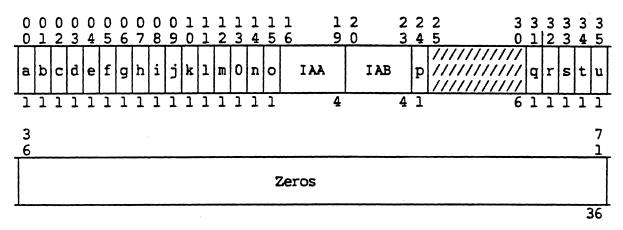

The machine word consists of 36 bits arranged as follows:

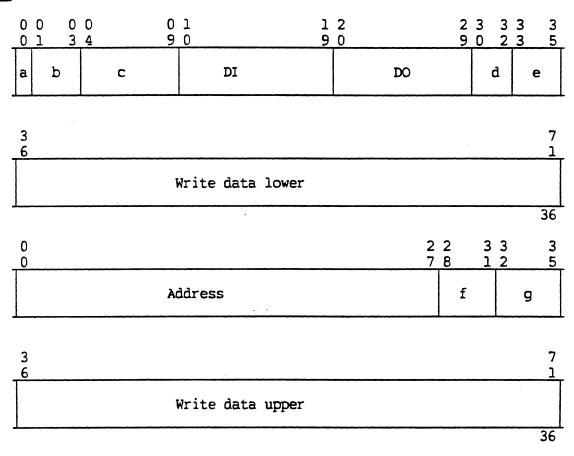

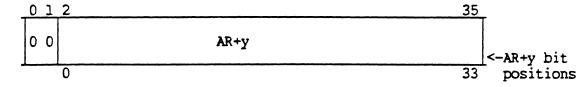

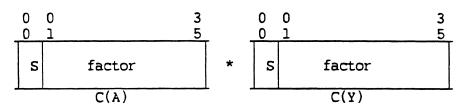

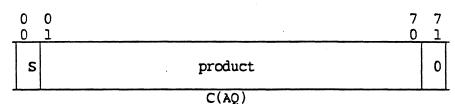

Data transfers between the processor and memory are double-word-oriented; 36 bits are used at a time for single-precision data and two parallel 36-bit word are used for double-precision data. When words are transferred to a memory unit, Error Detection and Correction (EDAC) bits are added to each word pair before the words are stored. When words are requested from a memory unit, the EDAC bits are read from memory, verified, and removed before sending the word pair to the processor.

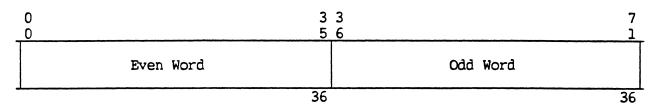

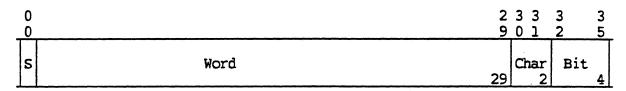

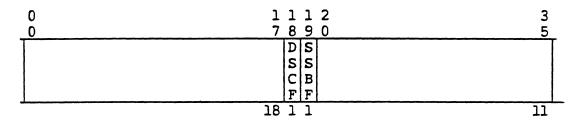

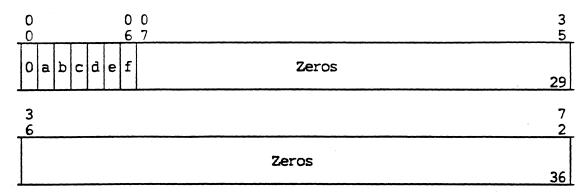

The processor has many built-in features for efficient transferring and processing of pairs of words. When a pair of words is transferred to or from memory, their addresses are an even number and the next higher odd number. A pair of words is arranged as follows.

Even Addresss

Odd Address

7

In an instruction intended for handling pairs of machine words, either of the two addresses may be used as the effective address (Y). Thus,

If Y is even, the pair of locations (Y, Y+1) is accessed. If Y is odd, the pair of locations (Y-1, Y) is accessed. The term "Y-pair" is used for each pair of addresses. Preferred coding practice refers to the even address; the GMAP assembler issues a warning diagnostic if Y is odd in an instruction intended for handling pairs of machine words.

#### CHARACTER-STRINGS

#### Character Positions

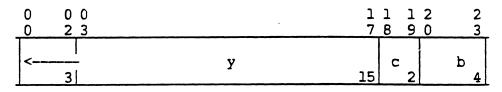

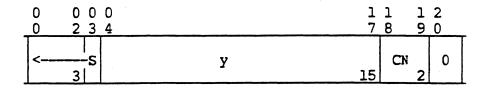

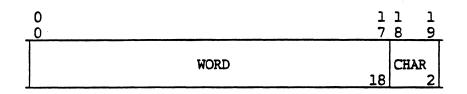

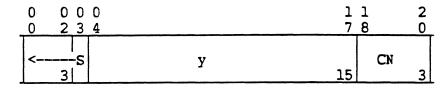

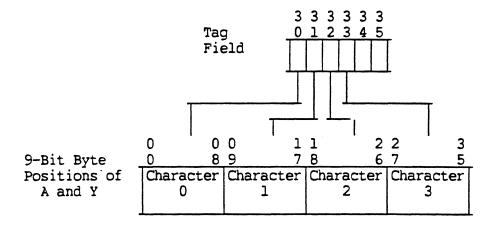

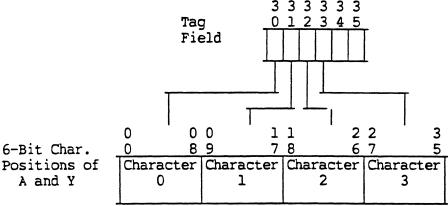

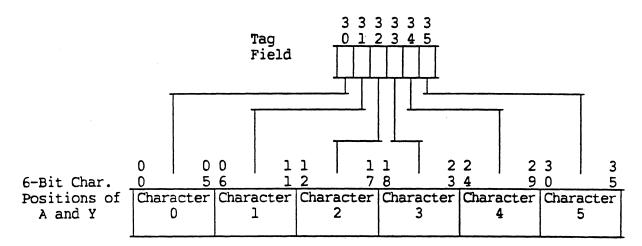

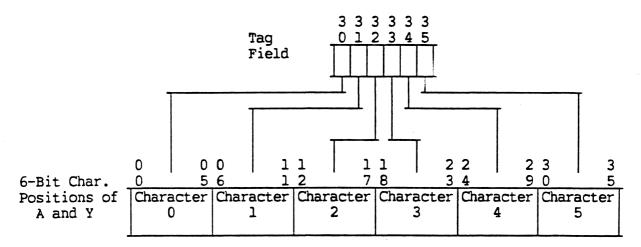

Alphanumeric data is represented by 9-bit, 6-bit, or 4-bit characters. A machine word contains either four, six, or eight characters, respectively. The character positions within the word are as follows:

9-Bit Character (Bytes):

| ( | 0 0 | 0 1<br>9 7 | 1 2<br>8 6 | 2 2 3<br>5 7 5 | < Bit positions within word           |

|---|-----|------------|------------|----------------|---------------------------------------|

|   | 0   | 1          | 2          | 3              | <pre>Syte positions within word</pre> |

6-Bit Characters:

|   | 0 5 | 0 1 1 | 1 1<br>2 7 | 1 2<br>8 3 | 2 2<br>4 9 | 3 3 5 |

|---|-----|-------|------------|------------|------------|-------|

| • | 0   | 1     | 2          | 3          | 4          | 5     |

4-Bit Characters (Packed Decimal):

| 0 | 0<br>1 | ( | )<br>1 | 0<br>5 |   | 0<br>9 |   | 1 | 1<br>4 | · | _ | 18 | 1 |   | 2 |   | 2 | 2<br>7 | 2<br>8 |   | 3 | 3 |   | 3<br>5 |

|---|--------|---|--------|--------|---|--------|---|---|--------|---|---|----|---|---|---|---|---|--------|--------|---|---|---|---|--------|

| z |        | 0 |        |        | 1 | z      | 2 |   |        | 3 | , | Z  |   | 4 |   | 5 |   | z      |        | 6 |   |   | 7 |        |

The Z represents the bit value 0; other numbers in the fields represent the character positions.

#### Bit Positions

Bit positions within a character are as follows:

0123 4-bit character

012345 6-bit character

012345678 9-bit character

Thus, both bit and character positions increase from left to right as in normal reading.

#### **LITERALS**

For information on literals refer to the GCOS 8 OS GMAP User's Guide.

#### BINARY NUMBERS

#### Fixed-Point Numbers

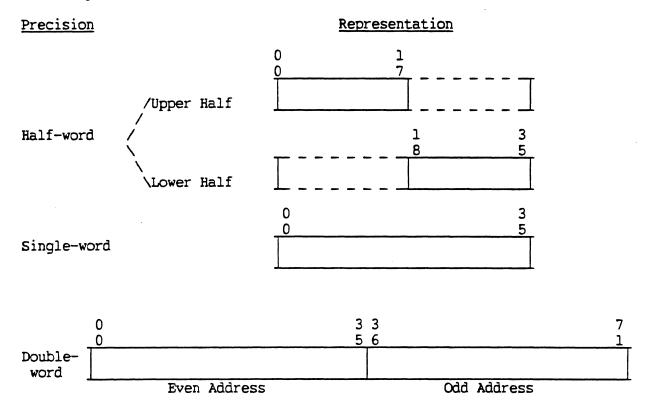

Binary fixed-point numbers are represented with half-word, single-word, and double-word precision as shown below.

Instructions can be divided into two groups according to the way in which the operand is interpreted: the "logic" group and the "algebraic" group.

For logic operations, operands and results are regarded as unsigned, positive binary numbers. In the case of addition and subtraction, the occurrence of an overflow is indicated by the carry out of the most significant (leftmost) bit position:

- 1. Addition If the carry out of the leftmost bit position equals 1 (Carry indicator ON), the sum is above the range.

- 2. Subtraction If the carry out of the leftmost bit position equals 0 (Carry indicator OFF), the difference is below the range.

In the case of comparisons, the zero and carry indicators show the relation.

For algebraic operations, operands and results are regarded as signed binary numbers, and the leftmost bit is used as a sign bit (a 0 being plus and 1 minus). When the sign is positive, all the bits represent the real value of the number; when the sign is negative, they represent the two's complement of the real value of the number.

In the case of addition and subtraction, the occurrence of an overflow is indicated by the carries into and out of the leftmost bit position (the sign position). If the carry into the leftmost bit position does not equal the carry out of that position, then overflow has occurred. If overflow has been detected and if the sign bit equals 0, the result is below range; if with overflow the sign bit equals 1, the result is above range.

In integral arithmetic, the location of the decimal point is assumed to the right of the least significant bit position; that is, depending on the precision, to the right of bit position 35 or 71 (17 for upper half-word).

The number ranges for the various cases of precision, interpretation, and arithmetic are given in Table 2-1.

Table 2-1. Ranges Of Fixed-Point Numbers

|                     |            | Precision                  |                                          |                                             |  |  |  |  |

|---------------------|------------|----------------------------|------------------------------------------|---------------------------------------------|--|--|--|--|

| Inter-<br>pretation | Arithmetic | Holf-word<br>(Xn, Yo17)    | Single-Word<br>(A,Q,Y)                   | Double-Word<br>(AQ,Y-pair)                  |  |  |  |  |

| Algebraic           | Integral   | -2 17 SNS(2 17-1)          | -2 <sup>35</sup> ≤N≤(2 <sup>35</sup> -1) | -2 <sup>71</sup> <n<(2<sup>71-1)</n<(2<sup> |  |  |  |  |

| , <b></b>           | Fractional | -1≤N≤(1-2 <sup>-17</sup> ) | -15Ns(1-2 <sup>-35</sup> )               | -1≤N≤(1-2 <sup>-71</sup> )                  |  |  |  |  |

| Logic               | Integral   | 0≤N≤(2 18-1)               | 0≤N≤(2 <sup>36</sup> -1)                 | 0≤N≤(2 <sup>72</sup> -1)                    |  |  |  |  |

| Logic               | Fractional | 0≤N≤(1-2 <sup>-18</sup> )  | 0≤N≤(1-2 <sup>-36</sup> )                | 0≤N≤(1-2 <sup>-72</sup> )                   |  |  |  |  |

#### Floating-Point Numbers

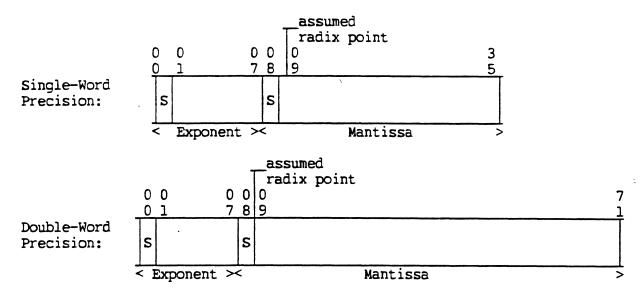

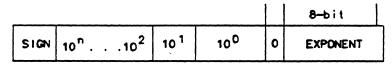

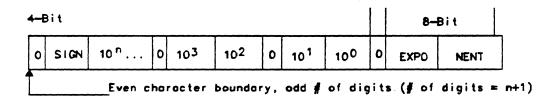

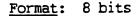

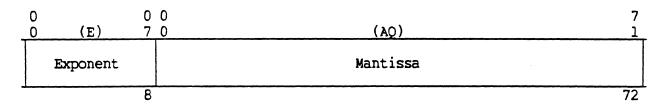

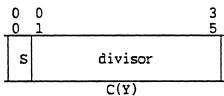

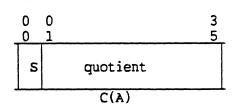

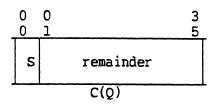

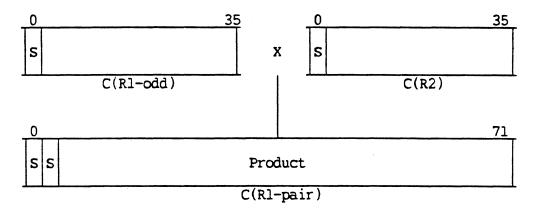

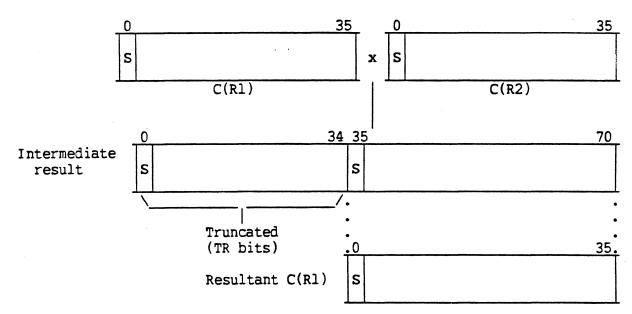

Floating-point numbers are represented with single-word and double-word precision. The upper 8 bits represent the integral exponent to the base 2 in two's complement form, and the lower 28 or 64 bits represent the fractional mantissa in two's complement form.

The format for a floating-point number is:

where S = sign bit

Before performing binary floating-point additions or subtractions, the processor aligns the number that has the smaller exponent. To maintain accuracy, the lowest permissible exponent of -128, together with the mantissa of zero, has been defined as the machine representation of the number zero (which has no unique floating-point representation). Whenever a floating-point operation yields an untruncated resultant mantissa equal to zero (71 bits plus sign because of extended precision), the exponent is automatically set to -128.

#### Hexadecimal Floating-Point Numbers

The hexadecimal option may be used in floating-point operations to declare hexadecimal constants, either explicitly or by default. The term hexadecimal refers to a floating-point format where the mantissa is a binary number, while the exponent represents a power of 16 (2\*\*4). The mantissa is shifted by the number of places for 4-bit groups as required by the exponent.

The hexadecimal floating-point mode is enabled only when bit 32 of the Indicator Register is set to 1 and bit 33 of the mode register is set to 1. After the hexadecimal floating-point mode is requested, the user controls the floating-point mode via the Indicator Register. If the bit 32 of the Indicator Register is not set to 1, the floating-point mode will be binary.

2-5 DZ51-00

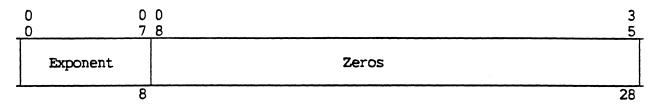

#### Quadruple-Precision Numbers

The data format used in quadruple-precision arithmetic is illustrated below. Notice that the format of data to be used in an operation is somewhat different from that of data to be stored after the operation.

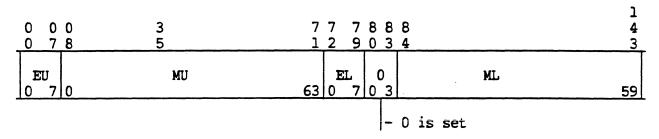

The format for data when an operand in main memory is used as arithmetic data:

|       | Y-pair | Y+2 pa       | ir |

|-------|--------|--------------|----|

| /     | ′      | $\vee$       | 1\ |

| 0 0 0 |        | 77 88        | 4  |

| 0 78  |        | 12 34        | 3  |

|       |        |              |    |

| EU    | MU     | \\\\\\\ ML   |    |

| 0 7 0 |        | 63 0\\\\11 0 | 59 |

|       |        | Ignored      |    |

The format for data when the result is stored in main memory is as follows:

- o The data in memory must reside on a double-word boundary.

- o The four words of data may span two pages.

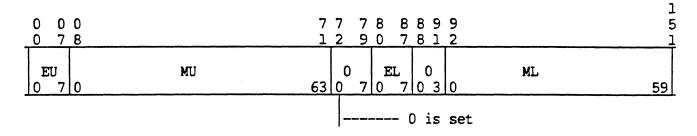

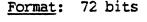

The registers E, AQ, and LOR are used for quadruple-precision arithmetic. The format for data used as operation data is as follows:

| _E    | <b>A</b> Q | LOR               |          |

|-------|------------|-------------------|----------|

| /     |            | V                 | 1\       |

| 0 0 0 |            | 7778 99           | 5        |

| 0 7 8 |            | 1290 12           | <u> </u> |

|       |            |                   |          |

| EU    | MU         | \\\\ \\\\\  ML    |          |

| 0 70  |            | 63 0\\7 0\\\\11 0 | 59       |

|       |            | Ignored           |          |

The contents of EAQ and LOR following an operation is as follows:

#### Field Values

EU Exponent

MU High Order Mantissa

EL EU -15 (residue)

ML Low-order mantissa

Quadruple-precision value  $N = (MU + ML)16^{EU}$

The quadruple-precision instructions operate with the exponent as a hexadecimal exponent regardless of the value of bit 32 of the indicator register (IR).

#### Normalized Binary Floating-Point Numbers

For normalized binary floating-point numbers, the binary point is placed at the left of the most significant bit of the mantissa (to the right of the sign bit). Numbers are normalized by shifting the mantissa left (and correspondingly adjusting the exponent) until no leading zeros are present in the mantissa for positive numbers, or until no leading ones are present in the mantissa for negative numbers. The vacated bit positions on the right are zero-filled.

The number ranges resulting from the various cases of precision, normalization, and sign are given in Table 2-2.

Table 2-2. Ranges Of Binary Floating-Point Numbers

|                      | Sign     | Single Precision                                  | Double Precision                                             |

|----------------------|----------|---------------------------------------------------|--------------------------------------------------------------|

| Normalized           | Positive | -2-129 SNS (1-2-27)2 127                          | 2 <sup>129</sup> SNS (1-2-63)2 <sup>127</sup>                |

| Normal 1240          | Negative | (-1+2 <sup>-26</sup> )2 <sup>-129</sup> ≥N≥-2 127 | (-1+2 <sup>-62</sup> )2 <sup>-129</sup> ≥N≥-2 <sup>127</sup> |

| Unnormalized         | Positive | 2-155 SNS (1-2-27)2127                            | 2 <sup>-191</sup> SNS (1-2 <sup>-63</sup> )2 <sup>127</sup>  |

| Olinovii B 1 1 2 e d | Negotive | -2 <sup>-155</sup> ≥N≥-2 127                      | -2 <sup>-155</sup> ≥N≥-2 <sup>127</sup>                      |

NOTE: The floating-point number zero is not included in the table.

#### Binary Representation Of Fractional Values

A decimal fraction of a given number of digits cannot necessarily be represented exactly by a binary fraction of any finite number of bits. Consider, for example, the value 1/5, which is represented in decimal notation as 0.2. Trying to represent it by a four-bit binary fraction, one obtains (.0011)<sub>2</sub> or 3/16; with eight bits, one obtains (.00110011)<sub>2</sub> or 51/256. In fact, the exact value must be written as

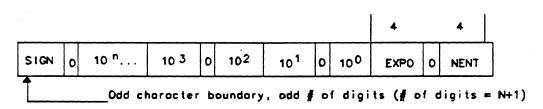

$$(0.2)_{10} = (0.0011)_2 \dots$$