| Honeywell                                | TITLE:       |                                | No. 43A                | 232215    |

|------------------------------------------|--------------|--------------------------------|------------------------|-----------|

| HONEYWELL<br>INFORMATION<br>SYSTEMS INC. |              | O CONTROLLER,<br>ERING PRODUCT | EPS-1<br>SPECIFICATION | , PART 1  |

|                                          |              | Total Pages 152                |                        | Page 1    |

| DIST:116-92                              | REVIS        | SION RECORD                    |                        |           |

| REVISION<br>LETTER DATE                  | PAGES AFFECT | ED /                           | APPROVALS              | AUTHORITY |

# HONEYWELL PROPRIETARY

The information contained in this document is proprietary to Honeywell Information Systems Inc. and is intended for internal Honeywell use only. Such information may be distributed to others only by written permission of an authorized Honeywell official. This restriction does not apply to vendor proprietary parts that may be disclosed in this document.

-----

J

CE 301 (6-71) document.

## Honeywell

Cont. on Page

Page 2

#### 1.0 GENERAL DESCRIPTION

Rev A

This document specifies the requirements for control of magnetic tape handlers, with the media recorded in either the phase encoded (PE) mode or in the non-return to zero (NRZI) mode. Both seven track and nine track handlers will be accommodated in this subsystem. The basic units of this subsystem are:

Microprogrammed Peripheral Controller (MPC) Link Adapter (LA) Tape Controller Adaptor (TCA) Magnetic Tape Hnadlers (MTH) Device Switch (SW)

This document defines the design requirements for the controller. The controller adaptor, switch and handlers are defined in other documents.

#### 1.1 SUBSYSTEM OBJECTIVES

The objectives of the phase encoded subsystem are to:

- Provide single channel and dual simultaneous channel operation

- Provide field upgrade from single channel to dual simultaneous channel, with increases in number of handlers up to maximum capability of the subsystem.

- Provide a high degree of subsystem modularity

- Provide on-line diagnosis, and off-line repair

- Provide 1600 bpi phase encoding (PE) as well as 200, 556, 800 bpi non-return to zero, change on ones (NRZI)

- Operate on systems with a peripheral subsystem interface (PSI) channel on an input/output multiplexer (IOM), or on systems providing an equivalent interface discipline.

- Control the magnetic tape units by microprograms residing in the microprogrammed peripheral controller (MPC)

- Maintain error statistics related to data transfers

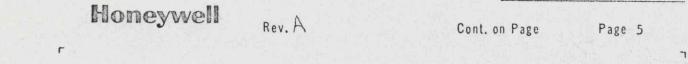

#### 1.2 APPLICABLE DOCUMENTS

- EPS-1 Microprogrammed Peripheral Controller (MPC), 43A177875

- EPS-1 Link Adapter (LA), 43A177879

- EPS-1 Peripheral Subsystem Interface (PSI), 43A177874

- EPS-1 IOM Peripheral Subsystem Interface Adapter, 43A177880

- EPS-1 Input/Output Multiplexor (IOM) Central, 43A219604

- EPS-1 Magnetic Tape Subsystem, 43A239623

- EPS-1 Magnetic Tape Handler MTH500 Series 59A502064 Common MPC Maintainability 43A237500

#### Cont. on Page Page 3

#### 1.2 APPLICABLE DOCUMENTS (continued)

Rev. A

EPS-1 General Design Requirements for GE655 System, 43A177851

NPL Device Level Interface (DLI) for Magnetic Tape Subsystem, BL0024

Area Objectives for New Product Line (NPL) Microprogrammed Peripheral Controller (MPC) Subsystems, BL0021

The following documents apply to media characteristics and to techniques for recording the media. In case of conflict between this controller specification and the referenced documents, the referenced documents shall take precedence.

X3B1/402 - April 1970

Draft USA Standard - Unrecorded Magnetic Tape for Information Interchange

#### X3B1/425 - April 1970

USA Standard - Recorded Magnetic Tape for Information Interchange (200 CPI. NRZI)

X3B1/426 - April 1970

USA Standard - Recorded Magnetic Tape for Information Interchange (800 CPI, NRZI)

X381/400 - April 1970

Proposed USA Standard - Recorded Magnetic Tape for Information Interchange (1600 CPI, Phase Encoded)

#### 1.3 DEFINITIONS

MPC Microprogrammed Peripheral Controller IOM Input/Output Multiplexor Tape Controller Adaptor TCA Link Adaptor LA Magnetic Tape Handler MTH EUS External User System refers to the central system which is making use of the magnetic tape subsystem PSIA PSI channel adaptor in the IOM Peripheral Subsystem Interface PSI IAI Internal Adaptor Interface

DLI Magnetic tape handler Device Level Interface

Cont. on Page

Page 4

#### 1.3 DEFINITIONS (continued)

Binary Mode - A PSIA mode in which the eight-bit bytes are packed contiguously in core

ASCII Mode - A PSIA mode in which the eight-bit bytes have a ZERO bit between them in core

ips Tape velocity at the MTH head in inches per second

bpi Bits per inch. Data recording density when considered longitudinally along tape. Corresponds to characters per inch in NRZI recording and to bytes per inch in PE recording.

fri Flux reversals per inch

Rev. A

PE Phase Encoded

NRZI Non Return to Zero, change on ones

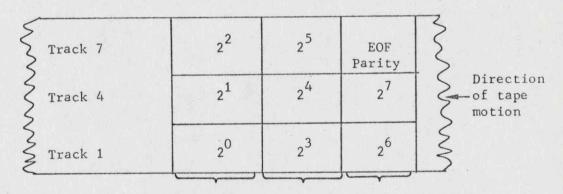

frame A set of bits when considered laterally across the tape. A frame in 7-channel tape has up to 7 bits; a frame in 9-channel has up to 9 bits.

byte As used in this specification, a byte is a group of 8 bits which are considered as a unit

character - A group of 6 bits considered as a unit

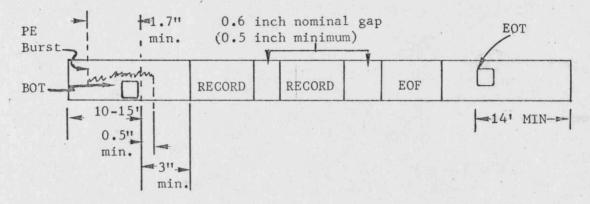

BOT marker - A reflective marker which is located at the logical beginning of tape

EOT marker - A reflective marker located near the physical end of tape

standby-loaded - A handler mode in which the tape is loaded, and operator intervention is required to bring the handler to the ready state

standby-unloaded - A handler state in which the tape is unloaded, but the handler is capable of responding to a Load Tape command; other actions to bring the handler to the ready state require operator intervention

controller - This is the unit consisting of MPC, LA(s), TCA(s) and SW.

- LCC Longitudinal Check Character

- CCC Cyclic Check Character

- ITR Integrated Test Routine

- BLT Basic Logic Test

### Honeywell

#### Cont. on Page

Page 6

\_

#### 2.0 SUBSYSTEM DESCRIPTION

Rev A

#### 2.1 SUBSYSTEM CAPABILITIES

This subsystem will control the movement of, recording on, and reading from  $\frac{1}{2}$  inch magnetic tape. The tape may be either seven track or nine track, and may be formatted in either the PE mode (for nine track) or NRZI mode (for seven or nine track). The tape may be moved at velocities ranging from 75 ips to 200 ips, and the data packing may vary from 200 bpi NRZI to 1600 bpi PE. The resulting nominal data transfer rates range from 11.25 K-bytes/sec (15 K-char/sec) to 320 K-bytes/sec (426.6 K-char/sec).

Both single channel and dual simultaneous data transfer operations are available, with up to sixteen magnetic tape handlers in the subsystem.

Special features include switched channels to the external user system, and optional code translation including ASCII to BCD (internal 6000 6-bit code), EBCDIC to BCD, and EBCDIC to ASCII. Dependent on the density code set in the handler, the code translation may be written on tape in either NRZI or PE modes.

The capabilities of this subsystem are summarized in figures 2.1.1, 2.1.2 and 2.1.3.

#### 2.2 SUBSYSTEM CONFIGURATIONS

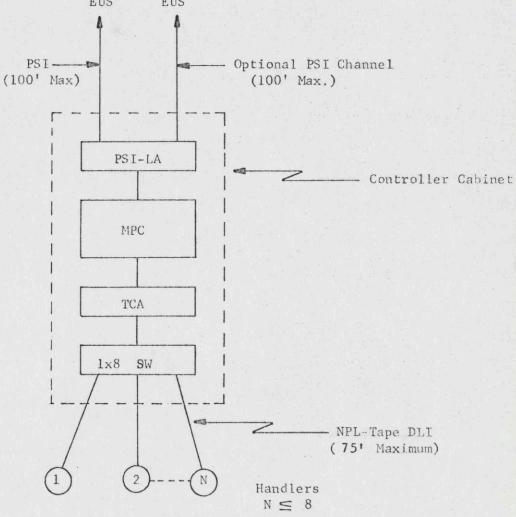

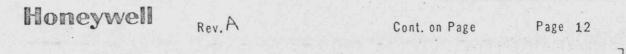

The single channel and dual-simultaneous channels subsystem configurations are illustrated in figures 2.2.1 and 2.2.2. The controller is composed of four major functional units -- link adaptor, microprogrammed controller, controller adaptor and device switch. These units are required in both the single and dual simultaneous configurations.

The link adaptor provides a hardware connection between the PSI cable and the back panel internal adaptor interface of the microprogrammed controller. The controller adaptor and device switch provide a hardware interface to the handlers, and also provide hardware control of certain device oriented functions. Finally, the microprogrammed controller (MPC) is the central intelligence unit which merges these functional units into a magnetic tape controller. This merging of functions is accomplished via microprograms contained in the MPC which personalizes it to become a magnetic tape controller.

## Honeywell

r

Rev.A

Cont. on Page 7

٦

4

| SPEED    | 75 ips              | 125 ips       | 200 ips                  |

|----------|---------------------|---------------|--------------------------|

| 200 bpi  | * 15K (20K)         | 25K (33.3k)   | 40K (53.3K)              |

| 556 bpi  | 41.7K (55.6K)       | 69.5K (92.6K) | <b>11</b> 1.2K (148.26K) |

| 800 bpi  | 60K (80K)           | 100K (133.3K) | 160K (213.3K)            |

| 1600 bpi | 120K (160K <b>)</b> | 200K (266.6K) | 320K (426.6K)            |

### FIGURE 2.1.1

Data Rates for Various Recording Densities and Handler Speeds for 9-Track Handlers

\* The data rates are given as bytes/sec (characters/sec), with K = 1000.

|   | Honeywell     |        |               |                       |

|---|---------------|--------|---------------|-----------------------|

|   | REGRECA AACES | Rev. A | Cont. on Page | Page 8                |

| F |               |        |               | the second states and |

| SPEED<br>DENSITY | 75 ips          | l25 ips         | 200 ips        |

|------------------|-----------------|-----------------|----------------|

| 200 bpi          | * 11.25K (15K)  | 18.75K (25K)    | 30K (40K)      |

| 556 bpi          | 31.275K (41.7K) | 52.125K (69.5K) | 83.4K (111.2K) |

| 800 bpi          | 45K (60K)       | 75K (100K)      | 120K (160K)    |

#### FIGURE 2.1.2

Data Rates for Various Recording Densities and Handler Speeds for 7-track Handlers

1

\* Data rates are given as bytes/sec (characters/sec), with  $K\,=\,1000$ .

-

1

## Honeywell

Г

Rev. A

| HANDLER<br>FORMAT<br>6000 FORMAT | 7 TRACK | 9 TRACK          |

|----------------------------------|---------|------------------|

| 6000 CODE<br>(6-bit)             | NONE    | EBCDIC           |

| 6000 CODE<br>(6-bit)             | NONE    | ASCII<br>(7-bit) |

| ASCII<br>(7-bit)                 | NONE    | EBCDIC           |

### FIGURE 2.1.3

Optional Code Translation in Subsystem

Page 10

٦.

1

г 2.2

SUBSYSTEM CONFIGURATION (continued)

Rev. A

The single channel and dual simultaneous channels subsystem configurations are illustrated in figures 2.2.1 and 2.2.2. The controller is composed of four major functional units -- link adaptor, microprogrammed controller, controller adaptor and device switch. These units are required in both the single and dual simultaneous configurations.

The link adaptor provides a hardware connection between the PSI cable and the back panel internal adaptor interface of the microprogrammed controller. The controller adapter and device switch provide a hardware interface to the handlers, and also provide hardware control of certain device oriented functions. Finally, the microprogrammed controller (MPC) is the central intelligence unit which merges these functional units into a magnetic tape controller. This merging of functions is accomplished via microprograms contained in the MPC which personalizes it to become a magnetic tape controller.

While the PSIA may have one, two, four, or eight logical channels assigned to it, the standard configuration for the MTC501 and MTC502 shall include two logical channels per PSIA.

1

FIGURE 2.2.1 - SINGLE CHANNEL SUBSYSTEM

#### SHOWING MAJOR FUNCTIONAL UNITS

EXTERNAL USER CHANNELS

FIGURE 2.2.2

DUAL-SIMULTANEOUS CHANNELS SUBSYSTEM

SHOWING MAJOR FUNCTIONAL UNITS

L

г

#### 2.3 GENERAL SUBSYSTEM CHARACTERISTICS

This subsystem will incorporate some features which are new to the 6000 line. This section summarizes the extent of these features.

o The controller does not contain any operator switches. Therefore, the modification of handler address formerly accomplished by configuration switches on magnetic tape controllers is not possible. Also, the set density commands (sections 5.4.15 through 5.4.18) have replaced the over-ride switches on the former Set High (now Set 800 BPI) and Set Low (now Set 556 BPI) commands.

- o While the initial offering includes only the MTH502 and MTH505 handlers, it is anticipated that 7-track and 200 ips handlers will be included. Therefore, this controller is specified to include these handlers.

- The controller contains four forms of code translation, three of which are optional (see Section 3.7).

- BCD Same as in previous 600 line subsystems (see Section 5.4.32 through 5.4.34). Not an option

- 6-bit to/from EBCDIC Conversion between 6000 line 6-bit format to/from 8-bit EBCDIC on tape (see Sections 5.4.35 and 5.4.36). (Optional features)

- 6-bit to/from ASCII Conversion between 6000 line 6-bit format to/from 8-bit ASCII-7 on tape. (See Section 5.4.37 and 5.4.38). Optional feature.

- ASCII to/from EBCDIC Conversion between ASCII-7 characters in 6000 to/from EBCDIC bytes on tape. (See sections 5.4.39 and 5.4.40). Optional Feature.

- Special Interrupt When a special interrupt is sent to an external user system, information is included which defines the interrupting device and reason for the interrupt. (See Section 6.6)

This subsystem is capable of being shared by independent external user systems. This is possible because of such features as the ability for the independent EUS's to communicate via the subsystem (See sections 5.6.5.7 through 5.6.5.9 - Lock Byte Application), and for these independent EUS's to selectively reserve any handler connected to the subsystem.

Cont. on Page

Page 14

7

#### 2.3 GENERAL SUBSYSTEM CHARACTERISTICS (continued)

Rev. A

- The subsystem will perform automatic retries for specified read type command (see Section 7.4) errors which have a Device Data Alert major status. This feature may be inhibited by the EUS using the technique of section 5.2.

- The subsystem will maintain an error log for specified errors occurring within the subsystem (see Section 7.5).

#### 2.4 STANDARDS AND OPTIONS

The features of the handlers and controllers are described in the next two sections.

MIRCEOI

2.4.1 Controller Features

|   |                                                                     | <u>MTC501</u>     | MTC502            |

|---|---------------------------------------------------------------------|-------------------|-------------------|

|   | Simultaneous data transfer                                          | No                | Yes               |

|   | Maximum No. Handlers                                                | 8                 | 16                |

|   | Recording Densities                                                 |                   |                   |

|   | 200, 556, 800 bpi NRZI<br>1600 bpi PE                               | Yes<br>Yes        | Yes<br>Yes        |

|   | No. Tracks                                                          | 7 & 9             | 7 & 9             |

|   | Standard Code Translation                                           |                   |                   |

|   | BCD                                                                 | Yes               | Yes               |

| ( | Optional Code Translation                                           |                   |                   |

|   | 6-bit to/from EBCDIC<br>6-bit to/from ASCII<br>ASCII to/from EBCDIC | Yes<br>Yes<br>Yes | Yes<br>Yes<br>Yes |

| Ι | Device Switch Modularity                                            |                   |                   |

|   | No handlers per module                                              | ۷4                | 4                 |

| F | Read Reverse Capability                                             | No                | No                |

| N | Multi-System External Users                                         | Yes               | Yes               |

|   |                                                                     |                   |                   |

| Hone  | ywell Rev. A                                                                         | Cont. on Page | Page 15       |

|-------|--------------------------------------------------------------------------------------|---------------|---------------|

| 2.4.2 | Handler Features                                                                     |               |               |

|       |                                                                                      | MTH 502       | <u>MTH505</u> |

|       | No. Tracks                                                                           | 9             | 9             |

|       | Speed Forward (ips)                                                                  | 75            | 125           |

|       | Rewind Speed (ips)                                                                   | 500           | 500           |

|       | Reverse Speed - Backspace (ips)                                                      | 75            | 125           |

|       | Recording Densities                                                                  |               |               |

|       | 200, 556, 800 bpi NRZI<br>1600 bpi PE                                                | Yes<br>Yes    | Yes<br>Yes    |

|       | Automatic Load                                                                       | Yes           | Yes           |

|       | Power Window                                                                         | Yes           | Yes           |

|       | Options                                                                              |               |               |

|       | 7-track, 200,556,800 bpi NRZI                                                        | Yes           | Yes           |

|       | 9-track, 1600 bpi PE only                                                            | Yes           | Yes           |

|       | Canister Load-Factory install                                                        | Yes           | Yes           |

|       | Canister Load - Field Upgrade                                                        | Yes           | Yes           |

|       | High altitude blower<br>Factory install                                              | Yes           | Yes           |

|       | High altitude blower<br>field upgrade                                                | Yes           | Yes           |

|       | D.C. Power Meter                                                                     | Yes           | Yes           |

|       | Tape Movement Meter                                                                  | Yes           | Yes           |

|       | ANSI Compatible Recording (per<br>reference specifications<br>listed in section 1.2) | Yes           | Yes           |

listed in section 1.2)

L

г

## Honeywell

Cont. on Page

Page 16

3.0

#### CONTROLLER DESCRIPTION

Rev. A

The controller utilized in this subsystem will use the MPC as a central control mechanism. The link adaptor will provide a hardware interface to the PSI channel, with microprograms residing in the MPC controlling the dialog on the PSI.

The portion of the controller which communicates with the handlers will be a combination of microprogram, controller adaptor and device switch. The switch provides a hardware interface between the controller adaptor and handlers, with the dialog controlled by microprograms in the MPC.

The controller adaptor provides hardware control for those deviceoriented functions which are not readily controlled by microprograms in the MPC. Functions which fall in this category include:

- o LCC generation

- o CCC generation

- o PE data recovery

- o PE/NRZI error detection/correction

- o Data Buffering

- o Code Translation

- o Pack/unpack associated with code translation

- o Generation of TCA status

- o PE Preamble/Postamble Detection and generation

- o BOT PE Identification Burst Generation

The MPC, in providing the major subsystem control, must include the following functions in its microprograms:

- o Interpret commands received by LA from EUS

- o Control dialog on PSI and IAI

- o Gather MTH, TCA, MPC status, format and transmit to EUS via LA

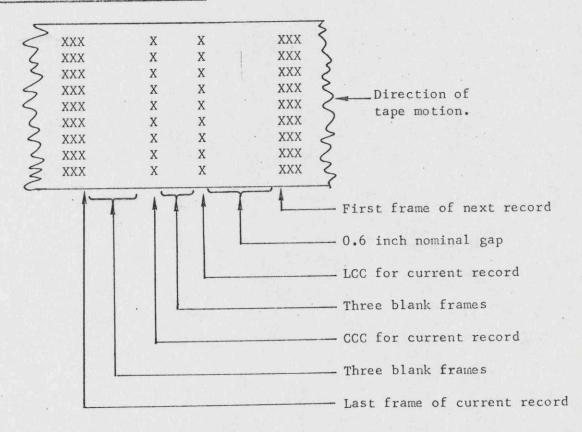

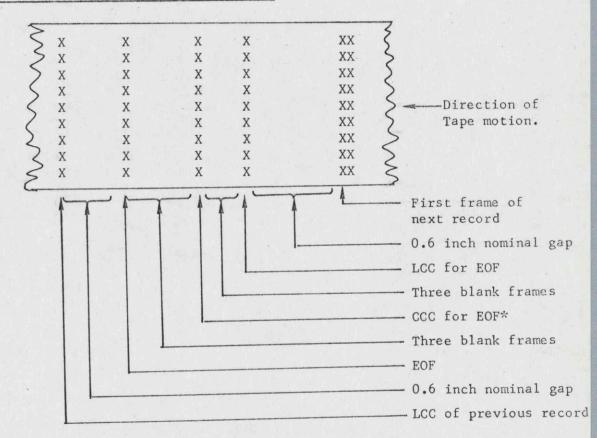

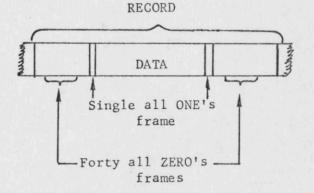

- o EOF generation/detection

### Honeywell

Cont. on Page

Page 17

#### 3.0 CONTROLLER DESCRIPTION (continued)

Rev. A

o Record and file gap control

- o CCC/LCC gap control

- o Write time base generation

- o Blank character time base generation

- o BOT PE identification burst detection

#### 3.1 NPL AREA OBJECTIVES

The design of this controller, including the LA, MPC, and TCA hardware, but excluding the control microprograms, shall not preclude accomplishing the NPL functions as described in the document Area Objectives for New Product Line (NPL) Microprogrammed Peripheral Controller (MPC) Subsystems issued 2/15/71, when the controller hardware is reimplemented in NPL packaging.

#### 3.2 DEVICE ADDRESSING

The controller in this subsystem shall be identified as device zero, and the handlers shall be numbered starting with number one. Thus, the handler numbers in a single-channel subsystem range between one and eight, and in a dual-channel subsystem the handler numbers range between one and sixteen.

Each device contains a five-bit code which is wired into the handler when the handler is installed in the subsystem. This wired-in number occupies bit positions 3 through 7 of summary status byte 4 (bit 3 = MSB) in the handler. This number, and the number on the front of the handler cabinet which is visible to the operator, must be made the same. These numbers are unique within the subsystem, and are not changed for the duration of the life of the handler on that subsystem. Since the visible number corresponds to the device code, the wired-in number also corresponds to the device code. The controller must maintain a table relating device codes to device switch ports. This table must be dynamic so that it is updated whenever a handler is added to or removed from the subsystem. Each time a command requires activity with a particular handler, and prior to initiating this activity. the controller will interrogate the summary status byte containing the wored-in number to be sure that the correct device is addressed.

## Honeywell

19 A L

٢

3.2

Cont. on Page

Page 18

٦.

## DEVICE ADDRESSING (continued)

Rev. A

The legal device codes for these subsystems are as follows:

| Device Code | Single-Channel | Dual-Channel |

|-------------|----------------|--------------|

| 0           | Controller     | Controller   |

| 1           | Handler 1      | Handler 1    |

| 2           | Handler 2      | Handler 2    |

| 3           | Handler 3      | Handler 3    |

| 4           | Handler 4      | Handler 4    |

| 5           | Handler 5      | Handler 5    |

| 6           | Handler 6      | Handler 6    |

| 7           | Handler 7      | Handler 7    |

| 8           | Handler 8      | Handler 8    |

| 9           | NL*            | Handler 9    |

| 10          | NL*            | Handler 10   |

| 11          | NL*            | Handler 11   |

| 12          | NL*            | Handler 12   |

| 13          | NL*            |              |

| 14          | NL*            | Handler 13   |

| 15          | NL*            | Handler 14   |

| 15          |                | Handler 15   |

| TO          | NL*            | Handler 16   |

\* NL means that this device code is not legal for single-channel subsystems.

Page 19

#### 3.3

#### CONTROLLER UTILIZATION OF HANDLER INTERFACE

Rev. A

The controller shall take special actions to verify that the correct handler is addressed, and that the interface to/from the handler is working properly. These activities are summarized as follows:

Prior to the execution of any command which will change the state of the handler, the controller will verify that the desired handler is addressed. This is accomplished by reading the address status byte stored in the handler.

Prior to the execution of any command involving a handler operation, and following the address verification mentioned above, the controller shall test the handler interface lines by executing DLI instruction Test.

Also, at the completion of execution of any command involving a handler, the controller shall read the handler status prior to formatting command termination status.

#### 3.4 CONFIGURATION SWITCHES

The controller contains a set of sixteen switches which are readable by microprogram control. The function of these switches include configuration control and operational information. They are defined as follows:

#### Switch

012

3

8 - 10

#### Application

| ITR BLT Bypass<br>ITR Loop Control                  |

|-----------------------------------------------------|

|                                                     |

| LA to be Used for Booting: $1 = LA$ on IAI Port 3   |

| 0 = LA  on IAI Port  2                              |

| Number of LA's in Subsystem: 1 = One LA (Port 2)    |

| 0 = Two LA's (Ports)                                |

| 3 and 2)                                            |

| Inhibit Interval Timer Runout Detection             |

| 1 = 9 track handler; $0 = 7$ track handler          |

| These two switches are defined as;                  |

| 00 Device 4                                         |

| 01 Device 1                                         |

| 가는 것 같은 것 않는 것 같은 것 같 |

| ~ ~ | 201200 | - |

|-----|--------|---|

| 10  | Device | 2 |

| 11  | Device | 3 |

The function of switches 5-7 is to provide information for the load-from-device process (see section 5.4.24).

1

These three switches are defined as follows:

| 000 | Not  | valid   | for   | this   | control | le |

|-----|------|---------|-------|--------|---------|----|

| 001 | 11   | 11      | *1    | 11     |         |    |

| 010 | Sing | gle cha | annel | l con  | troller |    |

| 011 | Dua  | l chani | nel d | contro | oller   |    |

## Honeywell Rev. A

Page 20

٦

L

| 2 | 1 |

|---|---|

| 5 | 4 |

r

CONFIGURATION SWITCHES (continued)

|    | 100                                      | Not  | valid | for | this    | controller     |  |  |  |  |  |

|----|------------------------------------------|------|-------|-----|---------|----------------|--|--|--|--|--|

|    | 101                                      |      |       | 11  |         |                |  |  |  |  |  |

|    | 110                                      |      |       | 11  |         | n              |  |  |  |  |  |

|    | 111                                      | 11   | 11    | **  |         | 11             |  |  |  |  |  |

| 11 | Not allo                                 | cate | d     |     |         |                |  |  |  |  |  |

| 12 |                                          |      |       |     | 1 (Sel) |                |  |  |  |  |  |

| 13 | Main Mem                                 | ory  | Size: |     |         | Words<br>Words |  |  |  |  |  |

| 14 | Error Interrupt Safestore Bypass Control |      |       |     |         |                |  |  |  |  |  |

| 15 | Not allo                                 | cate | d     |     |         |                |  |  |  |  |  |

|    |                                          |      |       |     |         |                |  |  |  |  |  |

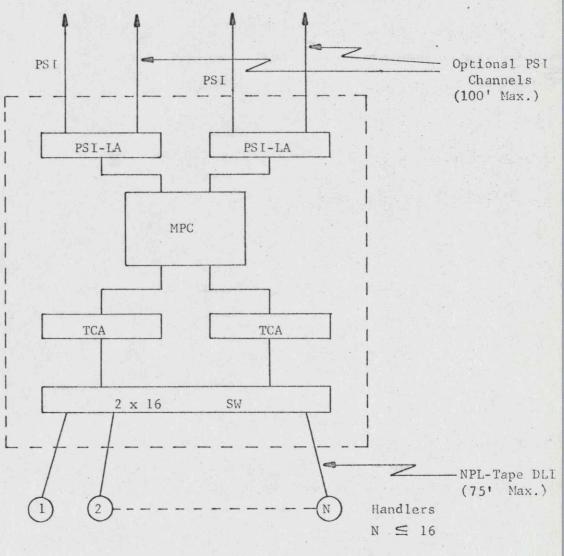

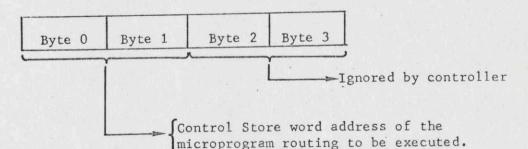

3.5

#### CONTROLLER MEMORY MAPS

The controller contains two memories -- Main Memory and Control Store. The map of the Main Memory shall be supplied as a part of the design documentation. The Control Store shall be mapped as shown below:

The personality firmware which makes this MPC function as a magnetic tape controller is located beginning at address 512, and extends to the end of the Control Store. Rev. A

Page 21

3.5

Г

Honeywell

#### CONTROLLER MEMORY MAPS (continued)

The Control Store Interrupt Entry locations are:

| T & D Mode :  | High-level EN-1 Interrupt<br>Low-level EN-1 Interrupt<br>Error Interrupt | 2 56<br>260<br>27 2 |

|---------------|--------------------------------------------------------------------------|---------------------|

| Normal Mode : | High-level EN-1 Interrupt<br>Low-level EN-1 Interrupt                    | 1024                |

|               | Error Interrupt                                                          | 1028<br>1040        |

\* All addresses given in this section are decimal addresses.

3..6

#### ERROR INTERRUPT IMPLEMENTATION

The basic MPC which is being used to implement the MTC500 magnetic tape controller has built-in logic to detect internal hardware errors such as parity errors on internal registers, parity errors on Main Memory data, parity errors on microinstructions accessed from Control Store, etc. The detection of any one of these internal hardware errors will result in the automatic execution of an error interrupt, which forces the MPC to branch to a fixed Control Store location, and establishes an "error interrupt in progress" state of the machine.

The microprogram which is automatically entered as a result of the error interrupt will first test the state of configuration switch number 14 (Section 3.4). If the switch is set, an immediate branch will be made to the Integrated Test Routine (ITR) module, located in the first 512 locations of Control Store. Setting of configuration switch 14 therefore implies that the controller will be put in the ITR mode upon the occurrence of an error interrupt.

If switch 14 is not set, the error interrupt microprogram will take the following actions:

- a) Safestore in a fixed Main Memory area the current contents of all pertinent hardware registers.

- b) Terminate all existing activity in progress, including device movement. Note however, that a handler which is executing a rewind operation will not be stopped. The execution of an active channel program will be aborted.

- c) Reset the error interrupt level, and return the controller to normal operation (i.e., waiting for a command from the external user system).

3.6

Page 22

٦

#### ERROR INTERRUPT IMPLEMENTATION (continued)

Rev. A

The occurrence of the error interrupt will force the Operational In line of the PSI to revert to the non-operational state. This line will stay in the non-operational state until the error intterrupt in progress state is reset by the microprogram. Repeated error detections will result in repeated error interrupts, and subsequent fluctuation of the Operational In line.

#### 3.7 CONTROLLER INITIALIZE

Two types of initialization must be considered in the controller. The first is a channel initialize which occurs when the Operational Out line of the PSI reverts from the operational to the non-operational state. This will cause the controller to reset all activity associated with the physical channel over which this action occurred. All allocation of devices, table entries, etc. must be reset. Activity associated with any other physical channel is not affected.

The second type of initialize is a controller initialize which affects the entire controller. This type of initialize causes the controller to be reset, and is caused by any one of the following:

- a) Actuation of the Initialize switch on the controller operator panel.

- b) Initialize signal from the MPC power supply during any power-up sequence.

- c) Remote initialize signal generated via the SCAM module.

- d) Signal on the Reset Out line of the PSI.

Initialization by means of (a) and (b) results in the controller being d-c initialized and left in the Halt Mode, and requires actuation of the Start Switch on the operator panel or initialization by means of (c) or (d) to begin microinstruction execution. Microinstruction execution begins (upon fall of the initialize signal) at Control Store location 0, which is the location at which the Basic Logic Test module will start.

The BLT module will execute a test of the basic MPC logic, including all attached Link Adaptors. If a hardware malfunction is detected during this test the BLT module will cause the controller to halt, with fault dictionary symptoms displayed on the controller maintenance panel. Configuration Switch 0 on the maintenance panel may be set to cause the BLT module to bypass the test of the basic MPC logic. Upon completion of the basic MPC logic test (or immediately upon

Rev. A

Page 23

3.7

#### CONTROLLER INITIALIZE (continued)

bypassing the test) the BLT module will accept either the Control Store Test Overlay command  $(11_8)$  or the Control Store Personality Overlay command  $(10_8)$  from the external user system. These commands are defined in Sections 5.4.24 and 5.4.23.

3.8

#### CODE TRANSLATION & PACK/UNPACK REQUIREMENTS

This subsystem includes the capability of code translation between selected character sets. Some of these translations which are valid only if the user has selected the particular option.

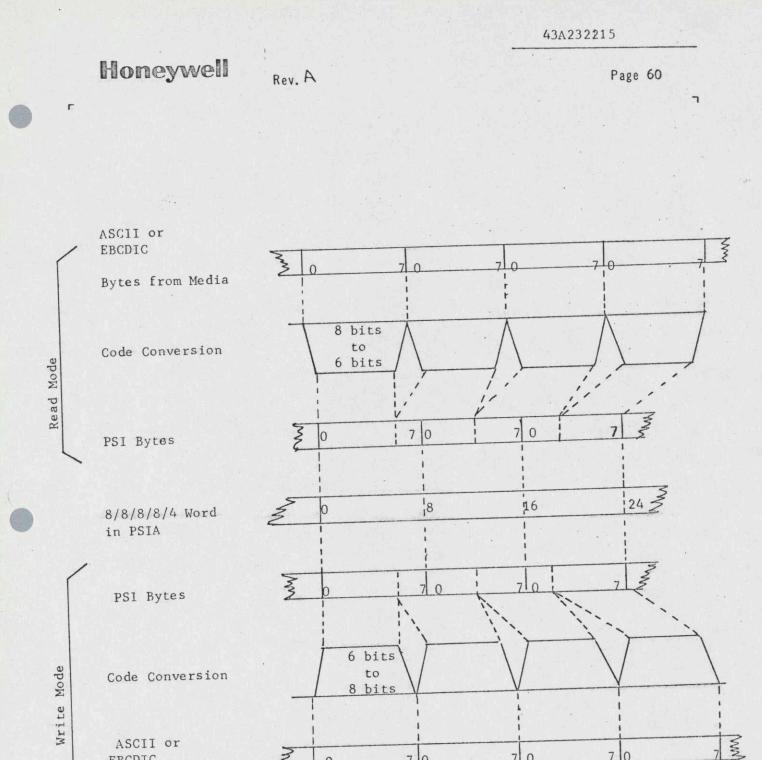

Related to these code translations is a pack/unpack activity which is necessitated in part by the PSI, and in part by the character formats. The controller must therefore be implemented to include the required translation as defined by the command, the related pack/unpack activity, and the control of the PSIA mode. The latter is the selection between the "binary mode" and the "ASCII mode" of the PSI adaptor in the IOM.

The following sections describe the translations and pack/unpack and PSIA mode for various data transfer commands to/from the handler.

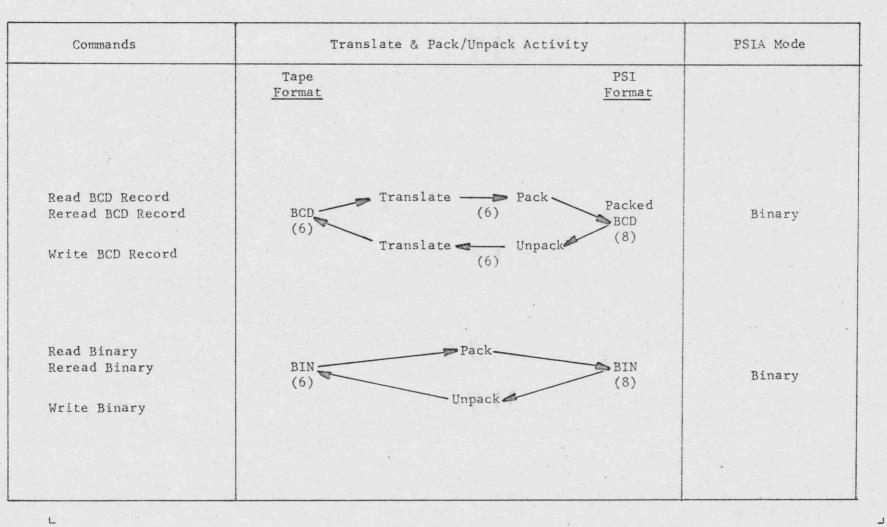

#### 3.8.1 Pack/Unpack Requirements for 7-channel Translation

The two basic modes of data transfer to/from a 7-channel handler are the Binary and the BCD modes. These commands require translation and pack/unpack as illustrated in Figure 3.8.1. It should be noted that the PSIA is in the "binary mode" for both data transfer modes.

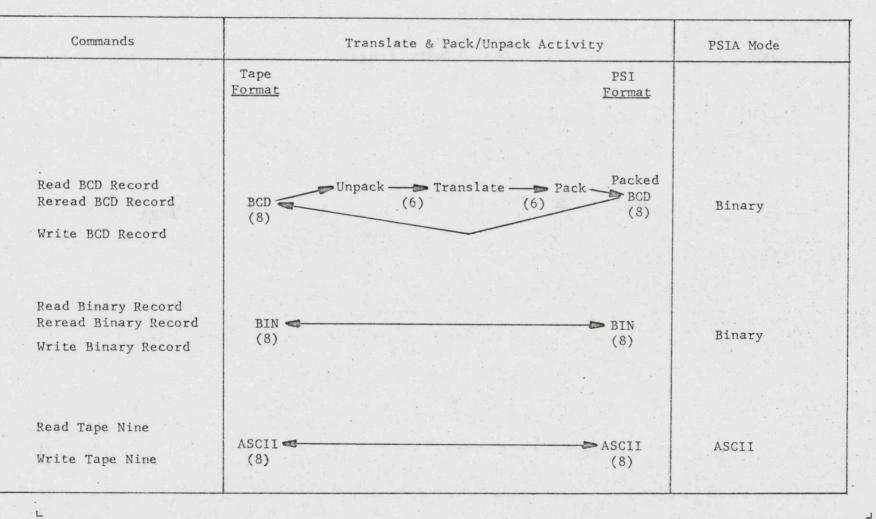

#### 3.8.2 Pack/Unpack Requirements for 9-channel Translation - Standard

There are three modes of data transfer to/from a 9-channel handler including the Binary, BCD,1 and Tape Nine. These are standard modes of data transfer for 9-channel tapes--the optional modes are described in section 3.8.3.

Only the BCD mode requires translation and pack/unpack as is shown in Figure 3.8.2. It should also be noted that the translation required in the BCD Read is for the single character 001010 as specified in section 8.6.4.4.

## Honeywell Rev. A

Page 24

٦

٦

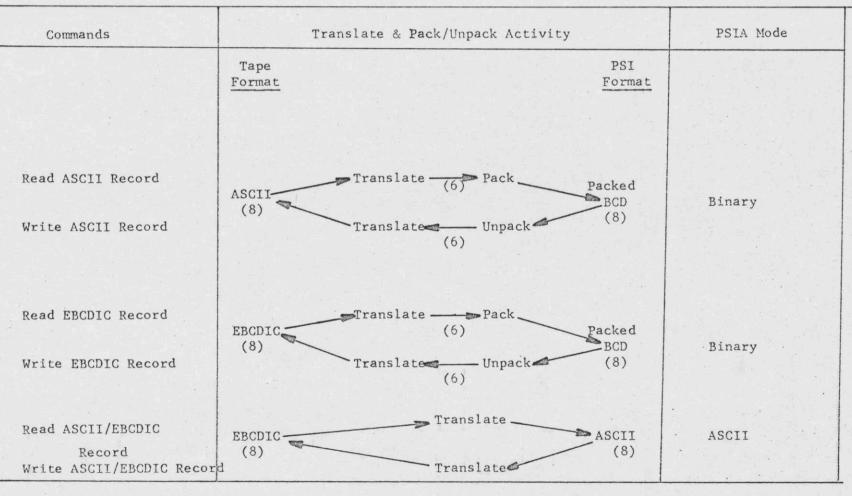

3.8.3

г

Pack/Unpack Requirements for 9-channel Translation - Optional

The three optional code translations offered by this subsystem require the pack/unpack activity illustrated in Figure 3.8.3. The tables defining these translations are given in sections 8.6.1 through 8.6.3.2.

Figure 3.8.1

4.

CE 301-1 (6-71)

Г

Pack/Unpack Requirements for 7-channel Translation

Honeywell

٦

Rev. A

43A232215

Page

25

#### Figure 3.8.2

Pack/Unpack Requirements for Standard 9-channel Translation

CE 301-1 (6-71)

Honeywell

7

Rev. A

43A232215

Page

26

#### Figure 3.8.3 Pack/Unpack Requirements for Optional 9-channel Translaction

Honeywell

Rev. A

43A232215

Page

N

1

L

CE 301-1

## Honeywell Rev. A

Page 28

#### INTERFACES

4.1

4.0

PERIPHERAL SUBSYSTEM INTERFACE

The peripheral subsystem interface (PSI) is the definition of the dialog and interface circuits for the exchange of information between the EUS and the magnetic tape subsystem. This interface exists between the PSI channel of the IOM (PSIA) and the link adaptor (PSI-LA) of the magnetic tape controller. The PSI dialog is controlled on the controller end by microprograms residing in the MPC.

This dialog places the heart of the control of the peripheral operation within the MPC. For example, when a data transfer is to occur, the MPC receives an IDCW from the PSIA and interprets this instruction, places the PSIA in the proper operating mode, and initiates the data transfer. At the termination of the instruction, the MPC formats the status and initiates a status transfer to the PSIA.

#### 4.2

#### MAGNETIC TAPE HANDLER DEVICE LEVEL INTERFACE

This interface defines the dialog and interface circuitry involved in the transfer of information between the device switch and the handler. It is an all-digital, radial interface which has been optimized for PE operation. Inherent in its definition is the requirement that PE deskew occur in the TCA, and that the NRZI deskew is accomplished in the handler. See the specification titled NPL Device Level Interface (DLI) for Magnetic Tape Subsystems.

#### 4.3 INTERNAL ADAPTOR INTERFACE

This interface is internal to the controller, and is implemented on the back-panel of the card cage. It provides a hardware and firmware interface between the MPC and the adaptors (link adaptors and controller adaptors).

4.4 EFFECTS OF PSI ON SIX-BIT CHARACTER MODE

The PSI presents some unique situations when working with an external user system which is oriented toward the six-bit character mode. This is due to the mis-match between the six-bit EUS and the eight-bit PSI. These situations are detailed in the following two sections.

#### 4.4.1 Effects of PSI on 7-channel Operation

When operating with 7-channel tapes the controller and IOS must take special precautions to ensure that only valid data is written

ŧ.

5

4.4.1

43A232215

Page 29

Effects of PSI on 7-channel Operation (continued)

on tape, and later read from tape.

Rev. A

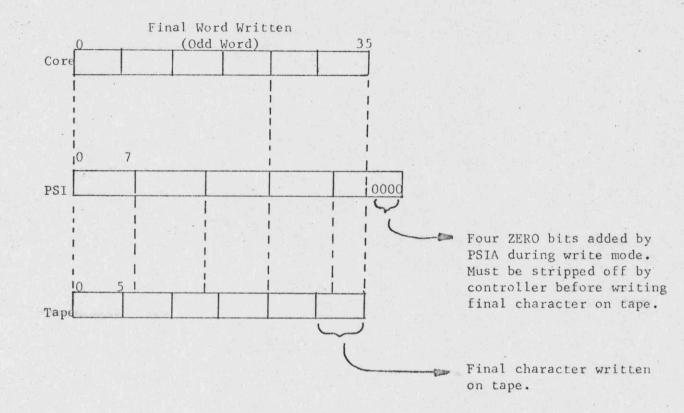

In the write mode the controller has the responsibility of writing only valid six-bit characters on tape. As illustrated in Figure 4.4.1.1, the 6000 systems write multiples of 36-bit words. If an odd number of words are written, the final byte transferred to the controller will contain four ZEROs padded by the PSIA. The controller must strip off these four bits, thus writing a valid final character on tape.

Read mode -

Write mode -

The situation in the read mode is more complicated because the tape may have been generated by a stranger system. In this case the final character on tape may correspond to any six-bit character position in the 36-bit 6000 word. Depending on the particular position of this final character in relation to the packing of previous characters into bytes for transmission across the PSI, the controller will pad 6, 4, 2, or 0 ZEROS on the final character.

The status supplied by the controller at termination will indicate the amount of ZERO-fill on the final character transferred, along with the terminate character position of the final byte transferred to the EUS. It is then the responsibility of IOS to map this terminate character position to the terminate character position as seen by subsystems operating on the former Common Peripheral Interface systems.

The relationship between characters on tape, bytes on the PSI, and words in 6000 core is illustrated in Figure 4.4.1.2. Also, Figure 4.4.1.3 defines the ZERO-fill performed by the controller, and the mapping required of IOS.

1

## Honeywell Rev. A

Page 30

٦

1

#### Figure 4.4.1.1

7-channel Write Operation for

Odd Number of Words Written

٢

Rev. A

43A232215

Page 31

- 7

| 0 | 1           | 2 | 3 | 4  | 5      | 6     | 7  | 8   | 9        | 10       | 1: |

|---|-------------|---|---|----|--------|-------|----|-----|----------|----------|----|

|   | 1           | 1 |   |    | 1      |       | 1  | 1   | I        | 1        |    |

|   |             |   |   |    | i      |       | 1  | 1   | 1        | 1        | 1  |

|   | i           | ! |   |    | i      |       | 1  |     | 1.100    | 1        | 1  |

|   |             | 1 |   | PS | I Bytq | s     | 1  | 1   | <u> </u> | <u>.</u> | 1  |

| 0 |             | 1 | 2 | 3  | 4      |       | 5  | 6   |          | 7        |    |

|   |             |   |   |    | 1      | 1     |    | 1   |          | 1        |    |

|   | 1           | 1 |   |    |        | 1     |    | i   | 1        |          |    |

|   | 1           | i |   |    |        | 1     |    | 1   | - 1-     | i i      |    |

|   | 1           |   |   | 3  | 6-bit  | Words |    | i - | 1        |          |    |

|   | T           | T |   |    |        |       | 17 |     |          | 1        |    |

|   | Section 151 |   |   |    |        |       |    |     |          |          |    |

Figure 4.4.1.2

Relationship Between Tape Characters, PSI Bytes, and Core Words for 7-channel Tape

Page 32

٦

1

|                     |                              | OUTPUT of IOS |                          |           |                    |     |             |  |

|---------------------|------------------------------|---------------|--------------------------|-----------|--------------------|-----|-------------|--|

| Final Char.<br>Read | Zero-fill Termin<br>Size Cha |               | ar. <sup>2</sup> Residue |           | Terminate<br>Char. |     | Substatu    |  |

| (No.)               | (No.bits)                    | TCP           | E/O                      |           | TCP                | E/O | au tha Para |  |

| 0                   | 2                            | 2             | 1                        | Actual    | 1                  | 0   | 00000X      |  |

| 1                   | 4                            | 3             | 1                        | 11        | 2                  | 0   | 11          |  |

| 2                   | 6                            | 4             | 1 1                      | 1         | 3                  | 0   | 11          |  |

| 3                   | 0                            | 4             | 1                        | 11        | 4                  | 0   | 11          |  |

| 4                   | 2                            | 0             | 1                        | 1 S 1     | 5                  | 0   | 11          |  |

| 5                   | 4                            | 1             | 0                        | Actual +1 | 0                  | 0   | н           |  |

| 6                   | 6                            | 2             | 0                        | Actual    | 1                  | 0   | 11          |  |

| 7                   | 0                            | 2             | 0                        | H H       | 2                  | 0   | п           |  |

| 8                   | 2                            | 4             | 0                        | 11        | 3                  | 0   | 11          |  |

| 9                   | 4                            | 5             | 0                        | п         | 4                  | 0   | 11          |  |

| 10                  | 6                            | 0             | 0                        | 11        | 5                  | 0   | п           |  |

| 11                  | 0                            | 0             | 0                        | 11        | 0                  | 0   |             |  |

The mapping required of the IOS is defined by the following table.

Rev. A

1 The formatting of the substatus under the Ready major status, for each of the Zero-fill conditions, is defined in section 6.5.

2 The definition of Terminate Character Position for PSI channels is given in 43A177880.

<sup>3</sup> The definition of Terminate Character Position for CPI channels is given in 43A219605.

Figure 4.4.1.3 Status Mapping

for

7-Channel Read Operation

#### Rev. A

43A232215

Page 33

#### 4.4.2

#### Effects of PSI on 9-channel Operation

When operating with 9-channel handlers the data transferred across the PSI corresponds directly to frames on tape for those operations requiring the PSIA to be in the binary mode. However, there are particular situations which occur, and are of such nature that the user data could be affected.

Write mode -

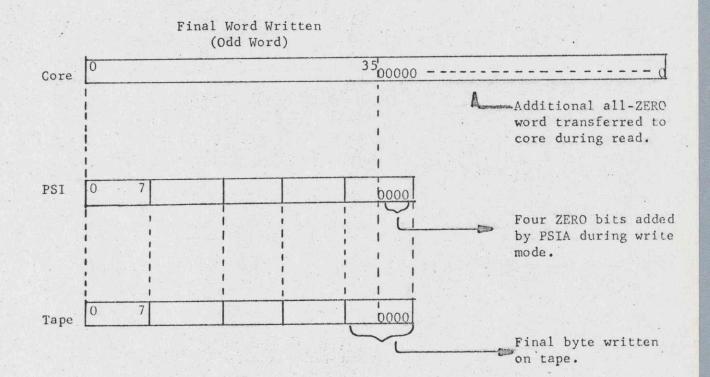

Two situations must be considered in the 9-channel write mode. The first arises when performing write operations with the PSIA in the binary mode, which is the mode of the PSIA for most non-ASCII operations (i.e., most non-Tape Nine operations as shown in Figure 3.8.2 and 3.8.3). In this case, a write operation with an odd number of 36-bit words transferred will result in a final byte with four high-order ZEROs. This final byte will be written on tape, and when read back will extend beyond the expected word count by the four ZERO bits as shown in Figure 4.4.2.1.

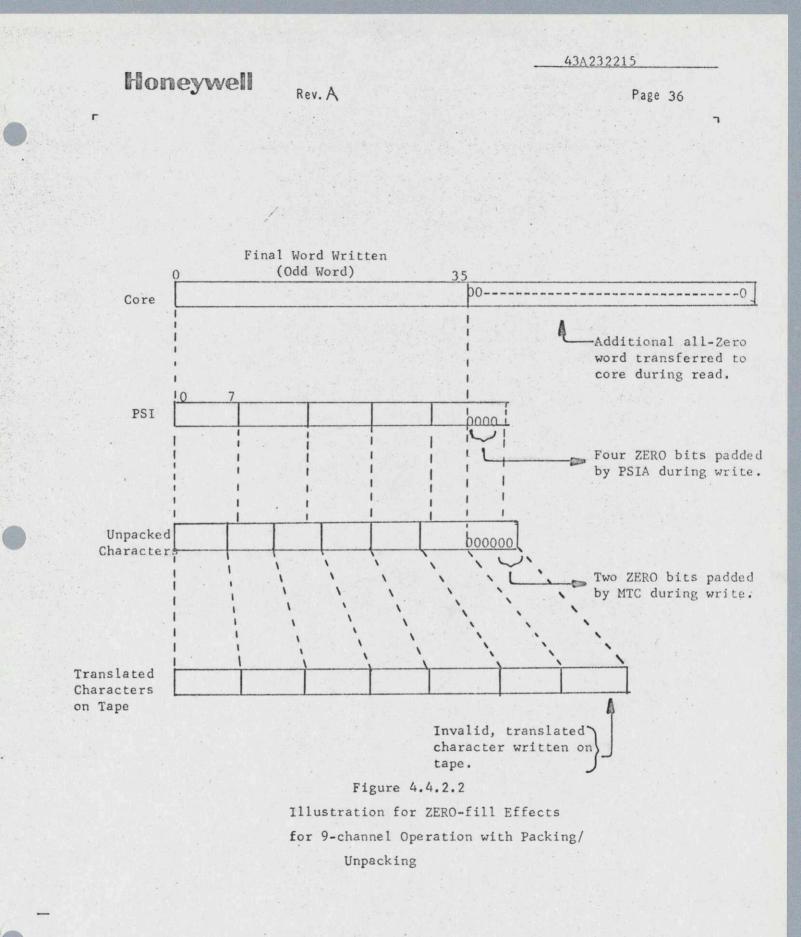

When performing code translation from the six-bit to the eight-bit representation during a write operation as shown in Figure 3.8.3, the final unpacked character may be the result of a ZERO-fill in the last byte transferred across the PSI. These four ZERO bits are padded with two ZEROs by the controller, translated, and written on tape. When reading, this last invalid frame will be transferred to the EUS as part of the record. See Figure 4.4.2.2.

Read mode -

If a 9-channel tape is read in a mode which does not require any packing/unpacking activity by the controller, the data contained in the bytes on the PSI should be completely valid. However, if any packing/unpacking is required, as would be the case for translation to an EUS six-bit code, the final byte transferred via the PSI may contain some invalid ZERO bits as illustrated in Figure 4.4.2.2. This final byte will result in the transfer to core of an extra word, zero-filled, whose first four bits result from the last four bits of the last byte on tape. This problem has existed since the orignal implementation of 9-channel tapes on the 600 Series. Software (GEFRC) has provided a test for correcting the residue, based on the assumption that for all 600/6000 Series created tape records of odd length,

Page 34

٦

1

## Honeywell

4:4.2

г

Effects of PSI on 9-channel Operation (continued)

Rev. A

the four bits in question will be zero bits. However, any "stranger" created 9-channel tape containing valid data in its last byte (of which the last four bits are zero), meeting the above criteria, will suffer the loss of the last four bits of the final byte.

I.

Rev. A

43A232215

Page 35

٦

٦

Figure 4.4.2.1

9-channel Binary Operations

for Odd Words Written

CE 301-1 (6-71)

ik:

1

1

CE 301-1 (6-7 1)

L

.

# Honeywell Rev. A

5.0

5.1

Page 37

#### SOFTWARE COMMANDS

The controller shall contain microprograms for proper interpretation of command codes received from the external user system. These command codes will be received via the PSI as described in Section 5.1.

TYPICAL PSI ACTION OF CONTROLLER

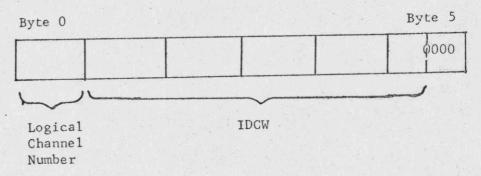

From the controller point of view, a typical command execution will be as described in the following general terms. Specific details for this interface may be found in the specification for the PSI as adapted to the 6000 (43A177874) and in the specification for the PSI adapter of the IOM (43A177880).

1. PSIA raises Channel Program Waiting (CPW) line to the controller.

- 2. The controller responds with the service code Initiate New Channel Program.

- 3. The PSIA responds with six bytes of information which contain the logical channel number in the first byte, followed by five bytes containing the IDCW in its standard format. A Terminate Out (TMO) signal will accompany the final byte. Details of the IDCW format will be found in Section 5.2.

- 4. The legality of various IDCW fields are checked as described in Section 5.2.

- 5. The controller interprets the command code, and takes appropriate action.

- 6. The data is transferred by appropriate applications of Strobe Out (STO) and Strobe In (STI) until the operation is terminated either by Terminate Out (TMO) or by Terminate In (TMI).

5.1

Rev. A

Page 38

TYPICAL PSI ACTION OF CONTROLLER (continued)

- 7. The controller will send the service code Store Terminate Status to the PSIA. The five status bytes will contain the major status and substatus as required by the standard 6000 status word, plus additional status information. See Section 6.0.

- 8. The controller will send the service code Move Pointer and Initiate Command Transfer, if required.

- 9. If step 8 above occurs, the sequence will start again at step 3.

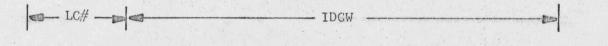

5.2 REQUIREMENTS FOR CONTROLLER CHECKING OF IDCW

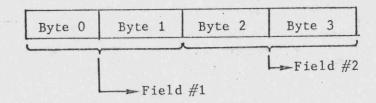

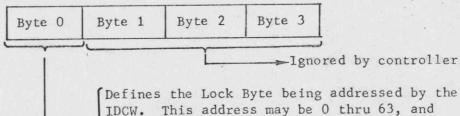

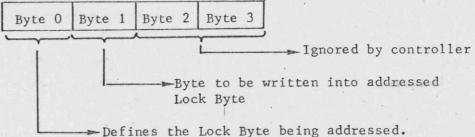

The controller will receive an IDCW from the external user system in the following format.

| Device Devi<br>Instruc- Addr | 방송에서 그 것은 이 것이다.      | 1BZ 11:               | I OINRI- | hannel  <br>nstruc- | Char.on<br>Record | 0000 |

|------------------------------|-----------------------|-----------------------|----------|---------------------|-------------------|------|

| <br>tion                     | and the second second | and the second second |          | LION                | . Lally I         |      |

| Byte O | Byte 1 | Byte 2 | Byte 3 | Byte 4 | Byte 5 |  |

|--------|--------|--------|--------|--------|--------|--|

| 0      | 7 .    |        |        |        |        |  |

#### Bits Description

0:0-0:7\* Logical Channel Number

Valid logical channel numbers are represented by 00000XXX, where the X's may be ZERO or ONE.

1:0-1:5 Device Instruction (Op. Code)

The codes found here are those of Section 5.3 and Section 5.5. If an illegal code is detected, the error is reflected to the external user system via the terminate status as described in Section 6.5.

1

\* 0:7 defines byte and bit (e.g., 0:7 = bit 7 of byte 0)

CE 301-1 (6-7 1)

43A232215

# Honeywell

## Rev. A

Page 39

5.2

REQUIREMENTS FOR CONTROLLER CHECKING OF IDCW (continued)

Description Bits

Device Address 1:6-2:3

> The legal codes are defined in Section 3.2. This field of the IDCW is valid only for the first IDCW in the channel program, and shall be ignored for all IDCWs other than the first in the program.

3:2-3:4

#### Must be 111,.

If this field is not correct, the controller will reflect Channel Status of 011, in the termination status as defined in Section 6.2.

3:5

3:6-3:7

Continue and Marker Bits

Ignored by the controller.

These two bits define the action to be taken by the controller upon completion of the operation:

Cont Mark

0

Х

1

The controller stores terminate status and causes a terminate interrupt at the end of this IDCW execution. This IDCW is the last in the list. The state of the mark bit is ignored by the controller

1

1

This is not last IDCW in list. Upon 0 completion of execution of this IDCW with no faults detected, the controller will issue a "Move Command Pointer" service code and obtain a new IDCW.

Upon completion of the execution of the IDCW, with ready status and no faults detected, the controller will store terminate status and cause a marker interrupt (This means that the technique of Section 6.1 is used to store terminate status except that the "Set Marker Interrupt" service code replaces the "Set Terminate Interrupt" service code), and then issue a "Move Command Pointer" service code to obtain a new IDCW.

43A232215

# Honeywell

## Rev. A

Page 40

5.2

REQUIREMENTS FOR CONTROLLER CHECKING OF IDCW (continued)

#### Description

4:0-4:5

Bits

Channel Instruction

This field has a two-fold purpose. First, it defines whether the command is to be executed as a Special Command (Section 5.5) or as a Regular Command (Section 5.3). Second, it defines the type of transaction which is to take place. This field must contain one of the following configurations:

For Regular Commands;

00<sub>8</sub> Unit record transfer

Peripheral action (non-data transfer; e.g., request status, backspace N records, set density)

068 Multi-record instruction

108

028

Single character record (e.g., write file mark as distinguished from EOF, tape mark, where the single character is contained in the tally field (4:6-5:3) of the IDCW Additional Codes for Regular Data Transfer Commands

| Octal | Turn Off                                                 | and the second second | apstain | Set Low   |

|-------|----------------------------------------------------------|-----------------------|---------|-----------|

| Code  | Automatic<br>Retry &<br>In-flight<br>Error<br>Correction | Slow                  | Fast    | Threshold |

| 22    | No                                                       | No                    | No      | No        |

| 21    | No                                                       | No                    | No      | Yes       |

| 22    | No                                                       | No                    | Yes     | No        |

| 23    | No                                                       | No                    | Yes     | Yes       |

| 24    | No ·                                                     | Yes                   | No      | No        |

| 25    | No                                                       | Yes                   | No      | Yes       |

| 26    | No .                                                     | No                    | No      | No        |

| 27    | No                                                       | No                    | No      | Yes       |

| 30    | Yes                                                      | No                    | No      | No        |

| 31    | Yes                                                      | No                    | No      | Yes       |

| 32    | Yes                                                      | No                    | Yes     | No        |

| 33    | Yes                                                      | No                    | Yes     | Yes       |

| 34    | Yes                                                      | No                    | No      | Yes       |

| 35    | Yes                                                      | No                    | No      | Yes J     |

| 36    | Yes                                                      | No                    | No      | No        |

| 37    | Yes                                                      | No                    | No      | Yes       |

Page 41

REQUIREMENTS FOR CONTROLLER CHECKING OF IDCW (continued)

for Special Controller Commands\*\*;

408 Unit record transfer

428 Peripheral action

Multi-record instruction 46 8

508 Single character record

\* These conditions are turned off for the duration of this current IDCW.

\*\* Channel Instruction fields of 4X<sub>8</sub> and 5X<sub>8</sub> are reserved for Special Controller commands.

All other configurations of this field are illegal, and will result in the controller generating a Channel Status of  $010_2$  in the termination status

### 4:6-5:3

Honeywell

Г

5.2

Character of Record Tally

This field contains the character for a single character record (Channel Instruction field =  $10_8$  or  $50_8$ ), or the number of times the device instruction is to be re-issued by the controller (Channel Instruction field =  $02_8$ ,  $06_8$ ,  $42_8$  or  $46_8$ ). In the magnetic tape controller application multiple record peripheral action commands are legal only for the Forward Space One Record and Backspace One Record commands. No specific checking of this field is required of the controller.

5:4-5:7

Must be zero.

CE 301-1 (6-71)

Rev. A

Page 42

5.3

г

### PERMISSABLE COMMANDS

The IDCW description given in section 5.2 indicates that the Channel Instruction field determines if the Device Instruction is to be interpreted as a Regular command, or as a Special Controller command. The former are summarized in the following list; the latter are summarized in Section 5.5.

| Command                  | Octal<br><u>Representation</u> | Section |

|--------------------------|--------------------------------|---------|

| Request Status           | 00                             | 5.4:1   |

| Reset Status             | 40                             | 5.4.2   |

| Request Device Status    | 50                             | 5.4.3   |

| Reset Device Status      | 51                             | 5.4.4   |

| Survey Devices           | 57                             | 5.4.5   |

| Read Control Registers   | 26                             | 5.4.6   |

| Write Control Registers  | 16                             | 5.4.7   |

| Set File Protect         | 62                             | 5.4.8   |

| Set File Permit          | 63                             | 5.4.9   |

| Rewind                   | 70                             | 5.4.10  |

| Tape Load                | 75 .                           | 5.4.11  |

| Rewind/Unload            | 72                             | 5.4.12  |

| Reserve Device           | 66                             | 5.4.13  |

| Release Device           | 67                             | 5.4.14  |

| Set 200 BPI              | 64                             | 5.4.15  |

| Set 556 BPI              | 61                             | 5.4.16  |

| Set 800 BPI              | 60                             | 5.4.17  |

| Set 1600 CPI             | 65                             | 5.4.18  |

| Forward Space One Record | 44                             | 5.4.19  |

| Forward Space One File   | 45                             | 5.4.20  |

| Backspace One Record     | 46                             | 5.4.21  |

| Backspace One File       | 47                             | 5.4.22  |

| Control Store Overlay    | 10                             | 5.4.23  |

| Load From Device         | 05                             | 5.4.24  |

| Erase                    | 54                             | 5.4.25  |

| Write End-of-File Record | 55                             | 5.4.26  |

| Write Tape Nine          | 13                             | 5.4.27  |

| Read Tape Nine           | 03                             | 5.4.28  |

|                          |                                |         |

L

43A232215

# Honeywell Rev. A

Page 43

-

5.3

#### PERMISSABLE COMMANDS (continued)

|                           | Octal          | 0       |

|---------------------------|----------------|---------|

| Command                   | Representation | Section |

| Write Binary Record       | 15             | 5.4.29  |

| Read Binary Record        | 05 .           | 5.4.30  |

| Reread Binary Record      | 07             | 5.4.31  |

| Write BCD Record          | 14             | 5.4.32  |

| Read BCD Record           | 04             | 5.4.33  |

| Reread BCD Record         | 06             | 5.4.34  |

| Write EBCDIC Record       | 34             | 5.4.35  |

| Read EBCDIC Record        | 24             | 5.4.36  |

| Write ASCII Record        | 37             | 5.4.37  |

| Read ASCII Record         | 27             | 5.4.38  |

| Write ASCII/EBCDIC Record | 35             | 5.4.39  |

| Read ASCII/EBCDIC Record  | 25             | 5.4.40  |

| Diagnostic Mode Control   | . 31           | 5.4.41  |

| Device Wraparound         | 32             | 5.4.42  |

| Device wraparound         |                |         |

| Write Timing Character    | 30             | 5.4.43  |

|                           |                |         |

### 5.4 DESCRIPTION OF TAPE COMMANDS

## 5.4.1 Request Status Command (00<sub>8</sub>)

This command results in the transmission to the external user system of the status conditions of the addressed device. This status shall be formatted as terminate status (see Section 6).

Since the exception conditions are stored for each handler, this information remains independent of controller communication with other handlers. Therefore, if an exception condition is reflected to the external user system at the termination of a command execution, and the external user system then addresses a second handler, the true status for the second handler will be returned as terminate status for the current command. The exception condition of the first handler remains unchanged.

Page 44

1

# Honeywell

## Rev.A

5.4.2

## Reset Status (408)

This command results in the resetting of all resettable status conditions within the addressed device. The resettable status conditions are defined as those exception conditions included in the following major status conditions:

Device Data Alert

#### End of File

The status reflected to the external user system as terminate status will be the status condition of the subsystem after resetting the resettable status.

#### 5.4.3 Request Device Status (50g)

Extensive status information is stored in each handler. Some of this status is descriptive of handler physical characteristics, and some is descriptive of the operational characteristics of the handler. The Request Device Status command will transfer this status to the external user system.

This command is not legal if addressed to device zero, and shall be rejected with Command Reject- Invalid Device Code status. The controller will place the PSIA in the "binary mode" prior to transmitting this status to the EUS.

Twenty-four bytes of handler status will be transmitted unless the EUS terminates the operation.

The first four (4) bytes are defined in the document defining the handler interface (NPL Device Level Interface (DLI) for Magnetic Tape Subsystem). The remaining bytes will be specified in the document defining the handler.

5.4.4 Reset Device Status (51<sub>8</sub>)

This command provides a mechanism for resetting the resettable status bits in the addressed handler. In response to this command, the controller will issue appropriate DLI commands to the addressed handler such that the status bits are reset to the ZERO state. Successful completion of this command will result in Ready status being transmitted to the EUS.

This command is not legal if addressed to Device Zero, and shall be rejected with Command Reject-Invalid Device Code status.

Same

Page 45

## .5.4.5 Survey Devices (57g)

Upon receipt of this command, the subsystem will interrogate each handler, assembling two bytes of information for each handler. The survey proceeds from handler 1 through handler 8 (for single channel controller) or through handler 16 (for dual channel controller). The controller will place the PSIA in the "ASCII mode" prior to transferring the first byte to the PSIA.

This command is legal only if addressed to device zero; otherwise it will be rejected with Command Reject-Invalid Device Code.

This command does not constitute an access request of a handler as described in section 6.6.

Successful completion of this command will result in Ready termination status being sent to the EUS.

The bytes assembled by the controller for each handler will contain the following format and information:

43A232215

# Honeywell

# Rev. A

Page 46

5.4.5 Survey Devices (57) (continued)

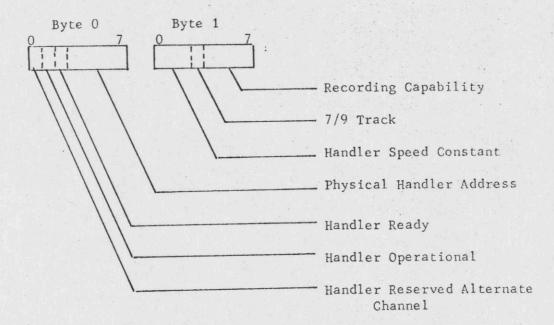

Bits Description

0:0

Handler Reserved Alternate Channel

A logical ONE in this bit position indicates that the handler is reserved for use by an alternate channel as the result of a Reserve Device command previously issued from another channel. If this bit is a logical ONE all other bits in the byte pair for that handler are invalid.

0:1

0:2

#### Handler Operational

A logical ONE indicates that the handler is capable of communication with the external user system; logical ZERO means handler is incapable of communication with EUS.

#### Handler Ready

A logical ZERO in this position indicates that the handler (a) is in the process of executing a rewind-type operation or the Tape Load command, (b) the device is in the standby state, or (c) the handler is in a fail state.

#### 0:3-0:7 Physical Handler Address

This is the 5-bit number which is wired into the handler at subsystem installation. For further description of the significance of this number, refer to section 3.2.

The low order bit is in position 0:7.

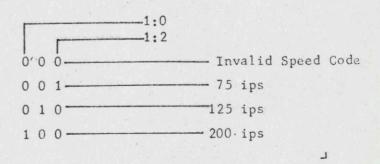

1:0-1:2 Handler Speed Constant

This field specifies the forward speed capability of the handler.

43A232215

# Honeywell <sub>R</sub>

## Rev. A

Page 47

| 5.4.5 | Survey Devices | (57.) | (continued) |

|-------|----------------|-------|-------------|

|       |                |       |             |

| Bits | Description |

|------|-------------|

| 1:3  | 7/9 Track   |

Logical ONE = 9-track handler.

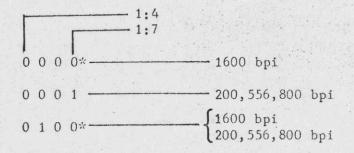

1:4-1:7 Recording Capability

This field describes the PE and NRZI recording capability of the handler.

\*These codes are not legal if 7/9 track bit is logical ZERO.

5.4.6

## Read Control Register (268)

This command provides a method by which the external user system may obtain the contents of error logs maintained in the controller. This command is valid only if addressed to a handler, and shall ' be rejected with Command Reject - Invalid Device code status if addressed to device ZERO.

When the Read Control Register command is addressed to some device other than zero, the contents of the counters related to the addressed handler will be returned to the EUS. In this case seven counts (two bytes each, plus two special bytes,) will be sent to the external user system. Prior to transmitting the first byte, the controller will place the PSIA in the "binary mode". Refer to section 7.5.2 for a description of the counters maintained by the controller for each handler in the subsystem.

### Rev. A

Page 48

1

## 5.4.7 Write Control Register (16g)

This command provides a mechanism by which the external user system may load particular data in the handler error logs maintained in the controller. This command shall be rejected with Command Reject-Invalid Device Code status if addressed to device zero.

In response to this command, the controller will place the PSIA in the binary mode, and prepare to receive eighteen bytes of information. These bytes shall be formatted by the EUS as shown in Figure 7.5.

The controller will extract the various counts, and store in the appropriate error logs.

5.4.8 Set File Protect (62)

The reception of the Set File Protect command will serve to unconditionally inhibit write operations on the selected handler regardless of the presence of a Write Permit Ring in the tape reel.

The handler shall remain in the File Protect condition until a new reel is loaded, or until the Set File Permit command is issued to this handler.

## 5.4.9 Set File Permit (63g)

This command will allow writing on a handler which has been protected previously by a Set File Protect command and has a Write Permit Ring in place.

If the Write Permit Ring is not in place, this command will be rejected with Command Reject - Invalid Operation Code status.

## 5.4.10 Rewind (70<sub>o</sub>)

CE 301-1 (6-7 1)

This command results in the tape on the selected tape unit being positioned on the Beginning of Tape (BOT) marker. The tape subsystem is free to accept commands directed to other tape units during the rewind execution. If any command other than a Rewind is directed to a tape unit which is executing a rewind operation, the command will be rejected with the Device Busy - In Rewind status. If a Rewind command is directed to a tape unit which is executing a rewind operation, the Peripheral Subsystem Ready status will be reflected.

Rev. A

Page 49

#### 5.4.10

### Rewind $(70_8)$ (continued)

Upon completion of this command, a special interrupt is sent to the EUS by using the technique of Section 6.6.

If at the time the Rewind command is received, the tape mounted on the specific tape unit is already positioned on BOT, the subsystem will reflect the Peripheral Subsystem Ready status to the EUS with the terminate status mode (section 6.1).

Prior to terminating this command the controller shall interrogate the "In Rewind" bit of the addressed handler to verify that the handler was set to the desired state. (This should take in the order of a few microseconds).

## 5.4.11 Tape Load (75<sub>8</sub>)

This command causes the tape mounted on the supply reel of the selected tape unit to be loaded automatically, and positioned at the beginning of Tape (BOT) marker. The status reflected will be Peripheral Subsystem Ready. The subsystem is free to accept commands directed to other tape units during the load operation. At the termination of the load operation special status will be sent to the EUS per section 6.6.

This command is valid only if the handler is in the Standby-unloaded state, which is the state at the end of a Rewind/Unload command.

If, at the time this command is received in the subsystem, the tape is already positioned at the BOT marker, the controller will send the terminate status Peripheral Subsystem Ready - Positioned at BOT to the EUS.

### 5.4.12 Rewind/Unload (72g)

CE 301-1 (6-7 1)

This command results in the tape on the selected tape unit being run back on the supply reel. The tape will stop in such a position that the tape reel may be readily dismounted from the tape unit.

Status reflected to the EUS during the reception of the Rewind/ Unload command will be Peripheral Subsystem Ready, provided the command is accepted. All subsequent commands will be rejected with the Device Attention - Standby status, except Tape Load and Request Stat

At termination of the unload operation, the controller will send special status to the EUS by using the method of section 6.6.

Page 50

## 5.4.13 <u>Reserve Device</u> (66<sub>9</sub>)

Rev A

This command permits an EUS to reserve an unreserved device for its exclusive use. This causes a device to be reserved to the link adapter port by which this command was received. This reserve condition may be erased by a Release Device command received via the same link adapter port which originally received the Reserve Device command.

When any other EUS (i.e., any other link adapter port) attempts to address a reserved device, the status Device Busy - Device Reserved will be returned as terminate status. The reserved state of the handler is maintained in tables within the controller.

## 5.4.14 Release Device (67,)

This command, when received via a link adapter port by which a Reserve Device command directed to the same device had been received, will cause the device reserve condition to be erased. The device is then available for use by any EUS.

When this command has been completed successfully, a special status/interrupt will be transmitted to all as defined in Section 6.6.

## 5.4.15 Set 200 BPI (64<sub>8</sub>)

The reception of this command by the subsystem will cause the addressed handler to be set to 200 bpi, if currently in a NRZI mode, or if at the BOT marker and capable of this density. The addressed tape unit will remain in this density until modified by one of the other set density commands.

If this command is directed to a handler which is not capable of 200 bpi operation, the command shall be rejected with Command Reject-Invalid Op Code.

If this command is directed to a handler which is currently set to 1600 bpi, and the tape is not at the BOT marker, this command will be rejected with Command Reject-Invalid Op Code.

## 5.4.16 Set 556 BPI (61<sub>8</sub>)

The reception of this command by the subsystem will cause the addressed handler to be set to 556 bpi, if currently in an NRZI mode, or if at the BOT marker and capable of this density. The addressed tape unit will remain in this density until modified by one of the other set density commands.

# Honeywell Rev A

Г

Page 51

## 5.4.16 Set 556 BPI (61<sub>o</sub>) (continued)

If this command is directed to a handler which is not capable of 556 bpi operation, the command shall be rejected with Command Reject-Invalid Op Code. If this command is directed to a handler which is currently set to 1600 bpi, and the tape is not at the BOT marker, this command will be rejected with Command Reject-Invalid Op Code.

## 5.4.17 Set 800 BPI (60g)

The reception of this command by the subsystem will cause the addressed handler to be set to 800 bpi, if currently in a NRZI mode, or if at the BOT marker and capable of this density. The addressed tape unit will remain in this density until modified by one of the other set density commands.

If this command is directed to a handler which is not capable of 800 bpi operation, the command shall be rejected with Command Reject-Invalid Op Code. If this command is directed to a handler which is currently set to 1600 bpi, and the tape is not at the BOT marker, this command will be rejected with Command Reject-Invalid Op Code.

### 5.4.18 Set 1600 BPI (65<sub>o</sub>)

The reception of this command by the subsystem will cause the addressed handler to be set to 1600 bpi, if at the BOT marker and capable of this density. The addressed tape unit will remain in this density until modified by one of the other set density commands (provided the next set density command is issued while at BOT marker).

If this command is directed to a handler which is not capable of 1600 bpi operation, the command shall be rejected with Command Reject-Invalid Op Code. If this command is directed to a handler which is currently set to a NRZI density, and the tape is not at the BOT marker, this command will be rejected with Command Reject-Invalid Op Code.

5.4.19

Forward Space One Record (44g)

This command results in the tape mounted on the specified handler being moved forward over the number of records specified by the record tally field of the IDCW, and positioned to read or write the next sequential record. There is no data transfer between the tape subsystem and the external user system during the execution of this command, and tape parity is not checked during the command execution.

# Honeywell Rev. A

Page 52

#### 5.4.19 Forward Space One Record (44,) (continued)

The tape subsystem remains busy during the execution of the command. Upon completion of the execution of this command, the terminate status is sent to the external user system. If a record spaced over was an End of File record, the status reflected to the external user system will be the End of File status, the operation will terminate, and the residue will reflect the unfulfilled record tally.

#### 5.4.20 Forward Space One File (45g)

This command results in the tape mounted on the specified handler being moved forward until an End of File record is detected. Tape is positioned to read or write over the record following the detected End of File record. There is no data transfer between the tape subsystem and the external user system during the execution of this command, and tape parity of the data records is not checked during the command execution. The controller will ignore the EOT marker. The tape subsystem remains busy during the execution of this command. Upon the completion of the execution of the command, the End of File terminate status is sent to the external user system.

## 5.4.21 Backspace One Record (46)

This command results in the tape mounted on the specified handler being moved backward over the number of records defined by the record tally field of the IDCW, and positioned to read or write the record just spaced over. There is no data transfer between the tape subsystem and the external user system during the execution of this command, and tape parity for data records is not checked during the command execution.

The tape subsystem remains busy during the execution of this command. Upon the completion of the execution of this command, appropriate terminate status is sent to the external user system. If a record just spaced over was an End of File record, the End of File terminate status will be sent, the operation will terminate, and the residue will reflect the unfulfilled record tally. If, at the time this command is received, the tape mounted on the specific tape unit is positioned at the BOT marker, the tape subsystem will not go busy, but will reflect the Command Reject-Positioned on Leader status to the external user system during the command sequence.

Rev. A

## Page 53

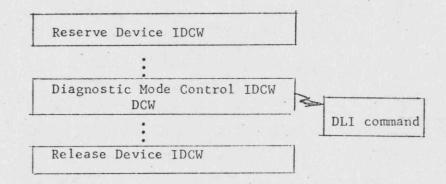

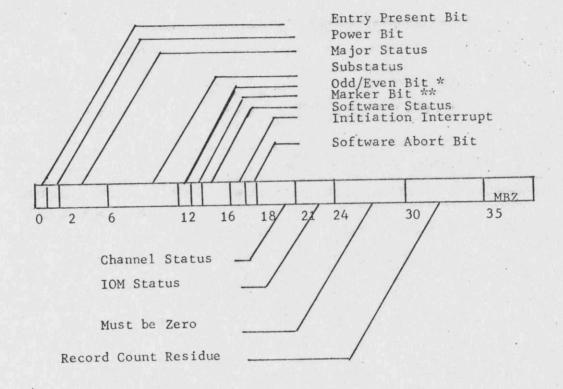

## 5.4.22 Backspace One File (47,)