Company without Department General Manager approval with legal concurrence.

CE 103 (12-69)

La

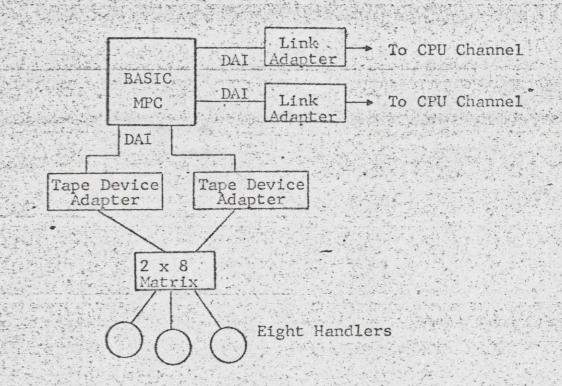

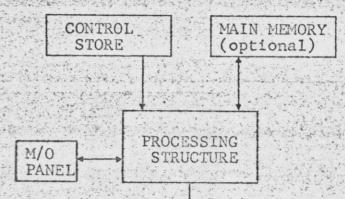

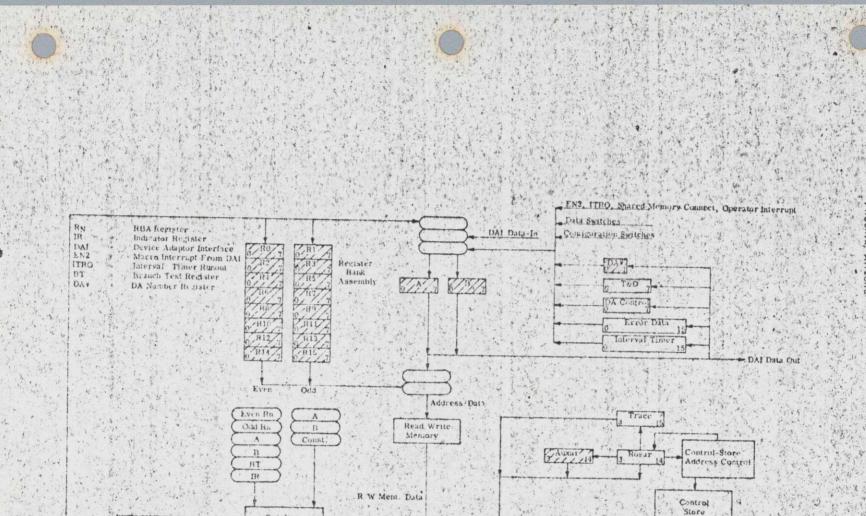

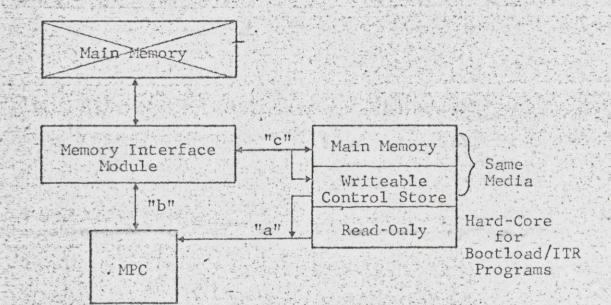

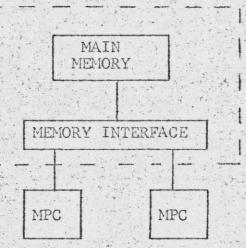

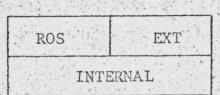

COMPANY CONFIDENTIAL And the second 43A177875 GENERAL ( ELECTRIC Cont. on Page 2.1 Page 2 Rev. TABLE OF CONTENTS GENERAL DESCRIPTION-----1. 3 1.1 MPC CONCEPT---1.1.1 Definition of Terms------1.2 PERFORMANCE CHARACTERISTICS--7 Microinstruction Execution------1.2.1 Concurrent Branch Execution------1.2.2 1.2.3 Connectability-----1.2.4 Device Control Capabilities-----1.2.5 Typical Application Configurations-----8 8 9 DOPT-1.3 REQUIRED SUPPORT-----14 1.3.1 Software Packages------14 Supporting Specifications for MPC 1.3.2 Configurations-----14 1.3.3 Common Firmware Packages for MPC------15 FUNCTIONAL DESCRIPTION-----2. 17 SING STRUCTURE----along the second second 2.1 PROCESSING STRUCTURE ---17 18 26 33 35 35 2.1.6 Error Detection-----36 and see all and CONTROL STORE-----2.2 37. -------2.2.1 Format-----37 2.2.2 Size/Modularity-----37 2.2.3 Writeable Control Store Capabilities ----38 MAIN MEMORY-----39 2.3

CE 302-1 (12-63)

COMPANY CONFIDENTIAL . GENERAL C ELECTRIC Rev.

43A177875

Cont. on Page 2.2 Page 2.1

|     |                   |                                  | Memory Modularity<br>Memory Width<br>Memory Accessibility<br>Memory Speed<br>Shared Memory Capability<br>NSTRUCTION REPERTOIRE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39<br>40<br>40<br>40<br>40<br>40 |

|-----|-------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| .3. | OPERA             | TIONAL                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 43                               |

|     | 3.1               | INITIAL                          | IZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43                               |

|     |                   | 3.1.1<br>3.1.2                   | Initialized State<br>Next Normal Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43<br>44                         |

|     | 3.2<br>3.3<br>3.4 | BOOTLO/<br>INTERRU<br>MICROIN    | 이 가지 않고 같은 것 같은 것을 다 가지 않는 것을 하는 것을 하는 것을 하는 것 같은 것을 하는 것이 가지 않는 것 같은 것을 하는 것을 수 있다. 것을 하는 것을 수 있다. 것을 하는 것을 수 있는 것을 하는 것을 하는 것을 수 있다. 같은 것을 하는 것을 하는 것을 수 있는 것을 수 있다. 것을 수 있는 것을 수 있다. 것을 것을 수 있는 것을 것을 것을 수 있는 것을 것을 수 있는 것을 것을 수 있는 것을 수 있는 것을 수 있는 것을 수 있는 것을 것을 수 있는 것을 것을 수 있는 것을 수 있는 것을 것을 수 있는 것을 것을 것을 것을 수 있는 것을 것을 것을 것을 것을 것을 것을 것을 것을 수 있는 것을 것을 것을 것을 수 있는 것을 것을 것 같이 않는 것을 것을 것을 것 같이 않는 것을 것을 것 같이 않는 것을 것 같이 않는 것을 것 같이 않는 것을 것 같이 않는 것 같이 않는 것을 것 같이 않는 것 않는 것 같이 않는 것 같이 않는 것 같이 않는 것 않는 | 45<br>45<br>46                   |

|     |                   | 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4 | Microinstruction Access from<br>Control Store                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46<br>47<br>50<br>50             |

|     | 3.5               | FIXED C                          | CONTROL STORE OPERATIONAL ADDRESSES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50                               |

|     |                   | 3.5.1<br>3.5.2<br>3.5.3          | Initialize State<br>Low-Level EN-1 Interrupt<br>Error Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 50<br>51<br>51                   |

| 4.  | INTER             | FACE RE                          | QUIREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 52                               |

|     |                   |                                  | ADAPTER INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 52                               |

|     |                   | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4 | Pomoto Initializa Function from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 52<br>53<br>53<br>54             |

CE 302-1 (12-69)

#### COMPANY CONFIDENTIAL GENERAL DELECTRIC Rev. Cont. on Page 2.3 Page 2.2 4.2 OPERATOR PANEL -----55 4.2.1 Power On/Power Off Switches-----55 4.2.2 Initialize Switch-----55 : 55 4.2.4 Auto/Manual Switch-----:56 4.2.5 Operator Interrupt Switch-----4.2.6 Error Reset Switch------4.2.7 Data Switches-----56 56 57 4.2.8 Configuration Switches------4.2.9 Address Switches-----57 59 59 60 4.3 MAINTENANCE PANEL-----60 4.4 MAIN MEMORY AS INTERFACE BETWEEN MPC'S----61 GENERAL DESIGN REQUIREMENTS------62 5. 62 5.2 PHYSICAL PACKAGING-----62 5.3 POWER SHARING/DISTRIBUTION-----62 i de 6. RELIABILITY AND MAINTAINABILITY REOUIREMENTS ---63 GENERAL-----6.1 63 6.1.1 General Maintainability Require-ments-----63 6.1.2 Isolation Test Routine Capability --63 DEFINITIONS-----6.2 64 MEASURING DEVICES-----6.3 64 Instrumentation-----6.3.1 64 6.3.2 Unit Identification-----64 OFFLINE REPAIRABILITY-----6.4 . 64 6.5 64 ADJUSTMENTS-----6.6 65 PREVENTATIVE MAINTENANCE (PM)-----6.7 65 6.8 65 STEP 4 REQUIREMENTS-----6.9 66 6.10 STEP 5 REQUIREMENTS-----66 6.11 UNRESTRICTED PRODUCTION-----67 6.12 FIELD PERFORMANCE MEASUREMENT-----67

| COMPANY CONFIDENTIAL                                                                                                              | 43A1778                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 375 - 2  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

| GENERAL 💮 ELECTRIC                                                                                                                | 45A177875                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |  |

|                                                                                                                                   | Cont. on Page 2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page 2.3 |  |

|                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |

| - 6.12.1 Incident Reports                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67       |  |

| 6.12.1 Incident Reports<br>6.12.2 Failure Analysis                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68       |  |

| 6.12.3 Data Reduction and Sto                                                                                                     | orage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 68       |  |

| 6.12.4 Equipment Selection<br>6.12.5 Evaluation Period                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68       |  |

| 6.12.5 Evaluation Period                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68       |  |

| 6.12.6 Performance Reports                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68       |  |

| A1. MICROINSTRUCTION REPERTOIRE                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 69       |  |

| A1.1 REGISTER NOTATION                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 69       |  |

|                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 70       |  |

| A2.1 BINARY ADD                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 70       |  |

| A2.2 BINARY SUBTRACT                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71       |  |

| A2.3 ADD CARRY<br>A2.4 SUBTRACT BORROW<br>A2.5 NEGATE                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72       |  |

| A2.4 SUBTRACT BORROW                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .73      |  |

| A2.5 NEGATE                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |

| A2.6 COMPLEMENT                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75       |  |

| A3. LOGICAL OPERATIONS                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76       |  |

| A3.1 Logical AND                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76       |  |

| A3.2 Logical OR                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 77       |  |

| A3.2 Logical OR<br>A3.3 Exclusive OR                                                                                              | Y CONTRACTOR OF THE PARTY OF TH | 78       |  |

| A4. SINGLE BYTE LOAD/STORE OPERATIONS                                                                                             | and the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 79       |  |

| A4.1 STORE A                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79       |  |

| A4.2 STORE B                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79       |  |

| A4.3 LOAD A                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79       |  |