| Hone     | eywell                     | TITLE:                                                                                                                                                                                                                             | No     | 43A1778 | 62         |

|----------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|------------|

| INFOR    | YWELL<br>MATION<br>MS INC. | ENGINEERING PRODUCT SPECIFICATION, PART 1<br>Device Channel Adapter (DCA)                                                                                                                                                          |        |         |            |

| L16-92   | OKL BGE 21                 | 7 TOS Total Pages 125                                                                                                                                                                                                              |        |         | Page 1     |

|          |                            | REVISION RECORD                                                                                                                                                                                                                    |        |         |            |

| REVISION | DATE                       | PAGES AFFECTED APPR                                                                                                                                                                                                                | OVALS  |         | AUTHORITY  |

| A ISSUED | JAN 21 197                 | 70                                                                                                                                                                                                                                 |        |         |            |

| B Rev.   | OCT 12 1971                | Ret.& Rev.Sh. 1,4,11,24, Oct<br>31,34,40,45,47,63,66,72,<br>77 & 90;Added Sh. 72.1;<br>Rev.Sh.2,3,5,7-10,12,13,<br>15,16,23,25-30,32,33,41-44,<br>46,48,53,55,57-62,64,65,<br>67,69,74,76,78,80,83,101,<br>105,108,110,111,115-121 | . 6, 1 | 971 CO  | ZEY-00-006 |

# HONEYWELL PROPRIETARY

The information contained in this document is proprietary to Honeywell Information Systems Inc. and is intended for internal Honeywell use only. Such information may be distributed to others only by written permission of an authorized Honeywell official. This restriction does not apply to vendor proprietary parts that may be disclosed in this document.

L

GENERAL BELECTRIC

Information Systems Equipment Division Phoenix, Arizona

### NUMBER: 43A177862 Rev. B

Cont. on Sh. 3 Sh. No.2

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

#### (TABLE OF CONTENTS)

|     |       |                                                    | Sheet No. |

|-----|-------|----------------------------------------------------|-----------|

| 1.0 | GENER | AL DESCRIPTION                                     |           |

|     | 1.1   | ELEMENTS OF THE SUBSYSTEM                          | 9         |

|     |       | REFERENCE DOCUMENTS                                | 13        |

| 2.0 | FUNCT | TIONAL CAPABILITIES                                | 13        |

|     | 2.1   | IBM FORMAT                                         | 14        |

|     | ~ • ± | 2.1.1 Track Layout                                 | 14        |

|     |       | 2.1.2 Field Structure                              | 16        |

|     |       | 2.1.3 Gap Structure                                | 18        |

|     | 2.2   | GE FORMAT                                          | 19        |

|     | 2.3   |                                                    | 22        |

|     | 2.0   | 2.3.1 Storage Capacity, General                    | 22        |

|     |       | 2.3.1.1 Storage Capacity, Fixed Format             | 22        |

|     |       |                                                    | 22        |

|     |       | 2.3.2 Data Transfer Rate<br>2.3.3 Access Times     | 23        |

|     |       | SUMMARY OF FUNCTIONS OF THE 355 (CONTROL SOFTWARE) | 23        |

|     | 2.4   |                                                    | 25        |

|     | 2.5   |                                                    | 26        |

|     |       | 2.5.1 DCA Data Transfer Techniques                 | 26        |

|     | 2.6   | SUMMARY OF FUNCTIONS OF THE DFE                    | 28        |

|     | 2.7   |                                                    | 29        |

|     | 2.8   | DCA BUFFER REQUIREMENTS                            | 30        |

|     |       | 2.8.1 DCA/355/IOM Bus Interface Buffer             | 30        |

|     |       | 2.8.2 DFE/DCA Interface Buffer                     | 30        |

|     |       |                                                    | 31        |

|     | 2.9   | DATA INTEGRITY                                     | 21        |

|     |       | 2.9.1 DCA/355 IOM Interface                        | 31        |

|     |       | 2.9.2 DCA/DFE Interface                            | 31        |

|     |       | 2.9.3 Status                                       | 31        |

|     |       | 2.9.3.1 Device Status Group                        | 32        |

|     |       | 2.9.3.2 DCA Status Group                           | 32        |

|     |       |                                                    |           |

B

B

GENERAL BELECTRIC

Information Systems Equipment Division Phoenix, Arizona

## NUMBER: 43A177862

Rev. B

Cont. on Sh. 4 Sh. No. 3

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

|     |       |             | <u>1</u>             | TABLE OF CONTENTS<br>(continued)                    |                            |

|-----|-------|-------------|----------------------|-----------------------------------------------------|----------------------------|

|     |       |             |                      |                                                     | Sheet No.                  |

|     | 2.10  | OTHER F     | EATURES              |                                                     | 34                         |

|     |       | 2.10.1      | Channel N            | Number Patch                                        | 34                         |

|     |       | 2.10.2      | Program 1            | Interrupt Level Patches                             | 34                         |

|     |       | 2.10.3      | Fixed Mer            | nory Address Patch                                  | 34                         |

| 3.0 | FUNCI | TIONAL DE   | SCRIPTION            |                                                     | 36                         |

|     | 3.1   | CONTROL     | SOFTWARE             | MECHANISMS                                          | 36                         |

|     |       | 3.1.1       | 355/Load             | External (LDEX)                                     | 36                         |

|     |       |             | 3.1.1.1              | General Format of LDEX                              | 36                         |

|     |       | 0 1 0       | 255/01-55            | Patamal (CTEV)                                      | 38                         |

|     |       | 3.1.2 3.1.3 |                      | e External (STEX)<br>/PCW/ICW/IDCW (General)        | 39                         |

|     |       |             | 0 1 0 1              | DOL Format                                          | 40                         |

|     |       |             | 3.1.3.1              | PCW Format<br>ICW Format                            | 41                         |

|     |       |             |                      |                                                     | 42                         |

|     |       |             |                      | IDCW Format<br>DCA Masked State                     | 48                         |

|     |       |             |                      | 3.1.3.4.1 IOM Fault Detected                        | 49                         |

|     |       |             | 3.1.3.5<br>3.1.3.6   | Conceptual Flowchart of ICW/IDC<br>Sample IDCW List | W List Operations 51<br>52 |

|     | 3.2   | DCA "RE     | EGISTER" F           | UNCTIONS                                            | 53                         |

|     |       | 0.0.1       | m Deed               | 에 환경화 감사는 것이 물건 귀엽을 많이 많은 것                         | 53                         |

|     |       |             | Tag Regi<br>File Bus |                                                     | 55                         |

|     |       |             | 3.2.2.1              | File Bus Functions                                  | 56                         |

|     |       | 3.2.3       | Device (             | Module) Select Register                             | 58                         |

|     |       |             |                      | ected Device Register                               | 60                         |

|     |       | 3.2.5       |                      | Address Bus Register                                | 61                         |

|     |       |             |                      |                                                     |                            |

B

43A177862

Honeywell

-

Rev. B

Page 4

# TABLE OF CONTENTS (Continued)

٦

٦

| 3.2.6                     | Gated Atte                                                                                                                                                                                                                                                  | ention Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 62                                                                                                                                           |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|                           | 3.2.6.1                                                                                                                                                                                                                                                     | Processing Gated Attention Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63                                                                                                                                           |

| 3.2.7                     | Device Sta                                                                                                                                                                                                                                                  | atus Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 64                                                                                                                                           |

|                           | 3.2.7.1                                                                                                                                                                                                                                                     | Device Status Detected by Control Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67                                                                                                                                           |

| 3.2.8                     | DCA Status                                                                                                                                                                                                                                                  | s Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67                                                                                                                                           |

|                           | 3.2.8.1<br>3.2.8.2<br>3.2.8.3<br>3.2.8.4<br>3.2.8.5<br>3.2.8.6<br>3.2.8.7<br>3.2.8.8<br>3.2.8.9<br>3.2.8.10<br>3.2.8.10<br>3.2.8.11<br>3.2.8.12<br>3.2.8.13<br>3.2.8.14<br>3.2.8.15<br>3.2.8.16<br>3.2.8.17<br>3.2.8.18<br>3.2.8.19<br>3.2.8.20<br>3.2.8.21 | Software Sync Bit<br>End of File Record<br>Compare Error (K or D Field)<br>Invalid IDCW Sequence<br>Sync Byte Failure<br>Data on Index Mark<br>Write Current Sense Error<br>Two Consecutive Index Marks Detected<br>TRO Error<br>Transfer Timing Error<br>ICW Address Indicator Bit<br>Check Character Error, K or D Field<br>Check Character Error, Count Field<br>CIOC/LDEX/STEX Received While Busy<br>DL or KL DL or DK Stored in Memory<br>Compare Count Field Error<br>Record Number Does Not Compare<br>Device/DCA Exception Condition<br>20410 (CC) Detected<br>SSI Bit Caused Interrupt<br>Command Parity Error | 67<br>68<br>68<br>69<br>69<br>69<br>69<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>71<br>71<br>71<br>71<br>71<br>72<br>72<br>72<br>72 |

| 3.2.9<br>3.2.10<br>3.2.11 | Key Lengt<br>Data Leng                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 72.1<br>72.1<br>73                                                                                                                           |

|                           | 3.2.11.2                                                                                                                                                                                                                                                    | Cyclic Check or Burst Check Register<br>Indicator Byte Function<br>Bit Count Checking Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73<br>73<br>74                                                                                                                               |

| 3.2.12                    | Memory Ad                                                                                                                                                                                                                                                   | ldress Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 75                                                                                                                                           |

|                           |                                                                                                                                                                                                                                                             | Non-Modulo 36 Data Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 75                                                                                                                                           |

|                           |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                              |

L

GENERAL CELECTRIC

Information Systems Equipment Division Phoenix, Arizona

NUMBER: 43A177862

Rev. B

Cont. on Sh. 6 Sh. No. 5

B

0

B

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

|     |         | TABLE OF CONTENTS<br>(continued)               |           |

|-----|---------|------------------------------------------------|-----------|

|     |         | (continued)                                    | Sheet No. |

|     |         |                                                | 76        |

|     |         | Serialization/Deserialization Register         | 76        |

|     |         | Data Buffer                                    | 76        |

|     | 3.2.15  | Set T&D Mode Function                          | 77        |

|     | 3.2.16  | Reset the DCA Function                         | 78        |

|     | 3.2.1/  | Simulated Clock Function                       | 78        |

|     |         | Force Check Character Alert Function           | 79        |

|     | 3.2.19  | T&D Register Command                           | 80        |

|     | 3.2.20  | Address of Hardware Register Functions         |           |

| 3.3 | REGISTE | R FUNCTIONS IN 355 MEMORY                      | 81        |

|     | 3.3.1   | Device/DCA Status (A, A+1)                     | 83        |

|     |         | Locations A+2 and A+3                          | 84        |

|     |         | Count Field Data Storage                       | 84        |

|     | 3.3.4   | Gap Area Data                                  | 85        |

|     |         |                                                | 85        |

|     |         | 3.3.4.1 Count Field Preamble                   | 86        |

|     |         | 3.3.4.2 Key Field Preamble                     | 87        |

|     |         | 3.3.4.3 Data Field Preamble                    | 0,        |

|     | 2 2 5   | Primary ICW Location                           | 87        |

|     | 3.3.6   |                                                | 87        |

|     | 5.5.0   | Alternate for house                            |           |

| 3.4 | 355/DCA | DATA TRANSFER COMMANDS                         | 87        |

|     | 3.4.1   | Common Characteristics of Commands             | 88        |

|     | 3.4.2   | Basic Data Transfer Operations                 | 89        |

|     |         |                                                | 89        |

|     |         | 3.4.2.1 CNC Operations                         | 90        |

|     |         | 3.4.2.2 Compare Operations (K or D Fields)     | 90        |

|     |         | 3.4.2.3 Write Operations                       | 90        |

|     |         | 3.4.2.4 Format Operations                      | 92        |

|     |         | 3.4.2.5 Idle Operations                        | 92        |

|     |         | 3.4.2.6 Other Read Operations                  |           |

|     | 3.4.3   | Table of Data Transfer Commands                | 92        |

|     |         | 0 / 0 1 Albertichions                          | 92        |

|     |         | 3.4.3.1 Abbreviations<br>3.4.3.2 Command Table | 93        |

|     |         | 3.4.3.2 Command Table                          |           |

## GENERAL BELECTRIC

Information Systems Equipment Division Phoenix, Arizona

B

B

B

#### NUMBER: 43A177862

Rev. B

Cont. on Sh. 8 Sh. No. 7

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

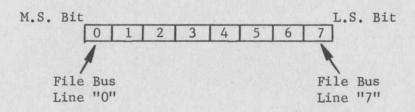

#### TABLE OF CONTENTS (continued) Sheet No. 108 4.2 DCA MODULE TO DFE 180 108 4.2.1 Interface Cables 108 4.2.2 Signal/Data Cable 111 Signal/Data Line Characteristics 4.2.3 111 Output Signal/Data Lines 4.2.4 4.2.4.1 File Bus Lines 4.2.4.2 Set Difference Tag Line 111 112 112 4.2.4.3 Set Cylinder Tag Line 113 4.2.4.4 Set Head Address Tag Line 4.2.4.5Set Control Tag Line4.2.4.6Module Select Lines 114 115 115 4.2.4.7 Release 115 4.2.4.8 Clear 115 4.2.4.9 Write Data Line 4.2.4.10 Write Control 116 116 4.2.4.11 Read Control 116 4.2.4.12 Operational Out 116 4.2.4.13 Resolution Inhibit 117 4.2.5 Input Signal/Data Lines 117 4.2.5.1 Cylinder Address Lines 117 4.2.5.1.1 Status on CAR Lines 118 4.2.5.2 Device unsafe 118 4.2.5.3 Selected Device (9) 4.2.5.4 Gated Attention 118 119 4.2.5.5 Pack Change 4.2.5.6 Seek Incomplete 4.2.5.7 Device Busy 4.2.5.8 Index 4.2.5.9 Write Current Sense 119 119 120 120 120 4.2.5.10 On-Line 4.2.5.11 End of Cylinder 4.2.5.12 Alt. Channel Desires Control 4.2.5.13 Reserved to Alt. Channel 120 120 120 4.2.5.14 5MHz Clock 120

1.

GENERAL CELECTRIC

NUMBER: 43A177862

Rev. B

Information Systems Equipment Division Phoenix, Arizona

### Cont. on Sh. 9 Sh. No. 8

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

|     | <u>TABLE OF CONTENTS</u><br>(continued)                         |                                |

|-----|-----------------------------------------------------------------|--------------------------------|

|     | 4.2.5.15 Stripped Clock<br>4.2.5.16 Stripped Data               | <u>Sheet No.</u><br>120<br>121 |

|     | 4.2.5.17 Operational In<br>4.2.5.18 DFE180 Identification Lines | 121<br>121                     |

| 5.0 | RELIABILITY, MAINTAINABILITY AND ACCURACY                       | 122                            |

| 6.0 | GENERAL DESIGN REQUIREMENTS                                     | 122                            |

|     | 6.1 U.L. REQUIREMENTS                                           | 122                            |

|     | 6.2 DCA CIRCUIT TECHNOLOGY                                      | 122                            |

|     | 6.3 DOCUMENT STANDARDS                                          | 122                            |

BB

#### GENERAL CEPELECTRIC

Information Systems Equipment Division Phoenix, Arizona

#### NUMBER: 43A177862 Rev. B

Cont. on Sh. 10 Sh. No. 9

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

#### 1.0 GENERAL DESCRIPTION

B

B

B

B

This Engineering Product Specification, Part 1, describes the Device Channel Adapter (DCA) module used in DSS175/180 disc storage subsystems. It has been prepared in response to Large Systems Department Product Planning Functional Specifications, 69-003 and 69-008, and the DSS175/180 Subsystem EPS-1, 43A177861.

This specification encompasses the Device Channel Adapter (DCA), and the interface to the Device File Electronics (DFE). Of necessity, functions and specifications outside of the arbitrary hardware limits of the DCA (i.e., the 355, DFE, and Drives) are included in order to clarify the role of the DCA within the subsystem.

1.1 ELEMENTS OF THE SUBSYSTEM

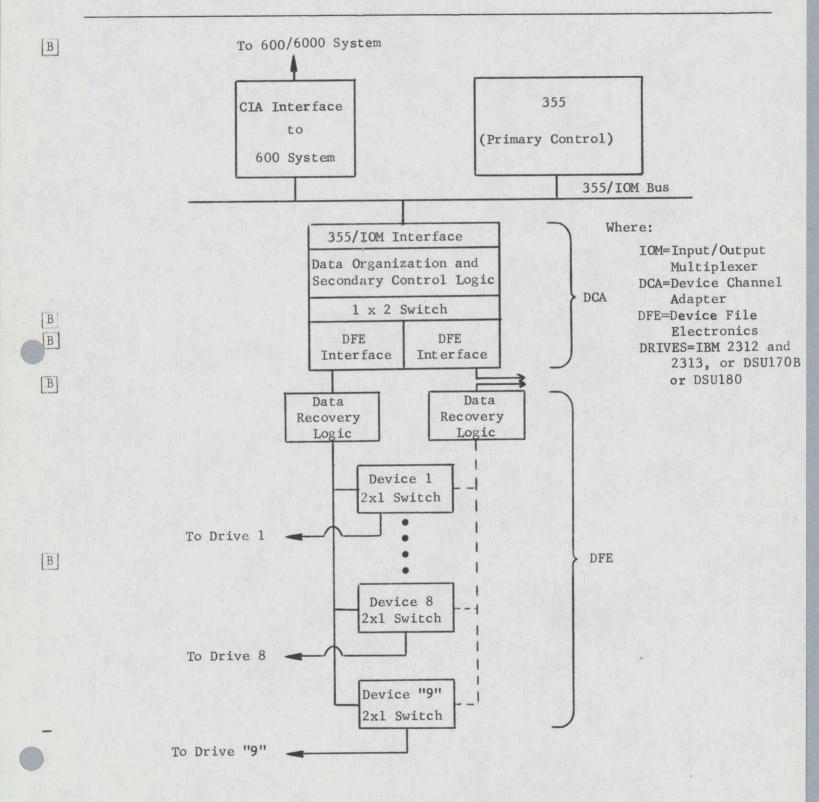

The following diagram illustrates the relationships of the various elements of the subsystem, and the major logical divisions of the 355/DCA/DFE complex.

- a) The 355 software functions as a primary controller (or sequencer) for the subsystem. As such, 355 software shall perform all functions which can be executed without exceeding the time constraints imposed on the 355/IOM and memory by the data transfer rate of the subsystem.

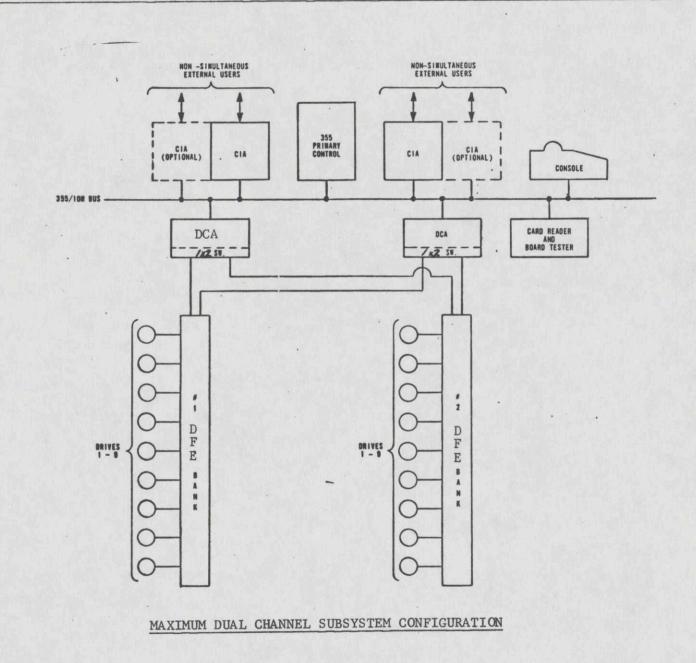

- b) The subsystem will include a maximum of two DCA's (where both may be executing data transfer simultaneously), and four CIA's. The CIA's will operate in switched channel pairs with only one of each pair transferring data at any one time.

- c) DCA channel adapters shall have priority over all other channel adapters connected to the 355/IOM.

- d) Each DCA shall require no more than 5 MQX type boards.

- e) The DCA shall perform those control functions which the 355 control software cannot execute because of insufficient response time. In addition, the DCA shall provide interfaces to the 355/IOM Bus and the DFE.

CM 287-2A (6-68)

## GENERAL CELECTRIC

Information Systems Equipment Division Phoenix, Arizona NUMBER: 43A177862 Rev. B

Cont. on Sh. 11 Sh. No. 10

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

## Honeywell

г

43A177862

Page 11

٦.

1

1.1 ELEMENTS OF THE SUBSYSTEM (continued)

Rev. B

- f) The DFE shall perform those functions which are of direct concern to the drive specified for this subsystem. In addition, the DFE shall provide interfaces to the DCA and the devices. The Drives (Devices) to be connected to this subsystem are the IBM 2312 and 2313, or the HIS DSU180 or HIS DSU170B. IBM and HIS drives shall not be intermixed on a DFE. If the HIS and IBM drive interfaces are different, only simple board replacement in the DSU170B or the DFE shall be acceptable as a means to make IBM and HIS drives plug compatible.

- g) The DCA and 355 Primary Controller shall write and read data on a discpack in a format compatible with the IBM 2314 removable disk subsystem.

The following diagram showing the maximum dual channel, single controller subsystem is included as an illustration of the connections of the subsystem elements. For a discussion of subsystem configurations refer to 43A177861.

L

## GENERAL DE ELECTRIC

Information Systems Equipment Division Phoenix, Arizona NUMBER: 43A177862 Rev. B

Cont. on Sh. 13 Sh. No. 12

TITLE: E

ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

#### GENERAL CE ELECTRIC

Information Systems Equipment Division Phoenix, Arizona

#### NUMBER: 43A177862 Rev. B

Cont. on Sh. 14 Sh. No. 13

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

1.2 REFERENCE DOCUMENTS

GE-355 EPS-1, 43A219608, Revision B Software EPS-1, 43A177865 Controller EPS-1, 43A177863 MQX Board Tester EPS-1, 43A177854 IBM 2312/2313 Drives: IBM File #S360-19, Form #A26-1586-1 IBM System 360 Component Descriptions, 2314 Direct Access Storage Facility, 2844 Auxiliary Storage Control: File #S360-07, Form #A26-3599-3 U.L. 478 IBM Field Engineering Manual, Theory of Operation, Y26-3671-3, March 1969 DAE EPS-1, M50EF00036 CIA EPS-1, 43A177858 DSS175/180 Subsystem EPS-1, 43A177861 DSU170B EPS-1, M50EB00775 DSU180 EPS-1, 59A301601 FUNCTIONAL CAPABILITIES

2.0

B

B

B

A requirement upon the DSS175/180 subsystem is that of IBM format compatibility. This format is characterized by variable field lengths, and the optional use of key fields as well as data fields. Also, the format includes the use of a Track Descriptor Record (Record 0) in addition to the Home Address identification of each track. The format is versatile, exhibits very useful user options. It is somewhat wasteful of storage space, and the use of fully variable key and data fields from sector to sector is probably operationally inefficient.

The discussion of functional capabilities must begin with the description of this format (paragraph 2.1). Paragraph 2.2 discusses the implementation of this format in GE 400/600 systems.

The DSS175/180 subsystem hardware includes the capability of fully implementing the IBM format. The DCA is capable of formatting, reading, and writing variable data fields as well as key fields. DCA data processing is accomplished on a field basis, with software supplied data control words identifying the fields and their requirements. Thus, the format on the data track is the responsibility of the controller software.

Operational requirement of GE 400/600 systems are met by the implementation of fixed sector lengths with no key fields. The resulting format is compatible with IBM, but only on a subset basis.

## GENERAL

Information Systems Equipment Division

Phoenix, Arizona

#### NUMBER: 43A177862

#### Rev. B

Cont. on Sh. 16 Sh. No. 15

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

- 2.1.1 Track Layout (continued)

- d) The Count field of a sector is fixed in length.

- e) The Key field of a sector (if present) can vary in length from 1 byte to 255 bytes.

- f) The Data field of a sector can vary from 0 byte to 7294 bytes.

- g) The length of the Data field can be set to zero. If so, an End of File status condition is indicated by the IBM 2314 controller. A Key field may be present with a length  $\neq$  0.

- h) "Gaps" between fields, within a sector, are fixed in length.

"Gaps" between sectors are variable and a function of the length of the key field plus the length of the Data field.

- Lengths of the fields of a sector are measured in bytes (8 bit multiples), as opposed to lengths being measured in words (36 bit multiples), or characters (6 bit multiples).

- j) A single data sector (including record zero) can be formatted, or a whole track can be formatted. If a single sector is formatted, the balance of the track is written with "ones" until the index mark is detected.

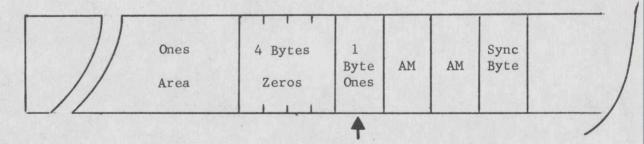

- k) A "sync byte" (the last byte in every gap area) identifies the type of field following it.

- 1) The last four bytes of every field are identified as:

| Burst | Burst | ID   | Bit |

|-------|-------|------|-----|

| CK    | CK    | Byte | CNT |

where:

Burst CK = Cyclic code bytes for error detection.

These bytes are calculated from the preceding data in the field, as described in the IBM Field Engineering Theory of Operation manual (Y26-3671-3) page 1-13.

B

#### GENERAL GE ELECTRIC

Information Systems Equipment Division Phoenix, Arizona

#### NUMBER: 43A177862

Rev. B

Cont. on Sh. 17 Sh. No. 16

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

2.1.1 Track Layout (continued)

В

- ID Byte = This byte identifies the DFE and device which wrote the field on the track. The format of this byte is identified in paragraph 3.2.11.2.

- Bit CNT = Bit count check byte. This byte records, modulo 8, the number of one-bits written in the field in ones complement form. Functionally, this byte is included as another code checking byte. Failure to compare the bit CNT is the same as a cyclic check compare failure.

These last four bytes are not part of the data of a field and are not usually transmitted beyond the DCA.

THE ABOVE DESCRIPTION OF THE LAST FOUR BYTES PERTAINS TO IBM 2314 MODEL A1 SUBSYSTEMS. IN EARLIER, MODEL 1, SUBSYSTEMS THE ID BYTE AND BIT CNT BYTE ARE NOT INCLUDED --- A FIELD ENDS WITH THE TWO BURST CHECK BYTES. THE DCA WRITES ALL OF THE FOUR BYTES DESCRIBED ABOVE IN THE MANNER OF MODEL A1. See paragraph 2.2.

#### 2.1.2 Field Structure

The fields discussed above exhibit the following structure:

### GENERAL S ELECTRIC

Information Systems Equipment Division Phoenix, Arizona NUMBER: 43A177862 Rev. B

Cont. on Sh. 24 Sh. No. 23

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

- 2.3.3 Access Times (Refer to the DSU170B EPS, M50EB00775)

- a) Latency Time:

The discpack rotates at 2400 rpm  $\pm$  2%. Therefore, the maximum rotational delay is 25 milliseconds  $\pm$  2% and the average rotational delay is 12.5 milliseconds.

b) Track Access Time:

The following access times are measured from "seek start" to "seek complete" and therefore, do not include any data transfer time.

Maximum Track Seek Time (Between track 000 and 202):

135 milliseconds (170B);60 milliseconds (180)

. Minimum Track Seek Time (Between Adjacent Tracks):

25 milliseconds (170B); 10 milliseconds (180)

. Average Random Track Seek Time:

75 milliseconds. (170B); 35 milliseconds (180)

SUMMARY OF FUNCTIONS OF THE 355 (CONTROL SOFTWARE)

From the DCA/DFE/Device point of view the 355 Control Software shall perform the following functions:

Interpret macro type instructions, received from the 600 system, into sequences of micro (type) commands for the DCA/DFE/Device combination.

Ex: Macro type: Seek, Read, Write, Request status, etc.

- Ex: Micro type: Load External, Store External, Select Channel, Connect.

- Provide sufficient data buffering in 355 memory to eliminate the possibility of a transfer timing error between the 600 system and 355/CIA.

If the control software finds that the total buffer space available is filled and cannot keep up with a given data transfer, it will provide the ability to take a latency and resume the data transfer.

B

B

B

B

2.4

## Honeywell Raw

Г

Rev. B

Page 24

1

2.4 SUMMARY OF FUNCTIONS OF THE 355 (Control Software) (continued)

2) (continued)

Therefore, the Control Software shall not initiate a data transfer sequence to the DCA unless it has buffered (or has buffer space available for) sufficient data for at least one full sector.

3) Data transfers at the 600 level shall not be limited to a length equal to the sector length, but shall only be limited by end of cylinder, encountering alternate and defective tracks, and similar physical constraints.

The Control Software shall initiate data transfer sequences to the DCA equal in length to the sector length. Therefore, if a data transfer from the 600 system exceeds the sector length, the 355 shall be responsible to initiate multiple data transfer sequences to the DCA until the data transfer is complete. The multiple command sequences (of the 355) shall be transparent to the 600.

- 4) The Control Software shall perform a status mapping function to convert status information received from the DCA/DFE/DRIVE into the Common Peripheral Status format.

- 5) The Control Software shall provide a switching matrix function for multiple DCA's (CIA's) connected to the IOM bus.

- 6) Simultaneous data transfers to/from devices are possible only with multiple DCA's (on any one 355 Primary Controller).

The 355 shall not be required to accommodate simultaneous data transfers on more than two (2) DCA's and more than two (2) CIA's; for a total of 4 transfers taking place simultaneously.

If additional CIA's are connected to the 355, the 355 shall treat the excess as switched channels.

## GENERAL CE ELECTRIC

Information Systems Equipment Division Phoenix, Arizona

7)

NUMBER: 43A177862 Rev. B

Cont. on Sh. 26 Sh. No. 25

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

- 2.4 SUMMARY OF FUNCTIONS OF THE 355 (Control Software) (continued)

- B B

- [B]

B

В

8) The Control Software shall process interrupts, and perform status checks of the DCA. The Control Software shall relate status to device (based on information received from the DCA). In addition, the Control Software shall be responsible to return status to the 600 system consistent with the Common Peripheral Interface priority structure for status.

The 355 shall initiate micro sequences to Reserve/Release drives

based on the macro type instructions received from the 600 system. Note that the DFE 2x1 switch (see paragraph 1.1) shall physically

Reserve/Release drives, and the 2xl switch shall remember the drives "reserve" status for later interrogation by the 355 control software.

- 9) The Control Software shall convert the continuous binary seek address, received from the 600, into the Cylinder-Head-Sector format required by the DCA.

- 2.5 SUMMARY OF FUNCTIONS OF THE DCA

- 1) Provide an interface compatible with the 355/IOM Bus. The data interface shall be 36 bits.

- 2) Provide sufficient data buffering to minimize transfer timing errors for a configuration consisting of two CIA's and two DCA's which are transferring data simultaneously.

- 3) The DCA shall respond to the following 355 commands in a manner to be defined in later paragraphs:

Load External

Store External

Connect (Sequence). See paragraph 2.5.1

- 4) The DCA shall communicate with the DFE (and ultimately the drives) across the DFE interface described in paragraph 4.

- 5) The DCA shall control the physical formatting of gaps and sectors on the disc pack (drive) in a format compatible with the IBM 2314 Model Al subsystem.

|        | on System  | ELECTRIC<br>Equipment Division<br>x, Arizona<br>NUMBER: 43A177862<br>Rev. B<br>Cont. on Sh. 27 Sh. No. 26                                                                                                                                                                                                                                                 |

|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TITLE: |            | NEERING PRODUCT SPECIFICATION, PART 1<br>CCE CHANNEL ADAP TER (DCA)                                                                                                                                                                                                                                                                                       |

| 2.5    | SUMM       | MARY OF FUNCTIONS OF THE DCA (continued)                                                                                                                                                                                                                                                                                                                  |

|        | 6)         | The DCA shall contain logic necessary to remember and act upon Key<br>length information and Data length information. Information for this<br>logic may originate from data read from a disc pack, or from the 355                                                                                                                                        |

|        | 7)         | during a Format operation.<br>The DCA shall convert the bit serial data received from the DFE into<br>the 36 bit format required by the 355/IOM Bus. The DCA shall convert<br>the 36 bit data of the 355/IOM bus into the bit serial stream of<br>"clock" and "data" bits required by the DFE (serialization/deserialization                              |

|        | 8)         | Provide miscellaneous control logic for the DFE.                                                                                                                                                                                                                                                                                                          |

|        | 9)         | Provide the "fill" characters and control logic required to write gap<br>areas between sectors and between fields within a sector.                                                                                                                                                                                                                        |

|        | 10)        | Provide Count Field (header) verification for data sectors (cylinder, head, record, track indicator bits, Key length, and Data length).                                                                                                                                                                                                                   |

|        | 11)        | Provide check character generation logic (Write) and comparison checking (Read).                                                                                                                                                                                                                                                                          |

|        | 12)        | Provide a memory address register for transferring data to/from the 355 memory.                                                                                                                                                                                                                                                                           |

|        | 13)        | Provide maintenance (T&D) "wrap around" functions.                                                                                                                                                                                                                                                                                                        |

|        | 14)        | Provide address mark detection and generation logic.                                                                                                                                                                                                                                                                                                      |

|        | 15)        | Provide field identification (Sync byte detection).                                                                                                                                                                                                                                                                                                       |

|        | 16)        | Provide gap timing counters.                                                                                                                                                                                                                                                                                                                              |

|        | 17)        | Detect whether sectors on a discpack have been formatted by an IBM 2314 Model 1 subsystem.                                                                                                                                                                                                                                                                |

| 2.5.1  | DCA        | Data Transfer Techniques                                                                                                                                                                                                                                                                                                                                  |

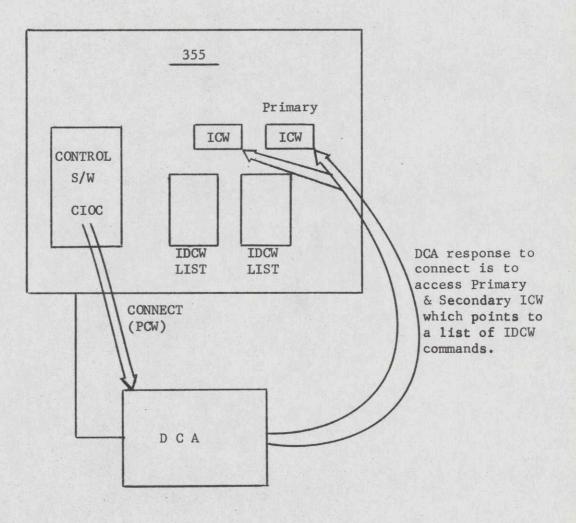

|        | sof<br>wit | order to provide continuous sector-to-sector data transfers, the control<br>tware will not generally handle each sector data transfer separately,<br>th a new "connect" for each. Instead, the software/DCA communication is<br>complished by means of a "list" of data transfer commands (IDCW's) prepared<br>control software, and executed by the DCA. |

## GENERAL SELECTRIC

Information Systems Equipment Division Phoenix, Arizona NUMBER: 43A177862 Rev. B

Cont. on Sh. 28 Sh. No. 27

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

2.5.1 DCA Data Transfer Techniques (continued)

The process is outlined briefly below and discussed in detail in Section 3 of the EPS.

## GENERAL DELECTRIC

NUMBER: 43A177862

Rev. B

#### Cont. on Sh. 29 Sh. No. 28

Information Systems Equipment Division Phoenix, Arizona

B

B

B

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

#### 2.5.1 DCA Data Transfer Techniques (continued)

The data transfer sequence begins by the issuance of a CONNECT to the DCA which causes it to access an ICW (Indirect Control Word) which points to the list of IDCW's. The IDCW is sent to the DCA by the 355/IOM.

The DCA depends on the following 355 and IOM functions for a data transfer operation:

- . The Connect/Peripheral Control Word (PCW) function initiates all data transfer operations.

- . The Indirect Control Word (ICW) function utilizes a list of field oriented DCA commands.

- The Instruction Data Control Word (IDCW) function provides the DCA with the location of data in 355/Memory and specifies the operation to be performed.

Once a data transfer operation has been initiated (by a Connect/PCW), the operation is sustained from field to field by allowing the DCA to access the ICW upon the successful completion of each field IDCW. The DCA shall continue to fetch IDCW's until the DCA is commanded to stop (by an IDCW), or ICW Tally Run Out occurs or some fault has occurred.

Data transfer capabilities are further enhanced by the ability of the control software to switch the DCA to a secondary ICW (which points to a separate list of IDCW's) by setting a switch bit wihtin an IDCW in the list.

B 2.6 SUMMARY OF FUNCTIONS OF THE DFE

The Device File Electronics shall include the following functions, (refer to paragraph 4.0 for further details on the DFE Interface).

- 1) Provide the Data Recovery logic necessary to translate the analog signals of the drives into serial streams of digital data bits and clock bits, for further processing by the DCA.

- 2) Provide the logic necessary to accept serial streams of clock and data bits to be written on the drives.

3) Provide a 2xl crossbar switching function for data and control signals to/from each drive.

#### GENERAL COS ELECTRIC

Information Systems Equipment Division Phoenix, Arizona

#### NUMBER: 43A177862

#### Rev. B

Cont. on Sh. 30 Sh. No. 29

#### TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

#### B 2.6 SUMMARY OF FUNCTIONS OF THE DFE (continued)

- 4) Provide and control both AC and DC power to the drives.

- 5) Provide physical drive status information to the DCA for eventual transmission to the 355.

- 6) Provide the device Reserve/Release function.

- 7) Provide a 5 megacycle clock.

- 8) Provide lines for DFE identification.

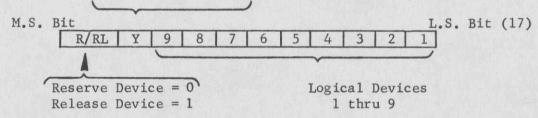

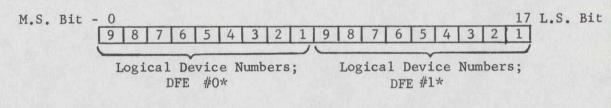

#### 2.7 DEVICE ADDRESSING

B

B

B

B

<u>Channel Number</u> is a 355 Control Software function necessary to select a channel adapter for I/O operations on the 355/IOM Bus. The DCA shall contain a wired "patch" corresponding to the channel number.

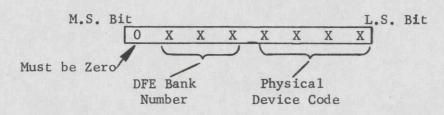

The DFE Bank Number sent to the DCA can only have an address of zero or one even though from 1 to 4 DFE Banks can be present within the subsystem. However, only two DFE's are physically possible on one DCA. The DFE Bank shall have physical addresses within the range 0 thru seven (binary). 355 Control Software shall have the capability to map the 600 system Device Code into the correct DFE bank. Once set, DFE Banks are not expected to change, but any DFE (Bank) address can be connected to any DCA.

The Device Code sent to the DCA shall be converted to the following form by 355 Control Software:

\* NOTE: A bit position designates a logical drive number. Only one drive bit can be set at any one time.

## GENERAL CELECTRIC

Information Systems Equipment Division Phoenix, Arizona

#### NUMBER: 43A177862 Rev. B

#### nev. D

#### Cont. on Sh. 31 Sh. No. 30

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

#### 2.8 DCA BUFFER REQUIREMENTS

#### 2.8.1 DCA/355/IOM Bus Interface Buffer

The DCA shall be required to have buffer storage for a minimum of 6 characters (36 bits) of data for this interface.

These Buffer requirements are based on the following conditions:

- DCA's shall always have the highest priority for data transfers on the 355/IOM/Bus.

- No more than two DCA's shall ever be connected to the 355/IOM Bus.

- No more than two DCA's and two CIA's are permitted to transfer data simultaneously on the 355/IOM Bus.

- Data transfers occur on a Field basis only.

- Data shall be transferred between the DCA and 355 memory on a "direct" by 36 bit basis.

- 355/IOM Bus service delays for a data transfer shall never exceed 13.8 microseconds for any reason.

#### B 2.8.2 DFE/DCA Interface Buffer

During a read operation, the DCA shall be required to convert the bit serial data received from the DFE into 36 bit parallel data for transmission to the 355.

During a write operation, the DCA shall be required to convert 36 bit parallel data received from the 355 into bit serial data for transmission to the DFE.

B

## Honeywell Rev. B

Page 31

#### 2.9 DATA INTEGRITY

F

#### 2.9.1 DCA/355 IOM Interface

The 355/IOM does not contain the logic necessary to transmit the memory parity bit to the DCA, nor does the 355/IOM contain the logic necessary to check parity generated by the DCA. Refer to paragraph 3.1.3.3 for description of DCA parity checking function.

#### 2.9.2 DCA/DFE Interface

Information is transferred between the DCA and the DFE in a bitserial manner. "Burst check" and "Bit count" check bytes are generated by the DCA and written with the data. On subsequent read operations, the DCA regenerates the check bytes based on the data read, and compares them to the check bytes read from the disk.

The check byte algorithm, designed into the DCA for write operations, shall be compatible with the IBM 2314 Model Al subsystem, and shall not cause an error condition to be detected by the IBM 2314 subsystem. The check byte algorithm, designed into the DCA for read operations, shall be compatible with the IBM 2314 Model 1 and Model Al subsystems.

All information fields written on the discpack shall contain check bytes (see paragraph 2.1.1).

#### 2.9.3 Status

Conceptually, status provided by the DCA can be separated into two logical groups:

- . Device oriented conditions.

- . DCA oriented conditions.

- a) Control Software shall be provided with the ability to receive both status groups. Accesses for device oriented status shall require a sequence of 355 LDEX and STEX commands. Control software shall interrogate device oriented status under the following conditions only:

- The DCA is in a static state (not busy). Therefore, 355 Control Software shall be required to remember whether the DCA is "busy" or not.

### GENERAL GE ELECTRIC

Information Systems Equipment Division Phoenix, Arizona

#### NUMBER: 43A177862

#### Rev. B

Cont. on Sh. 33 Sh. No. 32

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

- 2.9.3 Status (continued)

- a) (continued)

- A control software sequence is being executed which does not require a status return within a critical time period.

- b) Upon the termination of a data transfer type operation, the DCA automatically stores information from both status groups at a fixed ("patched") location in 355 memory.

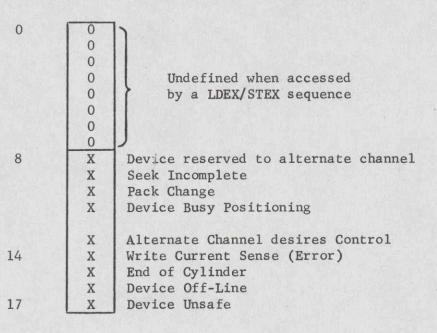

- 2.9.3.1 Device Status Group

The following conditions are reported as device status:

- . Device Unsafe \*\*

- Device Off-Line \*\*

- End of Cylinder \*\*

- . Write Current Sense (error)

- . Alternate Channel desire Control \*\*

- . Device Busy Positioning

- . Pack Change

- . Seek Incomplete

- . Device Reserved to the Alternate Channel

For detailed information concerning these status conditions, refer to paragraph 3.2.7.

\*\* NOTE: These status bits are also supplied during a DCA status service.

2.9.3.2 DCA Status Group

The following conditions are reported as DCA status:

- . Device/DCA exception condition detected.

- . Record Number did not compare\*

### GENERAL ( ELECTRIC

Information Systems Equipment Division Phoenix, Arizona

#### NUMBER: 43A177862

Rev. B

Cont. on Sh. 34 Sh. No. 33

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

- 2.9.3.2 DCA Status Group (continued)

- Count Field did not compare\*.

- . Data length or Key length < Data length or Key length in 355 Memory\*.

- . Connect/LDEX/STEX detected by the DCA while "busy".

- . Check character error (count field).

- . Check character error (key or data fields).

- . ICW address.

- . Transfer timing error (DCA/355 IOM).

- TRO caused terminate.

- Two consecutive index marks detected during a data transfer command.

- . Write current sense error.

- , Data transfer operation in progress at index mark.

- Sync Byte failure.

- Invalid IDCW sequence.

- . Compare error on Key or Data field.

- . End of File Record (Data length = 0).

20410 (CC) detected - discpack was generated on an IBM 2314 Model 1.

- Parity error during list service (IDCW).

- Control Software sync bit.

- SSI Bit Caused interrupt.

For detailed information concerning these status conditions, refer to paragraph 3.2.8.

\* NOTE: These status conditions are possible with the Compare ID (CNC) command only.

B

## Honeywell

Rev. B

Page 34

#### 2.10 OTHER FEATURES

Г

#### 2.10.1 Channel Number Patch

The channel number patch consists of a six-bit field which is switched into the IOM bus when the DCA requests service from the IOM. This field must be capable of being any six-bit code by "patching." This same physical "patch" will be used for both encode and decode in order to reduce the possibility of configuration problems. That is, the IOM will present the same six-bit code when it initiates a sequence to the DCA that the DCA would present when it initiates a sequence.

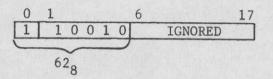

#### 2.10.2 Program Interrupt Level Patches

The DCA will use two interrupt levels, each of which shall be "patchable", allowing the DCA to use 2 of 8 of the highest priority interrupt levels. The  $2^3$  bit shall be a constant "0."

The two interrupt levels shall indicate the following events have occurred:

- A data transfer command has terminated.

- A "gated Attention" condition has occurred (such as seek complete) provided that the DCA is not busy with a data transfer command.

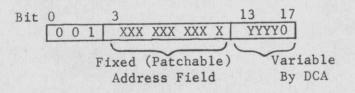

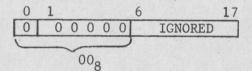

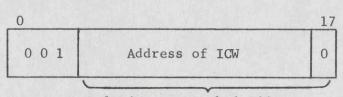

#### 2.10.3 Fixed Memory Address Patch

Each DCA shall require a reserved area of 32 (18 bit) words in 355 memory for its own operational use. (Refer to paragraph 3.3, Memory Map, for further details.) The starting address shall be designated by an address "patch" physically located in the DCA.

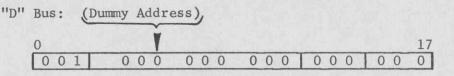

When the DCA executes an operation that requires access to the reserved area, it will access 36 bits at a time using the following address format:

## Honeywell Rev. B

Page 40

٦

1

3.1.3 355/CIOC/PCW/ICW/IDCW (General) (continued)

h) (continued)

An error was detected. The list of IDCW's shall be terminated prematurely. Error status shall be stored in 355/Memory.

Tally Run Out (TRO) was detected by the 355/IOM when it processed the ICW. Error status shall be stored in 355/Memory.

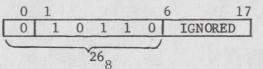

3.1.3.1 Peripheral Control Word Format (PCW):

Information contained in the 36 bit PCW shall conform to the following format:

The DCA shall not alter the contents of the PCW in 355 Memory. Refer to the 355 EPS-1, 43A219608, Revision B, for further details on the CIOC (Connect) instruction and the Peripheral Control Word (PCW).

a) Bit 0 thru 13, bit 15 thru 22, bit 24 thru bit 30, bit 32 and 33; The DCA shall ignore these bits.

Bit 14=1; The DCA shall go to secondary ICW list.

- b) Bit 23 = 1; The DCA shall be forced into the masked state. The DCA shall not initiate any further action. See paragraph 3.1.3.4 for further details on the Masked state.

- c) Bit 23 = 0; This bit is always zero during normal operation. See paragraph 3.1.3.4 for further details on the Masked state.

- Bit 31 = 1; This bit will put the DCA into Format mode when operation is to start with HA.

L

## GENERAL BELECTRIC

Information Systems Equipment Division Phoenix, Arizona NUMBER: 43A177862 Rev. B

Cont. on Sh. 42 Sh. No. 41

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

- 3.1.3.1 Peripheral Control Word Format (PCW) (continued):

- d) <u>Bit 34 = 1</u>; The next command in the List of IDCW's (i.e., the first command in the List) is a Home Address (HA) type command. The DCA shall wait for index mark before attempting to write or read, and shall expect a "Count" type field consisting of 5 bytes of data plus 4 "check" bytes.

- e) <u>Bit 35 = 1</u>; All Read type IDCW's in the list shall transfer 4 extra bytes to 355 memory. These 4 extra bytes consist of the 2 check bytes, the I.C. byte, and the Bit Count byte appended to each Field.

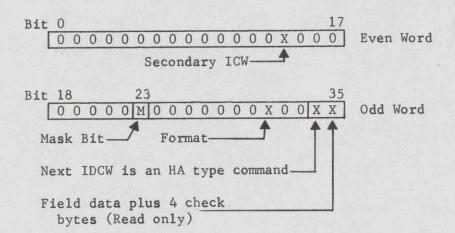

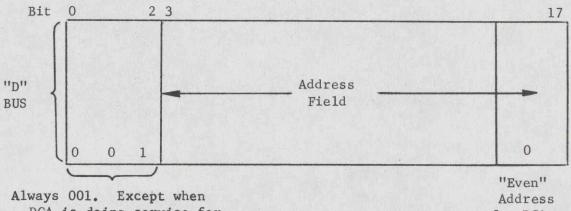

- 3.1.3.2 Indirect Control Word Format (ICW):

Information contained in the 36 bit ICW shall conform to the following format:

Even Word

The contents of the ICW are altered by the IOM each time the ICW is accessed by the DCA. Refer to the GE-355 EPS-1, 43A219608, Rev. B (paragraph 2.3.4.2) for a detailed description of the ICW.

a) Location of ICW's in 355 Memory:

The DCA is capable of accessing either of two ICW's located in 355 memory. The PRIMARY ICW shall be located in locations A + 16 and A + 17. The ALTERNATE ICW shall be located in locations A + 18 and A + 19. (Refer to paragraph 3.3, Memory Map.)

b) ICW Address Switching:

In response to a CONNECT/PCW sequence, the DCA shall access the PRIMARY ICW if bit 14 = 0.

## GENERAL CE ELECTRIC

Information Systems Equipment Division Phoenix, Arizona NUMBER: 43A177862

Rev. B

Cont. on Sh. 43 Sh. No. 42

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1. DEVICE CHANNEL ADAPTER (DCA)

3.1.3.2 Indirect Control Word Format (ICW): (continued)

b) ICW Address Switching: (continued)

The DCA shall be capable of alternating between the PRIMARY ICW and the ALTERNATE ICW. Each IDCW contains an ICW switching bit which commands the DCA to change ICW's. The DCA shall continue to access the new ICW until another ICW switching bit is encountered within a later IDCW in the list.

c) ICW Status Indication:

Status, stored in 355/Memory as the result of an SSI, shall contain a unique bit designating which ICW was accessed for the IDCW just completed.

#### 3.1.3.3 Instruction Data Control Word (IDCW):

Information contained in the 36 bit IDCW shall conform to the following format:

| Bit 0 X<br>X<br>2 X<br>3 A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A                                                                                                                                                                                                                                                                                                   |        | EVEN I<br>Location "B"                                                                                                      | ODD<br>Location "B + 1"                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| A       Address for Data       S         A       in 355 Memory.       26       X       Compare (Subt) on K or D Field.*@         A       A       X       This IDCW; Write=1, Read=0.*         A       X       Idle = 1, Data Transfer = 0.*@         A       29       X       Check Char. Alert override         X       CNC type command @       X         X       Format this Field       X | 2<br>3 | X Stop = 1, Continue = 0<br>X NEXT IDCW; Write = 1, Read=0<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A<br>A | <pre>S Sync Byte for<br/>This Field.<br/>S S S<br/>S S<br/>S S<br/>S S<br/>S S<br/>S S<br/>S S<br/>S S<br/>S S</pre> |

@ See NOTE on following page.

B

## GENERAL BELECTRIC

Information Systems Equipment Division Phoenix, Arizona NUMBER: 43A177862

Rev. B

Cont. on Sh. 44 Sh. No. 43

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

3.1.3.3 Instruction Data Control Word (IDCW): (continued) @ NOTE: These bits must form ODD parity.

\* NOTE: Valid Code combinations for these 3 bits are:

001 = Read from disc, no data transfer.

000 = Read from disc, data transfer.

010 = Write on disc, data transfer.

100 = Compare Data in Key or Data field.

011 = Write on disc, no data transfer.

The undefined codes: 101,110 and 111 will be interpreted as 001,010 and 011 respectively.

The DCA shall not alter the contents of the IDCW in 355 Memory. Each IDCW shall specify an operation to be performed on a single field. Therefore, more than one IDCW shall be required to process a single sector, or multiple sectors.

With the bit structure described in this paragraph, it is possible to build an extensive and extremely versatile set of command codes. Of all the commands possible, only a subset is potentially useful. These commands are described in paragraph 3.4.3.2. However, the DCA <u>shall not</u> test the validity of any op-code, and undefined commands (op-codes) shall have undefined results. The DCA will perform a parity check on the bits specified above.

a) Bit O; Store Status and Interrupt Bit (SSI):

Bit 0 = 1; SSI when this field (IDCW) has been completed.

After processing this field (IDCW), the DCA shall execute an SSI. Status shall be stored at fixed locations A and A + 1 (See paragraph 3.3.1 for status and paragraph 3.3, Memory Map). Termination of the IDCW list is not implied by the SSI bit unless the Stop bit is set also (Bit 1 = 1), or an error is detected. Conversely, if an error is detected, an SSI shall be executed by the DCA whether or not Bit 0 = 1.

The SSI sequence, executed by the DCA, shall be derived from the following IOM functions:

Double Precision data Word (36 bits). SCM - Store Channel in Memory. SXC - Set Interrupt Cell Unconditionally.

Refer to the GE-355 EPS-1, 43A219608, Rev. B., paragraph 4.0, for further requirements and detailed information.

В

B

## GENERAL BELECTRIC

Information Systems Equipment Division Phoenix, Arizona NUMBER: 43A177862 Rev. B

Cont. on Sh. 45 Sh. No. 44

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

- 3.1.3.3 Instruction Data Control Word (IDCW): (continued)

- a) (continued)

- . <u>Bit 0 = 0;</u> An SSI shall not occur unless an error is detected for the Field (IDCW).

- b) Bit 1; Stop/Continue Bit:

- . Bit 1 = 1; Stop:

After processing this field (this IDCW), the DCA shall terminate the data transfer operation. An SSI shall be executed by the DCA.

Bit 1 = 0; Continue:

After processing this field (this IDCW), the DCA shall fetch the next IDCW and continue unless an error has been detected. If bit 0 is set (1), the DCA shall execute an SSI before the next IDCW in the list is fetched.

c) Bit 2; Next IDCW Specifies a Read or Write:

Timing constraints impose the requirement that the DCA initiate head switching (Read to Write, Write to Read) at the earliest opportunity. Head switching (if any) shall take place in the "all ones" switching area of the gap immediately following the Field specified by the IDCW. Head switching shall begin before the next IDCW is requested from the 355/IOM. Control Software shall recognize that successive IDCW's are related by this (bit) function. Refer to paragraph 3.2.8.4, invalid IDCW sequence status for further details.

Bit 2 = 1; Next IDCW specifies a Write Operation:

Upon completion of the field specified by the IDCW, the DCA shall initiate a write operation to the selected device. If the DCA is already in the write mode, no head switching shall take place. The next IDCW must specify a Write Command.

43A177862

## Honeywell

Rev. B

Page 45

7

1

3.1.3.3 Instruction Data Control Word (IDCW): (continued)

c) (continued)

. Bit 2 = 0; Next IDCW specifies a Read Operation:

Upon completion of the field specified by the IDCW, the DCA shall initiate a read operation to the selected device. If the DCA is already in the read mode, no head switching shall take place.

The next IDCW must specify any one of the following commands; Read, Compare Next Count Field (CNC), Idle, or Compare (data in Key or Data Fields).

d) Bits 3 thru 17; Data Address:

These bits specify the even starting location in 355/Memory for data transfer operations.

The DCA shall save this address, but bit 17 shall be ignored. The DCA shall increment the data address by two after each 36 bit memory access. Key length and data length control the length of the data transfer; Refer to paragraph 3.2.9 and 3.2.10.

- e) Bit 18; This is the odd parity bit for command bits 26, 28, 30, 33, 34 & 35.

- f) Bits 19 thru 25; Sync Byte for this Field:

These 7 bits contain the bit configuration of the Sync byte (1-7) preceding the field to be read by the IDCW. Refer to paragraph 2.1.2 for the bit configurations necessary for IBM compatible sync bytes. Write and Format commands ignore these 7 bits. Bit 25 shall be the "least significant" bit.

g) Bits 26 thru 28; Valid/Invalid bit Combinations:

Together, these three bits specify the basic operation to be performed by the DCA.

The following bit combinations shall be valid:

001 specifies that the DCA shall read a field, but data shall not be transferred to 355/Memory. The data address contained in the IDCW shall be ignored by the DCA.

L

## GENERAL CELECTRIC

Information Systems Equipment Division Phoenix, Arizona

#### NUMBER: 43A177862

Rev. B

Cont. on Sh. 47 Sh. No. 46

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

3.1.3.3 Instruction Data Control Word (IDCW): (continued)

B

g) (continued)

000 specifies that the DCA shall read a field. Read commands shall transfer data to 355/Memory starting at the location designated by the IDCW.

However, the Compare Next Count Field (CNC) Command (bit 30 set) is an exception and shall cause the DCA to fetch data from 355/ Memory starting at the location designated by the IDCW.

010 specifies that the DCA shall Write, or Format, a field. Data shall be transferred from 355/Memory starting at the location designated by the IDCW.

<u>Oll</u> and Bit 31 together specify that the DCA shall Write (Format) a field, but the DCA shall require 36 bits of information from 355/Memory specifying Gap Length and Field Length. The DCA shall write zeros in the field. Information shall be transferred from the 355/Memory location designated by the IDCW.

100 specifies that the DCA shall perform a compare operation between data read from the disc and data in 355/ Memory. This comparison operation shall be valid for Key Fields and Data Fields only. The DCA shall implement the compare operation by utilizing the 355/IOM subtract command. In brief, data read from the disc is subtracted (on a 36 bit basis) from data stored in 355/Memory and the result is stored in 355/Memory. Therefore, data in 355/Memory shall be destroyed.

The data comparison shall start at the location designated by the IDCW.

101, 110, 111 specify invalid operations. The DCA shall not check for invalid operations. Therefore, the results of these invalid bit combinations shall be unpredictable.

## Honeywell

Rev. B

Page 47

3.1.3.3 Instruction Data Control Word (IDCW): (continued)

h) Bit 29; Check Character Alert Override:

If bit 29 is set (1), and a check character alert or sync failure is detected, the DCA shall not terminate, but shall request the next IDCW and continue. If the IDCW had the SSI bit set (bit 0 = 1) appropriate status shall be stored in 355/Memory. If the SSI bit was not set, the error status shall not be reset by the next IDCW.

i) Bit 30; Compare Next Count Field (CNC):

If bit 30 is set (1), the IDCW specifies that the DCA shall compare Count or Home Address Field data read from the disk against data stored in 355/Memory. The comparison shall start at the location designated by the IDCW. In performing the comparison, data stored in 355/Memory shall <u>not</u> be altered.

With one exception, the DCA shall automatically assume a field length of 9 bytes (72 data bits). If bit 34 of the PCW is set (1) and the IDCW is the first one requested by the DCA, the DCA shall automatically assume a field length of 5 bytes (40 data bits), implying a Home Address (HA) field.

j) Bit 31; Format This Field:

If bit 31 is set (1), the IDCW specifies that a Format operation shall be performed. The DCA shall request 36 bits of information from 355/Memory defining field length and gap length. The DCA shall remain in the Format mode until index mark is detected. Refer to paragraph 3.4.2.4, Format Operations for further details.

k) Bit 32; Switch ICW's:

The DCA shall provide the ability to alternate between the Primary ICW and the Alternate ICW. If bit 32 is set (1), the DCA shall not switch ICW's until the command specified by the IDCW has been completed. Refer to paragraph 3.1.3.2, ICW, for additional information.

### GENERAL CE ELECTRIC

Information Systems Equipment Division Phoenix, Arizona

#### NUMBER: 43A177862

Rev. B

Cont. on Sh. 49 Sh. No. 48

TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

- 3.1.3.3 Instruction Data Control Word (IDCW): (continued)

- 1) Bit 33, 34, 35; Field Designator Bits:

These three bit positions shall be used to identify the type of field to be processed by the DCA. These bits are mutually exclusive; i.e., only one bit of the three can be set (1) in any IDCW. The DCA shall not provide checking logic to determine if more than one bit is set.

Bit 33 = 1; Count Field Designator Bit:

The DCA shall perform any additional functions peculiar to Count Field processing.

Bit 34 = 1; Key Field Designator Bit:

The DCA shall perform any additional functions peculiar to Key Field processing.

Bit 35 = 1; Data Field Designator Bit:

The DCA shall perform any additional functions peculiar to Data Field processing.

- 3.1.3.4 DCA Masked State:

- a) The selected DCA shall be forced into the masked state by either an IOM fault, or by a one in bit position 23 of the PCW, or an LDEX (00) Initialize command, or a subsystem initialize pulse.

- b) If the Masked bit is set by the PCW, any additional information contained in the PCW shall effectively be ignored. Note that List processing cannot take place and an interrupt to the 355 shall not occur.

- c) Once the Mask Condition is set, the DCA shall be inhibited from initiating any further communication to the 355/IOM. However, the 355 shall be capable of initiating communications to the DCA. That is; the DCA shall accept, and process CONNECT(with mask bit reset), LDEX, and STEX, commands provided the DCA is not in the "Busy" state.

### GENERAL CELECTRIC

Information Systems Equipment Division Phoenix, Arizona NUMBER: 43A177862 Rev. B

Cont. on Sh. 54 Sh. No. 53

#### TITLE: ENGINEERING PRODUCT SPECIFICATION, PART 1 DEVICE CHANNEL ADAPTER (DCA)

#### 3.2 DCA REGISTER FUNCTIONS

- a) Subsequent paragraphs, as a matter of convenience, use the term "register" to describe "storage Like" functions and discrete functional elements. However, DCA hardware shall be designed to provide the functions only, and the term "register" shall not be construed as restricting design to a specific implementation technique.

- b) DCA Register Features:

Unless otherwise noted, all "registers" shall have the following characteristics:

- The register shall have a unique address, and shall be accessable by Control Software.