COMPACT COMPUTER FOR PROCESS CONTROL

SYSTEM

MANUAL

\*Reg. Trademark of General Electric Co.

GE PAG\* 402

COMPACT COMPUTER FOR PROCESS CONTROL

PROCESS COMPUTER BUSINESS SECTION PHOENIX, ARIZONA

# **CONTENTS**

| INTRODUCTION                           |                  |                                       |             |             |                   | . 1                    |

|----------------------------------------|------------------|---------------------------------------|-------------|-------------|-------------------|------------------------|

| THE GE/PAC 4020 CENTRAL PROCESSOR      | •<br>•<br>•<br>• | · · · · · · · · · · · · · · · · · · · |             |             | · ·<br>· ·<br>· · | 3<br>3<br>5<br>7<br>13 |

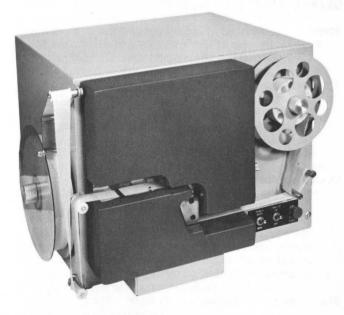

| BULK MEMORY SUBSYSTEMS                 | •                | • •                                   | •           | •           | • •               | 21                     |

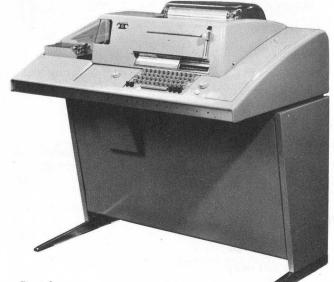

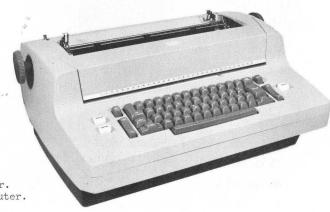

| PROGRAMMER INPUT-OUTPUT DEVICES        | •<br>•<br>•      | · ·                                   | •<br>•<br>• | •<br>•<br>• | ••••              | 23<br>24<br>27<br>28   |

| PROCESS INPUT-OUTPUT SUBSYSTEMS        | •                | · ·                                   | •           | •           | <br>              | 31<br>32               |

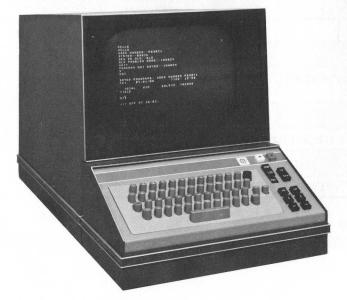

| PROCESS OPERATOR COMMUNICATIONS        |                  |                                       |             |             |                   | 37                     |

| REMOTES                                |                  |                                       |             |             |                   | 39                     |

| POWER AND ENVIRONMENTAL CONSIDERATIONS |                  | • •<br>• •<br>• •                     |             | •<br>•<br>• | • •<br>• •<br>• • | 43<br>43<br>43<br>43   |

| ALPHABETICAL INDEX                     | •                |                                       | •           | •           |                   | 45                     |

## INTRODUCTION

## SCOPE

This manual presents the specifications, internal organization, operation and machine-level programming characteristics of the GE/PAC 4020\* central processor, bulk memories, peripheral devices, remotes and subsystems.

The machine-level programming information is included to help explain how the equipment works, not how it should be programmed. Virtually all the real-time and input-output functions required for process monitoring and control are implemented by calling sequences to the GE/PAC 4020 computer's Real-Time Operating System (RTOS), which differ from the machine-level formats in both scope and detail. This manual will refer to RTOS occasionally, in those situations in which RTOS software substantially enhances or adds to the features wired into the equipment.

For information on how to program the GE/PAC 4020 computer, please refer to the GE/PAC 4020 Programming Manual and to the detailed reference manuals on the languages (FORTRAN, PAL, TASC), operating systems and other useful programs.

## FEATURES OF THE GE/PAC 4020 COMPUTER

Thanks to its monolithic integrated circuits and to its heritage from the GE 412 and the earlier members of the compatible GE/PAC 4000 process computer family, the GE/PAC 4020 computer combines high performance, high reliability, ease of programming and compactness. Its large command repertoire, long word, extensive input-output buffering, realistic process interface arrangements, and excellent safety characteristics offer unparalleled value for a wide variety of real-time applications. These features are aimed at reducing total project cost, not at reducing cost in one area at the expense of another.

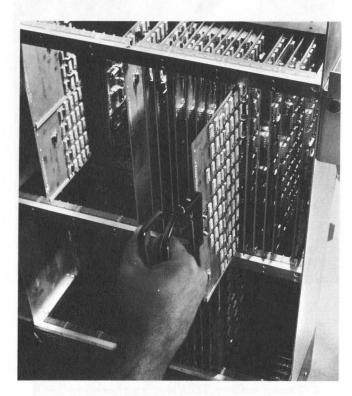

The monolithic integrated circuits used in the GE/PAC 4020 computer reduce the number of active components, connections and wiring by a factor of five, improving system reliability. These circuits also greatly reduce the physical area required for a given function, improving noise rejection characteristics and permitting safe and solid operation at clock frequencies higher than those usable with conventional or hybrid circuits.

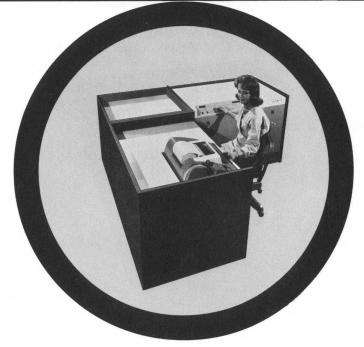

Accompanying the GE/PAC 4020 central processor is a full line of bulk memories, peripheral devices, process-oriented subsystems, and devices for remote communication and control, encompassing many application requirements.

\*Registered Trademark, General Electric Co.

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | JIIIIII.      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | 11 8 2 2      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |               | Contraction of the local division of the loc |

|          | anning the second secon |         |               | anning and a set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1. 10 A |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ,)<br>' |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |               | and the second s |

|          | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | <u>m 47</u> j | 11 IN 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| La a . y | e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | \       | . <u>.</u>    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Related General Electric products include GE/MAC electronic process instrumentation, GE/TAC remote telemetering and supervisory control, GE X-Ray Emission Gages (XEG's) and other special sensors, Directo-Matic II wired-program analog and digital control equipment, GE 400 and 600-series scientific and data processing computer systems, GE datasets and microwave, GE Mark Century numerical control and the full line of GE electrical apparatus. Software for the GE/PAC 4020 computer includes the Process Assembly Language (PAL), GE/PAC Process FORTRAN, the TASC control interpreter, the Real-Time and Free-Time Operating Systems, a full set of mathematical function subroutines, a Direct Digital Control package, numerous other specific application-oriented programs, the AID debugging program, and miscellaneous utility functions.

Unique features of the GE/PAC 4020 central processor include the TIM/TOM automatic inputoutput operations; Quadritect four-level core memory protection; and the use of quasi-instructions to encourage and make more efficient the use of floating-point arithmetic, circular lists, inverse to

memory and other advanced operations. Additional features are its flexible and powerful memory addressing capabilities and both word-logical and bit-logical hardware.

Process-oriented features of special value include automatic prevention of analog scanner and output controller multiple selections, avoiding upsets to processes caused by computer failures; three stall alarms covering a wide range of possible software and hardware problems; over-temperature detection in the cabinetry and on the bulk and working memories; and analog and contact output devices with enough current and power capability to remove the requirement for interposing devices or circuits.

## THE GE/PAC 4020 CENTRAL PROCESSOR

## ORGANIZATION

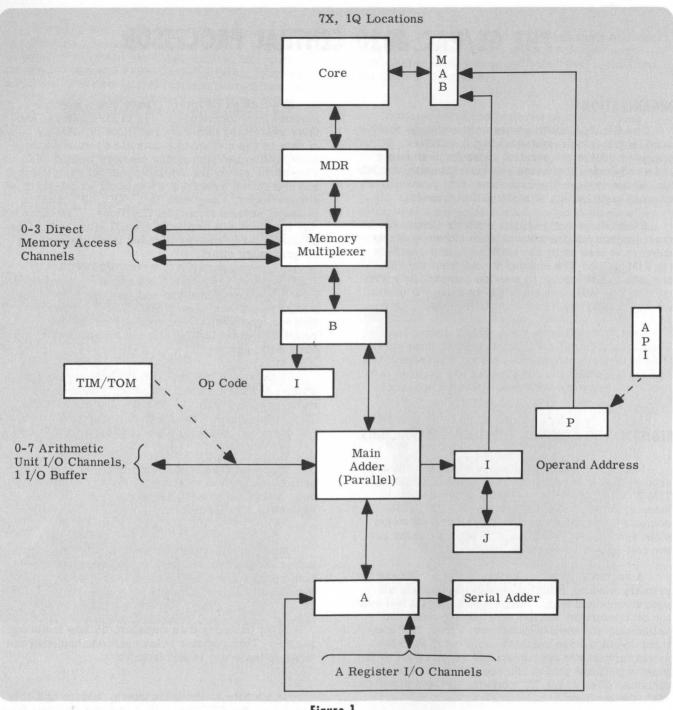

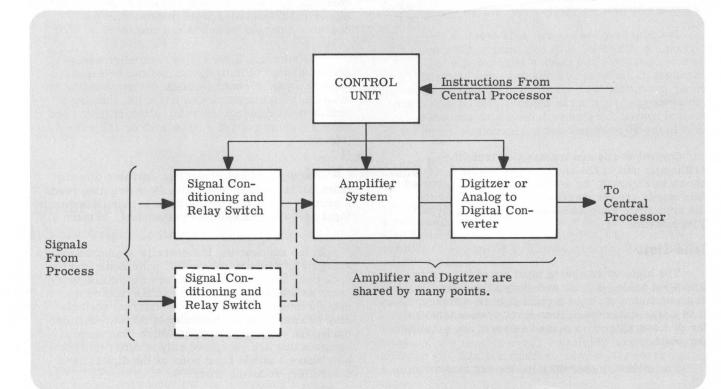

The GE/PAC 4020 computer is a binary, fixed word length, single-address, highly parallel computer utilizing a parallel adder for arithmetic and word-logical functions and a serial adder for bitlogical functions. Figure 1 shows this processor's internal organization in a simplified manner.

Of the three input-output methods shown, the great majority of the work is done either by direct memory access or by the arithmetic unit channels via TIM/TOM. The channel to and from the "A" register exists mainly to provide compatibility with the GE/PAC 4040 computer and to drive the contact sensing subsystem.

Certain functions - primarily indexing and the secondary accumulator ("Q" location) - are performed by a combination of dedicated core locations and special control hardware, but are programmed just as if they were active-component registers.

## **REGISTER AND CONTROL FLIP-FLOP DESCRIPTIONS**

Not counting the registers and other hardware used to implement its automatic program interrupt, TIM/TOM input-output or optional Quadritect memory protection features, the GE/PAC 4020 computer uses seven integrated circuit registers, eight special-purpose dedicated core locations and two full adders in executing programs:

<u>A register</u> (24 bits, including sign). This is the primary working register, involved in nearly all instructions and tests. "A" uses the serial full adder for bit operations and the parallel full adder for arithmetic and word-logical operations. "A" contains one of the two numbers involved in the elemental arithmetic operations and receives all or the most significant part of the result, except for division, after which "A" contains the remainder and "Q", the quotient.

<u>Q location</u> (24 bits, including sign). This special-purpose core location,  $10_8$  in all systems, supplemented by special hardware, acts as an extension of the "A" register during multiplication, division, double-length logical and arithmetic shifts, and double-length load, store, add and subtract operations.

<u>P register</u> (15 bits). This register contains the address from which the next instruction will be fetched. It works in conjunction with the parallel full adder and the "I" register to implement the GE/PAC computer's program control operations. The "P" register can address 32,768 core locations. <u>X locations</u> (15 bits). These seven specialpurpose core locations,  $1 - 7_8$  in all systems, and their associated hardware facilitate processing tables of data by the method of automatic operand address modification and addressing memory beyond 16K. Five of the seven are available without restriction and are stored by software whenever an interrupt is acknowledged, along with "A", "Q", "P", and the states of several important flip-flops. The other two "X" locations are usable in special situations. The unusually large number of index locations reduces programming effort.

<u>I register</u> (25 bits). This register contains the instruction being executed and with the main adder computes and holds the actual, direct operand address (up to 32K) that results from the four primary memory addressing modes and their combinations.

<u>J register</u> (five bits). This register contains the lengths of shift instructions  $(0-31_{10} \text{ places})$  and the count resulting from the bit-counting instructions. The contents of "J" can be transferred into any of the "X" locations by a single instruction, for further use.

<u>B register</u> (24 bits). This register acts as a buffer between the core registers, the arithmetic unit, and various input-output channels. It also assists in "Q" operations.

<u>MAB</u> (memory address buffer, 15 bits). This buffer consists of selection circuits and addresses both operands and instructions stored in up to 32K locations.

<u>MDR</u> (memory data register, 25 bits including parity). This register holds operands and instructions on their way to and from core.

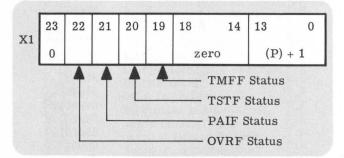

In addition to these registers, adders and core locations, the GE/PAC 4020 computer employs four control flip-flops. The states of these flip-flops are stored in memory during interrupts or subroutine entries by the save place and branch (SPB) instruction and are reloaded by load place and restore (LPR).

<u>Test flip-flop</u> (TSTF). Numerous test instructions set or reset this flip-flop, which then controls the direction of conditional branches. Separating these functions allows very efficient testing and branching in the numerous situations where there are only two possible exits from a series of conditions being tested.

Figure 1 GE/PAC 4020 Computer Simplified Block Diagram

Overflow flip-flop (OVRF). Operations exceeding the capacity of the "A" register cause a carry to propagate into the sign bit position, setting this flip-flop. Examples are all arithmetic operations, whether fixed-point or floating-point, and arithmetic shifts. Floating-point underflow is detected by the floating-point quasi's; the result is replaced by zero.

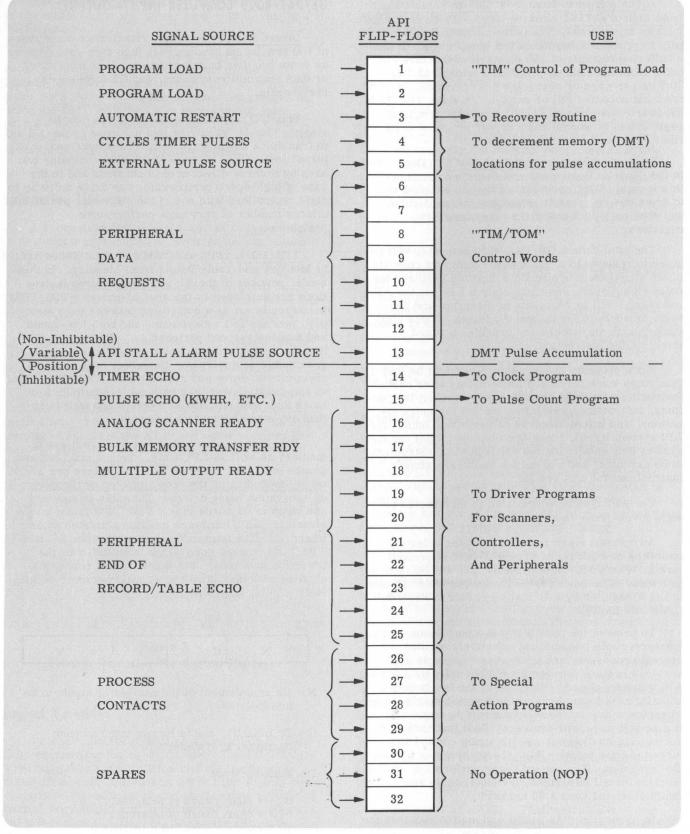

<u>Permit automatic interrupt flip-flop (PAIF)</u>. Actually two flip-flops, this function can permit all the interrupt levels, inhibit just the so-called "inhibitable" interrupts (IAI1), or inhibit all of them (IAI2). The first pulse reaching an inhibited portion of the API system will be stored in its flip-flop, but action will not be taken until a permit automatic interrupt (PAI) instruction enables the system again.

$\frac{\text{Trapping mode flip-flop (TMFF). This enables}}{\text{or disables the GE/PAC 4020 computer's Quadritect}}$  memory protection.

## **CORE MEMORY**

## General Characteristics and Operation

A coincident-current, three-wire magnetic core memory system is used in the GE/PAC 4020 computer, up to a maximum of 32,768 words.

Memory full-cycle time for the GE/PAC 4020 computer is 1.6 microseconds. The memory unit contains its own timing and control to enable external device controllers to share the core memory with the arithmetic unit, thereby reducing overall processing time.

Each word in the core memory contains 24 bits plus a parity bit. The parity circuitry generates an odd parity on the write cycle and checks on the read cycle for an odd total of "1's". The core word is restored as read, whether or not a parity error occurs.

Since 14 bits of each instruction are used for memory addressing, one instruction has direct access to 16,384 core locations and access to any of 32,768 locations by indexing or indirect addressing.

The numerous instructions that do not address memory use this field for microcoded elaborations on their basic operation code, device and channel selection, length of shift, or constants. This last use provides a form of "immediate mode" operation that saves both time and memory.

## **Memory Multiplexer**

This device switches the core memory between the arithmetic unit and three channels to external controllers. The arithmetic unit is given lowest priority because it can always wait for access if necessary. The external controllers drive high data-rate devices such as bulk memories, data links to other computers, data acquisition for telemetering systems, and high-speed peripherals. For highspeed peripherals, up to eight controllers can share a single channel. Each can operate up to four devices, one at a time.

The memory multiplexer operates on a true cycle-stealing basis. Once any of the controllers has made several accesses to core to load its control words, it makes only one access (1.6 us) for each succeeding operation. Even while cycles are being stolen in this manner, the arithmetic unit will continue to execute its current instruction, stopping only when it needs another access to core that cannot be granted at that instant.

Using these three cycle-stealing channels, the GE/PAC 4020 computer can communicate with a large number of high data-rate devices in the most efficient possible manner.

## **Dedicated Addresses**

The following dedicated memory locations are typical of the GE/PAC 4020 computer, if the named function is provided. Also, all are addressable and usable with any GE/PAC command.

| OCTAL                                                    | FUNCTION                                                                                                                                                                                                                                      |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

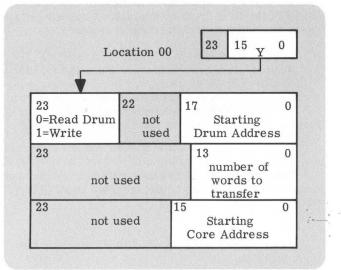

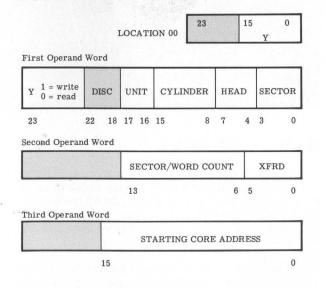

| 00                                                       | Primary bulk storage pointer word                                                                                                                                                                                                             |

| 01<br>07                                                 | Index location words                                                                                                                                                                                                                          |

| 10                                                       | Q location word                                                                                                                                                                                                                               |

| $\left. \begin{array}{c} 11 \\ 17 \end{array} \right\}$  | Additional bulk storage pointer words                                                                                                                                                                                                         |

| 20                                                       | Memory protect error exit location (SPB)                                                                                                                                                                                                      |

| 21                                                       | Memory protect, saved I-register word                                                                                                                                                                                                         |

| 22                                                       | Not dedicated                                                                                                                                                                                                                                 |

| 23                                                       | 11 11                                                                                                                                                                                                                                         |

| 24                                                       | API stall alarm error exit location                                                                                                                                                                                                           |

| 25                                                       | Not dedicated                                                                                                                                                                                                                                 |

| 26                                                       | " "                                                                                                                                                                                                                                           |

| 27                                                       | " "                                                                                                                                                                                                                                           |

| 30                                                       | " "                                                                                                                                                                                                                                           |

| $\left. \begin{array}{c} 31 \\ 37 \end{array} \right\}$  | Common peripheral pointer words                                                                                                                                                                                                               |

| $\left. \begin{array}{c} 40\\ 77\end{array} \right\}$    | Quasi instruction branch vectors                                                                                                                                                                                                              |

| $\left. \begin{array}{c} 100\\ 177 \end{array} \right\}$ | Memory protect status words                                                                                                                                                                                                                   |

| $\left. \begin{array}{c} 200\\ 377 \end{array} \right\}$ | 8 to 128 automatic program interrupt response locations. They may contain:                                                                                                                                                                    |

| (variable)                                               | <ul> <li>(a) Transfers to driver programs<br/>(SPB, BRU)</li> <li>(b) Memory decrement and test<br/>(DMT) for timing, counting</li> <li>(c) Table I/O (TIM/TOM) control<br/>words for input-output</li> <li>(d) No operation (NOP)</li> </ul> |

(d) No operation (NOP)

## **Quadritect Memory Protection**

This optional feature virtually assures that a new program being debugged on-line under the GE/PAC Free-Time System cannot interfere with running process programs, the Real-Time Operating System, the I/O equipment or any other part of the hardware, the software or the process.

Quadritect permits the identification of four possible types of protection for each 64-word block of core memory:

read, execute or write (anything allowable) -- 11

read or execute, but not write -- 01

read or write, but not execute -- 10

inaccessible (nothing allowable) -- 00

The instruction portions of the program being debugged will use as appropriate areas defined as 11 and 01; data portions, 10.

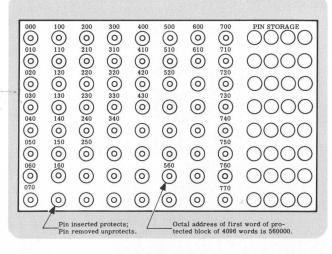

This status information is stored in up to 64 protect status words in core locations  $100 - 177_8$ , each of which gives the status for eight 64-word blocks, or 512 words. Figure 2 shows their layout.

When Quadritect is enabled (by setting the trapping mode flip-flop with a special "OUT" command), special hardware immediately begins examining instruction operation codes and operand addresses and fetching from core into the protect status word register (PSWR) the status word describing the block being referenced. When a reference is attempted to a block not described by the present word, the relevant word is fetched. The status word address register keeps track of which 512-word block is covered by the word presently in the PSWR.

In no case is any instruction in a program being debugged allowed to execute I/O instructions, to prevent errors and conflicts with the Real-Time Operating System (RTOS). I/O calls to RTOS and certain other situations too complex to handle solely by hardware, are trapped, examined by software, and executed only if they reference I/O devices or subsystems specified by the programmer as allowable. This feature, combined with the Quadritect hardware, allows the programmer to check out his program's logic under severe restrictions, then gradually remove constraints as he identifies and corrects errors and progresses toward his goal a correctly running program.

Attempted violations of Quadritect or the software restructions causes a branch to core location  $20_8$ , which in turn transfers control to a diagnostic program. This program then turns off

the offending program and prints out a summary of the attempted violation, to help the programmer diagnose and correct his error.

It is important to realize the Quadritect does require some software, is intended primarily for on-line debugging using the Free-Time System rather than for normal operations, and at any one instant can enforce only one of the four possible types of protection for each core block. If Quadritect were left enabled during normal operations, it could practically protect only those fixed areas (not subject to dynamic relocation) whose selected type of protection applied to all system programs.

In this Quadritect approach, GE offers flexible, in-depth protection useful when protection is really needed — during on-line debugging — rather than offering a modest level of protection active at all times and really adequate at no time.

| MPSW<br>Location       | MPSW Field<br>Bits |       | core Block<br>Protected |  |  |  |  |  |  |

|------------------------|--------------------|-------|-------------------------|--|--|--|--|--|--|

| 1008                   | 1, 0               |       | 0-778                   |  |  |  |  |  |  |

|                        | 4, 3               |       | 100-177                 |  |  |  |  |  |  |

|                        | 7, 6               |       | 200-277                 |  |  |  |  |  |  |

|                        | 10, 9              |       | 300-377                 |  |  |  |  |  |  |

|                        | 13, 12             |       | 400-477                 |  |  |  |  |  |  |

|                        | 16, 15             |       | 500-577                 |  |  |  |  |  |  |

|                        | 19, 18             |       | 600-677                 |  |  |  |  |  |  |

| *                      | 22, 21             |       | 700-777                 |  |  |  |  |  |  |

| 1018                   | 1, 0               | 1     | 000-1077                |  |  |  |  |  |  |

|                        | 4, 3               | 1     | 100-1177                |  |  |  |  |  |  |

| •                      | +                  |       | •                       |  |  |  |  |  |  |

| 23 20 17               | 14 11              | 8     | 5 2 0                   |  |  |  |  |  |  |

| not<br>used protect co | Ddes               |       |                         |  |  |  |  |  |  |

| Protect Code           | Read               | Write | Execute                 |  |  |  |  |  |  |

| 11                     | ~                  | 1     | 1                       |  |  |  |  |  |  |

| 01<br>10               | 1                  | x     | $\checkmark$            |  |  |  |  |  |  |

| 00                     | x                  | x     | X<br>X                  |  |  |  |  |  |  |

Figure 2 Memory Protect Status Words (MPSW)

## **ARITHMETIC UNIT**

## Commands

## **Major Types**

The GE/PAC 4020 computer accepts two types of commands, wired and quasi. The first is executed without further references to memory, except for operands; the second causes an automatic entry and return from a subroutine. This feature saves programming effort, bulk memory and running time, since it allows the GE/PAC 4020 central processor to have a larger and richer command repertoire, to be essentially program-compatible with the earlier GE/PAC 4000 computers, and to offer the programmer such powerful features as circular list processing and floating-point arithmetic.

The total amount of core required for the entire GE/PAC 4020 quasi package is approximately 700 words, which includes floating-point arithmetic. This block of words is included in the 5-6,000 words generally considered as RTOS's core requirement.

The GE/PAC 4020 computer's command repertoire consists of 112 commands -92 wired and 20 quasi's. There are 37 of these which reference memory -21 wired and 16 quasi's - and 60 which represent unique and useful microcoded variations of three of the GE/PAC 4020 computer's 44 primary operation codes. Of the unused operation codes, three -75, 76 and 77 - will cause quasi operation and can be used for special system instructions or macroinstructions.

## Formats

#### Instructions

Although the PAL Assembler takes care of assembling operation codes, addresses and parameters into the following formats, it is occasionally desirable to know them when debugging.

In all the formats, bits 23-18 are either the sole operation code or the primary one. Bits 17-15 specify the index location (if any) whose contents will be added to bits 13-0 of the instruction before execution. While the primary use of this feature is automatic address modification of full operand instructions, it will also produce the stated result when used with other types of instructions.

Bits 14-0 vary in significance depending on the instruction type.

The GE/PAC 4020 central processor's full operand mode references memory either directly or relative to the instruction's location, depending on

whether bit 14 is a zero or a one. The GE/PAC 4020 computer, like the rest of the GE/PAC 4000 series, uses relative addressing for locations within a program and direct addressing for fixed locations outside it. Then, whenever the Real-Time Operating System wants to bring a program from bulk memory into core and run it, RTOS only needs to find an area large enough without regard to its starting address, saving both running time and core. Since the internal memory references are relative to wherever the program happens to be, the program will still run correctly. This feature, called "dynamic relocatability", allows true multiprogramming.

The relative address may be positive or negative, as shown by bit 13. If bit 13 is a one, bits 12-0 contain the two's complement of the relative address.

Certain instructions, such as add constant to A (AKA) use the full operand format but carry their operands with them, in bits 13-0. A form of "immediate mode" addressing, this saves considerable memory and time when it is usable.

The second major format, called GEN 1, covers commands used for bit manipulation of the "A" register. Bits 14-5 are microcoded elaborations on the basic operation code for this format, 05, and bits 4-0 specify the particular bit position desired, counting down from left to right, or specify the length of shift. GEN 1 operations include right shifts, masking, testing, and counting.

GEN 2, distinguished from GEN 1 by its operation code, 25, is used for I/O operations involving the "A" register channels. Bits 14-12 are microcoding; bits 11-0 contain a device number. One instruction selects the device and transfers the data to or from it. A GE/PAC 4020 computer could address up to 2048 devices, if necessary.

GEN 3, 45, handles left shifts of A and left or right shifts of A and Q together. Bits 12-5 are microcoded; bits 4-0 specify the length of shift,  $0-31_{10}$  positions.

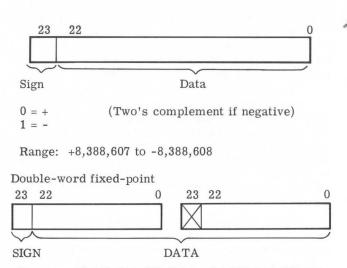

The GE/PAC 4020 computer offers the two formats below for fixed-point arithmetic. The double-word format is seldom necessary and is used mainly for large accumulations.

Multiply develops a 46-bit plus sign product from two 23-bit plus sign factors, and divide develops a 23-bit plus sign quotient and a 23-bit plus sign remainder from a 46-bit plus sign dividend and a 23-bit plus sign divisor.

The fixed-point formats represent negative numbers in two's complement form. The doubleword format ignores the second word's sign bit and uses the sign bit of the first word for the entire number.

|                                      | 23 22 21 20 19 10          | 11 10 13 | 14 15                                                         | 12 11 10 9 8 7 6 5                      | 5 4 3 2 1 0 |  |  |  |  |

|--------------------------------------|----------------------------|----------|---------------------------------------------------------------|-----------------------------------------|-------------|--|--|--|--|

| FULL OPERAND<br>Hardware             | ОР                         | OP X *   |                                                               |                                         |             |  |  |  |  |

| GEN 1                                | 000101                     | x        |                                                               | G                                       | K           |  |  |  |  |

| GEN 2                                | 010101                     | x        | S                                                             | S D                                     |             |  |  |  |  |

| GEN 3                                | 100101                     | x        | G K                                                           |                                         |             |  |  |  |  |

| OP Instruction octa                  | al                         |          | G                                                             | Micro-coded GEN 1 sub                   | command     |  |  |  |  |

| X Index word add                     | ress                       |          | K                                                             | Bit position of A-register or length of |             |  |  |  |  |

| <ul> <li>Relative address</li> </ul> | ssing indicator            |          |                                                               | shift                                   |             |  |  |  |  |

| Y Operand addres                     | ss (a few instructions use | Y        | S                                                             | GEN 2 subcommand                        |             |  |  |  |  |

| as the operand;<br>of the operand)   | others use Y as the add    | D        | I/O device address (bits 9, 10, $11 = 7/$ for high speed I/O) |                                         |             |  |  |  |  |

GE/PAC 4020 Computer Instruction Formats

Single-word fixed-point

Range: +70,368,744,177,633 to -70,368,744,177,664

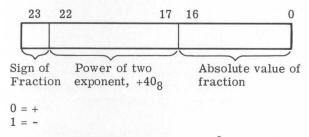

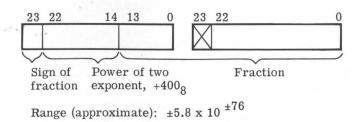

The GE/PAC 4020 computer's floating-point representation uses a sign and absolute value notation for the fractional part (mantissa) and an offset exponent for the characteristic. This is a selfnormalizing floating-point, to preserve maximum precision without extra programming effort.

Two modes of floating-point arithmetic are available. The single-length mode is adequate for the simpler mathematical process and control relationships, since it provides 17 bits of precision, equivalent to about five decimal digits. The doublelength mode is useful for more sophisticated models, linear programs, and other operations involving large matrices and provides about 11 digits. Both modes can be made available in the same central processor, selectable by the floating mode shift (FMS) command, though it remains the programmer's responsibility to use the modes and formats consistently and correctly. Accompanying this quasi package are fix and float conversion commands; they could be used with an FMS to convert between formats, or a new quasi could be written and assigned one of the unused quasi operation codes.

Single-word floating-point

Range (approximate):  $\pm 2.15 \times 10^{\pm 9}$

Double-word floating-point

## **Memory Addressability**

A single full operand instruction can address 16,384 words directly. In systems with more than 16K, direct addressing references the first 16K, in which the Real-Time Operating System subroutines and common data areas are generally found. In the relative mode, the GE/PAC 4020 computer can address any location within +8191 or -8192 locations of the instruction, regardless of memory size.

By using one of its seven index locations as a base address register, or by using its indirect load, store or branch instructions (LDI, STI, LPR), the computer can address any of its maximum 32,384 words of memory. The use of either mode for this purpose is rare, primarily because most instructions either reference locations within their own program (seldom as large as the 16K range available) or locations within the first 16K.

There are also available various interesting combinations of indexing and direct, indirect, relative, and "immediate mode" addressing. In the relative-indexed mode, the relative operation is carried out before the index location's contents are added.

## **Circular** Lists

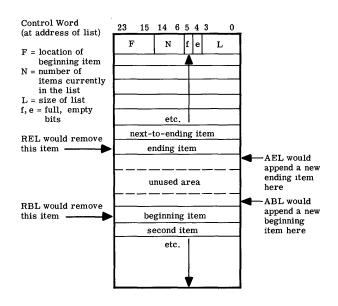

A circular list consists of a set of consecutive items contained within a fixed length block of memory. The first word of the block is a list control word. The size of the list must be a power of two, from one to eight.

Quasi-instructions append additional items to the beginning (ABL) or end (AEL) of the list and remove the beginning (RBL) or ending (REL) items. The address of the beginning and ending items changes as items are added and removed, as does the size of the unused area.

An item, when appended, becomes the new first or last item. The removal of an item forces the adjacent item to become the new beginning or ending item.

These lists are most useful for inter-program communication, since the appending and the removing programs can operate at different speeds and even at different times. Each program must know only the address of the control word. Each program must also incorporate logic to handle the "full" or "empty" conditions, depending on whether it is appending to or removing from the list.

Items processed through a list must either not require identification or must carry it with them; the

usual implicit identification of its contents by an address does not pertain.

Circular Lists

## **Counting and Time Keeping**

Any location in the GE/PAC 4020 computer's core memory can be used for counting external pulses, for maintaining a real-time or elapsed-time clock, or for program loop counting. The decrement memory and test (DMT) instruction, when used as an automatic program interrupt response command, acts as a one-instruction subroutine to accomplish this function.

When a pulse comes in, the DMT decrements a count preset into a designated core location. When the count passes from zero to minus one, the DMT generates an "echo" interrupt that notifies the relevant program to reset the count and take appropriate action.

The total time taken away from the running programs is only 4.8 us per event counted, since none of the AU's contents are disturbed, although some additional time is required to store and reload registers and to run the response program when the count runs down and the "echo" is processed.

Another advantage of this approach is that counts are not lost when the a-c power voltage or frequency goes out of limits, since the core's contents are protected against this contingency.

## GE/PAC 4020 COMPUTER INSTRUCTION SUMMARY

| CODE           | NAME                                                       | EXECUTE TIME                              | REL.     | ESSING<br>INDEX | OCTAL CODE           |

|----------------|------------------------------------------------------------|-------------------------------------------|----------|-----------------|----------------------|

|                |                                                            |                                           |          |                 |                      |

| ABL            | Append Item to Beginning of List                           | *130.0<br>*** 8 5 & 26 5                  | х        | X               | 57x*Y                |

| ABT            | Abort                                                      | 0.0 @ 20.0                                |          | X               | 25x3D                |

| ACT<br>ADD     | Activate Device<br>Add                                     | *** $8.5 \& 26.5$<br>3.2                  | x        | X<br>X          | 25x1D<br>11x*Y       |

| ADO            | Add One to Bit K                                           | 3.2<br>4.7                                | л        | X               | 05x0700K             |

| AEL            | Append Item to End of List                                 | *125.0                                    | х        | X               | 47x*Y                |

| AKA            | Add K to A                                                 | * 6.4                                     |          | x               | 60x0K                |

| ANA            | AND to A                                                   | 3.2                                       | х        | x               | 20x*Y                |

| BRU            | Branch unconditionally                                     | 1.6                                       | х        | х               | 14x*Y                |

| $\mathbf{BTR}$ | Branch if TSTF Reset                                       | 1.6                                       | х        | х               | 30x*Y                |

| BTS            | Branch if TSTF Set                                         | 1.6                                       | Х        | x               | 34x*Y                |

| СВК            | Change Bit                                                 | 4.7                                       |          | Х               | 05x4700K             |

| CLO            | Count Least Significant Ones                               | 4.7                                       |          |                 | 05004137             |

| CLZ            | Count Least Significant Zeros                              | 4.7                                       |          |                 | 05070137             |

| СМО            | Count Most Significant Ones                                | 4.7                                       |          |                 | 05004237             |

| CMZ            | Count Most Significant Zeros                               | 4.7                                       |          |                 | 05070237             |

| CPL            | Complement A                                               | 4.7<br>* 48.8                             | v        | 77              | 05010000<br>51+X     |

| DAD<br>DLA     | Double Add<br>Double Left Arithmetic Shift                 |                                           | х        | X<br>X          | 51x*Y                |

| DLA<br>DLD     |                                                            | 4.8 - 8.0<br>* 25.6                       | х        | X               | 45x0644K<br>41x*Y    |

| DLL            | Double Length Load<br>Double Left Logical Shift            | 4.8 - 8.0                                 | Λ        | X               | 45x0720K             |

| DMT            | Decrement Memory and Test                                  | 4.8                                       | х        | Λ               | 45X0720K<br>060*Y    |

| DRA            | Double Right Arithmetic Shift                              | 4.8 - 8.0                                 | Λ        | х               | 45x0440K             |

| DRC            | Double Right Circular Shift                                | 4.8 - 8.0                                 | <b>`</b> | X               | 45x0530K             |

| DRL            | Double Right Logical Shift                                 | 4.8 - 8.0                                 |          | x               | 45x0430K             |

| DST            | Double Length Store                                        | * 28.8                                    | х        | x               | 63x*Y                |

| DSU            | Double Subtract                                            | * 42.4                                    | х        | X               | 61x*Y                |

| DVD            | Divide                                                     | 13.7                                      | х        | х               | 65x*Y                |

| ERA            | Exclusive ''OR'' to A                                      | 3.2                                       | х        | х               | 10x*Y                |

| FAD            | Floating Add Single/Double                                 | *203.0/295.0                              | Х        | x               | 70x*Y                |

| FDV            | Floating Divide Single/Double                              | *182.0/288.0                              | Х        | x               | 73x*Y                |

| FIX            | Fix Floating Number Single/Double                          | *111.0/112.0                              |          | Х               | 74x0K                |

| FLO            | Float Fixed Number Single/Double                           | *123.0/145.0                              |          | X               | 74x2K                |

| FMP            | Floating Multiply Single/Double                            | *151.0/216.0                              | х        | Х               | 72x*Y                |