# TABLE OF CONTENTS

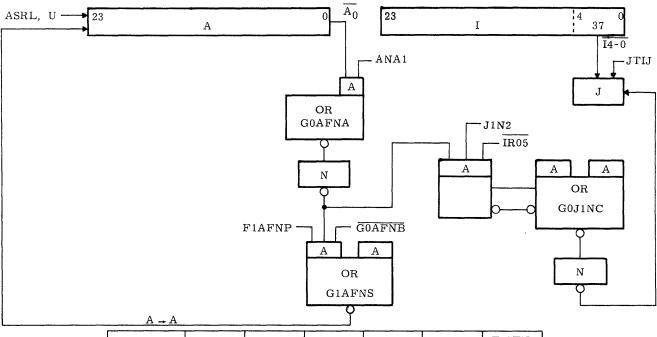

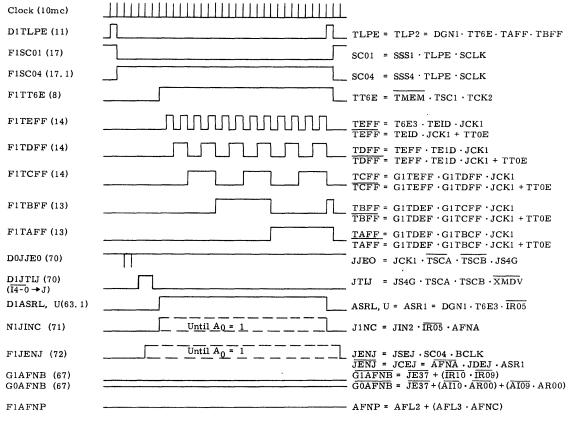

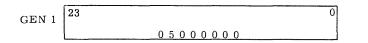

| ARITHMETIC UNIT 4022A               |      | Quasi                                       |

|-------------------------------------|------|---------------------------------------------|

| INTRODUCTION                        | INT  | BASIC TIMING OF FULL OPERAND COMMANDS       |

| SPECIFICATIONS                      |      | Instruction Sequencing                      |

| ARITHMETIC UNIT OPTIONS             |      | Sequence Control State 1                    |

|                                     |      | INDEXING                                    |

| ARITHMETIC UNIT DESCRIPTION         | DESC | RELATIVE ADDRESSING                         |

| A Register (Accumulator)            |      | MEMORY WRAP AROUND                          |

| B Register (Buffer)                 |      | COMMAND DESCRIPTION CONVENTIONS             |

| P Register (Program)                |      | ADD - ADD Z TO A ADD                        |

| J Register (Counter)                |      | ANA - LOGICAL AND TO A ANA                  |

| I Register (Instruction)            |      | BRU - BRANCH UNCONDITIONALLY BRU            |

| Parallel Full Adder                 |      | BTR - BRANCH IF TEST FLIP-FLOP RESET BTR    |

| Q Register (Multiplier/Quotient)    |      | BTS - BRANCH IF TEST FLIP-FLOP SET BTS      |

| Memory Address Buffer               |      | DMT - DECREMENT MEMORY AND TEST DMT         |

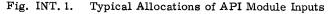

| Automatic Program Interrupt Control |      | DVD - DIVIDE DVD                            |

| Overflow Flip-Flop                  |      | ERA - EXCLUSIVE OR TO A ERA                 |

| Test Flip-Flop                      |      | GEN 1 COMMANDS GN1                          |

| Operators Console                   |      | ADO - Add One To Bit K                      |

| LOGIC SYMBOLS AND NOMENCLATURE      |      | CBK - Change Bit K                          |

| OPTIONS                             | OPT  | CLO - Count Least Significant Ones          |

| MEMORY PROTECT                      |      | CLZ - Count Least Significant Zeros         |

| Protect Status                      |      | CMO - Count Most Significant Ones           |

| Memory Protect Rules                |      | CMZ - Count Most Significant Zeros          |

| Theory of Operation                 |      | CPL - Complement A                          |

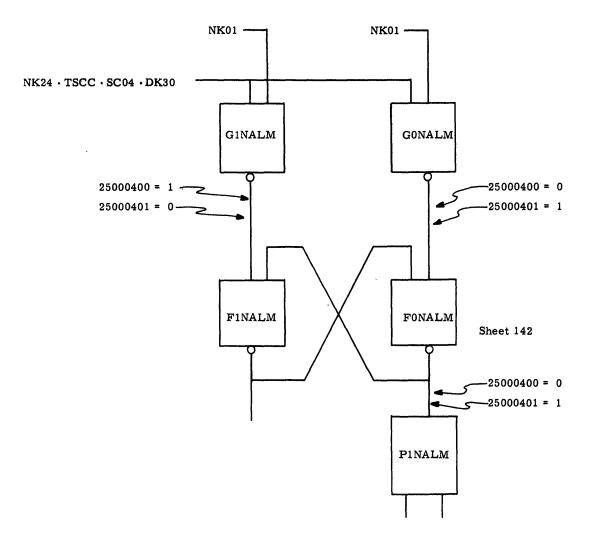

| STALL ALARM                         |      | IBK – Isolate Bit K                         |

| API WATCHDOG                        |      | LBM - Load Bit Mask                         |

| LINE FREQUENCY TIMER                |      | LDO - Load One Into Bit K                   |

| COMPUTER RESTART                    |      | LDZ - Load Zeros Into A                     |

| CONSOLE                             | CON  | LMO – Load Minus One Into A                 |

| INTRODUCTION                        |      | NEG - Negate                                |

| DESCRIPTION                         |      | RBK - Reset Bit K                           |

| Register Select - P, I, B, A        |      | REV - Reset Test Flip-Flop If Bit K is Even |

| Console to A, B                     |      | RNZ - Reset Test Flip-Flop If A Is Non-Zero |

| CLEAR Register                      |      | ROD - Reset Test Flip-Flop If K Is Odd      |

| MANual STEP Operation               |      | RST - Reset The Test Flip-Flop              |

| CONSOLE PROCEDURES                  |      | SBK - Set Bit K                             |

| Load A Bootstrap Routine            |      | SET – Set Test Flip-Flop                    |

|                                     | CND  | SEV – Set Test Flip-Flop If Bit K Is Even   |

|                                     | CMD  | SNZ - Set Test Flip-Flop If A Is Non-Zero   |

| COMMAND FORMATS                     |      | SOD - Set Test Flip-Flop If Bit K Is Odd    |

| Full Operand                        |      | SRA - Shift A Right Arithmetic              |

| GEN 1                               |      |                                             |

| GEN 2                               |      | SRC - Shift Right Circular                  |

| GEN 3                               |      | SRL - Shift Right Logical                   |

| TER - Test Even And Reset Bit K                                        |                               |                                     | ~ 10                          |

|------------------------------------------------------------------------|-------------------------------|-------------------------------------|-------------------------------|

|                                                                        |                               | COMMANDS                            | GN3                           |

| TES - Test Even And Set Bit K                                          |                               | A - (Shift) Double Left Arithmetic  |                               |

| TEV - Test Bit K Even                                                  |                               | L - (Shift) Double Left Logical     |                               |

| TNM - Test Not Minus One                                               | DF                            | A - (Shift) Double Right Arithmetic | :                             |

| TNZ - Test A Non-Zero                                                  | DF                            | C - (Shift) Double Right Circular   |                               |

| TOD - Test Bit K Odd                                                   | DF                            | L - (Shift) Double Right Logical    |                               |

| TOR - Test Odd And Reset Bit K                                         | M                             | AQ - Move A To Q                    |                               |

| TOS - Test Odd And Set Bit K                                           | SL                            | A - Shift Left Arithmetic           |                               |

| TSC - Test And Shift Circular                                          | SL                            | L - Shift Left Logical              |                               |

| TZC - Test Zero And Complement                                         | INDEXI                        | NG ADDRESS MODIFICATION             | INDEX                         |

| TZE - Test A Zero                                                      | INX -                         | INCREMENT X                         | INX                           |

| GEN 2 INPUT/OUTPUT COMMANDS                                            | $_{\rm N2}$ $^{\prime}$ LDA - | LOAD THE A REGISTER                 | LDA                           |

| ABT - Abort Device D's Operation                                       | LDP -                         | LOAD PLACE                          | LDP                           |

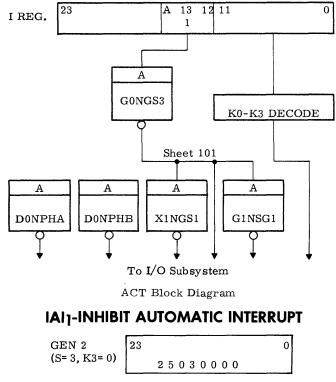

| ACT - Activate Device D's Interrupt                                    | LDQ -                         | LOAD THE Q REGISTER                 | LDQ                           |

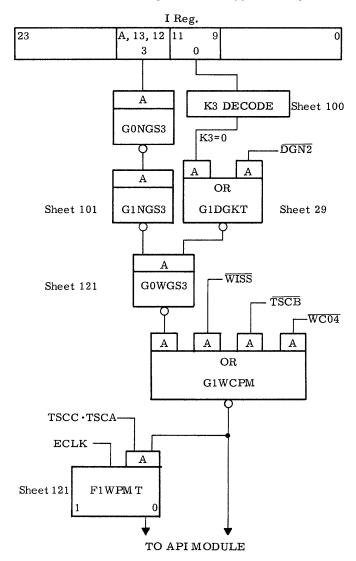

| IAI <sub>1</sub> - Inhibit Automatic Interrupt                         | LDX -                         | LOAD X LOCATION FROM Z              | LDX                           |

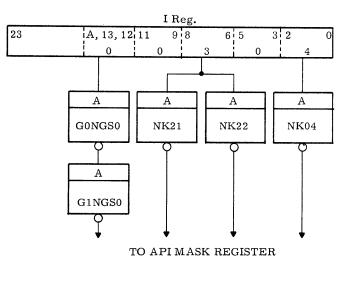

| IAI <sub>2</sub> - Inhibit Automatic Interrupt (Optional)              | LPR -                         | LOAD PLACE AND RESTORE              | LPR                           |

| IN - Input From Device D                                               | LXC -                         | LOAD X WITH COUNT                   | LXC                           |

| JCB - Jump If Channel Busy                                             | LXK -                         | LOAD X WITH K                       | LXK                           |

| * 0                                                                    | MPY '-                        | MULTIPLY                            | MPY                           |

| JDR - Jump If Data Ready                                               | NOP -                         | NO OPERATION                        | NOP                           |

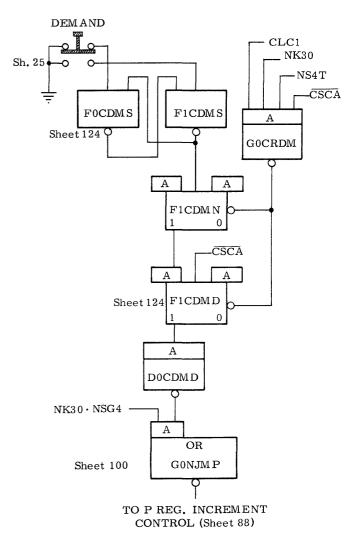

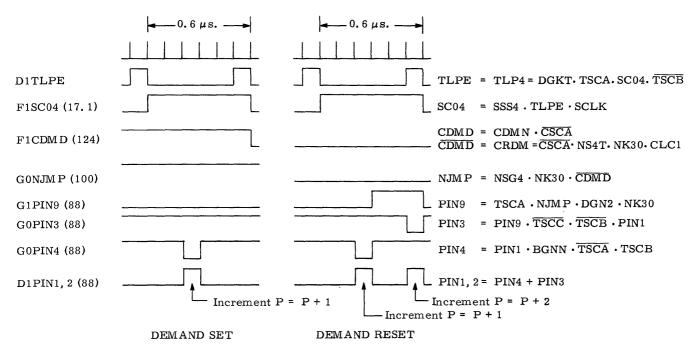

| JND - Jump If No Demand                                                | ORA -                         | LOGICAL OR TO A                     | ORA                           |

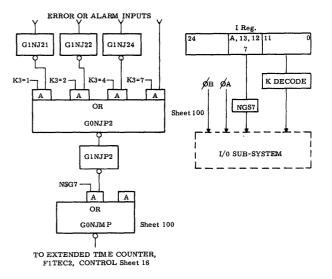

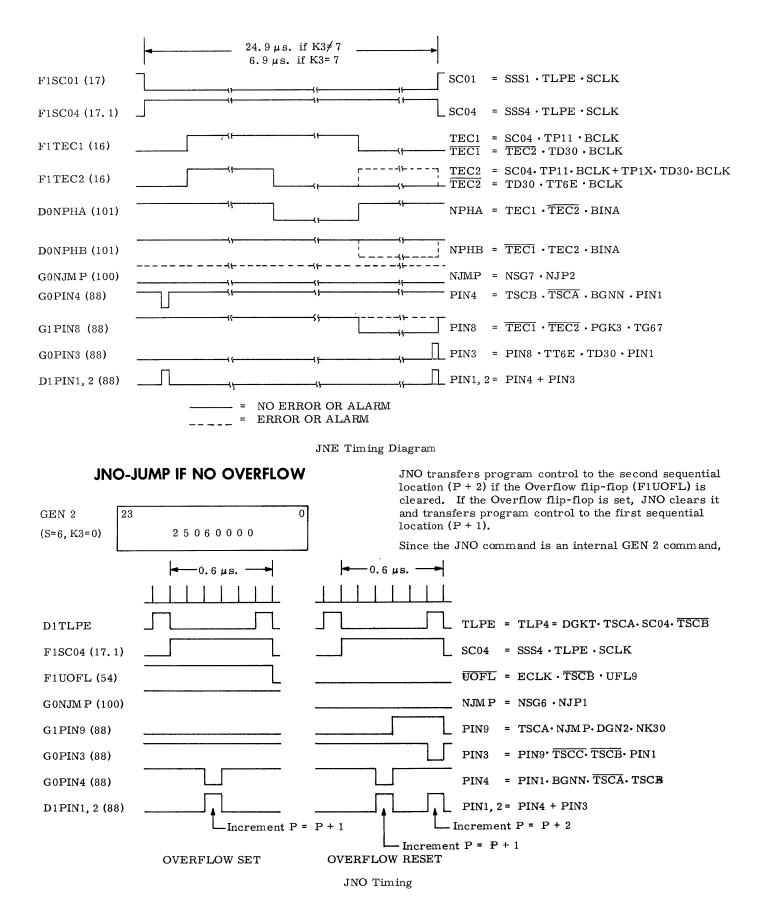

| JNE - Jump If Device D Not In Error                                    | QSI -                         | QUASI COMMANDS                      | QSI                           |

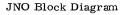

| JNO - Jump If No Overflow                                              | RELATIV                       | E ADDRESSING                        | RLT                           |

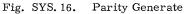

| JNP - Jump If No Parity Error                                          | SPB -                         | SAVE PLACE AND BRANCH               | SPB                           |

| JNR - Jump If Device D Not Ready                                       | STA -                         | STORE CONTENTS OF A                 | STA                           |

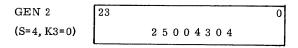

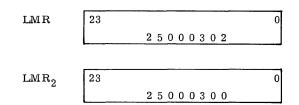

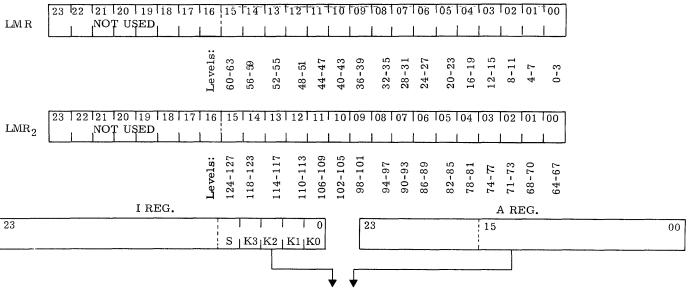

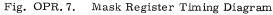

| LMR, LMR <sub>2</sub> - Load Mask Register (Optional)<br>OPR - Operate | STQ -                         | STORE CONTENTS OF Q                 | STQ                           |

| OUT - Output To Device D                                               | STX -                         | STORE X LOCATION INTO Z             | STX                           |

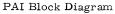

| PAI - Permit Automatic Interrupt                                       | SUB -                         | SUBTRACT Z FROM A                   | SUB                           |

| RCS - Read Console Switches                                            |                               |                                     | TIM/TOM                       |

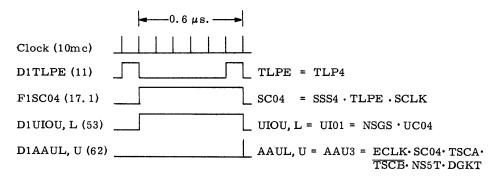

| SEL - Select Device D                                                  |                               | MEMORY/TABLE OUTPUT                 | 1 4 4 9 1 / 1 / 1 / 1 / 1 / 1 |

| SSA - Set Atall Alarm (Optional)                                       |                               | FROM MEMORY                         |                               |

| STM - Select Trapping Mode (Optional)                                  | TXH -                         | TEST X HIGH OR EQUAL                | TXH                           |

| PROGRAMMABLE ALARM                                                     | XEC -                         | EXECUTE                             | XEC                           |

\_\_\_\_\_

## INTRODUCTION

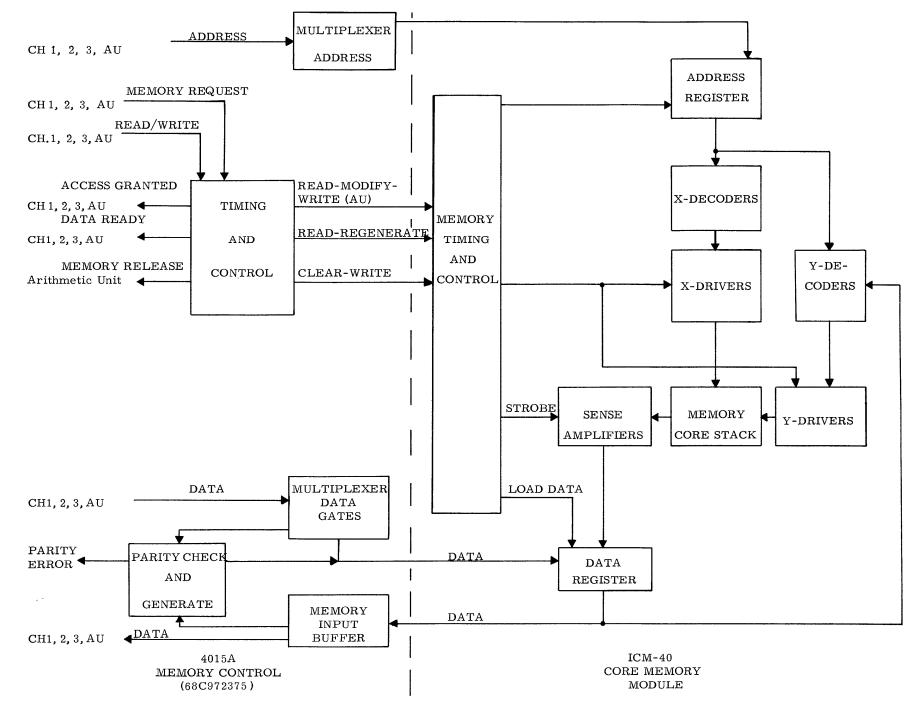

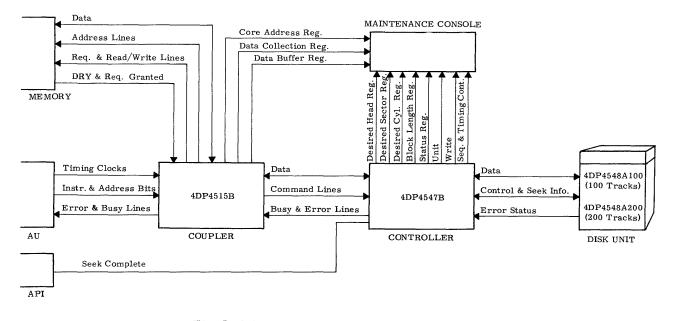

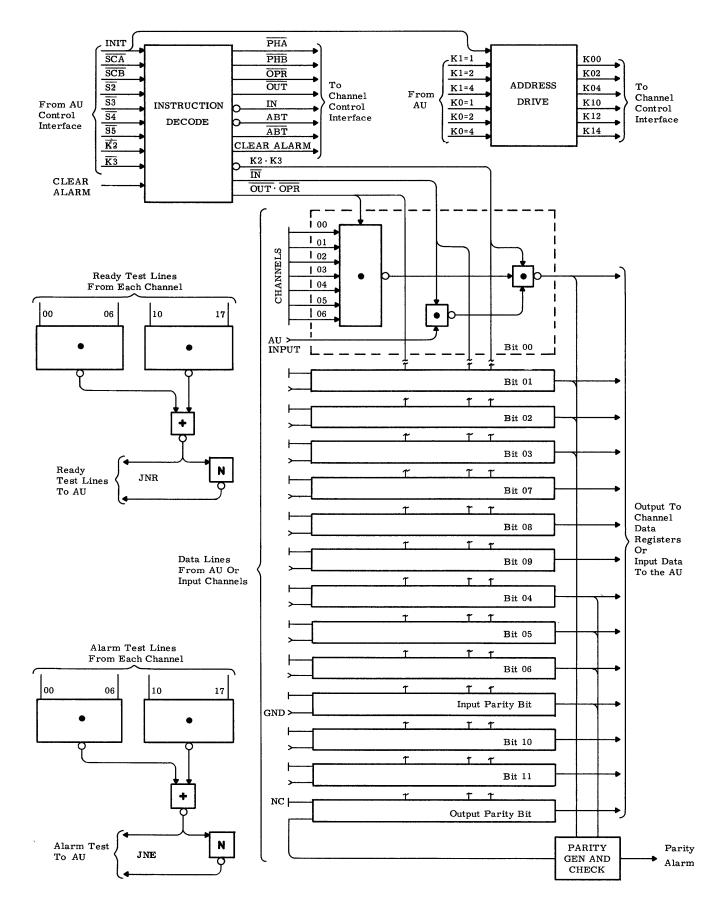

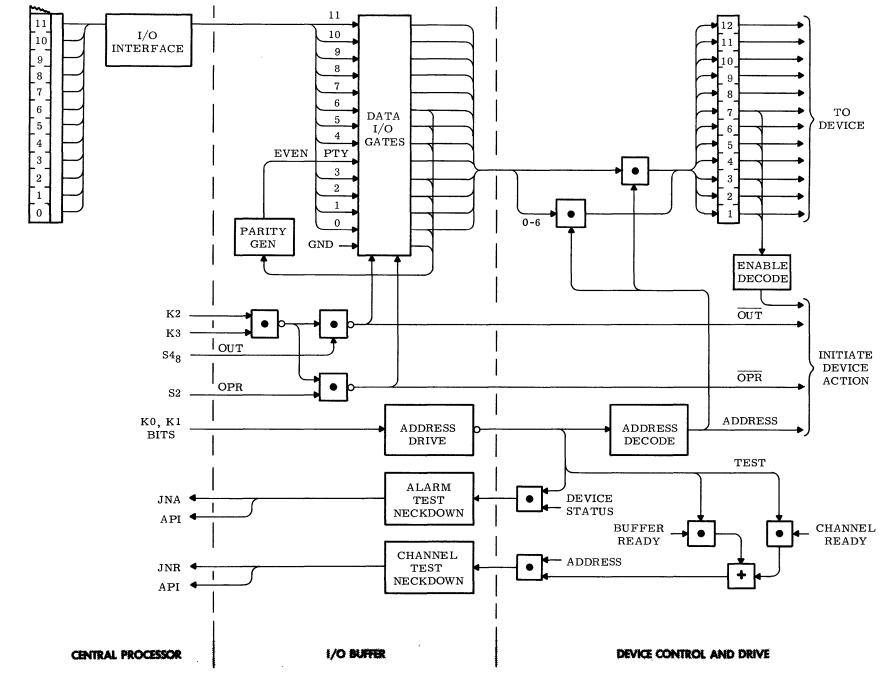

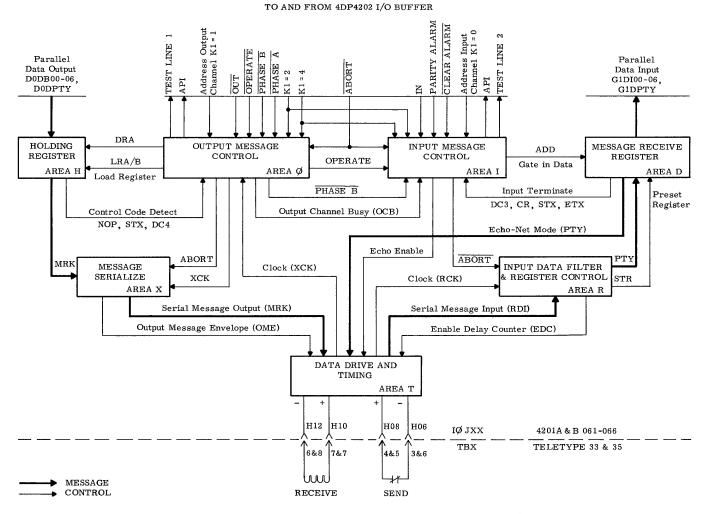

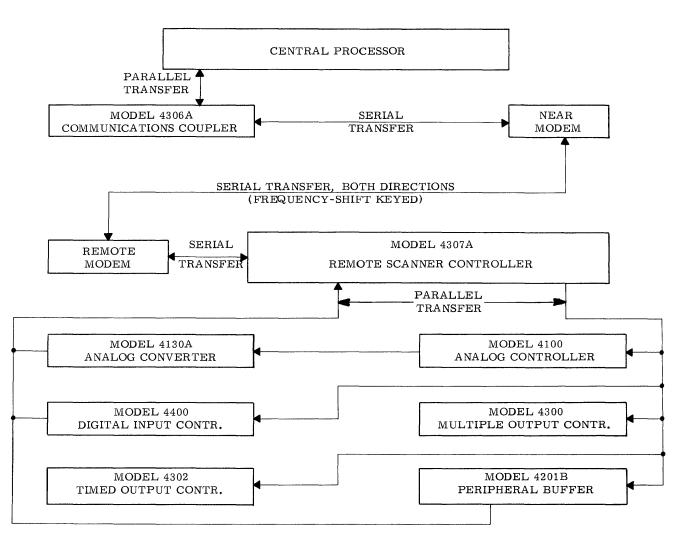

This section describes the functional operation of the GE-PAC\* 4022A Arithmetic Unit (GE Drawing Number 68C972367) which is the computational and control center for the GE-PAC 4020 Central Processing Unit.

The 4022A Arithmetic Unit performs calculations, a wide range of logical operations, and sequences and distributes data throughout the computer system. It supplies and receives information to/from the Core Memory, Automatic Program Interrupt Module, and Input/Output Peripheral Devices.

The Arithmetic Unit addresses sequential programmed commands stored in Core Memory. Each command addressed is transferred from the memory location to the Arithmetic Unit where the command is executed. Since execution of the command may require the transfer of data to or from one of the other modules of the system, the Arithmetic Unit becomes the communications hub of the system.

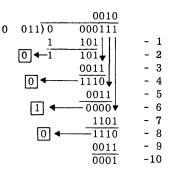

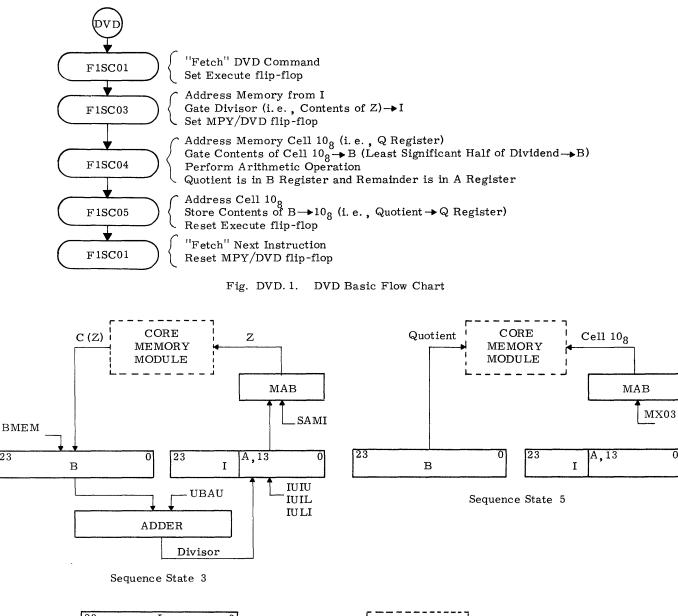

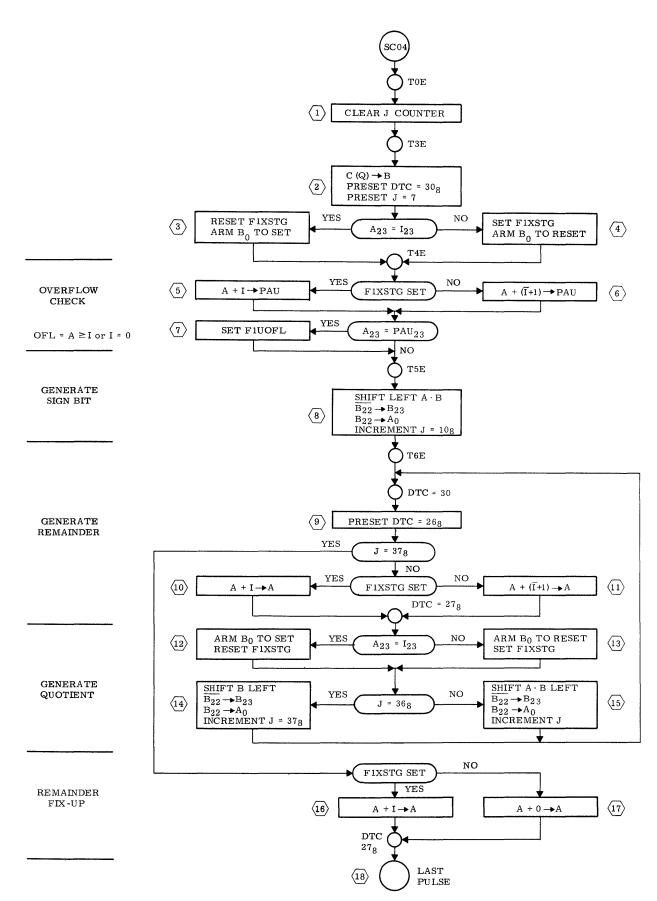

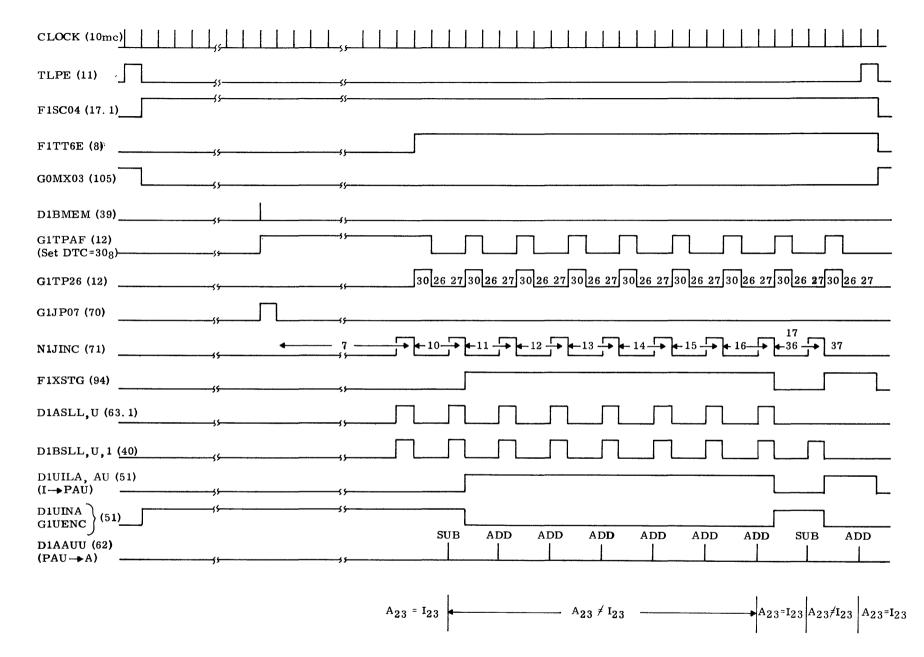

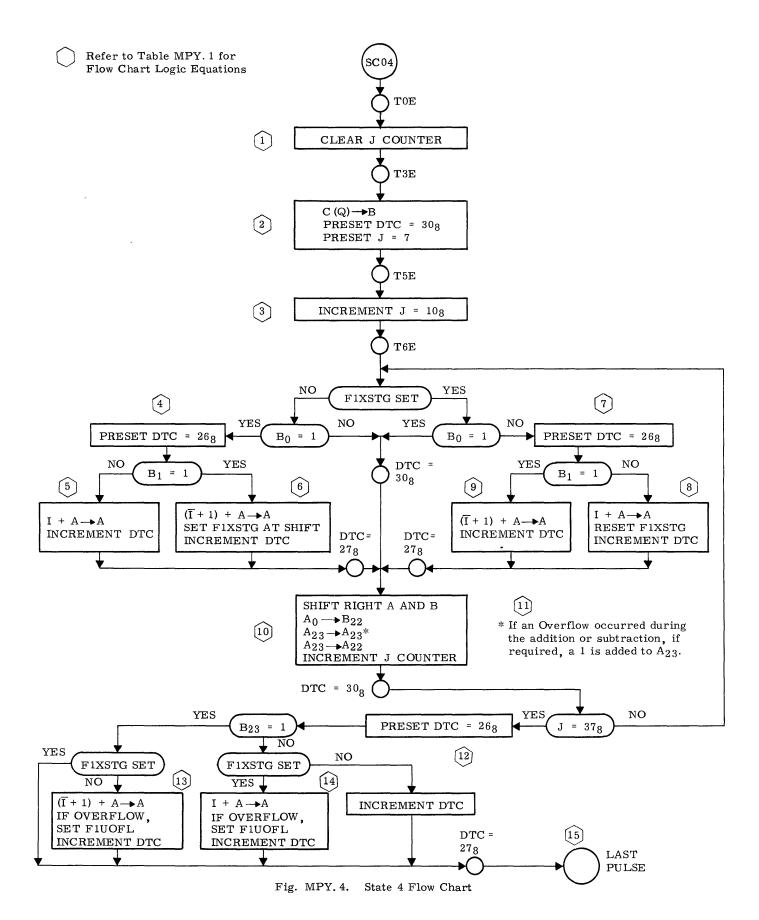

The arithmetic operations performed by the Arithmetic Unit include Add, Subtract, Multiply, and Divide. Addition and Subtraction are performed in 3.2 microseconds, while Multiply requires between 8.9 and 12.1 microseconds and Divide requires 13.6 microseconds. Add and Subtract use single length 24-bit numbers. Multiply operates on two 24-bit numbers to produce a double length (46 bits plus sign) product. Divide operates on a double length dividend and a single length divisor to produce a single length (23 bits plus sign) quotient and a single length remainder.

#### **SPECIFICATIONS**

- Electrical Requirements

- Voltage: 115/230 ±10%

- Phase: Single

- Frequency: 50 or 60 cps  $\pm 3\%$

Central Processor Power: 5.8 KW Maximum.

Environment

Temperature: 32° - 131°F Relative Humidity: 5 - 95%.

- Circuit Type Monolithic Integrated.

- Man/Machine Communication

Programming and Maintenance Console.

• Basic Clock Frequency

10 Megacycles

Pulse Width - 25 nanoseconds  $\pm 10\%$ .

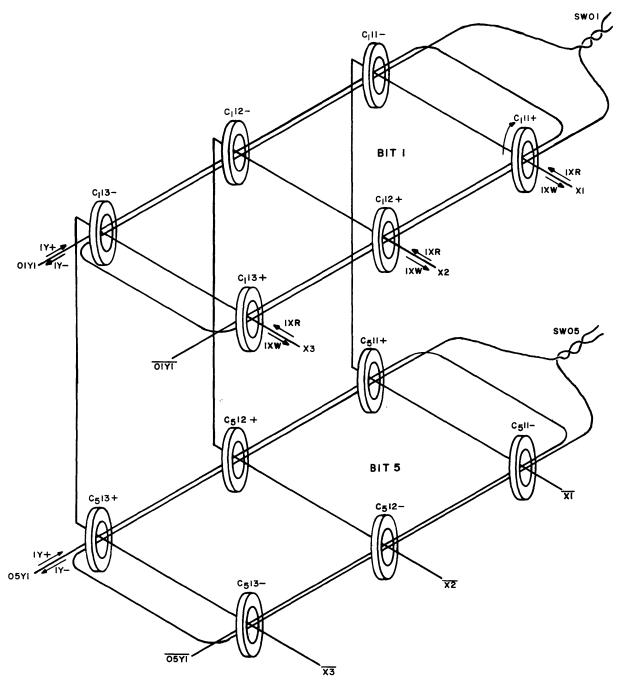

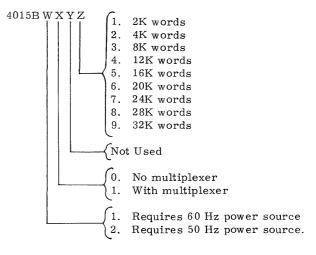

• Addressable Core Memory

4096 locations minimum, 32,768 locations maximum; directly 16,384, relative ( $\pm$  8K) and indexing to 32,768.

• Operation

Parallel and serial internal; parallel external.

• Arithmetic

Digital, binary, fixed point, and 2's complement; floating point by subroutine.

• Word Size

24-bits (23 through 00); bit 23 is sign and most significant bit.

• Index Words

Total of 7 words; 5 are unrestricted and 2 (1 and 2) are restricted by Quasi and sub-routine linkage.

### **ARITHMETIC UNIT OPTIONS**

The GE-PAC 4022A Arithmetic Unit may contain, as options, Memory Protect, Expanded Console, TIM/ TOM, Program Load, I/O Capability (future), and Stall/ Watchdog/Timer. These options are described under the mnemonic OPT in this section. The options for a particular system are contained in a special drawing for each system titled "Option List". The model numbers for each of the above options are listed below:

| Basic Arithmetic Unit                 | - | 4DP4022A0100  |

|---------------------------------------|---|---------------|

| Memory Protect Option                 | - | 4DP4022A0001  |

| TIM/TOM Option                        | - | 4DP4022A0002  |

| Console Option                        | - | 4DP4022A0003  |

| Program Load Option                   | - | 4DP4022A0004  |

| I/O Capability (future)               | - | 4DP4022A0005  |

| Stall Alarm/Timer/<br>Watchdog Option | - | 4DP4022A0006. |

\* Registered Trademark of General Electric Company

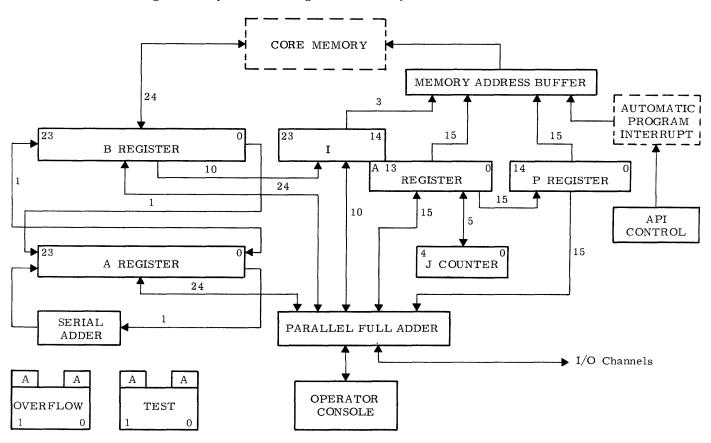

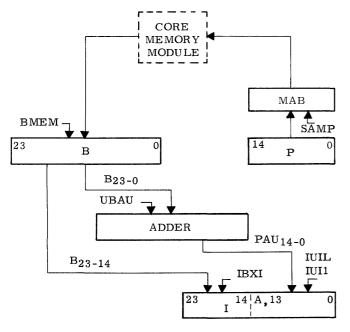

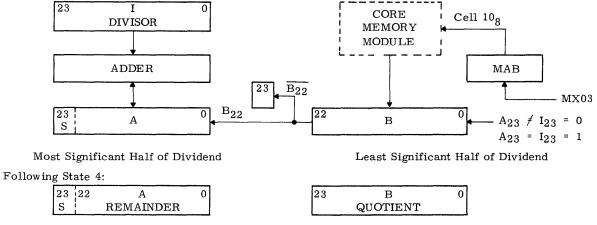

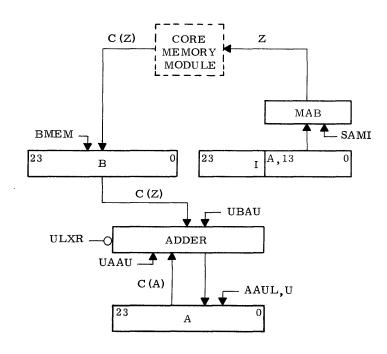

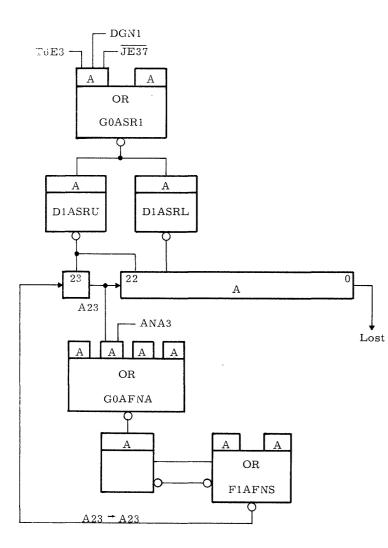

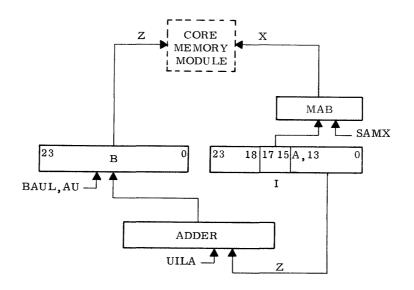

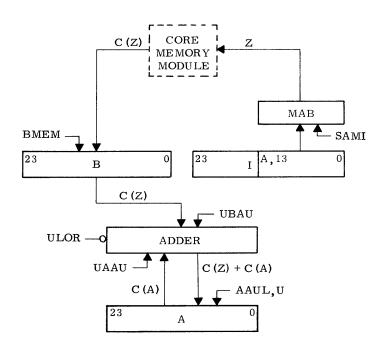

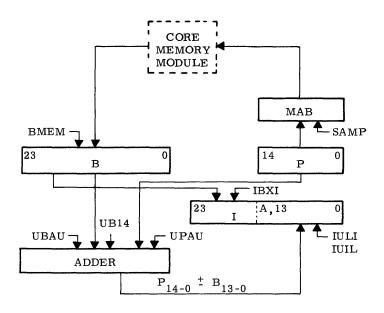

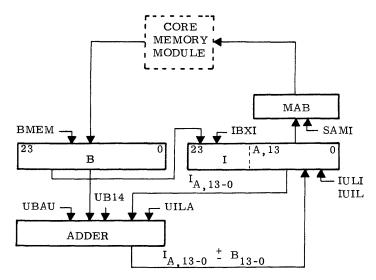

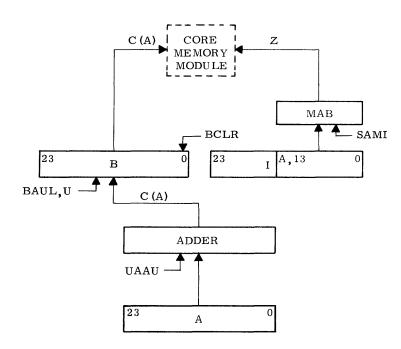

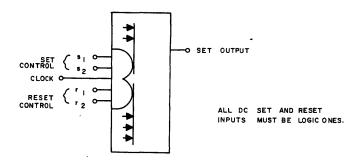

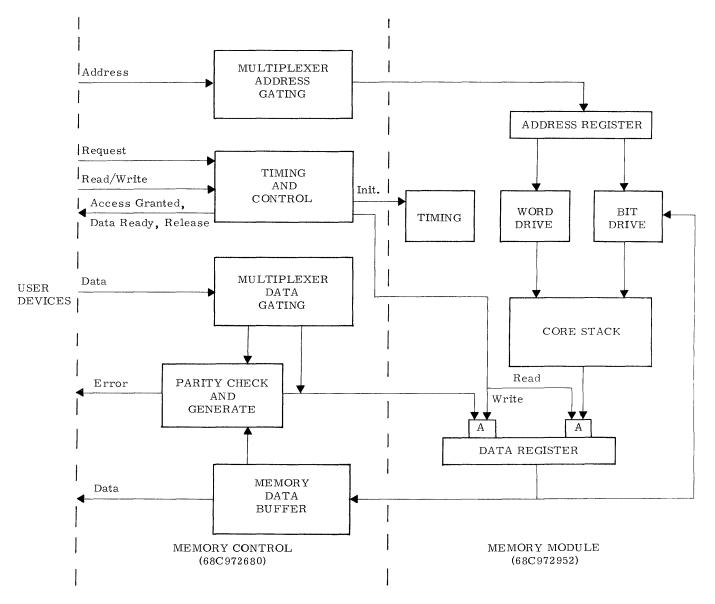

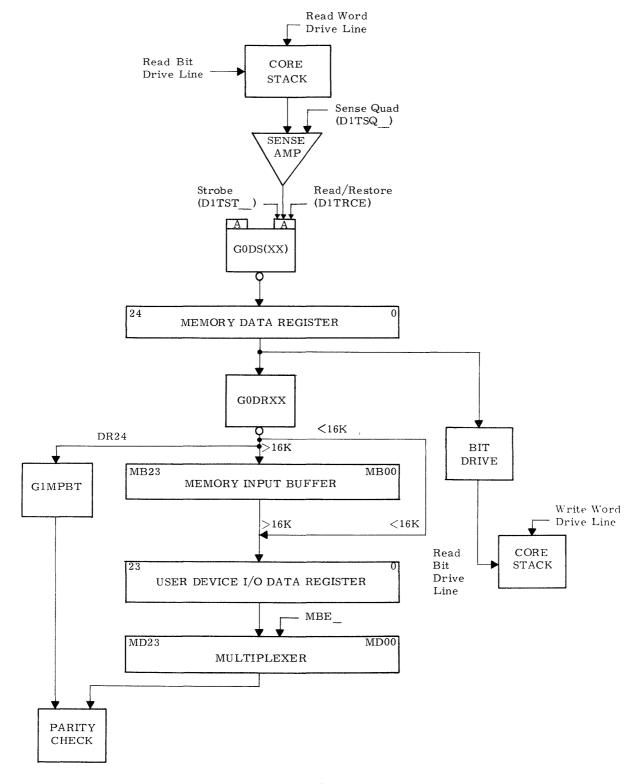

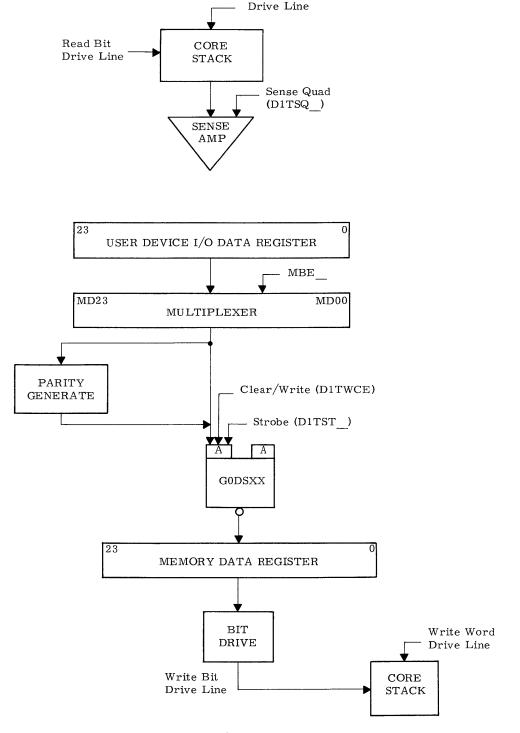

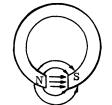

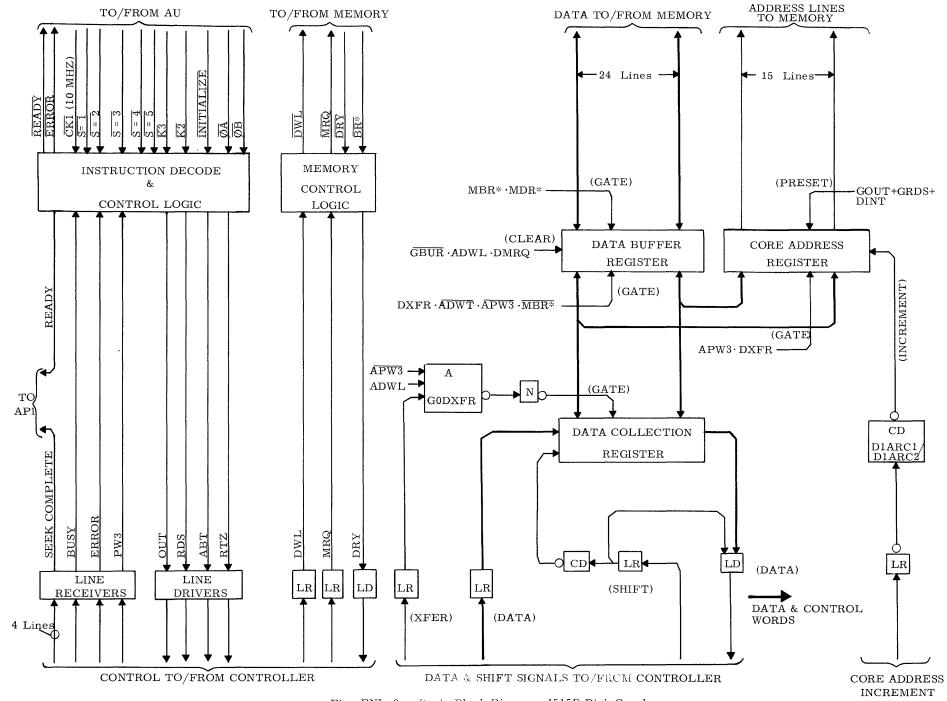

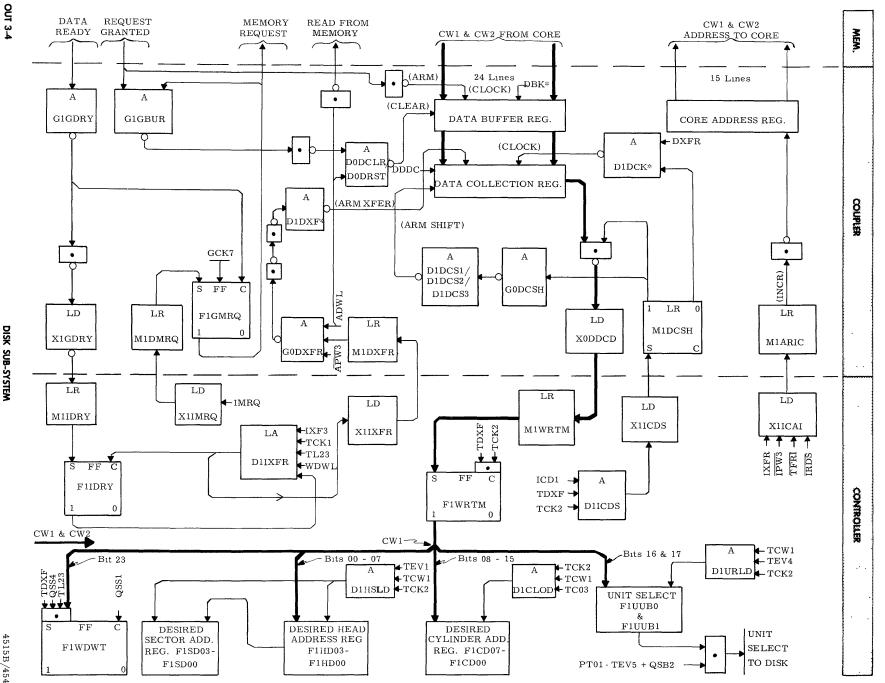

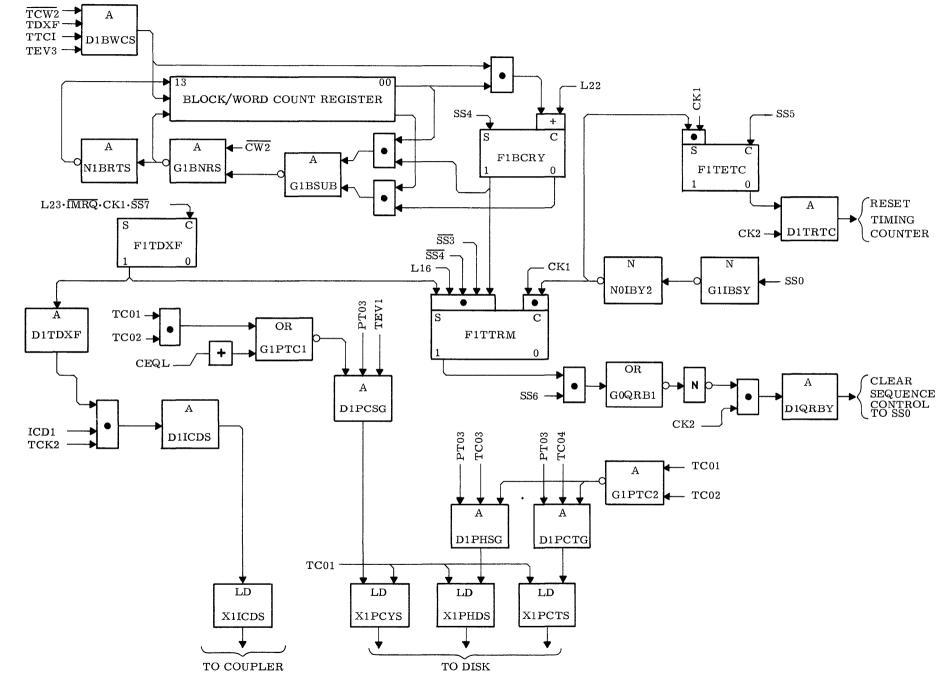

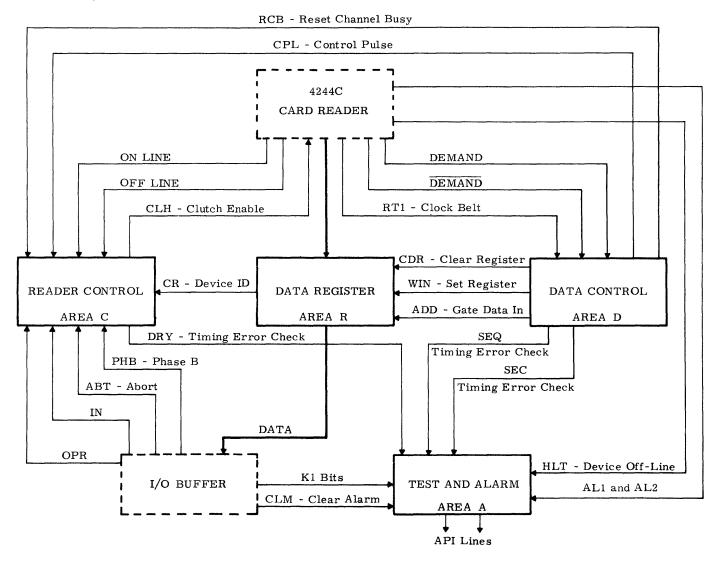

The following discussion describes the functional block diagram of the 4022A Arithmetic Unit. Fig. DESC. 1 contains a block diagram of the Arithmetic Unit illustrating the interconnection of the various registers, parallel adder unit, serial adder, and the associated core memory module. This diagram does not attempt to define timing, sequencing, or control organization.

#### A Register (Accumulator)

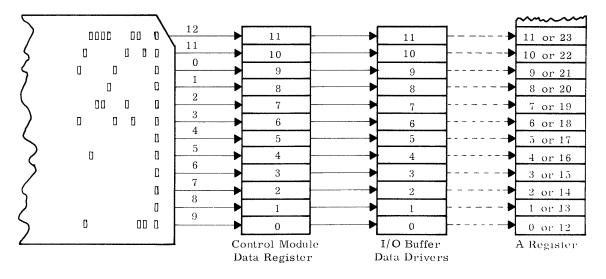

The A Register is the accumulator for arithmetic and bit manipulation operation and temporary storage for data coming from or going to the registers of the I/O equipment. It is comprised of 24 high-speed flip-flops in a bit configuration numbered 00-23 with bit 23 being the most significant.

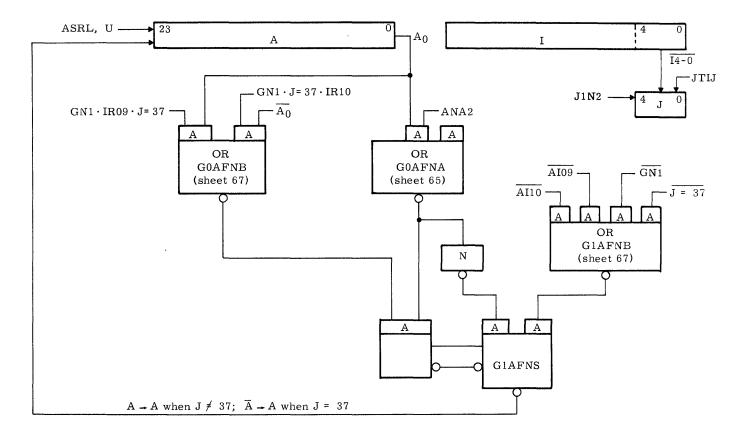

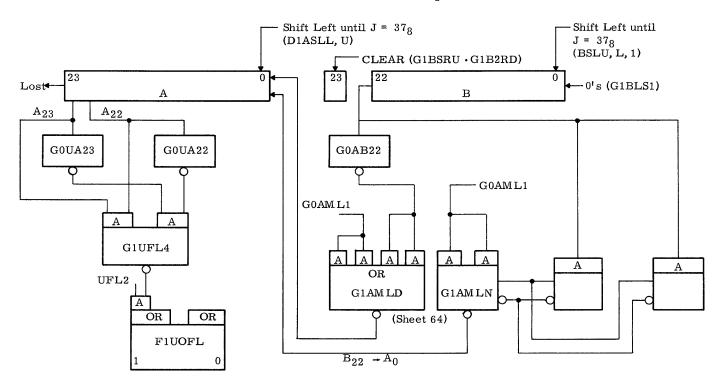

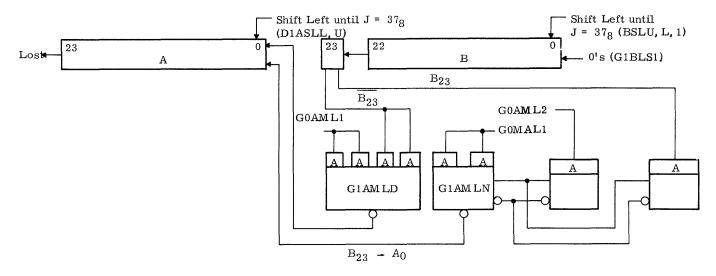

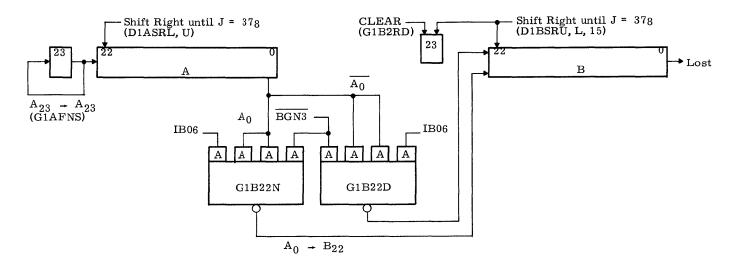

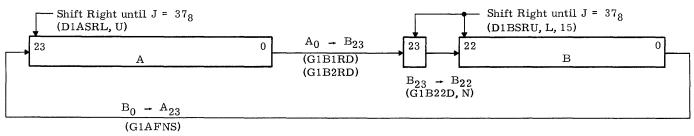

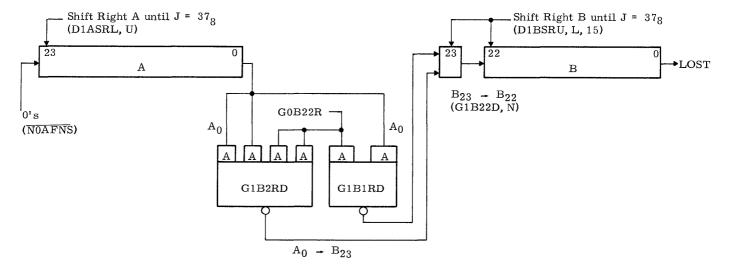

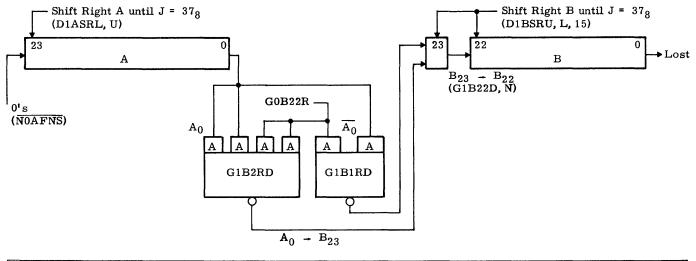

The A Register may be shifted right or left via the micro-coded GEN 1 command. However, the left shift (when using GEN 1) is accomplished by shifting right. A true left shift may be accomplished with a GEN 3 instruction where data from either B23 or B22 enters A0 and is shifted left. On a typical right shift, A0 passes through the serial full adder (where it may be altered) and back into A23. Position A23 may also enter the serial full adder, possibly modified, and routed back to A23 and at the same shift A23 may be applied to A22.

When A is shifted left, bit position 23 is lost. The contents of the A and B Registers may be shifted right where the contents of  $A_0$  enter either  $B_{23}$  or  $B_{22}$  as specified by the shift instruction.

The contents of the A Register may be gated in parallel to the Parallel Full Adder and the A Register may receive data in parallel from the Adder. The contents of A may be selectively displayed on the optional console.

### **B** Register (Buffer)

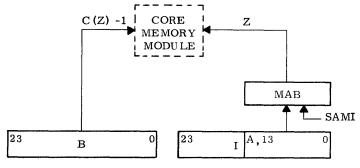

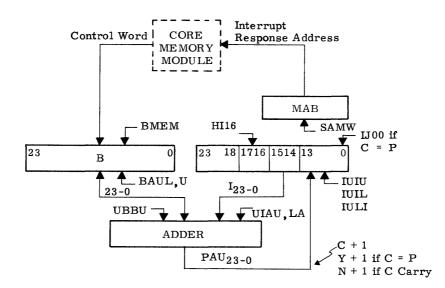

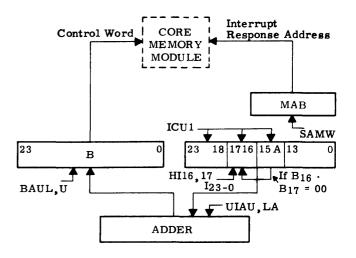

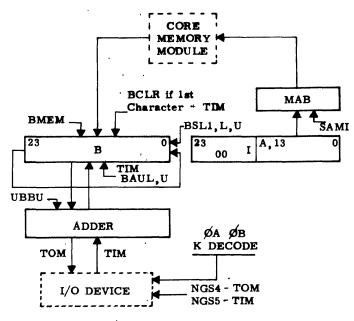

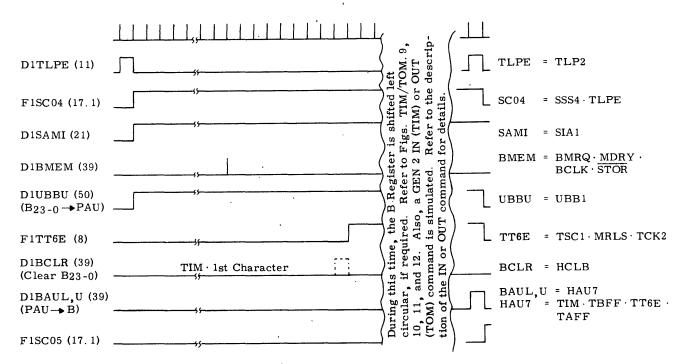

The B Register is a 24-bit register used to hold all instructions and AU data going to or coming from core memory. During the fetch portion of an instruction, the 10 most significant bits of the B Register are transferred in parallel to the I Register for decoding. The contents of the B Register are routed in parallel to the Parallel Full Adder in two fields: B13-0 for address modification, and B23-0 for full register operations. The contents of the Parallel Full Adder may be routed to the B Register in parallel.

The B Register may act as an extension to the A Register when performing right and left shifts (MPY, DVD, GEN 3, TIM/TOM). During a left shift, the contents of either B23 or B22 as specified by the instruction, enter position A<sub>0</sub> of the A Register. During a right shift, the contents of A<sub>0</sub> enter either B23 or B22 as specified by the instruction. The contents of B may be displayed on the optional console.

Fig. DESC. 1. GE/PAC 4022A Arithemtic Unit Block Diagram

#### ARITHMETIC UNIT

#### P Register (Program)

The P Register is a 15-bit binary counter register whose primary function is to control the addressing of the next instruction. Depending upon the instruction being executed, the P Register may be incremented by one or two. Information from the I Register (address) is transferred to the P Register during the operation of Branch commands. The contents of P may be selectively displayed on the console.

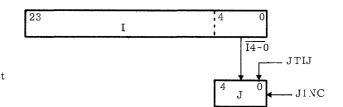

#### J Register (Counter)

The J Register is a 5-bit binary counter used to count shifts when executing shift instructions. Incrementation of J is controlled by the micro-coded GEN 1, GEN 3 instructions or Multiply, Divide, or TIM/TOM. The contents of J may be transferred to the I Register or the complement of the 5 least significant bits of I may be transferred to J. The contents of J are displayed on the optional console.

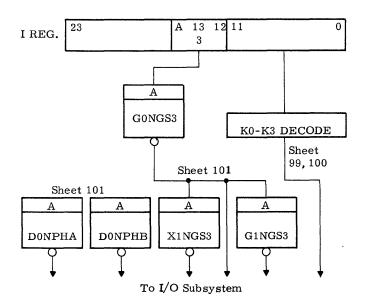

#### **I Register (Instruction)**

The I Register is a 24-bit register used to hold the instruction while it is being decoded, interpreted, and executed. An additional bit (14) position is used in the I Register to provide for relative addressing. In addition to holding the instruction to be executed, the I Register is also used to hold the divisor during Divide, the multiplicand during Multiply, and the TIM/TOM control during TIM/TOM operations.

The I Register may receive data in parallel from the Parallel Full Adder, B Register, and J Counter. Data is transferred from the I Register in parallel to the J Counter, P Register, Memory Address Buffer, and to the Parallel Full Adder. The contents of the I Register may be selected for display on the optional console.

#### Parallel Full Adder

The Parallel Full Adder is a 24-bit full adder. Most arithmetic operations within the arithmetic and control unit are accomplished through this adder. In addition to the normal add and subtract operations, the adder has the capability of accomplishing the following logical combinations:

Exclusive "OR" (if A = B, 0 out; if A  $\neq$  B, 1 out). Logical "AND" (if A = 1 and B = 1, 1 out; if A  $\neq$  1 or B  $\neq$  1, 0 out). Logical "OR" (if A = 0 and B = 0, 0 out; if A  $\neq$  0 or B  $\neq$  0, 1 out).

The adder may receive data in parallel from A, B, I, or the P Register. The adder also acts as a buffer for Input/Output operations. Data transferred into the central processor unit from Input/Output devices is channeled through the adder for distribution within the arithmetic and control unit. Data transmitted from memory to specified Input/Output devices is routed through the B Register to the Adder for distribution outside the arithmetic and control unit. Data transmitted from the A Register is routed through the adder for distribution outside the arithmetic and control unit.

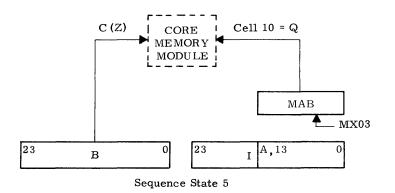

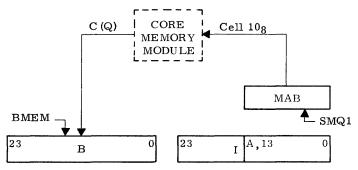

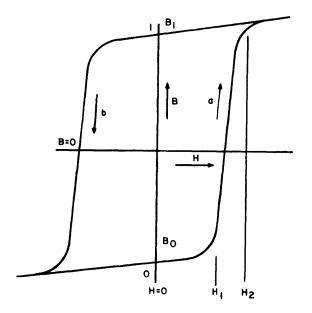

#### **Q** Register (Multiplier/Quotient)

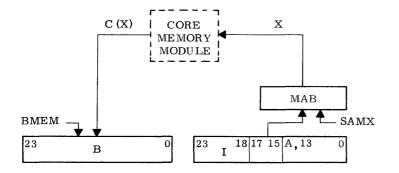

The Q Register is a pseudo register (located in core memory address 108) used as an auxiliary accumulator (MPY and DVD). The contents of Q are also used to define fields of the A and/or B Register during GEN 3 commands. The Q Register is addressed and gated to the B Register during the command execution.

#### **Memory Address Buffer**

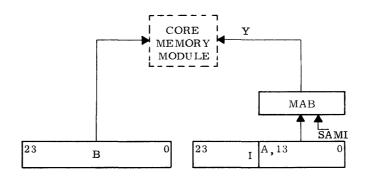

The Memory Address Buffer provides selection of the core memory address bits from the desired register or control circuit.

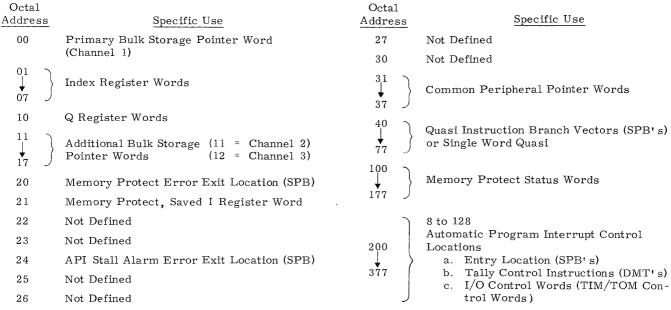

Certain memory locations are pre-assigned for specific use. These memory locations should be used only for the purpose intended unless hardware is not included to make use of the specific reserved address. The reserved memory locations and the pre-assigned uses are listed below.

| Octal |  |

|-------|--|

|       |  |

| Address                                             | Specific Use                                                                                                                                                                                |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00                                                  | Primary Bulk Storage Pointer Word<br>(Channel 1)                                                                                                                                            |

| 01 -<br>↓<br>07 _                                   | Index Register Words                                                                                                                                                                        |

| 10                                                  | Q Register Words                                                                                                                                                                            |

| $\begin{array}{c}11\\\downarrow\\17\\17\end{array}$ | Additional Bulk Storage (11 = Channel 2)<br>Pointer Words (12 = Channel 3)                                                                                                                  |

| 20                                                  | Memory Protect Error Exit Location (SPB)                                                                                                                                                    |

| 21                                                  | Memory Protect, Saved I Register Word                                                                                                                                                       |

| 22                                                  | Not Dedicated                                                                                                                                                                               |

| 23                                                  | Not Dedicated                                                                                                                                                                               |

| 24                                                  | API Stall Alarm Error Exit Location (SPB)                                                                                                                                                   |

| 25                                                  | Not Dedicated                                                                                                                                                                               |

| 26                                                  | Not Dedicated                                                                                                                                                                               |

| 27                                                  | Not Dedicated                                                                                                                                                                               |

| 30                                                  | Not Dedicated                                                                                                                                                                               |

| 31<br>$\downarrow$<br>37                            | Common Peripheral Pointer Words                                                                                                                                                             |

| 40 -<br>↓<br>77 _                                   | Quasi Instruction Branch Vectors (SPB's)<br>or Single Word Quasi                                                                                                                            |

| 100 -<br>↓<br>177 _                                 | Memory Protect Status Words                                                                                                                                                                 |

| 200<br>↓<br>377                                     | 8 to 128<br>Automatic Program Interrupt Control<br>Locations<br>a. Entry Location (SPB's, BRU)<br>b. Tally Control Instructions (DMT's)<br>c. I/O Control Words (TIM/TOM Con-<br>trol Words |

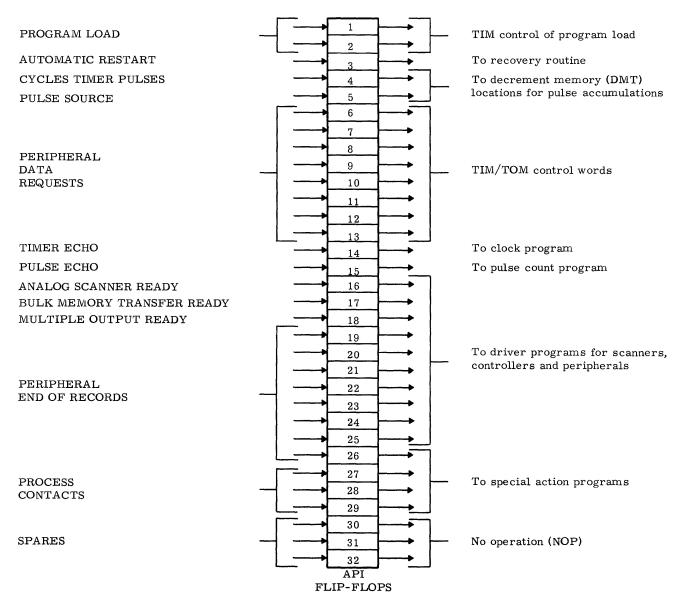

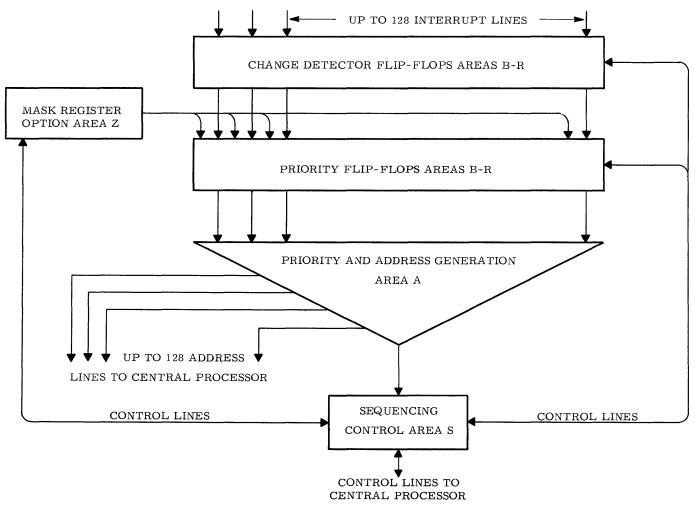

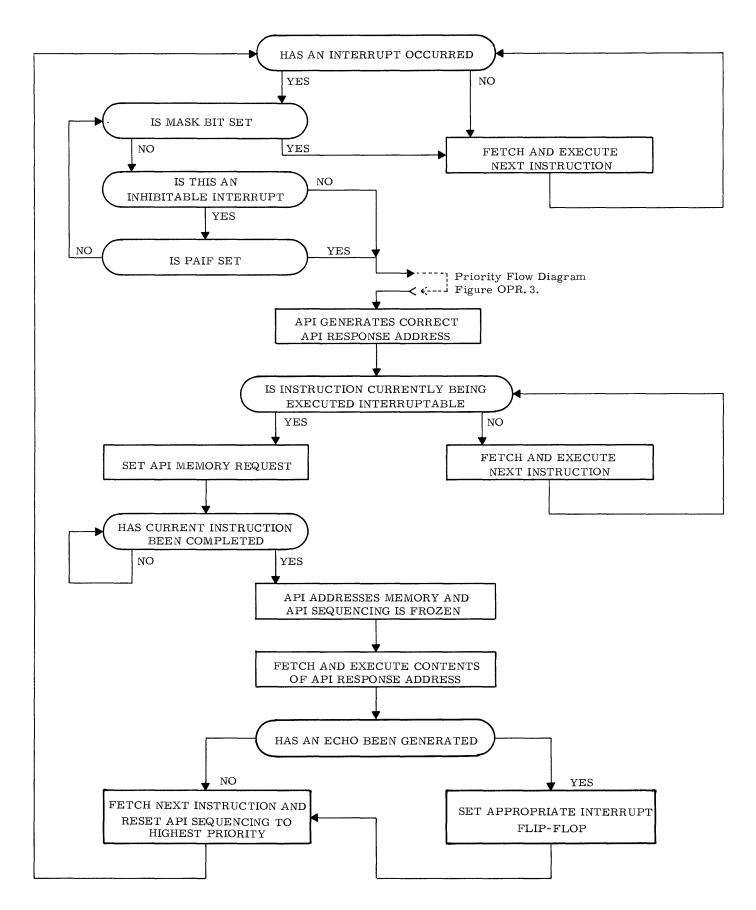

#### Automatic Program Interrupt Control

The Automatic Program Interrupt control logic within the Arithmetic Unit provides timing synchronization between the AU and API modules, inhibits interrupts during the execution of specific commands, inhibits inhibitable interrupts under program control, and provides an Echo interrupt signal to the API under certain conditions.

Each of these control functions and the logic elements providing these functions are described below.

• Enable API Gate, G1WENA (logic sheet 122), must be enabled to allow any interrupts to be serviced. This gate is enabled only during Time 3 Envelope (TSCA · TSCC) of Sequence Control State 4. Since some commands do not enter Sequence State 4 for execution, interrupts following these commands are inhibited. These commands include: BRU, BTS, BTR, and TXH.

In addition, the following commands inhibit G1WENA, thereby inhibiting interrupts follow-ing the command execution.

| Command                  | Logic Inhibit<br>Signal | Function                                                                          |

|--------------------------|-------------------------|-----------------------------------------------------------------------------------|

| CLO<br>CLZ<br>CMO<br>CMZ | DGN1· WI08 ·<br>WS67    | Allow J Count value<br>to be stored follow -<br>ing the commands                  |

| LPR<br>LDP<br>SPB        | XRMF                    | Allows the P Reg-<br>ister to be changed<br>before API                            |

| JNO<br>JNR<br>JDR<br>JCB | NGS6                    | Inhibits a TIM/TOM<br>interrupt from fol-<br>lowing JDR, JNR,<br>and JCB commands |

| LDX                      | WLDX                    | Allows Trap Error<br>detection                                                    |

| Volume<br>Difference     | MSSI                    | Allows Memory<br>Protect operation                                                |

| Trap Error               | 1                       |                                                                                   |

The API Lockout switch on the Console when in the Lockout position inhibits G1WENA.

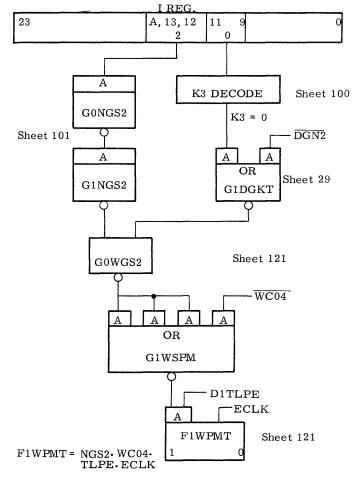

• The Permit Automatic Interrupt flip-flop, F1WPMT (logic sheet 121), when reset inhibits all inhibitable type interrupts. F1WPMT is reset during Time 3 Envelope (TSCA · TSCB · TSCC) of State 4 when there is not a Volume Difference or Memory Protect Error by an SPB, IAI, or LPR command.

> $\overline{F1WPMT}$  = TSCC · TSCA · WCPM · ECLK + Initialize.

G1WCPM when enabled to reset F1WPMT, also applies a signal to the API module to clear the priority flip-flops.

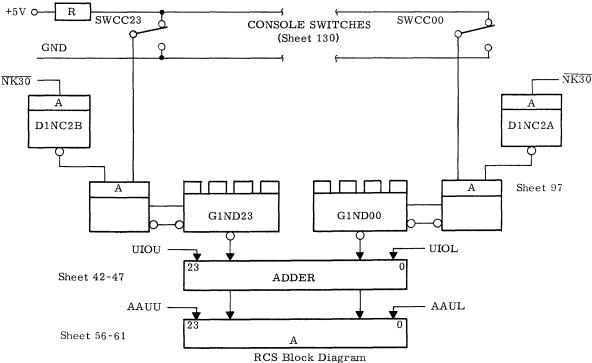

F1WPMT is set, allowing inhibitable interrupts, at Last Pulse of State 4 during the execution of a PAI or LPR command having bit 21 a "one".

$F1WPMT = WSPM \cdot TLPE \cdot ECLK.$

- G1WEKO applies a signal to the API to generate an "Echo" interrupt when a TIM/TOM operation is in progress and the last character of the last word is being transferred or when a DMT command decrements the memory cell from 0 to -1. Although the Echo signal is generated whenever the DMT decrements a cell from 0 to -1, a new interrupt is generated only if the DMT resulted from a previous interrupt.

- When an interrupt is generated by the API module, memory is addressed from the API module (GOSAMW) during the next Sequence State 1. This interrupt signal inhibits addressing memory from the P Register. GOSAMW enables memory address bit 7 (D1MA07) and in conjunction with the API Address Generator enables D1MA06-00 according to the interrupt level. In this manner an interrupt response address between 200g and 377g will be selected.

A detailed description of the API module is contained in the next section of this book set.

#### **Overflow Flip-Flop**

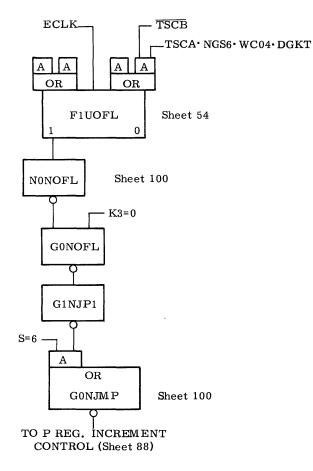

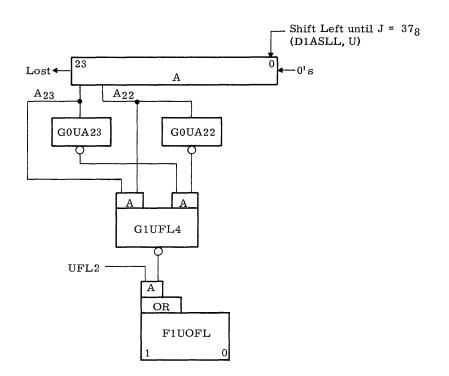

The Overflow flip-flop, F1UOFL (logic sheet 54), provides arithmetic overflow detection during the execution of ADD, DVD, MPY, and SUB commands. In addition, the Overflow flip-flop is set during the execution of GEN 3 commands when bit 5 of the command word is a "one" if the exclusive "OR" of  $A_{23}$  and  $A_{22}$  is a "one".

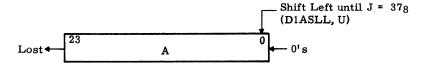

Arithmetic overflow occurs when the result of an arithmetic operation provides, or will provide, a result whose magnitude exceeds the capacity of 23 bits for single word length register (i.e.,  $2^{23}$ -1 or  $-2^{23}$ ) operations, or exceeds the capacity of 46 bits for double length register operations (i.e.,  $2^{46}$ -1 or  $-2^{46}$ ). During GEN 3 commands, when bit 5 of the command word is a "one", overflow occurs when bit 23 (sign bit) of the A Register is changed during a left shift.

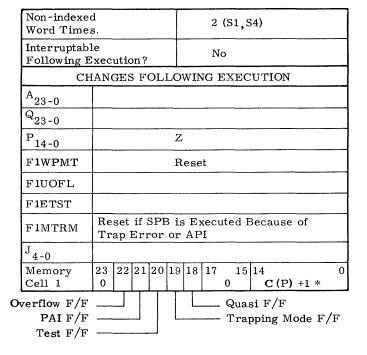

The status of the Overflow flip-flop is monitored and cleared by the JNO (GEN 2) command to establish program location control. The status of the Overflow flipflop is stored by the SPB command; restoring of the Overflow flip-flop status may then be accomplished by the LPR command.

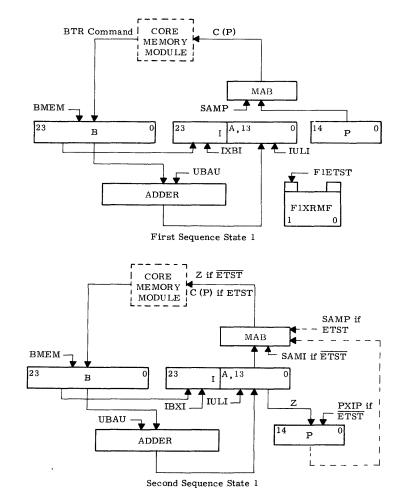

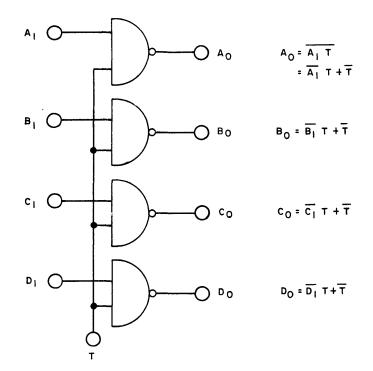

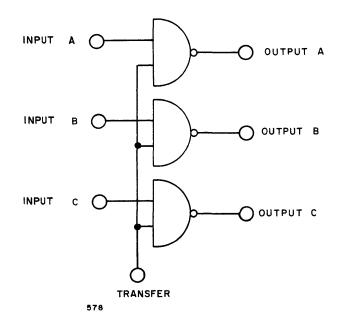

#### **Test Flip-Flop**

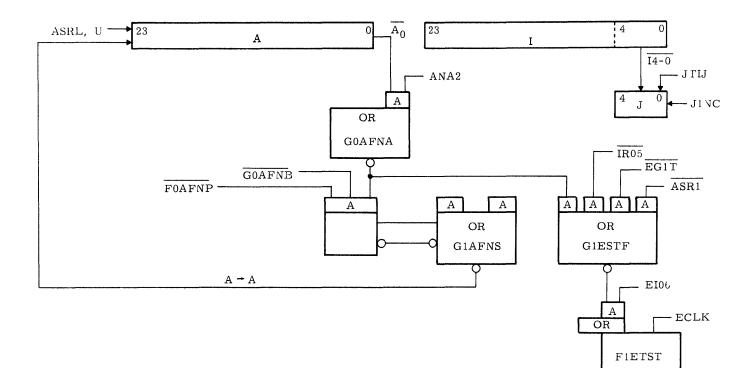

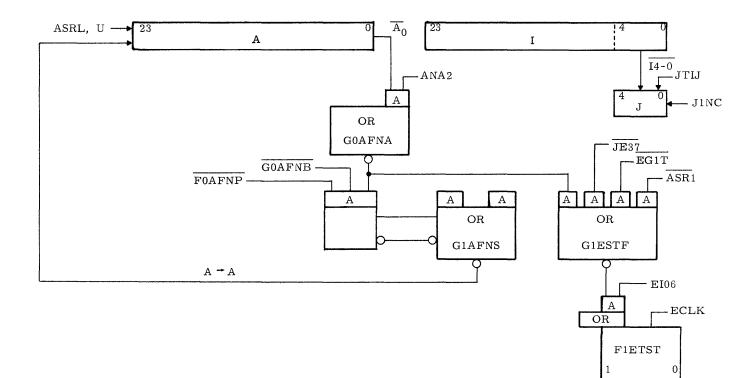

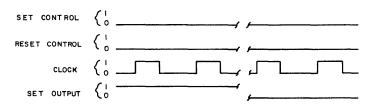

The Test flip-flop (F1ETST) serves as a memory element to remember the status of a previous test and to retain this status until changed by the program. The program may then use the status of the Test flip-flop to initiate a branch.

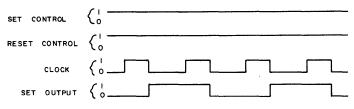

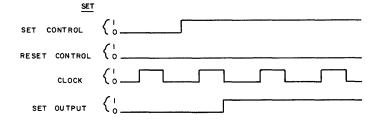

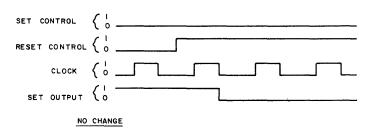

The Test flip-flop control logic provides the following functions:

- During the execution of DMT, GEN 1, and TXH commands, the Test flip-flop is used to remember the status of the condition tested.

- BTR and BTS commands will cause a branch in the program depending on the status of the Test flip-flop.

- The SPB command stores the status of the Test flip-flop; the status may be restored using the LPR command.

- The SET (GEN 1) command unconditionally sets the Test flip-flop; the RST (GEN 1) command unconditionally clears the Test flip-flop.

#### **Operators Console**

The Operators Console provides one method by which the operator may communicate with the computer in machine language. It allows the operator to load and execute programs and monitor the running program. A detailed description of the Operators Console is contained under the mnemonic CON in this section.

### LOGIC SYMBOLS AND NOMENCLATURE

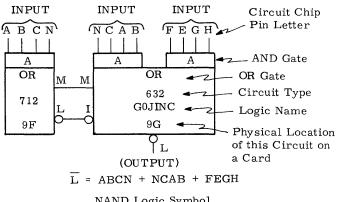

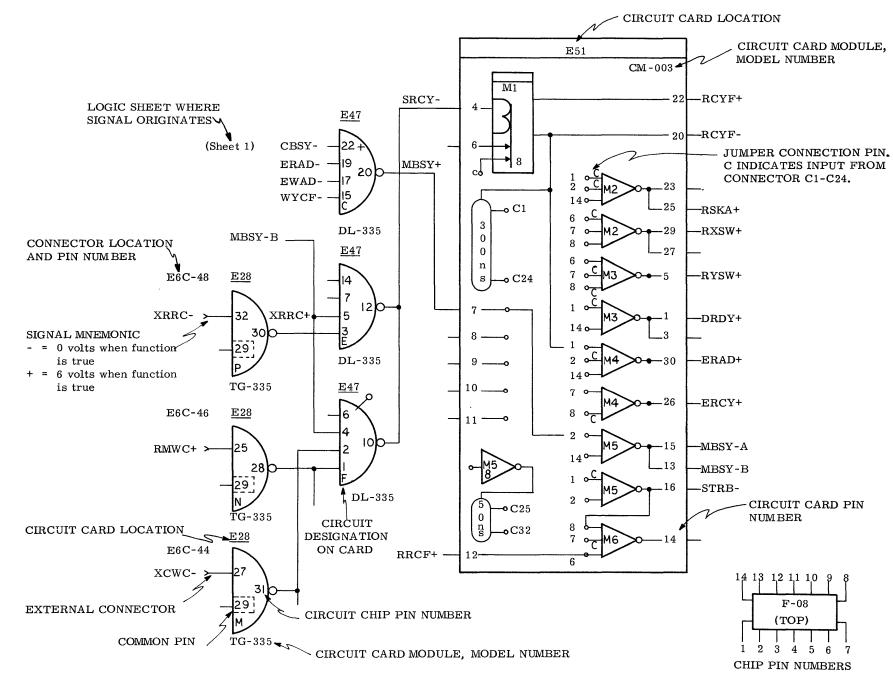

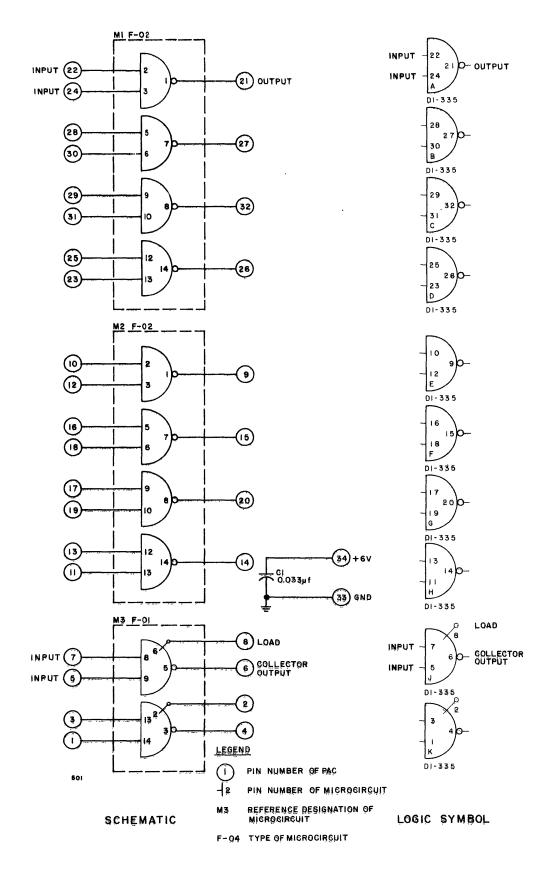

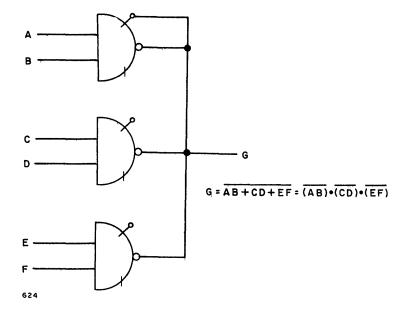

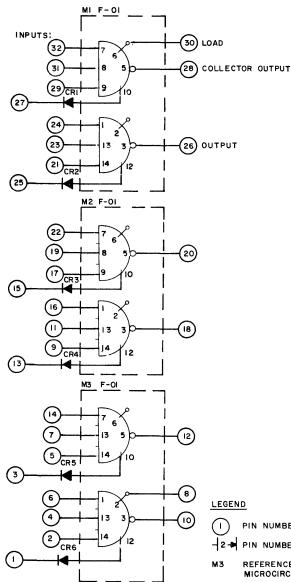

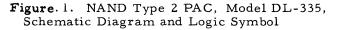

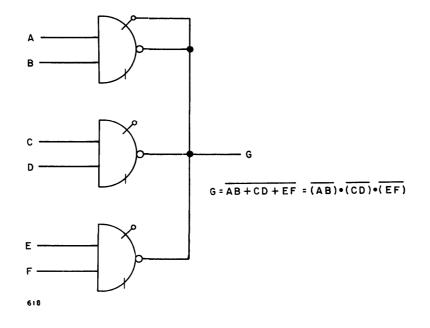

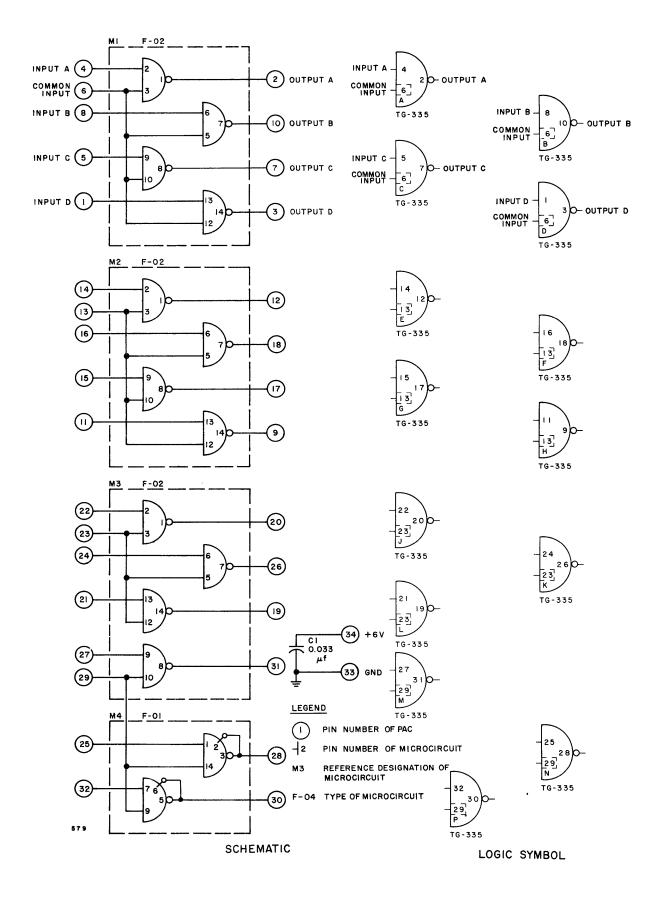

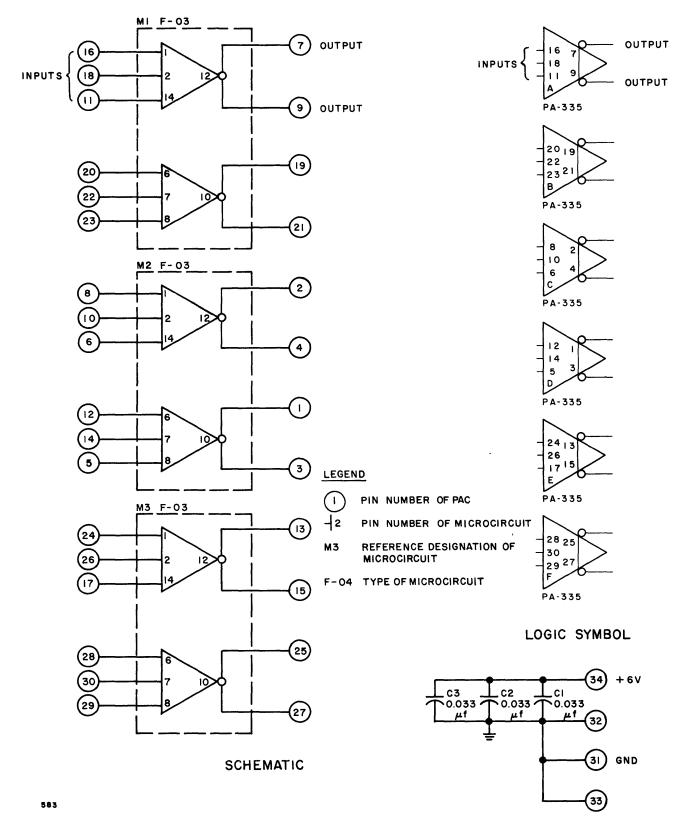

The following paragraphs provide a very brief discussion of the logic symbols and nomenclature used in the GE-PAC 4020 logic drawings.

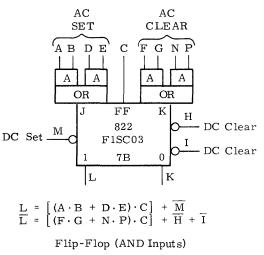

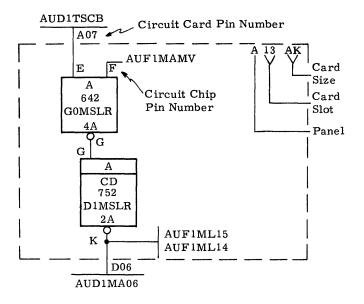

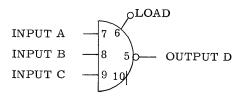

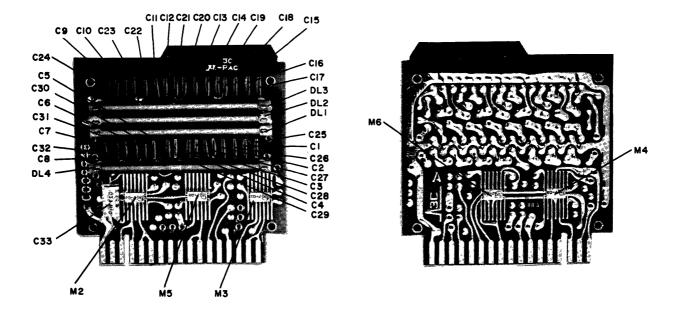

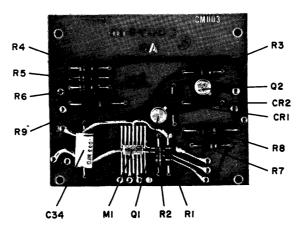

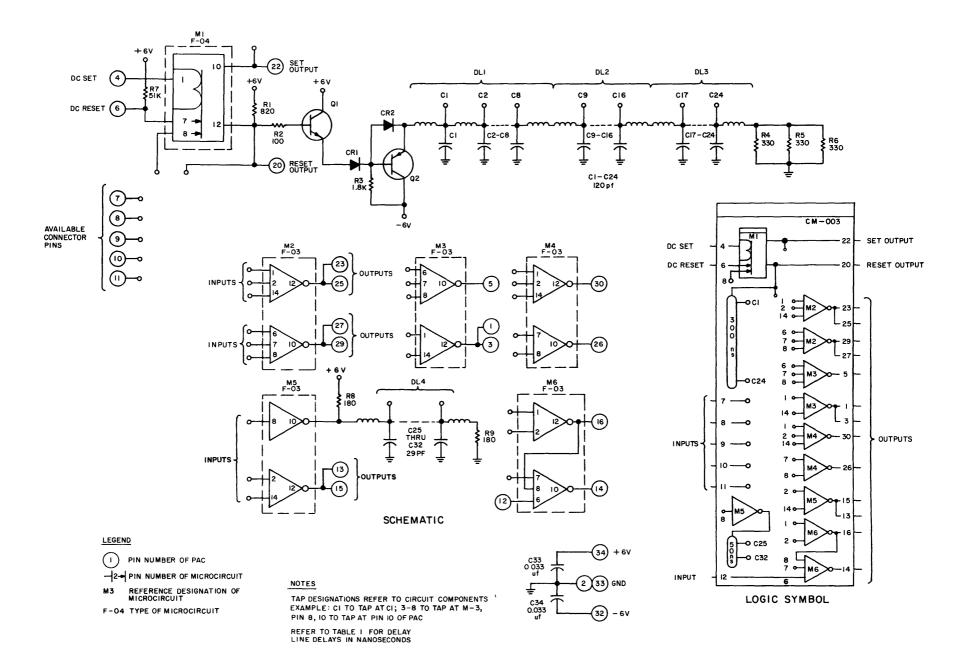

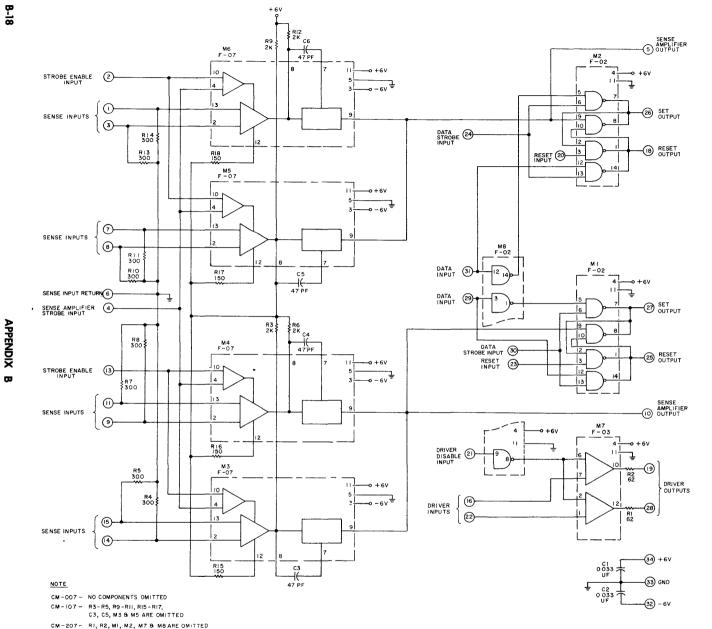

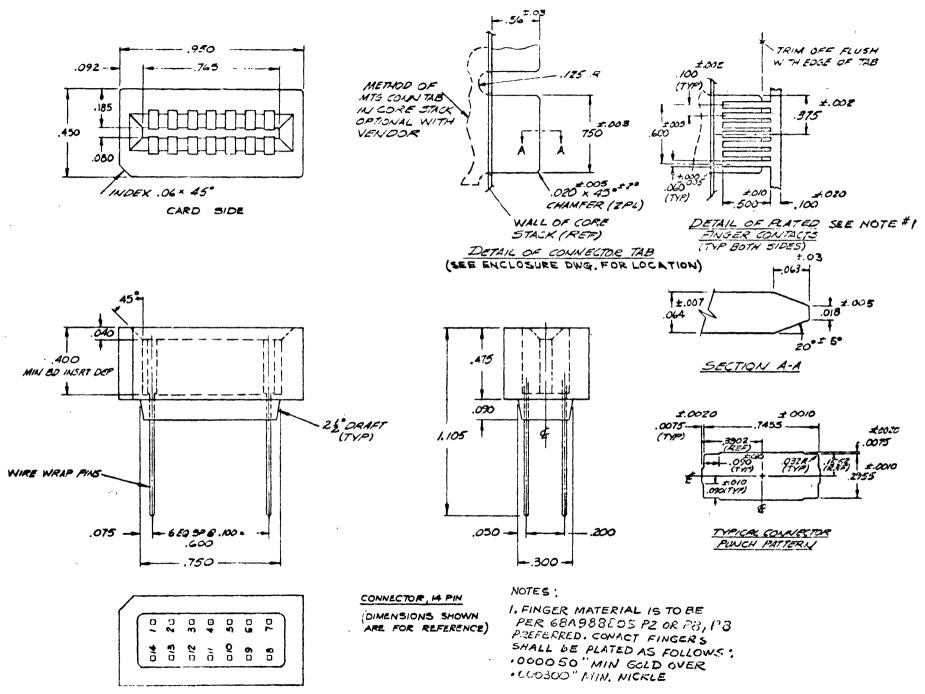

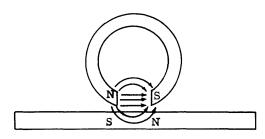

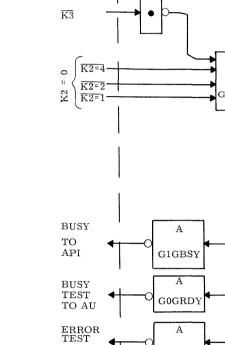

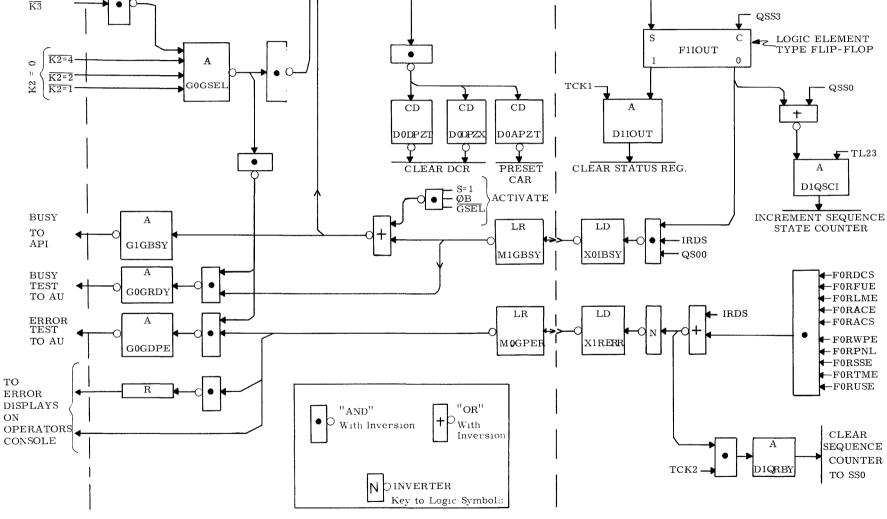

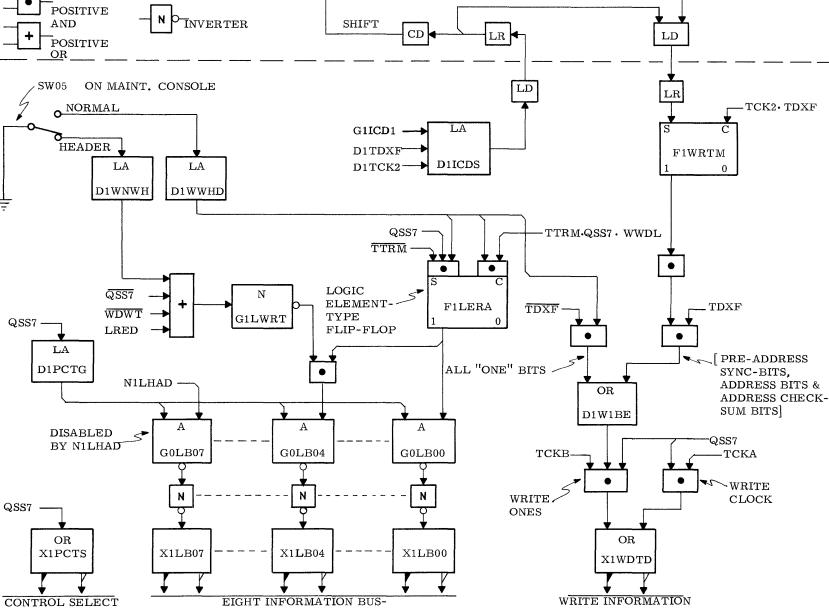

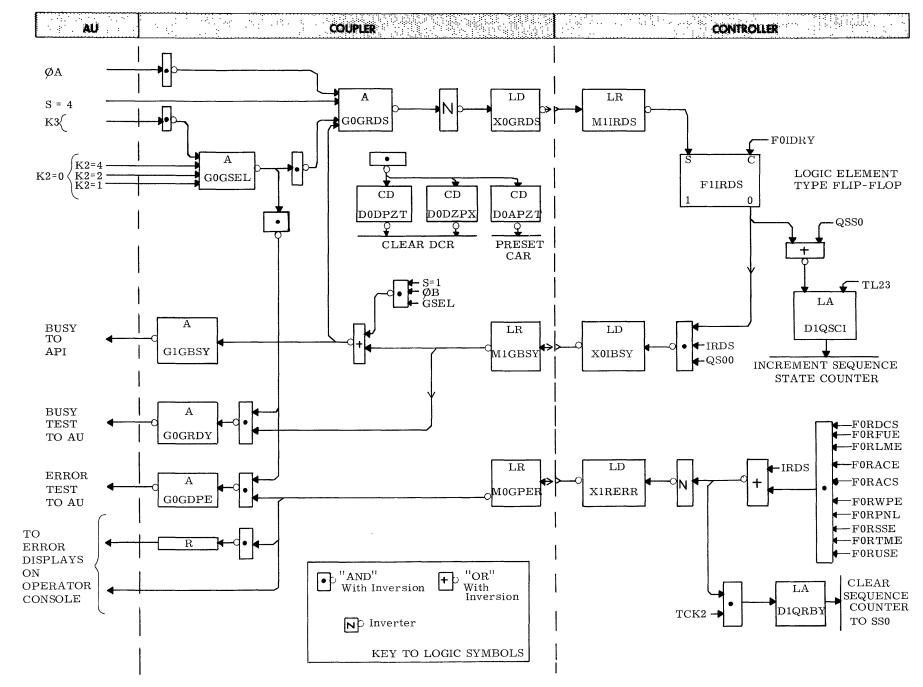

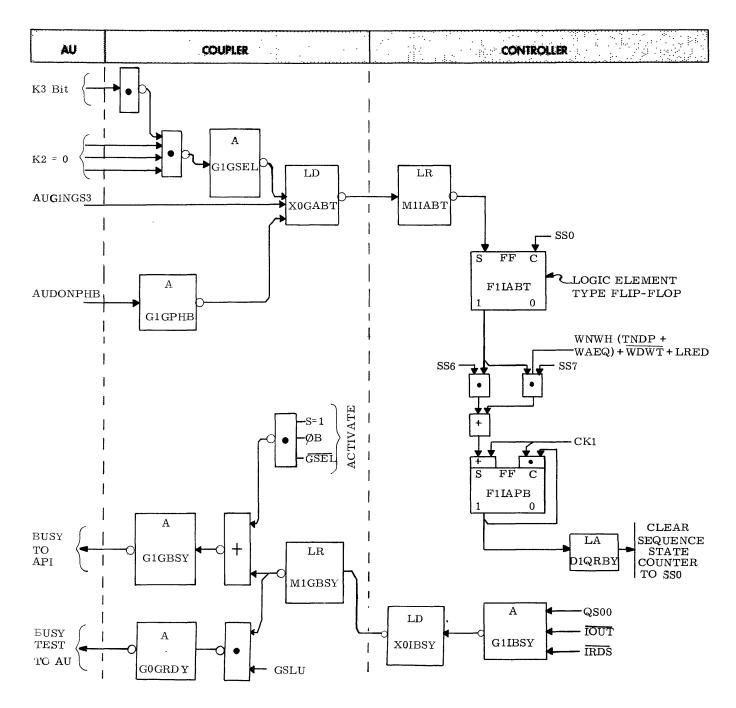

Fig. DESC. 2 illustrates the most commonly used logic symbols and the logic equation associated with each symbol. Each symbol designates the integrated circuit chip pin numbers, the AND (A) and OR inputs, an identification number of the circuit chip type, the logic name of the logic element, and the physical location of the logic element on the circuit card. Each of these designations will be discussed in the following paragraphs.

Since there are many different types of integrated circuit chips, each logic symbol identifies the type. This circuit type number is derived from the drawing number assigned to the individual circuit type. For instance, the drawing number for a 632 circuit is 68A8363P2; for a 752 circuit, 68A8375P2; for a 642, 68A8364P2; etc. Since the  $68A83_P$  part of the drawing number is the same for all circuits, it is deleted from the circuit type number contained in the logic symbol.

NAND Logic Symbol

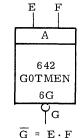

$\overline{K} = E \cdot G \cdot I \cdot F$ Clock Driver

Two-Input NAND/NOR Gate

1 = +3, 6V = True0 = 0V = False

The logic name consists of six digits to define four parts: Device Code, Polarity of output signal when the function is enabled, Functional Area of the logic prints, and the

mnemonic signal name. The logic name for the NAND symbol of Fig. DESC. 2 is described for clarity.

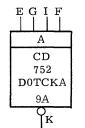

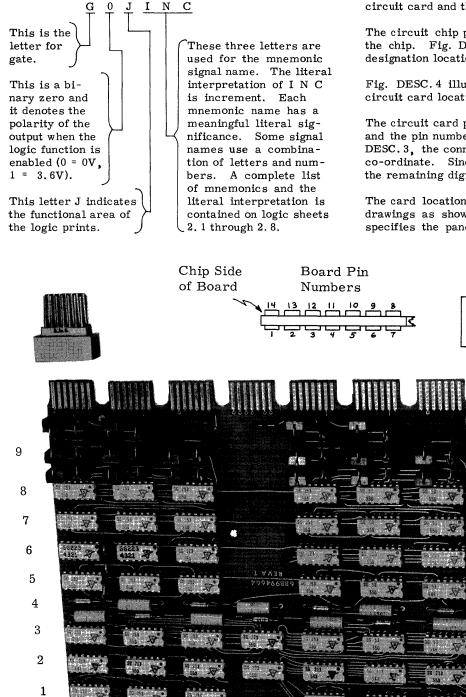

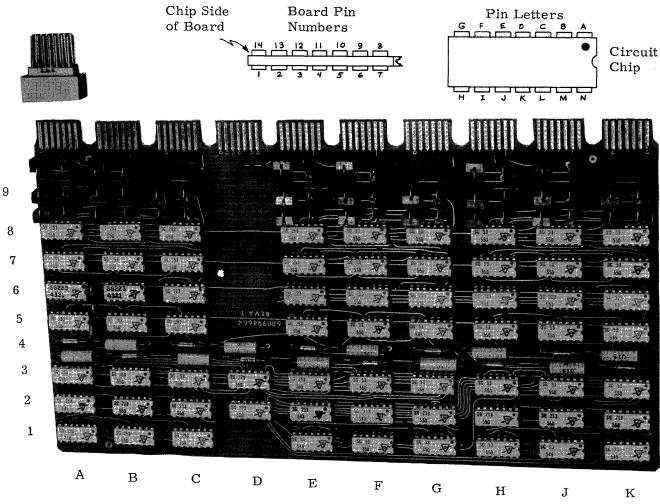

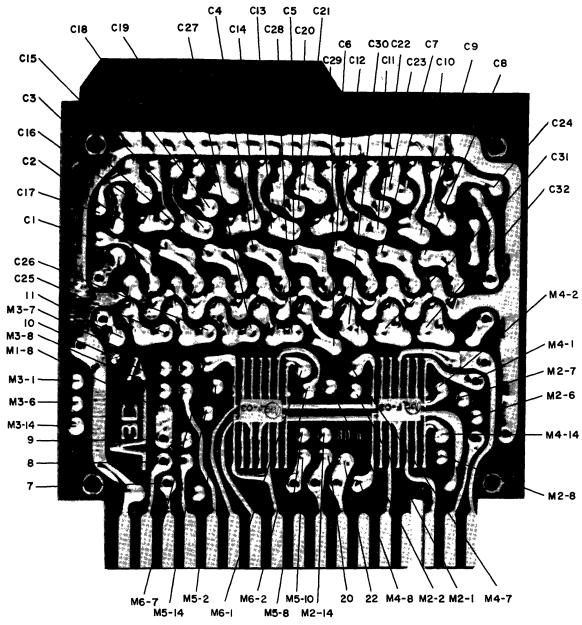

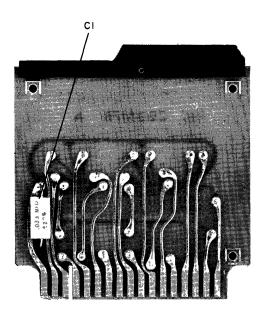

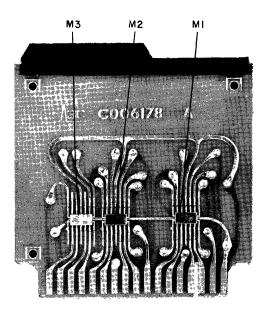

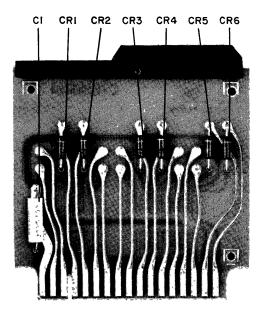

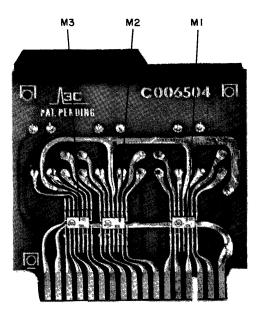

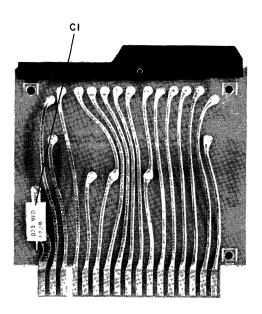

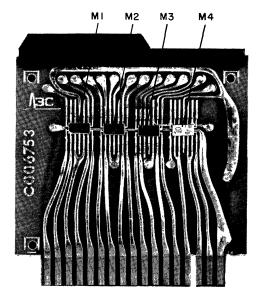

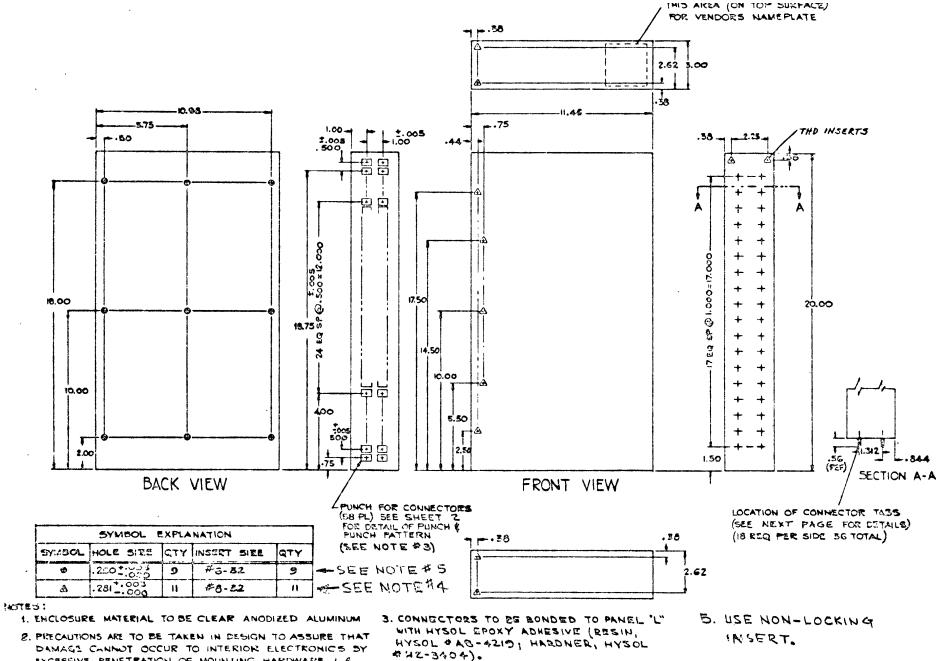

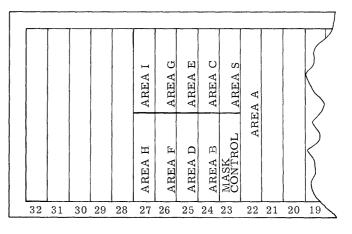

The physical location of this circuit on the card is designated by numbered and lettered co-ordinates of the circuit position of the card. Fig. DESC. 3 illustrates a circuit card and the co-ordinate designations.

The circuit chip pin letters specify the connections of the chip. Fig. DESC. 3 illustrates a chip and the pin designation locations.

Fig. DESC. 4 illustrates the wiring nomenclature and circuit card locations provided in the logic drawings.

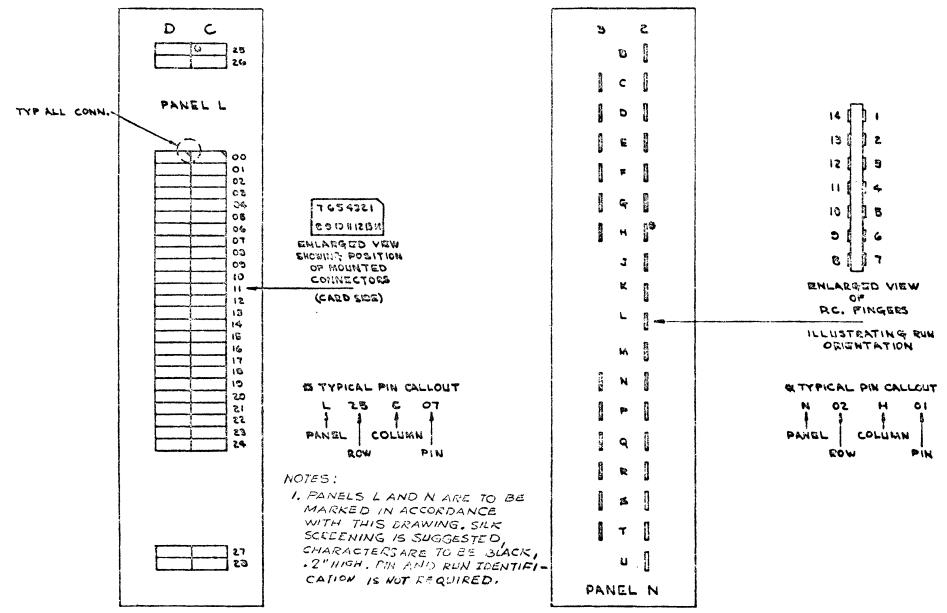

The circuit card pin number defines the card connector and the pin number of that connector. As shown in Fig. DESC.3, the connector may be defined by the lettered co-ordinate. Since each connector contains 14 pins, the remaining digits specify which pin of the connector.

The card location and size is also defined on the logic drawings as shown in Fig. DESC. 4. The first letter specifies the panel on which the card is located, the

Fig. DESC. 3. Circuit Card

next two numbers specify the card slot of the panel that the card is located, and the last two letters define the card size.

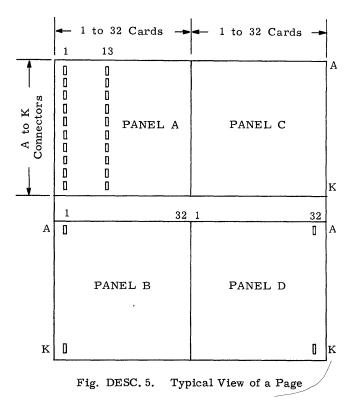

A typical page will contain up to four panels, as shown in Fig. DESC. 5. The first letter then designates in which panel the card is located. The next two numbered digits specify the card slot within the panel, since 32 card slots may be provided in a panel. The last two lettered digits indicate the size of the card by indicating the connectors provided. Therefore, AK is a 10-inch card utilizing connectors A through K. The letters AE would indicate a 5-inch card using connectors A through E, and the letters FK would indicate a 5-inch card using connectors F through K.

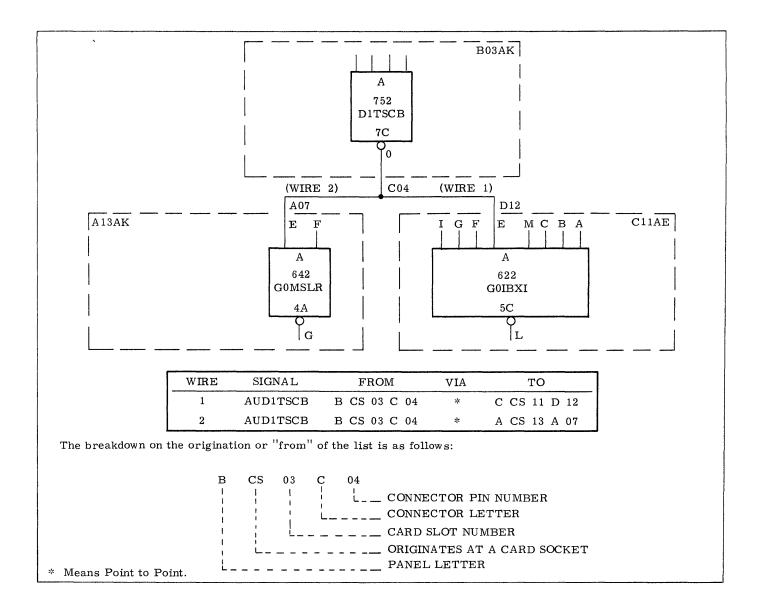

Since wire connections must be made between the individual circuit cards, a wire list is used to specify the required connections. Fig. DESC. 6 illustrates a sample logic drawing and the wire list associated with the logic drawing. The wire list gives the wire number, the name of the signal connected by the wire, where the wire originates, the route it must take, and the destination of the wire for each connection.

Fig. DESC. 4. Logic Wiring Nomenclature

## CONSOLE

### INTRODUCTION

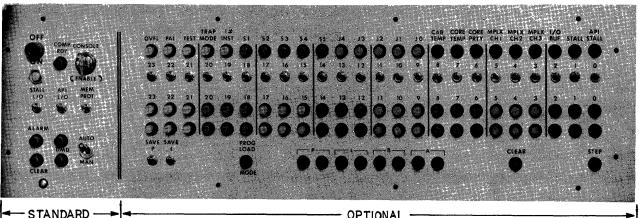

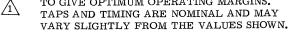

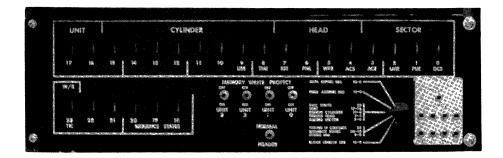

The GE-PAC 4020 Console (Fig. CON. 1) is the basic man/machine communication link and control element of the Central Processor. It provides all the necessary indications and switches to apply power, initialize, load programs and monitor the operation of the machine.

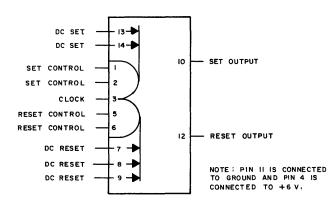

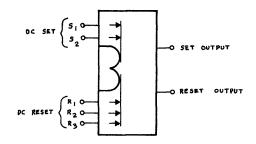

As shown in Fig. CON. 1, additional controls and indicators are provided on the console as an option (4DP4022A0013). All of these controls and indicators are described in the following text. Logic for the Console is contained in Drawing 68C972367, sheets 125 thru 132. Table CON. 1 lists the operation of the controls and indicators and the functions performed by each. The purpose of this discussion is to acquaint the reader with the operation of the Console and the function of the switches and indicators contained thereon. Basic procedures to enter data in a register, read in punched cards or paper tape, store words in memory locations, display memory locations, and to store a constant throughout all core memory locations are also provided.

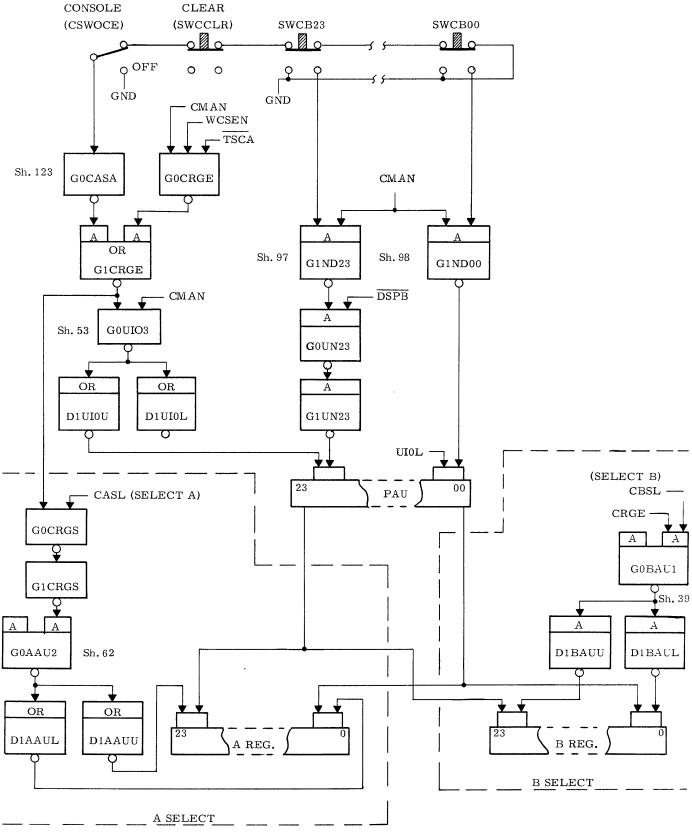

#### Console to A, B

Using the Register Entry Pushbuttons, data may be entered in the A or B Register as determined by the Register Select Switch. Fig. CON. 3 contains a block diagram of the logic utilized to implement this function. With the Console Enabled, in the MANual mode, and the A or B Register selected, pressing the Register Entry pushbuttons sets the corresponding bits in the A or B Register. The status of the pushbuttons are transferred to the A or B Register via the Parallel Adder Unit. As illustrated in the Register Select discussion above, the contents of the selected register are also gated to the Parallel Adder Unit. Therefore, the A or B Register must first be cleared prior to pressing the Register Entry pushbuttons. Operation to clear the A or B Register is described below.

### **CLEAR Register**

The CLEAR Reg. switch, when pressed, clears the B or A Register depending upon which is selected by the Register Select switch. In the MANual mode with the

OPTIONAL

Fig. CON.1. Operators Console

## DESCRIPTION

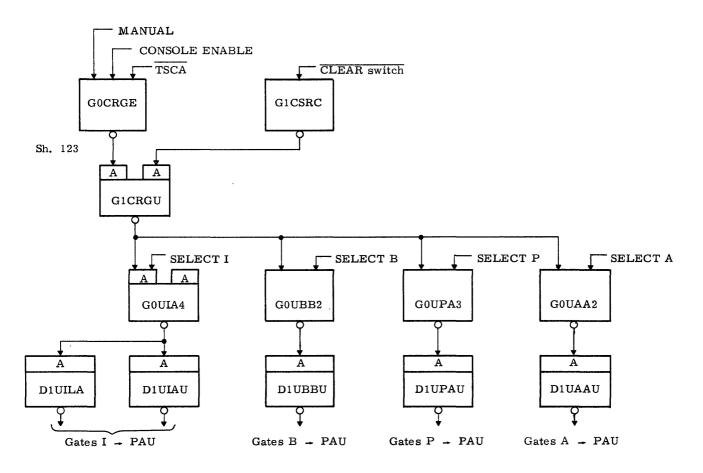

#### **Register Select-P,I,B,A:**

In the MANual mode, with the Console Enabled, the contents of the register selected by the Register Select switches are displayed by the Register Display indicators. In this manner, the operator may observe the contents of the P, I, B, or A Registers.

Fig. CON. 2 contains a block diagram of the logic circuits involved. The contents of the particular register selected is gated to the Parallel Adder Unit during TSCA when in the MAN mode, with the console enabled, and the CLEAR switch not pressed. The contents of the Parallel Adder Unit are then displayed by the indicators. Since sequencing is held in TSCA between pressing the STEP switch (see description below), a display of the selected register is provided.

Console Enabled, and the A or B Register Selected, the status of the Register Entry switches is gated to the selected Register via the Parallel Adder Unit. Since none of the Register Entry switches are pressed, this will clear the selected register. As shown in Fig. CON. 1, pressing the CLEAR Reg. switch, disables gating the contents of the Selected Register to the Parallel Adder Unit. In this manner, since no data is applied to the Parallel Adder Unit, the A or B Register will be cleared.

#### **MANual STEP Operation**

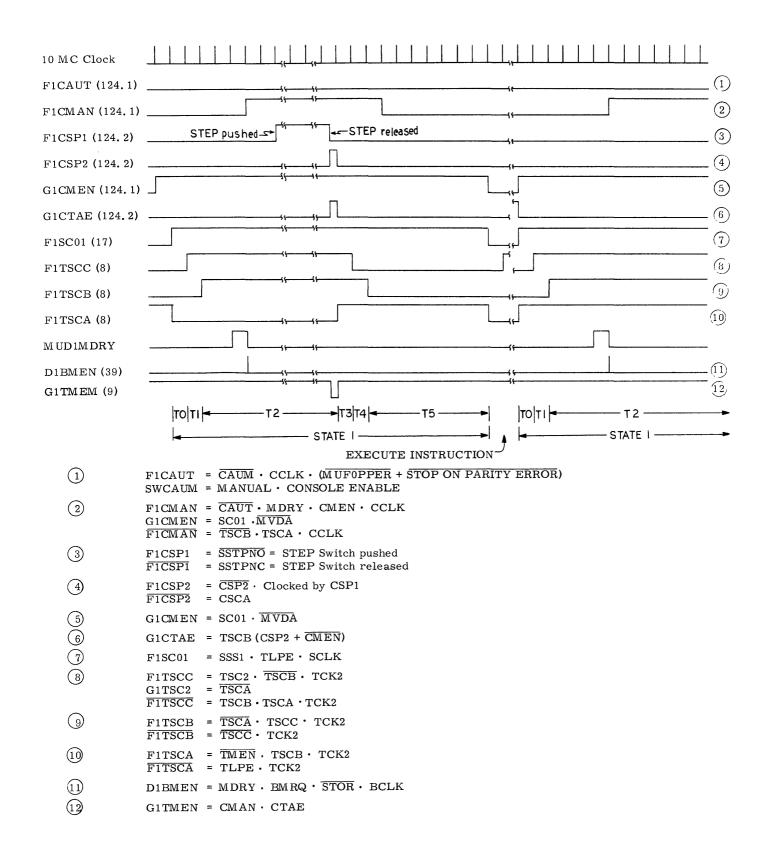

Pressing the STEP switch with the Console Enabled and in the MANual mode, will cause the instruction contained in the B Register to be executed. Instruction sequencing is halted after executing this instruction with the instruction just executed in the I Register and the next instruction in the B Register.

Fig. CON. 4 illustrates the basic timing, with logic

Fig. CON. 2. Register Select Block Diagram

equations, of the MANual STEP operation. When in the MANual mode, sequencing is halted in State 1, time 2 envelope. Pressing and releasing the STEP switch will allow the instruction contained in the B Register to be executed. Sequencing will then be halted during time 2 envelope of the following State 1. In the MANual Mode, sequencing is held in time 2 envelope by enabling G1TMEN and disabling G1CTAE during State 1. Pressing and releasing the STEP switch will enable G1CTAE and disable G1TMEN and allow sequencing to continue until the next State 1.

### **CONSOLE PROCEDURES**

The following procedures are provided to assist the operator of the Programming and Maintenance Console. To use these procedures, the Console must be enabled by both the key switch and CONSOLE OFF toggle switch (CSWOCE).

Enter Data in A or B Register

- 1. Place MAN AUTO toggle switch to MAN.

- 2. Select desired Register by pressing A or B Register Select switch.

- 3. Press the CLEAR Reg. switch.

- 4. Press the Data Entry pushbutton switches for desired bit pattern.

Store a Word in Core Memory Location Y

- 1. Place MAN AUTO toggle switch to MAN.

- 2. Press A Register Select switch.

- 3. Press CLEAR Reg. switch.

- 4. Press the Data Entry pushbuttons for desired bit pattern.

- 5. Press B Register Select switch.

- 6. Press CLEAR Reg. switch.

- 7. Using Data Entry pushbuttons, set a STA (320Y) in the B Register.

- 8. Press STEP switch.

Display the Contents of Memory Location Y

- 1. Place MAN AUTO toggle switch to MAN.

- 2. Press B Register Select Switch.

- 3. Press CLEAR Reg. Switch.

- 4. Press the Register Entry pushbuttons to set a LDA (000Y) into the B Register.

- 5. Press STEP switch.

- 6. Press A Register Select Switch. The contents of the addressed core cell will be displayed by the indicators.

ARITHMETIC UNIT

Fig. CON.3. Console To A, B Block Diagram

Fig. CON. 4. Manual Mode Step Sequencing

To Coat Core Memory With A Constant

- 1. Place MAN-AUTO toggle switch to MAN.

- 2. Press B Register Select switch.

- 3. Press CLEAR Reg. switch.

- 4. Press Register Entry switches for 07100001 bit pattern (LXK 1, 1).

- 5. Press STEP switch.

- 6. Press CLEAR Reg. switch.

- 7. Press Register Entry switches for 32100001 bit pattern (STA 1, 1)

- 8. Press A Register Select switch.

- 9. Press CLEAR Reg. switch.

- 10. Press Register Entry switches for the desired constant.

- 11. Press STEP switch.

- 12. Place SAVE I switch in save position.

- 13. Place MAN-AUTO toggle switch to AUTO.

- 14. The constant will now be stored in each memory location.

- 15. Place MAN-AUTO switch in MAN.

- 16. Lower SAVE I switch.

To Handload Instructions into Sequential Core locations Y, Y + 1, Y + 2, ... (Y  $\ge$  2).

- 1. Place MAN-AUTO toggle switch to MAN.

- 2. Press B Register Select switch.

- 3. Press CLEAR Reg. switch.

- Press Register Entry switches for 07100001 (LXK 1, 1) bit pattern.

- 5. Press STEP switch.

- 6. Press CLEAR Reg. switch.

- 7. Press Register Entry switches for 321XXXXX (STA Y-1, 1) where XXXXX = Y 1.

- 8. Press A Register Select switch.

- 9. Press CLEAR Reg. switch.

- 10. Press Register Entry switches to bit configuration of first instruction to be stored.

- 11. Press STEP switch.

- 12. Place SAVE I switch in save position.

- 13. For each instruction to be stored:

- a. Press CLEAR Reg. switch.

- b. Enter instruction in Register Entry switches.

- c. Press STEP switch.

The I Register contains the address of the last location stored.

Manually Display The Contents of Sequential Memory locations Y, Y + 1, Y + 2, ... (Y  $\ge$  2).

- 1. Place MAN-AUTO toggle switch to MAN.

- 2. Press B Register Select switch.

- 3. Press CLEAR Reg. switch.

- Press Register Entry switches for 07100001 (LXK 1, 1) bit pattern.

- 5. Press STEP switch.

- 6. Press CLEAR Reg. switch.

- Press Register Entry switches for 001XXXXX (LDA Y-1, 1) where XXXXX = Y - 1.

- 8. Press STEP switch.

- 9. Place SAVE I switch in save position.

- Press A Register select switch. Contents of selected memory location is displayed by Register Display indicators.

- 11. Press STEP switch for each sequential location display. The I Register contains the address of the location being displayed.

#### Load a Bootstrap Routine

The following procedure may be used to enter or load into memory a "Bootstrap" load routine contained by paper tape or punched tape. This routine assumes that the Bootstrap routine is assembled so that the first instruction is to be stored in memory location one.

- 1. Place MAN-AUTO toggle switch to MAN.

- 2. Ready the tape or card reader by inserting the proper tape or card and placing the device online.

- 3. Switch the API Lockout switch to the Lockout position.

- 4. Initialize computer by depressing the ON pushbutton.

- 5. Switch the Save-P switch to the Save-P position.

- <sup>6</sup> Hand load a "LDA" instruction into location zero.

- a. Press B Register Select switch.

- b. Press CLEAR switch.

- c. Press Register Entry switches for 320000008 (STA) bit pattern.

- d. Press A Register Select switch.

- e. Press CLEAR switch.

- f. Press STEP switch.

- 7 Hand load a "LDA" instruction into noninhibitable clock and DMT API response addresses.

- a. Press B Register Select switch.

- b. Press CLEAR switch.

- c. Press Register Entry switches for STA to noninhibitable clock (and DMT) API location.

- d. Press A Register Select switch.

- e. Press CLEAR switch.

- f. Press STEP switch.

- 8. Hand load the TIM Control Word into the corresponding API response address.

- a. Press Register Entry switches for "00000000" bit configuration for paper tape or to "00500000" bit configuration for cards.

- b. Press B Register Select switch.

- c. Press CLEAR switch.

- d. Press Register Entry switches for "32000202" (paper tape) or "3200020" (cards).

- e. Press STEP switch.

- 9. Hand load OPR command into B Register.

- a. Press Register Entry switches for 2502710D (D = Device Address)

- 10. Hand load DC1 code into A Register.

- a. Press A Register Select switch.

- b. Press CLEAR switch.

- c. Press Register Entry switches for "00000021" bit configuration.

- 11. Permit API's by placing API switch in nonlockout position.

- 12. Place AUTO/MAN switch to AUTO.

- 13. After card or read operation, place SAVE P switch in non-save position.

Bootstrap load program reads into memory starting at location one.

#### NOTE

Step 7 may be omitted by clearing core memory prior to step 1.

| CONTROL<br>OR<br>INDICATOR                | ACTIVE IN MODES<br>MANUAL, AUTO OR<br>CONSOLE OFF | PUSHBUTTON<br>OR TOGGLE<br>SWITCH | INDICATOR | LATCHING OR<br>M OM ENTARY | DESCRIPTION                                                                                                                                                                                                                                          |

|-------------------------------------------|---------------------------------------------------|-----------------------------------|-----------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| API STALL<br>(DRCD00)                     | ALL MODES                                         |                                   | x         |                            | Comes on when API Watchdog timer times out.                                                                                                                                                                                                          |

| API L/O<br>(SWCAPI)                       | AUTO & MAN                                        | т                                 |           | L                          | Inhibits all API's and disables API Watchdog<br>in the lockout mode. CONSOLE OFF enables<br>API and Watchdog. Refer to the API descrip-<br>tion in this book set.                                                                                    |

| AUTO/MAN<br>(SWCAUM)                      | AUTO & MAN                                        | Т                                 |           | L                          | In AUTO mode, computer sequencing enabled.<br>Computer runs automatically. In MAN mode<br>computer sequencing occurs each time STEP<br>switch is depressedFor one instruction.<br>CONSOLE OFF forces AUTO mode. Refer to<br>Manual Mode Description. |

| ALARM<br>(DRCERR)                         | ALL MODES                                         |                                   | х         |                            | Comes on when alarm or error condition<br>exists. Turned off by CLEAR ALARM Switch<br>or Initialize.<br>Comes on when the heat sink in the Bulk Power                                                                                                |

| CAB. TEM P.<br>(DRCD08)                   | ALL MODES                                         |                                   | х         |                            | Supply or Memory Power Supply reaches 260° ±<br>5° F. When the temperatures of the heat sink<br>reaches 287° ± 5° F, the power supplies will stop                                                                                                    |

| CLEAR ALARM<br>(SWCERR)                   | ALL MODES                                         | PB                                |           | м                          | operating, thus the system is shut down.<br>Clears all error/alarm conditions that are<br>ORed to the ALARM indicator.                                                                                                                               |

| CLEAR REG.<br>(SWCCLR)                    | MAN                                               | PB                                |           | M                          | Will clear the A or B Register as selected on<br>the Reg. Select switches. Refer to Clear<br>Register description.                                                                                                                                   |

| COM P<br>RDY(DRCRDY)                      | ALL MODES                                         |                                   | х         |                            | Comes on when power is applied. Turns off<br>when power is removed. Displays 5V logic<br>only. Refer to the Power Distribution section<br>of this book set for details.                                                                              |

| CORE PRTY<br>(DRCD06)                     | ALL MODES                                         |                                   | Х         |                            | Comes on when a memory parity error is<br>detected, CLEAR ALARM resets Parity<br>Error FF and turns off light. JNP and initi-<br>alize also clears the flip-flop and turns off<br>the light.                                                         |

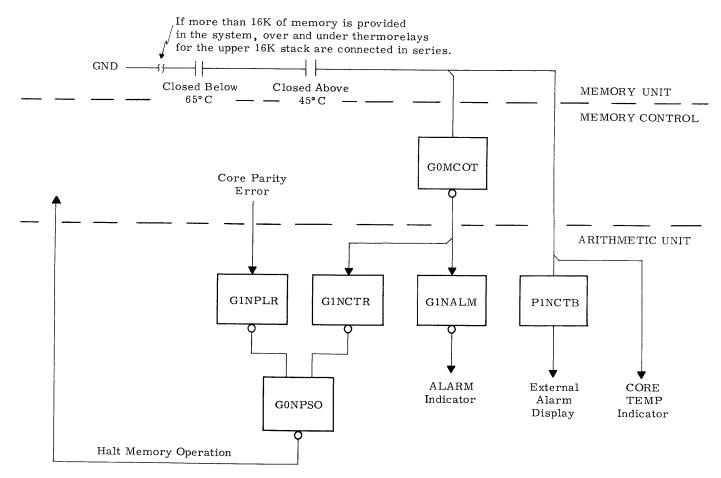

| CORE TEMP<br>(DRCD07)                     | ALL MODES                                         |                                   | х         |                            | Comes on when core stack temperature (4015B)<br>is not within allowable range. Turns off when<br>temperature is within allowable range. If parity<br>error occurs during out of limits time<br>memory sequencing is inhibited.                       |

| CONSOLE ENABLE<br>(SWCSEN)                | AUTO & MAN                                        | KEY                               |           | L                          | When in the disable position only the DMD,<br>RCS Switches, indicators, ALARM CLEAR<br>and OFF are active. Contacts 10, 11, and 12<br>may be used to provide optional external dis-<br>play or control.                                              |

| DM D<br>(LCDM D)<br>Continue On Next Page | ALL MODES                                         |                                   | x         | м                          | Sets Demand Flip-Flop when depressed and<br>released. Demand Flip-Flop is cleared and<br>light turned off by JND or initialize. Refer<br>to JND command description.                                                                                 |

Continue On Next Page

Table CON. 1. Controls and Indicators

~

| Table | CON. | 1. | (Cont. | ) |

|-------|------|----|--------|---|

|       |      |    |        |   |

| CONTROL<br>OR<br>INDICATOR                                 | ACTIVE IN MODES<br>MANUAL, AUTO OR<br>CONSOLE OFF | PUSHBUTTON<br>OR TOGGLE<br>SWITCH | INDICATOR | LATCHING OR<br>MOMENTARY | DESCRIPTION                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------|---------------------------------------------------|-----------------------------------|-----------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I ≠ INST<br>(DRCD19)                                       | ALL MODES                                         |                                   | x         |                          | Comes on at completion of Multiply/Divide or<br>prior to, and upon completion of TIM/TOM<br>to indicate I Register does not contain last<br>instruction. Cleared when next instruction<br>is executed.                                                                                                                                       |

| I/O BUF<br>(DRCD02)                                        | ALL MODES                                         |                                   | x         |                          | Comes on when a parity or timing error occurs in the I/O Buffer. Cleared by JNE.                                                                                                                                                                                                                                                             |

| J <sub>4</sub> - J <sub>0</sub><br>(DRCD13-09)             | ALL MODES                                         |                                   | x         |                          | Displays the contents of the J Counter. The J Counter is affected by GEN 1, GEN 3, MPY, DVD, and TIM/TOM operations.                                                                                                                                                                                                                         |

| MEM PROT<br>(SWCMEN)                                       | ALL MODES                                         |                                   |           | L                        | Disables Memory Protect when in Lockout<br>position, when in the non-lockout position<br>Memory Protect is active, if TMFF is set.                                                                                                                                                                                                           |

| MPLX CH. 1, CH. 2,<br>CH. 3<br>(DRCD03, 4, 5)              | ALL MODES                                         |                                   | x         |                          | Comes on when associated device produces<br>a parity error. Turned off by initialize or<br>OUT command.                                                                                                                                                                                                                                      |

| Overflow (OVFL)<br>(DRCD23)                                | ALL MODES                                         |                                   | x         |                          | Comes on when Arithmetic Overflow occurs.<br>Turned off by Initialize, JNO or LPR com-<br>mands. (See LPR & JNO commands.)                                                                                                                                                                                                                   |

| OFF<br>(SWCOFF)                                            | ALL MODES                                         | T                                 |           | м                        | Removes DC power from CPU. Refer to<br>Power Distribution section of this book set.                                                                                                                                                                                                                                                          |

| ON/Initialize<br>(SWCSON)                                  | MAN                                               | Т                                 |           | м                        | Applies DC power to CPU and Initializes CPU.<br>Initialize clears B, P, I Reg., $S_{2-5}$ , Demand,<br>PAI, All Alarms, and priority interrupt flip-<br>flops. Refer to the Power Distribution de-<br>scription of the book set.                                                                                                             |

| PAI<br>(DRCD22)                                            | ALL MODES                                         |                                   | x         |                          | Comes on when PAI command is executed to<br>indicate interrupts are permitted. Turned<br>off by IAI, LDP, LPR, SPB commands and<br>Initialize. See LPR, LDP, SPB command<br>description.                                                                                                                                                     |

| PROG LOAD<br>(SWCPGL)                                      | MAN & AUTO                                        | РВ                                |           | м                        | Not implemented at this printing. Refer to<br>Bootstrap load routine contained in this<br>section.                                                                                                                                                                                                                                           |

| Reg. Select<br>A, B, I, P<br>(SWCSLA, B, I, P)             | MAN                                               |                                   | x         | L                        | Each switch selects its associated register.<br>Used in conjunction with the register entry and<br>display switch lights. All Registers may be<br>displayed but only A & B may receive data from<br>the Reg. Entry switches. Activating any one<br>of the Reg. Select Switches disables the<br>others. Refer to Register Select discussions. |

| Reg. Entry/Display<br>(SWCB00-23)<br>Continue on Next Page | MAN                                               | PB                                | x         | М                        | The Switches are used in conjunction with the<br>Reg. Select Switch to enter data into A or B<br>Register. The lights will display the contents<br>of the register selected (I, P, B, orA) by the<br>Register Select Switch. Refer to Register<br>Select Discussions.                                                                        |

Continue on Next Page

| Table CON. 1. (Cont.)                          |                                                   |                                   |           |                          |                                                                                                                                                                                                                                   |

|------------------------------------------------|---------------------------------------------------|-----------------------------------|-----------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONTROL<br>OR<br>INDICATOR                     | ACTIVE IN MODES<br>MANUAL, AUTO OR<br>CONSOLE OFF | PUSHBUTTON<br>OR TOGGLE<br>SWITCH | INDICATOR | LATCHING OR<br>MOMENTARY | DESCRIPTION                                                                                                                                                                                                                       |

| Read Console Sw's.<br>(SWCC00-23)              | ALL MODES                                         | Т                                 |           | L                        | Used in conjunction with the RCS command<br>to enter the contents of these 24 switches<br>into the A Register. The up position re-<br>presents a 0, while the down position equals<br>a 1. Refer to the RCS command descriptions. |

| SAVE P<br>(SWCSSP)                             | AUTO & MAN                                        | Т                                 |           | L                        | When in the up position the P Register can-<br>not be altered. When in the down position,<br>P operates normally. CONSOLE OFF dis-<br>ables the SAVE P function.                                                                  |

| SAVE I<br>(SWCSSI)                             | AUTO & MAN                                        | т                                 |           | L                        | When in the up position the I Register can-<br>not be altered during the instruction fetch<br>cycle. In the down position I operates<br>normally. CONSOLE OFF disables the SAVE<br>I function.                                    |

| STEP<br>(SWCSTP)                               | MAN                                               | PB                                |           | м                        | In the MAN mode, each depression and re-<br>lease causes the computer to execute one<br>instruction. Refer to the Manual Mode<br>description.                                                                                     |

| S <sub>1</sub> - S <sub>5</sub><br>(DRCD18-14) | ALL MODES                                         |                                   | x         |                          | These indicators display the 5 sequence states of the CPU.                                                                                                                                                                        |

| STALL<br>(DRCD01)                              | ALL MODES                                         |                                   | x         |                          | Comes on when Stall Alarm timer times out.<br>May be cleared by Initialize, Stall L/O or<br>the SSA instruction.                                                                                                                  |

| STALL L/O<br>(SWCSTL)                          | AUTO & MAN                                        | т                                 |           | L                        | When in the Lockout mode the Stall Alarm is<br>disabled. CONSOLE OFF enables STALL<br>ALARM. Refer to the Stall Alarm description.                                                                                                |

| TRAP MODE<br>(DRCD20)                          | ALL MODES                                         |                                   | x         |                          | Comes on when trap or watchdog error<br>occurs. Turned off by SPB executed from<br>API response address 20 <sub>8</sub> or 24 <sub>8</sub> or Initialize.<br>Refer to Memory Protect descriptions.                                |

| TEST<br>(DRCD21)                               | ALL MODES                                         |                                   | x         |                          | Comes on when Test flip-flop is set. The<br>Test flip-flop can be set by: DMT, TXH,<br>some GEN 1 commands and LPR.                                                                                                               |

|                                                |                                                   |                                   |           |                          | The Test flip-flop may be reset by DNIT,<br>TXH, some GEN 1 instructions, LPR, and<br>Initialize. Refer to these command descrip-<br>tions.                                                                                       |

Table CON.1. Controls and Indicators

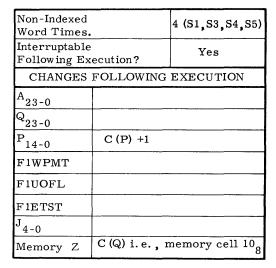

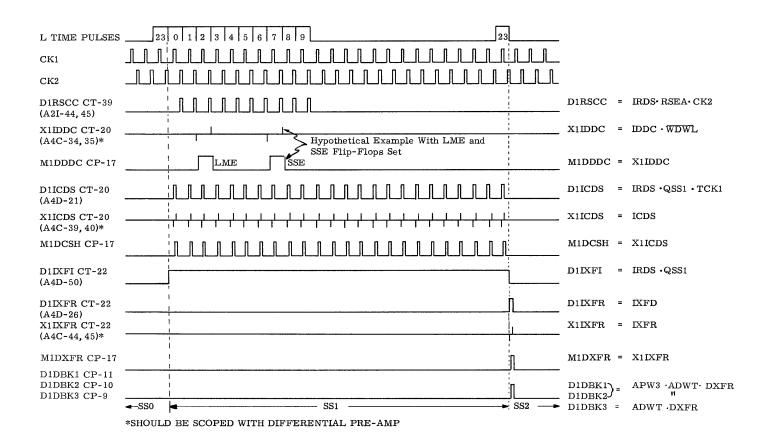

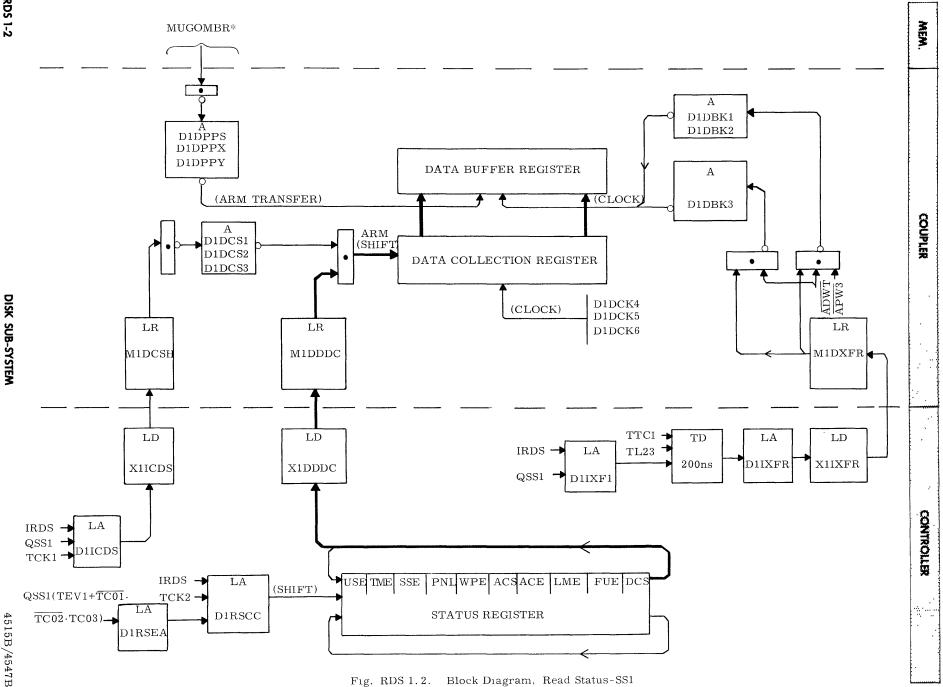

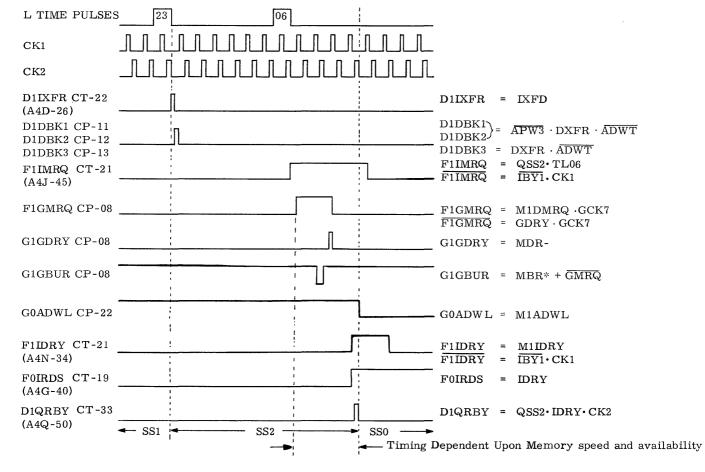

The following discussion is provided to assist the reader in a more thorough understanding of the individual command descriptions that follow.

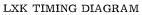

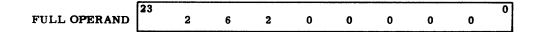

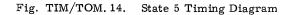

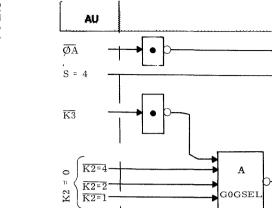

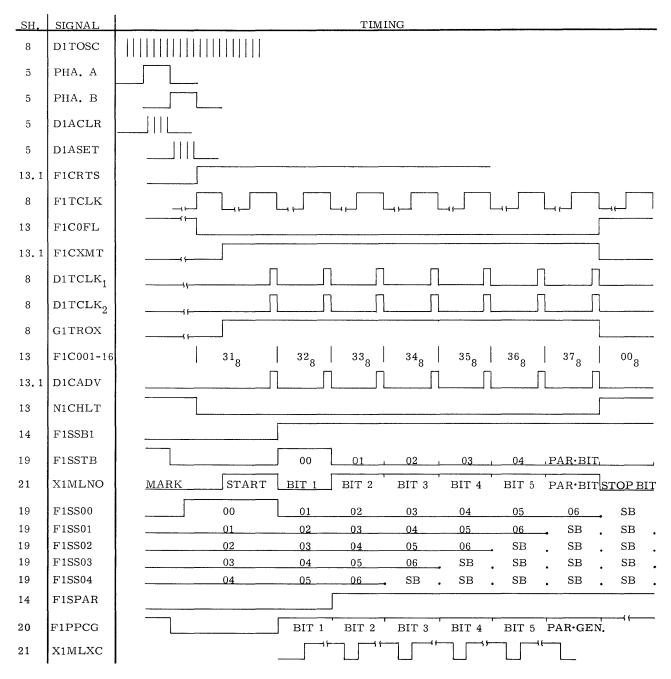

## **COMMAND FORMATS**

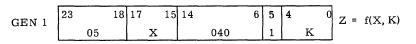

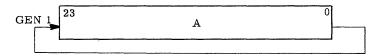

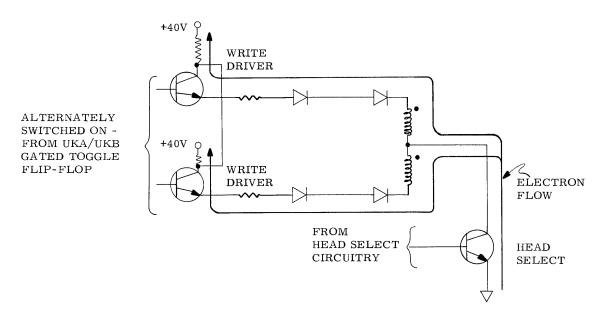

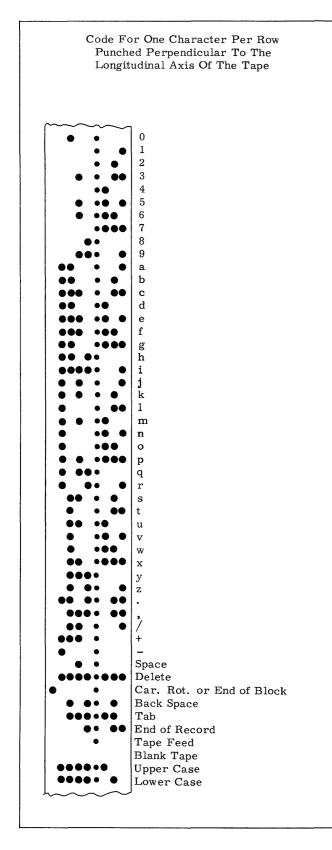

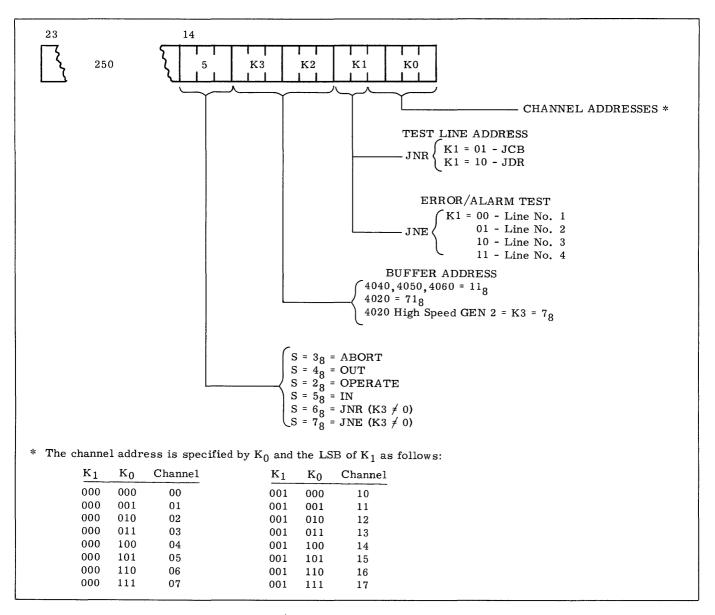

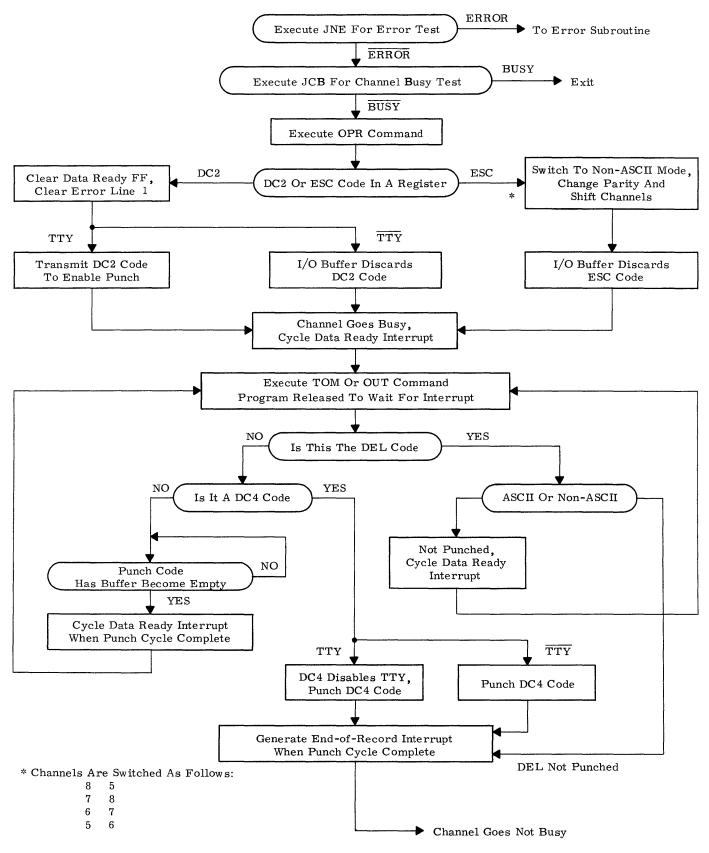

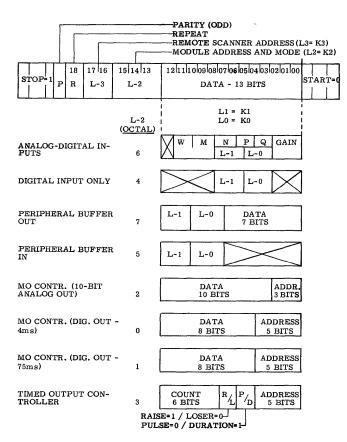

The commands, used by the GE-PAC 4022A Arithmetic Unit fall into five categories: Full Operand, GEN 1, GEN 2, GEN 3, and Quasi. The microcoded format of each of these command types is shown in Fig. CMD. 1.

#### Full Operand

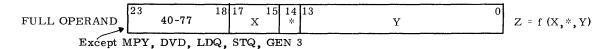

The Full Operand commands are the most widely used commands of the Arithmetic Unit. These commands are used to perform arithmetic operations, logical operations, index control operation, and data transfers to and from memory. These commands designate the core address for information in memory as an operand address. The operand address is a full 14 bits (13-0), which may be augmented by relative addressing (14) and/or indexing (17-15).

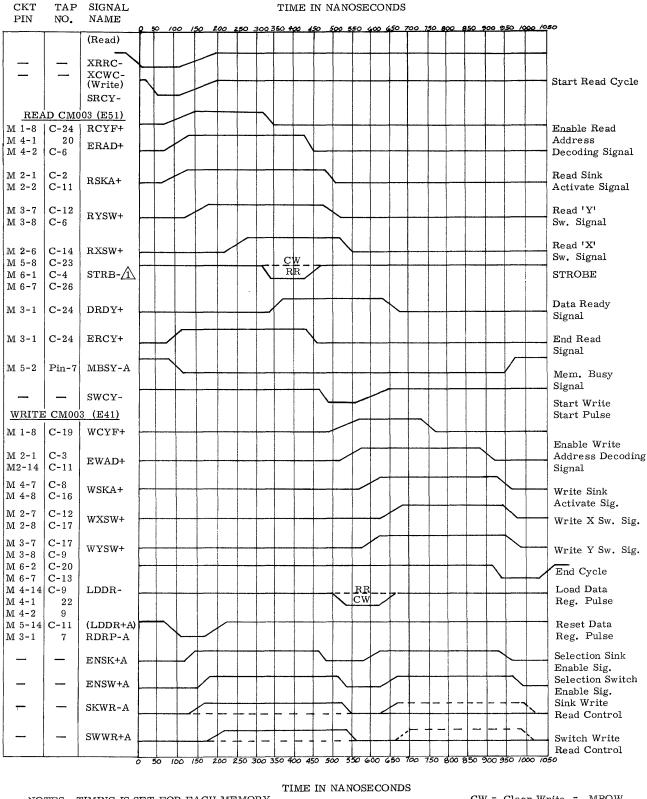

A detailed discussion of each of these commands is provided in alphabetical order. Each command description provides the mnemonic associated with the command, the command type, format, and a description of the command usage. In addition, a specific hardware oriented discussion is provided including a block diagram of the registers used, and a timing diagram including logic equations, of the more important control signals enabled within the Arithmetic Unit.

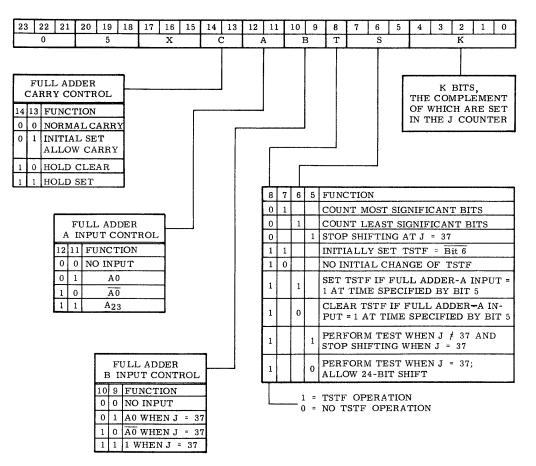

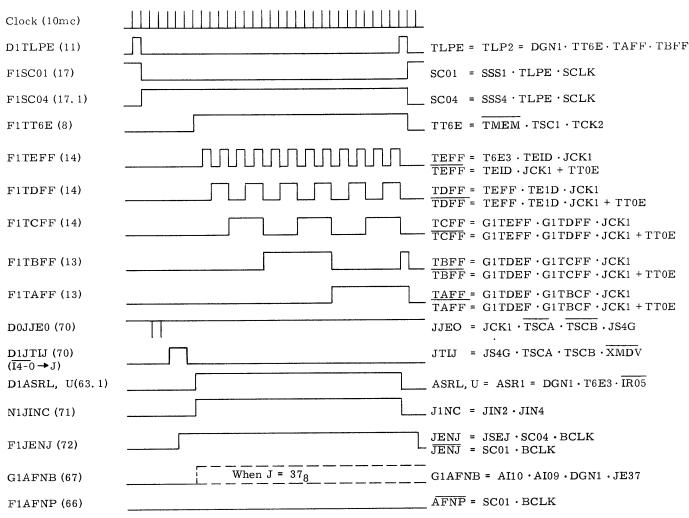

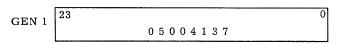

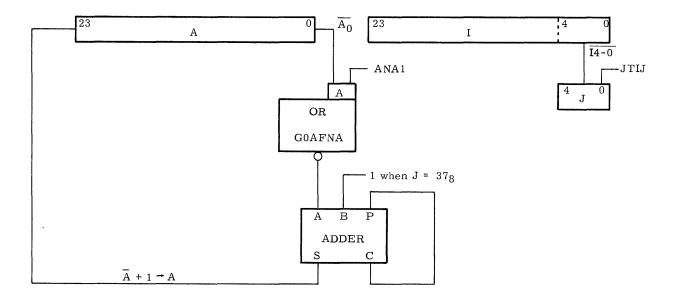

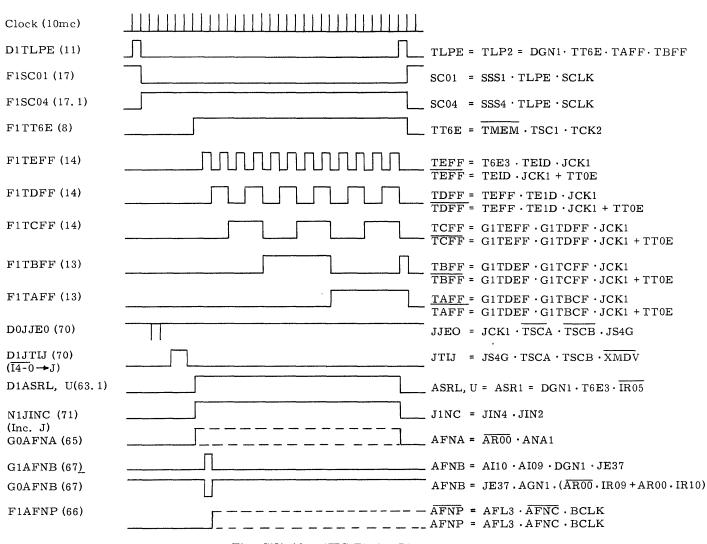

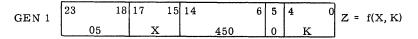

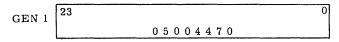

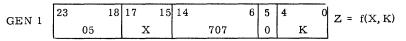

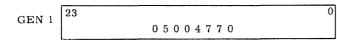

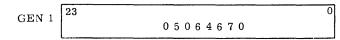

#### GEN 1

GEN 1 commands are differentiated from other commands by the OP Code (bits 23 through 18)  $05_8$ . GEN 1 commands are further subdivided into commands by the microcoding of the operation portion (bits 14 through 0) of the command word. GEN 1 commands are used primarily for bit manipulation of the A Register, but may be microcoded to affect the J Counter and Test flip-flop.

Thirty-seven different GEN 1 commands are described under the mnemonic GEN 1. Each description contains the microcoded format of the command, a description of the command usage, and a description of the hardware operation when executing the command.

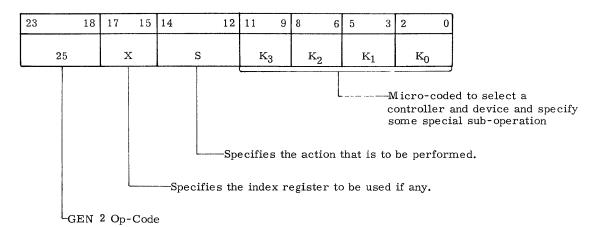

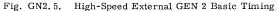

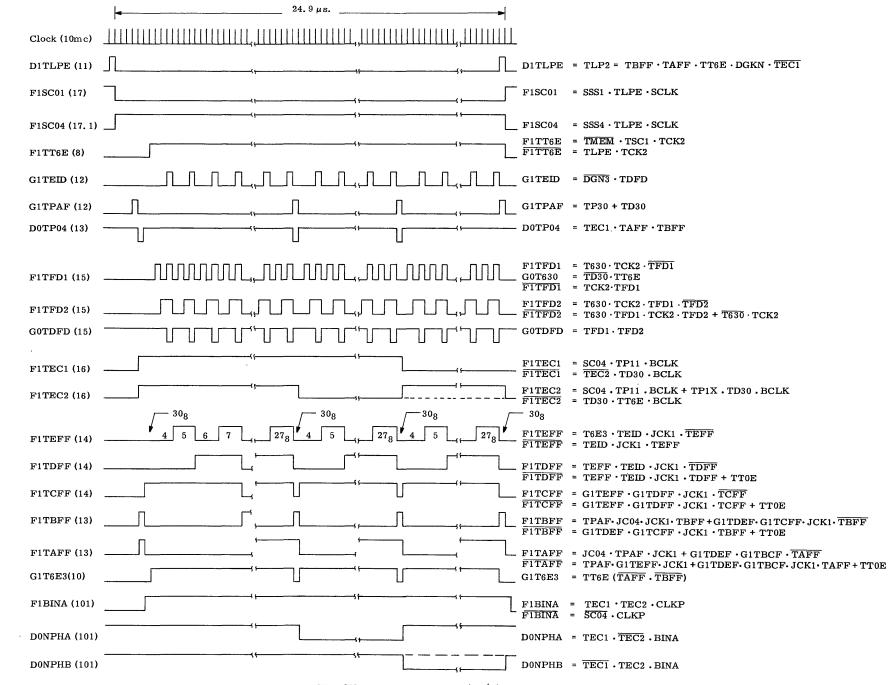

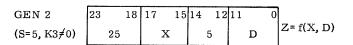

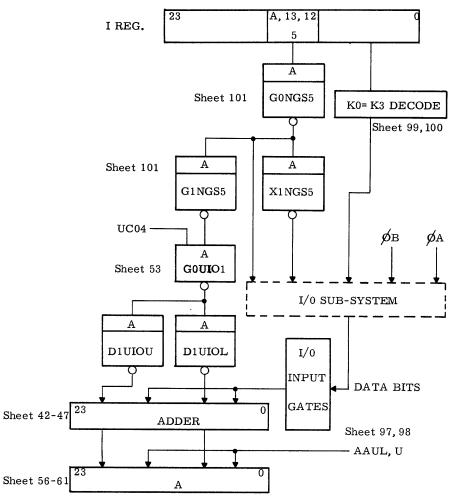

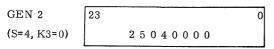

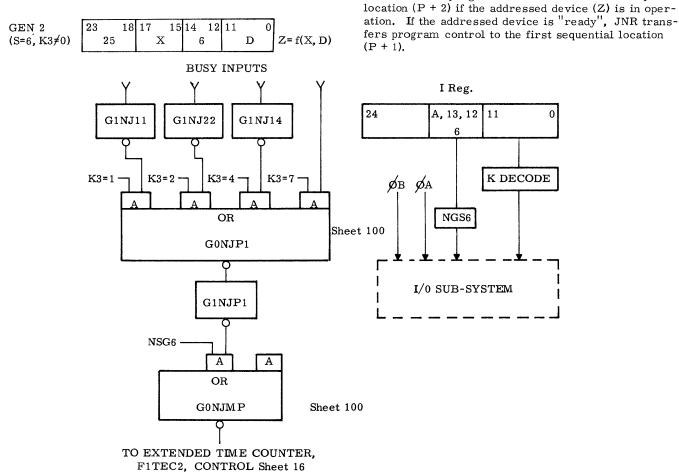

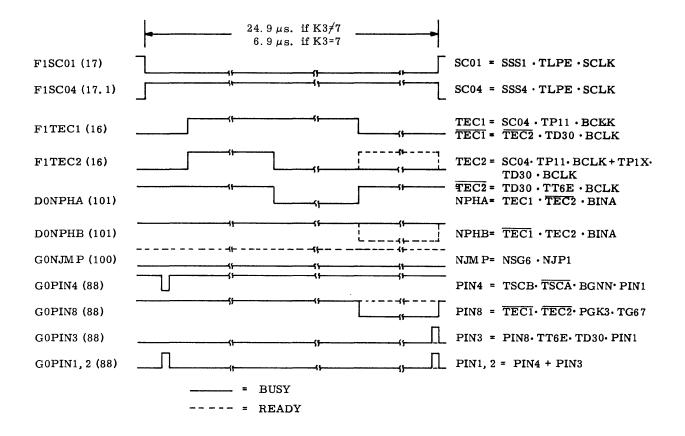

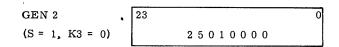

### GEN 2

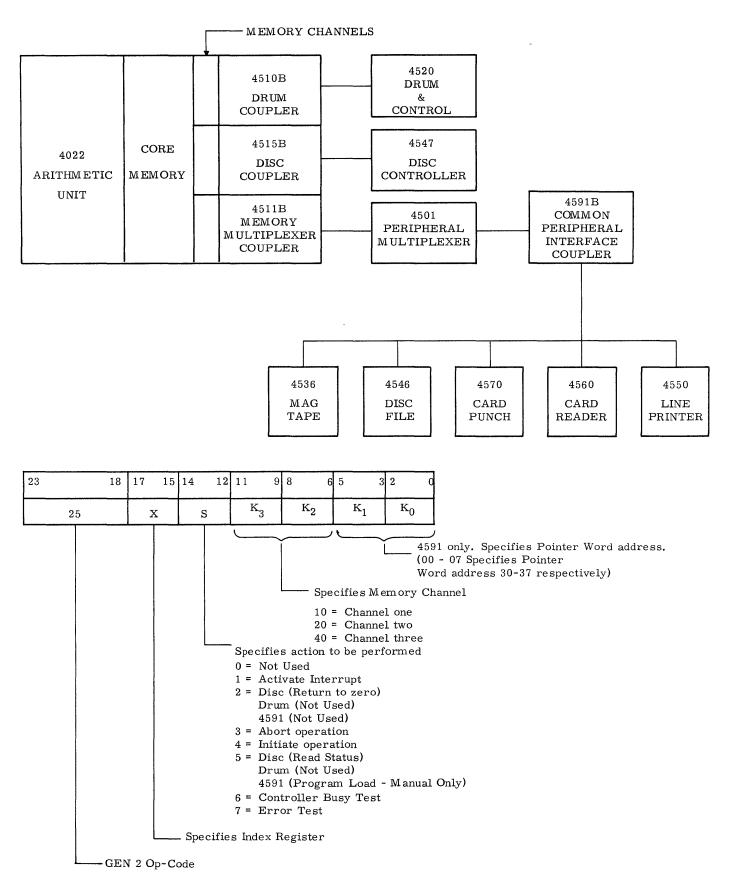

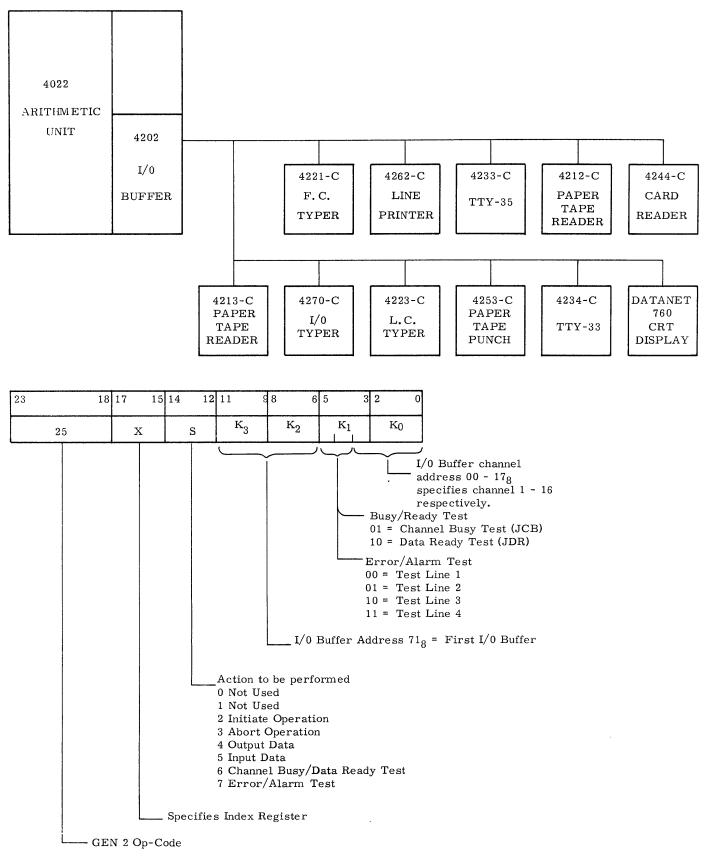

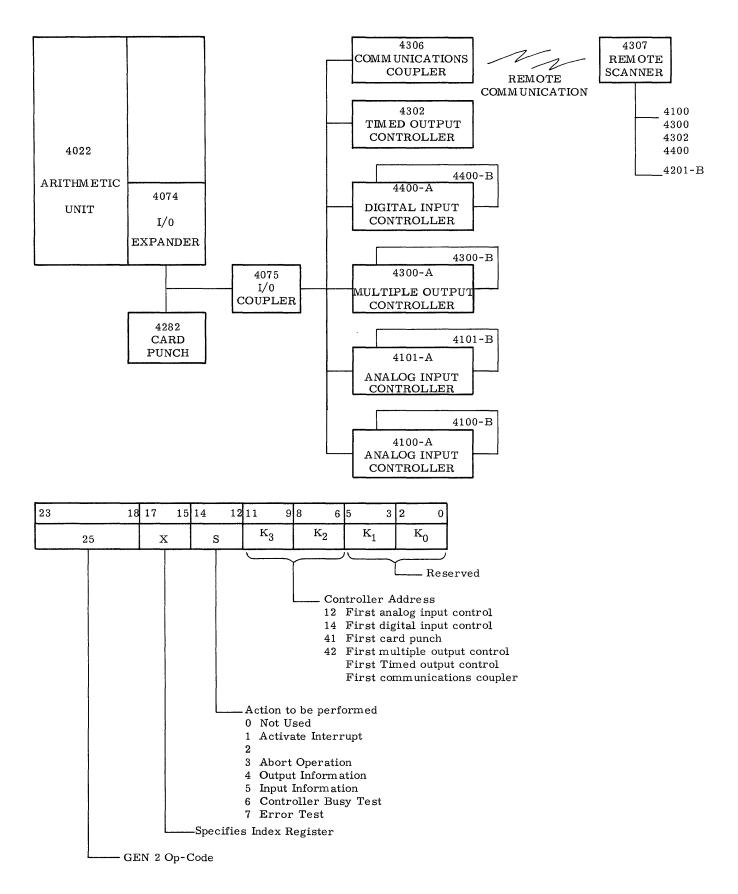

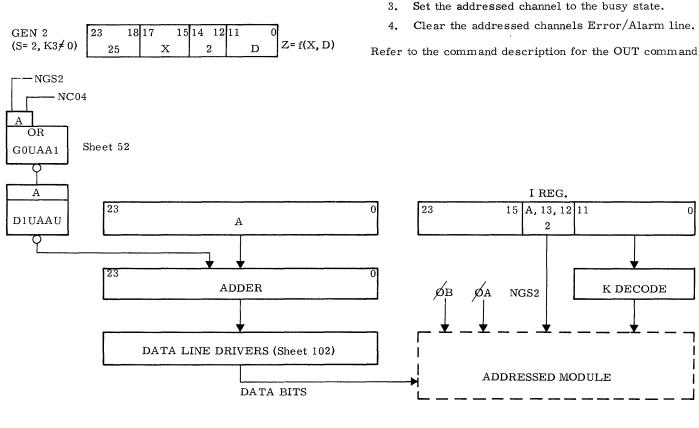

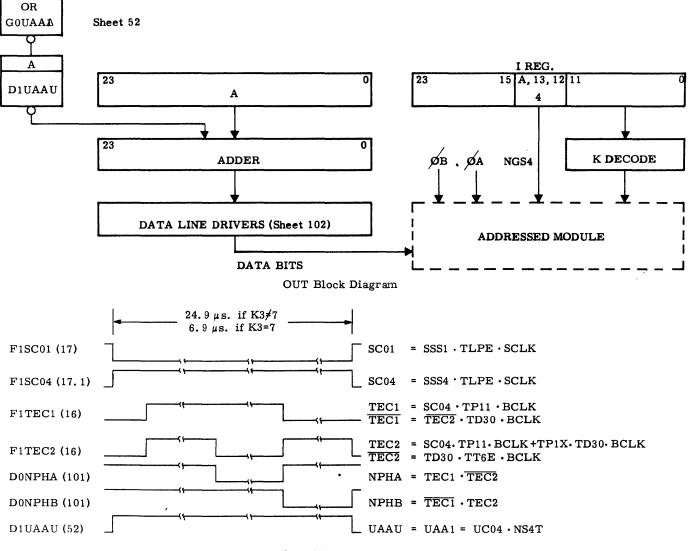

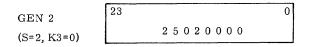

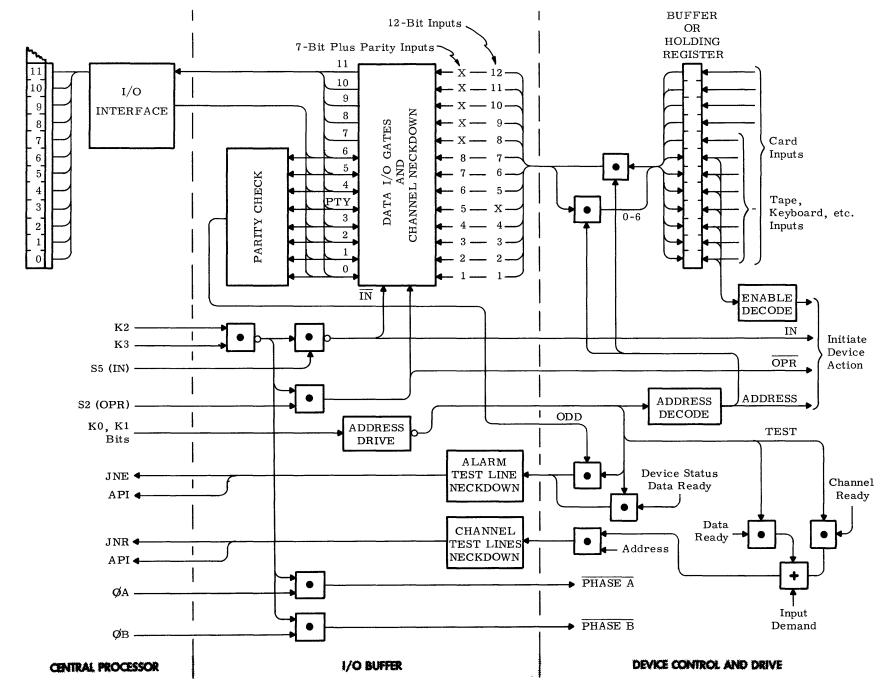

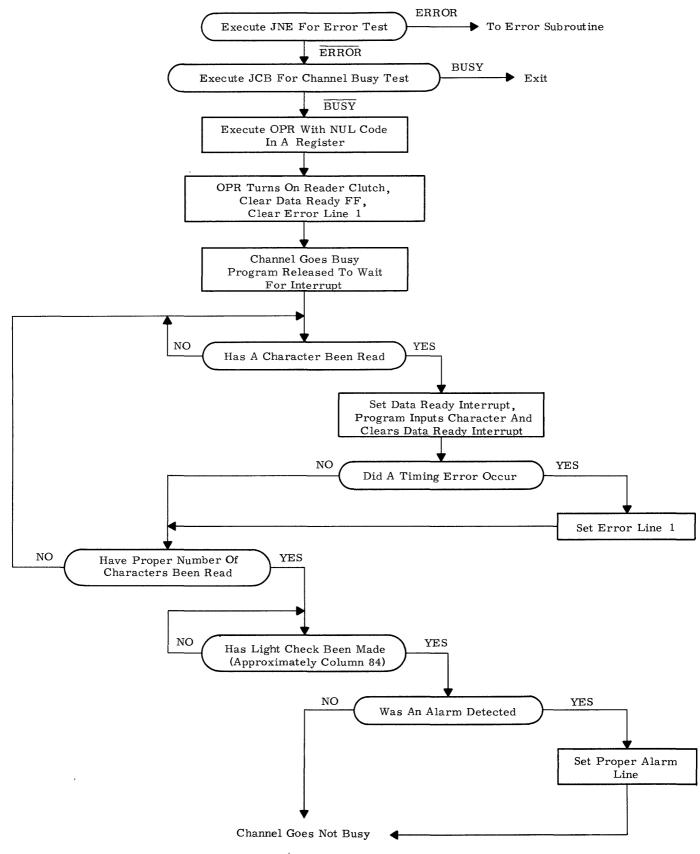

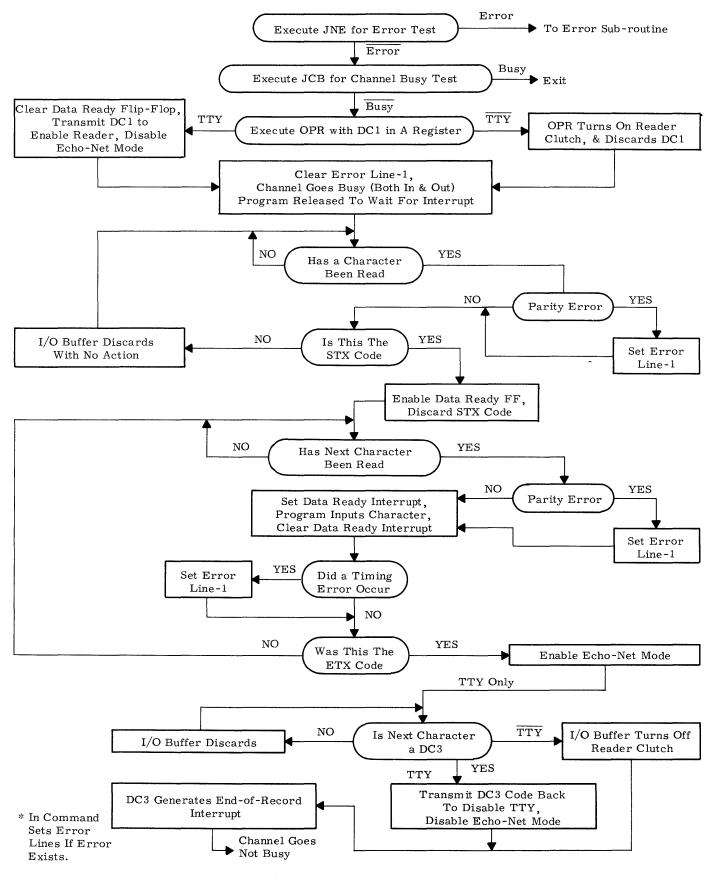

GEN 2 commands are differentiated from other commands by the OP Code (bits 23 through 18)  $25_8$ . GEN 2 commands are also subdivided into commands by the microcoding of the operation portion (bits 14 through 0) of the command word. These commands are employed by the GE-PAC system to: (1) select modules and devices in the input/output equipment, (2) transfer data to or from these devices, and (3) provide for program control transfers (jump) as determined by various internal and external conditions.

Twenty-one different GEN 2 commands are described under the mnemonic GEN 2. Each description contains the microcoded format, discussion of the command usage, and a detailed discussion of the hardware operation when executing the command.

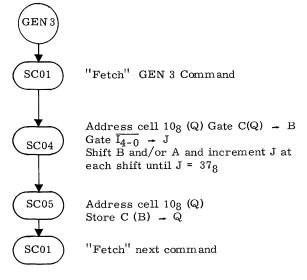

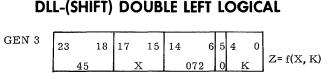

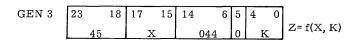

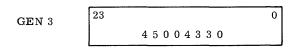

### GEN 3

GEN 3 commands are differentiated from other commands by the OP Code 458. GEN 3 commands are also subdivided into commands by the microcoding of the operation portion of the command word. These commands are used to manipulate the contents of the A and Q Registers, affect the J Counter, and optionally affect the Overflow flip-flop.

Eight individual GEN 3 commands are described in detail under the mnemonic GEN 3.

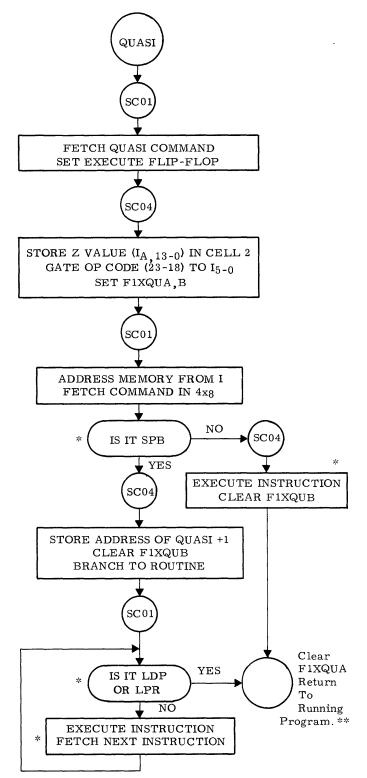

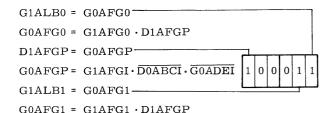

#### Quasi

Quasi commands provide operations not included in the hardware. These commands supply the programmer with a mnemonic which allows the running program to be linked with a subroutine. Quasi commands are identified by OP Codes  $40_8 - 77_8$  if the command is not an MPY, DVD, LDQ, STQ, or GEN 3.

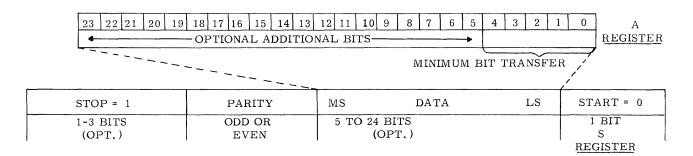

The Quasi command word is divided into four areas: bits 23 through 18, the next command address; bits 17

|                 | 23 | 22 | 21 | 20 | 19            | 18 | 17 | 16           | 15 | 14                      | 13 | 12  | 11 | 10 | 9 | 8  | 7    | 6    | 5  | 4 | 3 | 2  | 1 | 0 |    |  |

|-----------------|----|----|----|----|---------------|----|----|--------------|----|-------------------------|----|-----|----|----|---|----|------|------|----|---|---|----|---|---|----|--|

| FULL<br>OPERAND |    | OP |    | C  | CODE          |    |    | DEXI<br>DRE  |    | *                       |    |     |    |    |   | (  | OPEI | RANI | C  |   |   |    |   |   |    |  |

| GEN 1           |    | 0  |    |    | 5             |    |    | DEX.<br>DDRI |    | C                       |    | C A |    | F  |   | E  | 3    | т    |    | S |   |    |   | K | _  |  |

| GEN 2           |    | 2  |    |    | 5             |    |    | DEXI<br>DRE  |    | S                       |    | S   |    | S  |   | K3 |      |      | K2 |   |   | K1 |   |   | K0 |  |

| GEN 3           |    | 4  |    |    | 5             |    |    | DEXI<br>DRE  | -  | SEE GEN 3 DESCRIPTION K |    |     |    |    | К |    |      |      |    |   |   |    |   |   |    |  |

|                 |    |    |    |    | T MI<br>DR GI |    |    | DEXI<br>DRE  |    | * OPERAND               |    |     |    |    |   |    |      |      |    |   |   |    |   |   |    |  |

\*Relative Address Bit

Fig. CMD.1. Command Formats

through 15, index address modification; bit 14, relative addressing; and, 13 through 0, the operand.

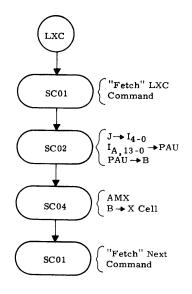

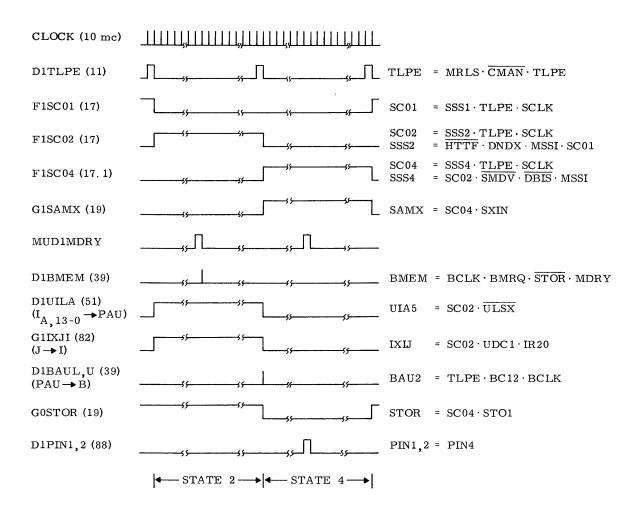

When a Quasi command is "fetched" from memory, indexing and/or relative address modification of the operand portion of the command is performed if specified. After modification, if required, the operand portion of the Quasi command is stored in index cell 2. The next instruction is then addressed from the OP Code portion of the Quasi command. Therefore, program control is transferred to a memory location between  $40_8$  and  $77_8$ . This location will normally contain an SPB command to a subroutine to accomplish the operation. This subroutine may, of course, use the contents of index cell (operand portion of the Quasi command) as an operand address or data value.

A detailed description of the Quasi command is contained under the mnemonic QSI.

## BASIC TIMING OF FULL OPERAND COMMANDS

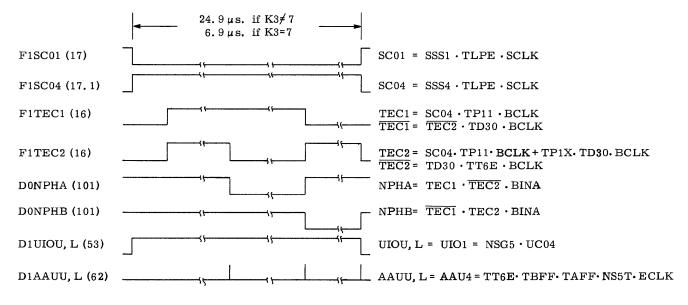

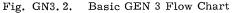

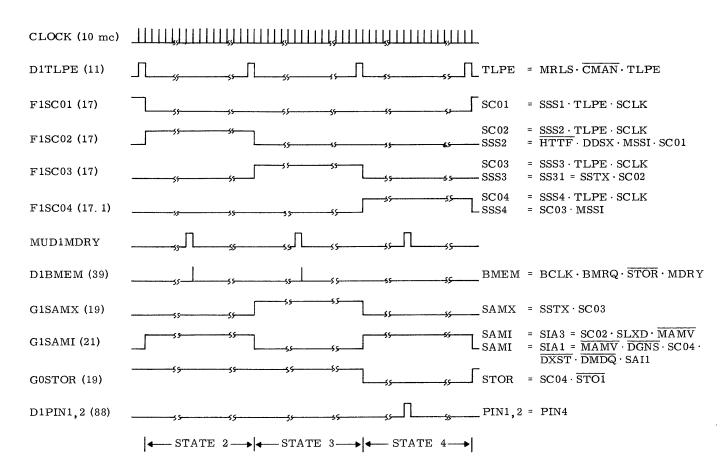

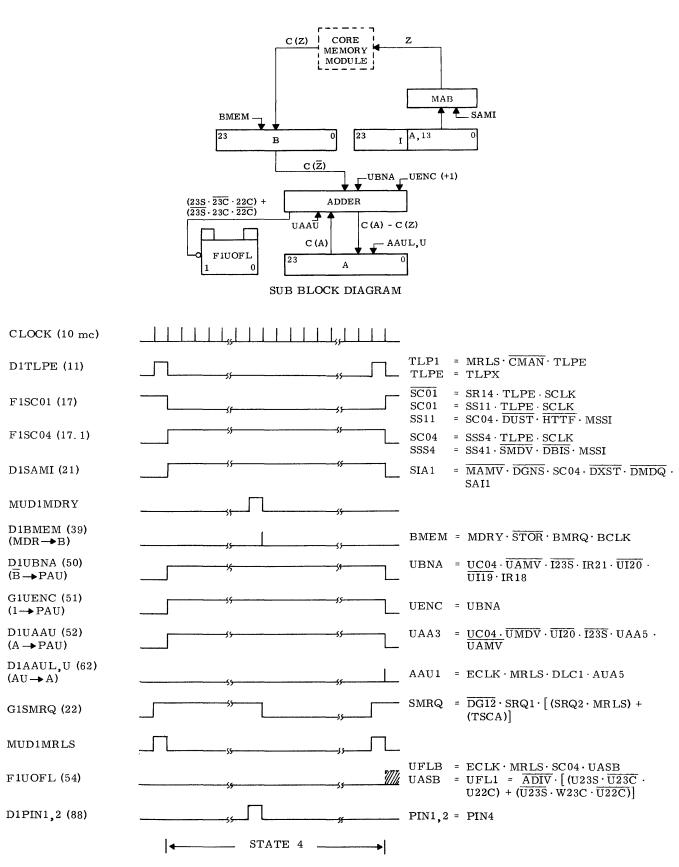

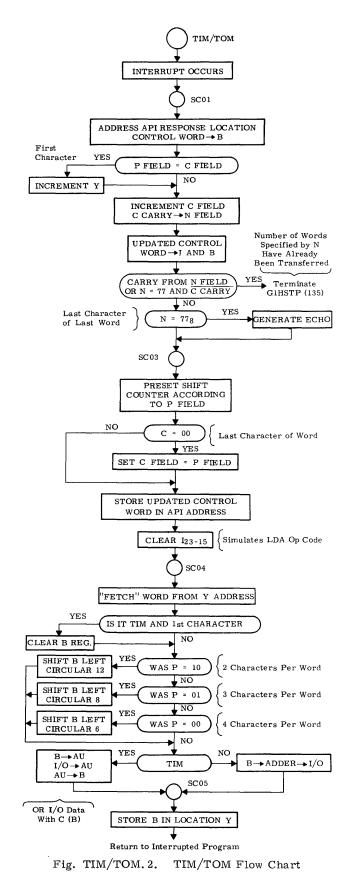

The following paragraphs describe the basic Arithmetic Unit timing for full operand commands. The basic timing for GEN 1, GEN 2, GEN 3, TIM/TOM, and the execution states of MPY and DVD are described with the command description of these commands.

Because the basic timing is identical for all Sequence States of most commands, the command descriptions that follow this section do not include this timing except where differences exist.

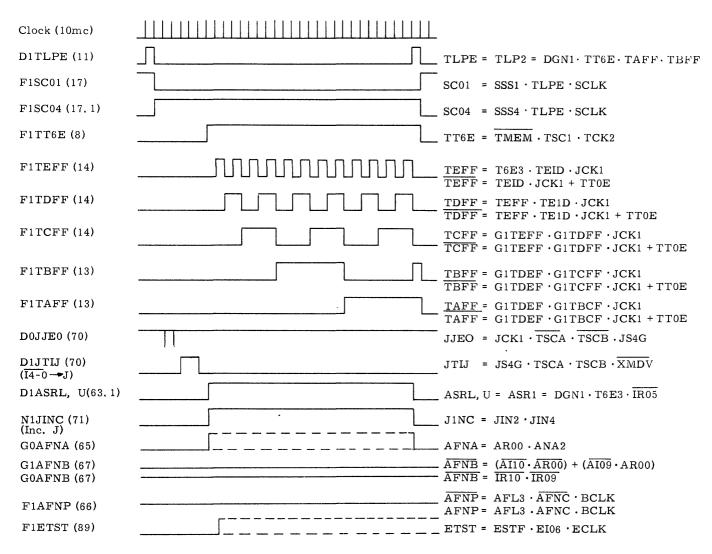

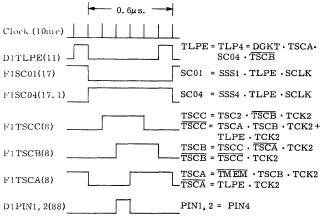

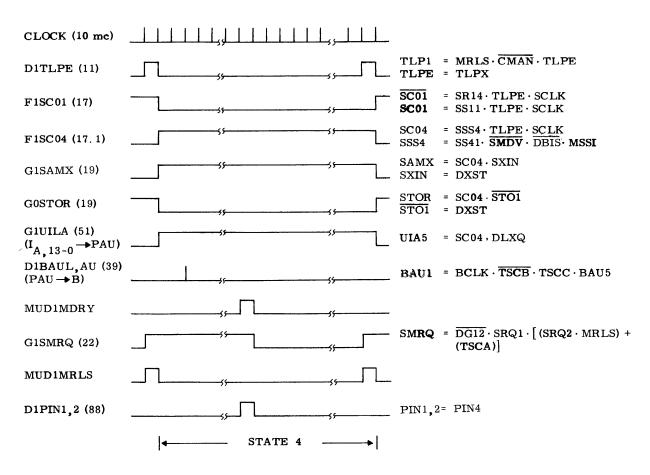

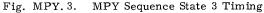

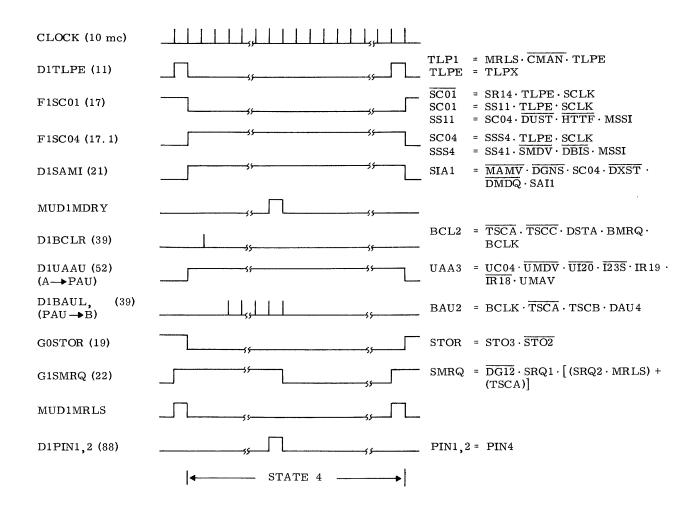

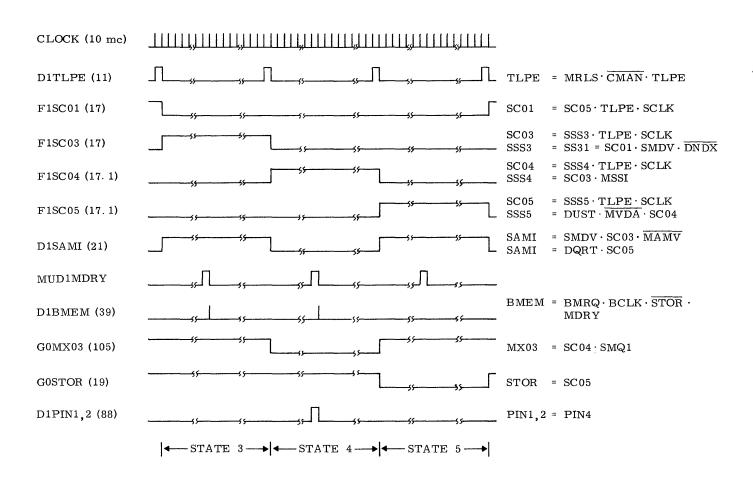

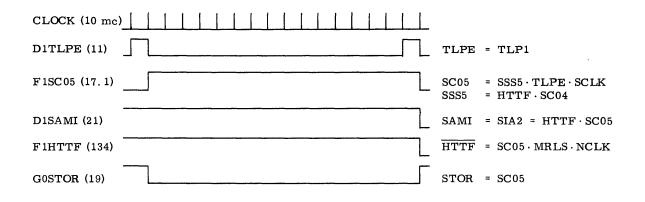

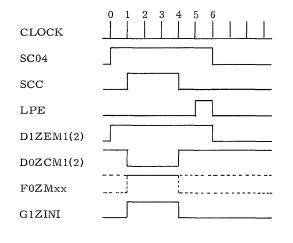

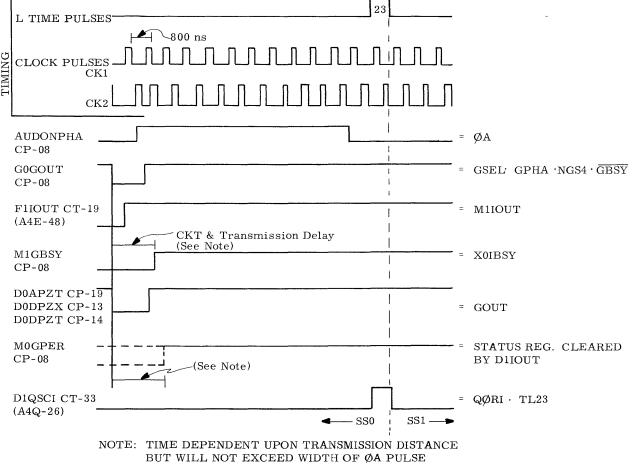

The basic clock signal used throughout the 4020 system is generated from a 10 megacycle crystal controlled oscillator (sheet 7). The output of the oscillator is applied through a variable 25 ( $^{\pm}10\%$ ) nanosecond single shot circuit. Therefore, out of the single shot, 25  $\pm 10\%$ nanosecond pulses occurring at a 10 megacycle rate are applied through clock drivers to the system.

Sequential timing within the Arithmetic Unit is controlled by a 3-state gray code counter (F1TSCA, F1TSCB, and F1TSCC). The condition of these flip-flops (set or clear) are used to specify specific time intervals to perform various functions. Six different time intervals are specified by this counter during the execution of full operand commands. For ease of description, the time intervals are called Time 0 Envelope through Time 5 Envelope. The count sequence and corresponding time envelope nomenclature are:

#### F1TSCA F1TSCB F1TSCC

| 0 | 0 | 0 | Time 0 Envelope |

|---|---|---|-----------------|

| 0 | 0 | 1 | Time 1 Envelope |

| 0 | 1 | 1 | Time 2 Envelope |

| 1 | 1 | 1 | Time 3 Envelope |

| 1 | 1 | 0 | Time 4 Envelope |

| 1 | 0 | 0 | Time 5 Envelope                                                                                                                                                                        |

|---|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | 0 | 1 | Time 6 Envelope -<br>This timing envelope<br>is entered only during<br>execution of MPY,DVD,<br>TIM/TOM, and GEN<br>commands. Refer to<br>these command de-<br>scriptions for details. |

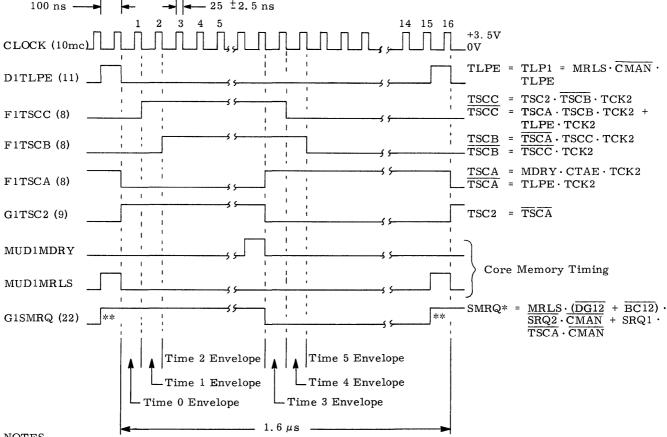

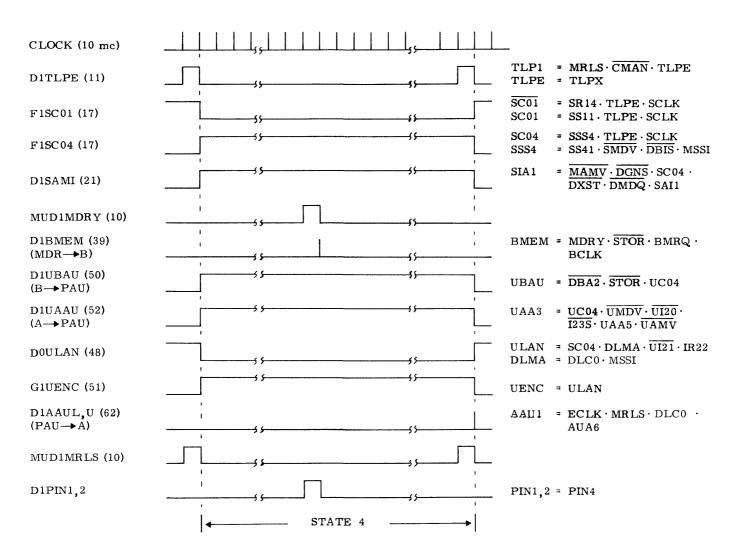

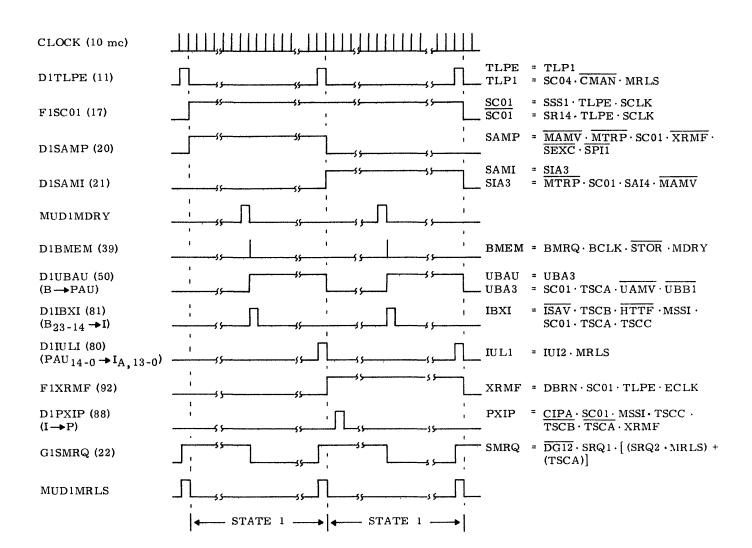

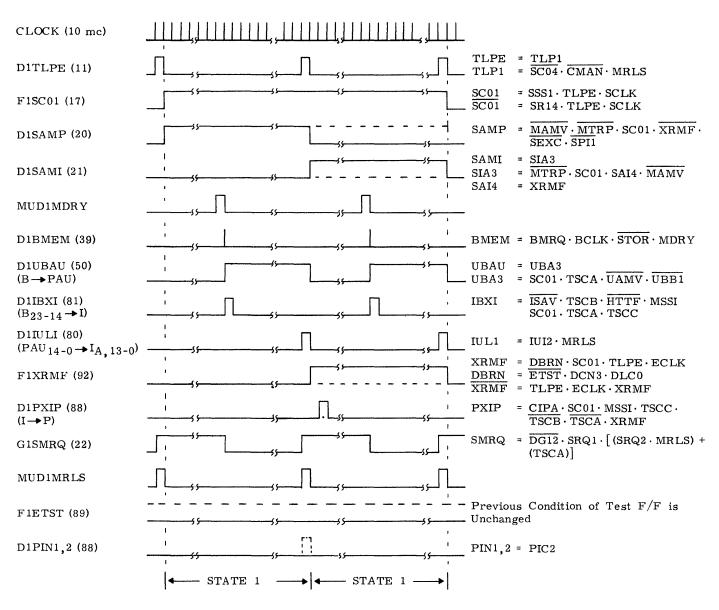

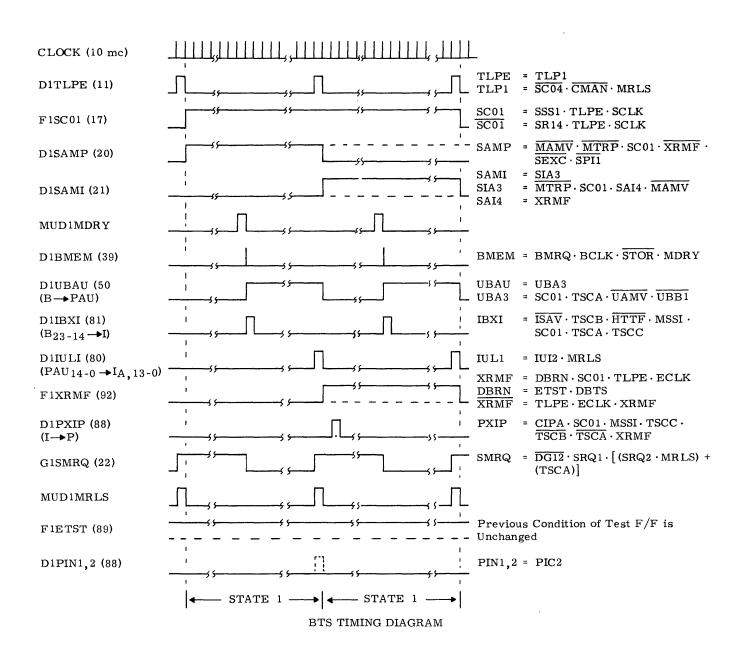

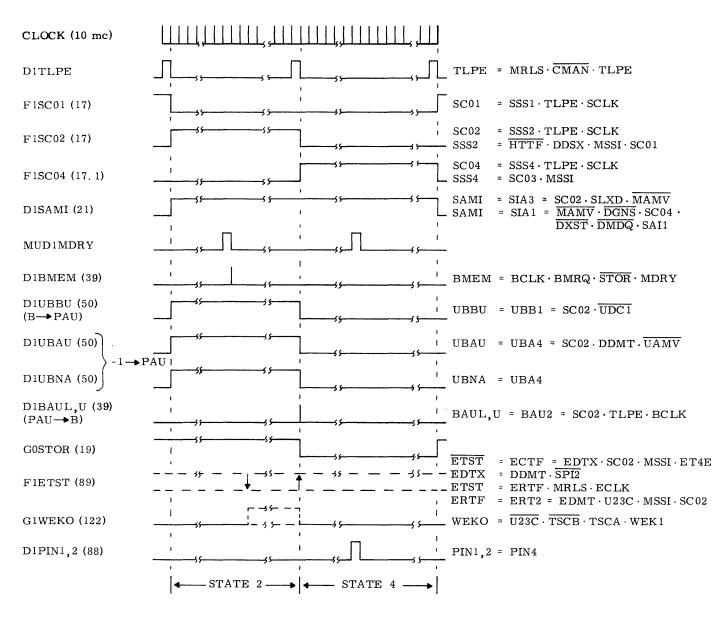

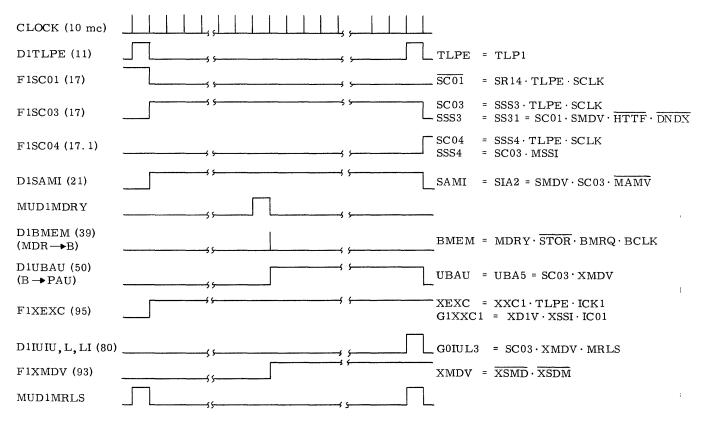

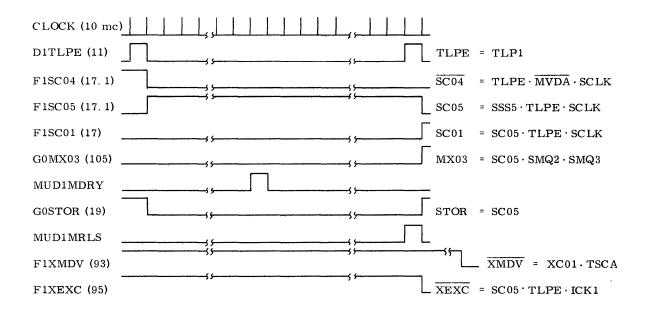

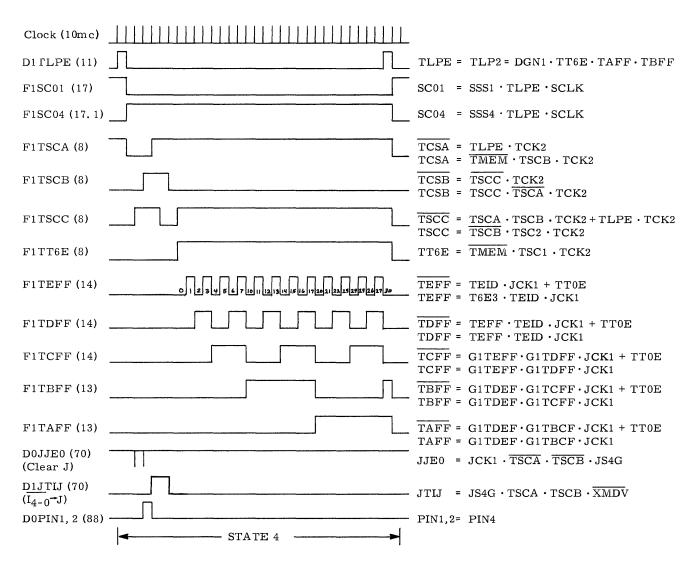

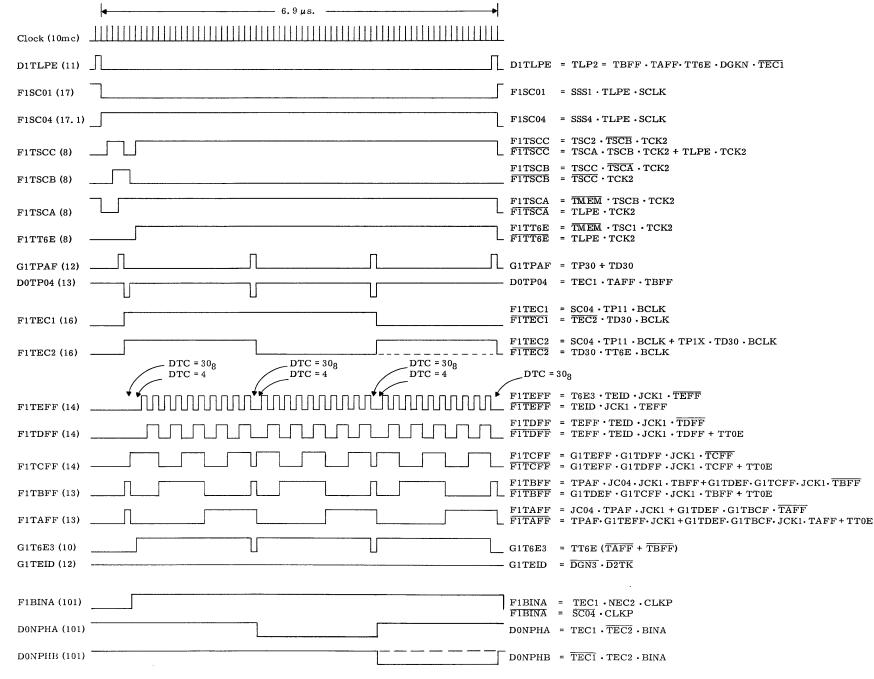

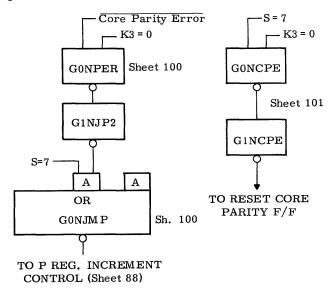

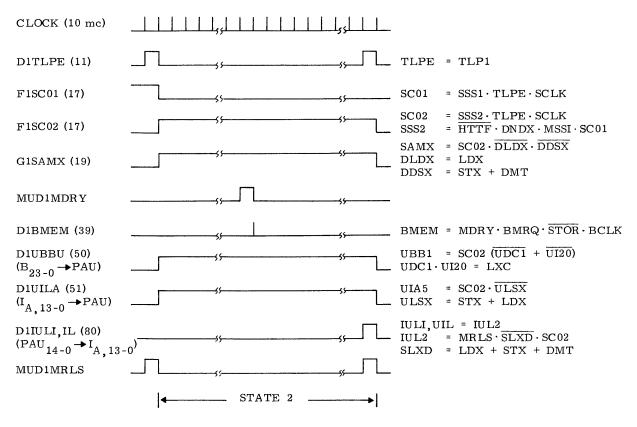

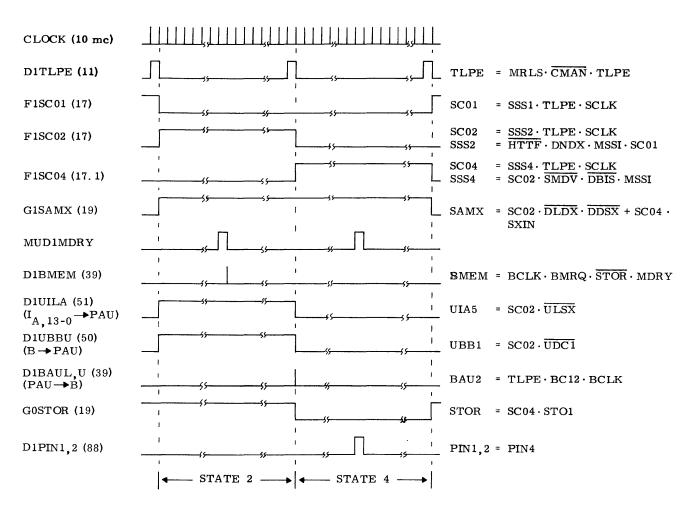

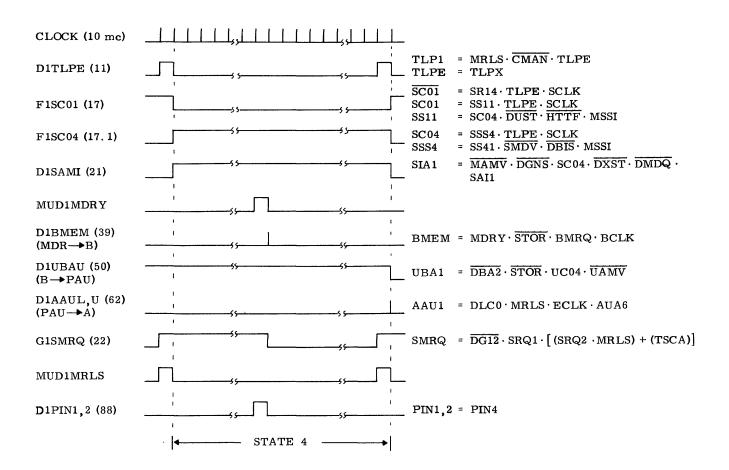

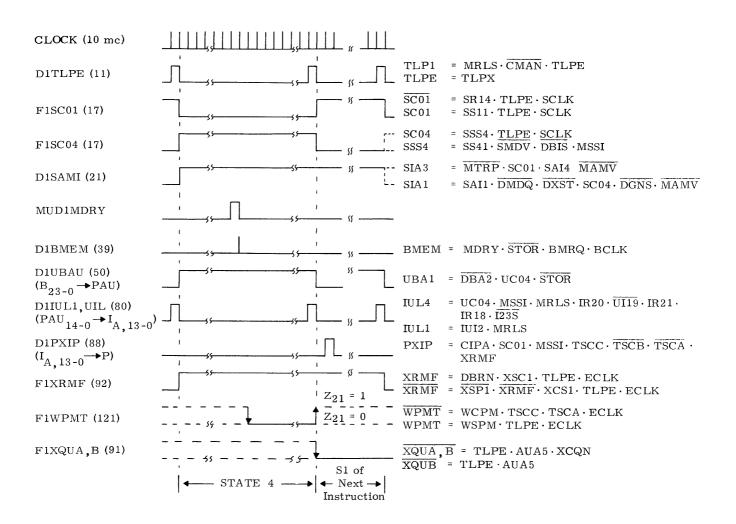

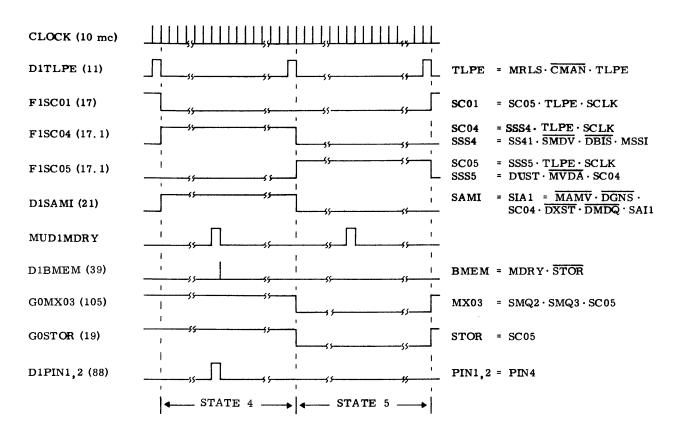

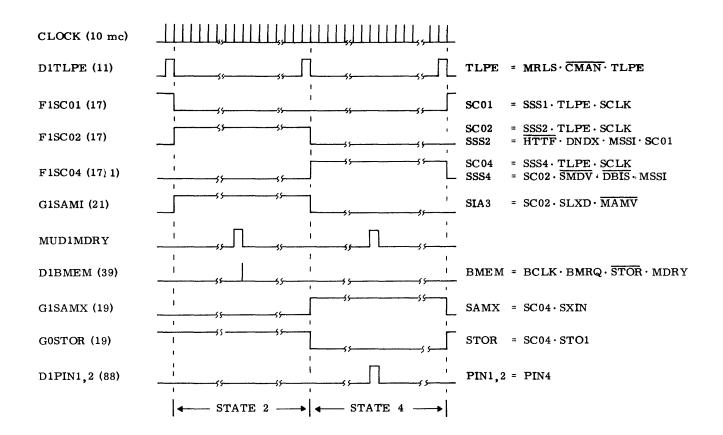

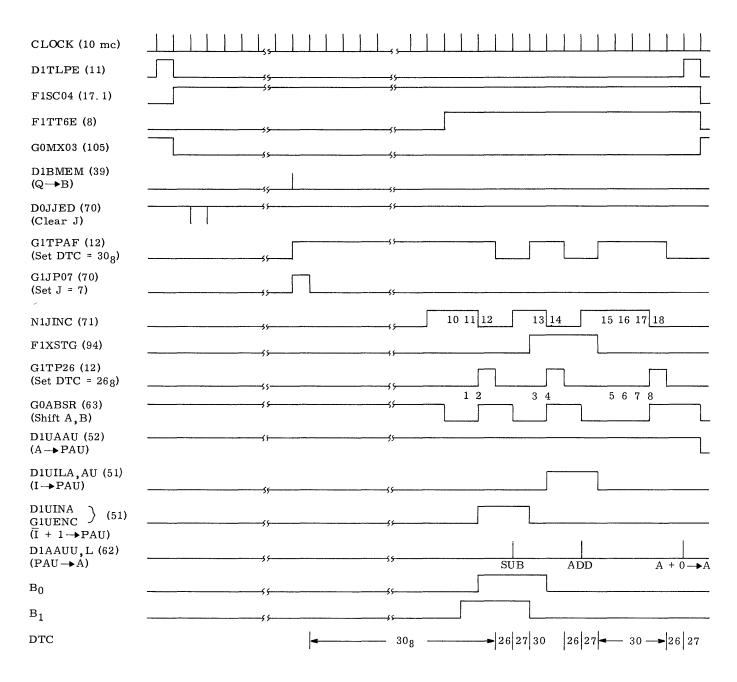

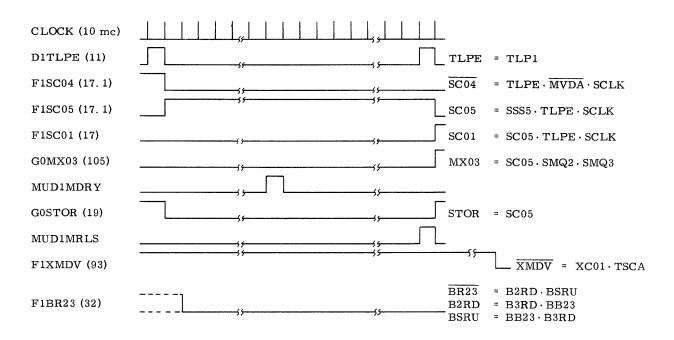

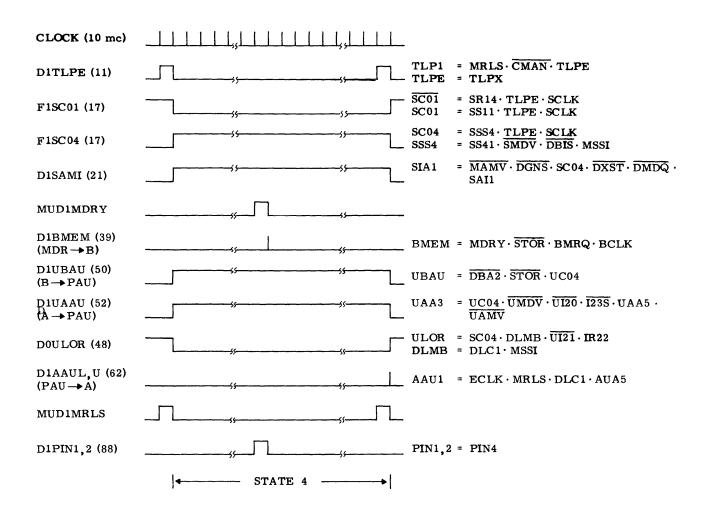

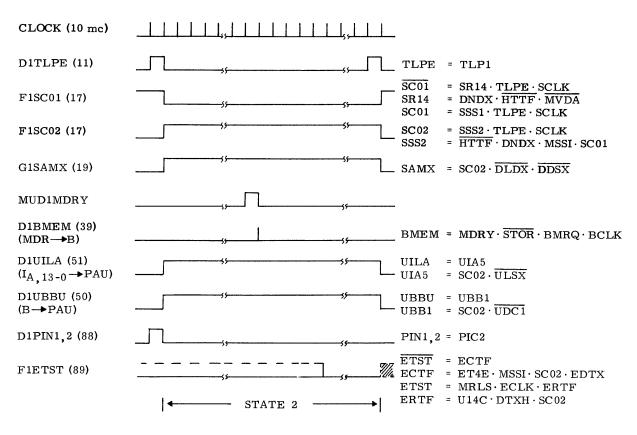

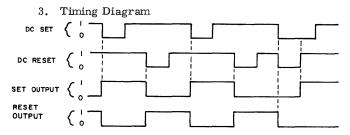

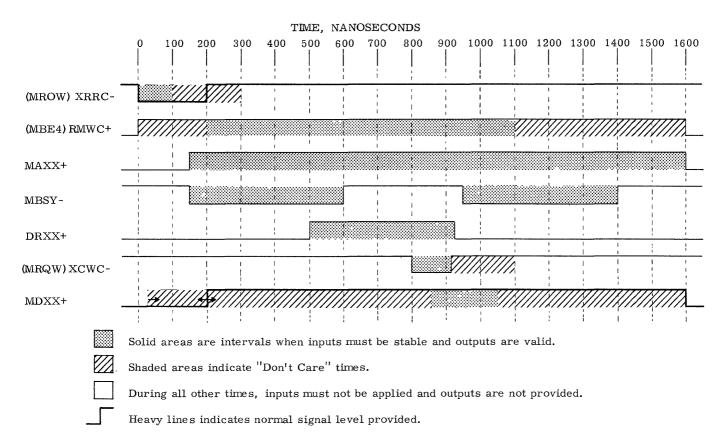

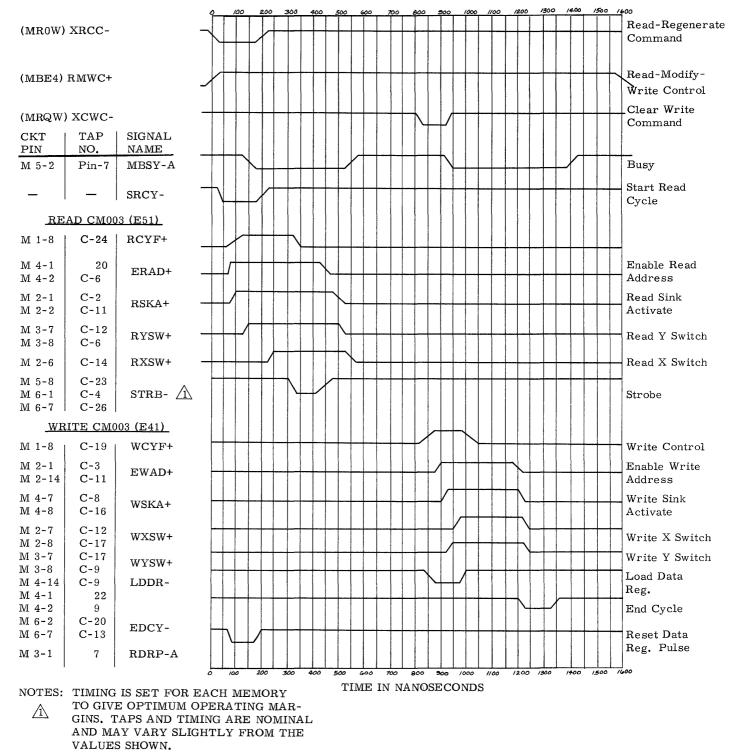

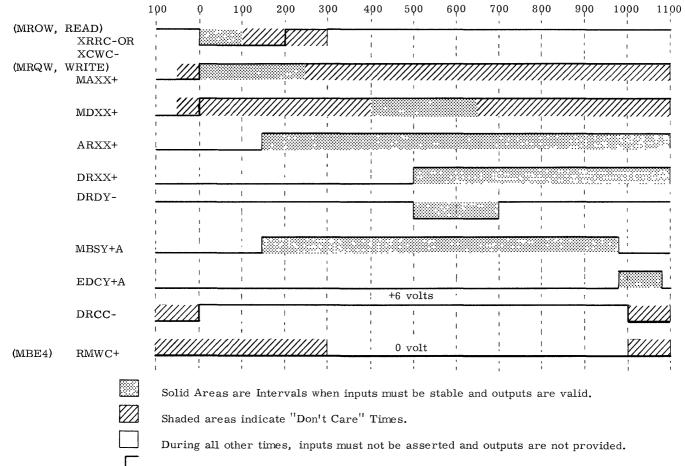

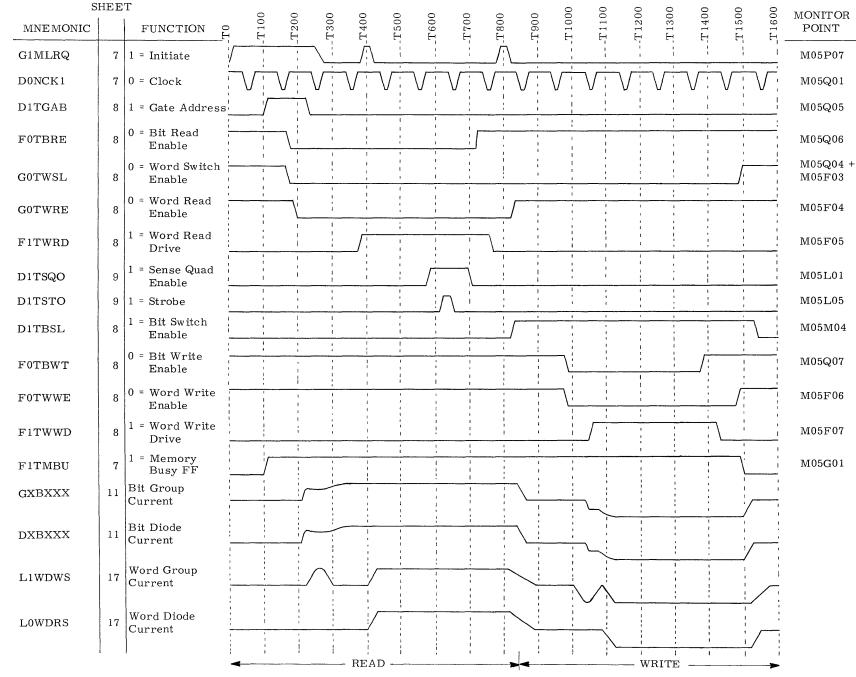

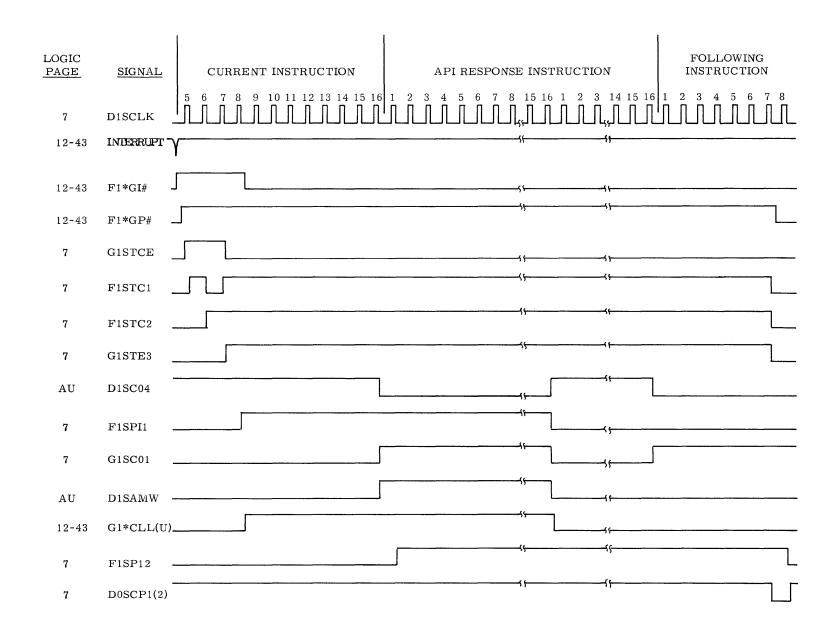

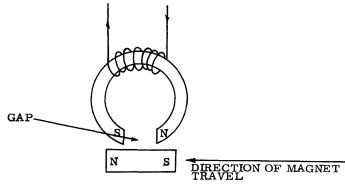

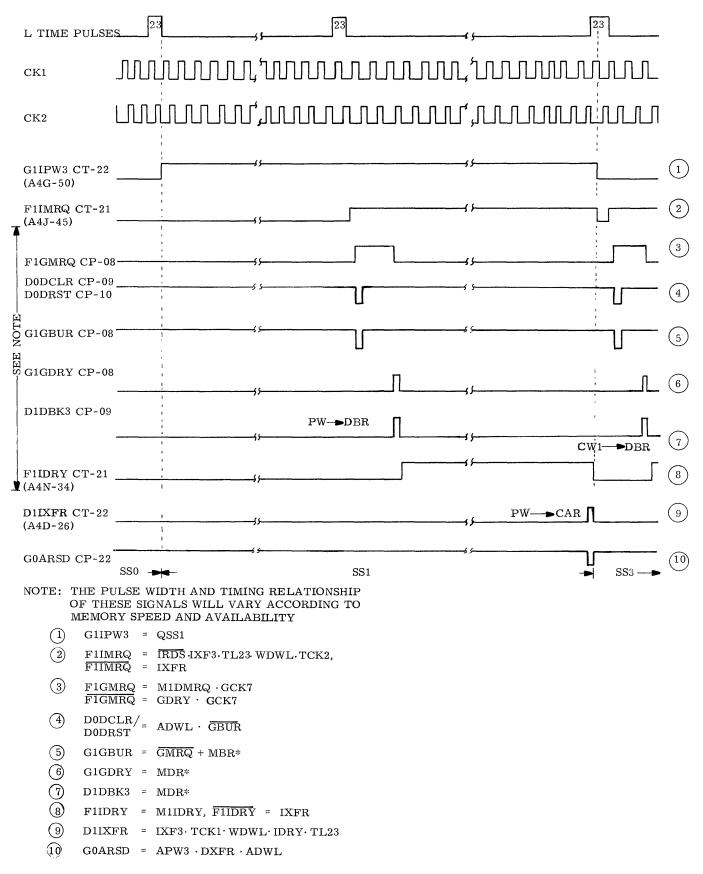

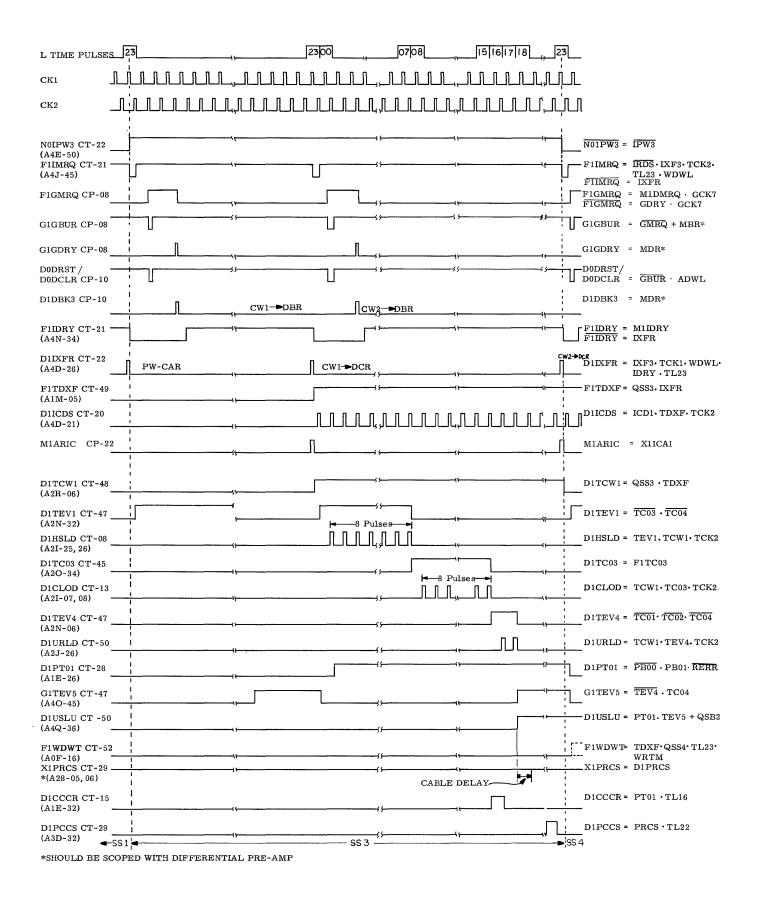

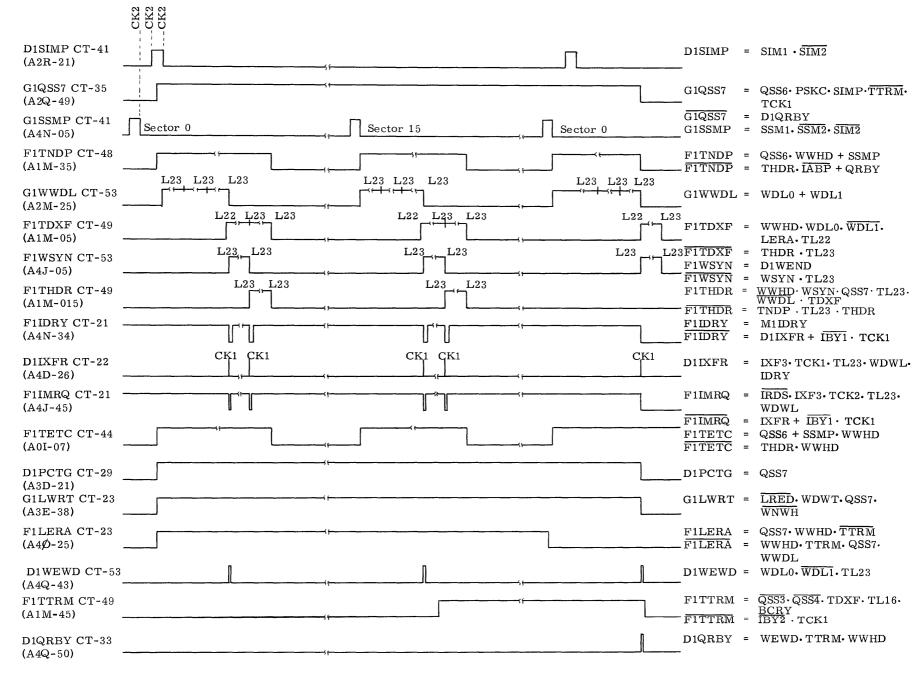

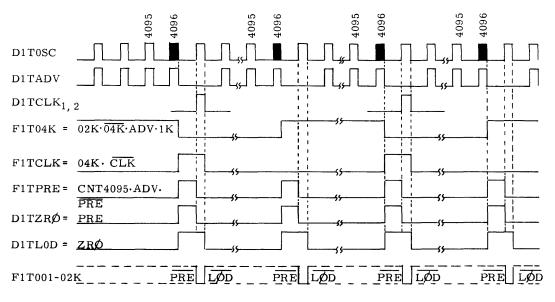

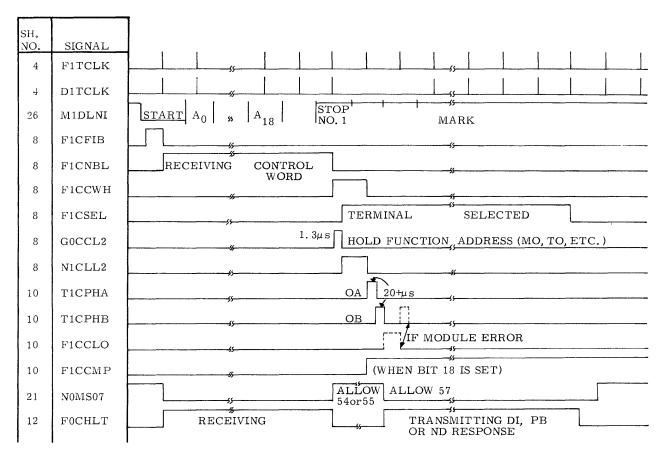

Fig. CMD.2 contains a timing diagram and logic equations of the Sequence Time Counter. This timing diagram applies to all commands except the execution states of GEN 1, GEN 2, GEN 3, MPY, DVD, and TIM/ TOM operations.

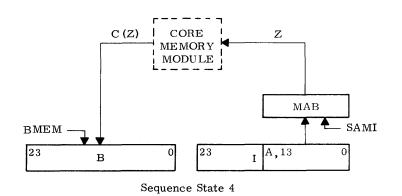

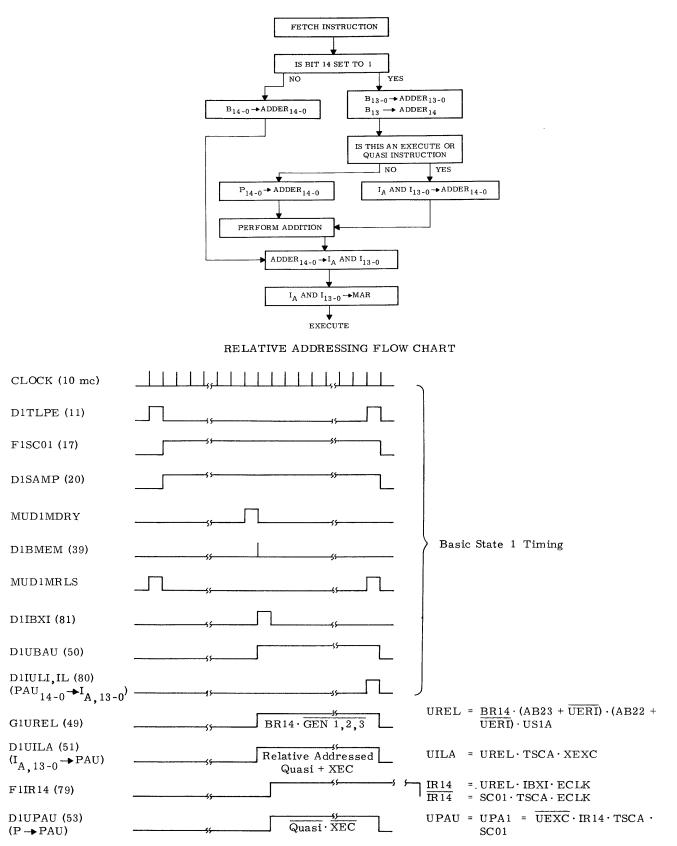

Last Pulse (D1TLPE) of any Sequence State or the Initialize signal (DOTINT) clears the gray code counter forming Time 0 Envelope. Clearing F1TSCA enables G1TSC2. With TSC2 enabled, the first clock pulse sets F1TSCC, forming Time 1 Envelope. The next clock pulse sets F1TSCB, forming Time 2 Envelope. Time 2 Envelope is enabled until Data Ready (MUD1MDRY) is received from the core memory module. This normally provides a duration of 6 clock pulses. The clock pulse during Data Ready sets F1TSCA, forming Time 3 Envelope. The next clock pulse clears F1TSCC, forming Time 4 Envelope. The next clock pulse clears F1TSCB, forming Time 5 Envelope. Time 5 Envelope is enabled until Last Pulse is generated. Last Pulse is generated from the Memory Release signal (MUD1MRLS), applied by the Core Memory module at the end of the memory timing cycle. This provides Time 5 Envelope with a duration of approximately 6 clock pulses. Last Pulse Envelope clears the Sequence Time Counter for the next timing cycle. The duration of Time 0 through Time 5 is approximately 1.6 microseconds.

As described above, the duration of Time 2 Envelope and the duration of Time 5 Envelope is dependent upon the memory cycle. The memory cycle begins with Memory Request (G1SMRQ) when access to memory is granted by the memory priority scheme. Memory Request is normally enabled by the Memory Release (MUD1MRLS) signal generated in the memory. If, however, the previous or next cycle does not require memory access (i.e., State 4 of GEN 1 or GEN 2 command, or when State 4 is extended for the execution of GEN 3, MPY, DVD, or TIM/TOM), the Memory Request signal is inhibited until Time 0 Envelope. In either condition, a time duration of 1.7 microseconds is required by the memory to determine access priority and to complete the memory cycle. Therefore, if Memory Request is inhibited until Time 0, the duration of Time 2 Envelope will be extended by one clock pulse while awaiting Data Ready. This is, of course, a comparatively rare occurrence.

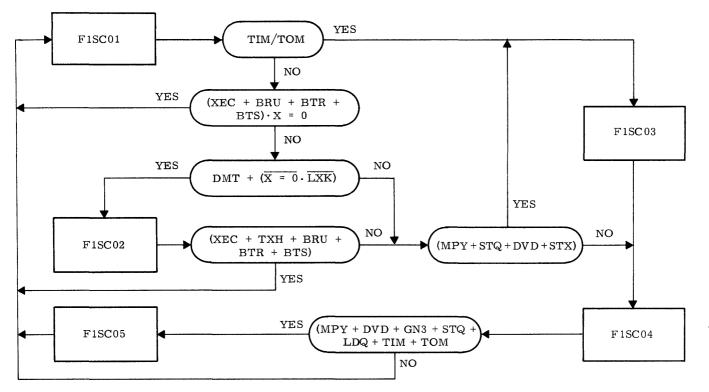

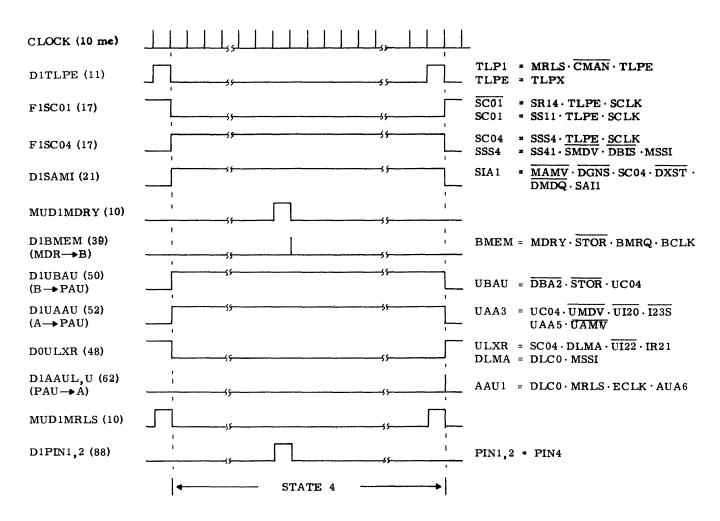

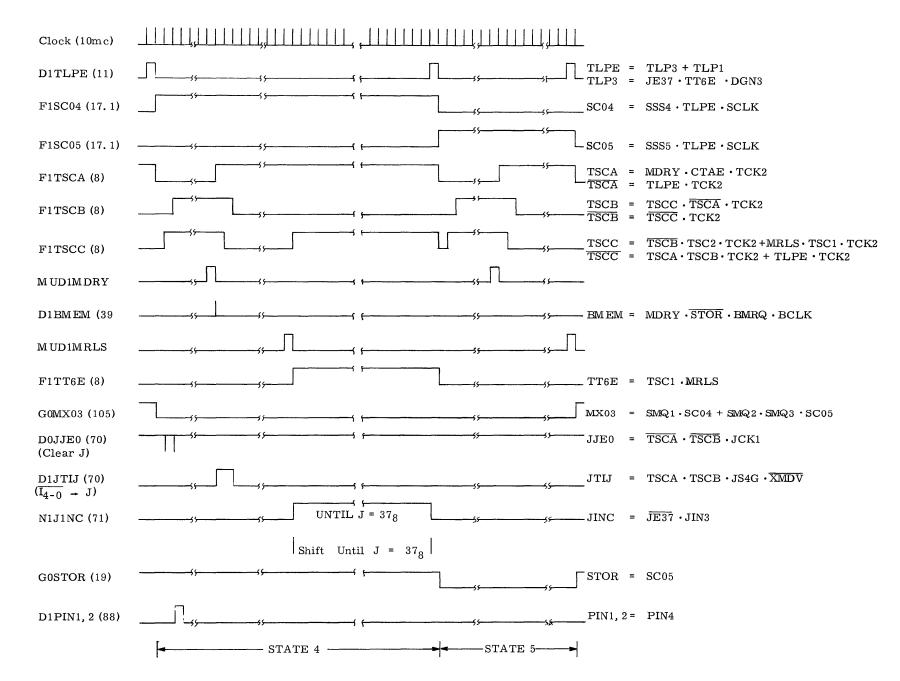

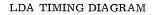

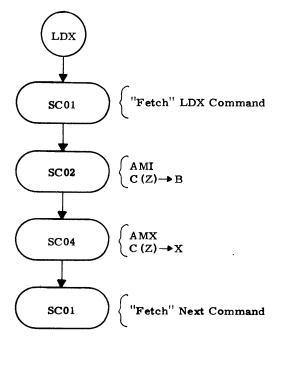

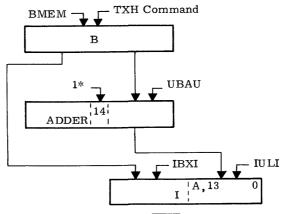

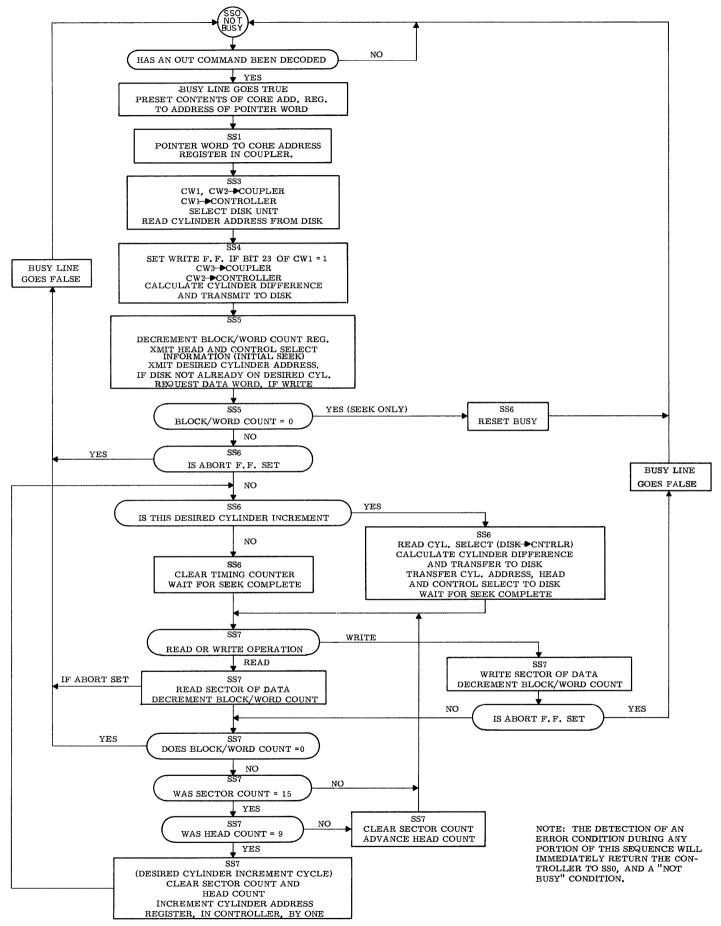

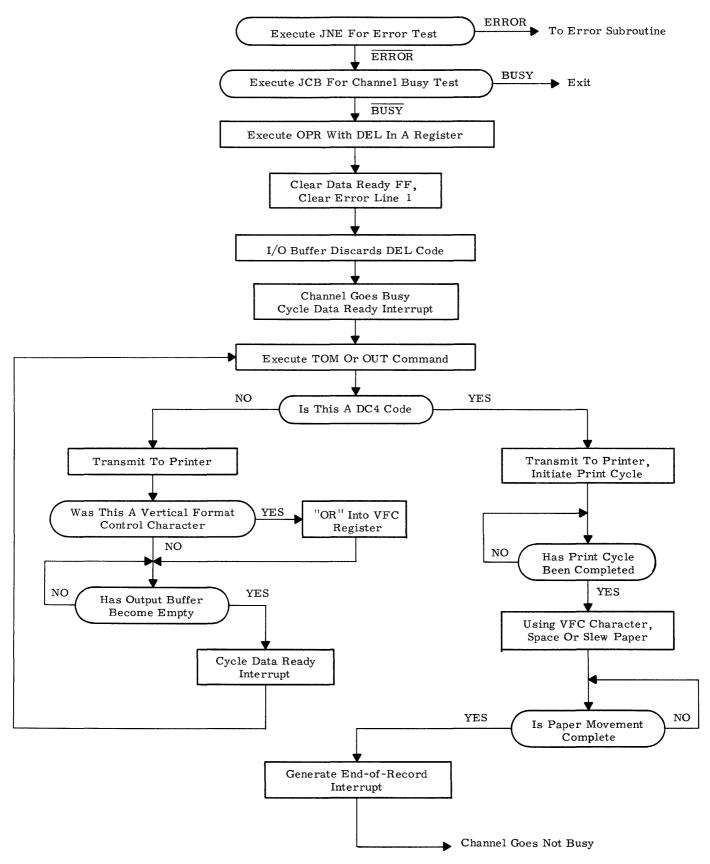

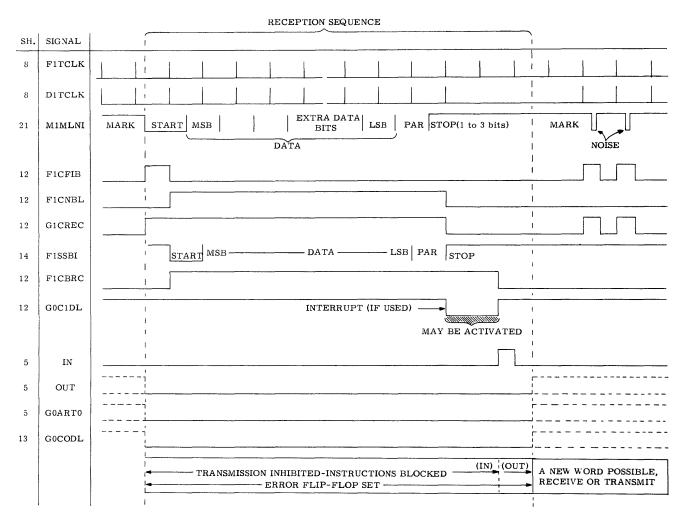

#### Instruction Sequencing

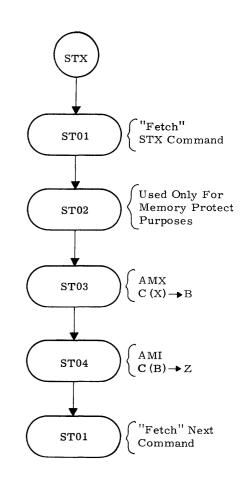

All instructions performed by the 4022A Arithmetic Unit follow a definite set pattern or sequence for "fetching" the instruction from memory, performing index address modification if required, and executing the instruction. Sequence Control State flip-flops F1SC01, F1SC02, F1SC03, F1SC04, and F1SC05 are provided to control this pattern or sequence.

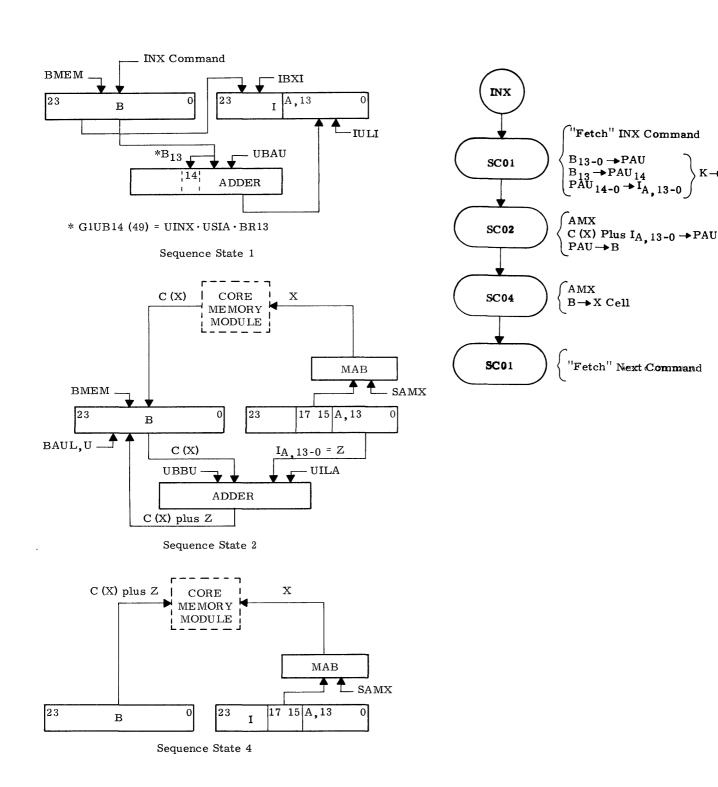

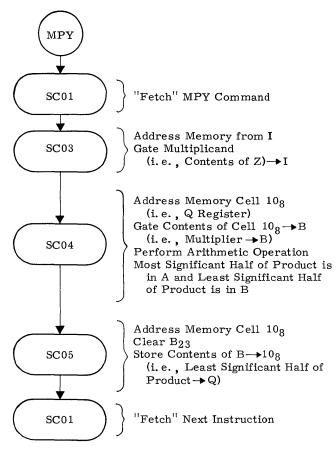

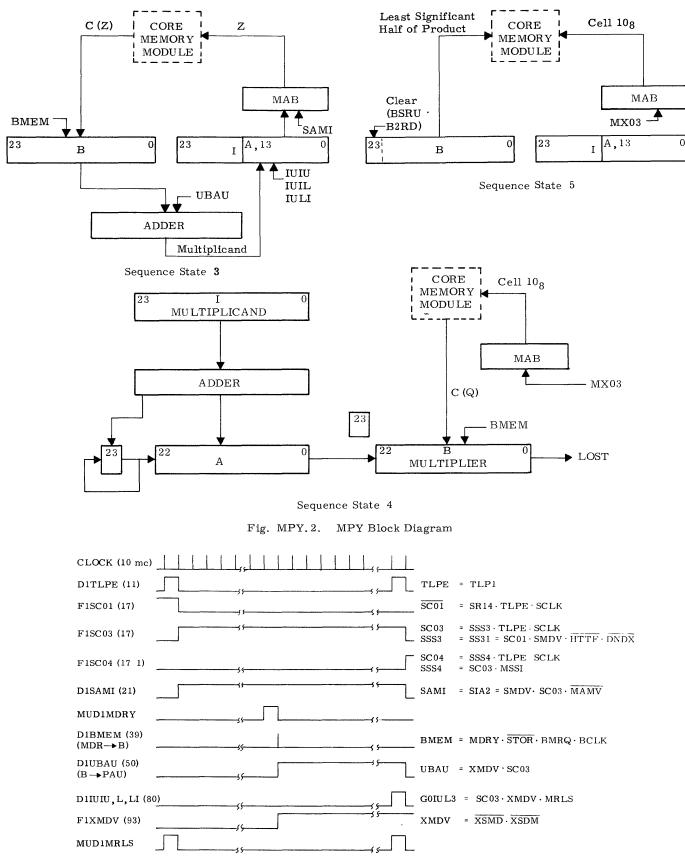

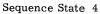

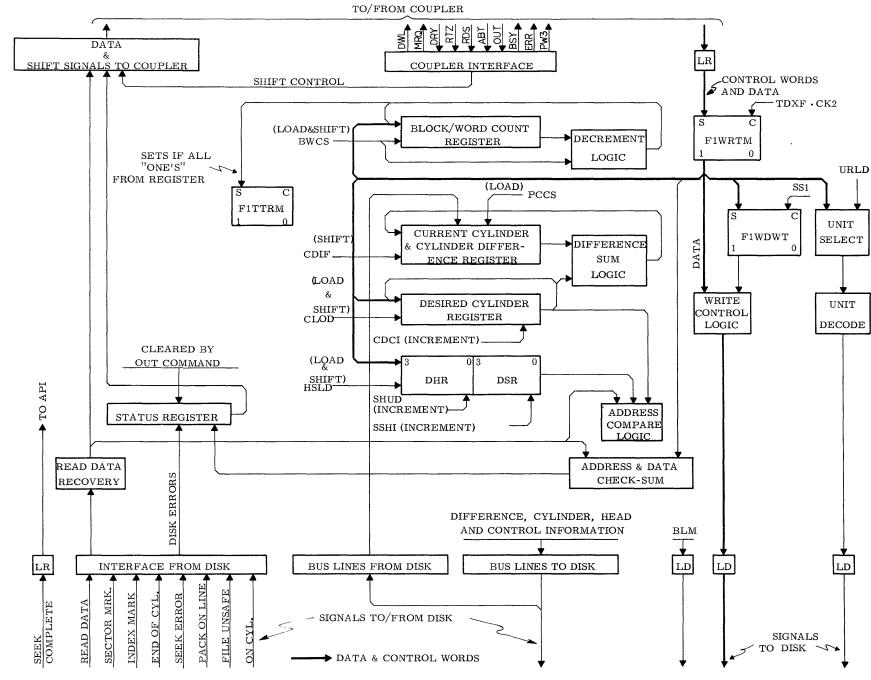

Fig. CMD. 3 graphically illustrates the Sequence States required to fetch, index, and execute any instruction. Briefly, the function performed during each Sequence Control State is described below.

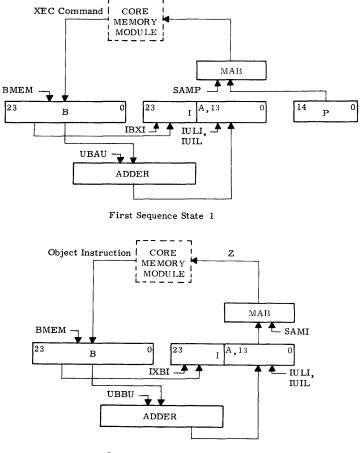

- Sequence Control State 1 F1SC01: During this Sequence State, all commands are "fetched" from memory. Non-indexed XEC, BRU, BTR, and BTS commands are also executed during Sequence Control State 1.

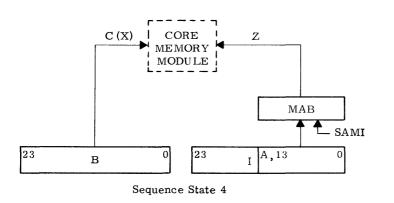

- Sequence Control State 2 F1SC02: During Sequence State 2 index address modification occurs. Also, STX, TXH, and DMT commands use State 2 for a portion of the execution.

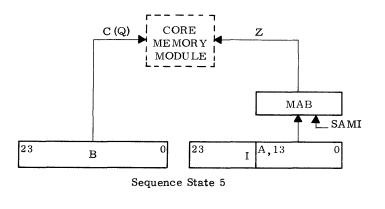

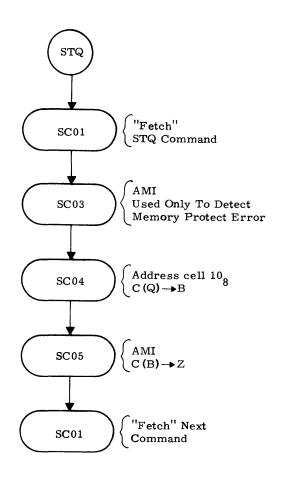

- Sequence Control State 3 F1SC03: State 3 is used during the execution of MPY, DVD, STQ, STX, and TIM/TOM operations.

- Sequence Control State 4 F1SC04: State 4 is the execution state for most commands.

- Sequence Control State 5 F1SC05: State 5 is used during MPY, DVD, GEN 3, STQ, LDQ, and TIM/TOM instructions to complete their execution cycle.

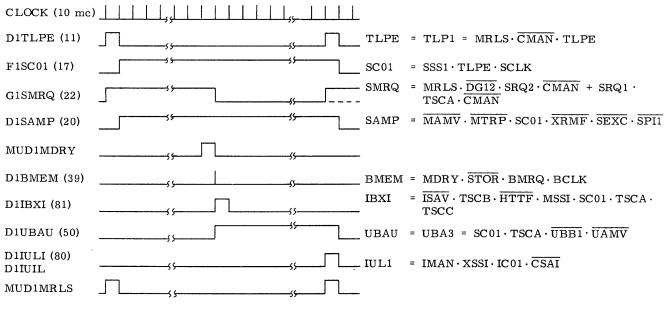

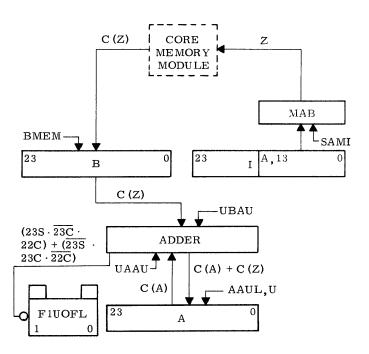

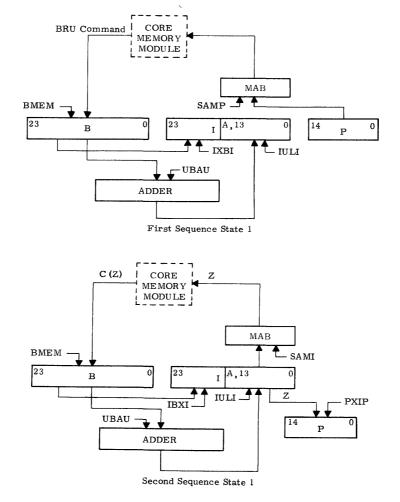

#### Sequence Control State 1

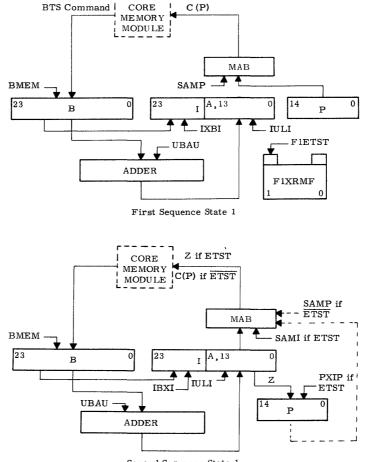

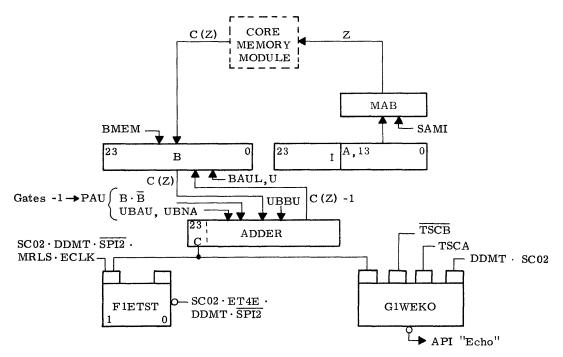

Sequence Control State 1 defines the "fetch" cycle for all instructions. Because State 1 is nearly the same for all commands, it is not described in the command descriptions later in this section unless it performs unique functions (e.g., XEC, BRU, TXH, BTR, and BTS). Therefore, the following discussion describes the detailed operation of the Arithmetic Unit during State 1. This discussion applies to all commands.

#### NOTES

- \* Memory Request is not enabled during State 4 of GEN 1 and GEN 2 commands.

- \*\* Memory Request is not enabled until Time 0 when following a Sequence State that does not use memory or a Sequence State that is extended (i.e., following State 4 of GEN. 1, 2, 3, MPY, DVD, or TIM/TOM). When Memory Request is not enabled until Time 0, Time 2 is extended by 1 clock pulse awaiting data ready.

Fig. CMD.2. Full Operand Basic Timing Diagram

#### **ARITHMETIC UNIT**

Fig. CMD. 3. Instruction Sequencing

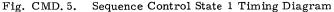

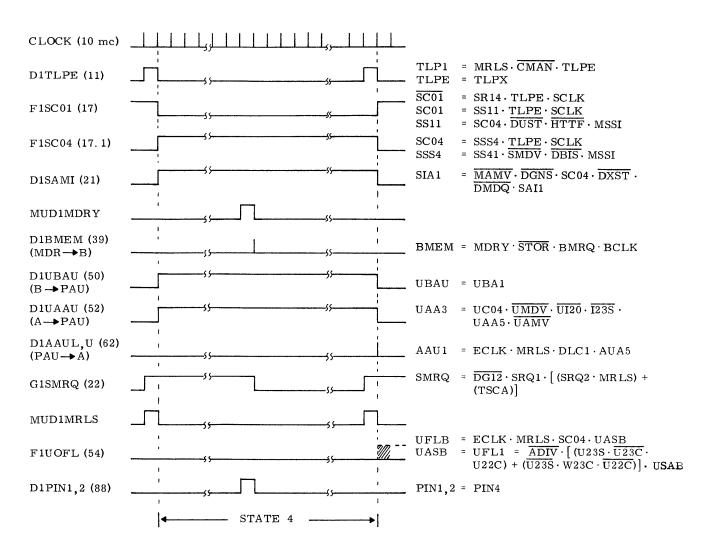

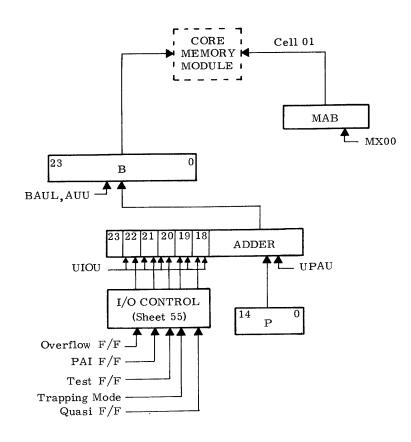

Fig. CMD. 4. State 1 Block Diagram

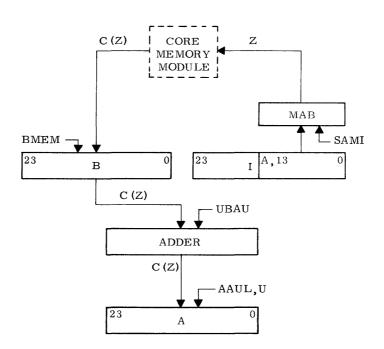

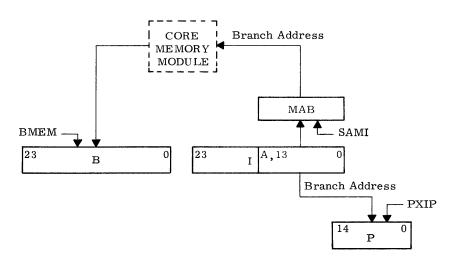

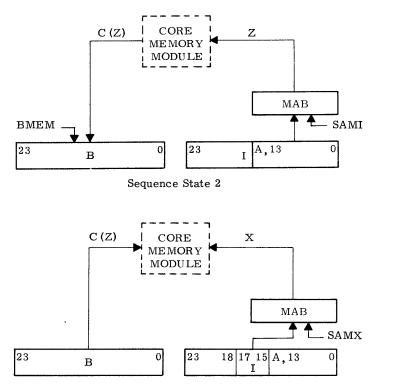

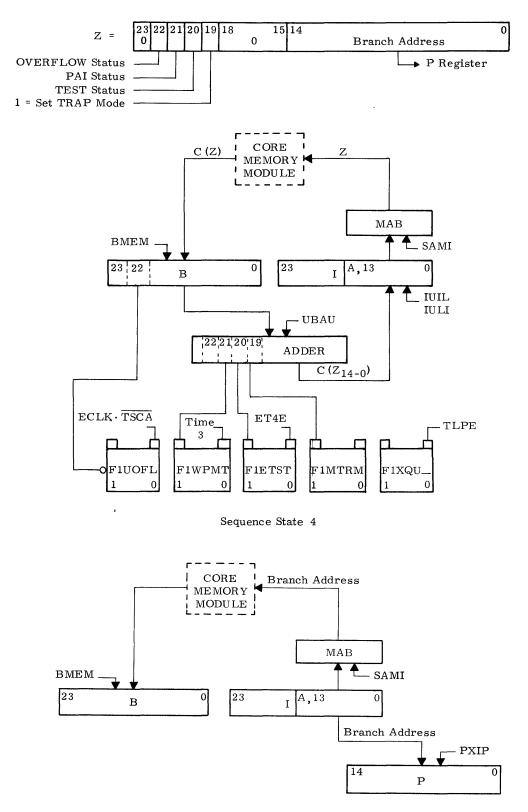

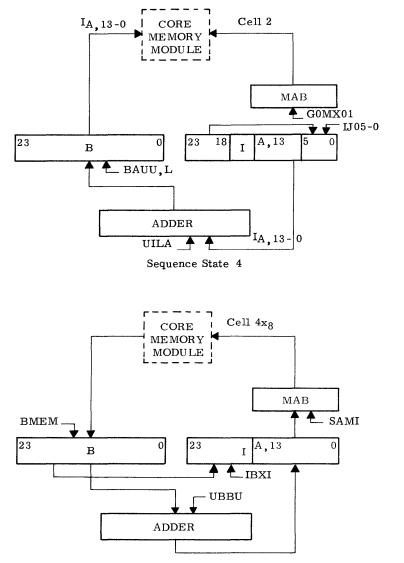

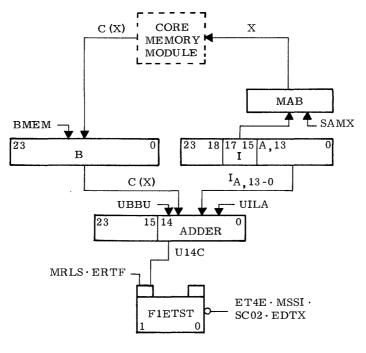

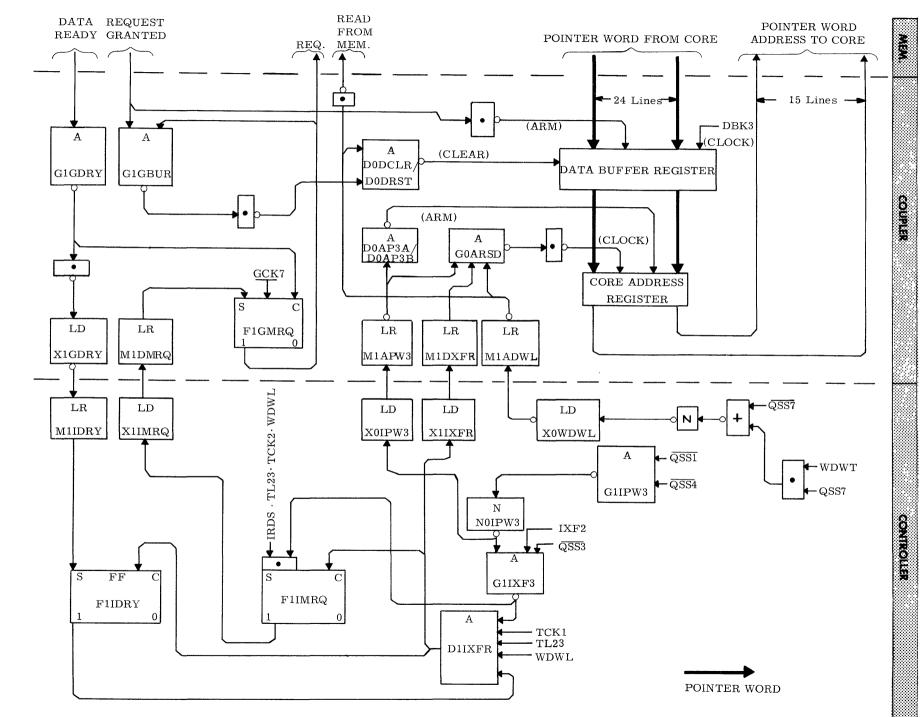

Fig. CMD. 4 contains a block diagram of the Arithmetic Unit operation during a normal Sequence State 1. A timing diagram and logic equations for State 1 are contained in Fig. CMD. 5. Refer to these aids during the following discussion. During Sequence State 1, memory is always requested (G1SMRQ) to "fetch" the next command from memory. Memory is addressed from the P Register during State 1 except when following a branch instruction (SPB, BRU, BTS, BTR, LDP, or LPR), an XEC command, an Automatic Program Interrupt, a Memory Protect Error, or when a new Protect Status Word is required for the optional Memory Protect logic. Upon receipt of the Data Ready signal from the core memory module, the command located in the addressed memory location is gated to the B Register by D1BMEN. Bits 23 through 14 of the command are gated from B to the I Register (IBXI). This places the OP Code of the instruction fetched in the I Register where it is decoded and the operation to be performed is determined. The operand address portion of the command (bits 13-0) is gated to the I Register via the Adder Unit. If the command is relative ad-dressed (bit 14 is a "one"), relative address modification of the operand address occurs in the Adder Unit prior to being transferred to the I Register. Relative Addressing is described separately under the mnemonic RLT in the command description portion of the description.

At memory release, Last Pulse Envelope is enabled to end State 1. Sequencing will then continue for execution of the command as described under the mnemonic of the command.

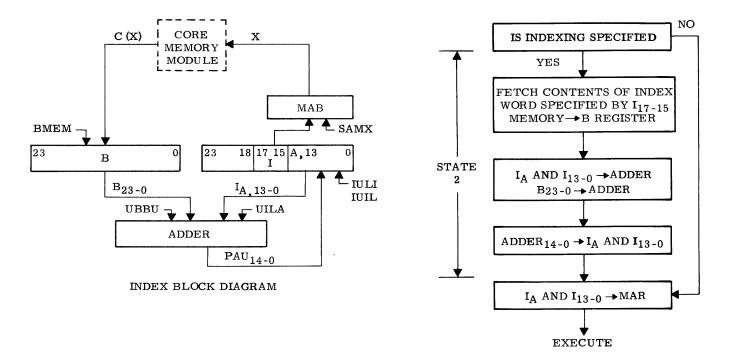

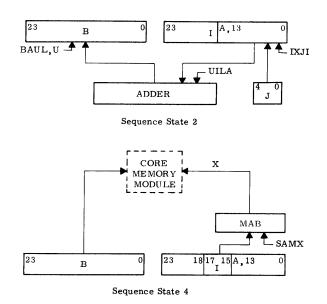

#### INDEXING