# GE-PAC 30-2 MICRO-PROGRAMMING MANUAL

\*Registered Trademark of General Electric Company

# GE-PAC 30-2 MICRO-PROGRAMMING MANUAL

General Electric reserves the right to make changes in the equipment (or software) and its characteristics (or functions) at any time without notice.

CONTENTS

INTRODUCTION PROCESSOR MICRO-INSTRUCTIONS ASSEMBLER ASSEMBLER OPERATION MICRO-SIMULATOR ROMWATS DESCRIPTION

# SECTION 1

# INTRODUCTION TO MICRO-PROGRAMMING THE GE-PAC 30-2

The General Electric GE-PAC 30-2 computer is a very fast, simple and uncomplicated machine. This computer is controlled by a Read-Only-Memory (ROM). A series of programs wired into the **ROM** control the flow of information within the registers and core storage of the machine. These programs are a sequence of very simple and elementary steps. These steps, or microinstructions, perform functions such as transferring the content of one register to another. A series of these micro-instructions can be combined to solve highly complex problems. The micro-program in the standard GE-PAC 30-2 is designed to emulate a third generation computer. This entire program, which handles all the instructions, interrupts and display function of the third generation computer represents less than one thousand micro-instructions in the ROM.

Any computer could be emulated by changing the micro-program directing the operation of the GE-PAC 30-2. Special instructions or functions can be added by developing a new microprogram. It is evident that the micro-program replaces the costly, complicated and failureprone hardware of a much more sophisticated computer or controlling device. The basic speed and non-destructable characteristics of this technique combined with ease of implementation and low cost make it the most attractive alternative to special purpose hardware yet available.

The micro-instructions for the machine are quite similar to the instructions for a conventional machine. For example, they are located at various addresses in the Read-Only-Memory, and they consist of operation codes that operate on various operands. To write programs for the micro machine, it is convenient to use the same kind of symbolism that is used for writing programs on conventional machines, and this means it is convenient to use an assembler. An assembler allows:

- 1. Operation codes to have symbolic names.

- 2. Operand to have symbolic names.

- 3. Numbers to be written in a natural way.

- 4. Memory locations to have symbolic names.

- 5. Error checking to be performed.

The GE-PAC 30-2 Micro-Code Assembler performs all of these functions and will run on any standard GE-PAC 30 computer with 8K bytes of memory and a teletypewriter.

Each micro-instruction is represented by a wire strung through the U-core ferrite transformers of the ROM. The data in a ROM is mechanically "loaded" during the manufacturing process by weaving the wires through an array of 32 U-cores. Each transformer corresponds to one binary bit of information. If the wire passes through the center of the U-core, a "one" will be read out of that bit position when that wire is pulsed. If the wire passes on the outside of the transformer, a "zero" will be read. Each wire is assigned a consecutive pair of hex addresses. The wire is woven according to the data to be stored in those addresses. Hence, each wire contains two 16-bit micro-instructions.

Since an error in a micro-program would require the restringing of the offending wires, it is highly desireable to wire a fully checked program. The GE-PAC 30-2 Micro-Code Simulator is used for testing and debugging GE-PAC 30-2

Micro-Code programs before they are wired into the ROM. It is an interactive program that enables the debugging process to proceed from a Teletypewriter keyboard under full control and continuous observation by the designer. The GE-PAC 30-2 Micro-Code Simulator will run on any standard GE-PAC 30 computer with 8K bytes of memory and a Teletypewriter.

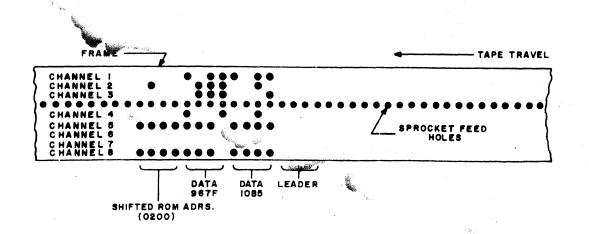

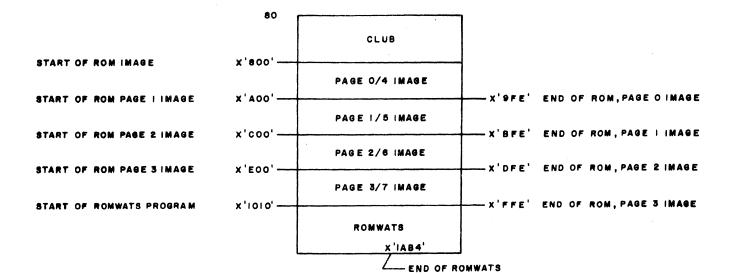

To aid on the production of ROM's, a machine called ROMWATS (ROM Wiring Aid and Test Set) has been developed. This machine is directed by paper tapes produced from the object tapes output

by the Micro-Code Assembler or the Simulator. The program that converts the object tape into the two tapes necessary to drive the machine is referred to as the ROMWATS program. The first tape produced by the ROMWATS program is used to wire the ROM. The second tape is used to check that the wires were strung correctly. The information presented in the GE-PAC 30-2 Micro-Programming Reference Manual will assist the designer in the production of good object tape, the production of the ROMWATS tapes is usually left to the manufacturer and should be of no concern to the user.

# SECTION 2

# THE MICRO-PROGRAMMED GE-PAC 30-2 PROCESSOR

The first problem a potential micro-programmer must encounter is that of visualizing the architecture of the micro-programmable machine. The information that is necessary is usually buried in a description of the instruction set or must be extracted from documents containing many references to boards, connectors, diodes, transistors and other such devices. We will try to solve this problem here and now.

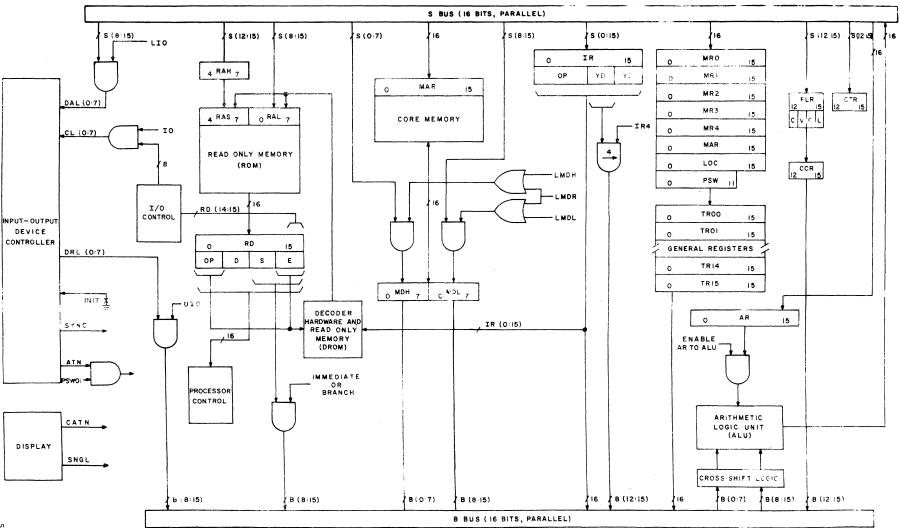

The first hurdle that must be overcome is the confusion between the emulated computer and the micro-programmable computer. The computer that is described in most GE-PAC 30 documentation (Reference Manual 29-004) is an emulated computer. This machine is similar to the IBM 360 family of machines and has a very powerful instruction set. This machine does not exist in hardware. A smaller and much less sophisticated micro-programmable computer has been programmed to appear as though it has the capabilities of the larger machine. The operation of the smaller machine is directed by a program wired into a Read-Only-Memory. (See GE-PAC 30-2 Hardware Block Diagram.) When executing the instructions of the emulated computer, the micro-program directs the hardware to read from core memory the next instruction to be executed. The microprogram then decodes the emulated instruction by performing logical and arithmetic operations on the data that was obtained from memory. Having decoded the instruction, the micro-program will then enter a micro-subroutine that has been designed to perform the emulated instruction. The loop is then closed by incrementing the instruction counter of the emulated machine and returning to the point in the micro-program that will fetch the next instruction from memory. By adding

the logic necessary to start, stop and select a starting address to the micro-program, the small machine is made to appear much larger without expending significant sums on hardware. All of this would be highly impractical if the micro-instructions were stored in a core memory. Core memories are either relatively slow devices or very expensive.

Read-Only-Memories (ROM) on the other hand are very fast, quite inexpensive and in addition, are non-volatile. It is evident, then, that this is an ideal device in which to store frequently used subroutines.

The small machine that uses the ROM must be designed to match the ROM's performance. The GE-PAC 30-2 has, therefore, been designed to execute most micro-operations in 400 nano seconds.

Now, the basic architecture will be described. The fine detail is left to the remaining sections of the Micro-Programming Manual.

The GE-PAC 30-2 has ten basic micro-instructions.

| SYMBOL       | DEFINITION   |

|--------------|--------------|

| A            | ADD          |

| S            | SUBTRACT     |

| X            | EXCLUSIVE OR |

| Ν            | AND          |

| 0            | INCLUSIVE OR |

| $\mathbf{L}$ | LOAD         |

| С            | COMMAND      |

| Т            | TEST         |

| В            | BRANCH       |

| D            | DECODE       |

|              |              |

# TABLE OF CONTENTS

·\*\*\*\*

| CHAPTER 1. | INTRODUCTION AND BLOCK DIAGRAM ANALYSIS 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 2. | WORD FORMAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CHAPTER 3. | SOURCE AND DESTINATION REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CHAPTER 4. | MICRO-INSTRUCTIONS 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|            | 4.1       ADD.       13         4.2       ADD IMMEDIATE.       15         4.3       SUBTRACT       16         4.4       SUBTRACT IMMEDIATE       18         4.5       EXCLUSIVE OR       19         4.6       EXCLUSIVE OR IMMEDIATE       21         4.7       AND.       22         4.8       AND IMMEDIATE       23         4.9       INCLUSIVE OR       24         4.10       INCLUSIVE OR IMMEDIATE       26         4.11       LOAD       26         4.12       LOAD IMMEDIATE       29         4.13       COMMAND.       30         4.14       TEST.       35         4.15       BRANCH ON CONDITION       36         4.16       BRANCH ON COUNTER       37 |

| CHAPTER 5. | USER ORIENTED PHASE DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CHAPTER 6. | MICRO-PROGRAMMING INPUT/OUTPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CHAPTER 7. | ADDITIONAL SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

.

# APPENDICES

ï

(

| APPENDIX 1. | REGISTER ADDRESSES          |

|-------------|-----------------------------|

| APPENDIX 2. | CODESA-2                    |

| APPENDIX 3. | INSTRUCTION EXECUTION TIMES |

### CHAPTER 1

# INTRODUCTION AND BLOCK DIAGRAM ANALYSIS

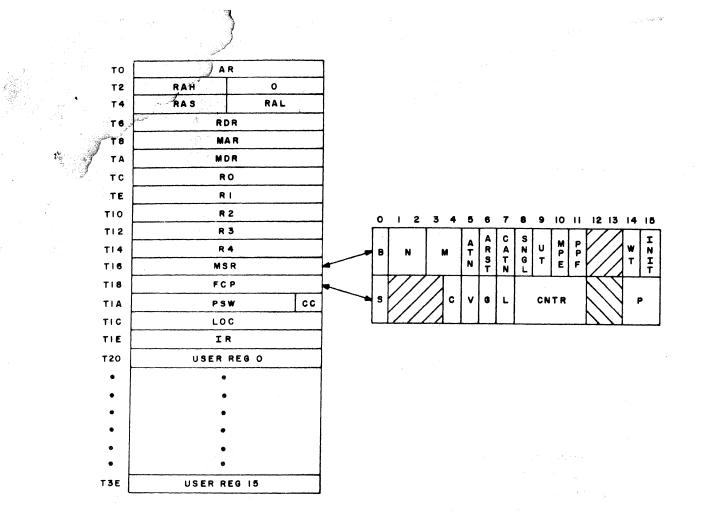

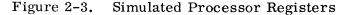

GE-PAC 30-2 Processor operation centers around the Read-Only-Memory (ROMO). ROM locations are addressed by a 12 bit register consisting of an 8 bit incrementing register (RAL) and a 4 bit non-incrementing page register (RAS) which is loaded from the 4 bit 'outer-rank' (RAH) register when RAL is loaded.

Information read from ROM is placed in a 16 bit Data Register (RD). Bits 0:3 of RD specify a micro-operation to be performed which, in turn, defines the meaning of the remaining bits.

ROM with its pre-wired micro-program, directs the Processor through the control unit. <u>Processor Control</u> can, depending on the micro-operation code, set-up the Arithmetic Logic Unit (ALU) to the desired mode of operation, test for specified hardware conditions, issue functional commands to establish hardware conditions, initiate memory cycles, or set-up micro-instruction loops, or load and unload selected registers in the hardware register stacks.

There are five general purpose Micro-Registers labeled MR0 through MR4. Each has a capacity of 16 bits and is directly addressable from RD.

<u>The Program Status Word</u> (PSW) is a 16 bit register which indicates the system status relative to the user program being executed (see Reference Manual, Publication Number 29-004). Bits 0:11 of PSW define machine status. Bits 12:15 are set apart in the Condition Code Register (CCR) which may be loaded only from the Flag Register (FLR). When PSW is loaded, bits 12:15 of the S Bus are loaded into the FLR instead of the CCR. This

permutes user status to the micro-level. The <u>Flag Register</u> and ultimately the <u>Condition</u> <u>Code Register</u> reflect the results of the micro-instruction (or instructions in the case of a user micro-routine) just performed.

The Location Counter (LOC) is a 16 bit appendum to PSW which holds the address of the next user instruction to be performed. LOC is directly addressable by RD, however, it may be forcibly selected, regardless of RD in the Decode micro-instruction.

The <u>Memory Address Register</u> (MAR) is a 16 bit register used to address core memory locations. MAR appears twice -- on the Memory Interface and in the Processor register stacks. When MAR is loaded, both registers are loaded at the same time. It was duplicated in the register stacks because the Address Register on the Memory Interface cannot be unloaded to the B Bus.

The <u>Memory Data Register</u> (MDR) is a 16 bit register used to hold data read from or written into core memory. MDR is directly addressable by RD. It is separated into two bytes (MDH and MDL) which may be loaded separately on cross-shift operations.

The 16 user's <u>General Registers</u> each have a capacity of 16 bits. The user's registers (TR0:TR15) are <u>not</u> directly addressable from RD. To access a particular user's register, one must address the appropriate Instruction Register (IR) fields which contain the address of the desired user's register (TR0:TR15). To access the register specified by IR bits 8:11, User's Destination (YD) is addressed; to access the register specified by IR bits 12:15, User's Source (S) is addressed; therefore, user's register selection is indirectly made. It is factofore necessary that IR contain the proper address before

$\mathbf{2}$

a 'user's register' is used. This is an over simplified description; there are numerous conditions which affect indirect addressing and will be discussed further in Chapter 3.

The <u>Instruction Register</u> (IR) is a 16 bit register used to hold the user's instruction currently being processed. IR is directly addressable by RD. In addition, provision

is made for unloading only bits 8:11 to the B Bus bits 12:15 (IR4) for comparison between the Mask (M1) field and the Flag Register when executing user's branches. Bits 0:7 of IR (User's Operation Code) are used to address locations in the <u>Decoder ROM</u> (DROM). This is a separate Read-Only-Memory consisting of up to 128 pre-wired words, each 12 bits long.

DROM is interrogated only on a Decode micro-instruction and the resulting 12 bit readout is immediately jammed into RAS and RAL. DROM holds the starting addresses of the micro-routines required to perform user's instructions. RAS and RAL may also be jammed with hardware generated addresses in the Decode micro-instruction.

The <u>Counter Register</u> (CNTR) is a 4 bit decrementing register. It may be pre-loaded with any number from 0 to 15 to count the number of repetitions of a single microinstruction or a block of micro-instructions. The counter is used in the Multiply or Divide sequences to cause 16 interations of the micro-instruction sets.

The <u>Arithmetic Register</u> (AR) is a 16 bit register used to hold the first operand in arithmetic or logical micro-operations. It is one of two direct inputs to the <u>Arithmetic Logic</u> <u>Unit</u> (ALU). The other input to the ALU is the 16 bit B Bus which receives data from any

1 of 29 possible sources. The two bytes of the B Bus may also be swapped with the cross shift logic.

The ALU consists of a 16 bit parallel adder-subtracter logic network with a one bit look ahead carry. The 16 bit arithmetic or logical result is gated to the S Bus which in turn is gated to 1 of 33 possible destinations.

Input-Output transfer (I/O) is accomplished by a single micro-instruction. The I/O control lines are decoded from RD bits 14 and 15. Input data is taken from the Data Request Lines (DRL 0:7) and placed directly on B Bus bits 8:15. Output data is taken from S Bus bits 8:15 and loaded directly to the Data Available Lines (DAL 0:7).

FIGURE 1 GE-PAC 30-2 HARDWARE BLOCK DIAGRAM

сı

# CHAPTER 2

# WORD FORMAT

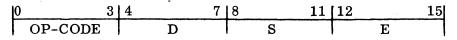

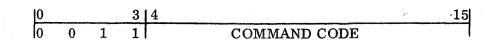

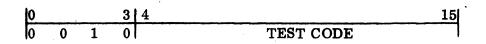

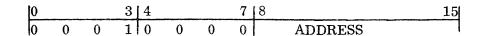

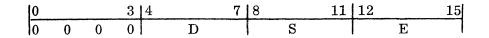

The GE-PAC 30 micro-instruction can have any one of four machine language formats, depending on the operation that the Op-Code specifies.

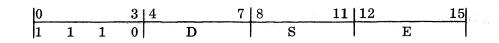

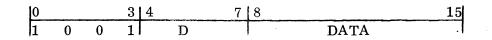

2.1 Arithmetic and Logic Format

S = Source field: the address of the register containing the second operand is in this field. The first operand comes from the A Register (AR).

D = Destination field: the result of the operation will be placed into the register whose address is in this field.

E = Extended Operation field: specifies options within the same

operation.

Bit 3 (of the Op-Code) in this format is always reset.

The following micro-instructions use the above format: Add, Subtract, Exclusive OR, AND, Inclusive OR, Load, and Decode.

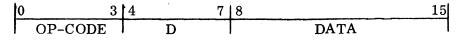

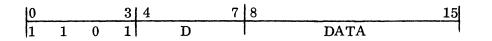

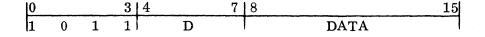

2.2 Immediate Format

DATA = the second operand itself is in this field. The first operand comes from the A Register (AR). D = Destination field: the result of the operation will be placed into the register whose address is in this field.

Bit 3 (of the Op-Code) in this format is always set.

The following micro-instructions use the above format: Add Immediate, Subtract Immediate, Exclusive OR Immediate, AND Immediate, Inclusive OR Immediate, and Load Immediate.

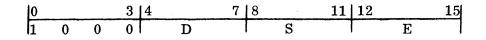

2.3 Test and Command Format

| 1 | 0 3     | 4       | 15 |

|---|---------|---------|----|

|   | OP-CODE | TC CODE |    |

TC CODE = Test or Command Code: specifies the signal to be tested or specifies the command to be performed.

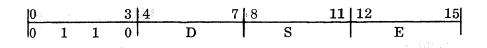

2.4 Branch on Condition Format

| - 1 | 0       | 3 | 4 | 5 | 6 | 7 | 8 15    |  |

|-----|---------|---|---|---|---|---|---------|--|

| 1   | OP-CODE |   | C | V | G | L | ADDRESS |  |

ADDRESS = if conditions (C, V, G, or L) are met, the program is transferred to the 8 bit address specified by this field.

C = carry

V = overflow

G =greater, than zero

L = less, than zero

If bits 4:7 are zero, the state of the Counter Register is examined. If the counter does not equal 'one', the counter is decremented by one and the program is transferred to the 8 bit address specified by the ADDRESS field.

The "Branch on Condition" micro-instruction uses this format.

### CHAPTER 3

# SOURCE AND DESTINATION REGISTERS

# 3.1 Source registers are only available to non-immediate micro-instructions,

(RD03 = 0). The following sources may be addressed.

| RD | <u>8</u> | <u>9</u> | <u>10</u> | <u>11</u> | SYMBOLIC |

|----|----------|----------|-----------|-----------|----------|

|    | 0        | 0        | 0         | 0         | MR0      |

|    | 0        | 0        | 0         | 1         | MR1      |

|    | 0        | 0        | 1         | 0         | MR2      |

|    | 0        | 0        | 1         | 1         | MR3      |

|    | 0        | 1        | 0         | 0         | MR4      |

|    | 0        | 1        | 0         | 1         | MAR      |

|    | 0        | 1        | 1         | 0         | LOC      |

|    | 0        | 1        | 1         | 1         | PSW      |

|    | 1        | 0        | 0         | 0         | NULL     |

| -  | 1        | 0        | 0         | 1         | IR       |

|    | 1        | 0        | 1         | 0         | MDR      |

|    | 1        | 0        | 1         | 1         | IR4      |

|    | 1        | 1        | 0         | 0         | NULL     |

|    | 1        | 1        | 0         | 1         | IO       |

|    | 1        | 1        | 1         | 0         | YD       |

|    | 1        | 1        | 1         | 1         | YDP1     |

3.2 There are two NULL sources. When address X'8' (the A Register) or address X'C' (the Counter) appear in the source field (RD 8:11), zeros are gated to all 16 bits of the B Bus.

3.3 When PSW is used as the source, bits 0:11 of the stack PSW are gated to B Bus bits 0:11 and the Condition Code Register (CCR bits 12:15) is gated to B Bus bits 12:15.

3.4 When IR4 is the source, IR bits 8:11 are gated to B Bus bits 12:15. The remainder of the B Bus is all zeros.

3.5 When IO (address X'D') appears as the source, an input operation is to be

performed. IO can only be a source in a Load instruction. The Processor is requesting a data response from an I/O device; IO is <u>not</u> a register. The nature of the request is encoded into the 'E' field of the Load instruction and will be discussed later in Chapter 4. The device response is gated from the Data Request Lines (DRL 0:7) to B Bus bits 8:15.

3.6 The 16 general purpose user's registers do not have individual source addresses. Instead, common symbolic addresses - YD (address X'E') and YDP1 (address X'F') - cause the general registers to be selected from the Instruction Register bits 8:11 or 12:15. The General Registers are Indirectly addressed.

3.7 There exists in the phase hardware, a flip-flop which specifies the IR field to be used for indirect source decoding. The flip-flop (PTYS), if set, causes the indirect source to be decoded from the User's Source (YS) field of IR, IR bits 12:15. If PTYS is reset, the indirect source is decoded from the User's Destination (YD) field of IR, IR bits 8:11. PTYS is set conditionally on a Decode micro-instruction and is reset when an indirect source is used.

3.8 If IR = X'nnA5 and PTYS is set when YD (address X'E') is the source, TR5 is unloaded to the B Bus. If PTYS is reset and YD is the source, TR10 is unloaded to the B Bus.

3.9 If YD plus 1 (YDP1) is the source, the indirect register decoding is done from the IR field YD or YS specified by the PTYS flip-flop. If the selected address is even, the next sequential address is forced and that register is unloaded to the B Bus. If the selected

address is odd, the next sequential address is <u>not</u> forced and the selected register is unloaded to the B Bus.

3.10 If IR = X'nn40' and PTYS is reset, YDP1 (address X'F') will cause TR5 to be unloaded to the B Bus. If IR = X'nn50' and YDP1 is the source, TR5 is unloaded to the B Bus.

3.11 The following Destinations may be addressed:

| RD | <u>4</u> | <u>5</u> | <u>6</u> | 7 | SYMBO          | LIC   |

|----|----------|----------|----------|---|----------------|-------|

|    | 0        | 0        | 0        | 0 | RAH*           | MR0** |

|    | 0        | 0        | 0        | 1 | RAL*           | MR1** |

|    | 0        | 0        | 1        | 0 | YS *           | MR2** |

|    | 0        | 0        | 1        | 1 | MR3            |       |

|    | 0        | 1        | 0        | 0 | $\mathbf{MR4}$ |       |

|    | 0        | 1        | 0        | 1 | MAR            |       |

|    | 0        | 1        | 1        | 0 | LOC            |       |

|    | 0        | 1        | 1        | 1 | PSW            |       |

|    | 1        | 0        | 0        | 0 | AR             |       |

|    | 1        | 0        | 0        | 1 | $\mathbf{R}$   |       |

|    | 1        | 0        | 1        | 0 | MDR            |       |

|    | 1        | 0        | 1        | 1 | $\mathbf{FLR}$ |       |

|    | 1        | 1        | 0        | 0 | CNTR           |       |

|    | 1        | 1        | 0        | 1 | ΙΟ             |       |

|    | 1        | 1        | 1        | 0 | YD             |       |

|    | 1        | 1        | 1        | 1 | YDP1           |       |

|    |          |          |          |   |                |       |

\* The Bank flip-flop must be reset to Load RAH, RAL, or YS.

\*\* The Bank flip-flop must be set to Load MR0, MR1, or MR2.

3.12 Loading RAH loads the outer rank page register only of ROM address register. ROM decodes page from the inner rank (RAS). When RAL is loaded, the data in RAH are loaded into RAS at the same time. All 12 bits of ROM address are loaded.

3.13 When User's Source (YS) is the destination, the S Bus is loaded to the

General Register specified by the YS field of IR, IR bits 12:15.

When User's Destination (YD) is the destination, the S Bus is loaded to the General Register specified by the YD field of IR, IR bits 8:11. PTYS has no affect on destinations. When User's Destination plus 1 (YDP1) is the destination, the same even/odd anomoly must be observed: if the address is even, the next sequential general register is loaded; if the address is odd, that register is loaded.

3.14 When the Program Status Word (PSW) is loaded, S Bus bits 12:15 are loaded into the Flag Register (FLR).

3.15 When IO appears as the destination, an output operation is to be performed.

IO can only be a destination in a Load micro-instruction. The Processor will transmit data to an external device. IO is <u>not</u> a register. The nature of the output data is encoded into the 'E' field of the Load instruction and will be discussed fully later in Chapter

4. The output byte is gated from S Bus bits 8:15 onto the Data Available Lines (DAL 0:7).

#### 3.16 For the cross shift option only

If MDR is the source

- and MAR is even, the cross shift operates normally.

- and MAR is odd, the cross shift is inhibited; the instruction behaves as a normal load.

If MDR is the destination

- and MAR is even, the lower byte of the source is stored as the higher byte in MDR - the lower byte of MDR remains unchanged.

- and MAR is odd, the lower byte of the source is stored as the lower byte in MDR - the upper byte of the MDR remains unchanged.

This option is used with MDR to get and store bytes in user memory.

# **CHAPTER 4**

### MICRO-INSTRUCTIONS

# 4.1 ADD

4.1.1 Description: the contents of the A Register (AR) are algebraically added to the contents of the register specified by the Source (S) field. The sum is then gated into the register specified by the Destination (D) field. For register addresses, see Appendix 1 and Chapter 3.

4.1.2 Options: Note that the character "x" in any bit position indicates a "don't care" state.

| <u>E field</u> | Definition                                                                                                                                           |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1xxx           | AR is not gated to the adder (Arithmetic<br>Logic Unit, ALU): zero is added to the<br>contents of the register specified by the<br>Source (S) field. |

| x1xx           | Set the flags.                                                                                                                                       |

| xx1x           | Carry flag (C), if set before this instruction, is added to the operands.                                                                            |

| xxx1           | If there is a carry from the most significant<br>bit position, the Carry flag (C) is set.                                                            |

4.1.3 Assembler Format: A D, S, E

A = symbol for Add

D = in this place there is a register symbol (e.g.: MAR, PSW, MR1), followed by a comma.

S = register symbol (e.g.: MR4, MDR, PSW), followed by a comma only if an assembler option is specified in the E field.

| Symbol | Definition                                                              |

|--------|-------------------------------------------------------------------------|

| CI     | Carry in, but not carry out. Bits 14 and 15 of the instruction = $10$ . |

| со     | Carry out, but not carry in. Bits 14 and 15 of the instruction = $01$ . |

| NC     | No carry. Bits 14 and 15 of the instruction $= 00.$                     |

| NF     | No flags. Bit 13 of the instruction $= 0$ .                             |

| NA     | No AR to ALU. Bit 12 of the instruction = $1$ .                         |

If there are no options stated in the E field of the symbolic assembler instruction, the following options are generated automatically: Carry in and out (bits 14 and 15 = 11), AR is an input to the ALU (bit 12 = 0), flags are changed (bit 13 = 1).

4.1.4 Examples: Binary

Overflow!

Decimal

=

| Sign | Data | <u>L</u> |      |      |       | Sign | Data   |

|------|------|----------|------|------|-------|------|--------|

| 0    | 011  | 0101     | 0010 | 1000 | AR    | +    | 13,608 |

| 0    | 010  | 1110     | 1001 | 0100 | B Bus | + .  | 11,924 |

| 0    | 110  | 0001     | 1011 | 1100 | S Bus | +    | 25,532 |

|      |      |          |      |      |       |      |        |

| 0    | 011  | 0101     | 0010 | 1000 | AR    | +    | 13,608 |

| 1    | 101  | 0001     | 0110 | 1100 | B Bus | -    | 11,924 |

| 0    | 000  | 0110     | 1001 | 0100 | S Bus | +    | 1,684  |

|      |      |          |      |      |       |      |        |

| 0    | 010  | 1110     | 1001 | 0100 | AR    | +    | 11,924 |

| 1    | 100  | 1010     | 1101 | 1000 | B Bus |      | 13,608 |

| 1    | 111  | 1001     | 0110 | 1100 | S Bus |      | 1,684  |

|      |      |          |      |      |       |      |        |

| 0    | 111  | 1111     | 1111 | 1111 |       | +    | 32,767 |

| 0    | 000  | 0000     | 0000 | 0101 |       | +    | 5      |

| 1    | 000  | 0000     | 0000 | 0100 |       |      | 33,472 |

|      |      |          |      |      |       |      | •      |

Unlike carrys from the sign (bit 0) and the most significant magnitude bit (bit 1) result in overflow: the sum is greater than 16 bits (including sign).

4.2 ADD IMMEDIATE

4.2.4

)

4.2.1 Description: the contents of the A Register (AR) are algebraically added to the 8 bits in the DATA field of this instruction. The sum is then gated into the register specified by the Destination (D) field. For register addresses, see Appendix 1.

4.2.2 Options: None. Note that the flags (C, V, G, or L) are not changed by this micro-instruction.

4.2.3 Assembler Format: A D, DATA

A = symbol for Add Immediate

- D = in this place there is a register symbol (e.g.: MR4, FLR, MAR), followed by a comma.

- DATA = either the operand expressed in hexadecimal (e.g.: X'9A') or as the low order 8 bits, L (DATA), or the high order 8 bits, H(DATA), of the value of a symbol defined by DATA.

| Examples | : <u>Bin</u> | ary  | •    | ==   | Dec  | imal  |      |         |

|----------|--------------|------|------|------|------|-------|------|---------|

|          | Sign         | Data |      |      |      |       | Sign | Data    |

|          | 0            | 011  | 0101 | 0010 | 1000 | AR    | +    | 13,608  |

|          | 0            | 000  | 0000 | 1011 | 1100 | B Bus | +    | 188     |

|          | 0            | 011  | 0101 | 1110 | 0100 | S Bus | +    | 13, 796 |

|          | 1            | 100  | 1010 | 1101 | 1000 | AR    | -    | 13,608  |

|          | 0            | 000  | 0000 | 1011 | 1100 | B Bus | +    | 188     |

|          | 1            | 100  | 1011 | 1001 | 0100 | S Bus |      | 13,420  |

Note: A negative B Bus is impossible.

| Binary    |      |      |      |      |      |       | Dec  | imal    |

|-----------|------|------|------|------|------|-------|------|---------|

|           | Sign | Data |      |      |      |       | Sign | Data    |

|           | 0    | 111  | 1111 | 1111 | 1111 | AR    | +    | 32, 767 |

|           | 0    | 000  | 0000 | 0000 | 0101 | B Bus | +    | 5       |

| Overflow! | 1    | 000  | 0000 | 0000 | 0100 | S Bus | +    | 33,472  |

# 4.3 SUBTRACT

4.3.1 Description: the contents of the register specified by the Source (S) field are algebraically subtracted from the contents of the A Register (AR). The difference is then gated into the register specified by the Destination (D) field. For register addresses, see Appendix 1.

4.3.2 Options: Note, that the character "x" in any bit position indicates a "don't care" state.

| E field | Definition                                                                                                                                 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 1xxx    | AR is not gated to the subtracter (ALU):<br>the contents of the register specified by<br>the Source (S) field are subtracted from<br>zero. |

| x1xx    | Set flags.                                                                                                                                 |

| xx1x    | Carry flag (C), if set before this instruc-<br>tion is also subtracted from the AR.                                                        |

| xxx1    | If there is a borrow from the most signi-<br>ficant bit position, the Carry flag (C) is                                                    |

4.3.3 Assembler Format: S D, S, E

)

- S = symbol for subtract

- D = in this place there is a register symbol (e.g.: MR4, AR, MAR), followed by a comma.

- S = register symbol (e.g.: MR3, MDR, MR2), followed by a comma only if an assembler option is specified in the E field.

The following symbolic options can appear in the E field:

| Symbol | Definition                                                               |

|--------|--------------------------------------------------------------------------|

| CI     | Carry in, but not carry out. Bits 14 and 15 of the instructions = $10$ . |

| CO     | Carry out, but not carry in. Bits 14 and 15 of the instructions = $01$ . |

| NC     | No carry. Bits 14 and 15 of the instruction $= 00.$                      |

| NF     | No flags. Bit 13 of the instruction $= 0$ .                              |

| NA     | No AR to ALU. Bit 12 of the symbolic instruction = 1.                    |

If there are no options stated in the E field of the symbolic assembler instruction, the following options are generated automatically: carry in and out (bits 14 and 15 = 11), AR is an input to the ALU (bit 12 = 0), flags are changed (bit 13 = 1).

| 4.3.4 | Examples: | Bin  | ary         |      |        |      | =     | Dec  | imal   |

|-------|-----------|------|-------------|------|--------|------|-------|------|--------|

|       |           | Sign | <u>Data</u> |      | ,<br>K | ·    |       | Sign | Data   |

|       |           | 0    | 011         | 0101 | 0010   | 1000 | AR    | +    | 13,608 |

|       |           | 0    | 010         | 1110 | 1001   | 0100 | B Bus | +    | 11,924 |

|       |           | 0    | 000         | 0110 | 1001   | 0100 | S Bus | +    | 1,684  |

|       |           |      |             | *    |        |      |       |      |        |

|       |           | 0    | 010         | 1110 | 1001   | 0100 | AR    | +    | 11,924 |

|       |           | 0    | 011         | 0101 | 0010   | 1000 | B Bus | +    | 13,608 |

|       |           | 1    | 111         | 1001 | 0110   | 1100 | S Bus | -    | 1,684  |

|       |           |      |             |      |        |      |       |      |        |

|           | Bin  | ary  |      |       |      | =     | Dec  | imal        |

|-----------|------|------|------|-------|------|-------|------|-------------|

|           | Sign | Data | :    | · · · | е.,  |       | Sign | <u>Data</u> |

|           | 0    | 011  | 0101 | 0010  | 1000 | AR    | +    | 13,608      |

|           | 1    | 101  | 0001 | 0110  | 1100 | B Bus |      | 11,924      |

|           | 0    | 110  | 0001 | 1011  | 1100 | S Bus | +    | 25,532      |

|           | 0    | 111  | 1111 | 1111  | 1111 | AR    | +    | 32,767      |

|           | 1    | 111  | 1111 | 1111  | 1011 |       |      | 5           |

| Overflow! | 1    | 000  | 0000 | 0000  | 0100 |       | +    | 33,472      |

Unlike borrows from the sign (bit 0) and the most significant magnitude bit (bit 1) result in overflow: the difference is greater than 16 bits (including sign).

# 4.4 SUBTRACT IMMEDIATE

4.4.1 Description: the contents of the DATA field are algebraically subtracted from the contents of the A Register (AR). The difference is then gated to the register specified by the Destination (D) field. For register addresses, see Appendix 1.

4.4.2 Options: None. Note, that the flags (C, V, G, or L) are not changed by this micro-instruction.

4.4.3 Assembler Format: S D, DATA

8 = symbol for Subtract Immediate

- D = there is a register symbol in this position (e.g.: MR4, LOC, MAR), followed by a comma

- DATA = either the operand expressed in hexadecimal (e.g.: X'9A') or as the low order 8 bits, L (DATA), or the high order 8 bits, H (DATA, of the value of a symbol defined by DATA.

Sign

0 0 0

1

0

1

000

100

| nary |      |      |      | =     | De   | cimal  |

|------|------|------|------|-------|------|--------|

| Data |      |      |      | 1     | Sign | Data   |

| 011  | 0101 | 0010 | 1000 | AR    | +    | 13,608 |

| 000  | 0000 | 1011 | 1100 | B Bus | +    | 188    |

| 011  | 0100 | 0110 | 1100 | S Bus | +    | 13,420 |

| 100  | 1010 | 1101 | 1000 | AR    | -    | 13,608 |

1100

1100

B Bus

S Bus

188

13,796

Note: A negative B Bus is impossible.

|           | 1 | 000 | 0000 | 0000 | 0001 | AR    |   | 32,767 |

|-----------|---|-----|------|------|------|-------|---|--------|

|           | 0 | 000 | 0000 | 0000 | 0101 | B Bus | + | 5      |

| Overflow! | 0 | 111 | 1111 | 1111 | 1100 |       |   | 33,472 |

1011

0001

Unlike borrows from the sign (bit 0) and the most significant magnitude bit (bit 1) result in Overflow: the difference is greater than 16 bits (including sign).

0000

1010

#### 4.5 EXCLUSIVE OR

4.5.1 Description: the contents of the register specified by the Source (S) field are logically subtracted (Exclusive ORed) from the contents of the A Register (AR). The logical difference (result) is then gated into the register specified by the Destination (D) field. For register addresses, see Appendix 1.

4.5.2 Options: Note, that the character "x" in any bit position indicates a "don't care" state.

#### E field Definition

1xxx

AR is not gated to the ALU: the contents of the register specified by the Source (S) field

# E field

Definition

is gated into the register specified by the Destination (D) field without any change.

x1xx Set flags.

xx1x No effect on this instruction.

No effect on this instruction.

4.5.3 Assembler Format: X D, S, E

X = symbol for Exclusive OR

xxx1

- D = in this place there is a register symbol (e.g.: MR4, LOC, MAR), followed by a comma

- S = register symbol (e.g.: MR3, MDR, MR0), followed by a comma only if an assembler option is specified in the E field

The following symbolic options can appear in the E field.

|                                            | Symbol | Definition                                                              |

|--------------------------------------------|--------|-------------------------------------------------------------------------|

|                                            | CI     | Carry in, but not carry out. Bits 14 and 15 of the instruction $=$ 10.  |

| and an | ÔÔ     | Carry out, but not carry in. Bits 14 and 15 of the instruction $= 01$ . |

| ana ang ang ang ang ang ang ang ang ang    | NC     | No carry. Bits 14 and 15 of the instruction $= 00.$                     |

|                                            | NF     | No flags. Bit 13 of the instruction = $0$ .                             |

|                                            | NA     | No AR to ALU. Bit 12 of the instruction $=$ 1.                          |

If there are no options stated in the E field of the symbolic assembler instruction, the following options are generated automatically: carry in and out (bits 14 and 15 = 11), AR is an input to the ALU (bit 12 = 0), flags are changed (bit 13 = 1).

# 4.5.4 Example:

| 0 | 101 | 1101 | 0010 | 0101 | AR    |

|---|-----|------|------|------|-------|

| 0 | 010 | 1000 | 0101 | 1110 | B Bus |

| 0 | 111 | 0101 | 0111 | 1011 | S Bus |

# 4.6 EXCLUSIVE OR IMMEDIATE

4.6.1 Description: the contents of the DATA field are logically subtracted (Exclusive ORed) from the contents of the A Register (AR). The logical difference (result) is gated into the register specified by the Destination (D) field. For register addresses, see Appendix 1.

4.6.2 Options: None. Note that the flags (C, V, G, or L) are not changed by this micro-instruction.

4.6.3 Assembler Format: X D, DATA

- X = symbol for Exclusive OR Immediate

- D = there is a register symbol in this position (e.g.: MR4, YD, MAR,) followed by a comma

- DATA = either the operand expressed in hexadecimal (e.g.: X'9A'), or as the low order 8 bits, L (DATA), or high order 8 bits, H (DATA), of the value of a symbol defined by DATA.

4.6.4 Example:

| 0 | 101 | 1101 | 0010 | 0101 | AR    |

|---|-----|------|------|------|-------|

| 0 | 000 | 0000 | 0101 | 1110 | B Bus |

| 0 | 101 | 1101 | 0111 | 1011 | S Bus |

4.7.1 Description: the contents of the register specified by the Source (S) field are logically multiplied (ANDed) by the contents of the A Register (AR). The logical product (result) is then gated into the register specified by the Destination (D) field. For register addresses, see Appendix 1.

4.7.2 Options: Note, that the character "x" in any bit position indicates a "don't care" state.

| <u>E field</u> | Definition                                                                                                                                   | an an an ar atra t |  |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|--|

| 1xxx           | AR is not gated to the ALU: the logical pro-<br>duct is zero, and zero is gated into the register<br>specified by the Destination (D) field. |                    |  |  |  |  |

| x1xx           | Set flags.                                                                                                                                   |                    |  |  |  |  |

| xx1x           | No effect on this instruction.                                                                                                               | 9                  |  |  |  |  |

| xxx1           | No effect on this instruction.                                                                                                               |                    |  |  |  |  |

190

4.7.3 Assembler Format: N D,S,E

N = symbol for AND

D = in this place there is a register symbol (e.g.: MR4, YD, MAR,) followed by a comma

S = register symbol (e.g.: MR0, MDR, LOC,) followed by a comma only if an assembler option is specified in the E field

The following symbolic options can appear in the E field.

| Symbol | Definition                                                              |

|--------|-------------------------------------------------------------------------|

| CI     | Carry in, but not carry out. Bits 14 and 15 of the instruction $=$ 10.  |

| CO     | Carry out, but not carry in. Bits 14 and 15 of the instruction $= 01$ . |

| NC     | No carry. Bits 14 and 15 of the instruction $= 00.$                     |

| NF     | No flags. Bit 13 of the instruction = $0$ .                             |

If there are no options stated in the E field of the symbolic assembler instruction, the following options are generated automatically: carry in and out (bits 14 and 15 = 11), AR is an input to the ALU (bit 12 = 0), flags are changed (bit 13 = 1).

4.7.4 Example:

| 0 | 101 | 1101 | 0010 | 0101 | AR    |

|---|-----|------|------|------|-------|

| 0 | 010 | 1000 | 0101 | 1110 | B Bus |

| 0 | 000 | 1000 | 0000 | 0100 | S Bus |

# 4.8 AND IMMEDIATE

4.8.1 Description: the contents of the DATA field are logically multiplied (ANDed) by the contents of the A Register (AR). The logical product (result) is gated into the register specified by the Destination (D) field. For register addresses, see Appendix 1.

4.8.2 Options: None. Note that the flags (C, V, G, or L) are not changed by this micro-instruction.

4.8.3 Assembler Format: N D, DATA

N = symbol for AND Immediate

- D = there is a register symbol in this position (e.g.: MR4, FLR, MAR,) followed by a comma

- DATA = either the operand expressed in hexadecimal (e.g.: X'9A'), or as the low order 8 bits, L (DATA), or high order 8 bits, H (DATA), of the value of a symbol defined by DATA.

# 3.8.4 Examples:

| 0 | 101 | 1101 | 0010 | 0101 | AR    |

|---|-----|------|------|------|-------|

| 0 | 000 | 0000 | 0101 | 1110 | B Bus |

| 0 | 000 | 0000 | 0000 | 0100 | S Bus |

# 4.9 INCLUSIVE OR

4.9.1 Description: the contents of the register specified by the Source (S) field arc logically added (ORed) by the contents of the A Register (AR). The logical sum (result) is then gated into the register specified by the Destination (D) field. For register addresses, see Appendix 1.

4.9.2 Options: Note that the character "x" in any bit position indicates a "don't care" state.

### E field

Definition

1 xxx

AR is not gated to the ALU: the contents of the register specified by the Source (S) field is gated into the register specified by the Destination (D) field without any change.

| E field | Definition                     |

|---------|--------------------------------|

| x1xx    | Set flags.                     |

| xx1x    | No effect on this instruction. |

| xxx1    | No effect on this instruction. |

4.9.3 Assembler Format: O D, S, E

- O = symbol for Inclusive OR

- D = in this place there is a register symbol (e.g.: MR0, LOC, MAR,) followed by a comma

- S = register symbol (e.g.: MR4, MDR, YD,) followed by a comma only if an assembler option is specified in the E field

The following symbolic options can appear in the E field.

| Symbol | Definition                                                              |

|--------|-------------------------------------------------------------------------|

| CI     | Carry in, but not carry out. Bits 14 and 15 of the instruction $=$ 10.  |

| CO     | Carry out, but not carry in. Bits 14 and 15 of the instruction $= 01$ . |

| NC     | No carry. Bits 14 and 15 of the instruction = 00.                       |

| NF     | No flags. Bit 13 of the instruction $= 0$ .                             |

| NA     | No AR to ALU. Bit 12 of the instruction = $1$ .                         |

If there are no options stated in the E field of the symbolic assembler instruction, the following options are generated automatically: carry in and out (bits 14 and 15 = 11), AR is an input to the ALU (bit 12 = 0), flags are changed (bit 13 = 1).

# 4.9.4 Examples:

| 0 | 101 | 1101 | 0010 | 0101 | AR    |

|---|-----|------|------|------|-------|

| 0 | 010 | 1000 | 0101 | 1110 | B Bus |

| 0 | 111 | 1101 | 0111 | 1111 | S Bus |

# 4.10 INCLUSIVE OR IMMEDIATE

| 0 |   |   | 3 | 4 | 7 8 |      | 15 |

|---|---|---|---|---|-----|------|----|

| 0 | 1 | 1 | 1 | D | 1.  | DATA |    |

4.10.1 Description: the contents of the DATA field are logically added (ORed) with the contents of the A Register (AR). The logical sum (result) is then gated into the register specified by the Destination (D) field. For register addresses, see Appendix 1.

4.10.2 Options: None. Note that the flags (C, V, G, or L) are not changed by this micro-instruction.

4.10.3 Assembler Format: O D, DATA

- O = symbol for Inclusive OR Immediate

- D = there is a register symbol in this position (e.g.: MR3, CNTR, MAR,) followed by a comma

- DATA = either the operand expressed in hexadecimal (e.g.: X'9A'), or as the low order 8 bits, L (DATA), or high order 8 bits, H(DATA), of the value of a symbol defined by DATA.

| 4.10.4    | Exampl | les: |       |     |      |      |                 |               |

|-----------|--------|------|-------|-----|------|------|-----------------|---------------|

|           |        |      | 0     | 101 | 1101 | 0010 | 0101            | $\mathbf{AR}$ |

|           |        |      | 0     | 000 | 0000 | 0101 | 1110            | B Bus         |

|           |        |      | 0     | 101 | 1101 | 0111 | 1111            | S Bus         |

| 4.11 LOAD |        |      |       |     |      |      |                 |               |

|           | 0      |      | 3   4 |     | 7 8  |      | 1 <b>1</b>   12 | 15            |

|           | 0 1    | 0    | 0     | D   |      | S    |                 | E             |

4.11.1 The contents of the register specified by the Source (S) field are loaded unaltered into the register specified by the Destination (D) field. For register addresses, see Appendix 1.

)

4.11.2 Note that the character "x" in any bit position indicates a "don't care" state. If the Destination or Source is not IO, the E field has the following meaning:

| <u>E field</u>   | Definition                                                                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00xx             | Load, no other options.                                                                                                                                                                                                                          |

| 01xx             | The contents of the Source register are shifted<br>right one bit and the shifted number is loaded<br>into the Destination register. Contents of<br>source register are unchanged unless same<br>register is both source and destination.         |

| 10xx             | The contents of the Source register are shifted<br><u>left</u> one bit and the shifted number is loaded in-<br>to the Destination register. Contents of source<br>register are unchanged unless same register is<br>both source and destination. |

| 11 <sub>xx</sub> | The source Data is byte swapped and loaded to<br>the Destination register. If MDR is either<br>Source or Destination, the cross shift will<br>occur only if MAR is even. See Chapter 3.                                                          |

| xx1x             | This is valid with the shift options only; if the<br>Carry flag (C) is set prior to this instruction,<br>a one will be shifted into the most significant<br>bit on a shift right, or into the least significant<br>bit on a shift left.          |

| xxx1             | With shift options only: if a one is shifted out,<br>the Carry flag (C) is set. Non-shift options:<br>the Carry flag (C) is reset.                                                                                                               |

4.11.3 If IO is Source or Destination, the E field takes on the following meaning. IO is Destination:

| <u>E field</u> | Definition                                           |

|----------------|------------------------------------------------------|

| xx01           | The S Bus is loaded to the DAL's as Address (ADRS).  |

| xx10           | The S Bus is loaded to the DAL's as Data (DA).       |

| xx11           | The S Bus is loaded to the DAL's as a Command (CMD). |

IO is Source:

| E field | Definition                                                                                                                    |  |  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| xx01    | Device interrupt is Acknowledged (ACK). The interrupting device address is loaded from the DRL's to the Destination register. |  |  |  |

| xx10    | Device Data is requested (DR). The data is loaded from the DRL's to the Destination Register.                                 |  |  |  |

| xx11    | Device Status is requested (STAT). The Status<br>byte is loaded from the DRL's to the Destination<br>Register.                |  |  |  |

# 4.11.4 Assembler Format: L D, S, E

L = symbol for Load.

D = in this place there is a register symbol (e.g.: MR4, IO, MAR,) followed by a comma

S = register symbol (e.g.: MR4, MDR, IO,) followed by a comma only if an assembler option is specified in the E field.

The following symbolic options can appear in the E field.

| Symbol | Definition                                               |                |

|--------|----------------------------------------------------------|----------------|

| CI     | Carry in, but not carry out. of the instruction $= 10$ . | Bits 14 and 15 |

| СО     | Carry out, but not carry in. of the instruction $= 01$ . | Bits 14 and 15 |

| Symbol        | Definition                                          |  |  |

|---------------|-----------------------------------------------------|--|--|

| NC            | No carry. Bits 14 and 15 of the instruction $= 00.$ |  |  |

| SR            | Shift Right option.                                 |  |  |

| $\mathbf{SL}$ | Shift Left option.                                  |  |  |

| CS            | Cross Shift option.                                 |  |  |

| ADRS          | I/O Address. I O in Destination.                    |  |  |

| DA            | I/O Data Available. I O in Destination.             |  |  |

| CMD           | I/O Command. I O in Destination.                    |  |  |

| ACK           | Acknowledge Interrupt. I O in Source.               |  |  |

| DR            | Data Request. IO in Source.                         |  |  |

| STAT          | Status Request. I O in Source.                      |  |  |

If there are no options stated in the E field of the symbolic assembler instruction, the following options are generated automatically: carry in and out (bits 14 and 15 = 11), no shifts (bits 12 and 13 = 00).

4.11.5 Examples:

| Before        | Symbolic<br>Instruction | After         |

|---------------|-------------------------|---------------|

| MR4 = X'1234' | L MR4, MR4, NC          | MR4 = X'1234' |

| MR4 = X'1234' | L MR4, MR4, SL          | MR4 = X'2468' |

| MR4 = X'1234' | L MR4, MR4, SR          | MR4 = X'091A' |

| MR4 = X'1234' | L MR4, MR4, CS          | MR4 = X'3412' |

|               |                         |               |

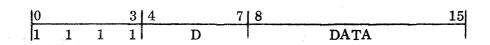

# 4.12 LOAD IMMEDIATE

4.12.1 Description: The 8 bits from the DATA field of this instruction are loaded into the register specified by the Destination (D) field. For register addresses, see Appendix 1. I/O is forbidden.

4.12.2 Options: None. Note that the flags (C, V, G, or L) are not changed by this micro-instruction.

4.13.3 Assembler Format: L D, DATA

L = symbol for Load Immediate

D = register symbol (e.g.: R5, SDR, MAH,) followed by a comma

DATA = either the operand expressed in hexadecimal (e.g.: X'9A') or as the low order 8 bits, L (DATA), or the high order 8 bits, H (DATA) of the value of a symbol defined by DATA.

#### 4.13 COMMAND

4.13.1 Description: The command micro-instruction results in the performance of the following machine functions as specified by the state of the COMMAND CODE bits.

# 4.13.2 Options:

| Bits set | Definition                                       |  |  |

|----------|--------------------------------------------------|--|--|

| 5        | Multiply Mode                                    |  |  |

| 4        | Divide Mode                                      |  |  |

| 4,5      | Repeat Mode                                      |  |  |

| 7        | Memory Read, Full Cycle                          |  |  |

| 6,7      | Memory Write, Full Cycle                         |  |  |

| 9        | Reset Bank*                                      |  |  |

| 8        | Set Bank*                                        |  |  |

| 8,9      | Trigger Bank                                     |  |  |

| 11       | Reset Utility*                                   |  |  |

| 10       | Set Utility*                                     |  |  |

| 10,11    | Trigger Utility*                                 |  |  |

| 12       | Clear Memory Parity Fail*                        |  |  |

| 13       | Set Wait Alarm*                                  |  |  |

| 14       | Reset Wait Alarm*                                |  |  |

| 15       | Power Down (this Command initializes the system) |  |  |

\* = flip-flops

4.13.3 Assembler Format: C F

C = symbol for Command

$\mathbf{F}$  = symbol for machine function

| Symbol      | Definition                |

|-------------|---------------------------|

| MPY         | Multiply                  |

| DIV         | Divide                    |

| RPT         | Repeat                    |

| MR          | Memory Read, Full Cycle   |

| MW          | Memory Write, Full Cycle  |

| СВ          | Reset Bank*               |

| SB          | Set Bank*                 |

| ТВ          | Trigger Bank*             |

| CUT         | Reset (clear) Utility*    |

| SUT         | Set Utility*              |

| TUT         | Trigger Utility*          |

| СМР         | Clear Memory Parity Fail* |

| SWA         | Set Wait Alarm*           |

| CWA         | Reset (clear) Wait Alarm* |

| POW         | Power Down                |

| * = flip-fl | ops                       |

A memory cycle consists of two half cycles: memory read, and memory write - in that order.

On a memory read, the memory location is read out, its contents are destroyed, then the memory location is restored and data is not lost.

On a memory write, the memory location is read out, but the data is not saved. Instead, the

(and

contents of the data register MDR are written back into the addressed memory location.

ŧ,

The following rules should be followed when programming around memory Commands:

- 1. Memory address register must always be loaded with the desired address before the memory command.

- 2. If a <u>write</u> operation is intended, the data register must always be loaded with the desired data before the memory command.

- 3. Observe this general rule: If memory registers are addressed by any micro-instruction when a memory cycle is in progress, that operation is inhibited until the memory cycle is completed.

The Bank flip-flop controls the addressing of certain registers. See Appendix 1.

The Utility flip-flop has no hardware function assigned to it, it is only for program control. Its condition can be tested with the Test micro-instruction.

The Wait Alarm is a flip-flop whose output is tied to the "wait" lamp on the display. Its purpose is to give a visual indication to the programmer when the Processor is halted or idling.

The Power Down Command initializes the entire system, and is generally used when "house keeping" operations are completed after the detection of a power failure.

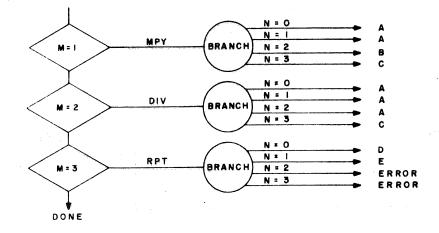

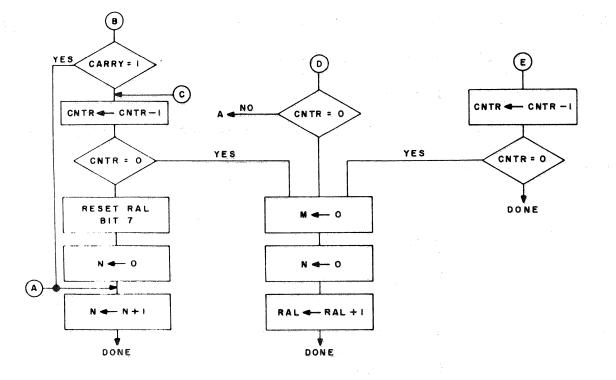

The Multiply command locks the Processor into a tight three instruction loop which is transversed 16 times until the Multiply function is completed. The command must be wired into an odd address. The Multiply loop would then follow:

odd addressCMPYnot part of the loopeven addressLYD, YD, SRodd addressAYD, YD, CO

The third instruction is not wired in. Instead, the Load is done twice: first with YD as Source and Destination, then with YDP1 as Source and Destination.

The add is done only if the hidden load resulted in a carry. If the above instruction set is not used, the results cannot be guaranteed.

The Divide command locks the Processor into a three instruction loop which is traversed 16 times until the Divide function is completed. The command must be wired into an odd address. The Divide loop would then follow:

> C DIV not part of the loop L YD, YD, SL A YD, YD, CO

The third instruction is not wired in. Instead, the load is done twice: first with YDP1 as Source and Destination, then with YD as Source and Destination. The Add modifies YD only if it results in a carry. If the above instruction set is not used, the results cannot be guaranteed.

The Repeat command, if the counter is not empty, causes the Processor to repeat the next sequential micro-instruction the number of times previously set in the counter register. Each execution causes the counter to decrement until zero is reached when the Processor resumes normal instruction sequencing. If the counter is zero when the repeat command is given, the next sequential micro-instruction is skipped.

The command Repeat must be wired into an odd address. Any instruction may be repeated that does not result in a branch, e.g. Branch, Load RAL, Decode. Also, it is suggested that memory commands not be repeated.

4.14.1 Description: If any of the machine functions specified by the TEST CODE is true, the Greater flag (G) is set and the Less flag (L) is reset. If the function specified by the TEST CODE is false, the Less flag (L) is set and the Greater flag (G) is reset.

4.14.2 Options: The testable functions are:

| Bit set | Definition                        |

|---------|-----------------------------------|

| 5       | I/O Interrupt                     |

| 6       | Auto Restart                      |

| 7       | Console Interrupt                 |

| 8       | <b>Console Single Instruction</b> |

| 9       | Utility flip-flop                 |

| 10      | Memory Parity Fail flip-flop      |

| 11      | Primary Power Fail                |

4.14.3 Assembler Format: T

T =

symbol for Test

$\mathbf{F}$  = symbol for machine function

| Symbol | Definition        |

|--------|-------------------|

| ATN    | I/O Interrupt     |

| ARST   | Auto Restart      |

| CATN   | Console Interrupt |

$\mathbf{F}$

| Symbol | Definition                 |

|--------|----------------------------|

| SNGL   | Console Single Instruction |

| UT     | Utility flip-flop          |

| MPF    | Memory Parity Fail         |

| PPF    | Primary Power Fail         |

### 4.15 BRANCH ON CONDITION

| 0 |   |   | 3 | 4 | 5 | 6 | 7 | 8 15    |

|---|---|---|---|---|---|---|---|---------|

| 0 | 0 | 0 | 1 | C | V | G | L | ADDRESS |

4.15.1 Description: the Branch on Condition micro-instruction results in a transfer in the micro-program sequence, if <u>any</u> of the specified conditions (Carry, oVerflow, Greater than zero, Less than zero) are true. The flags (in the Flag Register) are tested against the flags specified by bits (4:7) of the instruction. If <u>any flag and its corresponding bit</u> in the instruction are both set, control of the program is given to the location specified by the ADDRESS field, otherwise the next sequential instruction will be performed.

4.15.2 Options: None.

- 4.15.3 Assembler Format: B CC, ADDRESS

- B = symbol for Branch on Condition

- CC = Condition Code (C, V, G, or L: any one, any two e.g.: CV or VL etc., any three e.g.: CVG or VGL etc., or all four, CVGL, may be specified)

- ADDRESS = symbolic or hexadecimal address where the micro-program transfers if conditions are met

#### 4.16 BRANCH ON COUNTER

4.16.1 Description: the Branch on Counter micro-instruction results in a transfer in the micro-program sequence, if the Counter Register does not equal 'one'. If the condition is met, the Counter Register is decremented by 'one' and control of the program is given to the location specified by the ADDRESS field. If the counter does equal 'one', it is decremented to zero and the next sequential instruction will be performed.

4.16.2 Options: None.

4.16.3 Assembler Format: B CTR, ADDRESS

B = symbol for Branch

CTR = Counter Register

ADDRESS = symbolic or hexadecimal address where the micro-program transfers if conditions are met.

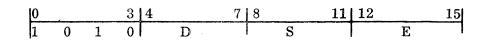

#### 4.17 DECODE

4.17.1 Qualifications: all zeros in RD are interpreted by the hardware as illegal and will result in an unconditional branch to location X'200' in ROM. Therefore, Decode is qualified by zeros in RD 0:3 and bits 4:15 are <u>not</u> all zeros. Only two sets of Destinations and Sources are allowed: the A Register (AR) as Destination and User's Destination (YD) as Source; or the Location Counter (LOC) as both Destination and Source.

4.17.2 Description: the Decode micro-instruction is primarily used to generate a phase change (see Chapter 5 for phase descriptions) although other options are available. Decodes are treated by the hardware as an Add or a Load. The Decode instruction terminating the Phase Zero micro-instruction set must have AR as its destination and YD as source. If the Instruction Register (IR) holds a user's Register to Register (RR) instruction, the contents of the General Register specified by IR 8:11 (YD) are <u>loaded</u> to the AR. If IR does not hold a user's RR instruction, the Location Counter (LOC) is forced to be both Source and Destination. The AR input to the ALU is forced to X'0002' and an Add is performed.

Only one Decode instruction is allowed in Phase Zero. Only the Phase Zero decode may result in a load or an add. Only the Phase Zero decode is written with AR the Destination and YD the Source. All other Decodes must have LOC as Source and Destination and are treated as Adds. The LOC will be incremented by two - AR input to ALU = X'0002' - unless we are exiting Phase Zero with user's RR instruction, exiting Phase One, or entering Phase Three. If the Decode is not to increment LOC, the AR input to ALU is X'0000' and LOC does not change. Other actions peculiar to the Decode micro-operation follow under options.

4.17.3 Options: Note that the character "x" in any bit position indicates a "don't care" state.

#### E field

### Definition

1 x x x

A Memory read is generated unless the conditions Phase Zero and RR user format exist.

|   | <u>E field</u> | Definition                                                                                                                                                                                                                                                                     |

|---|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | x1xx           | The contents of the Flag Register (FLR) are jammed to the Condition Code Register (CCR)                                                                                                                                                                                        |

|   | xx1x           | The Flag Register (FLR), Counter (CTR),<br>Utility Switch (UT), and Register Bank (BANK)<br>are cleared.                                                                                                                                                                       |

|   | xxx1           | The Phase Pointer and ROM Address will change.<br>The indirect Source Pointer (PTYS) will set if we<br>are exiting Phase Zero with an RR or indexed RS<br>or RX user's operation in the Instruction Register.<br>PTYS will reset the first time an indirect source<br>is used. |

| ł |                | NEW I INEW ROM                                                                                                                                                                                                                                                                 |

|    |                            | NEW                    |                                          | NEW ROM                                                                         |

|----|----------------------------|------------------------|------------------------------------------|---------------------------------------------------------------------------------|

| IR | INDEX?                     | PHASE                  | PTYS                                     | ADDRESS                                                                         |

| RR | NA                         | 2                      | Sets                                     | *                                                                               |

| RX | YES                        | 1                      | Sets                                     | X'00C'                                                                          |

| RX | NO                         | 1                      | Stays Reset                              | X'008'                                                                          |

| RS | YES                        | 1                      | Sets                                     | X'004'                                                                          |

| RS | NO                         | 2                      | Stays Reset                              | *                                                                               |

| NA | NA                         | 2                      | Resets                                   | *                                                                               |

|    | RR<br>RX<br>RX<br>RS<br>RS | RRNARXYESRXNORSYESRSNO | IRINDEX?PHASERRNA2RXYES1RXNO1RSYES1RSNO2 | IRINDEX ?PHASEPTYSRRNA2SetsRXYES1SetsRXNO1Stays ResetRSYES1SetsRSNO2Stays Reset |

## \*ROM Address generated by DROM

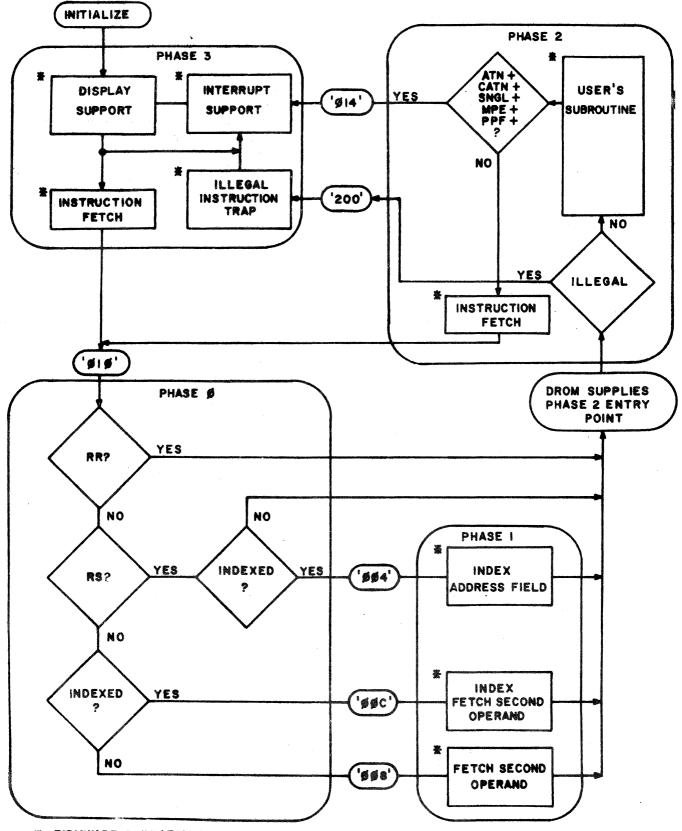

On exiting Phase Two, the Decode instruction tests for ATN, CATN, SNGL, MPE, and PPF. If any condition is true, Phase Three is entered and ROM Address is forced to X'014'. If none are true, Phase Zero is entered and ROM Address is forced to X'010'.

4.17.4 Assembler Format: D D, S, E

D = symbol for Decode

- D = A register symbol, either AR or LOC, followed by a comma

- S = A register symbol, either YD or LOC, followed by a comma if an assembler option is specified in the E field

The following symbolic options may appear in the E field:

| Symbol | Definition                                     |

|--------|------------------------------------------------|

| MR     | Memory Read. Bit $12 = 1$                      |

| JAM    | Load CCR from FLG. Bit 13 = 1                  |

| CL     | Clear FLR, CNTR, UT, and BANK.<br>Bit $14 = 1$ |

| PC     | Phase Change. Bit $15 = 1$                     |

| P0     | Phase Zero. Bits 12:15 = 1011                  |

| P1     | Phase One. Bits $12:15 = 1011$                 |

| P2J    | Phase Two, Jam. Bits 12:15 = 1111              |

| P2N    | Phase Two, No Jam. Bits $12:15 = 1011$         |

| P3     | Phase Three. Bits 12:15 = 1011                 |

#### **CHAPTER 5**

### USER ORIENTED PHASE DESCRIPTION

The GE-PAC 30-2 'Micro-Processor' is, to a certain extent, oriented toward the standard GE-PAC 30 user's instruction set. The user's instruction is decoded to define many hardware and firmware functions before actually entering the micro-routine that will execute the instruction.

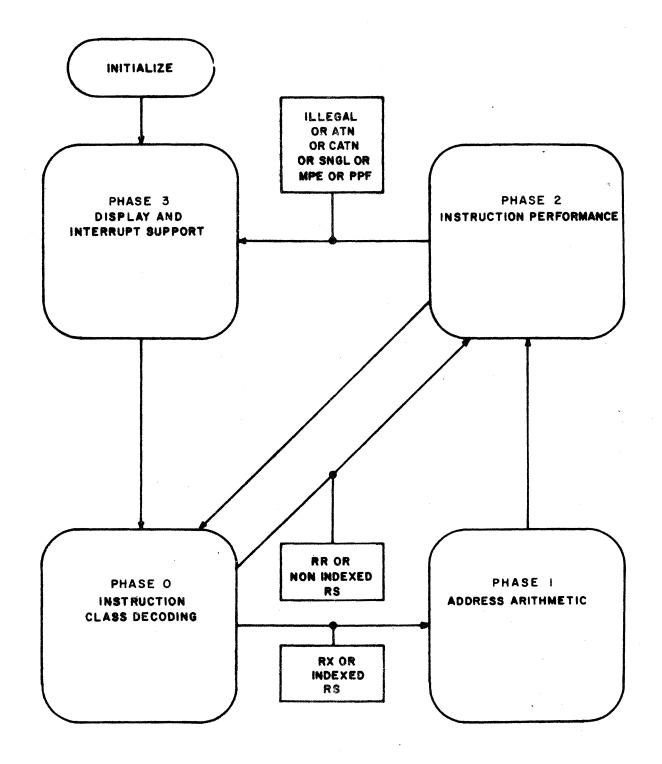

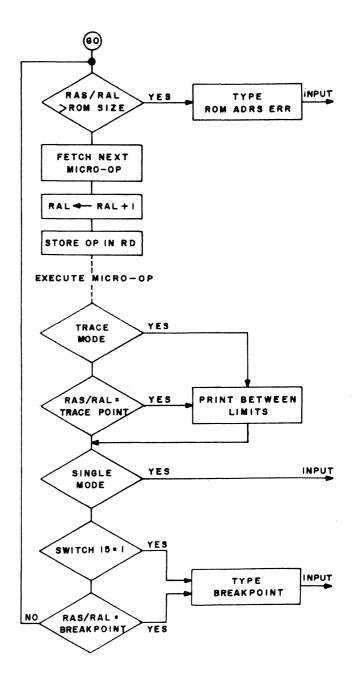

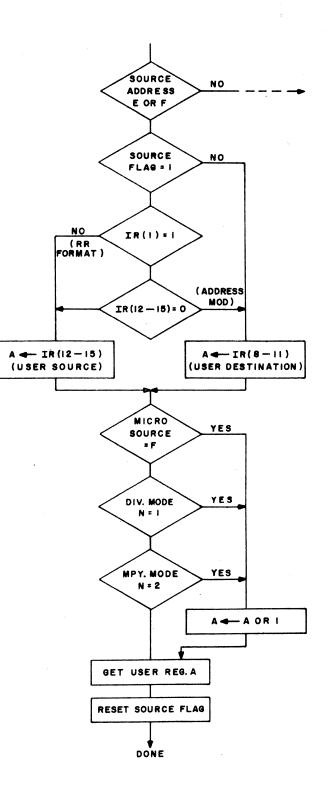

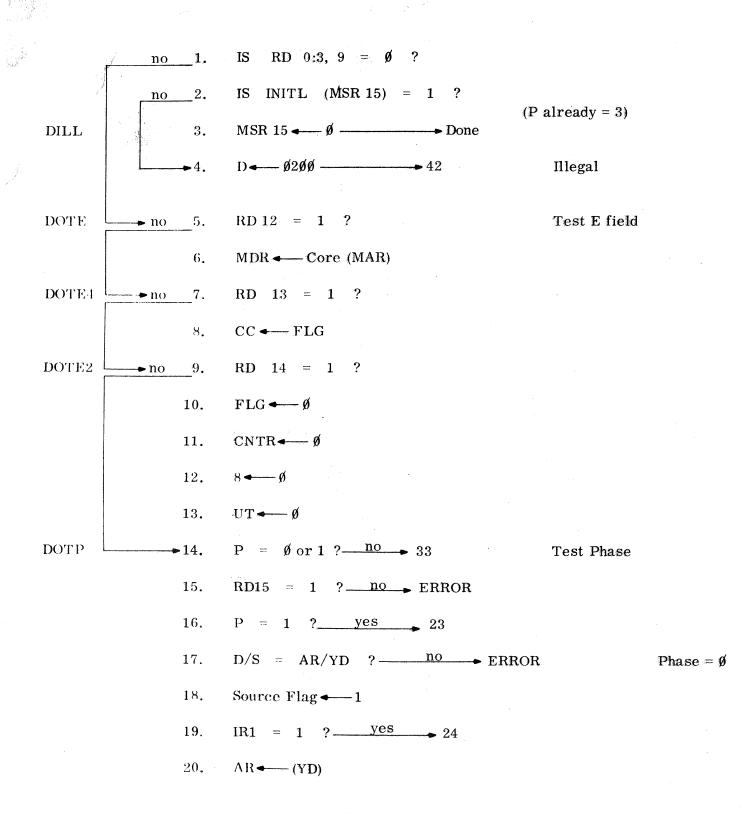

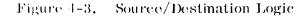

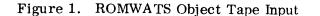

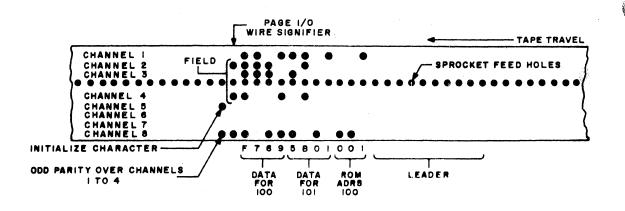

In the GE-PAC 30-2 there are four hardware conditions known as "phases". Each phase has corresponding sets of micro-instructions. In general, Phase Zero is dedicated to user's instruction fetch and class decoding: Phase One to indexing for the second operand; Phase Two to user's instruction execution; and Phase Three for interrupt service and display support. These phases effect and in-turn are effected only by the Decode micro-instruction. When the Decode micro-instruction is used to bring about a phase change, the subsequent state of the phase pointer is dependent on user's instruction format; whether or not the instruction is indexed and the current state of the phase pointer. (See Figure 1.)

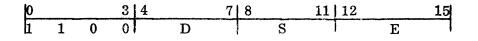

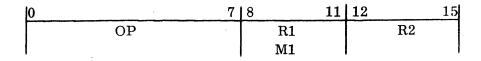

User instruction format is specified by bits 0:3 of the instruction word. The three formats are:

1. Register to Register (RR)

OP is an 8 bit field specifing, in all formats, the operation to be performed. R1 in all formats, is a 4 bit field containing the address of the register which holds the first operand or the mask (M1) for Branches. R2 is a 4 bit field containing the address of the

register which holds the second operand. Operation codes X'0n', '2n' and '9n' are recognized by the Processor as RR.

2. Register to Indexed Memory (RX)

| 0 7 | 8 11 | 12 15 | 16 31   | İ. |

|-----|------|-------|---------|----|

| OP  | R1   | X2    | ADDRESS |    |

|     | M1 , |       |         |    |

X2 is a 4 bit field containing the address of the register which holds the index value. Bits 16:31 specify an address which can be modified by the index value to specify where in core memory the second operand resides. Operation codes X'4n', '6n', and 'Dn' are recognized by the Processor as RX.

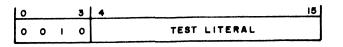

## 3. Register to Storage (RS)

| 0 7 | 8 11 | 12 15 | 16 31 |

|-----|------|-------|-------|

| OP  | R1   | X2    | DATA  |

Bits 16:31 contain the data constant to be used as the second operand (immediate). Operation codes X'Cn' and 'En' are recognized by the Processor as RS.

If bits 12:15 of RX and RS instructions are zero, no indexing is to take place.