# GE-635 System Manual

# GE-635 SYSTEM MANUAL

Rev. July 1964

# PREFACE

This manual introduces the GE-625 and the GE-635 Information Processing Systems, All significant features and capabilities of the two systems are identical, except for memory access times and instruction execution times. In the interests of clarity and readability, this manual discusses the GE-635 only, which has a one microsecond memory cycle. However, all information (except timing data) is applicable to the GE-625, which has a two microsecond memory cycle. The Appendix includes a listing of all machine instructions with execution times for both the GE-625 and the GE-635.

For more detailed information concerning either the GE-625 or the GE-635, refer to the GE-635 Programming Reference Manual, CPB-1004, and the GE-635 General Comprehensive Operating Supervisor Reference Manual, CPB-1002.

(c) 1964 by General Electric Company

# Contents

# I. INTRODUCTION

|      | Modularity and Configurations       Image: Configuration in the second sec | -1<br>-3<br>-7<br>-9 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| II.  | MEMORY MODULES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |

|      | Real-Time Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -1<br>-2<br>-2       |

| III. | PROCESSOR MODULES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

|      | System Configuration FlexibilityIIIRegister DescriptionsIIIWord FormatsIIIAddress ModificationIIIInstruction RepertoireIII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -2<br>-3<br>-7       |

| IV.  | INPUT/OUTPUT CONTROLLER MODULES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |

|      | Peripheral Equipment Capacity       IV         Data Transfer Capability       IV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -5<br>-7             |

| v.   | PROGRAMMING SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

|      | General Input/Output Supervisor       V         General File Record Control       V         General Loader       V         General Remote Terminal Supervisor       V         MACRO Assembler       V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10<br>10<br>11       |

| VI.  | REMOTE INPUT/OUTPUT AND REAL-TIME OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -2<br>-2             |

# VII. PERIPHERAL EQUIPMENT SUBSYSTEMS

| CR-20 Card Reader Subsystem. | VII-2<br>VII-3<br>VII-4<br>VII-5<br>VII-7<br>VII-8<br>VII-8<br>VII-9<br>/II-10<br>/II-11 |

|------------------------------|------------------------------------------------------------------------------------------|

| APPENDIX                     |                                                                                          |

| Instruction Summary          | A-1<br>A-8                                                                               |

# ILLUSTRATIONS

# Figure

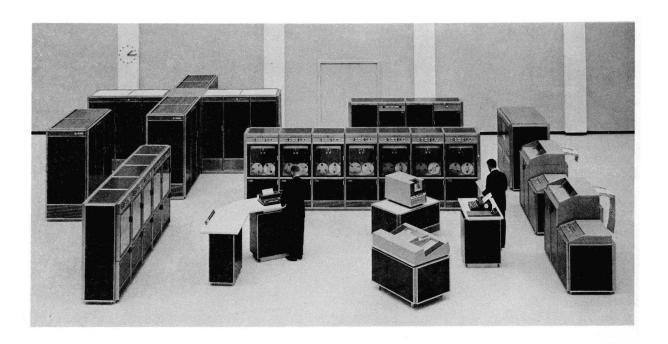

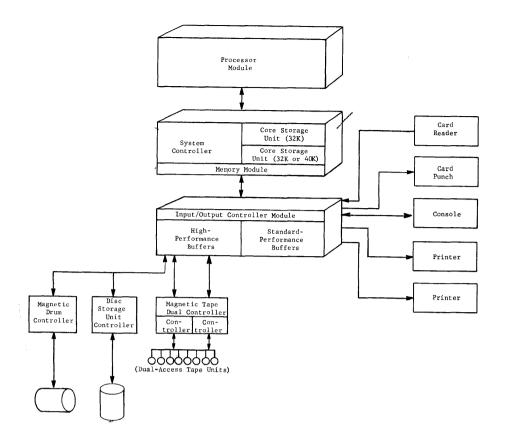

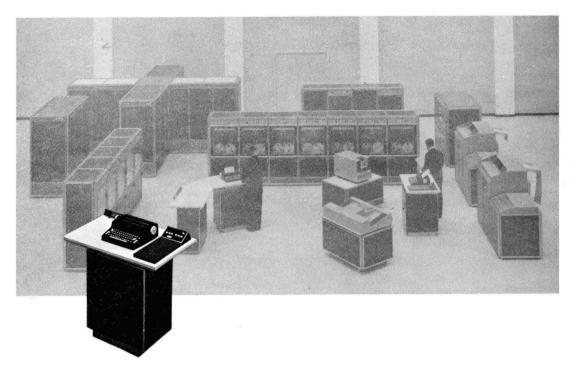

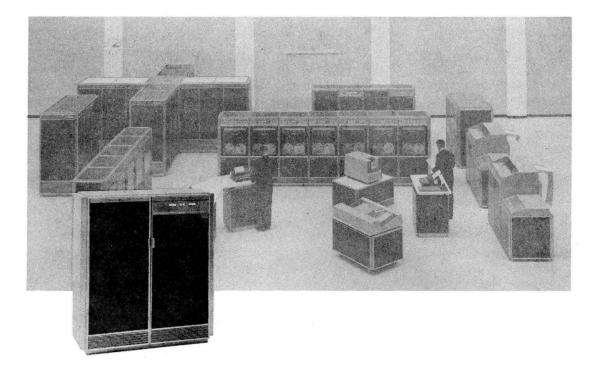

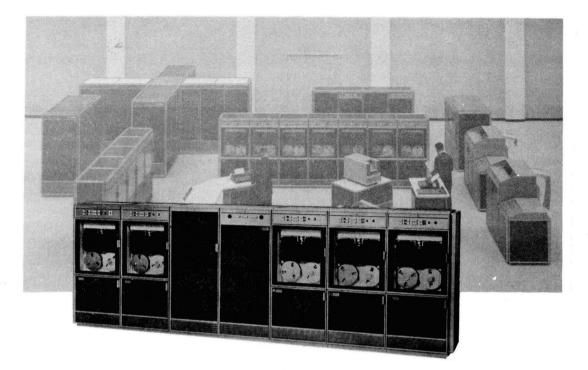

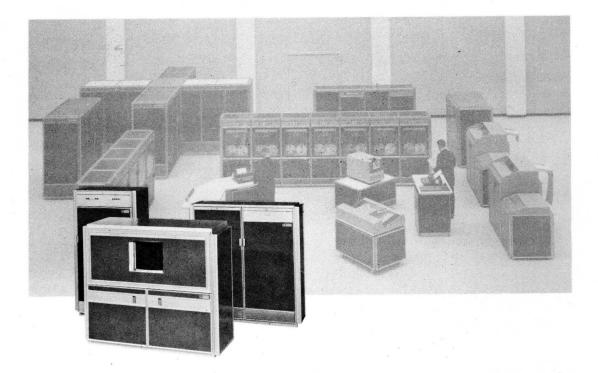

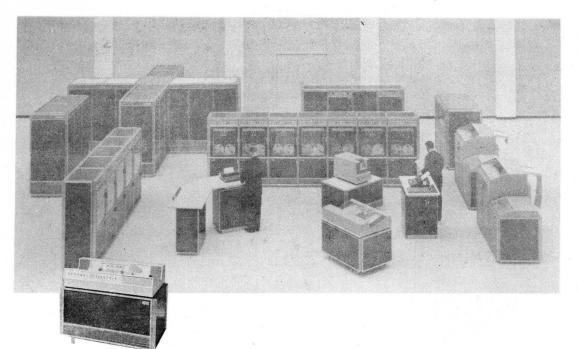

| Frontispiece<br>I-1<br>I-2<br>I-3<br>I-4 | GE-635 Information Processing SystemOn-Line ConfigurationMultiprocessor Configuration with Real-Time CapabilityI-4Multicomputer ConfigurationI-5Multicomputer Configuration with One SharedMemory ModuleI-6 |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| III-1                                    | Indicator Register Format                                                                                                                                                                                   |

| III-2                                    | Fixed-Point Data Formats                                                                                                                                                                                    |

| III-3                                    | Floating-Point Data Formats                                                                                                                                                                                 |

| III-4                                    | Alphanumeric Data Format                                                                                                                                                                                    |

| III-5                                    | General Instruction Format                                                                                                                                                                                  |

| III-6                                    | Indirect Word as Interpreted under I                                                                                                                                                                        |

| III-7                                    | Indirect Word as Interpreted under ID or DI                                                                                                                                                                 |

| III-8                                    | Indirect Word as Interpreted under SC                                                                                                                                                                       |

| III-9                                    | Indirect Word as Interpreted under CI                                                                                                                                                                       |

| III-10                                   | Indirect Word as Interpreted under AD                                                                                                                                                                       |

| III-11                                   | Indirect Word as Interpreted under IDC and DIC                                                                                                                                                              |

| III-12                                   | Typical Character Operations                                                                                                                                                                                |

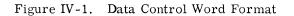

| IV-1                                     | Data Control Word Format                                                                                                                                                                                    |

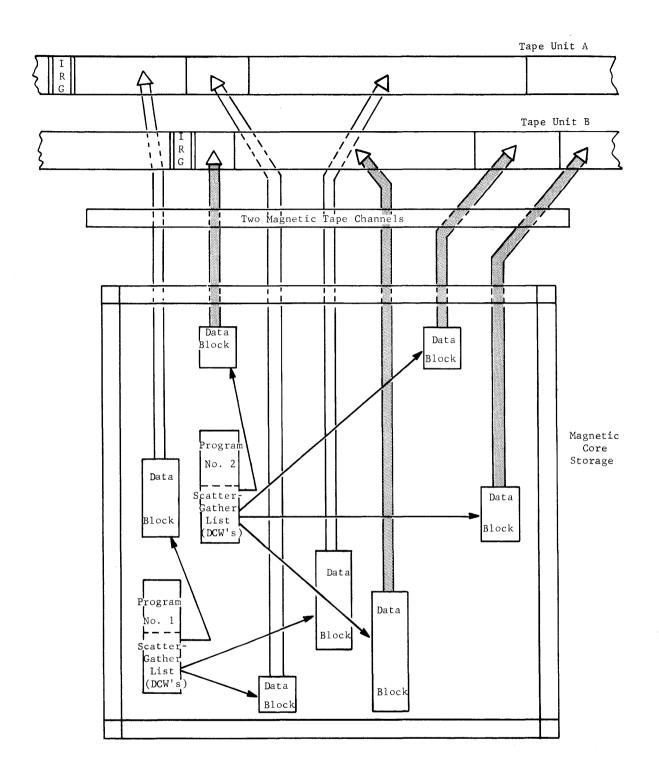

| IV-2                                     | Gather Writing on Magnetic Tape                                                                                                                                                                             |

# I. INTRODUCTION

The GE-635 Information Processing System is a modular, solid-state, digital computing system for large-scale business, scientific, military command and control and other real-time applications. The GE-635 equipment is complemented by a fully-integrated, yet modular, programming system that is controlled by the General Comprehensive Operating Supervisor (GECOS), an executive program that takes full advantage of the GE-635 equipment features.

The overall system design objectives for the GE-635 were to provide a user-oriented computation system with maximum reliability and the highest possible computation/cost ratio that would serve a user's present needs and could be expanded as his needs increased.

# SYSTEM CONCEPTS

System objectives were met in design through careful attention to four concepts:

Modularity Multiprogramming and multiprocessing capability Integrated programming and operating system Potential for growth

# Modularity

Modularity provides full configuration flexibility. Basic equipment modules permit establishing a configuration for current needs that can be expanded to other configurations to meet growing needs. The basic modules, which provide increased reliability through provision for self-backup, are:

- Memory Modules--This module type contains a System Controller and one or two core storage units. All communication and control functions are routed through a System Controller that accesses the core storage units.

- Processor Modules--This module type performs the data movement, arithmetic, logic, comparison, and control operations. Processor instructions can address up to 262,144 consecutive words of memory.

- Input/Output Controller Modules--This module type is the coordinator of all input/output operations between Memory modules and the peripheral subsystems.

Modular input/output control capabilities of the GE-635 permit the use of a full range of peripheral equipment, including real-time, data communication, remote terminal, and mass storage devices, as well as conventional input/output devices.

# Multiprogramming and Multiprocessing Capability

Multiprogramming is made possible through a combination of equipment and control program features.

The <u>General Comprehensive Operating Supervisor (GECOS)</u> is an operating system that adapts itself automatically to operate with any equipment configuration.

Dual mode operation restricts operating control of the multiprogramming environment to GECOS:

- Master mode, reserved for GECOS, allows unrestricted access to all of memory, permits input/output initiation through the Input/Output Controllers, and permits the setting of control registers.

- Slave mode, used by job programs and system programs such as FORTRAN, COBOL, Loader, Sort/Merge, etc., restricts address references to individual program boundary regions, and causes <u>all</u> memory references to be relative to the Base Address Register (BAR). The BAR is accessible <u>only</u> to control programs operating in the Master mode.

Dynamic relocation allows programs to be compacted in memory as individual programs are completed, allowing the system to use the released memory areas for new program allocation. In conjunction with dynamic relocation, these characteristics are significant:

- The Base Address Register is set by GECOS for each job program before that program gains control of the Processor.

- To insure GECOS control of the multiprogramming system, the programmer cannot set or restore the Base Address Register.

- Each programmer can look at memory as if his memory area always starts at zero, regardless of where his program ultimately resides in memory.

<u>Memory protection</u> insures complete program and data protection through program boundary limits imposed by the Processor and set by GECOS. Such boundary protection prevents job programs from erroneously affecting memory outside their assigned regions. Boundary protection for each program is automatically reset if the program is relocated during execution.

Effective interrupt orientation permits Processors and input/output devices to initiate interrupts whenever they require service from the operating system.

# Integrated Programming and Operating System

The General Comprehensive Operating Supervisor provides complete control over activity allocation, execution, and termination of all programs. This centralized computer operating system, together with the memory protection and interrupt features, maximizes utilization of memory and input/output devices, enabling the user to realize rapid throughput.

# Growth Potential

The user is assured that his GE-635 installation can grow as his needs increase. Modularity of design and a standardized memory interface permit additions of basic modules and peripheral devices as required.

Through data communications equipment, such as the DATANET-30, remote locations can be tied into the central computation system for remote inquiry and data processing, and multiple computer installations can communicate to form large computer complexes.

# MODULARITY AND CONFIGURATIONS

A GE-635 system is implemented in a combination of the three basic modules. These basic modules can be arranged in a variety of configurations using the number of:

- 1. Memory modules needed to provide the required amount of storage

- 2. Processor modules needed to provide the required amount of computational ability, and

- 3. Input/Output Controller modules required for the complement of peripheral equipment included.

This modular construction results in computer configurations that are tailored to the precise needs of an installation. System growth is accomplished by adding the appropriate modules as they are needed. Added reliability is obtained because identical modules are employed in expanded systems. These identical modules provide backup for each other if individual modules malfunction. Figure I-1 illustrates a typical on-line configuration of a GE-635 utilizing one Processor module, one Memory module, and one Input/Output Controller module.

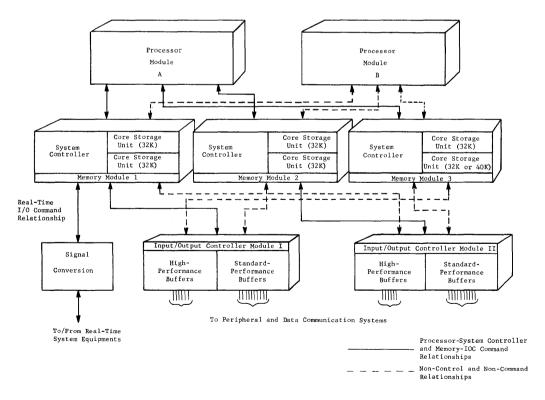

A system that uses multiple Processor modules is defined as a multiprocessor system. In such a system, only one Processor can be a Control Processor. All other Processors are subservient to the Control Processor. Subservient Processors can perform processing under the direction of the Control Processor; however, they cannot control system operations, nor can they directly initiate input/output transfers. The efficiency of multiprocessor configurations is inherently high. Figure I-2 illustrates a multiprocessor configuration with a real-time capability, using two Processor modules, three Memory modules, and two Input/Output Controller modules. In a multiprocessor system, the emphasis is on increased general-purpose system throughput.

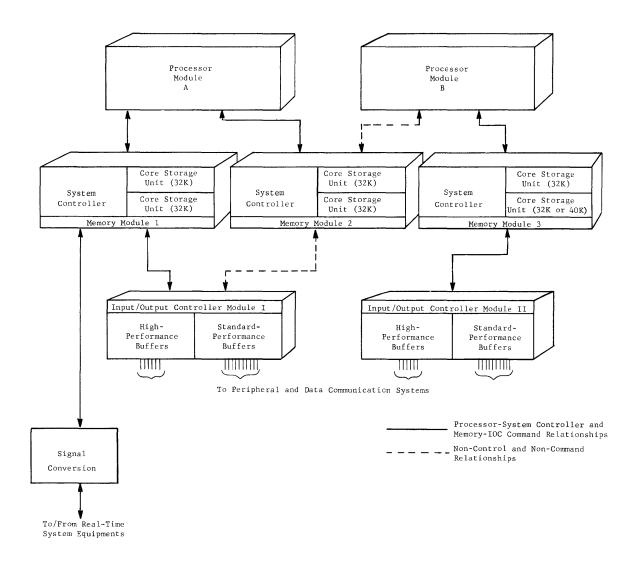

A system that includes multiple Processor modules and multiple Memory modules contains switches that permit the establishment of either a multiprocessor system or a multicomputer system. In the multicomputer system, two or more Processors operate as Control Processors, each controlling its own Memory modules and initiating input/output operations through its own Input/Output Controllers. A system of this type can be regarded as two or more separate computer systems; however, the separate computers can share common Memory modules. A multicomputer configuration is illustrated in Figure I-3.

Figure I-2. Multiprocessor Configuration with Real-Time Capability

COMPATIBLES//600-

Figure I-3. Multicomputer Configuration

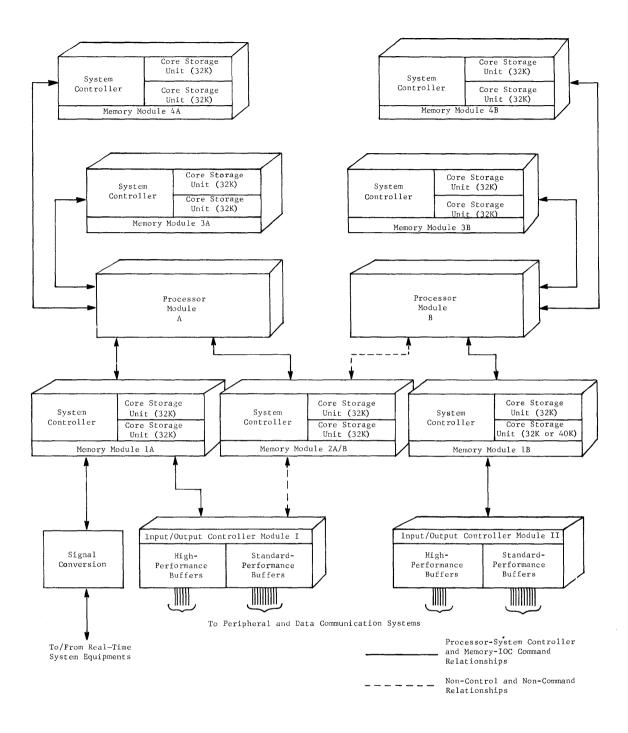

The maximum configuration for a GE-635 system in which each Processor and each Input/Output Controller has direct addressing of all associated Memory modules is limited to four System Controllers and associated core storage units. However, additional expansion of a multicomputer configuration can be accomplished if Processors communicate through shared Memory modules, rather than by direct addressing of each Memory module. The manner in which this can be done is shown in Figure I-4. Multicomputer configurations have enhanced reliability by permitting interchange of modules on a full system level as well as the individual module level.

Figure I-4. Multicomputer Configuration with One Shared Memory Module

# SYSTEM FEATURES

Certain GE-635 equipment features make significant contributions to the exceptional multiprogramming, high throughput, and rapid turn-around capabilities of the GE-635. These features, together with the integrated programming system under the control of GECOS, make possible the automatic supervision of the multiprogramming environment. These features permit GECOS to control:

Real-time interrupt response Job scheduling Hardware allocation Input/output supervision Local and remote media conversion Routine housekeeping and accounting functions

# Dual-Mode Operation

Dual mode operation is essential in a multiprogramming environment because only the operating system should be allowed to initiate input/output operations, set the interval timer, BAR, and other control registers. Without dual-mode operation, multiprogramming would require extreme discipline by the user to insure that he did not assume operating system functions.

Each Processor is capable of operating in two modes: the Slave mode or the Master mode. When a Processor is in the Master mode, no restrictions are imposed on a program. When a Processor is in the Slave mode, a program is inhibited from exercising a control relationship with Memory modules and associated peripheral devices. Also, while in the Slave mode, the Base Address Register (see below) controls relative addressing and memory limits protection for the program.

The General Comprehensive Operating Supervisor operates in the Master mode, whereas job programs operate in the Slave mode under control of GECOS. GECOS and job programs not currently being executed, together with their associated data, are protected from the job program being executed.

A Processor can be placed in the Slave mode at any time by program instruction. However, the Processor can be returned to the Master mode only by transfer to a legal system program entry from the job program, or by interrupt to a legal Master mode entry from a peripheral device. An attempt by a job program to access or transfer to any protected memory location at other than legal entry points, or to perform external control operations, results in an immediate fault routine. This feature provides positive protection for the entire system to allow it to operate in a multiprogramming-multiprocessing mode.

# Dynamic Program Relocation

When the Processor is in the Slave mode, memory references are controlled by the Base Address Register (BAR). This register contains a base address associated with the job program that is automatically added to all job program addresses at execution time. The BAR also contains a designation of the number of 1024-word memory blocks that are assigned to the specified job program, thereby limiting the area of memory to which the job program has access. Thus, all job programs are stored in memory relative to a zero address and, each time memory is referenced, the base address is added to the address of the instruction to determine the actual address.

The BAR can be reset only in the Master mode. This restriction is essential for the operating system to be able to relocate job programs dynamically. If the programmer were able to access the BAR at any time, then programs could not be safely relocated. Master mode addressing ignores the contents of BAR and is absolute through the entire address range. The BAR permits entire job programs to be relocated in memory. This capability is desirable when many programs reside in memory and must be relocated frequently in order to consolidate memory areas that have been relinquished upon program terminations. Thus, it is also possible to interrupt a job program temporarily, place it in temporary storage, and later return it to any available block of memory locations without the need for software relocation.

# Processor-Oriented Memory Protection

Two or more job programs simultaneously occupying the same Memory module must be protected from each other so that one program does not inadvertently store into the area outside its boundary limits. Each job program memory reference has the contents of the Base Address Register added to it, and a comparison is made to insure that this new address does not lie outside the allocated memory region. If it does, an out-of-bounds fault occurs.

# Input/Output Controller-Oriented Memory Protection

Input/output activities requested by one job program must not be permitted to disturb any other job program unintentionally. Thus, each input/output channel on an Input/Output Controller has provisions for checking data transfers to and from memory to assure that preassigned data transfer area limits are not violated.

## Interrupt Orientation

In an effective multiprogramming computer system, it is necessary to free both the equipment and the program from any specific timing requirements and from the burdens of checking other components of the system either for task completion or requests for service. Therefore, in the GE-635 system, devices that have completed tasks or that require service, generate interrupts to instruction processing. These interrupts can be generated by Processors as well as by input/ output devices. Specific equipment features are included in the system to implement this interruptoriented philosophy.

#### Interval Timer

Each Processor contains a timer that initiates a program interrupt at the end of a variable interval. The timer can be loaded or set only in the Master mode. It consists of a 24-bit register that is automatically decremented every 16 microseconds. When the count reaches zero, the timer generates an interrupt, but continues to count. This interrupt is masked in the Master mode. The interval timer is used by GECOS for system control of the multiprogramming environment to time job programs for automatic job termination, to prevent a job program from monopolizing a Processor, and to provide accounting information by monitoring processing and input/output elapsed time.

## Fault Interrupts

Because of the continuous access needs in a real-time multiprogramming application and in keeping with the interrupt-oriented philosophy of the GE-635 system, the Processor provides for continuous on-line operation by immediately responding to high-level interrupts called faults. Any operation that might otherwise cause the system to "hang up," causes a fault into

the Master mode control program automatically, so that immediate remedial action can be taken. Also, the system can call another job into execution if a current job encounters difficulty.

For each potential fault condition, two instructions in fixed memory locations are executed when the related fault occurs. The first instruction normally safe-stores the location counter and indicators; the second causes a transfer to the related fault routine. These fixed locations, reserved for Processor use only, are in the control supervisor area.

Fourteen conditions can cause faults:

| Exponent overflow<br>Exponent underflow<br>Arithmetic overflow<br>Memory parity                                                                                                                                                                    |   |              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|

| Connect (for Processor/Controller communication)<br>Time runout<br>Machine lockup<br>Illegal operation code<br>Command (Master/Slave mode violations)<br>Operation not complete<br>Divide check<br>Memory address violation<br>Shutdown<br>Startup | } | Non-maskable |

## Real-Time Interface

The GE-635 is designed to permit real-time devices to communicate directly with memory. The interface, together with memory, permits independent data movement and program initiation under complete control of the external device. Thus, the external device can operate in either the conventional processor-controlled mode or in a self-controlled mode which, for specialized applications, highly optimizes system performance.

# INTEGRATED PROGRAMMING AND OPERATING SYSTEM

The basic features of the GE-635 system and the manner in which these features interact implies a fundamental requirement for control program integration with the equipment. This overall system integration is achieved through the General Comprehensive Operating Supervisor, GECOS, which is provided by General Electric.

The GE-635, regardless of configuration, functions entirely under the control of GECOS. The integrated programming system is implemented in GECOS-controlled modules, enabling the user to select only the required modules for a given application and add or delete modules as needs change.

GECOS utilizes the previously-discussed equipment features to form a comprehensive system for the supervision of a multiprogramming environment. It controls all activities, including real-time interrupt response, job scheduling, equipment allocation, input/output supervision, local and remote media conversion, and routine housekeeping and accounting functions.

COMPATIBLES / 600

The entire programming system reflects the design objectives of providing user-oriented software. Programming system characteristics include:

- GECOS (and other system software) operates from a mass random access storage base. For this reason, magnetic tapes are not required for GECOS Library files, FORTRAN compilation, or other system program storage or execution. It is also permissible for GE-635 users to store their job programs on the magnetic disc included in the GE-635 system. This mass random access capability provides for maximum system throughput and minimum job turn-around time.

- To further facilitate throughput and turn-around time, the entire software system, under control of GECOS, is interrupt-oriented. Multiple levels of input/output interrupts are immediately serviced on a priority basis.

- Symbolic file assignments provide complete flexibility of peripheral allocation for dynamic scheduling and system reconfiguration.

- Control programs are written in modular form, are well-documented, and can be readily modified to tailor the system to specific operating conventions and application requirements. Also, special-purpose real-time and remote input/output control software can easily be interfaced with GECOS.

- Programmers writing for the GE-635 system need not be concerned that their programs will be executed in a multiprogramming environment. The same conventions that free the programmer from concern about absolute memory and peripheral requirements also provide for system growth without reprogramming.

A more complete description of GECOS is contained in Chapter V, Programming Systems. The compilers, MACRO Assembler, utility programs and subroutines, and other programming aids included in the integrated programming system are also described in that chapter.

# II. MEMORY MODULES

The Memory module is the hub for all information transferred between Processor modules and Input/Output Controller modules. The Memory module consists of a System Controller and either one or two associated core storage units. System Controllers are independent of each other and can function simultaneously, thus providing overlapped memory accesses in multiple-controller systems.

Normally, a memory size of 32k, 40k, 64k, or 72k words is associated with one System Controller. Each memory module represents a continuous portion of the total address range of associated modules. Only the highest-order Memory module can use the 40k or 72k memory size.

The System Controller has as many as eight channels for connection to Processor and Input/ Output Controller modules, and it also contains memory protection logic and program-interrupt cells.

# CHARACTERISTICS OF THE SYSTEM CONTROLLER

The System Controller performs most of the priority and control functions in the overall GE-635 system. These functions are:

- Control of communications between the system modules.

- Control of program interrupts for multiple-processor jobs and system programs, as well as Input/Output Controller requests for service.

- Protection of memory areas.

- Switching of control signals, addresses, and data to and from the Memory module.

- Provision for zone control (character handling).

The System Controller contains all the logic required for performing control functions and address checking. The controller also includes the following items:

- Eight memory ports for connection to the active modules (Processor, Input/Output Controllers, and other high-performance controllers and real-time devices). These ports are assigned a priority to permit the servicing of all demands in an orderly manner.

- A program-addressable memory port "lockout" mask that can be set by a control program to inhibit data transfers and interrupts.

- Sixteen program execute-interrupt cells. Any of the components interfacing with the System Controller can set the interrupt cells as required to initiate appropriate Control Processor activity.

- A program-addressable execute-interrupt mask. The control program can override the built-in priority of the interrupt cells and exercise complete control of all system interrupts as required.

- A Control-Processor-designation register. In a multiple-processor configuration it is desirable (for reliability and reconfiguration purposes) to designate different Processors alternately as the Control Processor for the system. The System Controller has an eight-position switch that corresponds to the eight channels to which the Processors and other active modules are connected. This switch is used to direct interrupt and control information to the appropriate Processor.

- A program-addressable memory protect register. In certain applications, it is advantageous to have a common data array that is not contiguously located with respect to the multiple-programs accessing it. A register in the System Controller can be set by the control program to protect various multiple, non-contiguous blocks of memory as required. The program-addressable memory protect register is a separate and independent feature that is unrelated to the standard Processor-oriented and Input/ Output Controller-oriented memory protection.

## REAL-TIME INTERFACE

The high-performance System Controller interface is derived from extensive experience with real-time military systems requirements. Its design provides maximum data handling capability with minimal interference with Processor activities.

The System Controller interface is basically bidirectional and word-oriented, and will accept a wide variety of real-time devices. It permits direct addressing of the memory locations involved without Processor intervention. This is of major importance with complex peripheral controllers requiring multiple queues, and for communication between a Processor or an Input/ Output Controller and a Memory module.

The System Controller interface can also initiate an interrupt, specifying the interrupt cell to be used and the action to be taken by the interrupted Processor.

Real-time capabilities are further discussed in Chapter VI.

# CORE STORAGE UNITS

Each Memory module contains either 32,768 or 65,536 words of magnetic core storage. Additionally, any one Memory module in a system contains an additional 8,192 words to accommodate the General Comprehensive Operating Supervisor (GECOS). Each word of core storage consists of 36 data bits, plus one parity bit. Although the single precision word size that is used throughout the system is 36 data bits, each access to memory, whether for data or instructions, obtains a double word of 72 data bits. The total memory cycle time for each Memory module is defined as the time from the start of command execution to the completion of the read-write cycle. Defined in this manner, the GE-635 memory cycle time is 1 microsecond for a full 74-bit access (two words plus a parity bit for each word). No overlap of memory operation is considered in determining this time.

# III. PROCESSOR MODULES

The Processor module has full program execution capability and conducts all actual computational processing within the GE-635 system. The Processor, which communicates only with System Controllers and associated memory, consists of an operations unit and a control unit. The operations unit contains the logic to execute arithmetic and logical operations. The control unit provides the interface between the operations unit and the System Controller. It also performs instruction fetching, address preparation, memory protection, and data fetching and storing. Both units operate with relative independence and maximum overlap to provide the highest rate of instruction execution.

# SYSTEM CONFIGURATION FLEXIBILITY

The GE-635 Processor includes standard features that directly contribute to the formation of multiprocessor and multicomputer system configuration flexibility or immediate reconfiguration.

The Processor is equipped with as many as four channels for connection to Memory modules and can directly address 262,144 words of memory. All instructions utilize a full 18-bit address field. Memory addresses are assigned consecutively, beginning with zero and continuing through the full available memory for those systems with less than a full complement of memory. Each Processor maintenance panel provides manual switches for assigning any 32k memory block to any modular 32k address within the range of continuous memory.

For example, in a two-Processor, three-Memory system (such as that illustrated in Figure I-3), both Processors can share the low-order 32k of memory, but address the upper 32k in different Memory modules.

In addition to provision for reassignment of basic memory block addresses, it is possible to assign fixed memory locations in a manner that avoids conflict in a multiprocessor system. The Processor always assumes that these locations are in low-order memory. However, if a low-order memory is common to several Processors, these fixed memory locations would overlay each other. To prevent this, manual reassignment of these fixed locations within low-order memory is permitted so that locations are uniquely defined for each Processor. Control relationships are thus established so that all interrupts are answered by one Processor, and all special locations are in one memory bank. Maximum multiprocessor effectiveness is thus achieved by relieving the balance of memory of all encumbrances and resolving potential conflict between Processors.

# **REGISTER DESCRIPTIONS**

The internal Processor registers that are accessible to the program are:

| Name                                          | Mnemonic | Length       |

|-----------------------------------------------|----------|--------------|

| Accumulator Register<br>Eight Index Registers | AQ       | 72 bits      |

| $(n = 0, 1, \dots, 7)$                        | Xn       | 18 bits each |

| Exponent Register                             | E        | 8 bits       |

| Base Address Register                         | BAR      | 18 bits      |

| Indicator Register                            | IR       | 18 bits      |

| Timer Register                                | TR       | 24 bits      |

| Instruction Counter                           | IC       | 18 bits      |

• The <u>AQ-Register</u> can be used:

In floating-point operations as a mantissa register for both single and double precision;

In fixed-point operations as an operand register for double precision, and each half independently of the other as two operand registers for single precision; the halves become the A-Register (bits 0 through 35) and the Q-Register (bits 36 through 71); and

In address modification each half of the A-Register and of the Q-Register can be the source of an index; these halves then become AU (bits 0 through 17), AL (bits 18 through 35), QU (bits 0 through 17), and QL (bits 18 through 35).

• The Xn-Registers can be used:

In fixed-point operations as operand registers for half-precision;

In address modification as sources of index quantities.

- The <u>E-Register</u> supplements the AQ-Register in floating-point operations as exponent register.

- The <u>Base Address Register</u> is used in address translation and protection. It denotes the base address and the number of 1024-word blocks assigned to the program being executed.

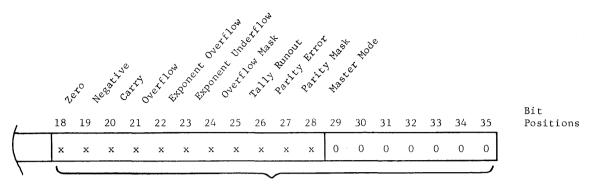

- The <u>Indicator Register</u> is a generic term for all of the program-accessible indicators within the Processor; the name is used where the set of indicators appears as a register, that is, as a source or destination of data. The format of the Indicator Register contents as they would be reflected in memory is shown in Figure III-1.

- The <u>Timer Register</u> is decremented by one each 16 microseconds and a Timer Runout fault occurs whenever its contents reach zero. If Timer Runout occurs in the Master mode, the fault does not occur until the Processor returns to the Slave mode.

Lower Half of a Memory Location

Figure III-1. Indicator Register Format

• The <u>Instruction Counter</u> stores the address of the next instruction to be executed.

#### WORD FORMATS

#### Fixed-Point Data

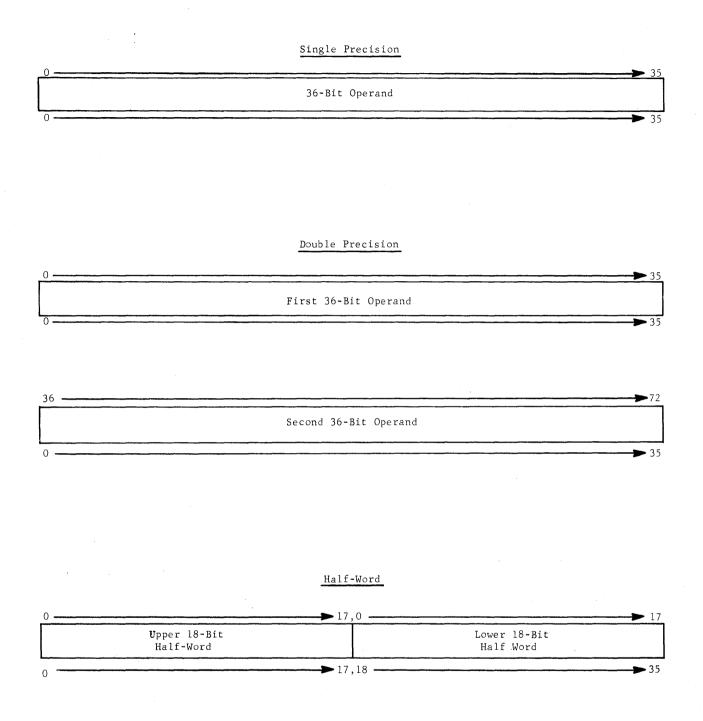

Fixed-point operations are conducted with 36-bit, single-precision operands; 72-bit doubleprecision operands; or 18-bit, half-word operands. The formats of the three types of operands are shown in Figure III-2.

Fixed-point data is represented in the two's complement number system. The range of single-precision numbers is  $2^{35-1}$  to  $-2^{35}$ , the range of double-precision numbers is  $2^{71-1}$  to  $-2^{71}$ , and the range of half-word operands is  $2^{17}-1$  to  $-2^{17}$ .

#### Floating-Point Data

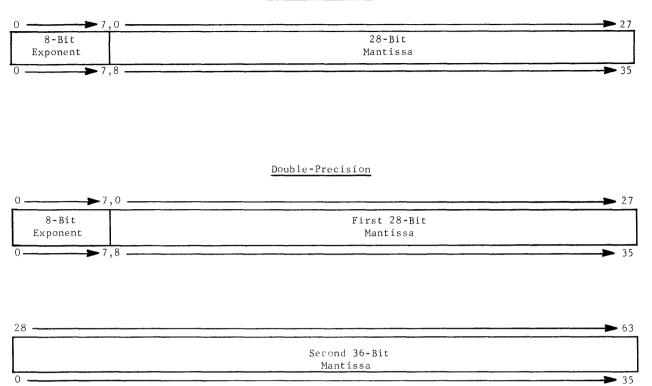

Floating-point operations are conducted with either 36-bit, single-precision operands or 72-bit, double-precision operands. The formats of each are illustrated in Figure III-3.

Floating-point numbers are represented by a mantissa of 28 or 64 bits and a binary exponent of 8 bits. Both the exponent and the mantissa are represented in the two's complement number system. The first bit of the mantissa indicates the sign of the quantity, and the exponent has a range of +127 to -128.

### Alphanumeric Data

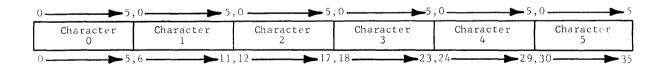

Six 6-bit characters are contained in each data word. The designation of the characters within the word is as shown in Figure III-4. Any combination of characters can be read or written to or from memory.

Figure III-2. Fixed-Point Data Formats

#### Single-Precision

Figure III-3. Floating-Point Data Formats

Figure III-4. Alphanumeric Data Format

#### Instruction Format

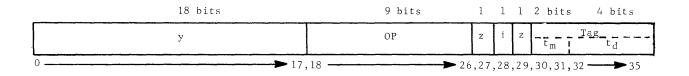

The instruction repertoire of the GE-635 Processor consists of 170 basic single-address instructions. With the exception of three Repeat instructions and the character-handling instructions. each instruction has the format shown in Figure III-5.

The operation (OP) part of the instruction specifies the operation to be performed and the registers that are involved.

The address (y) field of the instruction word specifies the storage location to obtain an operand or to place the result of the specified operation. Some of the exceptions to this general rule are:

- 1. Shift instruction, where the address field designates the number of bit positions to shift

- 2. Program sequence transfers, where the address field designates the location of the next instruction to be executed

- 3. A group of instructions where the address field specifies sub-operations.

The address modifier  $(t_m)$  portion of the tag field specifies how the address contained in the instruction word is to be modified to form the effective address Y of the resultant or the operand.

Figure III-5. General Instruction Format

The designator  $(t_d)$  portion of the tag field specifies the type of register modification to be used.

The interrupt inhibit (i) portion of the instruction word controls program interrupts in the Processor by either fault or program execute interrupts from the Memory.

The (z) fields must be zero, and are reserved for future compatibility with other General Electric 600-line systems.

COMPATIBLES//600-

# ADDRESS MODIFICATION

## Modification Types

The GE-635 performs address modification in four basic ways, using the identifiers R, RI, IR, and IT. The modification types R, RI, IR, or IT are specified by unique binary codes placed in the  $t_m$  field of the instruction word. The registers used to modify R, RI, or IR addresses are indicated in the  $t_d$  field of an instruction or indirect word.

- 1. Register modification (R)--Modify the address by adding to it the contents of the indicated register, producing the effective address of the operand. Indexing registers are X0-X7, AU, AL, QU, QL, and IC. The direct operand modifier symbols DU and DL may be used to treat the address directly as the operand.

- 2. Register then Indirect (RI)--First perform the indicated register modification of the address, as with R; then obtain an indirect word and conduct the modification specified in the indirect word.

- 3. Indirect then Register (IR)--First obtain the indirect word from the original address; then conduct the modification specified in the indirect word. Upon completion of the indirect addressing, perform the indicated register modification in the last IR word encountered. (Some special conditions for modification may be encountered in the indirect words; these involve R, RI, and IT.)

- 4. Indirect then Tally (IT)--Obtain the indirect word using the address modification type IT as specified in the  $t_m$  field of the instruction; then use the new address field of the indirect word to get the effective operand address. Next, follow one of nine possible variations, indicated in the  $t_d$  field of the instruction or indirect word that specified IT. (Two of the nine variations (SC and CI) are used for handling characters in the GE-635.)

The nine possible variations of the IT modification are listed and described below. When used, each variation mnemonic appears as a unique bit configuration in the  $t_d$  field of its instruction.

#### VARIATION SUMMARY UNDER IT MODIFICATION

|                                                                                                                                                                    | Mnemonic    | Name                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------------|

| = DIDecrement address, increment tally= SCSequence character= CICharacter from indirect= ADAdd delta= FFault= IDCIncrement address, decrement tally, and continued | $(t_d) = I$ |                                                  |

| = SCSequence character= CICharacter from indirect= ADAdd delta= FFault= IDCIncrement address, decrement tally, and continued                                       | = ID        |                                                  |

| = CICharacter from indirect= ADAdd delta= FFault= IDCIncrement address, decrement tally, and continued                                                             | = DI        | Decrement address, increment tally               |

| = ADAdd delta= FFault= IDCIncrement address, decrement tally, and continue                                                                                         | = SC        | Sequence character                               |

| = FFault= IDCIncrement address, decrement tally, and continue                                                                                                      | = CI        | Character from indirect                          |

| = IDC Increment address, decrement tally, and continue                                                                                                             | = AD        | Add delta                                        |

|                                                                                                                                                                    | = F         | Fault                                            |

| = DIC Decrement address, increment tally, and continu                                                                                                              | = IDC       | Increment address, decrement tally, and continue |

|                                                                                                                                                                    | = DIC       | Decrement address, increment tally, and continue |

#### IT Variation Descriptions

I

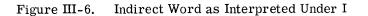

This tag is used to reference an indirect word without disturbing any part of the word. See Figure III-6.

COMPATIBLES/600

| 18 bits | 18 bits |

|---------|---------|

| Address |         |

| 0 17,   |         |

- ID This tag is used to reference an indirect word (Figure III-7) and to increment the address by 1 and decrement the tally of the indirect word by 1.

- DI This tag is used to reference an indirect word and to decrement the address by 1 and increment the tally of the indirect word by 1.

| 18 bits | 12 bits | 6 bits       |

|---------|---------|--------------|

| Address | Tally   |              |

| 0 17,   | 18      | ▶ 29,30 → 35 |

Figure III-7. Indirect Word as Interpreted under ID or DI

SC

This tag is used to reference an indirect word (Figure III-8) and to decrement the tally by 1, increment the character position by 1, and to specify the next character position--all in the indirect word.

| 18 bits | 12 bits | 3 bits           | 3 bits        |

|---------|---------|------------------|---------------|

| Address | Tally   | Z                | Char.<br>Pos. |

| 0 17,   | 18 29   | <b>, 30 —</b> 32 | ,33-> 35      |

Figure III-8. Indirect Word as Interpreted under SC

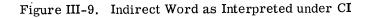

CI This tag is used to reference an indirect word (Figure III-9) and to operate on a particular character position without disturbing the indirect word.

|     | 18 bits      | 12 bits  | 3 bits  | 3 bits           |

|-----|--------------|----------|---------|------------------|

|     | Address      |          | Z       | Char.<br>Pos.    |

| 0 — | <b>———</b> 1 | 7,18 29, | 30 — 32 | ,33 <b>—</b> —35 |

COMPATIBLES // 600-

AD This tag is used to reference an indirect word (Figure III-10) and to increase the address field by the figure in the delta portion of the instruction. The tally portion of this indirect word is decremented by 1.

| 18 bits | 12 bits | 6 bits   |

|---------|---------|----------|

| Address | Tally   | Delta    |

| 0       |         | 29,30 35 |

| Figure III-10. | Indirect Word as Interpreted under AD |  |

|----------------|---------------------------------------|--|

|----------------|---------------------------------------|--|

- F The use of this address modification will cause a fault interrupt to occur.

- IDC This instruction modification is similar to ID modification, except that  $t_m$  and  $t_d$  fields specify further address modification. See Figure III-11 for indirect word interpretation.

- DIC

This tag modification is similar to DI modification, except that the  $t_{\rm m}$  and  $t_{\rm d}$  fields specify further address modification.

| 18 bits | 12 bits | 2 bits               | 4 bits              |

|---------|---------|----------------------|---------------------|

| Address | Tally   | Ta<br>t <sub>m</sub> | g<br>t <sub>d</sub> |

| 0 17,   | ,18 29  | ,30,31,32 <b>.</b>   | 35                  |

Figure III-11. Indirect Word as Interpreted under IDC and DIC

Address modification in the GE-635 using registers takes zero time; that is, under R, RI, IR modification, indexing the operand address of an instruction or indirect word adds no time to instruction execution. Under R modification, the DU and DL variations <u>reduce</u> normal execution time by 0.5 microseconds.

# Character Operations

Operations involving characters are performed using instructions that specify the IT type of address modification in the  $t_m$  field. The I of IT obtains an indirect word that, in turn, references a location containing the character or characters to be used. The indirect word holds tallying and character identifying information while the referenced location holds the character data. The  $t_d$  field of the original instruction must contain the sequence character (SC) or character from indirect (CI) designator variations.

Each time the original instruction is used under the SC variation, the tally and character position information in the indirect word (see Figure III-8) are automatically changed by one 1) to prepare for operating on the next sequential character and 2) for terminating the SC operations when the tally reaches zero. Characters are numbered 0 through 5. After operating on character

number 5, the Processor automatically increases the data word address by one and starts again at character 0 in the new location.

When a single character within a word is to be used repeatedly with the IT modification, the  $t_d$  field designates CI. The indirect word format is that shown in Figure III-9. The data movement process parallels that for the SC variation but the indirect word is not altered.

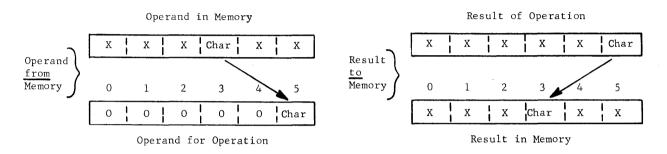

For both variations, the character position field of the indirect word (bits 33 through 35) specifies in octal the character position of the memory location to be used in instruction execution. Figure III-12 illustrates typical single-character operations to and from memory, assuming a character position designation of 3.

Figure III-12. Typical Character Operations

For operations where the operand is taken from memory, the <u>effective</u> operand is presented as a single word with the specified character right-justified to character position 5. The remaining positions (0 through 4 in Figure III-12) are presented as zeros.

For operations where the resultant is placed in memory, character 5 of the resultant replaces the specified character (3 in Figure III-12) in memory and the remaining character positions are not affected.

# INSTRUCTION REPERTOIRE

Most of the instructions available on the GE-635 system are familiar to experienced programmers of large-scale computers. However, additional instructions have been provided to give the programmer extended capability for character handling, decision-making, and advanced programming techniques involving list processing.

The 170 basic instructions available are grouped as follows:

| Data Movement and Shifting | 36 |

|----------------------------|----|

| Fixed-Point Arithmetic     | 34 |

| Boolean Operations         | 21 |

| Comparison                 | 16 |

| Floating-Point Arithmetic  | 30 |

| Transfer Control           | 14 |

| Special Operations         | 11 |

| Master Mode Operations     | 8  |

COMPATIBLES//600-

These basic instructions have provision for multiple variations by permitting the programmer to specify not only the type of address modification desired, but also the source registers associated with particular operation codes. For example, the operation field for a Transfer and Save Instruction Counter in Index instruction specifies the index in the operation field, leaving full address modification capability free for destination calculation.

A Processor module permits efficient operations to be performed on 18-, 36-, and 72-bit operands. The 18-bit operands are stored with, and fetched as, the left half of the instruction.

The following paragraphs briefly describe salient features of the major instruction types. A complete listing of the full instruction repertoire and execution times is included in the Appendix.

#### Data Movement

Character handling and manipulation is facilitated by the "indirect and tally" indexing option, and by instructions for directly loading and storing selected characters of the accumulator or quotient register.

Instructions are also included for directly loading the index registers from either memory or the A/Q-Register, directly storing any register into memory, and for loading registers with the complement of the memory location specified.

## Shifting

Shifting is accomplished using a "gear-shifting" algorithm, so that long shifts are executed essentially as fast as short shifts. The A- and Q-Registers can be shifted individually or as one unit. The Shift commands include right or left shift arithmetic, right shift logical, and left shift rotate (right shift rotate was omitted because the high speed of the left shift rotate makes the right shift rotate unnecessary).

#### Fixed-Point Arithmetic

Fractional and integer instructions for both multiplication and division afford the programmer freedom from scaling the results of such operations. Fractional multiplications are performed with the multiplicand in the A-Register; the result appears in bit positions 0 through 70 of the AQ-Register, automatically scaled with the binary point to the left of position 0. Integer multiplications are performed with the multiplicand in the Q-Register; the result appears in bit positions 1 through 71 of the AQ-Register, automatically scaled with the binary point to the right of position 71.

Fractional divisions use the full range of the AQ-Register for the dividend; the quotient appears in the A-Register with the remainder in the Q-Register. The binary point is automatically scaled to the left of position 0. Integer divisions have the integer dividend in the Q-Register, with the binary point to the right of position 35. After division, the quotient is in the Q-Register with the binary point automatically placed to the right of position 35, and the remainder is in the A-Register.

Normally, integer operations of divide and multiply occur in the Q-Register, and fractional operations of divide and multiply occur in the A-Register. This convention permits easy programming of fixed-point arithmetic operations.

Two arithmetic and three logic instructions used frequently in program coding are provided for combining the contents of memory locations directly with the contents of registers and storing the results in the same locations, without recourse to separate Store instructions. In all cases, the programmer can use the 18-bit indexing registers, X0 through X7, and the 36-bit A- and Q-Registers. In effect, the Add and Subtract to Storage instructions make arithmetic accumulators of all available memory locations. In all cases, the register contents are undisturbed.

#### Boolean Operations

The logical operations AND, Exclusive OR, and Inclusive OR are permitted between storage and the Xn-Registers, the A- and Q-Registers, and the AQ-Register.

## Comparison

Compare operations do not alter the contents of storage or the specified register, but merely set or clear the appropriate indicator as the result dictates. The compare instructions enable the programmer to make many types of program decisions.

The fixed-point compare instructions are:

| Instruction                          | Registers Used  | Principle Functions                                                        |

|--------------------------------------|-----------------|----------------------------------------------------------------------------|

| Compare Magnitude                    | А               | Compare absolute values                                                    |

| Compare with Register                | A, Q, AQ, X0-X7 | <ol> <li>Compares algebraic values</li> <li>Compares characters</li> </ol> |

| Comparative AND with<br>Register     | A, Q, AQ, X0-X7 | Tests for all zeros in word fields                                         |

| Comparative Not-AND<br>with Register | A, Q, AQ, X0-X7 | Tests for all 1's in word fields                                           |

| Compare Masked                       | Α               | Searches for identical, selectable<br>word fields                          |

| Compare with Limits                  | A, Q            | Searches for a value within selectable limits.                             |

Floating-point compare instructions are included for single- and double-precision operations on absolute values and algebraic values. All compare instructions are repeatable using the RPT, RPD, or RPL instructions described later under the heading, Special Operations.

# Floating-Point Arithmetic

Floating-point operations can be performed on both single- and double-precision data words; complete sets of data movement, arithmetic, and control instructions are provided for use in both types of operations. Unless otherwise specified by the programmer, the mantissas of all floating-point operation results are automatically normalized by the hardware. In additions and subtractions, addends and subtrahends are automatically aligned.

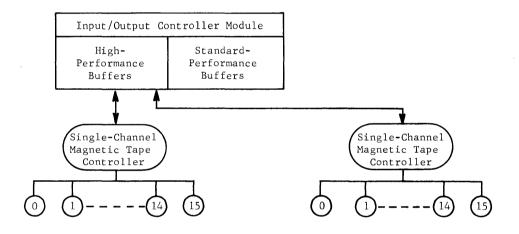

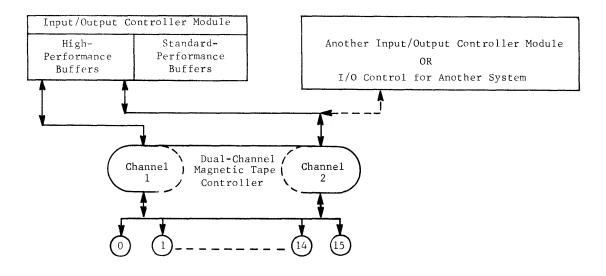

Operations on floating-point numbers are performed using an extended register composed of a 72-bit AQ-Register, which holds the mantissa, and a separate 8-bit exponent register; operations on the exponent and mantissa are performed by two separate adders. The existence of separate exponent and mantissa registers and adders enables the GE-635 programmer to intermix efficiently single- and double-precision instructions.