# Sentry 100 Hardware Manual

Part Number 67095483 Issued: June,1973

## Table of Contents

PREFACE

SECTION I

| GENERAL | INFORMATION |

|---------|-------------|

| CENEDAT | DECODIDETON |

| $1.0 \\ 1.1 \\ 1.1.1 \\ 1.1.2 \\ 1.1.3 \\ 1.1.4 \\ 1.1.5$ | GENERAL DESCRIPTION<br>SYSTEM HARDWARE DESCRIPTION<br>System Control Panel<br>System Power Modules<br>FST-1 Computer<br>Tester Controller<br>Test Station                                                                                                                                                                                                               | 1-1<br>1-2<br>1-4<br>1-4<br>1-4<br>1-8<br>1-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                           | Pin Electronics<br>Precision Measurement Unit<br>Load Boards<br>Power Supply Decoupling<br>Input Bias Voltage<br>MOS Input Pin Stressing<br>Clocking<br>Output Pin Loading<br>EUT Connection                                                                                                                                                                            | $1-8 \\ 1-10 \\ 1-10 \\ 1-10 \\ 1-10 \\ 1-10 \\ 1-10 \\ 1-10 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1-11 \\ 1$ |

| 1.2                                                       | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                  | 1-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SECTION II                                                | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                  | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.02.12.22.2.12.2.22.2.22.2.2.1                           | SYSTEM BLOCK DIAGRAM<br>REGISTERS & DATA BUSSES<br>COMPUTER & TESTER DATA FLOW<br>Peripheral Data Bus<br>Short Register Data Bus<br>Short Register Descriptions                                                                                                                                                                                                         | 2-1<br>2-3<br>2-5<br>2-6<br>2-6<br>2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

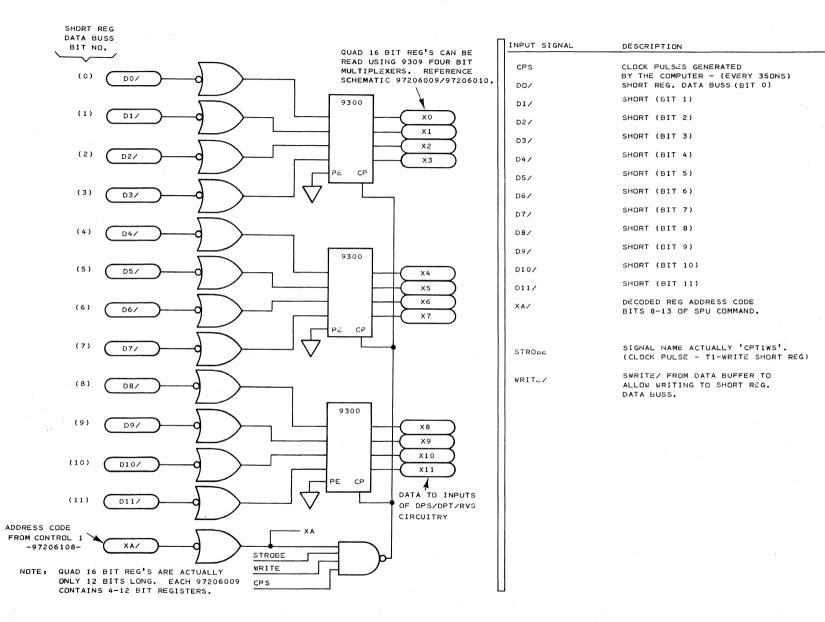

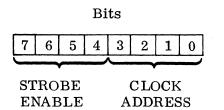

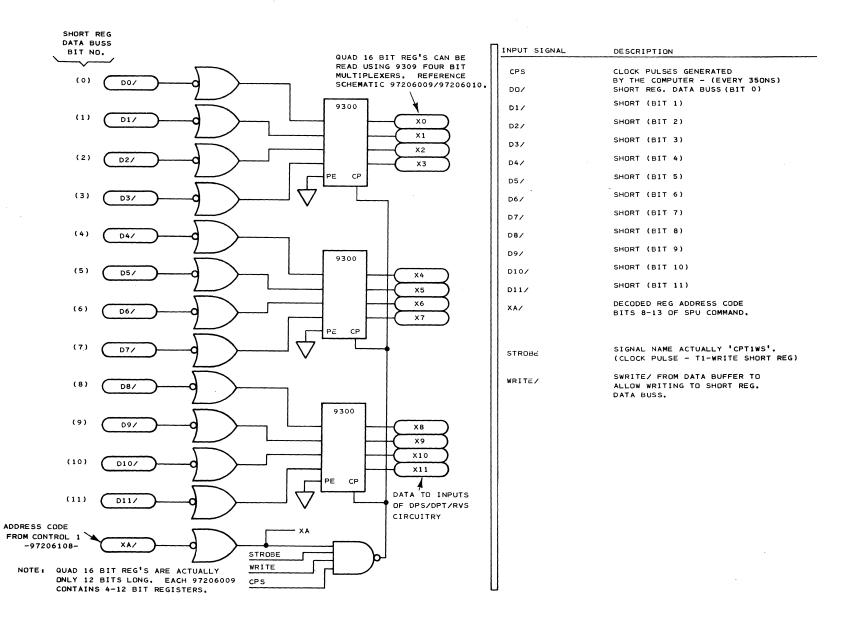

|                                                           | Register Address<br>Mode Register (01)<br>Status Register (02)<br>Memory Address Register, MAR (04)<br>Clock Burst Counter Register (10)<br>Time Delay Register (11)<br>Instruction Number Compare Register (14)<br>Instruction Number Display Register (15)<br>Data Buffer<br>Test Station Control Register (05)<br>Instruction Register (03)<br>Quad 16 Bit Registers | $\begin{array}{c} 2-7\\ 2-8\\ 2-10\\ 2-11\\ 2-12\\ 2-12\\ 2-12\\ 2-13\\ 2-13\\ 2-13\\ 2-13\\ 2-13\\ 2-14\end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Page

1-1

| Table of Cont                                                                                                                                 | ents (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2.3<br>2.2.3.1                                                                                                                              | Long Register Data Bus<br>Long Register Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $2-15 \\ 2-16$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| •                                                                                                                                             | D Register (Input/Output Definition Register)<br>M Register (Mask Register)<br>F Register (Function Register)<br>S Register (Select Reference Register)<br>C Register (Comparison Register)<br>R Register (Relay Register)<br>PA Register (Pin Address Register)<br>SID Register (Socket Identification Register)<br>SND Register (Statement Number Display<br>Register)<br>CS Register (Clock & Strobe Register)<br>PPS Register (Precision Power Supply Register)<br>PSL Register (Precision Sense Level Register)<br>EIR Register (External Interface Register)<br>DCT Register (DC Trip Register) | $\begin{array}{c} 2 - 17 \\ 2 - 17 \\ 2 - 17 \\ 2 - 17 \\ 2 - 17 \\ 2 - 18 \\ 2 - 19 \\ 2 - 19 \\ 2 - 20 \\ 2 - 20 \\ 2 - 20 \\ 2 - 20 \\ 2 - 21 \\ 2 - 21 \\ 2 - 21 \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.3 I<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5<br>2.3.6<br>2.3.7<br>2.3.8<br>2.3.8.1<br>2.3.8.2<br>2.3.8.3<br>2.3.8.4<br>2.3.8.5<br>2.3.9 | NDIVIDUAL BOARD DESCRIPTIONS<br>CPI 1 and CPI 2 (97166109<br>CPI 3 (97166108)<br>Register Address A (97340803)<br>Status Register A (97340804)<br>Mode Register (97206005)<br>Phase Loop Counter (97206006)<br>XDL Counter A (97340806)<br>T Count A (97206007)<br>Time Delay Counter<br>Clock Burst Counter<br>Instruction Number Display Counter<br>Instruction Number Counter<br>Readout Logic<br>Quad 16 Bit Register                                                                                                                                                                             | 2-22 2-24 2-24 2-27 2-30 2-33 2-35 2-39 2-39 2-39 2-39 2-39 2-40 2-40 2-40 2-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                               | Type 1 (97206008)<br>Type 2 (97206009)<br>Type 3 (97206010)<br>Statement Number Display Register<br>Clock, Sync, and Strobe Register<br>Socket Identification Register<br>External Interface Register                                                                                                                                                                                                                                                                                                                                                                                                 | $2-41 \\ 2-41 \\ 2-43 \\ 2-43 \\ 2-43 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ 2-45 \\ $ |

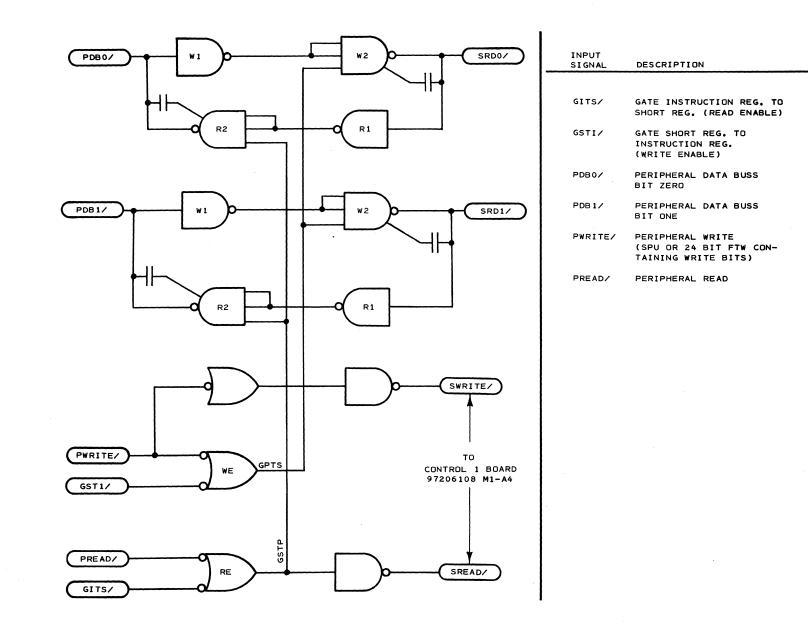

| $2.3.10 \\ 2.3.11 \\ 2.3.12 \\ 2.3.13 \\ 2.3.14$                                                                                              | Data Buffer (97206002)<br>Dual Multiplex Control (97236101)<br>Instruction Register (97206102)<br>Control 1 A (97340807)<br>Line Receiver II (97206113)                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-45<br>2-47<br>2-49<br>2-50<br>2-53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

ii

#### Table of Contents (Continued)

| Table of Cont                                    | cents (Continued)                                                                                                                                                                                                                                                             | Page                                                         |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

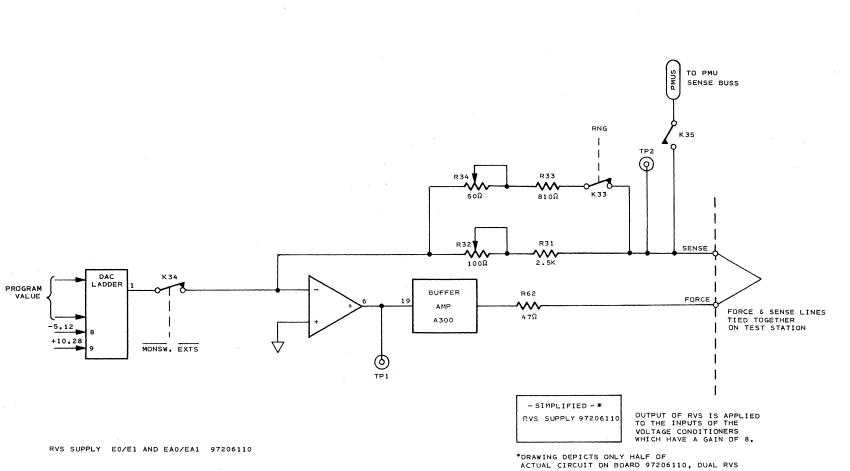

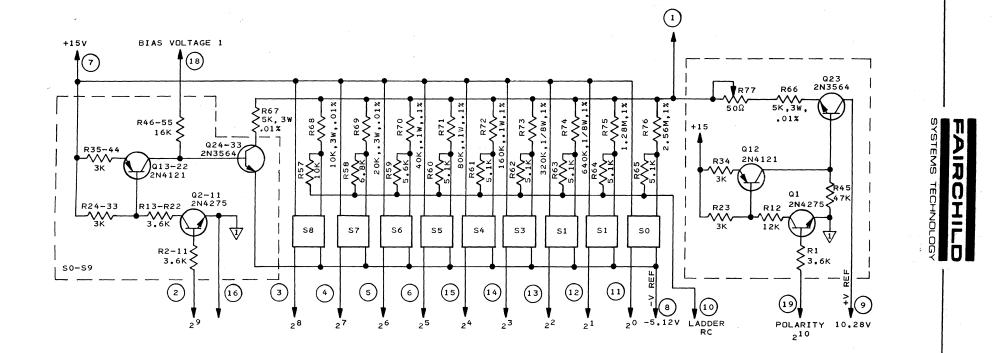

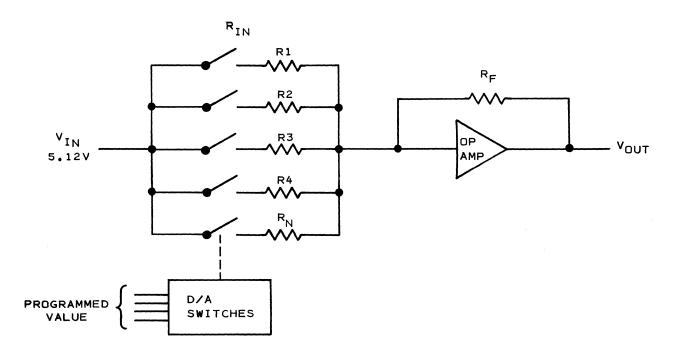

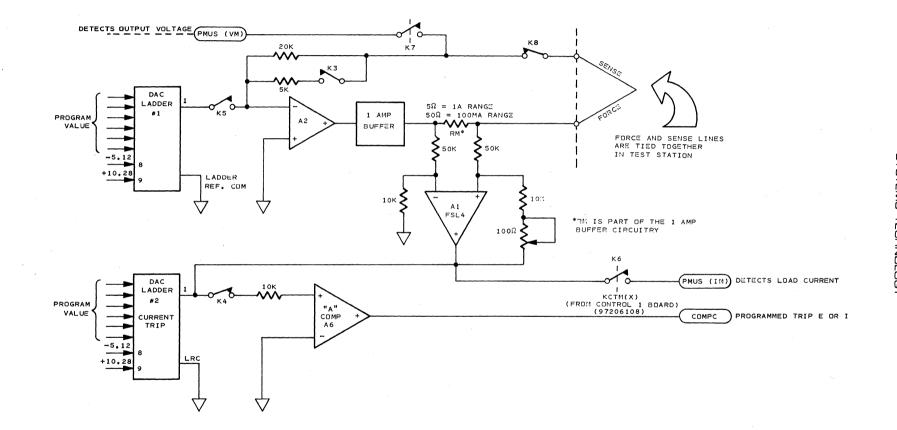

| 2.3.152.3.162.3.172.3.182.3.192.3.202.3.212.3.22 | T-Line Driver (97206206)<br>Reference Voltage Supply (97206110)(97206103)<br>Digitally Programmed Supply (97206104)<br>1 Amp Buffer (97206105)<br>Line Reference Voltage (97206111)<br>Analog Multiplexer (97209601)<br>Line Receiver (97206107)<br>15 Bit Decoder (97341603) | 2-53<br>2-53<br>2-59<br>2-64<br>2-64<br>2-65<br>2-65<br>2-65 |

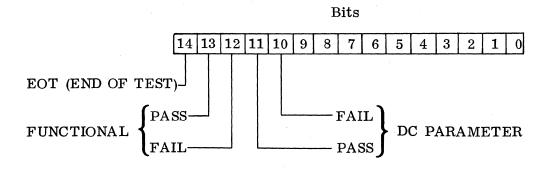

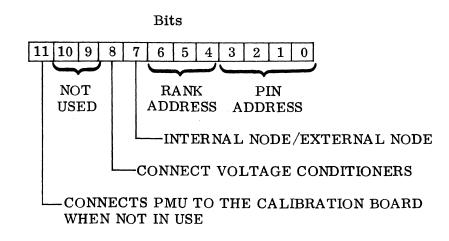

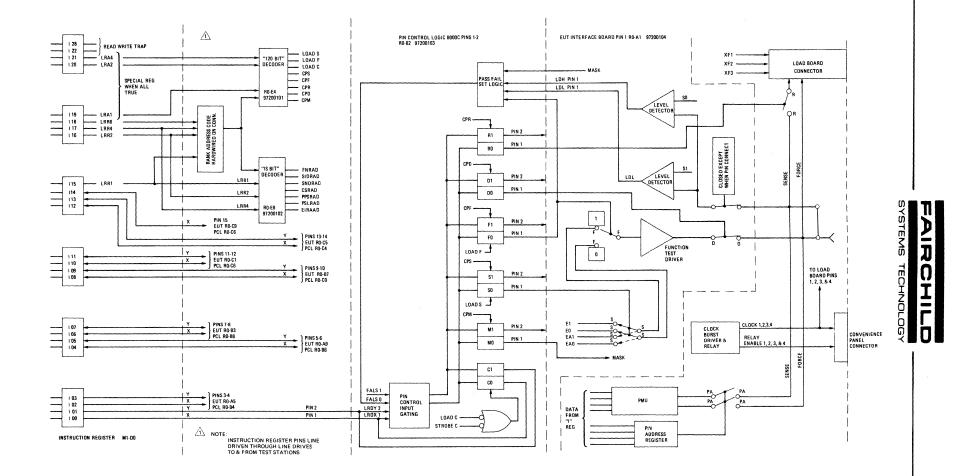

|                                                  | 120 Bit Register Decoder<br>Pin Address Register<br>PMU Addressing<br>Internal Node Decoding<br>Clock Relay Decoding<br>Connect Voltage Conditioner                                                                                                                           | 2-66<br>2-66<br>2-66<br>2-68<br>2-68<br>2-68                 |

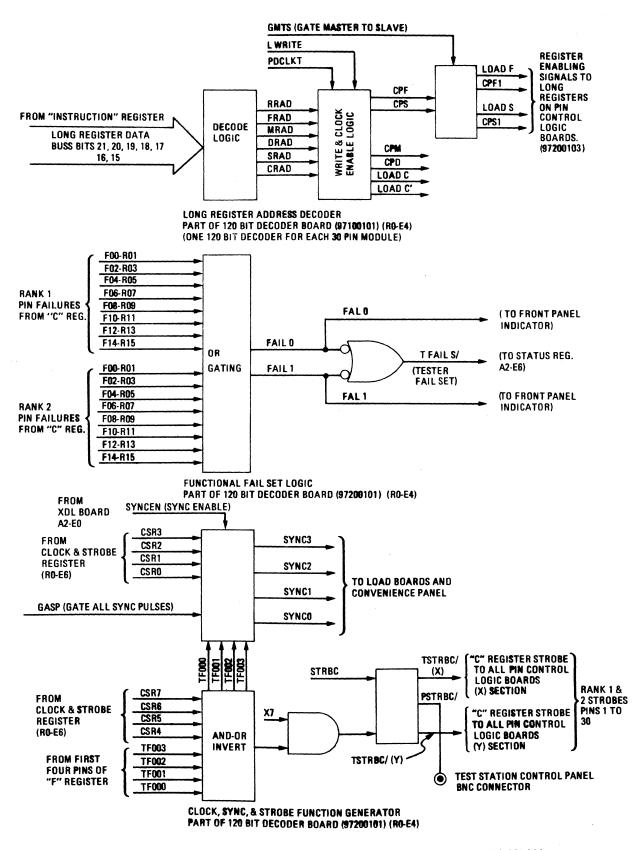

| 2.3.23                                           | 120 Bit Decoder (97200101)                                                                                                                                                                                                                                                    | 2-68                                                         |

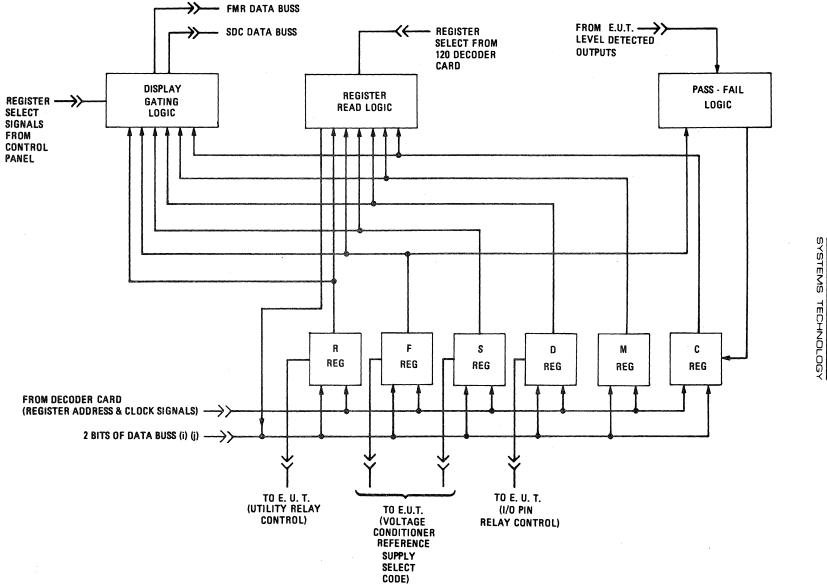

|                                                  | Long Register Decoding Logic<br>Sync and Strobe Logic<br>Fail Set Logic                                                                                                                                                                                                       | 2-68<br>2-70<br>2-70                                         |

| $2.3.24 \\ 2.3.25$                               | PEST Register (97201902)<br>Pin Control Logic (97200103)                                                                                                                                                                                                                      | 2-71<br>2-71                                                 |

|                                                  | Long Register Two-Bit Slices<br>Lamp Display Logic<br>Pass-Fail Set Logic                                                                                                                                                                                                     | 2-74<br>2-74<br>2-74                                         |

| 2.3.26<br>2.3.27<br>2.3.28<br>2.3.29             | EUT Interface (97200104)<br>Decoupling Board (97200110)<br>Monitor Control (97340801)<br>Power Supply Alarm (97204601)                                                                                                                                                        | 2-75<br>2-75<br>2-76<br>2-76                                 |

| SECTION III 7                                    | THEORY OF OPERATION                                                                                                                                                                                                                                                           | 3-1                                                          |

| 3.1 J<br>3.1.1                                   | TESTER OPERATING AND INSTRUCTION MODES<br>Operating Modes                                                                                                                                                                                                                     | 3-1<br>3-1                                                   |

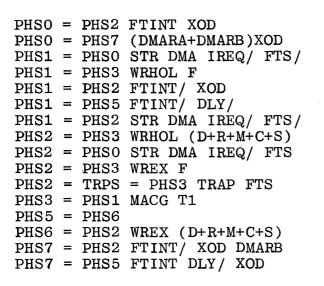

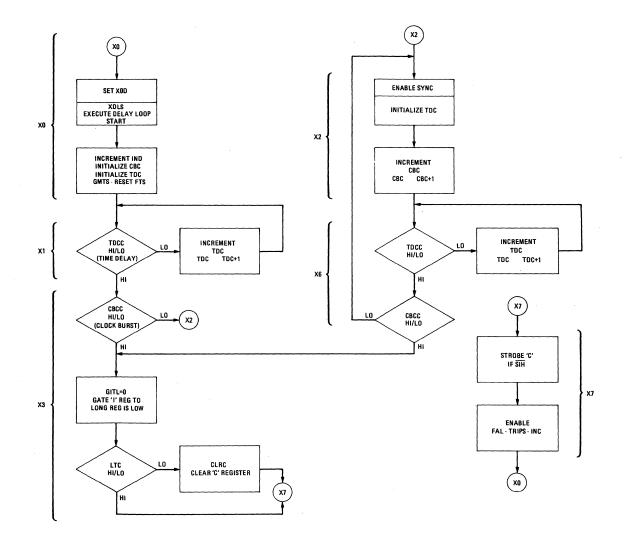

|                                                  | SPU and DMA Instructions<br>Short Register Loading<br>Short Register Addressing and Loading<br>DPS and RVS Addressing<br>Data Buffer Interface Operation<br>Long Register Loading and DMA Mode<br>DMA Instructions                                                            | 3-2<br>3-5<br>3-5<br>3-9<br>3-9<br>3-9<br>3-13               |

|                                                  |                                                                                                                                                                                                                                                                               | 3-14                                                         |

3-14

| Table of C | ontents (Continued)                       | Page         |

|------------|-------------------------------------------|--------------|

| 3.2        | DETAILED THEORY OF OPERATION              | 3-14         |

|            | Input Pins<br>Output Pins                 | 3-17<br>3-17 |

|            | Tester Strobe                             | 3-18         |

|            | Digitally Programmed Supplies (DPS)       | 3-18         |

|            | Clock Burst Counter                       | 3-18<br>3-18 |

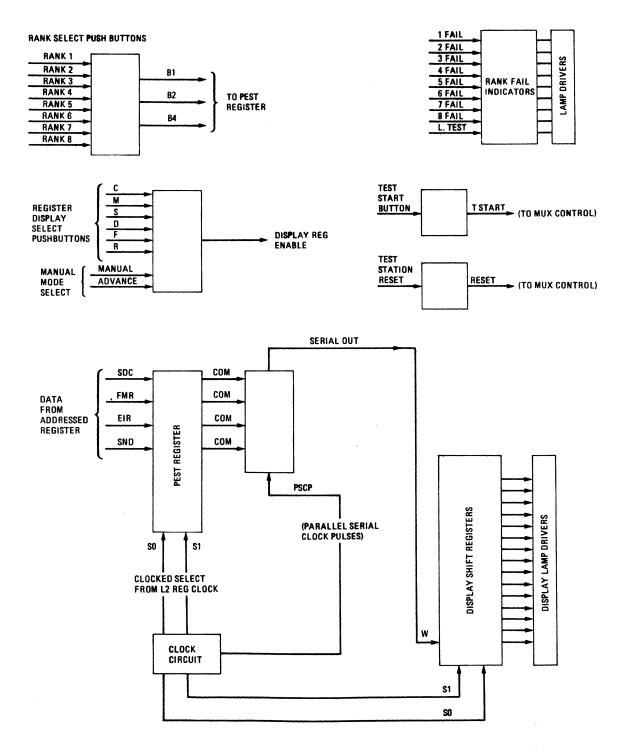

|            | Test Station Control Panel                | 3-18         |

|            | Rank Fail Indicators                      | 3-20         |

|            | Long Register Data Display                | 3-20         |

|            | External Interface Register (EIR) Display | 3-20         |

|            | Statement Number Readout                  | 3-20         |

|            | Pass/Fail Indicators                      | 5-20         |

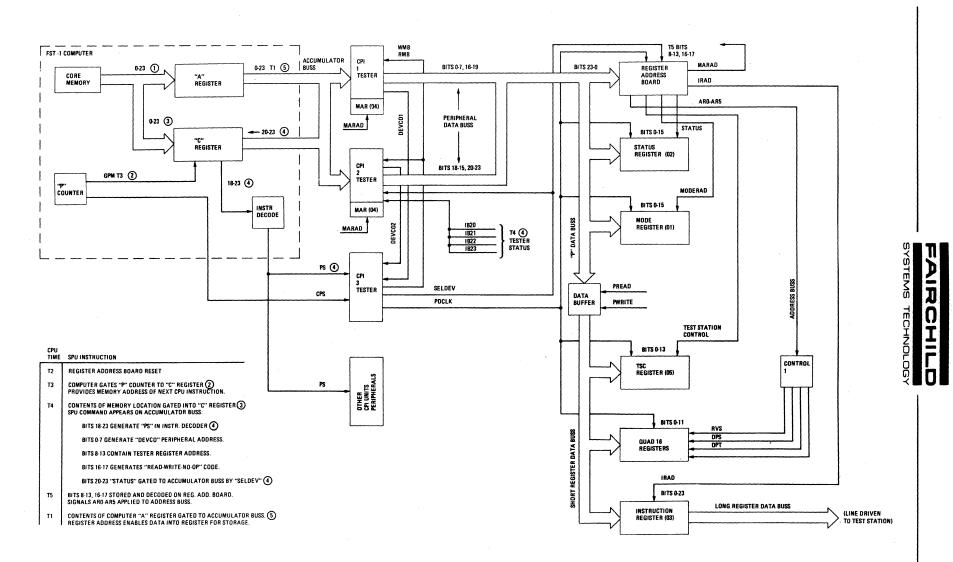

| 3.2.1      | SPU MODE                                  | 3-21         |

|            | Typical SPU Instruction                   | 3-21         |

|            | Read TSC (06602520B)                      | 3-21         |

|            | Write TSC (06402520B)                     | 3-27         |

|            | Write DPS1 (06410520B)                    | 3-29         |

|            | SPU Instruction to MAR                    | 3-30         |

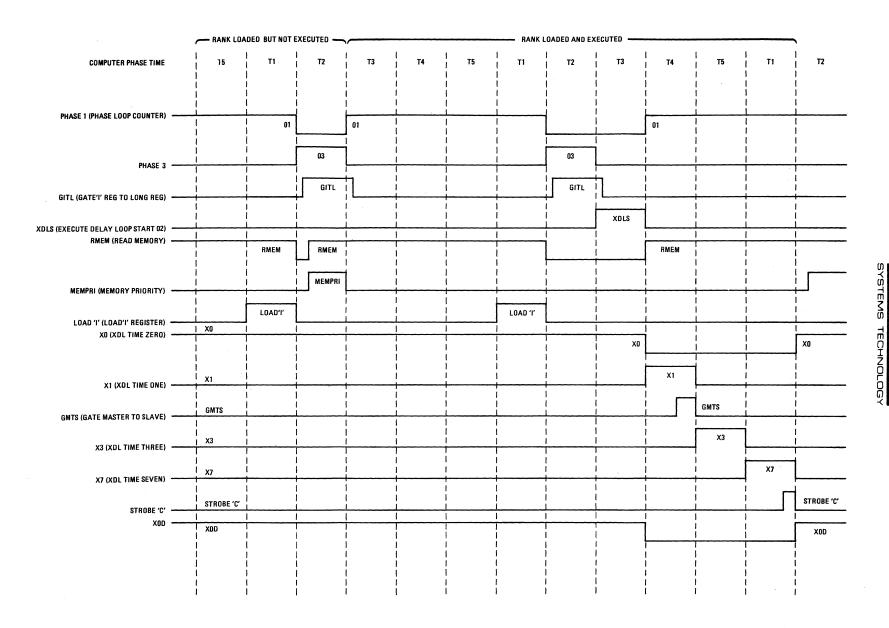

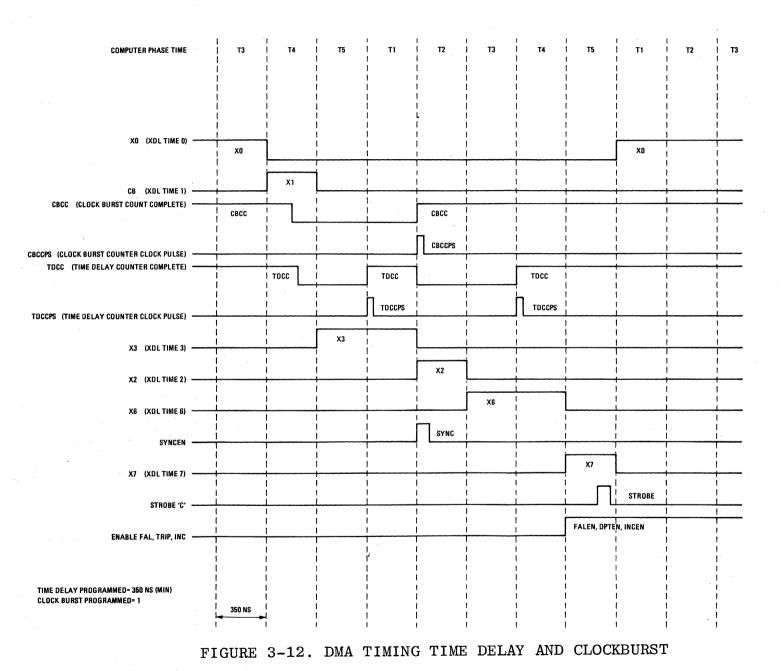

| 3.2.2      | DMA MODE                                  | 3-31         |

| 3.2.2.1    | DMA Sequence                              | 3-31         |

|            | Common Transitions                        | 3-33         |

|            | Read or Trap                              | 3-33         |

|            | Write to F Register                       | 3-33         |

|            | Write to non-F Registers                  | 3-34         |

|            | CPI Control                               | 3-34         |

|            | Function Test Suspended                   | 3-35         |

| 3.2.3      | PROGRAMMABLE VOLTAGE SUPPLIES             | 3-36         |

|            | Reference Voltage Supplies                | 3-36         |

|            | Digitally Programmable Supplies           | 3-37         |

| 3.2.4      | PMU - PRECISION MEASUREMENT UNIT          | 3-38         |

|            | INTRODUCTION                              | 3-38         |

|            | Functions                                 | 3-38         |

|            |                                           | 3-38         |

|            | Basic Operating Modes<br>Control          | 3-38         |

|            | CONTROL                                   | 5-40         |

### Table of Contents (Continued)

#### OPERATION

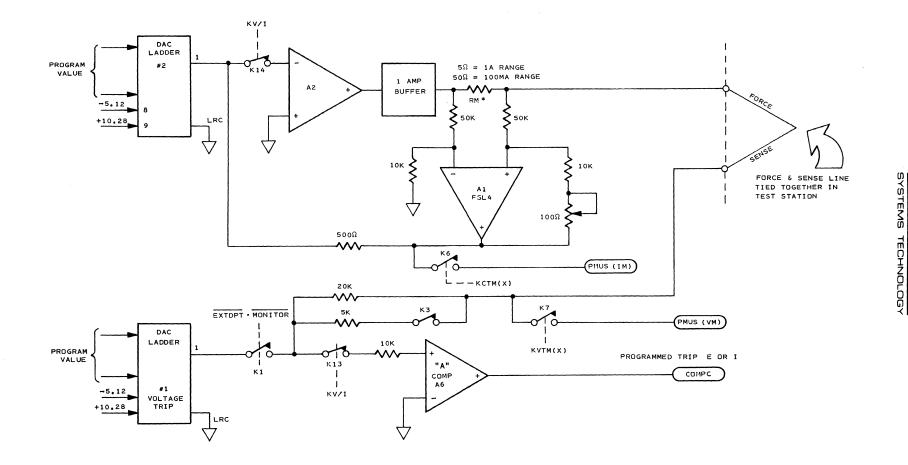

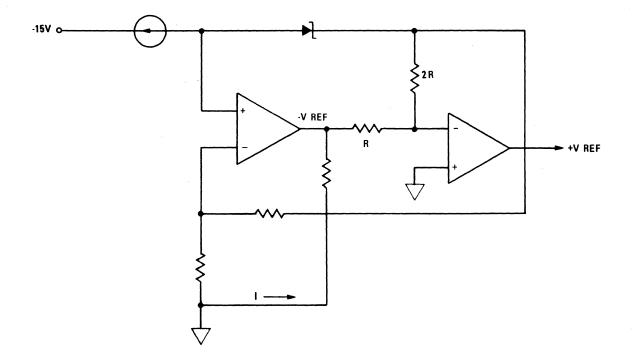

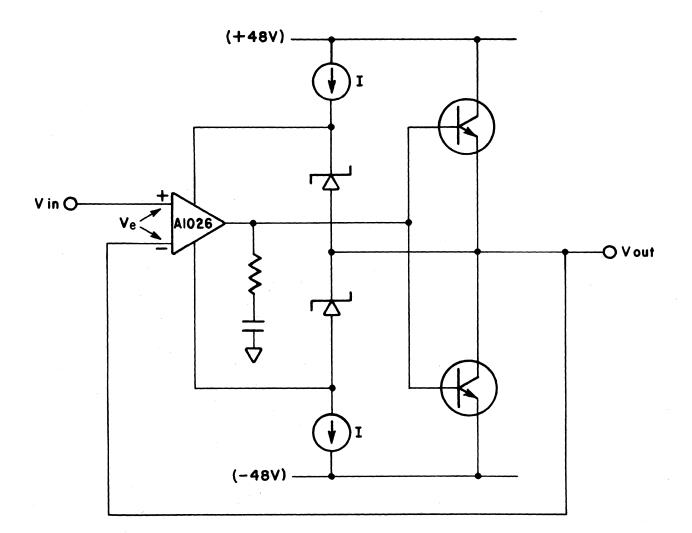

| Analog Circuits<br>Forcing and Measuring Circuits<br>Voltage Clamp Circuit<br>Control Circuits                                                                                                                                     | 3-41<br>3-41<br>3-44                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| PPS (Precision Power Supply) Register<br>DCT (DC Trip) Register<br>PLS (Precision Sense Level) Register<br>PA (Pin Address) Register                                                                                               | 3-47<br>3-48<br>3-50<br>3-51                         |

| DETAILED CIRCUIT DESCRIPTIONS                                                                                                                                                                                                      | 3-52                                                 |

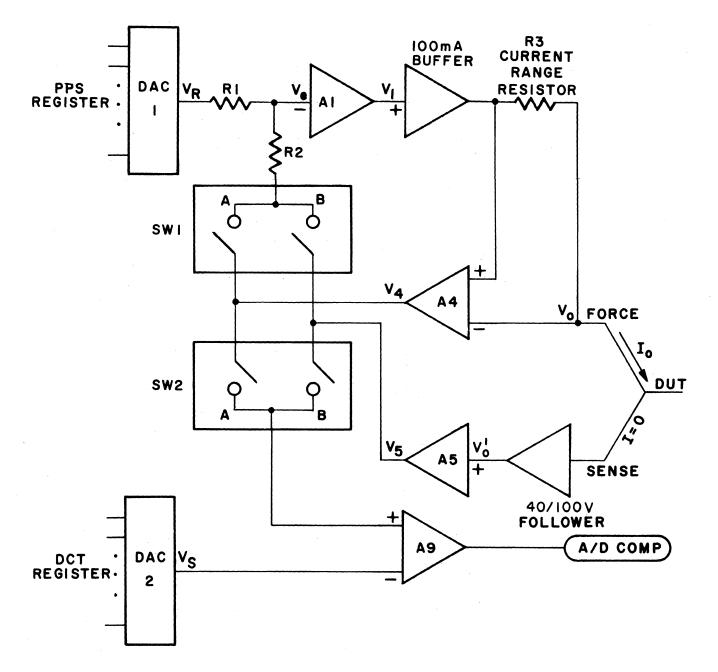

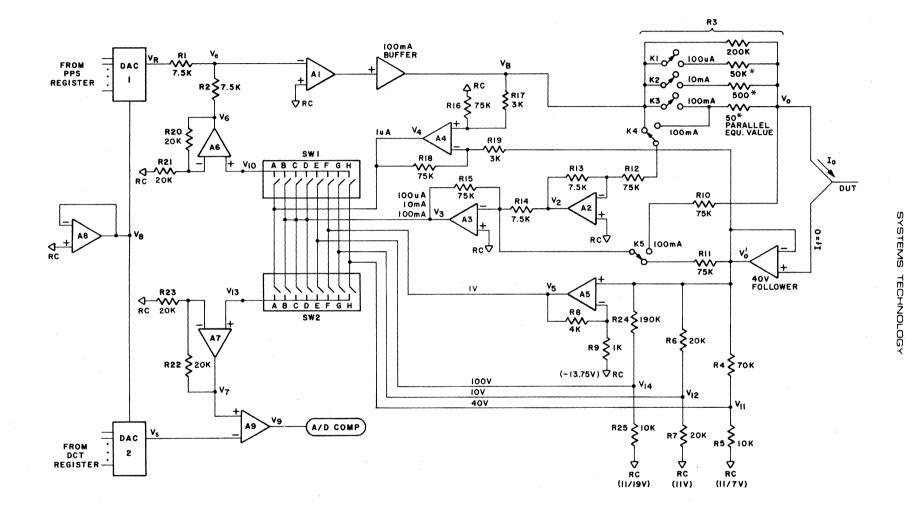

| Analog #1A Board (Refer to schematic<br>97341605-04)<br>Basic Forcing Loop and Sensing Circuitry<br>100mA Buffer Amplifier<br>MOS Switches<br>DAC 1 & DAC 2 (Forcing and Measuring DAC's)<br>Ground Buffer<br>Current Range Relays | 3-52<br>3-52<br>3-53<br>3-54<br>3-54<br>3-55<br>3-55 |

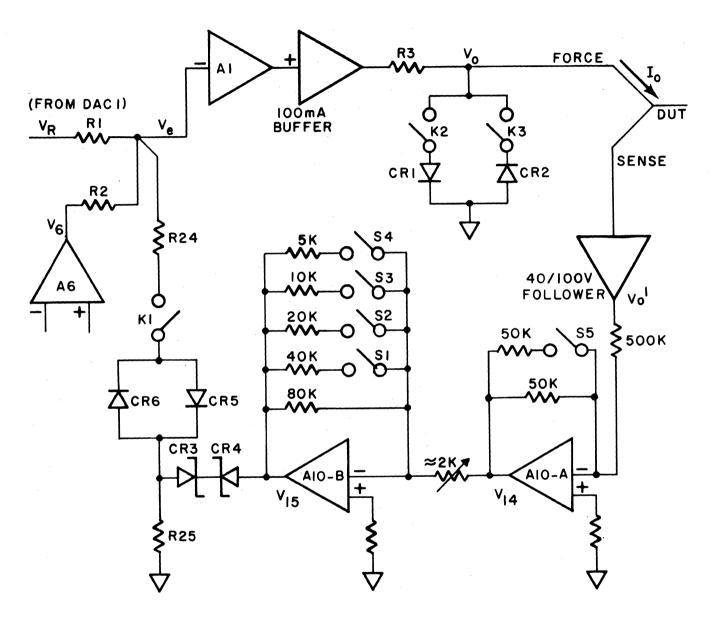

| Analog #2A Board (Refer to schematic<br>97341604-04)<br>40 Volt Follower<br>Voltage Clamp Circuit<br>Miscellaneous Relays                                                                                                          | 3-56<br>3-56<br>3-58<br>3-58                         |

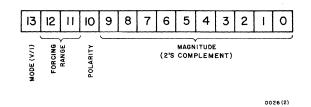

| PMU Control Board (Refer to schematic<br>97230104–04)<br>PPS Register<br>DCT Register<br>PSL Register<br>Current Range Relay Drivers                                                                                               | 3-59<br>3-59<br>3-60<br>3-61<br>3-61                 |

v.

## List of Illustrations

Page

| Figure 1-1<br>Figure 1-2<br>Figure 1-3<br>Figure 1-4<br>Figure 1-5<br>Figure 1-6                                                                                                                                                                                                                                                                                                          | S100 Test System<br>S100 Test System Control Panel<br>FST-1 Computer Control Panel<br>FST-1 Computer Simplified Block Diagram<br>S100 Simplified Block Diagram<br>S100 Simplified (Digital)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-3<br>1-5<br>1-7<br>1-9<br>1-12<br>1-14                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

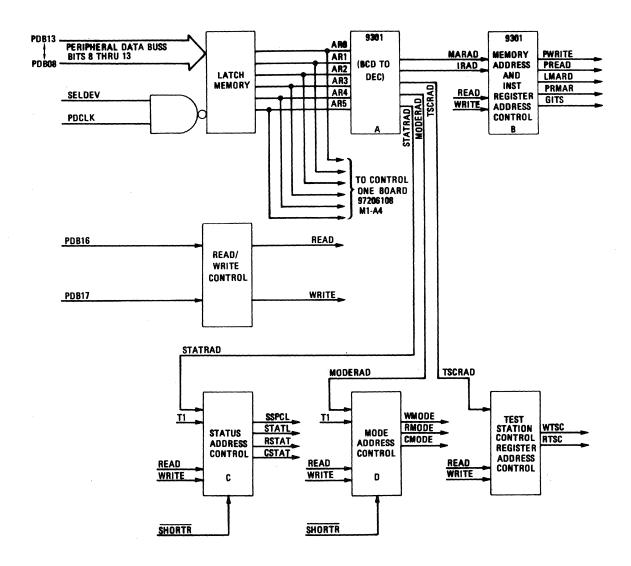

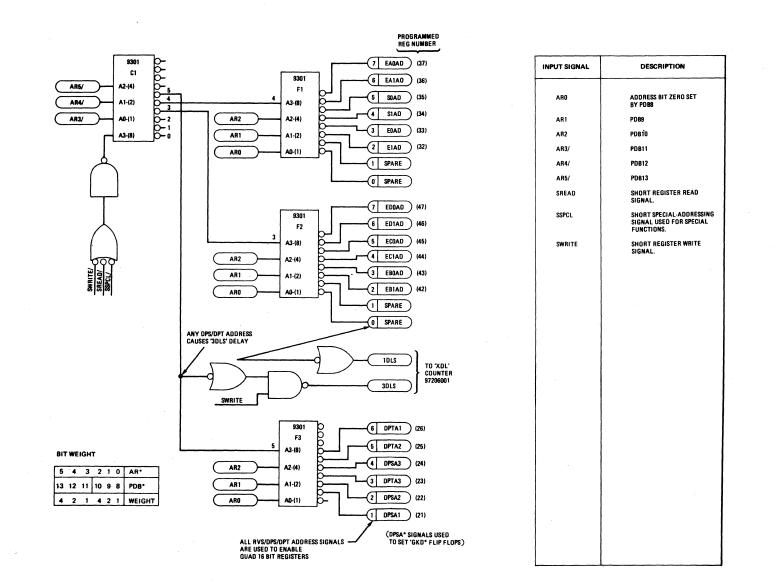

| Figure 2-1<br>Figure 2-2<br>Figure 2-3<br>Figure 2-4<br>Figure 2-5<br>Figure 2-6<br>Figure 2-7<br>Figure 2-8<br>Figure 2-9<br>Figure 2-10<br>Figure 2-11<br>Figure 2-12<br>Figure 2-12<br>Figure 2-13<br>Figure 2-13<br>Figure 2-14<br>Figure 2-15<br>Figure 2-15<br>Figure 2-17<br>Figure 2-18<br>Figure 2-19<br>Figure 2-20<br>Figure 2-22<br>Figure 2-22<br>Figure 2-22<br>Figure 2-22 | S100 Simplified Block Diagram<br>Tester CPI, Detailed Block Diagram<br>Register Address Simplified Block Diagram<br>Status Register Simplified<br>Mode Register Simplified<br>Phase Loop Counter Simplified<br>XDL Counter Flowchart<br>Quad 16-Bit Register<br>Data Buffer Simplified<br>Multiplex Control<br>Control 1A Simplified<br>Function Test, Signal Flowpath<br>Driver RVS Simplified<br>Detector RVS Simplified<br>RVS Simplified Block Diagram<br>D/A Converter Ladder Network<br>Simplified Op Amp<br>Simplified DPS Supply (V <sub>F</sub> I Trip)<br>Simplified DPS Supply (I <sub>F</sub> V Trip)<br>Line Reference Voltage Simplified<br>Pin Control Logic Simplified<br>S100 System Block Diagram (Sheet 1 of 3)<br>S100 System Block Diagram (Sheet 3 of 3) | 2-2<br>2-23<br>2-25<br>2-28<br>2-31<br>2-34<br>2-37<br>2-42<br>2-46<br>2-48<br>2-51<br>2-55<br>2-56<br>2-56<br>2-57<br>2-58<br>2-59<br>2-60<br>2-61<br>2-63<br>2-72<br>2-78<br>2-79 |

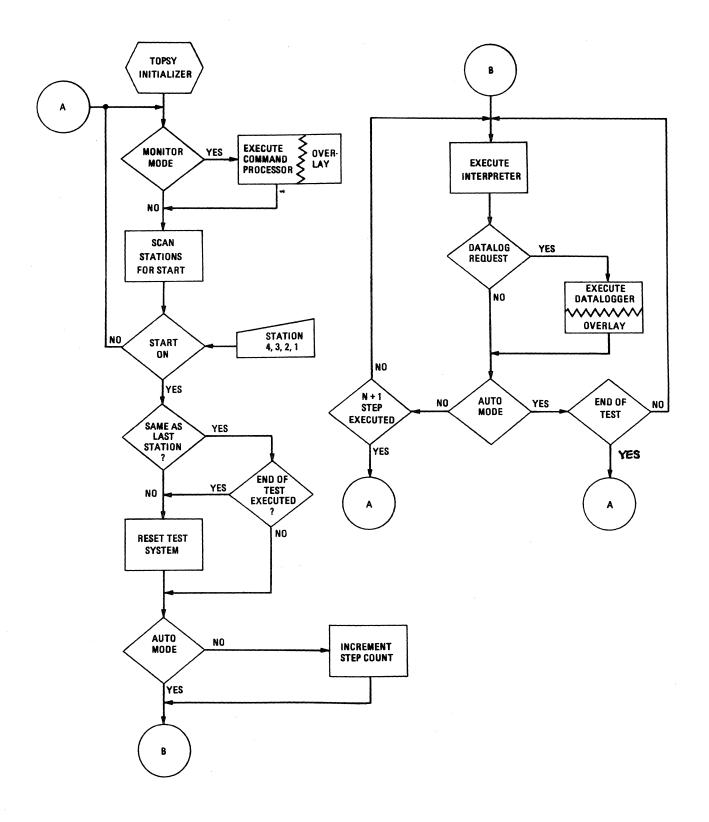

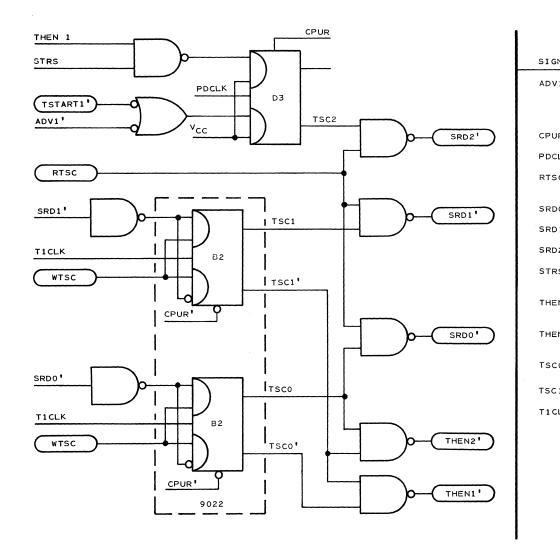

| Figure 3-1<br>Figure 3-2<br>Figure 3-3<br>Figure 3-4<br>Figure 3-5<br>Figure 3-6<br>Figure 3-7<br>Figure 3-7<br>Figure 3-9<br>Figure 3-10<br>Figure 3-11<br>Figure 3-12<br>Figure 3-13                                                                                                                                                                                                    | TOPSY Flowchart<br>Simplified Multiplex Control<br>Register Address Simplified<br>Control 1 Simplified<br>Quad 16 Bit Register Simplified<br>Data Buffer Simplified<br>Test Station Detailed Block Diagram,<br>Pin 1 (Typical)<br>120 Bit Decoder Simplified Diagram<br>Test Station Control Panel Logic Diagram<br>SPU Instruction Logic<br>SPU Instruction Timing<br>DMA Timing Time Delay And Clockburst<br>PMU Simplified Block Diagram                                                                                                                                                                                                                                                                                                                                    | 3-6<br>3-7<br>3-8<br>3-10<br>3-11<br>3-12<br>3-15<br>3-16<br>3-19<br>3-22<br>3-26<br>3-32<br>3-39                                                                                   |

List of Illustrations (Continued)

Page

| Figure 3-14 | PMU Simplified Schematic Diagram | 3-42 |

|-------------|----------------------------------|------|

| Figure 3-15 | Voltage Clamp Circuit Simplified |      |

|             | Schematic Diagram                | 3-45 |

| Figure 3-16 | 40V Follower Simplified          | 3-57 |

### List of Tables

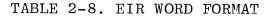

| Table 2-1<br>Table 2-2<br>Table 2-3<br>Table 2-4<br>Table 2-5<br>Table 2-6<br>Table 2-7<br>Table 2-8<br>Table 2-9<br>Table 2-9<br>Table 2-10<br>Table 2-11<br>Table 2-12 | Long Registers<br>Short Registers<br>Short Registers Loaded by Peripheral Data Bus<br>Mode Register Bit Description<br>Status Register Bit Description<br>Function of D, M, F, S, C, & R Registers<br>Clock, Sync, and Strobe Register, Word Format<br>EIR Word Format<br>15-Bit Register Decoding<br>Pin Address Format<br>Long Register Decoding<br>D, M, F, S, C, & R Register Functions | 2-4 2-6 2-8 2-10 2-18 2-44 2-44 2-67 2-67 2-69 2-73                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Table 3-1<br>Table 3-2<br>Table 3-3<br>Table 3-4<br>Table 3-5<br>Table 3-6<br>Table 3-7<br>Table 3-8<br>Table 3-9<br>Table 3-10<br>Table 3-11<br>Table 3-12              | <pre>SPU Instruction, Typical Format DMA Instruction, Typical Format Typical SPU Read Instruction Typical SPU Write Instruction Voltage and Current Ranges Voltage Clamp Values Voltage And Current Range Bit Format PPS Register DCT Register PSL Register PA Register</pre>                                                                                                               | 3-3<br>3-4<br>3-23<br>3-28<br>3-36<br>3-43<br>3-46<br>3-47<br>3-49<br>3-49<br>3-49<br>3-49<br>3-49 |

### Preface

This manual is intended to provide the reader with an appreciation of and in-depth familiarity with the tester portion of the Sentry 100 system -- its construction, organization, and operation -- from a hardware point of view.

Section I provides a general overall discussion of the S100 test System. This places the test system in the correct frame of reference with regard to the CPU memory and peripherals and will enable the reader to fully appreciate the following discussions on the tester.

Section 2 presents the basic system organization, showing how data is transferred along the three principal data buses -peripheral data bus, short register data bus, and long register data bus. Each register in the tester is discussed, in a manner which shows its function in the system, the information contained therein, and how that register is loaded from or read into one of the three data buses. A set of individual printed circuit board descriptions is provided, showing for each board its function in the system, the main input and output signals, and the circuitry contained on that board.

Section 3 presents the tester operation. The operating modes --Manual and Automatic -- and the instruction modes -- SPU and DMA -- are defined and explained.

Next, the detailed SPU and DMA instruction sequences are discussed, to provide an understanding of how the user-specified device testing algorithms are set up and run under program control. Finally, a complete description is given of the operation and circuitry of the PMU (Precision Measurement Unit).

SYSTEMS TECHNOLOGY

### Section I General Information

#### 1.0 GENERAL DESCRIPTION

The Sentry 100 Computer Controlled Test System provides the capability to test virtually all digital networks with up to 60 pins.

The system design is oriented to production testing of:

Wafers or discrete packages Static MOS, or Bi-Polar Integrated Circuits - using small to large scale integration (SSI, MSI, LSI) - using any technology (ECL, CML, CTL, TTL, DTL, RTL)

The S-100 system can also test other digital networks such as arrays and printed circuit cards.

The general purpose S-100 system software and hardware is driven by test plans programmed by the user, or, if desired, supplied by Fairchild. The system software utilizes a background/foreground approach which allows test plan creation, compilation, editing, etc., to be performed in the background mode while testing is in process in the foreground mode.

The system provides the capability to classify and bin integrated circuits according to a master test plan and up to 16 individual test specifications. Failure counters identified by the test type and device pin can be defined, when requested, in order to allow various problems in the manufacturing process to be detected easily and quickly. Histograms of related device test results can be created when requested. Also, the results of all tests or certain sets of tests (such as all fails) can be logged. Analysis aids are provided to simplify test plan development.

The Sentry 100 System performs two basic types of tests; functional tests (that determine whether the circuit performs the intended logic operations), and precision parametric tests (that determine whether component parameters meet specifications).

Functional tests are performed by forcing programmed logic levels on all input pins of the Element-Under-Test and comparing all

device outputs with the expected logic levels previously programmed. In functional testing, all device input pins are driven in parallel and all device output pins are tested in parallel after a programmed interval of time.

Parametric tests allow a voltage or current to be measured at any pin of the Element-Under-Test while forcing a current or voltage, respectively at that pin. The Precision Measurement Unit can force or sense voltages or currents which are positive or negative. This allows device parameters such as voltage levels of an output pin, input leakage current, etc., to be measured under desired load conditions. The functional testing capability of the system is generally used in conjunction with parametric testing in order to force the device into the desired state.

The Precision Measurement Unit may be connected to internal system nodes so that quantities such as the actual output voltages and load currents of the programmable Device Power Supplies or the functional logic levels actually generated by the Reference Voltage Supplies can be measured. This allows device power consumption to be calculated, and also allows system calibration to be checked by the system itself.

The maximum test rate of the system is 286,000 functional tests per second or approximately 875 D.C. tests per pin per second. The maximum number of tests that can be performed on a single element is virtually unlimited if subroutines or loops are used.

#### **1.1 SYSTEM HARDWARE DESCRIPTION**

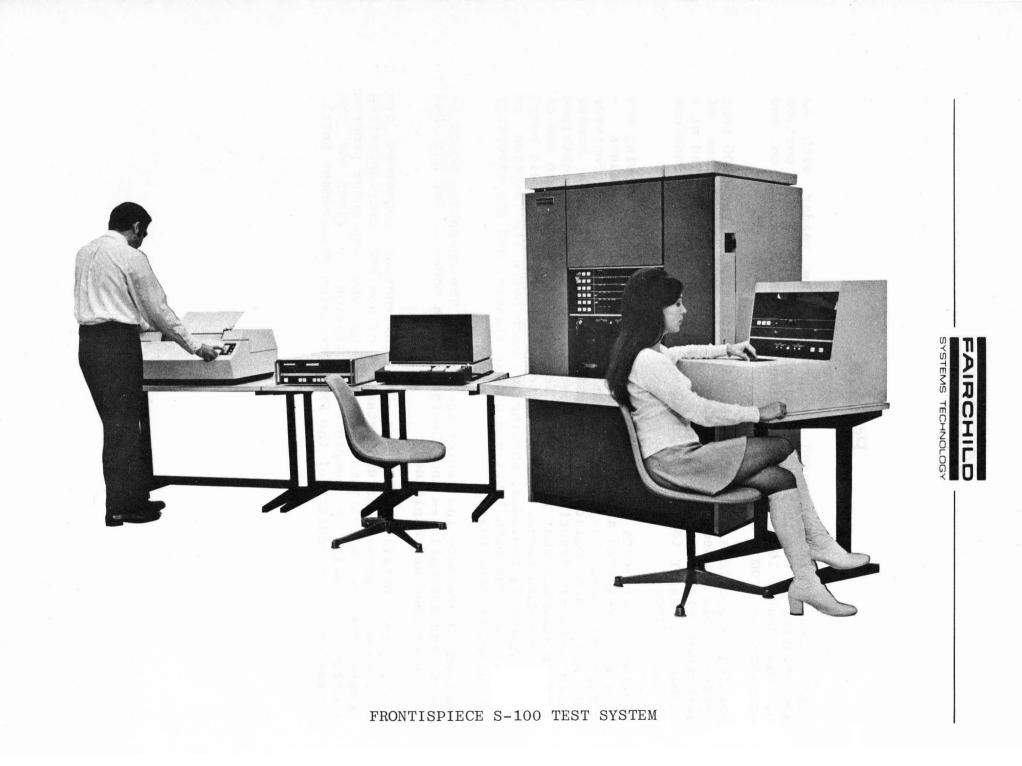

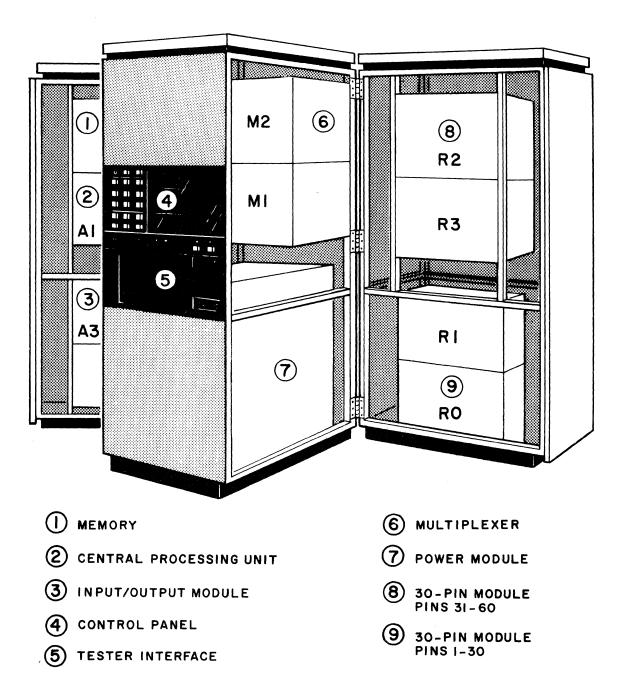

The basic Sentry 100 System consists of a single bay enclosing system power modules, the FST-1 computer, the tester controller, and the test station. A Teletype unit is supplied in addition to the basic mainframe. Optional peripheral items such as the VKT, tape cassette unit, line printer and submultiplex test stations are packaged independently to maximize system modularity.

Figure 1-1 is an illustration of the system with the side doors opened. The following paragraphs describe the functions of the various components of the system.

FIGURE 1-1. S100 TEST SYSTEM

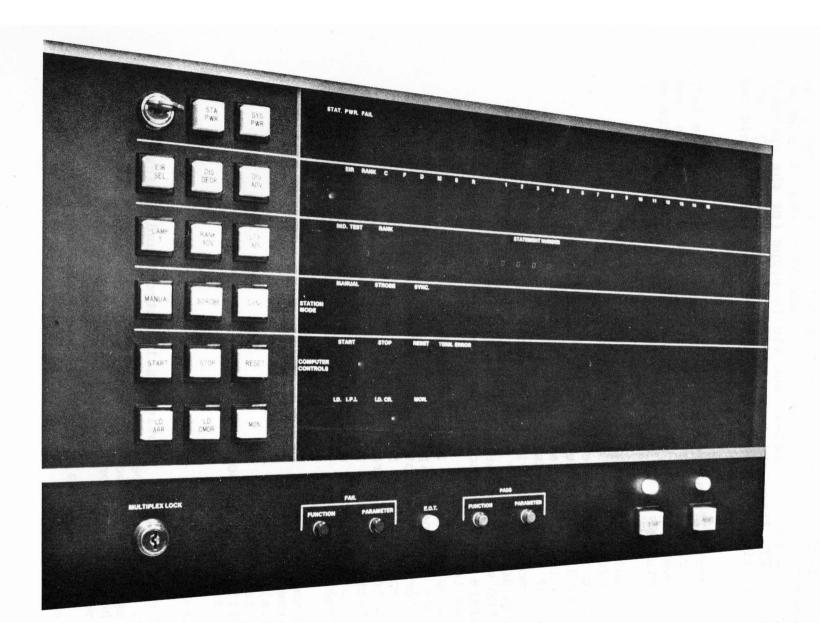

#### 1.1.1 System Control Panel

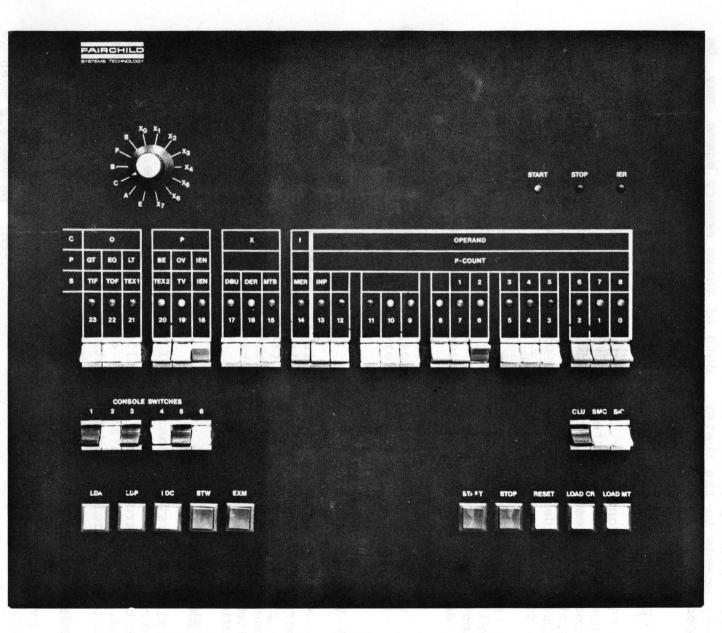

Controls and displays are separated into two areas. One provides the operator with station START and RESET pushbutton controls, and displays the pass/fail status of the element under test and the end-of-test status. The second area provides computer, tester operating mode, statement advance, register display, and indicator test controls. It also displays computer status, tester register contents, and the current program statement number.

Register Selector pushbuttons allow the operator to select various registers or the rank fail indicator whose contents will be displayed by a row of 15 register display lamps. There are four ranks to each register. By appropriate combination of rank selector and register selector the status of all 60 pins can be displayed.

The rank fail indicator illuminates, if selected, when a pin of a certain rank fails. The register contents may then be displayed on the register display lamps to determine which pin has failed. This type of display is useful while debugging prototype designs and during test program verification.

A numerical display of the test statement number which is currently in the tester is also provided. This is extremely valuable for program verification when the tester is in the manual mode and is being single stepped. It is always updated with the number of the last FACTOR statement executed when the test pauses. A detailed view of the system control panel is shown in figure 1-2.

#### 1.1.2 System Power Modules

The power modules are contained in the lower central section of the bay. Should one or more of the modules fail, an audible and visual alarm is generated. The modules are mounted so that all potentiometer controls are available for adjustment.

#### 1.1.3 FST-1 Computer

The FST-1 is a general-purpose digital computer located in the left door frame. Sufficient controls are available on the test station panel to control the FST-1 during normal operation.

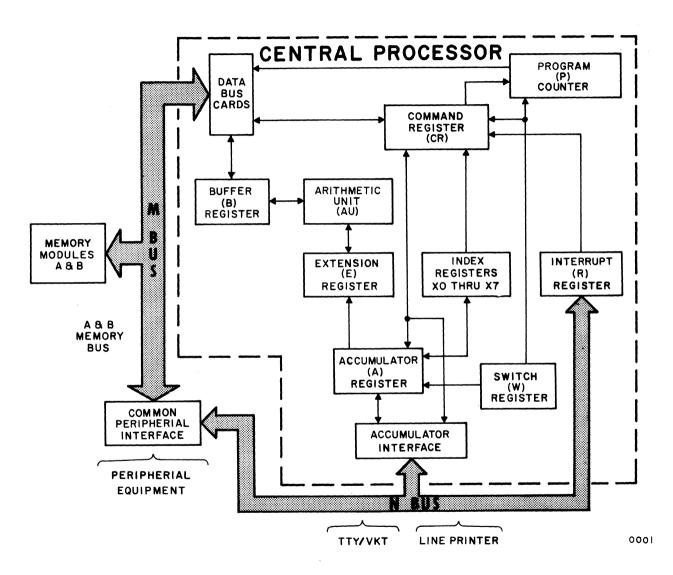

The FST-1 Computer consists of three subsystems; the central processing unit (A1), memory (A0), and interface (A3). Provisions are made for two memory modules each providing 8,192

FIGURE 1-2. S-100 TEST SYSTEM CONTROL PANEL

FAIRCHILD

FAIRCHILD

SYSTEMS TECHNOLOGY

word locations; they are positioned directly above the CPU. The interface module (A3) does not exist in the case of the S-100 and the tester Interface between the FST-1 system. is accomplished via three interface cards located in the M2 module. Interface between the FST-1 and the teletype (or the optional peripherals VKT line printer and tape cassette unit) are accomplished via interface cards physically located within the CPU module.

The FST-1 control panel (Figure 1-3) is located behind the left panel and is primarily for maintenance personnel; it is not normally accessible to the operator. Listed below are some of the FST-1 features:

(1) 24-bit data word

- (2) 1.75 microsecond memory-cycle time

- (3) Magnetic ferrite-core memory

- (4) 8192-word memory modules

- (5) Options to comprise a maximum of two memory modules, a total of 16,384 words per CPU

- (6) Dual memory-access via two memory buses

- (7) Random direct memory access, stored or retrieved at 571,000 words per second per memory bus

- (8) Separate interface control between memory modules and CPU or tester

- (9) Interrupt subsystem for communications and data transfer between CPU and peripheral units via accumulator bus

- (10) 16 external interrupt channels and a maximum of 63 interrupt locations in memory

- (11) Seven index registers for address modification

- (12) Indirect addressing for most instructions

- (13) A six-bit operation code for the following types of instructions:

load and store

arithmetic

logical operations

register and state

conditional and unconditional branch (transferof-control)

shift

input/output

The maintenance panel provides all controls and indicators for the FST-1. The switch register provides a means of manually setting up a 24-bit word. The up position represents a binary '1' and the down position a binary '0'. The contents of various working registers may be displayed on the lamps above the switches. In the bottom right hand corner are located the main computer switches; i.e., START, STOP, etc.

FIGURE 1-3. FST-1 COMPUTER CONTROL PANEL

FAIRCHILD

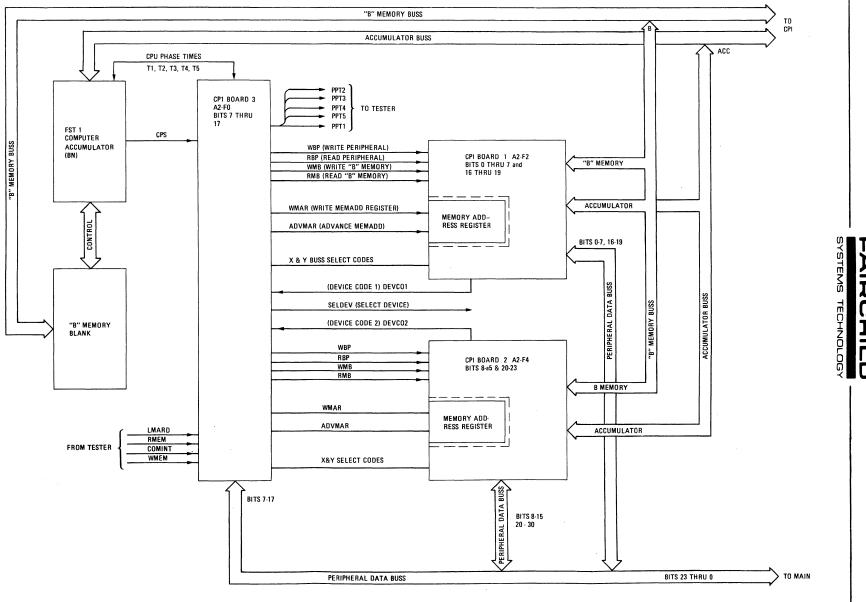

The basic configuration for the FST-1 is shown in Figure 1-4. The A memory and B memory data buses are interfaced to the memory and are primarily used for transmitting functional test data at memory speeds to the tester. Both of these memory buses may be in operation at the same time.

#### 1.1.4 Tester Controller

The Tester Controller is mounted on the backplane in the upper rear section of the center bay. The tester controller contains the computer/tester interface (M2) and various control and status registers. The controller contains such functions as initiation of hardware delays, execution of functional tests directly from the computer memory, etc.

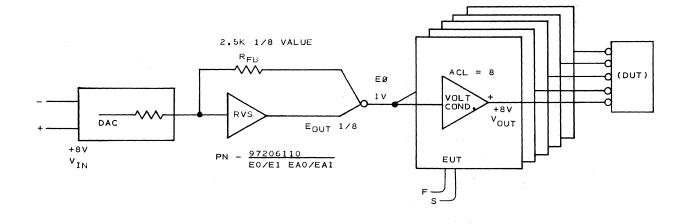

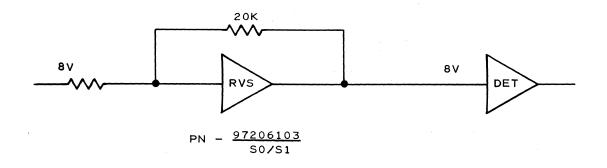

The programmable Device Power Supplies and Reference Voltage Supplies are also mounted in the tester controller (M1). The output of these supplies is furnished to the test station in analog form. The supplies included in the basic system are:

One Device Power Supplies (DPS1) One Pair of Functional Comparator Reference Supplies (S0, S1) One Pair of Functional Reference Voltage Supplies (E0, E1)

#### 1.1.5 Test Station

The Test Station is mounted in the right hand door frame. The lower backplane, where the Precision Measurement Unit is mounted, is present in all systems (RO). The upper backplane (R2) is present only in systems having more than 30 pins. On standard systems, one load board socket and input/output connector is provided for each backplane.

#### Pin Electronics

A minimum system consists of sufficient EUT Interface and Pin Control Logic circuit boards to drive 16 pins. Adding an additional card of each type allows an additional two pins to be used. These cards contain the driver amplifiers, comparators, and logic circuits used in functional testing.

#### Precision Measurement Unit

A Precision Measurement Unit is provided to measure the DC characteristics of the device-under-test. This type of testing is essential for specifying semiconductor parameters such as saturation voltage, input leakage, etc. The Precision Measurement Unit is capable of forcing a voltage or current on

FIGURE 1-4. FST-1 COMPUTER SIMPLIFIED BLOCK DIAGRAM

٢N

1-9

SYSTEMS TECHNOLOGY

any tester pin. The Precision Measurement Unit also is capable of measuring internal analog reference voltages and power supply voltages and currents for system self-checks. Measurements are made with a high-speed comparator with a 0.1% accuracy and resolution for voltages from 1 millivolt to 40 volts and currents from 1 nanoampere to 100 milliamperes. System software provides analog to digital conversion for data logging.

#### Load Boards

User designed load boards (or a performance board in the case of a sub multiplex station) allow unique requirements for a device or family of devices to be accomodated. The load board may be hardwired or switched under program control using the utility relay for each pin. The following list is typical of the hardware functions that may be implemented on the load board or performance board:

#### **Power Supply Decoupling**

Device power supply pins can be decoupled by connecting a capacitor in series with a utility relay. If it is necessary to perform a precision leakage test on the device supply pin, the utility relay can be opened prior to connecting the precision measurement unit to the device pin.

#### Input Bias Voltage

Unused power supplies can be connected to device input pins via utility relays to provide bias voltages. Up to two optional reference voltage supplies may be connected.

#### **MOS Input Pin Stressing**

Low-energy pulses can be applied to MOS input pins by connecting the user supplied pulse source to input pins via the utility relays. Control for the pulse source is derived from one of the external registers.

#### Clocking

An active circuit may be used to provide device clocking with pulse shaping if desired.

#### Output Pin Loading

Output pins can be loaded by either of the following methods:

(a) Connect a resistive load in series with the functional test driver and the device output pin (the functional

test level detector is also connected to the device output pin to allow concurrent GO/NO-GO testing). The load current for VOH/VOL is provided by switching the driver reference between EA1 and EA0 according to the output bit in the F register.

(b) Connect a resistive load to the device output pin in series with a utility relay and one of the programmable power supplies. Load current is then applied when the power supply is programmed to the appropriate voltage level.

#### **EUT** Connection

A connector for each backplane is mounted on pylons such that the connectors are positioned over a work surface when the right hand door of the system is closed. Each connector provides both force and sense connections for each tester pin. A mating connector may be used as a mount for a test socket for devices of less than 30 pins or connected via a cable to a remote socket, or a handler, or wafer prober, etc. Force and sense for each pin are tied together as close to the Element Under Test as practical so that line resistance does not affect measurement accuracy.

The system side of the connectors is wired to the load board sockets and the EUT Interface circuit boards.

#### 1.2 FUNCTIONAL DESCRIPTION

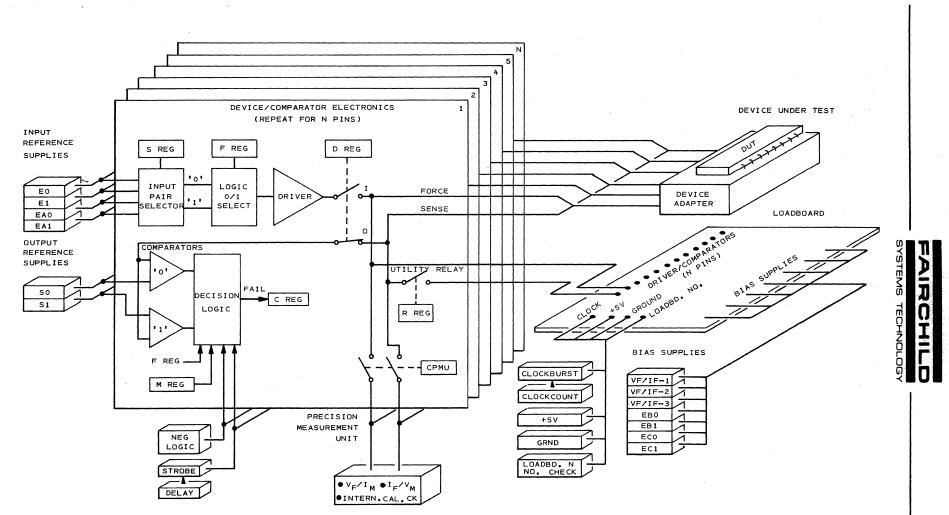

Figure 1-5 is a simplified block diagram of the Sentry 100 tester circuitry associated with one pin. A minimum system consists of circuitry for 16 pins. Driver/detector circuits are added in groups of 2 up to a maximum of 60 pins. The driver and detector permits each pin to be operated as an input pin, an output pin, both, or neither, depending upon programming of the registers.

The system provides two pairs of analog input references so that the programmer has the flexibility of choosing between two levels. One of the two input analog buses is selected by the 'S' register. Depending upon the excitation bit in the 'F' register, the driver is gated to produce a voltage equal to either the '1' or '0' level of the pair selected by the 'S' register.

If the device pin is an input pin, a '1' bit in the 'D' register closes relay R1. The output of the driver is applied to the pin of the DUT. If the device pin is an output pin, a 'O' bit in the 'D' register opens relay R1. The pin of the DUT is now connected only to the input of the detector. The detector also receives an input level proportional to the expected output. If the device

### FIGURE 1-5 S100 SIMPLIFIED BLOCK DIAGRAM

1-12

pin is an output, the expected output is compared with the actual output of the pin. If the inputs are within the programmed limits, the detector will provide a '0' output that is interpreted as a pass condition. If no comparison exists, the detector will provide a '1' output that is interpreted as a fail condition.

The detectors are always connected to the sense line through relay RO except when the PMU is addressed to that pin. The level on a pin can therefore be sensed whether it is an input pin or an output pin.

The detector also receives an input from the M register (mask register). If the programmer is interested in the output, the 'M' register is programmed as a '1'. The '1' condition enables the detector to make the comparison between the actual output and the expected output. If the programmer is not interested in the output level of the pin the 'M' register is programmed as a '0'. The '0' condition inhibits the output of the detector. The 'C' register and the function test fail output will indicate a pass.

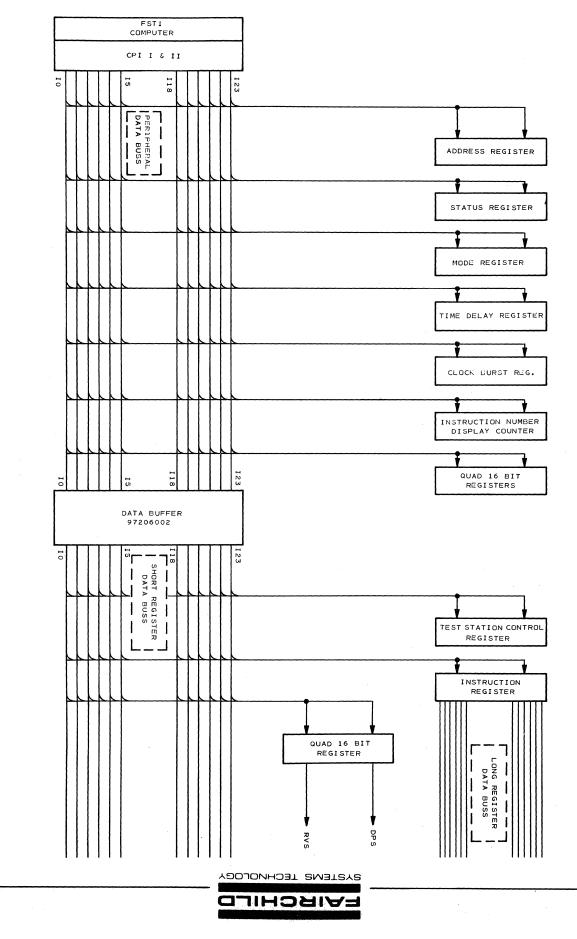

Figure 1-6 is a simplified block diagram of the digital portion of the tester. Interface between the FST-1 computer and the tester is provided by the CPI cards, which also contains the memory address register (MAR). Various other working registers are enterfaced to the peripheral data buss and to the long and short register data busses. Details of the operation and function of these registers are contained in the following sections. FIGURE 1-6. S100 SIMPLIFIED (DIGITAL)

₽1-14

### Section II Functional Description

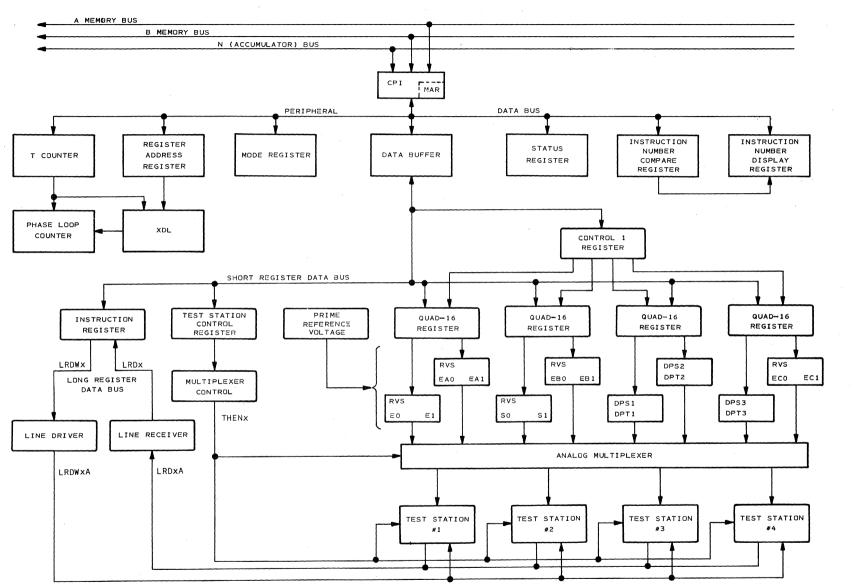

#### 2.0 SYSTEM BLOCK DIAGRAM

A simplified block diagram of the S100 system is shown in Figure 2-1. The computer and I/O peripherals are not represented on this diagram. The possibility for analog multiplexing to four test stations is indicated.

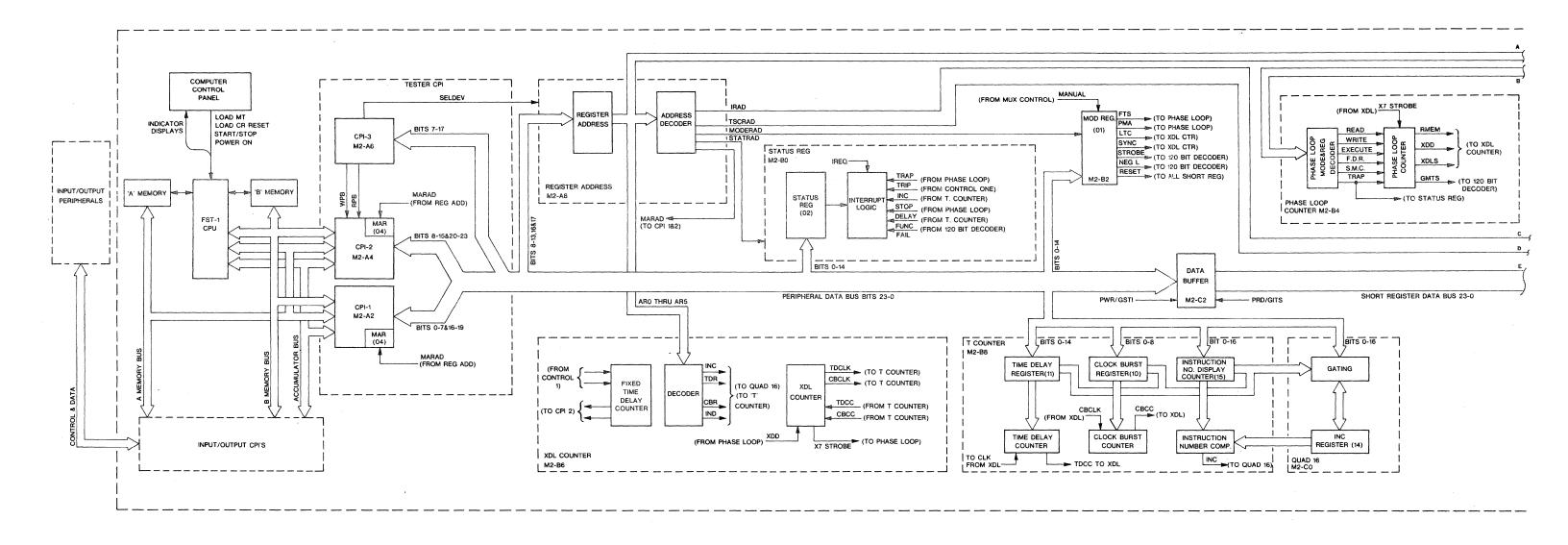

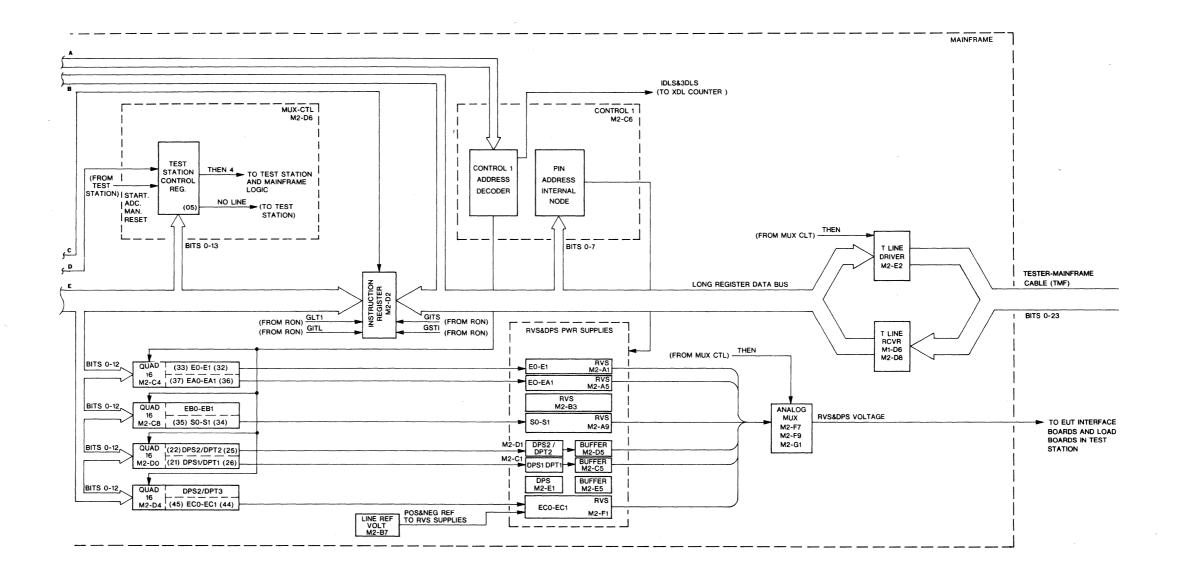

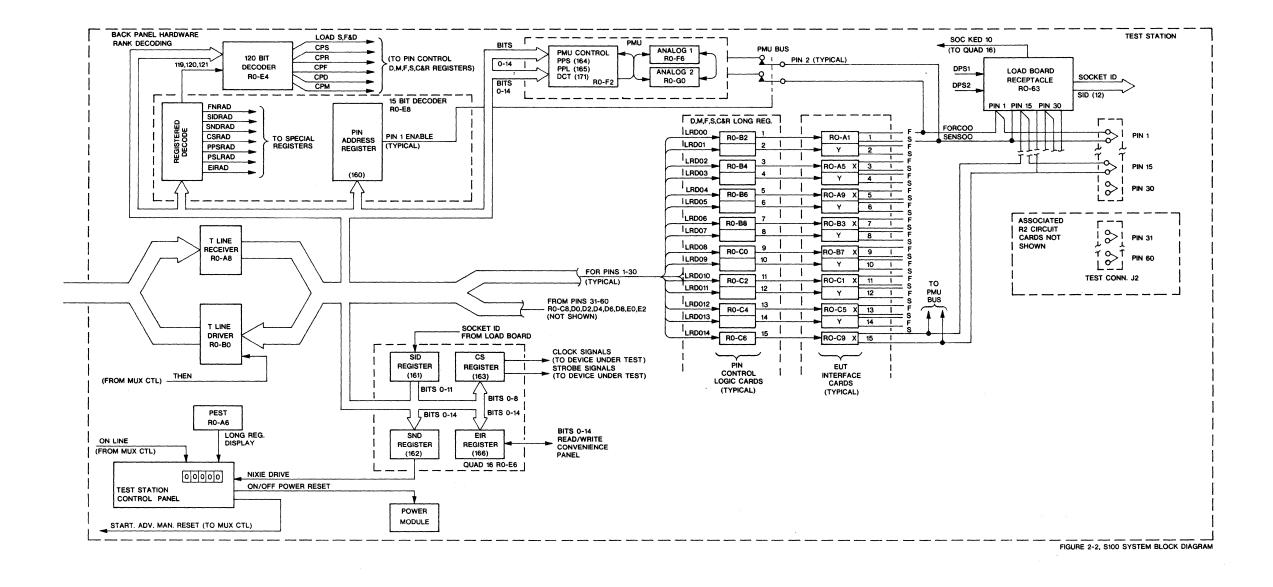

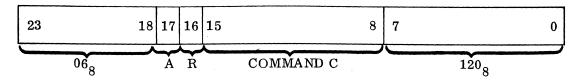

Figure 2-22 is a more detailed system block diagram. In this figure the computer and I/O peripherals are represented, and a single test station is detailed as a typical case. The system as shown in this figure is composed of four major blocks -- I/O Peripherals, Computer, Mainframe, and Test Station. The Computer block includes the CPU (Central Processing Unit), Core Memory, Computer Control Panel, I/O CPI's (Common Peripheral Interface), and Tester CPI.

The Mainframe Block contains all ShortRegisters and their associated logic circuitry, as well as the RVS and DPS power supplies. Also shown are the three 24-bit data buses (Peripheral Data Bus, Short Register Data Bus, and Long Register Data Bus). The functions of these registers and buses are discussed in detail in Section 2.2 below. The overall function of theMainframe block is to control the operation of the Test Station(s) in accordance with the programmed information resident in Computer Core Memory.

The Test Station block contains all long registers and pin electronics, including the PMU (Precision Measurement Unit).

In the S100 System, the Computer, Mainframe, and one Test Station are all physically housed in a single console. With a submux option (8438, 8439), up to four test stations may be accomodated, housed at remote locations.

Within each major block, dotted lines enclose individual printed circuit boards. Separate descriptions for each of these boards are presented in Section 2.3.

FIGURE 2-1. S100 SIMPLIFIED BLOCK DIAGRAM

2-2

FAIRCHIL

٥

TEMS TECHNOLOG

SYSTEMS TECHNOLOGY

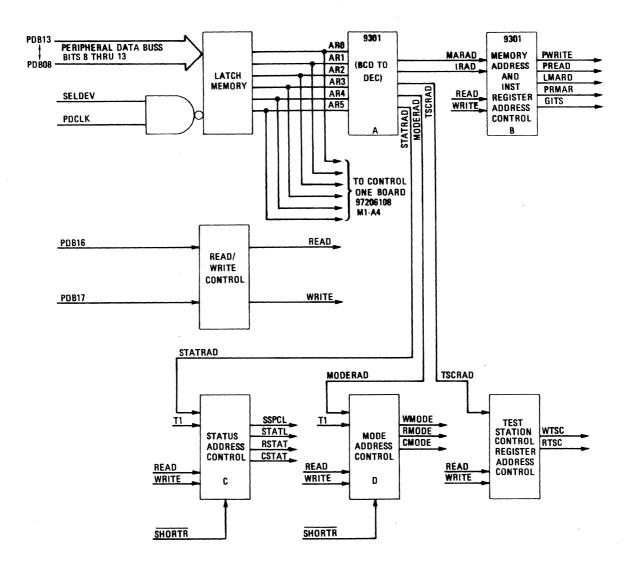

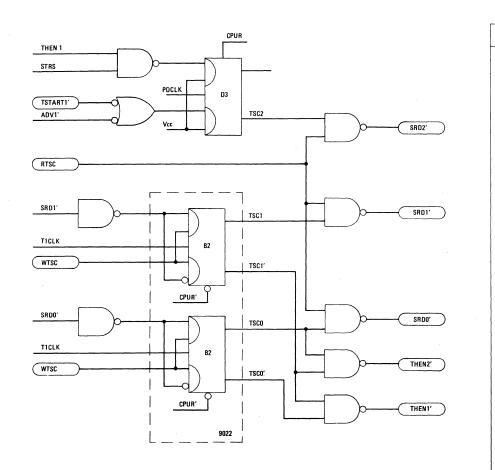

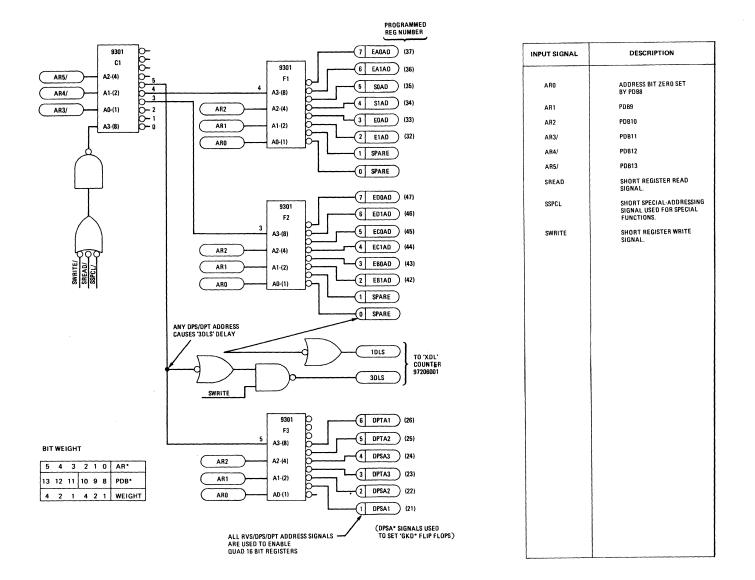

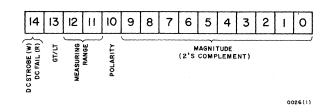

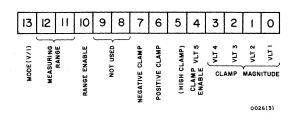

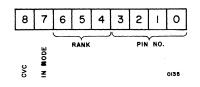

#### 2.1 REGISTERS & DATA BUSSES

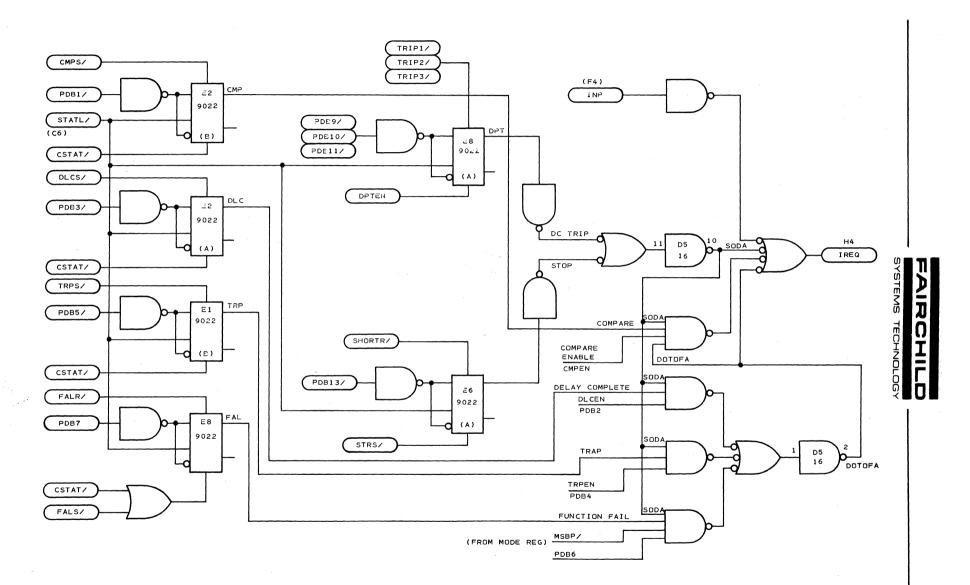

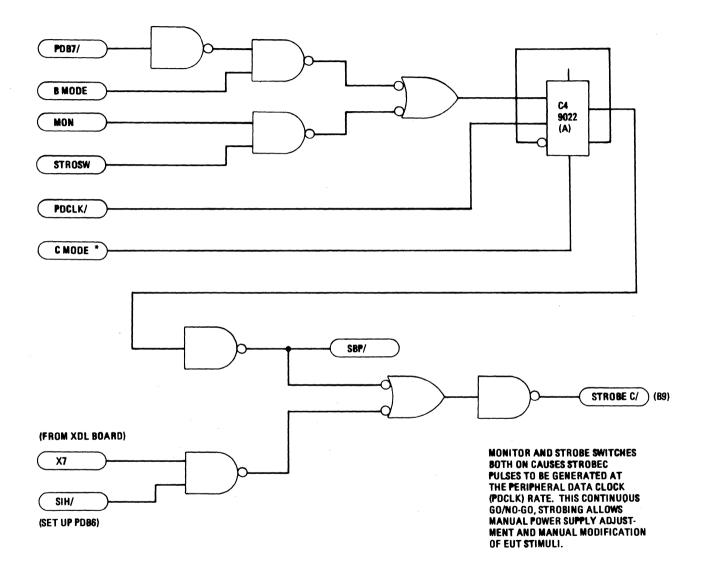

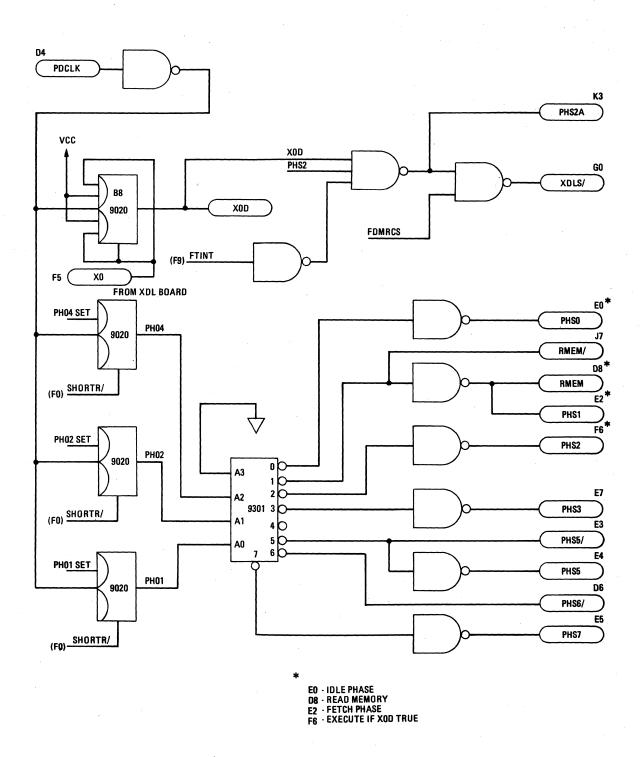

The registers in the S100 system are grouped into two categories -- short registers and long registers. Table 2-2 lists the short registers and table 2-1 lists the long registers. There are two groups of short registers. The first group is used for tester control. The second group controls the programmable dc power supplies which provide the functional logic level test voltages to the test station. There are also two groups of long registers, the variable length (D, M, F, S, C, and R) registers, and the fixed length special registers.