# **SENTRY**

# FACTOR PROGRAMMING LANGUAGE Reference Manual

# **SENTRY**

# **FACTOR PROGRAMMING LANGUAGE**

**Reference Manual**

Part Number: 67095738 Date Issued: March 1977

#### PREFACE

This manual discusses the Fairchild Sentry II and Sentry VII Programming Language called FACTOR (Fairchild Algorithmic Compiler-Tester ORiented). FACTOR is a procedural programming language that consist of two basic types of statements:

- (1) Arithmetic and logical control

- (2) Test control statements which set up and execute functional/parametric tests on electronic elements or devices.

This manual is intended for a person with a general knowledge of electronics and a working knowledge of programming concepts. It is suggested that the user become familiar with the glossary of terms before reading this manual. Sections 1 and 2 discuss elements and expressions as well as general format of the FACTOR language. Sections 3 through 5 discuss control statements, blocks and subprogram concepts and statements. Section 6 discusses FACTOR test statements and their format. Sections 7 through 9 discuss FACTOR I/O and operating procedures. A glossary of terms and acronyms, appendices and a comprehensive index are also included for user convenience.

The following manuals are suggested as supplementary reading and/or reference:

| Description                                                   | Publication Number |

|---------------------------------------------------------------|--------------------|

| Sentry VII User Reference Manual                              | 67095733           |

| Reference Manual<br>Sequence Processor (SPM)                  | 67095589           |

| Reference Manual                                              | •                  |

| Pattern Processor (PPM) User and Programming Reference Manual | 67095583           |

| Sentry Utility Reference Manual                               | 67095661           |

| FST-2 Computer Manual                                         | 67095701           |

## TABLE OF CONTENTS

|           |                                   | Page |

|-----------|-----------------------------------|------|

| PREFACE   |                                   |      |

| SECTION 1 | ELEMENTS OF FACTOR                |      |

| 1.1       | CHARACTER SET                     | 1-1  |

| 1.2       | FACTOR STATEMENTS                 | 1-1  |

| 1.3       | PROGRAM PREPARATION               | 1-1  |

| 1.3.1     | Record Format                     | 1-2  |

| 1.3.2     | Cards                             | 1-2  |

| 1.3.3     | Disc                              | 1-3  |

| 1.3.4     | Video Keyboard Terminal           | 1-3  |

| 1.4       | SYNTAX                            | 1-3  |

| 1.4.1     | Constant Parameters               | 1-3  |

| 1.4.2     | Variable Parameters               | 1-4  |

| 1.4.3     | Required Parameters               | 1-4  |

| 1.4.4     | Optional Parameters               | 1-4  |

| 1.4.5     | Syntax Characters                 | 1-5  |

| SECTION 2 | EXPRESSIONS                       |      |

| 2.1       | NUMBERS                           | 2-1  |

| 2.1.1     | Integers                          | 2-1  |

| 2.1.2     | Decimal Fractionals               | 2-2  |

| 2.1.3     | Exponentials                      | 2-2  |

| 2.2       | VARIABLES                         | 2-2  |

| 2.2.1     | System Global Variables           | 2-3  |

| 2.2.2     | User Variable Identifiers         | 2-4  |

| 2.2.3     | Scalar Values                     | 2-5  |

| 2.2.4     | Boolean Values                    | 2-5  |

| 2.2.5     | Array Values                      | 2-6  |

| 2.3       | FUNCTIONS                         | 2-6  |

| 2.4       | ARITHMETIC EXPRESSION EVALUATION  | 2-6  |

| 2.5       | LOGICAL EXPRESSIONS               | 2-7  |

| 2.5.1     | Logical Operators                 | 2-7  |

| 2.5.2     | Logical Expression Evaluation     | 2-8  |

| 2.6       | BOOLEAN EXPRESSIONS               | 2-8  |

| 2.6.1     | Relational Operators              | 2-8  |

| 2.6.2     | Evaluation of Boolean Expressions | 2-9  |

| 2.7       | MIXED EXPRESSIONS                 | 2-9  |

| SECTION 3    | CONTROL STATEMENTS                            |            |

|--------------|-----------------------------------------------|------------|

| 3.1          | PAUSE                                         | 3-1        |

| 3.2          | GOTO                                          | 3-1        |

| 3.2.1        | Indexed GOTO                                  | 3-2        |

| 3.3<br>3.3.1 | IF<br>The Conditional ELSE                    | 3-2<br>3-3 |

| 3.4          | BEGIN                                         | 3-3<br>3-4 |

| 3.5          | FOR                                           | 3-4<br>3-4 |

| 0.0          | Tolt                                          | 9 4        |

| SECTION 4    | SUBPROGRAMS AND BLOCK PROGRAM CONCEPTS        |            |

| 4.1          | BLOCKS                                        | 4-1        |

| 4.1.1        | Nesting Blocks                                | 4-1        |

| 4.2          | SUBPROGRAMS                                   | 4-2        |

| 4.2.1        | SUBR                                          | 4-3        |

| 4.3          | CALL                                          | 4-4        |

| 4.4          | FUNCT                                         | 4-5        |

| 4.4.1        | Function Call                                 | 4-5        |

| 4.5          | EXEC                                          | 4-7        |

| 4.5.1        | Writing the Assembly Language Program         | 4-8        |

| 4.5.2        | Referencing Parameters                        | 4-8        |

| 4.5.3        | Accessing System Routines                     | 4-9        |

| SECTION 5    | NOTATIONAL STATEMENTS AND COMPILER DIRECTIVES |            |

| 5.1          | NOISE                                         | 5-1        |

| 5.2          | REM                                           | 5-1        |

| 5.3          | PAGE                                          | 5-2        |

| 5.4          | LIST/NOLIST                                   | 5-2        |

| 5.5          | INSERT                                        | 5-3        |

| SECTION 6    | TEST STATEMENTS FORMATS                       | 6-1        |

| <b>6.</b> 1  | PROGRAM INITIALIZATION                        | 6-2        |

| 6.1.1        | Set Page                                      | 6-2        |

| 6.2          | ANALOG SUBSYSTEMS                             | 6-3        |

| 6.2.1        | Digital Power Supplies                        | 6-3        |

| 6.2.2        | Reference Voltage Supplies (RVS)              | 0 0        |

|              | and Clock Selection                           | 6-9        |

| 6.2.3        | Precision Measurement Unit (PMU)              | 6-13       |

| 6.2.4        | Analog System Time Delays                     | 6-26       |

| 6.2.5        | Miscellaneous Analog Subsystem                | 6-28       |

| 6.3          | FUNCTIONAL TEST TIMING SUBSYSTEMS             | 6-30       |

| 6.3.1        | Time Delay and Width Generators               | 6-30       |

| 6.3.2        | Test Rate Generator                           | 6-32       |

| 6.4          | PIN CONTROL LOGIC - FORMATTING AND            |            |

|              | FAIL RESPONSE                                 | 6-34       |

| 6.4.1     | Long Register Formatting               | 6-34 |

|-----------|----------------------------------------|------|

| 6.4.2     | Input Pin Definition Registers         | 6-40 |

| 6.4.3     | Output Mask Definition Registers       | 6-41 |

| 6.4.4     | Output Compartor Strobes               | 6-42 |

| 6.4.5     | Input Waveform Control                 | 6-42 |

| 6.4.6     | Input/Output Modes                     | 6-46 |

| 6.4.7     | Multiplexing Pin Channels              | 6-48 |

| 6.4.8     | Chaining Local Memory Channels         | 6-49 |

| 6.5       | LOCAL MEMORY TEST SEQUENCE LOGIC       | 6-50 |

| 6.5.1     | Loading Local Memory                   | 6-50 |

| 6.5.2     | Initiating Local Memory Function Tests | 6-54 |

| 6.5.3     | Function Test Execution                | 6-57 |

| 6.5.4     | Function Test Execution Options        | 6-61 |

| 6.5.5     | Function Test Termination              | 6-64 |

| 6.6       | MISCELLANEOUS TEST STATEMENTS          | 6-65 |

| 6.6.1     | Branch on Fail                         | 6-65 |

| 6.6.2     | Clearing Branch on Fail Flags          | 6-65 |

| 6.6.3     | Clearing Fail Indicators               | 6-66 |

| 6.6.4     | Controlling Load Board Utility Relays  | 6-66 |

| 6.6.5     | System Reset During Program Execution  | 6-66 |

| 6.6.6     | Enable Access                          | 6-67 |

| SECTION 7 | VARIABLE DECLARATION AND VALUE         |      |

| SECTION ? | ASSIGNMENT                             | 7-1  |

| 7.1       | DCL                                    | 7-1  |

| 7.1.1     | Single Variable Declaration            | 7-1  |

| 7.1.2     | Array Declaration                      | 7-2  |

| 7.1.3     | Literal Variable Capability            | 7-2  |

| 7.2       | VARIABLE ASSIGNMENT STATEMENT          | 7-4  |

| 1.2       | VARIABLE ASSIGNMENT STATEMENT          | (-4  |

| SECTION 8 | READ/WRITE STATEMENTS                  | 8-1  |

| 8.1       | READ                                   | 8-1  |

| 8.2       | WRITE                                  | 8-2  |

| 8.2.1     | Numeric Variables                      | 8-3  |

| 8.2.2     | Literal Variables                      | 8-4  |

| 8.3       | FACTOR DISC I/O                        | 8-5  |

| 8.3.1     | ON DIF EOF, LABEL                      | 8-5  |

| 8.3.2     | RESET FDIF                             | 8-5  |

| 8.3.3     | Programming Conventions for use with   | 5 0  |

|           | FACTOR Disc I/O                        | 8-5  |

| 8.4       | Examples of Programs that READ and     | 5 0  |

|           | WRITE to Disc                          | 8-6  |

|           |                                        |      |

| SECTION 9                                                                      | FACTOR OPERATING PROCEDURES AND ERROR MESSAGES                                                                                                                                                                                                                                                                                | 9-1                                                           |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 9.1<br>9.1.1<br>9.1.2<br>9.2<br>9.3                                            | PROGRAM INITIATION Input Output INTERPRETER INTERFACING ERROR MESSAGES                                                                                                                                                                                                                                                        | 9-1<br>9-1<br>9-1<br>9-2<br>9-3                               |

|                                                                                | LIST OF APPENDICES                                                                                                                                                                                                                                                                                                            |                                                               |

|                                                                                |                                                                                                                                                                                                                                                                                                                               | Page                                                          |

| GLOSSARY                                                                       |                                                                                                                                                                                                                                                                                                                               | Glossary-1                                                    |

| APPENDIX                                                                       | A - CHARACTER CODING (TRASCII)                                                                                                                                                                                                                                                                                                | A-1                                                           |

| APPENDIX<br>REGISTER                                                           | B - READING & WRITING OF LONG & SHORT<br>RS                                                                                                                                                                                                                                                                                   | B-1                                                           |

| B.1<br>B.1.1<br>B.1.2<br>B.2<br>B.2.1<br>B.3<br>B.3.1<br>B.3.2<br>B.3.3<br>B.4 | INTRODUCTION Long Registers Short Registers ADDRESSING SHORT REGISTERS Short Register Descriptions LONG REGISTER DESCRIPTION The D,M,S,R,F,RZ,ST,INVERT,TG and C Registers Format of Functional Test Word Special Test Station Registers FORMATTING OF FACTOR WRITE AND READ STATEMENTS LONG REGISTER ASSIGNMENT IN ALTERNATE | B-1<br>B-1<br>B-1<br>B-1<br>B-3<br>B-8<br>B-8<br>B-11<br>B-12 |

| <b>5.</b> 0                                                                    | BANK                                                                                                                                                                                                                                                                                                                          | В-30                                                          |

| APPENDIX                                                                       | C - DMA MODE STATEMENTS                                                                                                                                                                                                                                                                                                       | C-1                                                           |

| APPENDIX                                                                       | D - TIME DELAY RELATED STATEMENTS                                                                                                                                                                                                                                                                                             | D-1                                                           |

| APPENDIX                                                                       | E - EXECUTION TERMINAL ERROR NUMBERS                                                                                                                                                                                                                                                                                          | E-1                                                           |

| APPENDIX                                                                       | F - CALIBRATION RESISTOR TABLE                                                                                                                                                                                                                                                                                                | F-1                                                           |

| APPENDIX                                                                       | G - INTERNAL NODE MEASUREMENT                                                                                                                                                                                                                                                                                                 | G <b>-</b> 1                                                  |

| APPENDIX                                                                       | H - STATEMENT LIST                                                                                                                                                                                                                                                                                                            | H-1                                                           |

| H.1<br>H.2<br>H.3                                                              | BASIC STATEMENT FORMS INPUT/OUTPUT STATEMENT FORMS TESTER STATEMENTS                                                                                                                                                                                                                                                          | H-1<br>H-3<br>H-4                                             |

| H.4 ENABLE FORMS H.5 FORCE FORMS H.6 MISCELLANEOUS FORMS |                                                                                                    |              |  |  |  |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------|--|--|--|

| H.7                                                      | LOCAL MEMORY MANAGEMENT                                                                            | H-8          |  |  |  |

| APPENDIX I                                               | - READ/WRITE MAGNETIC TAPE STATEMENTS                                                              | I-1          |  |  |  |

| I.1                                                      | DEFINITION                                                                                         | I-1          |  |  |  |

| I.2                                                      | READ ERRORS                                                                                        | I-2          |  |  |  |

| I.2.1                                                    | Array Element Count Error                                                                          | I-2          |  |  |  |

| I.2.2                                                    | Data Transfer Error                                                                                | I-2          |  |  |  |

| I.2.3                                                    | End of Tape Error                                                                                  | I-2          |  |  |  |

| I.2.4                                                    | Memory Protect                                                                                     | I-3          |  |  |  |

| I.3                                                      | WRITE ERRORS                                                                                       | I-3          |  |  |  |

| I.3.1                                                    | Data Transfer Error                                                                                | I-3          |  |  |  |

| I.3.2                                                    |                                                                                                    | I-3          |  |  |  |

| I.3.3                                                    |                                                                                                    | I-3          |  |  |  |

|                                                          | Unrecoverable Errors                                                                               | I-3          |  |  |  |

| I.4                                                      | STANDARD MAG TAPE OPERATION IN TOPSY                                                               | I-3          |  |  |  |

| I.5                                                      | UNUSUAL MAG TAPE OPERATION IN TOPSY                                                                | I-4          |  |  |  |

| I.5.1                                                    | Catastrophic Errors                                                                                | I-4          |  |  |  |

| APPENDIX J                                               | - FLOATING POINT PACKAGE                                                                           | J-1          |  |  |  |

| APPENDIX K                                               | X - COMPILER GENERATED TESTER OP CODES DMA                                                         | K-1          |  |  |  |

| APPENDIX L                                               | - VOLTAGE AND CURRENT RANGE DEFINITIONS                                                            | L-1          |  |  |  |

| APPENDIX N                                               | 1 - STATEMENT LIST, REGISTERS WRITTEN, CODE                                                        |              |  |  |  |

|                                                          | TYPE, AND TIME DELAY                                                                               | M-1          |  |  |  |

|                                                          | LIST OF FIGURES                                                                                    |              |  |  |  |

|                                                          | hist of fidentis                                                                                   |              |  |  |  |

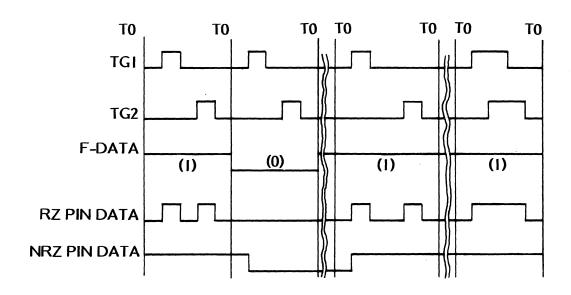

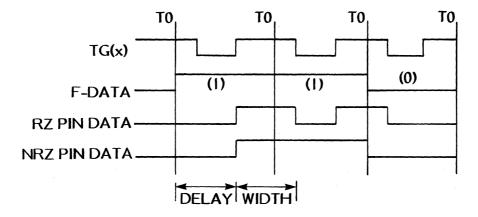

| Figure 6-1<br>Figure 6-2                                 | Timing Generator Pulse Generation for TG12<br>Period and Pulse Response for Pulse Exceeding Period | 6-31<br>6-32 |  |  |  |

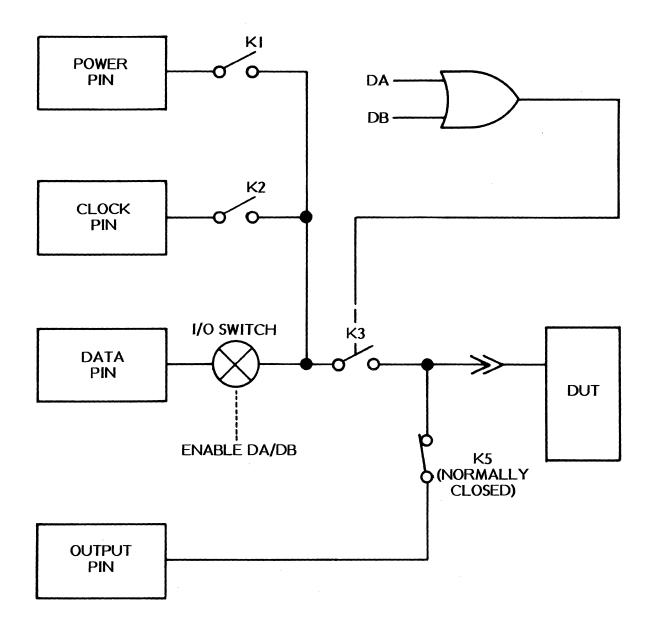

| Figure 6-3                                               | Pin Relay Sequence                                                                                 | 6-39         |  |  |  |

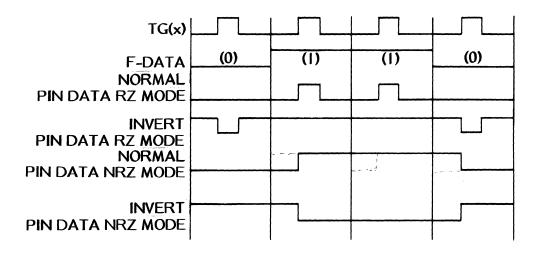

| Figure 6-4                                               | F-Data Inversion of RZ and NRZ Pins                                                                | 6-43         |  |  |  |

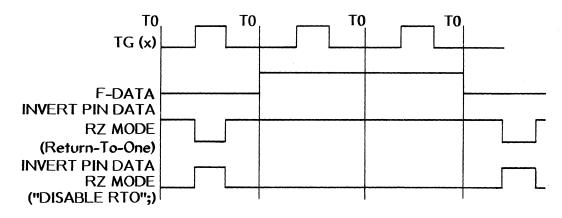

| Figure 6-5                                               | RTO Waveform and Inverted RTO Waveform                                                             | 6-44         |  |  |  |

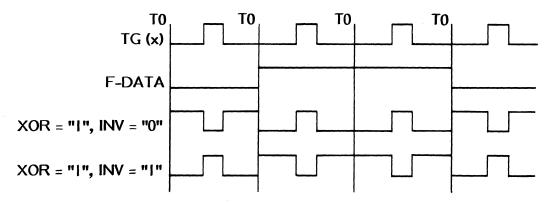

| Figure 6-6                                               | XOR Waveform for a Binary 1                                                                        | 6-45         |  |  |  |

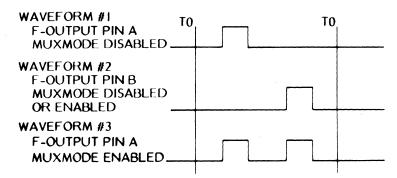

| Figure 6-7                                               | MUXMODE Example                                                                                    | 6-48         |  |  |  |

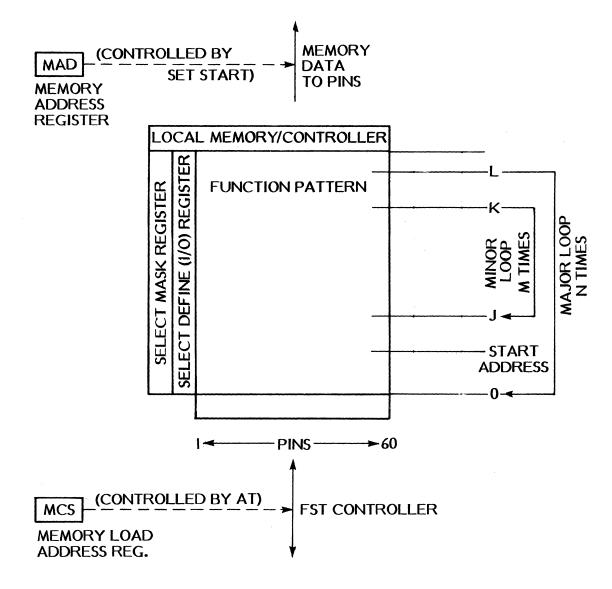

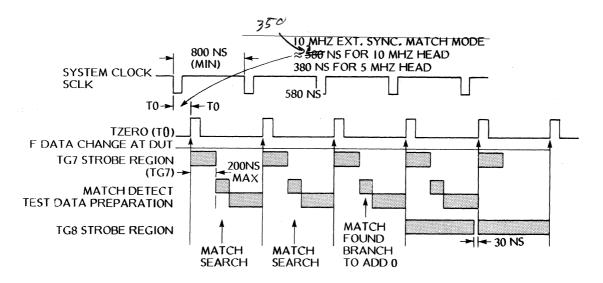

| Figure 6-8                                               | Local Memory Timing in Internal Same MATCH Made                                                    | 6-55         |  |  |  |

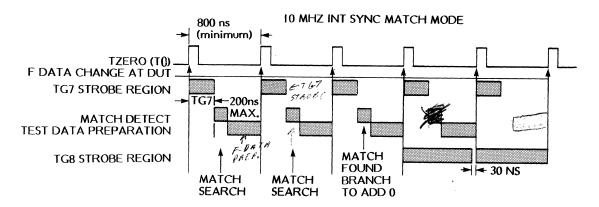

| Figure 6-9                                               | Timing in Internal Sync MATCH Mode                                                                 | 6-61         |  |  |  |

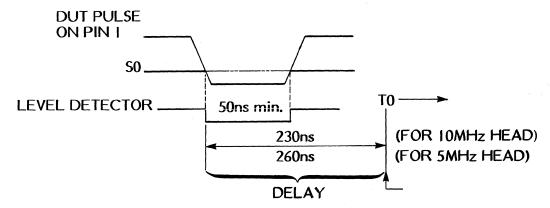

| Figure 6-10                                              | External Sync Pulse Characteristics                                                                | 6-62         |  |  |  |

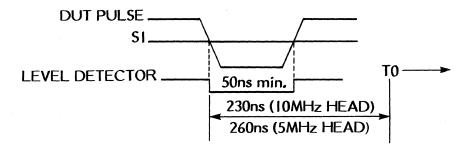

| Figure 6-11                                              | Timing in External Sync Match Mode                                                                 | 6-64         |  |  |  |

# LIST OF TABLES

| Table 2-1  | Precedence Values of Operators                  | 2-10 |

|------------|-------------------------------------------------|------|

| Table 4-1  | System Routines and Memory Address Locations    | 4-10 |

| Table 6-1  | Results of Set Page Integer Statement           | 6-2  |

| Table 6-2  | Clock Option, Power Supply, and Set F and Set S |      |

|            | Statements                                      | 6-10 |

| Table 6-3  | Comparator Pass/Fail Conditions                 | 6-13 |

| Table 6-4  | Voltage Statements                              | 6-29 |

| Table 6-5  | Timing Generator Range Scale and Resolution     | 6-30 |

| Table 6-6  | Period Range, Scale and Resolution              | 6-32 |

| Table 6-7  | Tester Surviving and Conditioning Pins          | 6-46 |

| Table 6-8  | IOM3 Extended Pin List                          | 6-47 |

| Table 6-9  | Set Chain Surviving Pin List                    | 6-49 |

| Table 6-10 | Results of SET PAGE Integer Statement           | 6-58 |

| Table 9-1  | Factor Error Messages                           | 9-3  |

| Table B-1  | SPU Command Format                              | B-2  |

| Table B-2  | Mode Register                                   | B-3  |

| Table B-3  | Status Register                                 | B-4  |

| Table B-4  | Instruction Register                            | B-4  |

| Table B-5  | Test Station Control Register                   | B-5  |

| Table B-6  | Digital Programmable Power Supply Register      | B-7  |

| Table B-7  | DPS Trip Registers                              | B-7  |

| Table B-8  | Reference Voltage Supply Registers              | B-8  |

| Table B-9  | Test Word Function Format                       | B-11 |

| Table B-10 | Pin Address Register                            | B-13 |

| Table B-11 | Test Rate Register                              | B-13 |

| Table B-12 | PPSR/PMUF Register                              | B-14 |

| Table B-13 | Precision Sense Level Register                  | B-15 |

| Table B-14 | External Interface Register                     | B-16 |

| Table B-15 | Local Memory Test Start/Delayed Memory          |      |

|            | Address Register (Address 1700)                 | B-16 |

| Table B-16 | Local Memory Address Register                   | B-17 |

| Table B-17 | DC Trip Limit Register                          | B-18 |

| Table B-18 | Chaining Register                               | B-19 |

| Table B-19 | Status and Mode Register A                      | B-19 |

| Table B-20 | Status and Mode Register B                      | B-20 |

| Table B-21 | Status and Mode Register C                      | B-20 |

| Table B-22 | Timing Generator Pulse Width Register           | B-21 |

| Table B-23 | Timing Generator Pulse Delay Register           | B-22 |

| Table B-24 | Power Pin Address Register                      | B-23 |

| Table B-25 | Timing Generator Delay/Width Vernier            | B-23 |

| Table B-26 | Short Register Reading and Writing Codes        | B-25 |

| Table B-27 | Long Register Reading & Writing Codes           | B-26 |

| Table B-28 | Long Register Assignment In Alternate Bank      | B-30 |

| Table C-1  | Statements Executed In DMA Mode                 | C-2  |

| Table D-1  | Time Delay Dependent Statements                 | D-1  |

| Table D-2  | Time Delay Generating Statements                | D-2  |

| Table E-1  | Execution Terminal Error Numbers                | E-1  |

| Table F-1  | Calibration Resistor Table                      | F-1  |

|            |                                                 |      |

| Table G-1 | Internal Nodes Measurement                  | G-1 |

|-----------|---------------------------------------------|-----|

| Table I-1 | Array Data Segment                          | I-2 |

| Table L-1 | Normal Force and Measure Ranges             | L-1 |

| Table L-2 | Force and Measure Ranges with 2V/2mV Option | L-2 |

#### SECTION 1.0

#### ELEMENTS OF FACTOR

This section defines the basic elements used in the FACTOR programming language, and the syntax information used to prepare programs for input to the compiler.

#### 1.1 CHARACTER SET

| Letters | A through Z and \$ #                     |

|---------|------------------------------------------|

| Digits  | 0 through 9                              |

| Special | () * + -/, .:; = @[] space † & work book |

| Other   | 106 7                                    |

|         | -> SEE 19 Complete list,                 |

The above characters are valid for a FACTOR source program. The "special" characters have meanings in FACTOR, the "other" characters may be used only in a FACTOR program REMARK statement. The meaning of a special character depends on the context in some cases. For example, the colon is used to define the immediately preceding identifier as a statement label; it also may be used in the binary pin pattern definition in a functional test statement. The correct meaning is chosen by the compiler from adjacent information in the statement. The meaning of all special characters is discussed in the text of this manual. Appendix A tabulates the internal code for the character set.

#### 1.2 FACTOR STATEMENTS

A FACTOR statement is the basic functional entity in a FACTOR program. Except for the IF statement, all statements are terminated by a semicolon.

Example:

LABEL: A = A + 1;

#### 1.3 PROGRAM PREPARATION

A FACTOR program is a group of statements designed to do a specific task, i.e., test a particular device. The program is compiled or translated into a set of object codes, which are interpreted by the system. The result of this translation is called the binary test program, test plan, or data file. The compiler input is called the source version of the test plan.

A SII/SVII FACTOR program begins with a <u>SET PAGE</u> statement followed by the main body of the program, and terminated with an <u>END</u> statement. A program is executed in the order <u>written</u> unless a specific statement alters the <u>flow</u> of control.

#### 1.3.1 Record Format

A record is an arbitrary amount of data read from or written into an input/output device. A record typically contains from 1 to 80 characters, depending on the input/output device type. For a VKT, a record is the amount of data from one carriage return character until the next carriage return character. For a line printer, a record is one line. Character position within the record is frequently called a column; independently of the the medium on which the record is written even if it is not punched cards. Only the first 72 columns of a record are used for FACTOR input. The next 8 columns are reserved for sequence numbers.

FACTOR provides free field input. That is, there is no implied correspondence between the end of the record and the end of the statement. Also, wherever one space is legal, as many spaces as desired can be used. Hence, a statement may start in the middle of a record and continue for as many records as desired. Conversely, more than one statement can be placed in one record. Statement labels need not start in a fixed field such as column 1, and so on. The restrictions are: (1) individual terms, such as variable names, reserved words, and noise words cannot be divided between two records, and the record may be terminated at any point where a space is a legal character; (2) only the first 72 columns of the record may be used for statements.

#### 1.3.2 Cards

When the user prepares the card deck of source statements there are several options. Up to 72 columns of the card may be used for one or more statements, providing a semicolon delimits each statement. Sequence characters are placed in columns 73 through 80 otherwise a portion of the statement is interpreted as a sequence symbol. A FACTOR statement may be started on one card and be carried over to the next, provided that individual words or tester instructions are not divided between two cards.

Cards can be sequenced either alphabetically, numerically, or both. The normal form of sequence numbers is a fixed alpha identifier in columns 73-75, followed by numeric digits in the remaining columns through column 80. These (five) digits ascend in sequence through the program by a convenient increment, one, ten, etc. Sequence symbols are checked for progression. Gaps (e.g. sequencing by tens) in the sequence may be left, so that program corrections and additions may be made without changing every sequence number in the deck. If a single deck contains more than one alpha identifier, these identifiers must be chosen so that the TRASCII (TRuncated ASCII) ascending collating sequence is maintained, otherwise a sequence error is produced.

When an error is detected, the compiler types the full current record and the warning message "SEQUENCE ERROR".

#### Examples:

Legal Sequences

| Illegal | Sequences |

|---------|-----------|

|---------|-----------|

| NUMERIC  | 1            | 3                 | 3   | 10 | 20 | 99999999 | 0 1 3 2 5 4 |

|----------|--------------|-------------------|-----|----|----|----------|-------------|

| COMBINED | 1LB          | $^{2}\mathrm{LB}$ | 3LB |    |    |          | IA OA 3A IA |

| ALPHA    | $\mathbf{A}$ | $\mathbf{C}$      | D   | E  | F  |          | A B P E C   |

|          |              |                   |     |    |    |          |             |

#### 1.3.3 Disc

Disc files may be used as a source program input to FACTOR. They must be type "string".

#### 1.3.4 Video Keyboard Terminal

Source programs may be entered <u>directly via</u> the <u>keyboard</u>. In this mode of operation the statements in each <u>input</u> record are compiled as they are entered.

Two editing characters may be entered from the VKT keyboard. A character back space is obtained by typing the "control" and "B" keys simultaneously. The number of times this key combination is typed corresponds to the number of previously entered characters which are to be ignored. A line delete is obtained by typing "control" and "L" simultaneously. This character deletes the current line only. It is necessary to type "carriage return" and "line feed" after the last END statement in the program.

#### 1.4 SYNTAX

Many FACTOR statements have numerous possible forms. Syntax notation provides a convenient method of identifying all options precisely and succinctly. Special syntactical characters are used to identify alternative forms of the statement. These characters are not entered as part of the statement; they simply define the statement's structure. Throughout this manual, the term "General Format", is used as notification that the next line is presented in syntax notation.

#### 1.4.1 Constant Parameters

Any word shown in upper case in the general form is a constant parameter and is always entered exactly as shown. The general form of a statement required to disconnect the precision measuring unit is as shown below.

Example:

XPMU PIN:

This statement has no options.

#### 1.4.2 Variable Parameters

Any word shown in <u>lower case</u> in the general form is a <u>variable parameter</u>; the word used indicates what <u>kind</u> of <u>information</u> is required. The <u>limits</u> on the value of the variable depend on the statement in which it is used.

#### Example:

CPMU PIN expression;

The word expression indicates a number or variable must be entered and not the ten characters that comprise the word expression.

CPMU PIN 3; is a legal statement.

#### 1.4.3 Required Parameters

Brackets are used to enclose a set of parameters where one, and only one, of the parameters in the set must be used. The parameters in the set are separated by the slash character. An underlined parameter identifies the default case if the entire statement is omitted.

#### Examples:

1. ON [FCT/DCT/TRIP], label;

Either FCT, DCT or TRIP must be specified.

2. [ENABLE/DISABLE] RELAY;

Either ENABLE or DISABLE must be used in this statement. If the entire statement is omitted, however, the disable relay state is assumed.

#### 1.4.4 Optional Parameters

Parentheses are used to enclose a set of optional parameters where, at most, one of the parameters in the set may be used. A slash is used to seperate parameters in the set. An underlined parameter identifies the default case if only that parameter is omitted.

#### Examples:

1. MEASURE VALUE (, LOG);

The ", LOG" is optional in this statement, if LOG is used, the comma must be used.

2. ...(, RNG2/,RNG3);

If the range is programmed, either ,RNG2 or ,RNG3 is used. If the range parameter is omitted, RNG3 is assumed.

#### 1.4.5 Syntax Characters

The brackets and parentheses characters are also used as a required part of the syntax for certain statements.

The brackets and parentheses are used to define pattern replication of binary pin pattern control statement (refer to section 6.4.1.1). In those patterns where the brackets and parentheses are shown, they are required and are not part of the syntax notation.

Parentheses are a required part of the input/output statements syntax (refer to section 8.0).

Brackets are required in the array declaration statements to designate array size (refer to section 7.1.2).

#### Examples:

- 1) SET F [8] (2:1);

The previous pin pattern is preserved to pin 8 and a new pattern starting at pin 8 is specified by the following pattern of two "ones".

- 2) READ (CR) & DEVNAM, &STAT; Information is read from the card reader and input data for literal variable DEVNAM and STAT is extracted.

- 3) DCL ARR [10];

Defines array size as 10 elements.

#### SECTION 2.0

#### **EXPRESSIONS**

An expression is a grouping of one or more numbers, variables, and functions combined with arithmetic or Boolean operators and parentheses so as to represent a quantity or an operation. Note that a single number or variable is considered an expression by this definition.

#### 2.1 NUMBERS

FACTOR accepts numbers in three forms:

(1) integers

(2) decimal fractionals

(3) exponentials

In all cases, numbers are converted to a <u>floating point internal representation</u> for manipulation in the computer (refer to Appendix J). The range of allowable decimal numbers is:

2.7105

$$\left(10^{-20}\right) \le |n| \le 9.2228 \left(10^{18}\right) \text{ or } n = 0$$

where: |n| means the "magnitude of n".

#### 2.1.1 Integers

An integer is defined as a whole number, including zero. It is interpreted as octal if it is immediately followed by a B, otherwise it is interpreted as decimal. It may be either signed (preceded by a + or -) or unsigned. If unsigned, it is interpreted as positive.

The limits for decimal and octal integers are:

Decimal integer

-8388607<u><</u>n<u>≤</u>+8388607

Octal integer

-37777777B≤n≤+37777777B (in two's complement form)

The following are examples of integers:

| ACCEPTABLE | UNACCEPTABLE         |                          |

|------------|----------------------|--------------------------|

| 0          | 4,000,000            | Commas not allowed       |

| 4000000    | 10000000000000000000 | Too large                |

| +2361      | 125_B                | Imbedded blank between   |

| -5         | -                    | number and octal identi- |

| 6B         |                      | fier                     |

#### 2.1.2 Decimal Fractionals

A decimal fractional is any signed or unsigned decimal number with a fractional part preceded by a period. Decimal fractionals cannot be octal. An attempt to use octal notation in combination with a decimal fractional results in an error message.

The following are examples of fractional numbers:

| ACCEPTABLE |                          | UNACCEPTABLE |                                                  |

|------------|--------------------------|--------------|--------------------------------------------------|

|            | 4.0<br>0.0               | 4.           | A number cannot end with a period                |

|            | .671<br>+.734650<br>42.0 | .1234B       | A fractional number cannot be specified as octal |

|            | 0.734650                 |              |                                                  |

#### 2.1.3 Exponentials

Exponentials may be signed or unsigned decimal integers or decimal fractionals followed immediately by an E and a positive or negative decimal integer.

The following are examples of exponential numbers:

| ACCEPTABLE        |                  | UNACCEPTABLE                                                                 |

|-------------------|------------------|------------------------------------------------------------------------------|

| 0.1E2<br>+1.23E-5 | 0.1E2+           | The sign must come between and its integer                                   |

| 7E-3<br>-1.0E+5   | 1E               | The exponent must have a number                                              |

| -5E+2             | .234 E5<br>2.BE2 | Imbedded spaces are illegal Octal numbers may not be exponentially specified |

#### 2.2 VARIABLES

In FACTOR, a variable denotes any quantity which is referred to by a name rather than by an explicit value. A variable may take on many values. The values

assigned may be any of the forms discussed above or they may be either scalar or Boolean. A variable identifier may reference either a single variable or a set of variables considered as an array.

Two general classes of variables may be referenced by the FACTOR program; system global variables and user variables. The values of the system global variables are retained from one execution of the program to the next. This allows the programmer to accumulate such information as total number of devices tested, number of parts passing or failing certain tests within the program. The values of all user variables are lost at the end of the test sequences and are reset to zero at the start of the next sequence. The system global variables are saved for each station or test position. System global variables are automatically declared.

#### 2.2.1 System Global Variables

There are twenty-three system global variables which are accessable from a FACTOR program. The names and special uses of these system global variables are:

SWITCH SWITCH is normally accessed through the TOPSY

> command SWITCH from the system PID. The global variable SWITCH may then be interrogated using a FACTOR statement to perform such operations as

conditional branching.

VALUE Contains the last value obtained by executing the

statement:

MEASURE VALUE/NODE/VARIABLE

TIME Value set by TIME is retained from one execution to the

next execution.

GLOB1 through May be assigned a single value each through a FACTOR GLOB20

variable assignment statement. May be set by a TOPSY

command for program control.

SeviAL Number In addition to the initialization procedures the TOPSY command LOAD also affects the system global variables contents depending upon whether or not the modifier SAVE is used with the command. If it is not used, the global variables are initialized to zero. If it is used, the current values of the global variables are

retained and may be used by the new program being loaded.

Examples:

GLOB1 = GLOB1 + 1;

WRITE 'DEVICE SERIAL NUMBER', GLOB1;

outputs an ascending device serial number to the POD each time the program is executed.

IF SWITCH EQ 2 THEN GOTO LOOP:

The global variable SWITCH may be interrogated using the following FACTOR statement to perform conditional branching.

SWITCH = SWITCH + 1

SWITCH may also be assigned a value from within the user's FACTOR program using a variable assignment statement.

```

MEASURE VALUE;

USERVAR = VALUE;

```

The content of the global variable VALUE may then be assigned to a user declared variable, if desired, using a FACTOR variable assignment:

```

SET PAGE 512;

:

TIME = TIME + 1;

XYZ = XYZ + 1;

WRITE TIME, XYZ;

END;

```

The results of TIME and XYZ would look as follows for 3 pressings of the START buttom:

| TIME | XYZ |

|------|-----|

| 1    | 1   |

| 2    | 1   |

| 3    | 1   |

This is because TIME is a global and its value is kept from one executio to the next, where as XYZ is a user variable and is set to 0 after each execution.

#### 2.2.2 User Variable Identifiers

Variable identifiers are names given to variables to aid the user's memory and make the program more intelligible. The identifier must begin with a letter ,#, or a dollar sign and may contain only letters, periods, dollar signs, pound signs, and digits. Identifiers can be of any length, however, FACTOR retains only the first eight characters. The first eight characters must be unique. System global variable names or reserved words must not be used as identifiers. The following is a list of reserved words:

| AND     | FOR     | PAUSE  |

|---------|---------|--------|

| AT      | FORCE   | PGEN   |

| BEGIN   | FUNCT   | PGM    |

| BLOCK   | GE      | RD     |

| BRANCH  | GOTO    | READ   |

| BY      | GT      | REM    |

| CALL    | IF      | RESET  |

| CGEN    | INSERT  | REXEC  |

| CLEAR   | LCGEN   | SET    |

| CONN    | LEQ     | SOCKET |

| CPMU    | LSET    | SPEC   |

| DCL     | LSUBR   | SUBR   |

| DISABLE | LT      | THEN   |

| DO      | MEASURE | THRU   |

| ELSE    | NEG     | UPDATE |

| ENABLE  | NEQ     | WR     |

| END     | NOISE   | WRITE  |

| EOR     | NOT     | XCON   |

| EQ      | ON      | XPMU   |

| EXEC    | OR      |        |

It is good programming practice to use identifier names that represent the meaning or use of a variable. For instance, TEMP could be the name given to a working variable. COUNTER might be the name given a variable that is used as a general purpose counter, and so on. Variables are assigned an initial value of zero. Arrays must be declared before the array is referenced. Refer to Section 7 for variable and array name declaration information.

The following are examples of variable identifiers:

| ACCEPTABLE       | UNACCEPTABLE |                                           |

|------------------|--------------|-------------------------------------------|

| A<br>CHISQUARE   | 123          | Identifiers may not<br>start with a digit |

| ALARGEIDENTIFIER | AB*C         | Special characters,                       |

| A1B2C3D4         |              | including blanks are not                  |

| DARRYL           |              | allowed                                   |

|                  | END          | Reserved words are                        |

|                  |              | illegal                                   |

#### 2.2.3 Scalar Values

The FACTOR variable in its simplest form is scalar. Scalars are defined as quantities having magnitude and no direction (i.e., no vectors). (Note that, as defined below, an array element may be a scalar value and/or a Boolean value.) In addition scalars may be any legal numbered value.

#### Example:

2.352 3.1414 +6 -3

To use the scalar value currently assigned to a variable, the user writes the variable's identifier in the program statements or expressions.

#### Example:

VCC=5; FORCE VF1 VCC,RNG2;

#### 2.2.4 Boolean Values

Boolean values are quantities which when evaluated have a value of either one (true) or zero (false). Expressions involving Boolean operators can only take on a true or false value thus expressions are not evaluated for any other absolute value. Whenever the user references the variable identifier the current Boolean value is returned.

#### 2.2.5 Array Values

An array is an ordered series of values which are grouped together positionally with respect to some variable identifier (usually the first array element identifier). The elements of the array are restricted to either signed or unsigned numbers (except alpha values are legal for literal variables). FACTOR arrays are restricted to one dimension.

To obtain an array value, the user must follow the array identifier with an expression which is enclosed in brackets. The value of the expression is the subscript which tells FACTOR which element of the array is wanted. If the subscript is zero, (i.e., A [0]) FACTOR returns the array size. Any other value of the subscript refers to the appropriate element in the array of values. For example, A [2] would reference the second element in array A.

#### NOTE

If the value of the expression is negative or greater than the array size, a terminal error results during execution.

#### 2.3 FUNCTIONS

Functions are parameterized calls and are used to obtain a value through a standardized set of operations. The FUNCT statement is described in Section 4.

#### 2.4 ARITHMETIC EXPRESSION EVALUATION

Arithmetic expressions are evaluated left-to-right according to the following rules.

- Parenthesized expressions are evaluated first. If parenthesized expressions are nested, the innermost expression is evaluated, then the next innermost until the entire expression has been evaluated.

- Within parenthesis and/or whenever parenthesis do not govern the order or evaluation, the hierarchy of operations in order of precedence are shown in Table 2-1. The arithmetic expressions are:

- (a) Negation (NEG)

- (b) Exponentiation (↑)

- (c) Multiplication or division (\*,/),

- (d) Addition or subtraction (+,-).

#### Example:

The expression

$$A*(Z-((B+C)/T)) + VAL$$

is evaluated in the following sequence.

$$\begin{array}{c} \mathbf{B}^{\uparrow}\mathbf{C}^{\rightarrow}\mathbf{e}_{1}\\ \mathbf{e}_{1}^{\prime}\mathbf{T}^{\rightarrow}\mathbf{e}_{2}\\ \mathbf{Z}^{-}\mathbf{e}_{2}^{\rightarrow}\mathbf{e}_{3}\\ \mathbf{e}_{3}^{\ast}\mathbf{A}^{\rightarrow}\mathbf{e}_{4}\\ \mathbf{e}_{4}^{+}\mathbf{VAL}^{\rightarrow}\mathbf{e}_{5} \end{array}$$

#### NOTE

The value of B is limited to positive or zero, since the general result for a negative quantity raised to a power is a complex number. C may be positive, negative or zero.

#### 2.5 LOGICAL EXPRESSIONS

#### 2.5.1 Logical Operators

The logical operators defined for the Test System operate on full word integers. The logical operators are:

|   | Symbol                  | <u>Operation</u>                                                |

|---|-------------------------|-----------------------------------------------------------------|

|   | AND<br>OR<br>EOR<br>NOT | Logical and<br>Inclusive or<br>Exclusive or<br>One's complement |

| 3 |                         |                                                                 |

With two expressions or constants P and Q, for each bit of P matched with the corresponding bit of Q, the following truth table holds:

| <u>P</u> | <u>Q</u> | P AND Q | P OR Q | P EOR Q | NOT P |

|----------|----------|---------|--------|---------|-------|

| 1        | 1        | 1       | 1      | 0       | 0     |

| 1        | 0        | 0       | 1      | 1       | 0     |

| 0        | 1        | 0       | 1      | 1       | 1     |

| 0        | 0        | 0       | 0      | 0       | 1     |

The order of precedence for the logical operators is shown in Table 2-2

#### Example:

Calculate a percentage and form an integer before printing:

```

PC = 100*X/Y;

PC = PC AND NOT 0;

WRITE 'PERCENT GOOD=', PC;

```

Prior to performing the logical operation the expression is evaluated and then fixed as an integer. The integer form is limited to 16 bits, therefore conversion underflow or overflow from floating point to fixed format must be considered by the programmer.

#### 2.5.2 Logical Expression Evaluation

Logical expressions are evaluated in order of operator precedence and from left to right when two or more operators of the same precedence exist.

Logical expressions are useful for specifying more than one option in a single variable. Using octal notation, suppose that the "hundreds" digit of the system variable SWITCH is used to select ABORT on first fail if the digit is non-zero, the tens digit is used to select a device grade, and the units digit is another quantity of interest. The logical AND operator can separate this information as follows:

```

SWITCH AND 700B extracts the "hundreds" octal digit.

SWITCH AND 70B extracts the "tens" digit.

SWITCH AND 7B extracts the "units" digit.

```

#### Example:

IF (SWITCH AND 700B) NEQ 0 THEN BEGIN

```

ON FCT, ABORT;

ON DCT, ABORT;

ON TRIP, ABORT:

```

END;

where ABORT is a label at the end of the program.

#### 2.6 BOOLEAN EXPRESSIONS

#### 2.6.1 Relational Operators

Relational operators deal with the comparison of two logical expressions, arithmetic expressions, variables, or constants in any combination. The result of the comparison is either true or false. The relational operators are:

| Symbol                             | Operation                                                                       |

|------------------------------------|---------------------------------------------------------------------------------|

| EQ<br>GE<br>GT<br>LT<br>LEQ<br>NEQ | equal greater than or equal greater than less than less than or equal not equal |

|                                    | <u> </u>                                                                        |

Consider the following examples:

A=16

B=25

A LT B

16 LT 25 This is a true statement.

B LT A This is a false condition.

All relational operators have the same precedence level. (Refer to Table 2-2).

#### 2.6.2 Evaluation of Boolean Expressions

A Boolean expression uses logical and relational operators and defines whether a true or a false condition exists. True and false conditions are represented by non-zero and zero respectively.

The order of operations for Boolean expressions depends upon the precedence values of the operators. The precedence order is shown in Table 2-1. The Boolean expressions are:

- (a) NOT

- (b) relational operators (LT, LEQ, EQ, GE, GT, NEQ)

- (c) AND

- (d) OR and EOR

The following are examples of Boolean expressions:

- 1. A (where A is either true or false)

- 2. A OR B EOR C

- 3. A GE B OR A LT C

In example 2, the expression is evaluated from left to right. A is ORed with B and then the result is EORed with C. In example 3, the expression A GE B is evaluated for a true or false condition: the expression A LT C is evaluated: the results of these two operations are ORed together.

#### 2.7 MIXED EXPRESSIONS

FACTOR allows mixing of arithmetic and Boolean expressions, without adhering to pure Boolean values. It is the responsibility of the programmer to ensure that values in mixed expressions are valid integers when they are involved in a Boolean expression. Arithmetic operators take precedence over Boolean operators in mixed expressions.

TABLE 2-1 PRECEDENCE VALUES OF OPERATORS

| Symbol                             | Operation                                                                          | Precedence Value       |

|------------------------------------|------------------------------------------------------------------------------------|------------------------|

| NEG<br>NOT                         | Unary negate<br>Not                                                                | 1 (highest precedence) |

| <b>†</b>                           | Exponentiation                                                                     | 2                      |

| /<br>*                             | Division<br>Multiplication                                                         | 3                      |

| +                                  | Addition<br>Subtraction                                                            | 4                      |

| LT<br>LEQ<br>EQ<br>GE<br>GT<br>NEQ | Less than Less than or equal Equal to Greater than or equal Greater than Not equal | 5                      |

| AND                                | Logical and                                                                        | 6                      |

| EOR<br>OR                          | Exclusive or<br>Inclusive or                                                       | 7 (lowest precedence)  |

#### SECTION 3.0

#### CONTROL STATEMENTS

Control statements are used to direct the flow of the program by a transfer of control to different parts of the program. Such a transfer may be imperative (e.g., GOTO) or conditional (e.g., IF).

The control statements discussed in this section are PAUSE; GOTO; IF; BEGIN; and FOR.

#### 3.1 PAUSE

The PAUSE statement is used to stop the execution of further statements until the START button is depressed. The general form is:

PAUSE expression;

The statement number and the value of the expression is output to the POD. The EIR register displays the pass/fail results of functional and DC tests which were executed since the last pause or beginning of test.

The PAUSE statement can be used to provide a programmed halt when debugging new FACTOR programs

#### NOTE

Refer to the Sentry User's Manual for use of the manual analysis PAUSE command

#### 3.2 GOTO

A program is essentially a series of statements which, in general, are executed sequentially, and thereby accomplish a particular task. The computer thus operates one step at a time. However, it is essential to be able to enter or leave the sequence of instructions at any desired point

This is the function of the GOTO statement. When executed, a GOTO statement always changes the program flow from the statement immediately following it to the one specified in the GOTO statement.

The simplest form of the GOTO statement is:

GOTO label;

where label is an identifier up to eight characters specifying the statement to be executed next. The statement label is terminated by a colon.

The label must be in the same block or a lower block (refer to Section 4), it is not permissible to jump into a subroutine from the main block or from another subroutine.

#### 3.2.1 Indexed GOTO

General Form:

GOTO (label1, label2, ..., labeln) expression;

As in a GOTO statement, program control is transferred to a specified location (defined by a label) in the FACTOR program. In the indexed GOTO statement, a multiple of such locations are allowed. The choice of one of the locations depends upon the result from evaluating the expression.

| GOTO Location                                       | Expression Value   |

|-----------------------------------------------------|--------------------|

| Label 1                                             | 1                  |

| Label 2                                             | $\cdot$ 2          |

| Label 3                                             | 3                  |

| Label n                                             | n                  |

| Next consecutive statement is fetched and executed. | 0, negative or > n |

In cases where the expression contains variables, the same indexed GOTO statement may cause branching to different locations at different times, depending upon the changing expression value.

#### 3.3 IF

The GOTO statement provides one method for altering the sequence of statement executions. It is also essential to be able to change the sequence of execution based on what happens as the program executes, i.e., a conditional change of execution. This is the principal use of the IF statement.

The simplest form of the IF statement is;

IF relation THEN statement1;

statement2;

Upon execution of the IF statement, if the relation is true, statement1 is executed followed by statement2 (unless statement1 carries control away from statement2). If the relation is false, statement2 is executed instead and statement1 is skipped.

#### Example:

IF A EQ 3 THEN GOTO LABEL;

If A is equal to 3, the sequence of execution is changed to the point in the program having a statement labeled LABEL. If A is not equal to 3 the next sequential statement, after the IF statement, is executed.

The true-false nature of the above relation gives a clue to the second general form of the IF relational clause. It is:

IF Boolean-expression THEN statement;

where Boolean-expression is any legal expression.

#### Example:

To continue doing something until the value of A and B, two variables being manipulated, both become less than some terminal value, 0. We could make this decision and monitor the values of A and B with one IF statement as follows:

IF A LT 0 AND B LT 0 THEN GOTO DONE;

In all cases of IF statement usage, the statements following THEN can introduce any type of FACTOR statement.

#### 3.3.1 The Conditional ELSE

The simple IF statement is one which causes a statement to execute if a relation or Boolean expression is true and skips statement execution if the relation or expression is false. A complete conditional statement does more. It specifies a second statement to be carried out if, and only if, the relation or expression is false. The general forms are:

IF relation THEN S1 ELSE S2; IF Boolean expression THEN S1 ELSE S2;

where S1 and S2 are any two statements. When the result of the IF operation is true, S1 executes and S2 is ignored. Notice here that ELSE terminates the first statement (S1) instead of a semicolon. When the result is false, S1 is skipped over and S2 executed. S2 may be any statement, including another IF statement. This nesting of conditionals can go to any depth.

#### Example:

IF relation THEN S1 ELSE IF relation THEN S2 ELSE S3;

#### 3.4 BEGIN

FACTOR allows the grouping of a series of statements between the statements BEGIN and END. The END, must immediately follow the last statement executed. Note that the semicolon is an integral part of the END; bracket. One purpose of this is to allow a compound statement to follow the THEN or the IF statement.

#### Example 1:

```

IF relation THEN

BEGIN

statement;

statement;

statement;

```

#### Example 2:

```

IF relation THEN

BEGIN

statement 1;

statement 2;

END ELSE BEGIN

statement 3;

statement 4;

END;

```

The above are examples of compound statements, and are an acceptable method of writing the IF statement. The statements between BEGIN and END; are legal and, as far as the IF statement is concerned, are considered to be one statement. In other words, if the relation is false the statement after the BEGIN-END; block is executed next. Any FACTOR statement may be part of the compound statement, including another IF statement.

#### 3.5 FOR

One of the techniques most widely used in programming is that of the program loop. This is the repetition of some program statement or statements over and over with different parameters. The FOR statement is the looping mechanism within FACTOR.

The general format of the FOR statement is:

FOR variable = expression THRU expression DO statement;

where variable expression and statement may be in any legal form defined in this manual.

Several statements may be included in the DO loop portion of the FOR statement by specifying a compound statement with BEGIN and END.

#### Example:

FOR variable=expression THRU expression BY expression DO

```

BEGIN

statement 1;

statement 2;

END;

```

An example of a typical loop is one designed to solve the following problem. Suppose it is desired to set the elements of an array to zero This can be achieved with the following IF statement sequence of statements:

```

I = 1

NEXT: A[I] =0;

I = I+1

IF I LEQ A [0] THEN GOTO NEXT;

```

but it is more easily programmed with the statement:

FOR

$$I = 1$$

THRU A  $[0]$  DO A  $[I] = 0$ ;

The simple FOR statement provides an index value which has three important features:

- (1) an initial value,

- (2) an (assumed) increment of +1,

- (3) a limit

In the above example, I takes on the values  $1, 2, 3, \ldots, A$  [0], where A [0] is the last value corresponding to the size of the array.

The implementation of the FOR causes the address of the index, the increment and the limit to be evaluated each time the loop is executed. Therefore, caution must be exercised within the loop when changing values that might affect this evaluation.

The loop is executed the number of times specified by the initial value, limit, and increment. (This may be zero.) Also, there is no restriction on transfers of control into or out of the loop. When the loop has finished its specified number of executions, control passes to the next sequentially executable statement, unless this sequence is interrupted by a statement in the DO loop.

In the above discussion an automatic increment of +1 from the initial value to the final value was assumed. There is a second form of the FOR statement which uses BY; this allows the user to specify some value which is used as the increment.

#### Example:

```

FOR I = 1 THRU A \begin{bmatrix} 0 \end{bmatrix} DO A \begin{bmatrix} I \end{bmatrix} = 0 BY 2;

```

It should be pointed out that because the values may be all positive, all negative, or mixed positive and negative, the user should consider the range of possible values expected. It makes sense to go from a negative number to a more negative number in negative increments or from a positive number to a negative number by negative increments. Going from positive to more positive or negative to positive, the increment must be positive. Going from -2 to +6 in increments of -2, as from +8 to +2 in increments of +2 is not logical and is flagged as an error at execution time.

Caution must be exercised when using fractional values for the index, since it is possible to introduce a step error. For example, a statement such as:

```

FOR I = 0 THRU 1000 BY 0.1 DO X = I + 1;

```

may operate the DO statement more than 10,000 times because of a rounding error in the floating point conversion of 0.1.

FOR statement also applies to a compounded set of statements written within a "BEGIN" and "END" pair. In the examples shown thus far, simple statements are used with the FOR statement. Consider the following example:

```

DCL ARRAY [100];

J = 1;

FOR I = 15E-6 THRU 5E-6 BY-100E-9 DO

BEGIN

ARRAY [J] = I;

J = J + 1;

WRITE I;

END;

WRITE ARRAY;

```

The FOR loop contains 3 statements compounded within the BEGIN-END pair of statements. The three statements are repeated for the number of times taken to reach the terminating value of I, the loop's variable. The FOR loop variable, I, is decrementing (instead of incrementing as previously shown) by 100E-9. The initial, the ending, and the incrementing values of I are all exponentiated instead of integers. The total number of looping times is 100.

#### Restriction:

The DO BEGIN words, even though they are written on two separate lines, must not have any other word or symbol in between them. Violation of this rule results in the error message, "WARNING NO STATEMENT INSIDE DO LOOP".

#### SECTION 4.0

#### SUBPROGRAMS AND BLOCK PROGRAM CONCEPTS

This section describes subprograms, and block program concepts.

#### 4.1 BLOCKS

Blocks are groups of program statements between the delineators, BLOCK and END. Local variable storage and local labels do not exist outside of the parent block they are in and cannot be referenced outside of the parent block. A block is an independent compilation. A program can consist of several completely independent blocks.

A block must have a beginning and a closing statement. In addition, a block can be either independent or dependent.

A block can be established in two ways:

- (1) It may be opened directly by writing the command BLOCK and closed by the command END.

- (2) A block may also be opened following the FUNCT and SUBR commands.

The initial BLOCK declaration need not be specified because FACTOR assumes a BLOCK  $\boldsymbol{0}_{\boldsymbol{\cdot}}$

#### 4.1.1 Nesting Blocks

Blocks do not need to be completely independent. One of the easiest methods of introducing block dependence is by "nesting" one block within another. This results in the execution of the inner block being dependent on the execution of the outer block. Nesting can occur up to eight levels on the Sentry. Nesting is illustrated in the following example:

```

BLOCK

BLOCK

END;

BLOCK

BLOCK

END;

END;

```

The inner block of a nested set is considered part of the enclosing blocks. Another form of dependence is that of global variables. A global quantity is one that is accessible to a block, but is not necessarily contained in (i.e., is not local to) that block. Variables and labels can be either local or global. This is illustrated in the following example:

```

BLOCK

L: DCL A, B/10/;

BLOCK

DCL A,C;

END;

END;

```

Each block in the above example contains the local variable A. The A in the inner block cannot be accessed from the outer block and vice versa. The variable B in the outer block is accessible from either block, but the variable C can be accessed only from the inner block. In this example, then, B is a global variable but C and the two variables A are all local.

Note, that if there had been a label L in the inner block, any reference to it within the inner block would have used that rather than the one in the outer block. Any nested set of blocks establishes a block context; i.e., a relationship of local and global variables. From the example, it can be seen that a reference to a variable or label is associated with the occurrence of that identifier or label in the same block, if it is present. If it is not, then the next outer block is examined, etc.

It should be noted that it is possible to make variables global from within a nested block in FACTOR by simply never declaring the variable as local. When the nested block is closed, the variable, and any residual value is relocated to the next outer block, where it may now be considered as global to any further nesting. When this outer block is closed, if it was nested, the variable again relocates to the next outer block and so forth until block 0 is closed.

#### NOTE

Compilation time can be decreased by declaring (in block 0) all the variables which are not local.

The fact that the declaration of a variable within a block makes it local has important implications for the FACTOR user. After leaving a block, i.e., closing it with an END command, the values of all variables declared within the block, and thus made local, are lost. Upon re-opening the block, the values of these variables are initialized to 0.

#### 4.2 SUBPROGRAMS

Programs frequently have groups of statements which can be used several times with different parameters. The required statements could be duplicated wherever they are needed in the program, but to do so is error prone, and wastes user time and machine storage. Therefore, it is desirable to be able to write statements so that they may be executed from any point in the program with a different set of parameters each time they are executed. The subroutine statement makes this possible.

#### 4.2.1 SUBR

The general formats of the subroutine declaration are as follows:

```

Format One:

SUBR 'entifier;

statement 1;

statement 2;

.

.

.

.

statement n;

END;

Format Two:

SUBR identifier (VI1, VI2, ..., VIn)

statement 1;

.

.

.

.

.

statement n;

```

The identifier after the SUBR command is used to reference the subroutine from the main program. The statements within the subroutine are not executed until the subroutine is called from the main program by the SUBR identifier. Any number of statements are allowed within the subroutine.

The END; statement is necessary because the SUBR command effectively opens a new block. When it is completed, it must be closed. The END; indicates the last statement in the subroutine.

Format Two indicates another important feature of the SUBR statement. The terms VI1 through VIn represent variable identifiers 1 through n. They are enclosed in parentheses and indicate to FACTOR that whenever a reference is made to this subroutine, the reference specifies actual values which are to be substituted at specific places within the subroutine body. These identifiers are called formal parameters There is a one for one correspondence between the position of the formal parameters and the position of the parameters or values used in the call. For reference and further explanation, see the next section on the CALL statement. The manner in which values transferred to the subroutine are used in the subroutine's statements is illustrated in the following example:

```

SUBR TOTAL (VI1, VI2, VI3);

VI1 = VI2 + VI3;

END;

```

When the above subroutine is referenced:

the values passed to it, obtained from the actual parameters A1, A2, and A3, positionally replace VI1, VI2, VI3 and are used in the arithmetic expression and assignment. The value of the variable represented by VI2 is added to that represented by VI3 and the total is assigned to the variable represented by the formal parameter VI1.

The following is an example of a subroutine with no formal parameters specified:

When TOTAL2 is called, the current values of the variables B and C are added and the total is assigned to the variable A. In this case A, B, and C are not formal parameters. They are working variables with current values in the outer blocks to the SUBR statement block.

Because the subroutine forms a new block, it must be remembered that any variables which are formally (i.e., DCL variable name/value;) declared in the subroutine are local.

#### 4.3 CALL

A subroutine is executed by using a CALL statement, which can be placed at any point in the program where the programmer can legally place a statement. The general formats are as follows:

```

CALL SI; CALL SI (expression 1, expression 2,..., expression n);

```

SI is the identifier of the subroutine block to be activated. The values, changed by the subroutine statements and by any other task executed, are accomplished as if the subroutine's body of statements has been placed at the point of the CALL statement. Then, the next sequential statement, following the CALL, is executed.

The expressions are evaluated at the time of the execution of the call and therefore, removes many constraints which are ordinarily placed on the CALL values. As the subroutine statements are executed, the value of expression 1 in the formal parameter list of the CALL statement is used wherever dummy parameter 1 was used. The same holds true for other dummy parameters and expressions. The only restriction is that when a dummy parameter recieves a result, the corresponding actual parameter from the formal parameter list in the CALL should not be an expression but a single variable identifier.

#### 4.4 FUNCT

The subroutine call, when encountered in the program execution, brings the subroutine statements into action to accomplish whatever processing is specified (ordinarily assigning new values to outer block variables). Control then usually passes to the next sequential statement.

When only one variable is assigned a new value, as a result of executing a subprogram, the call can be simplified by making the subprogram a function. When FUNCT is used, simply writing the identifier of the function causes its statements to execute. However, the identifier now represents a value that may be used wherever a variable is legal. Thus, it is as though the function call represents a variable of the same name.

The general form of the function statement is:

```

FUNCT identifier (VI1, ..., VIn); statement 1;

statement n;

```

END;