ELECTRONIC ASSOCIATES, INC. West Long Branch, New Jersey

EAI 8400

SCIENTIFIC COMPUTING SYSTEM

PRELIMINARY INFORMATION MANUAL

C ELECTRONIC ASSOCIATES, INC. 1988 ALL RIGHTS RESERVED

PRINTED IN U.S.A.

March 1965

# EAI 8400 SCIENTIFIC COMPUTING SYSTEM

# TABLE OF CONTENTS

| SECTION |     |            |          |                                                                        |             |

|---------|-----|------------|----------|------------------------------------------------------------------------|-------------|

| I       |     |            |          |                                                                        | PAGE        |

| •<br>•  | EAI | 8400       | SYSTEM I | DESCRIPTION                                                            |             |

|         | 1.0 | BASI       | C SYSTEM | 1 DESCRIPTION                                                          | 1-1         |

|         |     | 1.1        | Summary  | of 8400 Characteristics                                                | 1 <b>-1</b> |

|         |     | 1.2        | Basic S  | System Organization                                                    | 1-4         |

|         |     |            |          | The Memory                                                             | 1-4         |

|         |     |            |          | The Floating-Point Processor                                           | 1-4         |

|         |     |            |          | The Exchange Module                                                    | 1-4         |

|         |     |            |          | The Automatic Data Channel Processor<br>Expansibility                  | 1-5         |

|         |     |            | 1.2.2.9  | Expansionity                                                           | 1-5         |

|         | 2.0 | STOR       | AGE      |                                                                        | 2-1         |

|         |     | 2.1        |          | Characteristics                                                        | 2-1         |

|         |     |            | · · ·    | Storage Word                                                           | 2-1         |

|         |     |            |          | Storage Addressing                                                     | 2-1         |

|         |     |            |          | Storage Access                                                         | 2-1         |

|         |     |            | 2.1.4    | Storage Parity                                                         | 2-2         |

|         |     | <b>~</b> ~ | Fficio   | at Consolty Utilization                                                | 2-2         |

|         |     |            |          | ent Capacity Ut <b>ilization</b><br>ent Cycle Tim <b>e Utilization</b> | 2-2         |

|         |     | 2.00       |          | Concurrent Memory Operation                                            | 2-4         |

|         |     |            |          | Overlapped Memory Operation                                            | 2-4         |

|         |     |            |          | Combined Concurrent - Overlap                                          | 2-4         |

|         | 3.0 | FLOAT      | FING-POI | NT PROCESSOR                                                           | 3-1         |

|         |     | 2 1        | Control  | Functions                                                              | 2 2         |

|         |     | 2.1        |          | Instruction Characteristics                                            | 3-3<br>3-3  |

|         |     |            |          | The Flag Register                                                      | 3-5         |

|         |     |            |          | Interrupt System                                                       | 3-6         |

|         |     |            |          | Status and Function Line Control                                       | 3-9         |

|         |     |            |          | EXEC Bit Control System                                                | 3-10        |

|         |     |            |          | Interval Timer Register                                                | 3-12        |

|         |     |            |          | Rapid Access File                                                      | 3-12        |

|         |     | 3.2        | Arithme  | tic                                                                    | 3-13        |

|         |     | ·          | 3.2.1    | Arithmetic Characteristics                                             | 3-14        |

|         |     |            | 3.2.2    | Arithmetic Operations                                                  | 3-19        |

|         |     |            | 3.2.3    | Logical Operations                                                     | 3-23        |

|         | 4.0 | INSTI      | RUCTION  | REPERTOIRE                                                             | 4-1         |

|         |     | 4.1        |          | ming Ease and Power                                                    | 4-1         |

|         |     |            |          | Arithmetic Instructions                                                | 4-1         |

|         |     |            |          | Logical Instructions                                                   | 4-2         |

|         |     |            |          | Flag Transfer Instructions                                             | 4-3         |

|         |     |            |          | Index Jump Transfers                                                   | 4-4         |

|         |     |            | 4.1.5    | Assembly and Machine Language                                          | <b>.</b> .  |

|         |     | •          |          | Programming                                                            | 4-4         |

### SECTION

I

| I  | (cont.) |                                                |      |

|----|---------|------------------------------------------------|------|

|    | 5.0     | EXCHANGE MODULE                                | 5-1  |

|    |         | 5.1 Exchange Characteristics                   | 5-1  |

|    |         | 5.1.1 Data Channel System                      | 5-1  |

|    |         | 5.1.2 Automatic Data Channel Processor         | 5-7  |

|    |         | 5.1.3 External Systems Interface               | 5-10 |

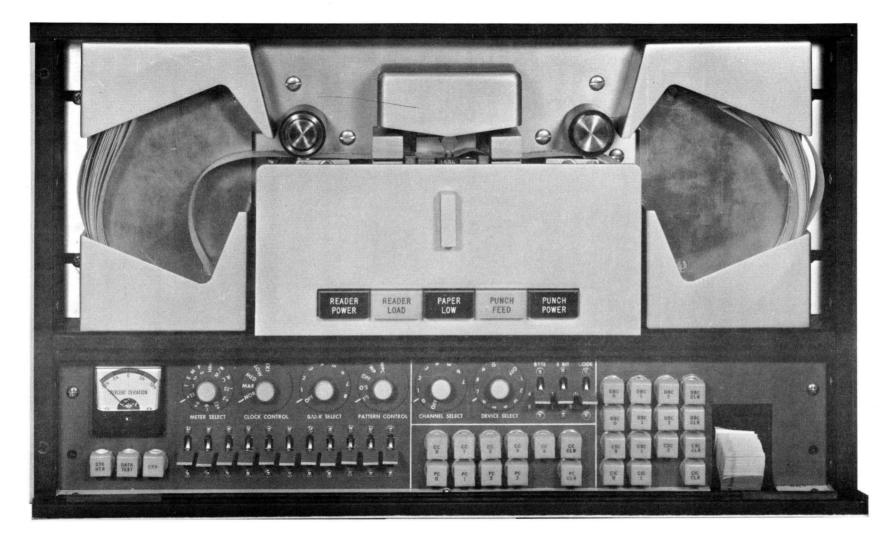

|    | 6.0     | SYSTEM ACCESS DEVICES                          | 6-1  |

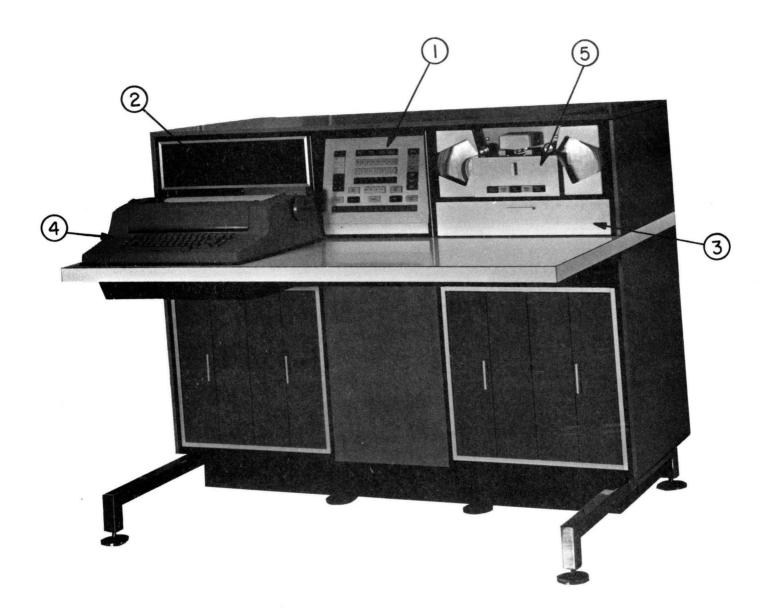

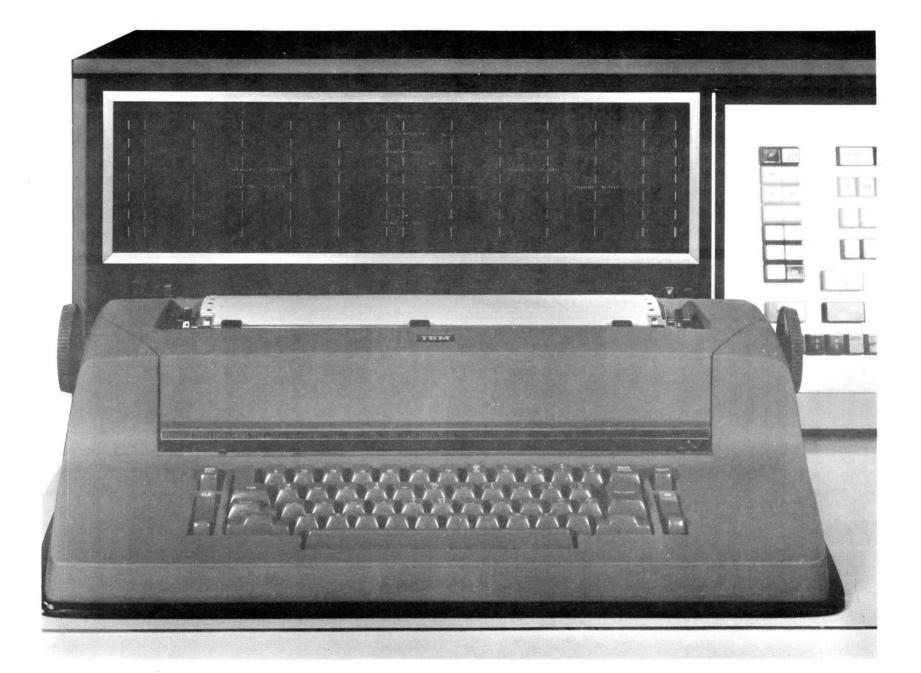

|    |         | 6.1 Control Desk                               | 6-1  |

|    |         | 6.2 Peripheral Equipment                       | 6-1  |

|    |         | 6.3 Teletype Model 35 ASR I/O Desk             | 6-2  |

| II | EAI     | 8400 PROGRAMMING SYSTEMS                       |      |

|    | 1.0     | STANDARD PROGRAMS AND PROGRAMMING SYSTEMS      | 1-1  |

|    | 2.0     | 8400 MONITOR SYSTEMS                           | 2-1  |

|    |         | 2.1 Standard Monitor System 84                 | 2-2  |

|    |         | 2.2 Simulation Monitor System 84               | 2-3  |

|    |         | 2.3 HYTRAN Monitor System                      | 2-4  |

|    | 3.0     | 8400 PROGRAM PREPARATION SOFTWARE              | 3-1  |

|    |         | 3.1 Macro Assembler 84                         | 3-1  |

|    |         | 3.1.1 Introduction                             | 3-1  |

|    |         | 3.1.2 Characteristics                          | 3-1  |

|    |         | 3.1.3 Coding Procedures                        | 3-7  |

|    |         | 3.2 FORTRAN IV Compiler 84 System              | 3-12 |

|    |         | 3.2.1 Introduction                             | 3-12 |

|    |         | 3.2.2 Characteristics                          | 3-12 |

|    |         | 3.2.3 FORTRAN System Organization              | 3-16 |

|    |         | 3.2.4 System Design                            | 3-17 |

|    | 4.0     | 8400 PROGRAM LOADING & RELOCATION SOFTWARE     | 4-1  |

|    |         | 4.1 Auto Load/Dump System                      | 4-1  |

| ·  |         | 4.2 Linking Relocatable Loader 84              | 4-1  |

|    | 5.0     | PROGRAM CHECKOUT SOFTWARE - DEBUG SYSTEM 84    | 5-1  |

|    |         | 5.1 General                                    | 5-1  |

|    |         | 5.2 System Operation                           | 5-1  |

|    |         | 5.3 Organization                               | 5-2  |

|    |         | 5.4 Symbolic Debugging                         | 5-3  |

|    |         | 5.5 Debugging Functions                        | 5-3  |

|    | 6.0     | RELOCATABLE SUB-ROUTINE LIBRARY 84             | 6-1  |

|    |         | 6.1 General                                    | 6-1  |

|    |         | 6.2 Arithmetic Subroutines - Single and Double |      |

|    |         | Precision Fixed and Floating-Point             | 6-1  |

|    |         | 6.3 Mathematical Subroutines                   | 6-2  |

|    |         | 6.4 Conversion Subroutines                     | 6-3  |

|    |         | 6.5 Input/Output and Data Display Subroutines  | 6-3  |

|    |         | 6.6 Compat Mode Subroutines                    | 6-3  |

PAGE

### SECTION

II (cont.)

| 7.0 | SIMULATION PROGRAMS GROUP     | 7-1 |

|-----|-------------------------------|-----|

|     | 7.1 Hybrid Mode Control       | 7-1 |

|     | 7.2 Integration Control       | 7-1 |

|     | 7.3 Function Generator Loader | 7-1 |

|     | 7.4 Hybrid Computer Set-Up    | 7-1 |

|     | 7.5 Hybrid Debug              | 7-2 |

| 8.0 | HYTRAN PROGRAMS GROUP         | 8-1 |

|     | 8.1 Static Check              | 8-1 |

|     | 8.2 Report Generator          | 8-2 |

|     | 8.3 Equipment Check-Out       | 8-2 |

| 9.0 | DIAGNOSTIC SYSTEM             | 9-1 |

### PAGE

#### 1.0 BASIC SYSTEM DESCRIPTION

The EAI 8400 is a new, exceptionally fast, scientific computing system that features a unique combination of capabilities for Real-Time Computation --

HIGH SPEED PROCESSING FLOATING POINT OPERATION, and FORTRAN LANGUAGE PROGRAMMING

With these capabilities, the 8400 is uniquely suited for real-time applications in -- scientific simulation, hybrid computation, laboratory or industrial on-line monitoring and control, and batch scientific processing as well.

#### 1.1 SUMMARY OF 8400 CHARACTERISTICS

#### GENERAL

- . Stored-program, scientific computer

- . Autonomous organization See P. 1-4

- . Parallel mode

- Silicon and micrologic circuitry

. 16 word fast memory, 250 nanoseconds cycle time or access time?

Priority interrupt system with mask registers

. Power fail safe

Save register See p. 3-1 3-14

. Real-time clock

#### PROCESSOR

- . Powerful instruction list over(750) commands

- . Floating-point arithmetic, 32 and 56 bit

24-bit mantissa, 8-bit exponent 48-hit mantissa, 8-bit exponent

Fixed-point arithmetic, 16 and 32-bit

fixed + floating

Integer, or mixed-mode arithmetic with.

16-bit fixed-point integers and 32-bit floating-point operands

Index arithmetic, 16-bit

Typical instruction execution times.

32-bit FLOATING ADD 3.50 usec 32-bit FLOATING MPY 6.25 usec 32-bit FLOATING DIV 9.50 usec 56-bit FLOATING ADD 6.00 usec 16-bit FIXED ADD 3.25 usec 16-bit FIXED MPY 5.25 usec 16-bit FIXED DIV 7.50 usec 32-bit FIXED ADD 4.00 usec

Byte manipulations with 1, 2, 4, 8, or 16 bits

Seven index registers

Indirect addressing

STORAGE

Magnetic core memory

Capacity to 65,536 words, directly addressable 2 words

Word size and utilization

32 data bits, 2 EXEC bits, and 2 parity bits; half-word or full-word, and  $t_{\Psi}$ te addressing

Expansion with 4k, 8k, and 16k banks

2 usec complete cycle time 750 nanosecond access time

Independent bank read write control

Storage access by up to four processors four proceeders operating simultaneously?

#### INPUT/ OUTPUT

buffer

Maleg Anonnels Bi-directional <u>buffered</u> data channels -- up to eight available -- each handling up to fifteen access devices

1-2

216= 64 K (full capacity)

ile lits for analog work?

Automatic Data Channel Processor available, providing simultaneous data exchange and compute capability direct memory access

Flexible systems interface for real-time, device-systems integration

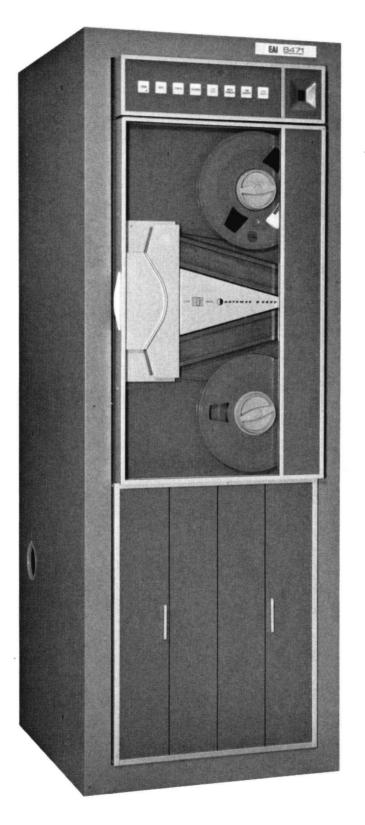

Peripherals

magnetic tape systems, card readers and punches, line printers, paper tape reader and punch.

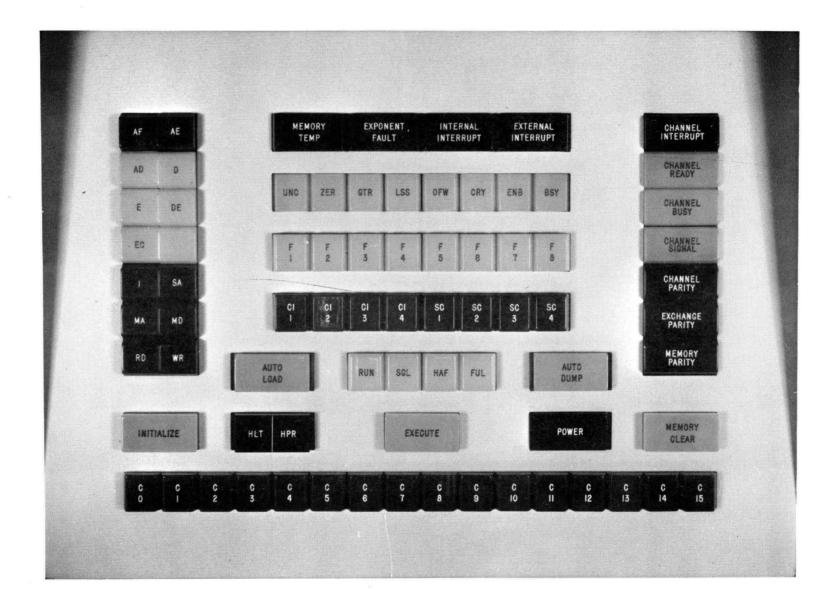

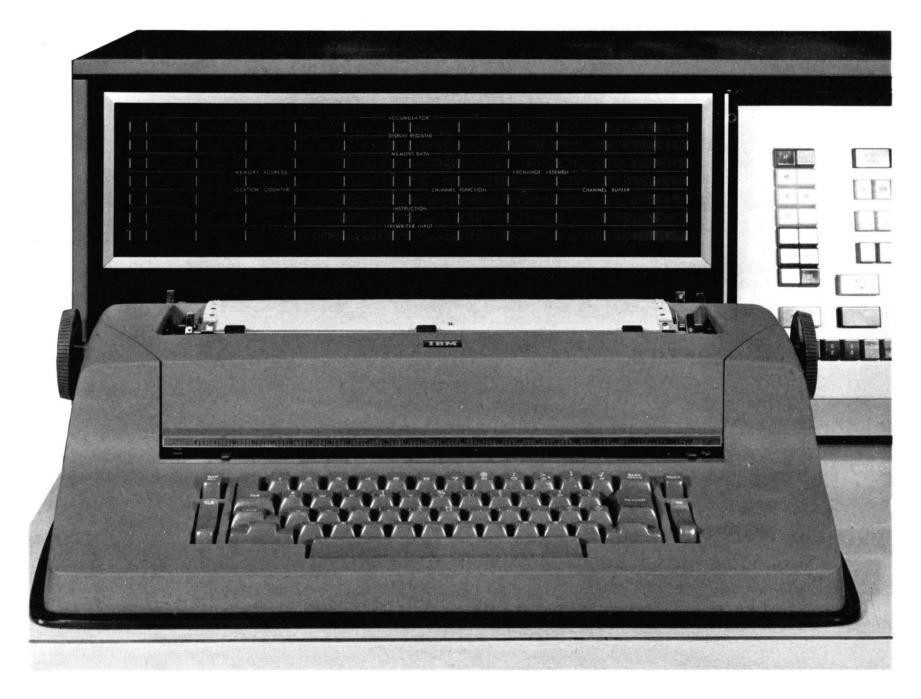

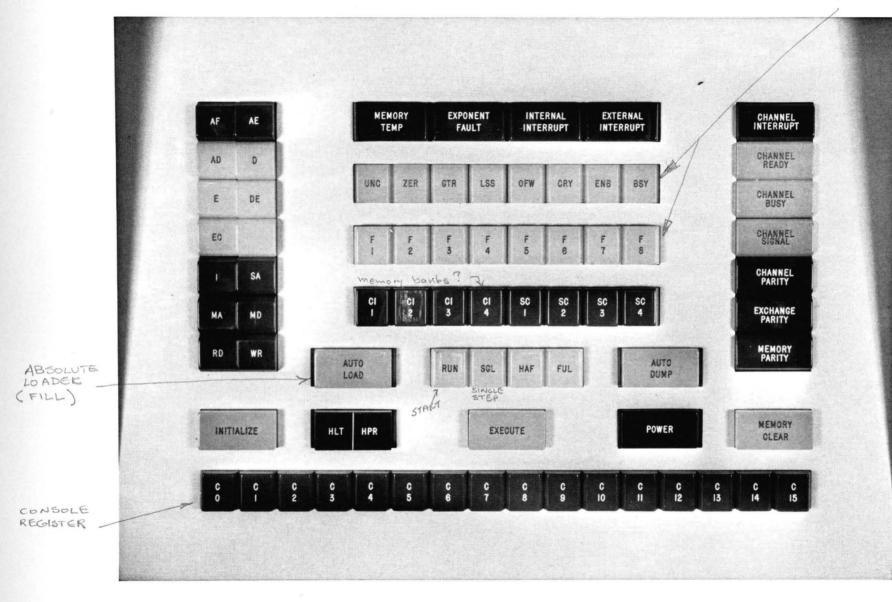

#### CONSOLE

Analog

The EAI 8400 System includes an operator's console with complete register display and on-line typewriter.

#### SOFTWARE

. 8400 Standard Monitor System

MACRO Assembler, FORTRAN IV, subroutine library, and programs for problem preparation, de-bugging, up-dating and modification

8400 Simulation Monitor System

Hybrid mode control, integration control, function generation, and other programming aids--for digital and hybrid scientific simulation

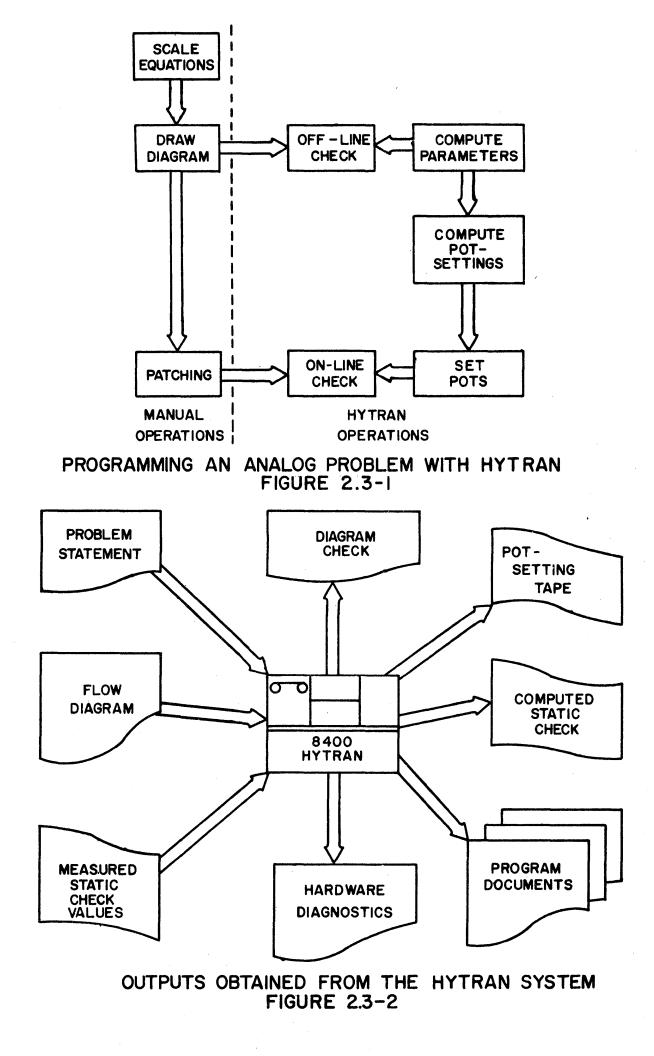

8400 HYTRAN<sup>S</sup> Monitor System

Designed primarily for processing programs used for preparation and check-out of analog and hybrid computer programs

Assembler - PHAP? Debugg I - SPECTRA Debugg I - CASPER?

<sup>s</sup> a service mark of Electronic Associates, Inc.

#### 1.2 BASIC SYSTEM ORGANIZATION

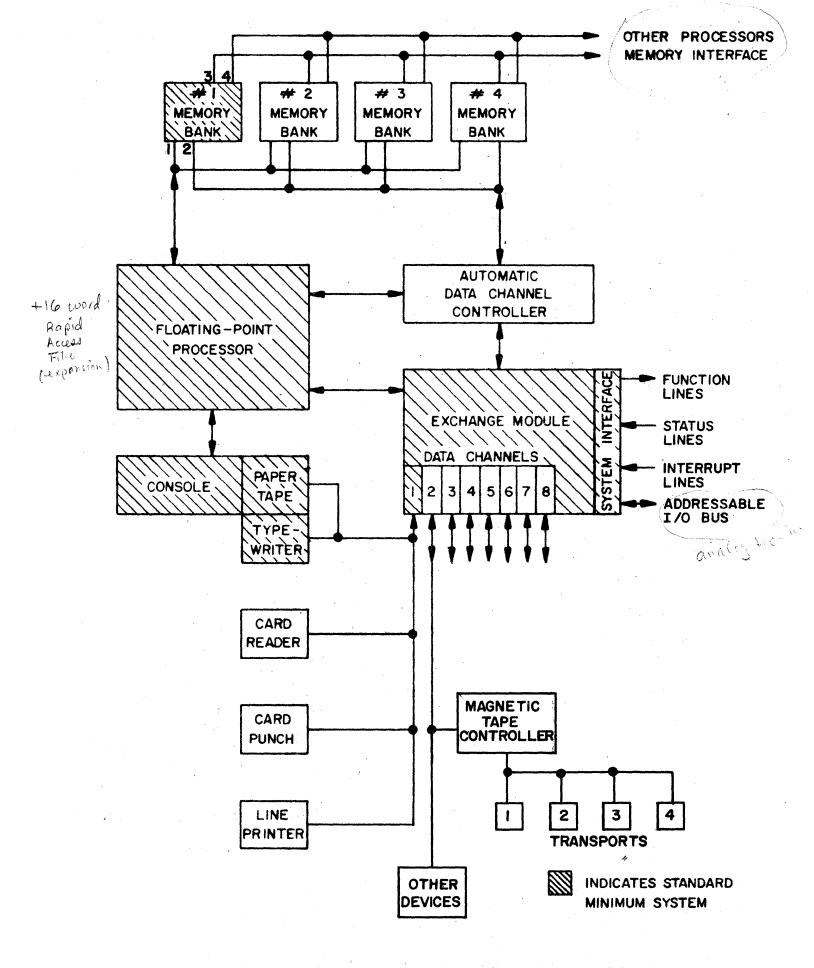

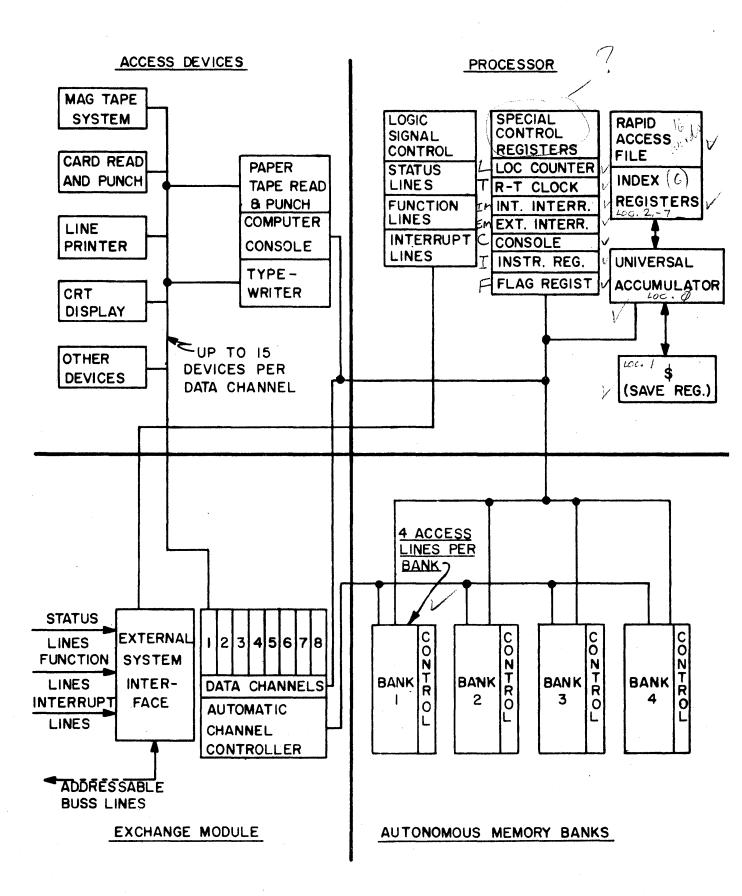

The basic system organization of the EAI 8400 integrates the operation of three <u>autonomous</u> subsystems; <u>Memory</u>, Floating-Point <u>Processor</u>, and <u>Exchange Module</u>. A fourth subsystem, the <u>Automatic Data Channel</u> Processor, is an optional expansion for the system. Each of these subsystems has independent timing and control facilities. System interrelationships are on a request/response basis. The control autonomy feature provides an unusual expansion flexibility for increasing machine throughput, as well as capacity. Figure 1-1 illustrates the internal system organization and various means of interfacing with external devices and systems.

#### 1.2.1 The Memory

BANK

8 OR 1614

D. CH.

card

m tape

MAIN PROCESSING

The Memory is structured with one, two, three, or four independent Memory Banks, each having autonomous control and data handling facilities for processing storage read and write requests from the system processors. Benks of 8192 and 16,384 word capacities are available, and may be used in any combination. Each Memory Bank has four storage access channels. In a typical multi-bank system, the first access channel of each bank is connected to a bus from the Floating-Point Processor and the second channel is connected to a separate bus from the Automatic Data Channel Processor. This configuration provides overlapped memory access by the Floating-Point Processor, as well as simultaneous Input/Output and Computation. The third and fourth access channels may be used for multiprocessor expansion and/or interfacing with external mass memory devices.

#### .2.2 The Floating-Point Processor

The Floating-Point Processor employs a 32-bit wordlength which provides for a powerful instruction repertoire (over 750 commands) and direct addressing of up to 65,536 words of memory. It has unusually extensive capabilities for both arithmetic and logical operations. The Processor is designed with <u>floating-point as a basic</u>, rather than expansion, capability. This concept is fundamental to the 8400's exceptional floating-point speed and storage efficiency characteristics.

#### 1.2.3 The Exchange Module

The Exchange Module contains a Data Channel System for interfacing/with standard external devices and a System Interface for special device and Systems integration. The Data Channel System provides communication paths and control for up to eight bi-directional Data Channels, each capable of handling fifteen device controllers (including A-D and D-A conversion equipment). The channels are designed for the new 8-bit ASCII and EBCDIC peripheral codes and have internal logic for byte assembly and disassembly, parity generation and checking, and collating

analog

4×16=64K

code conversion. Independent channel operation may be under program control, or under control of the Automatic Data Channel Processor. The Systems Interface includes a directly addressable input/output bus system and provision for control lines and external interrupt lines as required for hybrid or other system integration.

#### 1.2.4 The Automatic Data Channel Processor

The Automatic Data Channel Processor provides a means of control for the Data Channels that permits block data transfers independent of the Floating-Point Processor. Once initialized it executes a complete block data transfer between the selected peripheral devices and memory, with data transmission occurring over a separate memory bus. Access drauned Separate from the processor memory access drauned

#### 1.2.5 Expansibility

Modular expansibility in both capacity and speed are fundamental to the 8400's basic design.

Throughput of the Floating-Point Processor can be increased by increasing index register speed with optional conversion paks, or by the addition of an optional 16 word fast memory (Rapid Access File) for scratch-pad and high-speed looping techniques. Faster storage processing is obtained by over-lapping when the initial Memory is expanded with additional banks and Exchange Module throughput is increased by simultaneous channel operation when new Data Channels are added. Further increases in speed can be realized by expansion to a multi-processor system in which several Floating-Point Processors operate in parallel.

The control autonomy feature of the 8400 provides an unusual expansion flexibility permitting the up-dating of individual subsystems with new technological advances, without obsoleting the existing initial system hardware.

EAI 8400 SCIENTIFIC COMPUTING SYSTEM FIGURE 1-1

#### 2.0 STORAGE

The Memory provides high-speed, random access storage of instructions and data used by the Floating-Point Processor and Exchange Module. It has a maximum directly addressable storage capacity of 65,536 words, 131,072 half-words, or 262,144 8-bit bytes. The capacity is provided by independent banks each having control and data handling facilities for processing storage requests from four system processors. The banks are of a nonvolatile ferrite core construction and are characterized by a 2 microsecond complete cycle time and a storage access time that is 750 nanoseconds.

#### 2.1 <u>STORAGE CHARACTERISTICS</u>

#### 2.1.1 <u>Storage Word</u>

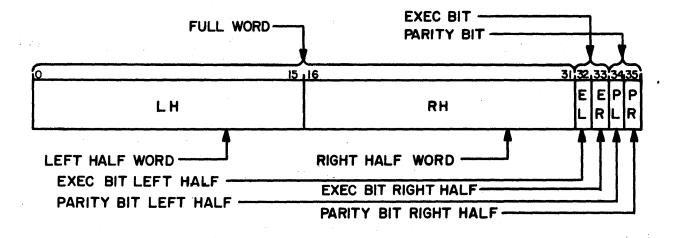

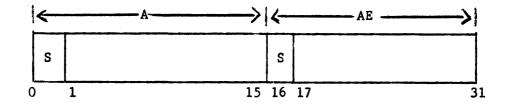

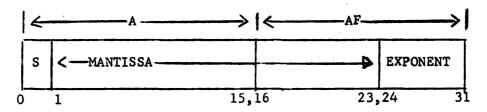

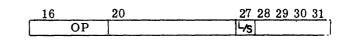

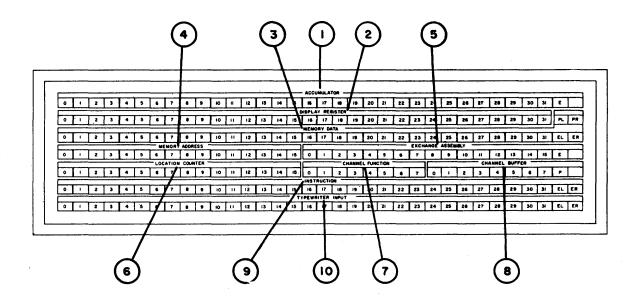

The memory word of the 8400 is comprised of 32 bits for information storage, 2 EXEC bits for special control functions and 2 parity bits; thus a memory word is 36 bits in length. The information portion may be used alternatively as one full-word location, for the storage of a 32-bit operand or instruction, or as two half-word locations for the storage of 16-bit operands or address fields. A parity bit and an EXEC bit are assigned to <u>each half-word</u>. The EXEC bits, an exclusive feature of the 8400, are used as markers for such purposes as dynamic re-location, V list processing and table manipulation. Figure 2-la shows the memory data word format.

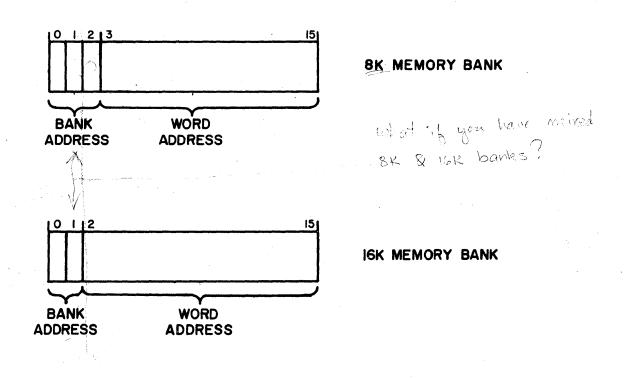

# 2.1.2 Storage Addressing field not a cond

The location of data in storage is identified by a 16-bit memory address word. The bit designations of the address word are interpreted differently by memory banks of different storage capacities. Figure 2-1b shows word format and its interpretations by an 8192 word bank and 16,384 word bank.

#### 2.1.3 Storage Access

The Memory Banks in an 8400 Memory may be accessed by up to four processors. These may be Floating-Point Processors, Automatic Data Channel Processors or external mass memory devices. The processor requesting access to storage transmits a request signal and a 16-bit address field to storage. The request signal specifies the read or write operation to be performed and whether full-word, half-word and/or EXEC bits are to be transfered. If the same bank is accessed simultaneously by two request sources, the bank control unit services the requests sequentially. According to what order.

or potr 2 with one D.D. CH

### MEMORY DATA WORD FORMAT FIGURE 2-1A

ADDRESS WORD FORMATS FIGURE 2-IB

#### 2.1.4 Storage Parity

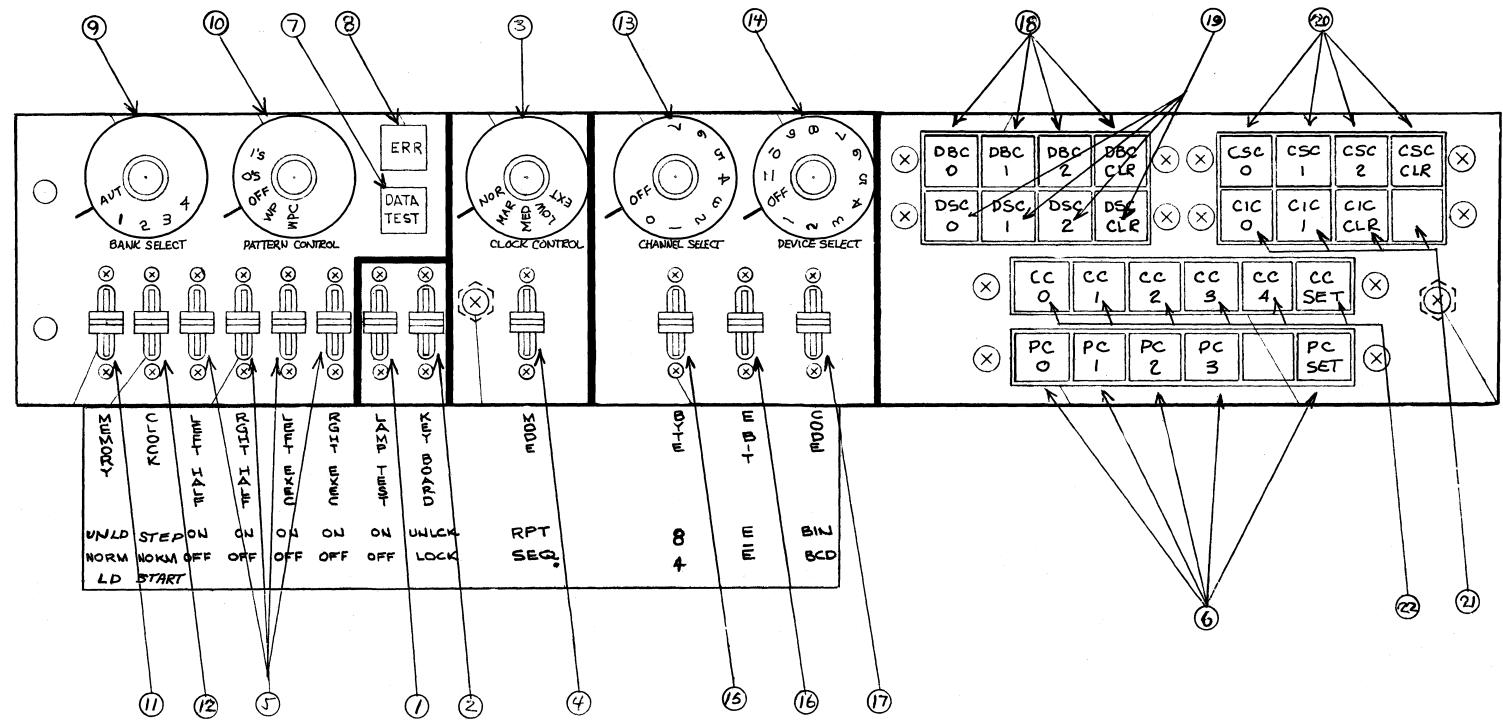

One parity bit accompanies each half-word transfer in the 8400 and two parity bits accompany full-word transfers. Odd parity is employed; that is, the parity bit is set such that the number of "1's" in a half-word, plus the parity bit, is always an odd number. During a write cycle, the correct parity bit is generated and stored automatically. During a read cycle, the detection of a parity error causes the Memory Parity Indicator to flash at the console and initiates an internal Parity Failure interrupt. The memory bank causing the error may be located by the interrupt subroutine or, alternatively, by the operator using the Bank Select Switch on the console maintenance panel.

#### 2.2 <u>EFFICIENT CAPACITY UTILIZATION</u>

Directly addressable data units which can be stored in one 8400 memory location include 32-bit full-words and 16-bit half-words, as previously noted. In addition, the Processor provides Double Precision Floating-Point Instructions which permit the direct sequential addressing of a contiguous word-pair and a set of Logical Connective Instructions which enable the direct addressing of 16, 8, 4, 2, and 1-bit bytes. Thus, the effective addressable storage capacity of the memory depends not only on the number of memory locations; but also on the sizes and mix of the data units to be stored. For example, a 64k memory has storage capacity for 64k floating-point or fixed point operands of 32-bit word length, 128k fixed-point operands of 16-bit word length or 256k ASCII or EBCDIC peripheral code characters. Figure 2-2 summarizes the effective storage capacities for all of the 8400 storage unit sizes and indicates the types of program information that utilize each of the sizes. The variety of useful types of information which can be stored in storage units of an exactly matching size results in highly efficient utilization of the available storage, by permitting dense packing of information with almost no waste capacity.

All memory addresses are available for general program use with the exception of a few addresses reserved for special purposes. The reserved addresses are listed below (in octal notation):

|                | · · · · ·    | 5x3+15 lints ? |                       | 00000                                                                    |

|----------------|--------------|----------------|-----------------------|--------------------------------------------------------------------------|

| V Swords       | Addresses    | 00000-00007:   |                       | for the Accumulator, Save                                                |

| à .<br>Martina |              | *              | Register              | and 6 Index Registers                                                    |

| 16 controls    | Addresses    | 00010-00027:   | Reserved<br>What's    | for the Rapid Access File<br>fue gap for ?.<br>for 16 Internal Interrupt |

| is about fi    | Addresses    | 00040-00060:   | Reserved              | for 16 Internal Interrupt                                                |

|                | novild be 41 |                | line loca             | ations                                                                   |

| 256            | Addresses    | 00061-00460?   | Reserved<br>line loca | for 256 External Interrupt<br>ations                                     |

$\phi \ll 0$

The Accumulator and Save Register are standard arithmetic hardware registers

### EFFECTIVE ADDRESSABLE STORAGE CAPACITY

| ADDRESSABLE<br>DATA UNIT | DATA UNITS/<br>MEMORY WORD | STORAGE CAPACITY<br>-WITH 64K MEMORY | TYPE OF INFORMATION                                                       |

|--------------------------|----------------------------|--------------------------------------|---------------------------------------------------------------------------|

| 64-BIT<br>WORD PAIRS     | ł                          | 32к                                  | DOUBLE PRECISION FLOATING<br>POINT OPERANDS                               |

| 32-BIT<br>FULL WORDS     | 1                          | 64К                                  | FLOATING POINT AND EXTEND-<br>ED FIXED POINT OPERANDS;<br>or INSTRUCTIONS |

| 16-BIT<br>WORD           | 2                          | 128K                                 | FIXED POINT, INDEX AND<br>INTEGER OPERANDS; or<br>ADDRESS FIELDS          |

| 16-BIT<br>BYTES          | 2                          | 128К                                 | 4 HEXADECIMAL CHARACTERS,<br>4-DIGIT BCD CODES; or<br>OTHER 16-BIT FIELDS |

| 8-BIT<br>Bytes           | 4                          | 256К                                 | ASCII AND EBCDIC 8-BIT<br>CHARACTER CODES; or 6-BIT<br>ALPHANUMERIC CODES |

| 4-BIT<br>BYTES           | 8                          | 512K                                 | BCD NUMERIC CHARACTER<br>CODES; or OTHER 4-BIT<br>FIELDS                  |

| 2-BIT<br>Bytes           | 16                         | 1024к                                | 2-BIT TEST OR DECISION<br>MAKING STATUS CONDITIONS                        |

| 1-BIT<br>Bytes           | 32                         | 2048K                                | 1-BIT TEST OR DECISION<br>MAKING STATUS CONDITIONS                        |

FIGURE 2-2

addressable as locations 00000 and 00001. The index registers and Rapid Access File are optional hardware registers whose functions are fulfilled with core memory locations in systems in which these options have not been elected. Any of the locations reserved for external interrupts may be used for other purposes in systems not requiring the full external interrupt line capacity of the 8400.

#### 2.3 <u>EFFICIENT CYCLE TIME UTILIZATION</u>

Each of the independent banks of which the Memory is comprised is an autonomous storage module capable of responding to read and write requests from up to four storage request sources. The control autonomy provided for the banks makes possible the use of several operational techniques that effectively increase the processing speed of the system. The techniques are as follows:

### 2.3.1 Concurrent Memory Operation

In this mode of operation, words in different memory banks are accessed simultaneously by different subsystems; for example a Floating-Point Processor and an Automatic Data Channel Processor.

standard memory prochap. Type tring - dead a may

#### 2.3.2 Overlapped Memory Operation

In this mode of operation words in different memory banks are accessed in "overlap" fashion by one subsystem; as in the case where a Floating-Point Processor while storing data in one bank begins fetching the next instruction from a different bank.

#### 2.3.3 Combined Concurrent-Overlap

norther Jean

In this mode of operation the requesting subsystems operate concurrently and overlap their individual memory accesses by addressing the same banks alternatively; and different banks simultaneously.

The use of these three modes of operation can significantly reduce operating time in multi-processor, multi-user and single user systems.

#### 3.0 FLOATING-POINT PROCESSOR

The Floating-Point Processor employs a 32-bit word length which provides for a powerful instruction repertoire (over 750 commands) and direct addressing of up to 65,536 words of memory. It has unusually extensive capabilities for both arithmetic and logical operations, as well as extensive control capabilities. The Processor is designed with Floating-Point as a basic, rather than expansion capability --- a concept fundamental to the 8400's exceptional floating-point speed and storage efficiency characteristics.

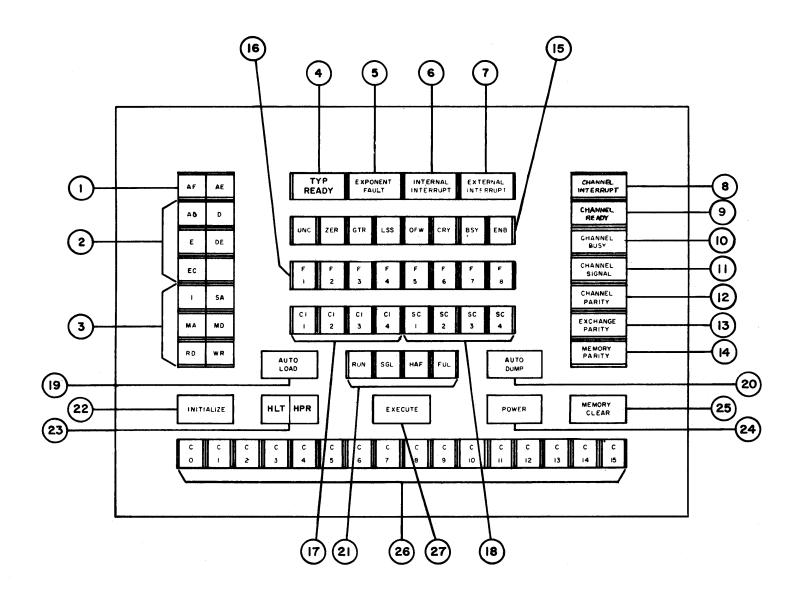

The processor provides system control for the 8400 system of autonomous functional modules, integrating its own operation with the operation of the Memory and Exchange Module. This role of systems control is illustrated by the diagram of Figure 3-1.

As the central processing unit of the 8400 Computing System, the Floating-Point Processor provides all of the capabilities for control and execution of the stored program. An indication of its powers and capability in this role is given by the following descriptions of the principle registers affecting operation:

#### Processor Registers

- 1. Instruction Register (I) contains the instruction currently being executed. /

- 2. Location Counter (L) contains the address of the next instruction to be executed. The register is addressable under program control.

- 3. Accumulator is designed to be "universal"; i.e. every variety of arithmetic and data manipulation is performed with the one register, making programming simpler. It consists of four sections: a 16-bit accumulator, a 16-bit extension for 32-bit fixed-point, a 16-bit extension for 32-bit floating-point, and a 24-bit second extension for 56-bit floating-point. All manipulations between the accumulator sections are handled automatically. The accumulator is addressable as memory location zero.

- 4. Save Register (\$) saves the current contents of the Accumulator concurrently with executing an arithmetic instruction. It is addressable as memory location one.

- 5. Index Registers (X) provide automatic address modification. Six core index registers and accumulator index capability are basic to the computer. The accumulator is index register 1, the rest are X2 thru X7.

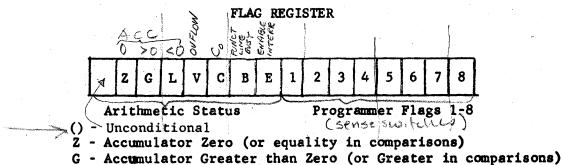

- 6. Flag Register (F) contains indicator bits, set as the result of arithmetic operations, exchange and interrupt status signals. The Flag Register is addressable. as what location?

- 7. Internal Mask Register (IM) contains a 16-bit priority pattern specifying which interrupt conditions should be acknowledged.

- 8. External Mask Register (EM) contains a 16-bit pattern as described above but for external interrupt conditions....

- 9. Interval Timer Register (T), provides an optional real-time clock whose contents are decremented by one, every millisecond. When contents are reduced to zero, an interrupt signal is generated, the initial value is reset, and the clock continues. The Timer register is addressable.

- 10. Rapid Access File provides 16 hardware registers of <u>32</u> bits and 2 EXEC bits. These registers have a 250 nanosecond access time for high speed data storage or instruction execution. When this option is not present in the system, 16 memory locations respond to Rapid Access File instructions.

- 11. Console Register (C) is accessible by the program and by the operator. It allows monitoring, data display, and data input while the program is running.

The control and arithmetic-logical capabilities of the Floating-Point Processor are described separately, in the immediately succeeding sections; 3.1 and 3.2, respectively.

NS

### EAI 8400 SYSTEM BLOCK DIAGRAM

#### 3.1 CONTROL FUNCTIONS

The control functions performed by the Processor include the sequencing of the computer through its program, the interpretation of instructions, the timing and gating of data flow, and the establishing of control relationships and priorities for the 8400 System. These functions are carried out through the use of the following control techniques:

- a) Logic timing and gating of the various system data busses, enabling the unique data paths required for the execution of each instruction; hardware control of other system elements as required by the operation being performed using the decoded instruction as its guide.

- b) Automatic Internal Interrupt System which provides the facility for continuously monitoring various conditions of the computer or its environment, and notifying the main program when certain conditions occur. If an interrupt signal is acknowledged, the main program will stop and transfer control to a subroutine, which services the condition. Use of the interrupt system permits immediate detection of system faults and facilitates the operation and coordination of asynchronous external devices.

- c) Program-controlled Internal Status and Function Lines which allow the programmer to monitor and set control lines throughout the system.

Several special registers are employed in some of the control functions. These include the Flag Register which provides on-line monitoring of the status of <u>sixteen</u> machine conditions during the course of a program and optional Interval Timer Register and Rapid Access File. An exclusive feature of the 8400 is its unique EXEC BIT Control System which enables the use of the EXEC bits marking each half word storage location in memory for special control functions, such as dynamic relocation of <u>subroutines</u> and <u>coding</u> sequences from one location in memory to another.

#### 3.1.1 Instruction Characteristics

but still requires a precty sophisticated exec rontine - not tilce RCA's hardware dynamic relocation sia content-addressed memory!

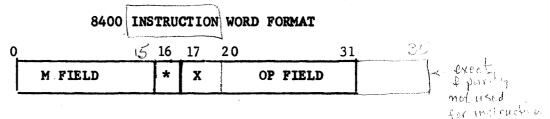

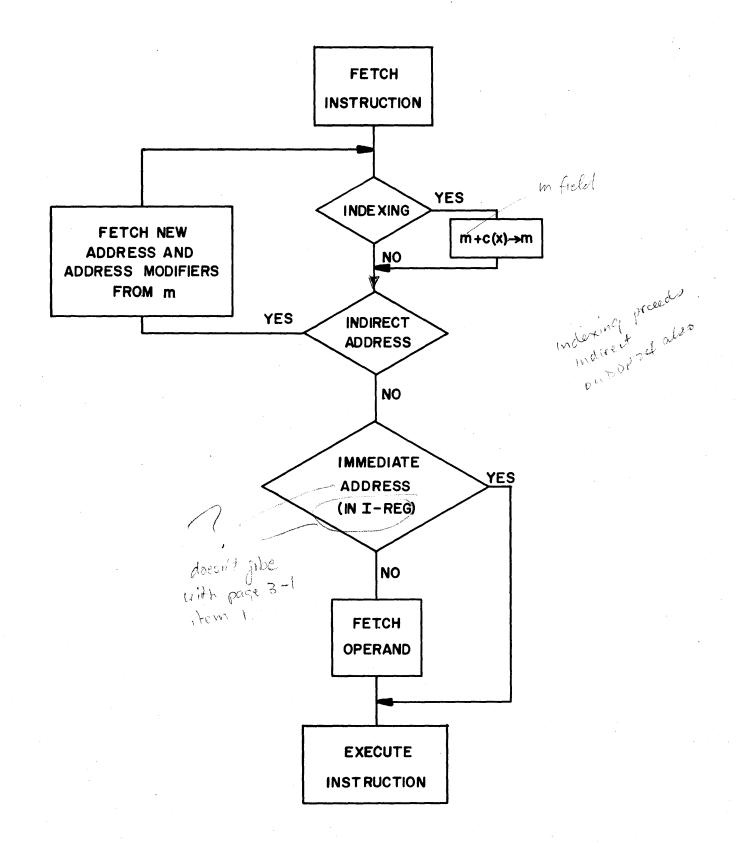

The 8400 is a single address computer employing a 32-bit instruction word. Under the normal mode of control the stored program is executed sequentially. The current instruction is contained in the Instruction Register (I) and the address of the next instruction is contained in the Location Counter (L). The execution of an individual program step is determined by the current instruction which is interpreted by logic and timing circuitry that implements the various functions to be performed. The normal program control capabilities therefore are indicated by the 8400 instruction word format which is shown below. These capabilities include addressing, address modification, and instruction interpretation and control.

M is a l6-bit address field. \* is an indirect address bit. X is a 3-bit index register field. OP is a 12-bit command.

#### Addressing

In arithmetic and logical instructions the 16-bit M Field may contain the address of a direct or an indirect operand, an immediate operand, or a shift count. In immediate addressing the address field itself is the operand. Both immediate operands and shift counts are signed numbers in two's complement notation.  $b_i t = sign b_i t$ ?

The addressable locations in which data may be found include any of the 32-bit memory locations, the Accumulator and the Save Register. Immediate addressing and half-word or byte positions in an addressable location are specified by bits in the operation field.

In control instructions the M Field may contain the address of an  $\frac{1}{2}$ internal or external sense or function line and registers of external devices that are interfaced to the Addressable Input/Output Bus of the Exchange Module.

#### Address Modification

The \* Bit in the instruction word determines whether or not indirect addressing is to be performed before an operand fetch. Multi-level indirect addressing is permissable, with optional address modification at every level.

The X Field specifies the index register to be used for address modification. This 3-bit field can address <u>seven</u> index registers. When indexed address modification is specified, the effective address is formed by <u>adding</u> (in two's complement notation) the contents of the selected index register to the base address contained in the M Field. A zero code in the X Field indicates that no modification is to be performed. That fearer 7 index registers

accumulator + 6 hardware

## FLOW CHART FOR ADDRESS MODIFICATION

WHERE INDEXING, INDIRECT ADDRESSING AND IMMEDIATE ADDRESS IS PERMISSABLE.

If both indirect addressing and address modification are specified, the modified effective address is used for indirect addressing at each level.

W. Jacquero

#### Instruction Interpretation and Control

The <u>12-bit</u> OP Field contains the operation code for the instruction to be performed. Instruction decoding logic interprets the OP code and sets the appropriate data paths and control circuitry required to execute the instruction.  $Q_{AC}Alle$

The length of the OP Field in the 8400 provides an unusually extensive instruction repertoire of over 750 commands. The **arder** code employed utilizes certain bits to designate <u>Basic</u> <u>Operations</u> (B) and other bits to designate <u>Operation Modifiers</u> (M). With this bit organization the programmer need remember only B + M codes to specify  $B \times M$  instructions. Two special modifiers specify unnormalized floating-point operation and the saving of the contents of the accumulator in the Save Register prior to instruction execution.

In data addressing, bits in the OP Field augment the address field, specifying immediate addressing; or, in the case of operations with half-word data or smaller bytes, specifying the position of the data at the addressed location.

#### 3.1.2 The Flag Register

The 8400 control system contains a <u>16-bit</u> Flag Register and associated circuitry that provide <u>continuous monitoring</u> of sixteen machine conditions during the course of a program. The individual bits of the Flag Register indicate the status of these conditions at the end of each instruction. Logic circuitry controlled by the current instruction enables testing, setting and resetting of the Flag Bits and provides a capability for conditional modification of the normal sequential control of the program in progress on the basis of a program condition monitored by one of the Flag Bits.

L - Accumulator Less than Zero (or Less in comparisons)

are manares!

- V Overflow of Accumulator (Cumulative)

- C Carry-out (Most Significant Bit)

- B Function Line or Data Channel Busy (not available)

- E Internal and External Interrupt System Enabled

- 1-8 Console Programmer Flag 1-8 set

- Note: complement testing of flag bits is also provided; Z bit can alternatively indicate a high (one) result for a Test Sense Line or Test EXEC Bit instruction

The Flag Register can be stored by the program, thereby enabling the internal status of the machine to be retained and later retrieved after program interruptions are completed.

### 3.1.3 Interrupt System

The fast and extensive interrupt system of the EAI 8400 provides the capability for altering the normal flow of sequential program control in response to the occurrence of any one of <u>sixteen</u> computer internal 256 external conditions and operating modes monitored by <u>sixteen</u> internal interrupt lines; and, up to <u>256 external</u> conditions monitored by the addition of external interrupt lines to the Exchange Module. When an interrupt condition occurs, the interrupt system automatically notifies the main program and, if acknowledged, stops the program and transfers control to an interrupt subroutine. The subroutine services the interrupt and returns control to the main program.

Conditions Monitored

External interrupt conditions are assigned at the users option when external interrupt lines are installed. The internal interrupt conditions are fixed by the design of the machine. These internal conditions are listed below in order of assigned priority (from highest to lowest).

#### INTERNAL CONDITIONS

- 0. Power Failure Detection of a drop in AC line voltage below operating level

- 1. Parity Failure- Parity check error in a memory bank or data channel

2. Reserved

| 3.               | EXEC Mode -                              | Presence of set EXEC bits in a word read from memory                                                                                                   |

|------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.               | Exponent Fault-                          | Presence of an exponent overflow or under-<br>flow in floating-point operations                                                                        |

| 5.               | Memory Protect-<br>Mode                  | Attempt to write in a protected location in memory                                                                                                     |

| 6.               | Interval Timer-                          | Down counting of Interval Timer register<br>to zero                                                                                                    |

| 7.               | Console -                                | Operator depressing one of <u>four</u> console<br>interrupt control buttons                                                                            |

| 8 <del>.</del> 1 | 5. Exchange Mod-<br>ule Data<br>Channels | Data Channel 1-8 interrupt control lines Hyperorites<br>(last four may be used as external lines tape<br>at users option if data channels not the ctc. |

#### System Structure and Priorities

The System interrupts are arranged in Groups of 16, each group having 16 individual interrupt levels, as follows:

| Group | 0   | Internal | interrupts | 0-15    |

|-------|-----|----------|------------|---------|

| Group | 1 . | External | interrupts | 0-15    |

| Group | 2   | External | interrupts | 16-31   |

| •     |     |          | •          |         |

| •     |     |          | •          |         |

| •     |     |          | •          |         |

| Group | 16  | External | Interrupts | 240-255 |

Each group of interrupts has priority over each succeeding group, and each level in a particular group has priority over lower levels. At the beginning of every instruction execution cycle, an interrupt scanning system sweeps through each group of interrupts, starting with Group 0.

Because of the scanning action of the interrupt system, interrupts of higher priority are always detected before interrupts of lower priority. Once an interrupt routine is given control, only interrupts of higher priority may interrupt the interrupt subroutine although this arrangement may be masked if desired. Detection of an active interrupt line takes place during the scan sweep, but the interruption of the normal program cycle by recognized interrupts takes place only after an instruction has been executed and before the next instruction is fetched. Exceptions are the EXEC and parity internal interrupts occurring on an instruction fetch which will interrupt before the instruction is executed.

#### System Enable-Disable

The entire interrupt system, both external and internal levels, may be enabled or disabled by setting or resetting the E-bit of the Flag Register. This bit may be appropriately set by the following instructions.

- (1) LDF load flag register

- (2) JSE, JRE, JTE, LRE and their complements JSNE, JRNE, etc. (See Flag Test Instructions in Instruction Repertoire Section).

A An exception is the Power Failure interrupt which can never be disabled.

#### Dynamic Priority Allocation

A very powerful feature of the 8400 interrupt system is the capability provided for Dynamic Priority Allocation of both external and internal interrupt lines, under program control. This is accomplished by means of Internal and External Mask Registers which provide masking control of the basic interrupt registers that continuously monitor the interrupt conditions assigned for detection.

The Internal Mask Register contains 16 masking bits corresponding to Interrupt Group O (internal conditions 0-15) and the External Mask Register contains 16 masking bits corresponding to Interrupt Group 1 (external conditions 0-15). The priority sequence of the interrupt lines in these two groups may be altered by resetting (to zero) the masking bits of lines to be inhibited; and setting (high) the bits of the lines to be recognized. This is accomplished by LDM and LDE instructions used to load the internal and external mask registers with the appropriate bit patterns. Additional groups of external interrupt can be inhibited under program control by means of the STATUS/FUNCTION LINE INSTRUCTION (SFL).

Through the use of mask control it is possible for the programmer to achieve the following results:

- Ensure an interrupt subroutine is not interrupted by one or more higher priority interrupts by resetting the corresponding mask bits for those higher order interrupts to be prevented.

- (2) Restructure the normal priority sequence by loading and "safestoring" mask configurations conforming to the order of priority desired.

- (3) Establish a dynamic "priority" level for the main program whereby only selected priority interrupts will be able to interfere. This is accomplished by altering the masking bits with instructions in the main program sequence and can be changed as the program progresses.

#### Interrupt Memory Locations

A unique memory location is assigned for each of the internal and possible external interrupt lines. Upon detection of an interrupt condition the normal program cycle is broken and an unconditional jump is effected to the memory location assigned to the particular interrupt line that is signalling for the program's interruption. The instruction which the programmer has stored in the interrupt's assigned memory location now determines the computers response. This instruction, which cannot be interrupted, controls the action taken by the interrupt logic in executing the interrupt subroutine. Three choices of instructions which may be used for this purpose are:

- (1) <u>a "Link" Instruction:</u> This is the normal interrupt subroutine linkage. <u>The address of the next unexecuted instruction of</u> the interrupted program (location counter contents) are stored in the memory address specified by the link instruction and the subroutine starts in the next memory cell. This avoids problems encountered in computers permitting only one such preassigned cell in handling interrupts of other interrupt routines.

- (2) an "Execute" Instruction: The instruction contained in the address specified by the Execute command will be singly executed without affecting the Location Counter (unless that instruction is a Jump or Link). This choice is used for single or chained "Execute" interrupt subroutines.

- (3) <u>any Other Instruction</u>: The instruction contained in the interrupt memory location is executed and control returns to the next instruction using the address in the Location Counter.

The variety of actions available through the choice of instructions that can be stored in an interrupt memory location adds another dimension of flexibility to that provided by the masking systems.

## 3.1.4 Status and Function Line Control Server lines & DCP

The capabilities provided by the Flag Register and Interrupt Systems, for modifying program control on the basis of internal and external conditions, are augmented in the 8400 by Status and Function lines which can be tested, set and reset under program control. Four banks of status and function lines are available; the first two of which are reserved for internal control purposes and the remainder for external systems control.

By using a set of Status and Function line commands (see Instruction repertoire section), internal conditions can be tested, and logic and data flow circuitry can be manipulated under program control. Control commands includes the selection of the appropriate bank and specific line or lines to be employed, using immediate addressing. When testing Status Lines, the Z bit of the Flag Register is made to correspond to the state of the line (s). The Busy Bit (B) of the Flag Register is set if a function line cannot be set, as a result of conflicting requirements.

The Status and Function Line Instructions for Bank 0 pertain to the Processor and Memory, while the instructions for Bank 1 pertain to the Exchange Module. The functions performed are listed below:

#### BANK O

- 1. Testing parity error flip-flops in the various memory banks.

- 2. Testing Console interrupt flip-flops.

- 3. Turning on/off the Real-Time Clock.

- 4. Establishing EXEC interrupt conditions.

#### BANK 1

- 1. Clearing a data channel.

- 2. Initializing a data channel.

- 3. Testing parity error flip-flops in the various data channels.

- 4. Enabling/disabling interrupt signal gates.

- 5. Device function control.

#### 3.1.5 EXEC Bit Control System

The EXEC bit Control System is an exclusive feature of the EAI 8400, which provides the programmer with many powerful programming techniques. The system operates in conjunction with the EXEC bits associated with each halfword in the 8400 memory. These word marking bits may be set, reset or tested by a group of EXEC bit control instructions. The result of a test of any half-word will set the Z bit in the Flag Register if the EXEC bit is high. Programmed decisions using the Flag Test Instruction Set can therefore be made, based on the state of any word's EXEC bit.

#### EXEC Mode Interrupt

The EXEC Bit Instructions enable the use of the EXEC bits under the direction of the stored program. In addition, the EXEC bits are monitored by the 8400's Internal Interrupt System. This allows <u>automatic</u> recognition of the EXEC bits for a variety of purposes.

The EXEC Mode Interrupt occurs whenever a word is read from memory and the EXEC bits for the word are set. The EXEC Mode Interrupt can be recognized at three points during the instruction cycle as follows:

- 1. After instruction fetch and before address modification; this would result from reading an instruction with one or both of its EXEC bits set.

- 2. After address modification and before operand fetch; this would result from indirect addressing.

- 3. After execution and before the next instruction fetch; this would result from reading an operand with the EXEC bits set.

The interrupt subroutine determines which case occurred, and acts accordingly.

#### Applications

The 8400 Programming Systems use the EXEC Bit Control System for a variety of purposes, the most significant of which is <u>dynamic relocation</u> of programs stored in memory. Both the Assembler and FORTRAN IV Compiler provide convenient means for setting the EXEC bits in individual half-words and word blocks, as appropriate. Thus other uses for the EXEC System are limited only by the programmer's imagination. Suggested possibilities are:

- Special simulations of other computers by trapping instructions marked with EXEC bits and executing them by interrupt software subroutines.

- 2. Implementation of special programming languages, such as list processors, compilers, interpreters, and generalized translators.

- 3. On-line breakpoint debugging for monitoring the progress of programs during execution.

- 4. Data Tagging for a special processing during input-output operations or table updating.

- 5. Implementation of push-down stack techniques using EXEC control.

# 3.1.6 Interval Timer Register (down counter with presetting)

As an optional control feature, the 8400 has available a 16-bit interval timer register which decrements the register once every millisecond. When the contents of the timer register, T, becomes zero, a Real-Time Clock Interrupt is generated. The clock does not stop counting when it reaches zero, but "returns" to its maximum value, and continues to decrement.

The Interval Timer has a maximum range of 65,535 milliseconds per count down and can be used for calculating elapsed time for periodic program interruption. Interruption can be programmed to occur every X seconds by loading the timer register with the binary equivalent of X in milliseconds. The timer counts down until it reaches zero and then generates an interrupt signal, which will initiate a subroutine to perform the desired services, and resets the timer for another X seconds. This feature permits flexible system integration, such as:

- 1. Synchronizing a program with a real-time device.

- 2. Outputting data periodically to certain peripheral devices.

- 3. Time-sharing multiple programs, or multiple consoles.

- 4. Periodically testing Sense Lines as an alternate to automatic interrupts.

#### 3.1.7 Rapid Access File

Another optional feature of the 8400 is the Rapid Access File, containing 16 high-speed registers. The individual locations in this file are specified in the same fashion as memory locations and can be used for the storage of instructions and operands. In the case of instruction storage, short high speed loops can be preloaded into the file and then operated upon from these high speed storage locations. This provides an increase in throughput for such functions as table searching with a wide variety of test criteria. Scratch pad memory programming techniques are another application of the Rapid Access File.

#### 3.2 ARITHMETIC

The Floating-Point Processor contains the logic and circuitry for performing the arithmetic and logical operations necessary for executing the stored program instructions. Some of the processor's important capabilities are:

1. <u>High-speed processing</u> - obtained by augmenting fast arithmetic circuitry with logic capabilities for powerful single instructions that enable a reduction in the total number of instructions necessary to perform a given function.

2. <u>Floating-point operations</u> - designed to be the normal arithmetic mode of operation for high speed, real time applications.

3. <u>A complete set of logical operations</u> - for fast and efficient programming language translation, input-output data handling and non-arithmetic problem requirements.

4. <u>Programming language features</u> - that provide ease of programming and reduce processing time as well as off-line preparation time.

5. <u>A "Universal Accumulator"</u> - that eliminates programmer concern with interregister transfer hardware considerations.

6. <u>High speed temporary storage</u> - that provides a simple effective means of holding intermediate computational results for subsequent reuse without additional memory referencing.

The Universal Accumulator and Save Register are particularly illustrative of the special programming features provided in the EAI 8400. The Accumulator is universal and directly addressable. It provides very high speed processing of both floating and fixed-point data in a variety of word formats. The Universal Accumulator concept saves the programmer the burden of transferring the result of a previous operation to the proper arithmetic register, of ensuring that the correct register is loaded or unloaded in transferring data to and from storage. All these functions are performed automatically by highspeed parallel logic. Not only are programmed instructions to accomplish these transfers unnecessary, but also one of the most frequent sources of programming errors is eliminated. The addressable nature of the Accumulator enables very high speed squaring and doubling. In addition, operations on data in the Accumulator can use the general set of instructions relating to memory. For example, the "Store after Rounding" instruction can be used to round quantities in the Accumulator by addressing location zero (the Accumulator's assigned address).

The SAVE Register provided in the Floating-Point Processor is a flexible high-speed storage register with configuration identical to that of the Universal Accumulator. It is addressable as location one. The SAVE Register allows the programmer to save the contents of the Accumulator prior to the execution of an arithmetic instruction. When this information is again required, it can be restored to the Accumulator by directly addressing the SAVE Register, an operation which requires 250 nanoseconds, considerably less than core memory access. The data is returned to the Accumulator automatically in the proper format for the arithmetic operation to be performed; all standard 8400 data formats may be accommodated.

#### 3.2.1 Arithmetic Characteristics

Operating modes and data formats

The Floating-Point Processor can operate in a variety of modes including the following:

Floating-point, 32 and 56-bit Fixed-point, 16 and 32-bit Integer, 16-bit Index, 16-bit Boolean, 16, 8, 4, 2 or 1-bit

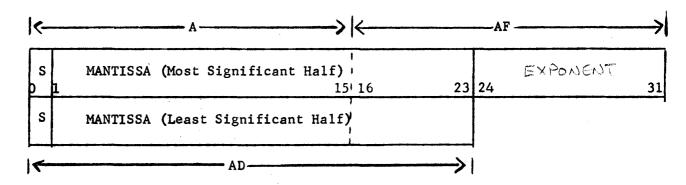

The data formats for these operating modes are diagrammed in figure 3.2-1, shown relative to the memory data word format. Supplemental numerical information is provided in the table below. <u>All binary formats</u> are in two's complement notation with sign bits high (one) for negative quantities.

Sing le Arec. Floating-Point 32 b.75 Binary format: [23 bit + sign] Mantissa from 1 to  $2^{-23}$  t [7 bit + sign] Exponent from  $2^{1/23}$  to  $(2^{-23}) 2^{1/28}$ Memory Storage: one 32-bit location hormalized scaling

Decimal Capacity: 8.388 x 10<sup>6</sup> max. Mantissa 1.280 x 10<sup>2</sup> max. Exponent

overall range 10-50 to 1

3-14

|                           |                     | 21            |

|---------------------------|---------------------|---------------|

| FLOATING POINT            | \$ 23               | S 7           |

| DOUBLE PRECISION {        | s 23                | · s 7         |

|                           | s 23                | 5 7           |

| INTEGER                   | <br> s  5           |               |

| FIXED POINT               | s 15                |               |

| EXTENDED FIXED POINT      | s 15                | s 15          |

| INDEX                     | s 15                |               |

| LOGICAL : I - IG BIT BYTE |                     |               |

| 2-8 BIT BYTES             |                     |               |

| 4 - 4 BIT BYTES           |                     |               |

| 8-2 BIT BYTES             |                     |               |

| 16- I BIT BYTES           |                     |               |

| INSTRUCTION               | ADDRESS             | * × OPERATION |

| MEMORY ADDRESS            |                     |               |

| MEMORY DATA               | LEFT HALF           | RIGHT HALF    |

| BIT SCALE                 | 0             7   0 | 916           |

.

EAI 8400 WORD FORMATS

FIGURE 3.2-1

56 loits

## Double Precision Floating Point

Binary Format: 46 bit + 2 sign Mantissa 7 bit + sign Exponent

Memory Storage: two 32-bit locations

Decimal Capacity: 7.056 x  $10^{13}$  max Mantissa 1.280 x  $10^2$  max Exponent

#### Fixed Point

Binary Format: 15-bit + sign Memory Storage: one half-word location Decimal Capacity: 3.277 x 10<sup>4</sup> max. magnitude

#### Extended Precision Fixed Point

Binary Format: 30-bit + 2 signs Memory Storage: one 32-bit location Decimal Capacity: 1.073 x 10<sup>9</sup> max. magnitude

#### Byte Modes

Binary Formats: 16, 8, 4, 2, 1 bits Memory Storage: 1, 1/2, 1/4, 1/8, 1/16 of one half-word location

As can be seen, all data words are based on the 16/32 bit balanced-word framework. This structure allows optimal hardware organization for rapid execution of arithmetic-logical operations in the various word sizes and conversions from one format to another.

#### Accumulator Configuration

As in all single address machines, arithmetic-logical operations are performed on information in the Accumulator and operands from storage (core memory, Rapid Access File, SAVE Register, the Accumulator itself).

The 8400 Universal Accumulator <u>automatically</u> forms the proper configuration of its internal registers, to handle the four arithmetic data formats involved in the operations to be performed, as follows:

16 Bit Fixed-Point, Integer, Index, Logical Connectives and Shifts: A Register A Register 32 Bit Extended Precision Fixed Point, Extended Shifts: A + AE Register

The AE Register is also used to hold 32 bit double length products and dividends of 16 bit Fixed-Point multiply/divide computation.

32 Bit Floating-Point A + AF Register

56 Bit Double Precision Floating-Point: A + AF + AD Register

The AD Register is used to hold double precision products and dividends of single precision floating-point multiply/divide computations.

The SAVE Register has a matching arrangement which is similarly adaptable. Other arithmetic registers are used to hold the operand and intermediate results.

#### Arithmetic Execution Speed

Figure 3.2-2 summarizes execution times for selected operation under several conditions. The significant feature is that Floating-Point execution times are equivalent to the times for comparative Fixed-Point operations. If the necessary scaling shifts are added to a typical fixed-point instruction mix, the 8400's floating-point solution will be faster. The differences in problem analysis and coding are, of course, appreciable.

#### Arithmetic Status Flags

In the course of running typical programs, a number of comparison operations and control steps are required. These include the ability to algebraically compare operands with respect to other operands, or with respect to zero. For example, the IF statement in algebraic compilers asks if an operand is "equal to", "greater than", or "less than" zero. Coupled with comparison operations are the actions desired as a function of the result. In the 8400 the Flag Register and its related Flag Test Transfer Instructions provide these capabilities.

The Flag Register's Zero (Z), greater than (G) and less then (L) bits continuously reflect the result in the Accumulator at the end of each instruction execution. In the COMPARE instructions included in the 8400 Arithmetic repertoire, their flag bits indicate that the data word in the Accumulator is equal to, greater than, or less than the referenced data word in memory. Flag settings are the only result of COMPARE operations; the Accumulator and Memory are unchanged. The Flag Test Transfer Instructions enable control transfer conditional upon arithmetic status through Jump, Link, Halt, and Execute operations.

#### Arithmetic Fault Detection

Three arithmetic fault indicators are provided in the 8400.

1. Exponent Fault Interrupt - occurs whenever the exponent of a floatingpoint number has become so large (positively or negatively) that the capacity of the exponent (Bits 24-31 of A + AF) is exceeded and Exponent Overflow or Underflow takes place. Because of the large range of exponents allowed in floating-point, this type of fault is relatively rare.

2. <u>Carry-Out Flag (C Bit) In Flag Register</u> - indicates that a carry of the most significant "magnitude" bit has occurred. Not truly a fault, carry-out is useful for initiating multiple step precisions in fixed-point operations.

3. Overflow Flag (V Bit) In Flag Register - signals that the result of an operation exceeded the capacity of the Accumulator in a positive or negative sense. Illegal multiplication, division, and "integerization" also set the V flag, which is <u>cumulative</u> and can be reset only by programmed Flag Test instructions. Due to the nature of two's complement notation, such a fault is sensed by the overflow logic whenever a carry of the most significant "magnitude" bit occurs with <u>NO</u> carry-out of the sign bit <u>or</u> a carry-out of the sign bit with <u>NO</u> carry from the first "magnitude" bit.

## ARITHMETIC SPEED CHART (times in microseconds)

| Type of          | Memory O | verlapped | No Memory | Overlap | Comment      |

|------------------|----------|-----------|-----------|---------|--------------|

| Operation        | Minimum  | Maximum   | Minimum   | Maximum | <u>Notes</u> |

| Load/Store       | 2.25     | 2.75      | 4.00      | 4.00    | 32 bit       |

| Floating Add     | 3.50     | 4.00      | 4.00      | 4.00    | 32 bit       |

| FloatingCompare  | 4.00     | 4.50      | 4.50      | 4.50    | 32 bit       |

| Floating Mult.   | 6.25     | 7.50      | 6.75      | 7.50    | 32 bit       |

| Floating Div.    | 9.50     | 10.00     | 10.00     | 10.00   | 32 bit       |

| Double Float Add | 6.00     | 6.50      | 6.00      | 6.50    | 56 bit       |

| Integer Add      | 3.50     | 4.00      | 4.00      | 4.00    | 16 bit       |

| Fixed Add        | 3.25     | 3.75      | 4.00      | 4.00    | 16 bit       |

| Fixed Multiply   | 5.25     | 6.25      | 5.75      | 6.25    | 16 bit       |

| Fixed Divide     | 7.50     | 8.00      | 8.00      | 8.00    | 16 bit       |

| Extended Fix Add | 4.00     | 4.50      | 4.50      | 4.50    | 32 bit       |

| Test/Branch      | 1.75     | 2.25      | 2.00      | 2.25    | -            |

| Logical          | 3.25     | 3.75      | 4.00      | 4.00    | . 🗕          |

| Shift            | 2.00     | 2.50      | 2.00      | 2.50    | Note 5       |

| No Ref to man.   | na       | na        | na        | na      | Note 6       |

- (1) Use of Save Register or addressable accumulator will decrease times shown for which all operand fetches are from core memory.

- (2) Minimum times assume no address modification and minimum operation execution time where applicable.

- (3) Maximum times assume indexing and maximum operation times where applicable.

- (4) For floating point operations add .25 u-sec for each pre-shift and normalize post shift.

- (5) For shifts add .25 u-sec for each place; however, with 8400 fast floating point fixed point scaling is nearly eliminated.

- (6) Inter-register transfers for arithmetic operations are not required with 8400 Universal Accumulator.

Figure 3.2.2

All arithmetic operations must produce a result which lies in the  $1 > R \ge -1$  range or a fault is produced. The 8400 handles arithmetic faults as shown in the following table.

|                                                                               | N N                                                                                                                                    |                                 |

|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Machine Operation(s)<br>Causing Fault                                         | Action Taken                                                                                                                           | Final State of<br>Overflow Flag |

| All Fixed Point, Index<br>Arithmetic Instructions                             | Operation Completed                                                                                                                    | SET                             |

| Floating Point and Integer<br>Clear & Subtract<br>Add<br>Subtract<br>Multiply | Operation is Completed;<br>Result is corrected.                                                                                        | RESET                           |

| Floating Point and Integer<br>Clear & Divide<br>Divide                        | Operation is Completed;<br>1. Answer meaningless if<br>Divisor < ∠ Dividend,<br>yielding R≥2.<br>2. Result is corrected if<br>2>R≥ +1. | SET<br>RESET                    |

| Floating Point Store Rounded                                                  | Operation is completed;<br>Result is corrected.                                                                                        | RESET                           |

| Integer Store and Store<br>Rounded                                            | Operation is completed.                                                                                                                | SET                             |

I where R is the characteristic only, of course!

## 3.2.2 Arithmetic Operations

Processing speed in the 8400 is achieved by augmenting fast arithmetic execution times with an extensive instruction repertoire, containing singly powerful instructions that result in shorter programs. Over 80 arithmetic instructions are provided.

The arithmetic instructions are readily learned and easily remembered through the use of a coding scheme which employs 10 basic operations and 6 class modifiers so that only 10 + 6 = 16 mnemonic symbols are required for  $10 \times 6 = 60$  instruction mnemonics. The coding scheme is indicated by the table on the following page which shows all of the 8400 arithmetic operations. Operations suffixed with a "U" indicate unnormalized floating-point. There are 24 of these operations. Characteristics and utilization of the six classes of operations are discussed below.

### Floating Point

Standard precision floating-point computations are the workhorse of the 8400. The word length and accumulator configuration are fundamentally designed to allow single memory access parallel floating-point capability. -The precision and range provided by the standard floating-point class of operations is adequate for most problem variables.

In standard precision Floating-Point operations, a full 32-bit memory word is transferred in parallel to the Accumulator where the computations are performed by the A + AF circuitry. For loading double length dividends and storing double precision products, the DCA or DCS and DST commands may be used in conjunction with two full-word contiguous memory cells. The AD register is also used in these operations.

Both normalized and unnormalized floating-point operations are provided for all instructions except Store and Compare.

Automatic scaling, implemented in floating-point operations by exponent arithmetic and normalization, is the prime advantage of normalized floatingpoint operations. It relieves the programmer from the time-consuming, and often complicated task of scaling his problem to the limited range of a computer. In each floating-point instruction, several operations are combined -- exponent equalization, the desired arithmetic operation, corrective measures for overflow, and post normalization. This results in the saving of processing time and storage.

While the majority of scientific applications use Normalized Floating-Point, the unnormalized capability has important applications as well. For example, this mode is used in the programming of multiple precision arithmetic operations. In such cases, the partial results are left unnormalized, and summarized to produce the multiple precision results. These final results may be normalized or still kept without normalization as the problem demands.

3-20

د) ؟

10 Install

Pre Modifiers: DF = 22 bit flooting 2) E = 32 bit fired (extended) 3) D = 56 bit Double Flooting 4) 7 = 16 bit Integer 5) X = 16 bit Integer

EAI 8400 INSTRUCTION LIST

## ARITHMETIC OPERATIONS

| Function                             | Mnemonic | Function                          | Mnemonic       |

|--------------------------------------|----------|-----------------------------------|----------------|

| 32 Bit <u>Floating</u> Point:        |          | 16 Bit Fixed Point:               |                |

| Subtract                             | F SB     | Subtract                          | SB             |

| Clear Subtract                       | FCS      | Clear Subtract                    | CS             |

| Clear Add                            | FCA      | Clear Add                         | CA             |

| bbb Partia                           | FAD      | Add                               | AD             |

| Compare                              | FCP      | Compare                           | CP             |

| Multiply                             | FMP      | Multiply                          | MP             |

| Store                                | FST      | Store                             | ST             |

| Store Rounded                        | FSR      | Store Rounded                     | SR             |

| Divide                               | FDV      | Divide                            | DV             |

| Clear Divide                         | FCD      | Clear Divide                      | CD             |

| 56 Bit <u>Double</u> Floating Point: |          | 32 Bit <u>Extended</u> Fixed Poir | nt•            |

| Subtract                             | DSB      | Subtract                          | ESB            |

| Clear Subtract                       | DCS      | Clear Subtract                    | ECS            |

| Clear Add                            | DCA      | Clear Add                         | ECA            |

| Add                                  | DAD      | Add                               | EAD            |

| Compare #                            | DCP      | Compare #                         | ECP            |

| Multiply #                           | DMP      | Multiply #                        | EMP            |

| Store                                | DST      | Store                             | EST            |

| Store Rounded #                      | DSR      | Store Rounded #                   | ESR            |

| Divide #                             | DDV      | Divide #                          | EDV            |

| Clear Divide #                       | DCD      | Clear Divide #                    | ECD            |

|                                      |          | order product w                   | LOD            |

| 16 Bit <u>Integer</u> :              |          | 16 Bit Index:                     |                |

| Subtract                             | ISB      | Subtract                          | XSB            |

| Clear Subtract                       | ICS      | Clear Subtract                    | XCS            |

| Clear Add                            | ICA      | Clear Add                         | XCA            |

| Add                                  | IAD      | Add                               | XAD            |

| Compare                              | ICP      | Compare                           | XCP            |

| Multiply                             | IMP      | Multiply #                        | XMP            |

| Store                                | IST      | Store                             | XST            |

| Store Rounded                        | ISR      | Store Rounded 🦸                   | XSR            |

| Divide                               | IDV      | Divide #                          | XDV            |

| Clear Divide                         | ICD      | Clear Divide #                    | XCD            |

| # Subroutine                         |          |                                   | н <sup>с</sup> |

# SHIFTING, ROTATION AND NORMALIZATION OPERATIONS $_{\beta^{1_k} \vdash^{\tau} \cup \mathcal{Z} \in \mathcal{T}}$

| Accumulator:     |     | Extended Accumulator: |      |

|------------------|-----|-----------------------|------|

| Arithmetic Shift | ASH | Arithmetic Shift      | EASH |

| Logical Rotate   | ROT | Logical Rotate        | EROT |

| Normalize        | NRM | Normalize             | ENRM |

#### Double Precision Floating Point

The double precision floating-point instructions operate on operands occupying two memory words, i.e., 64 bits. The word of lower address contains the most significant 23 bits of the fraction with its sign and the 7 bit exponent with its sign bit. The next higher memory address stores the least significant 23 bits of the fraction plus sign, and a 7-bit plus sign exponent differing from the exponent of the most significant half by 23. This two-word operand, when transferred into the Accumulator by a double precision floating-point instruction, will have a 46 bit fraction with duplicate signs and one exponent. The data word from the first memory word is loaded in the A + AF portion of the Accumulator, and the signed fraction from the higher memory location is transferred into AD. The exponent of the least significant part of the operand is ignored. During memory storage (DST) operations, the second exponent is generated automatically and inserted into the low end of the second memory cell, enabling the programmer to perform standard or double precision floatingpoint operations on the same operand word with no extra formatting necessary. It is also useful when multiple precision processing is required.

With the exception of word length and word format, these instructions are defined identically with their equivalent in the standard precision floatingpoint class, including the choice of normalized and unnormalized results.

## Fixed Point

The 8400 standard precision fixed-point class of computations employ a 16-bit half-word which is transferred in parallel from the Right or Left Half of a memory cell to the A register in the Accumulator. For loading double length (Extended Precision) dividends and storing Extended Precision products, the ECA and EST commands may be used, addressing a full-word memory location. The AE circuitry holds the least significant half of these numbers.

Because of the speed and efficiency of the -8400's floating-point circuitry, fixed-point operations take on a relatively minor significance. Standard precision fixed-point is used mainly for address arithmetic in conjunction with the Index class of operations, for function-generation, and for manipulation of constants and digitized analog or low-accuracy digital data before and after conversion to floating-point.