#### INCREMENTAL

#### INTERFACE REQUIREMENTS

#### DSR 1300, 1400, & 1500 SERIES

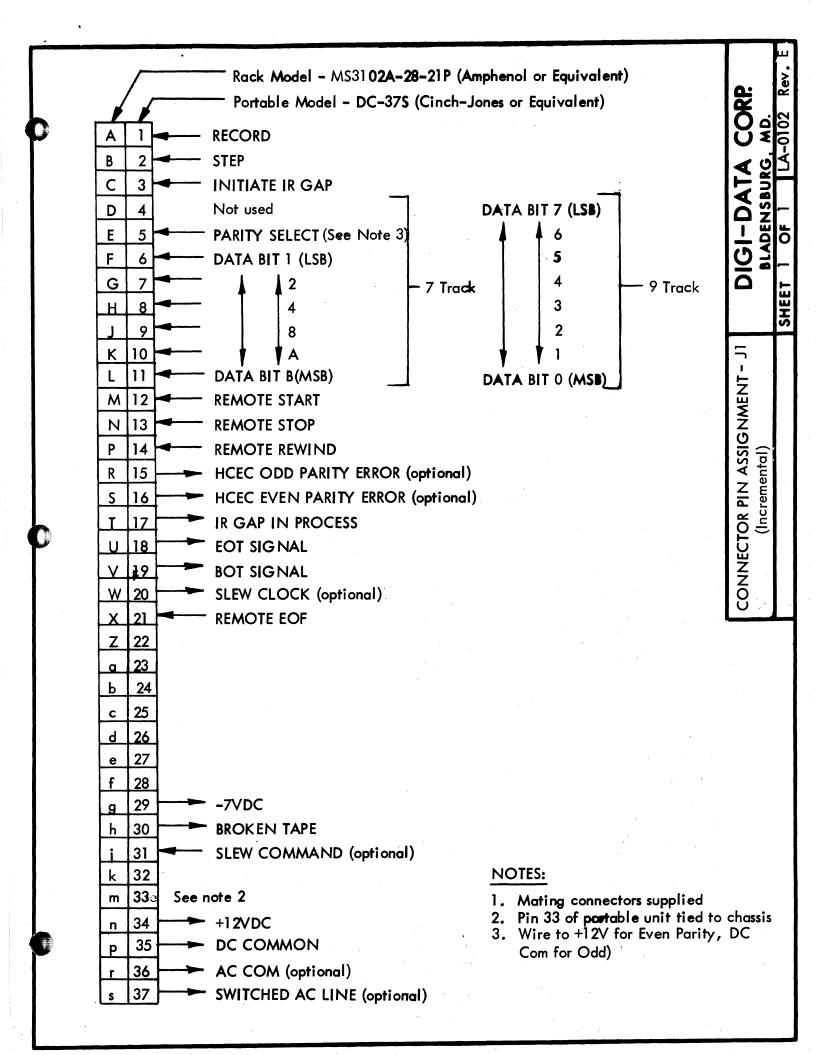

| ı | Ν | Ρ | U | T | S |

|---|---|---|---|---|---|

|---|---|---|---|---|---|

IC COMPATIBLE (STANDARD) Typical driver for T<sup>2</sup>L is SN 7401 with 1.5k to +5VDC. For DTL any element with 2k output to +5VDC.

Logic  $\emptyset = -5.0$  VDC to +0.5 VDC, less than 10 ua sink

Logic 1 = +3.0 VDC to +6.0 VDC, into nominal 3.0k ohm impedance to ground

HIGH LEVEL (OPTION)

Logic  $\emptyset = -0.5$  VDC to +0.5 VDC, less than 10 ua sink

Logic 1 = +6.0 VDC to +18.0 VDC, into nominal 15k ohm impedance to ground

DATA (6 lines - 7/track)

Positive level, coincident with or spanning record command, (8 lines - 9/track)

to record NRZI "one". Zero level during IRG sequence.

RECORD Minimum 50 usec positive pulse, return to zero minimum 50

usec before reactuation, records input data on tape

STEP Minimum 50 usec positive pulse, return to zero minimum 750 usec before reactuation, increments tape one character space

(4.7k impedance both options)

PARITY SELECT (7/Track)

Zero level to write odd parity, positive level to

write even parity

INITIATE IRG Minimum 50 usec positive pulse, return to zero minimum 2

msec before reactuation, writes CRCC (9/track) and LRCC on tape at four character spaces and 8 character spaces (9/track) respectively, inserts minimum .6 inches (9/track) or .75 inches

(7/track) erased tape gap, can be coincident with last step

command during incremental operation

REMOTE START Minimum 50 usec positive pulse, advances tape at slew speed

(stops at BOT marker)

REMOTE STOP Minimum 50 usec positive pulse, stops tape advance when in

BOT mode (overrides remote start)

REMOTE EOF 50 usec to 1 msec positive pulse, minimum 750 msec between

reactuations; generates internal IRG routine, then writes tape

mark and generates second internal IRG routine

REMOTE REWIND Positive level maintains rewind, zero level terminates (1400)

Positive pulse starts rewind, BOT internally stops. Positive level causes rewind past BOT. Use EOT to reset level. (1300)

(4.7k impedance both options)

POWER 105-125 VAC, 50-60 Hz

SLEW COMMAND (optional) Minimum 50 usec positive pulse, causes recorder to advance

tape in slew mode, positive level at end of IRG insertion causes recorder to continue in slew mode while zero level will

cause the recorder to halt (See Application Note)

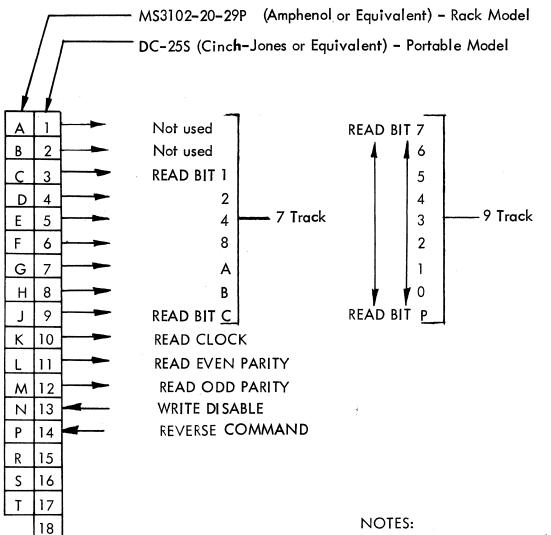

\* REVERSE Positive level to enable synchronous reverse tape motion,

zero level to enable synchronous forward tape motion

\*WRITE DISABLE Positive level disables write

### **OUTPUTS**

### IC COMPATIBLE (STANDARD)

Logic  $\emptyset$  = Maximum +0.5 VDC, 10 ma sink capability

Logic 1 = Nominal +5.0 VDC, 600 ohm source impedance (consult factory for other levels)

## HIGH LEVEL (OPTION)

Logic  $\emptyset$  = Maximum +0.5 VDC, 10 ma sink capability

Logic 1 = +12 VDC, 1.5k ohm source impedance

| GAP IN PROCESS                                               | Positive level during gap insertion, starting 3 msec after IRG cmd                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOT SIGNAL                                                   | Nominal 2 msec positive pulse occurring when BOT reflective marker is sensed (bi-directional)                                                                                                                                                                                                                                      |

| EOT SIGNAL                                                   | Positive level for duration EOT reflective marker is sensed (bi-directional)                                                                                                                                                                                                                                                       |

| BROKEN TAPE                                                  | Positive level when tape not loaded over head                                                                                                                                                                                                                                                                                      |

| DC POWER                                                     | +12VDC (2 pct regulation), -7VDC (10 pct regulation), DC common (consult factory for available power)                                                                                                                                                                                                                              |

| HCEC ODD PARITY ERROR                                        | Positive level, nominally 50 usec after record command, only if character being recorded on tape is even parity, output maintained until subsequent record command or initiate IRG, zero output when character is odd parity, and during IRG; positive level if head voltage fails or the unit is operated in rewind or read modes |

| HCEC EVEN PARITY ERROR                                       | Positive level, nominally 50 usec after record command, only if character being recorded on tape is odd parity, output maintained until subsequent record command or initiate IRG. Zero output when character is even parity and during IRG; positive level if head voltage fails or the unit is operated in rewind or read modes  |

| SLEW CLOCK (optional)                                        | Nominal 50 usec positive pulse occurring at slew rate of recorder (1.0 to 2.5k Hz nominal) first clock approximately 30 msec after initiating slew operation from halt, zero output during IRG                                                                                                                                     |

| * DATA (6 lines + parity 7/track) (8 lines + parity 9/track) | Nominal 10 usec positive pulse when bit is present, deskewed                                                                                                                                                                                                                                                                       |

| * READ CLOCK                                                 | Nominal 10 usec positive pulse nominally coincident with data                                                                                                                                                                                                                                                                      |

| * READ EVEN PARITY                                           | Nominal 10 usec positive pulse, nominally coincident with data; only occurs when character parity is even                                                                                                                                                                                                                          |

|                                                              |                                                                                                                                                                                                                                                                                                                                    |

Nominal 10 usec positive pulse, nominally coincident with

data; only occurs when character parity is odd

\* READ ODD PARITY

<sup>\*</sup> Standard features with read option

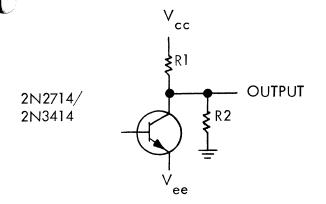

| INPUT | R1<br>C1 = | R2<br>: R3 <b>*</b> | v <sub>ee</sub> | 2N2714/<br>2N3414 |

|-------|------------|---------------------|-----------------|-------------------|

|-------|------------|---------------------|-----------------|-------------------|

# STANDARD INPUT INTERFACE

|    | LOW <sup>*</sup> | HIGH <sup>*</sup><br>LEVEL |

|----|------------------|----------------------------|

| R1 | 1.5K             | 1.5K                       |

| R2 | 1.5K             | 15K                        |

| R3 | 15K              | 47K                        |

| C1 | .001uf           | .001 uf                    |

$$0VDC \stackrel{\checkmark}{=} V \stackrel{\checkmark}{=} 0.2VDC$$

$6.0VDC \stackrel{\checkmark}{=} V \stackrel{\checkmark}{=} 8.0VDC$

|    | LOW <sup>*</sup> | HIGH*<br>LEVEL |

|----|------------------|----------------|

| R1 | 1.5K             | 1.5K           |

| R2 | 1.0K             | -              |

0VDC  $\leq$   $V_{ee} \leq 0.2$ VDC 11.5VDC  $\leq$   $V_{cc} \leq$  12.5VDC

# STANDARD OUTPUT INTERFACE

All resistors 1/4 watt, 5PCT, Metal Film; all capacitors disk ceramic, 10 PCT. Consult factory for alternate values.

- \* Low Level IC Compatible (Standard)

- \* High Level (Option)

1. Mating Connector Supplied