# HOW TO USE THE NOVA COMPUTERS

## How to use the Nova Computers

A System Reference Manual for the

Nova Supernova Nova 1200

Nova 800

Supernova SC

PRICE \$10.00

DIRECT COMMENTS CONCERNING THIS MANUAL TO

DATA GENERAL CORPORATION • SOUTHBORO, MASSACHUSETTS

DG NM-5

April 1971

Copyright © 1970, 1971 by Data General Corporation

The right to change specifications is reserved

Written for Data General Corporation by William English

Printed in the United States of America

### Contents

| 1   | INTRODUCTION                                                                                                                                                                                                            | 1-1  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1 | Instructions Instruction format 1-5                                                                                                                                                                                     | 1-4  |

| 1.2 | Memory                                                                                                                                                                                                                  | 1-6  |

| 2   | CENTRAL PROCESSOR                                                                                                                                                                                                       | 2-1  |

| 2.1 | Memory Reference Instructions<br>Move data instructions 2-5<br>Modify memory instructions 2-6<br>Jump instructions 2-7                                                                                                  | 2-2  |

| 2.2 | Arithmetic and Logical Instructions<br>Carry, shift and skip functions 2-12<br>Arithmetic and logical functions 2-14<br>Programming examples 2-17                                                                       | 2-10 |

| 2.3 | Input-Output<br>Special code-77 functions 2-26<br>Automatic program loading 2-30                                                                                                                                        | 2-21 |

| 2.4 | Program Interrupt                                                                                                                                                                                                       | 2-30 |

| 2.5 | Data Channel                                                                                                                                                                                                            | 2-38 |

| 2.6 | Processor Options<br>Real time clock 2-40<br>Power monitor and autorestart 2-41<br>Multiply-divide 2-42<br>Nova multiply-divide 2-42<br>Supernova high speed data channel 2-44<br>Memory allocation and protection 2-44 | 2-40 |

| 2.7 | Operation                                                                                                                                                                                                               | 2-50 |

| 3   | HARDCOPY EQUIPMENT                                                                                                                                                                                                      | 3-1  |

| 3.1 | Teletypewriter<br>Teletype output 3-2<br>Teletype input 3-3<br>Programming examples 3-3<br>Operation 3-5                                                                                                                | 3-1  |

| 3.2 | Paper Tape Reader                                                                                                                                                                                                       | 3-6  |

| 3.3 | Loading Programs<br>Automatic program load 3-9<br>Binary loader 3-10                                                                                                                                                    | 3-7  |

| 3.4 | Paper Tape Punch                                            | 3-11 |

|-----|-------------------------------------------------------------|------|

| 3.5 | Line Printer                                                | 3-12 |

| 3.6 | Plotter                                                     | 3-14 |

| 3.7 | Card Reader                                                 | 3-16 |

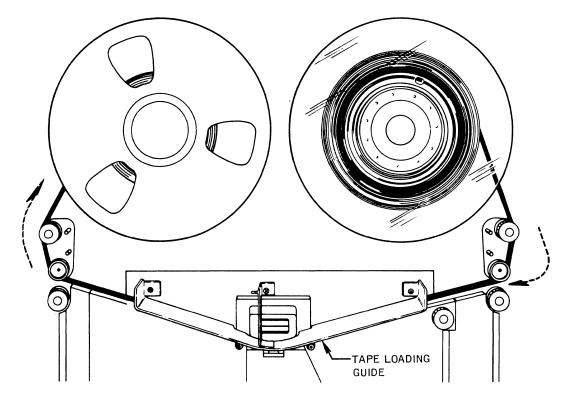

| 4   | MAGNETIC TAPE                                               | 4-1  |

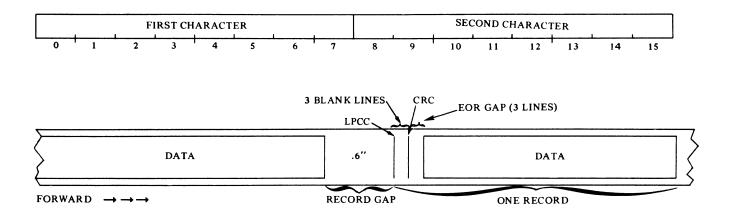

| 4.1 | Tape Format                                                 | 4-1  |

| 4.2 | Instructions                                                | 4-3  |

| 4.3 | Tape Commands                                               | 4-6  |

| 4.4 | Ampex Tape Transports                                       | 4-11 |

|     | TMZ transport 4-11                                          |      |

|     | TMX transport 4-13                                          |      |

|     | TM-16 transport 4-14                                        |      |

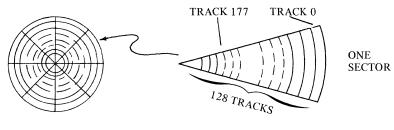

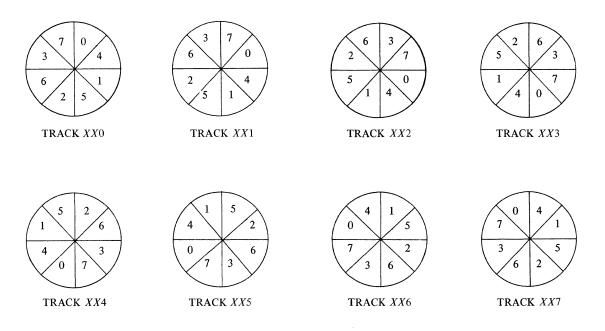

| 5   | DISK                                                        | 5-1  |

| 5.1 | Disk Format                                                 | 5-1  |

| 5.2 | Instructions                                                | 5-2  |

| 5.3 | Programming Considerations                                  | 5-5  |

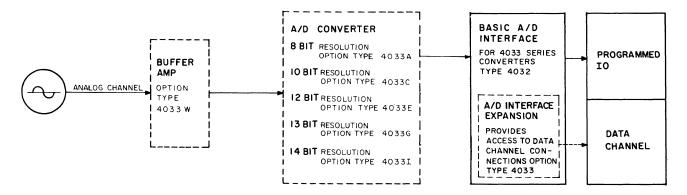

| 6   | ANALOG CONVERSION EQUIPMENT                                 | 6-1  |

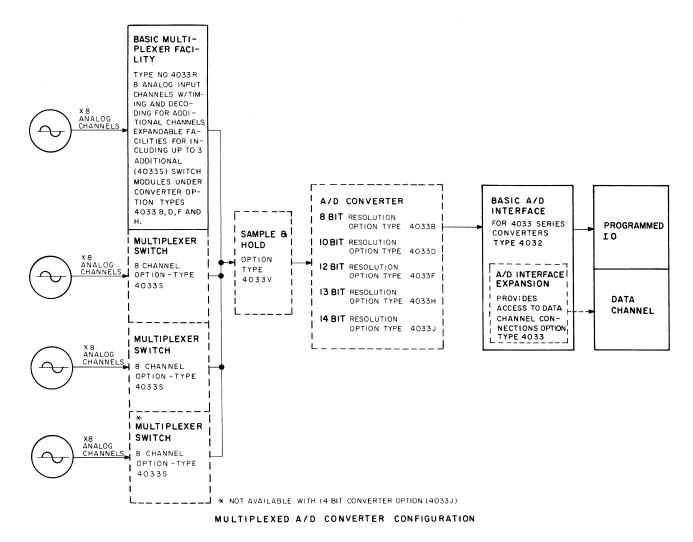

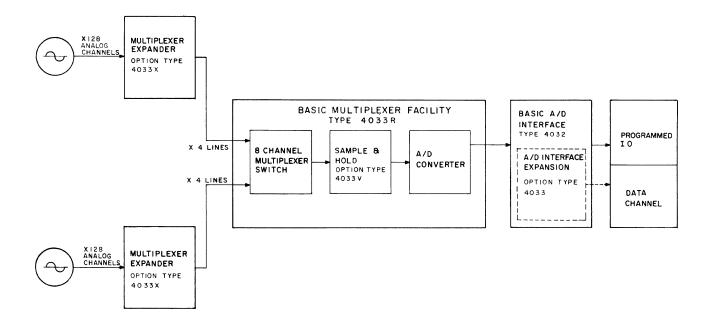

| 6.1 | A/D Conversion Equipment                                    | 6-1  |

|     | Basic A/D converter 6-2                                     |      |

|     | Multiplexed A/D converter 6-3                               |      |

|     | Multiplexer expander 6-4                                    |      |

|     | Programming the basic interface 6-4                         |      |

|     | Programming the extended interface 6-6                      |      |

|     | Physical data 6-9                                           |      |

|     | A/D conversion scaling 6-12                                 |      |

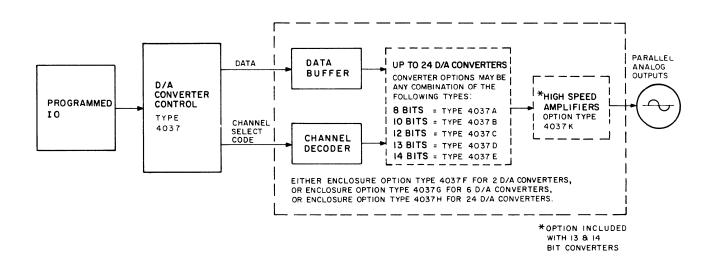

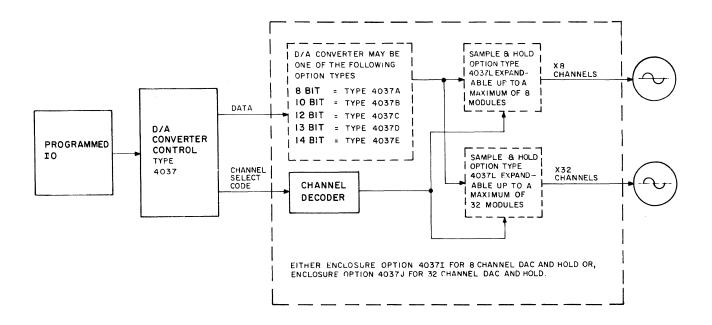

| 6.2 | D/A Conversion Equipment                                    | 6-13 |

|     | Standard D/A conversion equipment 6-13                      |      |

|     | D/A conversion equipment with sample and hold channels 6-14 |      |

|     | Physical data 6-16                                          |      |

|     | D/A conversion scaling 6-19                                 |      |

| 6.3 | Oscilloscope Control 4053                                   | 6-19 |

| 7   | DATA COMMUNICATIONS                                         | 7-1  |

| 7.1 | Communications Controller Type 4015                         | 7-1  |

|     | Receiver 7-1                                                |      |

|     | Transmitter 7-3                                             |      |

|     | Automatic answering 7-5                                     |      |

| 7.2 | Data Communications Multiplexer Type 4026                   | 7-5  |

| 7.3 | Modem Control Features 4023 and 4029                        | 7-7  |

| 7.4 | Multiprocessor Communications Adapter 4038                  | 7-9  |

|     | Receiver 7-10                                               |      |

|     | Transmitter 7-12                                            |      |

|     | Installation 7-14                                           |      |

#### APPENDICES

| A | Inter  | facing                                                                                                                                                | Al  |

|---|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

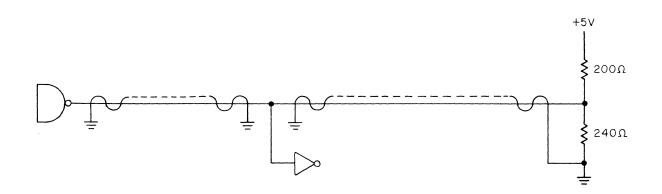

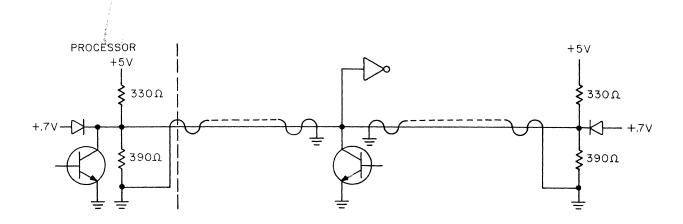

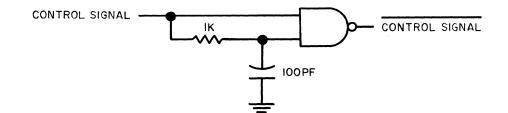

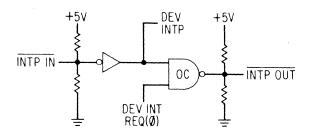

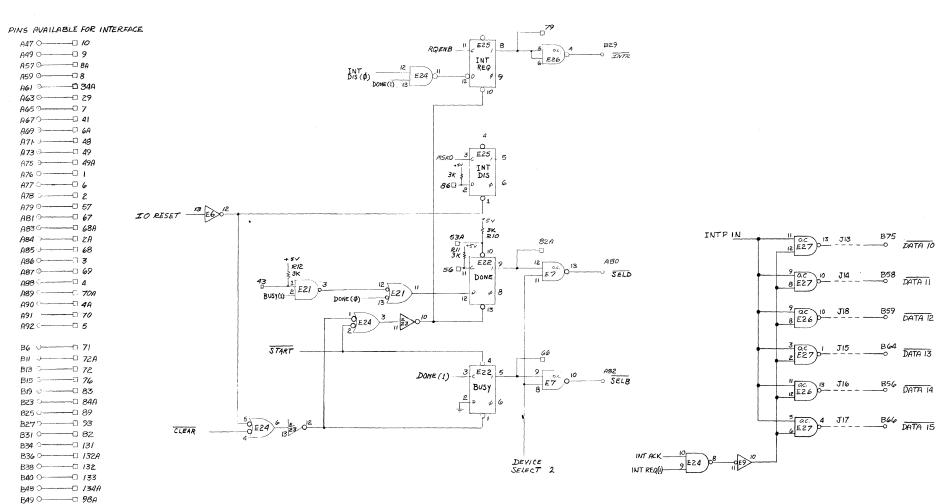

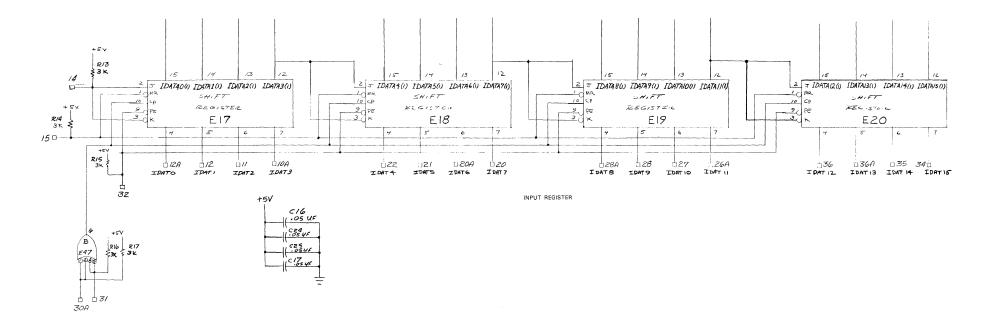

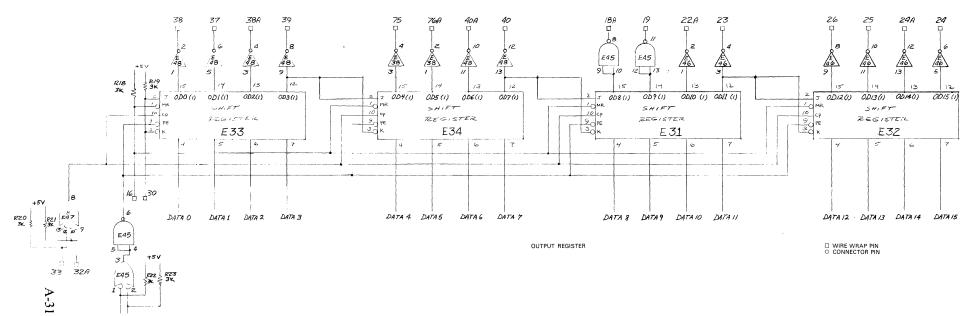

|   | Ι      | In-out Bus<br>Bus signals A3<br>Bus connections A6<br>Bus circuits A7                                                                                 | Al  |

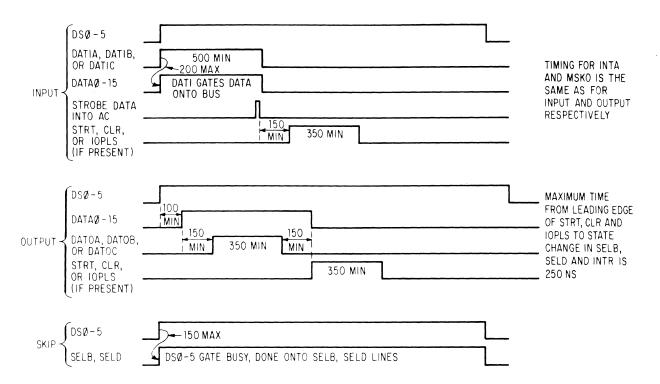

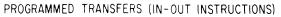

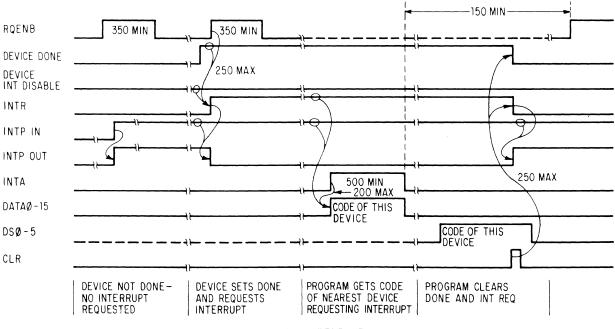

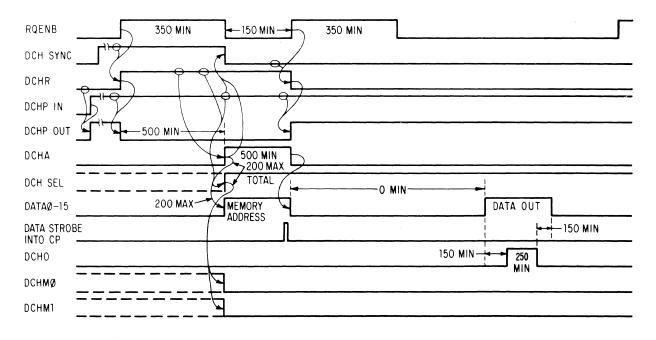

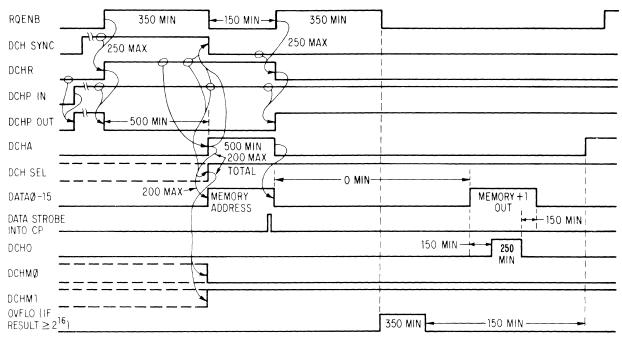

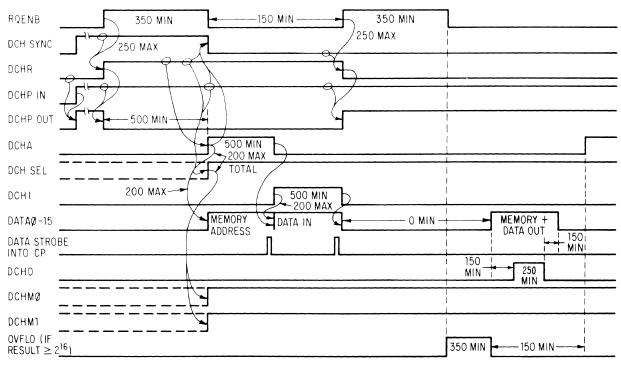

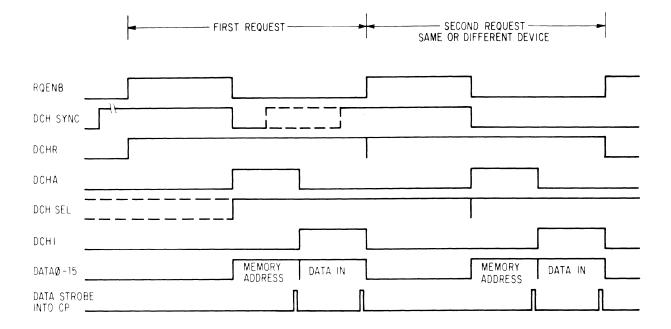

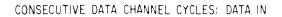

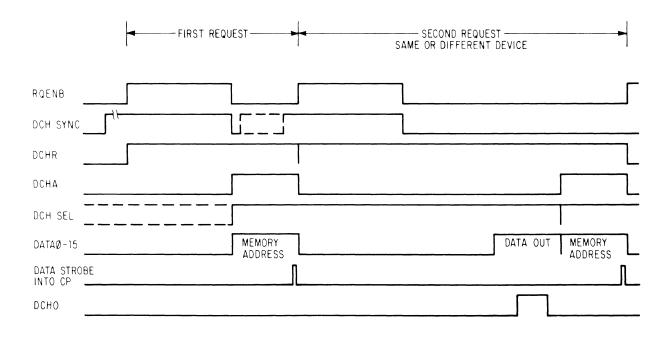

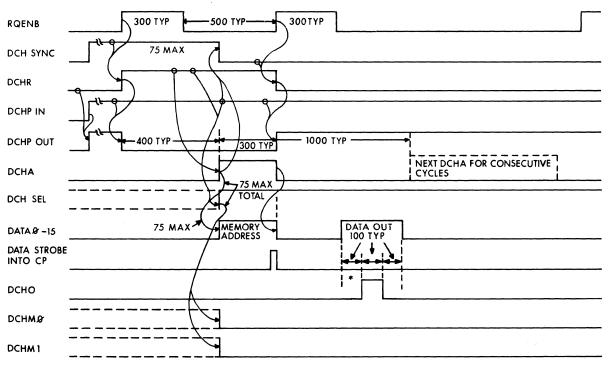

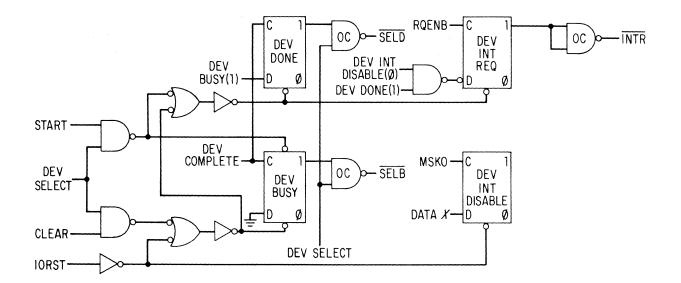

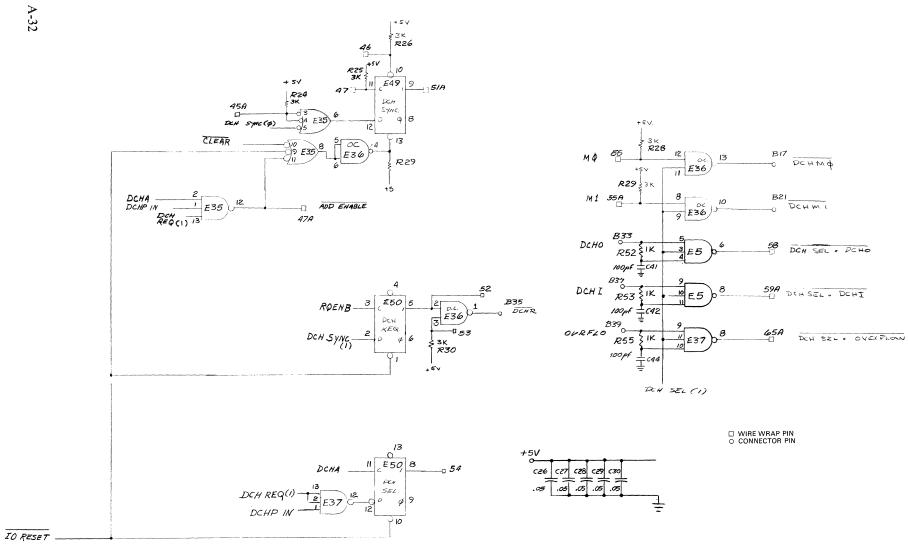

|   | II     | Interface Timing<br>Programmed transfers A11<br>Program interrupt A11<br>Standard data channel transfers A13<br>High speed data channel transfers A16 | A10 |

|   | III    | Design of Interface Equipment<br>Basic interface networks A19<br>Design examples A21                                                                  | A19 |

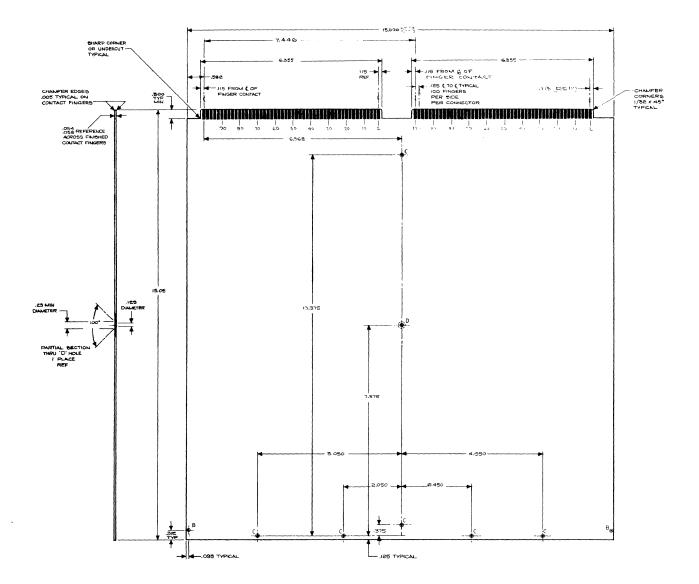

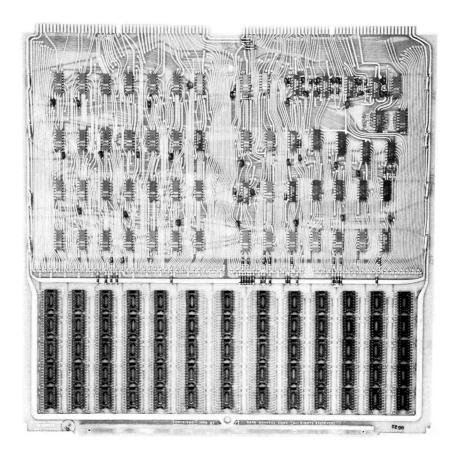

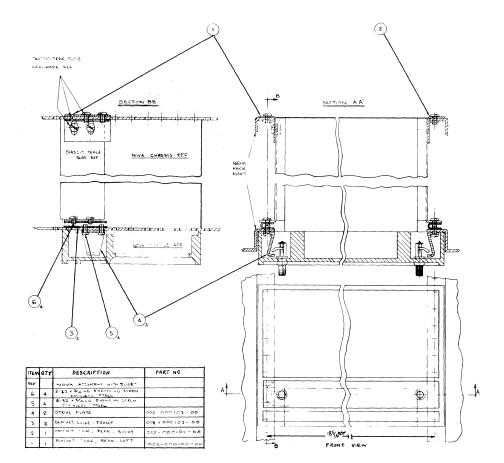

|   | IV     | Construction of Interface Equipment                                                                                                                   | A25 |

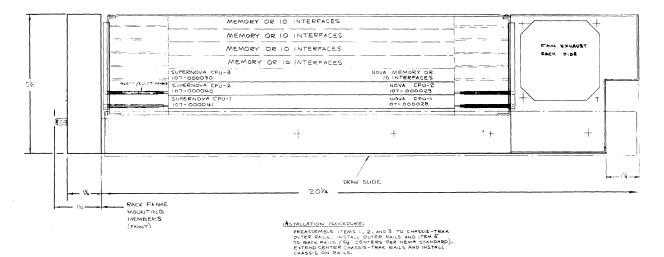

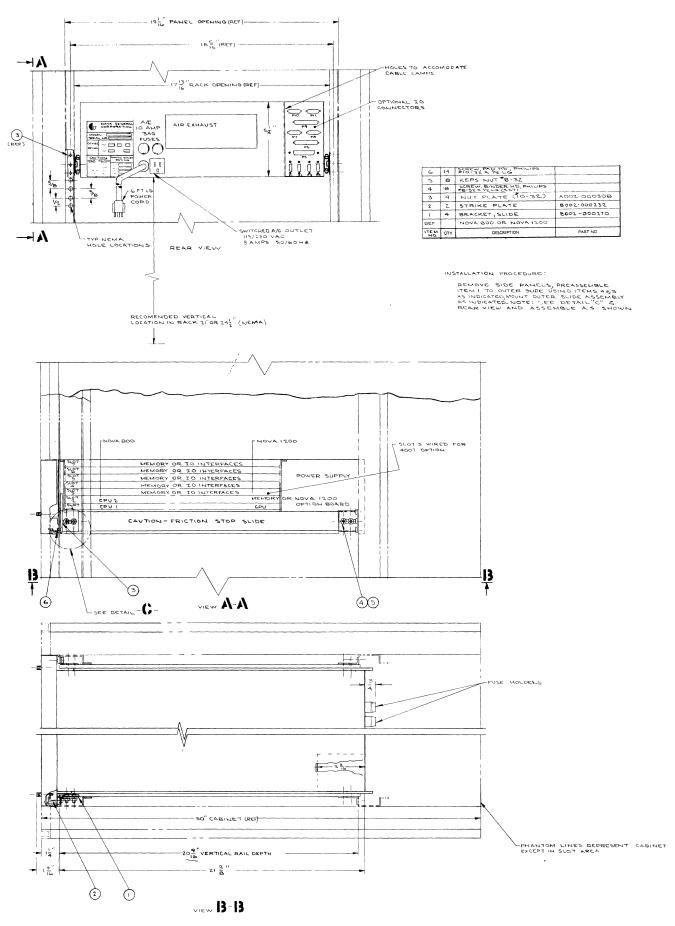

| В | Insta  | llation                                                                                                                                               | B1  |

| С | Float  | ing Point Arithmetic                                                                                                                                  | Cl  |

| D | Instru | uction Mnemonics and Timing<br>Numeric listing D2<br>Alphabetic listing D5<br>Instruction execution times D12                                         | D1  |

| Ε | In-ou  | It CodesIn-out devices E2<br>Teletype code E4                                                                                                         | E1  |

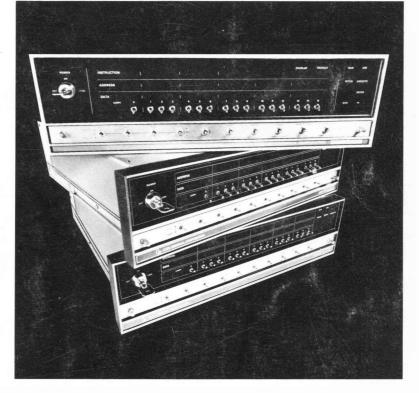

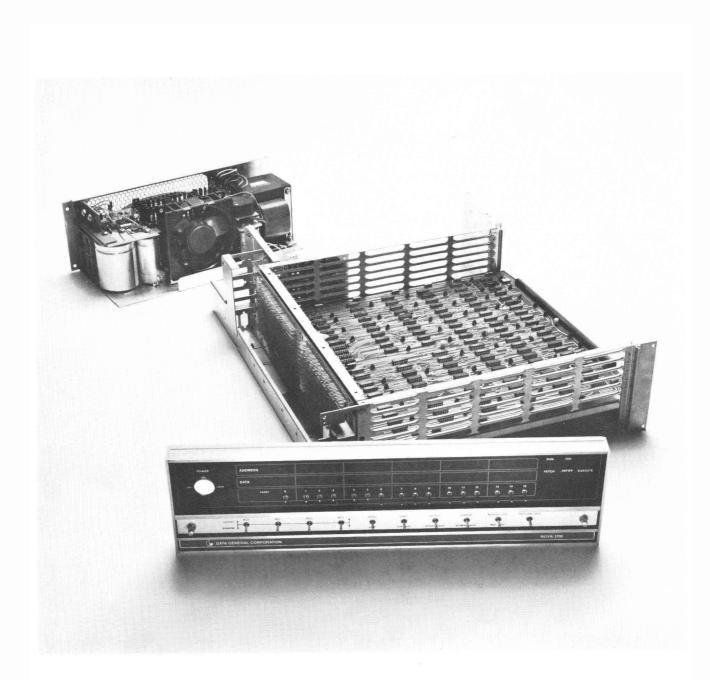

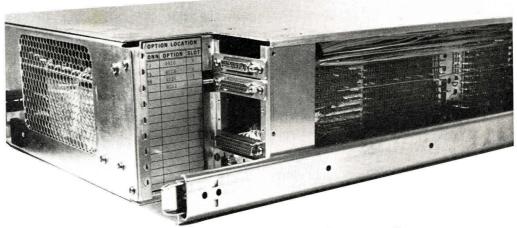

Nova 1200 front panel, chassis with central processor subassembly board, and power supply.

### Chapter I Introduction

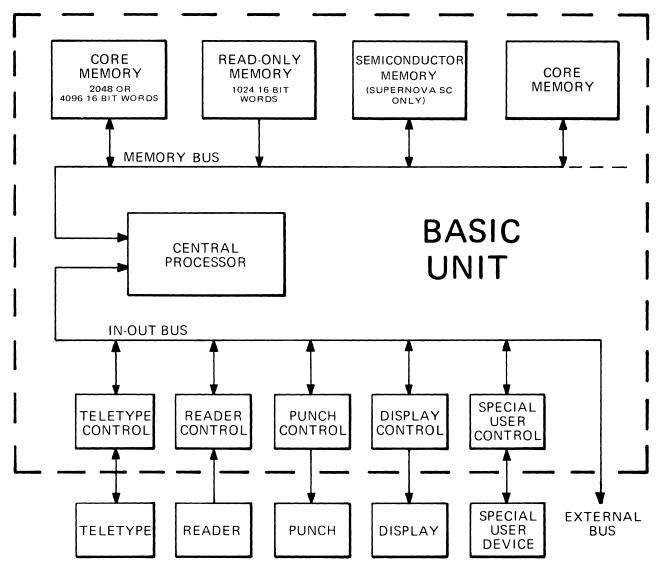

The Nova computers are general purpose computer systems with a 16-bit word length. All machines are organized around four accumulators, two of which can be used as index registers. This accumulator/index register organization provides great efficiency and ease in programming. The various machines differ from one another in features and speed, the Supernova SC being the fastest and most versatile. Programming for all machines is completely compatible except of course for programs that are time dependent.

Any Nova computer can have both alterable core memory and read-only memory, and the Supernova SC also has extremely fast semiconductor memory (in other respects the Supernova and Supernova SC are almost identical, and unless explicitly stated otherwise, any reference in this manual to the "Supernova" applies to both machines). With the console removed, a system can be operated as a hard-wired controller, whose functions can be altered simply by substituting different read-only memories.

Each computer requires only 5<sup>1</sup>/<sub>4</sub> inches mounted in a standard 19-inch rack. Processor options include real time clock, power failure detector, multiply-divide, and for the Supernova, memory allocation and protection. Available peripheral equipment includes teletypewriter, high speed paper tape reader and punch, card reader, line printer, incremental plotter, display, magnetic tape, magnetic disk, A-D and D-A conversion equipment, and data communications equipment.

The central processor is the control unit for the entire system: it governs all peripheral in-out equipment, performs all arithmetic, logical, and data handling operations, and sequences the program. It is connected to the memory by a memory bus and to the peripheral equipment by an in-out bus. The processor handles words of sixteen bits, which are stored in a memory with a maximum capacity of 32,768 words. The bits of a word are numbered 0 to 15, left to right, as are the bits in the registers that handle the words. Registers that hold addresses are fifteen bits, numbered according to the position of the address in a word, *ie* 1 to 15. Words are used either as computer instructions in a program, as addresses, or as operands, *ie* data for the program. The program can interpret an operand as a logical word, an address, a pair of 8-bit bytes, or a 16-digit signed or unsigned binary number. The arithmetic instructions operate on fixed point binary numbers, either unsigned or the equivalent signed numbers using twos complement conventions.

The processor performs a program by executing instructions retrieved from consecutive memory locations as counted by the 15-bit program counter PC. At the end of each instruction PC is incremented by one so that the next instruction is normally taken from the next consecutive location. Sequential program flow is altered by changing the contents of PC, either by incrementing it an extra time in a test skip instruction or by replacing its contents with the value specified by a jump instruction. The other internal registers of importance to the programmer are four 16-bit accumulators, AC0 to AC3. Data can be moved in either direction between any memory location and any accumulator. Although a word in memory can be incremented or decremented, all other arithmetic and logical operations are performed on operands in the accumulators, with the result appearing in an accumulator. Associated with the accumulators is the Carry flag, which indicates when a carry occurs out of bit 0 in an arithmetic instruction. The left and right halves of any accumulator can be swapped, the contents of any accumulator can be tested for a skip, and the 17-bit word contained in any accumulator combined with Carry can be rotated right or left. An instruction that references memory can address AC2 or AC3 as an index register, and transfers to and from peripheral devices are also made through the accumulators.

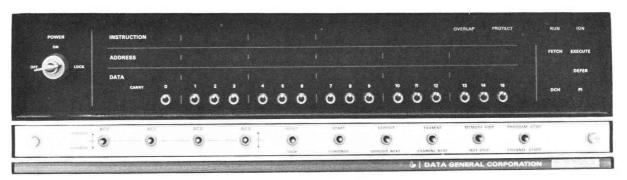

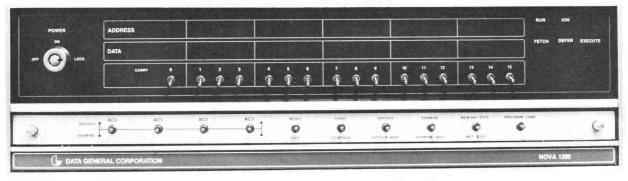

On the processor console is a set of data switches through which the operator can supply words and addresses to the program. The console also has a number of control switches that allow the operator to start

Nova Operator Console

Supernova Operator Console

Nova 800 and Nova 1200 Operator Console

and stop the program, to deposit the contents of the data switches in any memory location or accumulator, and to display the contents of any location or accumulator in the data lights. The Supernova also has switches for automatic loading when there is no program in memory; this feature is optional on the Nova 1200 and 800. The address lights display the contents of PC, the instruction lights on the Nova and Supernova display the left half of the instruction word currently being executed. The remaining lights display the Carry flag and a number of internal control conditions that are useful in program debugging.

Any instruction that references memory may address AC2 or AC3 as an index register. Instructions that move data to and from memory or the peripherals address a single accumulator as a source or destination of data while addressing a memory location or an in-out device. But the arithmetic and logical instructions do not have to reference memory; they simply address two accumulators, either or both of which may supply operands, and one of which may receive the result. Thus memory is used for storage of the program and permanent data, but 1-2

all calculations are carried out in the accumulators and intermediate results are held right in them. This reduces considerably the amount of data movement as compared with a single accumulator system, and thus saves instructions. For example, in as trivial an operation as exchanging the contents of two memory locations A and B, the multi-accumulator organization reduces the time by one third.

| Exchange with   | Exchange with    |

|-----------------|------------------|

| one accumulator | two accumulators |

| A→AC            | A→AC1            |

| AC→TEMP         | B→AC2            |

| B→AC            | AC1→B            |

| AC→A            | AC2→A            |

| TEMP→AC         |                  |

| AC→B            |                  |

Since an arithmetic or logical instruction does not contain a memory address, there are many bits that can be used for functions other than specifying the basic operation and the operands: the same instruction that adds or subtracts can also shift the result or swap its halves, test the result and/or carry for a skip, and specify whether or not the result shall actually be retained. Hence the percentage of time saved increases with the complexity of the program.

And there are advantages other than speed. The system is much more convenient to use, programming is much easier because the data being processed is much handier. The accumulators and their associated logic are essentially like the pad one uses at one's desk, whereas the memory fulfills the function of a set of reference books and a notebook kept on one's side. The results of address calculations are immediately available for index purposes to the memory reference instructions. One accumulator can be used for in-out data transmission without disturbing others being used continually for computations. Complex software routines such as multiplication, division and floating point can be performed without constantly referencing memory.

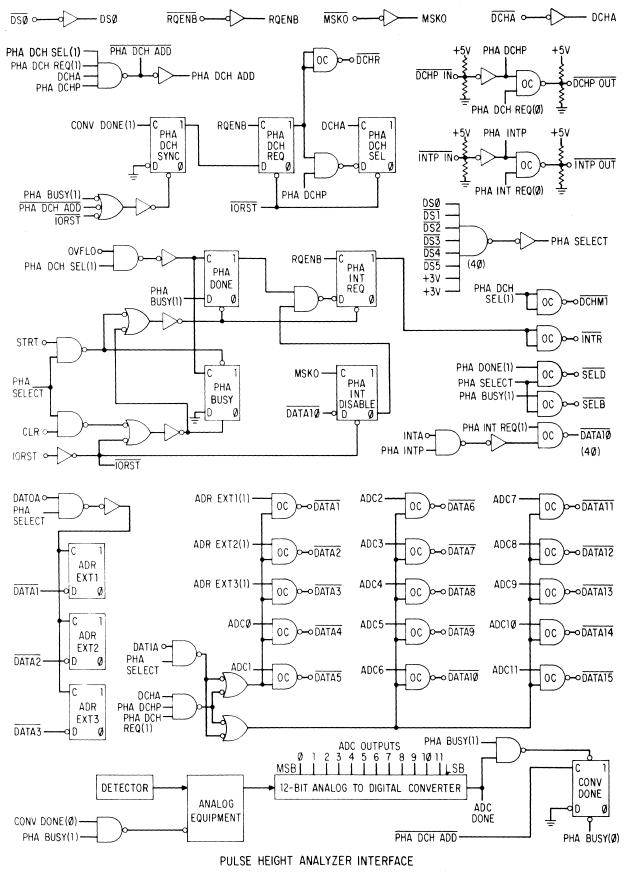

The input-output hardware allows the program to address up to sixty-two devices. A single instruction can transfer a word between an accumulator and a device and at the same time control the device operation. Included in the in-out system are facilities for program interrupts and high speed data transfers. The interrupt system facilitates processor control of the peripheral equipment by allowing any device to interrupt the normal program flow on a priority basis. The processor acknowledges an interrupt request by storing PC in location 0 and executing the instruction addressed by the contents of location 1. A high speed device, such as magnetic tape or disk, can gain direct access to memory through a data channel without requiring the execution of any instructions; the program simply pauses while access is made. The data channel logic allows the transfer of data to or from memory, incrementing of a memory word, and (in some machines) adding external data to a word already in memory. The latter two features allow such functions as pulse height analysis and signal averaging.

An option available only on the Supernova allows a number of programs to share processor time. With this option there are two modes of processor operation, supervisor and user. An executive program, which runs in supervisor mode, allocates areas of memory to the various users, write-protects (if necessary) part of any user's allocated area, schedules user programs and handles all input-output needs. Each user program is mapped into and restricted to its allocated area; and it is illegal for a user to write in a protected area, use more than two levels of indirect addressing, or give an in-out instruction. An attempt by a user to violate any of these restrictions results in a transfer of control back to the executive.

#### **1.1 INSTRUCTIONS**

The types of functions performed by instructions in most computers are the following.

- 1. Move data between memory and the operating registers.

- 2. Modify memory, usually in conjunction with a test to determine whether to alter the program sequence.

- 3. Alter the program sequence by jumping to a new location.

- 4. Perform an arithmetic or logical operation.

- 5. Test the value of a word or flag, or one word against another, to determine whether to alter the program sequence.

- 6. Transfer data to or from the peripheral equipment.

In many computers the first and fourth and the third and fifth groups overlap. In the NOVA groups 1 and 3 are unique. But groups 4 and 5 coincide: every arithmetic and logical instruction can test the result for a skip.

The following lists the registers that must be specified and the functions performed by the various instruction classes in the Nova computers.

| Move data            | One memory location, one accumulator. Either may be the source of the operation                                                                                                                                                                                                                                                               |  |  |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                      | the other is the destination.                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Modify memory        | One memory location. Increment or decrement contents; skip if result is zero.                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Jump                 | One memory location from which the next instruction is taken. A return address can be saved in AC3.                                                                                                                                                                                                                                           |  |  |  |  |  |

| Arithmetic and logic | Two accumulators. One or both may be source of operand(s). Perform arithmetic or logical function, with a bit-0 carry affecting the Carry flag as indicated. If desired, swap halves of answer or rotate it with Carry one place right or left, load result into either accumulator, and skip on condition specified for result and/or Carry. |  |  |  |  |  |

| Input-output         | One accumulator, one IO device. Transfer word in either direction between any accumulator and one of up to three registers in up to sixty-two devices. Also oper-<br>ate device as specified.                                                                                                                                                 |  |  |  |  |  |

|                      | Note: A subclass of these instructions executes no transfer and specifies only a device. The instruction either operates the device or skips on a selected condition in it.                                                                                                                                                                   |  |  |  |  |  |

Addressing. Instructions in the first three classes must address a memory location. Each instruction word contains information for determining the effective address, which is the actual address used to fetch or store the operand or alter program flow. The instruction specifies an 8-bit displacement which can directly address any location in four groups of 256 locations each. The displacement can be an absolute address, *ie* it may be used simply to address a location in page zero, the first 256 locations in memory. But it can also be taken as a signed number that is used to compute an absolute address by adding it to a 15-bit base address supplied by an index register. The instruction can select AC2 or AC3 as the index register; either of these accumulators can thus be used as an ordinary index register to vary the address computed from a constant displacement, or as a base register for a set of different displacements. The program can also select PC as the index register, so any instruction can address 256 words in its own vicinity (relative addressing).

Now the computed absolute (15-bit) address can be the effective address. However, the instruction can use it as an indirect address. *ie* it can specify a location to be used to retrieve another address. Bits 1-15 of the word read from an indirectly addressed location can be the effective address or they can be another indirect address.

Automatic Incrementing and Decrementing. The program can make use of an automatic indexing feature by indirectly addressing any memory location from 00020 to 00037 (addresses are always octal numbers). Whenever one of these locations is specified by an indirect address, the processor retrieves its contents, incre-1-4 ments or decrements the word retrieved, writes the altered word back into memory, and uses the altered word as the new address, direct or indirect. If the word is taken from locations 00020–00027, it is incremented by one; if taken from locations 00030–00037, it is decremented by one.

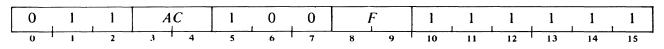

#### Instruction Format

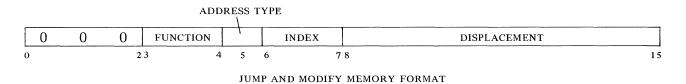

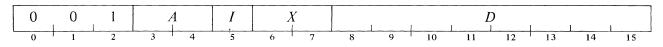

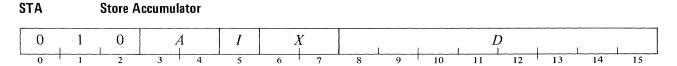

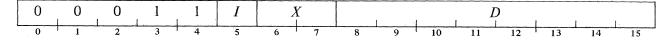

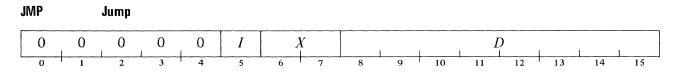

There are four basic formats for instruction words. In all but the arithmetic and logical instructions, bit 0 is 0. If bits 1 and 2 are also 0, bits 3 and 4 specify the function (jump or modify memory) and the rest of the word supplies information for calculating the effective address. Bits 8–15 are the displacement, bits 6 and 7 specify the index register if any, and bit 5 indicates the type of addressing, direct or indirect.

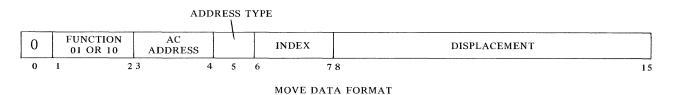

If bits 1 and 2 differ they specify a move data function. Bits 3 and 4 address an accumulator, the rest of the word is as above.

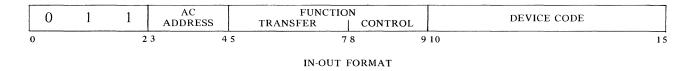

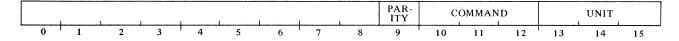

Bits 1 and 2 both being 1 indicate an in-out instruction. In this case the function is specified by bits 5-9, of which bits 5-7 indicate the direction of transfer and select one of three registers in the device. The transfer takes place between the accumulator addressed by bits 3 and 4 and the device selected by bits 10-15. Bits 8

and 9 of the function part specify an action to be performed, such as starting the device. If bits 5-7 are all 0 or all 1, there is no transfer and bits 8 and 9 specify a control or skip function respectively.

If bit 0 is 1, bits 5–7 specify an arithmetic or logical function. One operand is taken from the accumulator addressed by bits 1 and 2; a second operand, if any, from that addressed by bits 3 and 4. The rest of the word specifies the other functions that can be performed, including whether or not the result is to be loaded into the destination accumulator.

| 1 | AC<br>SOURCE<br>ADDRESS | AC<br>DESTINATION<br>ADDRESS | FUNCTION | SECONDARY FUNCTIONS<br>ROTATE, SWAP, CARRY, NO LOAD, SKIP |

|---|-------------------------|------------------------------|----------|-----------------------------------------------------------|

| 0 | 1 2                     | 23 4                         | 5        | 7 8                                                       |

ARITHMETIC AND LOGIC FORMAT

The Nova assembly programs recognize a number of mnemonics and other initial symbols that facilitate constructing complete instruction words and organizing them into a program [Appendix D]. In particular there are three-letter mnemonics for the 2- and 3-bit functions; these mnemonics also represent whatever bits are constant for the class the instruction is in. Eg the modify memory mnemonic

#### ISZ

assembles as 010000, the arithmetic mnemonic

SUB

assembles as 102400.

#### Note

Throughout this manual all numbers representing instruction words, register contents, codes and addresses are always octal, and any numbers appearing in program examples are octal unless otherwise specified. Computer words are represented by six octal digits wherein the left one is always 0 or 1 representing the value of bit 0. The ordinary use of numbers in the text to specify quantities of objects, such as words or locations, to count steps in an operation, or to specify word or byte lengths, bit positions, etc. employs standard decimal notation.

Characters are suffixed to the basic mnemonic to specify the control part of an IO function and most of the secondary functions in the arithmetic and logical class. The displacement and addresses of accumulators and index registers are separated from the mnemonic by a space and from each other by commas. Anything written at the right of a semicolon in a program listing is commentary that explains the program but is not part of it.

#### **1.2 MEMORY**

From the addressing point of view, the entire memory is a set of contiguous locations whose addresses range from zero to a maximum dependent upon the capacity of the particular installation. In a system with the greatest possible capacity, the largest address is octal 77777, decimal 32,767. But the memory is actually made up of a number of core or semiconductor memory modules, each having a capacity of 1024, 2048 or 4096 words, and can also contain read-only memory modules. The latter may be used for storage of pure (unalterable) programs and constants; they usually contain 1024 words but may be of any size. An address supplied by the program is actually decoded in two parts, the more significant to select a memory module and the less significant to select a location within that module, but this need not concern the programmer. From the point of view of the programmer, memory module size is irrelevant, and the read-only memory differs from the others only in that its contents cannot be altered electrically. Common arithmetic and in-out routines are available in standard read-only memory modules; others are available on a custom basis.

The basic processor cycle time of the Nova is 2.6 microseconds with a core memory, 2.4 microseconds with a read-only memory. The Nova 1200 and 800 have cycle times of 1200 and 800 nanoseconds respectively. The Supernova cycle time is 800 nanoseconds with core, but only 300 nanoseconds with semiconductor or read-only memory.

Memory Restrictions. The use of certain locations is defined by the hardware.

- 0–1 Program interrupt locations

- 20–27 Autoincrementing locations

- 30–37 Autodecrementing locations

- 1-6

### **Chapter II Central Processor**

This chapter describes all computer instructions but does not discuss the special effects of the in-out instructions when they address specific peripheral devices. The chapter treats the memory reference instructions and the arithmetic and logical instructions in detail, presents a general discussion of input-output, and describes the effects of the in-out instructions on processor elements, including the program interrupt, the real time clock, multiply-divide, and the memory allocation and protection option. Effects of in-out instructions on particular peripheral devices are discussed with the devices in the remaining chapters.

In the description of each instruction, the mnemonic and name are at the top, the format is in a box below them. The mnemonic assembles to the word in the box, where bits in those parts of the word represented by letters assemble as 0s. The letters indicate portions that must be added to the mnemonic to produce a complete instruction word.

Instruction execution times depend both on the processor and the type of memory; they are therefore given in a table at the end of Appendix D.

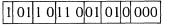

**Twos Complement Conventions.** The signed numbers used as displacements in referencing memory and as operands for the arithmetic instructions utilize the twos complement representation for negatives. In a word or byte used as a signed number, the leftmost bit represents the sign, 0 for positive, 1 for negative. In a positive number the remaining bits are the magnitude in ordinary binary notation. The negative of a number is obtained by taking its twos complement, with the sign bit included in the operation as though it were a more significant magnitude bit. If x is an n-digit binary number, its twos complement is  $2^n-x$ , and its ones complement is  $(2^n-1)-x$ , or equivalently  $(2^n-x)-1$ . Subtracting a number from  $2^n-1$  (*ie*, from all 1s) is equivalent to performing the logical complement, *ie* changing all 0s to 1s and all 1s to 0s. Therefore, to form the twos complement one takes the logical complement — usually referred to merely as the complement — of the entire word including the sign, and adds 1 to the result. A displacement of 89 and its negative would look like this in bits 8–15 of an instruction word where bit 8 is the sign.

| +8910 | = | +1318 | = |         | 01 01 | 1 001 |

|-------|---|-------|---|---------|-------|-------|

|       |   |       |   | <u></u> | 8     | 15    |

| -8910 | = | -1318 | = |         | 10 10 | 0 111 |

|       |   |       |   |         | 8     | 15    |

The same numbers used as operands in the accumulators would look like this.

$$+89_{10} = +131_8 = 00000001011001_{0}$$

$$-89_{10} = -131_8 = 111111110100111_{0}$$

Bit 0 is now the sign and bits 1-8 are not significant. It is thus evident that expanding an integer into a full word is accomplished simply by filling out the word to the left with the sign.

Zero is represented by a number containing all 0s; complementing this number produces all 1s, and adding 1 to that produces all 0s again. So there is only one zero representation and its sign is positive. Moreover there is one more negative number than there are nonzero positive numbers. Hence there are 256 displacements in an octal range -200 to +177. (The most negative number has a 1 in only the sign position.)

#### 2.1 MEMORY REFERENCE INSTRUCTIONS

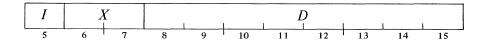

Bits 5-15 have the same format in every memory reference instruction whether the effective address is used for storage or retrieval of an operand or to alter program flow. Bit 5 is the indirect bit, bits 6 and 7 are the

index bits, and bits 8–15 are the displacement. The effective address E of the instruction depends on the values of I, X, and D. If X is 00, D addresses one of the first 256 memory locations, *ie* D is a memory address in the range 00000–00377. This group of locations is referred to as page zero.

If X is nonzero, D is a displacement that is used to produce a memory address by adding it to the contents of the register specified by X. The displacement is a signed binary integer in twos complement notation. Bit 8 is the sign (0 positive, 1 negative), and the integer is in the octal range -200 to +177 (decimal -128 to +127). If X is 01, the instruction addresses a location relative to its own position, *ie* D is added to the address in PC, which is the address of the instruction being executed. This is referred to as relative addressing. If X is 10 or 11 respectively, it selects AC2 or AC3 as a base register to which D is added.

| X  | Derivation of address                                                                                                      |

|----|----------------------------------------------------------------------------------------------------------------------------|

| 00 | Page zero addressing. <i>D</i> is an address in the range 00000–00377.                                                     |

| 01 | Relative addressing. D is a signed displace-<br>ment ( $-200$ to $+177$ ) that is added to the<br>address in PC.           |

| 10 | Base register addressing. <i>D</i> is a signed displacement $(-200 \text{ to } +177)$ that is added to the address in AC2. |

| 11 | Base register addressing. D is a signed dis-<br>placement ( $-200$ to $+177$ ) that is added<br>to the address in AC3.     |

If I is 0, addressing is direct, and the address already determined from X and D is the effective address used in the execution of the instruction. Thus a memory reference instruction can directly address 1024 locations: 256 in page zero, and three sets of 256 in the octal range 200 less than to 177 greater than the address in PC, AC2 and AC3. If I is 1, addressing is indirect, and the processor retrieves another address from the location 2-2

| Ι | A    |   |

|---|------|---|

| 0 | 1 15 | 5 |

specified by the address already determined. In this new word bit 0 is the indirect bit: bits1-15 are the effective address if bit 0 is 0; otherwise they specify a location for yet another level of address retrieval. This process continues until some referenced location is found with a 0 in bit 0; bits 1-15 of this location are the effective address *E*.

If at any level in the effective address calculation an address word is fetched from locations 00020–00037, it is automatically incremented or decremented by one, and the new value is both written back in memory and used either as the effective address or for the next step in the calculation depending on whether bit 0 is 0 or 1. Addresses taken from locations 00020–00027 are incremented, those from locations 00030–00037 are decremented.

Specific examples illustrating the various addressing methods are given on the next two pages.

The set of all addresses is cyclic with respect to the operations performed in an effective address calculation; regardless of the true sum or difference in any step, only the low order fifteen bits are used as an address. Hence the next address beyond 77777 is 00000, the next below 00000 is 77777.

#### CAUTION

Incrementing 77777 or decrementing 00000 changes the state of the indirect bit in the address word stored back in memory.

Programming Conventions. All memory reference functions are represented by three-letter mnemonics; eg

ISZ

assembles as 010000. For addressing page zero the displacement is simply an address. Thus

ISZ 344

assembles as 010344. When this word is executed as an instruction it increments the word in location 00344 and skips the next instruction if the incremented word is zero. For relative or base register addressing the displacement is a twos complement integer.

ISZ - 34,2

assembles as 011344 (0 001 001 011 100 100), in which bits 8-15 have the same configuration as in the previous example, but this time the instruction specifies a location whose address is  $34_8$  less than the address in AC2.

The initial symbol @ preceding the displacement places a 1 in bit 5 to produce indirect addressing. The examples given above use direct addressing, but

ISZ @ - 34,2

assembles as 013344 (0 001 011 011 100 100), and produces indirect addressing.

For memory reference with an accumulator, the AC address precedes the memory address information and is terminated by a comma. Eg

LDA

$$3, -34, 2$$

assembles as 035344 (0 011 101 011 100 100).

The assembler also allows the following addressing conventions. A period represents the current address, *ie* the address of the location containing the instruction being executed. Thus

LDA 3,.+6

is equivalent to

LDA 3,6,1

A colon following a symbol indicates that it is a symbolic location name.

A: ADD 2,3

indicates that the location that contains ADD 2,3 may be addressed symbolically as A. The assembler assigns a 15-bit value to the label A. When A is used in a statement such as

LDA 2,A+6

the treatment depends on the value of the expression in which A appears. In this case if A + 6 < 00400 its low order eight bits are simply placed in the displacement part of the instruction word and X is set to 00. If A + 6 is within range of PC, the indicated location is represented as a displacement relative to PC. Otherwise the assembler indicates an error as location A + 6 cannot be directly addressed by the instruction.

Addressing Examples. Suppose the following registers contain the numbers listed.

| Register | Contents |

|----------|----------|

| 6        | 100015   |

| 12       | 000035   |

| 15       | 000017   |

| 17       | 000023   |

| 23       | 000011   |

| AC3      | 000015   |

Now if the program executes the instruction

LDA 1,6

which loads AC1 from location 6, AC1 receives the number 100015. AC1 holds the same number after

is executed (effective address = C(AC3) - 7 = 15 - 7 = 6). But

LDA 1,@6

which indirectly addresses location 6, which in turn indirectly addresses location 15, which directly addresses location 17, loads 23 into the accumulator. AC1 also contains 23 following execution of

LDA 1,@15

On the other hand, AC1 contains 17 after

LDA 1,15

or

is executed. Now

LDA 1,6,3

does not address location 6; it addresses 23 (C(AC3)+6=15+6=23) and thus loads 11 into AC1. Note that addressing an autoincrementing location directly does not alter its contents; AC1 simply receives its contents as an operand. AC1 also receives 11 from

LDA 1,23

or

LDA 1,(a 17

But giving

LDA 1.(a 23

or

LDA 1, (*a* 6, 3

replaces the contents of location 23 with the number 12 and loads 35 (the contents of location 12) into AC1.

#### **Move Data Instructions**

These two instructions move data between memory and the accumulators. In the descriptions of all memory reference instructions, E represents the effective address.

#### LDA Load Accumulator

Load the contents of location E into accumulator A. The contents of E are unaffected, the original contents of A are lost.

Store the contents of accumulator A in location E. The contents of A are unaffected, the original contents of E are lost.

#### **Modify Memory Instructions**

These two instructions alter a memory location and test the result for a skip. They are used to count loop iterations or successively modify a word for a series of operations.

#### ISZ Increment and Skip if Zero

| 0 | 0 | 0 | 1 | 0 | Ι | 2 | Y   |   |   |    |    | Ð  |      |    |    |

|---|---|---|---|---|---|---|-----|---|---|----|----|----|------|----|----|

|   | 1 | 1 |   |   |   |   |     |   |   |    |    | 1  |      | 1  |    |

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | ' 7 | 8 | 9 | 10 | 11 | 12 | 1 13 | 14 | 15 |

Add 1 to the contents of location E and place the result back in E. Skip the next instruction in sequence if the result is zero.

#### DSZ Decrement and Skip if Zero

Subtract 1 from the contents of location E and place the result back in E. Skip the next instruction in sequence if the result is zero.

Consider a block of thirty words in locations 2000–2035 that we wish to move to locations 5150–5205 but in reverse order. We could autoincrement through one set, autodecrement through the other, and decrement a control count to determine when the block transfer is complete.

|       | LDA | 0,CNT   | ;Set up autoincrement location   |

|-------|-----|---------|----------------------------------|

|       | STA | 0,21    |                                  |

|       | LDA | 0,CNT+1 | ;Set up autodecrement location   |

|       | STA | 0,35    |                                  |

| LOOP: | LDA | 0,@21   | ;Get a word                      |

|       | STA | 0,@35   | ;Store it                        |

|       | DSZ | CNT+2   | ;Count down word count           |

|       | JMP | LOOP    | ;Jump back for next word         |

|       |     |         | ;Skip to here when count is zero |

|       | •   |         |                                  |

| CNT: | 001777 | ;1 before source block        |

|------|--------|-------------------------------|

|      | 005206 | ;1 after destination block    |

|      | 000036 | ;Word count: $30_{10} = 36_8$ |

Of course we could just as well put 177742 (-36) in CNT + 2 and replace the DSZ with an ISZ.

#### **Jump Instructions**

These two instructions allow the programmer to alter the normal program sequence by jumping to an arbitrary location. They are especially useful for calling and returning from subroutines.

Load E into PC. Take the next instruction from location E and continue sequential operation from there.

| J | SR |   | Jump to | o Subro | utine |   |   |   |   |   |    |    |    |    |    |    |

|---|----|---|---------|---------|-------|---|---|---|---|---|----|----|----|----|----|----|

| ſ | 0  | 0 | 0       | 0       | 1     | Ι | ) | Y |   |   |    | L  | )  | 1  |    |    |

| - | 0  | 1 | 2       | 3       | 4     | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Load an address one greater than that in PC into AC3 (hence AC3 receives the address of the location following the JSR instruction). Load E into PC. Take the next instruction from location E and continue sequential operation from there. The original contents of AC3 are lost.

NOTE: The effective address calculation is completed before PC+1 is loaded into AC3. Thus a JSR that specifies AC3 as a base register does execute properly; *ie* the previous contents of AC3 are used in the address calculation.

The usual procedure for calling a subroutine is to give a JSR whose effective address is the starting location of the routine. Since PC + 1 is saved in AC3, a subsequent return can be made to the location following the JSR simply by giving a JMP 0,3. Note also that PC + 1 is saved in an accumulator. Hence the subroutine can be reentrant (pure), *ie* memory is not modified by the act of calling it. If we wish to use AC3 in the subroutine, we can store the return address in a convenient place in page zero, say location B, with an STA 3,B and then return with a JMP (*a* B.

A convenient way to handle a number of subroutines that are called frequently is to store their starting addresses in page zero. Suppose we have subroutines starting at locations U, V, W, X, .... If we store these 15-bit addresses at locations UC, VC, WC, XC, ... respectively in page zero, then we can call a given routine, say the one beginning at X, simply by giving a JSR (a XC.

Consider a print subroutine that we wish to use to output fifty words beginning at TAB. The routine begins at PRT, which address is stored in PRTC in page zero. Our main program would contain this.

> JSR @PRTC ;Return here . . .

We use AC2 as a base register for counting through the table and AC0 to output the data. The starting address of the table is in TAB1, which is in the vicinity of PRT. The subroutine might look something like this.

| PRT:  | LDA | 2, <b>TAB</b> 1 | ;Set up AC2 as base for table               |

|-------|-----|-----------------|---------------------------------------------|

|       | LDA | 0,0,2           | ;Load word for output into AC0              |

|       | •   | * <sup>75</sup> | ;IO part of routine here                    |

|       | • 2 |                 |                                             |

|       | ISZ | PRT+1           | ;Increment displacement in load instruction |

|       | DSZ | CNT             | ;Done yet?                                  |

|       | JMP | PRT+1           | ;No, get next word                          |

|       | JMP | 0,3             | ;Yes, return by AC3                         |

| TAB1: | TAB |                 |                                             |

| CNT:  | 62  |                 | $;62_8 = 50_{10}$                           |

This routine is incomplete as it destroys itself; to be used again the displacement in location PRT+1 must be changed back to zero. The routine would be faster if we replaced the ISZ with an arithmetic instruction that increments AC2, thus using AC2 as an index register and leaving the LDA displacement alone (it would also be complete as AC2 is set up each time the subroutine is called). It would be even faster if we deleted the ISZ, stored the address TAB-1 in an autoincrementing location, say 23, and loaded AC0 with

> LDA 0,@23

Argument Passing. Suppose we have an arithmetic subroutine that operates on arguments in AC0 and AC1, leaving the result in AC1. The subroutine call looks like this:

|        | JSR         | VS1            | ;Call with arguments in ACO, AC1 |

|--------|-------------|----------------|----------------------------------|

|        |             |                | ;Return here with result in AC1  |

| the su | broutine lo | oks like this: |                                  |

|        |             |                |                                  |

VS1:

and

JMP 0.3

1100

IGD

In the above the program would have to load the accumulators before calling the routine. Now it is often convenient for the program simply to supply the arguments (or the addresses of the locations that contain them) along with the call and have the subroutine take care of the data transfers. With this version the program gives the arguments in the two memory locations immediately following the JSR,

;Arithmetic operations

:Return to call + 1

| JSR | VS2 |                                 |

|-----|-----|---------------------------------|

|     |     | ;Argument 1                     |

|     |     | ;Argument 2                     |

|     |     | ;Return here with result in AC1 |

|     |     |                                 |

2-8

and the return is made to the location following the second argument with the result in AC1.

| VS2: | LDA | 0,0,3 | ;Pick up argument 1 |

|------|-----|-------|---------------------|

|      | LDA | 1,1,3 | ;Pick up argument 2 |

|      | • . |       |                     |

|      | •   |       |                     |

|      | JMP | 2,3   | ;Return to call + 3 |

This version is called with the addresses of the arguments following the JSR; otherwise it is the same as version 2.

|      | JSR | VS3    |                        |

|------|-----|--------|------------------------|

|      |     |        | ;Address of argument 1 |

|      | ••• |        | ;Address of argument 2 |

|      | ••• |        |                        |

|      |     |        |                        |

|      | •   |        |                        |

| VS3: | LDA | 0,@0,3 | ;Pick up argument 1    |

|      | LDA | 1,@1,3 | ;Pick up argument 2    |

|      |     |        |                        |

|      | •   |        |                        |

|      | JMP | 2,3    | ;Return to call + 3    |

1

VS4

The next version is the same as version 3 except that the result replaces the second argument in memory.

|    | JSR   | VS4    |                                   |

|----|-------|--------|-----------------------------------|

|    |       |        | ;Address of argument 1            |

|    | •••   |        | ;Address of argument 2 and result |

|    | • • • |        |                                   |

|    | •     |        |                                   |

|    | •     |        |                                   |

| ł: | LDA   | 0,@0,3 | ;Pick up arguments                |

|    | LDA   | 1,@1,3 |                                   |

|    |       |        |                                   |

|    | •     |        |                                   |

|    | STA   | 1,@1,3 | ;Store result                     |

|    | JMP   | 2,3    |                                   |

|    |       |        |                                   |

The final version is the same as the fourth but AC0 and AC1 are not disturbed by its execution. The call is exactly the same as for VS4.

| VS5: | STA | 0,TM0  | ;Save ACs          |

|------|-----|--------|--------------------|

|      | STA | 1,TM1  |                    |

|      | LDA | 0,@0,3 | ;Pick up arguments |

|      | LDA | 1,@1,3 |                    |

|      | •   |        |                    |

|      | •   |        |                    |

|      | •   |        |                    |

|      | STA | 1,@1,3 | ;Store result              |

|------|-----|--------|----------------------------|

|      | LDA | 0,TM0  | ;Restore ACs               |

|      | LDA | 1,TM1  |                            |

|      | JMP | 2,3    |                            |

| TMO: | 0   |        | ;Temporary storage for ACs |

| TM1: | 0   |        |                            |

|      |     |        |                            |

#### 2.2 ARITHMETIC AND LOGICAL INSTRUCTIONS

To perform logical operations the hardware interprets operands as logical words. For arithmetic operations, operands are treated as 16-bit unsigned numbers, with a range of 0 to  $2^{16}$ -1. The program however can interpret them as signed numbers in twos complement notation as described at the beginning of this chapter. It is a property of twos complement arithmetic that operations on signed numbers using twos complement conventions are identical to operations on unsigned numbers; in other words the hardware simply treats the sign as a more significant magnitude bit. Suppose an accumulator contains this binary configuration:

| 1 | 000 | 000 | 001 | 011 | 001 |  |

|---|-----|-----|-----|-----|-----|--|

| 0 |     |     |     |     | 15  |  |

As an unsigned number this would be equivalent to

$100131_8 = 32857_{10}$

whereas interpreted as a signed number using twos complement notation it would be

$$-77647_8 = -32679_{10}$$

Insofar as processor operations are concerned, it makes no difference which way the programmer interprets the contents of the accumulators provided only that he is consistent.

Numbers in twos complement notation are symmetrical in magnitude about a single zero representation so all even numbers both positive and negative end in 0, all odd numbers in 1 (a number all 1s represents -1). If ones complements were used for negatives, one could read a negative number by attaching significance to the 0s instead of the 1s. In twos complement notation each negative number is one greater than the complement of the positive number of the same magnitude, so one can read a negative number by attaching significance to the rightmost 1 and attaching significance to the 0s at the left of it (the negative number of largest magnitude has a 1 in only the sign position). Assuming the binary point to be stationary, 1s may be discarded at the left in a negative integer, just as leading 0s may be dropped in a positive integer; equivalently an integer can be extended to the left by prefixing 1s or 0s respectively (*ie* by prefixing the sign). In a negative (proper) fraction, 0s may be discarded at the right; as long as only 0s are discarded, the number remains in twos complement form because it still has a 1 that possesses significance; but if a portion including the rightmost 1 is discarded, the remaining part of the fraction is now a ones complement. Truncation of a negative number thus increases its absolute value.

The computer does not keep track of a binary point; the programmer must adopt a point convention and shift the magnitude of the result to conform to the convention used. Two common conventions are to regard a number as an integer (binary point at the right) or as a proper fraction (binary point at the left); 2-10 in these two cases the range of signed numbers represented by a single word is  $-2^{15}$  to  $2^{15}-1$  or -1 to  $1-2^{-15}$ .

Since each bit position represents a binary order of magnitude, shifting a number is equivalent to multiplication by a power of 2, provided of course that the binary point is assumed stationary. Shifting one place to the left multiplies the number by 2. A 0 should be entered at the right, and no information is lost if the sign bit remains the same — a change in the sign indicates that a bit of significance has been shifted out. Shifting one place to the right divides by 2. Truncation occurs at the right, and a bit equal to the sign must be entered at the left.

Associated with the accumulators is the Carry flag, which is used to detect a carry out of bit 0 in an arithmetic operation. The circumstances that generate a carry out of the most significant bit are obvious when dealing with unsigned numbers. If addition or incrementing increases a number beyond  $2^{16}-1$ , a carry is produced. In subtraction the condition is the same if instead of subtracting we add the complement of the subtrahend and add 1 to the result (subtraction is performed by adding the twos complement). In terms of the original operands the subtraction A-B produces a carry if  $A \ge B$ . Forming the twos complement of zero generates a carry, for complementing zero produces a word containing all 1s, and adding 1 to that produces all 0s again plus a carry. The statement of the conditions given above if the numbers are simply interpreted as unsigned. In any event the complete conditions that produce a carry for numbers signed or unsigned are given in the instruction descriptions.

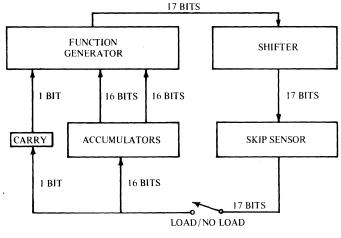

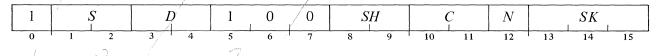

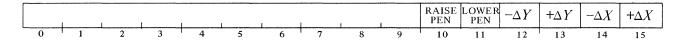

Arithmetic and Logical Processing. The logical organization of the arithmetic unit is illustrated below. Each instruction specifies one or two accumulators to supply operands to the function generator, which performs the function specified by the instruction. The function generator also produces a carry bit whose value depends upon three quantities: a base value specified by the instruction, the function performed, and the result obtained. The base value may be derived from the Carry flag. or the instruction may specify an independent value.

ORGANIZATION OF ARITHMETIC UNIT

The 17-bit output of the function generator, comprising the carry bit and the 16-bit function result, then goes to the shifter. Here the 17-bit result can be rotated one place right or left, or the two 8-bit halves of the 16-bit function result can be swapped without affecting the carry bit. The 17-bit shifter output can then be tested for a skip; the skip sensor can test whether the carry bit or the rest of the 17-bit word is or is not equal to zero. Finally the 17-bit shifted word can be loaded into Carry and one of the accumulators selected by the instruction. Note however that loading is not necessary: an instruction can perform a complicated arithmetic and shifting operation and test the result for a skip without affecting Carry or any accumulator.

#### **Carry, Shift and Skip Functions**

An instruction that has a 1 in bit 0 performs one of eight arithmetic and logical functions as specified by bits 5-7 of the instruction word. The function, which may be anything from a simple move to a subtraction, always uses the contents of the accumulator specified by bits 1 and 2; and if a second operand is required, it comes from the accumulator addressed by bits 3 and 4.

| 1 | AC<br>SOURCE<br>ADDRESS |   | A<br>DESTIN<br>ADD | - | FUNCTION |   | SHIFT |   | CARRY |    | NO<br>LOAD | SKIP |    |    |    |

|---|-------------------------|---|--------------------|---|----------|---|-------|---|-------|----|------------|------|----|----|----|

| 0 | 1                       | 2 | 3                  | 4 | 5        | 6 | 7     | 8 | 9     | 10 | 11         | 12   | 13 | 14 | 15 |

The instruction also supplies a carry bit to the shifter with the result. Bits 10 and 11 specify a base value to be used in determining the carry bit. The instruction supplies either this value or its complement depending upon both the function being performed and the result it generates. The mnemonics and bit configurations and the base values they select are as follows.

1

| Mnemonic | Bits 10–11 | Base value for carry bit             |

|----------|------------|--------------------------------------|

|          | 00         | Current state of Carry               |

| Z        | 01         | Zero                                 |

| Ο        | 10         | One                                  |

| С        | 11         | Complement of current state of Carry |

The three logical functions simply supply the listed values as the carry bit to the shifter. The five arithmetic functions supply the complement of the base value if the operation produces a carry out of bit 0; otherwise they supply the value given. The carry bit can be used in conjunction with the sign of the result to detect overflow in operations on signed numbers. But its primary use is as a carry out of the most significant bit in operations on unsigned numbers, such as the lower order parts in multiple precision arithmetic.

The 17-bit word consisting of the carry bit and the 16-bit result is operated on by the shifter as specified by bits 8 and 9.

| Mnemonic | Bits 8–9 | Shift operation                                                                              |

|----------|----------|----------------------------------------------------------------------------------------------|

|          | 00       | None                                                                                         |

| L        | 01       | Left rotate one place. Bit 0 is rotated into the carry position, the carry bit into bit 15.  |

|          |          | C -15                                                                                        |

| R        | 10       | Right rotate one place. Bit 15 is rotated into the carry position, the carry bit into bit 0. |

|          |          | C → 0-15                                                                                     |

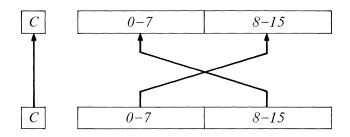

| S        | 11       | Swap the halves of the 16-bit result. The carry bit is not affected.                         |

The 17-bit output of the shifter is loaded into Carry and the accumulator addressed by instruction bits 3 and 4 provided bit 12 is 0. A 1 programmed in bit 12 inhibits the loading and prevents the instruction from affecting Carry or the accumulator. Note that it is the shifted result that is loaded: AC receives the result of the function and Carry the carry bit only if bits 8 and 9 are 0.

The shifter output is also tested for a skip according to the condition specified by bits 13–15. The processor skips the next instruction if the specified condition is satisfied.

| Bit | Effect of a 1 in the bit                                                                                                                        |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 13  | Selects the condition that the low order 16 bits of the shifter output are all 0.                                                               |

| 14  | Selects the condition that the bit in the carry position of the shifter output is 0.                                                            |

| 15  | Inverts the conditions selected by bits 13 and 14. In<br>other words a 1 in bit 15 causes 1s in the other bits<br>to select nonzero conditions. |

The combined effects of bits 13–15 taken together and the mnemonics for the various bit configurations are as follows.

| Mnemonic | Bits 13–15 | Skip function                             |

|----------|------------|-------------------------------------------|

|          | 0          | Never Skip                                |

| SKP      | 1          | Always Skip                               |

| SZC      | 2          | Skip on Zero Carry                        |

| SNC      | 3          | Skip on Nonzero Carry                     |

| SZR      | 4          | Skip on Zero Result                       |

| SNR      | 5          | Skip on Nonzero Result                    |

| SEZ      | 6          | Skip if Either Carry or Result is Zero    |

| SBN      | 7          | Skip if Both Carry and Result are Nonzero |

|          |            |                                           |

Remember that the test is made on the shifter output. Thus if the result of an addition is shifted left, SZC and SNC actually test the sign of the sum. Note also that the test is made whether or not the shifter output is loaded. The program can therefore test the result of an arithmetic function without disturbing the original operands or Carry.

Programming Conventions. The instruction

ADD 1,2

1 01 1 0 11 000 000 000

COM#

1,1,SZR

2-14

which assembles as 133000, adds the numbers in AC1 and AC2, loads the unshifted result in AC2, and complements Carry if there is a carry out of bit 0. Other carry and shift operations are selected simply by appending the appropriate letters to the function mnemonic, but the carry letter (if any) must appear first. Thus to generate a carry bit of 1 on a carry (0 otherwise) and load Carry and AC2 with the 17-bit result shifted left we give

which assembles as 133120. This instruction places the sign of the sum in Carry, the rest of the sum in bits 0-14 of AC2, and a 1 or a 0 in bit 15 depending on whether or not there is a carry out of the sign bit. To use the present state of Carry instead of 0 as the basis for adjusting bit 15, but otherwise produce the same effect, give

ADDL 1,2

ADDZL 1.2

which assembles as 133100. The instruction

ADDL 1,2,SZC

assembles as 133102, and affects Carry and AC2 in the same manner as the preceding instruction, but also causes the processor to skip the next instruction if the sign of the sum is positive.

The initial symbol # following the expanded function mnemonic places a 1 in bit 12 to prevent the loading of the shifter output. Hence we can skip the next instruction on a positive sum without affecting AC2 or Carry by giving

ADDL# 1,2,SZC

which assembles as 133112.

#### **Arithmetic and Logical Functions**

The eight functions are selected by bits 5-7 of the instruction word. For convenience the source and destination accumulators addressed by the S and D parts of the instruction are referred to as ACS and ACD.

| COIVI |   | Comple | ement |   |   |   |   |   |   |    |    |    |    |    |    |

|-------|---|--------|-------|---|---|---|---|---|---|----|----|----|----|----|----|

| 1     |   | S      | l     | ) | 0 | 0 | 0 |   | H |    | 7  | N  |    | SK |    |

| 0     | 1 | 2      | 3     | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Place the (logical) complement of the word from ACS and place the carry bit specified by C in the shifter. Perform the shift operation specified by SH. Load the shifter output in Carry and ACD unless N is 1. Skip the next instruction if the shifter output satisfies the condition specified by SK.

EXAMPLE. Suppose we wish to test AC1 for the unsigned integer  $2^{16}-1$  (177777, signed -1). The instruction

1 01 1 0 11 001 000 000

1 01 1 011 001 000 010

skips the next instruction if AC1 contains all 1s. The result is not loaded so we could specify any accumulator as the destination, eg

| NEG |   | Negate |   |       |   |   |   |   |   |    |    |    |    |    |    |

|-----|---|--------|---|-------|---|---|---|---|---|----|----|----|----|----|----|

| 1   |   | S      | l | )<br> | 0 | 0 | 1 | S | Η | (  | 7  | N  |    | SK |    |

| 0   | 1 | .2     | 3 | 4     | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Place the twos complement of the number from ACS into the shifter. If ACS contains zero, supply the complement of the value specified by C as the carry bit; otherwise supply the specified value. Perform the shift operation specified by SH. Load the shifter output in Carry and ACD unless N is 1. Skip the next instruction if the shifter output satisfies the condition specified by SK.

|   | MUV |   | Nove |   |   |   |   |   |   |   |    |    |    |    |    |    |

|---|-----|---|------|---|---|---|---|---|---|---|----|----|----|----|----|----|

| ļ | 1   |   | S    |   | ) | 0 | 1 | 0 | S | H | (  | Ţ. | N  |    | SK |    |

|   | 0   | 1 | 2    | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Place the contents of ACS and the carry bit specified by C in the shifter. Perform the shift operation specified by SH. Load the shifter output in Carry and ACD unless N is 1. Skip the next instruction if the shifter output satisfies the condition specified by SK.

EXAMPLES. The test for a zero word in AC1 is any of these:

| MOV        | 1,1,SZR          | MOV       | 1,1,SNR   | MOV# | 1,1,SZR | MOV# | 1,1,SNR |  |

|------------|------------------|-----------|-----------|------|---------|------|---------|--|

| se we wish | to divide the nu | mber in A | AC2 by 2. |      |         |      |         |  |

Suppos

| 2,2,SZC<br>2,2,SKP<br>2,2 | ;Is it positive?<br>;No, put in a 1 and skip<br>;Yes, put in a 0 | 101000000000000000000000000000000000000 |

|---------------------------|------------------------------------------------------------------|-----------------------------------------|

| -,<br>,                   | , 100, put in a 0                                                |                                         |

INC Increment

.....

| 1 | L | S |   | ) | 0 | 1 | 1 | S. | H | (  |    | N  |    | SK |    |

|---|---|---|---|---|---|---|---|----|---|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8  | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Add 1 to the number from ACS and place the result in the shifter. If ACS contains  $2^{16}-1$  (signed -1) supply the complement of the value specified by C as the carry bit; otherwise supply the specified value. Perform the shift operation specified by SH. Load the shifter output in Carry and ACD unless N is 1. Skip the next instruction if the shifter output satisfies the condition specified by SK.

ADC Add Complement

Add the (logical) complement of the number from ACS to the number from ACD, and place the result in the shifter. If ACD > ACS (unsigned), supply the complement of the value specified by C as the carry bit; otherwise supply the specified value. Perform the shift operation specified by SH. Load the shifter output in Carry and ACD unless N is 1. Skip the next instruction if the shifter output satisfies the condition specified by SK.

NOTE: For signed numbers the carry condition is that the signs of the operands are the same and ACD is the greater, or the signs differ and ACD is negative.

This instruction is often used to process high order words in multiple precision subtraction, wherein a negative is usually a ones complement instead of a twos complement. The overflow condition for signed numbers using ones complement conventions is the same as that given for SUB below.

| SUB |   | Subtrac | t |       |   |   |   |   |   |    |                |    |    |    |    |

|-----|---|---------|---|-------|---|---|---|---|---|----|----------------|----|----|----|----|

| 1   |   | S<br>I  | 1 | <br>) | 1 | 0 | 1 | S | Η | (  | $\overline{C}$ | N  |    | SK |    |

| 0   | 1 | 2       | 3 | 4     | 5 | 6 | 7 | 8 | 9 | 10 | 11             | 12 | 13 | 14 | 15 |

Subtract by adding the twos complement of the number from ACS to the number from ACD, and place the result in the shifter. If  $ACD \ge ACS$  (unsigned), supply the complement of the value specified by C as the carry bit; otherwise supply the specified value. Perform the shift operation specified by SH. Load the shifter output in Carry and ACD unless N is 1. Skip the next instruction if the shifter output satisfies the condition specified by SK.

NOTE: For signed numbers the carry condition is that the signs of the operands are the same and  $ACD \ge ACS$ , or the signs differ and ACD is negative.

EXAMPLES. This instruction can be used to clear an accumulator by subtracting it from itself.

SUB 2,2

clears AC2 and complements Carry,

SUBO 2,2

clears both AC2 and Carry.

SUB is also useful for comparing quantities, eg

SUB# 2,3,SNR

skips if AC2 and AC3 are unequal but does not affect either accumulator. 2-16

| _ |   |            |   |   |   |   |   |   |    |   |    |    |    |    |    |    |

|---|---|------------|---|---|---|---|---|---|----|---|----|----|----|----|----|----|

|   | 1 | 1 <u>S</u> |   | L | D |   | 1 | 0 | SH |   | C  |    | N  |    | SK |    |

|   | 0 | 1          | 2 | 3 | 4 | 5 | 6 | 7 | 8  | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Add the number from ACS to the number from ACD, and place the result in the shifter. If the unsigned sum is  $\ge 2^{16}$ , supply the complement of the value specified by C as the carry bit; otherwise supply the specified value. Perform the shift operation specified by SH. Load the shifter output in Carry and ACD unless N is 1. Skip the next instruction if the shifter output satisfies the condition specified by SK.

NOTE: For signed numbers the carry condition is that both summands are negative, or their signs differ and their magnitudes are equal or the positive one is the greater in magnitude.

| AND |   | And |   |   |   |   |   |   |   |    |    |    |    |    |    |

|-----|---|-----|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 1   |   | S   | I | ) | 1 | 1 | 1 | S | Ή | (  |    | N  | ÷  | SK |    |

| 0   | 1 | 2   | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Place the logical AND function of the word from ACS and the word from ACD in the shifter. Supply the value specified by C as the carry bit. Perform the shift operation specified by SH. Load the shifter output in Carry and ACD unless N is 1. Skip the next instruction if the shifter output satisfies the condition specified by SK.

This instruction operates bitwise on a pair of words, so it actually performs sixteen logical operations simultaneously. A given bit of the result is 1 if the corresponding bits of both operands are 1; otherwise the resulting bit is 0.

| $ACS_i$ | $ACD_i$ | Result <sub>i</sub> |

|---------|---------|---------------------|

| 0       | 0       | 0                   |

| 0       | 1       | 0                   |

| 1       | 0       | 0                   |

| 1       | 1       | 1                   |

#### **Programming Examples**

Together ADC and SUB allow the program to compare the magnitudes of unsigned numbers in every way. Eg

SUBZ# 1,0,SZC

skips if AC0<AC1, whereas,

ADCZ# 1,0,SZC

skips if AC0≤AC1.

ADD

Add

It is well known that the *n*th perfect square is the sum of the first n odd numbers. We can therefore find the largest integer contained in the square root of an integer held in AC0 by successively subtracting odd numbers in order from AC0 until overflow occurs, *ie* until AC0 becomes negative. The desired answer is the number of odd numbers successfully subtracted before a carry occurs. The routine is called by a JSR with effective address SQRT.

| SQRT: | SUBO  | 1,1              | ;Clear AC1 and Carry                                              |

|-------|-------|------------------|-------------------------------------------------------------------|

|       | MOVOL | 1,2              | ;AC2 gets 1 + twice AC1 $(2n + 1)$                                |

|       | SUBZ  | 2,0, <b>SN</b> C | ;Subtract next odd number; still positive?                        |

|       | JMP   | 0,3              | ;No, exit with <i>n</i> one less than number of odd numbers tried |

|       | INC   | 1,1              | ;Yes, increment n                                                 |

|       | JMP   | SQRT + 1         | ;and try next odd number                                          |

The instruction set has only one logical function of two variables, but the inclusive and exclusive OR functions can be performed by very simple routines. In an inclusive OR a bit of the result is 1 if either of the corresponding operand bits is 1, otherwise it is 0. The algorithm for full words is

$$A \land \sim B + B = A \lor B$$

Taking the arguments as single bits, if B is 1,  $A \land \sim B$  is 0 regardless of the state of A, and the expression on the right is 1. If B is 0, the expression is 1 or 0 as A is 1 or 0. In no case are  $A \land \sim B$  and B both 1, so the full word addition generates no carries. This sequence places the inclusive or of AC0 and AC1 in AC1 (AC0 = B, AC1 = A).

| COM | 0,0 | ;~ <i>B</i>                                                         |

|-----|-----|---------------------------------------------------------------------|

| AND | 0,1 | ; $\sim B \land A$ in AC1                                           |

| ADC | 0,1 | $;\sim \sim B + \sim B \land A = B + \sim B \land A \text{ in AC1}$ |

In an exclusive OR a bit of the result is 1 if the corresponding operand bits are different, otherwise it is 0. This is equivalent to the sum if carries from one bit position to the next are ignored. Now a carry out of the *i*th position is equal to twice the value of a 1 in the *i*th position, and a carry is generated only if the *i*th bits of both summands are 1, provided we compensate for any carry into the *i*th position. The algorithm is therefore.

$$A \stackrel{\checkmark}{=} B = A + B - 2(A \land B)$$

This sequence places the exclusive OR of AC0 and AC1 in AC1, destroying the contents of AC2 and Carry in the process (AC0 = B,AC1 = A).

| MOV   | 1,2 | ;Move A to AC2           |

|-------|-----|--------------------------|

| ANDZL | 0,2 | $(A \land B)$ in AC2     |

| ADD   | 0,1 | ;A + B                   |

| SUB   | 2,1 | $;A + B - 2(A \wedge B)$ |

**Double Precision Arithmetic.** A double length number consists of two words concatenated into a 32-bit string wherein bit 0 is the sign and bits 1-31 are the magnitude in twos complement notation. The high order part of a negative number is therefore in ones complement form unless the low order part is null (at the right

only 0s are null regardless of sign). Hence in processing double length numbers, twos complement operations are usually confined to the low order parts, whereas ones complement operations are generally required for the high order parts.

Suppose we wish to negate the double length number whose high and low order words respectively are in AC0 and AC1. We negate the low order part, but we simply complement the high order part unless the low order part is zero. Hence

| NEG | 1,1,SNR |                    |

|-----|---------|--------------------|

| NEG | 0,0,SKP | ;Low order zero    |

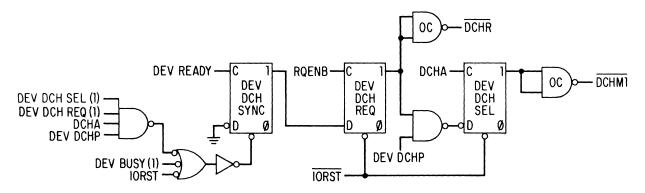

| COM | 0,0     | ;Low order nonzero |