AA-HD92A-TK

# *Technical Reference Manual Volume 1*

### LIBRARY

## DIGITAL EQUIPMENT CORP.

550 KING ST., LITTLETON MA 01460-1289 LOCATION LKG1-2/J10 DTN 226-7066

TELEPHONE (508) 466-7086

VAXmate

*Technical Reference Manual Volume 1*

#### First Printing, February 1987

© Digital Equipment Corporation 1987. All Rights Reserved.

The material in this document is for informational purposes and is subject to change without notice; it should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

Digital Equipment Corporation assumes no responsibility for the use or reliability of its software on equipment that is not supplied by Digital.

MS-DOS, MS-WINDOWS, and MS-NET are trademarks of Microsoft Corporation. Topview is a trademark of International Business Corporation. Motorola is a registered trademark of Motorola, Inc. IBM PC AT is a trademark of International Business Machines Corporation.

The following are trademarks of Digital Equipment Corporation.

| digital      | IAS      | Professional   |

|--------------|----------|----------------|

| DEC          | MASSBUS  | Rainbow        |

| DECmate      | MicroPDP | RSTS           |

| DECnet       | MicroVAX | RSX            |

| DECsystem-10 | MINC-11  | ThinWire       |

| DECSYSTEM-20 | OMNIBUS  | VAX            |

| DECUS        | OS/8     | VAXmate        |

| DECwriter    | PDP      | VMS            |

| DIBOL        | PDT      | VT             |

| EduSystem    | P/OS     | Work Processor |

|              |          |                |

Printed in U.S.A.

# Contents

| Preface                                | xxxiii |

|----------------------------------------|--------|

| VOLUME 1                               |        |

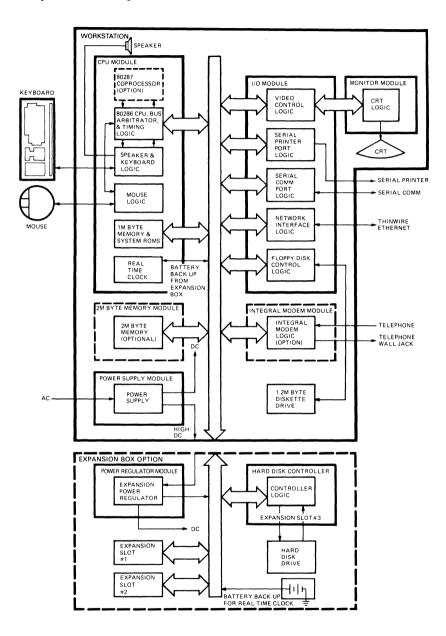

| Chapter 1 VAXmate Workstation Overview | 1-1    |

| Base System                            | 1-1    |

| Optional Components                    | 1-3    |

| Chapter 2 VAXmate Microprocessor       | 2-1    |

| Overview                               | 2-1    |

| Real Address Mode                      | 2-1    |

| Protected Virtual Address Mode         | 2-1    |

| Coprocessor.                           | 2-2    |

| Additional Sources of Information      | 2-2    |

| Memory Map                             | 2-3    |

| Input/Output Address Map               | 2-4    |

| Interrupt Vector Map                   | 2-6    |

| Bus Timing and Structure.              | 2-9    |

| Expansion Box Technical Specifications | 2-10   |

| Expansion Box Operating Ranges         | 2-10   |

| Chapter 3 Interrupt Controllers        | 3-1    |

| Overview                               | 3-1    |

| Additional Source of Information.      | 3-3    |

| Read/Write Control                     | 3-3    |

| Initialization Command Words                     | 3-5  |

|--------------------------------------------------|------|

| Initialization Command Word 1                    | 3-7  |

| Initialization Command Word 2                    | 3-8  |

| Initialization Command Word 3                    | 3-9  |

| ICW3 (Master)                                    | 3-9  |

| ICW3 (Slave)                                     | 3-9  |

| Initialization Command Word 4                    | 3-10 |

| Operation Command Words                          | 3-11 |

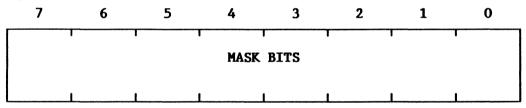

| Operation Command Word 1                         | 3-11 |

| Operation Command Word 2                         | 3-12 |

| Priority Rotation                                | 3-13 |

| Operation Command Word 3                         | 3-15 |

| Interrupt Request and In-Service Registers       | 3-16 |

| Interrupt Request Register                       | 3-16 |

| In-Service Register                              | 3-16 |

| Poll Command                                     | 3-17 |

| Poll Data Register                               | 3-17 |

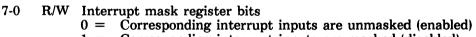

| Interrupt Sequence.                              | 3-18 |

| Programming Example                              | 3-21 |

| Constant Values and Data Structures              | 3-22 |

| Initialization Data                              | 3-22 |

| Initializing the Peripheral Interrupt Controller | 3-24 |

| Issuing an End-of-Interrupt Command              | 3-26 |

| Masking Interrupts                               | 3-26 |

|                                                  |      |

| Chapter 4 DMA Controller                         | 4-1  |

| Overview                                         | 4-1  |

| Additional Source of Information.                | 4-2  |

| Operation                                        | 4-2  |

|                                                  | 4-3  |

|                                                  | 4-3  |

| Single Transfer Mode                             | 4-3  |

| Block Transfer Mode                              | 4-3  |

| Demand Transfer Mode                             | 4-3  |

| Cascade Mode                                     | 4-4  |

| Data Transfers                                   | 4-4  |

| Auto-Initialize                                  | 4-4  |

| Priority                                         | 4-5  |

| Address Generation                               | 4-5  |

| Registers                                                                                                               | 4-7                                                          |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

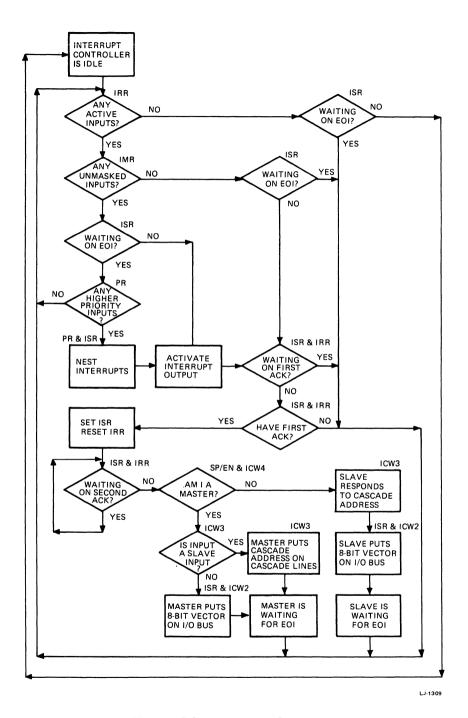

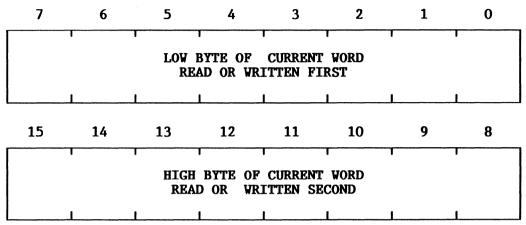

| Base and Current Address Register                                                                                       | 4-7                                                          |

| Base and Current Word Register                                                                                          | 4-8                                                          |

| Command Register                                                                                                        | 4-9                                                          |

| Write Single Mask Bit                                                                                                   | 4-11                                                         |

| Write All Mask Bits                                                                                                     | 4-11                                                         |

| Mode Register                                                                                                           | 4-12                                                         |

| Request Register                                                                                                        | 4-13                                                         |

| Status Register                                                                                                         | 4-14                                                         |

| Temporary Register                                                                                                      | 4-14                                                         |

| Programming Example                                                                                                     | 4-15                                                         |

| Constant Values                                                                                                         | 4-15                                                         |

| Data Structures                                                                                                         | 4-17                                                         |

| Initializing the DMA Controller                                                                                         | 4-18                                                         |

| Opening a DMA Channel                                                                                                   | 4-19                                                         |

| Preparing a Channel for Data Transfer                                                                                   | 4-20                                                         |

| Disabling a DMA Channel                                                                                                 | 4-22                                                         |

|                                                                                                                         |                                                              |

| Chapter 5 Real-Time Clock and CMOS RAM                                                                                  | 5-1                                                          |

| Overview                                                                                                                | 5-1                                                          |

| Additional Source of Information.                                                                                       | 5-2                                                          |

| Battery-Backup Considerations.                                                                                          | 5-2                                                          |

| Addressing the Real-Time Clock                                                                                          | 5-2                                                          |

| Real-Time Clock Registers                                                                                               | 5-3                                                          |

| Register A.                                                                                                             | 5-4                                                          |

| Register B                                                                                                              | 5-6                                                          |

| Register C.                                                                                                             | 5-8                                                          |

| Register D                                                                                                              | · 5-9                                                        |

| Real-Time Clock Data Registers                                                                                          | 5-10                                                         |

| Alarms                                                                                                                  | 5-12                                                         |

|                                                                                                                         | 5-13                                                         |

|                                                                                                                         | 5-14                                                         |

| Update-Ended Interrupt                                                                                                  | 5-14                                                         |

| Alarm Interrupt                                                                                                         | 5-14                                                         |

| Programming Example                                                                                                     | 5-15                                                         |

|                                                                                                                         |                                                              |

| Constant Values                                                                                                         |                                                              |

| Constant Values                                                                                                         | 5-18                                                         |

| Constant Values                                                                                                         | 5-18<br>5-20                                                 |

| Constant Values          Data Structures          Reading the Registers and RAM.          Writing the Registers and RAM | 5-18<br>5-20<br>5-21                                         |

| Constant ValuesData StructuresReading the Registers and RAMWriting the Registers and RAMCalculating the Checksum        | 5-18<br>5-20<br>5-21<br>5-22                                 |

| Constant Values          Data Structures          Reading the Registers and RAM.          Writing the Registers and RAM | 5-16<br>5-18<br>5-20<br>5-21<br>5-22<br>5-23<br>5-23<br>5-24 |

| Reading the Time                              | 5-25 |

|-----------------------------------------------|------|

| Displaying the Date                           | 5-26 |

| Displaying the Time                           | 5-27 |

| Displaying the Diskette Drive Type            | 5-28 |

| Displaying the Hard Disk Type                 | 5-29 |

| Handling the Clock Interrupts                 | 5-30 |

| Interpreting the RAM Contents                 | 5-32 |

| Initializing the Real-Time Clock              | 5-34 |

| Restoring the Interrupt Vectors               | 5-35 |

| Real-Time Clock Example                       | 5-36 |

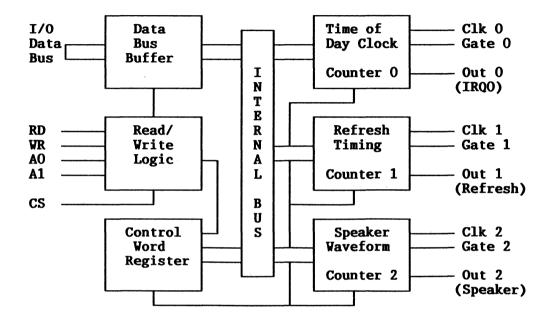

| Chapter 6 Three-Channel Counter and Speaker   | 6-1  |

| Overview                                      | 6-1  |

| Additional Source of Information.             | 6-1  |

| Block Diagram                                 | 6-2  |

| Counter Description                           | 6-2  |

| Mode Definitions                              | 6-3  |

| Mode 0 (Interrupt on Terminal Count)          | 6-4  |

| Initializing Mode 0                           | 6-4  |

| Mode 0 Cycle                                  | 6-4  |

| Mode 1 (Hardware Retriggerable One-Shot)      | 6-4  |

| Initializing Mode 1                           | 6-4  |

| Mode 1 Cycle                                  | 6-4  |

| Mode 2 (Rate Generator)                       | 6-5  |

| Initializing Mode 2                           | 6-5  |

| Mode 2 Cycle                                  | 6-5  |

| Mode 3 (Square Wave Mode)                     | 6-5  |

| Initializing Mode 3                           | 6-6  |

| Mode 3 Cycle.                                 | 6-6  |

| Mode 4 (Software Triggered Strobe)            | 6-6  |

| Initializing Mode 4                           | 6-6  |

| Mode 4 Cycle                                  | 6-7  |

| Mode 5 (Hardware Triggered Strobe)            | 6-7  |

| Initializing Mode 5                           | 6-7  |

| Mode 5 Cycle                                  | 6-7  |

| Registers.                                    | 6-8  |

| System Register                               | 6-9  |

| Control Word Register                         | 6-11 |

| Counter-Latch Command (Control Word Register) | 6-12 |

| Read-Back Command (Control Word Register)     | 6-13 |

| Status Response (Read-back Command)           | 6-14 |

| -                                             |      |

| Programming Example                           | 6-16 |

|-----------------------------------------------|------|

| Constant Values                               | 6-16 |

| Writing a Counter                             | 6-18 |

| Making a Bell Sound                           | 6-18 |

| Counter and Speaker Example                   | 6-20 |

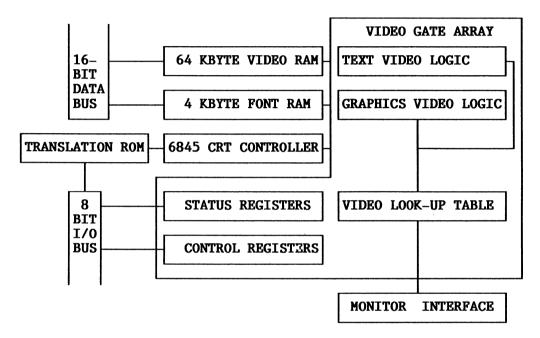

| Chapter 7 Video Controller                    | 7-1  |

| Introduction                                  | 7-1  |

| Industry-Standard Text and Graphics Features  | 7-1  |

| Enhancements to Industry-Standard Features    | 7-2  |

| Industry-Standard Features Not Available      | 7-2  |

| Extra Features                                | 7-2  |

| Block Diagram                                 | 7-3  |

| Additional Sources of Information             | 7-4  |

| Video Modes                                   | 7-5  |

| Text Modes                                    | 7-6  |

| Character Buffer Format                       | 7-6  |

| Character Position to Memory Location Mapping | 7-7  |

| Programmable Cursor                           | 7-8  |

| Programmable Character Generator (Font RAM)   | 7-9  |

| Graphics Mode                                 | 7-10 |

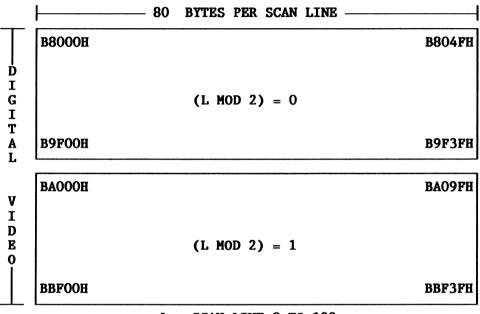

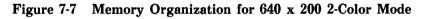

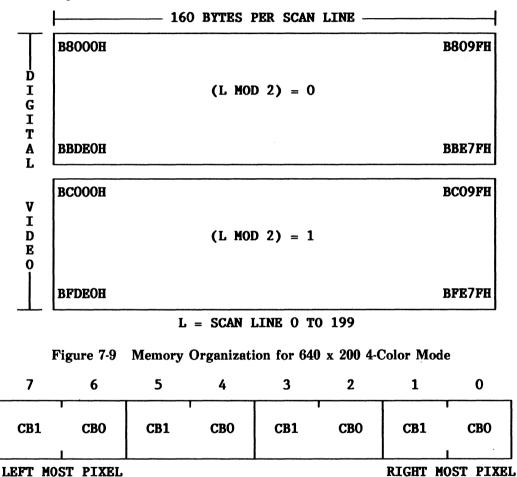

| Mapping the Display to Address                | 7-10 |

| Video Look-Up Table                           | 7-18 |

| Video System Registers                        | 7-22 |

| Special Purpose Register                      | 7-23 |

| CRTC Registers                                | 7-25 |

| Index Register                                | 7-25 |

| Data Register                                 | 7-25 |

| Register R0                                   | 7-28 |

| Register R1                                   | 7-28 |

| Register R2                                   | 7-29 |

| Register R3                                   | 7-29 |

| Register R4                                   | 7-30 |

| Register R5                                   | 7-30 |

| Register R6                                   | 7-31 |

| Register R7                                   | 7-31 |

| Register R8                                   | 7-32 |

| Register R9                                   | 7-33 |

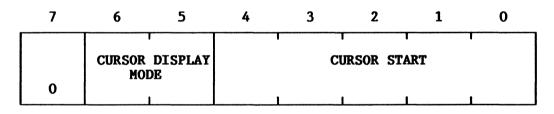

| Register R10                                  | 7-33 |

| Register R11                                  | 7-34 |

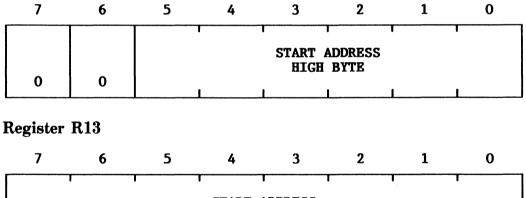

| Register R12                                  | 7-34 |

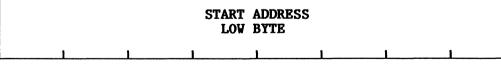

| Register R13                                  | 7-34 |

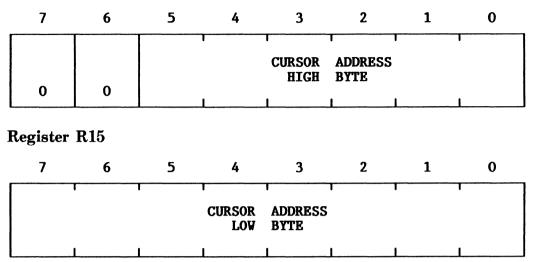

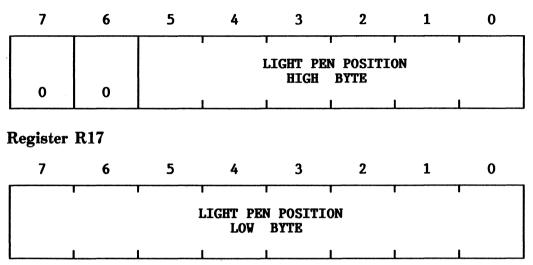

| Register R167-36Register R177-36Status Register A7-37Status Register B7-38Write Data Register7-39Color Select Register7-39Control Register A7-41Control Register B7-43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Register R14                                         | 7-35 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------|

| Register R17         7-36           Status Register A         7-37           Status Register B         7-38           Write Data Register         7-39           Color Select Register         7-39           Control Register A         7-41           Control Register B         7-43           Monitor Interface         7-44           Monitor Specification Summary         7-44           Monitor Specification Summary         7-44           Programming Example         7-45           Chapter 8 Keyboard-Interface Controller and Keyboard         8-1           Introduction         8-1           Physical Interface Controller         8-1           Physical Interface to the CPU         8-1           Physical Interface to the Keyboard         8-2           Logical Interface         8-2           Control Functions         8-3           Keyboard-Interface Controller Diagnostics         8-4           Keyboard-Interface Controller Registers         8-5           Data Register         8-6           Command Register         8-6           Command Register         8-10           Write Command Byte         8-10           Self-Test         8-12           I | Register R15                                         | 7-35 |

| Status Register A7-37Status Register B7-38Write Data Register A7-39Color Select Register7-39Control Register A7-41Control Register B7-43Monitor Interface7-44Monitor Specification Summary7-44Programming Example7-45Chapter 8 Keyboard-Interface Controller and Keyboard8-1Introduction8-1Keyboard-Interface Controller and Keyboard8-1Physical Interface to the CPU8-1Physical Interface to the CPU8-2Logical Interface Controller Registers8-3Keyboard-Interface Controller Registers8-5Data Register8-5Data Register8-6Command Register8-5Data Register8-6Command Register8-10Write Command Byte8-10Write Command Byte8-12Interface Test8-12Interface Test8-12Read Command Byte8-12Read Port 18-12Read Port 18-12Read Port 28-13Write Port 28-13Write Port 28-13Write Status Register8-13Port8-13Port8-13Prostatus Register8-13                                                                                                                                                                                                                                                                                                                                                          | Register R16                                         | 7-36 |

| Status Register B7-38Write Data Register7-39Color Select Register7-39Control Register A7-41Control Register B7-43Monitor Interface7-44Monitor Specification Summary7-44Programming Example7-45Chapter 8 Keyboard-Interface Controller and Keyboard8-1Introduction8-1Keyboard-Interface Controller8-1Physical Interface to the CPU8-1Physical Interface to the Keyboard8-2Logical Interface to the Keyboard8-2Control Functions8-3Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-6Command Register8-9Read Command Byte8-10Write Command Byte8-10Self-Test8-12Disable Keyboard8-12Read Port 18-12Read Port 18-12Read Port 18-13Write Status Register8-13Write Port 28-13Write Register8-13Write Port 28-13Read Test Inputs8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                               | Register R17                                         | 7-36 |

| Write Dat Register7-39Color Select Register7-39Control Register A7-41Control Register B7-43Monitor Interface7-44Monitor Specification Summary7-44Programming Example7-45Chapter 8 Keyboard-Interface Controller and Keyboard8-1Introduction8-1Physical Interface to the CPU8-1Physical Interface to the Keyboard8-2Logical Interface to the Keyboard8-2Control Functions8-3Keyboard-Interface Controller Diagnostics8-4Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-6Command Register8-6Command Register8-10Write Command Byte8-10Write Command Byte8-12Interface Test8-12Disable Keyboard8-12Read Port 18-12Read Port 18-12Read Port 18-13Write Status Register8-13Write Port 28-13Read Test Inputs8-13Write Status Register8-13                                                                                                                                                                                                                                                                                                                                                                                                                             | Status Register A                                    | 7-37 |

| Color Select Register7-39Control Register A.7-41Control Register B.7-43Monitor Interface7-44Monitor Specification Summary7-44Programming Example7-45Chapter 8 Keyboard-Interface Controller and Keyboard8-1Introduction8-1Keyboard-Interface Controller and Keyboard8-1Physical Interface to the CPU8-1Physical Interface to the Keyboard8-2Logical Interface controller Diagnostics8-3Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-6Command Register8-10Write Command Byte8-10Write Command Byte8-12Disable Keyboard8-12Interface Test8-12Interface Test8-12Read Port 18-12Read Port 18-13Write Status Register8-13Write Status Register8-13Price Test8-12Status Register8-12Status Register8-12Status Register8-12Status Register8-12Status Register8-12Status Register8-12Status Register8-12Status Register8-12Status Register8-13Status Register8-13Status Register8-13Status Register8-13Status Register8-13Status Register8-13                                                                                                                                                                                                                         | Status Register B                                    | 7-38 |

| Control Register A.7-41Control Register B.7-43Monitor Interface7-44Monitor Specification Summary.7-44Programming Example7-45Chapter 8 Keyboard-Interface Controller and Keyboard.8-1Introduction8-1Keyboard-Interface Controller8-1Physical Interface to the CPU8-1Physical Interface to the Keyboard8-2Logical Interface8-2Control Functions8-3Keyboard-Interface Controller Diagnostics8-4Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-6Command Register8-10Write Command Byte8-10Write Command Byte8-12Interface Test8-12Interface Test8-12Read Port 18-12Read Port 18-13Write Status Register8-13Write Status Register8-13Write Status Register8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Write Data Register                                  | 7-39 |

| Control Register B.7-43Monitor Interface7-44Monitor Specification Summary.7-44Programming Example7-45Chapter 8 Keyboard-Interface Controller and Keyboard.8-1Introduction8-1Keyboard-Interface Controller8-1Physical Interface to the CPU8-1Physical Interface to the Keyboard8-2Logical Interface8-2Control Functions8-3Keyboard-Interface Controller Diagnostics8-4Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-5Status Register8-6Command Register8-9Read Command Byte8-10Write Command Byte8-12Interface Test8-12Disable Keyboard8-12Read Port 18-12Read Port 18-13Write Status Register8-13Write Status Register8-13Write Port 28-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Color Select Register                                | 7-39 |

| Control Register B.7-43Monitor Interface7-44Monitor Specification Summary.7-44Programming Example7-45Chapter 8 Keyboard-Interface Controller and Keyboard.8-1Introduction8-1Keyboard-Interface Controller8-1Physical Interface to the CPU8-1Physical Interface to the Keyboard8-2Logical Interface8-2Control Functions8-3Keyboard-Interface Controller Diagnostics8-4Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-5Status Register8-6Command Register8-9Read Command Byte8-10Write Command Byte8-12Interface Test8-12Disable Keyboard8-12Read Port 18-12Read Port 18-13Write Status Register8-13Write Status Register8-13Write Port 28-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Control Register A                                   | 7-41 |

| Monitor Specification Summary7-44Programming Example7-45Chapter 8 Keyboard-Interface Controller and Keyboard.8-1Introduction8-1Keyboard-Interface Controller8-1Physical Interface to the CPU8-1Physical Interface to the Keyboard8-2Logical Interface8-2Control Functions8-3Keyboard-Interface Controller Diagnostics8-4Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-5Status Register8-6Command Register8-10Write Command Byte8-10Write Command Byte8-12Interface Test8-12Disable Keyboard8-12Read Port 18-12Read Port 18-12Read Port 18-13Write Status Register8-13Write Status Register8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      | 7-43 |

| Monitor Specification Summary7-44Programming Example7-45Chapter 8 Keyboard-Interface Controller and Keyboard.8-1Introduction8-1Keyboard-Interface Controller8-1Physical Interface to the CPU8-1Physical Interface to the Keyboard8-2Logical Interface8-2Control Functions8-3Keyboard-Interface Controller Diagnostics8-4Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-5Status Register8-6Command Register8-10Write Command Byte8-10Write Command Byte8-12Interface Test8-12Disable Keyboard8-12Read Port 18-12Read Port 28-13Write Status Register8-13Write Status Register8-13Write Status Register8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      | 7-44 |

| Programming Example7-45Chapter 8 Keyboard-Interface Controller and Keyboard.8-1Introduction8-1Keyboard-Interface Controller8-1Physical Interface to the CPU8-1Physical Interface to the Keyboard8-2Logical Interface8-2Control Functions8-3Keyboard-Interface Controller Diagnostics8-4Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-5Status Register8-6Command Register8-9Read Command Byte8-10Write Command Byte8-10Self-Test8-12Interface Test8-12Read Port 18-12Read Port 18-12Read Port 28-13Write Status Register8-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                      | 7-44 |

| Introduction8-1Keyboard-Interface Controller8-1Physical Interface to the CPU8-1Physical Interface to the Keyboard8-2Logical Interface8-2Control Functions8-3Keyboard-Interface Controller Diagnostics8-4Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-6Command Register8-6Command Register8-9Read Command Byte8-10Write Command Byte8-10Self-Test8-12Interface Test8-12Disable Keyboard8-12Read Port 18-12Read Port 28-13Write Port 28-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                      | 7-45 |

| Introduction8-1Keyboard-Interface Controller8-1Physical Interface to the CPU8-1Physical Interface to the Keyboard8-2Logical Interface8-2Control Functions8-3Keyboard-Interface Controller Diagnostics8-4Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-5Status Register8-6Command Register8-9Read Command Byte8-10Write Command Byte8-10Self-Test8-12Interface Test8-12Disable Keyboard8-12Read Port 18-12Read Port 28-13Write Port 28-13Write Status Register8-13Write Status Register8-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Chapter 8 Keyboard-Interface Controller and Keyboard | 8-1  |

| Keyboard-Interface Controller8-1Physical Interface to the CPU8-1Physical Interface to the Keyboard8-2Logical Interface8-2Control Functions8-3Keyboard-Interface Controller Diagnostics8-4Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-6Command Register8-6Command Register8-9Read Command Byte8-10Write Command Byte8-10Self-Test8-12Interface Test8-12Disable Keyboard8-12Read Port 18-12Read Port 18-12Read Port 18-13Write Port 28-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                      | 8-1  |

| Physical Interface to the CPU8-1Physical Interface to the Keyboard8-2Logical Interface to the Keyboard8-2Control Functions8-3Keyboard-Interface Controller Diagnostics8-4Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-6Command Register8-6Command Register8-9Read Command Byte8-10Write Command Byte8-10Self-Test8-12Interface Test8-12Disable Keyboard8-12Read Port 18-12Read Port 28-13Write Port 28-13Write Status Register8-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      | 8-1  |

| Physical Interface to the Keyboard8-2Logical Interface8-2Control Functions8-3Keyboard-Interface Controller Diagnostics8-4Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-6Command Register8-6Command Register8-9Read Command Byte8-10Write Command Byte8-10Self-Test8-12Interface Test8-12Disable Keyboard8-12Read Port 18-12Read Port 18-13Write Port 28-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      | 8-1  |

| Logical Interface8-2Control Functions8-3Keyboard-Interface Controller Diagnostics8-4Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-5Status Register8-6Command Register8-9Read Command Byte8-10Write Command Byte8-10Self-Test8-12Interface Test8-12Disable Keyboard8-12Read Port 18-12Read Port 28-13Write Status Register8-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                      | 8-2  |

| Control Functions8-3Keyboard-Interface Controller Diagnostics8-4Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-5Status Register8-6Command Register8-9Read Command Byte8-10Write Command Byte8-10Self-Test8-12Interface Test8-12Disable Keyboard8-12Read Port 18-12Read Port 28-13Write Port 28-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                                                    | 8-2  |

| Keyboard-Interface Controller Diagnostics8-4Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-6Command Register8-9Read Command Byte8-10Write Command Byte8-10Self-Test8-12Interface Test8-12Disable Keyboard8-12Read Port 18-12Read Port 28-13Write Port 28-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                      | 8-3  |

| Keyboard-Interface Controller Registers8-5Data Register8-5Command Register8-5Status Register8-6Command Register8-9Read Command Byte8-10Write Command Byte8-10Self-Test8-12Interface Test8-12Disable Keyboard8-12Read Port 18-12Read Port 28-13Write Port 28-13Write Status Register8-13Vrite Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                      | 8-4  |

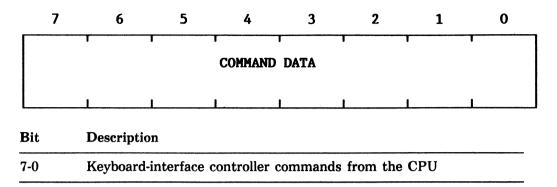

| Data Register8-5Command Register8-5Status Register8-6Command Register8-9Read Command Byte8-10Write Command Byte8-10Self-Test8-12Interface Test8-12Disable Keyboard8-12Enable Keyboard8-12Read Port 18-12Read Port 28-13Write Port 28-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | · •                                                  | 8-5  |

| Command Register8-5Status Register8-6Command Register8-9Read Command Byte8-10Write Command Byte8-10Self-Test8-12Interface Test8-12Disable Keyboard8-12Enable Keyboard8-12Read Port 18-12Read Port 28-13Write Status Register8-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      | 8-5  |

| Status Register.8-6Command Register8-9Read Command Byte.8-10Write Command Byte.8-10Self-Test8-12Interface Test8-12Disable Keyboard8-12Enable Keyboard8-12Read Port 1.8-12Read Port 2.8-13Write Port 28-13Write Status Register.8-13Pulse Output Port.8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                      | 8-5  |

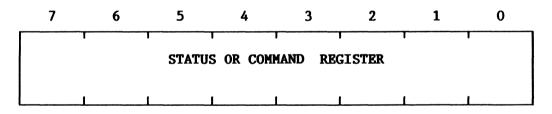

| Command Register8-9Read Command Byte8-10Write Command Byte8-10Self-Test8-12Interface Test8-12Disable Keyboard8-12Enable Keyboard8-12Read Port 18-12Read Port 28-13Write Port 28-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                      | 8-6  |

| Read Command Byte8-10Write Command Byte8-10Self-Test8-12Interface Test8-12Disable Keyboard8-12Enable Keyboard8-12Read Port 18-12Read Port 28-12Read Test Inputs8-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                      | 8-9  |

| Write Command Byte.8-10Self-Test8-12Interface Test8-12Disable Keyboard8-12Enable Keyboard8-12Read Port 1.8-12Read Port 2.8-13Write Port 28-13Write Status Register.8-13Pulse Output Port.8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      | 8-10 |

| Self-Test8-12Interface Test8-12Disable Keyboard8-12Enable Keyboard8-12Read Port 18-12Read Port 18-12Read Port 28-13Write Port 28-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                      | 8-10 |

| Interface Test8-12Disable Keyboard8-12Enable Keyboard8-12Enable Keyboard8-12Read Port 18-12Read Port 28-12Read Port 28-13Write Port 28-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                                                    | 8-12 |

| Disable Keyboard8-12Enable Keyboard8-12Read Port 1.8-12Read Port 1.8-12Read Port 2.8-13Write Port 28-13Read Test Inputs8-13Write Status Register.8-13Pulse Output Port.8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                      | 8-12 |

| Enable Keyboard8-12Read Port 1.8-12Read Port 1.8-12Read Port 2.8-13Write Port 2.8-13Write Port 2.8-13Read Test Inputs8-13Write Status Register.8-13Pulse Output Port.8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                      | 8-12 |

| Read Port 1.8-12Read Port 1.8-12Read Port 2.8-13Write Port 28-13Read Test Inputs8-13Write Status Register.8-13Pulse Output Port.8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                                                    | 8-12 |

| Read Port 1.8-12Read Port 2.8-13Write Port 28-13Read Test Inputs8-13Write Status Register.8-13Pulse Output Port.8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                      | 8-12 |

| Read Port 2.8-13Write Port 2.8-13Read Test Inputs8-13Write Status Register.8-13Pulse Output Port.8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                      |      |

| Write Port 28-13Read Test Inputs8-13Write Status Register8-13Pulse Output Port8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                      |      |

| Read Test Inputs8-13Write Status Register.8-13Pulse Output Port.8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                      |      |

| Write Status Register.8-13Pulse Output Port.8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                      |      |

| Pulse Output Port    8-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                      |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      | 8-14 |

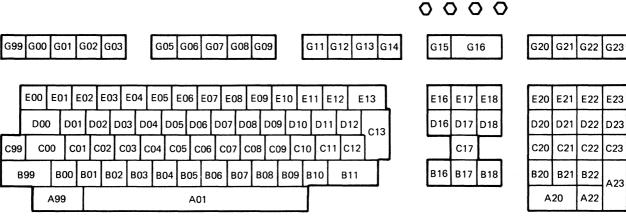

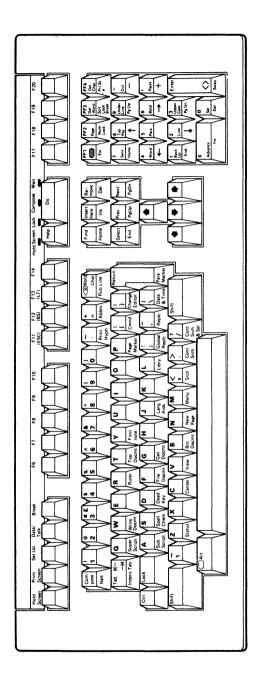

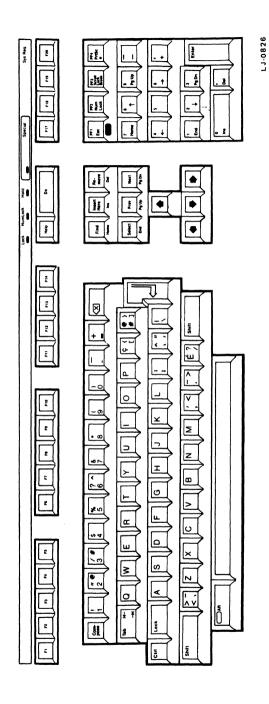

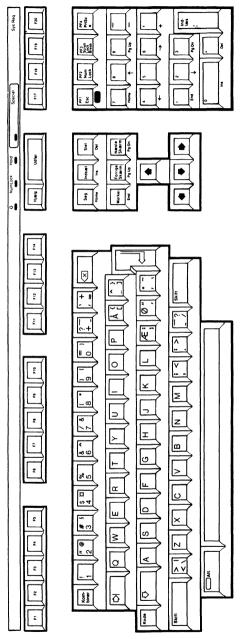

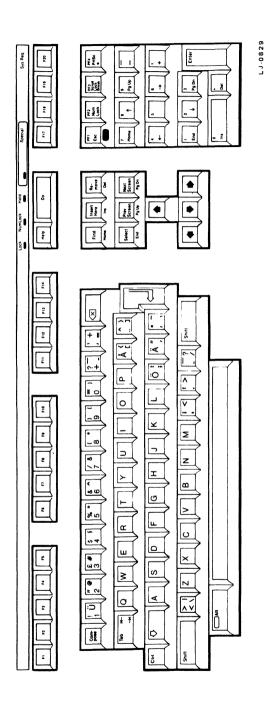

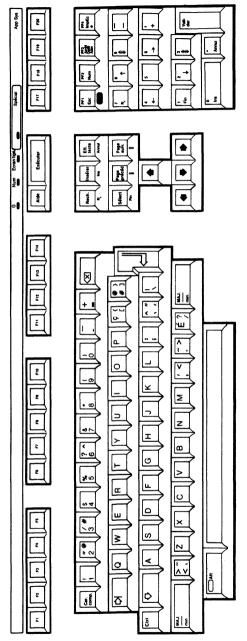

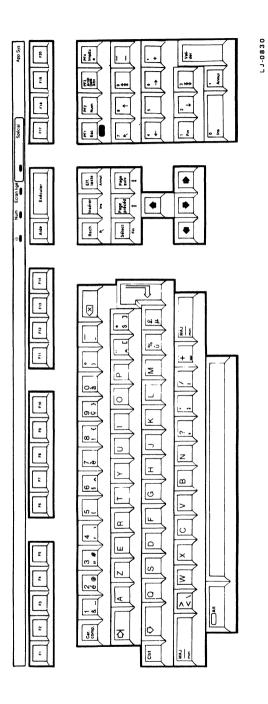

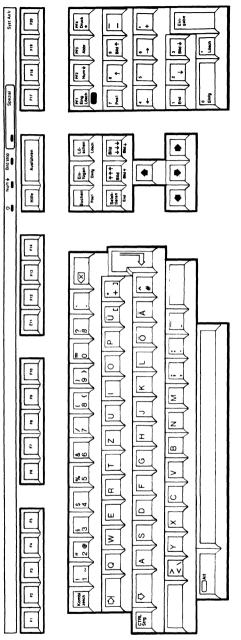

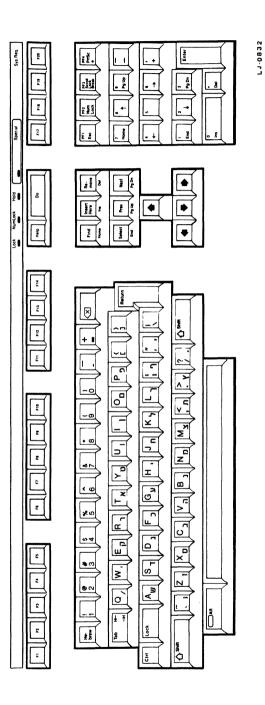

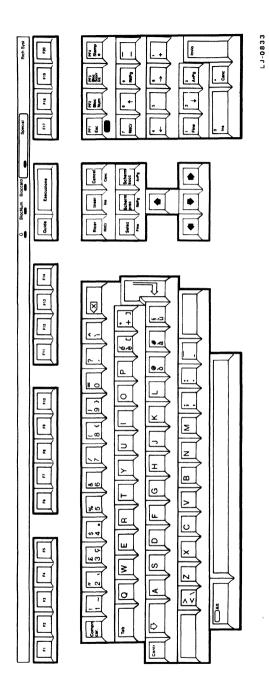

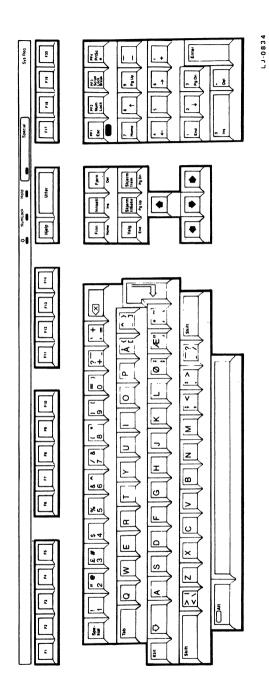

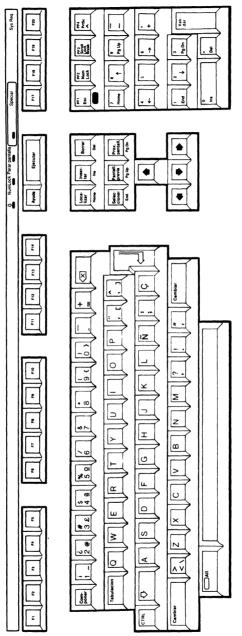

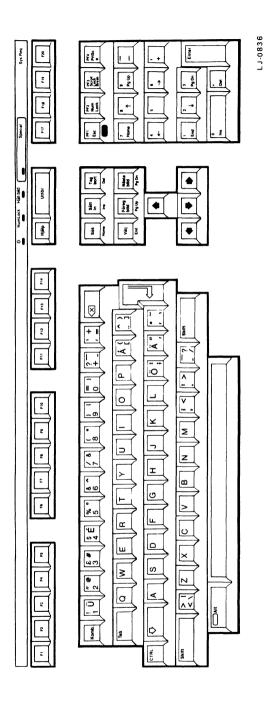

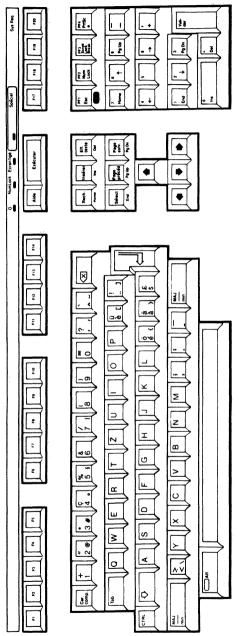

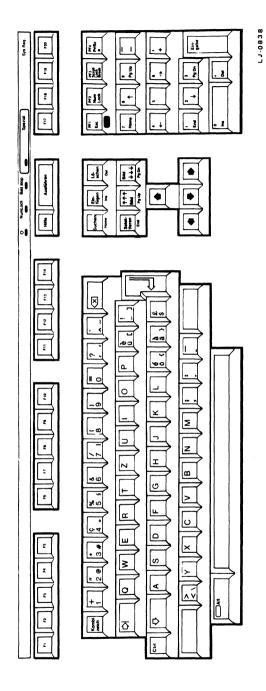

| LK250 Keyboard                               | 8-15 |

|----------------------------------------------|------|

| Scan Codes                                   | 8-15 |

| LK250 Keyboard Command Codes                 | 8-22 |

| Invalid Commands                             | 8-23 |

| Request Keyboard ID                          | 8-23 |

| Enter DIGITAL Extended Scan Code Mode        | 8-23 |

| Exit DIGITAL Extended Scan Code Mode         | 8-23 |

| Set Keyboard LED                             | 8-23 |

| Reset Keyboard LED                           | 8-24 |

| Set Keyclick Volume                          | 8-24 |

| Enable Autorepeat.                           | 8-24 |

| Disable Autorepeat                           | 8-24 |

| Keyboard Mode Lock                           | 8-25 |

| Keyboard Mode Unlock                         | 8-25 |

| Reserved                                     | 8-25 |

| LEDs On/Off                                  | 8-26 |

|                                              | 8-26 |

| Reserved                                     | 8-26 |

| Set Autorepeat Delay and Rate                | 8-27 |

| Enable Key Scanning                          | 8-28 |

| Disable Key Scanning and Restore to Defaults | 8-28 |

| Restore To Defaults.                         | 8-28 |

| Reserved                                     | 8-29 |

| Resend                                       | 8-29 |

| Reset                                        | 8-29 |

| LK250 Keyboard Responses                     | 8-30 |

| Buffer overrun                               | 8-30 |

| Self-test success                            | 8-30 |

| ЕСНО                                         | 8-30 |

| Release Prefix                               | 8-31 |

| Acknowledge (ACK)                            | 8-31 |

| Self-Test Failure                            | 8-31 |

| Resend                                       | 8-31 |

| LK250 Keyboard Error Handling                | 8-31 |

| U.S. and Foreign Keyboards                   | 8-31 |

| Programming Example                          | 8-46 |

| Chapter 9 Serial Communications.             | 9-1  |

| Overview                                     | 9-1  |

| Additional Sources of Information                    | 9-1   |

|------------------------------------------------------|-------|

| Receive Buffer Register/Transmitter Holding Register | 9-3   |

| Interrupt Enable Register                            | 9-4   |

| Interrupt Identification Register                    | 9-6   |

| Line Control Register                                | 9-7   |

| Modem Control Register                               | 9-9   |

| Diagnostic Loopback                                  | 9-10  |

| Line Status Register                                 | 9-11  |

| Modem Status Register                                | 9-13  |

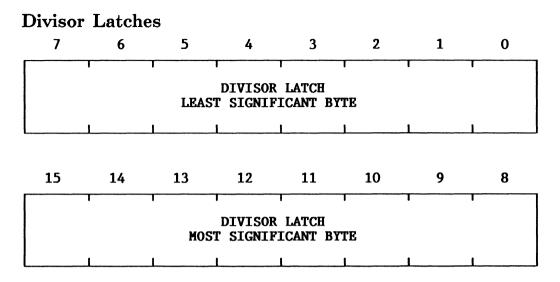

| Divisor Latches.                                     | 9-15  |

| Modem Control Programming Exceptions                 | 9-17  |

| Special Purpose Register                             | 9-18  |

| Communications Connector Signals                     | 9-19  |

| Printer Connector Signals                            | 9-20  |

| Modem Connector Signals.                             | 9-21  |

| Programming Example                                  | 9-22  |

| Program Description                                  | 9-23  |

|                                                      |       |

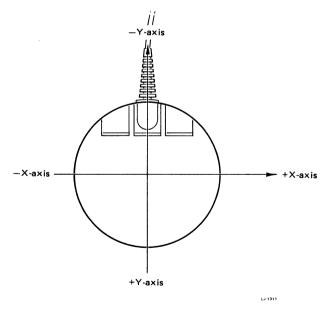

| Chapter 10 Mouse Information                         | 10-1  |

| Introduction                                         | 10-1  |

| Communication Requirements                           | 10-2  |

| Additional Source of Information.                    | 10-2  |

| Mouse Commands                                       | 10-2  |

| Prompt Mode Incremental Stream Mode                  | 10-3  |

| Request Mouse Position                               | 10-3  |

| Invoke Self-Test                                     | 10-3  |

| Vendor Reserved Function                             | 10-3  |

| Mouse Reports                                        | 10-4  |

| Position Report - Byte 1                             | 10-4  |

| Position Report - Byte 2                             | 10-5  |

| Position Report - Byte 3                             | 10-5  |

| Self-Test Report - Byte 1                            | 10-6  |

| Self-Test Report - Byte 2                            | 10-6  |

| Self-Test Report - Byte 3                            | 10-7  |

| Self-Test Report - Byte 4                            | 10-7  |

| Serial Interface                                     | 10-8  |

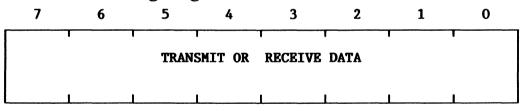

| Transmit Holding Register and Receive Buffer         | 10-8  |

| Status Register.                                     | 10-9  |

| Mode Register 1                                      | 10-10 |

| Mode Register 2                                      | 10-11 |

| Command Register                                     | 10-12 |

| Programming Example                                  | 10-14 |

| pter 11 Diskette Drive Controller            |

|----------------------------------------------|

| ntroduction                                  |

| iskette Drive Controller Registers           |

| Control Register                             |

| Main Status Register                         |

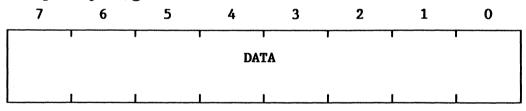

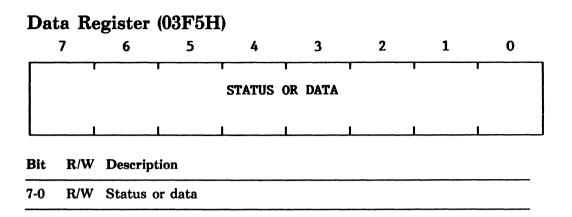

| Data Register                                |

| Data Transfer Rate Register                  |

| Change Register                              |

| Diskette Drive Controller Internal Registers |

| Internal Register - Command                  |

| Internal Register - Head/Unit Select         |

| Internal Register - Status Register 0        |

| Internal Register - Status Register 1        |

| Internal Register - Status Register 2        |

| Internal Register - Status Register 3        |

| Internal Register - SRT/HUT                  |

| Internal Register - HLT/ND                   |

| Internal Register - C                        |

| Internal Register - H                        |

| Internal Register - R                        |

| Internal Register - N                        |

| Internal Register - EOT                      |

| Internal Register - GPL                      |

| Internal Register - DTL                      |

| Internal Register - SC                       |

| Internal Register - D                        |

| Internal Register - STP                      |

| Internal Register - PCN                      |

| Internal Registers - NCN                     |

| iskette Drive Controller Programming         |

| Command State                                |

| Execution State                              |

| Result State                                 |

| Command and Result Register Sets             |

| rogramming Example                           |

| pter 12 Hard Disk Drive Controller           |

| -                                            |

| ntroduction                                  |

| Hard Disk Controller Registers                           | 12-1         |

|----------------------------------------------------------|--------------|

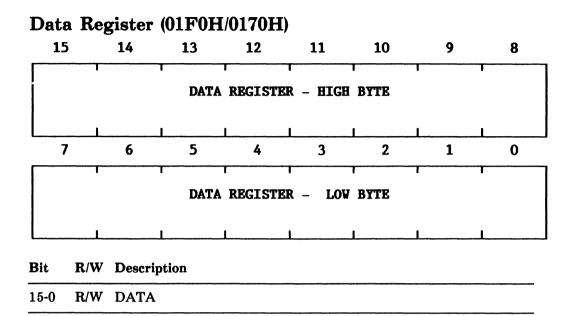

| Data Register                                            | 12-3         |

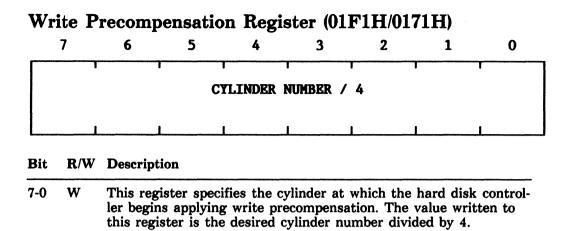

| Write Precompensation Register                           | 12-4         |

| Error Register                                           | 12-5         |

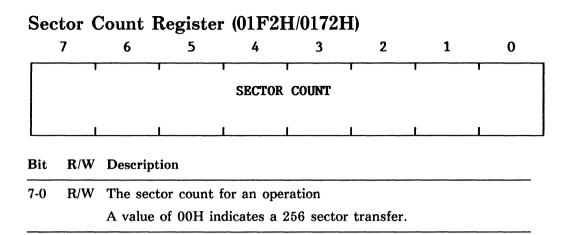

| Sector Count Register                                    | 12-7         |

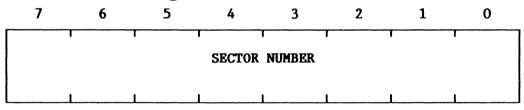

| Sector Number Register                                   | 12-7         |

| Cylinder Number Low Register                             | 12-8         |

| Cylinder Number High Register                            | 12-8         |

| SDH Register.                                            | 1 <b>2-9</b> |

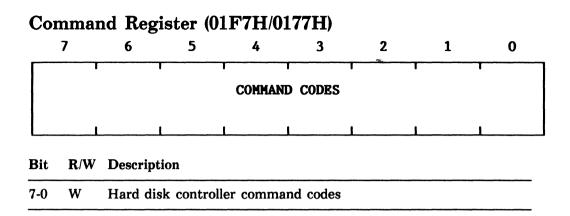

| Command Register                                         | 12-10        |

| Restore Command                                          | 12-11        |

| Seek Command                                             | 12-12        |

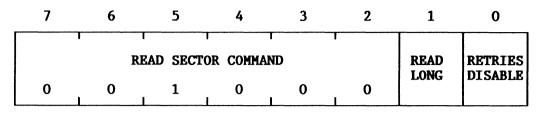

| Read Sector Command                                      | 12-13        |

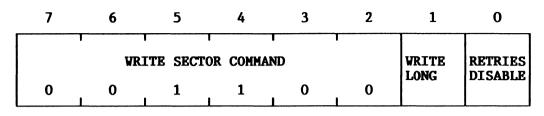

| Write Sector Command                                     | 12-15        |

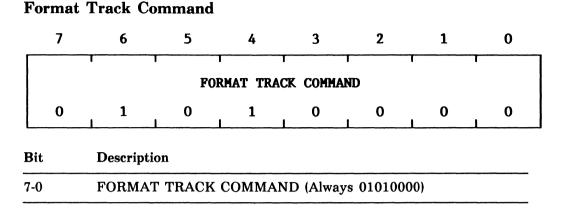

| Format Track Command                                     | 12-17        |

| Read Verify Command                                      | 12-19        |

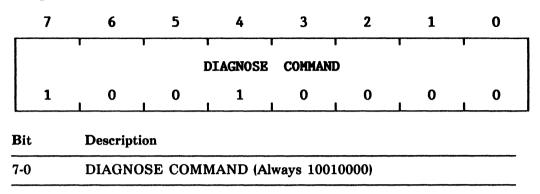

| Diagnose Command.                                        | 12-21        |

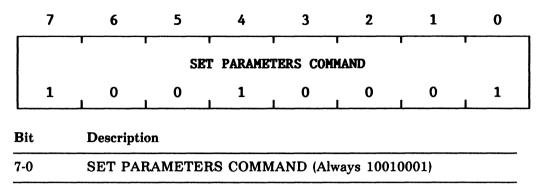

| Set Parameters Command                                   | 12-22        |

| Status Register.                                         | 12-23        |

| Alternate Status Register                                | 12-25        |

| Hard Disk Register                                       | 12-25        |

| Digital Input Register                                   | 12-26        |

| Programming Example                                      | 12-27        |

|                                                          |              |

| Chapter 13 Network Hardware Interface                    | 13-1         |

| Introduction to the LANCE                                | 13-1         |

| Additional Source of Information.                        | 13-2         |

| Functional Description of the Network Hardware Interface | 13-2         |

| The Coax Transceiver Interface                           | 13-2         |

| The Serial Interface Adapter ,                           | 13-2         |

| The Local Area Network Controller                        | 13-2         |

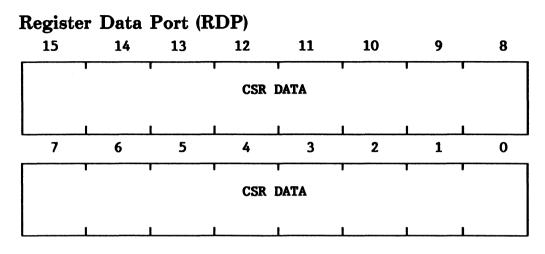

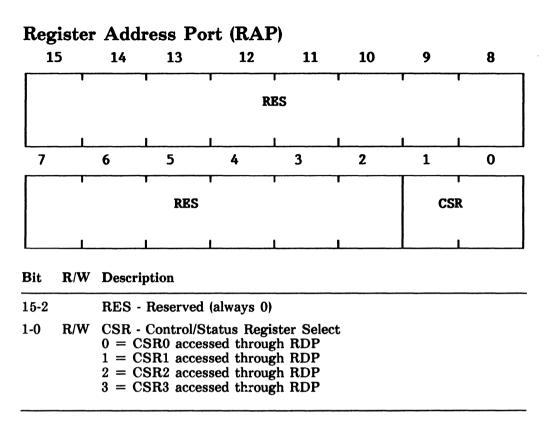

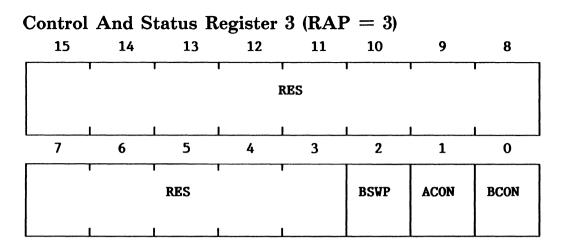

| Programming the LANCE                                    | 13-3         |

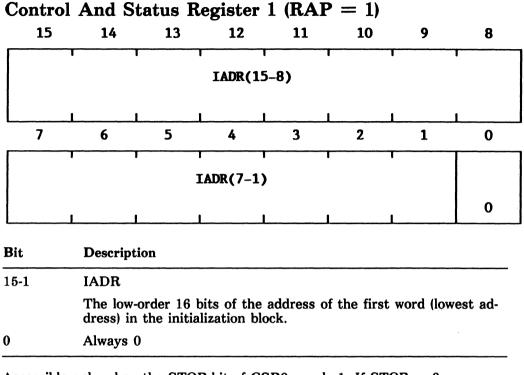

| Initialization Block                                     | 13-4         |

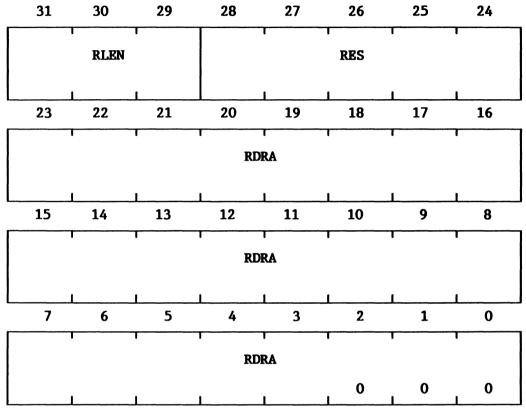

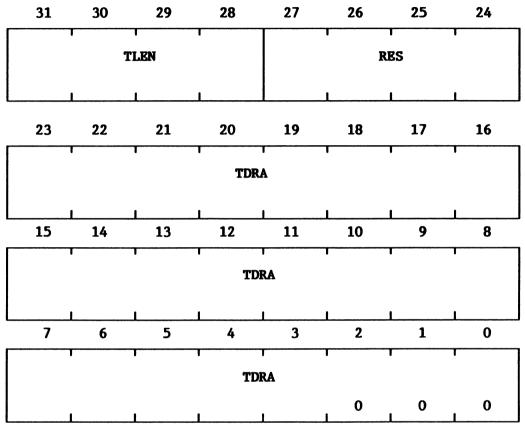

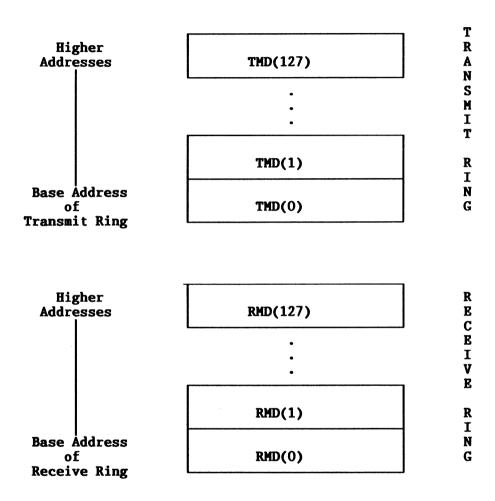

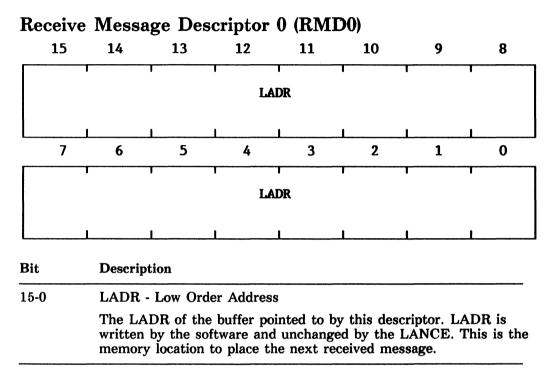

| Receive and Transmit Descriptor Rings                    | 13-4         |

| Data Buffers                                             | 13-4         |

| Programming Sequence                                     | 13-4         |