# VAX/VMS Guide to Writing a Device Driver Order No. AA-H499C-TE

### May 1982

This document explains how to write device drivers for devices that are not supported by VAX/VMS, and how to load these drivers into the VAX/VMS operating system.

### **REVISION/UPDATE INFORMATION:**

This document supersedes the VAX/VMS Guide to Writing a Device Driver (Order No. AA-H499B-TE), including Update Notice No. 1 (Order No. AD-H499B-T1).

#### SOFTWARE VERSION:

VAX/VMS Version 3.0

digital equipment corporation · maynard, massachusetts

First Printing, February 1979 Revised, March 1980 Updated, January 1981 Revised, May 1982

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright (c) 1979, 1980, 1981, 1982 by Digital Equipment Corporation All Rights Reserved.

#### Printed in U.S.A.

The postpaid READER'S COMMENTS form on the last page of this document requests the user's critical evaluation to assist in preparing future documentation.

The following are trademarks of Digital Equipment Corporation:

DEC DEC/CMS DECnet DECsystem-10 DECSYSTEM-20 DECUS DECWriter

5. 1

> DIBOL EduSystem IAS MASSBUS PDP PDT RSTS

RSX UNIBUS VAX VMS VT digital

ZK2140

| HOW TO ORDER ADDITION                                                                                                      | AL DOCUMENTATION                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| In Continental USA and Puerto Rico call 800-258-1710                                                                       | DIRECT MAIL ORDERS (CANADA)                                                                                         |

| In New Hampshire, Alaska, and Hawaii call 603-884-6660<br>In Canada call 613-234-7726 (Ottawa-Hull)                        | Digital Equipment of Canada Ltd.<br>940 Beifast Road<br>Ottawa. Ontario K1G 4C2                                     |

| 800-267-6146 (all other Canadian)                                                                                          | Attn: A&SG Business Manager                                                                                         |

| DIRECT MAIL ORDERS (USA & PUERTO RICO)*                                                                                    | DIRECT MAIL ORDERS (INTERNATIONAL)                                                                                  |

| Digital Equipment Corporation<br>P.O. Box CS2008<br>Nashua, New Hampshire 03061                                            | Digital Equipment Corporation<br>A&SG Business Manager<br>c/o Digital's local subsidiary or<br>approved distributor |

| <ul> <li>Any prepaid order from Puerto Rico must be placed<br/>with the local Digital subsidiary (809-754-7575)</li> </ul> |                                                                                                                     |

28214

## CONTENTS

PREFACE

SUMMARY OF TECHNICAL CHANGES

PART I

CHAPTER 1 INTRODUCTION TO DEVICE DRIVERS

| 1.1     | MACHINE DEPENDENCE AND MACHINE INDEPENDENCE 1-1  |

|---------|--------------------------------------------------|

| 1.2     | COMPONENTS OF A DEVICE DRIVER                    |

| 1.3     | ASYNCHRONOUS NATURE OF A DEVICE DRIVER .4 1-3    |

| 1.4     | FORK PROCESSES                                   |

| 1.5     | PROCESS CONTEXT AND INTERRUPT CONTEXT            |

| 1.6     | DEVICE DEPENDENCE AND DEVICE INDEPENDENCE 1-5    |

| 1.7     | THE I/O DATA BASE                                |

| 1.7.1   | Control Blocks In The I/O Data Base 1-6          |

| 1.7.1.1 | Device Data Block                                |

| 1.7.1.2 | Unit Control Block                               |

| 1.7.1.3 | Channel Request Block 1-7                        |

| 1.7.1.4 | Interrupt Dispatch Block 1-7                     |

| 1.7.1.5 | Adapter Control Block 1-7                        |

| 1.7.1.6 | Channel Control Block                            |

| 1.7.2   | I/O Request Packets                              |

| 1.8     | SYNCHRONIZATION                                  |

| 1.8.1   | Interrupt Priority Levels 1-8                    |

| 1.8.2   | Device Interrupts                                |

| 1.8.3   | Fork Queues                                      |

| 1.8.4   | Resource Wait Queues                             |

| 1.9     | FUNCTIONS OF A DEVICE DRIVER 1-10                |

| 1.9.1   | Initialization Routines 1-10                     |

| 1.9.2   | FDT Routines                                     |

| 1.9.3   | Start I/O Routine 1-11                           |

| 1.9.4   | Interrupt Service Routine 1-12                   |

| 1.9.5   | Device Timeout Handler 1-12                      |

| 1.9.6   | Cancel I/O Routine 1-12                          |

| 1.9.7   | Error-logging Routine 1-12                       |

| 1.10    | AN EXAMPLE OF A UNIBUS I/O REQUEST 1-12          |

| 1.11    | THE UNIBUS                                       |

| 1.12    | PROGRAMMED I/O AND DIRECT MEMORY ACCESS I/O 1-16 |

| 1.13    | BUFFERED I/O AND DIRECT I/O 1-16                 |

| 1.14    | LOADABLE DRIVERS                                 |

|         |                                                  |

CHAPTER 2 DISCUSSION OF A LINE PRINTER QUEUE I/O REQUEST

| 2.1 | DRIVER CODE FOR THE LP11 WRITE FUNCTION 2-1 |

|-----|---------------------------------------------|

| 2.2 | A USER PROCESS'S I/O REQUEST                |

| 2.3 | I/O PREPROCESSING BY VAX/VMS                |

| 2.4 | I/O PREPROCESSING BY THE DRIVER             |

| 2.5 | QUEUING THE I/O PACKET TO THE DRIVER        |

| 2.6 | DRIVER DEVICE ACTIVATION                    |

Page

xi

xv

|         |                                                                                                         | WAITING FOR A DEVICE INTERRUPT                                                                                                                                                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER | 3                                                                                                       | SYNCHRONIZATION OF I/O REQUEST PROCESSING                                                                                                                                                                                                                  |

|         | 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.1.6<br>3.1.7<br>3.1.8<br>3.1.8.1<br>3.1.8.2       | IPLs Defined for the Hardware3-2Interrupt Service Routines3-2Raising IPL3-3Lowering IPL3-3Dispatching Device Interrupts3-4Transferring Control to the Driver Fork Process3-5IPL Use During I/O Processing3-5IPL\$ ASTDEL (IPL 2)3-7IPL\$ IOPOST (IPL 4)3-8 |

|         | 3.1.8.3<br>3.1.8.4<br>3.1.8.5<br>3.1.9<br>3.1.9.1<br>3.1.9.2<br>3.1.9.3<br>3.1.9.4<br>3.1.9.5<br>3.1.10 | Driver Fork Processing (IPLs 8 through<br>11)                                                                                                                                                                                                              |

| 3.1.10   | Overview of IPL Use                               | 10  |

|----------|---------------------------------------------------|-----|

| 3.1.11   | Modifying IPL in Driver Code 3-                   | ·11 |

| 3.1.11.1 | Set Interrupt Priority Level Macro 3-             |     |

| 3.1.11.2 | Disable Interrupts Macro 3-                       | ·12 |

| 3.1.11.3 |                                                   |     |

| 3.1.11.4 |                                                   |     |

| 3.2 F    | ORK BLOCKS AND FORK DISPATCHING                   | 13  |

| 3.2.1    | Interrupt Service Routine for Fork Dispatching 3- | 14  |

| 3.3 R    | ESOURCE WAIT QUEUES                               |     |

| 3.3.1    | Competing for a Controller Data Channel 3-        | 16  |

|          |                                                   |     |

## CHAPTER 4 THE UNIBUS ADAPTER

| 4.1     | READING AND WRITING DEVICE REGISTERS 4-2       |

|---------|------------------------------------------------|

| 4.2     | MAPPING UNIBUS AND PHYSICAL ADDRESSES FOR DMA  |

|         | TRANSFERS                                      |

| 4.2.1   | UNIBUS Adapter Data Transfer Paths 4-3         |

|         | Direct Data Path                               |

|         | Buffered Data Paths 4-5                        |

| 4.2.1.3 | Byte Offset Data Transfers 4-7                 |

| 4.2.1.4 |                                                |

| 4.2.1.5 | Longword-Aligned 32-Bit Random Access Mode 4-8 |

| 4.3     | THE VAX-11/780 UNIBUS ADAPTER 4-8              |

| 4.4     | THE VAX-11/750 UNIBUS ADAPTER                  |

| 4.5     | THE VAX-11/730 UNIBUS ADAPTER 4-10             |

## CHAPTER 5 OVERVIEW OF I/O PROCESSING

| 5.1     | PREPROCESSING AN I/O REQUEST                         |

|---------|------------------------------------------------------|

| 5.1.1   | Process I/O Channel Assignment 5-3                   |

| 5.1.2   | Locating a Device Driver in the I/O Data Base $.5-3$ |

| 5.1.2.1 | Unit Control Block (UCB) 5-3                         |

| 5.1.2.2 | Channel Request Block (CRB) 5-4                      |

| 5.1.2.3 | Interrupt Dispatch Block (IDB) 5-5                   |

|         | 5.1.2.4 $5.1.3$ $5.1.4$ $5.1.5$ $5.1.6$ $5.2.1$ $5.2.1$ $5.2.2$ $5.2.3$ $5.2.4$ $5.2.5$ $5.3$ $5.3.1$                                                                                           | Device Data Block (DDB)                                                             |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| PART    | II                                                                                                                                                                                              |                                                                                     |

| CHAPTER | 6                                                                                                                                                                                               | TEMPLATE FOR AN I/O DRIVER                                                          |

|         | 6.1<br>6.2                                                                                                                                                                                      | CODING CONVENTIONS                                                                  |

| CHAPTER | 7                                                                                                                                                                                               | WRITING DEVICE DRIVER TABLES                                                        |

|         | 7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.2<br>7.2.1<br>7.2.2<br>7.3<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.3                                                                                              | DRIVER PROLOGUE TABLE (DPT)                                                         |

| CHAPTER | 8                                                                                                                                                                                               | WRITING FDT ROUTINES                                                                |

|         | $\begin{array}{c} 8.1 \\ 8.2 \\ 8.3 \\ 8.3.1 \\ 8.3.2 \\ 8.4 \\ 8.5 \\ 8.6 \\ 8.6.1 \\ 8.6.2 \\ 8.6.3 \\ 8.7 \\ 8.7.1 \\ 8.7.2 \\ 8.7.1 \\ 8.7.5 \\ 8.7.5 \\ 8.7.6 \\ 8.7.7 \\ 8.8 \end{array}$ | CONTEXT FOR FDT ROUTINE EXECUTION 8-1<br>REGISTERS PRESET FOR FDT ROUTINE EXECUTION |

v

| 8.8.1 | EXE\$ABORTIO                     |        |

|-------|----------------------------------|--------|

| 8.8.2 | EXE\$FINISHIO and EXE\$FINISHIOC | . 8-13 |

| 8.8.3 | EXE\$QIODRVPKT                   | . 8-14 |

| 8.8.4 | EXE\$ALTQUEPKT                   | . 8-16 |

## CHAPTER 9 WRITING THE START I/O ROUTINE

| 9.1<br>9.2 | TRANSFERRING CONTROL TO START I/O                |

|------------|--------------------------------------------------|

| 9.3        | ACTIVATING THE DEVICE                            |

| 9.3.1      | Obtaining Controller Access 9-2                  |

| 9.3.2      | Getting the I/O Function Code and Converting the |

|            | Code and Modifiers                               |

| 9.3.3      | Computing the Transfer Length 9-4                |

| 9.3.4      | Computing the Transfer Start Address 9-4         |

| 9.3.5      | Preparing the Device Activation Bit Mask 9-5     |

| 9.3.6      | Blocking All Interrupts 9-5                      |

| 9.3.7      | Checking for Power Failure 9-5                   |

| 9.3.8      | Activating the Device 9-5                        |

| 9.4        | WAITING FOR AN INTERRUPT OR TIMEOUT 9-5          |

| 9.4.1      | WFIKPCH and WFIRLCH Macro Formats 9-6            |

| 9.4.2      | Expansion of WFIKPCH Macro 9-6                   |

| 9.4.3      | IOC\$WFIKPCH Routine                             |

| 9.5        | RESPONDING TO AN EXPECTED DEVICE INTERRUPT 9-7   |

## CHAPTER 10 WRITING UNIBUS DMA TRANSFERS

| 10.1   | REQUESTING A BUFFERED DATA PATH               | 10-2   |

|--------|-----------------------------------------------|--------|

| 10.1.1 | Requesting a Permanent Buffered Data Path     | 10-2   |

| 10.1.2 | Requesting the Direct Data Path               | 10-3   |

| 10.1.3 | Mixed Direct and Buffered Data Path Transfers | 10-3   |

| 10.2   | REQUESTING UNIBUS ADAPTER MAP REGISTERS       | 10-3   |

| 10.2.1 | Allocation of Map Registers                   | 10 - 4 |

| 10.2.2 | Permanent Allocation of Map Registers         | 10 - 4 |

| 10.3   | LOADING THE UNIBUS ADAPTER MAP REGISTERS      | 10-5   |

| 10.4   | COMPUTING THE STARTING ADDRESS OF A TRANSFER  | 10-6   |

| 10.5   | ACTIVATING THE DEVICE                         | 10-6   |

| 10.6   | COMPLETION OF A DMA TRANSFER                  | 10-6   |

| 10.6.1 | Purging the Data Path                         | 10-7   |

| 10.6.2 | Releasing a Buffered Data Path                | 10-8   |

| 10.7   | RELEASING UNIBUS ADAPTER MAP REGISTERS        | 10-8   |

## CHAPTER 11 WRITING INTERRUPT SERVICE ROUTINES

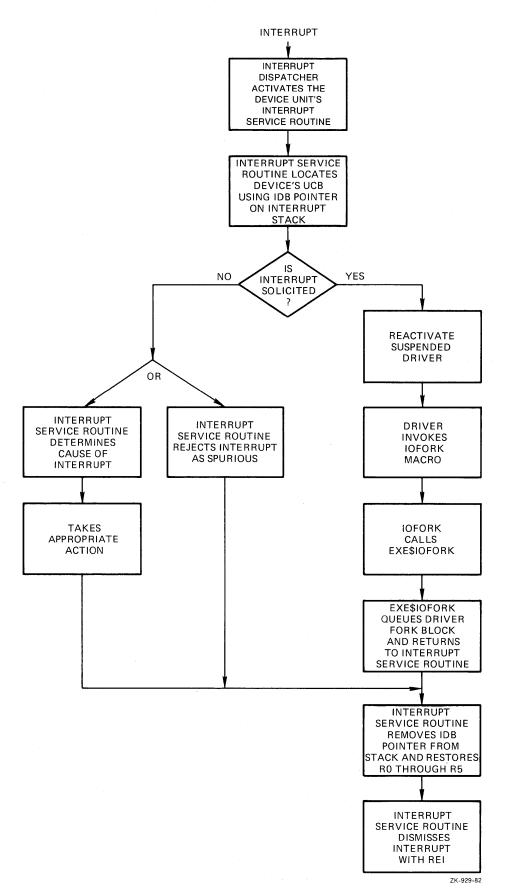

| 11.1   | DELIVERING A DEVICE INTERRUPT TO A DRIVER | 11-1 |

|--------|-------------------------------------------|------|

| 11.2   | INTERRUPT CONTEXT                         |      |

| 11.3   | SERVICING A SOLICITED INTERRUPT           | 11-4 |

| 11.4   | SERVICING AN UNSOLICITED INTERRUPT        | 11-5 |

| 11.4.1 | Examples of Unsolicited Input Handling    | 11-6 |

## CHAPTER 12 COMPLETING THE I/O REQUEST

|          | I/O POSTPROCESSING                           |      |

|----------|----------------------------------------------|------|

| 12.1.1   | EXE\$IOFORK                                  | 12-1 |

| 12.1.2   | Completing an I/O Request                    | 12-2 |

| 12.1.2.  | l Releasing the Controller                   | 12-2 |

| 12.1.2.1 | 2 Saving Status, Count, and Device-Dependent |      |

|          | Status                                       |      |

| 12.1.2.1 | 3 Returning to the Operating System          | 12-3 |

| 12.2     | TIMEOUT HANDLERS                             | 12-4 |

| 12.2.1   | Retrying the I/O Operation                   | 12-5 |

| Aborting the I/O Request                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WRITING INITIALIZATION, CANCEL I/O, AND ERROR-LOGGING ROUTINES                                                                                                                                                                                                                                                                                                          |

| <pre>INITIALIZATION ROUTINES</pre>                                                                                                                                                                                                                                                                                                                                      |

| LOADING A DEVICE DRIVER                                                                                                                                                                                                                                                                                                                                                 |

| PREPARATION FOR LOADING14-1LOADING THE DRIVER14-2LOAD Command14-2CONNECT Command14-3RELOAD Command14-6SHOW/ADAPTER14-7SHOW/CONFIGURATION14-8SHOW/DEVICE14-9The SYSGEN Autoconfiguration Facility14-10The SYSGEN Device Table14-16Floating Vector Address Calculation14-17Rules for Configuration14-17Rules for Configuration14-17Example of a UNIBUS Configuration14-18 |

| DEBUGGING A DEVICE DRIVER                                                                                                                                                                                                                                                                                                                                               |

| BOOTSTRAPPING THE SYSTEM WITH XDELTA                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                         |

CONTENTS

| 15.10.4 Open and Display Value Command 15-11            |

|---------------------------------------------------------|

| 15.10.5 Display Instruction Command 15-11               |

| 15.10.6 Close and Display Next Location Command 15-12   |

| 15.10.7 Display Range Command 15-12                     |

| 15.10.8 Indirect Command                                |

| 15.10.9 Display Previous Location Command 15-13         |

| 15.10.10 Show Value Command                             |

| 15.10.11 Step Instruction Command                       |

| 15.10.12 Step Instruction Over Subroutine Command 15-14 |

| 15.10.13 Setting Breakpoints                            |

| 15.10.14 Clearing Breakpoints                           |

| 15.10.15 Displaying Breakpoint List                     |

|                                                         |

|                                                         |

| 15.10.17 Proceeding from Breakpoints 15-15              |

| 15.10.18 Loading PC and Continuing 15-16                |

| 15.10.19 Display Mode Control                           |

| 15.10.20 The EXECUTE STRING Command 15-16               |

| 15.10.21 Setting Complex Breakpoints                    |

| 15.10.22 XDELTA Stored Commands                         |

| 15.10.23 Stored Base Registers                          |

| 15.11 DELTA                                             |

| 15.11.1 The EXIT Command                                |

| 15.11.2 Examining and Modifying Locations in Process    |

| Space                                                   |

| 15.12 GUIDELINES FOR DEBUGGING DEVICE DRIVERS 15-19     |

| 15.12.1 References to System Addresses                  |

| 15.12.2 Opening Device Registers in XDELTA 15-19        |

| 15.12.3 Incorrect References to Device Registers 15-19  |

|                                                         |

| 15.12.4 XDELTA and System Failures 15-20                |

PART III

APPENDIX A

### THE I/O DATA BASE

| A.1  | CONFIGURATION CONTROL BLOCK (ACF)        |  |

|------|------------------------------------------|--|

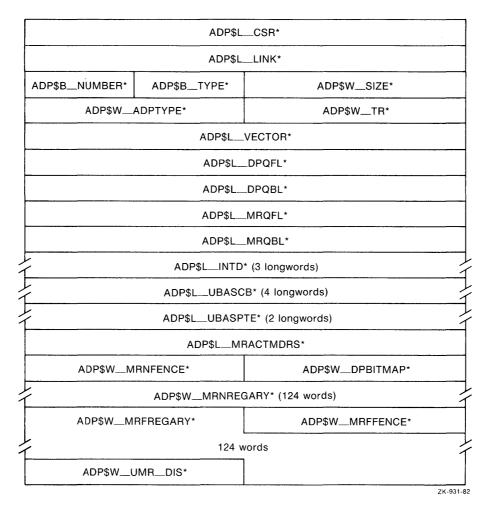

| A.2  | ADAPTER CONTROL BLOCK (ADP)              |  |

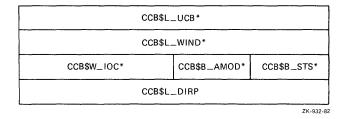

| A.3  | CHANNEL CONTROL BLOCK (CCB)              |  |

| A.4  | CHANNEL REQUEST BLOCK (CRB)              |  |

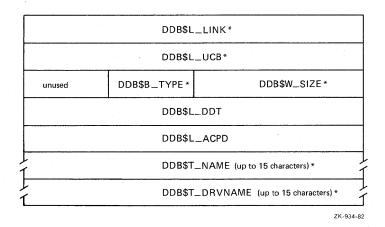

| A.5  | DEVICE DATA BLOCK (DDB)                  |  |

| A.6  | DRIVER DISPATCH TABLE (DDT)              |  |

| A.7  | DRIVER PROLOGUE TABLE (DPT)              |  |

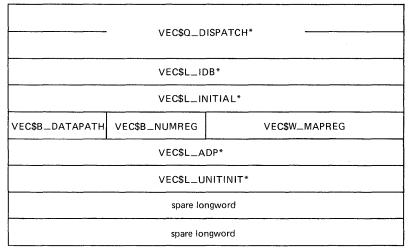

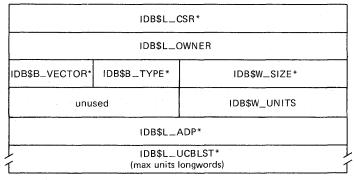

| A.8  | INTERRUPT DISPATCH BLOCK (IDB)           |  |

| A.9  | I/O REQUEST PACKET (IRP)                 |  |

| A.10 | I/O REQUEST PACKET EXTENSION (IRPE) A-31 |  |

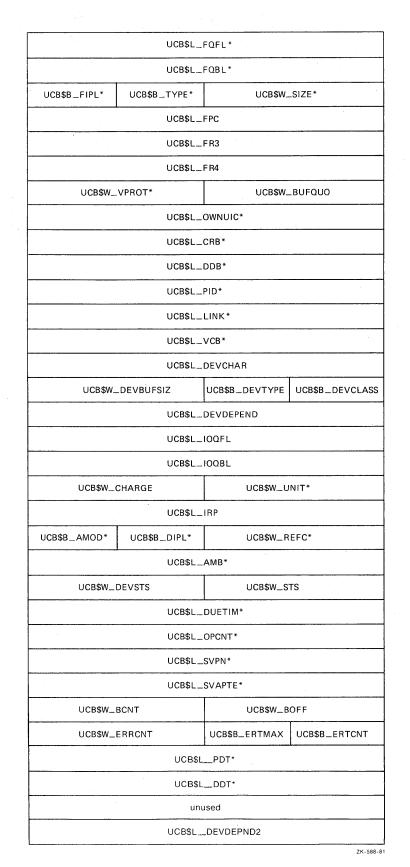

| A.11 | UNIT CONTROL BLOCK (UCB)                 |  |

|      |                                          |  |

APPENDIX B VAX/VMS MACROS INVOKED BY DRIVERS

APPENDIX C OPERATING SYSTEM ROUTINES

APPENDIX D SAMPLE DRIVER FOR AN ANALOG TO DIGITAL CONVERTER

APPENDIX E SAMPLE DRIVER FOR DR11-W DEVICES

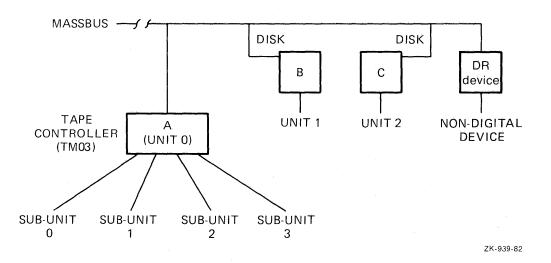

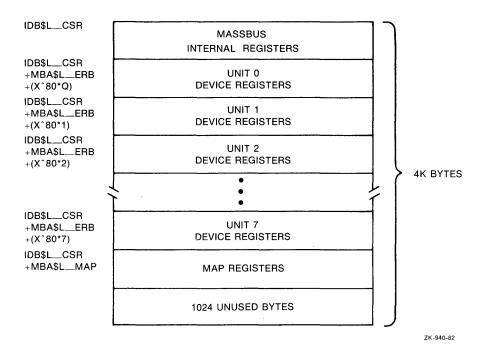

APPENDIX F MASSBUS ADAPTER

| F.l   | MASSBUS ADAPTER REGISTERS               |   | •   | • | • | • | F-2 |

|-------|-----------------------------------------|---|-----|---|---|---|-----|

| F.1.1 | Loading MASSBUS Adapter Registers       |   | •   | • | • | • | F-3 |

| F.1.2 | MASSBUS Adapter Registers and Offsets . | , | • ' | • | • | • | F-4 |

CONTENTS

| F.1.3   | Modification of MASSBUS Adapter Registers         | F-5 |

|---------|---------------------------------------------------|-----|

| F.2     | I/O DATA BASE FOR MASSBUS DEVICES                 | F-6 |

| F.3     | MASSBUS ADAPTER OPERATIONS                        | F-8 |

| F.4     | MASSBUS ADAPTER INTERRUPT DISPATCHING             | F-9 |

| F.4.1   | Checking for MASSBUS Adapter Ownership            | F-9 |

| F.4.2   | Dispatching the Interrupt F                       | -10 |

| F.5     | SPECIAL MBA CONSIDERATIONS FOR DRIVERS F          | -10 |

| F.5.1   | Considerations for Unit Initialization Routines F | -10 |

| F.5.2   | The MASSBUS Adapter and the I/O Data Base F       | -11 |

| F.5.3   |                                                   | -12 |

| F.5.3.1 | · · · · · · · · · · · · · · · · · · ·             | -12 |

| F.5.3.2 |                                                   | -12 |

| F.5.3.3 |                                                   | -13 |

| F.5.4   | Considerations for the DPTAB Macro F              | -13 |

| F.6     |                                                   | -13 |

| F.6.1   | Transferring Control to the Interrupt Service     |     |

|         |                                                   | -14 |

| F.6.2   |                                                   | -14 |

| F.6.3   | Considerations for Interrupt Service Routines F   | -15 |

APPENDIX G UNIBUS ADDRESSES FOR VAX-11 PROCESSORS

INDEX

GLOSSARY

## FIGURES

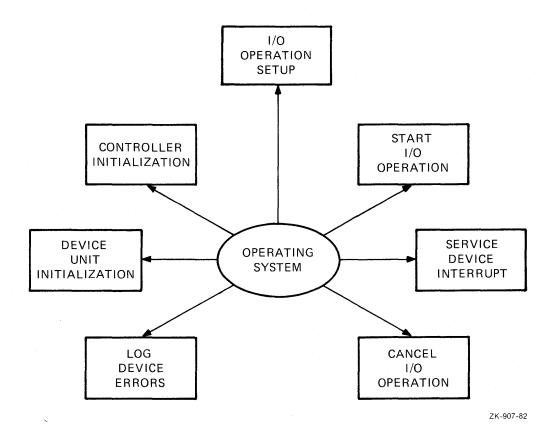

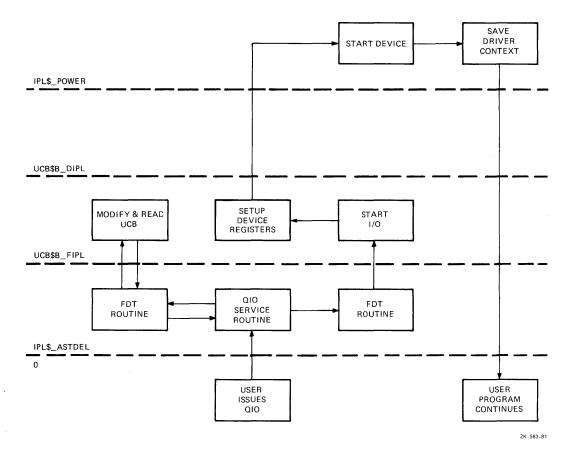

| 1-1  | VAX/VMS Calls to Driver Routines 1-3                                                                                                                                                                                                                                    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

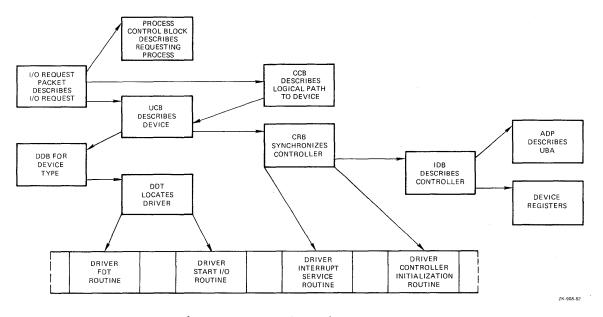

|      | The I/O Data Base                                                                                                                                                                                                                                                       |

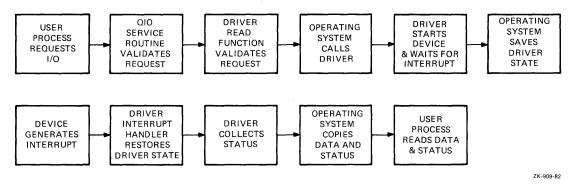

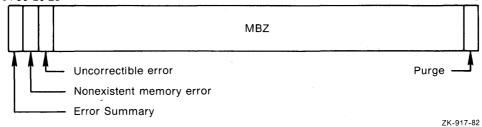

|      | Processing a Sample I/O Operation 1-12                                                                                                                                                                                                                                  |

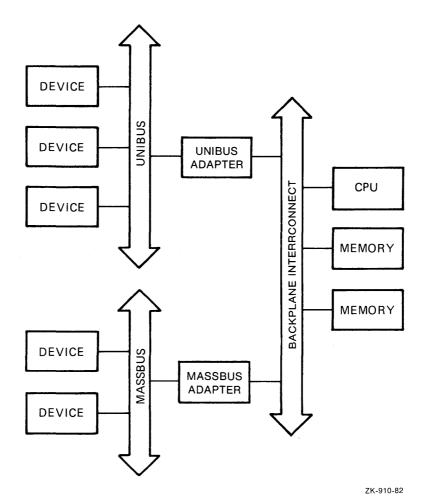

|      | VAX-11 Hardware Configuration 1-15                                                                                                                                                                                                                                      |

|      | A Line Printer Write Function                                                                                                                                                                                                                                           |

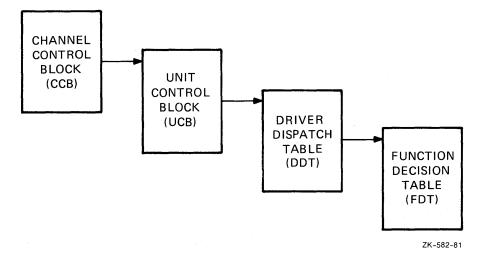

| 2-2  | Locating a Function Decision Table                                                                                                                                                                                                                                      |

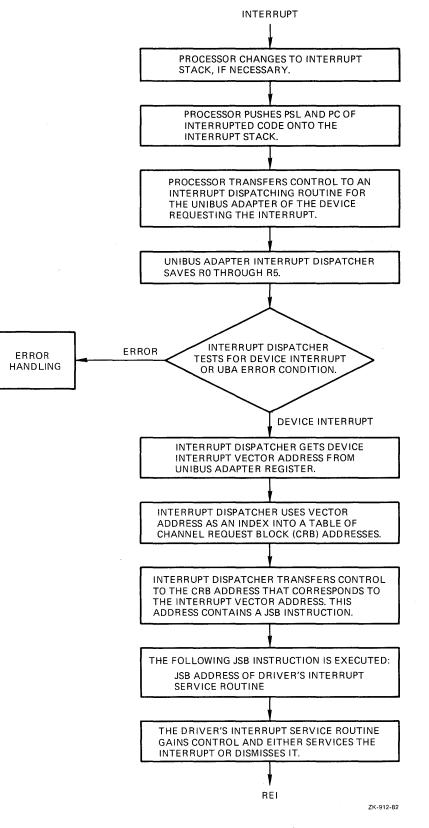

| 3-1  | Interrupt Dispatching of a Nondirect Vector                                                                                                                                                                                                                             |

|      | Interrupt                                                                                                                                                                                                                                                               |

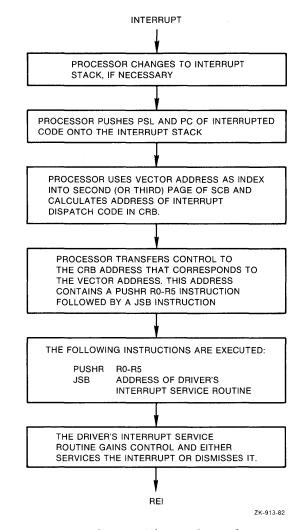

| 3-2  | Interrupt Dispatching of a Direct Vector Interrupt 3-7                                                                                                                                                                                                                  |

| 3-3  | IPL Conventions During I/O Processing 3-11                                                                                                                                                                                                                              |

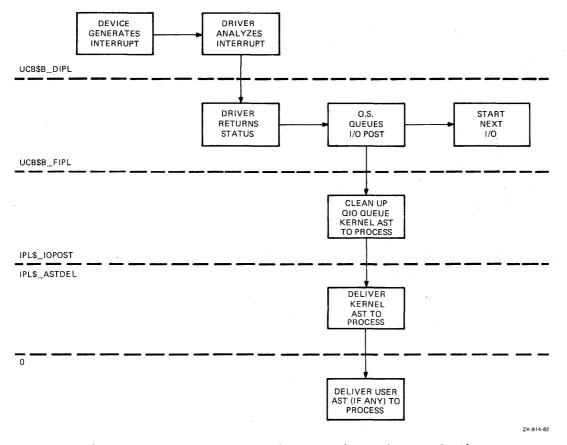

| 3-4  | IPL Conventions During I/O Completion 3-12                                                                                                                                                                                                                              |

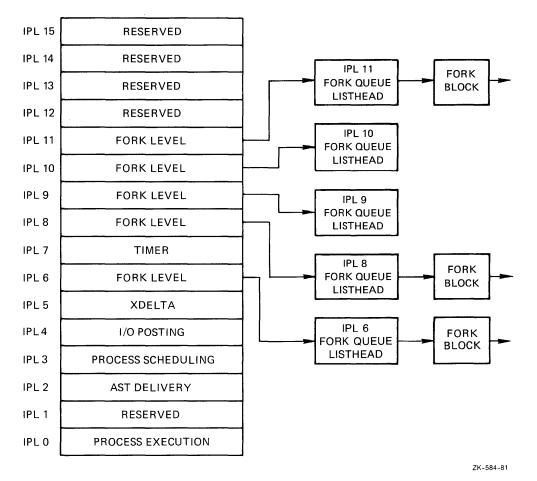

| 3-5  | Fork Dispatching Data Structure 3-15                                                                                                                                                                                                                                    |

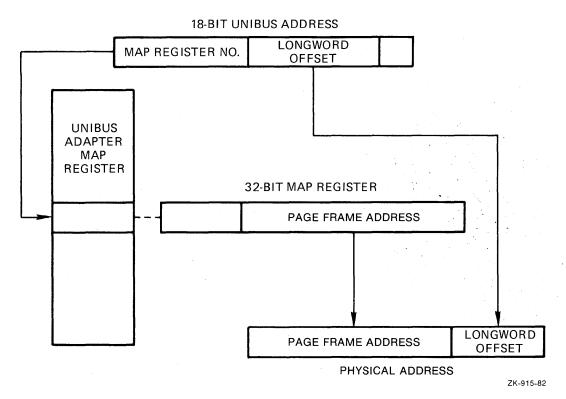

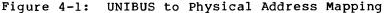

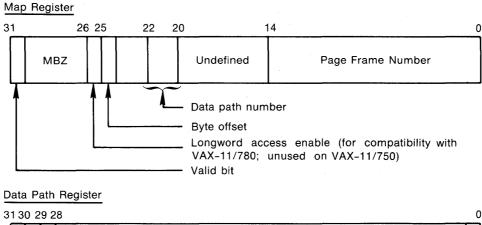

| 4-1  | UNIBUS to Physical Address Mapping 4-3                                                                                                                                                                                                                                  |

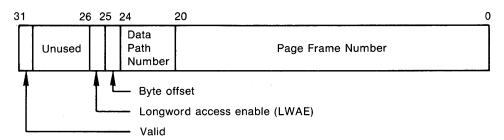

| 4-2  | VAX-11/780 UNIBUS Adapter Registers 4-9                                                                                                                                                                                                                                 |

| 4-3  | VAX-11/750 UNIBUS Adapter Registers 4-10                                                                                                                                                                                                                                |

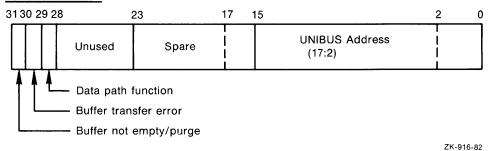

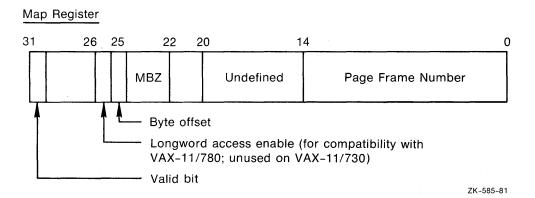

| 4-4  | VAX-11/730 UNIBUS Adapter Map Register 4-11                                                                                                                                                                                                                             |

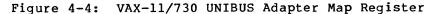

| 5-1  | Sequence of Driver Execution 5-2                                                                                                                                                                                                                                        |

| 5-2  | Locating the Target Device 5-4                                                                                                                                                                                                                                          |

| 5-3  | Data Structures for Three Devices on One                                                                                                                                                                                                                                |

|      | Controller                                                                                                                                                                                                                                                              |

| 5-4  | I/O Data Base for Two Controllers 5-6                                                                                                                                                                                                                                   |

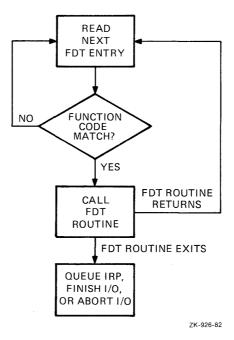

| 5-5  | Driver Function Decision Table 5-9                                                                                                                                                                                                                                      |

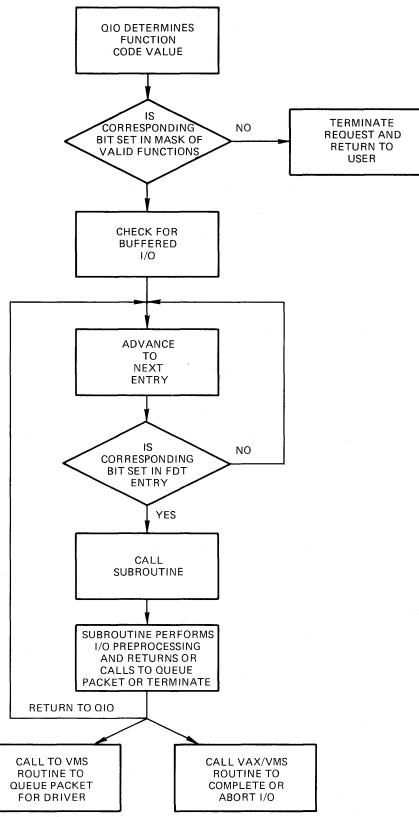

| 5-6  | FDT Routines and I/O Preprocessing 5-11                                                                                                                                                                                                                                 |

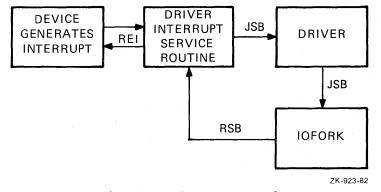

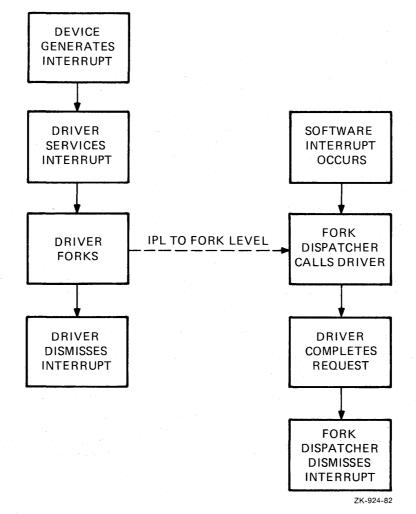

| 5-7  | Creating a Fork Process After an Interrupt 5-14                                                                                                                                                                                                                         |

| 5-8  | Reactivation of a Driver Fork Process 5-15                                                                                                                                                                                                                              |

| 6-1  | Driver Operation                                                                                                                                                                                                                                                        |

| 8-1  | Queue I/O Request Scan of a Function Decision                                                                                                                                                                                                                           |

|      | Table                                                                                                                                                                                                                                                                   |

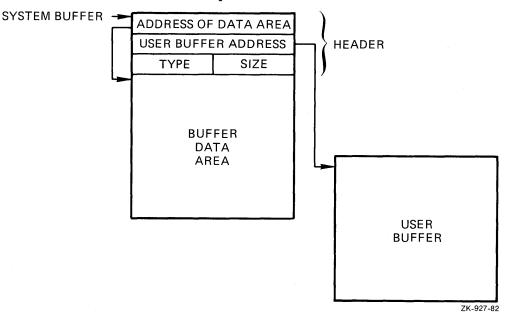

| 8-2  | Format of System Buffer for Buffered I/O Read                                                                                                                                                                                                                           |

|      | Operations                                                                                                                                                                                                                                                              |

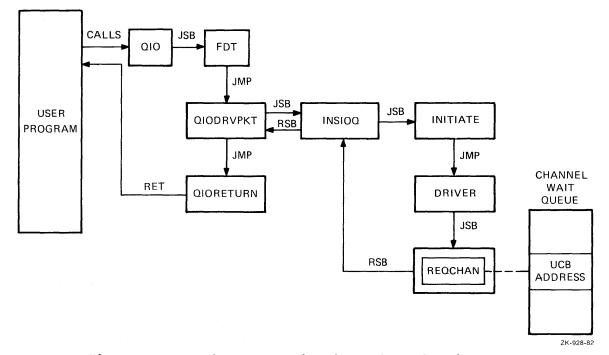

| 9-1  | Driver Insertion into Channel Wait Queue 9-3                                                                                                                                                                                                                            |

| 11-1 | Interrupt Handling Flow                                                                                                                                                                                                                                                 |

|      | $ \begin{array}{c} 1 - 2 \\ 1 - 3 \\ 1 - 4 \\ 2 - 1 \\ 2 - 2 \\ 3 - 1 \\ 3 - 2 \\ 3 - 3 \\ 3 - 4 \\ 3 - 5 \\ 4 - 1 \\ 4 - 2 \\ 4 - 3 \\ 4 - 4 \\ 5 - 1 \\ 5 - 2 \\ 5 - 3 \\ 5 - 4 \\ 5 - 5 \\ 5 - 6 \\ 5 - 7 \\ 5 - 8 \\ 6 - 1 \\ 8 - 1 \\ 8 - 2 \\ 9 - 1 \end{array} $ |

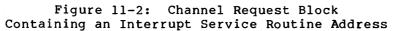

| 11-2 | Channel Request Block Containing an Interrupt     |

|------|---------------------------------------------------|

|      | Service Routine Address                           |

| 15-1 | Bootstrapping the System with XDELTA on a         |

|      | VAX-11/780                                        |

| 15-2 | Bootstrapping the System with XDELTA on a         |

|      | VAX-11/750                                        |

| 15-3 | Bootstrapping the System with XDELTA on a         |

|      | VAX-11/730                                        |

| 15-4 | Loading a Driver                                  |

| A-1  | Configuration Control Block                       |

| A-2  | Adapter Control Block                             |

| A-3  | Channel Control Block                             |

| A-4  | Channel Request Block                             |

| A-5  | Contents of CRB\$L INTD A-12                      |

| A-6  | Device Data Block                                 |

| A-7  | Driver Dispatch Table                             |

| A-8  | Driver Prologue Table                             |

| A-9  | Interrupt Dispatch Block                          |

| A-10 | I/O Request Packet                                |

| A-11 | I/O Request Packet Extension                      |

| A-12 | Unit Control Block                                |

| A-13 | UCB Error Log Extension                           |

| A-14 | UCB Disk Extension                                |

| F-1  | MASSBUS Configuration                             |

| F-2  | Location of MASSBUS Registers in Physical Address |

|      | Space                                             |

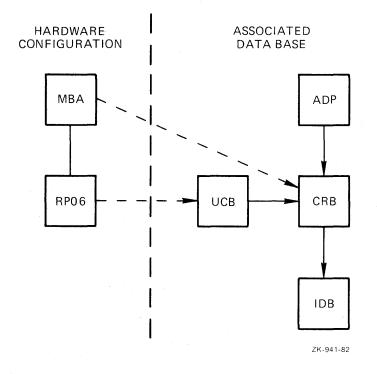

| F-3  | I/O Data Base for MASSBUS Disk Unit               |

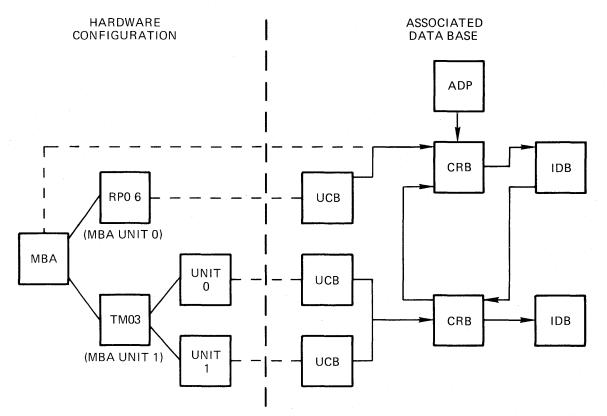

| F-4  | I/O Data Base for MASSBUS Disk and Tape Units F-7 |

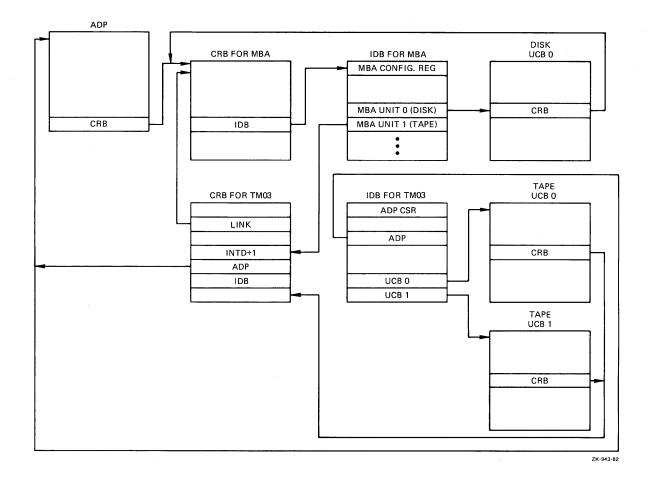

| F-5  | I/O Data Structures Used in Dispatching an        |

|      | Interrupt                                         |

## TABLES

TABLE

| 3-1<br>7-1 | IPLs Defined by VAX/VMS                           |

|------------|---------------------------------------------------|

|            | VAX/VMS I/O Function Codes                        |

| 8-1        | Registers Loaded by Queue I/O Request Service 8-2 |

| 8-2        | FDT Exit Methods                                  |

| 15-1       | XDELTA Command Summary                            |

| A-1        | Contents of the Configuration Control Block A-2   |

| A-2        | Contents of Adapter Control Block                 |

| A-3        | Contents of Channel Control Block                 |

| A-4        | Contents of Channel Request Block A-10            |

| A-5        | Fields of CRB\$L INTD A-12                        |

| A-6        | Contents of Device Data Block                     |

| A-7        | Contents of Driver Dispatch Table                 |

| A-8        | Contents of Driver Prologue Table                 |

| A-9        | Contents of Interrupt Dispatch Block A-23         |

| A-10       | Contents of an I/O Request Packet                 |

| A-11       | Contents of the I/O Request Packet Extension A-32 |

| A-12       | Contents of Unit Control Block                    |

| A-13       | UCB Error Log Extension                           |

| A-14       | UCB Disk Extension                                |

| F-1        | Major Offsets Defined by \$MBADEF                 |

#### PREFACE

The VAX/VMS Guide to Writing a Device Driver provides the information needed to write a device driver that runs under VAX/VMS Version 3.0 and to load that driver into the operating system. VAX/VMS makes no guarantee that drivers written for VAX/VMS Versions 1.0, through 1.6 and 2.0 through 2.5 will execute without modification on subsequent versions of the operating system. While the intent is to maintain the existing interface, some unavoidable changes may occur as new features are added. The use of internal executive interfaces other than those described in this manual is discouraged.

#### INTENDED AUDIENCE

This manual is intended for system programmers who are already familiar with the VAX-11 processor and the VAX/VMS operating system. The manual focuses on writing drivers for devices attached to the UNIBUS; however, Appendix F provides the additional information needed to write a driver for a device attached to the MASSBUS.

#### STRUCTURE OF THIS DOCUMENT

This manual is organized into two parts. The first part consists of the following chapters, which introduce VAX/VMS device drivers and those aspects of the VAX-11 processor and the VAX/VMS system that are essential to drivers:

- Chapter 1 introduces the main concepts associated with drivers on VAX/VMS.

- Chapter 2 describes an example of a line printer driver handling a data transfer.

- Chapter 3 discusses synchronization mechanisms: interrupt priority levels, fork processes and fork queues, and resource wait queues.

- Chapter 4 discusses UNIBUS considerations for direct memory access (DMA) transfers.

- Chapter 5 provides an overview of I/O processing and discusses the interaction between device drivers and VAX/VMS.

The second part of this document is a series of "how to" chapters that provide a sample approach to coding a device driver:

- Chapter 6 contains a template for writing a device driver.

- Chapter 7 details the macros that drivers invoke to create necessary tables.

#### PREFACE

- Chapter 8 describes the writing of function decision routines.

- Chapter 9 describes the writing of a start I/O routine.

- Chapter 10 describes the UNIBUS considerations for a start I/O routine.

- Chapter ll describes the writing of an interrupt service routine.

- Chapter 12 describes the writing of I/O completion and device timeout routines.

- Chapter 13 describes the writing of unit and controller initialization routines, I/O cancellation routines, and error-logging routines.

- Chapter 14 describes the loading of a driver into the system.

- Chapter 15 describes the debugging tool XDELTA that you can use to debug a device driver.

- Appendix A describes the I/O data base in detail. This is an important appendix for the programmer of a device driver.

- Appendix B describes the VAX/VMS macros that drivers can invoke.

- Appendix C describes the VAX/VMS routines that device drivers can call.

- Appendix D contains a sample driver for an analog-to-digital converter.

- Appendix E contains a sample driver for two connected DRlls.

- Appendix F contains information needed to write a device driver for a device attached to the MASSBUS.

- Appendix G lists the starting physical addresses for the UNIBUS memory address space associated with the VAX-11 processors.

- The glossary at the end of this manual defines I/O-related and driver-related terms.

#### ASSOCIATED DOCUMENTS

This document has the following prerequisites:

- VAX Hardware Handbook

- VAX/VMS Summary Description and Glossary

- I/O-related portions of the <u>VAX/VMS</u> <u>System</u> <u>Services</u> <u>Reference</u> <u>Manual</u>

- The appendix on naming conventions in the <u>VAX-11</u> <u>Guide to</u> <u>Creating Modular Library Procedures</u>

- VAX/VMS I/O User's Guide

## PREFACE

The following documents are associated with this manual:

- VAX/VMS System Dump Analyzer Reference Manual

- VAX/VMS System Management and Operations Guide

- VAX/VMS Internals and Data Structures

## CONVENTIONS USED IN THIS DOCUMENT

This manual describes code transfer operations in three ways:

- 1. The phrase "issues a system service call" implies the use of a CALL instruction.

- 2. The phrase "calls a routine" implies the use of a JSB or BSB instruction.

- 3. The phrase "transfers control to" implies the use of a BRB, BRW, or JMP instruction.

#### SUMMARY OF TECHNICAL CHANGES

This manual applies to Version 3.0 of VAX/VMS. The following list summarizes the major technical changes from the Version 2.2 manual:

- 1. DPTAB macro arguments -- The DPTAB macro has two optional arguments that allow drivers to control the SYSGEN utility's automatic configuration of the devices they operate:

- The DEFUNITS argument -- Specifies to AUTOCONFIGURE a default number of units to be configured for a given controller.

- The DELIVER argument -- Specifies the address of a driver-specific unit delivery action routine. See Chapter 7 and Chapter 14 for a discussion of these DPTAB arguments.

- 2. DDTAB macro argument -- The DDTAB macro has an optional argument, MNTVER, that specifies the address of a routine called at the start and end of a mount verification operation. See Chapter 7 for details.

- 3. SHOW command qualifiers -- The SYSGEN SHOW command has additional qualifiers that display values within the system configuration:

- SHOW/ADAPTER -- Displays adapter nexus values

- SHOW/CONFIGURATION -- Displays device CSR addresses, vector addresses, and associated adapter nexus values

The SHOW command qualifiers are briefly described in Chapter 14.

- 4. Configuration Control Block (ACF) -- The SYSGEN autoconfiguration facility uses this data structure to describe the device it is currently adding to the configuration. Appendix A contains a description of the fields within the ACF.

- 5. The VAX-11/730 -- The following chapters describe features specific to the VAX-11/730:

- Chapter 4 describes the VAX-11/730 UNIBUS adapter.

- Chapter 14 gives VAX-11/730 adapter nexus values.

- Chapter 15 describes how to bootstrap a VAX-11/730 with XDELTA.

- Appendix G gives starting physical addresses for VAX-11/730 UNIBUS memory address space.

PART I Introduction 11

#### CHAPTER 1

#### INTRODUCTION TO DEVICE DRIVERS

Under the VAX/VMS operating system, a device driver is a set of routines and tables that the system uses to process an I/O request for a particular device type. In order to understand how drivers are used by the VAX/VMS system, you must become familiar with the following basic concepts:

- Machine dependence and independence

- Asynchronous nature of a device driver

- Fork processes

- Process and interrupt context

- Device dependence and device independence

- I/O data base

- Synchronization mechanisms

The beginning sections of this chapter describe the concepts listed above. The later sections describe the more concrete aspects of drivers, such as the functions they perform.

#### 1.1 MACHINE DEPENDENCE AND MACHINE INDEPENDENCE

The VAX/VMS operating system can run on any of three VAX-11 processors: the VAX-11/780, VAX-11/750, or VAX-11/730. Although these processors conform to the VAX-11 architecture, there are some differences in design among the three machines. To achieve machine-independence, follow the conventions outlined in this manual when you write a device driver. The driver will then operate on any processor without modification.

To aid in driver debugging, sections of this manual discuss certain internal differences among the VAX-11/780, VAX-11/750, and the VAX-11/730. This section defines several terms that describe the hardware configuration of each of these processors in a machine-independent manner:

- Backplane interconnect -- An internal processor bus that UNIBUS and MASSBUS adapters use to communicate with main memory and the central processor.

- UNIBUS adapter -- An interface device between the backplane interconnect and a UNIBUS.

UNIBUS adapters may be direct vector or nondirect vector devices. On a direct vector UNIBUS adapter, UNIBUS device interrupts cause a direct processor interrupt that jumps to vectors in page two (or three) of the system control block (SCB). On nondirect vector UNIBUS adapters, UNIBUS device interrupts cause a UNIBUS adapter interrupt and are dispatched by the UNIBUS adapter interrupt service routine. Chapters 3 and 4 discuss these adapters in more detail.

- MASSBUS adapter -- An interface device between the backplane interconnect and a MASSBUS.

- Interrupt dispatcher -- A combination of hardware and software that routes UNIBUS and MASSBUS device interrupts to the appropriate device driver interrupt service routine. The interrupt dispatcher's routing mechanism works differently depending upon whether the VAX-11 processor in use accepts direct vector or nondirect vector UNIBUS interrupts and whether the adapter in use is a MASSBUS or UNIBUS adapter.

- Physical address -- The physical memory that UNIBUS and MASSBUS adapters address through the backplane interconnect. The different VAX-11 processors have different amounts of physical address space. Physical addresses of device registers also vary with processor type.

#### 1.2 COMPONENTS OF A DEVICE DRIVER

Normally, a device driver module consists of the following routines and tables:

- An I/O preprocessing routine or routines that validate device-specific parameters of an I/O request, format data, allocate system buffers, and lock pages in memory

- A start I/O routine that activates the device

- An interrupt service routine that responds to interrupts from the device unit

- An error recovery routine that retries I/O operations and performs other error handling

- An error-logging routine that writes the contents of device registers and other data into an error buffer for the system

- A cancel I/O routine that prevents further processing of an I/O request

- An initialization routine that readies a device or controller for operation when the system is bootstrapped or during recovery from a power failure

- A driver prologue table that describes the driver and the device type to the VAX/VMS procedure that loads drivers into the system

- A driver dispatch table that lists the entry point addresses of standard driver routines and records the size of diagnostic and error-logging buffers for the device type

• A function decision table that lists all valid function codes for the device and lists the addresses of I/O preprocessing routines associated with each valid function

With a few exceptions, which are noted in Chapter 7, the order of the various routines and tables within the driver module is not important.

#### 1.3 ASYNCHRONOUS NATURE OF A DEVICE DRIVER

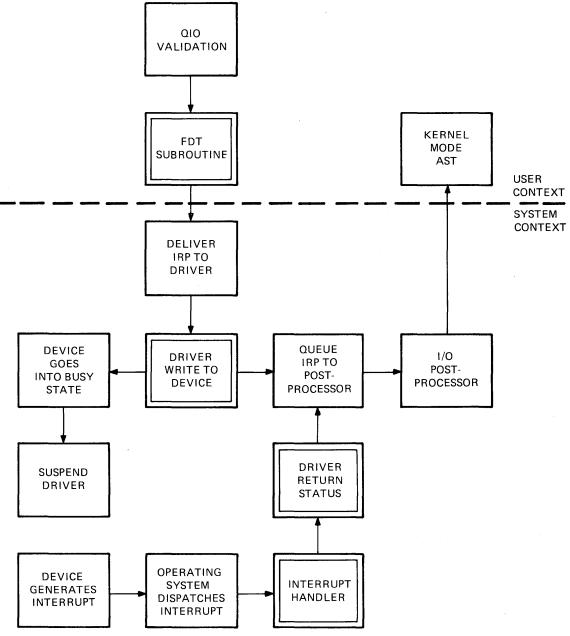

Using the driver tables and other information maintained by the driver and the operating system, the system determines which routines to activate and when they should be activated, as illustrated in Figure 1-1. For example, when a user process issues a Queue I/O Request system service, the system service calls various driver routines to perform preprocessing of the I/O request. Likewise, if a user process issues a Cancel I/O on Channel system service, the system service activates the driver's cancel I/O routine.

Figure 1-1: VAX/VMS Calls to Driver Routines

A device driver does not run from start to end. The system calls driver routines and suspends and resumes them; the central processor interrupts and reactivates driver routines. Because little sequential processing of driver code occurs, VAX/VMS must assume the responsibility for synchronizing the execution of the various driver routines and synchronizing the execution of all drivers in the system. The VAX/VMS operating system synchronizes driver execution using fork processes, interrupt priority levels, fork queues, and resource wait queues, described in the following sections.

#### 1.4 FORK PROCESSES

A fork process is a process that is created dynamically and has minimal context. Fork processes execute entirely within the system address space. The VAX/VMS operating system creates and schedules a fork process by constructing a specialized control block called a fork block, inserting the fork block in a fork queue, and requesting a software interrupt. Fork queues and fork process dispatching are described further in Section 1.7.3.

A driver fork process has the following context:

- Three general registers

- Program counter (PC)

- A unit control block in the I/O data base that describes the target device of the I/O request

The unit control block also contains the driver's fork block. Section 1.8 describes the unit control block and other control blocks in the I/O data base.

Like other processes, fork processes can be suspended and interrupted. VAX/VMS places a driver fork process in a wait state when the process requests an unavailable resource, for example, a controller data channel. The processor interrupts a fork process when the processor receives a request for an interrupt at a higher priority level.

Driver fork processes execute at raised interrupt priority levels to minimize the number of interruptions. Fork processes can raise the priority level to 31 to block all other interrupts, if necessary.

The system automatically saves registers for interrupted fork processes and restores these registers when the process is reactivated. The operating system does not swap fork processes because the fork block and all data about the fork process reside in nonpaged system memory.

#### 1.5 PROCESS CONTEXT AND INTERRUPT CONTEXT

Because a device driver consists of a number of routines that are activated by VAX/VMS, the operating system for the most part determines the context in which the routines execute. As an example, consider the following write request that occurs without error:

- A user process executing in user mode issues a write Queue I/O Request system service.

- The Queue I/O Request system service gains control in user process context but in kernel mode.

- The system service uses the driver's function decision table to call the appropriate preprocessing routines. These routines, called FDT routines, execute in full process context in kernel mode.

- When preprocessing is complete, a VAX/VMS routine creates a fork process to execute the driver's start I/O routine in kernel mode.

- The start I/O routine activates the device unit and suspends itself. At this point, VAX/VMS suspends the fork process executing the start I/O routine and saves sufficient context to reactivate the start I/O routine at the point of suspension.

- When the device completes the data transfer, it issues an interrupt. The interrupt causes the system to activate the driver's interrupt service routine.

- The interrupt service routine executes to handle the device interrupt. It then causes the start I/O routine to resume in interrupt context.

- The start I/O routine regains control in interrupt context but almost immediately issues a request to the operating system to transform its context to that of a fork process. This action dismisses the interrupt.

- When reactivated in fork process context, the start I/O routine performs device-specific I/O completion and passes control to the system for additional I/O postprocessing.

- VAX/VMS I/O postprocessing performs processing at a software interrupt priority level and then issues a kernel mode asynchronous system trap (AST) for the user process requesting I/O.

- When the kernel mode AST is delivered, the AST routine executes in full process context at kernel mode to deliver data and status to the process. If the original request specified a user mode AST, the kernel mode AST queues it.

- When the user process gains control, the user's AST routine executes in full process context in user mode.

It is essential, however, that the various driver routines not attempt to exceed the limitations of the context in which they execute. The majority of driver routines execute in fork process context.

#### 1.6 DEVICE DEPENDENCE AND DEVICE INDEPENDENCE

The VAX/VMS approach to I/O is that the operating system should perform as much of the processing of an I/O request as possible and that drivers should restrict themselves to the device-specific aspects of I/O processing. To accomplish this, the VAX/VMS operating system provides drivers with the following services:

- The Queue I/O Request system service preprocesses an I/O request by performing those functions and checks that are common to all devices; for example, it validates the arguments in the I/O request that are not device specific. This type of preprocessing is called device-independent preprocessing.

- The VAX/VMS operating system includes a number of routines that drivers can call to perform I/O preprocessing, allocate and deallocate resources, and synchronize driver execution.

- VAX/VMS I/O postprocessing performs the device-independent I/O postprocessing for all I/O requests.

Thus, drivers can leave the device-independent I/O processing to the operating system and concentrate on the device-dependent aspects of a device unit; that is, those aspects that vary from device type to device type. In addition, drivers can call the VAX/VMS system to perform many functions that are device specific but common to several devices.

#### 1.7 THE I/O DATA BASE

Because a driver and the operating system cooperate to process an I/O request, they must have a common I/O data base. Under VAX/VMS, the I/O data base consists of three main parts:

- Driver tables that allow the system to load drivers, validate device functions, and call drivers at their entry points

- Control blocks that describe every bus adapter, every device type, every device unit, every controller, and every logical path (channel) from a process to a device

- I/O request packets that define individual requests for I/O activity

The three driver tables are defined in every driver. Section 1.2 lists these tables. Appendix A describes each of the control blocks and the I/O request packet in detail.

Figure 1-2 illustrates some of the relationships among VAX/VMS I/O routines, the I/O data base, and a device driver.

Figure 1-2: The I/O Data Base

#### 1.7.1 Control Blocks In The I/O Data Base

Control blocks in the I/O data base permit access to and describe peripheral hardware. The VAX/VMS operating system creates these

control blocks either at system start-up or at the time a user-written driver is loaded into the system. Drivers refer to some or all of the following control blocks:

- Device data block (DDB)

- Unit control block (UCB)

- Channel request block (CRB)

- Interrupt dispatch block (IDB)

- Adapter control block (ADP)

- Channel control block (CCB)

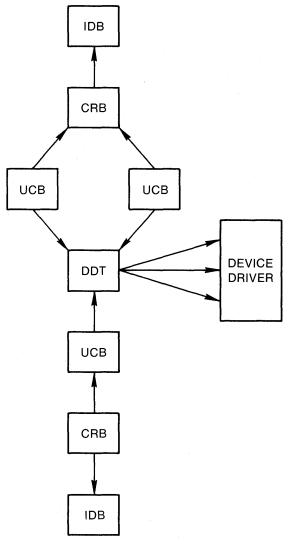

1.7.1.1 Device Data Block - A device data block contains information common to all devices of the same type that are connected to a particular controller. It records the generic device name concatenated with the controller designator, and the driver name and location for those devices. In addition, the device data block contains a pointer to the first unit control block for the device units attached to the controller.

1.7.1.2 Unit Control Block - The system defines a unit control block for each device attached to the system. A unit control block defines the characteristics and current state of an individual device unit. In addition, it contains the fork block used by the unit's device driver and the listhead for the queue of pending I/O request packets for the unit. Because drivers execute as fork processes that are created for each I/O operation on a unit, the unit control blocks are the focal point of the I/O data base. When a driver is suspended or interrupted, the UCB fork block holds the driver's context.

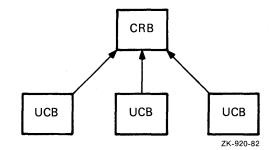

1.7.1.3 Channel Request Block - The operating system creates a channel request block for each controller. A channel request block defines the current state of the controller and lists the devices waiting for the controller's data channel. In addition, it contains the code that dispatches a device interrupt to the interrupt service routine for that unit's driver.

1.7.1.4 Interrupt Dispatch Block - The system creates an interrupt dispatch block for each controller. An interrupt dispatch block lists the device units associated with a controller and points to the unit control block of the device unit that the controller is currently servicing. In addition, an interrupt dispatch block points to device registers and the controller's UNIBUS adapter.

1.7.1.5 Adapter Control Block - An adapter control block defines the characteristics and current state of a UNIBUS or MASSBUS adapter. An adapter control block for the UNIBUS adapter contains the queues and allocation bit maps necessary to allocate adapter resources. VAX/VMS provides routines that drivers can call to interface with their UNIBUS adapter.

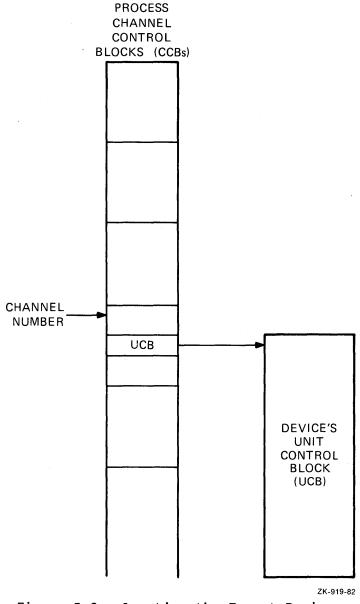

1.7.1.6 Channel Control Block - A channel is a logical path between a process and the unit control block of a specific device unit. The channel control block describes this path. Each process owns a number of channel control blocks. When a process issues the Assign I/O Channel system service, the system writes a description of the assigned device to the channel control block. Unlike the data structures mentioned earlier, a channel control block is not located in nonpaged system space, but in the process's control region (Pl space).

### 1.7.2 I/O Request Packets

The third part of the I/O data base is a list of I/O request packets (IRPs). When a process requests I/O activity, the operating system constructs a packet of data, called an I/O request packet, that describes the I/O request in standard form.

The I/O request packet contains fields into which the system and driver I/O preprocessing routines can write information, such as device-dependent parameters specified in the call to the Queue I/O Request system service. Later, the system sends the I/O request packet to the device driver start I/O routine. The driver start I/O routine uses the packet as its source of detailed instructions about the operation to be performed. The packet includes buffer addresses, a pointer to the target device, I/O function code, and further pointers to the I/O data base.

#### 1.8 SYNCHRONIZATION

The VAX/VMS operating system uses hardware and software interrupt priority levels (IPLs) with their associated interrupts, fork queues, and resource wait queues to synchronize the execution of all drivers within the system and to synchronize execution of various routines within a driver.

### 1.8.1 Interrupt Priority Levels

The VAX-11 processor defines 32 interrupt priority levels (0 through 31). The higher numbered IPLs are reserved for hardware interrupts, for example, device interrupts. The operating system uses the lower numbered IPLs. A higher IPL always takes precedence over a lower IPL. The VAX Hardware Handbook describes the VAX-11 processors' use of IPLs. The following IPLs are of particular interest to drivers:

- Hardware device IPLs (20 through 23); driver interrupt service routines execute at these IPLs.

- Driver fork processing IPLs (8 through 11); driver fork processes execute at these IPLs.

- I/O completion IPL (IPL 4); VAX/VMS gains control to begin its device-independent I/O postprocessing at this IPL.

- AST delivery IPL (IPL 2); VAX/VMS uses this IPL to coordinate the delivery of an AST to a user process. The Queue I/O Request system service also executes at this IPL.

#### 1.8.2 Device Interrupts

When the processor grants a device interrupt, the processor and the VAX/VMS interrupt dispatcher save the current process context. The processor pushes the PC and PSL at the time of the interrupt onto the interrupt stack. In addition, the interrupt dispatcher saves R0 through R5 on the stack.

The interrupt service routine activated as a result of the interrupt follows conventions to preserve all other context of the interrupted process, as follows:

- Uses only R0 through R5

- Cleans up the stack after use

When the interrupt has been serviced, the driver interrupt service routine restores RO through R5 from the stack. The processor restores the previous PC and PSL of the interrupted code. The interrupted process then resumes execution without any awareness of the interruption.

#### 1.8.3 Fork Queues

When an interrupt service routine completes the handling of a device interrupt, it transfers control to the driver to complete device-dependent processing of the I/O request. When the driver regains control, it is executing at device IPL. Almost immediately, the driver should lower IPL to driver fork IPL so that it does not block other device interrupts. A driver lowers IPL by invoking a VAX/VMS macro that creates a fork process to execute at driver fork IPL.

Each driver fork IPL has an associated fork queue. A VAX/VMS macro queues the driver's fork block in the fork queue that corresponds to the driver's fork IPL and issues a software interrupt request for that IPL. When the software interrupt is granted, the VAX/VMS fork dispatcher dequeues fork blocks from the driver fork queues and reactivates the driver at the point following the macro invocation.

## 1.8.4 Resource Wait Queues

Drivers compete for the following shared resources:

- Central processor

- UNIBUS adapter mapping registers, if the device is a DMA device

- UNIBUS adapter buffered data paths, if the device is a DMA device

- The controller data channel if the device is attached to a multiunit controller

When a driver fork process needs an unavailable resource, VAX/VMS resource management routines perform the following steps:

- Save fork process context in the device's UCB fork block

- Insert the address of the UCB fork block in a resource wait queue

- Suspend the driver fork process

When another driver fork process frees the necessary resource, the VAX/VMS resource management routines take the following steps to reactivate the next driver fork process:

- Remove the next UCB fork block from the resource wait queue

- Restore fork process context into the registers

- Reactivate the suspended driver fork process

The VAX/VMS resource management routines allow the driver fork process to be unaware of its suspension and reactivation.

#### 1.9 FUNCTIONS OF A DEVICE DRIVER

A VAX/VMS device driver controls I/O operations on a peripheral device by performing the following functions:

- Defines the peripheral device for the rest of VAX/VMS

- Defines the driver for the system procedure that loads the driver into system virtual address space and that creates the driver's associated data structures

- Readies the device and/or its controller for operation at system start-up and during recovery from a power failure

- Performs device-dependent I/O preprocessing

- Translates programmed requests for I/O operations into device-specific commands

- Activates the device

- Responds to hardware interrupts generated by the device

- Responds to device timeout conditions

- Responds to requests to cancel I/O on the device

- Reports device errors to an error-logging program

- Returns status from the device to the process that requested the I/O operation

The driver prologue table, described in Section 7.1, performs the first two functions listed above. Driver routines perform the remaining functions.

## 1.9.1 Initialization Routines

Most device controllers and device units require initialization when the VAX/VMS driver loading procedure loads the driver into memory and when the VAX/VMS system recovers from a power failure. The amount and type of initialization varies from device type to device type. Section 13.1 provides additional information about device driver initialization routines.

#### 1.9.2 FDT Routines

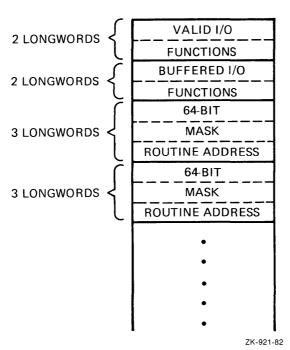

Every driver contains a function decision table (FDT) that indicates the I/O preprocessing routines that are to be executed for various functions on the device. When a user process issues a Queue I/O Request system service, the system service uses the I/O function code specified in the request to select one or more FDT routines for execution. FDT routines perform such functions as allocating buffers, locking pages in memory, and validating device-dependent parameters (P1 through P6) of the I/O request.

The driver contains FDT routines that are device-dependent. VAX/VMS provides additional FDT routines that perform processing common to many I/O functions, as described in Section 8.7. It is advisable for drivers to use FDT routines supplied by the operating system whenever possible.

Because FDT routines are called by the Queue I/O Request system service, they execute in full user process context. As a result, FDT routines have access to user-specified buffers located in the process address space; these buffers are not available to driver routines executing in fork context.

#### 1.9.3 Start I/O Routine

The start I/O routine executes in a driver fork process to perform the following device-dependent functions:

- Translate the I/O function code into a device-specific command

- Transfer the details of the request from the I/O request packet to the device's unit control block

- Obtain access to the controller if it is a multiunit controller

- Obtain the necessary UNIBUS resources if the transfer is direct memory access (DMA)

- Modify the device registers to activate the device

- Perform device-dependent I/O postprocessing after the transfer occurs

The start I/O routine may be forced to wait for the controller or UNIBUS resources to become available. In either case, VAX/VMS suspends the routine and reactivates it when the resources are free. Section 1.8.4 describes the context that VAX/VMS saves for the suspended routine.

After activating the device, the start I/O routine invokes the VAX/VMS wait for interrupt macro. The wait for interrupt macro suspends the driver. The driver remains suspended until the driver's interrupt service routine handles the interrupt and returns control to the driver. At that point, the driver performs device-dependent I/O postprocessing and then transfers control to VAX/VMS for device-independent I/O postprocessing.

#### 1.9.4 Interrupt Service Routine

When a device interrupt occurs, VAX/VMS transfers control to the device driver's interrupt service routine in interrupt context. The interrupt service routine determines whether the interrupt was expected or not and takes the appropriate action. Then the interrupt service routine reactivates the driver for I/O postprocessing.

#### 1.9.5 Device Timeout Handler

As the result of an error condition or a device's being offline, it is possible for a device to fail to complete a transfer in a reasonable period of time. This condition is called device timeout. When a start I/O routine invokes the wait for interrupt macro, it specifies the time interval in which the device can complete a transfer without timing out and the name of a timeout handler that the system is to invoke in the case of a timeout. This information is recorded in the device's unit control block.

Once every second, the VAX/VMS system timer checks all devices in the system for device timeout. When it locates a device that has timed out, it calls the timeout handler.

#### 1.9.6 Cancel I/O Routine

VAX/VMS provides the Cancel I/O on Channel system service that user processes can call to cancel I/O requests. The Cancel I/O on Channel system service, in turn, calls the driver's cancel I/O routine. VAX/VMS also calls the driver's cancel I/O routine when the device's reference count goes to zero; that is, when all users that assigned channels to the device have deassigned them.

#### 1.9.7 Error-logging Routine

The driver's error-logging routine fills an error log buffer with information about the error, for example, the register contentsat the time of the error. VAX/VMS provides a routine that drivers can call to allocate an error log buffer and transfer control to the register dump routine.

#### 1.10 AN EXAMPLE OF A UNIBUS I/O REQUEST

Figure 1-3 illustrates how the VAX/VMS operating system and the device driver process a user process request for a read I/O operation on a DMA UNIBUS device.

Figure 1-3: Processing a Sample I/O Operation

The processing of the sample I/O request illustrated in Figure 1-3 occurs in the following steps:

- A process requests I/O operation. A user process requests data from the device by issuing either of the following:

- A VAX-11 RMS get record function call (which results in a Queue I/O request)

- A Queue I/O Request system service

The user process specifies the target device, a read function code, and the address of a buffer in which the data is to be read.

- The operating system performs I/O preprocessing. The Queue I/O Request system service validates the request and locates I/O data base control blocks that describe the device and its driver. The system service also allocates and initializes an I/O packet to contain a description of the I/O request. The system service then calls a read function routine in the driver.

- The driver performs I/O preprocessing. The driver function decision table routine verifies that the user buffer resides in virtual memory pages that can be modified by the requesting process, locks the buffer pages in memory, and adds details of the I/O operation to the I/O request packet. The read FDT routine then calls the operating system to send the I/O request packet to the driver.

- VAX/VMS creates a driver fork process. A VAX/VMS routine creates a fork process in which the device driver can execute. The routine activates the driver fork process by transferring control to the driver's start I/O routine.

- The driver readies the UNIBUS adapter. For DMA transfers, the driver fork process calls VAX/VMS routines that control the UNIBUS adapter hardware to map UNIBUS addresses into physical addresses for the transfer.

- The driver activates the device. The fork process activates the device by setting bits in device registers.

- The driver waits for an interrupt. A VAX/VMS routine saves the context of the driver fork process and relinquishes the processor until an interrupt occurs.

- The device requests an interrupt. When the data transfer is complete, the device requests a hardware interrupt that causes the system to dispatch to the driver's interrupt service routine.

- The driver services the interrupt. The driver's interrupt service routine handles the interrupt and reactivates the driver, which reads device registers to obtain status information about the transfer.

- The operating system inserts the driver in a fork queue. The driver requests that the process be reactivated at a lower software interrupt priority level.

- The fork dispatcher reactivates the driver fork process. When processor priority permits, the VAX/VMS fork dispatcher reactivates the driver as a fork process.

- The driver completes the I/O operation. The driver fork process completes device-dependent I/O processing of the I/O request and returns the I/O status to VAX/VMS.

- VAX/VMS completes the I/O operation. The VAX/VMS I/O postprocessing routines copy the I/O status into process address space and/or general registers and return control to the user process.

Of the thirteen steps listed above, only four describe driver I/O preprocessing and driver fork processing. The VAX/VMS I/O support routines perform all I/O processing common to many or all I/O requests. Even in device driver routines, driver writing is simplified by the use of VAX/VMS routines that handle device-independent functions.

The thirteen-step example condenses and simplifies the processing of an I/O operation by ignoring such issues as the following:

- Association of a device with a process; that is, device assignment

- Simultaneous I/O requests for one device

- Hardware interrupt priority levels

- Driver competition for shared system and UNIBUS adapter resources

- Driver competition for I/O activity through a multiunit controller

- Driver recovery from device errors or power failure

Later chapters discuss each of these issues in relation to device drivers.

#### 1.11 THE UNIBUS

On a VAX-11 system, the backplane interconnect connects the central processor to memory. The backplane interconnect also connects the UNIBUS adapter and MASSBUS adapter to memory and to the central processor. Peripheral devices attach to either the UNIBUS, for UNIBUS devices, or the MASSBUS, for MASSBUS devices, as illustrated in Figure 1-4.

The VAX Hardware Handbook describes the hardware components diagrammed in Figure 4-1.

VAX/VMS provides device drivers for a number of standard devices supported by DIGITAL. These devices are connected to either the MASSBUS or the UNIBUS.

Nonstandard devices, that is, customer-supplied devices, normally are connected to the UNIBUS, but can also be attached to the MASSBUS or to the DR32 device interconnect. DIGITAL supplies a device driver and an application library for the DR32 device; see the chapter on the DR32 Interface Driver in the <u>VAX/VMS I/O</u> <u>User's</u> <u>Guide</u> for further information.

To activate a direct memory access (DMA) transfer on the UNIBUS, a driver must first obtain mapping registers, and, optionally, a buffered data path. The driver calls VAX/VMS routines that interface with the UNIBUS adapter to allocate these resources on behalf of the driver.

The direct data path maps each UNIBUS transfer to a backplane interconnect transfer. For each UNIBUS transfer, there is one backplane interconnect transfer. Each backplane interconnect operation transfers a single word or byte of data depending on the device. A buffered data path, on the other hand, allows multiple UNIBUS transfers to be assembled and transferred in one backplane interconnect operation.

Drivers performing other than DMA transfers are generally not concerned with UNIBUS adapter operation.

Instead of creating a complete device driver for a device that does not perform DMA transfers, you can connect the process to the device interrupt vector to program the device from a user process. For a description of how and when to connect to an interrupt vector, consult the VAX/VMS Real-Time User's Guide.

Figure 1-4: VAX-11 Hardware Configuration

#### 1.12 PROGRAMMED I/O AND DIRECT MEMORY ACCESS I/O

Devices transfer data using one of the following methods:

- Programmed I/O

- Direct memory access (DMA) transfers

Devices that perform programmed I/O transfer data as single words or bytes using device registers. After each transfer completes, the device notifies the central processor.

Devices that perform DMA transfers do not require the central processor so frequently. Once the driver activates the device, the device can transfer a large amount of data without requesting an interrupt after each of the smaller amounts. Normally, the driver of a DMA device allocates a UNIBUS buffered data path and UNIBUS map registers for I/O transfers.

#### 1.13 BUFFERED I/O AND DIRECT I/O

Drivers can perform I/O transfers using either of the following methods:

- Buffered I/O

- Direct I/O