EK-CI780-TD-001

# CI780 Hardware Technical Description

Prepared by Educational Services of Digital Equipment Corporation

#### Copyright © 1983 by Digital Equipment Corporation All Rights Reserved

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

#### Printed in U.S.A.

The manuscript for this book was created on a DIGITAL Word Processing System and, via a translation program, was automatically typeset on DIGITAL's DECset Integrated Publishing System. Book production was done by Educational Services Development and Publishing in South Lawrence, MA.

The following are trademarks of Digital Equipment Corporation:

## 8090080

DATATRIEVE DEC DECmate DECnet DECu: DECu: DECsystem-10 DECSYSTEM-20 DECtape DECUS DECWS DECwriter DIBOL MASSBUS PDP P/OS Professional Rainbow RSTS RSX <sup>+</sup> UNIBUS VAX VMS VT Work Processor

## CONTENTS

## CHAPTER 1 INTRODUCTION

| 1.1   | MANUAL SCOPE                                        | I-I |

|-------|-----------------------------------------------------|-----|

| 1.2   | THE COMPUTER INTERCONNECT (CI)                      |     |

| 1.3   | RELATED DOCUMENTS                                   |     |

| 1.4   | THE C1780 INTERFACE                                 |     |

| 1.4.1 | Link Module                                         |     |

| 1.4.2 | Packet Buffer Module (PB)                           |     |

| 1.4.3 | Data Path Module (DP)                               |     |

| 1.4.4 | The Synchronous Backplane Interconnect Module (SBI) | 1-8 |

| 1.4.5 | CI780 Power                                         |     |

### CHAPTER 2 LINK MODULE

| 2.1     | PACKET FORMATS                                     |     |

|---------|----------------------------------------------------|-----|

| 2.1.1   | Information Packet                                 | 2-1 |

| 2.1.1.1 | Bit Synchronization                                | 2-1 |

| 2.1.1.2 | Character Synchronization                          |     |

| 2.1.1.3 | Packet Type/Length (High)                          |     |

| 2.1.1.4 | Packet Length (Low).                               |     |

| 2.1.1.5 | Destinations (True and Complement)                 |     |

| 2.1.1.6 | Source                                             |     |

| 2.1.1.7 | Body                                               |     |

| 2.1.1.8 | Cyclical Redundancy Check (CRC) Bytes              |     |

| 2.1.1.9 | Trailer                                            |     |

| 2.1.2   | Acknowledge/Negative Acknowledge (ACK/NACK) Packet | 2-3 |

| 2.2     | LINK OVERVIEW                                      |     |

| 2.2.1   | Information Packet Reception                       | 2-4 |

| 2.2.2   | ACK/NACK Packet Transmission                       |     |

| 2.2.3   | Information Packet Transmission                    |     |

| 2.2.4   | ACK/NACK Packet Reception                          | 2-8 |

| 2.3     | LINK OPÉRATING STATES                              |     |

| 2.4     | NOTFIVE CHANNEL                                    |     |

| 2.4.1   | CI Carrier Detection and Path Selection            |     |

| 2.4.1.1 | Carrier Detect Logic                               |     |

| 2.4.1.2 | Receive Path Select Mux – ECL Logic                |     |

| 2.4.2   | Manchester Decoder                                 |     |

| 2.4.2.1 | Phase Encoding                                     |     |

| 2.4.2.2 | Decoder Logic                                      |     |

| 2.4.3   | Sync Character Detect Enable PAL                   |     |

| 2.4.4   | Byte Framer                                        |     |

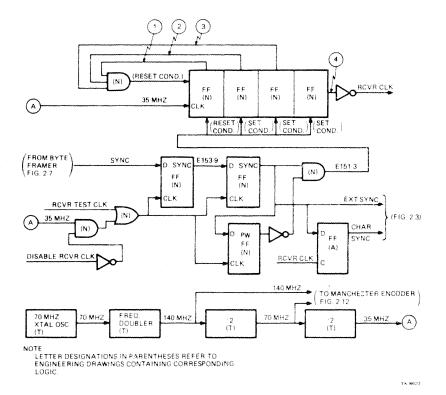

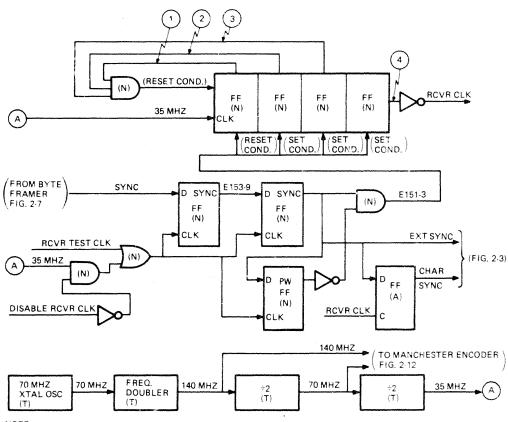

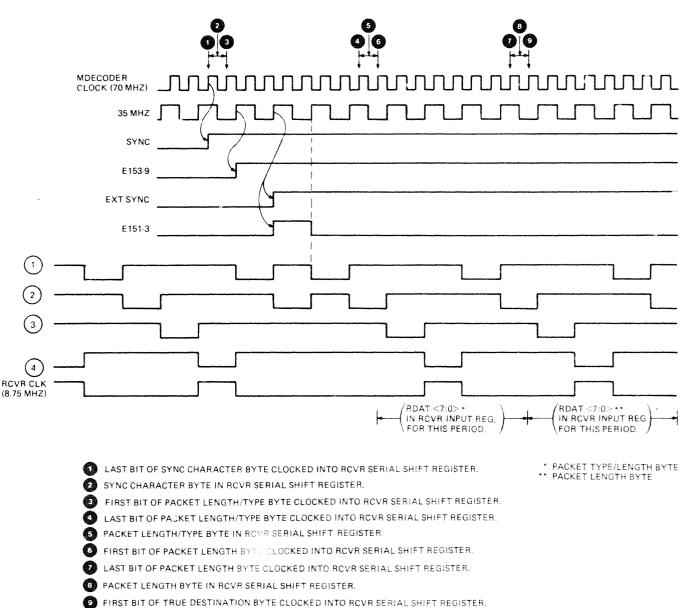

| 2.4.5   | RCVR CLK Generator                                 |     |

| 2.4.6   | CRC Check                                          |     |

| 2.4.7   | Destination Compare                                |     |

| 2.4.8   | ACK Source Comparison                              |     |

| 2.4.9   | Receive Data Parity and Channel Output             |     |

| 2.5     | TRANSMIT CHANNEL                                   |     |

| 2.5.1   | Transmit Data Input                                |     |

| 2.5.2   | Bit Sync, Sync Character, and Trailer Bytes        |     |

| 2.5.3    | ACK Packet Inserts                 |      |

|----------|------------------------------------|------|

| 2.5.3.1  | Packet Type Byte                   | 2-21 |

| 2.5.3.2  | Source Byte                        | 2-21 |

| 2.5.3.3  | Destination Bytes                  |      |

| 2.5.4    | Destination Address Register       | 2-23 |

| 2.5.5    | Transmit Data Parity Check         |      |

| 2.5.6    | CRC Generation                     | 2-23 |

| 2.5.7    | XMIT CLK Generator .               | 2-23 |

| 2.5.8    | Parallel to Serial Data Conversion | 2-23 |

| 2.5.9    | Manchester Encoder                 |      |

| 2.5.10   | XMIT ECL Drivers                   |      |

| 2.6      | CRC GENERATOR AND CHECKER          | 2-29 |

| 2.6.1    | CRC Generator                      | 2-29 |

| 2.6.2    | CRC Checker                        | 2-29 |

| 2.7      | ARBITRATION                        |      |

| 2.7.1    | General                            |      |

| 2.7.2    | Arbitration Logic                  |      |

| 2.8      | LINK FUNCTIONS                     | 2-36 |

| 2.9      | LINK INTERFACE SIGNALS             | 2-39 |

| 2.10     | OPERATING STATES                   | 2-43 |

| 2.10.1   | Message Transmit                   | 2-43 |

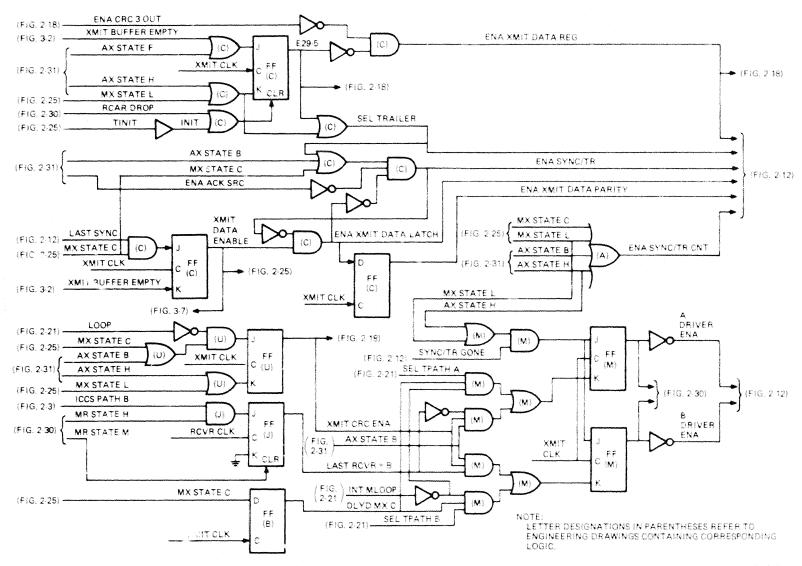

| 2.10.1.1 | Transmit Control Logic             | 2-45 |

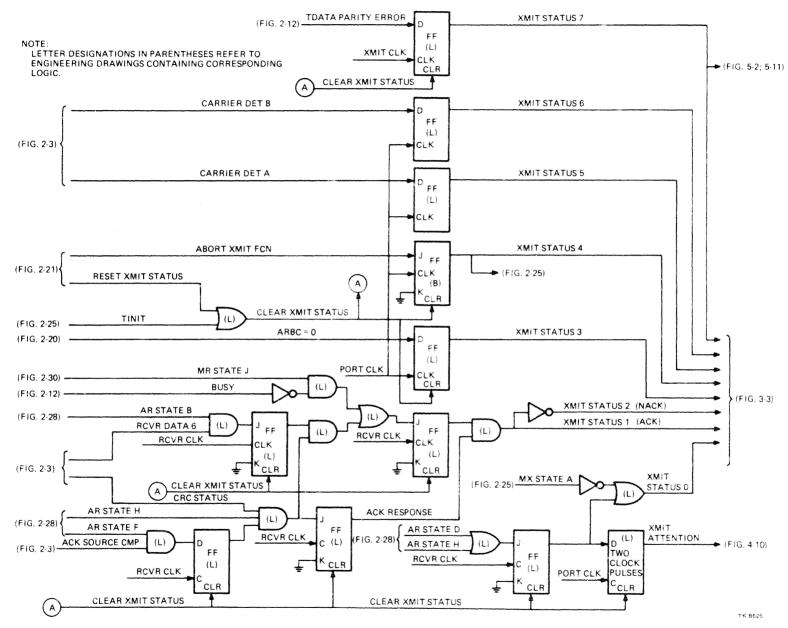

| 2.10.1.2 | Transmit Status                    | 2-47 |

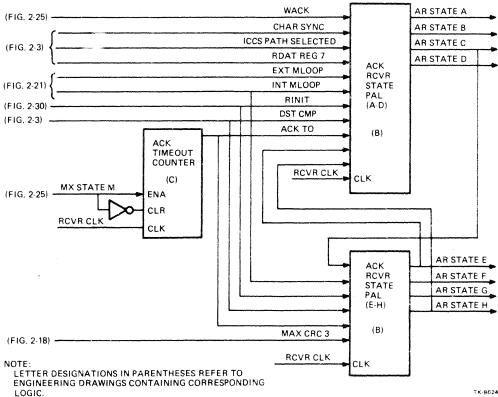

| 2.10.2   | ACK Receive                        | 2-49 |

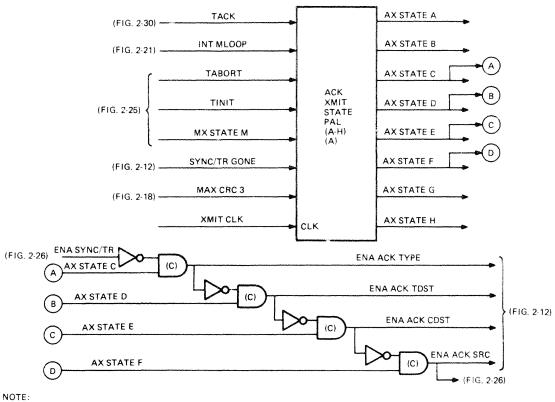

| 2.10.2.1 | ACK Receive PAL States             | 2-49 |

| 2.10.2.2 | Sync Character Detect Enable PAL   | 2-51 |

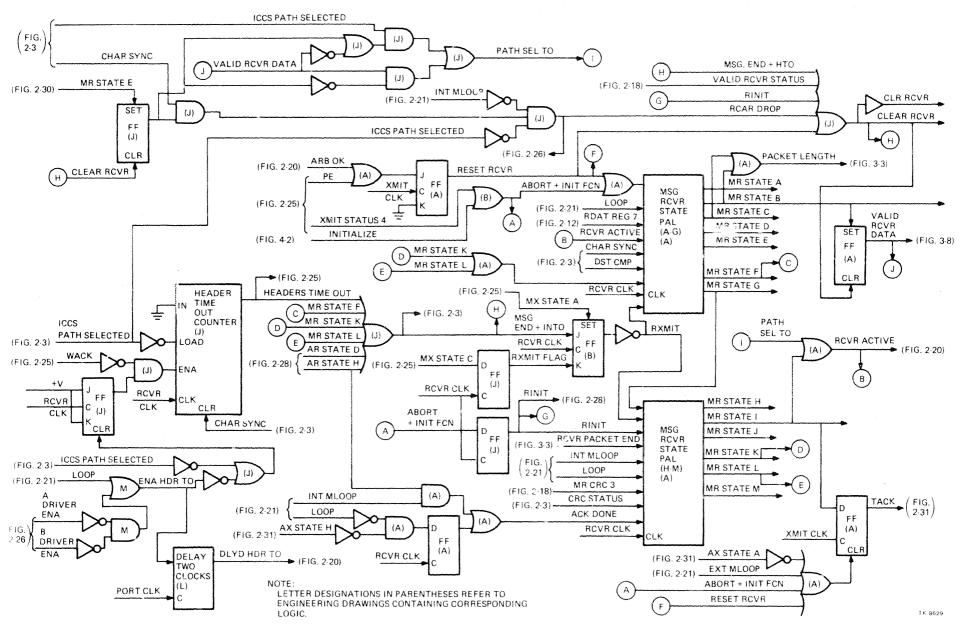

| 2.10.3   | Message Receive                    | 2-53 |

| 2.10.4   | ACK Transmit                       | 2-56 |

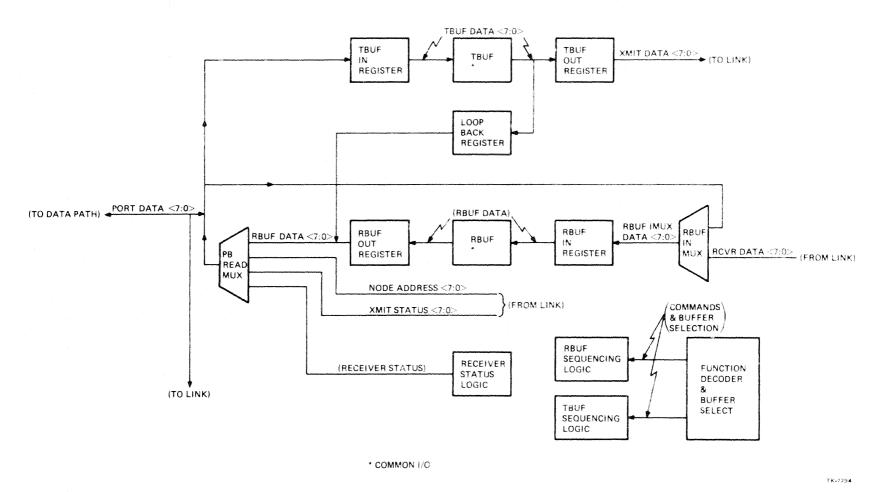

## CHAPTER 3 PACKET BUFFER MODULE

| 3.1   | DATA FLOW; GENERAL DISCUSSION |  |

|-------|-------------------------------|--|

| 3.1.1 | TBUF Load                     |  |

| 3.1.2 | Transmit                      |  |

| 3.1.3 | TBUF Read                     |  |

| 3.1.4 | Valid RCVR Drta               |  |

| 3.1.5 | RBUF MLOAD (Maintenance Load) |  |

| 3.1.6 | RBUF READ                     |  |

| 3.1.7 | PB Read Mux                   |  |

| 3.1.8 | Control Logic                 |  |

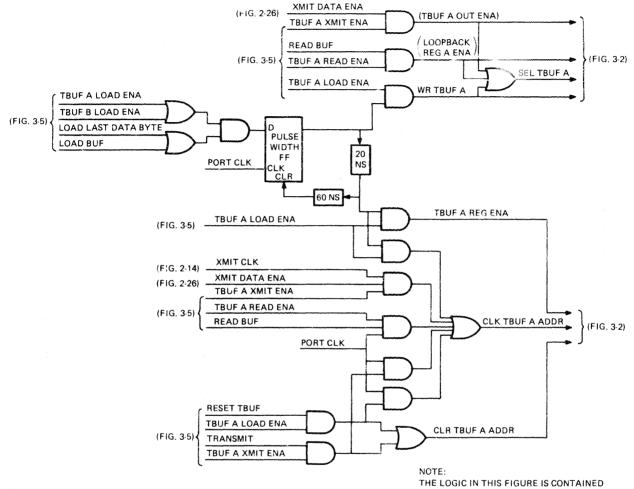

| 3.2   | TBUF DATA FLOW OPERATIONS     |  |

| 3.2.1 | TBUF LOAD                     |  |

| 3.2.2 | TRANSMIT                      |  |

| 3.2.3 | TBUF READ (Loopback)          |  |

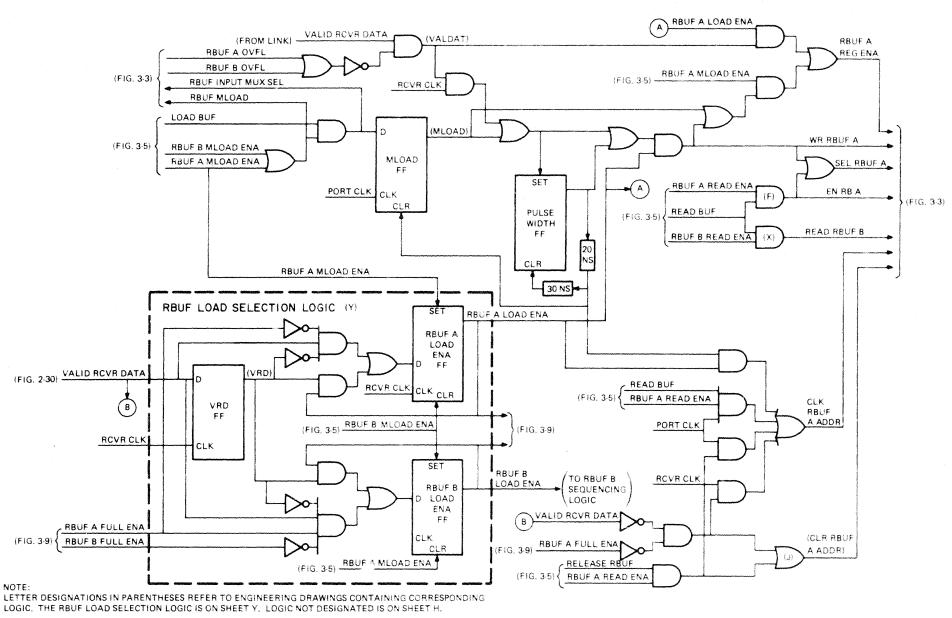

| 3.3   | RBUF DATA FLOW OPERATIONS     |  |

| 3.3.1 | VALID RCVR DATA               |  |

| 3.3.2 | RBUF MLOAD (Maintenance Load) |  |

| 3.3.3 | RBUF Read                     |  |

| 3.3.4 | PB Read Mux                   |  |

| 3.4   | CLOCKS                        |  |

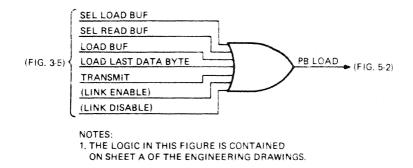

| 3.5    | FUNCTION DECODER AND BUFFER SELECT LOGIC |      |

|--------|------------------------------------------|------|

| 3.5.1  | SEL LOAD BUF                             |      |

| 3.5.2  | SEL READ BUF                             |      |

| 3.5.3  | LOAD BUF                                 |      |

| 3.5.4  | LOAD LAST DATA BYTE                      |      |

| 3.5.5  | READ BUF                                 |      |

| 3.5.6  | TRANSMIT                                 |      |

| 3.5.7  | RSET TBUF                                |      |

| 3.5.8  | RELEASE RBUF                             | 3-13 |

| 3.5.9  | READ NODE ADR                            |      |

| 3.5.10 | READ XMIT STATUS                         |      |

| 3.5.11 | READ RCVR STATUS                         |      |

| 3.5.12 | Link Enable and Link Disable             |      |

| 3.6    | PB LOAD                                  |      |

| 3.7    | SEQUENCING LOGIC                         |      |

| 3.7.1  | TBUF LOAD                                |      |

| 3.7.2  | TRANMIT                                  | 3-15 |

| 3.7.3  | TBUF READ (Loopback)                     |      |

| 3.7.4  | VALID RCVR DATA                          |      |

| 3.7.5  | RBUF MLOAD                               |      |

| 3.7.6  | RBUF READ                                |      |

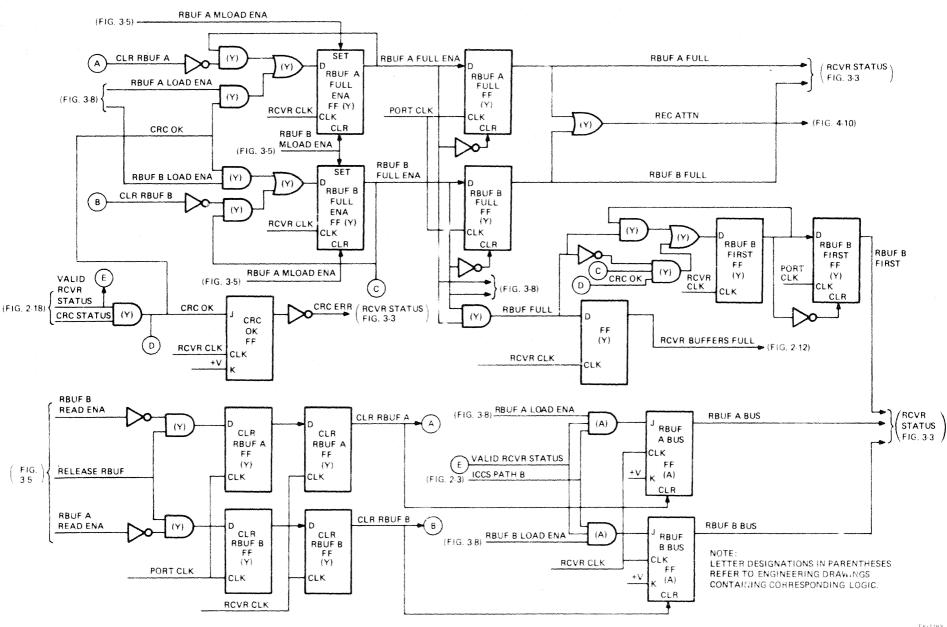

| 3.8    | RCVR STATUS                              |      |

| 3.8.1  | CRC ERR                                  |      |

| 3.8.2  | RBUF A FULL, RBUF B FULL                 |      |

| 3.8.3  | RBUF B FIRST                             |      |

| 3.8.4  | RBUF A BUS                               |      |

| 3.8.5  | RBUF B BUS                               |      |

| 3.8.6  | RCVR A ENABLE                            |      |

| 3.8.7  | RCVR B ENABLE                            |      |

## CHAPTER 4 CONTROL STORE

| 4.1     | SIMPLIFIED BLOCK DIAGRAM      |  |

|---------|-------------------------------|--|

| 4.2     | MICROWORD PARITY              |  |

| 4.3     | CS MICROWORD                  |  |

| 4.3.1   | Microword Fields              |  |

| 4.3.2   | Microword Register            |  |

| 4.4     | MAINTENANCE MUX               |  |

| 4.5     | CONTROL STORE SPACE AND LOGIC |  |

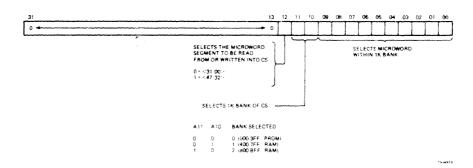

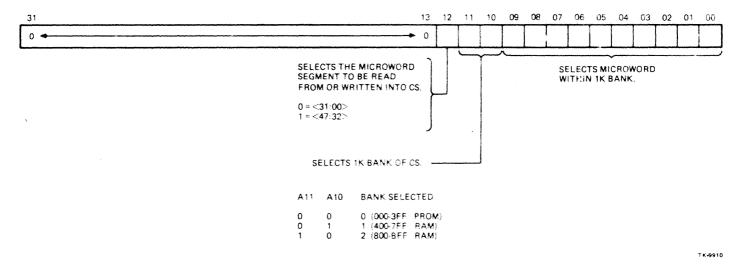

| 4.5.1   | Control Store Space           |  |

| 4.5.2   | Control Store Logic           |  |

| 4.6     | CONTROL STORE ADDRESS SOURCE  |  |

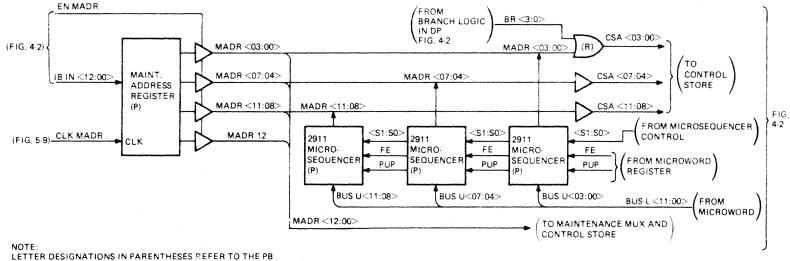

| 4.6.1   | Maintenance Address Register  |  |

| 4.6.2   | Microsequencer Logic          |  |

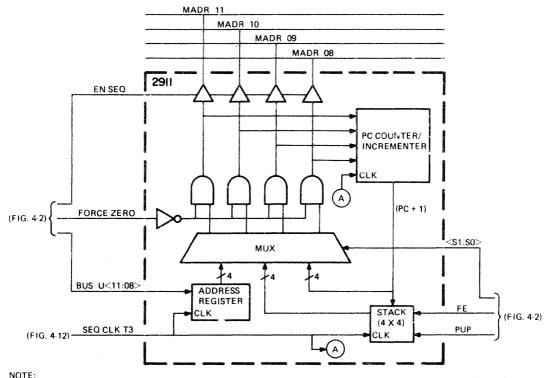

| 4.6.2.1 | 2911 Microsequencer           |  |

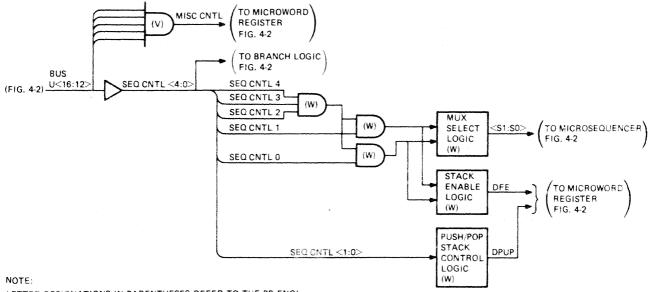

| 4.6.2.2 | Microsequencer Control Logic  |  |

| 4.6.2.3 | Branch Logic                  |  |

| 4.7     | MICROCODE START-UP            |  |

| 4.8     | CLOCKS                        |  |

|         |                               |  |

## CHAPTER 5 DATA PATH MODULE

| 5.1   | OVERVIEW                            |      |

|-------|-------------------------------------|------|

| 5.2   | DP BUSES AND PB INTERFACE           |      |

| 5.2.1 | DP-to-PB Interface                  |      |

| 5.2.2 | PB-to-DP Interface                  |      |

| 5.2.3 | LITERAL/PMCSR Mux                   |      |

| 5.3   | LS/VCDT                             |      |

| 5.3.1 | LS/VCDT Address Selection           |      |

| 5.3.2 | Write Control Logic                 |      |

| 5.4   | UNSOLICITED SBI REQUESTS            |      |

| 5.4.1 | Unsolicited Write Sequence          |      |

| 5.4.2 | Unsolicited Read Sequence           | 5-18 |

| 5.5   | CONTROL LOGIC                       |      |

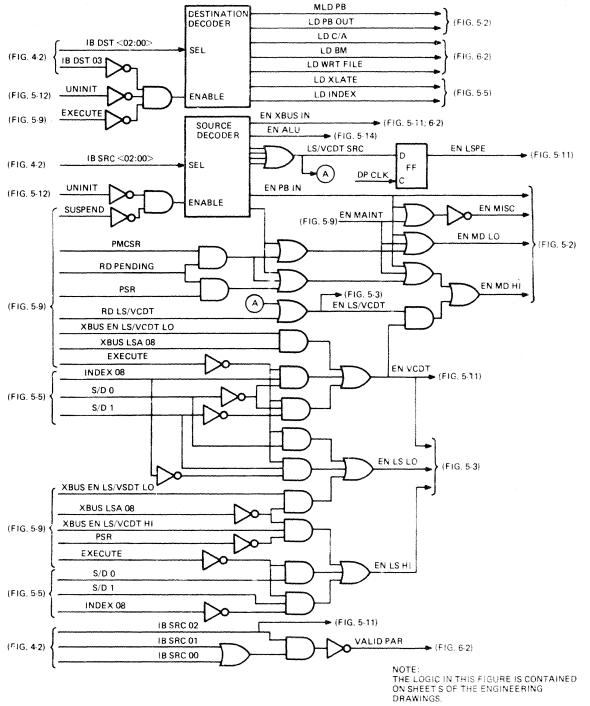

| 5.5.1 | BUS IB Destination                  |      |

| 5.5.2 | BUS IB Source                       |      |

| 5.5.3 | Control Signals                     |      |

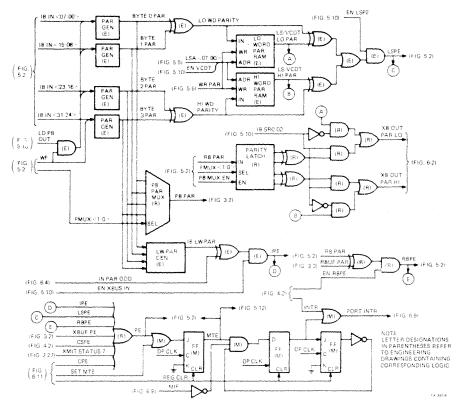

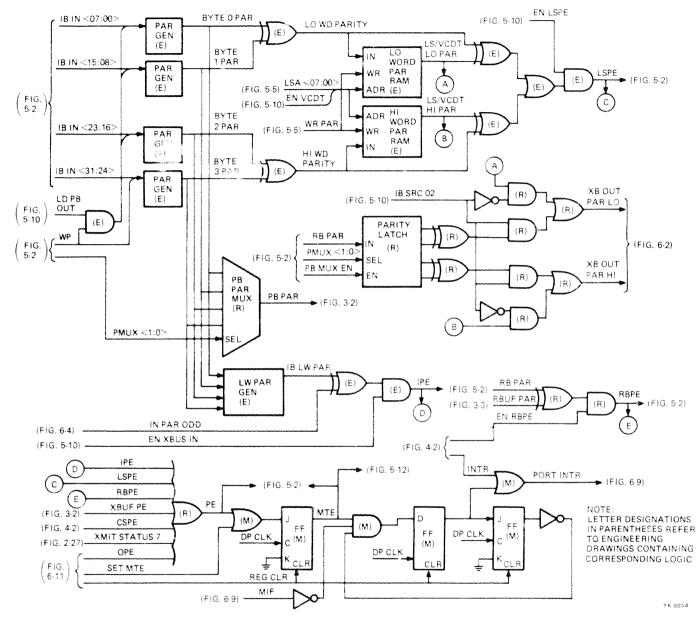

| 5.6   | DP PARITY GENERATOR/CHECKER         | -22  |

| 5.6.1 | PB PAR                              |      |

| 5.6.2 | Input Parity Error (IPE)            |      |

| 5.6.3 | Local Store Parity Error (LSPE)     |      |

| 5.6.4 | XBOUT PAR HI and XBOUT PAR LO.      |      |

| 5.6.5 | Receiver Buffer Parity Error (RBPE) |      |

| 5.6.6 | Parity Error (PE)                   |      |

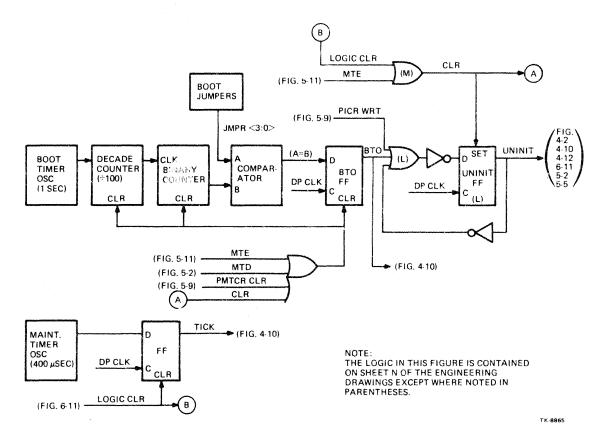

| 5.7   | BOOT TIMER AND MAINTENANCE TIMER    |      |

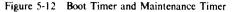

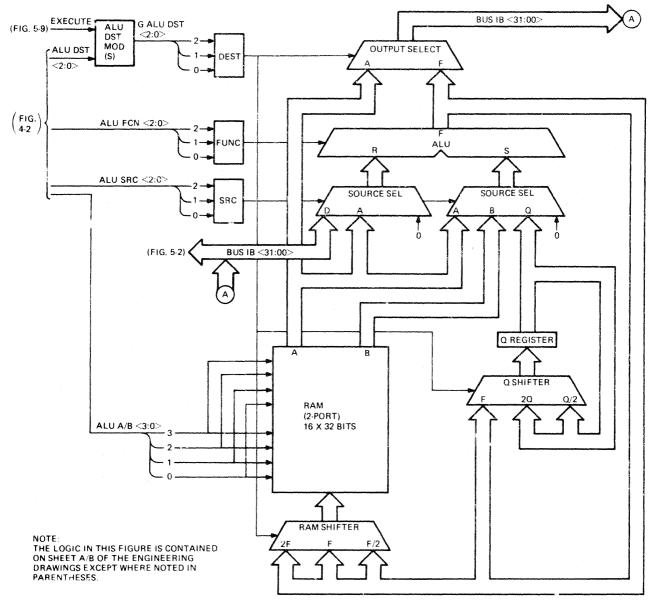

| 5.8   | 2901A MICROPROCESSOR                |      |

| 5.8.1 | Data Path                           |      |

| 5.8.2 | Data Manipulation                   |      |

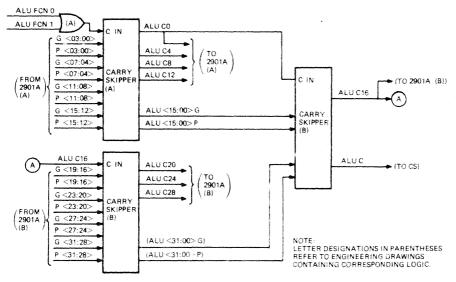

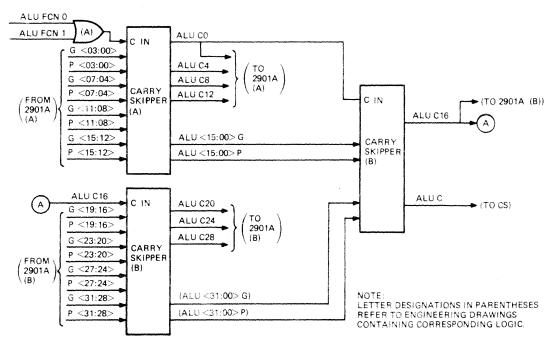

| 5.8.3 | Carry Look-Ahead Logic              |      |

## CHAPTER 6 SBI MODULE

| 6.1     | SBI OVERVIEW                       |      |

|---------|------------------------------------|------|

| 6.1.1   | Write Transfers                    |      |

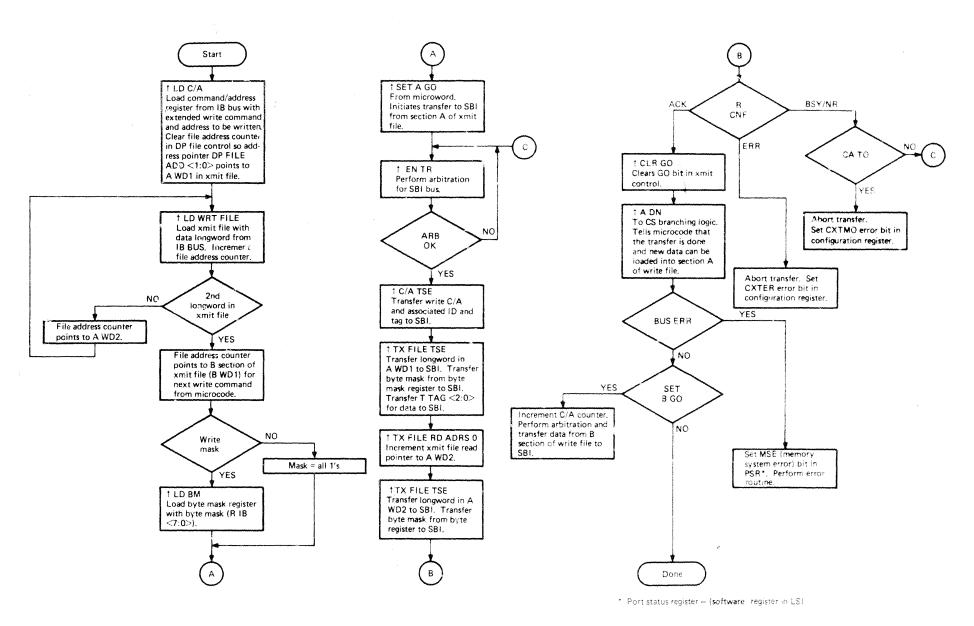

| 6.1.2   | Read Transfers                     |      |

| 6.2     | PORT-INITIATED TRANSFERS           |      |

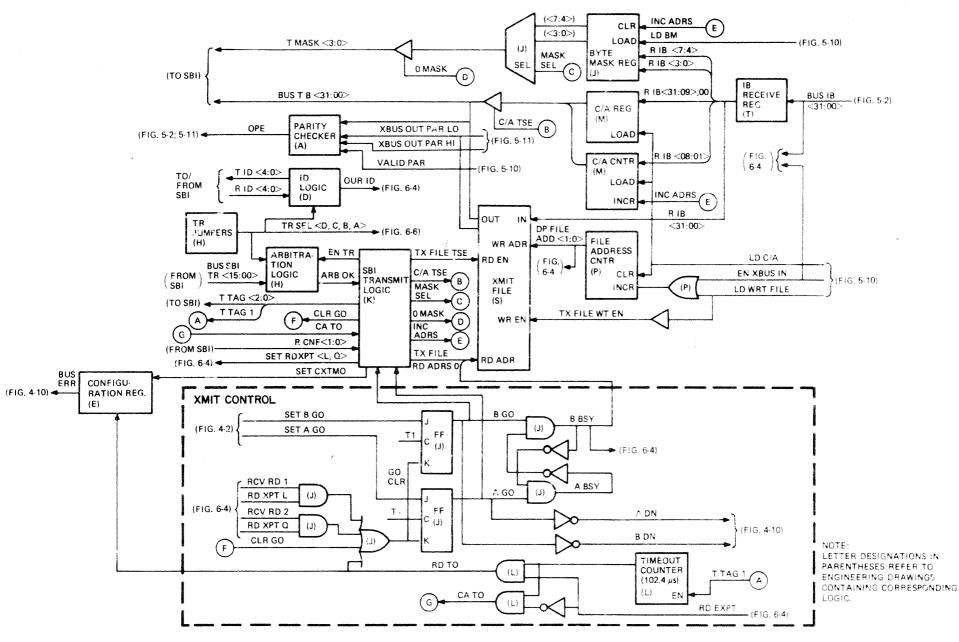

| 6.2.1   | SBI Extended Write Transfer        |      |

| 6.2.2   | SBI Extended Read Transfer         |      |

| 6.3     | UNSOLICITED SBI REQUESTS           |      |

| 6.3.1   | Unsolicited SBI Writes             |      |

| 6.3.1.1 | Writing a DP Register              |      |

| 6.3.1.2 | Writing the Configuration Register | 6-14 |

| 6.3.2   | Unsolicited SBI Reads              |      |

| 6.3.2.1 | Reading a DP Register              |      |

| 6.3.2.2 | Reading the Configuration Register | 6-16 |

| 6.4     | INTERRUPT SUMMARY REQUEST (ISR)    | 6-16 |

| 6.5     | INITIALIZATION AND RESTART LOGIC   |      |

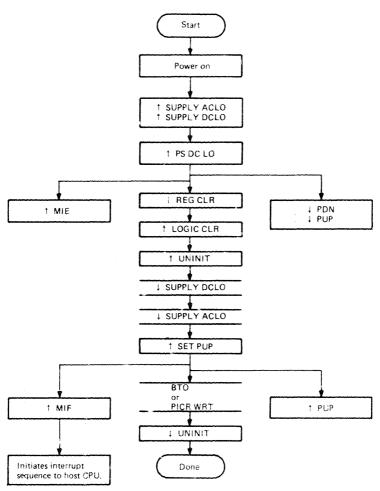

| 6.5.1   | Start-Up Sequence                  |      |

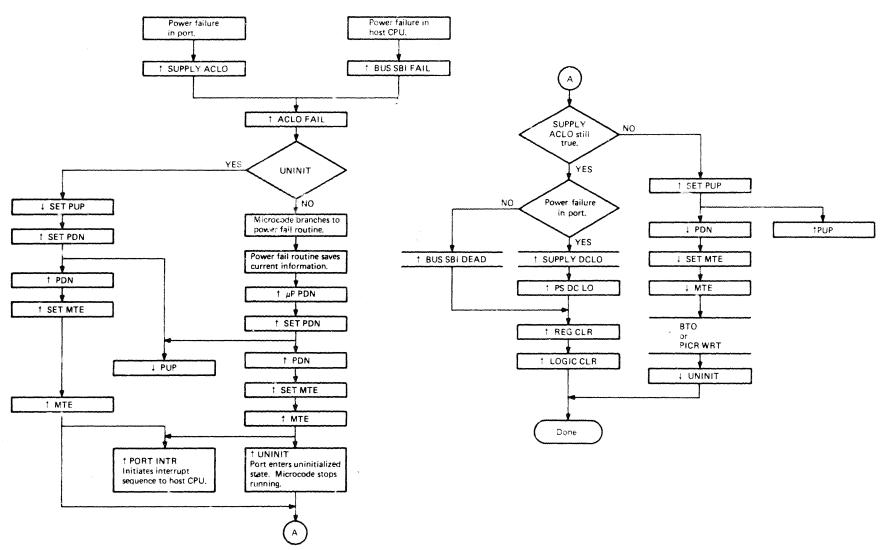

| 6.5.2   | Power-Fail Sequence                |      |

| 6.5.3   | Maintenance Mode                   |      |

| APPENDIX A               | CI780 MNEMONIC GLOSSARY                                                                                                                                        |     |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

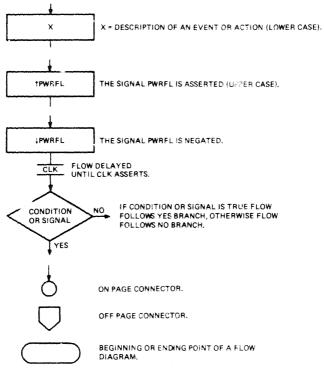

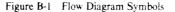

| APPENDIX B               | FLOW DIAGRAM SYMBOLS                                                                                                                                           | B-1 |

| APPENDIX C               | HARDWARE REGISTERS                                                                                                                                             |     |

| C.1<br>C.2<br>C.3<br>C.4 | MADR – Maintenance Address Register<br>MDATR – Maintenance Data Register<br>PMCSR – Port Maintenance Control/Status Register<br>CNFGR – Configuration Register |     |

## FIGURES

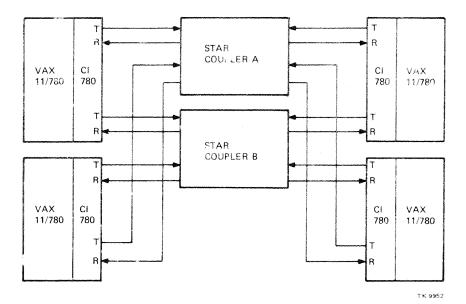

| 1-1  | Four-Node CI Cluster1-2                         |

|------|-------------------------------------------------|

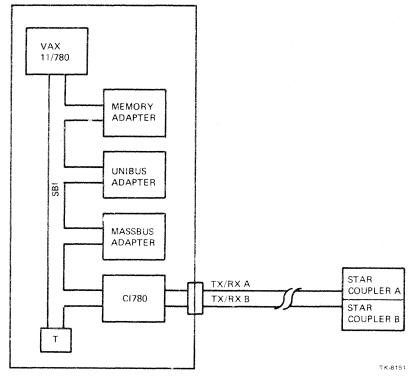

| 1-2  | CI780 Connection1-4                             |

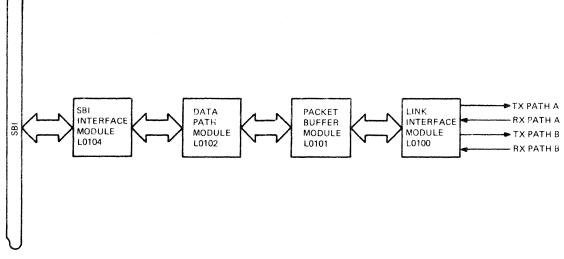

| 1-3  | CI780 Modules                                   |

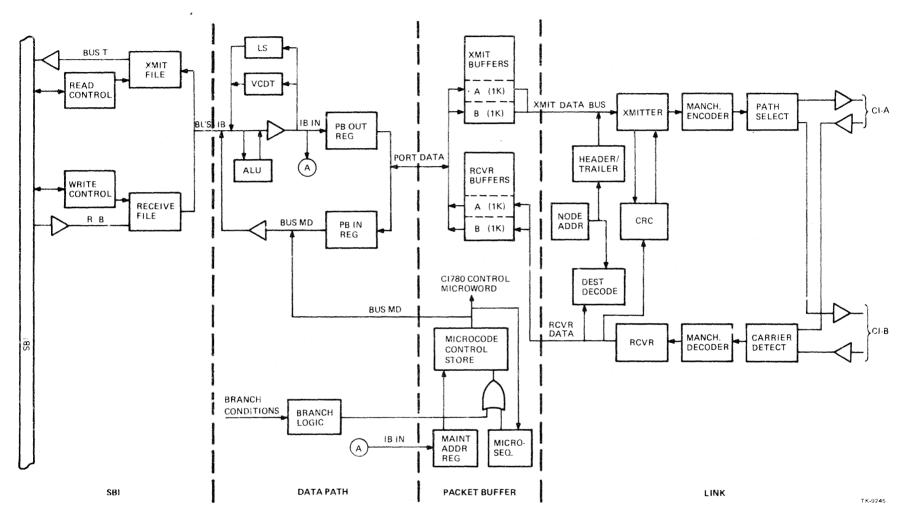

| 1-4  | C1780 Block Diagram 1-7                         |

| 1-5  | CI780 Power                                     |

|      |                                                 |

| 2-1  | Pocket Formats                                  |

| 2-2  | Link Simplified Block Diagram                   |

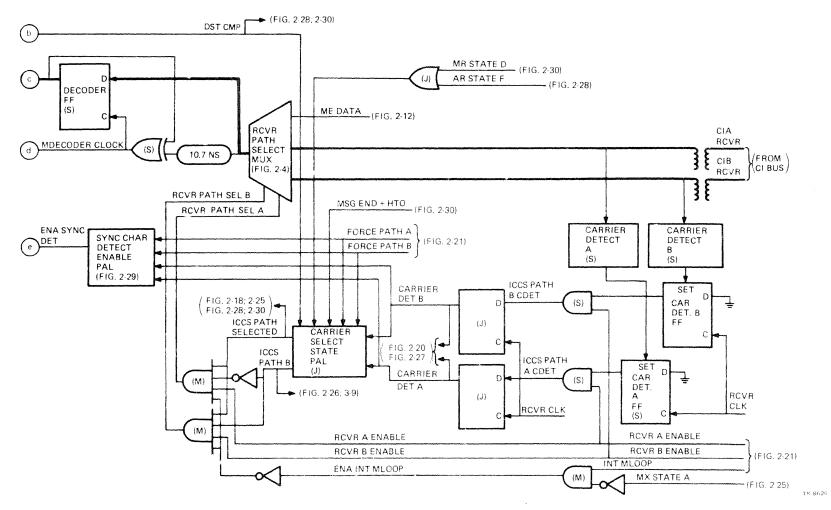

| 2-3  | Receive Channel Block Diagram                   |

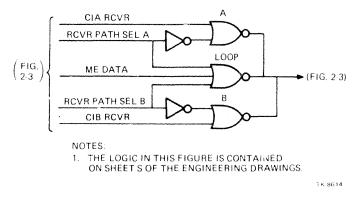

| 2-4  | Receive Path Select Mux-ECL Logic               |

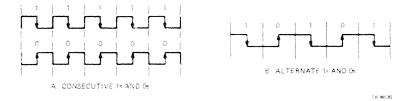

| 2-5  | PE (Phase Encoded) Data                         |

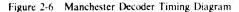

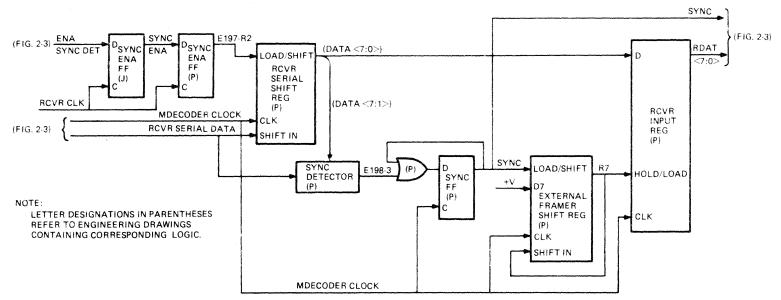

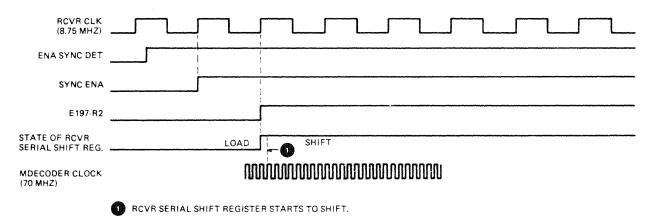

| 2-6  | Manchester Decoder Timing Diagram               |

| 2-7  | Byte Framer Block Diagram                       |

| 2-8  | Enabling the RCVR Serial Shift Register         |

| 2-9  | Lyte Framer Timing Diagram                      |

| 2-10 | RCVR CLK Generator                              |

| 2-11 | RCVR CLK Synchronization                        |

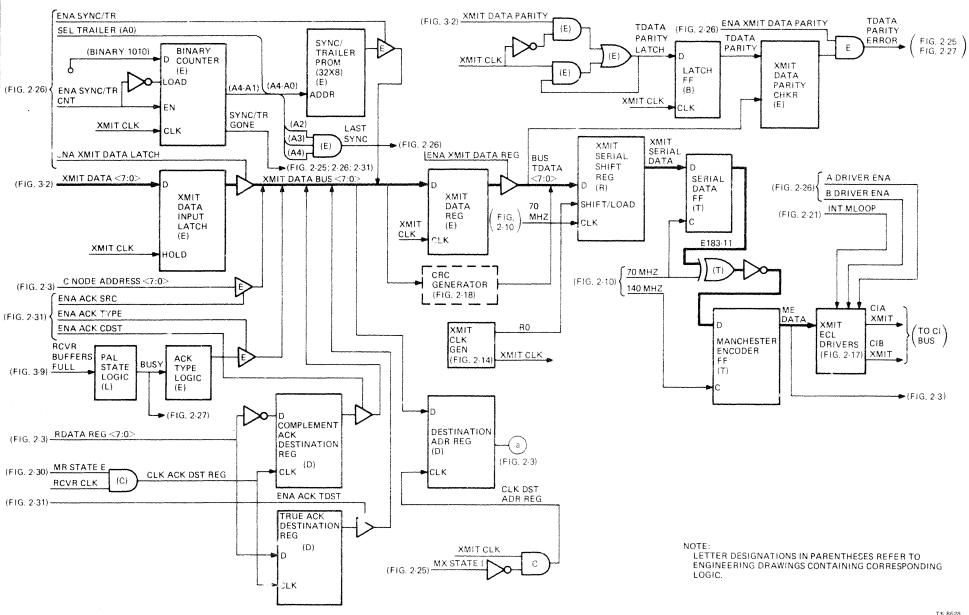

| 2-12 | Transmit Channel Block Diagram                  |

| 2-13 | Sync/Trailer PROM Space                         |

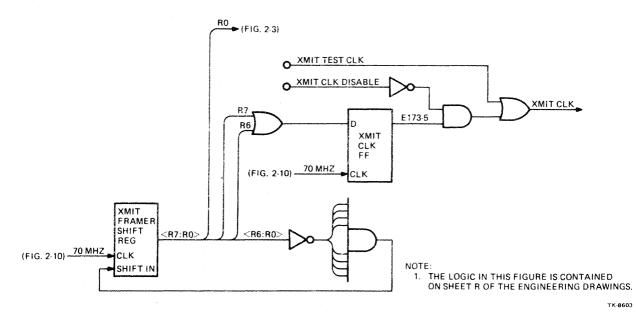

| 2-14 | XMIT CLK Generator Block Diagram                |

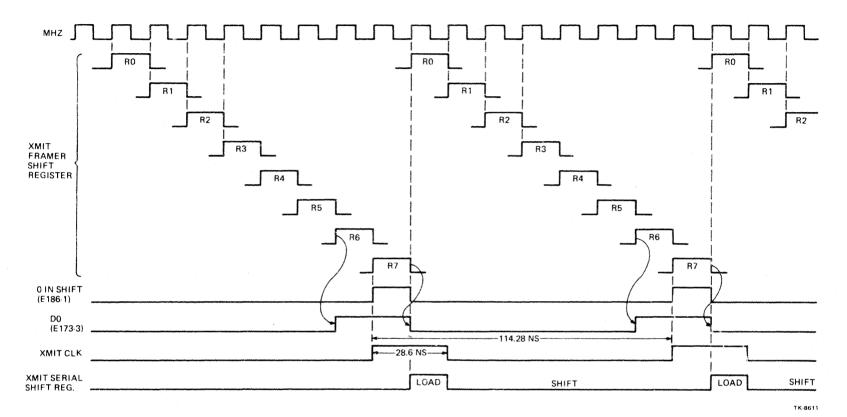

| 2-15 | XMIT CLK Generator Timing Diagram2-25           |

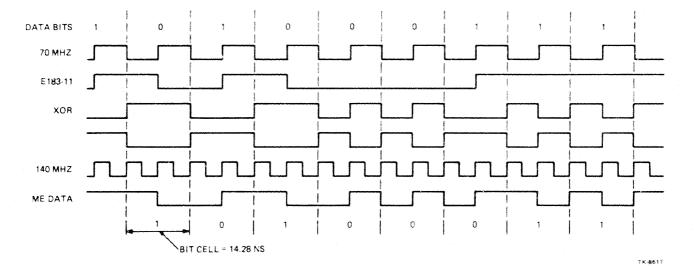

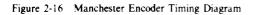

| 2-16 | Manchester Encoder Timing Diagram2-27           |

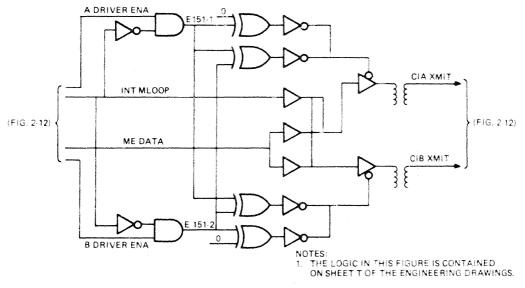

| 2-17 | XMIT ECL Drivers                                |

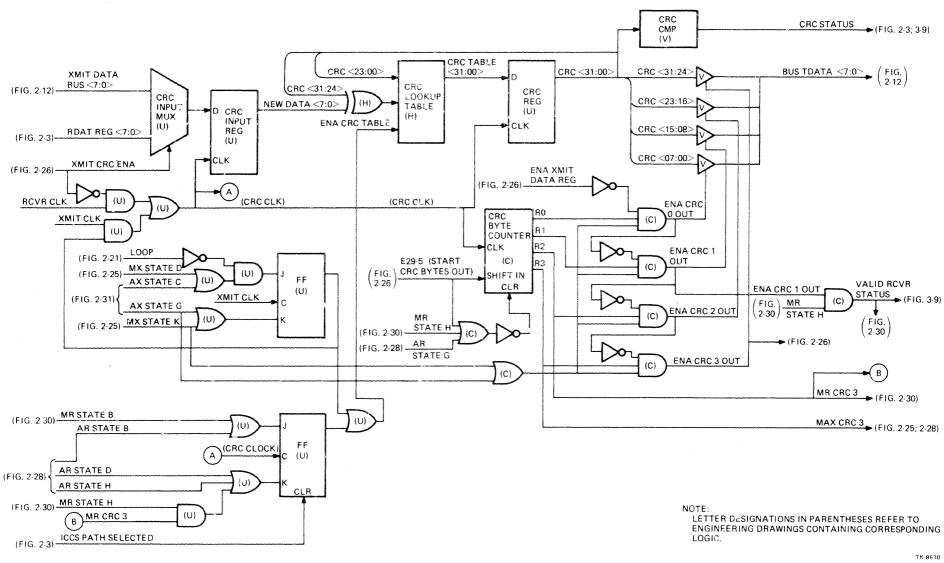

| 2-18 | CRC Generator/Checker                           |

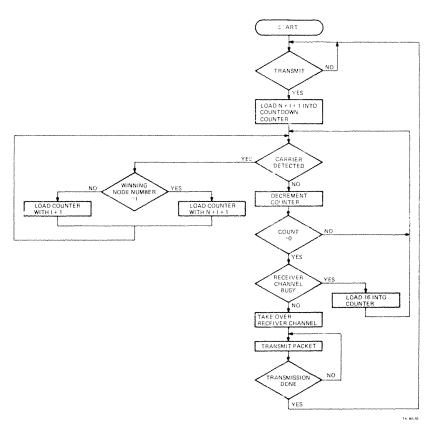

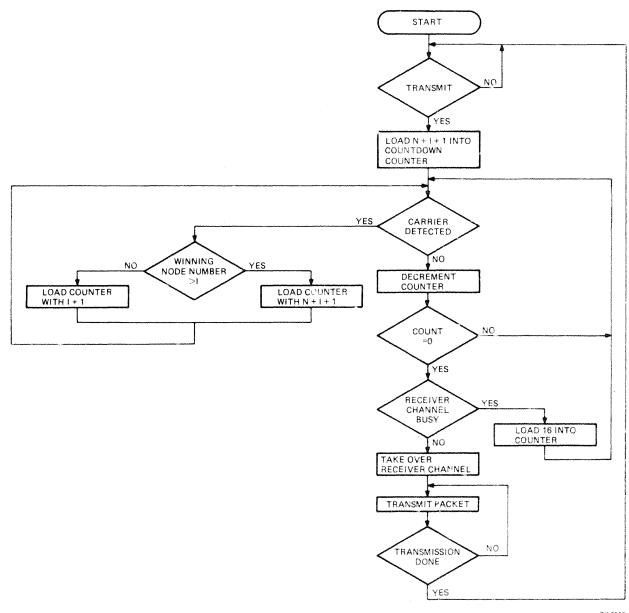

| 2-19 | Arbitration Flow Diagram                        |

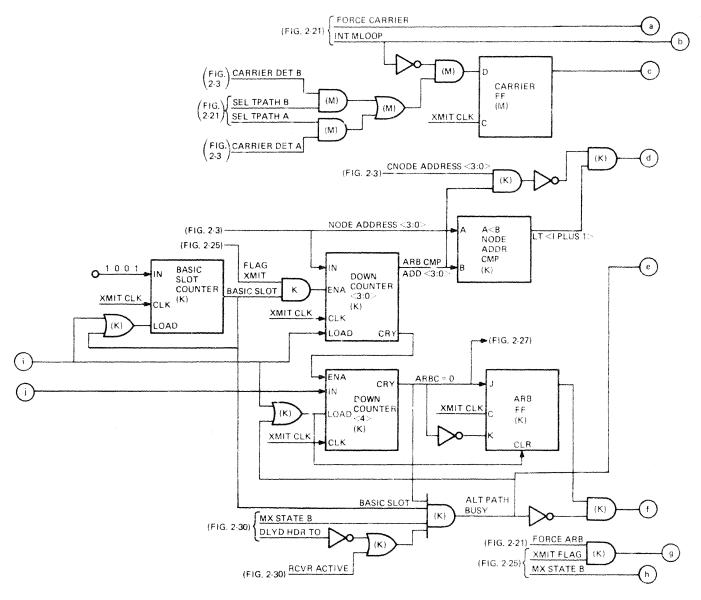

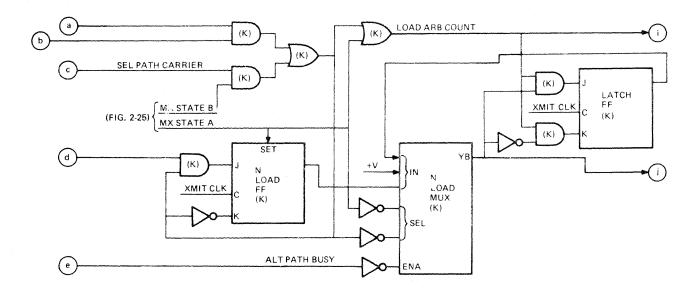

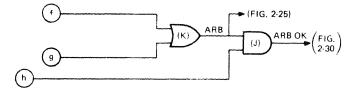

| 2-20 | Arbitration Block Diagram                       |

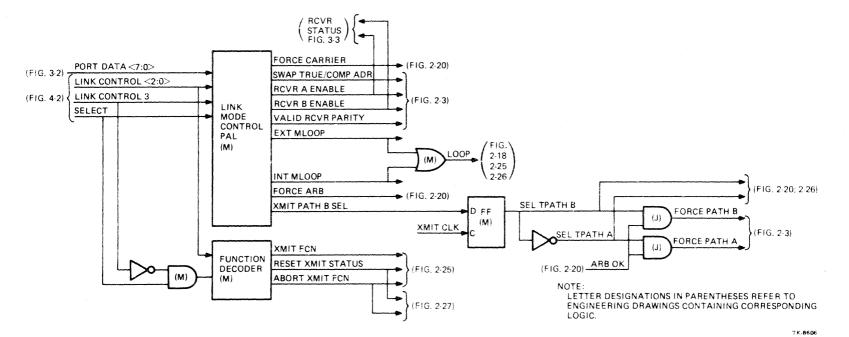

| 2-21 | Link Functions                                  |

| 2-22 | Link Interface Signals                          |

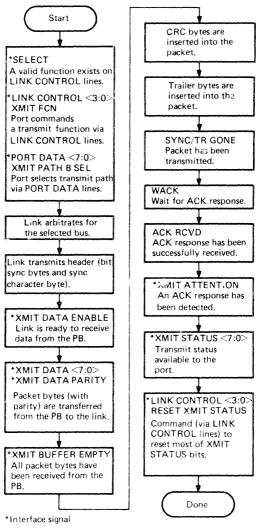

| 2-23 | Interface Flow Diagram - Transmit Operation2-41 |

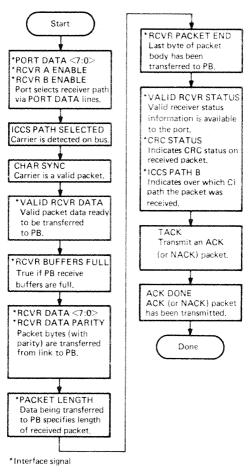

| 2-24 | Interface Flow Diagram - Receive Operation      |

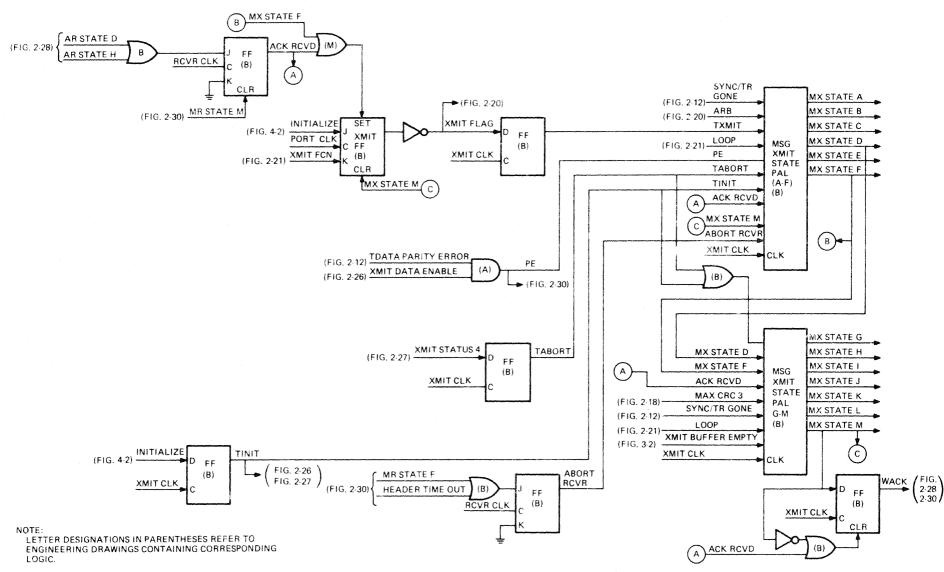

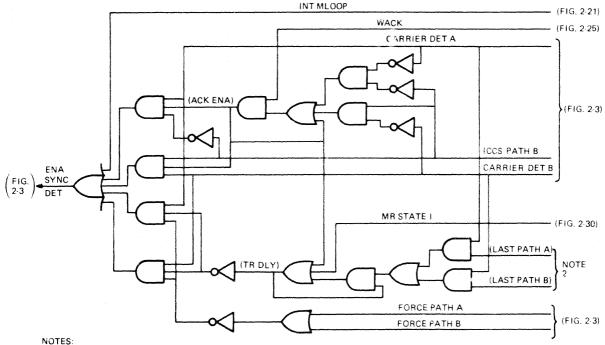

| 2-25 | Message Transmit State Logic                    |

| 2-26 | Transmit Control Logic                          |

| 2-27 | Transmit Status 2-48                            |

| 2-28 | ACK Receive State Logic                         |

| 2-29 | Sync Character Detect Enable PAL                |

| 2-30 | Message Receive State Logic                     |

| 2-31 | ACK Transmit State Logic                        |

|      |                                                 |

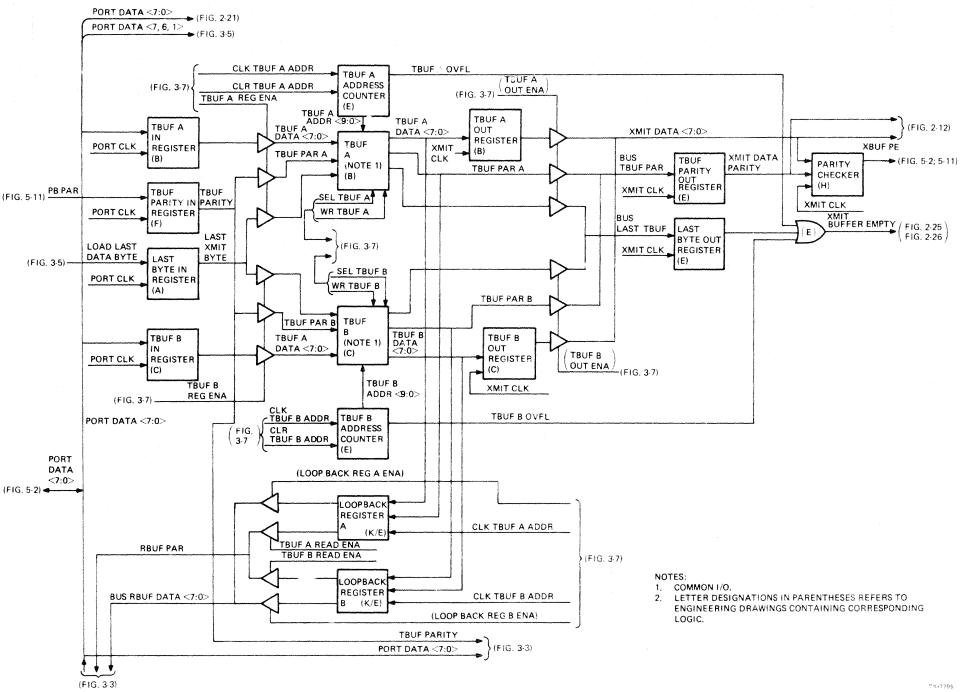

| 3-1     | Packet Buffer Data Flow                            | .3-2  |

|---------|----------------------------------------------------|-------|

| 3-2     | TBUF Operations                                    |       |

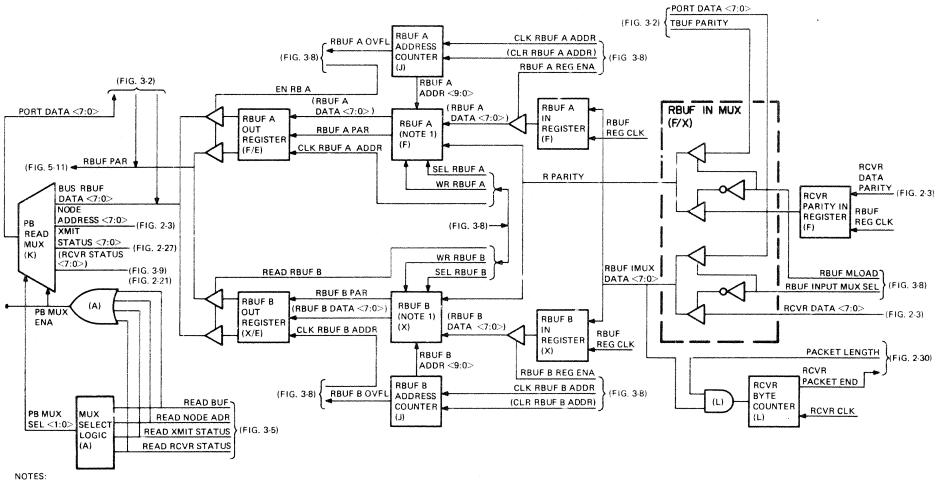

| 3-3     | RBUF Operations                                    |       |

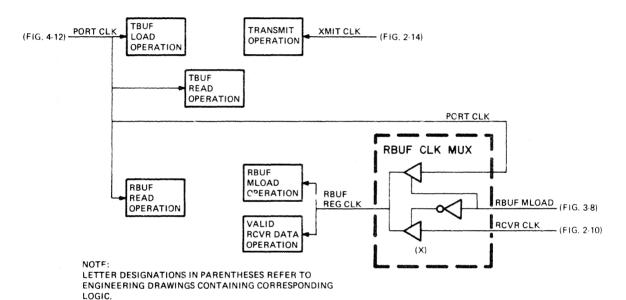

| 3-4     | Packet Buffer Clocks                               | 3-9   |

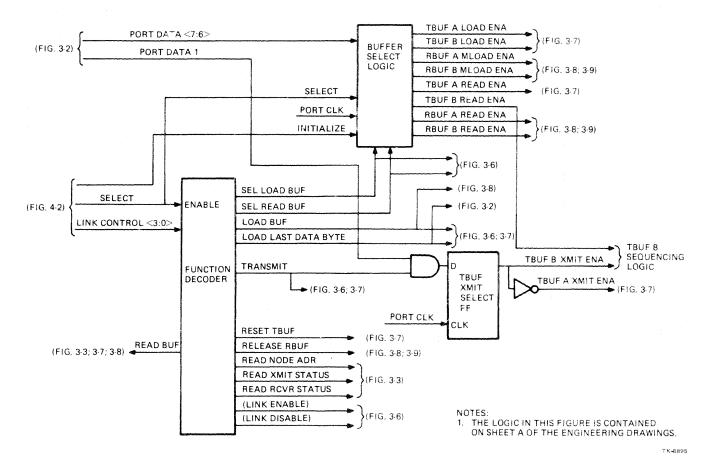

| 3-5     | Function Decoder and Buffer Select Logic           | 3-11  |

| 3-6     | PB Load Logic                                      | 3-14  |

| 3-7     | TBUF Sequencing Logic                              |       |

| 3-8     | RBUF Sequencing Logic                              |       |

| 3-9     | RCVR Status Logic                                  |       |

|         | Ke (K Status Logic                                 |       |

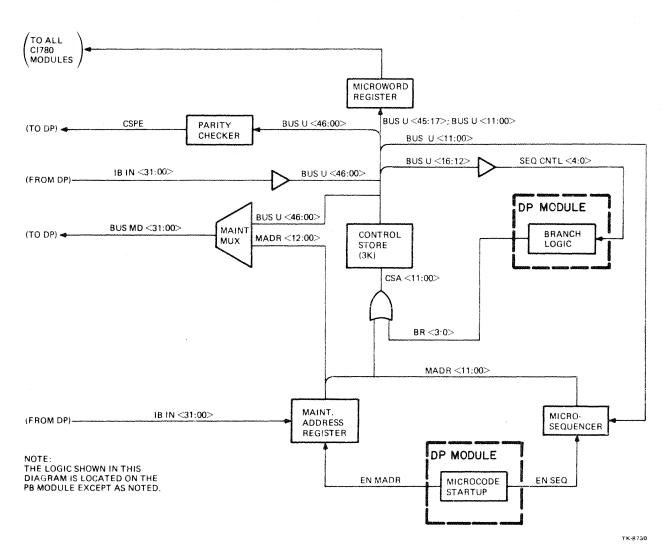

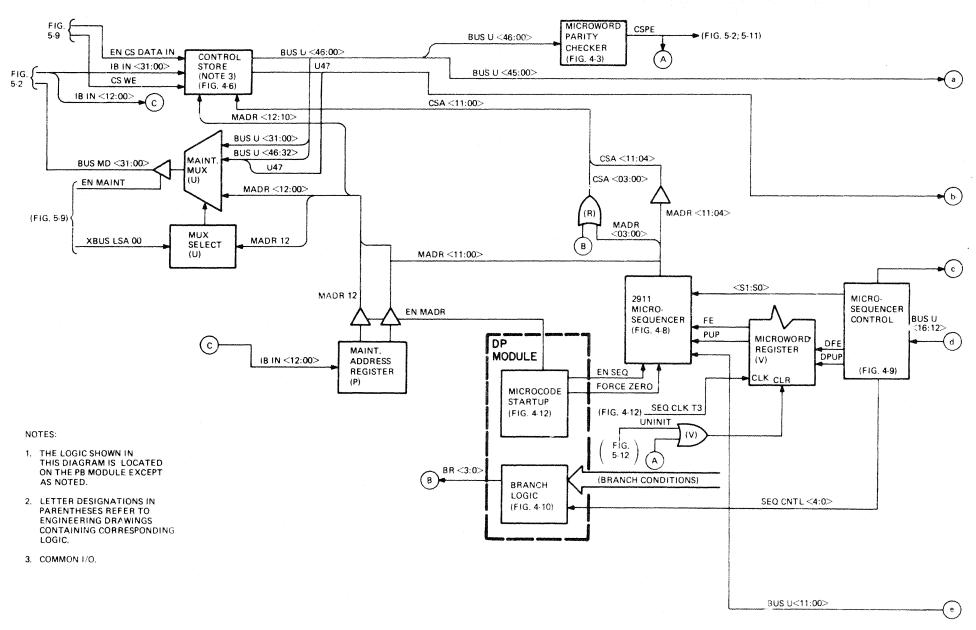

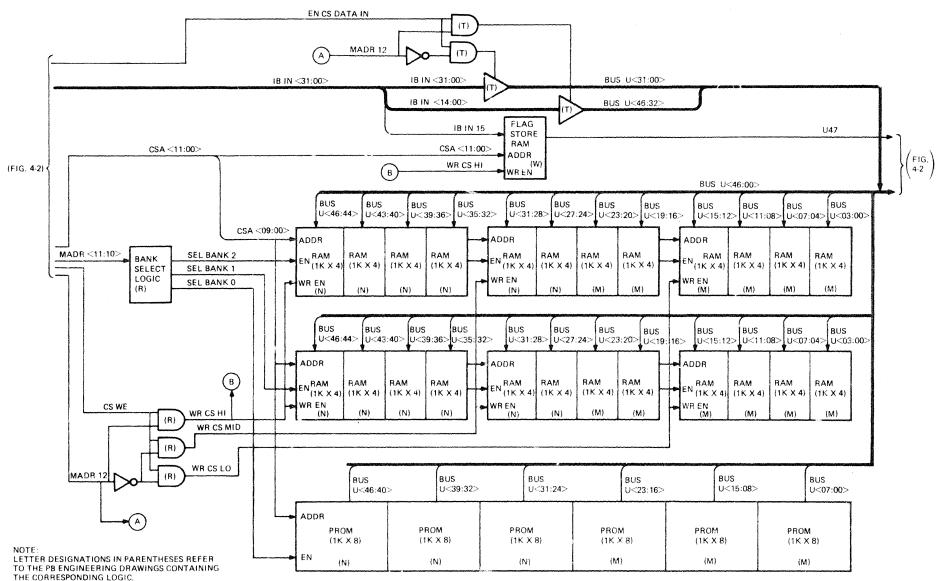

| 4-1     | Control Store Simplified Block Diagram             | 4-2   |

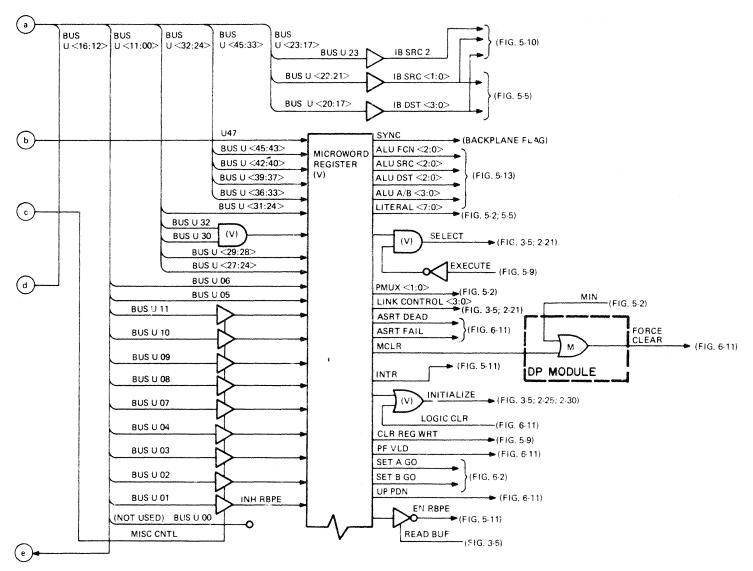

| 4-2     | Control Store Block Diagram.                       | 4-4   |

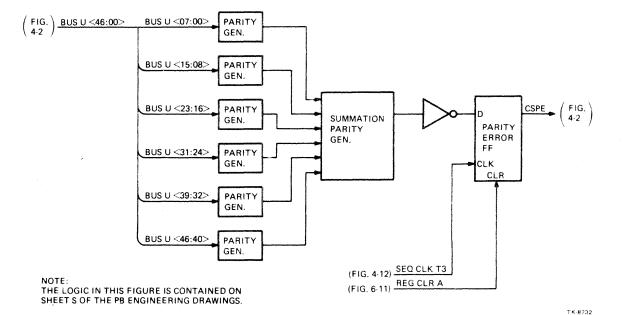

| 4-3     | Microword Parity Checker                           |       |

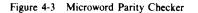

| 4-4     | Microword Fields                                   |       |

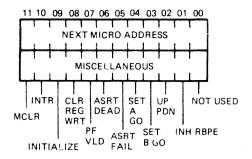

| 4-5     | Control Store Space                                |       |

| 4-6     | Control Store Logic                                |       |

| 4-7     | Control Store Address Multiplexing.                |       |

| 4-8     | 2911 Microsequencer                                |       |

| 4-9     | Microsequencer Control Logic                       |       |

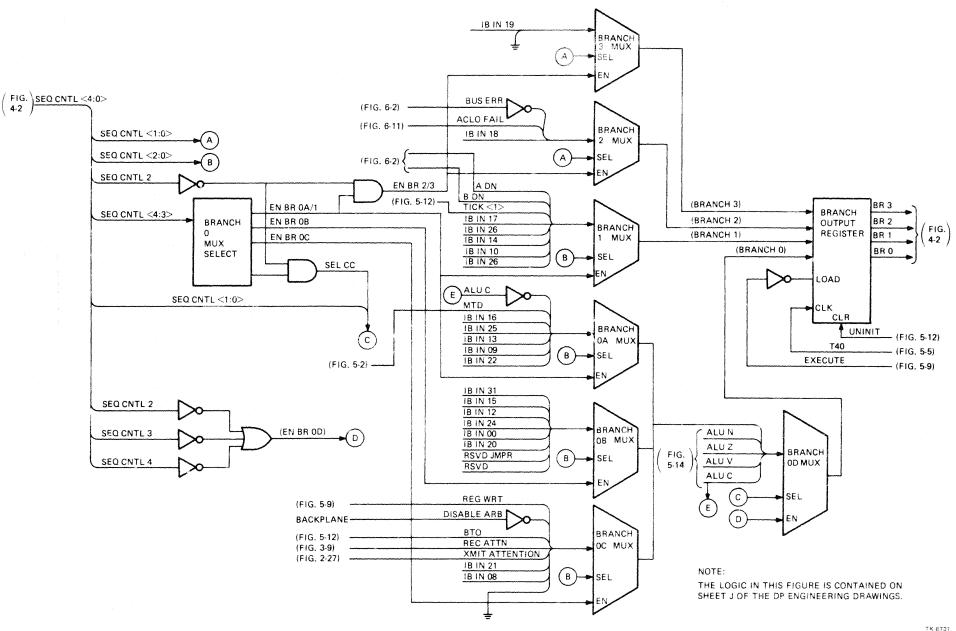

| 4-10    | Branch Logic                                       |       |

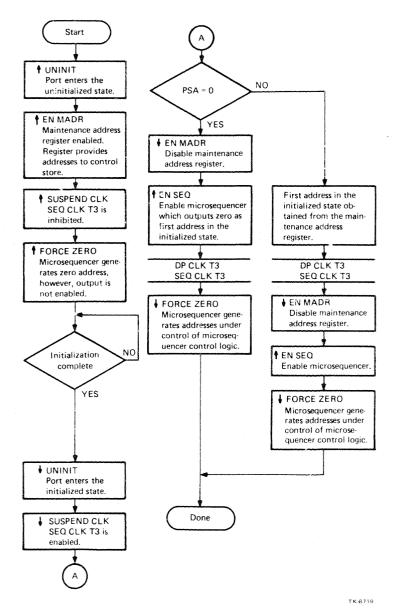

| 4-11    | Microcode Start-Up Flow Diagram                    | 1.33  |

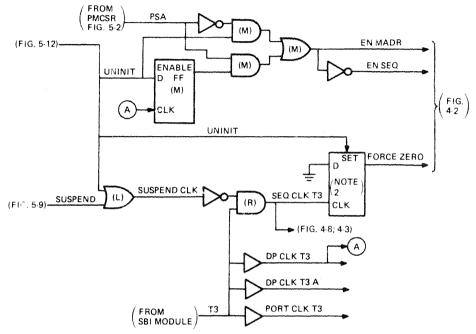

| 4-12    | Microcode Start-Up Logic                           | 1.24  |

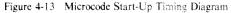

| 4-13    | Microcode Start-Op Logic                           |       |

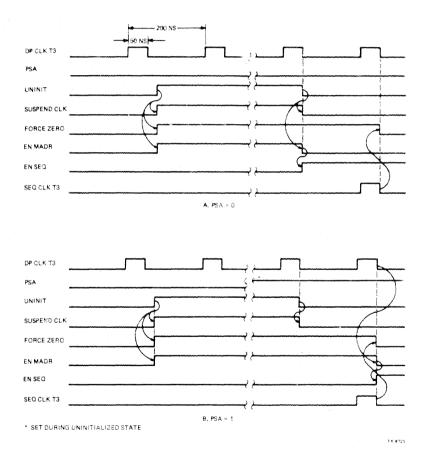

| 4-15    | Merocode Start-Op Timing Diagram                   | -20   |

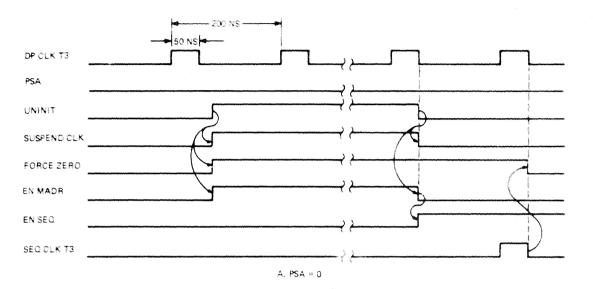

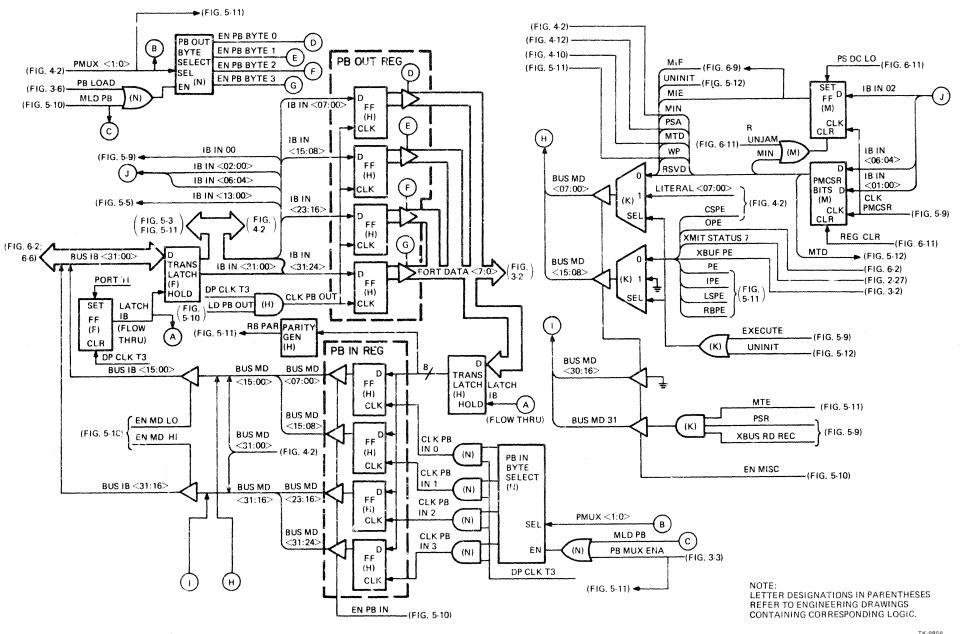

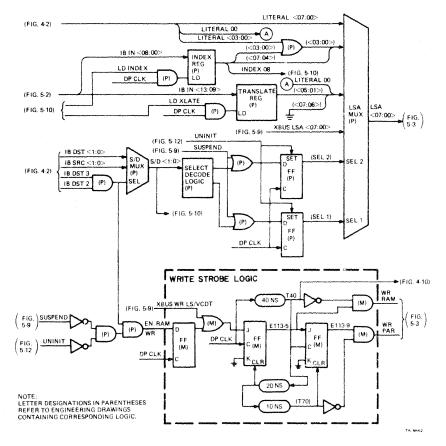

| 5-1     | Data Path Block Diagram                            | 5-2   |

| 5-2     | DP Buses and PB Interface                          |       |

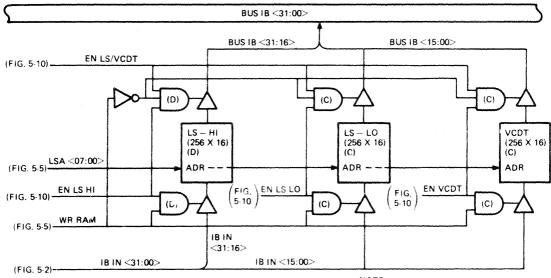

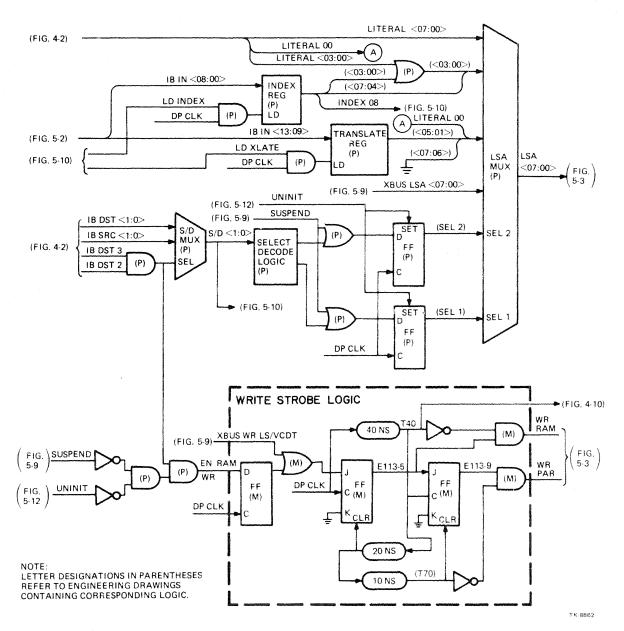

| 5-3     | LS/VCDT Block Diagram                              | 5-8   |

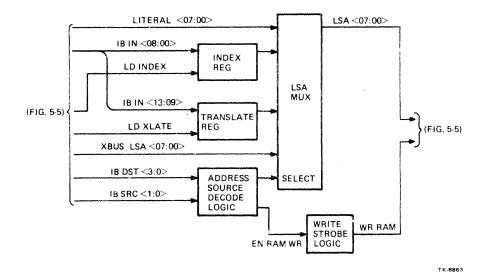

| 5-4     | LS/VCDT Address Selection Simplified Block Diagram |       |

| 5-5     | LS/VCDT Address Selection Block Diagram            | 5.10  |

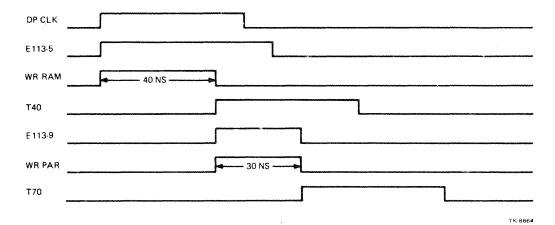

| 5-6     | Write RAM Timing Diagram                           | 5-12  |

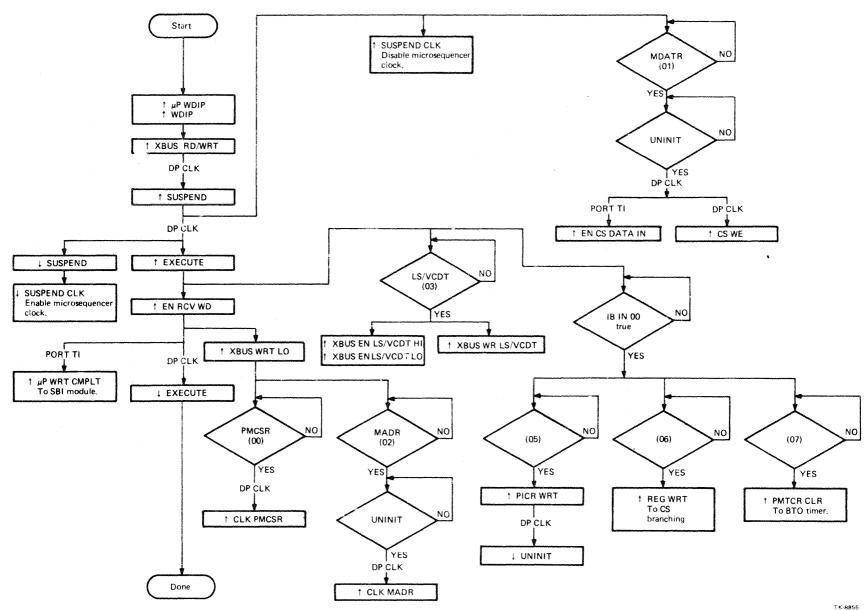

| 5-7     | Unsolicited SBI Write Request Flow Diagram         | 5-14  |

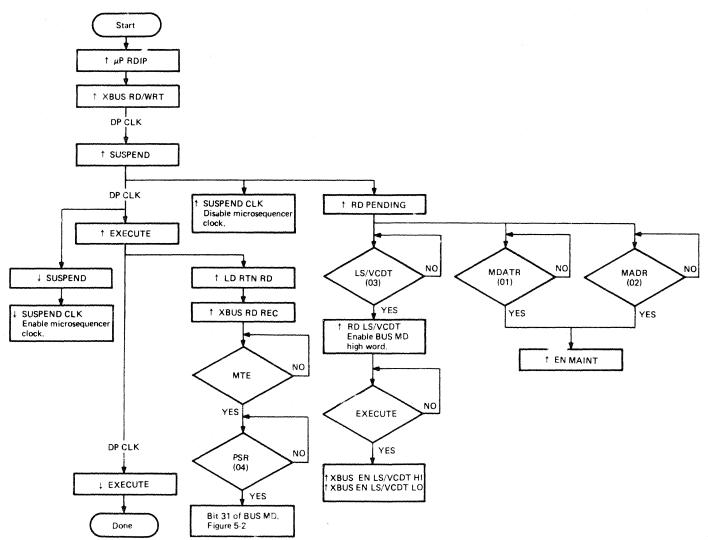

| 5-8     | Unsolicited SBI Read Request Flow Diagram          | 5.15  |

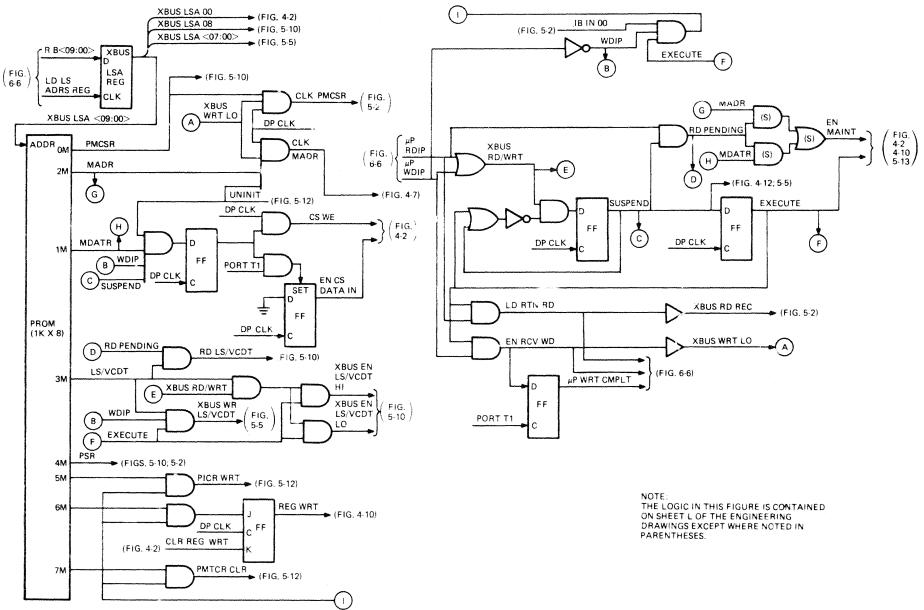

| 5-9     | Unsolicited SBI Request Logic                      |       |

| 5-10    | Control Logic                                      |       |

| 5-11    | Parity Generator/Cnecker Logic                     |       |

| 5-12    | Boot Timer and Maintenance Timer                   |       |

| 5-13    | 2901 A Microprocessor Simplified Block Diagram     |       |

| 5-14    | 2901A Microprocessor Block Diagram                 |       |

| 5-15    | Carry Look-Ahead Logic                             |       |

| 5-15    | Carry Look-Affead Logic                            | -51   |

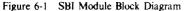

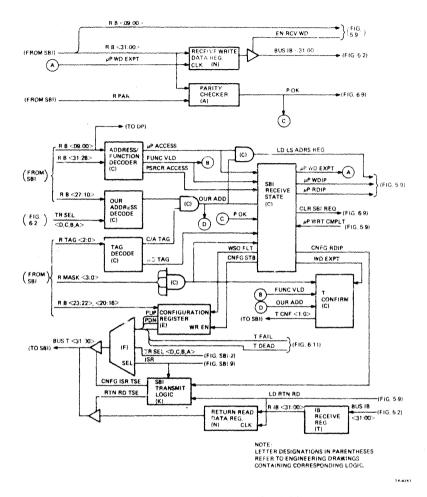

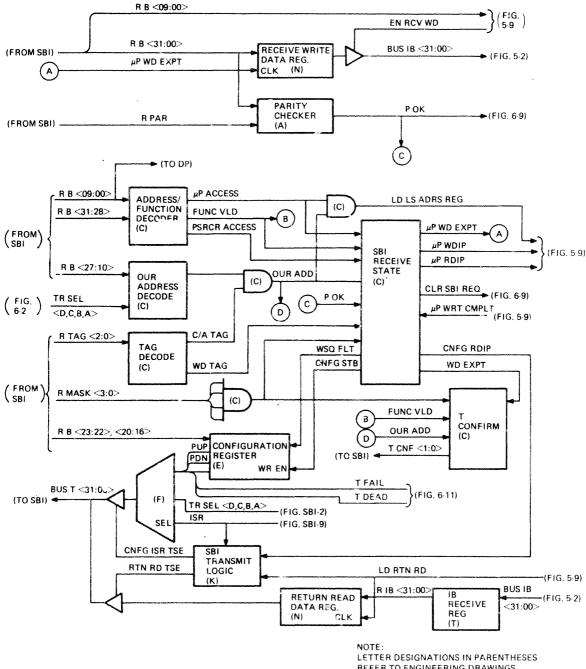

| 6-1     | SBI Module Block Diagram                           | .6-2  |

| 6-2     | Write Transfer Block Diagram                       |       |

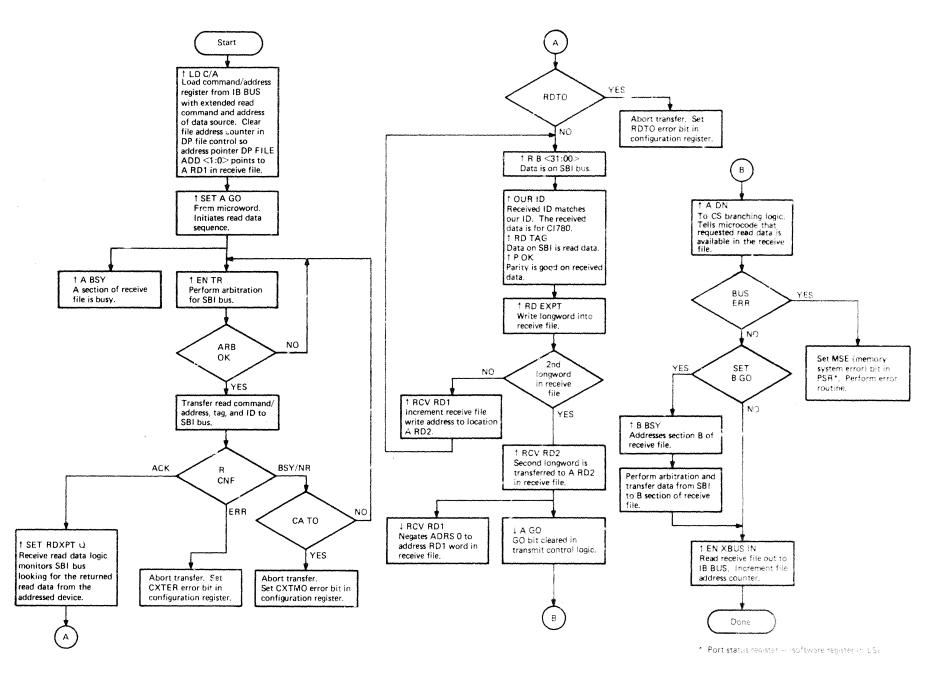

| 6-3     | Extended Write Flow Diagram                        | 6-6   |

| 6-4     | Read Transfer Block Diagram                        | 6-8   |

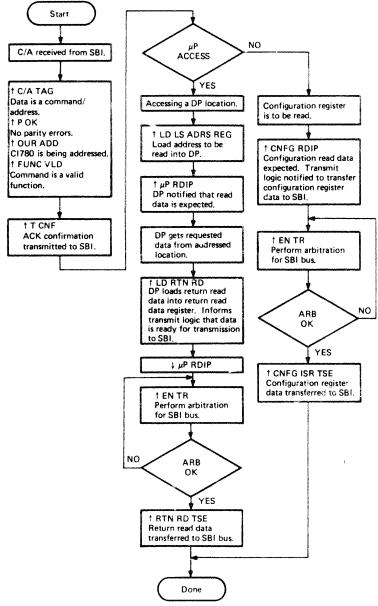

| 6-5     | Extended Read Flow Diagram                         |       |

| 6-6     | Unsolicited SBI Request Block Diagram              | -12   |

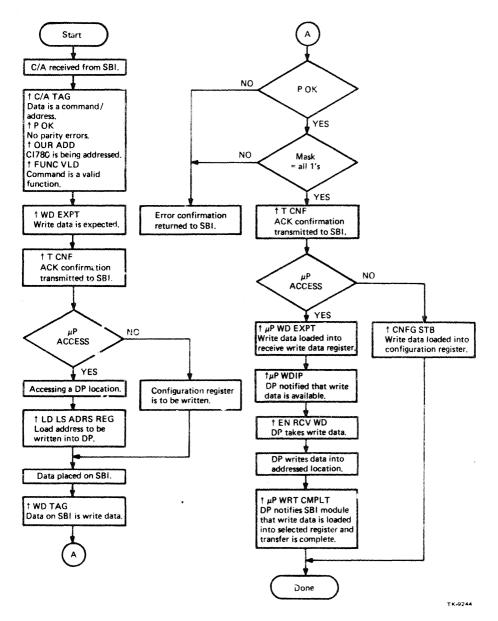

| 6-7     | Unsolicited SBI Write Flow Diagram                 | -13   |

| 6-8     | Unsolicited SBI Read Flow Diagram                  |       |

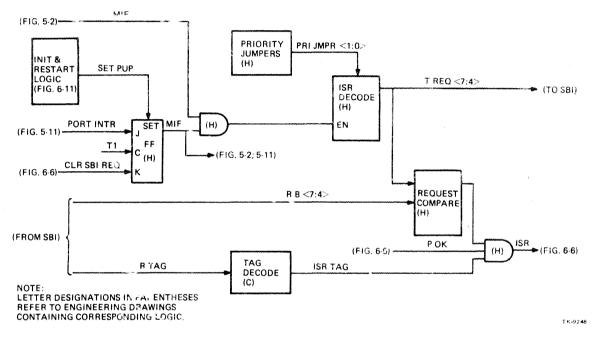

| 6-9     | ISR Block Diagram                                  |       |

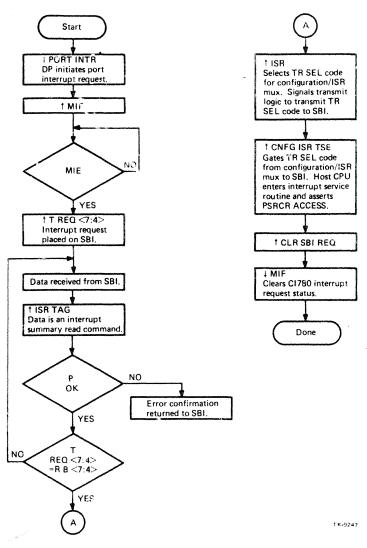

| 6-10    | ISR Flow Diagram                                   |       |

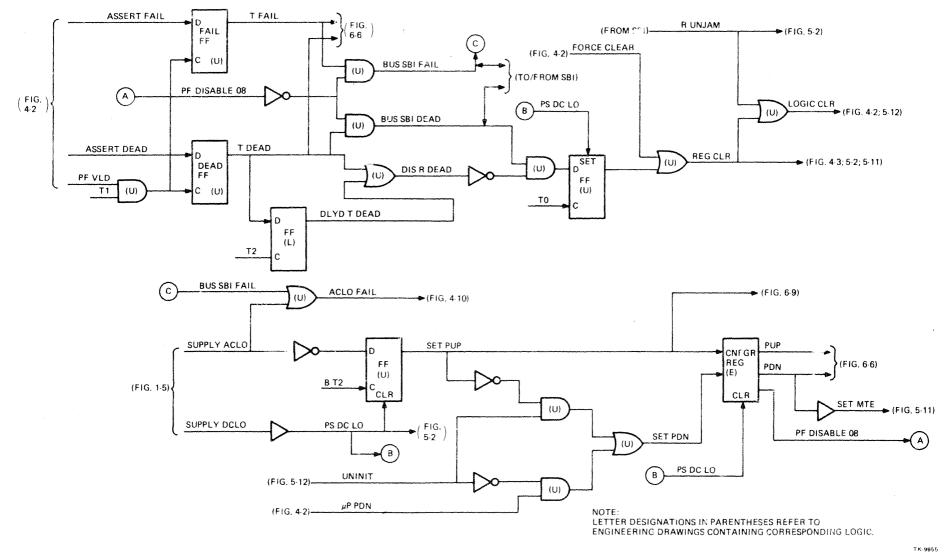

| 6-11    | Initialization and Restart Logic                   |       |

| 6-12    | Start-Up Sequence                                  |       |

| 6-13    | Power Fail Sequence.                               |       |

| · · · · |                                                    | · ~ / |

| B-1 | Flow Diagram Symbols                                        | B-1 |

|-----|-------------------------------------------------------------|-----|

| C-1 | Maintenance Address Register (MADR) Bit Fields              | C-1 |

| C-2 | Maintenance Data Register (MDATR) Bit Field                 | C-2 |

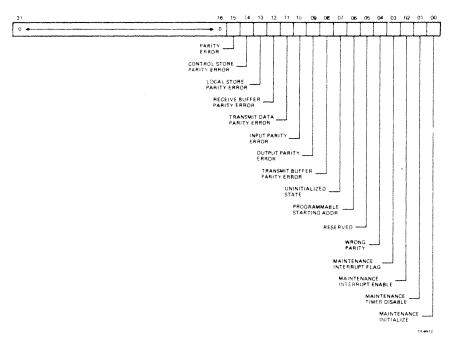

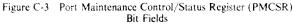

| C-3 | Port Maintenance Control/Status Register (PMCSR) Bit Fields | C-3 |

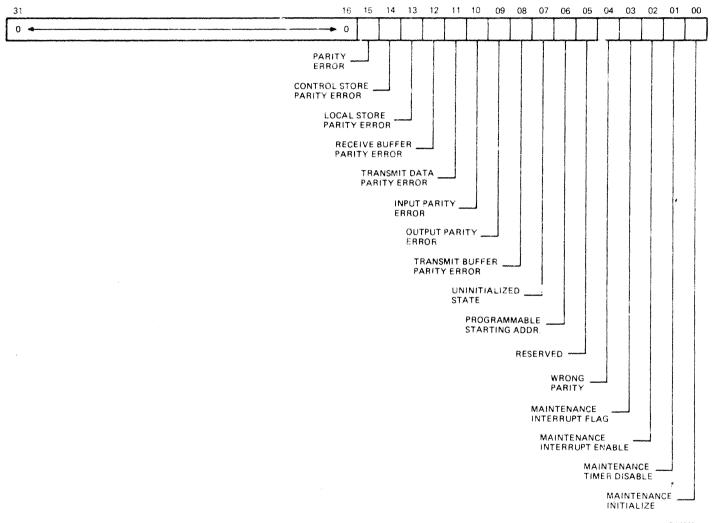

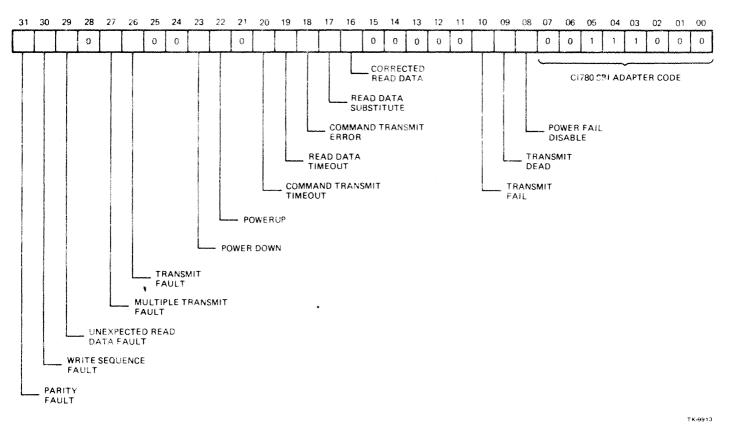

| C-4 | Configuration Register (CNFGR) Bit Fields                   | C-4 |

## TABLES

| 1-1 | CI780 Related Documents                    |     |

|-----|--------------------------------------------|-----|

| 2-1 | Link State Diagrams                        |     |

| 2-2 | Link Clocks                                |     |

| 2-3 | N Load Mux Selection                       |     |

| 3-1 | Link Control Codes Vs PB Function Commands |     |

| 3-2 | Load Buffer Select Code                    |     |

| 3-3 | Raad Buffer Select Code                    |     |

| 4-1 | Microword Fields                           |     |

| 4-2 | Maintenance Mux Selection Code             | 4-9 |

| 4-3 | Microsequencer Control Functions           |     |

| 4-4 | Branch Conditions                          |     |

| 5-1 | PMCSR Bits                                 |     |

| 5-2 | LSA Mux Selection Code                     |     |

| 5-3 | IB DST Codes                               |     |

| 5-4 | IB SRC Codes                               |     |

| 5-5 | ALU Source Code                            |     |

| 5-6 | ALU Function Code                          |     |

| C-1 | CNFGR Bits                                 | C-5 |

## CHAPTER 1 INTRODUCTION

#### 1.1 MANUAL SCOPE

This document provides a technical description of the CI780 computer interconnect hardware. It does not treat the CI780 port architecture or other software applications such as the CI780 port driver, command queues, or the VAX/VMS operating system.

A basic description of the CI780 computer interconnect is given in this chapter. Chapters 2, 3, 5 and 6 provide a detailed description of each of the four CI780 modules. Chapter 4 describes the microcode control store and associated control logic. By describing the control store, its addressing logic, and its branching logic in a separate chapter we can treat it as a single cohesive function although the hardware is distributed over two modules (packet buffer and data path).

Three appendixes supplement the information contained in this manual. Appendix A defines the mnemonics found within this document. Appendix B explains the symbology used in the flow diagrams. Appendix C is a description of hardware registers used for maintenance purposes.

#### **1.2 THE COMPUTER INTERCONNECT (CI)**

The computer interconnect (CI) (Figure 1-1) is a high-speed, serial data bus that is used to link computer subsystems (nodes) to form a CI cluster. Typically, the cluster is confined to a computer room environment. Nodes may consist of CPUs and memory. Nodes may also include intelligent mass storage, communication, or data acquisition subsystems.

Features of the CI include:

- Dual signal paths capable of simultaneous operation

- 70-megabit-per-second bandwidth and transfer rate

- 32-bit CRC generation and checking

- Low error rate

- Packet-oriented data transfers

- Immediate acknowledgement of the reception of a packet

- Contention arbitration at light loading and round-robin arbitration at heavy loading

- Internal and external data looping for diagnostic purposes.

Each node within a cluster connects to the computer interconnect via a CI780 interface that provides two separate signal paths. Dual paths provide a high degree of data availability between nodes. One pair of nodes can communicate over one path (path A) while another pair of nodes communicates over the second path (path B).

Each path contains a central star coupler (SC008) that receives the data transmitted by a node and distributes it to the other nodes within the cluster. A single CI path consists of a pair of bus cables (one for transmit, one for receive). These cables provide the connection between a node and the signal distribution coupler (star coupler) for that path.

Figure 1-1 Four-Node Cl Cluster

#### 1.3 RELATED DOCUMENTS

Fable 1-1 is a list of documents providing additional information related to the C1780.

| Title                                               | Document<br>Number                                                                                                                              | Contents                                                                                                                                                                                                                   |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1780 User's Guide                                  | EK-C1780-UG                                                                                                                                     | Contains instructions for unpack-<br>ing, installing, and acceptance test-<br>ing the CI780. A physical descrip-<br>tion of the CI780 is also provided.<br>Information is also provided on the<br>CI780 backplane jumpers. |

| SC008 Star Coupler<br>User's Guide                  | EK-SC008-UG                                                                                                                                     | Contains a description of the SC008<br>Star Coupler. Also provides instruc-<br>tions for unpacking and installing<br>the various Star Coupler<br>configurations.                                                           |

| VAX-11/780 Power<br>System Technical<br>Description | EK-PS780-TD                                                                                                                                     | Contains a technical description (physical and functional) of the H7100 option power supply and the H7101, $-5.2$ V regulator.                                                                                             |

| VAX Architecture<br>Handbook                        | EB19580-20                                                                                                                                      | Contains a description of the VAX<br>family architecture, including data<br>representations, instructions, regis-<br>ters, and operational modes.                                                                          |

| VAX Hardware Handbook                               | EB-21710-20                                                                                                                                     | Provides a hardware overview of<br>the VAX family. Hardware descrip-<br>tions include the 11/780, the<br>11/750, and 11/730.                                                                                               |

|                                                     | C1780 User's Guide<br>SC008 Star Coupler<br>User's Guide<br>VAX-11/780 Power<br>System Technical<br>Description<br>VAX Architecture<br>Handbook | TitleNumberCI780 User's GuideEK-C1780-UGSC008 Star Coupler<br>User's GuideEK-SC008-UGVAX-11/780 Power<br>System Technical<br>DescriptionEK-PS780-TDVAX Architecture<br>HandbookEB-19580-20                                 |

## Table 1-1 CI780 Related Documents

#### 1.4 THE CI780 INTERFACE

The CI780 is the interface used to connect a VAX-11/780 system to the CI cluster. It connects between the synchronous backplane interconnect (SBI) of the host system and the CI cluster. Figure 1-2 illustrates the CI780 connection.

The CI780 is an intelligent interface that performs the function of a buffered communications port. It utilizes the queue structure provided under the VAX/VMS operating system to transfer messages and blocks of data between the host's memory system and other nodes within the CI cluster. By providing data buffering, address translation, and serial encoding and decoding, the CI780 reduces the amount of overhead software processing required to complete high-level intercomputer communications.

The C1780 may be installed in any four-inch option slot in either the H9602-H SBI expansion cabinet or the standard CPU cabinet of the host system. The C1780 contains the following four modules functionally connected as shown in Figure 1-3:

- 1. Link Interface Module (ILI) L0100

- 2. Packet Buffer Module (IPB) L0101

- 3. Data Path Module (IDP) L0102

- 4. SBI Interface Module (ISI) L0104

Figure 1-2 CI780 Connection

Figure 1-3 CI780 Modules

TK-8150

Figure 1-4 is a block diagram of the C1780. It should be used with the following discussion of the C1780 modules.

#### 1.4.1 Link Module

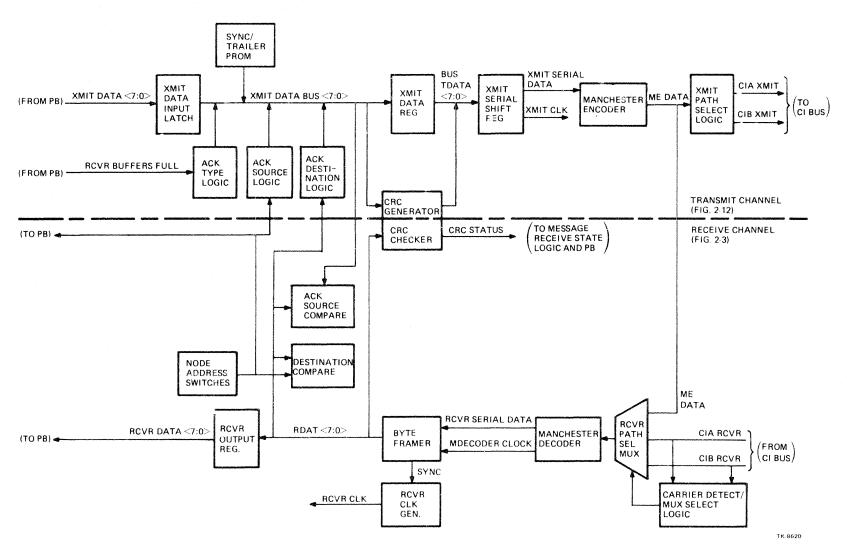

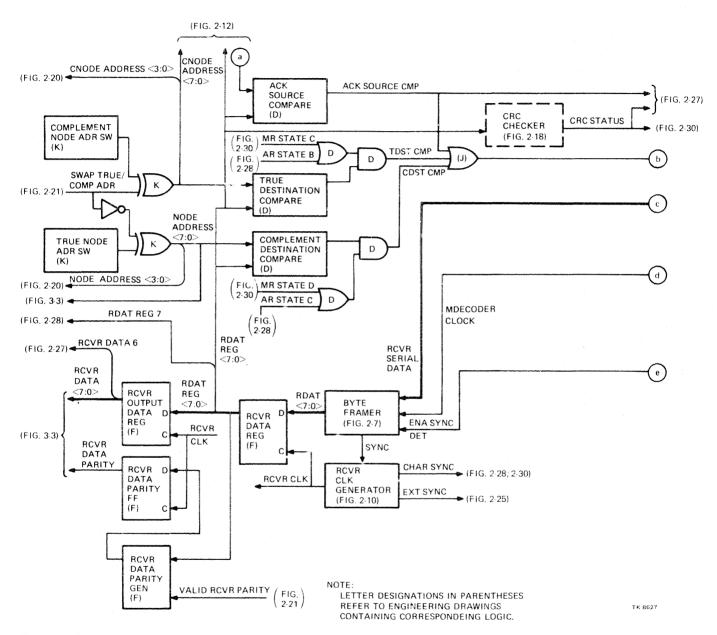

The link module provides the interface to the CI bus and has the capability of servicing both CI paths. The module is functionally divided into a transmit path and a receive path with a Cyclic Redundancy Check (CRC) function shared between the two channels. The link can transmit or receive over only one CI path at a time due to the common CRC logic being used by both channels.

Data packets are received from the packet buffer (PB) module over the XMIT DATA BUS, and are appended with header information and a trailer. The header functions to identify the source and destination of the packet. Node address switches provide the node with an address on the Cl cluster. The packet header contains this address as a source identification. The trailer serves to keep the node receiver locked up while the last data bytes in the packet are being processed.

The CRC logic uses the packet data bytes to generate four CRC check bytes that are appended to the data packet. The CRC bytes are unique for the specific data bytes in the packet. The bytes are used for error checking at the packet destination.

The link transmitter converts the data packet from a byte format to a 70-megabit-per-second serial format and then applies it to a Manchester encoder.

The Manchester encoder combines the serial data with the bit rate clock to produce a modulated (phase encoded) carrier for the CI bus.

The path selection logic selects the CI path (A or B) for the transmission. The path selection is under microcode control.

Carrier detection logic monitors the two CI paths and connects the receiver channel to whichever path is active.

The serial data from the CI is applied to a Manchester decoder which separates the signal into its clock and data components. The clock and data signal components are applied to the link receiver.

The link receiver converts the packet data from a 70 megabit-per-second serial format to a byte format.

The link receiver then supplies the packet data to the CRC logic. The CRC logic validates the packet by checking the packet data against the packet CRC bytes. If a CRC error is detected, no response (ACK or NACK) is returned to the transmitting node.

If there is no CRC error, the packet is sent to the PB module over the RCVR DATA bus. If the PB module can accept the packet, the link returns a positive acknowledgement (ACK) to the transmitting node. If the buffers on the PB module are full and cannot accept the packet, the link returns a NACK to the transmitting node which will then retransmit the packet.

#### 1.4.2 Packet Buffer Module (PB)

The PB module provides buffering for the data packets transferring through the C1780. Two transmit and two receive buffers (A and B) are provided. Each buffer has a capacity of 1K. When data packets are being transmitted, transmit buffer A is filled from the data path (DP) module over the PORT DATA bus. The next data packet is loaded into buffer B while the link is unloading the data from buffer A.

Likewise, received data packets are loaded into receive buffer A from the link module over the RCVR DATA bus. The following data packet is loaded into receive buffer B while the DP is unloading the data from receive buffer A.

Figure 1-4 CI780 Block Diagram

1-7

The C1780 microcode resides in a 3K RAM/PROM control store located on the PB module. The control store RAM/PROM outputs a 47-bit microword that controls and regulates operations throughout the C1780. Stepping of the microcode is controlled by a microsequencer which samples the next address field of the microword. The microcode is also subject to branching conditions via branching logic located in the DP module. The branching logic tests various conditions throughout the C1780. The test results are ORed with the microcode sequencer output to provide branching of the microcode sequences.

The C1780 control microword can be read by the host system via the BUS MD in the DP module.

Under certain conditions (system initialization or detection of an error) the host system can force a routine by inputting the starting address via the DP IB IN bus and the maintenance address register.

#### 1.4.3 Data Path Module (DP)

Conversion of data packets from longword to byte format and from byte to longword format is accomplished on the DP module. Data to be transmitted is input into a 32-bit PB OUT register from the IB IN bus (internal bus), in longword format. The PB OUT register is unloaded onto the PORT DATA bus a byte at a time.

Likewise, received data bytes from the PB module are input into a 32-bit PB IN register from the PORT DATA bus. When four bytes have been loaded into the register, the register outputs the 32-bit longword onto the MD (miscellaneous data) bus.

The DP module contains LS (local store) and VCDT (virtual circuit descriptor table) storage areas. The LS is a  $256 \times 32$  RAM area used to store software status blocks and software registers associated with the Cl780 port architecture. The VCDT is a  $256 \times 16$  RAM area used to store CI node parameters.

Also contained on the DP module is a 2901A ALU used to perform general purpose arithmetic and logical operations.

The data interface between the DP and the SBI module is the BUS IB bus. Data input to the DP on the BUS IB, has several possible destinations. It may be applied to the LS or the VCDT for storage, to the ALU for processing, or to the PB OUT register for transfer to the PB module.

Output data from the DP on the BUS IB, may be obtained from several sources. It may be data read from the LS or the VCDT area, it may be data obtained from the ALU after processing, or it may be data obtained from the BUS MD. Data from the BUS MD may be from the PB IN register or it may be the CI780 control microword read from the control store in the PB module.

The destination and source of the BUS IB data is selected by the CI780 microcode.

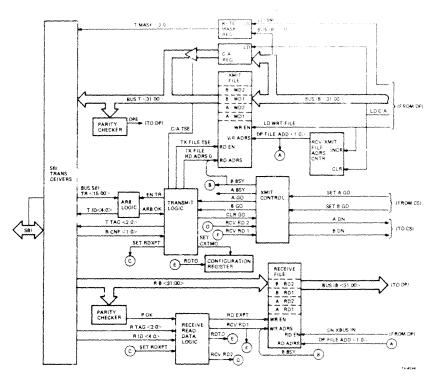

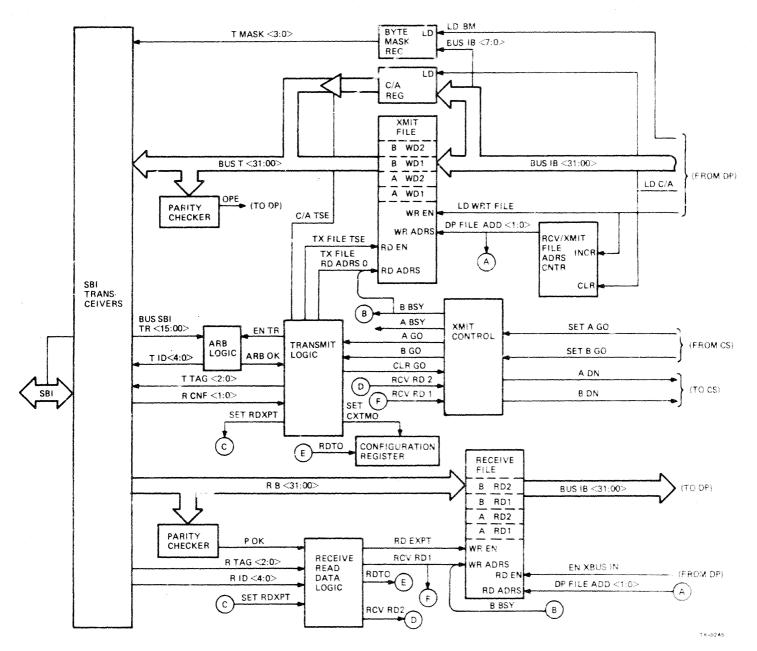

#### 1.4.4 The Synchronous Backplane Interconnect Module (SBI)

The basic function of the SBI module is to interface with the SBI. All SBI protocol and timing must be observed while transferring data to and from the SBI. A transmit and a receive file act as isolation buffers. The SBI side of the files are loaded and unloaded under SBI timing and control while the DP side of the files are loaded and unloaded under CI780 microcode control.

Data received from the DP over the BUS IB is loaded into the transmit file by the microcode. Up to two extended write transfers of data can be stored in the file. The microcode informs the read control that data is available in the file. The read control arbitrates for the SBI, receives and supplies information fields as required by SBI protocol, and unloads (reads) the data in the transmit file out to the SBI over the BUS T bus.

Data received from the SBI is loaded into the receive file by the write control. Up to two extended read transfers of data can be stored in the file. The write control receives and supplies the information fields required by SBI protocol and then loads (writes) the SBI data into the file over the RB bus. The write control informs the CI780 microcode that data is available in the file. The microcode unloads the data from the receive file onto the BUS IB for transfer to the DP module.

The SBI module provides for CPU access of CI780 registers via unsolicited SBI requests. Both reads and writes of the registers can be performed.

The SBI module also requests interrupts of the CPU when service routines are run on the CI780.

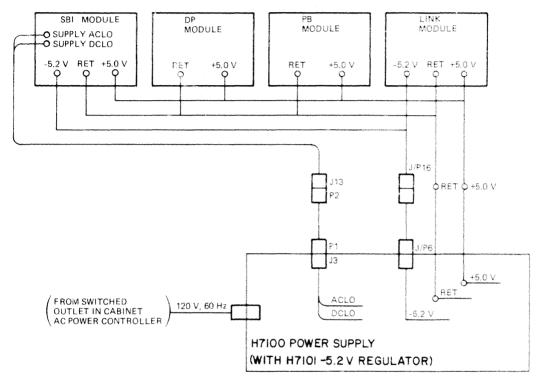

#### 1.4.5 - 1780 Power

Power is supplied to the C1780 from an H7100 option power supply with an H7101, -5.2 V regulator. The supply receives 120 V, 60 Hz from a switched outlet on the 869 power controller located in the cabinet. The supply provides +5.0 V to the four C1780 modules, and -5.2 V to the link and SBI modules. The supply also provides ACLO and DCLO to the SBI module.

Power signals and voltages pass from the power supply to the CI780 modules via the CI780 backplane. Figure 1-5 illustrates the routing of the power signals and voltages.

т K-9903

Figure 1-5 CI780 Power

## CHAPTER 2 LINK MODULE

#### NOTE

The functional block diagrams in Chapter 2 use logical AND and OR symbols. It does not necessarily follow that a corresponding gate exists on the link logic prints. The assertion of inputs A and B causing the assertion of output C may be represented on a block diagram by a single AND gate, yet the engineering drawing may show that several circuit stages are involved in the ANDing operation.

The functional block diagrams in this chapter are keyed to the link engineering circuit schematics (CS prints) by letter designations in parentheses. The letters specify the link CS sheet that contains the detailed logic associated with the functional blocks in the diagram.

The signal names used in the functional block diagrams are the names used on the engineering CS prints. Where other signal names or notes are used, they are enclosed in parentheses.

#### 2.1 PACKET FORMATS

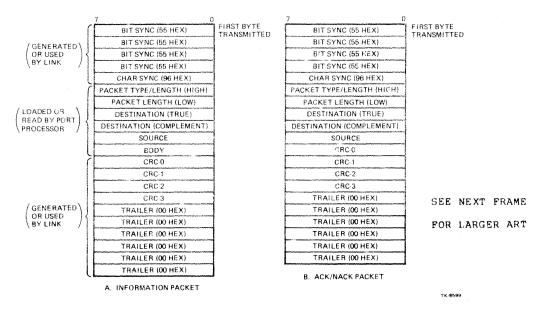

Formats of the two types of packets, information and ACK/NACK (acknowledge/negative acknowledge), are described below.

#### 2.1.1 Information Facket

Figure 2-1A illustrates the format of an information packet. The information packet is used to transmit both messages and data across the CI. Parts of the packet are generated by the link and inserted into the packet as it passes through the link to be transmitted.

**2.1.1.1** Bit Synchronization – The first five bytes of the packet are for bit synchronization within the link. The bytes are 55 hexadecimal which is an alternating pattern of 1's and 0's used to turn on the carrier detect circuits and to synchronize the Manchester decoder prior to the receipt of useful data. The link inserts the bit sync bytes into the packet.

**2.1.1.2** Character Synchronization – The character synchronization byte (96 hexadecimal) is used to indicate the start of useful data in the packet. When the sync character is recognized during packet reception, it starts the framing of the serial data into eight-bit bytes. The link inserts the sync character into the packet.

Figure 2-1 Packet Formats

**2.1.1.3** Packet Type/Length (High) – The packet type and length (high) byte specifies the type of packet (information or acknowledge) and contains the upper four bits of a 12-bit packet length word. Bits  $\langle 7:4 \rangle$  are the packet type bits. For an information packet bit 7 is a 0 (1 for an ACK/NACK packet) and bits  $\langle 6:4 \rangle$  are 0's.

Bits (3:0) are the upper four bits of the 12-bit word that specifies the packet length. Information packets are of variable length in one-byte increments up to 1K bytes\* with the minimum packet length being seven bytes. The packet length specified by the 12-bit packet length word includes all data from the packet type and length (high) byte up to and including the last byte of the body.

The port processor supplies the packet type and length (high) byte as part of the packet.

**2.1.1.4** Packet Length (Low) – This byte contains the low eight bits of the 12-bit packet length word. The port processor supplies this byte as part of the packet.

<sup>\*</sup> Limited by the capacity of the buffers in the PB. The link is capable of processing packets up to 4K bytes.

|               | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           | 7C                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ſ             | BIT SYNC (55 HEX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FIRST BYTE<br>TRANSMITTED | BIT SYNC (55 HEX)         | FIRST BYTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| /GENERATED\   | BIT SYNC (55 HEX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                           | BIT SYNC (55 HEX)         | (104100111120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| OR USED       | BIT SYNC (55 HEX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                           | BIT SYNC (55 HEX)         | and the second se |

| BY LINK '     | BIT SYNC (55 HEX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                           | BIT SYNC (55 HEX)         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|               | CHAR SYNC (96 HEX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           | CHAR SYNC (96 HEX)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| (             | PACKET TYPE/LENGTH (HIGH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                           | PACKET TYPE/LENGTH (HIGH) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|               | PACKET LENGTH (LOW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                           | PACKET LENGTH (LOW)       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LOADED OR     | DESTINATION (TRUE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           | DESTINATION (TRUE)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PROCESSOR     | DESTINATION (COMPLEMENT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                           | DESTINATION (COMPLEMENT)  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ,             | SOURCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                           | SOURCE                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|               | BODY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                           | CRC-0                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |