## VAXstation 2000 and MicroVAX 2000

Technical Manual EK-VTTAA-TM.001

)

$\mathbf{O}$

$\langle \mathbf{O} \rangle$

# VAXstation 2000 and MicroVAX 2000 Technical Manual

Order Number EK-VTTAA-TM-001

- Annalda

$\langle \bigcirc$

$\langle \rangle$

digital equipment corporation maynard, massachusetts

#### First Edition, July 1987

. . . . . . . . .

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright ©1987 by Digital Equipment Corporation.

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

BASEWAY BI Bus CompacTape DEC DEC/MAP DECmate DECnet DECUS DECwriter DIBOL FMS MASSBUS Micro/RSTS MIcro/PDP-11 Micro/RSX MicroVAX II MicroVAX 2000 PDP P/OS Q-bus Rainbow RSTS

RSX ThinWire ULTRIX-11 VAX VAXcluster VAXstation II VAXstation 2000 VMS

# Contents

## About This Manual

$\mathbb{C}$

$\bigcirc$

$\bigcirc$

## Chapter 1 System Introduction

| 1.1 VAXstation 2000 System Description      |

|---------------------------------------------|

| 1.1.1 VS410 System Box                      |

| 1.1.2 Video Monitor                         |

| 1.1.3 LK201 Keyboard                        |

| 1.1.4 VSXXX Mouse                           |

| 1.2 MicroVAX 2000 System Description        |

| 1.2.1 VS410 System Box                      |

| 1.2.2 Video Console Terminal                |

| 1.2.3 LK201 Keyboard 1-3                    |

| 1.3 Physical Characteristics                |

| 1.3.1 System Box                            |

| 1.3.1.1 KA410 System Module                 |

| 1.3.1.2 Network Interconnect Module         |

| 1.3.1.3 MS400 Memory Module                 |

| 1.3.1.4 Power Supply                        |

| 1.3.1.5 RX33 Diskette Drive                 |

| 1.3.1.6 RD32 Disk Drive                     |

| 1.3.1.7 DEC423 Converter (MicroVAX 2000)1-6 |

| 1.3.1.8 Resistor Load Module                |

| 1.3.2         BA40B Expansion Boxes         |

| 1.3.2.1 RD53 Disk Drive                     |

| 1.3.2.2 TZK50 Controller Board              |

| 1.3.2.3 TK50 Tape Drive 1-7                 |

| 1.3.3 BA40A Expansion Adapter               |

| <b>1.3.3.1</b> Disk Interface Module        |

## Chapter 2 Functional System Overview

| 2.1 | Central Processor Overview |

|-----|----------------------------|

| 2.2 | System Memory              |

| 2.3 | Time-Of-Year Clock         |

| 2.4 | DC524 Standard Cell        |

| 2.5 | DC503 Cursor Sprite Chip   |

| 2.6 | Serial Line Controller     |

| 2.7 | 9224 Disk Controller       |

| 2.8 | 5380 Tape Controller 2–15  |

| 2.9 | ThinWire Ethernet Circuits |

()

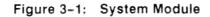

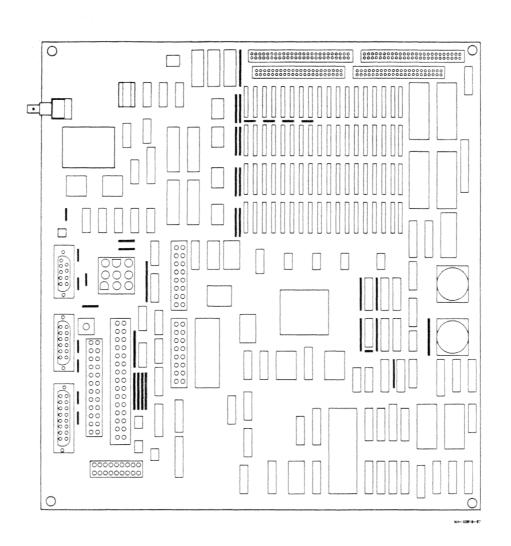

### Chapter 3 VS410 System Module Detailed Description

| 3.1 Introduction                                 | -1  |

|--------------------------------------------------|-----|

| 3.2 Central Processor                            | -3  |

| 3.2.1 DC333 CPU Chip Specifics                   | -4  |

| 3.2.1.1 CPU Bus Cycle Descriptions               | 11  |

| 3.2.1.2 General Registers 3-                     | 14  |

| 3.2.1.3 Processor Status Longword (PSL) Register | -14 |

| 3.2.1.4 Internal Processor Registers (IPR)       | -14 |

| 3.2.1.5 Interrupts and Exceptions                | 18  |

|                                                  | 25  |

|                                                  | 27  |

| 3.2.2.2 FPU/CPU Communications Protocol          | -28 |

| 3.2.3 40 MHz CPU/FPU Clock 3-                    | -29 |

| 3.2.4 DMA Bus Access                             | -29 |

|                                                  | -30 |

| 3.2.5.1 Virtual Memory Address Space             | 30  |

| 3.2.5.2 Physical Memory Address Space            | 30  |

| 3.2.5.3 Memory Management Control Registers      | 32  |

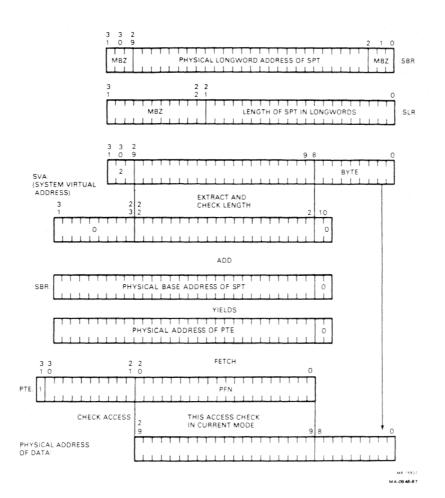

| 3.2.5.4 System Space Address Translation         | 33  |

|                                                  | 33  |

|                                                  | 37  |

| 3.2.6    | Processor Restarts                            |

|----------|-----------------------------------------------|

| 3.2.6.1  | Power-On Restart                              |

| 3.2.6.2  | HALT Restarts 3-39                            |

| 3.2.6.3  | HALT Code Register (HLTCOD) 3-39              |

| 3.3 Sys  | stem Memory                                   |

| 3.3.1    | RAM Memory                                    |

| 3.3.1.1  | System Module RAM 3-41                        |

| 3.3.1.2  | Video RAM                                     |

| 3.3.1.3  | Option Module RAM                             |

| 3.3.1.4  | Memory Parity Checking 3-44                   |

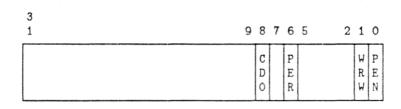

| 3.3.1.5  | Memory System Error Register (MSER)           |

| 3.3.1.6  | Memory Error Address Register (MEAR) 3-46     |

| 3.3.2    | ROM Memory                                    |

| 3.3.2.1  | System Module ROM 3-47                        |

| 3.3.2.2  | ThinWire Ethernet Address ROM                 |

| 3.3.2.3  | Option Module ROM                             |

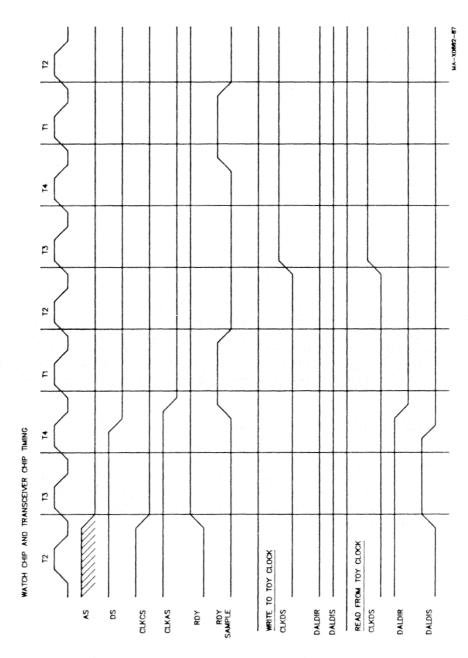

| 3.4 Tin  | ne-of-Year Clock (TOY) 3-58                   |

| 3.4.1    | Watch Chip Theory of Operation                |

| 3.4.2    | Watch Chip Registers 3-62                     |

| 3.4.2.1  | Control and Status Registers 3-64             |

| 3.4.2.2  | Date and Time-of-Year Registers 3-66          |

| 3.4.3    | Non-Volatile RAM Storage 3-67                 |

| 3.4.3.1  | Console Mailbox Register (CPMBX) 3-68         |

| 3.4.3.2  | Console Flags Register (CPFLG)                |

| 3.4.3.3  | Keyboard Type Register (LK201 ID) 3-70        |

| 3.4.3.4  | Console Type Register (CONSOLE ID) 3-71       |

| 3.4.3.5  | Scratch RAM Address Registers (SCR) 3-71      |

| 3.4.3.6  | Temporary Storage Registers (TEMPn) 3-71      |

| 3.4.3.7  | Battery Check Data Registers (BAT_CHK) 3-71   |

| 3.4.3.8  | Boot Device Registers (BOOT_DEV)              |

| 3.4.3.9  | Boot Flags Registers (BOOT_FLG)               |

| 3.4.3.10 | Scratch RAM Length Register (SCR_LENGTH) 3-72 |

| 3.4.3.11 | Tape Port Information Register (SCSI)         |

|          | nitialization                                 |

|          | Battery Backup                                |

| 3.5 DC   | 524 Standard Cell                             |

)

$\bigcirc$

$\bigcirc$

v

| 3.5.1    | Power-Up Initialization                                             |

|----------|---------------------------------------------------------------------|

| 3.5.2    | Memory Control                                                      |

| 3.5.2.1  | Multiplexed Address Signals (MEMAD8:0)                              |

| 3.5.2.2  | Memory Control Signals                                              |

| 3.5.2.3  | Memory and Peripheral Timing                                        |

| 3.5.2.4  | Control of CPU Cycle Slips 3-90                                     |

| 3.5.3    | Video Control 3-90                                                  |

| 3.5.3.1  | Video Shift Register Update and RAM Refresh 3-90                    |

| 3.5.3.2  | Video Timing Diagrams 3-91                                          |

| 3.5.3.3  | Video RAM and Cursor Data Combination and Output . 3-92             |

| 3.5.4    | Input/Output Control 3-95                                           |

| 3.5.4.1  | Configuration and Test Register Enable (SYSREGEN) 3-95              |

| 3.5.4.2  | System ROM Enable (ROMCS) 3-95                                      |

| 3.5.4.3  | Network Option ROM Enable (NIROMENA) 3–95                           |

| 3.5.4.4  | Video Option ROM Enable (OPTROMENA) 3-96                            |

| 3.5.4.5  | TOY Clock Control (CLKCS, CLKAS, and CLKDS) 3-96                    |

| 3.5.4.6  | System Error, Interrupt Control and Video Control<br>Registers      |

| 3.5.4.7  | Interrupt and Video Control Register (IVCR) 3–97                    |

| 3.5.4.8  | Serial Line Controller Enable (SLUENA) 3–98                         |

| 3.5.4.9  | Shift Silo (SHSILO)                                                 |

| 3.5.4.10 | 9224 Control Signals (CS9224, DS9224, and WR9224) 3-99              |

| 3.5.4.11 | Tape Port Control Signals (SCSICS, SCSIRD, and      SCSIWR)    3-99 |

| 3.5.4.12 | Disk RAM Buffer Control (DBUFCE)                                    |

| 3.5.4.13 | Ethernet/SID ROM Enable (EIDENA) 3-100                              |

| 3.5.4.14 | Network Interface Controller Enable (NIENA) 3-100                   |

| 3.5.4.15 | Cursor Chip Enable (CURSEL)                                         |

| 3.5.4.16 | Video RAM Enable (SRAM0 and SRAM1) 3-100                            |

| 3.5.4.17 | Video Option Enable (OPTVIDENA)                                     |

| 3.5.5    | Disk Control                                                        |

| 3.5.5.1  | Floppy Disks 3-101                                                  |

| 3.5.5.2  | Winchester Disks 3-102                                              |

| 3.5.5.3  | Common Signals                                                      |

| 3.5.6    | Tape Control (SCSI)         3-103                                   |

| 3.5.7    | Parity Generation and Checking (PBIT3:0)                            |

$\bigcirc$

vi

| 3.5.8    | Interval Timer Interrupt Generation (INTTIM) | 3-104 |

|----------|----------------------------------------------|-------|

| 3.5.9    | Interrupt Controller                         | 3-105 |

| 3.5.9.1  | Interrupt Request Register (INT REQ)         | 3-106 |

| 3.5.9.2  | Interrupt Mask Register (INT MSK)            | 3-106 |

| 3.5.9.3  | Interrupt Clear Register (INT CLR)           | 3-107 |

| 3.5.9.4  | Interrupt Vector Generation                  | 3-107 |

| 3.5.9.5  | Interrupt Sources and Ranking                | 3-108 |

| 3.5.9.6  | Video Interrupt Select Register (VDC_SEL)    | 3-109 |

| 3.5.10   | Monochrome Video Display Controller          | 3-110 |

| 3.5.10.1 | Video Timing                                 | 3-110 |

| 3.5.10.2 | End-of-Frame Interrupt                       | 3-111 |

| 3.5.10.3 | Data Plane Storage                           | 3-111 |

| 3.5.10.4 | Display Origin Register (VDC_ORG)            | 3-112 |

| 3.5.11   | Test Mode (TEST)                             | 3-112 |

| 3.5.11.1 | Interval Counter                             | 3-112 |

| 3.5.11.2 | Vertical Timing                              | 3-113 |

| 3.5.11.3 | Video RAM Shift Register Update/Refresh      | 3-113 |

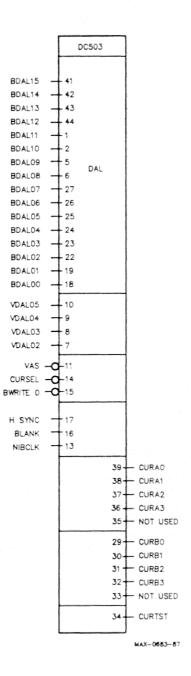

| 3.6 L    | OC503 Cursor Sprite Chip                     | 3-113 |

| 3.6.1    | Overview                                     | 3-113 |

| 3.6.2    | Cursor Coordinate Offsets                    | 3-116 |

| 3.6.3    | Cursor Generation                            | 3-117 |

| 3.6.4    | Cursor Control Registers                     | 3-117 |

| 3.6.5    | Cursor Command Register (DUR_CMD)            | 3-119 |

| 3.6.6    | Loading the Cursor Sprite Pattern            | 3-121 |

| 3.6.7    | Cursor Region Detector                       | 3-122 |

| 3.6.8    | Displaying a Sprite Cursor                   | 3-122 |

| 3.6.9    | Displaying a Crosshair Cursor                | 3-122 |

| 3.6.10   | Controlling Cursor Plane Outputs             | 3-123 |

| 3.6.11   | Blanking the Display                         | 3-123 |

| 3.6.12   | Cursor Chip Test                             | 3-123 |

| 3.6.13   | Power-Up Initialization                      | 3-124 |

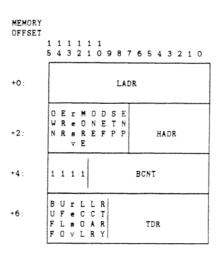

| 3.7 S    | erial Line Controller (DZ Controller)        | 3-125 |

| 3.7.1    | DZ Silo                                      | 3-129 |

| 3.7.2    | Line Identification                          | 3-129 |

| 3.7.3    | Diagnostic Terminal Connection               | 3-131 |

| 3.7.4    | Interrupts                                   | 3-132 |

)

0

vii

| 3.7.5    | Register Summary                                   | 3-132 |

|----------|----------------------------------------------------|-------|

| 3.7.5.1  | Control and Status Register (SER_CSR)              | 3-132 |

| 3.7.5.2  | Serial Line Receiver Buffer Register (SER_RBUF)    |       |

| 3.7.5.3  | Serial Line Parameter Register (SER_LPR)           |       |

| 3.7.5.4  | Serial Line Transmitter Control Register (SER_TCR) |       |

| 3.7.5.5  | Modem Status Register (SER MSR)                    |       |

| 3.7.5.6  | Transmitter Data Register (SER_TDR)                |       |

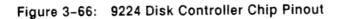

| 3.8 9    | 224 Disk Controller                                |       |

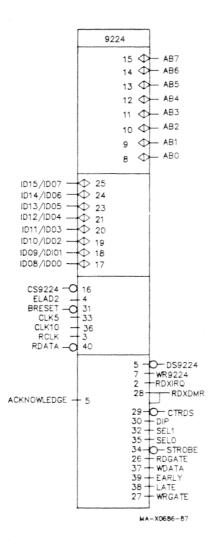

| 3.8.1    | Disk Data Buffer                                   |       |

| 3.8.2    | Disk Address Counters                              | 3-148 |

| 3.8.3    | Phase-Locked Loop                                  | 3-150 |

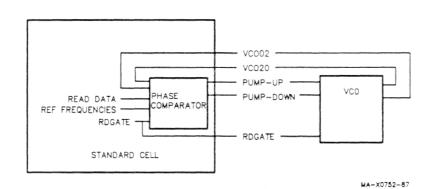

| 3.8.3.1  | Phase Comparator                                   | 3-151 |

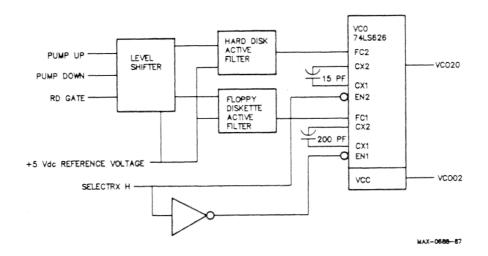

| 3.8.3.2  | Voltage-Controlled Oscillator (VCO)                | 3-152 |

| 3.8.4    | Hard Disk Data Bus                                 | 3-153 |

| 3.8.5    | Floppy Disk Data Bus                               | 3-153 |

| 3.8.6    | Controller Chip Organization                       | 3-153 |

| 3.8.6.1  | Disk Controller Chip Ports                         | 3-154 |

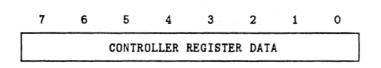

| 3.8.6.2  | Controller Chip Registers                          | 3-158 |

| 3.8.7    | Command Overview                                   | 3-170 |

| 3.8.7.1  | Read ID Sequence                                   | 3-172 |

| 3.8.7.2  | Verify Sequence                                    | 3-172 |

| 3.8.7.3  | Data Transfer Sequence                             |       |

| 3.8.8    | Command Descriptions                               |       |

| 3.8.8.1  | RESET Command                                      |       |

| 3.8.8.2  | SET REGISTER POINTER Command                       |       |

| 3.8.8.3  | DESELECT DRIVE Command                             |       |

| 3.8.8.4  | DRIVE SELECT Command                               |       |

| 3.8.8.5  | RESTORE DRIVE Command                              | 3-178 |

| 3.8.8.6  | STEP Command                                       |       |

| 3.8.8.7  | POLL DRIVES Command                                | 3-180 |

| 3.8.8.8  | SEEK/READ ID Command                               | 3-181 |

| 3.8.8.9  | FORMAT TRACK Command                               | 3-182 |

| 3.8.8.10 | READ TRACK Command                                 |       |

| 3.8.8.11 | READ PHYSICAL Command                              |       |

| 3.8.8.12 | READ LOGICAL Command                               |       |

| 3.8.8.13 | WRITE PHYSICAL Command                             | 3-188 |

()

viii

| 3.8.8.14 | WRITE LOGICAL Command                               |       |

|----------|-----------------------------------------------------|-------|

|          | Write Precompensation                               |       |

|          | Diskette Drive READY Condition                      | 3-191 |

| 3.8.11   | Disk Programming                                    | 3-193 |

| 3.8.11.1 | Diskette Motor Control                              | 3-193 |

| 3.8.11.2 | Implicit Seeks on Diskettes                         | 3-194 |

| 3.8.11.3 | Diskette Write Completion Delay                     | 3-194 |

| 3.8.11.4 | Using the Disk and Tape Controllers                 | 3-195 |

| 3.8.11.5 | Selecting the Diskette Drive                        | 3-195 |

| 3.8.11.6 | Drive Select Jumpers                                | 3-196 |

| 3.8.11.7 | Spurious Data CRC Errors                            | 3-196 |

| 3.8.12   | Diskette Drive Overview                             | 3-196 |

| 3.8.13   | Hard Disk Drives                                    | 3-197 |

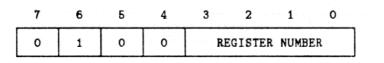

| 3.9 538  | 30 Tape Controller                                  | 3-198 |

| 3.9.1    | 5380 Tape Controller Overview                       | 3-200 |

| 3.9.2    | SCSI Overview                                       | 3-204 |

| 3.9.3    | 5380 Tape Controller Chip Registers                 | 3-206 |

| 3.9.3.1  | Mode Register (SCS MODE)                            | 3-207 |

| 3.9.3.2  | Initiator Command Register (SCS INI CMD)            | 3-209 |

| 3.9.3.3  | Target Command Register (SCS TAR CMD)               | 3-211 |

| 3.9.3.4  | Bus and Status Register (SCS STATUS)                | 3-212 |

| 3.9.3.5  | Current Bus Status Register (SCS CUR STAT)          | 3-214 |

| 3.9.3.6  | Select Enable Register (SCS_SEL_ENA)                | 3-214 |

| 3.9.3.7  | Output Data Register (SCS OUT DATA)                 | 3-215 |

| 3.9.3.8  | Current Data Register (SCS_CUR_DATA)                | 3-215 |

| 3.9.3.9  | Input Data Register (SCS IN DATA)                   | 3-215 |

| 3.9.3.10 | Start DMA Send Action (SCS DMA SEND)                | 3-216 |

| 3.9.3.11 | Start DMA Initiator Receive Action (SCS DMA IRCV) . | 3-216 |

| 3.9.3.12 | Start DMA Target Receive Action (SCS DMA TRCV)      | 3-216 |

| 3.9.3.13 | Reset Interrupt/Error Action (SCS RESET)            | 3-216 |

| 3.9.4    | DMA Register Operation                              | 3-217 |

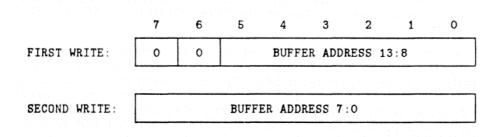

| 3.9.4.1  | DMA Address Register (SCD ADR)                      | 3-217 |

| 3.9.4.2  | DMA Count Register (SCD CNT)                        |       |

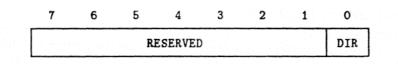

| 3.9.4.3  | DMA Direction Register (SCD DIR)                    | 3-219 |

and the second

| 3.9.5 Tape Controller Interrupts                | 3-219 |

|-------------------------------------------------|-------|

| 3.9.5.1 Selection or Reselection                | 3-220 |

| 3.9.5.2 DMA Count Reaches 0                     | 3-221 |

| 3.9.5.3 Bus Parity Error                        | 3-221 |

| 3.9.5.4 Phase Mismatch                          | 3-222 |

| 3.9.5.5 Bus Disconnect                          | 3-222 |

| 3.9.5.6 SCSI Tape Bus Reset                     | 3-222 |

| 3.9.6 Reset Conditions                          | 3-223 |

| 3.9.6.1 System Hardware Reset                   | 3-223 |

| 3.9.6.2 RST Received from SCSI Tape Bus         | 3-223 |

| 3.9.6.3 RST Issued to SCSI Tape Bus             | 3-223 |

| 3.9.7 Programming Notes                         | 3-223 |

| 3.9.7.1 Using the Tape and Disk Controllers     | 3-223 |

| 3.9.7.2 Device ID Values                        | 3-224 |

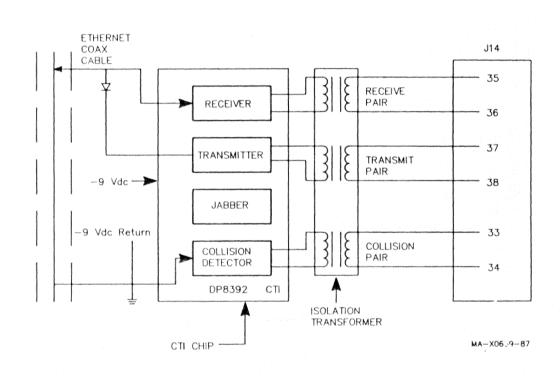

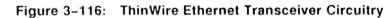

| 3.10 ThinWire Ethernet Circuits                 | 3-224 |

| 3.10.1 Coaxial Transceiver Interface            | 3-227 |

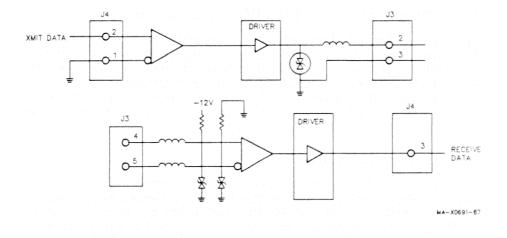

| 3.10.1.1 Transmitter                            | 3-228 |

| 3.10.1.2 Receiver                               | 3-228 |

| 3.10.1.3 Collision Detector                     | 3-229 |

| 3.10.1.4 Jabber                                 | 3-229 |

| 3.10.2 Network Address ROM                      | 3-229 |

| 3.11 Miscellaneous System Registers             | 3-229 |

| 3.11.1 HALT Code Register (HLTCOD)              | 3-230 |

| 3.11.2 Configuration and Test Register (CFGTST) | 3-230 |

| 3.11.3 I/O Reset Register (IORESET)             | 3-232 |

| 3.11.4 Address Strobe Delay Line                | 3-232 |

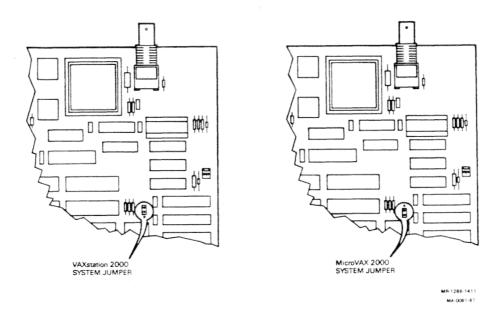

| 3.12 System Jumper Configuration                | 3-232 |

| 3.13 System Module Connector Pinouts            | 3-233 |

| 3.14 Power Requirements                         | 3-239 |

|                                                 |       |

|                                                 |       |

|                                                 |       |

|                                                 |       |

|                                                 |       |

|                                                 |       |

х

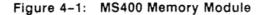

## Chapter 4 MS400 Option Memory Modules

| 4.1   | Introduction                                  |

|-------|-----------------------------------------------|

| 4.2   | Theory of Operation                           |

| 4.2.1 | Memory Module Control Signal Descriptions 4-2 |

| 4.2.2 | Memory Cycles                                 |

| 4.3   | Connector Pinouts                             |

| 4.4   | Configuration Jumpers 4-7                     |

| 4.5   | Power Requirements                            |

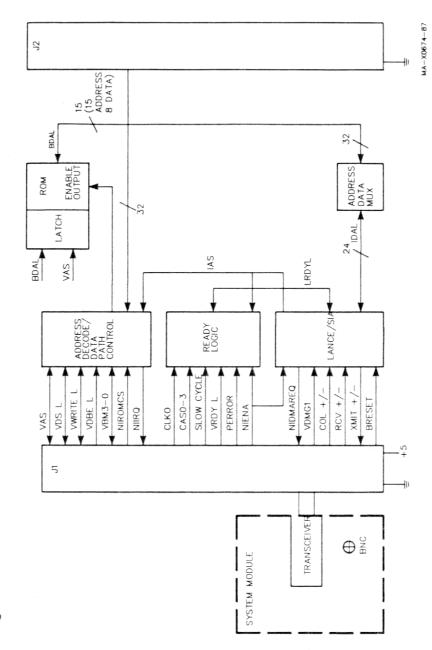

## Chapter 5 ThinWire Ethernet (DESVA) Option Module

| 5.1   | Introduction                            |

|-------|-----------------------------------------|

| 5.2   | Connector Pin Descriptions              |

| 5.3   | Ethernet Implementation                 |

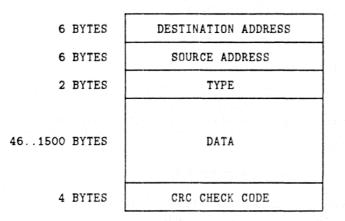

| 5.3.1 | Packet Format                           |

| 5.3.2 | Network Addresses                       |

| 5.4   | LANCE Chip Overview                     |

| 5.4.1 | LANCE Description                       |

| 5.4.2 | Transmit Mode                           |

| 5.4.3 | Receive Mode 5-9                        |

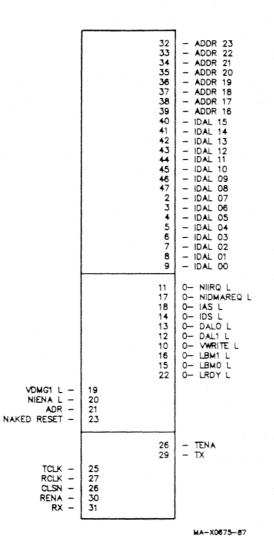

| 5.4.4 | LANCE Chip Pinout                       |

| 5.5   | SIA Chip Overview                       |

| 5.5.1 | SIA Description                         |

| 5.5.2 | Transmit Mode 5-18                      |

| 5.5.3 | Receive Mode 5-18                       |

| 5.6   | DMA Operation 5-19                      |

| 5.7   | Controller Firmware ROM                 |

| 5.7.1 | ROM Description                         |

| 5.8   | Program Control of the LANCE            |

| 5.8.1 | Register Address Port (NI RAP)          |

| 5.8.2 | Register Data Port (NI_RDP) 5-23        |

| 5.8.3 | Control and Status Register 0 (NI_CSR0) |

| 5.8.4 | Control and Status Register 1 (NI_CSR1) |

| 5.8.5 | Control and Status Register 2 (NI_CSR2) |

| 5.8.6 | Control and Status Register 3 (NI_CSR3) |

| 5.9   | Interrupts                              |

xi

| 5.10 Initialization Block                          | 5-30 |

|----------------------------------------------------|------|

| 5.10.1 Initialization Block MODE Word (NIB_MODE)   | 5-31 |

| 5.10.2 Network Physical Address (NIB_PADR)         | 5-33 |

| 5.10.3 Multicast Address Filter Mask (NIB LADRF)   | 5-34 |

| 5.10.4 Receive Descriptor Ring Pointer (NIB_RDRP)  | 5-35 |

| 5.10.5 Transmit Descriptor Ring Pointer (NIB_TDRP) | 5-36 |

| 5.11 Buffer Management                             | 5-37 |

| 5.11.1 Receive Buffer Descriptor                   | 5-38 |

| 5.11.2 Transmit Buffer Descriptor                  | 5-40 |

| 5.12 LANCE Operation                               | 5-42 |

| 5.12.1 Switch Routine                              | 5-43 |

| 5.12.2 Initialization Routine                      | 5-43 |

| 5.12.3 Look-For-Work Routine                       | 5-43 |

| 5.12.4 Receive Poll Routine                        | 5-44 |

| 5.12.5 Receive Routine                             | 5-44 |

| 5.12.6 Receive DMA Routine                         | 5-45 |

| 5.12.7 Transmit Poll Routine                       | 5-45 |

| 5.12.8 Transmit Routine                            | 5-46 |

| 5.12.9 Transmit DMA Routine                        | 5-46 |

| 5.12.10 Collision Detect Routine                   | 5-46 |

| 5.13 LANCE Programming Notes                       | 5-47 |

| 5.14 Power Requirements                            | 5-49 |

## Chapter 6 Resistor Load Module

## Chapter 7 Power Supply

| 7.1 Introduction        |             | <br> |

|-------------------------|-------------|------|

| 7.2 AC Input            |             | <br> |

| 7.3 DC Output           |             | <br> |

| 7.4 Battery for Time-of | -Year Clock | <br> |

| 7.5 Cooling             |             | <br> |

(

| Char | oter | 8 | Dr | iν | es  |

|------|------|---|----|----|-----|

|      |      |   |    |    | ~~~ |

| 8.1    | Introduction                           |

|--------|----------------------------------------|

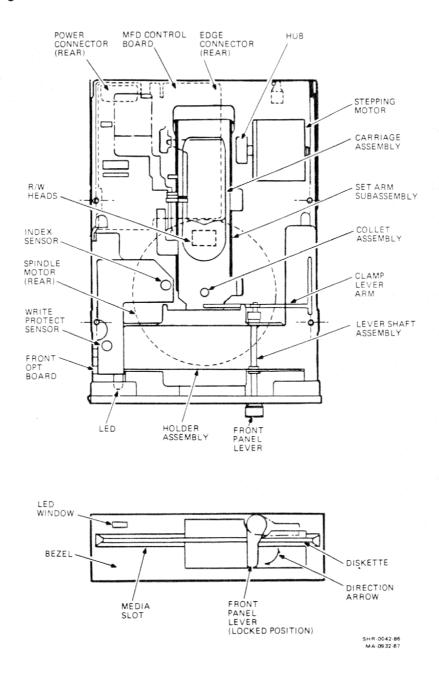

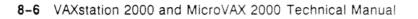

| 8.2    | RX33 Half-Height Diskette Drive        |

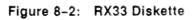

| 8.2.1  | RX33 Media                             |

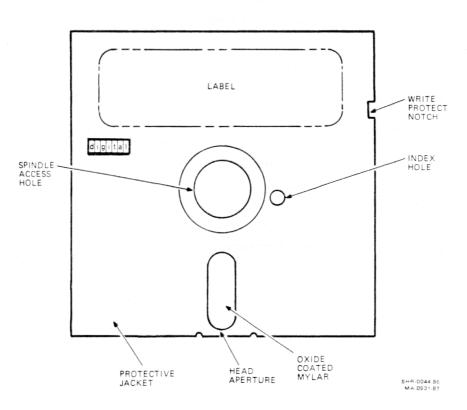

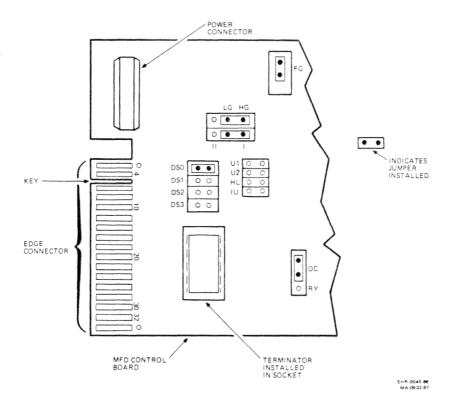

| 8.2.2  | RX33 Jumper Configuration              |

| 8.2.3  | Inserting/Removing a Diskette          |

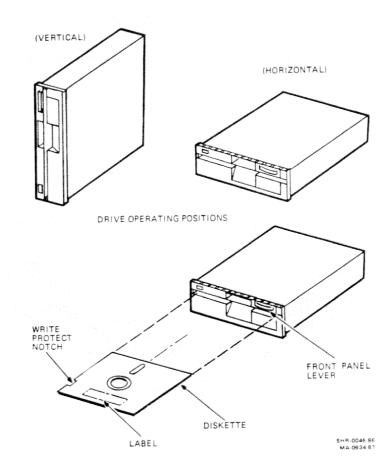

| 8.3    | RD32 Half-Height Hard Disk Drive       |

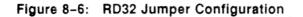

| 8.3.1  | RD32 Jumper Configuration              |

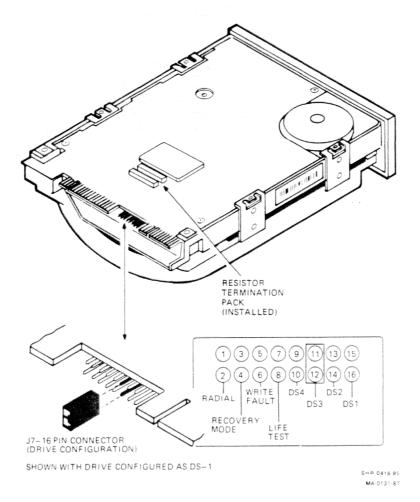

| 8.4    | RD53 Full-Height Hard Disk Drive       |

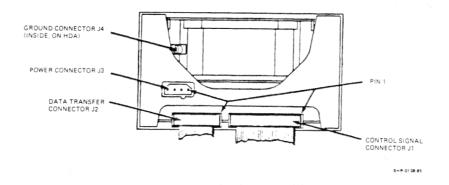

| 8.4.1  | RD53 Jumper Configuration 8-11         |

| 8.5    | TK50 Tape Drive                        |

| 8.5.1  | Using the TK50 8-13                    |

| 8.5.1. | 1 Loading/Unloading a Tape Cartridge   |

| 8.5.2  | Write Protecting a TK50 Tape Cartridge |

|        |                                        |

### Chapter 9 DEC423 Converter (MicroVAX 2000)

| 9.1   | Introduction                           | 9-1 |

|-------|----------------------------------------|-----|

| 9.2   | Physical Description                   | 9-1 |

| 9.2.1 | Converter Enclosure                    | 9-1 |

| 9.2.2 | Mounting                               | 9-2 |

| 9.2.3 | Circuit Board                          | 9-2 |

| 9.2.4 | Input/Output Connector Pinout          | 9-3 |

| 9.2.5 | Power Dissipation and Cooling          | 9-4 |

| 9.2.6 | Power Supply                           | 9-4 |

| 9.3   | Circuit Descriptions                   | 9-5 |

| 9.3.1 | Slew Rate                              |     |

| 9.3.2 | Failsafing                             | 9-6 |

| 9.3.3 | Pins 1 and 6 on the MMJ Connectors     |     |

| 9.3.4 | ESD/EOS Protection                     | 9-6 |

| 9.3.5 | Chokes                                 | 9-7 |

| 9.3.6 | EMI/RFI Isolation and Susceptability   | 9-7 |

| 9.4   | Loopback Connector H3103 (12-25083-01) | 9-7 |

## Chapter 10 Expansion Peripherals

| 10.1 In  | troduction               | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                              | 10-1 |

|----------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 10.1.1   | Hard Disk Expansion Box  | a a servici de la companya de la co<br>La companya de la comp | 10-1 |

| 10.1.2   | Tape Drive Expansion Box | a son a substantia de la calencia d<br>A ser este este este este este este este                                                                         | 10-3 |

| 10.1.3   | Expansion Adapter        |                                                                                                                                                                                                                                    |      |

| 10.1.3.1 | The Tape Port (Port A)   | la compositor de la constanta de la constanta<br>A constanta de la constanta de l  | 10-5 |

| 10.1.3.2 | The Disk Port (Port B)   |                                                                                                                                                                                                                                    | 10-6 |

## Appendix A Timing Diagrams

## Appendix B Physical Address Maps

| B.1   | System Module Addresses                       | B-1 |

|-------|-----------------------------------------------|-----|

| B.2   | Option Module Address Ranges                  | B-2 |

| B.2.1 | Ethernet Network Option Addresses             | B-3 |

| B.2.2 | Graphics (Color) Video Option Addresses       | B-4 |

| B.2.3 | Eight-port Asynchronous Serial Line Addresses | B-4 |

## Figures

| 1-1  | The VAXstation 2000 Computer System                      |

|------|----------------------------------------------------------|

| 1-2  | The MicroVAX 2000 Computer System                        |

| 2-1  | VS410 System Module Functional Block Diagram             |

| 2-2  | Block Diagram of the CPU Chip and the FPU Chip 2-3       |

| 2-3  | System Memory Functional Block Diagram                   |

| 2-4  | TOY Clock Functional Block Diagram                       |

| 2-5  | DC524 Standard Cell Functional Block Diagram 2-9         |

| 2-6  | DC503 Cursor Sprite Chip Functional Block Diagram 2-11   |

| 2-7  | Serial Line Controller Functional Block Diagram 2-12     |

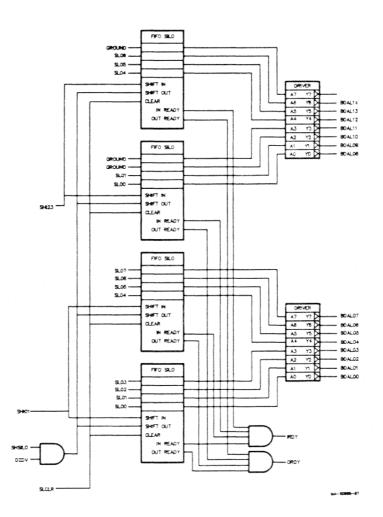

| 2-8  | 9224 Disk Controller Functional Block Diagram            |

| 2-9  | 5380 Tape Controller Functional Block Diagram            |

| 2-10 | ThinWire Ethernet Circuits Functional Block Diagram 2-17 |

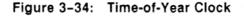

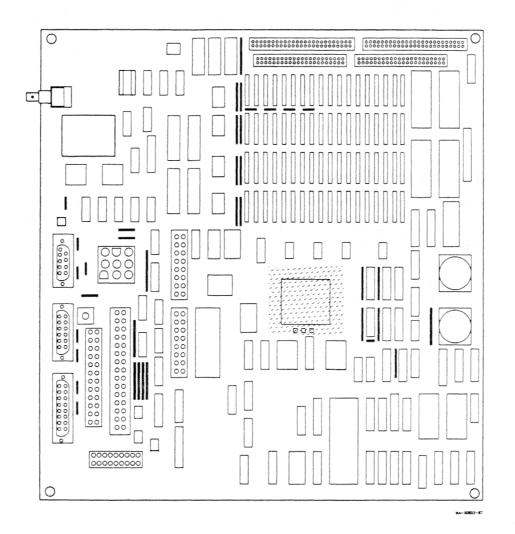

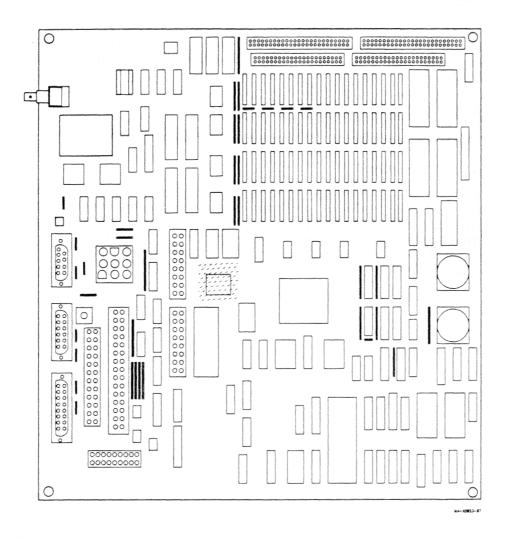

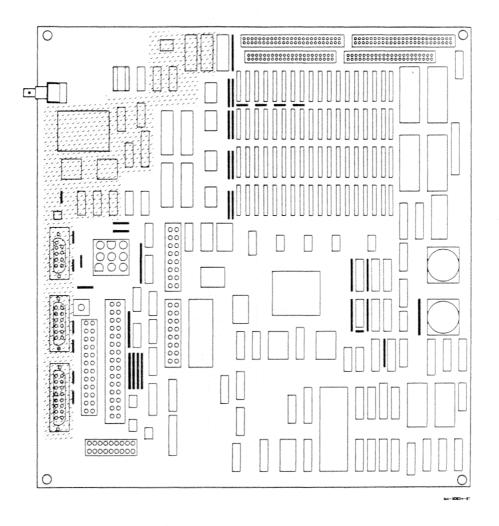

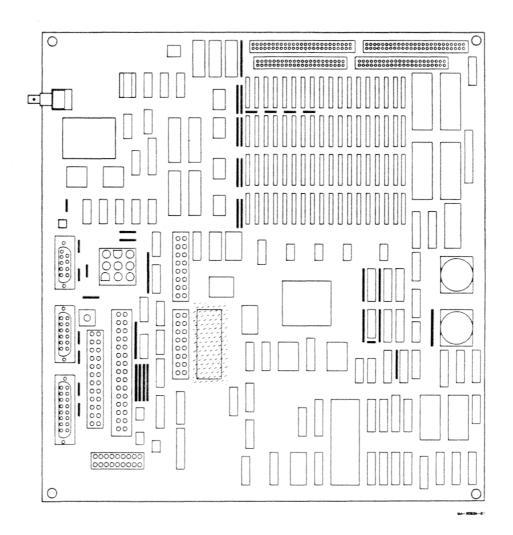

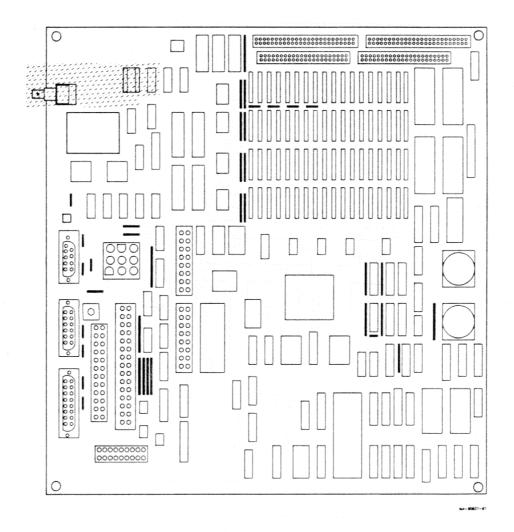

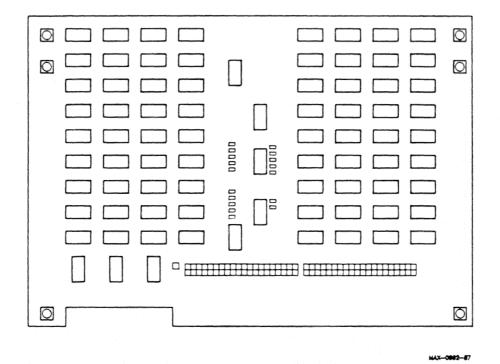

| 3-1  | System Module                                            |

| 3-2  | Central Processor Unit (CPU)                             |

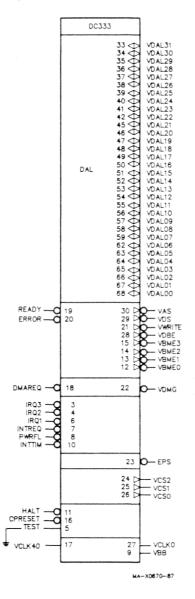

| 3-3  | CPU Chip Pinout                                          |

| 3-4  | Processor Status Longword Register                       |

| 3-5  | Interval Clock Control and Status Register (ICCS)    | 3-17 |

|------|------------------------------------------------------|------|

| 3-6  | System Identification Register (SID)                 | 3-17 |

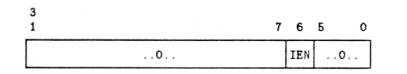

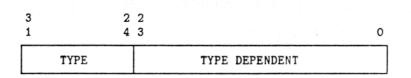

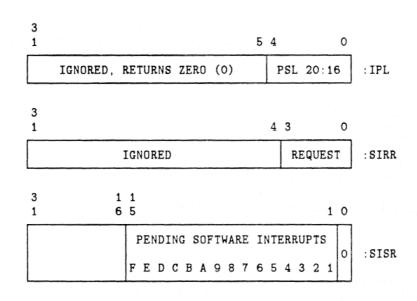

| 3-7  | Interrupt Control Registers (IPL, IRR, SISR)         | 3-18 |

| 3-8  | Machine Check Exception Parameters                   | 3-21 |

| 3-9  | System Control Block Base Register (SCBB)            |      |

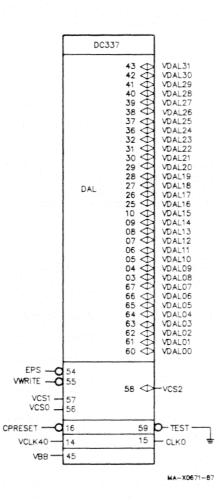

|      | DC337 FPU Chip Pinout                                |      |

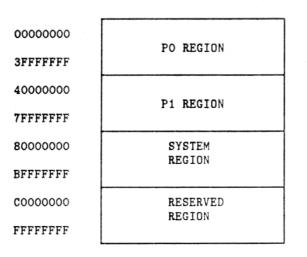

|      | Virtual Memory Address Space                         |      |

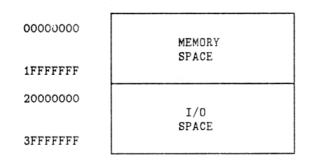

| 3-12 | Physical Memory Address Space                        | 3-31 |

|      | Memory Management (Mapping) Enable Register (MAPEN)  |      |

| 3-14 | Translation Buffer Invalidate Single Register (TBIS) | 3-32 |

| 3-15 | Translation Buffer Invalidate All Register (TBIA)    | 3-32 |

| 3-16 | System Space Virtual to Physical Address Translation | 3-34 |

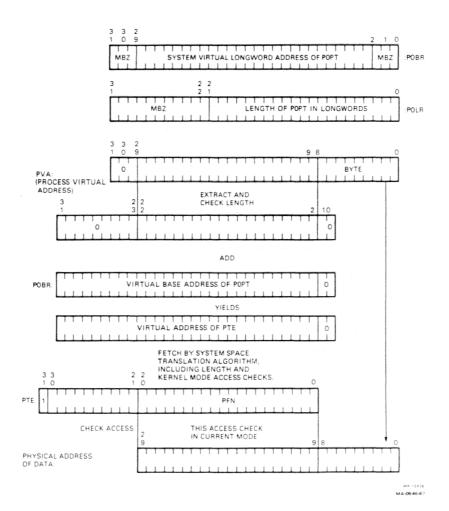

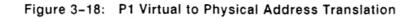

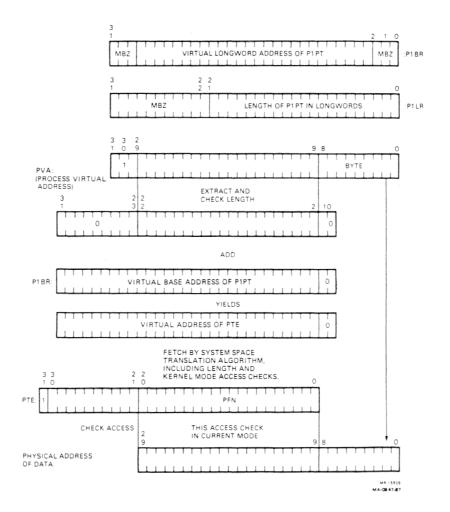

| 3-17 | P0 Virtual to Physical Address Translation           | 3-35 |

| 3-18 | P1 Virtual to Physical Address Translation           | 3-36 |

| 3-19 | Page Table Entry (PTE)                               | 3-37 |

|      | Halt Code Register (HLTCOD)                          |      |

|      | System Memory                                        |      |

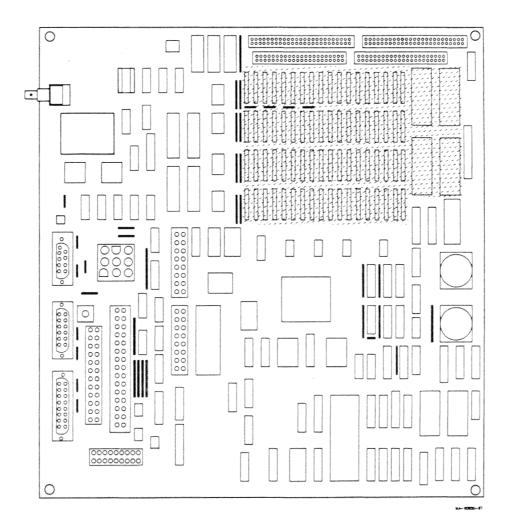

|      | RAM Zip Packs Block Diagram                          |      |

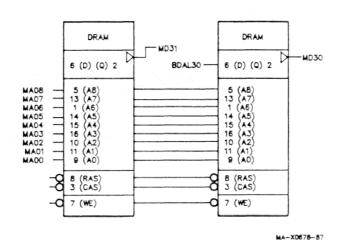

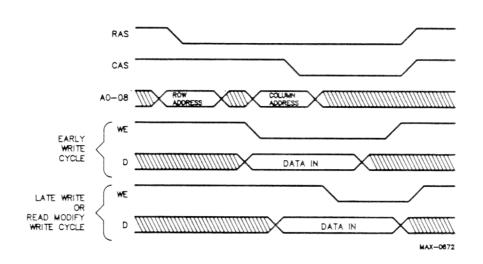

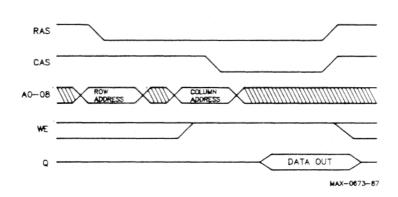

| 3-23 | Data In (Write) Memory Timing Cycle                  | 3-42 |

|      | Data Out (Read) Memory Timing Cycle                  |      |

|      | Memory System Error Register (MSER)                  |      |

| 3-26 | Memory Error Address Register (MEAR)                 | 3-46 |

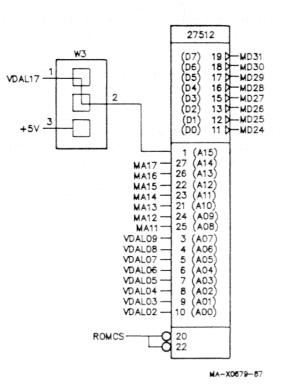

| 3-27 | System Module ROM Circuit Diagram (High Byte)        | 3-47 |

| 3-28 | System ROM Contents Layout                           | 3-49 |

| 3-29 | System Type Register (SYS_TYPE)                      | 3-52 |

| 3-30 | ThinWire Ethernet Address ROM diagram                | 3-53 |

| 3-31 | Option ROM Address Allocation                        | 3-55 |

|      | Option ROM Set Contents                              | 3-56 |

|      |                                                      | 3-57 |

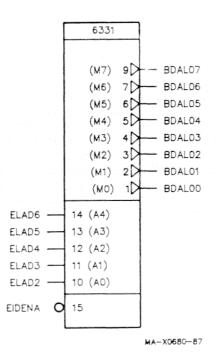

|      | Time-of-Year Clock                                   |      |

| 3-35 | Watch Chip and Transceiver Chip Diagram              | 3-59 |

|      | Watch Chip and Transceiver Chip Timing               |      |

|      | Watch Time Base Divisor (WAT_CSRA)                   |      |

|      | Watch Date Mode and Format (WAT_CSRB)                |      |

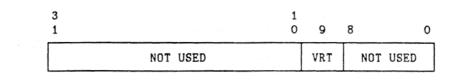

|      | Watch Valid RAM and Time Flag                        |      |

| 3-40 | Console Mailbox Register (CPMBX)                     | 3-68 |

No.

xv

| 3-41 | Console Flags Register (CPFLG)                         | . 3-69 |

|------|--------------------------------------------------------|--------|

| 3-42 | Tape Port Information Register (SCSI)                  | . 3-72 |

|      | Standard Cell                                          |        |

| 3-44 | DC524 Standard Cell Pinout                             | . 3-75 |

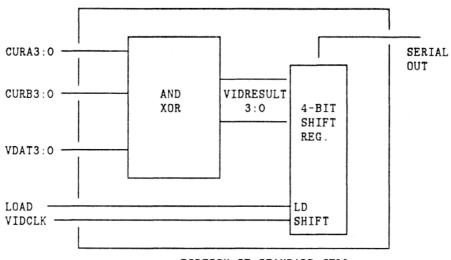

| 3-45 | Video RAM and Cursor Block Diagram                     | . 3-92 |

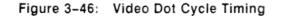

| 3-46 | Video Dot Cycle Timing                                 | . 3-93 |

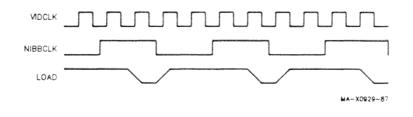

| 3-47 | Horizontal Timing Generation                           | . 3-94 |

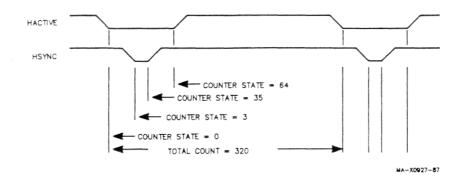

| 3-48 | Vertical Timing Generation                             | . 3-94 |

| 3-49 | Interrupt and Video Control Register (IVCR)            | . 3-97 |

| 3-50 | Interrupt Register Formats (INT REQ, INT MSK, INT CLR) | 3-105  |

| 3-51 | Interrupt Vector Longword                              | 3-107  |

| 3-52 | Video Interrupt Select Register (VDC SEL)              | 3-109  |

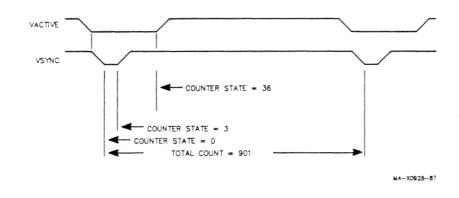

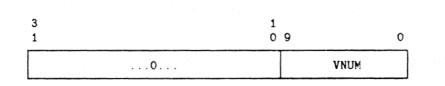

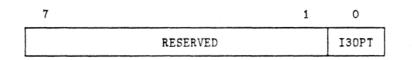

| 3-53 | DC503 Cursor Sprite Chip                               | 3-114  |

|      | DC503 Cursor Sprite Chip Pinout                        |        |

| 3-55 | Cursor Command Register (CUR_CMD)                      | 3-119  |

|      | Serial Line Controller                                 |        |

| 3-57 | DZ Controller Chip Pinout                              | 3-126  |

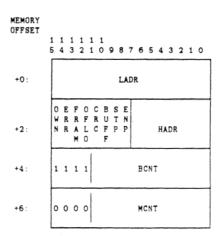

| 3-58 | DZ Silo Circuit Diagram                                | 3-130  |

| 3-59 | Serial Line Control and Status Register (SER_CSR)      | 3-133  |

| 3-60 | Serial Line Receiver Buffer Register (SER RBUF)        | 3-136  |

| 3-61 | Serial Line Parameter Register (SER LPR)               | 3-137  |

|      | Serial Line Transmitter Control Register (SER_TCR)     |        |

| 3-63 | Serial Line Modem Status Register (SER MSR)            | 3-141  |

| 3-64 | Serial Line Transmitter Data Register (SER_TDR)        | 3-142  |

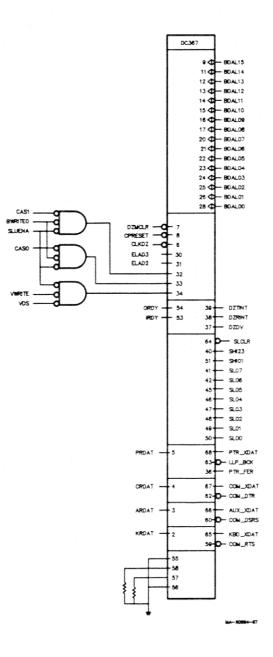

| 3-65 | 9224 Disk Controller                                   | 3-144  |

| 3-66 | 9224 Disk Controller Chip Pinout                       | 3-145  |

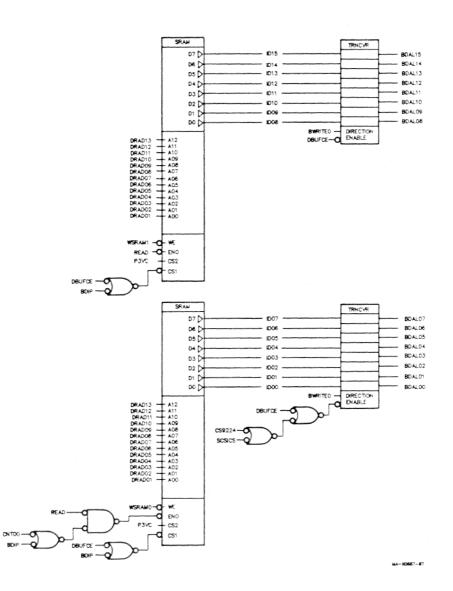

|      | Disk Data Buffer Circuit Diagram                       |        |

| 3-68 | Phase-Locked Loop Block Diagram                        | 3-150  |

| 3-69 | VCO Block Diagram                                      | 3-152  |

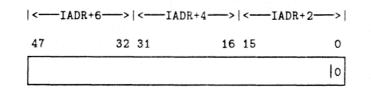

| 3-70 | Disk Register Data Access Port                         | 3-155  |

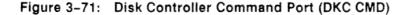

| 3-71 | Disk Controller Command Port (DKC_CMD)                 | 3-155  |

| 3-72 | Interrupt Status Port (DKC_STAT)                       | 3-155  |

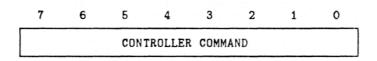

| 3-73 | DMA Address Registers (UDC DMAxx)                      | 3-159  |

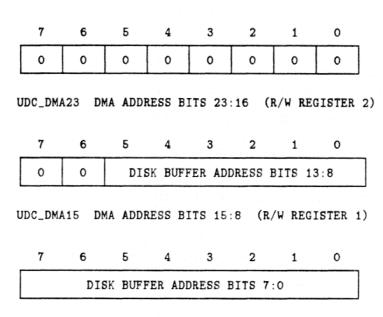

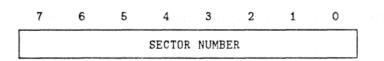

| 3-74 | Desired Sector Register (UDC DSECT)                    | 3-159  |

| 3-75 | Desired Head Register (UDC DHEAD)                      | 3-160  |

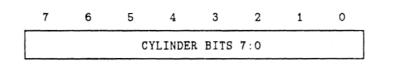

| 3-76 | Desired Cylinder Register (UDC DCYL)                   | 3-160  |

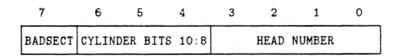

| 3-77  | Current Head Register (UDC_CHEAD)          | 3-161 |

|-------|--------------------------------------------|-------|

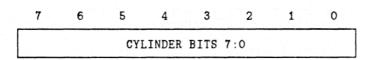

| 3-78  | Current Cylinder Register (UDC_CCYL)       | 3-161 |

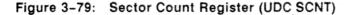

| 3-79  | Sector Count Register (UDC_SCNT)           | 3-161 |

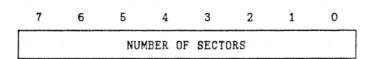

| 3-80  | Retry Count Register (UDC_RTCNT)           | 3-162 |

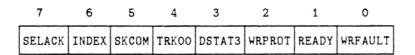

| 3-81  | Operating Mode Register (UDC_MODE)         | 3-163 |

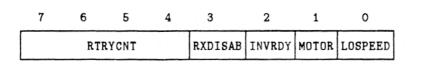

| 3-82  | Chip Status Register (UDC_CSTAT)           | 3-166 |

| 3-83  | Termination Conditions Register (UDC_TERM) | 3-167 |

| 3-84  | Drive Status Register (UDC_DSTAT)          | 3-168 |

| 3-85  | Disk Data Register (UDC_DATA)              | 3-170 |

|       | RESET Command                              | 3-174 |

|       | SET REGISTER POINTER Command               | 3-175 |

| 3-88  | DESELECT DRIVE Command                     | 3-175 |

| 3-89  | DRIVE SELECT Command                       | 3-176 |

| 3-90  | Restore Drive Command                      | 3-178 |

| 3-91  | STEP Command                               | 3-179 |

| 3-92  | POLL DRIVES Command                        | 3-180 |

| 3-93  | SEEK/READ ID Command                       | 3-181 |

| 3-94  | FORMAT TRACK Command                       | 3-182 |

|       | ID Field Bytes for Each Sector             | 3-183 |

|       | READ TRACK Command                         | 3-185 |

|       | READ PHYSICAL Command                      | 3-186 |

|       | READ LOGICAL Command                       | 3-187 |

|       | WRITE PHYSICAL Command                     | 3-188 |

|       | WRITE LOGICAL Command                      | 3-190 |

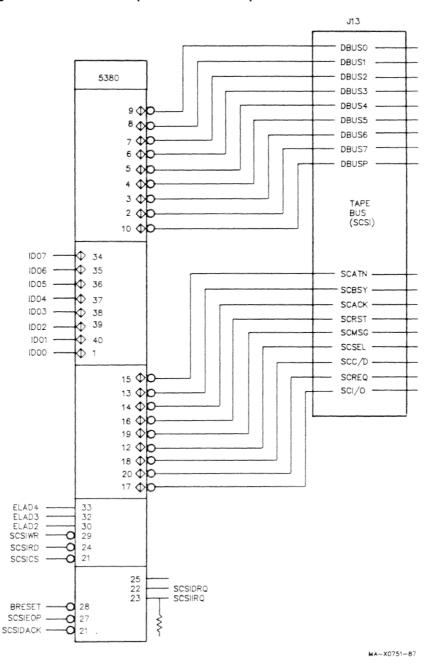

| 3-101 | 5380 Tape Controller                       | 3-199 |

| 3-102 | 5380 Tape Controller Chip Pinout           | 3-201 |

|       | Mode Register (SCS_MODE)                   | 3-207 |

|       | Intitiator Command Register                | 3-209 |

|       | Target Command Register                    | 3-212 |

|       | SCSI Tape Bus and Status Register          | 3-212 |

|       | Current Bus Status Register                |       |

|       | Select Enable Register (SCS_SEL_ENA)       |       |

|       | Output Data Register                       | 3-215 |

|       | Current Data Register (SCS_CUR_DATA)       |       |

|       | Input Data Register (SCS_IN_DATA)          |       |

| 3-112 | DMA Address Register (SCD ADR)             | 3-217 |

- Aller

xvii

| 3-113 | 3DMA Count Register (SCD_CNT)                          |

|-------|--------------------------------------------------------|

| 3-114 | 4DMA Direction Register                                |

| 3-115 | 5Transceiver Circuitry on System Module                |

| 3-110 | 6ThinWire Ethernet Transceiver Circuitry 3-226         |

| 3-112 | 7 Coaxial Transceiver Interface Chip Pinout            |

| 3-118 | 8Halt Code Register (HLTCOD) 3-230                     |

| 3-119 | 9Configuration and Test Register (CFGTST) 3-231        |

| 3-120 | 0VAXstation 2000 and MicroVAX 2000 System Jumper 3-233 |

| 4-1   | MS400 Memory Module 4-2                                |

| 5-1   | Network Interconnect Module                            |

| 5-2   | Ethernet Packet Format                                 |

| 5-3   | LANCE Chip Pinout 5-10                                 |

| 5-4   | SIA Chip Pinout                                        |

| 5-5   | Controller Firmware ROM 5-20                           |

| 5-6   | LANCE Register Address Port (NI_RAP) Format            |

| 5-7   | LANCE Control and Status Register 0 (NI_CSR0) 5-23     |

| 5-8   | LANCE Control and Status Register 1 (NI_CSR1) 5-27     |

| 5-9   | LANCE Control and Status Register 2 (NI_CSR2) 5-28     |

|       | LANCE Control and Status Register 3 (NI_CSR3) 5-29     |

|       | LANCE Initialization Block Format                      |

|       | Initialization Block Mode Word (NIB_MODE)              |

| 5-13  | Network Physical Address (NIB_PADR)                    |

|       | Multicast Address Filter Mask (NIB_LADRF) 5-34         |

|       | Receive Descriptor Ring Pointer (NIB_RDRP) 5-35        |

|       | Transmit Descriptor Ring Pointer (NIB_TDRP) 5-36       |

|       | Receive Buffer Descriptor                              |

| 5-18  | Transmit Buffer Descriptor                             |

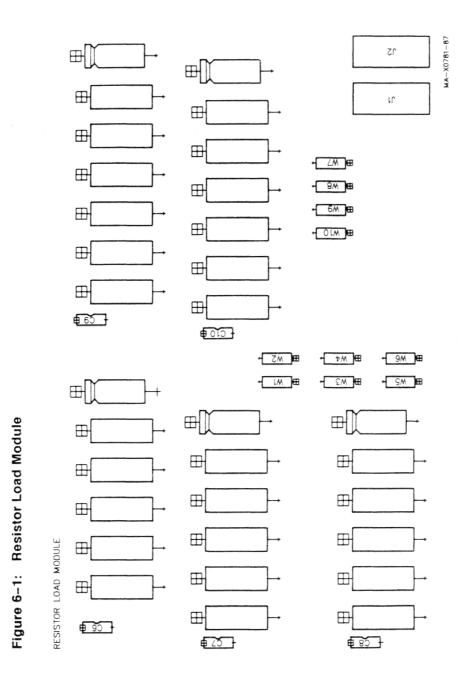

| 6-1   | Resistor Load Module                                   |

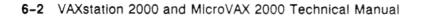

| 6-2   | Resistor Load Module Circuit Diagram                   |

| 8-1   | RX33 Diskette Drive                                    |

| 8-2   | RX33 Diskette                                          |

| 8-3   | RX33 Jumper Settings                                   |

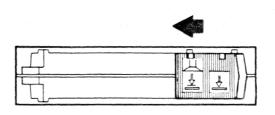

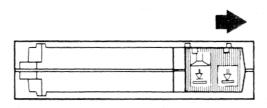

| 8-4   | Inserting a Diskette                                   |

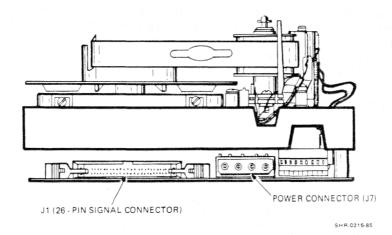

| 8-5   | RD32 Power and Data Connectors                         |

| 8-6   | RD32 Jumper Configuration                              |

| 8-7   | RD53 Power and Data Connectors                         |

xviii

| 8-8  | RD53 Jumper Configuration                            | 8-11  |

|------|------------------------------------------------------|-------|

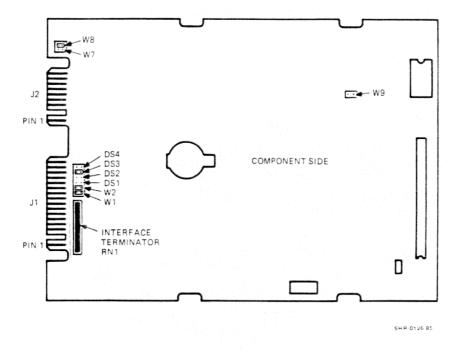

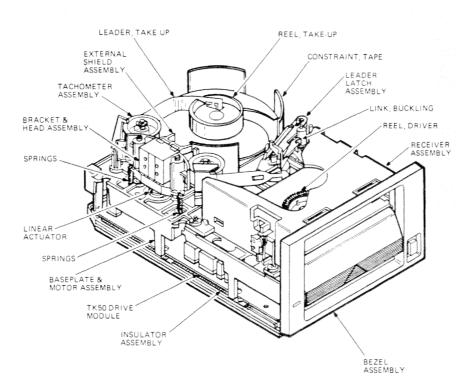

| 8-9  | Cutaway View of the TK50 Tape Drive                  | 8-12  |

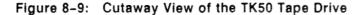

| 8-10 | TK50 Front View                                      | 8-13  |

| 8-11 | TK50 Rear View                                       | 8-14  |

| 8-12 | Write Protecting a Tape Cartridge                    | 8-16  |

| 8-13 | Disabling Write Protect on a Tape Cartridge          | 8-16  |

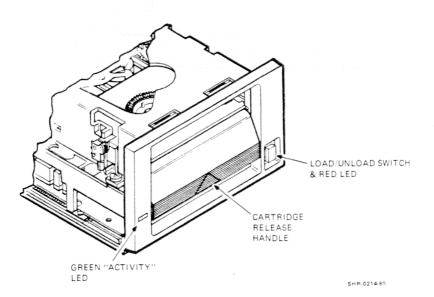

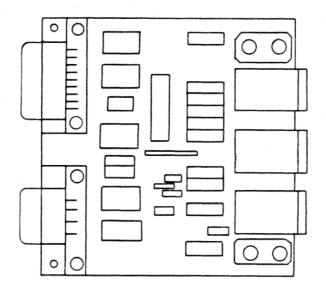

| 9-1  | DEC423 Converter Circuit Board                       |       |

| 9-2  | DEC423 Converter Block Diagram for Line 3            | . 9-5 |

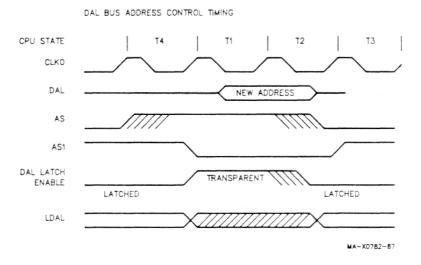

| A-1  | DAL Bus Address Control                              | . A-1 |

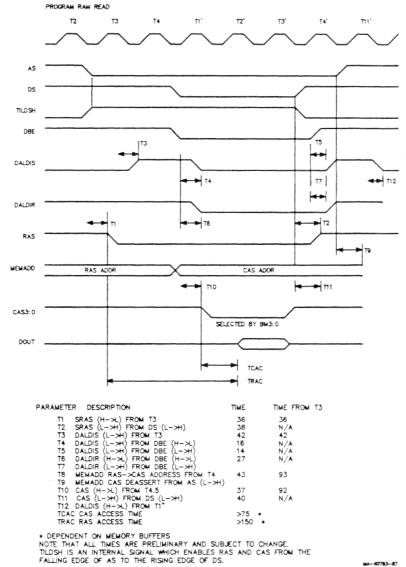

| A-2  | Program RAM Read                                     | . A-2 |

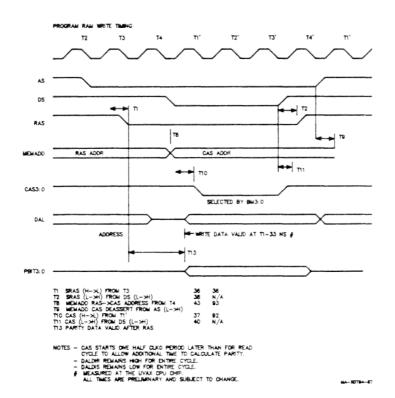

| A-3  | Program RAM Write                                    | A-3   |

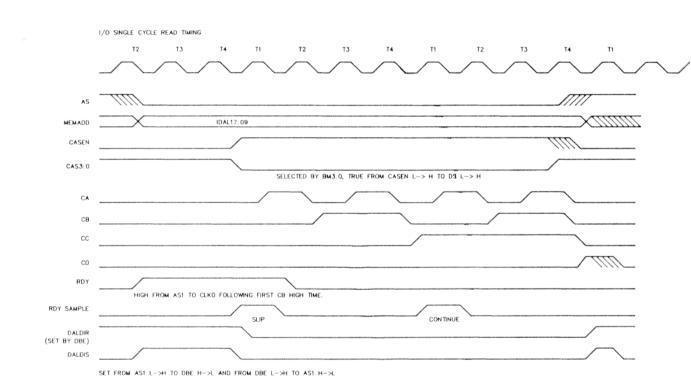

| A-4  | I/O Single Cycle Read                                | . A-4 |

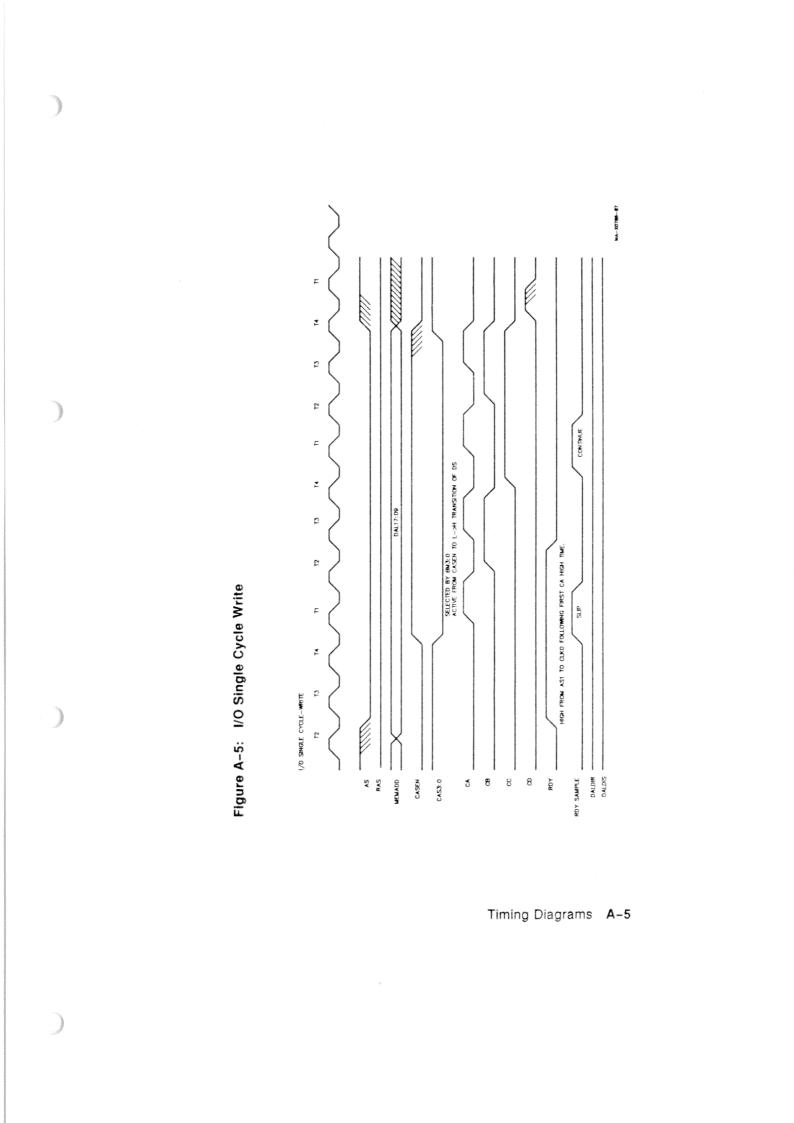

| A-5  | I/O Single Cycle Write                               | . A-5 |

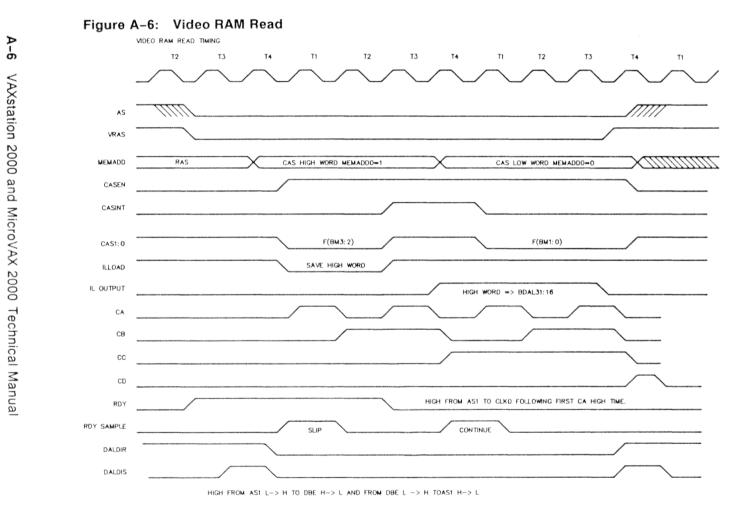

|      | Video RAM Read                                       |       |

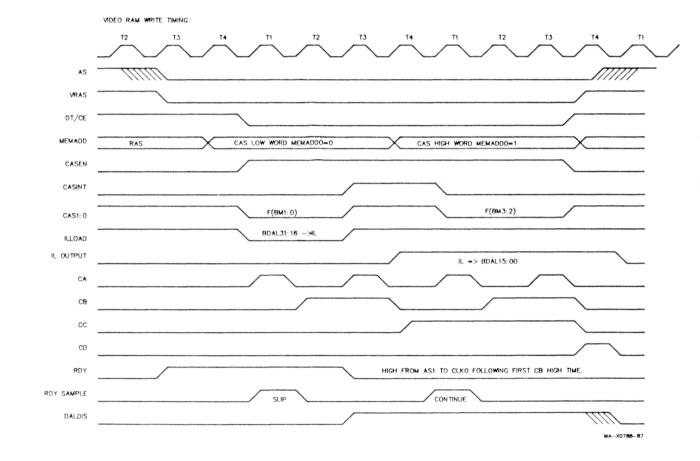

| A-7  | Video RAM Write                                      | . A-7 |

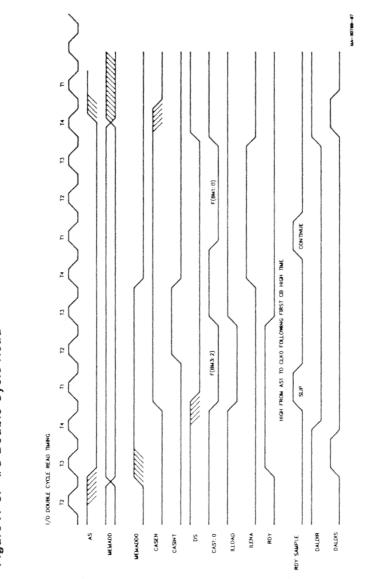

| A-8  | I/O Double Cycle Read                                | . A-8 |

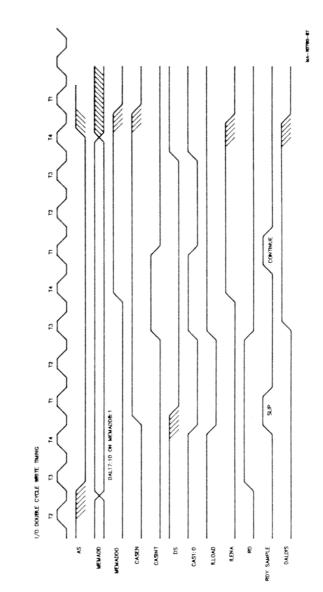

| A-9  | I/O Double Cycle Write                               | . A-9 |

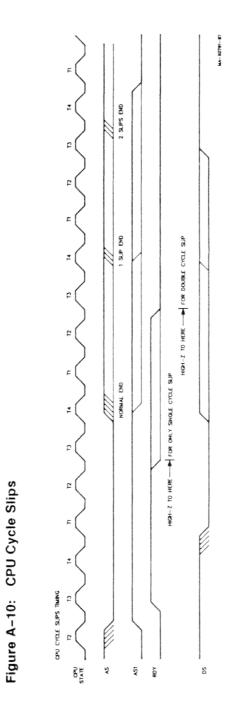

| A-10 | I/O Double Cycle Write                               | A-10  |

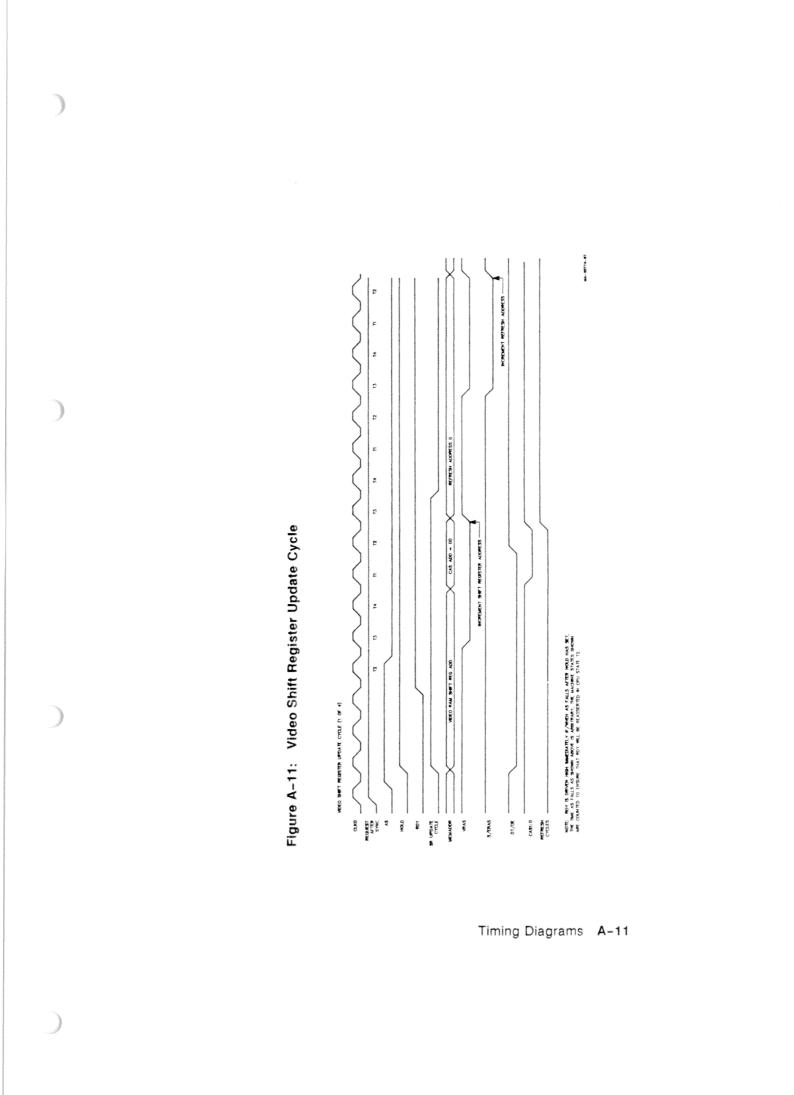

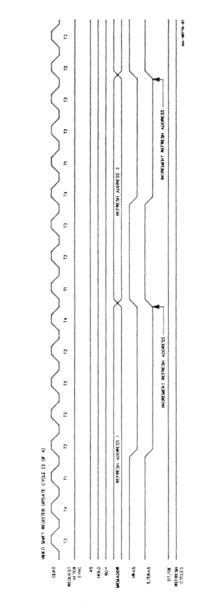

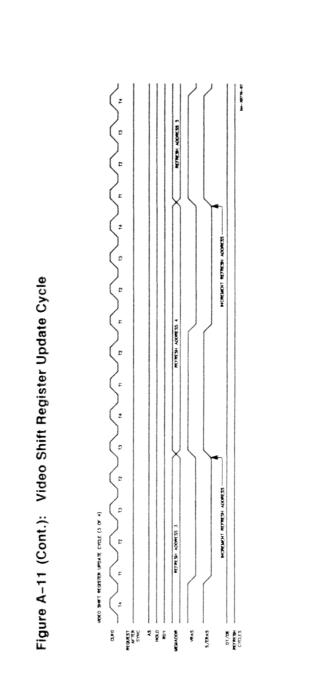

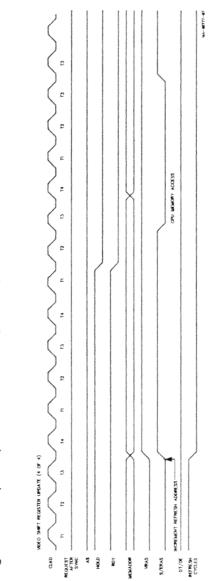

| A-11 | Video Shift Register Update Cycle                    | A-11  |

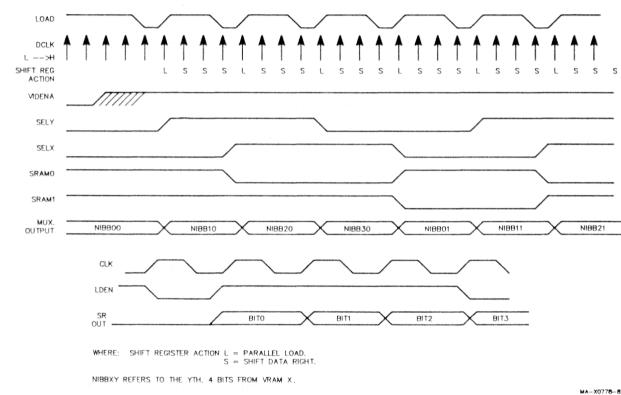

| A-12 | Start of Display/Region Line                         | A-15  |

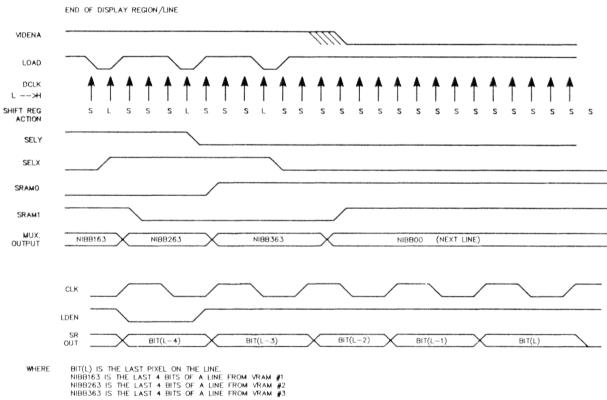

|      | End of Display/Region Line                           |       |

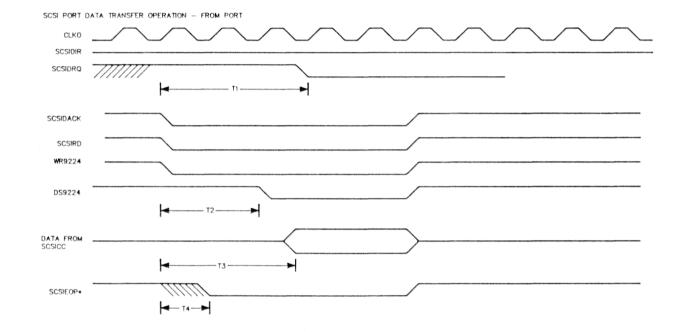

| A-14 | Tape (SCSI) Port Data Transfer Operation (From Port) | A-17  |

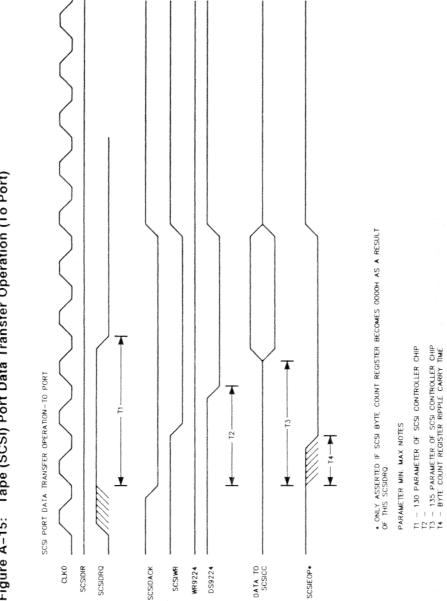

| A-15 | Tape (SCSI) Port Data Transfer Operation (To Port)   | A-18  |

|      |                                                      |       |

### Tables

1000

| 2-1  | FPU Instruction Times 2-                        | 5 |

|------|-------------------------------------------------|---|

|      | CPU Chip Pin Functions 3-                       |   |

| 3-2  | Internal Processor Registers                    | 6 |

| 3-3  | External Interrupts                             | 9 |

| 3-4  | System Control Block Format                     | 3 |

|      | DC337 FPU Chip Pin Functions 3-2                |   |

| 3-6  | Fixed ROM Address Allocations                   | 0 |

| 3-7  | ROM Address Locations Option Module ROMs 3-5    | 4 |

| 3-8  | Watch Chip Register Addresses 3-6               | 3 |

| 3-9  | Non-Volatile RAM Contents                       | 7 |

| 3-10 | LK201 Language Values for LK201 ID Register 3-7 | 0 |

| 3-11 Console Type Register Contents                                                                             |       |

|-----------------------------------------------------------------------------------------------------------------|-------|

| 3-12 DC524 Standard Cell Pinout                                                                                 |       |

| 3-13 DAL Bus Transceiver Enable Control Signal                                                                  |       |

| Functions                                                                                                       |       |

| 3-14 Internal Interrupt Registers                                                                               | 3-105 |

| · 전문 : [] 이 가지 이 이 이 나는 나는 이 이 이 것 이 이 가격하는 것 같은 것 이 가지 않아 있는 것 이 가지 않아요. 이 가는 것은 것 것 이 가지 않아요. 것 같은 것 이 나는 것 이 | 3-109 |

| $\mathbf{O}$                                                                                                    | 3-110 |

| 3-17 Standard Cell Test Mode Addressing                                                                         | 3-112 |

| 3-18 DC503 Cursor Sprite Chip Pin Description                                                                   | 3-116 |

|                                                                                                                 | 3-117 |

| 3-20 Cursor Generation Values                                                                                   | 3-117 |

| 3-21 Monochrome Cursor Control Registers                                                                        | 3-118 |

| 3-22 DZ Controller Chip Pin Functions                                                                           | 3-127 |

| 3-23 Serial Line Identification                                                                                 | 3-131 |

| 3-24 Serial Line Controller Register Addresses                                                                  | 3-132 |

| 3-25 9224 Disk Controller Pin Description                                                                       | 3-146 |

| 3–26 Disk Controller Chip Ports                                                                                 | 3-154 |

| 3-27 Disk Controller Register Numbers                                                                           | 3-158 |

| Na Man Mana Mana Mana Mana Mana Mana Man                                                                        | 3-165 |

| 3–29 Register Parameters                                                                                        | 3-184 |

| 그는 그는 것 같은 것 같                                                                    | 3-191 |

| 수가 가장 가장 가장 가장 가장 같은 것 같아요. 이렇게 가장                                          | 3-192 |

|                                                                                                                 | 3-194 |

|                                                                                                                 | 3-197 |

|                                                                                                                 | 3-198 |

|                                                                                                                 | 3-202 |

|                                                                                                                 | 3-205 |

| · · ·                                                                                                           | 3-206 |

|                                                                                                                 | 3-207 |

| 1 0                                                                                                             | 3-224 |

|                                                                                                                 | 3-228 |

|                                                                                                                 | 3-233 |

|                                                                                                                 | 3-233 |

|                                                                                                                 | 3-234 |

|                                                                                                                 | 3-234 |

|                                                                                                                 |       |

|                                                                                                                 |       |

| 3- | -46 Network Option Module Connector (J6)                | 35 |

|----|---------------------------------------------------------|----|

|    | -47 RD/RX Connector (J7)                                | 35 |

| 3- | -48 Graphics Option Port Connector (J8) 3-23            | 36 |

| 3- | -49 Expansion Disk Read/Write Cable Connector (J9) 3-23 | 36 |

| 3- | -50 Communication Connector (J10)                       | 37 |

| 3- | -51 Graphics Option Port Connector (J11)                | 37 |

|    | -52 Memory Option Module Connector (J12) 3-23           | 38 |

|    | -53 Tape Port Connector (J13)                           |    |

| 3- | -54 Network Option Module Connector (J14)               | 39 |

| 3- | -55 Memory Option Module Connector (J15) 3-23           | 39 |

| 4- | -1 Determining Memory Cycles                            | -4 |

| 4- | -2 Connector J1 Pinout                                  | -4 |

| 4- | -3 Connector J2 Pinout                                  |    |

| 4- | -4 Memory Module Configuration Jumpers                  | -7 |

| 5- | -1 Pin Assignments for Connector J1                     | -3 |

| 5- | -2 Pin Assignments for Connector J2                     | -5 |

| 5- | -3 LANCE Chip Pin Descriptions                          | 11 |

| 5- | -4 SIA Chip Pin Descriptions                            | 16 |

| 5- | -5 ROM Pin Descriptions 5-2                             | 20 |

| 7- | -1 AC Input Specifics                                   | -1 |

| 7- | -2 DC Output Specifications                             | -2 |

| ~  | -1 Drives                                               |    |

| 9- | -1 Connector J4 D-Sub Pinouts                           | -3 |

|    | -2 Connector J5 D-sub Pinouts                           |    |

| 9- | -3 MMJ Connector Pinouts for J1, J2, and J3             | -4 |

|    | 0-1 Hard Disk Expansion Box Internal Cable Pinout 10-   | -2 |

|    | 0-2 Tape Drive Expansion Box Internal Cable Pinout 10-  | -4 |

|    | 0-3 Tape Port Internal Cable Pinout (Port A) 10-        |    |

|    | 0-4 Disk Interface Module Pinout (Port B)               |    |

| B- | -1 System Module Address Locations                      | -1 |

| B- | -2 Option Module Address Ranges                         | -3 |

|    | -3 Ethernet Network Option Module Addresses             |    |

|    | -4 Graphics Video Option Module Addresses               |    |

| B- | -5 Asynchronous SLU Option Module Addresses             | -4 |

## **About This Manual**

This manual documents system design concepts and hardware functions for the VAXstation 2000 and MicroVAX 2000 computer systems. It describes options that support the systems, and provides hardware programming information.

Refer to the Reference Manuals section for a listing of documents that apply to the VAXstation 2000 and MicroVAX 2000 computer systems.

#### ORGANIZATION

The manual is divided into ten chapters and two appendices.

**Chapter 1 - System Introduction** describes the VAXstation 2000 and MicroVAX 2000 systems. It also lists the physical characteristics of the components that make up both systems.

**Chapter 2 - Functional System Overview** provides a functional overview of the system module in the VAX station 2000 and the MicroVAX 2000 systems.

Chapter 3 - VS410 System Module Detailed Description explains the system module in detail.

**Chapter 4 - MS400 Option Memory Modules** describes the MS400-AA and MS400-BA memory modules that are options to the KA410-AA system module.

Chapter 5 - ThinWire Ethernet (DESVA) Option Module describes the option that enables a VAXstation 2000 or MicroVAX 2000 system to connect to an Ethernet network.

**Chapter 6 - Resistor Load Module** explains the module that is used to regulate the power supply of expansion boxes when less than two drives are installed.

**Chapter 7 - Power Supply** lists the operating specifications of the H7848 power supply.

**Chapter 8 - Drives** provides an overview of the drives available for use with VAXstation 2000 and MicroVAX 2000 systems.

**Chapter 9 - DEC423 Converter (MicroVAX 2000)** describes the physical characteristics of the converter, which permits easy installation of terminals and printers using MMJ connectors. **Chapter 10 - Expansion Peripherals** describes the three expansion peripherals available with the VAXstation 2000 and MicroVAX 2000 systems.

Appendix A - System Timing Diagrams displays timing diagrams for the system.

Appendix B - Physical Address Maps lists system module and option module addresses.

| REFER | ENCE | ΜΑΝΙ | JALS |

|-------|------|------|------|

|-------|------|------|------|

| Manual                                                   | Order Number |

|----------------------------------------------------------|--------------|

| VAXstation 2000 Hardware Installation Guide              | EK-VAXAA-IN  |

| VAXstation 2000 Owner's Manual                           | EK-VAXAA-OM  |

| VAXstation 2000/MicroVAX 2000 Maintenance<br>Guide       | EK-VSTAA-MG  |

| MicroVAX 2000 Hardware Installation Guide                | EK-MVXAA-IN  |

| MicroVAX 2000 Owner's Manual                             | EK-MVXAA-OM  |

| VR290 Service Guide                                      | ED-VR290-SM  |

| VAXstation 2000, MicroVAX 2000, VAXmate<br>Network Guide | EK-NETAA-UG  |

#### NOTES, CAUTIONS, and WARNINGS

Notes, cautions, and warnings appear throughout this book.

- Notes contain general information about a topic.

- Cautions contain information to prevent damage to equipment.

- Warnings contain information to prevent personal injury.

# Chapter 1 System Introduction

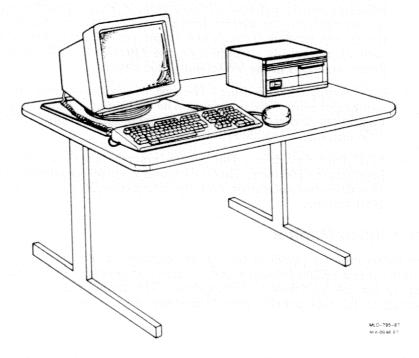

### 1.1 VAXstation 2000 System Description

The following paragraphs provide a physical description of the VAX station 2000 system. The VAX station 2000 consists of the following four hardware components (Figure 1–1).

- System box

- Video monitor

- Keyboard

- Mouse/Tablet

#### Figure 1-1: The VAXstation 2000 Computer System

System Introduction 1-1

#### 1.1.1 VS410 System Box

The VS410 system box contains the following components.

- KA410 system module The KA410 system module is central to the entire computer system. It is a printed circuit board mounted on the FCC shield. The system module contains all the control and interface electronics needed to support the CPU chip, support all I/O for the disks and tapes, support the video subsystem, and support the three option ports (memory, Ethernet network, and a graphics option port). This system module contains 2 megabytes of RAM and is used in both the VAXstation 2000 and MicroVAX 2000 systems. A jumper setting on the system module determines which system it is configured for.

- MS400 memory option module The memory module provides two to four additional megabytes of RAM memory. It is a printed circuit board mounted on standoffs on the system module and electrically connected to the system module through two 40-pin connectors. Although the memory module is called an option, additional memory is necessary to run the VMS or ULTRIX operating systems.

- Ethernet network option module The Ethernet network module provides an IEEE 802.3 interface to the ThinWire Ethernet communications network. It is a printed circuit board mounted on standoffs on the system module and electrically connected to the system module through two 40-pin connectors. This Ethernet network module is an option on the MicroVAX 2000 system but comes standard in the VAXstation 2000 system.

- RX33 floppy diskette drive The system box may contain an RX33 half-height floppy diskette drive. The RX33 media stores up to 1.23 megabytes of data. This drive is available on both the VAXstation 2000 and MicroVAX 2000 systems.

- RD32 hard disk drive The system box may contain an RD32 halfheight hard disk drive. The RD32 stores up to 40 megabytes of data. This drive is available on both the VAXstation 2000 and MicroVAX 2000 systems.

#### 1.1.2 Video Monitor

The video monitor provides the system display on the VAXstation 2000 system. It is a VR260 monochrome monitor that provides black and white display for the VAXstation 2000 system. The monitor has two display controls on the side panel to adjust brightness and contrast.

1-2 VAXstation 2000 and MicroVAX 2000 Technical Manual

#### 1.1.3 LK201 Keyboard

The operator uses the keyboard to enter data into the system. The keyboard contains three keypads (main, editing, and numeric) and a series of special function keys.

#### 1.1.4 VSXXX Mouse

The operator uses the mouse to position the cursor on the monitor screen. The mouse contains three keys and a position movement transducer for positioning the cursor on the display.

### 1.2 MicroVAX 2000 System Description

This section provides a physical description of the MicroVAX 2000 system. The MicroVAX 2000 consists of the following three hardware components (Figure 1–2).

- System box

- Video console terminal

- Keyboard

#### 1.2.1 VS410 System Box

The VS410 system box contains the same components as listed in Section 1.1.1, plus one additional component. The MicroVAX 2000 system has a DEC423 converter attached to the back of the system box and is mounted over the video and printer ports. The DEC423 converter changes the RS232 signals on the 15-pin video port and 9-pin printer port into DEC423 signals which go out to the three MMJ connectors.

#### 1.2.2 Video Console Terminal

The video console terminal provides the system display. The console terminal is a VT220 which provides a black and white display. It has two display controls for adjusting the brightness and contrast and also has a tilt control on the side panel for adjusting the viewing level.

#### 1.2.3 LK201 Keyboard

The operator uses the keyboard to enter data into the system. The keyboard contains three keypads (main, editing, and numeric) and a series of special function keys.

System Introduction 1-3

Figure 1-2: The MicroVAX 2000 Computer System

## **1.3 Physical Characteristics**

This section lists the physical characteristics of the components that comprise the VAX station 2000 and MicroVAX 2000 systems.

### 1.3.1 System Box

The VS410 system box is housed in a desk top enclosure. All cable access to it is from the rear panel. Cooling air intake is through the front panel and exhaust is through the rear panel. No clearance is required at the top or bottom, or either side of the box.

1-4 VAXstation 2000 and MicroVAX 2000 Technical Manual

| Width  | 12.75 inches | 323.85 mm |

|--------|--------------|-----------|

| Depth  | 11.25 inches | 285.75 mm |

| Height | 5.5 inches   | 139.7 mm  |

| Weight | 28 pounds    | 12.7 kg   |

The dimensions of the VS410 system box with  $\mathsf{BA40A}$  expansion adapter are as follows.

| Width  | 12.75 inches | 323.85 mm |

|--------|--------------|-----------|

| Depth  | 11.25 inches | 285.75 mm |

| Height | 7 inches     | 177.8 mm  |

| Weight | 30 pounds    | 13.6 kg   |

#### 1.3.1.1 KA410 System Module

(Same

| Width  | 10 inches   | 254 mm   |

|--------|-------------|----------|

| Length | 14 inches   | 355.6 mm |

| Height | 1.25 inches | 32 mm    |

#### 1.3.1.2 Network Interconnect Module

| Width  | 4 inches    | 102 mm  |

|--------|-------------|---------|

| Length | 7 inches    | 178 mm  |

| Height | 0.25 inches | 6.35 mm |

#### 1.3.1.3 MS400 Memory Module

| Width  | 4.6 inches  | 116.84 mm |

|--------|-------------|-----------|

| Length | 8 inches    | 203.2 mm  |

| Height | 0.38 inches | 9.65 mm   |

### 1.3.1.4 Power Supply

| Width  | 4.75 inches  | 120.65 mm |

|--------|--------------|-----------|

| Length | 10.25 inches | 260.35 mm |

| Height | 3.75 inches  | 95.25 mm  |

#### 1.3.1.5 RX33 Diskette Drive

| Width  | 5.75 inches | 146.05 mm |

|--------|-------------|-----------|

| Length | 8 inches    | 203.2 mm  |

| Height | 1.69 inches | 42.93 mm  |

Weight 2.9 pounds 1.32 kg

#### 1.3.1.6 RD32 Disk Drive

| Width  | 5.75 inches | 146.05 mm |

|--------|-------------|-----------|

| Length | 8 inches    | 203.2 mm  |

| Height | 1.63 inches | 41.4 mm   |

| Weight | 3.5 pounds  | 1.59 kg   |

#### 1.3.1.7 DEC423 Converter (MicroVAX 2000)

| Width  | 3 inches    | 76.2 mm  |

|--------|-------------|----------|

| Length | 3.3 inches  | 83.82 mm |

| Height | 1.23 inches | 31.24 mm |

| Weight | 5.6 ounces  | 159 g    |

#### 1.3.1.8 Resistor Load Module

| Width  | 4 inches   | 101.6 mm |

|--------|------------|----------|

| Length | 7 inches   | 177.8 mm |

| Height | 0.5 inches | 12.7 mm  |

### 1.3.2 BA40B Expansion Boxes

The power supply and resistor load modules in the expansion boxes are the same as in the system box. Dimensions of the BA40B storage expansion boxes are as follows.

| Width  | 12.75 inches | 323.85 mm |

|--------|--------------|-----------|

| Depth  | 11.25 inches | 285.75 mm |

| Height | 5.5 inches   | 139.7 mm  |

| Weight | 20 pounds    | 9.1 kg    |

1-6 VAXstation 2000 and MicroVAX 2000 Technical Manual

#### 1.3.2.1 RD53 Disk Drive

No.

| Width  | 5.75 inches | 146.05 mm |

|--------|-------------|-----------|

| Length | 8.2 inches  | 208.28 mm |

| Height | 3.37 inches | 85.6 mm   |

| Weight | 6.3 pounds  | 2.8 kg    |

#### 1.3.2.2 TZK50 Controller Board

| Width  | 5.7 inches   | 144.78 mm |

|--------|--------------|-----------|

| Length | 8 inches     | 203.2 mm  |

| Height | 0.625 inches | 15.88 mm  |

### 1.3.2.3 TK50 Tape Drive

| Width  | 5.75 inches | 146.05 mm |

|--------|-------------|-----------|

| Length | 8.4 inches  | 213.36 mm |

| Height | 3.25 inches | 82.55 mm  |

| Weight | 5 pounds    | 2.27 kg   |

## 1.3.3 BA40A Expansion Adapter

| Width  | 12.75 inches | 323.85 mm |

|--------|--------------|-----------|

| Length | 11.25 inches | 285.75 mm |

| Height | 1.5 inches   | 38.1 mm   |

| Weight | 2 pounds     | 0.9 kg    |

#### 1.3.3.1 Disk Interface Module

| Width  | 3.2 inches | 81.28 mm  |

|--------|------------|-----------|

| Length | 5.2 inches | 132.08 mm |

| Height | 0.4 inches | 10.16 mm  |

System Introduction 1-7

# Chapter 2 Functional System Overview

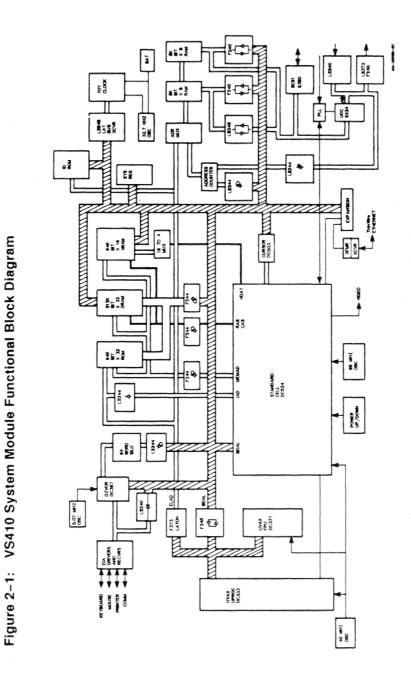

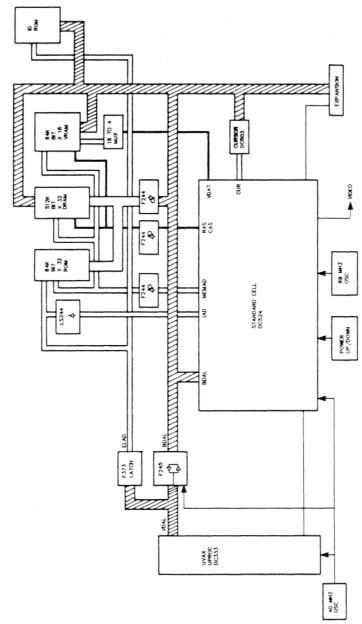

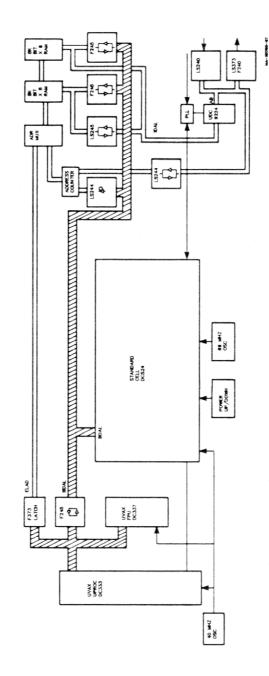

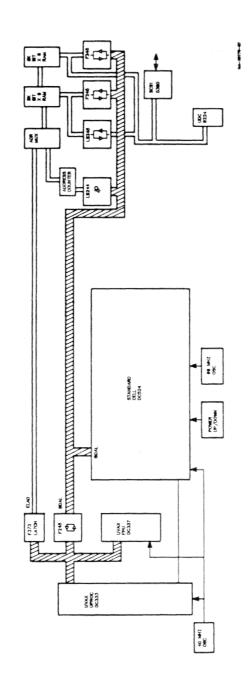

This chapter describes the functional overview of the system module in the VAXstation 2000 and MicroVAX 2000 systems. Functional overviews of the optional modules to these systems are described within their chapter and are not discussed here. Figure 2-1 shows the functional block diagram of the system module.

### 2.1 Central Processor Overview

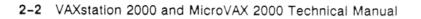

The central processor consists of a DC333 MicroVAX CPU chip and a DC337 MicroVAX FPU chip. The DC333 MicroVAX CPU chip is a 32-bit virtual memory microprocessor that implements a subset VAX-compatible central processor. The DC337 FPU chip implements a subset VAX-compatible floating point unit. The FPU chip provides floating point computation capabilities to the MicroVAX CPU chip. Each chip is contained in a 68-pin package and both chips reside on the VS410 system module.

Both chips use the 40 MHz oscillator and communicate to each other over the 32-bit VDAL CPU bus. The F373 latch and the F245 bidirectional bus transceiver buffer the VDAL CPU bus to the ELAD bus and BDAL bus, respectively. Figure 2-2 shows the functional block diagram of the CPU chip and the FPU chip.

Functional System Overview 2-1

#### Figure 2-2: Block Diagram of the CPU Chip and the FPU Chip

Key features supported by the DC333 MicroVAX CPU chip:

- Subset VAX data types The chip supports the following subset of the VAX data types: byte, word, longword, quadword, character string, and variable length bit field. Support for f floating, d floating, and g floating is available via the floating point unit chip. Support for the remaining VAX data types can be provided by macrocode emulation.

- Subset VAX instruction set The chip implements the following subset of the VAX instruction set: integer and logical, address, variable length bit field, control, procedure call, miscellaneous, queue, MOVC3/MOVC5, and operating system support. Floating point is implemented through the floating point unit chip. The remaining VAX instructions can be implemented via macrocode emulation (the chip provides microcode assists for the emulation of the character string, decimal string, EDITPC, and CRC instructions).

- Floating point The chip supports f floating, d floating, and g floating data types through the FPU; does not support h floating.

- Full VAX memory management The chip includes a demand paged memory management unit which is fully compatible with VAX memory management. System space addresses are virtually mapped through single-level page tables and process space addresses through double-level page tables.

- External interface based on industry standards The chip's external interface is a 32-bit extension of the industry standard microprocessor interface.

- Large virtual and physical address space The chip supports four gigabytes (2<sup>32</sup>) of virtual memory, and one gigabyte (2<sup>30</sup>) of physical memory.

- High performance At its maximum frequency, the chip achieves a 200 ns microcycle and a 400 ns I/O cycle.

- Single package The chip is packaged in a standard 68-pin surface mounted chip carrier.

Key features supported by the DC337 FPU chip:

- Subset VAX data types The chip supports the following subset of VAX data types: byte, word, longword, f floating, d floating, and g floating. The data type h floating is not supported.

- Subset VAX instruction set The chip implements a subset of the VAX floating point instruction set. (The remaining floating point instructions, except h floating, are implemented in the CPU chip.) Accuracy for the EMOD and POLY instructions will meet VAX architectural standards.

- Integer multiply and divide acceleration The chip supports signed integer multiply and unsigned integer divide.

- Simple external interface The chip's external interface is straightforward and requires no external support chips.

2-4 VAXstation 2000 and MicroVAX 2000 Technical Manual

- High performance At its maximum frequency, the chip achieves a 100 ns microcycle and a 200 ns I/O cycle.

- Package The chip is packaged in a 68-pin surface-mounted chip carrier.

- Fast instruction times Table 2-1 lists typical instruction times for the FPU. Note that times may be faster or slower depending on the operands used in the calculation.

| Instruction      | Single | Double |  |  |

|------------------|--------|--------|--|--|

| ADD <sup>1</sup> | 2.0    | 2.6    |  |  |

| MUL              | 2.6    | 4.2    |  |  |

| DIV              | 3.7    | 6.1    |  |  |

#### Table 2–1: FPU Instruction Times

<sup>1</sup>Digital FPU number uses operands separated by 11 in the exponent.

### 2.2 System Memory

The system memory consists of RAM and ROM memory located on the system module and also RAM memory located on the option memory module. Even though the optional RAM is not located on the system module, it is considered to be system memory. Figure 2–3 shows the functional block diagram of the system memory.

The system supports up to 16 megabytes of RAM (DRAM) memory, not including video RAM. The actual amount of RAM depends upon the option memory module installed. The data path to RAM memory is 32-bits wide. Data integrity is checked by a parity bit associated with each byte of memory. The RAM that is physically located on the system module contains 2048 kilobytes of memory.

The video RAM (VRAM) consists of 128 kilobytes of memory on the system module. It contains the video bitmap screen display information. The video bus caries the bitmap information from the VRAM through a multiplexer counter to the standard cell. The standard cell then generates the proper signals to display the video data, along with the cursor data, onto the video screen.

2-6 VAXstation 2000 and MicroVAX 2000 Technical Manual

Figure 2–3: System Memory Functional Block Diagram

73-40/DX-41

The optional memory module can contain up to 14,336 kilobytes of RAM, however, only 2048 kilobyte and 4096 kilobyte RAM option memory modules are supported. The system generates byte parity when writing to RAM memory and checks byte parity when reading from RAM memory.

The system module ROM contains 256k bytes of data that includes processor restart, diagnostic and console code, and I/O device drivers. The system ROM is addressed by the CPU chip over the ELAD bus and also by the standard cell over the MEMAD bus. The ROM outputs the data onto the MD bus which is buffered onto the BDAL bus and sent back to the CPU chip. The system ROM also contains interrupt vector routines that are addressed by the standard cell over the IAD bus.

The ThinWire Ethernet ID ROM on the system module contains 32 bytes of memory for a unique Ethernet network identification address for the system.

Each option module is required to have its own ROM memory that contains a standard signature to identify the option, as well as firmware initialization code and diagnostic code. This option ROM information is accessed through the memory option port.

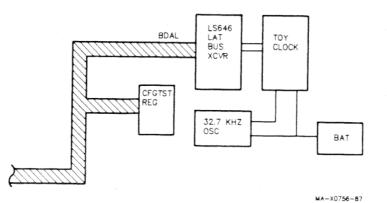

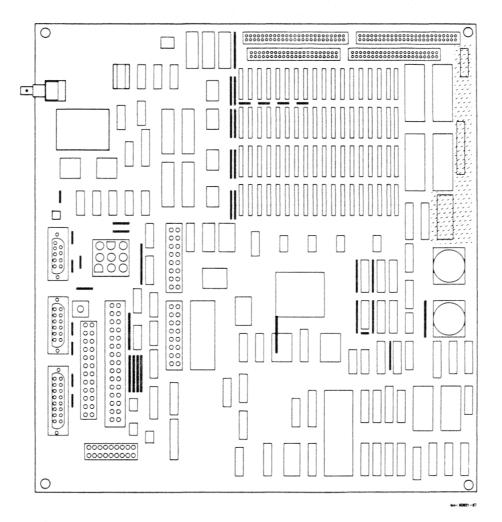

### 2.3 Time-Of-Year Clock

The time of year clock keeps the date, time of day, and 50 bytes of general purpose RAM. A 32.768 kHz time base oscillator provides the clock input and a rechargeable nickel-cadmium battery provides power to the chip and oscillator while system power is off. The TOY clock uses an LS646 transceiver to buffer and control the data and addresses to and from the CPU bus. Data from the TOY clock is used to determine the date and time during the power-up of the system. Within the 50 bytes of RAM are stored utilities such as the boot flags, boot device, halt action, and keyboard type as well as other volatile information. Figure 2–4 shows the functional block diagram of the TOY clock and also the configuration and test register.

A nickel-cadmium battery in the system box supplies power to the watch chip and its time base oscillator while system power is off. When starting from a fully charged condition, the battery maintains valid time and RAM data in the watch chip for a minimum of 100 hours. The battery recharges while system power is on.

Figure 2–4 also shows the configuration and test register. This register is an 8-bit register that contains system information such as whether the system is a VAX station 2000 or a MicroVAX 2000, whether an option module is installed in the option slots, whether the BCC08 cable is connected to the printer port, and cursor chip test results.

### Figure 2-4: TOY Clock Functional Block Diagram

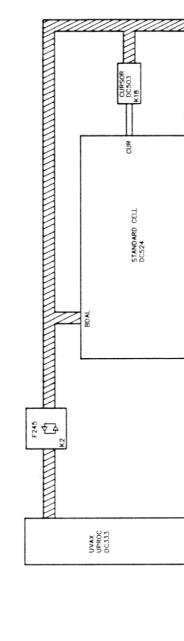

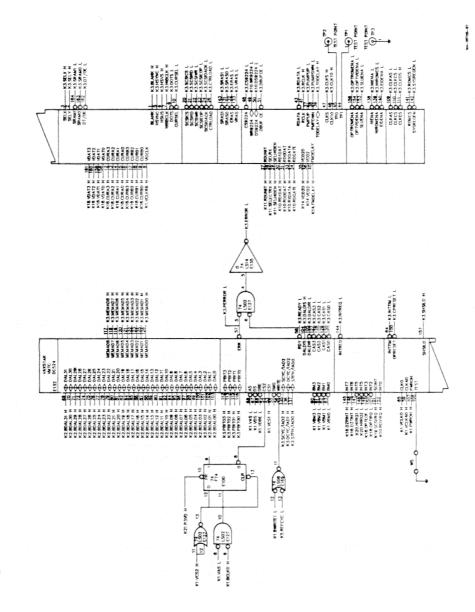

### 2.4 DC524 Standard Cell

The DC524 standard cell is the heart of the system. It controls the address decoding and the timing parameters for each device. It contains the interrupt controller, parity generation and checking, and all of the monitor timing circuitry internal to itself. The list below summarizes the functions of the standard cell and Figure 2–5 shows the functional block diagram of the standard cell.

- Power-up initialization

- Memory control

- Video control

- I/O control

- Disk control

- Tape control

- Parity generation and checking

- Interval timer interrupt generation

- Interrupt controller

- Monitor timing

- Chip test mode

2-8 VAXstation 2000 and MicroVAX 2000 Technical Manual

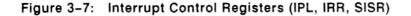

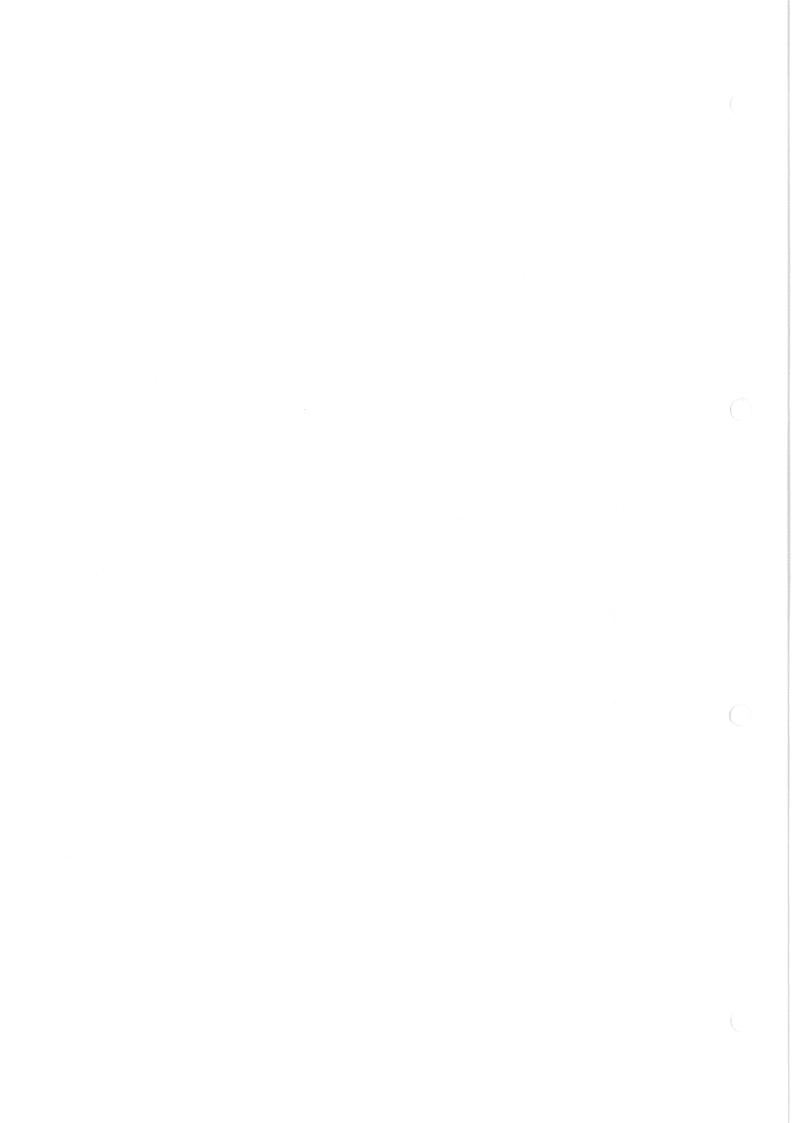

(3-15(0))-VM \*\*\*\* 2 - C BAT 1240 15240 1505 400 000 000 \*\*\*\* Л UDC 20 Π ĩ 32.7 1012 KCVA 85 å-( E e 2 de la ADORESS COUNTER 575 110 EXPANSION E 7 CURSON DC:503 18×5 2.00 5 VOAT WDE0 SI X BI De Ma ž0 F RAS 8 ¥⊢<sup>27</sup>a¥ 69 MH2 050 NEWAD STANDARD CELL DC324 q 5244 4 POWER UP //DOWN I DZVCR DC367 5.07 MHZ 05C 0425) X 2490 0442 F373 LATCH 20 KETROAND F EA NOUSE F DRIVERS PRINTER F AND COMM F CORS

Figure 2-5: DC524 Standard Cell Functional Block Diagram

$\mathbb{Z}$

)

### 2.5 DC503 Cursor Sprite Chip

The DC503 cursor sprite chip generates a cursor display on the video monitor. The cursor is generated from a two-plane memory array within the cursor chip. The cursor sprite chip receives commands over the BDAL bus for such things as cursor position, cursor pattern, and blanking of the cursor. The output of the cursor sprite chip is sent to the standard cell for inclusion in the video output signal to the monitor. Figure 2–6 shows the functional block diagram of the DC503 cursor sprite chip.

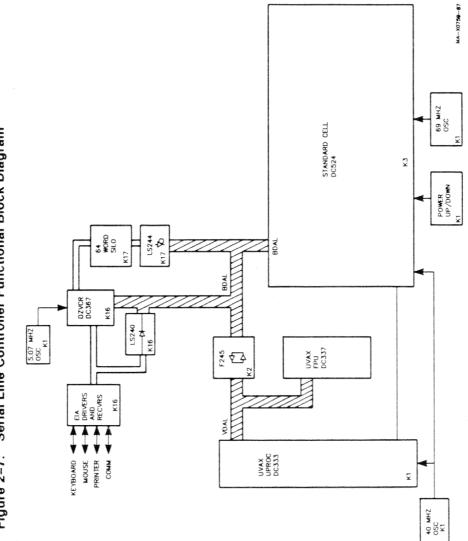

### 2.6 Serial Line Controller

The system module serial line controller handles four asynchronous serial lines. This controller is a DC367B gate array. Input characters from all four lines are buffered in a common 64-position silo. The silo is a true silo where a character drops through all 64 words in the silo before it is latched at the output. Only one line, the communication line, has full modem control signals. Figure 2–7 shows the functional block diagram of the serial line controller.

#### 2-10 VAXstation 2000 and MicroVAX 2000 Technical Manual

- Andrew

)

Functional System Overview 2-11

40 MHZ 0SC K1

ž

MA--X0578--87

WDED

69 MHZ 0SC K1

POWER UP/DOWN K1

ç

**EXPANSION**

### 2-12 VAXstation 2000 and MicroVAX 2000 Technical Manual

Figure 2-7: Serial Line Controller Functional Block Diagram

### 2.7 9224 Disk Controller

The disk controller supports both diskette drives (RX33) and ST506/412 hard disk drives (RD32 and RD53). The maximum configuration of the controller is one diskette drive and two hard disk drives. The controller is an HDC 9224 universal disk controller chip which uses a phase-locked loop (PLL) data recovery circuit, an address counter, and a 16-kilobyte dual port data buffer. Figure 2–8 shows the functional block diagram of the 9224 disk controller.

The disk data buffer is a 16-kilobyte block of RAM storage which is shared between the disk controller, the tape controller, and the CPU. This buffer uses two 8-kilobyte by 8-bit static RAM chips and is not included as part of the system module dynamic RAM. The disk and tape controller access the data buffer through the address counters. The address counters hold the data buffer address from the disk controller during normal RAM cycles as well as during DMA cycles. The disk data buffer is accessed by the CPU chip through the tri-state transceivers between the BDAL bus and the IDAL bus.

The phased locked loop (PLL) consists of a phase comparator and a voltagecontrolled oscillator (VCO). The phase comparator is inside the standard cell. The VCO is a dual oscillator chip for both hard disk and floppy diskette data frequencies. The phased lock loop is used to control the frequency of the raw read data from the disks. The individual modified frequency modulation (MFM) pulses that are read from the disks are sensitive to speed variations and the value of the pulse (1 or 0) may be lost if the frequency of the data stream is not precise. The VCO allows the tracking of any variation of the data stream and sends feedback to the phase comparator to compensate the variation so the loop recovers the data and sends the disk controller a steady and reliable data stream.

Figure 2-8: 9224 Disk Controller Functional Block Diagram

### 2.8 5380 Tape Controller

The tape controller is an NCR 5380 SCSI controller chip. It provides an ANSI Small Computer System Interface (SCSI) interface between the TZK50 tape controller in the tape expansion box and the data buffer on the system module. The tape controller is connected directly to the SCSI tape bus, which is port A on the expansion adapter, and it is also connected to the disk data buffer through the disk buffer data bus. The tape controller is controller is controller by the DC524 standard cell. Figure 2–9 shows the functional block diagram of the 5380 tape controller.

The SCSI interface is a bi-directional 8-bit wide bus to which up to eight devices can be attached. The system module is one of those devices, so up to seven additional devices can be attached. Devices may play one of two roles: initiator or target. An initiator originates an operation by sending a command to a specific target. A target performs an operation that is requested by an initiator. In this product, it is assumed that the system module is always an initiator and that all other SCSI devices attached to it are targets. Each device attached to the SCSI tape bus is identified by a unique device ID number in the range 0 through 7; the system module is normally 0.

Figure 2-9: 5380 Tape Controller Functional Block Diagram

### 2-16 VAXstation 2000 and MicroVAX 2000 Technical Manual

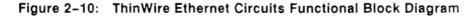

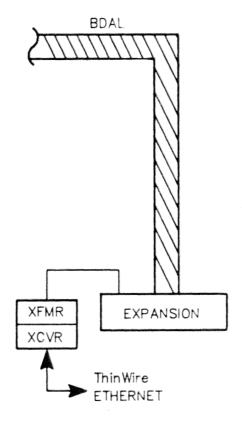

### 2.9 ThinWire Ethernet Circuits