EK-M8203-TM-002

# M8203 Line Unit Technical Manual

# M8203 Line Unit Technical Manual

digital equipment corporation • merrimack, new hampshire

#### 1st Edition, August 1979 2nd Edition (Rev), March 1981

Copyright <sup>©</sup> 1979, 1981 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10        | MASSBUS      |

|---------|---------------------|--------------|

| DEC     | <b>DECSYSTEM-20</b> | OMNIBUS      |

| PDP     | DIBOL               | <b>OS</b> /8 |

| DECUS   | EDUSYSTEM           | RSTS         |

| UNIBUS  | VAX                 | RSX          |

|         | VMS                 | IAS          |

# CONTENTS

### PREFACE

| CHAPTER 1                          | INTRODUCTION                                                          |              |

|------------------------------------|-----------------------------------------------------------------------|--------------|

| 1.1                                | PURPOSE                                                               |              |

| 1.2                                | DESCRIPTION                                                           |              |

| 1.3                                | MAJOR FUNCTIONAL AREAS                                                | 1-3          |

| 1.4                                | M8203 LINE UNIT/MICROPROCESSOR INTERFACE                              | 1-6          |

| CHAPTER 2                          | INTERFACE                                                             |              |

| 2.1                                | SCOPE                                                                 |              |

| 2.2                                | FULL-DUPLEX/HALF-DUPLEX OPERATION                                     |              |

| 2.3                                | STANDARD APPLICATIONS                                                 |              |

| 2.4                                | COMPATIBLE STANDARDS                                                  |              |

| 2.4.1                              | RS-232-C/CCITT V.28 (ISO 2110) Modem Interface                        |              |

| 2.4.2                              | EIA Standard RS-423-A                                                 |              |

| 2.4.3                              | EIA Standard RS-422-A                                                 |              |

| 2.4.4                              | EIA Standard RS-449                                                   |              |

| 2.4.5                              | CCITT V.35/ISO 2593                                                   |              |

| 2.5                                | INTERFACE SIGNALS                                                     |              |

| 2.6                                | ADDITIONAL LINE UNIT OPTIONS                                          |              |

| 2.7                                | HARDWARE VARIABLES                                                    |              |

| CHAPTER 3                          | TECHNICAL DESCRIPTION                                                 |              |

| 3.1                                | SCOPE                                                                 | 3-1          |

| 3.2                                | BERG PORT INTERFACE                                                   |              |

| 3.2.1                              | Read IBUS Registers                                                   |              |

| 3.2.2                              | OBUS Registers                                                        |              |

| 3.2.3                              | IBUS/OBUS Registers Bit Descriptions                                  |              |

| 3.2.4                              | Extended Registers/Indirect Addressing                                |              |

| 3.3                                | SILOS                                                                 |              |

| 3.3.1                              | Transmit Silo                                                         |              |

| 3.3.2                              | Receive Silo                                                          |              |

| 3.4                                | SEQUENCER                                                             |              |

| 3.5                                | DATA RATE GENERATOR                                                   |              |

| 3.6                                | USYRT                                                                 |              |

| 3.7                                | MODEM INTERFACE                                                       |              |

| 3.8                                |                                                                       |              |

|                                    | INTEGRAL MODEM SPECIFICATIONS                                         |              |

| 3.8.1                              | Receiver                                                              | 3-40         |

|                                    |                                                                       | 3-40         |

| 3.8.1                              | Receiver                                                              | 3-40         |

| 3.8.1<br>3.8.2                     | Receiver<br>Transmitter<br>SERVICE<br>SCOPE                           | 3-40<br>3-44 |

| 3.8.1<br>3.8.2<br>CHAPTER 4        | Receiver<br>Transmitter<br>SERVICE<br>SCOPE<br>MAINTENANCE PHILOSOPHY |              |

| 3.8.1<br>3.8.2<br>CHAPTER 4<br>4.1 | Receiver<br>Transmitter<br>SERVICE<br>SCOPE                           |              |

# **CONTENTS** (CONT)

### APPENDIX A MICRODIAGNOSTIC TESTS

| A.1 | INTRODUCTION              | .A-1 |

|-----|---------------------------|------|

| A.2 | HARDWARE REQUIREMENTS     |      |

| A.3 | INTERNAL MICRODIAGNOSTICS |      |

| A.4 | LINE UNIT TESTS           |      |

### APPENDIX B RECOMMENDED CABLES/CONNECTORS

| <b>B</b> .1 | SCOPE                            | <b>B</b> -1 |

|-------------|----------------------------------|-------------|

| B.2         | CABLING RECOMMENDATIONS          |             |

| B.3         | CABLE SPECIFICATIONS             | <b>B-1</b>  |

| B.3.1       | Cable Resistance Versus Distance | <b>B-4</b>  |

| B.3.1.1     | Twinax Cables                    | <b>B-4</b>  |

| B.3.1.2     | Triax Cables                     | <b>B-4</b>  |

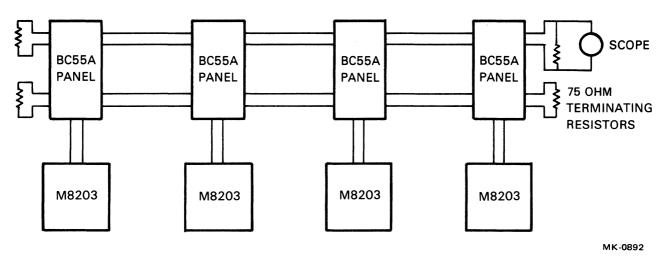

| B.3.2       | 75 Ohm Systems                   |             |

| B.3.3       | 150 Ohm Systems                  | <b>B-5</b>  |

| B.3.4       | Cable Attenuation                | <b>B-6</b>  |

| B.4         | INSTALLATION CONSIDERATIONS      | <b>B-6</b>  |

| B.5         | RECOMMENDED CONNECTORS           | <b>B-7</b>  |

| B.6         | GROUNDING RECOMMENDATIONS        | <b>B-9</b>  |

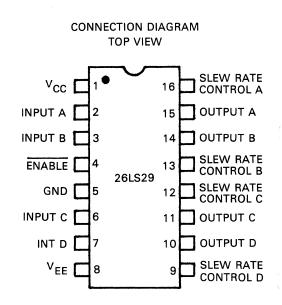

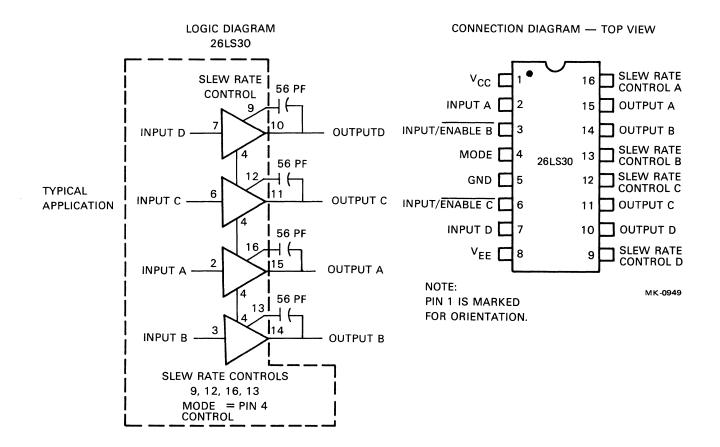

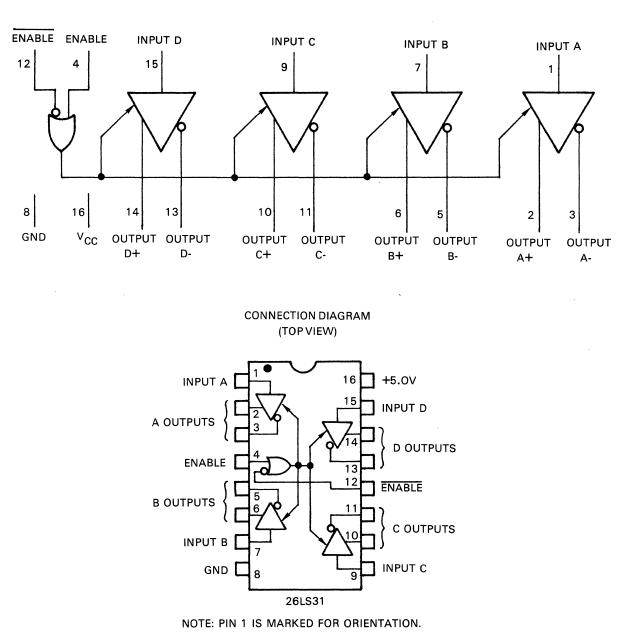

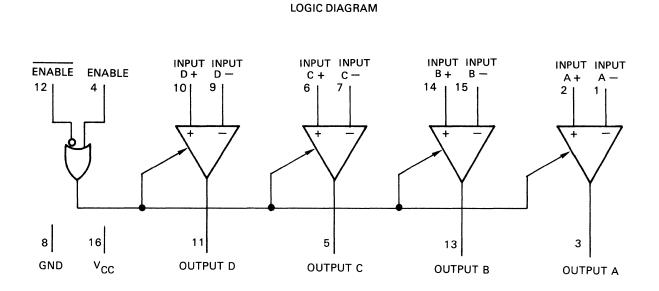

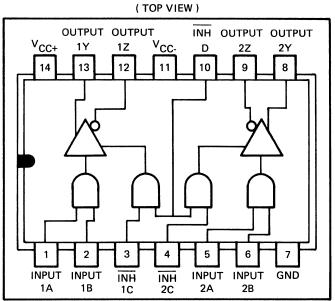

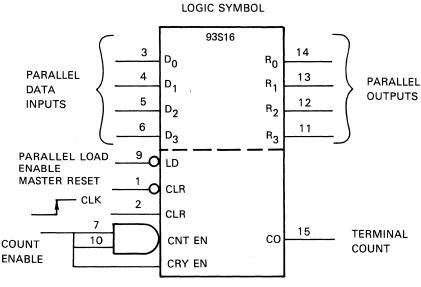

### APPENDIX C INTEGRATED CIRCUIT DESCRIPTIONS

| C.1 | INTRODUCTIONC-1                 |   |

|-----|---------------------------------|---|

| C.2 | SELECTED INTEGRATED CIRCUITSC-2 | • |

#### GLOSSARY

INDEX

Page

# **FIGURES**

# Figure No.

~

# Title

| 1 1  | Maion Expectional Amon                                  | 1 /    |

|------|---------------------------------------------------------|--------|

| 1-1  | Major Functional Areas.                                 | 1-4    |

| 1-2  | Typical PDP-11 Applications.                            | ·· 1-0 |

| 1-3  | Typical VAX-11/780 Applications                         | 1-/    |

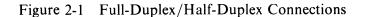

| 2-1  | Full-Duplex/Half-Duplex Connections                     | 2-2    |

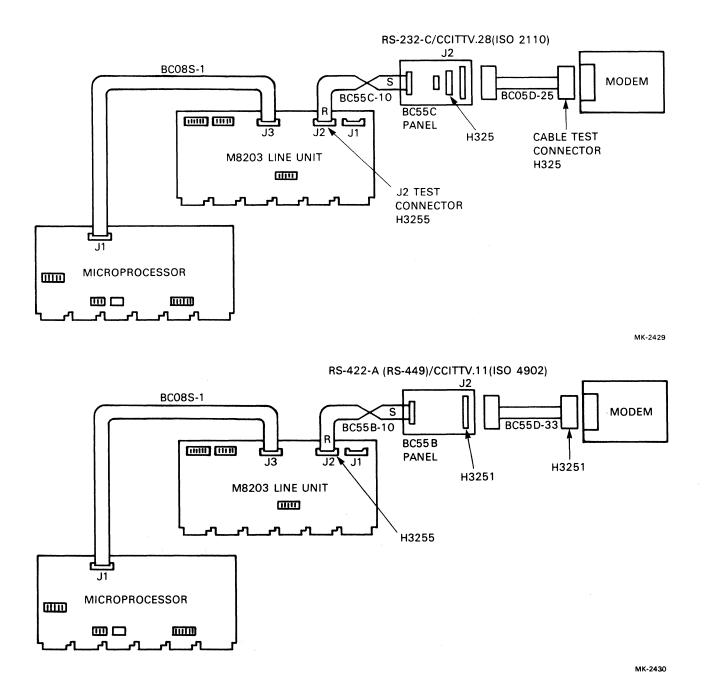

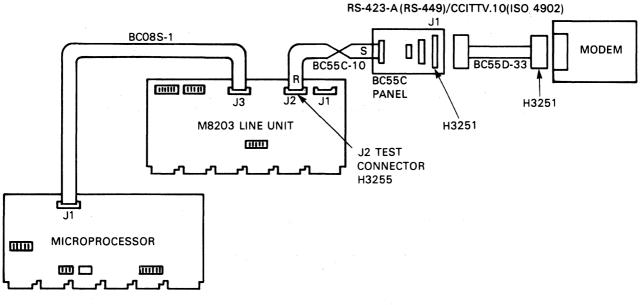

| 2-2  | Standard (Common) Interfaces                            |        |

| 2-3  | Special Application                                     | 2-4    |

| 2-4  | CCITT V.35 (ISO 2593) Interface                         | 2-5    |

| 3-1  | Input/Output Registers                                  |        |

| 3-2  | IBUS Register Select                                    |        |

| 3-3  | OBUS Register Select                                    |        |

| 3-4  | IBUS Register 10                                        |        |

| 3-5  | OBUS Register 10                                        | 3-7    |

| 3-6  | IBUS Register 11                                        | 3-8    |

| 3-7  | OBUS Register 11                                        | 3-9    |

| 3-8  | IBUS Register 12                                        | 3-10   |

| 3-9  | OBUS Register 12                                        | 3-11   |

| 3-10 | IBUS Register 13                                        | . 3-12 |

| 3-11 | OBUS Register 13                                        | 3-13   |

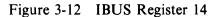

| 3-12 | IBUS Register 14                                        | 3-14   |

| 3-13 | OBUS Register 14                                        |        |

| 3-14 | IBUS Register 15                                        |        |

| 3-15 | OBUS Register 15                                        |        |

| 3-16 | IBUS Register 16                                        |        |

| 3-17 | OBUS Register 16                                        |        |

| 3-18 | IBUS Register 17                                        |        |

| 3-19 | OBUS Register 17                                        |        |

| 3-20 | AX0-15 Register                                         | 3-20   |

| 3-21 | AX0-16 Register                                         | 3-21   |

| 3-22 | AX1-15 Register                                         | 3-22   |

| 3-23 | AX1-15 Register                                         | 3_23   |

| 3-24 | A V2 15 Degister                                        | 3-23   |

| 3-25 | AX2-15 Register                                         | 3 24   |

|      | AX2-16 Register                                         | 3-24   |

| 3-26 | AX3-15 Register                                         | 3-25   |

| 3-27 | AX3-16 Register                                         | 3 20   |

| 3-28 | Transmit Silo                                           | 2 20   |

| 3-29 | Receive Silo                                            | 2 21   |

| 3-30 | Load Silo                                               | , 3-31 |

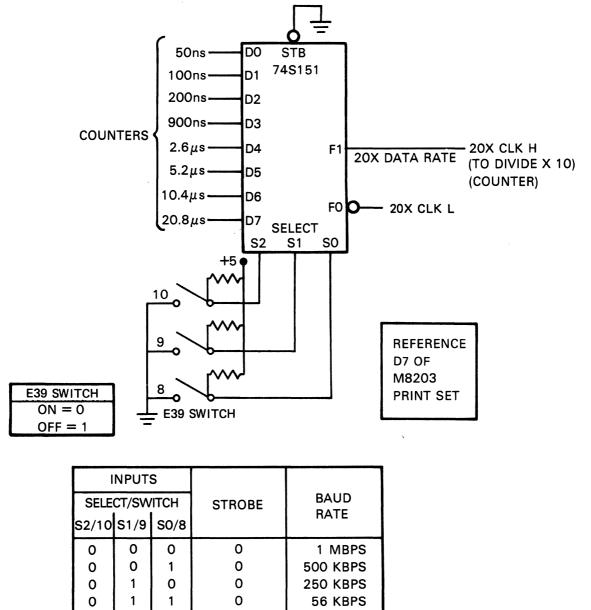

| 3-31 | Data Rate Generator                                     | . 3-33 |

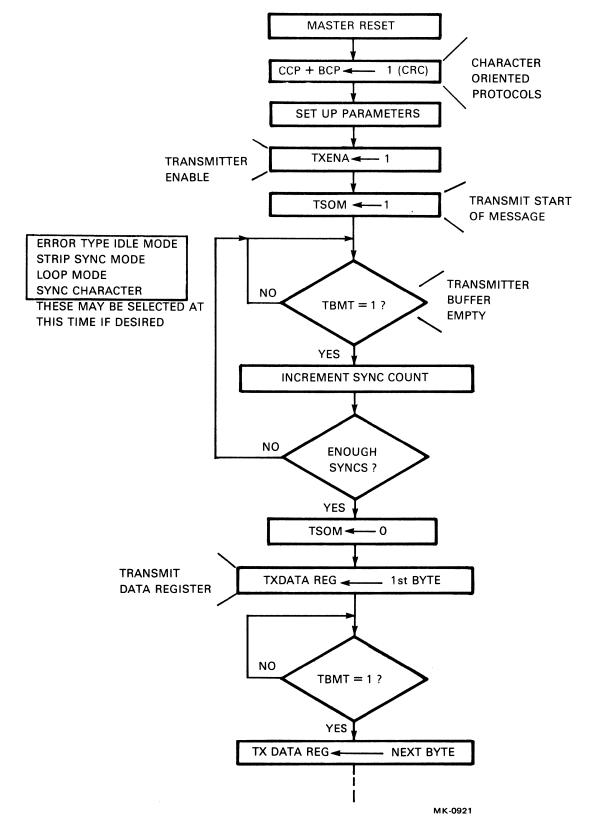

| 3-32 | Typical Start Sequence for the USYRT Bit Oriented       |        |

|      | Protocol Transmission Flowchart                         | . 3-34 |

| 3-33 | Typical Start Sequence for the USYRT Character Oriented |        |

|      | Protocol Transmission Flowchart                         | . 3-35 |

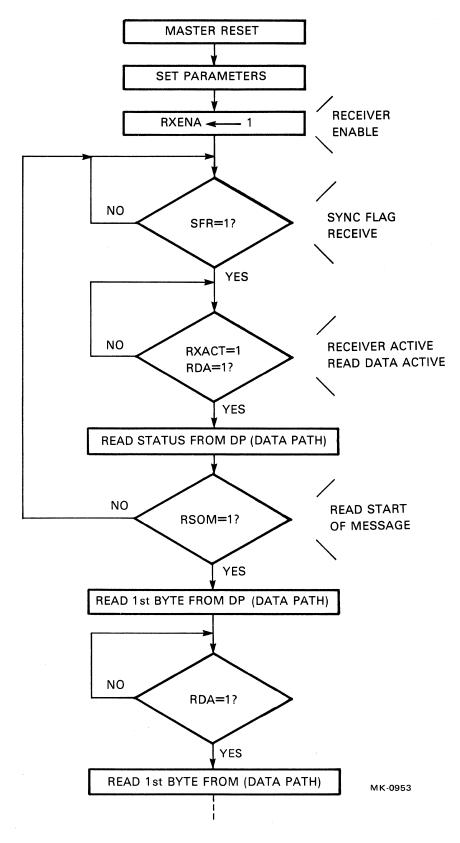

| 3-34 | Typical Receive Sequence for the USYRT Bit Oriented     |        |

|      | Protocol Flowchart                                      | . 3-36 |

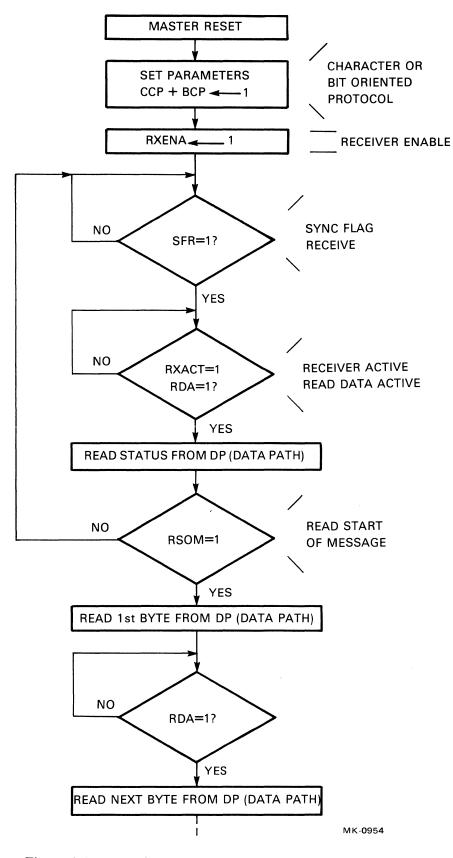

| 3-35 | Typical Receive Sequence for the USYRT Character        |        |

|      | Oriented Protocol Flowchart                             | . 3-37 |

| 3-36 | Data Rate Select                                        | . 3-38 |

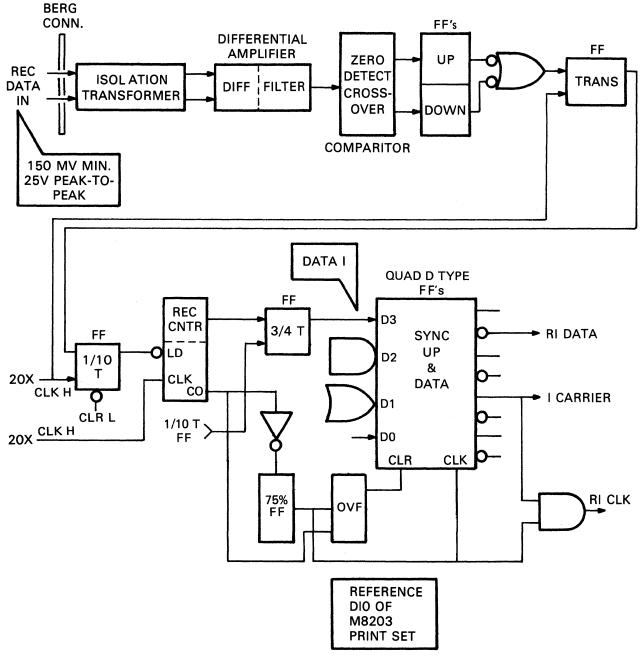

| 3-37 | Modem Receiver Block Diagram                            | . 3-40 |

|      |                                                         |        |

# FIGURES (CONT)

| Figure No.  | Title                                          | Page |

|-------------|------------------------------------------------|------|

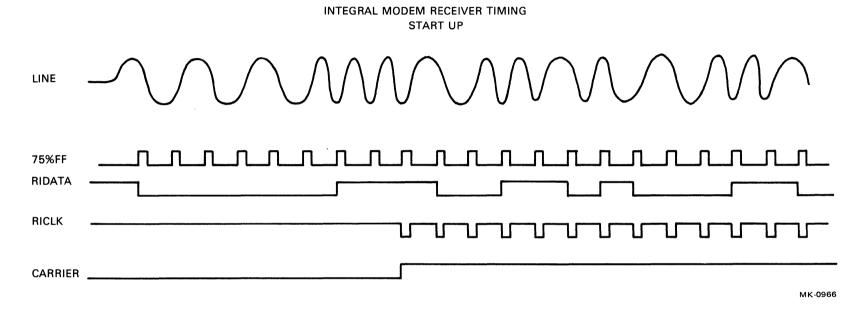

| 3-38        | Modem Receiver Timing Diagram – Start-Up       |      |

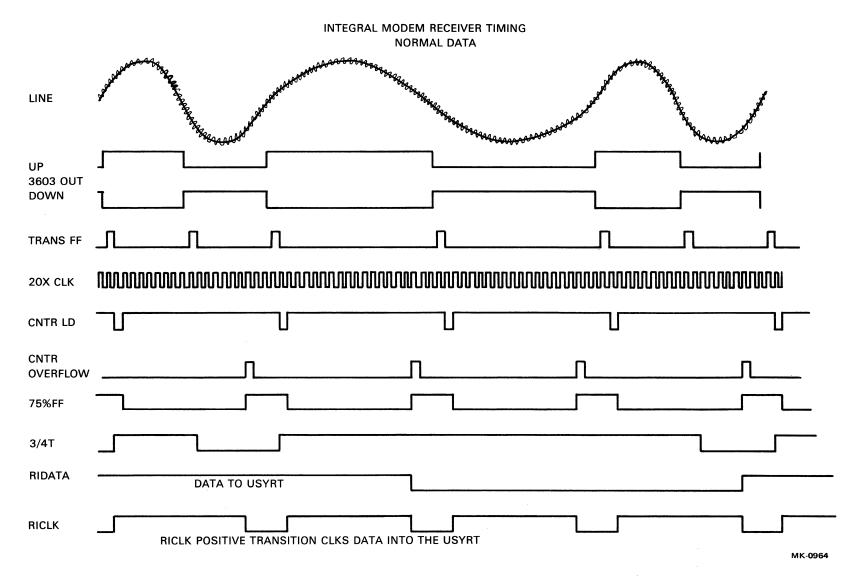

| 3-39        | Modem Receiver Timing Diagram – Normal Data    | 3-42 |

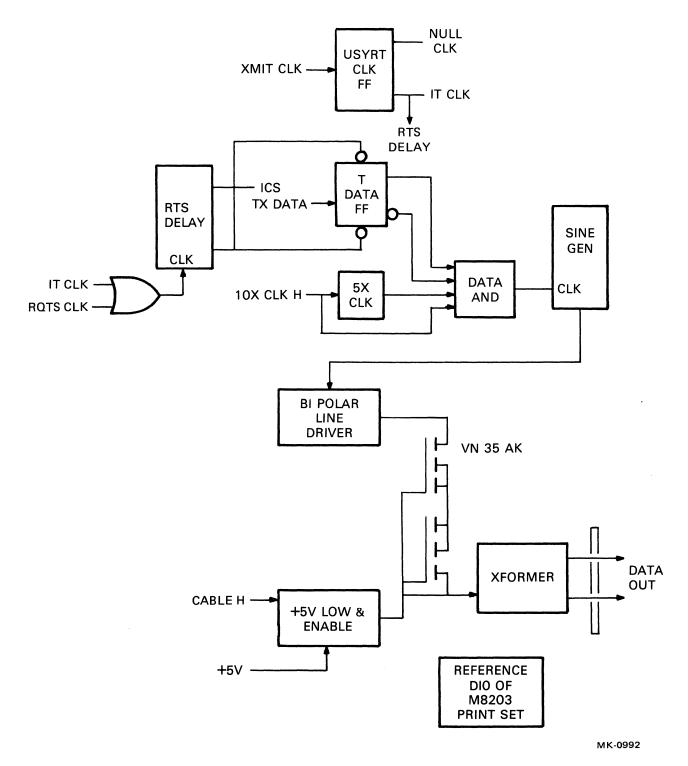

| 3-40        | Modem Transmitter Block Diagram                | 3-45 |

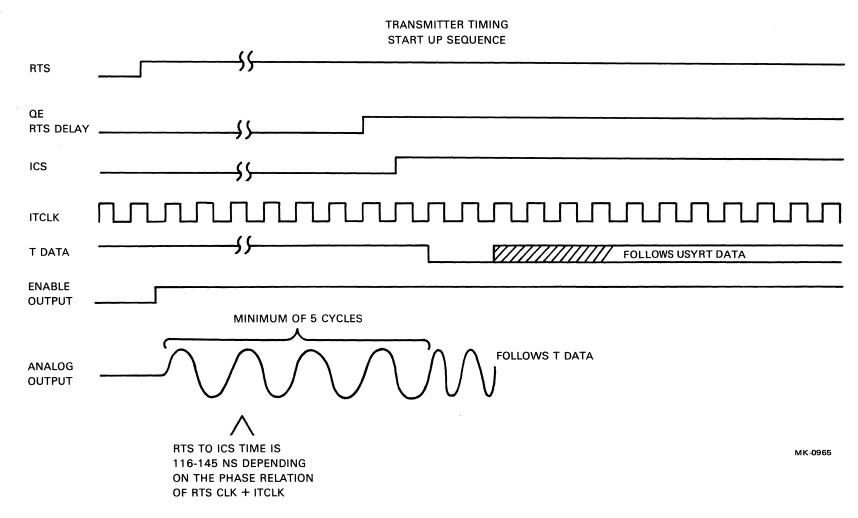

| 3-41        | Modem Transmitter Timing Diagram – Start-Up    |      |

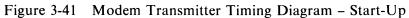

| 3-42        | Modem Transmitter Timing Diagram – Normal Data |      |

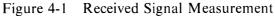

| 4-1 .       | Received Signal Measurement                    |      |

| 4-2         | Open and Short Circuit Resistance              |      |

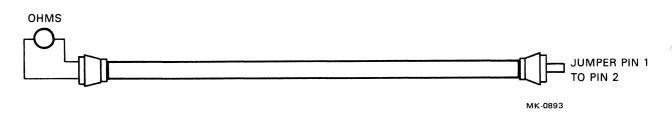

| 4-3         | Signal Reflections from a Line Fault           |      |

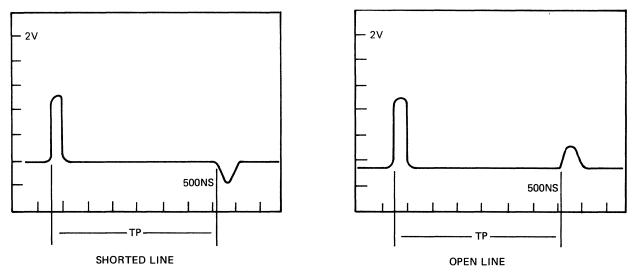

| <b>B-</b> 1 | Local Link Cable Connectors                    |      |

| C-1         | Terminal Connection (Identification)           |      |

|             | Diagram (2112517-01 Variation)                 | C-8  |

| C-2         | Suggested Block Diagram                        | C-10 |

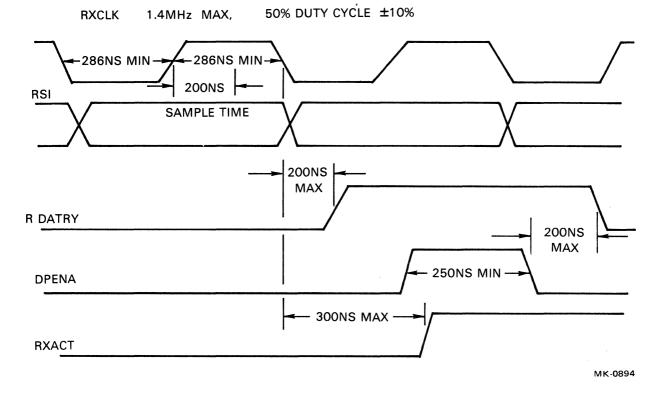

| C-3         | Receive Signal Timing Waveforms                |      |

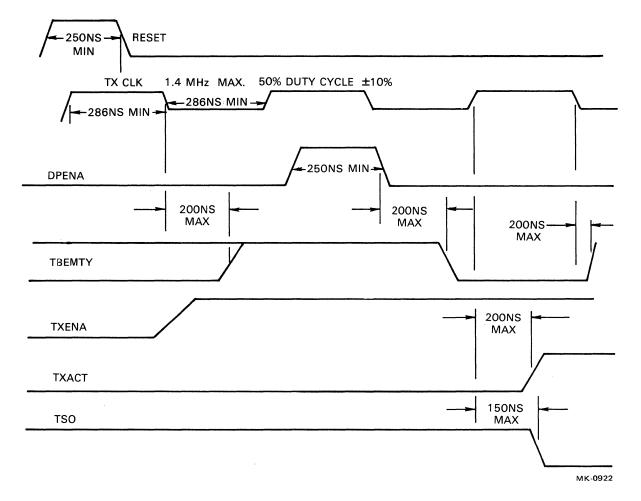

| C-4         | Transmit Signal Timing Waveforms               |      |

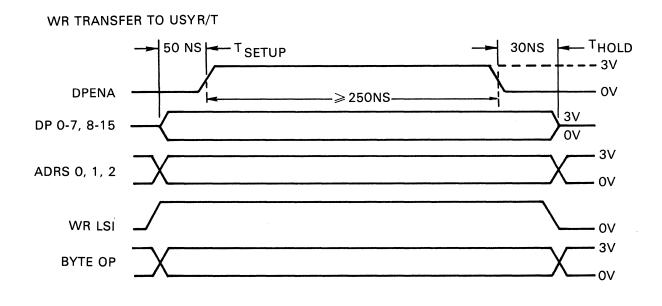

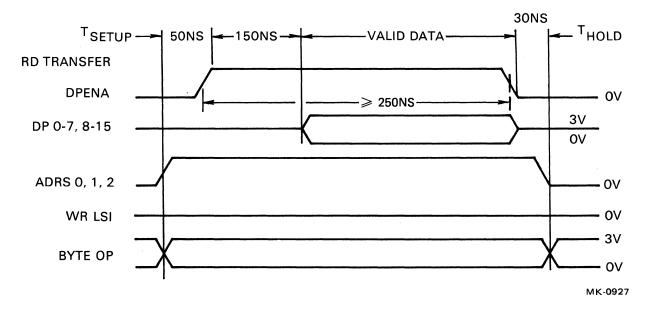

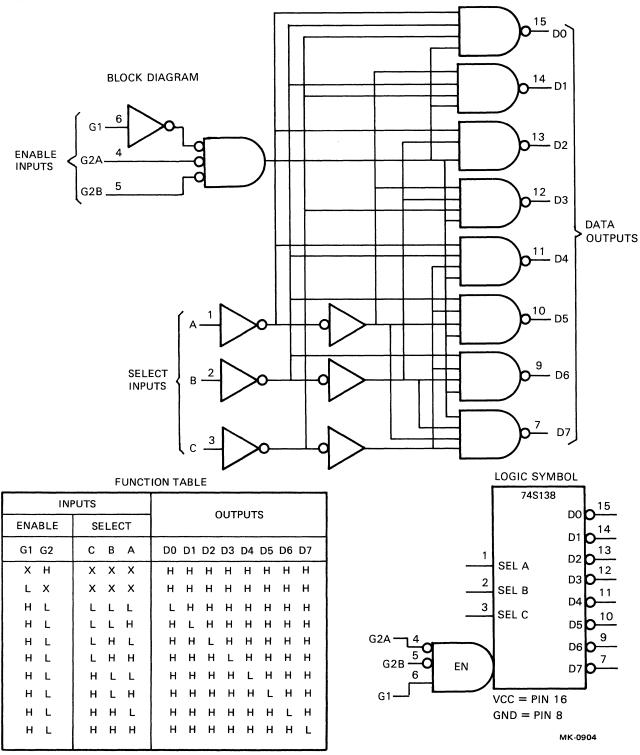

| C-5         | Tri-State Output Waveforms                     |      |

# TABLES

# Table No.

.

# Title

# Page

| 1-1 | M8203 Line Unit Interfaces                            |     |

|-----|-------------------------------------------------------|-----|

| 2-1 | Interface Signals/Pins at the Modem                   |     |

| 2-2 | Equivalency Table                                     |     |

| B-1 | Belden Twinax Cable Specifications                    | B-2 |

| B-2 | Belden Triax Cable Specifications                     | B-3 |

| C-1 | 2652 Internal Register Bit Map (2112517-01 Variation) | C-9 |

# PREFACE

The *M8203 Technical Manual* is a stand-alone document that describes typical line unit applications, circuit functions, and maintenance procedures based on a module replacement philosophy. Recommended cables and connectors, and installation considerations are provided in Appendix B. Detailed installation is provided in relevant systems documentation in which the line unit is implemented (such as the *DMP11-AD Technical Manual* – EK-DMP11-TM-001 or *DMR11 Technical Manual* – EK-DMR11-TM-002).

A Glossary of terms and abbreviations, selected integrated circuit descriptions, and microdiagnostic tests are also provided.

The following documents contain necessary reference information:

- M8207 Technical Manual (EK-M8207-TM-001)

- *M8207 Print Set* (D-CS-M8207-XX)

- *M8203 Print Set* (D-CS-M8203-XX)

- DMP11-AD Technical Manual (EK-DMP11-TM-001)

- DMR11 Technical Manual (EK-DMR11-TM-002)

- Electronic Industries Association (EIA) Specifications

# CHAPTER 1 INTRODUCTION

#### 1.1 PURPOSE

The M8203 is a high performance line unit designed for multipoint or point-to-point systems. The line unit is capable of cyclic redundancy check (CRC) or parity checking for both character and bit oriented protocols. Receive and Transmit Silos buffer the data to allow UNIBUS delays during transmission. However, for special bit and character oriented protocols, the line unit can be run without using the silos. Character oriented protocols use three types of error checking; CRC 16, even and odd, and vertical parity. The bit oriented protocols use two types of Comite Consultatif Internationale de Telegraphie et Telephone (CCITT) CRC 16 error checking; initialized to 0 and 1. Both protocols can be run without error checking for transparent or special operations.

#### **1.2 DESCRIPTION**

The M8203:

- is a full multilayer hex module containing three 40-pin berg connectors.

- has no cables permanently attached.

- contains three switch packs that must be set up when the module is installed.

- power consumption is +5V at 3 AMPS, +15V at 180 milliamps, and -15V at 150 milliamps.

- fits into any hex Small Peripheral Controller (SPC) slot or in a powered backplane (microprocessors are restricted to non-processor request (NPR) SPC slots DD11-C or D).

- is not a stand alone device; the line unit must be controlled by a microprocessor.

- provides no ac or dc loading to any UNIBUS signals.

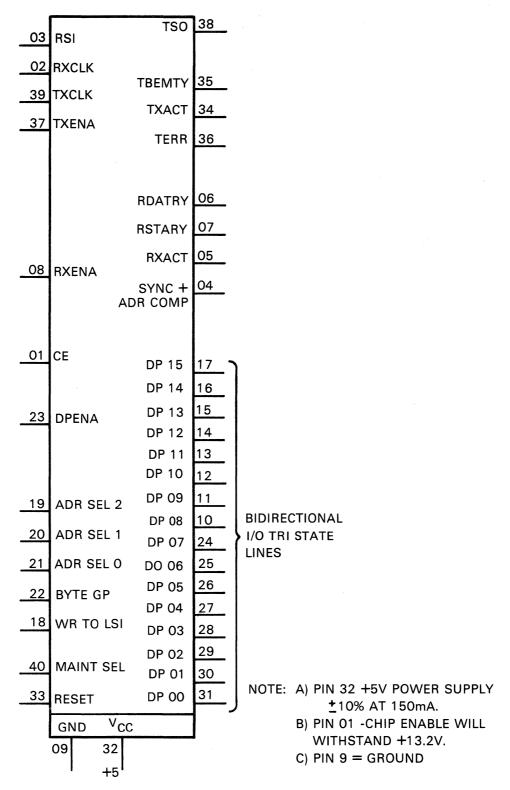

All data going to the line must go through the Universal Synchronous Receiver/Transmitter (USYRT). Transmit and Receive Silos are used to interface between the USYRT and the micro-processor.

M8203 Features:

- Addressing Addressed through the microprocessor IBUS and OBUS eight bit byte registers 10-17.

- Indirect Addressing Used to address the USYRT; bypasses the silos and standard hardware to run special protocols and variable character length operations.

- Berg Port The main interface to the microprocessor for all data and control of the line unit.

- Integral Modem Runs at 56K bps, 250K bps, 500K bps, and 1M bps. (Integral Modem specifications are provided in Chapter 3, Technical Description.) ٠

- Interfaces are listed in Table 1-1. ٠

| INTERFACE                             | SPEED                       | MODEM            | CABLE                                              |

|---------------------------------------|-----------------------------|------------------|----------------------------------------------------|

| EIA RS-232-C*<br>CCITT V.28/ISO 2110* | Up to 19.2K bps             | Bell 208,<br>209 | Panel Cable<br>BC55C-10<br>Modem Cable<br>BC05D-25 |

| EIA RS-423-A                          | Up to 56K bps <sup>†</sup>  |                  | Panel Cable<br>BC55C-10                            |

| Compatible with                       |                             |                  | Modem Cable<br>BC55D-33                            |

| Federal 1030;                         |                             |                  | BC35D-55                                           |

| CCITT V.10/ISO                        |                             |                  |                                                    |

| 4902 and X.26                         |                             |                  |                                                    |

| EIA RS-422-A                          | Up to 1M bps                |                  | Panel Cable<br>BC55B-10                            |

| Compatible with                       |                             |                  | Modem Cable<br>BC55D-33                            |

| Federal 1020;                         |                             |                  | BC35D-33                                           |

| CCITT V.11/ISO                        |                             |                  |                                                    |

| 4902 and X.27                         |                             |                  |                                                    |

| CCITT V.35/ISO 2953                   | Up to 250K bps              | Bell 500A        | BCO5Z-25                                           |

| INTEGRAL MODEM<br>using Twinax/Triax  | 56, 250, 500K bps<br>1M bps | Integral         | BC55A-10                                           |

#### Table 1-1 M8203 Line Unit Interfaces

\*Drivers are protected to  $\pm 10$  Volts not  $\pm 15$  Volts †Limited to 20K bps by RS-449 and 9600 bps by ISO 4902

#### **1.3 MAJOR FUNCTIONAL AREAS**

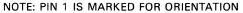

A simplified block diagram of the M8203 is provided in Figure 1-1. A brief description of the subject areas is as follows:

- INBUS Registers 10-17 Functions (as seen by the microprocessor):

- Read data and status in the Receive Silo and Shift Silo

- Microcode uses switches for line status (switches set up at installation time)

- Receiver status

- Status and control of the Modem Interface

- Extended address bits

- Maintenance functions

- Full or half-duplex on all interfaces

- OUTBUS Registers 10-17 Functions (loaded by the microprocessor):

- Load data and status into Transmit Silo and Shift Silo

- Control transmit circuitry

- Enable maintenance mode

- Status and control of Modem Interface

- Extended address bits

- Load data into data registers (only in extended mode)

- Maintenance functions

- Switch Packs:

- Defined by microcode (see specific options manual)

- Receive Silo:

- First in first out (FIFO)  $64 \times 12$

- Loaded from the USYRT via a crystal controlled sequencer.

- Transmit Silo:

- FIFO 64 × 12

- Loaded from the microprocessor

Figure 1-1 Major Functional Areas

- Sequencer:

- Controls all data in and out of the USYRT and all clear functions on the module

- Timing is controlled by a crystal (20 MHz for 100 ns increments)

- USYRT:

- All received data to the line unit must go through the USYRT

- Handles the basic protocol and error detection

Character Oriented Protocol:

- 1. Parallel to serial conversion

- 2. Synchronous (Sync) character recognition and generation

- 3. Sync character stripping

- 4. CRC checking if enabled

- 5. Vertical parity if enabled

Bit Oriented Protocol:

- 1. Parallel to serial conversion

- 2. Zero stuffing (insertion) and stripping

- 3. CRC checking if enabled

- 4. Flag recognition and generation

- 5. Abort recognition and generation

- 6. Go-Ahead recognition and generation

- Modem Interface

A summary of the Modem Interfaces is provided in this section. Detailed descriptions are contained in Chapter 2, Interface.

- RS-449/International Standards Organization (ISO) 4902/CCITT V.24: Common interface defined by all Electronic Industries Association (EIA) interfacing cables used with RS-422-A and RS-423-A.

- RS-232-C: EIA defined signals and characteristics for older modems (drivers are not protected from shorts to signals over 10 volts).

- RS-422-A (Federal Standard 1020) (ISO 4902/CCITT V.11 and X.27): Differential balanced interface used in conjunction with RS-449.

- RS-423-A (Federal Standard 1030) (ISO 4902/CCITT V.10 and X.26): Single-ended (unbalanced) signal levels used with RS-449 cables.

- V.35: CCITT Standard/ISO 2593 Standard

- Integral Modem: Diphase-space modulation compatible with the DMC11 Integral Modem and the encoding/decoding of the DIGITAL DC017 IC chip.

Transmitter output = 5.6 volts peak-to-peak minimum into a 30-ohm load.

Receiver signal = 150mV peak-to-peak minimum @ 20% maximum distortion.

Transformer coupled 500 volt common mode.

#### NOTE

#### Modules do not include any modem or Modem Interface cables.

#### 1.4 M8203 LINE UNIT/MICROPROCESSOR INTERFACE

The M8203 Line Unit connects to the network via (1), the twinax or triaxial cables in local network applications or (2), the modems and common carrier facilities in remote network applications. The M8203 runs up to 1M bps on both Modem Interface and Integral Modems.

MK-2426

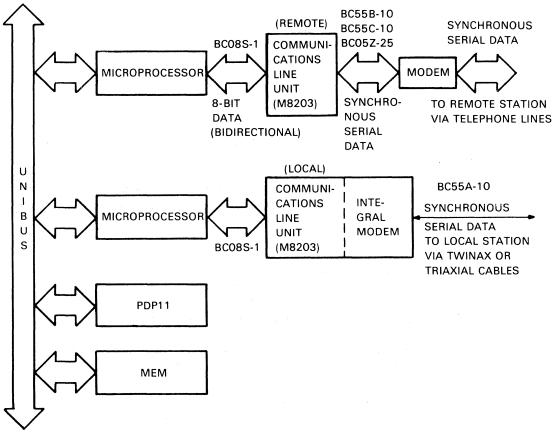

Figure 1-2 Typical PDP-11 Applications

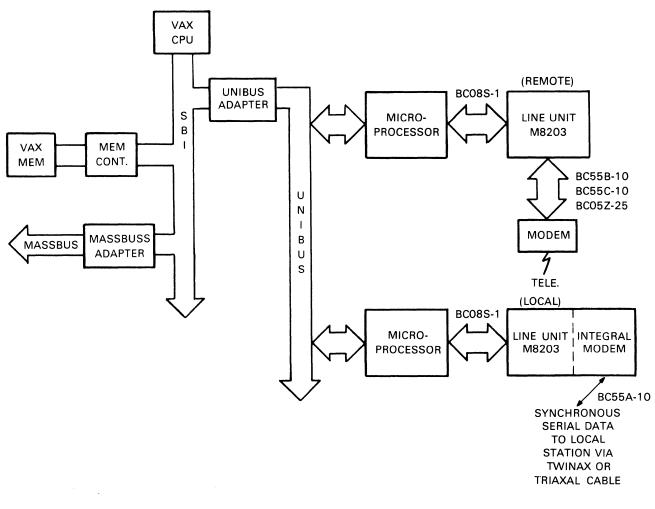

Figure 1-2 shows typical PDP-11 local/remote applications, while Figure 1-3 illustrates similar VAX-11/780 applications. Local stations are connected by a single twinaxial or triaxial cable for half-duplex operation or two cables for full-duplex operation. Remote stations are connected via modems that use common carrier facilities.

MK-2425

Figure 1-3 Typical VAX-11/780 Applications

# CHAPTER 2 INTERFACE

#### 2.1 SCOPE

The M8203 Line Unit is used in a wide range of synchronous communications applications. The M8207 or M8204 Microprocessors can be used with the line unit and can be programmed to handle a variety of protocols and interfaces. This section presents full and half-duplex connections, standard and special applications, compatible standards, and interfacing information.

#### 2.2 FULL-DUPLEX/HALF-DUPLEX OPERATION

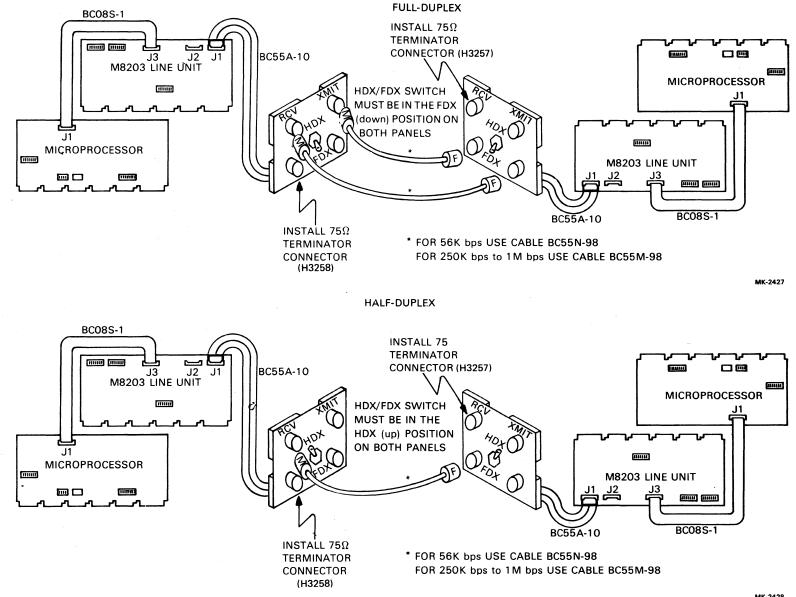

The M8203 Line Unit is capable of either full-duplex or half-duplex operation. The microprogram controls selection of half-duplex mode; the line unit controls and eliminates contention problems.

Operation of the M8203 Line Unit requires hardware considerations. The full-duplex operation requires two separate local link cables while half-duplex operation requires only one.

Although full-duplex operation requires two cables, it also provides full throughput potential. Halfduplex operation implies half the throughput potential but requires only one cable. The following questions should be considered when selecting full-duplex or half-duplex operation.

- 1. Traffic Flow Is most of the data going one way or is data flow nearly equal in both directions?

- 2. Data Rate

- a. Is it necessary to use maximum data rate now and in the foreseeable future?

- b. Will the maximum data rate cause UNIBUS latency problems?

#### NOTE

#### Each UNIBUS system has a maximum Non-Processor Request (NPR) activity rate. Consider all NPR devices on the UNIBUS using the maximum activity rating.

3. Cable Expense – Is the two cable full-duplex operation worth the expense?

Wiring for half-duplex operation is done by connecting the transmitter and receiver together. A switch setting, defined by microcode, must be selected on the line unit to inform the microprocessor that the line unit is installed (Figure 2-1).

#### NOTE

# Refer to the appropriate option Technical Manual for switch definitions and jumper configurations.

2-2

MK-2428

#### **2.3 STANDARD APPLICATIONS**

The most common application is the Integral Modem which runs at four switch selectable speeds. The system should be designed in accordance with the guidelines provided in the description of the Integral Modem in Chapter 3, Technical Description.

There are three interfaces (RS-423-A, RS-422-A, and RS-232-C) that use RS-449 common interface and standard cables to meet Electronic Industries Association (EIA) specifications. See Figure 2-2 and Table 1-1.

Figure 2-2 Standard (Common) Interfaces (Sheet 1 of 2)

MK-2431

#### **2.4 COMPATIBLE STANDARDS**

All cables used with the Modem Interfaces are described in the following sections and must be ordered separately. (See Figures 2-3 and 2-4.)

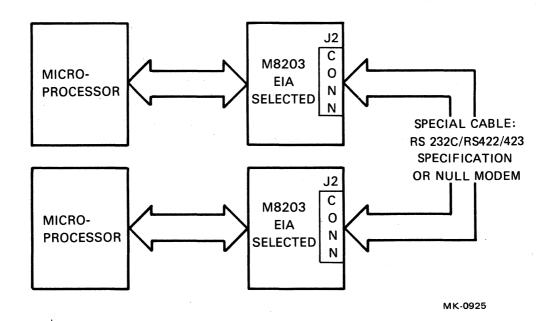

Figure 2-3 Special Application

MK-2432

Figure 2-4 CCITT V.35 (ISO 2593) Interface

#### 2.4.1 RS-232-C/CCITT V.28 (ISO 2110) Modem Interface

The RS-232-C interface uses the BC55C-10 panel cable, the BC05D-25 modem cable, and the H325 test connector or alternate. (See Figure 2-2.) M8203 implementation meets RS-232-C standards except driver protection against shorts to other lines over 10 volts and the drive impedance. RS-232-C states minimum drive impedance of 300 ohms without controlled rise and fall times. The new drivers have a 500 ohm impedance on the line accomplishing the same effect. A switch in the Modem Interface Selection Circuitry of the M8203 Line Unit (D7 of the M8203 Print Set) must be set to the single-ended output.

RS-232-C interfacing is limited to a maximum speed of 19.2K bps and is designed to interface to existing modems. The new EIA interface specifications RS-449 and RS-422-A/RS-423-A should be implemented.

The speed of the NULL clock is switch selectable and should not be set above 19.2K bps (see Section 3.5, Data Rate Generator). The maximum cable length for the RS-232-C interface is 15.24 meters (50 feet).

#### NOTE

- 1. In some configurations, the BC05C-25 cable can be used in place of the BC05D-25 cable for RS-232-C applications. However, some options such as the DMR11 do not support using the alternate cable. Refer to specific options manual for use of the BC05C-25.

- 2. In configurations where the BC05C-25 cable is used, removal of certain M8203 jumpers may be necessary to ensure acceptable operation.

| Jumper    | Condition                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------|

| <b>W7</b> | To disable Signal Rate (on some modems used as a test clock)                                                          |

| W8        | To disable Data Mode– May cause prob-<br>lems with some modems where pin 18 is<br>used for dibit clock                |

| W9        | To disable Null Clock– May cause prob-<br>lems with some modems                                                       |

| W10       | To disable Terminal Ready– May cause<br>problems with some modems where pin<br>10 is used for a negative test voltage |

| W12       | To disable Terminal in Service – May cause problems on some modems                                                    |

#### 2.4.2 EIA Standard RS-423-A

The RS-423-A is compatible with the Federal Standard 1030 and the Comite Consultatif Internationale de Telegraphie et Telephone (CCITT)V.10 and X.26/International Standards Organization (ISO) 4902. RS-423-A interface is single-ended and is subject to the RS-449 and Federal Standard 1031 interface with a new cable and test connector. Panel cable BC55C-10, modem cable BC55D-33, and test connector H3251 are used. The BC55C panel cable is a flat cable and the BC55D-33 modem cable is a round extension cable used for unprotected external runs.

A switch (E39-7) in the Modem Interface Selection Circuitry of the M8203 Line Unit (D7 of the *M8203 Print Set*) must be set to the single-ended mode. Signal levels are provided in Section 2.4.4. The maximum speed is limited to 56K bps by the rise time (limited to 20K b/s by RS-449 and 9600 b/s by ISO 4902). (Refer to the RS-423-A specification for more detail.) The maximum cable length is 60.48 meters (200 feet) as defined by the rise time used in the RS-423-A specification.

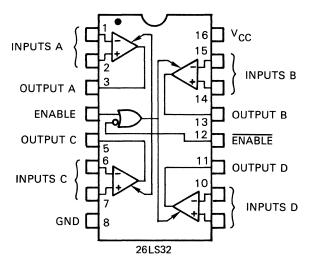

The RS-423-A interface standard specifies unbalanced circuits, but the M8203 uses a balanced differential receiver (26LS32) with a common return for improved performance at greater distances. The speed limitation of the M8203 electrical circuits under RS-423-A implementation without RS-449 implementation is limited to 56K bps which is imposed by software and other factors.

Applications using RS-423-A with RS-449 implementation are limited to a maximum speed of 20K bps and for ISO 4902 the speed is limited to 9600 bps.

#### 2.4.3 EIA Standard RS-422-A

RS-422-A is compatible with Federal Standard 1020 and CCITT V.11 and X.27/ISO 4902. It is a differential interface and subject to EIA specification RS-449 and Federal Standard 1031 (signal levels are provided in Section 2.4.4). RS-422-A uses the panel cable BC55B-10, modem cable BC55D-33, and test connector H3251.

A switch (E39-7) in the Modem Interface Selection Circuitry of the M8203 Line Unit (D7 of the *M8203 Print Set*) must be set to the differential mode as defined in the RS-449 specification. The maximum data rate for the RS-422-A interface is limited to 1M bps by the line unit. The rise time is less than 200 ns. Maximum cable length is defined by RS-422-A.

The balanced circuits of RS-422-A use differential generators and receivers over a pair of wires for each signal. This type of circuit requires more wires in a cable to support all the signals, but only circuits that are speed sensitive generally use this interface standard. The circuits which are speed sensitive are defined as Category I type circuits under the RS-449 Interchange Standard, and those that are not speed sensitive as Category II type circuits. The speed sensitive circuits are data signals, timing signals, and any control signal that must respond quickly. These speed sensitive circuits (Category I type) usually implement balanced type circuits using the RS-422-A Electrical Standard. Terminating resistors ( $R_T$ ) are used at the receiver to achieve top performance for distance and speed.

#### NOTE Terminating resistors of 100 ohms are built into the BC55B-10 cable.

If properly terminated, the maximum cable length is 1.22 km (3865 feet); if terminating resistors are not used, the maximum cable length is 12.19 meters (40 feet).

#### 2.4.4 EIA Standard RS-449

The RS-449 is compatible with CCITT Standards V.24, ISO Standard 4902, and Federal Standard 1031. RS-449 is used by all EIA interfacing cables, either single-ended or differential. The switch (E39-7) in the Modem Interface Selection Circuitry of the M8203 Line Unit (D7 of the M8203 Print Set) can be set to single-ended (unbalanced) or differential (balanced) mode with no interlock between the cable and the interface. The maximum speed for each EIA interface is specified in relevent sections of this manual and in more detail in the EIA specifications.

#### NOTE EIA Specifications may be obtained from:

EIA Engineering Department Electronic Industries Association 2001 Eye Street N.W. Washington, D.C. 20006

#### **RISE TIMES**:

- Single-ended = 5 microseconds

- Differential = 200 nanoseconds

#### **RISE TIME LIMITATIONS:**

- Provides a means of calculating maximum cable length for use with each EIA interfacing level

- Rise times may be adjusted for specific variations of the M8203

#### CABLE LENGTHS:

- RS-232-C limited to 15.24 meters (50 feet) by specification

- RS-423-A limited to 60.48 meters (200 feet) by rise time

- RS-422-A must be terminated with a maximum limit of 1.22 km (3865 feet) if all the guidelines in the RS-422-A specification are followed

- Standard cables are all modem interfaces of 7.62 meters (25 feet) for older cables and 10 meters (33 feet) for new cables

- Special cable or NULL modem arrangements (Contact Computer Special Systems (CSS))

SIGNAL LEVELS (New RS-449 Specifications):

- Maximum output voltage =  $\pm 6$  volts

- Minimum output voltage with no load  $= \pm 5$  volts (single-ended outputs)

- A 450 ohm resistor used as a load will not drop the output voltage more than 10 percent

- The differential outputs maximum output  $= \pm 5$  volts (referenced between the outputs with no load). With a balanced 100 ohm load, the output will not drop more than 10 percent

- The minimum output with no load =  $\pm 2$  volts

- The balance error will not exceed 0.4 volts

- System ground differences cannot exceed 3 volts

- The output is protected to  $\pm 10$  volts at 150 milliamps from voltages applied to the wrong pins when the modem is connected

- RECEIVE COMMON is tied to ground by a 100 ohm resistor for a fail-safe condition when no receiver ground is supplied to the interface

- SEND COMMON is tied directly to ground and is not current limited

- The shield grounds also tie directly to ground and are not current limited

The receivers are set up to accommodate differential inputs for the RS-422-A (see Section 2.4.3). Resistors are provided for fail-safe operation. The differential signals can be changed to single-ended (or when not connected) and allow the receivers to go to the fail-safe state. The receivers also go to the failsafe state when power is off on the modem. The maximum signal off-set is 3 volts. The receivers can withstand a maximum voltage of plus or minus 25 volts without damage to the components. The operating range is  $\pm 15$  volts. The RS-449 is a fail-safe interface when no signal is provided or the wire is open for that particular receiver. The Integral Modem Cable selects the interface when the cable is plugged in.

#### NOTE

#### The software is unable to tell if the cable is not connected or if the modem is not operating.

The M8203 reports that the RS-449 interface is enabled for either single-ended or differential mode. The RS-449 interface is made as fail-safe as possible. If a ground line or return line is open, there are pull-up resistors that compensate for the open-line. The signals received are pulled to a fail-safe state when power is off on the modem or when any of the lines except data and timing are open or left unterminated. The M8203 supports the following RS-449 category 1 signals:

| Circuit | Description                                |

|---------|--------------------------------------------|

| SD      | Send Data                                  |

| RD      | Receive Data                               |

| TT      | Terminal Timing (Null Clock)               |

| ST      | Send Timing                                |

| RT      | Receive Timing                             |

| RS      | Request to Send                            |

| CS      | Clear to Send                              |

| RR      | Receiver Ready (Carrier)                   |

| TR      | Terminal Ready (Data Terminal Ready = DTR) |

| DM      | Data Mode (Modem Ready)                    |

These circuits are supported in differential and single-ended mode for RS-449. The receivers and drivers are all fail-safe circuits so the differential receivers handle single-ended lines. Drivers are selected by a switch and must match the interface cable.

#### 2.4.5 CCITT V.35/ISO 2593

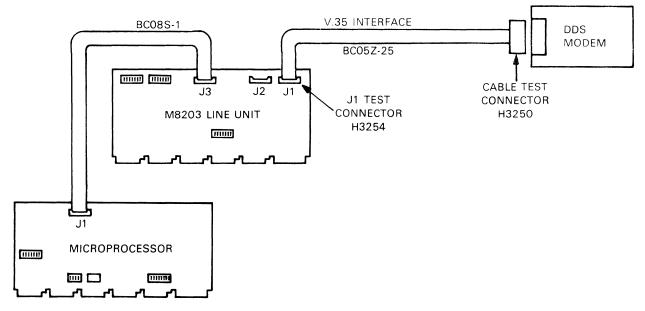

The V.35 interface uses the BCO5Z-25 cable and the H3250 test connector (the same connector used by the Integral Modem). When the cable is plugged in, a bit is set in the extended registers (see Chapter 3, Technical Description) that indicates that the V.35 mode has been selected. The maximum speed is 250K bps. The NULL clock is switch selectable from 2.4K bps to 1M bps (see Chapter 3, Technical Description).

#### 2.5 INTERFACE SIGNALS

Table 2-1 lists all the signals handled by the standards described in the previous sections and the associated pins at the modem.

A list of interchange circuits showing the nearest equivalent RS-232-C, RS-449, and CCITT identification in accordance with recommendation V.24 is presented in Table 2-2. It should not be inferred that circuit definitions given are in exact accord with RS-232-C, RS-449, and CCITT recommendations.

#### 2.6 ADDITIONAL LINE UNIT OPTIONS

The M8203 Line Unit is set up so the CRC 32 chip can be used with the Universal Synchronous Receiver/Transmitter (USYRT) by cutting four etches and installing the chip.

#### NOTE

# This option must be factory installed. It may not be installed in the field.

#### **2.7 HARDWARE VARIABLES**

The M8203 contains three switch packs (E39, E121, and E134) and 17 jumpers (W1 through W17) which are used to select certain features and/or configuration variations. Some of these switches and

jumpers may be used differently in specific options such as the DMR11. For a more detailed description of each switch and jumper, refer to the specific options manual.

The purpose of this section is to identify each switch and jumper, and to provide a general description of each.

- Jumper Functions Jumpers W1-W17 are used to select various interface standard parameters and modem interface signals, depending on application and modem type. Additional jumpers are available on the BC55C (panel) cable for additional interface signal selection.

- Switch Pack E39 Functions This switch pack allows proper selection of interface driver and receiver control logic and different line speeds for various applications.

- Switch Pack E121 Functions This switch pack is physically connected to internal registers. The function of each switch is microprogram dependent and may be different depending on the option selected. Refer to specific option manual for details.

- Switch Pack E134 Functions This switch pack is physically connected to internal registers. The function of each switch is microprogram dependent and may be different depending on the option selected. Refer to specific option manual for details.

| SIGNALS                         | PIN AT MODEM |          |          |      |

|---------------------------------|--------------|----------|----------|------|

|                                 | RS-449       |          |          |      |

|                                 | RS-232-C     | RS-423-A | RS-422-A | V.35 |

| CLEAR TO SEND (+)               | 5            | 9        | 9        | D    |

| CLEAR TO SEND (-)               |              | 27       | 27       |      |

| DATA MODE(+)                    | 6            | 11       | 11       | Е    |

| DATA MODE (-)<br>(Modem Ready)  |              | 29       | 29       |      |

| INCOMING CALL<br>(Ring)         | 22           | 15       | 15       |      |

| LOCAL LOOP                      | 18*          | 10       | 10       |      |

| NEW SIGNAL                      |              | 34       | 34       |      |

| PROTECTIVE GROUND               | 1            |          |          |      |

| RECEIVE COMMON                  |              | 20       | 20       |      |

| RECEIVE DATA (+)                | 3            | 6        | 6        | R    |

| RECEIVE DATA (-)                |              | 24       | 24       | Т    |

| RECEIVER READY (+)              | 8            | 13       | 13       | F    |

| RECEIVER READY (-)<br>(Carrier) |              | 31       | 31       |      |

Table 2-1 Interface Signals/Pins at the Modem

\*Selected by a jumper on the BC55C-10 cable.

| SIGNALS             | PIN AT MODEM<br>RS-449 |          |          |      |

|---------------------|------------------------|----------|----------|------|

|                     |                        |          |          |      |

|                     | RS-232-C               | RS-423-A | RS-422-A | V.35 |

| RECEIVE TIMING (+)  | 17*                    | 8        | 8        | V    |

| RECEIVE TIMING (-)  |                        | 26       | 26       | х    |

| REMOTE LOOP         | 21*                    | 14       | 14       |      |

| REQUEST TO SEND (+) | 4                      | 7        | 7        | С    |

| REQUEST TO SEND (-) |                        |          | 25       |      |

| SELECT STANDBY      |                        | 32       | 32       |      |

| SEND COMMON         |                        | 37       | 37       |      |

| SEND DATA (+)       | 2                      | 4        | 4        | Р    |

| SEND DATA (-)       |                        |          | 22       | S    |

| SEND TIMING (+)     | 15*                    | 5        | 5        | Y    |

| SEND TIMING (-)     |                        | 23       | 23       | а    |

Table 2-1 Interface Signals/Pins at the Modem (Cont)

\*Selected by a jumper on the BC55C-10 cable.

| SIGNALS                                           | PIN AT MODEM |          |          |      |

|---------------------------------------------------|--------------|----------|----------|------|

|                                                   | RS-449       |          |          |      |

|                                                   | RS-232-C     | RS-423-A | RS-422-A | V.35 |

| SHIELD GROUND                                     | 1*           | 1*       | 1        |      |

| SIGNAL GROUND                                     | 7            | 19       | 19       | А    |

| SIGNAL QUALITY                                    | 21*          | 33       | 33       |      |

| SIGNAL RATE INDICATOR                             | 23*          | 2        | 2        |      |

| SIGNAL RATE SELECT                                | 23*          | 16       | 16       |      |

| STANDBY INDICATION                                | 25*          | 36       | 36       |      |

| TERMINAL IN SERVICE                               | 25*          | 28       | 28       |      |

| TERMINAL READY (+)                                | 20           | 12       | 12       | Н    |

| TERMINAL READY (-)<br>(Data Terminal Ready = DTR) |              |          | 30       |      |

| TERMINAL TIMING (+)                               | 24 .         | 17       | 17       | U    |

| TERMINAL TIMING (-)<br>(Null Clock)               |              |          | 35       | W    |

| TEST MODE                                         | 25*          | 18       | 18       |      |

Table 2-1 Interface Signals/Pins at the Modem (Cont)

\*Selected by a jumper on the BC55C-10 cable.

| EIA RS-449             | EIA RS-232-C              | CCITT<br>RECOMMENDATION<br>V.24 | J2<br>BERG CONN<br>PIN |

|------------------------|---------------------------|---------------------------------|------------------------|

|                        | AA SHIELD GROUND          |                                 | UU                     |

| SG SIGNAL GROUND       | AB SIGNAL GROUND          | 102 SIGNAL GROUND               | vv                     |

|                        | AA PROTECTIVE GROUND      |                                 | A/B                    |

| SC SEND COMMON         |                           | 102a DTE COMMON                 | A                      |

| RC RECEIVE COMMON      |                           | 102b DCE COMMON                 | В                      |

| IS TERMINAL IN SERVICE |                           |                                 | с                      |

| IC INCOMING CALL       | CE RING INDICATOR         | 125 CALLING INDICA-<br>TOR      | X                      |

| TR TERMINAL READY (+)  | CD DATA TERMINAL<br>READY | 108/2 DATA TERMIN-<br>AL READY  | DD                     |

| TR TERMINAL READY (-)  |                           |                                 | w                      |

| DM DATA MODE (+)       | CC DATA SET READY         | 107 DATA SET READY              | Z                      |

| DM DATA MODE (-)       |                           |                                 | U                      |

| SD SEND DATA (+)       | BA TRANSMITTED DATA       | 103 TRANSMITTED<br>DATA         | F                      |

| SD SEND DATA (-)       |                           |                                 | КК                     |

| RD RECEIVE DATA (+)    | <b>BB RECEIVED DATA</b>   | 104 RECEIVED DATA               | s                      |

| RD RECEIVE DATA (-)    |                           |                                 | J                      |

Table 2-2

Equivalency Table

| EIA RS-449             | EIA RS-232-C                                            | CCITT<br>RECOMMENDATION<br>V.24                               | J2<br>BERG CONN<br>PIN |

|------------------------|---------------------------------------------------------|---------------------------------------------------------------|------------------------|

| TT TERMINAL TIMING     | DA TRANSMITTER SIGNAL<br>ELEMENT TIMING<br>(DTE SOURCE) | 113 TRANSMITTER<br>SIGNAL ELE-<br>MENT TIMING<br>(DTE SOURCE) | L                      |

| TT TERMINAL TIMING (–) |                                                         | (DIE SOURCE)                                                  | EE                     |

| ST SEND TIMING (+)     | DB TRANSMITTER SIGNAL<br>ELEMENT TIMING<br>(DCE SOURCE) | 114 TRANSMITTER<br>SIGNAL ELE-<br>MENT TIMING<br>(DCE SOURCE) | Ν                      |

| ST SEND TIMING (-)     |                                                         | (DEE SOOREE)                                                  | TT                     |

| RT RECEIVE TIMING (+)  | DD RECEIVER SIGNAL<br>ELEMENT TIMING                    | 115 RECEIVER SIGNAL<br>ELEMENT TIMING                         | SS                     |

| RT RECEIVE TIMING (-)  |                                                         | (DCE SOURCE)                                                  | R                      |

| RS REQUEST TO SEND (+) | CA REQUEST TO SEND                                      | 105 REQUEST TO SEND                                           | v                      |

| RS REQUEST TO SEND (-) |                                                         |                                                               | AA                     |

| CS CLEAR TO SEND (+)   | CB CLEAR TO SEND                                        | 106 READY FOR SEND-                                           | Т                      |

| CS CLEAR TO SEND (-)   |                                                         | ING                                                           | РР                     |

| RR RECEIVER READY (+)  | CF RECEIVED LINE SIG-<br>NAL DETECTOR                   | 109 DATA CHANNEL RE-<br>CEIVED LINE SIGNAL                    | Β̈́Β                   |

| RR RECEIVER READY (-)  |                                                         | DETECTOR                                                      | Н                      |

| SQ SIGNAL QUALITY      | CG SIGNAL QUALITY DE-<br>TECTOR                         | 110 DATA SIGNAL QUAL-<br>ITY DETECTOR                         | ММ                     |

Table 2-2

Equivalency Table (Cont)

| EIA RS-449                                               | EIA RS-232-C                                    | CCITT<br>RECOMMENDATION<br>V.24                                                           | J2<br>BERG CONN<br>PIN |

|----------------------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------|

| NS NEW SIGNAL                                            |                                                 |                                                                                           | НН                     |

| SF/SR* SELECT FREQUENCY/<br>SIGNALING RATE SE-<br>LECTOR | CH DATA SIGNAL RATE<br>SELECTOR (DTE<br>SOURCE  | 126 SELECT TRANS-<br>MIT FREQUENCY<br>111 DATA SIGNALING<br>RATE SELECTOR<br>(DTE SOURCE) | RR                     |

| SI SIGNALING RATE IN-<br>DICATOR                         | CI DATA SIGNAL RATE<br>SELECTOR (DCE<br>SOURCE) | 112 DATA SIGNALING<br>RATE SELECTOR<br>(DCE SOURCE)                                       | Y                      |

| LL LOCAL LOOPBACK                                        |                                                 | 141 LOCAL LOOPBACK                                                                        | К                      |

| RL REMOTE LOOPBACK                                       |                                                 | 140 REMOTE LOOPBACK                                                                       | FF                     |

| TM TEST MODE                                             | · · · ·                                         | 142 TEST INDICATOR                                                                        | Е                      |

| SS SELECT STANDBY                                        |                                                 | 116 SELECT STANDBY                                                                        | CC                     |

| SB STANDBY INDICATOR                                     |                                                 | 117 STANDBY INDICA-<br>TOR                                                                | М                      |

| DTE = Data Terminal Equipment                            |                                                 |                                                                                           |                        |

| DCE = Data Circuit-terminating<br>Equipment              |                                                 |                                                                                           |                        |

Table 2-2

Equivalency Table (Cont)

\* SF and SR share the same pin.

2-16

# CHAPTER 3 TECHNICAL DESCRIPTION

#### 3.1 SCOPE

The technical description and programming of the M8203 Line Unit Circuitry is presented at the functional level. The intent is to provide the Field Service representative with enough information to troubleshoot the line unit. Logic block diagrams supplement the text and make reference to the M8203 *Print Set* thereby providing the additional information required to troubleshoot to the gate level. Definition of the register bits and special chips may be useful to the programmer as well as the technician.

The major functional areas shown in Figure 1-1 are described in the following sections in the sequence given below.

- Berg Port Interface

- Silos

- Sequencer

- Data Rate Generator

- Universal-Synchronous Receiver/Transmitter (USYRT) Device

- Modem Interface

- Integral Modem

#### NOTE

D(x) references in the text are based on the signal map rather than actual sheet numbers of the M8203 Print Set.

#### **3.2 BERG PORT INTERFACE**

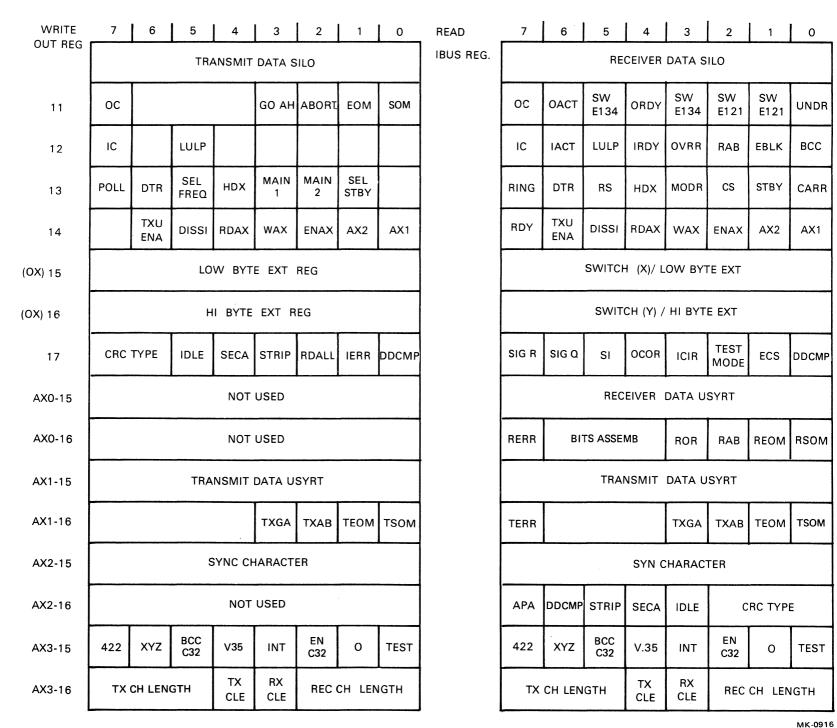

The Berg Port Interface has eight basic input and output registers expanded by second level addressing to eight more registers (See Figure 3-1).

.

WIK-0510

INBUS/OUTBUS and INBUS\*/OUTBUS\* refer to two register groups or categories within, and accessed by, the microprocessor. This terminology is used in microinstruction formatting. It defines the group of registers to be accessed by the microprocessor and whether the particular register is used as a source or destination for data.

- The "\*" indicates one register group; the absence of the "\*" indicates the other register group.

- The "IN" portion of the term identifies the specific register as the data source.

- The "OUT" portion of the term identifies the specific register as the destination for data.

- The "BUS" portion of the term does not refer to a physical BUS.

- The following terms are synonymous:

OUTBUS and OUT INBUS\* and IBUS\* OUTBUS\* and OUT\* INBUS and IBUS

Registers in the "\*" group (IBUS\*/OUT\*) are located in the Microprocessor Multiport Random Access Memory (RAM):

| CSR Bytes 0-7    | (Registers 0 to 7 are $R/W$ ) |

|------------------|-------------------------------|

| NPR Control      | (Register 10 is $R/W$ )       |

| μP Miscellaneous | (Register 11 is $R/W$ )       |

Registers in the INBUS/OUTBUS group located in the microprocessor:

| IN DATA LB    | Register $0 - R/W = Low Byte$  | DMA data from memory to the                             |

|---------------|--------------------------------|---------------------------------------------------------|

| IN DATA HB    | Register $1 - R/W = High Byte$ | microprocessor                                          |

| OUT DATA LB   | Register $2 - R/W = Low Byte$  | DMA data from the microprocessor to                     |

| OUT DATA HB   | Register $3 - R/W = High Byte$ | memory                                                  |

| IN BA <7:0>   | Register $4 - R/W = Low Byte$  | DMA address for<br>data from memory<br>to the micropro- |

| IN BA <15:8>  | Register $5 - R/W = High Byte$ | cessor                                                  |

| OUT BA <7:0>  | Register $6 - R/W = Low Byte$  | DMA address for<br>data from the<br>microprocessor to   |

| OUT BA <15:8> | Register 7 – $R/W$ = High Byte | memory                                                  |

Registers in the INBUS/OUTBUS group located in the line unit:

| RECEIVER DATA SILO | Register 10 - Read = Receive Data FIFO                                                                                    |

|--------------------|---------------------------------------------------------------------------------------------------------------------------|

| TRANSMIT DATA SILO | Register 10 – Write = Transmit Data FIFO                                                                                  |

| OUT CONT           | Register $11 - R/W = Output Control$                                                                                      |

| IN CONT            | Register $12 - R/W = Input Control$                                                                                       |

| MODEM CONT         | Register $13 - R/W = Modem Control$                                                                                       |

| SYNC REG           | Register $14 - R/W = SYNC$ Character/Secondary Address                                                                    |

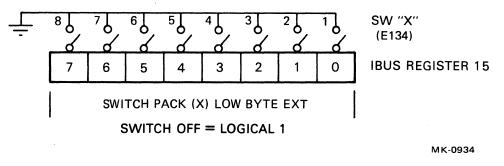

| SW PACK (X)        | Register 15 – Read only – Contents = Switch Pack                                                                          |

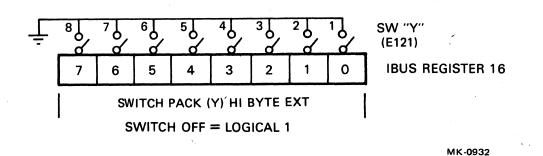

| SW PACK (Y)        | X/Low Byte of Extended Register.<br>Register 16 – Read only – Contents = Switch Pack<br>Y/High Byte of Extended Register. |

| MAINT REG          | Register $17 - R/W = Maintenance$                                                                                         |

#### NOTE

- 1. Address Extended (AX) registers are indirectly addressed by using AX1 and AX2 for address, Write to Extended registers (WAX) for write, Read to Extended registers (RDAX) for read, registers 15 and 16 for data, Enable Extended registers (ENAX) going to a one to start the operation, and Ready (RDY) to tell when the operation is complete.

- 2. The bit map as seen by the KMC11 and DMC11 Microprocessors.

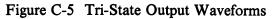

#### 3.2.1 Read IBUS Registers

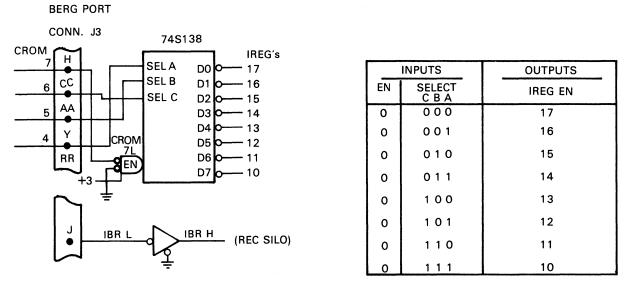

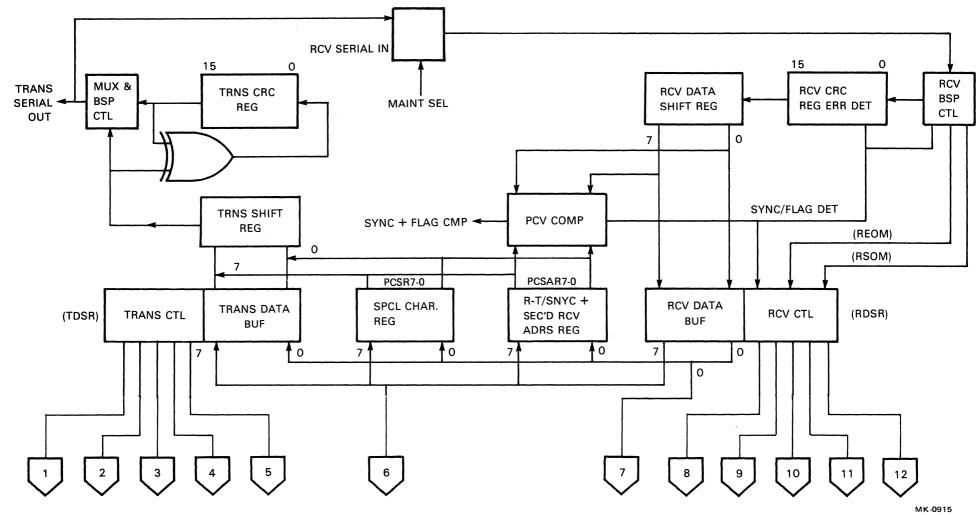

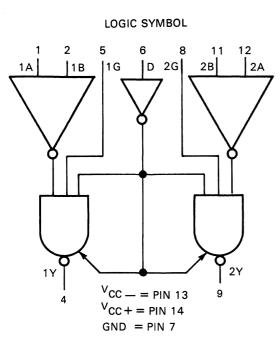

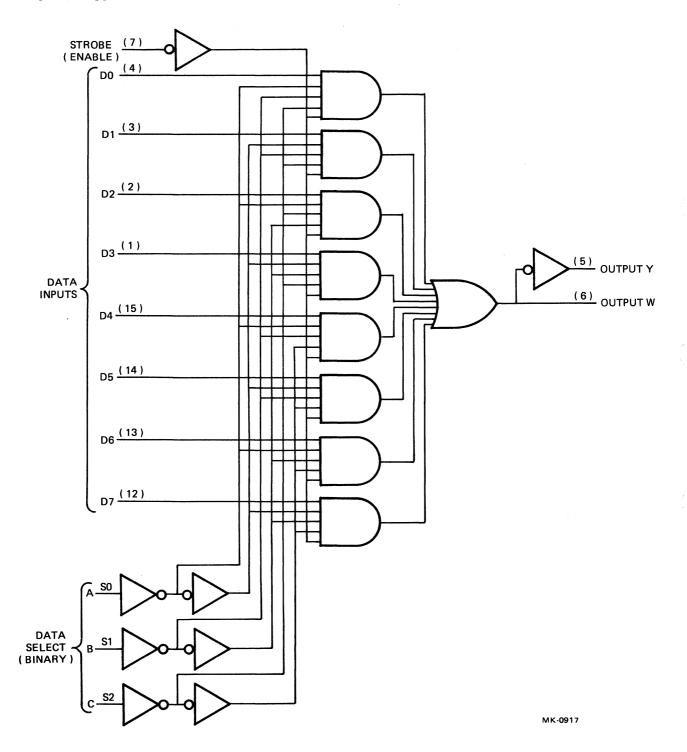

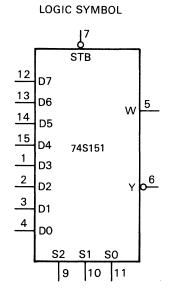

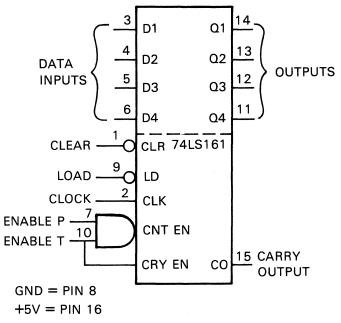

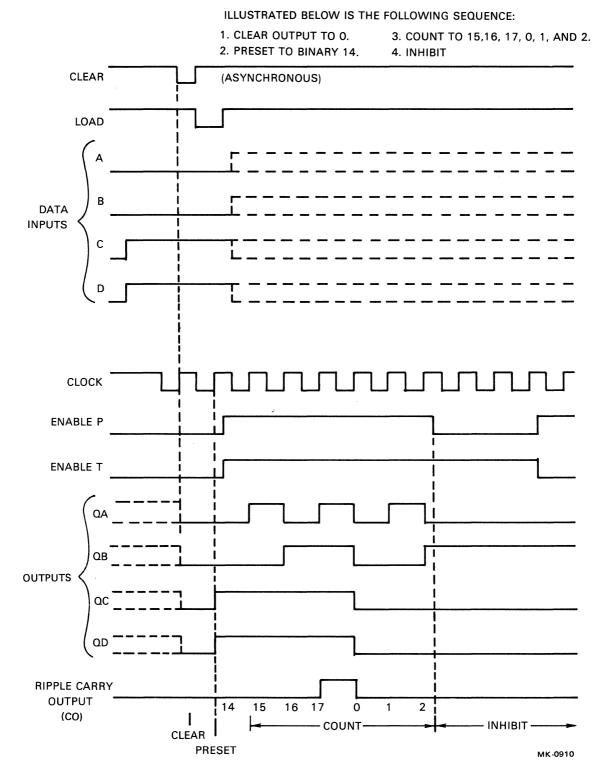

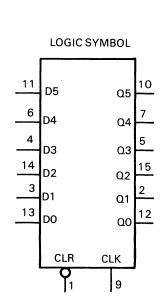

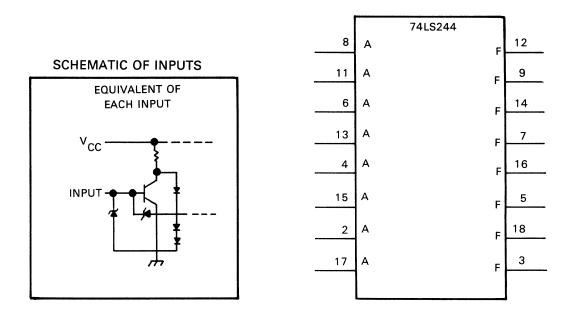

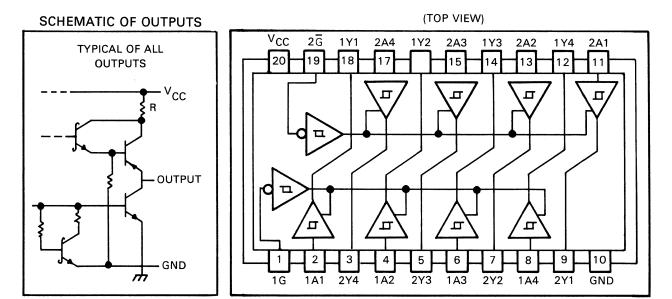

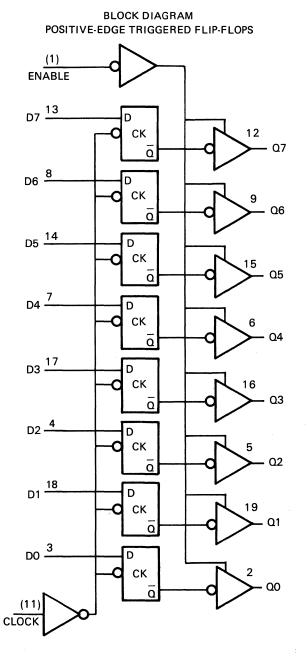

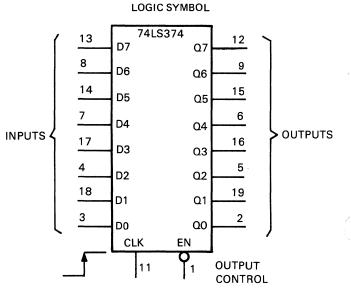

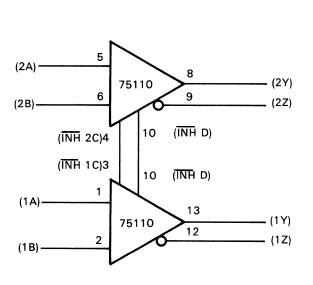

The line unit input registers are 12 tristate D-Type flip-flops (74LS374s). Extended registers are primarily used to load or verify USYRT registers. They can also be used for special protocols. IBUS and extended IBUS register selection is done by the microprocessor Control Read Only Memory (CROM) lines 4-7. The lines are decoded via a 74S138 decoder/multiplexer and used to enable the selected input register (See Figure 3-2). INBUS Read (IBR H) is used to shift data out of the receive silo (D5 of the *M8203 Print Set*).

MK-0924

Figure 3-2 IBUS Register Select

#### **3.2.2 OBUS Registers**

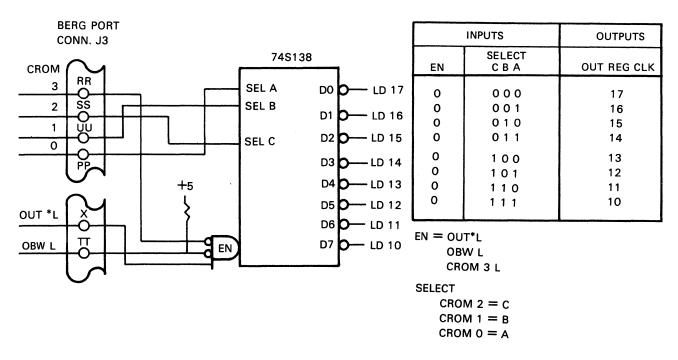

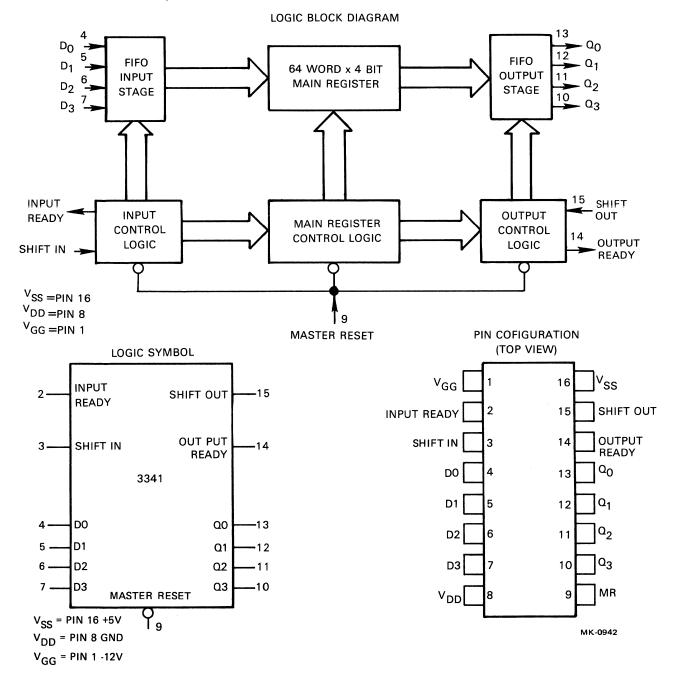

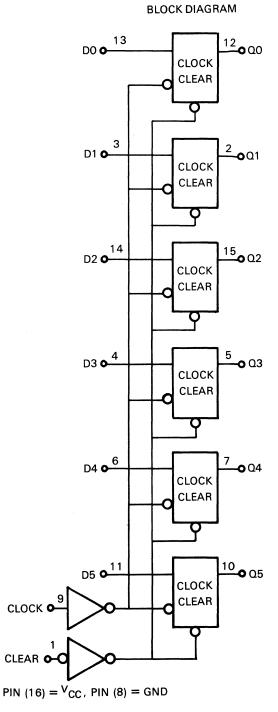

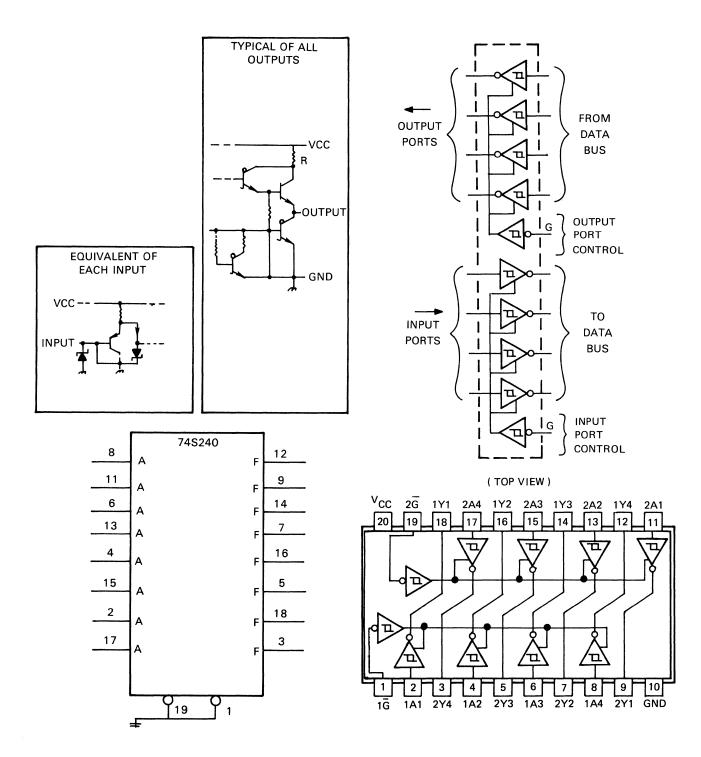

The buffered Arithmetic Logic Unit (ALU) lines from the microprocessor are inverted via a 74S240 then routed to the output register inputs. Selection of the output registers is done by the microprocessor CROM lines 3-0 which are decoded via a 74S138 decoder/multiplexer (See Figure 3-3). OUTBUS Write (OBWL) is used to gate the load pulse to the registers (D3 of the *M8203 Print Set*).

MK-0929

#### Figure 3-3 OBUS Register Select

# 3.2.3 IBUS/OBUS Registers Bit Descriptions

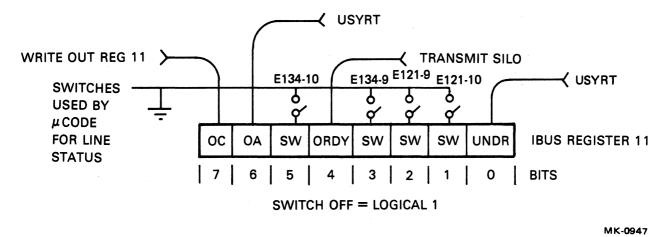

Figures 3-4 through 3-19 provide the input and output registers, bit descriptions, and qualifications for read and write operations.

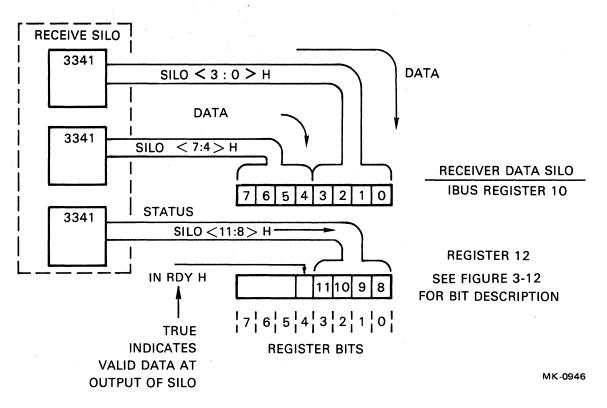

Figure 3-4 IBUS Register 10

- Reads data in and shifts the silo.

- Status bits (register 12) are read first.

- Register 12 status bit 4, in RDY H, must be true before any data is read from the silo.

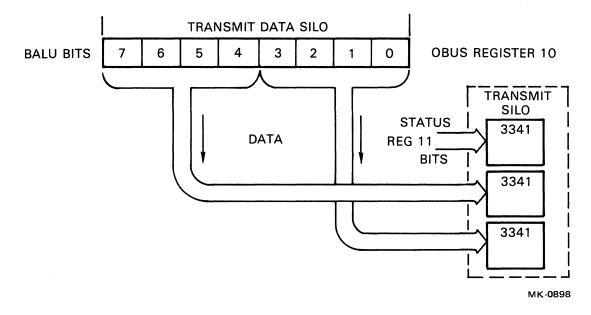

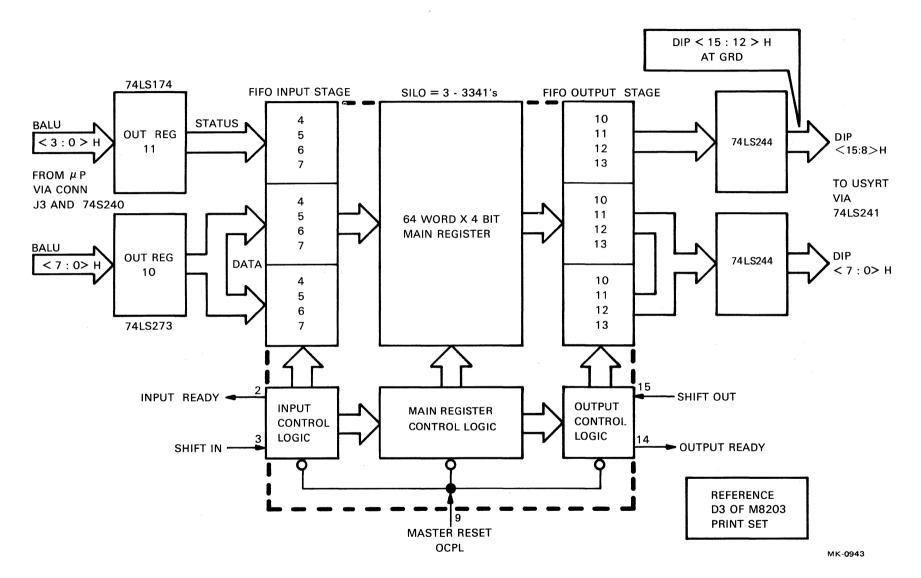

#### LOAD DATA TO BE TRANSMITTED

Figure 3-5 OBUS Register 10

Write Operation:

- Loads data to be transmitted into and shifts the silo.

- Status bits (BALU 3-0) from OBUS register 11 are also loaded into the silo when OBUS register 10 loads the silo. The status bits, if they are required, should be loaded first.

- All bits are cleared when the silo is shifted.

- Data should not be written into register 10 unless status Bit 4 of read IBUS register 11 (Out Ready) is set.

#### LINE STATUS

- Bits 1-3 and 5 (switch) have no hardware control. They should be set up when the module is installed in the field according to the customer link (the microcode and microprocessor used). Refer to the appropriate Options Technical Manual.

- Bit 0 = a transmitter underrun has occurred meaning characters have not been supplied to the transmitter fast enough, causing the USYRT to go to the IDLE state. (Can only be cleared by the next Start of Message (SOM) or by clearing the transmitter.)

- Bit 4 = Out Ready the silo is ready for another character. If the silo is disabled, it indicates that the USYRT is ready for another character.

- Bit 6 = Out Active the USYRT is in the process of transmitting data. If Out Active is set and Request to Send is not set, no characters are processed (check Modem Ready and Clear to Send bits in IBUS register 13).

- Bit 7 = Out Clear transmitter is in the process of being cleared and should not be addressed. This bit must not be set until In Clear (IBUS register 12, bit 7) is clear; that is, Out Clear should not be set when an In Clear is in progress.

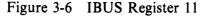

#### CONTROL TRANSMIT CIRCUITRY

Figure 3-7 OBUS Register 11

Write Operation:

- Bits 0 to 3 are loaded into the silo before register 10 loads the silo and are used to transmit characters or cyclic redundancy check (CRC).

- Bit 0 = Start of Message (SOM) used to transmit flags (01111110) in bit oriented protocols or is loaded with a sync character to set up the transmitter and receiver for data that is to follow.

- Bit 1 = End of Message (EOM) used to send the CRC character, if CRC is enabled in both protocols, and the trailing flag or sync character.

# NOTE A minimum of two SOMs must be sent at the start of a character oriented message.

Bit 2 = Send Abort – used in bit oriented protocol (11111111).

Bit 3 = Send Go-Ahead – used in bit-oriented protocols only (01111111).

• Bit 7 = Clear the Transmit Circuitry – Out Clear (OC, IBUS register 11) must be 0 before loading the transmitter.

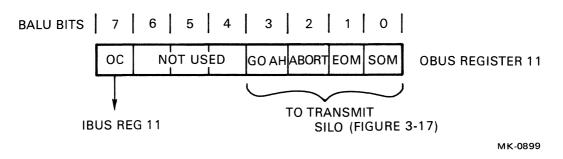

NOTE If the transmit silo is full, the Out Clear function will not clear the transmitter. **RECEIVER STATUS**

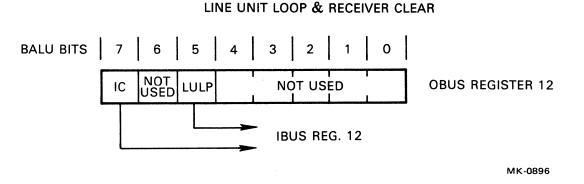

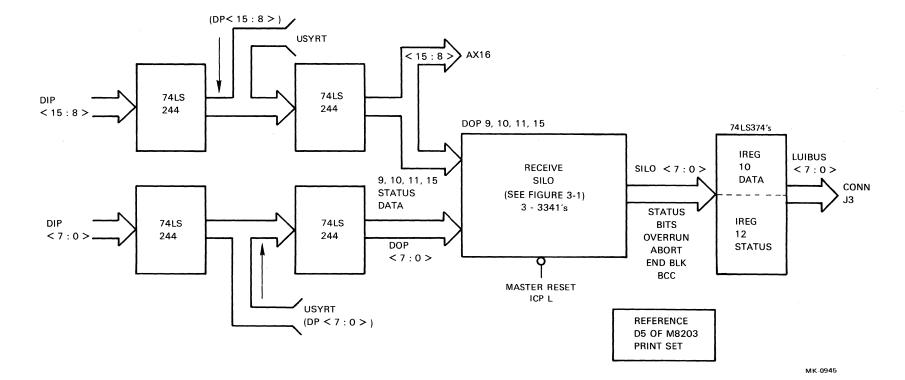

Figure 3-8 IBUS Register 12

Read Operation:

- Bits 0-3 = status of the USYRT (data character in IBUS register 10). When IBUS register 10 is read, bits 0-3 are updated to the next character.

- 0 = Block Check Character (BCC) match only valid at the end of the message or after the last data character (bit oriented protocol when EOM is set).

# NOTE BCC match is valid two characters before the previous DMC11 Line Units (M8201 and M8202).

One = correct CRC or match in character oriented protocol.

Zero = correct CRC or match in bit oriented protocol.

- Bit 1 = End of Block in bit oriented protocol indicates End of Message & BCC match is valid.

- Bit 2 =Received Abort bit oriented protocol, 7 ones received.

- Bit 3 = Receiver Overrun data is not being removed fast enough from the receiver silo meaning data for this message is not valid and should be discarded. OVRR will clear when receiver is cleared (IC).

- Bit 4 = In Ready the next character is ready to be read from the receiver silo. If the silo is disabled, a character is ready to be read from the USYRT.

- Bit 5 = Line Unit Loop line unit is in maintenance mode and transmit data is being turned around in the USYRT.\*

\*Strictly internal to the USYRT; not to be confused with the line unit loop set in the microprocessor CSR 0 which is a loop back mode that is external to the USYRT. If RUN on the microprocessor:

- (1) is set, the USYRT is run at 24K bps.

- (2) is not set, the clock is generated from the Step Line Unit bit 12 of CSR 0.

- Bit 6 = Receiver Active receiver has started to process data. The carrier bit M IBUS register 13 must be set or the receiver will not become active.

- Bit 7 = In Clear receiver circuit of USYRT and the silos are in the process of being cleared.

Figure 3-9 OBUS Register 12

Write Operation:

- Bit 5 = Line Unit Loop enables the maintenance mode of the USYRT which loops the data back internally to the USYRT. Selects internal clock if RUN is set or Step Line Unit if RUN is not set.

- Bit 7 = Clear the Receiver Circuit of the USYRT (silos also cleared) used to clear the receiver CRC in byte oriented protocol. In Clear must not be set until Out Clear (IBUS register 12, Bit 7) is clear; that is, In Clear should not be set when Out Clear is in progress.

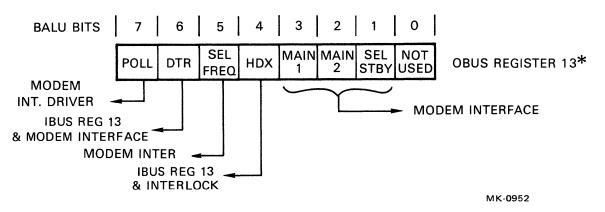

#### STATUS AND CONTROL OF MODEM INTERFACE MODEM RECEIVERS **OUTPUT REG** USYRT 13 RS HDX MODR CS STBY CARR RING DTR **IBUS REGISTER 13** 2 0 7 6 5 4 3 1 BITS MK-0901

Figure 3-10 IBUS Register 13

- Bit 0 = Carrier (Receiver Ready) indicates that the Integral Modem or Modem Interface is active. The carrier signal must be set before the USYRT receiver processes characters. The carrier is used by the USYRT to clear the CRC registers between messages.

- Bit 1 = Standby references standby indication from the modem (see EIA specification).

- Bit 2 = Clear to Send a reply from the modem used by hardware to start sending data. Clear to Send must be low for Request to Send to set. With the Integral Modem, a 100  $\mu$ s delay occurs before Clear to Send is set.

- Bit 3 = Modem Ready (Data Mode) modem is in service. Used with Modem Interface and is a hardware lockout of Request to Send until modem ready is set (see EIA specification).

- Bit 4 = Half-Duplex the line unit logic is set in the half-duplex mode.

- Bit 5 = Request to Send the USYRT is ready to start transmitting data and will start as soon as Clear to Send is true. Request to Send does not set unless Out Active is set, Modem Ready is set, and Clear to Send is not set.

- Bit 6 = Data Terminal Ready (Terminal in Service) signal to modem from the line unit indicating that the line unit is available and on line (see EIA specification).

- Bit 7 = Ring or Incoming Call the modem has just been dialed and data is forthcoming (see EIA specification).

#### STATUS AND CONTROL OF MODEM

Figure 3-11 OBUS Register 13

# Write Operation:

- Bit 1 = Select Standby when a modem interface is used (see EIA specification).

- Bit 2 = Maintenance Mode 2 remote loopback using the modem interface and the external modem. It is used to test the modem (see EIA specification).

- Bit 3 = Maintenance Mode 1 local loop using the Modem Interface and the external modem tests the interface to the modem (see EIA specification).

- Bit 4 = Half-Duplex sets the line unit in the half-duplex mode; the line unit either transmits or receives at any given time (hardware interlocked controlling the line unit).

- Bit 5 = Select Frequency used on Modem Interface to change modem data rates (see EIA specification).

- Bit 6 = Data Terminal Ready (Terminal Ready) indicates to the modem that the line unit is ready to receive or transmit data. It must be set when the Modem Interface is used, otherwise, the modem ignores other control signals from the line unit.

- Bit 7 = Polling a new function for RS-422-A, RS-423-A, and RS-449 (not clearly defined). Intended for use with multidrop modems.

<sup>\*</sup>For switched line booting, OBUS Register 13 is not cleared by a Master Clear or Initialize.

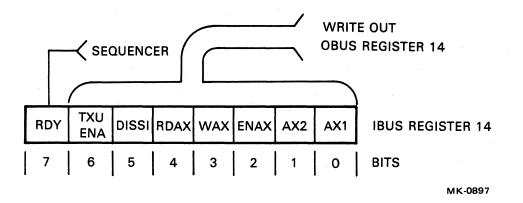

Read/Write Operations:

#### NOTE

Sync character or secondary address must be loaded through the extended registers. Register 14 is used for extended register control (unlike previous DMC11 line units).

- Bit 0 = Extended Address Bit 1 used to select the USYRT register that is being written to or read from.

- Bit 1 = Extended Address Bit 2.

- Bit 2 = enables the extended registers starts the extended operation when set.

- Bit 3 = selects a write operation through the extended registers.

- Bit 4 = selects a read operation through the extended registers.

- Bit 5 = disables the silos so that the USYRT can be loaded and read directly.

- Bit 6 = Transmitter Enable must be set before characters are loaded into the USYRT when the line unit is programmed with the silos disabled. When the silo is enabled, keeps Request to Send set.

- Bit 7 = Ready (Read only) the operation executed through the extended registers is completed. Other bits in registers 14, 15, and 16 should not change unless the Ready bit is set.

The normal operation using extended registers:

- Extended address must be loaded first.

- If a write: data must be loaded in write out (OBUS) registers 15 & 16. Set WAX and the enable bit.

- If a read: Set RDAX and the enable bit.

- The operation is complete when Bit 7 becomes true.

#### LOADING THRU EXTENDED REGISTERS 7 6 5 4 3 2 1 0 BALU BITS NOT TXU **OBUS REGISTER 14** DISSIRDAX WAX ENAX AX2 AX1 USED ENA **IBUS REG 14** 74S174 FUNCTION LATCH < 3: 0 > (D6 OF M8203 PRINT SET) MK-0958

Figure 3-13 OBUS Register 14

Read/Write Operations:

Refer to Figure 3-13 for bit definitions.

Figure 3-14 IBUS Register 15

- A normal read from register 15 is a switch pack defined by microcode. Refer to the appropriate Options Technical Manual.

- In extended addressing mode, IBUS register 15 is the low byte of data read from the extended register defined by the extended address bits. (See Extended Register Description, Section 3.2.4.)

- The extended address data is only true when the relevant bits are set for the extended address and Bit 7 of register 14 is set. (See Extended Register Description, Section 3.2.4.)

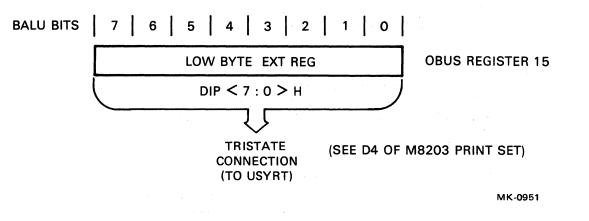

Figure 3-15 OBUS Register 15

# Write Operation:

- A write to OBUS register 15 in normal mode is not valid.

- A write to OBUS register 15 is only valid in extended mode.

- Any write to OBUS register 15 is loaded in the extended data register (low byte), but data is not used until the extended address is set up and WAX and ENAX are set, except AX3-15, which must be selected before data is written into OBUS register 15.

- See Extended Register Description, Section 3.2.4.

Figure 3-16 IBUS Register 16

- Similar to Register 15.

- A normal read is from the switch pack defined by microcode.

- In extended mode, the register is the high data byte for extended addressing, whose data is only valid when Bit 7 of register 14 is set.

- Refer to Extended Register Description, Section 3.2.4.

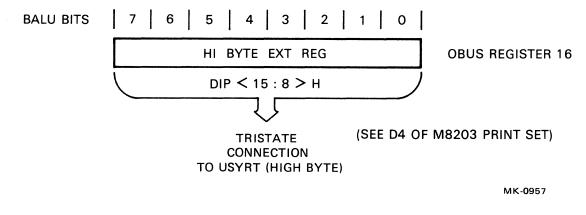

Figure 3-17 OBUS Register 16

Write Operation:

- A write to register 16 loads data only into the data register for the extended addressing function.

- The data is used after the address is set up and WAX and ENAX are set.

- Refer to Extended Register Description, Section 3.2.4.

#### MAINTENANCE FUNCTIONS

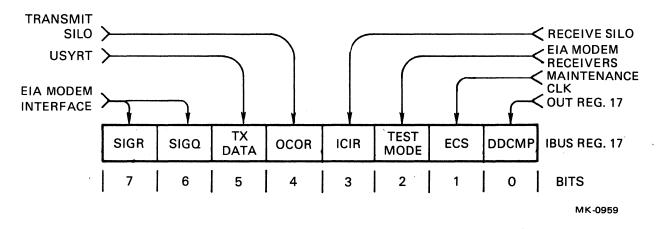

Figure 3-18 IBUS Register 17

- Bit 0 =Line unit mode

- 0 = Bit oriented protocol

- 1 = Character oriented protocol (initializes to a 1).

- Bit 1 = Maintenance clock step line unit or 48 KHz.

- Bit 2 = Test mode, modem attached to EIA interface is in the test mode (see EIA specification).

- Bit 3 = In composite ready, the receive silos are ready to receive another character (maintenance mode only).

- Bit 4 = Out composite ready, data is present at the bottom of the transmit silo for transfer to the USYRT (maintenance mode only).

- Bit 5 = indicates that a data bit is present on the output of the USYRT serial data stream (maintenance mode only).

- Bit 6 = Signal quality indication from the EIA Modem Interface (see EIA specification).

- Bit 7 = Signal rate from EIA Modem Interface (see EIA specification).

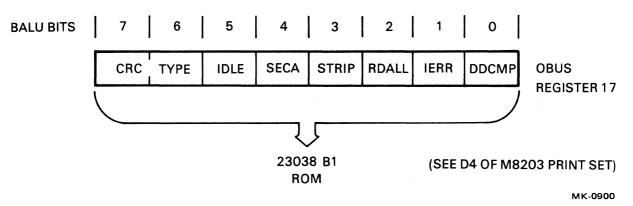

#### MAINTENANCE AND PROTOCOL FUNCTIONS

Figure 3-19 OBUS Register 17

Write Operation:

- Bit 0 = Mode of line unit initializes to a 1. 1 = Character oriented protocol

- 0 = Bit oriented protocol

- Bit 1 = Insert error when line unit loop is set in microprocessor CSR; all bits are shifted into the USYRT when this bit is set to 1.

- Bit 2 = Read All Parties used in bit oriented protocol; all parties address (11111111) and the normal secondary address.

- Bit 3 = Strip sync character in character oriented protocol after the first two characters.

- Bit 4 = Secondary address mode for bit oriented protocol. Enables auto detection of the secondary address and accepts messages with its secondary address or the all parties address if bit 3 is set.

- Bit 5 = Idle Uses the 23038B1 ROM, which normally sets Idle in the USYRT (sync characters must be loaded by the microprocessor). With Idle clear the USYRT will MARK when underrun occurs.

• Bits 6 & 7 = Determine the type of error checking being used:

| Bits | Character Oriented   | Bit Oriented                    |

|------|----------------------|---------------------------------|

| 76   | Protocol             | Protocol                        |

| 0 0  | CRC 16               | CCITT 16 initialized to one     |

| 0 1  | Odd vertical parity  | CCITT 16 initialized<br>to zero |

| 1 0  | Even vertical parity | Not used                        |

| 1 1  | No error checking    | No error checking               |

Register 17 initializes to character oriented protocol with CRC 16.

## 3.2.4 Extended Registers/Indirect Addressing

Indirect addressing is used to address the USYRT directly, thereby bypassing the silos and standard hardware to run special protocols and variable word lengths. Indirect addressing is accomplished by setting up address AX in OUT/IBUS register 14, then the data in extended registers 15 and 16.

- Extended address must be loaded first.

- For a write operation, set Enable AX and WAX. Data must be loaded in OBUS registers 15 and 16.

- For a read operation, set Enable AX and RDAX.

When bit 7 of IBUS register 14 is set, the operation is complete. Figures 3-20 through 3-27 provide the write IBUS/OBUS register bit descriptions and qualifications for read operations.

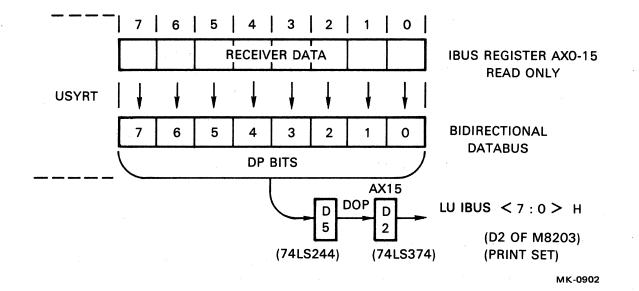

Figure 3-20 AX0-15 Register

Read only:

- Receiver data is directly from the USYRT.

- The silo must be disabled (DISSI must be set).

- Set RDAX and Enable AX.

- IBUS register 15 is the low byte of the data read from AXO-15 as defined by the extended address bits.

- The operation is complete when Ready bit 7 (IBUS register 14) becomes true.

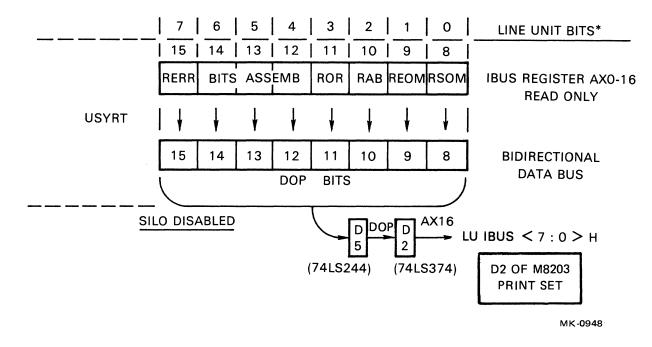

Figure 3-21 AX0-16 Register

Read only: Receiver status of each character from USYRT.

- Bit 0 = Received Start of Message (bit oriented protocol). A flag has been received followed by a non-flag character.

- Bit 1 = Received End of Message (bit oriented protocol). The closing flag has been received. The RERR bit is valid if CRC is enabled.

- Bit 2 = Received Abort (bit oriented protocol). Seven or eight ones have been received. Invalid character in bit oriented protocol.

- Bit 3 = Receiver Overrun (data is invalid, the message should be discarded indicating that the data characters have not been removed fast enough).

- Bits 4, 5, 6 = Number of bits assembled in the last data character when the closing flag was received (used in variable length bit oriented protocols).

- Bit 7 = Receiver Error (BCC match or parity error). Valid with the last character when CRC is enabled. A one indicates an error in bit oriented protocol.

\*USYRT bits <15:8> are interpreted (seen) by the microprocessor as line unit bits <7:0>.

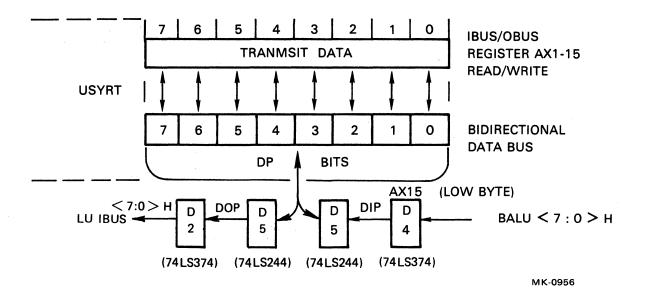

Figure 3-22 AX1-15 Register

# Read/Write:

- Transmit data loaded into USYRT should only be used with the silos disabled (DISSI) and only read when the clock is disabled as a maintenance function.

- With the silos disabled, OUT RDY Bit 4 (ORDY) in IBUS register 11 indicates when the next register can be loaded into AX1-15.

- AX1-15 should not be read unless IN RDY Bit 4 of IBUS register 12 is set.

- IBUS register 16 is the high byte of the data read from AX1-15.

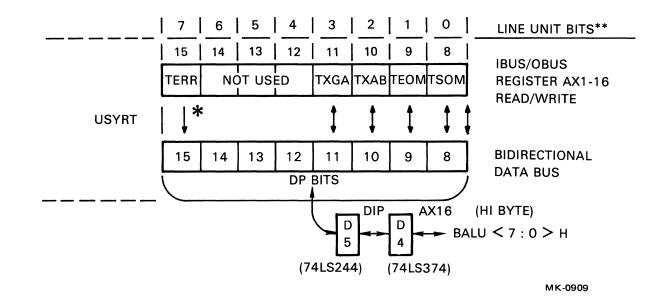

Figure 3-23 AX1-16 Register

Read/Write (Transmitter Control):

- Bit 0 = Transmit Start of Message generates sync or flag character and starts CRC calculation.

- Bit 1 = Transmit End of Message ends CRC generation, transmits CRC 16-bit character and flag or sync character.

- Bit 2 = Transmit Abort, (bit oriented protocol) transmits an abort character if IDLE Bit 5 of OBUS register 17 is cleared, or a flag character if IDLE is set.

- Bit 3 = Transmit Go Ahead; special for bit oriented protocol (0111111).

- Bit 7 = Transmitter Underrun (read only). Characters have not been supplied to the transmitter fast enough.

# \*READ ONLY

\*\*USYRT bits <15:8> = line unit bits <7:0> as seen by the microprocessor

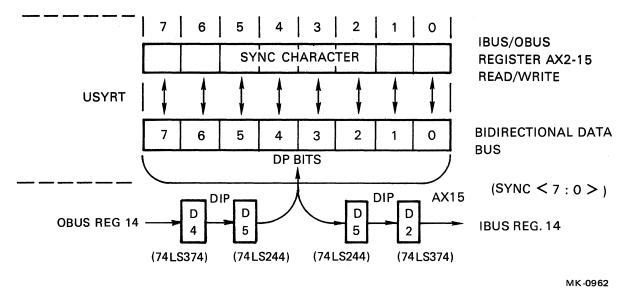

Figure 3-24 AX2-15 Register

Read/Write:

• Sync character in character oriented protocol or secondary address for bit oriented protocol.

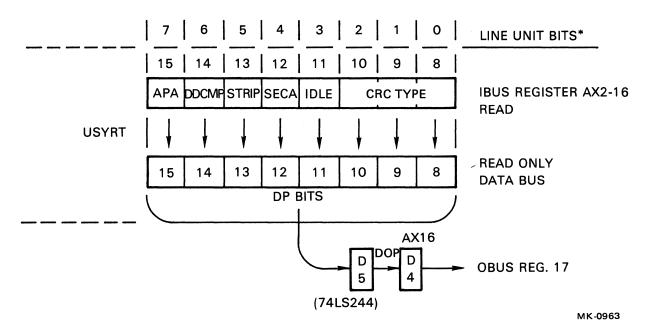

Figure 3-25 AX2-16 Register

Read: (Functions set via OBUS register 17)

• Bits 2, 1, 0 = CRC/Error Checking

\*USYRT bits <15:8> = line unit bits <7:0> as seen by the microprocessor.

| Bi<br>2 | ts<br>1 | 0 | Character Oriented<br>Protocol | <b>Bit Oriented Protocol</b>                    |

|---------|---------|---|--------------------------------|-------------------------------------------------|

| 0       | 0       | 0 | _                              | CCITT 16 initialized                            |

| 0       | 0       | 1 | -                              | to a one.<br>CCITT 16 initialized<br>to a zero. |

| 0       | 1       | 0 | Not used                       | Not used.                                       |

| 0       | 1       | 1 | CRC 16                         | _                                               |

| 1       | 0       | 0 | Odd parity                     | _                                               |

| 1       | 0       | 1 | Even parity                    | _                                               |

| 1       | 1       | 0 | Not used                       | Not used.                                       |

| 1       | 1       | 1 | No error checking              | No error checking.                              |

- Bit 3 = Idle: Determines what will be sent when an underrun occurs or when Transmit Abort Bit 2 of AX1-16 is set (0 = marks are sent, 1 = flags or syncs are sent in transparent modes, usually run with CRC disabled).

- Bit 4 = Secondary address enable for bit oriented protocol.

- Bit 5 = Strip sync characters for character oriented protocols.

- Bit 6 = 1 for character oriented protocol = 0 for bit oriented protocols.

- Bit 7 = Receive all parties (SEC address 377).

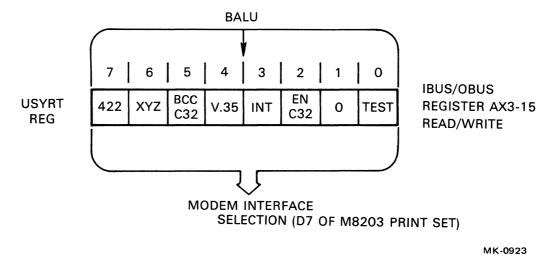

Figure 3-26 AX3-15 Register

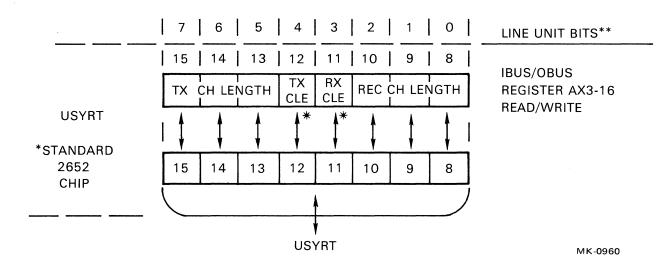

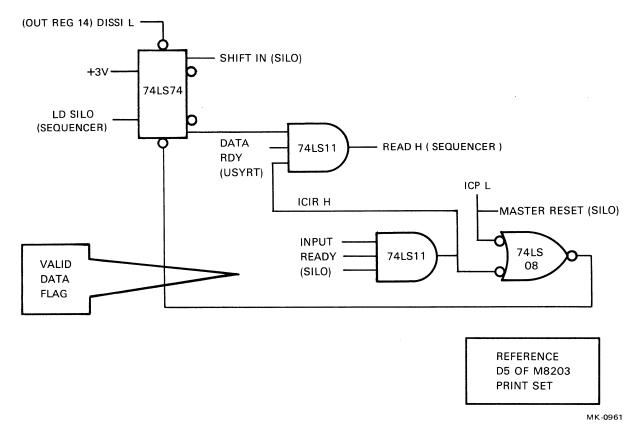

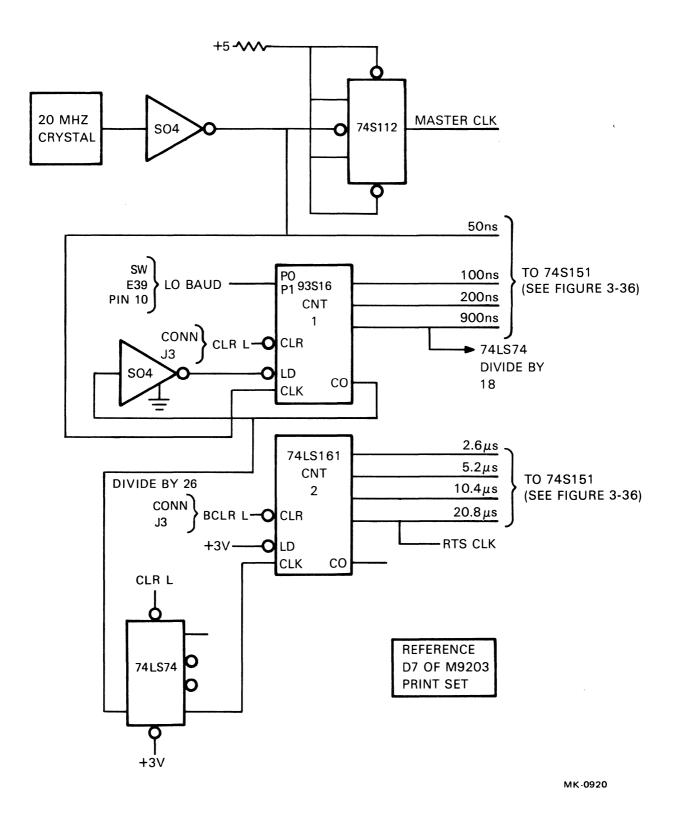

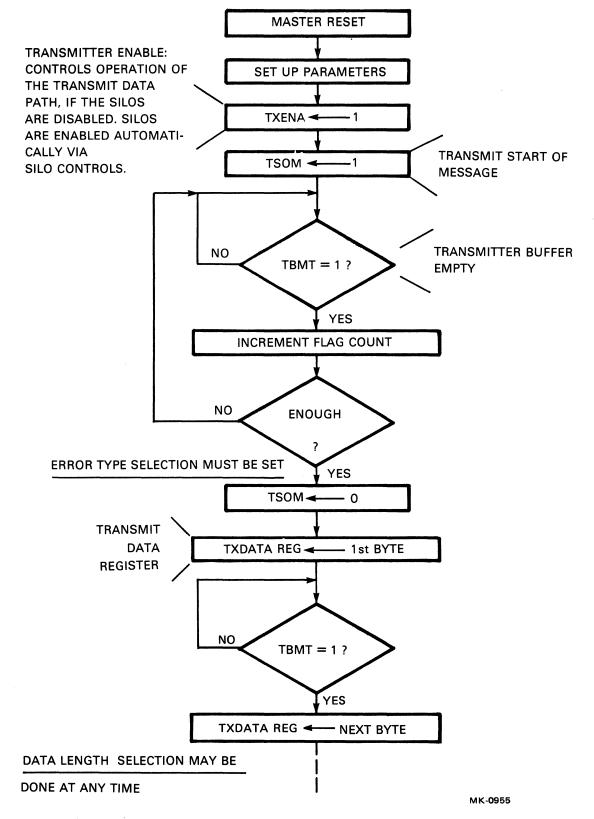

## Read/Write: