# LA36/LA35 DECuriter II Maintenance Manual Volume II

EK-2LA36-MM-001

# LA36 DECwriter II MAINTENANCE MANUAL Volume II

digital equipment corporation • maynard, massachusetts

# Copyright © 1976 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC          | DECtape | PDP              |

|--------------|---------|------------------|

| DECCOMM      | DECUS   | RSTS             |

| DECsystem-10 | DIGITAL | <b>TYPESET-8</b> |

| DECSYSTEM-20 | MASSBUS | TYPESET-11       |

|              |         | UNIBUS           |

# CONTENTS

| CHAPTER 9                                                  | UPGRADED LA36                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9.1                                                        | GENERAL                                                                                                                                                                                                                                                                                                                                                                        |

| 9.2                                                        | LA35/LA36 MODEL VARIATIONS                                                                                                                                                                                                                                                                                                                                                     |

| 9.3                                                        | EASY IDENTIFICATION OF LOGIC BOARDS                                                                                                                                                                                                                                                                                                                                            |

| 9.3.1                                                      | Major Functional Differences Between M7722 and M7723 Logic Boards 9-2                                                                                                                                                                                                                                                                                                          |

| 9.3.2                                                      | M7723 Jumper Configurations                                                                                                                                                                                                                                                                                                                                                    |

| 9.3.3                                                      | Functional Differences Between M7723 and M7728 Logic Boards                                                                                                                                                                                                                                                                                                                    |

| 9.3.4                                                      | M7728 Jumper Configurations                                                                                                                                                                                                                                                                                                                                                    |

| 9.3.5                                                      | M7728 Cabling Configurations                                                                                                                                                                                                                                                                                                                                                   |

| 9.4                                                        | MAJOR POWER SUPPLY CHANGES                                                                                                                                                                                                                                                                                                                                                     |

| 9.4.1                                                      | New Power Transformers                                                                                                                                                                                                                                                                                                                                                         |

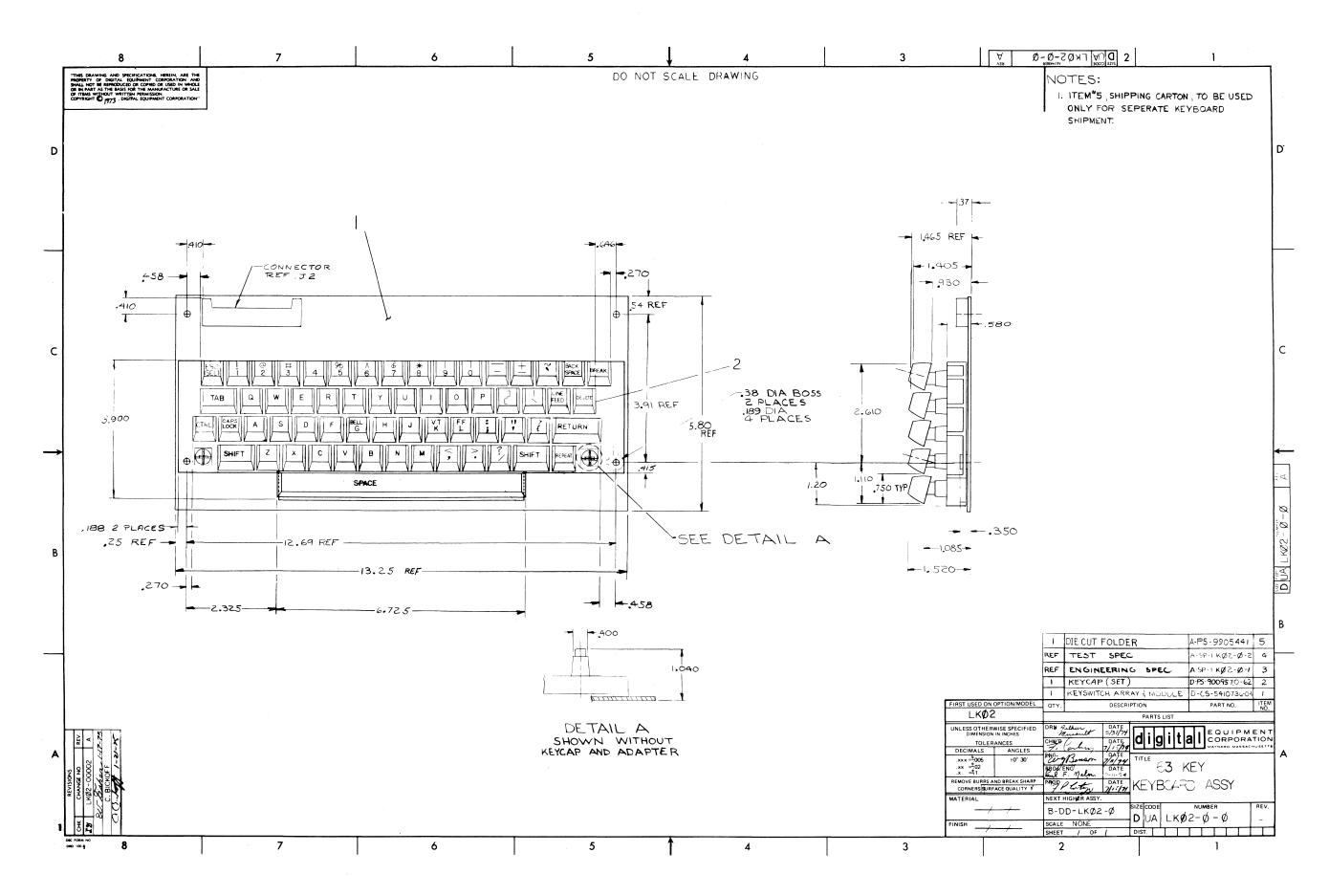

| 9.5                                                        | NEW KEYBOARD BEZELS                                                                                                                                                                                                                                                                                                                                                            |

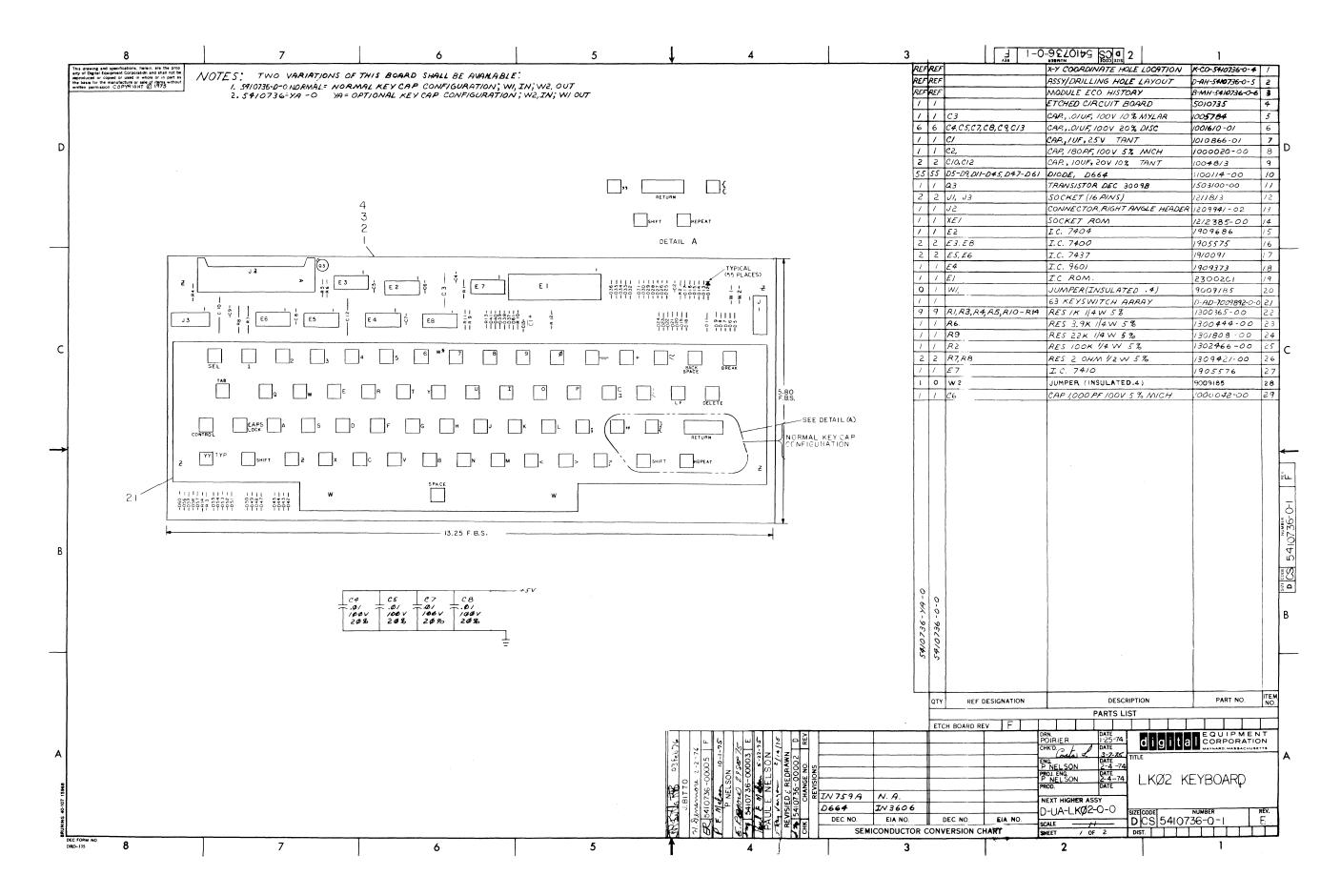

| 9.6                                                        | CAPS LOCK KEYBOARD                                                                                                                                                                                                                                                                                                                                                             |

| 9.7                                                        | LA35/LA36 OPTIONS                                                                                                                                                                                                                                                                                                                                                              |

| 9.8                                                        | UPGRADED LA36 FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                           |

| 9.8.1                                                      | New Transmit Path                                                                                                                                                                                                                                                                                                                                                              |

| 9.8.2                                                      | New Receive Path                                                                                                                                                                                                                                                                                                                                                               |

| 9.8.3                                                      | Transmit Operation with Options Installed                                                                                                                                                                                                                                                                                                                                      |

| 9.8.4                                                      | Receive Operation with Options Installed                                                                                                                                                                                                                                                                                                                                       |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                |

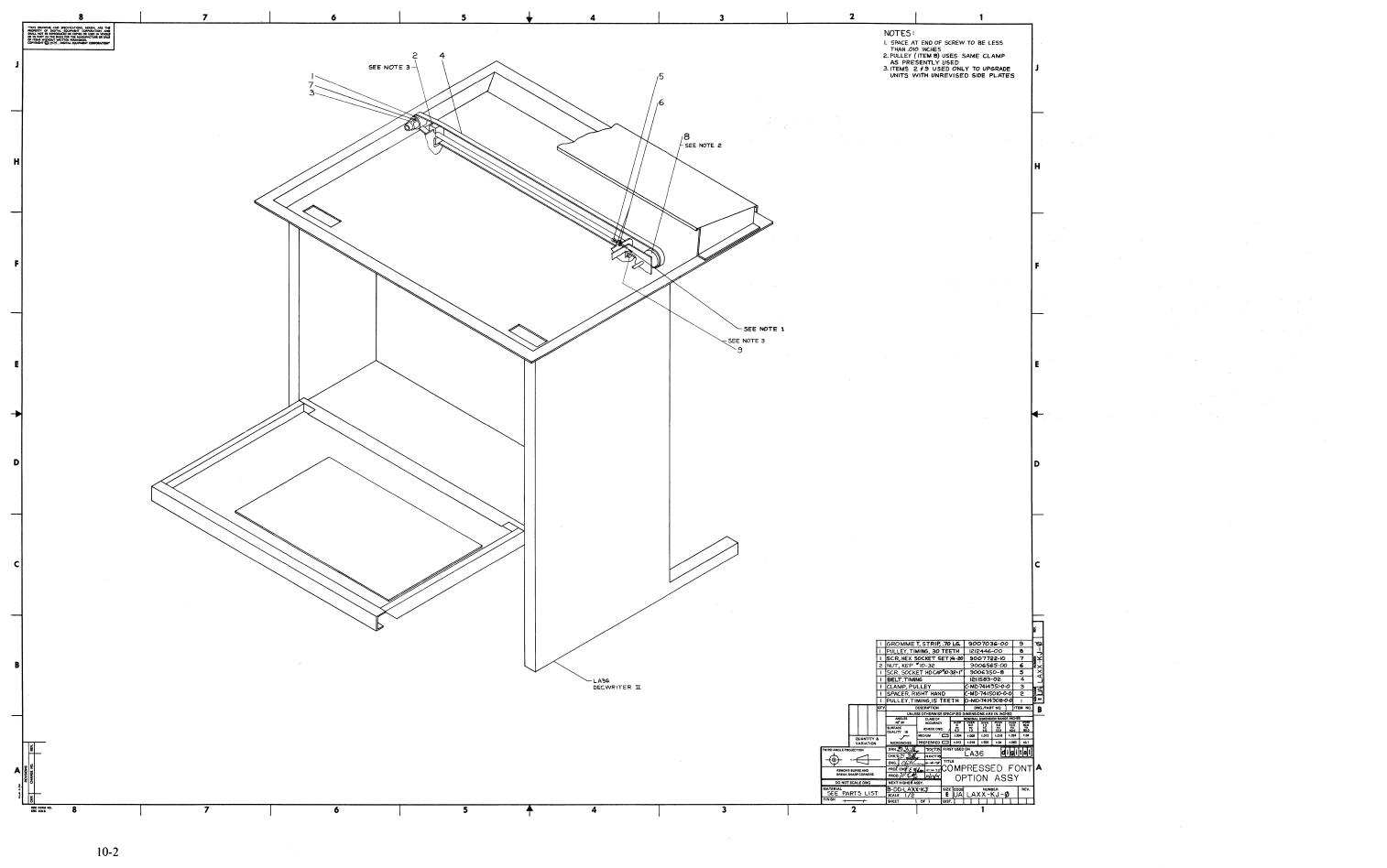

| CHAPTER 10                                                 | COMPRESSED FONT OPTION KIT (LAXX-KJ)                                                                                                                                                                                                                                                                                                                                           |

| 10.1                                                       | INTRODUCTION TO COMPRESSED FONT                                                                                                                                                                                                                                                                                                                                                |

| 10.2                                                       | LAXX-KJ PRINT SET                                                                                                                                                                                                                                                                                                                                                              |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                |

| CHAPTER 11                                                 | FORMS CONTROL OPTION KIT (LAXX-KV)                                                                                                                                                                                                                                                                                                                                             |

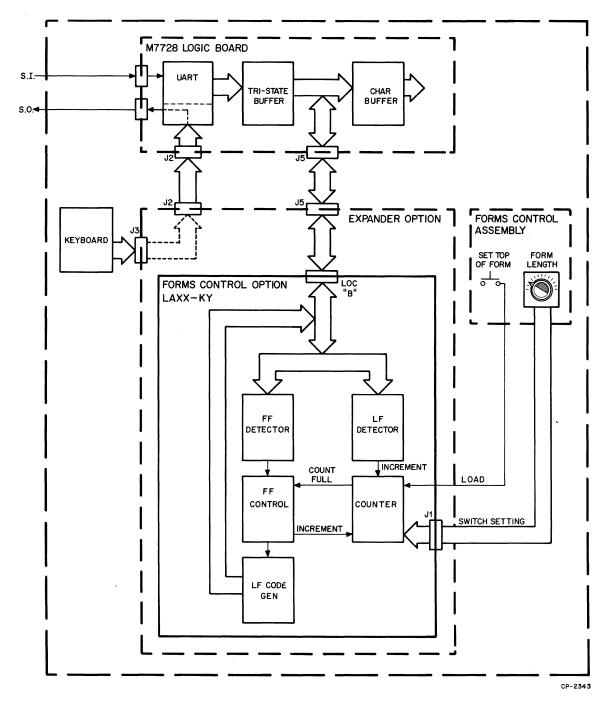

| 11.1                                                       | FORMS CONTROL INTRODUCTION                                                                                                                                                                                                                                                                                                                                                     |

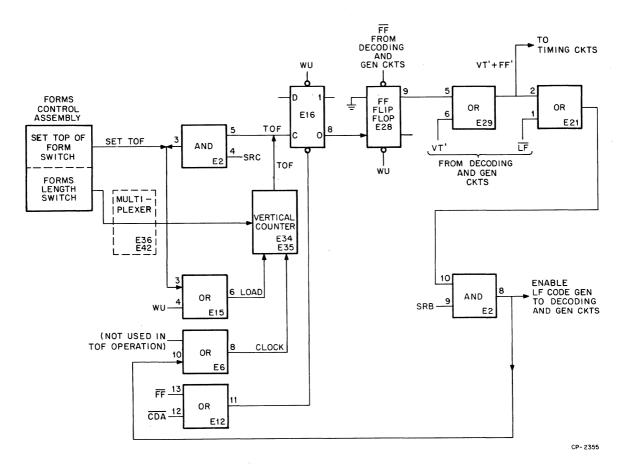

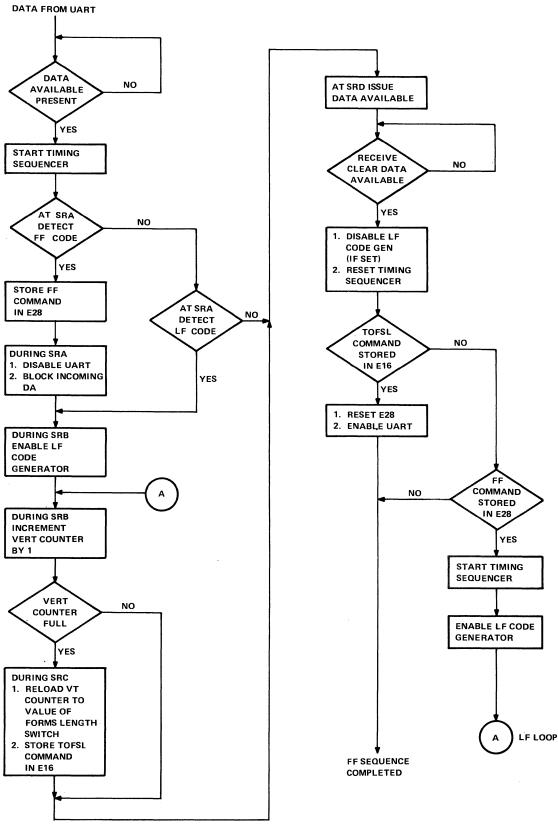

| 11.2                                                       | FORMS CONTROL FUNCTIONAL DIAGRAM                                                                                                                                                                                                                                                                                                                                               |

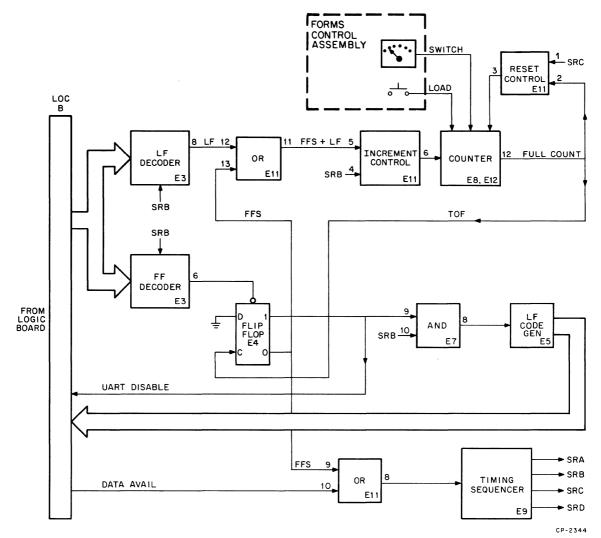

| 11.3                                                       | FORMS CONTROL BASIC BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                              |

| 11.3.1                                                     | Counter Circuit                                                                                                                                                                                                                                                                                                                                                                |

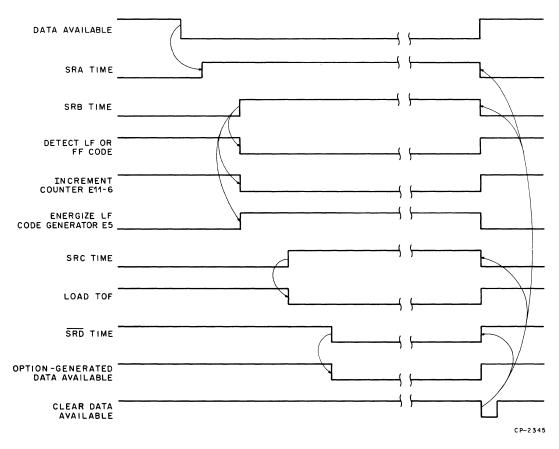

| 11.3.2                                                     | Option Timing                                                                                                                                                                                                                                                                                                                                                                  |

| 11.4                                                       | OPERATIONAL SEQUENCES                                                                                                                                                                                                                                                                                                                                                          |

| 11.4.1                                                     | Any Character Received                                                                                                                                                                                                                                                                                                                                                         |

| 11.4.2                                                     | Line Feed Code Decoded                                                                                                                                                                                                                                                                                                                                                         |

| 11.4.3                                                     | Form Feed Code Decoded                                                                                                                                                                                                                                                                                                                                                         |

| 11.5                                                       | TROUBLESHOOTING                                                                                                                                                                                                                                                                                                                                                                |

| 11.6                                                       | LAXX-KV PRINT SET                                                                                                                                                                                                                                                                                                                                                              |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                |

|                                                            |                                                                                                                                                                                                                                                                                                                                                                                |

| CHAPTER 12                                                 | SELECTIVE ADDRESSING OPTION (LAXX-KW)                                                                                                                                                                                                                                                                                                                                          |

| CHAPTER 12<br>12.1                                         |                                                                                                                                                                                                                                                                                                                                                                                |

|                                                            | SELECTIVE ADDRESSING OPTION (LAXX-KW)                                                                                                                                                                                                                                                                                                                                          |

| 12.1                                                       | SELECTIVE ADDRESSING OPTION (LAXX-KW)<br>SELECTIVE ADDRESSING INTRODUCTION                                                                                                                                                                                                                                                                                                     |

| 12.1<br>12.1.1                                             | SELECTIVE ADDRESSING OPTION (LAXX-KW)         SELECTIVE ADDRESSING INTRODUCTION         Transmit Conditions                                                                                                                                                                                                                                                                    |

| 12.1<br>12.1.1<br>12.1.2                                   | SELECTIVE ADDRESSING OPTION (LAXX-KW)         SELECTIVE ADDRESSING INTRODUCTION         Transmit Conditions         Receive Conditions         12-1         Receive Conditions                                                                                                                                                                                                 |

| 12.1<br>12.1.1<br>12.1.2<br>12.1.3                         | SELECTIVE ADDRESSING OPTION (LAXX-KW)         SELECTIVE ADDRESSING INTRODUCTION         Transmit Conditions         Receive Conditions         Operational Modes                                                                                                                                                                                                               |

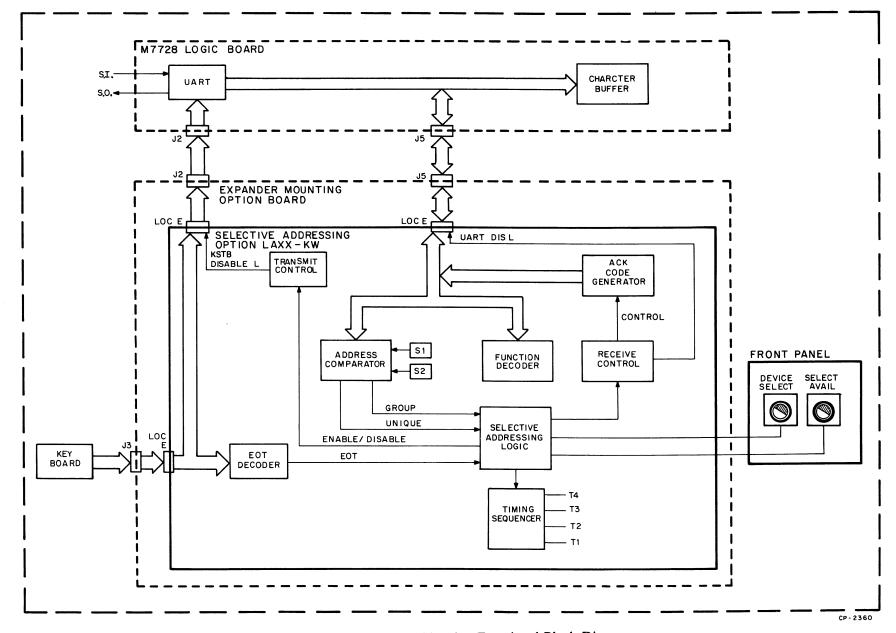

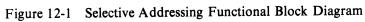

| 12.1<br>12.1.1<br>12.1.2<br>12.1.3<br>12.2                 | SELECTIVE ADDRESSING OPTION (LAXX-KW)         SELECTIVE ADDRESSING INTRODUCTION         Transmit Conditions         Receive Conditions         Operational Modes         SELECTIVE ADDRESSING FUNCTIONAL BLOCK DIAGRAM                                                                                                                                                         |

| 12.1<br>12.1.1<br>12.1.2<br>12.1.3<br>12.2<br>12.3         | SELECTIVE ADDRESSING OPTION (LAXX-KW)         SELECTIVE ADDRESSING INTRODUCTION       12-1         Transmit Conditions       12-1         Receive Conditions       12-1         Operational Modes       12-2         SELECTIVE ADDRESSING FUNCTIONAL BLOCK DIAGRAM       12-2         SELECTIVE ADDRESSING BASIC BLOCK DIAGRAM       12-4                                      |

| 12.1<br>12.1.1<br>12.1.2<br>12.1.3<br>12.2<br>12.3<br>12.3 | SELECTIVE ADDRESSING OPTION (LAXX-KW)         SELECTIVE ADDRESSING INTRODUCTION       12-1         Transmit Conditions       12-1         Receive Conditions       12-1         Operational Modes       12-2         SELECTIVE ADDRESSING FUNCTIONAL BLOCK DIAGRAM       12-2         SELECTIVE ADDRESSING BASIC BLOCK DIAGRAM       12-4         Power-Up Sequence       12-4 |

# **CONTENTS** (Cont)

|            |                                                                                | Page   |

|------------|--------------------------------------------------------------------------------|--------|

| 12.3.2.3   | Unique One-Way Slaves                                                          | . 12-7 |

| 12.3.2.4   | Unique Two-Way Slaves                                                          | 12-7   |

| 12.3.2.5   | Select Add-On Slaves                                                           | . 12-7 |

| 12.4       | TROUBLESHOOTING                                                                |        |

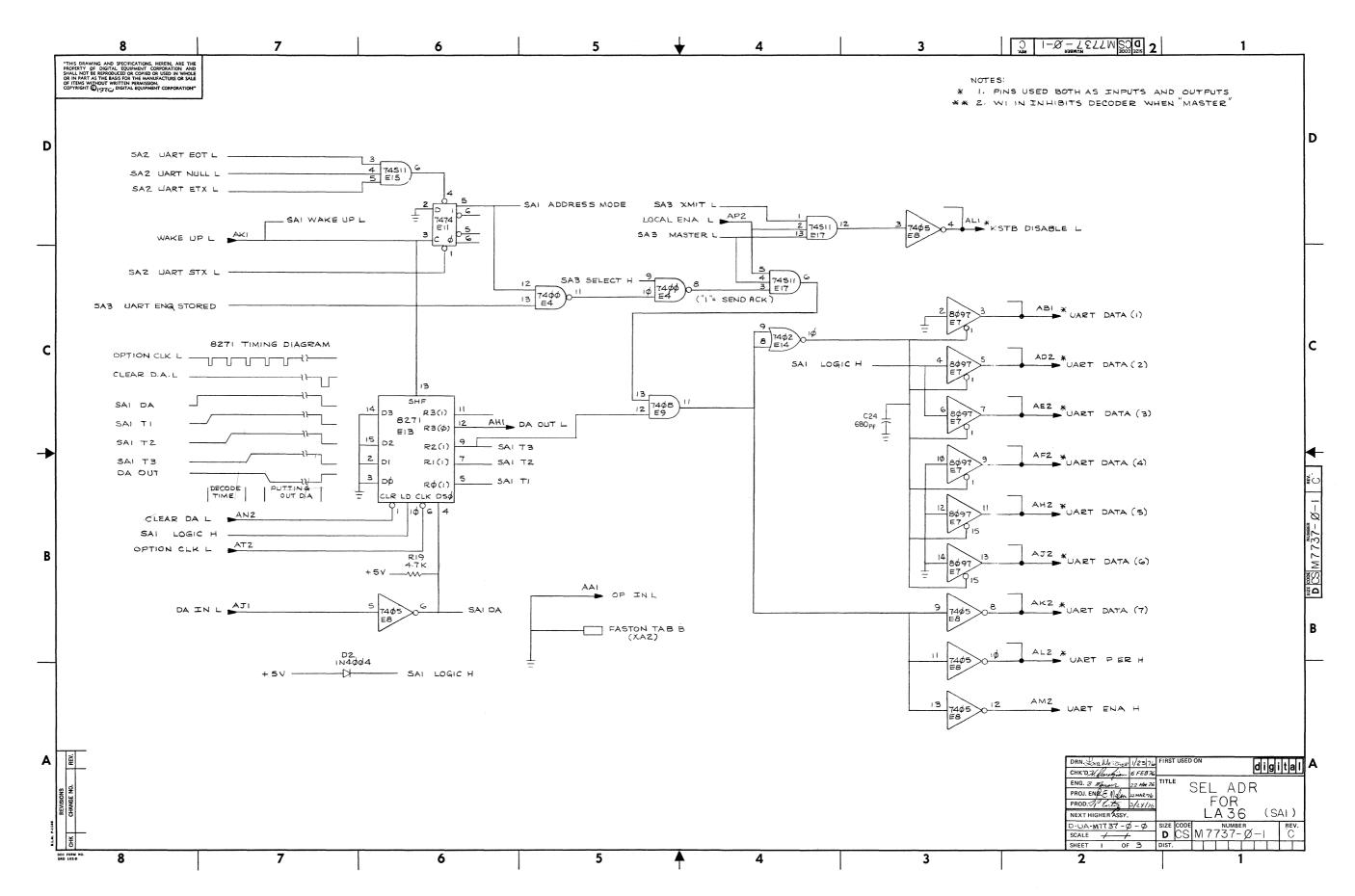

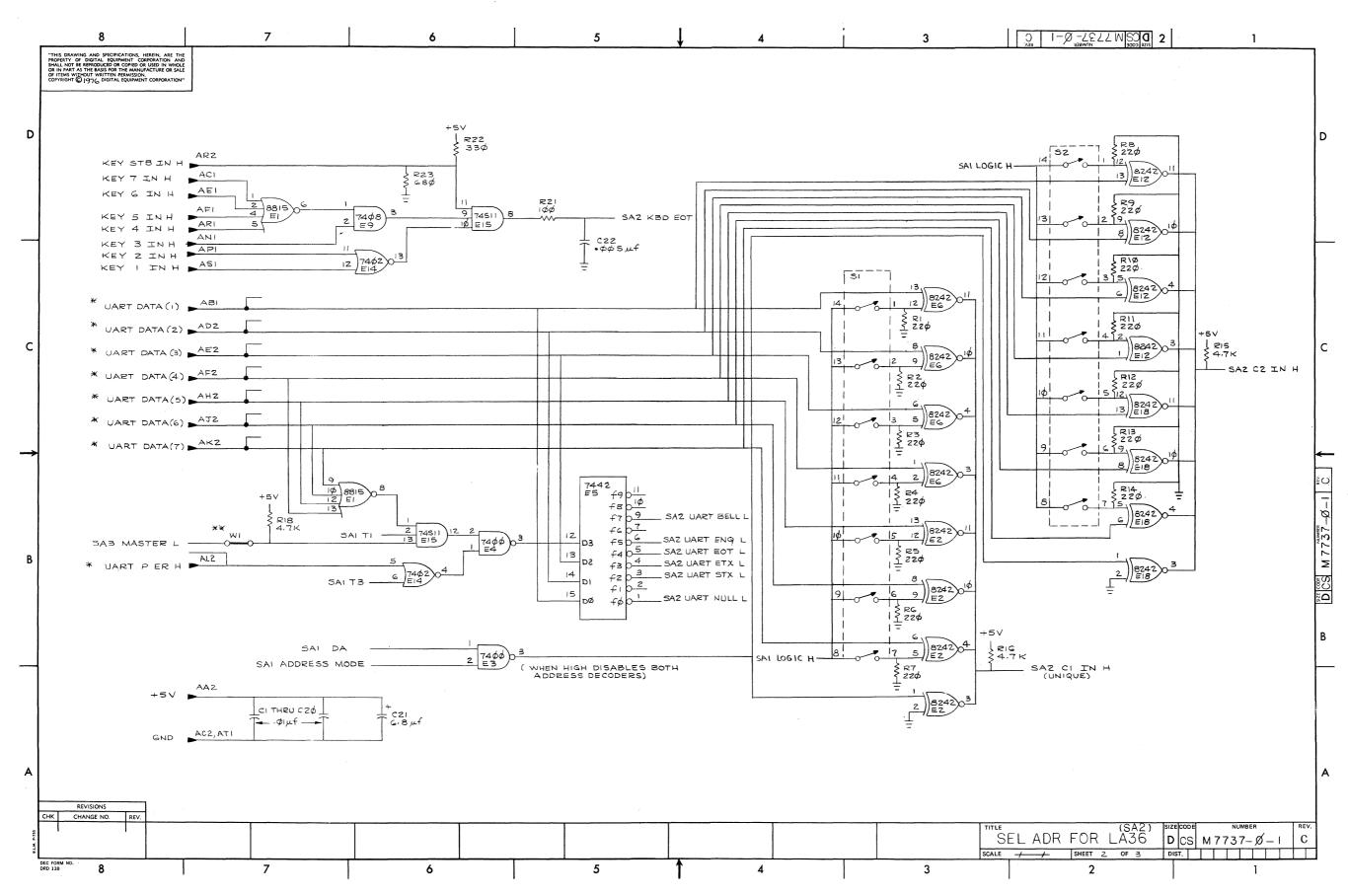

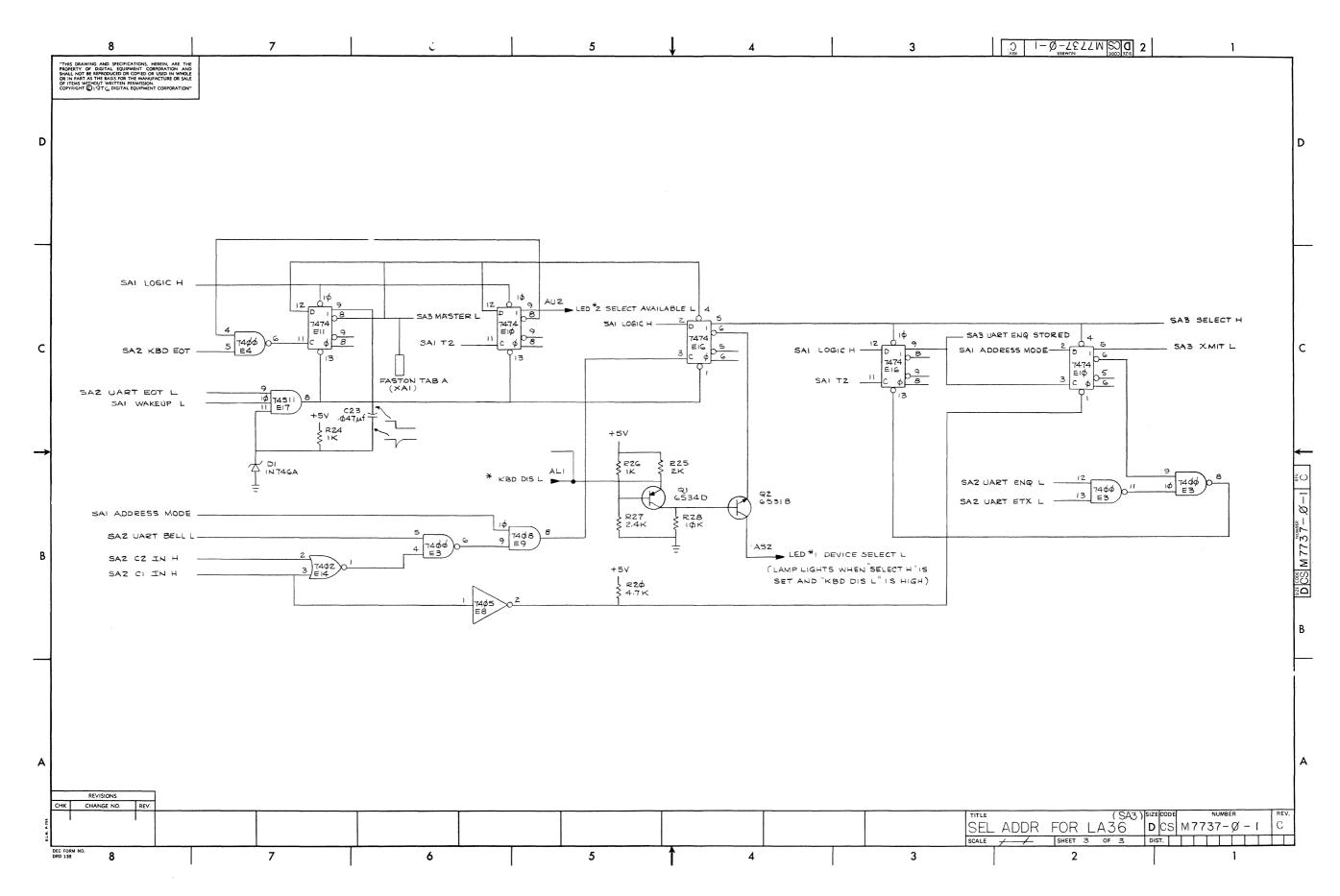

| 12.5       | LAXX-KW PRINT SET                                                              | . 12-7 |

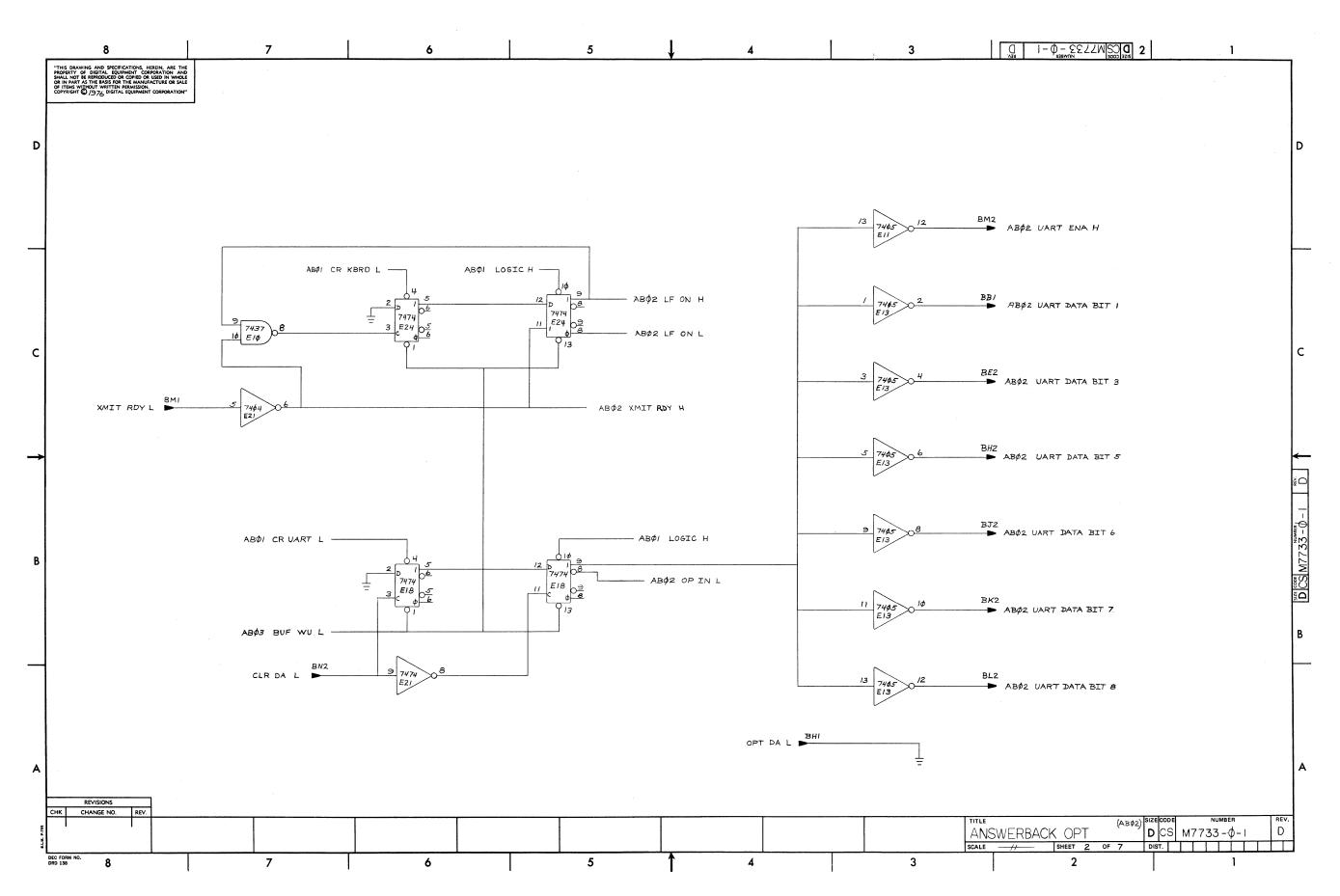

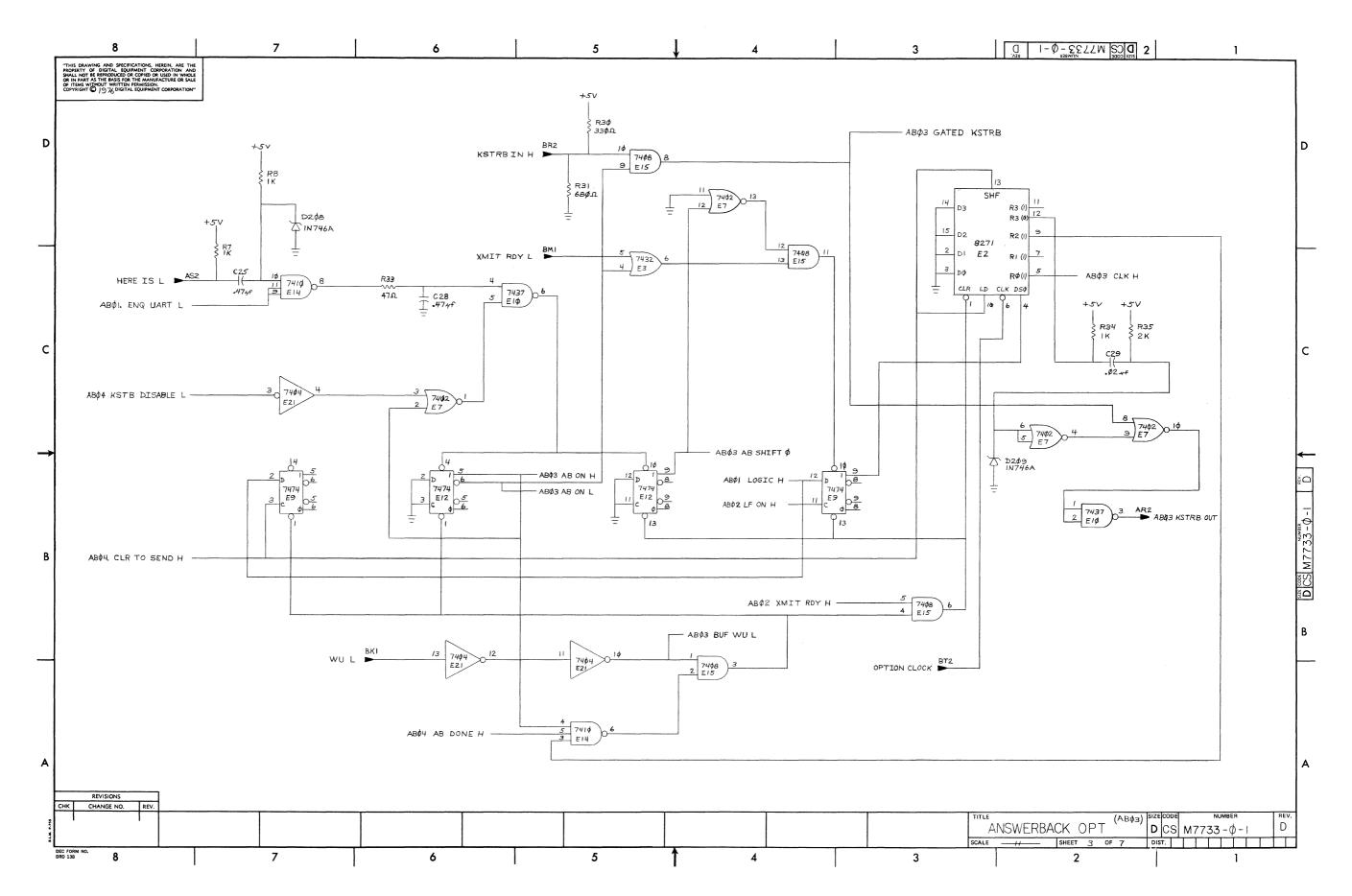

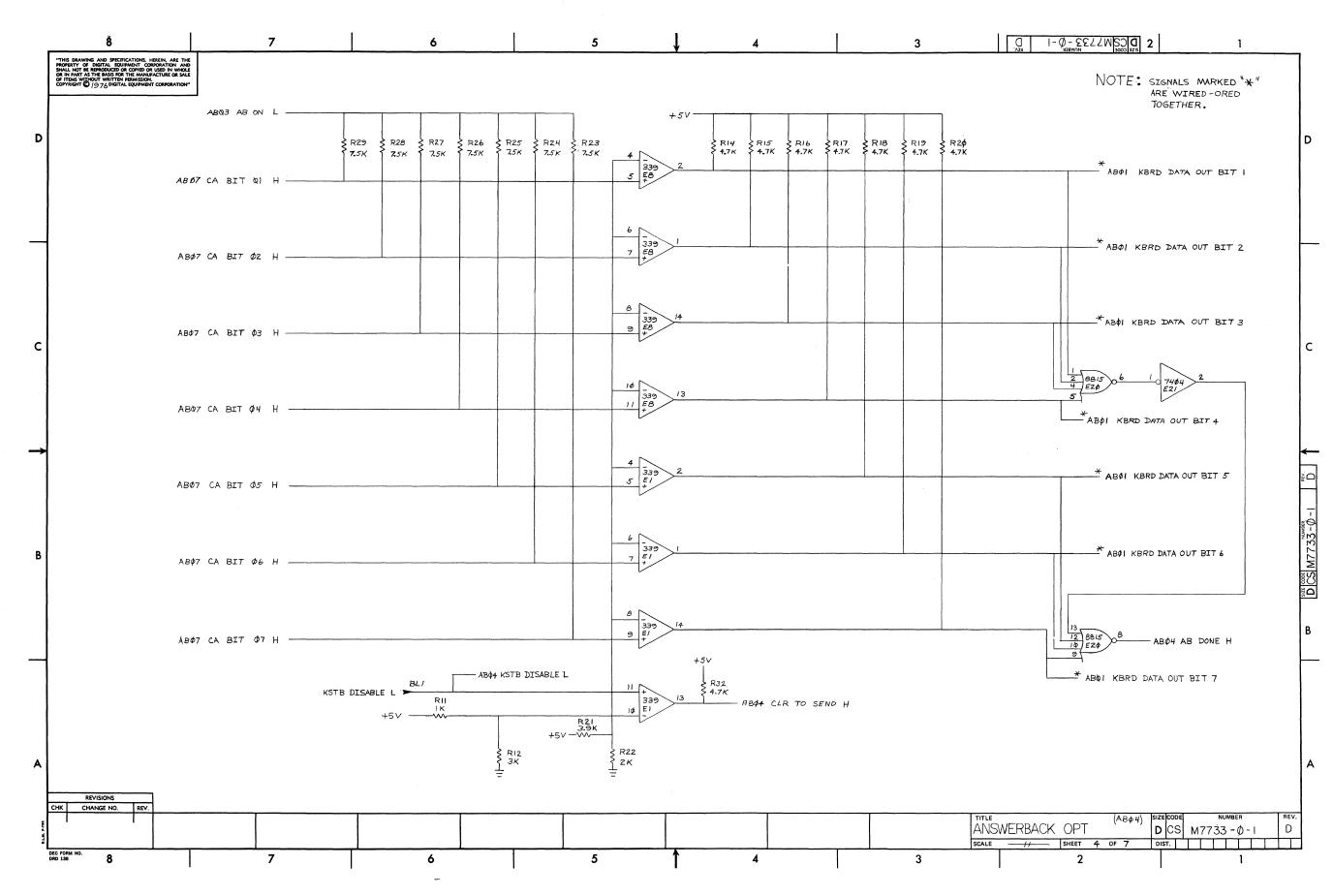

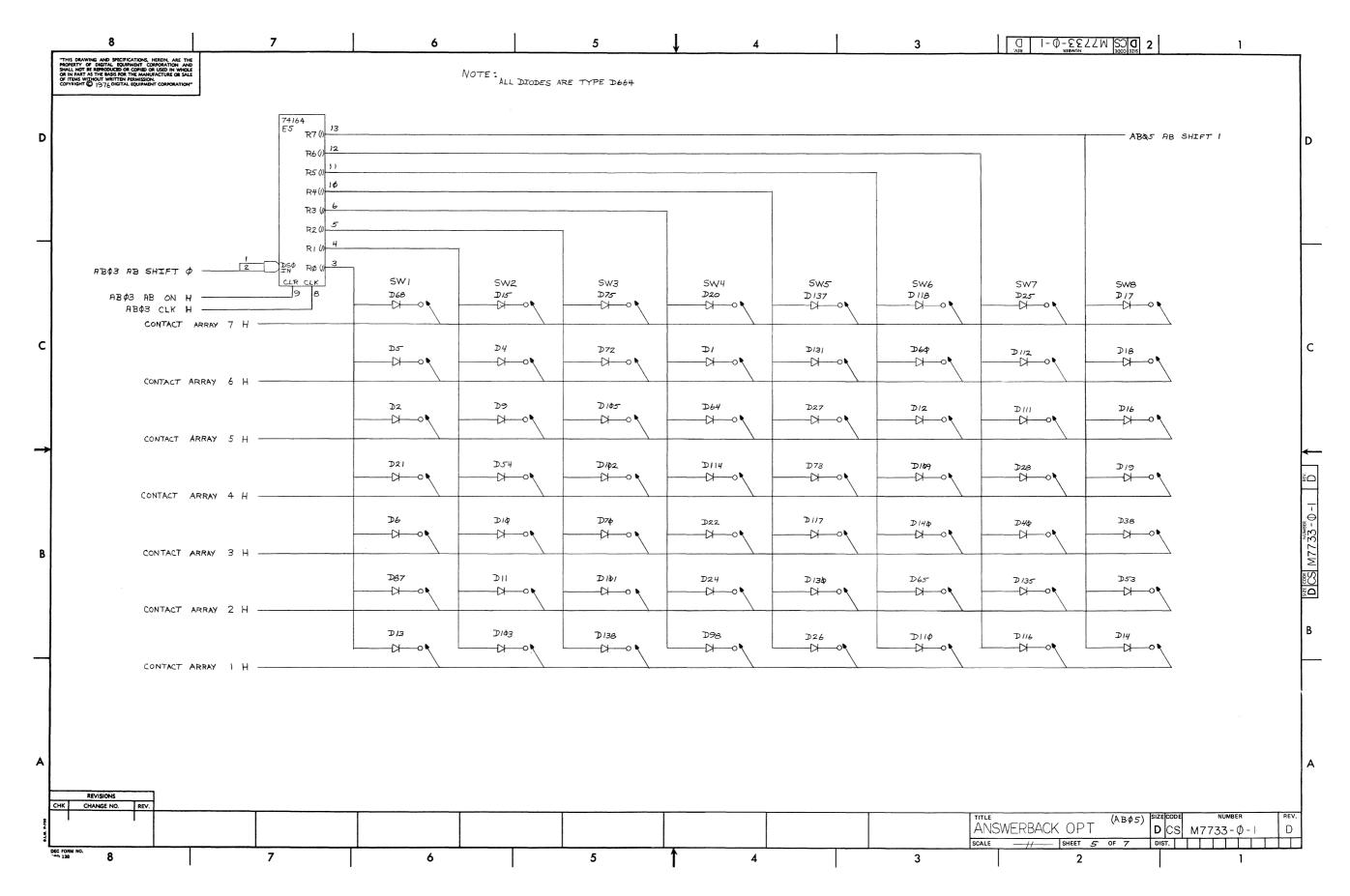

| CHAPTER 13 | AUTOMATIC ANSWERBACK OPTION (LAXX-KX)                                          | 44     |

| 13.1       | AUTOMATIC ANSWERBACK INTRODUCTION                                              | 13-1   |

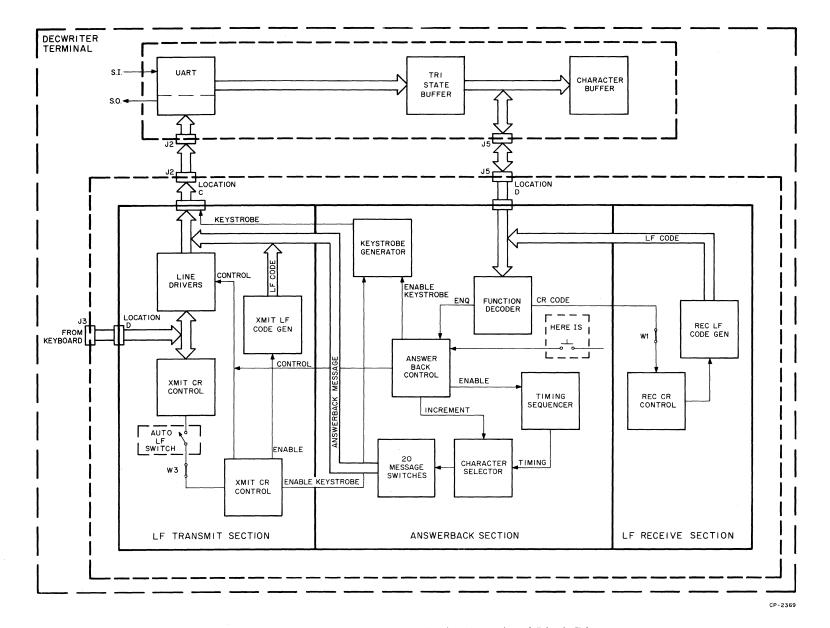

| 13.2       | ANSWERBACK OPTION FUNCTIONAL BLOCK DIAGRAM                                     |        |

| 13.2.1     | Operation of LF Transmit Section                                               |        |

| 13.2.2     | Operation of LF Receive Section                                                |        |

| 13.2.3     | Operation of Answerback Section                                                |        |

| 13.3       | AUTOMATIC ANSWERBACK BASIC BLOCK DIAGRAM                                       |        |

| 13.3.1     | LF Transmit Section Basic Block Diagram                                        |        |

| 13.3.2     | LF Receive Section Basic Block Diagram                                         |        |

| 13.3.3     | Answerback Section Basic Block Diagram                                         |        |

| 13.4       | TROUBLESHOOTING                                                                |        |

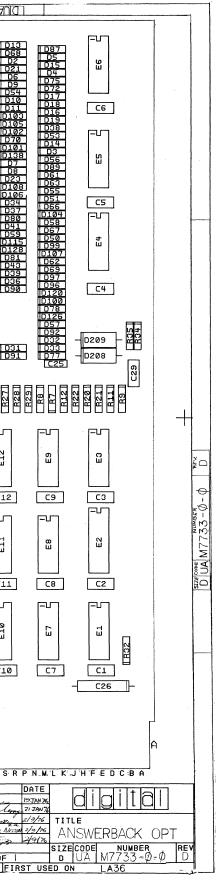

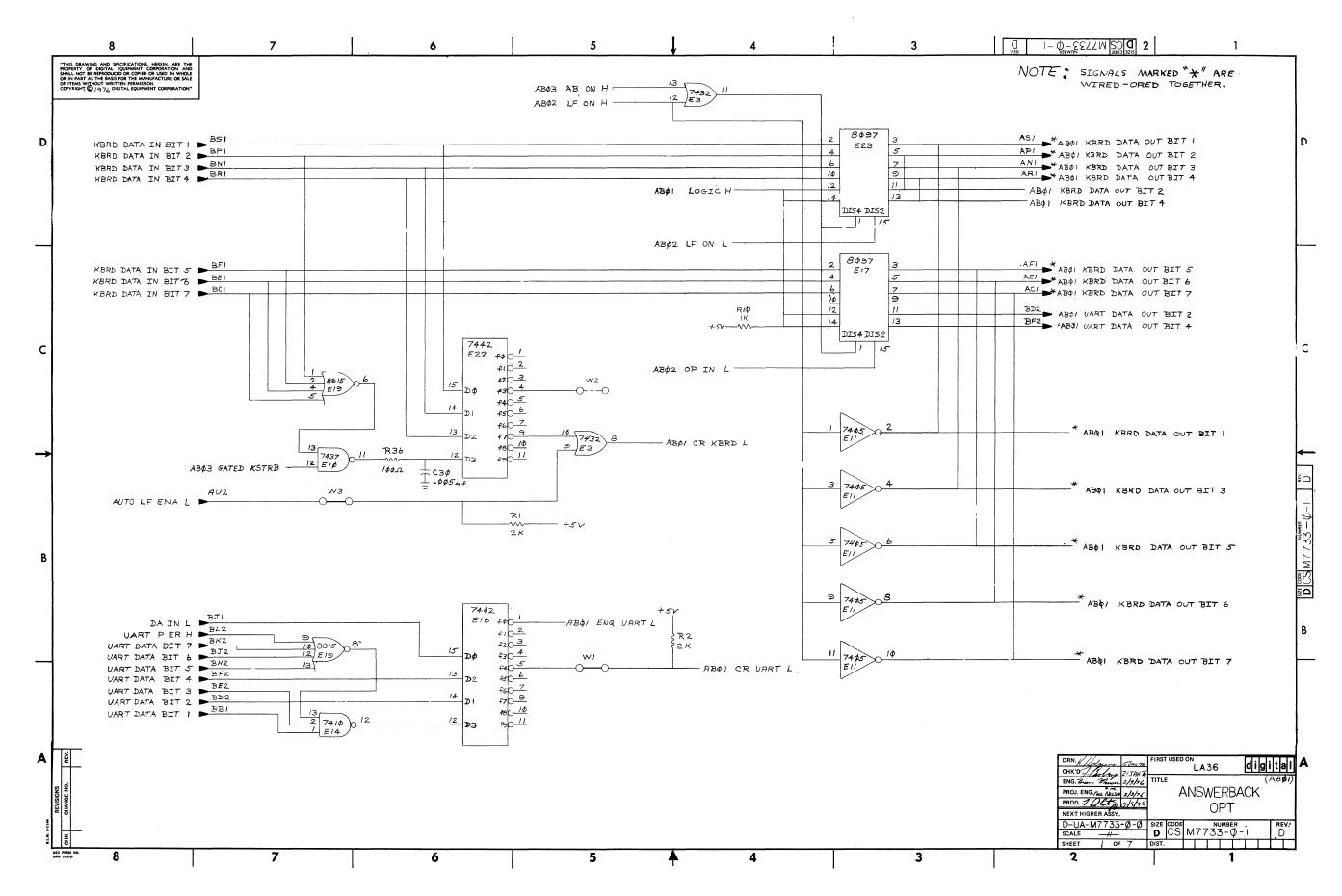

| 13.5       | LAXX-KX PRINT SET                                                              |        |

| 1010       |                                                                                | 15 14  |

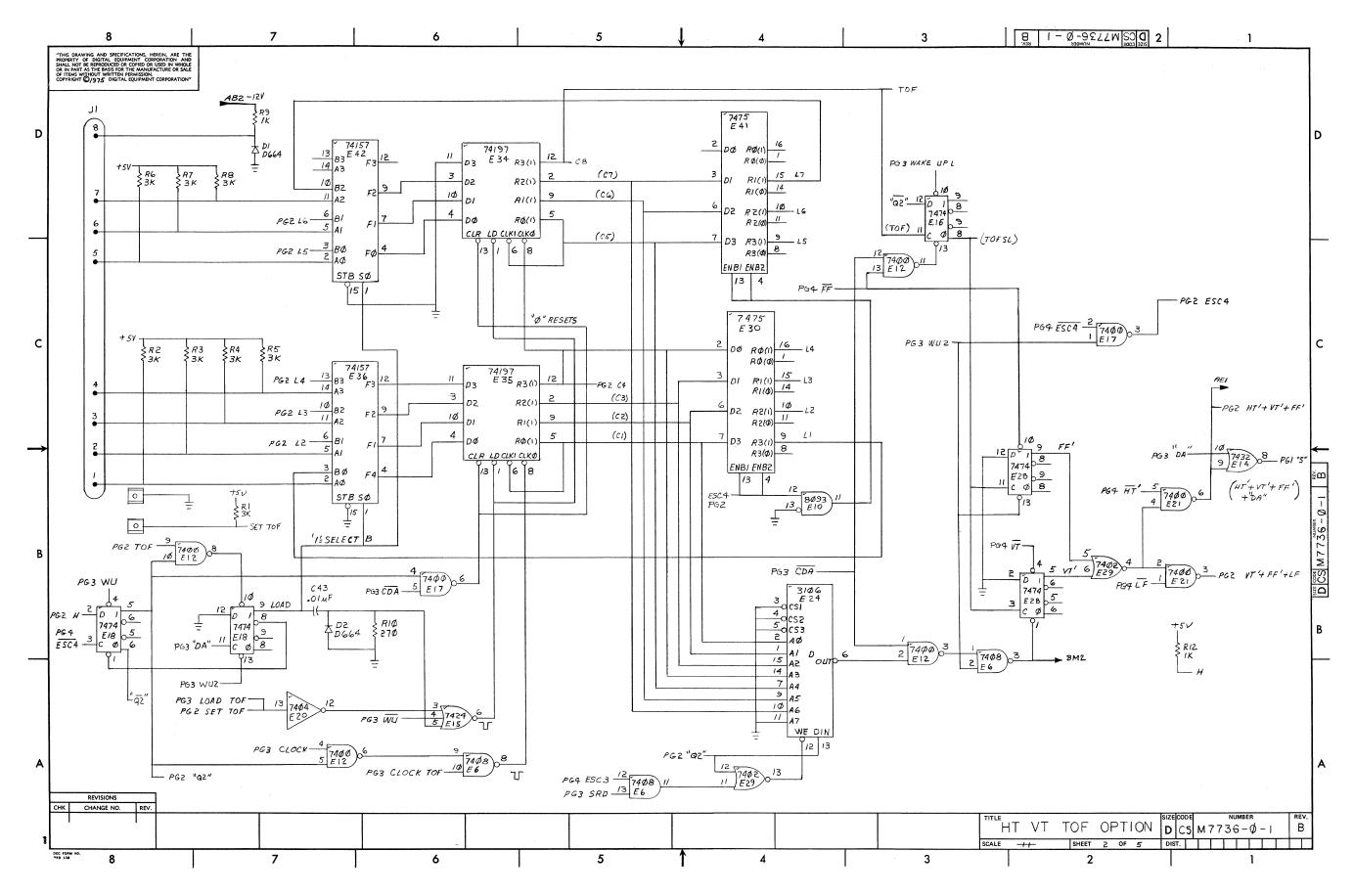

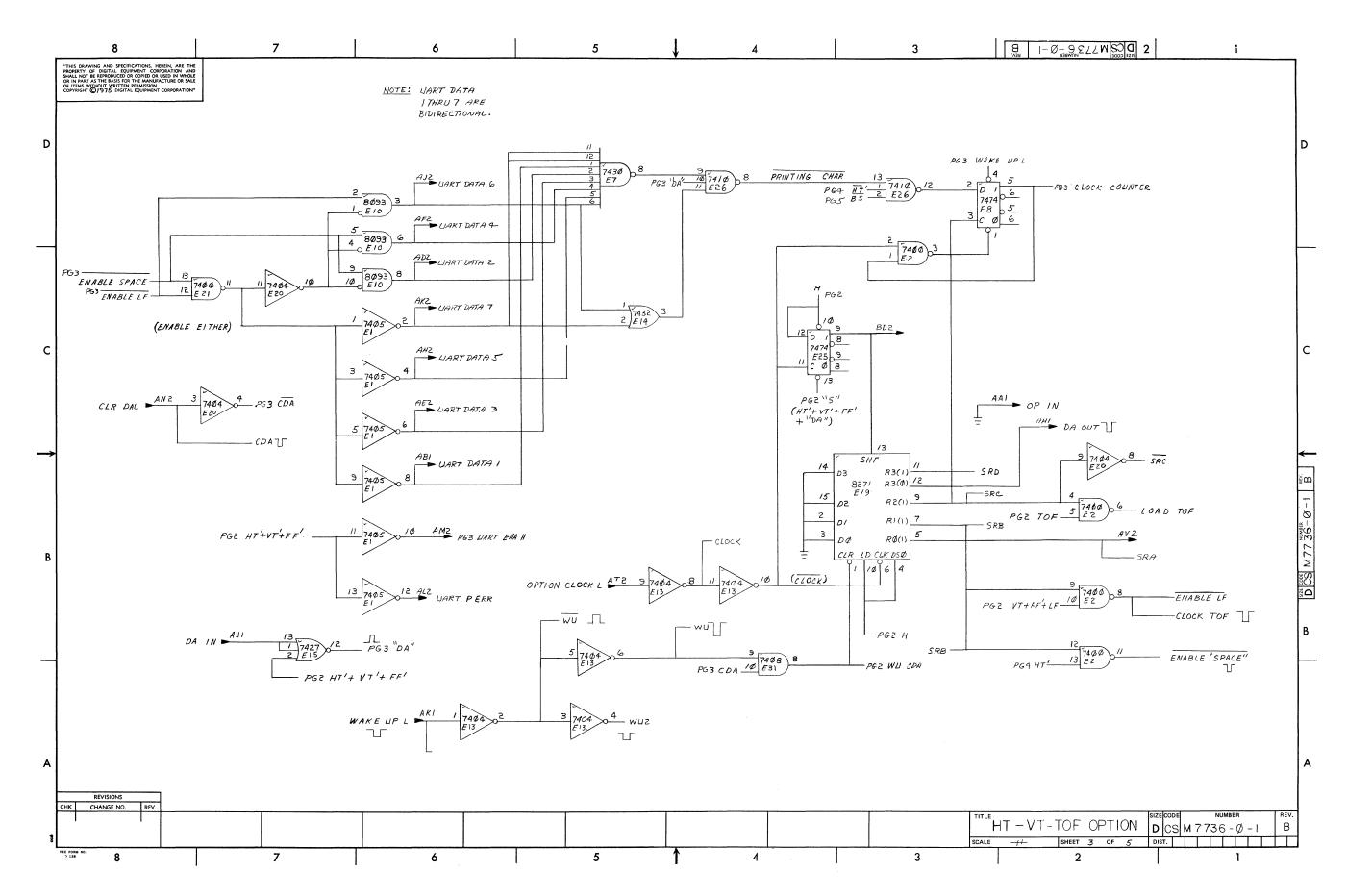

| CHAPTER 14 | FORMS CONTROL, VERTICAL TABULATION, AND HORIZONTAL TABULATION OPTION (LAXX-KY) |        |

| 14.1       | TABS OPTION INTRODUCTION                                                       | 14-1   |

| 14.2       | TABS OPTION FUNCTIONAL DIAGRAM                                                 | 14-1   |

| 14.3       | SIMPLIFIED OPERATION OF TABS OPTION                                            |        |

| 14.3.1     | Horizontal Tabs Operation                                                      |        |

| 14.3.2     | Top of Form (TOF) Operation                                                    |        |

| 14.3.3     | Vertical Tabs Operation                                                        |        |

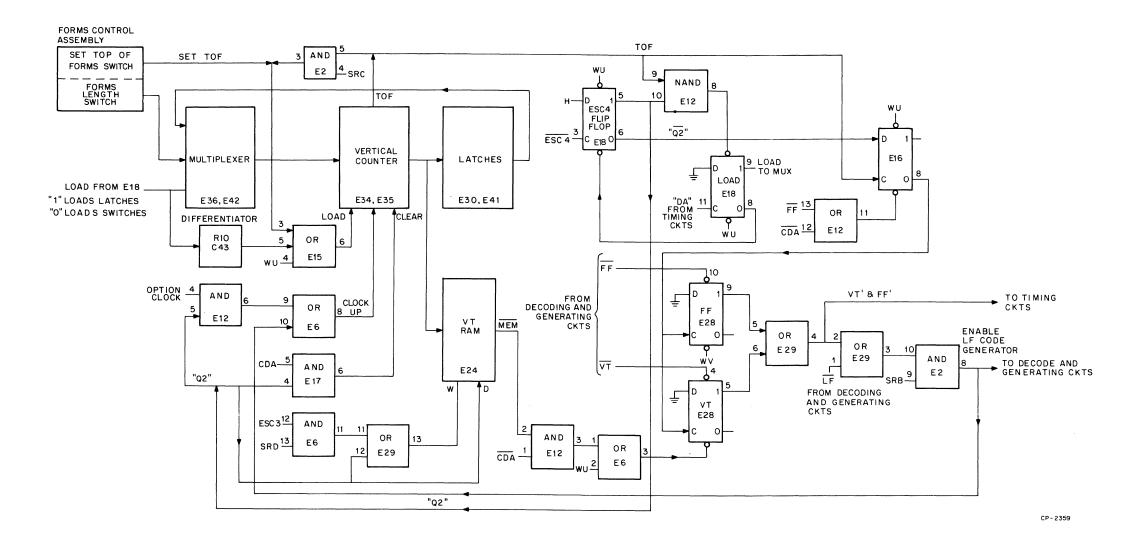

| 14.4       | TABS OPTION BASIC BLOCK DIAGRAM                                                |        |

| 14.4.1     | Decoding and Generating Circuits Basic Block Diagram                           |        |

| 14.4.1.1   | Decoding                                                                       |        |

| 14.4.1.2   | Generating                                                                     |        |

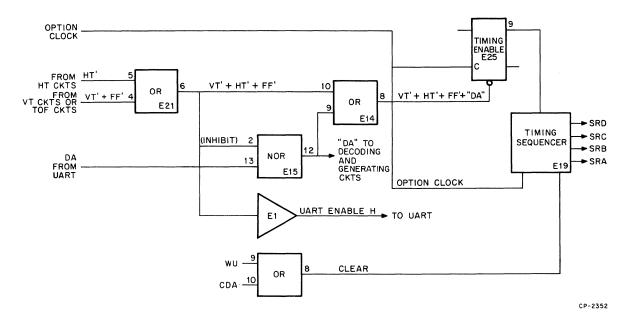

| 14.4.2     | Timing Circuits Basic Block Diagram                                            |        |

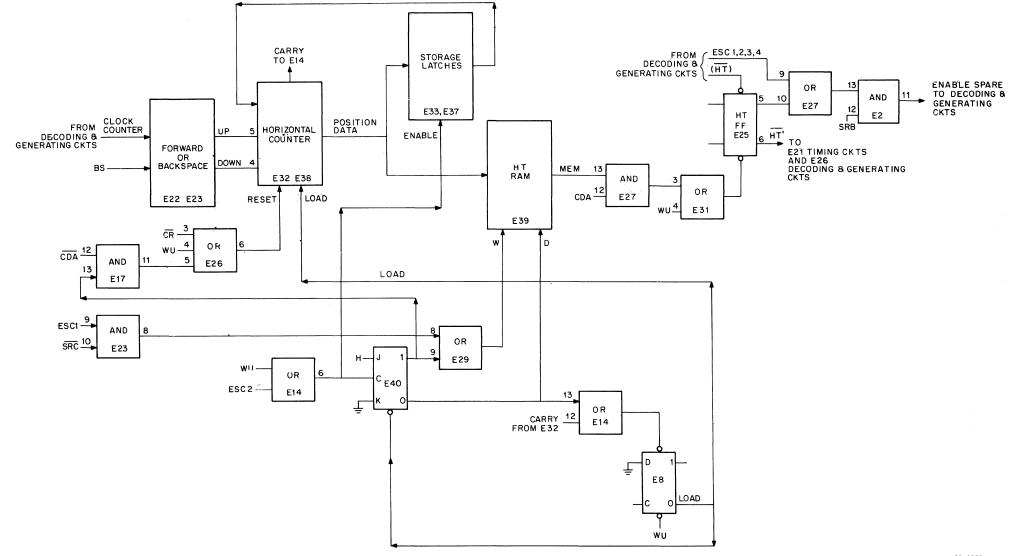

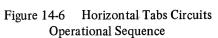

| 14.4.3     | Horizontal Tabs Circuits Basic Block Diagram                                   |        |

| 14.4.3.1   | Monitoring                                                                     |        |

| 14.4.3.2   | Setup                                                                          |        |

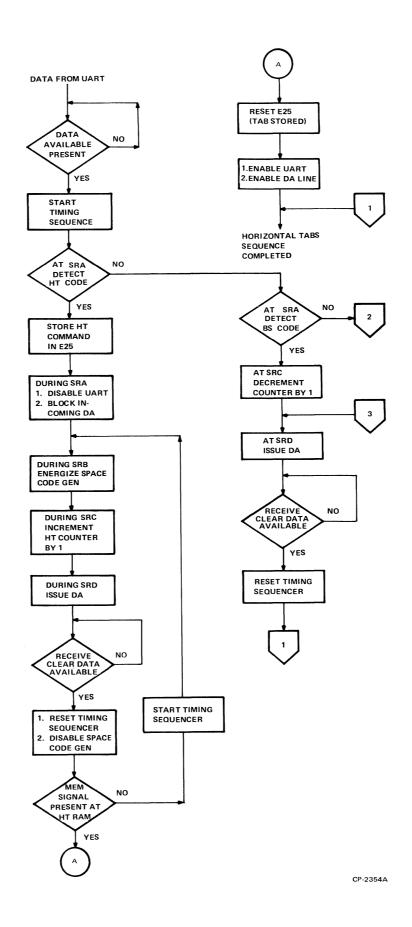

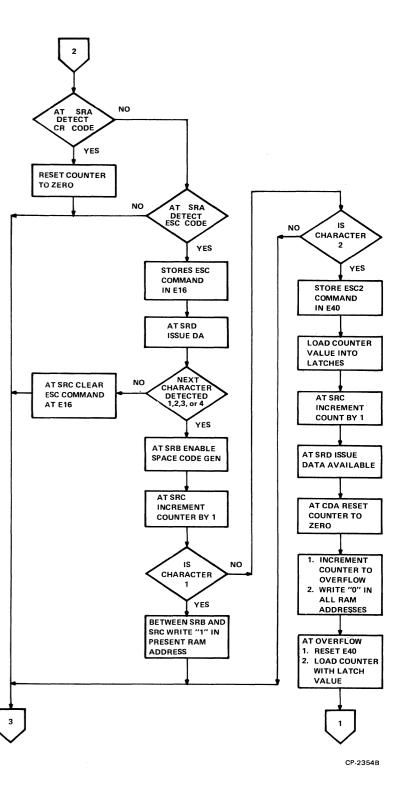

| 14.4.3.3   | Horizontal Tab Action                                                          |        |

| 14.4.3.4   | Clearing Horizontal Tabs                                                       |        |

| 14.4.4     | Top of Form (TOF) Circuits Basic Block Diagram                                 |        |

| 14.4.4.1   | Monitoring                                                                     |        |

| 14.4.4.2   | Form Feeding                                                                   |        |

| 14.4.4.3   | Setup and Wake-Up                                                              |        |

| 14.4.5     | Vertical Tabs Circuits Basic Block Diagram                                     |        |

| 14.4.5.1   | Monitoring                                                                     |        |

| 14.4.5.2   | Vertical Tab Setup                                                             |        |

| 14.4.5.3   | •                                                                              | 14-20  |

| 14.4.5.4   | Clearing Vertical Tabs                                                         |        |

| 14.5       | TROUBLESHOOTING                                                                |        |

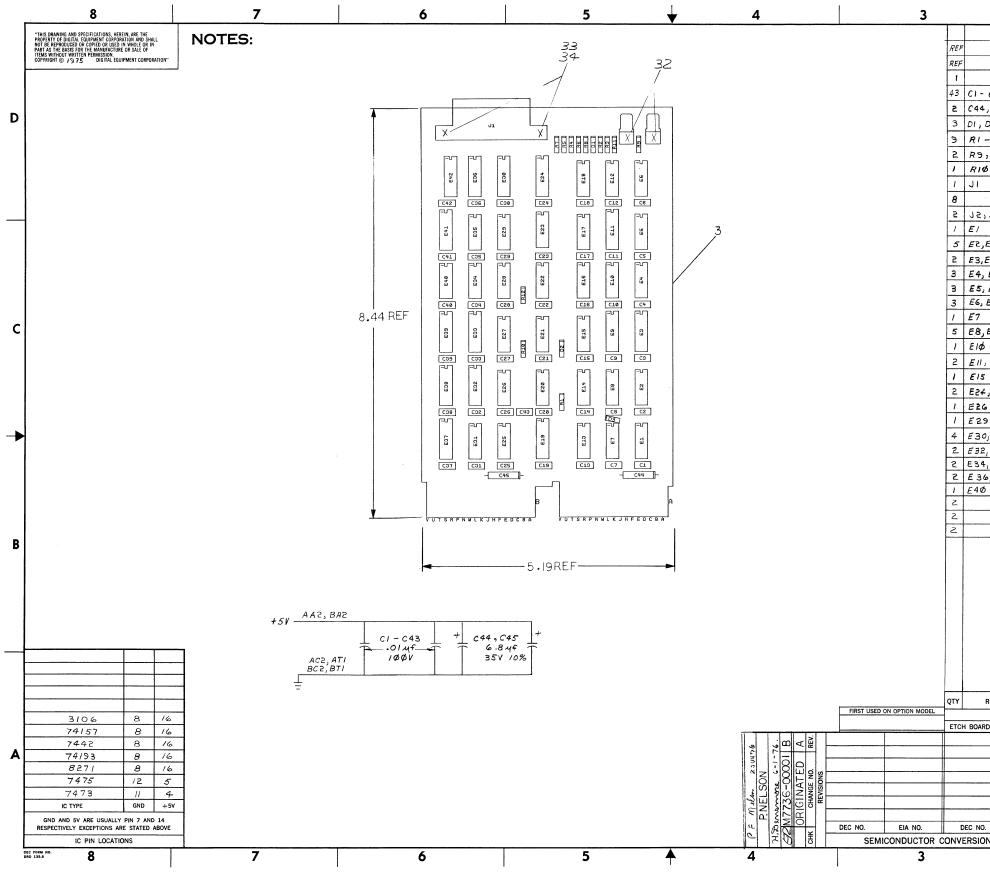

| 14.6       | LAXX-KY PRINT SET                                                              |        |

|            |                                                                                | 1 44   |

.

#### CONTENTS (Cont)

Page

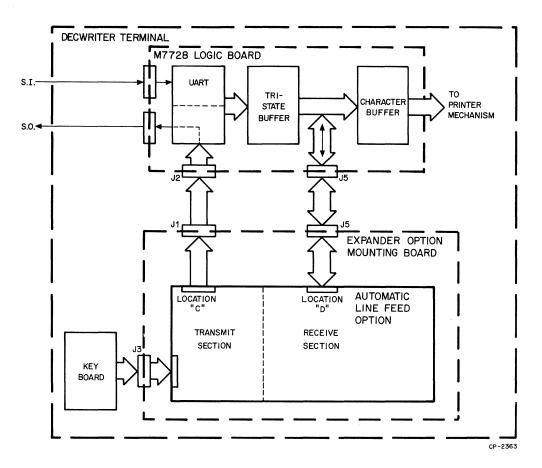

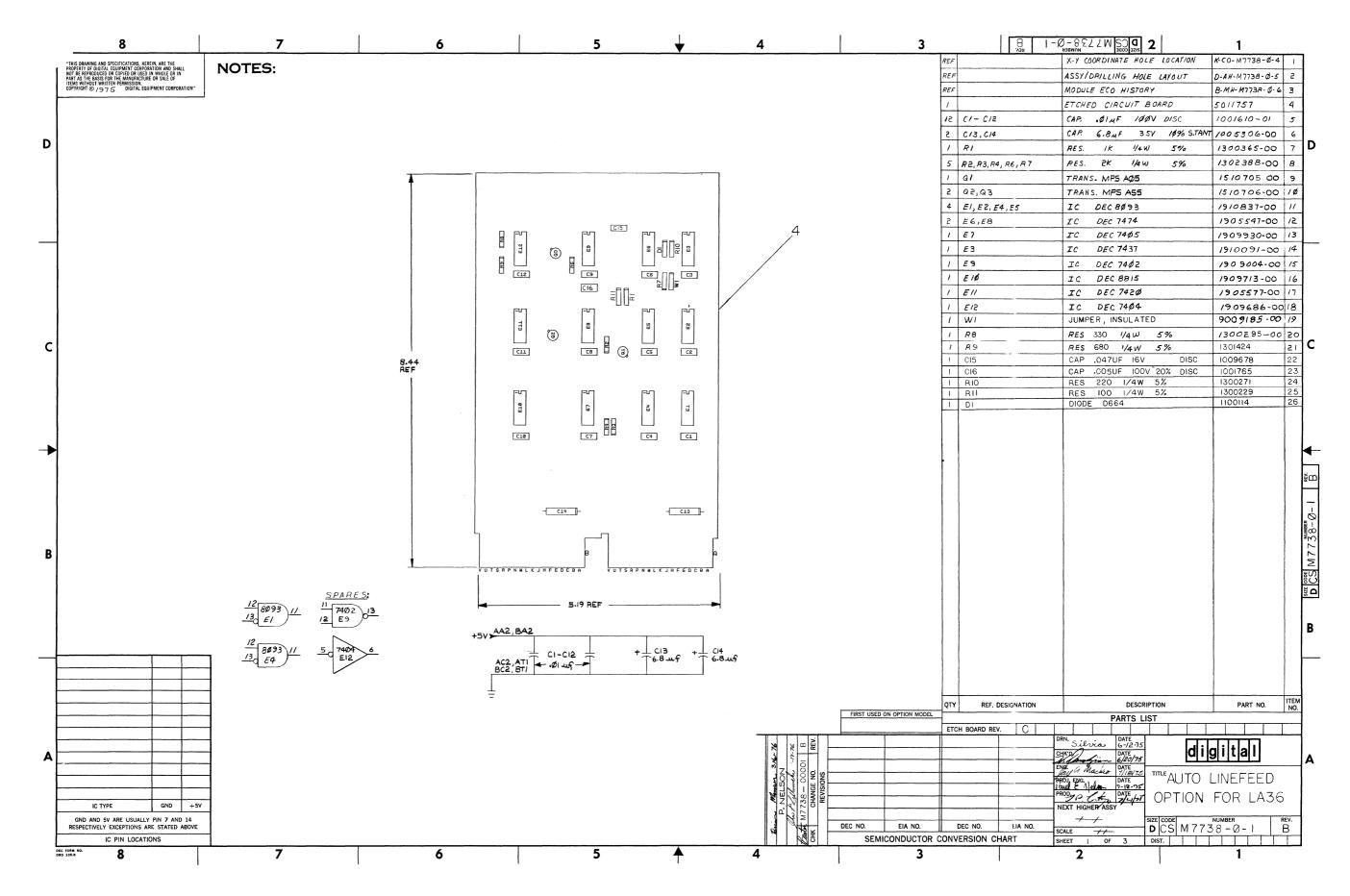

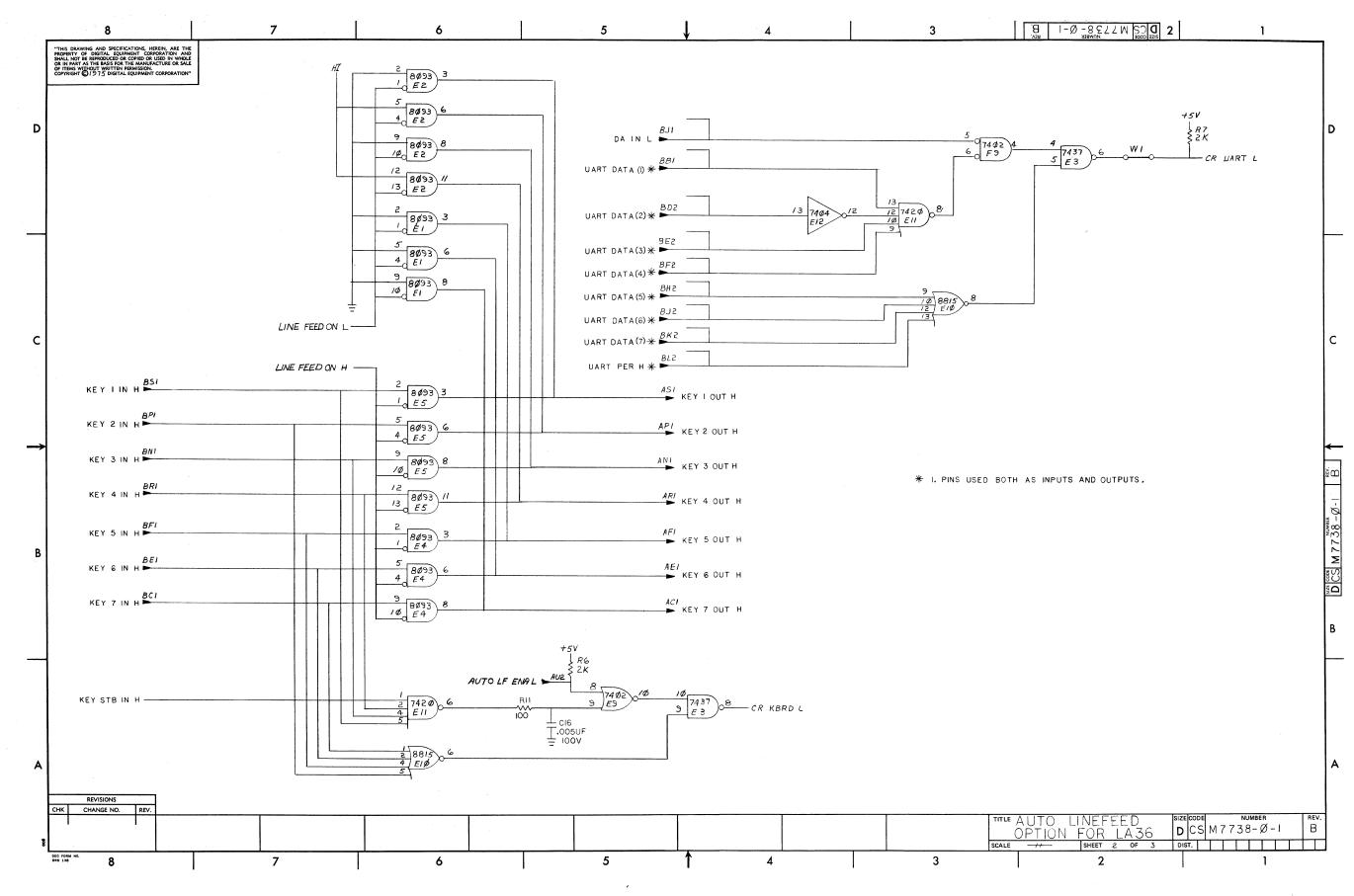

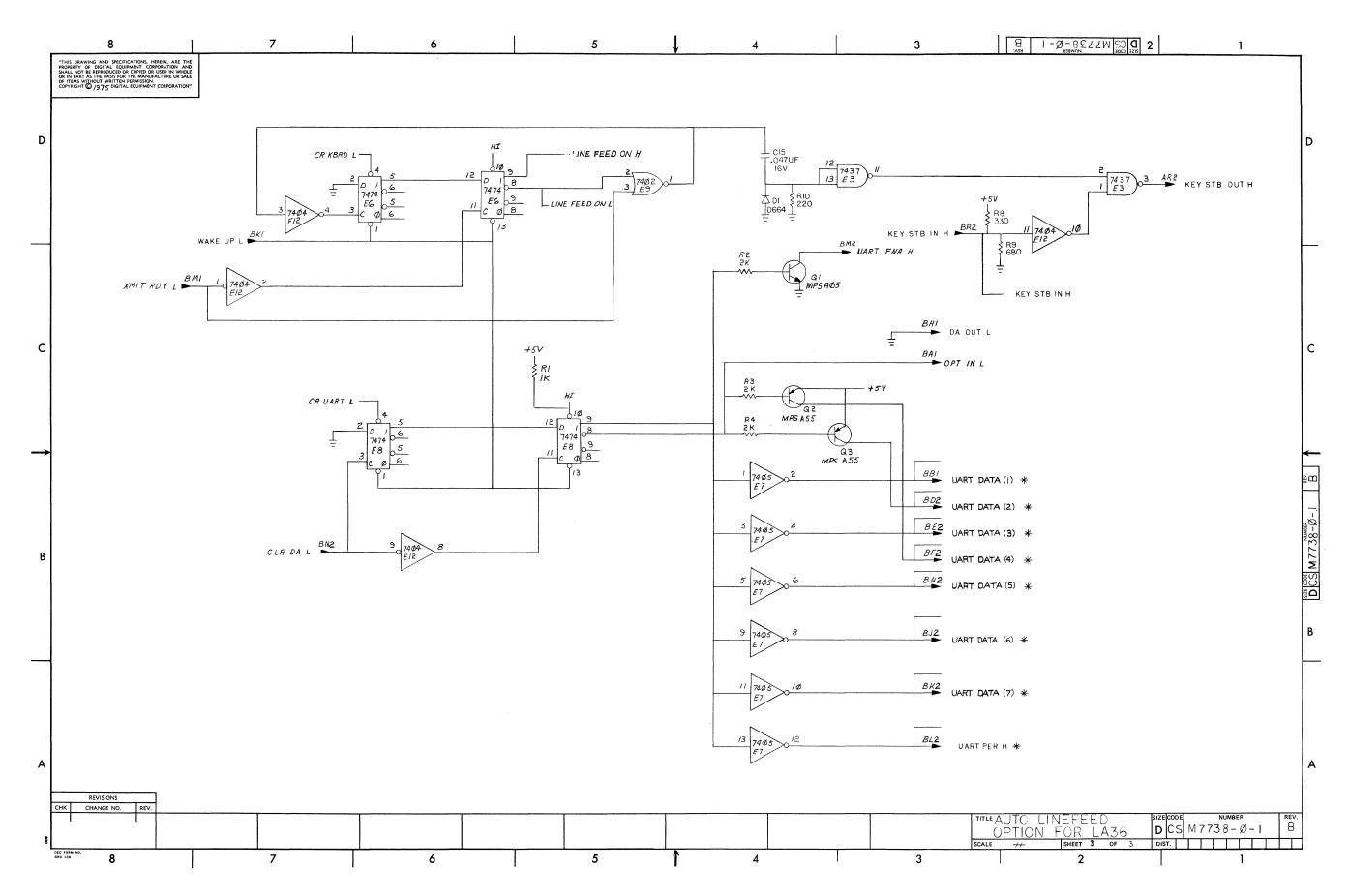

| CHAPTER 15       | AUTOMATIC LINE FEED OPTION (LAXX-LA)                                       |

|------------------|----------------------------------------------------------------------------|

| 15.1             | AUTOMATIC LINE FEED INTRODUCTION                                           |

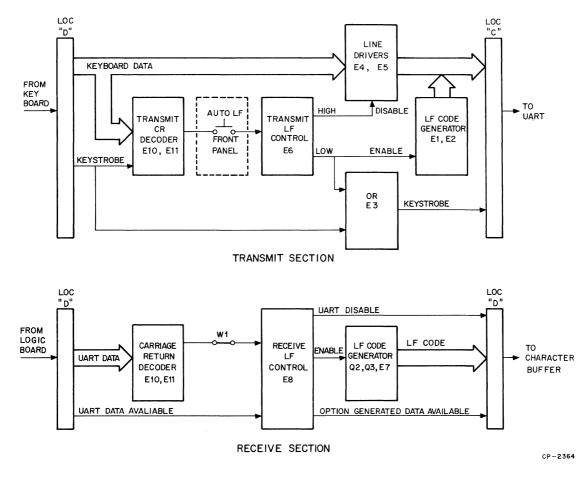

| 15.2             | AUTOMATIC LINE FEED FUNCTIONAL BLOCK DIAGRAM                               |

| 15.3             | AUTOMATIC LINE FEED BASIC BLOCK DIAGRAM                                    |

| 15.3.1           | Transmit Section                                                           |

| 15.3.2<br>15.4   | Receive Section                                                            |

| 15.5             | TROUBLESHOOTING         15-7           LAXX-LA PRINT SET         15-7      |

| 15.5             |                                                                            |

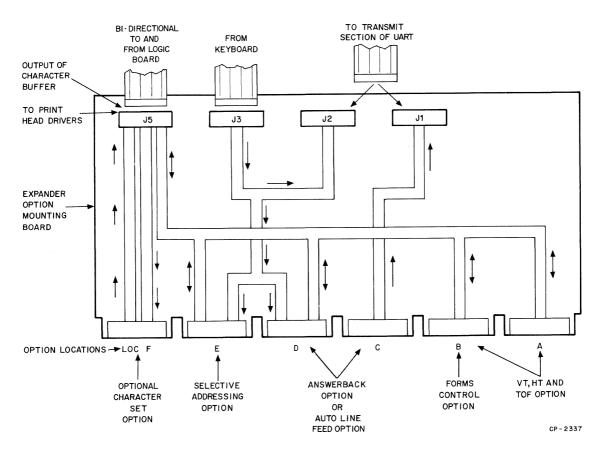

| CHAPTER 16       | EXPANDER OPTION MOUNTING KIT (LAXX-LB)                                     |

| 16.1             | EXPANDER OPTION MOUNTING KIT INTRODUCTION                                  |

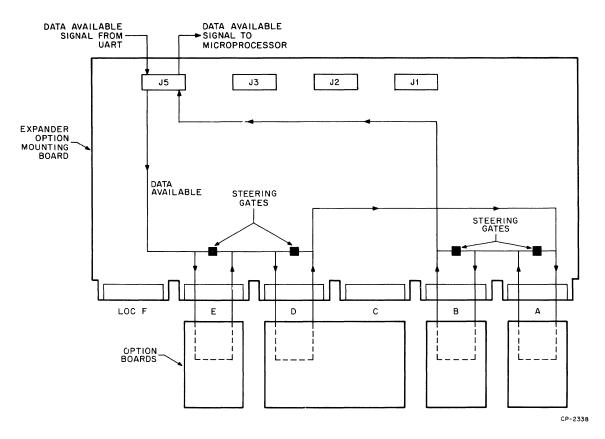

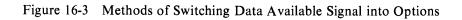

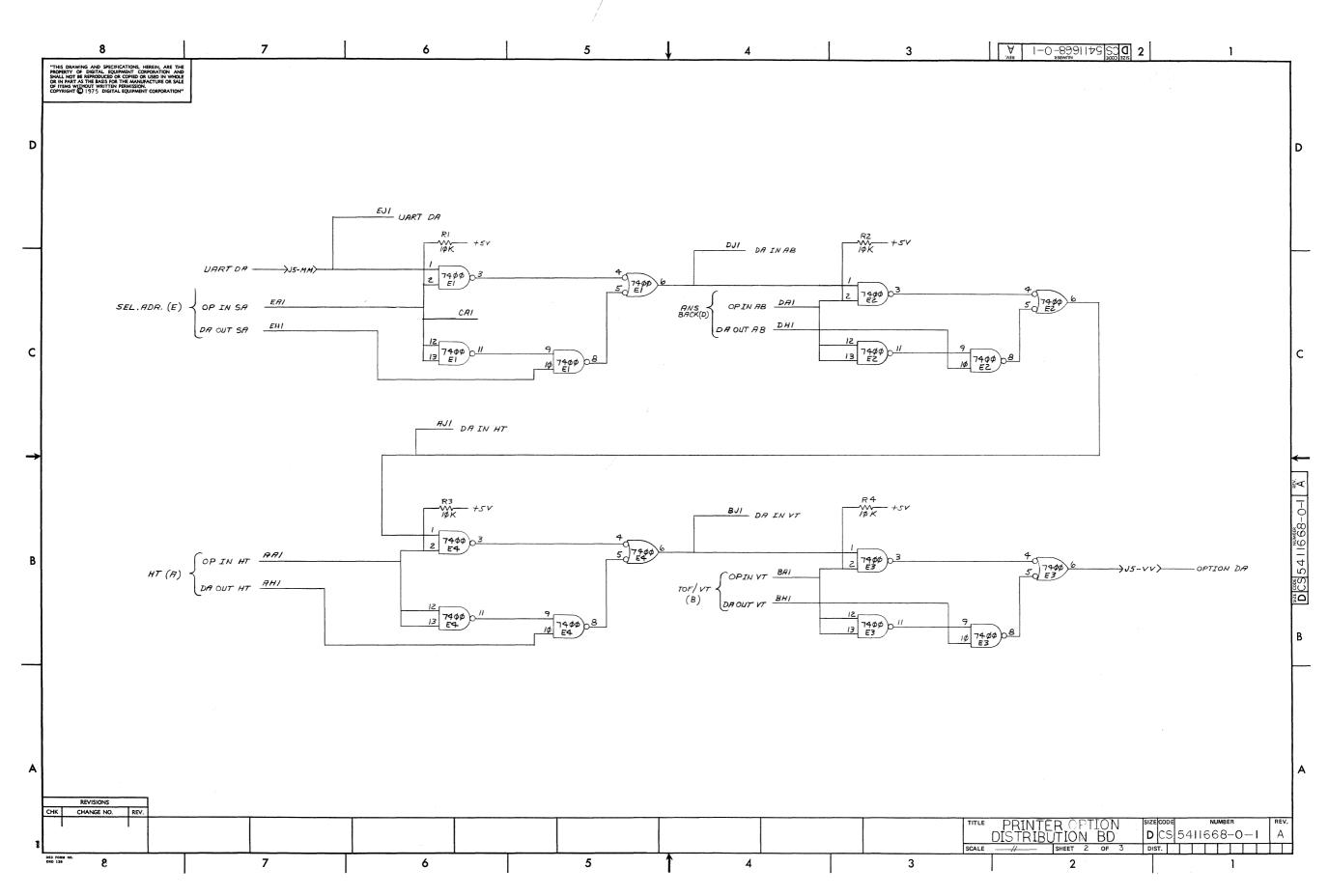

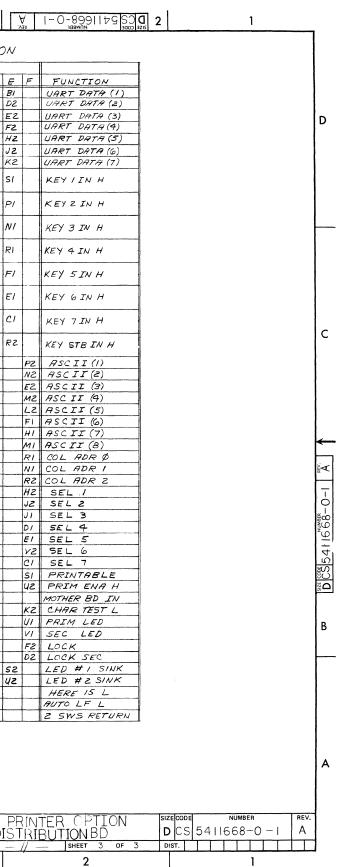

| 16.2             | EXPANDER BOARD DATA DISTRIBUTION                                           |

| 16.3             | EXPANDER BOARD CONTROL SIGNAL DISTRIBUTION                                 |

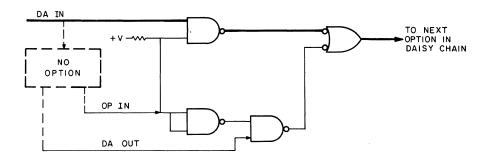

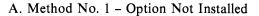

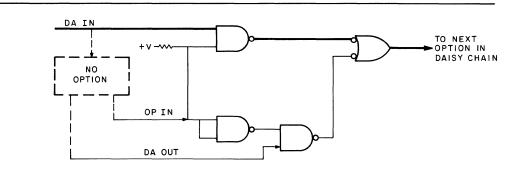

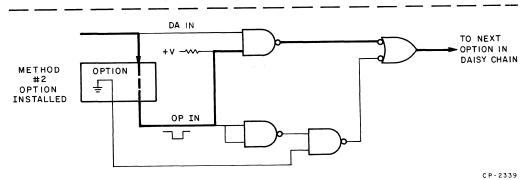

| 16.3.1           | Routing of DATA AVAILABLE Signal                                           |

| 16.3.2<br>16.4   | Routing of KEYSTROBE Signal    16-5      TROUBLESHOOTING    16-5           |

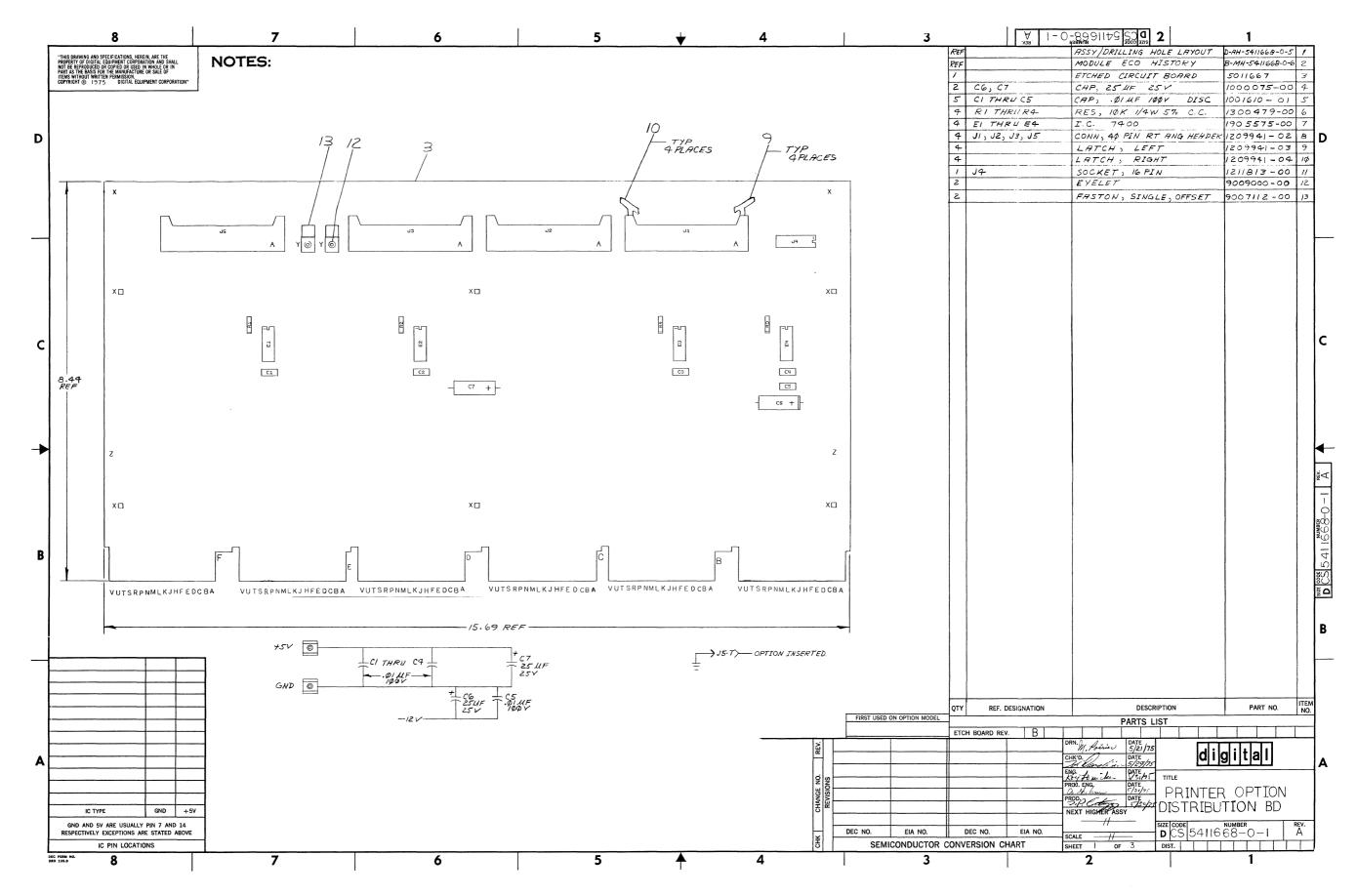

| 16.5             | LAXX-LB PRINT SET                                                          |

| 10.5             |                                                                            |

| CHAPTER 17       | EIA INTERFACE OPTION KIT (LAXX-LG)                                         |

| 17.1             | EIA INTERFACE INTRODUCTION                                                 |

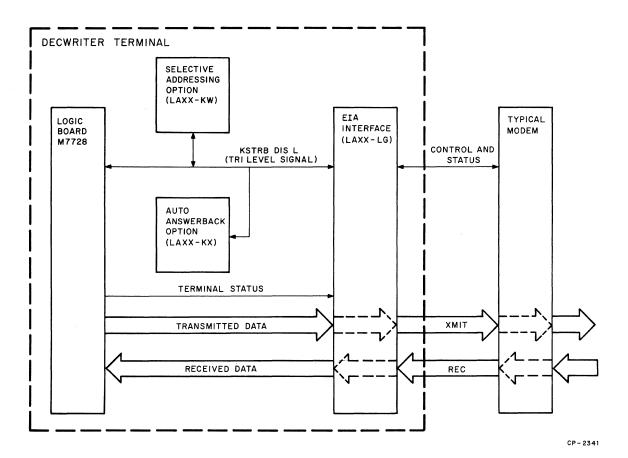

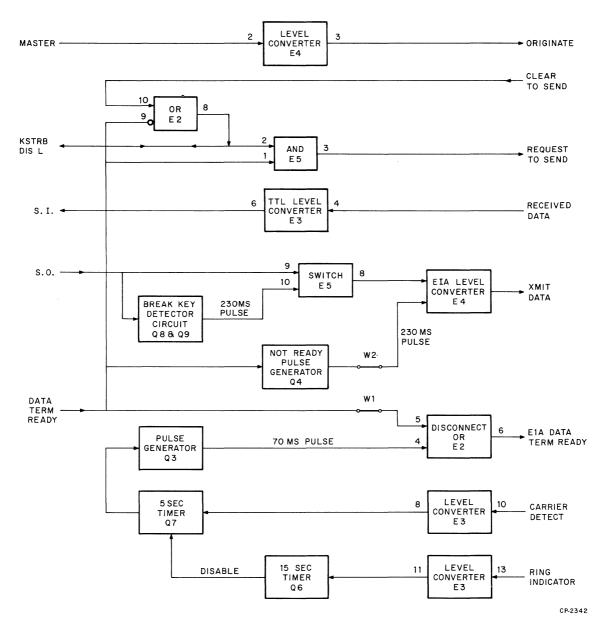

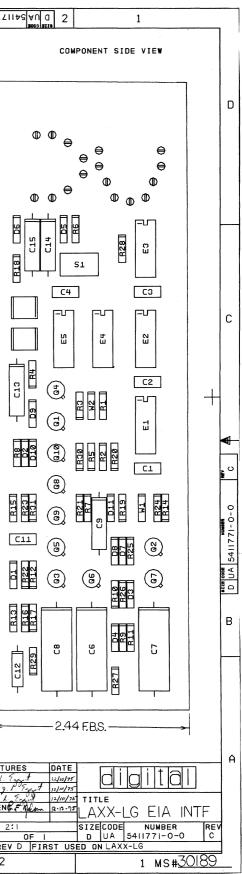

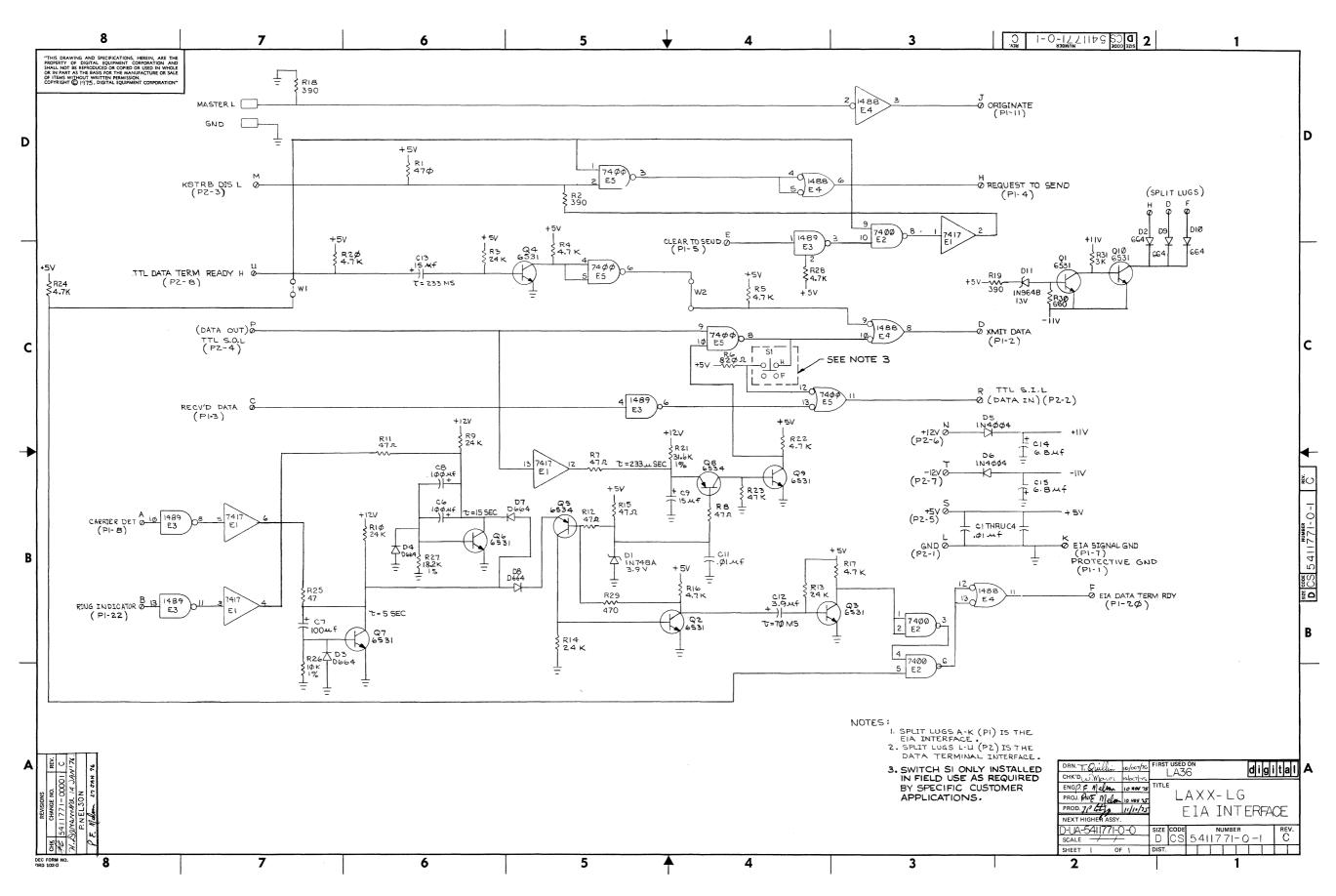

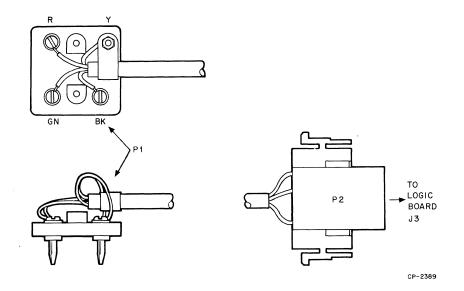

| 17.2             | EIA INTERFACE FUNCTIONAL BLOCK DIAGRAM                                     |

| 17.3             | EIA INTERFACE BASIC BLOCK DIAGRAM 174                                      |

| 17.3.1           | Data Path                                                                  |

| 17.3.2<br>17.3.3 | Connection Protocol                                                        |

| 17.4             | Disconnect Functions                                                       |

| 17.4             | LAXX-LG PRINT SET                                                          |

| 17.5             |                                                                            |

| CHAPTER 18       | 20 mA INTERFACE CABLE OPTION KITS (LAXX-LK DEC 10<br>AND LAXX-LH STANDARD) |

| 10.1             | 20 mA INTERFACE CABLE INTRODUCTION                                         |

| 18.1             | 20 MA INTERFACE CABLE INTRODUCTION                                         |

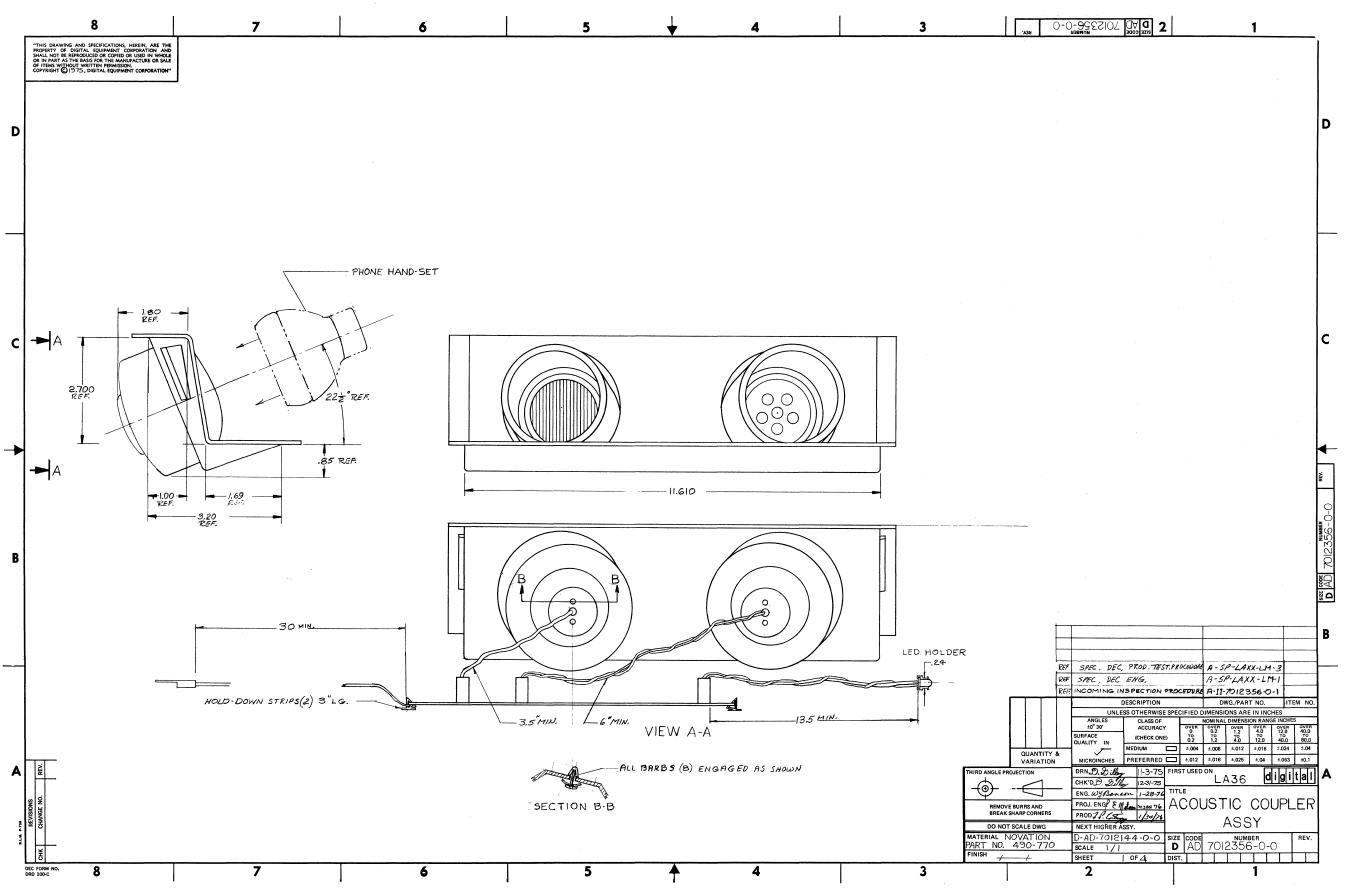

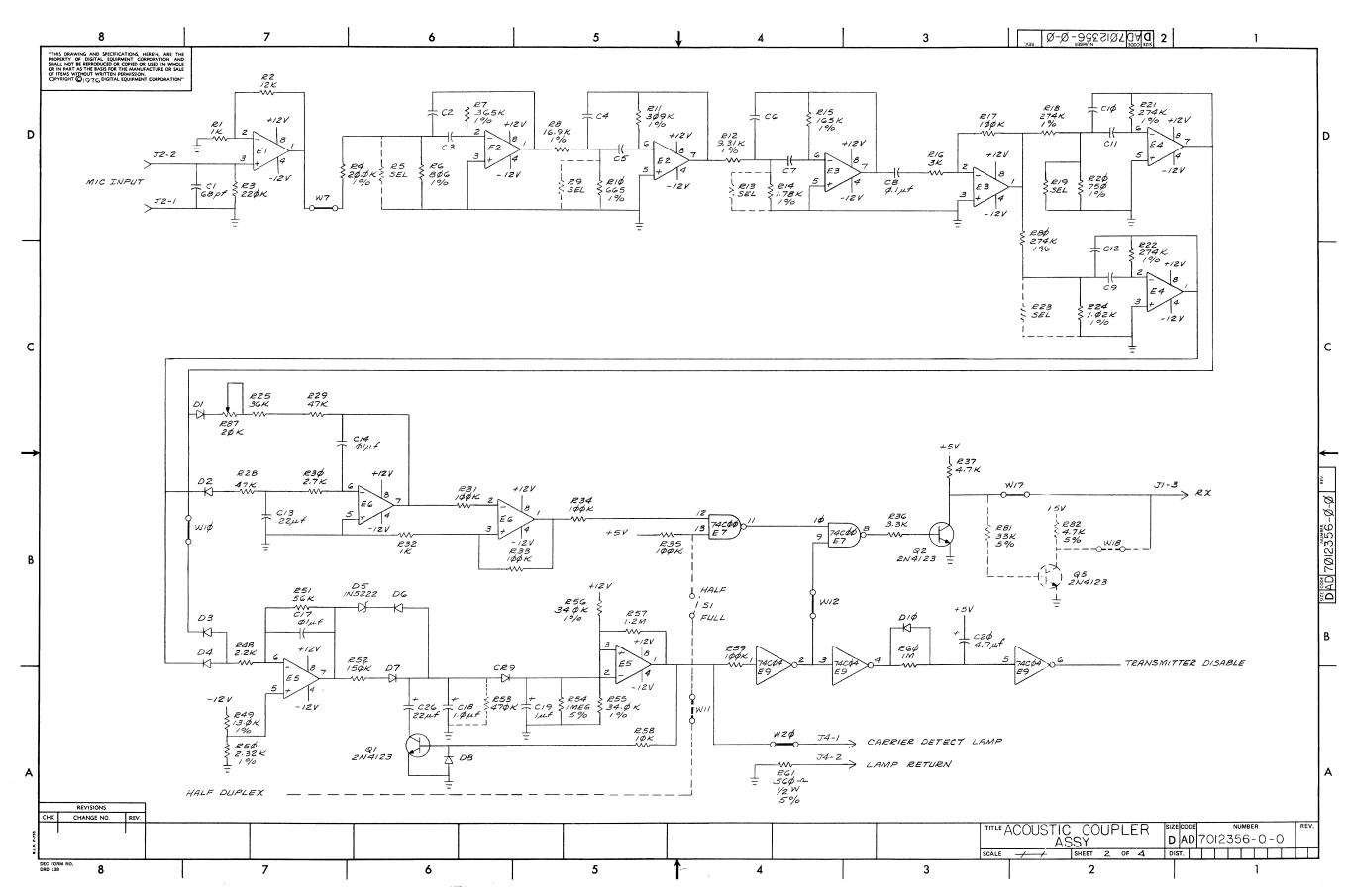

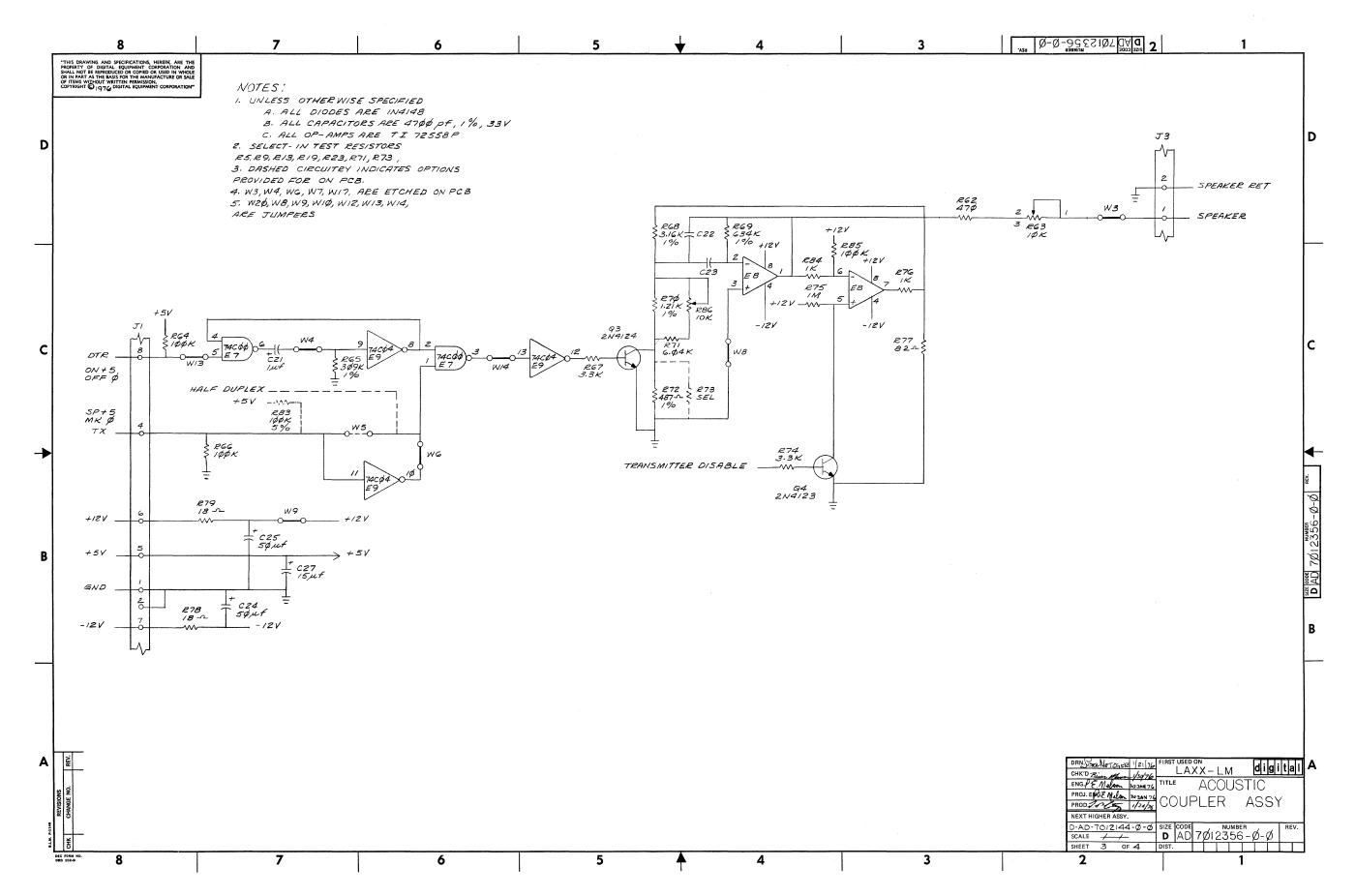

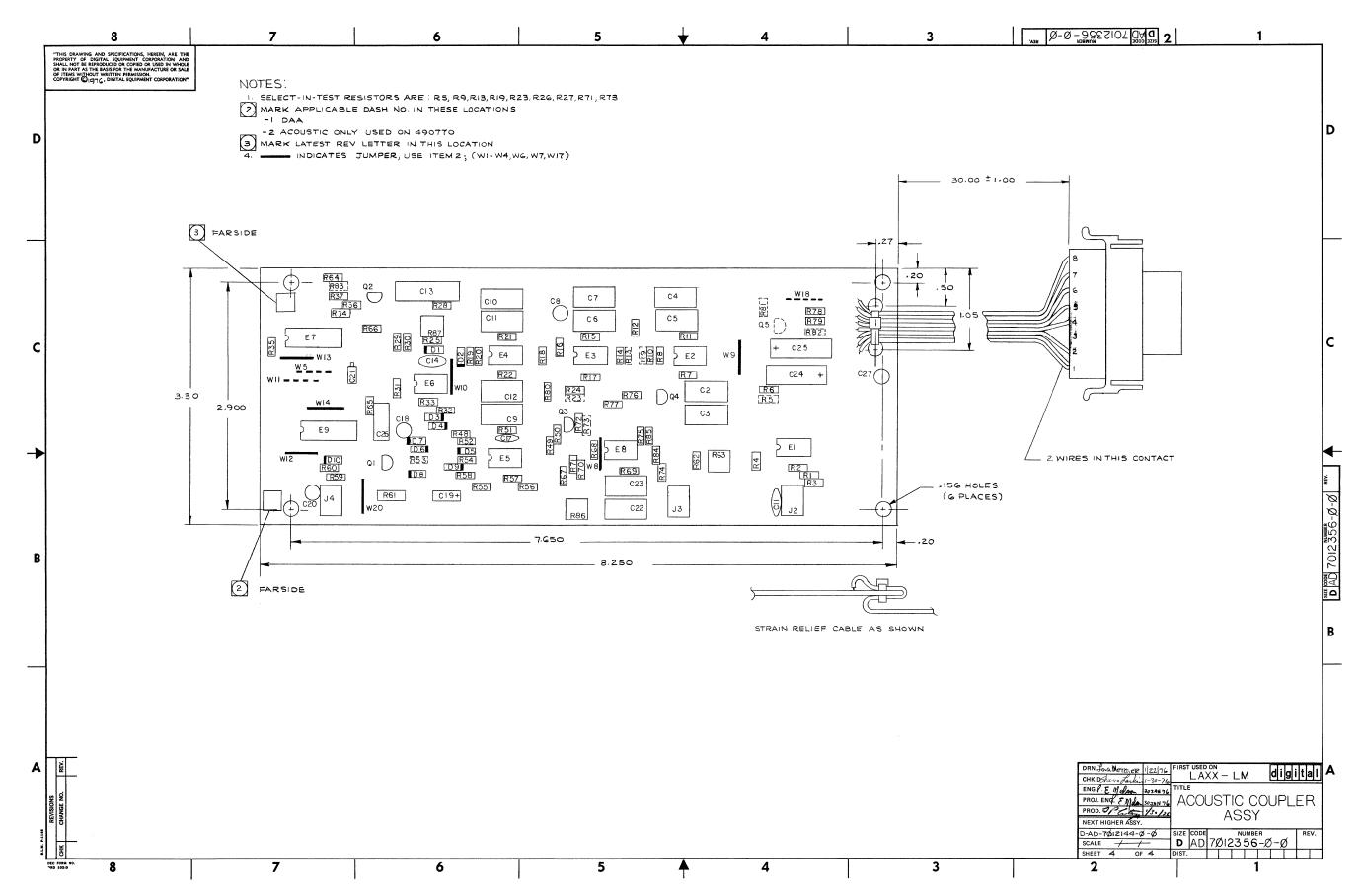

| CHAPTER 19       | ACOUSTIC COUPLER OPTION KIT (LAXX-LM)                                      |

| 19.1             | INTRODUCTION TO THE ACOUSTIC COUPLER                                       |

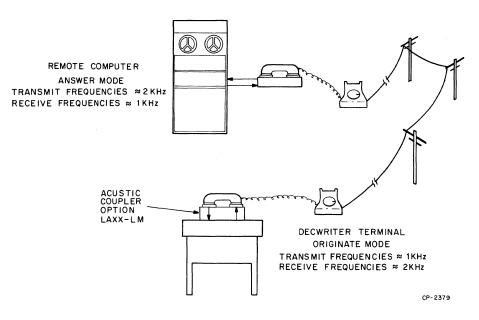

| 19.2             | TYPICAL ACOUSTIC COUPLER OPERATION                                         |

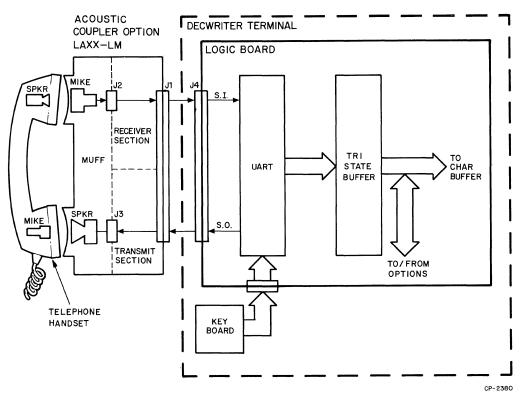

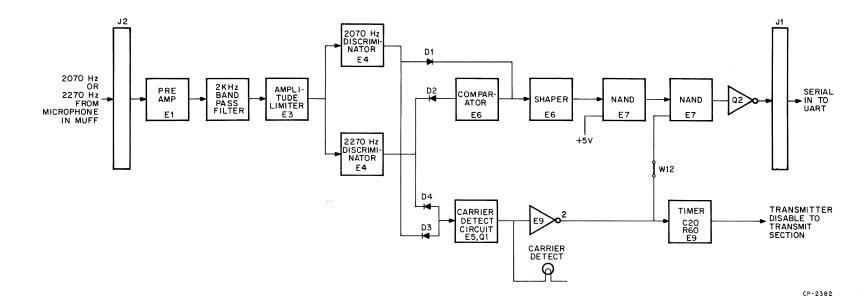

| 19.3             | ACOUSTIC COUPLER FUNCTIONAL BLOCK DIAGRAM 19-2                             |

| 19.4             | ACOUSTIC COUPLER BASIC BLOCK DIAGRAM 19-3                                  |

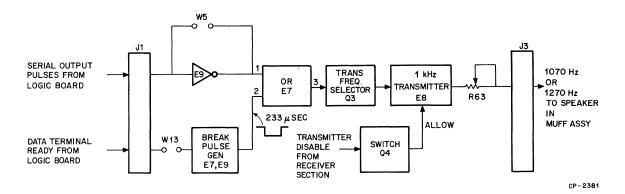

| 19.5             | TRANSMIT SECTION                                                           |

| 19.6             | RECEIVE SECTION                                                            |

| 19.7<br>19.8     | TROUBLESHOOTING         19-6           LAXX-LM PRINT SET         19-6      |

| 19.0             | LAXX-LM PRINT SET                                                          |

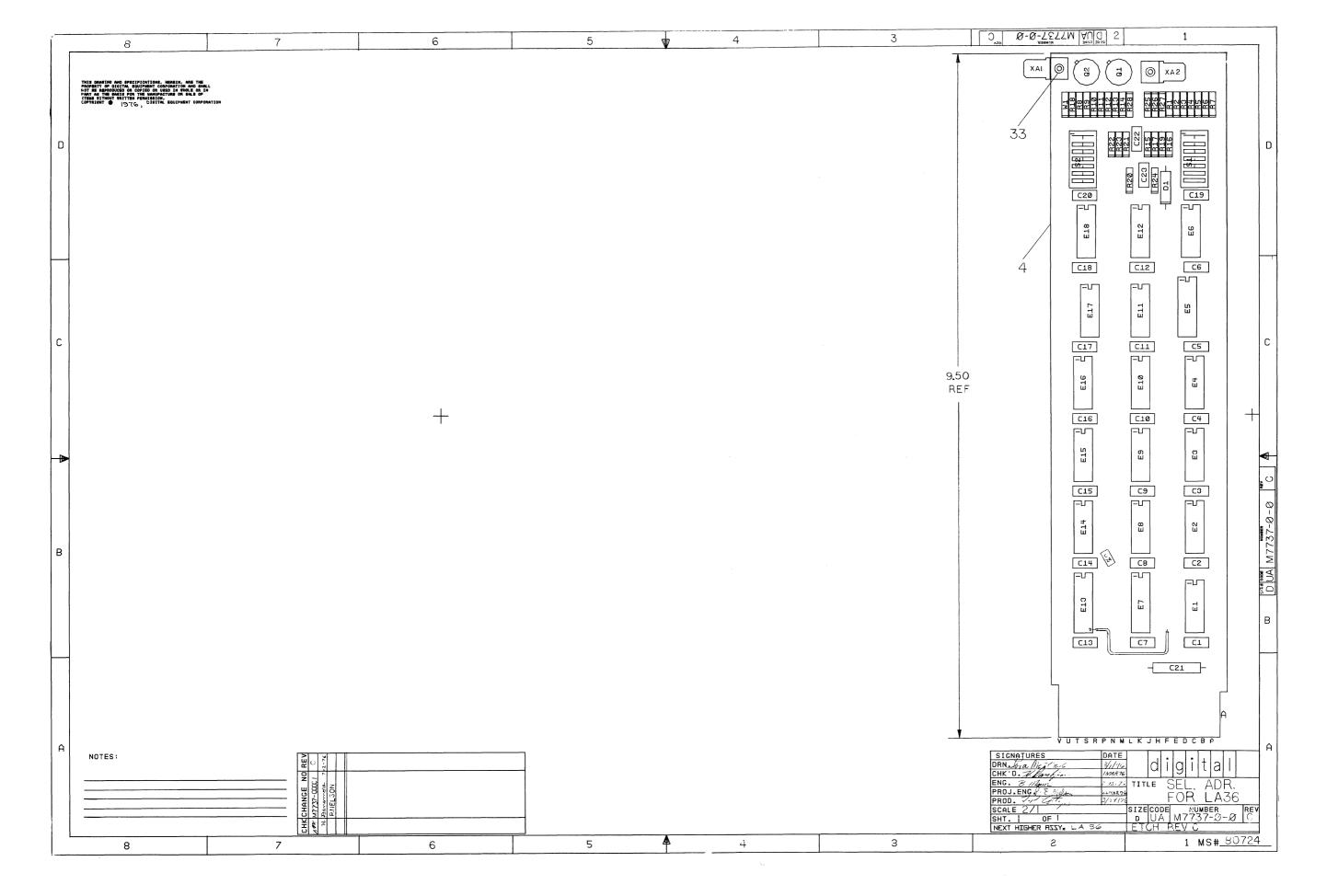

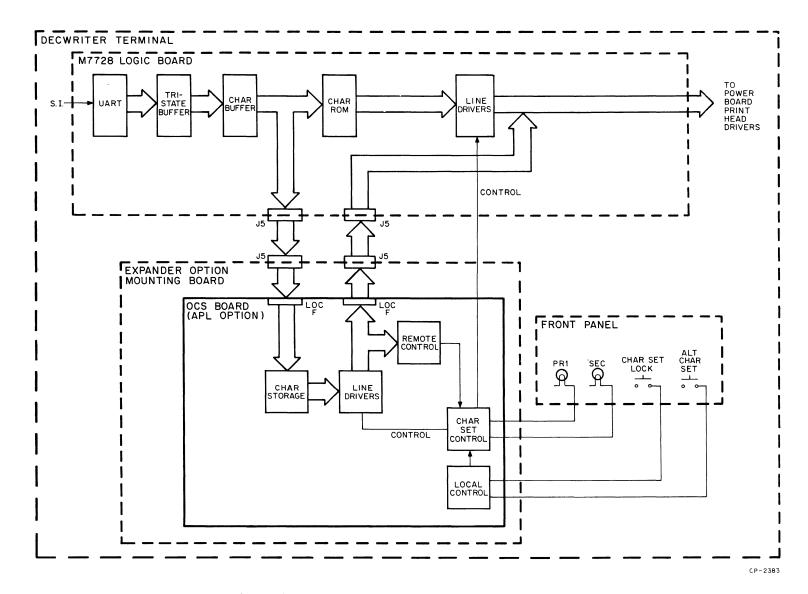

| CHAPTER 20       | APL OPTION KIT (LAXX-PK)                                                   |

| 20.1             | APL INTRODUCTION                                                           |

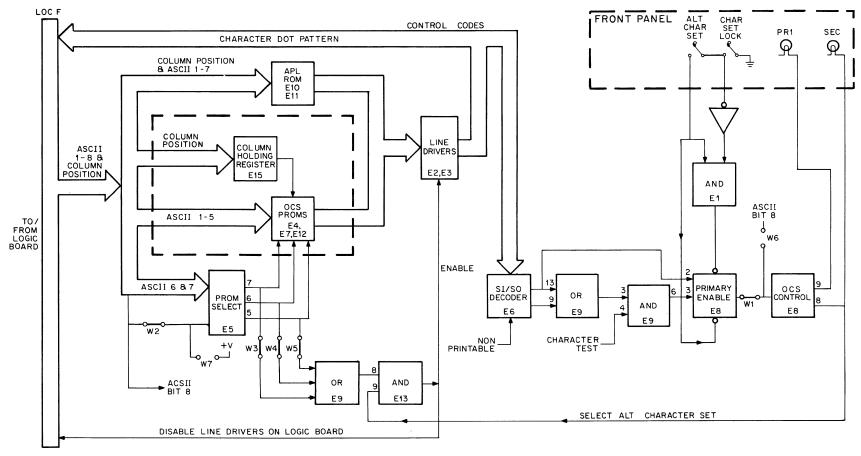

| 20.2             | APL FUNCTIONAL BLOCK DIAGRAM                                               |

| 20.3             | APL BASIC BLOCK DIAGRAM                                                    |

| 20.4             | CHARACTER STORAGE                                                          |

# CONTENTS (Cont)

| 20.5 | CHARACTER SET SELECTION | 20-6 |

|------|-------------------------|------|

| 20.6 | TROUBLESHOOTING         | 20-9 |

| 20.7 | LAXX-PK PRINT SET       | 20-9 |

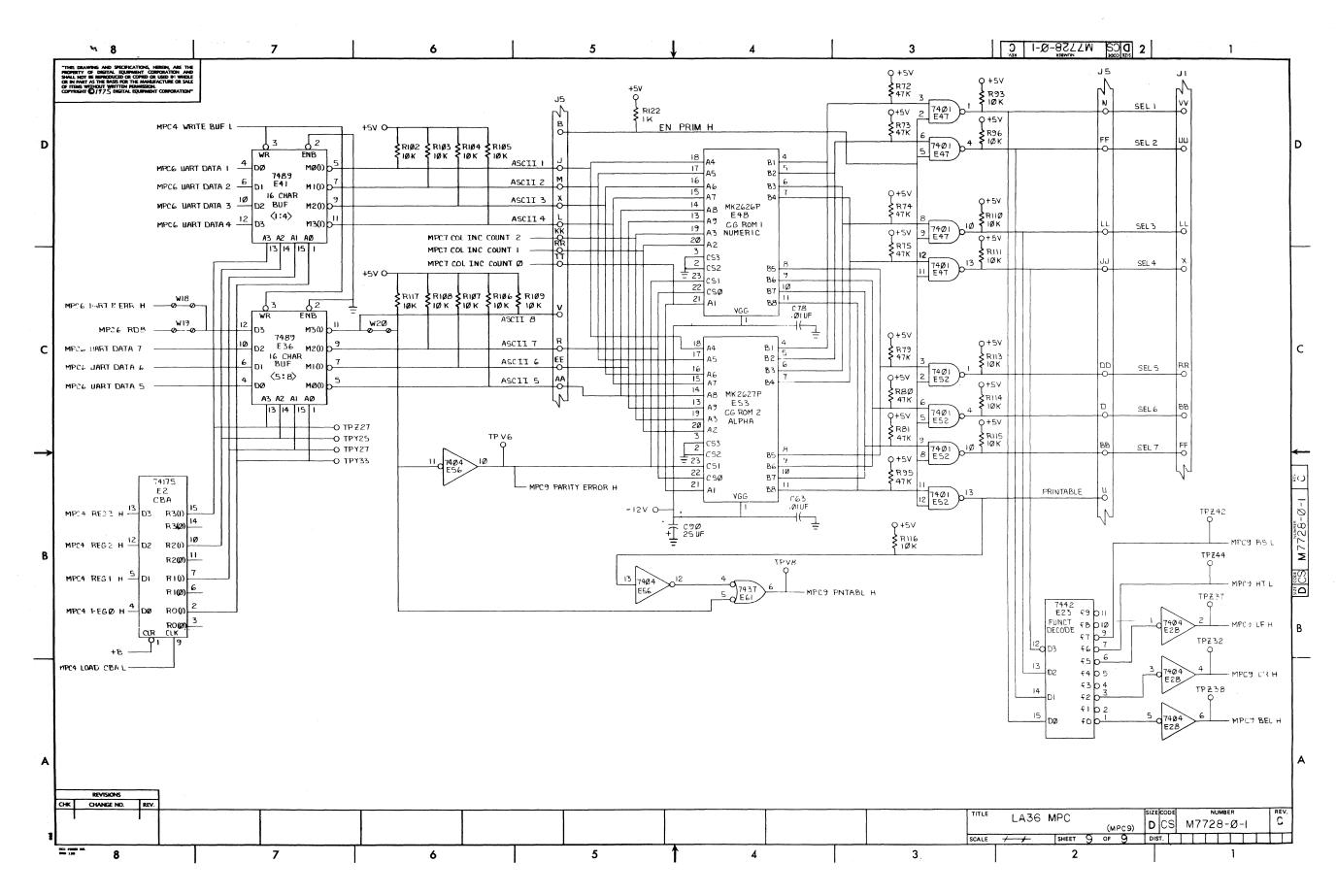

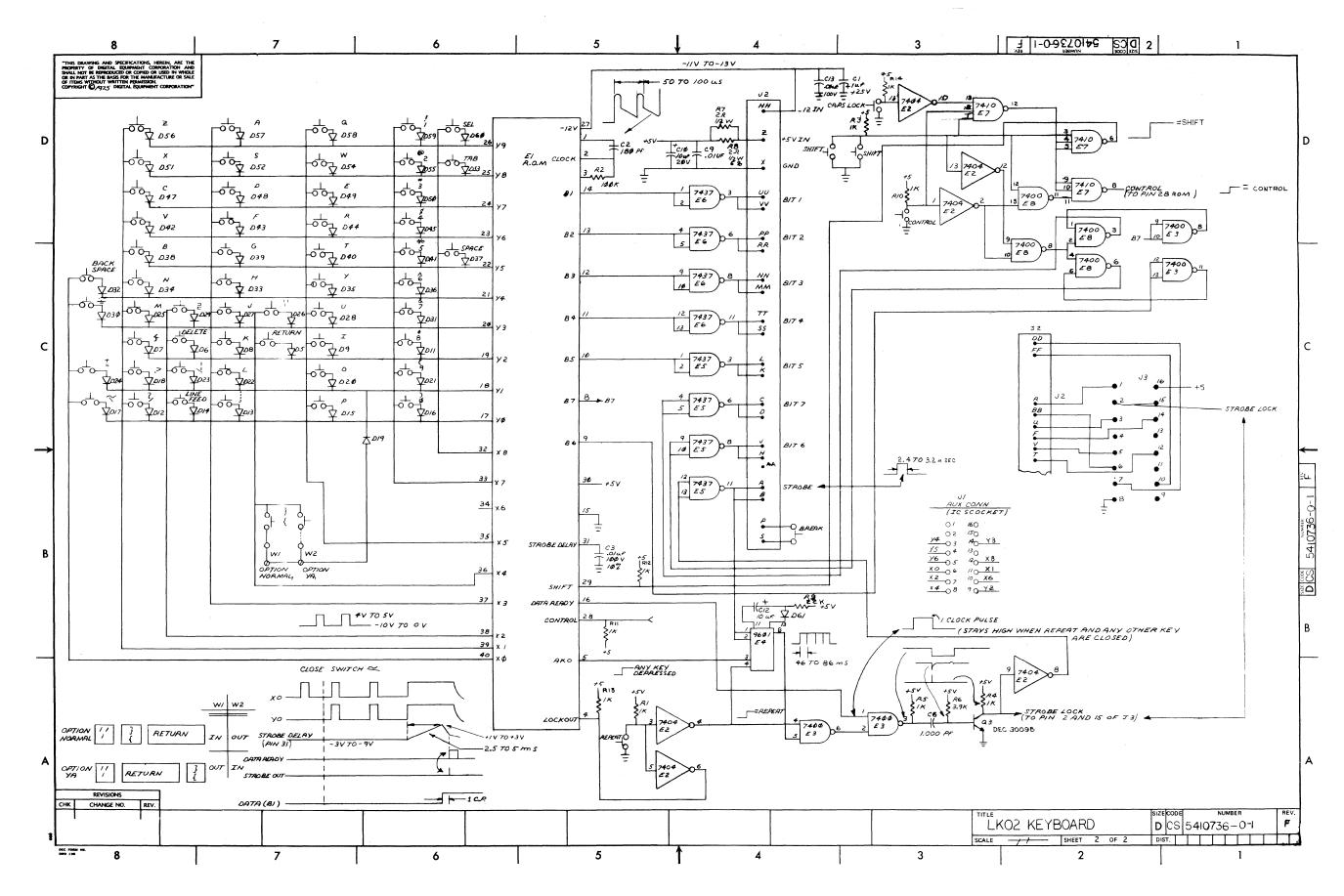

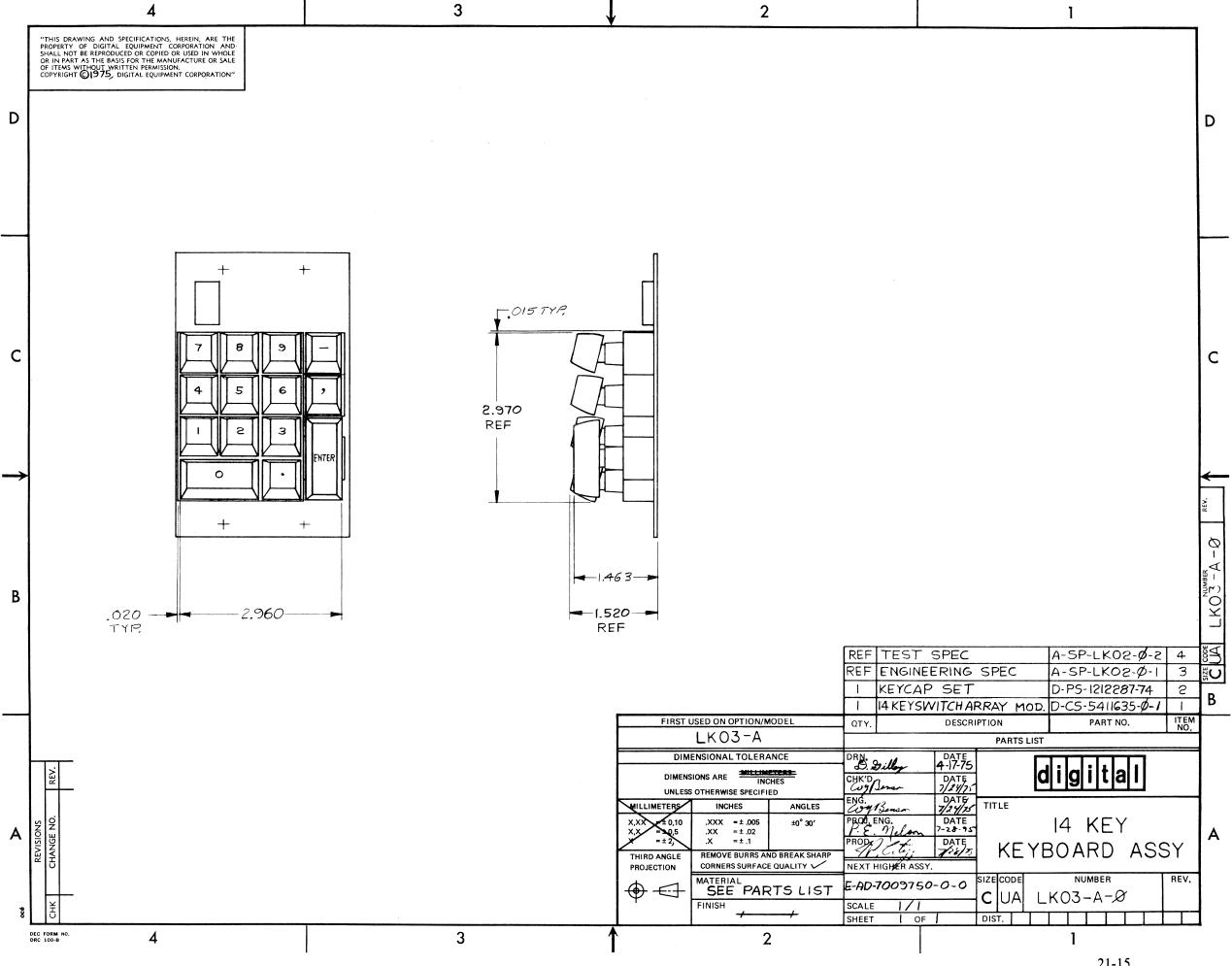

# CHAPTER 21 M7728 PRINT SET

| REFERENCE DATA               |

|------------------------------|

| ABBREVIATIONS A-1            |

| SIGNAL GLOSSARY A-1          |

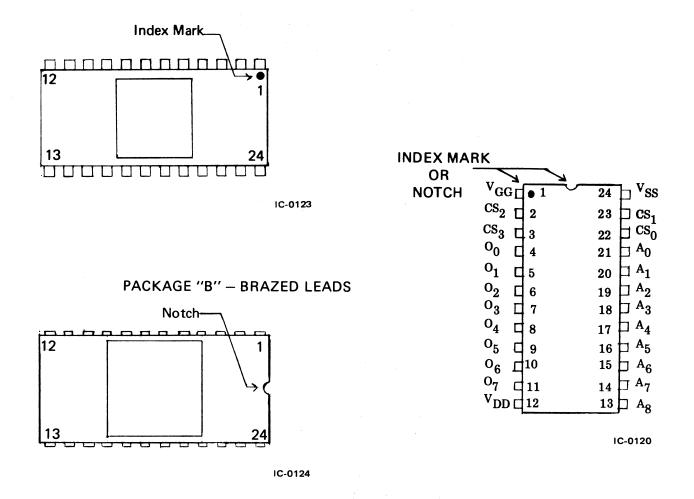

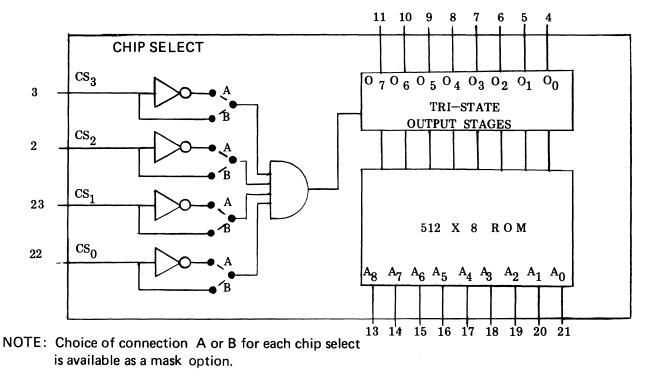

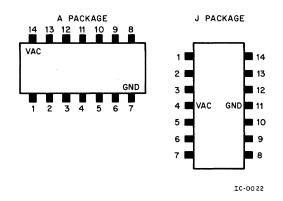

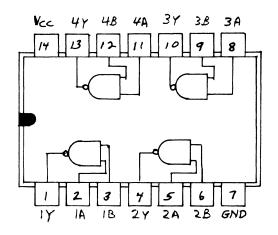

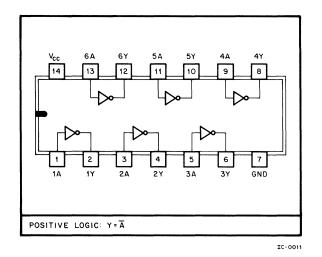

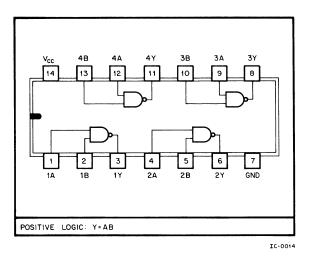

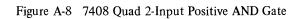

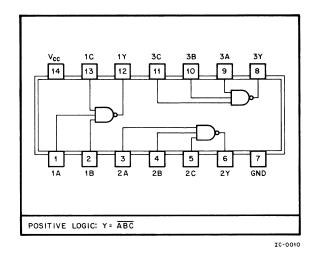

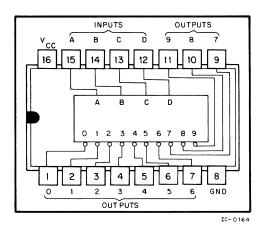

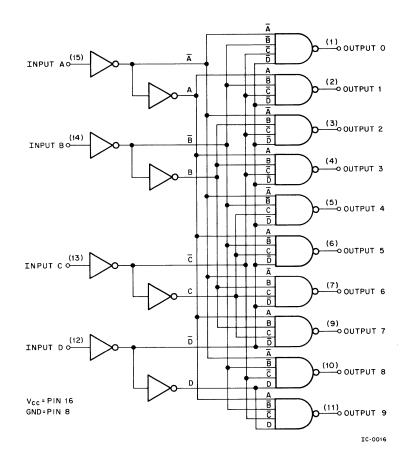

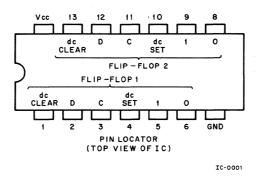

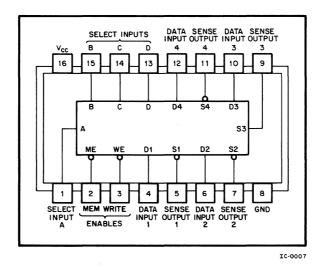

| IC PIN LOCATION DRAWINGS A-1 |

|                              |

# ILLUSTRATIONS

Title

# Figure No.

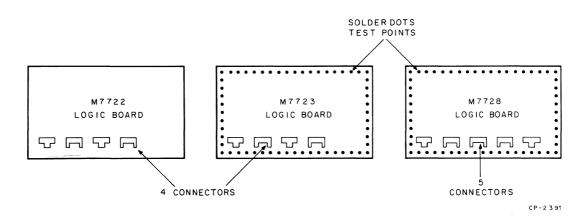

| 9-1 Physical Characteristics of M7722, M7723, and M7728 Logic Boards | 0.0     |

|----------------------------------------------------------------------|---------|

|                                                                      |         |

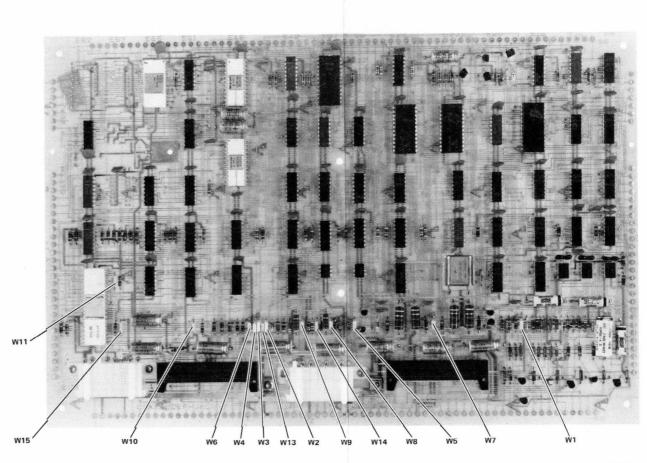

| 9-2 Location of Jumpers on M7723 Logic Board                         |         |

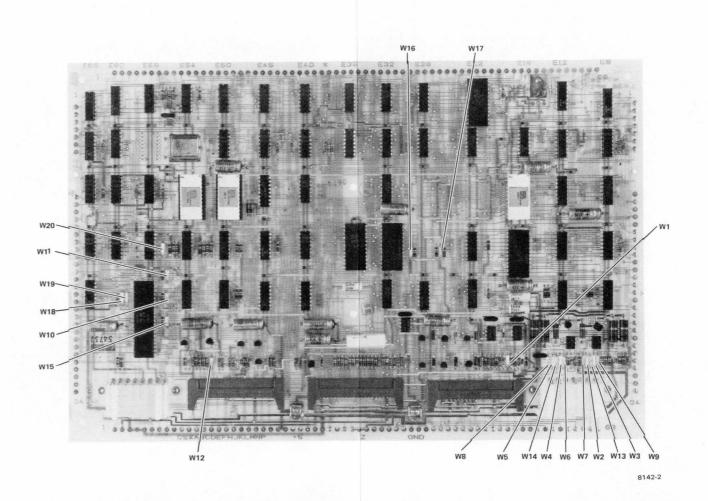

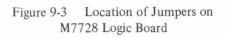

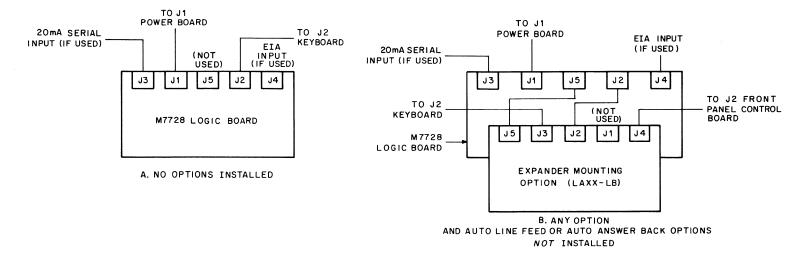

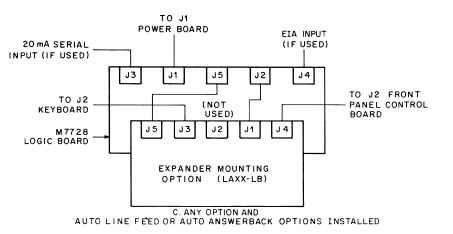

| 9-3 Location of Jumpers on M7728 Logic Board                         | 9-5     |

| 9-4 Cabling Configurations for the M7728 Logic Board                 | 9-6     |

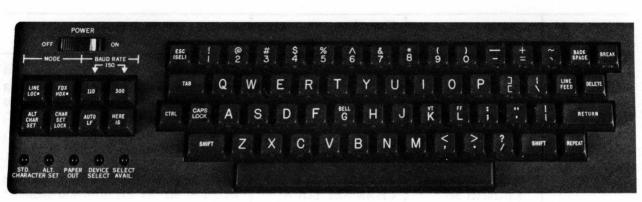

| 9-5 LA36 Keyboard Bezel                                              | 9-7     |

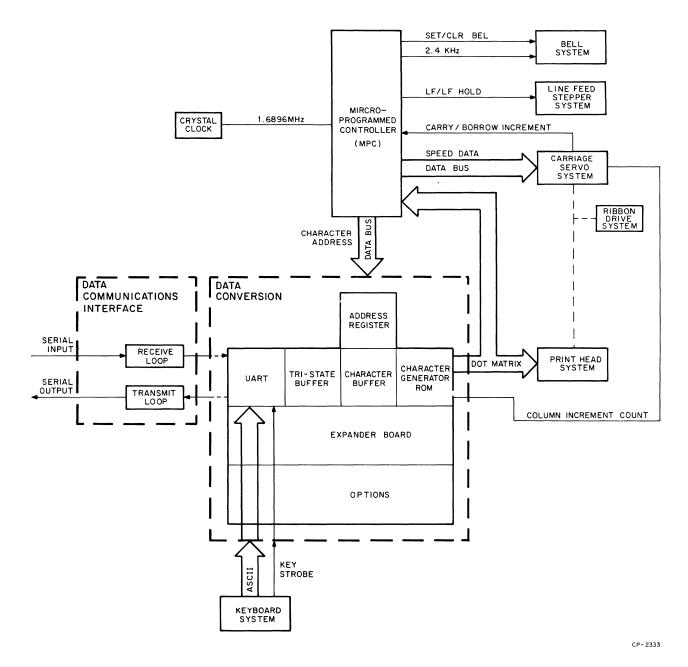

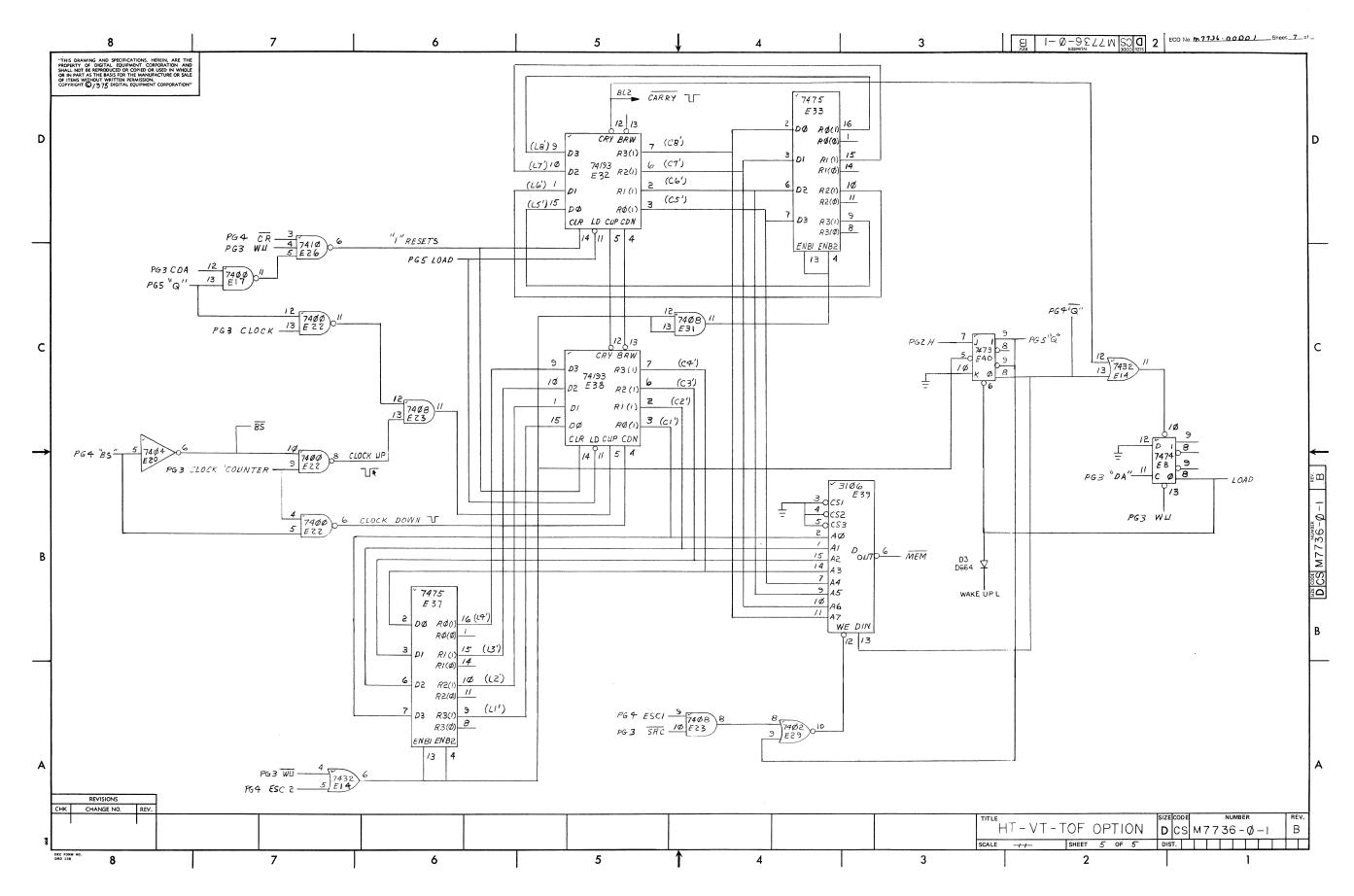

| 9-6 Basic Block Diagram of M7728 Logic Board                         | 9-11    |

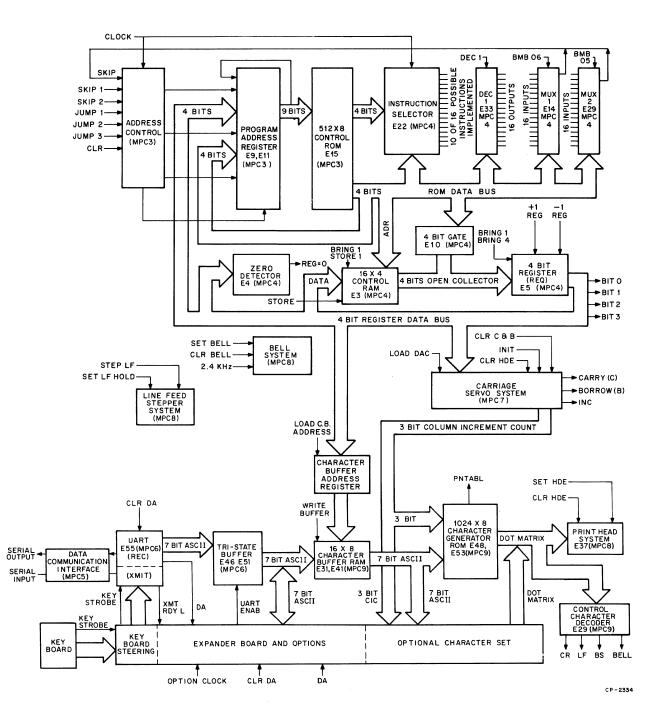

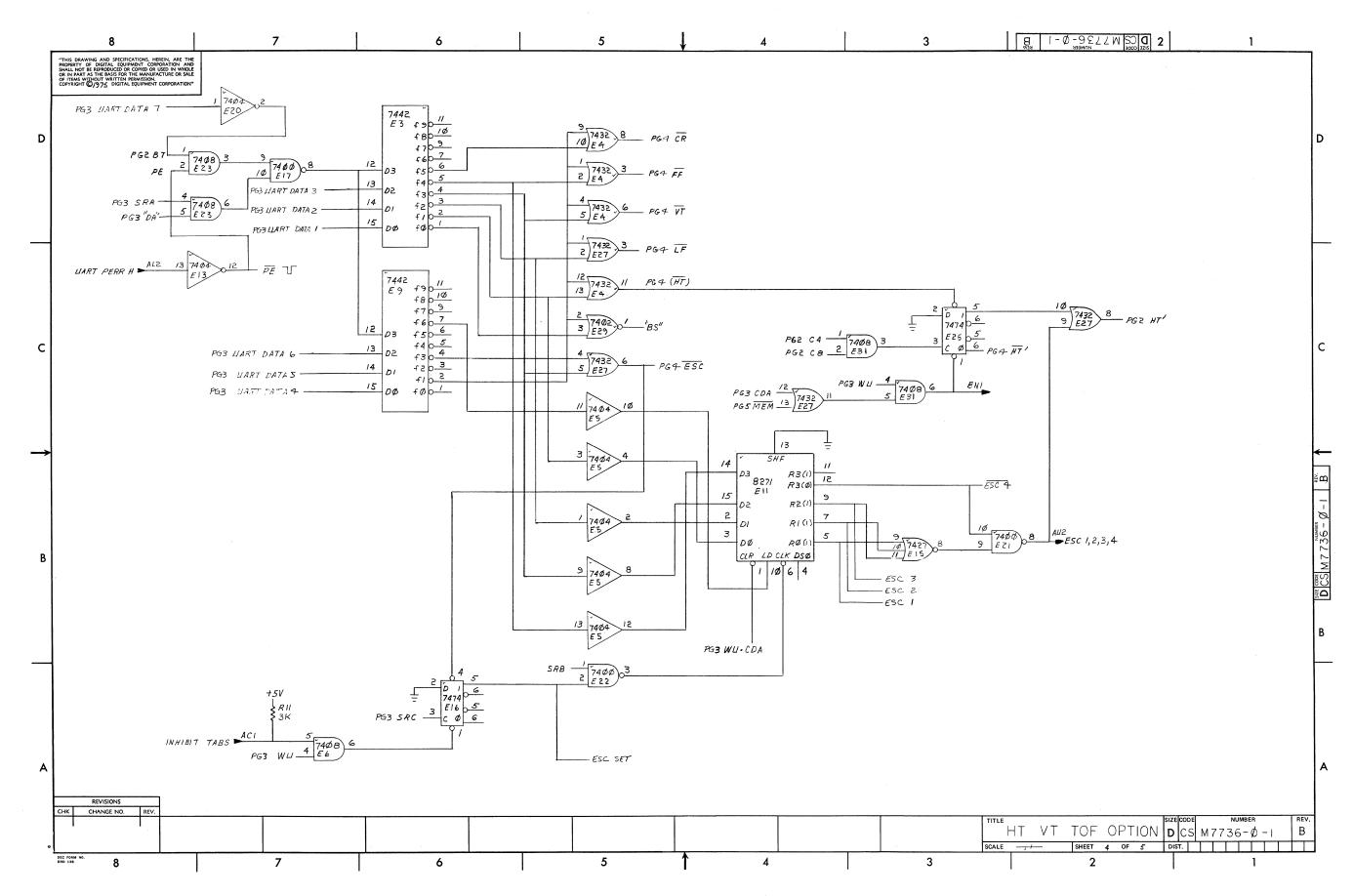

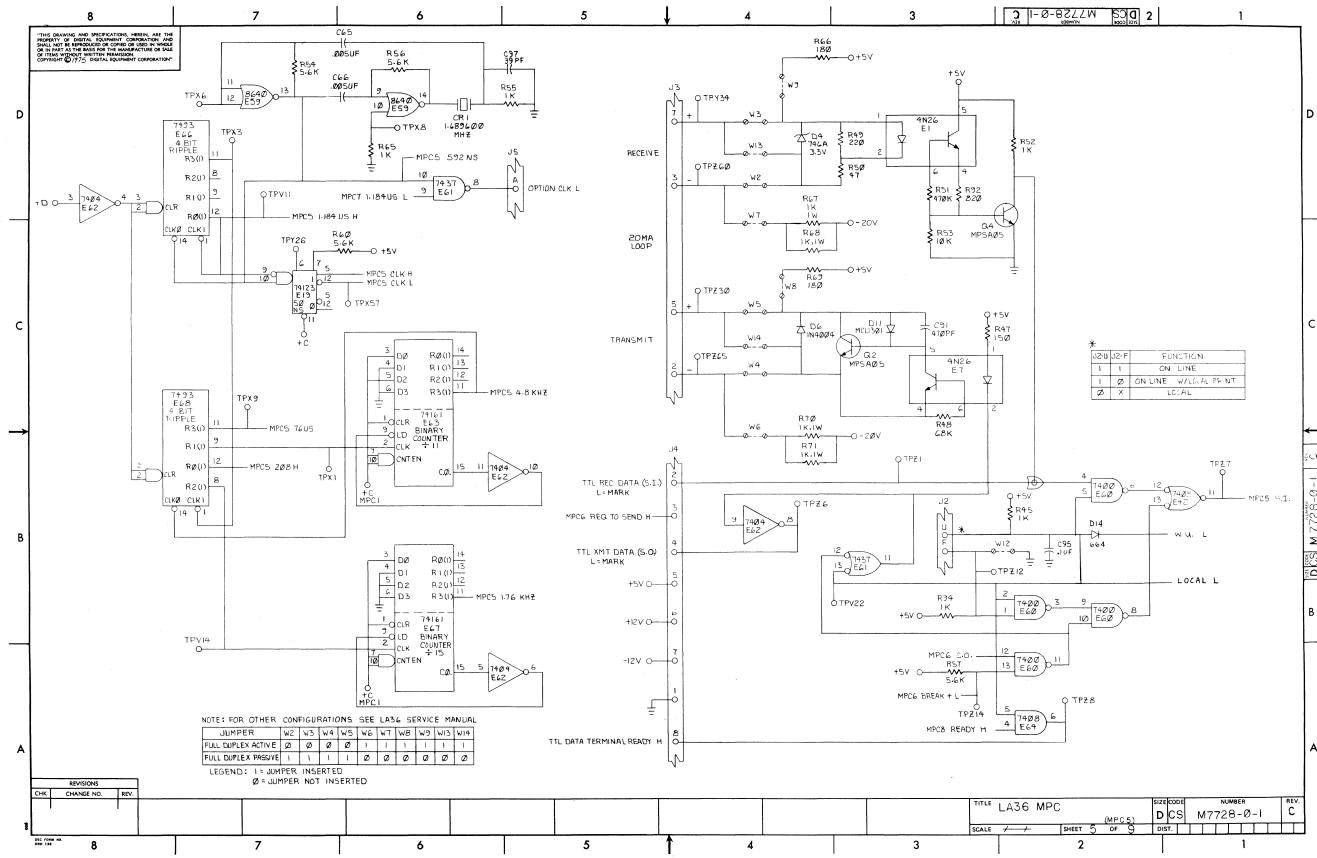

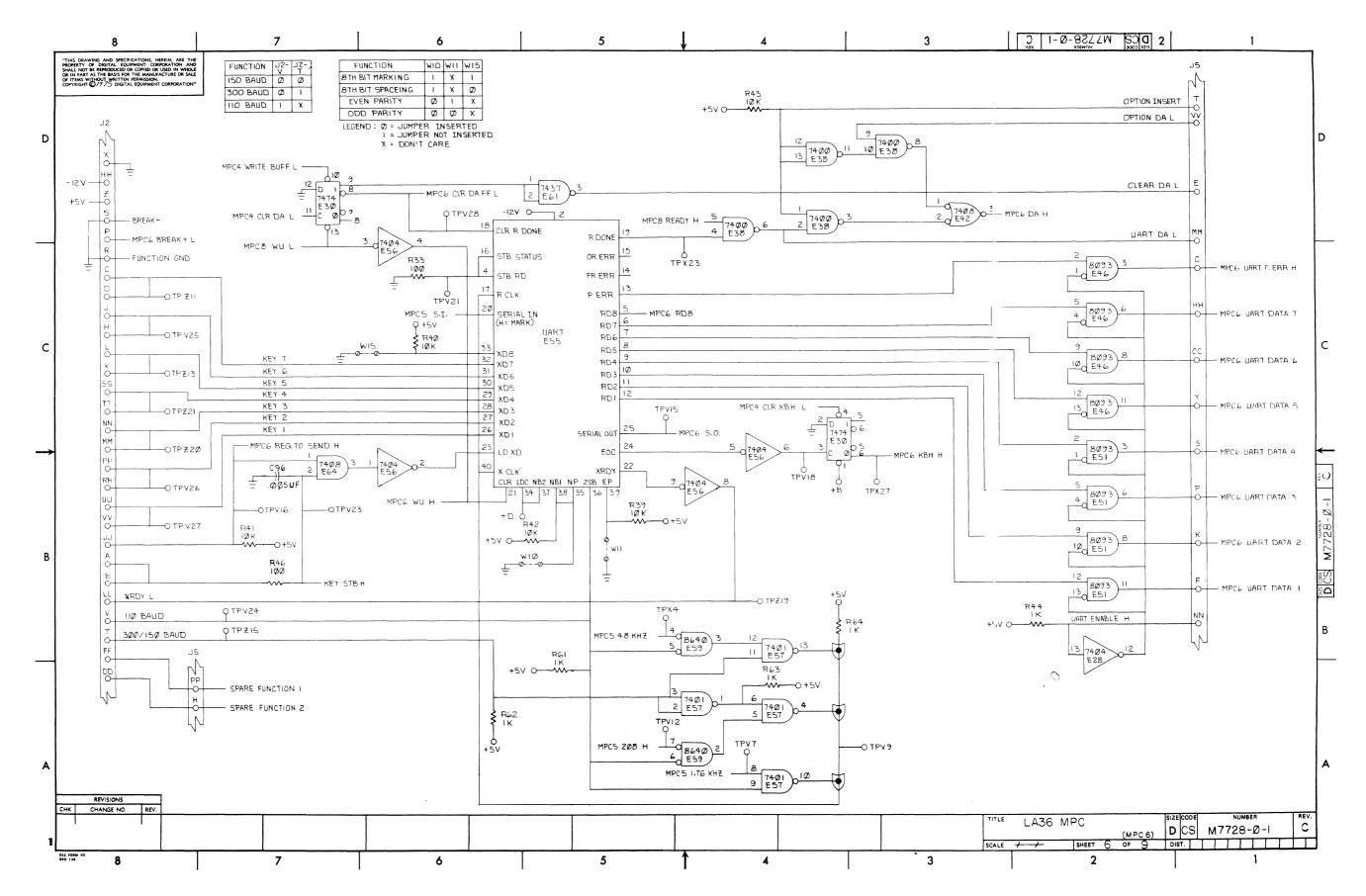

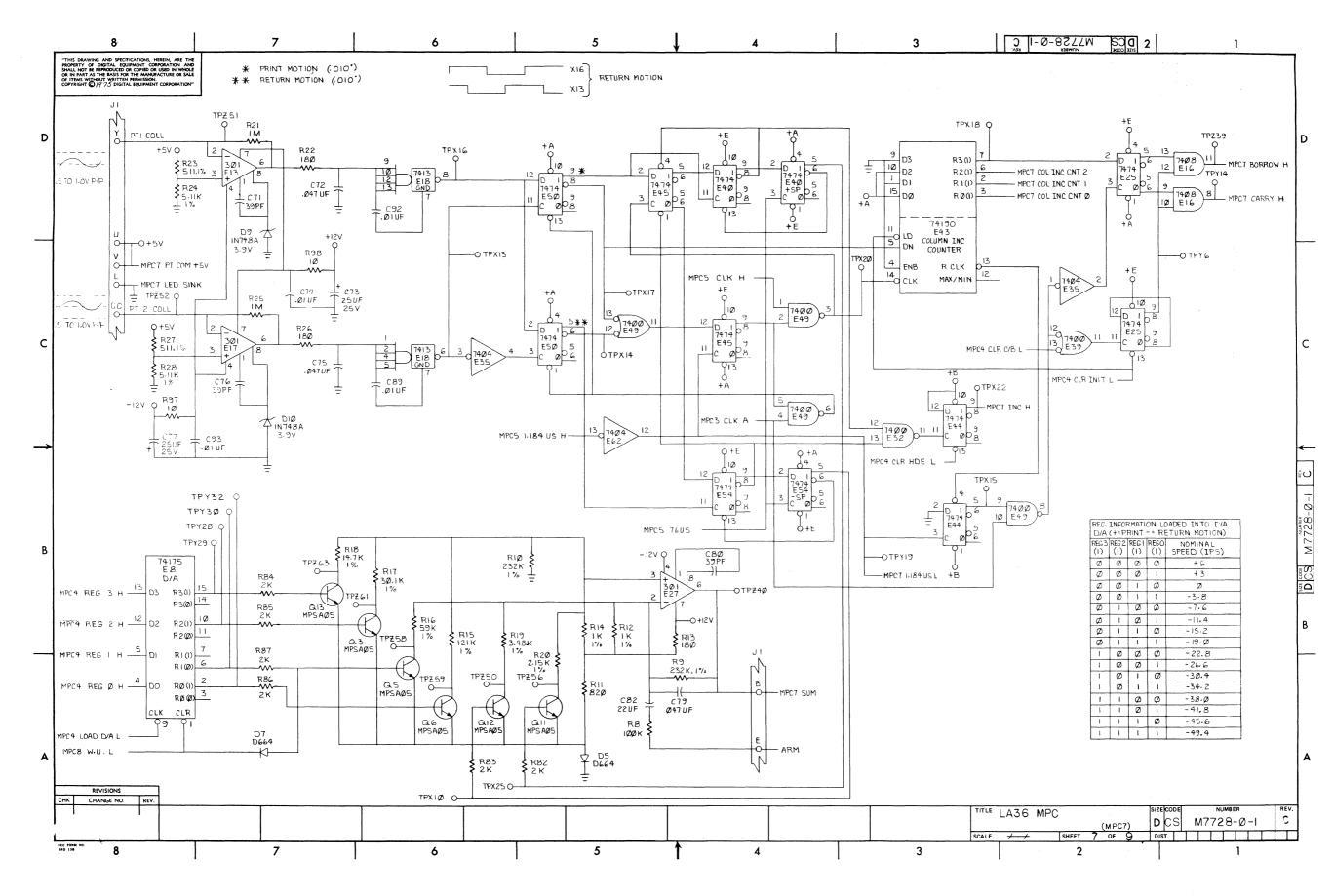

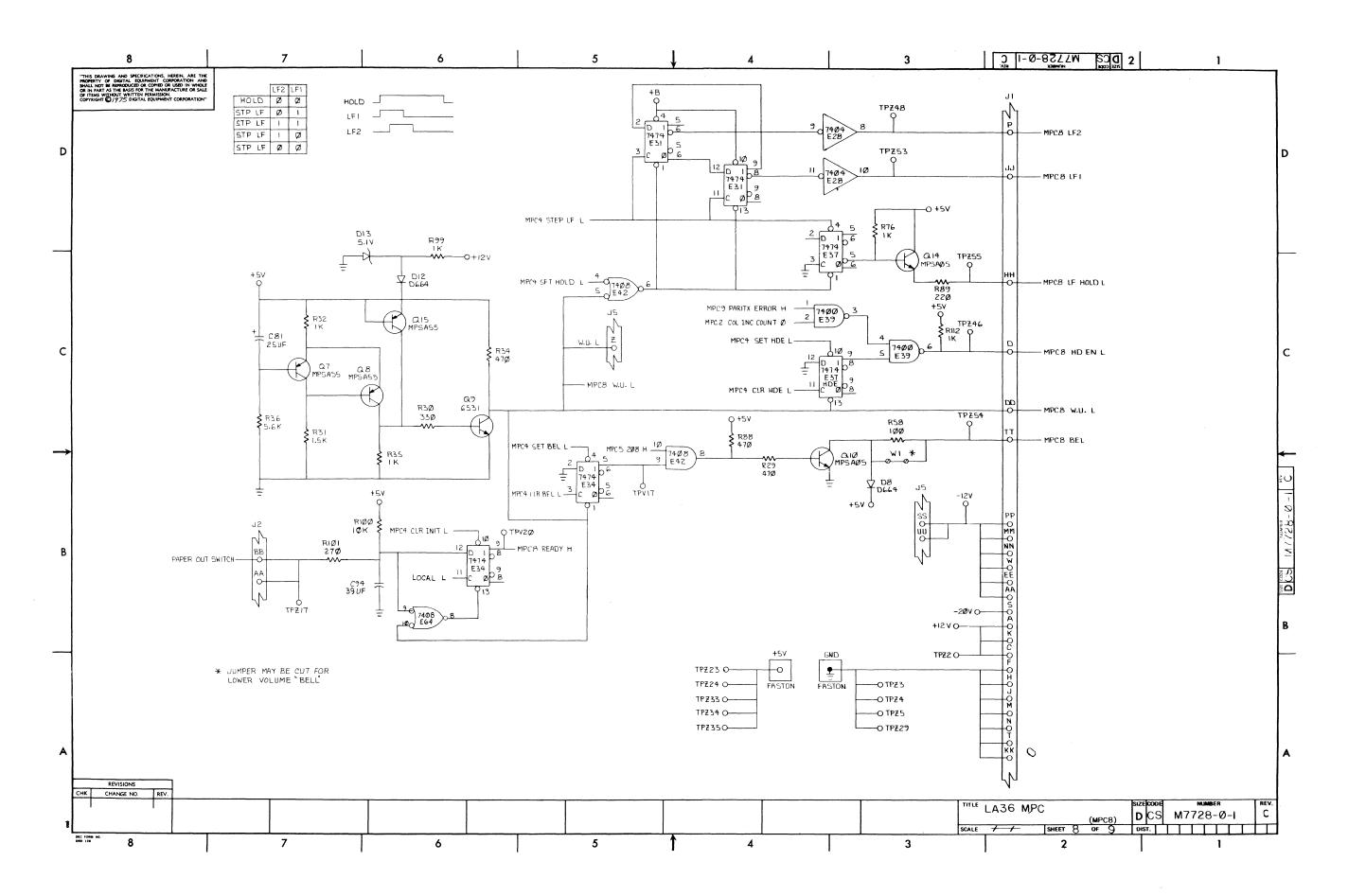

| 9-7 M7728 Control Logic Diagram                                      | 9-12    |

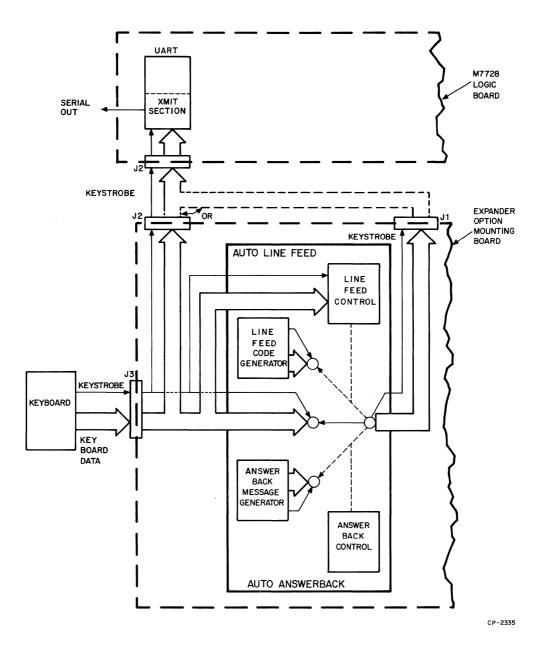

| 9-8 Steering of Keyboard Data                                        | 9-13    |

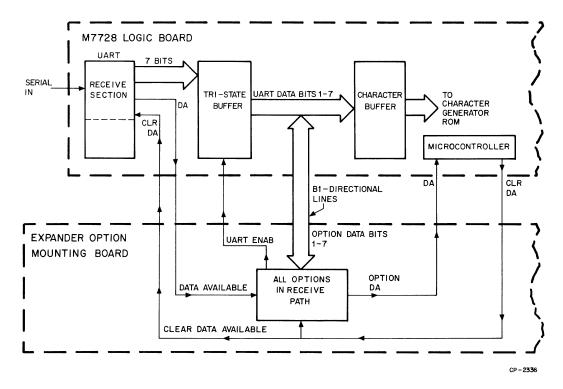

| 9-9 Receive Operations of M7728 Logic Board                          | 9-15    |

| 11-1 Forms Control Functional Block Diagram                          |         |

| 11-2 Forms Control Basic Block Diagram                               | 11-3    |

| 11-3 Timing Sequence for Forms Control Option                        | 11-5    |

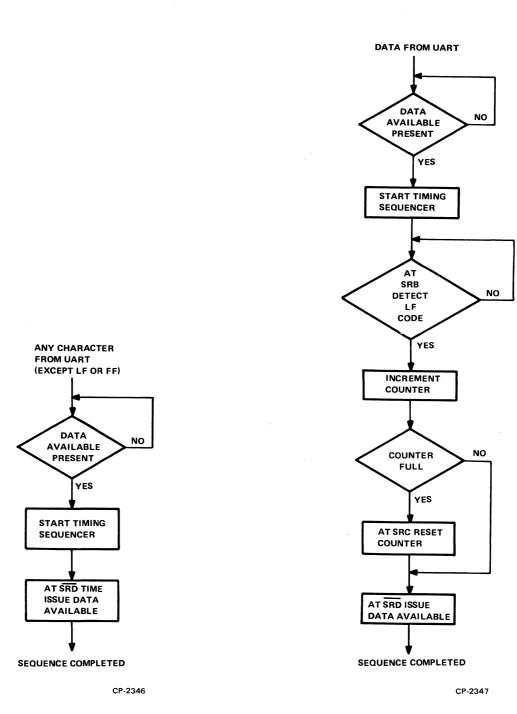

| 11-4 Forms Control Operational Sequence When Any Character Received  | 11-6    |

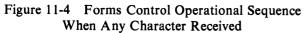

| 11-5 Forms Control Operational Sequence When Line Feed Code Received | 11-6    |

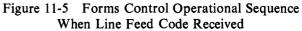

| 11-6 Forms Control Operational Sequence When Form Feed Code Received | 11-8    |

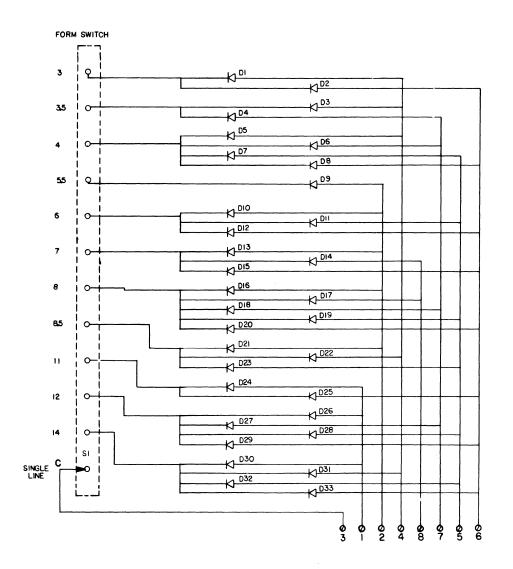

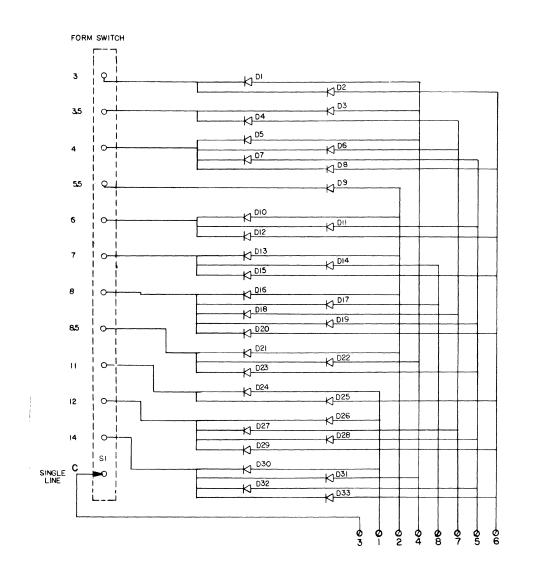

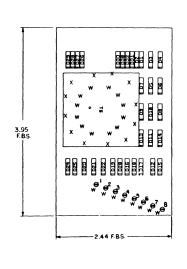

| 11-7 LAXX-KV Form Feed Diode Matrix                                  | . 11-10 |

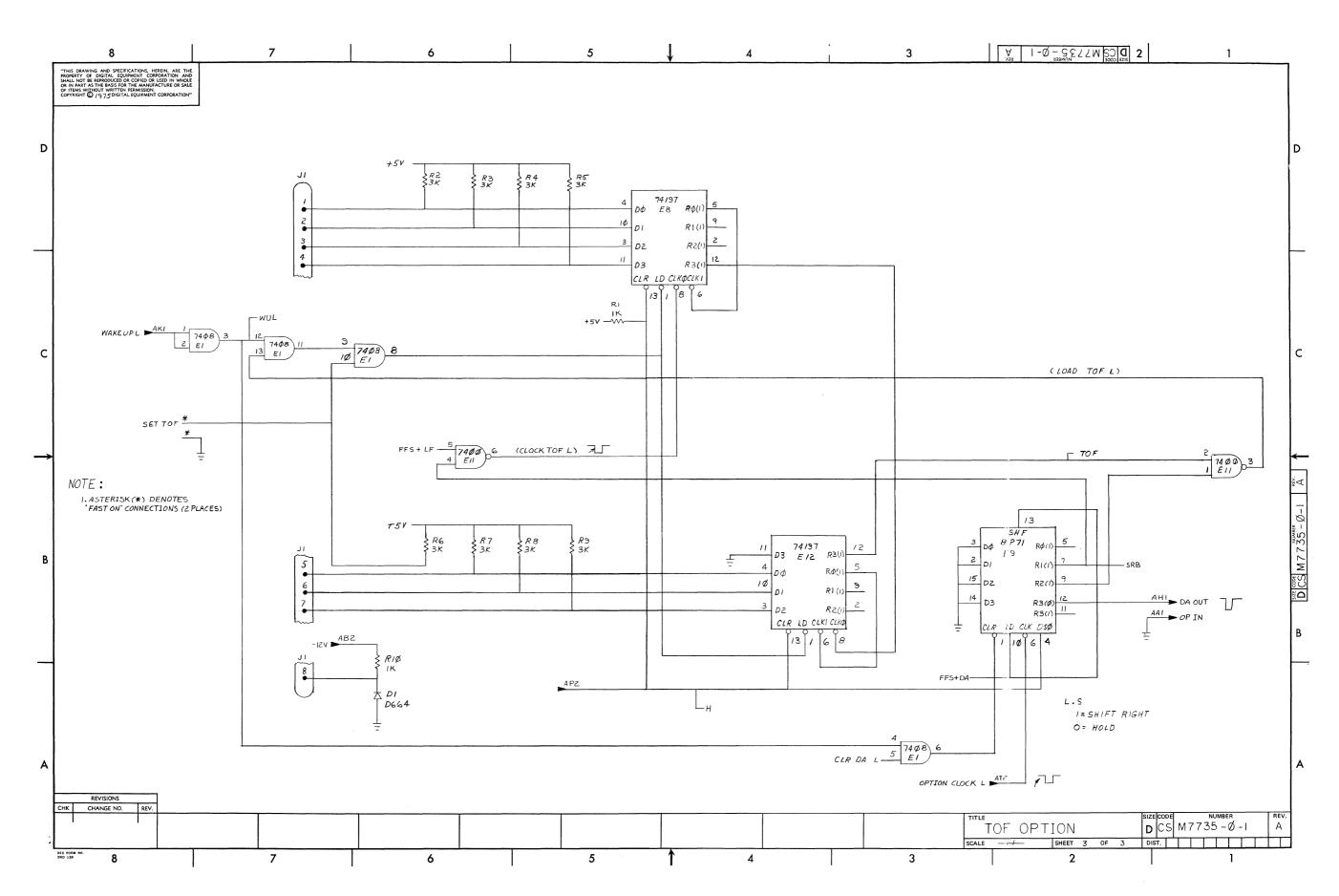

| 12-1 Selective Addressing Functional Block Diagram                   | 12-3    |

| 12-2 Selective Addressing Basic Block Diagram                        | 12-5    |

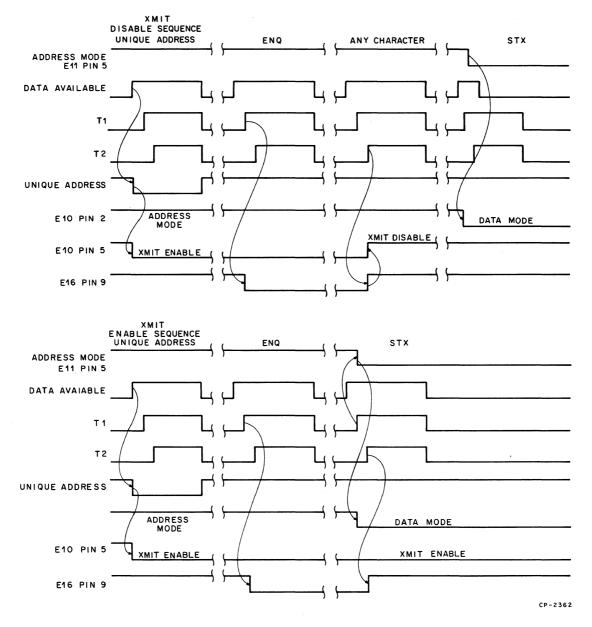

| 12-3 Timing Diagram for Transmit Enable and Disable Sequence         | 12-8    |

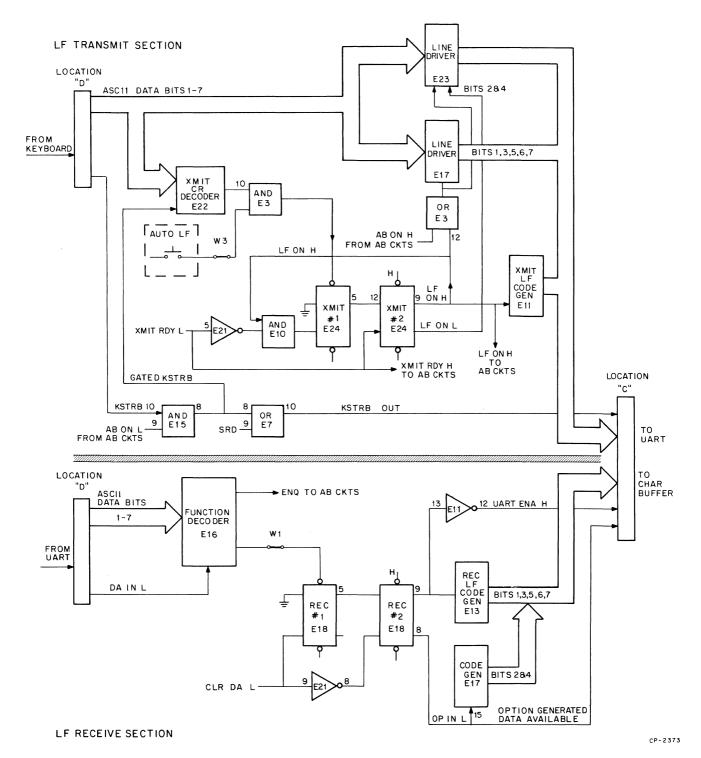

| 13-1 Automatic Answerback Option Functional Block Diagram            | 13-2    |

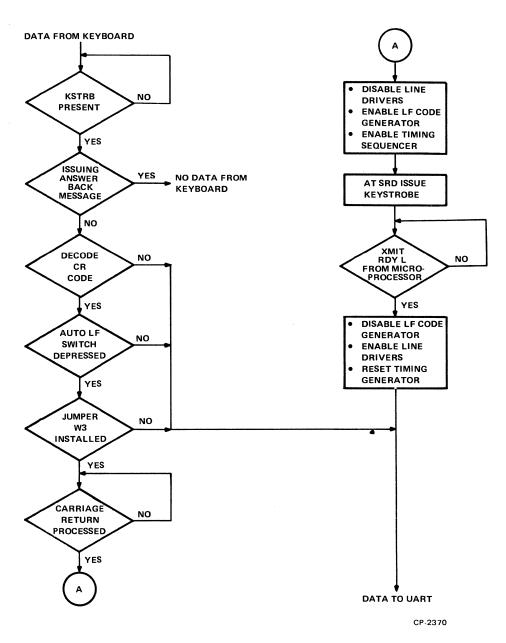

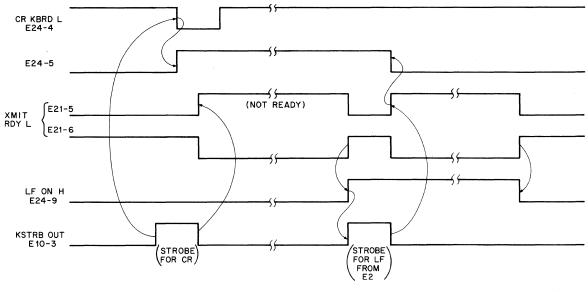

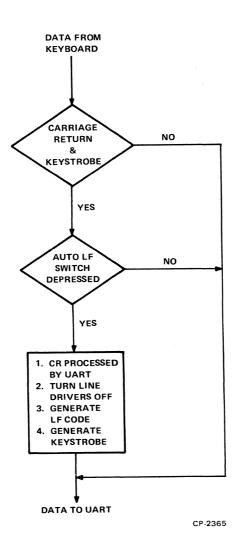

| 13-2 Operational Sequence for LF Transmit Section                    | 13-4    |

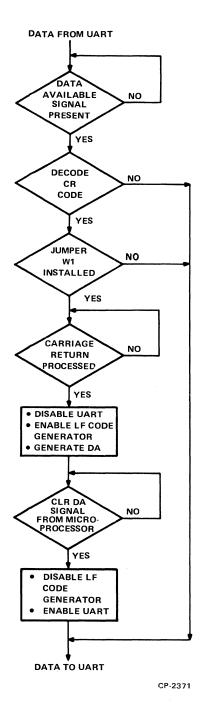

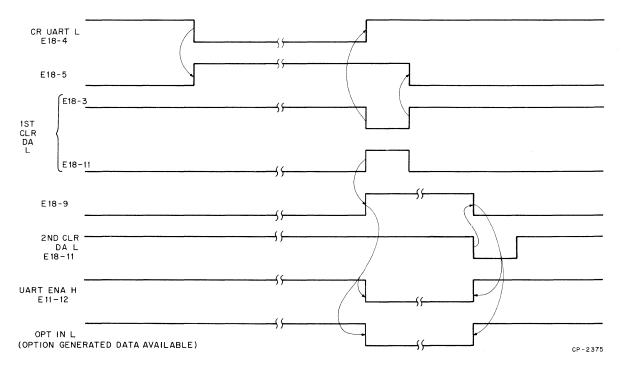

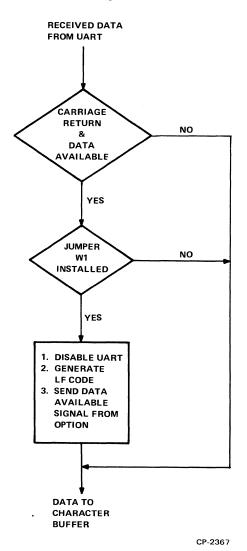

| 13-3 Operational Sequence for LF Receive Section                     | 13-6    |

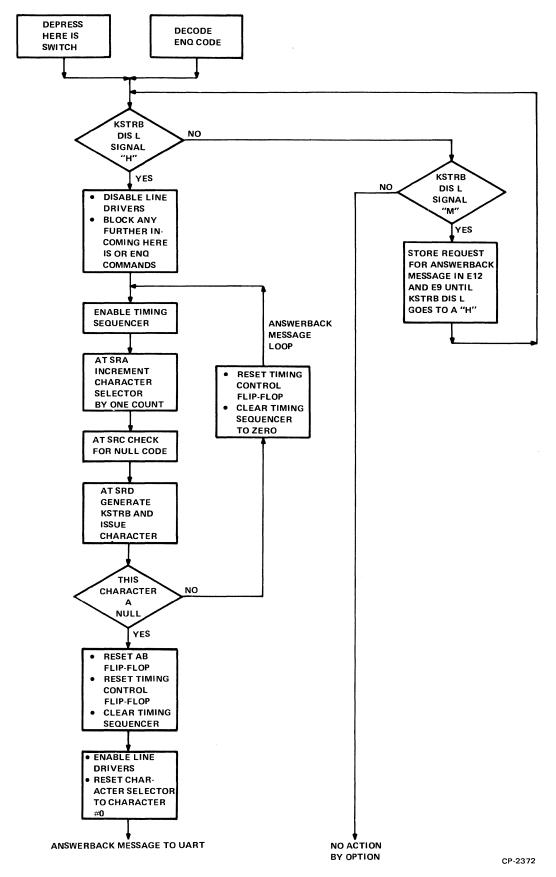

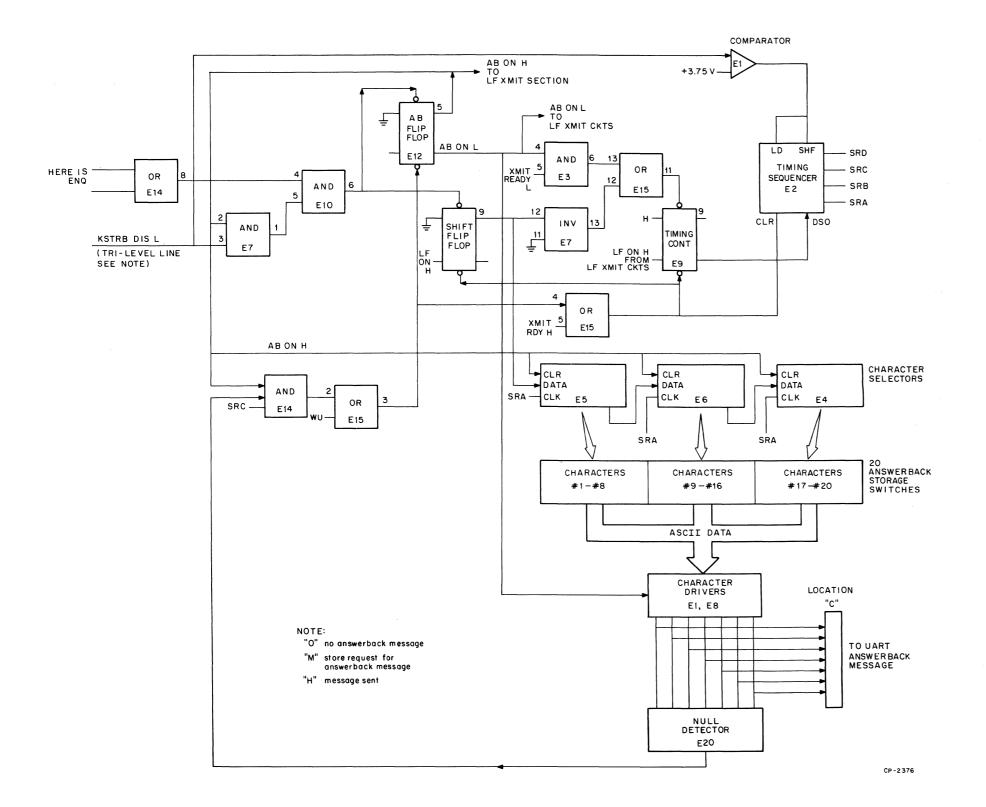

| 13-4 Operational Sequence for Answerback Section                     | 13-7    |

| 13-5 LF Sections of Answerback Option                                | 13-9    |

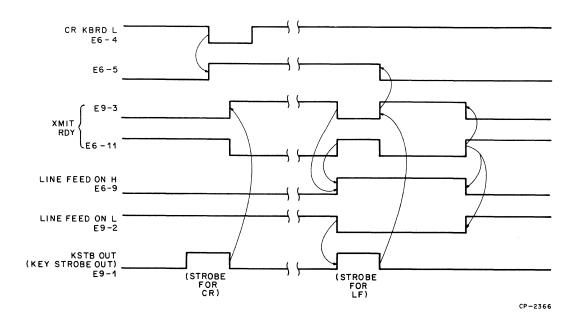

| 13-6 LF Transmit Section Timing Sequence                             | . 13-10 |

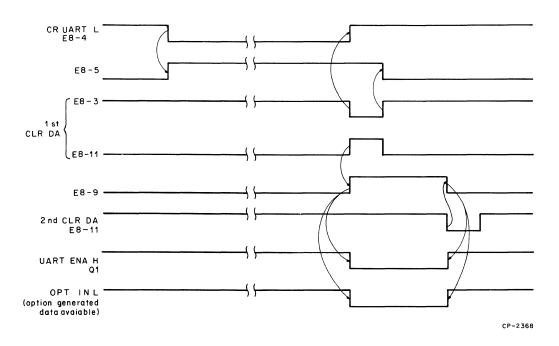

| 13-7 LF Receive Section Timing Sequence                              | . 13-11 |

| 13-8 Answerback Section Basic Block Diagram                          | . 13-12 |

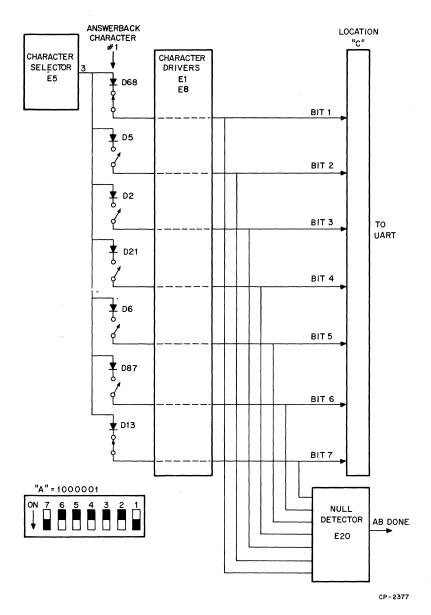

| 13-9 Typical Answerback Character Programming                        | . 13-14 |

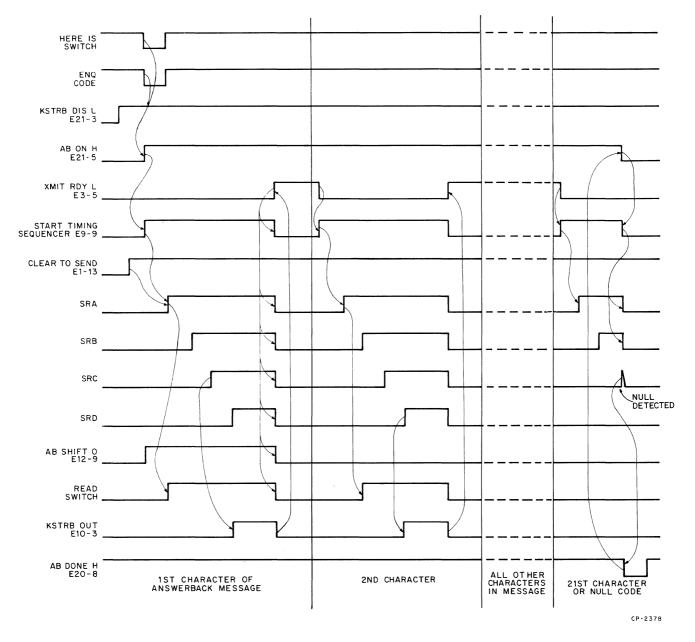

| 13-10 Answerback Section Timing Sequence                             | . 13-15 |

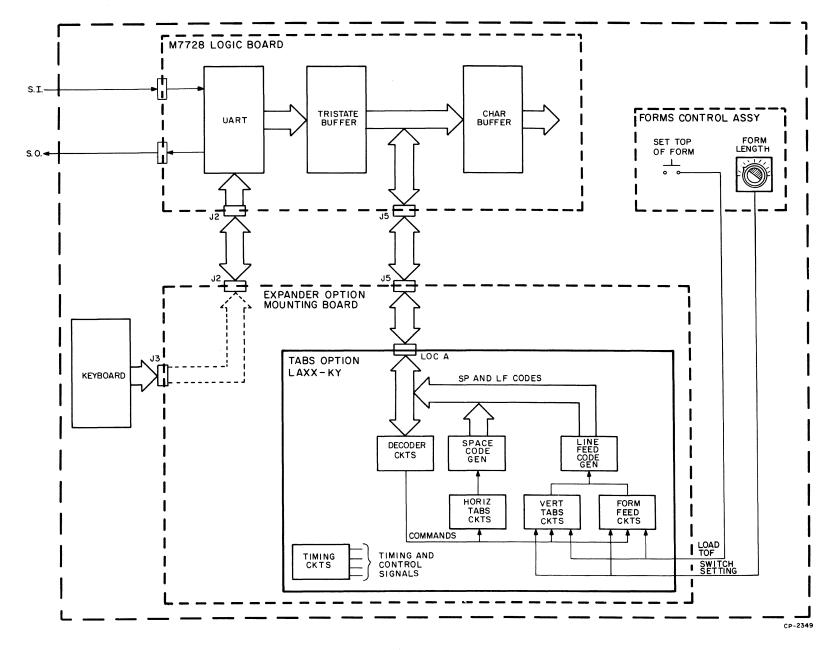

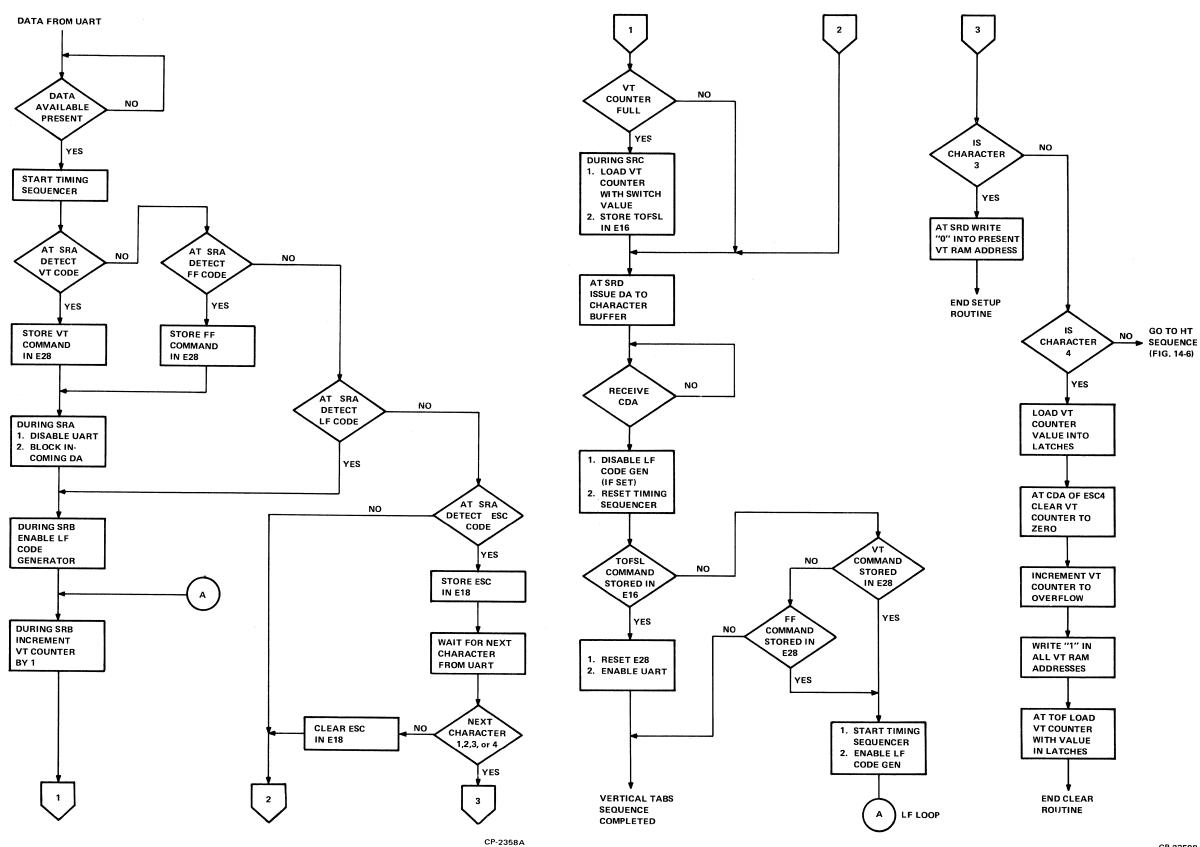

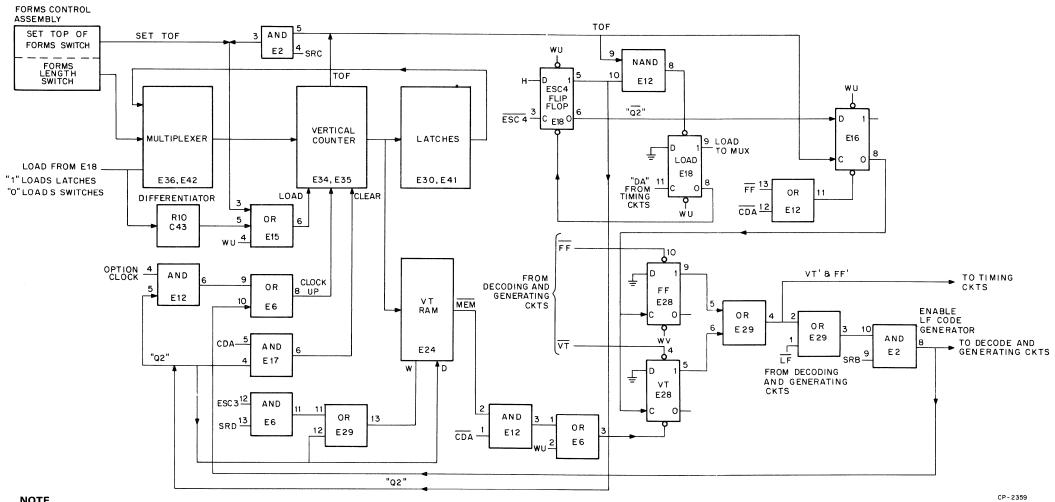

| 14-1 Tabs Option Functional Block Diagram                            |         |

| 14-2 Decoding and Generating Circuits Basic Block Diagram            |         |

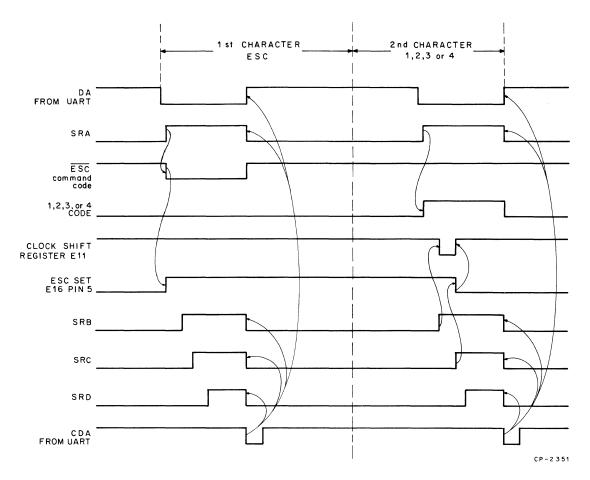

| 14-3 Timing for ESC Command Decoding                                 |         |

Page

Page

# ILLUSTRATIONS (Cont)

| 14-5       Horizontal Tabs Circuits Basic Block Diagram       14-10         14-6       Horizontal Tabs Circuits Operational Sequence       14-11         14-7       Top of Form Circuits Basic Block Diagram       14-14         14-8       Top of Form Circuits Basic Block Diagram       14-17         14-9       Vertical Tabs Circuits Operational Sequence       14-17         14-10       Vertical Tabs Circuits Operational Sequence       14-18         14-11       Common Components of Vertical Tabs and TOP Circuits       14-19         14-12       LAXX-KY Diode Matrix       14-24         15-1       Automatic Line Feed Functional Diagram       15-3         15-2       Automatic Line Feed Block Diagram       15-3         15-3       Operational Sequence for Automatic Line Feed Transmit Section       15-4         15-4       Transmit Line Feed Control Timing Sequence       15-5         15-5       Operational Sequence for Automatic Line Feed Receive Section       15-6         16-2       Data Available Signal Distribution on Expander Board       16-3         16-3       Methods of Switching Data Available Signal Into Options       16-4         16-4       Keystrobe Distribution on Expander Board       16-5         17-1       EIA Interface Block Diagram       17-2                                                                                                                          | Figure No.   | Title                                               | Page  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------|-------|

| 14-6       Horizontal Tabs Circuits Operational Sequence       14-11         14-7       Top of Form Circuits Basic Block Diagram       14-14         14-8       Top of Form Circuits Operational Sequence       14-15         14-9       Vertical Tabs Circuits Operational Sequence       14-18         14-10       Common Components of Vertical Tabs and TOF Circuits       14-19         14-11       Common Components of Vertical Tabs and TOF Circuits       14-19         14-12       LAXX-KY Diode Matrix       14-24         15-1       Automatic Line Feed Functional Diagram       15-2         15-2       Automatic Line Feed Mutomatic Line Feed Transmit Section       15-4         15-3       Operational Sequence for Automatic Line Feed Receive Section       15-5         15-4       Transmit Line Feed Control Timing Sequence       15-7         16-5       Receive Line Feed Control Timing Sequence       15-7         16-6       Receive Line Feed Control Timing Sequence       15-7         16-7       Data Available Signal Distribution on Expander Board       16-3         16-8       Receive Line Feed Control Timing Sequence       15-7         16-9       Data Available Signal Distribution on Expander Board       16-3         16-1       ASCII Data Distribution on Expander Board       16-3                                                                                                      | 14-4         | Timing Circuits Basic Block Diagram                 | 14-8  |

| 14-7       Top of Form Circuits Basic Block Diagram       14-14         14-8       Top of Form Circuits Operational Sequence       14-15         14-9       Vertical Tabs Circuits Basic Block Diagram       14-17         14-10       Vertical Tabs Circuits Sais Block Diagram       14-18         14-11       Common Components of Vertical Tabs and TOF Circuits       14-19         14-12       LAXX-KY Diode Matrix       14-23         15-2       Automatic Line Feed Iock Diagram       15-3         15-3       Operational Sequence for Automatic Line Feed Transmit Section       15-4         15-4       Transmit Line Feed Control Timing Sequence       15-5         15-5       Operational Sequence for Automatic Line Feed Receive Section       15-6         15-6       Receive Line Feed Control Timing Sequence       15-7         16-1       ASCII Data Distribution on Expander Board       16-3         16-2       Data Available Signal Distribution on Expander Board       16-5         16-3       Methods of Switching Data Available Signal into Options       16-64         16-4       Keystrobe Distribution on Expander Board       16-75         17-1       EIA Interface Cable Option (LAXX-LK) Pin Assignments       18-1         18-2       20 mA Interface Cable Option (LAXX-LK) Pin Assignments       18-                                                                                            | 14-5         | Horizontal Tabs Circuits Basic Block Diagram        | 14-10 |

| 14-8       Top of Form Circuits Operational Sequence       14-15         14-9       Vertical Tabs Circuits Operational Sequence       14-17         14-10       Common Components of Vertical Tabs and TOF Circuits       14-18         14-11       Common Components of Vertical Tabs and TOF Circuits       14-19         14-12       LAXX-KY Diode Matrix       14-24         15-1       Automatic Line Feed Functional Diagram       15-3         15-3       Operational Sequence for Automatic Line Feed Transmit Section       15-4         15-4       Transmit Line Feed Control Timing Sequence       15-5         15-5       Operational Sequence for Automatic Line Feed Receive Section       15-6         15-6       Receive Line Feed Control Timing Sequence       15-7         16-1       ASCII Data Distribution on Expander Board       16-2         16-2       Data Available Signal Distribution on Expander Board       16-3         16-3       Methods of Switching Data Available Signal into Options       164         16-4       Keystrobe Distribution on Expander Board       16-5         17-1       EIA Interface Cable Option (LAXX-LK) Pin Assignments       18-1         17-2       EIA Interface Cable Option (LAXX-LH) Pin Assignments       18-2         17-3       Typical Telephone Communication Configuration <td>14-6</td> <td>Horizontal Tabs Circuits Operational Sequence</td> <td> 14-11</td> | 14-6         | Horizontal Tabs Circuits Operational Sequence       | 14-11 |

| 14-9       Vertical Tabs Circuits Basic Block Diagram       14-17         14-10       Vertical Tabs Circuits Operational Sequence       14-18         14-11       Common Components of Vertical Tabs and TOP Circuits       14-19         14-12       LAXX-KY Diode Matrix       14-24         15-1       Automatic Line Feed Block Diagram       15-3         15-2       Automatic Line Feed Block Diagram       15-3         15-3       Operational Sequence for Automatic Line Feed Transmit Section       15-4         15-4       Transmit Line Feed Control Timing Sequence       15-5         15-5       Operational Sequence for Automatic Line Feed Receive Section       15-6         16-1       ASCII Data Distribution on Expander Board       16-3         16-2       Data Available Signal Distribution on Expander Board       16-3         16-4       Keystrobe Distribution on Expander Board       16-5         16-5       Methods of Switching Data Available Signal into Options       16-6         16-4       Keystrobe Distribution on Expander Board       16-5         16-5       Uption (LAXX-LK) Pin Assignments       18-1         18-2       20 mA Interface Cable Option (LAXX-LK) Pin Assignments       18-2         18-2       20 mA Interface Cable Option (LAXX-LK) Pin Assignments       18-2                                                                                                           | 14-7         | Top of Form Circuits Basic Block Diagram            | 14-14 |

| 14-10       Vertical Tabs Circuits Operational Sequence       14-18         14-11       Common Components of Vertical Tabs and TOF Circuits       14-19         14-12       LAXX-KY Diode Matrix       14-24         15-1       Automatic Line Feed Floretional Diagram       15-3         15-2       Automatic Line Feed Block Diagram       15-3         15-3       Operational Sequence for Automatic Line Feed Transmit Section       15-4         15-4       Transmit Line Feed Control Timing Sequence       15-5         15-5       Operational Sequence for Automatic Line Feed Receive Section       15-6         16-6       Receive Line Feed Control Timing Sequence       15-7         16-7       Data Available Signal Distribution on Expander Board       16-3         16-8       Methods of Switching Data Available Signal into Options       16-4         16-4       Keystrobe Distribution on Expander Board       16-5         17-1       ElA Interface Functional Diagram       17-5         18-1       20 mA Interface Cable Option (LAXX-LK) Pin Assignments       18-1         18-2       20 mA Interface Cable Option (LAXX-LK) Pin Assignments       18-2         19-1       Typical Telephone Communication Configuration       19-2       Acoustic Coupler Fransmit Section Basic Block Diagram       19-3 <t< td=""><td>14-8</td><td>Top of Form Circuits Operational Sequence</td><td> 14-15</td></t<>     | 14-8         | Top of Form Circuits Operational Sequence           | 14-15 |

| 14-11       Common Components of Vertical Tabs and TOF Circuits       14-19         14-12       LAXX-KY Diode Matrix       14-24         15-1       Automatic Line Feed Eunctional Diagram       15-3         15-2       Automatic Line Feed Block Diagram       15-3         15-3       Operational Sequence for Automatic Line Feed Transmit Section       15-4         15-4       Transmit Line Feed Control Timing Sequence       15-5         15-5       Operational Sequence for Automatic Line Feed Receive Section       15-6         16-1       ASCII Data Distribution on Expander Board       16-2         16-2       Data Available Signal Distribution on Expander Board       16-5         16-4       Keystrobe Distribution on Expander Board       16-5         16-5       Bitribution on Expander Board       16-5         16-6       Receive Line Feed Option (LAXX-LK) Pin Assignments       18-1         16-7       EIA Interface Eable Option (LAXX-LK) Pin Assignments       18-1         17-2       EIA Interface Cable Option (LAXX-LK) Pin Assignments       18-2         18-1       20 mA Interface Cable Option (LAXX-LK) Pin Assignments       18-2         19-1       Typical Telephone Communication Configuration       19-3         19-2       Acoustic Coupler Transmit Section Basic Block Diagram       19                                                                                            | 14-9         | Vertical Tabs Circuits Basic Block Diagram          | 14-17 |

| 14-12       LAXX-KY Diode Matrix       14-24         15-1       Automatic Line Feed Functional Diagram       15-2         15-2       Automatic Line Feed Block Diagram       15-3         15-3       Operational Sequence for Automatic Line Feed Transmit Section       15-4         15-4       Transmit Line Feed Control Timing Sequence       15-5         15-5       Operational Sequence for Automatic Line Feed Receive Section       15-6         16-6       Receive Line Feed Control Timing Sequence       15-7         16-1       ASCII Data Distribution on Expander Board       16-3         16-2       Data Available Signal Distribution on Expander Board       16-4         16-3       Methods of Switching Data Available Signal into Options       16-4         16-4       Keystrobe Distribution on Expander Board       16-5         17-1       ELA Interface Functional Diagram       17-2         18-1       20 mA Interface Cable Option (LAXX-LK) Pin Assignments       18-1         18-2       20 mA Interface Cable Option (LAXX-LK) Pin Assignments       18-2         19-1       Typical Telephone Communication Configuration       19-2         19-2       Acoustic Coupler Functional Block Diagram       19-3         19-3       Acoustic Coupler Transmit Section Basic Block Diagram       19-3     <                                                                                                 | 14-10        | Vertical Tabs Circuits Operational Sequence         | 14-18 |

| 14-12       LAXX-KY Diode Matrix       14-24         15-1       Automatic Line Feed Functional Diagram       15-2         15-2       Automatic Line Feed Block Diagram       15-3         15-3       Operational Sequence for Automatic Line Feed Receive Section       15-4         15-4       Transmit Line Feed Control Timing Sequence       15-5         5-5       Operational Sequence for Automatic Line Feed Receive Section       15-6         15-6       Receive Line Feed Control Timing Sequence       15-7         16-1       ASCII Data Distribution on Expander Board       16-3         16-2       Data Available Signal Distribution on Expander Board       16-4         16-3       Methods of Switching Data Available Signal into Options       16-4         16-4       Keystrobe Distribution on Expander Board       16-5         17-1       EIA Interface Functional Diagram       17-2         18-1       20 mA Interface Cable Option (LAXX-LK) Pin Assignments       18-2         18-2       20 mA Interface Cable Option (LAXX-LK) Pin Assignments       18-2         19-1       Typical Telephone Communication Configuration       19-2         19-2       Acoustic Coupler Functional Block Diagram       19-3         19-3       Acoustic Coupler Transmit Section Basic Block Diagram       19-4 <td>14-11</td> <td>Common Components of Vertical Tabs and TOF Circuits</td> <td> 14-19</td>             | 14-11        | Common Components of Vertical Tabs and TOF Circuits | 14-19 |

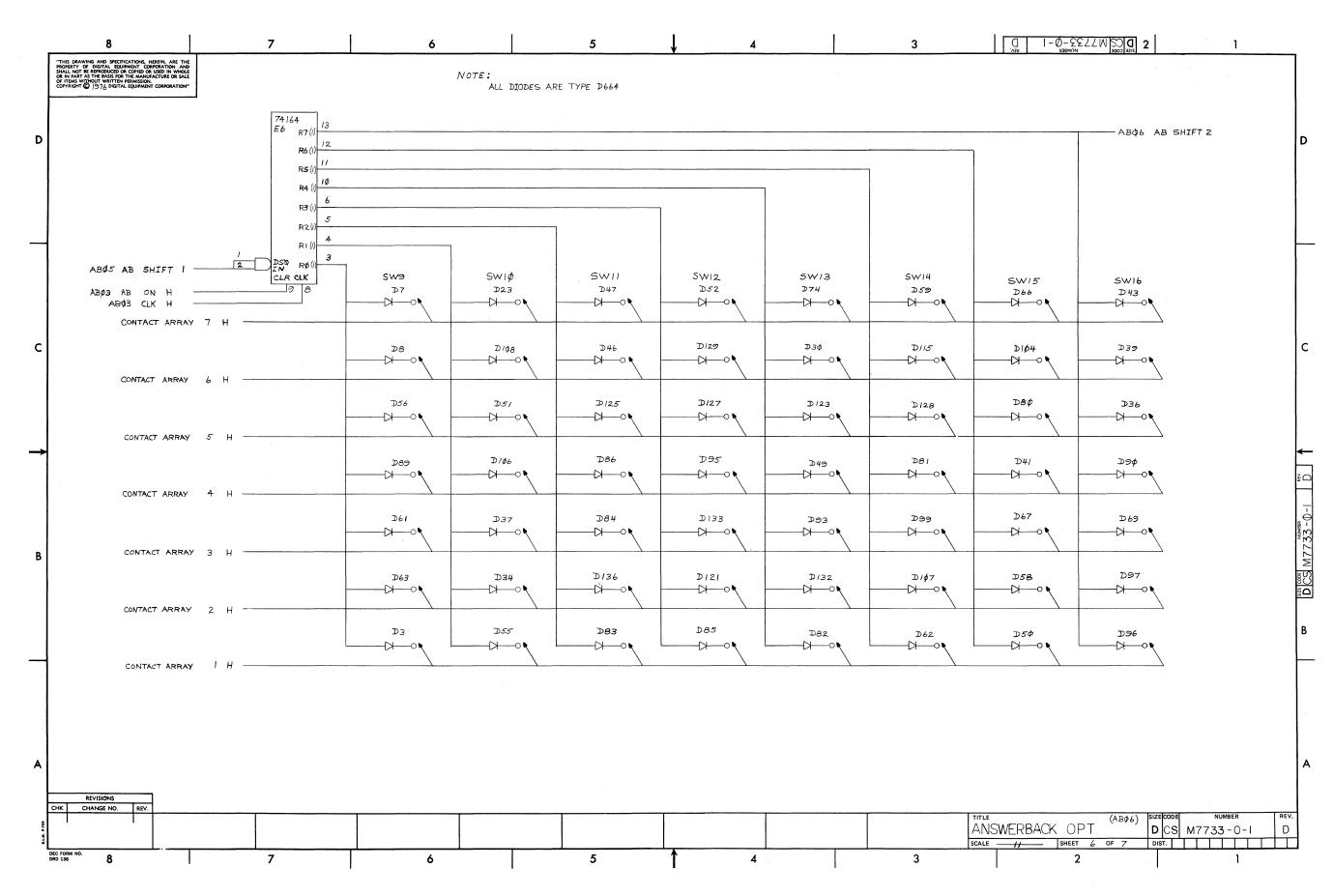

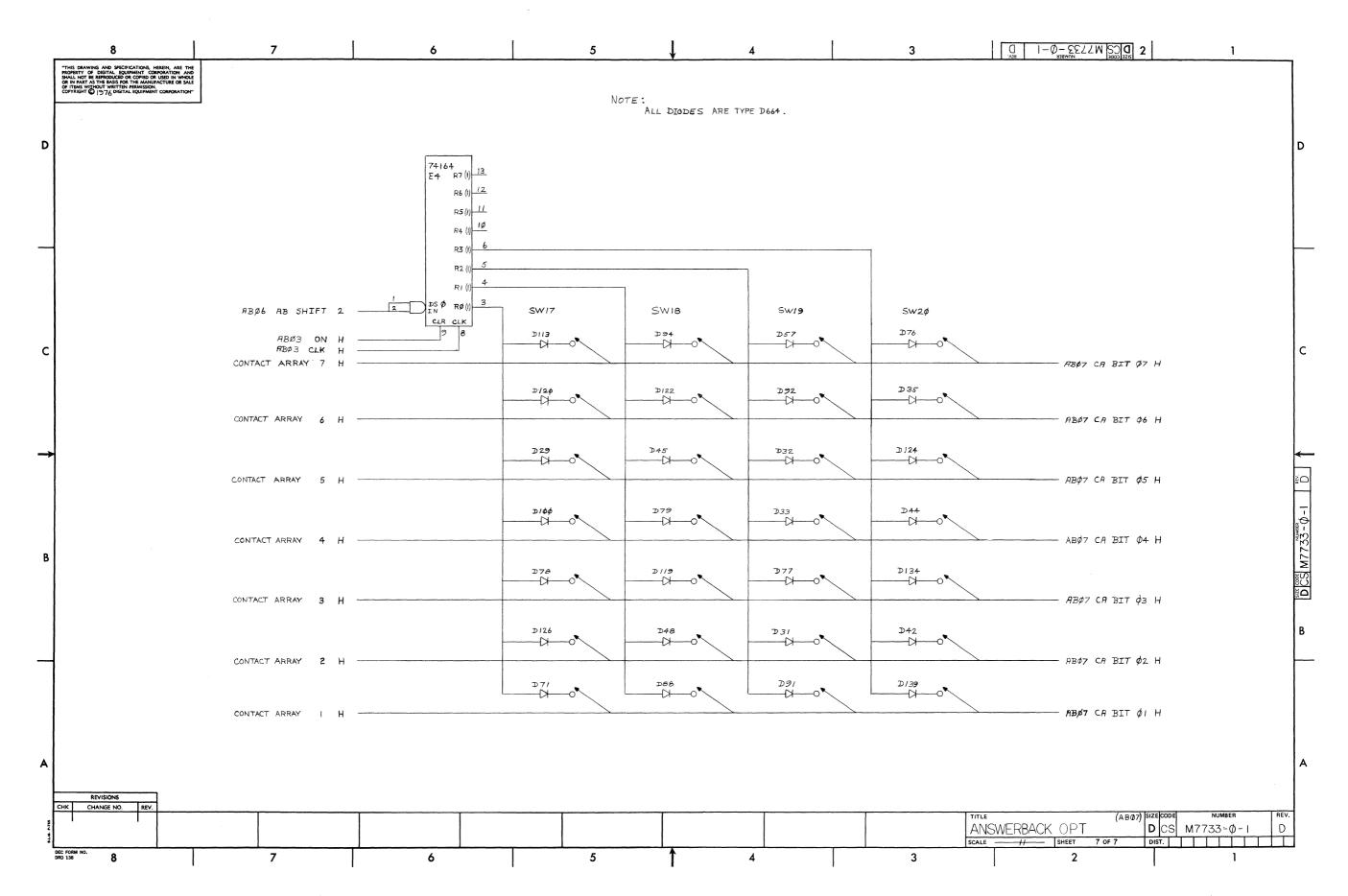

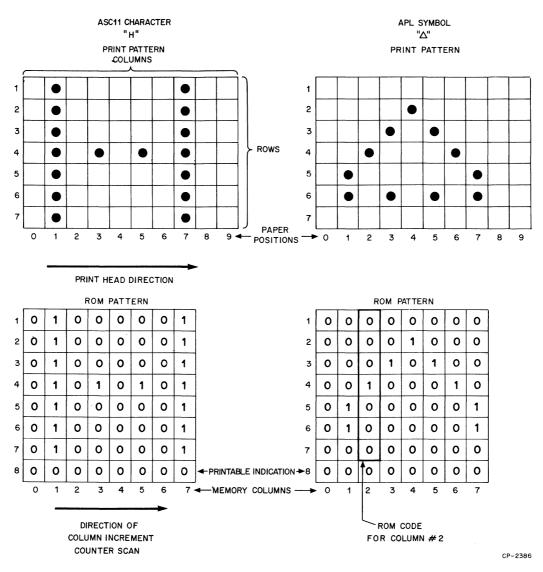

| 15-1Automatic Line Feed Functional Diagram15-215-2Automatic Line Feed Block Diagram15-315-3Operational Sequence for Automatic Line Feed Transmit Section15-415-4Transmit Line Feed Control Timing Sequence15-515-5Operational Sequence for Automatic Line Feed Receive Section15-615-6Receive Line Feed Control Timing Sequence15-716-1ASCII Data Distribution on Expander Board16-216-2Data Available Signal Distribution on Expander Board16-316-3Methods of Switching Data Available Signal into Options16-416-4Keystrobe Distribution on Expander Board16-517-1EIA Interface Block Diagram17-518-120 mA Interface Cable Option (LAXX-LK) Pin Assignments18-118-220 mA Interface Cable Option (LAXX-LK) Pin Assignments18-219-1Typical Telephone Communication Configuration19-2Acoustic Coupler Functional Block Diagram19-319-3Acoustic Coupler Transmit Section Basic Block Diagram19-320-4Bit Assignments for ASCII and APL Character Sets20-420-5Jumper Control over Character Set Selection20-720-6Jumper Control over Character Set Selection20-720-7Jupical ASCII/APL ROM Mapping and Print Pattern20-720-6Jumper Control over Character Set Selection20-820-7Jupical ASCII/APL ROM Mapping and Print Pattern20-720-6Jumper Control over Character Set Selection20                                                                                                                                                            | 14-12        | -                                                   |       |

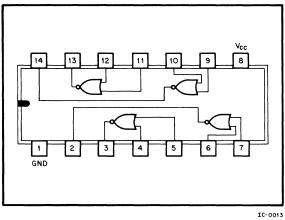

| 15-2Automatic Line Feed Block Diagram15-315-3Operational Sequence for Automatic Line Feed Transmit Section15-415-4Transmit Line Feed Control Timing Sequence15-515-5Operational Sequence for Automatic Line Feed Receive Section15-615-6Receive Line Feed Control Timing Sequence15-716-1ASCII Data Distribution on Expander Board16-216-2Data Available Signal Distribution on Expander Board16-316-3Methods of Switching Data Available Signal into Options16-416-4Keystrobe Distribution on Expander Board16-517-1ElA Interface Functional Diagram17-217-2ElA Interface Block Diagram17-518-120 mA Interface Cable Option (LAXX-LK) Pin Assignments18-118-220 mA Interface Cable Option (LAXX-LK) Pin Assignments18-219-1Typical Telephone Communication Configuration19-319-3Acoustic Coupler Functional Block Diagram19-319-4Acoustic Coupler Receive Section Basic Block Diagram19-320-1API Character Set Functional Block Diagram20-320-2Bit Assignments for ASCII and API: Character Sets20-420-3APIL Option Basic Block Diagram20-520-4Typical ASCII/API. ROM Mapping and Print Pattern20-720-5Jumper Control over Character Set Selection20-820-6Operational Sequence for OCS Set20-10A-1380 Quad 2-Input NOR GateA-16A-32627P                                                                                                                                                                                                 | 15-1         |                                                     |       |

| 15-3Operational Sequence for Automatic Line Feed Transmit Section15-415-4Transmit Line Feed Control Timing Sequence15-55-5Operational Sequence for Automatic Line Feed Receive Section15-615-6Receive Line Feed Control Timing Sequence15-716-1ASCII Data Distribution on Expander Board16-316-2Data Available Signal Distribution on Expander Board16-316-3Methods of Switching Data Available Signal into Options16-416-4Keystrobe Distribution on Expander Board16-517-1EIA Interface Functional Diagram17-518-120 mA Interface Cable Option (LAXX-LK) Pin Assignments18-118-220 mA Interface Cable Option (LAXX-LK) Pin Assignments18-118-220 mA Interface Cable Option (Configuration19-219-1Typical Telephone Communication Configuration19-319-2Acoustic Coupler Functional Block Diagram19-319-3Acoustic Coupler Receive Section Basic Block Diagram20-319-4Acoustic Coupler Receive Section Basic Block Diagram20-320-2Bit Assignments for ASCII and APL Character Sets20-420-3APL Option Basic Block Diagram20-520-4Jumper Control over Character Set Selection20-820-5Jumper Control over Character Set Selection20-820-6Operational Sequence for OCS Set20-120-7Jumper Control over Character Set Selection20-820-6Operational Sequence for OCS Set4-13<                                                                                                                                                                     | 15-2         | -                                                   |       |

| 154       Transmit Line Feed Control Timing Sequence       15.5         15.5       Operational Sequence for Automatic Line Feed Receive Section       15.6         15.6       Receive Line Feed Control Timing Sequence       15.7         16.1       ASCII Data Distribution on Expander Board       16.2         16.2       Data Available Signal Distribution on Expander Board       16.3         16.3       Methods of Switching Data Available Signal into Options       16.4         16.4       Keystrobe Distribution on Expander Board       16.5         17.1       EIA Interface Functional Diagram       17.2         17.2       EIA Interface Block Diagram       17.5         18.1       20 mA Interface Cable Option (LAXX-LK) Pin Assignments       18.1         18.2       20 mA Interface Cable Option (LAXX-LK) Pin Assignments       18.2         19.1       Typical Telephone Communication Configuration       19.3         19.2       Acoustic Coupler Transmit Section Basic Block Diagram       19.3         19.3       Acoustic Coupler Runcitonal Block Diagram       20.3         20.2       Bit Assignments for ASCII and APL Character Sets       20.4         20.3       APL Option Basic Block Diagram       20.3         20.4       Typical ASCII/APL ROM Mapping and Print Pattern       20.7 <td>15-3</td> <td></td> <td></td>                                                                        | 15-3         |                                                     |       |

| 15:5Operational Sequence for Automatic Line Feed Receive Section15:615:6Receive Line Feed Control Timing Sequence15:716:1ASCII Data Distribution on Expander Board16:316:2Data Available Signal Distribution on Expander Board16:316:3Methods of Switching Data Available Signal into Options16:416:4Keystrobe Distribution on Expander Board16:517.1EIA Interface Functional Diagram17:217.2EIA Interface Cable Option (LAXX-LK) Pin Assignments18:118:220 mA Interface Cable Option (LAXX-LK) Pin Assignments18:118:220 mA Interface Cable Option (LAXX-LK) Pin Assignments18:219:1Typical Telephone Communication Configuration19:219:2Acoustic Coupler Functional Block Diagram19:319:3Acoustic Coupler Functional Block Diagram19:420:1APL Character Set Functional Block Diagram20:320:2Bit Assignments for ASCII and APL Character Sets20:420:3APL Option Basic Block Diagram20:520:4Typical ASCII/APL ROM Mapping and Print Pattern20:720:5Jumper Control over Character Set Selection20:820:6Operational Sequence for OCS set4.13A:326:27P A6-01 Character Generator Alpha4.13A:326:27P A6-01 Character Generator Alpha4.14A:43101 Random Access Memory4.16A:57400 Quad 2-Input Positive NAND Gate4.16A:67401 NAND Gate-Quad 2-P                                                                                                                                                                                                | 15-4         |                                                     |       |

| 15-6Receive Line Feed Control Timing Sequence15-716-1ASCII Data Distribution on Expander Board16-216-2Data Available Signal Distribution on Expander Board16-316-3Methods of Switching Data Available Signal into Options16-416-4Keystrobe Distribution on Expander Board16-517-1EIA Interface Functional Diagram17-217-2EIA Interface Cable Option (LAXX-LK) Pin Assignments18-118-220 mA Interface Cable Option (LAXX-LH) Pin Assignments18-219-1Typical Telephone Communication Configuration19-219-2Acoustic Coupler Transmit Section Basic Block Diagram19-319-3Acoustic Coupler Transmit Section Basic Block Diagram19-319-4Acoustic Coupler Receive Section Basic Block Diagram20-320-2Bit Assignments for ASCII and APL Character Sets20-420-3APL Option Basic Block Diagram20-520-4Typical ASCII/APL ROM Mapping and Print Pattern20-720-5Jumper Control over Character Set Selection20-820-6Operational Sequence for OCS Set20-1A-1380 Quad 2-Input NOR GateA-13A-21702A 8-Bit Reprogrammable ROMA-13A-3267PP AG-01 Character Generator AlphaA-14A-43101 Random Access MemoryA-15A-57400 Quad 2-Input Positive NAND GateA-16A-77404 Hex InverterA-16A-774104 Hex InverterA-16A-87408 Quad 2                                                                                                                                                                                                                                    | 15-5         |                                                     |       |

| 16-1ASCII Data Distribution on Expander Board16-216-2Data Available Signal Distribution on Expander Board16-316-3Methods of Switching Data Available Signal into Options16-416-4Keystrobe Distribution on Expander Board16-517-1EIA Interface Functional Diagram17-217-2EIA Interface Block Diagram17-517-110 mA Interface Cable Option (LAXX-LK) Pin Assignments18-118-220 mA Interface Cable Option (LAXX-LK) Pin Assignments18-219-1Typical Telephone Communication Configuration19-219-2Acoustic Coupler Functional Block Diagram19-319-3Acoustic Coupler Receive Section Basic Block Diagram19-319-4Acoustic Coupler Receive Section Basic Block Diagram19-420-1APL Character Set Functional Block Diagram20-320-2Bit Assignments for ASCII and APL Character Sets20-420-3APL Option Basic Block Diagram20-520-4Typical ASCII/APL ROM Mapping and Print Pattern20-720-5Jumper Control over Character Set Selection20-820-4Typical ASCII/APL ROM Mapping and Print Pattern20-10A-1380 Quad 2-Input NOR GateA-13A-21702A 8-Bit Reprogrammable ROMA-13A-32627P A6-01 Character Generator AlphaA-14A-43101 Random Access MemoryA-15A-57400 Quad 2-Input Positive NAND GateA-17A-7744 Hex InverterA-16A-7                                                                                                                                                                                                                                | 15-6         |                                                     |       |

| 16-2Data Available Signal Distribution on Expander Board16-316-3Methods of Switching Data Available Signal into Options16-416-4Keystrobe Distribution on Expander Board16-517-1EIA Interface Functional Diagram17-217-2EIA Interface Cable Option (LAXX-LK) Pin Assignments18-118-220 mA Interface Cable Option (LAXX-LK) Pin Assignments18-219-1Typical Telephone Communication Configuration19-219-2Acoustic Coupler Functional Block Diagram19-319-3Acoustic Coupler Transmit Section Basic Block Diagram19-319-4Acoustic Coupler Transmit Section Basic Block Diagram20-320-2Bit Assignments for ASCII and APL Character Sets20-420-3APL Option Basic Block Diagram20-520-4Typical ASCII/APL ROM Mapping and Print Pattern20-720-5Jumper Control over Character Set Selection20-820-6Operational Sequence for OCS Set20-10A-1380 Quad 2-Input NOR GateA-14A-32627P A6-01 Character Generator AlphaA-14A-43101 Random Access MemoryA-15A-57400 Quad 2-Input Positive NAND GateA-16A-77404 Hex InverterA-16A-87408 Quad 2-Input Positive NAND GateA-17A-97410 Triple 3-Input Positive NAND GateA-18A-117416 Hex InverterA-16A-77404 Hex InverterA-16A-77404 Hex InverterA-18                                                                                                                                                                                                                                                           | 16-1         |                                                     |       |

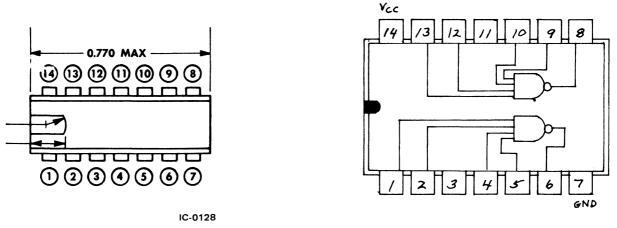

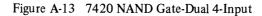

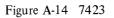

| 16-3Methods of Switching Data Available Signal into Options16-416-4Keystrobe Distribution on Expander Board16-517-1EIA Interface Functional Diagram17-217-2EIA Interface Gable Option (LAXX-LK) Pin Assignments18-118-120 mA Interface Cable Option (LAXX-LK) Pin Assignments18-118-220 mA Interface Cable Option (LAXX-LK) Pin Assignments18-219-1Typical Telephone Communication Configuration19-219-2Acoustic Coupler Functional Block Diagram19-319-3Acoustic Coupler Transmit Section Basic Block Diagram19-319-4Acoustic Coupler Receive Section Basic Block Diagram20-320-2Bit Assignments for ASCII and APL Character Sets20-420-3APL Option Basic Block Diagram20-520-4Typical ASCII/APL ROM Mapping and Print Pattern20-720-5Jumper Control over Character Set Selection20-820-6Operational Sequence for OCS Set20-10A-1380 Quad 2-Input NOR GateA-13A-21702A 8-Bit Reprogrammable ROMA-14A-43101 Random Access MemoryA-15A-57400 Quad 2-Input Positive NAND GateA-16A-77404 Hex InverterA-16A-77410 Triple 3-Input Positive NAND GateA-17A-97410 Triple 3-Input Positive NAND GateA-18A-107413 Schmidt TriggerA-18A-117420 NAND Gate-Quad 2-In put MA GateA-19A-127417 Hex Buffers/Driver                                                                                                                                                                                                                                     | 16-2         |                                                     |       |

| 164Keystrobe Distribution on Expander Board16-517.1EIA Interface Functional Diagram17-217.2EIA Interface Block Diagram17-517.2EIA Interface Cable Option (LAXX-LK) Pin Assignments18-118-220 mA Interface Cable Option (LAXX-LH) Pin Assignments18-118-220 mA Interface Cable Option (LAXX-LH) Pin Assignments18-219-1Typical Telephone Communication Configuration19-219-2Acoustic Coupler Functional Block Diagram19-319-3Acoustic Coupler Functional Block Diagram19-319-4Acoustic Coupler Receive Section Basic Block Diagram20-320-1APL Character Set Functional Block Diagram20-320-2Bit Assignments for ASCII and APL Character Sets20-420-3APL Option Basic Block Diagram20-520-4Typical ASCII/APL ROM Mapping and Print Pattern20-720-5Jumper Control over Character Set Selection20-820-6Operational Sequence for OCS Set20-10A-1380 Quad 2-Input NOR GateA-13A-21702A 8-Bit Reprogrammable ROMA-13A-32627P A6-01 Character Generator AlphaA-14A-43101 Random Access MemoryA-16A-77404 Hex InverterA-16A-77404 Hex InverterA-16A-87400 Quad 2-Input Positive NAND GateA-17A-107413 Schmidt TriggerA-18A-117416 Hex Inverter Buffer/DriverA-18A-127417 H                                                                                                                                                                                                                                                                        |              |                                                     |       |

| 17-1       EIA Interface Functional Diagram       17-2         17-2       EIA Interface Block Diagram       17-5         18-1       20 mA Interface Cable Option (LAXX-LK) Pin Assignments       18-1         18-2       20 mA Interface Cable Option (LAXX-LK) Pin Assignments       18-2         19-1       Typical Telephone Communication Configuration       19-2         19-2       Acoustic Coupler Functional Block Diagram       19-3         19-3       Acoustic Coupler Receive Section Basic Block Diagram       19-4         20-1       APL Character Set Functional Block Diagram       20-3         20-2       Bit Assignments for ASCII and APL Character Sets       20-4         20-3       APL Option Basic Block Diagram       20-5         20-4       Typical ASCII/APL ROM Mapping and Print Pattern       20-7         20-5       Jumper Control over Character Set Selection       20-8         20-6       Operational Sequence for OCS Set       20-10         A-1       380 Quad 2-Input NOR Gate       A-13         A-2       1702A 8-Bit Reprogrammable ROM       A-14         A-3       2627P A6-01 Character Generator Alpha       A-14         A-4       3101 Random Access Memory       A-15         A-5       7400 Quad 2-Input Positive NAND Gate       A-16 <td></td> <td></td> <td></td>                                                                                                              |              |                                                     |       |

| 17-2EIA Interface Block Diagram17-518-120 mA Interface Cable Option (LAXX-LK) Pin Assignments18-118-220 mA Interface Cable Option (LAXX-LH) Pin Assignments18-219-1Typical Telephone Communication Configuration19-219-2Acoustic Coupler Functional Block Diagram19-319-3Acoustic Coupler Transmit Section Basic Block Diagram19-319-4Acoustic Coupler Receive Section Basic Block Diagram19-420-1APL Character Set Functional Block Diagram20-320-2Bit Assignments for ASCII and APL Character Sets20-420-3APL Option Basic Block Diagram20-520-4Typical ASCII/APL ROM Mapping and Print Pattern20-720-5Jumper Control over Character Set Selection20-820-6Operational Sequence for OCS Set20-10A-1380 Quad 2-Input NOR GateA-13A-21702A 8-Bit Reprogrammable ROMA-13A-32627P A6-01 Character Generator AlphaA-14A-43101 Random Access MemoryA-16A-77404 Hex InverterA-16A-77404 Hex InverterA-16A-87408 Quad 2-Input Positive NAND GateA-17A-97410 Triple 3-Input Positive NAND GateA-18A-117416 Hex Inverter Buffer/DriverA-18A-127417 Hex Buffers/DriversA-19A-137420 NAND Gate-Quad 2 In Buffer, I4 PinA-20                                                                                                                                                                                                                                                                                                                         |              | • •                                                 |       |

| 18-120 mA Interface Cable Option (LAXX-LK) Pin Assignments18-118-220 mA Interface Cable Option (LAXX-LH) Pin Assignments18-219-1Typical Telephone Communication Configuration19-219-2Acoustic Coupler Functional Block Diagram19-319-3Acoustic Coupler Transmit Section Basic Block Diagram19-319-4Acoustic Coupler Receive Section Basic Block Diagram19-420-1APL Character Set Functional Block Diagram20-320-2Bit Assignments for ASCII and APL Character Sets20-420-3APL Option Basic Block Diagram20-720-4Typical ASCII/APL ROM Mapping and Print Pattern20-720-5Jumper Control over Character Set Selection20-820-6Operational Sequence for OCS Set20-10A-1380 Quad 2-Input NOR GateA-13A-21702A 8-Bit Reprogrammable ROMA-14A-32627P A6-01 Character Generator AlphaA-14A-43101 Random Access MemoryA-15A-57400 Quad 2-Input Positive NAND GateA-16A-77404 Hex InverterA-16A-87408 Quad 2-Input Positive NAND GateA-17A-97410 Triple 3-Input Positive NAND GateA-17A-107413 Schmidt TriggerA-18A-117416 Hex Inverter Buffer/DriverA-18A-127417 Hex Buffers/DriversA-19A-137420 NAND Gate-Dual 4-InputA-19A-14A-117416 Hex Inverter Buffer/DriverA-20A-13 </td <td></td> <td>•</td> <td></td>                                                                                                                                                                                                                                      |              | •                                                   |       |

| 18-220 mA Interface Cable Option (LAXX-LH) Pin Assignments18-219-1Typical Telephone Communication Configuration19-219-2Acoustic Coupler Functional Block Diagram19-319-3Acoustic Coupler Receive Section Basic Block Diagram19-319-4Acoustic Coupler Receive Section Basic Block Diagram19-320-1APL Character Set Functional Block Diagram20-320-2Bit Assignments for ASCII and APL Character Sets20-420-3APL Option Basic Block Diagram20-520-4Typical ASCII/APL ROM Mapping and Print Pattern20-720-5Jumper Control over Character Set Selection20-820-6Operational Sequence for OCS Set20-10A-1380 Quad 2-Input NOR GateA-13A-21702A 8-Bit Reprogrammable ROMA-13A-32627P A6-01 Character Generator AlphaA-14A-43101 Random Access MemoryA-15A-57400 Quad 2-Input Positive NAND GateA-16A-77404 Hex InverterA-16A-77404 Hex InverterA-16A-87408 Quad 2-Input Positive NAND GateA-17A-97410 Triple 3-Input Positive NAND GateA-17A-107413 Schmidt TriggerA-18A-117416 Hex Inverter Buffer/DriverA-18A-127417 Hex Buffers/DriversA-19A-137420 NAND Gate-Dual 4-InputA-19A-14743A-20                                                                                                                                                                                                                                                                                                                                                     |              |                                                     |       |

| 19-1Typical Telephone Communication Configuration19-219-2Acoustic Coupler Functional Block Diagram19-319-3Acoustic Coupler Transmit Section Basic Block Diagram19-319-4Acoustic Coupler Receive Section Basic Block Diagram19-420-1APL Character Set Functional Block Diagram20-320-2Bit Assignments for ASCII and APL Character Sets20-420-3APL Option Basic Block Diagram20-520-4Typical ASCII/APL ROM Mapping and Print Pattern20-720-5Jumper Control over Character Set Selection20-820-6Operational Sequence for OCS Set20-10A-1380 Quad 2-Input NOR GateA-13A-21702A 8-Bit Reprogrammable ROMA-13A-32627P A6-01 Character Generator AlphaA-14A-43101 Random Access MemoryA-15A-57400 Quad 2-Input Positive NAND GateA-16A-77404 Hex InverterA-16A-77404 Hex InverterA-17A-97410 Triple 3-Input Positive NAND GateA-17A-107413 Schmidt TriggerA-18A-117416 Hex Inverter Buffer/DriverA-18A-127417 Hex Buffers/DriversA-19A-137420 NAND Gate-Dual 4-InputA-19A-147423A-19A-19A-157437 NAND Gate-Quad 2 In Buffer, 14 PinA-20                                                                                                                                                                                                                                                                                                                                                                                                         |              |                                                     |       |

| 19-2Acoustic Coupler Functional Block Diagram19-319-3Acoustic Coupler Transmit Section Basic Block Diagram19-319-4Acoustic Coupler Receive Section Basic Block Diagram19-420-1APL Character Set Functional Block Diagram20-320-2Bit Assignments for ASCII and APL Character Sets20-420-3APL Option Basic Block Diagram20-520-4Typical ASCII/APL ROM Mapping and Print Pattern20-720-5Jumper Control over Character Set Selection20-820-6Operational Sequence for OCS Set20-10A-1380 Quad 2-Input NOR GateA-13A-21702A 8-Bit Reprogrammable ROMA-13A-32627P A6-01 Character Generator AlphaA-14A-43101 Random Access MemoryA-15A-57400 Quad 2-Input Positive NAND GateA-16A-77404 Hex InverterA-16A-87408 Quad 2-Input Positive AND GateA-17A-97410 Triple 3-Input Positive NAND GateA-18A-107413 Schmidt TriggerA-18A-117416 Hex Inverter Buffer/DriverA-18A-127417 Hex Buffer/DriversA-18A-137420 NAND Gate-Dual 4-InputA-19A-137420 NAND Gate-Dual 4-InputA-20A-147423A-19A-20                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |                                                     |       |

| 19-3Acoustic Coupler Transmit Section Basic Block Diagram19-319-4Acoustic Coupler Receive Section Basic Block Diagram19-420-1APL Character Set Functional Block Diagram20-320-2Bit Assignments for ASCII and APL Character Sets20-420-3APL Option Basic Block Diagram20-520-4Typical ASCII/APL ROM Mapping and Print Pattern20-720-5Jumper Control over Character Set Selection20-820-6Operational Sequence for OCS Set20-10A-1380 Quad 2-Input NOR GateA-13A-21702A 8-Bit Reprogrammable ROMA-13A-21702A 8-Bit Reprogrammable ROMA-14A-43101 Random Access MemoryA-15A-57400 Quad 2-Input Positive NAND GateA-16A-67401 NAND Gate-Quad 2-Pin Open CollectorA-16A-77404 Hex InverterA-16A-87408 Quad 2-Input Positive NAND GateA-17A-97410 Triple 3-Input Positive NAND GateA-18A-107413 Schmidt TriggerA-18A-117416 Hex Inverter Buffer/DriverA-18A-127417 Hex Buffer/DriversA-19A-137420 NAND Gate-Dual 4-InputA-19A-147423                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                                     |       |

| 194Acoustic Coupler Receive Section Basic Block Diagram19420-1APL Character Set Functional Block Diagram20-320-2Bit Assignments for ASCII and APL Character Sets20-420-3APL Option Basic Block Diagram20-520-4Typical ASCII/APL ROM Mapping and Print Pattern20-720-5Jumper Control over Character Set Selection20-820-6Operational Sequence for OCS Set20-10A-1380 Quad 2-Input NOR GateA-13A-21702A 8-Bit Reprogrammable ROMA-13A-32627P A6-01 Character Generator AlphaA-14A-43101 Random Access MemoryA-15A-57400 Quad 2-Input Positive NAND GateA-16A-77404 Hex InverterA-16A-87408 Quad 2-Input Positive AND GateA-17A-97410 Triple 3-Input Positive NAND GateA-18A-117413 Schmidt TriggerA-18A-127417 Hex Buffer/DriversA-19A-137420 NAND Gate-Dual 4-InputA-19A-147423A-19A-157437 NAND Gate-Quad 2 In Buffer, 14 PinA-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                                                     |       |

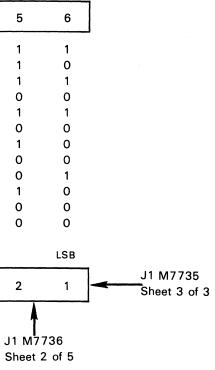

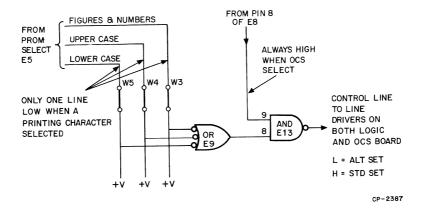

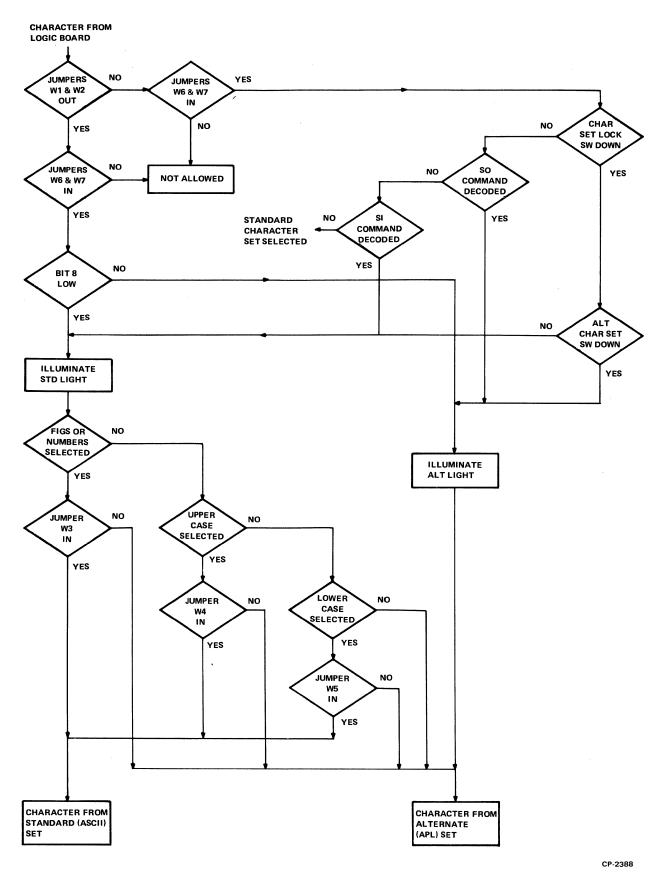

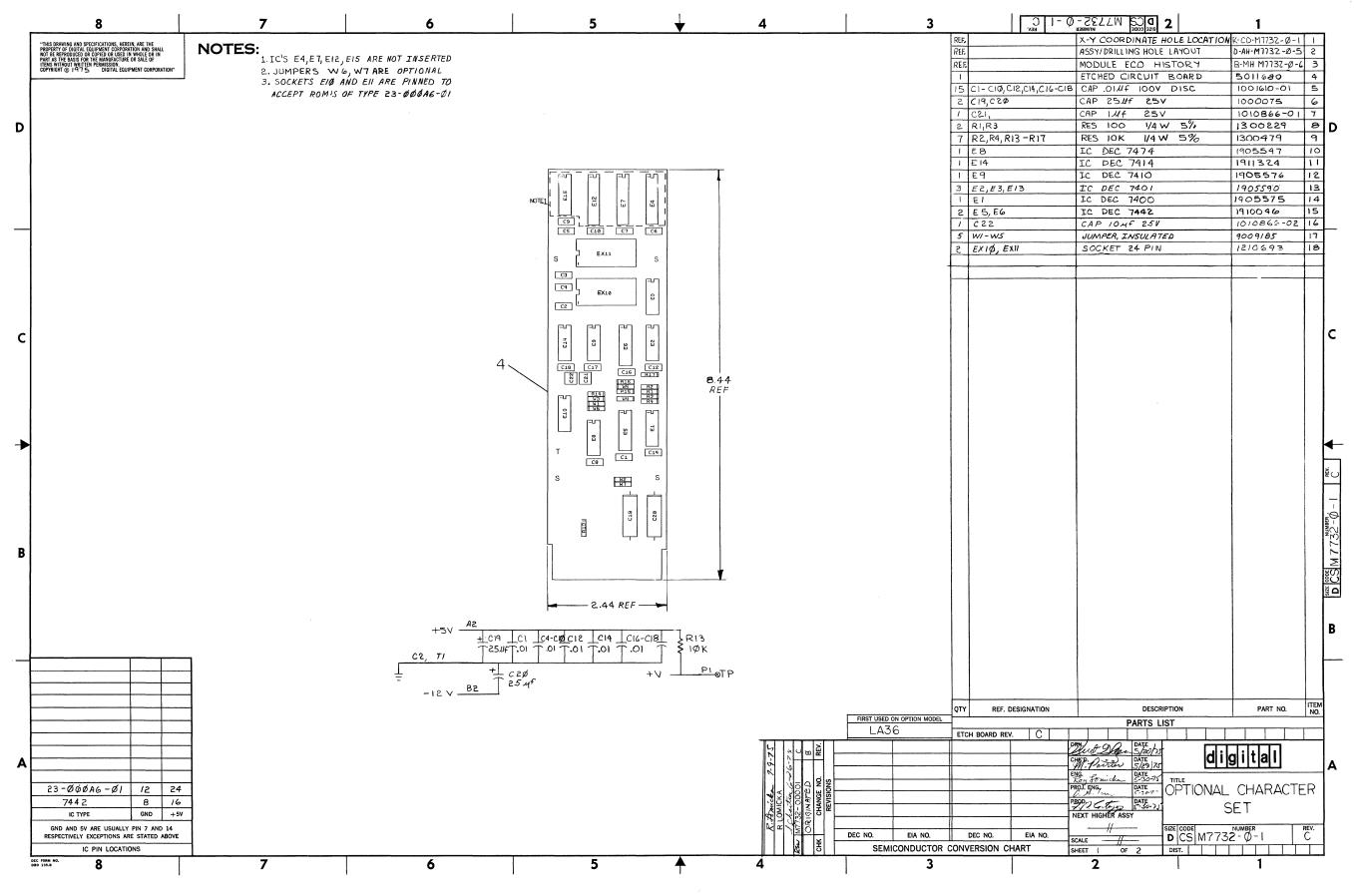

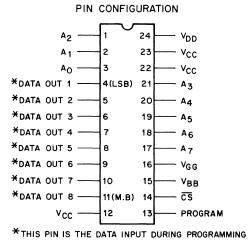

| 20-1APL Character Set Functional Block Diagram20-320-2Bit Assignments for ASCII and APL Character Sets20-420-3APL Option Basic Block Diagram20-520-4Typical ASCII/APL ROM Mapping and Print Pattern20-720-5Jumper Control over Character Set Selection20-820-6Operational Sequence for OCS Set20-10A-1380 Quad 2-Input NOR GateA-13A-21702 A 8-Bit Reprogrammable ROMA-13A-32627P A6-01 Character Generator AlphaA-14A-43101 Random Access MemoryA-15A-57400 Quad 2-Input Positive NAND GateA-16A-67401 NAND Gate-Quad 2-Pin Open CollectorA-16A-77404 Hex InverterA-16A-87408 Quad 2-Input Positive AND GateA-17A-97410 Triple 3-Input Positive NAND GateA-17A-107413 Schmidt TriggerA-18A-117416 Hex Inverter Buffer/DriverA-18A-127417 Hex Buffers/DriversA-19A-137420 NAND Gate-Dual 4-InputA-19A-137423A-20A-147423A-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              |                                                     |       |