# WRL Research Report 95/9

# Memory Consistency Models for Shared-Memory Multiprocessors

Kourosh Gharachorloo

Western Research Laboratory 250 University Avenue Palo Alto, California 94301 USA

The Western Research Laboratory (WRL) is a computer systems research group that was founded by Digital Equipment Corporation in 1982. Our focus is computer science research relevant to the design and application of high performance scientific computers. We test our ideas by designing, building, and using real systems. The systems we build are research prototypes; they are not intended to become products.

There are two other research laboratories located in Palo Alto, the Network Systems Lab (NSL) and the Systems Research Center (SRC). Another Digital research group is located in Cambridge, Massachusetts (CRL).

Our research is directed towards mainstream high-performance computer systems. Our prototypes are intended to foreshadow the future computing environments used by many Digital customers. The long-term goal of WRL is to aid and accelerate the development of high-performance uni- and multi-processors. The research projects within WRL will address various aspects of high-performance computing.

We believe that significant advances in computer systems do not come from any single technological advance. Technologies, both hardware and software, do not all advance at the same pace. System design is the art of composing systems which use each level of technology in an appropriate balance. A major advance in overall system performance will require reexamination of all aspects of the system.

We do work in the design, fabrication and packaging of hardware; language processing and scaling issues in system software design; and the exploration of new applications areas that are opening up with the advent of higher performance systems. Researchers at WRL cooperate closely and move freely among the various levels of system design. This allows us to explore a wide range of tradeoffs to meet system goals.

We publish the results of our work in a variety of journals, conferences, research reports, and technical notes. This document is a research report. Research reports are normally accounts of completed research and may include material from earlier technical notes. We use technical notes for rapid distribution of technical material; usually this represents research in progress.

Research reports and technical notes may be ordered from us. You may mail your order to:

Technical Report Distribution DEC Western Research Laboratory, WRL-2 250 University Avenue Palo Alto, California 94301 USA

Reports and technical notes may also be ordered by electronic mail. Use one of the following addresses:

| Digital E-net: | JOVE::WRL-TECHREPORTS             |

|----------------|-----------------------------------|

| Internet:      | WRL-Techreports@decwrl.pa.dec.com |

| UUCP:          | decpa!wrl-techreports             |

To obtain more details on ordering by electronic mail, send a message to one of these addresses with the word "help" in the Subject line; you will receive detailed instructions.

Reports and technical notes may also be accessed via the World Wide Web: http://www.research.digital.com/wrl/home.html.

# Memory Consistency Models for Shared-Memory Multiprocessors

Kourosh Gharachorloo\*

December 1995

Also published as Stanford University Technical Report CSL-TR-95-685.

\*This report is the author's Ph.D. dissertation from Stanford University. In addition to Digital Equipment's support, the author was partly supported by DARPA contract N00039-91-C-0138 and by a fellowship from Texas Instruments.

## Abstract

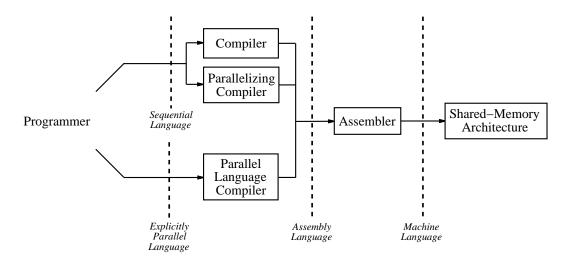

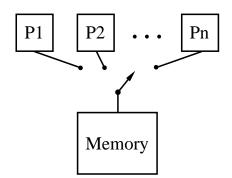

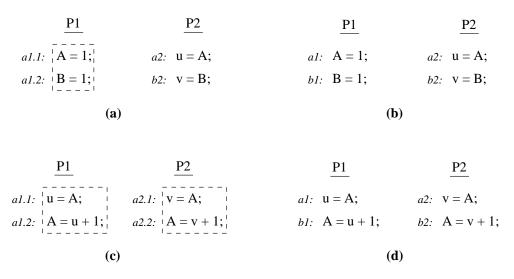

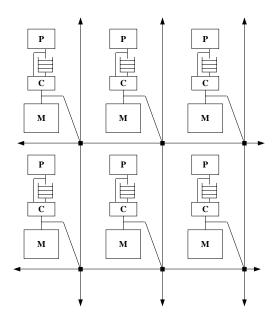

The memory consistency model for a shared-memory multiprocessor specifies the behavior of memory with respect to read and write operations from multiple processors. As such, the memory model influences many aspects of system design, including the design of programming languages, compilers, and the underlying hardware. *Relaxed models* that impose fewer memory ordering constraints offer the potential for higher performance by allowing hardware and software to overlap and reorder memory operations. However, fewer ordering guarantees can compromise programmability and portability. Many of the previously proposed models either fail to provide reasonable programming semantics or are biased toward programming ease at the cost of sacrificing performance. Furthermore, the lack of consensus on an acceptable model hinders software portability across different systems.

This dissertation focuses on providing a balanced solution that directly addresses the trade-off between *programming ease* and *performance*. To address programmability, we propose an alternative method for specifying memory behavior that presents a higher level abstraction to the programmer. We show that with only a few types of information supplied by the programmer, an implementation can exploit the full range of optimizations enabled by previous models. Furthermore, the same information enables automatic and efficient *portability* across a wide range of implementations.

To expose the optimizations enabled by a model, we have developed a formal framework for specifying the low-level ordering constraints that must be enforced by an implementation. Based on these specifications, we present a wide range of architecture and compiler implementation techniques for efficiently supporting a given model. Finally, we evaluate the performance benefits of exploiting relaxed models based on detailed simulations of realistic parallel applications. Our results show that the optimizations enabled by relaxed models are extremely effective in hiding virtually the full latency of writes in architectures with blocking reads (i.e., processor stalls on reads), with gains as high as 80%. Architectures with non-blocking reads can further exploit relaxed models to hide a substantial fraction of the read latency as well, leading to a larger overall performance benefit. Furthermore, these optimizations complement gains from other latency hiding techniques such as prefetching and multiple contexts.

We believe that the combined benefits in hardware and software will make relaxed models universal in future multiprocessors, as is already evidenced by their adoption in several commercial systems.

# Acknowledgements

Many thanks go to my advisors John Hennessy and Anoop Gupta for their continued guidance, support, and encouragement. John Hennessy's vision and enthusiasm have served as an inspiration since my early graduate days at Stanford. He has been a great source of insight and an excellent sounding board for ideas. His leadership was instrumental in the conception of the DASH project which provided a great infrastructure for multiprocessor research at Stanford. Anoop Gupta encouraged me to pursue my early ideas on memory consistency models. I am grateful for the tremendous time, energy, and wisdom that he invested in steering my research. He has been an excellent role model through his dedication to quality research. I also thank James Plummer for graciously serving as my orals committee chairman and my third reader.

I was fortunate to be among great friends and colleagues at Stanford. In particular, I would like to thank the other members of the DASH project, especially Jim Laudon, Dan Lenoski, and Wolf-Dietrich Weber, for making the DASH project an exciting experience. I thank the following people for providing the base simulation tools for my studies: Steve Goldschmidt for TangoLite, Todd Mowry for Dixie, and Mike Johnson for the dynamic scheduled processor simulator. Charles Orgish, Laura Schrager, and Thoi Nguyen at Stanford, and Annie Warren and Jason Wold at Digital, were instrumental in supporting the computing environment. I also thank Margaret Rowland and Darlene Hadding for their administrative support. I thank Vivek Sarkar for serving as a mentor during my first year at Stanford. Rohit Chandra, Dan Scales, and Ravi Soundararajan get special thanks for their help in proof reading the final version of the thesis. Finally, I am grateful to my friends and office mates, Paul Calder, Rohit Chandra, Jaswinder Pal Singh, and Mike Smith, who made my time at Stanford most enjoyable.

My research on memory consistency models has been enriched through collaborations with Phil Gibbons and Sarita Adve. I have also enjoyed working with Andreas Nowatzyk on the Sparc V9 RMO model, and with Jim Horning, Jim Saxe, and Yuan Yu on the Digital Alpha memory model.

I thank Digital Equipment Corporation, the Western Research Laboratory, and especially Joel Bartlett and Richard Swan, for giving me the freedom to continue my work in this area after joining Digital. The work presented in this thesis represents a substantial extension to my earlier work at Stanford.

I would like to thank my friends and relatives, Ali, Farima, Hadi, Hooman, Illah, Rohit, Sapideh, Shahin, Shahrzad, Shervin, Siamak, Siavosh, and Sina, who have made these past years so enjoyable. Finally, I thank my family, my parents and brother, for their immeasurable love, encouragement, and support of my education. Most importantly, I thank my wife, Nazhin, who has been the source of happiness in my life.

ii

To my parents Nezhat and Vali and my wife Nazhin

iv

# Contents

| Ac | cknowledgements |         |                                                              | i  |

|----|-----------------|---------|--------------------------------------------------------------|----|

| 1  | Intr            | oductio | )n                                                           | 1  |

|    | 1.1             | The Pr  | oblem                                                        | 2  |

|    | 1.2             | Our A   | pproach                                                      | 3  |

|    |                 | 1.2.1   | Programming Ease and Portability                             | 4  |

|    |                 | 1.2.2   | Implementation Issues                                        | 4  |

|    |                 | 1.2.3   | Performance Evaluation                                       | 4  |

|    | 1.3             | Contri  | butions                                                      | 5  |

|    | 1.4             | Organi  | ization                                                      | 5  |

| 2  | Bac             | kgroun  | d                                                            | 7  |

|    | 2.1             | What i  | s a Memory Consistency Model?                                | 7  |

|    |                 | 2.1.1   | Interface between Programmer and System                      | 7  |

|    |                 | 2.1.2   | Terminology and Assumptions                                  | 8  |

|    |                 | 2.1.3   | Sequential Consistency                                       | 9  |

|    |                 | 2.1.4   | Examples of Sequentially Consistent Executions               | 10 |

|    |                 | 2.1.5   | Relating Memory Behavior Based on Possible Outcomes          | 15 |

|    | 2.2             | Impact  | t of Architecture and Compiler Optimizations                 | 15 |

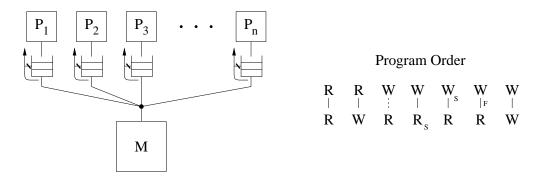

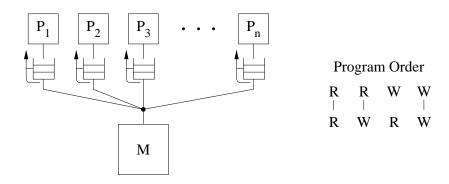

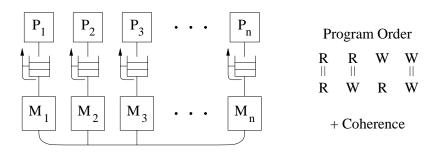

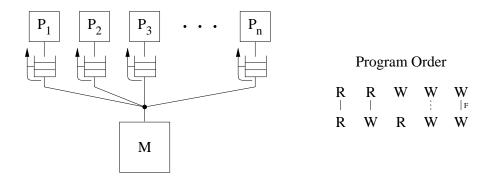

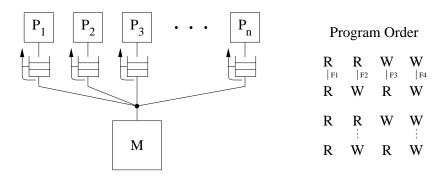

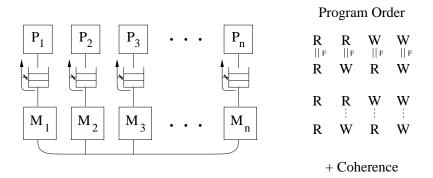

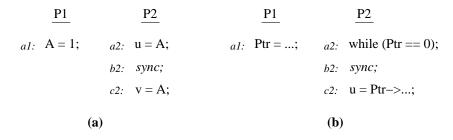

|    |                 | 2.2.1   | Architecture Optimizations                                   | 15 |

|    |                 | 2.2.2   | Compiler Optimizations                                       | 19 |

|    | 2.3             | Implic  | ations of Sequential Consistency                             | 20 |

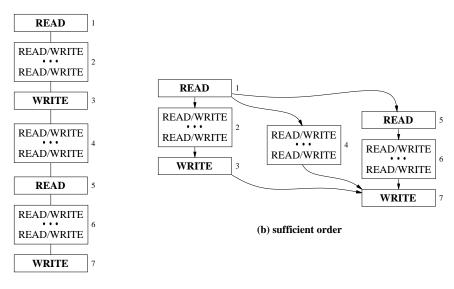

|    |                 | 2.3.1   | Sufficient Conditions for Maintaining Sequential Consistency | 21 |

|    |                 | 2.3.2   | Using Program-Specific Information                           | 22 |

|    |                 | 2.3.3   | Other Aggressive Implementations of Sequential Consistency   | 23 |

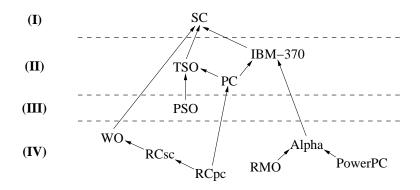

|    | 2.4             | Altern  | ative Memory Consistency Models                              | 24 |

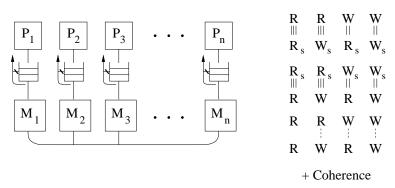

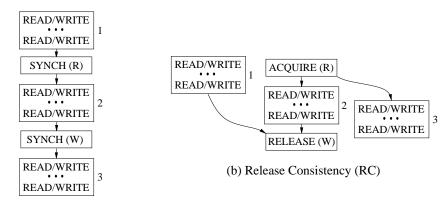

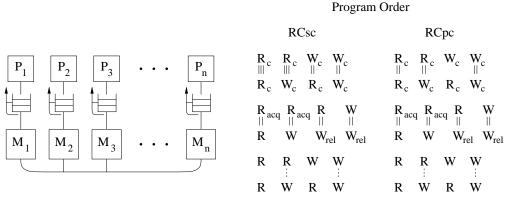

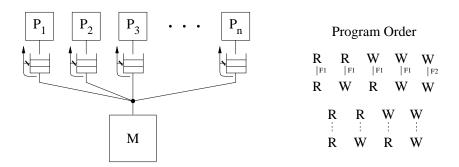

|    |                 | 2.4.1   | Overview of Relaxed Memory Consistency Models                | 24 |

|    |                 | 2.4.2   | Framework for Representing Different Models                  | 25 |

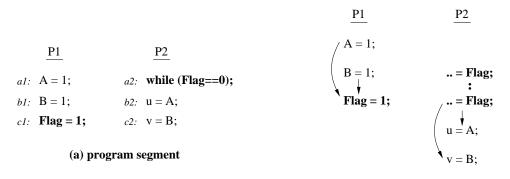

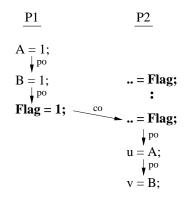

|    |                 | 2.4.3   | Relaxing the Write to Read Program Order                     | 26 |

|   |     | 2.4.4     | Relaxing the Write to Write Program Order                               | 31 |

|---|-----|-----------|-------------------------------------------------------------------------|----|

|   |     | 2.4.5     | Relaxing the Read to Read and Read to Write Program Order               | 31 |

|   |     | 2.4.6     | Impact of Relaxed Models on Compiler Optimizations                      | 38 |

|   |     | 2.4.7     | Relationship among the Models                                           | 39 |

|   |     | 2.4.8     | Some Shortcomings of Relaxed Models                                     | 39 |

|   | 2.5 | How to    | • Evaluate a Memory Model?                                              | 40 |

|   |     | 2.5.1     | Identifying the Target Environment                                      | 40 |

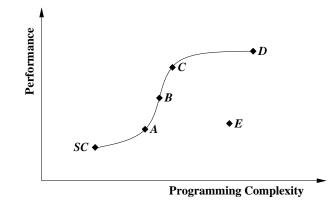

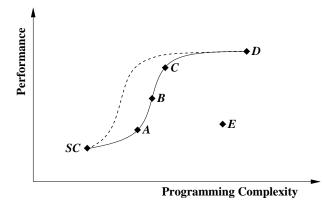

|   |     | 2.5.2     | Programming Ease and Performance                                        | 41 |

|   |     | 2.5.3     | Enhancing Programming Ease                                              | 42 |

|   | 2.6 | Related   | d Concepts                                                              | 43 |

|   | 2.7 | Summ      | ary                                                                     | 44 |

| 3 | App | proach f  | for Programming Simplicity                                              | 45 |

|   | 3.1 | Overvi    | ew of Programmer-Centric Models                                         | 45 |

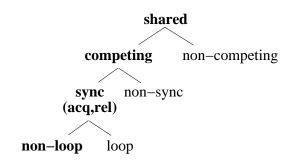

|   | 3.2 | A Hier    | archy of Programmer-Centric Models                                      | 47 |

|   |     | 3.2.1     | Properly-Labeled Model—Level One (PL1)                                  | 48 |

|   |     | 3.2.2     | Properly-Labeled Model—Level Two (PL2)                                  | 52 |

|   |     | 3.2.3     | Properly-Labeled Model—Level Three (PL3)                                | 55 |

|   |     | 3.2.4     | Relationship among the Properly-Labeled Models                          | 60 |

|   | 3.3 | Relatir   | ng Programmer-Centric and System-Centric Models                         | 61 |

|   | 3.4 | Benefi    | ts of Using Properly-Labeled Models                                     | 63 |

|   | 3.5 | How to    | Obtain Information about Memory Operations                              | 65 |

|   |     | 3.5.1     | Who Provides the Information                                            | 65 |

|   |     | 3.5.2     | Mechanisms for Conveying Operation Labels                               | 67 |

|   | 3.6 | Progra    | ms with Unsynchronized Memory Operations                                | 70 |

|   |     | 3.6.1     | Why Programmers Use Unsynchronized Operations                           | 70 |

|   |     | 3.6.2     | Trade-offs in Properly Labeling Programs with Unsynchronized Operations | 71 |

|   |     | 3.6.3     | Summary for Programs with Unsynchronized Operations                     | 74 |

|   | 3.7 | Possib    | le Extensions to Properly-Labeled Models                                | 74 |

|   |     | 3.7.1     | Requiring Alternate Information from the Programmer                     | 74 |

|   |     | 3.7.2     | Choosing a Different Base Model                                         | 75 |

|   |     | 3.7.3     | Other Possible Extensions                                               | 76 |

|   | 3.8 | Related   | d Work                                                                  | 76 |

|   |     | 3.8.1     | Relation to Past Work on Properly-Labeled Programs                      | 76 |

|   |     | 3.8.2     | Comparison with the Data-Race-Free Models                               | 78 |

|   |     | 3.8.3     | Other Related Work on Programmer-Centric Models                         | 79 |

|   |     | 3.8.4     | Related Work on Programming Environments                                | 80 |

|   | 3.9 | Summ      | ary                                                                     | 81 |

| 4 | Spe | cificatio | on of System Requirements                                               | 82 |

|   | 4.1 | Frame     | work for Specifying System Requirements                                 | 82 |

|   |     | 4.1.1     | Terminology and Assumptions for Specifying System Requirements          | 83 |

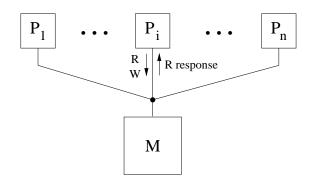

|   |     | 4.1.2   | Simple Abstraction for Memory Operations                                            | 86  |

|---|-----|---------|-------------------------------------------------------------------------------------|-----|

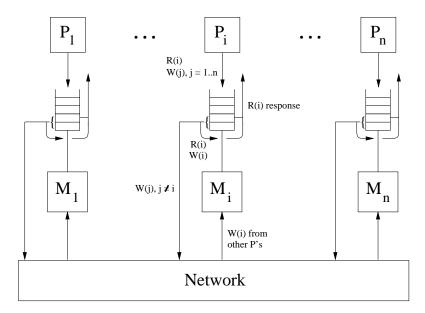

|   |     | 4.1.3   | A More General Abstraction for Memory Operations                                    | 88  |

|   | 4.2 | Suppor  | rting Properly-Labeled Programs                                                     | 97  |

|   |     | 4.2.1   | Sufficient Requirements for PL1                                                     | 97  |

|   |     | 4.2.2   | Sufficient Requirements for PL2                                                     | 107 |

|   |     | 4.2.3   | Sufficient Requirements for PL3                                                     | 109 |

|   | 4.3 | Expres  | sing System-Centric Models                                                          | 109 |

|   | 4.4 | Porting | g Programs Among Various Specifications                                             | 114 |

|   |     | 4.4.1   | Porting Sequentially Consistent Programs to System-Centric Models                   | 115 |

|   |     | 4.4.2   | Porting Programs Among System-Centric Models                                        | 120 |

|   |     | 4.4.3   | Porting Properly-Labeled Programs to System-Centric Models                          | 121 |

|   | 4.5 | Extens  | ions to Our Abstraction and Specification Framework                                 | 126 |

|   | 4.6 | Related | d Work                                                                              | 126 |

|   |     | 4.6.1   | Relationship to other Shared-Memory Abstractions                                    | 126 |

|   |     | 4.6.2   | Related Work on Memory Model Specification                                          | 128 |

|   |     | 4.6.3   | Related Work on Sufficient Conditions for Programmer-Centric Models                 | 129 |

|   |     | 4.6.4   | Work on Verifying Specifications                                                    | 130 |

|   | 4.7 | Summa   | ary                                                                                 | 131 |

|   |     |         |                                                                                     |     |

| 5 | -   |         | ation Techniques                                                                    | 132 |

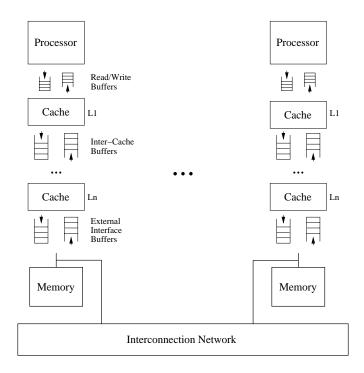

|   | 5.1 |         | Coherence                                                                           | 133 |

|   |     | 5.1.1   | Features of Cache Coherence                                                         |     |

|   |     | 5.1.2   | Abstraction for Cache Coherence Protocols                                           |     |

|   | 5.2 |         | nisms for Exploiting Relaxed Models                                                 |     |

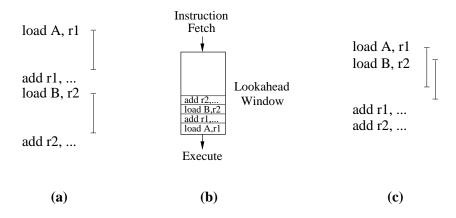

|   |     | 5.2.1   | Processor                                                                           |     |

|   |     | 5.2.2   | Read and Write Buffers                                                              |     |

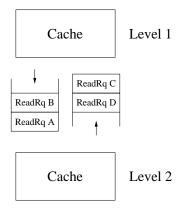

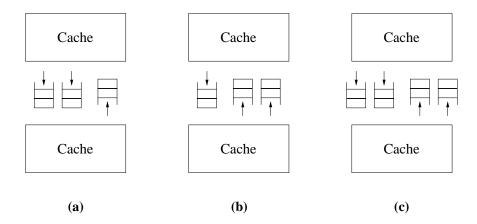

|   |     | 5.2.3   | Caches and Intermediate Buffers                                                     |     |

|   |     | 5.2.4   | External Interface                                                                  |     |

|   |     | 5.2.5   | Network and Memory System                                                           |     |

|   |     | 5.2.6   | Summary on Exploiting Relaxed Models                                                | 150 |

|   | 5.3 | Mainta  | ining the Correct Ordering Among Operations                                         | 150 |

|   |     | 5.3.1   | Relating Abstract Events in the Specification to Actual Events in an Implementation | 151 |

|   |     | 5.3.2   | Correctness Issues for Cache Coherence Protocols                                    | 154 |

|   |     | 5.3.3   | Supporting the Initiation and Uniprocessor Dependence Conditions                    | 158 |

|   |     | 5.3.4   | Interaction between Value, Coherence, Initiation, and Uniprocessor Dependence Con-  |     |

|   |     |         | ditions                                                                             | 160 |

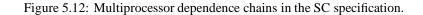

|   |     | 5.3.5   | Supporting the Multiprocessor Dependence Chains                                     | 162 |

|   |     | 5.3.6   | Supporting the Reach Condition                                                      | 183 |

|   |     | 5.3.7   | Supporting Atomic Read-Modify-Write Operations                                      | 184 |

|   |     | 5.3.8   | Comparing Implementations of System-Centric and Programmer-Centric Models           | 185 |

|   |     | 5.3.9   | Summary on Maintaining Correct Order                                                | 186 |

|   | 5.4 | More A  | Aggressive Mechanisms for Supporting Multiprocessor Dependence Chains               | 186 |

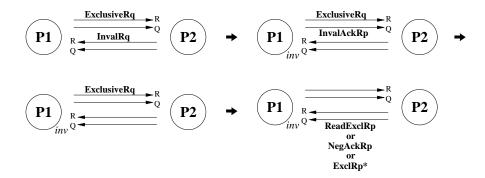

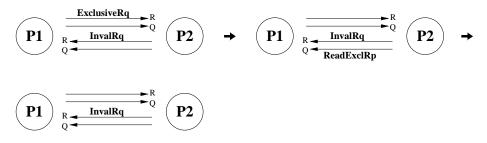

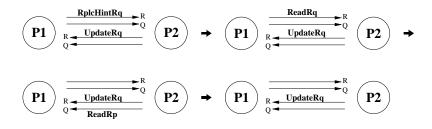

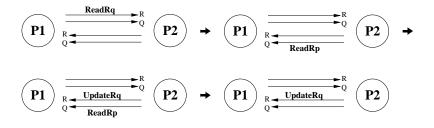

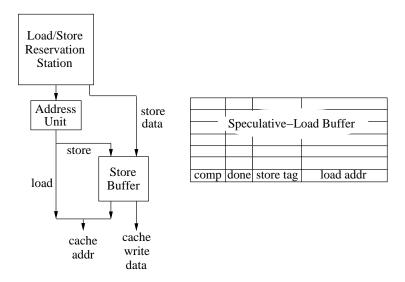

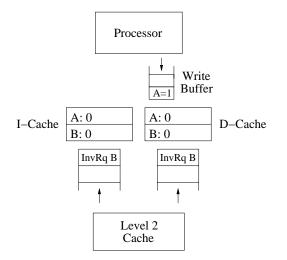

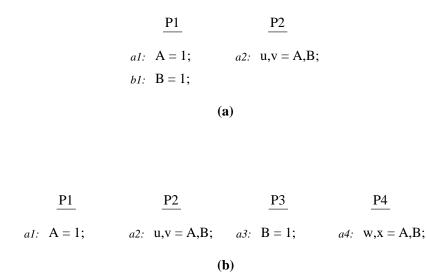

| 5.4.3       Exploiting the Roll-Back Mechanism in Dynamically-Scheduled Processors         5.4.4       Combining Speculative Reads with Hardware Prefetching for Writes         5.4.5       Other Related Work on Aggressively Supporting Multiprocessor Dependence Chains         5.5       Restricted Interconnection Networks         5.5.1       Broadcast Bus         5.5.2       Hierarchies of Buses and Hybrid Designs         5.5.3       Rings         5.5.4       Related Work on Restricted Interconnection Networks         5.5.5       Rystems with Software-Based Coherence         5.7       Interaction with Thread Placement and Migration         5.7.1       Thread Migration         5.7.2       Thread Placement         5.8       Interaction with Other Latency Hiding Techniques         5.8.1       Prefetching         5.8.2       Multiple Contexts         5.8.3       Synergy Among the Techniques         5.10.1       Problems with Current Compilers         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture -         5.10.3       Reasoning about Compiler Optimizations         5.10.4       Determining Safe Compiler Optimizations         5.10.5       Summary of Compiler Issues         5.11       Summary of Compiler Issues                                                                                 |   |      | 5.4.1   | Early Acknowledgement of Invalidation and Update Requests                      | 187 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|---------|--------------------------------------------------------------------------------|-----|

| 5.4.4       Combining Speculative Reads with Hardware Prefetching for Writes         5.4.5       Other Related Work on Aggressively Supporting Multiprocessor Dependence Chains         5.5       Restricted Interconnection Networks         5.5.1       Broadcast Bus         5.5.2       Hierarchies of Buses and Hybrid Designs         5.5.3       Rings         5.5.4       Related Work on Restricted Interconnection Networks         5.6       Systems with Software-Based Coherence         5.7       Interaction with Thread Placement and Migration         5.7.1       Thread Migration         5.7.2       Thread Placement         5.8       Interaction with Other Latency Hiding Techniques         5.8.1       Prefetching         5.8.2       Multiple Contexts         5.8.3       Synergy Among the Techniques         5.10       Implications for Compilers         5.10.1       Problems with Current Compilers         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture .         5.10.3       Reasoning about Compiler Optimizations         5.10.4       Determining Safe Compiler Optimizations         5.10.5       Summary of Compiler Issues         5.10.1       Summary of Blocking Reads         6.2.1 <t< td=""><td></td><td></td><td>5.4.2</td><td>Simple Automatic Hardware-Prefetching</td><td>196</td></t<>       |   |      | 5.4.2   | Simple Automatic Hardware-Prefetching                                          | 196 |

| 5.4.5       Other Related Work on Aggressively Supporting Multiprocessor Dependence Chains         5.5       Restricted Interconnection Networks         5.5.1       Broadcast Bus         5.5.2       Hierarchies of Buses and Hybrid Designs         5.5.3       Rings         5.5.4       Related Work on Restricted Interconnection Networks         5.6       Systems with Software-Based Coherence         5.7       Interaction with Thread Placement and Migration         5.7.1       Thread Migration         5.7.2       Thread Placement         5.8       Interaction with Other Latency Hiding Techniques         5.8.1       Prefetching         5.8.2       Multiple Contexts         5.8.3       Synergy Among the Techniques         5.9       Supporting Other Types of Events         5.10.1       Problems with Current Compilers         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture         5.10.3       Reasoning about Compiler Optimizations         5.10.4       Determining Safe Compiler Optimizations         5.10.5       Summary of Compiler Issues         5.11       Summary of Compiler Issues         6.1       Overview         6.2       Experimental Framework <td< td=""><td></td><td></td><td>5.4.3</td><td>Exploiting the Roll-Back Mechanism in Dynamically-Scheduled Processors</td><td>199</td></td<> |   |      | 5.4.3   | Exploiting the Roll-Back Mechanism in Dynamically-Scheduled Processors         | 199 |

| 5.5       Restricted Interconnection Networks         5.5.1       Broadcast Bus         5.5.2       Hierarchies of Buses and Hybrid Designs         5.5.3       Rings         5.5.4       Related Work on Restricted Interconnection Networks         5.6       Systems with Software-Based Coherence         5.7       Interaction with Thread Placement and Migration         5.7.1       Thread Placement         5.8       Interaction with Other Latency Hiding Techniques         5.8.1       Prefetching         5.8.2       Multiple Contexts         5.8.3       Syngray Among the Techniques         5.9       Supporting Other Types of Events         5.10.1       Problems with Current Compilers         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture          5.10.3       Reasoning about Compiler Optimizations         5.10.4       Determining Safe Compiler Optimizations         5.10.5       Summary of Compiler Issues         5.11       Summary of Compiler Issues         5.11       Summary         6       Performance Evaluation         6.1       Overview         6.2       Experimental Results         6.3       Interaction with Other Latency Hiding Techniques <td></td> <td></td> <td>5.4.4</td> <td>Combining Speculative Reads with Hardware Prefetching for Writes</td> <td>201</td>                        |   |      | 5.4.4   | Combining Speculative Reads with Hardware Prefetching for Writes               | 201 |

| 5.5.1       Broadcast Bus         5.5.2       Hierarchies of Buses and Hybrid Designs         5.5.3       Rings         5.5.4       Related Work on Restricted Interconnection Networks         5.6       Systems with Software-Based Coherence         5.7       Interaction with Thread Placement and Migration         5.7.1       Thread Migration         5.7.2       Thread Placement         5.8       Interaction with Other Latency Hiding Techniques         5.8.1       Prefetching         5.8.2       Multiple Contexts         5.8.3       Synergy Among the Techniques         5.8.4       Supporting Other Types of Events         5.101       Irplications for Compilers         5.102       Memory Model Assumptions for the Source Program and the Target Architecture         5.10.3       Reasoning about Compiler Optimizations         5.10.4       Determining Safe Compiler Optimizations         5.10.5       Summary of Compiler Issues         5.11       Summary         6 <b>Performance Evaluation</b> 6.1       Overview         6.2.1       Experimental Results         6.2.2       Experimental Results         6.3       Interaction with Other Latency Hiding Techniques                                                                                                                                                                                   |   |      | 5.4.5   | Other Related Work on Aggressively Supporting Multiprocessor Dependence Chains | 202 |

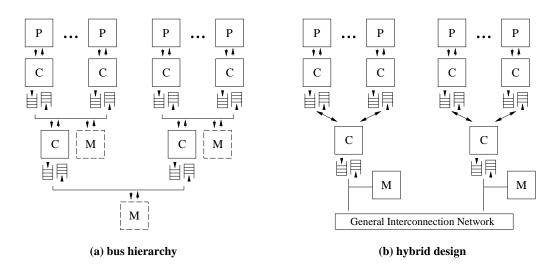

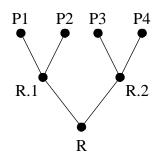

| 5.5.2       Hierarchies of Buses and Hybrid Designs         5.5.3       Rings         5.5.4       Related Work on Restricted Interconnection Networks         5.6       Systems with Software-Based Coherence         5.7       Interaction with Thread Placement and Migration         5.7.1       Thread Migration         5.7.2       Thread Placement         5.8       Interaction with Other Latency Hiding Techniques         5.8.1       Prefetching         5.8.2       Multiple Contexts         5.8.3       Synergy Among the Techniques         5.9       Supporting Other Types of Events         5.10       Implications for Compilers         5.10.1       Problems with Current Compilers         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture          5.10.3       Reasoning about Compiler Optimizations         5.10.4       Determining Safe Compiler Optimizations         5.10.5       Summary of Compiler Issues         5.11       Summary of Compiler Issues         5.11       Summary of Compiler Issues         6.1       Overview         6.2       Experimental Framework         6.2.3       Effect of Varying Architectural Assumptions         6.2.4       Summary                                                                                                                                                |   | 5.5  | Restric | ted Interconnection Networks                                                   | 204 |

| 5.5.3       Rings         5.5.4       Related Work on Restricted Interconnection Networks         5.6       Systems with Software-Based Coherence         5.7       Interaction with Thread Placement and Migration         5.7.1       Thread Migration         5.7.2       Thread Placement         5.8       Interaction with Other Latency Hiding Techniques         5.8.1       Prefetching         5.8.2       Multiple Contexts         5.8.3       Synergy Among the Techniques         5.9       Supporting Other Types of Events         5.10       Implications for Compilers         5.10.1       Problems with Current Compilers         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture         5.10.3       Reasoning about Compiler Optimizations         5.10.4       Determining Safe Compiler Optimizations         5.10.5       Summary of Compiler Issues         5.11       Summary of Compiler Issues         5.11       Summary of Compiler Reads         6.2.1       Experimental Framework         6.2.2       Experimental Results         6.3       Interaction with Other Latency Hiding Techniques         6.3       Interaction with Prefetching         6.3.2       Inte                                                                                                                                               |   |      | 5.5.1   | Broadcast Bus                                                                  | 204 |

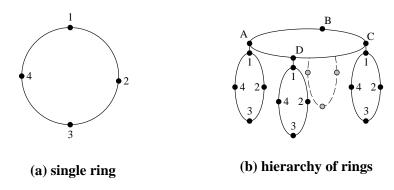

| 5.5.4       Related Work on Restricted Interconnection Networks         5.6       Systems with Software-Based Coherence         5.7       Interaction with Thread Placement and Migration         5.7.1       Thread Migration         5.7.2       Thread Placement         5.8       Interaction with Other Latency Hiding Techniques         5.8.1       Prefetching         5.8.2       Multiple Contexts         5.8.3       Synergy Among the Techniques         5.9       Supporting Other Types of Events         5.10       Implications for Compilers         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture         5.10.3       Reasoning about Compiler Optimizations         5.10.4       Determining Safe Compiler Optimizations         5.10.5       Summary of Compiler Issues         5.11       Summary of Compiler Issues         5.11       Summary of Compiler Issues         6.1       Overview         6.2       Experimental Framework         6.2.3       Effect of Varying Architectural Assumptions         6.2.4       Summary of Blocking Read Results         6.3.1       Interaction with Other Latency Hiding Techniques         6.3.2       Interaction with Multiple Contexts                                                                                                                                       |   |      | 5.5.2   | Hierarchies of Buses and Hybrid Designs                                        | 205 |

| 5.6       Systems with Software-Based Coherence       5.7         5.7       Interaction with Thread Placement and Migration       5.7.1         5.7.1       Thread Migration       5.7.2         5.7.2       Thread Placement       5.8         5.8       Interaction with Other Latency Hiding Techniques       5.8.1         5.8.1       Prefetching       5.8.1         5.8.2       Multiple Contexts       5.8.3         5.8.3       Synergy Among the Techniques       5.9         5.9       Supporting Other Types of Events       5.10.1         5.10.1       Problems with Current Compilers       5.10.2         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture         5.10.3       Reasoning about Compiler Optimizations       5.10.5         5.10.4       Determining Safe Compiler Optimizations       5.10.5         5.10.5       Summary of Compiler Issues       5.11         5.11       Summary       6         6.1       Overview       6.2.1         6.2       Architectures with Blocking Reads       6.2.3         6.2.1       Experimental Framework       6.2.3         6.2.2       Experimental Results       6.3.1         6.3       Interaction with O                                                                                                                                                                     |   |      | 5.5.3   | Rings                                                                          | 207 |

| 5.7       Interaction with Thread Placement and Migration         5.7.1       Thread Migration         5.7.2       Thread Placement         5.8       Interaction with Other Latency Hiding Techniques         5.8.1       Prefetching         5.8.2       Multiple Contexts         5.8.3       Synergy Among the Techniques         5.9       Supporting Other Types of Events         5.10       Implications for Compilers         5.10.1       Problems with Current Compilers         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture          5.10.3       Reasoning about Compiler Optimizations         5.10.4       Determining Safe Compiler Optimizations         5.10.5       Summary of Compiler Issues         5.11       Summary         6       Performance Evaluation         6.1       Overview         6.2.1       Experimental Framework         6.2.2       Experimental Results         6.3.1       Interaction with Other Latency Hiding Techniques         6.3.1       Interaction with Multiple Contexts         6.3.2       Interaction with Multiple Contexts         6.3.3       Summary of Other Latency Hiding Techniques         6.4       Architectures with Non-Blocki                                                                                                                                               |   |      | 5.5.4   | Related Work on Restricted Interconnection Networks                            | 209 |

| 5.7.1       Thread Migration       5.7.2         5.7.2       Thread Placement       5.8         5.8       Interaction with Other Latency Hiding Techniques       5.8.1         5.8.1       Prefetching       5.8.2         5.8.2       Multiple Contexts       5.8.3         5.8.3       Synergy Among the Techniques       5.9         5.9       Supporting Other Types of Events       5.10         5.10       Implications for Compilers       5.10.2         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture       5.10.3         5.10.4       Determining Safe Compiler Optimizations       5.10.4         5.10.5       Summary of Compiler Issues       5.11         5.11       Summary of Compiler Issues       5.11         5.11       Summary of Compiler Issues       5.11         6.1       Overview       6.2         6.2       Architectures with Blocking Reads       6.2.1         6.2.1       Experimental Framework       6.2.3         6.2.2       Experimental Results       6.3.1         6.3.3       Interaction with Other Latency Hiding Techniques       6.3.1         6.3.1       Interaction with Multiple Contexts       6.3.3         6.3.2                                                                                                                                                                                |   | 5.6  | System  | s with Software-Based Coherence                                                | 210 |

| 5.7.2       Thread Placement         5.8       Interaction with Other Latency Hiding Techniques         5.8.1       Prefetching         5.8.2       Multiple Contexts         5.8.3       Synergy Among the Techniques         5.9       Supporting Other Types of Events         5.10.1       Problems with Current Compilers         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture         5.10.3       Reasoning about Compiler Optimizations         5.10.4       Determining Safe Compiler Optimizations         5.10.5       Summary of Compiler Issues         5.11       Summary         6       Performance Evaluation         6.1       Overview         6.2.1       Experimental Framework         6.2.2       Experimental Results         6.2.3       Effect of Varying Architectural Assumptions         6.2.4       Summary of Blocking Read Results         6.3       Interaction with Other Latency Hiding Techniques         6.3.1       Interaction with Multiple Contexts         6.3.2       Interaction with Multiple Contexts         6.3.3       Summary of Other Latency Hiding Techniques         6.4       Architectures with Non-Blocking Reads         6.5.3       Summar                                                                                                                                               |   | 5.7  | Interac | tion with Thread Placement and Migration                                       | 212 |

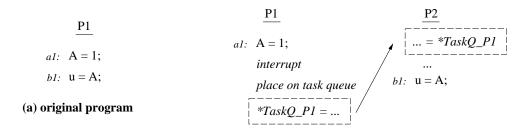

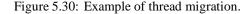

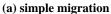

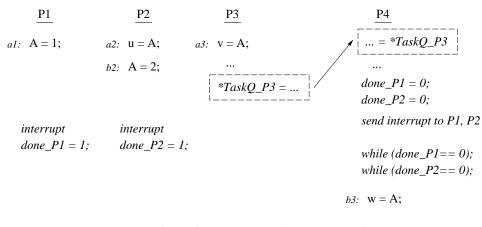

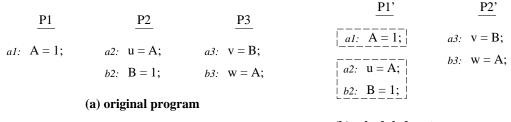

| 5.8       Interaction with Other Latency Hiding Techniques       5         5.8.1       Prefetching       5         5.8.2       Multiple Contexts       5         5.8.3       Synergy Among the Techniques       5         5.9       Supporting Other Types of Events       5         5.10       Implications for Compilers       5         5.10.1       Problems with Current Compilers       5         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture       5         5.10.3       Reasoning about Compiler Optimizations       5         5.10.4       Determining Safe Compiler Optimizations       5         5.10.5       Summary of Compiler Issues       5         5.11       Summary       6         6.1       Overview       6         6.2.1       Experimental Framework       6         6.2.2       Experimental Results       6         6.3       Interaction with Other Latency Hiding Techniques       6         6.3.1       Interaction with Multiple Contexts       6         6.3.2       Interaction with Multiple Contexts       6         6.3.3       Summary of Other Latency Hiding Techniques       6         6.4       Architectures with Non-Block                                                                                                                                                                              |   |      | 5.7.1   | Thread Migration                                                               | 213 |

| 5.8.1       Prefetching       5.8.2         Multiple Contexts       5.8.3         5.8.3       Synergy Among the Techniques         5.9       Supporting Other Types of Events         5.10       Implications for Compilers         5.10.1       Problems with Current Compilers         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture         5.10.3       Reasoning about Compiler Optimizations         5.10.4       Determining Safe Compiler Optimizations         5.10.5       Summary of Compiler Issues         5.11       Summary         6       Performance Evaluation         6.1       Overview         6.2.1       Experimental Framework         6.2.2       Experimental Results         6.2.3       Effect of Varying Architectural Assumptions         6.2.4       Summary of Blocking Read Results         6.3       Interaction with Other Latency Hiding Techniques         6.3.1       Interaction with Multiple Contexts         6.3.2       Interaction with Multiple Contexts         6.3.3       Summary of Other Latency Hiding Techniques         6.4       Architectures with Non-Blocking Reads         6.4.1       Experimental Framework         6.4.2                                                                                                                                                               |   |      | 5.7.2   | Thread Placement                                                               | 215 |

| 5.8.2       Multiple Contexts         5.8.3       Synergy Among the Techniques         5.9       Supporting Other Types of Events         5.10       Implications for Compilers         5.10.1       Problems with Current Compilers         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture         5.10.3       Reasoning about Compiler Optimizations         5.10.4       Determining Safe Compiler Optimizations         5.10.5       Summary of Compiler Issues         5.11       Summary         6       Performance Evaluation         6.1       Overview         6.2       Architectures with Blocking Reads         6.2.1       Experimental Framework         6.2.2       Experimental Results         6.2.3       Effect of Varying Architectural Assumptions         6.2.4       Summary of Blocking Read Results         6.3       Interaction with Other Latency Hiding Techniques         6.3.1       Interaction with Multiple Contexts         6.3.2       Interaction with Multiple Contexts         6.3.3       Summary of Other Latency Hiding Techniques         6.4       Architectures with Non-Blocking Reads         6.4.1       Experimental Framework         6.4.2       E                                                                                                                                               |   | 5.8  | Interac | tion with Other Latency Hiding Techniques                                      | 221 |

| 5.8.3       Synergy Among the Techniques       5.9         5.9       Supporting Other Types of Events       5.10         5.10       Implications for Compilers       5.10.1         5.10.1       Problems with Current Compilers       5.10.2         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture       5.10.3         5.10.3       Reasoning about Compiler Optimizations       5.10.4         5.10.4       Determining Safe Compiler Optimizations       5.10.5         5.10.5       Summary of Compiler Issues       5.11         Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |      | 5.8.1   | Prefetching                                                                    | 221 |

| 5.9       Supporting Other Types of Events         5.10       Implications for Compilers         5.10.1       Problems with Current Compilers         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture         5.10.3       Reasoning about Compiler Optimizations         5.10.4       Determining Safe Compiler Optimizations         5.10.5       Summary of Compiler Issues         5.11       Summary of Compiler Issues         5.11       Summary of Compiler Issues         6.1       Overview         6.2       Architectures with Blocking Reads         6.2.1       Experimental Framework         6.2.2       Experimental Results         6.2.3       Effect of Varying Architectural Assumptions         6.3.1       Interaction with Other Latency Hiding Techniques         6.3.1       Interaction with Multiple Contexts         6.3.3       Summary of Other Latency Hiding Techniques         6.4.1       Experimental Framework         6.4.2       Experimental Results                                                                                                                                                                                                                                                                                                                                                           |   |      | 5.8.2   | Multiple Contexts                                                              | 222 |

| 5.10       Implications for Compilers       2         5.10.1       Problems with Current Compilers       2         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture       2         5.10.3       Reasoning about Compiler Optimizations       2         5.10.4       Determining Safe Compiler Optimizations       2         5.10.5       Summary of Compiler Issues       2         5.11       Summary of Compiler Issues       2         5.11       Summary of Compiler Issues       2         6       Performance Evaluation       2         6.1       Overview       2         6.2       Architectures with Blocking Reads       2         6.2.1       Experimental Framework       2         6.2.2       Experimental Results       2         6.2.3       Effect of Varying Architectural Assumptions       2         6.3.1       Interaction with Other Latency Hiding Techniques       2         6.3.1       Interaction with Multiple Contexts       2         6.3.3       Summary of Other Latency Hiding Techniques       2         6.4       Architectures with Non-Blocking Reads       2         6.4.1       Experimental Framework       2         6.4.2       <                                                                                                                                                                          |   |      | 5.8.3   | Synergy Among the Techniques                                                   | 224 |

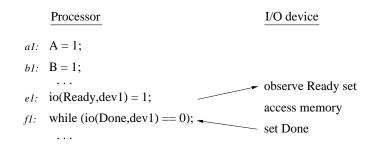

| 5.10.1       Problems with Current Compilers       5.10.2         5.10.2       Memory Model Assumptions for the Source Program and the Target Architecture       5.10.3         5.10.3       Reasoning about Compiler Optimizations       5.10.4         5.10.4       Determining Safe Compiler Optimizations       5.10.5         5.10.5       Summary of Compiler Issues       5.11         Summary       5.11       Summary       5.11         6       Performance Evaluation       6.2         6.1       Overview       6.2         6.2.1       Experimental Framework       6.2.2         6.2.2       Experimental Results       5.2.3         6.2.3       Effect of Varying Architectural Assumptions       5.2.4         6.3.1       Interaction with Other Latency Hiding Techniques       6.3.1         6.3.2       Interaction with Multiple Contexts       5.3.3         6.3.3       Summary of Other Latency Hiding Techniques       5.3.3         6.4       Architectures with Non-Blocking Reads       5.4.1         6.4.1       Experimental Framework       5.4.2         6.4.2       Experimental Results       5.3.3                                                                                                                                                                                                                                                          |   | 5.9  | Suppor  | ting Other Types of Events                                                     | 224 |

| 5.10.2 Memory Model Assumptions for the Source Program and the Target Architecture       2         5.10.3 Reasoning about Compiler Optimizations       2         5.10.4 Determining Safe Compiler Optimizations       2         5.10.5 Summary of Compiler Issues       2         5.11 Summary       2         6 Performance Evaluation       2         6.1 Overview       2         6.2 Architectures with Blocking Reads       2         6.2.1 Experimental Framework       2         6.2.2 Experimental Results       2         6.2.3 Effect of Varying Architectural Assumptions       2         6.3 Interaction with Other Latency Hiding Techniques       2         6.3.1 Interaction with Multiple Contexts       2         6.3.2 Interaction with Multiple Contexts       2         6.3.3 Summary of Other Latency Hiding Techniques       2         6.4.1 Experimental Framework       2         6.4.1 Experimental Framework       2         6.4.2 Experimental Results       2                                                                                                                                                                                                                                                                                                                                                                                                       |   | 5.10 | Implica | ations for Compilers                                                           | 225 |

| 5.10.3 Reasoning about Compiler Optimizations       5.10.4 Determining Safe Compiler Optimizations         5.10.4 Determining Safe Compiler Optimizations       5.10.5 Summary of Compiler Issues         5.11 Summary       5.11 Summary         6 Performance Evaluation       6.1 Overview         6.2 Architectures with Blocking Reads       6.2.1 Experimental Framework         6.2.2 Experimental Results       6.2.3 Effect of Varying Architectural Assumptions         6.2.4 Summary of Blocking Read Results       6.3.1 Interaction with Other Latency Hiding Techniques         6.3.1 Interaction with Multiple Contexts       6.3.3 Summary of Other Latency Hiding Techniques         6.4.1 Experimental Framework       6.4.1 Experimental Framework         6.4.2 Experimental Results       6.4.2 Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |      | 5.10.1  | Problems with Current Compilers                                                | 225 |

| 5.10.4 Determining Safe Compiler Optimizations       2         5.10.5 Summary of Compiler Issues       2         5.11 Summary       2         6 Performance Evaluation       2         6.1 Overview       2         6.2 Architectures with Blocking Reads       2         6.2.1 Experimental Framework       2         6.2.2 Experimental Results       2         6.2.3 Effect of Varying Architectural Assumptions       2         6.2.4 Summary of Blocking Read Results       2         6.3 Interaction with Other Latency Hiding Techniques       2         6.3.1 Interaction with Multiple Contexts       2         6.3.3 Summary of Other Latency Hiding Techniques       2         6.4 Architectures with Non-Blocking Reads       2         6.4 Experimental Framework       2         6.4.1 Experimental Results       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      | 5.10.2  | Memory Model Assumptions for the Source Program and the Target Architecture    | 227 |

| 5.10.5       Summary of Compiler Issues       2         5.11       Summary       2         6       Performance Evaluation       2         6.1       Overview       2         6.2       Architectures with Blocking Reads       2         6.2.1       Experimental Framework       2         6.2.2       Experimental Results       2         6.2.3       Effect of Varying Architectural Assumptions       2         6.2.4       Summary of Blocking Read Results       2         6.3       Interaction with Other Latency Hiding Techniques       2         6.3.1       Interaction with Prefetching       2         6.3.2       Interaction with Multiple Contexts       2         6.3.3       Summary of Other Latency Hiding Techniques       2         6.4       Architectures with Non-Blocking Reads       2         6.4.1       Experimental Framework       2         6.4.2       Experimental Results       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      | 5.10.3  | Reasoning about Compiler Optimizations                                         | 228 |

| 5.11       Summary       2         6       Performance Evaluation       2         6.1       Overview       2         6.2       Architectures with Blocking Reads       2         6.2.1       Experimental Framework       2         6.2.2       Experimental Results       2         6.2.3       Effect of Varying Architectural Assumptions       2         6.2.4       Summary of Blocking Read Results       2         6.3       Interaction with Other Latency Hiding Techniques       2         6.3.1       Interaction with Prefetching       2         6.3.2       Interaction with Multiple Contexts       2         6.3.3       Summary of Other Latency Hiding Techniques       2         6.4       Architectures with Non-Blocking Reads       2         6.4.1       Experimental Framework       2         6.4.2       Experimental Results       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |      | 5.10.4  | Determining Safe Compiler Optimizations                                        | 229 |

| 6       Performance Evaluation       2         6.1       Overview       2         6.2       Architectures with Blocking Reads       2         6.2.1       Experimental Framework       2         6.2.2       Experimental Results       2         6.2.3       Effect of Varying Architectural Assumptions       2         6.2.4       Summary of Blocking Read Results       2         6.3       Interaction with Other Latency Hiding Techniques       2         6.3.1       Interaction with Prefetching       2         6.3.2       Interaction with Multiple Contexts       2         6.3.3       Summary of Other Latency Hiding Techniques       2         6.4       Architectures with Non-Blocking Reads       2         6.4.1       Experimental Framework       2         6.4.2       Experimental Results       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      | 5.10.5  | Summary of Compiler Issues                                                     | 233 |

| 6.1       Overview       2         6.2       Architectures with Blocking Reads       2         6.2.1       Experimental Framework       2         6.2.2       Experimental Results       2         6.2.3       Effect of Varying Architectural Assumptions       2         6.2.4       Summary of Blocking Read Results       2         6.3       Interaction with Other Latency Hiding Techniques       2         6.3.1       Interaction with Prefetching       2         6.3.2       Interaction with Multiple Contexts       2         6.3.3       Summary of Other Latency Hiding Techniques       2         6.4       Architectures with Non-Blocking Reads       2         6.4.1       Experimental Framework       2         6.4.2       Experimental Results       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 5.11 | Summa   | ary                                                                            | 233 |

| <ul> <li>6.2 Architectures with Blocking Reads</li> <li>6.2.1 Experimental Framework</li> <li>6.2.2 Experimental Results</li> <li>6.2.3 Effect of Varying Architectural Assumptions</li> <li>6.2.4 Summary of Blocking Read Results</li> <li>6.3 Interaction with Other Latency Hiding Techniques</li> <li>6.3.1 Interaction with Prefetching</li> <li>6.3.2 Interaction with Multiple Contexts</li> <li>6.3.3 Summary of Other Latency Hiding Techniques</li> <li>6.4 Architectures with Non-Blocking Reads</li> <li>6.4.1 Experimental Framework</li> <li>6.4.2 Experimental Results</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6 | Perf | forman  | ce Evaluation                                                                  | 234 |

| <ul> <li>6.2.1 Experimental Framework</li> <li>6.2.2 Experimental Results</li> <li>6.2.3 Effect of Varying Architectural Assumptions</li> <li>6.2.4 Summary of Blocking Read Results</li> <li>6.3 Interaction with Other Latency Hiding Techniques</li> <li>6.3.1 Interaction with Prefetching</li> <li>6.3.2 Interaction with Multiple Contexts</li> <li>6.3.3 Summary of Other Latency Hiding Techniques</li> <li>6.4 Architectures with Non-Blocking Reads</li> <li>6.4.1 Experimental Framework</li> <li>6.4.2 Experimental Results</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 6.1  | Overvi  | ew                                                                             | 234 |

| 6.2.2       Experimental Results       2         6.2.3       Effect of Varying Architectural Assumptions       2         6.2.4       Summary of Blocking Read Results       2         6.3       Interaction with Other Latency Hiding Techniques       2         6.3.1       Interaction with Prefetching       2         6.3.2       Interaction with Multiple Contexts       2         6.3.3       Summary of Other Latency Hiding Techniques       2         6.4       Architectures with Non-Blocking Reads       2         6.4.1       Experimental Framework       2         6.4.2       Experimental Results       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 6.2  | Archite | ectures with Blocking Reads                                                    | 235 |

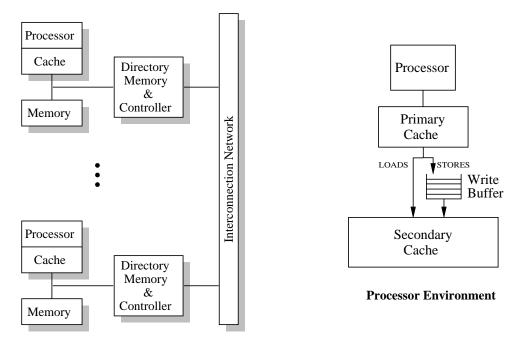

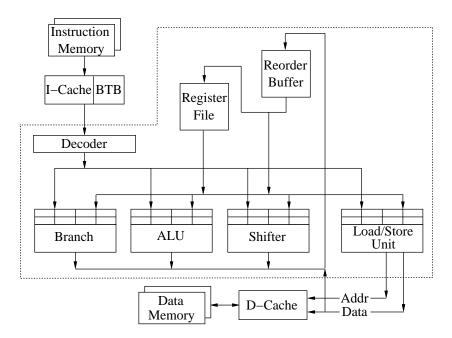

| 6.2.3       Effect of Varying Architectural Assumptions       2         6.2.4       Summary of Blocking Read Results       2         6.3       Interaction with Other Latency Hiding Techniques       2         6.3.1       Interaction with Prefetching       2         6.3.2       Interaction with Multiple Contexts       2         6.3.3       Summary of Other Latency Hiding Techniques       2         6.4       Architectures with Non-Blocking Reads       2         6.4.1       Experimental Framework       2         6.4.2       Experimental Results       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      | 6.2.1   | Experimental Framework                                                         | 235 |

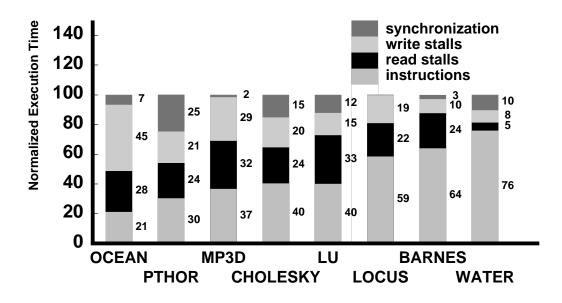

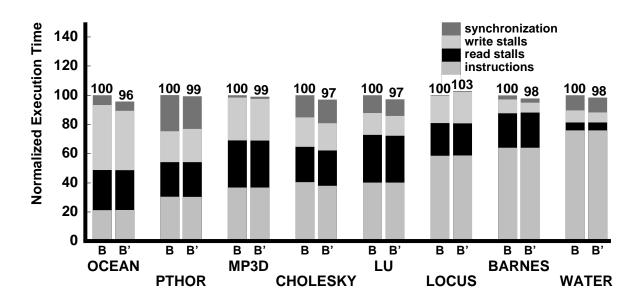

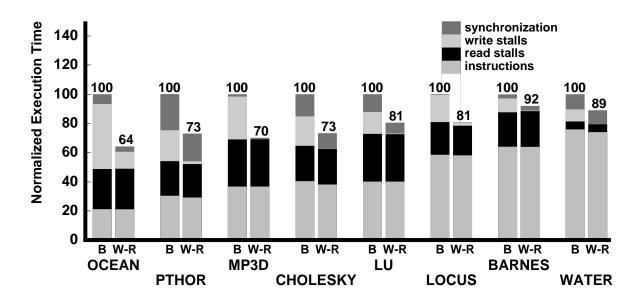

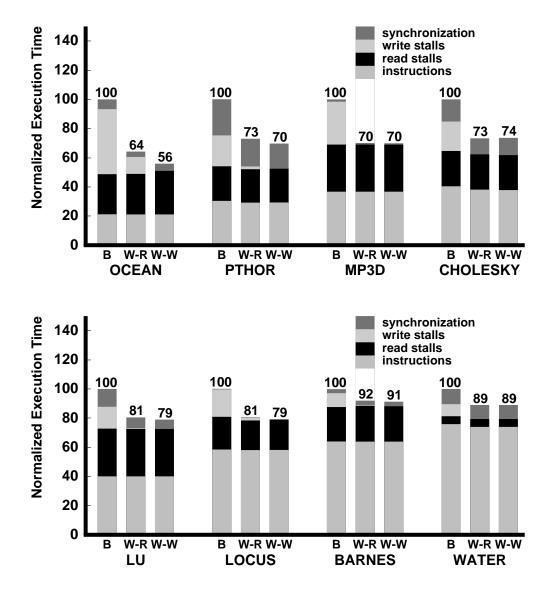

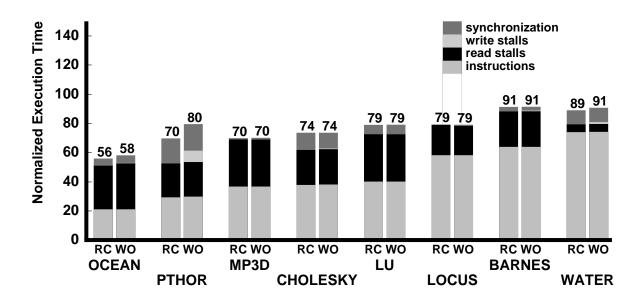

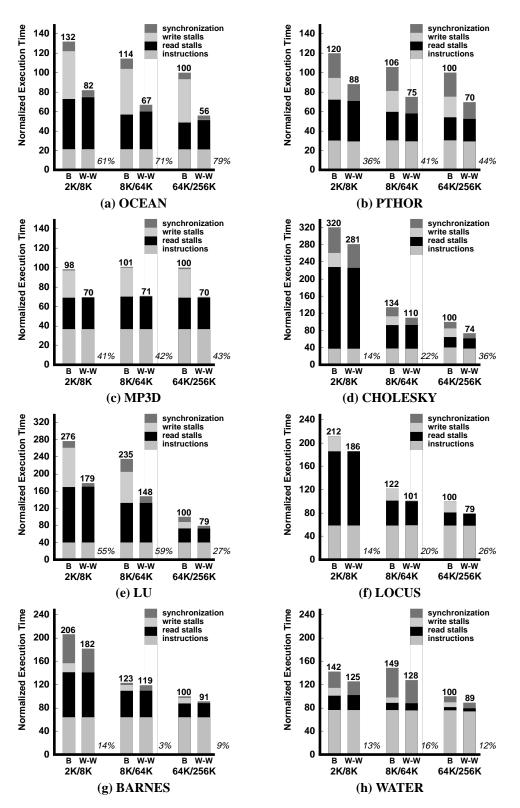

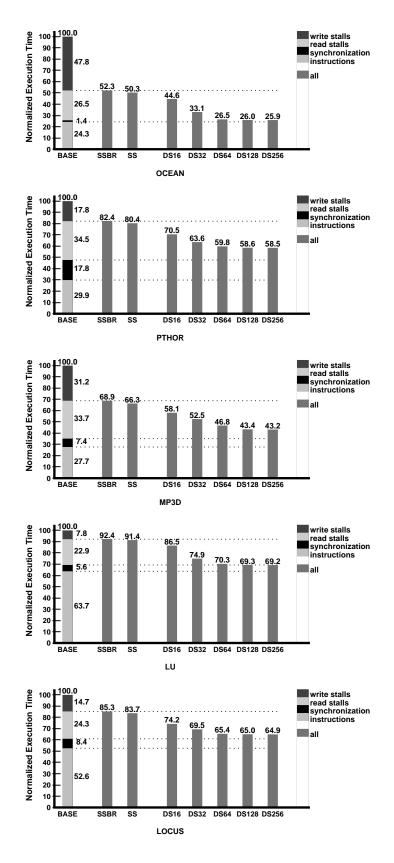

| 6.2.4       Summary of Blocking Read Results       2         6.3       Interaction with Other Latency Hiding Techniques       2         6.3.1       Interaction with Prefetching       2         6.3.2       Interaction with Multiple Contexts       2         6.3.3       Summary of Other Latency Hiding Techniques       2         6.4       Architectures with Non-Blocking Reads       2         6.4.1       Experimental Framework       2         6.4.2       Experimental Results       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |      | 6.2.2   | Experimental Results                                                           | 240 |

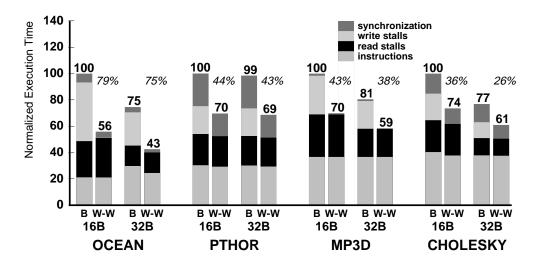

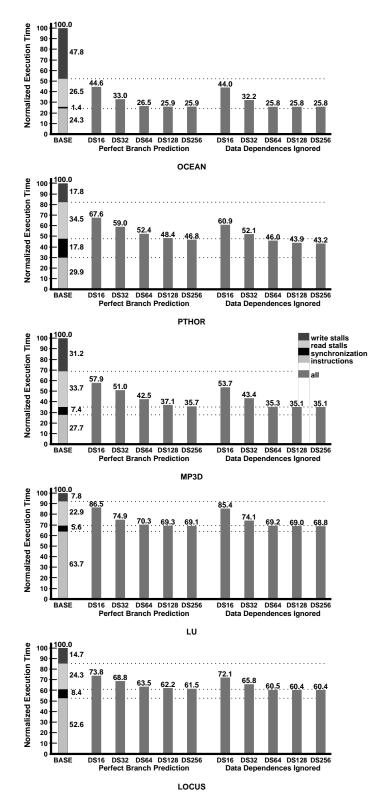

| 6.3 Interaction with Other Latency Hiding Techniques       2         6.3.1 Interaction with Prefetching       2         6.3.2 Interaction with Multiple Contexts       2         6.3.3 Summary of Other Latency Hiding Techniques       2         6.4 Architectures with Non-Blocking Reads       2         6.4.1 Experimental Framework       2         6.4.2 Experimental Results       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      | 6.2.3   | Effect of Varying Architectural Assumptions                                    | 248 |

| 6.3.1       Interaction with Prefetching       2         6.3.2       Interaction with Multiple Contexts       2         6.3.3       Summary of Other Latency Hiding Techniques       2         6.4       Architectures with Non-Blocking Reads       2         6.4.1       Experimental Framework       2         6.4.2       Experimental Results       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |      | 6.2.4   | Summary of Blocking Read Results                                               | 255 |

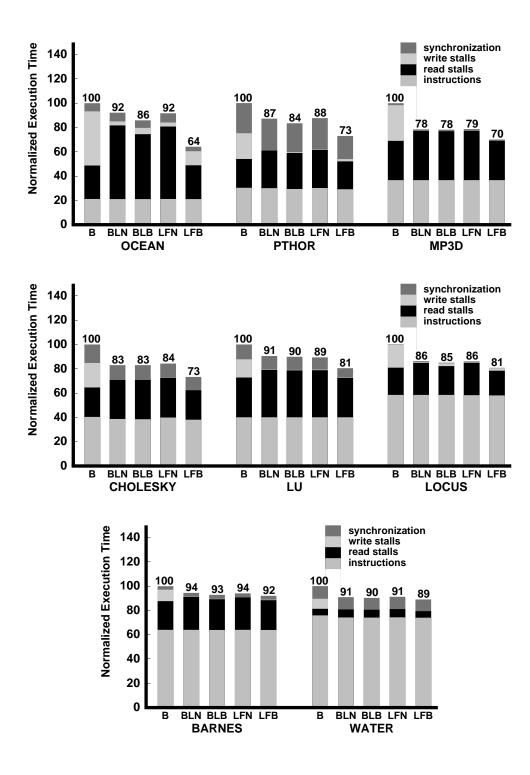

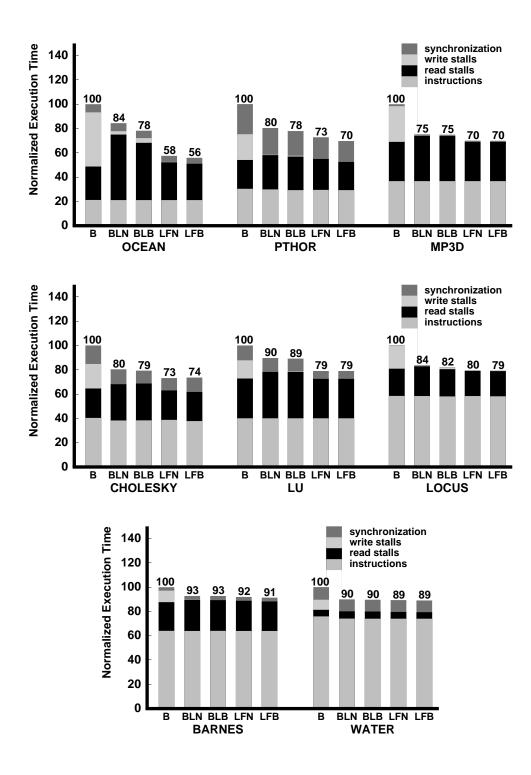

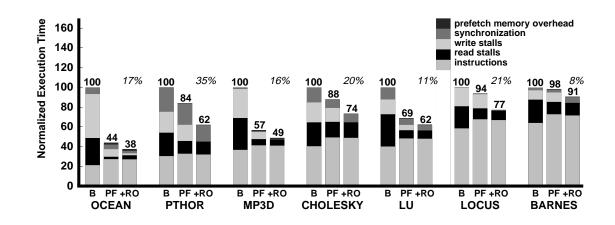

| 6.3.2       Interaction with Multiple Contexts       2         6.3.3       Summary of Other Latency Hiding Techniques       2         6.4       Architectures with Non-Blocking Reads       2         6.4.1       Experimental Framework       2         6.4.2       Experimental Results       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 6.3  | Interac | tion with Other Latency Hiding Techniques                                      | 256 |

| 6.3.3       Summary of Other Latency Hiding Techniques       2         6.4       Architectures with Non-Blocking Reads       2         6.4.1       Experimental Framework       2         6.4.2       Experimental Results       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |      | 6.3.1   | Interaction with Prefetching                                                   | 256 |

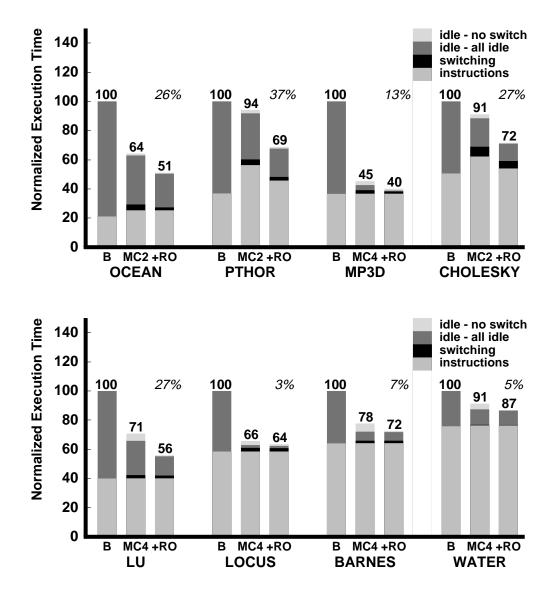

| 6.4       Architectures with Non-Blocking Reads       2         6.4.1       Experimental Framework       2         6.4.2       Experimental Results       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |      | 6.3.2   | Interaction with Multiple Contexts                                             | 258 |

| 6.4.1 Experimental Framework    2      6.4.2 Experimental Results    2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |      | 6.3.3   | Summary of Other Latency Hiding Techniques                                     | 259 |

| 6.4.2 Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 6.4  | Archite | ectures with Non-Blocking Reads                                                | 261 |